|                                                                                                                                                                                                                                   | A Forward On-The-Fly Approach for Safety and Reachability Controller Synthesis of Timed Systems |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|

| Auteur:<br>Author:                                                                                                                                                                                                                | Parisa Heidari                                                                                  |  |  |

| Date:                                                                                                                                                                                                                             | 2012                                                                                            |  |  |

| Type:                                                                                                                                                                                                                             | Mémoire ou thèse / Dissertation or Thesis                                                       |  |  |

| Référence: Heidari, P. (2012). A Forward On-The-Fly Approach for Safety and Reachab<br>Controller Synthesis of Timed Systems [Thèse de doctorat, École Polytech<br>de Montréal]. PolyPublie. https://publications.polymtl.ca/979/ |                                                                                                 |  |  |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/979/ |

|------------------------------------------|--------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Hanifa Boucheneb                     |

| Programme: Program:                      | Génie informatique                   |

# UNIVERSITÉ DE MONTRÉAL

# A FORWARD ON-THE-FLY APPROACH FOR SAFETY AND REACHABILITY CONTROLLER SYNTHESIS OF TIMED SYSTEMS

# PARISA HEIDARI DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIÆ DOCTOR (GÉNIE INFORMATIQUE) NOVEMBRE 2012

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée :

# A FORWARD ON-THE-FLY APPROACH FOR SAFETY AND REACHABILITY CONTROLLER SYNTHESIS OF TIMED SYSTEMS

présentée par : HEIDARI Parisa

en vue de l'obtention du diplôme de : <u>Philosophiæ Doctor</u> a été dûment acceptée par le jury d'examen constitué de :

M. QUINTERO Alejandro, Doct., président.

Mme BOUCHENEB Hanifa, Doctorat, membre et directrice de recherche.

M. <u>BELTRAME Giovanni</u>, Ph.D., membre.

M. BENTAHAR Jamal, Ph.D., membre.

$\begin{tabular}{ll} \it To Mom and Dad, \\ \it for their unfailing love. . . \\ \end{tabular}$

To Fariba and Keivan for being there!

### **ACKNOWLEDGEMENTS**

I would like to thank my advisor, Professor Hanifa Boucheneb, for having led me in this research. I appreciate her valuable directives and continuous moral support. She came with me step by step along the way. I'm honored to have worked with her and had the chance to profit from her experiences.

I would also like to thank Dr. Rachid Hadjidj for his collaboration in this research.

## RÉSUMÉ

Cette thèse s'intéresse à la synthèse de contrôleurs pour des systèmes temps réel (systèmes temporisés). Partant d'un système temps réel modélisé par un réseau de Petri temporel composé de transitions contrôlables et non contrôlables (TPN), le contrôle vise à forcer, en restreignant les intervalles de franchissement des transitions contrôlables, le système à satisfaire les propriétés souhaitées.

Nous proposons, dans cette thèse, un algorithme pour synthétiser de tels contrôleurs pour des propriétés de sûreté et d'accessibilité. Cet algorithme, basé sur la méthode de graphe de classes d'états, calcule à la volée les classes d'états atteignables du TPN tout en collectant progressivement les sous-intervalles de tir à éviter, afin de satisfaire les propriétés souhaitées. Avec cet algorithme, il n'est plus nécessaire de calculer les prédécesseurs contrôlables et de partitionner récursivement les classes d'états jusqu'à atteindre un point fixe, comme c'est le cas dans les autres approches basées sur l'exploration, en avant et en arrière, de l'espace des états du système. Nous prouvons formellement la correction de l'algorithme, puis nous montrons que dans la catégorie des contrôleurs basés sur la restriction des intervalles de tir, l'algorithme, proposé dans cette thèse, synthétise un contrôleur optimal (le plus permissif possible).

Afin d'atténuer davantage le problème d'explosion combinatoire, nous montrons comment combiner cette approche avec une abstraction par l'inclusion, par union-convexe ou par enveloppe-convexe. Nous montrons également comment exploiter cet algorithme pour générer des contrôleurs décentralisés.

Enfin, nous proposons d'appliquer cet algorithme pour contrôler des TPN par des chronomètres. Notre algorithme permet de partitionner les intervalles des transitions en "bons" et "mauvais" sous-intervalles (à éviter). L'idée est d'utiliser des chronomètres pour suspendre les tâches (transitions) durant leurs mauvais sous-intervalles et les activer dans leurs "bons sous-intervalles". Il s'agit donc de contrôler les réseaux de Petri temporels en associant des chronomètres aux transitions contrôlables, pour obtenir ainsi des réseaux de Petri temporels contrôlés.

#### **ABSTRACT**

This thesis deals with controller synthesis for real time systems (timed systems). Given a real time system modeled as a Time Petri Net (TPN) with controllable and uncontrollable transitions, the control aims at forcing the system to satisfy properties of interest, by limiting the firing intervals of controllable transitions. We propose, in this thesis, an algorithm to synthesize such controllers for safety / reachability properties.

This algorithm, based on the state class graph method, computes on-the-fly the reachable state classes of the TPN while collecting progressively firing subintervals to be avoided so that the property is satisfied. It does not need to compute controllable predecessors and then split state classes until reaching a fixpoint, as it is the case for other approaches based on backward and forward exploration of state space of the system. We prove formally the correctness of the algorithm and show that, in the category of state dependent controllers based on the restriction of firing intervals, the algorithm proposed in this thesis, synthesizes maximally permissive controllers.

In order to attenuate the state explosion problem, we show how to combine efficiently this approach with an abstraction by inclusion, convex union or convex hull. Afterwards, we discuss the compatibility of this method with distributed systems and decentralized controllers.

Finally, we apply this algorithm to control TPN with controllable and uncontrollable transitions by stopwatch. In this approach, we find the subintervals violating the given properties and our objective is to suspend the tasks (transitions) during their bad subintervals and to resume them later. The controller is synthesized through the same algorithm already introduced. In this approach, we suggest to control time Petri nets by associating stopwatches to controllable transitions and to achieve a controlled time Petri nets.

# TABLE OF CONTENTS

| DEDIC  | CATION                                                       | iii |

|--------|--------------------------------------------------------------|-----|

| ACKNO  | OWLEDGEMENTS                                                 | iv  |

| RÉSUM  | ИÉ                                                           | v   |

| ABSTR  | RACT                                                         | vi  |

| TABLE  | E OF CONTENTS                                                | vii |

| LIST O | OF TABLES                                                    | Х   |

| LIST O | OF FIGURES                                                   | xii |

| GLOSS  | SARY AND ABBREVIATIONS                                       | xiv |

| CHAPT  | ΓΕR 1 INTRODUCTION                                           |     |

| 1.1    | Thesis Contributions                                         |     |

| 1.3    | Impact and potentials of the thesis                          |     |

| 1.4    | Thesis organization                                          |     |

| СНАРТ  | ΓΕR 2 Preliminaries and Basic Concepts                       |     |

| 2.1    | Property-specification Languages                             |     |

| 2.2    | Timed Automata                                               | 13  |

| 2.3    | Time Petri Nets                                              |     |

|        | 2.3.1 Definition and behavior                                |     |

|        | 2.3.2 Zone Based Graph                                       |     |

|        | 2.3.3 The state class graph method                           | 19  |

| СНАРТ  | ΓER 3 Controller Synthesis in Real Time Systems              | 22  |

| 3.1    | Introduction to controller synthesis                         | 22  |

| 3.2    | Literature review                                            | 24  |

| 3.3    | A forward method for computing predecessors of state classes | 29  |

| 3.4    | On-the-fly algorithm for safety controller synthesis         | 32  |

|        | 3.4.1 Operations over real intervals                         | 33  |

|       | 3.4.2 | Our algorithm                                                           | 37 |

|-------|-------|-------------------------------------------------------------------------|----|

|       | 3.4.3 | Definitions: Bad sequences, bad/winning intervals, losing/winning sub-  |    |

|       |       | classes                                                                 | 38 |

|       | 3.4.4 | Formalization and proof of the correctness Algorithm1 for safety con-   |    |

|       |       | troller synthesis                                                       | 40 |

|       | 3.4.5 | Independent controllable state classes                                  | 41 |

|       | 3.4.6 | Legal safety controllers                                                | 43 |

|       | 3.4.7 | Maximally permissive controllers                                        | 44 |

|       | 3.4.8 | Illustrative examples                                                   | 46 |

| 3.5   | Contr | oller for reachability properties                                       | 51 |

|       | 3.5.1 | Formalization and proof of the correctness of Algorithm3 for reachabil- |    |

|       |       | ity controller synthesis                                                | 54 |

|       | 3.5.2 | State dependent controller                                              | 54 |

|       | 3.5.3 | Legal reachability controllers                                          | 54 |

|       | 3.5.4 | Maximally permissive reachability controllers                           | 55 |

|       | 3.5.5 | An example of reachability controller synthesis                         | 56 |

| 3.6   | Concl | usion                                                                   | 58 |

| CHAP' | TER 4 | Abstraction                                                             | 59 |

| 4.1   | _     | luction to the state space abstraction                                  | 59 |

| 4.2   |       | action by inclusion, convex union or convex hull                        | 59 |

| 7.2   | 4.2.1 | Inclusion test, convex union test and convex hull of two state classes. | 60 |

|       | 4.2.2 | How to use an abstraction by inclusion?                                 | 60 |

|       | 4.2.3 | Can we use an abstraction by convex union?                              | 62 |

|       | 4.2.4 | Can we use an abstraction by convex hull?                               | 63 |

| 4.3   |       | riments                                                                 | 64 |

| 1.0   | 4.3.1 | Production cell                                                         | 65 |

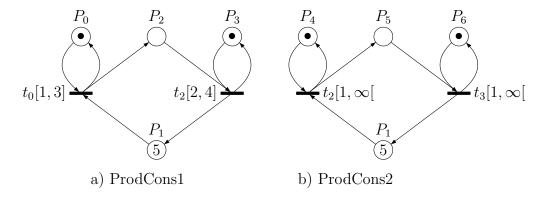

|       | 4.3.2 | Producer/consumer model                                                 | 67 |

| 4.4   |       | usion                                                                   | 70 |

| O 1   |       |                                                                         |    |

| CHAP' |       | Decentralized Controller for Modular Systems                            | 72 |

| 5.1   |       | luction to decentralized controller                                     | 72 |

| 5.2   |       | ture review                                                             | 74 |

|       | 5.2.1 | Case of uniform modules and uniform local controllers                   | 74 |

|       | 5.2.2 | Case of various local properties                                        | 75 |

|       | 5.2.3 | Case of an identical global property                                    | 76 |

| 5.3   | A dec | entralized controller for TPN models                                    | 79 |

|       | 5.3.1    | Case of static local controllers                                        | 81   |

|-------|----------|-------------------------------------------------------------------------|------|

|       | 5.3.2    | Case of marking dependent local controllers                             | 81   |

|       | 5.3.3    | Case of state dependent local controllers                               | 86   |

|       | 5.3.4    | Decentralized implementation with the possibility of intercommunication | . 87 |

|       | 5.3.5    | Illustrative examples                                                   | 91   |

| 5.4   | Conclu   | ısion                                                                   | 101  |

| CHAPT | ΓER 6    | Controller Synthesis with Stopwatch                                     | 102  |

| 6.1   | Introd   | uction to timed models associated with stopwatch                        | 102  |

| 6.2   | Literat  | ture review                                                             | 105  |

| 6.3   | Contro   | oller synthesis and stopwatch                                           | 108  |

|       | 6.3.1    | Why inhibitor hyperarcs?                                                | 111  |

| 6.4   | Illustra | ative example                                                           | 112  |

| 6.5   | Conclu   | nsion                                                                   | 116  |

| CHAPT | TER 7    | CONCLUSION                                                              | 118  |

| 7.1   | Analys   | sis of the achievements                                                 | 118  |

| 7.2   | Limita   | tions of the approach                                                   | 119  |

| 7.3   | Future   | e work                                                                  | 120  |

| REFER | RENCES   |                                                                         | 122  |

# LIST OF TABLES

| Table 2.1 | State zones of the TPN presented at Fig.2.5                                  | 21 |

|-----------|------------------------------------------------------------------------------|----|

| Table 2.2 | The state classes of the TPN presented at Fig.2.5                            | 21 |

| Table 3.1 | A marking dependent controller for the TPN of Fig.2.4                        | 48 |

| Table 3.2 | State classes of the TPN at Fig.3.8                                          | 48 |

| Table 3.3 | Tracing Algorithm 1 on the example of Fig.3.8                                | 50 |

| Table 4.1 | State classes of the SCG at Fig.4.2.a                                        | 65 |

| Table 4.2 | State classes of the TPN presented at Fig.4.3                                | 67 |

| Table 4.3 | Results for different abstraction implementations and different number       |    |

|           | of available plates of the system of Fig.4.3. The first category $aa$ is for |    |

|           | non-abstracted state class graph, $bb$ is for abstraction by inclusion, $cc$ |    |

|           | is for abstraction by convex union. The second line of each row is the       |    |

|           | reduction percentage over SCG construction                                   | 68 |

| Table 4.4 | Results for different number of available plates of the system of Fig.4.3.   |    |

|           | The first category $aa$ is for non-abstracted state class graph, $dd$ is for |    |

|           | abstraction by convex hull. The second line of each row is the reduction     |    |

|           | percentage over SCG construction                                             | 69 |

| Table 4.5 | Results for different abstraction implementations and different config-      |    |

|           | urations of the system of Fig.4.5. The first category aa is for non-         |    |

|           | abstracted state class graph, $bb$ is for abstraction by inclusion, $cc$ is  |    |

|           | for abstraction by convex union. The second line of each row is the          |    |

|           | reduction percentage over SCG construction                                   | 70 |

| Table 4.6 | Results for different abstraction implementations and different config-      |    |

|           | urations of the system of Fig.4.5. The first category aa is for non-         |    |

|           | abstracted state class graph, $dd$ is for abstraction by convex hull. The    |    |

|           | second line of each row is the reduction percentage over SCG construc-       |    |

|           | tion                                                                         | 71 |

| Table 5.1 | A marking dependent controller for the TPN of Fig.3.8. The chosen            |    |

|           | scenario forces $t_1$ to fire before $t_2$                                   | 82 |

| Table 5.2 | Trace of Algorithm 5 on Fig.5.5 (Module L)                                   | 92 |

| Table 5.3 | Trace of Algorithm 5 on Fig.5.5 (Module R)                                   | 92 |

| Table 5.4 | State classes of Fig.5.7 for $t_3 = [2, 4]$                                  | 96 |

| Table 5.5 | State classes of Fig.5.7 for $t_3 = [2, 3]$                                  | 97 |

| Table 5.6 | Trace of Algorithm 5 on Fig.5.8 (block a)                                    | 99 |

| Table 5.7 | Trace of Algorithm 5 on Fig.5.8 (block b)      | 100 |

|-----------|------------------------------------------------|-----|

| Table 5.8 | Trace of Algorithm 5 on Fig.5.8 (block c)      | 100 |

| Table 6.1 | State classes of the TPN presented at Fig.6.14 | 117 |

# LIST OF FIGURES

| Model-checking                                                                      |                                                      |

|-------------------------------------------------------------------------------------|------------------------------------------------------|

| A simple example of timed automata from (Alur, 1999)                                | 13                                                   |

| Three levels of abstraction (Boucheneb et Hadjidj, 2008)                            |                                                      |

| A bounded TPN with an infinite ZBG reported from (Boucheneb $et\ al.$ ,             |                                                      |

| 2009)                                                                               | 19                                                   |

| A simple Petri net with $T_c = \{t_1\}, \ldots, t_r$                                | 21                                                   |

| The state graph of the TPN presented at Fig.2.4                                     | 21                                                   |

| Controller of a system                                                              | 23                                                   |

| Controllable predecessors                                                           | 26                                                   |

| On-the-fly algorithm for timed game automata proposed in (Cassez                    |                                                      |

| et al., 2005)                                                                       | 29                                                   |

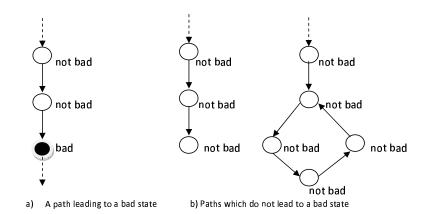

| Paths satisfying or not a safety property. Black state is to be avoided             | 34                                                   |

| The winning and losing subclasses of $\alpha_0$ in TPN of Fig.2.4 for AG not $p_1+$ |                                                      |

| $p_3 = 0.\dots$                                                                     | 40                                                   |

| Applying Algorithm 1 on the TPN of Fig.2.4 for $AG$ not $p_1 + p_3 = 0$ .           | 47                                                   |

| The controlled TPN obtained for the TPN of Fig.2.4 for $AG$ not $p_1$ +             |                                                      |

| $p_3 = 0.\dots$                                                                     | 48                                                   |

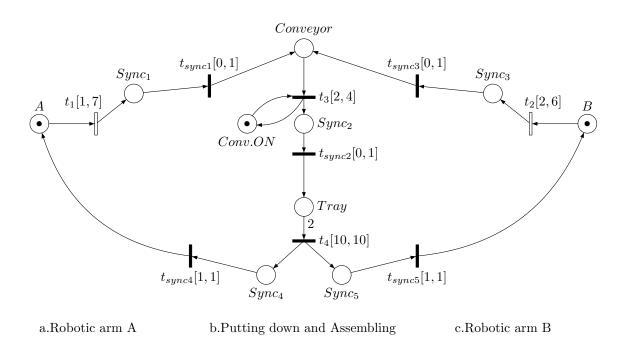

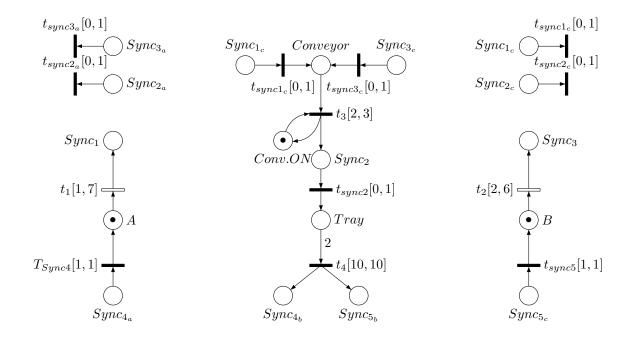

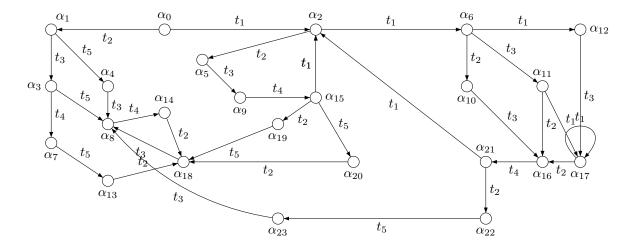

| The TPN model of the assembling section in a manufacturing line                     | 49                                                   |

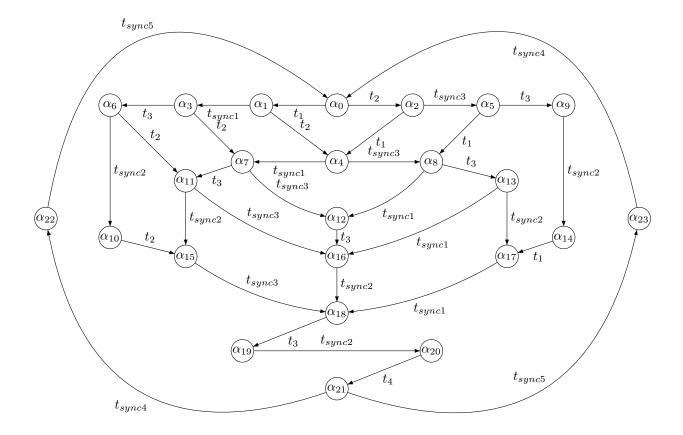

| The state graph of the TPN presented at Fig.3.8                                     | 49                                                   |

| The winning and bad subclasses of $\alpha_0$ in the TPN of Fig.3.8, w.r.t.          |                                                      |

| $AG\ Convoyer < 2. \dots \dots \dots \dots \dots \dots \dots$                       | 49                                                   |

| Paths satisfying or not a reachability property. Black states are to be             |                                                      |

| avoided                                                                             | 51                                                   |

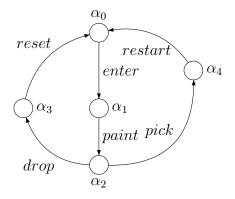

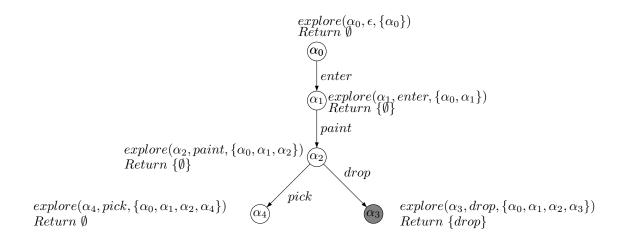

| A box painting production system                                                    | 56                                                   |

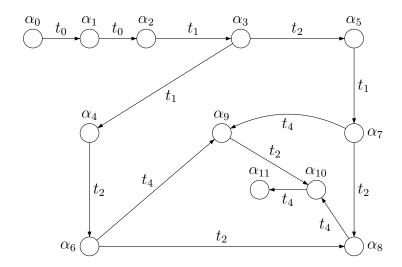

| The state class graph of the TPN presented at Fig.3.12                              | 57                                                   |

| The state class information of the TPN presented at Fig.3.12                        | 57                                                   |

| Applying Algorithm 3 on the TPN of Fig.3.12 for AF picked                           | 57                                                   |

| A TPN with finite SCG and infinite convex hull abstraction                          | 63                                                   |

| SCG and abstraction by convex hull of the TPN at Fig.4.1                            | 64                                                   |

| A production cell system                                                            | 66                                                   |

| The state class graph of the production cell system of Fig.4.3                      | 66                                                   |

| Producer/consumer model                                                             | 70                                                   |

|                                                                                     | A simple example of timed automata from (Alur, 1999) |

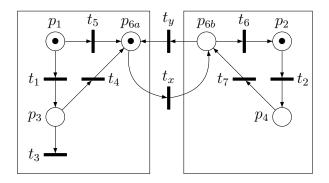

| Figure 5.1 An example of the overlapped Petri nets taken from (Aydin et    |                                                                                      |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                                                            | 2009)                                                                                |

| Figure 5.2                                                                 | Expanded Petri nets of Fig.5.1                                                       |

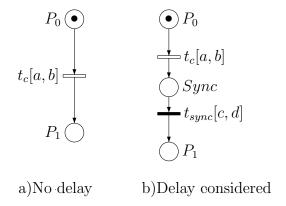

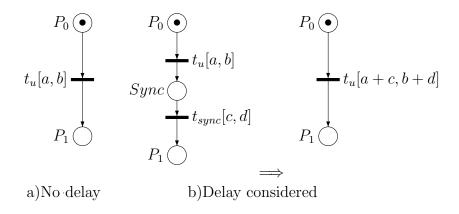

| Figure 5.3                                                                 | A controllable transition, considering synchronization delay 85                      |

| Figure 5.4 An uncontrollable transition, considering synchronization delay |                                                                                      |

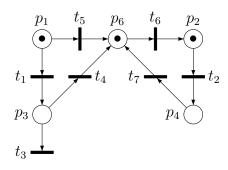

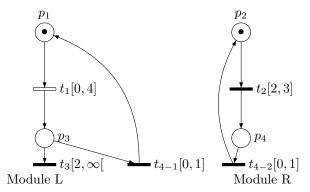

| Figure 5.5                                                                 | The example of Fig.2.4 in modules                                                    |

| Figure 5.6                                                                 | The TPN model of the assembly section of a manufacturing line con-                   |

|                                                                            | sidering intercommunication delay among the modules                                  |

| Figure 5.7                                                                 | The state class graph of the model depicted in Fig.5.6 95                            |

| Figure 5.8                                                                 | The modular TPN model of the system depicted in Fig.5.6 99                           |

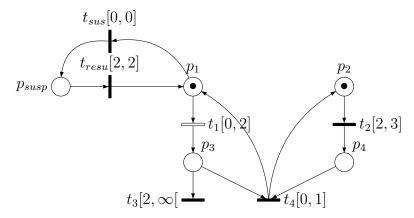

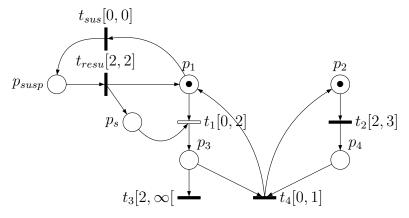

| Figure 6.1                                                                 | A simple example of time Petri nets with inhibitor hyperarc. $t_1$ is active         |

|                                                                            | if $p_2$ is not marked, otherwise it is suspended                                    |

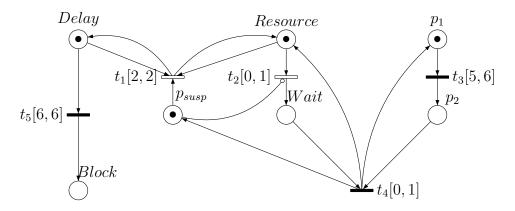

| Figure 6.2                                                                 | An interruptible task modeled by SWPN, reported from (Allahham et                    |

|                                                                            | Alla, 2008)                                                                          |

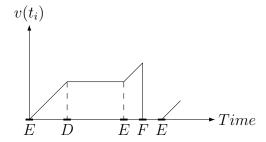

| Figure 6.3                                                                 | Time elapses, $t_i$ is an interruptible transition                                   |

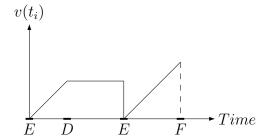

| Figure 6.4                                                                 | Time elapses, $t_i$ is a non-interruptible transition                                |

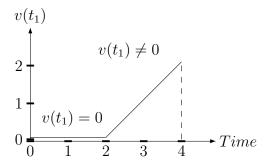

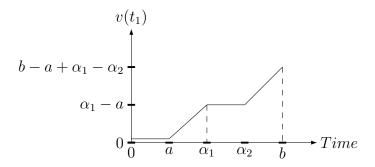

| Figure 6.5                                                                 | Clock evaluation of $t_1$ in the controlled TPN of Fig.6.6 109                       |

| Figure 6.6                                                                 | Time Petri net of Fig.2.4, controlled by inhibitor hyperarcs $(T_c = \{t_1\})$ . 110 |

| Figure 6.7                                                                 | A simple time Petri net $(T_c = \{t_1\})$                                            |

| Figure 6.8                                                                 | The controlled TPN of Fig.6.7 using inhibitor hyperarcs $(T_c = \{t_1\})$ .          |

|                                                                            | Forbidden interval is $]\alpha_1, b]$ where $a \leq \alpha_1 < b$                    |

| Figure 6.9                                                                 | Clock evaluation of $t_1$ in the controlled TPN of Fig.6.7. Forbidden                |

|                                                                            | interval is $]\alpha_1, b]$ where $a \leq \alpha_1 < b$                              |

| Figure 6.10                                                                | A simple time Petri net controlled by inhibitor hyperarcs $(T_c = \{t_1\});$         |

|                                                                            | bad subinterval is $[\alpha_1, \alpha_2]$ where $a < \alpha_1 < \alpha_2 \le b$      |

| Figure 6.11                                                                | Clock evaluation of $t_1$ in a controlled TPN of Fig.6.7. Forbidden inter-           |

|                                                                            | val is $]\alpha_1, \alpha_2]$ where $a < \alpha_1 < \alpha_2 < b$                    |

| Figure 6.12                                                                | Controlling the example of Fig.2.4 using stopwatch of (Allahham et                   |

|                                                                            | Alla, 2008). The controller fails                                                    |

| Figure 6.13                                                                | Controlled model of Fig.2.4 using stopwatch of (Allahham et Alla, 2008).115          |

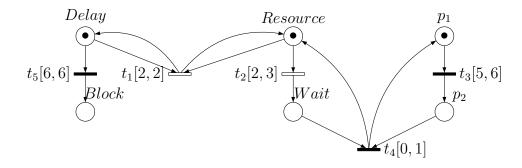

| Figure 6.14                                                                | A Periodic system with $T_c = \{t_1, t_2\}$                                          |

| Figure 6.15                                                                | The state class graph of the TPN presented at Fig.6.14                               |

| Figure 6.16                                                                | Controlled model of Fig.6.14 using inhibitor hyperarcs                               |

### GLOSSARY AND ABBREVIATIONS

BCFCF Backward Conflict and Forward Concurrent Free

BCS Backward Concurrent Structure

CTL Computational Tree Logic

DBM Difference Bound Matrix

DES Discrete Event System

GMEC Generalized Mutual Exclusion Constraints

IHTPN Time Petri Nets with Inhibitor Hyperarcs

LTL Linear Temporal Logic SWA Stopwatch Automata SCG State Class Graph

SWPN Post and Pre-initialized Stopwatch Petri Nets

TA Timed Automata

TCTL Timed Computational Tree Logic

TL Temporal LogicTPN Time Petri NetsTS Transition System

TTS Timed Transition System

ZBG Zone Based Graph

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation and problem statement

Real time systems are systems with specific timing requirements. In real time systems, well functionality is a two-sided concept where correctness is as important as respecting timing requirements. A request cannot be answered later than a given delay. These systems are widely used in our daily life from little electronic devices like a digital camera, to traffic lights, avionic systems and missile firing.

In the real time field, *critical systems* refer to the systems where a failure in functionality is too costly, critical or harmful. Considering the cost of a failure in such systems, their well functionality should be guaranteed at the design level, before implementation. In fact, a design needs to be verified formally before being implemented. What we mean by verification is to prove that a system is safe or to find a counterexample (i.e. an error or a failure). Verification is different from simulation. Simulation gives an idea about how a system works, it may show an error but it does not prove the absence of errors.

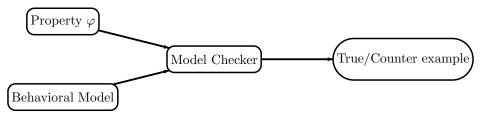

With this objective, the system is first modeled based on the mathematical expression of its behaviors and then, some techniques such as model-checkers are applied on the model to verify its correctness or give a counterexample (Fig.1.1). What we mean by correctness is satisfaction of the given properties and meeting the given timing requirements. Some known models are modeling languages, (timed) automata and (time or timed) Petri nets. Albeit having a mathematical nature, the two last ones are represented graphically, making them more user friendly and understandable. Automata and Petri nets are bi-similar most of the time. However, in some contexts one is more suitable than the other. For example, Petri nets are more convenient for modeling parallelism. An infinite system can be modeled by finite Petri nets. In general, the semantics of the models are defined by a transition system. Properties are formulas to declare requirements and desired specifications. Formulas are based on Temporal Logics (TL).

Model-checking is effective in locating bottlenecks. In the case a system does not guarantee to satisfy the properties of interest, a complementary object, a controller, is needed to

Figure 1.1 Model-checking.

fix the failures and guarantee the satisfaction of the given properties. Finding a controller for a system to force a given property is the subject of the *controller synthesis*. A model is analyzed to design the suitable controller using some algorithms. Many researches and case studies have been done to find an appropriate controller to guarantee the satisfaction of the property of interest. The objective is to have a controller running in parallel with the system under study and preventing any violation of given properties. In other words, another agent is added to the system such that the model-checker proves that the new compound system is safe and correct.

Model-checking detects the issues of an existing model and controller synthesis provides a solution to resolve them. In fact, a controller will make an open-loop system to be closed-loop. In an open-loop system, environment can affect the system in such a way that it violates the desired specifications. A closed-loop system adapts its reactions against the environmental undesired behaviors and keeps the requirements satisfied. Controller synthesis or supervisory controller, as in model checking, categorizes the properties and finds an algorithm to synthesize them.

In the concept of controller synthesis, two questions, Control Problem and Controller Synthesis Problem need to be addressed. The first question, Control Problem, investigates if for a given system S and a property  $\varphi$ , a controller C exists for the system S such that when S is running in parallel with C, the property  $\varphi$  is satisfied. The Controller Synthesis Problem, answers the question of if such controller exists, whether or not there is a solution to implement it.

The concept of controller synthesis is also described by game theory (Altisen *et al.*, 2005). Game theory considers a problem as a game with some players and a game *strategy*. A strategy is simply the actions to be played in each situation. Hence, game theory describes the

controller synthesis for a timed system, as a timed game with two players, the system under study against the environment. The control problem is then declared as: "Is there a strategy to make the controller the winner of the game?". In such a game, actions are partitioned into two disjoint sets, controllable and uncontrollable. Controllable actions are those that can be managed by the controller (forced to happen or prevented from happening). Uncontrollable actions are those that the controller has no control on. Players have equal chances to win. The control problem consists in searching a strategy such that the environment never wins the game against the controller. A strategy consists of the sequence of actions leading to the winning game outcome where the controller always wins against the environment.

In the controller synthesis, actions are observable or unobservable (Bouyer et al., 2005). While an unobservable action is uncontrollable by default, an observable action is either controllable or uncontrollable. As an example, suppose a multitasking system with different processes, each of them having an execution time and period; and they access some possibly shared resources. Process arrival depends on its period and its termination depends on the execution time. Then, both process arrival and termination of execution are uncontrollable, whereas access to the shared resources and starting the execution are controllable. Unobservable actions are most internal actions with no available output event. An example of unobservable action is an internal counter in a digital system. With each clock cycle, the counter is modified, but it is unobservable, unless it is captured by a predefined value; at this time, an observable action happens and the external observer is aware.

There are various approaches in the literature to control different properties. Most of the available solutions do not take into account timing properties. In order to control these kinds of properties in timed models (Timed Automata and Time Petri Nets), several approaches have been proposed in the literature (Cassez et al., 2005; Gardey et al., 2006b; Tripakis, 1998). Two known methods are the backward fixpoint method and the backward-forward on-the-fly method. The first one is proposed for time Petri nets but it cannot guarantee to give a controller when it exists (Gardey et al., 2006b). The second one is proposed for timed automata and guarantees to give the controller when it exists (Cassez et al., 2005).

However, both above-mentioned approaches require some expensive operations such as calculating the difference between states. The difference between two states is not necessarily one state and then may result in several states which need to be handled separately. It would be interesting to investigate if there is an approach which does not need to split states.

In the context of controller synthesis, a scheduler is a kind of controller that manages shared resources and timing specifications of the system. In a multitasking system, a newly arrived task waits for accessing resources. After accessing the required resources, each task uses those resources for its execution time and then releases them. If the task is periodic, it stays in a passive state before its next arrival. A scheduler cannot modify timing specifications of the system such as period and execution time. In order to manage the shared resources among different periodic tasks with different levels of priority, the solution is to suspend a task with lower priority and let the other tasks with higher priorities to use the resources. Then, the suspended task is retrieved until it finishes its execution. When a task is suspended, the execution time is not progressing. It is interesting to see if controller synthesis can be used to synthesize a scheduler.

#### 1.2 Thesis Contributions

This thesis consists of a number of contributions. We are interested in modeling the behavior of the real time systems by time Petri nets. Our main objective is to investigate controller synthesis of a real time system modeled by time Petri nets for safety and reachability properties.

#### Contribution 1: Safety controller synthesis

Our first contribution is an algorithm for controller synthesis of safety properties in time Petri nets. The goal is to have some general algorithms achieving suitable controllers and replacing case based solutions where the approach works for a particular case study. Our proposed algorithm is a forward on-the-fly semantic approach and is based on processing of the state class graph of the model. Our approach answers both control problem and controller synthesis problem mentioned above. It gives a controller if it exists. If the algorithm fails to give the controller, the controller does not exist. We prove that our approach gives a maximally permissive controller and apply the solution on some case studies.

#### Contribution 2: Reachability controller synthesis

In our next contribution, we study reachability controller synthesis. In our first contribution, we have suggested a forward on-the-fly algorithm for controller synthesis of real time systems modeled by time Petri nets. In the second contribution, we extend the algorithm to reachability properties. We prove the correctness of our algorithm and show that it is maximally permissive. We test it on some case studies.

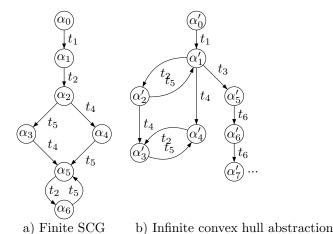

## Contribution 3: Optimization of the suggested approach by abstraction

In semantic approach, the algorithm processes the state space of the model and then, state space explosion is a common issue. In this thesis, we optimize the devised algorithm and investigate how to combine our approach with different methods of abstraction. Abstraction consists in agglomeration of some similar states and helps to have a more compact state space while decreasing the risk of state space explosion. During the construction of an abstraction, each newly computed abstract state is compared with the previously computed ones. We discuss the possibility of abstraction by inclusion and convex union. We also investigate if it is possible to use abstraction by convex hull. In the literature it was never proven if abstraction by convex hull preserve boundedness property. In this thesis, we present a new result. We give a counterexample to show that in our context, abstraction by convex hull is less appropriate as it does not preserve the boundedness property of TPN. Some case studies are also presented to show the scalability and effectiveness of each of the above-mentioned abstraction methods.

#### Contribution 4: Decentralized implementation on modular systems

Being optimized by abstraction, our algorithm is a good candidate for controller synthesis of large-scale systems. Large-scale systems are usually modular by their nature. In the other contribution, implementation of our centrally synthesized controllers on modular system is studied. We discuss how to implement the controller computed by the devised algorithm on modular systems and achieve a set of decentralized controllers. We answer the controller synthesis problem and investigate if our approach is implementable on modular, large-scale systems. Note that, we investigate how to implement a centralized computed controller on a decentralized system rather than synthesizing a "decentralized controller".

### Contribution 5: Preemptive controller and scheduling

Our next contribution is to investigate if our controller synthesis approach can be used to synthesize a scheduler for managing shared resources and timing specifications. A scheduler needs to suspend and retrieve some tasks. Clocks are stopped during suspension. Our approach in its original form can initialize a clock but it cannot stop it. In this contribution, we synthesize the controller (scheduler) using the stopwatch which provides the possibility of suspending and retrieving the clocks. The solution we suggest in this thesis, is to synthesize the time Petri net model and to carry out the controller (scheduler). Then, the scheduler equips the appropriate transitions with stopwatch and controls the model by suspending the transitions. In other terms, we assume that every controllable action can be suspended (be

associated with stopwatch). This way considering, first, we calculate some subintervals in which the system violates the given properties and then the controller suspends the corresponding transition during those subintervals. This approach is very useful and interesting for preemptive scheduling purposes and managing shared resources.

The contributions of this thesis can be summarized as follows:

- Proposal of a forward on-the-fly algorithm for controller synthesis in time Petri nets.

Formalization, proof of correctness and calculation of the complexity for the proposed algorithm. Providing some case studies.

- Extending the devised algorithm to reachability controllers. Formalization and proof of correctness. Providing some examples.

- Optimization of the proposed algorithm by state space abstraction. Investigating how

to combine some known abstraction methods with the proposed approach. Providing

some scalability analysis through some case studies.

- Investigation of the implementation of the proposed algorithms on large-scale modular systems. Discussing independent local controllers and local controllers with intercommunication among them.

- Extending the suggested controller synthesis approach to Petri nets equipped with stopwatch in order to support preemptive scheduling.

## 1.3 Impact and potentials of the thesis

In this thesis, we suggest an algorithm for controller synthesis of real time systems, modeled by time Petri nets. We propose a semantic approach which is not dependent on the specifications of a particular system. The available solutions in the literature for controller synthesis of real time systems are often case based and are dependent on the specifications of the system under study (Buy et al., 2005; Iordache et Antsaklis, 2010; Wu et al., 2008). Our approach is a completely forward method (not backward and forward), based on time Petri nets which restricts time intervals. Unlike previously existing general semantic approaches, our algorithm does not need to compute controllable predecessors, then split state classes and handle them separately (which is very costly). Therefore, our approach is less expensive and more efficient in comparison with the other general semantic approaches available in the literature. In the category of state dependent controllers based on the restriction of firing intervals, our algorithm synthesizes maximally permissive controllers. We prove the correctness of this algorithm and discuss its decentralized implementation. In addition, this

algorithm is extended to be used for preemptive scheduling purposes.

Considering the fact that controller synthesis of real time systems are widely used in different areas like web service applications, robotic manipulators, cooperative robotic, networked control systems, work flow applications, manufacturing, production chain, wireless sensing and actuators, a software tool for automatically controller synthesis can facilitate system design and verification. A generic solution is required to be implemented in a software tool then, case based solutions of (Buy et al., 2005; Iordache et Antsaklis, 2010; Wu et al., 2008) are less appropriate. The backward approaches (Cassez et al., 2005; Gardey et al., 2006b) are general but expensive. They require to calculate controllable predecessors and consequently need to compute the difference between states. This in turn may split states that should be handled separately. The approach suggested in this thesis does not split the states and is a good alternative to be implemented in a software tool with a graphical environment for automatically controller synthesis of time Petri net models. Such a tool is suitable for both professional and less professional users as it hides the complicated mathematical computations in the background.

## 1.4 Thesis organization

This document is organized as follows: in Chapter 2, we introduce some basic concepts and preliminaries. In Chapter 3, we focus on controller synthesis, and available approaches in the literature. We suggest our algorithm for safety properties and prove its correctness. We also discuss how to extend the devised approach to reachability controllers. In Chapter 4, we discuss different methods of state space abstraction and investigate the compatibility of our algorithm with those methods. Chapter 5 is dedicated to distributed systems and decentralized controllers; it includes a survey on the literature and shows that our algorithm is implementable on modular systems. Chapter 6 is devoted to controller synthesis using stopwatch for preemptive scheduling purposes. It includes a literature review on different Petri nets associated with stopwatch. Then, it suggests that the controller adds stopwatch to some appropriate controllable transitions to achieve a controlled system. Finally, we finish this document with the conclusion and future work in Chapter 7.

#### CHAPTER 2

## Preliminaries and Basic Concepts

This chapter explains some preliminary concepts and definitions which will be used later in this document:

- Transition system: A Transition System(TS) is defined by  $(\mathcal{Q}, \to, q_0)$  tuple where  $\mathcal{Q}$  is the set of states,  $q_0 \in \mathcal{Q}$  is the initial state and  $\to$  is the transition relation between the states. The notion  $q \to q'$  denotes that q is in relation with q' and  $(q, q') \in \to$ . A transition system is called finite (infinite) if  $\to$  is finite (infinite), respectively.

- Run: A run is an execution path denoted by  $\rho$ . The notion  $\rho_q$  stands for an execution path starting from q:

$$\rho_q = q_0 \to q_1 \to q_2 \dots \tag{2.1}$$

where  $q = q_0$ .

$q = \rho(i)$  is the  $i_{th}$  state of  $\rho$ , while  $\rho^i$  is a suffix of  $\rho$  starting from the state number i. Note that counting the states of an execution path starts from 1 (not 0).

- **Labeled Transition System**: A labeled transition system is defined by  $Q = (\mathcal{Q}, q_0, \Sigma, \rightarrow)$  where  $\Sigma$  is the set of labels and  $\rightarrow \subseteq (\mathcal{Q} \times \Sigma \times \mathcal{Q})$ . Labeled transition system is either discrete or dense; dense system is also called continuous (e.g. timed systems).

- **Discrete Transition System**: A discrete transition system is a labeled transition system where  $\Sigma$  is the set of actions also denoted by A. In these systems,  $q \stackrel{\alpha}{\to} q'$  denotes that  $(q, \alpha, q') \in \to$ . And  $q \stackrel{\alpha}{\to} q'$  with  $\alpha \in A$  is called a discrete transition. In a discrete transition system a run is defined by:

$$\rho_q = q_0 \stackrel{\alpha_0}{\to} q_1 \stackrel{\alpha_1}{\to} \dots q_i \stackrel{\alpha_i}{\to} \dots \tag{2.2}$$

where the action  $\alpha_i \in A$  and  $q = q_0$ . If q is not determined, the corresponding run is denoted by  $\rho$  and the initial state of the model is considered as the starting state. Finally,  $q = \rho(i)$  refers to the  $i^{th}$  state of a run and  $\rho^i$  stands for a suffix of  $\rho$  starting from the state number i.

- **Timed Transition System**: Let A be the set of actions. A timed transition system (TTS) is a labeled transition system, labeled by  $\Sigma = A \cup \mathbb{R}^+$ , such that  $A \cap \mathbb{R}^+ = \emptyset$ . A transition  $q \xrightarrow{\theta} q'$  where  $\theta \in \mathbb{R}^+$  is called a timed transition.

In a timed system, a transition is either a discrete action  $\alpha$ , or time elapsing  $\theta$  denoted by  $q \xrightarrow{\theta} q'$ . Consequently, in a timed system a run contains both discrete and timed transitions:

$$\rho_q = q_0 \stackrel{\alpha_0}{\to} q_1 \stackrel{\theta_0}{\to} \dots q_i \stackrel{\alpha_i}{\to} q_{i+1} \stackrel{\theta_i}{\to} \dots$$

(2.3)

A timed transition  $q_1 \stackrel{\theta}{\to} q_2$  means  $q_2 = q_1 + \theta$ . A timed transition system is an example of dense or continuous transition system.

Runs(q) signifies all runs starting from the state q.

- **Reachability**: For a given timed transition system  $(\mathcal{Q}, q_0, \Sigma, \rightarrow)$ , state  $q_n$  is reachable from  $q_0$  if  $\rho_q$  exists, where  $q = q_0$  such that,  $q_0 \stackrel{\rho_q}{\to} q_n$ . Let  $Reach(q_0)$  be the set of all reachable states from  $q_0$  then:

$$q' \in Reach(q_0) \ if \ \exists \ t, \ \exists \ \theta \ q \xrightarrow{\theta \ t} q'.$$

(2.4)

- Formula: Let Y be the set of real variables. A linear inequality over Y or every logic conjunction of linear inequalities are called Formula.

- **Atomic constraint**: An atomic constraint on Y is a linear inequality; it can come under two forms:  $(x \prec c)$  or  $(x y \prec c)$ , called *simple* and *triangular* respectively. In these inequalities  $x, y \in Y$ ,  $c \in \mathbb{Q} \cup \{\infty, -\infty\}$  and  $\prec \in \{<, \leq, \geq, =, >\}$  where  $\mathbb{Q}$  is the set of rational numbers. The set of all atomic constraints on Y is denoted by  $\mathcal{C}(Y)$ .

- **Hyperplane**: A hyperplane H on Y (a set of real variables), is a set of valuations satisfying an atomic constraint.

- Polyhedron: A Polyhedron P is the set of union or intersection of a finite number of hyperplanes.

- **Region**: A Region is represented by a set of constraints of the form k < x < k + 1 or x = k, where k is a constant on each dimension. Each variable can be equal with an integer or limited by two consecutive integers. For a two dimensional region represented by x and y, (x = 2, y = 2), (x = 1, 2 < y < 3), (2 < x = y < 3) and (1 < x < 2, 2 < y < 3) are all regions whereas,  $(1 < x \le 2, y = 2)$  and (1 < x < 3, 1 < y < 2) are not regions.

- **Zone**: A zone is a convex polyhedron. A polyhedron P is called convex if:  $\forall v_1, v_2 \in P \text{ and } \lambda \in \mathbb{R}, 0 < \lambda < 1, \lambda v_1 + (1 \lambda)v_2 \in P.$

- Informally, each two points of a zone can make a line; if all points of such a line are in the zone, this zone is convex. If a polyhedron is non-convex, it can be broken into finite number of zones.

- **Bound**: Considering  $c \in \mathbb{Q}$  and  $\prec in\{<, \leq\}$ , the couple  $(c, \prec)$  is called a bound. Some operations are defined on bounds:

- $-(c, \prec) = (c', \prec') \iff c = c' \text{ and } \prec = \prec'.$

- $-(c, \prec) < (c', \prec') \iff (c < c') \text{ or } (c = c' \text{ and } \prec < \prec').$

- $-(c, \prec) \leq (c', \prec') \Longleftrightarrow (c, \prec) = (c', \prec') \text{ or } (c, \prec) < (c', \prec').$

- $(c, \prec) + (c', \prec') = (c + c', min(\prec, \prec')).$

- **Difference Bound Matrix (DBM)**: Let Y be a set of real variables and F a set of atomic constraints (conjunction of atomic constraints) over Y. Consider  $x_i, x_j \in Y$ . Add an element 0 (denoted by  $x_0$  or 0) to Y. Every atomic constraint from F on Y, is written as:

- $x_i x_j \prec_{i,j} c_{i,j}$  where  $c_{i,j} \in \mathbb{Q} \cup \{\infty, -\infty\}, \prec_{i,j} \in \{<, \leq\}$ . Thus, a matrix can represent all atomic constraints of F where each element of the matrix  $(b_{i,j})$  is the bound of  $x_i x_j \prec_{i,j} c_{i,j}$ . This matrix is called *Difference Bound matrix* of F (Bengtsson, 2002).

- Reflexive, symmetrical and transitive relation: A binary relation  $\approx$  on the set  $\mathcal{Q}$  is a subset of  $(\mathcal{Q} \times \mathcal{Q})$ . The relation  $\approx$  is reflexive if and only if  $q \approx q, \forall q \in \mathcal{Q}$ . The relation  $\approx$  is symmetrical if and only if  $q \approx q' \Rightarrow q' \approx q, \forall q, q' \in \mathcal{Q}$ . The relation  $\approx$  is transitive if and only if

$$\forall q, q', q'' \in \mathcal{Q}, q \approx q' \land q' \approx q'' \Rightarrow q \approx q''.$$

- Simulation: Let  $(\mathcal{Q}, q_0, \Sigma, \to)$  and  $(\mathcal{Q}', q_0', \Sigma, \to)$  be two labeled transition systems, labeled by the set of labels  $\Sigma$ . Let  $\approx \subseteq (\mathcal{Q} \times \mathcal{Q}')$  be a binary relation on the set of states of these two systems. The relation  $\approx$  is a simulation if and only if  $\forall (q, q') \in (\mathcal{Q} \times \mathcal{Q}')$  such that  $q \approx q'$ , the following condition holds:

$$q \xrightarrow{a} q_1 \Rightarrow \exists \ q_1^{'} \ s.t. \ q' \xrightarrow{a} q_1^{'} \land q_1 \approx q_1^{'}.$$

- **Bi-simulation**: The relation  $\approx$  is bi-simulation if and only if  $\approx$  and its inverse are both

simulation. Consider two labeled transition systems  $(\mathcal{Q}, q_0, \Sigma, \to)$  and  $(\mathcal{Q}', q_0', \Sigma, \to)$ , labeled by the set of labels  $\Sigma$ . The systems  $\mathcal{Q}$  and  $\mathcal{Q}'$  are bi-similar if and only if there exists a bi-similar relation  $\approx$  such that  $(q_0, q_0') \in \approx$ .

## 2.1 Property-specification Languages

In this section, we present a brief survey on the languages declaring the properties and the behavior of the system. In general, temporal logics are used to express the properties and specifications of the system consist of three types of elements:

- a propositional variable from PV, the set of propositional variables.

- boolean logic operators  $(\neg, \lor, \land)$ ;  $\neg$  stands for not (e.g.  $\neg \varphi$ ).

- some operators (A, E, U, X, R).

Let  $\varphi$  and  $\psi$  be two properties, the operators are defined as follows:

- **A**: signifies that the given property holds for all paths and is also denoted by  $\forall$  (e.g.  $A\varphi$  means that  $\varphi$  is held in all paths).

- **E**: signifies that the given property holds at least in a path and is also denoted by  $\exists$  (e.g.  $E\varphi$  means that  $\varphi$  is held at least in one path).

- U: stands for until (e.g.  $\varphi \cup \psi$  denotes that  $\varphi$  is true until  $\psi$  happens).

- **X**: stands for next and means that the given property is true at the immediate next state of the computation.

- **R**: stands for release (e.g.  $\varphi R \psi$  is read as  $\varphi$  releases  $\psi$ , and it denotes that  $\psi$  is true forever or it is true until  $\varphi$  happens for the first time).

Not, And, Until and Next are the basic operators. Others are defined using these three ones. A and E quantify the path while U and X are operators on the state.

Two major types of formalism exist: *linear time* and *branching time*. In linear time, properties are considered on runs as the set of executions, whereas in branching time properties are observed on the execution trees.

The following languages and their semantics are defined (Penczek et Polrola, 2004):

- CTL\*: CTL\* is the most generalized language which contains all the operators named above. Other languages are subclasses of CTL\* eliminating some operators. The words respect the grammar below where  $\varphi_s$  and  $\varphi_p$  represent the formula on the state and execution path respectively and  $\varphi \in PV$  is a propositional variable.

$$\varphi_s := \wp | \neg \varphi_s | \varphi_s \wedge \varphi_s | \varphi_s \vee \varphi_s | \forall \varphi_p | \exists \varphi_p.$$

$$\varphi_p := \varphi_s \mid \varphi_p \wedge \varphi_p \mid \varphi_p \vee \varphi_p \mid X\varphi_p \mid \varphi_p \cup \varphi_p \mid \varphi_p R\varphi_p.$$

Two operators F (also denoted by  $\Diamond$ ) and G (also denoted by  $\Box$ ) are defined as follows:

- $-\exists \Diamond \varphi = \exists (true \cup \varphi).$

- $\ \forall \ \Diamond \varphi = \forall (true \cup \varphi).$

- $\exists \Box \varphi = \neg \forall \Diamond \neg \varphi.$

- $\ \forall \ \Box \varphi = \neg \exists \Diamond \neg \varphi.$

The semantics of CTL\* is defined on a structure of Kripke  $\mathcal{MD} = (Q, \mathcal{V})$ , where:

- $-Q=(Q,\rightarrow,q_0)$  is a transition system,

- $-\mathcal{V}:\mathcal{Q}\to 2^{PV}$  is a function that assigns to each state the set of atomic propositions it satisfies.

Let  $\mathcal{MD}$  be a model of the system,  $\varphi$  and  $\psi$  two CTL\* formulas, q a state, Runs(q) the set of all runs starting from q and  $\varphi$  a propositional variable. In the following, the formal semantics of  $CTL^*$  is defined inductively, using the notation of  $satisfaction(\models)$  (Hadjidj, 2006). The expression  $\mathcal{MD}, x \models \varphi$  is read: in the model  $\mathcal{MD}$ , x satisfies the property  $\varphi$ .

- $-\mathcal{MD}, q \models \wp \text{ iff } \wp \in \mathcal{V}(q).$

- $\mathcal{MD}, x \models \neg \varphi \text{ iff } \mathcal{MD}, x \nvDash \varphi, \text{for } x \in \{q, \rho\}.$

- $-\mathcal{MD}, x \models \varphi \lor \psi \text{ iff } \mathcal{MD}, x \models \varphi \text{ or } \mathcal{MD}, x \models \psi, \text{ for } x \in \{q, \rho\}.$

- $\mathcal{MD}, x \models \varphi \wedge \psi \text{ iff } \mathcal{MD}, x \models \varphi \text{ and } \mathcal{MD}, x \models \psi, \text{ for } x \in \{q, \rho\}.$

- $\mathcal{MD}, q \models \forall \varphi \text{ iff } \forall \rho \in Runs(q), \mathcal{MD}, \rho \models \varphi.$

- $\mathcal{MD}, q \models \exists \varphi \text{ iff } \exists \rho \in Runs(q), \mathcal{MD}, \rho \models \varphi.$

- $\mathcal{MD}, \rho \models \varphi$  iff  $\mathcal{MD}, \rho(1) \models \varphi, \ \varphi$  is a state formula.

- $-\mathcal{MD}, \rho \models X_{\varphi} \text{ iff } \mathcal{MD}, \rho^2 \models \varphi.$

- $\mathcal{MD}, \rho \models \psi U \varphi \text{ iff } (\exists j \geq 1)(\mathcal{MD}, \rho^j \models \varphi \text{ and} (\forall 1 \leq i < j), \mathcal{MD}, \rho^i \models \psi).$

- LTL(Linear Temporal Logic): Words can be in the form of  $\forall \varphi$  where  $\varphi$  does not include A and E. There is no quantifier.

- CTL(Computation Tree Logic): The words are positive subset of CTL\* words. There is no ¬ operator in CTL. In CTL timed operators are combined with quantifiers e.g.

AF, EF, AG, EG, AU, EU, AX, EX or their boolean combinations.

-  $\mathbf{L}_{-X}$ :There is no operator X in this language.

When we add the concept of time to the temporal logic, the above-mentioned languages change to TCTL\* and TCTL. In such models, formulas are associated with time intervals or clocks.

Two known timed models widely used for modeling various systems are timed automata and timed Petri nets.

#### 2.2 Timed Automata

A timed automaton (Alur, 1999) is an automaton extended with clocks and constraints on clocks. These constraints specify the stay time in each location and the timing condition of transitions.

Let Y be a finite set of real-valued variables called clocks. The notion  $\prec$  stands for a binary relation and  $\mathcal{C}(Y)$  denotes the set of constraints  $\varphi$  and it follows this grammar:

$$\varphi ::= x \prec k \mid x - y \prec k \mid \varphi \land \varphi$$

, where  $k \in \mathbb{Z}$  and  $x, y \in Y$ .

The set  $\mathcal{B}(Y)$  is a subset of  $\mathcal{C}(Y)$  with only rectangular constraints  $(x \prec k)$ .

Then, timed automata are defined formally by a tuple  $(L, l_0, Y, A, E, I)$ , where L is the set of locations,  $l_0 \in L$  is the initial location, Y is the set of clocks, A is the set of actions,  $E \subseteq L \times A \times \mathcal{B}(Y) \times 2^Y \times L$  is the set of edges between locations with an action, a guard (a condition serving as a label) and a set of clocks to be reset, and  $I: L \to \mathcal{B}(Y)$  assigns invariants to locations.

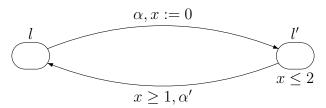

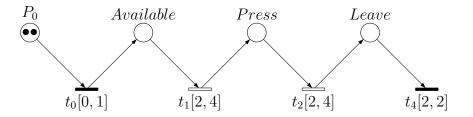

Figure 2.1 A simple example of timed automata from (Alur, 1999).

A clock valuation is a function  $v: Y \to \mathbb{R}^+$  from the set of clocks to the non-negative reals.  $\mathbb{R}^Y$  is the set of all clock valuations and  $\forall x \in Y, \ v_0(x) = 0$ . Let  $x \in Y$  and  $\theta \in \mathbb{R}^+$ ,  $(v+\theta)(x) = v(x) + \theta$ . We consider invariants and constraints as sets of clock valuations. For  $g \in \mathcal{C}(Y)$  and  $v \in (\mathbb{R}^+)^Y$ , if v satisfies g we denote  $v \models g$ .

In timed automata, we define state q = (l, v). Fig.2.1 taken from (Alur, 1999) shows a simple example of timed automata with the initial location l and the clock x. The system may remain in l infinitely as there is no invariant to restrict that. Once the action  $\alpha$  happens and the system goes to l', x is reset. It may remain in l' until 2 time units and action  $\alpha'$  may happen only after at least one time unit.

The semantics of timed automata is defined by a timed transition system  $(Q, q_0, \Sigma, \rightarrow)$  where Q is the set of locations  $Q = L \times (\mathbb{R}^+)^Y$  and  $q_0 = (l_0, v_0)$ :

- $-(l,v) \xrightarrow{\theta} (l,v+\theta) \text{ if } \forall \theta' : 0 \le \theta' \le \theta \Rightarrow v+\theta' \in I(l).$

- $(l, v) \stackrel{\alpha}{\to} (l', v')$  if there exists a transition  $l \stackrel{g,\alpha,Y}{\longrightarrow} l' \in E$  s.t.  $v \models g, v' = v[Y]$  and,  $v' \models I(l')$ .

Kronos (Bozga *et al.*, 1998) and UPPAAL (Behrmann *et al.*, 2006b) are two known tools for formal verification of timed automata. UPPAAL-TIGA (Behrmann *et al.*, 2007) is an extension to UPPAAL that can be used for controller synthesis in timed automata.

#### 2.3 Time Petri Nets

#### 2.3.1 Definition and behavior

A time Petri net (TPN in short) is a Petri net augmented with time intervals associated with transitions (Merlin, 1974).

Formally, a time Petri net (TPN) is a tuple  $(P, T, Pre, Post, M_0, Is)$  where:

- P and T are finite sets of places and transitions such that  $(P \cap T = \emptyset)$ ,

- Pre and Post are the backward and the forward incidence functions ( $Pre, Post : P \times T \to \mathbb{N}, \mathbb{N}$  is the set of nonnegative integers),

- $M_0$  is the initial marking  $(M_0: P \to \mathbb{N})$ , and

- Is is the static interval function  $(Is: T \to \mathbb{Q}^+ \times (\mathbb{Q}^+ \cup \{\infty\}))$ .  $\mathbb{Q}^+$  is the set of nonnegative rational numbers. Is associates with each transition t an interval called the static firing interval of t. Bounds  $\downarrow Is(t)$  and  $\uparrow Is(t)$  of the interval Is(t) are the minimum and maximum firing delays of t respectively.

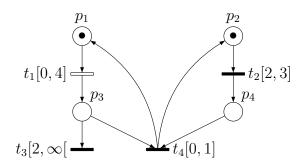

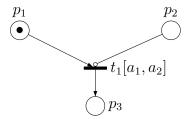

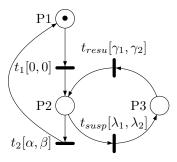

In a controllable time Petri net, transitions are partitioned into controllable and uncontrollable transitions, denoted by  $T_c$  and  $T_u$  (with  $T_c \cap T_u = \emptyset$  and  $T = T_c \cup T_u$ ), respectively. For the sake of simplicity and clarification, in this manuscript the controllable transitions are depicted as white bars, while the uncontrollable ones as black bars.

In TPN, marking is a function of  $P \to \mathbb{N}$ . Let M be a marking and t be a transition. Transition t is enabled for M if and only if all the required tokens for firing t are present in M, i.e.,  $\forall p \in P, M(p) \geq Pre(p,t)$ . In this case, the firing of t leads to the marking M' defined by:  $\forall p \in P, M'(p) = M(p) - Pre(p,t) + Post(p,t)$ . We denote by En(M) the set of transitions enabled for M, i.e.,  $En(M) = \{t \in T \mid \forall p \in P, Pre(p,t) \leq M(p)\}$ . A TPN, is called bounded if:

$$\forall p \in P, M(p) \leq b.$$

For  $t \in En(M)$ , we denote CF(M,t) to be the set of transitions enabled in M but in conflict with t, i.e.,  $CF(M,t) = \{t' \in En(M) \mid t' = t \vee \exists p \in P, M(p) < Pre(p,t') + Pre(p,t) \}$ .

Let  $t \in En(M)$  and M' be the successor marking of M by t, a transition t' is said to be newly enabled in M' iff t' is not enabled in the intermediate marking (i.e., M - Pre(.,t)) or t' = t. We denote New(M',t) the set of transitions newly enabled M', by firing t from M, i.e.,  $New(M',t) = \{t' \in En(M') | t = t' \lor \exists p \in P, M'(p) - Post(p,t) < Pre(p,t')\}$ .

Among the different semantics proposed for time Petri nets (Roux *et al.*, 2005), the research presented in this thesis focuses on the classical one, called intermediate semantics in (Roux *et al.*, 2005), in the context of mono-server and strong-semantics (Boyer et Vernadat, 2000).

There are two known characterizations for the TPN state. The first one, based on clocks, associates with each transition  $t_i$  of the model a clock to measure the time elapsed since  $t_i$  became enabled most recently. The TPN clock state is the pair  $(M, \nu)$ , where M is the marking and  $\nu$  is the clock valuation function,  $\nu : En(M) \to \mathbb{R}^+$ . For a clock state  $(M, \nu)$  and  $t_i \in En(M)$ ,  $\nu(t_i)$  is the value of the clock associated with transition  $t_i$ . The initial clock state is  $q_0 = (M_0, \nu_0)$  where  $\nu_0(t_i) = 0$ , for all  $t_i \in En(M_0)$ . The TPN clock state evolves either by time progression or by firing transitions. When a transition  $t_i$  becomes enabled, its clock is initialized to zero. The value of this clock increases synchronously with time until  $t_i$  is fired or disabled by the firing of another transition.  $t_i$  can fire, if the value of its clock is inside its static firing interval  $Is(t_i)$ . It must be fired immediately, without any additional

delay, when the clock reaches  $\uparrow Is(t_i)$ . The firing of a transition takes no time, but may lead to another marking (required tokens disappear while produced ones appear).

Let  $q = (M, \nu)$  and  $q_0 = (M_0, \nu_0)$  be two clock states of the TPN model,  $\theta \in \mathbb{R}^+$  and  $t_f \in T$ . We write  $q \xrightarrow{\theta} q'$ , also denoted by  $q + \theta$ , if and only if state q' is reachable from the state q after a time progression of  $\theta$  time units, i.e.:

$$\bigwedge_{t' \in En(M)} \nu(t) + \theta \le \uparrow Id(t_i), M' = M, \text{ and } \forall t_j \in En(M'), \nu'(t_j) = \nu(t_j) + \theta.$$

We write  $q \stackrel{t_f}{\to} q'$  if and only if state q' is immediately reachable from state q by firing transition  $t_f$ , i.e.:  $t_f \in En(M), \ \nu(t_f) \ge \downarrow Is(t_f), \ \forall p \in P, M'(p) = M(p) - Pre(p, t_f) + Post(p, t_f),$  and  $\forall t_i \in En(M'), \ \nu'(t_i) = 0$ , if  $t_i \in New(M', t_f), \ \nu'(t_i) = \nu(t_i)$  otherwise.

The second characterization, based on intervals, defines the TPN state as a marking and a function which associates with each enabled transition the time interval in which the transition can fire (Berthomieu et Vernadat, 2003).

The TPN state is defined as a pair (M, Id), where M is a marking and Id is a firing interval function  $(Id : En(M) \to \mathbb{Q}^+ \times (\mathbb{Q}^+ \cup \{\infty\}))$ . The initial state is  $(M_0, Id_0)$  where  $M_0$  is the initial marking and  $Id_0(t) = Is(t)$ , for  $t \in En(M_0)$ .

Let (M, Id) and (M', Id') be two states of the TPN model,  $\theta \in \mathbb{R}^+$  and  $t \in T$ . The transition relation  $\longrightarrow$  over states is defined as follows:

- $(M, Id) \xrightarrow{\theta} (M', Id')$ , also denoted by  $(M, Id) + \theta$ , if and only if from state (M, Id), we will reach the state (M', Id') by a time progression of  $\theta$  units, i.e.,  $\bigwedge_{t' \in En(M)} \theta \le \uparrow Id(t'), M' = M$ , and  $\forall t'' \in En(M'), Id'(t'') = [Max(\downarrow Id(t'') \theta, 0), \uparrow Id(t'') \theta]$ .

- $(M, Id) \xrightarrow{t} (M', Id')$  if and only if the state (M', Id') is reachable from state (M, Id) by immediately firing transition t, i.e.,  $t \in En(M), \downarrow Id(t) = 0, \forall p \in P, M'(p) = M(p) Pre(p, t) + Post(p, t)$ , and  $\forall t' \in En(M'), Id'(t') = Is(t')$ , if  $t' \in New(M', t), Id'(t') = Id(t')$ , otherwise.

The TPN state space is the labeled transition system  $(Q, q_0, \Sigma, \longrightarrow)$ , where  $q_0 = (M_0, Id_0)$  is the initial state of the TPN,  $\Sigma = T \cup R^+$  and  $Q = \{q|q_0 \xrightarrow{*} q\}(\xrightarrow{*} \text{being the reflexive}$  and transitive closure of the relation  $\longrightarrow$  defined above) is the set of reachable states of the model. A run in the TPN state space  $(Q, q_0, \Sigma, \longrightarrow)$  of a state  $q \in Q$  is a maximal sequence  $\rho = q_1 \xrightarrow{\theta_1} q_1 + \theta_1 \xrightarrow{t_1} q_2 \xrightarrow{\theta_2} q_2 + \theta_2 \xrightarrow{t_2} q_3...$ , such that  $q_1 = q$ . By convention, for any state  $q_i$ , the relation  $q_i \xrightarrow{0} q_i$  holds. The sequence  $\theta_1 t_1 \theta_2 t_2...$  is called the timed trace of  $\rho$ . The

sequence  $t_1t_2...$  is called the firing sequence (untimed trace) of  $\rho$ . A marking M is reachable if and only if  $\exists q \in \mathcal{Q}$  s.t. its marking is M. Runs (resp. timed / untimed traces) of the TPN are all runs (resp. timed / untimed traces) of the initial state  $q_0$ .

To use enumerative analysis techniques with time Petri nets, an extra effort is required to abstract their generally infinite state spaces. Abstraction techniques aim to construct a finite contraction of the state space of the model by removing some irrelevant details. This contraction of the state space preserves the properties of interest. For best performances, the contraction should be the smallest possible and computed with the minimal resources in terms of time and space. The preserved properties are usually verified using standard analysis techniques on the abstractions (Penczek et Polrola, 2004).

Several state space abstraction methods have been proposed, in the literature, for time Petri nets (e.g. the state class graph (SCG) (Berthomieu et Diaz, 1991), the zone based graph (ZBG) (Boucheneb et al., 2009), etc). These abstractions may differ mainly in the characterization of the states (interval states or clock states), the agglomeration criteria of the states, the representation of the agglomerated states (abstract states), the kind of properties they preserve (markings, linear or branching properties) and their size.

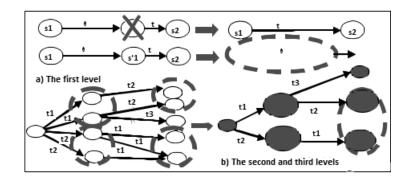

Abstraction consists of agglomeration of some states with similar behaviors. Agglomeration methods are different in the type of properties they preserve (LTL,CTL,...), the time characterization they use (clock, interval or firing date), and also the agglomeration policy they consider. There are three levels for abstraction criteria:

- At the first level, states being the result of time elapsing are agglomerated and only states being the result of transitions are considered as distinct states.

- At the second level, all states being the result of a similar transition are regrouped.

- At the third level, all states being the result of the same transitions with different sequences are regrouped as equivalent nodes. For example, a state being the result of  $t_1, t_2$  is agglomerated with a state being the result of  $t_2, t_1$ .

Fig.2.2 from (Boucheneb et Hadjidj, 2008) shows the three levels of abstraction.

Expressing the state of a model by either intervals or clocks are completely bi-similar. When time elapses in a model, its state is modified. The new state is declared by increasing clock values in clock characterization or decreasing the corresponding bounds in interval characterization. In some cases, using intervals instead of clocks helps to better abstract the

Figure 2.2 Three levels of abstraction (Boucheneb et Hadjidj, 2008).

state space, because bounds are positive values and whenever decreasing an interval yields to a negative value, it will be considered zero. In some other cases like construction of the state space graph, using clocks helps to better distinguish the states.

These abstractions are finite for all bounded time Petri nets. However, abstractions based on clocks are less interesting than the interval based abstractions when only linear properties are of interest. Indeed, abstractions based on intervals are finite for bounded TPN with unbounded intervals, while this is not true for abstraction based on clocks. The finiteness is enforced using an approximation operation, which may involve some overhead computation.

#### 2.3.2 Zone Based Graph

In the Zone Based Graph (ZBG) (Boucheneb et al., 2009), all clock states reachable by runs supporting the same firing sequence are agglomerated in the same node and considered modulo some over-approximation operation (Behrmann et al., 2006a; Gardey et al., 2006a). This operation is used to ensure the finiteness of the ZBG for the bounded TPNs with unbounded firing intervals. An abstract state, called state zone, is defined as a pair  $\beta = (M, FZ)$  combining a marking M and a formula FZ which characterizes the clock domains of all the states agglomerated in the state zone. In FZ, the clock of each enabled transition for M is represented by a variable with the same name. The domain of FZ is convex and has a unique canonical form represented by the pair (M, Z), where Z is a DBM of the order  $|En(M) \cup \{o\}$  defined by:  $\forall (x,y) \in (En(M) \cup \{o\})^2$ ,  $z_{xy} = Sup_{FZ}(x-y)$ . Here o represents the value of 0. State zones of the ZBG are in the relaxed form.

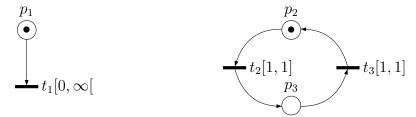

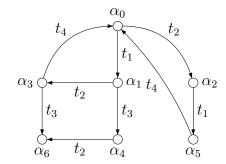

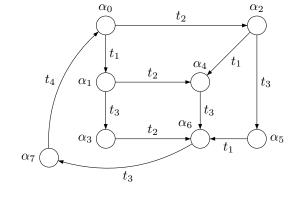

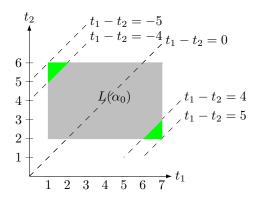

The initial state zone is the pair  $\beta_0 = (M_0, FZ_0)$ , where  $M_0$  is the initial marking and  $FZ_0 = \bigwedge_{t_i,t_j \in En(M_0)} 0 \le ti = tj \le \bigwedge_{t_u \in En(M_0)} I_s(t_u)$ . As an example, consider the TPN given in (Gardey et al., 2006b) and reported at Fig.2.4. Its state zone graph is reported at Fig.2.5 and its state zone graphs are reported in Table 2.1. More information about computing ZBG could be find in (Boucheneb et al., 2009).

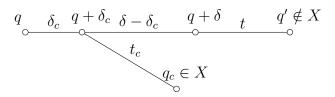

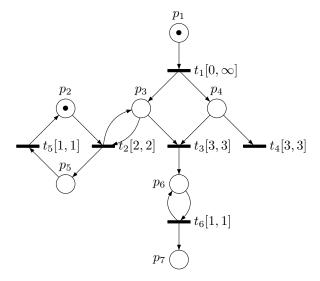

The ZBG of a bounded TPN is not necessarily bounded. Fig. 2.3 given in (Boucheneb et al., 2009) shows a bounded TPN with an infinite ZBG. For this reason, zone based graphs require some over-approximation.

Figure 2.3 A bounded TPN with an infinite ZBG reported from (Boucheneb et al., 2009).

In this work, we consider the state class method and study the possibility of enforcing the behavior of a given TPN in order to satisfy a safety / reachability property. The idea is to construct on-the-fly the reachable state classes of the TPN and at the same time collect progressively firing subintervals to be avoided so that the properties of interest are satisfied.

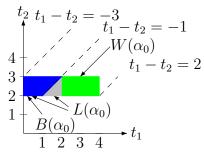

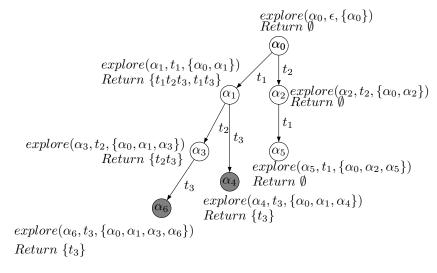

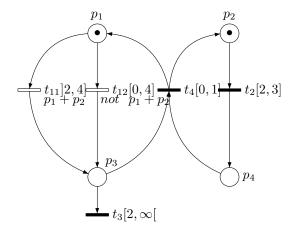

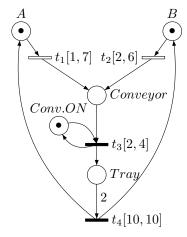

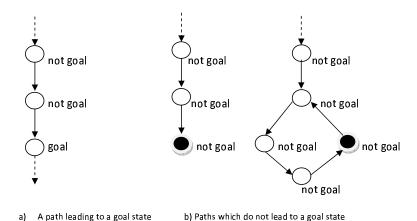

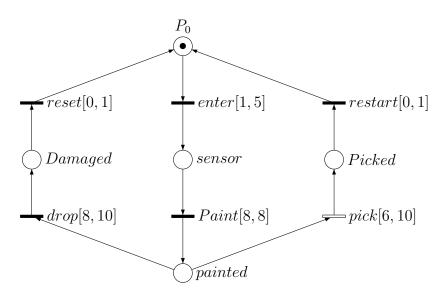

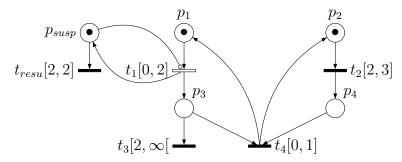

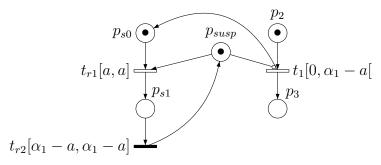

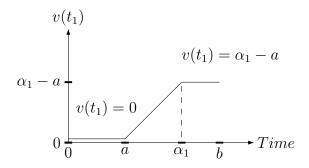

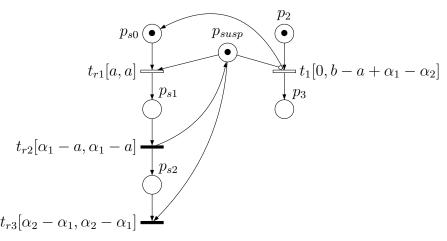

#### 2.3.3 The state class graph method