|                         | Architectures and Methodology for the Design of Real-time Power Converter Simulators on FPGAs                                                                                                                                                                   |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Federico Montano                                                                                                                                                                                                                                                |

| Date:                   | 2021                                                                                                                                                                                                                                                            |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                       |

| Référence:<br>Citation: | Montano, F. (2021). Architectures and Methodology for the Design of Real-time Power Converter Simulators on FPGAs [Ph.D. thesis, Polytechnique Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/9191/">https://publications.polymtl.ca/9191/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/9191/  |

|------------------------------------------|----------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Jean Pierre David, & Tarek Ould-Bachir |

| Programme: Program:                      | Génie électrique                       |

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

| Architectures and methodology for the design of real-time power | converter |

|-----------------------------------------------------------------|-----------|

| simulators on FPGAs                                             |           |

# FEDERICO MONTANO

Département de génie électrique

Thèse présentée en vue de l'obtention du diplôme de Philosophix Doctor Génie électrique

Août 2021

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Cette thèse intitulée :

Architectures and methodology for the design of real-time power converter simulators on FPGAs

présentée par Federico MONTANO

en vue de l'obtention du diplôme de *Philosophiæ Doctor* a été dûment acceptée par le jury d'examen constitué de:

Yvon SAVARIA, président

Jean Pierre DAVID, membre et directeur de recherche

Tarek OULD-BACHIR, membre et codirecteur de recherche

Pierre LANGLOIS, membre

Handy FORTIN-BLANCHETTE, membre externe

# **DEDICATION**

To all the people that have been next to me in this long s-path...

# ACKNOWLEDGEMENTS

This doctoral thesis represents for me the achievement and culmination of a long academic career that would not have been possible without the help of all the people who supported me along this long winding road.

First of all, I would like to thank my directors, Professor Jean Pierre David for having confidence in me and guiding me through this process and Professor Tarek Ould-Bachir for his constant support, excellent ideas and challenging discussions. Also to Professor Yvon Savaria who guided me at the beginning of my academic journey when I arrived at Polytechnique.

I would also like to thank my close family, my son Nicolas and my wife Beatriz Elena for their unconditional support and for putting up with me every day. To my extended family, my father who is no longer here, my mother, my sisters, my brothers and my countless nieces and nephews who have always been there for me.

I would also like to thank the members of the jury for taking the time to evaluate this work.

I would also like thanks to OPAL-RT Technologies and MITACS for their financial support.

Finally, I would like to thank my friends and lab partners Shiva, Roberto and Hemin who made this journey more enjoyable.

# RÉSUMÉ

Cette thèse porte sur une méthodologie pour la mise en œuvre sur FPGA de simulateurs en temps réel des convertisseurs de puissance. Un simulateur en temps réel donne un aperçu du comportement des convertisseurs. La complexité du simulateur peut changer dépendamment de la topologie du convertisseur à simuler. Le simulateur permet d'évaluer les spécifications, de vérifier le comportement des convertisseurs modélisés au cours des différentes phases de développement et de simplifier leur intégration. L'utilisation de simulateurs en temps réel facilite, par exemple, le test d'un convertisseur de puissance et de son contrôleur dans une configuration avec matériel dans la boucle (hardware-in-the-loop – HIL). Il permet de réduire les risques et les coûts associés à l'utilisation d'un banc d'essai réel.

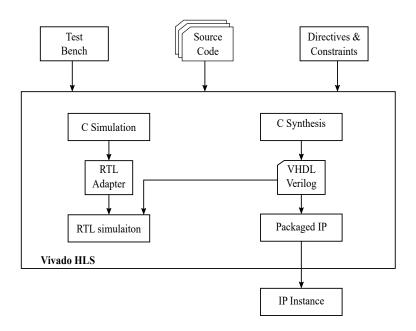

La mise en œuvre de simulateurs en temps réel sur FPGA est une tâche complexe réservée aux experts. De plus, le cycle de développement sur des FPGA est relativement long. Actuellement, il existe des outils de conception à haut niveau d'abstraction tel que Vivado HLS de Xilinx qui permettent de générer du matériel à partir d'un module programmé en C/C++/SystemC et d'utiliser des directives pour guider le processus de synthèse. HLS fournit une approche logicielle qui réduit le temps de vérification fonctionnelle et facilite la génération de matériel. Toutefois, selon l'application, ces outils n'atteignent pas toujours des performances équivalentes à celles d'un expert utilisant une description RTL (register transfer level). L'une des principales limitations de l'approche HLS est qu'elle ne fournit pas de mécanismes permettant d'instancier efficacement des modules personnalisés préfabriqués.

Cette recherche propose l'utilisation des approches combinées des architectures de superposition (overlay architectures — OA) et de la conception insensible à la latence (latency insensitive design — LID) comme méthodologie pour la mise en œuvre de simulateurs en temps réel basés sur les FPGA. Ce travail a été développé en trois étapes principales. Premièrement, nous avons réalisé une étude sur l'utilisation d'un outil HLS (Vivado HLS) pour la mise en œuvre de simulateurs en temps réel pour les convertisseurs de puissance. Deuxièmement, nous proposons la conception d'un réseau d'interconnexion multi-niveaux (multi-stage interconnection network — MIN) en utilisant le paradigme de conception insensible à la latence — LID. Ce MIN peut être reprogrammé et paramétré. Il offre des capacités de contention de données pour éviter les conditions de blocage. Le MIN a une conception et un algorithme de routage simples, qui permettent un haut débit à des fréquences élevées (>500 MHz) tout en gardant une consommation de ressources faible. Il est utilisé comme mécanisme d'interconnexion pour le routage des données entre les principaux modules du sys-

tème. Finalement, nous avons généralisé l'approche LID en ajoutant des unités de contrôle distribuées aux modules fonctionnels (opérateurs arithmétiques et mémoires) pour permettre des transferts synchronisés par les données et nous avons relié les modules pour former une architecture de superposition d'un solveur linéaire paramétrable et reprogrammable. Une nouvelle architecture peut être facilement générée en modifiant certains paramètres, par exemple, le nombre et le type d'opérateurs. Une architecture déjà synthétisée peut être reprogrammée pour simuler différents types de convertisseurs. Trois architectures ont été générées et testées sur différents circuits. Elles opèrent à des fréquences d'horloge allant jusqu'à 300 MHz et permettent d'atteindre des pas de calcul inférieurs à la microseconde — un requis fort pour la simulation en temps réel des convertisseurs de puissance modernes.

La génération automatique de l'implémentation matérielle obtenue avec la méthodologie de conception proposée dans cette recherche facilite l'utilisation des FPGA aux spécialistes des applications et aux développeurs de logiciels pour la mise en œuvre de simulateurs de convertisseurs de puissance pour les applications HIL.

# ABSTRACT

This thesis focuses on a methodology for the implementation of real-time FPGA-based simulators for power converters. A real-time simulator provides a preview of the behavior of converters. Its complexity may change depending on the converters' topology. The real-time simulator allows evaluating the specifications, verifying the behavior of modeled systems during the various phases of development, and simplifying their integration. The use of real-time simulators facilitates, for example, the testing of a power converter and its controller in a hardware-in-the-loop (HIL) configuration. It helps to reduce the risks and costs associated with the use of a physical test bench.

The implementation of real-time simulators on FPGAs is a complex task reserved for experts. Moreover, the development cycle for FPGAs is relatively long. Currently, there are high level synthesis tools such as Vivado HLS from Xilinx that allow the generation of hardware from a module programmed in C/C++/SystemC and the use of directives to guide the synthesis process. HLS provides a software approach that reduces the time of functional verification and facilitates the generation of hardware. However, depending on the application, these tools do not always reach a performance equivalent to that achieved by an expert using RTL description. One of the main limitations of the HLS approach is that it doesn't provide a mechanism to effectively instantiate custom-made modules.

This research proposes the use of the combined approaches of overlay architectures (OA) and latency insensitive design (LID) as a methodology for the implementation of real-time simulators based on FPGA. This work has been developed in three main stages. Firstly, we performed a study of the use of an HLS tool (Vivado HLS) for implementing real-time simulators for power converters. Secondly, we propose the design of a multi-stage interconnection network (MIN) using the latency insensitive design paradigm — LID. This MIN can be reprogrammed and parametrized. It provides data contention capabilities to avoid blocking conditions. The MIN has a simple design and routing algorithm, which enables high throughput at high frequencies (>500 MHz) while maintaining low resource consumption. It is used as an interconnection mechanism for data routing between the main modules of the target simulation system. Finally, we generalized the LID approach by adding distributed control units to the functional modules (arithmetic operators and memories) to allow synchronized data transfers and interconnected the modules to form a parametrizable and reprogrammable linear solver overlay architecture. New architectures can be easily generated by modifying certain parameters, for example, the number and type of operators. An architecture already

synthesized can be reprogrammed to simulate different types of converters. Three architectures have been generated and tested on different circuits. They support clock frequencies up to 300 MHz, and generate computation time-steps lower than one microsecond which is a requirement for real-time simulation of modern power converters.

The automatic hardware implementation obtained with the design methodology proposed in this research facilitates the use of the FPGA by application specialists and software developers for the implementation of power converter simulators for HIL applications.

# TABLE OF CONTENTS

| DEDIC  | ATION   |                                                  | iii               |

|--------|---------|--------------------------------------------------|-------------------|

| ACKNO  | OWLED   | GEMENTS                                          | iv                |

| RÉSUM  | ΙÉ      |                                                  | v                 |

| ABSTR  | ACT     |                                                  | vii               |

| TABLE  | OF CO   | ONTENTS                                          | ix                |

| LIST O | F TAB   | LES                                              | xiii              |

| LIST O | F FIGU  | JRES                                             | xiv               |

| LIST O | F SYM   | BOLS AND ACRONYMS                                | vii               |

| СНАРТ  | ER 1    | INTRODUCTION                                     | 1                 |

| 1.1    | Proble  | m Definition                                     | 2                 |

| 1.2    | Resear  | ch Objectives                                    | 3                 |

| 1.3    |         | Outline                                          | 4                 |

| СНАРТ  | TER 2   | BACKGROUND                                       | 6                 |

| 2.1    | Introd  | uction                                           | 6                 |

| 2.2    | Electri | c Circuit Equations                              | 6                 |

|        | 2.2.1   | State-Space Representation Method                | 7                 |

|        | 2.2.2   | Nodal Method                                     | 8                 |

|        | 2.2.3   | The Modified and Augmented Nodal Analysis Method | 8                 |

|        | 2.2.4   | Switch Models                                    | 9                 |

| 2.3    |         | of Simulations                                   | 11                |

|        | 2.3.1   | Offline Simulation                               | 11                |

|        | 2.3.2   | Real-Time Simulation                             | 12                |

|        | 2.3.3   | Use of Real-Time Simulators                      | 12                |

| 2.4    |         | ercial Simulation Tools                          | 13                |

| ⊿.च    | 2.4.1   | Offline Simulation Tools                         | 13                |

|        | 2.4.1   | CPU-Based Real-Time Simulators                   | 14                |

|        | 2.4.3   | FPGA-Based Real-Time Simulators                  | 1 <del>4</del> 15 |

|        | ۷.4.ئ   | TI GA-Dased Real-Tille Sillidatols               | TO                |

| 2.5   | Conclu | asion                                                                                                                      |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------|

| СНАРТ | ER 3   | LITERATURE REVIEW                                                                                                          |

| 3.1   | Introd | uction                                                                                                                     |

| 3.2   |        | -based Real-Time Methods for Simulation of Power Electronics 18                                                            |

|       | 3.2.1  | Latency Insertion Method                                                                                                   |

|       | 3.2.2  | Switching Elements Based Partitioning                                                                                      |

|       | 3.2.3  | Methods for Naturally Commuted Devices                                                                                     |

| 3.3   | Hardw  | are Development Approaches                                                                                                 |

|       | 3.3.1  | RTL                                                                                                                        |

|       | 3.3.2  | High-Level Synthesis Approach (HLS)                                                                                        |

|       | 3.3.3  | Overlay Architectures (OA)                                                                                                 |

|       | 3.3.4  | Latency Insensitive Design (LID)                                                                                           |

| 3.4   | Summ   | ary                                                                                                                        |

| 3.5   |        | sion                                                                                                                       |

| СНАРТ | ER 4   | CONTENT ORGANIZATION AND RESEARCH APPROACH 33                                                                              |

| СНАРТ | ER 5   | ARTICLE 1: AN EVALUATION OF A HIGH-LEVEL SYNTHESIS AP-                                                                     |

| PRC   | ACH 7  | TO THE FPGA-BASED SUB-MICROSECOND REAL-TIME SIMULA-                                                                        |

| TIO   | N OF F | POWER CONVERTERS                                                                                                           |

| 5.1   | Introd | uction $\dots \dots \dots$ |

| 5.2   | Relate | d Work                                                                                                                     |

| 5.3   | Design | Exploration                                                                                                                |

|       | 5.3.1  | Custom Design                                                                                                              |

|       | 5.3.2  | VHLS Approaches                                                                                                            |

|       | 5.3.3  | Implementation Results                                                                                                     |

| 5.4   | Case S | tudy: Power Converter                                                                                                      |

|       | 5.4.1  | Implementation Results                                                                                                     |

|       | 5.4.2  | Offline Simulation Results                                                                                                 |

|       | 5.4.3  | Online Simulation Results                                                                                                  |

| 5.5   | Conclu | asion                                                                                                                      |

| 5.6   | Appen  | dix—Power Circuit Modeling                                                                                                 |

| СНАРТ | ER 6   | ARTICLE 2: A LOW-LATENCY RECONFIGURABLE MULTISTAGE                                                                         |

| INT   | ERCON  | NNECTION NETWORK 57                                                                                                        |

| 6.1   | Introd | uction                                                                                                                     |

| 6.2   | MIN A  | Architecture                                         | 8 |

|-------|--------|------------------------------------------------------|---|

|       | 6.2.1  | Butterfly Topology                                   | 8 |

|       | 6.2.2  | Proposed Switch Architecture                         | 0 |

|       | 6.2.3  | Routing Scheme                                       | 1 |

|       | 6.2.4  | MIN Capacity and Data Contention                     | 2 |

|       | 6.2.5  | Generic Structure                                    | 2 |

| 6.3   | Imple  | mentation Results                                    | 3 |

| 6.4   | Conclu | asion                                                | 4 |

| СНАРТ | TER 7  | ARTICLE 3 : A LATENCY-INSENSITIVE DESIGN APPROACH TO |   |

| PRO   | OGRAN  | MABLE FPGA-BASED REAL-TIME SIMULATORS 6              | 6 |

| 7.1   | Introd | uction                                               | 6 |

| 7.2   | Relate | d Work                                               | 8 |

|       | 7.2.1  | Switch Model                                         | 8 |

|       | 7.2.2  | Hardware Description Languages                       | 9 |

|       | 7.2.3  | Number Format                                        | 9 |

| 7.3   | Backg  | round                                                | 0 |

|       | 7.3.1  | Overlay Architectures                                | 0 |

|       | 7.3.2  | Latency-Insensitive Design                           | 2 |

| 7.4   | Propo  | sed Solution                                         | 2 |

|       | 7.4.1  | Mathematical Formulation                             | 3 |

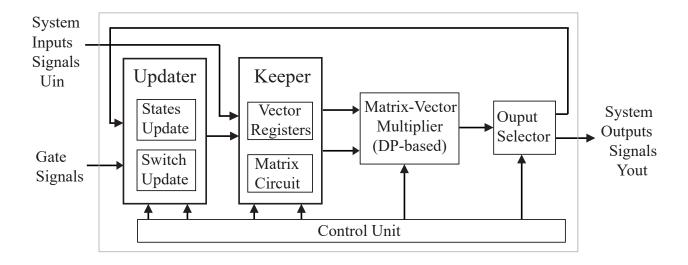

|       | 7.4.2  | Hardware Solver Architecture                         | 4 |

|       | 7.4.3  | Programming Model                                    | 5 |

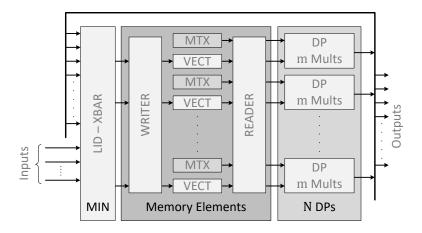

|       | 7.4.4  | Interconnection Network                              | 5 |

|       | 7.4.5  | Memory Elements                                      | 7 |

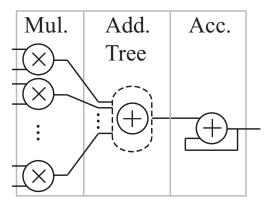

|       | 7.4.6  | Dot-Product Operator                                 | 8 |

| 7.5   | Result | s                                                    | 8 |

|       | 7.5.1  | Synthesis Results                                    | 9 |

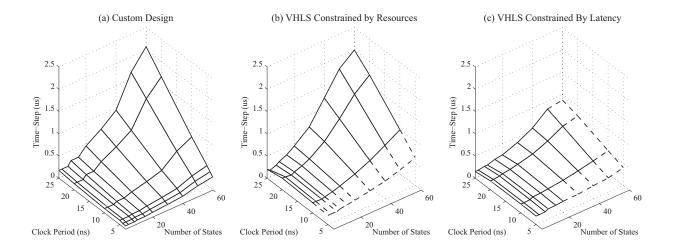

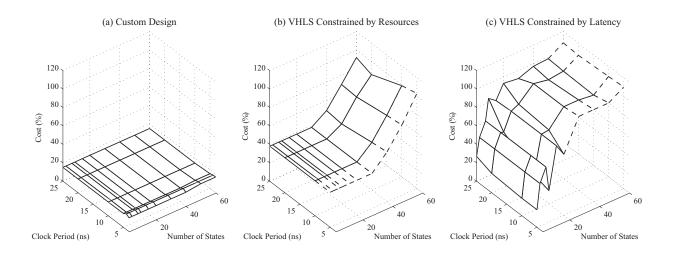

|       | 7.5.2  | Time-step Exploration                                | 0 |

|       | 7.5.3  | Open-Loop Test Case 1                                | 2 |

|       | 7.5.4  | Open-Loop Test Case 2                                | 6 |

|       | 7.5.5  | Closed-Loop Test Case                                | 6 |

| 7.6   | Discus | sion                                                 | 8 |

| 7.7   | Concl  | ısions                                               | 0 |

| СНАРТ | TER 8  | GENERAL DISCUSSION                                   | 1 |

|                                          | xii |

|------------------------------------------|-----|

| CHAPTER 9 CONCLUSION AND RECOMMENDATIONS | 94  |

| 9.1 Synopsis of the work                 | 94  |

| 9.2 Limitations of the Proposed Solution | 95  |

| 9.3 Future Research                      | 96  |

| REFERENCES                               | 97  |

# LIST OF TABLES

| Table 3.1: | Synthesis Results from State of the Art                  | 31 |

|------------|----------------------------------------------------------|----|

| Table 3.2: | Design Characteristics from State of the Art             | 31 |

| Table 5.1: | DP Latency for the Various Operation Frequencies         | 40 |

| Table 5.2: | Circuit Parameters                                       | 46 |

| Table 5.3: | Synthesis Results for the Kintex XC7K325T                | 47 |

| Table 5.4: | Implementation results for the Virtex 7VX485T            | 49 |

| Table 6.1: | Design Exploration                                       | 65 |

| Table 7.1: | Synthesis Results for Xilinx Virtex 7 (7vx485tffg1157-1) | 80 |

| Table 7.2: | Synthesis results from literature                        | 81 |

| Table 7.3: | ACDCAC Converter parameters                              | 83 |

| Table 7.4: | 2-Norm Error Relative Error                              | 83 |

| Table 7.5: | THD Comparison                                           | 85 |

| Table 7.6: | PR controller parameters                                 | 88 |

| Table 8.1: | Synthesis Results from State of the Art                  | 93 |

| Table 8.2: | Design Characteristics from State of the Art             | 93 |

# LIST OF FIGURES

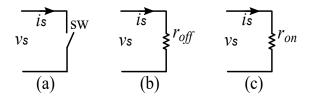

| Figure 2.1:  | Resistive switch model (a) Ideal switch; (b) OFF state; (c) ON state.        | 1 |

|--------------|------------------------------------------------------------------------------|---|

| Figure 2.2:  | ADC Switch model (a) Ideal switch; (b) ON state; (c) OFF state; (d)          |   |

|              | Discrete model                                                               | 1 |

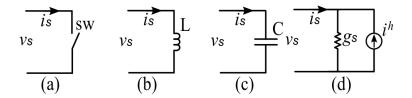

| Figure 2.3:  | Types of simulation: (a) Offline simulation. (b) Real-time simulation        | 1 |

| Figure 2.4:  | Use of real-time simulation. (Inspired from $[1]$ )                          | 1 |

| Figure 3.1:  | FPGA Design Flow                                                             | 2 |

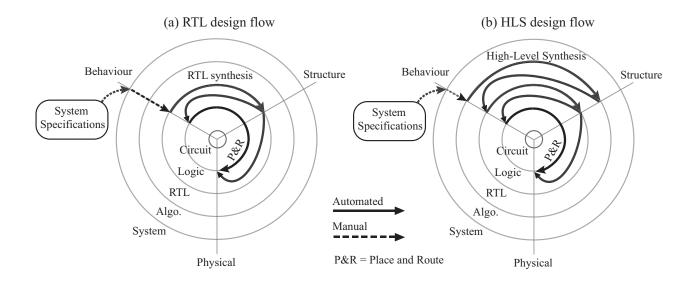

| Figure 3.2:  | HLS Design Flow                                                              | 2 |

| Figure 3.3:  | Design flow with Vivado HLS. (Inspired from [2])                             | 2 |

| Figure 3.4:  | Design flow with Intel SDK. (Inspired from [3])                              | 2 |

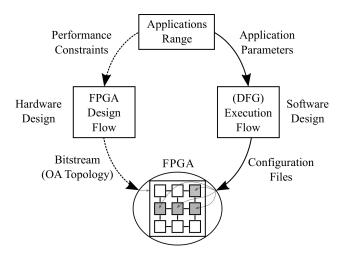

| Figure 3.5:  | OA Design —General flow (Inspired from [4])                                  | 2 |

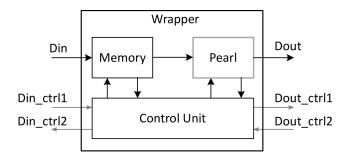

| Figure 3.6:  | LID module —General structure(Inspired from [5])                             | 2 |

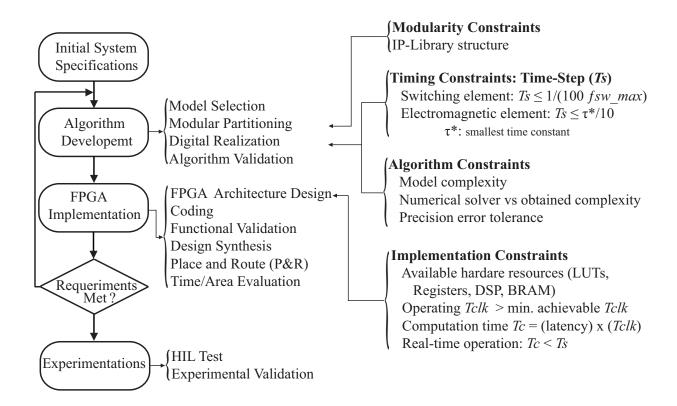

| Figure 5.1:  | Design guideline for FPGA-based real-time simulator design. Adapted          |   |

|              | from [6]                                                                     | 3 |

| Figure 5.2:  | Y-chart for (a) RTL and (b) HLS. Adapted from [7]                            | 3 |

| Figure 5.3:  | Custom design hardware solver architecture                                   | 4 |

| Figure 5.4:  | DP operator structure                                                        | 4 |

| Figure 5.5:  | Excerpt from the C-code used for the design of the HS in VHLS $$ . $$ .      | 4 |

| Figure 5.6:  | Directives for the VHLS approach constrained by resources                    | 4 |

| Figure 5.7:  | Directives for VHLS approach constrained by latency                          | 4 |

| Figure 5.8:  | Minimum Time-step: (a) Custom design; (b) VHLS constrained by                |   |

|              | resources; (c) VHLS constrained by latency                                   | 4 |

| Figure 5.9:  | Implementation cost: (a) Custom design; (b) VHLS constrained by              |   |

|              | resources; (c) VHLS constrained by latency                                   | 4 |

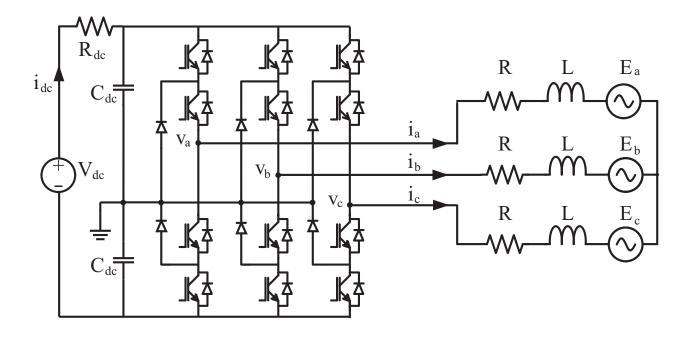

| Figure 5.10: | Case study: NPC converter connected to an RLE load                           | 4 |

| Figure 5.11: | Simulation results: (a) Load current $i_a$ ; (b) Relative errors; (c) Close- |   |

|              | up view on relative errors                                                   | 5 |

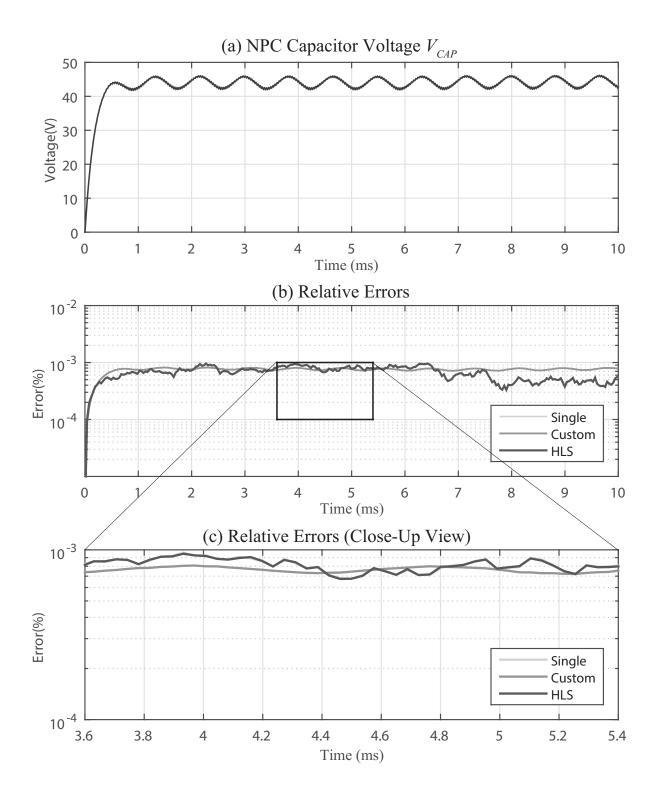

| Figure 5.12: | Simulation results: (a) Capacitor voltage $V_{CAP}$ ; (b) Relative errors;   |   |

|              | (c) Close-up view on relative errors                                         | 5 |

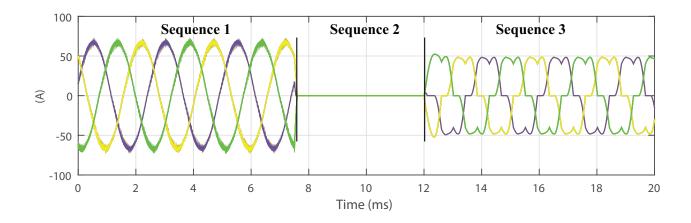

| Figure 5.13: | Load currents from a SPS offline simulation with 3 sequences: (1) In-        |   |

|              | version mode; (2) Gates turned-off; (3) Rectification mode $\dots$           | 5 |

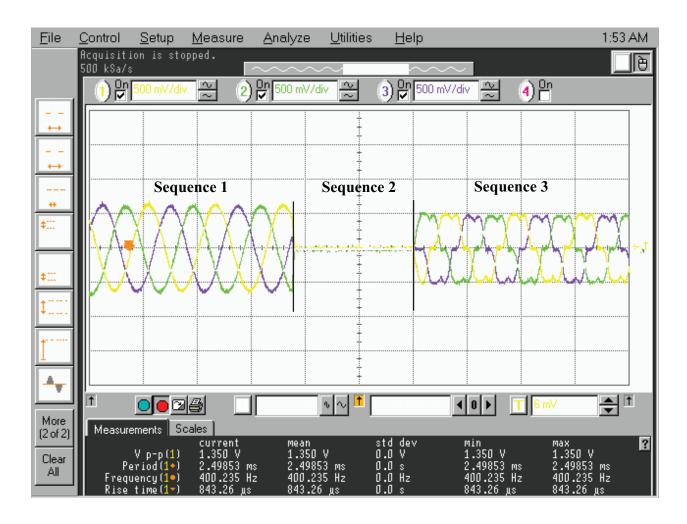

| Figure 5.14: | Load currents from an online simulation with 3 sequences: $(1)$ Inversion    |   |

|              | mode; (2) Gates turned-off; (3) Rectification mode                           | 5 |

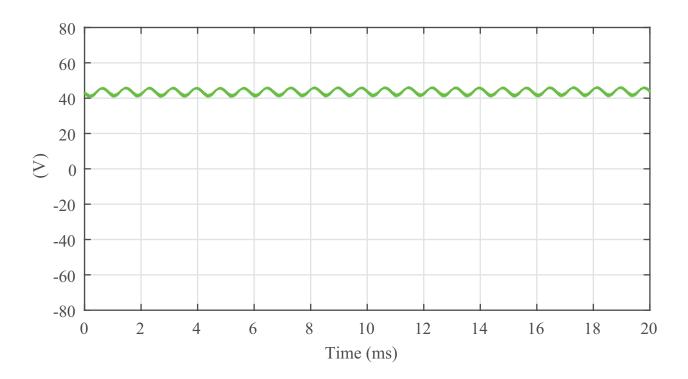

| Figure 5.15: | Capacitor voltage from an SPS offline simulation in inversion mode .         | 5 |

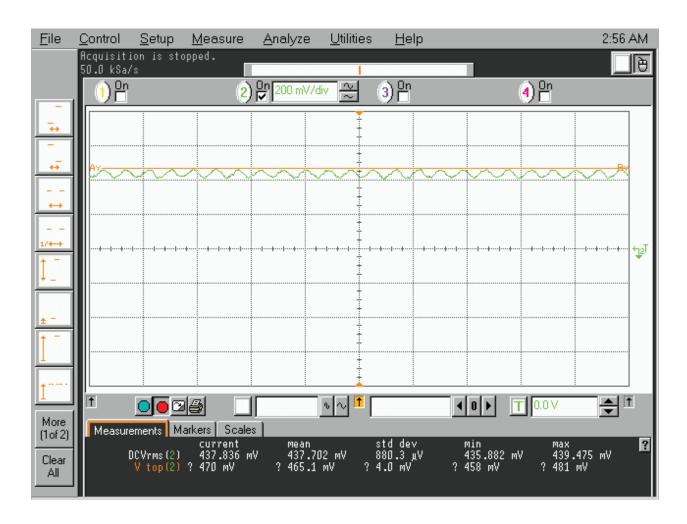

| Figure 5.16: | Capacitor voltage from an online simulation in inversion mode                | 56 |

|--------------|------------------------------------------------------------------------------|----|

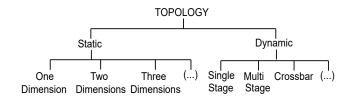

| Figure 6.1:  | Taxonomy of interconnection networks                                         | 59 |

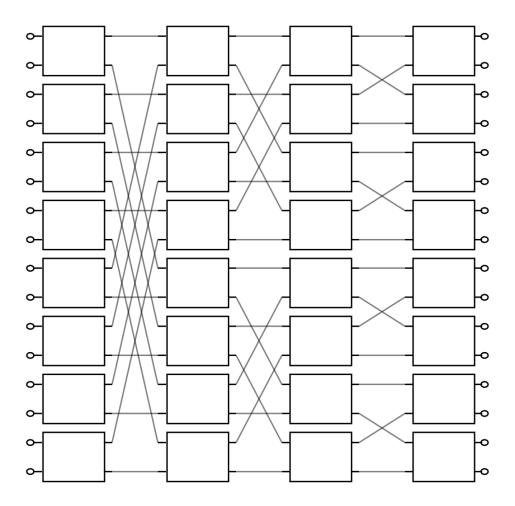

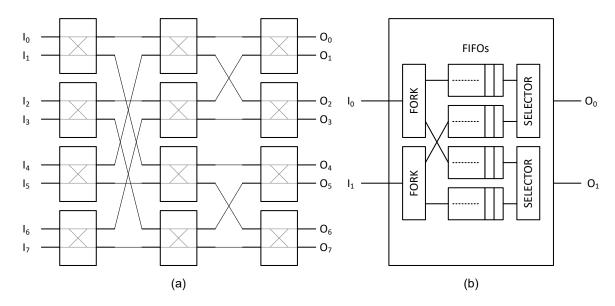

| Figure 6.2:  | Butterfly topology: $16 \times 16$ MIN                                       | 59 |

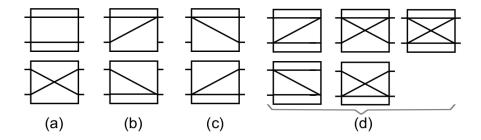

| Figure 6.3:  | Basic switch modes and conditions: a) One-to-one non-blocking; b) One-       |    |

|              | to-one blocking; c) Multicast non-blocking; d) Multicast blocking            | 60 |

| Figure 6.4:  | Proposed Switch: a) Internal structure; b) Transmission without data         |    |

|              | contention; c) Transmission with use of data contention                      | 61 |

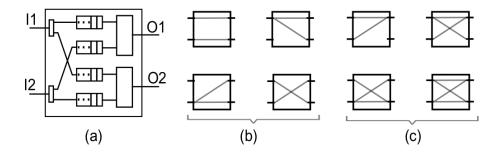

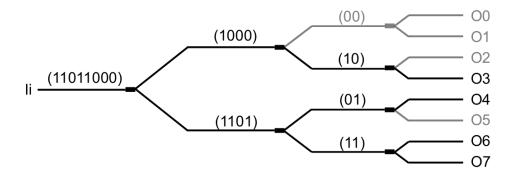

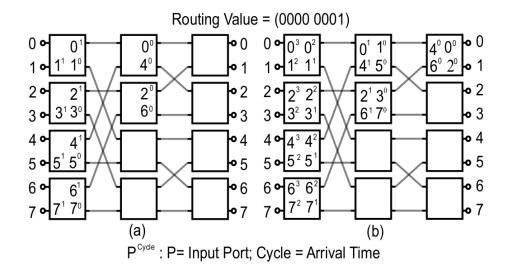

| Figure 6.5:  | Multi-cast routing example: routing commands are given between paren-        |    |

|              | thesis. Target outputs are O3, O4, O6 and O7 , i.e. $11011000$               | 61 |

| Figure 6.6:  | Data flow in $N$ -to-one transmission targeting output port 0: a) Status     |    |

|              | at cycle 2; b) Status at cycle 4                                             | 63 |

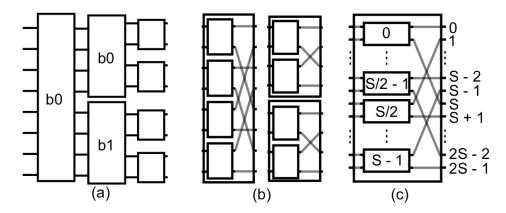

| Figure 6.7:  | Block representation: a) Inter-block connection; b) Output cross con-        |    |

|              | nections; c) Switch-Block output interconnection                             | 63 |

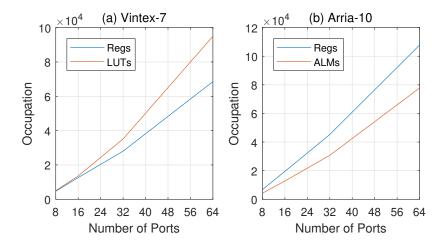

| Figure 6.8:  | Resource consumption as function of number of ports $(N)$                    | 65 |

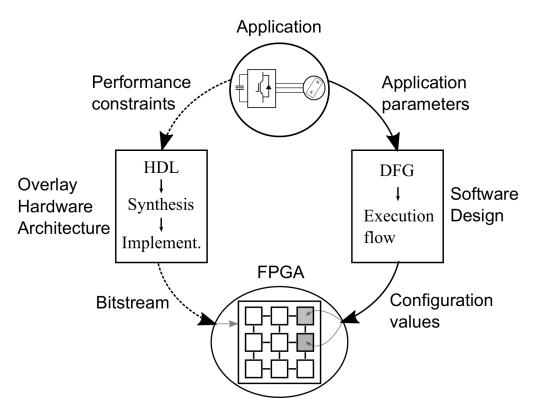

| Figure 7.1:  | Overlay development cycle (Inspired from [4])                                | 71 |

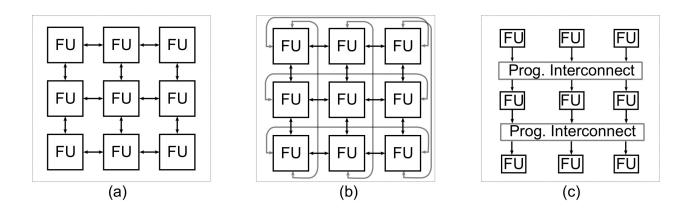

| Figure 7.2:  | Basic topologies of overlay architectures: a) Nearest neighbor [4],          |    |

|              | b) Torus [8], c) Linear [9]                                                  | 73 |

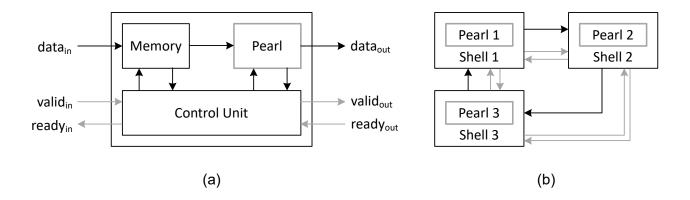

| Figure 7.3:  | (a) General architecture of a shell; (b) LID-based design with intercon-     |    |

|              | nected shells                                                                | 73 |

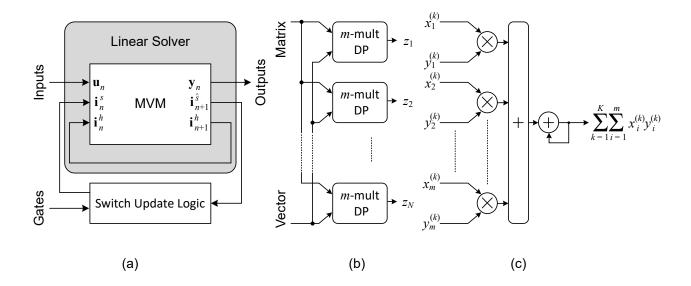

| Figure 7.4:  | Solver Architecture                                                          | 76 |

| Figure 7.5:  | Linear Solver Architecture                                                   | 76 |

| Figure 7.6:  | Multilevel Interconnection Network. (a) $8 \times 8$ Butterfly topology; (b) |    |

|              | $2 \times 2$ MIN Cell                                                        | 77 |

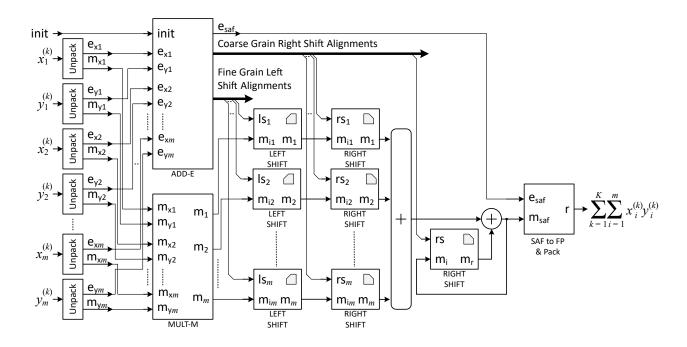

| Figure 7.7:  | Dot product operator implemented using a fused path self-alignment           |    |

|              | format                                                                       | 79 |

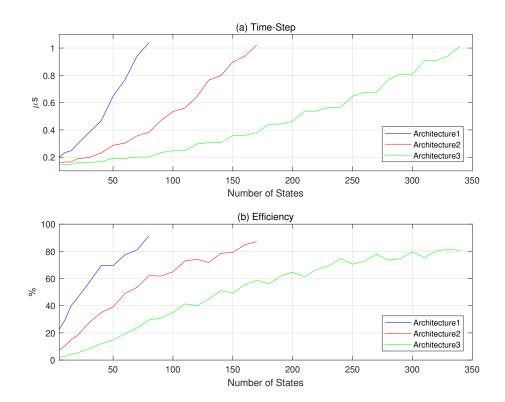

| Figure 7.8:  | Overlay performance. (a) Min. time-step vs nb states; (b) Efficiency .       | 81 |

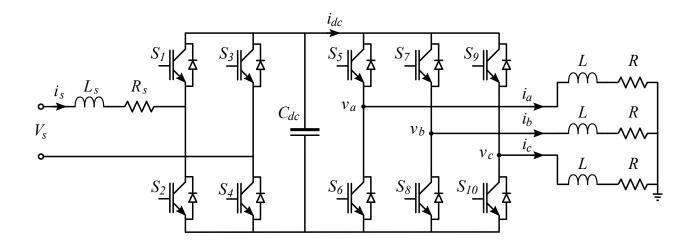

| Figure 7.9:  | AC-DC-AC Power Converter. Adapted from [10]                                  | 83 |

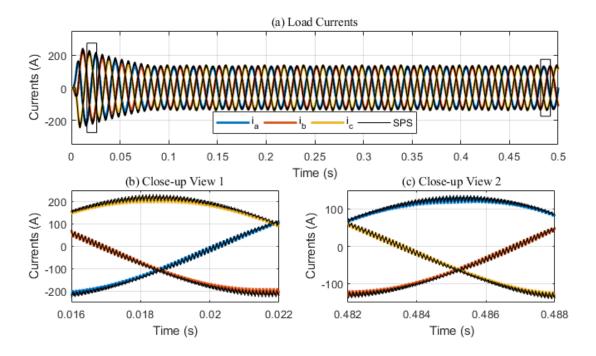

| Figure 7.10: | 3-phase load currents: (a) Whole sequence view with indications for          |    |

|              | close-up views; (b) Close-up view #1; (c) Close-up view #2                   | 84 |

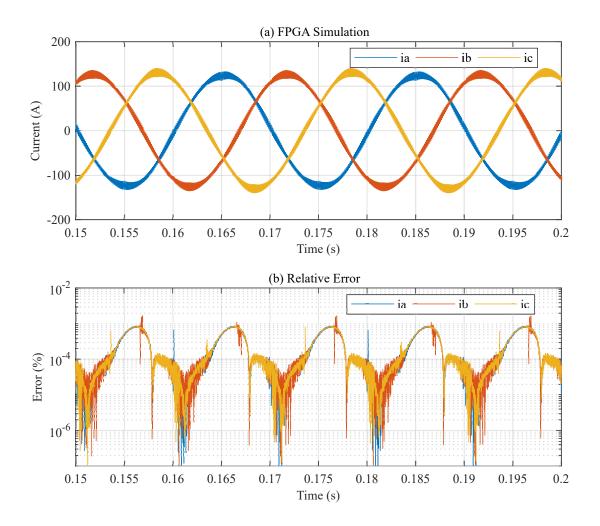

| Figure 7.11: | Close-up view of 3-phase load currents (a) HS FPGA-simulation; (b)           |    |

|              | Relative error for each time-point of the simulation                         | 85 |

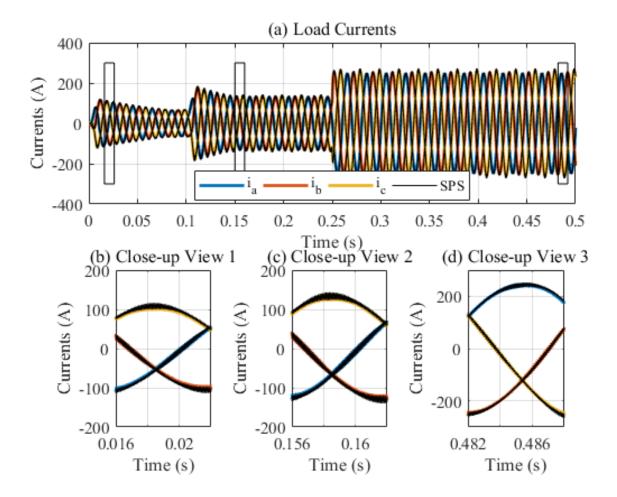

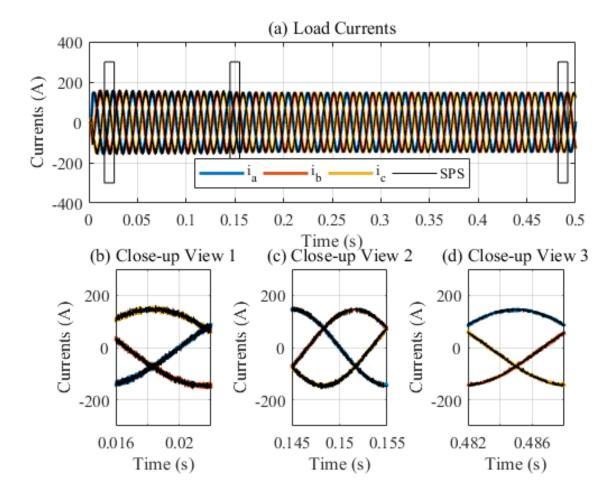

| Figure 7.12: | Three-phase load currents: (a) Whole sequence view with indications          |    |

|              | for close-up views; (b) Close-up view #1; (c) Close-up view #2; (c)          |    |

|              | Close-up view #3                                                             | 87 |

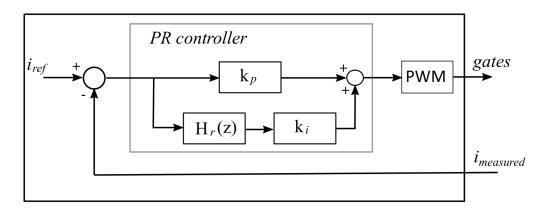

| Figure 7.13: | Control strategy block diagram                                               | 87 |

| Figure 7.14: | Three-phase load currents in closed-loop: (a) Whole sequence view           |    |

|--------------|-----------------------------------------------------------------------------|----|

|              | with indications for close-up views; (b) Close-up view $\#1$ ; (c) Close-up |    |

|              | view #2 and (d) Close-up view #3                                            | 89 |

#### LIST OF SYMBOLS AND ACRONYMS

ADC Associated Discrete Circuit

CP Computing Power

DAE Differential Algebraic Equations

DP Dot Product

DSP Digital Signal Processor

EMT Electro-Magnetic Transient

FDP Fused Datapath

FLOPS FLoating-point OPerations per Second

FP Floating-Point

FPGA Field Programmable Gate Array

FXP Fixed-Point

HIL Hardware-In-the-Loop

HLS High Level Synthesis

HS Hardware Solver

LID Latency-Insensitive Design

LUT Look-Up Table

MANA Modified-Augmented Nodal Analysis

MIN Multi-stage Interconnection Network

MVM Matrix-Vector Multiplication

NoC Network on Chip

NTT Network Tearing Technique

OA Overlay Architecture

PEC Power Electronic Circuit

RAM Random Access Memory

RSM Resistive Switch Model

RTL Register-Transfer Level

RTS Real-Time Simulator

SAF Self-Alignment Format

SNP Switching Network Partitioning

SPS SimPowerSystem

THD Total Harmonic Distortion

VHDL Very high speed integrated circuit Hardware Description Language

XBAR Crossbar

#### CHAPTER 1 INTRODUCTION

The complexity associated with modern electrical networks used in industries such as generation, transport and distribution of electricity, electrical vehicles, and aerospace requires multiple iterations during their development cycle to warrant proper functioning. For many decades, simulation has been used in research and industry as an efficient method to reduce the cost and risk related to the development, test, and deployment of new systems. The use of a simulator allows foreseeing the system behavior before its physical implementation. The physical system (typically a plant) is modeled using a set of equations that describe its behavior under the operation range. The computing power and time required to perform the associated calculations depend on the complexity of the model.

The simulation can be performed in offline or real-time modes. An offline simulation means that the computing power is used to solve the system's equations and obtain its state and outputs regardless of the time required to perform all the calculations. Offline simulation offers flexibility and is normally used during the initial stages of the development process. However, the lack of time synchronicity makes offline simulation unusable during the later stages of the development process, when the response time must be considered. In contrast, real-time simulation performs all the model calculations within the time-step duration and produces outputs in a synchronized way under a hard real-time constraint.

Real-time simulation eases the test and the verification of real systems during the multiple phases of the development process. It helps shortening the development iteration loop, to reduce costs and implementation time. For this reason, real-time simulation is the preferred technique to apply in the development of devices and systems rather than hardware prototyping. Furthermore, real-time simulation enables testing the system under development at the limits of its normal operation, avoiding the risks associated with doing such tests with physical devices. Typically, real-time simulators are used for testing the controller of a plant in a hardware-in-the-loop (HIL) configuration. In such an approach, the real controller is connected to the simulator and cannot see any difference between the simulator and the real real system.

Historically, real-time simulators were designed using PC clusters to accommodate for complex models. However, real-time simulation implies that all calculations pertaining to a time-point are completed within the duration of the simulation time-step. In certain applications such a modern power electronics, this condition introduces heavy constraints on the round-trip time due to the latency associated with the communication links in CPU-based

simulation. For example, a power converter requires that the simulator solves the system equations within a 1  $\mu$ s time when the switching frequencies are over tens of kHz. Hence, real-time simulation manufacturers started considering the use of FPGAs as a hardware platform.

The digital design of FPGA-based real-time simulators is mainly performed at low level, following a register-transfer level (RTL) approach and using hardware description languages (HDL) such as VHDL and Verilog. Graphical tools such as Xilinx System Generator are also used. This comes at a cost, due to the complexity associated with the RTL approach, as time to market increases. Additionally, an FPGA specialist is usually required to perform the design. An update to the digital design can take many days before implementation. Hence, there is clearly a need for a high-level solution for the design and implementation of real-time simulators on FPGA.

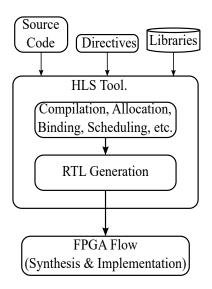

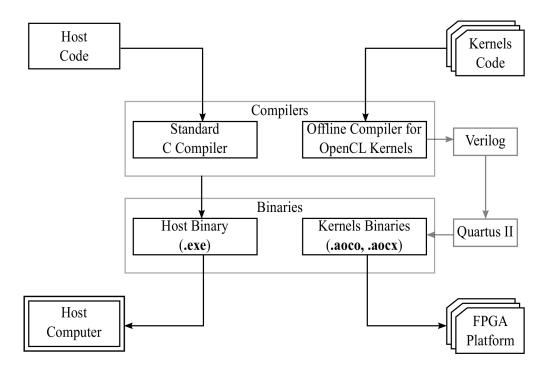

Nowadays, there are commercial and academic tools that use the high-level synthesis (HLS) design for FPGA development. These tools allow the use of languages like C/C++ as entry points, then a specialized compiler translates the C/C++ description into a hardware module. Following this approach, the usage of FPGA can be facilitated to software developers or application specialists. However, it has been shown that the hardware produced with such tools can hardly compete with hand-crafted designs for real-time simulation purposes.

# 1.1 Problem Definition

Modern simulators used in the industry are platforms combining general processors (CPUs) and FPGAs. In applications requiring short calculation time, the FPGAs are used to complement or replace the CPUs when the latter are unable to meet the timing requirements on their own. FPGA-based real-time simulators require high computing power, good flexibility, efficient interconnection systems, and short response times.

The architecture of FPGAs offers high parallelism capacity and structural flexibility. These features make the FPGAs suitable for the development of high-speed hardware solvers for real-time simulation of electrical networks. Hardware development on FPGAs isn't necessarily a task that can be easily performed by a power application engineer. Frequently, the support of a hardware specialist for the low-level design, or the use of high level approaches can ease the task. Two main aspects are affected by this condition: i) If the design is performed at low level (RTL-HDL), the time and complexity attached to the development increase the total cost; ii) If commercial HLS tools are used for the design of real-time simulators, at their current state, such tools can fail to achieve the required performance. There are other

design alternatives, such as latency insensitive design (LID) and overlay architectures (OAs), which are known to facilitate modularity and reprogramming. Although OAs are already in use in the industry, none have considered LID in the implementation of hardware real-time simulators. These conditions lead to the interest of this research to establish a methodology for implementing real-time simulators over FPGAs using LID and OA approaches to generate architectures that are easy to configure and reprogram.

In this research, we show that:

- 1. The ever-increasing resources and performance of modern FPGAs make them the privileged hardware platform for the implementation of real-time simulators.

- 2. Solving the system of equations of power systems implies matrix operations that offer parallel processing opportunities.

- 3. The combination of LID and OA allows a fast implementation of FPGA-based real-time simulators that are accurate by design. This methodology leads to an automatic generation of hardware implementations.

# 1.2 Research Objectives

The main goal of this research to provide a design methodology for FPGA-based real-time simulators. This methodology allows the automatic generation of hardware solvers aimed at the real-time simulation of power converters on FPGAs. Thus, facilitating the use of FPGAs to application specialists for the implementation of power converters simulators for HIL applications and reducing design time. In order to achieve our goal we:

- 1. Propose and develop predefined hardware solver architectures that can be parameterized and re-configurable. These architectures use an OA design that can be reprogrammed after synthesis.

- 2. Introduce the latency insensitive design approach to the development of FPGA-based real-time simulators. This approach facilitates the integration of modules.

- 3. Propose and develop a cost-effective interconnection system that allows data transfer among the different modules forming the simulator at high throughput and low cost.

- 4. Propose a methodology to wrap the specialized operators already built by hardware specialists to allow their reuse.

#### 1.3 Thesis Outline

This chapter presented an introduction to the real-time simulation, the problems associated with their development, and the overview of the objectives for this research. The following chapters show a layout for the rest of this work.

- Chapter 2: This chapter introduces the basic concepts related to real-time simulation. The most used mathematical formulations and switch models are presented. The offline and online simulation are differentiated, and a context of utilisation of real-time simulators is presented;

- Chapter 3: This chapter reviews the works more related to this research. It explains the different techniques for the implementation of real-time simulations for power converters over FPGAs, as well as the implementation approaches and their limitations. Finally, it presents the state-of-art of real-time simulation;

- Chapter 4: This chapter describes the process followed to generate and assemble the main chapters that form this thesis;

- Chapter 5: This chapter presents a comparative evaluation between custom design and the use of a high-level synthesis tool. Both techniques were used as design methods for the hardware solvers implementation. A detailed study for the performance, latency, and resource consumption over multiple circuits of different sizes is presented. This is the first paper issued from this work [11]. It has been published in IEEE Transactions on Industrial Electronics in 2018;

- Chapter 6: This chapter presents the system interconnection mechanism conceived as a re-configurable (low latency/high throughput) multistage interconnection network (MIN). The latency insensitive design approach is first introduced in this chapter. This topic is our second paper [12]. It has been presented at IEEE-CCECE in 2019;

- Chapter 7: This chapter presents the complete methodology used for the implementation of a re-configurable and re-programmable overlay architecture following a LID approach to implement hardware solvers, its advantages, and limitations. The real-time simulation of power converters is presented as an application case. This topic is our third paper [13]. It has been published in MDPI-Electronics in 2020;

- Chapter 8: This chapter presents a general discussion of the approaches and results obtained in this work;

• Chapter 9: Conclusion and recommendations: This last chapter summarizes the results and presents the main teachings obtained from this thesis. This chapter ends by suggesting that further research must be done to create a mathematical model to predict the achievable time step for each circuit to be simulated on any of the implemented architectures.

#### CHAPTER 2 BACKGROUND

# 2.1 Introduction

Real-time simulation is an industry practice used for designing and implementing power systems. It is widespread in industrial sectors such as the generation, transmission and distribution of electric power, electric and hybrid vehicles, and in the aerospace field. Real-time simulation allows systems to be tested before their construction, thereby reducing risk, costs and development time.

The evolution of real time simulators started with the Transient Network Analyzer (TNA), where the models were recreated at a small scale with a configuration of analog components. TNAs have been used to perform simulations with Hardware-In-the-Loop (HIL) to test control equipment and protections [14]. Then, computer evolution allowed the use of CPU-based architectures to replace progressively the TNAs on real-time simulation also increasing their flexibility [15, 16]. Finally, FPGAs were integrated into these simulators. Initially as efficient interfacing mechanisms, then as high performance parallel computing units in applications that require small time-steps, thus increasing the application range of real-time simulators [6, 17].

In this chapter we present briefly some concepts, methods, models and tools associated with the usage and design of digital real-time simulators of electrical networks, particularly for those implemented on FPGAs.

# 2.2 Electric Circuit Equations

Electric network simulation tools meet different needs, including the study of switchgear, analysis of harmonics on the network, electricity generation, power distribution on the network, failure conditions, machine behavior, and their controls, etc. [14]. This work mainly focuses on the simulation of the network's transient in the time domain, better known as the electromagnetic transient simulation (EMT) [18]. The system to be simulated is described by a mathematical model which reflects its behavior for the studied conditions. The network model is generally of a discrete nature and involves Differential Algebraic Equations (DAE) [19]. An EMT simulator must assemble, discretize and solve the DAEs. Network equations are composed using either state-space or nodal analysis methods.

# 2.2.1 State-Space Representation Method

The representation of states for a linear differential equation system is given by:

$$\begin{cases} \dot{\mathbf{x}} = \mathbf{A}\mathbf{x} + \mathbf{B}\mathbf{u} \\ \mathbf{y} = \mathbf{C}\mathbf{x} + \mathbf{D}\mathbf{u} \end{cases}$$

(2.1)

where  $\mathbf{x}$ ,  $\mathbf{u}$ , and  $\mathbf{y}$  are the state, input, and output vectors respectively.  $\mathbf{A}$  is the dynamic matrix,  $\mathbf{B}$  the control matrix,  $\mathbf{C}$  the observation matrix and  $\mathbf{D}$  the direct action matrix. With certain reservations, a power circuit can be described by a representation of states. This is the approach adopted by software such as SimPowerSystems [20] from Hydro Québec or PLECS [21] from PLEXIM.

If the time step is many folds smaller than the time constants of the system, a low order integration method such as the implicit Backward Euler (BE) method can be used to discretize the state-space equations, which yields:

$$\begin{cases} \mathbf{x_{n+1}} &= \mathbf{A}_d \mathbf{x_n} + \mathbf{B}_d \mathbf{u_{n+1}} \\ \mathbf{y_{n+1}} &= \mathbf{C}_d \mathbf{x_n} + \mathbf{D}_d \mathbf{u_{n+1}} \end{cases}, \tag{2.2}$$

with

$$\begin{cases}

\mathbf{A}_{d} = (\mathbf{I} - \Delta t \mathbf{A})^{-1} \\

\mathbf{B}_{d} = (\mathbf{I} - \Delta t \mathbf{A})^{-1} \Delta t \mathbf{B} \\

\mathbf{C}_{d} = \mathbf{C} (\mathbf{I} - \Delta t \mathbf{A})^{-1} \\

\mathbf{D}_{d} = \mathbf{D} + \mathbf{C} (\mathbf{I} - \Delta t \mathbf{A})^{-1} \Delta t \mathbf{B}

\end{cases} (2.3)$$

$\mathbf{A}_d$ ,  $\mathbf{B}_d$ ,  $\mathbf{C}_d$  and  $\mathbf{D}_d$  are the discretized matrices of  $\mathbf{A}$ ,  $\mathbf{B}$ ,  $\mathbf{C}$ , and  $\mathbf{D}$  respectively.  $\mathbf{x_n}$ ,  $\mathbf{y_n}$ , and  $\mathbf{u_n}$  are respectively the sampled version of vectors  $\mathbf{x}$ ,  $\mathbf{y}$ , and  $\mathbf{u}$ , and  $\mathbf{I}$  is the identity matrix. It was shown in [22] that rewriting Eq. (2.2) in a matrix-vector multiplication form as follows:

$$\begin{bmatrix} \mathbf{x_{n+1}} \\ \mathbf{y_n} \end{bmatrix} = \begin{bmatrix} \mathbf{A}_d & \mathbf{B}_d \\ \mathbf{C}_d & \mathbf{D}_d \end{bmatrix} \begin{bmatrix} \mathbf{x_n} \\ \mathbf{u_n} \end{bmatrix}, \tag{2.4}$$

the parallelism associated with processing on FPGAs helps to warrant small-time steps for solving the system.

#### 2.2.2 Nodal Method

The (classical) nodal analysis method gives the system equations as:

$$\mathbf{Y}\mathbf{v} = \mathbf{i},\tag{2.5}$$

where  $\mathbf{v}$  is the vector of node voltages (unknown),  $\mathbf{i}$  is the vector of node current injections and  $\mathbf{Y}$  is the admittance matrix. In power circuits, it is customary to replace electrical components (L, C, etc.) by their Norton equivalent, as obtained by a discretization rule (the trapezoid rules and BE are most often used) [23]. The Norton equivalent of a two-terminal device connected to nodes a and b is given by:

$$g_{ab}(v_a^{n+1} - v_b^{n+1}) = i_{ab}^{n+1} + j^{n+1}, (2.6)$$

where  $(v_a^{n+1} - v_b^{n+1})$  is the voltage drop between nodes a and b,  $i_{ab}^{n+1}$  is the current flowing through the device from node a to node b,  $g_{ab}$  is the equivalent conductance of the device, and  $j^{n+1}$  is the history term. Using BE, the equivalent conductance of an inductance L is  $g_L = \Delta t/L$ , and  $g_C = C/\Delta t$  for a capacitance C. The history term  $j^{n+1}$  is  $-i_{ab}^n$  for L, and  $g_c(v_a^n - v_b^n)$  for C.  $\Delta t = t^{n+1} - t^n$  is the simulation time step.

# 2.2.3 The Modified and Augmented Nodal Analysis Method

The classical nodal method does not support independent voltage sources, more so when the independent source has none of its terminals connected to the ground. The Modified and Augmented Nodal Analysis (MANA) method overcomes these (and many other) shortcomings [24]. The system equations are augmented and yield:

$$\mathbf{A}\mathbf{x} = \mathbf{b},\tag{2.7}$$

where  $\mathbf{A}$  is the modified and augmented nodal matrix,  $\mathbf{x}$  is a vector containing unknown node voltages and certain branch currents, and  $\mathbf{b}$  is a vector composed of known sources and history terms. More specifically, Eq. (2.7) reads as follows:

$$\begin{bmatrix} \mathbf{Y} & \mathbf{V_{c}} & \mathbf{D_{c}} & \mathbf{S_{c}} \\ \mathbf{V_{r}} & \mathbf{0} & \mathbf{0} & \mathbf{0} \\ \mathbf{D_{r}} & \mathbf{0} & \mathbf{0} & \mathbf{0} \\ \mathbf{S_{r}} & \mathbf{0} & \mathbf{0} & \mathbf{S_{d}} \end{bmatrix} \begin{bmatrix} \mathbf{v} \\ \mathbf{i_{V}} \\ \mathbf{i_{D}} \\ \mathbf{i_{S}} \end{bmatrix} = \begin{bmatrix} \mathbf{i} \\ \mathbf{v_{b}} \\ \mathbf{0} \\ \mathbf{0} \end{bmatrix}, \tag{2.8}$$

where  $\mathbf{Y}$ ,  $\mathbf{v}$ , and  $\mathbf{i}$  represent the admittance matrix, the unknown node voltages and the current injections from the classical nodal analysis. Subscripts  $\mathbf{r}$ ,  $\mathbf{c}$ , and  $\mathbf{d}$  refer to row, column and diagonal respectively.  $\mathbf{V}_{\mathbf{r}}$  is the voltage source connection matrix.  $\mathbf{D}_{\mathbf{r}}$  holds dependent branch equations (ideal transformers). Sub-matrices  $\mathbf{S}$  contains the equations of the ideal switches with  $\mathbf{S}_{\mathbf{d}}$  representing the state of switches. The column matrices are the transposed of row matrices, and the rest of sub-matrices are very often null. This representation fixes the rank of the matrix giving the possibility of easily reformulating the equations for any change on the switch statuses.

To facilitate the implementation over FPGAs, the MANA equations can also be represented by matrix-vector multiplication as done for the state-space representation. Defining  $\mathbf{b_n} = \mathbf{K_c}[\mathbf{u_n}, \ \mathbf{j_n}]^T$ , where  $\mathbf{K_c}$  is the incidence matrix,  $\mathbf{u_n}$  is a vector containing the independent sources of the network,  $\mathbf{j_n}$  is the vector of historic for reactive (L/C) components and switches. Considering  $\mathbf{A^s}$  to be the matrix for a given combination of switch statuses. Eq. (2.7) becomes

$$\mathbf{x}_n = (\mathbf{A}^s)^{-1} \mathbf{K}_c \begin{bmatrix} \mathbf{u}_n \\ \mathbf{j}_n \end{bmatrix}, \tag{2.9}$$

we can have:

$$\begin{bmatrix} \mathbf{j}_{n+1} \\ \mathbf{y}_n \end{bmatrix} = \begin{bmatrix} \mathbf{H^s}_{ju} & \mathbf{H^s}_{jj} \\ \mathbf{H^s}_{yu} & \mathbf{H^s}_{yj} \end{bmatrix} \begin{bmatrix} \mathbf{u}_n \\ \mathbf{j}_n \end{bmatrix}, \tag{2.10}$$

where the matrices  $\mathbf{H}_{ju}^{\mathbf{s}}$ ,  $\mathbf{H}_{jj}^{\mathbf{s}}$ ,  $\mathbf{H}_{yu}^{\mathbf{s}}$ , and  $\mathbf{H}_{yj}^{\mathbf{s}}$  are obtained from Eq. (2.9).

# 2.2.4 Switch Models

It is common to find power semiconductors such as diodes, IGBTs, GTOs or MOSFETs in power converters. These components can be treated as ideal switches. Two currently used models were born from this idea:i) the resistive switch model (RSM) and the associated discrete circuit (ADC) switch model.

The RSM represents the switch by a high resistor  $R_{off}$  when OFF and by a low one  $R_{on}$  when ON, as shown in Fig. 2.1:. Replacing the switch by changing the status of these switches alters the topology of the network. Solving each topology involves a new factorization of the circuit matrix [25]. For real-time simulation, it is common to pre-compute the inverse of the matrix for the different combinations of switch statuses. In these conditions, the memory requirements increase as  $2^n$  (where n is the number of switches) limiting the size of the circuit to be simulated. To tackle this limitation, often the associated discrete circuit (ADC) switch model is used. The ADC switch model [26] proposes to replace the switch by an

Figure 2.1: Resistive switch model (a) Ideal switch; (b) OFF state; (c) ON state

Figure 2.2: ADC Switch model (a) Ideal switch; (b) ON state; (c) OFF state; (d) Discrete model

inductance when it is in the ON state, and by a capacitance when it is in the OFF state as shown in Fig. 2.2:. The inductance and capacitance are replaced by their Norton equivalent circuits obtained by the discretization of the L/C equations. The conductance of the Norton equivalent associated with the inductance (ON) is given by:

$$\mathbf{gs_{ON}} = \mathbf{g_L} = \frac{\Delta \mathbf{t}}{\mathbf{L}},\tag{2.11}$$

The conductance of the Norton equivalent associated with the capacitance (OFF) is given by:

$$gs_{OFF} = g_C = \frac{C}{\Delta t}, \qquad (2.12)$$

Where  $\Delta t$  is the fixed simulation time step. By making sure that  $\Delta t = \sqrt{LC}$  we get  $gs_{ON} = gs_{OFF}$ . In this case, the circuit equations become constant regardless of the condition (ON-OFF) of the switches, so it suffices to precompute the inverse of a single matrix. As A is invariant when using the ADC model, Eq. 2.9 becomes:

$$\begin{bmatrix} \mathbf{y_n} \\ \mathbf{i_{n+1}^{\hat{s}}} \\ \mathbf{i_{n+1}^{h}} \end{bmatrix} = \mathbf{H} \begin{bmatrix} \mathbf{u_n} \\ \mathbf{i_n^{s}} \\ \mathbf{i_n^{h}} \end{bmatrix}, \tag{2.13}$$

where  ${\bf H}$  is a matrix obtained by algebraic manipulation of  ${\bf A}^{-1}$  and  ${\bf K_c}.$   ${\bf y_n}$  represents the

wanted outputs of the system,  $i_{n+1}^{\hat{s}}$  represents the historic of switches for both conditions (ON and OFF) computed, whilst  $i_{n+1}^{s}$  contains only one of two historic for each switch based on its actual status. This system can be solved by a processing architecture composed by a linear solver and a switch logic treatment module. The details of design, implementation, and performance of this solver are presented in chapter 7. It is important to notice that the ADC model introduces faulty oscillations during switching times, what requires an execution with small steps of calculation to keep the precision of the results [27].

# 2.3 Types of Simulations

A digital simulation is the representation for the functioning of a system by using the computing power to solve its model equations. It is used to facilitate different tasks, from the evaluation of electrical components characteristics to the analysis and design of complex electrical networks. The simulation methods and characteristics considered in this work will try to reproduce the real wave forms at different points of the circuit network (EMT-type). We assume that the simulation is at discrete time with constant time step. Based on the relation between the calculation time and the real-time system operation, we will distinguish two types of simulations, namely offline and real-time simulation.

# 2.3.1 Offline Simulation

An offline simulation refers to the execution of the circuit model, usually on a computer, in order to have an idea of its behavior. It offers a wide variety of numerical methods and programming flexibility. Some of the objectives of using offline simulation is to optimize the accuracy for the different modeling techniques and help to find the range of values for the parameters that must be tuned on the network whilst maximizing the computing speed. In an offline simulation, the execution time of a calculation step differs from the network response time (real time). In a real-time simulation, the execution of a calculation step is synchronized with the response time of the system. On a discretized time basis with a constant computation step, the offline simulation starts each computation step independently of the real time. Two conditions arise when comparing the time evolution of the offline simulation and the network response as shown in figure Fig. 2.3:.a. If the requirements on computation are low comparative to the computation power, the time for a simulation step can be lower than the network response. This condition leads to an accelerated simulation as shows the upper part of figure Fig. 2.3:.a. However, the regular condition is that the complexity of the models on modern networks requires a high amount of computations. The time consumed by the computation is often longer than the time response of the network as shown in the bottom

Figure 2.3: Types of simulation: (a) Offline simulation. (b) Real-time simulation

part of Fig. 2.3:.a. As offline simulation doesn't have time constraints, the simulation can be performed with a higher precision considering the models and mathematical operations.

# 2.3.2 Real-Time Simulation

In a real-time simulation, Fig.2.3: .b, the execution time of a computation step must always be smaller than the real time and the start of the simulation step is synchronized with the beginning of the computation step. The idle time (difference between the computation time and the real time) must suffice to treat inputs and outputs. The time constraint limits the flexibility in programming and the precision on the results. However, As the results are synchronized with the real time, these tools offer the possibility of being interfaced with real systems.

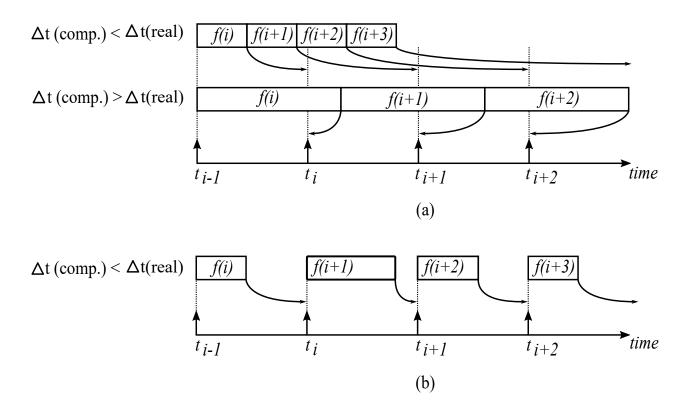

# 2.3.3 Use of Real-Time Simulators

HIL simulation requires that all calculations and communication between the simulator and the rest of the system be performed in a time smaller than the established calculation step [28].

Figure 2.4: Use of real-time simulation. (Inspired from [1])

First, the simulator receives the input signals coming from devices on the connection environment. Then the simulator calculates and sends the new operating conditions (state) back to the rest of the system (or DUT). This completes the simulation cycle. The HIL technique allows changes to be made quickly if the results are not compliant. It also allows validating operation while avoiding significant power consumption and minimizing potential risks associated with malfunction. Real-time simulators are used in different phases of project development [1]. Fig. 2.4: shows different phases in which real-time simulators are used. In the design phase, the speed of the simulator helps reduce simulation time. The real-time simulator is also used for prototyping and testing real components of systems such as HVDC, FACTS, and their control, thus facilitating their implementation and verification.

# 2.4 Commercial Simulation Tools

The increasing industry demand has pushed the creation or adaptation of multiple tools for offline and for real-time simulation that continues to evolve.

# 2.4.1 Offline Simulation Tools

Offline simulation is performed on hardware platforms with one or more general-purpose processors (CPUs). Several offline simulation tools use the nodal method proposed in 1969 by Dommel for transient analysis in electrical networks [29]. These tools are known as the

EMT (electromagnetic transient) type. Among them we have: ATP [30] and PSCAD / EMTDC [31], which uses the trapezoidal integration method with a fixed calculation step. Also, EMTP-RV, the simulation software developed by Hydro-Québec is based on a modified version of nodal analysis (MANA) [24, 32]. A second group of tools is based on the state representation method and allows the simulation to be carried out with a fixed or variable calculation step. These simulators are used for modeling systems in electronics, automation, transport and electrical networks, among others. The best known are Hydro-Québec's Sim-PowerSystems SPS [20] and PLECS from PLEXIM [21]. These two programs are marketed as a toolbox in Matlab / Simulink. PLECS is also sold as a stand-alone application.

# 2.4.2 CPU-Based Real-Time Simulators

The first commercial digital simulator was developed by RTDS Technologies and used to test HVDC devices [33]. This simulator was organized in racks whose hardware platform was formed by three main modules. The processing module, made up of two DSPs, had a few digital and analog input and output ports. The interface module used to communicate the rack to the workstation (host). The inter-rack communication module used to interconnect up to four racks. The software platform consisted of a graphical interface (PSCAD) for inputting circuits. A compiler produced the code to be executed in the processing module, the circuit distribution reports, and a set of libraries with the models of the components encoded in machine language. This simulator was limited in terms of interfaces, libraries of components, and computing capacity. However, it allowed the testing of protective relays and control equipment [34]. This technology continues to evolve and several other commercial digital simulators have been developed to cover many applications in modern industry [35], among them, are:

- The modern version of the RTDS simulator, from RTDS Technologies. It uses RSCAD software for development. The platform is configured in racks based on the RISC PowerPC processor. This simulator is used for testing protection and control systems, HVDC, FACTS and HIL among others.

- HYPERSIM [15] developed by the Hydro-Québec Research Institute. The open hardware platform is based on parallel computers and capable of interfacing with FPGAs. The Hypersim Toolkit has a model library, schematic editor, data acquisition system, and signal processing system. This tool is capable of automatically distributing the simulation tasks on the different available cores in the system. This simulator is mainly used for electromagnetic transient simulations in huge electrical networks (FACTS and HVDC among others). The calculation steps are greater than 10  $\mu$ s.

- ARTEMiS [36] from OPAL-RT, this simulator has a hardware platform based on multicore processors and RT-Lab software. Capable of interfacing with Matlab/Simulink, it contains model libraries of components for the simulation of power systems and power electronics. This simulator is used in the design and testing of protective equipment, relays and controllers in power electronics and HIL.

- rtxd from ADI [37] This simulator has a CPU-based hardware platform and uses AD-vantageDE for development. It is mainly used in the simulation of avionics systems.

Processor-based real-time simulators offer modularity, programming flexibility and support for multiple data types which ease the implementation of the ever-increasing size and complexity systems. However, data transmission between processors and I/O interfaces introduces delays that limit the minimum computational step to several microseconds [23].

### 2.4.3 FPGA-Based Real-Time Simulators

The advances in technology, the increasing I/O requirements for data transfer, and the increased needs for computing capacity at a short time step have pushed the introduction of FPGAs in the development of simulators. Mixed platforms (FPGA-CPU) and pure FPGA platforms have been introduced into the market. Among them we can find the following:

- OPAL-RT's eFPGAsim [38] uses FPGAs to simulate power electronics, control systems, electrical protection and HIL. It uses the homemade solver (eHS) to solve the system of equations and is supported by several editors (PSIM, SPS, PLECS).

- dSPACE [39] with a platform based on CPU and on FPGA uses a library for the simulation of power electronic systems (RTI) under Simulink for development. It is mainly used for the implementation and testing of control systems in mechatronics.

- Typhoon RTDs [40] uses the Typhoon schematic editor. It is used for testing power electronics controllers.

- PLECS RT BOX by PLEXIM [41] on a SoC platform (Zync7000 CPU-FPGA) uses the editor and the PLECS code generator under Matlab. It is used for HIL testing of power converters.

- Speedgoat and Simulink real-time use combined CPU-FPGA platforms to perform HIL and RCP.

These tools are used in various industrial sectors for hardware-in-loop simulation (HIL), rapid prototyping of power systems, power electronics and their control. Several conditions to be considered when building FPGA simulators will be discussed in the next chapter.

#### 2.5 Conclusion

This chapter presented the concepts related to the simulation of electrical networks. It presented the main mathematical formulations for state-space and nodal analysis. A view of how this formulation can be solved using matrix-vector multiplication was also presented. The more frequently switch models used for real-time simulation and the consideration for FPGA implementations were presented. The special consideration shown for the ADC model presented its principal benefit and drawback. This model will be used for the work performed in this research. The difference between offline and real-time simulation was treated showing their benefits and drawbacks. In the same line, the conditions for the utilization of real-time simulation were shown. Finalizing this chapter, we presented a brief summary of the commercial tools to perform offline simulation. Similarly, the best-known commercial tools for real-time simulation based on CPU or CPU/FPGA were presented. The latest is the most related to this research. This work is centered on the development of real-time simulation of power converters on FPGA. For this reason, the more recent techniques used for the development of real-time simulators on FPGA will be presented in the following chapter.

#### CHAPTER 3 LITERATURE REVIEW

# 3.1 Introduction

Real-time simulation of electrical networks has passed from using scaled model circuit representations to computer-aided simulations. During the 1990s, the use of simulators with one or more general-purpose processors (CPUs) was common. However, the latency associated with their communication systems limited their usage when short time steps were required. The FPGA has been introduced to real-time simulators as mechanisms to improve the I/O interface. The growth in the computing power of FPGAs has promoted the arrival of simulators using CPU and FPGA as processing elements. In recent literature, we can find the design of simulators purely based on FPGAs for systems with high dynamic characteristics such as power converters. The latest is the core of this research.

As a general rule, the development of real-time simulators starts by creating models and algorithms that describe the behavior of the electrical network to be simulated. At this point, offline simulation tools can be used to verify the specs. Once its behavior has been validated, the portion of the network to be simulated on FPGA is separated. The discretization chosen for the representation of the equations depends on the precision, time constraint, and stability required. The main constraints to fulfill are calculation time, accuracy, and the area of the design. However, the design of real-time simulator of power converters on FPGA has multiple challenges:

- Time constraints: In modern power converters, for example, the switching frequencies are high [42]. It is suggested that the calculation step (Ts) be 20 times smaller than the system dynamics (transient and harmonics), and 50 to 100 smaller than the switching period [6, 43]. This allows to have a better accuracy, and to catch changes inferior to 2 % of the duty cycle. Thus, if we assume a switching frequency of 10 kHz, the computation time must be less than 1  $\mu$ s.

- Area: FPGAs have limited resources, this condition limits the size of the network to be simulated while keeping the required calculation time-step fixed.

- Numerical resolution: The numerical representation, fixed-point or floating point, is

chosen according to the dynamic range of values. In modern applications, operators

capable of handling floating point numbers are increasingly required. Several works

have deepened the development of floating point operators.

- Modeling methods: The circuit component model must have enough detail for an accurate representation of the real power circuit. However, good optimizations should be achieved to reduce resources consumption and make the circuit fit on the FPGA.

- Design approaches: The complexity inherent to FPGA development limits its utilization and increases the time to market. However, this limitation can be mitigated if appropriated tools or development environments are available to the application specialists.

This chapter presents the state-of-the-art of FPGA-based real-time simulators for electrical networks. It presents the limitations found in currents development and puts our research in context. It also presents the commercial tools and design approaches used in the development of the real-time simulation for power converters on FPGAs. This includes the use of the high-level synthesis (HLS), overlay architectures, and LID approaches in the design of FPGA computing engines, whether in the context of real-time simulation or as calculation acceleration units over FPGA. At the end of this chapter, the works most related to this research are summarized and compared.

#### 3.2 FPGA-based Real-Time Methods for Simulation of Power Electronics

Modern power converters are known for their high-dynamic operation which increases the challenges bound to their real-time simulation. Multiple methods have been proposed at the application level to meet the requirements. These methods aim to increase parallelism, reduce the simulation time step and simplify the power converters' real-time simulation.

# 3.2.1 Latency Insertion Method

The LIM method proposes to represent the circuit using connections of LIM compatible branches (series circuit R, L, and voltage source), and LIM compatible nodes (parallel circuit G, C, and current sources) [44]. Branches and nodes are computed and updated alternatively as time progresses. Originally proposed for offline simulations, this method improves the simulation time. It has been adapted to be used in FPGA as the LB-LMC method presented in [25] which separates the circuits in two parts (linear and nonlinear). The linear part will be solved with the nodal method. Each nonlinear element is treated independently and is represented as a current or voltage source (with its discretized equation of state explicitly) whose solution can be calculated in one step with the previous step results. LB-LMC method has been used in other publications and more recently is the core of the project

ORTiS Code Gen [45]. A new version of LIM for FPGA is presented in [46]. The circuit is divided in LIM compatible branches (series R, L, V) and nodes (parallel G, C, I). A hardware instance is created for each LIM branch and node to offer a higher granularity and to increase parallelism. The number of operations for each LIM entity remains constant. However, the FPGA occupation grows as the number of LIM entities increases.

#### 3.2.2 Switching Elements Based Partitioning

The circuit partitioning is one of the most used methods. It allows dividing large circuits into multiple subcircuits to increase parallelism. In power converters, the dynamics of switches are fast comparatively to the dynamics of large capacitors and inductors. Often, parallel capacitors and serial inductors are used to determine the partition points [47]. Although the partitioning techniques were originally proposed for offline simulation, modern adaptations have made it possible to use them in real time with FPGA. Some of them are presented below.

The network tearing technique (NTT) [48], used for power converters proposes to divide the circuit into separate parts (subcircuits) and replace these with multi-port networks using the hybrid Norton-Thévenin equivalent. The resistive model is used for switches. Only the current and voltage variables in each port are considered when putting all the modules together. Using this method, a Neutral Point Clamped (NPC) converter of 18 switches is divided into 5 subcircuits, 3 of which are formed by the branches containing the switches of the converter. With this distribution, a reduction in memory requirements is obtained (from 218 systems of equations to 26 per branch) to keep the different configurations of the switches in the circuit. An extension for the utilization of NTT for more generic topologies is presented in [49].

A switching network partitioning (SNP) method for multiple converters using the two-value resistor switch model is presented in [50]. The SNP method proposes to analyze the power converter in three stages: i) equivalent circuit external to the switching network, ii) equivalent variables for the switching network, iii) equivalent of switching network variables as sources. One entity determines the states of all switches considering only the gates control signals and the external circuit. However it requires  $2^l$  permutations to be stored in RAM for each converter, where l is the number of legs in the converter.

As a sub-module must wait for the result of another, partitioning the circuit often introduces latency that can cause instability. To tackle this effect, the predictor-corrector method [10] proposes to separate the switch network from the circuit element part. Then, compute them at the same time with a parallel architecture. At each time step, the predictor generates

the results for the future time step based on the results obtained by the corrector. This architecture is known to spend the double of DSP resources.

#### 3.2.3 Methods for Naturally Commuted Devices

The voltage and current on the terminals of a naturally commuted switch (e.g., a diode) determines its status ON-OFF. As these variables evolve, the conditions of the switch can change producing errors in the results. Multiple iterations are often needed to correctly establish the switch status. However, the iterations increase the computational demand which limits the real-time simulation when small time-steps are required.

The Zero Regulation method (ZR) proposed in [51] presents a method for reducing the zero-crossing error. An SLR (series load resonant converter) is used as a case study case. A threshold is set around the zero-crossing (chattering region) to limit the iterations. The predictor-corrector is used to determine the condition. A flag is used to identify if the simulation is in the zero-crossing zone, the values around the zero point are counted (the zero is marked as a region). This limits the value of the chattering to be neglected and reduces the iterations. This technique reduces the zero-crossing error from 20% to 0.3% potentially.

The Direct Mapped Method (DMM [52]) proposes to eliminate the iterations for circuits with diodes. In a single-phase full rectifier, the possible combinations of the diode statues are obtained by a map that links the history terms to the possible statuses of the diodes. The regions obtained by the map determine the status of all diodes, avoiding iterations. Two units are used to solve the system, one to calculate historic and outputs. The second to evaluate the mapping function. The results report a time-steps of 25 ns for an LLC converter.

The mentioned methods intend to simplify the analysis of the network or optimize and facilitate the implementation of FPGA. However, they can be considered custom solutions from the point of view that if the circuit changes, the hardware must be synthesized again. Some of them can even require further adjustments.

#### 3.3 Hardware Development Approaches

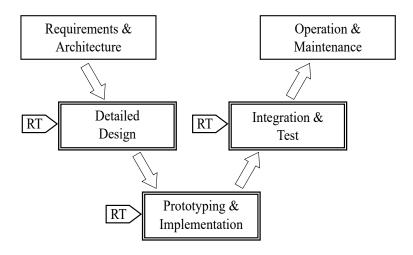

#### 3.3.1 RTL

The FPGA design flow requires several steps to be taken to ensure the functionality of the circuits implemented. The first step is the circuit description. Traditionally, the hardware description languages VHDL and Verilog are used at this stage. The quantity and types of

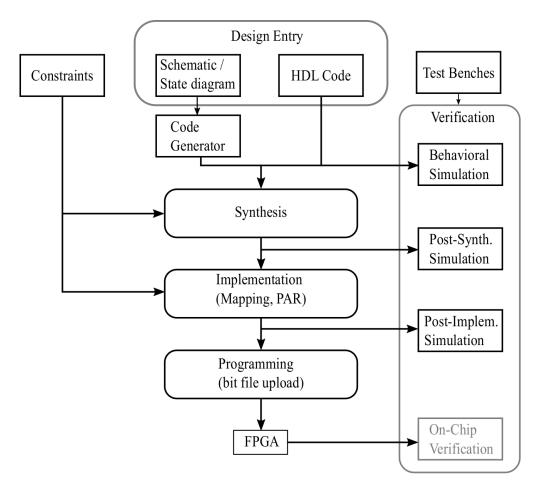

Figure 3.1: FPGA Design Flow

available operators (IPs) depend on the capacity and the technology of the FPGA chosen as a development platform. With these elements in hand, the hardware expert carries out a description (behavioral or structural) of the circuit based on the specification and the algorithms. It is a manual process, prone to errors, and requires great skill from the designer. Once the description step is done, the rest of the process can be automated at a certain degree by using the tools. In a second step, the circuits are synthesized. This task is performed using tools like Xilinx ISE / Vivado, Altera Quartus, Actel Libero, Synopsis Symplify. The third step concerns the implementation process (map, place and route) which is specific to each manufacturer. Fig. 3.1: shows the design flow over FPGAs. The simulation is a fundamental step that allows verifying the functioning of the described circuit. It can be performed at different stages of the development. FPGA manufacturers offer tools for simulation purpose e.g., ISIM from Xilinx. However, other tools such as ModelSim from Mentor Graphics are often used. Finally, the circuit is implemented and programmed on the FPGA.