**Titre:** Réalisation de la mémoire partagée dans les systèmes répartis

Title:

**Auteur:** Hugues Notouom

Author:

**Date:** 1996

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Notouom, H. (1996). Réalisation de la mémoire partagée dans les systèmes répartis [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/9011/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/9011/>

PolyPublie URL:

**Directeurs de recherche:** Louis Granger

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

RÉALISATION DE LA MÉMOIRE PARTAGÉE

DANS LES SYSTÈMES RÉPARTIS

par

Hugues NOTOUOM

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (M.Sc.A)

(GÉNIE GÉLECTRIQUE )

JUILLET 1996

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-26501-3

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

RÉALISATION DE LA MÉMOIRE PARTAGÉE

DANS LES SYSTÈMES RÉPARTIS

Présenté par: Hugues NOTOUQM

en vue de l'obtention du diplôme de: Maîtrise Ès Sciences Appliquées

a été dûment accepté par le jury d'examen constitué de:

M. Jean-Louis HOULE, Ph.D., président

M. Claude ÉVÉQUOZ, Ph.D., membre et directeur de recherche

M. Louis GRANGER, M.Sc., membre et substitut du directeur de recherche

M. Hai Hoc Hoang, Ph.D., membre

## **Dédicace**

À ma feue grand-mère, Madame Méwa Odette, en souhaitant que son âme se repose en paix.

## **REMERCIEMENTS**

L'auteur tient à remercier tous ceux qui ont participé de près ou de loin à la réalisation de ce mémoire.

Je remercie surtout mon directeur de recherche Monsieur Claude Évéquoz, pour les idées qu'il a apportées pour la réalisation de ce projet ainsi que le temps qu'il a consacré pour lire et corriger la version finale et les versions préliminaires de ce document.

## RÉSUMÉ

Pour augmenter la puissance de calcul, on utilise de plus en plus les systèmes répartis. On constate cependant que l'absence d'une mémoire commune les rendent difficile à programmer, car le paradigme de programmation par messages qu'ils offrent à l'usager est différent du paradigme de programmation qui lui est offert par les machines mono-processeurs et auxquelles ils sont habitués.

L'objectif principal de ce projet est triple:

- implanter dans les systèmes répartis et par une approche serveur, une mémoire partagée et globale en utilisant les modules mémoires disponibles à chaque poste de travail;

- proposer un modèle analytique pour évaluer rapidement les performances du système résultant;

- étudier l'impact des paramètres sur ce dernier.

Ce mémoire décrit donc une approche vers la réalisation de ces objectifs.

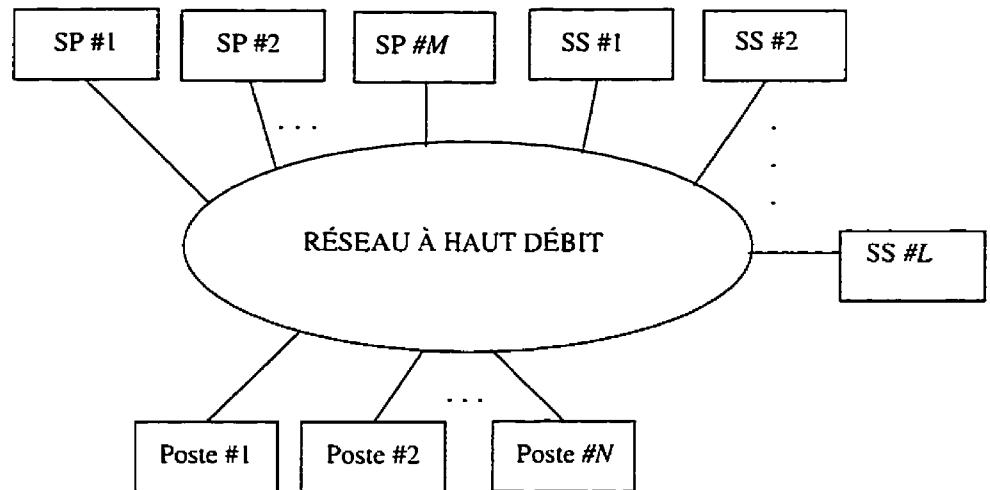

Le système que nous avons retenu est composé de postes de travail, de serveurs principaux et de serveurs secondaires, tous reliés par un réseau de communications à grand débit. La cohérence entre les données partagées est maintenue d'une part par un protocole de mise à jour en écriture, et de l'autre par un protocole d'invalidation en écriture. Ces deux protocoles utilisent le schéma du propriétaire de la donnée ainsi que le schéma de la copie initiale. Pour transmettre une information locale à plusieurs sites, le système utilise une des trois techniques suivantes: la diffusion, la diffusion simulée et le chaînage. Ces techniques de diffusions sont couplées à un mécanisme de verrouillage à deux phases pour s'assurer que la donnée propagée est correctement reçue par tous les sites participants.

Pour chaque protocole utilisé, un modèle analytique hiérarchisé a été développé. Ce modèle est composé d'une chaîne de Markov de l'état des données, d'une chaîne de Markov du nombre de copies des données, ainsi que d'un modèle du processeur formé d'un réseau mixte de files d'attente ouvertes et fermées. Dans chaque cas, un modèle de simulation a également été proposé afin de valider le modèle analytique. Une des caractéristiques de chaque modèle obtenu est qu'il tient compte de l'effet du protocole de cohérence, de la technique de diffusion ainsi que de chaque paramètre sur les performances du système. Pour réduire la complexité du modèle du processeur, un modèle équivalent formé de plusieurs chaînes de routages ouvertes et d'une seule chaîne de routage fermée a été proposé.

Pour chaque modèle analytique obtenu, un programme de mesure de performance a été implanté. L'avantage de ce programme est qu'il ne nécessite pas beaucoup d'espace mémoire, et qu'il donnent un temps de réponse rapide sur un ordinateur personnel, et ceci, quel que soit la taille du système. D'autre part, il permet d'étudier le rôle et la contribution de chaque paramètre sur les performances du système.

Les résultats numériques montrent que pour implanter une mémoire partagée dans les systèmes répartis en utilisant notre approche, il faut que le réseau de communication soit très rapide. Dans ce cas, il faut maximiser le nombre de serveurs principaux et minimiser le nombre de serveurs secondaires afin d'obtenir les meilleures performances, et d'annuler l'effet du protocole de cohérence ainsi que l'effet la technique de diffusion. Si le réseau n'est pas rapide, il est préférable d'utiliser le protocole de mise à jour couplé à la technique de diffusion.

## ABSTRACT

Distributed systems are used more and more to increase computation power. However, they have no common memory. This lack of memory makes them difficult to program, because the message communication paradigm they offer to the user is different from the shared memory communication paradigm with which he is familiarized.

The main objective of our research is triple:

- to build a distributed shared memory using memories modules available in any workstation by a server approach;

- to develop an analytic model to evaluate rapidly the performance of the resulting system;

- to study the impact of the parameters on the performance of the system.

This thesis presents an approach to reach this goal.

The system consists of workstations, main and backup servers. This system can use either write-update protocol, or write-invalidate protocol. It can also support true or simulated broadcast, or chain-bond communications. To make sure that data are correctly propagated, these techniques are coupled to a weak form of consistency by two-phase locking.

For each of these protocols and for both broadcast communications, an analytic model is developed. It is composed of a Markov chain representing the states of data in the local memory, a Markov chain representing the number of copies of data in the system, and a processor model. This processor model consists of mixed multiple chain queueing networks. A simulation model is developed to validate the analytic model. To reduce the complexity of the processor model, an equivalent model is proposed. It is composed of a single closed chain and of multiple open chain queueing networks.

For each model, a computer program is wrote. The advantage of these programs is that they quickly give results on personal computers. Furthermore, it facilitate the study of the impact of the parameters on the system performance.

Numerical results obtained from the model show that, to build a shared memory on top of a distributed system using our approach, one needs a high bandwidth interconnection network. In this case, the number of main servers has to be maximized and the number of backup servers minimized in order to obtain better performance and cancel the effect of the coherence protocol and also the broadcast communication. If the network is not fast enough, the write-update protocol should be used with the true broadcast.

## TABLE DES MATIÈRES

|                                                  |           |

|--------------------------------------------------|-----------|

| DÉDICACE .....                                   | iv        |

| REMERCIEMENTS .....                              | v         |

| RÉSUMÉ .....                                     | vi        |

| ABSTRACT .....                                   | viii      |

| TABLE DES MATIÈRES .....                         | x         |

| LISTE DES FIGURES .....                          | xiii      |

| LISTE DES TABLEAUX .....                         | xvi       |

| LISTE DES ANNEXES .....                          | xvii      |

| <b>CHAPITRE 1: INTRODUCTION .....</b>            | <b>1</b>  |

| 1.1 Évolution des systèmes répartis .....        | 4         |

| 1.2 Caractéristiques des systèmes répartis ..... | 5         |

| 1.3 Mémoire partagée .....                       | 7         |

| 1.3.1 La spécification physique .....            | 8         |

| 1.3.2 Fonctionnement logique .....               | 8         |

| 1.4 Analyse de performance .....                 | 10        |

| 1.5 Contributions .....                          | 11        |

| 1.6 Contenu du mémoire .....                     | 12        |

| <b>CHAPITRE 2: REVUE DE LA LITTÉRATURE .....</b> | <b>14</b> |

| 2.1 Choix du design .....                        | 14        |

| 2.1.1 Structure et granularité .....             | 15        |

| 2.1.2 La sémantique de la cohérence .....        | 16        |

| 2.1.3 Hétérogénéité .....                        | 18        |

| 2.1.4 Extensibilité.....                         | 18        |

| 2.2 Implantation .....                           | 19        |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| 2.2.1 Accès et localisation des données .....               | 19        |

| 2.2.2 Protocole de cohérence .....                          | 22        |

| 2.2.3 Protocole d'invalidation en écriture .....            | 22        |

| 2.2.4 Protocole de mise à jour en écriture .....            | 28        |

| 2.2.5 Stratégies de remplacement .....                      | 32        |

| 2.3 Analyse de performance des systèmes à DSM .....         | 35        |

| <b>CHAPITRE 3: LES MODÈLES .....</b>                        | <b>37</b> |

| 3.1 Le modèle physique .....                                | 37        |

| 3.2 Organisation de la mémoire .....                        | 41        |

| 3.2.1 RéPLICATION des données .....                         | 42        |

| 3.2.2 Accès et localisation des données .....               | 44        |

| 3.2.3 Protocoles de cohérence .....                         | 47        |

| 3.3 Protocole de mise à jour en écriture .....              | 48        |

| 3.3.1 Scénarios des transactions à travers le système ..... | 50        |

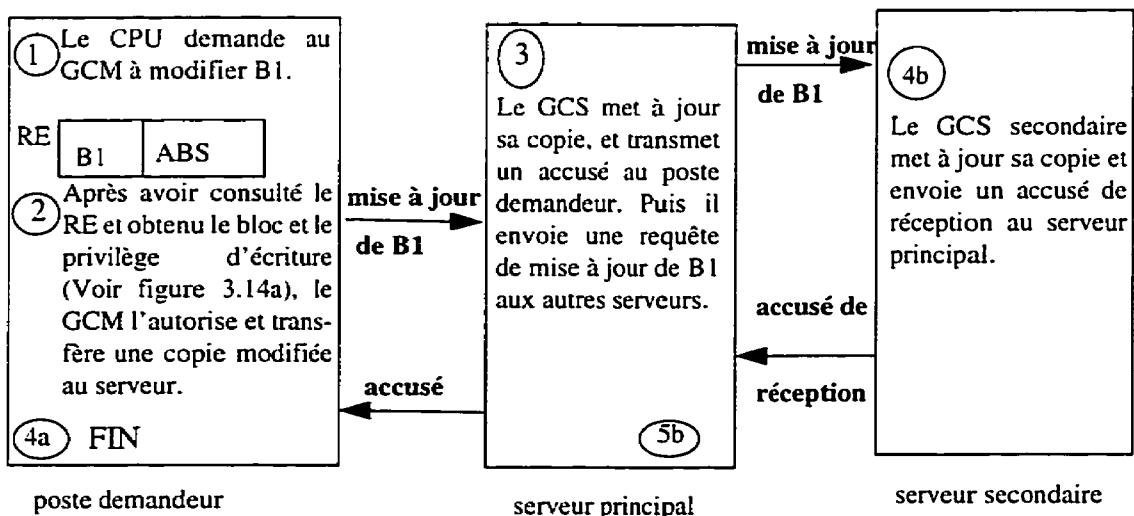

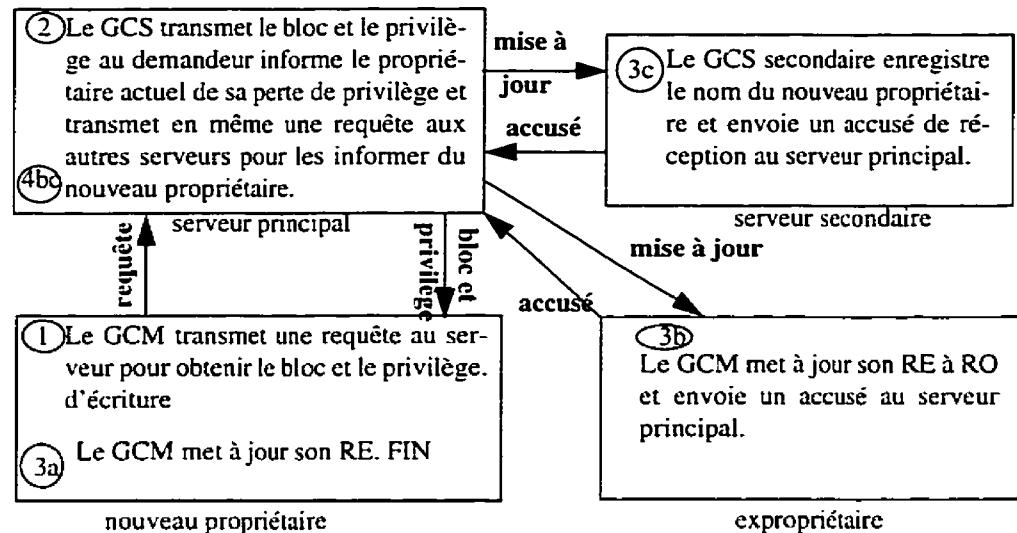

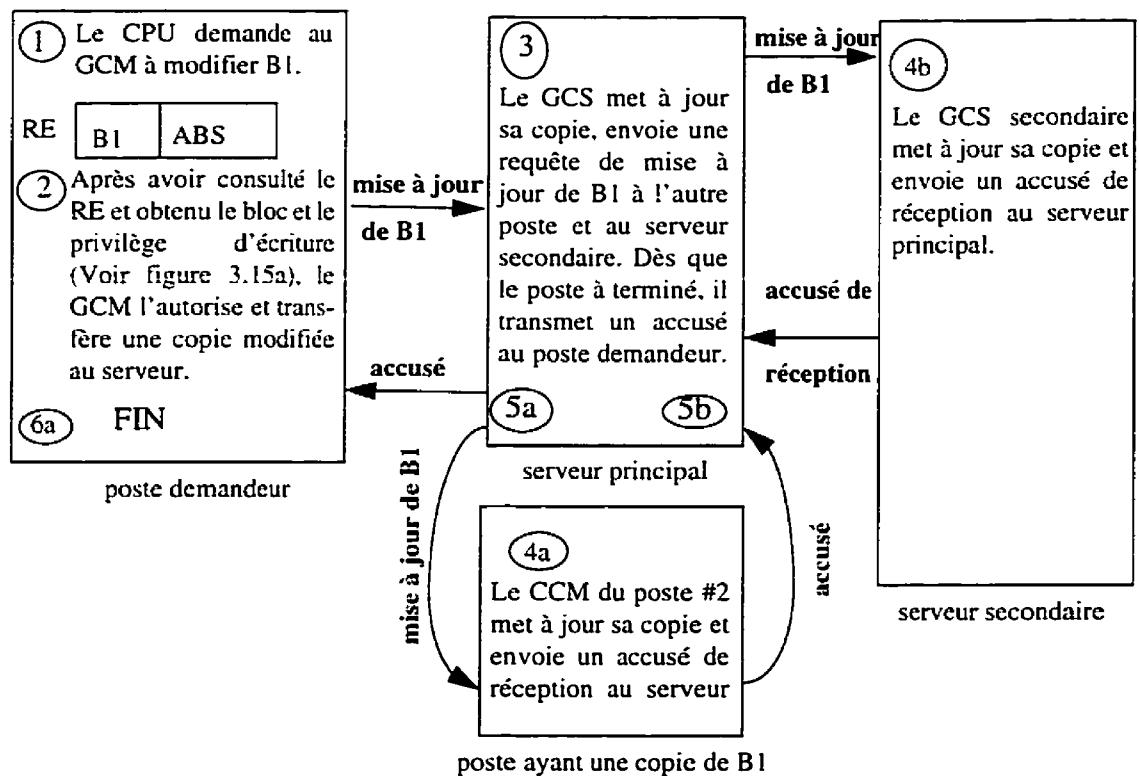

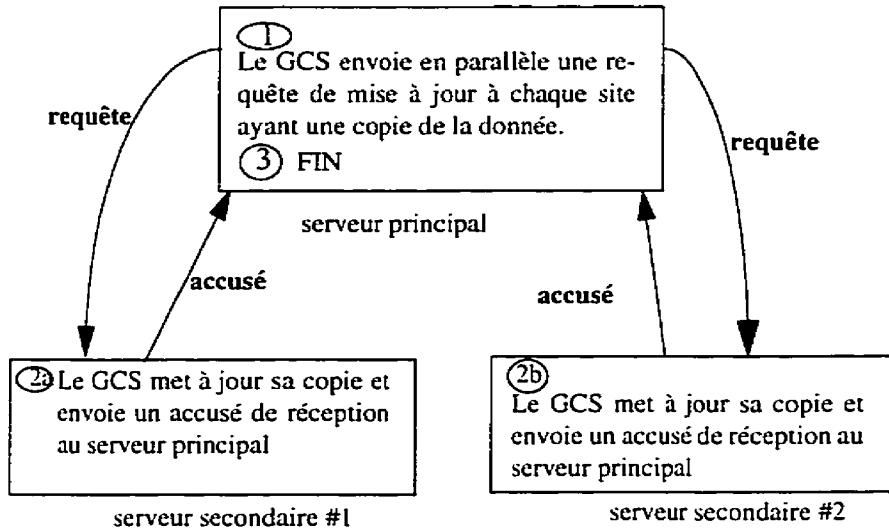

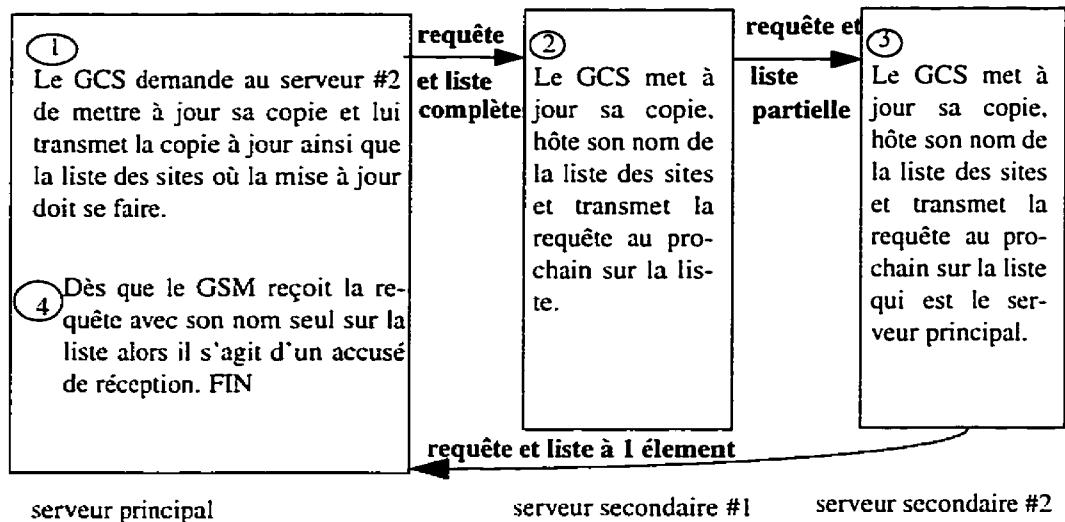

| 3.4 Protocole de mise à jour des serveurs .....             | 59        |

| 3.5 Protocole d'invalidation en écriture .....              | 61        |

| 3.5.1 Scénario des transactions à travers le système .....  | 62        |

| <b>CHAPITRE 4: MODÈLES MATHÉMATIQUES .....</b>              | <b>66</b> |

| 4.1 Hypothèses des modèles .....                            | 66        |

| 4.2 Modèle à mise à jour .....                              | 69        |

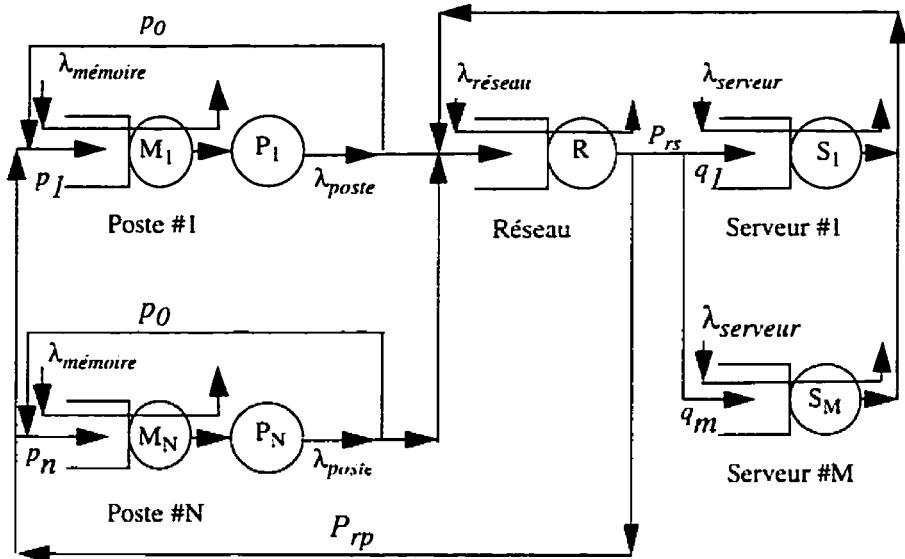

| 4.2.1 Modèle des processeurs .....                          | 69        |

| 4.2.1.1 Description du modèle .....                         | 69        |

| 4.2.1.2 Le modèle .....                                     | 72        |

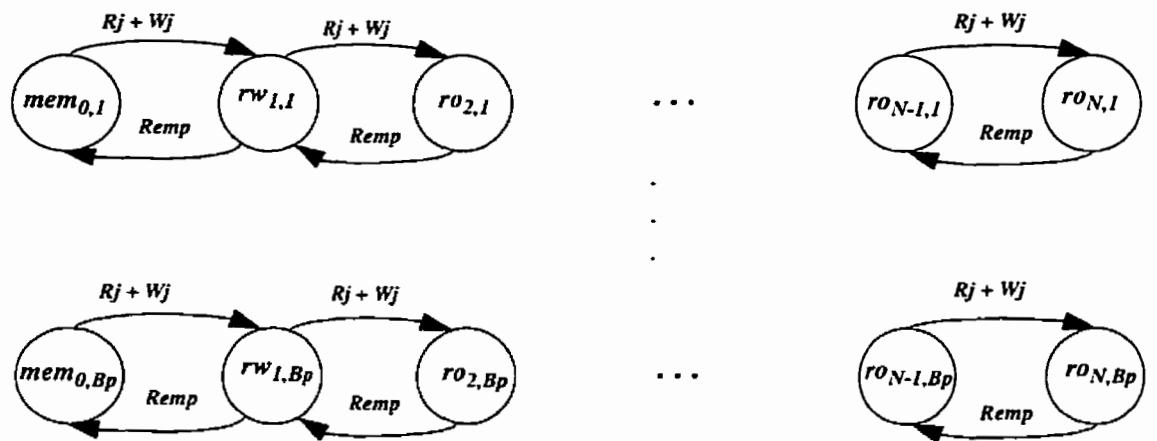

| 4.2.2 Modèle des données .....                              | 76        |

| 4.2.3 Solutions du modèle .....                             | 82        |

|                                                                       |            |

|-----------------------------------------------------------------------|------------|

| 4.2.3.1 Probabilités de routage .....                                 | 88         |

| 4.2.3.2 Débit des chaînes ouvertes .....                              | 89         |

| 4.2.3.3 Algorithme .....                                              | 92         |

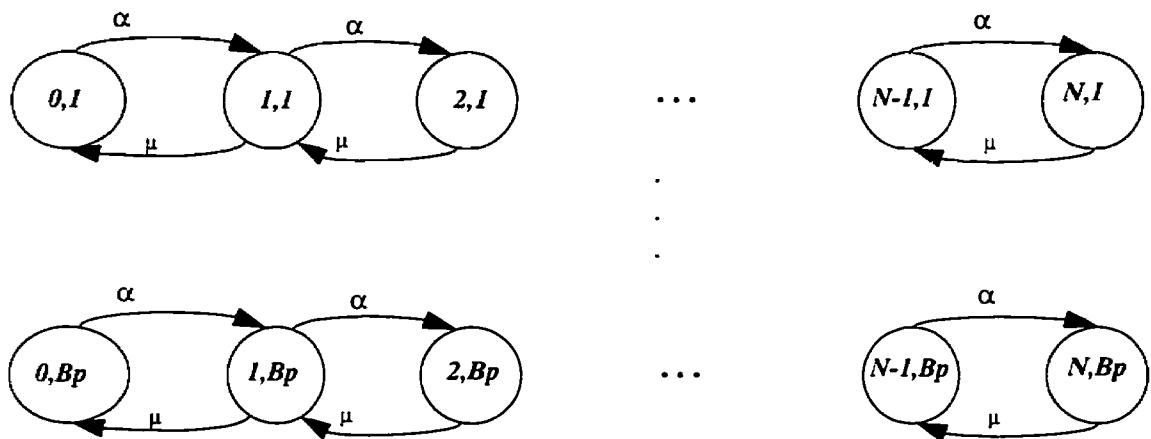

| 4.3 Le modèle à invalidation .....                                    | 93         |

| 4.3.1 Modèle du processeur .....                                      | 93         |

| 4.3.2 Modèle des données .....                                        | 94         |

| 4.3.3 Solution du modèle .....                                        | 96         |

| 4.3.3.1 Résolution .....                                              | 100        |

| 4.4 Validation des modèles .....                                      | 100        |

| 4.4.1 Modèles de simulation .....                                     | 101        |

| 4.4.1.1 Description des identificateurs du modèle de simulation ..... | 101        |

| <b>CHAPITRE 5: RÉSULTATS ET DISCUSSIONS .....</b>                     | <b>111</b> |

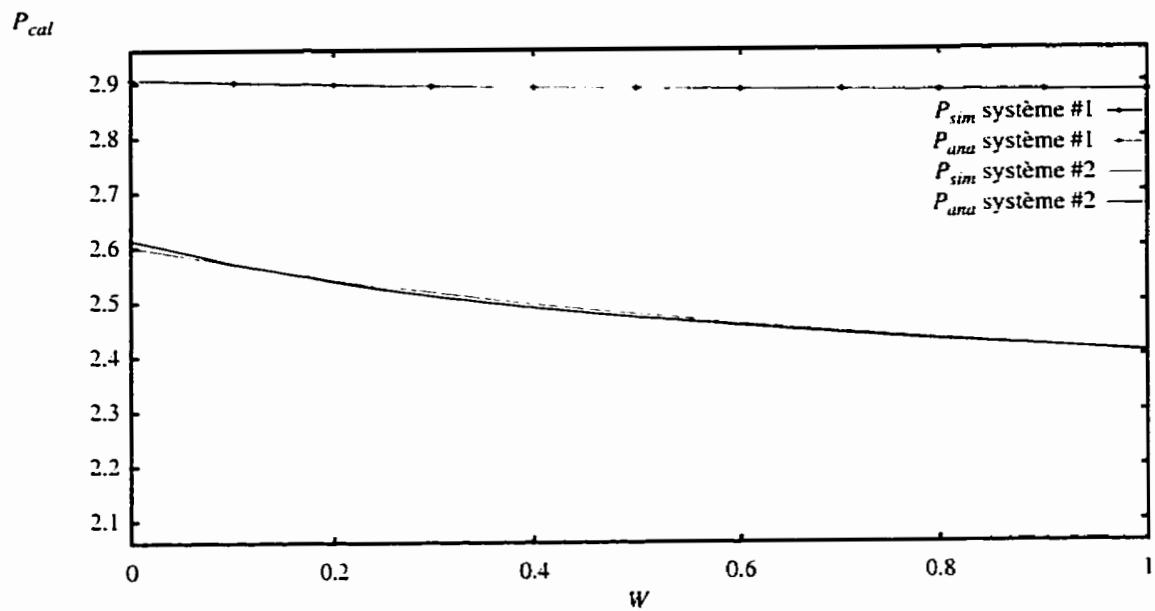

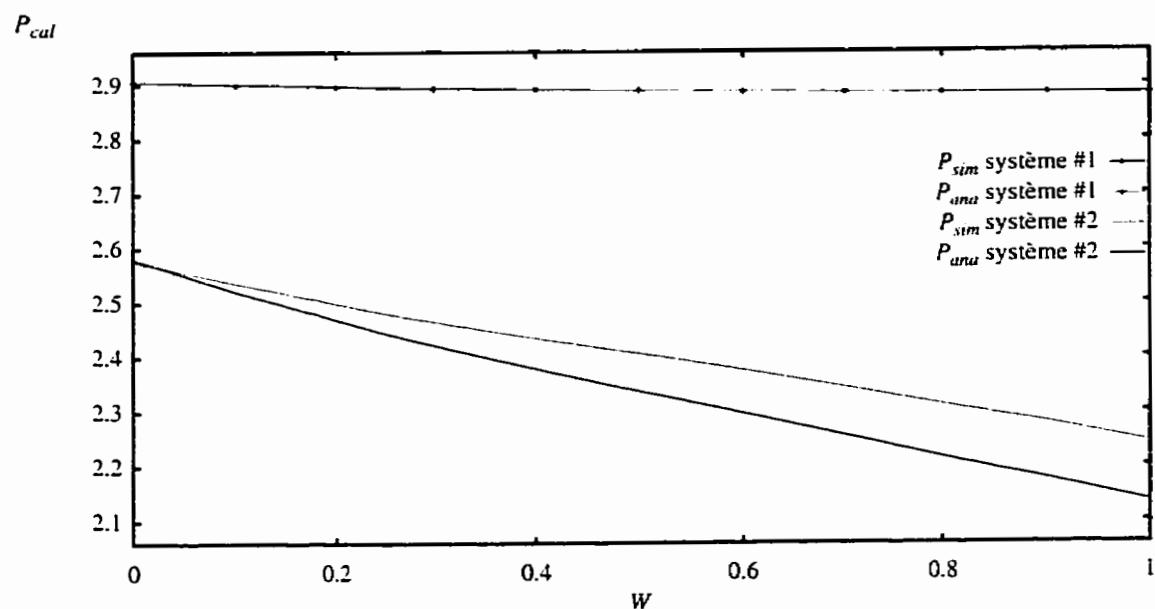

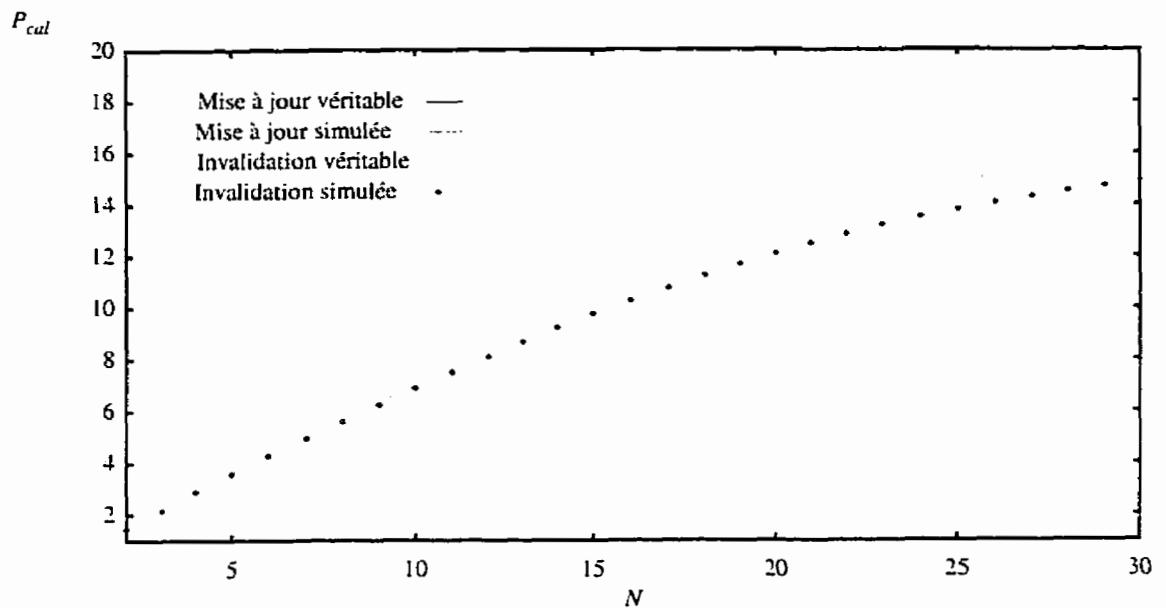

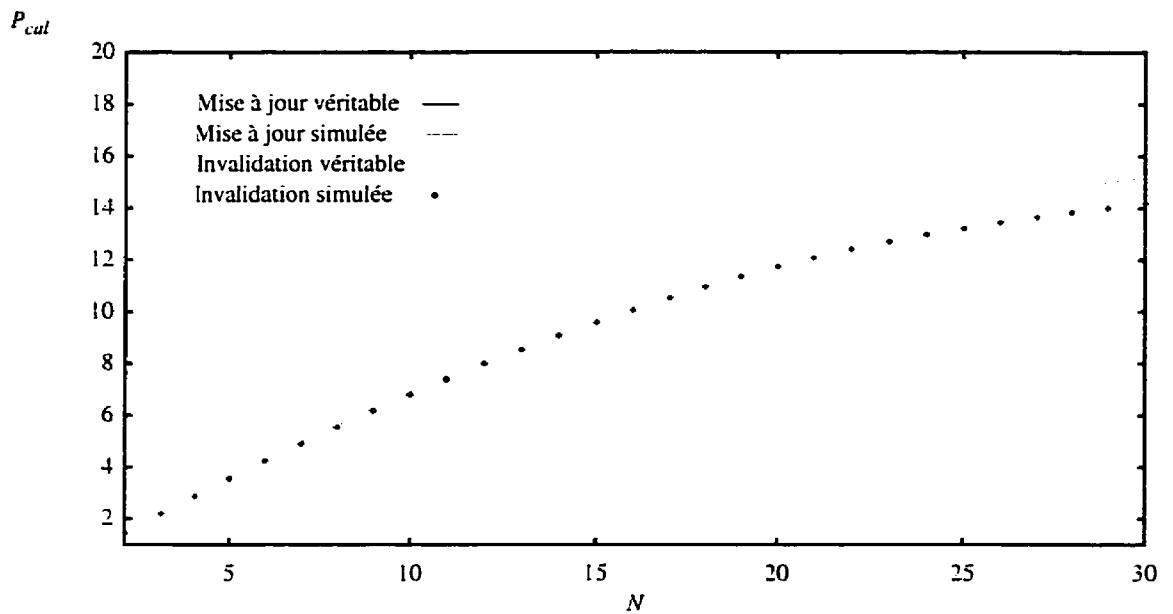

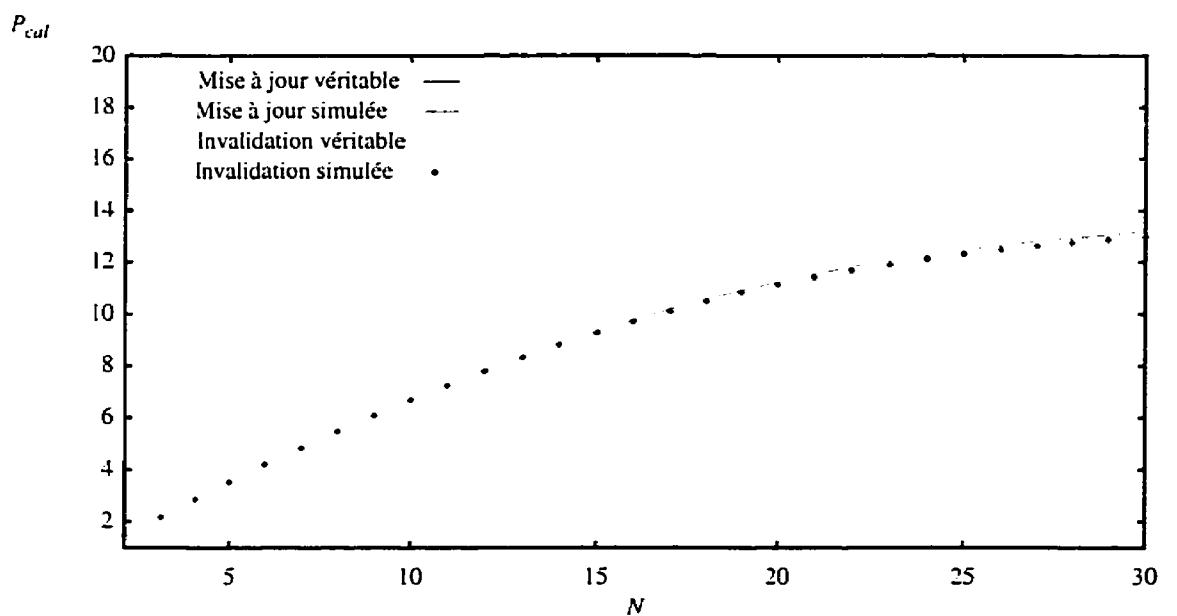

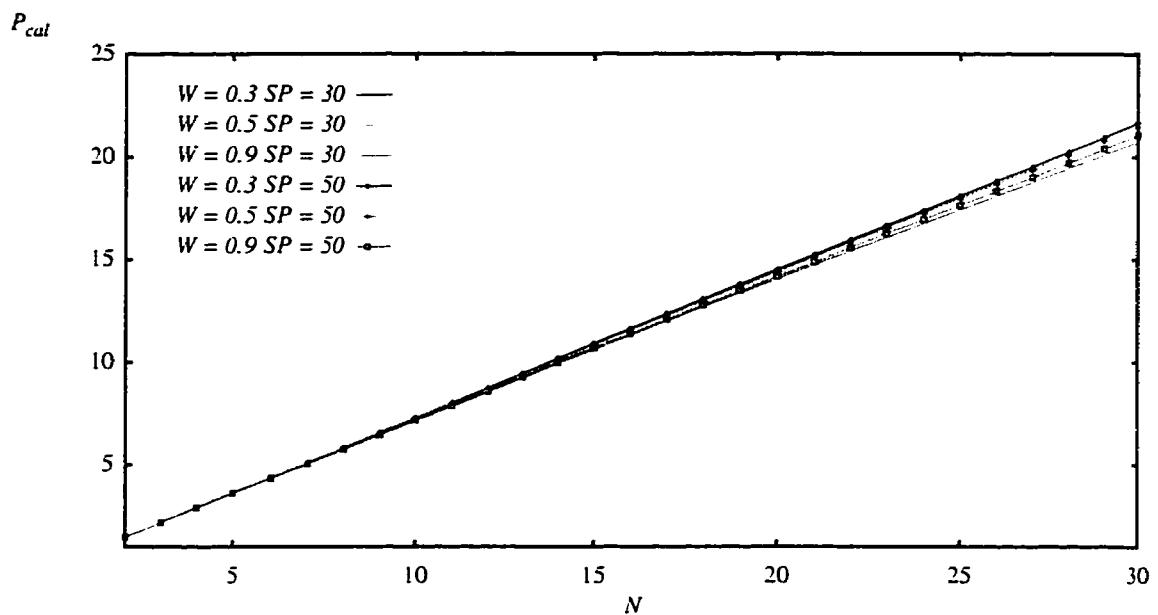

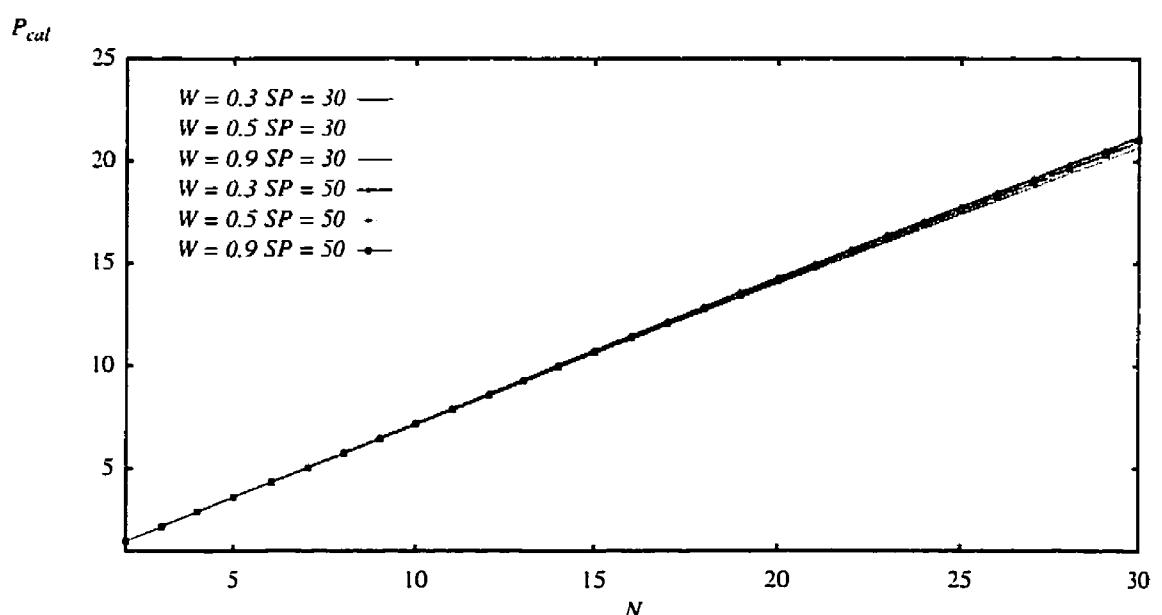

| 5.1 Validation des modèles .....                                      | 111        |

| 5.1.1 Choix des paramètres .....                                      | 111        |

| 5.1.2 Résultats numériques .....                                      | 113        |

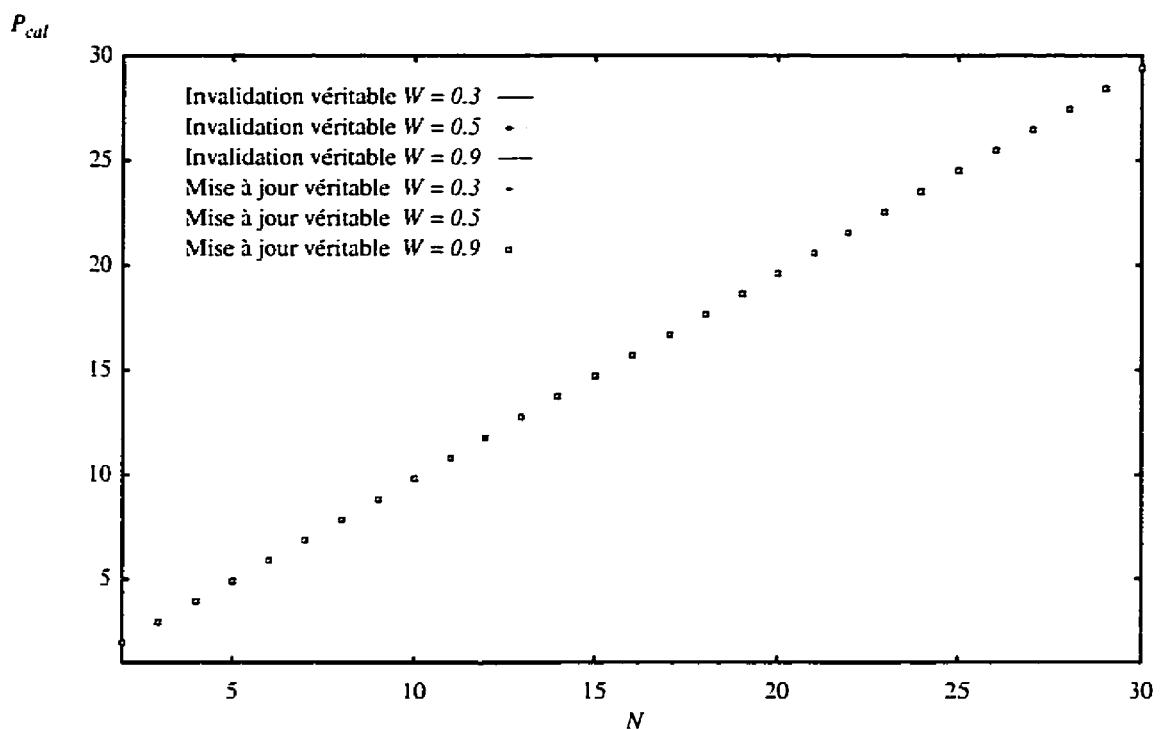

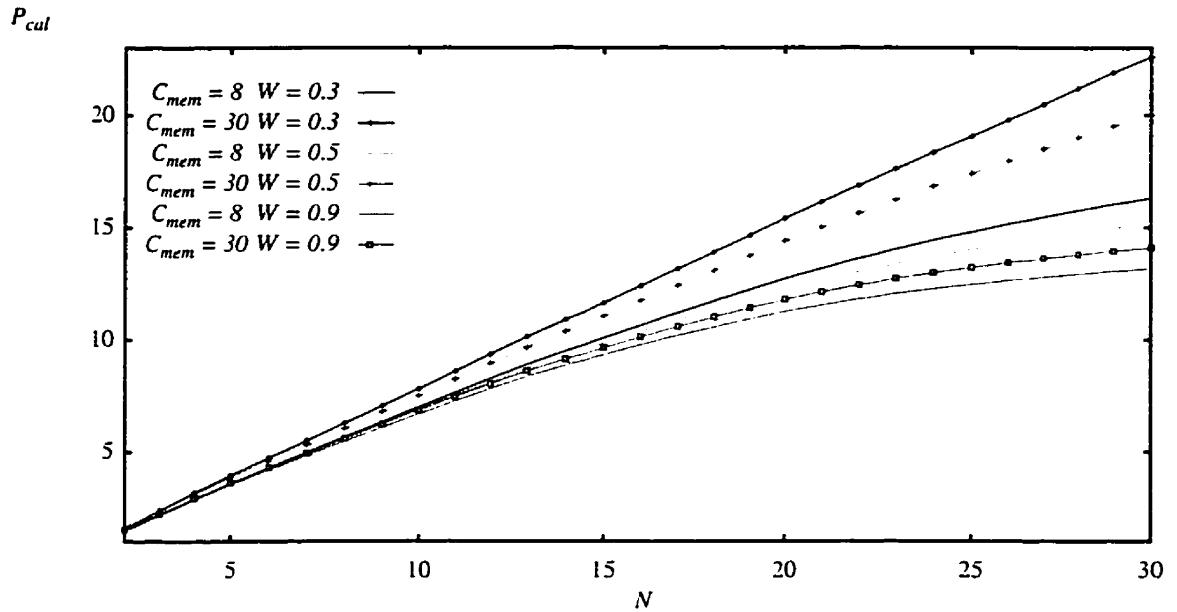

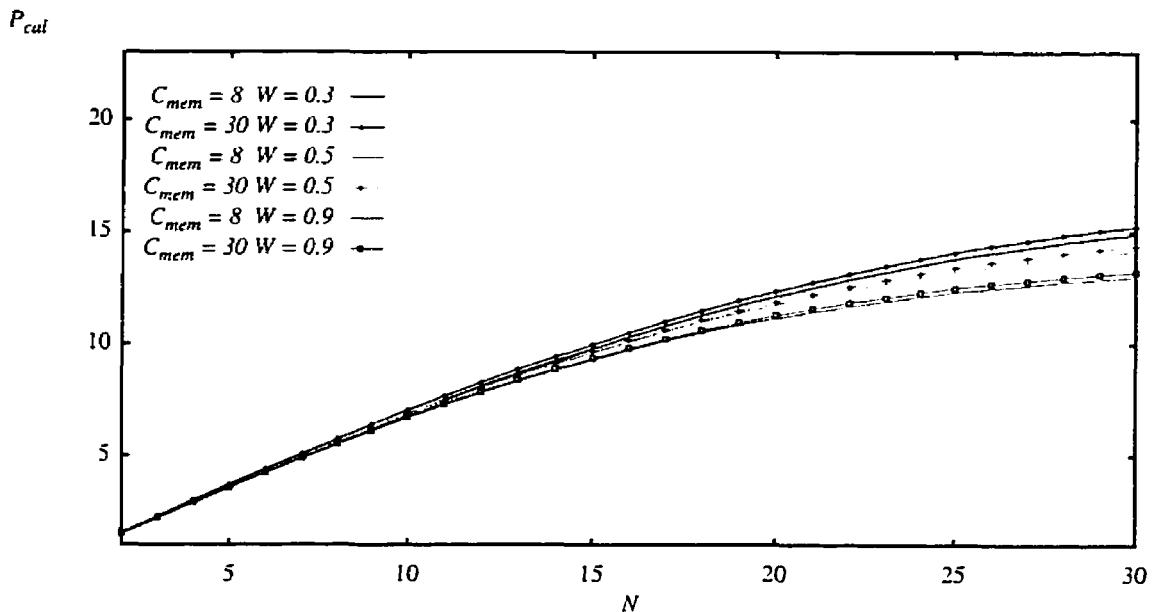

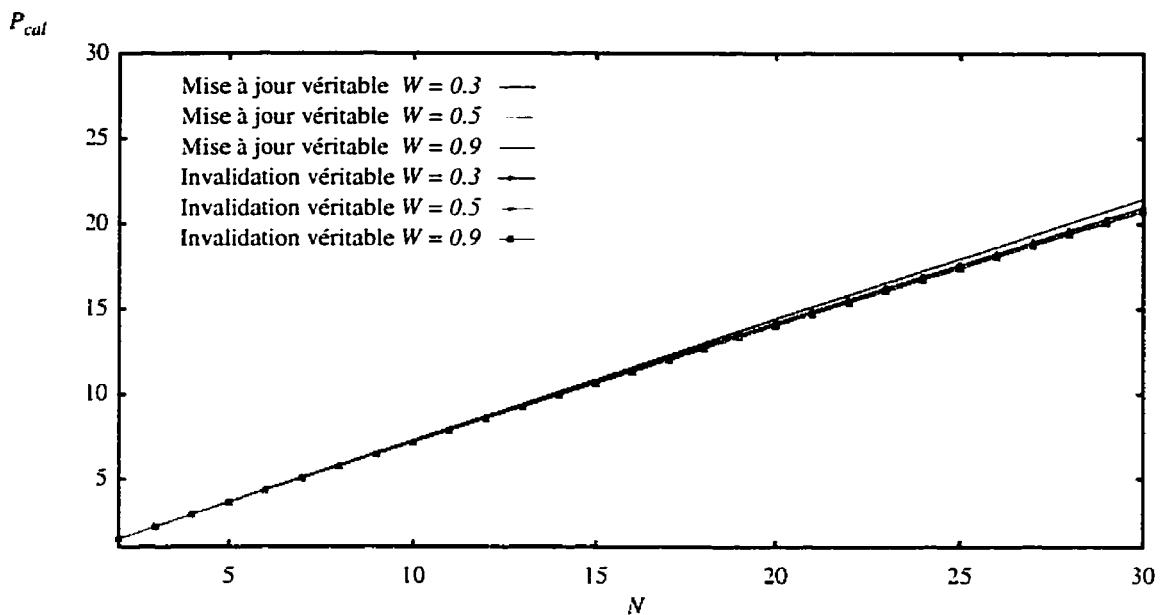

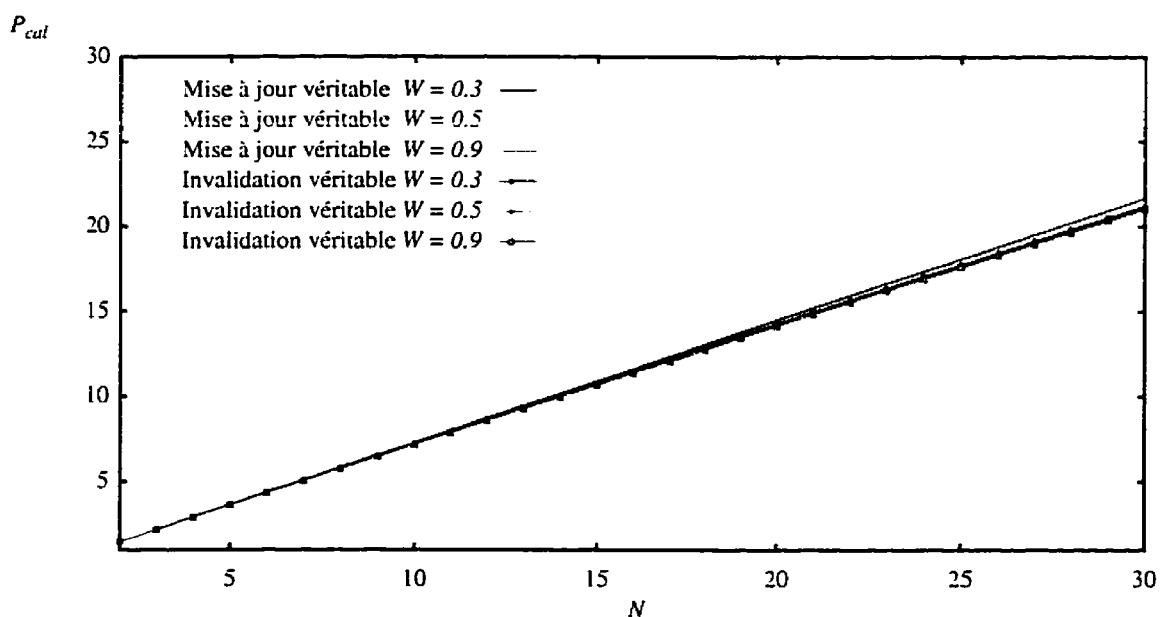

| 5.2 Étude du système sous certaines conditions de charge .....        | 117        |

| 5.2.1 Choix du système de référence .....                             | 117        |

| 5.2.2 Performances du système de base .....                           | 118        |

| 5.2.3 Effet du temps d'interarrivée .....                             | 120        |

| 5.2.4 Effet de la taille de la mémoire locale .....                   | 122        |

| 5.2.5 Effet du nombre des serveurs principaux .....                   | 123        |

| 5.2.6 Effet du nombre des serveurs secondaires .....                  | 127        |

| 5.2.7 Effet de la vitesse du réseau .....                             | 129        |

| <b>CHAPITRE 6: CONCLUSIONS .....</b>                                  | <b>132</b> |

| <b>RÉFÉRENCES:.....</b>                                               | <b>135</b> |

## LISTE DES FIGURES

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| Figure 1.1 Un système multiprocesseur .....                                   | 2  |

| Figure 1.2 Un Système réparti .....                                           | 3  |

| Figure 2.1 Protocole d'invalidation en écriture de DASH .....                 | 27 |

| Figure 2.2 Protocole mise à jour en écriture de PLUS .....                    | 31 |

| Figure 3.1 Le système physique .....                                          | 37 |

| Figure 3.2 Modèle à analyser .....                                            | 40 |

| Figure 3.3 Exemple d'un répertoire d'état .....                               | 41 |

| Figure 3.4 Problèmes de cohérence avec des copies multiples .....             | 43 |

| Figure 3.5 Exemple d'un répertoire de copies .....                            | 44 |

| Figure 3.6 Modèle du poste de travail .....                                   | 46 |

| Figure 3.7 Modèle du serveur .....                                            | 47 |

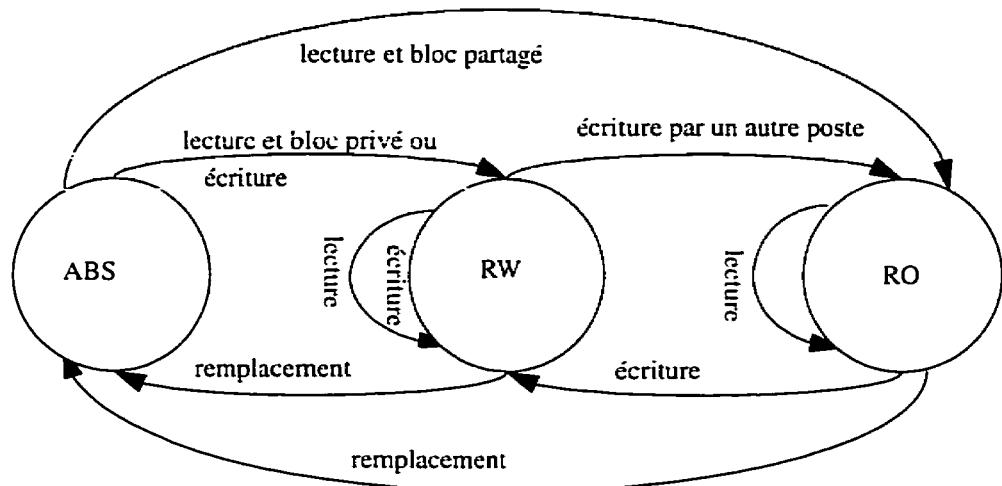

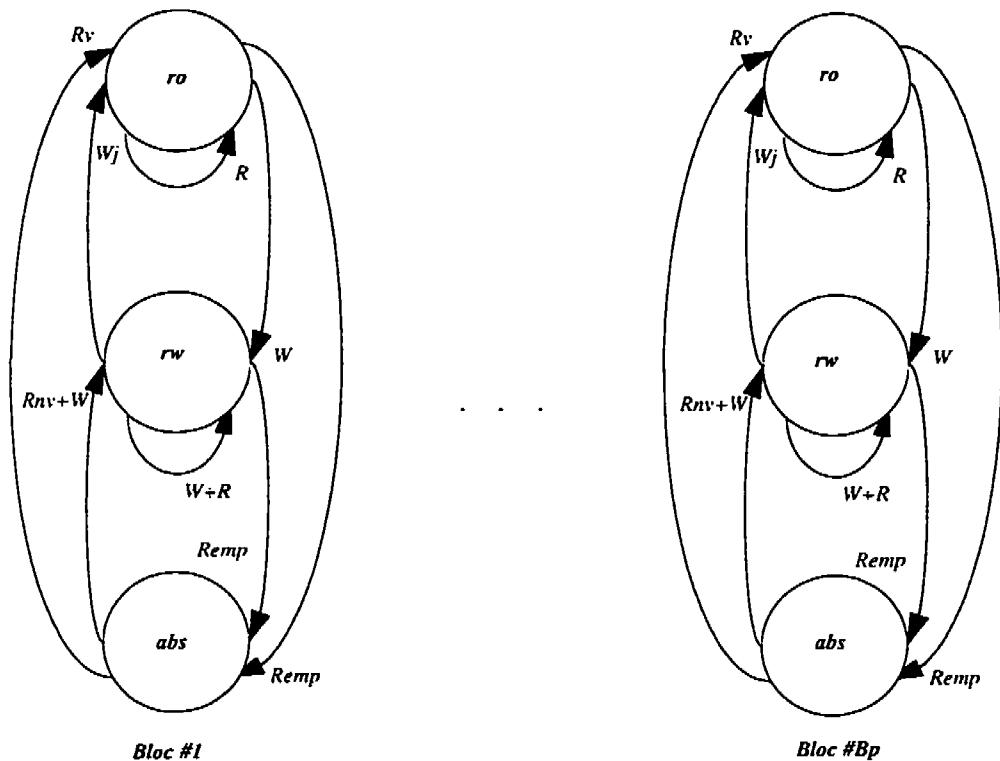

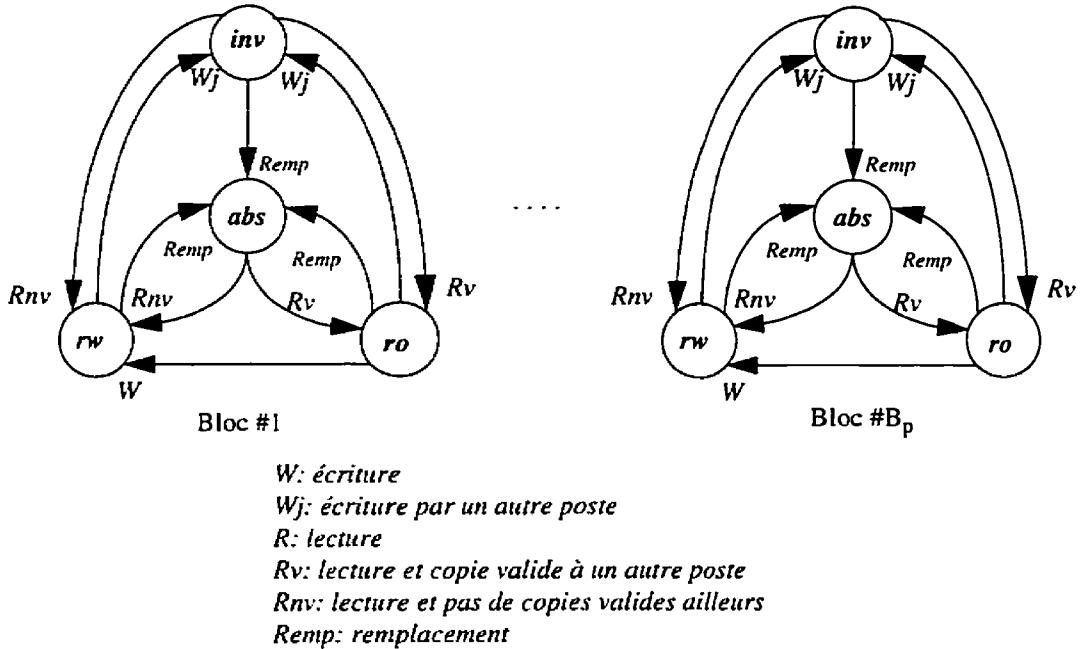

| Figure 3.8 Diagramme de transition d'état d'un bloc en mémoire locale .....   | 50 |

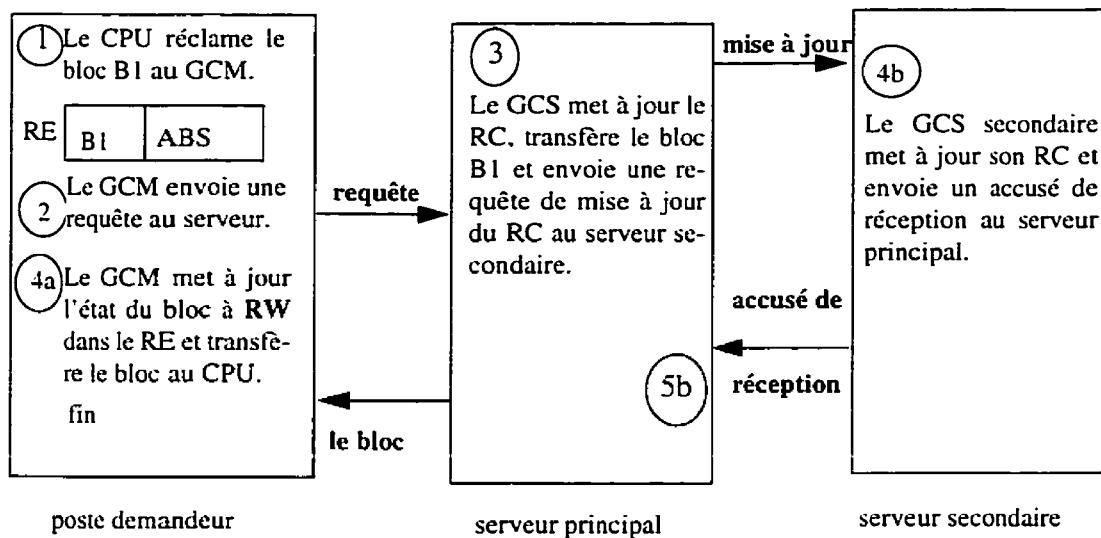

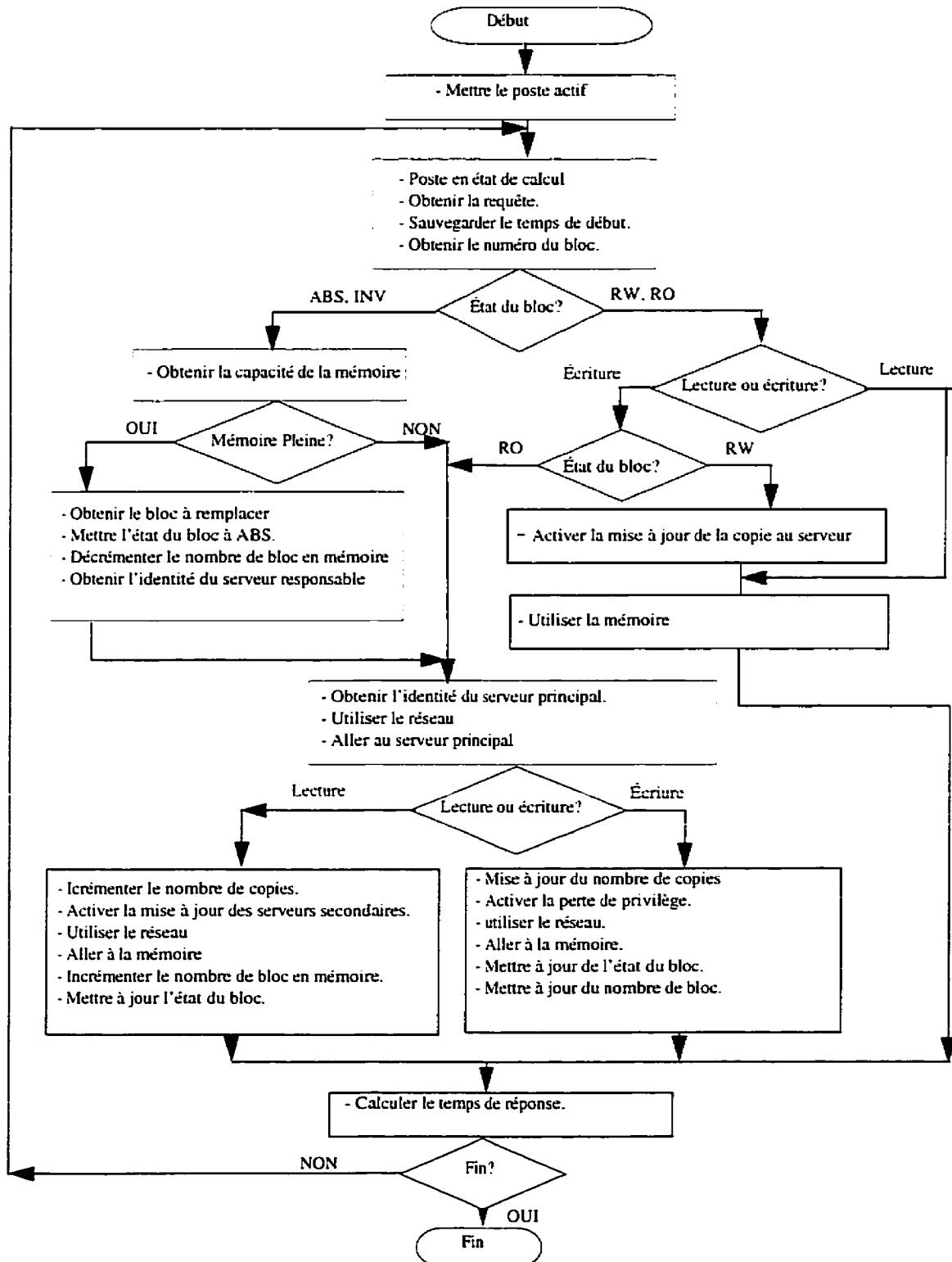

| Figure 3.9 Obtention d'un bloc .....                                          | 51 |

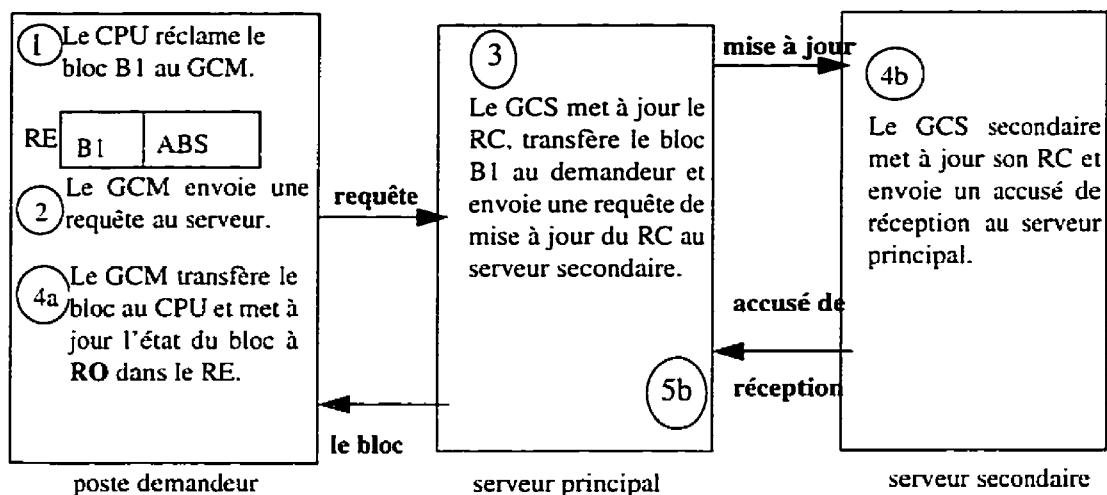

| Figure 3.10 Obtention d'un bloc avec copie existante .....                    | 52 |

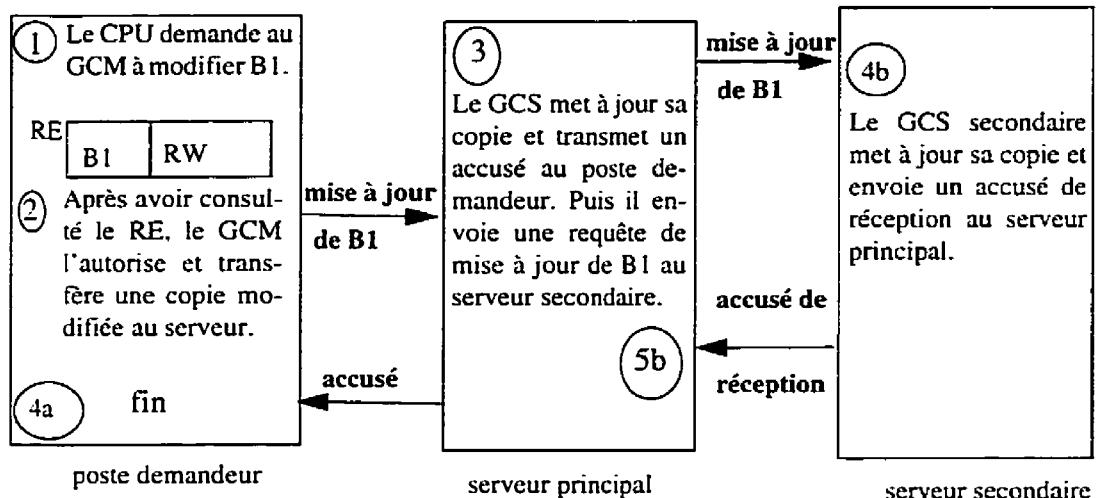

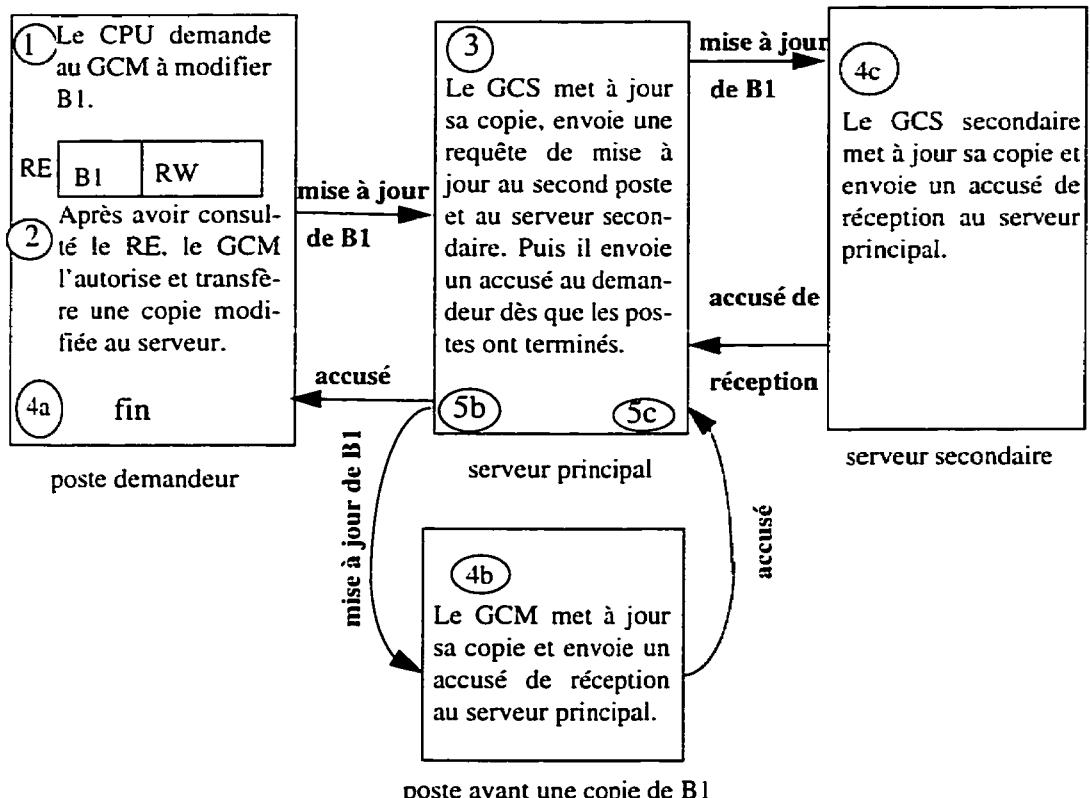

| Figure 3.11 Modification d'un bloc RW .....                                   | 53 |

| Figure 3.12 Modification d'un bloc RW avec copie RO existante .....           | 53 |

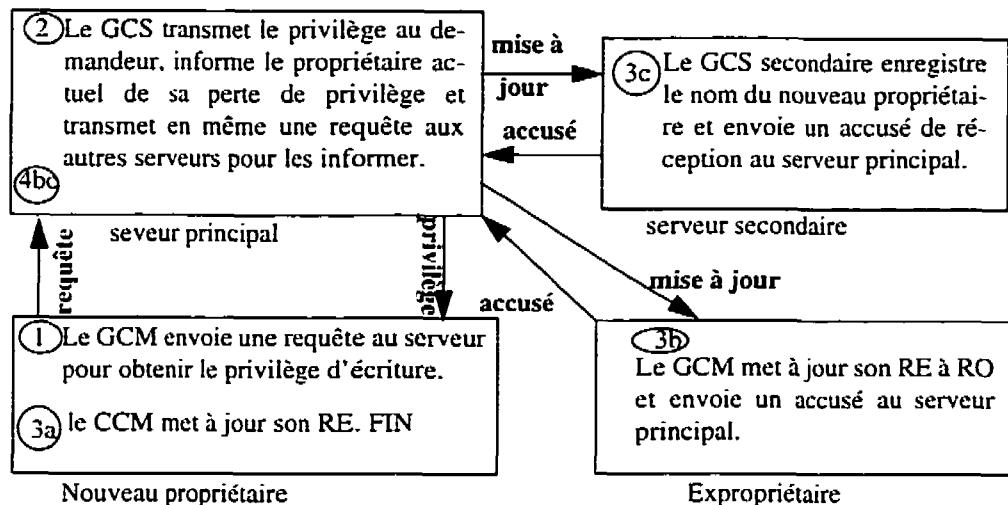

| Figure 3.13a Obtention d'un bloc et du PE .....                               | 55 |

| Figure 3.13b Modification d'un bloc RO avec copies existantes .....           | 55 |

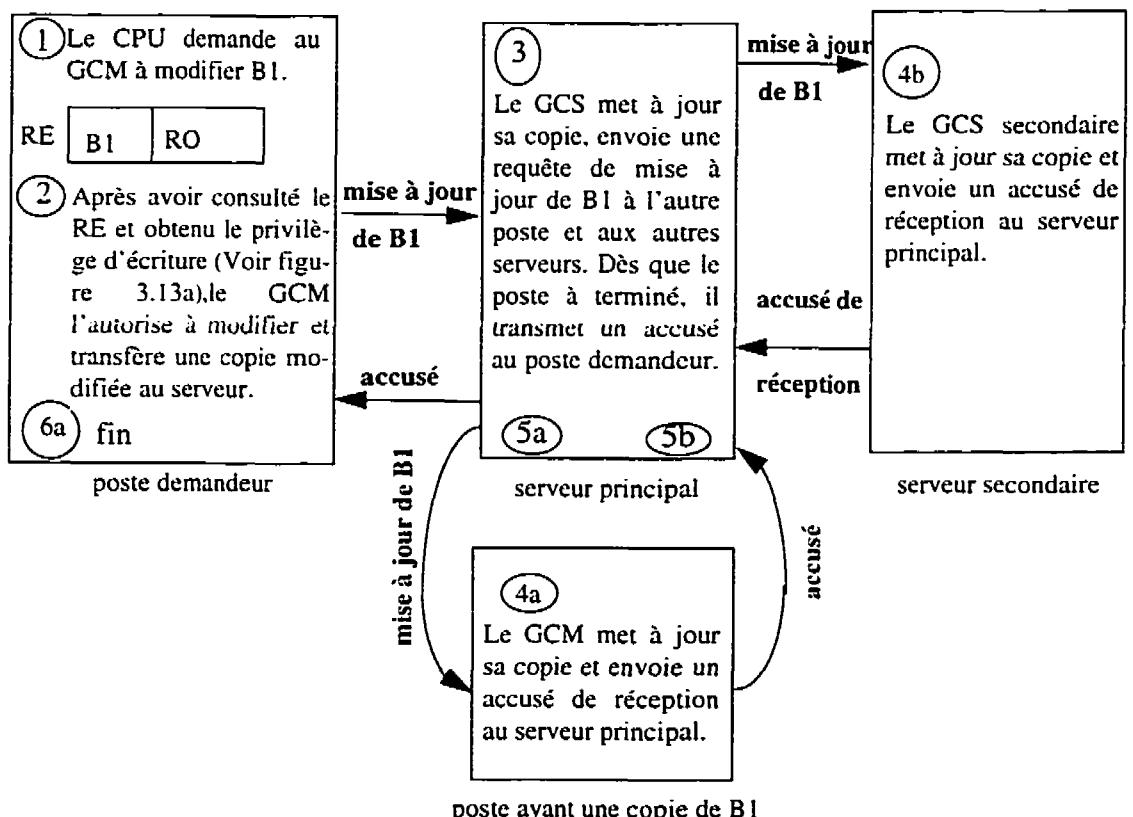

| Figure 3.14a Obtention d'un bloc unique et du PE sans copies aux postes ..... | 57 |

| Figure 3.14b Modification d'un bloc ABS sans copie existante .....            | 57 |

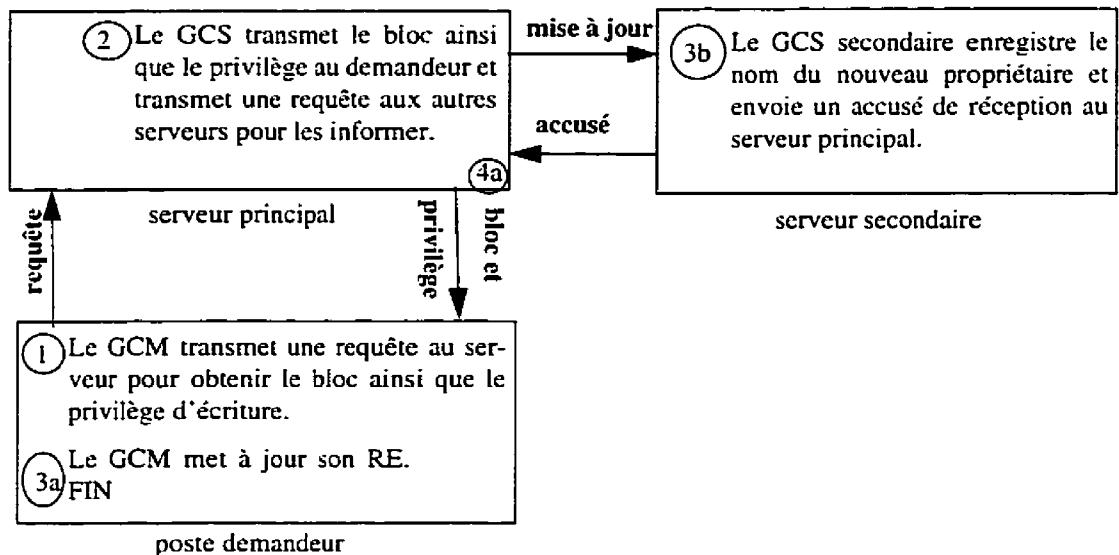

| Figure 3.15a Obtention d'un bloc ABS et du PE avec copie RW disponible .....  | 58 |

| Figure 3.15b Modification d'un bloc ABS avec copie existante .....            | 58 |

| Figure 3.16 Mise à jour par diffusion .....                                   | 60 |

|                                                                                         |     |

|-----------------------------------------------------------------------------------------|-----|

| Figure 3.7 Mise à jour par chaînage .....                                               | 61  |

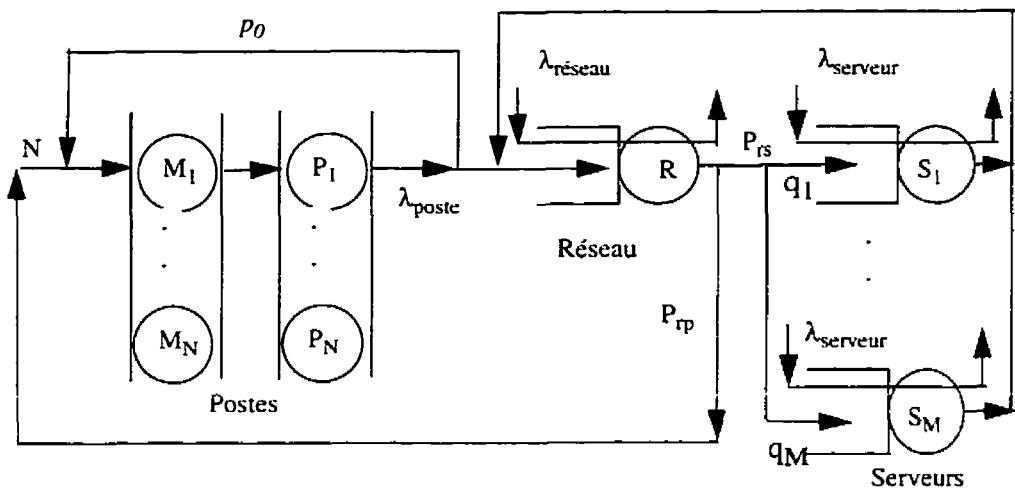

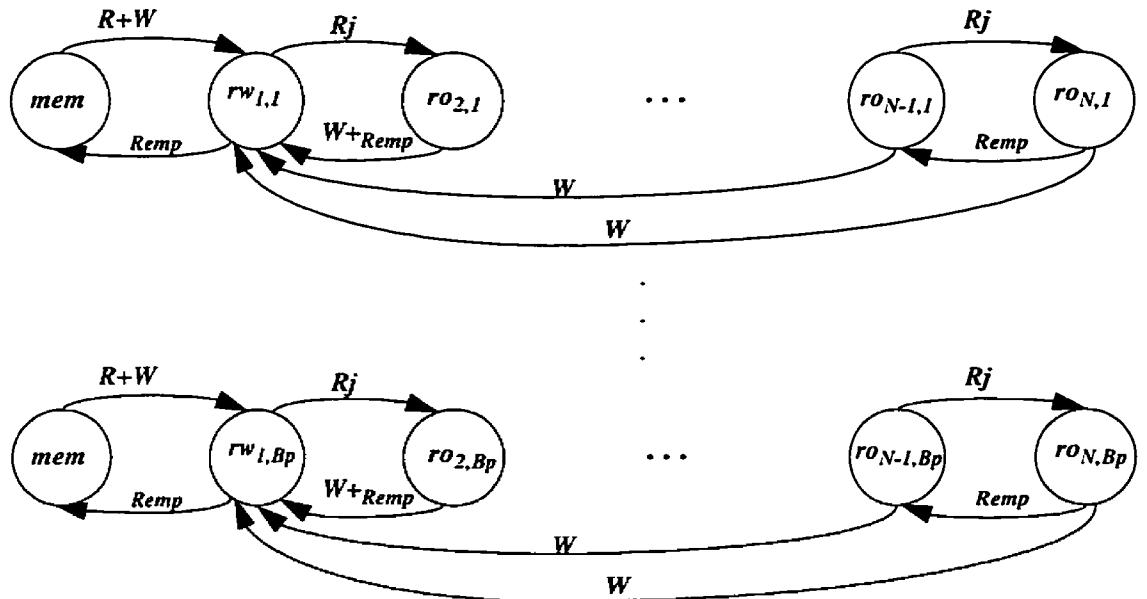

| Figure 4.1 Modèle du processeur .....                                                   | 73  |

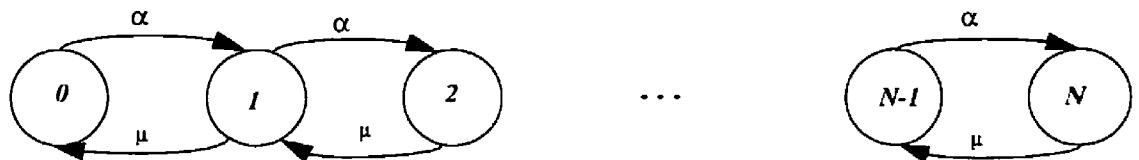

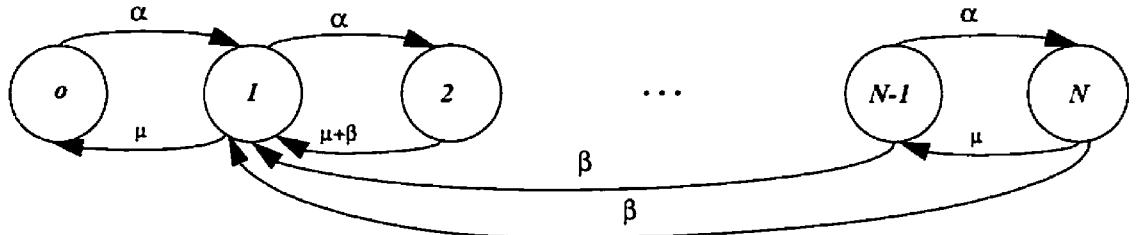

| Figure 4.2 Diagramme de transition du nombre de copies des blocs dans le système .....  | 77  |

| Figure 4.3 Chaîne de Markov représentant le nombre de copies des blocs dans le système  | 78  |

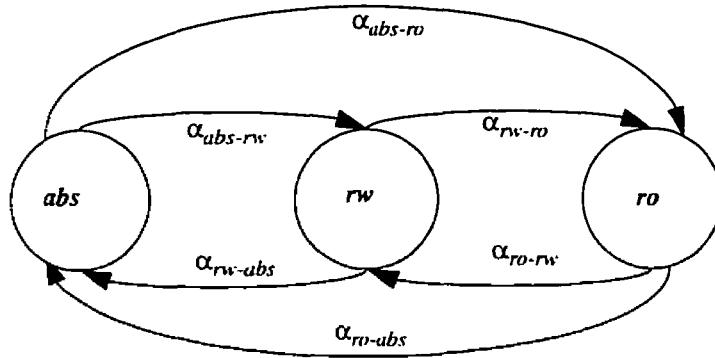

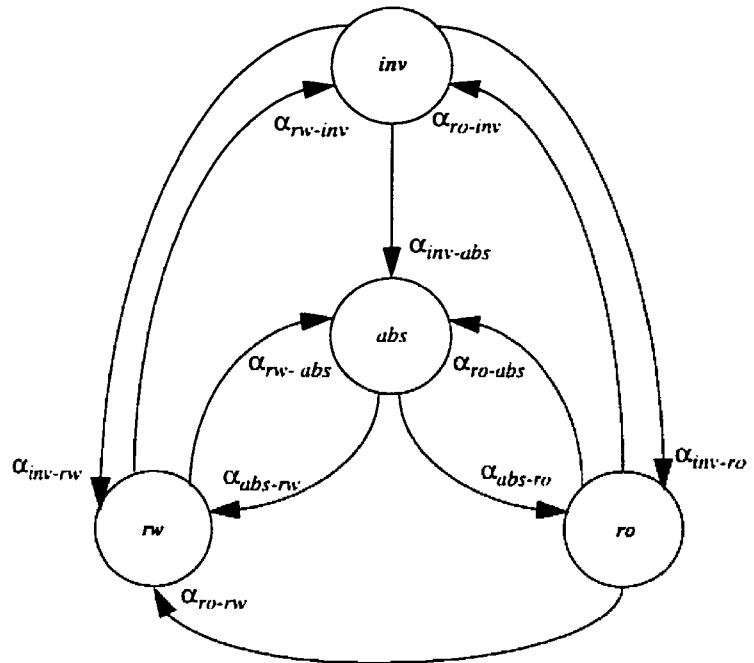

| Figure 4.4 Diagramme de transitions des états des blocs en mémoire locale .....         | 80  |

| Figure 4.5 Chaîne de Markov des états des blocs en mémoire locale .....                 | 81  |

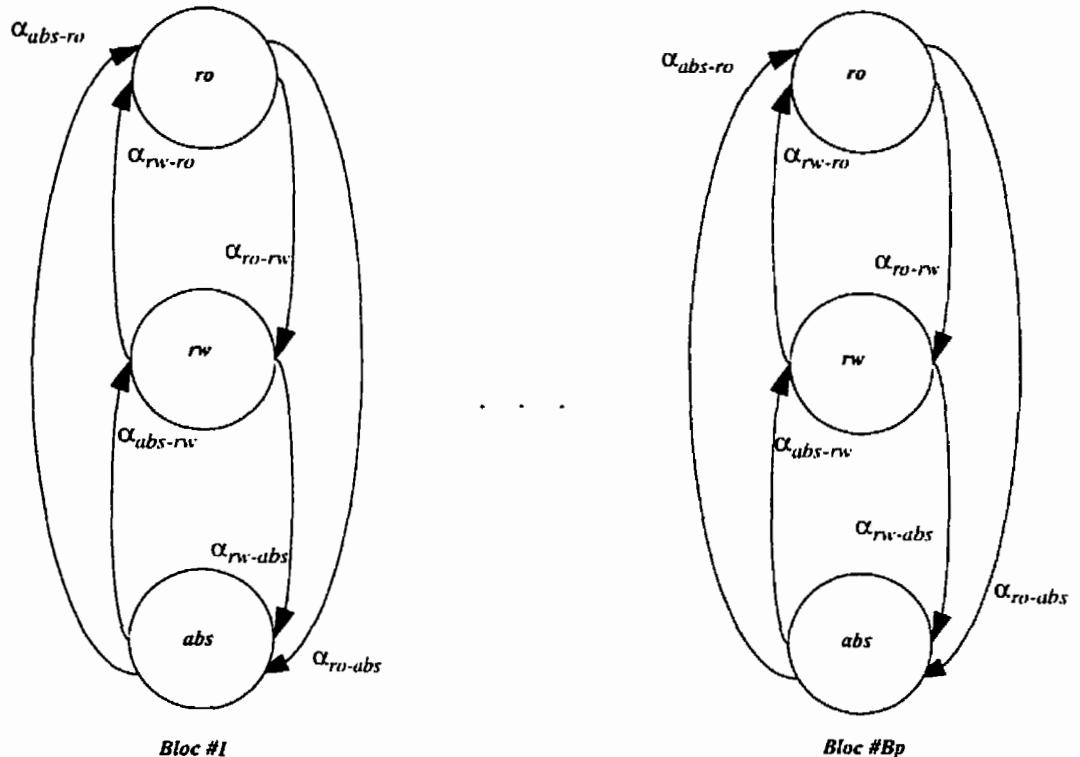

| Figure 4.6 Interactions entre les modèles .....                                         | 83  |

| Figure 4.7 Modèle du processeur avec une chaîne de routage et $N$ clients .....         | 84  |

| Figure 4.8 Chaîne de Markov du nombre de copies d'un bloc .....                         | 85  |

| Figure 4.9 Chaîne de Markov pour le changement d'état d'un bloc en mémoire locale ..... | 86  |

| Figure 4.10 Diagramme d'état pour le nombre de copies d'une donnée .....                | 95  |

| Figure 4.11 Diagramme de transition d'un bloc dans une mémoire locale .....             | 96  |

| Figure 4.12 Chaîne de Markov du nombre de copies d'un bloc .....                        | 97  |

| Figure 4.13 Chaîne de Markov des états d'un bloc en mémoire locale .....                | 98  |

| Figure 4.14 Modèle pour le calcul du temps de réponse .....                             | 107 |

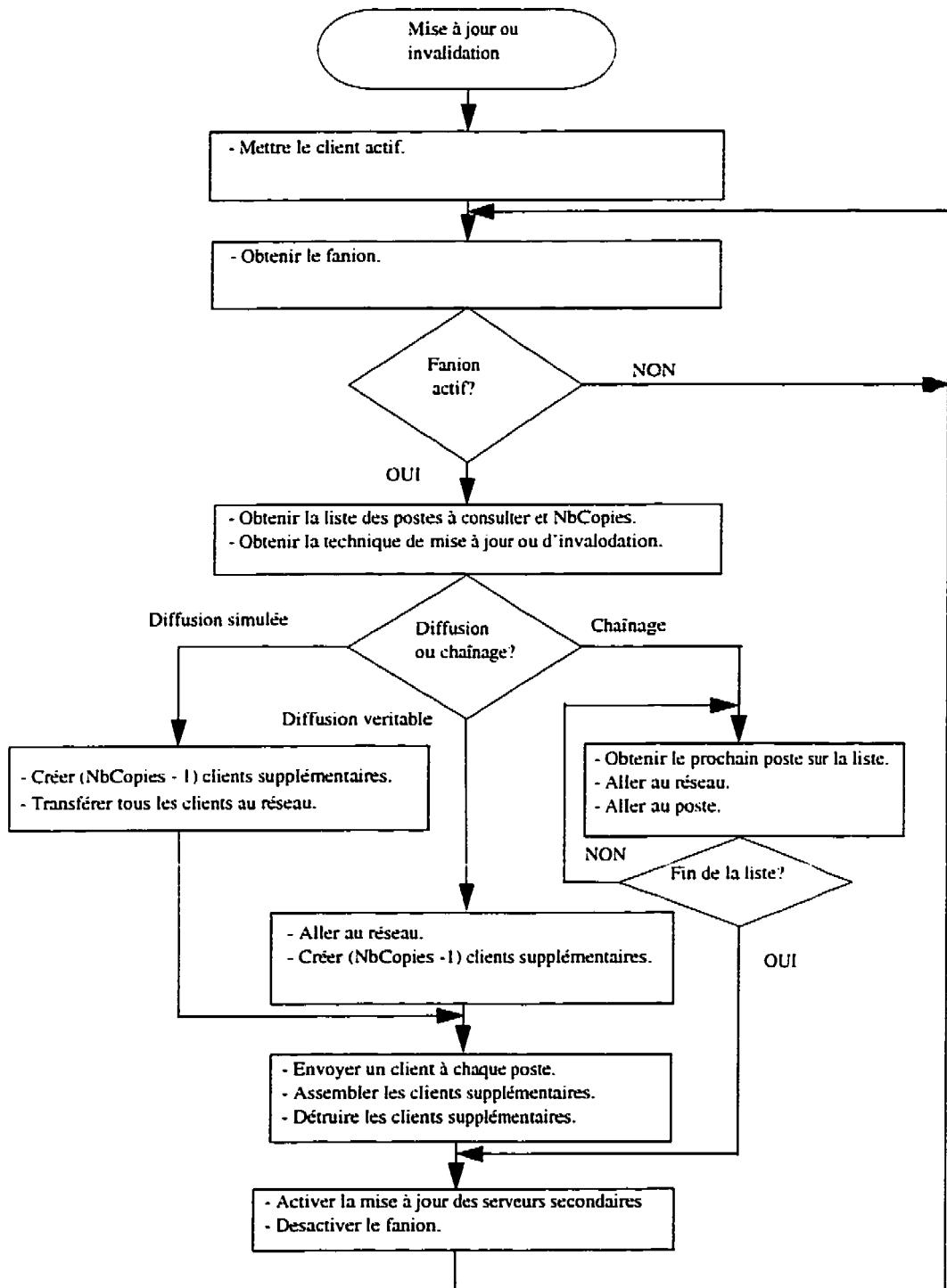

| Figure 4.15 Modèle pour la mise à jour ou l'invalidation des postes .....               | 108 |

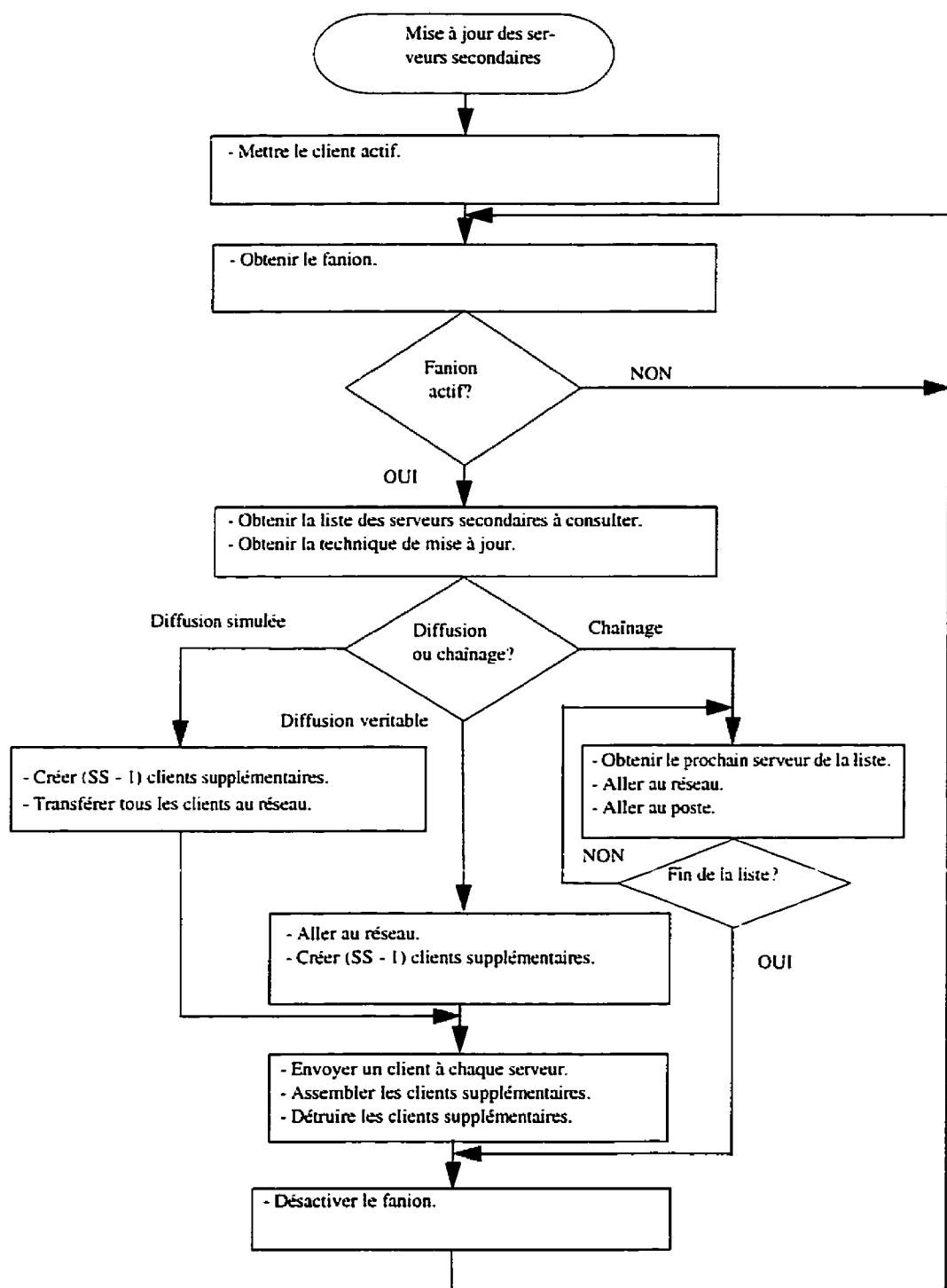

| Figure 4.16 Modèle pour la mise à jour des SS .....                                     | 109 |

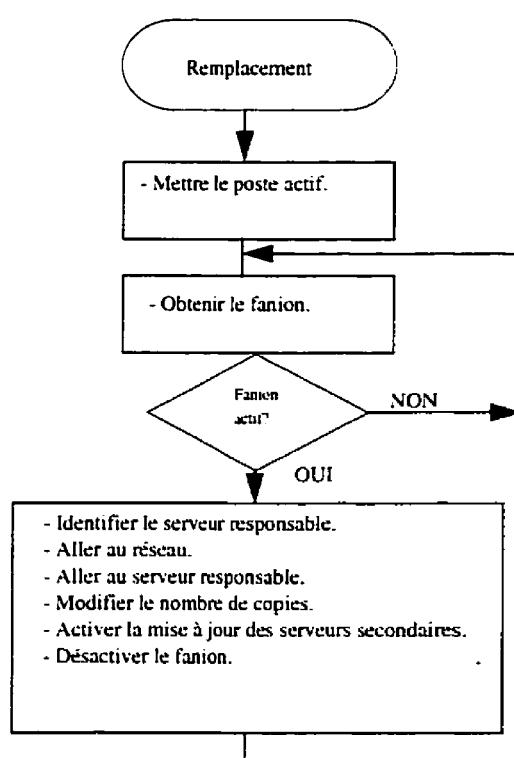

| Figure 4.17a Remplacement .....                                                         | 110 |

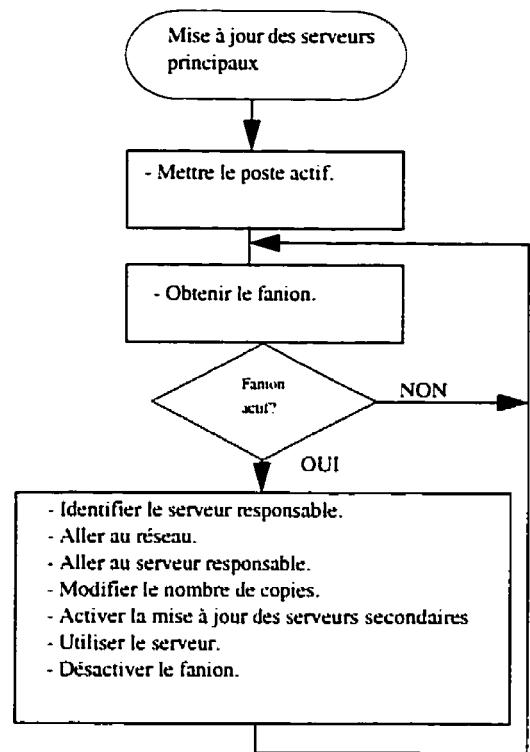

| Figure 4.17b Mise à jour des SP .....                                                   | 110 |

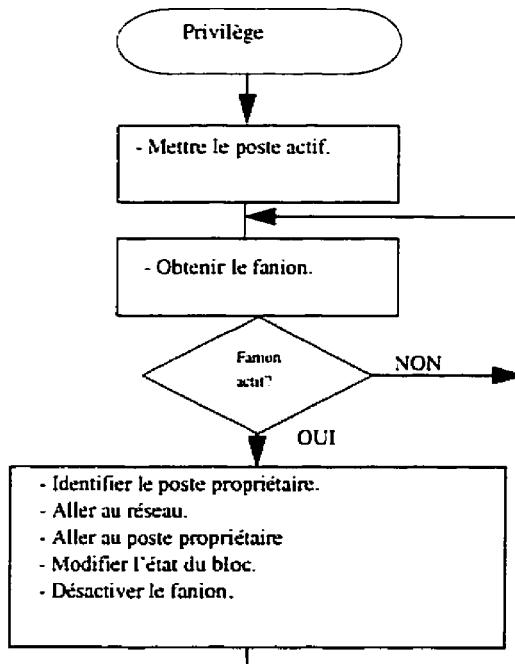

| Figure 4.17c Transfert de privilège .....                                               | 110 |

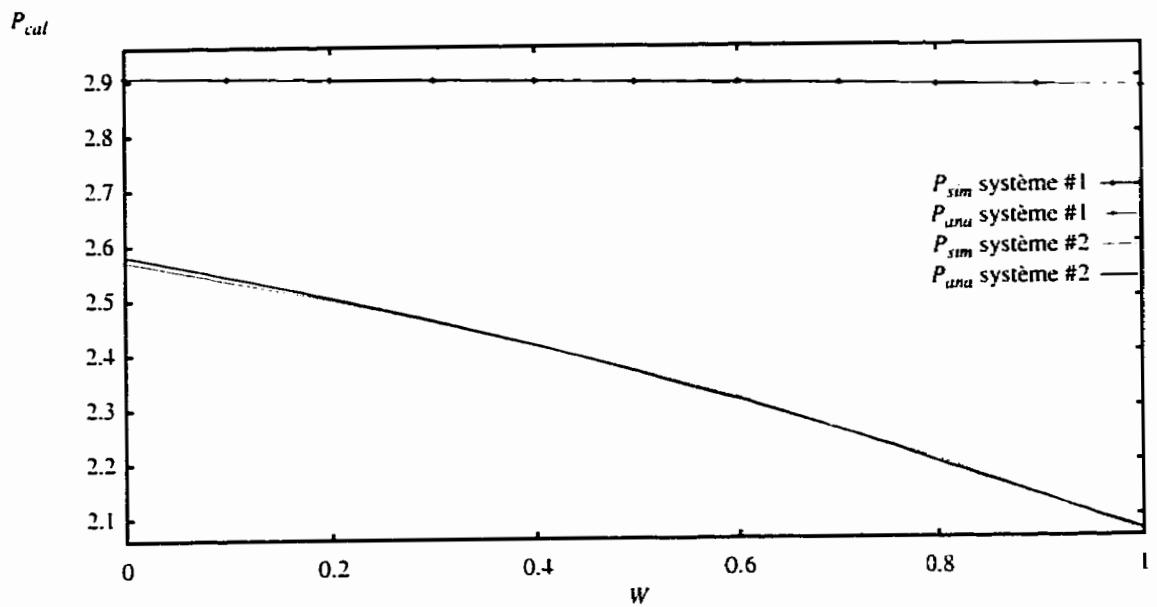

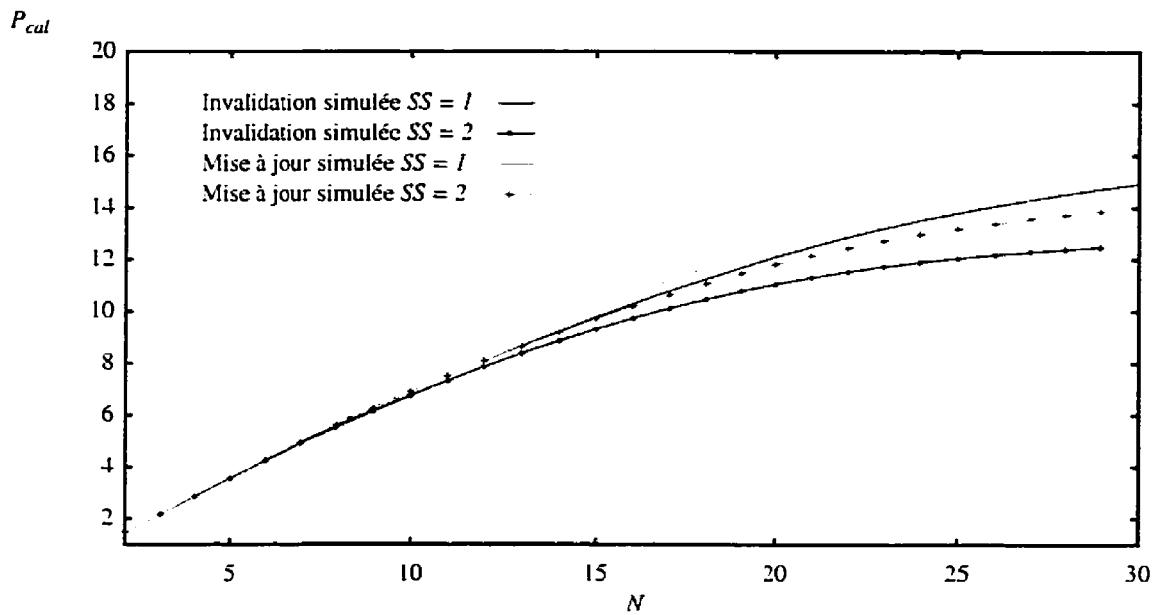

| Figure 5.1 Validation des modèles pour une mise à jour simulée .....                    | 114 |

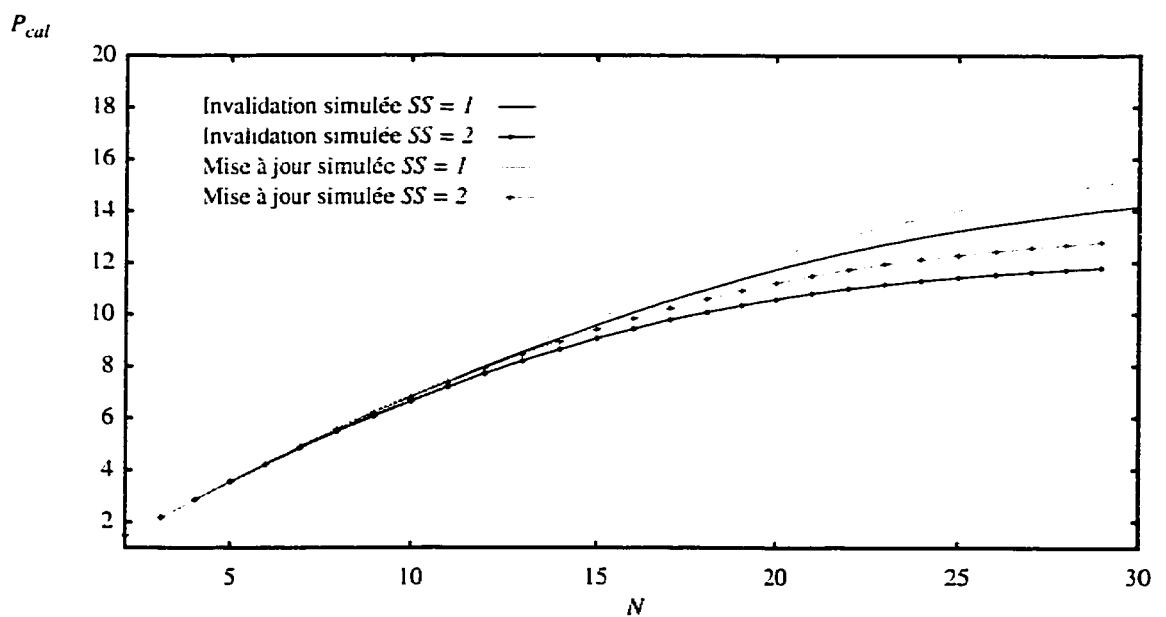

| Figure 5.2 Validation des modèles pour une mise à jour véritable .....                  | 114 |

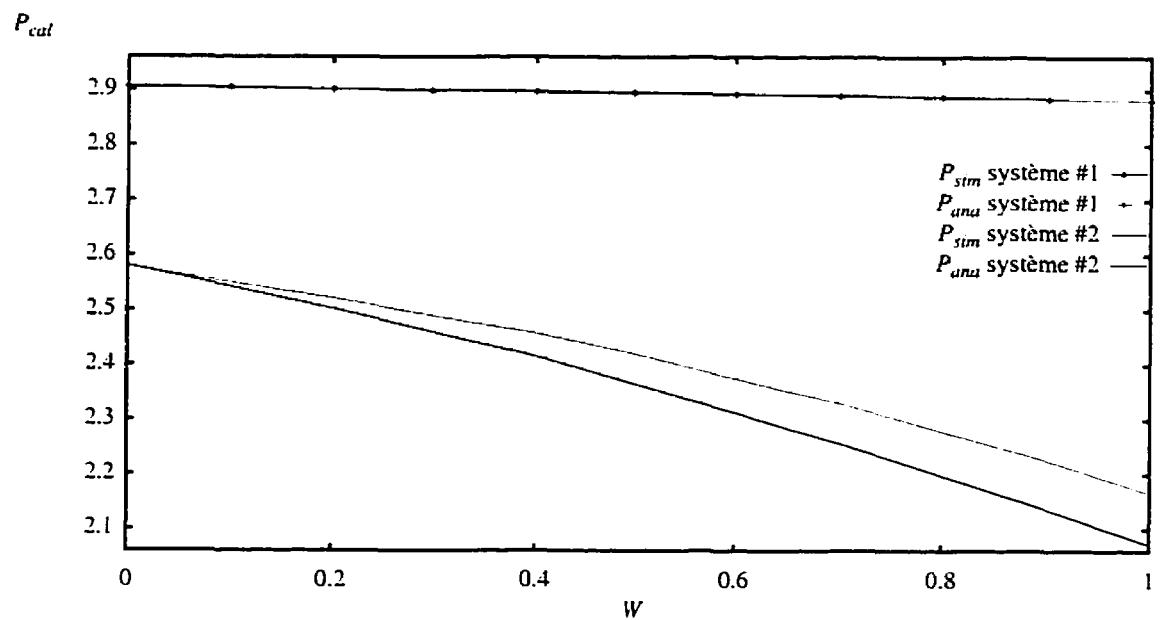

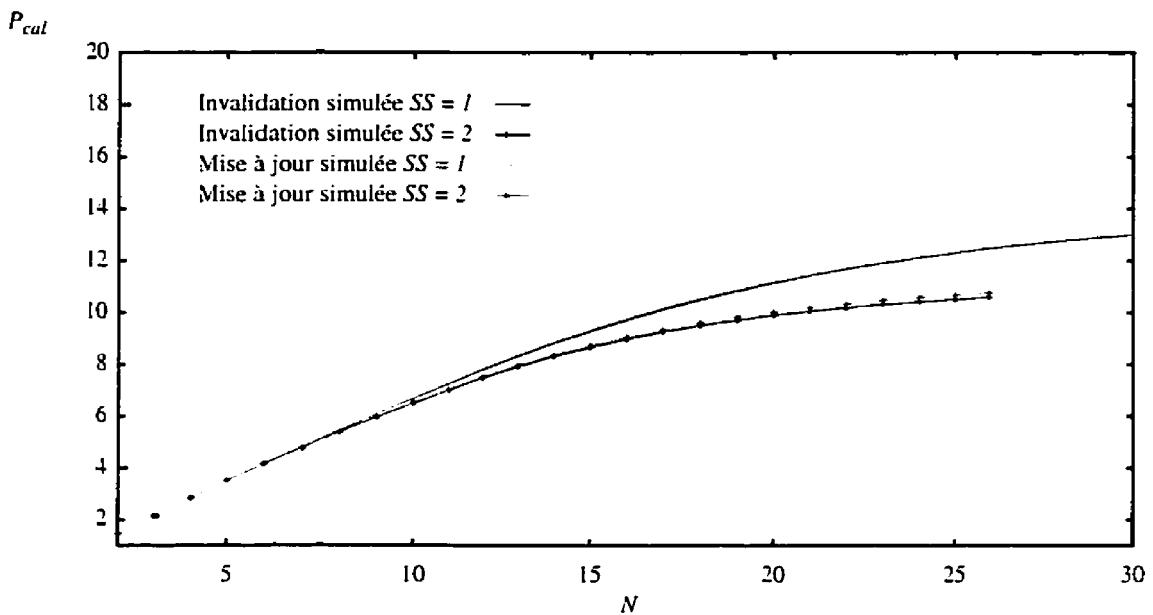

| Figure 5.3 Validation des modèles pour une mise à jour par chaînage .....               | 115 |

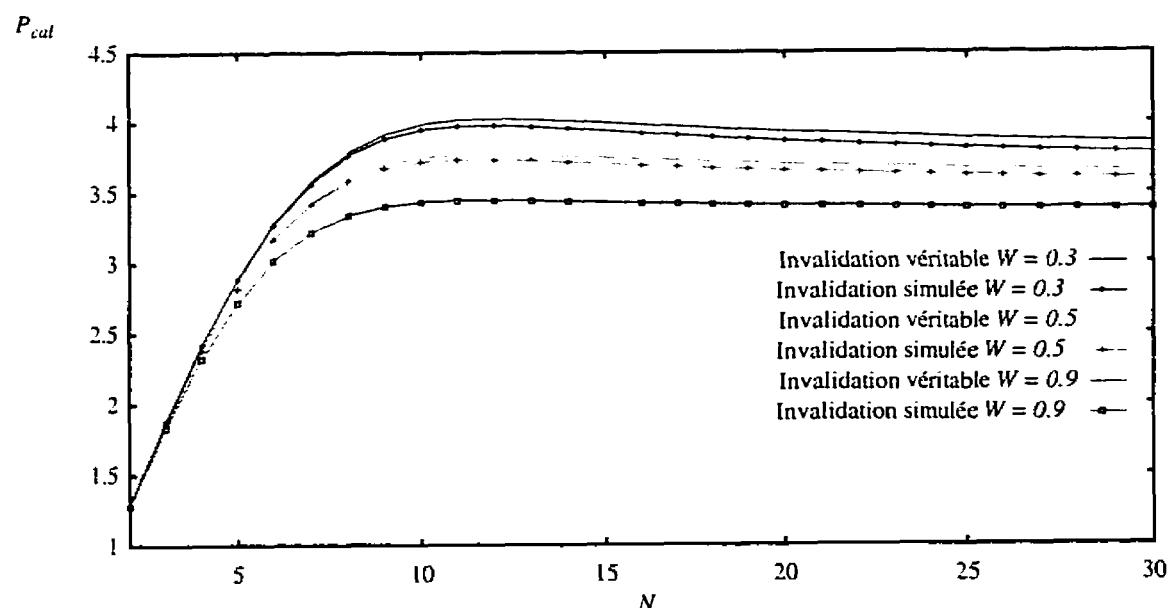

| Figure 5.4 Validation des modèles pour une invalidation simulée .....                   | 115 |

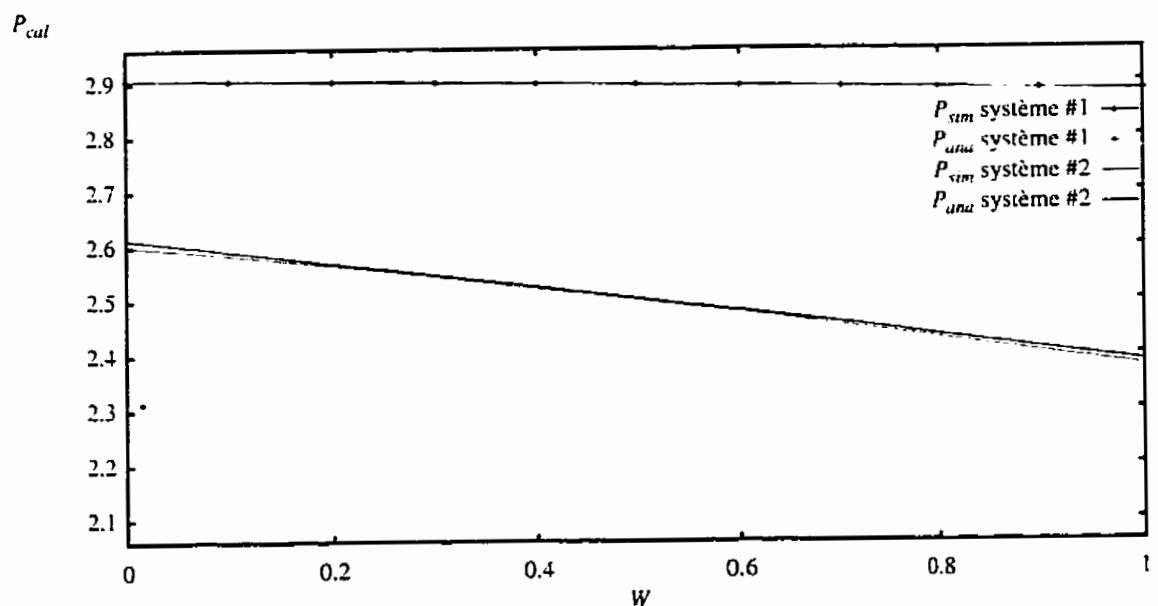

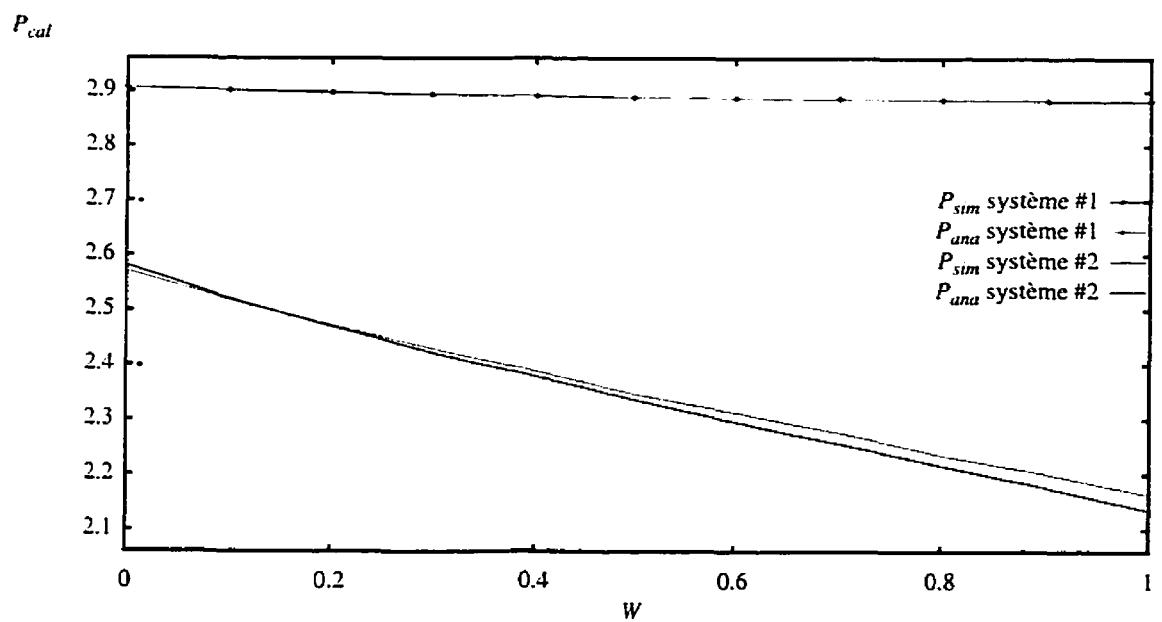

| Figure 5.5 Validation des modèles pour une invalidation véritable .....                 | 116 |

|                                                                                                  |     |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 5.6 Validation des modèles pour une invalidation par chaînage .....                       | 116 |

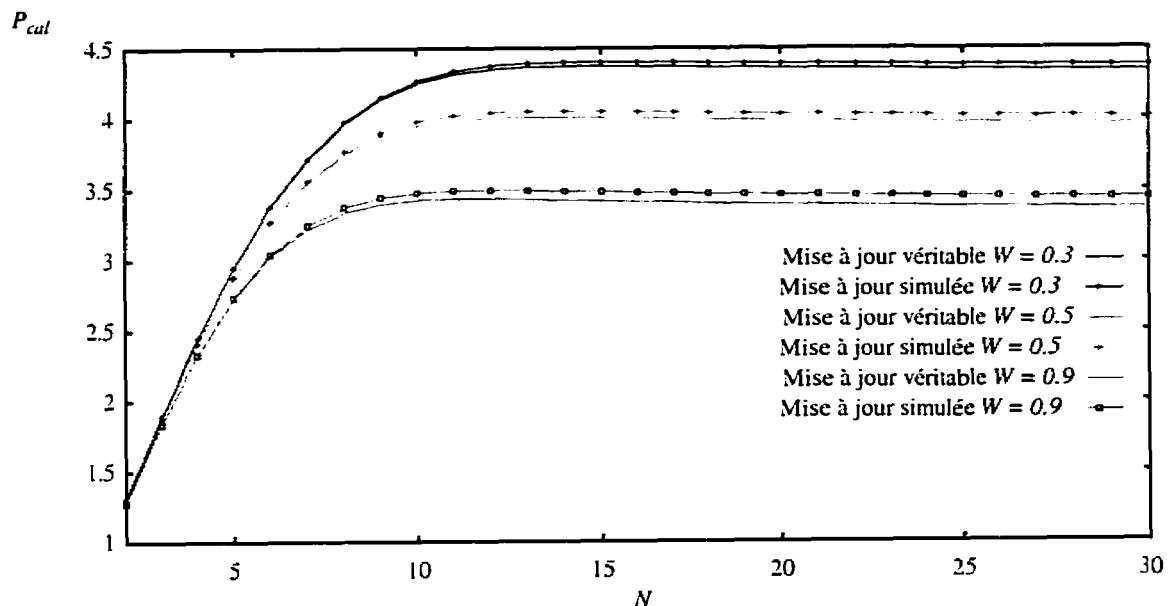

| Figure 5.7 Performance du système pour un taux d'écriture faible ( $W = 0.3$ ) .....             | 118 |

| Figure 5.8 Performance du système de base pour un taux d'écriture moyen ( $W = 0.5$ ) ...        | 119 |

| Figure 5.9 Performance du système pour un taux d'écriture élevé ( $W = 0.9$ ).....               | 119 |

| Figure 5.10 Effet du temps du temps d'interarrivée $T_{arr} = 20$ .....                          | 121 |

| Figure 5.11 Effet des mémoires locales pour une mise à jour véritable .....                      | 123 |

| Figure 5.12 Effet des mémoires locales pour une invalidation véritable .....                     | 124 |

| Figure 5.13 Effet du nombre de serveurs principaux pour une mise à jour véritable .....          | 125 |

| Figure 5.14 Effet du nombre de serveurs principaux pour une invalidation véritable .....         | 125 |

| Figure 5.15 Comparaison des protocoles pour $SP = 30$ .....                                      | 126 |

| Figure 5.16 Comparaison des protocoles pour $SP = 50$ .....                                      | 126 |

| Figure 5.17 Effet du nombre de serveurs secondaires: $W = 0.3$ .....                             | 128 |

| Figure 5.18 Effet du nombre de serveurs secondaires: $W = 0.5$ .....                             | 128 |

| Figure 5.19 Effet du nombre de serveurs secondaires: $W = 0.9$ .....                             | 129 |

| Figure 5.20 Effet de la vitesse du réseau sur le protocole de mise à jour $T_{réseau} = 0.05..$  | 130 |

| Figure 5.21: Effet de la vitesse du réseau sur le protocole d'invalidation $T_{réseau} = 0.05..$ | 130 |

## **LISTE DES TABLEAUX**

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| Tableau 4.1 Description des variables globales .....                              | 102 |

| Tableau 4.2 Description des variables locales de l'algorithme de simulation ..... | 104 |

| Tableau 5.1 Paramètres de simulation .....                                        | 112 |

| Tableau 5.2 Paramètres du système de référence .....                              | 117 |

## **LISTE DES ANNEXES**

|                                                                     |     |

|---------------------------------------------------------------------|-----|

| ANNEXE 1: Résultats numériques .....                                | 139 |

| ANNEXE 2: Programmes des modèles analytiques et de simulation ..... | 145 |

# CHAPITRE 1

## INTRODUCTION

Un ensemble d'ordinateurs forment un système réparti lorsqu'ils peuvent s'échanger de l'information à l'aide d'un système de communication. Selon le degré de couplage, on distingue les multiprocesseurs dont la communication se réalise généralement par l'intermédiaire d'une mémoire partagée et les réseaux d'ordinateurs. C'est à ces derniers types de système que nous restreignons tout au long de ce mémoire, le qualificatif de réparti.

Depuis l'avènement des ordinateurs, leurs vitesses n'ont jamais cessé d'augmenter pour satisfaire les exigences des applications pour lesquelles ils étaient utilisés. Cependant, avec la limitation physique imposée par la vitesse de la lumière, il est impossible de croire que cette vitesse va croître indéfiniment. Aujourd'hui, on note l'apparition de nouvelles applications ayant des contraintes temporelles d'exécution alors que les performances des ordinateurs saturent. Pour rencontrer les exigences imposées par ces applications, il faut augmenter la puissance de calcul en utilisant plusieurs processeurs en parallèle.

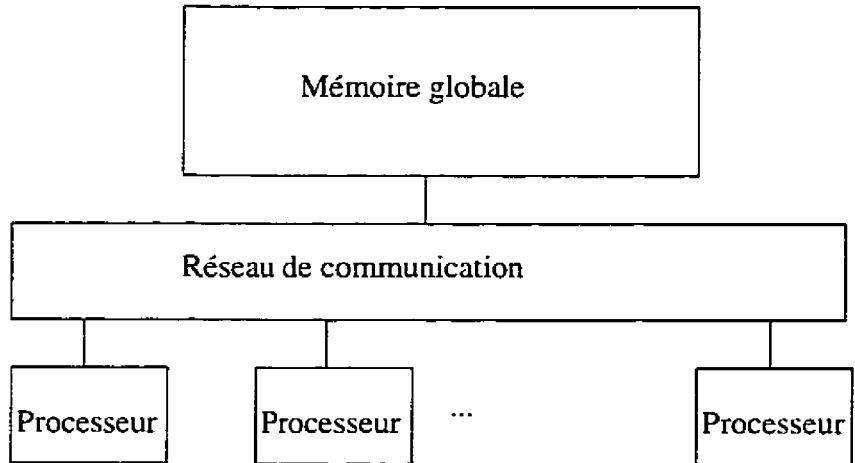

Deux genres de machines parallèles sont devenus populaires: les multiprocesseurs et les systèmes répartis. Les multiprocesseurs sont constitués de plusieurs processeurs et d'une seule mémoire physique globale. L'avantage de ces systèmes est qu'ils sont faciles à programmer étant donné qu'ils sont naturellement assimilables aux machines monoprocesseurs. Cependant, leurs performances sont affectées par le goulot d'étranglement qui apparaît au niveau de la mémoire principale lorsque le nombre de processeurs augmente. En effet, la mémoire ne dispose en général que d'un seul port

d'accès et par conséquent traite les requêtes séquentiellement. Cette faiblesse limite le nombre de processeurs qu'on peut coupler à la mémoire et réduit l'efficacité du traitement parallèle. Les systèmes répartis, quant à eux, ne souffrent pas des mêmes problèmes.

Figure 1.1 Un système multiprocesseur

Avec la chute du prix des processeurs et des mémoires, jumelée à l'accroissement de leurs performances, on a assisté à la pénétration de l'informatique dans plusieurs secteurs d'activité sous la forme de micro-ordinateurs. Pour plusieurs applications, un terminal d'accès à un système à temps partagé peut être remplacé avantageusement par un micro-ordinateur. Cependant, il faut noter que:

- la communication entre usagers et le partage des ressources que permettaient les systèmes à temps partagé ne sont plus possibles avec des micro-ordinateurs isolés.

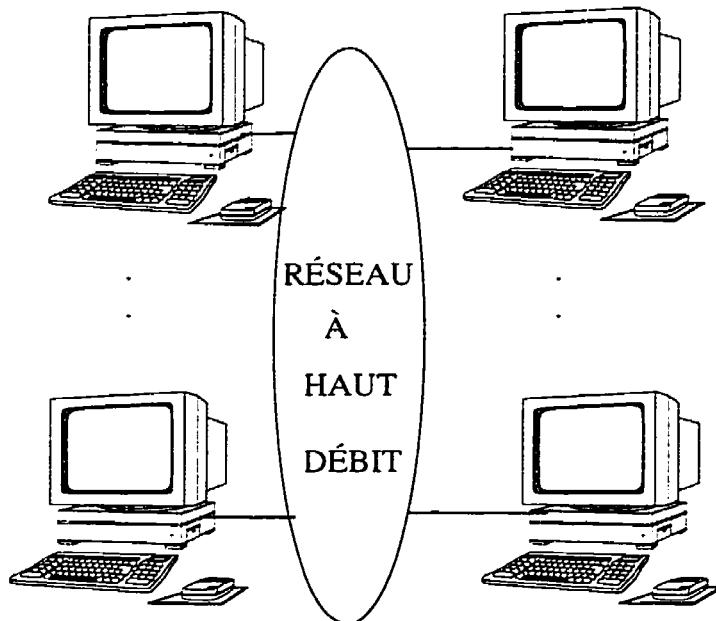

Ces problèmes justifient le développement des systèmes répartis interconnectant des postes de travail individuels et des serveurs spécialisés à travers un réseau de communication à grand débit. Si la topologie du réseau est bien conçue, ces systèmes peuvent contenir plus de sites que les multiprocesseurs.

Figure 1.2 Un système réparti

Un système informatique réparti doit permettre le partage des ressources, l'autonomie et la disponibilité de ses composants, une extensibilité ainsi qu'une hétérogénéité.

**Le partage des ressources:** Dans un système réparti, certaines ressources peuvent être jugées très coûteuses ou sous-utilisées. Si plusieurs postes de travail se partagent les mêmes ressources, alors on augmente leur taux d'utilisation et on réduit en même temps le

coût associé au système. Ce partage permet aussi la répartition de la charge par la migration des données.

**L'autonomie:** Ceci permet d'interconnecter des applications déjà existantes, développées de manière indépendante pour former un système unique intégré. Le fonctionnement des postes est indépendant les uns des autres mais ceux-ci peuvent communiquer entre eux.

**La disponibilité:** Le mauvais fonctionnement d'un composant ne doit pas entraîner la panne du système. Celui-ci doit être capable de détecter un composant défectueux pour permettre son remplacement par un composant équivalent. Il faut donc prévoir un logiciel pour gérer la reconfiguration ou la reprise en cas d'incident. C'est à dire que le système doit être tolérant aux fautes ou aux défaillances.

**L'extensibilité:** Un système réparti est toujours appelé à grossir. Ainsi le système doit supporter en tout temps, l'ajout de nouvelles applications et de nouveaux composants sans pour autant affecter la qualité de son service.

**L'hétérogénéité:** Plusieurs équipements d'origines différentes doivent cohabiter au sein du même système. Étant donné que ces composants n'ont pas les mêmes normes, il faut prévoir un mécanisme permettant de les uniformiser.

## 1.1 Évolution des systèmes répartis

Vers la fin des années 50, on notait l'apparition des premiers systèmes répartis, notamment le système SABRE utilisé pour la réservation des places d'avion ou le système SAGE

servant à la surveillance du territoire [Krakowiak 87]. La caractéristique commune de ces systèmes était qu'ils étaient très spécialisés et utilisaient tous la technique de communication point à point pour l'échange d'information. Par la suite les efforts ont été orientés vers la conception des systèmes répartis très généraux. Un des premiers projets d'envergure a été ARPANET qui fut lancé au début des années 60 [Bertekas 89]. Ces projets ont permis de mettre au point la technique de commutation par paquet et de développer des protocoles de communication, notamment pour le transfert de fichiers.

Au cours des années 70, on note l'élaboration du principe du réseau local ETHERNET, des réseaux à anneau à jeton et de l'organisation client-serveur pour le partage des ressources. Ces principes ont permis au cours des années 80 de développer des systèmes répartis intégrés.

Avec l'introduction des réseaux à fibre optique qui présentent l'avantage d'offrir des taux de transmission élevés et une transmission sans erreur, les projets actuels s'orientent vers le développement des systèmes répartis pouvant gérer des applications qui nécessitent une grande largeur de bande comme le multimédia.

## 1.2 Caractérisques des systèmes répartis

Un système réparti doit être muni d'un système d'exploitation. Ce système d'exploitation doit être vu par l'usager comme étant un système d'exploitation ordinaire qui fonctionne dans plusieurs processeurs; c'est à dire que le système d'exploitation doit être transparent. En d'autres termes, l'utilisation de plusieurs processeurs doit être invisible par l'usager. Celui-ci voit le système comme une machine monoprocesseur virtuelle et pas comme une

collection de machines distinctes.

Les systèmes répartis présentent plusieurs attraits. Premièrement, le gain en performance de processeurs associé à la chute de leurs prix font que leurs rapports prix/performance est avantageux par rapport à certains systèmes traditionnels tels que les mini-ordinateurs. Un autre facteur qui joue en faveur des systèmes répartis est leur extensibilité. Si on veut accroître la puissance de calcul d'un certain pourcentage, il suffit d'augmenter le nombre de processeurs par la même proportion. Enfin, les systèmes répartis offrent une très grande disponibilité. Si une partie du système tombe en panne, les autres ne sont pas trop affectées. Cependant, l'efficacité du système en est affectée car le nombre de processeurs à allouer est réduit.

Plusieurs modèles ont été proposés pour construire les systèmes répartis. Ces modèles peuvent être classés en trois catégories: le modèle à mini-ordinateurs, le modèle à postes de travail et le modèle à banque de processeurs [Tanenbaum 85].

Dans le modèle à mini-ordinateurs, le système est constitué d'environ une douzaine de mini-ordinateurs (VAX par exemple) chacun ayant plusieurs clients. Chaque client se connecte à une machine spécifique avec un accès sur les autres. Ce modèle n'est qu'une extension du modèle à temps partagé.

Dans le modèle à postes de travail, chaque client possède une machine comportant un processeur puissant, une mémoire, un écran, et un disque. Tout le travail s'effectue au niveau du poste de travail. Un tel système commence à devenir réparti lorsqu'il dispose d'un système de fichiers global unique et où les données sont obtenues sans préciser leur

endroit d'origine. Autrement dit, l'accès aux données est transparent pour l'utilisateur.

Le modèle à banque de processeurs est la prochaine étape d'évolution après le modèle à postes de travail. Si un client veut une certaine puissance de calcul, un ou plusieurs processeurs peuvent lui être alloués temporairement. Dès que le travail se termine, les processeurs sont remis dans la banque et attendent leur prochaine utilisation. Un modèle hybride peut être conçu en combinant ce modèle à celui des postes de travail. Ainsi, chaque utilisateur dispose d'une banque de plusieurs processeurs pour ses calculs intensifs en plus de son propre poste de travail.

### 1.3 Mémoire partagée

Les systèmes répartis présentent un degré de parallélisme. Malgré qu'ils ne disposent pas de mémoire commune, ils peuvent néanmoins exécuter des programmes parallèles. Dans ces applications, les programmes créent des processus qui manipulent des données qu'ils partagent. L'accès à une variable partagée se fait par l'échange de messages. Ces systèmes sont difficiles à programmer car le modèle de programmation est basé sur le paradigme de communication par message, technique qui est différente du paradigme de programmation par mémoire partagée utilisé dans les langages procéduraux auxquels le programmeur est habitué. Pour faciliter la programmation, certains systèmes ont implanté une mémoire commune virtuelle dans les systèmes répartis. L'idée est de donner au programmeur l'illusion que le système dispose d'une mémoire partagée et de lui permettre ainsi d'utiliser le paradigme de programmation par mémoire partagée.

L'implantation d'une mémoire partagée se fait en deux étapes:

- la spécification physique;

- la spécification du fonctionnement logique.

### **1.3.1 La spécification physique**

Dans cette première étape, il faut d'abord déterminer la répartition physique de la mémoire partagée. Deux méthodes sont généralement utilisées pour implanter physiquement une mémoire globale: la manière répartie où l'espace adressable est local et l'accès à une variable globale se fait par l'émission de messages à travers le réseau, et la manière partagée où l'espace adressable comprend toutes les mémoires du système. Avec la première approche, le système peut supporter un nombre important de composants mais il devient difficile à programmer pour les raisons que nous avons énumérées auparavant. Avec la deuxième approche, les systèmes sont faciles à programmer mais au point de vue architecturale, ils sont inefficaces car lorsque le système devient grand, la mémoire partagée devient un goulot d'étranglement. Une manière de réunir les deux paradigmes consiste à utiliser l'avantage de chacun: il s'agit d'une mémoire physiquement répartie mais à espace adressable partagé. Par la suite on spécifie la structure et l'organisation de la mémoire ainsi que de la taille des objets manipulés et leurs représentations internes.

### **1.3.2 Fonctionnement logique**

Dans cette deuxième étape, on décrit comment les données partagées sont gérées par le système. Deux approches sont généralement utilisées: la méthode statique et la méthode dynamique [Nitzberg 91]. Pour le premier cas, les données sont disponibles à un endroit précis et les localiser devient facile. Cependant, l'efficacité du système dépend de la

répartition des données partagées. Dans ce cas, il est possible que toutes les données se retrouvent à un seul site créant ainsi un goulot d'étranglement. Pour le second cas, on a une répartition des données là où elles ont été utilisées. Cette approche permet donc une migration des données dans le système. Dans ce dernier cas, localiser une donnée devient plus difficile et requiert un algorithme. Si l'algorithme est bien conçu, les données seront équitablement réparties et la charge ainsi que les performances du système seront meilleures que dans le cas précédent.

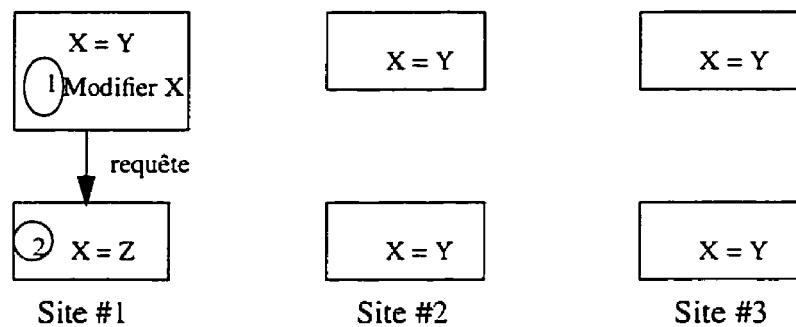

Pour augmenter la disponibilité des données, un système réparti doit permettre leurs replications: c'est-à- dire conserver plusieurs copies d'une donnée dans le système. Ainsi plusieurs postes différents peuvent accéder en même temps à la même donnée. Ceci peut créer des problèmes d'incohérence entre les copies d'une donnée. Supposons que nous disposons de deux copies de la variable  $X$  dans deux sites  $p$  et  $q$ . Si le site  $p$  modifie la valeur de  $X$ , alors deux valeurs distinctes se retrouvent dans le système: la variable est incohérente. Or si la valeur de  $X$  au site  $q$  est invalidée ou mise à jour, alors  $X$  redevient cohérente. Pour que le système fonctionne bien, il faut donc prévoir un mécanisme pour maintenir la cohérence entre les données. Il s'agit donc de définir un protocole de cohérence.

L'une des deux familles de protocoles suivantes est utilisée pour maintenir la cohérence entre les données partagées: le protocole d'invalidation en écriture et le protocole de mise à jour en écriture [Stenström 90]. Ces deux familles de protocoles fonctionnent identiquement lorsqu'il s'agit de lire une donnée. Par contre, lorsqu'il faut modifier une donnée, les mécanismes diffèrent. Pour ce qui est du protocole d'invalidation en écriture, il faut invalider toutes les autres copies sauf celle qu'il faut modifier. Pour ce qui est du

protocole de mise à jour en écriture, il faut modifier toutes les copies de la donnée dans le système.

Il faut par la suite définir un mécanisme de synchronisation pour empêcher une incohérence entre les données lors d'un accès concurrent. En effet, considérons le cas où une opération d'écriture doit mettre à jour toutes les autres copies du système. Si nous autorisons une opération de lecture sur une des copies précédentes avant la fin des mises à jour, alors l'initiateur de la requête travaillera avec une copie périmée. D'où l'importance d'établir un ordre lorsque l'on veut opérer sur les données partagées. En dernier, on spécifie l'algorithme de traitement lors d'une faute d'objets c'est-à-dire l'ensemble des procédures à suivre pour obtenir une donnée qui est localement absente.

L'objectif principal de ce mémoire est de déterminer les bénéfices et les mérites de ces familles de protocoles. Pour réaliser ce but, nous avons recours à l'analyse de performance que nous introduisons brièvement ci-dessous.

## 1.4 Analyse de performance

Pour évaluer les performances des systèmes informatiques, on effectue généralement une modélisation analytique du système ou un modèle de simulation.

Pendant la phase de conception, ce modèle analytique permet:

- d'avoir les caractéristiques globales du système;

- d'obtenir la mesure de certains paramètres critiques;

- de déterminer des éventuels goulots d'étranglement;

- de caractériser le système sous certaines conditions d'utilisation.

L'usage de tels modèles est généralement économique en temps d'exécution car il permet d'obtenir rapidement les paramètres recherchés. Cependant, lorsqu'on souhaite une plus grande précision, ou que les hypothèses des modèles ne sont pas satisfaites, on doit avoir recours à la simulation. Dans le cadre de ce mémoire, nous utilisons la simulation pour valider les modèles analytiques que nous avons développés.

Omis les considérations économiques, la simulation est plus complète par rapport à la modélisation analytique en ce sens qu'elle représente fidèlement le comportement du système modélisé dans ses moindres détails. Les résultats produits par le modèle analytique ne sont généralement valable qu'en régime permanent alors que la simulation fournit en plus des résultats en régime transitoire.

## 1.5 Contributions

Le travail effectué dans le cadre ce mémoire est indispensable pendant la phase de conception d'une mémoire partagée répartie. Ses contributions sont diverses.

Qualitativement, la démarche proposée est indépendante du protocole et elle est valable pour l'évaluation des performances de tous systèmes informatiques. Cette démarche est la suivante:

- Dans un premier temps, extraire du système un premier modèle mettant en jeux les activités de toutes les ressources physiques ainsi que de la façon dont elles sont sollicitées.

- Deuxièmement, obtenir un second modèle mettant en jeu les données sur lesquelles les ressources physiques opèrent.

- Troisièmement, établir la relation entre les deux modèles pour exprimer la dynamique du système et obtenir ainsi un modèle analytique global.

- Quatrièmement, résoudre le modèle analytique obtenu.

Quantitativement, la solution proposée converge rapidement. Elle fournit les paramètres caractéristiques du modèle physique. Ces paramètres guident les concepteurs sur:

- le choix du protocole à utiliser;

- le choix des ressources physiques du système;

- le choix de la taille du système.

Ce qui fait la force de la solution proposée est qu'elle se comporte très bien lorsque la taille du système augmente, ne consomme pas beaucoup d'espace mémoire et en plus fournit un temps de réponse raisonnable sur un ordinateur personnel.

## 1.6 Contenu du mémoire

Ce chapitre nous a permis d'introduire la problématique du partage de mémoire dans les systèmes répartis. Le chapitre suivant sera consacré à une revue de la littérature. Dans ce chapitre nous ferons une présentation ainsi qu'une analyse des résultats et des algorithmes qui sont utilisés dans les systèmes existantes. Nous le terminerons par un exposé de la méthodologie utilisé par le passé pour obtenir les performances de ces systèmes. Ce chapitre nous sera très utile car il nous permettra d'aborder le chapitre 3 avec la connaissance de tous les paramètres à retenir dans notre modèle. Le chapitre 3 sera donc consacré à la description des modèles sur lesquelles nous allons travailler dans le reste du

mémoire. Ce chapitre présentera d'abord le modèle physique retenu. Par la suite, nous allons décrire les différents protocoles retenus pour assurer son bon fonctionnement. Le chapitre 4 sera consacré à la modélisation. Dans un premier temps des modèles analytiques seront obtenus à partir du système physique et des différents protocoles en utilisant une combinaison de réseau de files d'attente et de chaînes de Markov, ainsi qu'une méthode pour les résoudre. Par la suite des modèles de simulation seront développés pour valider les modèles analytiques précédents. Les résultats obtenus à l'aide de ces différents modèles seront présentés au chapitre 5. Enfin le chapitre 6 présentera les conclusions de ce travail.

## CHAPITRE 2

# REVUE DE LA LITTÉRATURE

Dans ce chapitre, nous donnons un aperçu des résultats et des algorithmes qui ont servis par le passé à concevoir et à implanter des systèmes à mémoire partagée et répartie (DSM). Nous nous attarderons aussi sur les systèmes qui illustrent le mieux les aspects spécifiques des systèmes à DSM.

Un système réparti est conçu pour exécuter des programmes parallèles. Pour que le système soit efficace, il faut favoriser l'accès simultané aux données, éviter le plus possible les traitements séquentiels et empêcher l'apparition des goulots d'étranglement. Dans les systèmes répartis, les facteurs qui participent à la dégradation du système sont les accès à distance aux données et les opérations de synchronisation. L'effet de ces opérations peut être réduit lors de la phase de conception en faisant un choix judicieux des paramètres qui les influencent ainsi que des algorithmes qui assurent le fonctionnement du système. Ces choix sont généralement très complexes à cause du fait que ces paramètres ne sont pas indépendants les uns des autres. Il s'avère donc primordial de décrire le choix de ces derniers et de leurs implantations dans les systèmes existants.

### 2.1 Choix du design

Pour concevoir une DSM, il faut trancher sur les points suivants: la structure et la granularité des données partagées, leurs accès, leur cohérence et les problèmes liés à l'hétérogénéité du système [Nitzberg 91, Balter 91]

### 2.1.1 Structure et granularité

Lorsqu'on parle de structure, on fait référence à l'unité sémantique des données partagées en mémoire. La granularité du partage définit la grandeur de l'unité. Il peut s'agir d'octets, de mots, de pages ou de structures de données complexes.

Parmi les systèmes qui ont été mis au point, on en trouve qui ne structurent pas leur mémoire. Nous pouvons citer IVY et DASH, dont les unités de partage sont respectivement des pages de 1 kiloctets et de 16 octets [Nitzberg 91, Lenoski 90]. D'autres, par contre, structurent leurs mémoires. LINDA organise sa mémoire partagée comme une base de données [Carriero 89] et MUNIN la structure en objets [Bennett 90]. Cependant, il faut noter que:

- Une grande granularité augmente le débit du système car le nombre de messages circulant dans le système est réduit. Par contre, la probabilité que deux processus accèdent à la même unité de partage est grande.

- Une petite granularité diminue le débit du système car le nombre de messages circulant dans le système est élevé. Par contre, la probabilité que deux processus accèdent à la même unité de partage est faible.

Au niveau des serveurs, il serait plus avantageux d'avoir une grande granularité, ce qui réduirait la taille des structures nécessaires pour identifier les données et accélérerait leurs accès. Par contre au niveau des machines autonomes, on gagnerait à avoir une granularité plus petite pour permettre l'utilisation des structures de données fournies par les langages de programmation procéduraux tels que Pascal, C, etc.

## 2.1.2 La sémantique de la cohérence

Le programmeur doit comprendre comment la mise à jour des données partagées se réalise à travers le système. Un système implante l'un des types de cohérences suivants: stricte, séquentielle, processeur, faible ou libre [Nitzberg 91].

Pour une cohérence stricte, une lecture retourne toujours la valeur la plus récemment écrite. Quelques exemples de systèmes mis au point sont MERMAID, MIRAGE, IVY et SHIVA [Nitzberg 91].

Dans une cohérence séquentielle, l'exécution d'un programme réparti donne exactement le même résultat si l'exécution s'était effectuée sur un seul processeur. L'ordre de l'exécution des processeurs doit suivre l'ordre imposé par le programme.

Pour une cohérence processeur, les requêtes d'écriture générées par un processeur sont toujours exécutées en ordre. Cependant les écritures générées par des processeurs différents peuvent être exécutées en désordre. Cette cohérence est implantée dans PLUS [Bisiani 90].

Dans le cas d'une cohérence faible, une cohérence séquentielle est imposée pour l'accès aux variables de synchronisation, par contre il n'y a pas de contrainte quant à l'accès aux autres types de variables. Elle est utilisée dans DASH [Lenoski 90].

Pour une cohérence libre, il s'agit d'utiliser une consistance faible avec deux opérations de synchronisation: acquérir et libérer; chaque type d'opération doit être implanté selon une

cohérence de type processeur. DASH l'utilise dans son système.

La gestion de la cohérence peut être transparente à l'usager ou effectuée manuellement par le programmeur. Plusieurs programmeurs prennent pour acquis que dans les systèmes à DSM, le résultat d'une séquence d'écritures générée par un processeur est directement visible par les autres processeurs dans le même ordre. Ces systèmes sont cohérents séquentiellement et laissent au programmeur le choix d'utiliser des opérations de lecture et d'écriture pour implanter les primitives de synchronisation. Lorsqu'il y a plusieurs mémoires physiques, la mise au point d'une cohérence stricte ou séquentielle est très coûteuse en terme de temps, car au niveau du système, toutes les opérations sont traitées en série. Cependant, dans plusieurs applications, des formes de cohérences dans lesquelles les actions générées par un poste ne sont pas immédiatement détectables par les autres postes sont suffisantes. Typiquement, un programme parallèle alterne entre plusieurs opérations de lecture successives et des écritures sur des variables partagées ou des variables de synchronisation. Ainsi, imposer un ordre strict sur toutes des opérations de lecture et d'écriture n'est pas nécessaire si le programmeur comprend que les opérations de synchronisation doivent être utilisées dans certain cas spécifiques seulement; par exemple lorsqu'une opération de lecture suit immédiatement une opération d'écriture sur la même donnée. Dans ces cas, pour que les programmes donnent des résultats corrects, le programmeur doit explicitement utiliser des opérations sur des variables de synchronisation. Il faut noter que plus on avance vers les formes de cohérences plus faibles, un gain de performance est fait au coût d'un modèle de programmation plus complexe et difficile à comprendre par l'usager. Ce gain en performance est dû au fait que le fonctionnement du système requiert moins de synchronisation.

### 2.1.3 Hétérogénéité

Il s'agit de greffer une mémoire partagée sur des machines ayant des architectures différentes. Ceci paraît difficile car ces machines peuvent utiliser des représentations différentes pour leurs types de données de base tels que les entiers et les réels. Il est plus facile d'implanter une DSM si la mémoire est structurée en variables ou en objets dans un langage de haut niveau. Ainsi il devient possible à un compilateur DSM d'insérer des routines de conversion pour accéder à la mémoire partagée. AGORA utilise cette approche [Nitzberg 91]. MERMAID pour sa part utilise une nouvelle approche. Sa mémoire est partagée en pages et une page ne peut contenir qu'un seul type de données. Dès qu'une page passe par deux architectures différentes, une routine convertit ses données dans un format approprié [Nitzberg 91].

Il est possible d'avoir des DSM hétérogènes. Cependant, le temps mis pour faire la conversion des formats peut affecter les performances du système. Puisqu'un des buts visés lors de la conception des DSM est d'obtenir des performances élevées, il est préférable d'utiliser des machines homogènes.

### 2.1.4 Extensibilité

Les systèmes à DSM doivent supporter le plus grand nombre possible de processeurs. Pour le faire, il faut éviter des situations pouvant donner naissance aux goulots d'étranglement. On a donc intérêt à:

- privilégier des traitements répartis au détriment des traitements centralisés;

- favoriser les solutions ne donnant pas de goulots d'étranglement;

- éviter le plus possible des opérations qui font intervenir tous les postes du système comme la diffusion car ils surchargent le réseau de communication.

Il faut aussi noter que le choix de la topologie du réseau de communication est très déterminant quant à l'agrandissement du système. Un exemple de système est IVY qui utilise ETHERNET et qui est limité à 100 noeuds alors que SHIVA qui utilise l'hypercube iPSC/2 d'INTEL peut supporter plus de postes [Nitzberg 91].

## 2.2 Implantation

Une DSM devrait transformer un accès à une variable partagée en une communication interprocessus. Ceci requiert des algorithmes pour localiser les données partagées, les maintenir cohérentes et les mettre à jour.

### 2.2.1 Accès et localisation des données

Dans un système à DSM, tout programme parallèle doit être capable de localiser et d'accéder aux données dont il a besoin. On distingue une distribution statique où les données sont réparties dans chaque site selon un algorithme de répartition. Selon ce schéma, un site peut devenir surchargé, et même maintenir des variables qu'il n'utilise plus.

La distribution dynamique répartit les données là où elles ont été utilisées. Dans ce cas la localisation d'une donnée devient difficile car la donnée change de site au fur et à mesure qu'elle est utilisée. La solution naturelle est l'utilisation d'un serveur centralisé. Le serveur peut poser des problèmes car les requêtes qui lui sont soumises sont traitées séquentiellement. Il peut être surchargé car il peut devenir très sollicité ce qui augmente le temps d'accès aux variables partagées. Tous ces facteurs contribuent à réduire l'efficacité du traitement parallèle. Une stratégie possible consiste à décentraliser le serveur. Dans ce cas, chaque requête se traduit par une diffusion à travers le réseau et seul le site qui possède cette donnée répond à la requête. S'il y a un grand partage entre les données, le réseau devient rapidement surchargé, ce qui a pour conséquence de réduire l'efficacité du système.

Une autre solution consiste à utiliser le schéma de la répartition du propriétaire des données partagées [Nitzberg 91]. Chaque donnée partagée est associée à un propriétaire qui est en fait le site privilégié et ayant la copie de la donnée. Cependant, au fur et à mesure que les données transitent à travers le réseau, le propriétaire change également. Si un site veut une copie de la donnée, il envoie une requête au propriétaire reconnu de cette donnée. Si celui-ci possède toujours la dernière copie mise à jour, il la lui envoie. Par contre si le propriétaire a transféré cette donnée à un autre, il transmet la requête au nouveau propriétaire. Le seul problème avec ce schéma est la surcharge éventuelle du réseau car pour trouver la donnée, il faut consulter tous les sites par où elle a transité. Ceci augmente le temps de réponse de la requête. La solution est de maintenir une liste de tous les propriétaires probables. C'est la technique réalisée par IVY [Nitzberg 91]. Ainsi, dans chaque site et pour chaque donnée partagée, on dispose d'une liste de tous les propriétaires potentiels qu'il suffit d'aller consulter pour avoir la localisation de la donnée voulue.

Lorsqu'il y a réPLICATION de données, une DSM devrait pouvoir localiser toutes les copies existantes dans le système. Deux grandes familles de méthodes sont utilisées. Il s'agit des techniques à répertoire et à chaînage.

Dans les systèmes DASH [Lenoski 90], la réUNION des méMOIRES LOCALES de chaque site CONSTITUE la méMOIRE GLOBALE. Ainsi, cette méMOIRE GLOBALE n'est FORMÉE que d'une méMOIRE LOGIQUE et pour laquelle CHAQUE PORTION de cette méMOIRE est GÉRÉE par le SITE où SE trouve la portion. Les sites EMPLOIENT un réPERTOIRE RÉPARTI, IMPLANTÉ MATÉRIELLEMENT. Pour un SITE donné, le réPERTOIRE CONTIENT l'ADRESSE de tous les BLOCS PHYSIQUES qui SE trouvent dans sa portion de la méMOIRE GLOBALE. Chaque BLOC est REPRÉSENTÉ par un réPERTOIRE qui SPÉCIFIE son étAT et où trouver toutes les autres COPIES. Le SITE où EST DISPONIBLE ce réPERTOIRE est APPELÉ le SITE *initial*. Ainsi, pour LOCALISER une donnée NE se trouvant pas dans un POSTE, il faut COMMUNIQUER avec le SITE *initial*.

IVY [Nitzberg 91] pour sa part, UTILISE à chaque SITE, une TABLE DES PAGES qui CONTIENT pour CHAQUE PAGE, la LISTE DES SITES PROBABLES posséDANT la PAGE. Ainsi, pour LOCALISER une donnée, il faut CONSULTER les PROPRIÉTAIRES PROBABLES.

Par contre, PLUS [Bisiani 90] UTILISE une LISTE CHAÎNÉE RÉPARTIE pour MAINTENIR une TRACE DES COPIES RÉPLIQUÉES. Cette LISTE a DEUX CHAMPS d'INFORMATION. Le PREMIER est l'IDENTITÉ du SITE ayant la PREMIÈRE COPIE à CONSULTER, et le SECOND est l'IDENTITÉ du PROCHAIN SITE ayant une COPIE. Chaque SITE possèDE une TABLE DES PAGES qui ASSOCIE le NUMÉRO d'UNE PAGE au SITE le plus proche posséDANT une COPIE. Ainsi, pour ACCÉDER à toutes les COPIES d'UNE donnée, il faut CONSULTER la TABLE DES PAGES et la LISTE DES SITES VOISINS afin d'obtenir l'ADRESSE du SITE le plus proche ayant une COPIE de cette donnée. Par la SUITE il faut

consulter la liste des copies disponibles sur le site obtenu précédemment.

### **2.2.2 Protocole de cohérence**

S'il n'existe qu'une seule copie d'une donnée partagée à travers le système, tous les accès à cette donnée sont traités séquentiellement car le site qui a la donnée reçoit des requêtes et les traite au fur et à mesure qu'elles arrivent. Pour accroître le parallélisme, il faudrait dupliquer les données; ainsi plusieurs accès à la même donnée peuvent se faire simultanément. On distingue deux types de protocoles de cohérence: l'invalidation en écriture et la mise à jour en écriture.

### **2.2.3 Protocole d'invalidation en écriture**

Ce protocole partage les copies en deux groupes d'usagers: ceux qui peuvent accéder à la donnée en lecture et ceux qui peuvent la modifier. Ici, il peut y avoir plusieurs copies d'une donnée que l'on peut accéder en lecture uniquement et une seule copie de la donnée que l'on peut accéder en écriture. Le protocole invalide toutes les autres copies sauf celle qui peut être accédée en écriture.

Lors d'un accès en lecture, la donnée est obtenue localement si elle est valide. Autrement, une demande de lecture est transmise à un site possédant une copie valide et cette copie est retournée. La copie demeure valide jusqu'à ce qu'une demande d'invalidation soit reçue.

Pour un accès en écriture, la modification de la donnée peut être satisfaite immédiatement si cette donnée n'est pas partagée avec un autre site et que le site auquel elle réside a le privilège d'écriture. Par contre si la donnée est partagée et que le site possède le privilège d'écriture, alors le poste envoie une requête d'invalidation à tous les sites ayant une copie valide. Dès que l'opération d'invalidation est complétée, la donnée peut être modifiée.

#### **Exemple: protocole d'invalidation en écriture de DASH**

DASH est constitué de plusieurs sites reliés par un réseau de communication à haut débit. La mémoire globale est répartie sur chaque site et est accessible par tous. Chaque site est formé de plusieurs processeurs ayant chacun une antémémoire, une portion de la mémoire partagée, une antémémoire partagée pour les accès à distance, un répertoire pour les blocs qui se trouvent dans la portion de la mémoire globale du site, ainsi qu'une interface de communication. Pour présenter le protocole de cohérence, nous utilisons les désignations suivantes: Le *processeur local* est le processeur qui génère la requête; Les *processeurs voisins* sont les processeurs qui partagent la même mémoire locale; le *site initial* est le site qui dispose du répertoire renfermant les informations pour localiser la donnée. Un *site distant* est n'importe quel autre site; la *mémoire locale* fait référence à la portion de la mémoire globale associée au *processeur local* alors que la *mémoire distante* est n'importe quelle autre mémoire.

Un bloc en mémoire peut être dans l'un des trois états suivants: PRIVÉ, s'il n'est présent dans aucun autre poste; PARTAGÉ, s'il est présent dans au moins un autre poste et qu'il n'est pas modifié; SALE, s'il est présent dans un seul poste et qu'il est modifié. Le protocole définit la notion de site propriétaire pour chaque bloc mémoire. 'Le site

propriétaire est le *site initial*. Cependant, dans le cas où le bloc mémoire est présent dans un poste mais dans l'état SALE, alors celui-ci devient le propriétaire. Seul le propriétaire de la donnée peut autoriser une modification de la donnée et mettre à jour l'état du répertoire.

Comme pour les blocs mémoires, un bloc dans une antémémoire peut être dans l'un des états suivants: INVALIDE, PARTAGÉ, ou SALE. Dans l'état PARTAGÉ, il y a plusieurs processeurs qui partagent le bloc. L'état SALE signifie qu'il y a un seul processeur qui contient une copie du bloc mémoire et que cette copie a été modifiée.

Les sections suivantes décrivent les primitives que le protocole de cohérence de DASH met à la disposition du système: *la lecture*, *l'écriture*, et *l'écriture en mémoire*.

### La primitive *lecture*

Lors d'une lecture, si le bloc est présent dans l'antémémoire du poste qui la demande, alors l'antémémoire s'occupe de transférer la donnée au *processeur local*. Par contre, si le bloc est absent, alors le demandeur communique avec les postes avec lesquels il partage la même portion de la mémoire globale. Si le bloc est présent dans l'une des antémémoires et qu'il est à l'état PARTAGÉ, alors la donnée est tout simplement transférée à travers le bus jusqu'au demandeur et il n'y a pas d'accès au *site initial*. Si par contre l'état du bloc est SALE, alors ce site va récrire le bloc en mémoire au *site initial* et transférer la donnée au demandeur. Si la lecture ne peut être satisfaite localement, alors le demandeur transfère sa requête au *site initial* qui obtient l'état de ce bloc en mémoire. Si le bloc est PRIVÉ ou PARTAGÉ, alors la donnée est transférée au demandeur par le contrôleur du répertoire. Il

enregistre aussi le fait que le demandeur a une copie de la donnée. Si le bloc par contre est dans l'état SALE, alors la requête est transférée au site où se trouve la copie SALE.

Ce site propriétaire envoie deux messages en réponse à la demande de lecture. Un message contenant la donnée est envoyée directement au demandeur et une demande de mise à jour est envoyée au site maison. Cette demande d'écriture écrit le contenu du bloc SALE en mémoire et en même temps met à jour le répertoire.

### La primitive écriture

Lors d'une écriture, si la donnée ne peut être satisfaite par le demandeur, alors elle est transmise aux *processeurs voisins* à travers le bus. Si dans l'antémémoire d'un des processeurs on trouve le bloc et que celui-ci est à l'état SALE, alors ce poste transfère le bloc et invalide sa propre copie. Si la donnée ne se trouve pas dans les postes locaux, alors la requête est transférée au site maison. Si le bloc mémoire est PRIVÉ ou PARTAGÉ, alors la donnée est transférée au demandeur ainsi qu'un message indiquant qu'il est le nouveau propriétaire. En plus, si la donnée est PARTAGÉE, alors un message d'invalidation est envoyé à chaque poste contenant le bloc. La donnée ainsi qu'un compteur du nombre d'invalidations sont également envoyées au demandeur. Chacun de ces postes après avoir complété son invalidation renvoie un accusé de réception au demandeur. Si le répertoire indique que le bloc est SALE, alors la requête est transférée au poste ayant cette copie. Ce poste invalide sa copie et envoie un message au demandeur, comportant la donnée et le fait qu'il est le nouveau propriétaire du bloc. Une requête est envoyée également au *site initial* afin de mettre à jour le propriétaire du bloc. Après avoir reçu le message, le *site initial* en informe le nouveau propriétaire.

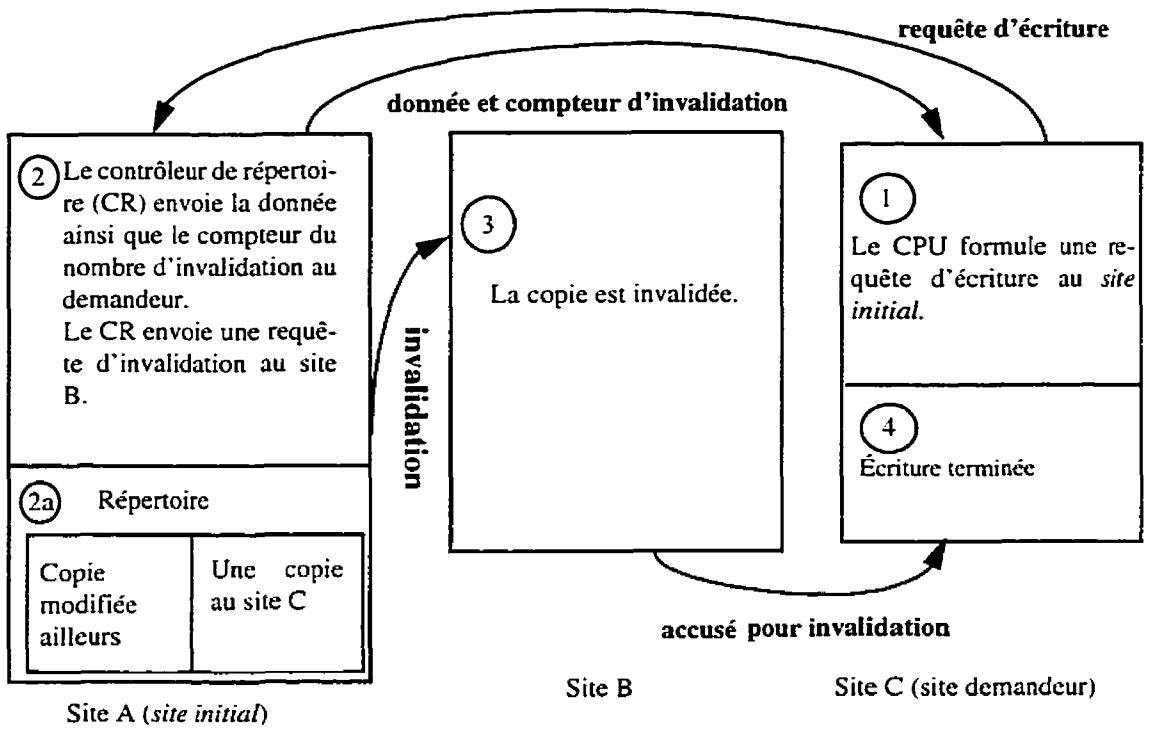

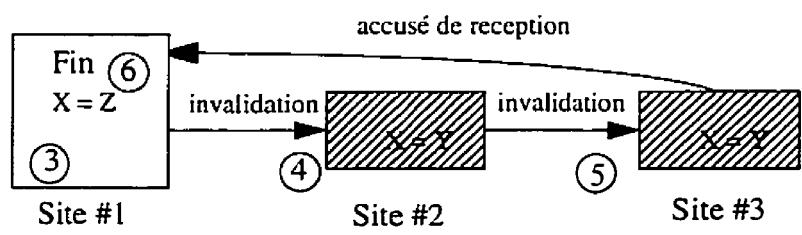

La figure 2.1a illustre une opération d'écriture dans le cas où la donnée est partagée. Le site demandeur est le site C. Le site A est le *site initial* alors que le site B contient une copie du bloc. Le site demandeur formule sa requête et l'envoie au *site initial*. Celui-ci après avoir reçu la requête met à jour son répertoire de copies et envoie un message d'invalidation au site B ayant une copie valide de la donnée. Il envoie également au demandeur un compteur pour le nombre d'accuser de réception à recevoir pour mettre fin à l'opération d'écriture. Dès que le site B finit d'invalider sa copie, il envoie un accusé d'invalidation au demandeur. La réception de cet accusé par le demandeur permet de mettre fin à cette transaction.

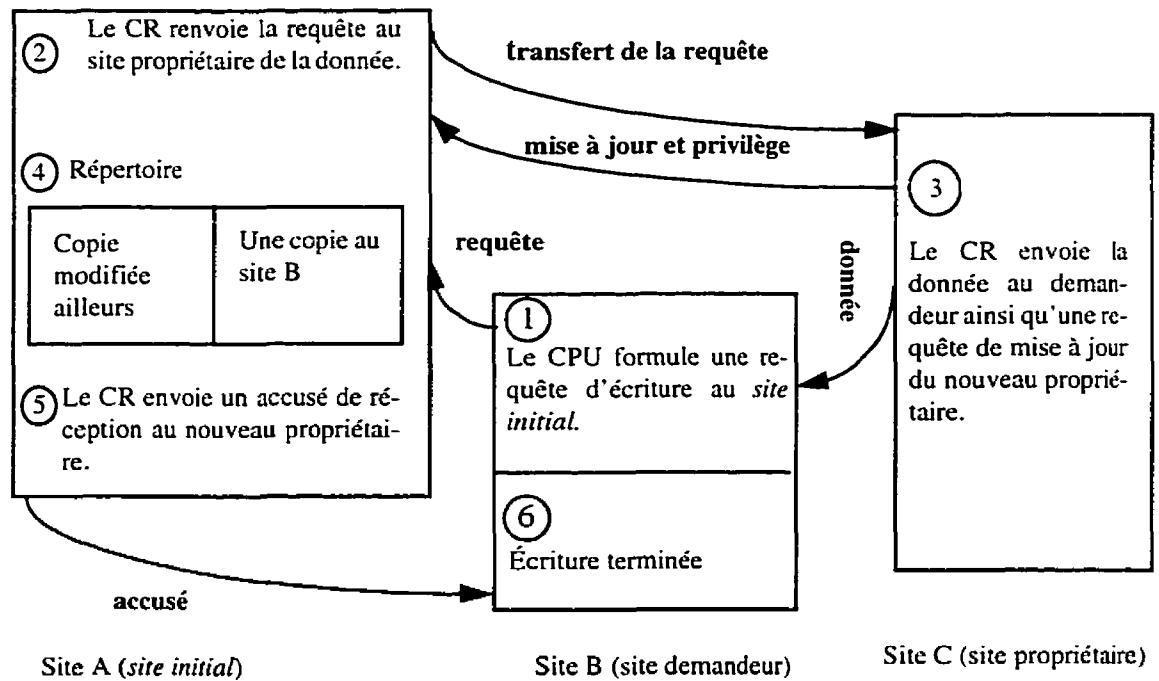

La figure 2.1b illustre une opération d'écriture dans le cas où la donnée est SALE. Le site B est le site demandeur, le site A le *site initial* et le site C le site propriétaire de la donnée. Le demandeur génère sa requête et la transmet au *site initial*. Celui-ci envoie la requête au site propriétaire de la donnée. Ce dernier transmet le bloc au demandeur, et envoie l'identité du nouveau propriétaire au *site initial*. Le *site initial* met à jour son répertoire de copies et envoie un accusé au demandeur. La réception de cet accusé par le demandeur met fin à l'opération d'écriture.

### La primitive écriture mémoire

Tout bloc SALE contenu dans une antémémoire et qui doit être remplacé doit être récrit en mémoire locale. Si le bloc est dans le *site initial*, alors le bloc est tout simplement récrit en mémoire principale. Si par contre il ne se trouve pas dans le *site initial*, alors un message est envoyé au *site initial* qui met à jour la mémoire principale et change l'état du bloc en PRIVÉ.

(a) Donnée PARTAGÉE

(b) Donnée SALE

Figure 2.1 Protocole d'invalidation en écriture de DASH

## 2.2.4 Protocole de mise à jour en écriture

Ce protocole partage les copies en deux groupes d'usagers: ceux qui peuvent accéder à la donnée en lecture et ceux qui peuvent la modifier. Le protocole met à jour toutes les autres copies du système lors d'une opération d'écriture.

Lors d'un accès en lecture, la donnée est obtenue localement si elle est valide. Autrement, une demande de lecture est transmise à un site possédant une copie valide et cette copie est renvoyée. La copie demeure intacte jusqu'à ce qu'une demande de mise à jour soit reçue. Pour un accès en écriture, la modification de la donnée peut être satisfait immédiatement si cette donnée n'est pas partagée et que le site sur lequel elle réside a le privilège d'écriture. Par contre si la donnée est partagée avec un privilège d'écriture, alors le poste envoie une requête pour obtenir le privilège d'écriture ainsi qu'une requête pour une copie de la donnée si la copie locale n'est pas valide. Dès que la donnée devient disponible au site, il la modifie et demande une mise à jour des autres copies du système.

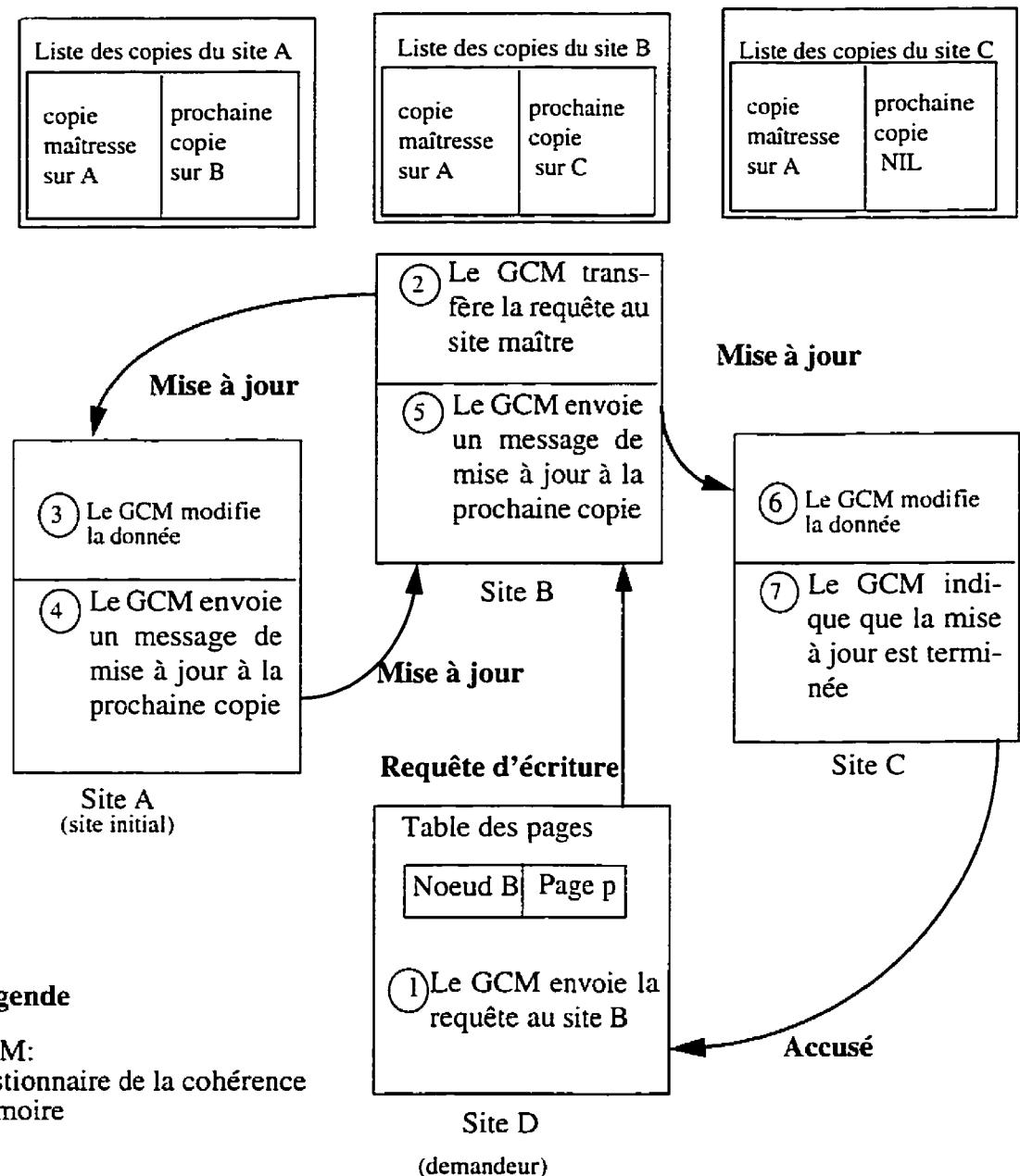

### **Exemple:** protocole de mise à jour en écriture de PLUS [Bisiani 90]

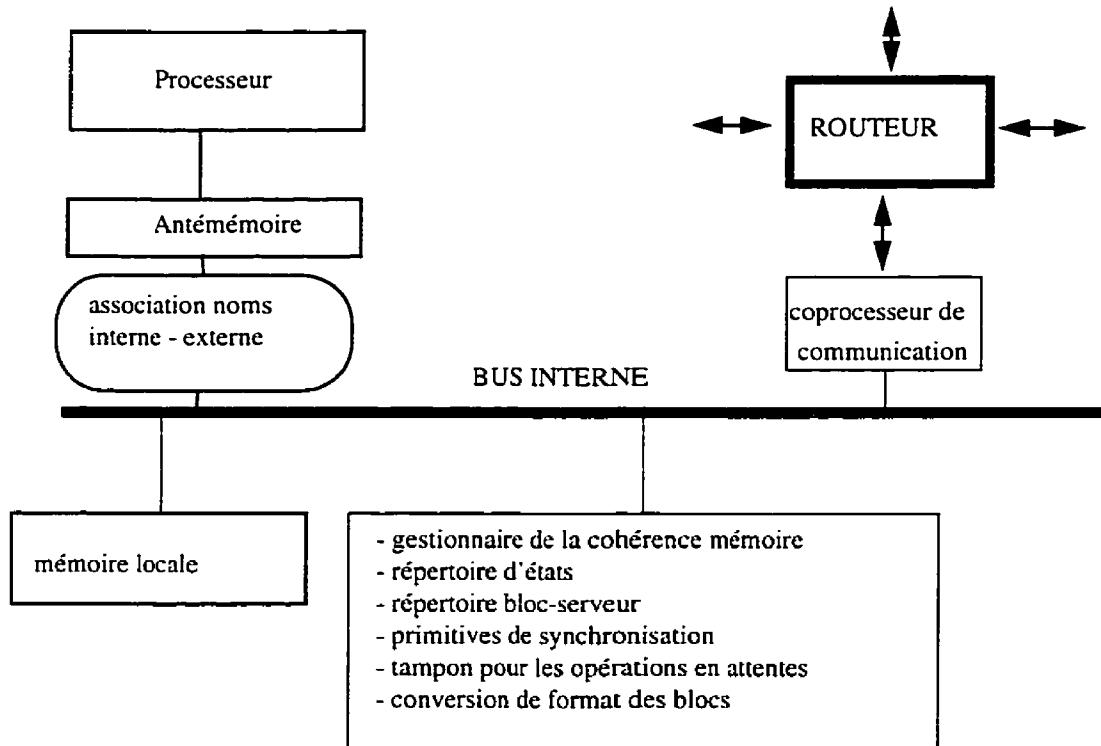

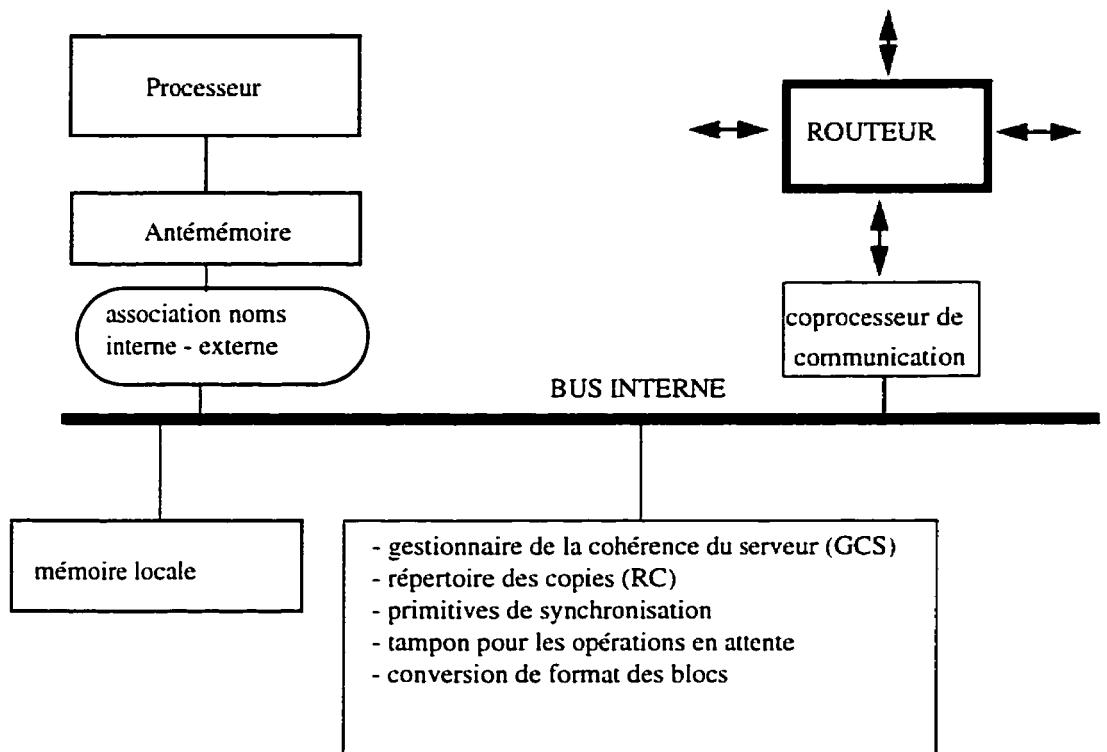

Pour localiser et accéder aux données répliquées, PLUS utilise le protocole de mise à jour en écriture. PLUS est constitué de plusieurs postes reliés par un réseau de communication à haut débit. Chaque site comprend un processeur muni de son antémémoire, une mémoire locale et un gestionnaire de la cohérence mémoire (GCM) qui fait le lien entre la mémoire et le réseau. La mémoire locale est utilisée comme une mémoire vive et comme une antémémoire pour les données qui sont absentes localement et qui se trouvent dans les mémoires des sites.

Une table des pages réunit, la liste des pages physiques répliquées dans les différents sites. Le premier élément de cette liste est l'identité du site ayant la *copie maîtresse* c'est-à-dire la première copie créée. L'adresse globale d'une page physique est le couple formée par l'identité du site ainsi que le numéro de la page que nous notons  $\langle\langle \text{site.id}, \text{page.id} \rangle\rangle$  qui est généré directement par le mécanisme de correspondance de la mémoire du processeur. Le champ *site.id* de l'adresse physique détermine quel site est adressé et le champ *page.id* spécifie le numéro de la page dans ce site. Dans chaque site, l'identité des sites ayant une copie répliquée est accessible au GCM, par la liste des copies qui comporte deux champs dont un pour l'adresse de la copie maîtresse et l'autre pour l'adresse de la prochaine copie. Les sections suivantes décrivent les primitives de lecture et d'écriture du protocole de cohérence de PLUS.

#### La primitive *lecture*

Si le site local est indiqué, alors la mémoire locale est lue. Autrement, le GCM envoie une requête de lecture au site identifié, attend la réponse et envoie la donnée au processeur.

#### La primitive *écriture*

Cette opération est plus compliquée car elle va porter sur toutes les copies. L'écriture est d'abord effectuée sur la copie maîtresse avant d'être propagée sur les autres copies contenues dans la table des pages.

Si l'adresse physique indique un autre site, alors le GCM envoie une requête d'écriture à ce site. Autrement, il consulte la table de la copie maîtresse pour localiser la première

copie. Si la copie maîtresse est locale, alors il procède à l'écriture de la mémoire locale et envoie un message de mise à jour à la prochaine copie si jamais il y en a une. Si par contre la copie maîtresse n'est pas locale, alors la requête est transférée au site contenant la copie maîtresse.

Un GCM qui reçoit une requête d'écriture de son site demande une mise à jour par la copie maîtresse puis l'opération se propage sur les prochaines copies. Finalement, le site contenant la dernière copie sur la liste des copies envoie un accusé de réception au processeur qui a généré la requête originale. Ainsi se termine la requête.

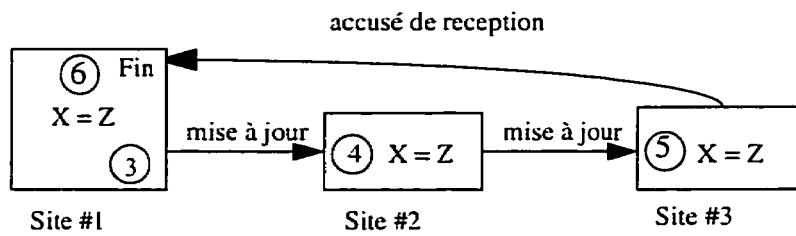

La figure 2.2 représente le protocole mise à jour en écriture de PLUS. Il s'agit d'une opération d'écriture. Tous les sites ont une copie de la donnée sauf le site D qui est demandeur. Le site A est le site ayant la copie maîtresse. La requête d'écriture est formulée par le demandeur puis envoyé au site B. Celui-ci consulte sa liste des copies pour obtenir l'adresse du site ayant la copie maîtresse et lui transmet la requête. Celui-ci met à jour sa copie et transmet la requête au site B ayant la prochaine copie. Le site B procède de la même façon. Dès que la requête parvient au site C, la liste des copies est terminée et ce dernier envoie un accusé au demandeur. On constate que les mises à jour commencent toujours par la copie maîtresse et ensuite se propagent sur les autres sites de la liste des copies. L'opération d'écriture est terminée lorsque le dernier noeud de la liste envoie un accusé de réception au demandeur de la requête d'écriture.

Figure 2.2 Protocole mise à jour en écriture de PLUS

## 2.2.5 Stratégies de remplacement

À la suite d'une faute d'objet [Tanenbaum 87], le GCM doit, pour libérer de la place mémoire, retirer un objet de sa mémoire pour l'objet manquant. Si l'objet a été modifié depuis son chargement en mémoire, il faut l'écrire en zone sûre sinon l'objet lu remplace simplement l'objet supprimé.

Le choix de l'objet peut se faire au hasard. Mais si on choisit un objet qui sera peu utilisé, on améliore sensiblement les performances du système. Si par contre on choisit un objet très demandé, alors il est possible que des références ultérieures lui soient adressées ce qui entraîne une perte de temps inutile. Plusieurs algorithmes de remplacement ont été décrits dans la littérature. Nous allons en présenter dans les paragraphes suivants quelques algorithmes parmi les plus utiles.

### 1 - Algorithme optimal

Lors d'une faute d'objet, l'algorithme optimal choisit un objet à remplacer qui ne fera pas l'objet d'une référence ultérieure, ou à défaut, un objet auquel on fera la référence la plus tardive. L'algorithme optimal suppose la connaissance à priori de l'ensemble des chaînes de référence, c'est-à-dire l'identité des objets auxquels on accédera.

### 2- Remplacement d'un objet non récemment utilisé.

Dans cet algorithme, deux bits d'information sont associés à chaque objet utilisé. Le premier bit R ou bit de référence est positionné par le matériel à chaque lecture ou écriture

de l'objet. Le second bit M ou bit de modification est positionné quand on écrit dans l'objet. Ces bits doivent être mis à jour à chaque référence. Il est donc important qu'il soit fait par le matériel. Dès qu'un bit est mis à 1, il reste dans cet état jusqu'à ce que le GCM vienne le mettre à 0. Le fonctionnement du système est le suivant: au déclenchement d'un processus (programme en exécution), le GCM met à 0 les bits de tous les objets. Périodiquement (par exemple à chaque interruption d'horloge), le bit R est mis à 0 pour différencier les objets qui n'ont pas été récemment référencés des autres. Lorsqu'une faute de d'objet se produit et que la mémoire est pleine, le GCM parcourt tous les objets et les répartit dans l'une des quatre catégories suivantes en fonction des différentes valeurs des bits R et M:

- 0: non référencé, non modifié;

- 1: non référencé, modifié;

- 2: référencé, non modifié;

- 3: référencé, modifié.

Ces différentes catégories permettent plus tard de faire un choix de l'objet à remplacer.

Il faut noter que les interruptions ne réinitialisent pas le bit M car il permet de savoir si l'objet a été modifié ou non. L'algorithme de l'objet le moins récemment utilisé retire un objet au hasard de la catégorie qui à le plus petit numéro. Cet algorithme est relativement efficace et fournit des performances qui sont souvent suffisantes même si elles ne sont pas optimales.

### 3- Cercle chronologique d'utilisation (Least Recently Used (LRU))

Puisque les objets récemment utilisés ont une probabilité plus élevée d'être utilisés dans un futur proche, une objet inutilisé depuis longtemps a une probabilité faible d'être réutilisé prochainement. On choisit donc comme victime l'objet ayant fait la référence la plus ancienne. Cet algorithme est théoriquement réalisable mais très coûteux. En effet, il faut mémoriser une liste chaînée de tous les objets en mémoire, l'objet le moins utilisé étant à la fin de la liste et le plus utilisé à la tête de la liste. La difficulté de cet algorithme vient du fait que cette liste doit être mise à jour chaque fois que la mémoire est adressée. Localiser un objet, le supprimer puis la déplacer au début de la liste sont des opérations très coûteuses en temps de processeur.

### 4- Cercle chronologique de changement (FIFO)

Il s'agit d'une approximation de la précédente. Cet algorithme choisit comme victime l'objet le plus anciennement chargé. Pour le faire, le GCM maintient une liste de tous les objets en mémoire, l'objet le plus ancien étant en tête et l'objet le plus récent étant à la fin. Dès qu'il faut remplacer un objet, la premier objet de la liste est retiré et on insère le nouvel objet à la fin de la liste.

Une modification simple de l'algorithme FIFO consiste à examiner le bit R et M de l'objet le plus ancien. Si cet objet appartient à la catégorie 0 (non référencé et non modifié), cet objet est supprimé. Sinon on vérifie le bit R et M de l'objet un peu moins ancien et ainsi de suite. S'il n'y a pas d'objet de la catégorie 0, on applique la même procédure aux catégories 1, 2, puis 3.

## 5- Algorithme de la seconde chance

C'est une variante de l'algorithme précédent. L'idée ici est de tester le bit R de l'objet le plus ancien. S'il est à 0, l'objet est immédiatement remplacé. Sinon ce bit est mis à 0 et l'objet est mis en fin de la liste des objets comme s'il venait d'être chargé en mémoire et la recherche continue. Cet algorithme cherche donc un ancien objet qui n'a pas été référencé. Si tous les objets ont été référencés, l'algorithme de la seconde chance est équivalent à l'algorithme FIFO parce que la liste sera ordonnée de manière à avoir l'objet le plus anciennement référencé à la tête et le plus récemment référencé à la fin.

### 2.3 Analyse de performance des systèmes à DSM

Dans la section précédente, nous avons passé en revue les différents paramètres et algorithmes à tenir compte pour l'implantation d'une DSM. Cependant pour avoir un estimé des performances attendues du système une fois construit, il faut recourir à l'analyse de performance.

Des évaluations de performance des protocoles de cohérence des multiprocesseurs ont déjà été réalisées. Un modèle de simulation a été proposé par Achibald et Baer [Archibald 86] pour comparer les différents protocoles. Une technique basée sur les réseaux de Pétri temporisés généralisés a été décrite dans [Vernon 86], mais la complexité de la technique la rend peu appropriée pour les systèmes de grande envergure. Le modèle des réseaux de file d'attente a d'abord été utilisé pour la modélisation des réseaux à commutation de paquets [Yang 88]. Par la suite ces concepts furent appliqués à l'analyse de performance des multiprocesseurs. Qing Yang et Laxmi N. Bhuyan proposent un concept basé sur la

décomposition hiérarchique [Bhuyan 89]. Ils utilisent un modèle à deux niveaux pour obtenir les mesures de paramètres caractéristiques du système. Le modèle de haut niveau est constitué d'une chaîne de Markov dont les états représentent les différents états que peuvent prendre les données dans les antémémoires du système dû au protocole de cohérence. Au bas niveau, les taux des transitions entre les états de la chaîne de Markov du niveau supérieur peuvent être calculés en résolvant le réseau de file d'attente qui représente le système physique et logique. Le modèle de haut niveau fournit des probabilités stationnaires pour la détermination des probabilités de routage dans le modèle de bas niveau. La solution complète est obtenue en itérant d'un modèle à l'autre jusqu'à convergence.

Ce chapitre nous a permis de constater que la conception des systèmes DSM est très complexe car il faut faire des choix qui ne sont pas nécessairement indépendants et qui sont d'autant plus importants qu'ils affectent directement la performance du système. Le chapitre suivant sera donc consacré à la spécification physique du système et de son fonctionnement logique.

# CHAPITRE 3

## LES MODÈLES

Dans le chapitre précédent, nous avons présenté quelques paramètres nécessaires pour la conception d'une mémoire partagée répartie ainsi que décrit leurs influences sur les performances du système qui en résulte. Nous avons également décrit la méthodologie utilisée pour évaluer les performances de ces systèmes. Il ressortait de cette description que la spécification du système physique et de son protocole de cohérence étaient suffisant pour sa modélisation analytique. Dans le présent chapitre, nous allons nous inspirer de cette étude pour décrire l'architecture de notre système ainsi que son fonctionnement logique.

### 3.1 Le modèle physique

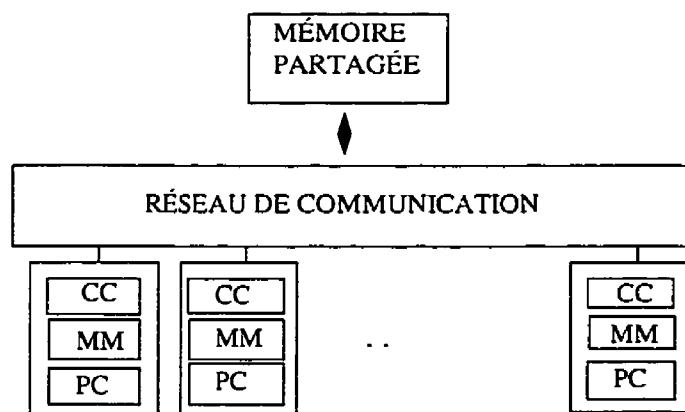

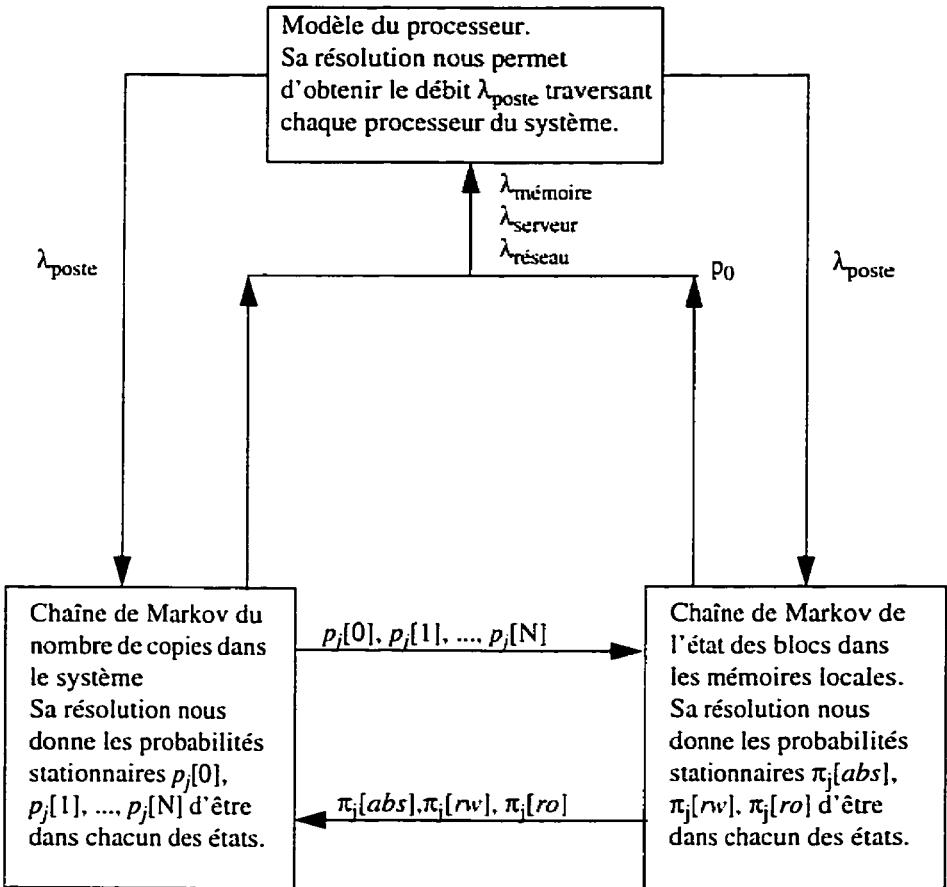

Le système que nous voulons analyser peut être représenté par le modèle de la figure 3.1.

Figure 3.1 Le système physique

Dans ce modèle, plusieurs postes de travail sont reliés par un réseau à grande vitesse. Chaque poste de travail possède un processeur de calcul (PC), un module mémoire (MM) et un ou plusieurs coprocesseurs de communication (CC). Le but de notre travail est d'implanter une mémoire partagée à partir des modules mémoires disponibles localement à chaque poste de travail.

Le réseau de communication fournit une interface au niveau transport sur laquelle nous faisons les hypothèses ci-dessous.

- Tous les postes peuvent communiquer entre eux en émettant des messages. Il n'y a donc pas de poste isolé du reste du réseau.

- Il n'y a pas d'altération, ni de duplication, ni de perte des messages émis par les postes, c'est-à-dire que le délai d'acheminement des messages est non nul mais fini.

- Il n'y a pas de déséquencement des messages, c'est-à-dire que les messages sont reçus par un site, dans le même ordre qu'ils ont été émis par le site émetteur.

- Un site peut détecter une panne du système de communication ou d'un autre poste.

Dans le cas où c'est le réseau qui est défectueux il annule sa requête. Dans le cas où c'est le poste récepteur qui est défectueux, il change de destinataire.

Le système est asynchrone en ce sens qu'il n'y a pas une horloge centrale qui diffuse son heure aux autres sites. Lorsqu'un poste a une donnée à transmettre, il formule une requête en spécifiant son adresse et celle du récepteur dans un paquet et le transmet au réseau. Une fois le paquet transmis, le réseau redevient libre et peut être utilisé par un autre poste. Le récepteur envoie une réponse de manière similaire à l'émetteur.