|                   |                                                                                                                                                            |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Titre:</b>     | Capteur d'images intégré en mode courant et à résolution variable                                                                                          |

| Title:            |                                                                                                                                                            |

| <b>Auteur:</b>    | Jonathan Coulombe                                                                                                                                          |

| Author:           |                                                                                                                                                            |

| <b>Date:</b>      | 2000                                                                                                                                                       |

| <b>Type:</b>      | Mémoire ou thèse / Dissertation or Thesis                                                                                                                  |

| <b>Référence:</b> | Coulombe, J. (2000). Capteur d'images intégré en mode courant et à résolution variable [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. |

| Citation:         | <a href="https://publications.polymtl.ca/8878/">https://publications.polymtl.ca/8878/</a>                                                                  |

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

|                           |                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------|

| <b>URL de PolyPublie:</b> | <a href="https://publications.polymtl.ca/8878/">https://publications.polymtl.ca/8878/</a> |

| PolyPublie URL:           |                                                                                           |

|                                 |               |

|---------------------------------|---------------|

| <b>Directeurs de recherche:</b> | Mohamad Sawan |

| Advisors:                       |               |

|                   |              |

|-------------------|--------------|

| <b>Programme:</b> | Non spécifié |

| Program:          |              |

**UNIVERSITÉ DE MONTRÉAL**

**CAPTEUR D'IMAGES INTÉGRÉ EN MODE COURANT**

**ET À RÉSOLUTION VARIABLE**

**JONATHAN COULOMBE**

**DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE**

**ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION**

**DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES**

**(GÉNIE ÉLECTRIQUE)**

**NOVEMBRE 2000**

**©Jonathan Coulombe, 2000.**

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Notre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-60892-1

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

**CAPTEUR D'IMAGES INTÉGRÉ EN MODE COURANT**

**ET À RÉSOLUTION VARIABLE**

présenté par : JONATHAN COULOMBE

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. SAVARIA Yvon, Ph.D., président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

Mme. WANG Chunyan, Ph.D., membre et codirectrice de recherche

M. BRAULT Jean-Jules, Ph.D., membre

## **REMERCIEMENTS**

Je souhaiterais en premier lieu adresser mes sincères remerciements au professeur Mohamad Sawan qui m'a accueilli dans son équipe de recherche et m'a permis d'effectuer mes travaux dans d'excellentes conditions. Ces mots de remerciements s'adressent également à Chunyan Wang, pour ses recommandations qui ont significativement contribué à l'avancement de mes travaux, ainsi qu'aux professeurs Yvon Savaria et Jean-Jules Brault, qui ont accepté de participer au jury d'examen de ce mémoire.

Le fait de côtoyer les membres de l'équipe de recherche PolySTIM a aussi été pour moi un atout important. Les nombreuses discussions techniques qu'ils m'ont permis d'avoir, ainsi que leur franche camaraderie, ont rendu l'ensemble des mes travaux des plus agréables.

Je ne saurais oublier mes parents et mon frère pour leur soutien moral inconditionnel et pour leur encouragement tout au long de mes études. Merci aussi à ceux qui m'ont côtoyé quotidiennement pour une longue période pendant mes travaux, Martin et Sophie.

Je tiens à exprimer toute ma gratitude envers ceux qui n'ont pas hésité à me fournir un généreux coup de main aux moments les plus opportuns : Steve, Éric, Karine, Jasmin, Caro, Guru et, tout particulièrement, Marie-Jo, qui m'a offert, tous les jours de la rédaction, un support d'une importance et d'une qualité inestimables.

Finalement, je souhaite remercier le Fonds pour la Formation de Chercheurs et pour l'Aide à la Recherche ainsi que le Groupe de Recherche Inter-universitaire en Architecture des Ordinateurs et VLSI pour leur soutien financier.

## RÉSUMÉ

Que ce soit pour le divertissement, la recherche scientifique, la robotique ou nombre d'autres applications, les capteurs d'images sont des éléments déterminants pour les performances des systèmes auxquels ils se rattachent. En effet, ils constituent le premier élément dans la chaîne d'acquisition et de traitement de l'information. Aussi, les nouvelles applications de haute technologie rendent les spécifications auxquelles doivent se soumettre les capteurs de plus en plus contraignantes. C'est pourquoi le domaine de l'acquisition d'images est en constante évolution et qu'il est intéressant de s'y attarder.

L'objectif du travail présenté est de concevoir un circuit d'acquisition d'images intégré présentant une interface entièrement numérique, une souplesse d'utilisation et qui soit applicable dans des situations variées sans compensation par pièces mécaniques ou optiques. Il doit être possible d'utiliser le capteur pour une large variété d'applications; toutefois, les principales contraintes prises en considération au cours de sa conception sont celles soumises par un système de stimulation intracorticale destiné aux victimes de cécité profonde.

La première de ces contraintes est la nécessité de limiter l'énergie consommée par le système. Ensuite, pour pallier la faiblesse de la résolution de l'image qui peut être transmise au cerveau, un zoom est une fonctionnalité recherchée afin de pourvoir l'utilisateur du maximum d'information visuelle selon les conditions d'utilisation. En combinaison avec une matrice de cellules photosensibles comportant plus de pixels que l'image que l'on désire acquérir, une résolution variable permet de réaliser un véritable zoom électronique. Le fait d'effectuer cette opération au niveau même de la capture d'image plutôt que par un traitement numérique subséquent minimise le transfert et le traitement des données. Par conséquent, la consommation s'en voit diminuée. L'évaluation de la moyenne de la sortie de pixels adjacents permet de réduire la perte

d'information associée à la réduction de la résolution par rapport à une approche de sous-échantillonnage de la matrice.

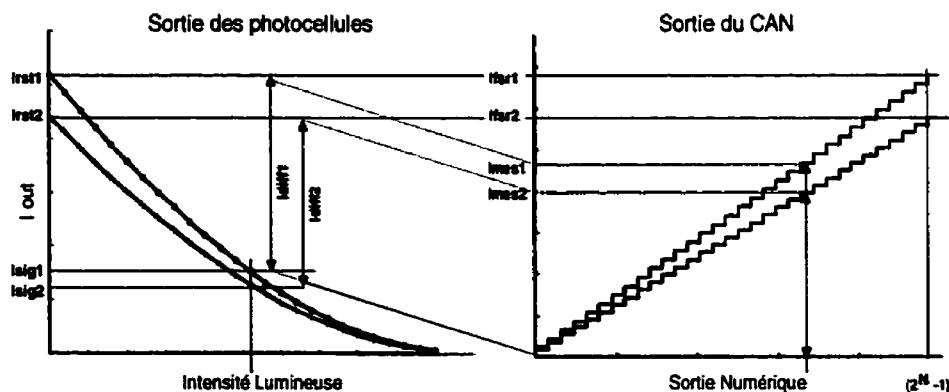

Une première proposition de circuit répondant aux principales spécifications mentionnées plus haut est détaillée et les choix sont justifiés. La première caractéristique fondamentale du circuit est que le signal analogique est véhiculé en tout point en mode courant. Ceci permet au système de fonctionner à faible tension d'alimentation, minimisant ainsi la puissance dissipée. L'utilisation du mode courant est cependant peu répandue dans la littérature, puisque plusieurs éléments liés à la fabrication rendent la réponse significativement différente d'un pixel à l'autre, détériorant ainsi la qualité de l'image. Cette erreur, désignée « Fixed Pattern Noise (FPN) », est croissante avec la luminosité incidente. Une nouvelle technique de réduction de l'erreur, basée sur la méthode usuelle de double échantillonnage corrélé, mais où la sortie de chaque pixel est normalisée sur une échelle qui lui est propre à même la conversion analogique à numérique, élimine l'erreur linéaire de gain interpixel. Ceci permet de réduire le niveau d'erreur total sur toute la plage d'intensité lumineuse. Aussi, une méthode simple permettant l'évaluation instantanée de la valeur moyenne de groupes de  $1 \times 1$ ,  $2 \times 2$  ou  $4 \times 4$  pixels, n'affectant pas le rapport signal sur bruit, est proposée et utilisée. Ceci procure trois niveaux de zoom au niveau de la capture d'image.

Un circuit a été fabriqué afin de vérifier la fonctionnalité des modules proposés. Le circuit comporte différentes caractéristiques rendant possible la vérification des différents modules analogiques de façon indépendante. On présente aussi un système de tests dédié au capteur comprenant un circuit de mesures analogiques, un contrôleur externe implanté sur un circuit programmable, ainsi qu'un logiciel d'interface permettant de commander les tests facilement à partir d'un ordinateur personnel.

Le système a démontré la fonctionnalité de tous les blocs du capteur intégré. Il a permis, notamment, d'évaluer certaines caractéristiques du procédé utilisé en tant que capteur

d'images. La technique de réduction du FPN proposée a été comparée avec la technique de double échantillonnage corrélé et confirme la validité de la méthode utilisée.

Les observations expérimentales font aussi ressortir certaines limitations de l'approche proposée. En effet, la réduction du bruit n'est pas complète et il persiste des erreurs dues aux contributions non linéaires des différents éléments actifs des photocellules. L'approche en mode courant avec la méthode proposée de réduction du FPN se limite donc à des applications où une excellente qualité d'images n'est pas une nécessité. Aussi, on remarque que la présence d'un obturateur électronique réduit les plages dynamiques intrascène et interscène du capteur. Cette constatation est plus préoccupante dans le cas du stimulateur visuel considérant que ceci diminue les conditions de luminosité dans lesquelles peut être utilisé le capteur à un taux de lecture d'images donné.

Une autre approche est alors proposée afin d'améliorer principalement la plage dynamique interscène de la caméra. Les modifications proposées améliorent aussi la souplesse d'utilisation du capteur en permettant des niveaux arbitraires de zoom. Ceci implique cependant l'utilisation d'une nouvelle architecture et d'un nouveau convertisseur. Des simulations sur ce dernier indiquent que le capteur proposé est en mesure d'atteindre un taux de lecture d'images de 30 Hz à résolution maximale, soit  $128 \times 128$  pixels, tout en offrant une faible consommation. Des considérations pratiques importantes à appliquer lors de la réalisation d'un circuit mixte de taille importante sont aussi présentées.

Ce travail constitue une première itération concluante dans le processus de conception et de réalisation d'un système d'acquisition d'image versatile et peu énergivore. Des efforts visant à améliorer la plage intrascène du capteur devraient permettre à court terme de réaliser une caméra intégrée particulièrement adaptée pour un système de stimulation du cortex visuel pour aveugles.

## ABSTRACT

Image sensors are the first link in the chain of image acquisition and processing systems. They tend to determine the performance of any system to which they belong, be they used in entertainment, scientific research, robotics, or for other purposes. They are governed by ever more stringent specifications, arising from new high technology applications. The field of image retrieval is thus constantly evolving, which makes it worthy of further study.

The aim of this project is to design an integrated image acquisition circuit with a fully digital interface, flexible and able to adapt to a variety of situations, without requiring additional mechanical and optical parts. Although the sensor must be suitable for use in a broad range of applications, the main requirements considered during its design were those of an intracortical stimulation system intended for the profoundly blind.

The first of these requirements is the need to limit the system's power consumption. The second is to offset the poor resolution of the image sent to the brain by incorporating a zoom, which gives the user the maximum amount of visual information available for each given circumstance. Together with a matrix of light sensitive cells containing more pixels than the image one wants to retrieve, a variable resolution function makes it possible to achieve a true electronic zoom. Because this operation is completed at the image acquisition phase rather than by means of subsequent digital processing, transfer and processing of data are minimized, which in turn keeps down power consumption. An evaluation of the average output of adjacent pixels allows for a greater reduction in the loss of information associated with the reduction in resolution than would be the case with a matrix sub-sampling approach.

The project describes and sets out justifications for an initial circuit that complies with the principal specifications listed above. The first fundamental characteristic of the circuit is that the analog signal is transmitted throughout in current mode. This enables the system to operate at low voltage, thus reducing power consumption. However, the use of current mode is not widespread in the literature, since a number of factors cause the response to vary significantly from pixel to pixel, which leads to a loss of image quality. This error, called, Fixed Pattern Noise (FPN), expands with any increase in incident luminosity. The linear error of interpixel gain is eliminated by a method that combines correlated double sampling with analog to digital conversion scaling for each pixel. This makes it possible to reduce the error level throughout a wide range of light intensity. A simple method is proposed to instantaneously average groups of 1x1, 2x2, or 4x4 pixels without influencing the signal/noise ratio. This creates three levels of zoom in the image acquisition process.

A circuit was manufactured to verify the practicality of the proposed modules. This circuit features various characteristics which make it possible to evaluate the various analog modules independently. A test system for the sensor is also presented, comprising an analog measurement circuit, an external controller implemented on a programmable circuit, as well as an interface software that allows for easy test control from a PC.

The system demonstrated the functionality of all the modules of the integrated sensor. The validity of the proposed FPN reduction scheme was assessed and confirmed by a comparison with the correlated double sampling method.

Experimental observations also highlighted a number of limitations of the proposed approach. It was determined that noise reduction is not complete, and that errors persist owing to non linear contributions of transistors in the photocells. The current mode approach with the proposed FPN reduction method is thus limited to applications that do not require excellent image quality. It was also noted that the presence of an electronic

shutter reduces the intrascene and interscene dynamic ranges of the sensor. This fact is of concern with respect to the visual stimulator, since it limits the light conditions under which the sensor can be used at a given image frame rate.

Another approach is thus proposed, mainly with a view to improving the camera's interscene dynamic range. The proposed modifications also enhance the sensor's flexibility by allowing for arbitrary zoom levels. However, this implies the use of a new architecture and a new converter. Simulations on the latter indicate that the proposed sensor enable image acquisition at a frame rate of 30 Hz at maximum resolution (128×128 pixels), while consuming little power.

This project is a first conclusive iteration in the process of designing and creating a versatile image acquisition system requiring little power. Efforts to improve the intrascene dynamic range of the sensor should make it possible in the near future to create an integrated camera that is tailored to the needs of a system to stimulate the visual cortex of the blind.

## TABLE DES MATIÈRES

|                                                                     |             |

|---------------------------------------------------------------------|-------------|

| <b>REMERCIEMENTS.....</b>                                           | <b>iv</b>   |

| <b>RÉSUMÉ.....</b>                                                  | <b>v</b>    |

| <b>ABSTRACT .....</b>                                               | <b>viii</b> |

| <b>TABLE DES MATIÈRES .....</b>                                     | <b>xi</b>   |

| <b>LISTE DES TABLEAUX.....</b>                                      | <b>xiv</b>  |

| <b>LISTE DES FIGURES .....</b>                                      | <b>xv</b>   |

| <b>LISTE DES ANNEXES .....</b>                                      | <b>xxi</b>  |

| <b>LISTE DES ABBRÉVIATIONS ET SYMBOLES .....</b>                    | <b>xxii</b> |

| <b>INTRODUCTION.....</b>                                            | <b>1</b>    |

| <b>CHAPITRE 1 : GÉNÉRALITÉS SUR LES CAPTEURS D'IMAGES.....</b>      | <b>5</b>    |

| 1.1    Introduction .....                                           | 5           |

| 1.2    Captation lumineuse à l'aide de semi-conducteurs .....       | 6           |

| 1.3    Capteurs d'images numériques .....                           | 9           |

| 1.3.1    Critères de performance .....                              | 10          |

| 1.3.2    Capteurs d'images à « Charge Coupled Devices (CCD) » ..... | 12          |

| 1.3.3    Capteurs d'images CMOS.....                                | 14          |

| 1.4    Types de capteurs CMOS.....                                  | 15          |

| 1.4.1    Capteur Passif.....                                        | 15          |

| 1.4.2    Capteurs actifs .....                                      | 16          |

| 1.5    Techniques de réduction du FPN .....                         | 22          |

| 1.6    Exemples de fonctions spécialisées de capteurs CMOS .....    | 25          |

|                                                |                                                           |    |

|------------------------------------------------|-----------------------------------------------------------|----|

| 1.6.1                                          | <b>Capteurs à résolution variable</b>                     | 27 |

| 1.7                                            | <b>Conclusion</b>                                         | 30 |

| <b>CHAPITRE 2 : DESCRIPTION DU CAPTEUR</b>     |                                                           | 31 |

| 2.1                                            | <b>Introduction</b>                                       | 31 |

| 2.2                                            | <b>Vue d'ensemble du système</b>                          | 32 |

| 2.2.1                                          | <b>Fonctions programmables du capteur</b>                 | 32 |

| 2.3                                            | <b>Description détaillée du système</b>                   | 34 |

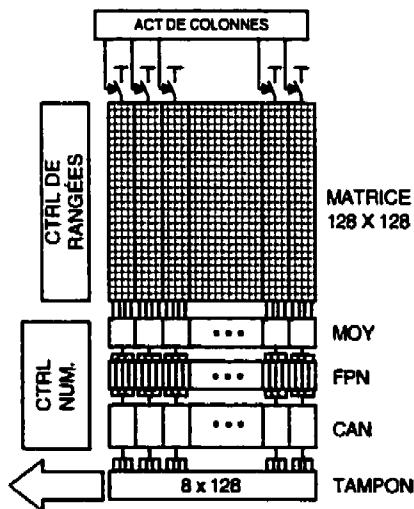

| 2.3.1                                          | <b>Schéma bloc</b>                                        | 34 |

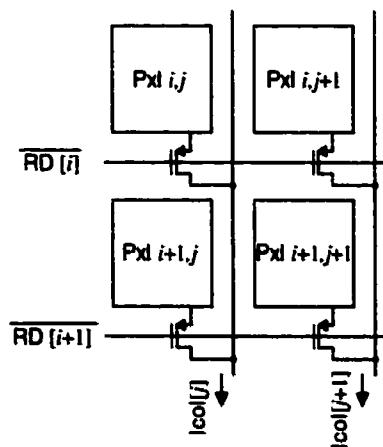

| 2.3.2                                          | <b>Matrice APS</b>                                        | 35 |

| 2.3.3                                          | <b>Cellule unitaire</b>                                   | 37 |

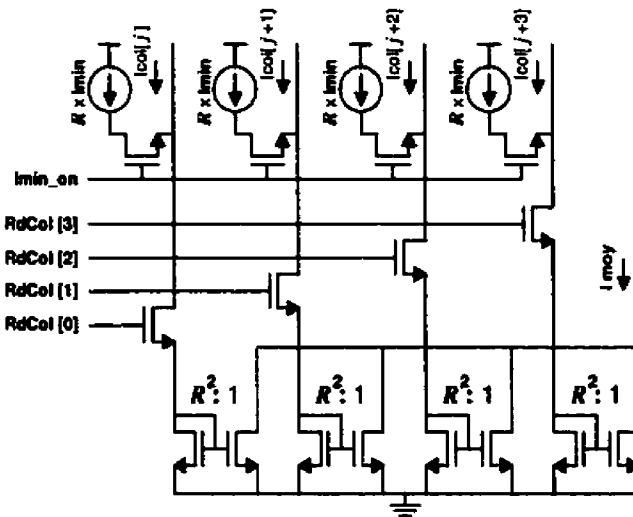

| 2.3.4                                          | <b>Circuit de multiplexage et d'évaluation de la VMPA</b> | 38 |

| 2.3.5                                          | <b>Circuit de réduction du FPN</b>                        | 40 |

| 2.3.6                                          | <b>Convertisseur Analogique à Numérique</b>               | 45 |

| 2.3.7                                          | <b>Mémoire tampon</b>                                     | 50 |

| 2.4                                            | <b>Conclusion</b>                                         | 52 |

| <b>CHAPITRE 3 : SYSTÈME DE CARACTÉRISATION</b> |                                                           | 54 |

| 3.1                                            | <b>Introduction</b>                                       | 54 |

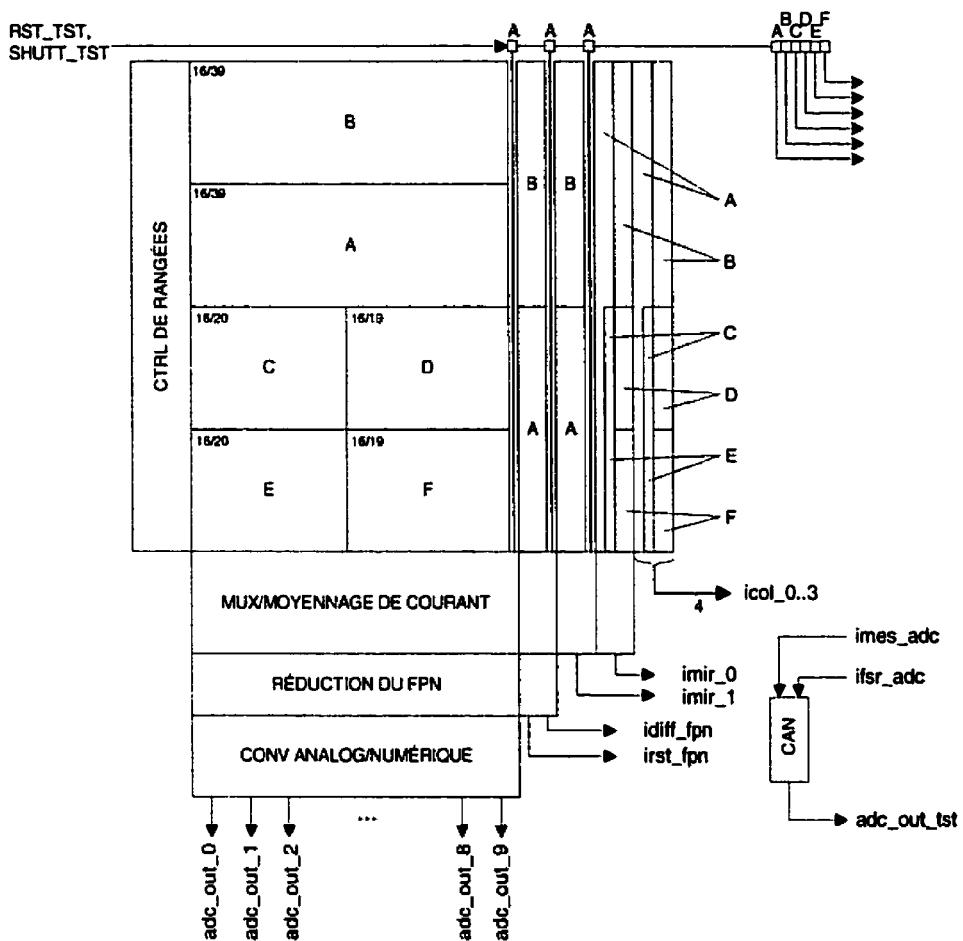

| 3.2                                            | <b>Capteur d'images de tests</b>                          | 54 |

| 3.2.1                                          | <b>Matrice de Cellules Photosensibles</b>                 | 55 |

| 3.2.2                                          | <b>Évaluation de la VMPA</b>                              | 55 |

| 3.2.3                                          | <b>Réduction du FPN</b>                                   | 56 |

| 3.2.4                                          | <b>Contrôle numérique</b>                                 | 56 |

| 3.2.5                                          | <b>Polarisation des modules constituant le capteur</b>    | 60 |

| 3.2.6                                          | <b>Testabilité</b>                                        | 61 |

| 3.2.7                                          | <b>Dessin des masques</b>                                 | 63 |

| 3.3                                            | <b>Description du système de tests</b>                    | 67 |

| 3.3.1                                          | <b>Installation matérielle</b>                            | 68 |

| 3.3.2                                          | <b>Logiciel du système de tests</b>                       | 70 |

|                                                     |                                                   |            |

|-----------------------------------------------------|---------------------------------------------------|------------|

| 3.3.3                                               | Contrôleur du Capteur de Tests.....               | 71         |

| 3.4                                                 | Conclusion.....                                   | 77         |

| <b>CHAPITRE 4 : EXPÉRIMENTATION ET ANALYSE.....</b> |                                                   | <b>78</b>  |

| 4.1                                                 | Introduction .....                                | 78         |

| 4.2                                                 | Résultats expérimentaux .....                     | 78         |

| 4.2.1                                               | Réponse à la lumière du capteur .....             | 78         |

| 4.2.2                                               | Plage dynamique optique .....                     | 81         |

| 4.2.3                                               | Uniformité de la réponse.....                     | 84         |

| 4.2.4                                               | Réduction du FPN .....                            | 85         |

| 4.2.5                                               | Évaluation de la VMPA .....                       | 87         |

| 4.2.6                                               | Performances du CAN .....                         | 88         |

| 4.2.7                                               | Principales sources du bruit de lecture.....      | 92         |

| 4.3                                                 | Principales modifications à apporter.....         | 95         |

| 4.3.1                                               | Vue d'ensemble du système proposé .....           | 98         |

| 4.3.2                                               | Convertisseur Analogique à Numérique .....        | 100        |

| 4.3.3                                               | Évaluation de la valeur moyenne de colonnes ..... | 104        |

| 4.4                                                 | Conclusion.....                                   | 105        |

| <b>CONCLUSION.....</b>                              |                                                   | <b>107</b> |

| <b>BIBLIOGRAPHIE .....</b>                          |                                                   | <b>111</b> |

| <b>ANNEXES.....</b>                                 |                                                   | <b>120</b> |

## **LISTE DES TABLEAUX**

|             |                                                                                                       |     |

|-------------|-------------------------------------------------------------------------------------------------------|-----|

| Tableau 3.1 | Signaux de communication entre le PC et le contrôleur de tests .....                                  | 71  |

| Tableau 3.2 | Description des champs des mots d'instructions.....                                                   | 72  |

| Tableau 3.3 | Modules du séquenceur du contrôleur du système de tests.....                                          | 74  |

| Tableau 3.4 | Définition des registres de paramètres .....                                                          | 75  |

| Tableau 4.1 | Mesure de la plage dynamique intrascène des photocellules avec<br>8 bits de résolution en sortie..... | 82  |

| Tableau 4.2 | Erreur maximale du rapport $I_{mes}/I_{ref}$ après réduction du FPN .....                             | 86  |

| Tableau 4.3 | Performances simulées du CAN algorithmique .....                                                      | 89  |

| Tableau 4.4 | Performances simulées du convertisseur en cascade .....                                               | 103 |

| Tableau E.1 | Liste et définition des broches du capteur d'images de tests .....                                    | 153 |

## LISTE DES FIGURES

|             |                                                                                                                                                                   |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1  | Absorption d'un photon dans une jonction PN .....                                                                                                                 | 7  |

| Figure 1.2  | Architecture d'un capteur CCD.....                                                                                                                                | 12 |

| Figure 1.3  | Mécanisme de transfert de charges dans un capteur CCD (tiré de [5])....                                                                                           | 13 |

| Figure 1.4  | Cellule photosensible CMOS passive .....                                                                                                                          | 16 |

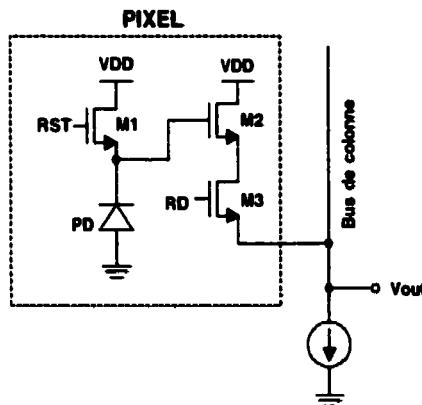

| Figure 1.5  | Pixel à photodiode en mode tension.....                                                                                                                           | 17 |

| Figure 1.6  | Pixel à photodiode en mode courant .....                                                                                                                          | 18 |

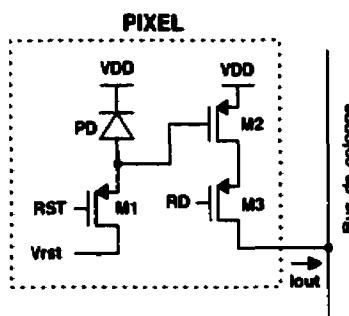

| Figure 1.7  | Pixel à modulation de durée d'impulsions (tiré de [14]).....                                                                                                      | 20 |

| Figure 1.8  | Pixel à modulation de fréquence d'impulsions (tiré de [57]).....                                                                                                  | 20 |

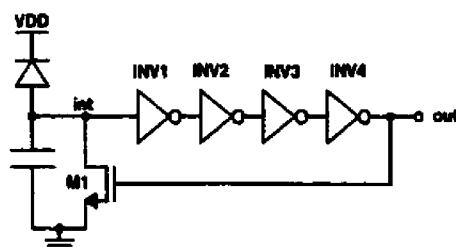

| Figure 1.9  | Pixel à transistor à photogrille.....                                                                                                                             | 22 |

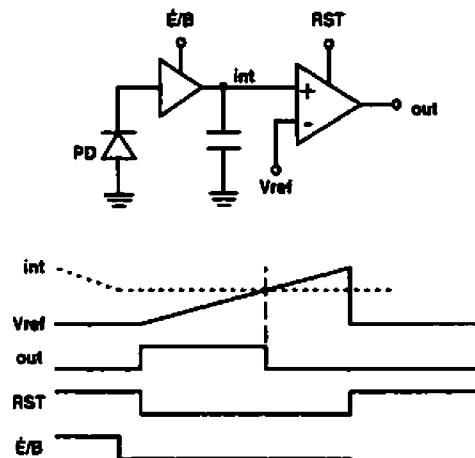

| Figure 1.10 | Circuit de réduction du FPN par CDS.....                                                                                                                          | 23 |

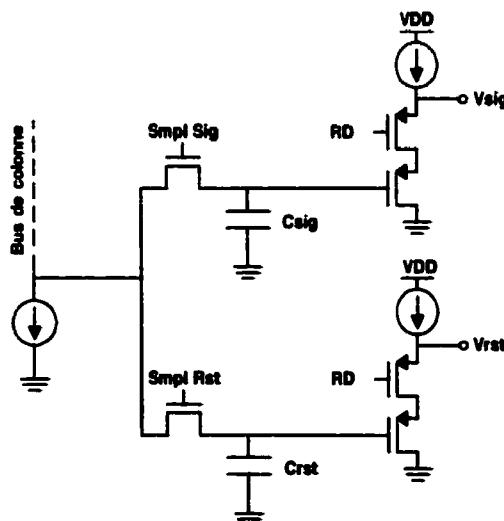

| Figure 1.11 | Réduction du FPN par CDS en mode courant.....                                                                                                                     | 24 |

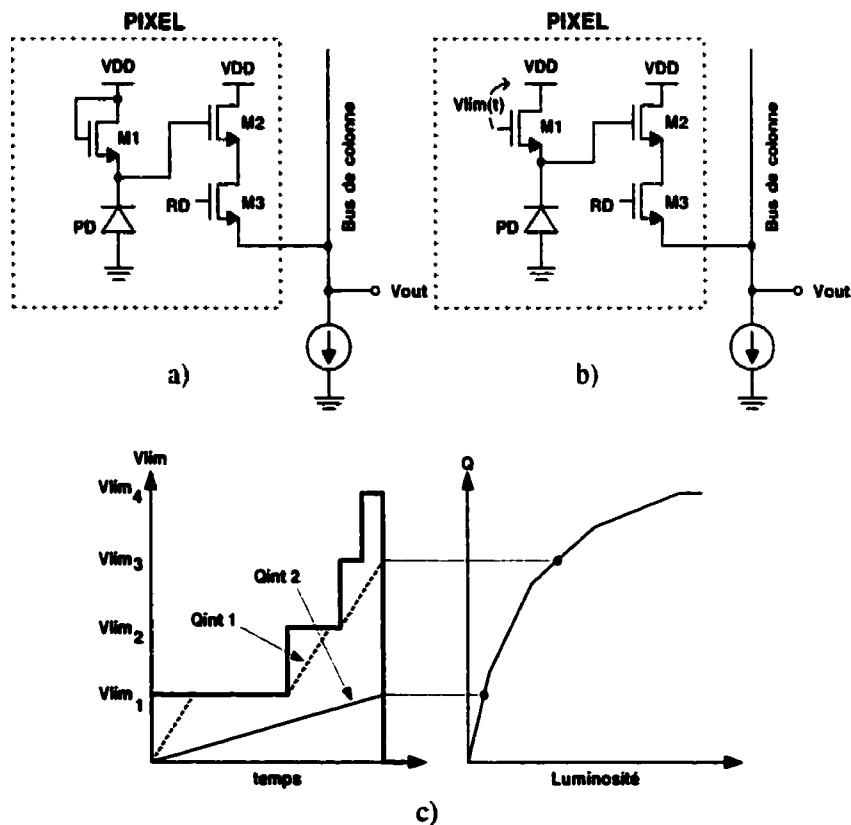

| Figure 1.12 | Cellules à réponse (a) logarithmique et (b) pseudo-logarithmique<br>ainsi que (c) l'évolution des charges accumulées dans la cellule<br>pseudo-logarithmique..... | 26 |

| Figure 1.13 | Étapes d'acquisition d'image pour le calcul de la VMPA à<br>résolution réduite (3x3) .....                                                                        | 29 |

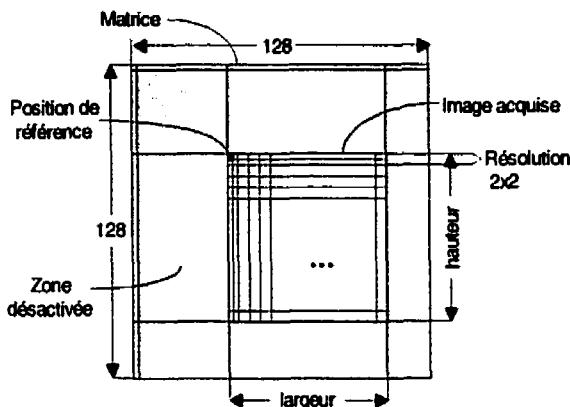

| Figure 2.1  | Illustration d'une configuration d'acquisition d'image.....                                                                                                       | 33 |

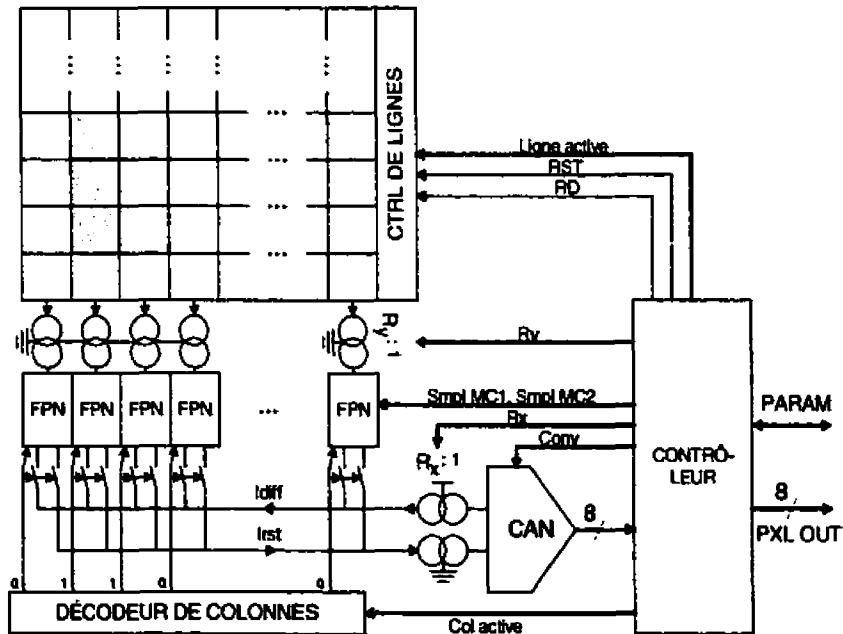

| Figure 2.2  | Schéma bloc de la caméra intégrée .....                                                                                                                           | 34 |

| Figure 2.3  | Configuration de la matrice APS .....                                                                                                                             | 36 |

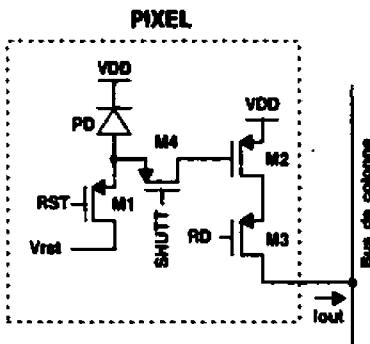

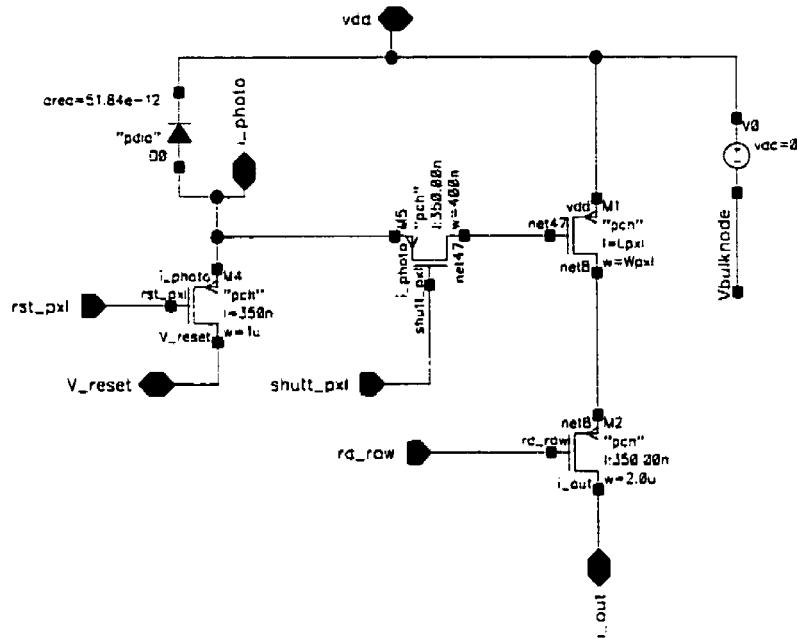

| Figure 2.4  | Pixel avec obturateur électronique .....                                                                                                                          | 38 |

|                    |                                                                                               |           |

|--------------------|-----------------------------------------------------------------------------------------------|-----------|

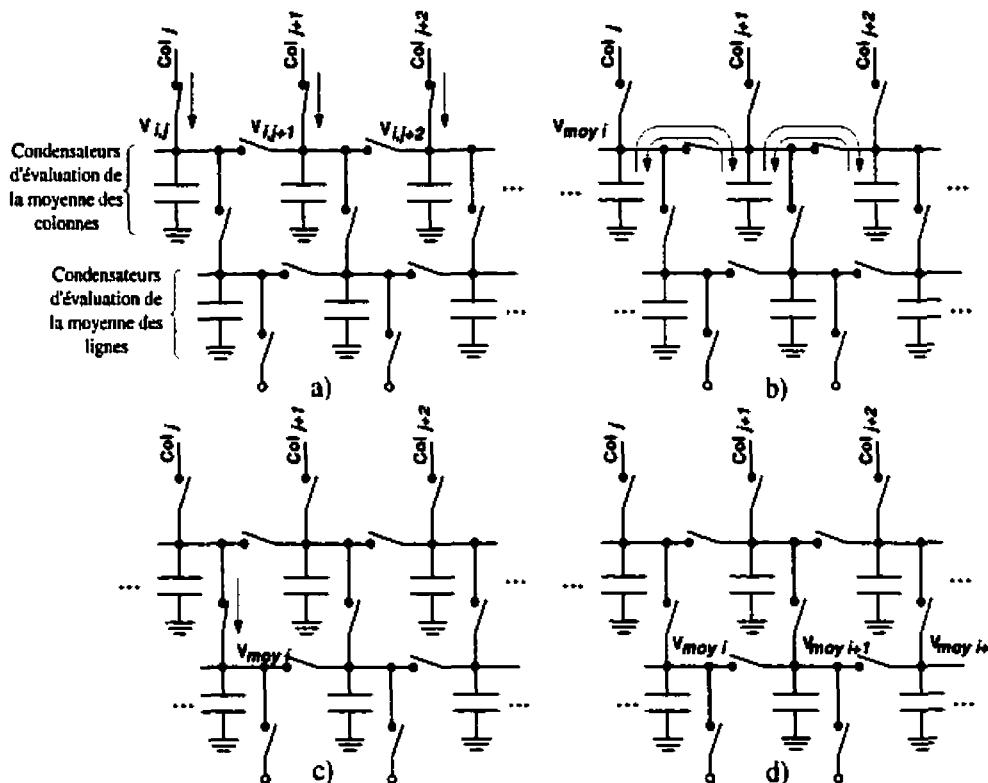

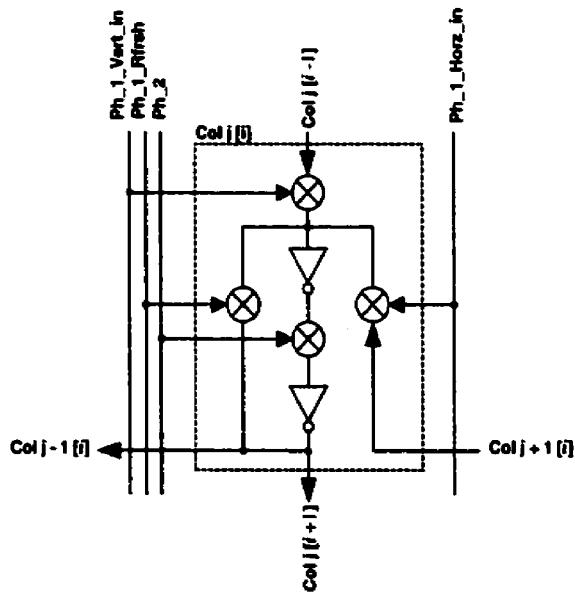

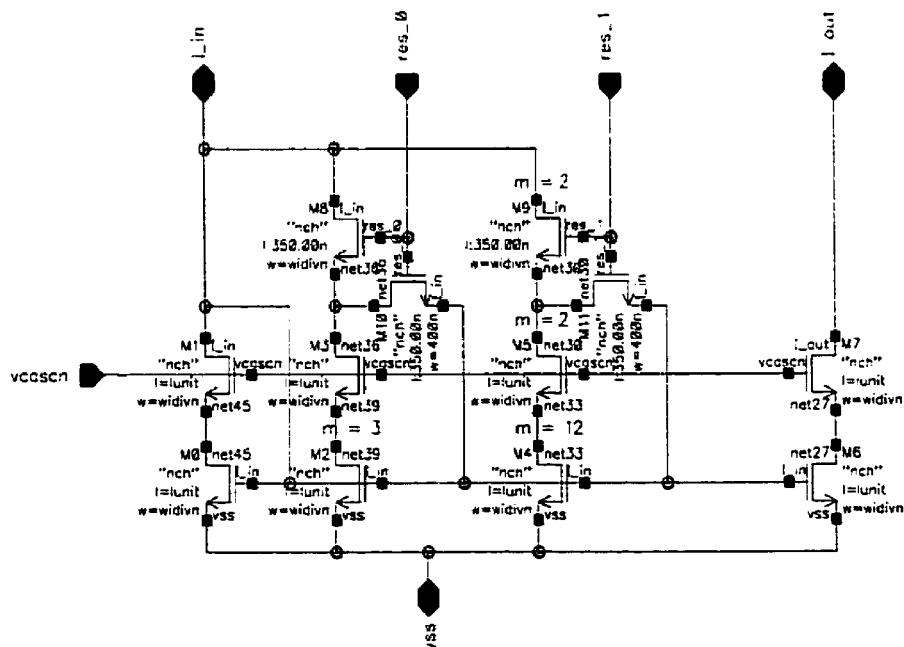

| <b>Figure 2.5</b>  | <b>Circuit de multiplexage et d'évaluation de la Valeur Moyenne de Pixels Adjacents .....</b> | <b>39</b> |

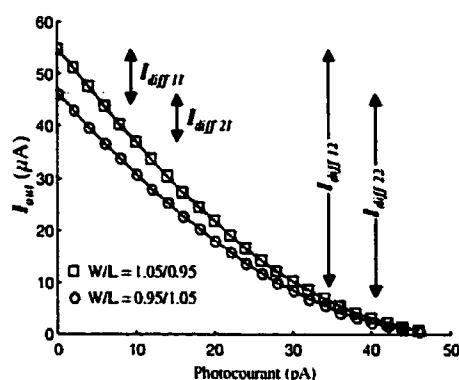

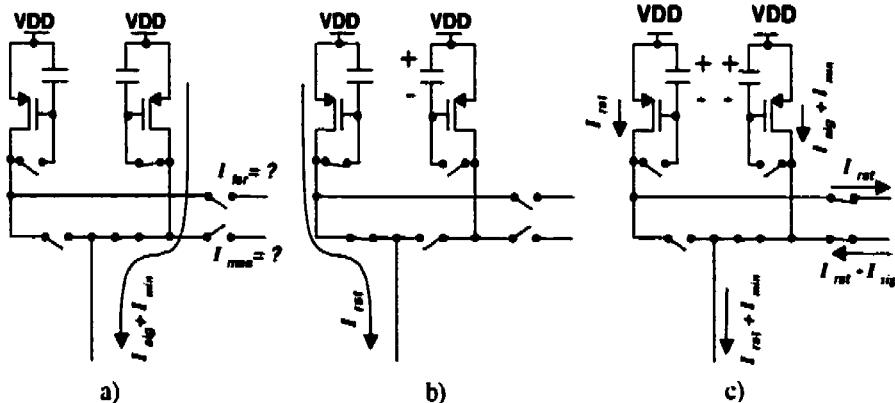

| <b>Figure 2.6</b>  | <b>Sorties de deux pixels aux gains différents .....</b>                                      | <b>41</b> |

| <b>Figure 2.7</b>  | <b>Conversions du signal Lumineux à Analogique à Numérique .....</b>                          | <b>42</b> |

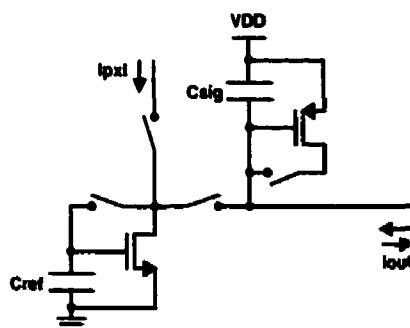

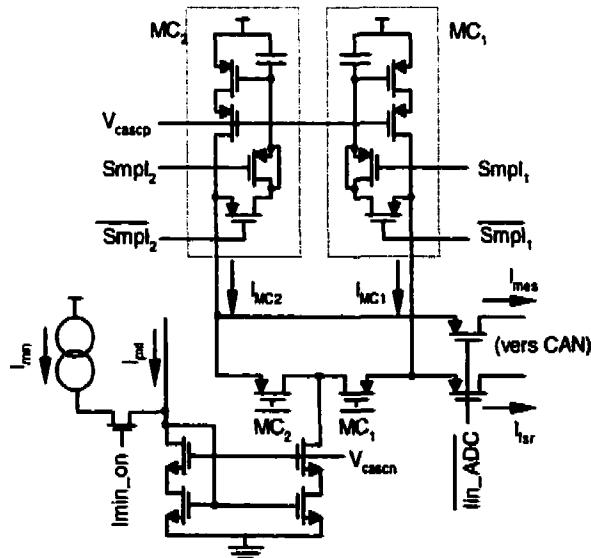

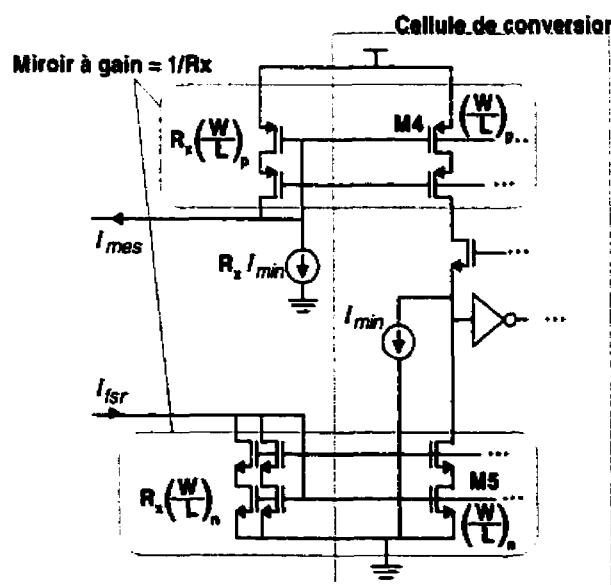

| <b>Figure 2.8</b>  | <b>Circuit de réduction du FPN .....</b>                                                      | <b>43</b> |

| <b>Figure 2.9</b>  | <b>Utilisation du circuit de réduction du FPN .....</b>                                       | <b>44</b> |

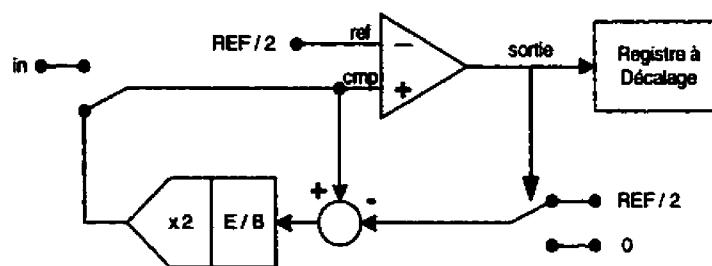

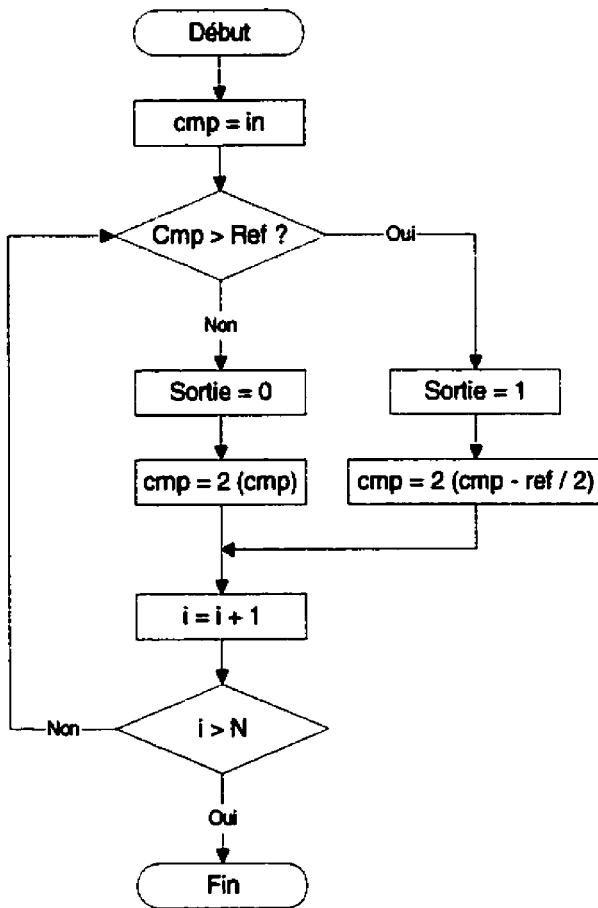

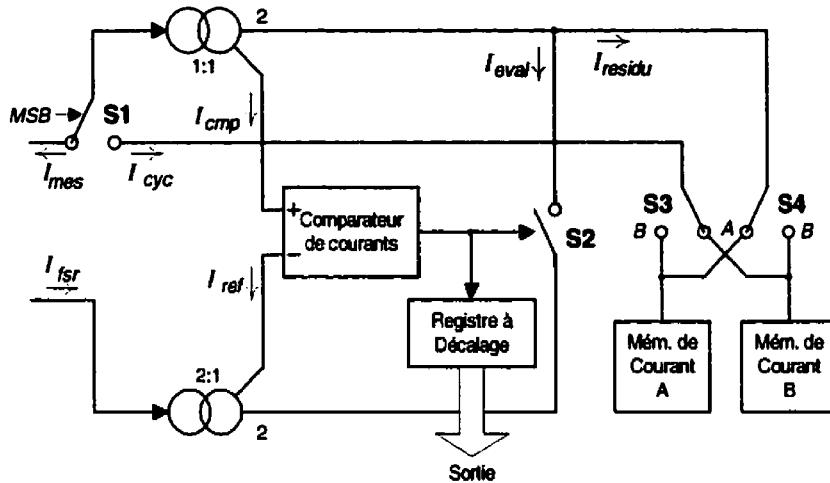

| <b>Figure 2.10</b> | <b>Convertisseur Algorithmique-Cyclique .....</b>                                             | <b>45</b> |

| <b>Figure 2.11</b> | <b>Organigramme de conversion .....</b>                                                       | <b>46</b> |

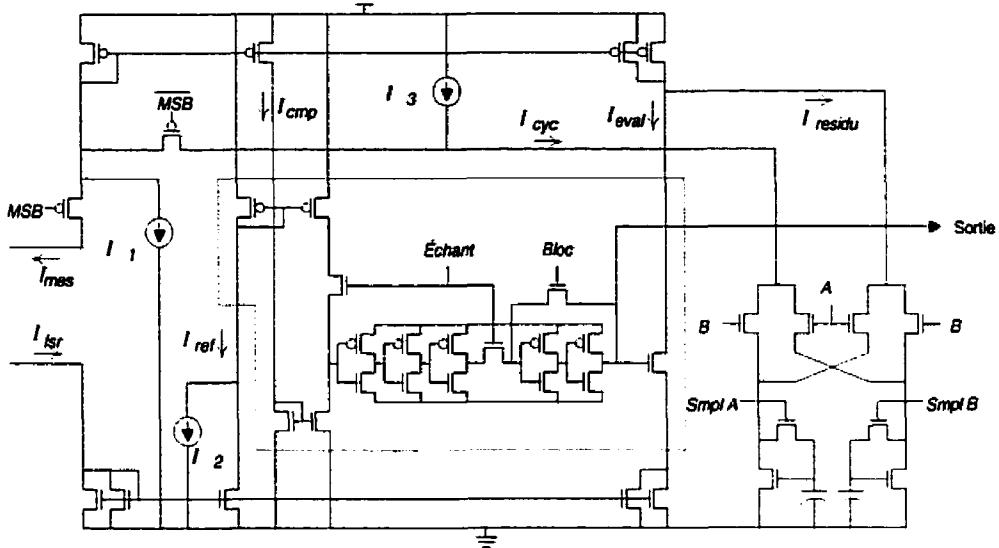

| <b>Figure 2.12</b> | <b>Convertisseur Algorithmique-Cyclique en mode courant.....</b>                              | <b>47</b> |

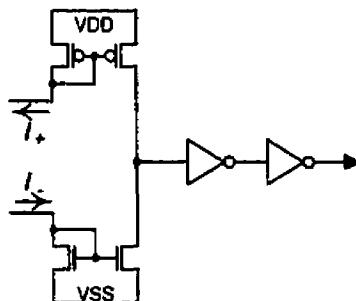

| <b>Figure 2.13</b> | <b>Comparateur de courants de base.....</b>                                                   | <b>48</b> |

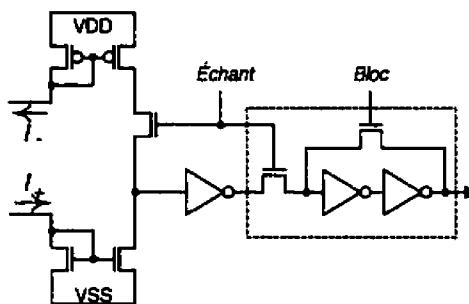

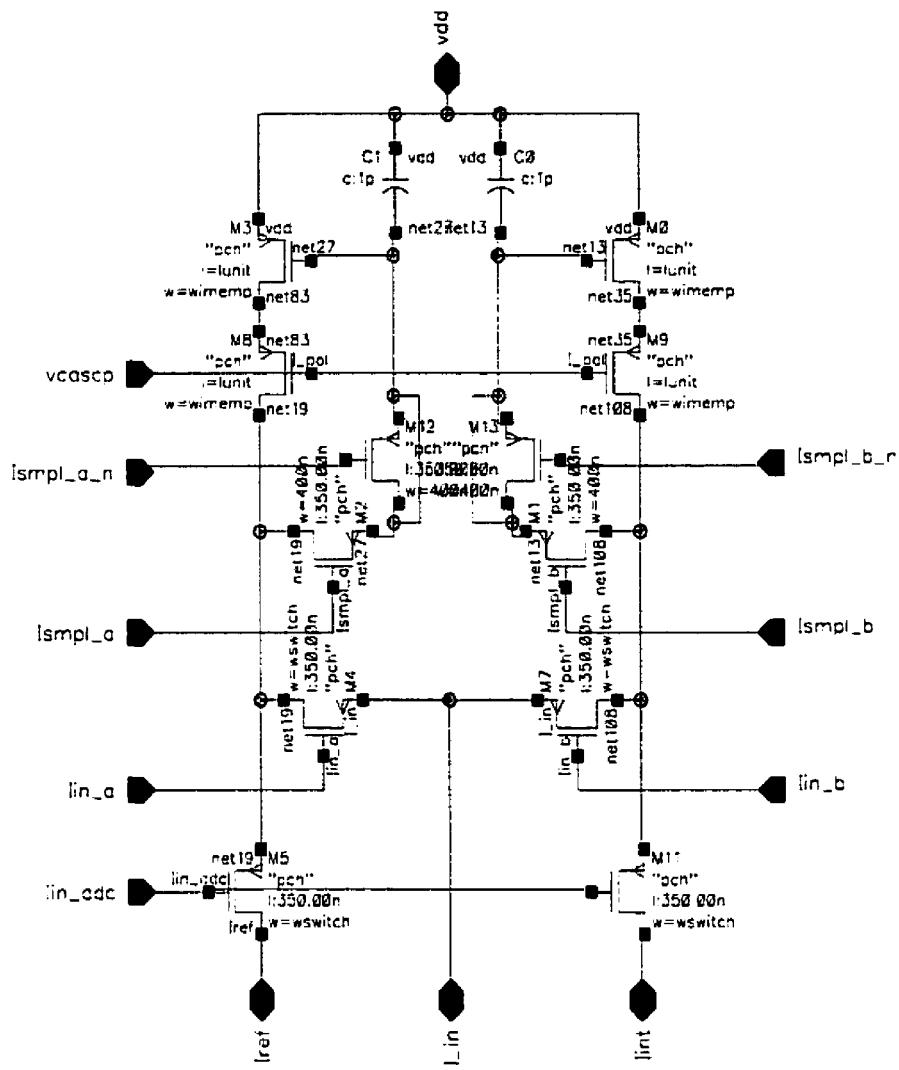

| <b>Figure 2.14</b> | <b>Comparateur de courants Échantillonneur-Bloqueur.....</b>                                  | <b>49</b> |

| <b>Figure 2.15</b> | <b>Convertisseur Analogique-Numérique.....</b>                                                | <b>50</b> |

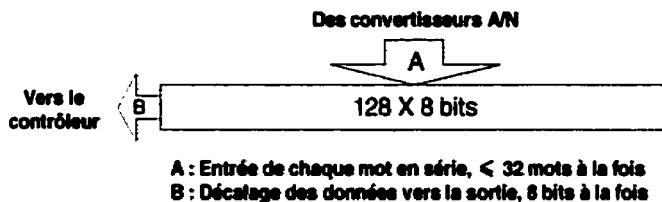

| <b>Figure 2.16</b> | <b>Transfert des données dans la mémoire tampon .....</b>                                     | <b>51</b> |

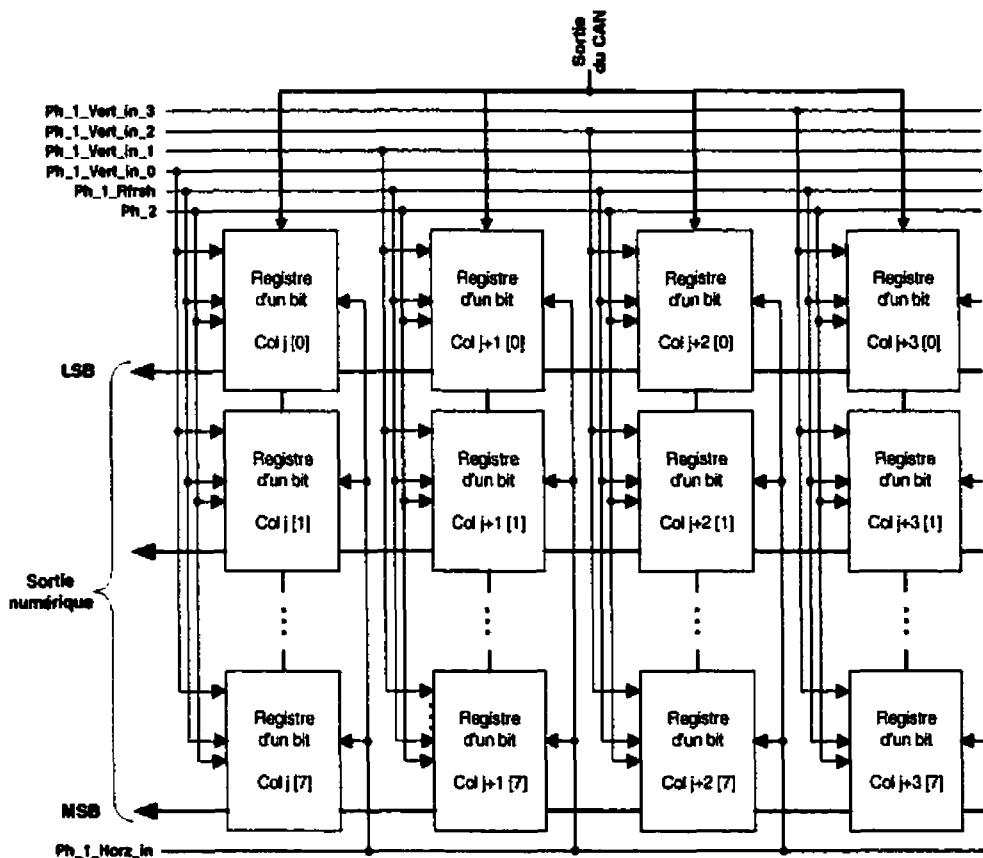

| <b>Figure 2.17</b> | <b>Registre d'un bit de la mémoire tampon .....</b>                                           | <b>51</b> |

| <b>Figure 2.18</b> | <b>Structure de la mémoire tampon .....</b>                                                   | <b>52</b> |

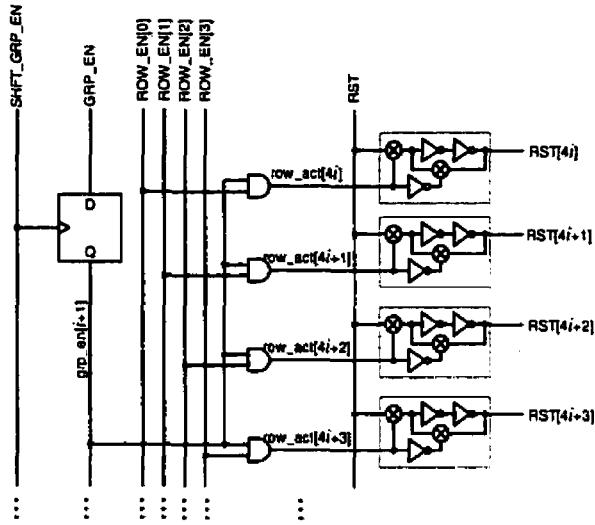

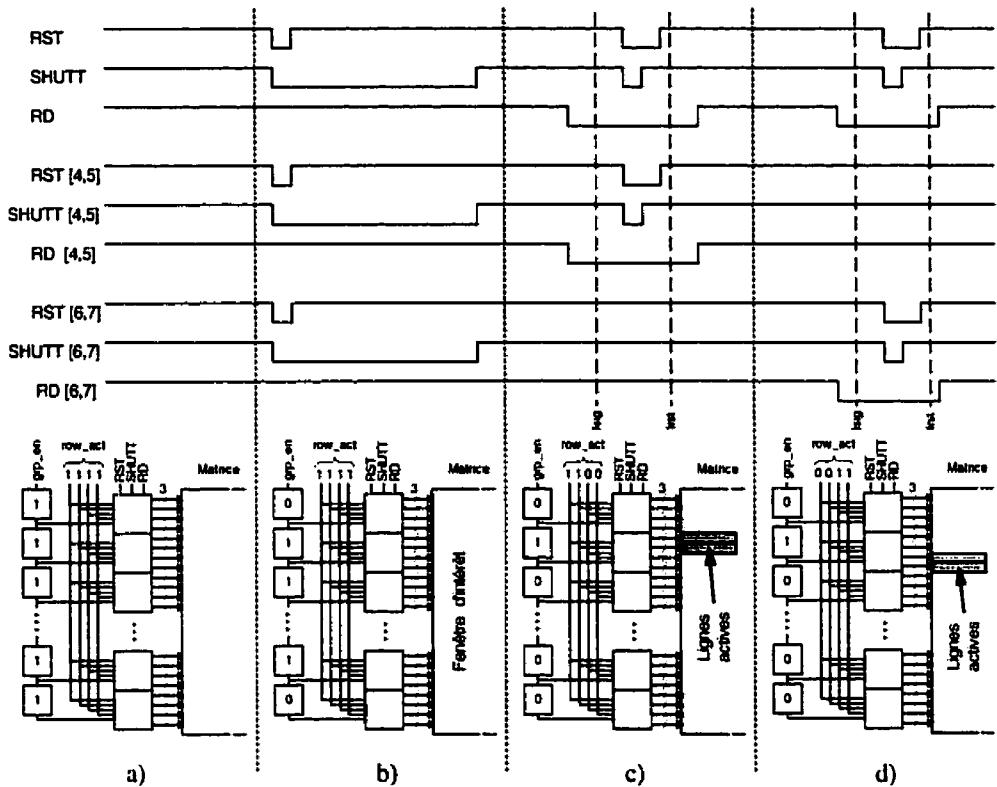

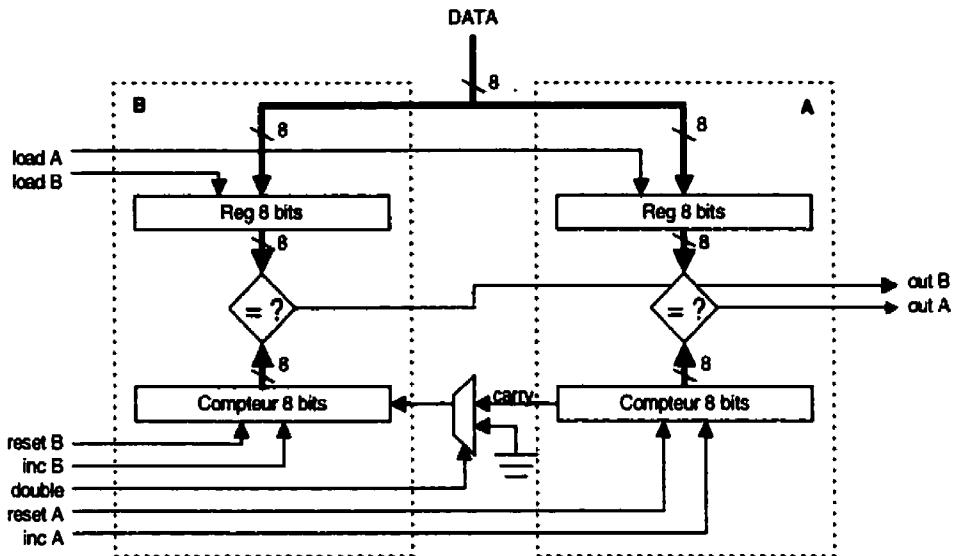

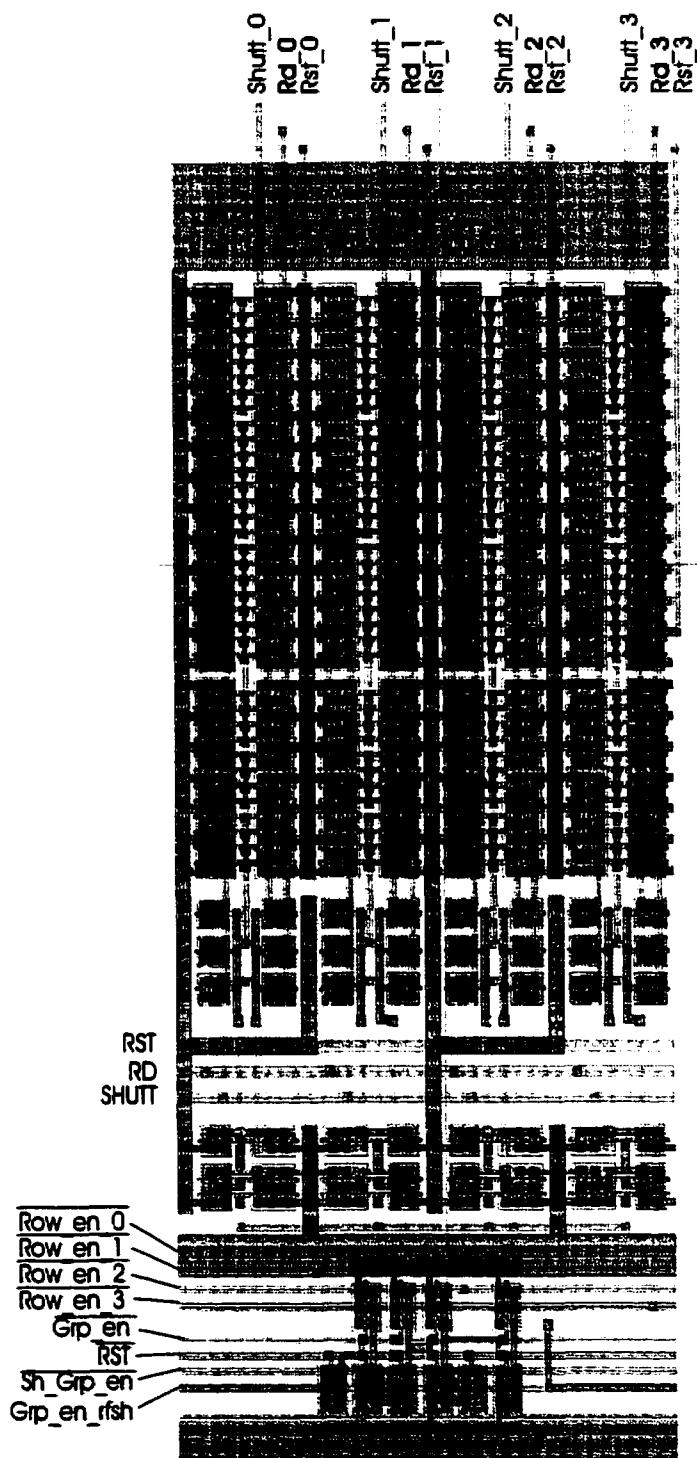

| <b>Figure 3.1</b>  | <b>Circuit de contrôle de 4 rangées .....</b>                                                 | <b>58</b> |

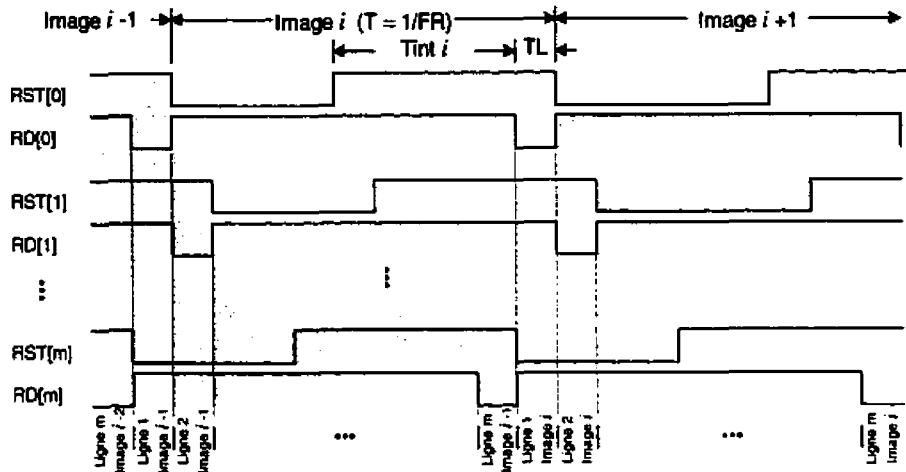

| <b>Figure 3.2</b>  | <b>Étapes d'acquisition d'une image .....</b>                                                 | <b>59</b> |

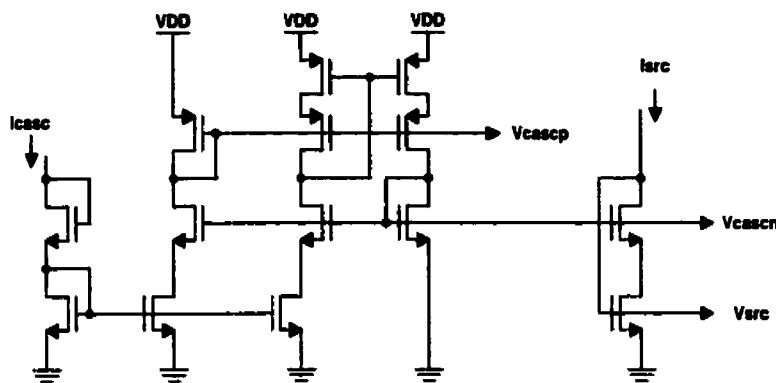

| <b>Figure 3.3</b>  | <b>Circuit de polarisation .....</b>                                                          | <b>61</b> |

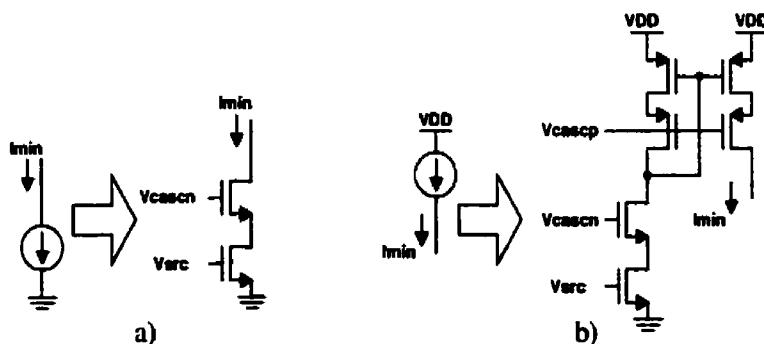

| <b>Figure 3.4</b>  | <b>Implémentation des sources a) N et b) P à partir d'une tension Vsrc .....</b>              | <b>61</b> |

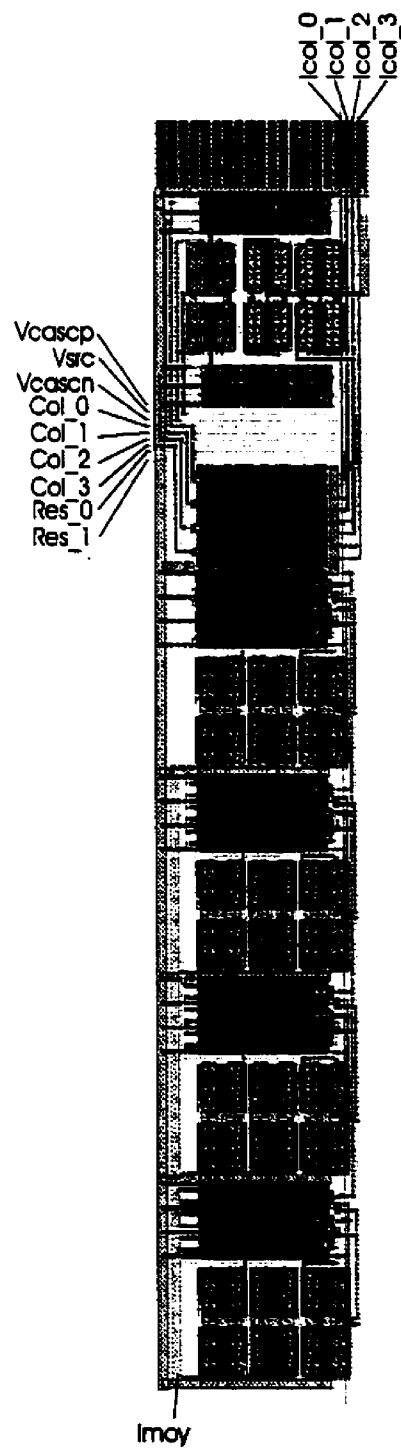

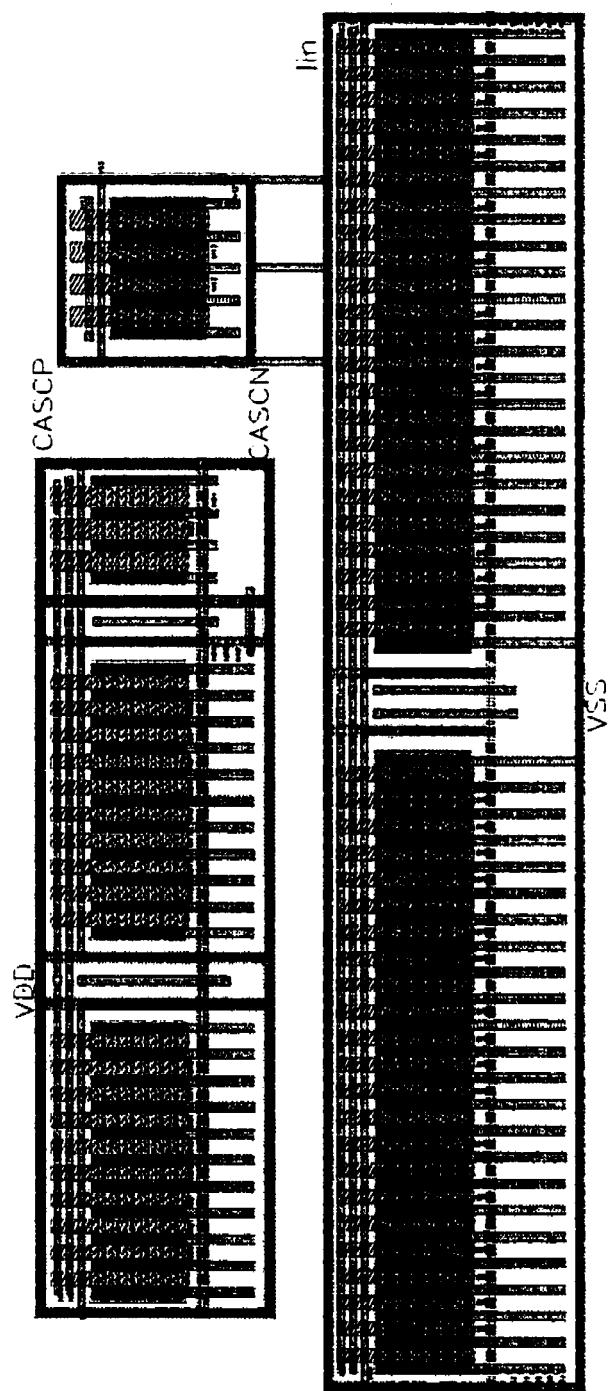

| <b>Figure 3.5</b>  | <b>Disposition des éléments et principaux signaux du capteur de tests.....</b>                | <b>63</b> |

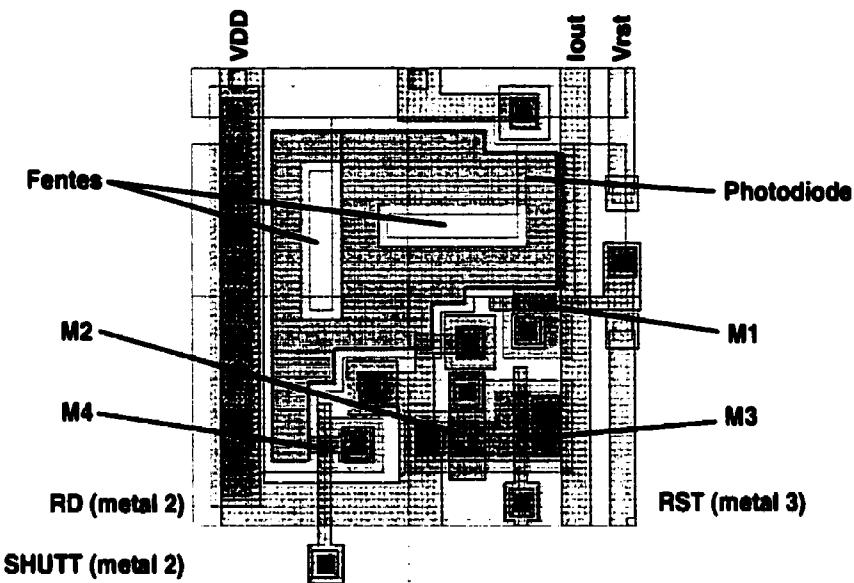

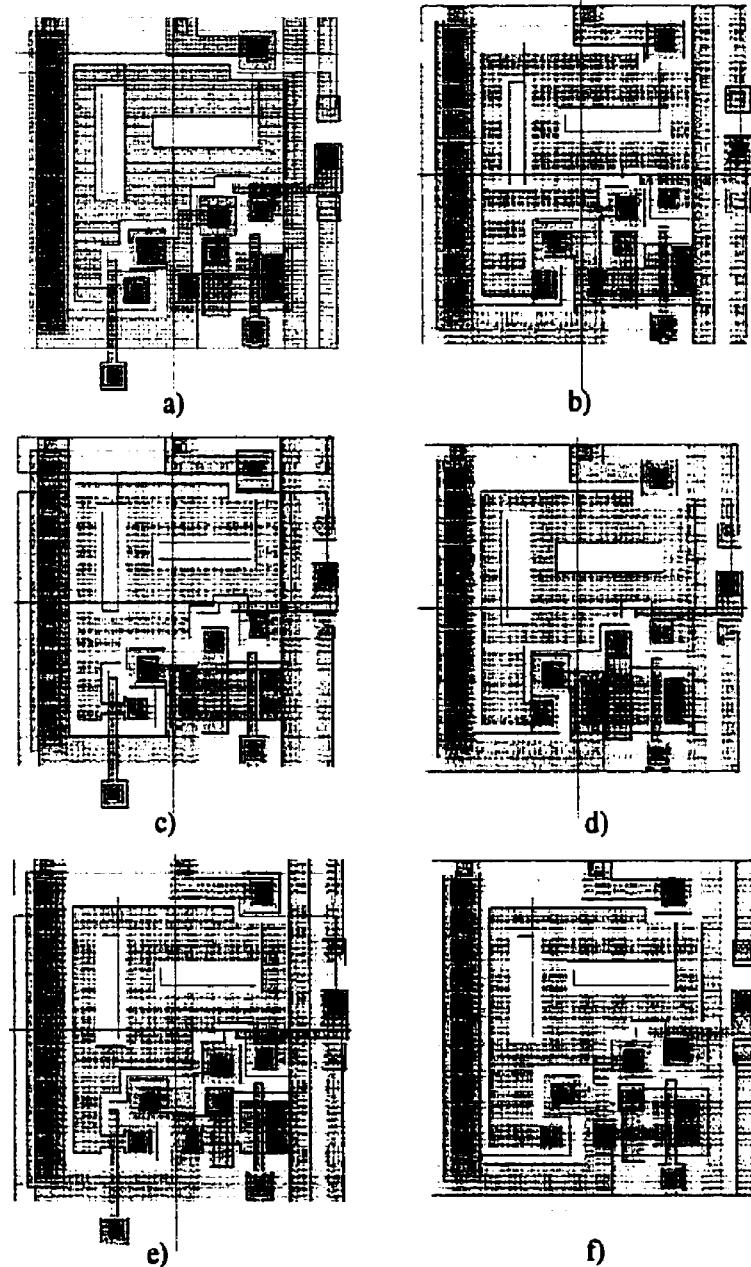

| <b>Figure 3.6</b>  | <b>Masques d'une cellule photosensible .....</b>                                              | <b>64</b> |

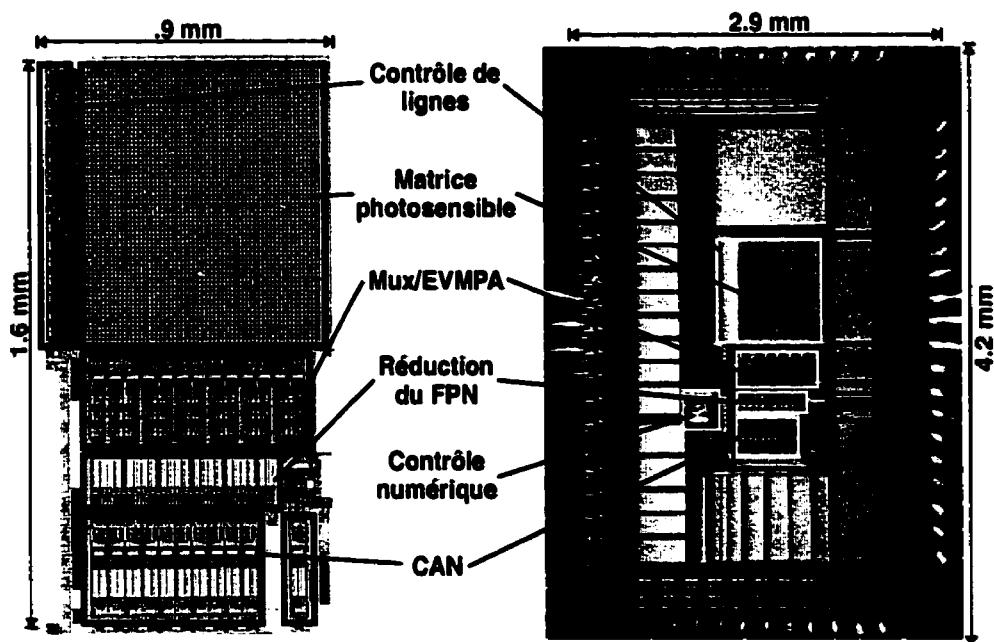

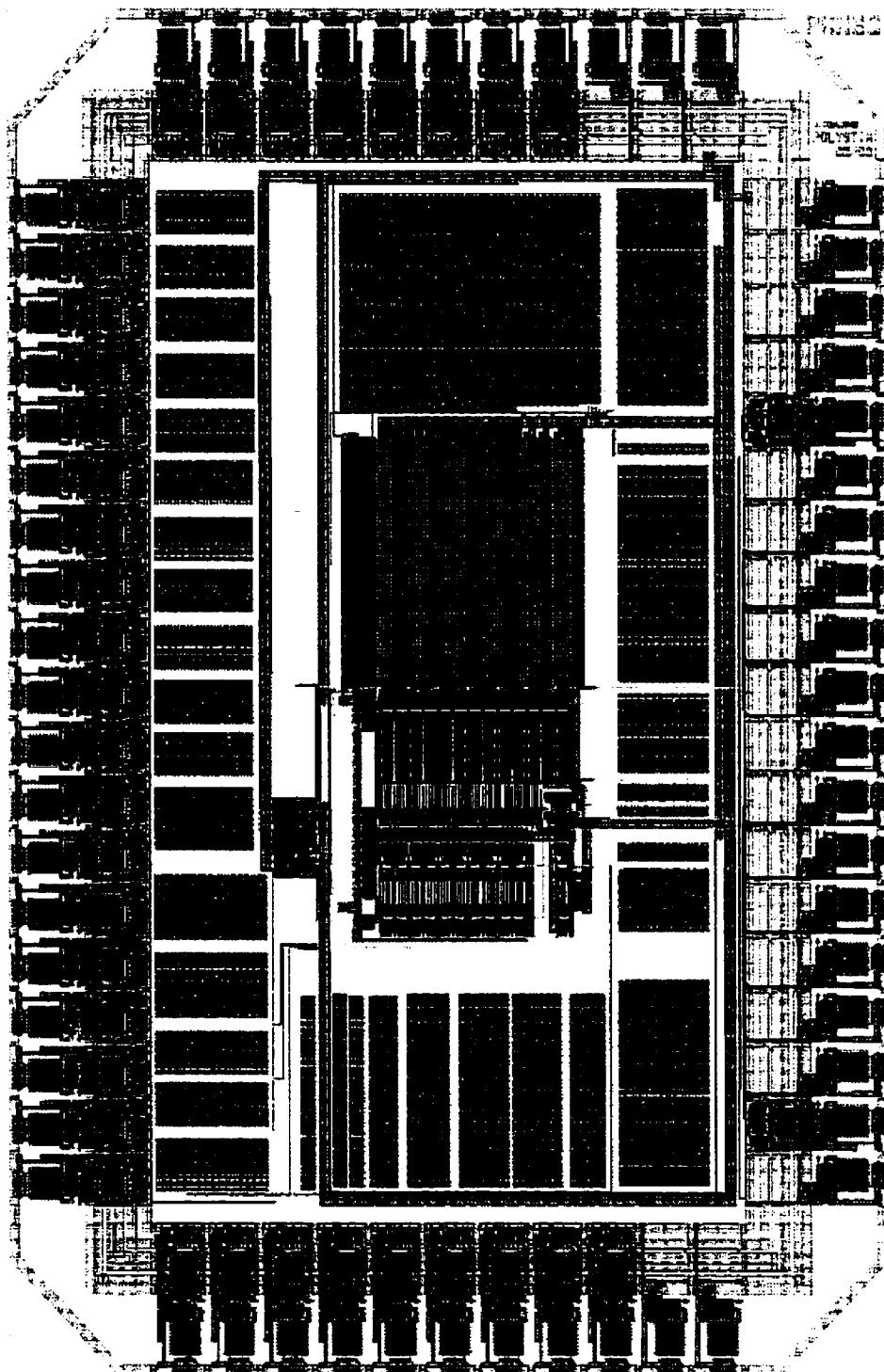

| <b>Figure 3.7</b>  | <b>Masques et photo du circuit intégré .....</b>                                              | <b>66</b> |

|             |                                                                                                                      |    |

|-------------|----------------------------------------------------------------------------------------------------------------------|----|

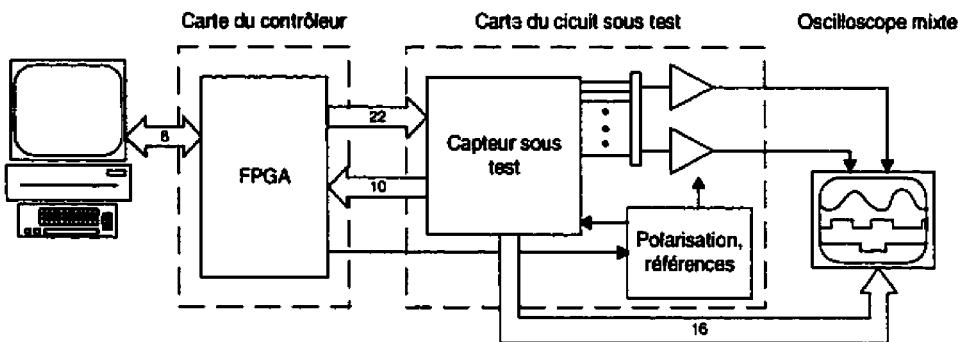

| Figure 3.8  | Schéma bloc du système de tests.....                                                                                 | 68 |

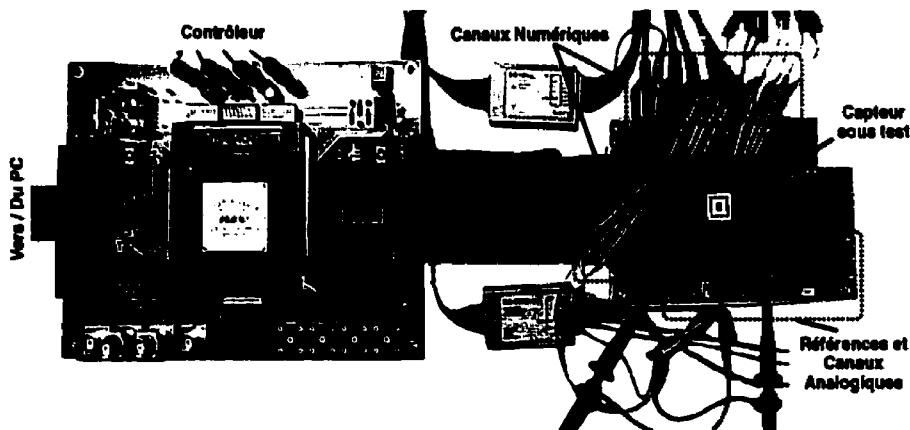

| Figure 3.9  | Photographie du système de tests.....                                                                                | 69 |

| Figure 3.10 | Interface du logiciel de tests.....                                                                                  | 70 |

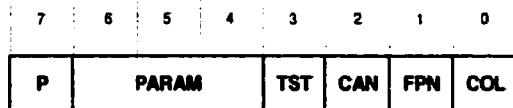

| Figure 3.11 | Contenu des mots d'instructions du contrôleur.....                                                                   | 72 |

| Figure 3.12 | Schéma bloc du contrôleur.....                                                                                       | 73 |

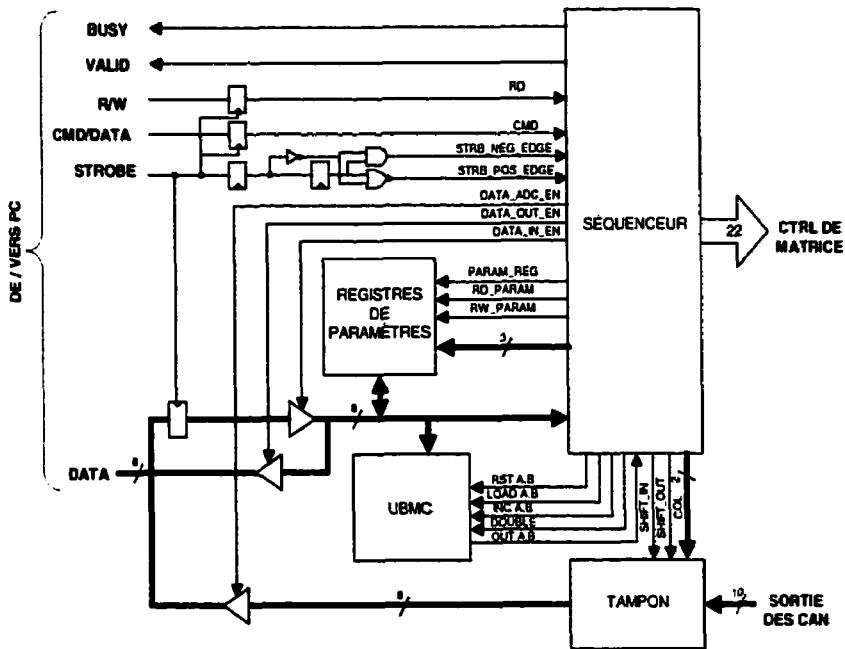

| Figure 3.13 | Contenu des registres de paramètres .....                                                                            | 75 |

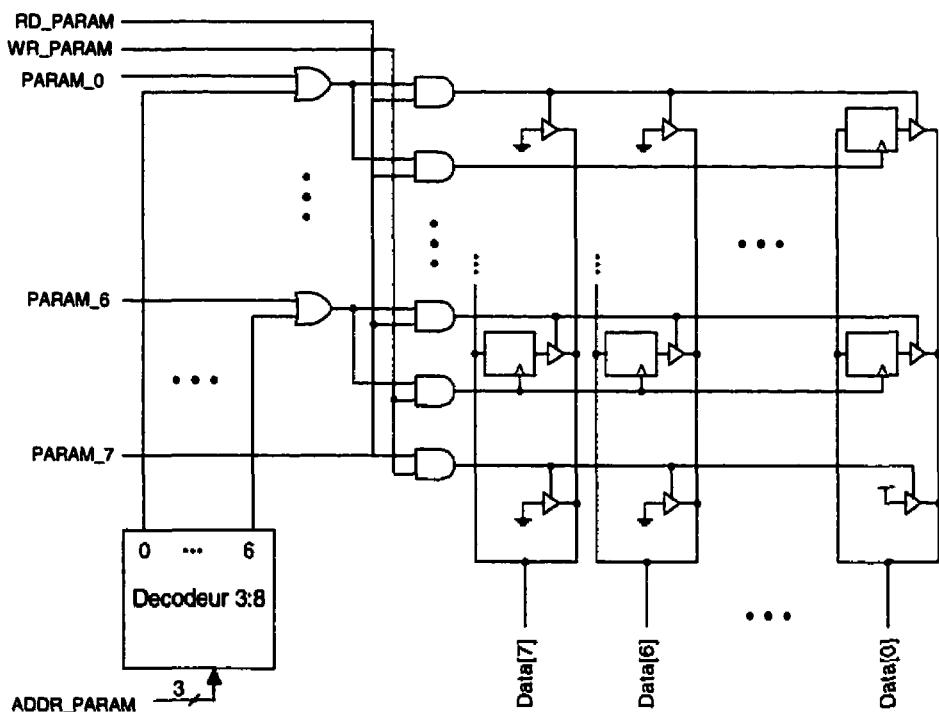

| Figure 3.14 | Registres de paramètres.....                                                                                         | 76 |

| Figure 3.15 | Unité de balayage de la matrice et de chronométrage.....                                                             | 77 |

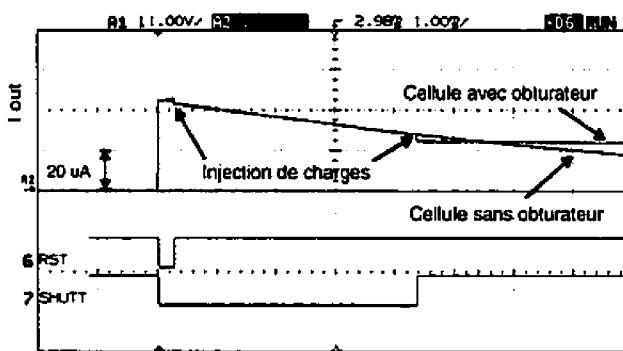

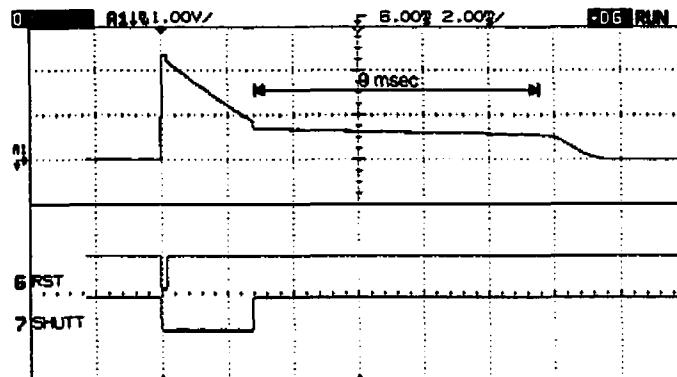

| Figure 4.1  | Réponse temporelle à la lumière d'une photocellule .....                                                             | 79 |

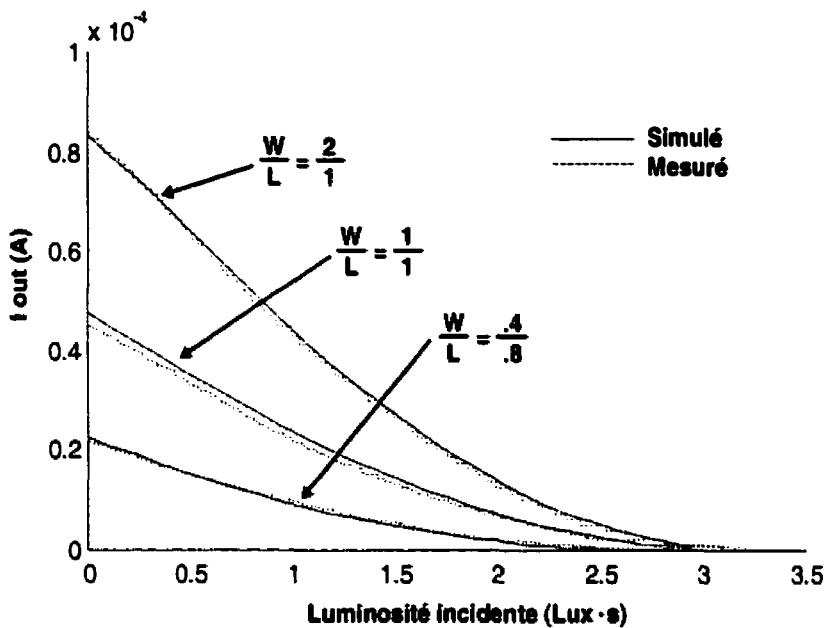

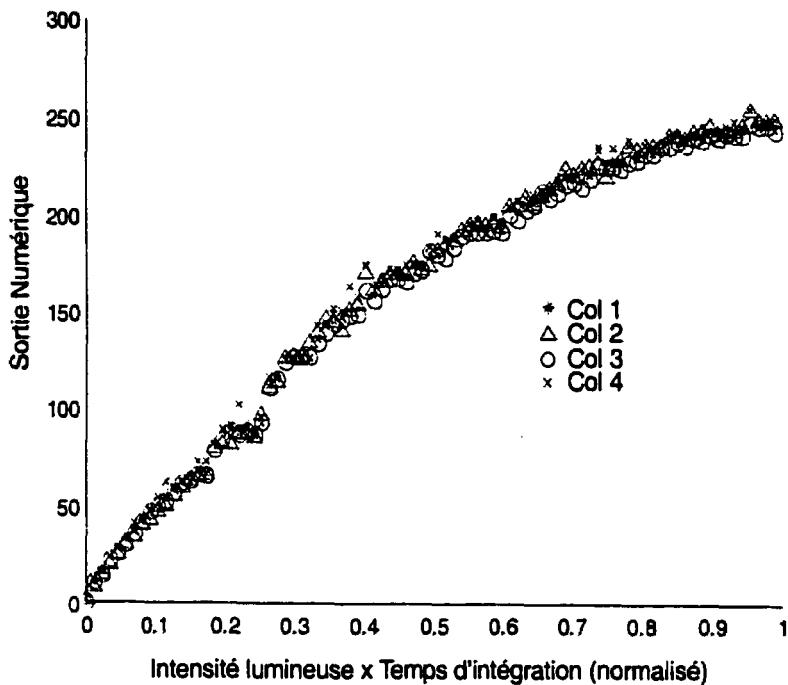

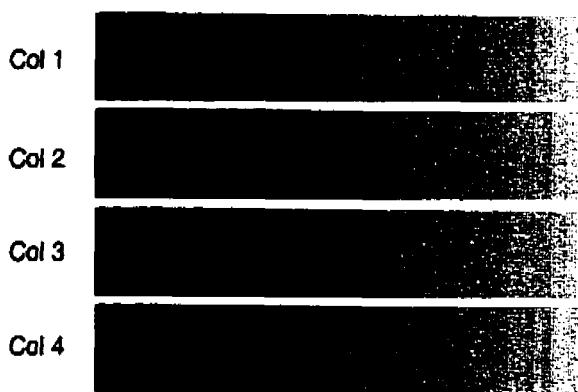

| Figure 4.2  | Caractéristiques de sortie des photocellules.....                                                                    | 80 |

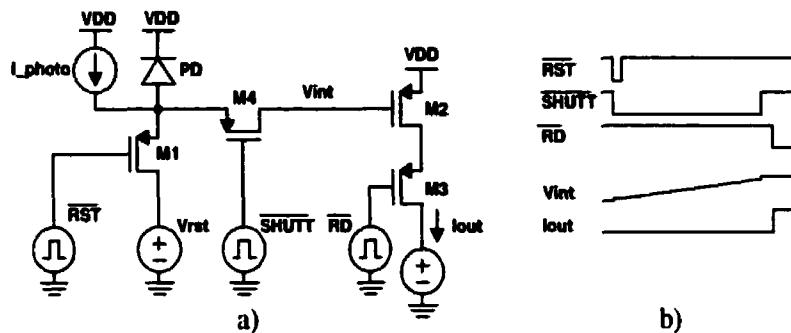

| Figure 4.3  | a) Configuration et b) Signaux de stimulation et de sortie d'une cellule photosensible pour fins de simulation ..... | 81 |

| Figure 4.4  | Corruption du courant de sortie en mode maintient.....                                                               | 84 |

| Figure 4.5  | Sortie directe de 56 pixels d'une colonne .....                                                                      | 84 |

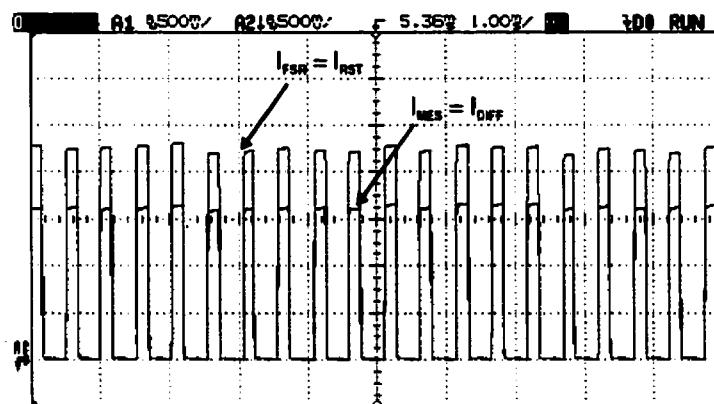

| Figure 4.6  | Sorties du circuit réducteur de FPN .....                                                                            | 85 |

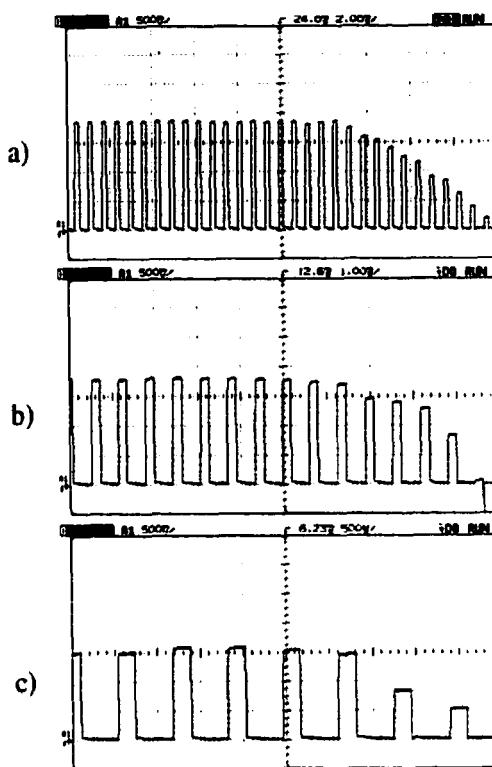

| Figure 4.7  | Gradient d'intensité lumineuse aux résolutions<br>a) $1 \times 1$ ; b) $2 \times 2$ ; c) $4 \times 4$ .....          | 88 |

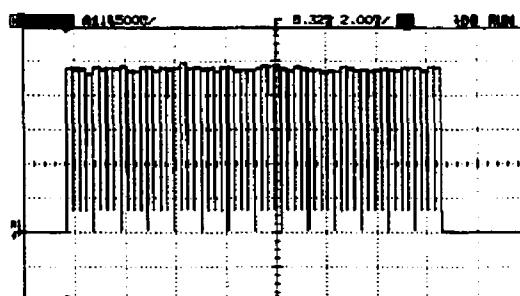

| Figure 4.8  | Caractéristique de sortie numérique de 4 colonnes.....                                                               | 91 |

| Figure 4.9  | Degrade d'intensité de 4 colonnes .....                                                                              | 91 |

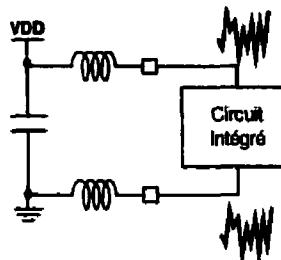

| Figure 4.10 | Effet inductif des plots sur l'alimentation du circuit.....                                                          | 93 |

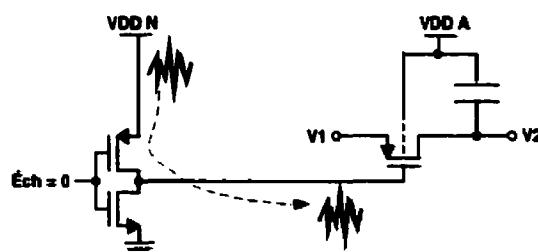

| Figure 4.11 | Corruption de la charge maintenue à un nœud capacitif relié à VDD par bruit d'alimentation numérique .....           | 93 |

|                                                                                                                                          |     |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.12 Corruption de la charge maintenue à un nœud capacitif relié à VSS par effet résistif de la masse .....                       | 94  |

| Figure 4.13 Chronogramme de synchronisation des signaux de contrôle pour une matrice de cellules sans obturateur électronique .....      | 96  |

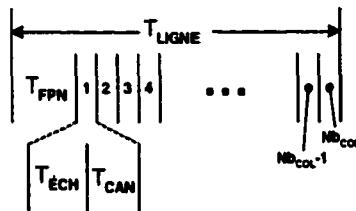

| Figure 4.14 Décomposition des étapes de lecture d'une ligne .....                                                                        | 97  |

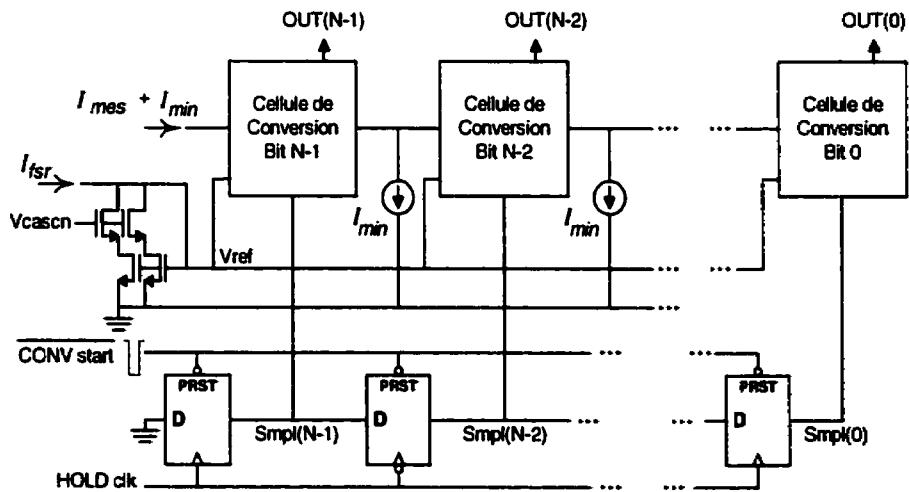

| Figure 4.15 Schéma bloc de l'architecture proposée d'un capteur à CAN unique.....                                                        | 98  |

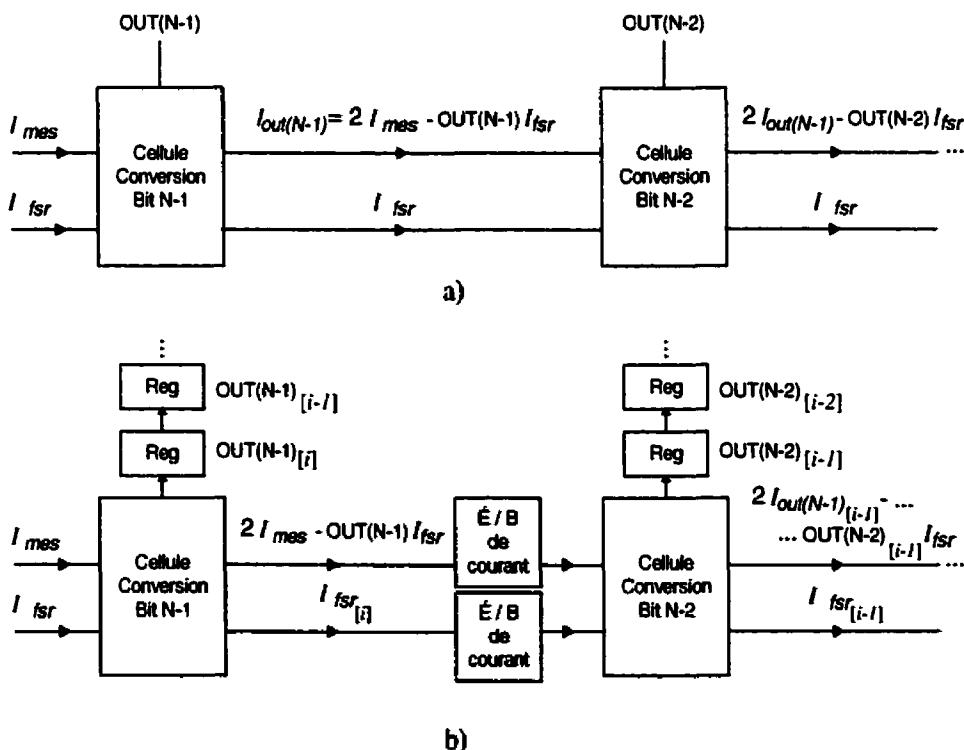

| Figure 4.16 Configurations de cellules de conversion d'un bit pour convertisseur a) en cascade et b) pipeline .....                      | 100 |

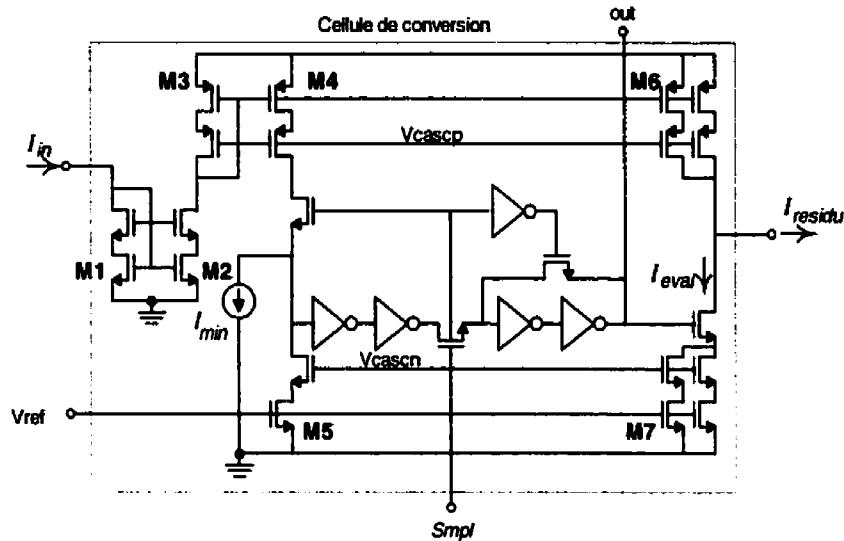

| Figure 4.17 Cellule de conversion d'un bit .....                                                                                         | 102 |

| Figure 4.18 Configuration en cascade du CAN .....                                                                                        | 102 |

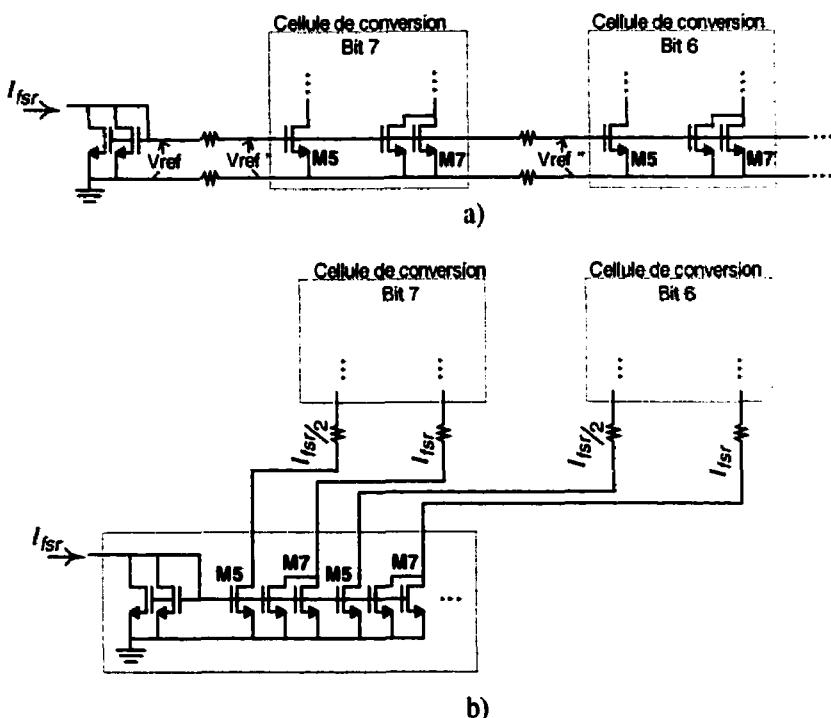

| Figure 4.19 Séparations physiques des miroirs de courant en fonction des cellules de conversion d'un bit ; a) fautive, b) correcte ..... | 104 |

| Figure 4.20 Division du courant de somme des colonnes .....                                                                              | 105 |

| Figure A.1 Cellule photosensible .....                                                                                                   | 121 |

| Figure A.2 Circuit de division du courant de sortie .....                                                                                | 121 |

| Figure A.3 Circuit de réduction du FPN .....                                                                                             | 122 |

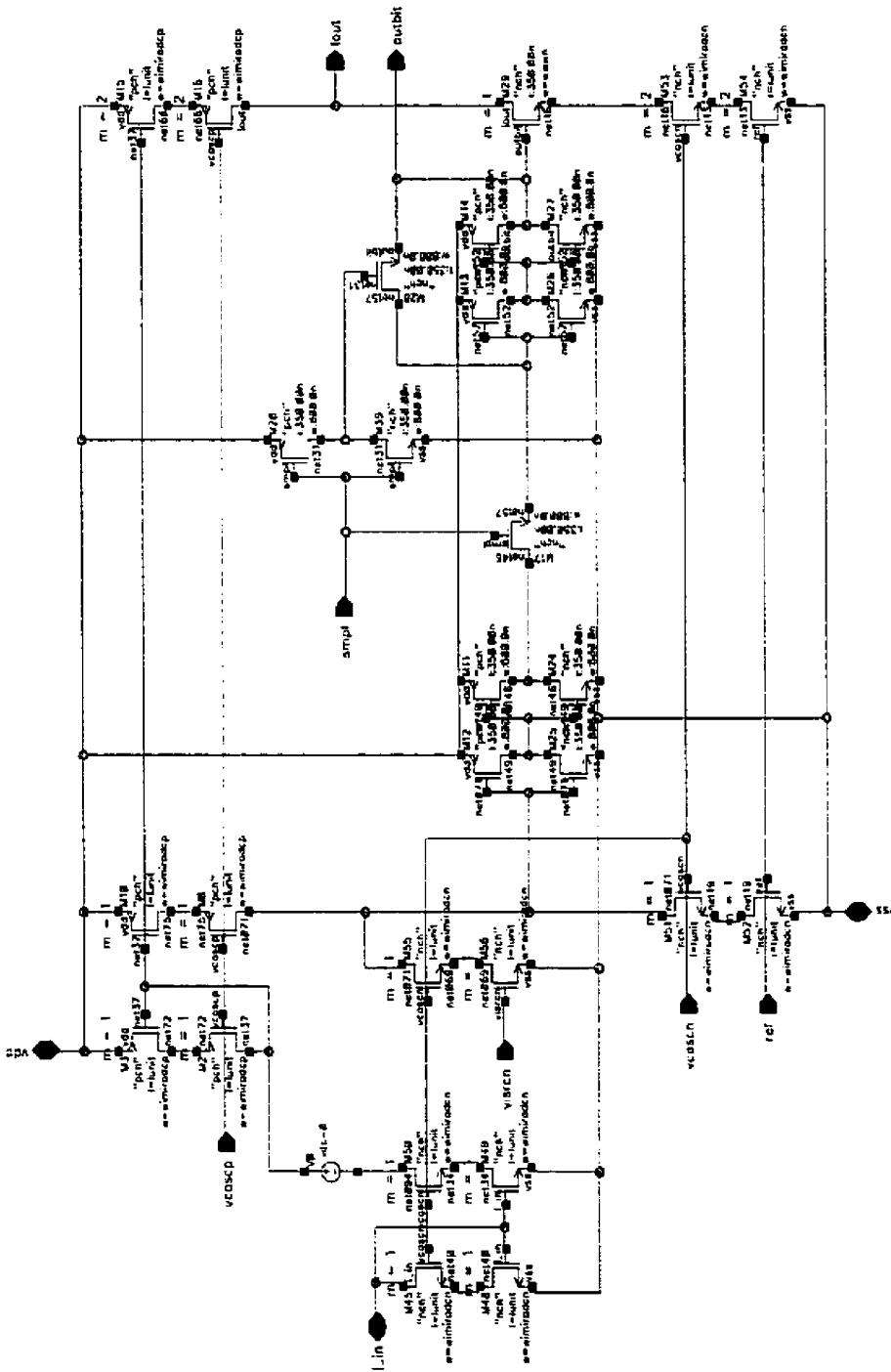

| Figure A.4 CAN algorithmique cyclique .....                                                                                              | 123 |

| Figure A.5 Cellule de conversion du CAN en cascade .....                                                                                 | 124 |

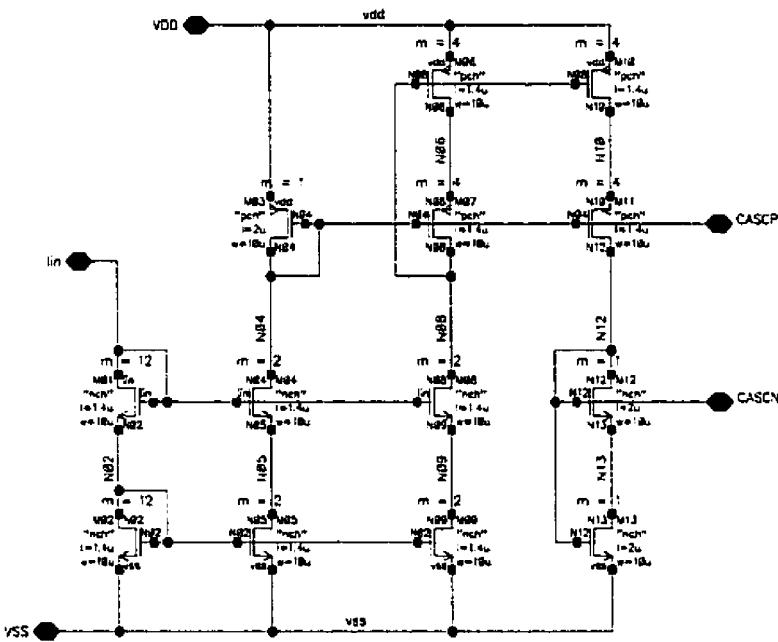

| Figure A.6 Circuit de génération des tensions de polarisation des transistors cascode .....                                              | 125 |

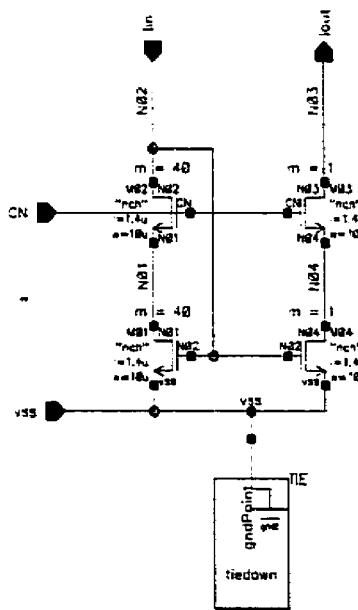

| Figure A.7 : Circuit de génération de la tension de polarisation des sources de courant $I_{min}$ .....                                  | 125 |

|            |                                                                                                                |     |

|------------|----------------------------------------------------------------------------------------------------------------|-----|

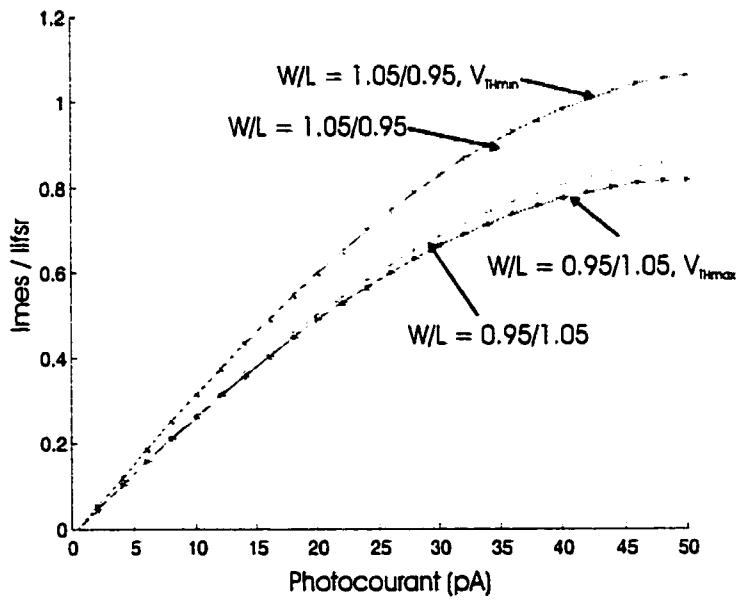

| Figure C.1 | Caractéristique de sortie directe de photocellules non appareillées .....                                      | 135 |

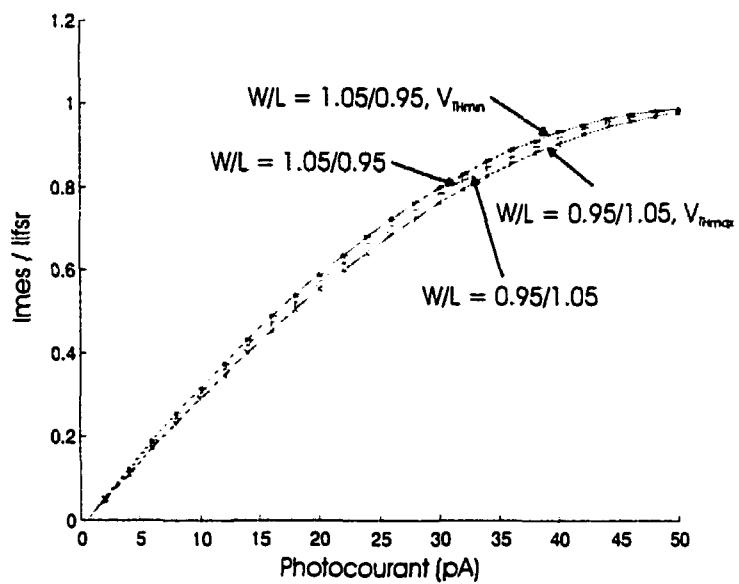

| Figure C.2 | Caractéristique de sortie de photocellules non appareillées avec<br>CDS à référence fixe .....                 | 135 |

| Figure C.3 | Caractéristique de sortie de photocellules non appareillées avec<br>ajustement de la plage de conversion ..... | 136 |

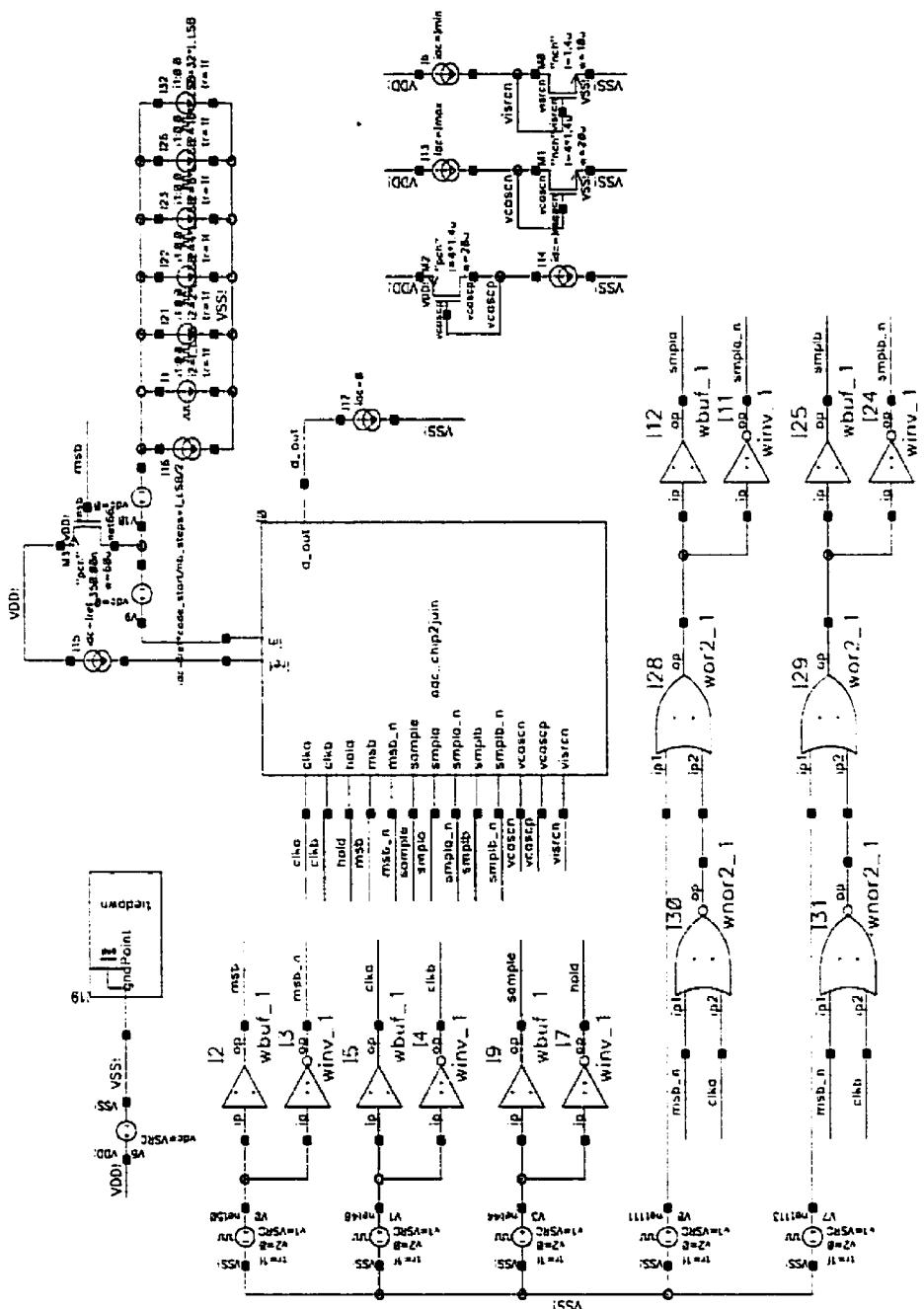

| Figure C.4 | Circuit de simulation du CAN algorithmique cyclique.....                                                       | 137 |

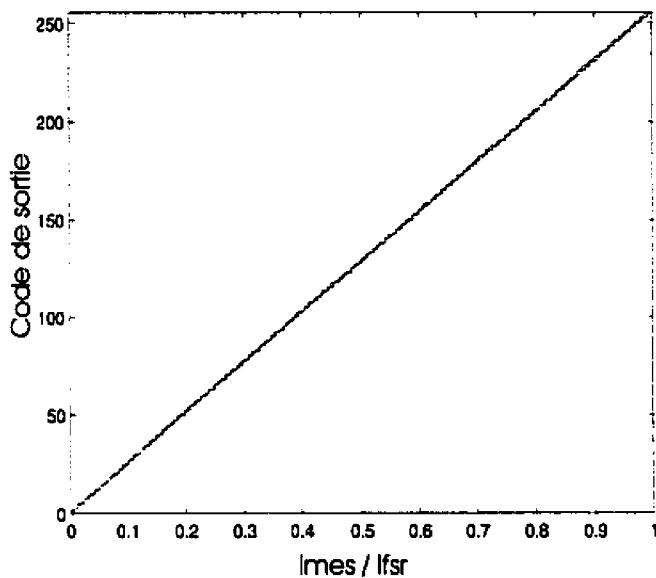

| Figure C.5 | Caractéristique de sortie du CAN algorithmique cyclique (idéale et<br>simulée) .....                           | 138 |

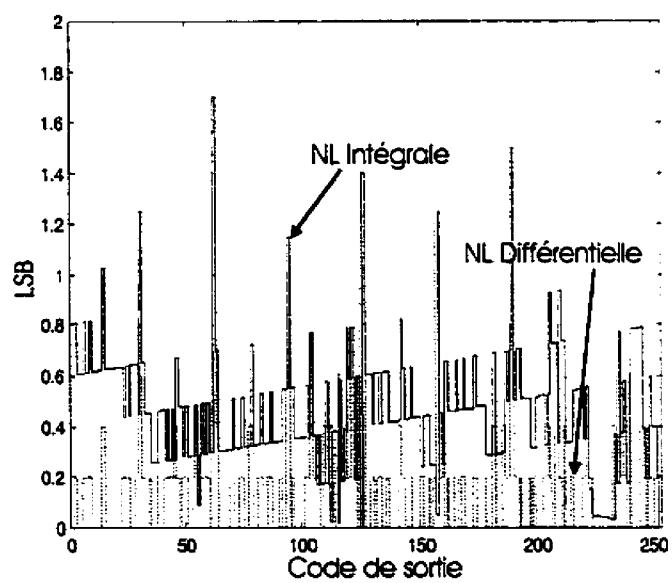

| Figure C.6 | Non-linéarités différentielle et intégrale du CAN algorithmique<br>cyclique .....                              | 138 |

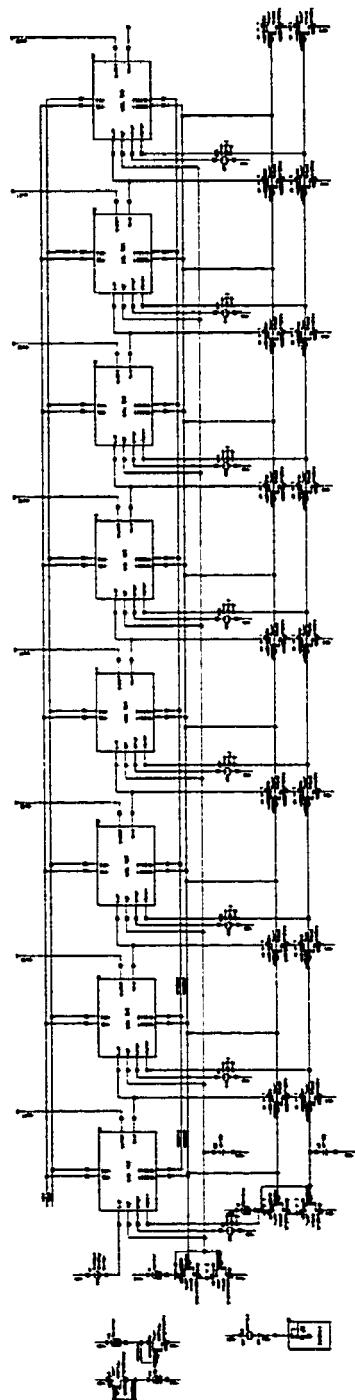

| Figure C.7 | Circuit de simulation du CAN en cascade .....                                                                  | 139 |

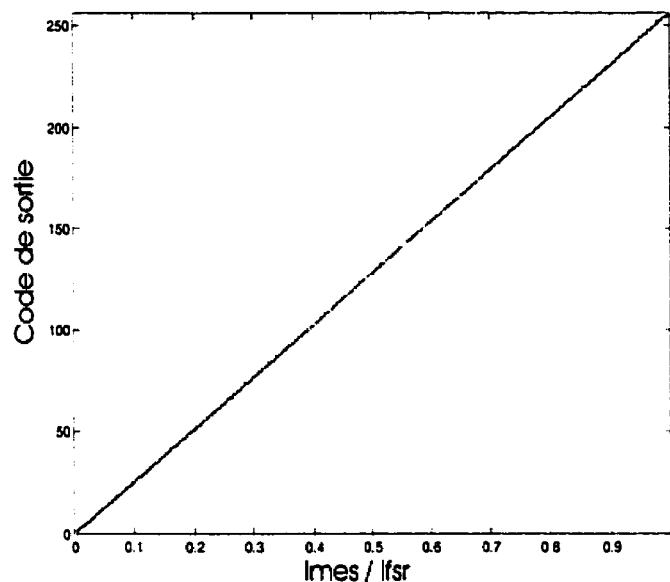

| Figure C.8 | Caractéristique de sortie du CAN en cascade (idéale et simulée).....                                           | 140 |

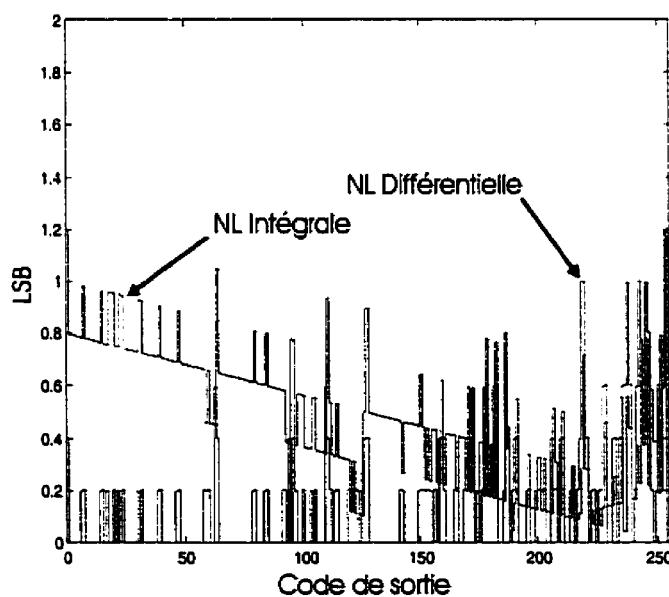

| Figure C.9 | Non-linéarités différentielle et intégrale du CAN en cascade.....                                              | 140 |

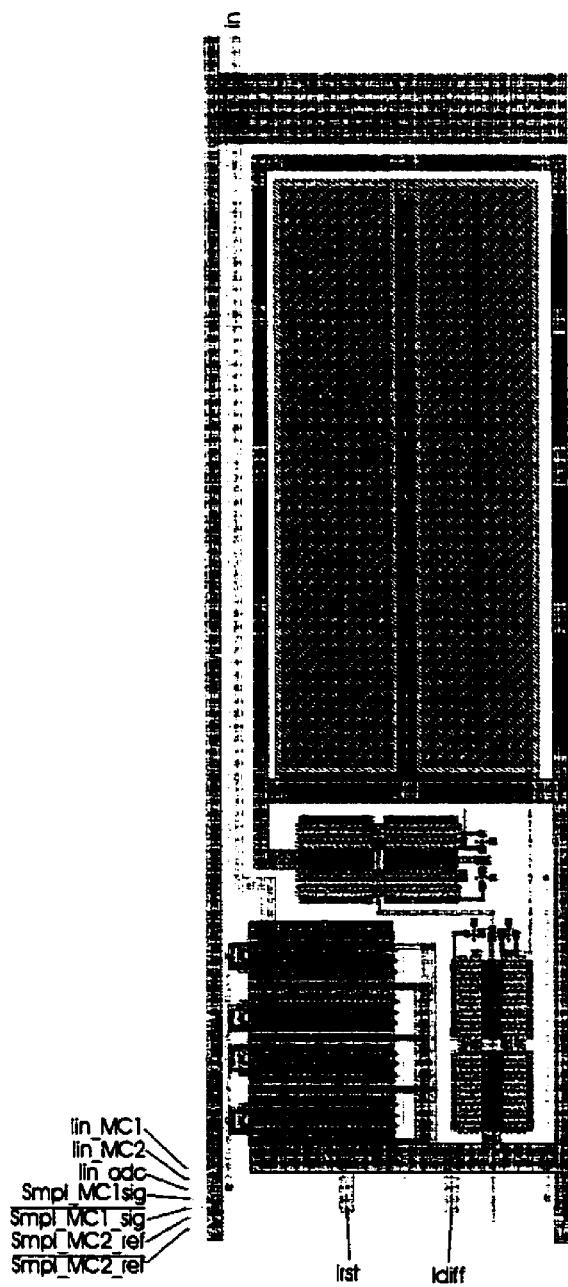

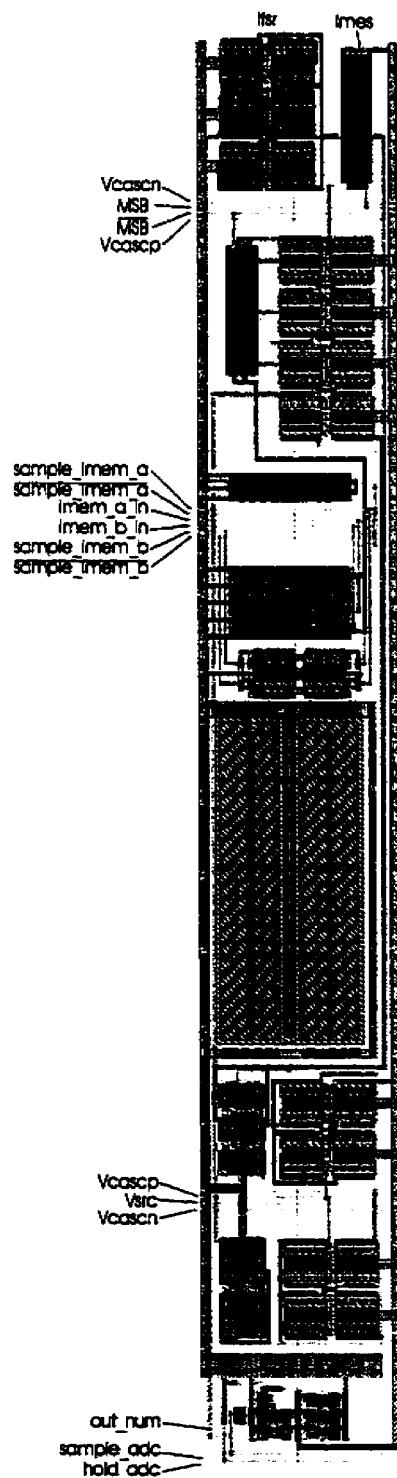

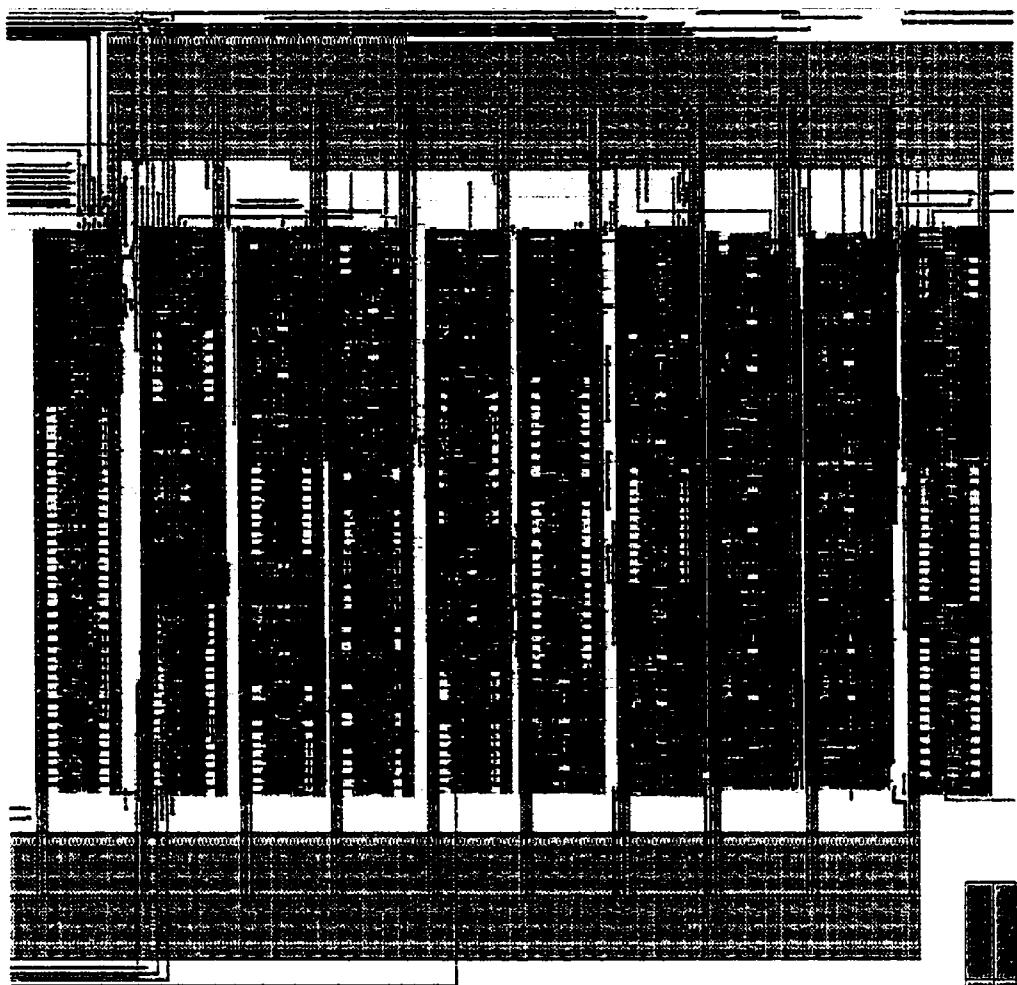

| Figure D.1 | Cellules photosensibles .....                                                                                  | 142 |

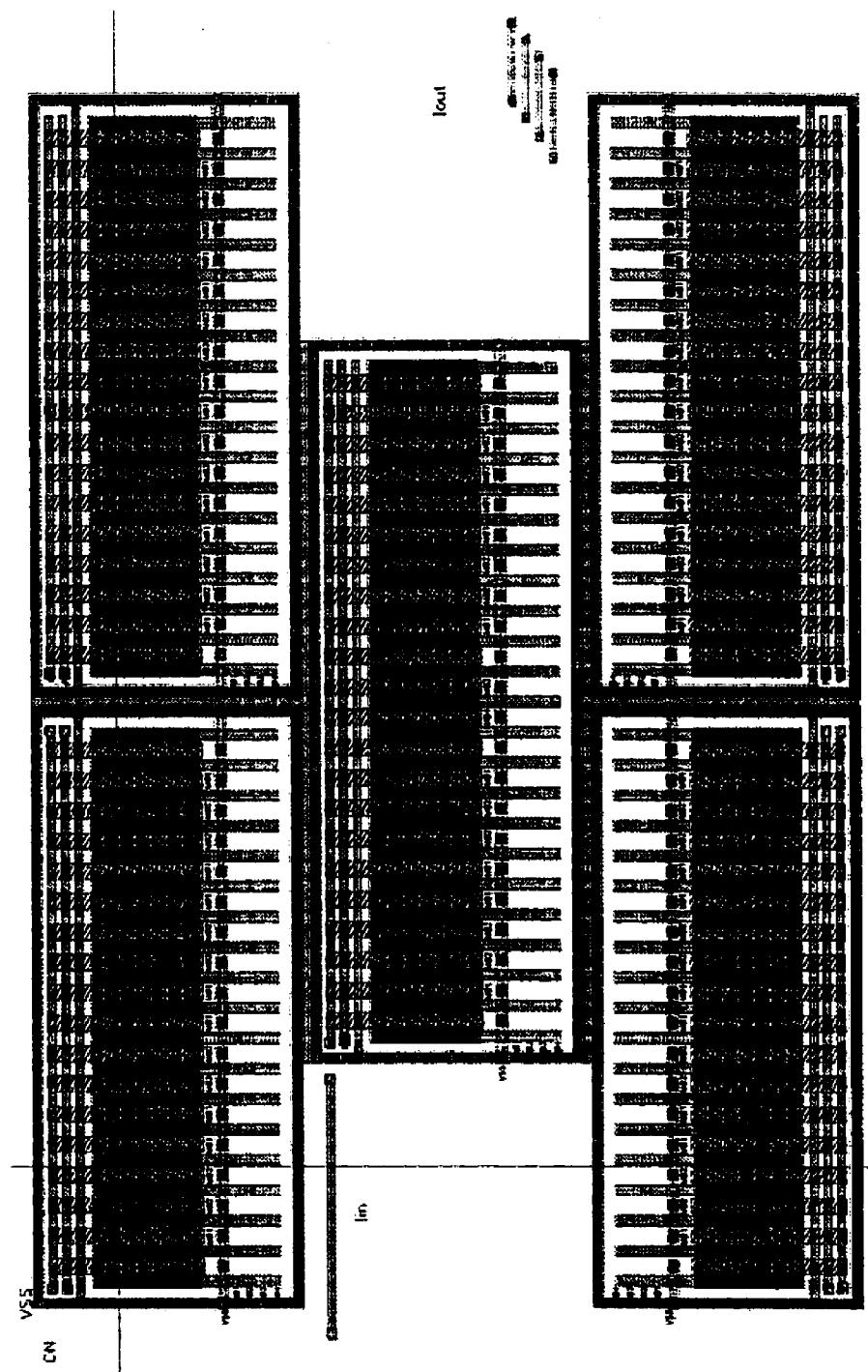

| Figure D.2 | Circuit de multiplexage et d'évaluation de la moyenne des<br>colonnes.....                                     | 143 |

| Figure D.3 | Circuit de réduction du FPN .....                                                                              | 144 |

| Figure D.4 | CAN algorithmique cyclique .....                                                                               | 145 |

| Figure D.5 | Circuit de génération des tensions de polarisation des transistors<br>cascode .....                            | 146 |

| Figure D.6 | Circuit de génération de la tension de polarisation des sources de<br>courant $I_{min}$ .....                  | 147 |

|                   |                                                              |            |

|-------------------|--------------------------------------------------------------|------------|

| <b>Figure D.7</b> | <b>Circuit de contrôle de groupes de quatre lignes .....</b> | <b>148</b> |

| <b>Figure D.8</b> | <b>Circuits numériques générés par synthèse .....</b>        | <b>149</b> |

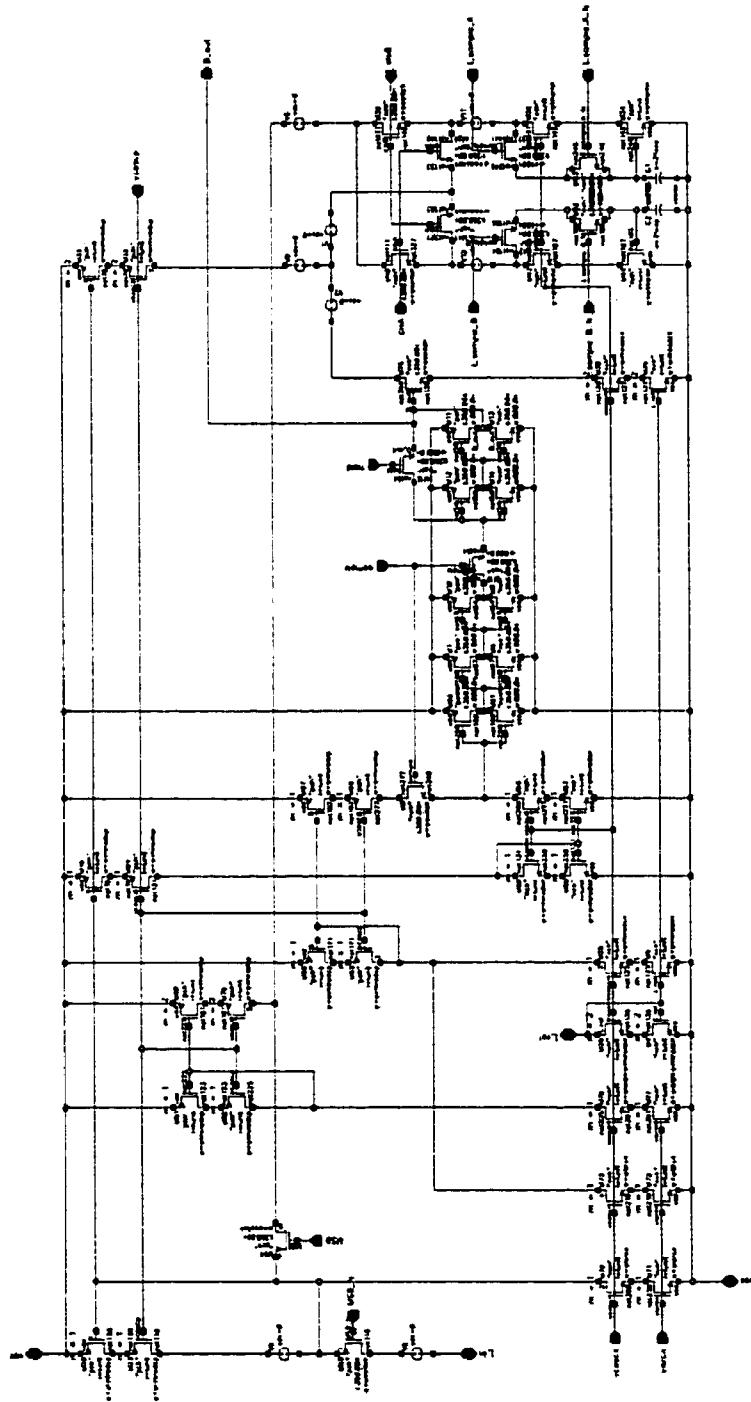

| <b>Figure D.9</b> | <b>Capteur d'images de tests.....</b>                        | <b>150</b> |

| <b>Figure E.1</b> | <b>Broches du capteur d'images de tests .....</b>            | <b>152</b> |

## **LISTE DES ANNEXES**

|                 |                                                                  |            |

|-----------------|------------------------------------------------------------------|------------|

| <b>Annexe A</b> | <b>Schémas des modules analogiques.....</b>                      | <b>120</b> |

| <b>Annexe B</b> | <b>Fichier de simulation des modules analogiques.....</b>        | <b>126</b> |

| <b>Annexe C</b> | <b>Simulations des modules analogiques.....</b>                  | <b>134</b> |

| <b>Annexe D</b> | <b>Masques de fabrication.....</b>                               | <b>141</b> |

| <b>Annexe E</b> | <b>Définition des broches du capteur d'images de tests .....</b> | <b>151</b> |

## **LISTE DES ABBRÉVIATIONS ET SYMBOLES**

### **ABBRÉVIATIONS**

|             |                                                            |

|-------------|------------------------------------------------------------|

| <b>APS</b>  | <b>Active Pixel Sensor</b>                                 |

| <b>CAN</b>  | <b>Convertisseur Analogique à Numérique</b>                |

| <b>CCD</b>  | <b>Charge Coupled Device</b>                               |

| <b>CDS</b>  | <b>Correlated Double Sampling</b>                          |

| <b>CMOS</b> | <b>Complementary Metal Oxyde Semiconductor</b>             |

| <b>FPGA</b> | <b>Field Programmable Gate Array</b>                       |

| <b>FPN</b>  | <b>Fixed Pattern Noise</b>                                 |

| <b>FR</b>   | <b>Frame Rate</b>                                          |

| <b>HDL</b>  | <b>Hardware Description Language</b>                       |

| <b>LSB</b>  | <b>Least Significant Bit</b>                               |

| <b>MOS</b>  | <b>Metal Oxyde Semiconductor</b>                           |

| <b>NLD</b>  | <b>Non-Linéarité Différentielle</b>                        |

| <b>NLI</b>  | <b>Non-Linéarité Intégrale</b>                             |

| <b>SPP</b>  | <b>Standard Parallel Port</b>                              |

| <b>UBMC</b> | <b>Unité de Balayage de la Matrice et de Chronométrage</b> |

| <b>VLSI</b> | <b>Very Large Scale Integration</b>                        |

| <b>VMPA</b> | <b>Valeur Moyenne de Pixels Adjacents</b>                  |

## PRINCIPAUX SYMBOLES

|                        |                                                                                         |

|------------------------|-----------------------------------------------------------------------------------------|

| <i>Icas</i>            | Courant d'entrée du circuit de polarisation des transistors cascode                     |

| <i>Idiff</i>           | Courant différentiel avant et après intégration lumineuse ( <i>Irst</i> – <i>Isig</i> ) |

| <i>Ifsr</i>            | Courant de pleine plage de conversion du CAN                                            |

| <i>Imes</i>            | Courant à convertir par le CAN                                                          |

| <i>Imin</i>            | Courant de polarisation des miroirs de courant                                          |

| <i>Iphoto</i>          | Photocourant dû à l'exposition à la lumière de l'élément photosensible                  |

| <i>Ipxl</i>            | Courant de sortie d'une ou d'un groupe de cellules photosensibles                       |

| <i>Irst</i>            | Sortie d'une ou d'un groupe de pixels suite à une réinitialisation                      |

| <i>Isig</i>            | Sortie d'une ou d'un groupe de pixels suite à l'intégration lumineuse                   |

| <i>Isrc</i>            | Courant d'entrée du circuit de polarisation des sources de courant <i>Imin</i>          |

| <i>L</i>               | Longueur de la grille d'un transistor MOS                                               |

| <i>R</i>               | Résolution de l'image acquise                                                           |

| <i>Rx</i>              | Résolution horizontale de l'image acquise                                               |

| <i>Ry</i>              | Résolution verticale de l'image acquise                                                 |

| <i>T<sub>CAN</sub></i> | Temps de conversion analogique à numérique                                              |

| <i>T<sub>ECH</sub></i> | Temps de stabilisation des entrées du CAN                                               |

| <i>T<sub>FPN</sub></i> | Temps requis pour la réduction du FPN                                                   |

| <i>T<sub>int</sub></i> | Période d'intégration lumineuse                                                         |

| <i>TI</i>              | Temps de lecture et de transfert des données d'une image                                |

| <i>TL</i>              | Temps de lecture et de transfert des données d'une ligne                                |

| <i>Vcascn</i>          | Tension de polarisation des transistors cascode à canal 'N'                             |

| <i>Vcascp</i>          | Tension de polarisation des transistors cascode à canal 'P'                             |

| <i>Vint</i>            | Tension aux bornes de l'élément photosensible                                           |

| <i>Vrst</i>            | Tension de réinitialisation des photocellules                                           |

| <i>Vsrc</i>            | Tension de référence pour les sources de courant <i>Imin</i>                            |

| <i>W</i>               | Largeur de la grille d'un transistor MOS                                                |

## INTRODUCTION

Depuis la commercialisation du premier appareil photographique du Français Daguerre il y a de cela déjà près de deux siècles, les systèmes d'acquisition d'images sont devenus, au fil du temps, aussi indispensables qu'omniprésents. Non seulement profitons-nous aujourd'hui des capteurs d'images sur une base quotidienne, par exemple pour des applications liées au divertissement, mais ceux-ci trouvent aussi leur place dans une panoplie d'applications avec lesquelles nous sommes moins familiers. Ils sont utilisés, notamment, en contrôle de qualité des procédés industriels, en aéronautique, pour des systèmes de haute sécurité et bien plus. De nouvelles approches rendent d'ailleurs les systèmes d'acquisition d'images de plus en plus performants et l'évolution des technologies de pointe repousse constamment les limites des domaines d'applications de l'imagerie numérique.

L'équipe de recherche PolySTIM, de l'École Polytechnique de Montréal œuvre actuellement au développement d'un implant visuel destiné à restituer aux gens atteints de cécité profonde une vision limitée mais fonctionnelle par stimulation du cortex visuel à l'aide d'un système électronique. Un des éléments clés d'un tel système est son capteur d'image, premier élément de la chaîne de traitement de l'information transmise au cerveau. Plusieurs contraintes sont fixées par cette application et n'importe quel capteur ne peut prétendre s'y prêter convenablement. Étant donné qu'il s'agit d'un système de vision destiné à être utilisé en permanence, ou presque, par les patients, sa durée d'utilisation est évidemment bien supérieure à celle de n'importe quelle caméra vidéo portative. Son autonomie doit donc être maximale. Aussi, pour la même raison, son encombrement doit être minimal.

Malheureusement, les populaires capteurs d'image commerciaux à « Charge Coupled Devices (CCD) » présentent certaines caractéristiques qui les rendent peu attrayants pour

des applications semblables. En effet, bien qu'ils permettent l'acquisition d'images dont la qualité est à ce jour inégalée, ces capteurs nécessitent plusieurs alimentations et sont plutôt énergivores. De plus, étant donné qu'ils nécessitent un procédé de fabrication particulier, un système externe complet pour l'implant visuel incluant un capteur d'images et une unité de traitement ne pourraient être implanté sur un seul circuit intégré à faible coût. Pour ces raisons, la technologie des capteurs fabriqués sur procédés dits « Complementary Metal Oxyde Semiconductor (CMOS) », étant définitivement avantageuse sur chacun de ces points, se présente comme une solution incontournable.

Cette dernière technologie a d'ailleurs fait l'objet de recherches intenses au cours des dernières années. Les récents procédés de fabrication permettent de réaliser de capteurs aux dimensions adéquates afin de traiter la lumière du spectre visible. Aussi, des techniques efficaces d'acquisition et de conversion d'images ont significativement amélioré les performances des capteurs CMOS, faisant apparaître un engouement certain pour ce domaine.

Le capteur développé et présenté ici vise à répondre aux exigences spécifiées par le système de stimulation visuelle et s'inscrit dans cet effort récent de miniaturisation et d'amélioration de la qualité des capteurs CMOS. Toutefois, il n'est pas conçu de manière totalement dédiée, mais plutôt de façon à être d'usage général.

Ledit système est basé sur une matrice de pixels photosensibles actifs, communément appelé « Active Pixel Sensor (APS) ». Il possède tous les éléments nécessaires à son utilisation de façon entièrement numérique. De plus, il présente certaines caractéristiques qui le distinguent de la majorité des caméras intégrées disponibles sur le marché ou dans la littérature. En effet, ladite caméra fonctionne en mode courant, ce qui lui confère la capacité de fonctionner à faible tension d'alimentation afin de minimiser sa consommation de puissance. Cette approche reste minoritaire dans les applications courantes, principalement en raison de son fort patron de bruit fixe, ou « Fixed Pattern

Noise (FPN) », difficile à éliminer. Ce dernier est principalement causé par le gain de transconductance des cellules photosensibles fortement dépendant des paramètres du transistor d'amplification, par opposition au mode tension où le gain unitaire est pratiquement indépendant du transistor d'amplification. Nous proposons une technique de réduction du FPN par le biais d'un nouveau capteur pour réduire significativement ce bruit et par le fait même augmenter la précision de l'APS.

De plus, sa résolution peut être modifiée instantanément. L'attrait principal de cette fonctionnalité est concevable, particulièrement pour l'application de l'implant visuel à un non voyant, étant donné la faible taille de l'image implantée [4,36]. En effet, en conservant le nombre de pixels de l'image constant, la variation de résolution a pour conséquence de modifier la superficie de l'image captée par la caméra. Ainsi, l'utilisateur a accès à un zoom électronique, ne nécessitant aucun déplacement de pièces mécaniques ou optiques. Ceci devrait permettre au patient de jouir d'une autonomie maximale dans les situations variées de la vie courante. Au choix, un large champ de vision peut être utilisé pour des déplacements, alors qu'une plus haute résolution dans une zone restreinte peut être préférable afin de discerner les détails d'un point d'intérêt ou pour la lecture. Le fait de réaliser la modification de la résolution directement au niveau de la capture d'image contribue significativement à réduire la consommation du système, par opposition à une approche où le traitement serait effectué dans une étape ultérieure.

Ce mémoire présente les différentes décisions de conception et évolutions menant à la conception d'une caméra intégrée d'utilisation générique, mais particulièrement adaptée pour l'implant visuel. Avant de présenter un système satisfaisant, deux architectures ont été élaborées, la seconde étant une évolution de la première en termes de souplesse d'utilisation et de performances, notamment au niveau des conditions de luminosité dans lesquelles il peut être utilisé. Une stratégie différente au niveau de l'architecture et du mode de lecture des données permet de réaliser ces améliorations.

Le premier chapitre constitue une introduction aux capteurs d'images. Les différentes technologies permettant de réaliser des capteurs d'images à partir de semi-conducteurs y sont présentées et comparées. Quelques exemples de capteurs CMOS ayant fait l'objet de publications récentes sont ensuite présentés.

Le second chapitre présente le concept d'une caméra intégrée présentant les caractéristiques mentionnées. Les différents composants du système et leurs principes de fonctionnement sont présentés. Les nombreux choix de conception sont alors présentés et justifiés.

Avant de réaliser un système de l'ampleur de ce qui est décrit dans ce deuxième chapitre, il convient de réaliser un premier circuit, plus modeste, comportant les éléments innovateurs ou potentiellement problématiques. Ce circuit est donc présenté au chapitre trois. Dans ce même chapitre, le système développé permettant de caractériser le circuit intégré est aussi présenté et explicité.

Finalement, le quatrième et dernier chapitre présente les résultats de caractérisation du système introduit dans les chapitres précédents. Suite à certaines observations, des modifications sont proposées afin de réaliser un système plus performant à partir des modules conçus et testés.

## CHAPITRE 1

### GÉNÉRALITÉS SUR LES CAPTEURS D'IMAGES

#### 1.1 Introduction

Les capteurs d'images font partie d'une sphère particulière de la microélectronique puisqu'ils font appel à des notions peu utilisées dans les autres applications d'intégration à très grande échelle (« Very Large Scale Integration », VLSI). C'est pourquoi il convient de s'attarder ici sur la présentation des concepts de base de la transduction photonique à électronique et sur les caractéristiques propres aux performances des caméras numériques avant de plonger le lecteur dans des discussions relatives à la conception d'une caméra intégrée. Le présent chapitre se veut donc une introduction au domaine de l'acquisition d'images numériques à l'aide de semi-conducteurs.

L'emphase est portée particulièrement sur les capteurs CMOS, bien que d'autres types soient répandus dans le domaine. Aussi, le présent ouvrage ne traite que de capteurs monochromes. Toutefois, la seule différence fondamentale entre ces capteurs et les capteurs couleurs est une mince couche de micro-filtres chromatiques qui recouvre la matrice de photosenseurs. Par conséquent, à l'exception de modules numériques de correction de couleurs présents afin de compenser l'effet non idéal des filtres, le contenu des blocs fonctionnels des deux types de capteurs est identiques au niveau VLSI.

Le chapitre est entamé avec une explication sommaire des phénomènes physiques qui sous-tendent le fonctionnement des capteurs d'images numériques modernes. Les capteurs sont ensuite présentés d'un point de vue général, en portant une attention particulière sur les principaux critères de performances qui les définissent, de manière à permettre au lecteur de mieux comprendre les discussions suivantes. Les capteurs à « Charge Coupled Devices (CCD) » sont brièvement présentés, et laissent place aux

capteurs de technologie CMOS standard. Les configurations de cellules photosensibles de base des différents types capteurs CMOS sont présentés. Ensuite, la méthode de réduction du bruit qui est la référence, ainsi que ses principaux circuits, sont brièvement exposés. Finalement, une présentation de quelques travaux représentatifs du domaine de recherche complète cette introduction sur le sujet, avec une attention particulière sur les capteurs dont la résolution est variable en temps réel, directement au moment de l'acquisition d'image.

## 1.2 Captation lumineuse à l'aide de semi-conducteurs

Lorsqu'un photon pénètre la surface d'un semi-conducteur, il existe une forte probabilité que son énergie soit absorbée par un électron si elle est supérieure à l'énergie qui sépare les bandes de valence et de conduction du matériau [2,46,48]. L'électron ainsi excité peut alors quitter la bande énergétique de valence qu'il occupe pour se retrouver dans la bande de conduction, créant ainsi une paire électron-trou. Ces charges, désignés porteurs en excès, sont alors libres de circuler dans le matériau.

Il existe plusieurs dispositifs permettant de tirer profit de ce phénomène de manière à mesurer une intensité lumineuse. Deux de ces éléments, la photodiode et le photocondensateur, constituent la base des capteurs optiques modernes et se doivent d'être présentés ici.

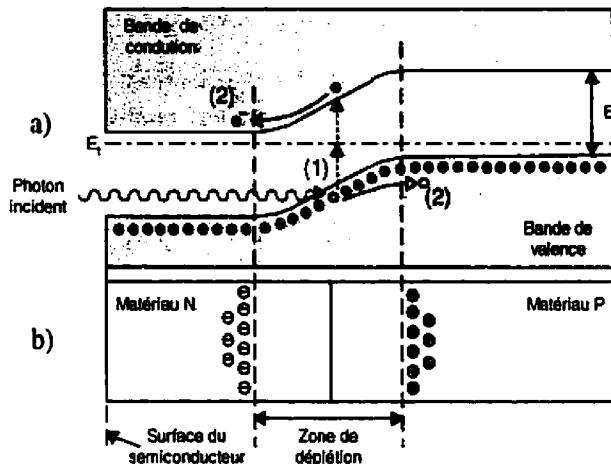

Le principe de la photodiode consiste à permettre à des photons de pénétrer dans un semi-conducteur afin qu'ils génèrent des paires électrons-trous à l'intérieur de la zone de déplétion d'une jonction P-N polarisée en inverse. Le champ électrique présent dans la zone de déplétion sépare alors rapidement les deux porteurs en excès. Ceci crée un courant de dérive à travers la jonction P-N qui est directement proportionnel au nombre de photons dont l'énergie est appropriée pénétrant dans le semi-conducteur. Le mécanisme d'interaction entre le photon et l'électron dans la zone de déplétion est illustré à la Figure 1.1. Le phénomène d'absorption du photon (1) et de séparation des charges

par le champ électrique (2) sont représentés sur le diagramme de bandes d'énergie en a), alors que b) représente l'accumulation de charges en excès dans le semi-conducteurs.

**Figure 1.1 : Absorption d'un photon dans une jonction PN**

Il est alors possible de déduire l'intensité du signal lumineux au moyen de senseurs électriques en mesurant l'une des deux variables suivantes : le courant de dérive généré par le signal lumineux (photocourant), ou la charge accumulée d'un côté de la jonction P-N au cours d'une période déterminée [50]. Il est à noter que les charges accumulées sont de type opposé à celles forcées par la tension inverse aux bornes de la diode. L'accumulation de charges se traduit donc par une diminution de la tension aux bornes de l'élément photosensible.

Le photocondensateur est l'autre élément de détection lumineuse fréquemment utilisé pour les capteurs d'images modernes. Le condensateur en question est constitué d'une plaque de conducteur transparent séparée d'un substrat semi-conducteur par une mince couche d'oxyde isolant. Par analogie avec le transistor dit à « Metal Oxyde Semiconductor (MOS) » qui partage la même structure, on y fait régulièrement référence à l'aide des appellations photoMOS, phototransistor ou transistor à photogrille.

En appliquant une tension à la grille du phototransistor, une zone de déplétion se forme dans le semi-conducteur, à l'image de ce qui se produit lors de la formation d'un canal sous la grille d'un transistor MOS. La grille conductrice et l'isolant étant transparent, ou presque, les photons sont libres de pénétrer la surface du substrat semi-conducteur. Les charges libérées par les interactions entre photons et électrons dans le substrat peuvent alors être accumulées dans la région, située sous la grille, que l'on nomme puits de potentiel.

Le principal avantage du photoMOS est que, grâce au fait que ses bornes soient électriquement isolées, aucun courant ne circule lorsque la tension est appliquée pour générer la zone de déplétion, comme il se produit dans le cas de la photodiode (courant de polarisation inverse). Ceci lui procure donc une meilleure sensibilité à de très faibles niveaux d'éclairage, puisque le signal ne se confond avec aucun courant présent par défaut (courant de noirceur).

Dans le cas du photoMOS, comme dans celui de la photodiode, les paramètres qui définissent les performances du dispositif (sensibilité, nombre de charges générées par photon incident, intensité du courant, réponse spectrale, courant de noirceur) dépendent principalement du substrat et du dopage du semi-conducteur. Le concepteur d'un capteur optique utilisant ces photosenseurs dans une technologie donnée n'a donc que très peu de contrôle sur ces performances.

En réalité, la sensibilité d'un semi-conducteur à une longueur d'onde est maximale lorsque l'énergie photonique est légèrement supérieure à l'énergie qui sépare ses bandes énergétiques de valence et de conduction. En effet, si l'énergie du photon est trop largement ou trop faiblement supérieure à celle qui sépare les bandes énergétiques du matériau, l'absorption du photon a de très fortes probabilités de se produire respectivement trop en surface ou trop en profondeur dans le semi-conducteur pour que les charges générées soient accumulées par l'élément photosensible [3]. Le premier cas

est d'autant plus vrai lorsqu'un photoMOS est utilisé, car le photon risque de se faire absorber directement par la photogrille.

Heureusement, le silicium présente de bonnes caractéristiques dans la plage des fréquences associées à la lumière visible. L'énergie qui sépare les bandes énergétiques du silicium, soit 1.11 eV, permet de capter des photons dont la longueur d'onde est inférieure à environ 1.1  $\mu\text{m}$ . Ceci couvre généralement adéquatement tout le spectre de lumière visible, qui s'étend d'environ 390 à 770 nm, du bleu au rouge, respectivement.

### 1.3 Capteurs d'images numériques

Un capteur d'images numérique se compose normalement d'une matrice bidimensionnelle de cellules photosensibles (pixels) et d'un circuit d'appoint chargé de lire l'information analogique emmagasinée dans les cellules et de synchroniser les différentes étapes requises lors de l'acquisition d'une image.

Une large variété de capteurs optiques existe, mais un moyen domine largement quant au traitement du signal de sortie des photodéTECTeurs. La méthode d'accumulation des charges générées par l'interaction avec la lumière pendant un temps déterminé (nommé temps d'intégration) est largement plus utilisée que la lecture directe du courant de dérive à travers la jonction P-N dans le cas où des photodiodes sont utilisées.

Une lecture s'effectue généralement de la manière suivante. Dans un premier temps, les éléments photosensibles de la matrice sont initialisés en les vidant de toute charge préalablement accumulée et en fixant un potentiel prédéterminé à leurs bornes. Ensuite, l'intégration a lieu, produisant ainsi un voltage qui est fonction de la quantité de charge générée par la lumière et de la valeur capacitive au nœud où la tension est lue. Le condensateur d'accumulation des charges est souvent formé simplement des capacités parasites se retrouvant au nœud en question. Généralement, il s'agit du photodéTECTeur lui-même et, dans plusieurs cas, de la grille d'un transistor. Une fois l'intégration terminée,

les cellules sont lues séquentiellement, rangée par rangée. Les pixels d'une même rangée peuvent par contre être lus parallèlement.

### 1.3.1 Critères de performance

Avant de comparer les principales technologies utilisées pour la réalisation de capteurs d'images, il convient de définir les principaux critères permettant d'évaluer les forces et faiblesses des différents systèmes. Les critères de performance des capteurs sur lesquels le concepteur de circuits VLSI a une influence sont donc brièvement présentés dans les paragraphes suivants.

En premier lieu, deux caractéristiques de base déterminent à quel point l'image acquise pourra être une représentation fidèle de l'image réelle, même en faisant fi de toute caractéristique dynamique du système. Celles-ci sont la **Résolution** et le **facteur de remplissage de la matrice**. La première représente la densité des pixels en nombre par unité de surface. La seconde est exprimée comme la fraction de la superficie du pixel utilisé pour la détection lumineuse.

Le **couplage parasite**, communément nommé « cross-talk » est une mesure plutôt qualitative qui fait référence au degré d'influence d'un pixel sur ses voisins. Il peut se présenter de différentes manières et origine de plusieurs sources. Celles-ci peuvent être d'origine optique (diffraction de la lumière sur les matériaux translucides au dessus du pixel ou aux frontières des éléments avoisinants), ou électrique (débordement d'un pixel sursaturé en intensité lumineuse, migration des charges générées en profondeur).

Le **taux de lecture d'une image** est la fréquence à laquelle l'information d'une image peut être recueillie à la sortie du capteur.

La **plage dynamique intrascène** est le rapport de l'intensité lumineuse saturant le signal de sortie sur la plus petite intensité détectable dans une même image. La plage

dynamique intrascène est fortement affectée par le rapport signal sur bruit du signal de sortie. La plage dynamique interscène, quant à elle, fait référence à la plus forte et la plus faible des intensités lumineuses qui peuvent être mesurées sur différentes acquisitions. Cette caractéristique détermine donc les conditions extrêmes de luminosité dans lesquelles le capteur peut être utilisé. Elle est dépendante du plus court et du plus long temps d'intégration que peut supporter le capteur. La vitesse de lecture des données ainsi que le taux de lecture des images sont donc des facteurs déterminants pour la plage dynamique interscène.

Le bruit de lecture est le niveau de bruit associé à la conversion de l'information lumineuse en signal électrique et au transfert de ce dernier. Ce bruit est aléatoire et il n'existe aucune corrélation de ce bruit d'une lecture à l'autre. Certaines contributions sont non négligeables et incontournables au niveau design (« shot noise » de la diode, « flicker noise » du transistor [21]), mais le bruit de lecture global peut être réduit par une conception méticuleuse des circuits de lecture et de conversion analogique à numérique ou par une réduction du taux de lecture.

Le bruit spatial fixe est le niveau de bruit invariant dans le temps associé aux disparités entre les réponses de différents pixels au travers de la matrice. Ce type de bruit, particulier aux capteurs d'images numériques, mérite ici une attention particulière. Les différences entre les caractéristiques des différents éléments au travers de la matrice, qui apparaissent au moment de la fabrication, procurent des réponses différentes d'un pixel à l'autre. En conséquence, une variance dans la réponse des cellules photosensibles est présente et se traduit par une image irrégulière en sortie, même sous une illumination homogène au dessus de la matrice. Ces irrégularités sont cependant fonction de l'espace, et non du temps, et se répètent d'une image à l'autre. Pour cette raison, ce bruit est désigné sous l'appellation de patron de bruit fixe, traduit de l'anglais « Fixed Pattern Noise (FPN) ».

### 1.3.2 Capteurs d'images à « Charge Coupled Devices (CCD) »

La présente section explique brièvement le fonctionnement et les caractéristiques des capteurs communément référencés sous l'acronyme CCD, de l'anglais « Charge Coupled Devices ». Bien que le sujet du présent mémoire soit d'un type différent, on ne peut passer sous silence les dispositifs CCD. En effet, vu leur grande popularité dans le monde de l'acquisition d'images numériques, ils demeurent la référence.

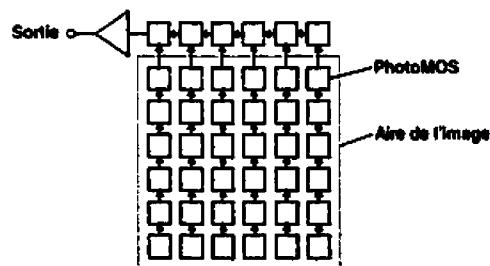

La Figure 1.2 schématisé l'architecture globale d'un capteur de type CCD. L'élément photosensible utilisé est le photocondensateur. Une matrice de photogrilles, situées à proximité les unes des autres, permet d'intégrer et de déplacer les charges créées par la lumière. Afin de balayer toute la matrice, les charges sont transférées, comme dans des registres à décalage, vers un amplificateur situé à la sortie. En décalant les charges lentement à la verticale et rapidement à l'horizontale, l'image est présentée à l'extérieur du circuit intégré sous forme d'un signal vidéo analogique.

**Figure 1.2 : Architecture d'un capteur CCD**

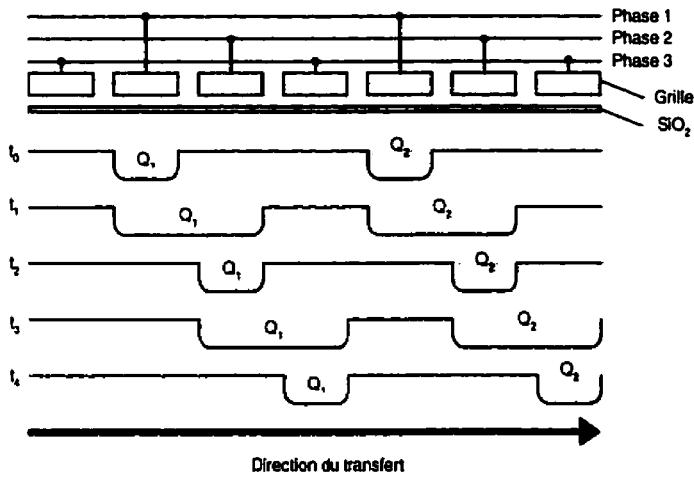

La Figure 1.3 présente le mécanisme permettant d'arriver à cette fin. Sur ce schéma, les charges sont initialement intégrées sous les grilles formées par le signal *Phase 1*. Par la suite, l'activation appropriée des différents signaux *Phase x* permet, en quelques étapes ( $t_0$  à  $t_4$  sur la figure), de former et de détruire des puits de potentiel afin de contraindre le déplacement des charges ( $Q_x$ ) dans la direction voulue.

**Figure 1.3 : Mécanisme de transfert de charges dans un capteur CCD (tiré de [5])**

La technologie CCD offre des performances très intéressantes en détectant et transférant les signaux avec un niveau de bruit relativement faible et uniforme. Il s'agit aussi d'une technologie mature en termes de rendement et de performances. Celles-ci ont en général atteint des niveaux près de leurs limites théoriques ou qui n'a pas subi d'améliorations significatives depuis des années [18].

Cependant, quelques points rendent cette technologie non désirable dans certaines applications. Premièrement, un sous échantillonnage de la matrice est impossible. En effet, on ne peut avoir accès à la valeur de chaque pixel qu'en accédant à tous les pixels des lignes et colonnes qui le précédent dans la matrice. Ensuite, pour une bonne efficacité de transfert des charges de chaque site vers la sortie, plusieurs niveaux de tensions sont nécessaires. De plus, les dispositifs CCD représentent des charges capacitives très importantes, qui rendent leur consommation plutôt grande [22,25]. Finalement, les circuits de ce type ont besoin d'un procédé de fabrication spécial, ce qui rend leur intégration à des systèmes plus complexes sur une seule puce impossible, ou tout au moins inefficace [11].

### 1.3.3 Capteurs d'images CMOS

Il est aussi possible de réaliser des capteurs au moyen de procédés CMOS standards. Cette option a été introduite initialement pour l'avantage qu'elle présente au niveau des coûts, puisque les procédés et usines de fabrication CMOS sont abondants et facilement disponibles. Cependant, de nos jours, on s'accorde plutôt pour dire que les principaux avantages de cette technologie se situent aux niveaux de sa faible consommation de puissance et des fonctionnalités qu'elle permet d'intégrer au capteur [22,28,53].

Au niveau de la qualité d'image, les capteurs CMOS se comparent aux capteurs CCD de milieu de gamme, mais ils demeurent inférieurs aux capteurs de haut de gamme [3]. Ceci est une conséquence de leur plus faible sensibilité à la lumière et de leur plus grand courant de noirceur. En effet, contrairement aux capteurs CCD, les procédés CMOS standards n'ont pas été optimisés pour les caractéristiques optiques de leurs éléments, mais plutôt pour la réalisation des circuits numériques ou mixtes.

Cependant, toujours au niveau de la qualité d'image, l'attrait des capteurs CMOS actifs augmente avec le nombre de pixels et cette technologie deviendra sûrement bientôt la référence pour les capteurs de quelques millions de pixels [18]. Ceci est principalement dû à leur plus faible bruit de lecture à des fréquences au dessus de 10 MHz, grâce à l'amplification possible à l'intérieur même du pixel, comme il sera présenté à la prochaine section. Aussi, le fait d'effectuer la conversion directement sur la puce améliore la qualité du signal, en éliminant le bruit qui s'introduit dans les interconnexions entre composants. Le transfert de l'information à l'extérieur du chip de façon numérique est bien sûr mieux immunisé au bruit que le transfert analogique. La vitesse de lecture est aussi améliorée, puisque la distance qui sépare les photodétecteurs et les circuits de lecture est réduite, et que la charge capacitive des plots est ainsi éliminée.

Toutefois, les dispositifs CMOS étant particulièrement sujets à de fortes disparités de leurs caractéristiques dans une technologie donnée, le FPN constitue une sévère limite

aux performances d'un capteur s'il n'est pas traité adéquatement. Dans la plupart des cas, des efforts pour réduire ce type de bruit sont essentiels pour procurer une image de qualité acceptable. Heureusement, le bruit se répétant d'une image à l'autre, des moyens efficaces d'amélioration d'image existent et seront présentés plus loin dans ce chapitre.

## 1.4 Types de capteurs CMOS

Les capteurs CMOS peuvent être divisés en deux grandes catégories selon les éléments qui composent leurs cellules photosensibles. Il s'agit des capteurs passifs et des capteurs actifs.

Les premiers sont les plus simples et ils permettent la plus grande résolution et le meilleur facteur de remplissage. Les capteurs actifs, quant à eux, possèdent des transistors d'amplification et/ou de conversion directement au niveau de leurs cellules photosensibles. De cette manière, il est habituellement possible d'améliorer de façon significative le rapport signal sur bruit et la vitesse de lecture du senseur. Nous faisons communément référence à ces capteurs au moyen de l'acronyme APS, signifiant « Active Pixel Sensor ».

Nous présentons dans les sections suivantes les configurations de base pour chacun des types de photodétecteurs les plus populaires, soient la photodiode et le transistor à photogrille. Cependant, le lecteur doit noter que plusieurs modifications peuvent être apportées aux circuits présentés ici, de manière à intégrer différentes fonctionnalités directement au niveau des pixels. Certaines de ces fonctionnalités seront cependant présentées plus loin, à la section 1.6.

### 1.4.1 Capteur Passif

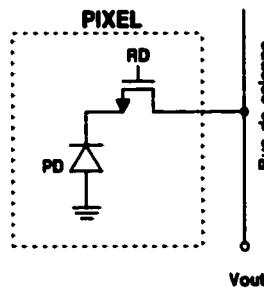

Un capteur qui utilise l'approche du pixel passif consiste en une matrice de pixels qui contiennent tous une photodiode et un transistor de sélection [30], tel que schématisé à la Figure 1.4. Les charges de la photodiode sont transférées à un amplificateur situé au bas

du bus de colonne une fois la période d'intégration terminée. C'est une impulsion sur la grille des transistors des pixels qui permet le transfert de ces charges. La lecture d'une image complète se fait généralement rangée par rangée. L'amplificateur de chaque colonne convertit la charge reçue en une tension proportionnelle à cette charge. Notons toutefois que deux transistors de sélection sont parfois utilisés afin de permettre un adressage x-y de manière à activer les pixels un à la fois.

Les capteurs à cellules passives offrent le plus grand facteur de remplissage et la plus grande densité. Néanmoins, ils souffrent de faibles rapport signal à bruit et vitesse de lecture, dus à la grande distance qui sépare les pixels de leur amplificateur.

**Figure 1.4 : Cellule photosensible CMOS passive**

## 1.4.2 Capteurs actifs

### 1.4.2.1 Capteurs actifs à photodiodes

Contrairement au pixel passif, où le signal véhiculé est constitué de la charge accumulée à une borne de la diode, le pixel actif peut transmettre à sa sortie n'importe quel type de signal, selon le choix du concepteur. Plusieurs types de cellules, significativement différentes, sont donc présentées ici et sont identifiées selon le mode de propagation de leur signal de sortie. Il s'agit des modes tension, courant et impulsions.

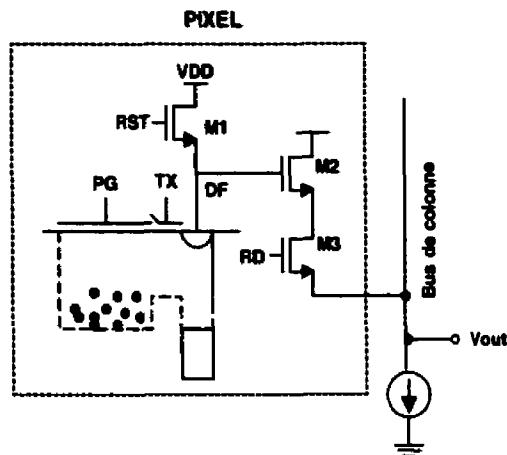

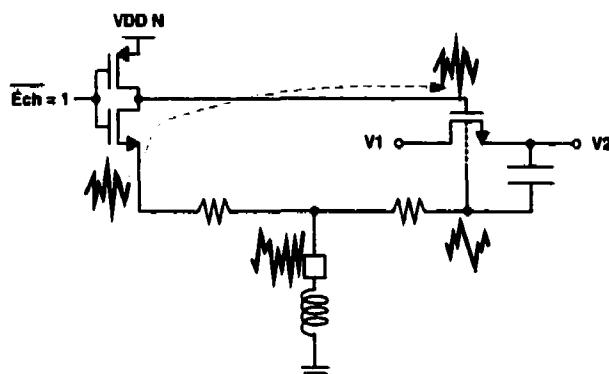

### a) Mode Tension

Une cellule typique de capteur actif à photodiode possède trois transistors, tel que schématisé à la Figure 1.5. Pour la décrire, expliquons sa procédure d'utilisation. Afin d'initialiser la cellule, avant chaque cycle de lecture, une impulsion sur l'entrée **RST** ramène le potentiel de la diode à la tension de référence, dans ce cas **VDD**. La période d'intégration suit. Pendant cette période, le photocourant fait baisser la tension présente aux bornes de la diode. Lorsque vient le temps de la lecture, une impulsion **RD** est envoyée à la grille de **M3**, activant ainsi la cellule. La tension **Vout**, dépendant de la tension aux bornes de la diode peut donc être lue par l'amplificateur de colonne (connecté à **Vout**) via le suiveur **M2** alors polarisé par la source de courant.