| <b>Titre:</b> Title:    | CMOS low voltage preamplifier based on 1/F noise cancellation                                                                                                                          |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Yamu Hu                                                                                                                                                                                |

| Date:                   | 2000                                                                                                                                                                                   |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                              |

| Référence:<br>Citation: | Hu, Y. (2000). CMOS low voltage preamplifier based on 1/F noise cancellation [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. https://publications.polymtl.ca/8872/ |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:                  | https://publications.polymtl.ca/8872/ |

|--------------------------------------------------------|---------------------------------------|

| <b>Directeurs de</b><br><b>recherche:</b><br>Advisors: | Mohamad Sawan, & Jean-Jules Brault    |

| <b>Programme:</b> Program:                             | Non spécifié                          |

### UNIVERSITÉ DE MONTRÉAL

# CMOS LOW VOLTAGE PREAMPLIFIER BASED ON 1/F NOISE CANCELLATION

#### YAMU HU

# DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2000

© YAMU HU, 2000.

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottowa ON K1A 0N4 Canada

Your file Vote riddrance

Our life Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-60898-0

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

#### CMOS LOW VOLTAGE PREAMPLIFIER BASED ON 1/F NOISE CANCELLATION

présenté par : <u>YAMU HU</u>

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. SAVARIA Yvon, Ph.D., président

M. <u>SAWAN Mohamad</u>, Ph.D., membre et directeur de recherche

M. JEAN-JULES BRAULT, Ph.D., membre et codirecteur de recherche

M. MARCEL LAPOINTE, Ph.D., membre

# **DEDICATE**

To all my friends

#### **ACKNOWLEDGEMENTS**

First, I would like to thank my advisor, Professor Mahamad Sawan, for his patient guidance and support during my stay at École Polytechnique de Montréal. In addition to providing guidance in microelectronic system design, he also provided help in technical writing and presentation style, and I found this guidance extremely valuable for me.

I would like also thank my co-director, Professor Jean-Jules Brault, for his valuable guidance and encouragement along the way.

I would like to thank Professor Yvon Savaria, École Polytechnique de Montréal, and Doctor Marcel Lapointe, Goal Semiconductor Inc., for their acceptance to participate in the jury exam of this thesis. I am especially grateful to Dr. Marcel Lapointe for answering numerous technical questions and providing me so much advice.

I also appreciate my colleagues of POLYSTIM past and present for their friendship and all of their help over years. Adnan Harb and Abdelouahab Djemouai helped me get up to speed and were patient with questions at the start of this project. Christian Fayomi was a valuable resource and friend to me. I also appreciate him for listening to my ideas and providing feedback. Also, Hicham Elhallabi, Jonathan Coulombe, Jean-François Delage, Jean-François Harvey and Eric Schneider all are good friends and I really enjoyed the atmosphere in this research group.

Finally, I would like to thank my family for their love and support. I couldn't have completed this thesis without them.

This work was supported by the MICRONET. CMOS fabrication was offered by Canadian Microelectronics Coropration (CMC).

#### RÉSUMÉ

L'utilisation des préamplificateurs analogiques de haute performance devient de plus de plus incontournable avec l'évolution rapide de la microélectronique. Celle-ci est due au fait que les préamplificateurs définissent le niveau minimum de signal pouvant être traité. Dans les applications à basse fréquence telles que les applications biomédicales, le facteur limite est le bruit 1/f et le décalage continue ou DC du circuit d'amplification. La décroissance rapide de la taille minimale des transistors en technologie CMOS, impose une contrainte additionnelle sévère à la conception des circuits analogiques de haute performance.

L'objectif principal de ce mémoire est la conception en technologie CMOS d'un préamplificateur possédant une bonne performance de bruit 1/f avec un niveau faible de la tension de décalage. Le circuit proposé est en mesure de fonctionner à basse alimentation puisqu'elle est destinée aux applications biomédicales.

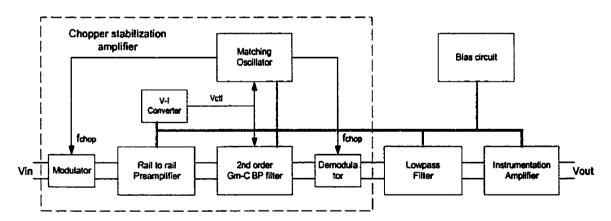

Une analyse de la source de bruit aux basses fréquences en technologie CMOS a été effectuée. La technique de «CHopper Stabilisation (CHS) », qui est une méthode fréquemment utilisée pour réduire à la fois le bruit à basse fréquence ainsi que la tension de décalage, a été étudiée tant au niveau théorique qu'au niveau implementation VLSI. Le circuit de préamplification proposé fonctionne avec une alimentation de 1.8 V tout en présentant une large bande dynamique (0 à 1.8 V) et a été fabriqué dans un procédé

CMOS  $0.35\mu m$ . Il est composé d'un circuit d'appariement d'horloge, d'un filtre passe-bas continu d'ordre 4 et d'un amplificateur d'instrumentation. Le gain DC de l'amplification est de 51 dB avec une bande passante de 4.5 kHz. Le bruit équivalent d'entrée est de l'ordre de  $45 \text{ nV} / \sqrt{Hz}$ . Le circuit occupe une surface approximative  $1150\times450 \ \mu \text{m}^2$  et dissipe seulement 775  $\mu \text{W}$  en simulation. Bien que le circuit a été originalement conçu pour les applications biomédicales, sa versatilité fait qu'il peut être utilisé dans des applications nécessitant la mesure de signaux basses fréquences de très faible amplitude.

#### **ABSTRACT**

Nowadays, with the ongoing development of microelectronics, high performance analog preamplifier plays a critical role in mixed-signal analog-digital interfaces. It often limits the minimum signal level that can be processed. For the low-frequency applications, such as implantable devices in biomedicine that require to monitor several neuromuscular activities, the main factors that limit the signal dynamic range are the flicker noise and the DC offset of the preamplifier. In addition, the ongoing downscaling of the CMOS technology introduces more difficulty on designing high performance analog circuits.

The aim of this master thesis is to design a CMOS preamplifier without being limited by its inherent flicker noise and DC offset, which allows handling smaller signals. Furthermore, apart from low-noise and low-offset, the circuit should work under a low-voltage supply since it is designed for an implantable stimulate application.

This thesis examines the noise sources and means to minimize their impact in CMOS technology used at low frequency. An emphasis is placed on providing noise minimizing solutions. Chopper Stabilization technique (CHS) is used to realize low-noise and low-offset. This thesis deals both with theoretical analysis and circuit implementations. The proposed circuit works under low power supply (1.8V), and has a wide common mode input range (0-1.8V). It features a 51dB gain with a bandwidth of 4.5 KHz. The equivalent input noise is about 45  $nV/\sqrt{Hz}$ . The proposed preamplifier includes a

matching clock generator, a  $4^{th}$  order continuous time low-pass filter and an instrumentation amplifier, and it has been implemented in a  $0.35\mu m$  n-well CMOS process with an active die area of  $1150\times450~\mu m^2$ . The total data acquisition device consumes only 775  $\mu W$  in simulation. Although the analog front-end preamplifier was originally designed for biomedical applications, it can be used for any low frequency application to monitor ultra low-amplitude signals.

# **CONDENSÉ EN FRANÇAIS**

#### I. INTRODUCTION

Pour les applications de mesure de signaux, le bruit intrinsèque du système limite souvent la plage du signal d'entrée. Il existe deux sortes de sources de bruit dans un circuit MOS.

#### 1. Le bruit thermique

Le bruit thermique dans un transistor MOS résulte du mouvement aléatoire des électrons. La densité du bruit peut être représentée par  $N_{iw} = 4kT/gm$ , qui est du bruit blanc.

#### 2. Le bruit 1/f

Bien que l'origine de ce bruit est partiellement inconnue, il est possible de l'identifier par sa densité spectrale qui est inversement proportionnelle à la fréquence, comme le montre l'équation.

$$N_{t/f}(f) = \frac{K}{f^{7}}$$

où,  $0.7 < \gamma < 1.3$

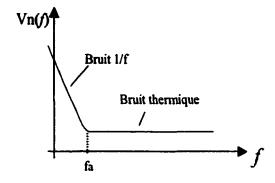

Comme le bruit en 1/f est plus élevé que le bruit thermique à basse fréquence, le bruit en 1/f est particulièrement important dans les circuits MOS. La figure 1 illustre la densité spectrale de bruit typique d'un transistor MOS en fonction de la fréquence. Le bruit

thermique et le bruit en 1/f se croisent à la fréquence fa, qui est appelée fréquence de coin (corner frequency).

Figure 1. Densité spectrale de bruit typique d'un transistor MOS

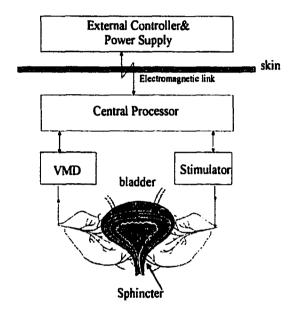

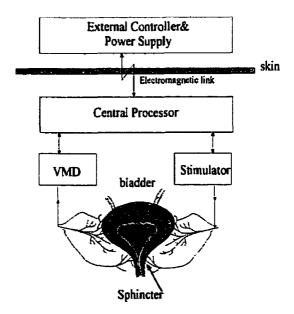

Plusieurs applications nécessitent le traitement des signaux à basse amplitude tels que les dispositifs électroniques implantables dédiés à des applications biomédicales afin de coordonner les nombreuses activités neuromusculaires [1][2][3]. Parmi ces dispositifs, on retrouve le contrôleur de la vessie, dédié à la mesure du volume urinaire et à l'évacuation de l'urine par la stimulation électrique via des électrodes [1]. Le système implantable correspondant se compose par conséquent de trois parties principales, tel que présenté sur la figure 2: un processeur central (CP), un module de mesure du volume urinaire « Volume Monitoring Device (VMD) » et un micro-stimulateur.

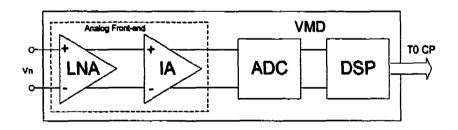

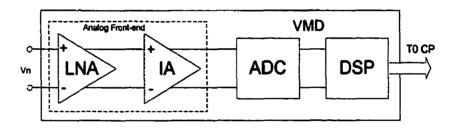

Le module VMD prélève le signal nerveux qui contient l'information sur le volume de la vessie. Le schéma fonctionnel du VMD est illustré sur la figure 3. L'amplitude du signal nerveux  $V_n$  est généralement très basse, de l'ordre 1 à 10  $\mu V$  [2][3], et souvent submergée par le bruit dans un amplificateur opérationnel conventionnel CMOS à deux

étages. Par conséquent, le signal doit être faiblement amplifié, tout d'abord par un amplificateur à faible bruit (LNA), afin de limiter le bruit 1/f et d'augmenter le niveau du signal au-dessus de celui du bruit de l'amplificateur d'instrumentation (AI). La sortie de l'AI est alors convertie en signal numérique et envoyée au bloc traitant le signal numérique.

Figure 2. Schéma bloc simplifié du system globale dédié à la régulation de la vessie.

Figure 3. Schéma bloc du module VMD

La source dominante de bruit dans les applications de systèmes électroniques implantables est le bruit 1/f de l'étage différentiel d'entrée. La technologie récente utilisé

pour les masque et l'emploi de longueurs de transistors réduites associée à la réduction d'échelle tend généralement à augmenter le niveau du bruit 1/f [11]-[14]. Le bruit peut être réduit par un certain nombre de méthodes [4]-[10]. La technique de « CHopper Stabilisation (CHS) » est une méthode fréquemment utilisée pour réduire à la fois le bruit à basse fréquence ainsi que la tension de décalage due au "mismatch".

# II. CARACTÉRISTIQUES DE LA TECHNIQUE DE STABILISATION CHOPPER

Cette dernière méthode tire profit d'une technique de modulation qui n'augmente pas le bruit à large bande ni le bruit blanc à bande de base. Ainsi le CHS est une méthode très pertinente pour le traitement des signaux en temps réel, tel que la surveillance des activités neuromusculaires dans les applications biomédicales.

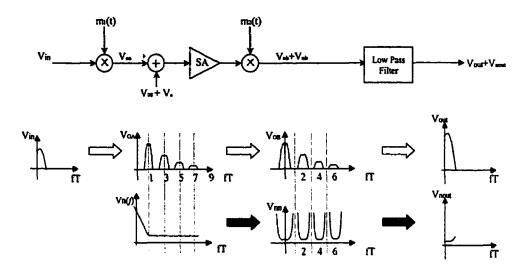

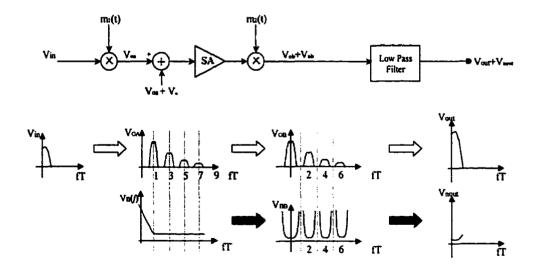

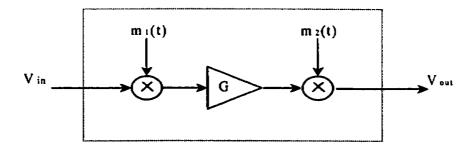

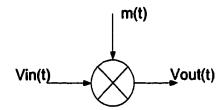

Le principe de base du CHS est présenté à la figure 4. Le signal d'entrée  $V_{in}(t)$  est modulé par un signal d'une onde carrée  $m_1(t)$  à une fréquence  $f_{chop}$ . Après cette modulation, le spectre du signal d'entrée  $(V_{in})$  est transposé aux fréquences des harmoniques impaires du signal  $m_1(t)$ . Il est alors amplifié par un amplificateur sélectif (SA) et démodulé par le signal  $m_2(t)$ , et cela transpose de nouveau le signal  $m_1(t)$  à la bande initiale. Si le spectre du signal d'entrée est limité à la moitié de la fréquence de chopper, aucun chevauchement de signal ne se produira.

Figure 4. Principe de la technique CHS

Le bruit à basse fréquence ainsi que le décalage de tension de l'amplificateur (représentée par V<sub>n</sub> et V<sub>os</sub> respectivement sur la figure 4) sont modulés une première fois par le démodulateur et leurs spectres se retrouvent aux harmoniques impaires, laissant par le fait même le bruit blanc dans la bande de base. Après démodulation (soit une deuxième modulation), le signal est filtré passe-bas à la moitié de la fréquence de chopper. Ainsi, les signaux et le bruit à contenu fréquentiel élevé seront éliminés.

Quelques études sur la technique CHS ont été publiés récemment [4][5][6][7]. La partie critique du CHS est de concevoir un amplificateur sélectif optimal, qui amplifie non seulement le signal dans une bande de fréquence, mais peut également réduire le décalage résiduel (figure 5) provenant de l'horloge du modulateur d'entrée. Deux publications [5][6] ont démontré qu'un filtre passe-bande du deuxième ordre (BPF) sera un meilleur compromis entre la réduction du décalage et la complexité du circuit. Dans [5], l'effet de

la modulation CHS sur le bruit de l'amplificateur a été illustré en détail, mais le circuit utilisé était un filtre passe-bas de premier ordre au lieu d'un filtre passe-bande de second ordre, tel qu'il a été utilisé dans la pratique. Dans [6][7], les auteurs ont complété une autre étude sur le taux de rejet en mode commun (CMRR) et le décalage dans les CHS. Dans ce mémoire, plusieurs caractéristiques complémentaires et importantes du CHS sont fournis, et l'analyse du rapport de signal sur bruit (SNR) avec CHS et sans CHS est démontrée. Ceci afin de fournir un aperçu supplémentaire sur la réduction du bruit du signal par le filtre passe-bande du deuxième ordre. Les résultats ont été vérifiés par un modèle de comportement établi pour l'outil SIMULINK [28].

#### Le décalage résiduel

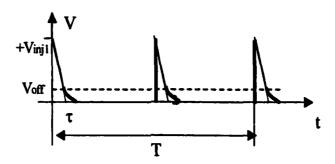

Le décalage en tension dans un amplificateur sélectif est quasi nul, car il a été décalé aux harmoniques impaires de la fréquence  $f_{chop}$ , puis filtré par le filtre passe bas (LPF). Mais les niveaux crêtes des signaux résultants du modulateur d'entrée présentent un décalage en tension résiduel après la seconde modulation, tel que présenté sur la figure 5. On démontrera que ce décalage résiduel est proportionnel au carré du taux (la constante de temps du niveau crête sur la\_période T du signal modulé), si un filtre passe-bande de deuxième ordre est choisi comme amplificateur sélectif. La constante de temps  $\tau$  est égale à RC, où R est la résistance de la source du signal d'entrée et C est la capacité parasite de l'amplificateur.

Figure 5. Le décalage résiduel

#### Les bruit thermique du CHS

Après que le bruit blanc soit passé par un filtre passe-bande de deuxième ordre, un bruit résultant à bande étroite est obtenu. Ceci augmente le SNR (CHS sur bruit blanc) de  $16/\pi^2 = 1.62$  par rapport à un système sans CHS. Ce phénomène est dû au fait que le modulateur d'entrée présente un coefficient  $k=4/\pi$  à la première harmonique qui est principalement la partie du signal restauré. Le signal augmenté améliore donc le SNR d'un taux de  $k^2$ .

#### III. IMPLEMENTATION DU CIRCUIT

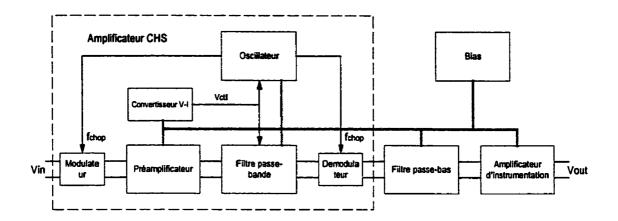

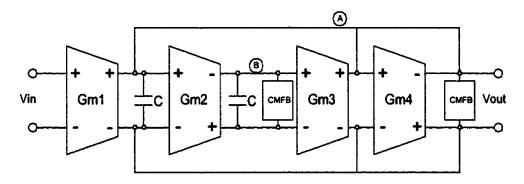

#### 1.Schéma bloc du circuit

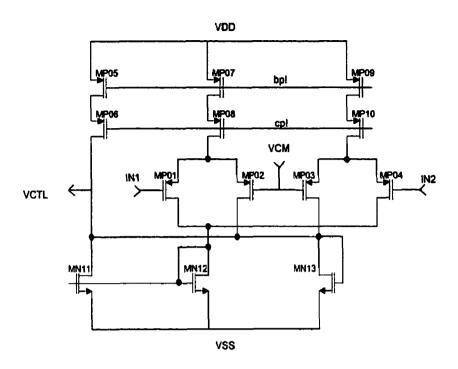

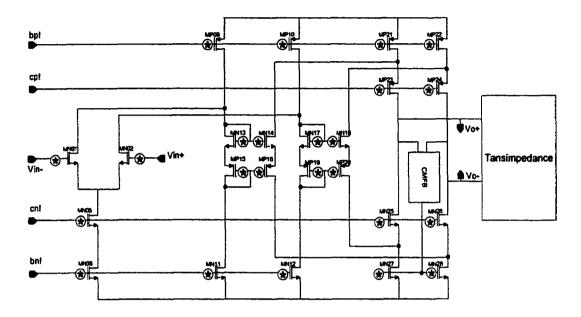

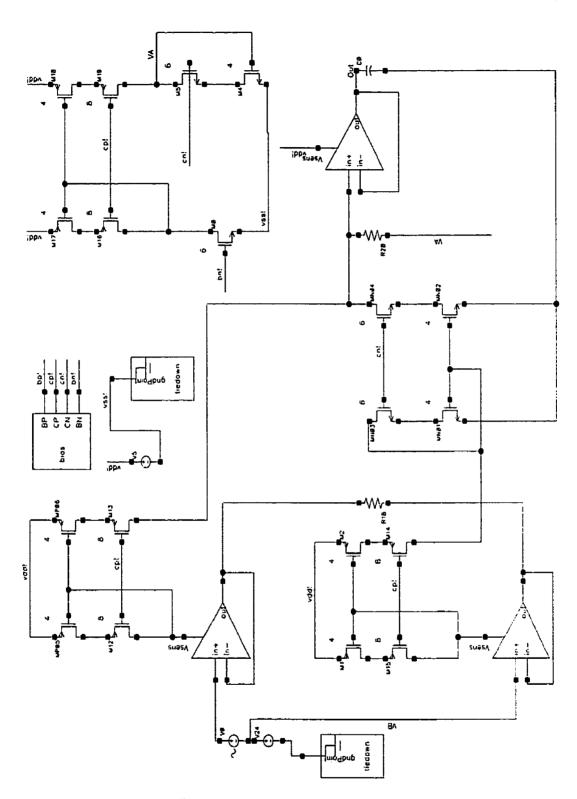

Le VMD sera implanté dans le corps humain, ainsi toutes les composantes analogiques d'entrée incluant le générateur à horloge et le filtre passe bas devraient être entièrement intégrée sur une seule puce. Le schéma bloc simplifié du système est donné à la figure 6.

Figure 6. Schéma bloc de l'amplificateur d'entrée analogique

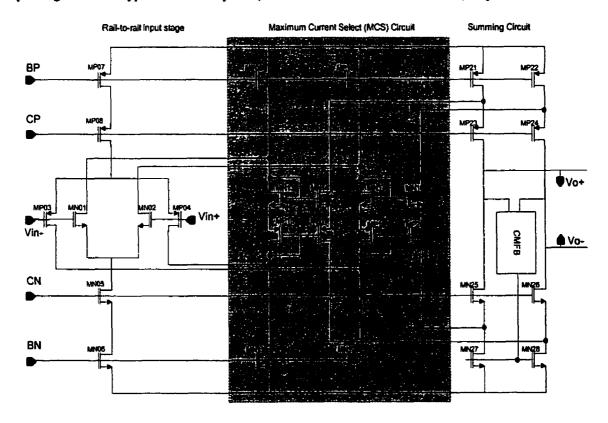

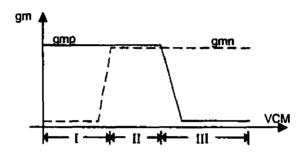

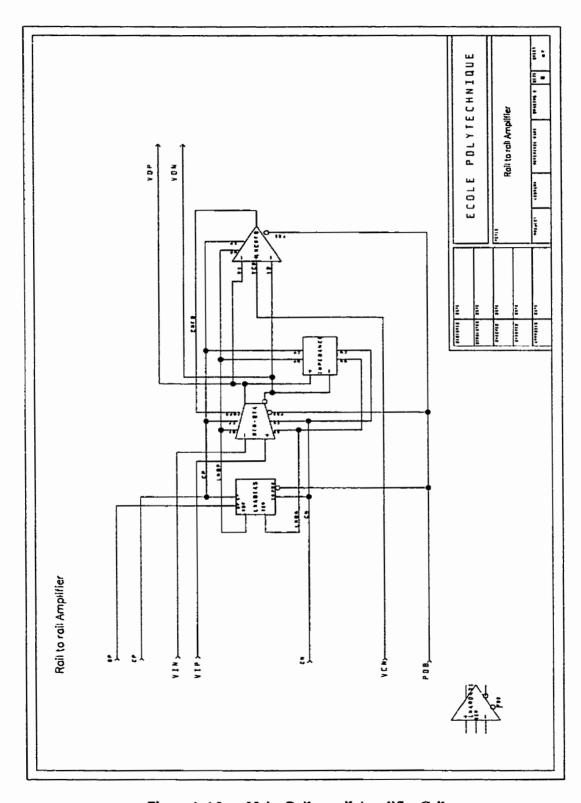

Dans notre application, l'amplificateur sélectif est réalisé par deux étages, un préamplificateur à large bande et faible bruit suivi d'un filtre passe-bande. Cette structure présente deux avantages: d'abord, une large gamme d'entrée en mode commun peut être réalisée en utilisant un OTA (Amplificateur Opérationnel à Transconductance) ayant une topologie rail à rail au premier étage, sans pour autant affecter la linéarité du filtre g<sub>m</sub>-C (combinaison de cellules de transconductances et de condensateurs). En second lieu, la valeur de la transconductance d'entrée du BPF n'a pas besoin d'être très haute pour réaliser un gain DC élevé, d'où la non nécessité de compenser le décalage provenant de la paire d'entrée.

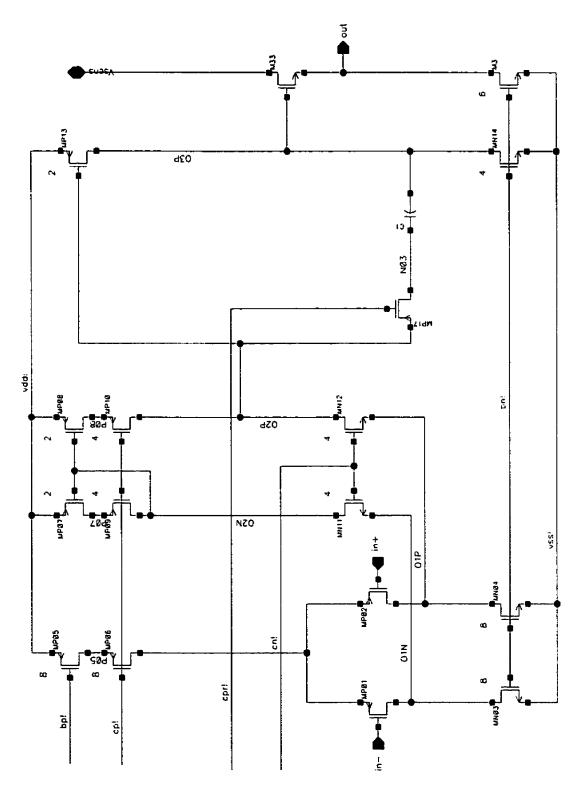

#### 2. Le préamplificateur à faible bruit

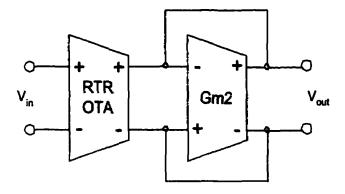

Le préamplificateur est composé d'un OTA rail à rail suivi d'un étage à transimpédance.

Le gain DC de l'amplificateur est égal au rapport de Gm1/Gm2, où Gm1 et Gm2 sont les valeurs des transconductances de l'OTA et de l'étage à transimpédance respectivement.

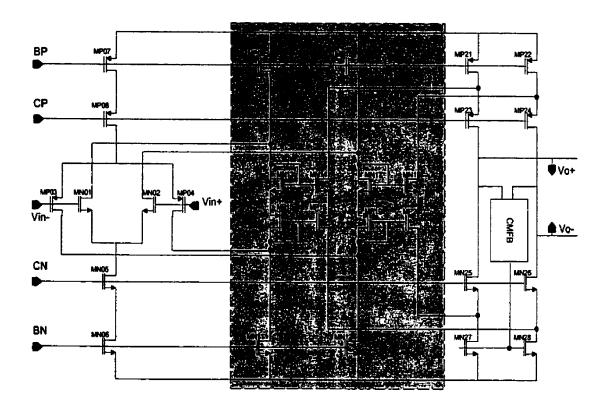

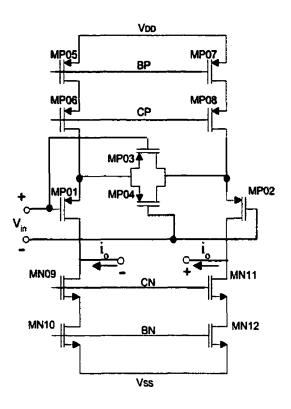

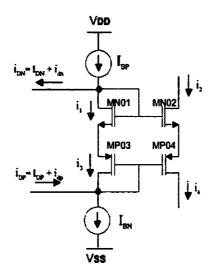

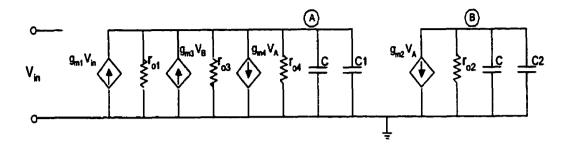

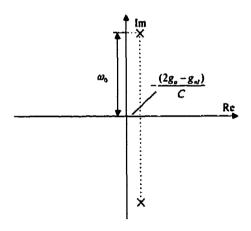

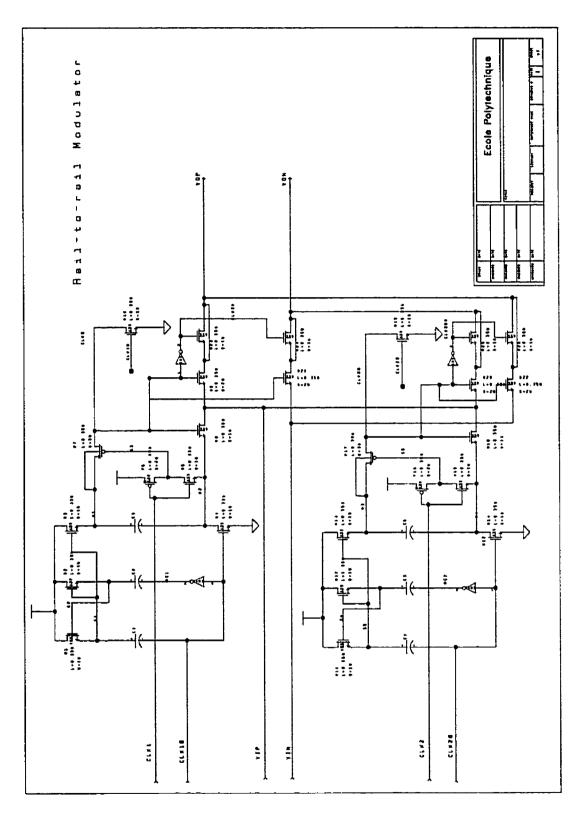

La largeur de bande de l'amplificateur est choisie élevée afin d'éviter qu'un faible gain ainsi qu'une distortion de la phase n'apparaisse dans le système. L'amplificateur rail à rail (plage d'entrée de 0V à VDD) à faible bruit est présenté à la figure 7. L'étage à transimpédance proposé utilise un étage à transconductance linéaire avec une rétroaction négative, tirant avantage de deux transistors en triode afin d'améliorer la linéarité.

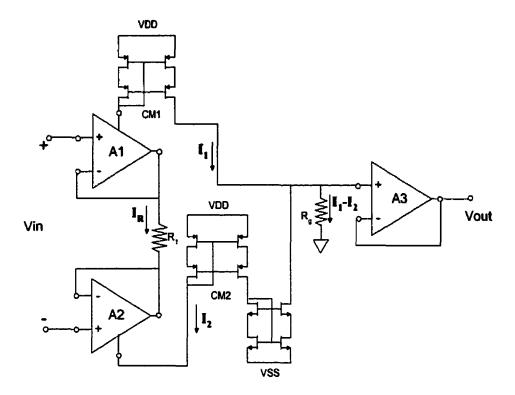

Figure 7. Schéma de l'amplificateur rail à rail

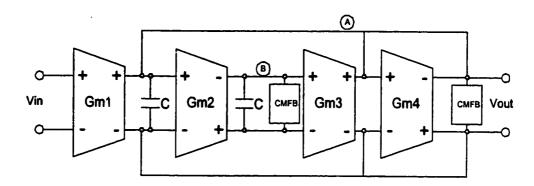

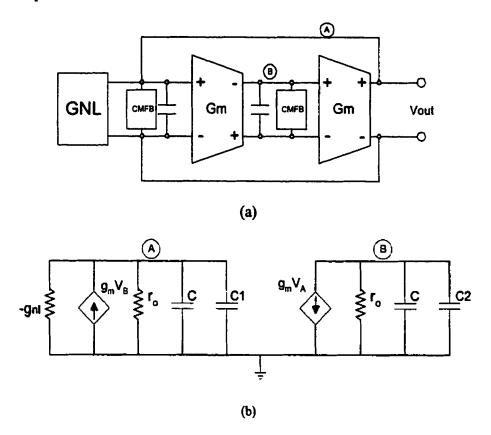

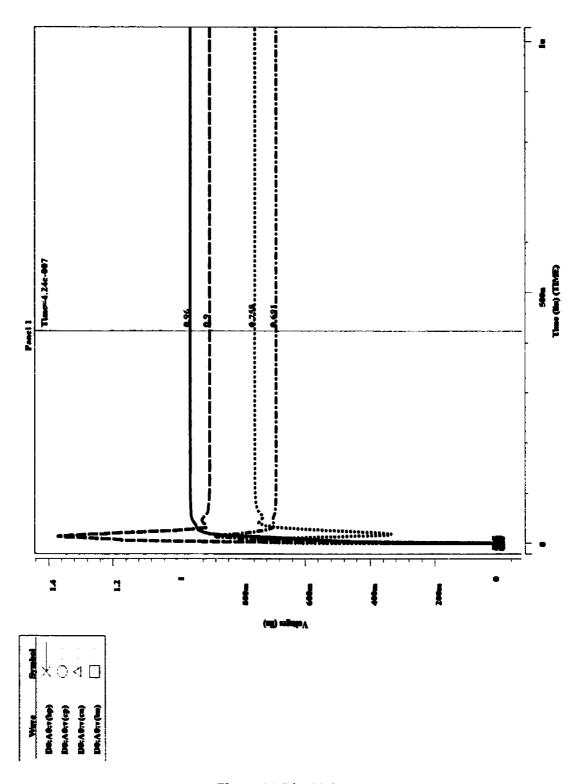

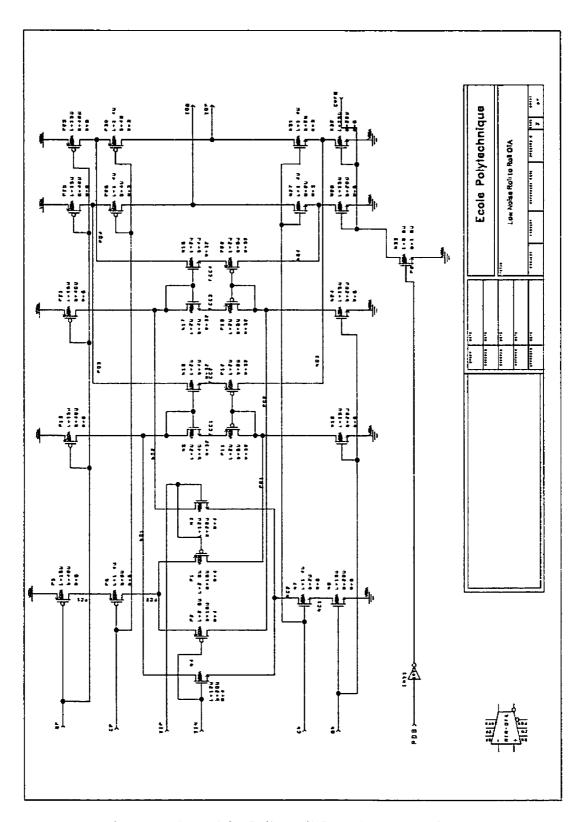

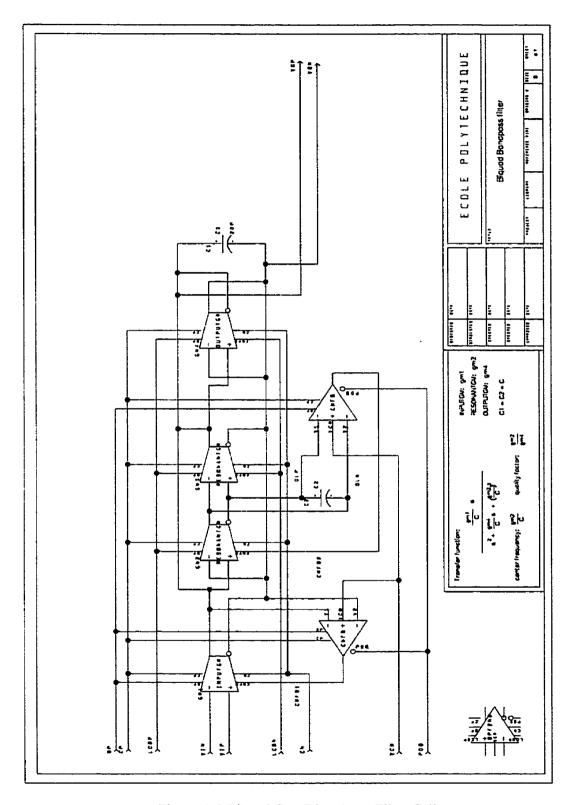

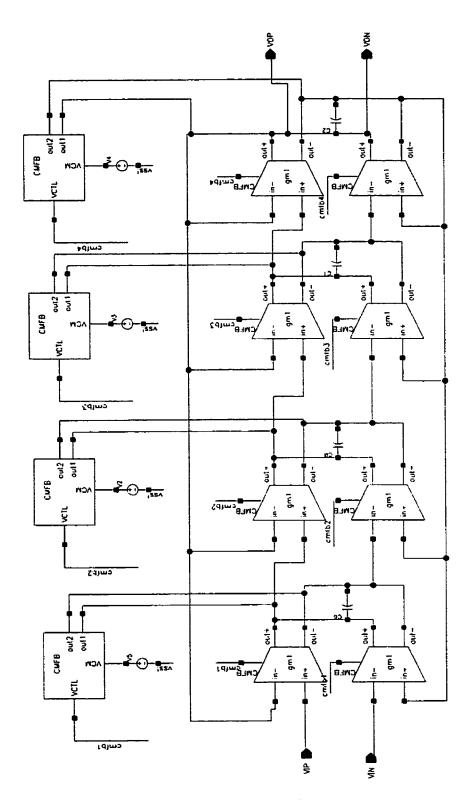

#### 3. Le filtre passe-bande et l'oscillateur

Le deuxième étage de l'amplificateur sélectif est constitué d'un filtre Gm-C de 2ième ordre. La fréquence f<sub>chop</sub> et la fréquence centrale sont doivent être égaler, et supérieures à

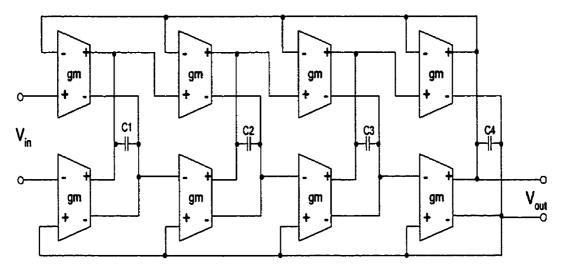

la fréquence de coin (corner frequency). Le facteur de qualité Q sera limité par la largeur de bande et est égal à 4. Ainsi la bande passante du signal peut aller jusqu' à 5 kHz. Le schéma bloc est présenté à la figure 8. Les cellules GM utilisent des étages à transconductance linéaire [22].

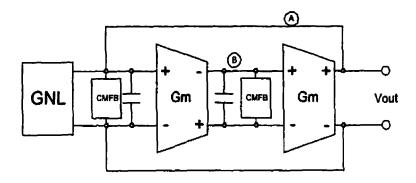

Figure 8. Schéma bloc du filtre passe-bande

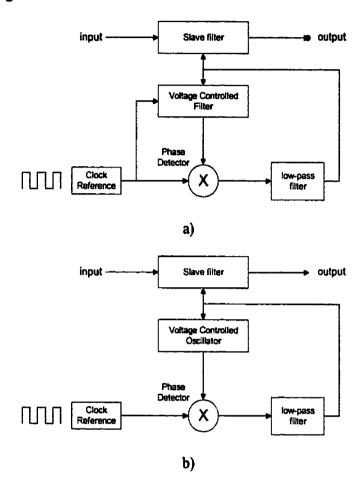

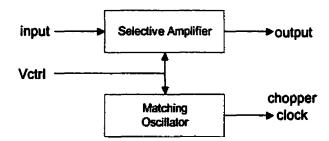

En raison du manque de masses virtuelles et de nœuds à basse impédance, les filtres gm-C sont sensibles aux capacités parasites. Par conséquent, il est nécessaire d'ajouter un circuit de calibration automatique dans le filtre passe bande, pour verrouiller sa fréquence centrale  $f_c$  avec le  $f_{chop}$ . La calibration automatique des filtres continus a été analysée dans la littérature [21]-[26]. Mais pour l'amplificateur CHS, la valeur de la fluctuation du  $f_{chop}$  ne présentera pas d'impact significatif sur les performances du CHS. Donc, le point clé de la calibration dans le CHS étant de suivre la fréquence centrale du filtre, plutôt que de le fixer avec une horloge à référence. Ainsi nous pouvons utiliser un oscillateur intégré avec le filtre passe bande qui joue le rôle d'un générateur d'horloge  $f_{chop}$ . Deux structures identiques du circuit de résonance sont utilisées dans l'oscillateur et dans le filtre passebande. Cette structure réduira la complexité du système entier. Cela est particulièrement

important dans cette application, où l'horloge  $f_{chop}$  est générée sur la même puce. Le schéma de l'oscillateur est présenté à la figure 9.

Figure 9. Schéma bloc de l'oscillateur

#### IV. SIMULATION ET RÉSULTATS EXPÉRIMENTAUX

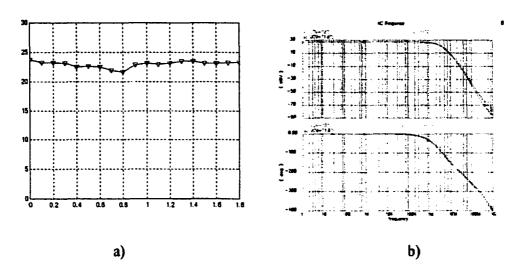

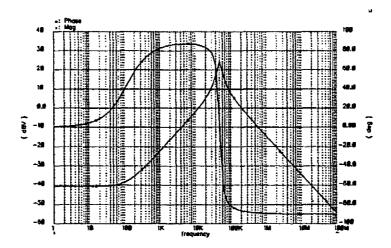

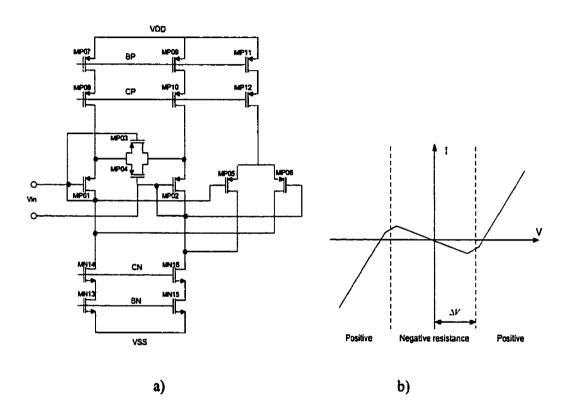

Le design proposé du CHS a été implémenté et fabriqué en technologie CMOSP35 de la Société Canadienne en Microélectronique (SCM). Les résultats de mesure de l'amplificateur d'entrée rail à rail sont montrés sur la figure 10 a). La variation du Gm est inférieure à 5%, et les autres performances sont meilleurs que celle d'un OTA conventionnel rail à rail. La réponse en fréquence du préamplificateur à faible bruit est présentée sur la figure 10 b). Son gain DC est de 26 dB et la fréquence de coupure à -3dB est environ 1.2 MHz, beaucoup plus grande que le f<sub>chop</sub> (47 kHz dans notre cas). La figure 11 montre le spectre du filtre passe bande. Un zéro supplémentaire apparaît en basse fréquence à cause de l'impédance de sortie finie de l'étage à transconductance. Le gain à la fréquence centrale est de 25 dB. Le gain de l'amplificateur sélectif incluant deux étages est de 51 dB. L'amplificateur d'instrumentation (AI) a été également intégré dans cette

puce. La structure de l'AI proposé par notre équipe PolySTIM a été illustrée dans [27]. L'AI permet de réaliser un taux de rejet en mode commun (CMRR) assez élevé sans calibration. Le bruit équivalent à l'entrée est de  $45 \text{ nV}/\sqrt{Hz}$ . La puissance consommée en simulation est de seulement 775  $\mu$ W pour une alimentation de 3.3 V.

Figure 10. Résultats de mesure de l'amplificateur d'entrée rail à rail

a) Variation du Gain b) Réponse en fréquence

Figure 11. Simulation du filtre passe bande

#### V. CONCLUSION

La technique de modulation 'CHOPPER' a été choisie pour réduire le bruit à basse fréquence ainsi que l'offset au niveau de l'amplificateur opérationnel CMOS. La basse tension d'alimentation et la grande marge de tension en mode commun sont réalisées en utilisant le préamplificateur rail à rail à faible bruit au niveau du premier étage. Le système a été intégré dans la technologie CMOSP 0.35 µm. Cet amplificateur a été initialement conçu pour des applications biomédicales, toutefois il peut être employé pour des applications à basses fréquences pour traite des signaux de basse amplitude.

# TABLE OF CONTENTS

| DEDICATE                                     | iv     |

|----------------------------------------------|--------|

| ACKNOWLEDGEMENTS                             | v      |

| RESUMÉ                                       | vii    |

| ABSTRACT                                     | ix     |

| CONDENSÉ EN FRANÇAIS                         | xi     |

| TABLE OF CONTENTS                            | xxiv   |

| LIST OF TABLES                               | xxvi   |

| LIST OF FIGURES                              | xxvii  |

| LIST OF ABBREVIATIONS AND SYMBOLS            | xxxii  |

| LIST OF ANNEXS                               | xxxvii |

|                                              |        |

| Chapter 1 Introduction                       | 1      |

| 1.1 Motivation                               | 1      |

| 1.2 Research Goals                           | 4      |

| 1.3 Thesis Organization                      | 5      |

| Chapter 2 Noise in CMOS Integrated Circuits  | 7      |

| 2.1 Introduction                             | 7      |

| 2.2 Noise Sources in MOSFET Transistors      | 8      |

| 2.2.1 Channel Thermal Noise Mechanism        | 8      |

| 2.2.2 Flicker (1/f) Noise in MOS Transistors | 10     |

| 2.2.3 Impact of Scaling                                    | 13 |

|------------------------------------------------------------|----|

| 2.3 Low Noise Techniques                                   | 13 |

| 2.3.1 Autozero Technique                                   | 15 |

| 2.3.2 Chopper Stabilization Technique                      | 21 |

| 2.4 Low Noise Circuits within Recent Literatures           | 27 |

| 2.5 Conclusion                                             | 30 |

| Chapter 3 Chopper Stabilization Technique                  | 32 |

| 3.1 Introduction                                           | 32 |

| 3.2 A CHS Behavior Model in MATLAB/SIMULINK                | 33 |

| 3.2.1 Model Description                                    | 33 |

| 3.2.2 Non-idealities Consideration                         | 41 |

| 3.2.3 A Simulation Example                                 | 41 |

| 3.3 Supplemental analyses of CHS                           | 43 |

| 3.3.1 Characteristics of CHS                               | 43 |

| 3.3.2 Chopper Amplifier with the 2 <sup>nd</sup> order BPF | 44 |

| 3.4 Summary                                                | 54 |

| Chapter 4 Low Voltage Operation & Elementary Circuits      | 55 |

| 4.1 Introduction                                           | 55 |

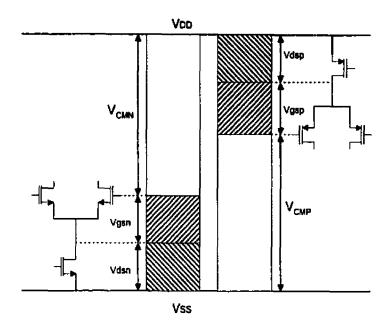

| 4.2 Voltage Requirements of Analog Circuits                | 56 |

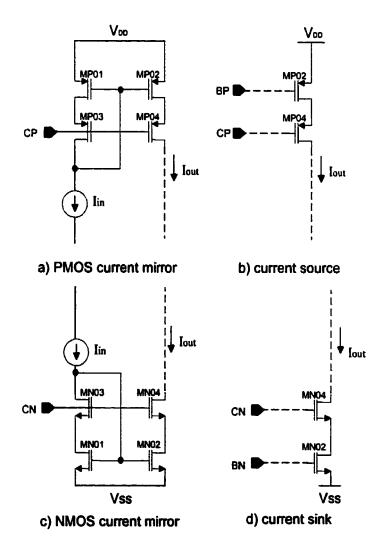

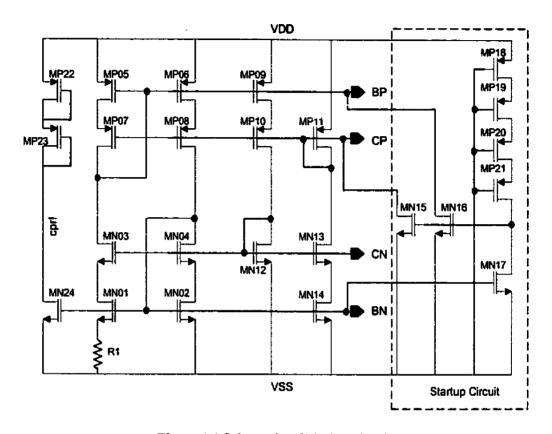

| 4.3 Basic Circuits and Functions                           | 59 |

| 4.3.1 High-swing Current Source/Sink                       | 59 |

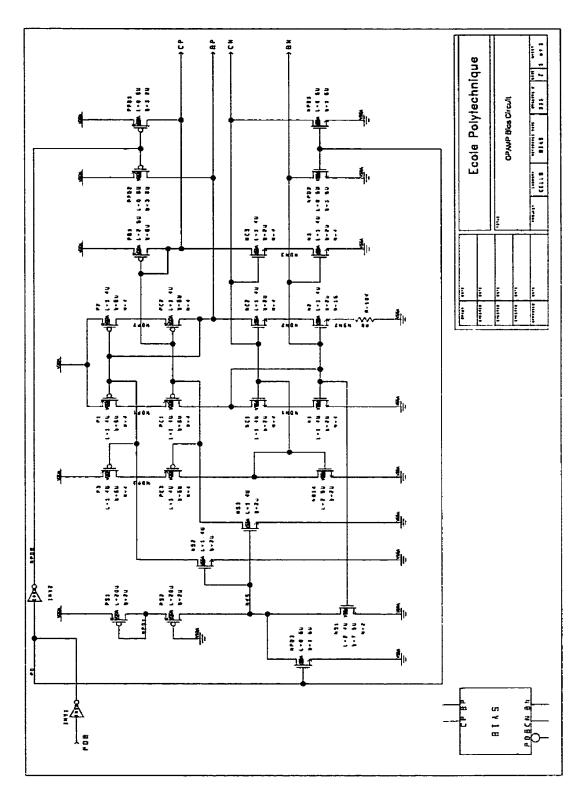

| 4.3.2 BIAS Circuit Design                                  | 61 |

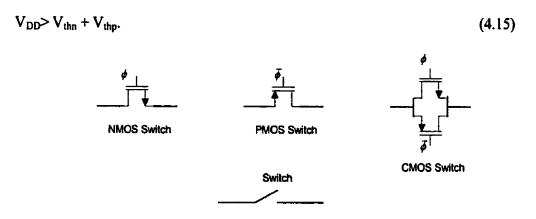

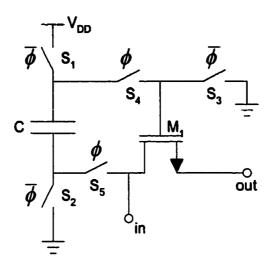

| 4.3.3 MOSFET Switch                                     | 64  |

|---------------------------------------------------------|-----|

| 4.3.4 Transconductor                                    | 69  |

| 4.3.5 Common Mode Feed-back (CMFB)                      | 71  |

| 4.4 Summary                                             | 72  |

| Chapter 5 Implementation of the CHS Modules             | 73  |

| 5.1 Introduction                                        | 73  |

| 5.2 Noise in Cascaded Stages                            | 74  |

| 5.3 Modulators                                          | 75  |

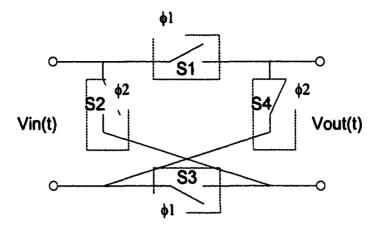

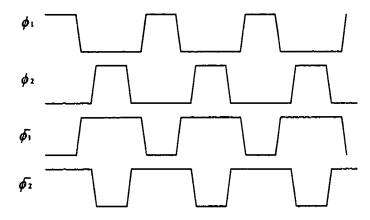

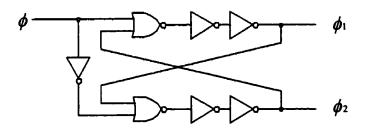

| 5.3.1 Circuit Implementation                            | 75  |

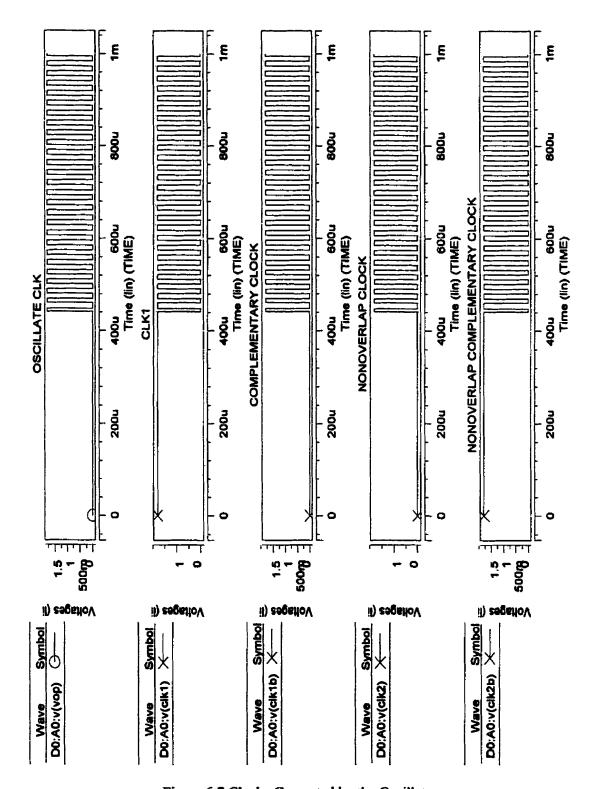

| 5.3.2 Clock Signals of Modulator                        | 76  |

| 5.3.3 Noise in Modulator                                | 77  |

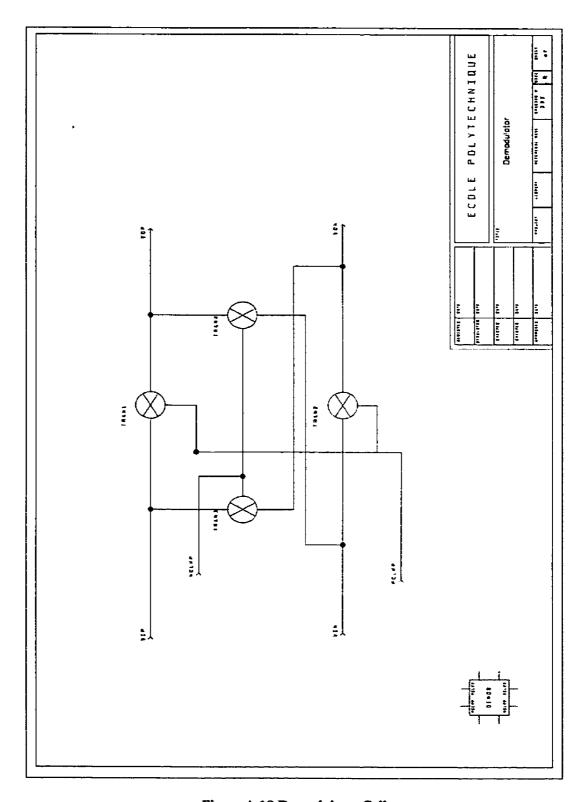

| 5.3.4 Demodulator                                       | 79  |

| 5.4 Selective Amplifier                                 | 79  |

| 5.4.1 Low Noise Preamplifier                            | 80  |

| 5.4.2 Second order BP Filter Design                     | 89  |

| 5.5 Automatic Tuning & Matching Oscillator              | 92  |

| 5.6 Summary                                             | 99  |

| Chapter 6 Simulation Results and Experimental Prototype | 100 |

| 6.1 Simulation Results                                  | 100 |

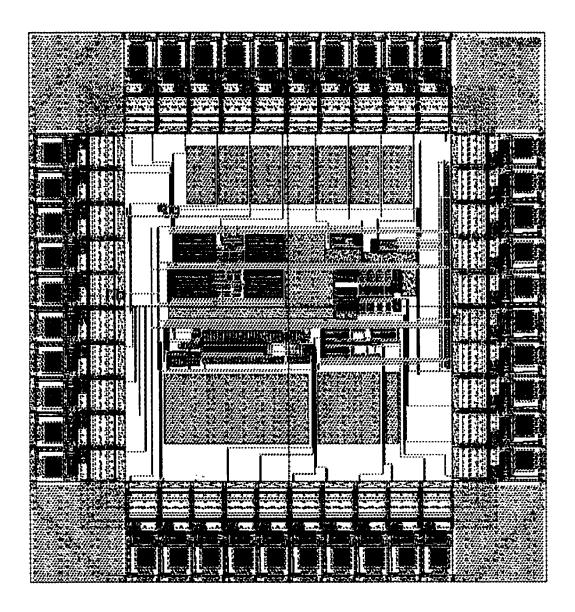

| 6.2 Prototype Chip                                      | 114 |

| Chapter 7 Conclusion                                    | 118 |

| REFERENCES                                              | 121 |

# LIST OF TABLES

| Table 2.1 Main characteristics of reported low-noise preamplifiers | 30  |

|--------------------------------------------------------------------|-----|

| Table 4.1 Specifications of the system design.                     | 59  |

| Table 6.1 Simulation results of the proposed analog front-end      | 103 |

| Table 6.2 Measurement results of the experimental chip             | 117 |

# LIST OF FIGURES

| Figure 1.1 Simplified block diagram of the global system dedicated to bladd | er control.2 |

|-----------------------------------------------------------------------------|--------------|

| Figure 1.2 Block diagram of VMD                                             | 3            |

| Figure 2.1 Cross section of NMOS transistor                                 | 9            |

| Figure 2.2 Basic principle of AZ technique                                  | 15           |

| Figure 2.3 Autozero sample clocks                                           | 16           |

| Figure 2.4 a) Hold phase signal and b) its spectrum                         | 17           |

| Figure 2.5 Spectrum representation of AZ                                    | 18           |

| Figure 2.6 Increased white noise by aliasing                                | 20           |

| Figure 2.7 Principle of Chopper Stabilization technique                     | 21           |

| Figure 2.8 Modulate signal and its spectrum                                 | 22           |

| Figure 2.9 Noise modulation                                                 | 23           |

| Figure 2.10 Chopper modulated white noise versus bandwidth                  | 24           |

| Figure 2.11 Residual offset                                                 | 25           |

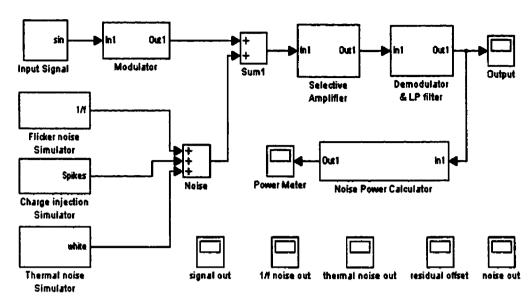

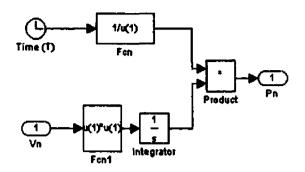

| Figure 3.1 A CHS model in SIMULINK                                          | 34           |

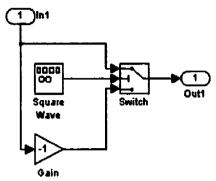

| Figure 3.2 Modulator sub-system                                             | 35           |

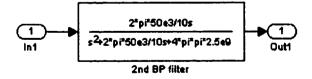

| Figure 3.3 Selective Amplifier model                                        | 35           |

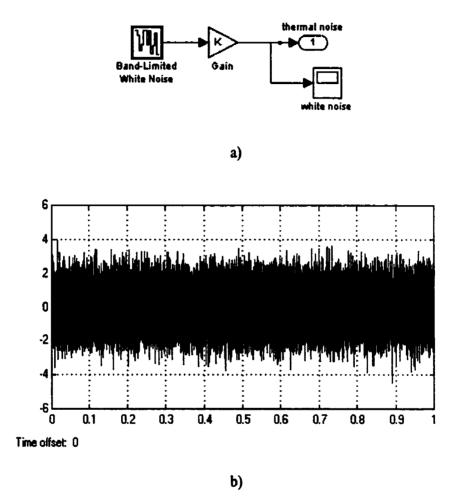

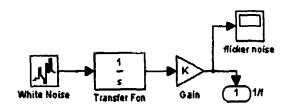

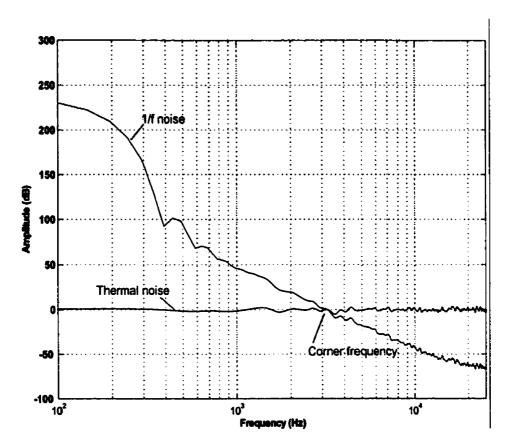

| Figure 3.4 a) Thermal noise module and b) generated thermal noise           | 37           |

| Figure 3.5 a) Input noise module and b) generated input 1/f noise           | 38           |

| Figure 3.6 Spectrums of 1/f noise and white noise                           | 39           |

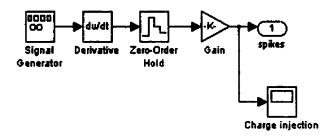

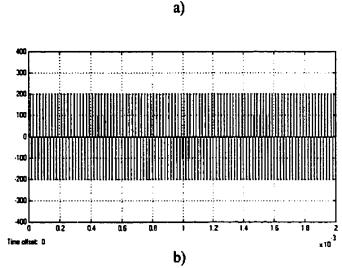

| Figure 3.7 (a) Charge injection simulator (b) modulator spikes              | 40           |

| Figure 3.8 Noise power calculator module                                | 41 |

|-------------------------------------------------------------------------|----|

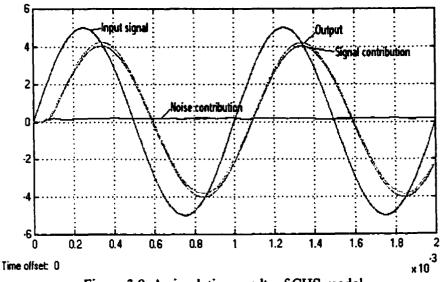

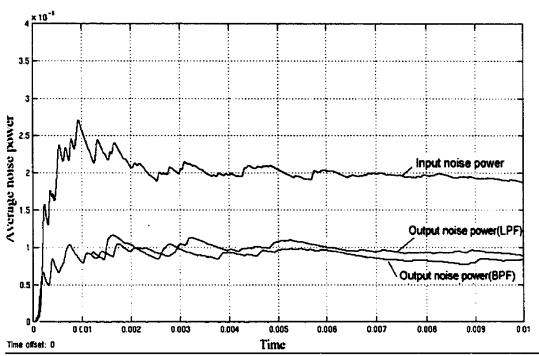

| Figure 3.9 A simulation result of CHS model                             | 42 |

| Figure 3.10 Signal path in CHS                                          | 45 |

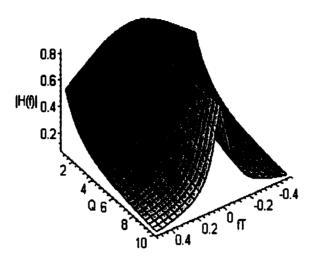

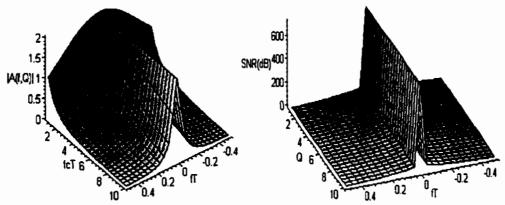

| Figure 3.11 Transfer function of CHS                                    | 47 |

| Figure 3.12 Thermal noise simulation                                    | 49 |

| Figure 3.13 Calculation result of flicker noise reduction               | 51 |

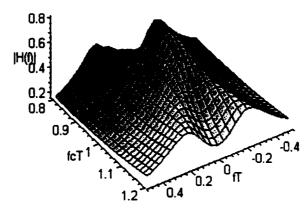

| Figure 3.14 Transfer function variation due to the tuning error         | 52 |

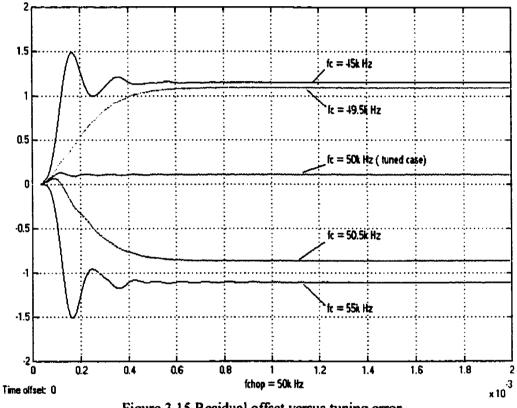

| Figure 3.15 Residual offset versus tuning error                         | 53 |

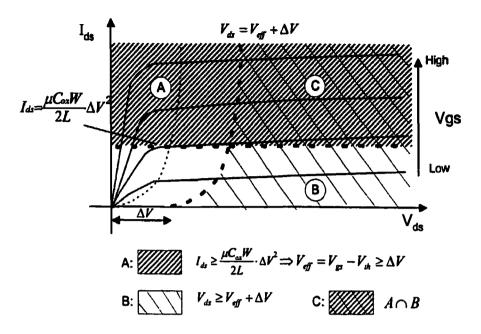

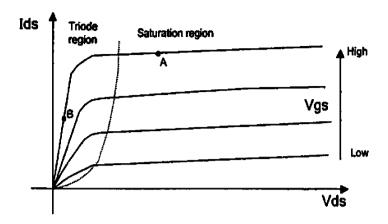

| Figure 4.1 I-V characteristic of MOSFET transistor                      | 57 |

| Figure 4.2 Common mode range of N-pair, P-pair                          | 58 |

| Figure 4.3 High swing current mirror                                    | 60 |

| Figure 4.4 Schematic of biasing circuit                                 | 62 |

| Figure 4.5 MOSFET switches                                              | 64 |

| Figure 4.6 Charge in the NMOS transistor channel                        | 65 |

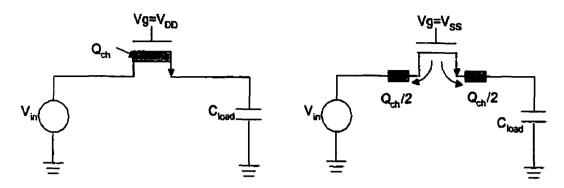

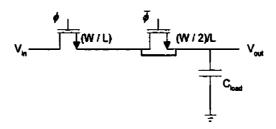

| Figure 4.7 Charge injection cancellation using a half size dummy switch | 67 |

| Figure 4.8 Bootstrapped MOS switch                                      | 68 |

| Figure 4.9 Linear transconductor circuit                                | 70 |

| Figure 4.10 Common mode feedback circuit                                | 72 |

| Figure 5.1 The block scheme of the analog front-end preamplifier        | 73 |

| Figure 5.2 Noise sources of a cascade stage amplifier                   | 74 |

| Figure 5.3 Modulator function block                                     | 75 |

| Figure 5.4 Modulator based on four switches                             | 76 |

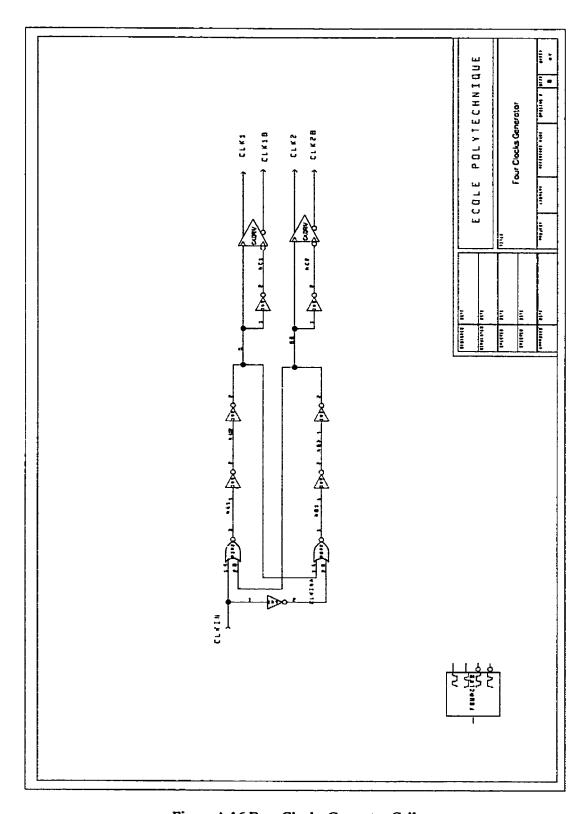

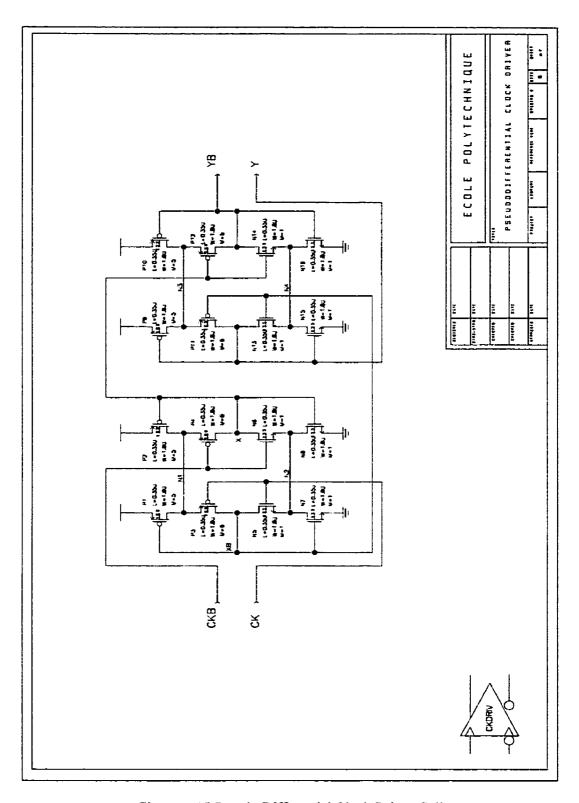

| Figure 5.5 Clocks in the modulator77                                                     |

|------------------------------------------------------------------------------------------|

| Figure 5.6 Non-overlap clock generator                                                   |

| Figure 5.7 Noise model of the MOS switch in "on" state                                   |

| Figure 5.8 Block scheme of the preamplifier80                                            |

| Figure 5.9 Rail-to-rail Operational Transconductor Amplifier (OTA)81                     |

| Figure 5.10 Gm of three regions                                                          |

| Figure 5.11 Maximum current select circuit                                               |

| Figure 5.12 I-V characteristic of MOS transistor85                                       |

| Figure 5.13 Noise model of the rail-to-rail OTA                                          |

| Figure 5.14 Block scheme of the biquad filter                                            |

| Figure 5.15 Small signal model of the filter                                             |

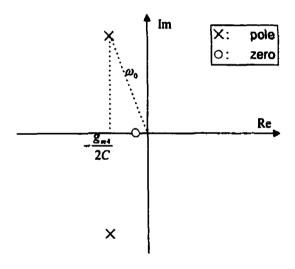

| Figure 5.16 Poles and zero of the 2 <sup>nd</sup> order BPF91                            |

| Figure 5.17 Automatic tuning techniques of the filter design based on a) VCF b)VCO       |

| 93                                                                                       |

| Figure 5.18 Matching oscillator to lock with filter94                                    |

| Figure 5.19 On-chip oscillator a) block scheme b) Small signal model of the oscillator9. |

| Figure 5.20 Poles of the oscillator                                                      |

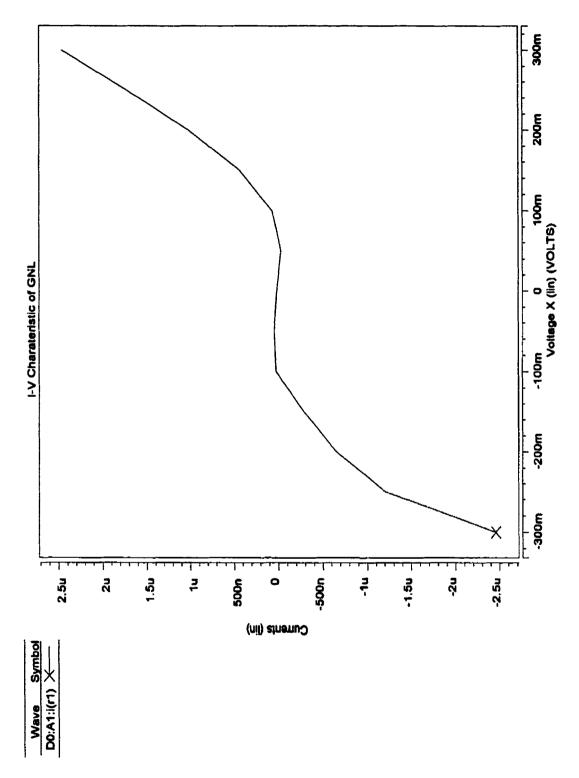

| Figure 5.21 Non-linear transconductor (GNL) block a) schematic b) I-V transfer           |

| characteristic98                                                                         |

| Figure 6.1 Bias Voltages104                                                              |

| Figure 6.2 Input Modulator Simulation Result (1)                                         |

| Figure 6.3 Input Modulator Simulation Result (2)                                         |

| Figure 6.4 Constant Gm of the rail-to-rail OTA107                         | 7 |

|---------------------------------------------------------------------------|---|

| Figure 6.5 Low Noise Rail-to-rail Amplifier AC Response & Noise result108 | 3 |

| Figure 6.6 Magnitude and Phase Spectrum of the 2 <sup>nd</sup> BPF        | ) |

| Figure 6.7 Clocks Generated by the Oscillator110                          | ) |

| Figure 6.8 I-V Transfer Characteristic of the GNL                         | l |

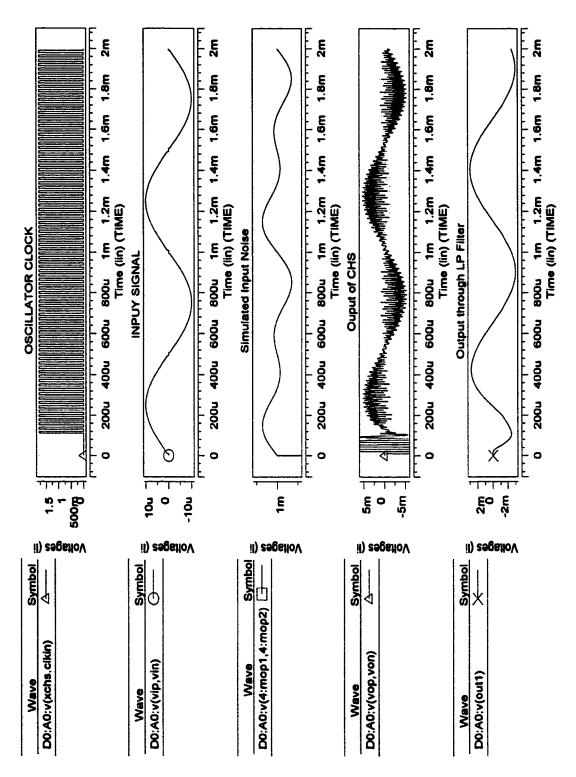

| Figure 6.9 Simulation Result of the Chopper Amplifier                     | 2 |

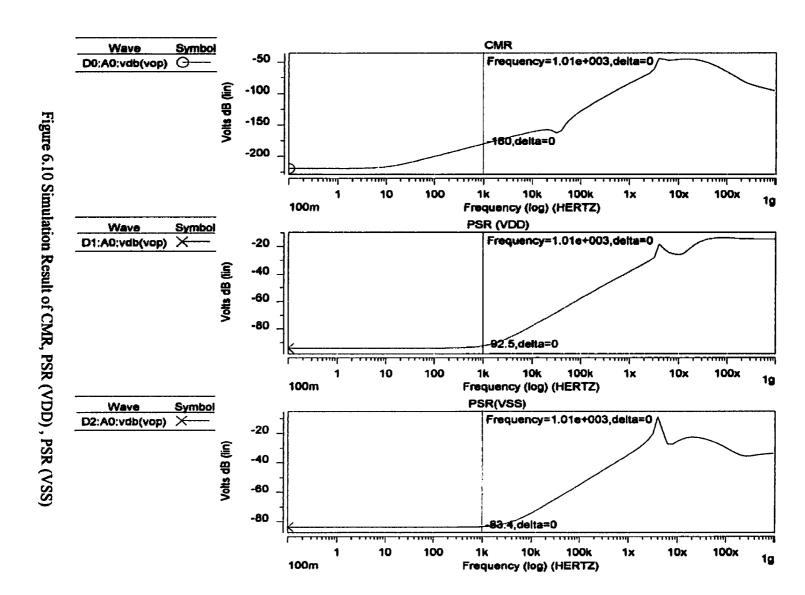

| Figure 6.10 Simulation Result of CMR, PSR (VDD), PSR (VSS)113             | 3 |

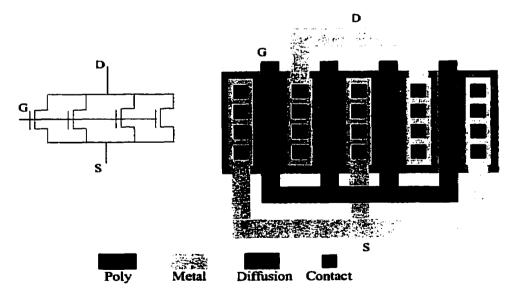

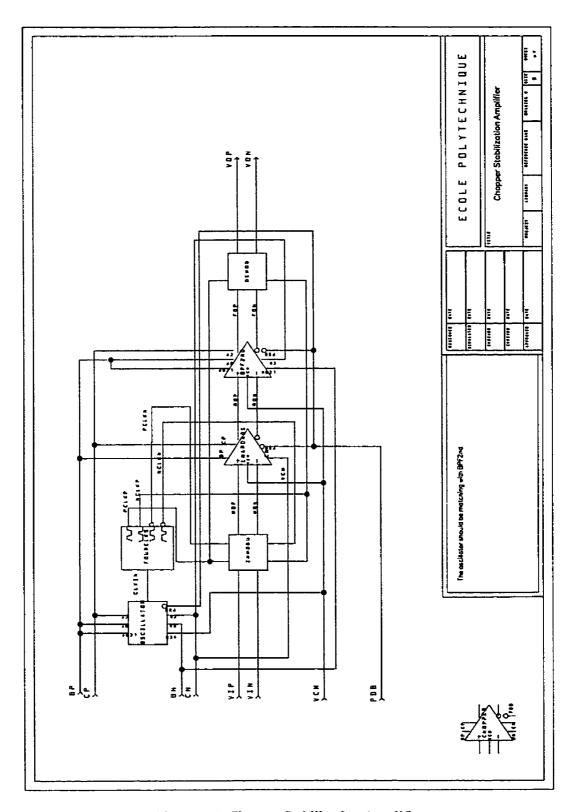

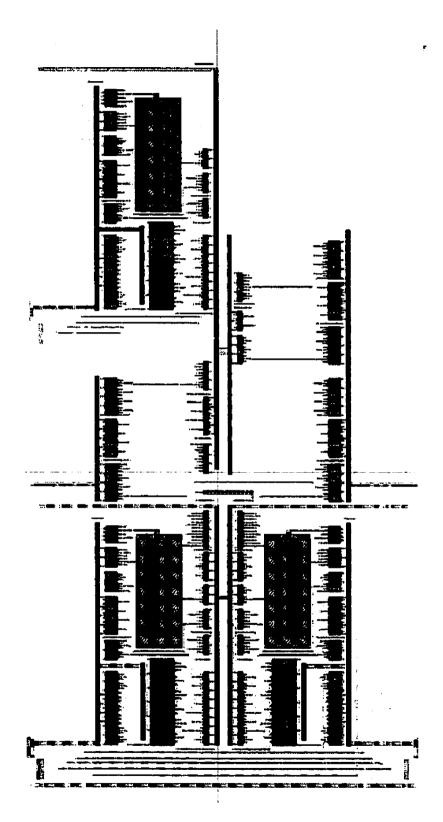

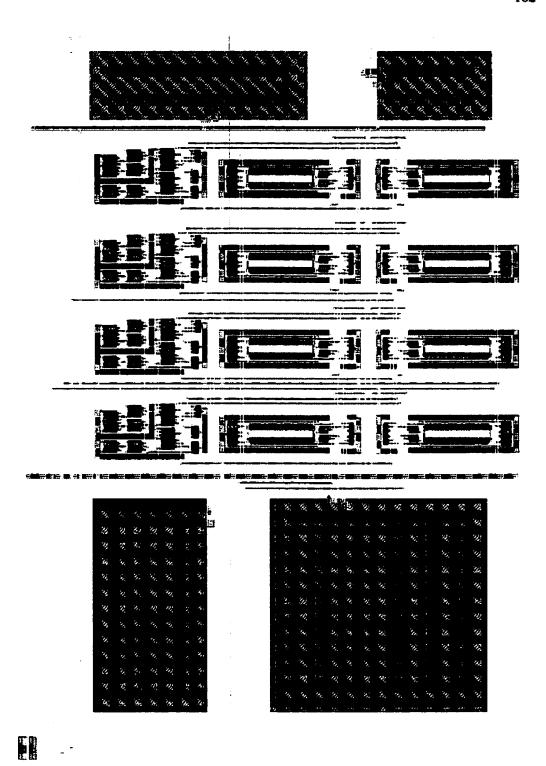

| Figure 6.11 Layout of a split transistor (M=4)                            | 4 |

| Figure 6.12 Layout of a differential pair with interdigitizing            | 5 |

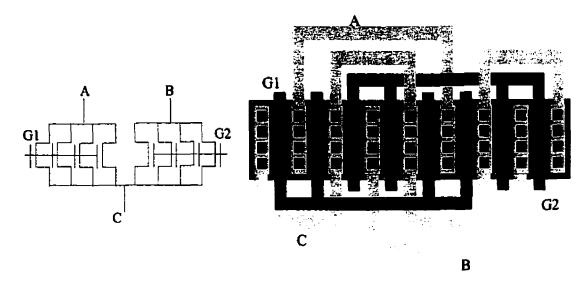

| Figure 6.13 Layout of the Analog Front-end Amplifier                      | 5 |

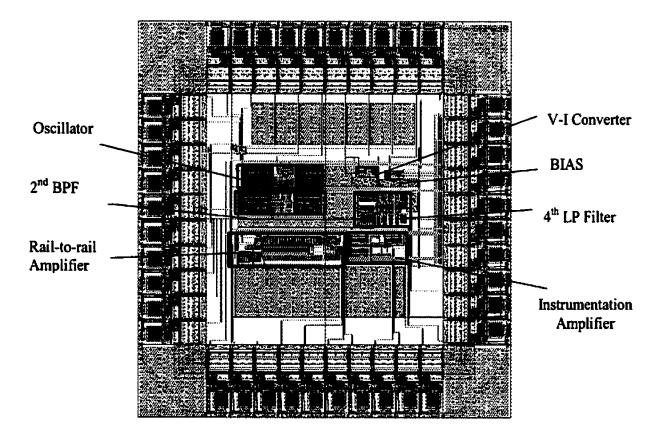

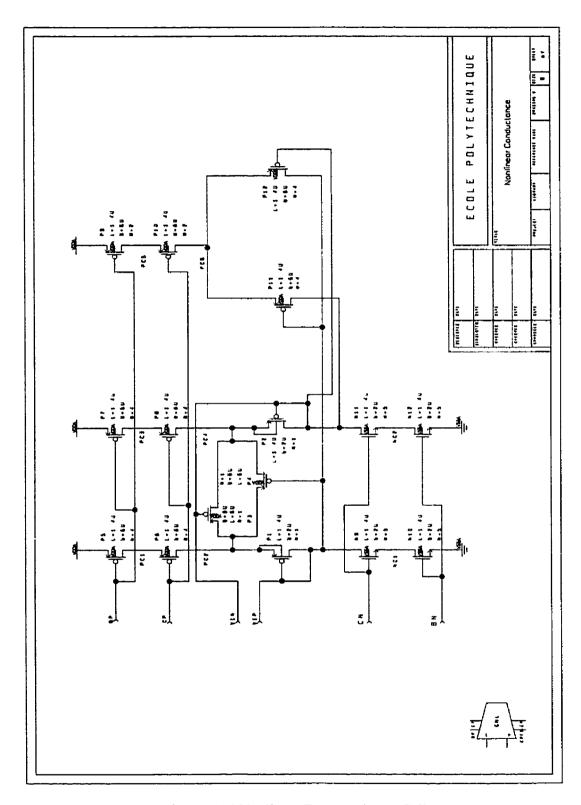

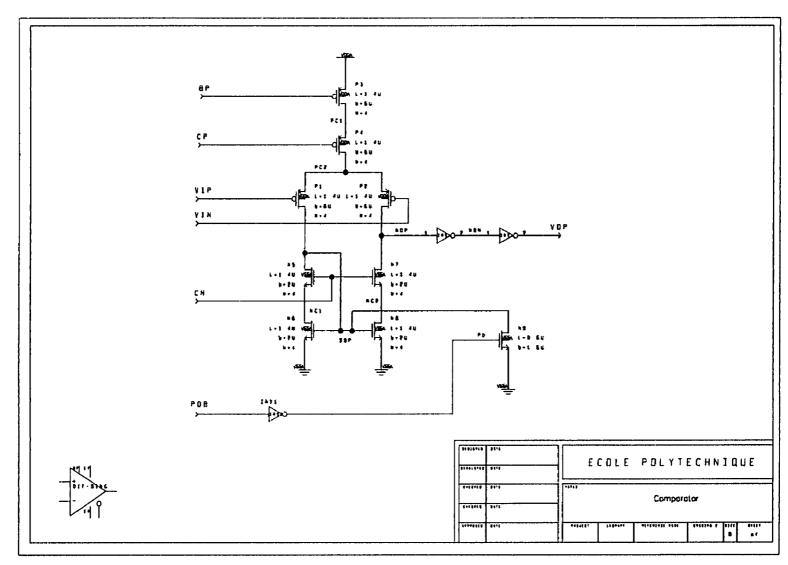

| Figure A.1 Chopper Stabilization Amplifier                                | 7 |

| Figure A.2 Input Modulator Cell                                           | 8 |

| Figure A.3 BIAS Cell                                                      | 9 |

| Figure A.4 Low Noise Rail-to-rail Amplifier Cell                          | 0 |

| Figure A.5 Low Noise Rail-to-rail Operational Amplifier Cell              | 1 |

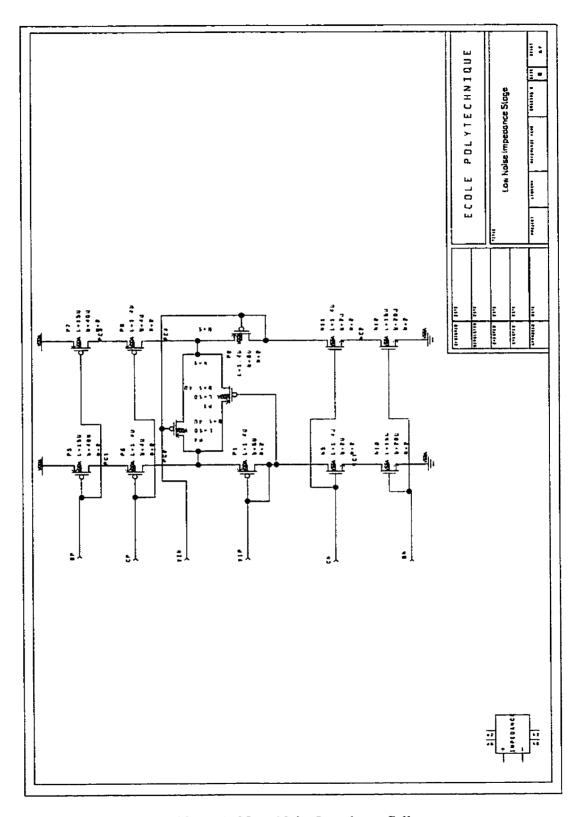

| Figure A.6 Low Noise Impedance Cell                                       | 2 |

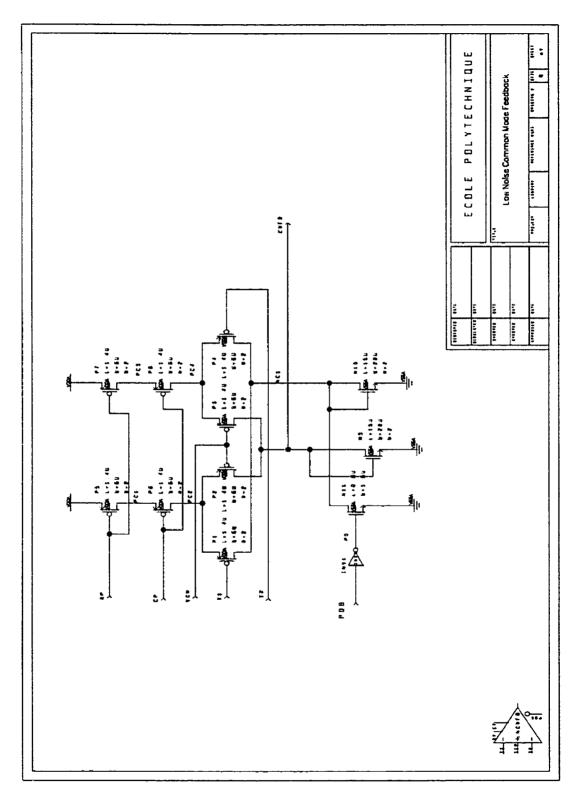

| Figure A.7 Low Noise Common Mode Feedback Cell                            | 3 |

| Figure A.8 Biquad Gm-C bandpass Filter Cell                               | 4 |

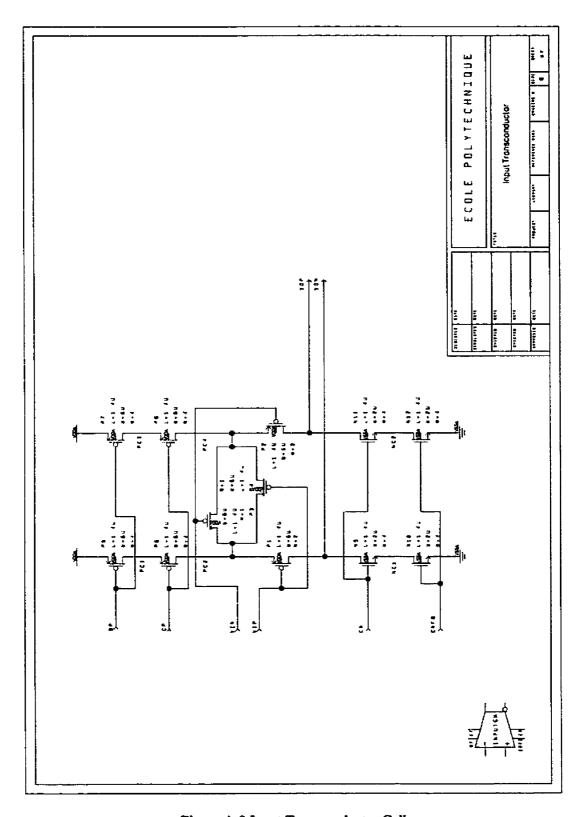

| Figure A.9 Input Transconductor Cell                                      | 5 |

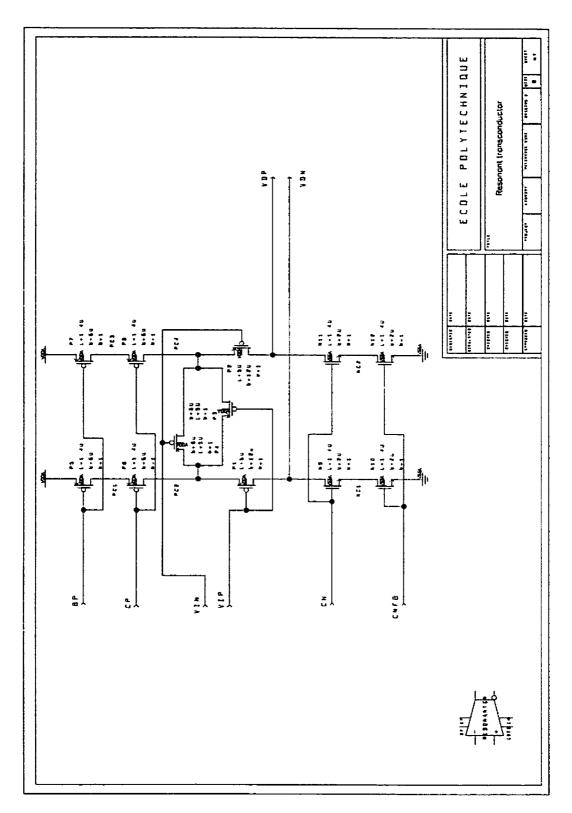

| Figure A.10 Resonant Transconductor Cell                                  | 6 |

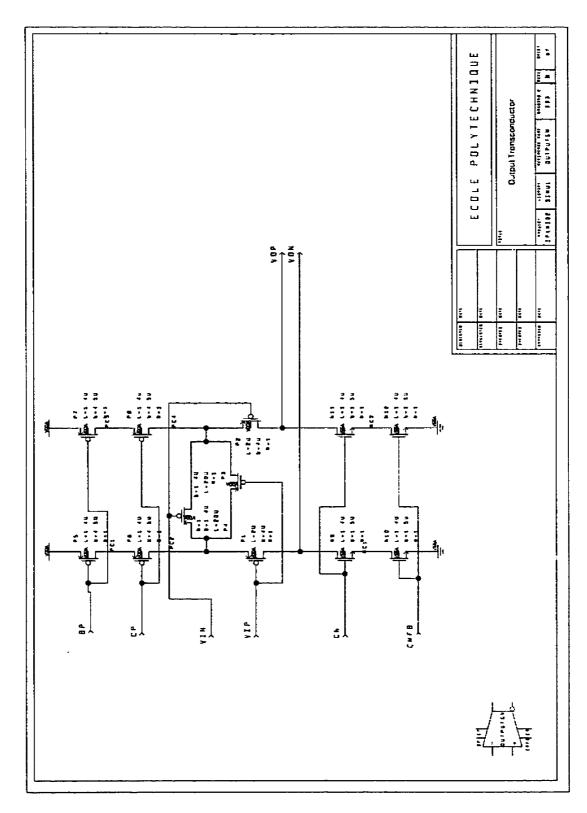

| Figure A.11 Output Transconductor Cell                                    | 7 |

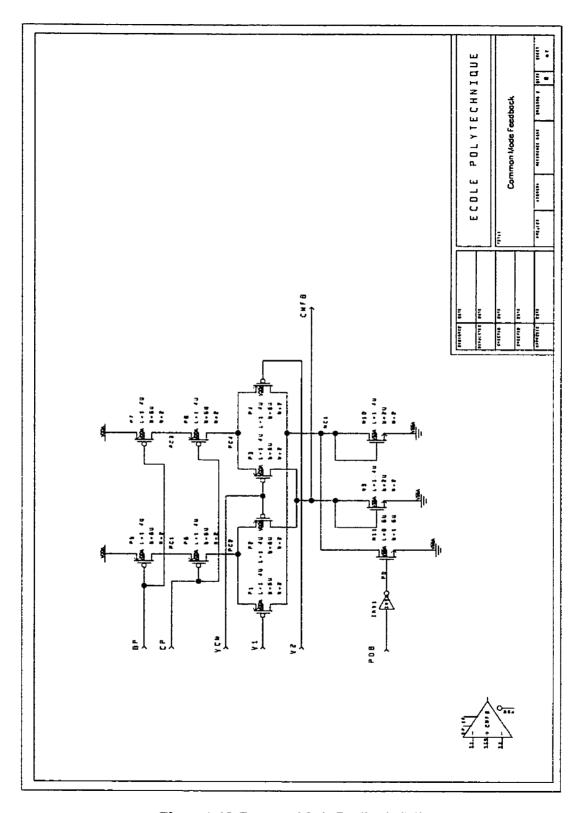

| Figure A.12 Common Mode Feedback Cell                                     | 8 |

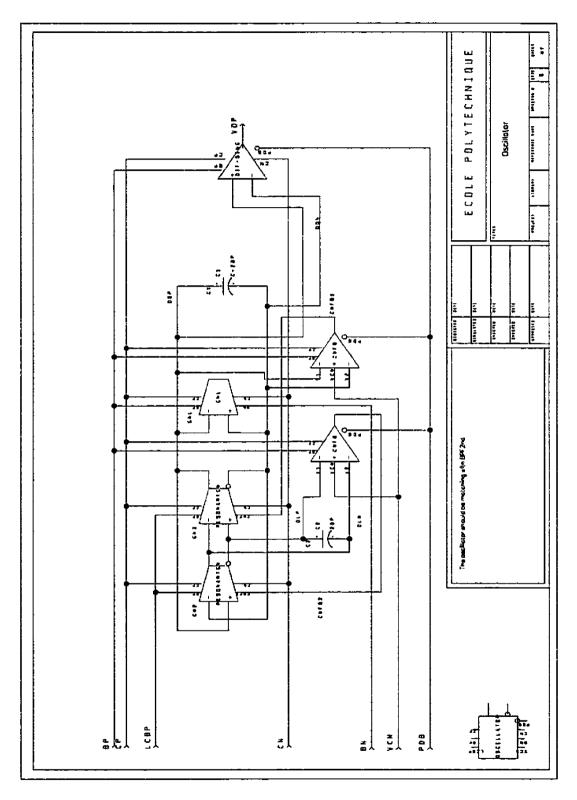

| Figure A.13 Matching Oscillator Cell                           |

|----------------------------------------------------------------|

| Figure A.14 Nonlinear Transconductor Cell                      |

| Figure A.15 Differential-to-Single Converter Cell              |

| Figure A.16 Four Clocks Generator Cell                         |

| Figure A.17 Pseudo Differential Clock Driver Cell              |

| Figure A.18 Demodulator Cell                                   |

| Figure A.19 Instrumentation Amplifier                          |

| Figure A.20 OPAMP                                              |

| Figure A.21 4th order LP Filter                                |

| Figure D.1 Topology of the Instrumentation Amplifier (IA)      |

| Figure D.2 Block Scheme of the 4 <sup>th</sup> order LP filter |

#### LIST OF ABBREVIATIONS AND SYMBOLS

#### **ABBREVIATIONS**

ADC Analog-to-Digital Converter

AZ Autozero technique

BPF, BP Band Pass Filter

CHS Chopper Stabilization Amplifier

CMFB Common Mode Feedback

CMOS Complementary Metal Oxide Semiconductor

CMR Common Mode Range

CMRR Common Mode Rejection Ratio

CP Central Processing

DOA Differential Opamp

DSB Double Sideband

DSP Digital Signal Processing

GNL Non Linear Transconductor

IA Instrumentation Amplifier

IC Integrated Circuit

LNA Low Noise Amplifier

LPF, LP Low Pass Filter

LTI Linear Time Invariable

MCS Maximum Current Select circuit

#### xxxiv

MOSFET Metal Oxide Field Effect Transistor

NF Noise Figure

NMOS Channel-N Metal Oxide Semiconductor

OTA Operational Transconductor Amplifier

PLL Phase Lock Loop

PMOS Channel-P Metal Oxide Semiconductor

PSD Power Spectral Density

PSRR Power Supply Rejection Ratio

RMS Root Mean Square value

SA Selective Amplifier

SNR Signal to Noise Ratio

SOA Single-end Opamp

SOC System-On-Chip

VCF Voltage Controlled Filter

VCO Voltage Controlled Oscillator

VLSI Very Large Scale Integration

VMD Volume Measure Device

#### **SYMBOLS**

k Boltzman Constant

T Absolute temperature

μ Channel mobility of MOSFET transistor

W Width of MOSFET transistor

L Length of MOSFET transistor

C<sub>ox</sub> Gate capacitance per unit area

λ Output impedance constant of MOSFET transistor

γ Body-effect constant of MOSFET transistor

Q Quality Factor

id Drain current of MOSFET transistor

g<sub>m</sub> Transconductance of MOSFET transistor

V<sub>n</sub> Low frequency noise voltage

V<sub>off</sub> DC offset voltage

f<sub>chop</sub> Chopper modulating frequency

f<sub>c</sub> Cut-off frequency

V<sub>eff</sub> Effective voltage of MOSFET transistor

V<sub>th</sub> Threshold voltage of MOSFET transistor

V<sub>sat</sub> Saturation voltage of MOSFET transistor (also named V<sub>eff</sub>)

V<sub>gs</sub> Gate-source voltage of MOSFET transistor

VDD Positive supply voltage

VSS Negative supply voltage

VCM Common Mode voltage

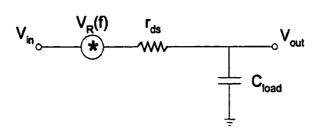

r<sub>ds</sub> Drain-source resistance of MOSFET transistor

# LIST OF ANNEXS

| Annex A | Schematics                                         | 126 |

|---------|----------------------------------------------------|-----|

| Annex B | Hspice Netlist file                                | 148 |

| Annex C | Layouts                                            | 156 |

| Annex D | Instrumentation amplifier & Output Low-pass filter | 164 |

#### CHAPTER 1

#### INTRODUCTION

### 1.1 Motivation

With the continuous growth of microelectronic, the pervasiveness of digital circuits does not make the analog part diminish. On the contrary, it becomes a key factor for the increased pervasiveness of analog circuits in mixed signal chips. There are two main reasons for this: the need to interface the digital signal processing (DSP) part to the analog world and the need for analog-enhanced digital performance.

Advances in MOS technology in the past decades allow digital circuits to benefit more from the downscaling, however the new trends of the mixed-signal IC which include low voltage, low power, low noise, high-frequency operation and high-resolution make the analog IC designers job more difficult.

Sensors, detectors, and transducers are basic functions to the instrumentation and control fields, which translate the characteristics of the physical world into electrical signals. In recent years, new high-precision sensors and high-performance data acquisition systems have been developed. However all sensors have an offset or limiting noise level. The system designer must interface the sensor with electronic circuitry that contributes a

minimum of additional noise. To raise the signal to noise ratio (SNR), a high performance analog front-end signal conditioning stage must be designed.

Nowadays, more and more applications require an ultra low-amplitude signal measurement system, such as the implantable devices in biomedical applications intended to monitor several neuromuscular activities [1][2][3]. Among these devices, the bladder controller, dedicated to measure the volume of the urine and to stimulate via neural pathways the detrusor and sphincter muscle when necessary, is an important rehabilitation application [1]. The implantable part of the corresponding system consists of three main blocks as shown in figure 1.1: Central Processor (CP), Volume-Monitoring Device (VMD) and stimulator.

Figure 1.1 Simplified block diagram of the global system dedicated to bladder control

The VMD senses the nerve signal that contains information about volume of the bladder. The block diagram of the VMD is illustrated in figure 1.2. Nerve signal, of which the amplitude is very low and generally ranged from 1 to 10  $\mu$ V [2][3], is submerged in the noise of a conventional CMOS two stages topology Opamp. Hence, the signal needs to be first weakly amplified by a Low Noise Amplifier (LNA), to overcome the 1/f noise, and to rise this signal above the noise level of the instrumentation amplifier (IA), which amplifies the signal with a programmable gain and rejects the common mode signal. The output of IA is then converted to digital signals and is sent to the Digital Signal Processing (DSP) block. At this level, the useful information is then extracted and sent to the CP block to analyze the data about the bladder volume, such as the filled volume percentage and estimation of time needed to fully filling the bladder.

Figure 1.2 Block diagram of VMD

All functions of the implantable system must be integrated in one chip. Although it makes the analog part design more difficult, the single-chip solution offers several advantages:

The size of the system is reduced, which is a very important characteristic in implantable system.

- The speed of operation can be increased. The analog and digital circuits do not have to communicate via off-chip interconnects, which are plagued by parasitic capacitances.

- The power dissipation is decreased.

- Other factors such as the design flexibility, the reliability and the system cost all benefit from system integration.

#### 1.2 Research Goals

The primary aim of this master thesis is to design a low noise CMOS analog front-end amplifier, to overcome the low frequency noise and DC offset, when detecting signals on peripheral nerves. Note that it does not reduce the inherent noise of the electrodes, but it reduces the additional 1/f noise created by the circuits. Due to the special environment where the implantable system will be located, the analog front-end of the system, which includes the low-noise preamplifier and the instrumentation amplifier, must be low noise and have low DC offset. In addition, it must also meet the following characteristics:

- ♦ Low-supply voltage and low-power consumption, because the needed energy is transmitted from outside the body through the skin and should be minimized.

- High Power Supply Rejection Ratio (PSRR), since the variation of the power supply caused by the bi-directional link must not affect the stimulation operations.

- High Common Mode Rejection Ratio (CMRR) to overcome the relatively high common mode input voltage.

Fully integrated device in a low-die-area in order to reduce the physical dimensions of the implant.

### 1.3 Thesis Organization

Following this chapter, chapter 2 provides an overview of the noise sources that exist in MOS amplifiers. The noise reduction techniques that include autozero (AZ) and chopper stabilization (CHS) methods will also be reviewed in chapter 2.

Chapter 3 focuses on presenting detailed characteristics and further analysis of the chopper stabilization technique. First an analysis method by virtue of a behavioral model in MATLAB/SIMULINK to simulate the chopper stabilization amplifier, will be introduced. Then the signal transfer function, signal to noise ratio (SNR), and non-ideality effects to the CHS will be further analyzed respectively and verified by the behavioral model.

In Chapter 4, low voltage requirements of the system are first examined. Then some elementary circuits which are compatible with low voltage operation are covered. Chapter 5 illustrates detailed circuit implementation of the needed blocks of a CHS amplifier, which include a modulator (demodulator), a rail-to-rail low noise preamplifier, a 2<sup>nd</sup> order bandpass filter and an oscillator.

The simulation and measurement results of an experimental prototype chip are the subject of chapter 6. Some layout rules which are utilized to reduce mismatching are also discussed. Conclusions from this project and future work are presented in the last part of this thesis.

#### **CHAPTER 2**

# **NOISE IN CMOS INTEGRATED CIRCUITS**

#### 2.1 Introduction

Noise in integrated circuits is one of the most critical factors that determine the performance of integrated signal processing systems, such as ultra low-amplitude signal monitor, detector readout systems, transducer, AM/FM radio receivers, etc. It represents a lower limit of the electrical signal level that can be handled by an integrated circuit without significant deterioration in signal quality.

As the noise performance of any integrated system is determined by the noise characteristic of the integrated components, this chapter first presents a brief overview of the noise sources that exist in MOSFET transistors. Then the impacts of CMOS downscaling on system noise performance are discussed in the next section. The Autozero (AZ) and Chopper Stabilization (CHS) circuit techniques that reduce the low frequency noise and DC offset will be illustrated in the third section. The main previous works on two methods published by Enz (1996) and Menolfi (1997) will be briefly reviewed. The last section completes the literature review on the low noise amplifier design.

#### 2.2 Noise sources in MOSFET transistors

Two important noise sources can be distinguished in a MOSFET transistor: the thermal noise associated with the conducting resistive channel and the flicker noise or so called 1/f noise. Other noise sources also exist in MOS transistors, such as the noise associated with the resistive poly-gate and the noise due to the distributed substrate resistance [34][43]. However for low frequency applications, it is sufficient to calculate and analyze the noise performance of circuits by considering only the thermal noise and the flicker noise. Thus the two noise mechanisms will be discussed in the following.

#### 2.2.1 Channel Thermal Noise Mechanism

When a MOS transistor is in the "on" state, the current flowing between its drain and source is based on the existence of an inverse resistive channel between them. The inverse resistive channel is formed by the minority carriers of substrate under an appropriate gate control voltage. In analogy to a resistance, the random motion of the free carriers in the channel generates thermal noise at the device terminals. In the extreme case where there is no voltage potential difference between the drain and the source ( $V_{ds} = 0V$ ), the inversed channel can be treated as a homogeneous resistance. According to the Nyquist theorem, the short circuit thermal noise current spectral density  $i_d$  is then given by [34]

$$i_d^2 = 4kTg_0 \tag{2.1}$$

where k is the Boltzman constant, T represents the absolute temperature and g<sub>0</sub> denotes the channel conductance at zero drain-source voltage.

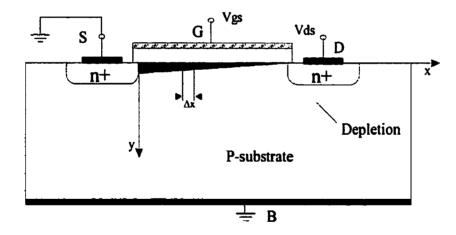

However, for analog applications, MOS transistors mostly operate in the saturation region, in which the channel can't be considered as a homogeneous resistance. In this case, the short-circuit drain current noise must be calculated by dividing the channel into a large number of small sections  $\Delta x$ , as shown in figure 2.1. For each section  $\Delta x$ , the output current noise which stem from the noise electromotive force generated in the section  $\Delta x$ , can be calculated separately, and finally be integrated along the whole channel to obtain the total drain current noise.

Figure 2.1 Cross section of NMOS transistor

The transistor drain current noise spectral density is derived by

$$i_d^2 = 4kT \frac{\mu^2 W^2}{L^2 I_{DS}} \int_0^2 Q_n^2(V) dV = 4kT \frac{2}{3} g_m$$

(2.2)

where W and L are the channel width and length respectively,  $\mu$  is the effective channel mobility,  $I_{DS}$  is the drain-source current,  $Q_n(x)$  represents the inversion channel charge per unit area and  $g_m$  is the transconductance of the MOSFET. Equation (2.2) predicts well the channel thermal noise behavior of MOSFET with negligible substrate effect.

## 2.2.2 Flicker (1/f) Noise in MOS Transistors

The 1/f noise phenomenon has been observed in almost all kinds of devices, from homogeneous metal films and different kinds of resistors to semiconductor devices and even chemical concentration cells. Among all active integrated devices, MOS transistor shows the highest 1/f noise due to its surface conduction mechanism. In spite of more than 30 years of research, the mechanisms involved in the 1/f noise of MOSFET transistor are not yet fully understood. Two main 1/f noise theoretical models exist: the carrier density or number fluctuation model ( $\Delta n$  model) and the mobility fluctuation model ( $\Delta n$  model).

### 2.2.2.1 Number Fluctuation Model (An model)

In this model, the 1/f noise is believed to be caused by the random trapping and detrapping of the mobile carriers in the traps located at the Si-SiO<sub>2</sub> interface and within the gate oxide. Each trapping and detrapping event results in a Random Telegraph Signal (RTS) corresponding to a Lorentzian spectrum or generation-recombination spectrum. The superposition of a large number of such Lorentzians with a proper time constant

distribution results in the 1/f noise spectrum. The general expression for the spectrum of the drain 1/f current noise can be written by

$$i_d^2(f)_{y_f} = \frac{\mu q^2 I_{DS}}{L^2 C_{ox}} \frac{kTN_t}{\alpha f} \frac{1}{8} \ln \left[ \frac{2}{2(\frac{V_{SAT} - V_{DS}}{V_{SAT}})^2 + (\frac{n_i}{n_{s0}})^2} \right]$$

(2.3)

where  $N_t$  is the trap density,  $\alpha$  (=10<sup>8</sup> cm<sup>-1</sup>) is the McWhorter tunneling constant,  $n_{s0}$  is the surface carrier concentration value at source side. In the saturation region where  $V_{DS} > V_{SAT}$ , equation (2.3) is reduced to

$$i_d^2(f)_{\gamma_f} = \frac{\mu q^2 I_{DS}}{L^2 C_{ox}} \frac{kTN_t}{cof} \frac{1}{16} \ln \left[ \frac{\sqrt{2} n_{s0}}{n_i} \right] = \frac{K_F I_{DS}}{C_{ox} L^2 f}$$

(2.4)

where

$$K_F = \frac{\mu q^2 kTN_i}{\alpha} \frac{1}{16} \ln \left[ \frac{\sqrt{2}n_{r0}}{n_i} \right]$$

The transconductance of a MOS transistor in saturation is given by

$$g_{m} = \sqrt{2\mu C_{\alpha x} \frac{W}{L} I_{DS}} \tag{2.5}$$

Combining (2.4) and (2.5), the equivalent input 1/f noise can be easily calculated as

$$v^{2}(f)_{\gamma_{f}} = \frac{i_{d}^{2}(f)_{\gamma_{f}}}{g_{m}^{2}} = \frac{K_{F}}{2\mu C_{cr}^{2}WL_{f}} = \frac{K_{f}}{C_{cr}^{2}WL_{f}}$$

(2.6)

where  $K_f = K_F/2\mu$ . Note that according to equation (2.6) the flicker noise is only determined by the transistor channel area size and is independent of the DC bias condition. The expression (2.6) is widely used in 1/f noise analysis and in CMOS amplifier design.

### 2.2.2.2 Mobility Fluctuation Model (Δμ model)

In the mobility fluctuation model, the 1/f noise is assumed to be attributed to the fluctuation in mobility of free carriers when they collide with the crystal lattices. This model is described by the Hooge empirical equation [44]

$$\frac{i_{Vf}^2}{I^2} = \frac{\alpha_l}{N \cdot f} \tag{2.7}$$

where  $\alpha_l$  is so called Hooge 1/f noise parameter, N is the total number of the free carriers in the device and I is the short circuit current through the device. Integrating over the whole channel the total 1/f noise power spectrum at saturation is obtained as [34]

$$i_{11f}^{2} = \alpha_{l} \frac{q \mu_{f} (V_{GS} - V_{T}) I_{DS}}{L^{2} f}$$

(2.8)

Combining the equation (2.5) and (2.8), the equivalent input 1/f noise voltage spectrum density is then

$$v_{llf}^{2} = \frac{i_{llf}^{2}}{g_{m}} = \alpha_{l} \frac{q \mu_{f} (V_{GS} - V_{r})}{2 \mu_{eff} C_{\alpha x} W L f}$$

(2.9)

According to equation (2.9), the input referred 1/f noise voltage is directly proportional to the effective gate voltage  $V_{GS}$ - $V_T$ , rather than being independent of it as in the  $\Delta n$  model. In this case, noise analysis and simulation is much more complex. Although the 1/f noise of the CMOSP35 technology used to implement the system is dependent on the DC bias condition, we will ignore this dependence to simplify the noise analysis.

### 2.2.3 Impact of scaling

The tendency to downscale the average feature size in today's CMOS, which is the leading edge technology world-wide, brings up continuous changes in the device processing and architecture. As the minimal device length is reduced by a factor K, in order to obtain a reasonable threshold voltage and to minimize short channel effects, one should modify the gate dielectric thickness and substrate doping density accordingly. This requires major technological changes, the development of new processing steps and the use of new lithographical techniques and equipment. As 1/f noise is strongly technology sensitive, the introduction of advanced processing steps may lead to observations which in many cases can hardly be predicted and/or modeled by the existing theories. But, it has been demonstrated, both theoretically and experimentally, that scaling a technology by a factor K (>1) increases the average noise level accordingly [11][12]. In addition, it has been observed that the noise dispersion (the sample-to-sample and wafer-to-wafer variation) increases significantly with scaling.

## 2.3 Low noise techniques

For implantable electronic system applications, the dominant noise source is often the 1/f noise component of the differential input stage. This component is directly proportional to the surface state density ( $N_t$  in equation 2.3) in the channel and inversely proportional to the gate area [10]. The 1/f noise can be reduced by a number of different methods.

- One approach is to simply make use of large input device geometries to reduce the 1/f noise associated with these devices. This approach has been widely used in the past, and works particularly well in process technologies that have a low level of surface states at the outset. For processes that have high surface state densities, however, this approach can give uneconomically large input transistor geometries for applications requiring extremely high dynamic range.

- The second approach is to use buried channel devices so as to remove the channel from the influence of surface states. This approach requires process steps which are not usually included in standard LSI technologies used to manufacture the needed circuits in high volume.

- The third approach is to make the input transistors be operated in the lateral bipolar mode that is compatible with CMOS process. The 1/f noise is strongly reduced because the minority carrier flow is pushed away from the oxide-silicon interface. But it is not well suited for high impedance requirements due to the bipolar transistor base current.

- The fourth approach is to use some special circuit techniques to reduce the 1/f noise and the offset. Popular approaches include the auto-zero technique (AZ) and the chopper stabilization technique (CHS). The latter is the main subject of this thesis.

The next section will review some details about the two circuit techniques, Autozero (AZ) technique and Chopper Stabilization (CHS) technique, to reduce the 1/f noise and DC offset. Readers are referred to [4][5][6][7] for a more comprehensive and in-depth review of the underlying concepts and related issues.

## 2.3.1 Autozero technique

### 2.3.1.1 Basic principle

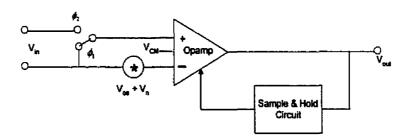

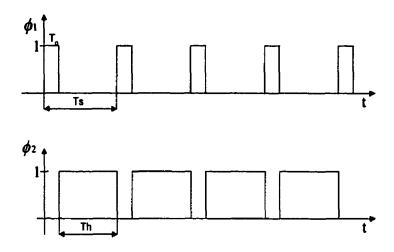

The basic principle of the auto-zero technique is presented in figure 2.2. In the sampling phase  $\phi_I$ , as illustrated in figure 2.3, the output in accordance with the noise  $V_n$  and the offset voltage  $V_{os}$  are sampled and stored. During this phase, the amplifier is disconnected from the signal path and its inputs are short-connected and set to an appropriate common-mode voltage. The sampled noise and offset value are stored by means of an analog or a digital method. Then, in the amplification phase  $\phi_2$ , the input terminals of the amplifier are connected back to the signal source for amplification.

Figure 2.2 Basic principle of AZ technique

Figure 2.3 Autozero sample clocks

If the amplifier is used under the same conditions as during sampling, the instantaneous noise and DC offset can be compensated by the stored value in the sampling phase. Thus, ideally, the amplifier is free from offset. However, unlike the offset voltage, which can be considered as a constant, the amplifier's noise, and particularly its wide-band thermal noise component is time-varying and random. The efficiency of the AZ process for the low-frequency noise reduction strongly depends on the correlation between the noise sample and the instantaneous noise value from which this sample is subtracted.

### 2.3.1.2 The effect of AZ on the noise

Suppose the analog switch in sample-and-hold circuit is ideal ( $T_0=0$ ), the sample-and-hold (S/H) process can be expressed as

$$y_s(t) = \sum_{n=-\infty}^{\infty} x(nT_s)h(t - nT_s)$$

(2.10)

where y(t) and x(t) denote the output and input signals which correspond to  $V_{out}$  and  $V_{in}$  in figure 2.2 respectively,  $x(nT_s)$  denotes the signal value ideally sampled at the time  $nT_s$ ,

h(t) represents the hold signal which is a rectangular pulse of unit amplitude and duration  $T_s$ , defined as

$$h(t) = \begin{cases} 1 & 0 < t \le T_s \\ 0 & otherwise \end{cases}$$

(2.11)

As the instantaneous sampled signal x<sub>s</sub>(t) can be written as

$$x_s(t) = x(t)\delta r_s(t) = \sum_{n=-\infty}^{\infty} x(nT_s)\delta(t-nT_s)$$

(2.12)

According to (2.10) and (2.12), it can be derived that  $y_s(t)$  is the convolution of  $x_s(t)$  with the hold signal pulse h(t), that is

$$y_2(t) = x_2(t) * h(t)$$

(2.13)

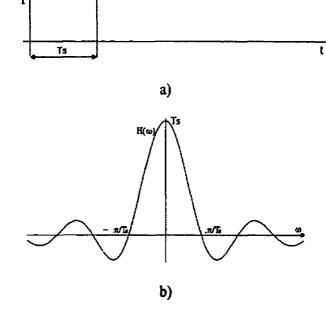

Figure 2.4 a) Hold phase signal and b) its spectrum

In the frequency domain, by using Fourier transform, we obtain

$$Y_s(\omega) = X_s(\omega)H(\omega) = \frac{1}{T_s} \sum_{n=-\infty}^{\infty} X(\omega - n\omega_s)H(\omega)$$

(2.14)

where the spectrum

$$|H(\omega)| = T_s \frac{\sin(\omega T_s)}{\omega T_s}$$

(2.15)

The signal h(t) and its spectrum are shown in figure 2.4. Note that the sampling-and-hold process is equivalent to passing an ideal sampled signal through a filter having the frequency response  $G(\omega) = H(\omega)$ .

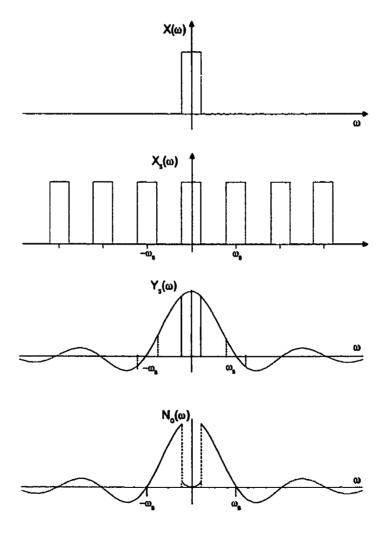

Figure 2.5 Spectrum representation of AZ

Thus the spectrum of the output noise with the autozero process can be expressed as:

$$N_o(\omega) = X(\omega) - Y_s(\omega) = X(\omega) - \frac{\sin(\omega T_s)}{\omega T_s} \sum_{n=-\infty}^{\infty} X(\omega - n\omega_s)$$

(2.16)

Figure 2.5 illustrates a graphical interpretation of equation (2.16), with the assumed  $X(\omega)$ . It illustrates that the auto-zero technique effectively imposes a high-pass filters on the noise. For DC or very low-frequency noise, this results in an effective cancellation.

However, for the wide-band thermal noise, which has a spectrum wider than Nyquist frequency, the output noise spectrum foldover (aliasing) is inevitable. This can be understood clearly if we assume that the amplifier's wide-band noise is an ideally low-pass filtered white noise having bandwidth equal to  $F_B$ . The aliasing effect introduced by the sampling process in this case is illustrated in figure 2.6, which assumes that  $F_BT_s = 2$ . The original noise power spectrum is shifted by multiplying n of the sampling frequency and summed, resulting in a white noise of Power Spectrum Density (PSD) value approximately equal to  $N \times S_0$ , where N is the integer closest to the undersampling factor defined by  $2F_BT_s$ . Thus the output thermal noise PSD will be increased to [5]

$$S_{white}(f) = (2F_B T_S - 1) So \sin c^2 (\pi f T_S)$$

(2.17)

If the undersampling factor  $2F_BT_x$  is much larger than unity, the autozeroed white noise is thus dominated by the aliased broadband noise component.

Figure 2.6 Increased white noise by aliasing

A similar analysis can be carried out for the 1/f noise, although 1/f noise has a narrow bandwidth, it still has a foldover component due to the aliasing of all the tails of the 1/f noise. It had been demonstrated that the aliasing increases log-arithmetically to  $f_cT_s$  [5], rather than increasing proportionally as the white noise, thus the effect of aliasing on the 1/f noise is not as dramatic as that observed on the broadband white noise.

In conclusion, the auto-zero technique can effectively reduce the DC offset and low frequency noise, but at the cost of an increased white noise foldover component as well as 1/f noise.

# 2.3.2 Chopper Stabilization technique

An alternate approach to 1/f noise reduction is the CHopper Stabilization technique (CHS). This technique has been used for more than fifty years when the best DC performance was required. It was first used with vacuum tubes and mechanical relay choppers [10]. Recently, CHS has been used to reduce the low frequency noise and DC offset in CMOS technology.

## 2.3.2.1 Basic principle

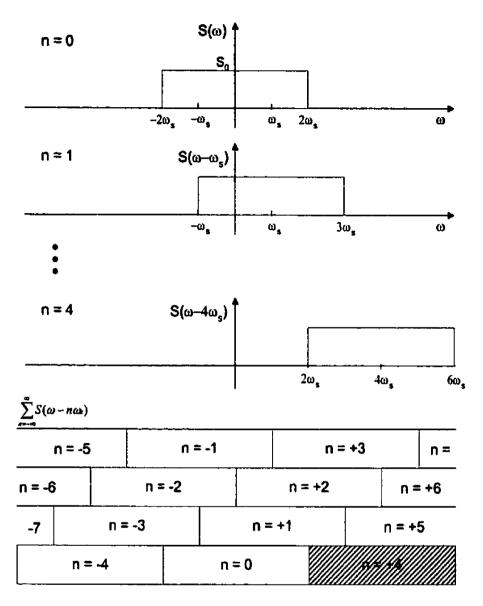

The basic principle of CHS is reviewed in figure 2.7

Figure 2.7 Principle of operation of the chopper stabilization technique

The input signal  $V_{in}(t)$  is modulated by a square-wave signal  $m_1(t)$  with frequency  $f_{chop}$ . After this modulation, the signal spectrum is transposed to the odd harmonic frequencies of the signal  $m_1(t)$ . It is then amplified by a selective amplifier (SA) and demodulated by signal  $m_2(t)$  back to the original band. Suppose that the input signal has a spectrum limited to half the chopper frequency, then no signal aliasing occurs.

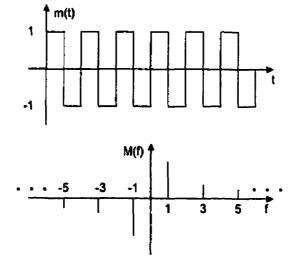

Modulating Signal m(t) is a square wave function which is shown in figure 2.8. Its Fourier series and frequency spectrum are given in equations (2.18).

$$\begin{cases} m(t) = \frac{2}{\pi} \sum_{\substack{n = -\infty \\ n \text{ odd}}}^{\infty} \frac{1}{\sin(2\pi n \frac{t}{T})} \\ M(f) = \frac{2}{j\pi} \sum_{\substack{n = -\infty \\ n \text{ odd}}}^{\infty} \frac{1}{n} \delta(f - \frac{n}{T}) \end{cases}$$

(2.18)

Figure 2.8 Modulation signal and its spectrum

Note that the low frequency noise and offset of the amplifier (represented by  $V_n$  and  $V_{os}$  respectively in figure 2.7) are only modulated once by the demodulator and translated to

the odd harmonics, leaving essentially white noise in the baseband. After demodulation, the signal is filtered at half the chopper frequency by a low pass filter, thus high-frequency components, which also include the 1/f noise and offset of the amplifier, will then be removed.

# 2.3.2.2 The effect of CHS on the amplifier noise

From the description of the CHS principle of operation, we know that the 1/f noise and DC offset will be reduced. However, the effect on thermal noise needs to be further discussed.

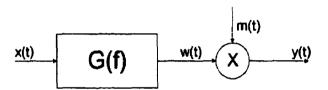

Figure 2.9 Noise modulation

The noise path is extracted from figure 2.7 as shown in figure 2.9, where x(t) represents the amplifier noise and DC offset, y(t) denotes its output. Enz presented in [4][5]: the power spectrum density (PSD) of the output white noise was

$$S_{white}(f) \approx S_{white}(0) = S_0 \cdot \left(1 - \frac{\tanh(\frac{\pi}{2} f_c T)}{\frac{\pi}{2} f_c T}\right)$$

(2.19)

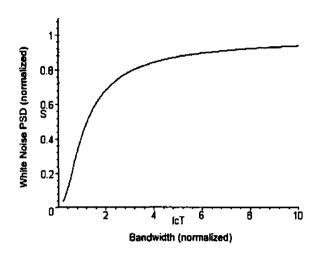

where  $S_0$  represents the input thermal noise. The PSD is plotted in figure 2.10 against the white-noise bandwidth normalized to the chopper frequency. It shows that the chopper-modulated white noise power is always smaller than the power of the original white

noise. This implies that the CHS technique not only reduces the 1/f noise but also decreases the output thermal noise level.

Figure 2.10 Chopper modulated white noise versus bandwidth

And according to [4][5], the PSD of the output 1/f noise

$$S_{1/f}(f) \cong 0.8525 S_0 f_k T \tag{2.20}$$

where fk represents the chopper frequency.

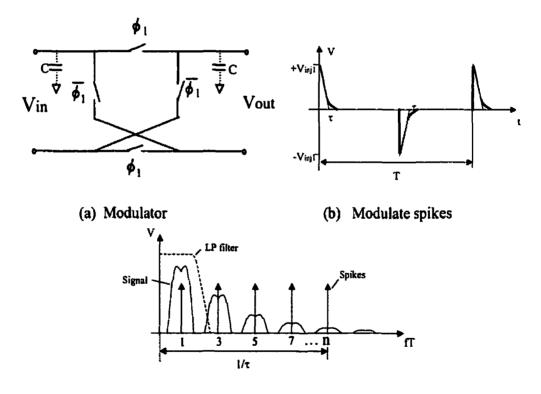

# 2.3.2.3 Residual Offset

The inherent DC offset in the selective amplifier is completely removed, since it has been shift to the odd harmonics of the chopper frequency, and filtered by the low pass filter (LPF). In MOS circuits, the modulators are composed of four switches. It is inevitable that the charge injection through these switches, especially in the input modulator, will introduce a residual offset to the chopper amplifier. This charge injection and parasitic coupling cause spikes appearing at the input of the amplifier. Each time a MOS switch turns off, a certain amount of charge  $\Delta Q$  flows into parasitic capacitors C, and causes a

"spike" with peak voltage  $V_{inj} = \Delta Q/C$  as presented in figure 2.11. The time constant  $\tau$  of the spikes has a value RC, where R represents the resistance of the input signal source.

This "spike" signal has a period of T ( $1/f_{chop}$ ). Since the demodulation signal is also periodic with period T, a substantial part of this spike energy will be translated back to DC which result in a residual offsets. If care is taken to limit the time constant  $\tau$  of those spikes to a value much smaller than T/2, most of the spike energy will remain on frequencies higher than the chopper frequency, as shown in figure 2.11 (c).

(c) Spectrum of spikes and signals

Figure 2.11 Residual offset

The spectrum of the spike's signal is represented by impulses at the odd harmonics of the chopper frequency with an equivalent bandwidth proportional to  $1/\tau$  and much larger than

f<sub>chop</sub>. Meanwhile, figure 2.11 shows the spectrum of a modulated signal. Since the spectral envelope of the signal is inversely proportional to the frequency, the output signal after amplification and demodulation can be essentially reconstituted by its fundamental harmonic. This poses a problem of choosing an amplifier bandwidth in order to be capable of restoring the modulated signal while rejecting most of the spike's spectral components.

The spikes can be represented by the Fourier series [6]

$$x_{spike}(t) = \sum_{\substack{n=1\\ odd}}^{\infty} \frac{4\tau}{T} V_{inj} \frac{1}{\sqrt{1 + (n\omega\tau)^2}} \cos(n\omega t - \arctan(n\omega\tau))$$

(2.21)

Amplified by the selective amplifier (SA), the spikes become

$$x_f(t) = \sum_{\substack{n=1\\ \text{odd}}}^{\infty} A_n \cdot \frac{4\tau}{T} V_{inj} \frac{1}{\sqrt{1 + (n\omega\tau)^2}} \cos(n\omega t - \arctan(n\omega\tau) + \phi_n)$$

(2.22)

where  $A_n$  and  $\phi_n$  represent the amplitude and phase response of the SA at the frequency  $n\omega$ , respectively. Thus after demodulating, the residual offset can be written as:

$$V_{off} = \Im_{LP}(x_f(t) \cdot m(t))$$

$$= \sum_{\substack{n=1 \ odd}}^{\infty} A_n \cdot \frac{4\tau}{T} \cdot \frac{2}{n\pi} V_{inj} \frac{1}{\sqrt{1 + (n\omega\tau)^2}} \cos(-\arctan(n\omega\tau) + \phi_n - \frac{\pi}{2})$$

(2.23)

where  $\Im_{tr}$  represents an ideal low pass filter function having a cutoff frequency of one half of the modulation signal frequency  $f_{mod}$ . It illustrates that the effectiveness of the offset reduction depends on the transfer function of the selective amplifier.

It has been demonstrated that the  $2^{nd}$  order bandpass filter (BPF) is the best choice between offset reduction and complexity of the circuit [5][6]. Equation (2.24) presents the optimized residual offset of the CHS, which illustrates that in this case the residual offset is proportional to the square of the ratio between spike time constant  $\tau$  and modulating signal period T.

$$V_{off} \approx 4A_0 V_{inj} \left(\frac{2\tau}{T}\right)^2 \tag{2.24}$$

## 2.3.2.4 Comparison with AZ

Unlike the AZ process, the CHS approach does not use sampling techniques, but it is based on a modulation method. It does not alias the wideband noise, thus does not increase the baseband white noise. In addition, the amplifier is always connected with signal in CHS unlike in the autozero technique where during one of the phase the amplifier is disconnected. Furthermore, the AZ technique also suffers the charge injection, which result from the non-ideal MOS switches. Therefore the CHS is more effective for continuous time signal processing, such as monitoring the neuromuscular activities in the biomedical application. In this project we will take advantage of the chopper stabilization technique to reduce the 1/f noise and DC offset.

## 2.4 Low noise circuits within recent literatures

So far, a few papers have discussed the low noise circuit techniques. Timothy et al. [29] presented a compact low noise operational amplifier in 1.2 um digital CMOS technology,

which used the lateral PNP transistors as the input stage to reduce the 1/f noise. Due to the inherent low 1/f noise attribute of the bipolar transistor, the circuit features a input referred noise of 23.8 nV/ $\sqrt{Hz}$  at 1 Hz, with a closed loop gain 20.8 dB, a minimum PSRR of 68 dB and a CMRR of 100 dB. It worked under a  $\pm 2.5$  V supply. The chip area of the fabricated amplifier is 0.211 mm<sup>2</sup> only. However, the bipolar input stage of the amplifier makes it only suitable for applications that can tolerate its low input impedance, not applications like urine monitor system, where the source impedance is about 10k  $\Omega$  [1].

Wong et al. introduced a switched differential Op-amp with low offset and reduced 1/f noise [10]. The authors proposed a dynamic technique for implementing fully differential op-amps (DOA) by time-sharing conventional single-output op-amps (SOA), which took advantages of the auto-zero technique to reduce the input DC offset and 1/f noise. The authors analyzed the reduction of offset and 1/f noise produced by the technique, unfortunately they did not mention its impact on the input thermal noise. The circuit was implemented using a 5-um polysilicon-gate CMOS process. The Opamp realized 52 dB gain with input noise density of 200 nV/ $\sqrt{Hz}$  at 1k Hz. The offset was reduced to 0.4 mV. It worked under a  $\pm$ 5V power supply.

Enz discussed chopper stabilization to reduce the DC offset and 1/f noise of conventional monolithic CMOS opamp [4][5][29]. The author provided a detailed mathematical analysis of the effect on Opamp thermal noise, 1/f noise and the residual offset

introduced by a non-ideal modulator. The author also compared the CHS technique with the auto-zero technique. He demonstrated that CHS is more adaptable in continuous time signal applications than other known techniques. Furthermore, the authors pointed out that the critical part of CHS amplifier design is to use an optimized selective amplifier to reduce the residual offset. The selective amplifier presented in [5] made use of a 2nd order continuous time gm-C BP filter only. It realized a 56 dB DC gain, however an offset compensation circuit was necessarily associated with the high gm value of the input transconductor. Its equivalent input-referred noise was  $47 \text{nV}/\sqrt{Hz}$  under a 5V supply voltage.

Menolfi et al. presented further insight on the chopper stabilization technique to reduce the offset and the flicker noise [6][7]. The authors analyzed the residual offset in the time domain, and illustrated that a band-pass filter provides the best choice between the residual offset reduction and the circuit complication. The authors also suggested that the common mode rejection ratio can be improved by CHS. Moreover, a low noise amplifier based on the CHS technique has been implemented and used successfully in a thermoelectric infrared detectors. Two stages [6] and three stages [7] amplifiers were used as the selective amplifier respectively which allow to easily realize a high gain. The equivalent input-referred noise in the case of two stage amplifier was  $15 \text{ nV}/\sqrt{Hz}$  [6]. The supply voltage was 5V and the power consumption was 3 mW.

Table 2-1 depicts a summary of those techniques and their respective performance.

|                | Timothy et al         | Wong et al           | Enz.              | Menolfi et al     |

|----------------|-----------------------|----------------------|-------------------|-------------------|

| Key Words      | Lateral BJT           | Switched Opamp       | CHS               | CHS               |

| Power Supply   | ±2.5 V                | ±5V                  | 5V                | 5V                |

| Utilize        | 1.2 um                | 5-um                 | SACMOS            | l-um              |

| technology     |                       |                      |                   |                   |

| Input referred | 23.8 nV/√ <i>Hz</i> @ | 200 nV/√ <i>Hz</i> @ | 43 nV/√ <i>Hz</i> | 15 nV/√ <i>Hz</i> |

| noise          | l Hz                  | lk Hz                |                   |                   |

| Input DC       | N/A                   | 0.4 mV               | 0.62μV            | 0.5μV             |

| offset         |                       |                      |                   |                   |

| DC gain        | 20.8 dB               | 52 dB                | 56 dB             | 52 dB             |

| Surface area   | 0.211 mm <sup>2</sup> | N/A                  | N/A               | 1260×1150         |

| size           |                       |                      |                   | μm²               |

| Reference      | [29]                  | [10]                 | [4][5]            | [6]               |

Table 2.1 Main characteristics of reported low-noise preamplifiers

### 2.5 Conclusion

This chapter has reviewed the important concepts in the design of CMOS low noise circuits. First two dominant noise sources in MOSFET transistors were introduced. And the effect of downscaling of the CMOS technology on the system noise was presented. This was followed by a discussion on the two circuit low noise techniques. Based on the

comparison of two techniques, The CHS technique will be used in this project to reduce the low frequency noise and DC offset.

#### CHAPTER 3

## **CHOPPER STABILIZATION TECHNIQUE**

#### 3.1 Introduction

The basic principle of Chopper stabilization technique has been introduced in the last chapter and main previous CHS analysis works have been reviewed. It has also been illustrated that one of the critical parts of CHS is to design an optimized selective amplifier, which not only amplifies the signal to a high level, but also can reduce the residual offset that stems from the charge injections of the input modulator.

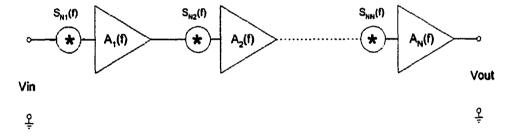

Enz and Menolfi both have demonstrated that making use of a 2<sup>nd</sup> order bandpass filter (BPF) as the SA is the best compromise between offset reduction and complexity of circuit. However their analyses and conclusions of the effect of CHS on amplifier noise (equations (2.19) and (2.20)) were based on analyzing a 1<sup>st</sup> order low-pass filter from the viewpoint of simplicity, rather than a 2<sup>nd</sup> order BPF used in practice. Thus in this chapter, detailed discussions of the CHS amplifier with a 2<sup>nd</sup> order BPF and illustration of its two supplementary characteristics of CHS will be given. The next section will first introduce a CHS behavior model that is built under SIMULINK toolbox in Matlab. The proposed model can be used to simulate the practical behavior of chopper stabilization technique in

a view of theory and mathematical consideration, so that we can use it to verify our analyses and conclusions later.

#### 3.2 A CHS Behavior Model in MATLAB/SIMULINK

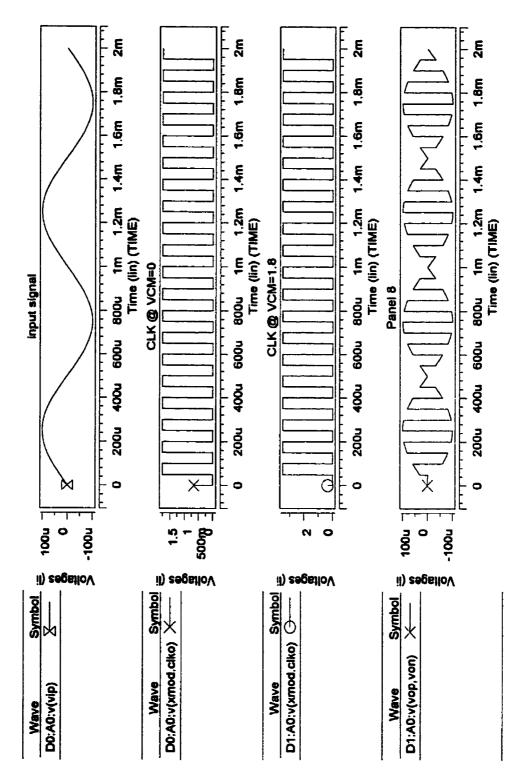

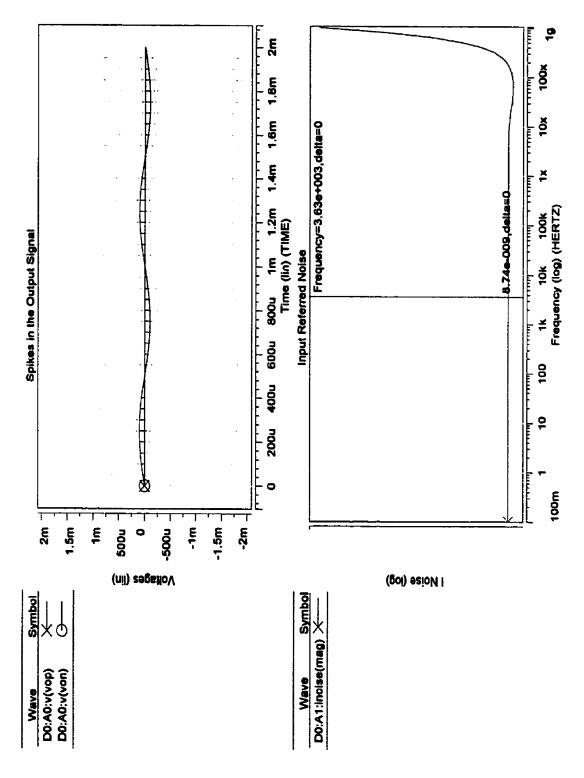

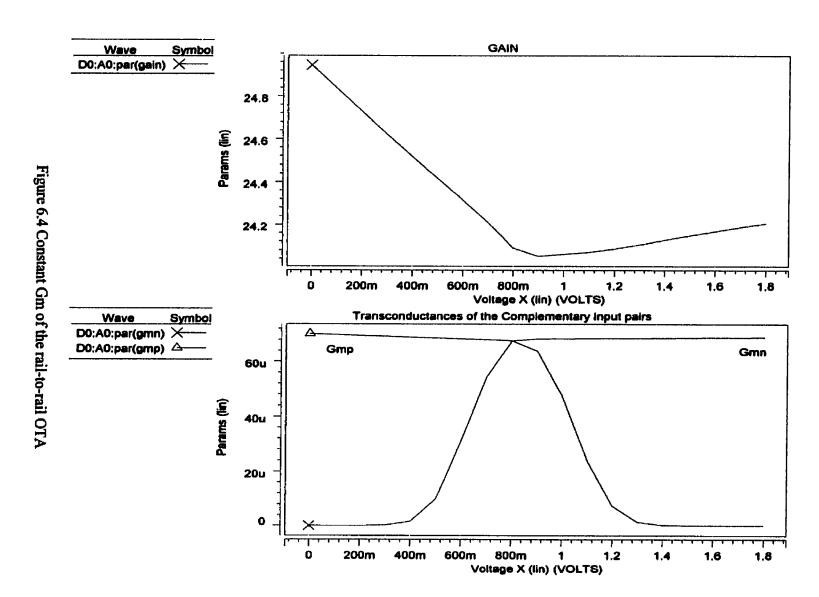

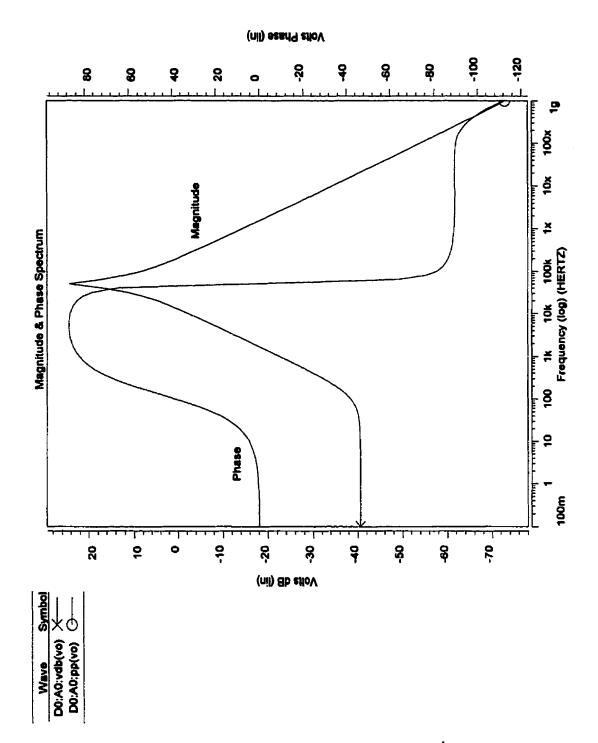

With the rapid evolution of the design technology, time-to-market is one of the crucial factors in the ultimate success of a component. Designers have, therefore, increasingly adhered to design methodologies and strategies that are more amenable to design automation and flexible analysis. Chopper stabilization technique has been known for a long time to realize high-precision DC gains with AC-coupled amplifiers and reduce the low frequency noise. However, its relatively complicated mathematical model which refers to twice frequency transforms and once non-ideal filter, makes that designing and optimizing the CHS circuit be a bewildering and tedious work. Moreover, the random attribute of the noise and other practical non-idealities in circuit implementation, further contribute to the complexity and difficulty of CHS analysis. These problems will be identified by the CHS behavior model built with MATLAB/SIMULINK.