**Titre:** Réalisation de filtres analogiques Gm-C configurables dans les circuits intégrés

Title: Circuits intégrés

**Auteur:** Jean-Charles Voghell

Author:

**Date:** 2000

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Voghell, J.-C. (2000). Réalisation de filtres analogiques Gm-C configurables dans les circuits intégrés [Mémoire de maîtrise, École Polytechnique de Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/8869/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8869/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

RÉALISATION DE FILTRES ANALOGIQUES Gm-C CONFIGURABLES

DANS LES CIRCUITS INTÉGRÉS

JEAN-CHARLES VOGHELL

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUIN 2000

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file: Votre référence

Our file: Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-60919-7

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

RÉALISATION DE FILTRES ANALOGIQUES Gm-C CONFIGURABLES

DANS LES CIRCUITS INTÉGRÉS

présenté par: VOGHELL Jean-Charles

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. SAVARIA, Yvon, Ph.D., Président

M. SAWAN, Mohamad, Ph.D., membre et directeur de recherche

M. GUARDO, Robert, Ph.D., membre

À Aline et Benoit ...

## **REMERCIEMENTS**

**Je tiens à remercier personnellement plusieurs personnes qui ont grandement contribué à la réalisation de ce mémoire par leur support et leurs encouragements constants. Je tiens donc à remercier ma famille, mes parents, mes grand-parents et plus particulièrement Julie, ma future épouse, à qui j'espère pouvoir donner autant d'encouragements qu'elle l'a fait pour moi dans l'accomplissement de sa maîtrise.**

**Bien évidemment, je dois remercier le professeur Mohamad Sawan pour m'avoir offert la chance de réaliser ce projet et qui m'a guidé patiemment et sagement en cours de route.**

**De plus, je tiens à remercier mes collègues de l'équipe Polystim, dirigée par Mohamad Sawan pour leur présence, leur support technique et pour avoir mis de la vie dans le laboratoire.**

**Finalement, je tiens à remercier la Société Canadienne de Microélectronique pour la fabrication des composants et pour les équipements mis à notre disposition, ainsi que le CRSNG pour le support financier de ce projet.**

## RÉSUMÉ

La fabrication d'appareils électroniques de petites dimensions et de faible consommation de puissance est de nos jours une préoccupation constante. On retrouve un intérêt similaire pour l'utilisation de filtres analogiques dans les circuits intégrés dédiés à des applications biomédicales, aux appareils portables, ou tout simplement pour la réduction de la surface exploitée des circuits en général.

Ce projet de maîtrise consiste à réaliser des filtres analogiques actifs à l'aide d'intégrateurs transconductance-condensateur ( $Gm-C$ ) dans des circuits intégrés. L'avantage que procure l'utilisation des cellules de transconductance ( $Gm$ ), par rapport aux autres techniques existantes, c'est qu'il s'agit d'éléments simples, capables de fonctionner à des vitesses élevées, tout en permettant d'ajuster les paramètres des filtres réalisés.

Nous avons développé, dans le cadre de ce projet, une nouvelle cellule  $Gm$  contrôlée par une source de courant programmable et commandée par un convertisseur numérique-analogique. Cette cellule a été conçue en effectuant les compromis nécessaires pour obtenir des caractéristiques s'approchant d'un intégrateur idéal. Plusieurs exemples d'applications utilisant ces dispositifs pour réaliser des filtres sont présentés dans ce mémoire. Nous présentons aussi les simulations nécessaires à la conception des circuits et les résultats expérimentaux obtenus avec des composants fabriqués dans la technologie CMOS  $0.35\mu m$ , soit une source de courant programmable et un filtre passe-bande du second et du huitième ordre. Nous présentons enfin une analyse montrant les effets

causés par les éléments non idéaux sur les caractéristiques des filtres communément utilisés.

## ABSTRACT

Since the interest in manufacturing small devices is continuously growing, several applications require miniaturization of electronic systems by using integrated circuits. We note such a tendency in analog signal processing circuits (eg. analog filtering) used in implantable biomedical devices, handheld devices or simply for area reduction of circuits.

The main objective of this project is to realize tunable continuous time analog filters by using a transconductance-capacitor (Gm-C) pair as an integrator in integrated circuits. Simplicity, high speed operation and programmability give transconductor cells (Gm) great advantages over alternative techniques.

In this project, a new current tunable Gm cell architecture is proposed by using a programmable current source based on a digital to analog converter. All efforts and compromises have been made to obtain integrator characteristics that approach the ideal case. Also, examples of specific applications where Gm cells are used in filters are presented. Moreover, simulation and test results of two experimental integrated circuits fabricated in a  $0.35\mu\text{m}$  CMOS technology are reported. These components are respectively a programmable current source based on a digital to analog converter and a programmable eight order bandpass filter. Finally, an analysis of the effects of non-ideal characteristics on the most commonly used filter classes is made.

## TABLE DES MATIÈRES

|                                                                                                                     |      |

|---------------------------------------------------------------------------------------------------------------------|------|

| DÉDICACE .....                                                                                                      | iv   |

| REMERCIEMENTS .....                                                                                                 | v    |

| RÉSUMÉ .....                                                                                                        | vi   |

| ABSTRACT .....                                                                                                      | viii |

| TABLE DES MATIÈRES .....                                                                                            | ix   |

| LISTE DES TABLEAUX .....                                                                                            | xiii |

| LISTE DES FIGURES .....                                                                                             | xiv  |

| LISTE DES SYMBOLES ET DES ABRÉVIATIONS .....                                                                        | xix  |

| LISTE DES ANNEXES .....                                                                                             | xxii |

| INTRODUCTION .....                                                                                                  | 1    |

| CHAPITRE I: APERÇU DES ARCHITECTURES DE TRANSCONDANCE<br>ET DES TECHNIQUES DE RÉALISATION<br>DES FILTRES Gm-C ..... | 6    |

| 1.1 INTRODUCTION .....                                                                                              | 6    |

| 1.2 CONCEPTION DES FILTRES ANALOGIQUES DANS LES CIRCUITS INTÉGRÉS .....                                             | 6    |

| 1.3 TECHNIQUES DE RÉALISATION DES FILTRES .....                                                                     | 8    |

| 1.3.1 Sections quadratiques mises en cascade .....                                                                  | 8    |

| 1.3.2 Modèle du gyrateur .....                                                                                      | 10   |

| 1.3.3 Modèle à variables d'état .....                                                                               | 11   |

| 1.4 SURVOL DES ARCHITECTURES DE TRANSCONDANCES .....                                                                | 15   |

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

| 1.4.1 Cellule opérant dans la région ohmique.....                                        | 16 |

| 1.4.2 Cellule basée sur des inverseurs.....                                              | 17 |

| 1.4.3 Cellule différentielle simple.....                                                 | 18 |

| 1.4.4 Cellule différentielle simple avec étage de sortie.....                            | 19 |

| 1.4.5 Cellule différentielle double et résistance négative.....                          | 21 |

| 1.5 CONCLUSION.....                                                                      | 25 |

| <br>                                                                                     |    |

| CHAPITRE II: CONTRÔLE DES FILTRES Gm-C.....                                              | 26 |

| 2.1 INTRODUCTION.....                                                                    | 26 |

| 2.2 PROCÉDURE DE CONTRÔLE EN MODE COURANT.....                                           | 26 |

| 2.3 IDENTIFICATION DES CARACTÉRISTIQUES ET DES MODULES ÉLECTRONIQUES<br>RECHERCHÉES..... | 27 |

| 2.3.1 Caractéristiques de l'intégrateur.....                                             | 27 |

| 2.3.2 Caractéristiques de la source de courant programmable.....                         | 31 |

| 2.4 PROPOSITION D'UNE NOUVELLE CELLULE DE TRANSCONDUCTANCE.....                          | 31 |

| 2.4.1 Étage d'entrée.....                                                                | 32 |

| 2.4.2 Étage de sortie.....                                                               | 36 |

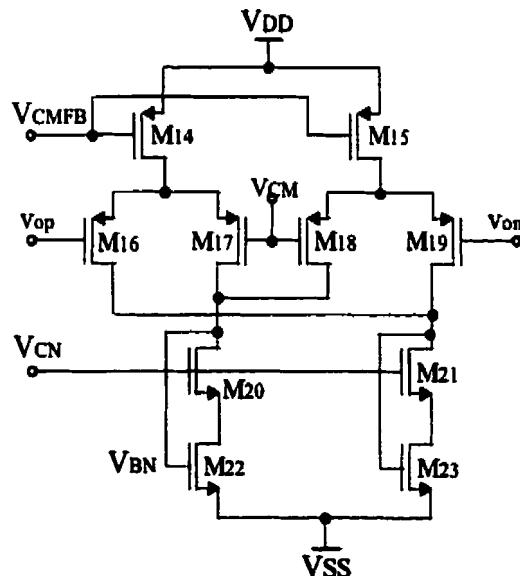

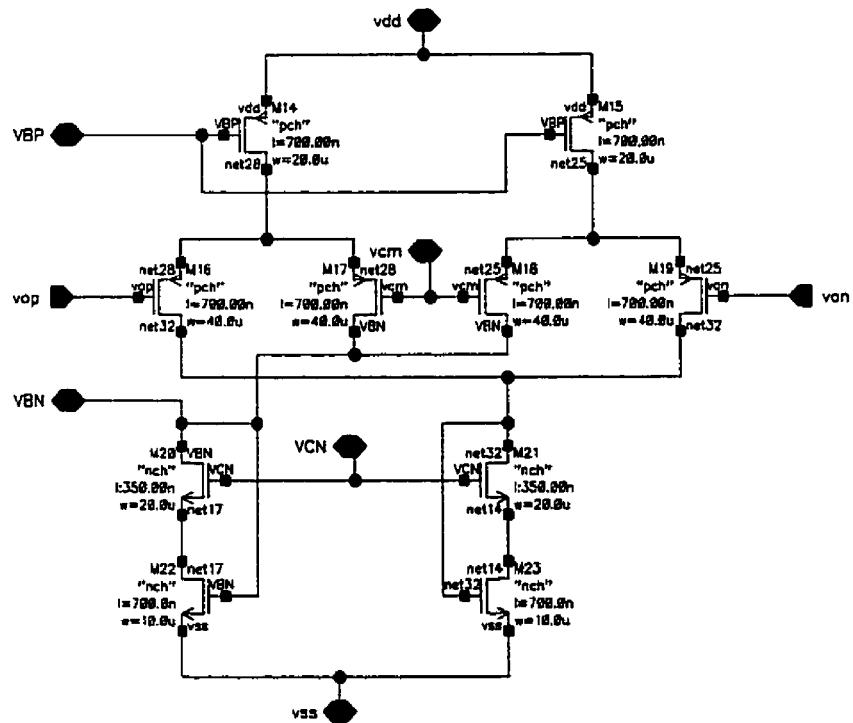

| 2.4.3 Circuit de rétroaction en mode commun (CMFB).....                                  | 38 |

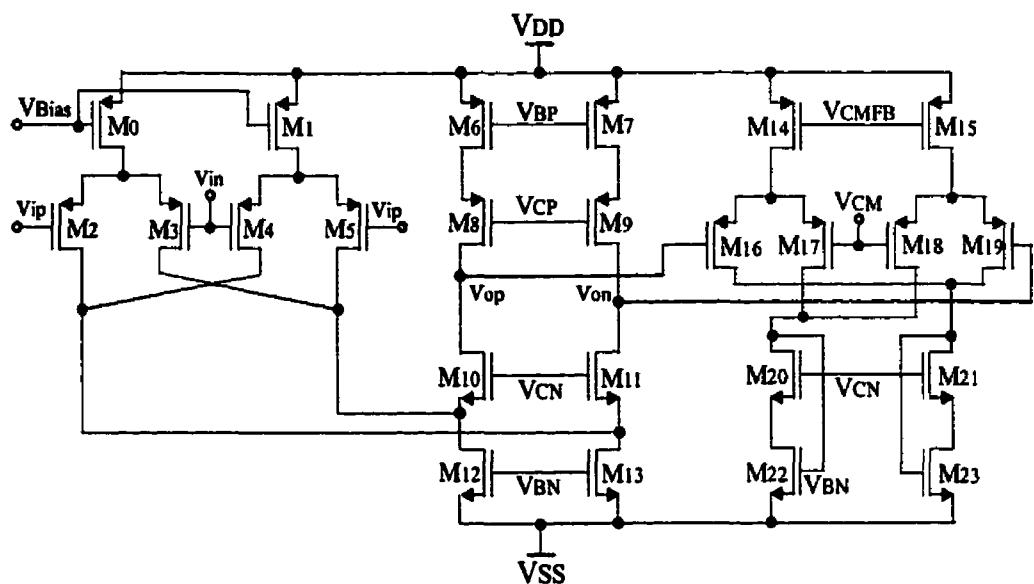

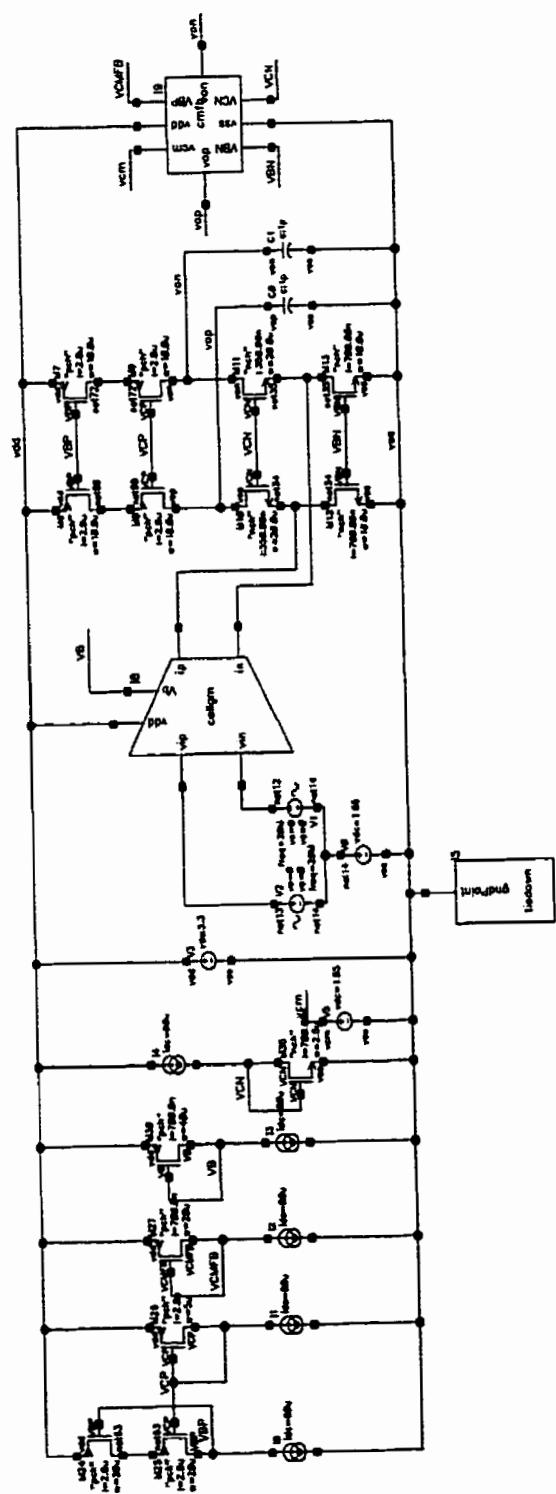

| 2.4.4 Circuit final et circuit de polarisation.....                                      | 39 |

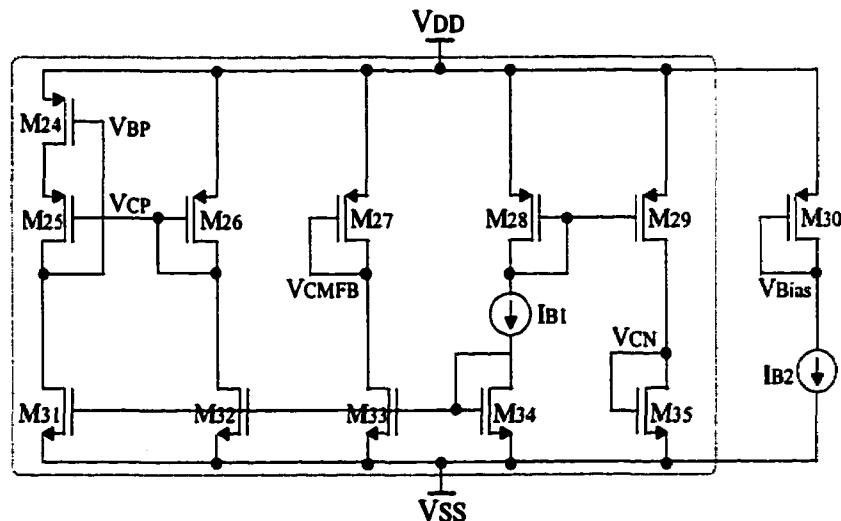

| 2.5 PRÉSENTATION D'UNE SOURCE DE COURANT PROGRAMMABLE.....                               | 43 |

| 2.6 CONCLUSION.....                                                                      | 46 |

|                                                                                                     |           |

|-----------------------------------------------------------------------------------------------------|-----------|

| <b>CHAPITRE III: CONCEPTION DE FILTRES CONFIGURABLES DÉDIÉS À DES APPLICATIONS SPÉCIFIQUES.....</b> | <b>48</b> |

| <b>    3.1 INTRODUCTION.....</b>                                                                    | <b>48</b> |

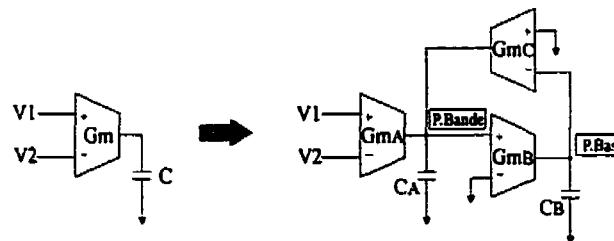

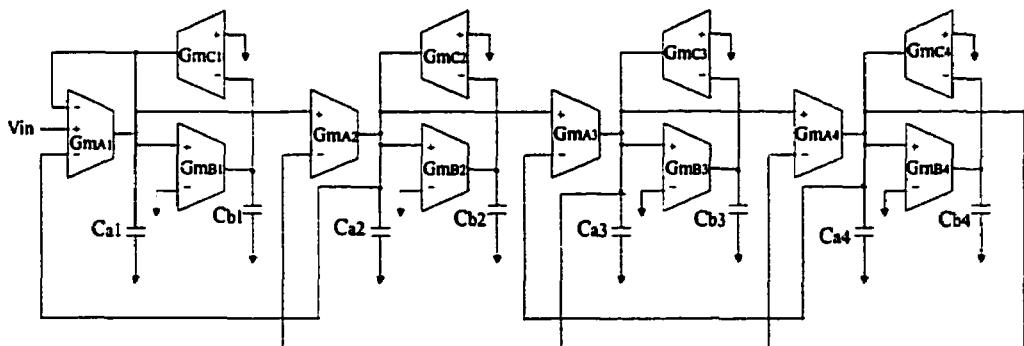

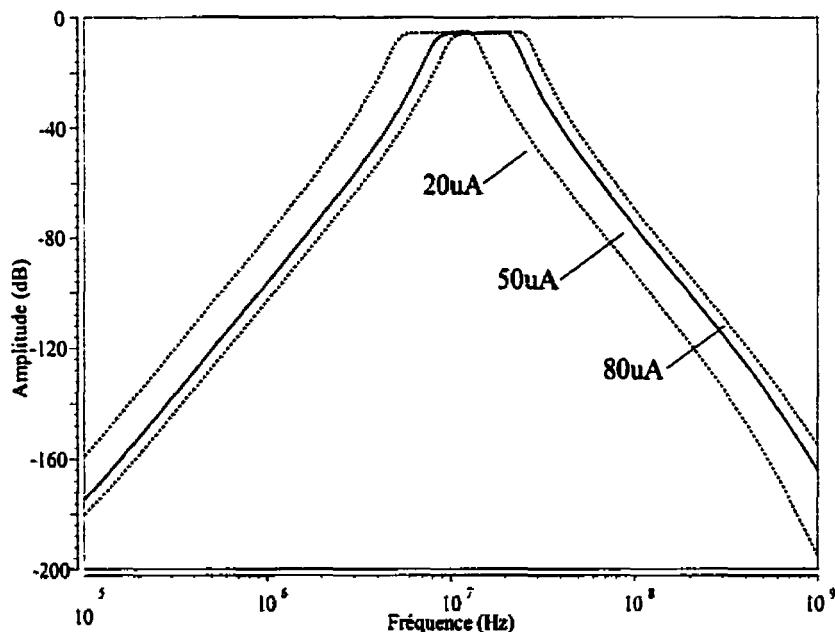

| <b>    3.2 DESCRIPTION D'UN FILTRE PASSE-BANDE QUADRATIQUE ET DU HUITIÈME ORDRE.....</b>            | <b>48</b> |

| <b>        3.2.1 Filtre passe-bande .....</b>                                                       | <b>49</b> |

| <b>        3.2.2 Filtre passe-bande du huitième ordre de configuration LF .....</b>                 | <b>50</b> |

| <b>        3.2.3 Simulation du filtre passe-bande de huitième ordre.....</b>                        | <b>53</b> |

| <b>    3.3 ÉTAGE D'ENTRÉE D'UN RÉCEPTEUR DÉDIÉ AUX STIMULATEURS NEURO-MUSCULAIRES.....</b>          | <b>54</b> |

| <b>        3.3.1 Récepteur FSK.....</b>                                                             | <b>56</b> |

| <b>        3.3.2 Récepteur PSK.....</b>                                                             | <b>60</b> |

| <b>    3.4 CONCLUSION.....</b>                                                                      | <b>64</b> |

| <br>                                                                                                |           |

| <b>CHAPITRE IV: RÉSULTATS EXPÉRIMENTAUX.....</b>                                                    | <b>65</b> |

| <b>    4.1 INTRODUCTION.....</b>                                                                    | <b>65</b> |

| <b>    4.2 RÉSULTATS DE SIMULATIONS DE LA CELLULE DE TRANSCONDUCTANCE.....</b>                      | <b>65</b> |

| <b>        4.2.1 Analyse AC de la cellule de transconductance.....</b>                              | <b>66</b> |

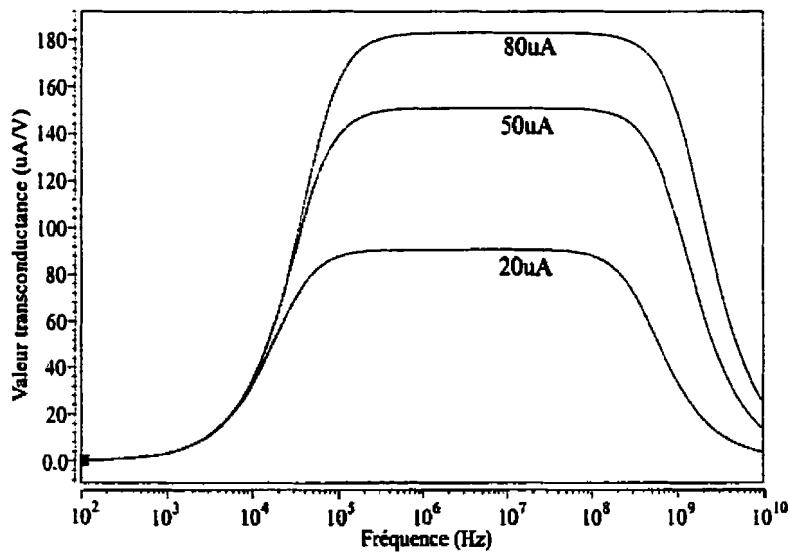

| <b>        4.2.2 Plage de transconductance.....</b>                                                 | <b>69</b> |

| <b>        4.2.3 Impédance d'entrée et de sortie .....</b>                                          | <b>70</b> |

| <b>        4.2.4 Taux de rejet du signal en mode commun (TRMC) .....</b>                            | <b>70</b> |

| <b>        4.2.5 Taux de rejet des tensions d'alimentation (PSRR) .....</b>                         | <b>71</b> |

|                                                                                           |           |

|-------------------------------------------------------------------------------------------|-----------|

| <b>4.3 SIMULATIONS ET PERFORMANCES DE LA SOURCE DE COURANT. . . . .</b>                   | <b>71</b> |

| <b>4.3.1 Paramètres servant à caractériser la source de courant programmable. . . . .</b> | <b>72</b> |

| <b>4.3.2 Présentation des résultats de simulation. . . . .</b>                            | <b>74</b> |

| <b>4.3.3 Dessin des masques et réalisation du composant. . . . .</b>                      | <b>76</b> |

| <b>4.3.4 Performances de la source de courant finale. . . . .</b>                         | <b>77</b> |

| <b>4.4 SIMULATIONS ET TESTS D'UN FILTRE DE HUITIÈME ORDRE. . . . .</b>                    | <b>80</b> |

| <b>4.4.1 Présentation des résultats de simulation. . . . .</b>                            | <b>80</b> |

| <b>4.4.2 Dessin des masques et réalisation du composant. . . . .</b>                      | <b>83</b> |

| <b>4.4.3 Performances du composé réalisé. . . . .</b>                                     | <b>84</b> |

| <b>4.5 INTERPRÉTATION DES EFFETS D'UN INTÉGRATEUR NON-IDÉAL . . . . .</b>                 | <b>88</b> |

| <b>4.5.1 Effet sur les filtres passe-bande. . . . .</b>                                   | <b>89</b> |

| <b>4.5.2 Effet sur les filtres passe-bas. . . . .</b>                                     | <b>90</b> |

| <b>4.6 CONCLUSION. . . . .</b>                                                            | <b>91</b> |

| <b>CONCLUSIONS. . . . .</b>                                                               | <b>92</b> |

| <b>RÉFÉRENCES. . . . .</b>                                                                | <b>97</b> |

## LISTE DES TABLEAUX

|             |                                                                                                                            |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 2.1 | Dimensions des transistors. . . . .                                                                                        | 42 |

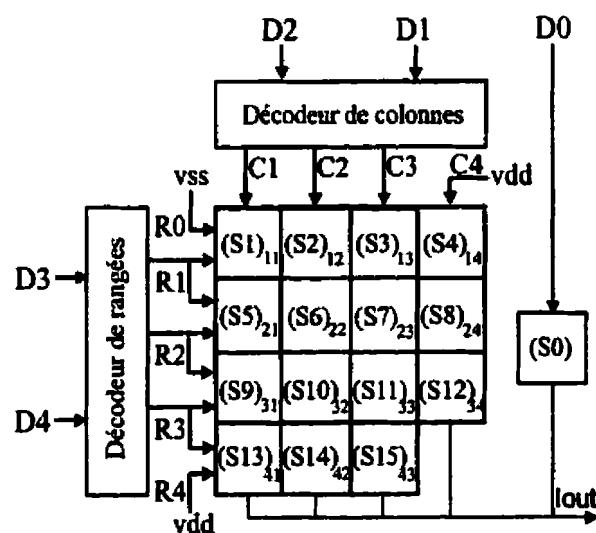

| Tableau 2.2 | Table de correspondance des décodeurs . . . . .                                                                            | 45 |

| Tableau 4.1 | Caractéristiques simulées de la cellule de transconductance:<br>variations en fonction du courant de polarisation. . . . . | 66 |

| Tableau 4.2 | Résultats de simulation de la source de courant. . . . .                                                                   | 74 |

| Tableau 4.3 | Présentation des résultats expérimentaux<br>des deux sources de courant . . . . .                                          | 78 |

| Tableau 4.4 | Résumé des résultats de simulation<br>du filtre passe-bande du second ordre. . . . .                                       | 81 |

| Tableau 4.5 | Résumé des résultats de simulation<br>du filtre passe-bande du 8 <sup>ième</sup> ordre. . . . .                            | 83 |

| Tableau 4.6 | Résultats expérimentaux pour le filtre<br>passe-bande du second ordre. . . . .                                             | 85 |

| Tableau 4.7 | Résultats expérimentaux pour le filtre<br>passe-bande du huitième ordre . . . . .                                          | 87 |

## **LISTE DES FIGURES**

|                    |                                                                                                                 |           |

|--------------------|-----------------------------------------------------------------------------------------------------------------|-----------|

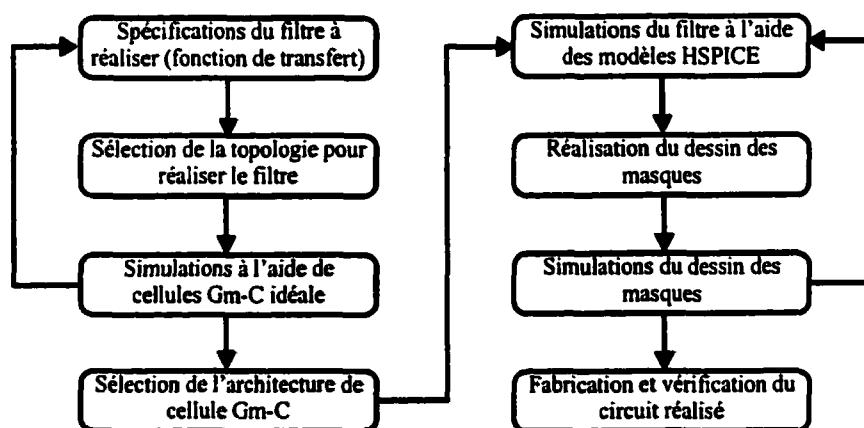

| <b>Figure 1.1</b>  | <b>Processus de conception des filtres Gm-C.....</b>                                                            | <b>7</b>  |

| <b>Figure 1.2</b>  | <b>Section de filtre quadratique différentielle généralisée<br/>tiré de John &amp; Martin .....</b>             | <b>9</b>  |

| <b>Figure 1.3</b>  | <b>Résistance réalisée à l'aide d'une cellule Gm.....</b>                                                       | <b>11</b> |

| <b>Figure 1.4</b>  | <b>Représentation d'une inductance.....</b>                                                                     | <b>11</b> |

| <b>Figure 1.5</b>  | <b>Configuration FLF pour un système du troisième ordre.....</b>                                                | <b>12</b> |

| <b>Figure 1.6</b>  | <b>Configuration IFLF pour un système du troisième ordre.....</b>                                               | <b>13</b> |

| <b>Figure 1.7</b>  | <b>Représentation d'un filtre passe-bas normalisé du troisième ordre ..</b>                                     | <b>14</b> |

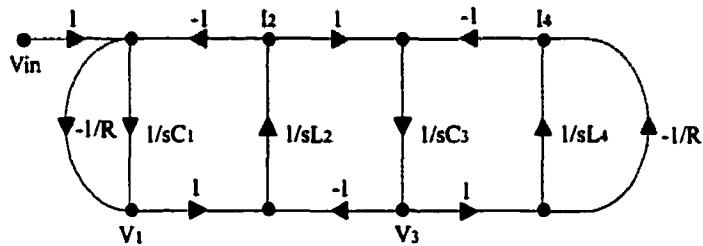

| <b>Figure 1.8</b>  | <b>Graphe de fluence du circuit équivalent.....</b>                                                             | <b>14</b> |

| <b>Figure 1.9</b>  | <b>Filtre Gm-C équivalent.....</b>                                                                              | <b>14</b> |

| <b>Figure 1.10</b> | <b>Cellule opérant dans la région ohmique, <math>i_o</math> est le courant de sortie<br/>différentiel .....</b> | <b>16</b> |

| <b>Figure 1.11</b> | <b>Cellule Gm basée sur des inverseurs.....</b>                                                                 | <b>17</b> |

| <b>Figure 1.12</b> | <b>Cellule différentielle simple de type N .....</b>                                                            | <b>18</b> |

| <b>Figure 1.13</b> | <b>Cellule différentielle avec étage de sortie <i>folded-cascode</i>.....</b>                                   | <b>20</b> |

| <b>Figure 1.14</b> | <b>Cellule différentielle double avec résistance négative .....</b>                                             | <b>22</b> |

| <b>Figure 1.15</b> | <b>Cellule différentielle double avec résistance négative.....</b>                                              | <b>23</b> |

| <b>Figure 1.16</b> | <b>Technique de compensation par rétroaction positive.....</b>                                                  | <b>24</b> |

| <b>Figure 2.1</b>  | <b>Intégrateur basé sur une cellule de transconductance.....</b>                                                | <b>27</b> |

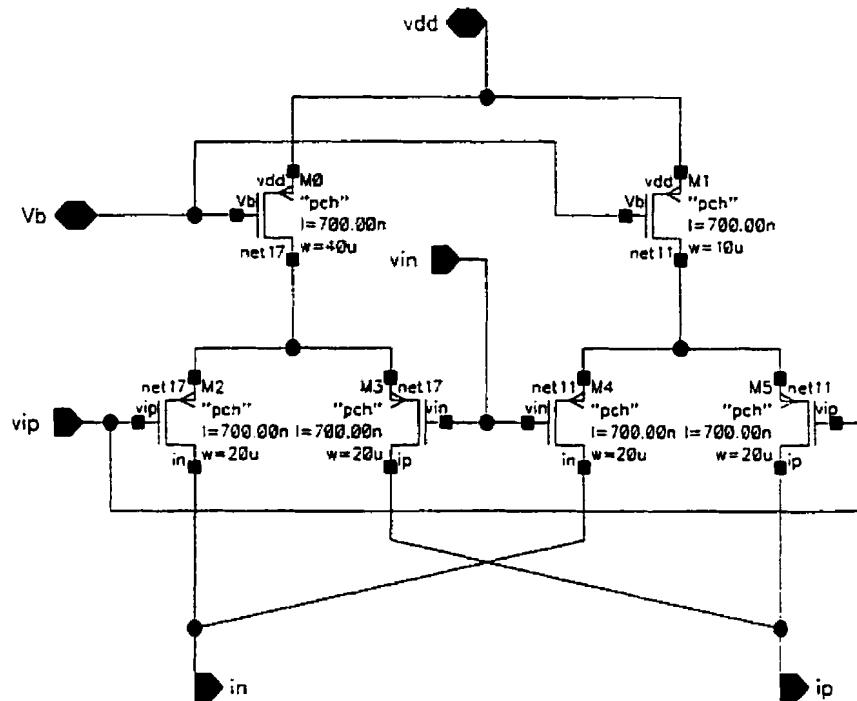

| <b>Figure 2.2</b>  | <b>Étage d'entrée proposé.....</b>                                                                              | <b>32</b> |

|             |                                                                                                                                                                    |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

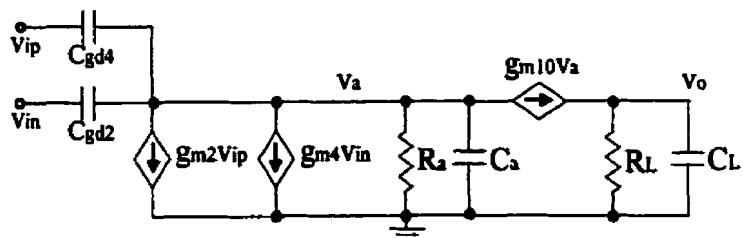

| Figure 2.3  | Modèle petit signal équivalent du circuit. . . . .                                                                                                                 | 34 |

| Figure 2.4  | Étage de sortie ( <i>Folded cascode</i> ). . . . .                                                                                                                 | 37 |

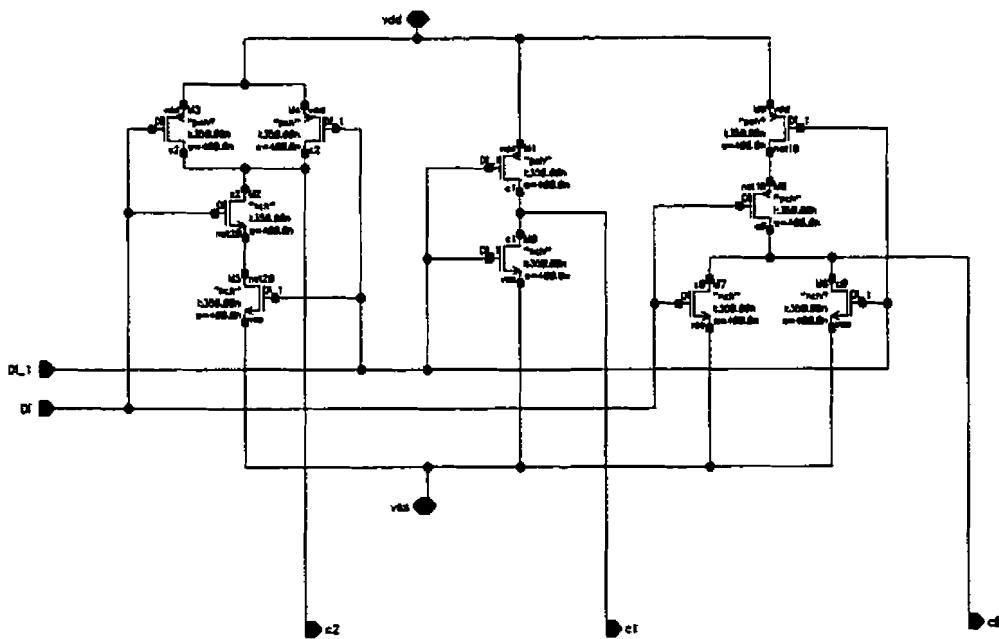

| Figure 2.5  | Circuit de rétroaction en mode commun (CMFB) . . . . .                                                                                                             | 38 |

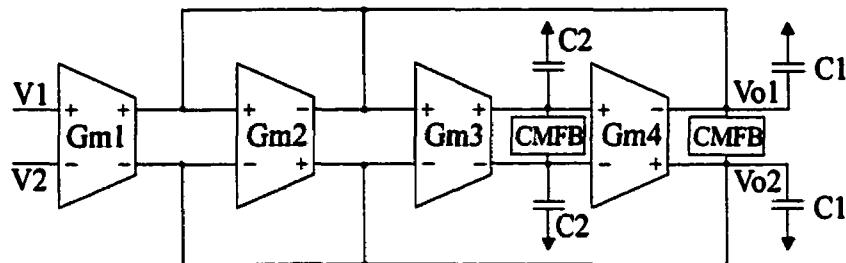

| Figure 2.6  | Cellule de transconductance proposée . . . . .                                                                                                                     | 40 |

| Figure 2.7  | Circuit de polarisation. . . . .                                                                                                                                   | 40 |

| Figure 2.8  | Schéma bloc du CNA à 5-bits proposé. . . . .                                                                                                                       | 44 |

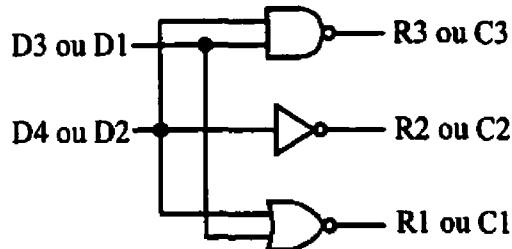

| Figure 2.9  | Schéma logique des décodeurs de colonnes et de rangées. . . . .                                                                                                    | 45 |

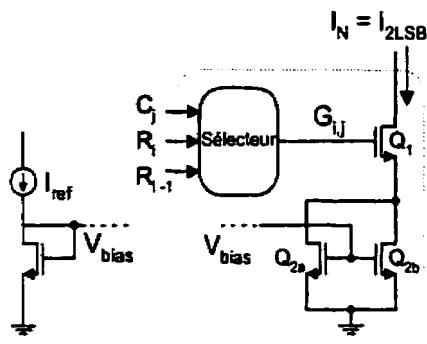

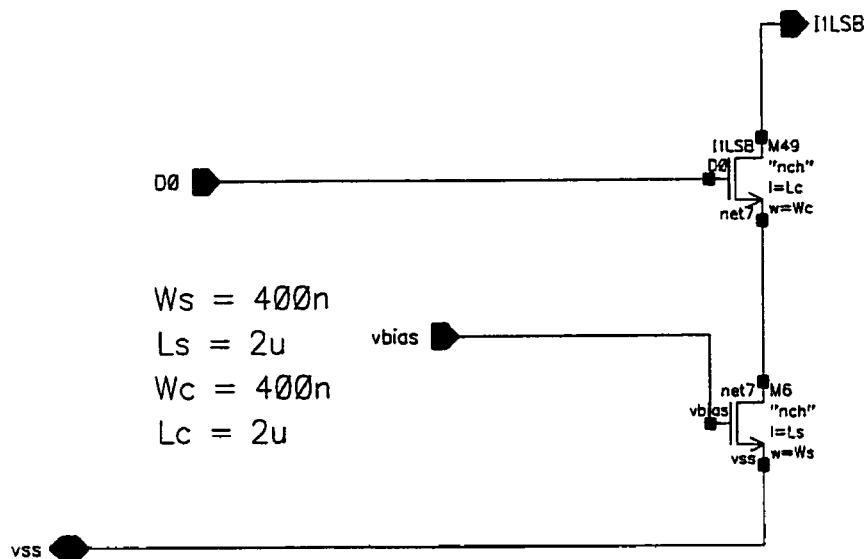

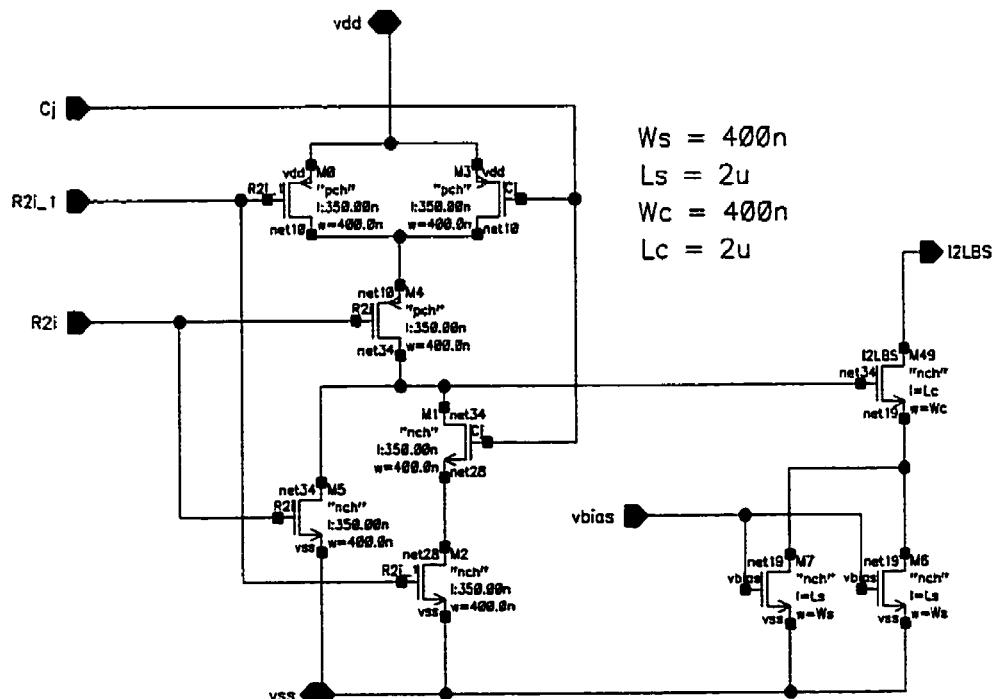

| Figure 2.10 | Source de courant individuelle à 2 LSB . . . . .                                                                                                                   | 46 |

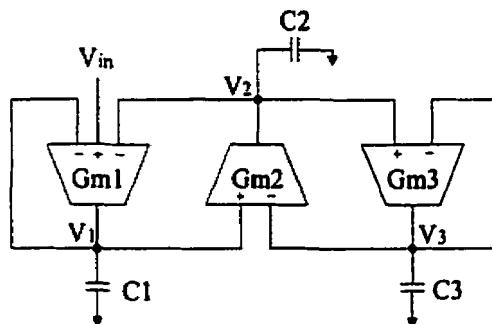

| Figure 3.1  | Section quadratique (passe-bande). . . . .                                                                                                                         | 49 |

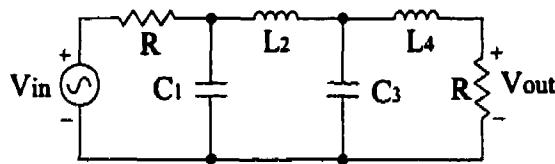

| Figure 3.2  | Représentation d'un filtre passe-bas du quatrième ordre. . . . .                                                                                                   | 51 |

| Figure 3.3  | Représentation graphique du filtre passe-bas. . . . .                                                                                                              | 51 |

| Figure 3.4  | Transformation de passe-bas à passe-bande. . . . .                                                                                                                 | 52 |

| Figure 3.5  | Représentation du filtre du huitième ordre. . . . .                                                                                                                | 52 |

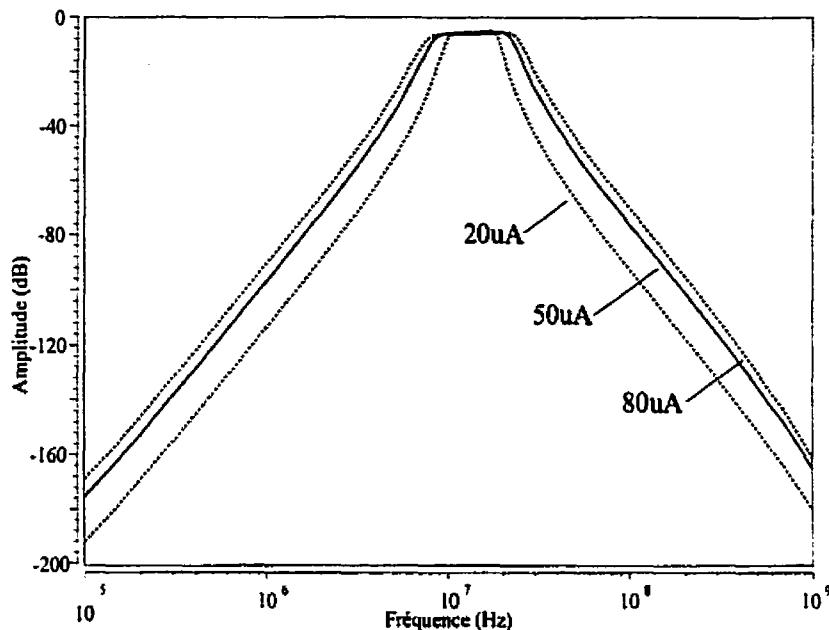

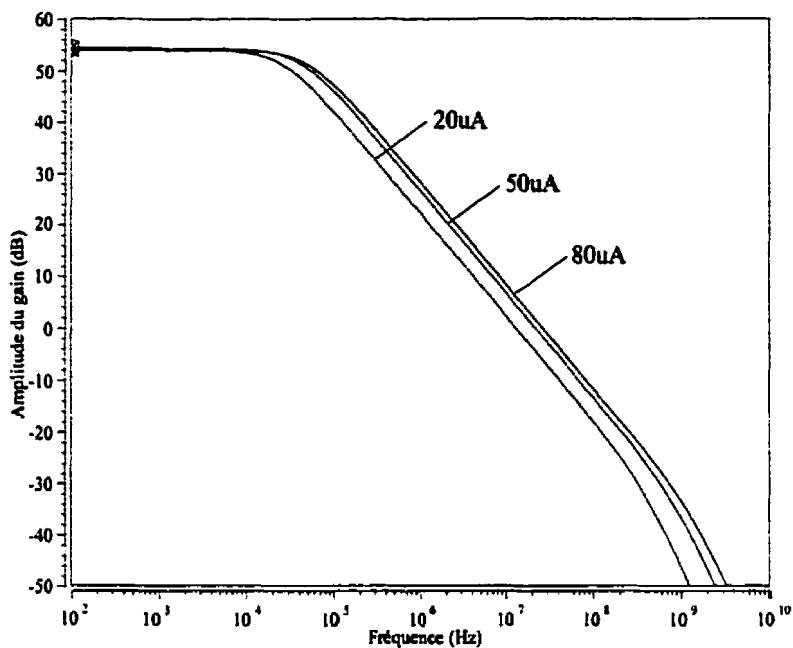

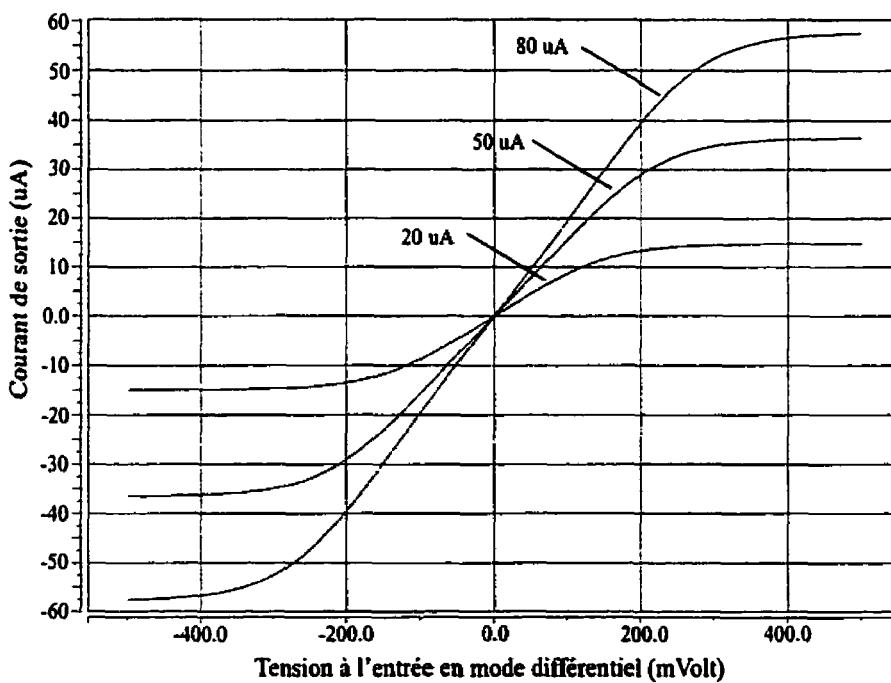

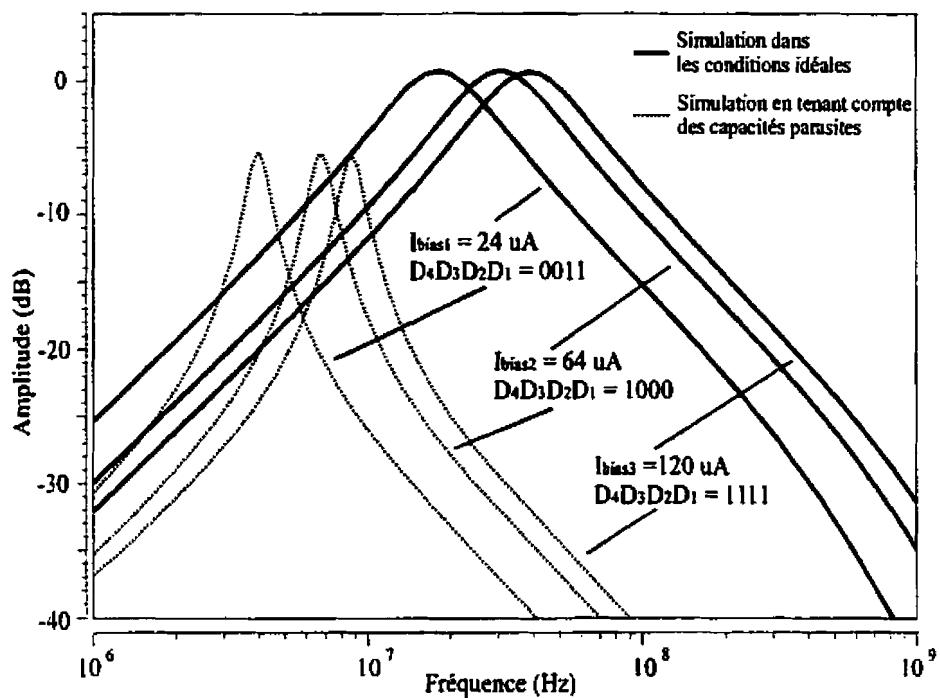

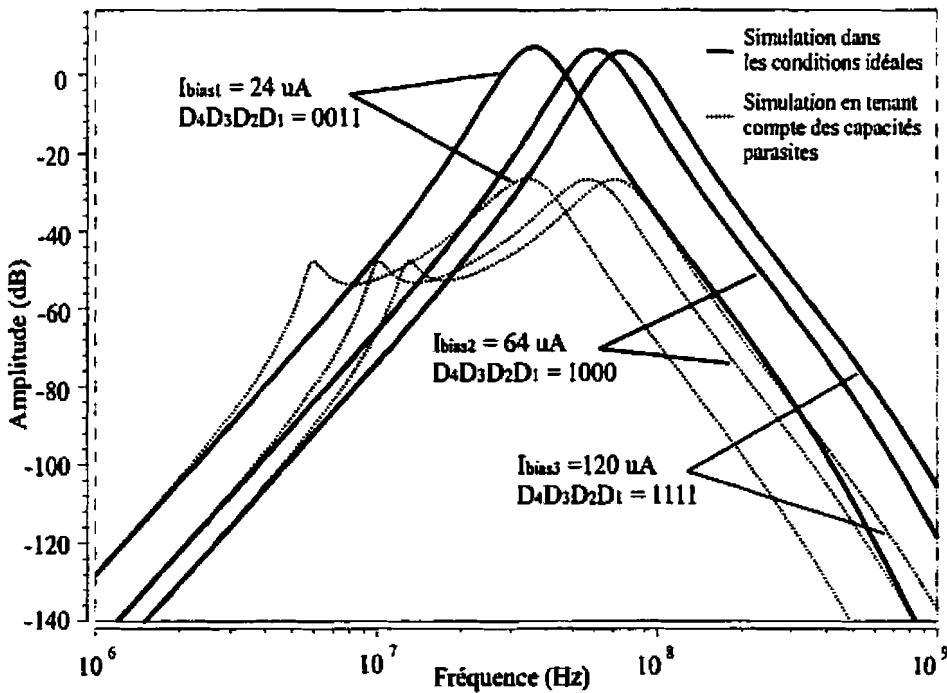

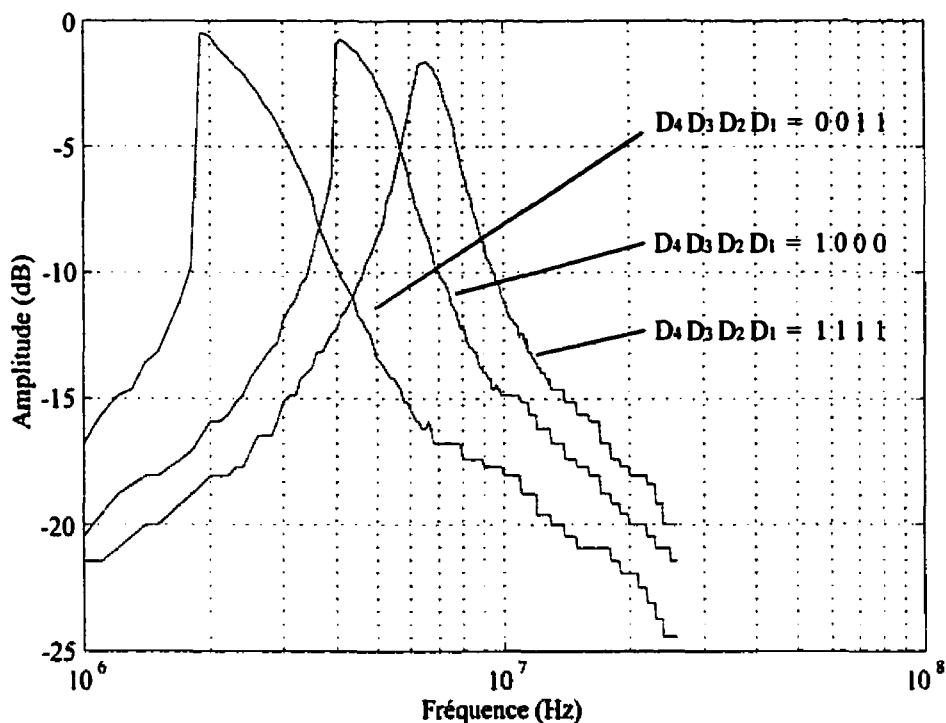

| Figure 3.6  | Modification de la fréquence centrale du filtre du huitième ordre<br>en variant le courant de polarisation des cellules à 20, 50 et 80 $\mu$ A. . . . .            | 53 |

| Figure 3.7  | Modification du facteur de qualité du filtre de huitième ordre<br>en variant le courant de polarisation des cellules $G_{mAx}$<br>de 20, 50 et 80 $\mu$ A. . . . . | 54 |

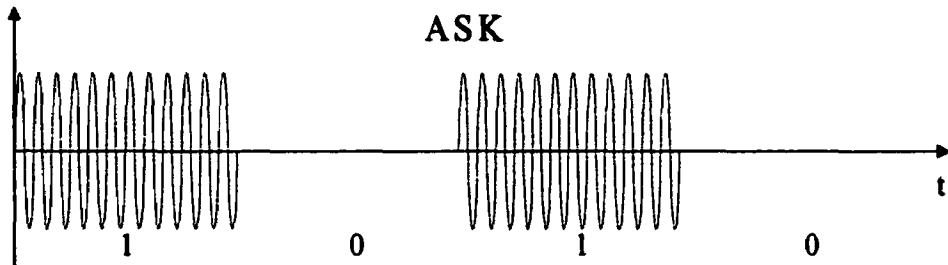

| Figure 3.8  | Représentation simplifiée d'un signal ASK . . . . .                                                                                                                | 55 |

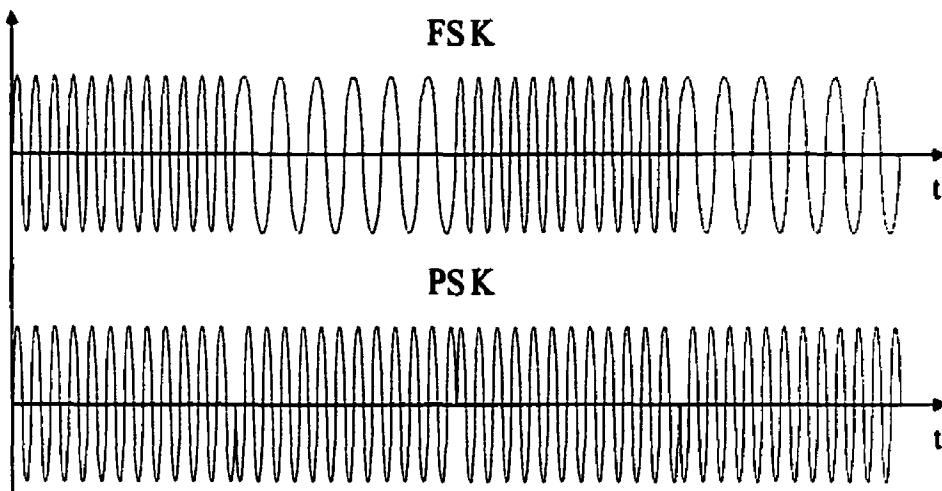

| Figure 3.9  | Représentation simplifiée des signaux FSK et PSK . . . . .                                                                                                         | 56 |

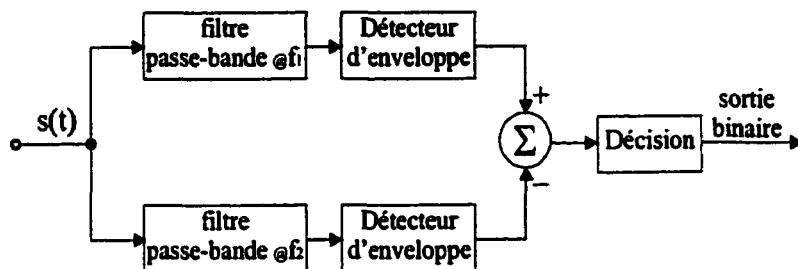

| Figure 3.10 | Schéma simplifié d'un récepteur FSK. . . . .                                                                                                                       | 57 |

|                    |                                                                                                                                                                |    |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

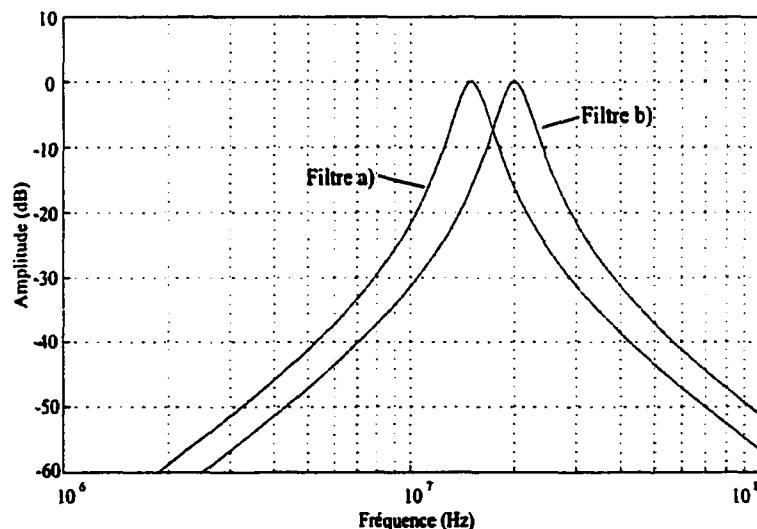

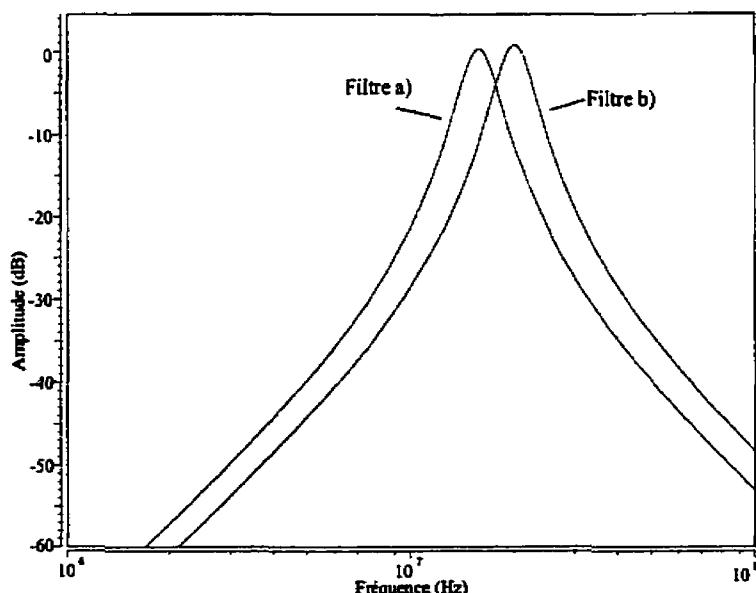

| <b>Figure 3.11</b> | <b>Réponse en fréquence théorique des filtres de fréquence centrale:</b>                                                                                       |    |

|                    | a) 15MHz, b) 20MHz .....                                                                                                                                       | 58 |

| <b>Figure 3.12</b> | <b>Réponse en fréquence des filtres passe-bande servant à la réalisation d'un récepteur FSK: <math>f_1=15\text{MHz}</math>, <math>f_2=20\text{MHz}</math>.</b> | 59 |

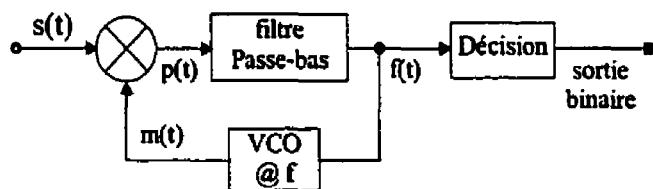

| <b>Figure 3.13</b> | <b>Schéma simplifié d'un récepteur PSK</b>                                                                                                                     | 60 |

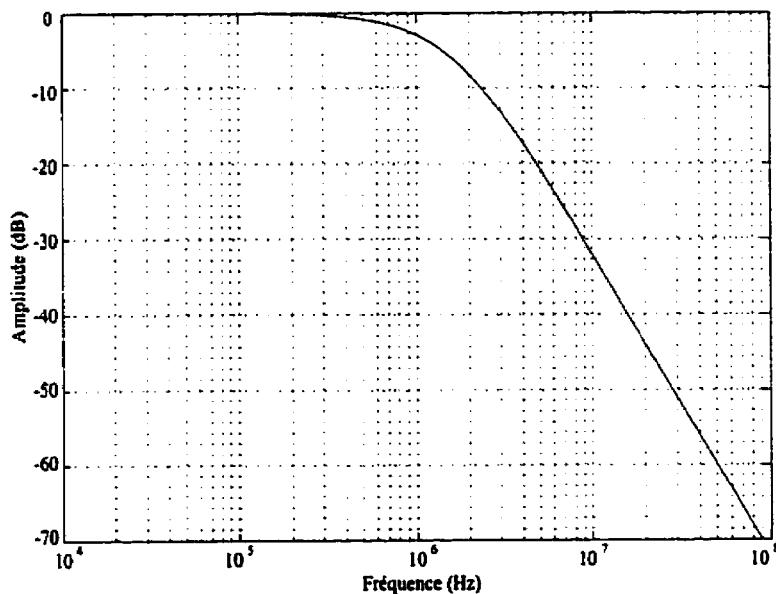

| <b>Figure 3.14</b> | <b>Réponse en fréquence théorique du filtre passe-bas</b>                                                                                                      | 62 |

| <b>Figure 3.15</b> | <b>Réponse en fréquence du filtre passe-bas servant à la réalisation d'un récepteur PSK</b>                                                                    | 63 |

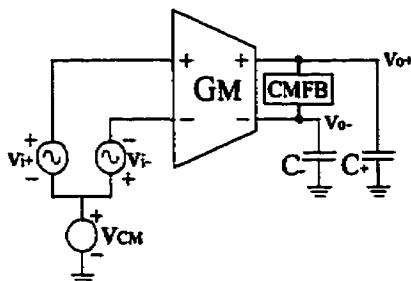

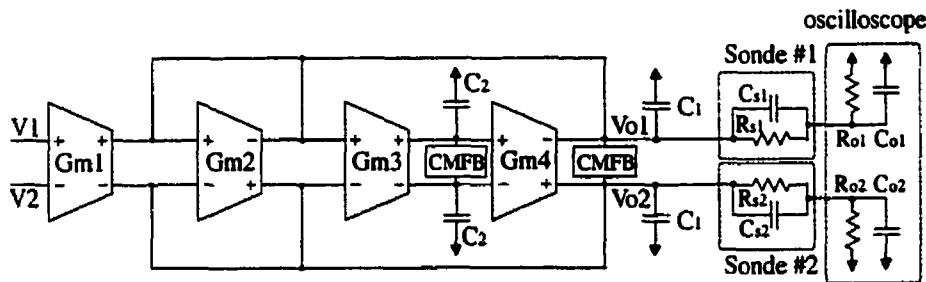

| <b>Figure 4.1</b>  | <b>Configuration de la cellule pour l'analyse AC</b>                                                                                                           | 67 |

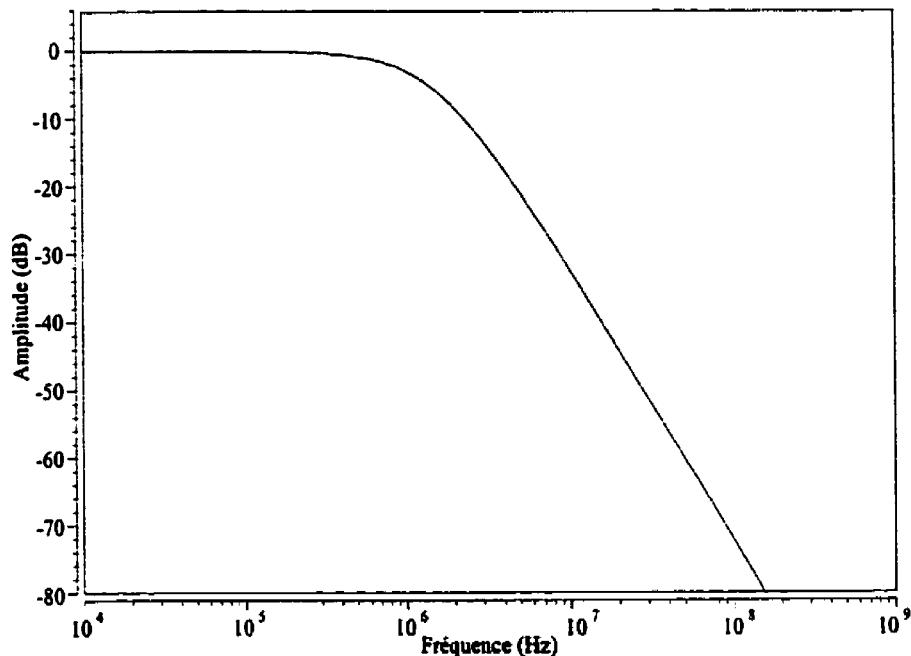

| <b>Figure 4.2</b>  | <b>Analyse AC de la cellule de transconductance.</b>                                                                                                           | 68 |

| <b>Figure 4.3</b>  | <b>Plage d'opération de l'intégrateur (Gm-C).</b>                                                                                                              | 68 |

| <b>Figure 4.4</b>  | <b>Variation possible de la valeur de la transconductance.</b>                                                                                                 | 69 |

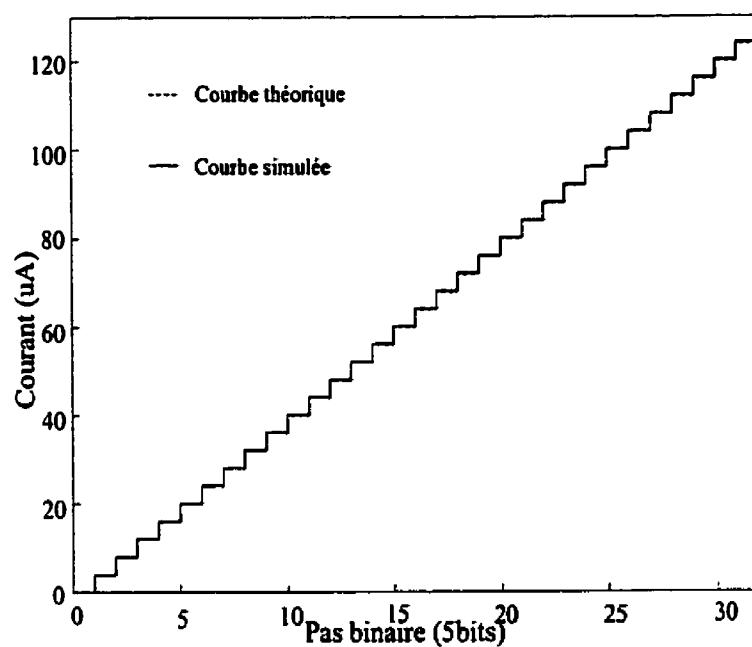

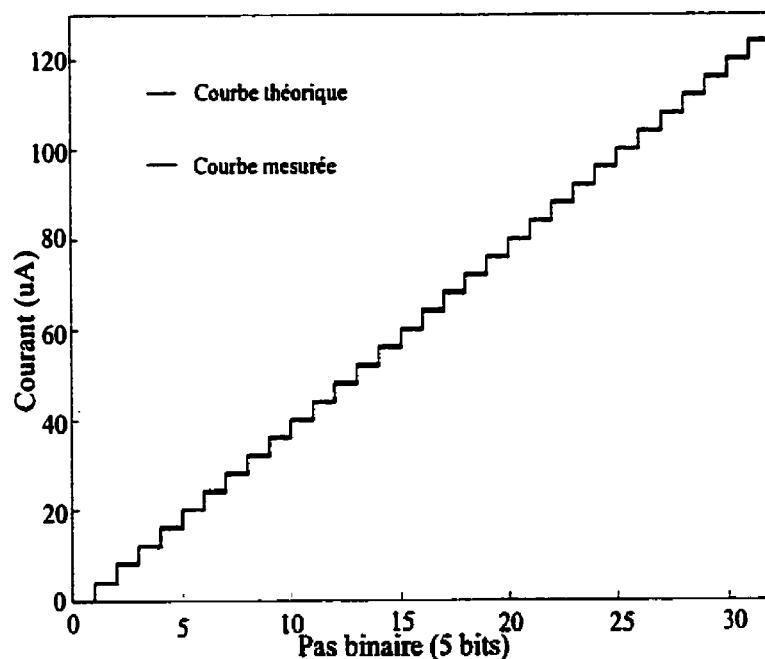

| <b>Figure 4.5</b>  | <b>Comparaison des rampes simulée et théorique.</b>                                                                                                            | 75 |

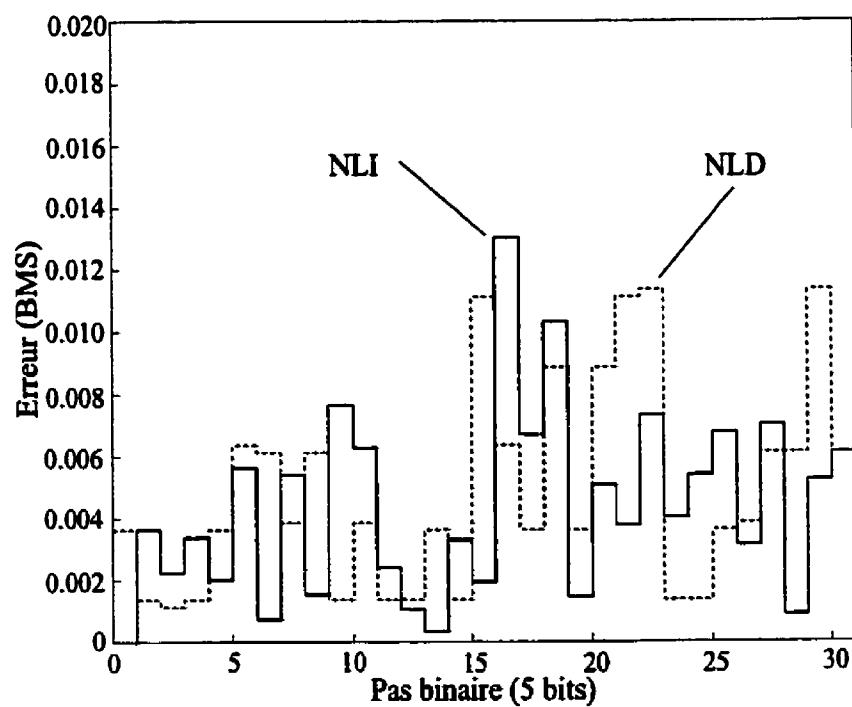

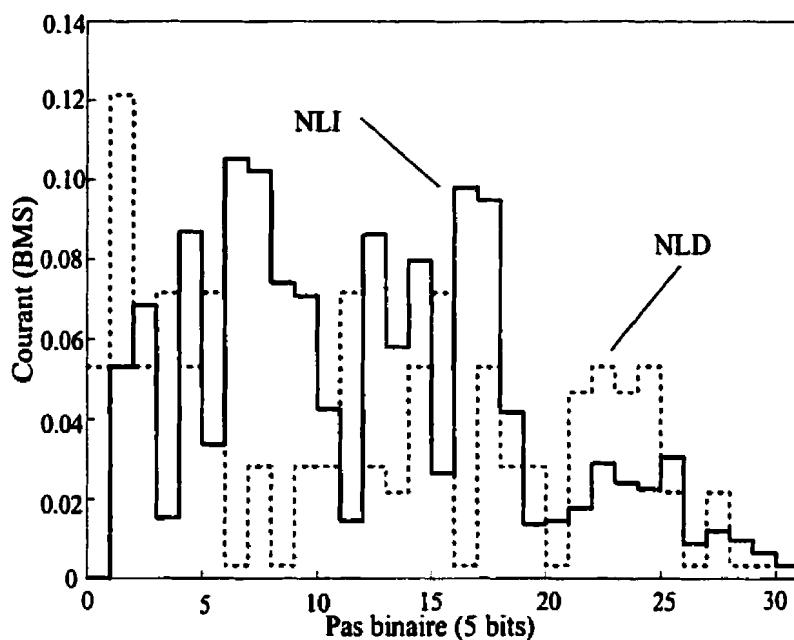

| <b>Figure 4.6</b>  | <b>Représentation de l'erreur de non-linéarités différentielle et intégrale.</b>                                                                               | 75 |

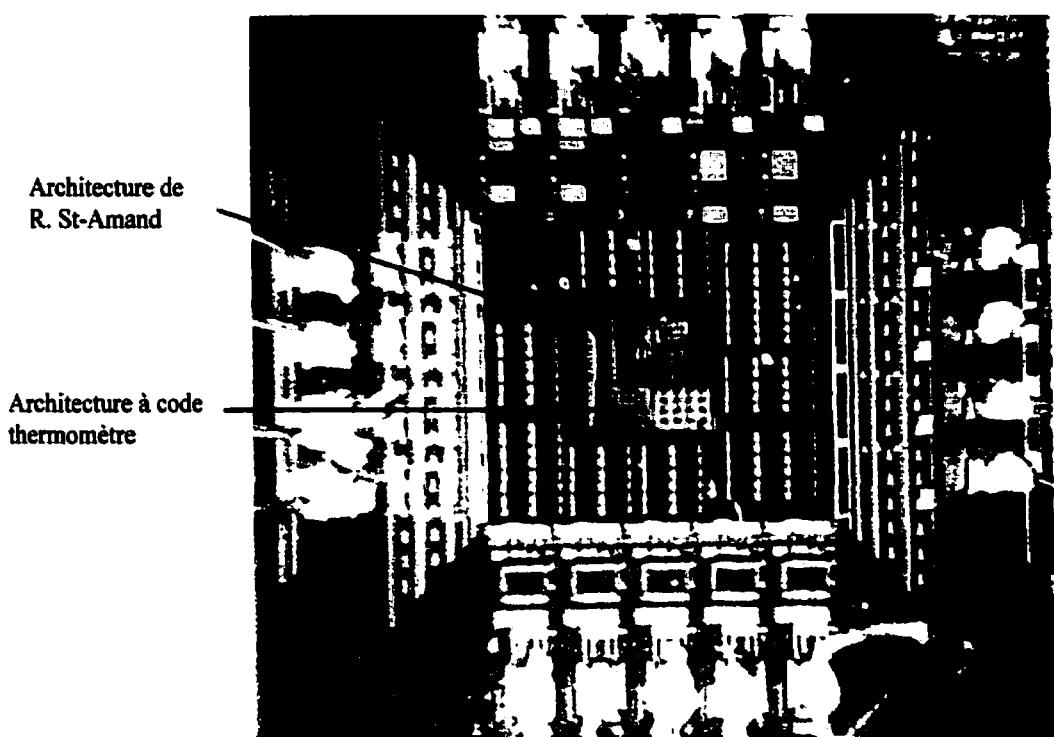

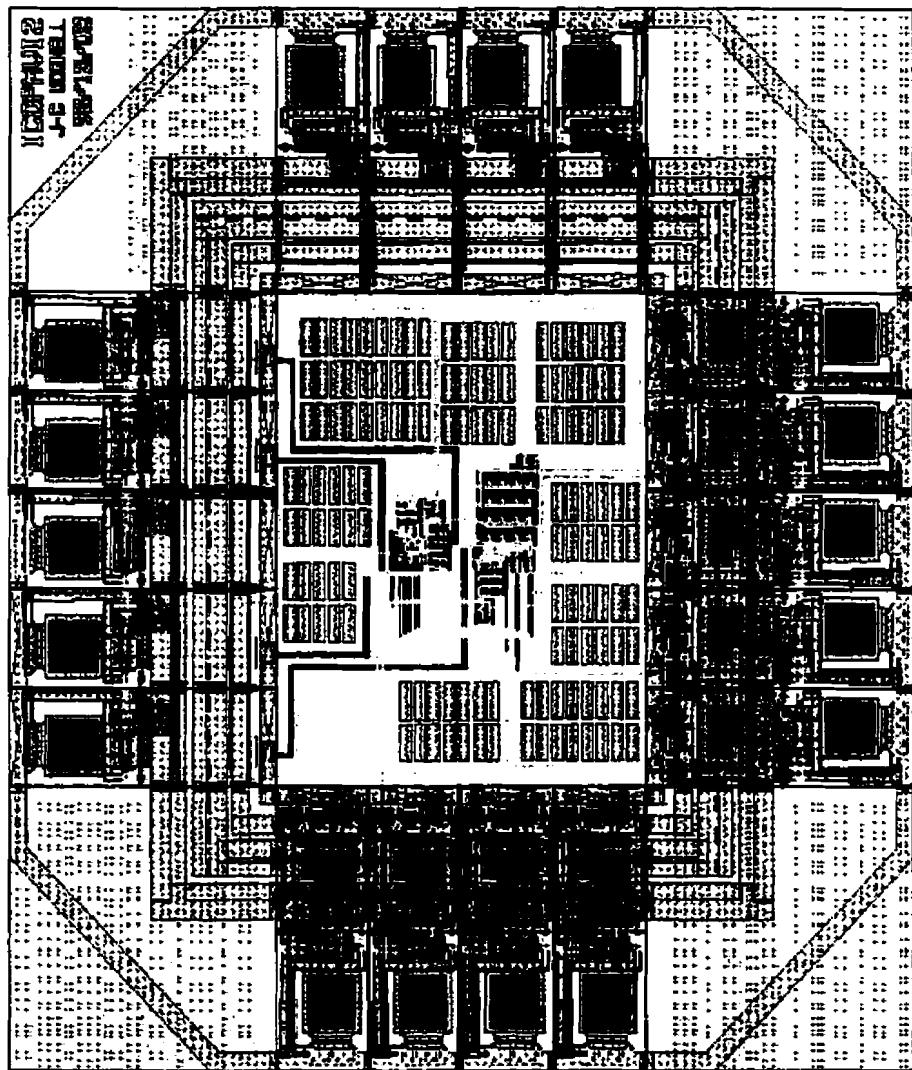

| <b>Figure 4.7</b>  | <b>Photographie du composant regroupant les deux sources de courant</b>                                                                                        | 77 |

| <b>Figure 4.8</b>  | <b>Rampe mesurée de la source à code thermomètre pour une charge de <math>1\text{ k}\Omega</math> comparée à la rampe théorique</b>                            | 78 |

| <b>Figure 4.9</b>  | <b>Erreur NLI et NLD de la source à code thermomètre.</b>                                                                                                      | 79 |

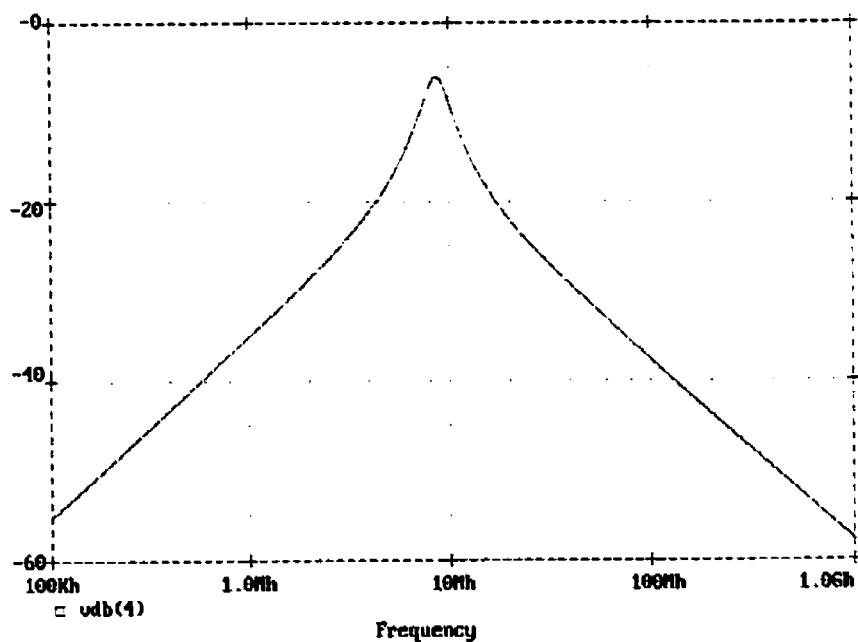

| <b>Figure 4.10</b> | <b>Réponse en fréquence du filtre passe-bande du second ordre.</b>                                                                                             | 82 |

| <b>Figure 4.11</b> | <b>Réponse en fréquence du filtre passe-bande du huitième ordre.</b>                                                                                           | 82 |

|                    |                                                                                                                                                   |            |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>Figure 4.12</b> | <b>Réponse en fréquence mesurée du filtre passe-bande<br/>du second ordre.....</b>                                                                | <b>85</b>  |

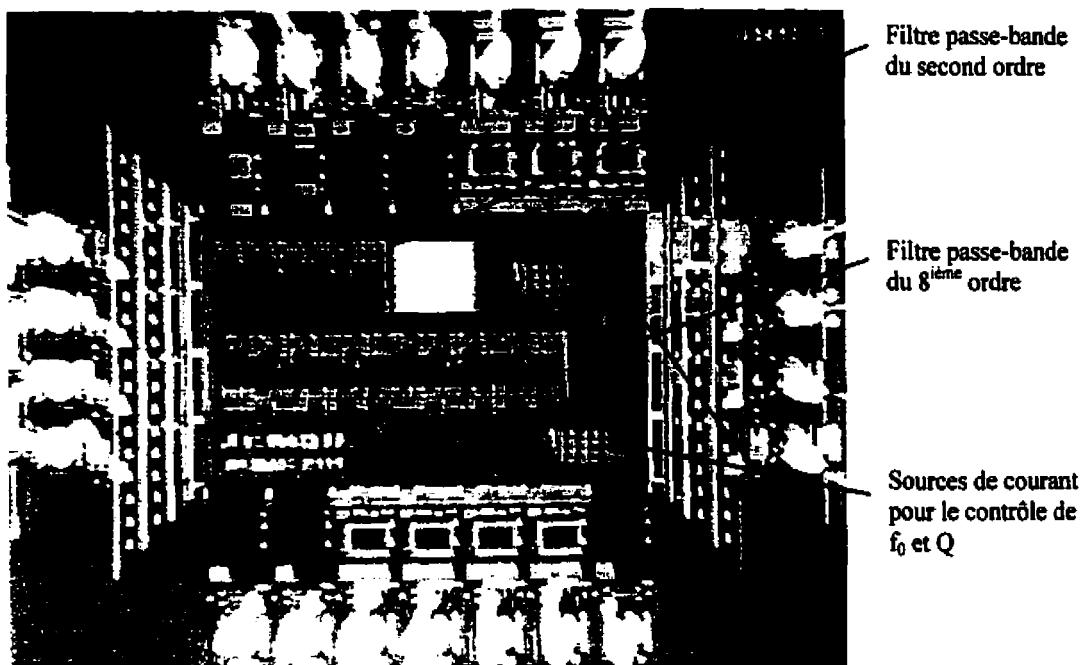

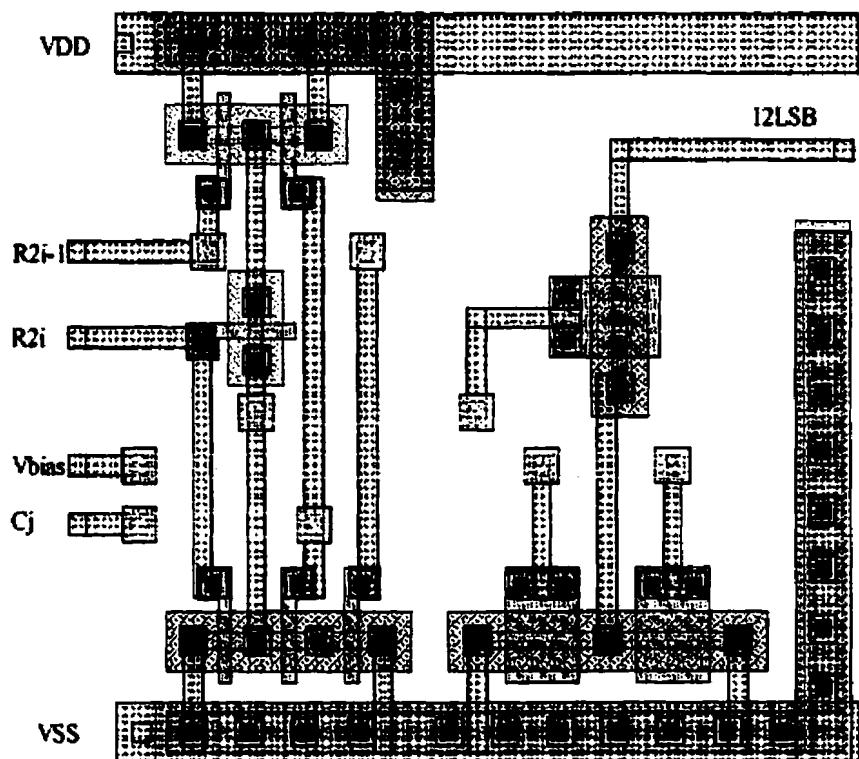

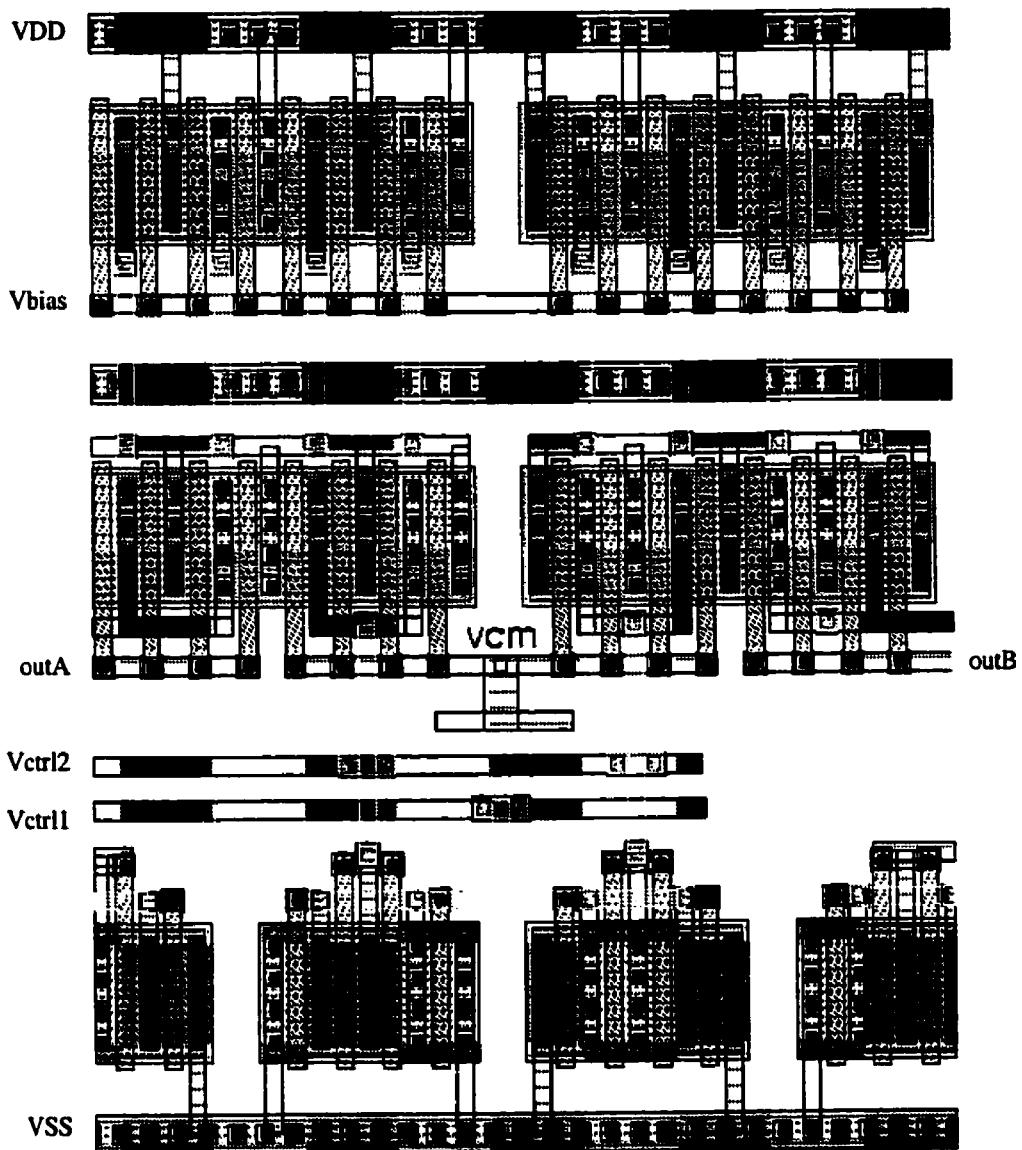

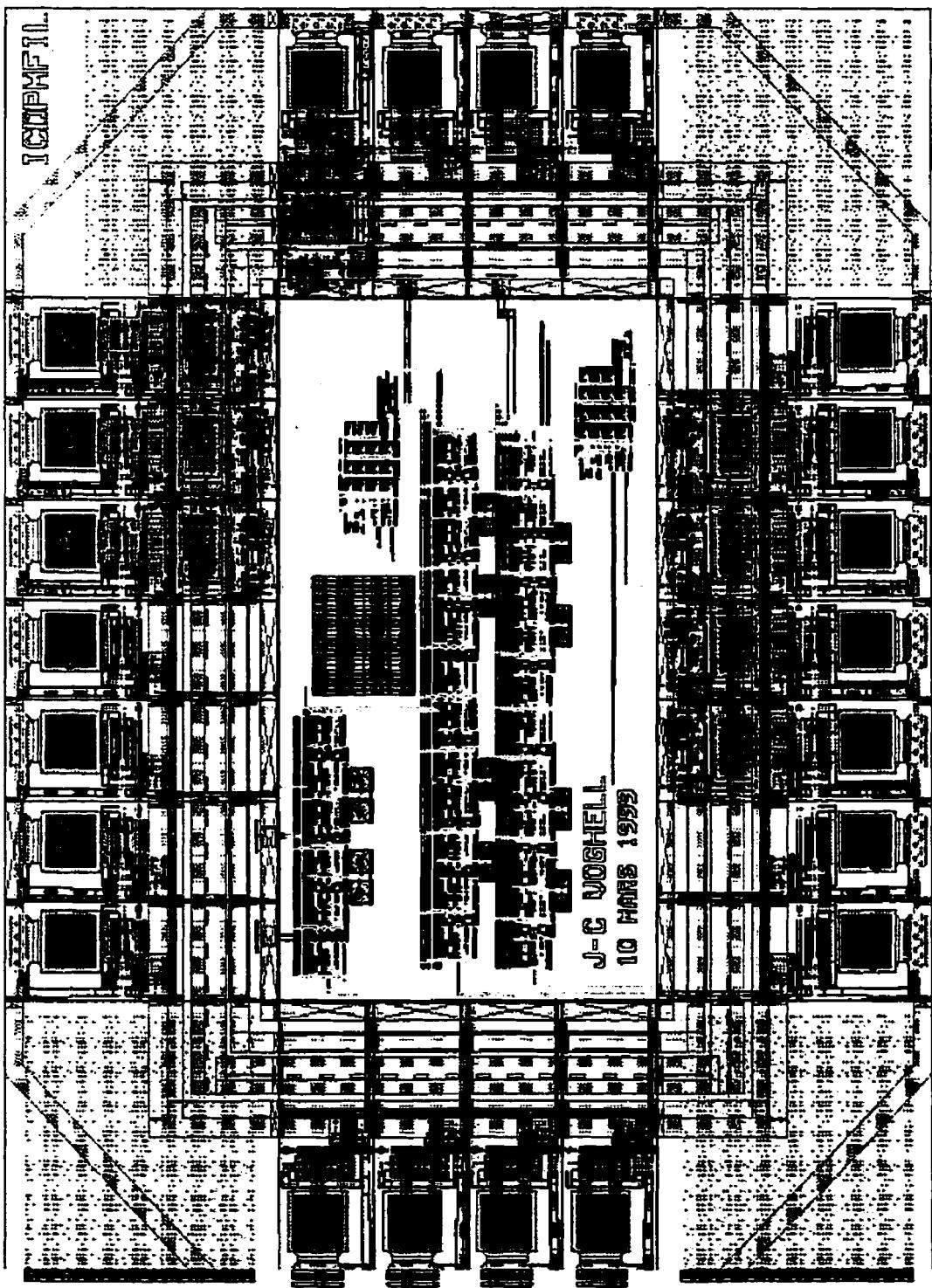

| <b>Figure 4.13</b> | <b>Photographie du composant comprenant les filtres réalisés<br/>et les sources de courant permettant de contrôler <math>f_0</math> et Q.....</b> | <b>88</b>  |

| <b>Figure A.1</b>  | <b>Cellule Gm-C non-idéale.....</b>                                                                                                               | <b>102</b> |

| <b>Figure B.1</b>  | <b>Représentation simplifiée d'une moitié de cellule<br/>de transconductance.....</b>                                                             | <b>104</b> |

| <b>Figure B.2</b>  | <b>Modèle petit signal du circuit simplifié .....</b>                                                                                             | <b>104</b> |

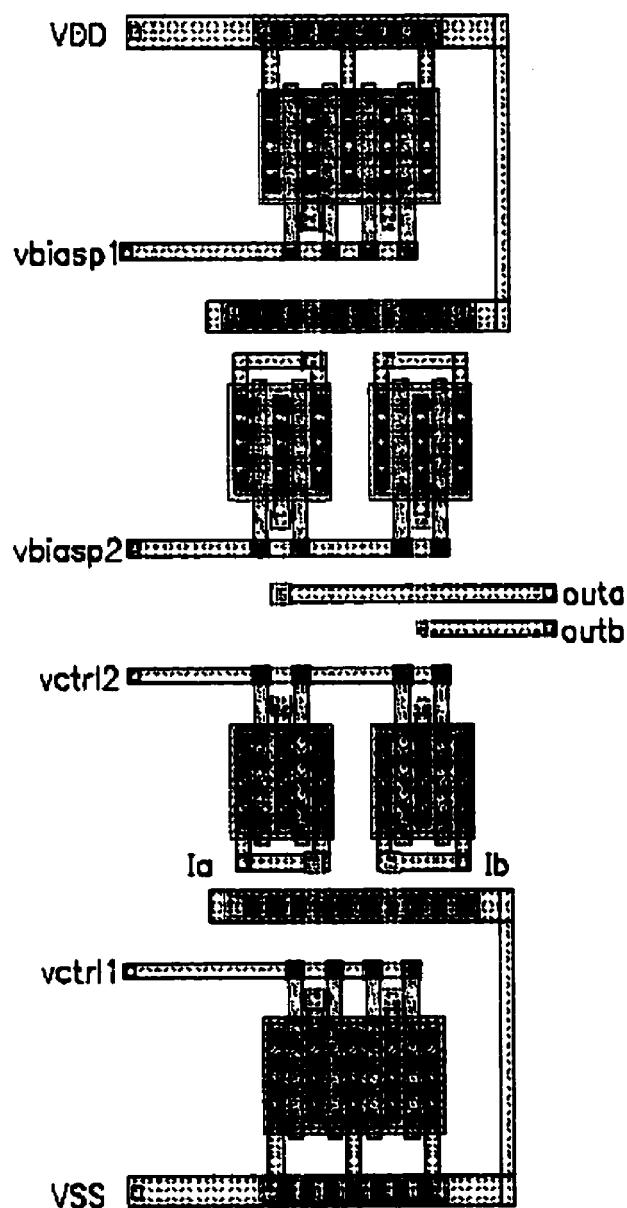

| <b>Figure D.1</b>  | <b>Étage d'entrée de la cellule de transconductance .....</b>                                                                                     | <b>117</b> |

| <b>Figure D.2</b>  | <b>Circuit de rétroaction en mode commun (CMFB).....</b>                                                                                          | <b>118</b> |

| <b>Figure D.3</b>  | <b>Cellule de transconductance proposée .....</b>                                                                                                 | <b>119</b> |

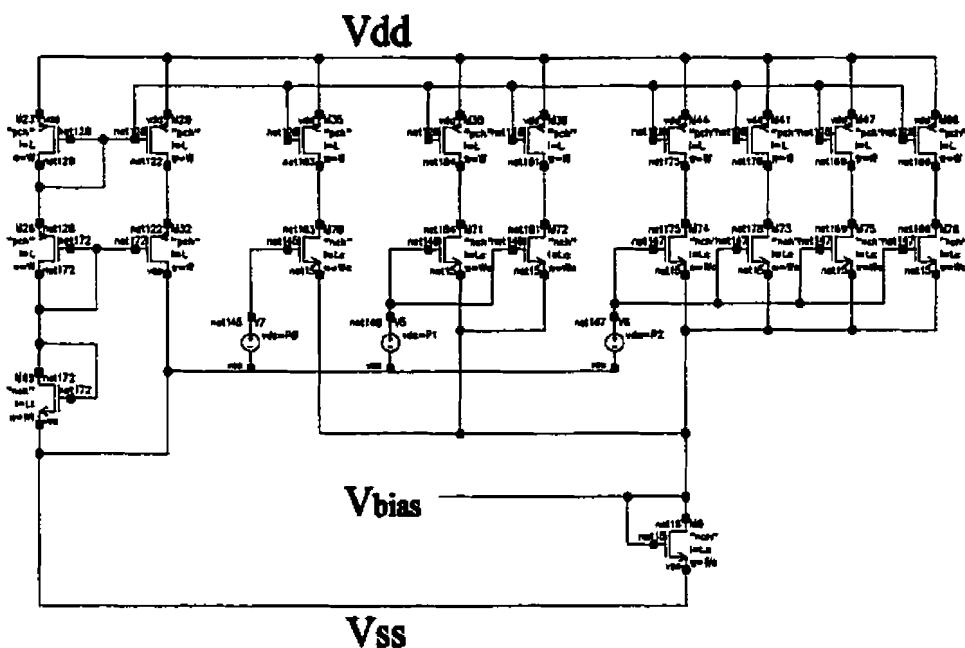

| <b>Figure E.1</b>  | <b>Schéma de la source de courant à code thermomètre.....</b>                                                                                     | <b>123</b> |

| <b>Figure E.2</b>  | <b>Sélecteur de plage de courant maximale .....</b>                                                                                               | <b>124</b> |

| <b>Figure E.3</b>  | <b>Décodeur de colonnes et de rangées .....</b>                                                                                                   | <b>124</b> |

| <b>Figure E.4</b>  | <b>Source de courant de 1 BMS .....</b>                                                                                                           | <b>125</b> |

| <b>Figure E.5</b>  | <b>Source de courant de 2 BMS .....</b>                                                                                                           | <b>125</b> |

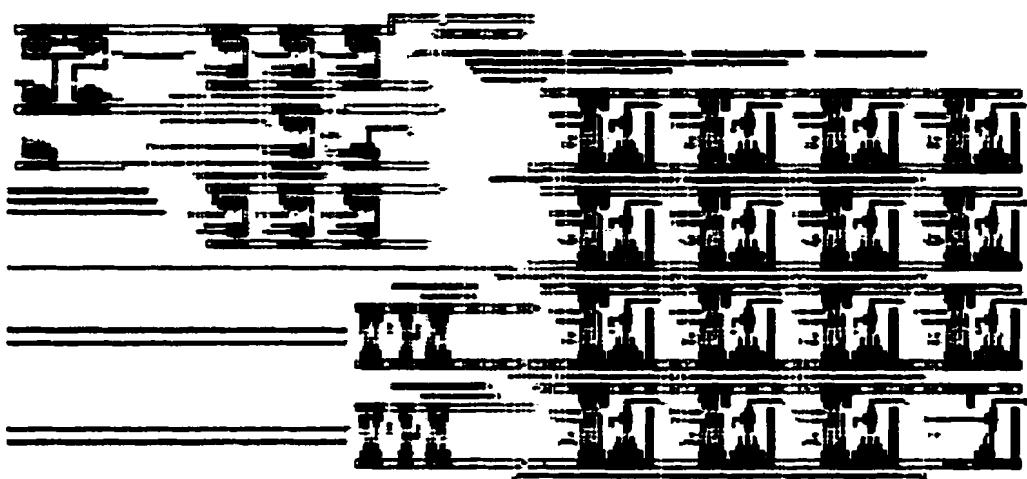

| <b>Figure E.6</b>  | <b>Dessin du masque de la source de courant à code thermomètre ...</b>                                                                            | <b>126</b> |

| <b>Figure E.7</b>  | <b>Dessin du masque de la source de courant de R. St-Amand .....</b>                                                                              | <b>126</b> |

| <b>Figure E.8</b>  | <b>Dessin du masque d'une source de courant individuelle générant un<br/>courant égal à 2 LSB .....</b>                                           | <b>127</b> |

| <b>Figure E.9</b>  | <b>Dessin du masque du composant comprenant les deux sources de<br/>courant .....</b>                                                             | <b>128</b> |

|                   |                                                                                                                                                                                                                                         |            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

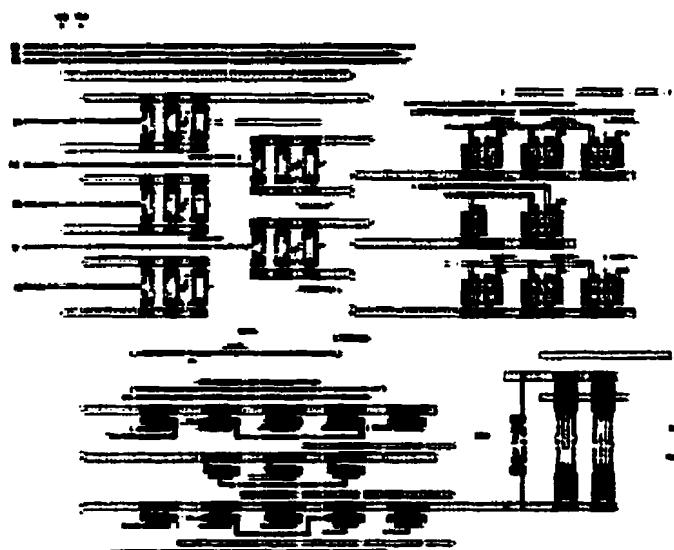

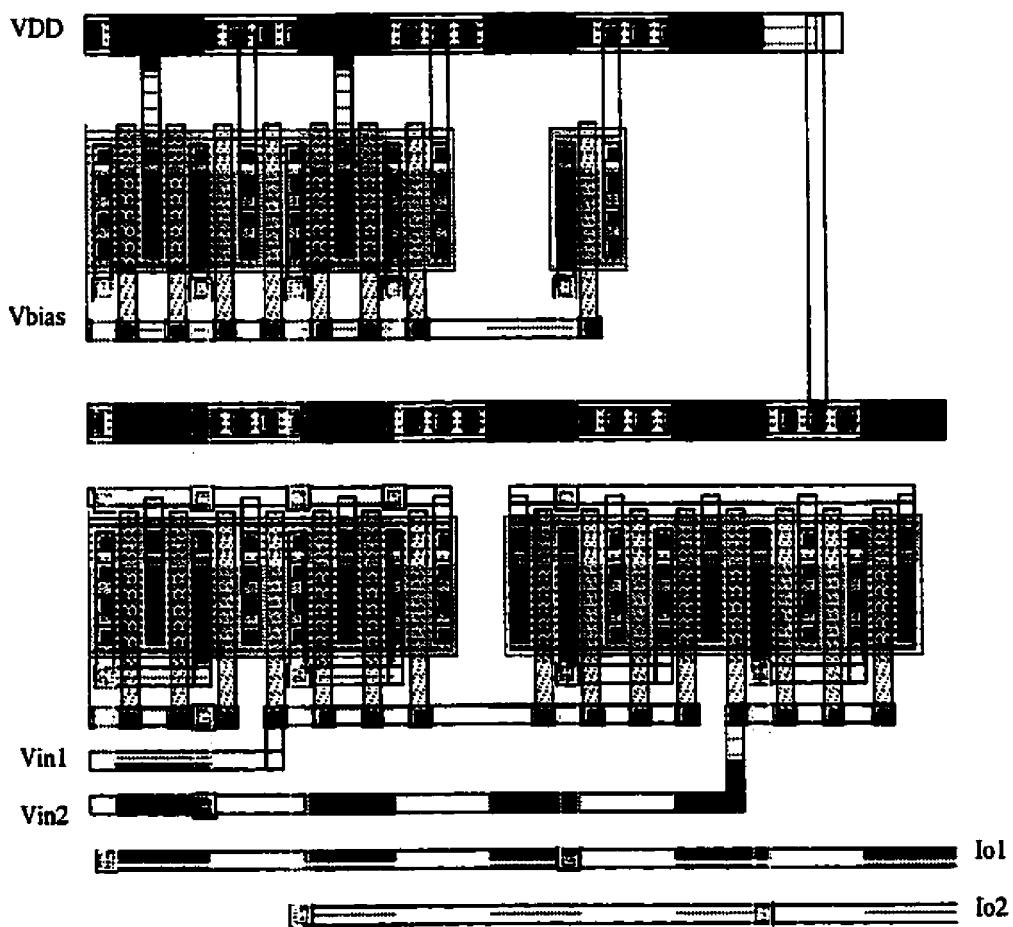

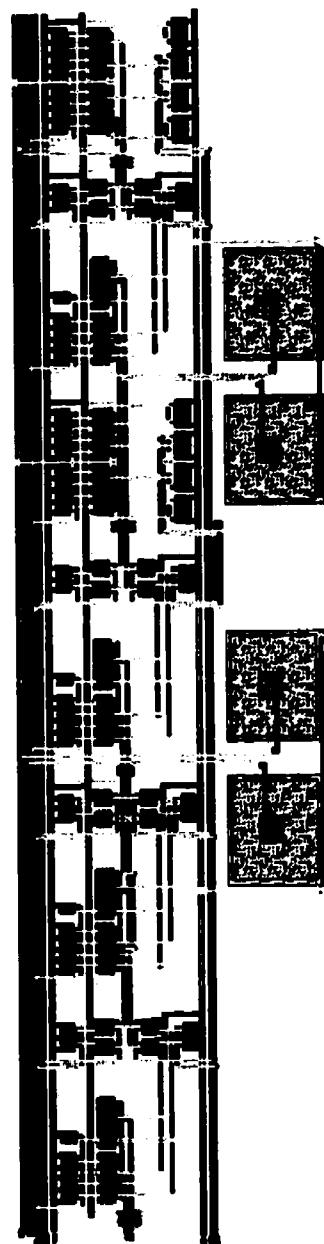

| <b>Figure F.1</b> | <b>Dessin du masque de l'étage d'entrée de la cellule de transconductance .....</b>                                                                                                                                                     | <b>129</b> |

| <b>Figure F.2</b> | <b>Dessin du masque de l'étage de sortie <i>Folded Cascode</i>. . . . .</b>                                                                                                                                                             | <b>130</b> |

| <b>Figure F.3</b> | <b>Dessin du masque du circuit de rétroaction en mode commun (CMFB) . . . . .</b>                                                                                                                                                       | <b>131</b> |

| <b>Figure F.4</b> | <b>Dessin du masque d'une section quadratique . . . . .</b>                                                                                                                                                                             | <b>132</b> |

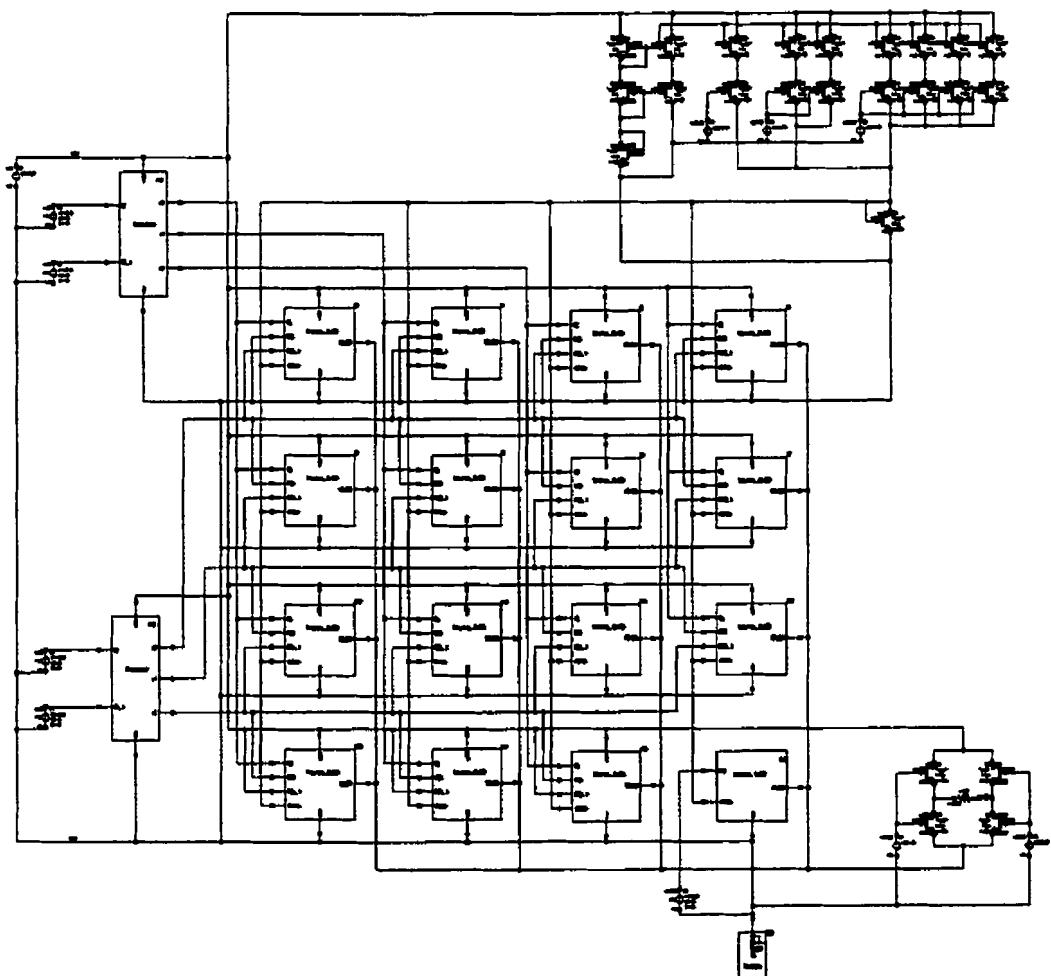

| <b>Figure F.5</b> | <b>Dessin du masque de l'ensemble du composant . . . . .</b>                                                                                                                                                                            | <b>133</b> |

| <b>Figure G.1</b> | <b>Représentation d'une section quadratique avec les éléments internes aux appareils de mesure . . . . .</b>                                                                                                                            | <b>141</b> |

| <b>Figure G.2</b> | <b>Simulation d'une section quadratique idéale avec les éléments internes des appareils de mesure . . . . .</b>                                                                                                                         | <b>142</b> |

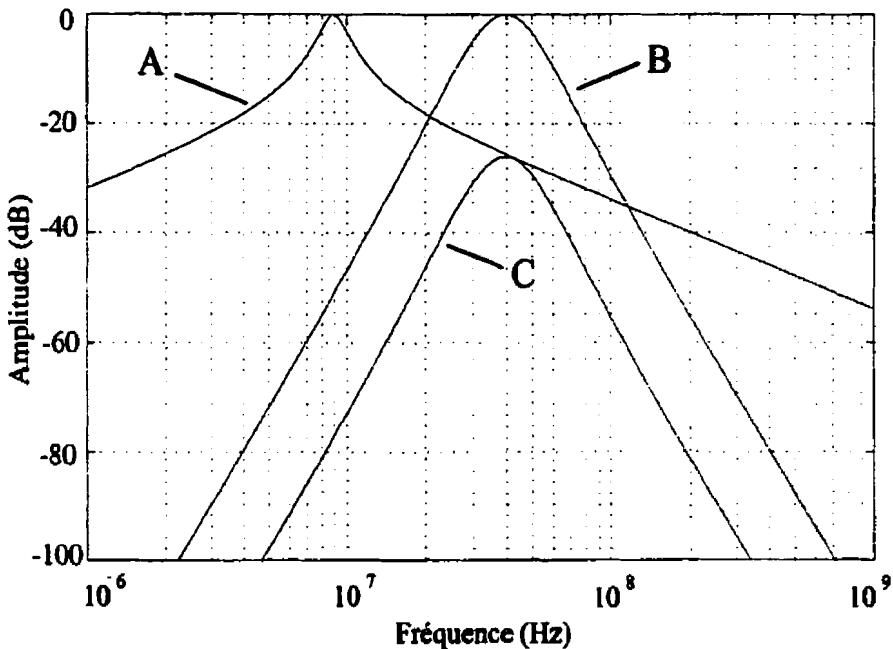

| <b>Figure G.3</b> | <b>Réponse en fréquence théorique du filtre du huitième ordre:<br/>A) réponse de la section quadratique de sortie, B) réponse des trois premières sections et C) superposition des réponses des quatre sections du filtre . . . . .</b> | <b>143</b> |

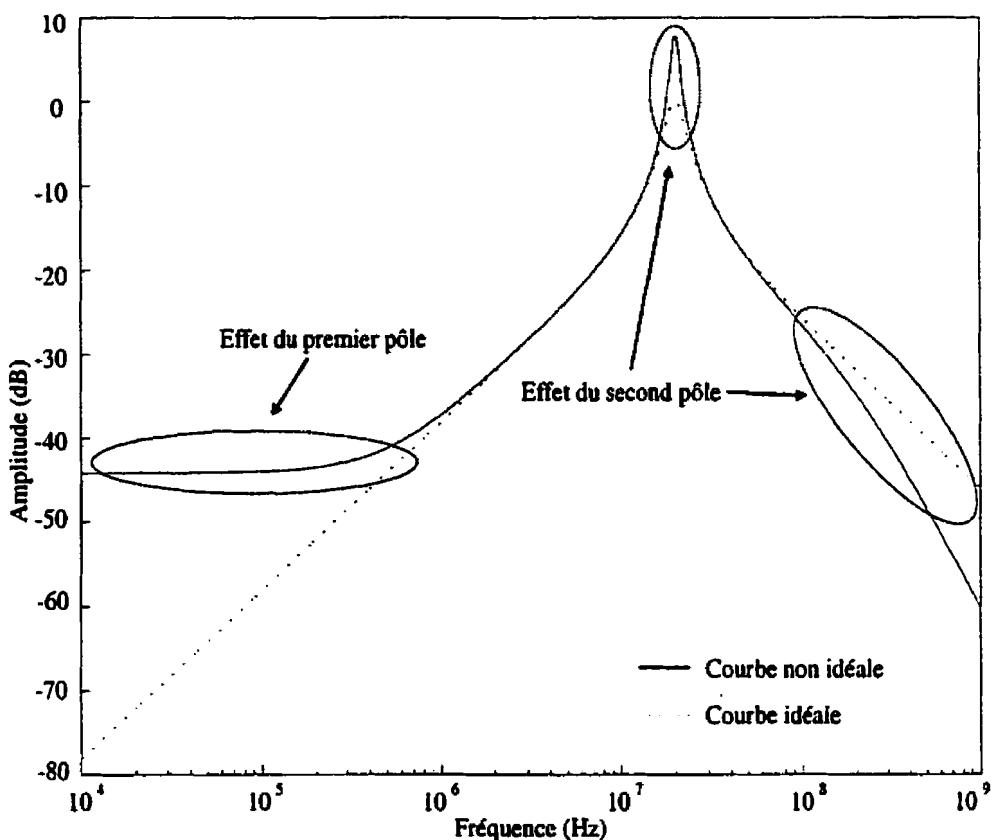

| <b>Figure H.1</b> | <b>Effet d'une cellule non-idéale sur un filtre passe-bande. . . . .</b>                                                                                                                                                                | <b>146</b> |

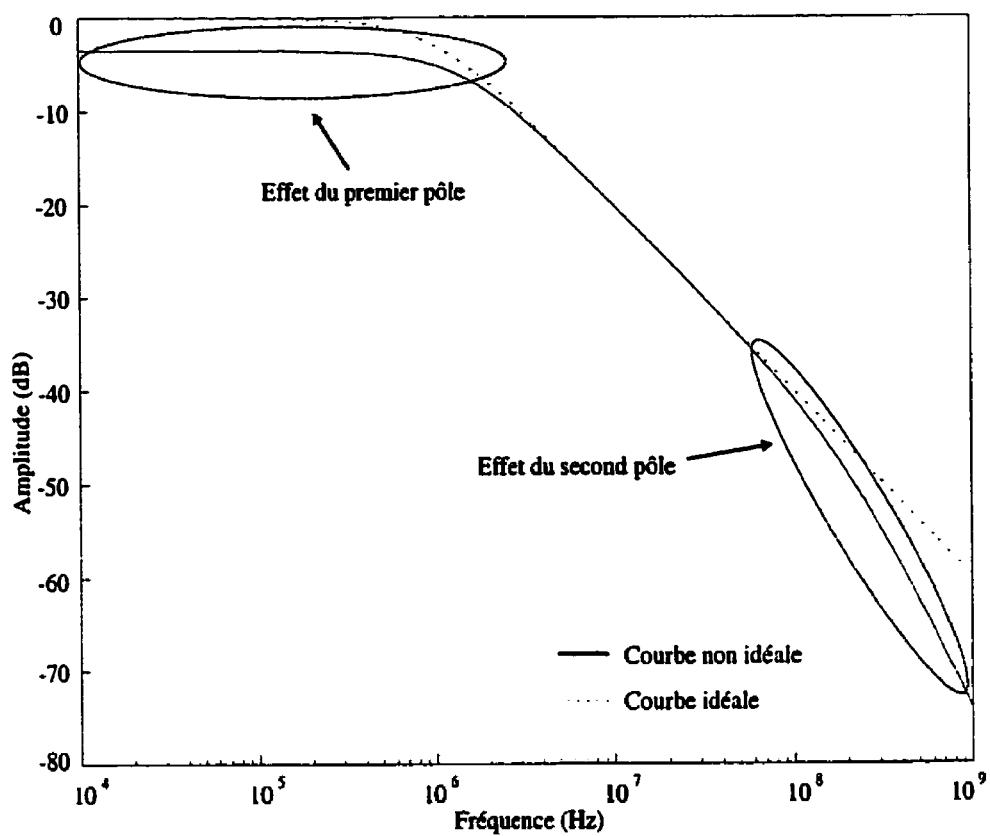

| <b>Figure H.2</b> | <b>Effet d'une cellule non-idéale sur un filtre passe-bas . . . . .</b>                                                                                                                                                                 | <b>147</b> |

## LISTE DES SYMBOLES ET DES ABRÉVIATIONS

### SYMBOLES

|                       |                                                    |

|-----------------------|----------------------------------------------------|

| $A_{\text{md}}$       | Amplitude en mode différentiel                     |

| $A_{\text{mc}}$       | Amplitude en mode commun                           |

| $C$                   | Capacité de charge                                 |

| $C_{\text{ox}}$       | Capacité de grille par unité de surface            |

| $C_{\text{gd}}$       | Capacité grille-drain                              |

| $\text{dB}$           | Décibel                                            |

| $E_{\text{gain}}$     | Erreur de gain d'un CNA                            |

| $G_m$                 | Transconductance                                   |

| $G_m \cdot C$         | Intégrateur transconductance-condensateur          |

| $\text{Hz}$           | Hertz                                              |

| $I$                   | Courant de polarisation d'un transistor            |

| $I_{\text{décalage}}$ | Courant de décalage à la sortie d'un CNA           |

| $I_{\text{BMS}}$      | Courant correspondant au bit le moins significatif |

| $I_{\text{MAX}}$      | Courant maximal de la source de courant            |

| $L$                   | Longueur des transistors                           |

| $r_{\text{ds}}$       | Résistance drain-source                            |

| $\mu_n$               | Mobilité des porteurs de charge                    |

| $\mu_p$               | Mobilité des trous                                 |

| $Q$                   | Facteur de qualité d'un filtre                     |

|            |                                                  |

|------------|--------------------------------------------------|

| $R$        | Résistance en Ohm ( $\Omega$ )                   |

| $v_{gs}$   | Tension grille-source                            |

| $V$        | Tension (Volt)                                   |

| $V_{bias}$ | Tension de polarisation de l'étage d'entrée      |

| $V_{BN}$   | Tension de polarisation des transistor N         |

| $V_{BP}$   | Tension de polarisation des transistor P         |

| $V_{CN}$   | Tension de polarisation des transistor cascode N |

| $V_{CM}$   | Tension en mode commun                           |

| $V_{CP}$   | Tension de polarisation des transistor cascode P |

| $V_{tp}$   | Tension de seuil des transistors de type P       |

| $w_{cb}$   | Fréquence de coupure basse (rad/sec)             |

| $w_{ch}$   | Fréquence de coupure haute (rad/sec)             |

| $w_o$      | Fréquence centrale (rad/sec)                     |

| $W$        | Largeur des transistors                          |

| $Z_p$      | Impédance parasite de sortie en Ohm ( $\Omega$ ) |

## ABRÉVIATIONS

|      |                                         |

|------|-----------------------------------------|

| ASK  | Amplitude Shift Keying                  |

| BMS  | Bit le moins significatif               |

| CMFB | Common-mode feedback                    |

| CMOS | Complementary Metal Oxyde Semiconductor |

| CNA  | Convertisseur numérique à analogique    |

|      |                                        |

|------|----------------------------------------|

| FLF  | Follow the Leader Feedback             |

| FSK  | Frequency Shift Keying                 |

| IFLF | Inverse Follow the Leader Feedback     |

| LF   | Leapfrog                               |

| MOS  | Metal Oxyde Semiconductor              |

| NLD  | Erreur de non-linéarité différentielle |

| NLI  | Erreur de non-linéarité intégrale      |

| NMOS | Channel-N Metal Oxyde Semiconductor    |

| NRL  | Negative Resistance Load               |

| PLL  | Phase Lock Loop                        |

| PSK  | Phase Shift Keying                     |

| PMOS | Channel-P Metal Oxyde Semiconductor    |

| SÉF  | Stimulation Électrique Fonctionnelle   |

| VCO  | Voltage controlled oscillator          |

## **LISTE DES ANNEXES**

|                 |                                                                                          |            |

|-----------------|------------------------------------------------------------------------------------------|------------|

| <b>ANNEXE A</b> | <b>Calcul de la représentation non-idéale d'une cellule de transconductance.....</b>     | <b>102</b> |

| <b>ANNEXE B</b> | <b>Détails du calcul de la fonction de transfert de la cellule proposée .....</b>        | <b>104</b> |

| <b>ANNEXE C</b> | <b>Fichiers de simulation des applications présentées au chapitre 3 .....</b>            | <b>107</b> |

| <b>ANNEXE D</b> | <b>Présentation de la cellule de transconductance .....</b>                              | <b>117</b> |

| <b>ANNEXE E</b> | <b>Présentation et dessin des masques de la source de courant réalisée .....</b>         | <b>123</b> |

| <b>ANNEXE F</b> | <b>Présentation du composant réalisé comprenant les filtres passe-bandes.....</b>        | <b>129</b> |

| <b>ANNEXE G</b> | <b>Explications théoriques des résultats expérimentaux obtenus .....</b>                 | <b>141</b> |

| <b>ANNEXE H</b> | <b>Calcul de la représentation non-idéale des filtres passe-bas et passe-bande .....</b> | <b>144</b> |

## INTRODUCTION

Dans un monde guidé par les développements technologiques rapides, la tendance actuelle est à la miniaturisation des circuits électroniques existants. Il en est de même pour les applications nécessitant l'utilisation de filtres analogiques dans les circuits intégrés. Certes, la réalisation des filtres externes (discrets) est un sujet qui a été largement traité par le passé et où la documentation est abondante. À l'inverse, la conception des filtres opérant à haute fréquence dans les circuits intégrés a longtemps été limitée par les différentes méthodes proposées antérieurement. En effet, l'utilisation des circuits à condensateurs commutés ou encore à courants commutés est limitée à des fréquences peu élevées, alors qu'il est difficile d'intégrer précisément les inductances et les condensateurs. De plus, étant donné les variations relatives aux procédés de fabrication des caractéristiques des circuits réalisés, il est nécessaire de pouvoir modifier certains éléments du filtre afin d'ajuster adéquatement la réponse en fréquence désirée. Ceci est cependant difficilement réalisable par les techniques énoncées précédemment.

Récemment, la conception des filtres analogiques utilisant des intégrateurs Gm-C a acquis une grande popularité. Les cellules de transconductance (Gm) sont des circuits relativement simples, qui permettent d'opérer à des fréquences élevées, tout en minimisant la puissance consommée. L'intérêt de réaliser des filtres à l'intérieur des composants électroniques s'est ainsi renouvelé. En effet, la question de savoir s'il était préférable de réaliser le filtre à l'intérieur ou à l'extérieur des composants était jusqu'à tout

récemment à l'ordre du jour. Les avantages relatifs au filtrage extérieur étaient la possibilité de réaliser toutes les fonctions de transfert tout en permettant de les ajuster. L'inconvénient majeur est qu'il est nécessaire de passer par les ports d'entrée et de sortie des composants, ce qui peut altérer la réponse en fréquence. De plus, certaines applications nécessitent une intégration complète du système de façon à augmenter les performances ou encore de réduire au maximum l'encombrement du circuit. Les applications biomédicales, où l'on utilise les techniques de stimulation électrique fonctionnelle (SÉF) en vue de corriger certaines dysfonctionnements du corps humain, sont un excellent exemple de cette situation, étant donné que les systèmes doivent être portés par le patient.

Nous savons maintenant qu'il est possible de réaliser et d'ajuster les filtres dans les circuits intégrés. Plusieurs travaux ont été réalisés en ce sens. Bien que le fait de modifier la valeur de la transconductance ( $G_m$ ) pour changer les caractéristiques de la fonction de transfert d'intérêt apparaît simple, il est nécessaire de franchir certaines étapes pour atteindre cet objectif. Il faut d'abord choisir la technique adéquate pour disposer les intégrateurs  $G_m-C$  afin de réaliser les filtres. La sélection d'un circuit simple et facile à ajuster est une seconde étape importante. En effet, la sélection des dimensions des transistors, la stratégie de contrôle des transconductances (que ce soit par courant ou tension) ainsi que les façons de concevoir les cellules qui minimisent les effets parasites sont des domaines où il est plus rare de trouver la documentation adéquate.

## Objectifs poursuivis

Le principal objectif du présent projet de maîtrise est de développer une approche pour réaliser des filtres analogiques programmables à l'aide d'intégrateurs Gm-C dans les circuits intégrés. Ces filtres doivent fonctionner dans une plage de fréquences de 100KHz à 100MHz, où l'accent doit être mis sur le contrôle des caractéristiques des filtres. Sachant que la transconductance des cellules peut être ajustée, il est possible de contrôler les paramètres (fréquence centrale, facteur de qualité et gain) des filtres.

Dans un premier temps, nous déterminerons la méthode adéquate de disposition des cellules de transconductance, où les paramètres des filtres seront clairement identifiés mathématiquement de façon à prioriser les éléments responsables de la réponse du filtre. La sensibilité du filtre réalisé aux procédés de fabrication est évidemment dépendante de la méthode employée. Dans un deuxième temps, nous proposerons une cellule de transconductance performante réalisée en technologie CMOS et nous identifierons explicitement les paramètres (dimension des transistors, tension et courant de référence) qui déterminent la transconductance. Un des principaux critères de sélection sera la facilité avec laquelle on peut varier les valeurs des transconductances.

Le présent mémoire se distingue des travaux précédents par le fait que l'ajustement des transconductances est réalisé en mode courant, alors que la majorité des techniques existantes privilégient une approche de contrôle des transconductances par tension.

L'approche de contrôle par courant est préférée étant donné qu'il est plus simple de réaliser des sources de courant linéaires programmables que des tensions de références variables dans les circuits intégrés CMOS. Finalement, dans un contexte où la majorité des travaux sont axés sur l'amélioration d'un seul aspect à la fois, tel les architectures de transconductance ou encore la présentation de méthodes de génération de filtres, le présent projet fera le lien entre ces divers éléments. Le travail proposé est cependant plus axé sur le développement de la cellule de transconductance plutôt que sur le développement des topologies de filtres.

### **Organisation du mémoire**

Le mémoire est subdivisé en quatre chapitres. Le premier chapitre consiste en une revue de la littérature afin d'avoir un aperçu des architectures des cellules de transconductance et des techniques de réalisation des filtres Gm-C. Au terme de ce chapitre, nous serons en mesure d'apprécier les derniers développements dans le domaine. Dans le second chapitre, nous analyserons le contrôle des filtres Gm-C où une nouvelle architecture de cellule de transconductance ainsi qu'une source de courant programmable performante seront présentées. Le troisième chapitre permettra de montrer diverses applications de filtres Gm-C. Finalement, les différents résultats expérimentaux des circuits réalisés seront présentés dans le quatrième chapitre.

Le mémoire comporte aussi huit annexes. L'annexe A montre le calcul de la représentation théorique non idéale d'une cellule de transconductance, tandis que l'annexe B expose les détails du calcul de la fonction de transfert de la cellule proposée à partir du circuit. L'annexe C présente différents fichiers de simulation permettant de réaliser les applications du chapitre 3. L'annexe D montre la cellule de transconductance proposée, incluant les schémas et les fichiers de simulations HSPICE de cette dernière. Les annexes E et F présentent respectivement le dessin des masques et les fichiers de simulation des deux composants réalisés au cours de ce mémoire, soit une source de courant programmable et un filtre passe-bande programmable. L'annexe G propose une explication des résultats expérimentaux obtenus. Finalement, l'annexe H décrit le calcul de la représentation non idéale des filtres passe-bas et passe-bande et montre les effets d'une cellule non idéale.

## CHAPITRE I

# APERÇU DES ARCHITECTURES DE TRANSCONDUCTANCE ET DES TECHNIQUES DE RÉALISATION DES FILTRES Gm-C

### 1.1 Introduction

La réalisation des filtres analogiques utilisant les cellules Gm-C (transconductance-C) dans les circuits intégrés est actuellement en pleine effervescence. Afin de saisir l'état actuel des connaissances, nous proposons dans ce chapitre une revue de littérature orientée vers les différentes techniques de réalisation de ce type de filtres. Cette revue tentera notamment de sélectionner les méthodes offrant la possibilité de contrôler les paramètres des filtres tout en étant aussi insensibles que possible aux variations des procédés de fabrication. Par la suite, nous présenterons brièvement les différentes architectures de transconductance CMOS et leurs applications aux filtres Gm-C.

### 1.2 Conception des filtres analogiques dans les circuits intégrés

La conception des filtres analogiques dans les circuits intégrés pour une technologie donnée est un processus qui demande plusieurs étapes (Figure 1.1). Il est important de bien accomplir chacune d'entre elles pour arriver au produit final. Les premières étapes

consistent à déterminer les spécifications du filtre à réaliser en fonction de l'application choisie. Il faut alors choisir la topologie adéquate et simuler celle-ci avec des cellules idéales pour vérifier l'exactitude du circuit. Ensuite, il est nécessaire d'identifier l'architecture qui sert à réaliser un intégrateur répondant aux exigences de simplicité, performances et facilité de contrôle. L'intégrateur constitue l'élément principal de la conception des filtres. À ce stade, il suffit de réaliser le dessin des masques en appliquant les techniques servant à minimiser les variations aléatoires du procédé de fabrication et de simuler le tout. Parfois, il peut s'avérer essentiel de réajuster certains paramètres du circuit afin de contrebalancer les effets des capacités parasites. Après ces étapes, on peut procéder à la fabrication du circuit et à la mesure des performances réelles sur un prototype.

Figure 1.1 Processus de conception des filtres Gm-C

### **1.3 Techniques de réalisation des filtres**

Les différentes techniques pour réaliser les filtres Gm-C ont été développées bien avant l'apparition de ces derniers. Ces techniques ont été développées dans le but de faciliter l'analyse des circuits plus imposants afin de réaliser des filtres discrets (Wing, 1956). Celles-ci, demeurent évidemment utilisables dans le cadre de nos applications. Depuis lors, une multitude de méthodes ont été proposées pour générer des filtres d'ordre élevé, en vue de minimiser la sensibilité, permettre le contrôle ou encore réduire le nombre de cellules des circuits élaborés. Étant donné le choix impressionnant offert, il devient impératif d'effectuer un bref rappel des méthodes utilisées afin de trouver la plus adéquate. Tel est l'objectif principal de cette section.

#### **1.3.1 Sections quadratiques mises en cascade**

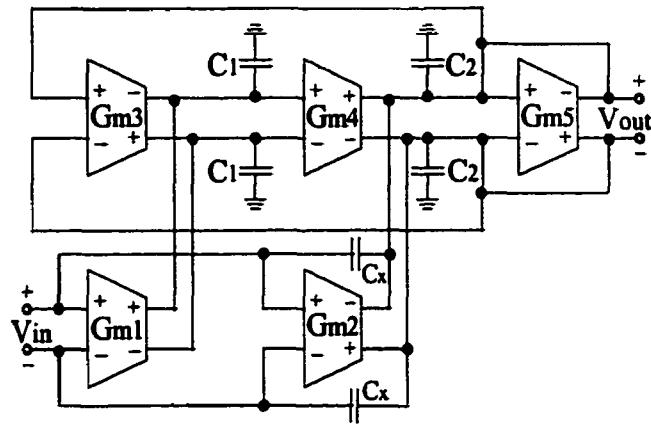

Une méthode couramment employée dans les travaux actuels est la mise en cascade de sections quadratiques en vue de réaliser des filtres d'ordre plus élevé (Minot, Degruillier, 1998), (Wyszynski, Schaumann, 1994). Cette façon de procéder allie la simplicité à un bon accès aux paramètres de contrôle des filtres. Pour ce faire, il faut d'abord choisir un modèle de section quadratique parmi ceux existants. La section quadratique généralisée (figure 1.2) proposée par John et Martin (1997) représente une option intéressante.

Figure 1.2 Section de filtre quadratique différentielle généralisée

tiré de John & Martin (1997)

La fonction de transfert de cette section quadratique peut être représentée par l'équation

1.1. On remarque qu'il est possible de réaliser avec ce circuit toutes les fonctions de transfert pouvant être représentées par un quotient de deux polynômes. Par exemple, si l'on désire obtenir un filtre passe-bande, il suffit d'éliminer la cellule  $G_{m1}$  ainsi que le condensateur  $C_x$ . De même, on obtient un filtre passe-bas en retirant la cellule  $G_{m2}$  et le condensateur  $C_x$ .

$$H(s) = \frac{\left(\frac{C_x}{C_x + C_2}\right)s^2 + \left(\frac{G_{m2}}{C_x + C_2}\right)s + \frac{G_{m1}G_{m4}}{C_1(C_x + C_2)}}{s^2 + \left(\frac{G_{m5}}{C_x + C_2}\right)s + \left(\frac{G_{m3}G_{m4}}{C_1(C_x + C_2)}\right)} \quad (1.1)$$

Les équations 1.2 et 1.3 font ressortir les éléments du circuit agissant respectivement sur la fréquence centrale et le facteur de qualité. Nous sommes donc en présence d'un circuit offrant un contrôle total sur les paramètres des filtres résultants.

$$w_0 = \sqrt{\frac{G_{m3}G_{m4}}{C_1(C_x + C_2)}} \quad (1.2)$$

$$Q = \sqrt{\left(\frac{G_{m3}G_{m4}}{G_{m5}^2}\right)\left(\frac{C_x + C_2}{C_1}\right)} \quad (1.3)$$

En résumé, en plus d'offrir un accès facile aux paramètres, cette méthode permet de réduire le temps requis pour réaliser l'intégration des modules, étant donné les similitudes entre les différentes sections mises en cascade. Cependant, selon une étude de Laker, Schaumann et Ghausi (1979), cette façon de procéder a l'inconvénient d'être sensible aux variations des caractéristiques des composants du système.

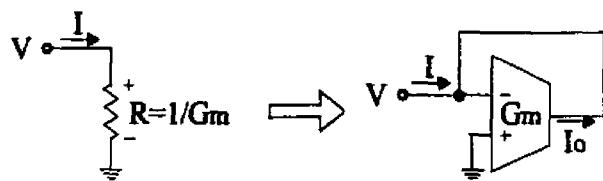

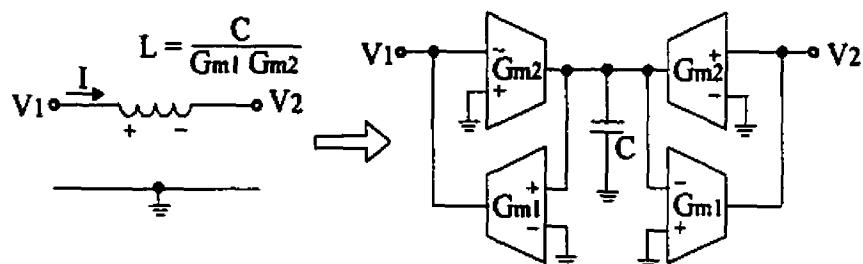

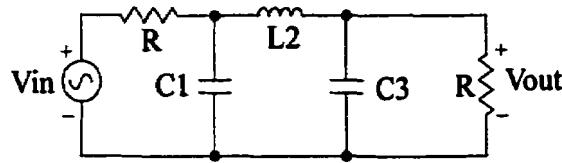

### 1.3.2 Modèle du gyrateur

Cette technique consiste à remplacer tous les éléments discrets d'un filtre passif tels les résistances, condensateurs et inductances, par leurs équivalents réalisés à l'aide de cellules Gm-C. En premier lieu, il faut choisir le modèle du filtre à réaliser à l'aide des éléments passifs usuels. Ces éléments sont par la suite remplacés par des cellules de transconductance simulant leurs propriétés respectives, ce qui permet de réaliser la même fonction de transfert. À titre d'exemple, une résistance mise à la masse peut être réalisée à l'aide d'une seule cellule Gm telle que montrée par la figure 1.3. De même, il est possible de réaliser une inductance flottante (figure 1.4) (Kardontchik, 1992) avec quatre cellules Gm et un condensateur.

Figure 1.3 Résistance réalisée à l'aide d'une cellule  $G_m$

Figure 1.4 Représentation d'une inductance

Comme on peut l'imaginer, la réalisation d'un filtre quelconque peut nécessiter un grand nombre de cellules  $G_m-C$ , qu'il faut ajuster individuellement afin de simuler correctement chaque élément passif. Conséquemment, il peut s'avérer difficile de modifier le comportement du filtre étant donné le nombre de cellules impliquées. Malgré ces désavantages, cette méthode permet de réaliser tous les types de fonction de transfert.

### 1.3.3 Modèle à variables d'état

Sachant que l'état d'un système peut-être représenté comme une série d'équations différentielles du premier ordre, diverses techniques de généralisation basées sur le modèle à variable d'état ont été proposées afin de réaliser rapidement des filtres  $G_m-C$ .

Ces équations permettent de décrire les comportements ainsi que les signaux de sorties d'un système donné. On distingue trois modèles principaux de représentation de filtres à l'aide de variables d'états. On reconnaît les modèles FLF (*follow the leader feedback*), IFLF (*inverse follow the leader feedback*) et LF (*leapfrog*). Ces modèles sont décrits dans l'ouvrage de Dorf et Bishop (1995).

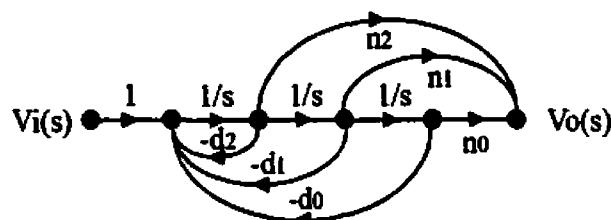

La configuration FLF nécessite l'utilisation d'une cellule de transconductance à plusieurs entrées, puisqu'elle reçoit les boucles de rétroaction de toutes les autres cellules constituant le filtre. Cette façon de faire n'apparaît pas comme une solution viable pour la réalisation des filtres Gm-C d'ordre élevé, puisqu'il est difficile de réaliser simplement un tel type de cellule (Chiang, Schaumann, 1996). La figure 1.5 montre un exemple de filtre du troisième ordre (équation 1.4) réalisé avec cette méthode. On peut obtenir toutes les fonctions de transfert (passe-bas, passe-haut, etc.) dont la valeur du numérateur est inférieure à celle du dénominateur. Il est à noter que l'on remplace les intégrateurs ( $1/s$ ) par les cellules Gm-C.

Figure 1.5 Configuration FLF pour un système du troisième ordre

$$H(s) = \frac{V_o(s)}{V_i(s)} = \frac{n_2 s^2 + n_1 s + n_0}{s^3 + d_2 s^2 + d_1 s + d_0} \quad (1.4)$$

Afin d'éviter la complexité de la réalisation d'une cellule à plusieurs entrées, on utilise la configuration IFLF présentée à la figure 1.6. L'équipe de Chiang et Schaumann (1996, 1998) l'a d'ailleurs utilisée pour réaliser des filtres Gm-C. L'équation 1.4 correspond à la fonction de transfert de cette configuration. Elle nécessite, dans le pire des cas, des cellules de transconductance à trois entrées pour exécuter la sommation aux nœuds. De plus, il faut ajouter des cellules pour réaliser les coefficients  $n_1$  et  $n_2$ .

Figure 1.6 Configuration IFLF pour un système du troisième ordre

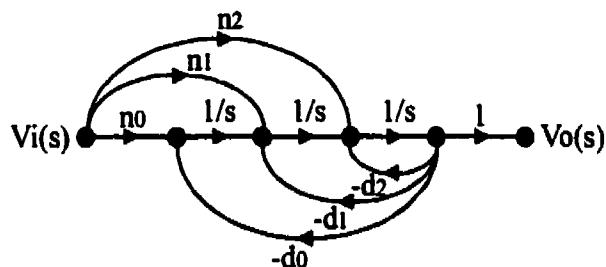

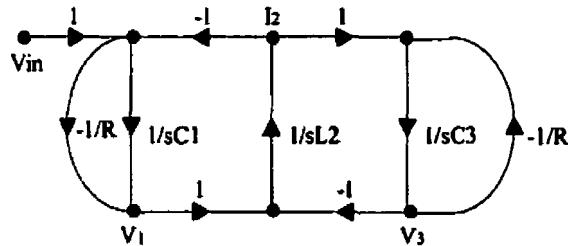

La troisième configuration LF consiste à déduire les équations d'états à partir d'un prototype de circuit en échelle passif obtenu de la fonction de transfert normalisée. Par exemple, en partant de la fonction de transfert d'un filtre passe-bas du troisième ordre (équation 1.5), on obtient le circuit passif de la figure 1.7. De même, on en déduit le graphe de fluence (Figure 1.8) et on réalise à partir de ce dernier le circuit final (Figure 1.9). Cette méthode nécessite des cellules à deux entrées et une cellule à trois entrées pour traiter le signal d'entrée.

$$H(s) = \frac{1}{s^3 + 2s^2 + 2s + 1} \quad (1.5)$$

Figure 1.7 Représentation d'un filtre passe-bas normalisé du troisième ordre

Figure 1.8 Graphe de fluence du circuit équivalent

Figure 1.9 Filtre Gm-C équivalent

Pour réaliser les filtres passe-bande avec cette méthode, il est possible de remplacer les intégrateurs par une section quadratique (équation 1.6) pour faire la transformation passe-bas à passe-bande, tout en conservant un accès facile aux paramètres de contrôle du filtre (Chang *et al.*, 1997). Les variables  $w_0$ ,  $w_{cb}$  et  $w_{ch}$  sont respectivement les fréquences centrale, de coupure basse et de coupure haute du filtre passe-bande.

$$s \rightarrow \frac{s^2 + w_0^2}{(w_{ch} - w_{cb})s} \quad (1.6)$$

Les méthodes présentées sont toutes applicables pour la réalisation de filtres Gm-C. En effet, elles permettent de réaliser rapidement des filtres peu sensibles aux variations des caractéristiques des composants (Laker *et al.*, 1979). Cependant, il en ressort une difficulté pour programmer les filtres pour la majorité des méthodes présentées, puisque les coefficients Gm, bien qu'accessibles, ne permettent pas de contrôler tous les paramètres des filtres.

#### **1.4 Survol des architectures de transconductances**

Parallèlement, de nombreux développements ont récemment été réalisés en vue d'améliorer les performances des cellules de transconductance (Gm). Ainsi, plusieurs architectures de G<sub>m</sub> ont été proposées afin de répondre aux exigences de diverses applications. On distingue deux grandes classes d'architectures: les Gm opérant dans la région ohmique et celles opérant dans la région active (saturation). Bien que les cellules du premier type offrent en général une meilleure linéarité, les cellules opérant dans la zone active donnent de meilleures performances à plus haute fréquence. Nous examinerons donc dans de cette section les principales architectures CMOS de transconductances retrouvées dans la littérature.

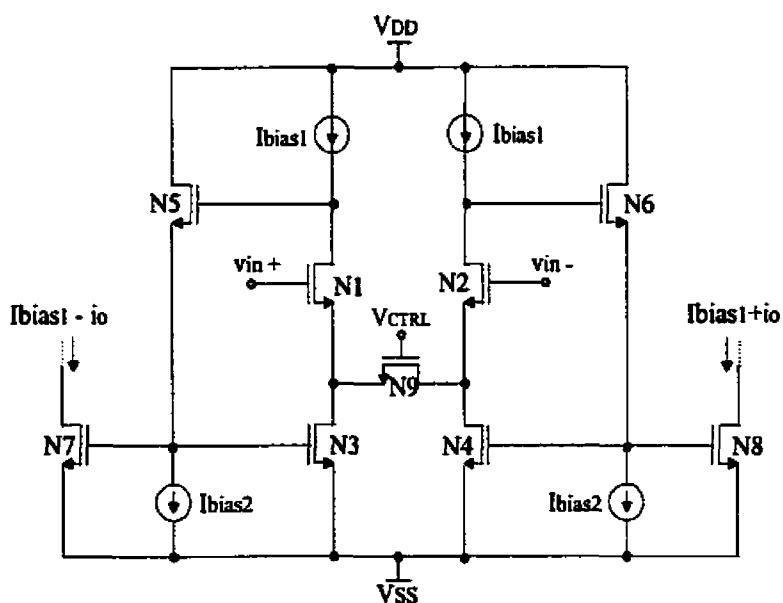

### 1.4.1 Cellule opérant dans la région ohmique

Il existe plusieurs types de cellules de transconductance opérant dans la région ohmique. Le circuit montré à la figure 1.10, présente une architecture typique à cette catégorie (Welland et al., 1994). Bien qu'ayant le nom d'une cellule opérant dans la région ohmique, seul le transistor N9 se trouve dans ce mode, les autres transistors étant en saturation. La transconductance de ce circuit, qui peut être modifiée par le signal  $V_{CTRL}$ , est égale à l'inverse de la résistance  $r_{ds9}$  du transistor N9, (équation 1.7). En effet, le fait de changer les tensions de grilles de N1 et N2 permet de modifier le courant des transistors N3 et N4 par l'entremise de N9 puisqu'il apparaît une différence de potentiel entre les drains de N3 et N4. Les transistors N7 et N8 constituent les miroirs de courant des transistors N3 et N4. Cette architecture est limitée en fréquence puisqu'elle présente de nombreux nœuds internes.

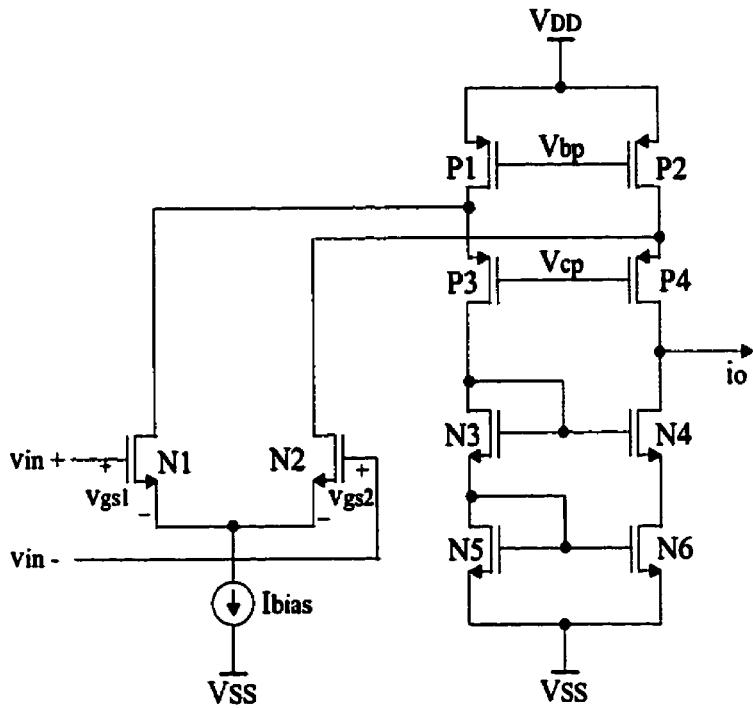

Figure 1.10 Cellule opérant dans la région ohmique,  $i_o$  est le courant de sortie différentiel

$$Gm = \mu_n C_{ox} \frac{W_{N9}}{L_{N9}} (v_{g9} - v_m) \quad (1.7)$$

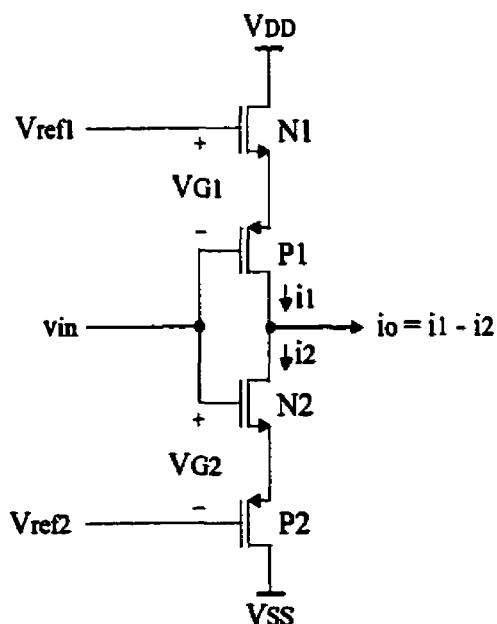

### 1.4.2 Cellule basée sur des inverseurs

Une des premières architectures de cellule Gm contrôlable, dédiée à la réalisation des filtres, a été proposée par Park et Schaumann (1986) pour améliorer les performances de simples inverseurs utilisés comme transconductance. Le circuit basé sur un simple inverseur CMOS (figure 1.11), est constitué de quatre transistors de taille identique opérant en saturation. Cette configuration permet d'éviter les problèmes relatifs à l'ajustement du rapport de largeur des transistors de type P et de type N. En effet, la linéarité du circuit repose en grande partie sur l'équivalence, c'est-à-dire le rapport des longueurs et des largeurs des paires de transistors N1, P1 et N2, P2.

Figure 1.11 Cellule Gm basée sur des inverseurs

La valeur de la transconductance totale, décrite par l'équation 1.8, peut être modifiée dynamiquement en variant la tension de référence  $V_{ref}$ . Le circuit jouit d'une grande impédance d'entrée et d'une impédance de sortie plutôt faible.

$$Gm = \frac{2\mu_p \mu_n C_{ox}^2 (W/L)^2}{(\sqrt{\mu_n C_{ox} (W/L)} + \sqrt{\mu_p C_{ox} (W/L)})^2} (V_{ref} - (V_n - V_p)) \quad (1.8)$$

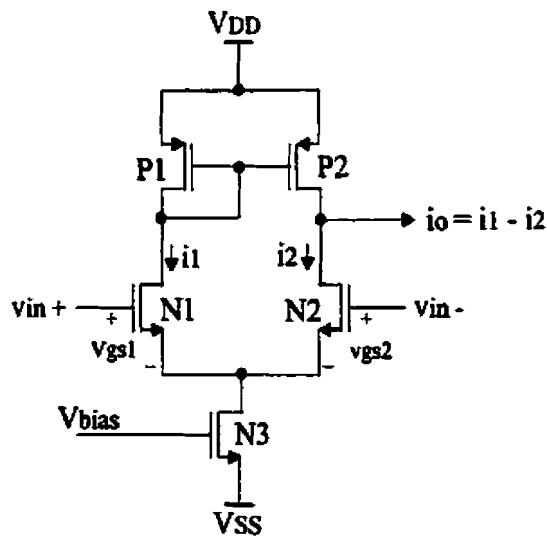

#### 1.4.3 Cellule différentielle simple

On peut considérer la cellule différentielle simple (figure 1.12) comme une architecture de base pour réaliser un intégrateur Gm-C. Cette dernière, qui a été étudiée comme un élément pouvant servir à la réalisation de filtres (Torrance *et al.*, 1985), sert normalement d'étage d'entrée dans la plupart des amplificateurs opérationnels (John et Martin, 1997).

Figure 1.12 Cellule différentielle simple de type N

Il est possible de modifier la transconductance en variant la tension de polarisation  $V_{bias}$  pour affecter la tension de grille à source  $v_{gs1}$  et  $v_{gs2}$  tel que décrit par l'équation 1.9 (les transistors N1 et N2 ayant les mêmes dimensions).

$$Gm = \frac{i_o}{v_{in+} - v_{in-}} = \mu_n C_{ox} \frac{W_{N1}}{L_{N1}} (v_{gs} - v_m) \quad (1.9)$$

Le problème principal de ce circuit, qui pourtant offre une bonne linéarité, est qu'il possède une faible impédance de sortie. Cette dernière est équivalente à seulement quelques centaines de kilo Ohms, puisqu'elle provient des résistances drain-source ( $r_{ds}$ ) des transistors N2 et P2 mises en parallèle. Une fois la charge ajoutée (condensateur), le circuit est loin d'offrir un comportement d'intégrateur idéal.

Il est à noter que la sortie peut être totalement différentielle, en autant qu'un circuit de rétroaction en mode commun (CMFB) soit ajouté pour stabiliser les tensions de sorties (Kardontchik, 1992).

#### **1.4.4 Cellule différentielle simple avec étage de sortie**

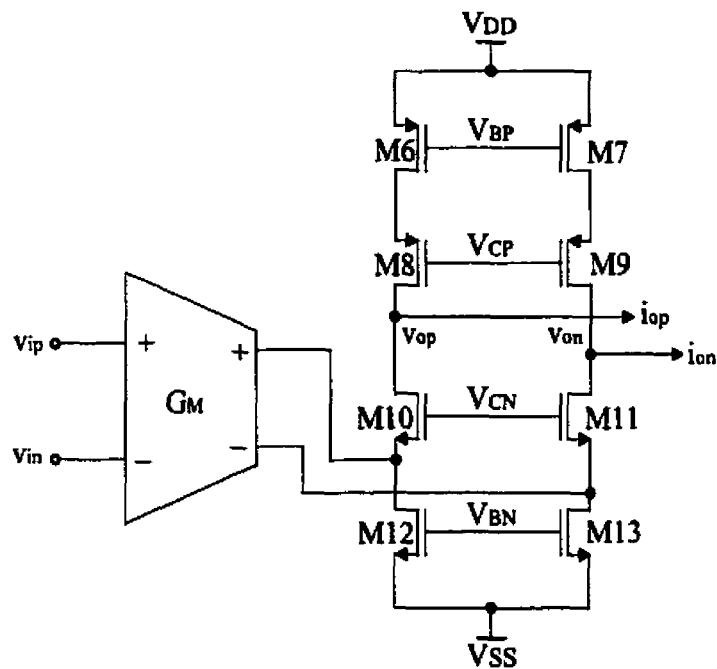

Afin de remédier aux problèmes associés à la faible impédance de sortie de la cellule différentielle simple, un étage de sortie folded-cascode a été ajouté (figure 1.13) pour former un amplificateur de transconductance opérationnel OTA (Kardontchik, 1992).

Figure 1.13 Cellule différentielle avec étage de sortie *folded-cascode*

L'équation 1.10 montre que la transconductance totale du circuit dépend uniquement de l'étage d'entrée différentiel.

$$G_m = \frac{i_o}{v_{in+} - v_{in-}} = \mu_n C_{ox} \frac{W_N}{L_N} (v_{gs} - v_m) \quad (1.10)$$

avec  $W_{N1} = W_{N2} = W_N$ ,  $L_{N1} = L_{N2} = L_N$  et  $v_{gs1} = v_{gs2} = v_{gs}$

On obtient cette fois-ci un circuit ayant une impédance de sortie beaucoup plus élevée que celui décrit à la section précédente. L'ajout de cet étage de sortie a cependant le désavantage de réduire la plage de la tension de sortie disponible, en plus de diminuer la fréquence maximale d'opération de la cellule de transconductance, dû à la présence de nœuds internes.

#### 1.4.5 Cellule différentielle double et résistance négative

Afin d'augmenter la linéarité d'une simple paire différentielle, Nedungadi et Viswanathan (1984) ont étudié une nouvelle cellule à partir de deux paires différentielles où tous les transistors opèrent dans la région de saturation. Quelques années plus tard, l'utilisation de cellules de transconductance complètement différentielles en utilisant deux sorties à la place d'une seule est devenue une tendance générale. Cette structure permet d'éliminer les harmoniques paires qui se trouvent à la sortie du circuit (Walker et Green, 1994). La distorsion harmonique totale s'en trouve alors améliorée, puisque dans la majorité des cas, la deuxième harmonique est souvent dominante. De plus, on obtient un circuit beaucoup moins sensible au bruit provenant des sources d'alimentation.

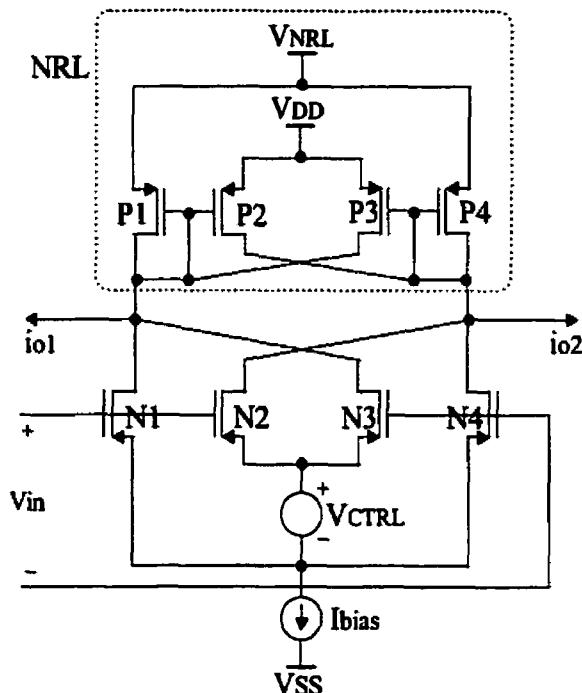

Ces travaux ont ainsi donné naissance à un nouveau type d'architecture proposé par Szczechanski *et al.* (1997). Ce circuit (figure 1.14) est en fait réalisé à l'aide de deux cellules, chacune constituée d'une paire différentielle, dont l'une est connectée en rétroaction positive (résistance négative NRL) dans le but d'augmenter le gain DC, c'est à dire l'impédance de sortie.

Figure 1.14 Cellule différentielle double avec résistance négative

(tiré de Szccepanski, 1997)

En plus de contribuer à augmenter le gain DC de la cellule, le NRL a pour autre rôle de stabiliser la tension de sortie en mode commun, ce qui permet d'éviter l'utilisation d'un circuit de rétroaction en mode commun (CMFB). La valeur de la transconductance est alors modifiable en changeant la source de tension flottante  $V_{CTRL}$ , tandis que l'on modifie la résistance négative avec la tension  $V_{NRL}$ , tel que le démontrent les équations 1.11 et 1.12 respectivement.

$$G_M = \mu_n C_{ox} \frac{W_n}{L_n} V_{ctrl} \quad (1.11)$$

avec  $W_n = W_{n1} = W_{n2} = W_{n3} = W_{n4}$  et  $L_n = L_{n1} = L_{n2} = L_{n3} = L_{n4}$

$$G_{MNRL} = \frac{1}{R_N} = \mu_p C_{ox} \frac{Wp}{Lp} (V_{DD} - V_{NRL}) \quad (1.12)$$

avec  $Wp = Wp1 = Wp2 = Wp3 = Wp4$  et  $Lp = Lp1 = Lp2 = Lp3 = Lp4$

Assi et Sawan (1999), de l'équipe de recherche Polystim, ont proposé leur propre cellule (figure 1.15). On ajuste la transconductance en modifiant la tension  $V_{CTRL}$  ainsi que la résistance négative avec la tension  $V_{NRL}$  selon les équations 1.13 et 1.14. La tension en mode commun est, dans le cas présent, contrôlée par la tension  $V_{bias}$ .

**Figure 1.15:** Cellule différentielle double avec résistance négative

(tiré de Assi, 1999)

$$G_M = \mu_p C_{ax} \frac{Wp_a}{Lp_a} (V_{ctrl}) \quad (1.13)$$

avec  $Wp_a = Wp_{a1} = Wp_{a2} = Wp_{a3} = Wp_{a4}$  et  $Lp_a = Lp_{a1} = Lp_{a2} = Lp_{a3} = Lp_{a4}$

$$G_{MNRL} = \mu_p C_{ax} \frac{W p_b}{L p_b} (V_{DD} - V_{NRL}) \quad (1.14)$$

avec  $Wp_b = Wp_{b5} = Wp_{b6} = Wp_{b7} = Wp_{b8}$  et  $Lp_b = Lp_{b5} = Lp_{b6} = Lp_{b7} = Lp_{b8}$

Tous les circuits présentés jusqu'ici ont pour objectif d'éliminer les nœuds internes afin qu'ils puissent fonctionner à haute fréquences. En effet, les capacités parasites sont, pour la plupart, situées en parallèle avec la capacité de charge, ce qui élimine la présence des pôles parasites. Ces architectures permettent ainsi d'obtenir de bonnes performances jusqu'à des fréquences de 500MHz.

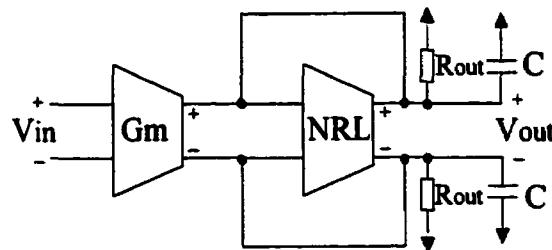

Afin de bien identifier la technique de compensation par rétroaction positive (NRL), il est possible de représenter les circuits précédents de façon simplifiée par la figure 1.16. En analysant ce circuit, on trouve la fonction de transfert décrite par l'équation 1.15. On y voit alors que lorsque  $1/R_{out}$  est égal à  $Gm_{NRL}$ , un gain théorique infini est obtenu.

Figure 1.16 Technique de compensation par rétroaction positive

$$\frac{V_{out}}{V_{in}} = \frac{Gm}{sC + \frac{1}{R_{out}} - Gm_{NRL}} \quad (1.15)$$

Les performances des circuits utilisant une NRL sont réalisées au détriment de la flexibilité, puisqu'il est nécessaire d'ajuster un paramètre additionnel. Il faut d'ailleurs remarquer que l'ajustement de la résistance négative est dépendante de la valeur de la transconductance totale, puisque la modification de cette dernière a une influence sur

l'impédance de sortie. La transconductance doit être ajustée à chaque variation de Gm sachant que  $R_{out}$  dépend directement de cette dernière valeur, ce qui complique grandement le changement des caractéristiques des filtres.

Parallèlement, il faut être en mesure de garantir un minimum de précision à la tension  $V_{NRL}$ , afin de s'assurer une impédance de sortie élevée, au risque de dégrader les résultats au cas où la valeur de la résistance négative serait supérieure à la résistance de sortie. Ceci représente un défi important à relever, sachant qu'il faudra appliquer la tension sur un nœud de faible impédance. La difficulté est similaire pour le contrôle de la transconductance et vient s'ajouter à celle décrite précédemment.

## 1.5 Conclusion

Au cours du présent chapitre, nous avons présenté une revue des principales techniques de réalisation des filtres Gm-C, ainsi qu'un survol des architectures de cellules de transconductances CMOS. Nous avons aussi souligné les inconvénients de ces éléments. Le prochain chapitre consistera à proposer notre propre cellule de transconductance et les circuits connexes, en mettant l'accent sur le thème du contrôle des filtres.

## **CHAPITRE II**

### **CONTRÔLE DES FILTRES Gm-C**

#### **2.1 Introduction**

Nous venons d'examiner les principales façons de réaliser des filtres Gm-C, ainsi que les différentes cellules de transconductance servant à leur fabrication. Nous allons, au cours de ce chapitre, qui constitue en fait le cœur du présent mémoire, nous consacrer à la conception d'un intégrateur et à ses circuits connexes. Les principaux attributs recherchés pour cet intégrateur sont une architecture simple, facile à contrôler et ayant des caractéristiques s'approchant le plus possible d'un élément idéal. Une nouvelle cellule de transconductance, ainsi qu'une source de courant programmable pour le contrôle de la transconductance seront proposés.

#### **2.2 Procédure de contrôle en mode courant**

Contrairement à ce que nous avons vus au chapitre 1, une approche de contrôle en mode courant est préférée à un contrôle par tension, du fait qu'il est plus simple de réaliser une source de courant de référence programmable jouissant d'une bonne linéarité. Dans la plupart des travaux réalisés auparavant, on utilisait une source de tension contrôlable afin de modifier la transconductance des cellules Gm. Or, la précision requise de ce type de dispositif, pour obtenir un ajustement adéquat de la transconductance, est de l'ordre du

millivolt. La réalisation d'un tel circuit peut s'avérer difficile. Dans cette perspective, il est difficile de fixer précisément la valeur des transconductances à partir des équations. Avec une approche en mode courant, il est possible de contourner ces problèmes en adoptant un outil de contrôle précis tout en étant simple à réaliser. Le présent défi consiste à extraire mathématiquement la variable du courant de l'équation de la transconductance de l'intégrateur choisi.

## 2.3 Identification des caractéristiques des modules électroniques recherchés

L'objet de cette section est d'identifier les principales caractéristiques de l'intégrateur et de la source de courant programmable qui sert à le contrôler.

### 2.3.1 Caractéristiques de l'intégrateur

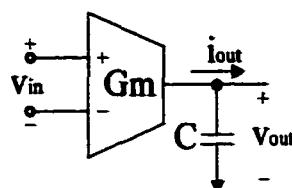

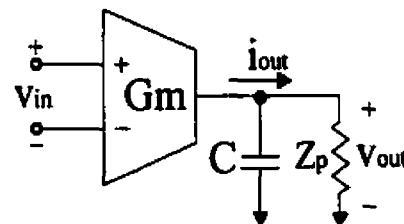

Essentiellement, le rôle de la cellule  $Gm$  est de convertir la tension appliquée à ses bornes d'entrée en un courant proportionnel à la valeur de sa transconductance. Pour obtenir un intégrateur, il suffit d'y ajouter une charge capacitive à sa sortie. On obtient alors le circuit présenté à la figure 2.1.

Figure 2.1 Intégrateur basé sur une cellule de transconductance

Si tout le courant généré par la cellule Gm se dirige vers la capacité C, c'est-à-dire si la tension  $V_{out}$  est lue par un voltmètre idéal, on obtient la fonction de transfert de l'intégrateur tel que démontré par les équations 2.1:

$$i_{out}(s) = G_m v_{in}(s) \quad (2.1a)$$

$$v_{out}(s) = \frac{i_{out}(s)}{sC} \quad (2.1b)$$

$$H(s) = \frac{v_{out}(s)}{v_{in}(s)} = \frac{G_m}{sC} \quad (2.1c)$$

Puisqu'il est possible de modifier la valeur de Gm en variant soit la tension ou le courant de référence de la cellule, on peut ajuster à volonté la fonction de transfert d'un filtre qui serait réalisé avec plusieurs intégrateurs.

Idéalement, l'intégrateur devrait avoir des impédances d'entrée et de sortie élevées. En effet, il est important d'avoir une impédance d'entrée élevée sachant que la conception d'un filtre nécessite la mise en cascade de plusieurs cellules. L'ajout d'une cellule ne devrait pas affecter les performances des cellules précédentes. Ce point est relativement facile à réaliser, étant donné que l'entrée de la cellule de transconductance est généralement connectée à la grille d'un transistor MOS qui possède une impédance très élevée. Par contre, il est plus difficile d'obtenir une impédance de sortie élevée sans compromettre d'autres caractéristiques. En réalité, l'impédance de sortie finie de la cellule Gm-C limite le gain DC effectif de cette dernière. Il est ainsi nécessaire de prévoir un mécanisme pour augmenter ce gain de façon à éviter la détérioration des

caractéristiques des filtres. L'équation 2.2 montre l'effet d'une impédance finie ( $Z_p$ ) sur la fonction de transfert de la cellule Gm-C. Notons que les détails du calcul permettant d'obtenir cette représentation sont présentés à l'annexe A.

$$\frac{v_{out}(s)}{v_{in}(s)} = \frac{G_m}{1/Z_p + Cs} \quad (2.2)$$

De la même façon, la cellule de transconductance devrait être la plus linéaire possible, afin d'éviter la distorsion du signal d'entrée. La plage de tension maximale à l'entrée peut être limitée; cependant, la cellule doit être linéaire autour de la tension en mode commun où l'on compte utiliser le circuit.

Finalement, dans le but de garantir une bonne largeur de bande à la cellule Gm, c'est-à-dire une plage fréquentielle où la transconductance demeure constante, il est nécessaire d'éloigner le plus possible le second pôle de la fréquence d'opération de la cellule. La plage où Gm est constant en fréquence est en effet limitée par le premier et le second pôle. Il est possible de représenter l'effet du second pôle par l'équation 2.3 à une fréquence égale à  $w_p$ . Ce dernier provient de la présence de capacités parasites dans les nœuds internes du circuit.

$$\frac{v_{out}(s)}{v_{in}(s)} = \frac{G_m}{Cs} \cdot \frac{1}{1+s/w_p} \quad (2.3)$$

En combinant les effets de l'impédance de sortie finie et d'une fréquence d'opération maximale limitée (équations 2.2 et 2.3), on obtient une représentation de la fonction de transfert d'un intégrateur Gm-C réel (Équation 2.4). On remarque qu'en faisant tendre  $w_p$

et  $Z_p$  vers l'infini, on obtient la relation  $H(s)=G_m/sC$  d'un intégrateur idéal. Rappelons que les détails permettant d'obtenir ces équations sont présentés à l'annexe A.

$$\frac{v_{out}(s)}{v_{in}(s)} = \frac{G_m}{s^2(C/w_p) + s(C + 1/w_p Z_p) + 1/Z_p} \quad (2.4)$$

En résumé, les caractéristiques essentielles d'un bon intégrateur sont:

- impédance d'entrée élevée

- impédance de sortie élevée

- bonne linéarité sur la plage de tension d'intérêt

- largeur de bande élevée

Tout en tenant compte de ces paramètres pour concevoir un intégrateur le plus près possible de l'idéal, il est important de veiller à ce que le circuit donne un accès facile au contrôle des caractéristiques des filtres qui sont composés de plusieurs intégrateurs. Voilà donc le principal défi à relever.

### 2.3.2 Caractéristiques de la source de courant programmable

Désirant contrôler les caractéristiques des filtres à l'aide d'un courant de référence, il est important d'avoir une source de courant programmable très linéaire et offrant plusieurs niveaux de courant. La façon la plus simple de réaliser une telle source est d'utiliser un convertisseur numérique à analogique (CNA). Dans un convertisseur à codage binaire, le nombre de niveaux de courant constant est lié au nombre de bits N (*nb. niveaux =  $2^N$* ). Il est important de maximiser ce nombre. La linéarité dépend principalement du type d'architecture choisi. En tenant compte de ces principaux critères pour réaliser le convertisseur, la solution retenue devra être en plus simple à réaliser.

## 2.4 Proposition d'une nouvelle cellule de transconductance

Dans la poursuite des travaux précédents (Szczepanski *et al.*, 1997 et Assi, Sawan, 1999), il en ressort qu'une approche complètement différentielle (i.e. entrée différentielle et sortie différentielle) doit être privilégiée à une méthode à sortie unique. Un circuit différentiel a en effet l'avantage d'éliminer les signaux non désirés en mode commun se présentant à l'entrée de la cellule. Nous allons dans cette section présenter successivement les étages d'entrée et de sortie de la cellule de transconductance ainsi que le circuit de rétroaction en mode commun.

### 2.4.1 Étage d'entrée

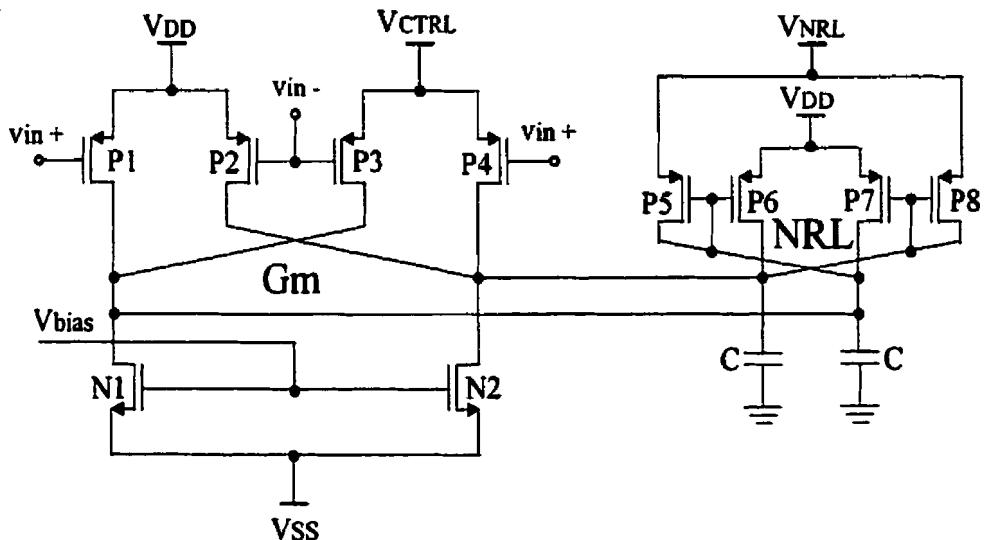

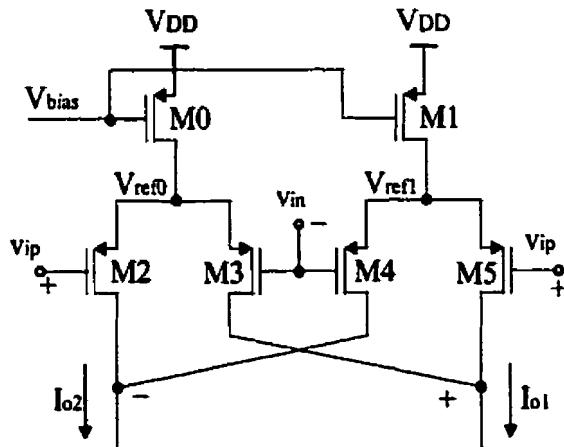

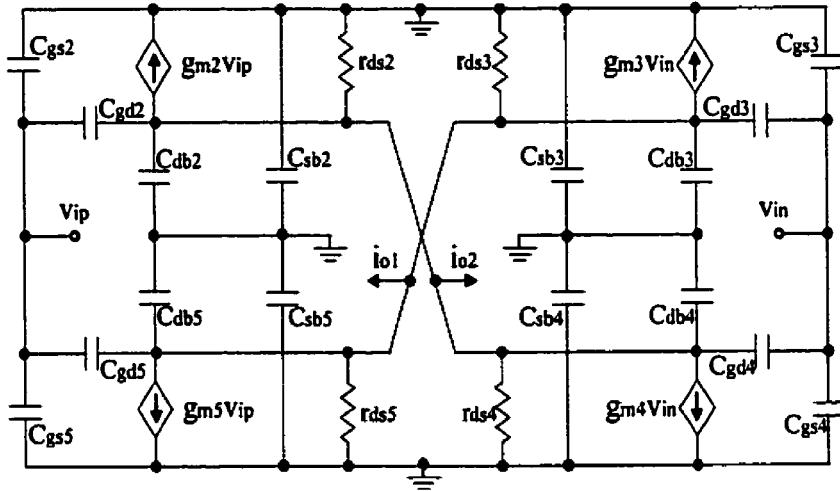

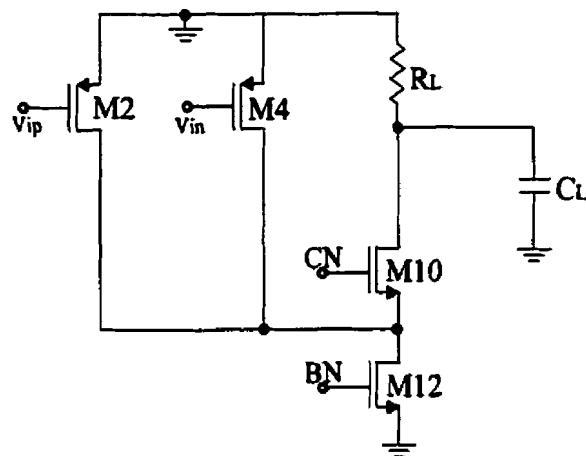

L'étage d'entrée de la nouvelle cellule de transconductance est basée sur les travaux réalisés par Assi et Sawan (1999). Cet étage d'entrée est construit à partir de deux étages d'entrées différentiels simples entrecroisés. Quelques ajouts demeurent nécessaires afin de contrôler la transconductance avec le courant de référence. Rappelons d'abord que cet étage représente une évolution d'une architecture où l'on désirait améliorer la linéarité et la réponse en fréquence en éliminant les nœuds internes. Ainsi, en ajoutant respectivement les transistors M0 et M1 à la source des transistors M2, M3 et M4, M5, on obtient le circuit présenté à la figure 2.2.

Figure 2.2 Étage d'entrée proposé

En dimensionnant les transistors M0 et M1 avec un rapport de largeur sur longueur égal à un entier  $k$  tel que:

$$k = \frac{W_0/L_0}{W_i/L_i} \quad \text{où } k > 1 \quad (2.5a)$$

Les valeurs des tensions de référence  $V_{ref0}$  et  $V_{ref1}$  sont liées par:

$$V_{ref0} > V_{ref1} \quad (2.5b)$$

Sachant que l'on a une entrée différentielle, la tension du signal d'entrée est égale à: