**Titre:** Conception d'une bibliothèque et d'un convoluteur 3\*3TSPC

Title:

**Auteur:** Bertrand Le Chapelain

Author:

**Date:** 1999

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Le Chapelain, B. (1999). Conception d'une bibliothèque et d'un convoluteur 3\*3TSPC [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/8856/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8856/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & Yvon Savaria

Advisors:

**Programme:** Non spécifié

Program:

**UNIVERSITÉ DE MONTRÉAL**

**CONCEPTION D'UNE BIBLIOTHÈQUE

ET

D'UN CONVOLUEUR 3\*3 TSPC**

**BERTRAND LE CHAPELAIN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GENIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)**

**JUIN 1999**

© Bertrand Le Chapelain, 1999.

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-48861-6

Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

CONCEPTION D'UNE BIBLIOTHÈQUE TSPC

ET

D'UN CONVOLUEUR 3\*3 TSPC

présenté par: Le Chapelain Bertrand

en vue de l'obtention du diplôme de: Maîtrise ès Sciences Appliquées

a été dûment accepté par le jury d'examen constitué de:

M. SAWAN Mohamed, Ph. D., président

M. BOIS Guy, Ph. D., membre et directeur de recherche

M. SAVARIA Yvon, Ph. D., membre et directeur de recherche

M. BLAQUIÈRE Yves, Ph. D., membre

## REMERCIEMENTS

Je désire remercier mon directeur de recherche M. Guy Bois pour son attention, ses conseils et sa disponibilité en tout temps. Son appui et sa compréhension, tout au long de ma maîtrise, m'ont permis de me sentir à l'aise pour discuter ouvertement de tout problème. J'aimerais également exprimer ma gratitude envers mon codirecteur de recherche, M. Yvon Savaria pour m'avoir accepté dans son groupe de recherche en microélectronique. Je le remercie d'avoir trouvé le temps de suivre le déroulement de mes travaux et de les avoir orientés dans de nouvelles directions. Le partage de sa vision des choses, en particulier pour les applications de mes travaux, a été une source de réflexion constante. Je les remercie pour leur soutien matériel, ainsi que Design Workshop et Hyperchip pour m'avoir financé lors de mes études.

Je tiens également à remercier les nombreuses personnes qui ont contribué aux différents projets de ma maîtrise lors d'application de cours et de stages. Kamel Ridouh pour m'avoir formé sur la plupart des outils de la microélectronique, Youcef Fouzar, Alexandre Méchain, Robert Chehi, Jean-Christophe Petit et Ginette Monté pour leur participation au convolueur. Jérôme Laporte et Bernard Antaki pour m'avoir aidé à développer des bibliothèques de cellules TSPC.

Enfin, je profite de l'occasion pour dire merci à tous les étudiants du laboratoire GRM94 qui ont pu m'offrir leurs conseils lors des deux dernières années, notamment Mathieu Gagnon pour ses nombreux conseils sur Cadence et Réjean Lepage pour le maintien d'un réseau stable.

## RÉSUMÉ

Dans ce mémoire, nous présentons une heuristique des bascules bâtie selon le style de conception des circuits à horloge monophasée (True Single Phase Clock, TSPC). Des études précédentes ont montré que les circuits TSPC peuvent opérer à de très grandes fréquences. Notre but est d'implémenter de gros blocs logiques qui peuvent opérer à 1 GHz ou plus (en technologie CMOS 0.35 um). Notre stratégie a débuté avec le développement d'une bibliothèque de base selon une méthode ad-hoc. Une méthode rapide semi-automatique a alors été développée pour réduire le nombre de simulations. Basé sur l'expérience acquise lors des optimisations TSPC, nous proposons un algorithme d'optimisation automatique des cellules TSPC et une méthode pour réaliser des bibliothèques de cellules logiques standards. Ce mémoire décrit les différentes étapes à suivre pour élaborer une bibliothèque TSPC. La méthode et la bibliothèque de cellules sont validées par la caractérisation de petits blocs logiques.

Une version TSPC (True Single Phase Clock) très haute fréquence d'un convoluteur  $3 \times 3$  est également développée. La régularité de l'opération de convolution en fait une candidate idéale pour une réalisation basée sur la technique de conception TSPC. Ce convoluteur TSPC permet d'entrevoir les limites de performance d'un coprocesseur conçu à l'aide d'une technologie CMOS à 0.35 microns.

## ABSTRACT

In this memory, we present a heuristic study of split-output latches built according to the true single-phase clocked circuits (TSPC) design style. Previous studies have shown that TSPC circuits can operate at very high frequencies. Our goal is to implement large digital building blocks operating at 1 GHz or more (in 0.35  $\mu$ m CMOS technology). Our methodology started with the development of a first set of cells based on ad-hoc design. A fast semi automatic method was then developed to reduce the number of simulations. Based on the experience acquired with TSPC optimization, we proposed an automatic algorithm to optimize TSPC cells and a method to realize libraries of logical standard cells. This memory describes the different steps followed to elaborate the TSPC library. The method and the cell library are validated by characterizing small digital building blocks.

A very high speed TSPC (True Single Phase Clock) version of the 3\*3 convolver's datapath is also shown. The regularity of the 2-D convolution makes it an ideal candidate for the fine-grained pipelining associated with the TSPC scheme. The design of the TSPC convolver shows the performance limits which can be achieved by a coprocessor based on a CMOS 0.35 micron technology.

## TABLE DES MATIÈRES

|                                                                                            |            |

|--------------------------------------------------------------------------------------------|------------|

| <b>REMERCIEMENTS.....</b>                                                                  | <b>IV</b>  |

| <b>RÉSUMÉ.....</b>                                                                         | <b>V</b>   |

| <b>ABSTRACT .....</b>                                                                      | <b>VI</b>  |

| <b>TABLE DES MATIÈRES.....</b>                                                             | <b>VII</b> |

| <b>LISTE DES TABLEAUX.....</b>                                                             | <b>X</b>   |

| <b>LISTE DES FIGURES .....</b>                                                             | <b>XI</b>  |

| <b>INTRODUCTION.....</b>                                                                   | <b>1</b>   |

| <b>CHAPITRE 1 : METHODE DE CONCEPTION D'UNE</b>                                            |            |

| <b>BIBLIOTHEQUE TSPC .....</b>                                                             | <b>10</b>  |

| 1.1    Bascules dynamiques synchronisées par des horloges monophasées.....                 | 10         |

| 1.1.1    Introduction .....                                                                | 10         |

| 1.1.2    Configurations de bascules et de portes TSPC .....                                | 11         |

| 1.2    Méthode d'optimisation d'une bibliothèque TSPC. ....                                | 14         |

| 1.2.1    Introduction .....                                                                | 14         |

| 1.2.2    Une méthode d'optimisation systématique.....                                      | 15         |

| 1.2.3    Méthode d'optimisation des bascules selon trois dimensions. ....                  | 18         |

| 1.2.4    Méthode d'optimisation à partir d'un outil d'optimisation d'un<br>simulateur..... | 19         |

| 1.3    Méthode d'optimisation de la taille des transistors.....                            | 20         |

|                                                              |                                                                                    |           |

|--------------------------------------------------------------|------------------------------------------------------------------------------------|-----------|

| 1.3.1                                                        | Règles d'optimisation.....                                                         | 22        |

| 1.3.1.1                                                      | Banc d'essai .....                                                                 | 22        |

| 1.3.1.2                                                      | Critères d'optimisation .....                                                      | 23        |

| 1.3.1.3                                                      | Modèle utilisé pour la simulation. ....                                            | 24        |

| 1.3.2                                                        | Étapes d'optimisation pour élaborer une bibliothèque TSPC.....                     | 24        |

| 1.3.2.1                                                      | Modèle utilisé pour la simulation. ....                                            | 25        |

| 1.3.2.2                                                      | Algorithme d'optimisation automatique d'une bibliothèque<br>de cellules TSPC ..... | 27        |

| 1.3.3                                                        | Résultats de la bibliothèque de cellules TSPC.....                                 | 29        |

| 1.3.3.1                                                      | Tailles des différentes cellules:.....                                             | 29        |

| 1.3.3.2                                                      | Performance obtenue dans la technologie 0.35 mm .....                              | 30        |

| 1.3.3.3                                                      | Étude d'une cellule xor TSPC. ....                                                 | 33        |

| 1.3.3.4                                                      | Problèmes des cellules TSPC à sortie partagée .....                                | 36        |

| 1.4                                                          | Conclusion.....                                                                    | 38        |

| <b>CHAPITRE 2 : ARCHITECTURE DU CONVOLUEUR 3*3 TSPC.....</b> |                                                                                    | <b>40</b> |

| 2.1                                                          | Introduction .....                                                                 | 40        |

| 2.1.1                                                        | La convolution 2D.....                                                             | 41        |

| 2.2                                                          | Fonction au niveau système du convoluteur 3*3 .....                                | 43        |

| 2.2.1                                                        | Oscillateur à tension commandé .....                                               | 43        |

| 2.2.2                                                        | Générateur de vecteurs pseudo-aléatoires .....                                     | 43        |

| 2.2.3                                                        | Filtres de convolution (ROM).....                                                  | 44        |

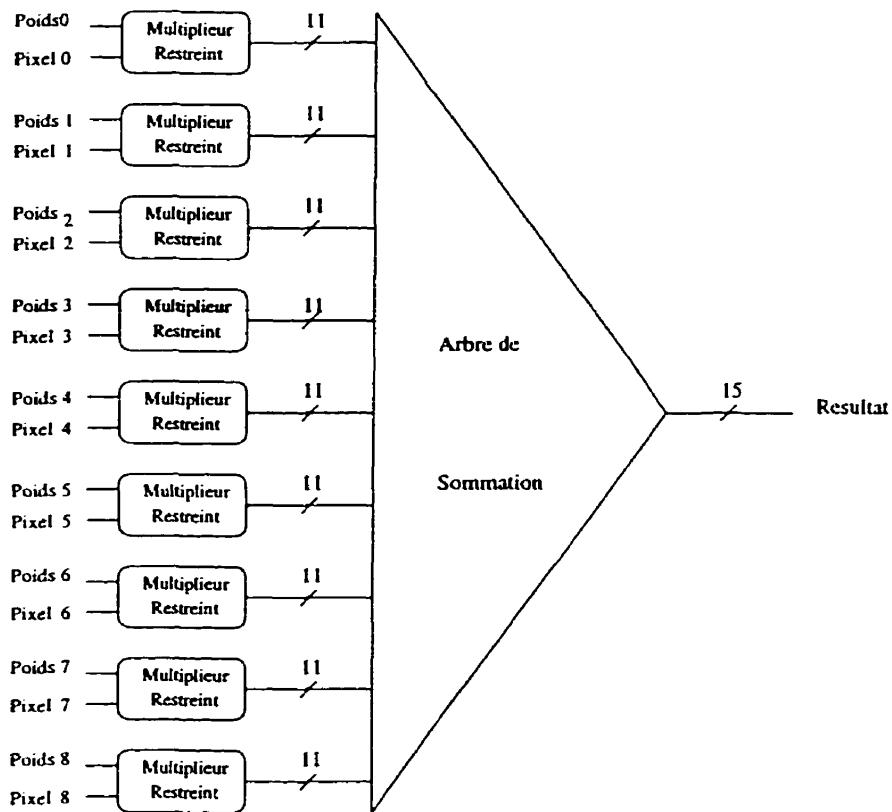

| 2.2.4                                                        | Multiplieurs restreints .....                                                      | 45        |

| 2.2.5                                                        | Module de sommation.....                                                           | 46        |

| 2.2.6                                                        | Compacteur (analyse de signatures).....                                            | 48        |

| 2.2.7                                                        | Démultiplexeur.....                                                                | 49        |

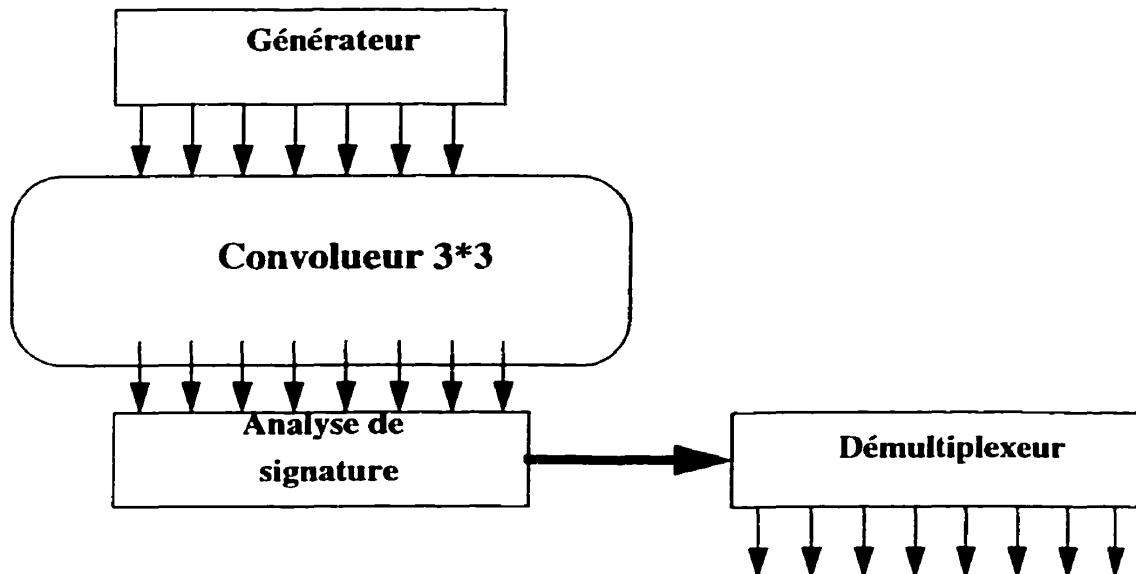

| 2.2.8                                                        | Schéma bloc (figure 2.5) et signaux.....                                           | 49        |

| 2.3                                                          | Conception des cellules de base du convoluteur 3*3 TSPC.....                       | 52        |

|       |                                                           |    |

|-------|-----------------------------------------------------------|----|

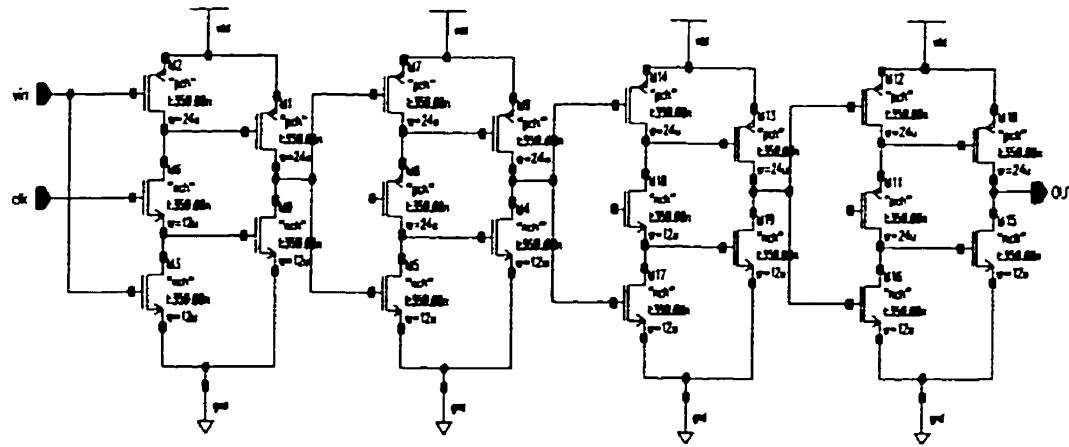

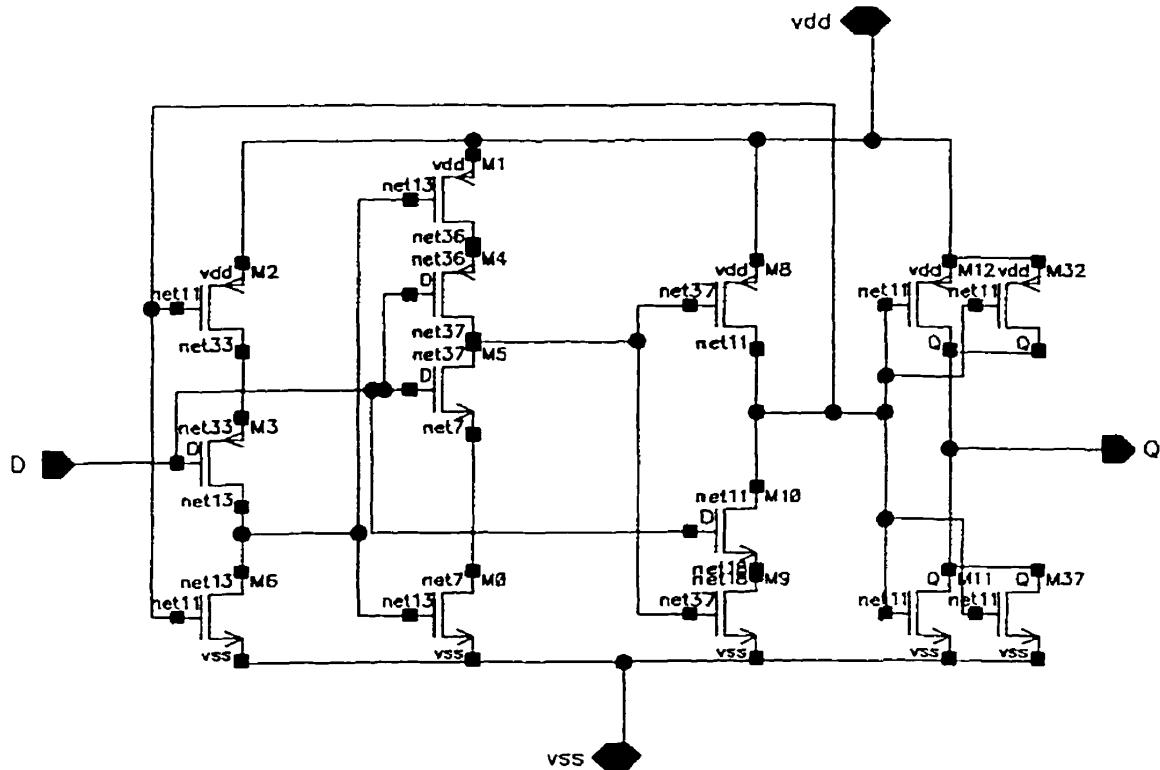

| 2.3.1 | La cellule registre à décalage .....                      | 53 |

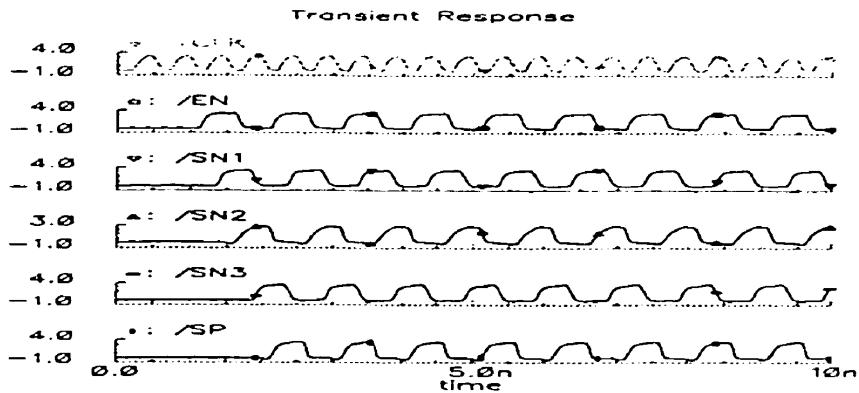

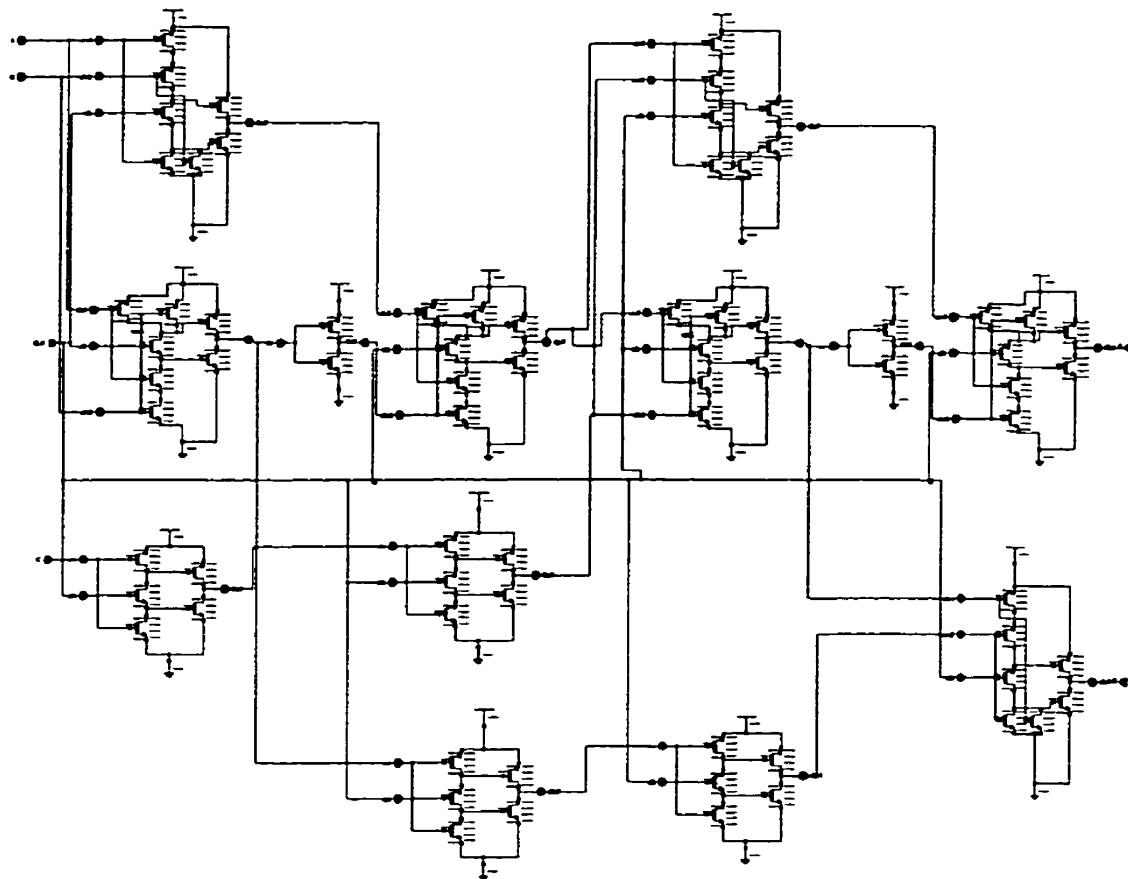

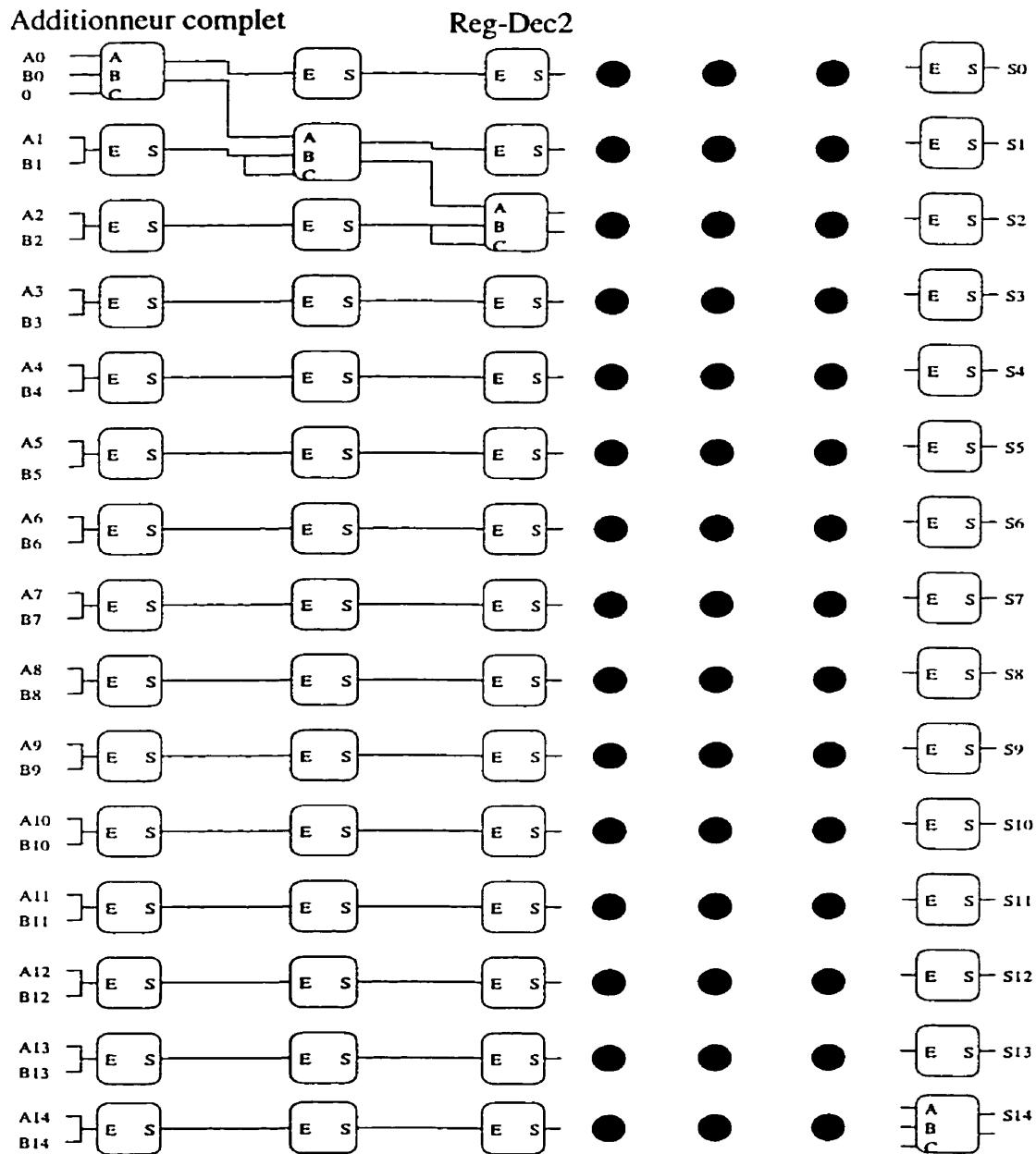

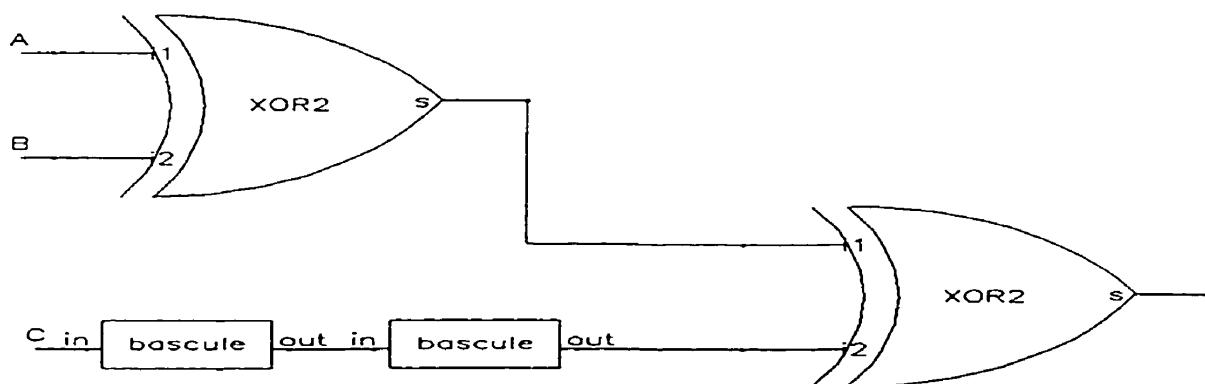

| 2.3.2 | Additionneur complet.....                                 | 55 |

| 2.3.3 | Multiplieur-restreint .....                               | 60 |

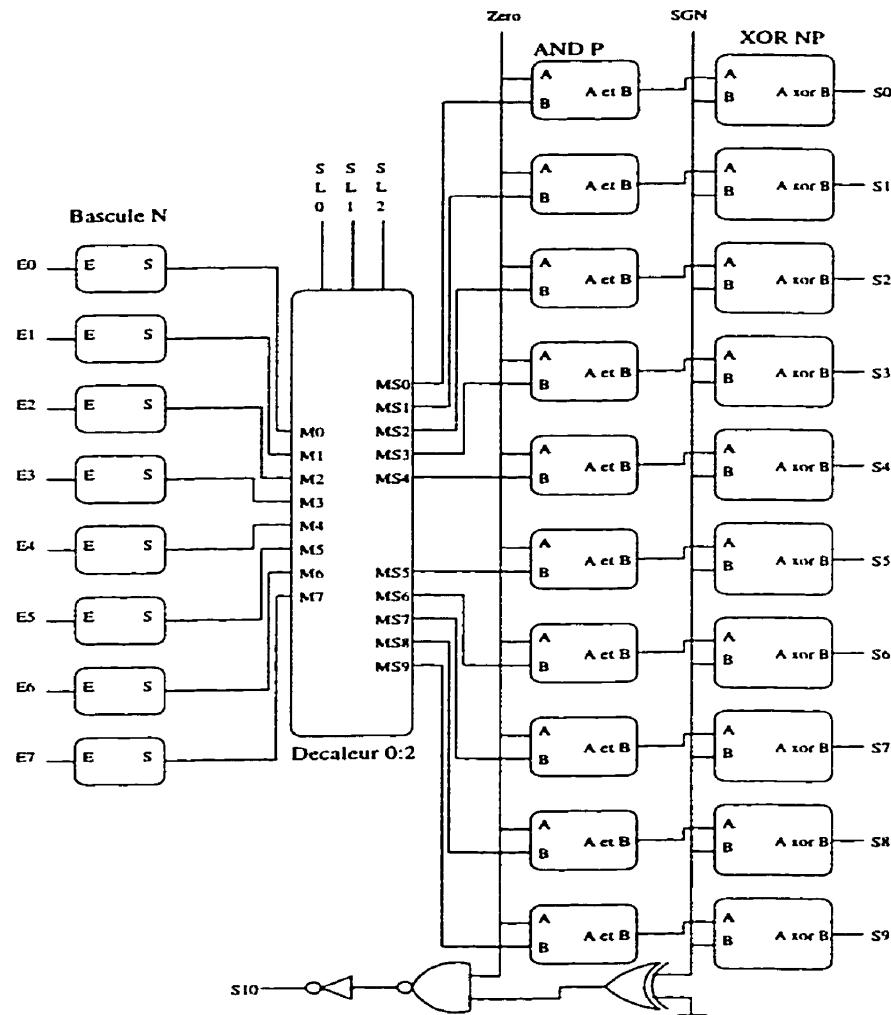

| 2.4   | Architecture du chemin de données du convoluteur 3*3..... | 67 |

| 2.4.1 | Les multiplieurs restreints .....                         | 67 |

| 2.4.2 | L'Arbre de sommation .....                                | 68 |

## **CHAPITRE 3 : BLOCS DE TEST ET MÉTHODE DE CONCEPTION DU CONVOLUEUR 3\*3..... 75**

|       |                                                             |     |

|-------|-------------------------------------------------------------|-----|

| 3.1   | Introduction .....                                          | 75  |

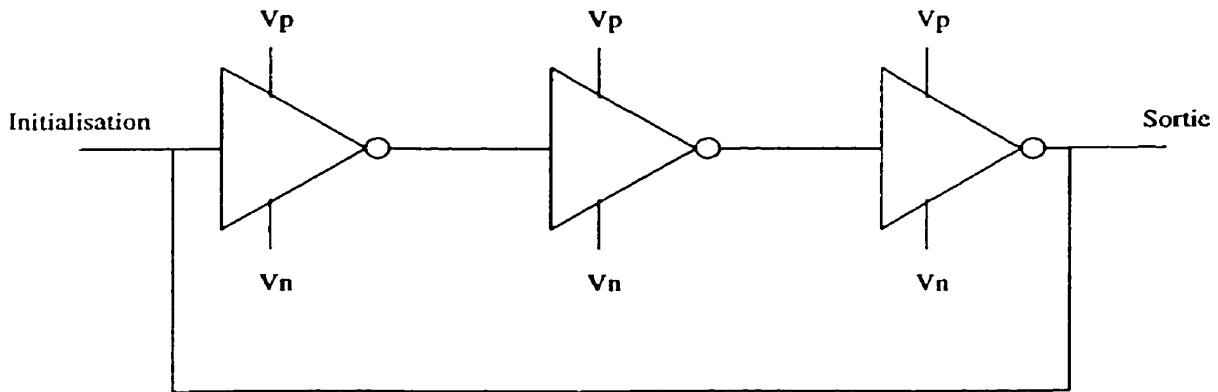

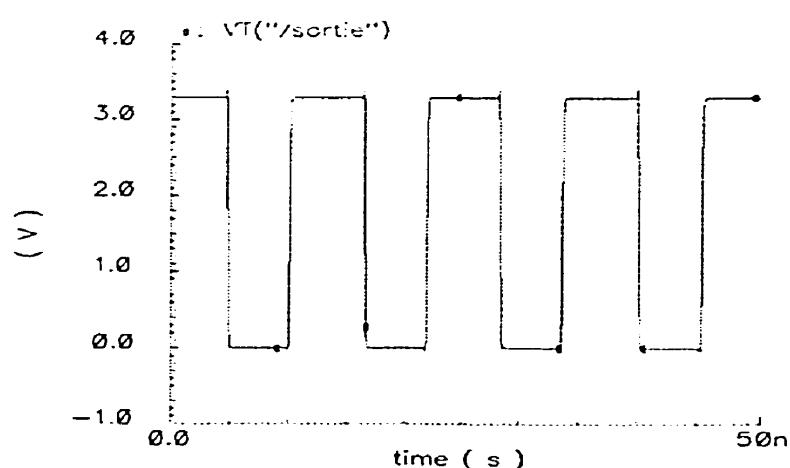

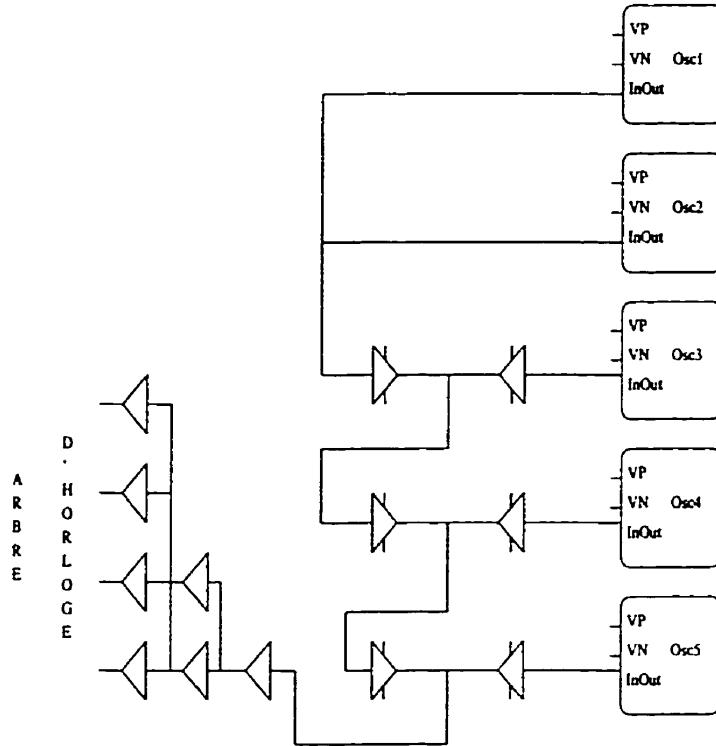

| 3.2   | Bloc "oscillateurs" .....                                   | 75  |

| 3.2.1 | Oscillateurs utilisés .....                                 | 75  |

| 3.2.2 | Assemblage des oscillateurs.....                            | 82  |

| 3.2.3 | Diviseur de fréquence .....                                 | 83  |

| 3.3   | Bloc Générateur de vecteurs pseudo-aléatoires.....          | 84  |

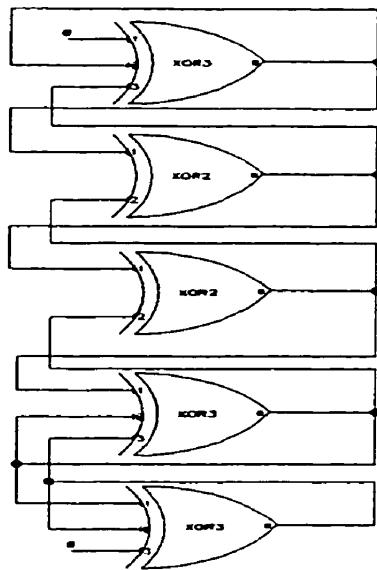

| 3.3.1 | Principe des Automates Cellulaires .....                    | 86  |

| 3.3.2 | Représentation d'une règle d'Automate Cellulaire .....      | 88  |

| 3.3.3 | Représentation TSPC d'une règle d'Automate Cellulaire ..... | 90  |

| 3.4   | Bloc "Analyse de signature" .....                           | 94  |

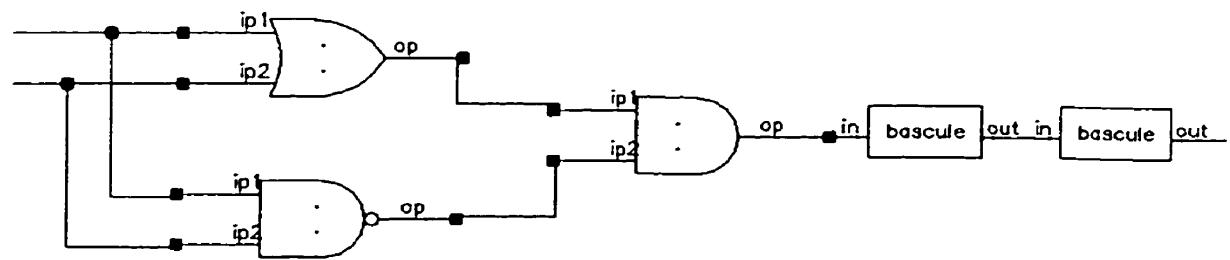

| 3.4.1 | Présentation du circuit Analyse de Signature.....           | 94  |

| 3.5   | Démultiplexeur de haute performance .....                   | 97  |

| 3.6   | ROM .....                                                   | 102 |

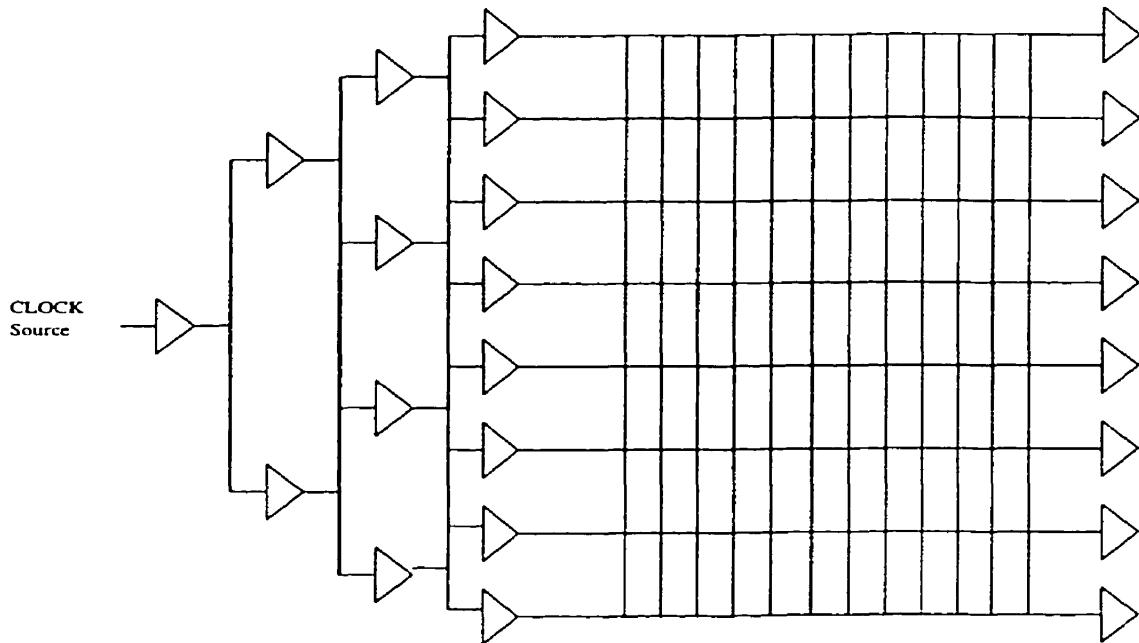

| 3.7   | Méthode de Distribution de l'Horloge .....                  | 106 |

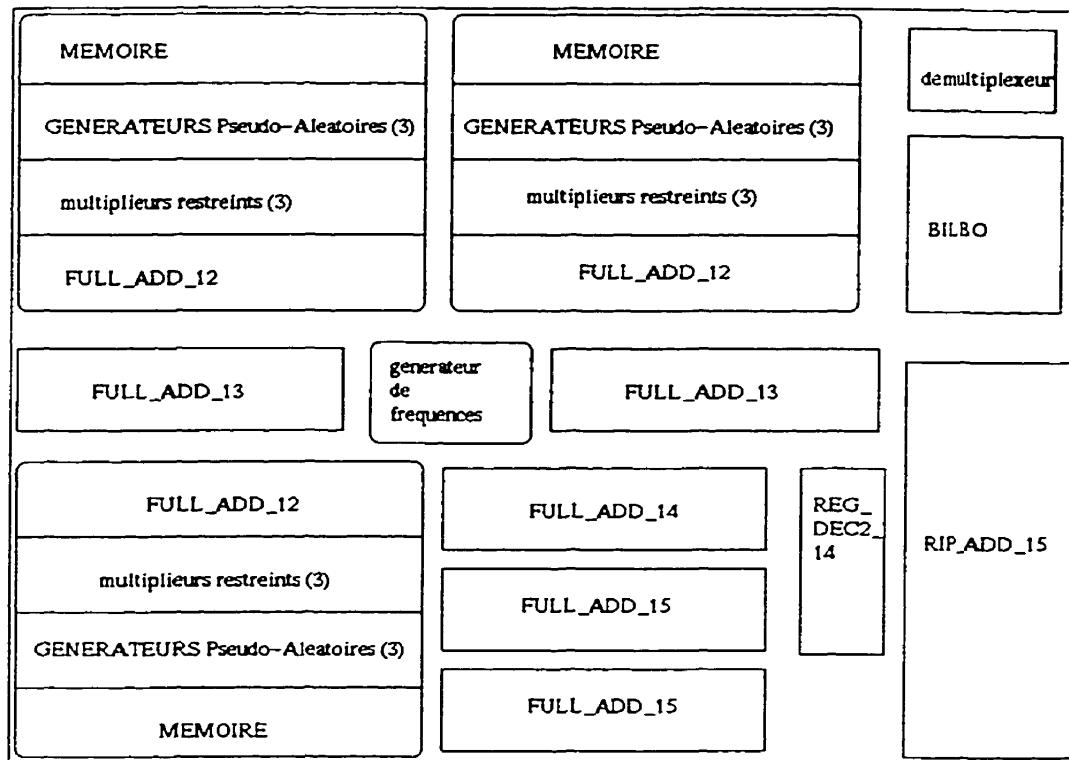

| 3.8   | Méthode de Placement et Routage .....                       | 109 |

| 3.8.1 | Outils Utilisés .....                                       | 113 |

| 3.8.2 | Dissipation de puissance .....                              | 113 |

| 3.9   | Conclusion .....                                            | 115 |

|                            |            |

|----------------------------|------------|

| <b>CONCLUSION .....</b>    | <b>116</b> |

| <b>BIBLIOGRAPHIE .....</b> | <b>119</b> |

| <b>ANNEXES .....</b>       | <b>122</b> |

## LISTE DES TABLEAUX

|                                                                                                        |     |

|--------------------------------------------------------------------------------------------------------|-----|

| Tableau 2.1 : Opérations du multiplicateur restreint.....                                              | 45  |

| Tableau 2.2 : Complexité du multiplicateur restreint.....                                              | 66  |

| Tableau 2.3 : Complexité de l'arbre de sommation.....                                                  | 72  |

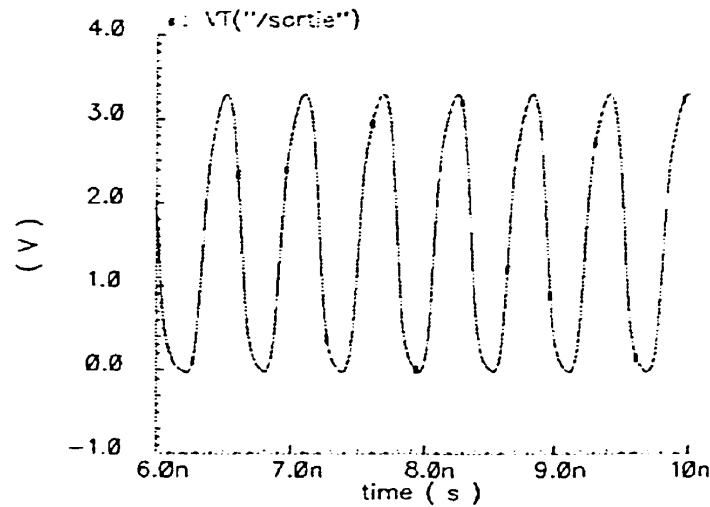

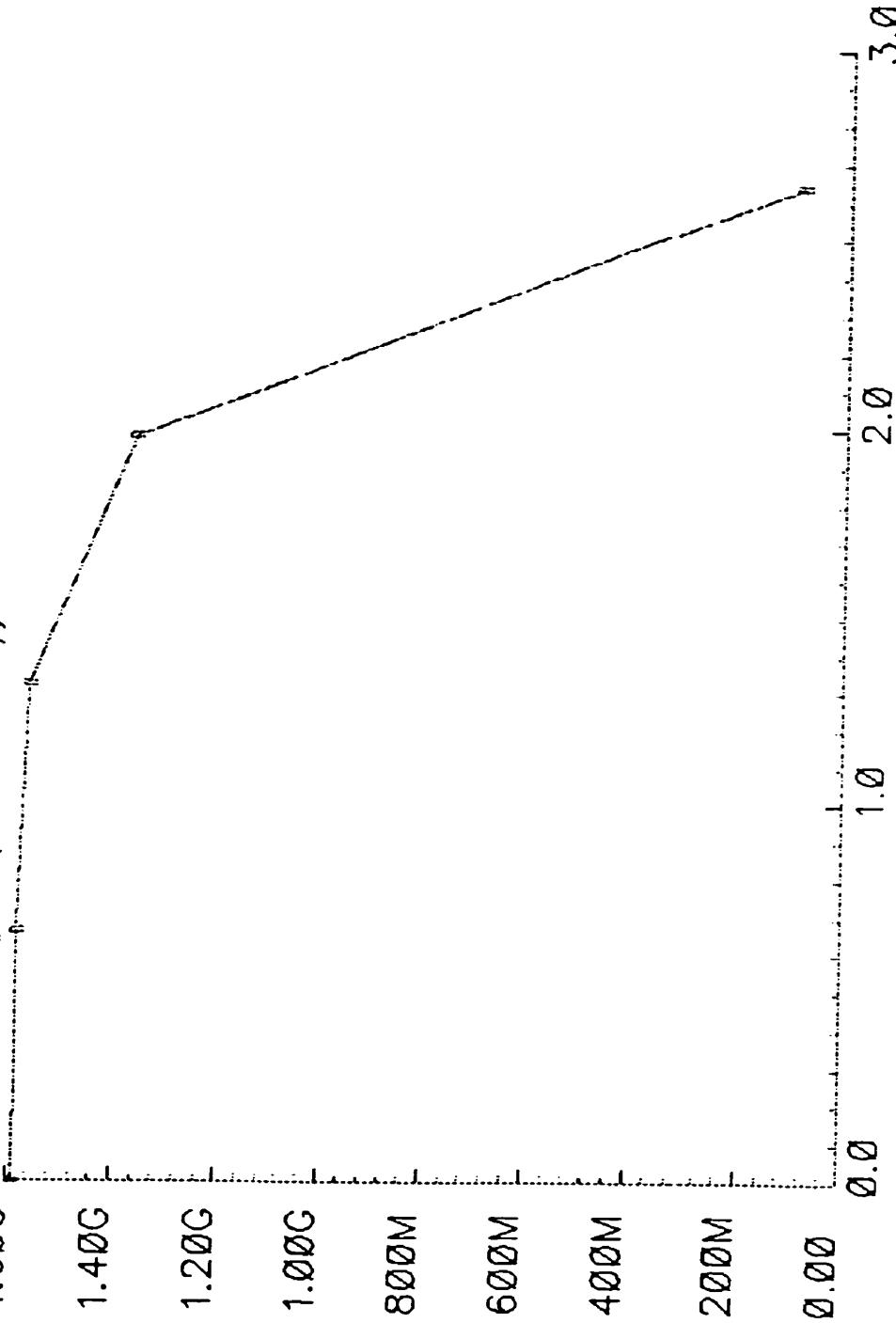

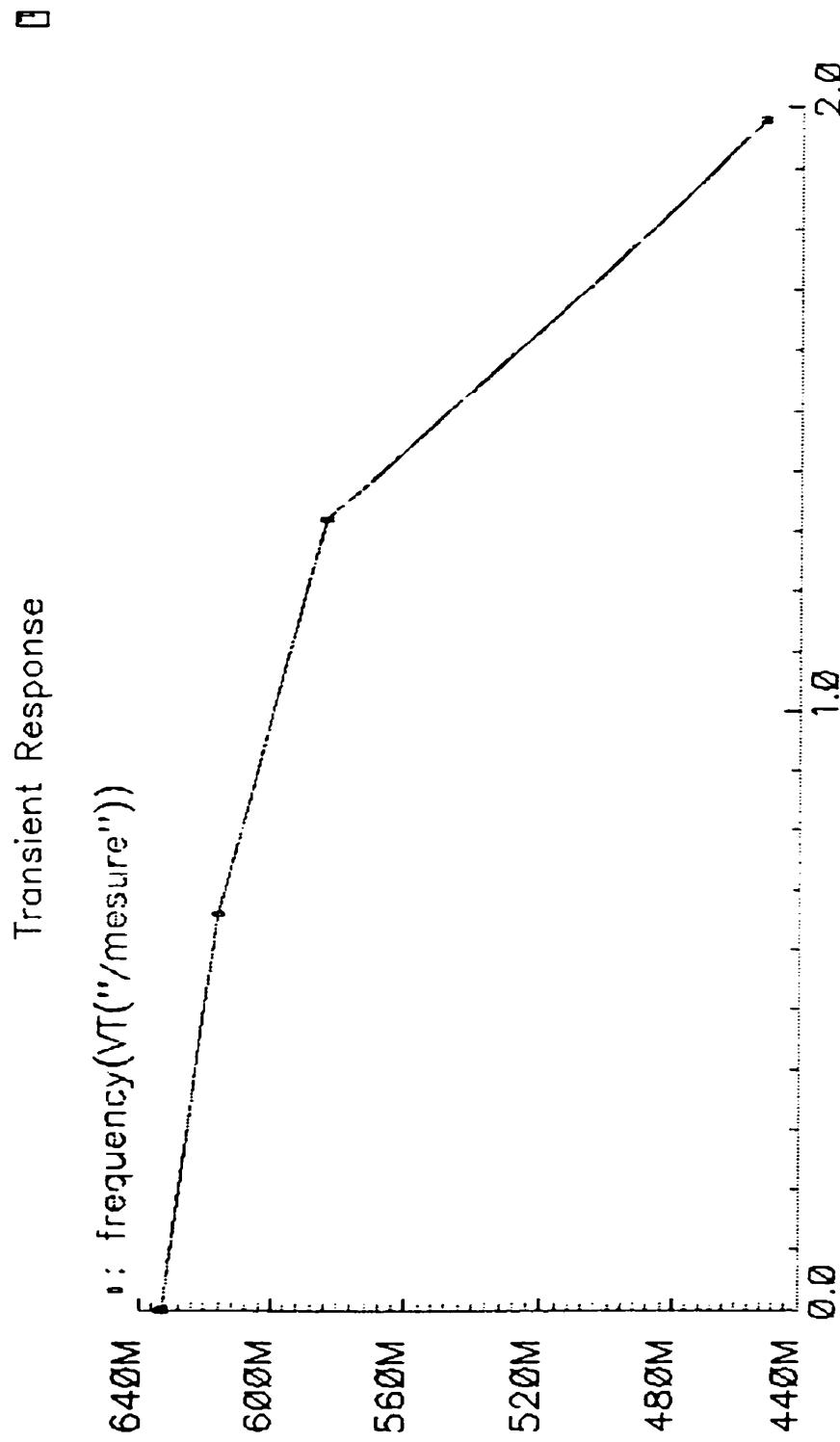

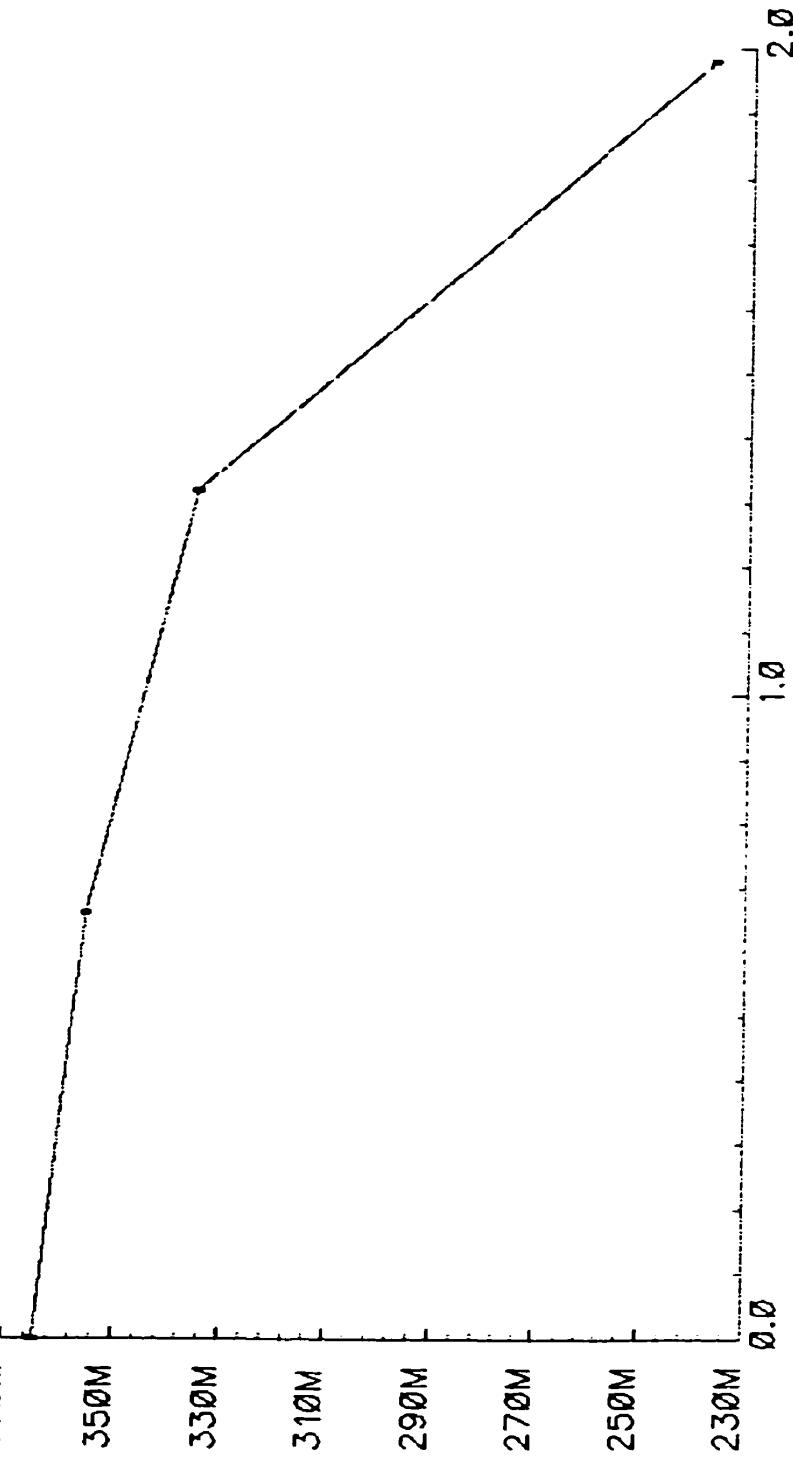

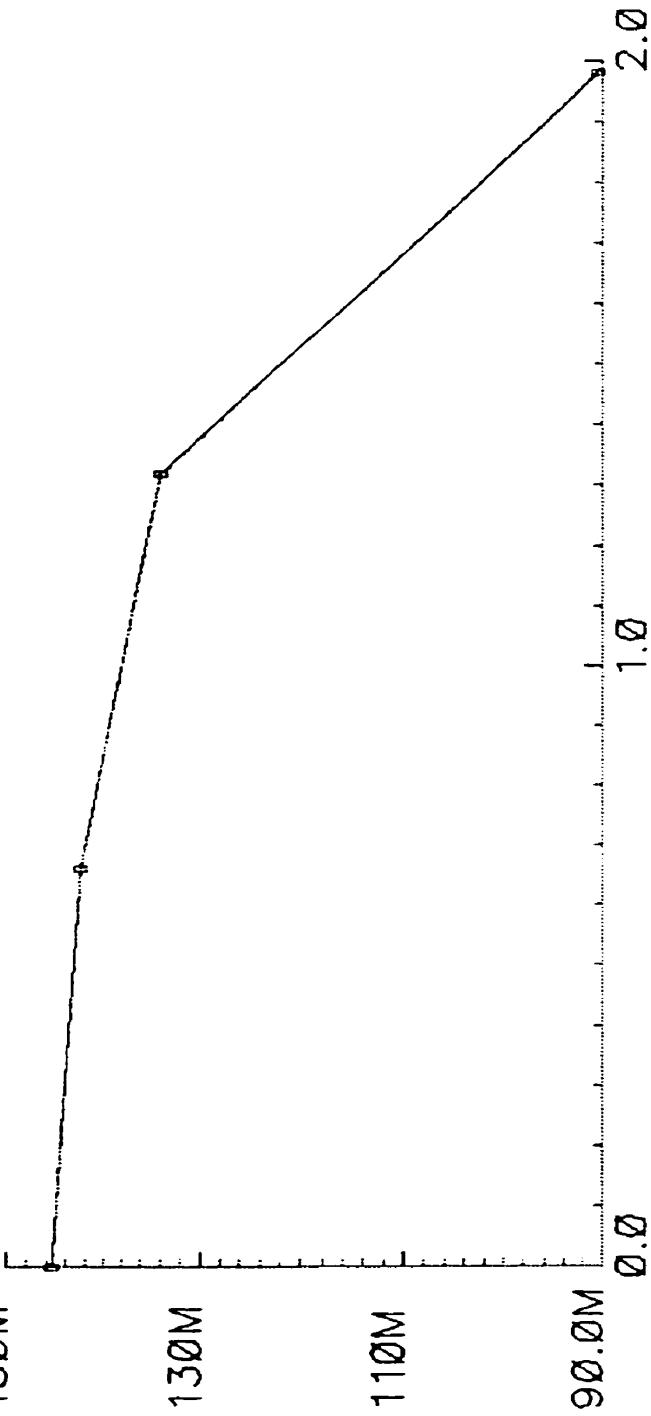

| Tableau 3.1 : fréquence d'oscillation(GHz) pour Osci1 en fonction de la polarisation<br>vp et vn. .... | 76  |

| Tableau 3.2 : fréquence d'oscillation(GHz) pour Osci2 en fonction de la polarisation<br>vp et vn. .... | 77  |

| Tableau 3.3 : fréquence d'oscillation(GHz) pour Osci3 en fonction de la polarisation<br>vp et vn. .... | 77  |

| Tableau 3.4 : fréquence d'oscillation(GHz) pour Osci4 en fonction de la polarisation<br>vp et vn. .... | 78  |

| Tableau 3.5 : fréquence d'oscillation(GHz) pour Osci5 en fonction de la polarisation<br>vp et vn. .... | 79  |

| Tableau 3.6 : Paramètres des oscillateurs utilisés.....                                                | 80  |

| Tableau 3.7 : Table de vérité de la règle 90 .....                                                     | 87  |

| Tableau 3.8 : Règles de construction .....                                                             | 89  |

| Tableau 3.9 : Complexité du compteur 10.....                                                           | 96  |

| Tableau 3.10 : Valeur des poids de convolution .....                                                   | 102 |

## LISTE DES FIGURES

|              |                                                                    |    |

|--------------|--------------------------------------------------------------------|----|

| Figure 0.1:  | Technique dynamique NORA.....                                      | 5  |

| Figure 0.2:  | Bascules TSPC.....                                                 | 5  |

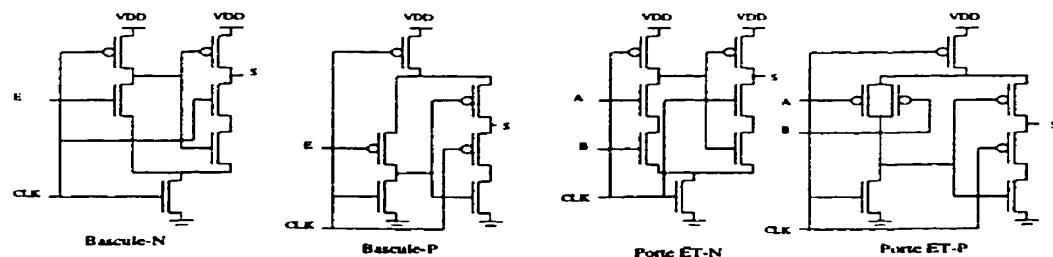

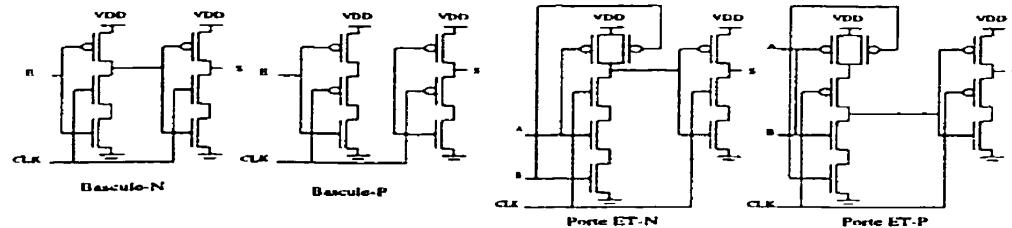

| Figure 1.1:  | Différentes configurations des cellules TSPC .....                 | 12 |

| Figure 1.2:  | Banc d'essai typique (AND à 2 entrées).....                        | 20 |

| Figure 1.3:  | Différentes étapes d'optimisation pour une bascule de type N ..... | 23 |

| Figure 1.4:  | Différentes étapes d'optimisation pour AND TSPC de type NMOS ..... | 26 |

| Figure 1.5:  | Résultats de la bibliothèque de cellules TSPC .....                | 29 |

| Figure 1.6:  | Simulation d'une chaîne de 6 bascules à 2 GHz.....                 | 30 |

| Figure 1.7:  | Schéma en logique statique d'un demi additionneur.....             | 31 |

| Figure 1.8:  | Simulation d'un demi additionneur à 1.6 GHz.....                   | 32 |

| Figure 1.9:  | Schématique et schéma des masques du Xor TSPC.....                 | 33 |

| Figure 1.10: | Simulation du Xor TSPC à 1 GHz.....                                | 34 |

| Figure 2.1:  | Fenêtre de convolution.....                                        | 40 |

| Figure 2.2:  | Exemples de masque de convolution: (masques Lapaciens) .....       | 41 |

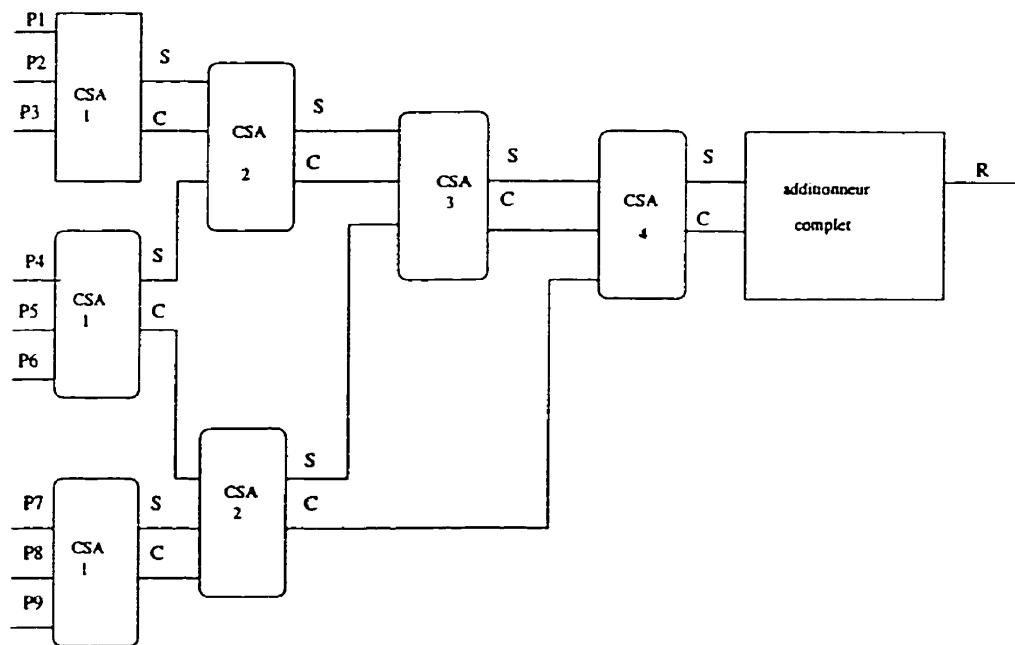

| Figure 2.3:  | Arbre de sommation .....                                           | 46 |

| Figure 2.4:  | Principe de fonctionnement du CSA .....                            | 47 |

| Figure 2.5:  | Schéma Bloc du prototype convoluteur 3*3 .....                     | 49 |

| Figure 2.6:  | chemin de données.....                                             | 52 |

| Figure 2.7:  | Registre à décalage 2 bits.....                                    | 53 |

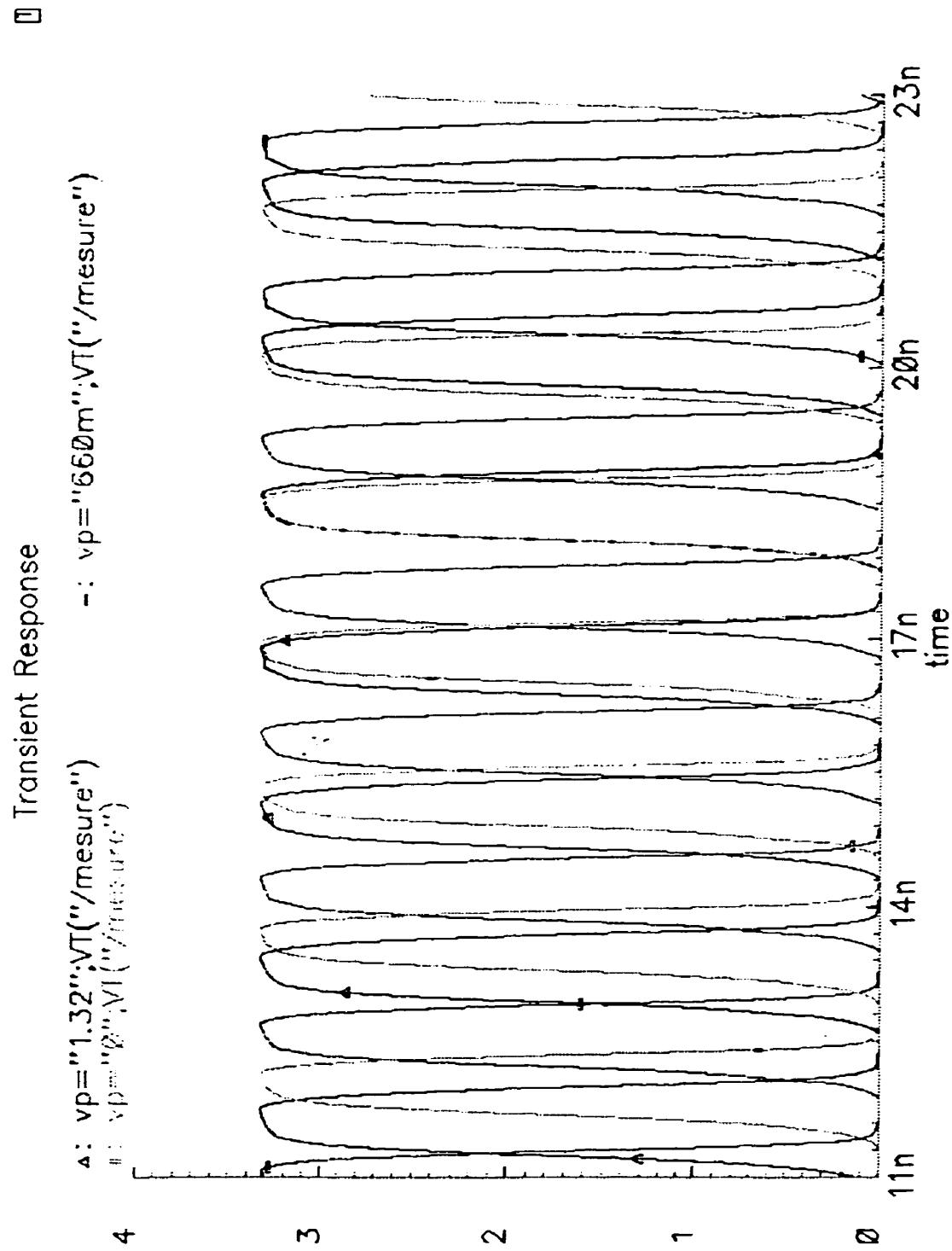

| Figure 2.8:  | Simulation à 2 GHz de la cellule registre à décalage 2 bits.....   | 54 |

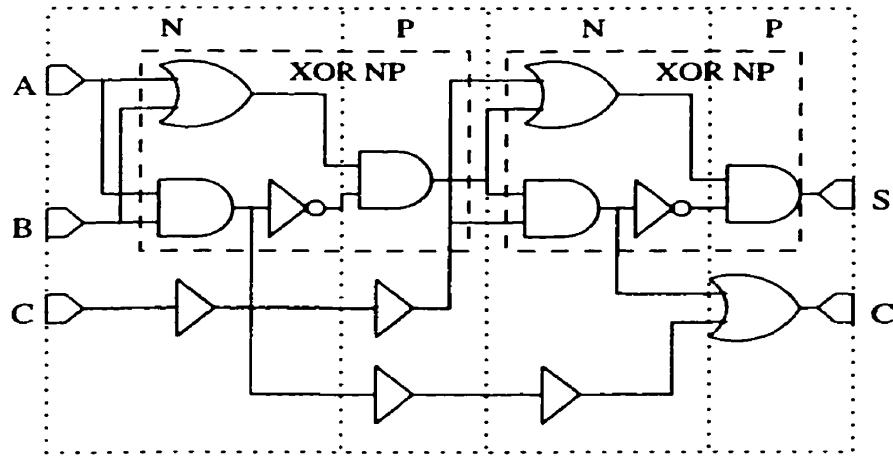

| Figure 2.9:  | Sommateur Complet du convoluteur 3*3 .....                         | 55 |

| Figure 2.10: | Schématique du additionneur complet en logique statique .....      | 57 |

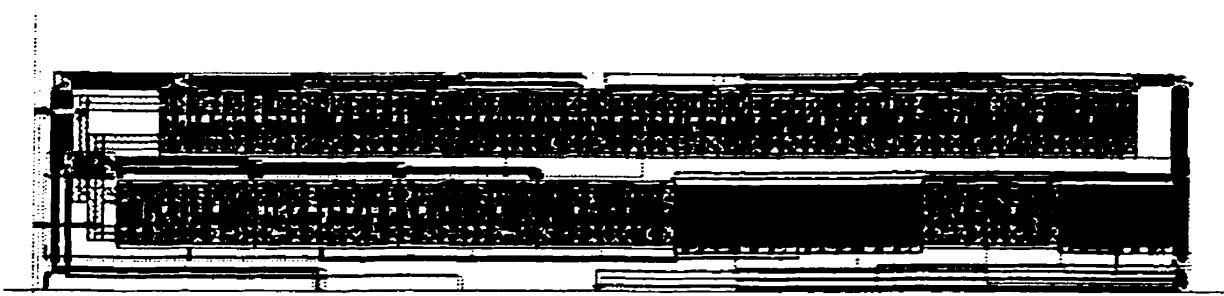

| Figure 2.11: | Simulation de l'additionneur complet à 1 GHz .....                 | 58 |

|              |                                                                                        |    |

|--------------|----------------------------------------------------------------------------------------|----|

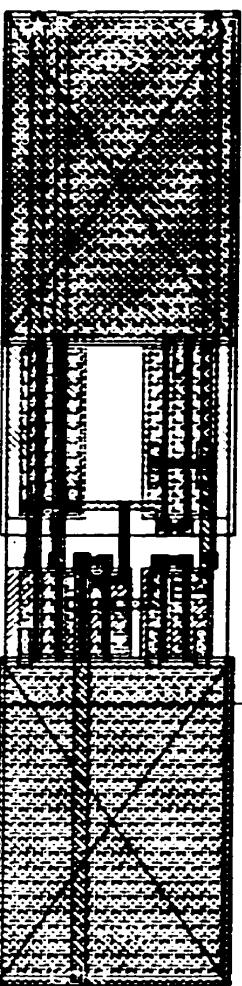

| Figure 2.12: | Schéma des masques de l'additionneur complet .....                                     | 59 |

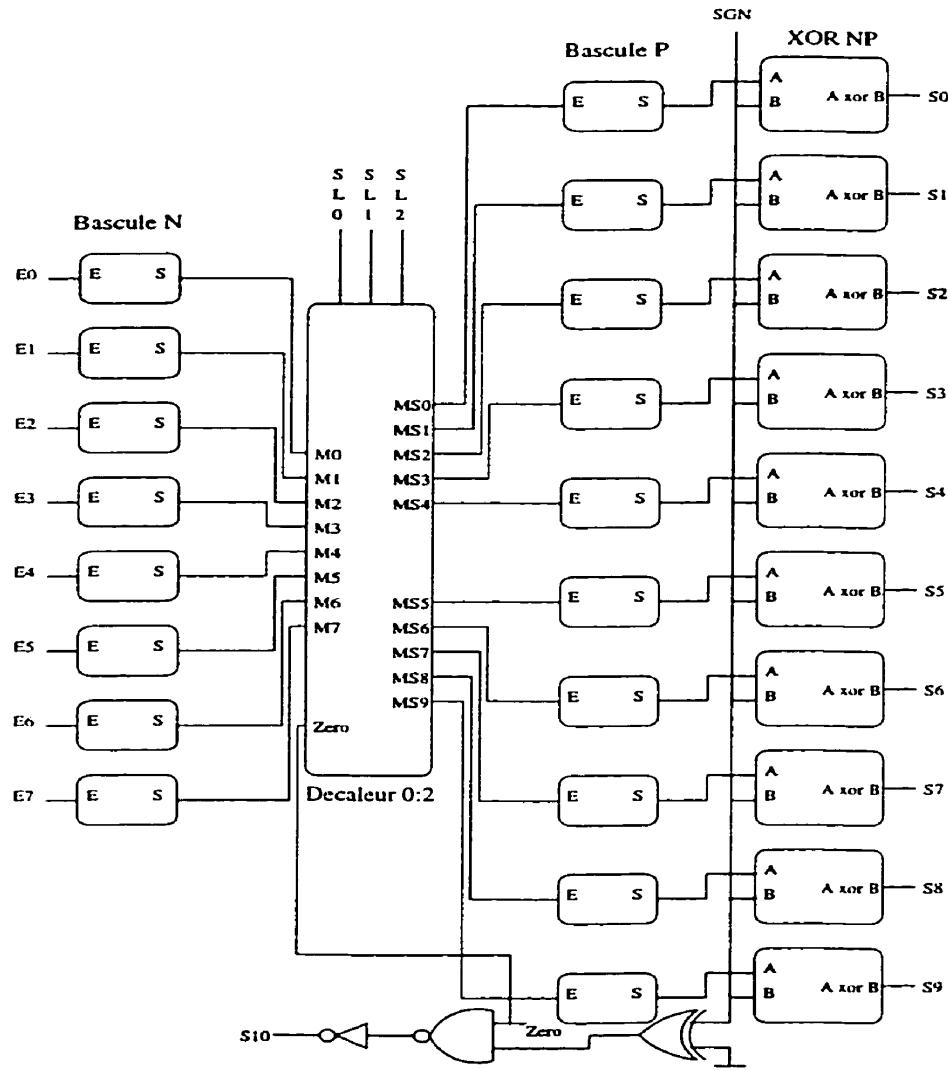

| Figure 2.13: | Cellule multiplicateur restreint .....                                                 | 60 |

| Figure 2.14: | Multiplicateur restreint avec 4 sélection dans le décaleur .....                       | 62 |

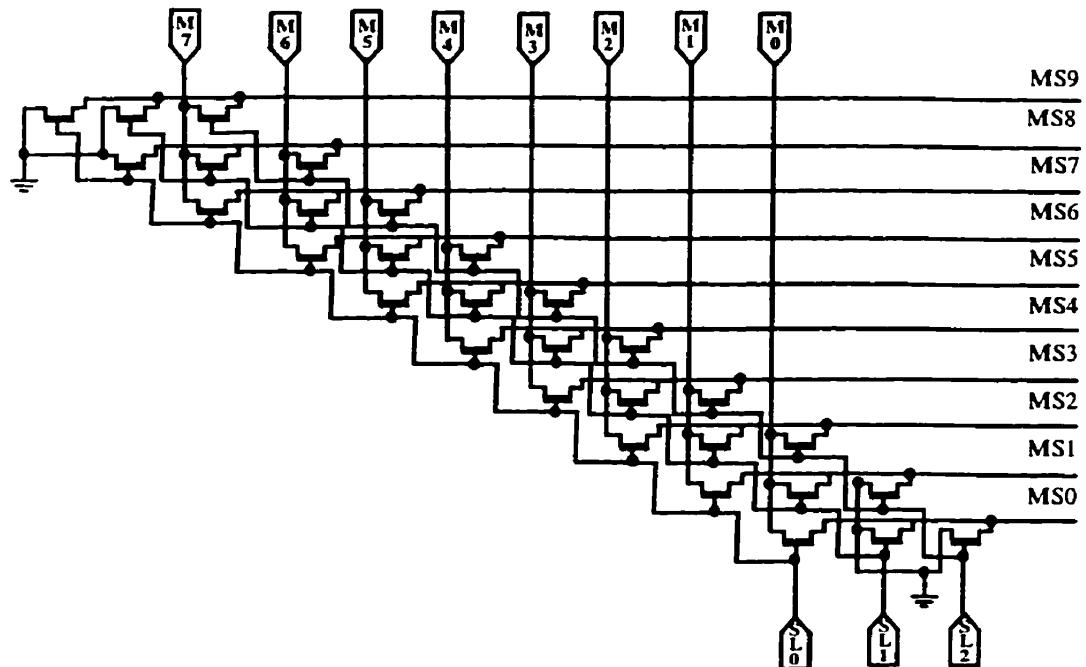

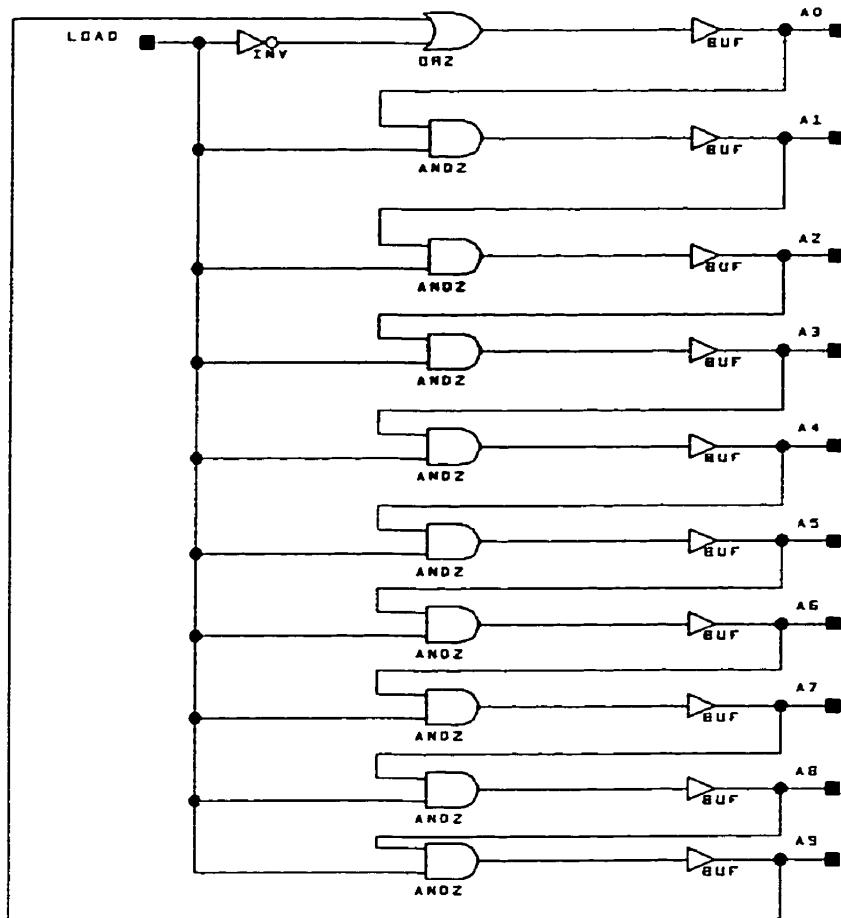

| Figure 2.15: | Décaleur (0:2) .....                                                                   | 63 |

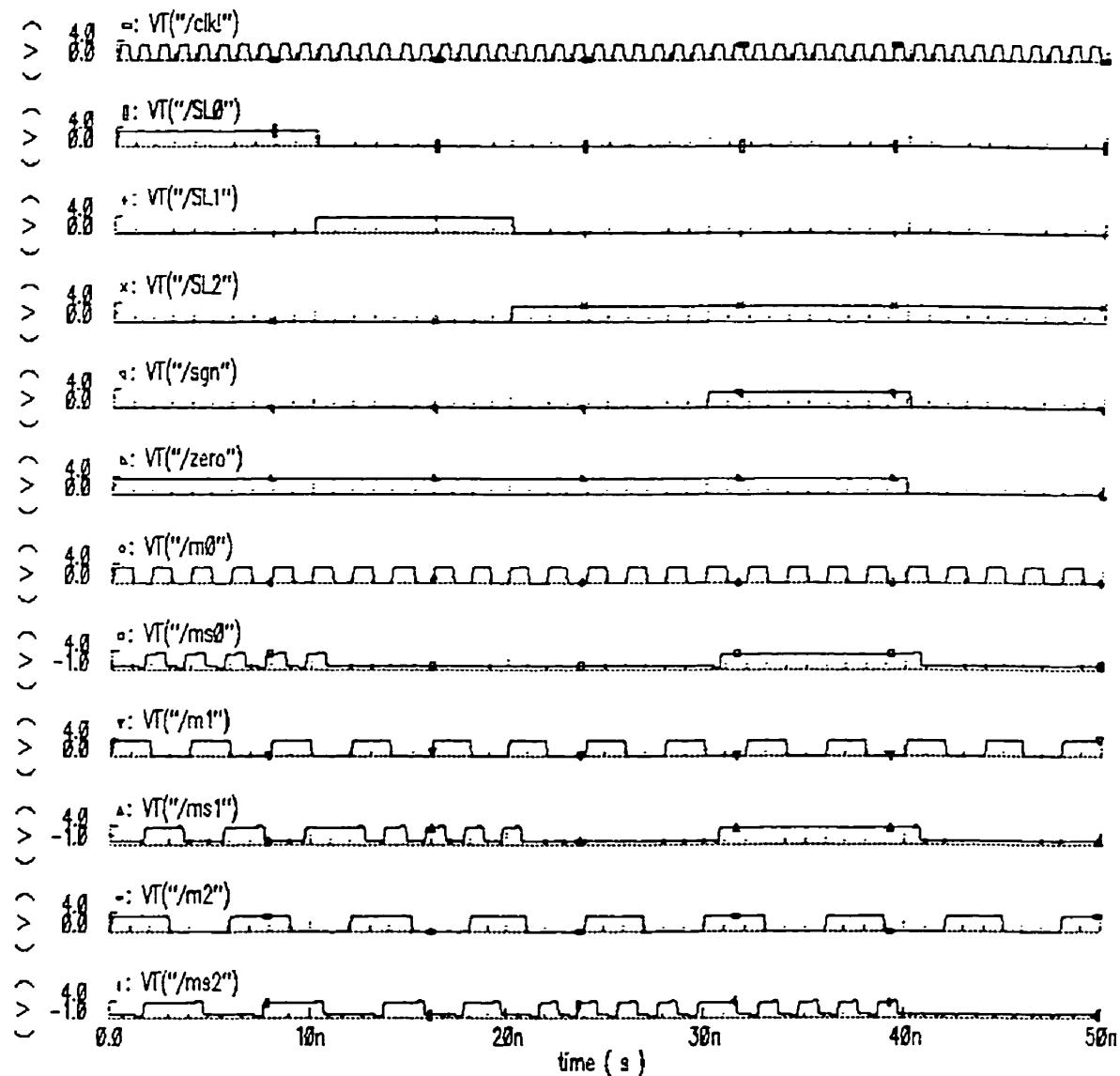

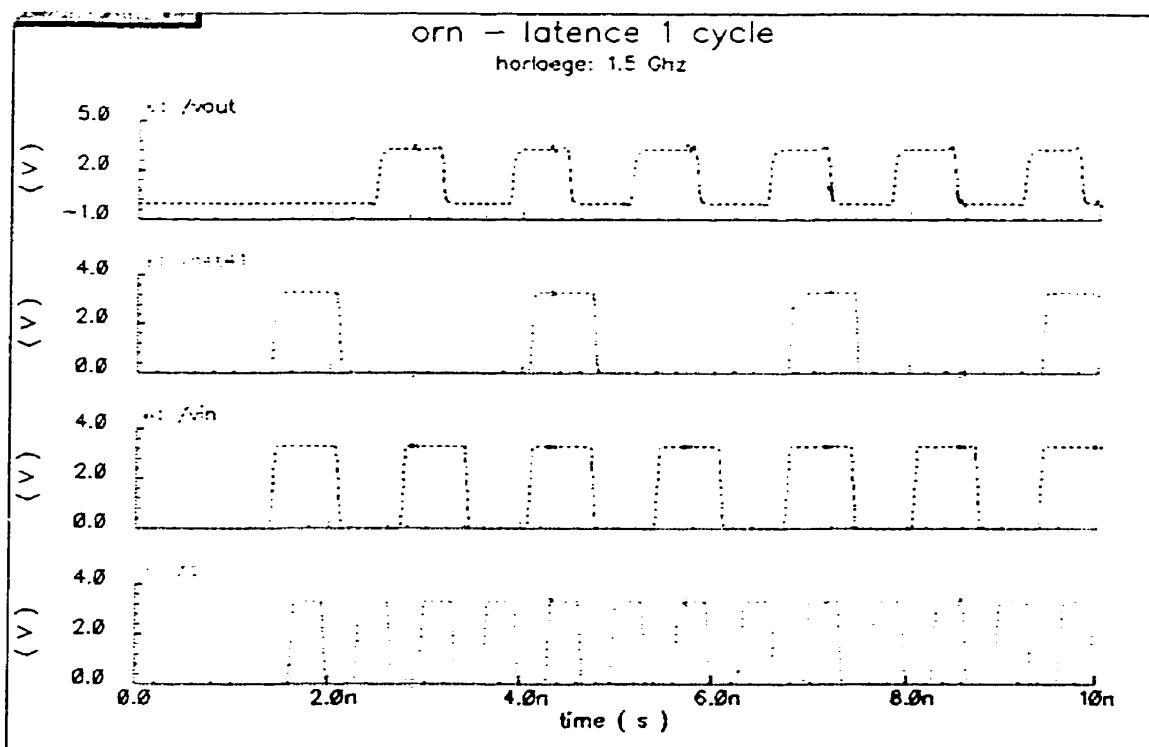

| Figure 2.16: | Simulation du multiplicateur restreint (a) .....                                       | 64 |

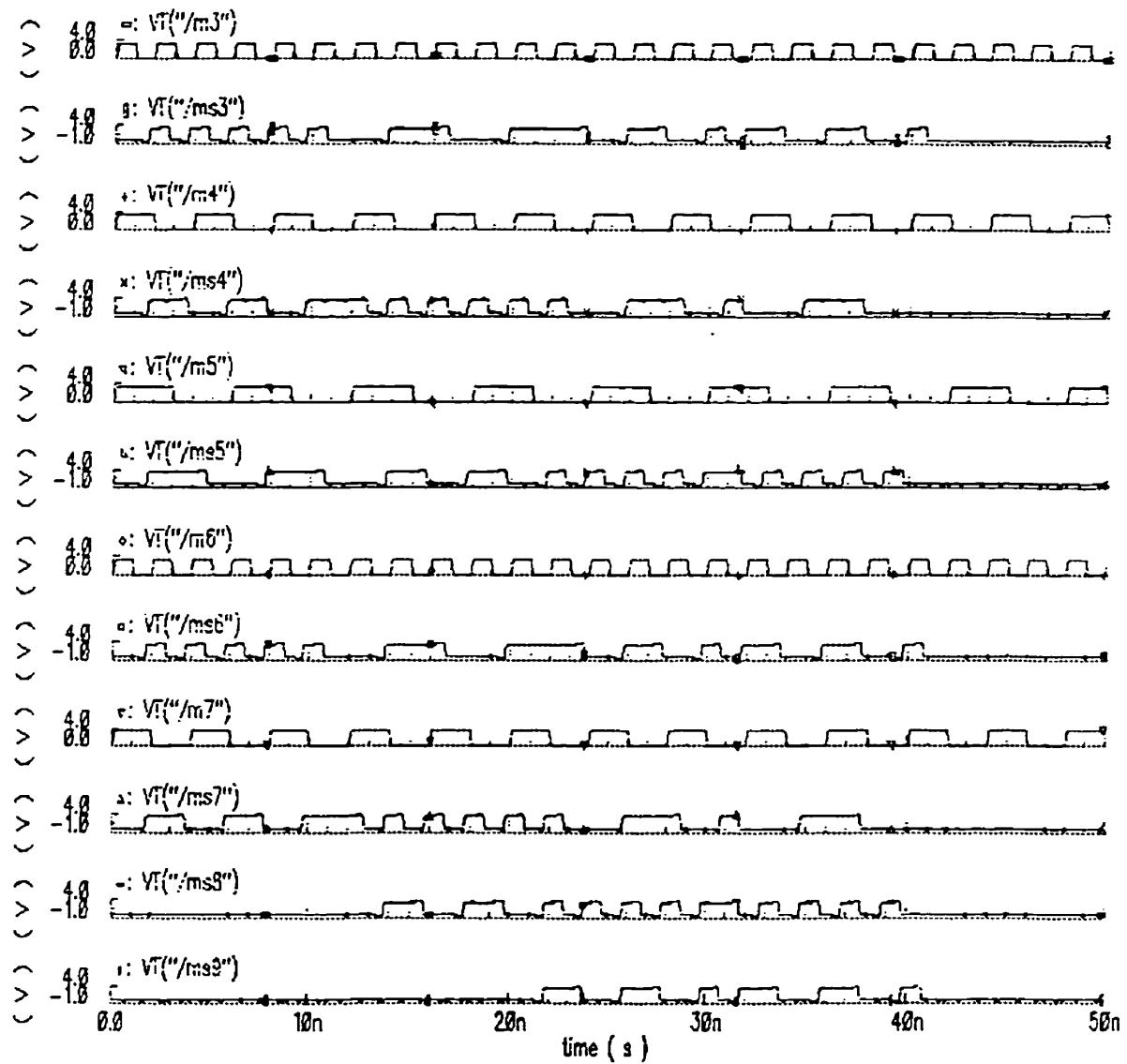

| Figure 2.17: | Simulation du multiplicateur restreint (b) .....                                       | 65 |

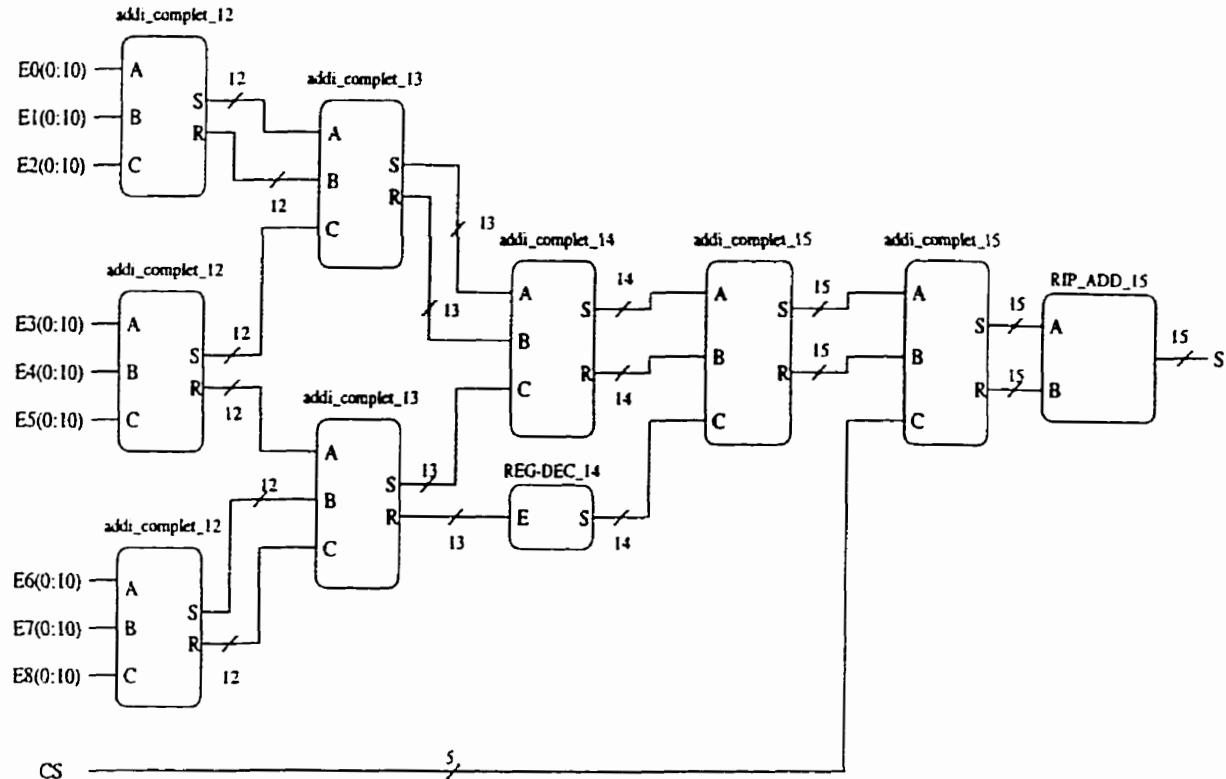

| Figure 2.18: | Arbre de sommation .....                                                               | 69 |

| Figure 2.19: | Rip-Add_15 .....                                                                       | 71 |

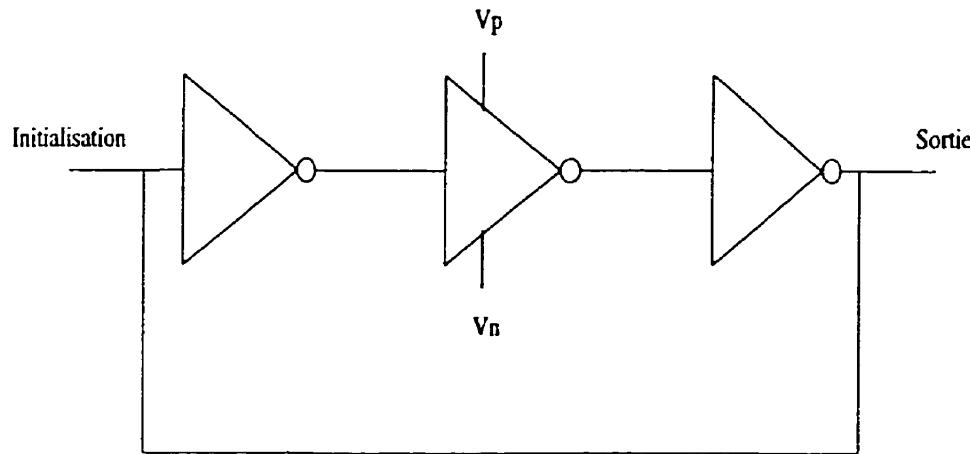

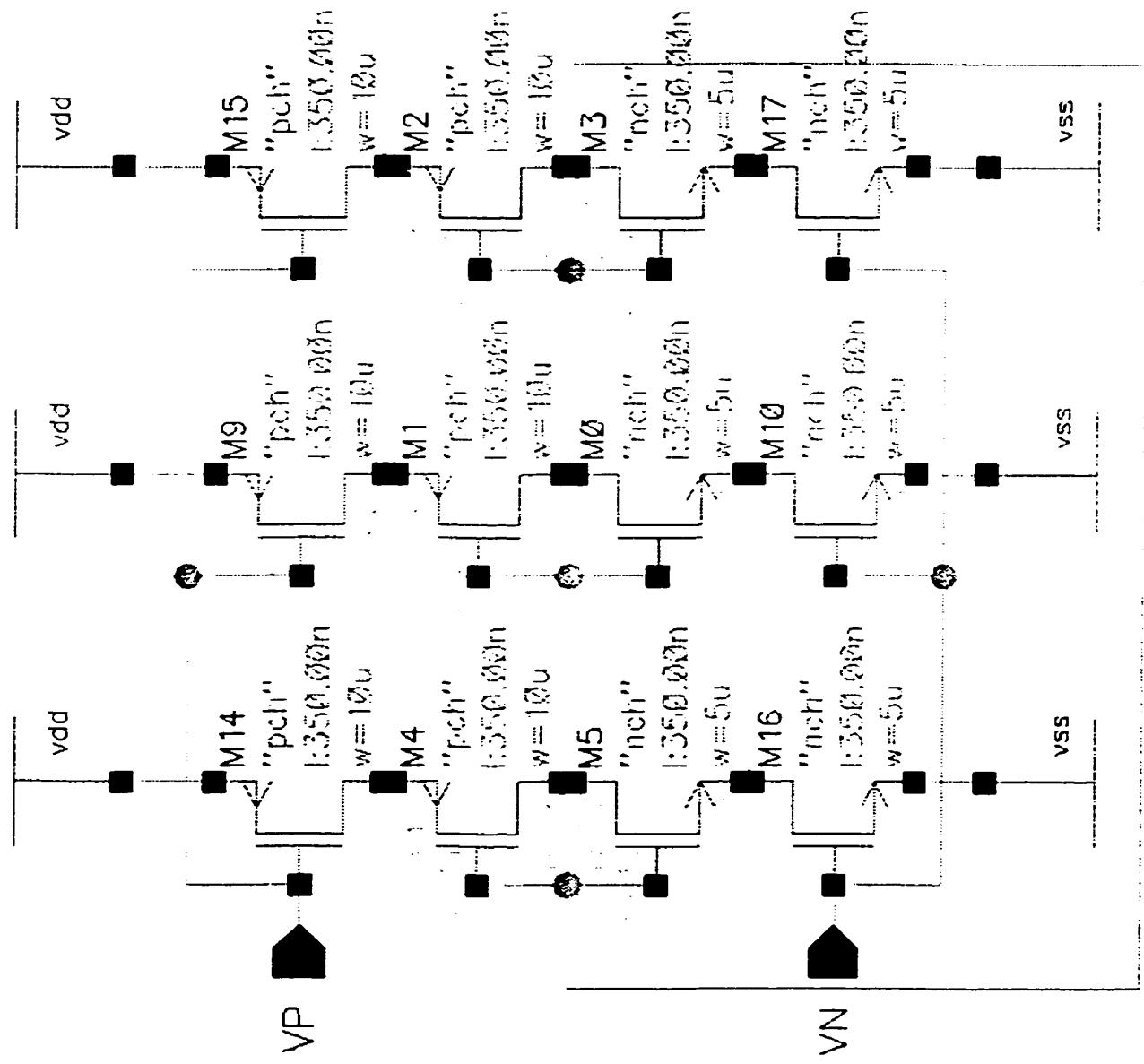

| Figure 3.1:  | oscillateurs en Anneau à Tension commandée .....                                       | 75 |

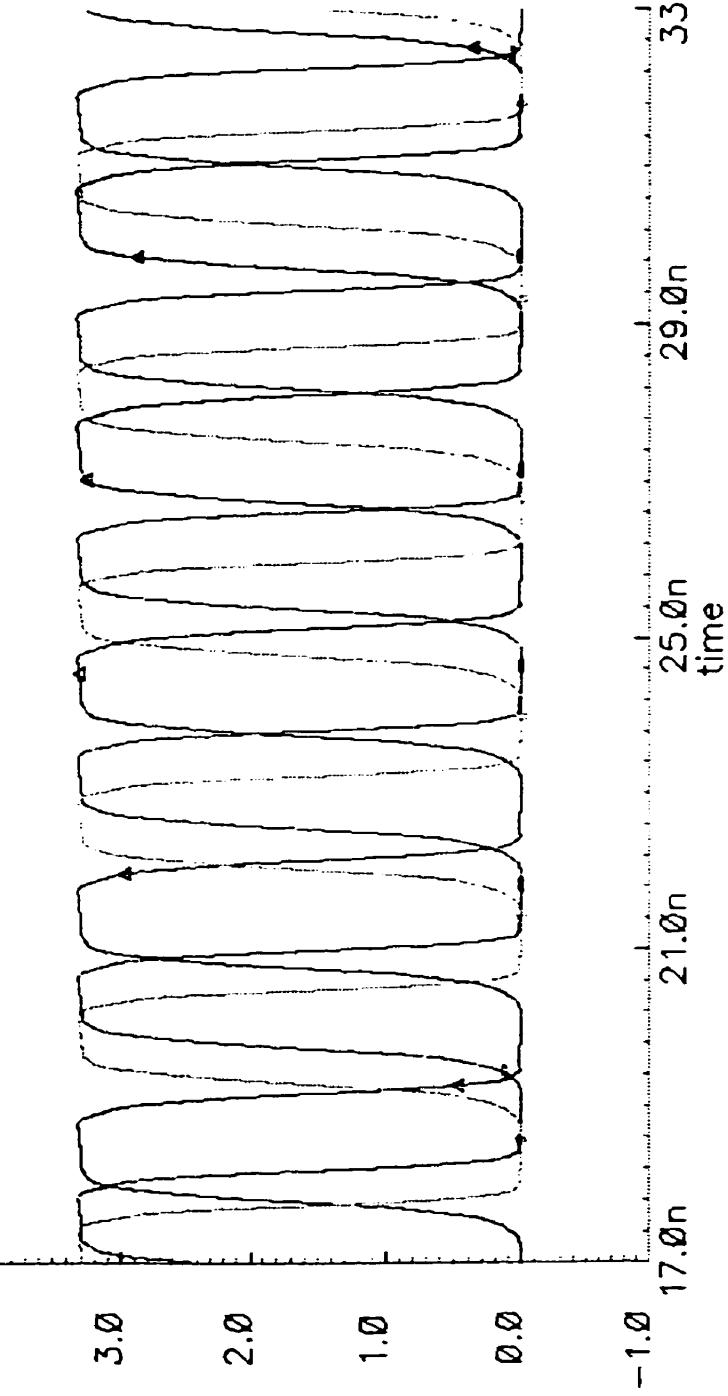

| Figure 3.2:  | Signal de sortie de l'oscillateur 1 à 185 MHz.....                                     | 76 |

| Figure 3.3:  | Oscillateurs en Anneau proposé par Nikili .....                                        | 78 |

| Figure 3.4:  | Oscillateur5 à 1.7 GHz .....                                                           | 80 |

| Figure 3.5:  | Bloc d'oscillateurs .....                                                              | 81 |

| Figure 3.6:  | Diviseur dynamique de fréquence .....                                                  | 83 |

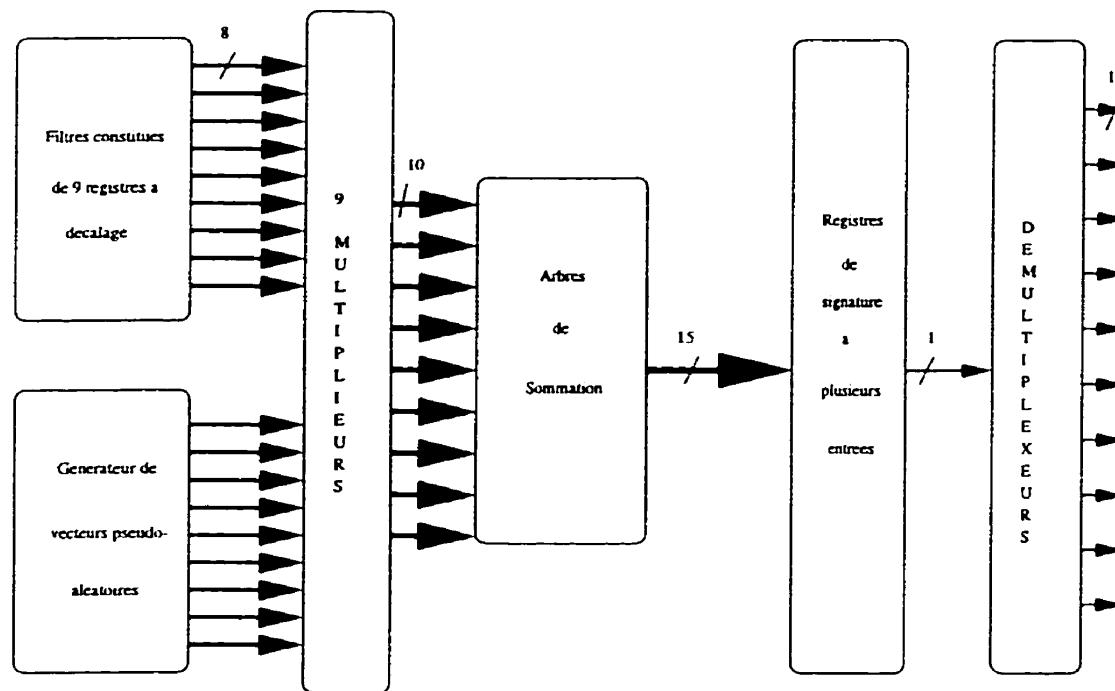

| Figure 3.7:  | Structure du BIST .....                                                                | 85 |

| Figure 3.8:  | Exemple d'une règle 90 d'un AC .....                                                   | 87 |

| Figure 3.9:  | Schéma du générateur de vecteurs par automate cellulaire .....                         | 90 |

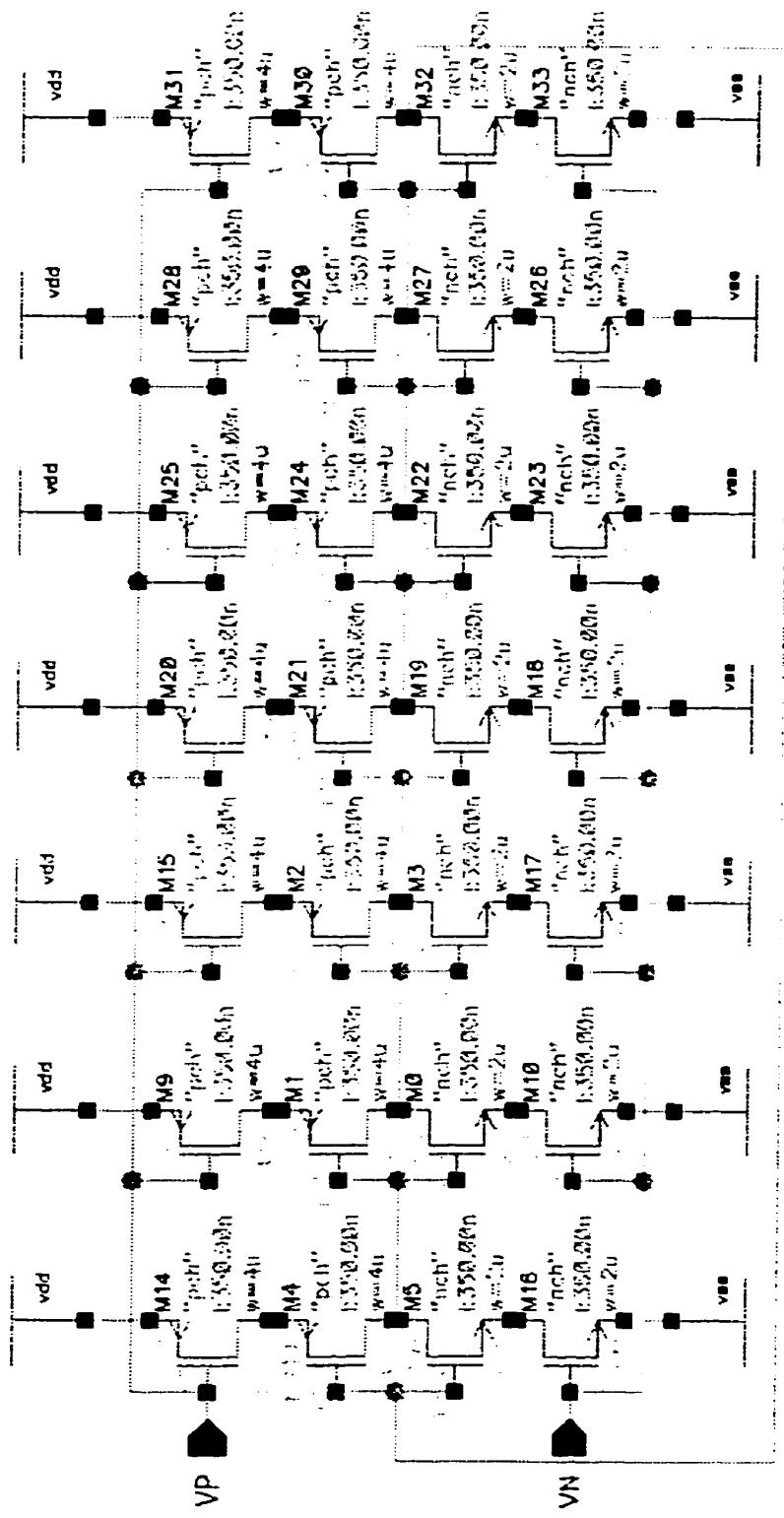

| Figure 3.10: | Schéma de la règle 90 .....                                                            | 91 |

| Figure 3.11: | Schéma de la règle 150 .....                                                           | 91 |

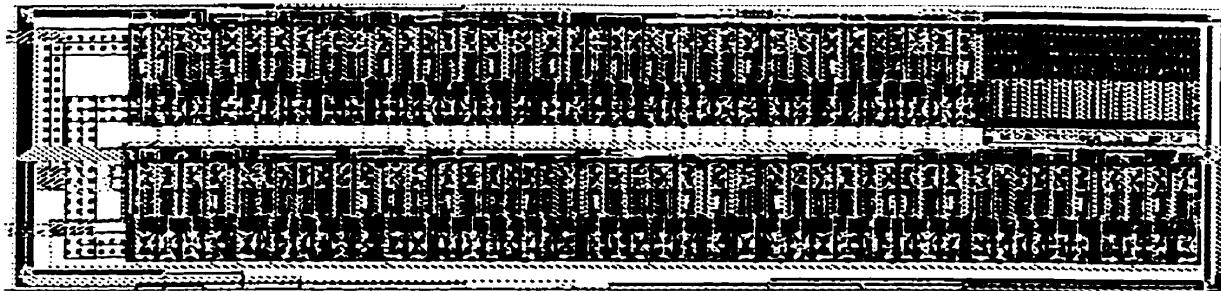

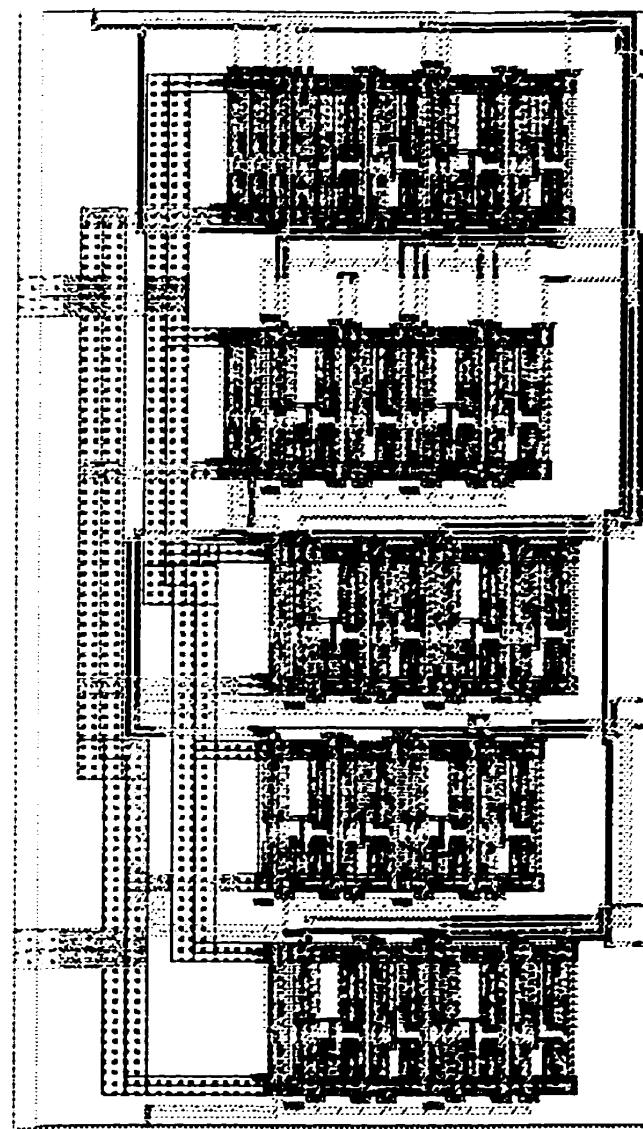

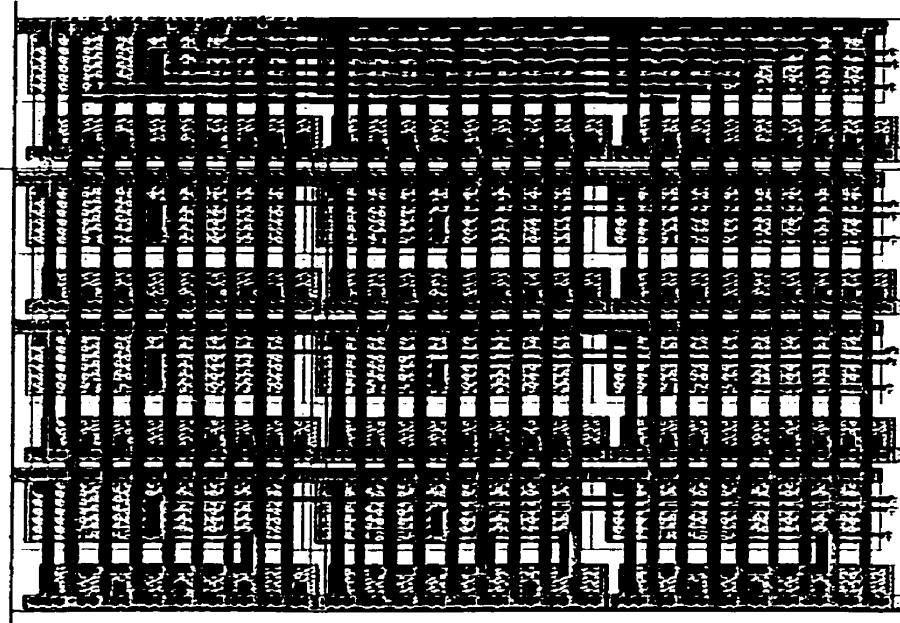

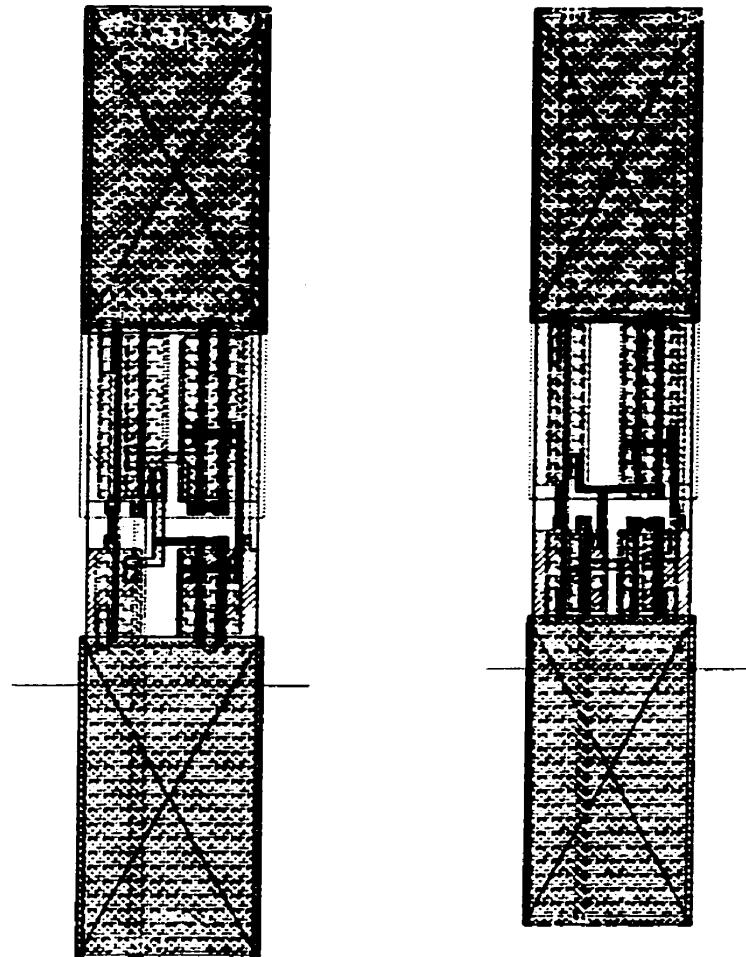

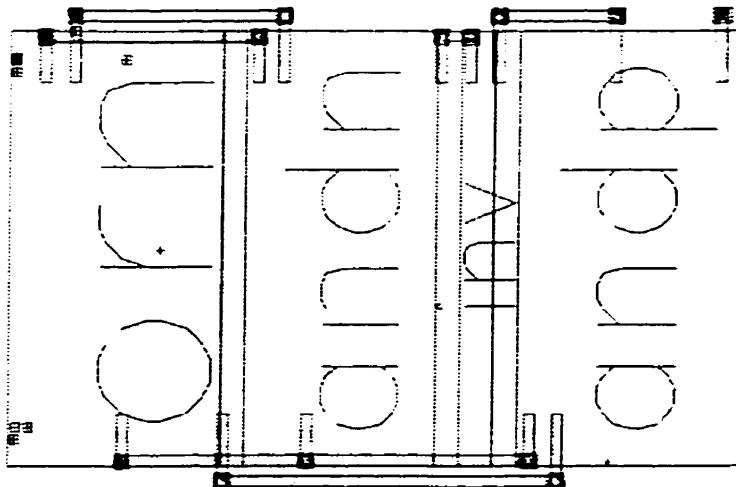

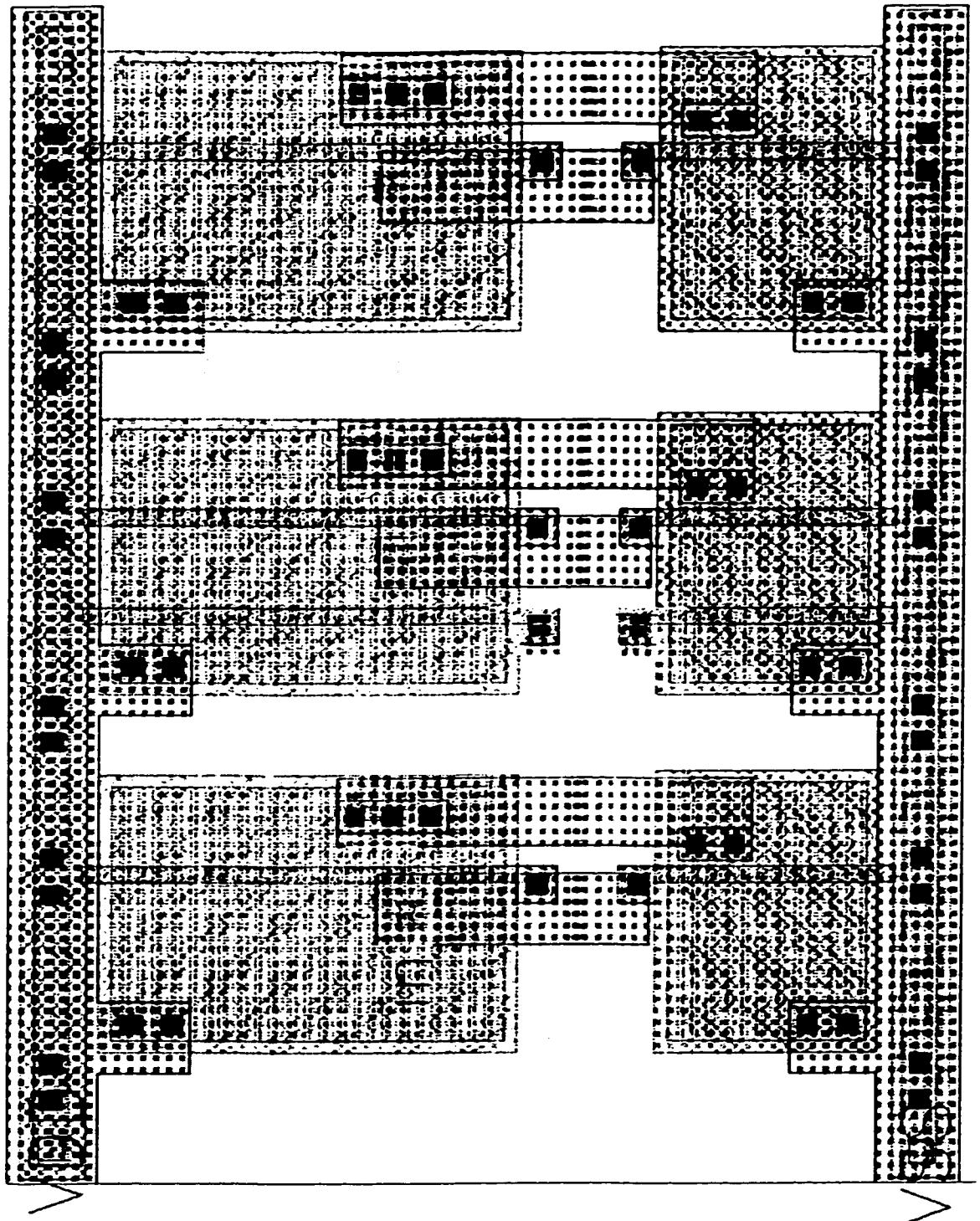

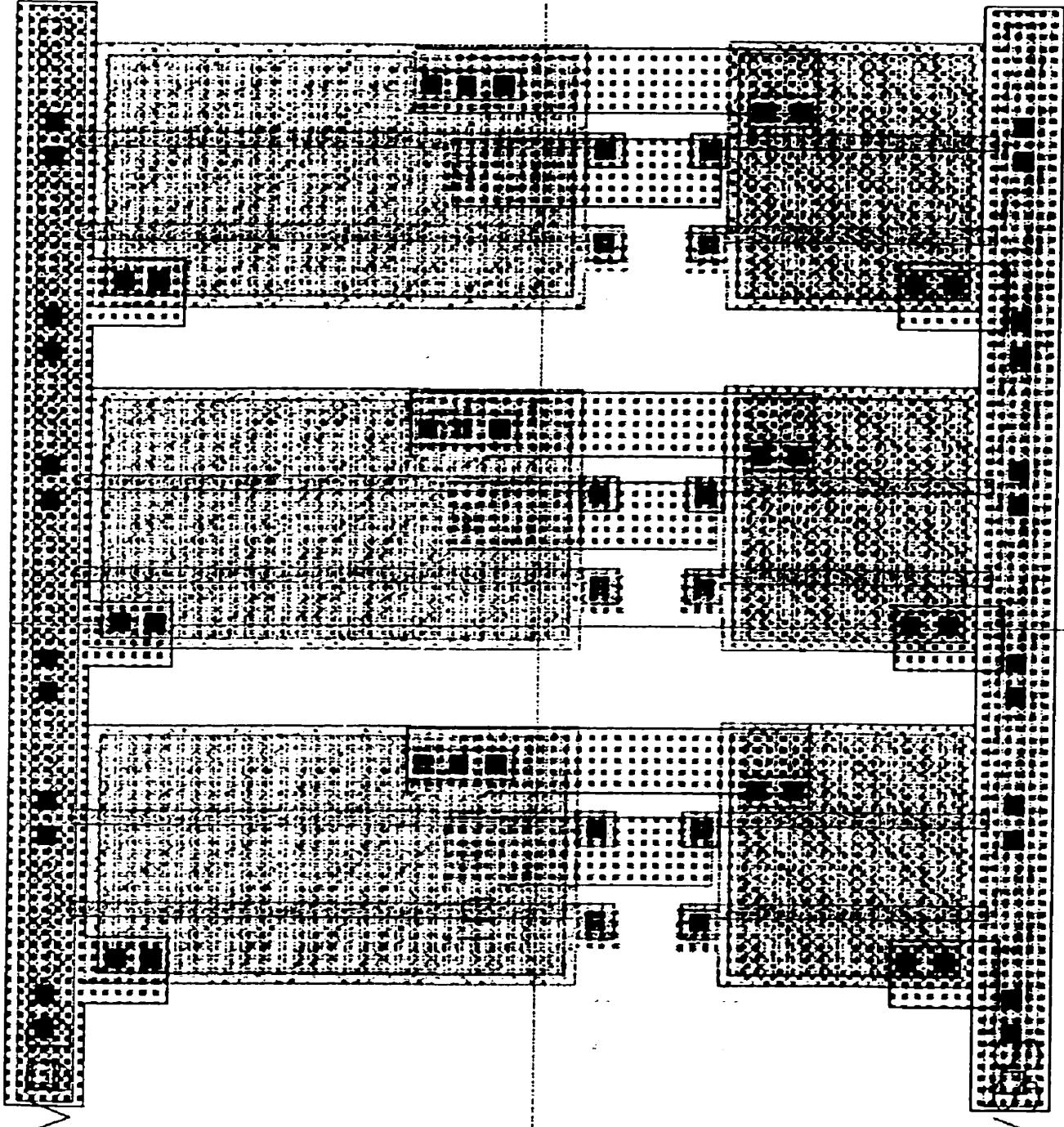

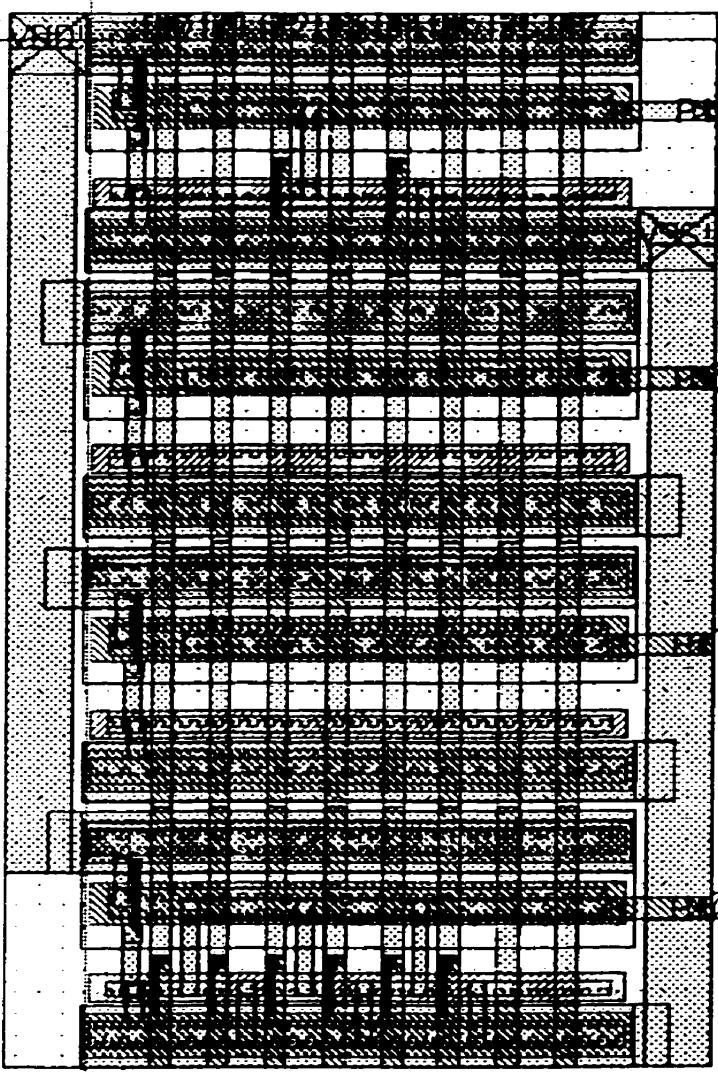

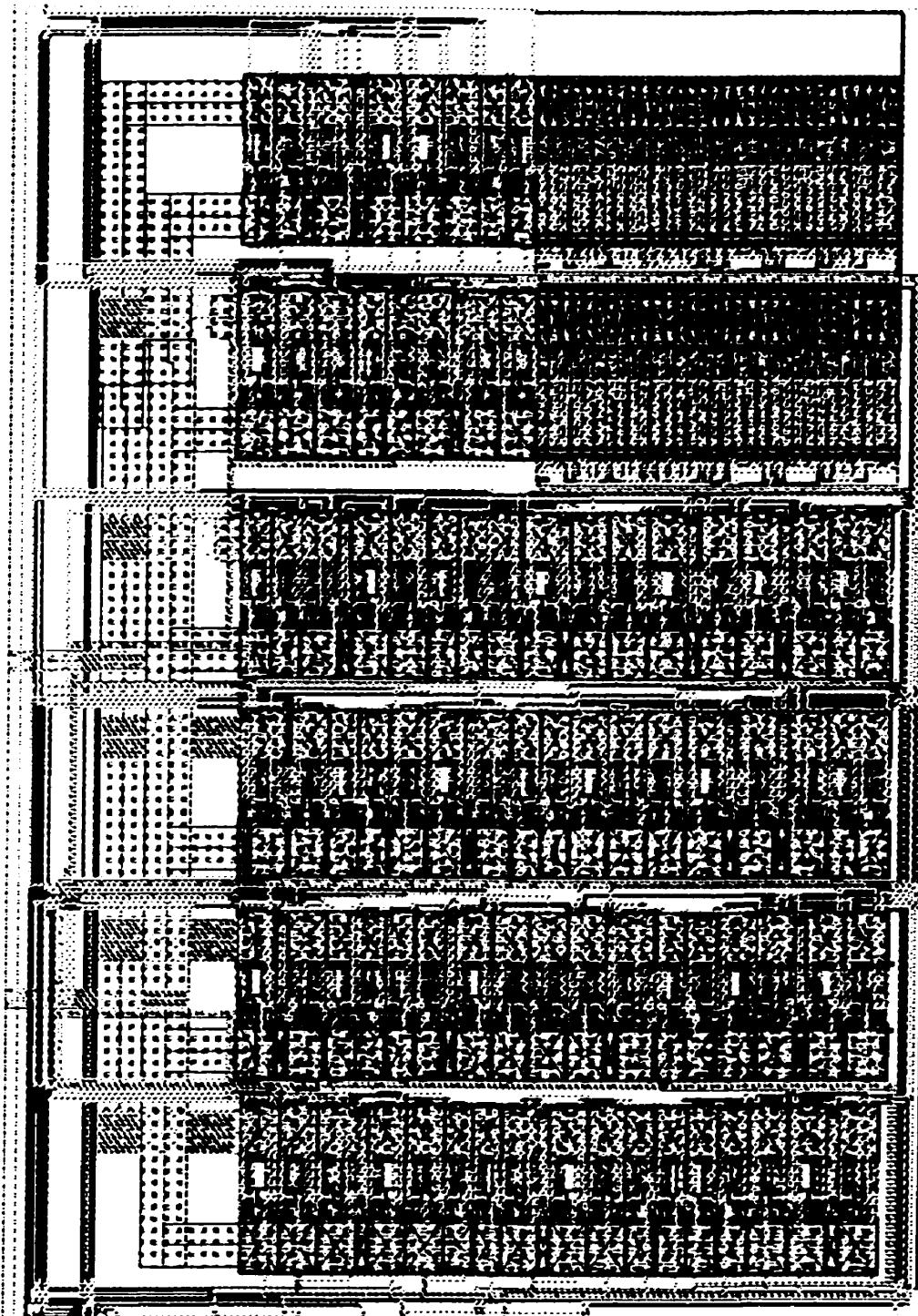

| Figure 3.12: | Masques d'un compteur pseudo-aléatoire de 10 bits.....                                 | 92 |

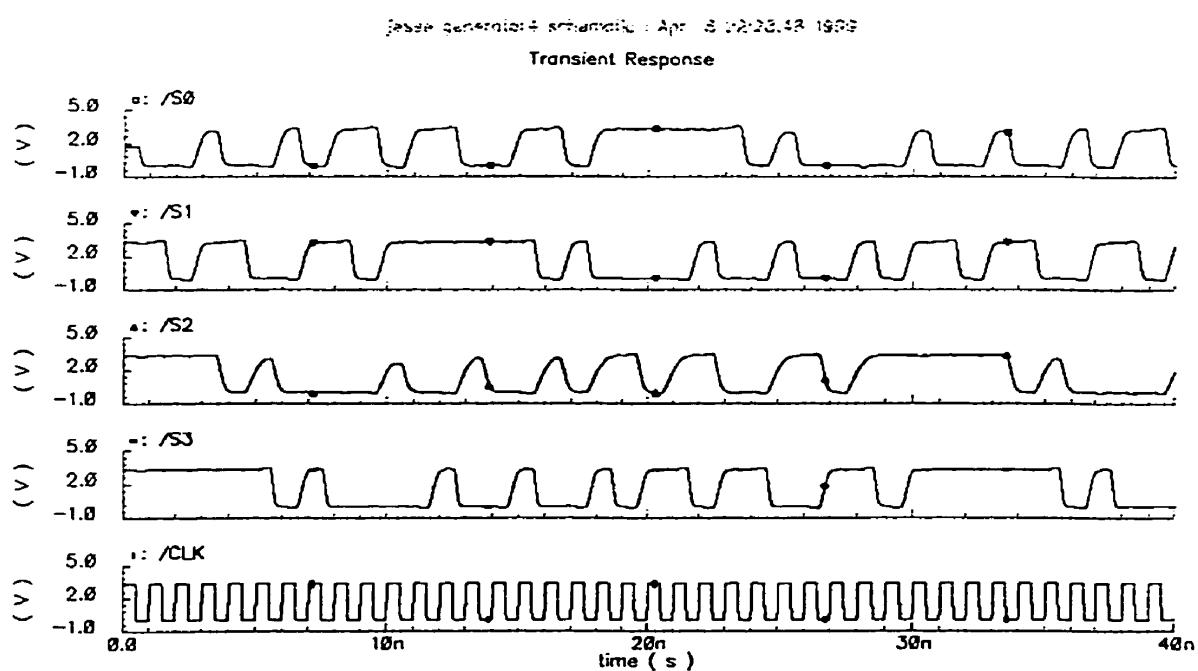

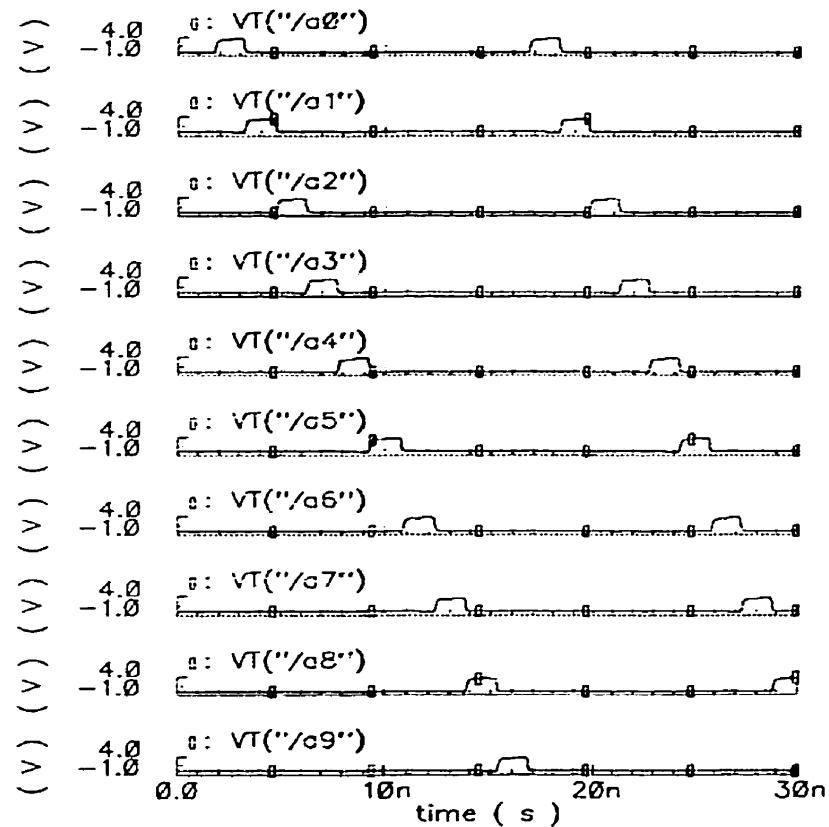

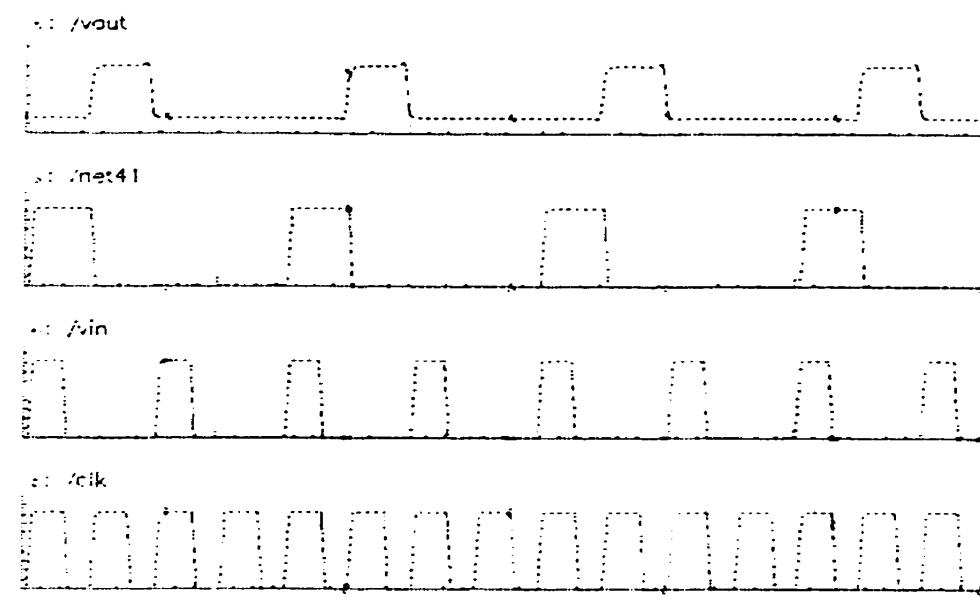

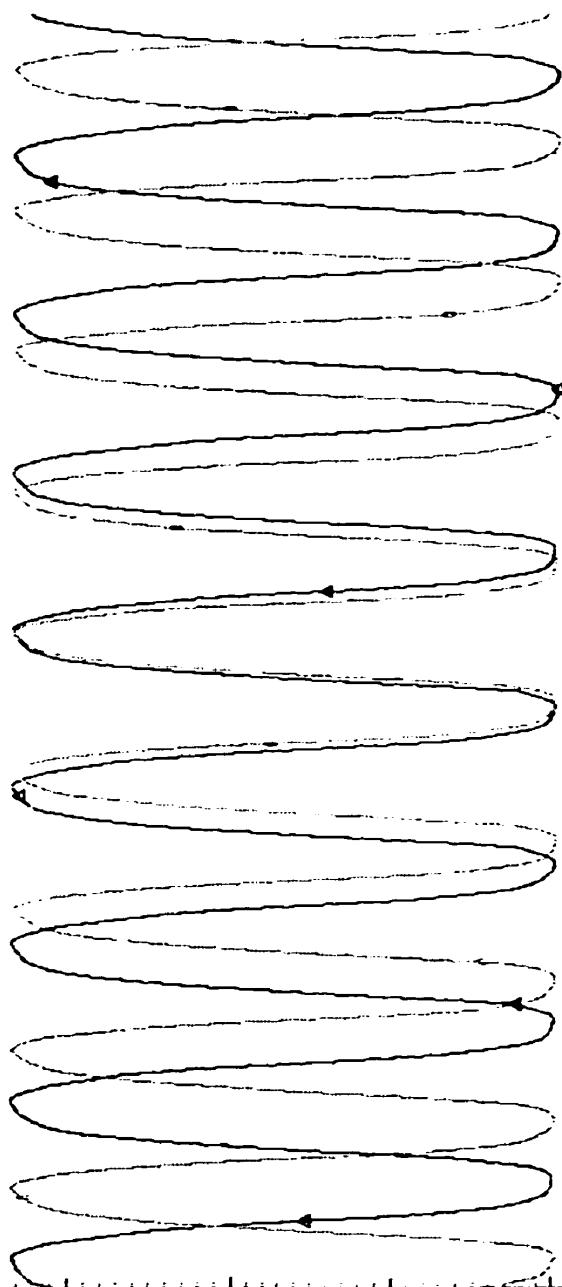

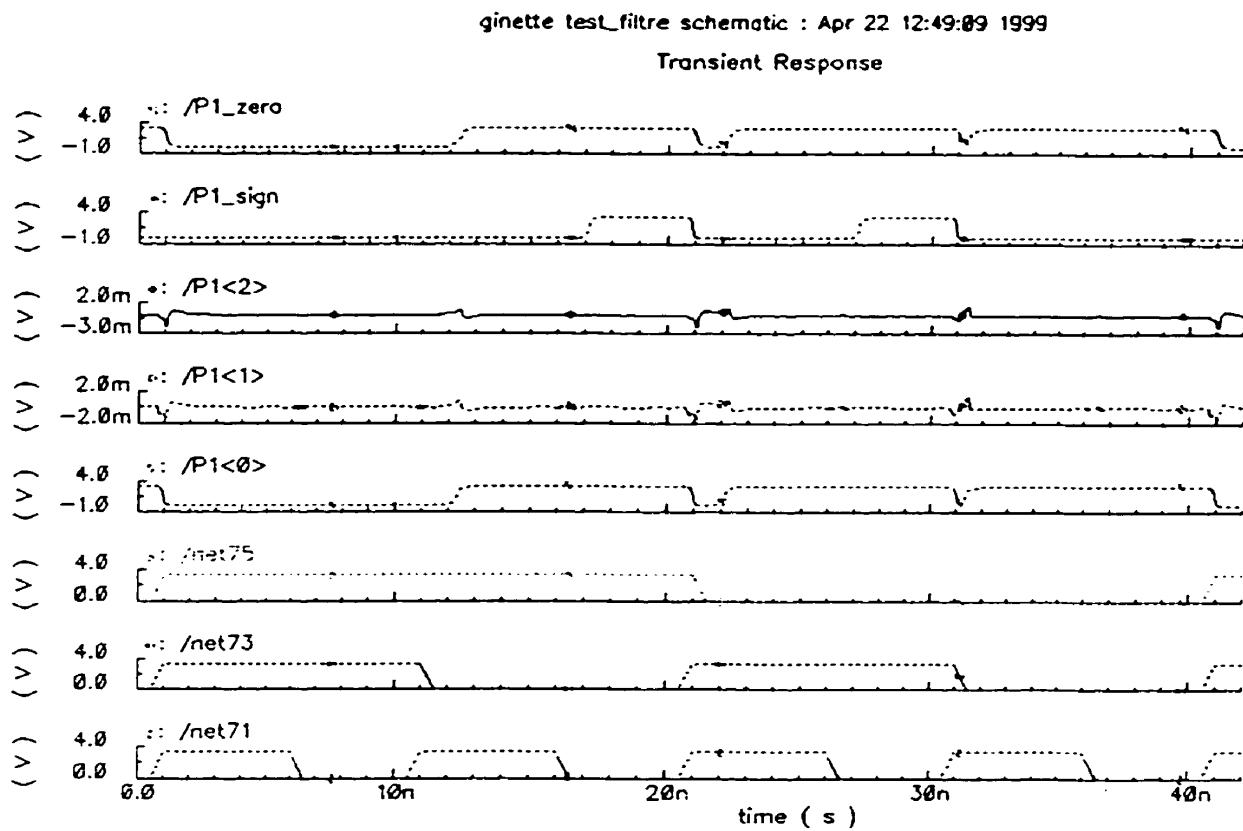

| Figure 3.13: | Simulation avec HSPICE du circuit extrait de la figure 3.12 .....                      | 92 |

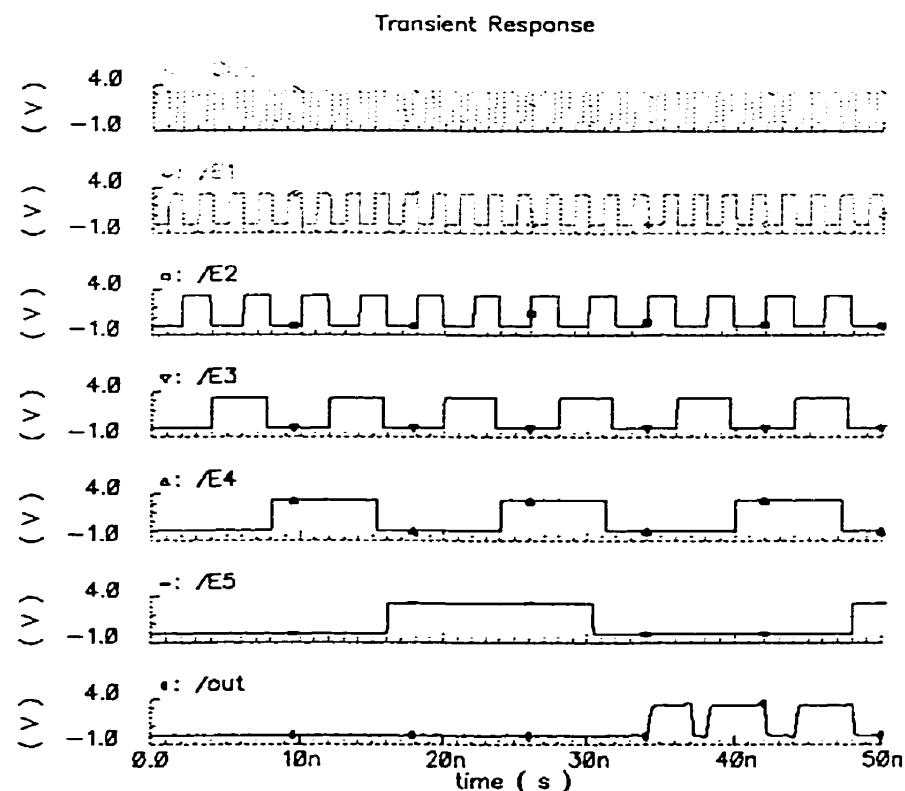

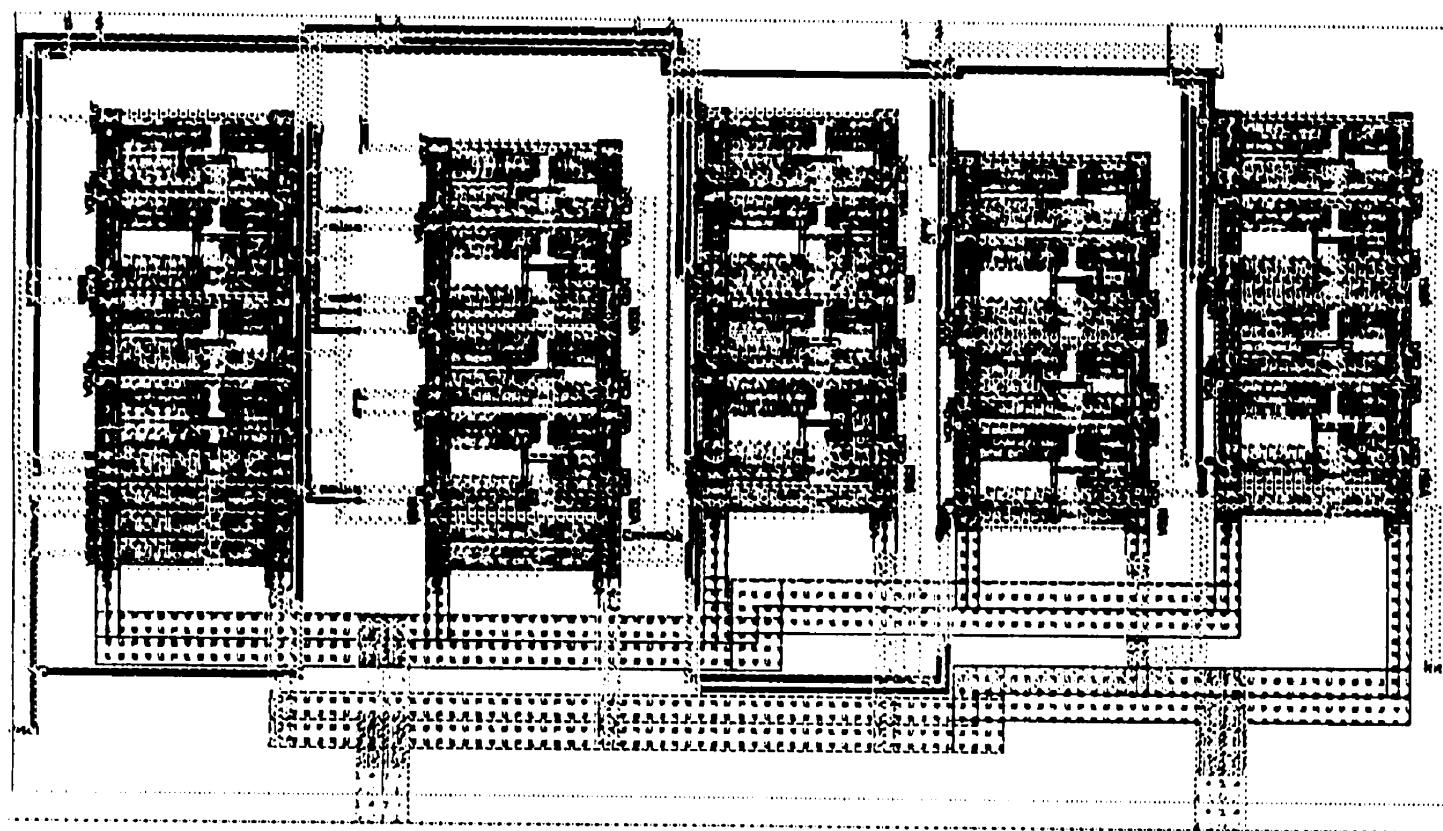

| Figure 3.14: | Simulataion du bloc analyse de signature.....                                          | 94 |

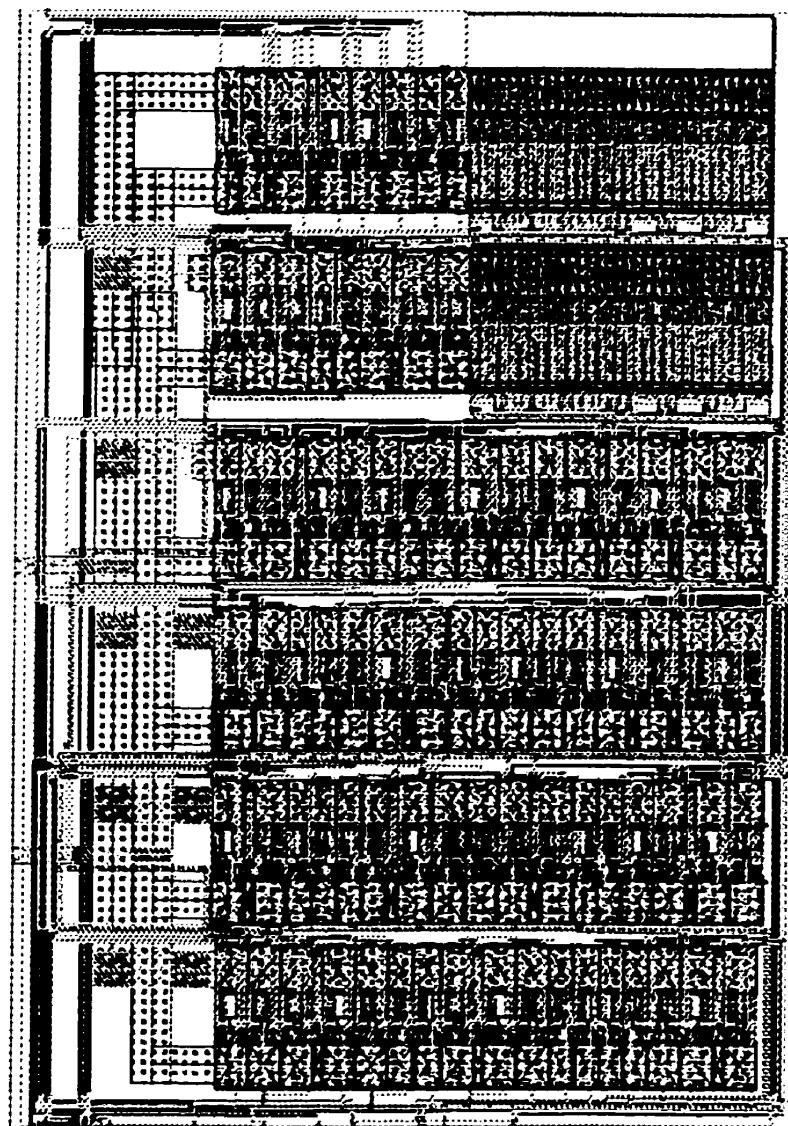

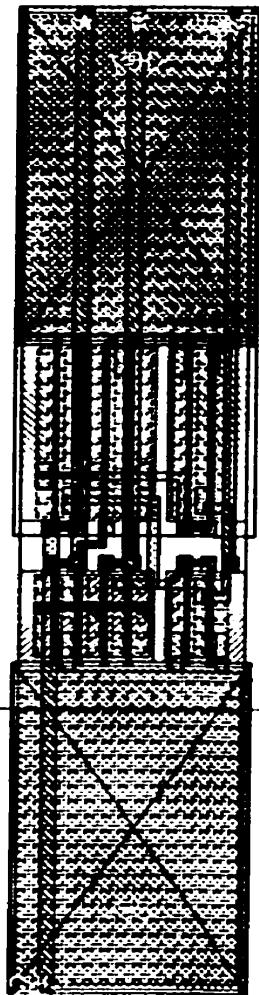

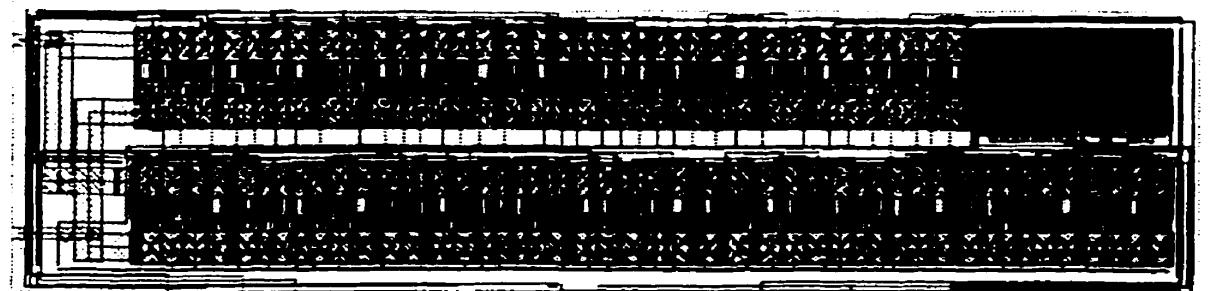

| Figure 3.15: | Schéma des masques du bloc analyse de signature .....                                  | 95 |

| Figure 3.16: | Exemple d'un compteur par 10 en anneau (réalisé en TSPC) .....                         | 97 |

| Figure 3.17: | Simulation du compteur par 10 en anneau à partir d'un modèle extrait des masques ..... | 98 |

|              |                                                                 |     |

|--------------|-----------------------------------------------------------------|-----|

| Figure 3.18: | Schéma du compteur par 10 en anneau au niveau des masques ..... | 99  |

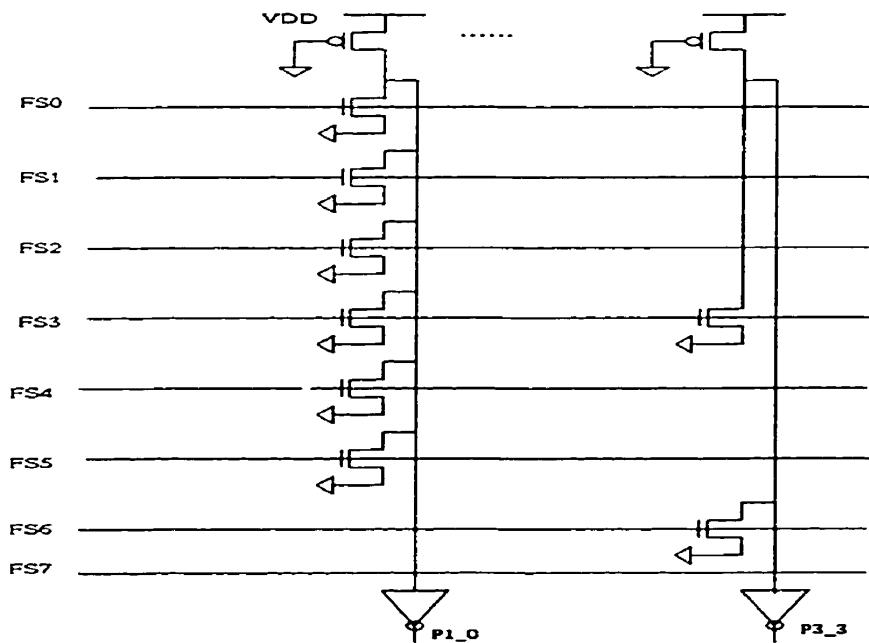

| Figure 3.19: | Un filtre de type pseudo NMOS .....                             | 100 |

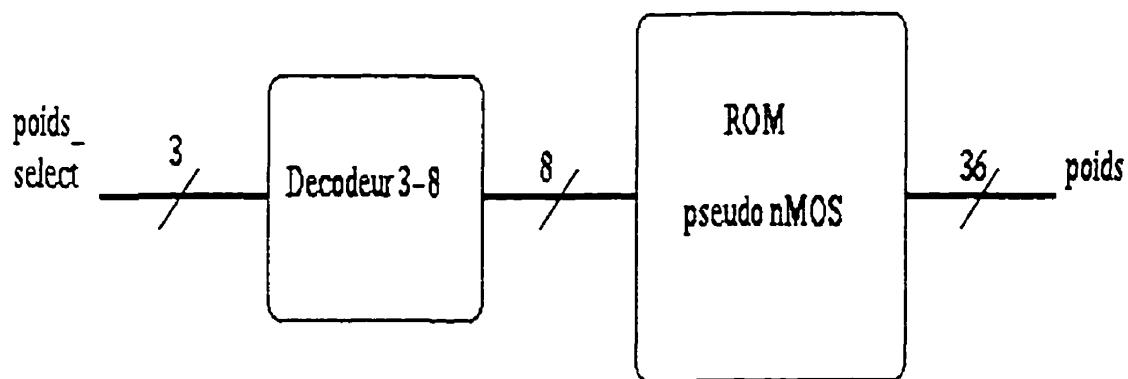

| Figure 3.20: | Décodeur 3-8 .....                                              | 101 |

| Figure 3.21: | Schéma des masques du décodeur 3-8.....                         | 104 |

| Figure 3.22: | Réseau de distribution d'horloge du DEC Alpha .....             | 106 |

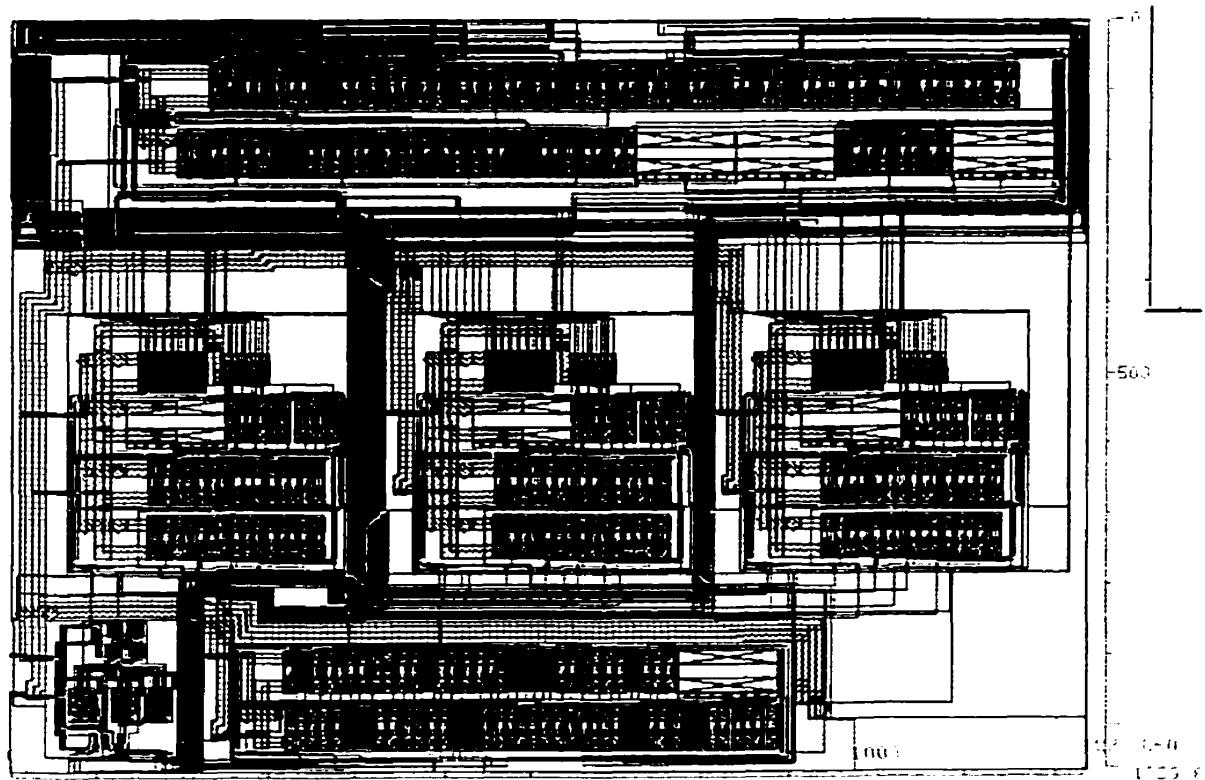

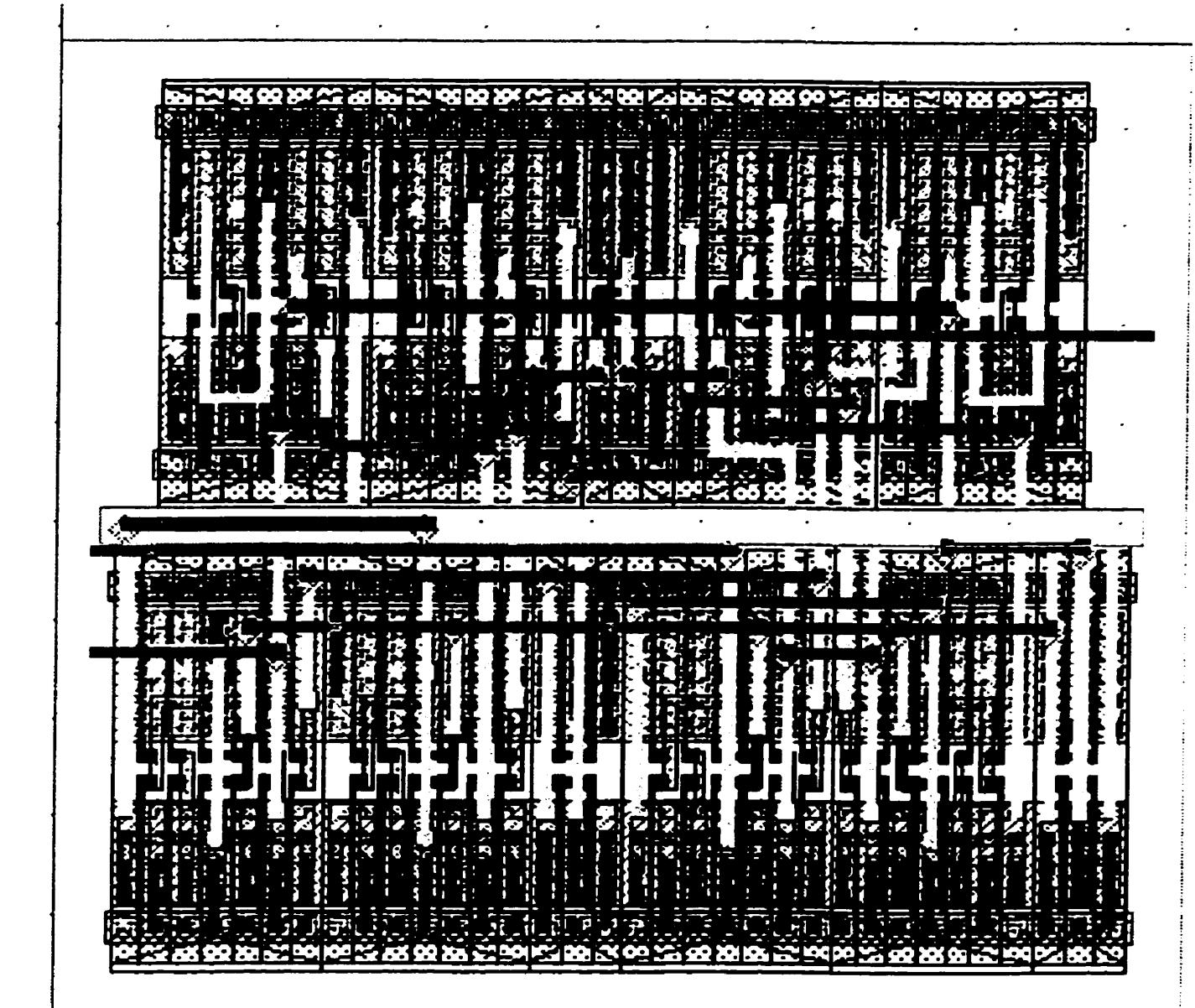

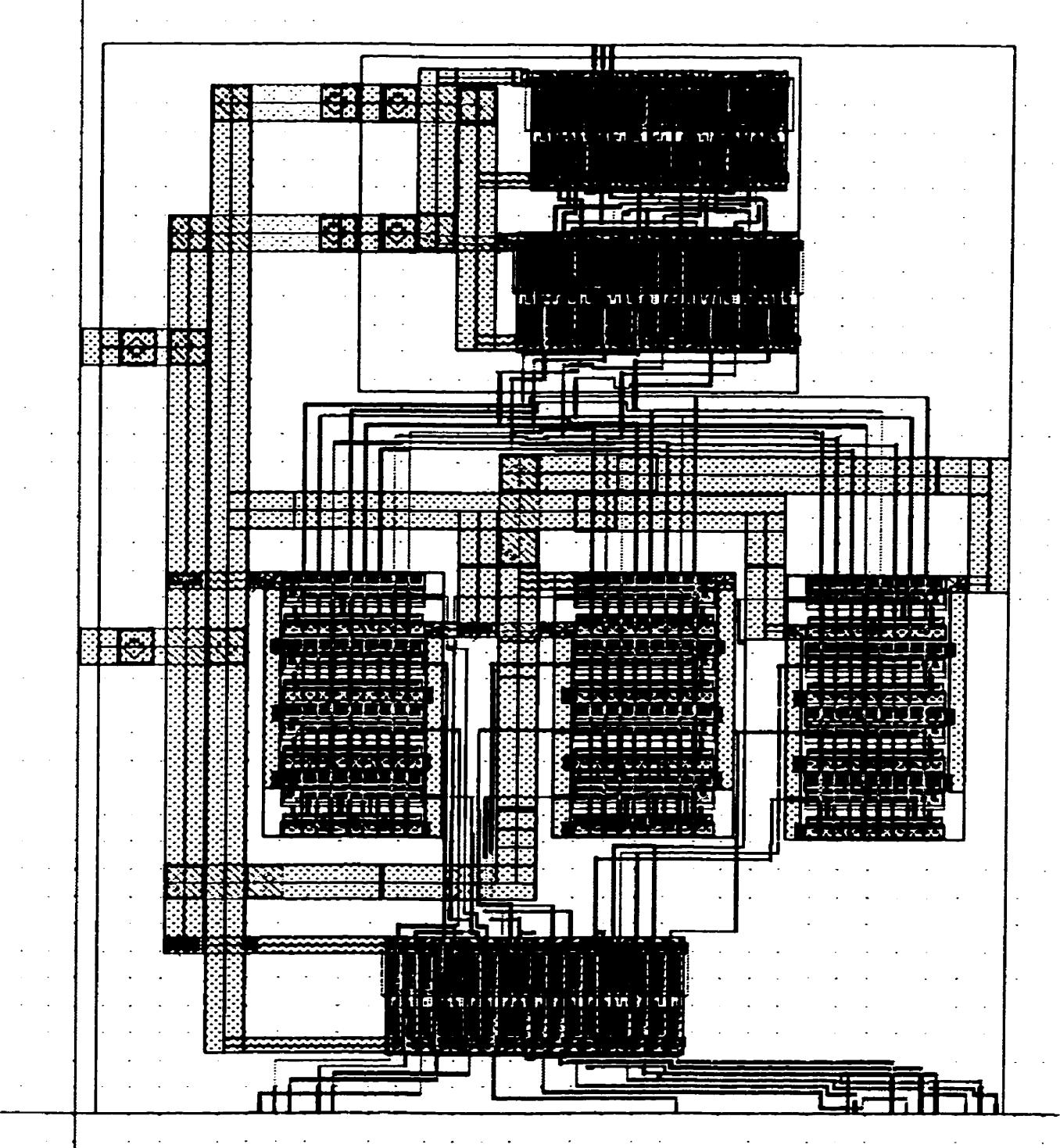

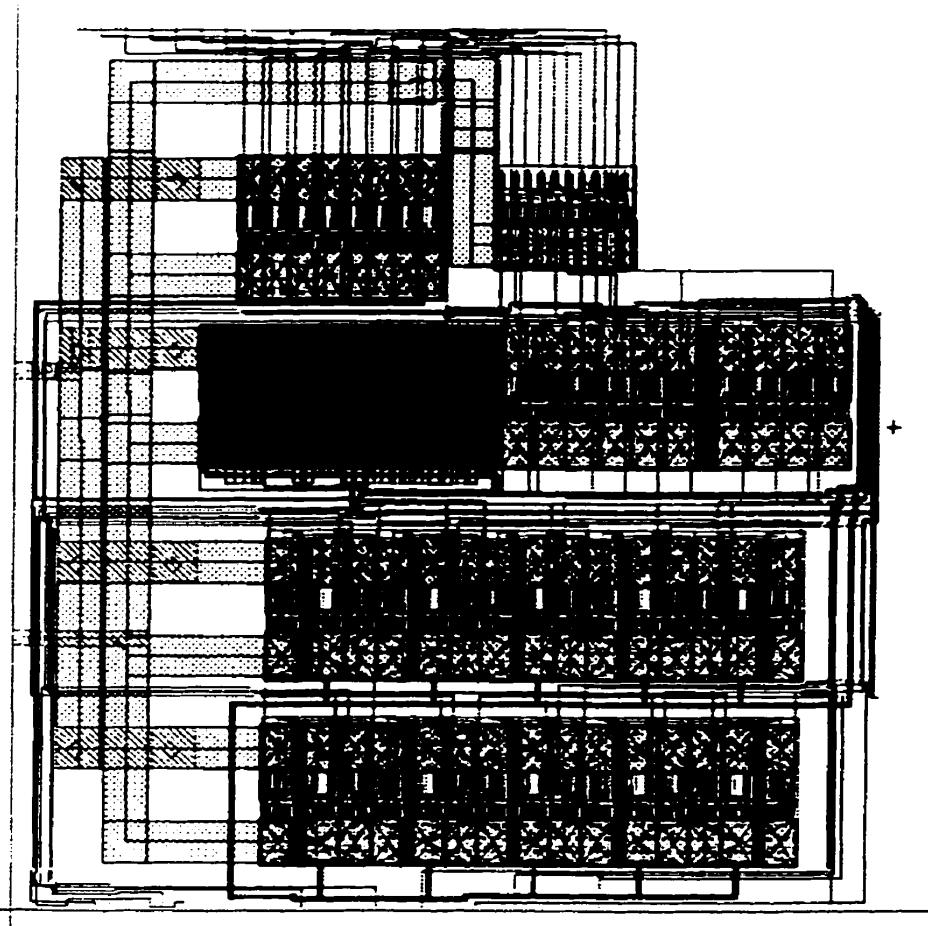

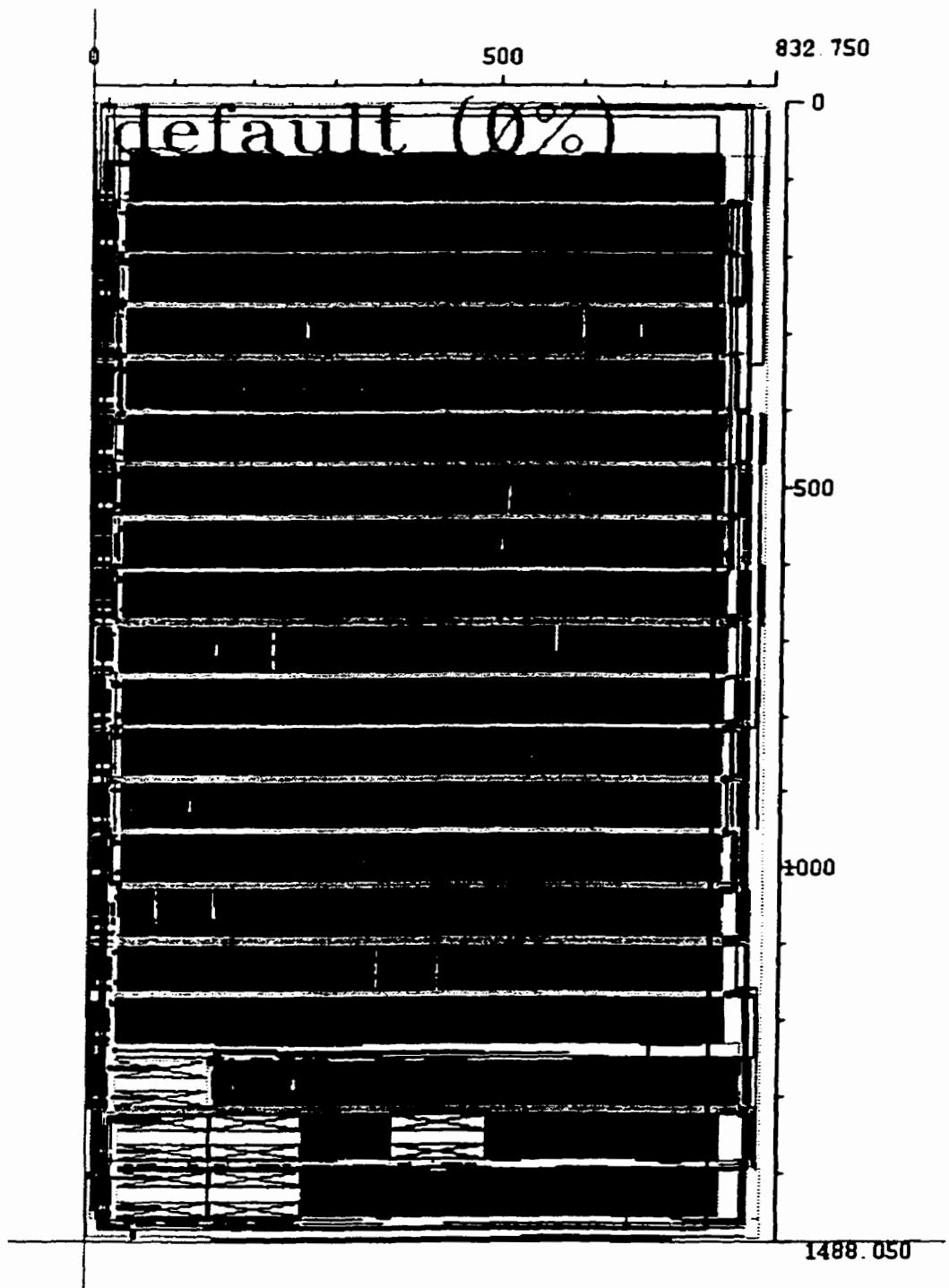

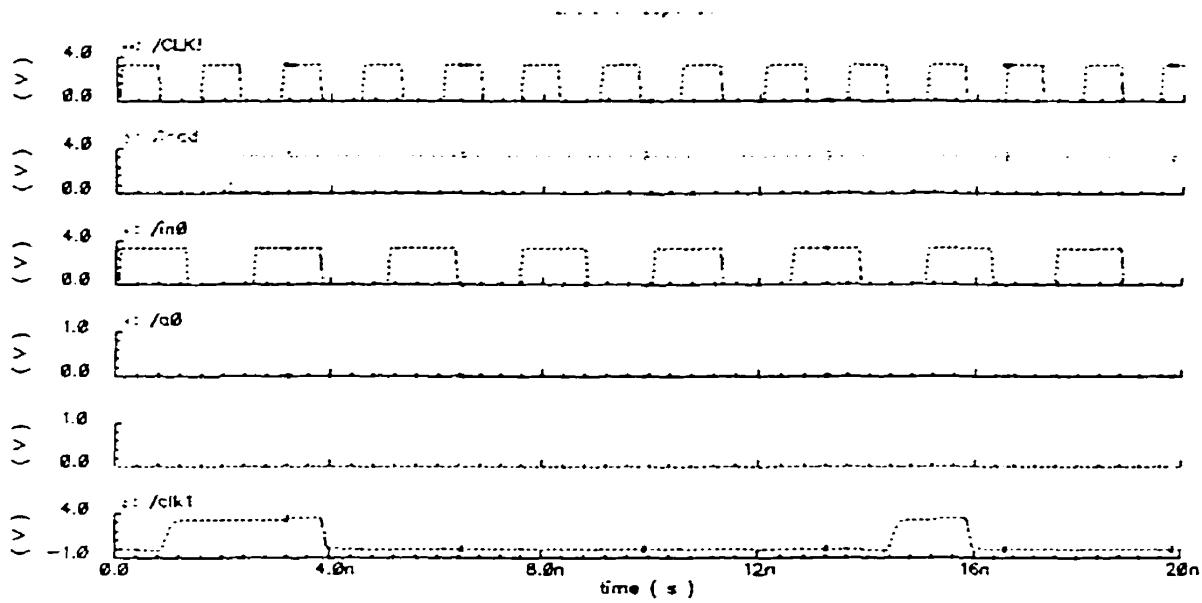

| Figure 3.23: | Placement des différents blocs du convoluteur 3*3 TSPC .....    | 108 |

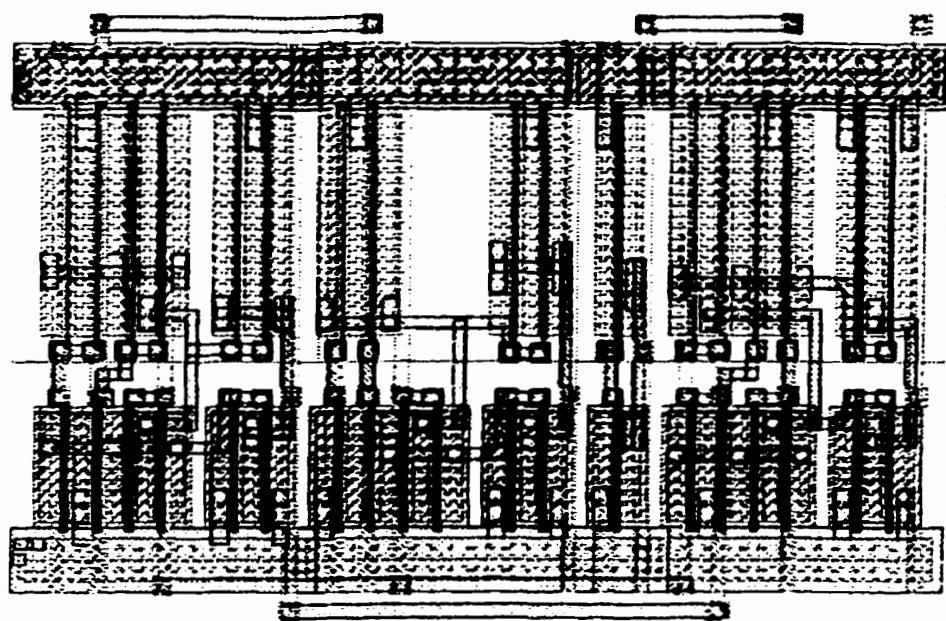

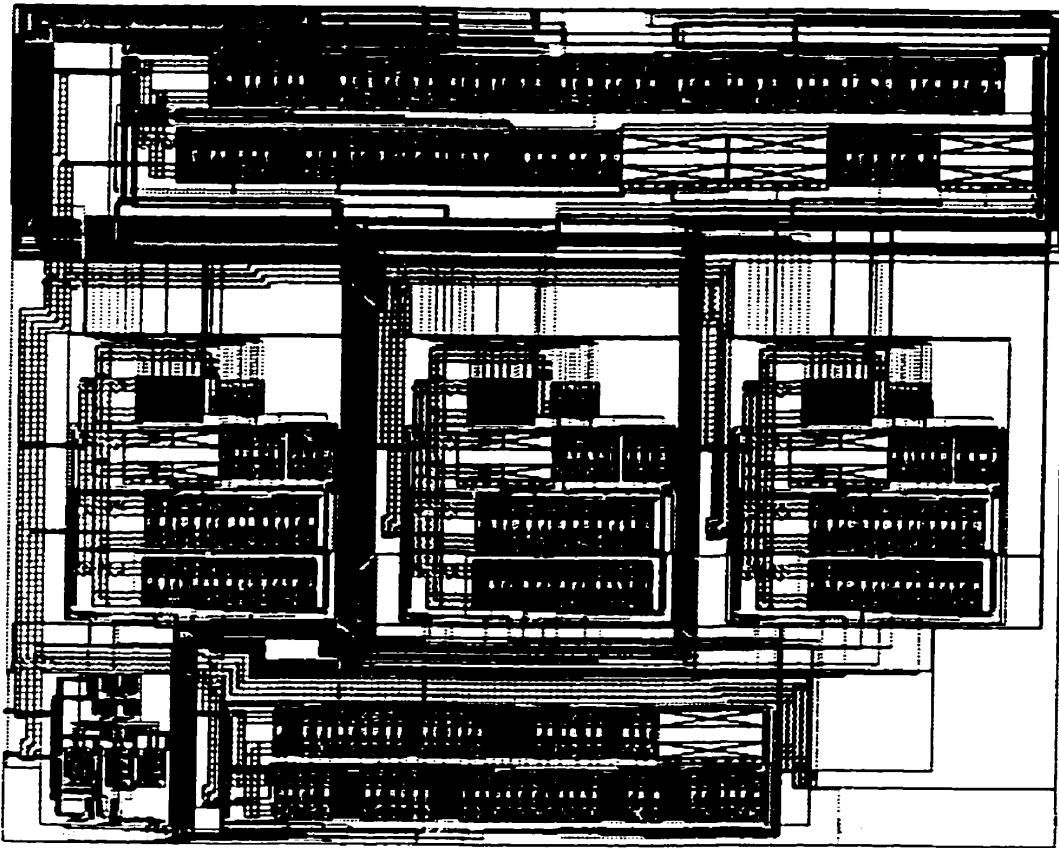

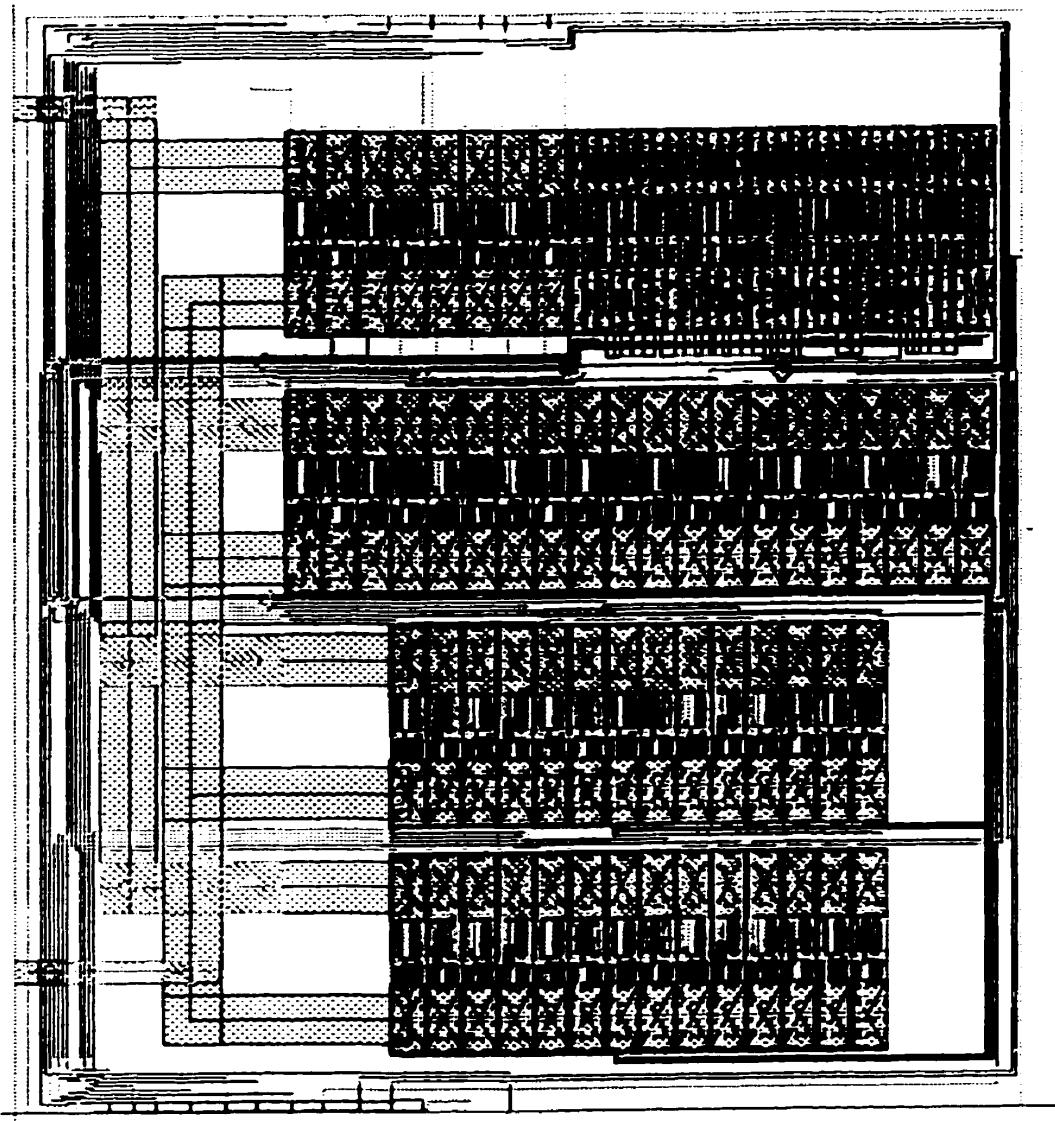

| Figure 3.24: | Placement et routage d'un des 3 modules du convoluteur.....     | 110 |

## INTRODUCTION

Les concepteurs de microprocesseurs essaient continuellement d'augmenter les performances des machines qu'ils réalisent. Actuellement, une façon d'améliorer les micro-architectures est d'augmenter la granularité du pipeline afin de diminuer le nombre de cycles d'horloge des instructions. Les processeurs fonctionnent à des fréquences très élevées, maintenant à 500 MHz et bientôt à 1 GHz. Cette croissance des fréquences d'opération est principalement due à une recherche très efficace dans le développement de nouvelles technologies CMOS offrant maintenant des résolutions de 0.25  $\mu\text{m}$  et 0.18  $\mu\text{m}$ , et de 0.15  $\mu\text{m}$  dans un an.

À la conférence IEEE International Solid-State Circuits en février 1999, le laboratoire d'IBM d'Austin [1] a présenté un processeur expérimental à 64 bits appelé guTS (giga-hertz unit Test Site). Le but de ce processeur était de démontrer que des techniques de conception de circuit couplées à un centrage de ces circuits pouvaient augmenter de façon significative la performance des microprocesseurs, donc d'ouvrir une nouvelle voie de recherche pour contribuer à augmenter la performance des microprocesseurs et de la technologie CMOS. Pour clairement distinguer les améliorations découlant des méthodes de conception de celles découlant des nouvelles technologies de fabrication, une technologie de 1997 avait été choisie (CMOS 0.25  $\mu\text{m}$  1.8 V). Maintenant encore, une telle perfor-

mance n'est pas accessible même avec les dernières technologies 0.18  $\mu$ m, en utilisant des techniques de conception conventionnelles.

Le processeur "guTS" est un circuit dédié, composé presque à 100% de circuits dynamiques. Il est capable d'exécuter 96 instructions entières du jeu d'instruction de l'architecture Power PC. Toutes les instructions, dont les chargements et les rangements, sont exécutées en un seul cycle. Ce processeur montre qu'il est possible de concevoir des circuits de très hautes performances sans être dépendant exclusivement de nouvelles technologies pour progresser.

Les cellules dynamiques utilisées par IBM étaient des cellules Domino. Nelson F. Goncalves et Hugo J. De Man [2] ont élaboré des techniques de conception de cellules dynamiques NORA, pour des structures logiques pipelinées. Dans les circuits conventionnels, il existe une redondance d'information. À chaque dispositif de type N correspond un dispositif de type P. En fait, une fonction logique complète est fabriquée avec des dispositifs de type N, doublés de dispositifs de type P. Ainsi une grande quantité de silicium est gaspillée, spécialement pour les réseaux logiques complexes. Un autre problème des réseaux de portes statiques CMOS provient des courses dans les circuits pipelinés. Pour propager l'information entre deux circuits pipelinés, des portes de transmission sont habituellement utilisées.

En logique CMOS, ces portes de transmission sont généralement implémentées avec deux transistors de type N et P en parallèles et contrôlées par des horloges  $\phi$  et  $\bar{\phi}$ . L'utilisation

de simples portes de type P ou N est à éviter, à cause de la dissipation de puissance et de la faible marge de bruit. Ces portes de transmission de type N et P souffrent également de courses intenses. En effet, pendant la phase d'évaluation, toutes les portes de transmission sont activées, ce qui peut corrompre le flot d'information, dépendant du rapport entre le délai de la porte et le biais de synchronisation de l'horloge.

Dans la technique Domino, Krambeck et al. [3] ont résolu le problème en plaçant des inverseurs statiques après chaque bloc dynamique. Une limitation de la technique Domino est le manque de signaux inversés. La combinaison d'un bloc dynamique avec des inverseurs statiques donne un signal non inversé. Cette solution diminue la flexibilité logique et nécessite par conséquent plus de transistors pour une fonction logique. Le problème de course d'horloge n'est toujours pas résolu dans cette technique. La technique NORA permet de palier à ces problèmes. Les fonctions logiques sont alors implémentées à partir de cellules dynamiques CMOS de type N et P et de fonctions C<sup>2</sup>MOS. Pour résoudre les problèmes de courses entre signaux dans les circuits pipelinés, l'information doit toujours être enregistrée dans une fonction C<sup>2</sup>MOS. De plus, les signaux inversés et non inversés sont préservés. Quand des couplages entre des blocs dynamiques sont désirés, les fonctions logiques sont implémentées par l'alternance de blocs N et P. Les blocs de même type peuvent communiquer à l'aide d'inverseurs comme dans la technique Domino.

Un circuit pipeliné Nora est insensible aux problèmes de course si le nombre total d'inversions (statiques et dynamiques) entre deux bascules C<sup>2</sup>MOS est semblable.

Les cellules NORA sont limitées par des problèmes de partage de charge et de marge de bruit. Le signal de sortie des cellules dynamiques est relié aux noeuds de stockage. Lors d'une commutation d'un transistor d'un état inactif à un état actif, un effet de redistribution de charge peut apparaître entre la capacité de sortie et les capacités parasites du réseau logique. Ces limites sont communes à toutes les techniques dynamiques.

Cependant, avec la NORA, comme il n'existe pas de temps mort et de problème de biais de synchronisation, nous pouvons nous attendre à atteindre de plus hautes fréquences d'horloge qu'avec la technique C<sup>2</sup>MOS. Un développement plus profond de la stratégie de distribution d'horloges devrait utiliser encore moins de signaux d'horloge. La technique dynamique CMOS à vraie horloge monophasée (TSPC) [4] utilise seulement un signal d'horloge qui n'est jamais inversé. Donc, il n'existe aucun biais entre une horloge et son complément, excepté pour les problèmes de délai de l'horloge, ainsi une plus grande fréquence d'horloge peut être atteinte. Comme nous l'expliquons ensuite, la conception à vraie horloge monophasée peut remplacer non seulement les cellules dynamiques mais également les cellules statiques et dans la plupart des cas la technique CMOS NORA.

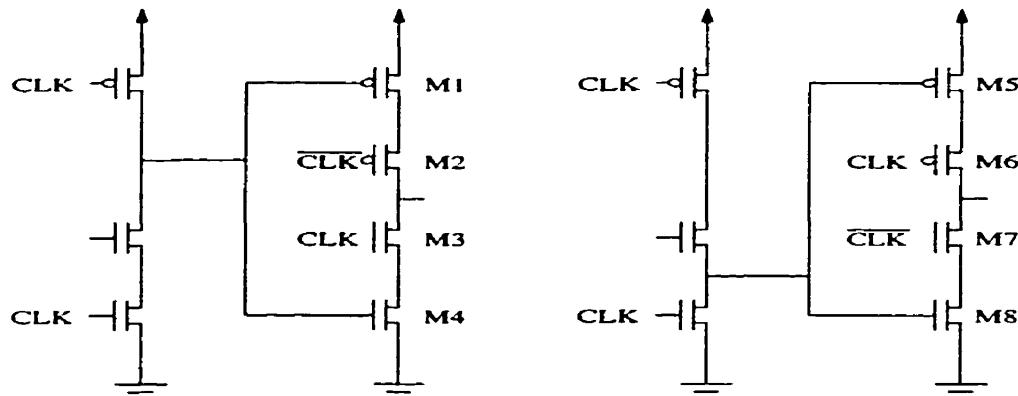

Figure 0.1: Technique dynamique NORA

Figure 0.2: Bascules TSPC

Dans la Figure 0.1, nous avons deux bascules C<sup>2</sup>MOS contrôlées par deux signaux d'horloge  $CLK$  et  $\overline{CLK}$ . La nécessité d'utiliser  $\overline{CLK}$  réside dans le contrôle des transistors M2 et M7. Cependant, ceci peut être donné par un signal d'horloge  $CLK$  connecté aux deux bascules par des inverseurs comme nous le voyons à la figure 0.2. Nous appelons les deux différentes unités étage N-C<sup>2</sup>MOS et étage P-C<sup>2</sup>MOS, respectivement, et si nous utilisons

ces étages en série, ils deviennent des bascules TSPC. Les blocs logiques de type N et P sont utilisés alternativement avec le même signal d'horloge. Tant que le délai du signal d'horloge est inférieur au délai de la porte, le système est stable. Apparemment, c'est mieux que la stratégie de pseudo horloge à deux phases sans recouvrement, et aussi du point de vue des contraintes logiques, cela peut se comparer avec la stratégie d'horloge à deux phases NORA. Il est également possible de n'utiliser que des portes TSPC avec de la logique NMOS si les blocs sont séparés par des inverseurs une fois sur deux. Les blocs logiques TSPC sont expliqués davantages dans le chapitre 1. Le principal problème des cellules dynamiques est de pouvoir les utiliser dans des outils de synthèse afin de concevoir rapidement des circuits de taille respectable. Il est possible de les utiliser dans des circuits dédiés ou dans les points critiques des gros circuits. Edefors [5] a proposé un outil afin de réaliser la synthèse et le placement et routage des cellules TSPC. Une bibliothèque de base a été conçue de façon dédiée en respectant les sortances. Ces cellules sont compatibles avec une horloge rapide qui impose de nombreuses contraintes sur les règles de conception. Chaque cellule est balancée, avec des temps de montée et de descente semblables. De plus toutes les cellules ont des délais similaires. D'autre part, entre chaque cellule, il faut mettre des longueurs de fil comparables. En effet, les fils engendrent, à haute fréquence, une capacité non négligeable qui peut empêcher les signaux d'arriver en même temps si les distances entre les interconnexions sont trop importantes.

La dissipation de puissance est devenue un important domaine de recherche dans les circuits numériques, surtout dans les équipements portables. Ainsi, de nombreuses techniques de circuits à faible consommation apparaissent pour allonger la durée de vie des

batteries. Dans les circuits CMOS, la majorité de la consommation de puissance est dûe aux commutations. Dans les circuits synchrones, une bonne part de la consommation de puissance est liée à l'activité de l'horloge, indépendamment de l'activité logique. La logique dynamique peut ainsi offrir un potentiel pour réduire l'énergie dissipée car les portes dynamiques sont plus petites que les portes statiques. Farnsworth, Edwards et Sikand [6] expliquent l'intérêt d'utiliser des portes dynamiques pour réduire la dissipation de puissance dans les circuits asynchrones. Un exemple intéressant réalisé avec des cellules TSPC est le processeur Alpha de DEC où l'horloge est responsable de 40% de la dissipation de puissance. On voit donc l'importance de diminuer le nombre de noeuds commandés par l'horloge. Pour atteindre cet objectif, la méthode TSPC a été utilisée dans la conception de tous les registres, à partir des cellules proposées par Svensson and Yuan [4]. Les deux principaux avantages de cette technique sont qu'un seul noeud d'horloge est nécessaire, et que seulement quatre transistors de taille minimale par registre sont connectés au noeud d'horloge avec la configuration retenue. Ceci permet une diminution de près de 50% de la puissance d'horloge par rapport aux horloges à deux phases sans recouvrement. Un autre avantage est que le nombre total de transistors est de 11, comparé aux bascules sans recouvrement, ce qui permet un gain d'intégration en surface. Le fait d'utiliser un seul noeud d'horloge permet également d'utiliser un seul canal de routage, et donc de réduire encore la surface. Il existe deux inconvénients à la méthode TSPC. D'abord, il s'agit d'un registre dynamique, donc l'horloge a besoin d'une fréquence minimale d'opération. Les mesures ont montré que ce minimum était de l'ordre de 500 Hz à 25°C. Un autre inconvénient est une course interne qui apparaît à l'entrée de l'inverseur sur le front

montant de l'horloge. Ce phénomène a été observé en simulation sans charge, mais il n'a jamais été vu dans un contexte d'utilisation réaliste où chaque porte a au moins une sor-tance de une porte.

Le premier chapitre de ce mémoire est consacré au développement de bibliothèques de cellules TSPC. Nous présentons tout d'abord les différentes cellules TSPC, leur avan-tages, puis différents travaux qui leur sont dédiés. Une fois que ces travaux ont été présen-tés et analysés, nous présentons notre propre méthode de conception de bibliothèque qui est valable pour toutes les cellules dynamiques. L'heuristique présentée est dédiée aux cellules TSPC. Enfin, nous mettons en valeur certains points faibles des cellules TSPC à sortie partagée.

Le second chapitre présente l'architecture d'un convoluteur  $3 \times 3$  TSPC et la solution que nous avons choisie. Une brève description de chaque module est présentée. Ensuite, sont présentés les cellules de base du convoluteur  $3 \times 3$  TSPC, puis le chemin de données qui réalise l'opération de convolution.

Le troisième chapitre explique davantage la méthode que nous avons adopté pour déve-lopper un circuit de haute performance avec la présentation de circuits de test efficaces à plus d'un GHz. Ce chapitre présente aussi la stratégie de distribution d'horloge et les mé-thodes de placement que nous avons utilisées.

## CHAPITRE 1

### METHODE DE CONCEPTION D'UNE BIBLIOTHEQUE TSPC

#### 1.1 Bascules dynamiques synchronisées par des horloges monophasées

##### 1.1.1 Introduction

La technologie CMOS conventionnelle utilise des formes de logiques statiques et dynamiques. Une technique de synchronisation très en vogue pour les circuits à logique dynamique est celle de la synchronisation pseudo double-phase (Suzuki, Odagawa et Abe, 1973; Weste et Eshraghian, 1985). Celle-ci requiert quatre signaux d'horloge. Les cellules dynamiques permettent d'atteindre des fréquences très élevées tout en étant synchronisées. Les cellules dynamiques les plus courantes sont les cellules C<sup>2</sup>MOS, Domino et Nora. Toutes ces cellules ont en commun un système de précharge et des transistors commandés par une horloge qui libèrent les charges à la fréquence voulue. Évidemment, plus la fréquence est élevée, moins le réseau logique de ces portes est complexe. Les avantages de la synchronisation multiphasée sont la sécurité et l'efficacité mesurée en terme du nombre de transistors. Cependant, la distribution des horloges requiert une superficie de silicium relativement élevée. Des circuits récents basés sur l'horloge monophasée permettent d'atteindre des vitesses supérieures à 1 GHz avec une technologie comme la CMOS 0.8 μ m. La synchronisation à horloge monophasée s'avère aussi sécuritaire et efficace en terme du nombre de transistors que la technique à quatre phases (Yuan, Karlson et Sven-

son, 1987). Elle permet également des fréquences d'horloge plus élevées que les techniques multiphasées (Yuan et Svensson. 1989).

La première partie de ce chapitre est consacrée à la définition des cellules TSPC. Dans la deuxième partie, nous présentons et analysons les différentes méthodes d'optimisation qui ont été explorées. Notre méthode d'optimisation, ainsi que ses résultats, sont proposées dans la troisième partie.

### **1.1.2 Configurations de bascules et de portes TSPC**

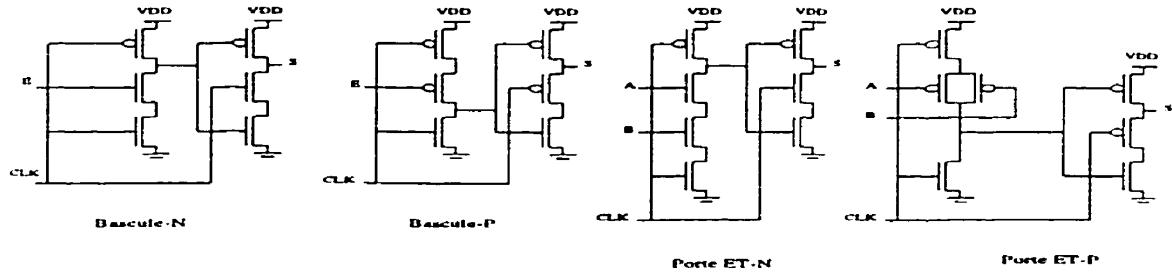

Les cellules TSPC sont dynamiques et se caractérisent par l'utilisation d'une horloge à phase unique. Ces cellules font appel à l'utilisation de transistors de précharge et à des noeuds dynamiques, afin d'accroître la vitesse de commutation et de réduire la complexité des éléments de mémoire. Il est ainsi possible d'associer une bascule logique à chaque porte logique. Nous pouvons donc former un pipeline à granularité très fine dont chaque étage correspond à une porte logique. Il faut seulement alterner des étages de polarité N avec des étages de polarité P, comme pour les cellules Nora. Pour une cellule de type N, le niveau haut de l'horloge active un transistor d'évaluation, alors que la précharge se réalise sur son niveau bas. Pour une cellule de type P, le niveau bas de l'horloge active le transistor d'évaluation, alors que la précharge se réalise sur le niveau opposé.

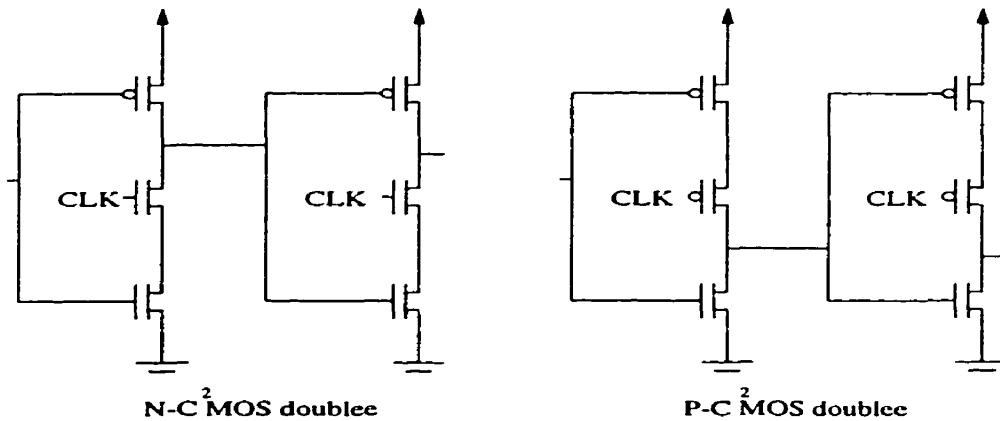

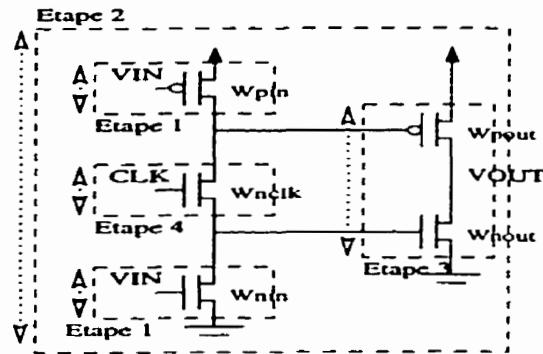

La figure 1.1 présente différentes configurations de bascules et de portes TSPC, telles que définies par Yuan et Svensson [4]. Pour chacune des configurations (TSPC-1, TSPC-2,

$C^2MOS$  double et sortie partagée), des bascules N et P sont illustrées ainsi que des portes ET de type N et P.

### Configuration TSPC-1

### Configuration TSPC-2

Figure 1.1: Différentes configurations des cellules TSPC

### Configuration C<sup>2</sup>MOS double

### Configuration à sortie partagée

Figure 1.1: Différentes configurations des cellules TSPC

Bosi [8] et Chtchvyrkov [9] ont présenté une bonne description du fonctionnement des différentes classes de cellules TSPC. Chtchvyrkov a montré que la configuration TSPC à sortie partagée donnait les meilleurs résultats en terme de vitesse maximale. Le fonctionnement d'une bascule TSPC à sortie partagée de type N est assez simple. Lorsque l'horloge est à 0, si l'entrée est à 0, nous avons une précharge à 1 sur le drain du transistor d'horloge. Lorsque l'horloge passe à 1, elle agit comme une porte de transmission et propage le 1 à sa source, ce qui active le transistor nMOS de sortie. Le transistor Nmos de

sortie envoie alors un 0 sur le noeud de sortie. Le fonctionnement est similaire si on veut propager un 1. En fait, il faut analyser cette cellule comme deux inverseurs en série. Le premier inverseur produit une précharge à l'opposé logique de l'entrée. Le second inverseur inverse alors la précharge propagée par l'horloge. Pour des cellules efficaces et capables de supporter les charges typiquement rencontrées dans un circuit logique, nous pouvons nous attendre à ce que les transistors de l'inverseur de sortie soient plus grands que les transistors de l'inverseur d'entrée. Nous nous sommes donc concentrés sur ce type de cellule afin de réaliser une bibliothèque de cellules TSPC. Les études précédentes [8] [9] s'étaient surtout concentrées sur la réalisation de bascules et nous les avons prolongées pour couvrir la réalisation d'une bibliothèque TSPC portable d'une technologie à l'autre.

## 1.2 Méthode d'optimisation d'une bibliothèque TSPC.

### 1.2.1 Introduction

Plusieurs personnes ont essayé de développer des bibliothèques de cellules TSPC en exploitant la puissance des outils de conception et de simulation qui sont à notre disposition. En fait, lorsqu'une nouvelle technologie arrive il faut développer une nouvelle bibliothèque de cellules TSPC. Chtchyrkov a tout d'abord testé les diverses familles de cellules TSPC. Ses nombreuses simulations ont permis de confirmer que la technique TSPC à sortie partagée donne les meilleurs résultats. Il travaillait à l'époque en technologie CMOS 3 μ m. Il a également mis au point un algorithme d'optimisation de cellules dynamiques que nous allons exposer puis analyser. Bosi a également développé une bibliothèque de

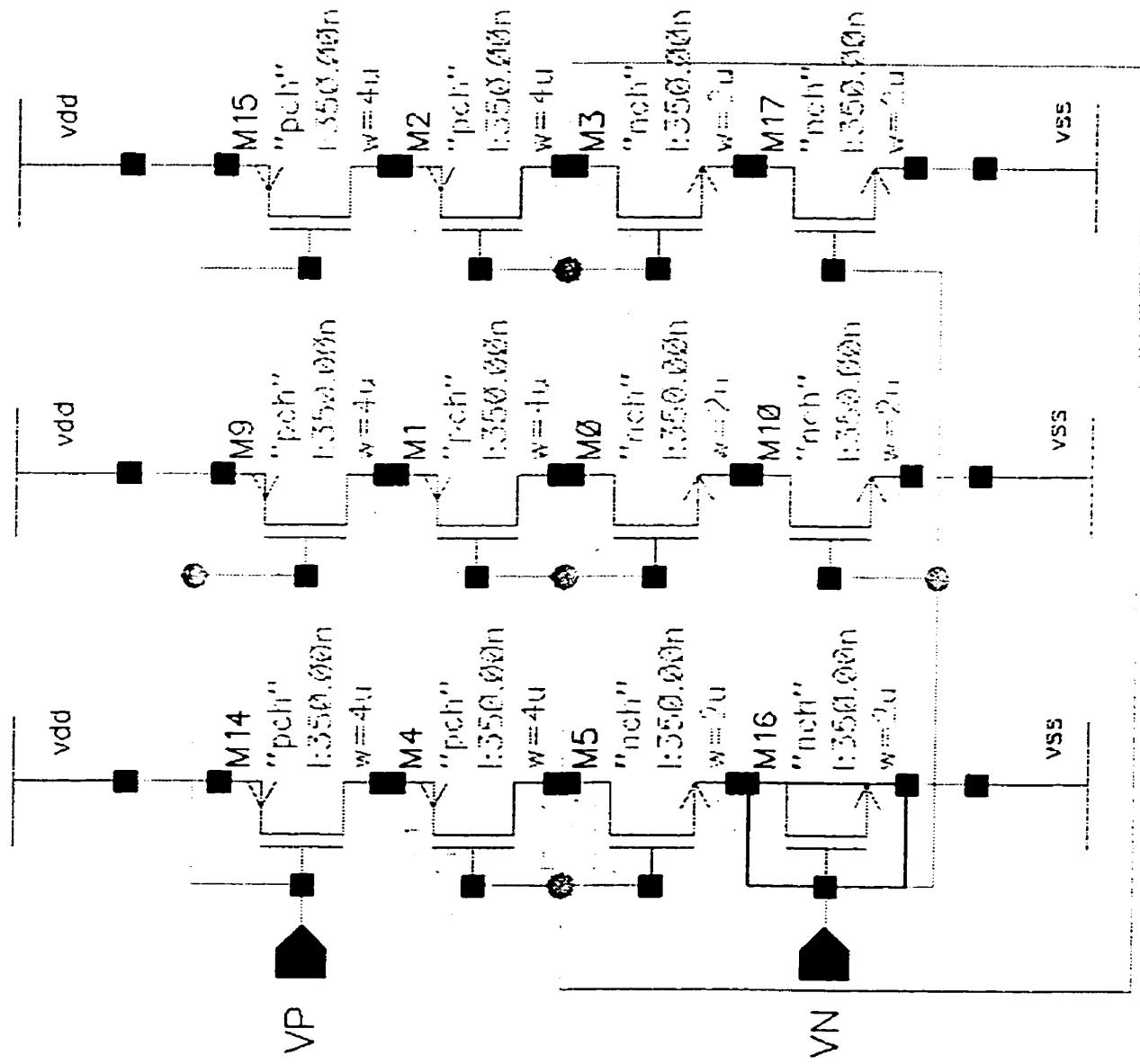

cellules TSPC en schématique pour la technologie CMOS 1.2  $\mu$ m en vue d'implanter un convolveur 3\*3 TSPC. Il a, pour ce faire, exploité les algorithmes d'optimisation disponibles dans HSPICE. Antaki et Patenaude [10] se sont également intéressés à l'importance du transistor d'horloge dans les cellules TSPC à sortie partagée. Ils ont travaillé sur des chaînes de bascules en proposant un algorithme d'optimisation séduisant par sa simplicité. Les sections 2.1, 2.2 et 2.3 sont relatives à la description et à l'évaluation des différentes méthodes de développement de bibliothèques de cellules TSPC, dont découle la section 3 consacrée à une nouvelle méthode d'optimisation des cellules TSPC.

### **1.2.2 Une méthode d'optimisation systématique**

Chtchvyrkov a étudié les cellules TSPC1, TSPC2, C<sup>2</sup>MOS et SP (Sortie partagée). Il a réalisé une étude de chaque cellule. Deux versions de chaque bascule furent considérées: l'une étant en configuration positive (sensible à une valeur positive de l'horloge, type N), l'autre négative (type P). Il a ainsi pu évaluer les avantages et inconvénients de chaque technique selon les vitesses d'évaluation, de précharge, de temps de montée et de descente. Pour évaluer ces techniques de conception, il a d'abord conçu des bascules selon chaque technique en les optimisant à l'aide d'un algorithme d'optimisation automatique. Il a établi un certain nombre de critères qui sont partiellement repris dans la section 3. Son programme d'optimisation a été réalisé en langage ANSI C. Son logiciel fournit une netlist à HSPICE qui lui renvoie des paramètres de temps de montée, de descente, de tension maximale... Ces données sont analysées par son logiciel qui renvoie une nouvelle Netlist à Hspice, qui renvoie à son tour des données jusqu'à l'obtention d'une convergence.

Son algorithme d'optimisation se résume ainsi:

- 1) à chaque étape, le logiciel choisit une des configurations possibles et exécute une simulation HSPICE pour en établir les performances;

- 2) les résultats sont comparés aux résultats antérieurs;

- 3) la meilleure configuration est retenue et le processus continue, jusqu'à la satisfaction d'un critère d'arrêt.

Pour réduire le nombre de simulations, un algorithme introduisant des perfectionnements graduels a été proposé afin d'accélérer la recherche. La recherche s'effectue sur une dimension à la fois, c'est-à-dire que toutes les largeurs de transistors sont fixées, sauf une. Une fois que la meilleure solution est déterminée pour une dimension, elle sert de point de départ dans la recherche de la dimension suivante. La complexité de ce genre de recherche est linéaire relativement au nombre de dimensions à explorer.

En fait, dans cet algorithme, la fréquence d'opération à laquelle les cellules sont simulées est constante. Il faut donc déterminer la fréquence de travail et être certain que la bibliothèque pourra entièrement être conçue à cette fréquence. Le but de cette opération est de réaliser une bibliothèque de cellules balancées. Chaque cellule doit avoir des temps de montée et de descente proches et des délais semblables. Il faut donc mettre des critères sur chaque paramètre afin que le signal de sortie de chaque porte se conforme à un gabarit imposé.

Donc, dans cet algorithme, une largeur de transistor est proposée et sa valeur évolue tant que les performances s'améliorent. La méthode optimise tous les transistors de la cellule en suivant un gradient de performance. La rapidité d'exécution pourrait être accrue en utilisant une recherche dichotomique pour le meilleur rendement de la taille d'un transistor. Cet algorithme consomme un temps de calcul considérable, car il prend en compte un nombre important de paramètres et peut demander plusieurs passes avant de converger. Il semble donc nécessaire de diminuer l'effort de recherche, cependant on peut remarquer que cet algorithme donne de bons résultats malgré un nombre d'itérations important. Notons que dans l'algorithme implanté par Chchvyrkov, la charge peut varier et les inverseurs d'entrée produisant un signal de format typique sont fixes. Il aurait été bon de laisser varier les inverseurs d'entrée afin d'avoir des signaux correspondant à la taille variable de la nouvelle bibliothèque. En effet, si les inverseurs d'entrée ont une taille importante, les transistors d'entrée de la cellule à optimiser ont un grand degré de liberté et ils peuvent ainsi atteindre une taille importante. Dans la réalité, lorsque les étages N et P sont alternés, nous pouvons rencontrer des erreurs. L'étage de sortie des bascules est configuré pour commander deux inverseurs en espérant n'en rencontrer qu'un ou deux. Si les transistors d'entrée sont trop importants, l'étage de sortie sera insuffisant pour contrôler la bascule suivante. Il faut donc que les transistors qui commandent l'entrée soient ajustées avec ceux de la cellule en voie d'optimisation. Il faut également tenir compte des interconnexions

### 1.2.3 Méthode d'optimisation des bascules selon trois dimensions.

Patenaude et Antaki [10] ont étudié l'importance du transistor d'horloge sur des registres à décalage TSPC réalisés avec des cellules à sortie partagée. Ce transistor est très important dans ces cellules, car il joue le rôle d'une demi-porte de transmission. Dans leur recherche, ils évaluent l'importance de la taille de ce transistor ainsi que l'effet de la sortance et des longues interconnexions en sortie. Pour ce faire, ils ont développé un outil d'optimisation automatique. Cet outil réalisé en langage C invoque également Hspice, de façon itérative, en vue de converger vers une solution qui n'est pas forcément la meilleure, mais qui correspond quand même à un résultat valable.

Dans cette chaîne de bascules, seules trois dimensions peuvent évoluer en fonction de la fréquence. On ne travaille que sur trois variables: les transistors Nmos, Pmos et le transistor d'horloge à partir d'une Netlist extraite de Cadence. Il est ainsi possible de connaître la fréquence maximale que peut atteindre une configuration de tailles de transistors et de faire varier cette configuration pour accroître les performances. En modifiant l'algorithme, il est également possible d'obtenir la meilleure configuration de transistors à la fréquence de travail souhaitée. L'algorithme proposé est plus complexe que le précédent, mais il tient compte de moins de variables.

Les résultats ont démontré l'importance du transistor d'horloge et dévoilé également les limites des simulateurs à hautes fréquences. Ainsi, lorsque seul le transistor d'horloge évolue linéairement, on s'attend à des résultats qui progressent linéairement, hors ce n'est

pas le cas. Des zones d'ombre, où se produisent des chutes de performance inexplicées et des pics de performance pour une taille de transistor montrent les limites des modèles des transistors à haute fréquence. Ceci s'explique par des changements de modèles de transistors lorsque les tailles changent. Les modèles de transistors d'une technologie varient selon la longueur de la grille et la largeur du transistor ainsi que le procédé de fabrication. Donc, lorsque la taille des transistors évolue, il peut apparaître des pics dans les résultats qui sont encore plus importants à haute fréquence. Évidemment, le fait de ne faire varier que les transistors Nmos et Pmos diminue le degré d'optimisation des résultats, car nous n'avons que 2 paramètres, mais cette méthode peut donner rapidement des résultats. Nous jugeons que la qualité des solutions obtenue est insuffisante lorsqu'il s'agit de développer une bibliothèque de cellules.

#### **1.2.4 Méthode d'optimisation à partir d'un outil d'optimisation d'un simulateur**

Bosi [8] a également développé une bibliothèque de cellules TSPC en technologie CMOS 1.2  $\mu\text{m}$ . Ces cellules ont été réalisées au niveau schématique. Pour cette optimisation, seul l'outil d'optimisation disponible dans HSPICE est utilisé. Cet outil permet aux transistors de varier selon une table prédéfinie, dans le but de rencontrer un certain nombre de critères. En fait, Hspice réalise des mesures et ne conserve que les configurations qui atteignent un certain nombre d'objectifs en terme de performance. Cette méthode rejoint celle de Chtchvyrkov et permet d'obtenir rapidement une bibliothèque de cellules balancées . Il est par exemple possible de demander que le temps de montée soit à 90% de VDD et inférieur à 0.2 ns. En fait, il faut dessiner un gabarit et Hspice fait varier les tailles de tran-

sistors tant que les objectifs n'ont pas été atteints. Évidemment, Hspice ne tient pas compte de résultats aberrants sur les dimensions des transistors et peut offrir des solutions peu élégantes. Il faut vraiment se méfier de telles optimisations. De plus, il faut travailler à fréquence constante et il est difficile de connaître la meilleure configuration dans une technologie donnée. Cette méthode est tout de même intéressante pour obtenir une première idée des tailles de transistors pour une bibliothèque.

### 1.3 Méthode d'optimisation de la taille des transistors

Cette section présente une heuristique pour optimiser des bascules TSPC à sortie partagée. Les études précédentes ont montré que les circuits TSPC peuvent opérer à de très hautes fréquences. Notre but est d'implémenter de larges blocs numériques pouvant opérer à 1 GHz ou davantage (dans une technologie CMOS 0.35 µm). Notre méthode a débuté avec le développement d'un premier ensemble de cellules basées sur un design ad-hoc.

Une méthode semi-automatique fut alors développée pour réduire le nombre de simulations. Basé sur l'expérience acquise dans l'optimisation de cellules TSPC, nous proposons un algorithme pour optimiser automatiquement les cellules TSPC et une méthode pour réaliser des bibliothèques de cellules logiques normalisées. Cette section décrit les différentes étapes à suivre pour élaborer une bibliothèque TSPC. La méthode et la bibliothèque de cellules sont validées par la caractérisation de petits blocs numériques.

Les concepteurs de systèmes électroniques luttent pour augmenter les performances qu'ils obtiennent. Chaque fois qu'une nouvelle technologie apparaît, les concepteurs rencontrent la nécessité de développer de nouvelles bibliothèques. Pour éviter cette tâche, une méthode qui optimise les performances des cellules TSPC est proposée. Le but de la méthode est de réduire, autant que possible, le nombre de simulations requises pour atteindre un design quasi optimal. L'optimisation dépend des critères adoptés. Nous avons pu observer dans des travaux précédents que les cellules pouvaient être balancées pour une fréquence cible spécifique, et, dans ce cas, le but général est de minimiser la surface pour atteindre cette fréquence. La section 1.3.1 décrit des critères d'optimisation. La section 1.3.2 propose une méthode qui utilise ces critères, suivie d'un ensemble d'étapes. La section 1.3.3 présente quelques résultats comprenant une bibliothèque de base avec ses tailles de transistors et son utilisation pour réaliser de petits blocs logiques.

### 1.3.1 Règles d'optimisation

#### 1.3.1.1 Banc d'essai

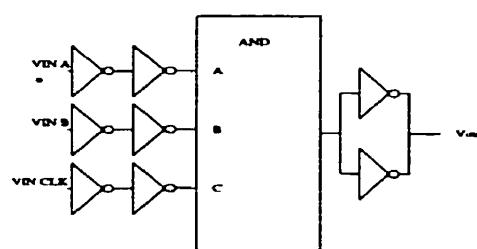

**Figure 1.2: Banc d'essai typique (AND à 2 entrées)**

Des bancs d'essai similaires à ceux montrés à la figure 1.2 furent utilisés lors de l'optimisation de la bibliothèque de cellules de base. Tous les signaux d'entrée d'un circuit testé passent à travers des paires d'inverseurs pour produire des transitions réalistes. Les inverseurs utilisés sont ceux de notre bibliothèque standard. La vitesse maximale d'un bloc TSPC tend à être contrôlée par la vitesse de la cellule la plus lente. Il est donc nécessaire d'optimiser au maximum toutes les cellules lentes, en l'occurrence celles qui ont un transistor Pmos pour l'horloge. Une charge réaliste doit être introduite pour obtenir des résultats valides. Nous avons pu remarquer que les sortances de nos blocs logiques, numériques et arithmétiques étaient d'un ou de deux avec une grande fréquence. Donc deux inverseurs ont été utilisés pour représenter cette charge. Notons que pendant l'optimisation, les tailles des transistors de tous les inverseurs (entrée et sortie) varient selon celles des transistors dans les cellules (tous liés à un même paramètre de variation). Il faut également ajouter une capacité d'interconnexion pour la sortance.

### 1.3.1.2 Critères d'optimisation

Une bibliothèque convenablement optimisée doit être en mesure de propager tous les signaux d'entrée. Cependant, un petit nombre de vecteurs d'entrée sont suffisants pendant la phase d'optimisation pour atteindre cet objectif. Par exemple, les vecteurs 000100010... et 11101110... testent la faculté d'un chemin sensibilisé à répondre à des valeurs 0 et 1 isolées, tandis que le vecteur 010101010 force la cellule à réagir rapidement à des signaux qui varient constamment. Les cellules à deux entrées sont testées avec les quatre combinaisons logiques possibles. À chaque fois, nous conservons le résultat du pire vecteur.

L'optimisation permet de trouver la fréquence maximale atteignable par une cellule et la plus petite taille de transistor nécessaire pour une cellule à une fréquence et à une sortance spécifique. Un ensemble de critères sont utilisés pour établir la faculté du circuit à propager le signal à une vitesse donnée. Ces critères sont:

\* Le niveau haut logique de la tension de sortie doit atteindre 90% de VDD et le niveau bas logique doit être inférieur à 10% de VDD;

\*Si l'on considère le signal d'entrée 010101 dont la période est de deux cycles d'horloge, quand ce signal est propagé à travers une cellule, la durée des signaux valides 0 et 1 en sortie devront être de plus de 5% de la durée d'un cycle d'horloge.

\*les transitions de montée et de descente des sorties doivent être de moins de 40% du cycle d'horloge.

### **1.3.1.3 Modèle utilisé pour la simulation.**

Afin d'utiliser un bon modèle pour l'optimisation, une première version de chaque cellule a été conçue au niveau schéma des masques. Pour le schéma des masques, tous les transistors ont la même taille ( $W=7 \mu m$  dans notre exemple). Les éléments parasites typiques sont extraits du schéma des masques afin de générer une *netlist* plus complète.

### 1.3.2 Étapes d'optimisation pour élaborer une bibliothèque TSPC.

Cette section commence par la description des différentes étapes d'optimisation qui peuvent être combinées lors du développement d'une bibliothèque TSPC. Un algorithme utilisant ces étapes sera proposé ensuite. Deux technologies ont été supportées dans nos exemples [11,12]

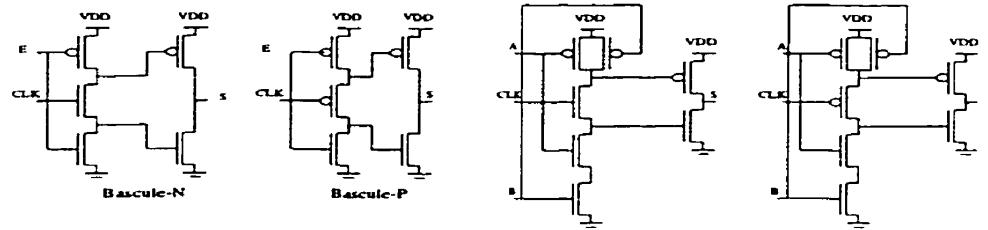

**Figure 1.3: Différentes étapes d'optimisation pour une bascule de type N**

#### 1.3.2.1 Modèle utilisé pour la simulation.

Les quatre étapes d'optimisation sont liées à la structure des cellules TSPC à sorties partagées, et elles sont donc applicables à tous les types de portes, comme montré aux figures 1.3 et 1.4, pour une bascule et une porte ET respectivement.

Étape 1:

Cette étape est utilisée pour trouver le meilleur rapport  $x$  entre les largeurs des transistors Nmos et Pmos, c'est à dire:  $W_p/W_n$  où:

$$W_p = W_{pin} = W_{pclk} = 0.5 * W_{pout} \quad (1)$$

$$W_n = W_{nin} = W_{nclk} = 0.5 * W_{nout} \quad (2)$$

Tout d'abord,  $W_n$  est fixé et nous déterminons  $W_p$  en considérant l'espace  $[W_n, \dots, 5W_n]$ .

Différents incrément peuvent être utilisés à l'intérieur de l'espace à différentes phases du processus d'optimisation. Pour simplifier, nous avons utilisé un incrément de  $5 \mu\text{m}$  à différentes phases de l'algorithme. Donc  $W_p \in \{W_n, W_{n+5}, W_{n+10}\dots\}$ . Évidemment, d'autres incrément peuvent être utilisés pour obtenir une meilleure résolution. Toutefois, de petits incrément augmenteront les ressources matérielles de calcul. Il est également possible de débuter avec des incrément plus importants pour effectuer une première évaluation, puis de diminuer la valeur des incrément lorsque l'algorithme progresse. Quand l'algorithme est appliqué à une technologie CMOS  $0.35 \mu\text{m}$ , la solution converge à  $W_p=4*W_n$  pour une porte ET de type N et à  $W_p=2*W_n$  pour une porte ET de type P.

### Étape 2:

Dans cette étape, nous déterminons la meilleure hauteur des cellules pour une technologie. Le rapport  $W_p = x * W_n$  a été obtenu de l'étape précédente. Ainsi la valeur des transistors p est liée à celle des transistors n. La recherche d'une hauteur idéale amène à la remarquable conclusion que la performance continue de croître lorsque la hauteur croît. Le circuit tend vers une performance asymptotique maximale. Dans une technologie  $1.5 \mu\text{m}$ , cette asymptote était plus ou moins atteinte avec une taille de  $50 \mu\text{m}$  et 95% de la

performance maximale était obtenu avec  $W_n=12 \mu\text{m}$ . Par contre, dans une technologie  $0.35 \mu\text{m}$ , cette asymptote était plus ou moins atteinte avec une taille de  $30 \mu\text{m}$  et 95% de la performance maximale était déjà atteinte avec une largeur  $W_n=5 \mu\text{m}$ . Dans cette étape, des équations similaires à (1) et (2) sont utilisées mais  $W_p$  est remplacé par  $x^*W_n$ .

#### Étape 3:

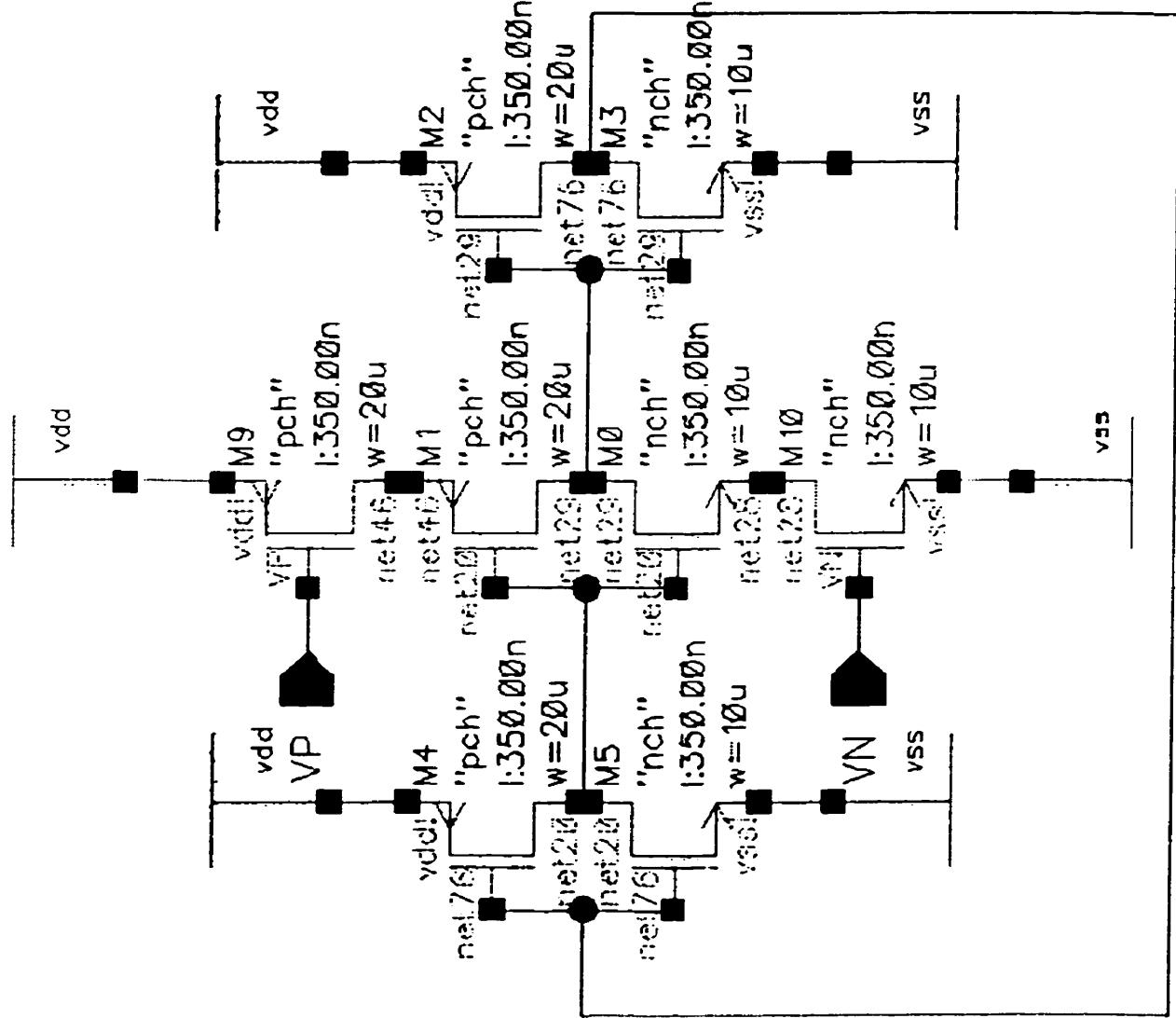

Dans cette étape, nous optimisons la taille des transistors de sortie. Leur taille peut changer jusqu'à l'obtention de la meilleure performance pour une sortance donnée. Après avoir obtenu le meilleur rapport  $y$  entre  $W_{pout}$  et  $W_{nout}$ ,  $W_{pout}$  est remplacé par  $y^*W_{nout}$ . La taille des transistors varie jusqu'à l'obtention des meilleurs résultats. À cette étape seuls deux transistors varient. Dans notre exemple (technologie CMOS  $0.35 \mu\text{m}$ ), nous avons utilisé un incrément de  $5 \mu\text{m}$  et trouvé un rapport de 2 pour chaque cellule de la bibliothèque ( $W_{pout}=20 \mu\text{m}$  et  $W_{nout}=10 \mu\text{m}$ ).  $W_{pout}$  et  $W_{nout}$  dépendent de la sortance. Les transistors de sortie jouent un rôle très important car ils restaurent le signal de sortie.

#### Étape 4:

Cette étape optimise la taille du transistor d'horloge. Sa largeur varie jusqu'à l'obtention des meilleurs résultats. Dépendant de la polarité de la grille,  $n$  ou  $p$ ,  $W_{nclk}$  ou  $W_{pclk}$  changent de  $1 \mu\text{m}$  à 5 fois la valeur de  $W_{nin}$  selon la valeur de l'incrément d'optimisation.

**Figure 1.4: Différentes étapes d'optimisation pour AND TSPC de type NMOS**

### 1.3.2.2 Algorithme d'optimisation automatique d'une bibliothèque de cellules TSPC

L'algorithme débute avec une phase d'initialisation qui est suivie par la boucle principale. La phase d'initialisation commence avec une chaîne de bascules TSPC dont la polarité des transistors d'horloge est alternée afin d'obtenir  $W_p=x^*W_n$ . L'étape 2 est alors utilisée pour caractériser la performance selon le rapport taille/asymptote. L'utilisateur peut choisir une fréquence cible ou sélectionner un point d'opération sur l'asymptote, qui sera par exemple la largeur des transistors qui correspond à la hauteur de sa bibliothèque. Il faut noter que dans la recherche du paramètre de taille optimale, la charge et les transistors de commande doivent varier en même temps que les bascules. Dans une technologie CMOS 0.35  $\mu\text{m}$ , nous avons obtenu  $W_{n\text{in}}=5 \mu\text{m}$  et  $W_{p\text{in}}=10 \mu\text{m}$ , comme l'indiquent les figures 1.3 et 1.5 pour des bascules de type N et P.

La principale boucle d'optimisation optimise chaque cellule de la bibliothèque. Les étapes 1,3 et 4 sont utilisées dans cette tâche. Ces étapes peuvent être répétées dans un ordre différent. Elles peuvent également être renouvelées plus d'une fois afin d'améliorer le résultat. Pour obtenir la bibliothèque présentée à la figure 4, la séquence d'étape 1,3,4,1,4 et 3 a été utilisée sur chaque cellule. Il faut noter que l'étape 1 change après sa première utilisation. Seuls  $W_{pin}$  et  $W_{nin}$  changent, tandis que  $W_{clk}$  et  $W_{out}$  conservent leur valeur obtenue lors de la précédente optimisation.

Les inverseurs prennent les valeurs  $W_{pinv} = W_{pin}$  et  $W_{ninv} = W_{nin}$ , obtenues lors de l'initialisation, pendant la phase d'optimisation. Quand la bibliothèque est finie, les inverseurs de la nouvelle bibliothèque adoptent les tailles des transistors  $W_{pout}$  and  $W_{nout}$  obtenues pour la bascule TSPC Nmos. Ainsi, pour obtenir un NON-ET, nous avons juste à ajouter un inverseur au ET. Quand des tailles stables ont été obtenues ou après un nombre spécifié d'itérations, nous pouvons optimiser davantage les cellules en faisant varier seulement un transistor à la fois, tandis que les autres restent statiques comme dans l'algorithme proposé par Chtchvyrkov.

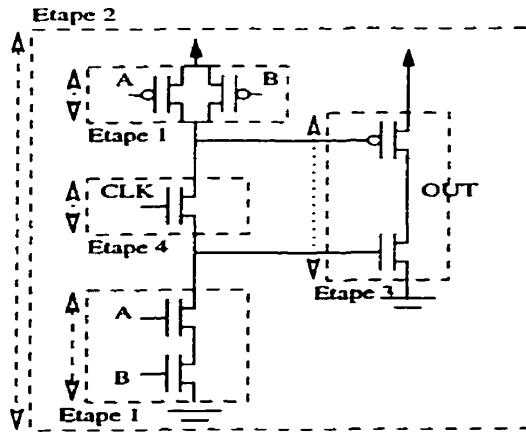

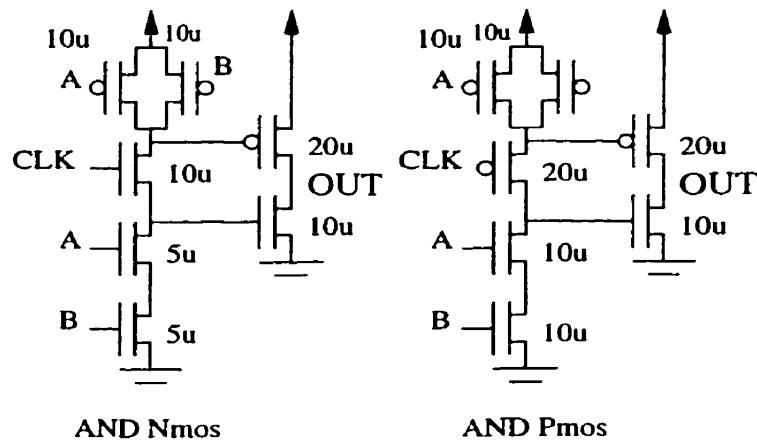

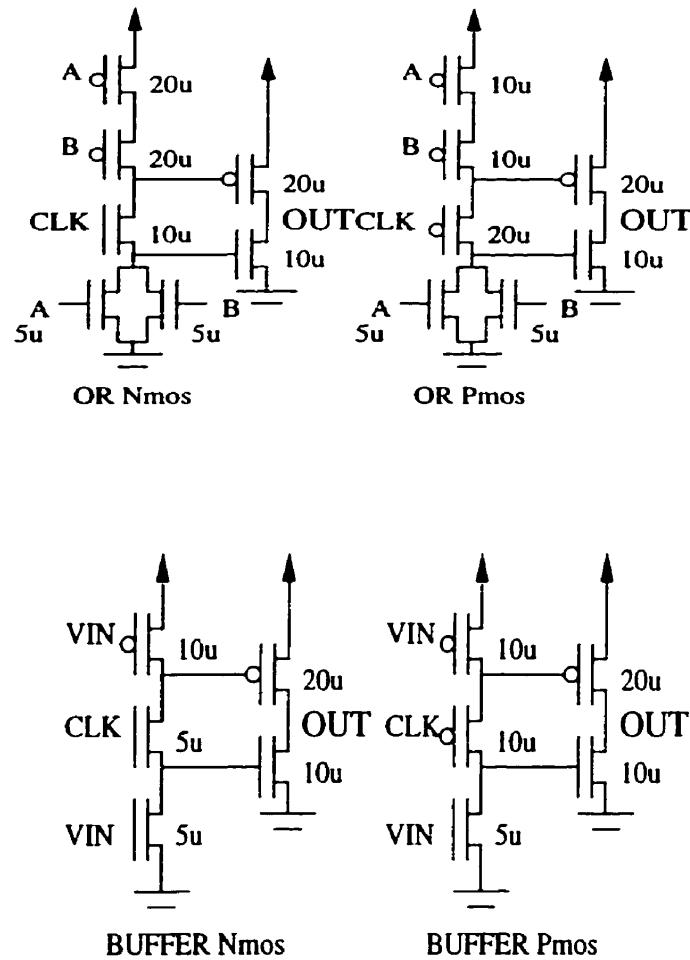

Les quatre étapes d'optimisation ont produit les six cellules présentées à la figure 1.5.

### 1.3.3 Résultats de la bibliothèque de cellules TSPC

#### 1.3.3.1 Tailles des différentes cellules:

La figure 1.5 présente les résultats obtenus par notre algorithme dans une technologie CMOS 0.35  $\mu\text{m}$ .

Figure 1.5: Résultats de la bibliothèque de cellules TSPC

**Figure 1.5: (suite) Résultats de la bibliothèque de cellules TSPC**

### 1.3.3.2 Performance obtenue dans la technologie $0.35 \mu\text{m}$

Cette section valide les performances de la bibliothèque. Nous avons réalisé des circuits typiques utilisant la plupart des cellules comme l'additionneur complet et nous démontrons les performances des circuits TSPC avec un registre à décalage qui fonctionne à une fréquence proche de la vitesse limite de la technologie.

=> Chaîne de six bascules TSPC avec une sortance de deux inverseurs.

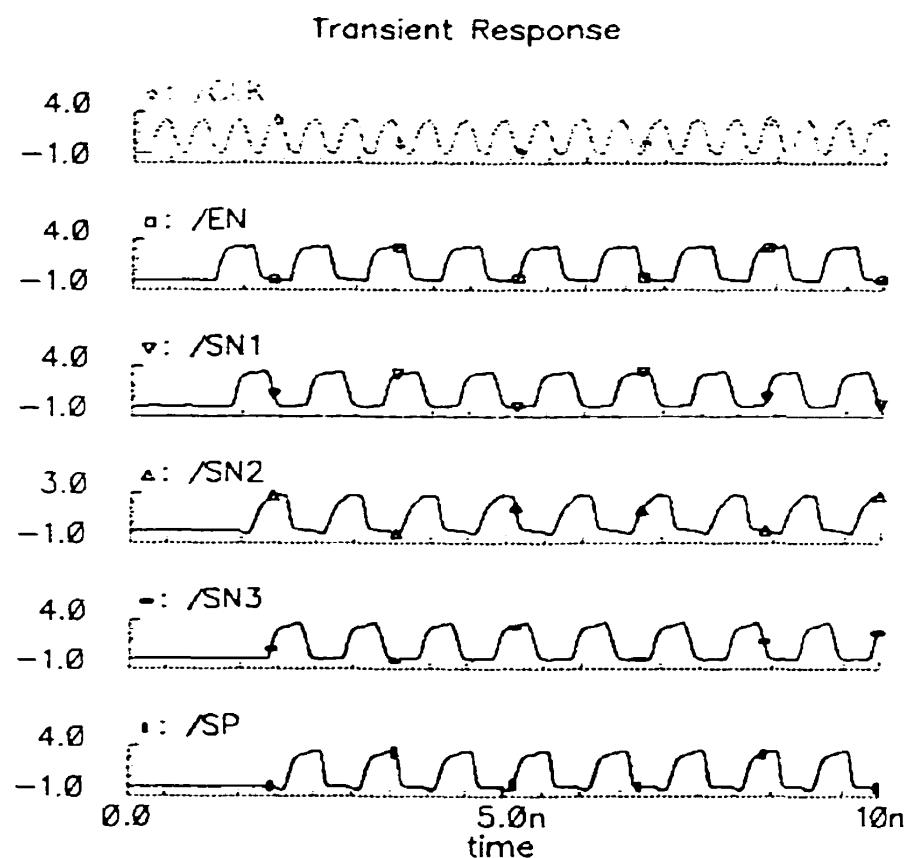

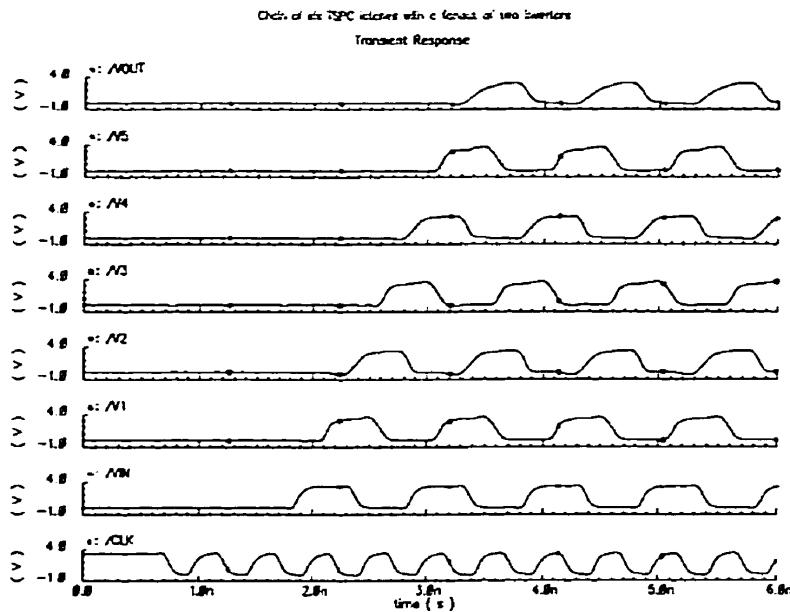

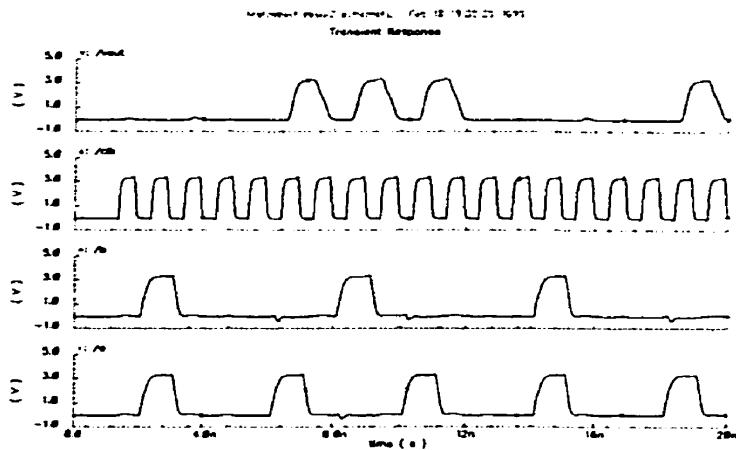

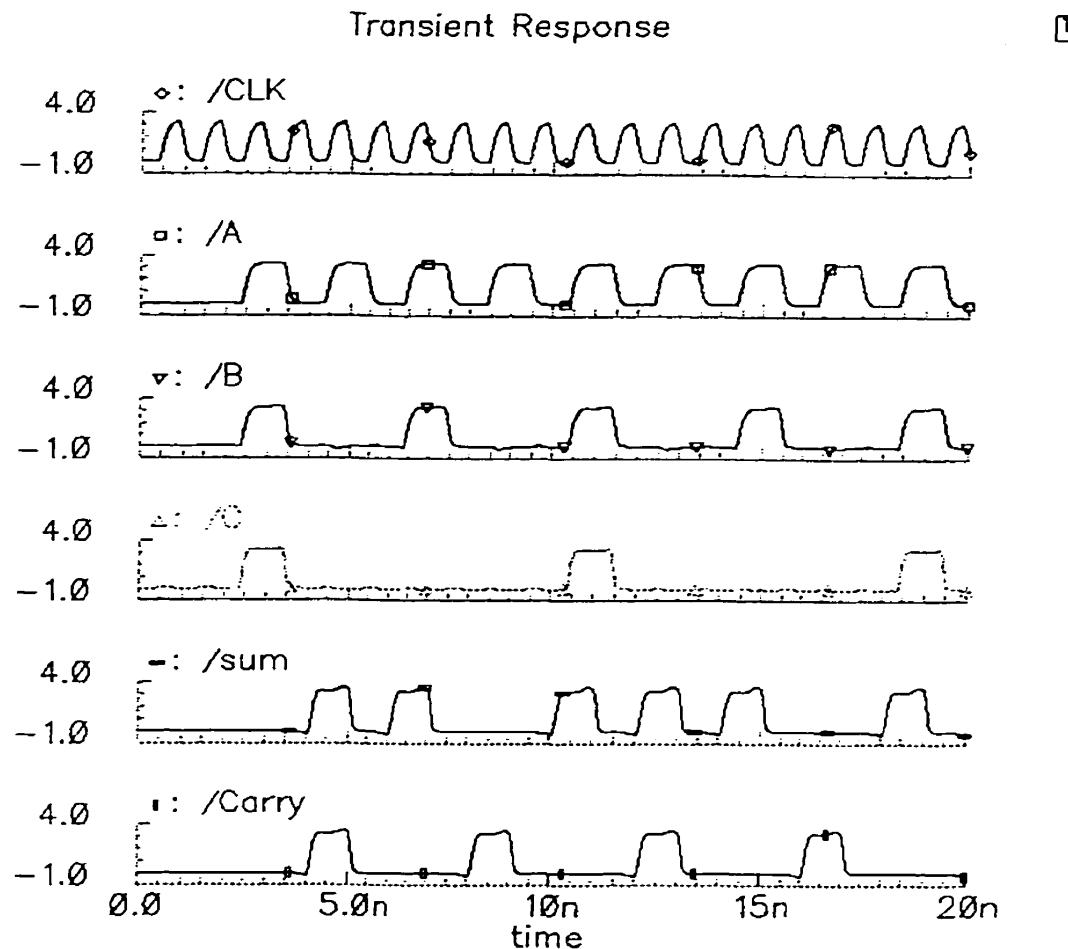

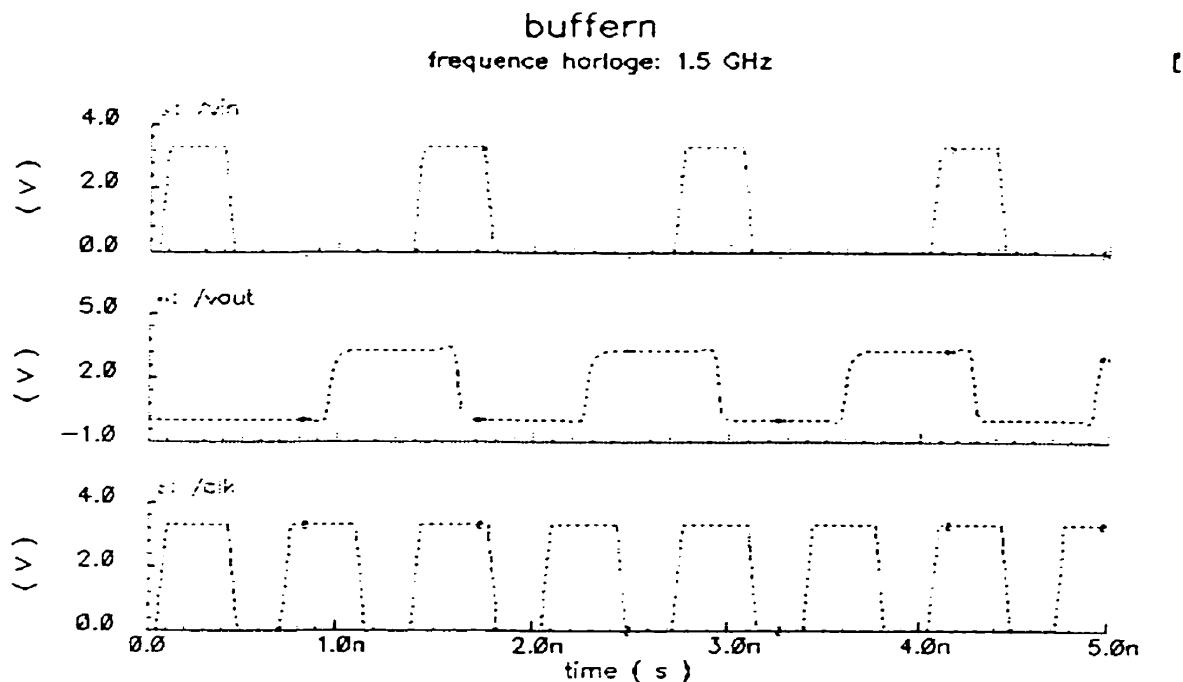

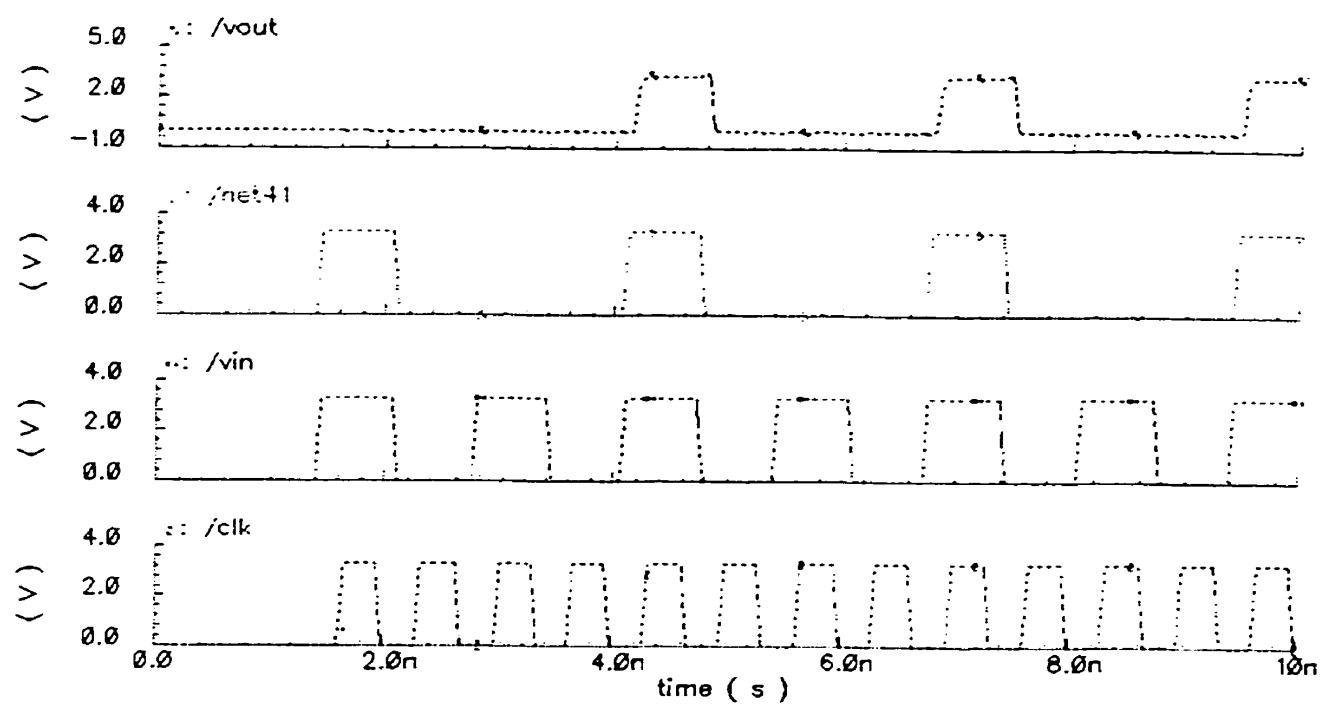

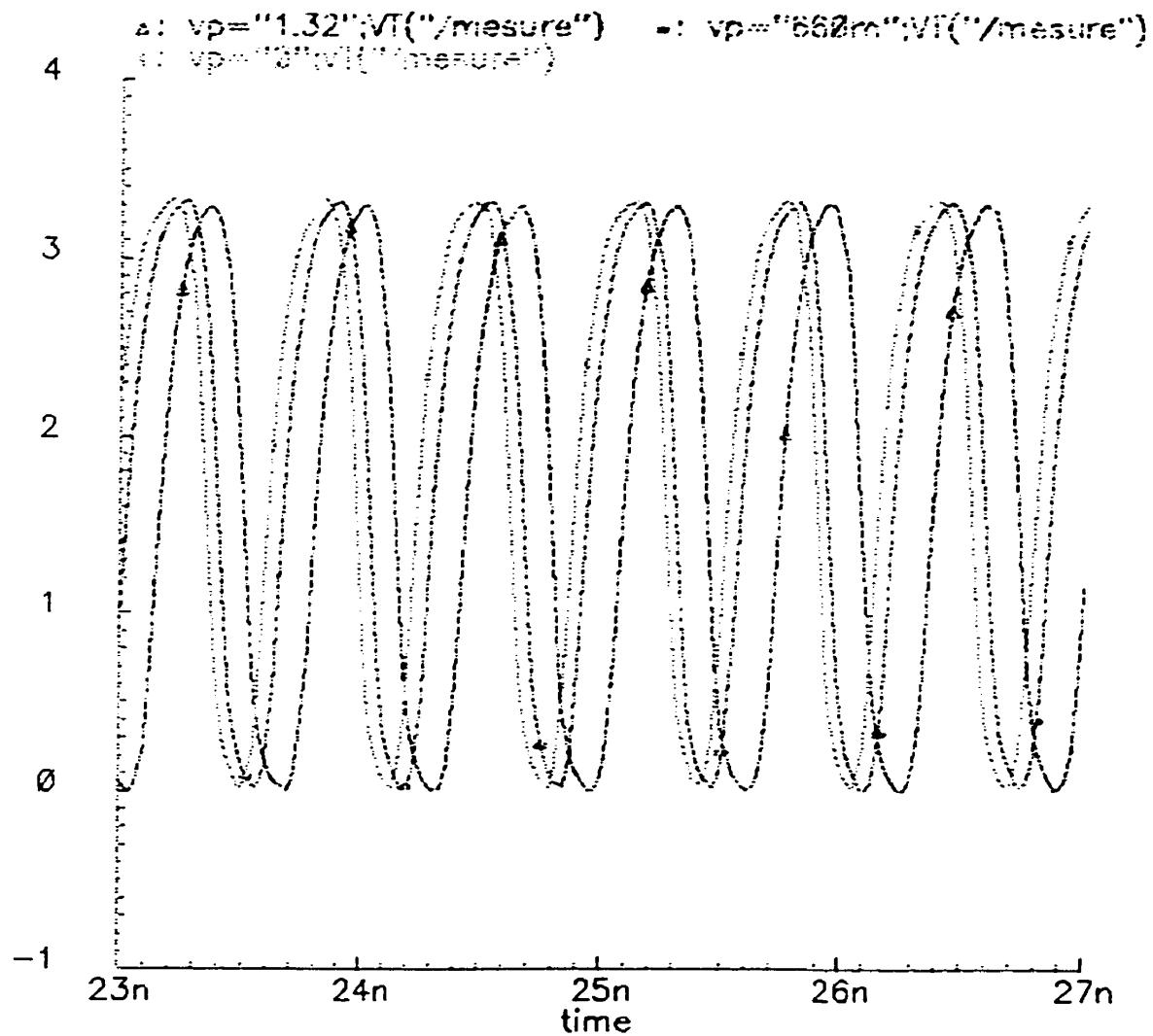

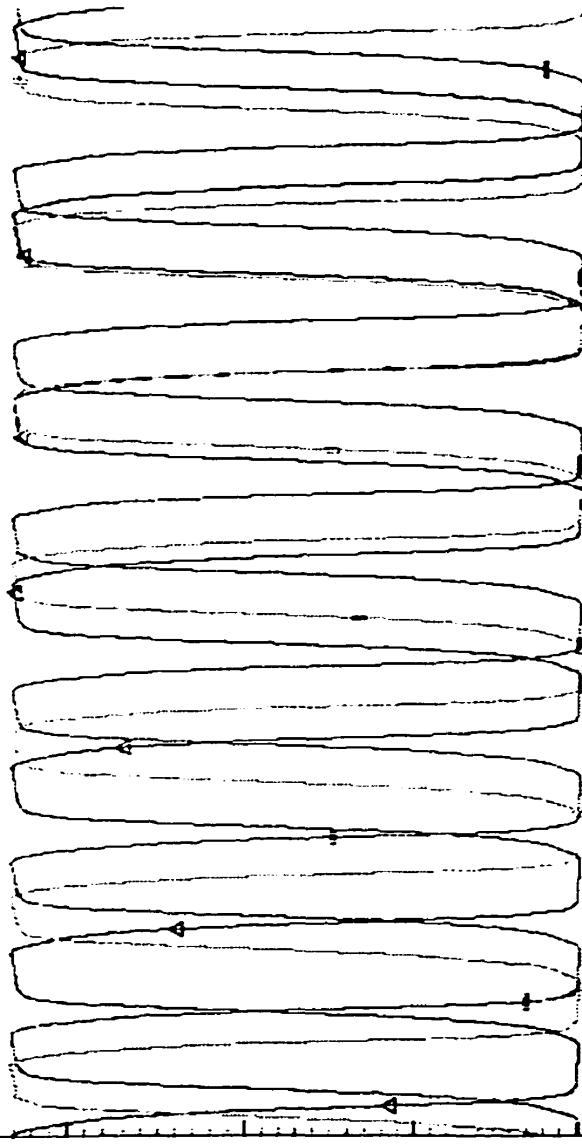

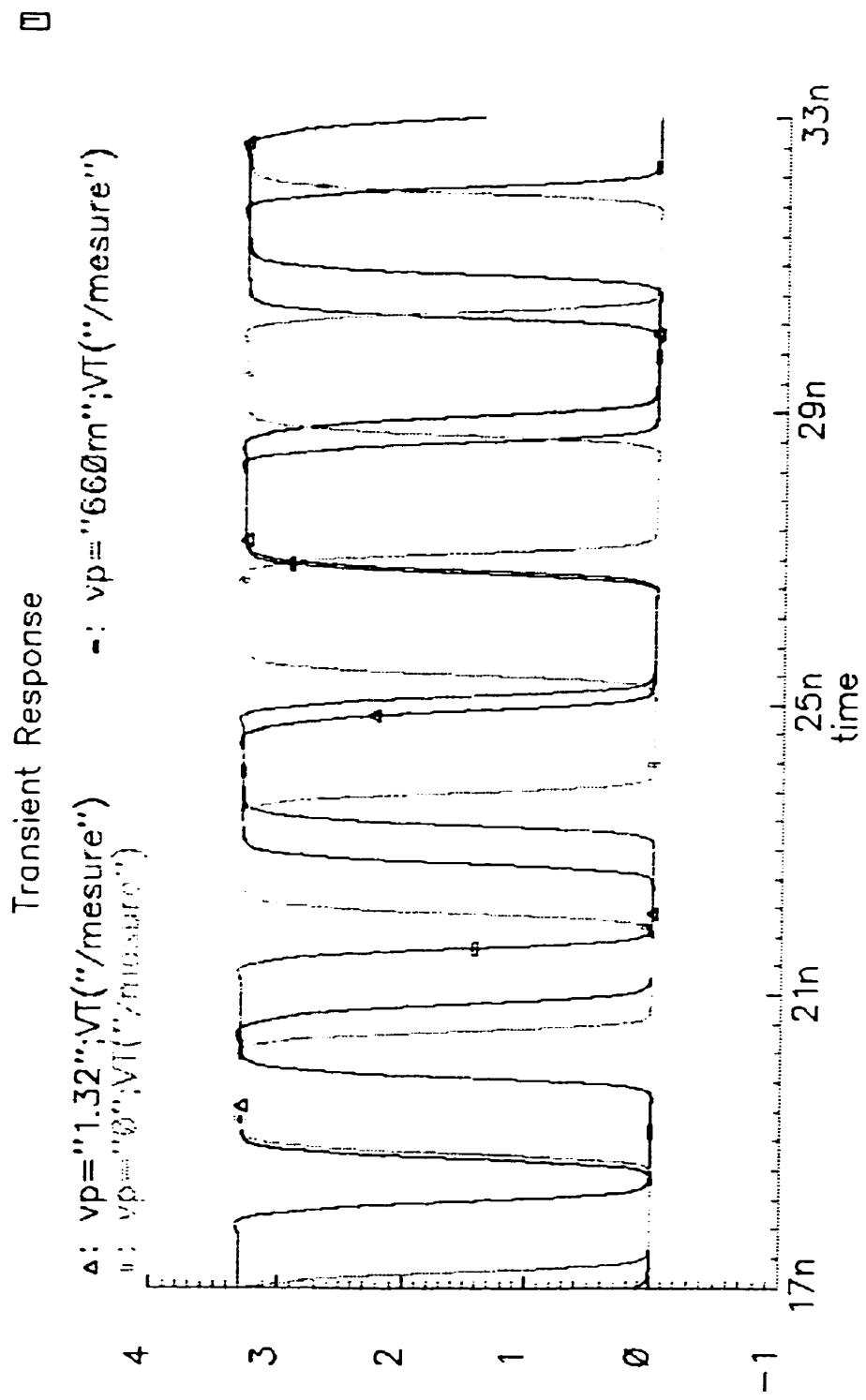

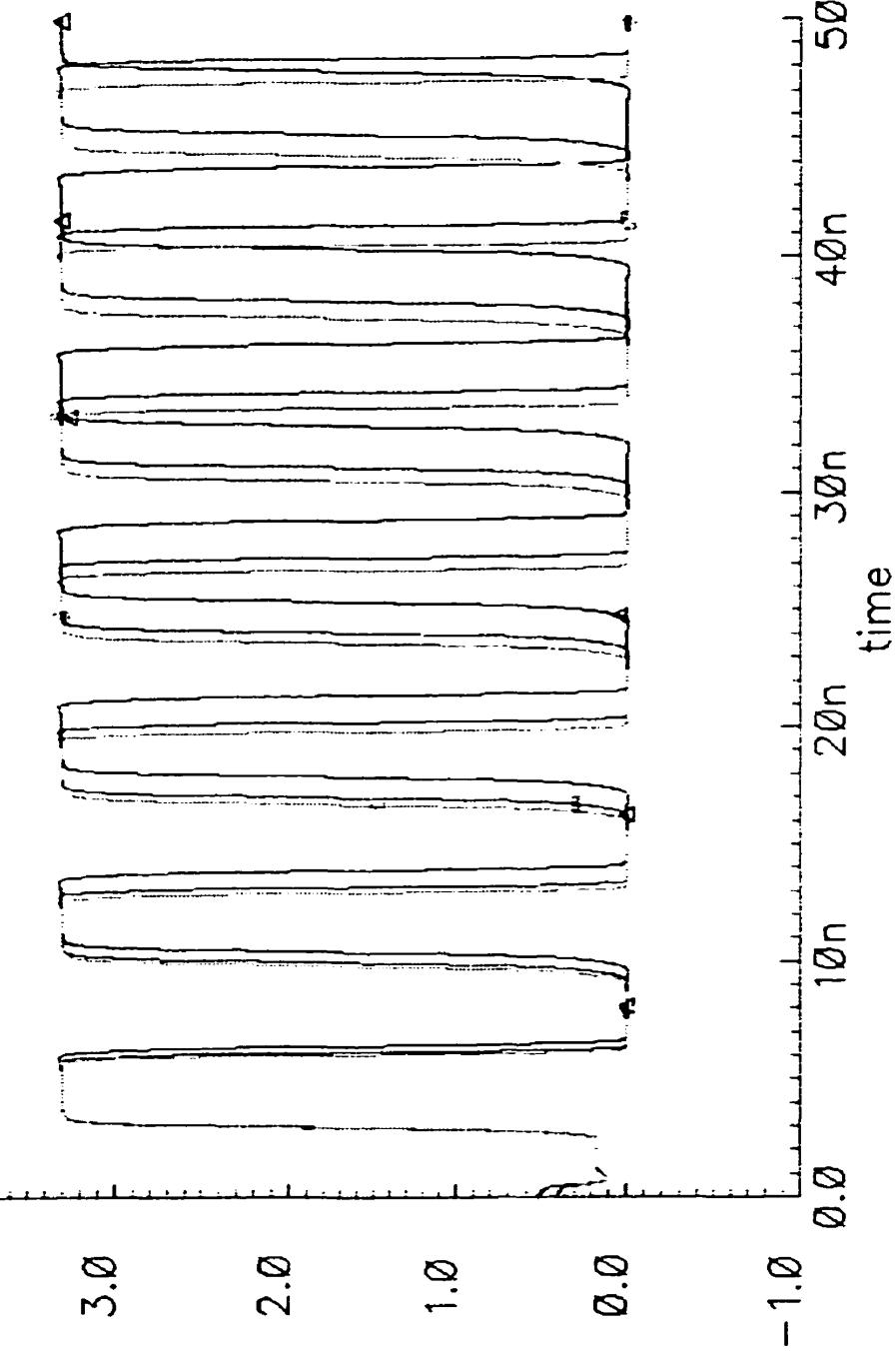

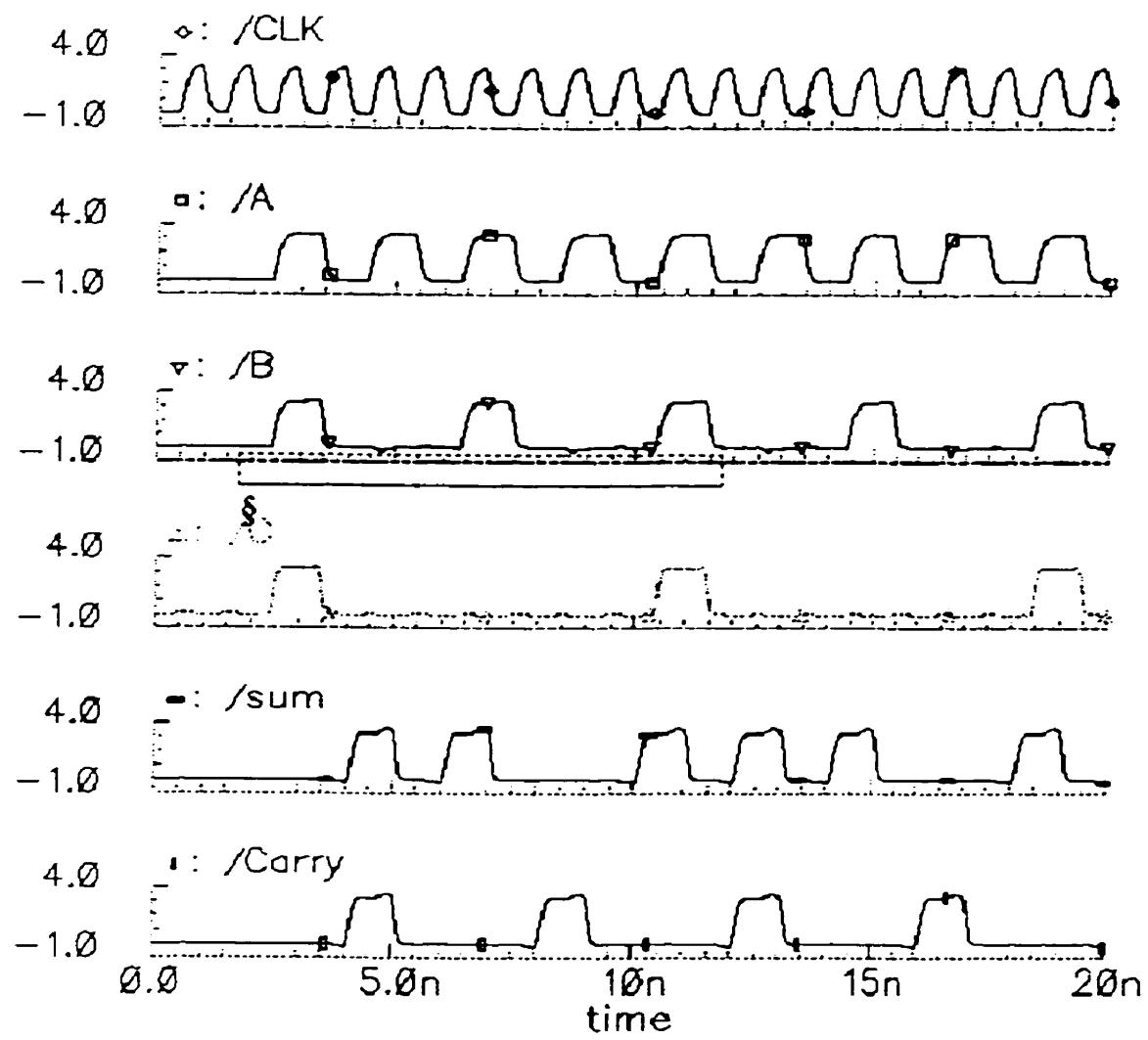

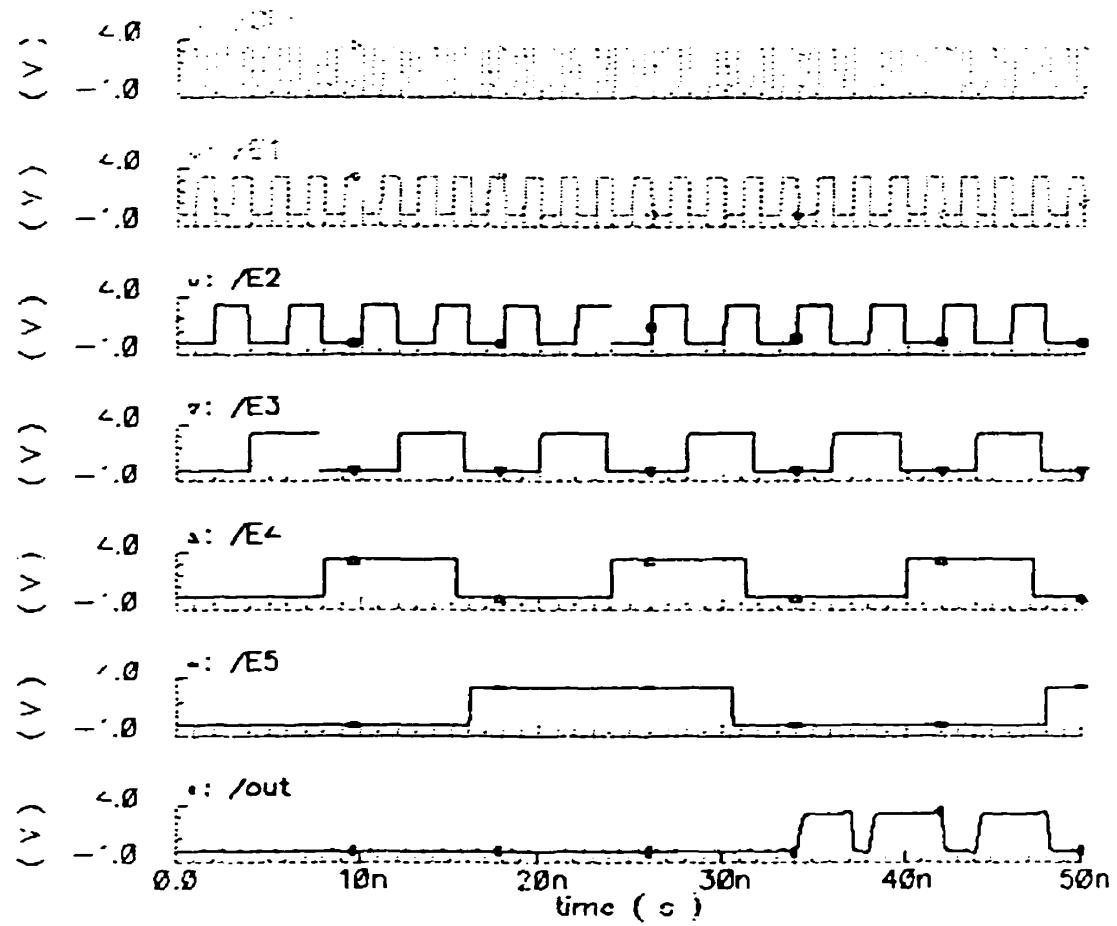

**Figure 1.6: Simulation d'une chaîne de 6 bascules à 2 GHz**

La figure 1.6 présente les résultats d'une simulation d'une chaîne de six bascules opérant à 2 GHz. Cette chaîne est composée de 6 bascules à polarités Nmos et Pmos alternées. La sortance est toujours de deux inverseurs en parallèle comme dans le banc d'essai.

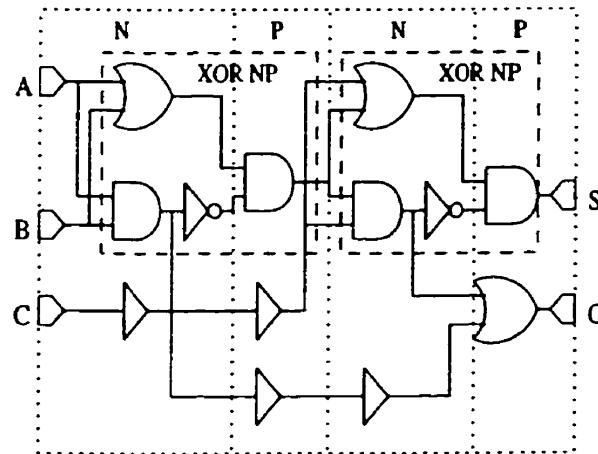

=> Additionneur Complet

Un additionneur complet dont la structure est illustrée à la figure 1.7 a été caractérisé par simulation. Le chemin critique de cette cellule est situé au niveau de la porte NAND Nmos du XOR. Ce type de circuit doit éviter la logique négative autant que possible, car

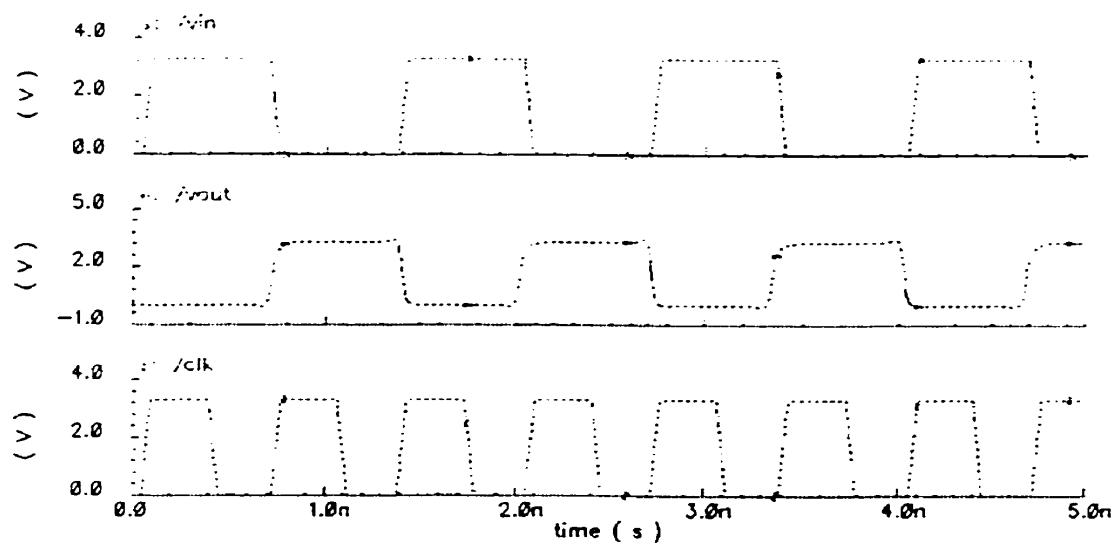

les inverseurs ajoutent du délai. La fréquence d'horloge maximale du NAND Nmos est 1.6 GHz. La fréquence d'horloge de l'additionneur complet, tel que montré à la figure 1.8, est également de 1.6 GHz lorsqu'il est chargé par deux inverseurs.

Figure 1.7: Schéma en logique statique d'un additionneur complet

**Figure 1.8: Simulation d'un additionneur complet à 1.6 GHz**

Il est pertinent de mentionner que les simulations réalisées avec Hspice donnent une fréquence maximale de 1.6 GHz, tandis que celles réalisées avec Spectre de Cadence donnent une fréquence de 1.9 GHz et ce pour un modèle de transistor très proche, le modèle de transistor est le BSIM3v3, développé par l'université de Berkeley.

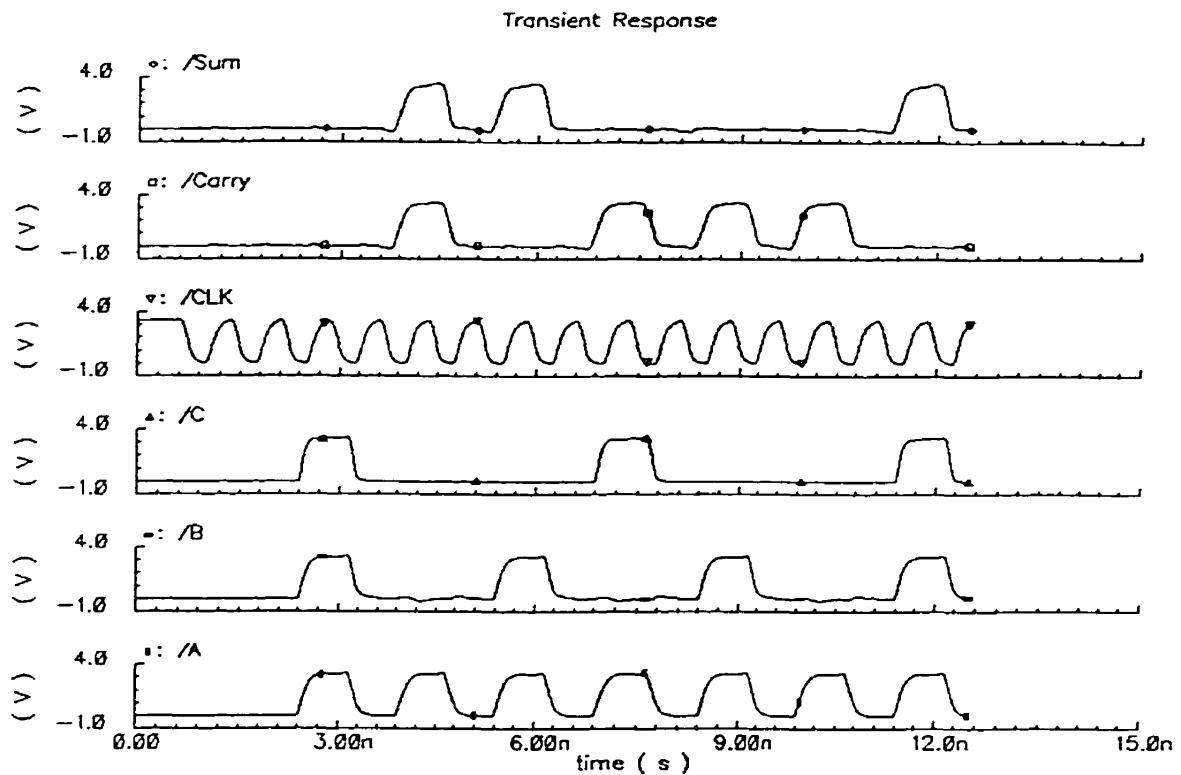

### 1.3.3.3 Étude d'une cellule xor TSPC.

Nous avons vu que la technique TSPC repose sur un pipeline d'une granularité très fine.

Il est également possible de concevoir des blocs plus importants au détriment de la vites-

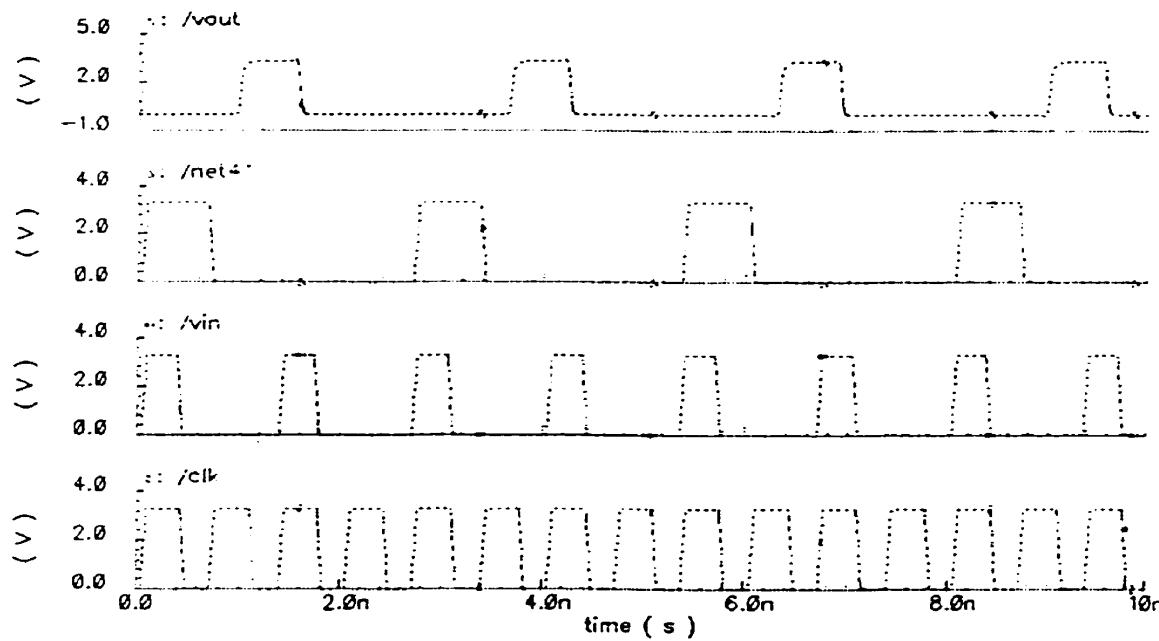

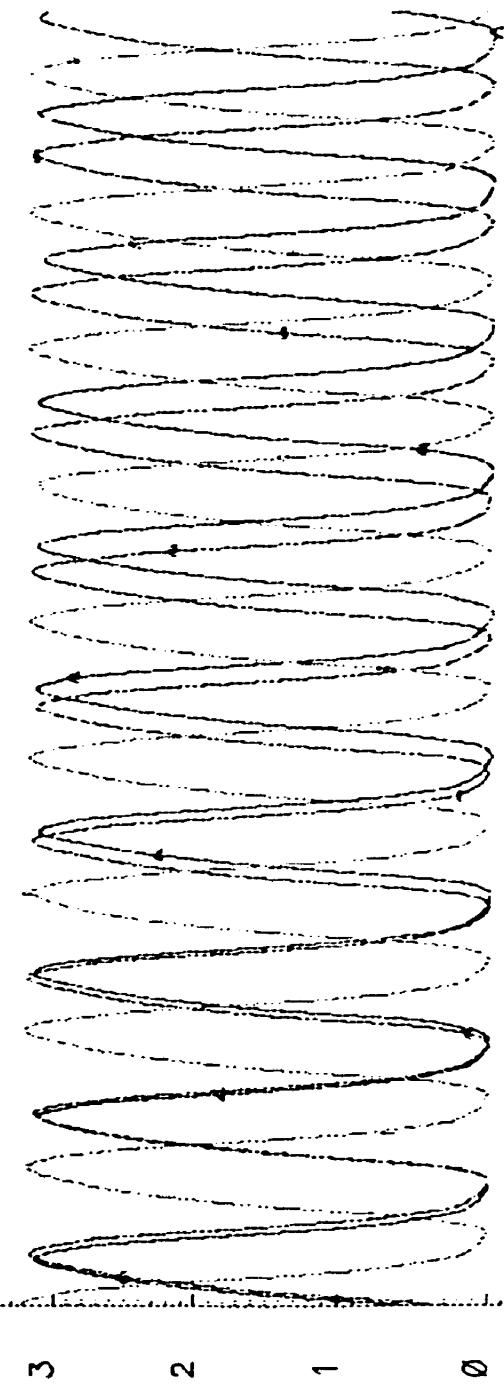

se, mais en diminuant la latence. Un exemple concret est la porte XOR TSPC de polarité N ou P. Nous avons vu à travers le sommateur qu'il est possible de réaliser des XOR à l'aide de trois portes élémentaires. La fréquence atteinte était alors de 1.6 GHz pour cette cellule. Il est également possible de réaliser le XOR avec une seule cellule et des performances moindre. La fréquence atteinte pour le XOR N est alors de 1 GHz.

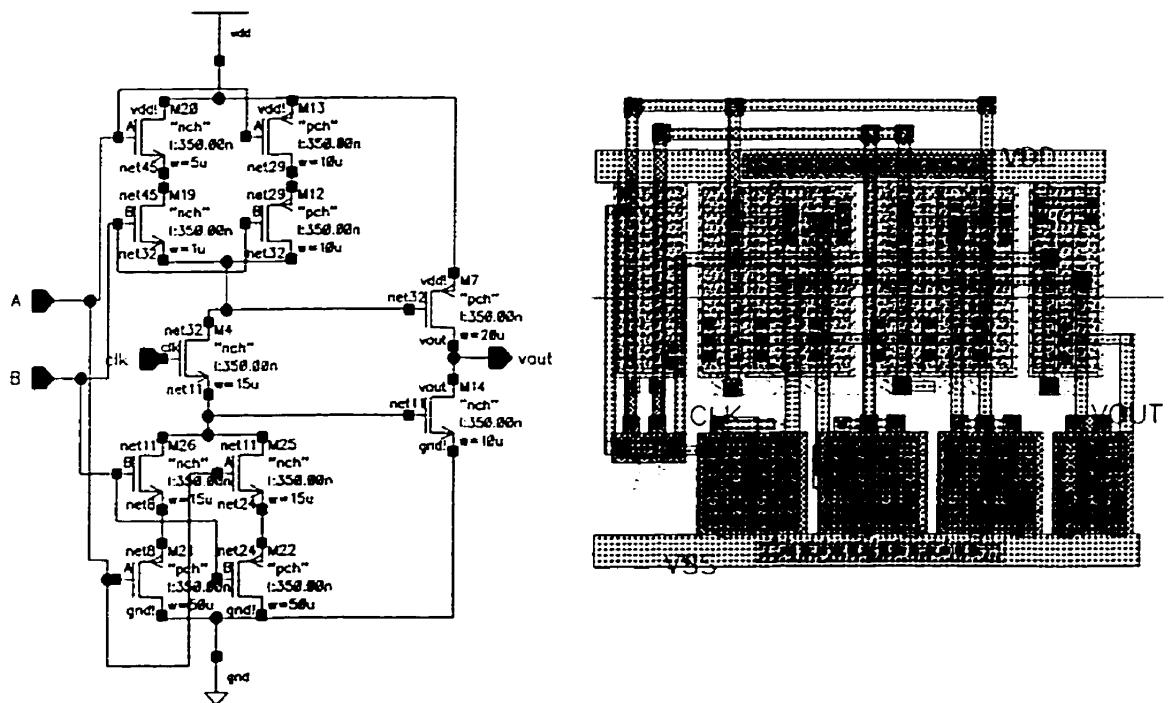

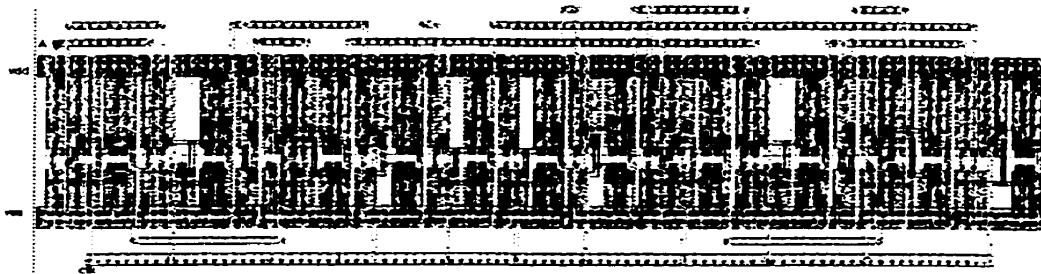

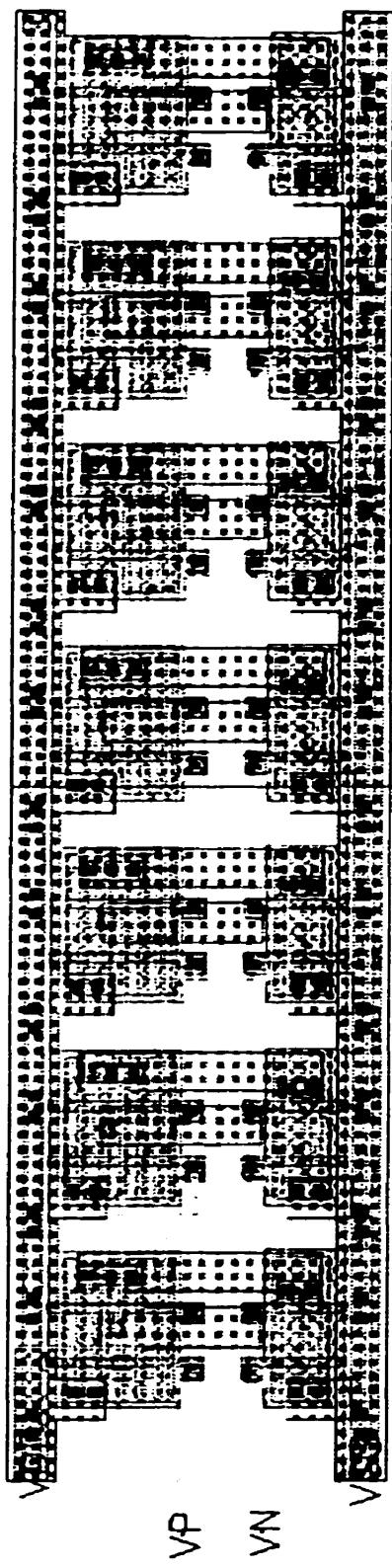

**Figure 1.9:** Schématique et schéma des masques du Xor TSPC

**Figure 1.10: Simulation du Xor TSPC à 1 GHz**

Cette optimisation a demandé un effort plus important que pour les autres cellules. Nous avons toutefois utilisé la même méthode. Les résultats sont présentés dans les figures 1.9 et 1.10. Un résultat surprenant concerne les transistors Nmos au dessus de l'horloge. En fait, seul le transistor Nmos au-dessus de l'horloge est vraiment critique. Sa taille doit être proche de la taille minimale. Quand sa taille augmente, la performance de la cellule chute. Si  $A=1$  et  $B=0$  dans une séquence, puis que  $A=0$  et  $B=1$  dans la séquence suivante, lorsque l'horloge fait passer un 0, le transistor Nmos M19 conduit et se décharge. Le transistor de sortie Pmos n'a plus alors un vrai 0 à sa grille et conduit moins vite pouvant entraîner une faute logique à haute fréquence. Pour palier à ce problème, le transistor Nmos qui est plus rapide que les transistors Pmos doit être “ralenti”. Pour ce faire, il suffit de diminuer sa largeur. En effet, les meilleurs résultats ont été obtenu, lorsque le transistor Nmos 19 avait une taille minimale. La technique TSPC offre également de bonnes performances pour des cellules un peu plus importantes. L'avantage d'utiliser des cellules plus complexes est

également de diminuer la charge de l'horloge qui est considérable dans un pipeline aussi profond que celui que nous utilisons.

#### 1.3.3.4 Problèmes des cellules TSPC à sortie partagée

Lors de la conception de blocs logiques assez importants, nous avons pu remarquer que ces derniers dissipait beaucoup de puissance et nécessitaient de grands fils d'alimentation. Une étude approfondie des cellules a permis de relever deux problèmes. Le premier inconvénient des cellules TSPC à sortie partagée réside dans leur transistor d'horloge qui agit comme une demi-porte de transmission. Les tensions sur les drains et sources de ce transistor sont donc sujettes à des pertes de tensions de seuil. Nous n'aurons donc pas toujours un vrai 0 ou 1 à l'issue de la transmission de notre précharge. Les inverseurs de sortie recevant des 0 ou des 1 altérés vont donc commuter moins vite et ils propagent des signaux imparfaits. De plus, comme les commutations des transistors de sortie sont moins rapides, ils dissipent davantage de puissance par le mécanisme de courant de court-circuit.

Le XOR TSPC a permis de mettre davantage en évidence le problème de partage de charges associé aux courses internes. Ce problème se répercute sur la plupart des cellules TSPC à sortie partagée, sauf sur les bascules. Nous retrouvons ce problème à chaque fois que deux transistors PMOS ou NMOS sont en série. Dans une porte OU, par exemple, nous avons les deux transistors PMOS d'entrée en série. Pour l'analyse qui suit, nous supposons que dans un premier temps les entrées sont à 0. Lorsqu'une entrée passe à 1 et que l'autre ne change pas, nous pouvons avoir une faute logique. En effet, lors de l'évaluation,

la valeur découlant de la précharge essaie d'activer le transistor Pmos de sortie alors que le transistor PMOS d'entrée qui est toujours à 0 libère ses charges. Le problème est évidemment amplifié lorsque nous utilisons une porte OR TSPC de type PMOS, car la demi-porte de transmission du transistor de l'horloge amène une perte de seuil. Nous n'avons donc plus tout à fait un 0 logique. Dans la porte XOR que nous avons présenté dans la section 3.3.3, le problème est doublement accru, car nous avons à chaque extrémité du transistor d'horloge une paire de transistors en parallèle avec une autre paire de transistors, le problème de charge partagée est encore plus important. Dans la configuration présentée, nous avons éliminé ce problème en nous assurant que les transistors aux extrémités du transistor d'horloge aient des entrées différentes. Le problème majeur de la porte XOR TSPC et de toutes les grosses cellules TSPC est que la précharge doit commander une grosse capacité; deux transistors aux extrémités du transistor d'horloge ont été ajoutés pour ralentir la propagation de la précharge. Ce dernier problème est vraiment fonction de la fréquence d'utilisation. Il faut bien remarquer que lorsque le transistor d'horloge conduit, il propage le VDD ou le VSS sélectionnés par les entrées. Si la fréquence est peu élevée, la charge emmagasinée par le OR TSPC sur le transistor PMOS d'entrée à 0 a le temps de passer à 0 et nous aurons donc seulement un problème de perte de seuil au pire des cas. Lorsque le transistor d'horloge est désactivé, nous avons une vraie précharge qui continue d'activer le transistor de sortie jusqu'à la prochaine évaluation ou jusqu'au changement des signaux d'entrée. Nous avons pu remarquer qu'à des fréquences proches de 1.5 GHz, nos blocs logiques donnaient des réponses cohérentes.

Notre bibliothèque n'est pas sensible au phénomène de courses intenses dans les fréquen-

ces d'utilisation de l'ordre de 800 MHz à 1 GHz. À des fréquences supérieures nous pouvons avoir des courses intenses et donc des fautes logiques.

Ces deux problèmes nous montrent la difficulté de développer une bibliothèque de cellules TSPC à sortie partagée ainsi que ceux qui surviennent quand on veut concevoir des cellules complexes.

#### 1.4 Conclusion

Dans ce chapitre, nous avons étudié en détail la conception des cellules TSPC, ainsi que diverses méthodes d'optimisation. La méthode que nous proposons pourrait être davantage optimisée en la programmant dans un outil en langage C. Pour avoir une optimisation optimale, il faudrait coupler notre outil avec un outil de génération de cellules automatique qui dessineraient les cellules au niveau schéma des masques à partir des paramètres que lui propose notre outil. En effet, le fait d'avoir un fichier extrait tenant compte des capacités réelles des interconnexions serait très utile pour obtenir rapidement des résultats précis. La simplicité de notre algorithme permet de développer très rapidement une bibliothèque de cellules sans la nécessité d'un outil automatique qui est difficile à mettre en place à cause du nombre de paramètres à contrôler. Grâce à la méthode proposée, une bibliothèque de cellules de base TSPC efficaces peut-être développée en un mois, quelque soit la technologie employée.

Après avoir développé une bibliothèque de cellules dans la technologie CMOS 0.35 μm,

nous avions besoin d'un circuit assez important pour valider notre bibliothèque à une fréquence élevée. Nous avons ainsi développé un convoluteur  $3 \times 3$  TSPC que nous présentons au chapitre 2.

## CHAPITRE 2

### Architecture du convolueur 3\*3 TSPC

#### 2.1 Introduction

Après avoir présenté les performances et la méthode de conception de notre bibliothèque de cellules TSPC, nous souhaitons évaluer ses performances dans un circuit de grande complexité pour valider nos cellules et connaître davantage le potentiel des cellules dynamiques. Les circuits, construits à partir de cellules TSPC, entraînent une architecture fortement pipelinée qui induit une latence importante mais qui procure une très grande vitesse d'exécution. Il est donc nécessaire d'utiliser une application nécessitant un flot de données continues suffisamment long pour justifier une grande latence. Les applications liées au traitement de l'image nécessitent un effort prolongé et spécifique des microprocesseurs variant selon la taille de l'image à traiter. Il est donc intéressant de se doter de co-processeur spécialisés dans ce genre d'application.

Bosi [8] a proposé une première architecture d'un convolueur 3\*3 TSPC que nous avons analysé, puis optimisé, afin de pouvoir le concevoir au niveau schéma des masques. Nous nous proposons donc de concevoir un circuit intégré avec une architecture complètement dédiée pouvant fonctionner à de très hautes fréquences.

La section 2.1 définit la convolution 2D, tandis que la section 2.2 présente la fonction au niveau système. La section 2.3 est consacrée à la conception des cellules de base du con-

volueur 3\*3 TSPC et la section 2.4 à leur assemblage. Par la suite, le chapitre III présentera les blocs spécifiques de notre convoluteur, la distribution d'horloge, la méthode de conception et les résultats obtenus.

### 2.1.1 La convolution 2D

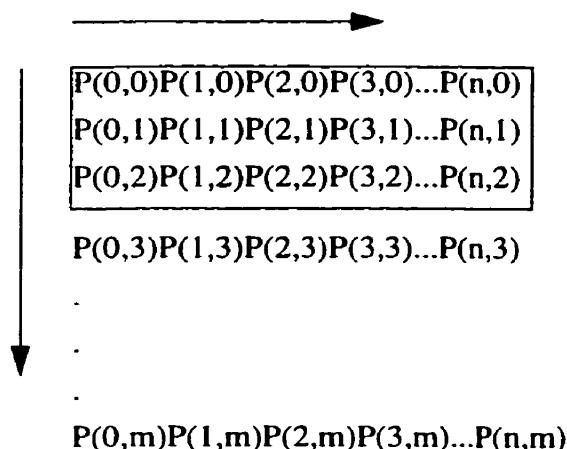

L'opération de convolution 2-D permet d'effectuer différents types de filtrages sur des images. La figure 2.1 illustre comment est effectuée une convolution 3\*3 sur une image.

**Figure 2.1: Fenêtre de convolution**

L'opération consiste à déplacer un masque couvrant 3\*3 pixels sur la totalité de l'image; à chaque déplacement du masque (un pixel à la fois, une direction à la fois) le calcul de la convolution est exécuté. La convolution 3\*3 revient à faire une somme de produits de pixels (P) et de poids (W), comme l'indique l'équation 2.1:

$$\hat{P}(x, y) = \sum_{\substack{i=-1 \\ \text{Somme des produits des poids et des pixels}}}^1 \sum_{j=-1}^1 P(x+i, y+j) \times W(i, j) \quad (2.1)$$

Chacun des poids du masque de convolution est multiplié à un pixel de la fenêtre de convolution selon la règle illustrée à la figure 2.1. La somme des 9 produits pixels\*poids représente alors la convolution 3\*3 du pixel central de la fenêtre considérée. Ainsi, en déplaçant une fenêtre de convolution semblable à celles proposées dans la figure 2.2, un produit de convolution peut être calculé pour chacun des pixels de l'image.

|    |    |    |

|----|----|----|

| 0  | -1 | 0  |

| -1 | 4  | -1 |

| 0  | -1 | 0  |

■

|    |    |    |

|----|----|----|

| -1 | -1 | -1 |

| -1 | 8  | -1 |

| -1 | -1 | -1 |

■

|    |    |    |

|----|----|----|

| 1  | 2  | 1  |

| -2 | 4  | -2 |

| 1  | -2 | 1  |

**Figure 2.2: Exemples de masque de convolution: (masques Laplaciens)**

Parmi les applications de la convolution 2-D, on retrouve toute la gamme des filtres spatiaux FIR (Finite Impulse Response). Par exemple, le filtre moyen est un passe-bas qui permet de réduire le niveau de bruit dans une image et d'interpoler les valeurs de pixels bruités à partir des pixels avoisinants. Le filtre Laplacien permet de détecter les contours dans une image et il met en évidence les maxima et les minima locaux rencontrés.

## 2.2 Fonction au niveau système du convoluteur 3\*3

### 2.2.1 Oscillateur à tension commandé

L'oscillateur représenté dans le schéma-bloc de la figure 2.5 sert à générer l'horloge interne du système. Il devra pouvoir fonctionner entre 100 MHz et 2 GHz. Afin de couvrir toute notre plage de fréquence, nous avons choisi d'utiliser cinq oscillateurs ayant chacun des plages de fonctionnement différentes: à 100 MHz, de 100 MHz à 300 MHz, de 400 MHz à 1.2 GHz, de 1 GHz à 1.5 GHz et de 1.5 à 2 GHz . Il s'agit des différents oscillateurs en anneaux présentés dans le chapitre 3. Pour commander ces oscillateurs, nous avons besoin d'une entrée sur laquelle la tension de commande est amenée, et une entrée de sélection de l'oscillateur et d'initialisation.

### 2.2.2 Générateur de vecteurs pseudo-aléatoires

Le générateur de vecteurs pseudo-aléatoires transmet au convoluteur des vecteurs correspondant aux pixels d'une image. Nous effectuons la convolution de 9 pixels par 9 poids. Chaque poids est constitué de 4 bits et un pixel a une largeur de 8bits(non signé). Donc nous avons besoin d'un circuit BIST (Built In Self Test), détaillé dans le chapitre 3, à 8 entrées au minimum (on peut concevoir d'avoir un générateur pour chaque pixel). Si nous voulons générer une séquence de vecteurs de dimension 8\*8 pixels ( $2^{12}$  bits), nous devons prévoir que le nombre minimal de bits du générateur sera de 13 de façon à couvrir un nombre suffisant de vecteurs. Ce BIST a également été conçu en VHDL afin de vérifier toute

la logique du convoluteur et de générer les vecteurs de sortie. Grâce au BIST réalisé en VHDL, nous pourrons également valider le BIST conçu au niveau schématique et schéma des masques. Les contraintes découlant du placement font que l'utilisation de plusieurs générateurs de vecteurs à des positions différentes évite des problèmes de synchronisation entre des entrées très éloignées. Une approche définitive n'a pas été arrêtée: les options retenues sont d'avoir 3 générateurs de 24 bits ou encore 9 générateurs de 13 bits; la décision se prendra par rapport aux contraintes de placement. Le générateur de vecteurs pseudo-aléatoires est développé selon une architecture TSPC afin d'atteindre les performances souhaitées ainsi que des entrées toujours synchronisées sur l'horloge.

### 2.2.3 Filtres de convolution (ROM)