**Titre:** Conception et mise en oeuvre d'un système de reconfiguration dynamique

Title: [Conception et mise en oeuvre d'un système de reconfiguration dynamique](#)

**Auteur:** Cynthia Cousineau

Author: [Cynthia Cousineau](#)

**Date:** 2000

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Cousineau, C. (2000). Conception et mise en oeuvre d'un système de reconfiguration dynamique [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/8807/>

Citation: [Cousineau, C. \(2000\). Conception et mise en oeuvre d'un système de reconfiguration dynamique \[Mémoire de maîtrise, École Polytechnique de Montréal\]. PolyPublie. https://publications.polymtl.ca/8807/](#)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8807/>

PolyPublie URL: [https://publications.polymtl.ca/8807/](#)

**Directeurs de recherche:** Yvon Savaria, & Mohamad Sawan

Advisors: [Yvon Savaria](#), [Mohamad Sawan](#)

**Programme:** Non spécifié

Program: [Non spécifié](#)

UNIVERSITÉ DE MONTRÉAL

CONCEPTION ET MISE EN ŒUVRE D'UN SYSTÈME DE

RECONFIGURATION DYNAMIQUE

CYNTHIA COUSINEAU

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE

MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JANVIER 2000

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

*Our file Notre référence*

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-53566-5

Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

CONCEPTION ET MISE EN OEUVRE D'UN SYSTÈME DE RECONFIGURATION

DYNAMIQUE

présenté par : COUSINEAU Cynthia

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. BOIS Guy, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. SAWAN Mohamad, Ph.D., membre et codirecteur de recherche

M. HOULE Jean-Louis, Ph.D., membre

## **REMERCIEMENTS**

La réalisation de ce projet de maîtrise n'aurait pu être possible sans l'aide de Monsieur Yvon Savaria, mon directeur de recherche, qui m'a proposé ce sujet et qui m'a soutenu et aidé tout au long de son développement ainsi que Monsieur Mohamad Sawan, mon co-directeur de recherche. Également, je tiens à remercier Monsieur Pierre Popovic et toute l'équipe de MiroTech Microsystems Inc. qui m'ont fourni ressources et supports pour le développement de ce projet ainsi qu'un milieu de travail propice à la conception. En dernier lieu, je tiens à remercier Madame Virginie Cousineau qui a critiqué de manière constructive ce mémoire ainsi que mon conjoint et mes parents qui m'ont supporté moralement durant ce travail. Merci.

## RÉSUMÉ

Ce mémoire traite de la reconfiguration dynamique des FPGA. La reconfiguration dynamique, ou RTR pour *Run Time Reconfiguration*, est une technique qui permet de conserver une partie d'un système en traitement pendant que l'autre se fait reconfigurer. Cette nouvelle approche de reconfiguration se divise principalement en deux champs, soit la reconfiguration dynamique des FPGA reprogrammables partiellement et la reconfiguration dynamique utilisant des FPGA conventionnels. Ces deux branches de la reconfiguration dynamique sont passablement différentes et apportent des avantages et inconvénients distincts. Le travail de recherche qui a été effectué pour ce mémoire repose sur la reconfiguration dynamique utilisant les FPGA conventionnels. Toutefois, nous avons tout de même démontré les points que nous tentons d'améliorer par rapport à l'autre technique de reconfiguration dynamique, celle utilisant les FPGA reconfigurables partiellement.

Le système proposé a été implanté sur une carte, commercialement disponible, du nom de X-C436 et produite par MiroTech Microsystems Inc. de Ville St-Laurent. La compagnie nous a approché pour tenter l'implantation d'un système de reconfiguration dynamique sur cette carte moyennant l'utilisation d'un lien de communication secondaire, le lien série JTAG, régit par le protocole IEEE 1149.1 (*Boundary Scan*). Dans ce projet, on utilise la technique de reconfiguration dynamique avec des FPGA conventionnels, puisque la carte est munie de ce type de FPGA, des XC4036EX de Xilinx. La modification de la carte est la partie principale de ce projet. Elle consistait en un remaniement du contrôleur de la carte, le CSU, sigle de *Configuration and Shutdown Unit*. Ce contrôleur est, quant à lui, un FPGA de la famille XC3000 de Xilinx.

Le concept de reconfiguration dynamique de la carte repose sur le fait que celle-ci possède deux unités de traitement. Ainsi, en utilisant toujours une de ces unités pour effectuer un traitement, nous pouvons reconfigurer la deuxième pour que celle-ci soit en mesure de poursuivre le traitement débuté par la première. Le type de système qui peut bénéficier de la reconfiguration dynamique est un système qu'on peut décortiquer en plusieurs séries de traitements. Ces traitements unitaires sont par la

suite implantés, un à un, dans les unités de traitement. On réalise ainsi une grande économie matérielle grâce à la reconfiguration dynamique.

Une fois que l'implantation matérielle fut réalisée, nous avons procédé à une démonstration qui nécessitait également l'implantation d'une partie logicielle. Étant donné que la carte X-C436 est conçue pour être utilisée avec des DSP TMS320C4x de Texas Instruments, la démonstration réalisée utilisait deux de ces DSP pour effectuer un traitement d'image continu. En effet, la démonstration consistait en l'application, sur une image vidéo noir et blanc, d'une série de filtres Sobel, dont la progression créait l'effet d'une rotation dans l'angle de projection d'une détection de contour.

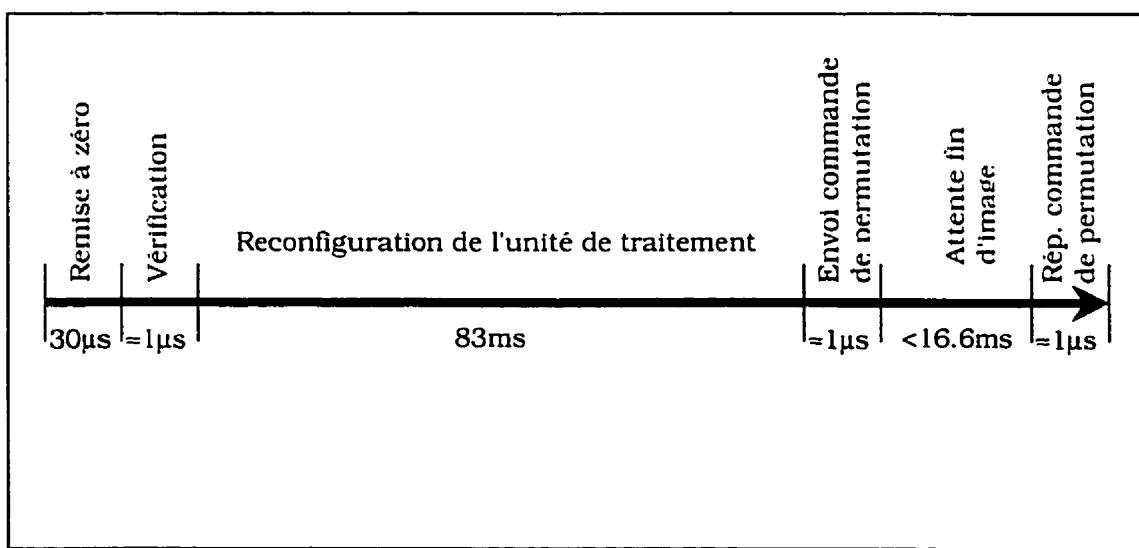

L'implantation nous a permis de mesurer exactement le temps de reconfiguration nécessaire pour chaque filtre. C'est à l'aide du lien JTAG que nous transmettions le fichier de configuration de l'unité de traitement à configurer. La vitesse de ce lien série était de 8.25 MHz en théorie, ce qui nous aurait permis d'effectuer une reconfiguration complète, incluant le temps de permutation entre les deux unités traitantes, en deçà de 100 ms. Cependant, les mesures faites nous ont malheureusement prouvé que ce temps théorique n'est pas réalisable, du moins, avec l'utilisation d'un composant nommé TBC (Test Bus Controller) pour effectuer la transmission des données selon le protocole JTAG. En effet, avec cet élément dans la chaîne de transmission des données de configuration, nous devons tenir compte de certains temps de pause qui lui sont nécessaires pour recharger ses FIFO de données. Le temps complet de reconfiguration d'une unité de traitement se situe alors entre 220 et 230 ms. Même si le temps de reconfiguration optimal n'a pas été atteint, le système conçu montre une réalité de reconfiguration dynamique qui n'a encore jamais été vu à ce jour sur le marché.

## ABSTRACT

This master's thesis deals with Run Time Reconfiguration of FPGAs. Run Time Reconfiguration is a relatively new technique that allows to change the hardware configuration of a system while computing. Two distinct paths seem to impose themselves: run time reconfiguration using FPGAs that can be partially reconfigured and run time reconfiguration using conventional FPGAs. These branches are quite different and bring distinct advantages and inconveniences. This research is based on run time reconfiguration using conventional FPGAs, but we have also considered the other run time reconfiguration technique using partially reconfigurable FPGAs.

The prototype system that we have implemented is based on a commercially available board called the X-C436, from MiroTech Microsystems Inc of Ville St-Laurent. This company mandated us to implement a run time reconfiguration system based on their product using a secondary communication link supporting IEEE 1149.1 Boundary Scan standard, also known as JTAG. In this project, we implemented run time reconfiguration with conventional FPGAs, since the board is equipped with this kind of FPGA, two XC4036EX from Xilinx. We have to adapt this existing board to support RTR by modifying its controller, the CSU. This unit is implemented with another FPGA of the XC3000 family from Xilinx.

Run time reconfiguration on the X-C436 is based on the fact that the board has two processing elements. Thus, we can use one of them to compute while the other is reconfigured. Processing can continue while we reconfigure one of the processing elements. The kind of systems for which that run time reconfiguration can be beneficial is those that can be partitioned in multiple sub-systems. Each sub-system can be implemented, one after the other, in the processing element. The hardware complexity of the system can be significantly reduced by using this technique, since we systematically reuse the same two processing elements of the X-C436 board.

Since the hardware mechanisms were already built, we implemented the software to control it and a demonstration application to validate the system. Since the

board is designed to be used with TMS320C4x DSP from Texas Instruments, the demonstration uses two of these DSPs. This demonstration consists in a flow of several Sobel filters that detect edges with an intensity projected on a rotating vector.

That implementation allowed to measure the reconfiguration time required for each filter. Using the JTAG link, we transmit the configuration file to the board and data is transmitted serially at 8.25 MHz. The complete reconfiguration of a processing element including the time required to switch from one processing element to the other can be, in theory, less than 100 ms. However, measurements showed that this time is not really feasible if we use a component called the TBC (Test Bus Controller) to do data transmission. Indeed, with this component, the transmission chain must pause while the TBC reloads its FIFOs to transmit new data. The complete reconfiguration time was measured to be between 220 and 230 ms. Even if the optimal reconfiguration time has not been reached, the system shows a real run time reconfigurable operation which has no equivalent at this time on the market.

**TABLE DES MATIÈRES**

|                                                                                       |      |

|---------------------------------------------------------------------------------------|------|

| <b>REMERCIEMENTS.....</b>                                                             | iv   |

| <b>RÉSUMÉ.....</b>                                                                    | v    |

| <b>ABSTRACT.....</b>                                                                  | vii  |

| <b>TABLE DES MATIÈRES.....</b>                                                        | ix   |

| <b>LISTE DES TABLEAUX.....</b>                                                        | xiii |

| <b>LISTE DES FIGURES.....</b>                                                         | xiv  |

| <b>LISTE DES SIGLES ET ABRÉVIATIONS.....</b>                                          | xvi  |

| <br>                                                                                  |      |

| <b>INTRODUCTION.....</b>                                                              | 1    |

| <br>                                                                                  |      |

| <b>CHAPITRE PREMIER - REVUE DE LITTÉRATURE.....</b>                                   | 5    |

| 1.0 Introduction .....                                                                | 5    |

| 1.1 Reconfiguration dynamique de FPGA pouvant être reconfigurés<br>partiellement..... | 6    |

| 1.1.1 Xilinx XC6200 ou CAL 'Algotronix.....                                           | 6    |

|                                                                                                            |           |

|------------------------------------------------------------------------------------------------------------|-----------|

| 1.1.2 CLAy de National SemiConductor.....                                                                  | 9         |

| 1.1.3 Atmel 6000.....                                                                                      | 11        |

| 1.2 Reconfiguration dynamique utilisant des FPGA conventionnels.....                                       | 13        |

| 1.3 Les outils .....                                                                                       | 15        |

| 1.4 Développement de nouveaux FPGA ou de systèmes dynamiquement reconfigurables.....                       | 21        |

| 1.5 Études et analyses sur l'efficacité de la reconfiguration dynamique .....                              | 23        |

| 1.6 Discussion et conclusion.....                                                                          | 27        |

| <br>                                                                                                       |           |

| <b>CHAPITRE DEUXIÈME -DÉVELOPPEMENT.....</b>                                                               | <b>30</b> |

| 2.0 Introduction .....                                                                                     | 30        |

| 2.1 Exposé du problème .....                                                                               | 31        |

| 2.1.1 Description du fonctionnement de la carte avant l'implantation de la reconfiguration dynamique ..... | 33        |

| 2.2 Le lien JTAG, Protocole IEEE 1149.1 Boundary Scan .....                                                | 37        |

| 2.3 Fonctionnalités désirées et difficultés prévues.....                                                   | 43        |

| 2.3.1 Fonctionnalités désirées .....                                                                       | 43        |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| 2.3.2 Difficultés prévues .....                             | 45        |

| 2.4 Conclusion.....                                         | 54        |

| <br>                                                        |           |

| <b>CHAPITRE TROISIÈME - IMPLANTATION.....</b>               | <b>55</b> |

| 3.0 Introduction .....                                      | 55        |

| 3.1 L'implantation matérielle.....                          | 56        |

| 3.2 L'implantation logicielle.....                          | 62        |

| 3.2.1 Notions de base.....                                  | 62        |

| 3.2.2 L'application implantée : suite de filtres Sobel..... | 63        |

| 3.2.2.1 Mécanisme de reconfiguration.....                   | 64        |

| 3.2.2.2 Déroulement du programme implanté.....              | 65        |

| 3.2.3 Processus de reconfiguration dynamique .....          | 72        |

| 3.3 Résultats et analyse.....                               | 74        |

| 3.4 Conclusion.....                                         | 77        |

|                                            |           |

|--------------------------------------------|-----------|

| <b>CHAPITRE QUATRIÈME -DISCUSSION.....</b> | <b>78</b> |

| <b>CONCLUSION.....</b>                     | <b>82</b> |

| <b>BIBLIOGRAPHIE.....</b>                  | <b>84</b> |

## LISTE DES TABLEAUX

|                                                                                                                         |           |

|-------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Tableau 2.1 Description des instructions JTAG disponibles avec les FPGA de la famille XC4000 de Xilinx.....</b>      | <b>41</b> |

| <b>Tableau 2.2 Description des instructions JTAG disponibles chez les FPGA de la famille Virtex de Xilinx.....</b>      | <b>42</b> |

| <b>Tableau 2.3 Commande JTAG auxquelles répond le CSU afin d'implanter un système de reconfiguration dynamique.....</b> | <b>45</b> |

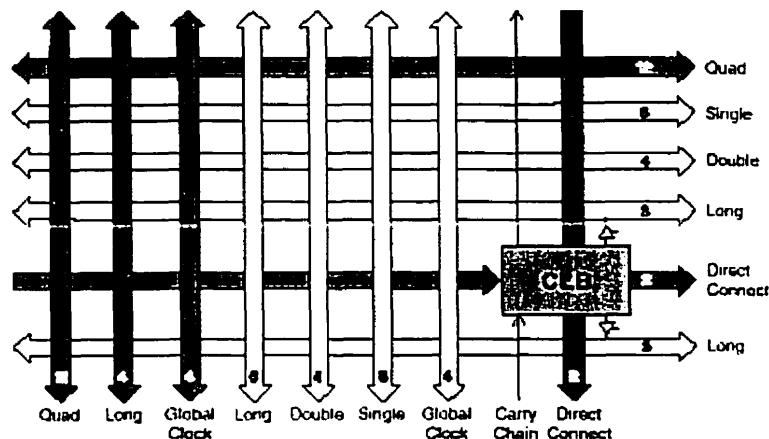

| <b>Tableau 2.4 Ressources de routage par CLB chez les FPGA de la famille XC4000.....</b>                                | <b>50</b> |

## LISTE DES FIGURES

|                                                                                                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figure 1.1</b> Classification des FPGA selon leur configurabilité.....                                                                                                  | 24 |

| <b>Figure 2.1</b> Schéma bloc de la carte X-C436.....                                                                                                                      | 32 |

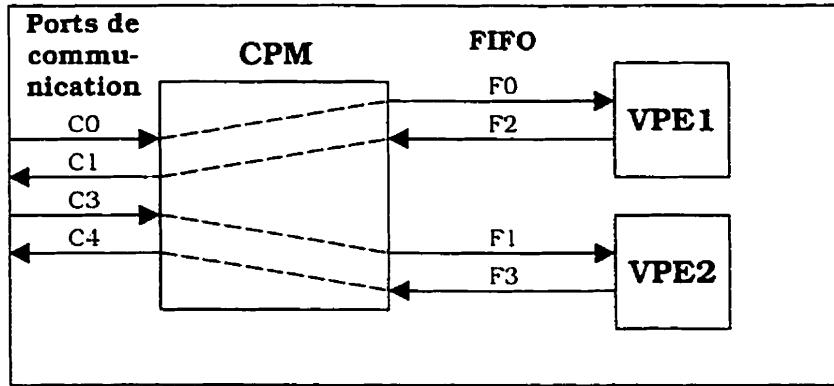

| <b>Figure 2.2</b> Schéma des interconnexions à l'intérieur du CPM.....                                                                                                     | 34 |

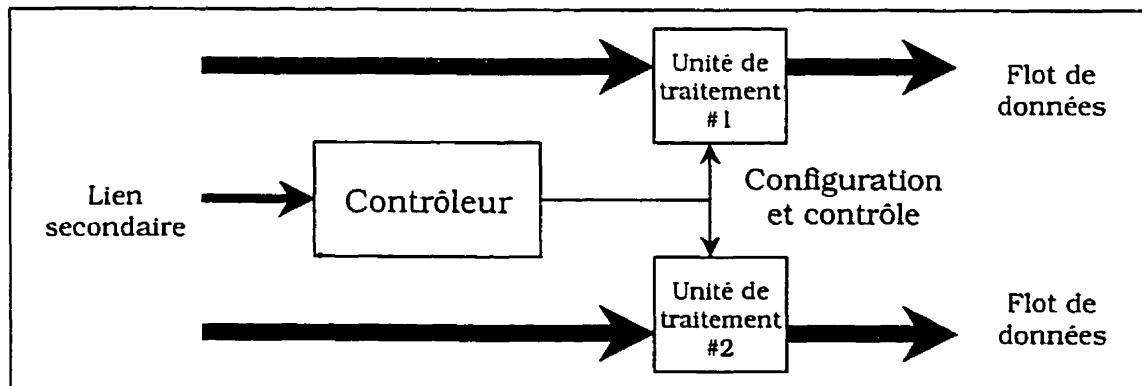

| <b>Figure 2.3</b> Schéma représentant le flot de données principal versus le lien secondaire.....                                                                          | 36 |

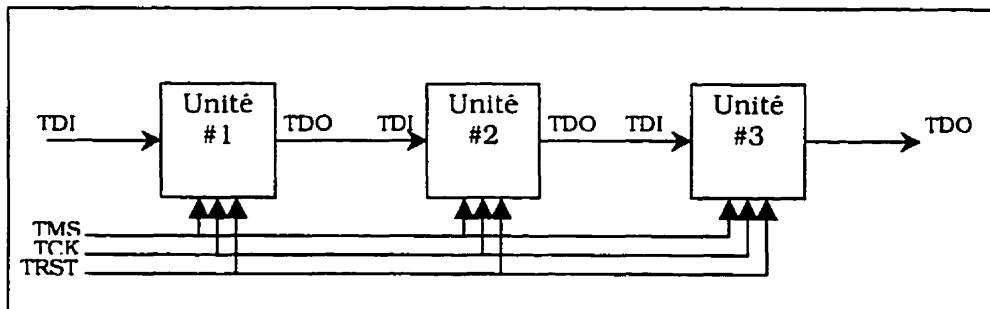

| <b>Figure 2.4</b> Schéma représentant une chaîne JTAG conventionnelle.....                                                                                                 | 37 |

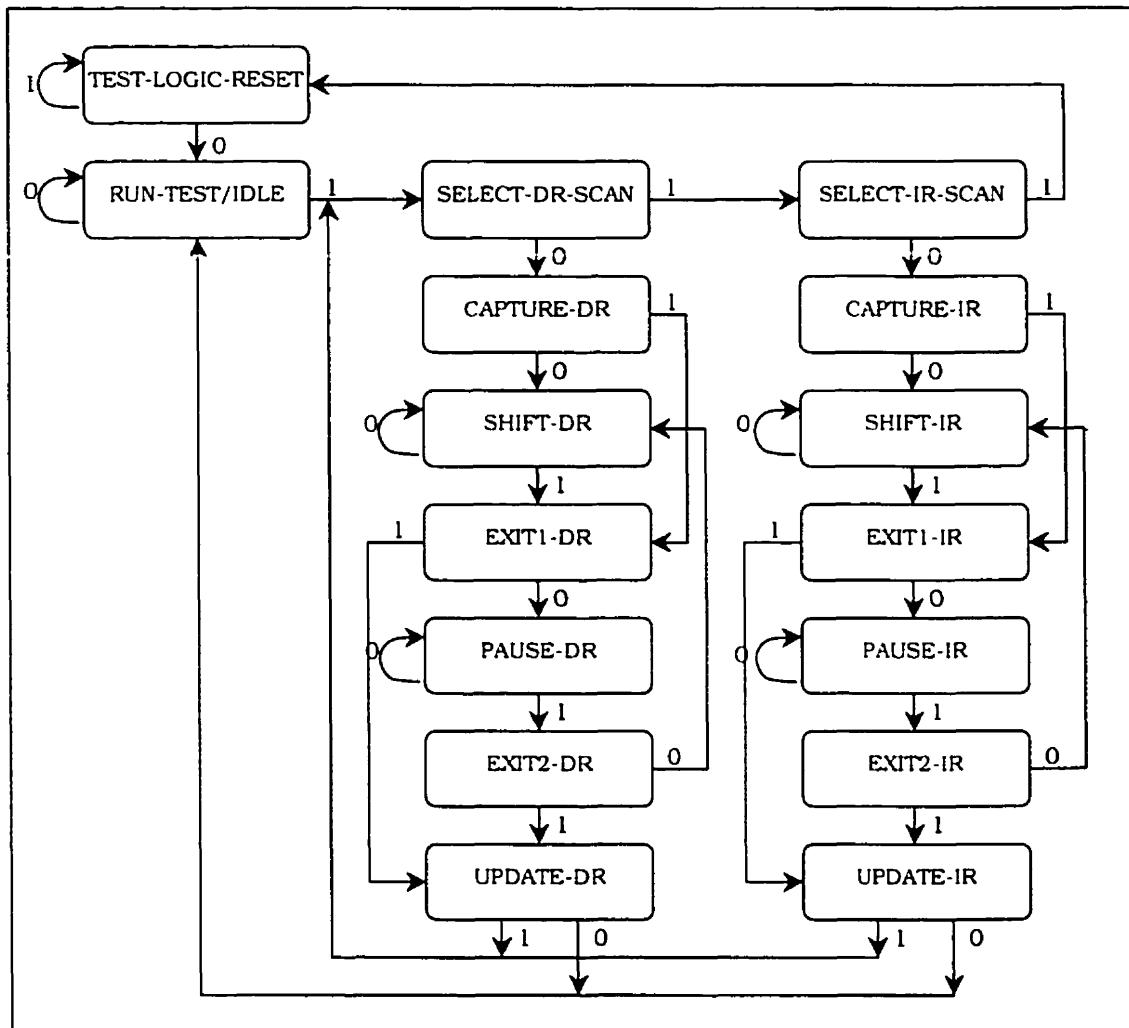

| <b>Figure 2.5</b> Diagramme d'états du <i>TAP controller</i> .....                                                                                                         | 39 |

| <b>Figure 2.6</b> Représentation du décalage de données pour les états <i>CAPTURE</i> et <i>SHIFT</i> .....                                                                | 40 |

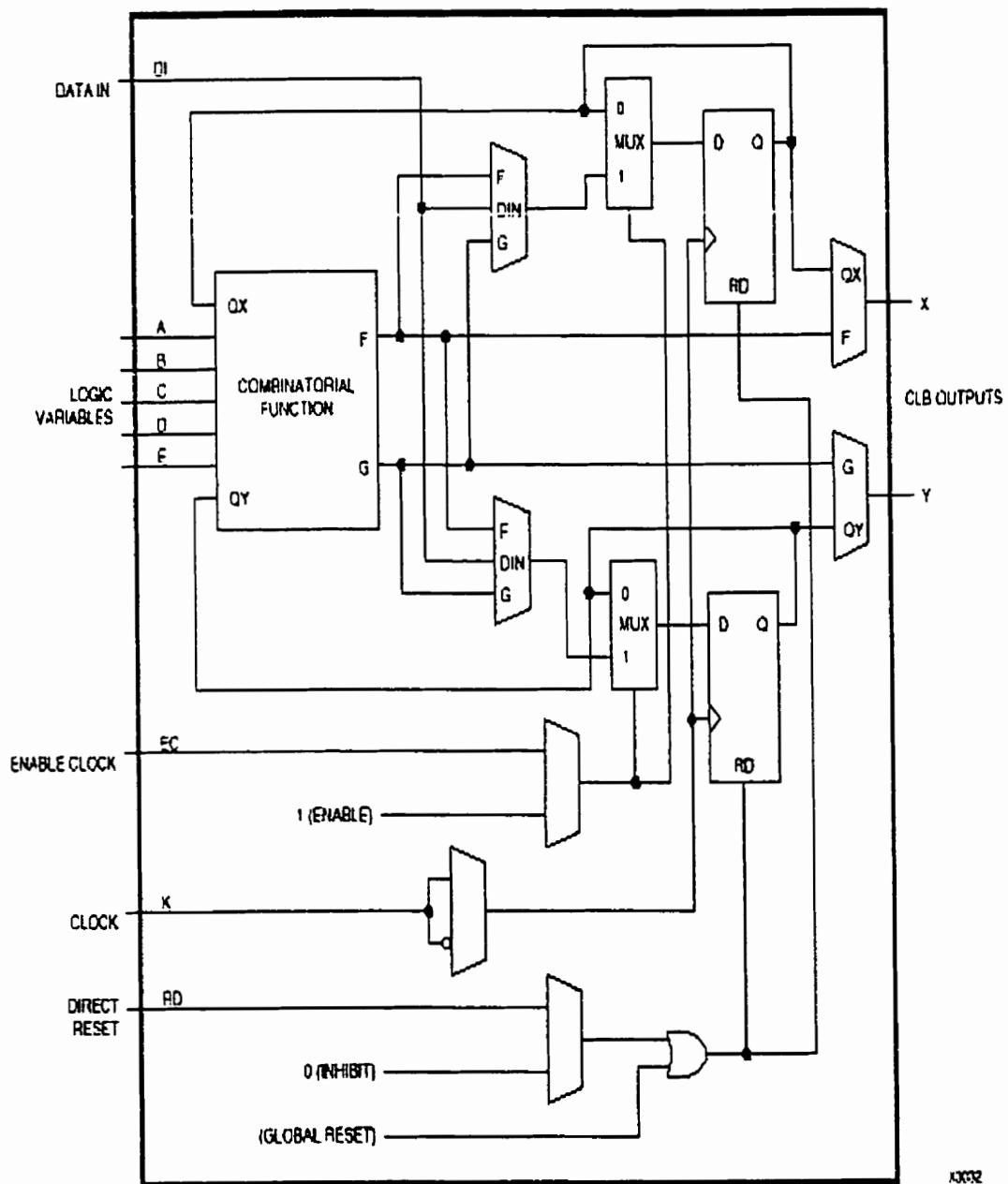

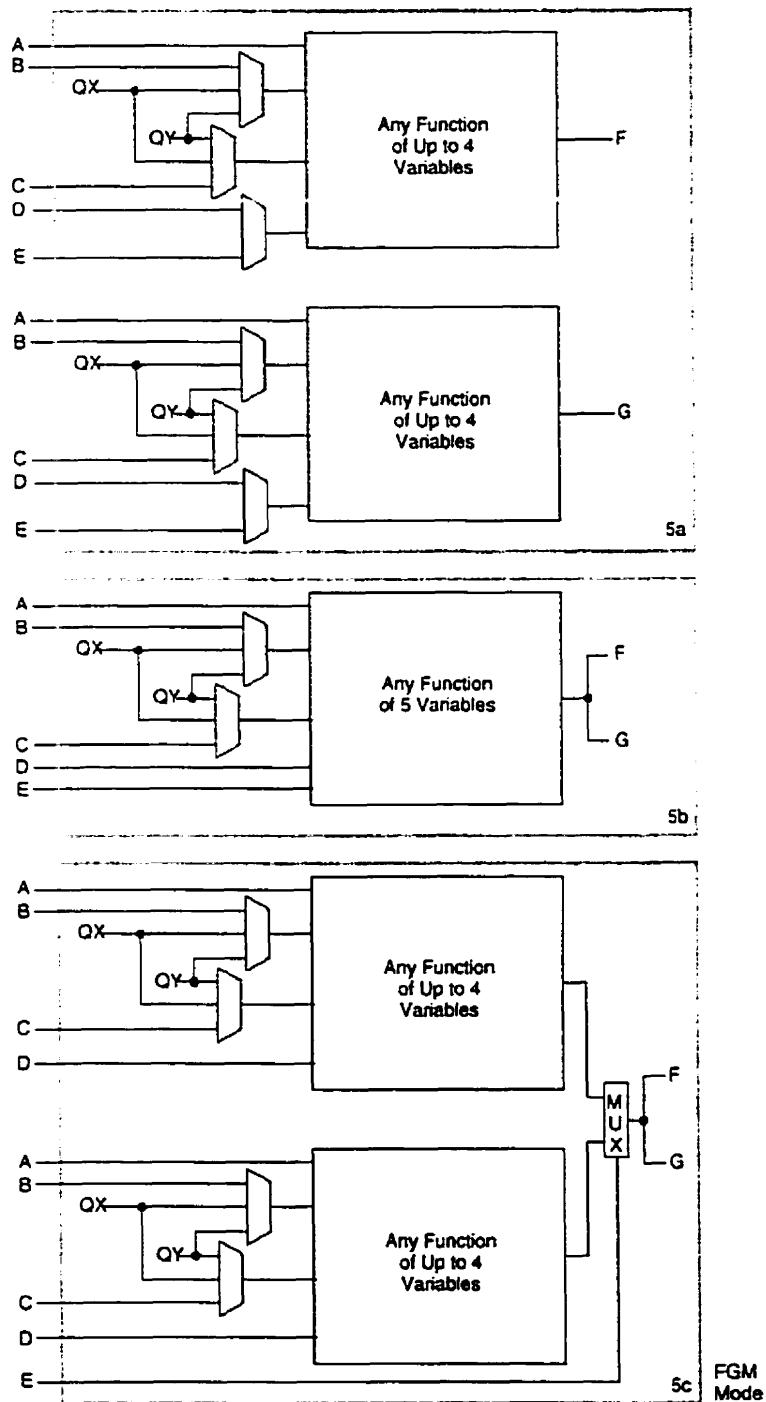

| <b>Figure 2.7</b> Détails d'un CLB pour un FPGA de la famille XC3000 de Xilinx.....                                                                                        | 47 |

| <b>Figure 2.8</b> Représentation des possibilités de combinaisons pour l'utilisation des cinq entrées et deux sorties d'un CLB de FPGA de la famille XC3000 de Xilinx..... | 48 |

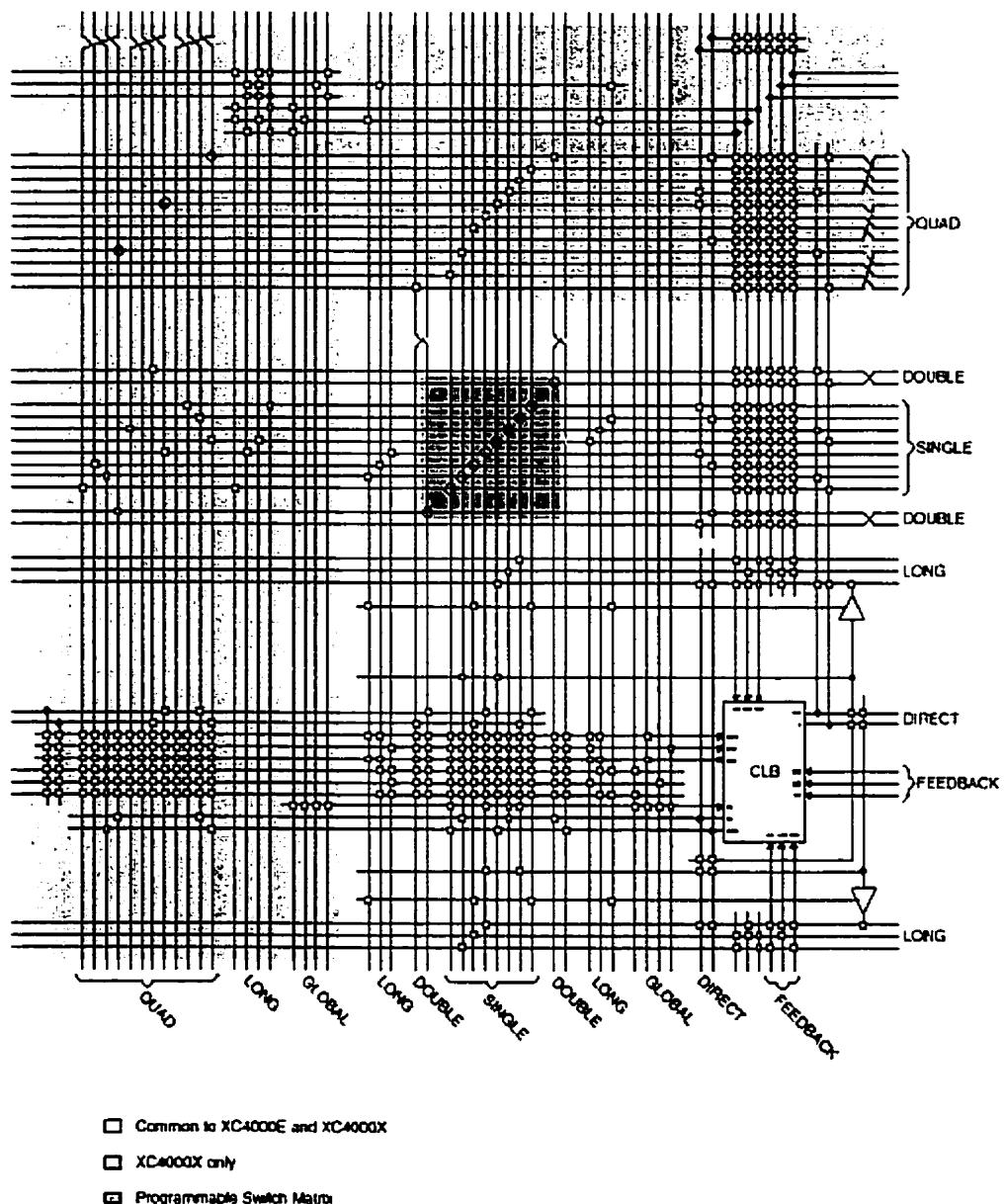

| <b>Figure 2.9</b> Représentation des fils disponibles autour d'un CLB d'un FPGA de la famille XC4000.....                                                                  | 51 |

| <b>Figure 2.10</b> Représentation des matrices d'interconnexions ainsi que des différents types de lignes autour d'un CLB d'un FPGA de la famille XC4000.....              | 52 |

|                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------|----|

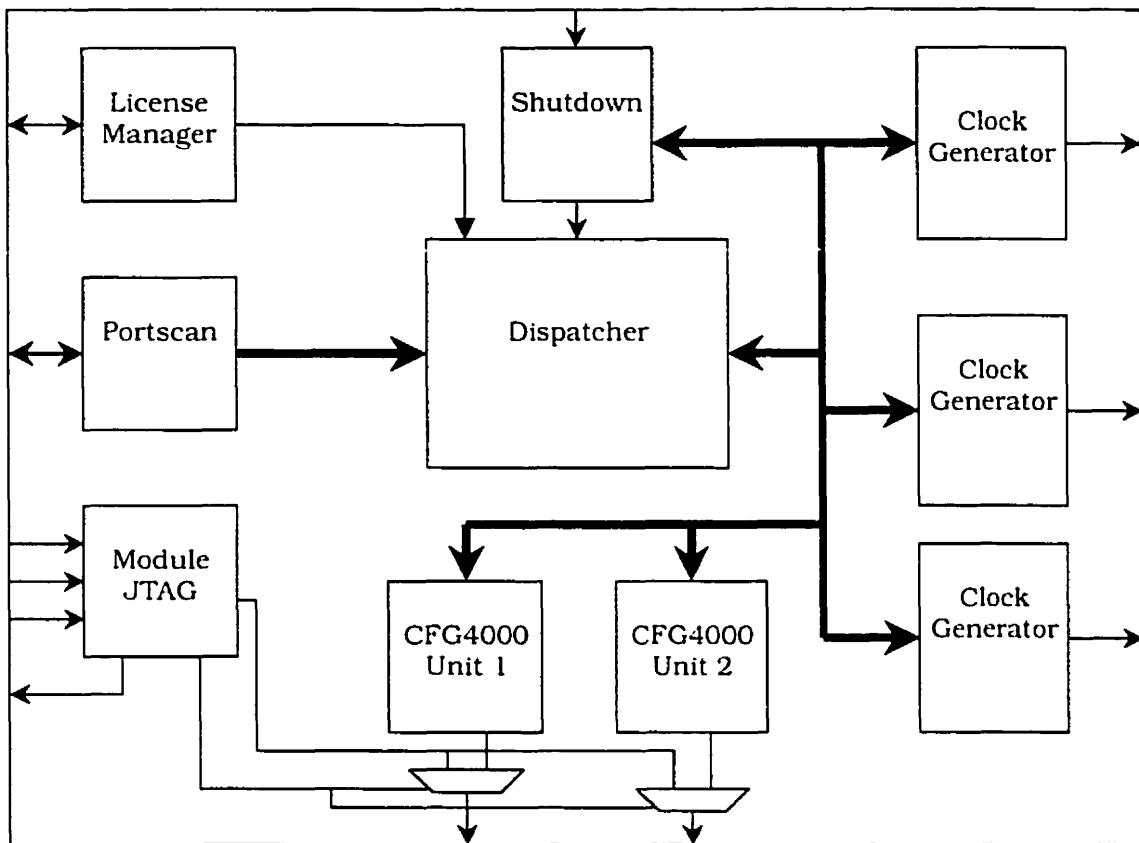

| <b>Figure 3.1</b> Schéma bloc du CSU (Configuration and Shutdown Unit).....                                          | 57 |

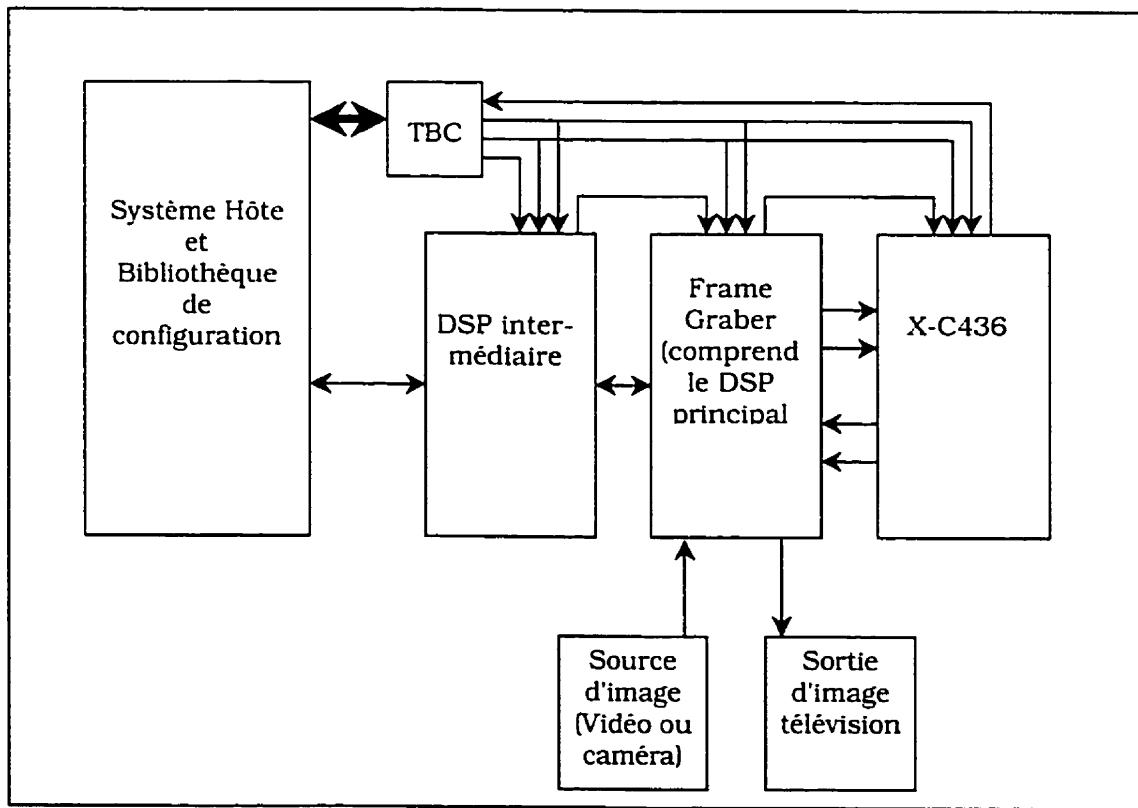

| <b>Figure 3.2</b> Schéma bloc du système avec l'application de suite de filtres d'image.....                         | 66 |

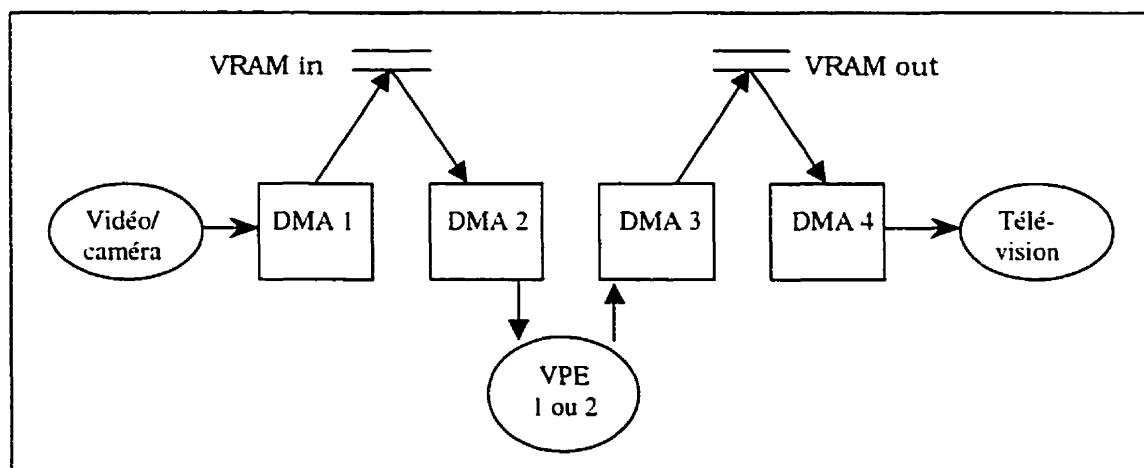

| <b>Figure 3.3</b> Flot de données du traitement d'image.....                                                         | 67 |

| <b>Figure 3.4</b> Représentation temporelle d'un cycle de reconfiguration dynamique.                                 | 75 |

| <br>                                                                                                                 |    |

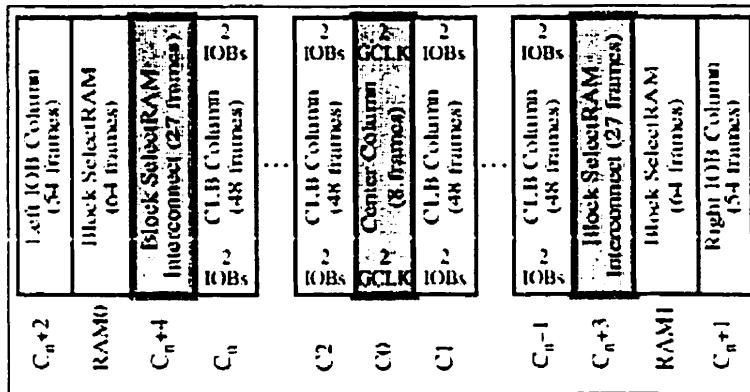

| <b>Figure 4.1</b> Représentation du nombre de blocs de configuration par colonne chez les FPGA Virtex de Xilinx..... | 80 |

## **LISTE DES SIGLES ET ABRÉVIATIONS**

|      |                                           |

|------|-------------------------------------------|

| ASIC | Application Specific Integrated Circuit   |

| C40  | Processeur TMS320C40 de Texas Instruments |

| CCM  | Custom Computing Machine                  |

| CLB  | Configurable Logic Block                  |

| CPLD | Complex Programmable Logic Device         |

| CPM  | Communication Port Manager                |

| CPS  | Connexions par Seconde                    |

| CSU  | Configuration and Shutdown Unit           |

| DMA  | Direct Memory Address                     |

| DR   | Data Register                             |

| DRAM | Dynamic Random Access Memory              |

| DSP  | Digital Signal Processing                 |

| FIFO | First In First Out                        |

| FPGA | Field Programmable Gate-Array             |

| GAL  | Generic Array Logic                       |

| IR   | Instruction Register                      |

| JTAG | Join Test Action Group                    |

| LUT  | Look Up Table                             |

| MHz  | Méga Hertz                                |

| ms   | milli seconde                             |

| μs   | micro seconde                             |

| ns   | nano seconde                              |

| PAL  | Programmable Array Logic                  |

| PCB  | Printed Circuit Board                     |

| PCI  | Peripheral Component Interconnect         |

| PLA  | Programmable Logic-Array                  |

| PROM | Programmable Read-Only Memory             |

| RAM  | Random Access Memory                      |

| RISC | Reduce Instruction Set Computer           |

| RTR  | Run Time Reconfiguration                  |

| SLU  | Swappable Logic Unit                      |

|              |                                            |

|--------------|--------------------------------------------|

| <b>TAP</b>   | <b>Test Access Port (Contrôleur)</b>       |

| <b>TBC</b>   | <b>Test Bus Controller</b>                 |

| <b>TCK</b>   | <b>Test Clock</b>                          |

| <b>TDI</b>   | <b>Test Data In</b>                        |

| <b>TDO</b>   | <b>Test Data Out</b>                       |

| <b>TMS</b>   | <b>Test Mode Select</b>                    |

| <b>TRST</b>  | <b>Test Reset</b>                          |

| <b>VHDL</b>  | <b>VHSIC Hardware Description Language</b> |

| <b>VHSIC</b> | <b>Very High Speed Integrated Circuit</b>  |

| <b>VPE</b>   | <b>Virtual Processing Element</b>          |

## INTRODUCTION

Le monde de la micro-électronique a énormément évolué dans les 50 dernières années. Depuis l'avènement des premiers circuits intégrés dans les années 60, le nombre d'applications découlant de l'utilisation de tels composants n'a cessé de croître. Pour réaliser des circuits complexes, le choix se portait alors soit sur les microprocesseurs à prédominance logicielle, ou encore sur les circuits intégrés dédiés à prédominance matérielle, en plus de disposer d'une myriade de composants élémentaires de type portes logiques de base. Les circuits intégrés dédiés qu'on nomme aussi ASIC pour *Application Specific Integrated Circuit* sont des composants qui ont, certes, beaucoup évolués depuis leur début en terme de capacité, mais qui n'en demeurent pas moins longs et coûteux à concevoir. Les microprocesseurs ont eux aussi évolués. Ils sont en mesure d'accomplir des instructions plus complexes et atteignent des vitesses de traitement toujours plus rapides. Ils conservent cependant un champ d'application restreint, c'est-à-dire strictement logiciel. À l'aide de ces deux ressources principales, soit le microprocesseur et le ASIC, nous avons pu, par le passé, construire des systèmes efficaces, basés soit sur l'un ou sur l'autre, sans toutefois atteindre la rapidité de développement que requiert le marché.

Au milieu des années 80 est né le tout premier FPGA (Field Programmable Gate Array). Ce composant de la logique programmable regroupe un nombre fixe de portes logiques de base qui peuvent ou non être utilisées afin de former un circuit spécifique. Le FPGA se différencie des autres membres de la logique programmable, puisqu'il permet de construire des circuits plus complexes et permet ainsi de servir à autre chose que de la "colle" logique (*glue logic*). En effet, ayant en général plus de ressources matérielles et une architecture plus étendue, le FPGA permet de concevoir des circuits adaptés à des applications aussi différentes que le contrôle et le traitement de données. Il possède une mer de portes logiques de bas niveau regroupées en cellules qui possèdent chacune au moins un élément de mémoire (bascule D ou *latch*). Ces cellules peuvent être interconnectées entre elles au moyen d'une multitude de réseaux possibles, pré-tracés à l'intérieur du composant.

On catégorise les FPGA par famille selon l'architecture, le type ou la quantité de routage qu'ils offrent et la structure de leurs cellules logiques. Par exemple, certains FPGA avantagent le traitement de données, puisqu'ils ont de grosses cellules logiques et fournissent moins de matrices d'interconnexions. On parle alors d'une grosse granularité. D'autres allouent une plus grande flexibilité, fournissant de petites cellules logiques et une grande quantité de routage. On parle alors de granularité fine et ces types de FPGA répondent mieux aux besoins d'un circuit de contrôle par exemple. Les FPGA ont aussi comme avantage d'être plus rapides que les microprocesseurs dans certaines applications et ils sont définitivement plus flexibles que les circuits intégrés dédiés. Ils peuvent donc rallier le meilleur des deux mondes à moindre coût de développement qu'un circuit intégré dédié.

Plusieurs avantages militent en faveur des FPGA. Le premier est sans doute sa reprogrammabilité. Plusieurs applications utilisent les FPGA soit à titre d'élément de base (traitement) ou à titre de soutien (contrôle). On voit aussi très souvent les FPGA comme coprocesseur à certains systèmes, exécutant une tâche spécifique qui permet de libérer le processeur principal. Les machines de calcul dédiées (traduction de *Custom Computing Machines* ou CCM) utilisent de plus en plus les FPGA à la base du système. La popularité des FPGA fait en sorte qu'on exige plus de rendement, et plus de flexibilité de leur part. On veut à la fois des outils plus performants pour le placement routage, et pouvoir les reprogrammer le plus rapidement possible afin de construire des systèmes de traitement temps réel moins coûteux.

La demande pour une flexibilité accrue a poussé les chercheurs et les industriels vers un type particulier de reprogrammation, qui s'effectue pendant que le système traite. C'est ce qu'on appelle la reconfiguration dynamique, traduction de RTR pour *Run Time Reconfiguration*. En résumé, plusieurs visions du concept sont développées et les voies se séparent entre une reprogrammation complète du FPGA versus une reprogrammation partielle. La reconfiguration dynamique partielle d'un FPGA sous-entend qu'un mécanisme, interne au FPGA, permet de garder une partie de la circuiterie en fonction alors qu'il reçoit des données de reprogrammation pour une région seulement. La reconfiguration dynamique totale, quant à elle, consiste à reconfigurer le FPGA en entier pendant que celui-ci effectue un traitement. Bien

entendu, celui-ci ne doit plus être fonctionnel et un arrêt de traitement doit donc être envisagé.

Les industriels et les universitaires se sont majoritairement tournés vers la reprogrammation dynamique impliquant la reconfiguration partielle du FPGA. On a donc vu apparaître sur le marché des FPGA supportant cette fonctionnalité. Par contre, ces composants n'ont pas remporté un succès commercial significatif. En effet, même si la moitié des FPGA reprogrammables partiellement était issue du milieu académique et n'était destinée qu'à des fins de recherche, les autres composants provenant du milieu industriel n'ont guère fait meilleure figure et n'ont survécu que quatre ans sur le marché. Toutefois, tout récemment, un chef de file dans le marché des FPGA, la compagnie Xilinx, a créé un FPGA pouvant être configuré partiellement, le Virtex. Celui-ci brille davantage pour sa taille et ses capacités d'implantation que pour ses aptitudes à supporter la reconfiguration partielle.

La reconfiguration dynamique utilisant la reprogrammation totale du FPGA a tout de même intéressé quelques chercheurs au tout début des années 90. Ceux-ci ont fourni la preuve que des systèmes dédiés, basés sur des technologies de FPGA conventionnels, pouvaient fournir des résultats remarquables sans inconvénients. En effet, les FPGA reconfigurables partiellement ont causé plusieurs maux de tête aux développeurs, étant donné qu'aucun outil efficace de placement routage et de développement n'était disponible sur le marché pour ces FPGA. Malheureusement, l'intérêt pour ce type de reconfiguration dynamique s'est estompé et, à ce jour, l'ensemble des recherches sur la reconfiguration dynamique est orienté vers les FPGA partiellement reprogrammables.

Ce mémoire contribue à démontrer qu'on peut toujours faire des systèmes performants basés sur la reconfiguration dynamique de FPGA conventionnels. Pour ce faire, nous présenterons d'abord plusieurs études sur le sujet qui ont, d'une manière ou d'une autre, fait évoluer les connaissances sur le sujet. Nous ferons ressortir les lacunes visibles des systèmes utilisant les FPGA reconfigurables partiellement et nous fixerons, de cette manière, les objectifs de notre projet. Le concept et les notions de bases relatifs à ce projet seront présentés au chapitre deux, tandis que l'implantation en tant que telle sera le thème du chapitre trois. De plus, à la fin de ce mémoire, nous

ferons une analyse critique de ce projet, des manières de l'améliorer et de comment nous pouvons l'étendre à des systèmes plus performants.

## CHAPITRE PREMIER - REVUE DE LITTÉRATURE

### 1.0 INTRODUCTION

Ce chapitre vise à familiariser le lecteur au sujet traité dans le cadre de ce mémoire en le situant parmi les recherches antérieures et actuelles du milieu académique et industriel. Cette revue de littérature se veut exhaustive afin de favoriser chez le lecteur une compréhension plus affinée pour les chapitres subséquents. Après une brève description des tendances actuelles, une discussion visant à faire ressortir les points forts et les points faibles de ces recherches sera faite. Finalement, nous présenterons le sujet de cette recherche en démontrant quels types de problèmes nous tentons de résoudre.

Le milieu académique et le milieu industriel ont présenté des recherches et des produits ayant trait à la reconfiguration dynamique des FPGA depuis les années 90 environ. Dans le but de faciliter la présentation et la compréhension de ces recherches, nous les regrouperons en différents thèmes. Tout d'abord, nous présenterons les recherches qui traitent de la reconfiguration dynamique des FPGA supportant la reconfiguration partielle (RTR partiel) et la reconfiguration dynamique des systèmes comportant des FPGA conventionnel (RTR total). Ensuite, nous présenterons des recherches qui se penchent sur des outils de placement et routage ou des outils de développement pour des systèmes supportant le RTR. Nous exposerons également des recherches qui ont mené au développement de nouvelles architectures de FPGA qui supporteraient également une forme de reconfiguration dynamique. Finalement, nous présenterons les quelques recherches qui ont fait une analyse du RTR au point de vue rendement et avenir.

## **1.1 RECONFIGURATION DYNAMIQUE DE FPGA POUVANT ÊTRE RECONFIGURÉS PARTIELLEMENT**

La reconfiguration dynamique de FPGA qui supportent la reconfiguration partielle est sans contredit le sujet le plus répandu des recherches portant sur le RTR. En effet, avec l'avènement sur le marché de FPGA ayant de telles capacités, beaucoup y ont vu la solution idéale pour plusieurs applications. Quatre compagnies principalement ont produit pour le marché ou pour le milieu académique des FPGA pouvant être reconfigurés partiellement. Déjà vers la fin des années 80 (1988), Algotronix, une compagnie d'Écosse, présente une première version de son FPGA CAL1024, qui supporte la reconfiguration partielle. Cette entreprise est, vers la fin de 1995, achetée par Xilinx, qui en fait la base de sa famille XC6200. Le FPGA CLAy de National SemiConductor a, quant à lui, toujours servi à des fins académiques et a alimenté plusieurs des recherches présentées plus loin. Finalement, la famille 6000 d'Atmel, disponible commercialement, a été utilisée dans quelques recherches. À ce jour, les produits d'Atmel et de Xilinx sont encore disponibles, par contre, les XC6200 de Xilinx ne sont plus supportés. Xilinx a plutôt misé sur une toute nouvelle famille de FPGA qui offre, en plus d'une capacité d'implantation de circuits de grande taille, la possibilité de supporter la reconfiguration dynamique en utilisant un processus de reconfiguration par colonne du FPGA. Cependant, puisque cette toute nouvelle fonction de reconfiguration partielle n'est annoncée publiquement que depuis le milieu de l'été 1999, nous n'avons pu étudier ce nouvel aspect dans le cadre de ce mémoire. Nous y consacrons toutefois une attention particulière au chapitre quatre. Mentionnons finalement qu'une compagnie anglaise du nom de Plessey SemiConductors avait commercialisé durant un bref temps des FPGA de ce type au tout début des années 90, mais nous n'avons retracé aucune recherche les ayant utilisés.

### **1.1.1 XILINX XC6200 OU CAL D'ALGOTRONIX**

Les recherches qui sont présentées dans cette section concernent des applications ayant été réalisées avec les FPGA de la famille XC6200 de Xilinx ou CAL

d'Algotronix. En effet, plusieurs outils de placement/routage, ainsi que des outils de développement de systèmes RTR à base de ces FPGA ont été réalisés, mais nous en discuterons à la partie 1.3 qui traite des outils.

Même si les FPGA d'Algotronix sont apparus sur le marché en 1988, ce n'est pas avant 1993 qu'un article relatant l'utilisation de ce FPGA est publié (Foulk, 1993). Le système traité dans cet article a trait à une technique nommée data-folding (pliage de données) spécialement appliquée à des recherches à l'intérieur de textes. Le FPGA d'Algotronix est, selon l'auteur, idéal pour la reconfiguration dynamique, puisqu'il possède une fine granularité, c'est-à-dire que de très petites fonctions logiques (2 entrées) sont garnies d'une excellente structure de routage interne. L'auteur mentionne qu'il est possible de sauver plus de la moitié de l'espace prévu pour implanter le circuit. Ainsi, son circuit ne nécessite-t-il que deux FPGA CAL d'Algotronix à la place de cinq. Finalement, l'auteur traite d'un aspect qui est rarement abordé dans les recherches sur le sujet, soit l'implantation d'un système pour commuter d'une configuration à l'autre. Dans ce cas précis, l'auteur mentionne que le FPGA CAL d'Algotronix offre la possibilité de relire l'état de chacune des cellules. Générant une petite logique de vérification, il est en mesure de connaître en tout temps le moment adéquat pour la commutation. Le mécanisme est automatique. De cette manière, on peut augmenter la vitesse de commutation du système.

Le tout premier article répertorié qui traite de la reconfiguration partielle avec les XC6200 de Xilinx est l'article de Brebner et Gray (1995), qui utilise ces FPGA pour la détection de codes de longueur variable à la rapidité d'un signal vidéo (temps réel). Ces codes sont fournis selon la norme fax T.4 et le codage des symboles est fait selon un codage de Huffman. Ce type de codage fait en sorte qu'on peut encoder les symboles à transmettre selon leur fréquence d'apparition. Les symboles les plus souvent lus possèdent un code binaire court (au minimum 2 bits) et les symboles les moins souvent rencontrés ont un code binaire plus long (maximum 13 bits). Le signal à décoder est série et passe à travers un arbre de décodage qui peut décoder les symboles qui ont un maximum de 6 bits. Au-delà de ce nombre, le FPGA doit être reconfiguré partiellement en sélectionnant un parmi les 64 sous-arbres afin d'être en mesure de traiter les symboles de plus de 6 bits. La reconfiguration de ce sous-arbre de décodage nécessite 10 cycles d'écriture (dû à leur architecture de système). Mais

compte tenu que 90 % des symboles possèdent un code plus petit ou égal à 6 bits, le temps de reconfiguration nécessaire lors des codes plus long peut être amorti et on peut compter une moyenne d'un cycle d'écriture par mot binaire (peu importe sa longueur). Donc, d'après leurs calculs, l'équipe comptait obtenir une sortie traitée qui rencontrait la bande passante vidéo. Étant donné que les FPGA XC6200 n'étaient pas disponibles sur le marché au moment où les travaux ont été effectués, les auteurs n'ont pu planter cette application.

L'année suivante (1996), Gunther, Milne et Narasimhan publient sur une application faite à partir d'un système de 16 FPGA CAL d'Algotronix. Ce groupe étudie la recherche de mots à l'intérieur de textes. Une liste contenant une série de mots choisis devient la base de la comparaison pour chacun des mots du texte. À la fin du texte, celui-ci obtient un score qui est proportionnel au nombre de mots correspondants à la liste. Le mécanisme de recherche est composé d'un circuit fixe et d'un chemin de données reconfigurable. Cette logique, qui utilise 57% de l'espace total du système de 16 FPGA, est synthétisée juste avant d'être configurée. Selon leurs résultats, ils sont en mesure d'effectuer une recherche de 91 mots-clés en 3.21 secondes, ce qui inclut 0.16 seconde pour la synthèse des chemins de données et 3.05 secondes pour leur configuration à l'intérieur du système de FPGA. Mentionnons également que la recherche s'est effectuée sur plusieurs textes totalisant une base de données de dizaines de mégaoctets.

Une équipe de l'Université de Glasgow en Écosse, Royaume-Uni (Burns et al., 1997) s'est intéressée à la reconfiguration dynamique de systèmes à base de FPGA partiellement reconfigurables. Le but de leur recherche était d'établir une interface pour un système exécutant une application dynamiquement reconfigurable. Pour ce faire, ils ont d'abord étudié les besoins de tels systèmes en démontrant trois applications. De celles-ci, ils ont pu caractériser le système à bâtir. Le système est conçu pour utiliser un FPGA de la famille XC6200, mais le concept pourrait aussi être implanté sur d'autres FPGA partiellement reprogrammables. Leur système nommé RAGE contient quatre modules principaux, en plus de la banque d'applications et du FPGA lui-même. Ces modules sont le *Virtual Hardware Manager*, le module *Transformation Manager*, le module *Configuration Manager* et finalement le module *Device Driver*. Le premier est le contrôleur du système qui interagit avec tous les

modules sauf le FPGA. Le second module, *Transformation Manager*, est un outil qui permet de réorganiser les parties à reconfigurer du FPGA pour que celui-ci puisse demeurer performant d'une configuration à l'autre. Le module *Configuration Manager* configure le FPGA par l'entremise du *Device Driver*, tandis que ce dernier s'occupe du transfert de données/résultats, ainsi que des données de reconfiguration. Sur la base de ce que l'on retrouve dans la littérature, le projet semble en être resté au stade d'une proposition non développée.

Dans un autre ordre d'idée, une équipe de l'Université du Massachusetts à Amherst (Park et Burleson, 1998) a développé une technique qui utilise les FPGA partiellement reconfigurables pour une application dédiée à l'estimation de mouvements. Cette technique de compression d'images est, selon les auteurs, la plus exigeante au niveau temps de calcul parmi toutes les techniques utilisées dans le codage vidéo. La quantité de CLB à reconfigurer est autour de 64. De ce nombre, ils concluent que le temps de reconfiguration de leur système sera autour de 20 microsecondes, étant donné que d'après les spécifications du composant, le temps de reconfiguration d'un CLB est autour de 40 nano secondes. Ceci est amplement suffisant pour du traitement temps réel à raison de trente images par seconde, 2 champs par image, un pair et un impair. On ne parle pas de l'implantation physique de cette recherche.

Étant donné leur grande disponibilité, les FPGA de la famille XC6200 de Xilinx ont été amplement cités et utilisés dans le milieu académique. Comme il est impossible de relater tous les travaux de recherche ayant utilisé de tels FPGA, nous nous sommes limités aux recherches qui sont les plus importantes dans le contexte de ce mémoire.

### 1.1.2 CLAY DE NATIONAL SEMICONDUCTOR

Le FPGA CLAy de National SemiConductor a essentiellement été utilisé par le milieu académique à des fins de développement. Les premières recherches qui traitent de ce FPGA datent de 1995.

Un des plus importants systèmes ayant été construits à partir des FPGA CLAy de National SemiConductor est sans doute le DISC de L'Université Brigham Young,

Utah par Wirthlin et Hutchings (1995). Le système reflète l'essence même de toute application dite dynamiquement reconfigurable, c'est-à-dire qu'une certaine logique de base est fixe et qu'une instruction à la fois est portée à l'intérieur du FPGA selon le cours de l'exécution du programme. Cette instruction fait partie d'une suite d'instructions pré-compilées qui constitue un module spécifique dans une bibliothèque d'instructions. Le système qui entoure DISC interagit avec un ordinateur hôte via un bus ISA. Par la suite, deux FPGA CLAy31 sont utilisés, le premier est le processeur DISC qui reçoit toutes les instructions et le deuxième agit à titre de contrôleur pour exécuter la configuration. Le processeur a également à sa disposition de la mémoire RAM. Jusqu'à cinq instructions peuvent être présentes à la fois dans le processeur, mais une à la fois est exécutée. Lorsque le processeur contient cinq instructions et qu'une autre instruction doit être configurée, la plus ancienne est effacée. Ainsi, le processeur agit à titre de cache des cinq plus récentes instructions.

Les suites de ce projet apparaissent dans un autre article de Wirthlin et Hutchings l'année suivante avec DISC II. La seconde version de ce système est un peu plus élaborée que la première avec plus de mémoire, plus de registres et un FPGA de plus. La logique fixe est moindre, afin de donner plus de place à la partie dynamique. Le FPGA supplémentaire a hérité de la partie instruction, le processeur garde seulement le programme épuré. La mémoire est accessible par le processeur et par le FPGA contenant les instructions. Le processeur fonctionne maintenant sur 16 bits au lieu de 8 et à une vitesse de 8 MHz au lieu de 7.5.

Une autre équipe de l'Université Brigham Young, Hadley et Hutchings (1995) a utilisé les FPGA CLAy de National SemiConductor pour construire un réseau de neurones artificiel. Le système RRANN2 pour *Rapidly Reconfigurable Artificial Neural Network*, tire sa source d'études antérieures qui exploitaient des FPGA conventionnels (XC3010 de Xilinx). Les réseaux de neurones auraient avantage à utiliser la reconfiguration dynamique, puisqu'elle peut augmenter la densité fonctionnelle du réseau de 500% à comparer des réseaux implantés sur des systèmes n'utilisait pas la reconfiguration dynamique. Le but du projet RRANN2 est d'atteindre les mêmes performances que son prédecesseur, mais avec encore moins de neurones. De plus, l'équipe voulait approfondir le développement d'une méthodologie de conception avec les FPGA partiellement reconfigurables. En effet, en maximisant la taille du circuit

statique et en minimisant la partie dynamique, le temps de reconfiguration en sera d'autant diminué. Les auteurs mentionnent finalement qu'il existe un manque important au niveau des outils de synthèse et de simulation qui tiennent compte de tous les mécanismes impliqués dans le développement de systèmes à base de FPGA partiellement reconfigurables.

Au niveau application concrète, Schoner, Jones et Villasenor présentaient en 1995 un système de codage vidéo sans fils utilisant des FPGA reconfigurables dynamiquement. L'application utilise trois configurations consécutives qui conservent une grande partie du circuit de base de l'une à l'autre. Cette suite de configurations est effectuée pour chaque champs d'images. Le temps total de ces reconfigurations est de 3 ms, ce qui correspond à 10 % du temps d'un cadre. À l'écriture de l'article, la réalisation du projet n'était pas terminée.

### 1.1.3 ATMEL 6000

La famille de FPGA Atmel 6000 était autrefois offerte sous la bannière de Concurrent Logic et elle portait le nom de Cli6000. Les recherches faisant état de l'utilisation de ces FPGA ne sont pas nombreuses: quelques unes en 93-94 et une en 1996. Le manque d'intérêt du milieu académique est curieux, puisque Atmel est à ce jour la seule compagnie qui fournit sur le marché des FPGA programmables partiellement. Un FPGA plus récent, le AT40k, est lui aussi reprogrammable partiellement. Cette famille offre de 5k à 50k portes logiques utilisables. On peut donc se questionner sur la qualité du support de ces FPGA, car un manque d'outils veut dire immédiatement perte d'intérêt dans le domaine du FPGA.

Ross, Vellacott et Turner (1993) ont développé un système dédié au traitement d'images. Leur système nommé *imputer* pour **imaging - computer** utilise des FPGA Atmel 6000 comme unités de traitement, mais un FPGA conventionnel (Actel) comme contrôleur. Une mémoire RAM est accessible par ces deux composants pour des fins de traitement et une autre mémoire est utilisée à titre de bibliothèque des configurations à être implantées. Des résultats sur des traitements d'images comme un filtre Sobel sont présentés à titre de comparaison avec un système compétiteur. Selon les auteurs, leur système serait jusqu'à dix fois plus rapide avec cette implantation de

reconfiguration dynamique. Malheureusement, aucune donnée relative à la taille de l'image traitée n'est fournie, ce qui nous empêche de véritablement évaluer les performances de ce système.

En 1993 et 1994, deux groupes de recherche ont présenté une étude d'implantation d'un réseau de neurones artificiel sur les FPGA de Atmel (Concurrent Logic pour l'un d'eux). Le premier groupe dirigé par van Daalen (van Daalen, Jeavons et Shawe-Taylor, 1993) de l'Université Royal Holloway de Londres n'a pas implanté concrètement son architecture sur ces FPGA. Par contre, tout le projet a été pensé en conséquence de cette implantation. Le deuxième groupe, de l'Université de Strathclyde (Lysaght et al., 1994), donne plus de détails quant à l'implantation et aux résultats. En effet, pour leur architecture, le réseau de neurones implanté sur un système dynamiquement reconfigurable obtient 38 fois les performances qu'ils auraient obtenues avec un système basé sur des FPGA conventionnels. Leur système offre une performance de 770K CPS (Connexions par seconde) à 24KHz comparativement à 20K CPS, 625 Hz si la même architecture avait utilisé des FPGA conventionnels. Par contre, l'équipe mentionne que de bien meilleurs résultats avaient été obtenus avec des systèmes plus volumineux basés sur des FPGA conventionnels. Ils nomment GANGLION, un projet de Cox et Blanz (1992) qui utilise 30 FPGA XC3010 de Xilinx. Ces circuits sont relativement plus gros que les AT6005 utilisés dans le projet de Lysaght. Les performances de GANGLION sont impressionnantes, 4.5 milliards de connexions par seconde (4.45G CPS).

Finalement, une dernière étude utilisant les FPGA de Atmel a été publiée, celle d'Eggers et al., (1996). Cette fois-ci, l'application touche un système rapidement reconfigurable de commutation croisée (Crossbar Switching). Cette application, destinée au domaine biomédical, avait comme contrainte une reconfiguration totale du système en deçà de 200 micro secondes. Le FPGA 6005 de Atmel peut se configurer totalement en 800 micro secondes, en utilisant le mode le plus rapide de reconfiguration. La reconfiguration dynamique utilisant le procédé de reconfiguration partielle ne peut donc pas s'effectuer aussi rapidement. En effet, si l'on considère que la reconfiguration complète du composant prend environ 255 nano secondes par cellule (3136 cellules individuelles), la reconfiguration partielle est environ 6 à 7 fois plus lente avec un temps de 1.7 micro secondes par cellule. Le temps requis par cellule

pour entrer dans la contrainte de 200 micro secondes est de 3.125 micro secondes par cellule. L'implantation n'atteint toutefois pas les performances d'un système dédié à cette application (FPIID de I-Cube). Par contre, en considérant le rapport performance sur prix, la conception sur FPGA reprogrammable est la plus avantageuse. L'équipe de recherche note en terminant que les FPGA de Xilinx, plus récents, promettent d'être plus performants dans le sens où l'on peut les reconfigurer plus rapidement que les FPGA d'Atmel en mode reconfiguration partielle.

## **1.2 RECONFIGURATION DYNAMIQUE UTILISANT DES FPGA CONVENTIONNELS**

Peu de recherches relatent l'utilisation de FPGA conventionnels pour concevoir un système pouvant être reconfiguré dynamiquement. Les recherches qui ont toutefois été publiées ont été faites au tout début des études portant sur la reconfiguration dynamique de systèmes à base de FPGA.

Le tout premier article traitant de la reconfiguration dynamique de systèmes de FPGA conventionnels apparaît en 1991. Lysaght, de l'Université de Strathclyde à Glasgow, Écosse, Royaume-Uni, fait état d'une architecture développée dans le cadre de projets de fin d'études de deux étudiants en génie électrique de l'Université. Ces deux projets, qui se soutiennent mutuellement, proposent un système simple avec une application simple. Deux FPGA de la famille XC2000 de Xilinx interagissent pour former un système qui dirige sa propre reconfiguration. En fait, un seul des FPGA exécute toute l'application tandis que l'autre agit à titre de contrôleur. C'est pourquoi, selon leur application, pour passer d'une configuration à une autre, on doit attendre le temps de reconfiguration total du FPGA traitant. Ce temps d'arrêt est court, puisque les FPGA XC2000 sont petits, mais l'auteur mentionne tout de même que l'utilisation des FPGA reprogrammables partiellement pourrait être envisagée, puisqu'en configurant le système partiellement, le temps de reconfiguration est diminué.

Un impressionnant système de 30 FPGA XC3090 de Xilinx est présenté en 1992. Il s'agit de GANGLION, de Cox et Blanz dont nous avons parlé auparavant (section 1.1.3). Cet article démontre l'implantation d'un classificateur de connexions ou

encore réseau de neurones. Ces chercheurs ont développé un concept intéressant qui consiste à générer de la logique spécifique à chaque nouvelle application. Ainsi, à titre d'exemple, ils ont implanté un multiplicateur de 8 bits variables par 8 bits constants. Les 8 bits constants sont fixés à l'intérieur de LUT (Look Up Table), ce qui permet ainsi d'avoir un multiplicateur consommant moins de CLB, en plus d'être plus rapide qu'un multiplicateur conventionnel. Le système en lui-même est très performant. Comme nous l'avons déjà mentionné, il est en mesure d'effectuer 4.48G connexions par seconde et 20 millions de décisions par seconde. Selon les auteurs, leur système utilise pleinement toutes les capacités de la reprogrammabilité des FPGA conventionnels.

En continuant avec les réseaux de neurones, Eldredge et Hutchings (1994) ont publié deux articles relatifs à une implantation sur des FPGA XC3090 de Xilinx. Le projet RRANN pour Run-time Reconfiguration Artificial Neural Network procède à l'implantation d'un algorithme dit de *backpropagation*. Pour ce faire, ils divisent le processus en trois parties distinctes qui sont tour à tour implantées dans le même FPGA. Basé sur la propagation d'erreur, le système effectue les mêmes trois étapes (i.e. calcul, propagation de l'erreur, rafraîchissement) jusqu'à ce que le réseau soit suffisamment entraîné. Le système a été monté avec 12 FPGA, dont un dédié à être le contrôleur et les autres supportent chacun six neurones matériels. Comparativement à un système n'utilisant pas de reconfiguration dynamique, la densité de neurones implantés serait augmentée de 500%. Par contre, il est bon de mentionner que le système utilisant la reconfiguration dynamique surpassé le système qui ne l'utilise pas, lorsque le nombre de FPGA XC3090 est plus grand que 23. Nous pouvons facilement comparer ce système avec GANGLION présenté précédemment, puisque celui-ci utilisait également des FPGA XC3090 de Xilinx. En vérifiant les résultats fournis par les auteurs dans une charte de leur article, avec 30 FPGA XC3090, leur système serait en mesure de fournir environ 110M CPS ( $1.1 \times 10^8$  connexions par seconde) alors que le système GANGLION avait comme performance 4.48G CPS soit 40 fois mieux.

Une dernière application présentée en 1995 par Lemoine et Merceron utilise une plate-forme DECPeRLe-1 du laboratoire de recherche de Digital à Paris. Ils ont implanté un système pour traiter une base de données contenant tout le génome humain. La carte DECPeRLe-1 utilise 23 FPGA XC3090 de Xilinx et permet

l'implantation d'un système utilisant la reconfiguration dynamique des FPGA. Deux types de reconfiguration dynamique sont envisageables selon les auteurs. La première synthétiserait un fichier de configuration totalement nouveau, conçu pour satisfaire des contraintes connues durant le traitement. La deuxième modifierait un fichier de configuration de base selon des informations connues durant le traitement. Il est clair que générer un fichier de configuration totalement nouveau pendant que le système traite ralentit celui-ci d'un délai considérable. Cependant, selon les auteurs, ce processus permettrait d'augmenter la vitesse de traitement du FPGA, ainsi que sa densité. Cette équipe a démontré que le traitement de 3.5 milliards de nucléotides pouvait s'effectuer en 100 secondes environ. Ils ont comparé ce temps avec celui d'un processeur RISC 3000 40MHz (même vitesse que leur système) et ils ont obtenu un temps dans les dizaines de millier de secondes.

### 1.3 LES OUTILS

La quantité de recherches sur le développement d'outils de placement/routage, ou d'outils de développement et de simulation pour les FPGA partiellement reprogrammables, en dit long sur la volonté du milieu académique de travailler sur de tels FPGA et l'intérêt que l'industrie y voit. Clairement, pour construire un système reprogrammable dynamiquement, on a besoin d'outils de placement et de routage, ainsi que d'outils de simulation adéquats. Ces outils, les fabricants de FPGA les ont et ils sont généralement suffisamment performants pour répondre aux besoins des utilisateurs, quoiqu'ils ne soient pas développés pour supporter des applications utilisant la reconfiguration dynamique. Par contre, lorsque les FPGA partiellement reprogrammables sont impliqués, les choses se compliquent. Les articles dont nous discuterons dans cette section ont aussi et surtout fait état d'outils de niveau système qui supportent tout le processus de développement de circuits dynamiquement reconfigurables.

Un des premiers articles traitant de la réalisation d'outils liés au développement des systèmes dynamiquement reconfigurables est celui d'un groupe logiciel du David Sarnoff Research Center au New Jersey (Gokhale et Marks, 1995). Cet outil vise à

partitionner un programme parallèle afin de l'implanter dans un processus de reconfiguration dynamique. L'outil est développé pour les FPGA CLAy de National Semiconductor qui sont partiellement reconfigurables. Dans le processus de partitionnement, le compilateur conserve les "variables globales" (sic) entre chaque reconfiguration, ce qui forme la circuiterie fixe. Leur compilateur génère à la fois le VHDL à être synthétisé par les outils conventionnels et le code C qui exécutera l'application sur le système hôte. Au moment où cet article était en rédaction, le travail à effectuer sur le compilateur n'était pas encore terminé.

Un auteur qui a constamment travaillé sur des outils de reconfiguration dynamique est Brebner du département d'informatique de l'Université d'Edinburgh en Écosse, Royaume-Uni. Depuis 1996, Brebner raffine les outils qui supporteraient son concept de SLU (Swappable Logic Unit). Le FPGA qui est jusqu'alors visé est le XC6200 de Xilinx. Le concept de SLU repose sur l'identification de fonctions spécifiques, localisées à un endroit fixe et utilisant un certain nombre d'entrées/sorties définies. La manipulation de SLU est la base de leur outil logiciel. Trois articles de 1996 et 1997 exposent le concept sous tous ses angles et l'auteur promet des résultats quant à son implantation. En 1998, Brebner et Donlin s'attaquent au problème de routage, mais sans toutefois montrer de résultats concrets, qu'ils promettent encore pour des travaux futurs. De plus, l'outil qu'ils prévoient développer est toujours destiné au FPGA XC6200 de Xilinx et ils mentionnent même que l'outil est dépendant de la famille de FPGA utilisé, donc non portable. Rappelons également qu'à cette date, les FPGA XC6200 de Xilinx n'étaient plus disponibles commercialement mais placés à la disposition du milieu académique seulement.

Une équipe de l'Imperial College à Londres (Luk, Shirazi et Cheung, 1996) a développé un modèle d'outil pouvant aider à tous les processus de conception d'un système basé sur la reconfiguration dynamique de FPGA. À partir des spécifications, l'outil permettrait de visualiser un système en cours de développement. À cette date, seulement le modèle était développé, l'imbrication de l'aspect temporel entre autre était un manque important. En 1997, l'équipe fournit un compilateur qui est basé sur le langage formel RUBY et le VHDL. L'outil est compatible avec les outils de simulation et de synthèse de l'industrie. L'insertion de la notation formelle RUBY apporte une base pour la vérification formelle et la validation, notions qui n'ont pas encore été exploitées

dans la communauté. Même si l'outil n'est pas développé pour une famille de FPGA en particulier, les FPGA XC6200 de Xilinx ont servi de plate-forme d'essai pour deux exemples.

La même équipe (Shirazi, Luk et Cheung) publie en 1998 un outil un peu plus substantiel, qui introduit le concept d'identification et de planification de région reconfigurable à l'intérieur du composant visé. Le principal objectif de l'outil est qu'il soit en mesure de reconnaître la partie commune à deux circuits distincts dans le but de les planter consécutivement. Cette partie fait toujours allusion au tout premier plan de travail que l'équipe avait démontré en 1996. Bizarrement, l'outil présenté dans cet article concerne la toute première étape de leur plan de travail, qui comprend les étapes suivantes: décomposition du circuit, séquencement, évaluation partielle, calcul de configuration incrémentielle, génération de configuration simultanée et validation. La représentation des deux configurations selon un graphe bipartie permet de décomposer les deux circuits et d'en faire ressortir, selon un système de poids, les parties semblables entre les deux. En utilisant les meilleurs résultats de cette analyse, la position de l'insertion de multiplexeurs est identifiée et les deux circuits sont ainsi combinés. Les auteurs ont démontré pour quelques applications une évaluation du nombre de cellules ainsi que du nombre de cycles de reconfiguration nécessaires pour la réalisation du circuit. Jusqu'à 32 cycles de reconfiguration sont nécessaires pour l'implantation d'un *pattern matcher*. La méthode proposée permet de réduire le nombre de cellules implantées de moitié et d'augmenter sa rapidité du double. Pour ce qui est de la notion de rapidité, le terme est mal défini. Les auteurs ne mentionnent pas le temps requis pour une reconfiguration, ils mentionnent que le temps de reconfiguration est plus long que le temps de traitement ce qui peut être un désavantage de l'utilisation d'une telle méthode.

Une application intéressante a été produite des suites de ces recherches de l'Imperial College de Londres. En effet, Luk et al. ont publié récemment (FCCM99) un article portant sur l'utilisation de leur outil de développement pour une application vidéo. La réalité augmentée (Augmented Reality) est une technique qui permet de juxtaposer des images réelles et des images synthétiques, pour enrichir la perception de l'environnement ainsi que l'interaction avec le milieu.

Une autre équipe qui provient cette fois de l'Université de Strathclyde à Glasgow, Écosse, Royaume-Uni (Lysaght et Stockwood, 1996) publie le premier outil de simulation et de développement destiné aux systèmes reconfigurables dynamiquement. Comme le soulignent les auteurs, une partie importante des outils reste encore à développer, soit ceux pour l'estimation du temps de reconfiguration, le placement routage automatique, la planification de l'espace (*floorplanning*) et la synthèse du contrôleur de reconfiguration. Toutefois, leur approche est intéressante pour la simulation des systèmes dynamiquement reconfigurables, puisqu'elle permet d'introduire la simulation beaucoup plus tôt dans le processus de développement, en utilisant des approximations de l'effet de la reconfiguration dynamique sur le système.

En 1998, Robinson, McGregor et Lysaght publient une suite du développement de l'outil décrit par la dernière équipe. Cette équipe, qui est également de l'Université de Strathclyde, a orienté sa recherche dans le développement d'un outil complet et plus étendu, qui aide tout au long du processus de développement, le concepteur de systèmes dynamiquement reconfigurables. Leur modèle semble bien défini, basé essentiellement sur la très importante étape de simulation. Ils présentent des chemins et des évaluations bien distincts pour la partie simulation fonctionnelle et simulation avec délais. Une fois les simulations terminées, un de leurs outils nommé DCSTech entreprend la tâche de décomposer le circuit reconfigurable dynamiquement en une série de composants statiques. Les signaux communs sont fixes, ce qui facilite le routage mais constraint le placement. L'implantation physique de ce système n'est toutefois pas encore opérationnelle. En effet, une partie très importante qui concerne le contrôleur de configuration n'est pas encore réalisée. Un autre manque relaté par l'équipe est un estimateur de temps de reconfiguration pour évaluer les latences dans le traitement ou tout simplement pour évaluer si le circuit possède les performances attendues lorsqu'implanté sur un système dynamiquement reconfigurable.

Toujours en Écosse, mais à l'Université de Glasgow cette fois, des chercheurs (Singh, Hogg et McAuley, 1996) ont présenté un outil presque totalement basé sur les méthodes formelles. C'est plutôt sous forme d'étude que les chercheurs nous présentent leur méthode de reconfiguration qui serait basée sur l'évaluation partielle du système. Un exemple simple qu'ont démontré les auteurs pour illustrer l'évaluation partielle est le suivant:

Soit la fonction suivante:

**(A et B) ou C.**

Si l'évaluation partielle du système permet de définir par exemple que A vaut 1, alors l'expression définie plus haut se résume maintenant à:

**B ou C.**

La réalisation d'une évaluation partielle sur le système a permis d'éliminer une porte logique, ce qui réduit la complexité matérielle tout en augmentant la rapidité, puisqu'il y a moins de portes logiques à parcourir. Sachant que cette reconfiguration partielle est variable selon le circuit à évaluer, dans quelle situation est-il vraiment avantageux d'utiliser une telle méthode? Étant donné que les auteurs n'avaient pas implanté leur système au moment de la rédaction de l'article, cette question restera probablement en suspend.

Tout récemment, à la dernière conférence FPGA for Custom Computing Machines (avril 1999, Napa Valley, Californie, Etats-Unis), la presque totalité des articles sur la reconfiguration dynamique de FPGA concernait des outils de développement pour de tels systèmes. Certains étaient conçus expressément pour les FPGA de Xilinx XC6200, tandis que d'autres étaient plus génériques. Notons que depuis près d'un an, Xilinx ne supporte plus les FPGA de la famille XC6200.

Nous n'aborderons pas en détail les recherches portant sur le développement d'outils pour les FPGA de la famille XC6200 de Xilinx pour les raisons nommées plus haut. Nous présenterons donc brièvement trois recherches présentées lors de la conférence FPGA for Custom Computing Machines d'avril dernier. La plus originale de ces recherches est probablement celle de Vasilko et Cabanis qui introduit un nouveau type de données dans la bibliothèque déjà définie de IEEE (std\_logic\_1164). Ce nouveau type de données, "V" pour *Virtual*, permettrait d'indiquer la partie de logique reconfigurée dynamiquement et propagerait la valeur de ce signal aux composants touchés.

Une autre étude portant sur un outil de développement pour les XC6200 de Xilinx est présentée par Cardoso et Neto à la même conférence. Cette équipe de l'INESC du Portugal a développé un outil basé sur le langage Java. Leur compilateur serait en

mesure de décortiquer toute l'information nécessaire à la synthèse matérielle d'un système dynamiquement reconfigurable. Selon la taille du circuit, le système choisit le FPGA dans lequel il sera implanté parmi ceux disponibles de la famille XC6200 de Xilinx.

Poursuivant probablement les travaux entrepris plus tôt à l'Université de Glasgow en Écosse, McKay et Singh ont publié à la même conférence un article portant sur les techniques de déverminage pour les systèmes dont la partie matérielle est dynamiquement reconfigurable. On se souviendra que ce groupe avait poussé leurs recherches vers l'implantation d'un système basé sur l'évaluation partielle du circuit. Ils ont donc jumelé leurs outils à ceux de Xilinx supportant la famille XC6200 soit XACTstep.

Dans un sens plus général, l'équipe de l'Université Brigham Young en Utah (Hutchings et al. 1999), a poursuivi depuis 1998 des travaux en vue de concevoir un outil de développement conçu originellement pour les systèmes dynamiquement reconfigurables. JHDL, pour Java Hardware Description Language, a été porté pour supporter les familles de FPGA non dynamiquement reconfigurables. À la base, (1998), l'outil possédait des constructeurs et des destructeurs d'objets pour décrire les structures de circuits qui sont dynamiquement reconfigurables. Il pouvait également fournir un environnement de simulation et d'exécution, dans lequel l'usager pouvait passer directement de l'environnement logiciel de simulation au domaine matériel permettant l'exécution. De plus, un support particulier est fourni pour les applications de type logiciel/matériel intégré. Une interface logicielle permet à l'usager de visualiser à la fois, le circuit développé, une simulation et l'état des signaux internes. Selon les auteurs, la bibliothèque serait à ce jour plus développée pour les FPGA de la famille 4000 de Xilinx qu'elle ne l'était pour la famille 6000.

## 1.4 DÉVELOPPEMENT DE NOUVEAUX FPGA OU DE SYSTÈMES DYNAMIQUEMENT RECONFIGURABLES

Le développement de nouvelles architectures de FPGA supportant la reconfiguration dynamique est apparu très tôt dans les recherches sur le sujet. En effet, le manque de support des quelques FPGA existant qui supportaient la reconfiguration dynamique ainsi que l'architecture même des FPGA disponibles ont poussé les chercheurs vers la création de FPGA faits "sur mesure". Les résultats sont très diversifiés et intéressants, mais malheureusement, aucune de ces recherches n'a abouti à une implantation réelle avec mise en marché.

L'équipe de Ling et Amano (1993 et 1995) a été l'une des premières à discuter du principe de *Virtual Hardware* (matériel virtuel) et de l'implanter sur un système conçu pour cette fin. Leur argument principal justifiant la conception d'un nouveau composant est que les FPGA actuels demandent trop de temps pour effectuer une reconfiguration complète. Cette reconfiguration s'effectue habituellement à partir d'une ROM externe au FPGA. C'est pourquoi en créant un FPGA qui possède un certain nombre de configurations à l'intérieur du même composant, le temps de reconfiguration en serait diminué d'autant. À l'aide seulement de multiplexeurs, les multiples configurations pourraient permettre d'une à l'autre en très peu de temps. Le composant, nommé WASMII, pourrait même faire partie d'un réseau de composants du même type et ainsi créer un système de taille aussi grande que voulue. C'est essentiellement pour du traitement de chemin de données que les concepteurs ont pensé leur puce.

Une équipe du Virginia Polytechnic Institute (Bittner et al., 1996) a proposé une machine dédiée au traitement de flot de données basé sur les concepts disponibles avec les technologies de FPGA. Leur concept ne se concentre pas seulement au niveau composant, mais il supporte aussi le niveau système comprenant toute la partie développement et logicielle. Les applications visées avec ce système sont le traitement numérique, les applications DSP (Digital Signal Processing), le traitement d'images, les systèmes de communication, les filtres numériques, le traitement de sons, le contrôle de système temps réel et l'accélération de simulation. Les performances, quant au temps de reconfiguration, ne sont pas divulguées et aucun exemple d'application n'a

été démontré. Il devient donc difficile de comparer ce système avec ceux des autres recherches. L'année suivante, Bittner et Athanas publient un nouvel article sur leur puce Colt, mais encore une fois, les auteurs n'ont pas illustré les aspects de reconfiguration dynamique de leur système, ils se sont plutôt concentrés sur la présentation de l'architecture du composant.

Dans le même ordre d'idées, une équipe de Northwestern University, en Illinois (Hauck et al., 1997) a présenté un système du nom de Chimaera. Le système propose une solution au problème d'engorgement qui se présente souvent dans le transfert d'information entre un processeur et un FPGA qui joue le rôle de son co-processeur. En combinant l'aspect reprogrammable du FPGA au système hôte, les auteurs croient pouvoir créer un système plus de deux fois plus rapide que les systèmes conventionnels de traitement. Ils veulent, de plus, intégrer au système la propriété de se reconfigurer partiellement pour réduire le temps de reconfiguration de la partie reconfigurable. À partir d'une banque d'instructions complète, le système retient seulement celles nécessaires pour l'opération courante et sert de ce fait de cache d'opération.

Du côté industriel, une équipe de recherche de chez Xilinx (Trimberger et al., 1997) a publié un article à propos d'une nouvelle architecture de FPGA basée sur ceux de la famille 4000 de la même compagnie. Huit configurations pourraient être logées à même ce nouveau FPGA. Ces configurations seraient disposées tout autour du FPGA, ce qui permettrait à celui-ci de se reconfigurer en aussi peu qu'un cycle d'horloge: 30 ns. Les modifications apparentes quant aux fonctionnalités existantes chez le XC4000E sont l'ajout de la possibilité de sauvegarder les états de cellules et une augmentation de la quantité de routage. Les configurations peuvent même être installées lorsque le FPGA est en traitement. Pour contenir ces huit configurations sur le composant et posséder un temps de reconfiguration aussi bas que 30 ns, l'équipe a pourvu chaque cellule de huit blocs de mémoire. Trois modes de configuration sont décrits, soit le mode de temps partagé, le mode "machine logique" (*logic engine*) et le mode statique. Pour le premier mode, un signal interne ou externe permet de déclencher le processus de reconfiguration. Dans le deuxième mode, le processus de reconfiguration est prédéfini et de manière cyclique les reconfigurations se succèdent.

Finalement, dans le mode statique, le contenu des CLB ne change pas. Ce FPGA n'a jamais été commercialisé même si des prototypes ont été construits.

Une équipe de l'Université de Californie à Santa Barbara (Chang et Marek-Sadowska, 1998) a présenté une étude portant sur une nouvelle architecture de FPGA dynamiquement reconfigurable. En particulier, l'équipe s'est penchée sur le partitionnement du système en morceaux de circuits séquentiels, en développant un algorithme de partitionnement. Cet algorithme permet de trouver le partitionnement optimal, qui possède les coûts minimum en matériel et en communication, tout en gardant la performance. Le but de cet article est de supporter l'étude faite sur le développement de l'algorithme, sans toutefois aller vers l'implantation du système. Leur approche de développement est de retourner au niveau porte logique, ce qui permettrait selon eux de construire un réseau de communications processeur/FPGA beaucoup moins coûteux, puisque plus direct. Les performances estimées de leur système montrent qu'ils peuvent réduire le coût relié à la communication de près de 35%.

Un dernier travail de ce type est recensé, il s'agit de celui de Chiricescu et Vai, 1998, du Northeastern University à Boston au Massachusetts. L'article traite du développement d'un FPGA tridimensionnel possédant de la mémoire intégrée pour conserver les données requises pour reconfigurer dynamiquement le système. D'une configuration à l'autre, le système permet de conserver les parties constantes. Le système n'étant pas conçu, il est trop tôt pour connaître les performances réelles de ce circuit.

## **1.5 ÉTUDES ET ANALYSES SUR L'EFFICACITÉ DE LA RECONFIGURATION DYNAMIQUE**

Travailler sur un sujet jeune comme la reconfiguration dynamique peut parfois devenir aveuglant. En effet, comme c'est souvent le cas dans le milieu de la recherche, lorsqu'un sujet devient populaire, une masse de gens se rue vers un travail traitant dudit sujet. Il est bien important de garder à l'esprit que ce n'est pas toutes les

applications qui peuvent tirer bénéfice de l'utilisation de techniques de reconfiguration dynamique. Le système doit pouvoir être séparé de manière séquentielle afin qu'il puisse être exécuté par partie. De plus, certaines applications ont déjà fait l'objet de création de composants dédiés, ce qui pousse loin derrière les performances que peut fournir un système construit sur un FPGA par exemple. C'est pourquoi on retrouve dans la littérature scientifique quelques articles faisant état d'une analyse ou une réflexion sur les caractéristiques d'un système avantage par l'utilisation d'une technique de reconfiguration dynamique. Il sera intéressant de remarquer la qualité de ces études par rapport à l'époque à laquelle celles-ci sont publiées. On y verra qu'une certaine maturité émane des études plus récentes, mais il reste que le sujet est peut-être encore trop jeune et l'engouement trop fort pour bien percevoir les avantages réels de la reconfiguration dynamique.

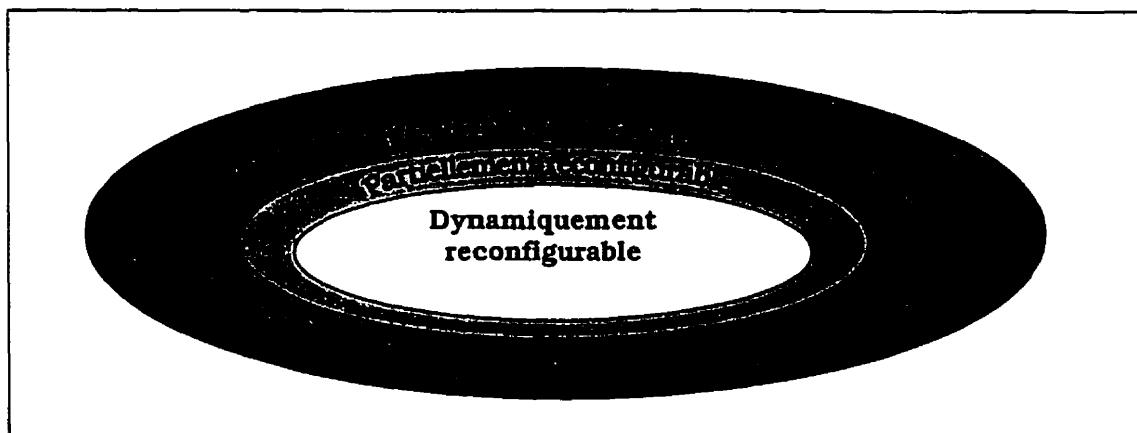

Une toute première étude qui analyse les conséquences de la reconfiguration dynamique est publiée par Lysaght et Dunlop de l'Université de Strathclyde à Glasgow en Écosse (1993). Les auteurs précisent d'abord les termes "reconfigurable partiellement" et "reconfigurable dynamiquement". Une figure intéressante est la figure 1.1, publiée avec le même article.

Les auteurs considèrent, selon ce schéma, que la seule manière efficace de faire de la reconfiguration dynamique d'un système est l'utilisation de FPGA partiellement

Figure 1.1 Classification des FPGA selon leur configurabilité

reconfigurables. Cependant, comme nous l'avons relaté dans la section 1.2, Lysaght a publié (1991) un article portant sur l'utilisation de FPGA conventionnels comme base de système dynamiquement reconfigurable. C'est là qu'il faut faire une distinction entre FPGA reconfigurable dynamiquement et système reconfigurable dynamiquement. Les auteurs relèvent cependant un point intéressant dans les avantages de la reconfiguration partielle: ils n'écartent pas complètement l'utilisation de FPGA conventionnels pour construire des systèmes reconfigurables dynamiquement, par contre, ils mentionnent que plus la complexité et la taille des FPGA sont imposantes, plus le temps de reconfiguration devient long. C'est pourquoi ils considèrent que la seule manière de construire des systèmes reconfigurables dynamiquement lorsque la taille des FPGA sera encore plus importante devrait être l'utilisation de la reconfiguration partielle. De la même manière, on pourrait considérer que les FPGA de la famille XC6200 de Xilinx sont trop petits pour considérer une implantation réaliste d'un système reconfigurable dynamiquement. En effet, parmi tous les articles cités, aucun ne fait de réelle implantation d'application, complexe et volumineuse sur ces FPGA. Rappelons que les systèmes de taille comme le projet du génome humain de Lemoine et Merceron en 1995 ou encore le système GANGLION de Cox et Blanz, 1992 utilisent des FPGA conventionnels pour les réalisations concrètes. L'énergie se concentre alors uniquement sur le développement du contrôleur de configuration, puisque les outils de placement/routage sont efficaces pour ce type de FPGA, tandis que les utilisateurs de FPGA reconfigurables partiellement doivent investir du temps dans le développement et la réalisation d'un placement/routage serré et complexe, puisqu'il doit imbriquer plusieurs configurations et conserver le plus de logique fixe possible entre chacune d'elles.