**Titre:** Développement d'estimateurs de performance pour des applications de co-design matériel/logiciel

Title: [Développement d'estimateurs de performance pour des applications de co-design matériel/logiciel](#)

**Auteur:** Lévis Thériault

Author: [Lévis Thériault](#)

**Date:** 2000

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Thériault, L. (2000). Développement d'estimateurs de performance pour des applications de co-design matériel/logiciel [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/8800/>

Citation: [Thériault, L. \(2000\). Développement d'estimateurs de performance pour des applications de co-design matériel/logiciel \[Mémoire de maîtrise, École Polytechnique de Montréal\]. PolyPublie. https://publications.polymtl.ca/8800/](#)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8800/>

PolyPublie URL: [https://publications.polymtl.ca/8800/](#)

**Directeurs de recherche:** Yvon Savaria

Advisors: [Yvon Savaria](#)

**Programme:** Non spécifié

Program: [Non spécifié](#)

UNIVERSITÉ DE MONTRÉAL

DÉVELOPPEMENT D'ESTIMATEURS DE PERFORMANCE POUR

DES APPLICATIONS DE CO-DESIGN MATÉRIEL/LOGICIEL

LÉVIS THÉRIAULT

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (M.Sc.A.)

(GÉNIE ÉLECTRIQUE)

AOÛT 2000

**National Library

of Canada**

**Acquisitions and

Bibliographic Services**

395 Wellington Street

Ottawa ON K1A 0N4

Canada

**Bibliothèque nationale

du Canada**

**Acquisitions et

services bibliographiques**

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

*Our file Notre référence*

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-57429-6

**Canadä**

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Scénario

sans frontières

Ce mémoire intitulé:

DÉVELOPPEMENT D'ESTIMATEURS DE PERFORMANCE POUR

DES APPLICATIONS DE CO-DESIGN MATÉRIEL/LOGICIEL

présenté par: THÉRIAULT Lévis

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. BOIS Guy, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. AUDET Daniel, Ph.D., membre et codirecteur de recherche

M. ABOULHAMID El Mostapha, Ph.D., membre

À mes parents qui m'ont toujours soutenu

À mon épouse pour son soutien et sa patience

À mes proches

# Remerciements

Avant de vous proposer le résultat de ma recherche personnelle, qu'il me soit permis ici d'adresser mes remerciements les plus profonds et les plus sincères à quelques personnes qui ont été associées plus étroitement à moi tout au long de ce parcours inoubliable dans ma formation universitaire.

En premier lieu et de façon très particulière, je tiens à remercier Monsieur Yvon Savaria, professeur à l'École Polytechnique de Montréal, qui a bien voulu me servir de premier directeur de recherche, qui m'a offert un indispensable support non seulement scientifique mais également financier et qui en plus m'a constamment nourri de ses précieux conseils dans le cadre de fréquents dialogues fort enrichissants sur le sujet, ce qui a contribué pour une très large part à la réalisation de ce présent mémoire.

En deuxième lieu, je voudrais adresser un merci tout spécial à Monsieur Daniel Audet, professeur à l'Université du Québec à Chicoutimi et co-directeur de mon présent mémoire, qui a bien voulu assurer presque quotidiennement la supervision de cette recherche et qui en outre n'a jamais refusé de répondre à mes nombreuses et incalculables interrogations.

Je m'en voudrais ici de ne pas ajouter un remerciement explicite à plusieurs autres personnes qui, en raison de leur situation particulière, ont joué un rôle significatif dans la réalisation de ce mémoire de maîtrise.

Aux membres du jury de ce présent mémoire, je souhaite exprimer toute ma reconnaissance et ma gratitude.

Au Conseil de Recherches en Sciences Naturelles et en Génie du Canada (CRSNG), je dis un gros merci pour la qualité de son soutien financier.

À Madame Ghislaine Éthier Carrier, aux étudiants et aux membres du Groupe de Recherche en Microélectronique (GRM) de l'École Polytechnique de Montréal, que j'ai eu la chance de rencontrer et de joindre grâce à mon directeur ainsi qu'à tous les membres de l'Équipe de Recherche en Microélectronique et Traitement Informatique des Signaux (ERMETIS) de l'Université du Québec à Chicoutimi, je voudrais également adresser mes sincères remerciements pour leur soutien technique. Sur ce plan, je ne peux passer sous silence la grande collaboration, l'inconditionnelle disponibilité et l'indispensable aide que m'a offert en tout temps Monsieur André Falgueyret.

Au soutien scientifique, financier et technique vient s'ajouter parfois le support moral, ce dont j'ai eu quelques fois besoin au cours de cet itinéraire, aux courbes souvent imprévues. Pour cette raison, je me dois d'adresser de chaleureux remerciements à Monsieur Jean-Guy Girard et à quelques autres professeurs de l'Université du Québec à Chicoutimi, qui, entre autres, m'ont permis de prendre du recul et de ne jamais baisser les bras. Sous cet angle, je désire également remercier tous ceux et celles qui ont contribué à l'élaboration de ce travail, dont principalement mon épouse bien-aimée.

Ce n'est pas tout de développer son intelligence et de développer son savoir-faire. Il faut également construire constamment son savoir-être. Aussi, au terme de cette recherche, je dois reconnaître devant tous que la réalisation de ce mémoire n'a pas été une tâche facile et qu'il m'a fallu me dépasser moi-même presque à chaque jour. Outre les exigences intellectuelles, qui ne sont pas à négliger, j'avoue bien humblement que j'ai dû faire preuve d'autonomie et de débrouillardise, deux qualités qui sont essentielles pour réussir à mener à terme une recherche de ce type.

À chacun de vous et à tous, je dis merci, un gros merci et mille fois merci.

# Résumé

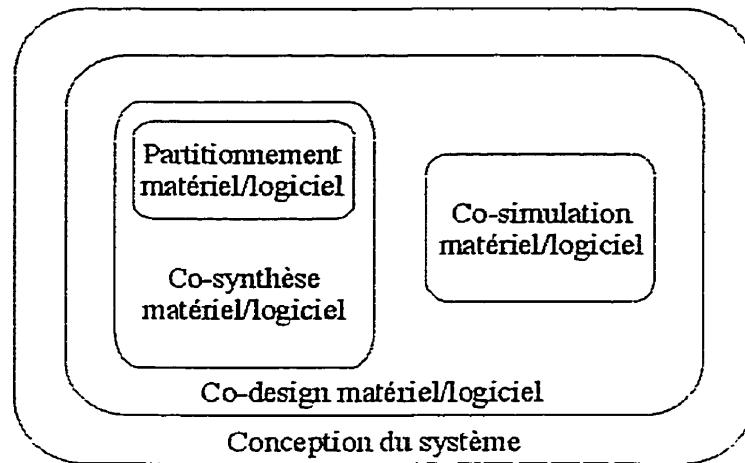

Le partitionnement matériel/logiciel constitue une tâche fondamentale en conception de systèmes basés sur une méthodologie de co-design matériel/logiciel. La pertinence de ces éventuels partitionnements va non seulement dépendre de l'architecture matérielle ciblée, mais aussi des estimateurs de performance considérés. Ces derniers affectent directement l'accélération des calculs selon la qualité du partitionnement matériel/logiciel. Toutefois, peu d'outils de co-design matériel/logiciel sont disponibles et sont souvent trop spécifiques à un environnement donné, ce qui limite leur utilisation et leur performance.

Nous proposons dans ce mémoire un nouvel environnement intégré de co-design matériel/logiciel, conçu essentiellement d'estimateurs ou métriques de performance permettant d'évaluer la structure logicielle d'applications écrites en langage C ANSI. Les métriques permettent de caractériser, en fonction de l'architecture cible, chacun des blocs de base (boucles ou nids de boucles) d'une application en vue de prédire la pertinence de ses éventuels partitionnements matériel/logiciel. Le partitionnement s'effectuera sur une architecture matérielle reconfigurable de type FPGA, afin d'accentuer la vitesse d'exécution des blocs les plus prometteurs et ainsi d'accélérer l'exécution de toute l'application. Ces métriques sont le temps d'exécution requis, l'espace mémoire requis, la bande passante requise et finalement, la surface matérielle utilisée.

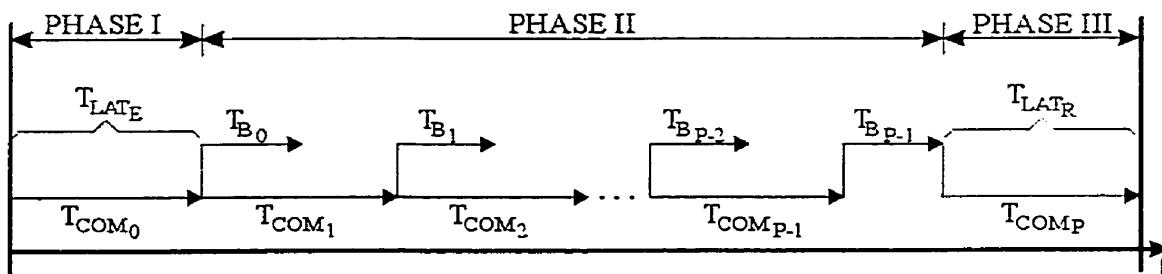

Les temps d'exécution considérés incluent le temps requis sur un Pentium pour exécuter chacun des blocs en logiciel et, le temps requis sur un FPGA pour exécuter ces mêmes blocs en matériel. Ce dernier tient compte à la fois du temps de communication, ainsi que du temps de latence s'y rattachant. À ce stade, l'architecture offrant une efficacité d'exécution optimale pour chacun des blocs est connue. Si le temps requis sur un Pentium est inférieur à celui requis sur un FPGA, pour un même bloc, alors le processus d'analyse est terminé et ledit bloc sera éventuellement exécuté en logiciel. Dans le cas contraire, une deuxième phase d'analyse est enclenchée consistant à vérifier si la quantité de mémoire, la bande passante et la surface matérielle requises pour exécuter le bloc en question, sont suffisantes.

Pour ce faire, les séquences d'accès à chacun des tableaux sont enregistrées, dans le but de mesurer la durée de vie de chacune des variables et de déterminer l'espace mémoire minimal requis pour réaliser tous les passages dans la boucle. Par la suite, la bande passante est estimée en fonction du taux de transfert des données fournies à l'unité de calcul (FPGA) pour effectuer une tâche spécifique. Finalement, la surface matérielle du FPGA utilisée est estimée selon le nombre de CLBs requis. Cette métrique permet, d'une part, d'analyser la structure logique qui doit être disponible et, d'autre part, de déterminer si les blocs analysés peuvent être transposés en matériel.

Une fois les valeurs de métriques trouvées, une fonction paramétrique est utilisée pour caractériser chacun des blocs de base. La mise en œuvre de cette fonction repose sur l'algorithme de partitionnement matériel/logiciel développé qui permet de déterminer s'il est possible et profitable de transposer et d'exécuter en matériel chacun des blocs de base analysés. Pour qu'un partitionnement soit possible et profitable, il faut que toutes les conditions soient gagnantes, c'est-à-dire qu'elles respectent les contraintes de temps, ainsi que celles imposées par l'architecture matérielle.

Les métriques de performance que nous avons proposées permettent de caractériser l'exécution de chacun des blocs de base et de détecter les blocs les plus prometteurs ("boucles chaudes"). Ces blocs seront éventuellement transposés et exécutés sur une

architecture matérielle reconfigurable afin d'accentuer la vitesse d'exécution de ces blocs et ainsi d'accélérer l'exécution de toute l'application.

Les résultats obtenus montrent la pertinence de notre travail et constituent une base solide pour le développement futur de nouveaux outils d'analyse plus élaborés. Ces outils nous permettront de prédire la pertinence d'éventuels partitionnements matériel/logiciel sur des architectures matérielles reconfigurables.

# Abstract

Hardware/software partitioning constitutes a fundamental task in the design of systems based on a hardware/software co-design methodology. The performance of these possible partitioning will not only depend on targeted architecture, but also on the performance of considered estimators. The latter ones directly speed up the computation according to the hardware/software partitioning quality. However, few hardware/software co-design tools are available and they are often too specific to a given environment, which limits their use and their performance.

This thesis proposes a new integrated co-design environment, which includes hardware/software performance estimators or metrics allowing to evaluate the software structure of applications written in ANSI C language. The metrics allow us to characterize, according to the target architecture, which basic block (loops or nested loops) of an application is worth embedding in hardware. The process targets a FPGA based reconfigurable hardware architecture, in order to increase the execution speed of the most promising blocks and to accelerate the execution of the whole application. These metrics include the required execution time, the required memory capacity, the required bandwidth and finally, the complexity of the hardware partition.

The considered execution time takes into account the time required by a Pentium processor to execute each block in software and, the time required by a suitably

configured FPGA chip to execute these same blocks in hardware. The latter takes into account both the communication time and the corresponding latency time. At this stage, the architecture that offers optimal execution speed for each block is known. If the required time for a given block on a Pentium is lower than that on a FPGA, then the analysis is stopped and this block is left for software implementation. Otherwise, a second phase of analysis is engaged. It checks the availability of the required memory, bandwidth and hardware resources to implement this block.

To realize this, the access sequences to each table are recorded, in order to measure the lifespan of each variable and to determine the minimal memory capacity required to execute all the steps of the loops. Next, the bandwidth is estimated according to the data transfer rate to the processing unit (FPGA) required to carry out a specific task. Finally, the tool estimates the required FPGA complexity measured by the number of configurable logic blocks (CLBs). These metrics allow to determine if the analyzed blocks can be implemented in hardware.

Once the metrics are known, a parametric function is used to characterize each basic block. A block is retained for hardware implementation if its mapping to hardware is advantageous and feasible.

Our proposed metrics allow characterizing the execution of each basic block and to detect the most promising ones ("hot loops"). Mapping these blocks to hardware accelerates the execution of the overall application.

The results obtained show the relevance of the proposed method and constitutes a solid base for future developments of more elaborate tools. Such tools would allow predicting the performance of possible hardware/software partitions on reconfigurable architectures.

# Table des matières

|                                                        |       |

|--------------------------------------------------------|-------|

| REMERCIEMENTS .....                                    | v     |

| RÉSUMÉ.....                                            | vii   |

| ABSTRACT.....                                          | x     |

| TABLE DES MATIÈRES .....                               | xvii  |

| LISTE DES TABLEAUX.....                                | xviii |

| LISTE DES FIGURES .....                                | xcix  |

| LISTE DES ANNEXES.....                                 | xxii  |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                 | xxiv  |

| INTRODUCTION.....                                      | 1     |

| Chapitre 1                                             |       |

| SURVOL DES DIFFÉRENTES STRATÉGIES D'OPTIMISATION ..... | 3     |

| 1.1 Les méthodes d'évaluation de performance.....      | 3     |

| 1.1.1 Méthodes logicielles.....                        | 4     |

---

|                                                     |                                          |    |

|-----------------------------------------------------|------------------------------------------|----|

| 1.1.2                                               | Méthodes matérielles.....                | 6  |

| 1.2                                                 | Les architectures matérielles .....      | 7  |

| 1.2.1                                               | Les FPGAs .....                          | 7  |

| 1.2.2                                               | Les ASICs .....                          | 8  |

| 1.3                                                 | Les stratégies de partitionnement.....   | 9  |

| 1.3.1                                               | Les outils existants .....               | 9  |

| 1.3.1.1                                             | Les outils commerciaux .....             | 13 |

| 1.3.2                                               | Les algorithmes de partitionnement ..... | 14 |

| 1.4                                                 | Le choix de la méthodologie suivie.....  | 15 |

| 1.4.1                                               | Le projet CODE .....                     | 15 |

| 1.4.2                                               | Les spécifications de l'outil.....       | 16 |

| 1.4.2.1                                             | Les objectifs .....                      | 16 |

| 1.4.2.2                                             | La méthodologie.....                     | 17 |

| <br>Chapitre 2                                      |                                          |    |

| LA MÉTHODOLOGIE DE CO-DESIGN MATÉRIEL/LOGICIEL..... |                                          | 18 |

| 2.1                                                 | La problématique.....                    | 18 |

| 2.2                                                 | Les spécifications du système .....      | 20 |

| 2.2.1                                               | Structure générale du système.....       | 20 |

| 2.2.2                                               | Système formel de départ .....           | 21 |

---

|                                                        |           |

|--------------------------------------------------------|-----------|

| 2.2.3 Système formel d'arrivée .....                   | 22        |

| 2.2.4 L'architecture matérielle .....                  | 23        |

| 2.2.4.1 Les FPGA .....                                 | 24        |

| 2.2.4.2 Le langage VHDL .....                          | 26        |

| 2.2.5 Règles de traduction .....                       | 27        |

| 2.2.6 Métriques de performance .....                   | 27        |

| 2.3 La structure logicielle de l'outil d'analyse ..... | 27        |

| 2.3.1 Le flux de données du système .....              | 27        |

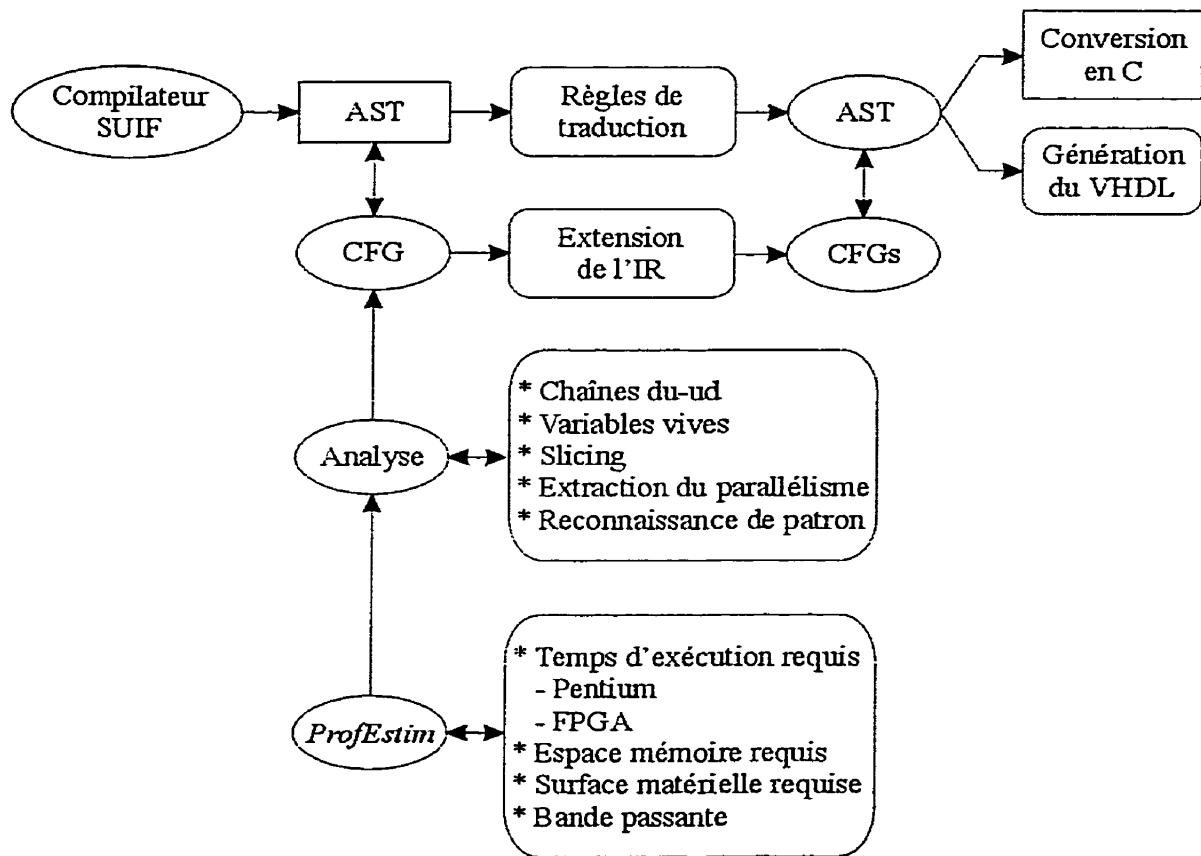

| 2.3.2 Le compilateur SUIF .....                        | 29        |

| 2.3.3 Le co-design matériel/logiciel .....             | 30        |

| 2.3.4 Le partitionnement matériel/logiciel .....       | 31        |

| 2.3.5 La partie logicielle .....                       | 32        |

| 2.3.6 La partie matérielle .....                       | 32        |

| <br><b>Chapitre 3</b>                                  |           |

| <b>LES MÉTRIQUES DE PERFORMANCE .....</b>              | <b>34</b> |

| 3.1 L'approche suivie .....                            | 34        |

| 3.1.1 Introduction .....                               | 34        |

| 3.1.2 Modèle architectural de l'outil .....            | 35        |

| 3.1.2.1 Généralités .....                              | 35        |

---

|                |                                          |    |

|----------------|------------------------------------------|----|

| 3.1.2.2        | Interface entre les modules.....         | 35 |

| 3.1.2.3        | Description du module ProfEstim .....    | 37 |

| 3.1.3          | Modèle de l'architecture matérielle..... | 38 |

| 3.2            | Les métriques de performance .....       | 38 |

| 3.2.1          | Le temps d'exécution .....               | 39 |

| 3.2.1.1        | Sur le Pentium.....                      | 39 |

| 3.2.1.2        | Sur le FPGA .....                        | 40 |

| 3.2.2          | L'espace mémoire .....                   | 47 |

| 3.2.3          | La surface matérielle du FPGA.....       | 53 |

| 3.2.4          | La bande passante.....                   | 55 |

| 3.3            | La fonction paramétrique .....           | 55 |

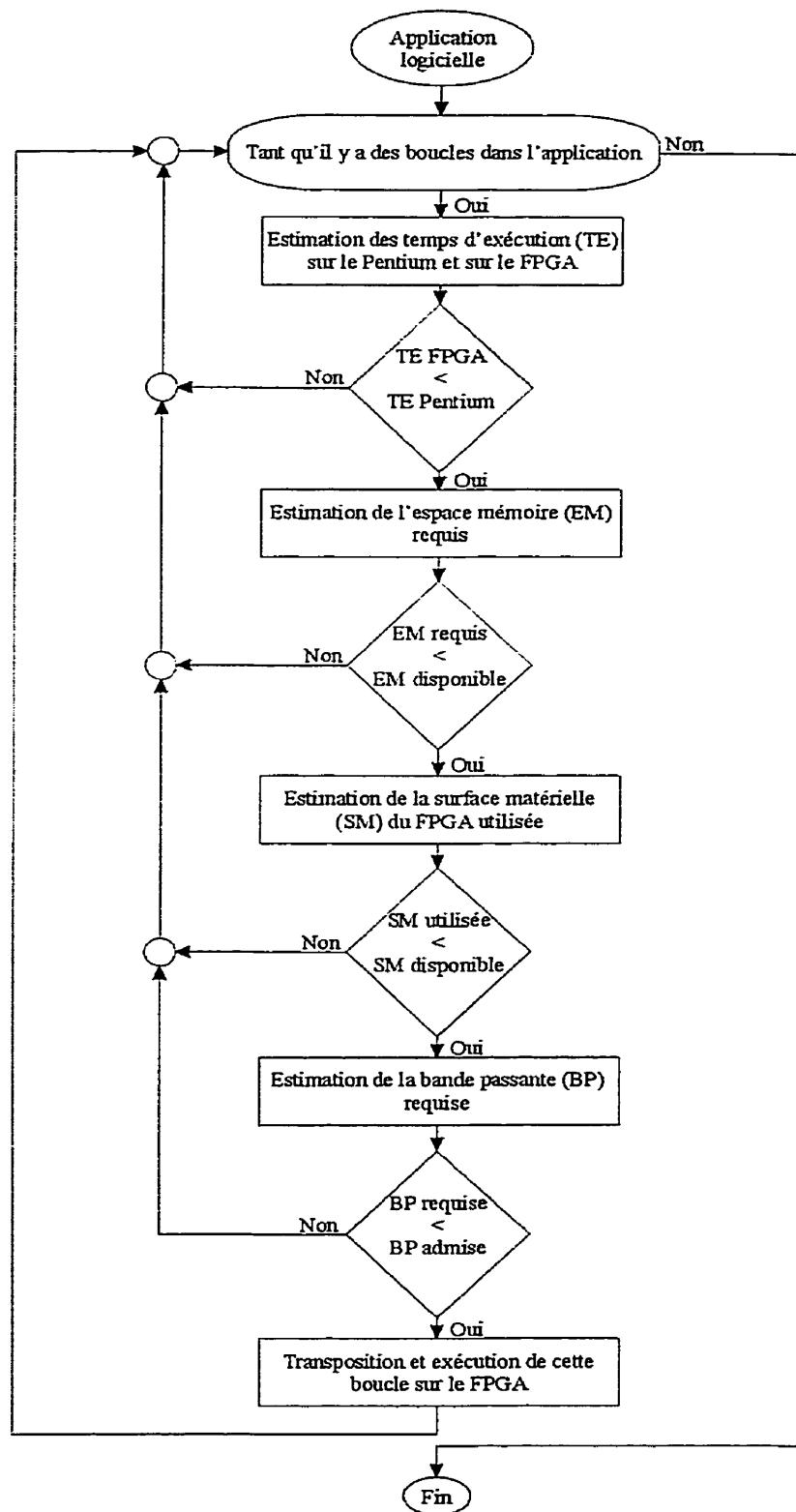

| 3.4            | L'algorithme de partitionnement.....     | 56 |

| <br>Chapitre 4 |                                          |    |

|                | LES RÉSULTATS ET ANALYSES .....          | 59 |

| 4.1            | Paramètres initiaux.....                 | 59 |

| 4.2            | Résultats obtenus.....                   | 60 |

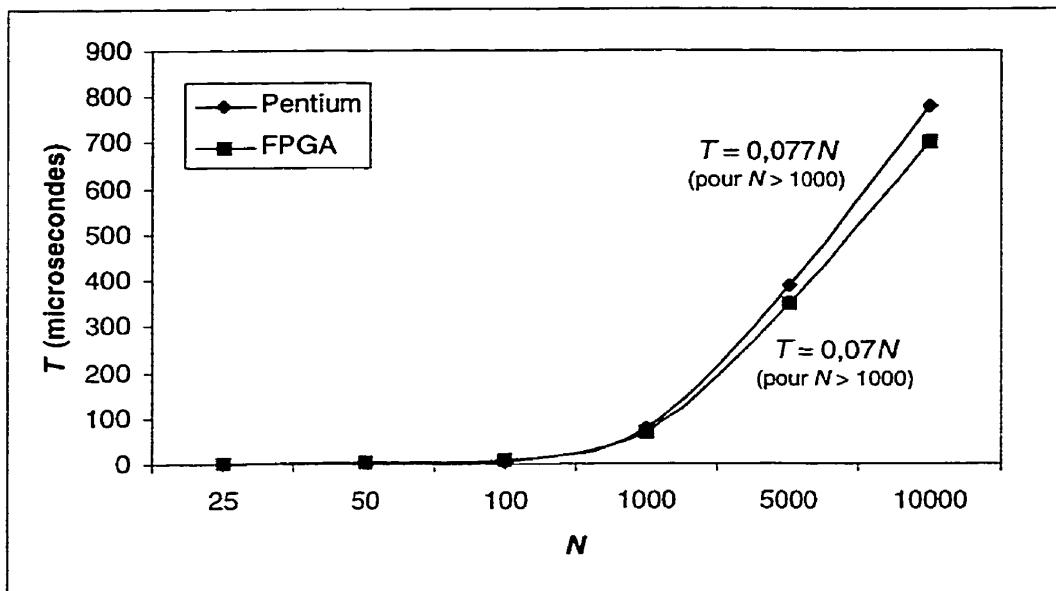

| 4.2.1          | Temps d'exécution requis .....           | 61 |

| 4.2.2          | Espace mémoire requis.....               | 64 |

| 4.2.3          | Surface matérielle utilisée .....        | 67 |

---

|                                               |    |

|-----------------------------------------------|----|

| 4.2.4 Bande passante .....                    | 71 |

| 4.2.5 Partitionnement matériel/logiciel ..... | 71 |

| 4.3 Discussion .....                          | 74 |

| CONCLUSION .....                              | 76 |

| RÉFÉRENCES .....                              | 79 |

| BIBLIOGRAPHIE .....                           | 89 |

| ANNEXES .....                                 | 92 |

# Liste des tableaux

|             |                                                                                                                                                                   |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 3.1 | Cycles d'horloge requis sur le Pentium 233 MHz pour exécuter le programme qui calcule la suite de Fibonacci lorsque $Fibnum = 45$ .....                           | 40 |

| Tableau 3.2 | Cycles d'horloge requis sur le FPGA XCV300-200 MHz en fonction des opérateurs et de la taille des opérandes .....                                                 | 42 |

| Tableau 3.3 | Temps d'exécution relatif à une éventuelle exécution logicielle et matérielle .....                                                                               | 47 |

| Tableau 3.4 | Nombre de CLB nécessaires pour mettre en œuvre les opérateurs additionneur et soustracteur en fonction des différentes configurations possibles sur le FPGA ..... | 54 |

| Tableau 3.5 | Nombre de CLB nécessaires pour mettre en œuvre l'opérateur multiplicateur en fonction des différentes configurations possibles sur le FPGA.....                   | 54 |

| Tableau 3.6 | Nombre minimum et maximum de CLBs pour mettre en œuvre la suite de Fibonacci sur le FPGA .....                                                                    | 55 |

---

|             |                                                                                                                                                               |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 4.1 | Valeurs relatives à la métrique du temps d'exécution requis pour effectuer chacun des cas sur le Pentium et sur le FPGA en fonction de la valeur de $N$ ..... | 62 |

| Tableau 4.2 | Valeurs relatives à la métrique de l'espace mémoire requis pour réaliser chacun des cas sur le FPGA en fonction de la valeur de $N$ .....                     | 65 |

| Tableau 4.3 | Valeurs relatives à la métrique du nombre de CLBs requis pour mettre en œuvre les fonctionnalités de chacun des cas sur le FPGA .....                         | 68 |

| Tableau 4.4 | Valeurs relatives à la métrique de bande passante requise pour le transfert des données .....                                                                 | 72 |

| Tableau 4.5 | Indicateur de pertinence relatif à chacun des cas analysés en fonction de la valeur de $N$ .....                                                              | 73 |

# Liste des figures

|           |                                                                    |    |

|-----------|--------------------------------------------------------------------|----|

| Fig. 2.1  | Structure générale du système .....                                | 21 |

| Fig. 2.2  | Architecture logique du système initial .....                      | 21 |

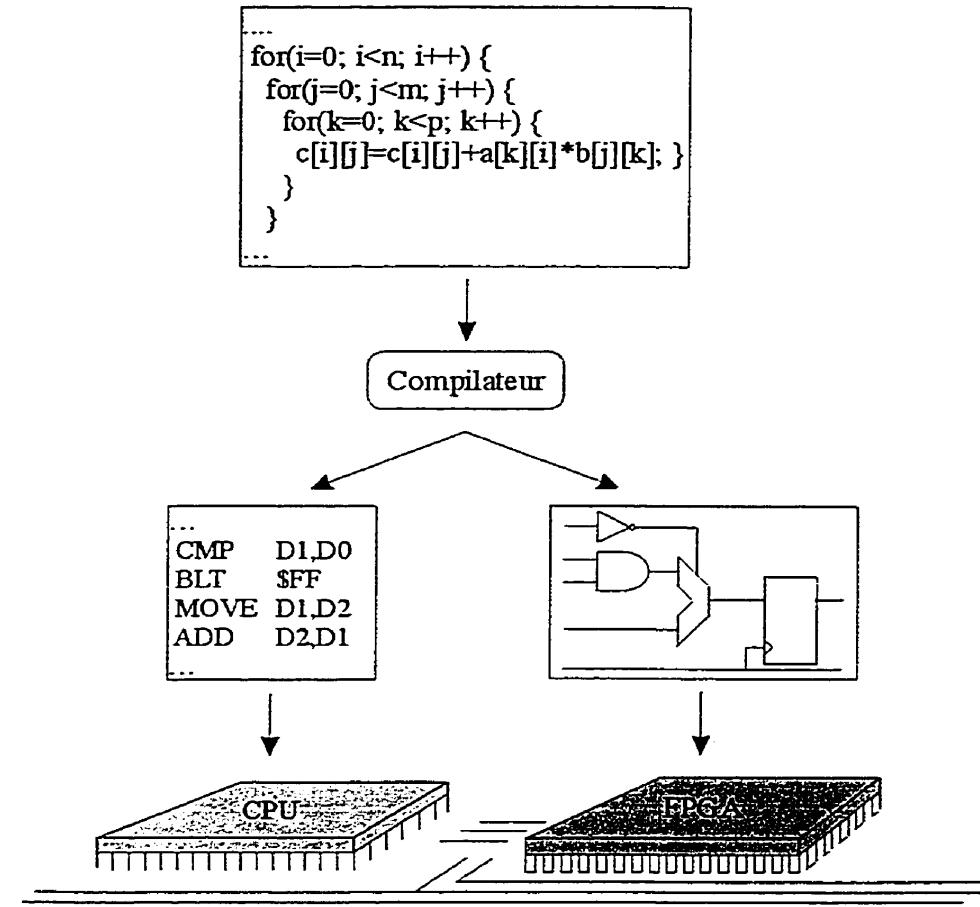

| Fig. 2.3  | Flux de compilation traditionnel .....                             | 22 |

| Fig. 2.4  | Architecture logique cible du système hybride reconfigurable ..... | 23 |

| Fig. 2.5  | Flux de compilation recherché .....                                | 24 |

| Fig. 2.6  | Vue d'ensemble de l'architecture Virtex .....                      | 25 |

| Fig. 2.7  | Vue schématique d'un bloc logique programmable (CLB) .....         | 25 |

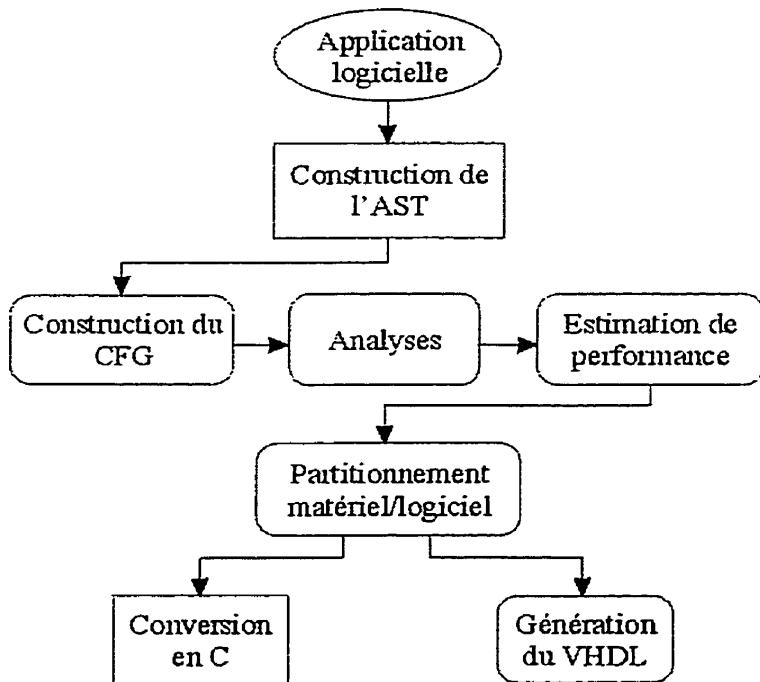

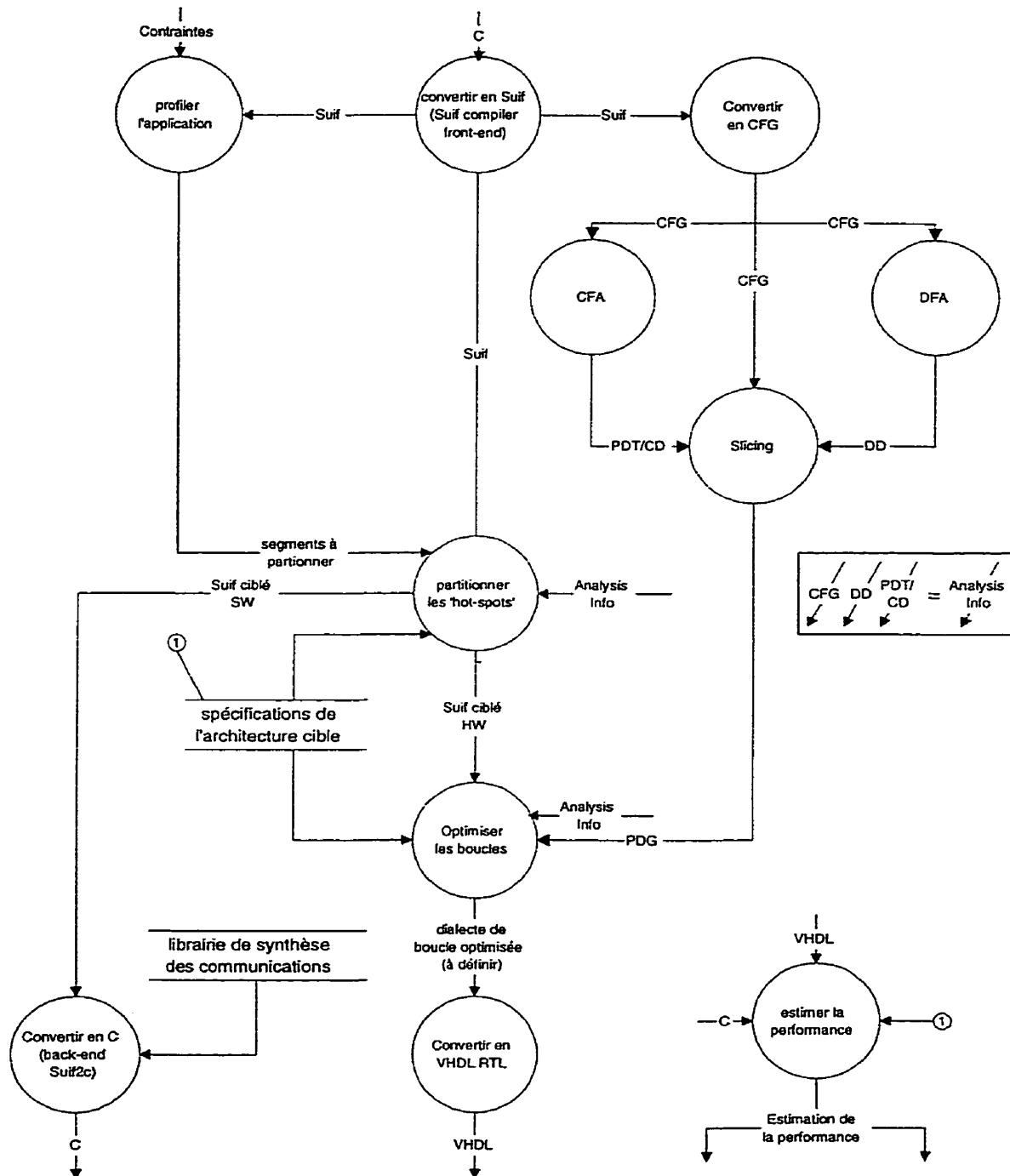

| Fig. 2.8  | Diagramme de flux de données .....                                 | 28 |

| Fig. 2.9  | Phases d'une conception conjointe matériel/logiciel .....          | 31 |

| Fig. 2.10 | Configuration type d'un système de partitionnement .....           | 32 |

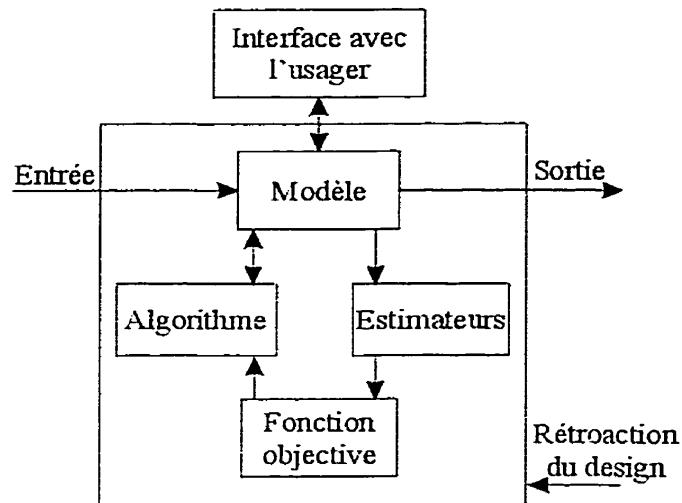

| Fig. 3.1  | Diagramme bloc du modèle architectural de l'outil .....            | 36 |

| Fig. 3.2  | Code source augmenté des fonctions de comptage .....               | 41 |

|          |                                                                                         |    |

|----------|-----------------------------------------------------------------------------------------|----|

| Fig. 3.3 | Chronogramme de synchronisation des différents temps considérés .....                   | 42 |

| Fig. 3.4 | Code source modifié illustrant les fonctions d'accès au tableau $F[i]$ .....            | 48 |

| Fig. 3.5 | Programme permettant de visualiser les séquences d'accès au tableau $F[i]$ ...          | 49 |

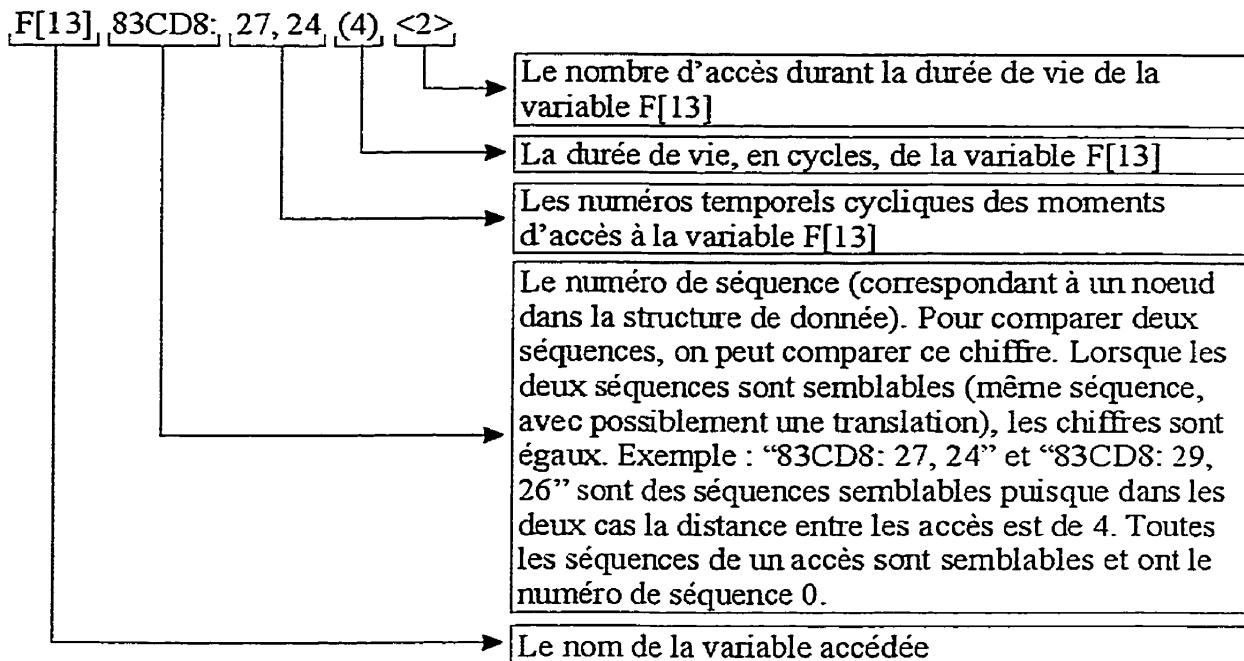

| Fig. 3.6 | Liste des enregistrements des séquences d'accès au tableau $F[i]$ .....                 | 51 |

| Fig. 3.7 | Séquences d'accès au tableau $F[i]$ .....                                               | 52 |

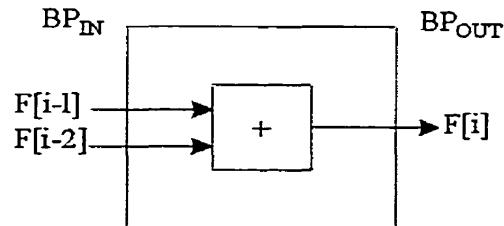

| Fig. 3.8 | Modèle de calcul de la bande passante.....                                              | 55 |

| Fig. 3.9 | Algorithme de partitionnement développé dans le cadre de cette étude .....              | 58 |

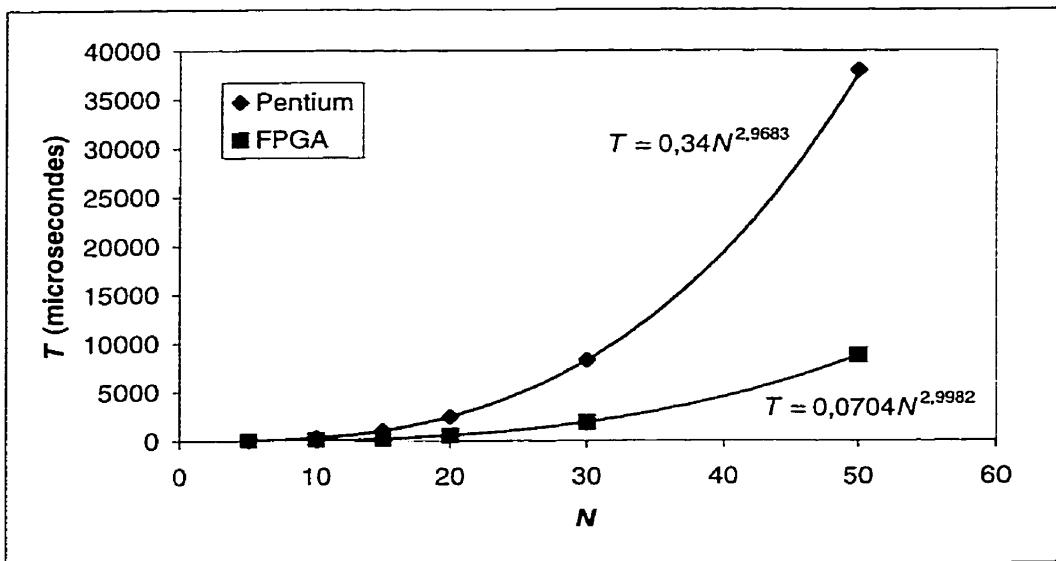

| Fig. 4.1 | Variation de $T$ en fonction du $N^{\text{ième}}$ terme .....                           | 63 |

| Fig. 4.2 | Variation de $T$ en fonction de la dimension $N$ des deux matrices .....                | 63 |

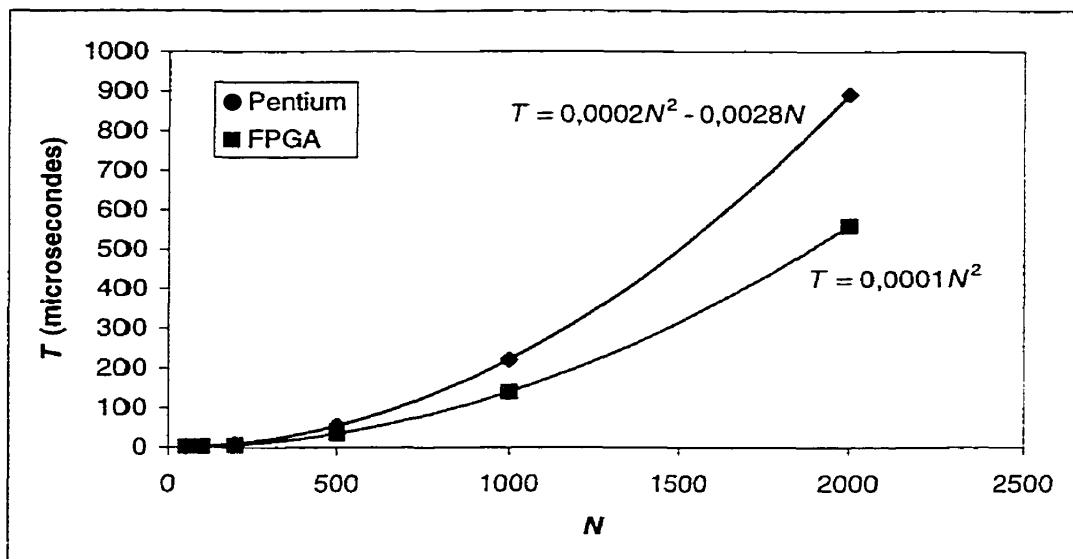

| Fig. 4.3 | Variation de $T$ en fonction de la dimension $N$ des deux vecteurs .....                | 64 |

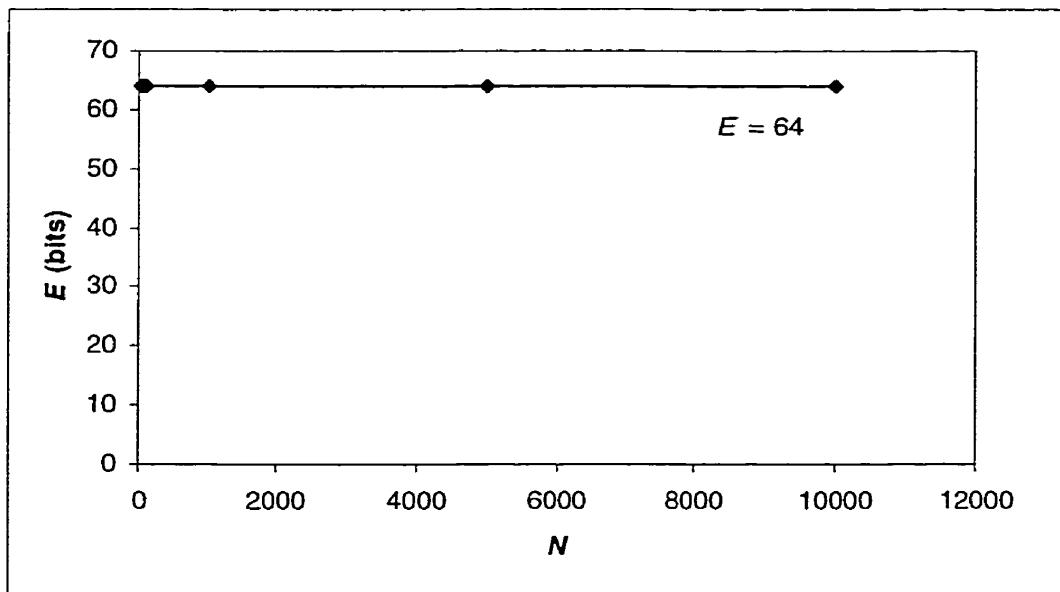

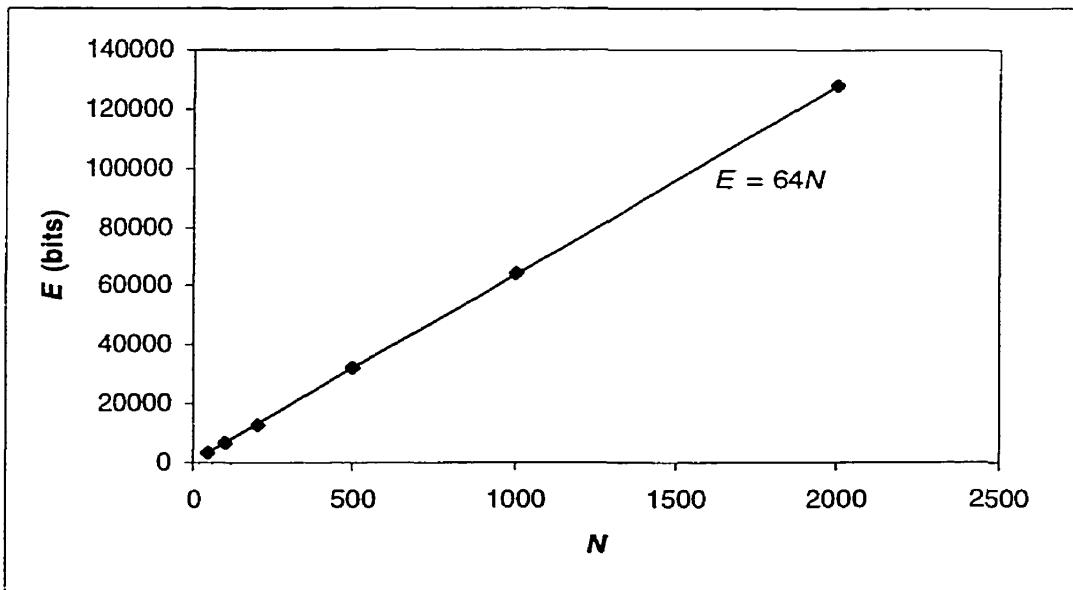

| Fig. 4.4 | Variation de $E$ en fonction du $N^{\text{ième}}$ terme.....                            | 66 |

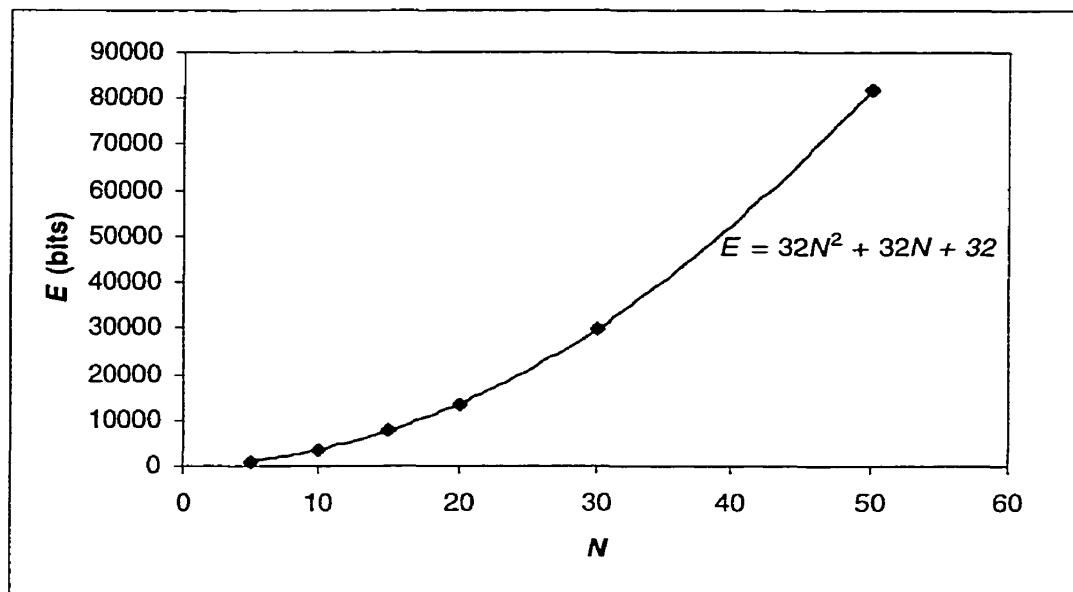

| Fig. 4.5 | Variation de $E$ en fonction de la dimension $N$ des deux matrices .....                | 67 |

| Fig. 4.6 | Variation de $E$ en fonction de la dimension $N$ des deux vecteurs .....                | 67 |

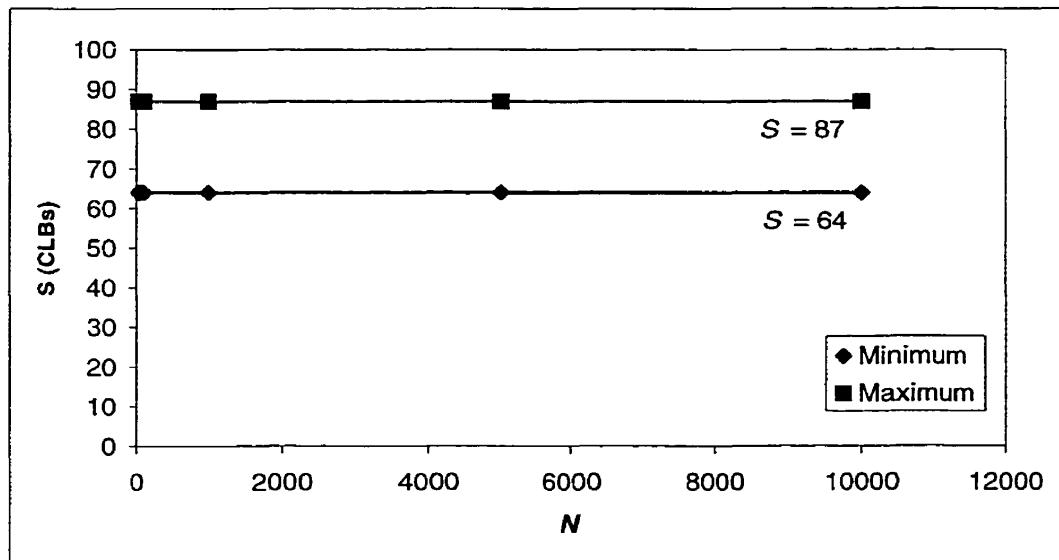

| Fig. 4.7 | Variation de $S$ en fonction du $N^{\text{ième}}$ terme .....                           | 69 |

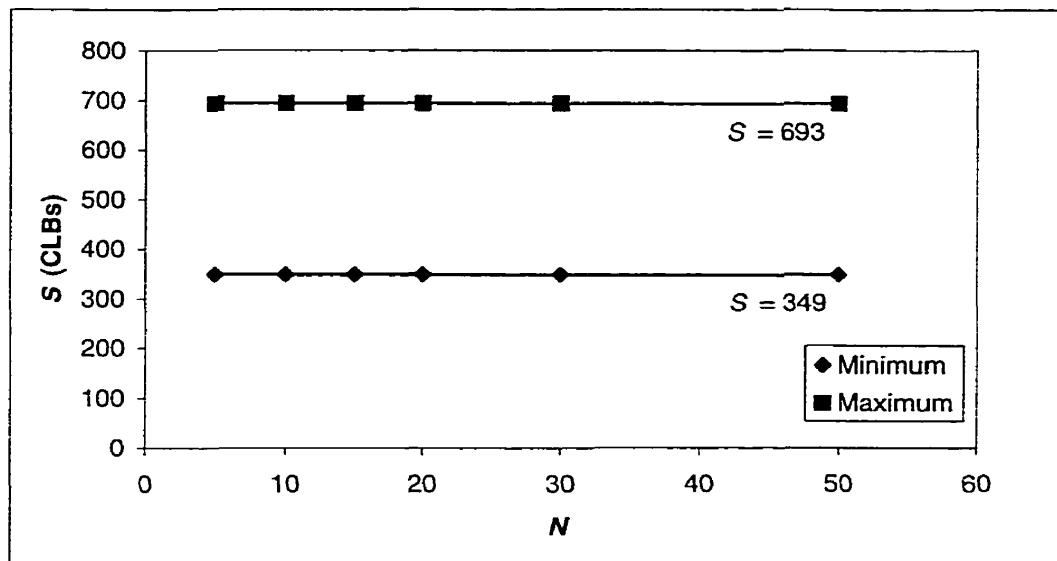

| Fig. 4.8 | Variation de $S$ en fonction de la dimension $N$ des deux matrices .....                | 70 |

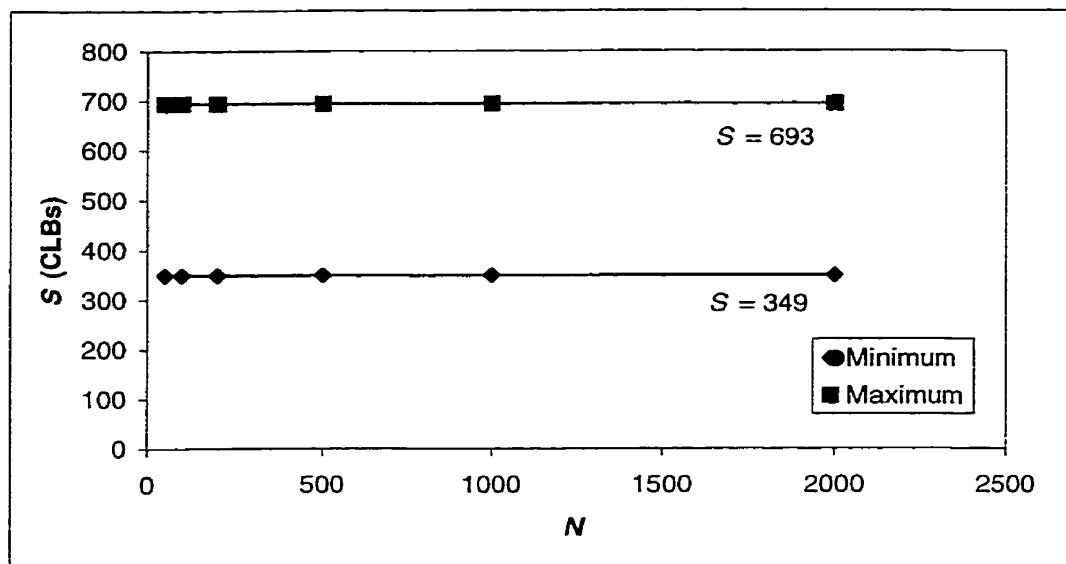

| Fig. 4.9 | Variation de $S$ en fonction de la dimension $N$ des deux vecteurs.....                 | 71 |

| Fig. A.1 | Diagramme détaillé de flux de données global (d'après [DOU98]).....                     | 94 |

| Fig. B.1 | Exemple illustrant les fonctions de comptage à l'intérieur d'une application type ..... | 99 |

---

|                                                                                                    |     |

|----------------------------------------------------------------------------------------------------|-----|

| Fig. B.2 Code source calculant la suite de Fibonacci.....                                          | 101 |

| Fig. B.3 Code source modifié de la figure B.2.....                                                 | 101 |

| Fig. B.4 Procédure permettant l'affichage des moments d'accès du code source de la figure B.3..... | 102 |

# Liste des annexes

## Annexe A

|                                                                    |    |

|--------------------------------------------------------------------|----|

| PROPOSITION D'UN DIAGRAMME DÉTAILLÉ DE FLUX DE DONNÉES GLOBAL..... | 93 |

|--------------------------------------------------------------------|----|

## Annexe B

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| PROTOTYPE D'UN OUTIL D'ANALYSE DE PERFORMANCE : GUIDE DE L'UTILISATEUR..... | 95 |

|-----------------------------------------------------------------------------|----|

|                    |    |

|--------------------|----|

| B.1 Préambule..... | 95 |

|--------------------|----|

|                     |    |

|---------------------|----|

| B.2 Objectifs ..... | 96 |

|---------------------|----|

|                        |    |

|------------------------|----|

| B.3 Introduction ..... | 96 |

|------------------------|----|

|                        |    |

|------------------------|----|

| B.4 Installation ..... | 97 |

|------------------------|----|

|                     |    |

|---------------------|----|

| B.5 Lancement ..... | 98 |

|---------------------|----|

|                                                     |    |

|-----------------------------------------------------|----|

| B.5.1 Temps d'exécution requis sur un Pentium ..... | 98 |

|-----------------------------------------------------|----|

|                                                                    |     |

|--------------------------------------------------------------------|-----|

| B.5.2 Métriques relatives à l'architecture matérielle du FPGA..... | 100 |

|--------------------------------------------------------------------|-----|

|                                     |     |

|-------------------------------------|-----|

| B.5.3 L'espace mémoire requis ..... | 100 |

|-------------------------------------|-----|

|                                   |            |

|-----------------------------------|------------|

| <b>B.5.4 Bande passante .....</b> | <b>103</b> |

| <b>B.6 Contact .....</b>          | <b>103</b> |

# Liste des sigles et abréviations

|         |                                         |

|---------|-----------------------------------------|

| ANSI    | American National Standards Institute   |

| ASIC    | Application Specific Integrated Circuit |

| AST     | Abstract Syntactic Tree                 |

| CD      | Control Dependency                      |

| CFA     | Control Flow Analysis                   |

| CFG     | Control Flow Graph                      |

| CFSM    | Codesign Finite State Machine           |

| CLB     | Configurable Logic Block                |

| COREGEN | CORE GENerator                          |

| CPU     | Central Processing Unit                 |

| DD      | Data Dependency                         |

| DFA     | Data Flow Analysis                      |

---

|              |                                         |

|--------------|-----------------------------------------|

| <b>DFG</b>   | Data Flow Graph                         |

| <b>DSP</b>   | Digital Signal Processor                |

| <b>FFT</b>   | Fast Fourier Transform                  |

| <b>FIFO</b>  | First In First Out                      |

| <b>FPGA</b>  | Field Programmable Gate Array           |

| <b>FSM</b>   | Finite State Machine                    |

| <b>HDL</b>   | Hardware Description Language           |

| <b>IR</b>    | Intermediate Representation             |

| <b>MDFG</b>  | Multiple Data Flow Graph                |

| <b>MIPS</b>  | Million d'Instructions Par Seconde      |

| <b>PDG</b>   | Program Dependency Graph                |

| <b>PDT</b>   | Post Dominator Tree                     |

| <b>PRAM</b>  | Parallel Random Access Machines         |

| <b>RTL</b>   | Register Transfer Level                 |

| <b>SUIF</b>  | Stanford University Intermediate Format |

| <b>VHSIC</b> | Very High-Speed Integrated Circuits     |

| <b>VHDL</b>  | VHSIC Hardware Description Language     |

| <b>VLIW</b>  | Very Large Instruction Word             |

# Introduction

Depuis quelques années, les ordinateurs à architectures reconfigurables ont fait leur apparition. Ces machines permettent une répartition de l'exécution du programme sur des plates-formes étroitement couplées. Ces systèmes offrent des possibilités substantielles d'accélération [EDW94, HAR96].

Ces systèmes offrent un grand potentiel, car il est bien connu qu'une grande partie du temps d'exécution des programmes scientifiques et de traitement des signaux est passée dans les nids de boucles [GEN96]. L'accélération globale d'un programme passe nécessairement par l'optimisation de ces portions de code. L'exploitation du parallélisme inhérent aux nids de boucles et la réutilisation des données sont des moyens de réduire les temps d'exécution. La détection des nids de boucles offrant le meilleur potentiel est donc essentielle pour qui veut accélérer l'exécution d'un traitement.

L'approche générale que nous proposons consiste à transporter l'exécution des nids de boucles sur une structure à base de logique reconfigurable. En d'autres termes, il s'agit, pour un traitement donné, de synthétiser l'application décrite par les nids de boucles, puis de l'implanter sur un support reconfigurable.

Pour ce faire, il faut auparavant prédire la pertinence de déporter des segments<sup>1</sup> de code en matériel afin d'accentuer la vitesse d'exécution de certains segments d'une tâche. Des métriques permettant de caractériser chacun des segments analysés doivent donc être définies. Notre objectif consiste à intégrer un certain nombre de métriques de performance à l'intérieur d'un environnement de co-design matériel/logiciel et de voir les différentes adaptations requises en fonction des autres environnements disponibles sur le marché tels que Cosyma, SpecSyn, etc.

L'originalité du travail repose sur le développement de métriques permettant la détection et la caractérisation de "boucles chaudes" à l'intérieur d'une application donnée, écrite en langage C ANSI. Une fois les valeurs des métriques trouvées, suite à une analyse statistique de chacun des blocs de base [BAL92], elles sont intégrées dans une fonction paramétrique. La mise en œuvre des blocs repose finalement sur l'algorithme de partitionnement choisi. La combinaison des métriques et d'un algorithme de partitionnement permet d'établir la pertinence d'un éventuel partitionnement matériel/logiciel dudit bloc de base, accentuant la vitesse d'exécution de l'application.

L'emploi de FPGA (Field Programmable Gate Arrays) pour mettre en œuvre des co-processeurs programmables n'est pas nouvelle. Certains des travaux les plus pertinents sont présentés dans le chapitre 1. Le chapitre suivant (chap. 2) contiendra les différentes étapes de la méthodologie de co-design matériel/logiciel que nous avons élaborée. L'approche suivie et les métriques associés à notre outil sont décrites dans le chapitre 3. La validité de notre approche est démontrée à l'aide d'exemples concrets présentés au chapitre 4.

---

<sup>1</sup> Dans le présent ouvrage, *segment*, *région*, *partie* et *bloc de base* sont synonymes et représentent tous une boucle ou nid de boucles dans une application.

# *Chapitre 1*

## **Survol des différentes stratégies d'optimisation**

Dans le présent chapitre, nous faisons un tour d'horizon des différents ouvrages traitant, d'une part, des méthodes d'évaluation de performance logicielle et matérielle, et, d'autre part, des techniques de partitionnement matériel/logiciel utilisant des co-processeurs reconfigurables et dédiés. Enfin, notre positionnement par rapport à l'ensemble de ces ouvrages sera exposé à la fin de ce chapitre.

### **1.1 Les méthodes d'évaluation de performance**

Cette section fait état des différents ouvrages les plus pertinents sur les techniques utilisées pour mesurer les performances des systèmes. La plupart du temps, les applications scientifiques, exécutées par ces systèmes, ont été mises en œuvre en utilisant une philosophie de conception séquentielle. D'où l'intérêt de mesurer les performances de ce genre d'applications, afin d'exploiter le parallélisme en respectant les dépendances des données, en vue d'un éventuel ordonnancement ou partitionnement du code.

### 1.1.1 Méthodes logicielles

Plusieurs chercheurs ont proposé un certain nombre d'approches pour caractériser l'exécution des logiciels [GON94]. Une méthode simple d'estimation du temps d'exécution est présentée dans [DAM94]. Dans cette étude, les temps d'exécution sont calculés en effectuant le produit du nombre d'instructions exécutées par le temps moyen d'exécution. Le traitement est effectué sur un processeur MIPS. L'étude se limite à caractériser le temps d'exécution sur ce processeur et n'évalue en aucun temps la pertinence de transposer des segments de code sur un co-processeur de type FPGA.

Dans [HAR93] et [WOL93], on propose des méthodes statistiques pour modéliser l'exécution sur l'unité centrale de traitement de sorte que plusieurs types de CPU peuvent être évalués en regard du programme devant être exécuté. Parallèlement, [SMI91] propose un système de synthèse logiciel, où toutes les primitives pour construire un programme sont définies dans une séquence d'instructions fixe. Le temps d'exécution requis pour effectuer un bloc d'instructions donné est pré-calculé. Par conséquent, ces primitives peuvent être employées pour effectuer des prévisions précises d'exécution.

Un modèle proposé dans [GUP94] estime le temps d'exécution d'un programme par le nombre de cycles d'exécution nécessaires pour chaque instruction dans le programme, la quantité de mémoire en lecture/écriture, et le nombre de cycles pour chaque accès mémoire. Cependant, ce modèle ne tient pas compte des caractéristiques intrinsèques de l'architecture matérielle cible, ce qui est essentiel pour optimiser l'exécution via un partitionnement efficace.

Dans [YE93], la méthode d'évaluation employée dans le système COSYMA est présentée. Dans cette méthode, le système cible exécutant le programme est également synthétisé. L'approche consiste à "exécuter" le code sur un modèle du système cible au niveau RT (Register-Transfer) pour en extraire des caractéristiques de synchronisation à partir des résultats de simulation. Cette méthode d'évaluation considère le code source dans son ensemble et non pas bloc de base par bloc de base.

Une autre variante intéressante pour calculer le temps d'exécution du logiciel est d'utiliser un modèle d'estimation. Il peut être spécifique à un processeur ou générique, de façon à pouvoir être indépendant du processeur choisi [GAJ94c, KNI96]. Un profilage [CON96] peut être fait sur les différents blocs du logiciel, de façon à déterminer le nombre de fois où chacun des blocs sera exécuté, par exemple. Ce profilage peut se faire de façon dynamique en faisant exécuter plusieurs fois les blocs sur le processeur cible ou en utilisant un outil tel que QPT2 [BAL92]. Le profilage statique n'utilise pas les données pour déterminer le nombre de fois où chacun des blocs sera exécuté. Il doit donc être capable de déterminer les bornes supérieures et inférieures. À cet effet, l'outil Cinderella [CIN00] peut être utilisé pour ce type de profilage.

Une étude dans [BAL96] compare PP à QPT2. PP est un outil de profilage qui emploie la bibliothèque EEL [LAR95] pour insérer une instrumentation dans les programmes exécutables. QPT2 est un autre outil de profilage construit avec EEL, qui utilise un algorithme [BAL94] profilant les effets de bord (les débuts et les fins de boucles). QPT2 requiert habituellement moins de temps système, mais les deux systèmes donnent des résultats similaires. Encore une fois, ces outils de profilage ne considèrent pas les caractéristiques de l'architecture matérielle cible, ce qui est un handicap important lorsque l'on désire effectuer un partitionnement matériel/logiciel pertinent et efficace.

Young et Smith ont employé une forme limitée du traçage de programme afin d'enregistrer les voies d'accès permettant ainsi d'étudier la corrélation des branchements [YOU94]. Dans une mémoire tampon de type FIFO, les  $N$  derniers branchements sont enregistrés, où chacun d'eux se compose d'un nombre de blocs de base et les résultats de branchements s'y rattachant. Notons que cette technique coûte plus cher que celle du profilage par voie d'accès et exige également un niveau supplémentaire d'adressage indirect, associé au compteur des voies d'accès, composé d'une séquence de nombre de blocs. À la différence du profilage par voie d'accès, cette technique n'a pas besoin de distinguer la répétition des voies d'accès acycliques, puisque cette répétition se tronque de part et d'autre à la borne du FIFO.

Martin Edwards [EDW93] décrit un système en C qui rassemble l'information de profilage par la compilation et l'exécution du programme. Puisqu'il ne considère que les fonctions ou procédures (dans les programmes sources) comme étant des régions à accélérer, il ne peut considérer des plus petites régions plus prometteuses comme les boucles. Comme dans le travail d'Athanas [ATH91], les régions sont choisies par un utilisateur humain et aucune analyse automatique n'est effectuée.

### 1.1.2 Méthodes matérielles

Il existe principalement deux méthodes permettant d'évaluer les performances d'une application lorsque celle-ci est exécutée sur une plate-forme matérielle. La première utilise une technique de synthèse. Cette technique réalise essentiellement une synthèse rapide sans aucune optimisation. Le bloc matériel est donc transformé depuis sa description comportementale à partir d'un graphe de flots de données. Une allocation d'opérateurs est effectuée pour chacune des opérations. Ces opérateurs sont ensuite ordonnancés. Par la suite, une estimation du nombre d'étapes de contrôle est faite, suite à l'exécution dudit bloc matériel afin d'obtenir un temps d'exécution approximatif. Pour ce faire, un outil de synthèse comme Monet de Mentor Graphics peut être utilisé.

La seconde, consiste à réaliser une traduction du langage C vers un langage de description matérielle, tels que le VHDL ou le Verilog. Différents outils sont disponibles à cet effet [COM90, RUN90], cependant ceux-ci ne supportent qu'un sous-ensemble limité du langage et ils sont souvent orientés vers des architectures de type VLIW, par exemple. De nos jours, on retrouve des outils commerciaux de conception de systèmes sur puce (System-on-Chip, SoC), tel que SystemC [ARN00, SYS00]. L'apparition et la grande popularité de ce type de méthodologie de conception de système sur puce a apporté avec lui une variété de suggestions pour un langage simple qui peut décrire toutes les conditions fonctionnelles pour ces conceptions fortement complexes. Ces systèmes favorisent la conception de blocs matériel qui peuvent être réutilisés éventuellement. Par la suite, différentes techniques peuvent être utilisées pour estimer le temps d'exécution du

bloc matériel. Par exemple, le même programme peut être exécuté plusieurs fois et le temps maximal d'exécution pourra être choisi comme étant le temps d'exécution du bloc matériel. De cette façon, on obtient une quantité considérable de statistiques permettant ainsi d'évaluer les performances de chacun des blocs matériels analysés.

## 1.2 Les architectures matérielles

Cette section présente une synthèse des différentes plates-formes les plus utilisées lors de la conception de systèmes matériel/logiciel. Principalement, on y retrouvera les circuits reprogrammables ainsi que quelques systèmes embarqués.

### 1.2.1 Les FPGAs

Bertin, Roncin et Vuillemin [BER92] enregistrent des vitesses impressionnantes pour dix algorithmes réalisés sur des co-processeurs FPGAs. Les algorithmes utilisés ont été soigneusement conçus pour convenir, de façon optimale, à l'architecture matérielle. Certains de leurs exemples présentant des accélérations du traitement considérables sont à l'origine d'une reformulation des algorithmes, afin d'orienter leurs mises en œuvre de façon très étroite avec les caractéristiques intrinsèques de l'architecture ciblée. Leurs exemples sont simples et ils décrivent des applications spécifiques (non génériques), par opposition aux programmes classiques qui seront étudiés dans ce mémoire.

Luk, Lok et Page [LUK93] ont effectué une étude qui montre comment une application logicielle peut être accélérée, en utilisant des FPGAs qui lui sont disponibles, lors d'un partitionnement matériel/logiciel soigneux qui adapte la partition matérielle en fonction de l'architecture cible. Cependant, l'avantage principal repose essentiellement sur un choix judicieux ou une conception soigneuse de l'algorithme en fonction de l'architecture logicielle et matérielle disponible. En d'autres termes, tous ces facteurs doivent être connus de la part de l'utilisateur. Malheureusement, cette approche n'est pas faisable pour un partitionnement matériel/logiciel automatique d'une application donnée

quelconque. Notre but est d'automatiser ce processus, en utilisant des estimateurs de performance afin de prédire la pertinence d'un éventuel partitionnement matériel/logiciel.

Koch et Golze décrivent un système embarqué de co-processeurs [KOC93], lequel est utilisé dans la conception, et le but de son utilisation est semblable à [JAN94a]. Cependant, ils se concentrent d'avantage sur la conception de systèmes embarqués et moins sur des méthodologies de partitionnement. De plus, ils ne mettent en application aucun algorithme de partitionnement.

Le travail sur l'architecture Mark-I par Lewis et al. [LEW93] a pour but l'accélération d'une classe de programmes définissant une application spécifique représentée par un ensemble d'instructions qui sont exécutées sur un support matériel constitué de 16 FPGA Xilinx. La disposition d'un tel positionnement d'instructions, pour un programme donné, est semblable à identifier des régions critiques pour une éventuelle implantation matérielle sur des FPGAs. Lewis et al. n'ont pas automatisé le partitionnement, mais se sont concentrés particulièrement sur le développement de l'architecture matérielle cible.

### 1.2.2 Les ASICs

Dans [CAR96], la méthodologie de co-design matériel/logiciel est vue comme une approche rentable et prometteuse pour mettre en œuvre des systèmes complexes. La rentabilité est dérivée d'un partitionnement approprié des tâches du système parmi les composantes matérielles (applications spécifiques ASICs) qui sont rapides mais chères et les composantes logicielles (exécutées dans un ou plusieurs dispositifs, habituellement des processeurs standards) qui sont plus lents mais peu coûteux. En outre, certains comportements sont plus efficaces suite à une mises en œuvre matérielles ou logicielles.

Dans la phase de spécification, le système est décrit en utilisant le langage formel LOTOS [BOL87, DEL95]. LOTOS a les caractéristiques requises pour définir les spécifications au niveau du système. Les buts et les contraintes, guidant le processus de

co-design, sont dans la description même du système. Des transformations formelles sont appliquées pour l'optimiser.

Après cette phase, la syntaxe et la sémantique sont analysées afin d'établir une forme intermédiaire avec laquelle le partitionnement matériel/logiciel sera effectué. L'architecture matériel/logiciel cible se compose d'un processeur exécutant le logiciel, d'un ASIC mettant en application le matériel et d'une mémoire partagée consultée par un bus commun. Des modules d'interfaces sont utilisés pour relier le processeur et l'ASIC au bus, tout en tenant compte des transmissions et des transferts de données entre elles. Cette architecture est paramétrable en ce qui concerne le nombre de processeurs et/ou d'ASICs.

## 1.3 Les stratégies de partitionnement

Cette section énumère les différents outils de co-design matériel/logiciel disponibles sur le marché. Elle présente aussi les avantages et les inconvénients relatifs à chacun d'eux. De plus, elle examine leurs limites de fonctionnement qui sont déterminées par les contextes d'utilisation.

### 1.3.1 Les outils existants

Plusieurs recherches essayent d'intégrer le matériel et le logiciel dans un même processus de conception : COSMOS de TIMA/INPG [ISM95], SpecSyn de Irvine [GAJ94a], CODES de Siemens [BUC93], Thomas de CMU [THO93], Gupta et De Micheli de Stanford [GUP93b], Ptomeley [CHI93] et POLIS [SUZ96] de Berkeley.

COSMOS est un environnement de co-design matériel/logiciel basé sur le format intermédiaire SOLAR [ISM94] pour modéliser et synthétiser des systèmes hybrides. La description intermédiaire peut être produite par différents langages comme SDL, LOTOS, etc. Le partitionnement est effectué en utilisant un ensemble hiérarchique de processus de communication qui caractérise une fonction de coût et de performance. Ce

partitionnement est transformé en appliquant quatre opérations différentes, le résultat de celui-ci est ensuite utilisé lors de la synthèse. De ce partitionnement, une combinaison gagnante et qui satisfait les différentes contraintes de conception est choisie. SOLAR supporte différents niveaux comportementaux des spécifications du système. COSMOS inclut des outils de synthèse, utilisés pour synthétiser la transmission et le partitionnement du système. AMICAL est un outil comportemental de synthèse pour le matériel utilisé dans COSMOS. La version courante de COSMOS procède à partir du langage SDL et produit une architecture hétérogène comprenant des descriptions matérielles en langage VHDL et des descriptions logicielles en langage C.

SpecSyn est un cadre de conception de système qui aide le concepteur à obtenir des descriptions pouvant être synthétisées afin d'obtenir des modules pouvant être mis en œuvre sur une architecture matérielle. Les spécifications du système abstrait sont données par les langages SpecCharts ou VHDL. Les principales tâches de conception de SpecSyn sont: l'allocation des objets structuraux (c.-à-d. modules et bus), le partitionnement des spécifications du système (c.-à-d. que les objets fonctionnels sont alloués aux objets structuraux) et finalement, une liaison entre les objets structuraux et les bibliothèques de composants est effectuée.

CODES est un environnement de conception qui intègre un nouvel outil de modélisation avec plusieurs outils existants permettant de définir les spécifications du système pour la mise en œuvre du matériel et du logiciel. L'outil de modélisation est basé sur le modèle algébrique abstrait PRAM (Parallel Random Access Machines) et sur une extension des réseaux de Pétri. L'entrée pour cet outil peut être un Statemate ou une spécification SDL. Les environnements intégrés dans l'outil existant sont: les générateurs de C et de VHDL pour StateChart et SDL, l'outil de conception et de simulation Matrix, et l'outil SIDECON pour la configuration de base des cartes électroniques. Actuellement, CODES vise la conception de systèmes à base de processeurs.

L'approche de co-synthèse de Thomas consiste à indiquer au système un ensemble de tâches et d'assigner ces tâches aux processus effectuant la mise en œuvre sur le

matériel spécialisé ou sur le logiciel d'application fonctionnant sur un CPU commercial. Thomas propose de spécifier dans le langage de description matérielle Verilog, les processus qui seront mis en œuvre en matériel. Le matériel et le logiciel communiquent à l'aide des sockets BSD disponibles sur Unix et par un module Verilog correspondant à un bus d'interface abstraite. Une co-simulation du système est possible en utilisant un simulateur du langage Verilog.

Gupta et De Micheli [GUP92, GUP93a] proposent une approche orientée matériel qui utilise un sous-ensemble limité du langage C, appelé Hardware C, comme langage décrivant les spécifications du système. Ce dernier est le langage d'entrée du système Olympus. Leur système de conception permet d'entrer graduellement des fonctions, qui seront effectuées en matériel, dans le programme source, tout en considérant les contraintes de temps et de synchronisation. À partir des spécifications du système, on dérive le graphe de flot de données (DFG). Celui-ci est utilisé pour évaluer une fonction de coût de partitionnement matériel/logiciel. L'approche orientée matériel et l'utilisation de Hardware C limitent la complexité du système global.

L'environnement de conception Ptolemy permet le développement et la simulation des modules matériels et logiciels. L'environnement supporte, pour la partie matérielle, les architectures de type "behavioral" et "structural", décrivant le comportement de chaque entité et, pour la partie logicielle, un module de génération du code d'assemblage ciblé pour des microprocesseurs DSP. Un utilisateur de Ptolemy peut synthétiser le logiciel, modéliser le matériel et simuler des algorithmes donnés. Il indique à l'entrée de Ptolemy les structures de flots de données synchrones et les graphiques fonctionnels en utilisant les deux niveaux d'abstraction suivants : au niveau porte et au niveau comportemental. Il peut obtenir comme sortie un code assembleur ciblé pour un processeur DSP, pour la partie logicielle et, pour la partie matérielle, une description "Netlist" pouvant être utilisée pour la synthèse logique.

Dans le système POLIS, la partition, la vérification de la synchronisation et l'optimisation au niveau CFSM (Codesign Finite State Machine) et au niveau des graphes

sont guidés par une évaluation de la mise en œuvre finale. Cette évaluation est basée sur des modèles du système cible et de la structure du code.

Outre ces nombreux projets, d'autres chercheurs ont essayé aussi de concevoir des outils de partitionnement matériel/logiciel intégrant à la fois le logiciel et le matériel dans un même processus de conception. Les travaux les plus pertinents sur le sujet sont présentés ci-dessous, les auteurs ainsi que leurs méthodologies respectives y seront cités.

Barros da Silva [BAR93] présente un outil de partitionnement basé sur une description conforme à UNITY. Cette description peut être séquentielle ou parallèle. Un processus d'affectation permet de rassembler, en deux étapes, d'une part, les différentes mises en œuvre possibles et, d'autre part, les dépendances de données, les ressources partagées ainsi que les performances s'y rattachant. La gestion des affectations est ordonnée pour l'architecture ciblée. Ce processus est réitéré afin de satisfaire toutes les contraintes de conception.

O'Nils et al. [ONI95] présente un outil de partitionnement nommé AKKA. Cet outil est basé sur la même approche que dans [JAN94b], mais cependant, plusieurs améliorations ont été apportées. La première consiste à permettre à l'utilisateur, lors du partitionnement, d'imposer des contraintes en assignant des candidats potentiels au matériel ou au logiciel afin d'obtenir l'information résultante reliée à un éventuel profilage. Cette information est visible via une interface graphique. La seconde repose sur le fait que l'information relative au profilage peut être utilisée lors du transfert des données, ce qui réduit considérablement les goulots d'étranglement lors de la transmission.

L'ambition d'Athanas [ATH91] est le partitionnement automatique d'un programme, écrit en langage C, dans des parties logicielles et matérielles et planter les parties matérielles sur des FPGAs. Par contre, son approche considère seulement les circuits combinatoires purs, sans utiliser des techniques de synthèse de haut niveau. Il ne permet

pas l'accès mémoire disponible sur les FPGAs et le processus de partitionnement est guidé lui aussi par un utilisateur humain.

Ernst et Henkel [ERN92, ERN98] utilisent une extension du langage C, comme langage de spécification, pour un contrôleur embarqué lors de la conception. Leur objectif est d'extraire des segments de code qui seront éventuellement implantés sur une architecture matérielle. Leur système de partitionnement matériel/logiciel est basé sur le recuit simulé et considère chaque segment de code logiciel comme étant des régions prometteuses. Cette approche est inefficace, puisque la plupart de ces segments de code ne sont pas des régions critiques. Les données de profilage sont recueillies par un simulateur qui est beaucoup plus lent que la compilation et l'exécution du programme source. Ceci est d'autant plus fastidieux lorsque l'on exécute des longs programmes.

Cette revue sur les outils de co-design matériel/logiciel est certes incomplète, puisque ce domaine évolue tellement rapidement, il est fort probable que déjà d'autres types d'outils sont présentement sur le marché et que d'autres ont complètement été laissés de côté. À ce titre, le lecteur peut consulter les ouvrage spécialisés cités aux références [EET00, GAJ00, SUM00]. Ces ouvrages actualisent et répertorient les principaux travaux dans ce domaine.

#### 1.3.1.1 *Les outils commerciaux*

Il est important de noter que quelques outils de co-design matériel/logiciel ont vu le jour dernièrement et sont présentement disponibles. Parmi les principaux on note CoWare [BOL97, COW00] et Arexsys [ARE00]. On peut les catégoriser comme des outils de partitionnement semi-automatique permettant, entre autre, un raffinement intéressant au niveau des communications entre le logiciel et le matériel.

CoWare est un environnement de co-design matériel/logiciel permettant la mise en œuvre de systèmes hétérogènes basée sur des spécifications hétérogènes. Cet environnement permet à un concepteur de mettre en œuvre une application basée sur une conception de raffinement. Tout d'abord, le système est spécifié complètement en

langage C. Ensuite, selon le choix du partitionnement matériel/logiciel, le C fonctionnel correspondant à la partie matérielle est traduit manuellement en une description comportementale. Puis, CoWare génère automatiquement une description Verilog ou VHDL de niveau RTL équivalente, ainsi que l'interface de communication entre la partie logicielle et matérielle. Finalement, CoWare supporte également la co-simulation avec des simulateurs Verilog et VHDL.

Arexsys est une amorce de technologie sur le marché naissant de la conception assistée par ordinateur de système (System Design Automation, SDA). SDA entoure les outils et les méthodologies qui permettent à des concepteurs, selon des caractéristiques de systèmes électroniques, de mettre en œuvre des modules en logiciel et en matériel. Le processus commence par un cahier des charges formel écrit en langages standard d'industrie tels que C, SDL ou VHDL et fournit des descriptions matérielles au niveau transfert de registre (RTL) ciblées pour les langages VHDL et Verilog et des descriptions logicielles ciblées pour le langage C.

### 1.3.2 Les algorithmes de partitionnement

Une fois la modélisation du système complétée, un algorithme de partitionnement doit être utilisé afin d'examiner les différentes configurations possibles. Il existe des algorithmes précis comme le "branch-and-bound" [AXE97] qui examine l'ensemble des configurations possibles pour une même modélisation. Cependant, la plupart de ces procédures sont des heuristiques qui essaient, à partir d'une modélisation donnée, de faire des changements à une configuration de départ dans le but de l'améliorer. Les heuristiques les plus répandues sont la recherche taboue [HEN97], le recuit simulé [AXE97], la méthode vorace [GAJ94c] et les procédures génétiques [GAJ94c].

Peng's et Kuchcinski's [ELE94] proposent un partitionnement basé sur le recuit simulé et la représentation interne est basée sur les réseaux de Petri. Elle utilise les informations de profilage, qui sont obtenues par un simulateur, ainsi que l'information reliée à la connectivité statique entre les opérations effectuées.

Jantsch et al. [JAN94a] présente un algorithme de partitionnement basé sur un arrangement hiérarchique de présélection qui utilise des techniques de programmation dynamique. Cette approche permet: (a) une collecte efficace des données relatives au profilage possible grâce à l'utilisation des langages de haut niveau, tels que C et C++, comme langage de spécification; (b) une rapidité du partitionnement due à la présélection des candidats potentiels; (c) un niveau de complexité supérieur du partitionnement matériel permettant une émulation logique du système entier.

Le lecteur intéressé par les méthodes de partitionnement les plus répandues peut consulter l'ouvrage cité à la référence [EDW97].

## **1.4 Le choix de la méthodologie suivie**

Dans cette dernière section, nous allons identifier les spécifications, les objectifs et les contraintes du projet. Nous allons y décrire le choix des fonctionnalités que nous avons implantées, afin de bien faire ressortir la méthodologie préconisée dans ce travail. Mais tout d'abord, présentons une vue d'ensemble du projet CODE.

### **1.4.1 Le projet CODE**

Le projet CODE du Groupe de Recherche en Microélectronique de l'École Polytechnique de Montréal consiste à étudier la structure d'un compilateur C ciblé vers un ordinateur d'une architecture hybride reconfigurable. Ce projet propose de tenter de capter le flux de design de ce type d'application dans un compilateur d'un langage de haut niveau. Cet outil intégrera à la fois le flux de design logiciel et matériel dans un même processus de conception.

## 1.4.2 Les spécifications de l'outil

### 1.4.2.1 *Les objectifs*

Tout d'abord, les spécifications du cahier des charges initiales étaient de concevoir et de mettre en œuvre des estimateurs de performance. Ces estimateurs permettant de prédire la pertinence d'un éventuel partitionnement matériel/logiciel automatique, sur une architecture matérielle reconfigurable de type FPGA, afin d'accentuer la vitesse d'exécution d'une tâche donnée. Ceux-ci identifiant les "boucles chaudes" ou régions critiques présentes à l'intérieur de programmes, écrits en langage C ANSI. En d'autres termes, nous devions développer des outils permettant d'analyser la structure logicielle d'une application quelconque écrite en C et d'extraire les informations relatives aux caractéristiques de cette application lors de son exécution.

Initialement, cinq fonctionnalités de base ont été définies afin d'élaborer un premier embryon d'outil de mesure et d'analyse de performance. Ces fonctionnalités recherchées sont : un compilateur du langage C, un module permettant la génération de deux codes cibles, soit : le C et VHDL, une bibliothèque de modules générique afin de supporter plusieurs architectures matérielles, un module de profilage servant à quantifier le squelette d'exécution de l'application et, enfin, un module d'estimation de la performance de chacune des applications, mesurant ainsi la pertinence d'un éventuel partitionnement matériel/logiciel sur une architecture matérielle reconfigurable.

Cependant, un certain nombre de contraintes s'ajoutent à la complexité de l'outil. Citons les trois plus importantes contraintes qui imposent, en quelque sorte, la structure logicielle que devra prendre l'outil. Tout d'abord, le code cible (C et VHDL) doit pouvoir être synthétisé et compilé par des outils commerciaux de base. On ne veut pas réécrire un "front-end", donc celui-ci doit être récupéré du compilateur C utilisé. Enfin, l'outil doit supporter la simulation et le déverminage des codes cibles générés.

### 1.4.2.2 *La méthodologie*

Afin de bien présenter le portrait général de la méthodologie suivie et de la pertinence de celle-ci, on doit se rapporter, de façon très étroite, aux spécifications fonctionnelles du futur outil d'analyse.

Notons que, dans le cadre de cette étude, nous avons focalisé nos efforts essentiellement sur la conception et la mise en œuvre du module effectuant un profilage dynamique et du module permettant d'estimer la performance de chacune des applications analysées. Le module de profilage dynamique sert à quantifier le squelette d'exécution de l'application et le module d'estimation de performance mesure la pertinence d'un éventuel partitionnement matériel/logiciel sur une architecture matérielle reconfigurable.

Pour y parvenir, voici les grandes étapes de la méthode suivie lors de la conception. La première étape du processus est la revue de la littérature sur le sujet des processeurs et des circuits reconfigurables. À ce stade, la décision d'utiliser une architecture reconfigurable de type FPGA ou autre chose, découle en général des contraintes de performance et de coût. Le choix d'un compilateur, du domaine public, devrait normalement découler des spécifications fonctionnelles et des contraintes du système. Le développement d'une stratégie d'optimisation permet de localiser les "boucles chaudes" d'un programme et d'en évaluer les coûts d'exécution selon la quincaillerie disponible. Cela constitue les dernières étapes de la méthodologie de conception.

Le chapitre qui suit passe à travers tous ces points d'une façon plus détaillée, en commençant par la description de la structure générale d'un système hybride reconfigurable.

## *Chapitre 2*

# **La méthodologie de co-design matériel/logiciel**

Dans ce chapitre, nous présenterons d'abord une vue d'ensemble de la problématique de recherche relative au choix d'une méthodologie de co-design matériel/logiciel débouchant sur la réalisation d'un système hybride reconfigurable. Par la suite, nous traiterons de la structure modulaire de l'outil d'analyse, puis nous décrirons les spécifications respectives rattachées à chacun des modules.

Une partie des concepts de base sur le co-design utilisés dans ce chapitre proviennent du travail de Doucet [DOU99] sur la définition de l'architecture générale du système.

### **2.1 La problématique**

La conception d'applications hybrides de type matériel/logiciel a longtemps été un art exercé par de petits groupes de chercheurs universitaires et privés. L'apparition d'une telle philosophie de conception vient probablement du besoin qu'a eu l'industrie, dans le secteur des hautes technologies, de systèmes de plus en plus performants pour être en mesure d'exécuter des applications de plus en plus complexes et ce, le plus rapidement possible. Cependant, le partitionnement s'effectue manuellement et selon l'expérience du concepteur. Ces tâches sont souvent réservées aux ingénieurs les plus expérimentés ayant

la capacité, en fonction de leurs expériences en conception, de déterminer quels seront les blocs qui seront plus efficace en matériel et ceux qui seront plus efficace en logiciel respectivement. Il y a donc quasi absence de procédures automatisées permettant d'obtenir de l'information sur la nature des programmes analysés. Les mécanismes d'interface entre les partitions logicielles et matérielles sont souvent improvisés et sont décrites dans des langages non-formels et non-standardisés. Un langage standard est généralement un gage de compatibilité, de portabilité, de stabilité et de pérennité. Ce manque de formalisme réduit de façon importante la performance globale des systèmes, un certain nombre de facteurs provoquent ces pertes de performance. Le premier de ces facteurs est, sans contredit, que la conception et la mise en œuvre de ces partitions repose sur une méthodologie de conception ponctuelle ne respectant aucune spécification fonctionnelle commune. Le second découle des délais importants reliés à l'intégration de ces partitions afin de respecter, d'une part, les spécifications fonctionnelles respectives à chacune et, d'autre part, la synchronisation de ces deux processus, ainsi que leur mode de fonctionnement spécifique. Pour palier à ces problèmes, les concepteurs ont tendance à mettre en œuvre le plus de segments du système en logiciel et de minimiser les partitions matérielles. Par conséquent, ce genre d'approche résulte très souvent en des partitionnements matériel/logiciel plus ou moins efficaces et non-optimaux. Cependant, on retrouve actuellement sur le marché des outils de co-simulation comme Eagle de Synopsys et Seamless CVE de Mentor Graphics qui permettent de vérifier la synchronisation d'une façon automatisée. Ces outils sont mature et très efficace.

Au cours de la dernière décennie, une nouvelle méthodologie de conception a vu le jour. Cette méthodologie se nomme le co-design et elle inclut, dans un même processus, à la fois les parties logicielles et les parties matérielles. Le co-design permet, lors de la conception, de séparer les parties qui seront en logiciel des parties qui seront en matériel selon des critères rigoureux. Cependant, peu d'outils de co-design sont disponibles et sont souvent orientés pour des applications spécifiques ou des grammaires pré-sélectionnées.

Notre approche propose un certain nombre de critères ou métriques de performance servant à détecter et à caractériser chacun des segments de code d'une application donnée écrite en langage C ANSI. À partir des valeurs de métriques trouvées, une fonction paramétrique a été développée pour quantifier chacun de ces segments afin de prédire la pertinence d'éventuels partitionnements matériel/logiciel sur une architecture matérielle reconfigurable de type FPGA. La mise en œuvre de cette fonction est basée sur un algorithme de partitionnement respectant à la fois les contraintes de temps et les contraintes imposées par l'architecture matérielle ciblée.

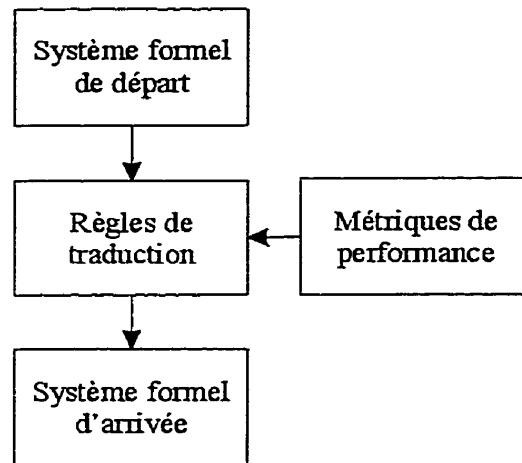

## 2.2 Les spécifications du système

Comme nous venons de le voir, ce travail de recherche consiste à développer un outil d'analyse afin de prédire la pertinence de transposer et d'exécuter des segments de code en matériel afin d'accélérer la vitesse d'exécution de certains segments d'une tâche. Essentiellement, cet outil devra transformer une description dans un système formel de départ vers une description dans un système formel d'arrivée, en utilisant les règles de traduction appropriées selon les résultats des métriques de performance. Évidemment, cette section présente une vue d'ensemble du projet afin de permettre au lecteur de se faire une idée générale des différents facteurs considérés.

### 2.2.1 Structure générale du système

La structure générale du système, illustrée à la figure 2.1, permet d'identifier les différentes fonctionnalités du système. Les domaines de fonctionnalité couverts par les systèmes formels de départ et d'arrivée ne sont pas les mêmes. On cherche à traduire les segments de code qui sont dans l'intersection des domaines de fonctionnalité. La détermination des segments se trouvant dans cette intersection est obtenue via les résultats des métriques de performance.

FIG. 2.1 Structure générale du système

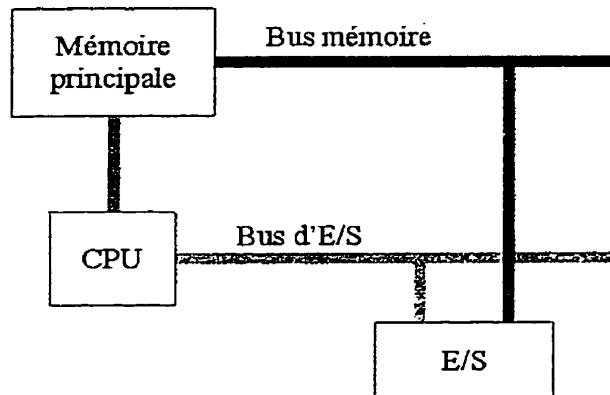

## 2.2.2 Système formel de départ

Le système formel de départ décrit des applications dans un langage de haut niveau ciblé pour un ordinateur avec un microprocesseur séquentiel. La figure 2.2 illustre l'architecture d'un tel ordinateur sous sa forme la plus simplifiée.

FIG. 2.2 Architecture logique du système initial

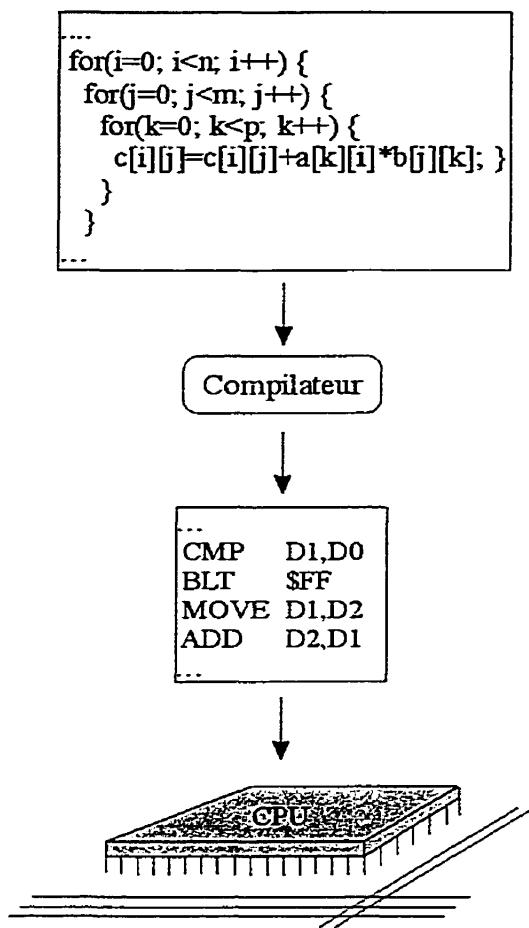

La description de chacune des applications séquentielles est écrite en langage C ANSI. La figure 2.3 illustre le flux de compilation traditionnel relatif au système formel de départ.

FIG. 2.3 Flux de compilation traditionnel

Essentiellement, la compilation effectue une traduction d'un programme écrit en langage évolué en un programme équivalent en langage machine. Le programme qui exécute la compilation utilise le programme source écrit en langage source comme données et produit, comme résultat, un programme objet en langage objet, ce dernier pouvant être en fait le langage assembleur ou directement le langage machine, qui sera exécuté séquentiellement sur le microprocesseur cible.

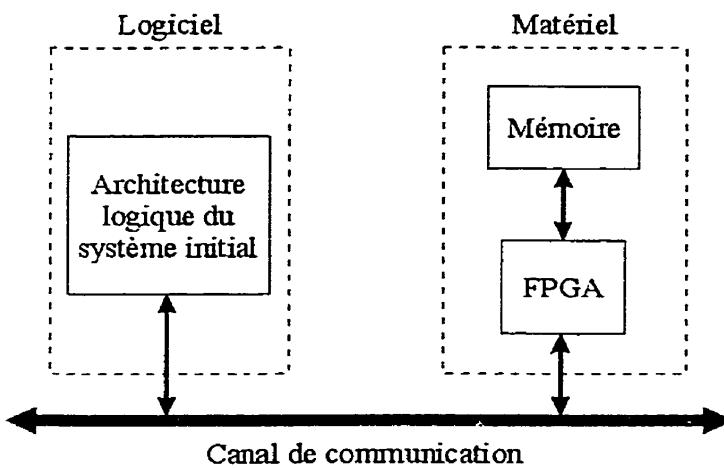

### 2.2.3 Système formel d'arrivée

Le système formel d'arrivée décrit des applications dans un langage ciblé pour un processeur reconfigurable de type FPGA. L'architecture d'un tel processeur est illustrée,

sous sa forme la plus simplifiée, à la figure 2.4. Notons que le bloc de gauche, dans cette figure, intitulé *Architecture logique du système initial*, correspond exactement à ce qui est illustré à la figure 2.2. On veut schématiser, ici, que l'architecture logique cible du système hybride reconfigurable est constituée, d'une part, de l'architecture logique du système initial et, d'autre part, de l'architecture logique du co-processeur FPGA. Rappelons que le FPGA possède à la fois de la mémoire interne et externe.

FIG. 2.4 Architecture logique cible du système hybride reconfigurable

La description de chaque application, pour le système hybride, est écrite dans une combinaison de deux langages, soient le langage C ANSI et le langage VHDL. Le VHDL est un langage compilé vers des descriptions matérielles au niveau des registres et des portes logiques. Ces descriptions sont chargées par la suite dans le processeur reconfigurable. La figure 2.5 illustre le flux de compilation relatif au système formel d'arrivée.

## 2.2.4 L'architecture matérielle

Dans la présente section, nous présentons d'abord une vue d'ensemble des caractéristiques de la plate-forme matérielle. Ensuite, nous traitons des différents éléments programmables présents dans cette architecture. Après quoi, nous abordons le

langage de description matérielle VHDL, puis nous proposons une brève introduction qui permet de mettre en évidence certains facteurs importants reliés au choix de ce langage.

FIG. 2.5 Flux de compilation recherché

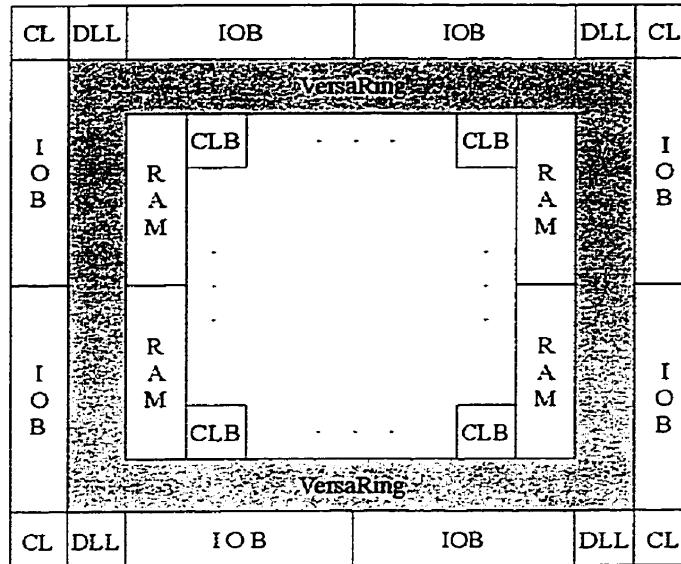

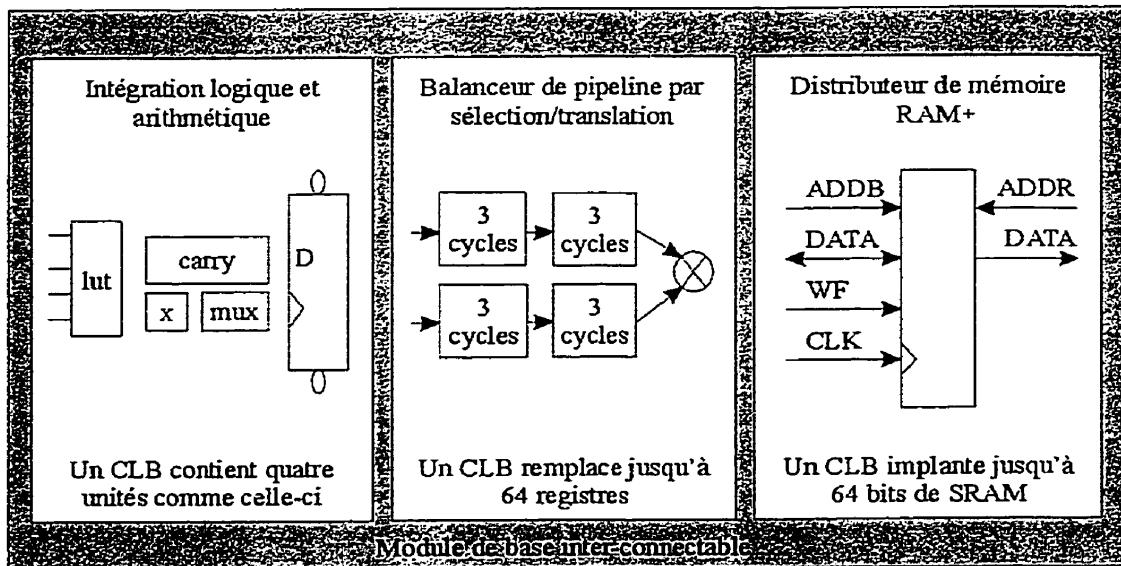

#### 2.2.4.1 Les FPGA

Un FPGA est un circuit reconfigurable. Son architecture interne, présentée à la figure 2.6, est constituée essentiellement de blocs logiques programmables (CLBs), de matrices de routage et de blocs mémoire. Un CLB (Configurable Logic Block) est un module logique qui met en œuvre une table de vérité. La figure 2.7 illustre les différents composants constituant un CLB. Les matrices de routage établissent les liens entre les CLBs, la mémoire et les broches physiques de la puce. En combinant chacun des CLBs, on arrive à implanter diverses fonctions logiques. Le lecteur intéressé par les circuits

programmables (FPGAs, ASICs, etc.) et leurs architectures respectives peut consulter divers ouvrages spécialisés [DUT97, SMI97, XIL99a].

FIG. 2.6 Vue d'ensemble de l'architecture Virtex

Une description en langage VHDL peut être compilée vers une description de séries de tables logiques. Ensuite, un placement et un routage détermine les liens à établir entre les CLBs pour réaliser matériellement les fonctionnalités sur le FPGA.

FIG. 2.7 Vue schématique d'un bloc logique programmable (CLB)

#### 2.2.4.2 *Le langage VHDL*

C'est dans le courant des années 1970 que le ministère américain de la défense (DoD) lança le programme VHSIC (Very High Speed Integrated Circuits), une initiative de grande ampleur destinée à produire des circuits intégrés complexes de très haute performance. Il apparut rapidement que, compte tenu du grand nombre de sociétés concernées, le défi majeur résidait moins dans l'effort technologique que dans la normalisation de la communication entre les différents intervenants. La plus grande diversité régnait parmi les outils utilisés, non seulement entre les différentes compagnies contractées, mais aussi bien entre les différents départements d'une même compagnie, voire entre différents projets gérés par un même département. Cet état de fait a motivé l'émergence du VHDL (VHSIC Hardware Description Language), qui visait entre autres à fournir un environnement de développement matériel complet unifié. Standardisé en décembre 1987 par l'Institute of Electrical and Electronics Engineers sous la référence IEEE-1076, le VHDL se présente donc comme un langage unique pour la description, la modélisation, la simulation, la synthèse et la documentation [LAR97].

Son utilisation pour la synthèse logique, autrement dit la création de circuits à partir de descriptions textuelles, est plus récente, et est notamment reliée à l'essor extraordinaire des composants logiques programmables, qu'ils se nomment CPLD ou FPGA. Il fallait, à ces architectures devenues complexes, un langage descriptif de haut niveau, en remplacement des langages de première génération aux fonctionnalités limitées ou aux méthodes de capture schématique. Il leur fallait également un langage universel, ne verrouillant pas l'utilisateur à une architecture unique. Il leur fallait enfin un langage démocratique, apte à promouvoir des environnements de développement économiques. Toutes ces conditions sont aujourd'hui remplies : le VHDL est devenu le langage descriptif le plus répandu parmi les concepteurs de circuits.

Cette présentation est certes incomplète, puisque nous ne donnons pas nécessairement au lecteur l'information relative à l'utilisation de ce langage. Cependant, le lecteur intéressé peut toujours consulter divers ouvrages [AUM96, LAR97].

### 2.2.5 Règles de traduction

À cette étape, on cherche à traduire les segments de code de l'application qui sont dans l'intersection des domaines de fonctionnalité. On va pouvoir déterminer quels sont les segments qui sont dans cette intersection à l'aide des informations fournies par les métriques de performance. Ces informations permettront de choisir les règles de traduction appropriées.

### 2.2.6 Métriques de performance