**Titre:** Conception et réalisation d'un prototype de la partie implantable

d'un stimulateur visuel cortical

Title: d'un stimulateur visuel cortical

**Auteur:** Martin Roy

Author:

**Date:** 1999

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Roy, M. (1999). Conception et réalisation d'un prototype de la partie implantable

d'un stimulateur visuel cortical [Mémoire de maîtrise, École Polytechnique de

Montréal]. PolyPublie. <https://publications.polymtl.ca/8754/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8754/>

PolyPublie URL:

**Directeurs de

recherche:** Mohamad Sawan

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

CONCEPTION ET RÉALISATION D'UN PROTOTYPE DE

LA PARTIE IMPLANTABLE D'UN STIMULATEUR VISUEL CORTICAL

MARTIN ROY

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

NOVEMBRE 1999

©Martin Roy, 1999.

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

*Our file Notre référence*

**The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.**

**L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.**

**The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.**

**L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.**

**0-612-48870-5**

**Canada**

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

CONCEPTION ET RÉALISATION D'UN PROTOTYPE

DE LA PARTIE IMPLANTABLE D'UN STIMULATEUR VISUEL CORTICAL

présenté par : ROY Martin

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. SAVARIA Yvon, Ph.D., président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

M. BRAULT Jean-Jules, Ph.D., membre

## **REMERCIEMENTS**

Je tiens premièrement à remercier mon directeur de recherche, Mohamad Sawan, pour m'avoir proposé un sujet de recherche passionnant et ensuite me guider durant l'accomplissement de mes travaux.

Un grand merci à Gaétan Décarie pour sa contribution dans le projet et pour ses judicieux conseils.

Je tiens à saluer mes collègues de l'équipe de recherche PolySTIM pour leur bonne compagnie et pour leur aide.

Un merci spécial à ma compagne, Guylaine Renaud, pour m'avoir épaulé tous le long de mes études.

Finalement, un grand merci à tous mes amis, à ma famille et particulièrement à mes parents, Pierre Roy et Monique Denis pour leur aide et leur encouragement.

## RÉSUMÉ

Les récents progrès dans le domaine de la microélectronique ont permis la réalisation de stimulateurs physiologiques de plus en plus complexes et performants. Parmi ces progrès, la miniaturisation des circuits intégrés et la diminution de la puissance requise pour leur fonctionnement laissent entrevoir la réalisation de nouvelles avenues dans le domaine de la stimulation électrique. L'une de ces avenues consiste à stimuler le cortex visuel d'un non-voyant afin de lui redonner une vision partielle. En effet, les expériences de plusieurs chercheurs ont permis de constater qu'il est possible de faire apparaître un petit point lumineux, appelé phosphène, dans le champ visuel d'un non-voyant en lui injectant des courants de stimulation dans son cortex visuel. Il semble donc possible de réaliser un système permettant de produire une sensation d'image pixelisée chez les non-voyants en stimulant plusieurs endroits de leur cortex visuel. Un tel système comportera un contrôleur externe pour l'acquisition et l'amélioration des images et un implant qui, selon les données transmises par le contrôleur externe, injectera les courants de stimulation.

Le but de ce mémoire de maîtrise est de réaliser un prototype d'implant visuel cortical (PIVC). Le prototype, qui possède la même architecture que l'implant cortical anticipé, est réalisé à partir de composants discrets et comporte une matrice de diodes électroluminescentes (DEL) permettant de visualiser les « images » obtenues suite à la réception de données du contrôleur externe. Le PIVC n'est donc pas utilisé pour stimuler le cortex visuel, mais employé pour donner une idée de l'image perçue par le non-voyant suite à une opération de stimulation. Le prototype permet donc de valider une architecture d'implant mais pourra également servir comme outil de développement car la principale composante du prototype est reconfigurable.

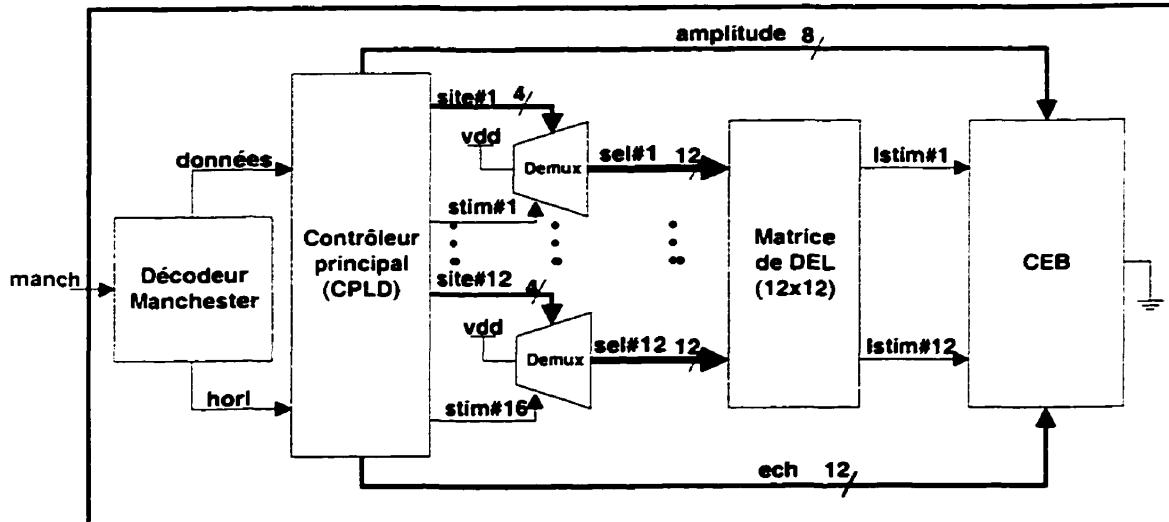

Deux architectures de prototype de l'implant furent développées au cours du projet mais seule la première fût utilisée pour réaliser un prototype complet du stimulateur. La différence entre les deux architectures se situe au niveau du circuit de conversion numérique analogique qui contrôle les intensités des courants de stimulation. La première architecture utilise un circuit intégré et des composants discrets commerciaux pour réaliser cette fonction alors que la deuxième architecture utilise un circuit intégré prédiffusé. La partie analogique de la deuxième architecture comprenant un convertisseur numérique analogique et des échantillonneurs-bloqueurs fonctionnant en mode courant est donc entièrement intégrée à l'intérieur d'une seule puce. Les résultats de simulation indiquent que la topologie du circuit prédiffusé est fonctionnelle. Toutefois, la technologie choisie ne permet pas une grande densité d'interconnexion (une seule couche de métal) ce qui a empêché le bon fonctionnement du circuit de la deuxième architecture.

Cependant, les résultats obtenus de la réalisation de la première architecture du prototype ont donné lieu au fonctionnement attendu. Ainsi il est possible de faire afficher des images sur la matrice de diodes électroluminescentes suite à la réception des données provenant du contrôleur externe. Ces données correspondent aux paramètres de stimulation qui permettent de moduler l'intensité lumineuse des DEL. Ces paramètres sont les amplitudes des courants et les durées de phase et d'interphase des opérations de stimulation. Le protocole de communication établit entre le contrôleur externe et le prototype permet, suite à une étape de configuration, de définir un taux de transfert variable de l'information selon les besoins. Cette flexibilité est requise par cette application car les paramètres idéaux pour obtenir une stimulation efficace ne sont pas encore connues. Les images obtenues sur la matrice de DEL laissent croire qu'un implant visuel cortical comportant essentiellement la même architecture que le prototype permettrait à un non-voyant de lire et de reconnaître des objets facilement même si le nombre de pixels de l'image est relativement faible.

## ABSTRACT

With the recent advances in microelectronics, it is now possible to fabricate physiological stimulator devices which are more complex and efficient than ever. Among these advances, the miniaturisation and power consumption diminution of integrated circuit devices are some of the characteristics that allow to anticipate new avenues in electrical stimulations.

The stimulation of the visual cortex of a blind person in order to give him back a partial sight is one of these avenues. Several research experiments have shown that it is possible to induce the perception of a small spot of light called phosphene, into the visual field of the blind, following the injection of stimulation currents into his visual cortex. It seems that it is now possible to design a system that allows to produce pixelized image sensation to the blind following the stimulation of several sites into his visual cortex. Such a system will have an external controller for image acquisition and improvement and an implant to produce stimulation currents.

The main goal of the project is to design and fabricate a cortical visual implant prototype (CVIP). The prototype has the same architecture as the envisioned implant, which is realised from discrete electronics components and contains a LED array that allows the visualisation of obtained images following the reception of visual data from the external controller. The CVIP is not used for visual cortex stimulation but to give an idea of what a blind person would see after a stimulation operation. The prototype allows the validation of the anticipated implant architecture and can be used as a development tool because the main component is reconfigurable.

Two architectures have been designed but only the first one has been used to prototype a complete visual stimulator. The difference between the architectures is the digital to

analogue conversion circuit used to control the intensities of stimulation currents. The first architecture uses a commercial integrated circuit and several discrete components to make the conversion, while the second architecture uses a bipolar array integrated circuit. The analog part of the second architecture, composed of a digital to analog converter and several current mode samples and holds, is then entirely integrated into a single chip.

The simulation results indicates the full operation of the bipolar array integrated circuit topology, but the selected technology doesn't allow more than one interconnection layer which gave high integrated complexity and prevent the circuit of the second architecture of the prototype to operate properly.

However, results obtained following the fabrication of the first architecture of the prototype show the expected operation of the circuit. Thus, it is possible to display images on the LED array following the reception of data from the external controller. These data are the stimulation parameters that allow to modulate the light intensities of LEDs. The parameters are the amplitudes of the currents and the phase and interphase delays of the stimulation operations. The established communication protocol between the external controller and the prototype allows, following a configuration step, to define a variable transfer rate of the information. This flexibility is required by this application since the ideal parameters to obtain efficient stimulation results are not known.

The obtained images on the LED array let us believe that a cortical visual implant that has essentially the same architecture as the proposed prototype would allow, for a blind person, to read and recognize objects easily even if the number of image pixels is relatively low.

**TABLE DES MATIÈRES**

|                                                                 |             |

|-----------------------------------------------------------------|-------------|

| <b>REMERCIEMENTS .....</b>                                      | <b>iv</b>   |

| <b>RÉSUMÉ .....</b>                                             | <b>v</b>    |

| <b>ABSTRACT .....</b>                                           | <b>vii</b>  |

| <b>TABLE DES MATIÈRES .....</b>                                 | <b>ix</b>   |

| <b>LISTE DES TABLEAUX .....</b>                                 | <b>xiii</b> |

| <b>LISTE DES FIGURES .....</b>                                  | <b>xiv</b>  |

| <b>LISTE DES ANNEXES .....</b>                                  | <b>xix</b>  |

| <b>LISTE DES SIGLES ET ABRÉVIATIONS .....</b>                   | <b>xx</b>   |

| <b>INTRODUCTION .....</b>                                       | <b>1</b>    |

| <b>CHAPITRE 1 : ÉTUDE DES STIMULATEURS PHYSIOLOGIQUES .....</b> | <b>5</b>    |

| 1.1 Introduction .....                                          | 5           |

| 1.2 La cellule nerveuse .....                                   | 6           |

| 1.3 Classification des stimulateurs électriques .....           | 8           |

| 1.4 Les technologies .....                                      | 11          |

| 1.5 Les techniques analogiques .....                            | 12          |

| 1.5.1 Transmission et réception de données et d'énergie .....   | 13          |

| 1.5.2 Convertisseur numérique analogique (CNA) .....            | 17          |

| 1.6 Electrodes et réseaux d'électrodes .....                    | 19          |

|                                                                               |        |

|-------------------------------------------------------------------------------|--------|

| 1.6.1 Modélisation de l'interface électrode-tissu .....                       | 20     |

| 1.7 Considérations d'ordre biomédicales .....                                 | 21     |

| 1.7.1 Biocompatibilité des implants .....                                     | 22     |

| 1.7.2 Excitabilité et lésion neuronale .....                                  | 22     |

| 1.8 Conclusion .....                                                          | 23     |

| <br><b>CHAPITRE 2 : LES PROTHÈSES VISUELLES .....</b>                         | <br>24 |

| 2.1 Introduction .....                                                        | 24     |

| 2.2 Le système visuel humain et les maladies de la vision .....               | 24     |

| 2.3 Les avenues de recherche pour récupérer partiellement la vision .....     | 27     |

| 2.3.1 L'implant rétinien .....                                                | 27     |

| 2.3.2 Le stimulateur du nerf optique .....                                    | 29     |

| 2.3.3 L'implant cortical .....                                                | 29     |

| 2.3.4 Comparaison entre les différentes avenues de recherche .....            | 30     |

| 2.4 Les connaissances actuelles sur la stimulation du cortex visuel .....     | 32     |

| 2.4.1 Bref historique .....                                                   | 32     |

| 2.4.2 Les travaux de l'équipe de Hambrecht .....                              | 33     |

| 2.5 Architecture et travaux de pointe sur l'implant cortical .....            | 35     |

| 2.5.1 La première version du stimulateur visuel miniaturisé de PolySTIM ..... | 36     |

| 2.5.2 Le démultiplexeur physiologique de Jones et Normann .....               | 38     |

| 2.5.3 L'implant de Troyk .....                                                | 40     |

| 2.6 Efficacité d'une vision obtenue à l'aide d'un implant cortical .....      | 40     |

| 2.7 Conclusion .....                                                          | 41     |

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| <b>CHAPITRE 3 : CONCEPTION MATÉRIELLE DU PROTOTYPE .....</b>           | <b>43</b> |

| 3.1 Introduction .....                                                 | 43        |

| 3.2 Élaboration de la structure de base des prototypes .....           | 44        |

| 3.3 Structure du prototype du stimulateur visuel cortical (PSVC) ..... | 46        |

| 3.4 Architecture de la première version du PIVC .....                  | 47        |

| 3.4.1 Décodeur Manchester .....                                        | 48        |

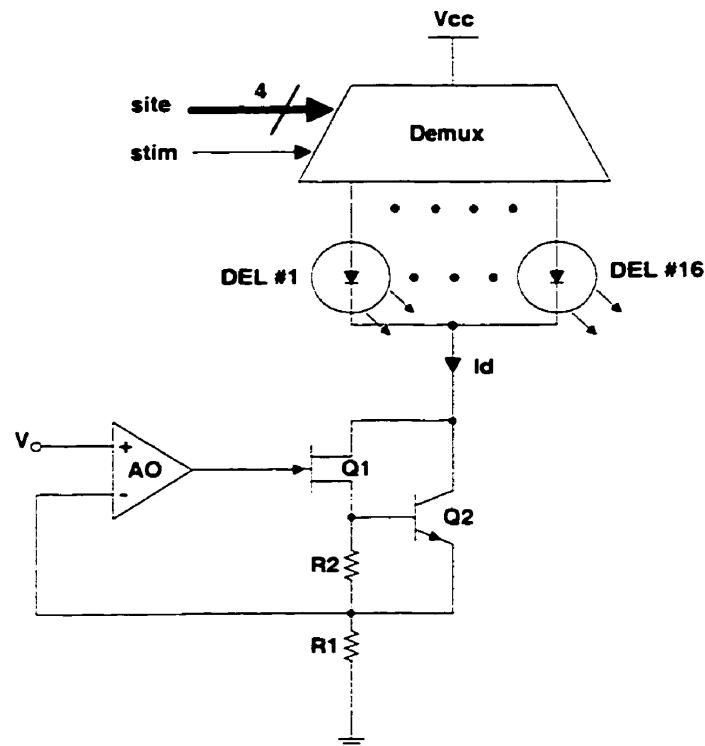

| 3.4.2 Sélection d'une DEL et contrôle de l'intensité du courant .....  | 50        |

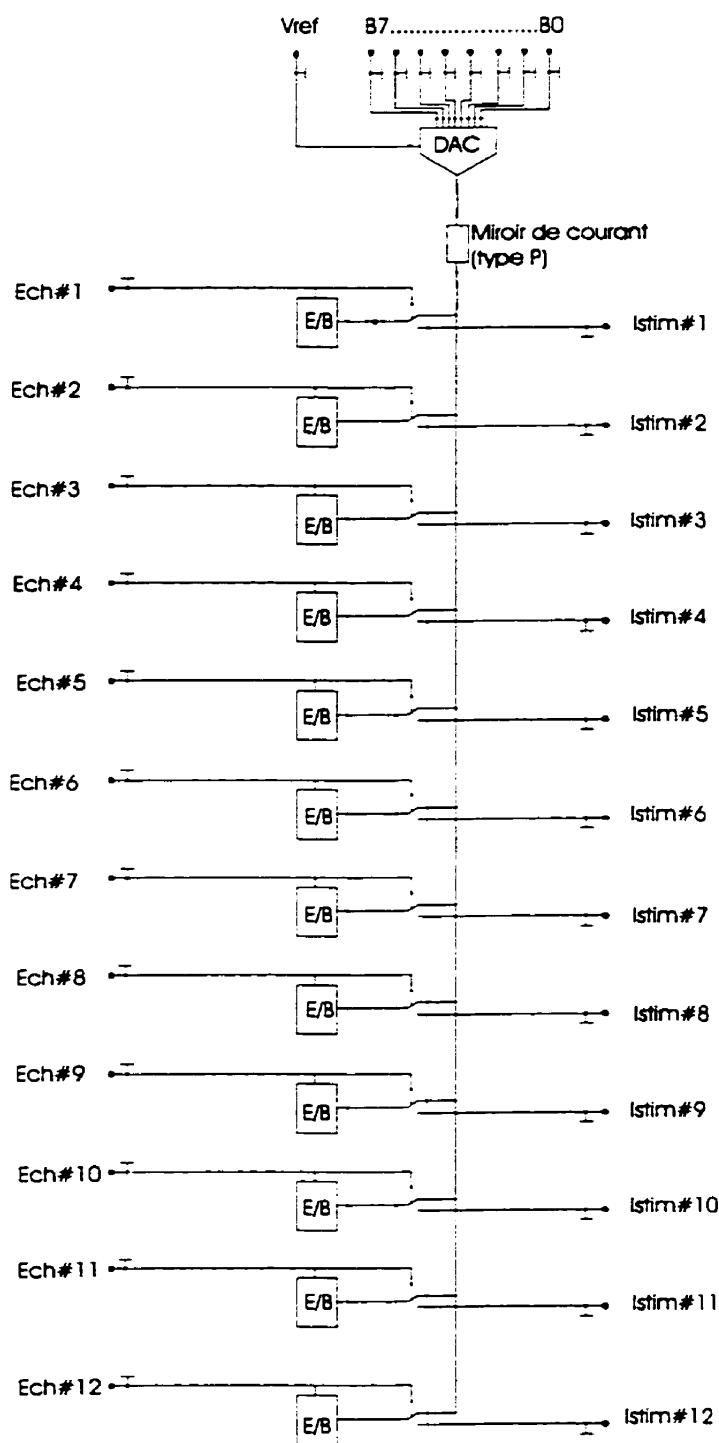

| 3.5 Architecture de la deuxième version du PIVC .....                  | 52        |

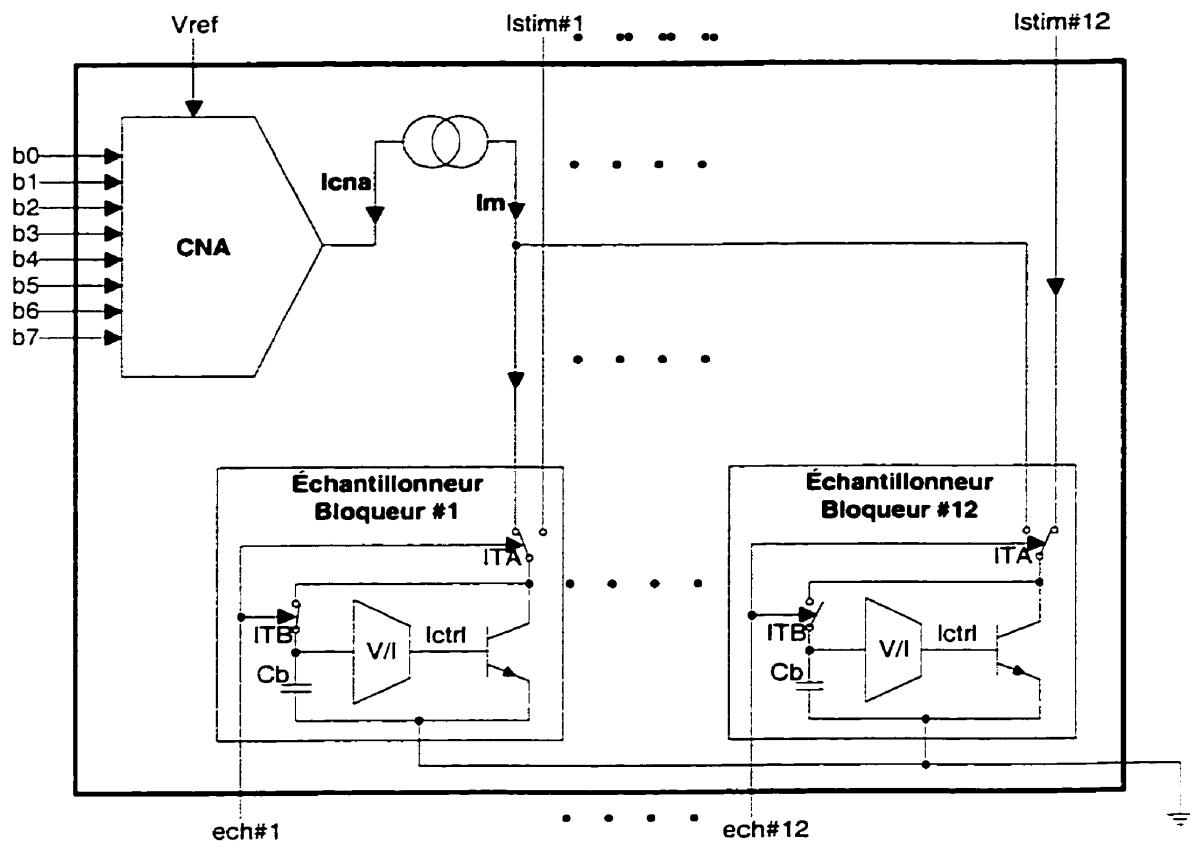

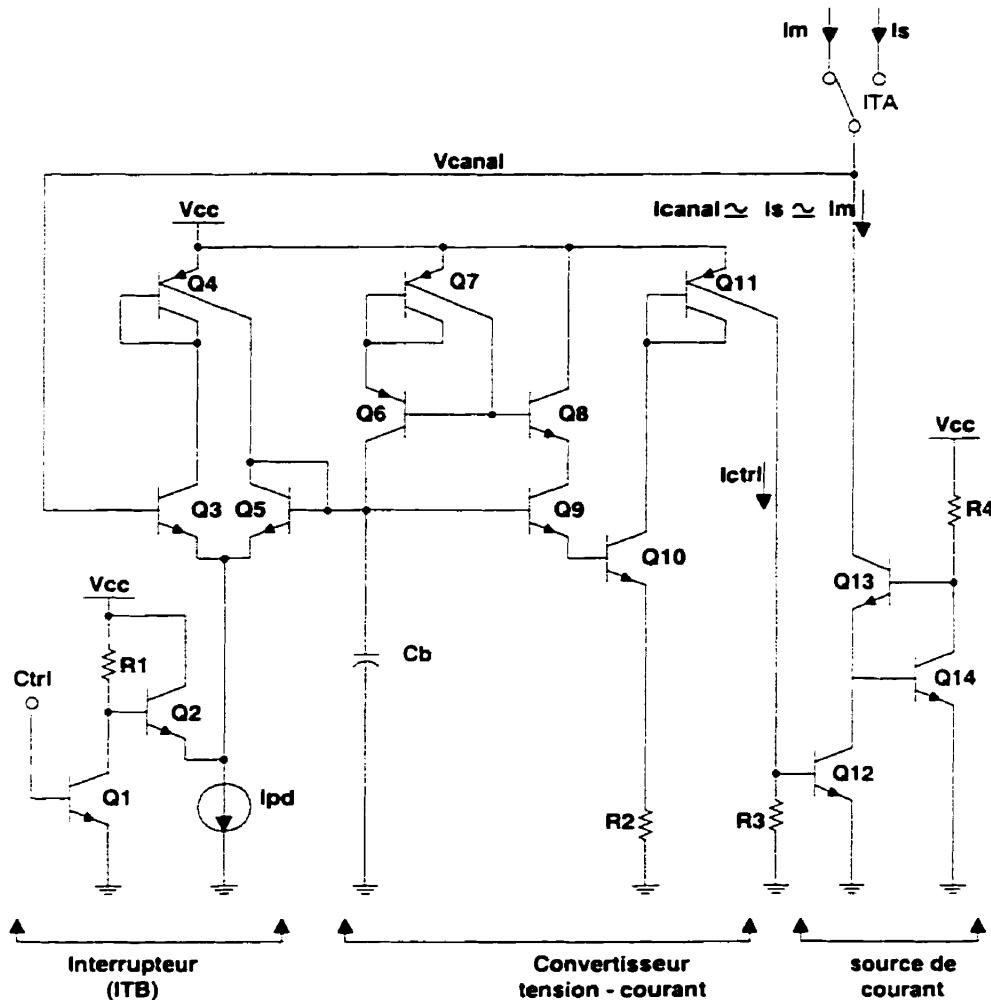

| 3.5.1 Principe de fonctionnement du CEB .....                          | 53        |

| 3.5.2 L'échantillonneur-bloqueur du CEB .....                          | 55        |

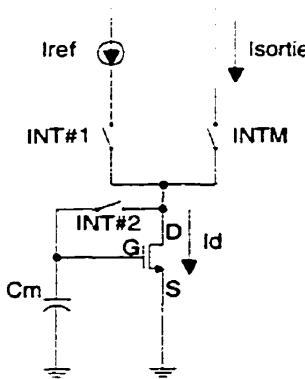

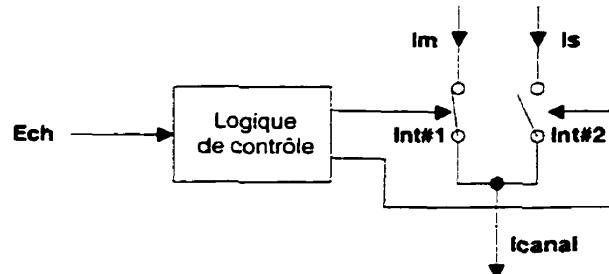

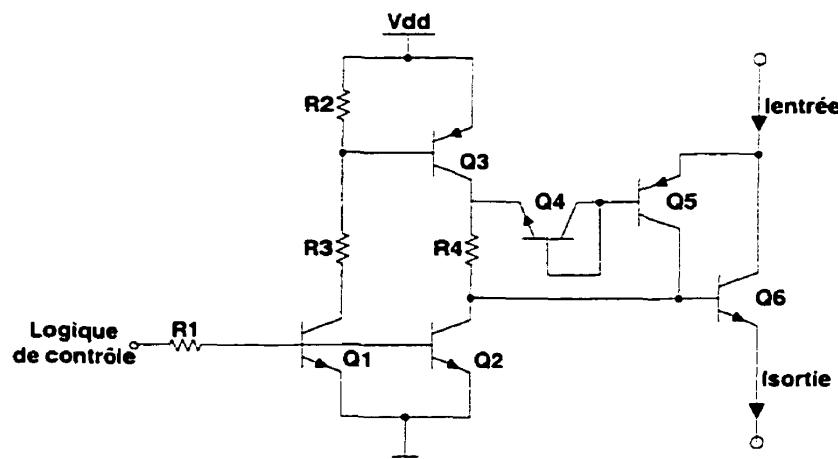

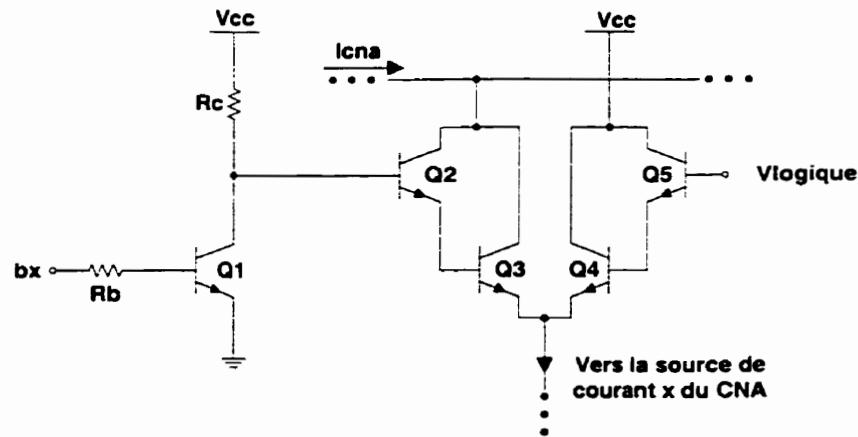

| 3.5.3 Le commutateur de courant ITA .....                              | 57        |

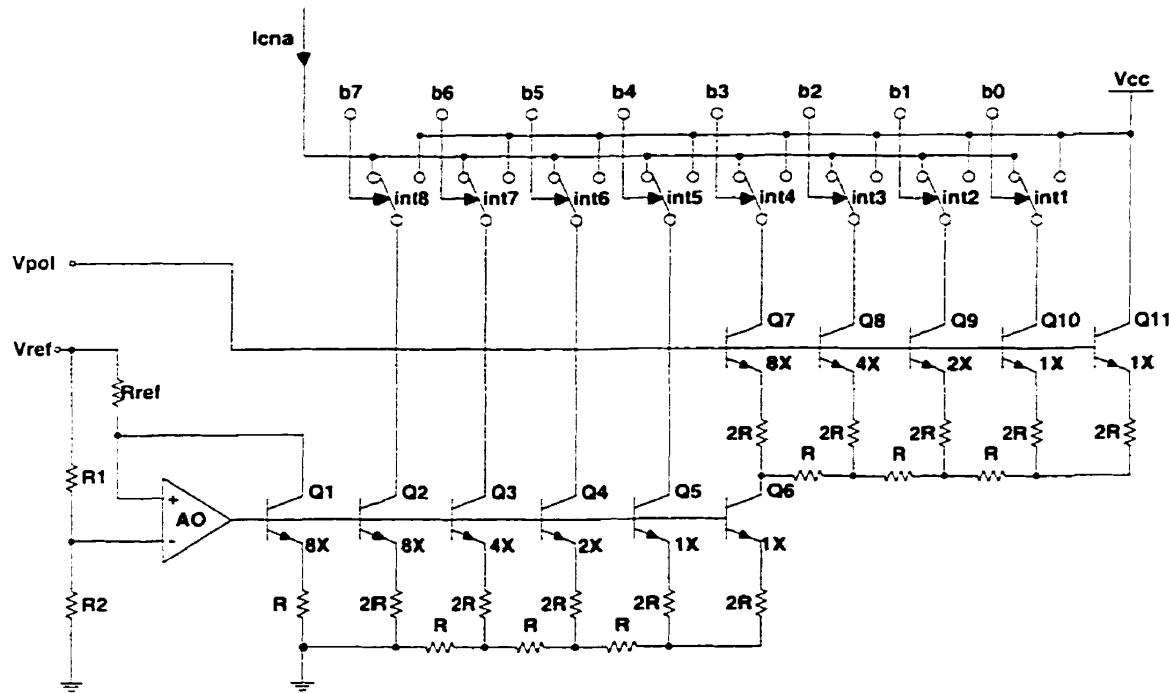

| 3.5.4 Le CNA du CEB .....                                              | 59        |

| 3.6 Conclusion .....                                                   | 61        |

| <b>CHAPITRE 4 : LE CONTRÔLEUR DU PIVC .....</b>                        | <b>63</b> |

| 4.1 Introduction .....                                                 | 63        |

| 4.2 Les modes de fonctionnement .....                                  | 63        |

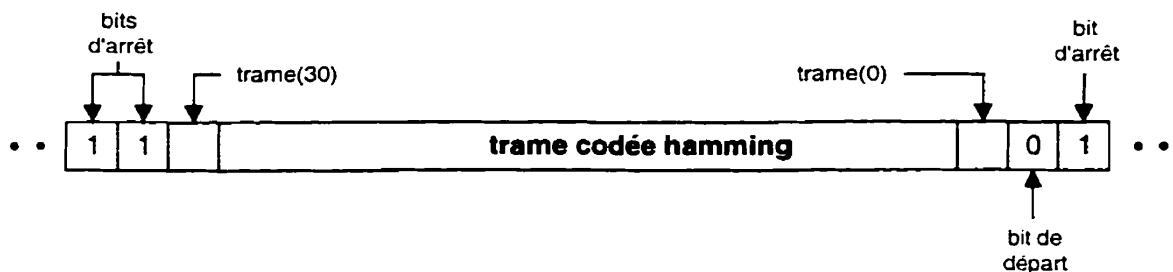

| 4.3 Le protocole de communication .....                                | 65        |

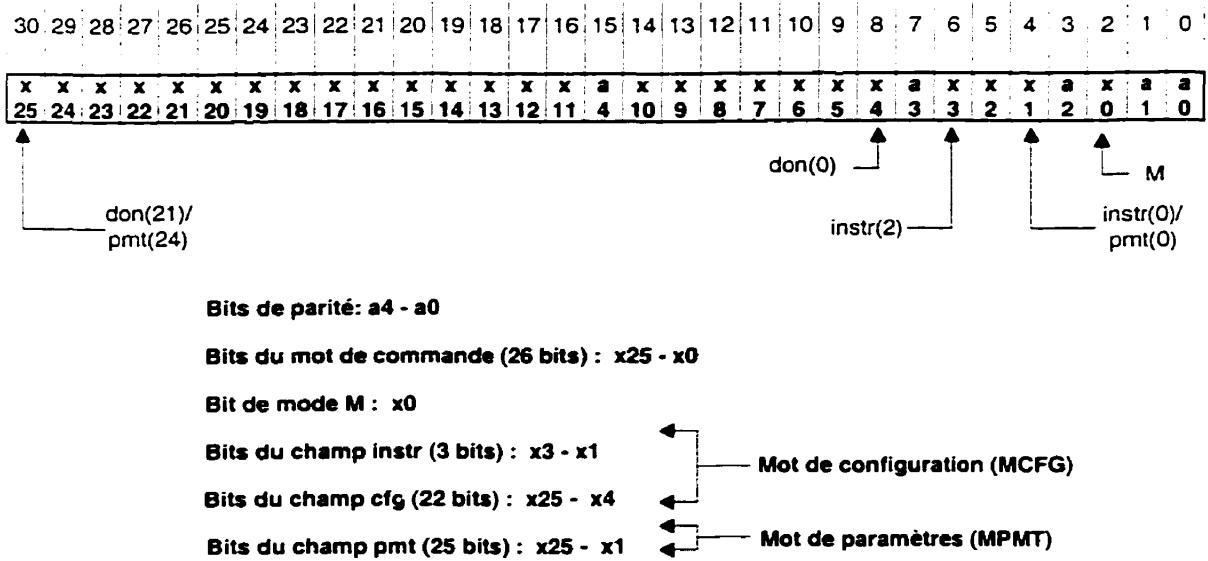

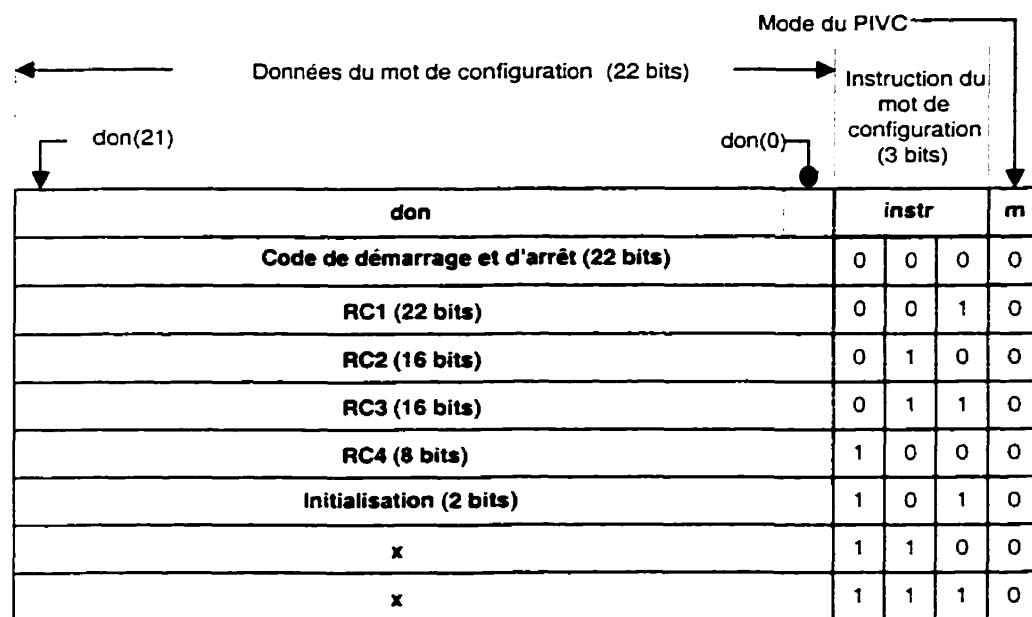

| 4.3.1 Le mot de configuration .....                                    | 66        |

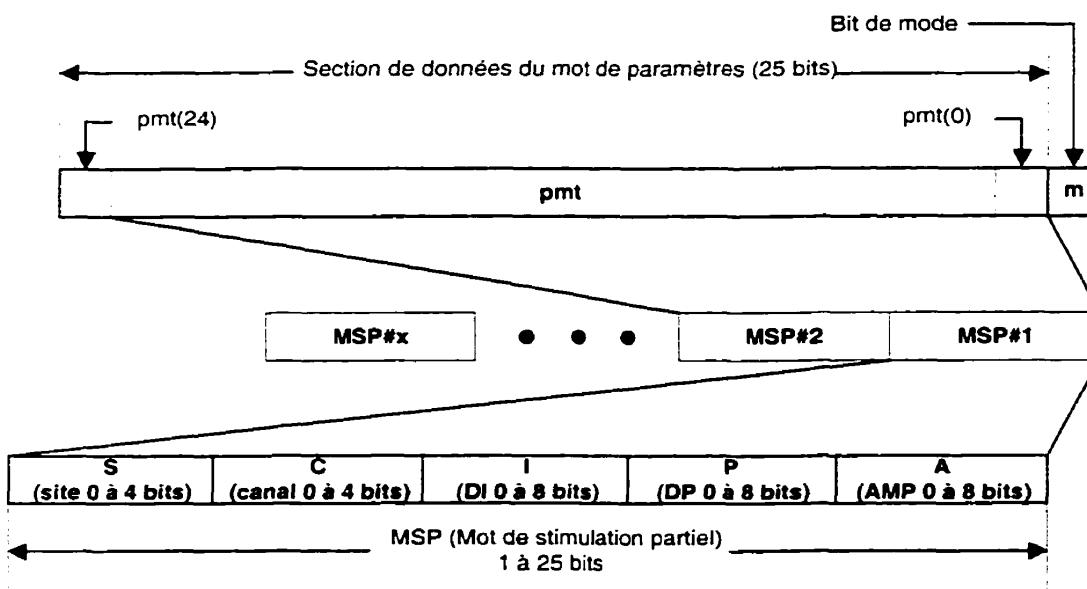

| 4.3.2 Le mot de paramètres .....                                       | 69        |

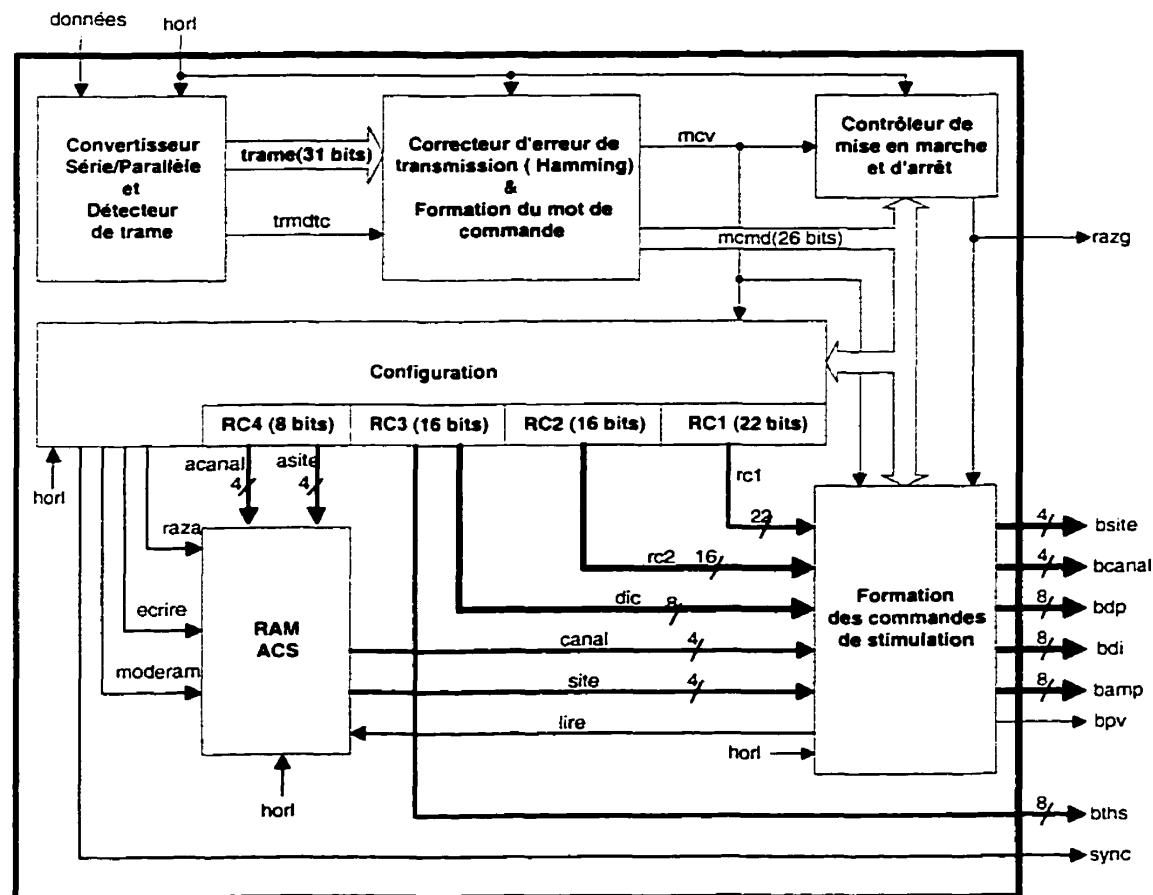

| 4.4 Architecture générale du contrôleur du PIVC .....                  | 70        |

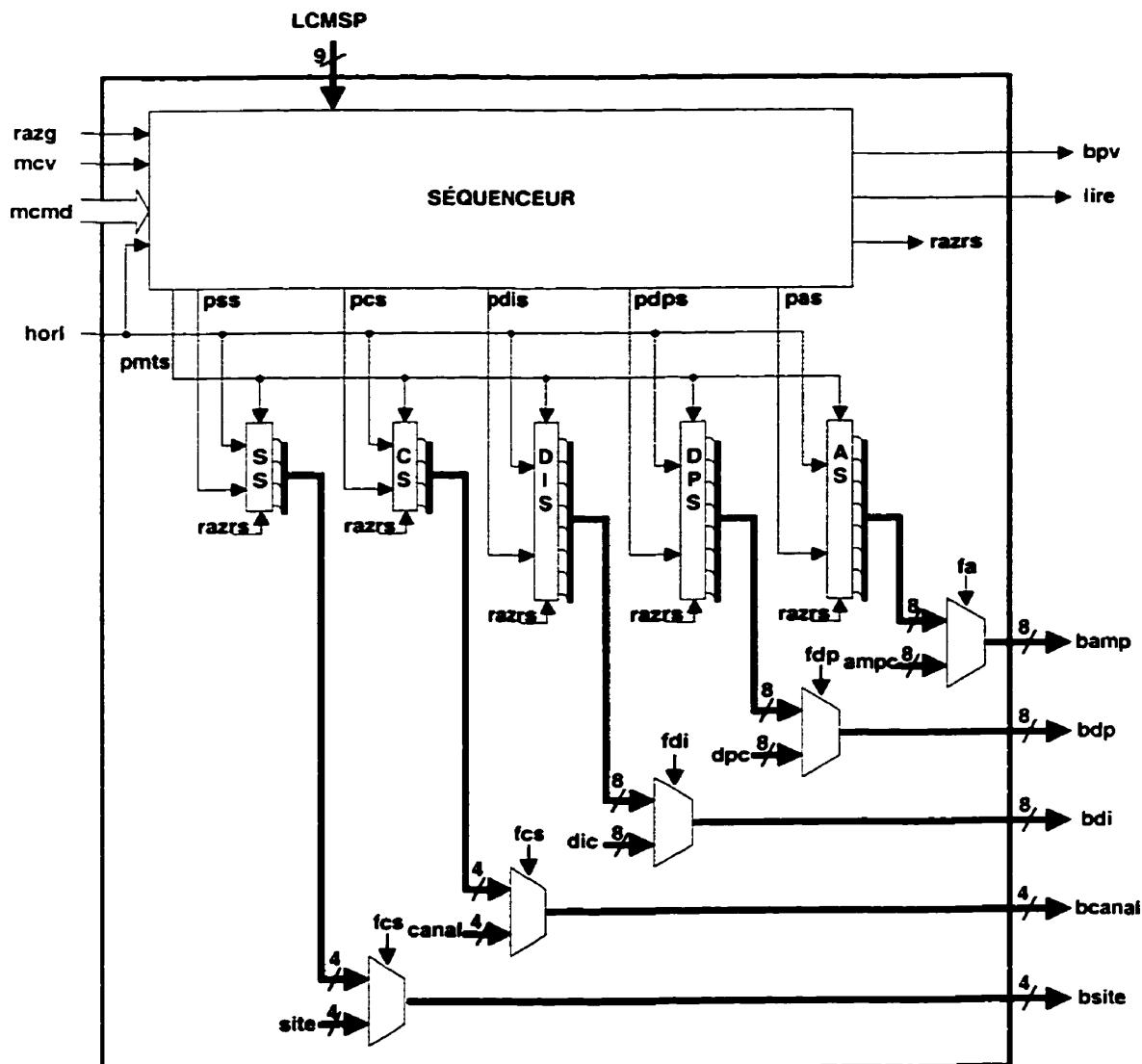

| 4.4.1 Le contrôleur principal (CPIVC) .....                            | 72        |

|                                                                 |            |

|-----------------------------------------------------------------|------------|

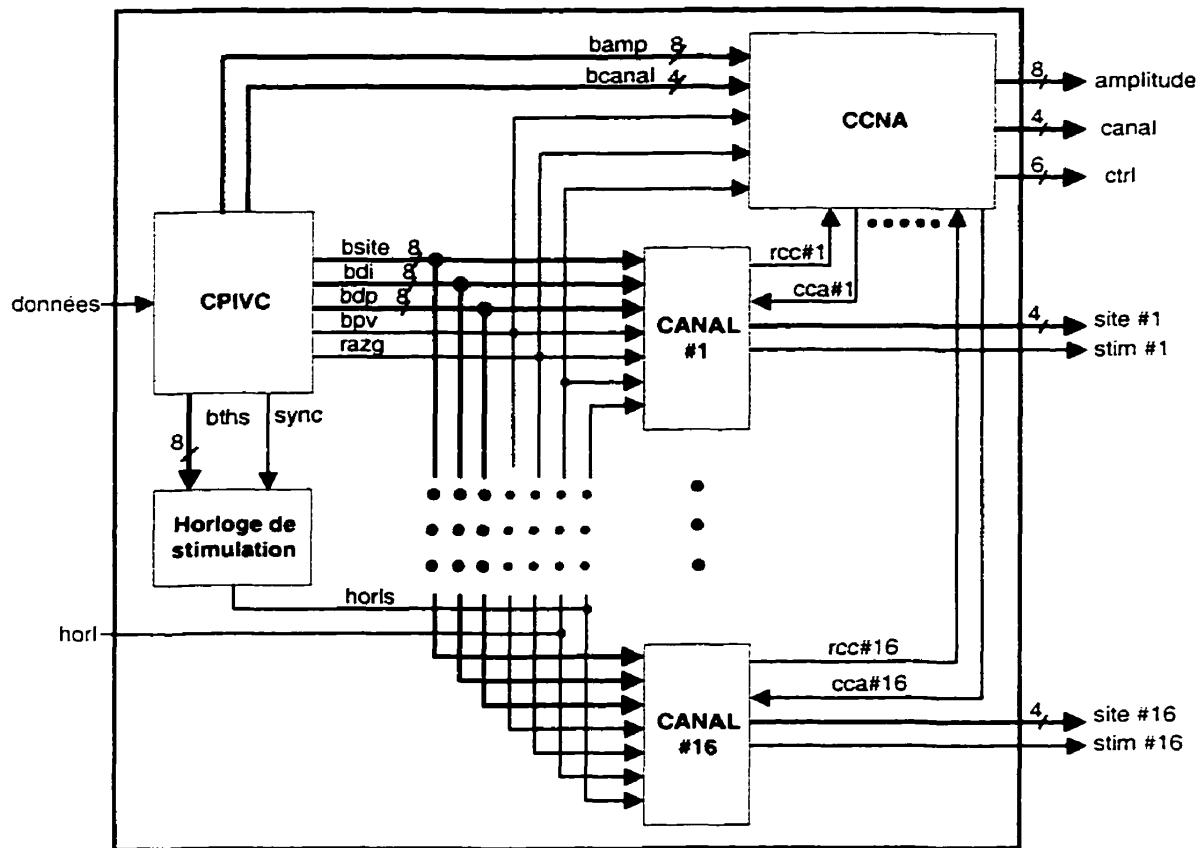

| 4.4.2 Le module de formation des commandes de stimulation ..... | 74         |

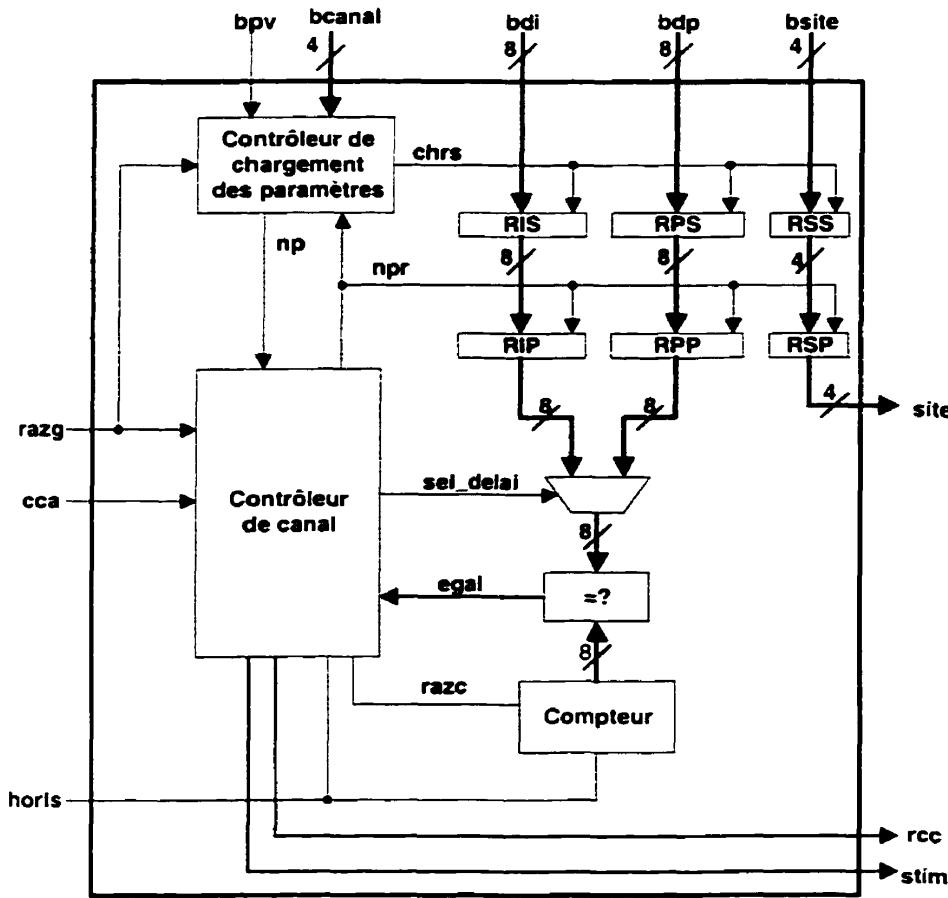

| 4.4.3 Les canaux de stimulation .....                           | 75         |

| 4.5 Conclusion .....                                            | 77         |

| <b>CHAPITRE 5 : RÉALISATION ET RÉSULTATS .....</b>              | <b>78</b>  |

| 5.1 Introduction .....                                          | 78         |

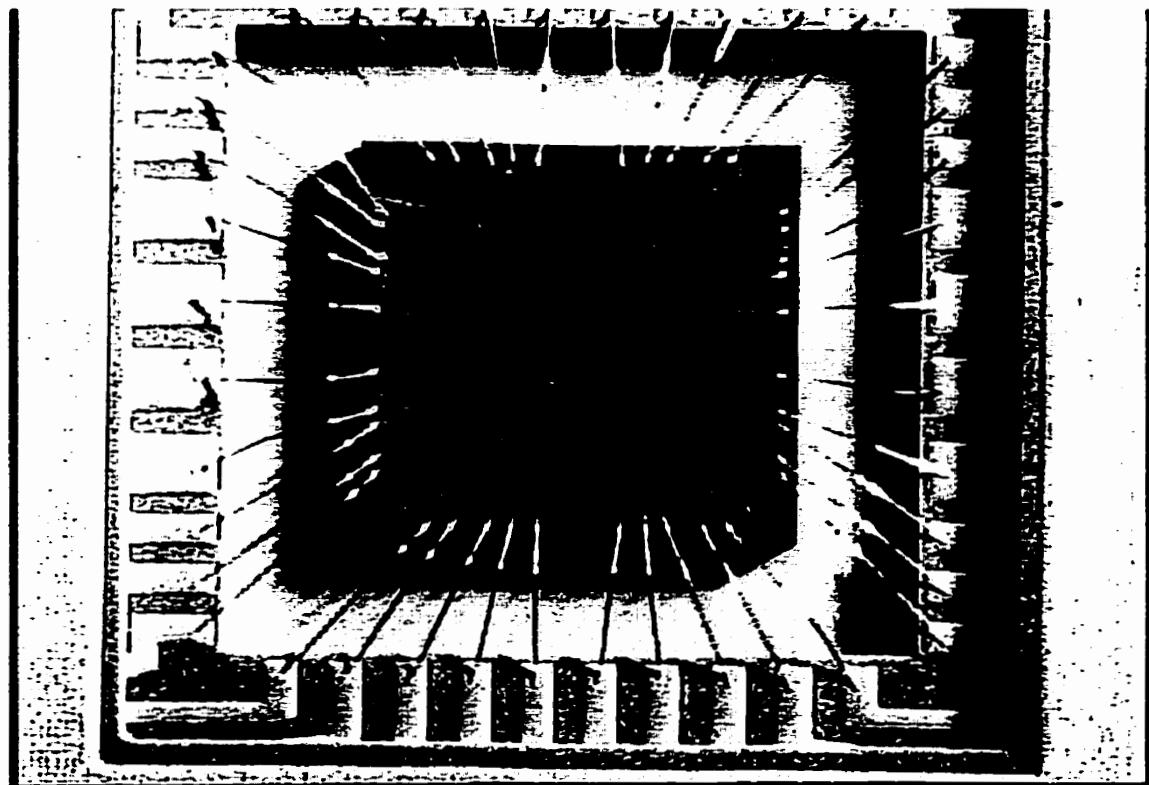

| 5.2 Réalisation du CEB .....                                    | 78         |

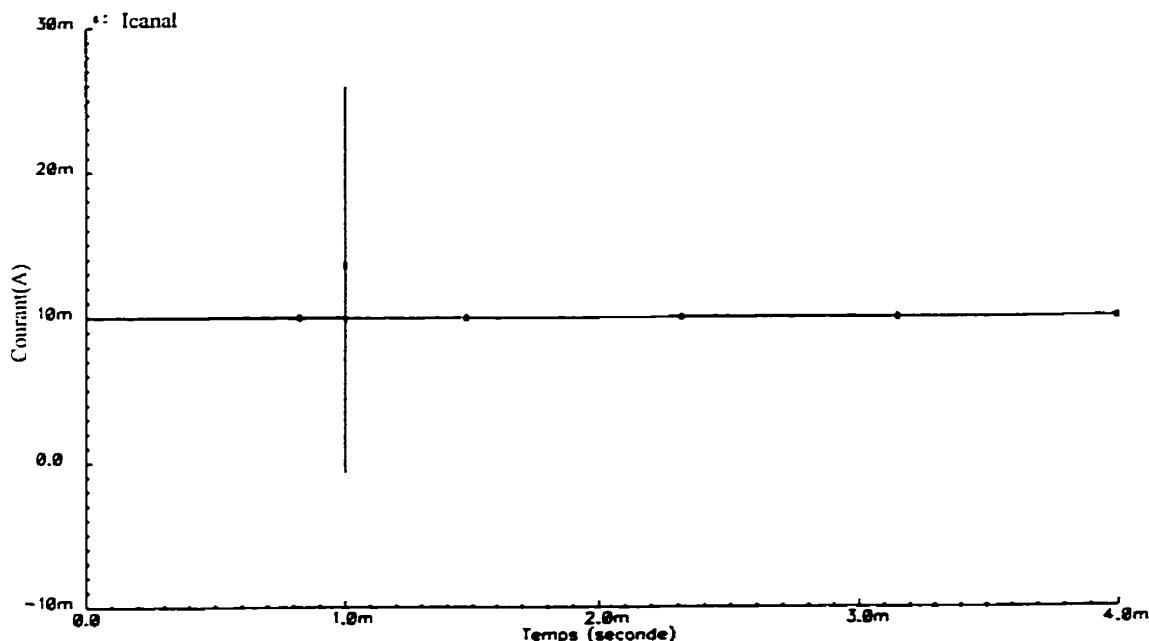

| 5.3 Simulation du CEB .....                                     | 80         |

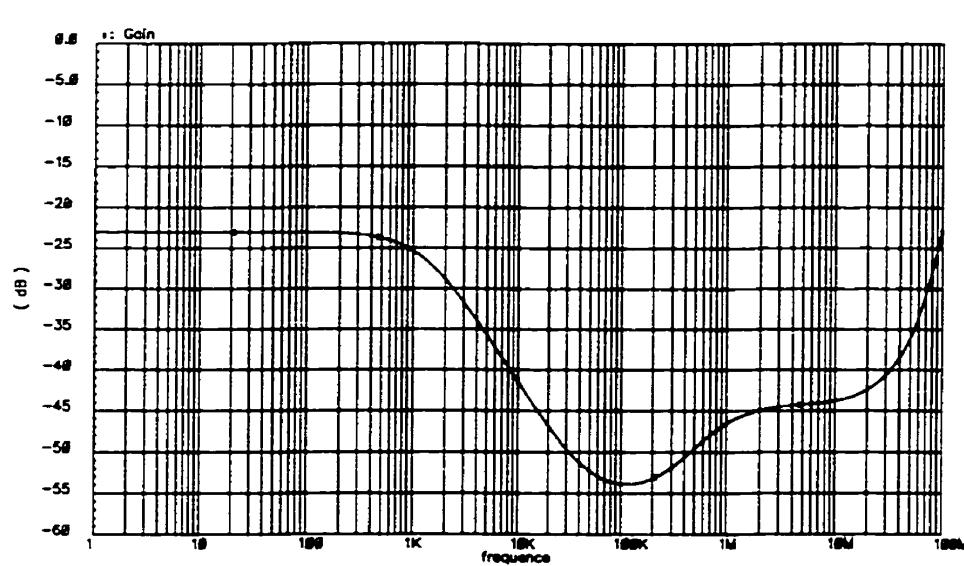

| 5.3.1 L'amplificateur opérationnel .....                        | 80         |

| 5.3.2 Le CNA et le miroir de courant .....                      | 82         |

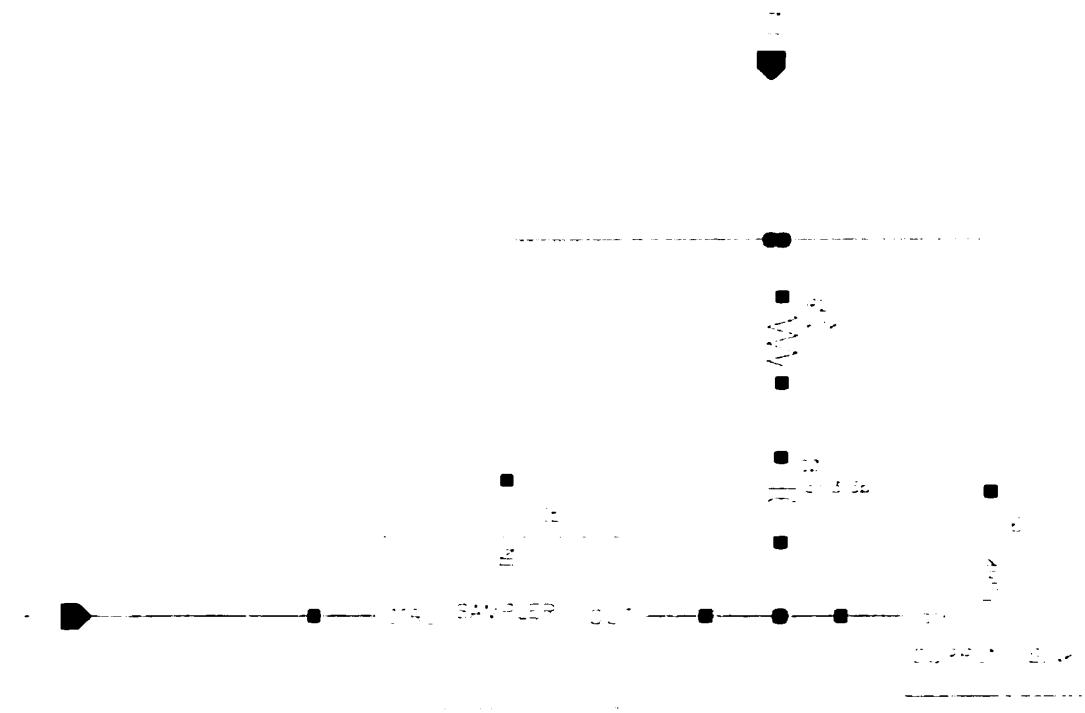

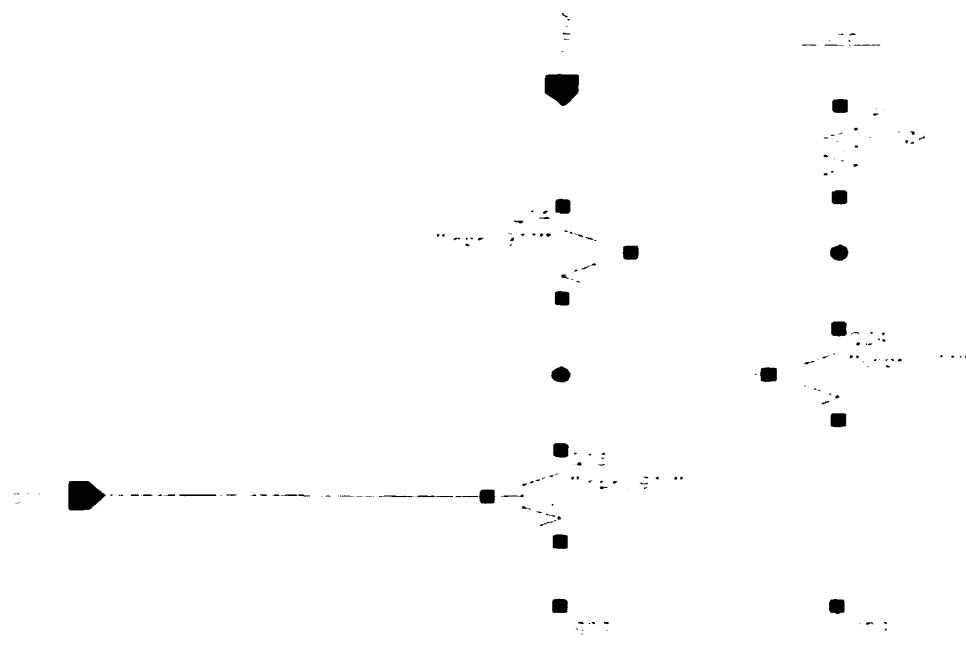

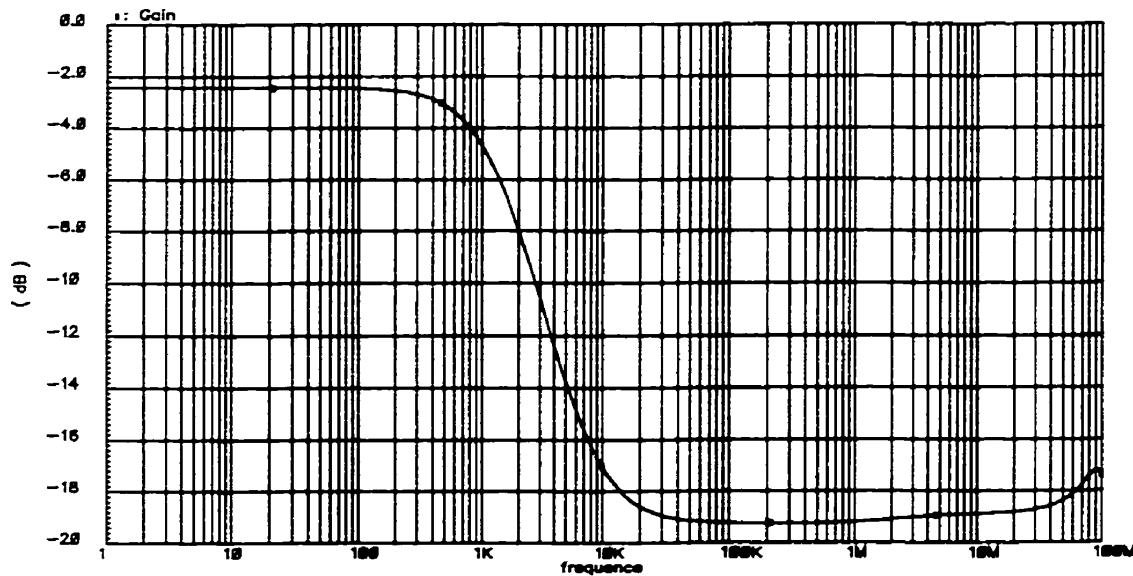

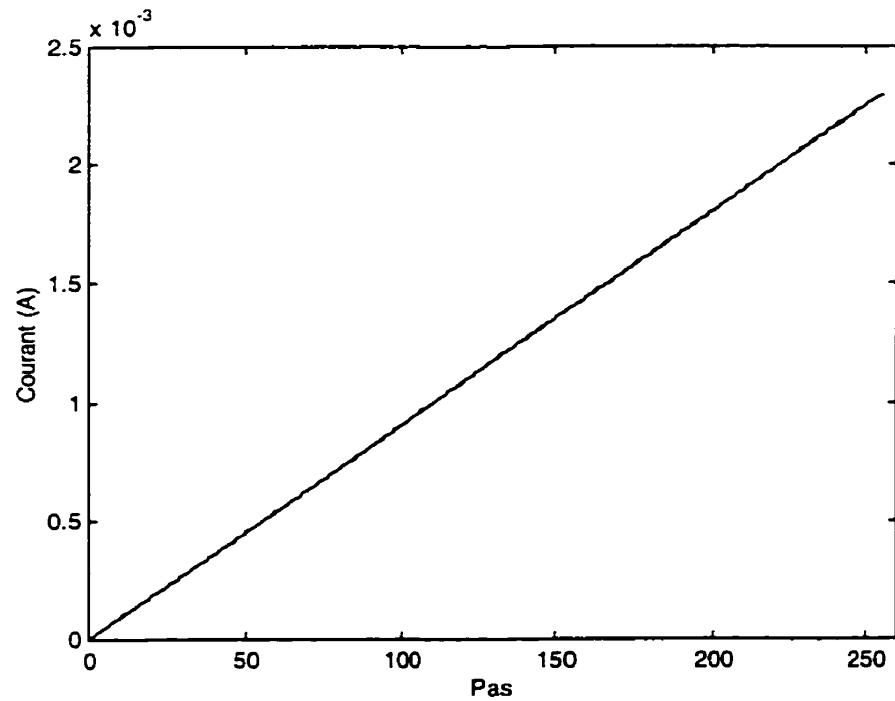

| 5.3.3 L'échantillonneur-bloqueur (EB) .....                     | 83         |

| 5.3.4 Caractéristiques globales du CEB .....                    | 85         |

| 5.3.5 Précision des simulations et causes de défectuosité ..... | 87         |

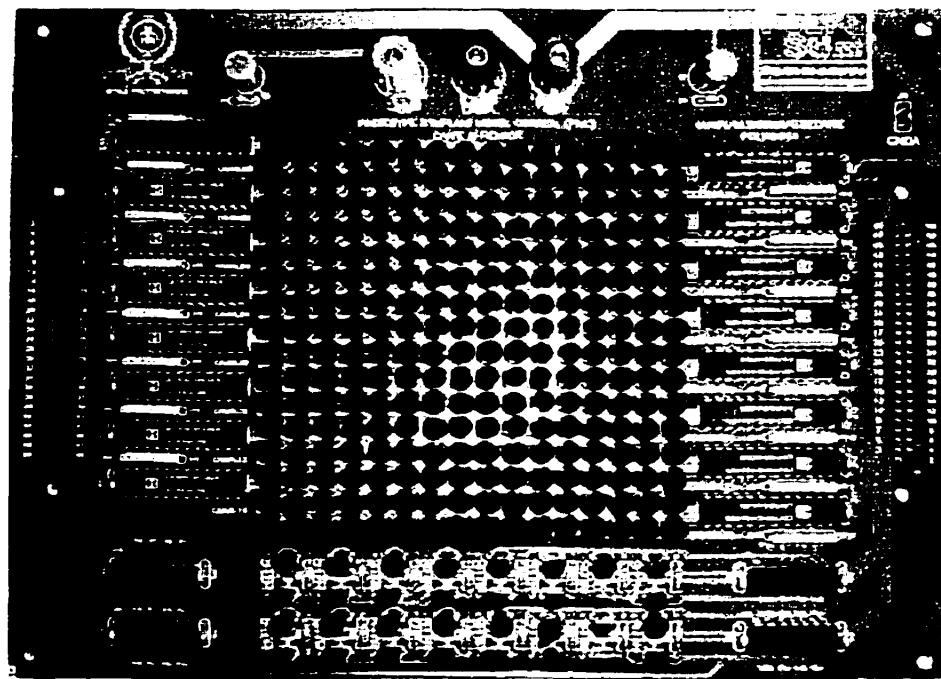

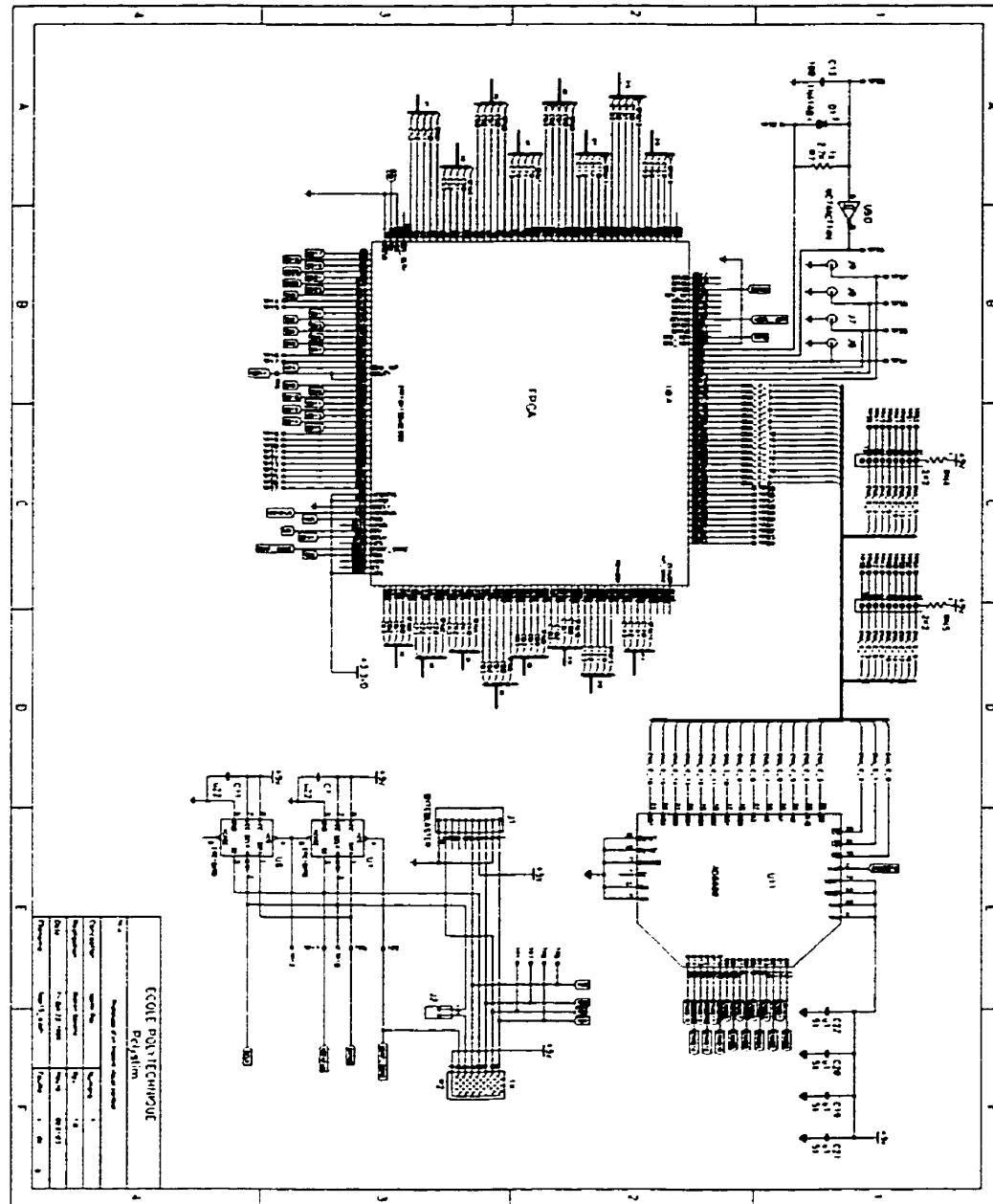

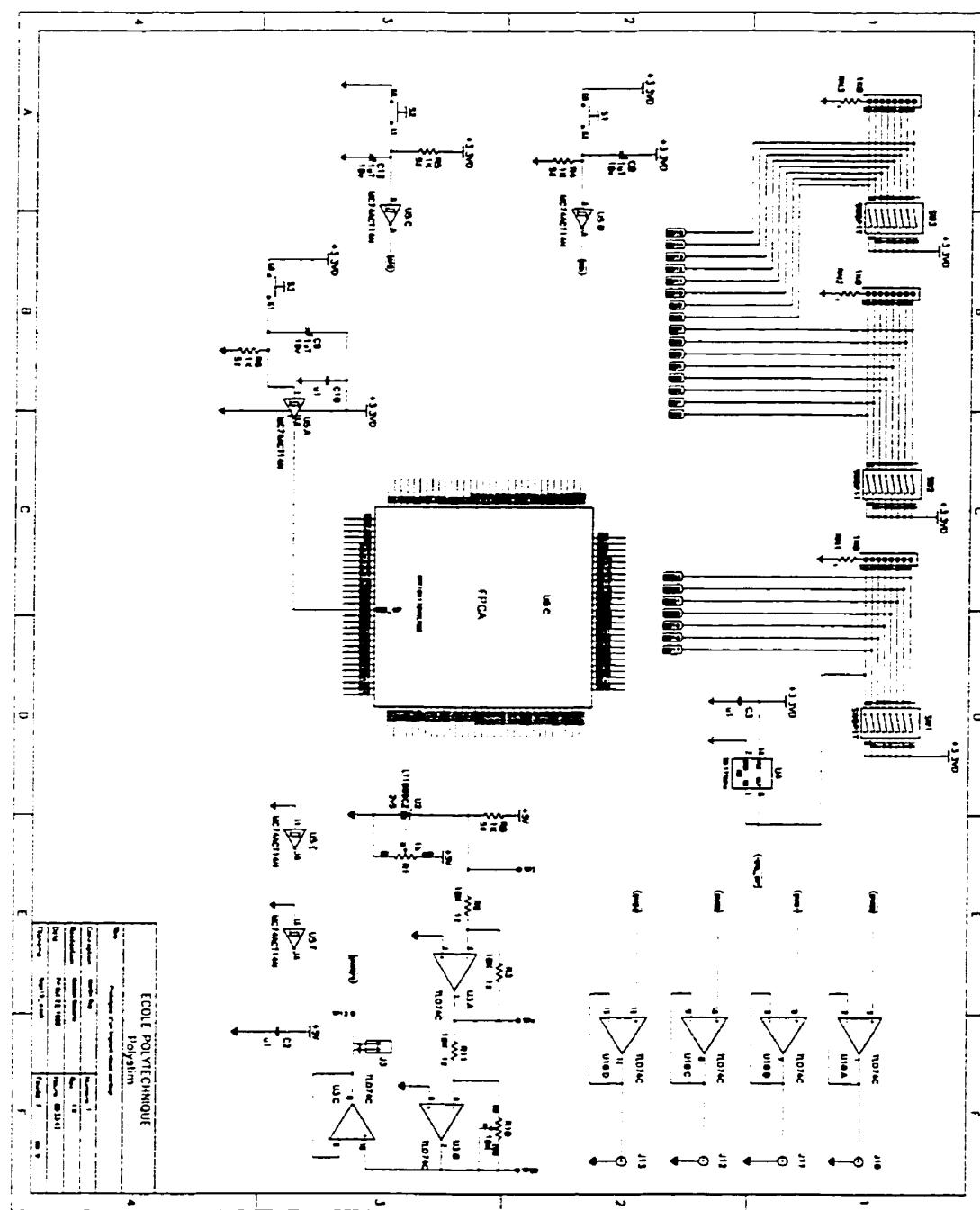

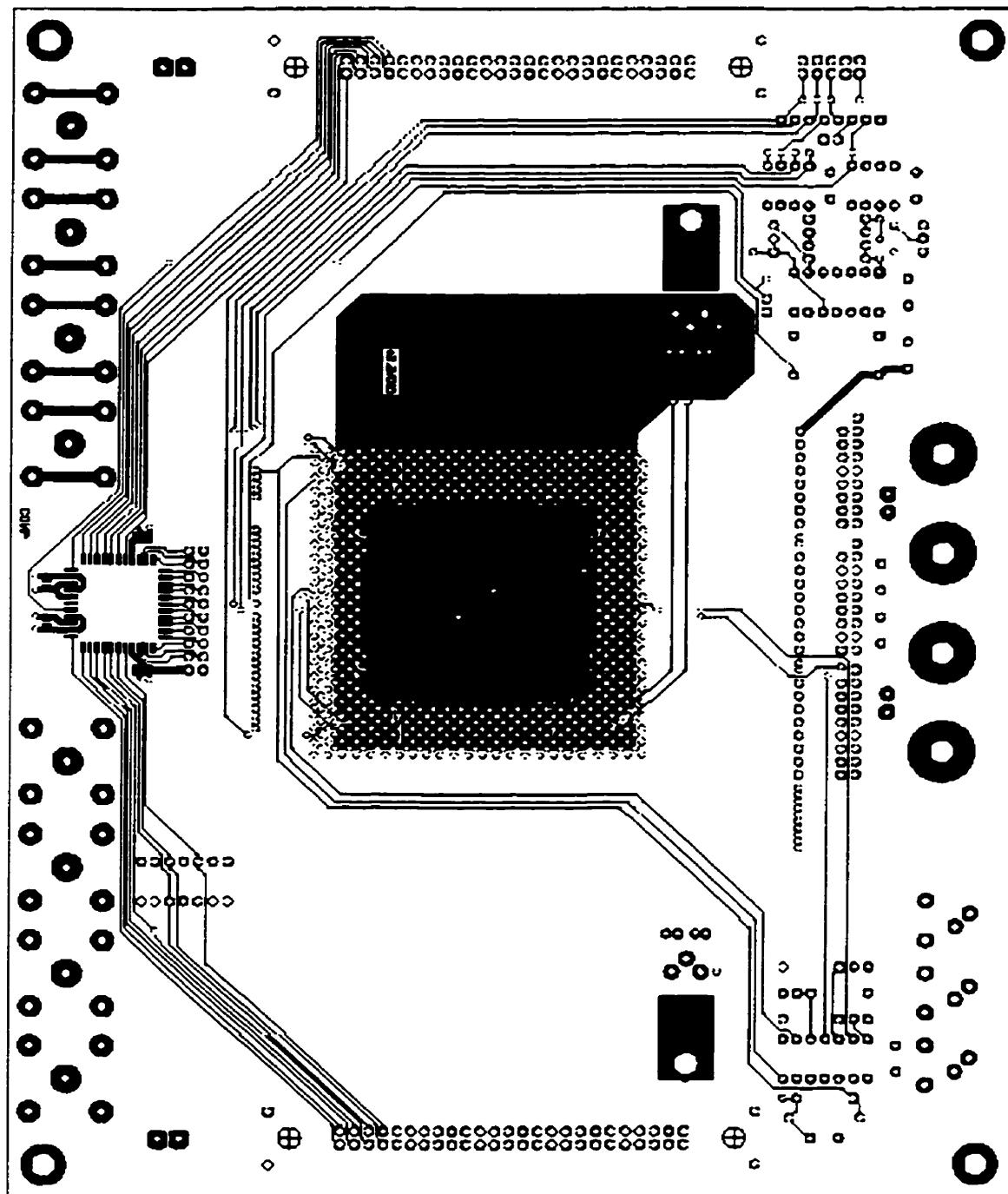

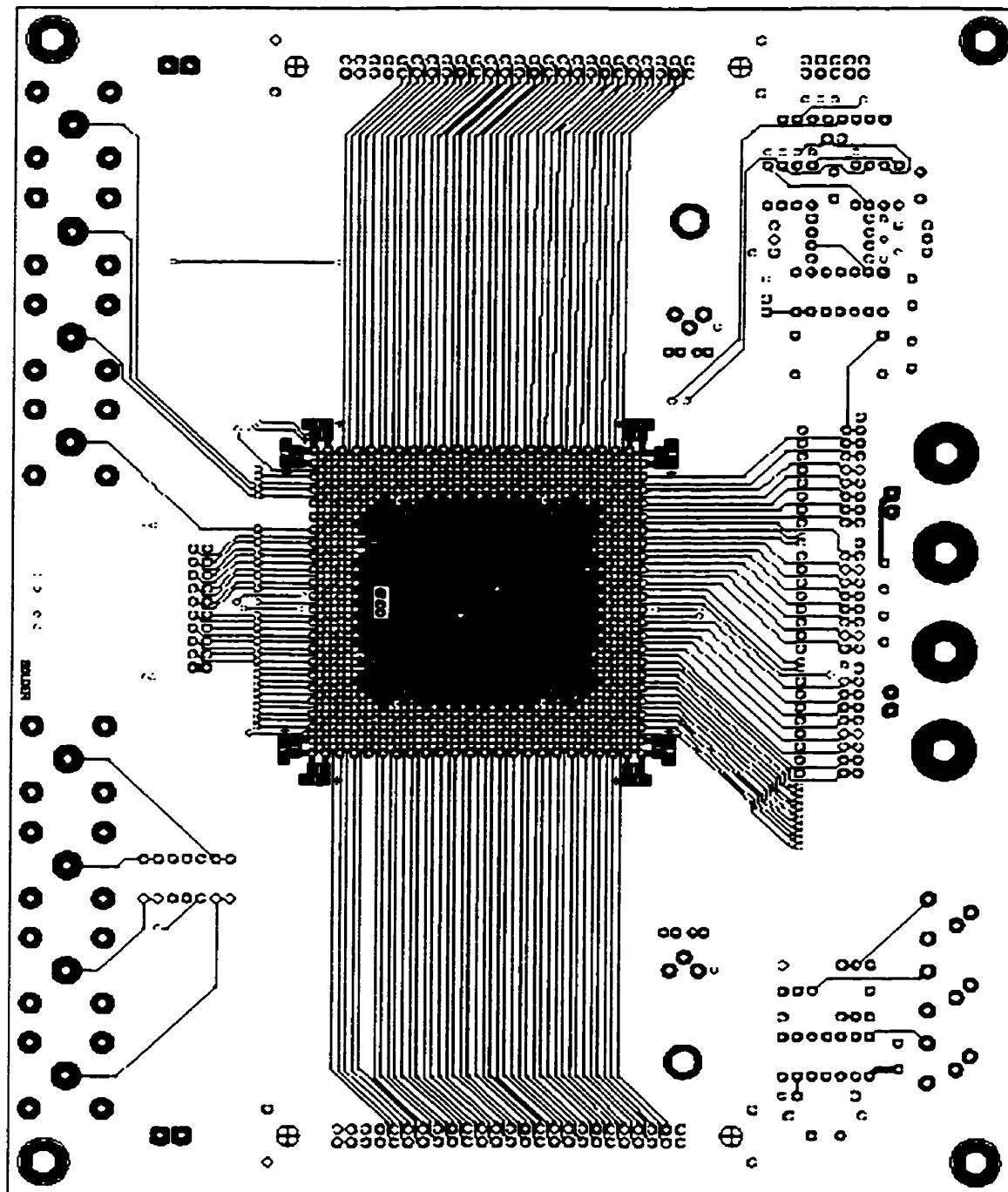

| 5.4 Réalisation du PIVC .....                                   | 87         |

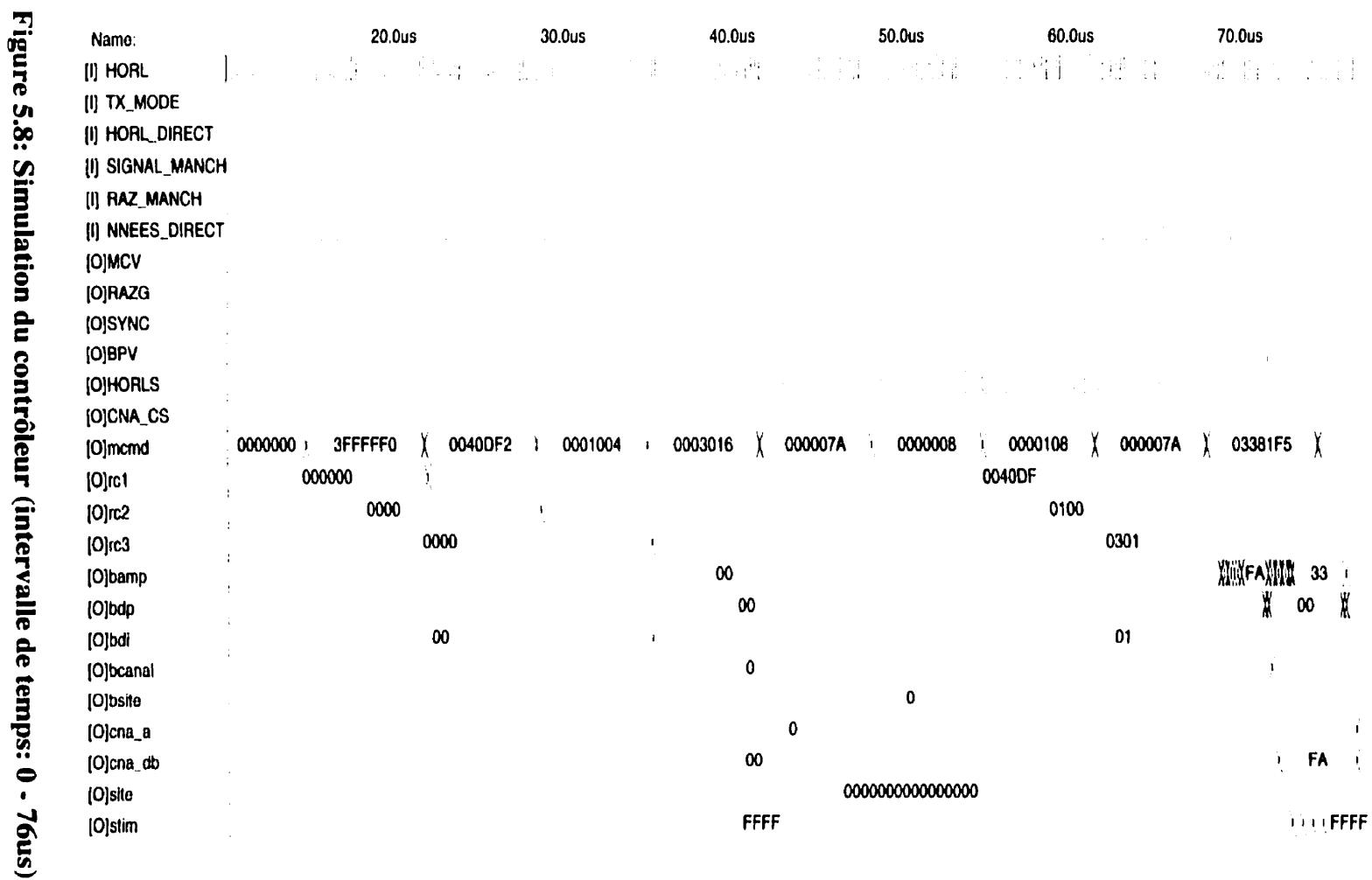

| 5.5 Résultats de simulation du contrôleur du PIVC .....         | 90         |

| 5.6 Vérification de la fonctionnalité du prototype .....        | 94         |

| 5.7 Conclusion .....                                            | 95         |

| <b>CONCLUSION .....</b>                                         | <b>97</b>  |

| <b>BIBLIOGRAPHIE .....</b>                                      | <b>101</b> |

| <b>ANNEXES .....</b>                                            | <b>111</b> |

**LISTE DES TABLEAUX**

|                                                                                        |     |

|----------------------------------------------------------------------------------------|-----|

| Tableau 2.1 : Historique de la stimulation du cortex visuel .....                      | 32  |

| Tableau 4.1 : Description des champs des registres de configuration .....              | 68  |

| Tableau 5.1 : Caractéristiques simulées de l'amplificateur opérationnel .....          | 81  |

| Tableau 5.2 : Caractéristiques simulées du CNA avec et sans le miroir de courant ..... | 82  |

| Tableau 5.3 : Caractéristiques simulées d'un EB .....                                  | 85  |

| Tableau 5.4 : Caractéristiques simulées du CEB .....                                   | 86  |

| Tableau A.1 : Liste des broches spéciales et d'alimentation du CPLD .....              | 121 |

| Tableau A.2 : Liste des entrées du contrôleur et broches associées .....               | 124 |

| Tableau A.3 : Liste des sorties du contrôleur et broches associées .....               | 125 |

| Tableau A.4 : Liste des points de test du contrôleur et broches associées .....        | 129 |

| Tableau D.1 : Liste des fichiers de la description VHDL du contrôleur du PIVC .....    | 147 |

| Tableau G.1 : Contenu des registres de configuration .....                             | 213 |

| Tableau G.2 : Description des types de test .....                                      | 215 |

## LISTE DES FIGURES

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| Figure 1.1 : La cellule nerveuse .....                                        | 7  |

| Figure 1.2 : Schéma bloc typique d'un stimulateur multicanaux .....           | 10 |

| Figure 1.3 : Circuit simplifié d'un lien inductif .....                       | 14 |

| Figure 1.4 : Récepteur et modulateur LSK .....                                | 15 |

| Figure 1.5 : Codage Manchester .....                                          | 16 |

| Figure 1.6 : CNA à miroirs de courant simple .....                            | 17 |

| Figure 1.7 : CNA en BiCMOS .....                                              | 18 |

| Figure 1.8 : CNA proposé par St-Amand [62] .....                              | 19 |

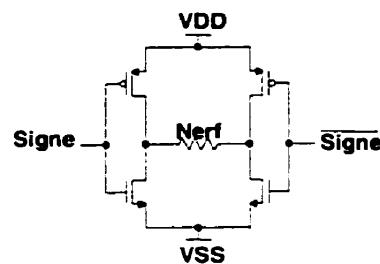

| Figure 1.9 : Contrôle du sens du courant .....                                | 19 |

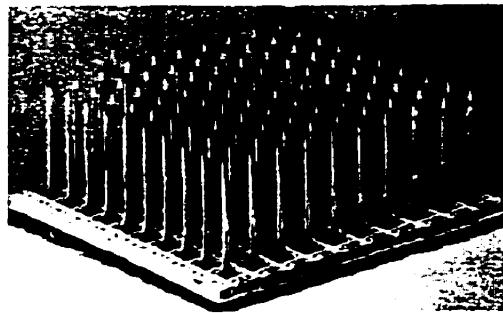

| Figure 1.10 : Réseau d'électrodes (tiré de [33]) .....                        | 20 |

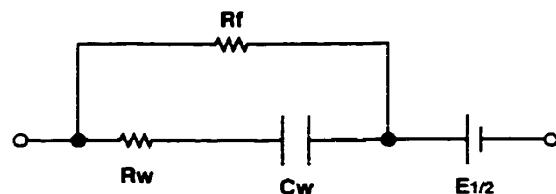

| Figure 1.11 : Modèle de l'interface électrode-électrolyte .....               | 21 |

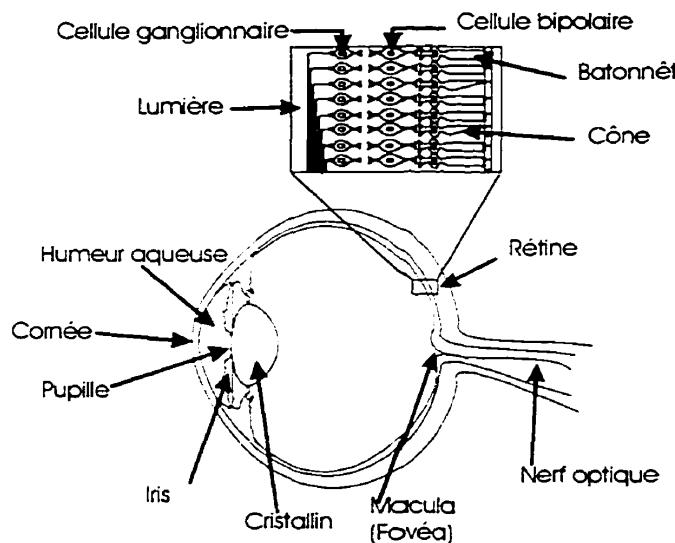

| Figure 2.1 : Vue en coupe d'un oeil .....                                     | 25 |

| Figure 2.2 : Le système visuel humain .....                                   | 26 |

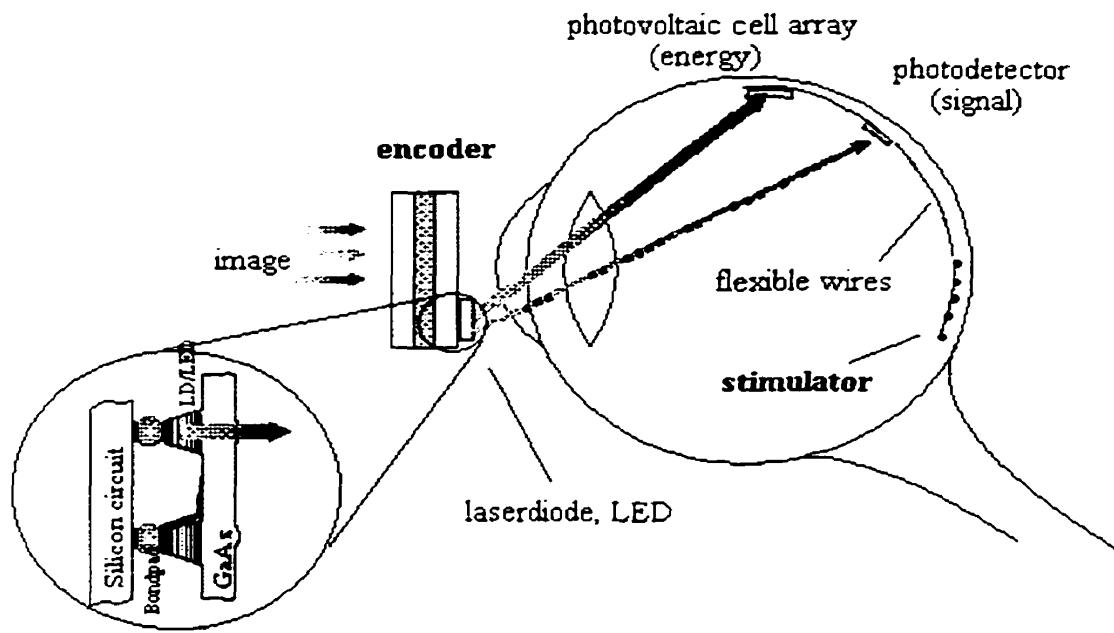

| Figure 2.3 : Implant rétinien (tiré de [8]) .....                             | 28 |

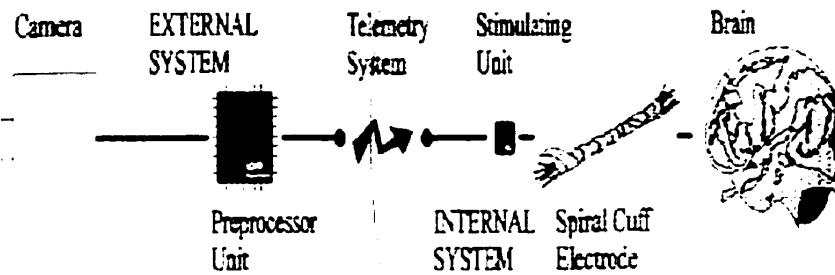

| Figure 2.4 : Stimulateur du nerf optique (tiré de [10]) .....                 | 29 |

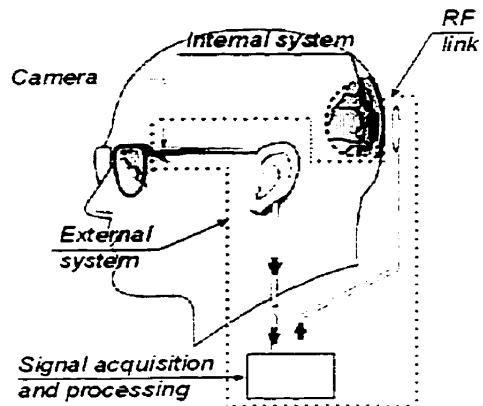

| Figure 2.5 : Implant cortical (adapté de [14]) .....                          | 30 |

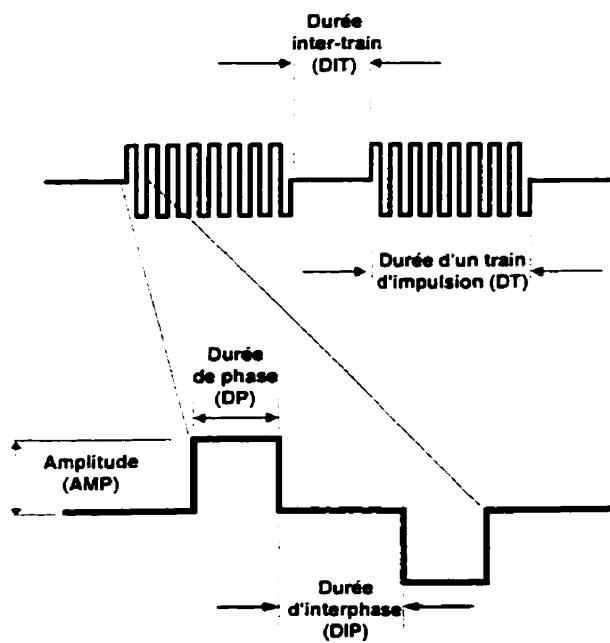

| Figure 2.6 : Formes d'onde utilisées pour la stimulation intracorticale ..... | 34 |

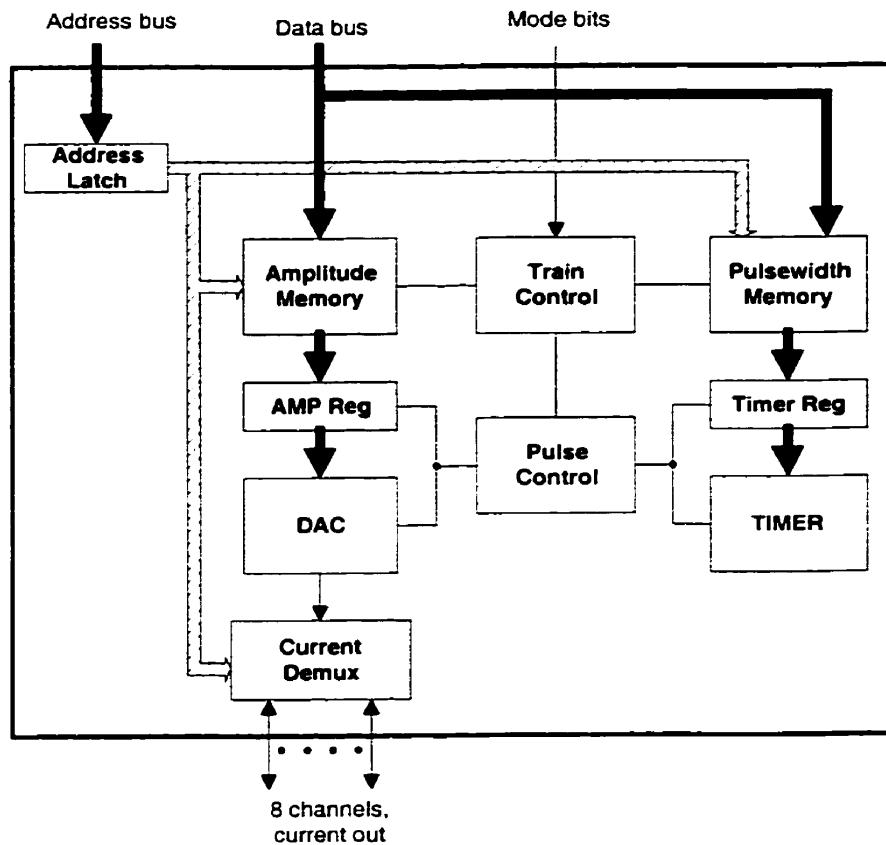

| Figure 2.7 : Stimulateur visuel miniaturisé de Boyer [52] .....               | 37 |

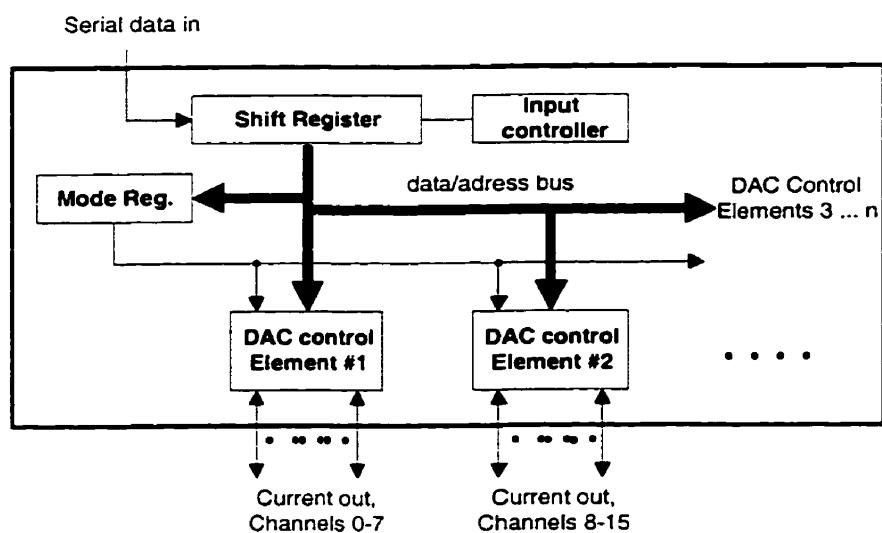

| Figure 2.8 : Structure générale du CI de Jones et Normann [39] .....          | 38 |

| Figure 2.9 : Structure d'un canal de stimulation (DAC control element) .....  | 39 |

| Figure 3.1 : Prototype du stimulateur visuel cortical .....                   | 46 |

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

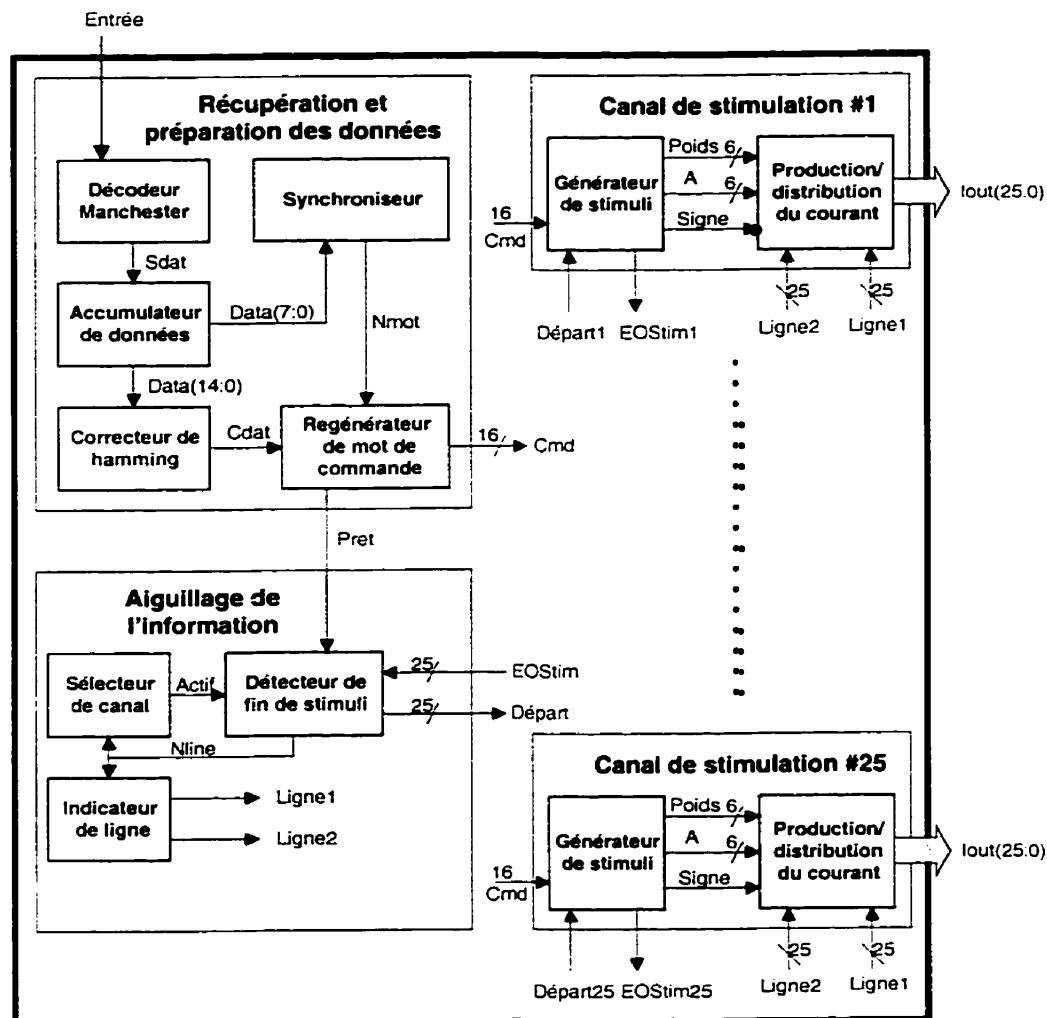

| Figure 3.2 : Schéma bloc de la première architecture du PIVC .....                | 47 |

| Figure 3.3 : Décodeur Manchester (tiré de [80]) .....                             | 49 |

| Figure 3.4 : Exemple de formes d'onde des E/S du décodeur Manchester.....         | 50 |

| Figure 3.5 : Sélection d'une DEL et contrôle de l'intensité de son courant.....   | 51 |

| Figure 3.6 : Schéma bloc de la deuxième architecture du PIVC .....                | 52 |

| Figure 3.7 : Schéma bloc simplifié du CEB.....                                    | 54 |

| Figure 3.8 : Miroir de courant dynamique .....                                    | 55 |

| Figure 3.9 : Échantillonneur- bloqueur en mode courant .....                      | 56 |

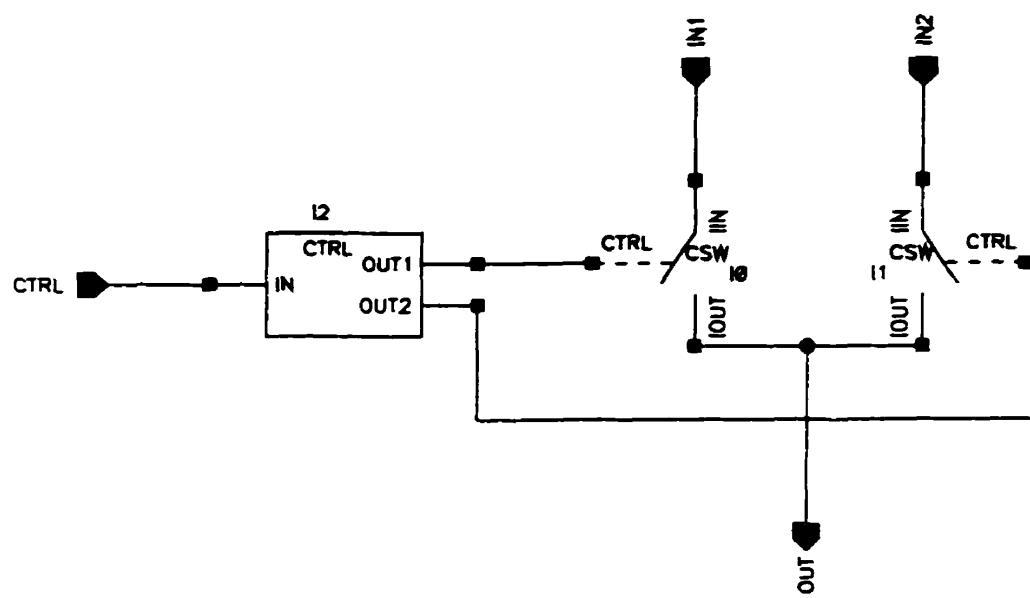

| Figure 3.10 : Schéma bloc du commutateur ITA .....                                | 58 |

| Figure 3.11 : Circuit d'un commutateur de courant .....                           | 58 |

| Figure 3.12 : Schéma simplifié du convertisseur numérique-analogique .....        | 60 |

| Figure 3.13 : Schéma d'un commutateur utilisé dans le CNA .....                   | 61 |

| Figure 4.1 : Format d'une trame de données .....                                  | 65 |

| Figure 4.2 : Disposition des bits dans une trame de données.....                  | 66 |

| Figure 4.3 : Format des mots de configuration .....                               | 67 |

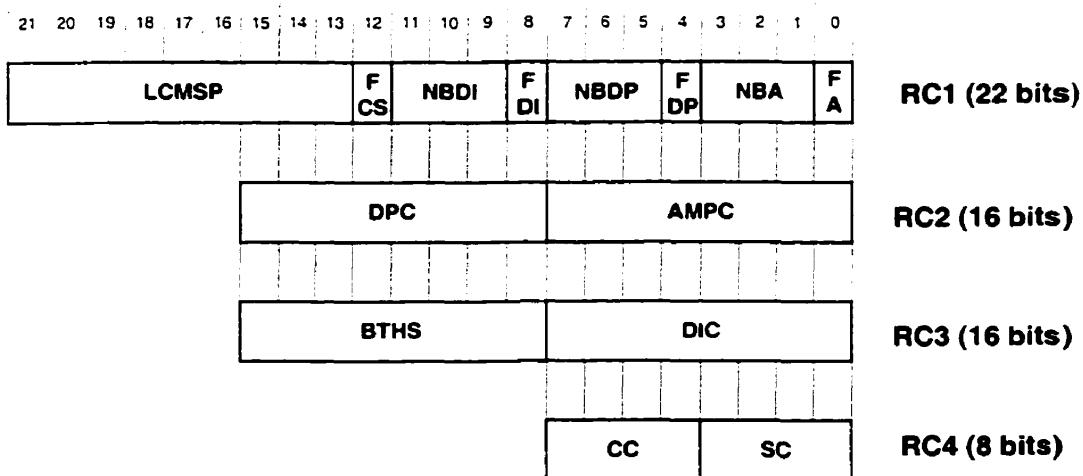

| Figure 4.4 : Contenu des registres de configuration.....                          | 67 |

| Figure 4.5 : Composition d'un mot de paramètres (MPMT) .....                      | 69 |

| Figure 4.6 : Schéma bloc du circuit numérique de contrôle du PIVC .....           | 71 |

| Figure 4.7 : Schéma bloc simplifié du CPIVC .....                                 | 72 |

| Figure 4.8: Schéma bloc du module de formation des commandes de stimulation ..... | 75 |

| Figure 4.9 : Schéma bloc d'un canal de stimulation .....                          | 76 |

| Figure 5.1 : Photographie du CEB .....                                            | 79 |

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

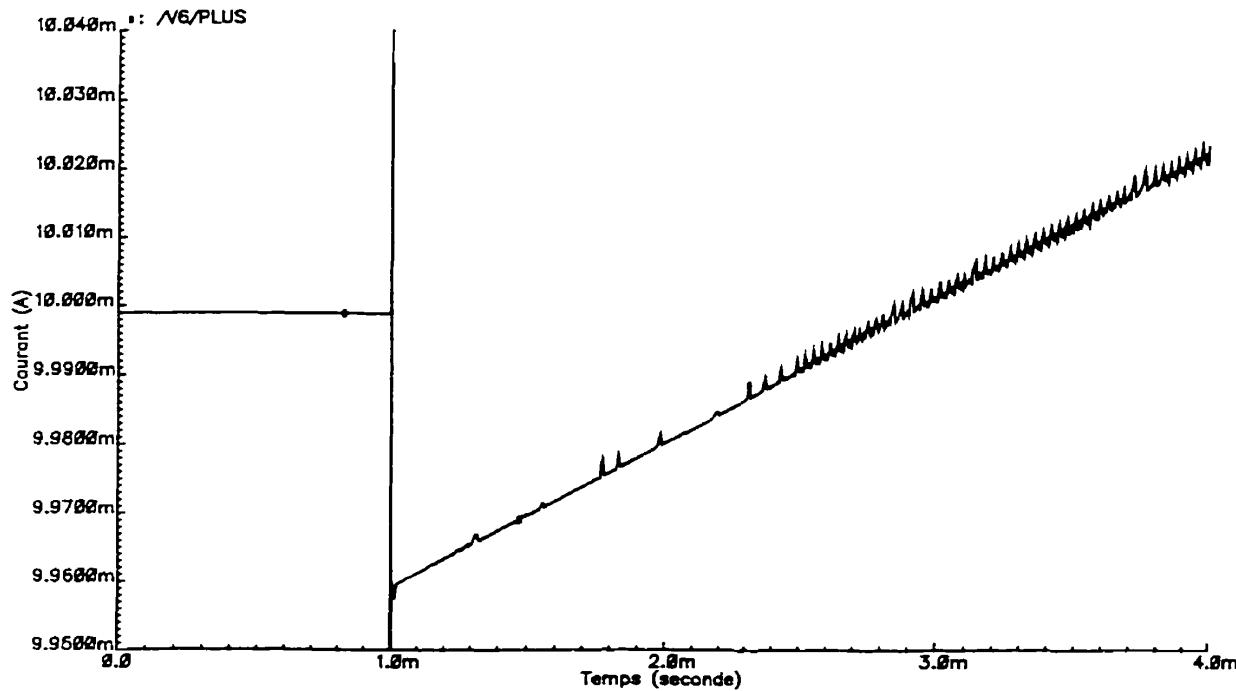

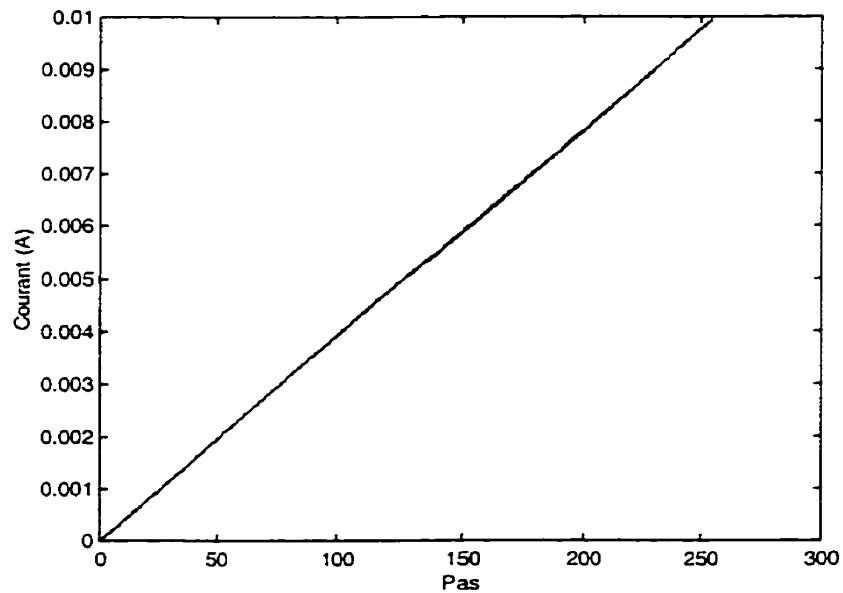

| Figure 5.2 : Opération (échantillonnage/maintient) d'un EB .....                  | 83  |

| Figure 5.3 :Dérive du courant d'un EB en mode maintient .....                     | 84  |

| Figure 5.4 : Réponses simulée et idéale du CEB (mode maintient) .....             | 86  |

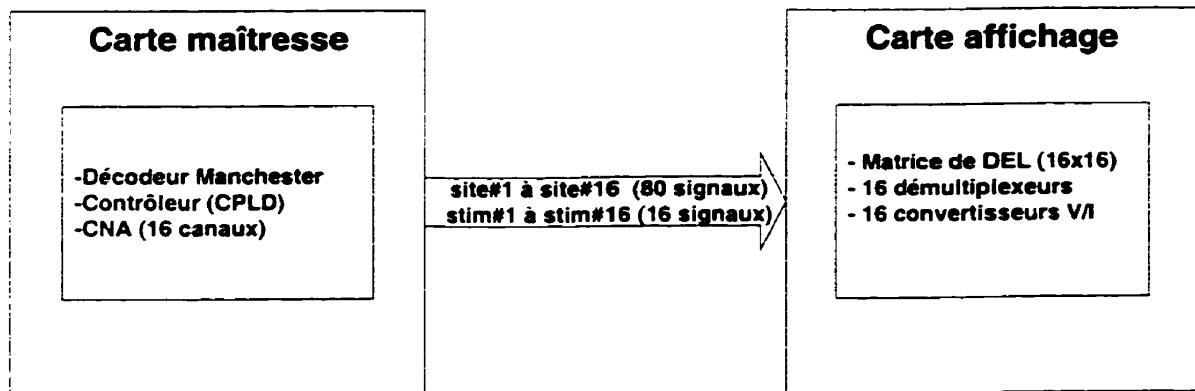

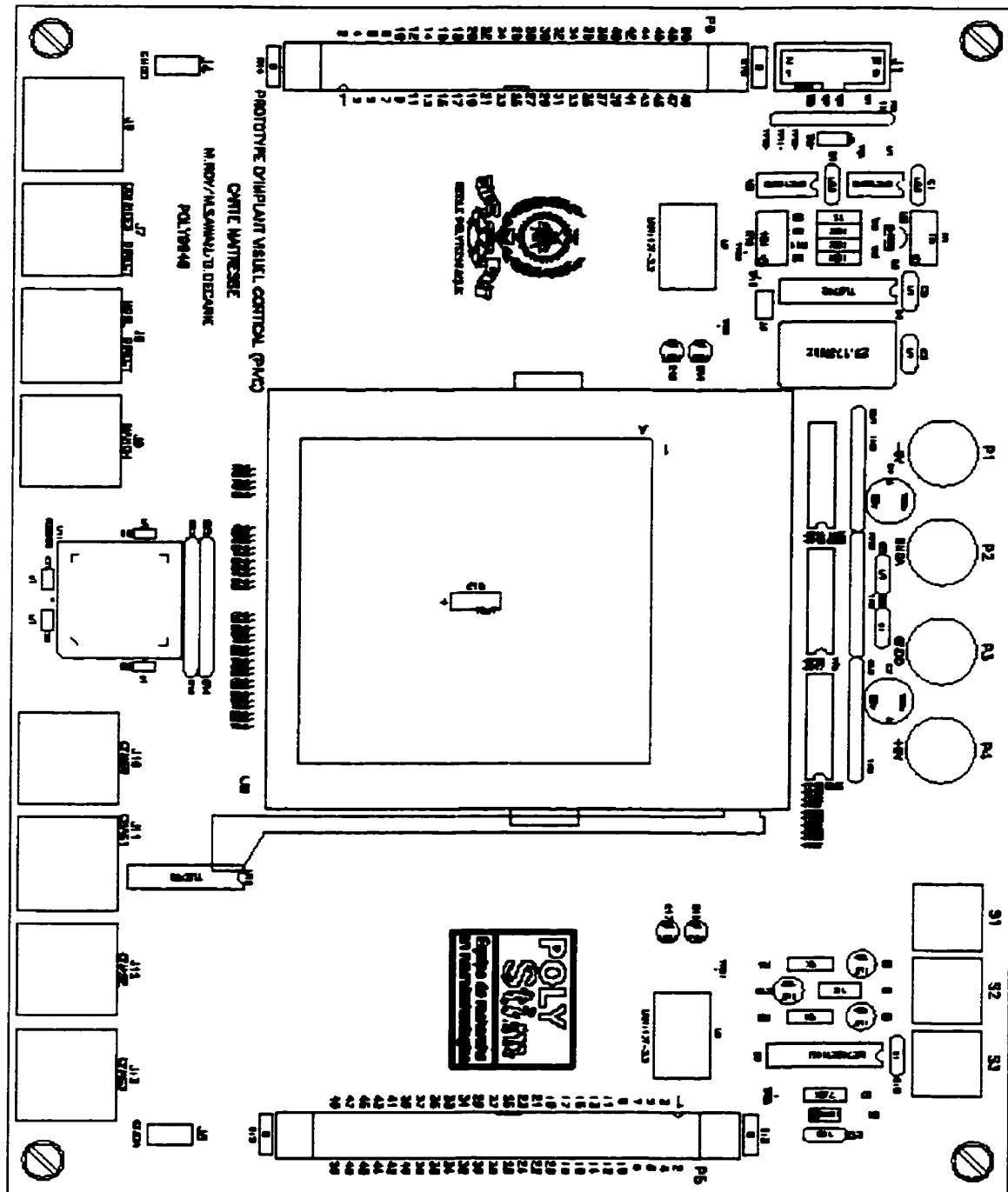

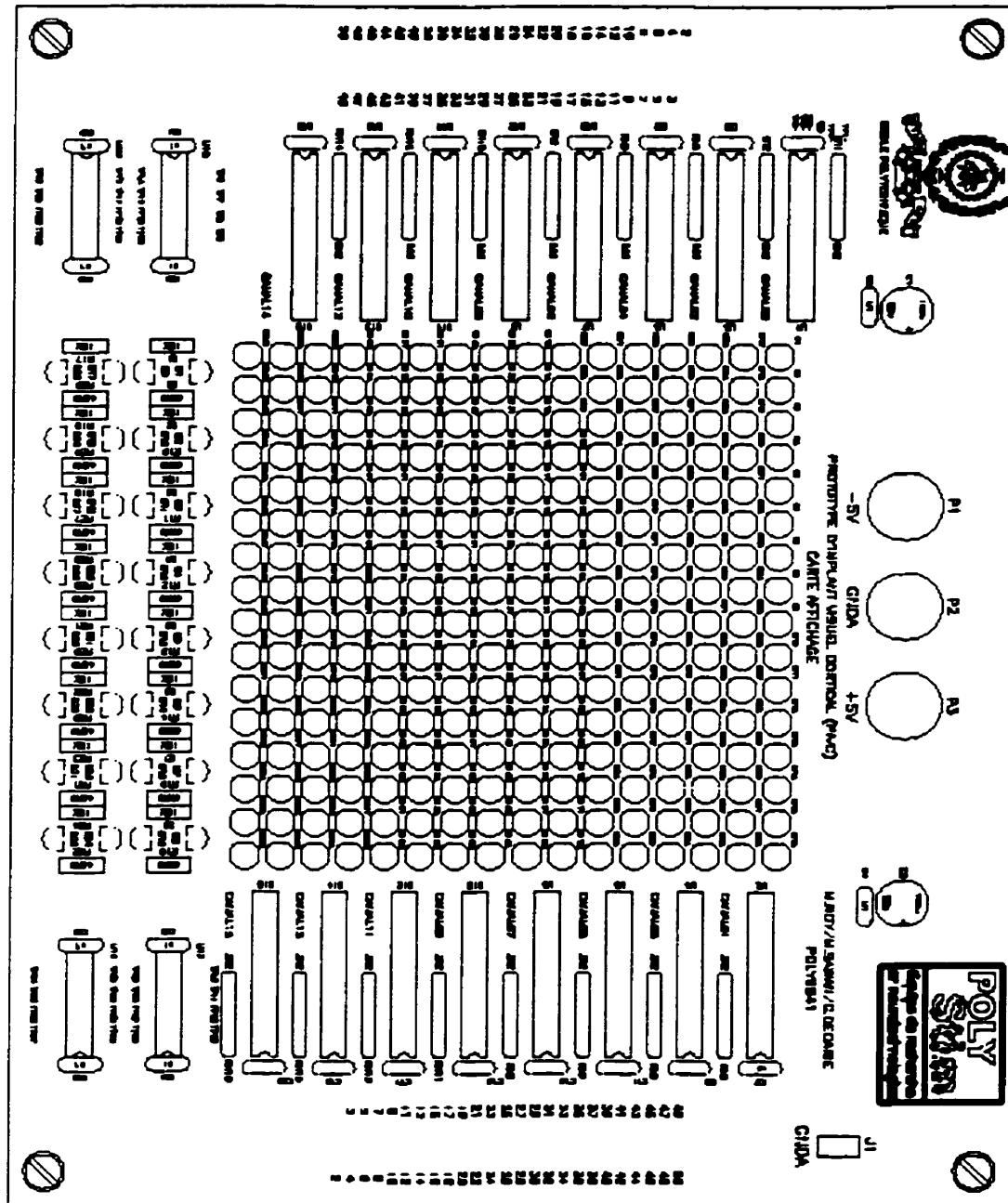

| Figure 5.5 : Principaux éléments de chaque carte du prototype .....               | 88  |

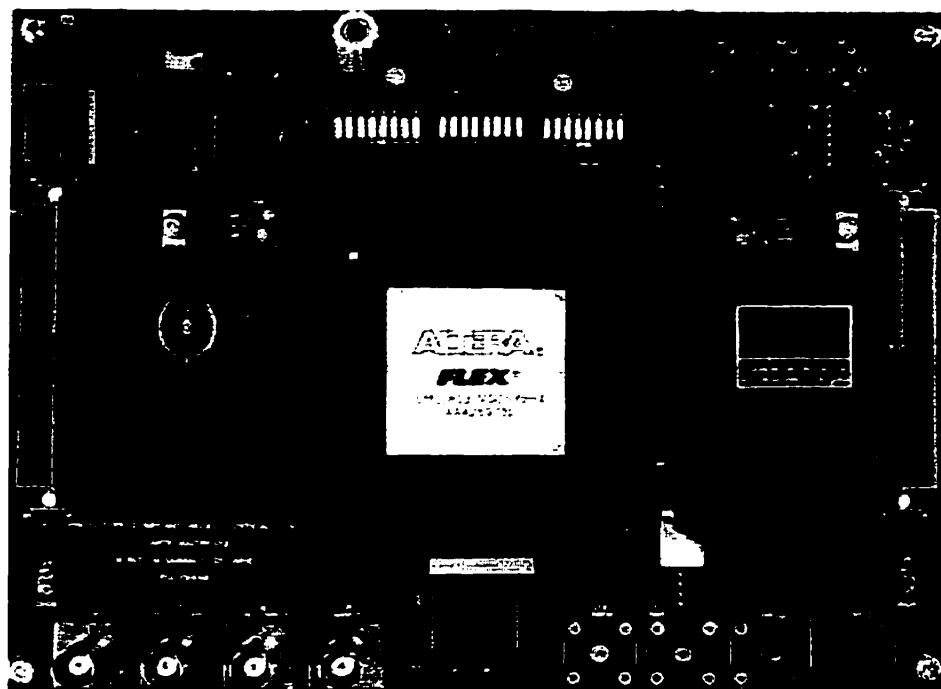

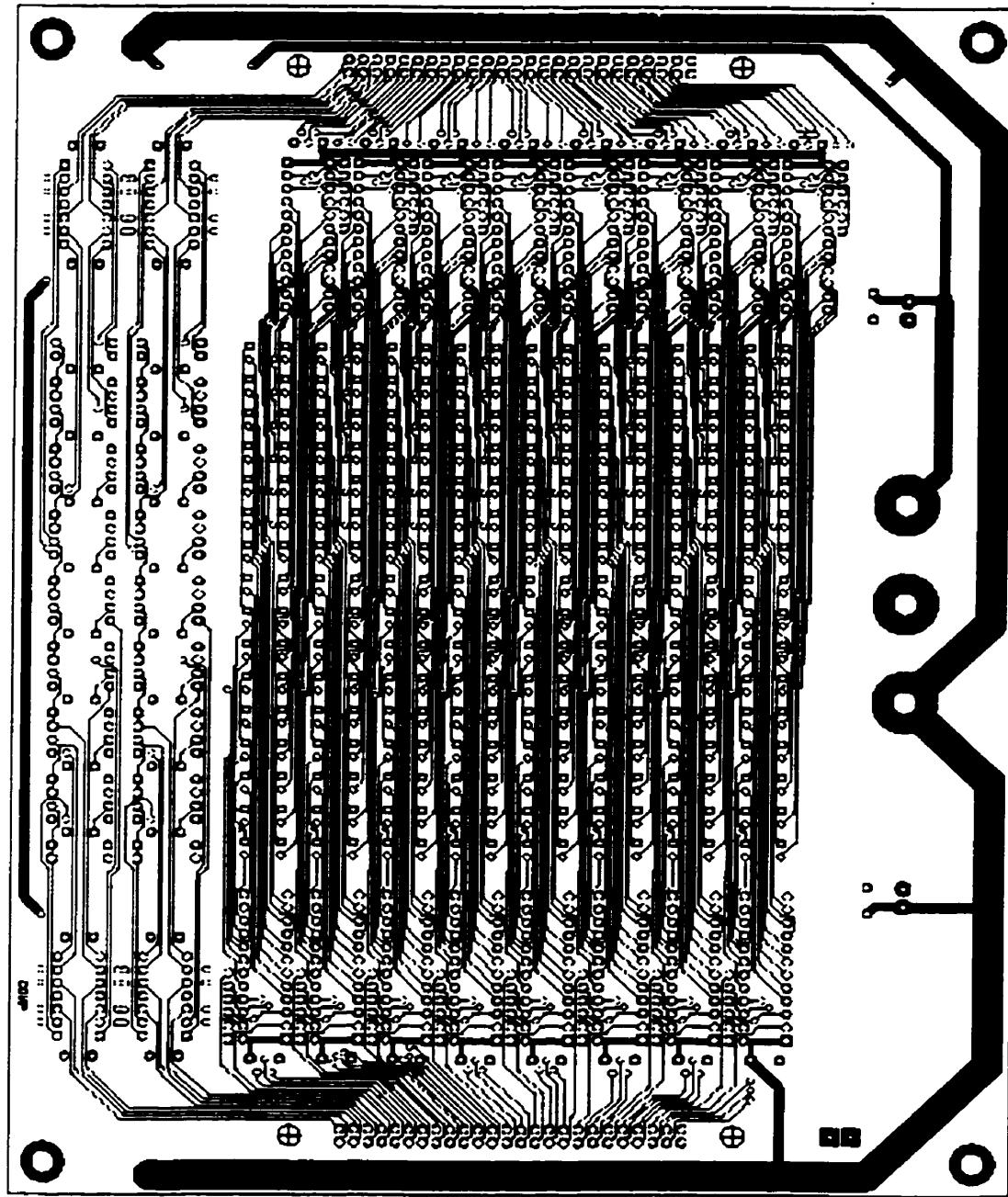

| Figure 5.6 : Photographie du circuit imprimé de la carte maîtresse .....          | 89  |

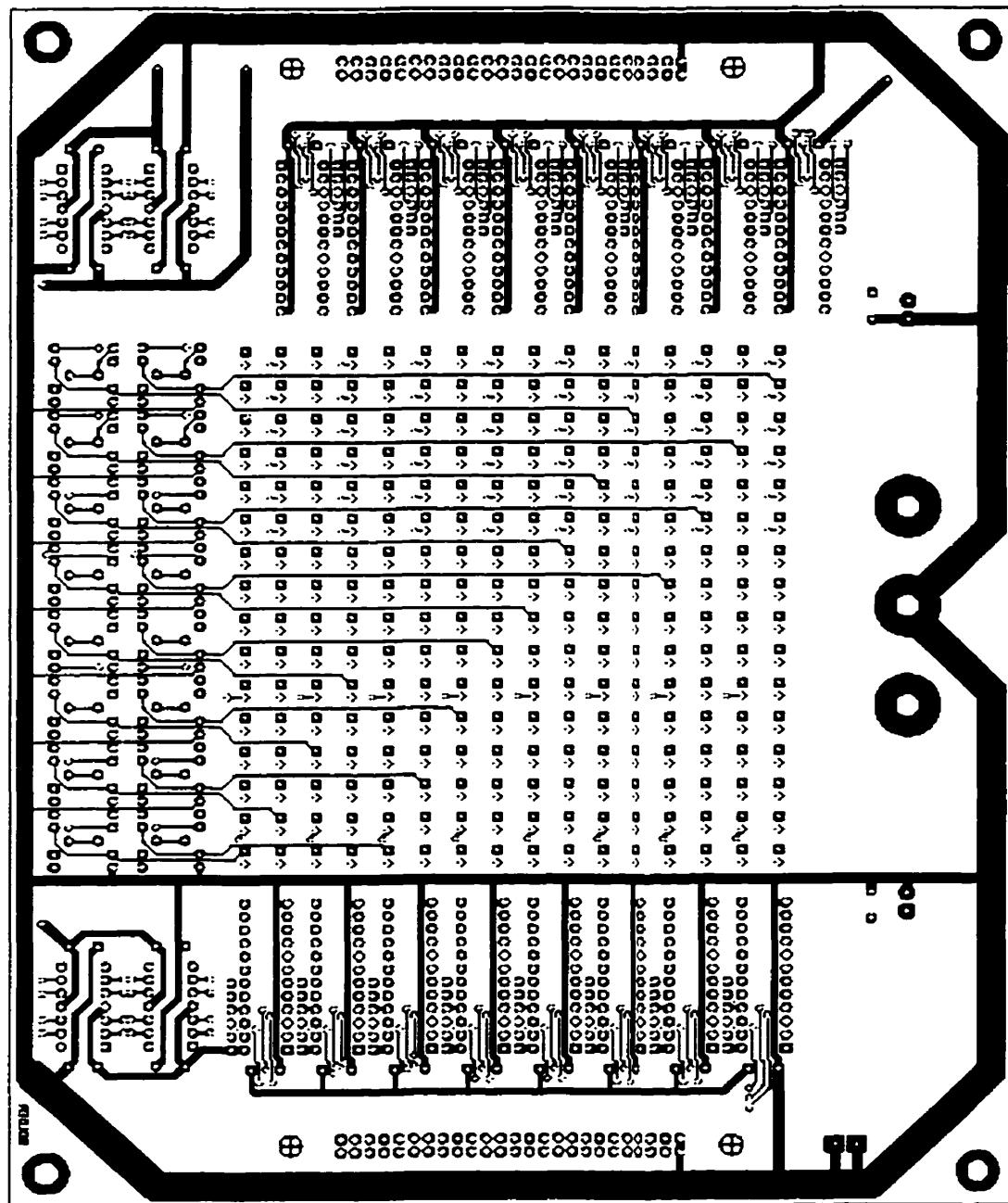

| Figure 5.7 : Photographie du circuit imprimé de la carte affichage .....          | 89  |

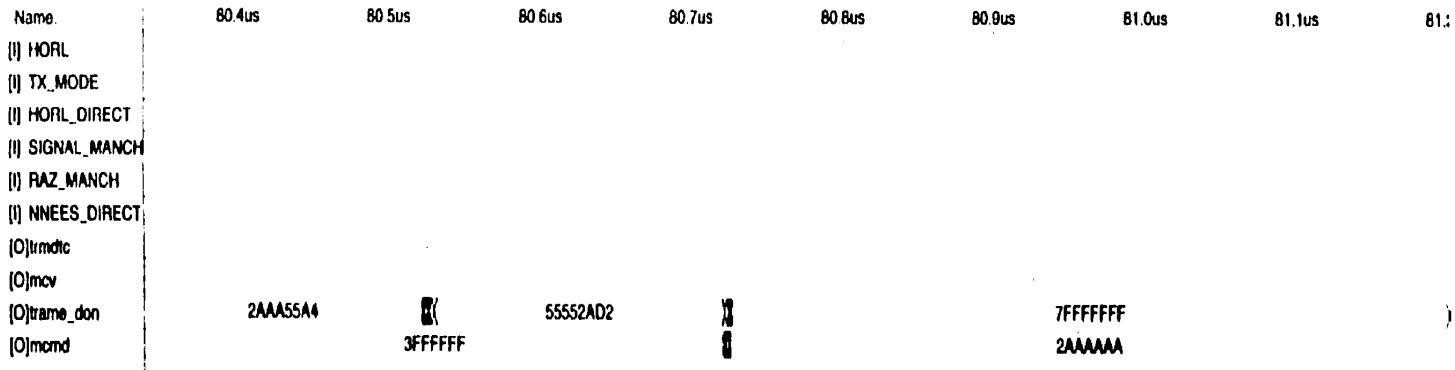

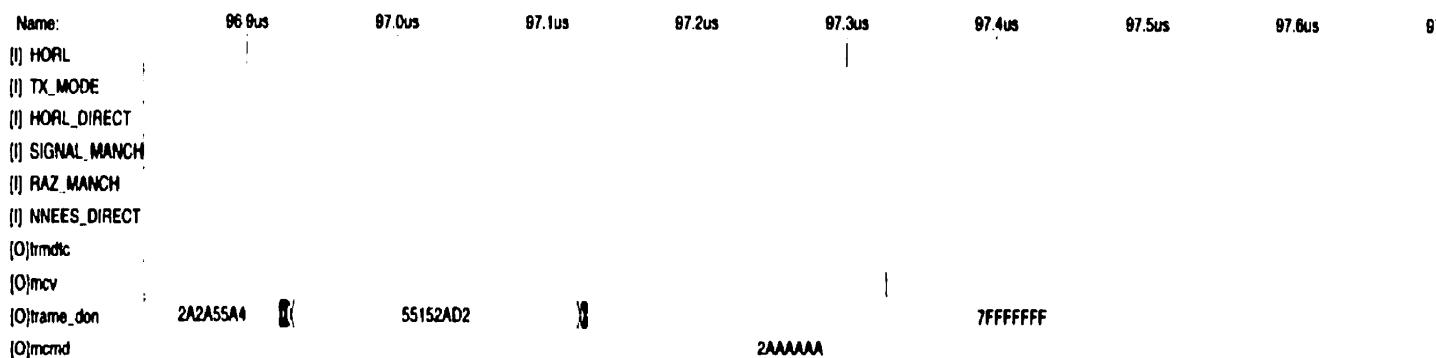

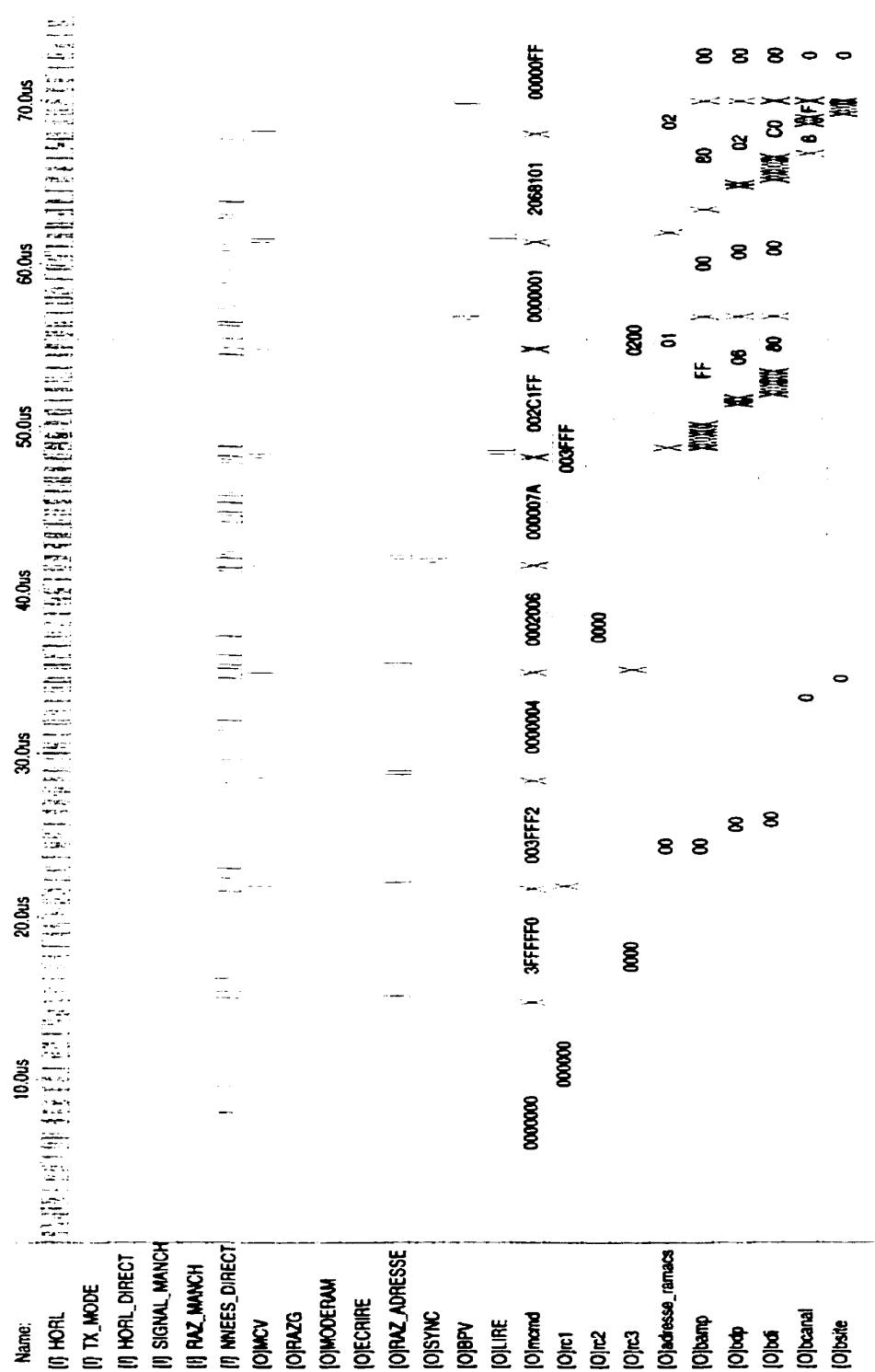

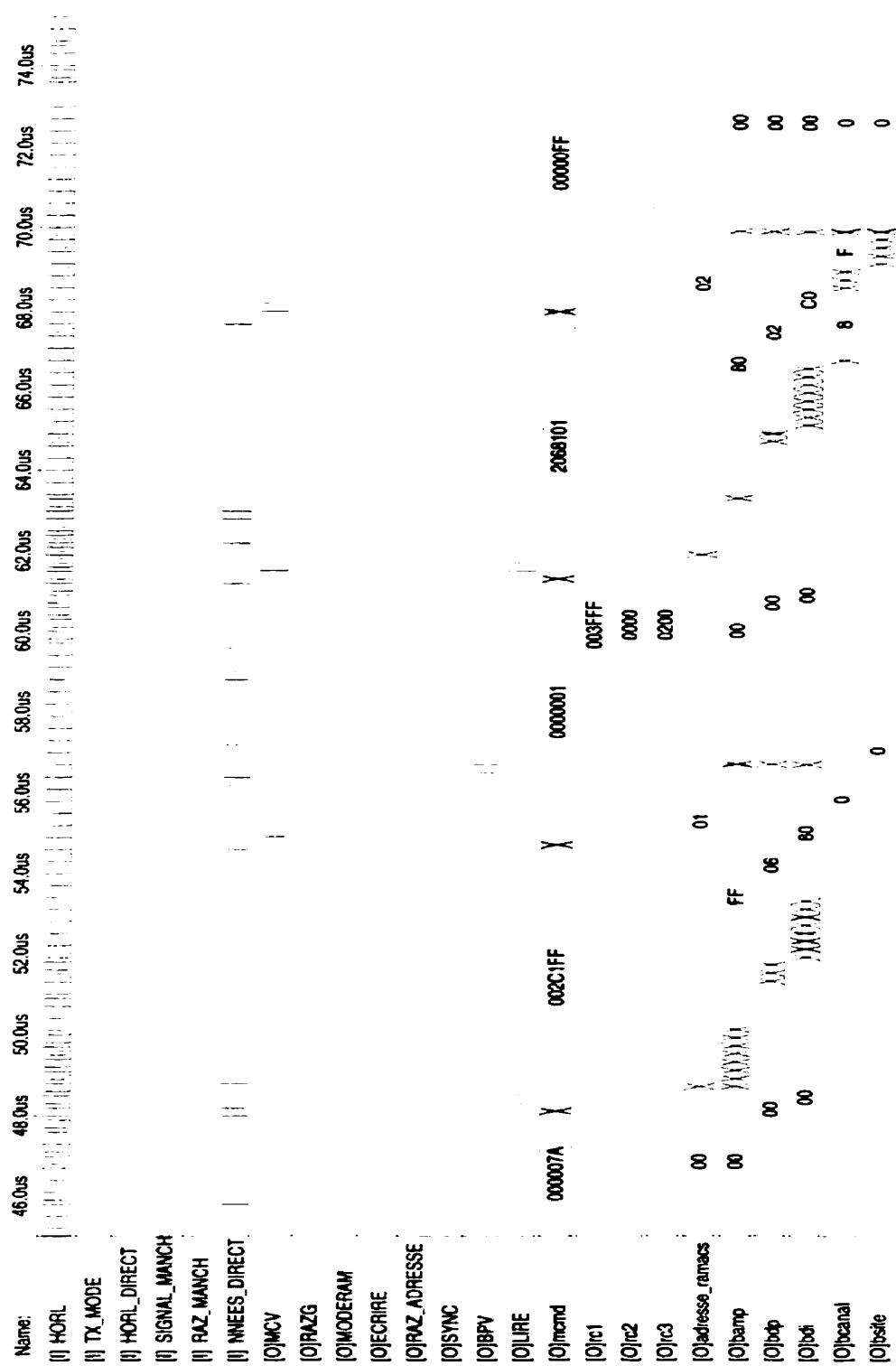

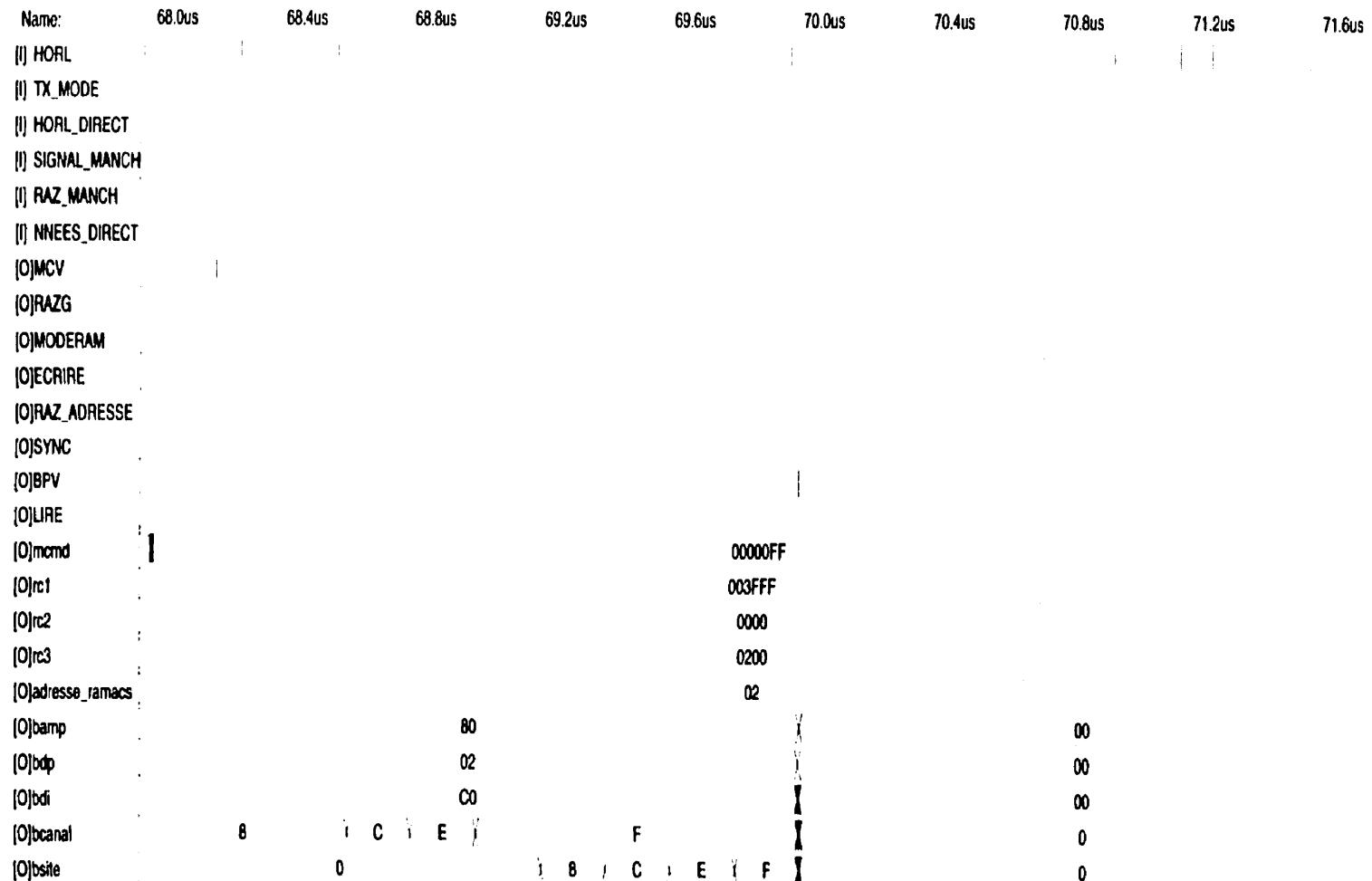

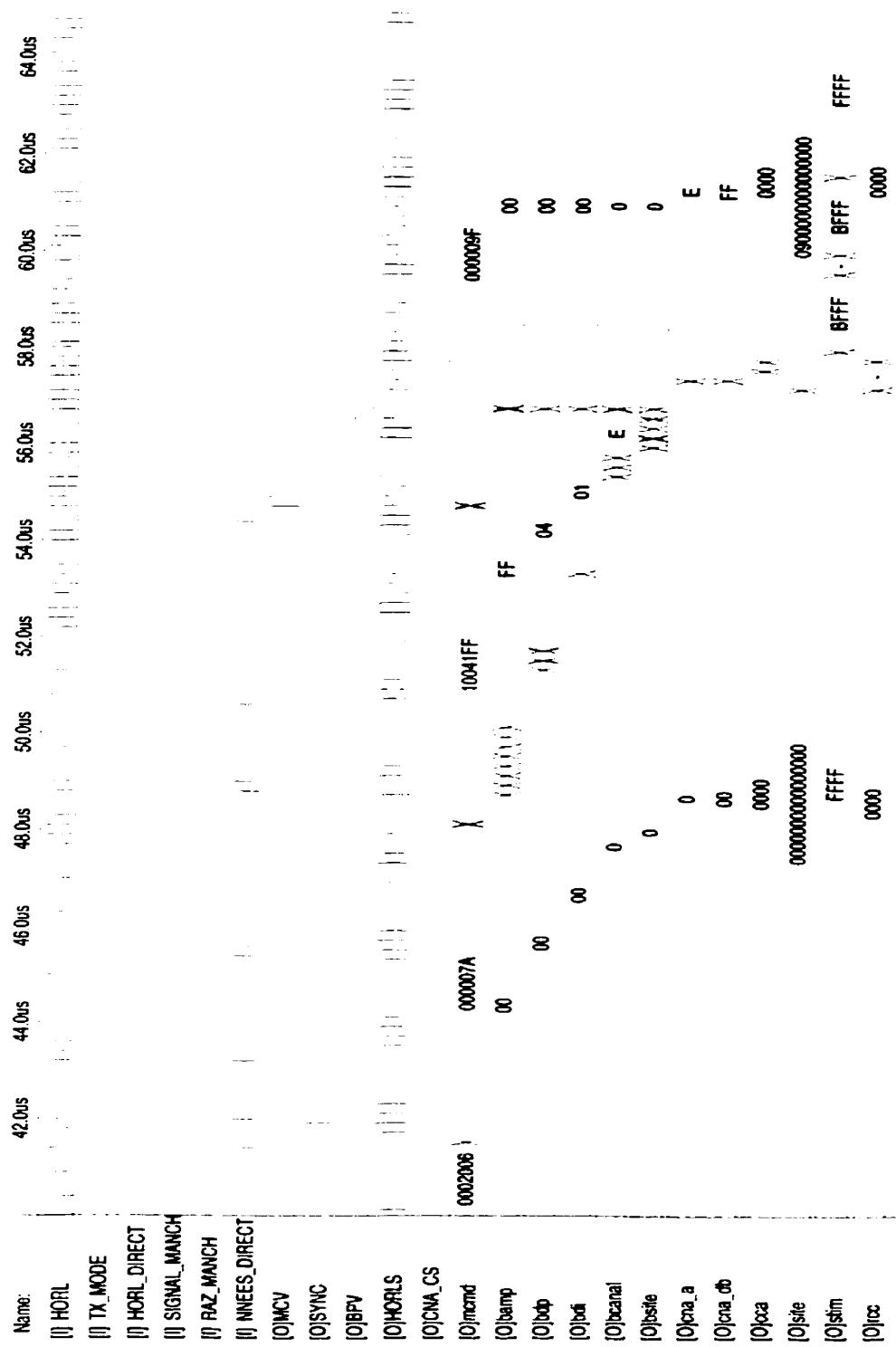

| Figure 5.8 : Simulation du contrôleur (intervalle de temps : 0 - 76 us).....      | 91  |

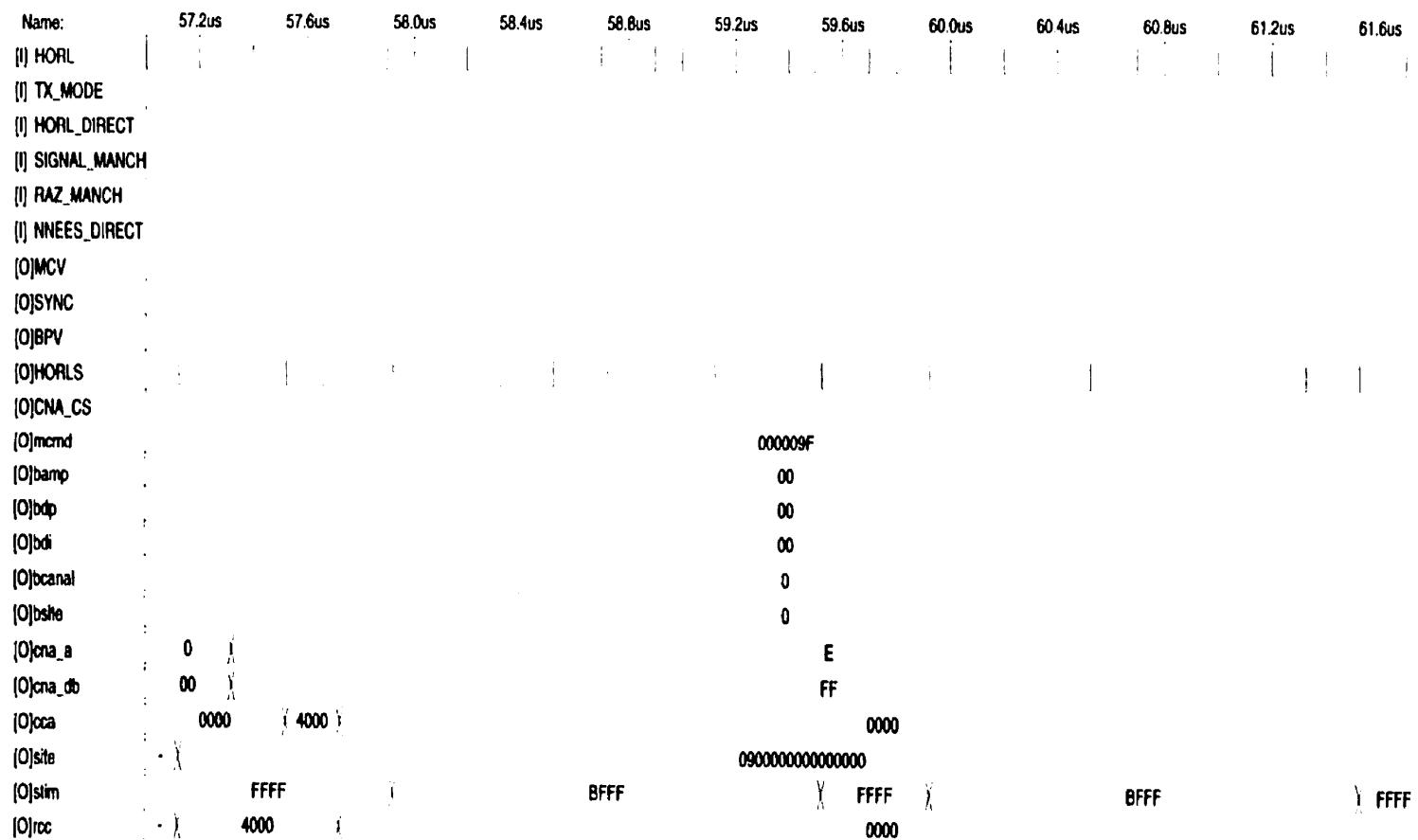

| Figure 5.9 : Simulation du contrôleur (intervalle de temps : 71.2us – 80 us)..... | 93  |

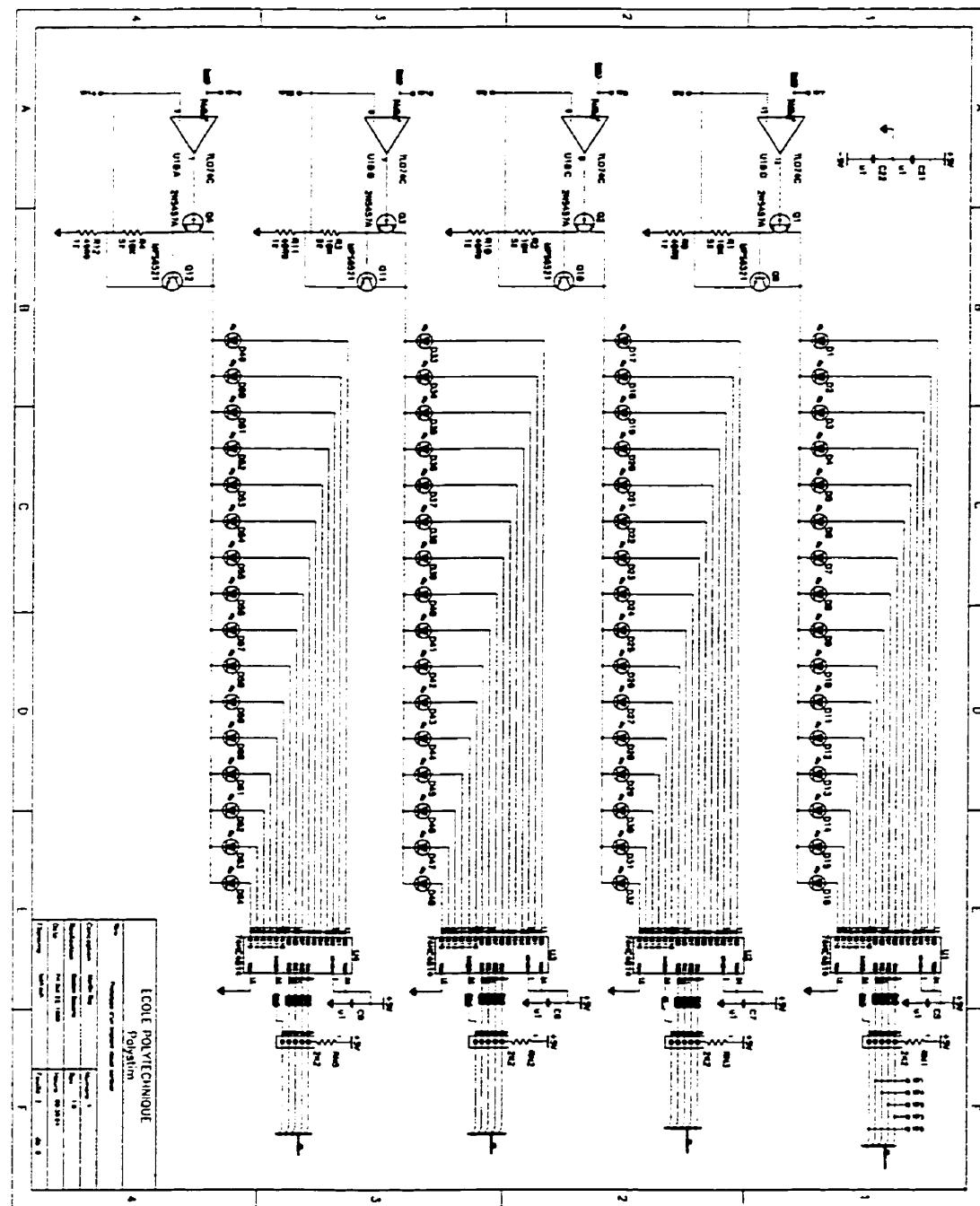

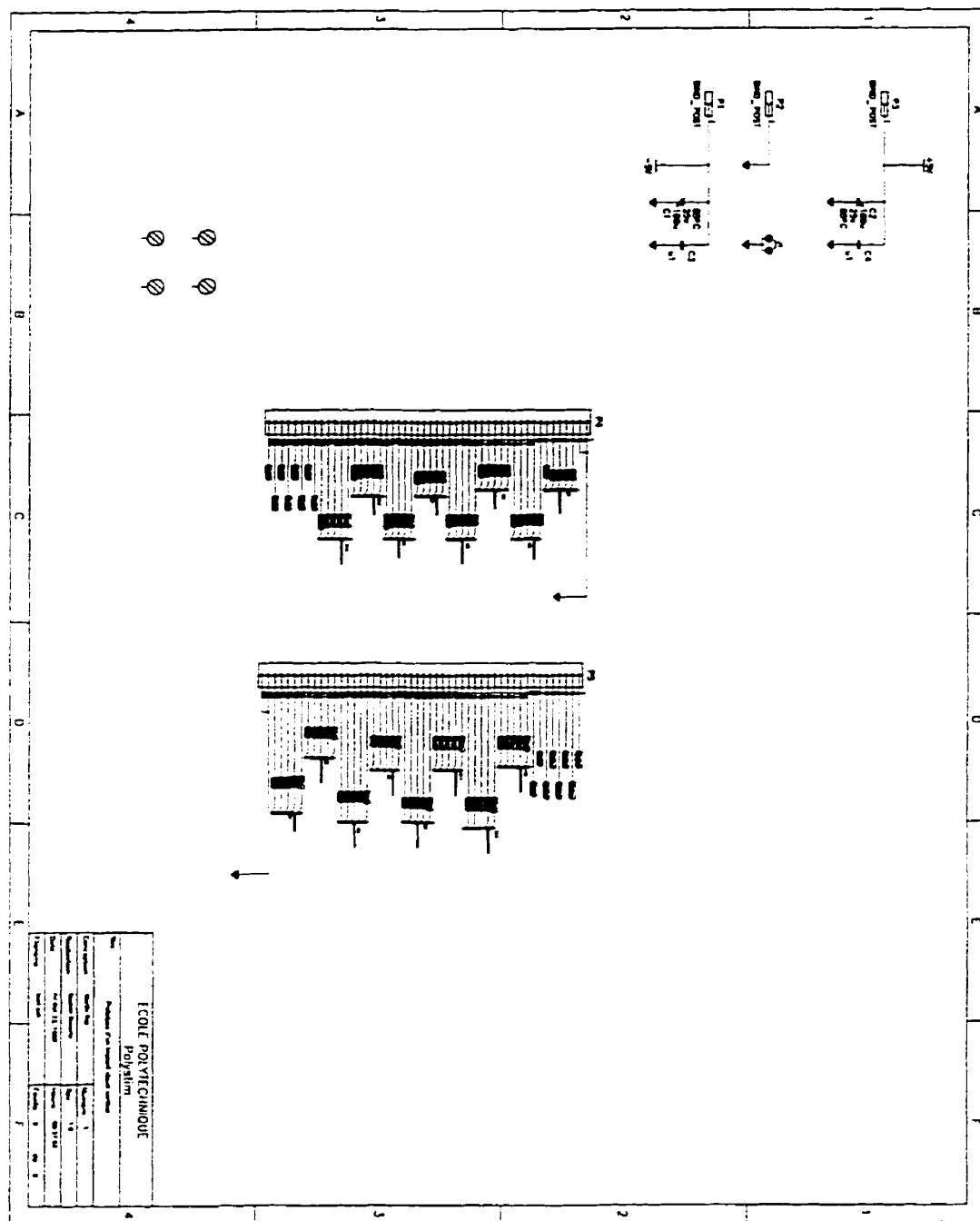

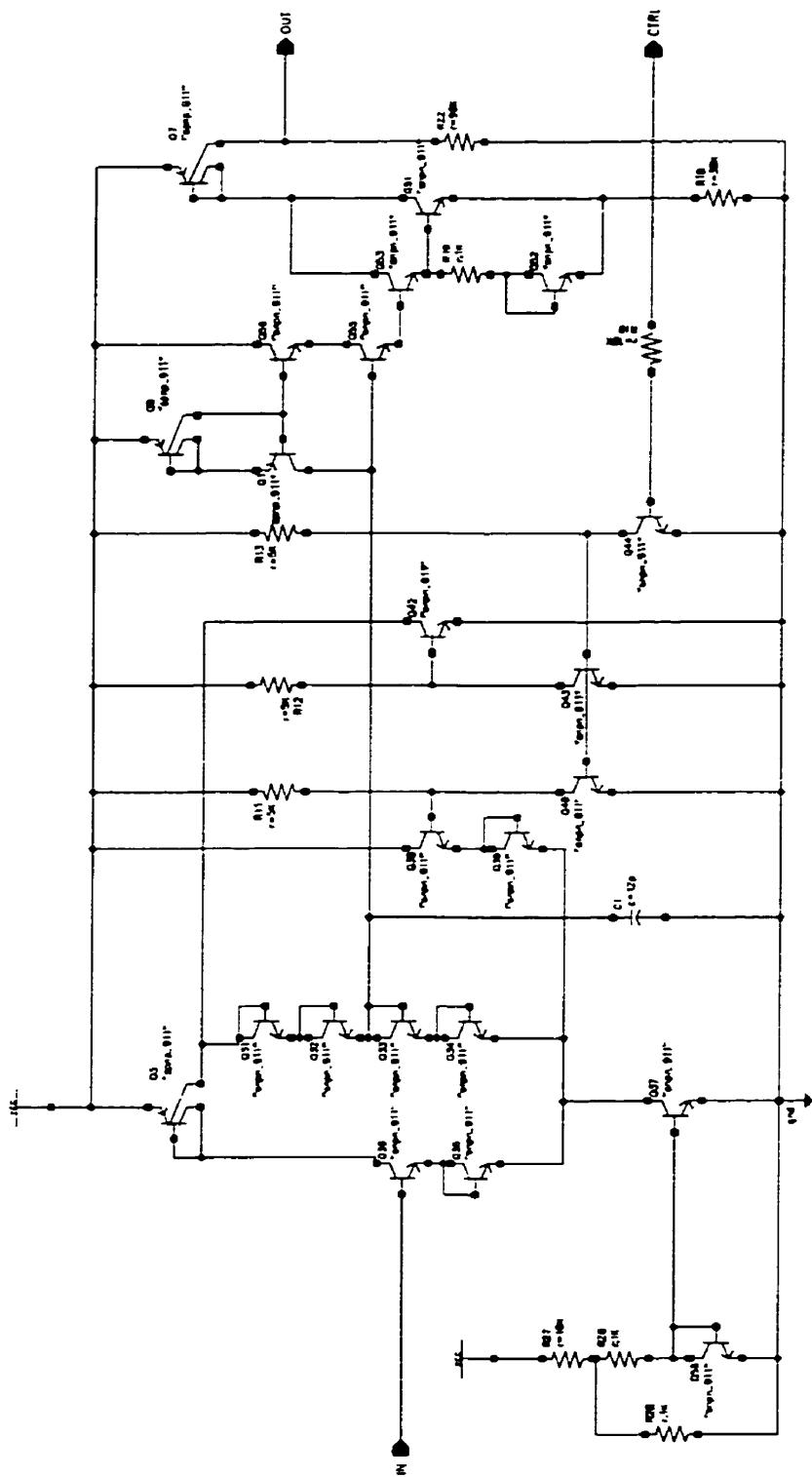

| Figure A.1 : Circuit de la carte maîtresse (1/3).....                             | 113 |

| Figure A.2 : Circuit de la carte maîtresse (2/3).....                             | 114 |

| Figure A.3 : Circuit de la carte maîtresse (3/3) .....                            | 115 |

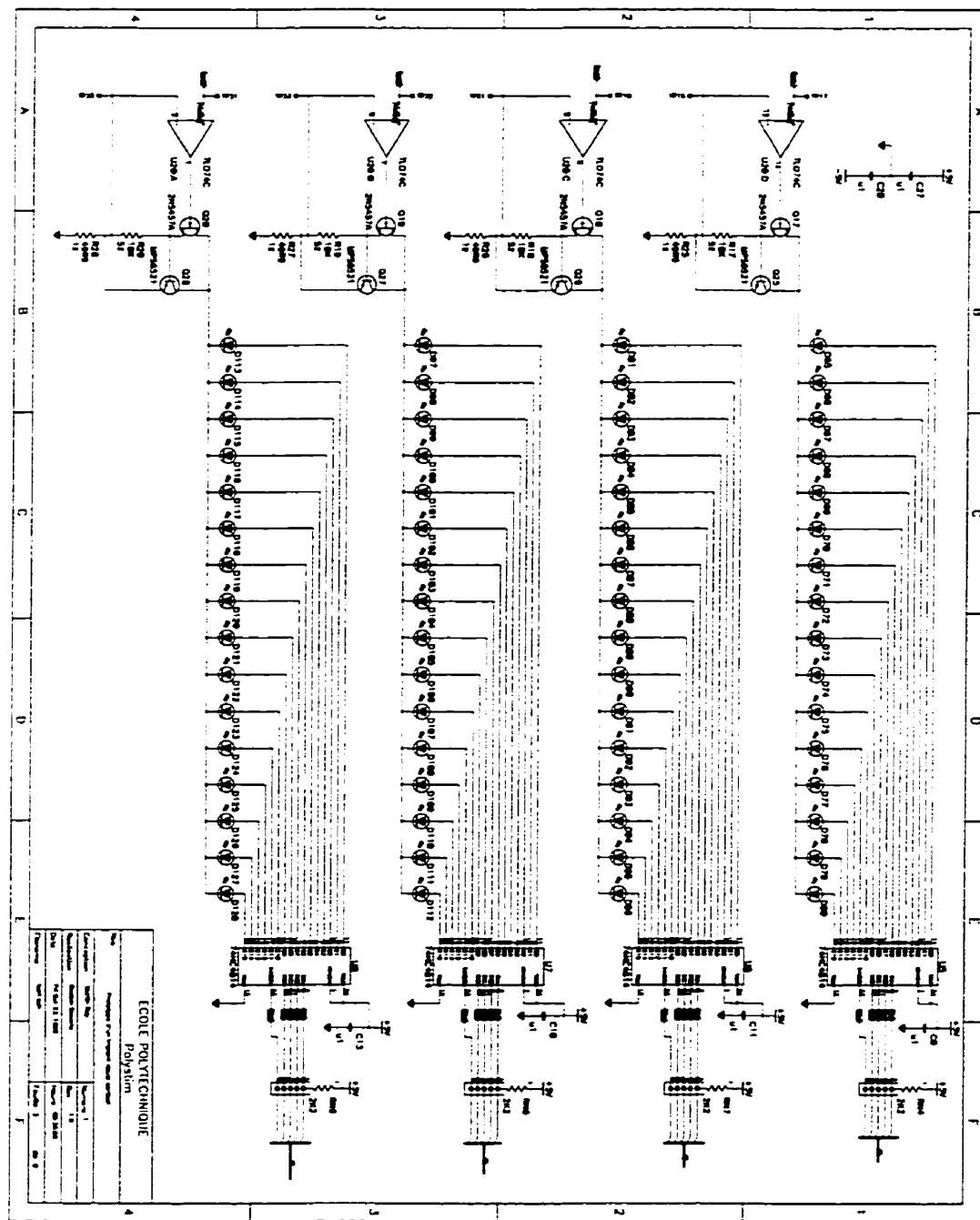

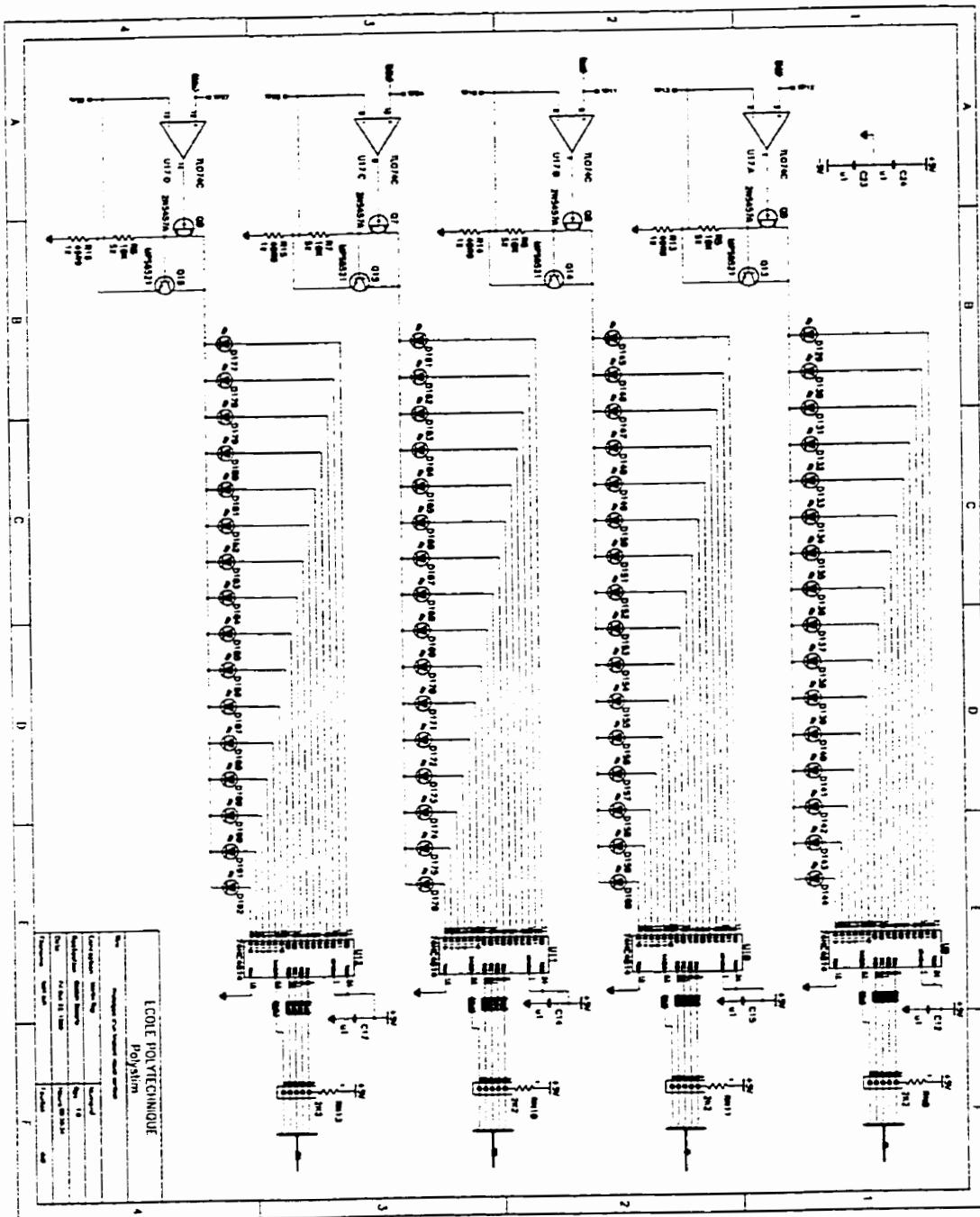

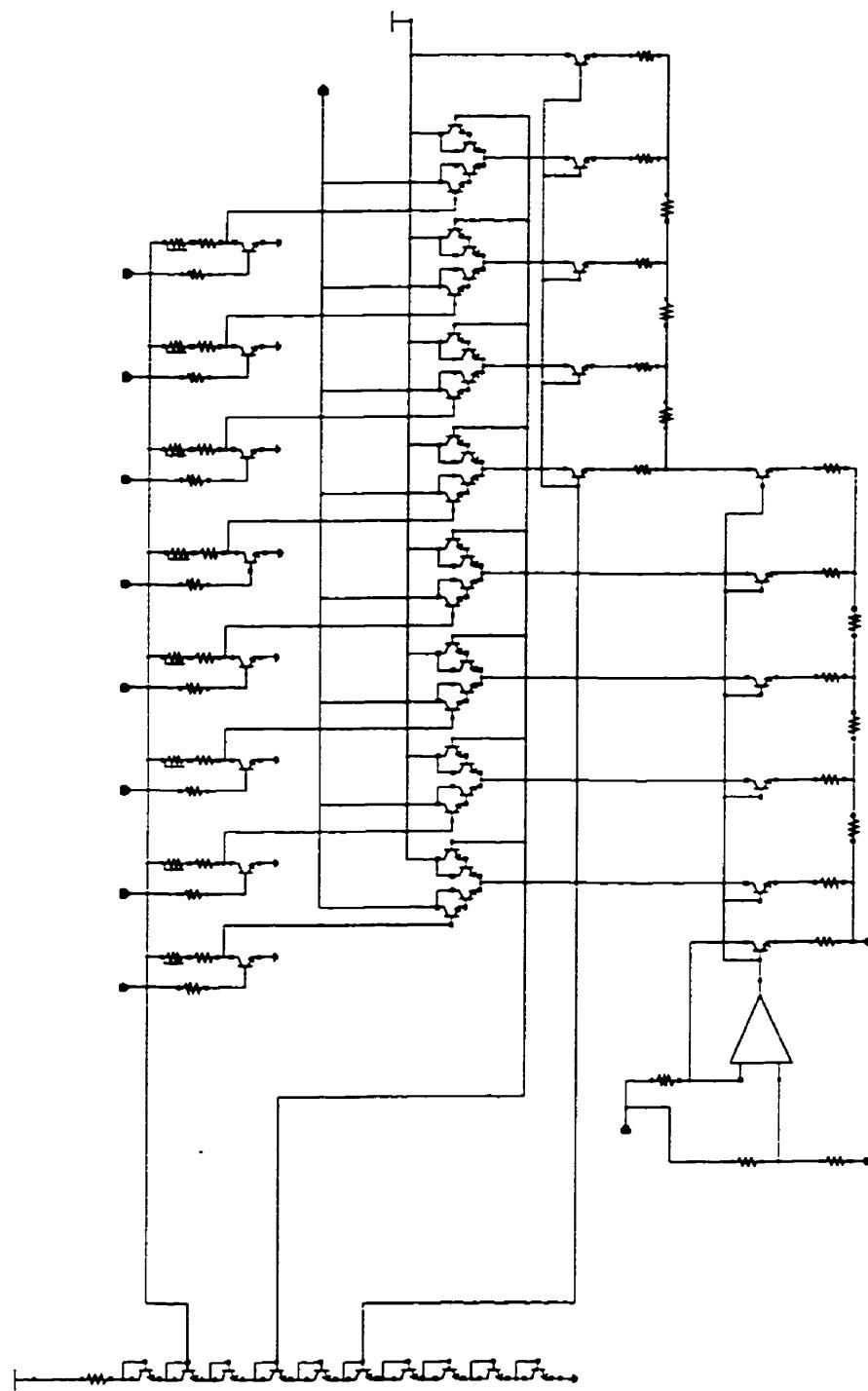

| Figure A.4 : Circuit de la carte affichage (1/5) .....                            | 116 |

| Figure A.5 : Circuit de la carte affichage (2/5) .....                            | 117 |

| Figure A.6 : Circuit de la carte affichage (3/5) .....                            | 118 |

| Figure A.7 : Circuit de la carte affichage (4/5) .....                            | 119 |

| Figure A.8 : Circuit de la carte affichage (5/5) .....                            | 120 |

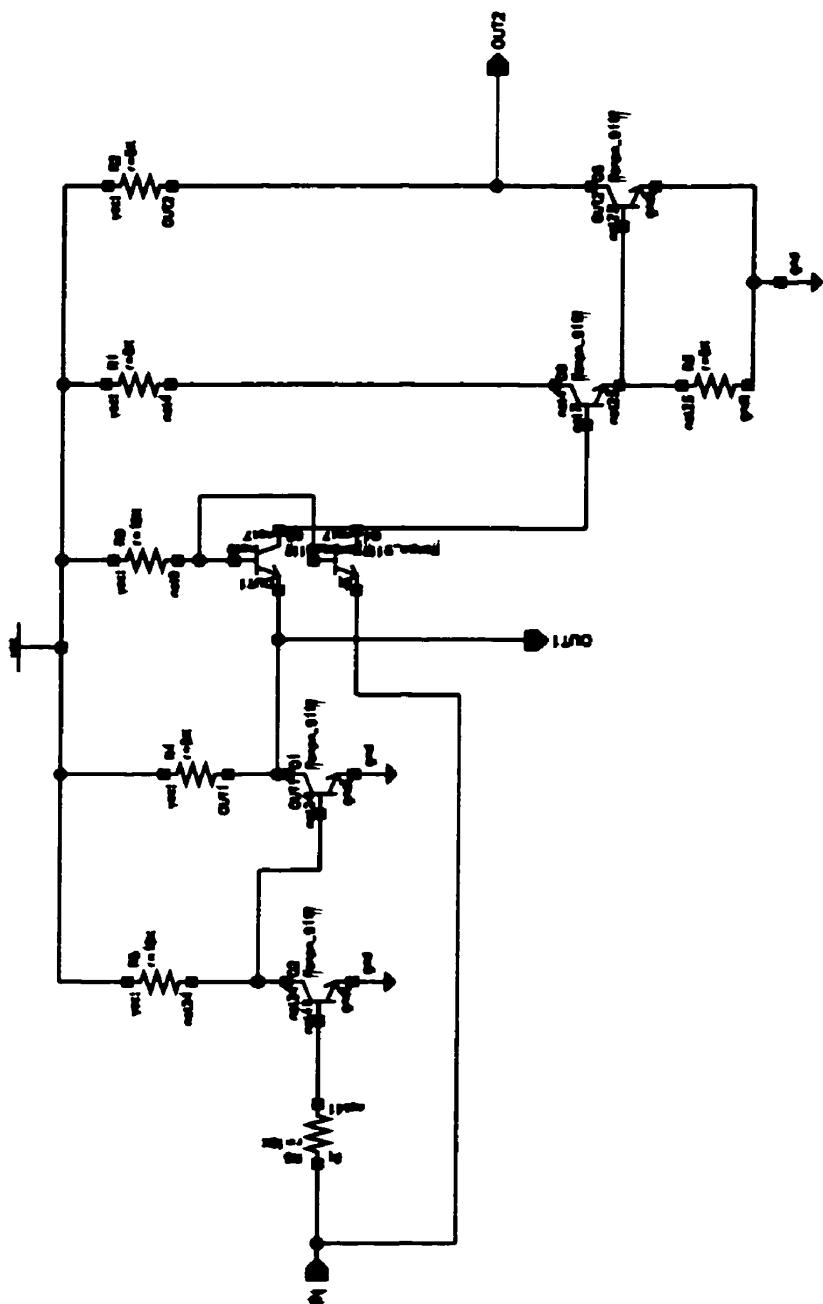

| Figure B.1 : Schéma bloc du CEB .....                                             | 131 |

| Figure B.2 : Structure interne d'un EB .....                                      | 132 |

| Figure B.3 : Source de courant d'un EB .....                                      | 132 |

| Figure B.4 : Échantillonneur-bloqueur du EB .....                                 | 133 |

| Figure B.5 : Miroir de courant (type P).....                                      | 134 |

| Figure B.6 : Convertisseur numérique-analogique (CNA) .....                       | 135 |

|                                                                                       |     |

|---------------------------------------------------------------------------------------|-----|

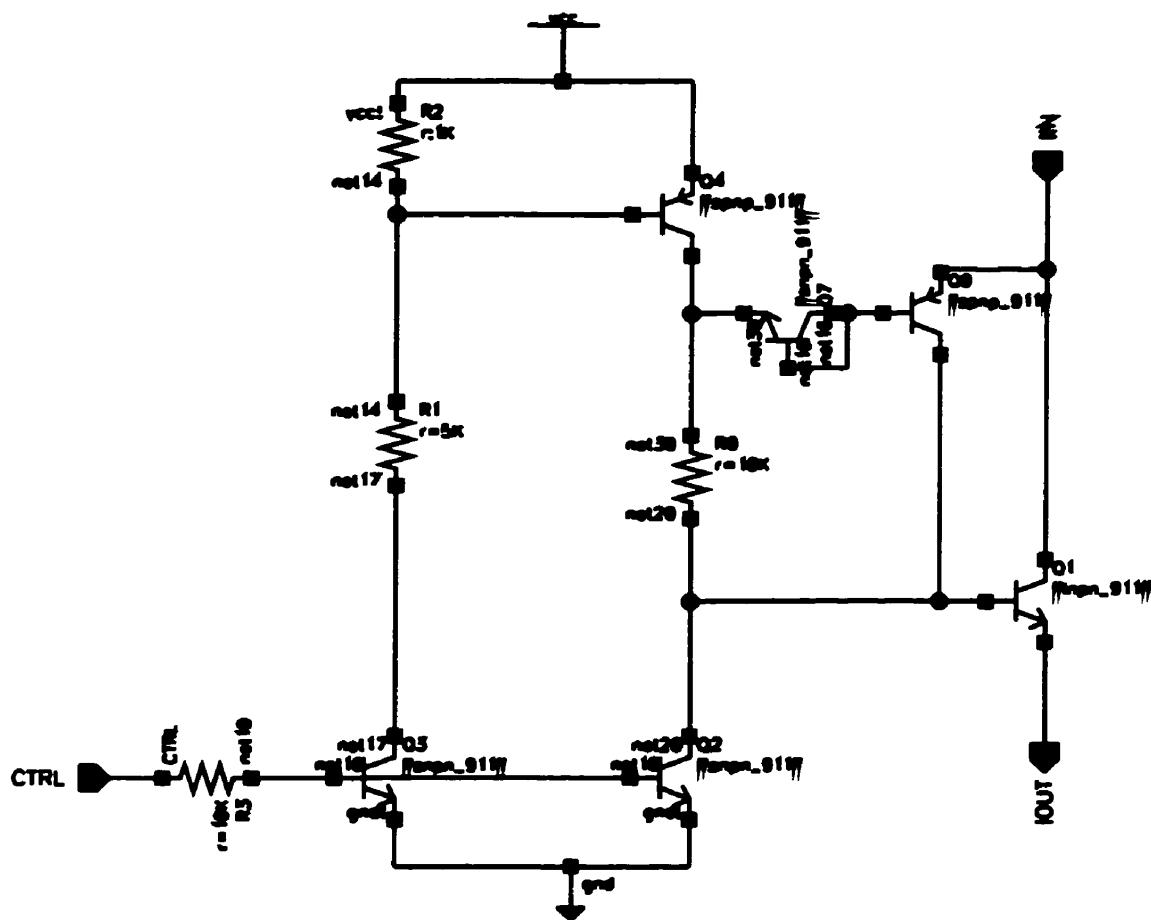

| Figure B.7 : Amplificateur opérationnel utilisé par le CNA .....                      | 136 |

| Figure B.8 : Schéma bloc du commutateur de courant .....                              | 137 |

| Figure B.9 : Circuit de contrôle du commutateur de courant .....                      | 138 |

| Figure B.10 : Circuit du commutateur de courant .....                                 | 139 |

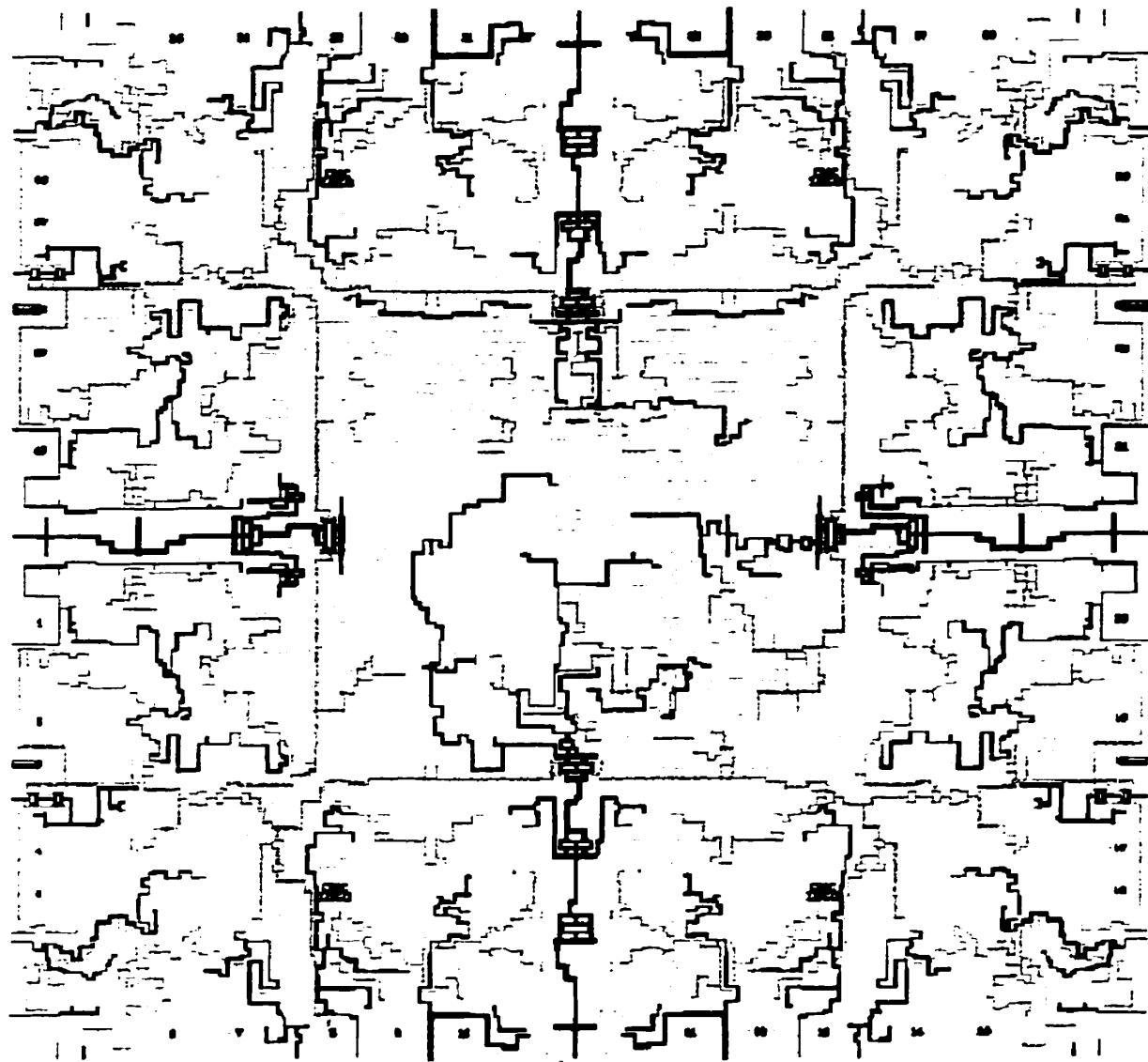

| Figure B.11 : Dessin du masque de métal du CEB .....                                  | 140 |

| Figure C.1 : Réponse en fréquence de l'amplificateur opérationnel .....               | 141 |

| Figure C.2 : Gain en mode commun de l'amplificateur opérationnel .....                | 141 |

| Figure C.3 : Gain Vsortie/Valim pour mesure du PSSR du OPAMP .....                    | 142 |

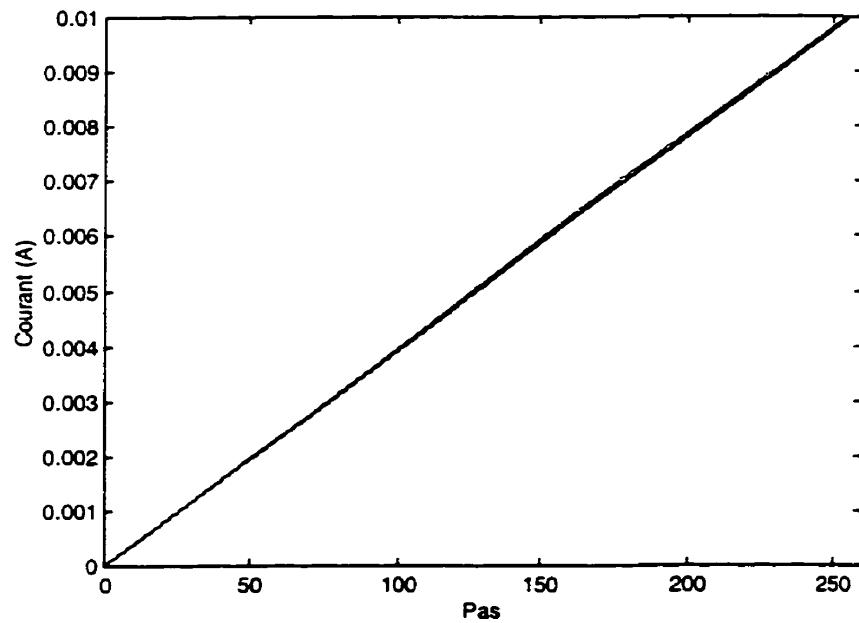

| Figure C.4 : Réponses théorique et simulée du CNA .....                               | 142 |

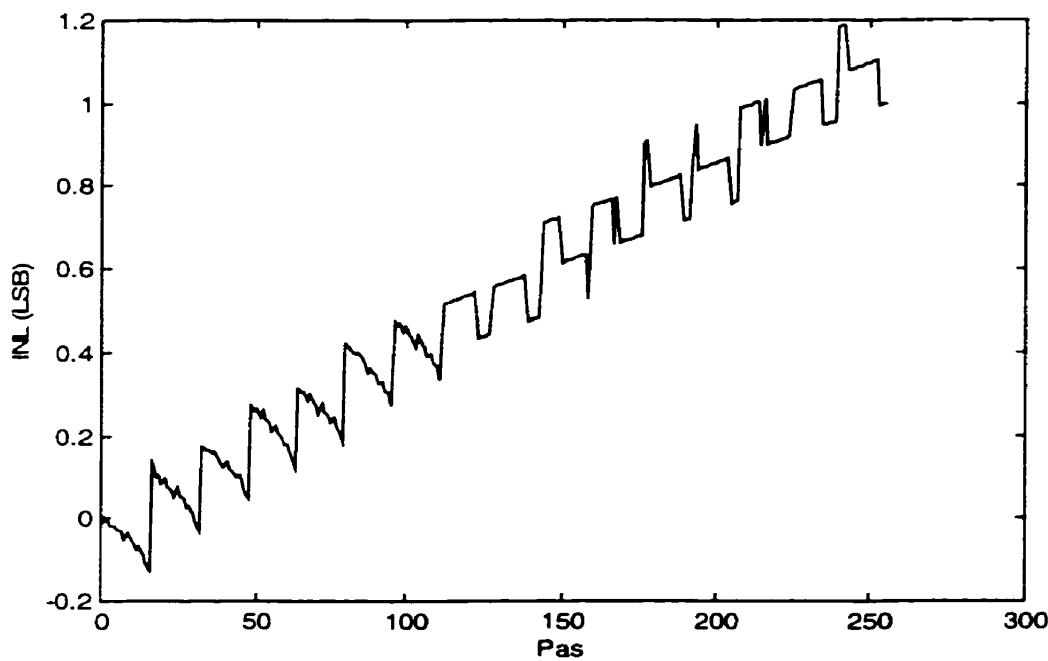

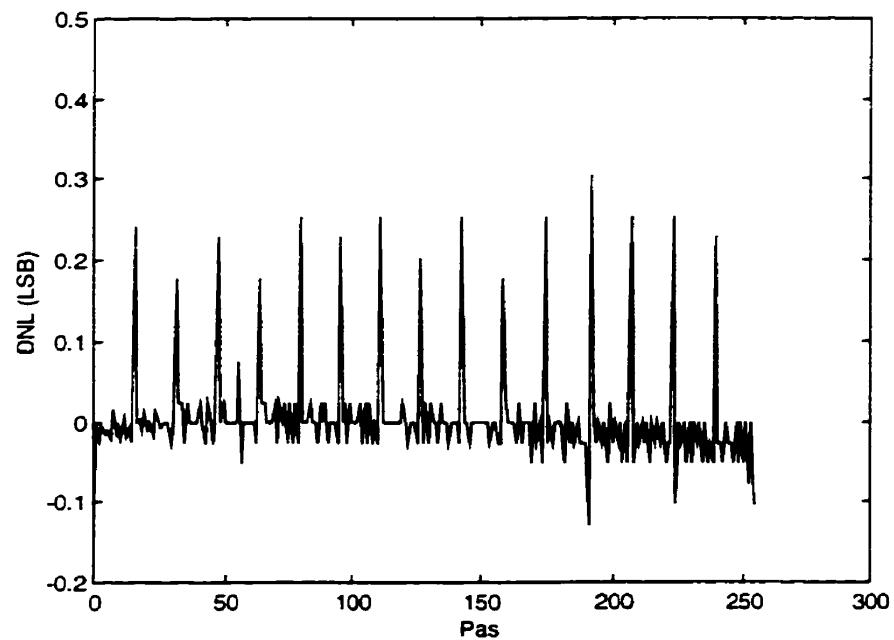

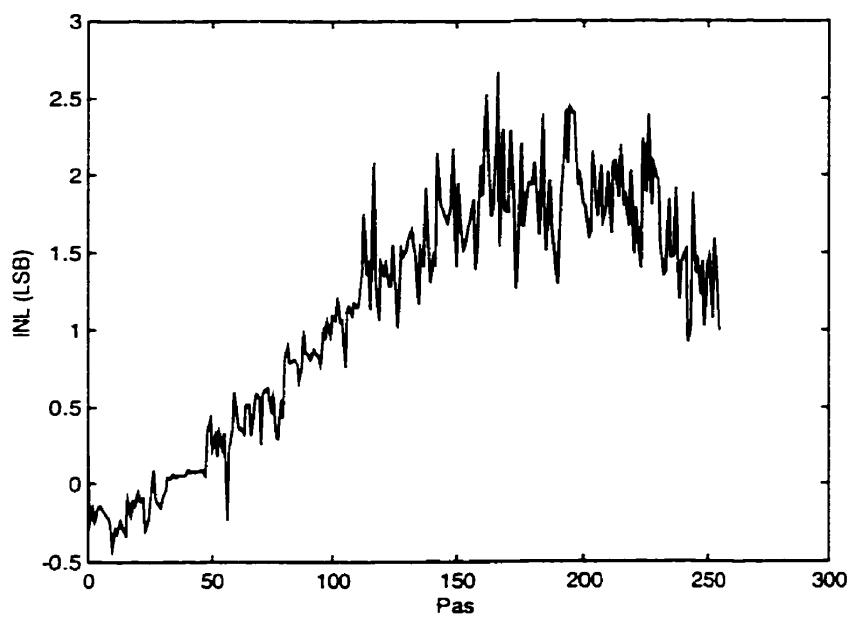

| Figure C.5 : Non-linéarité intégrale (INL) du CNA .....                               | 143 |

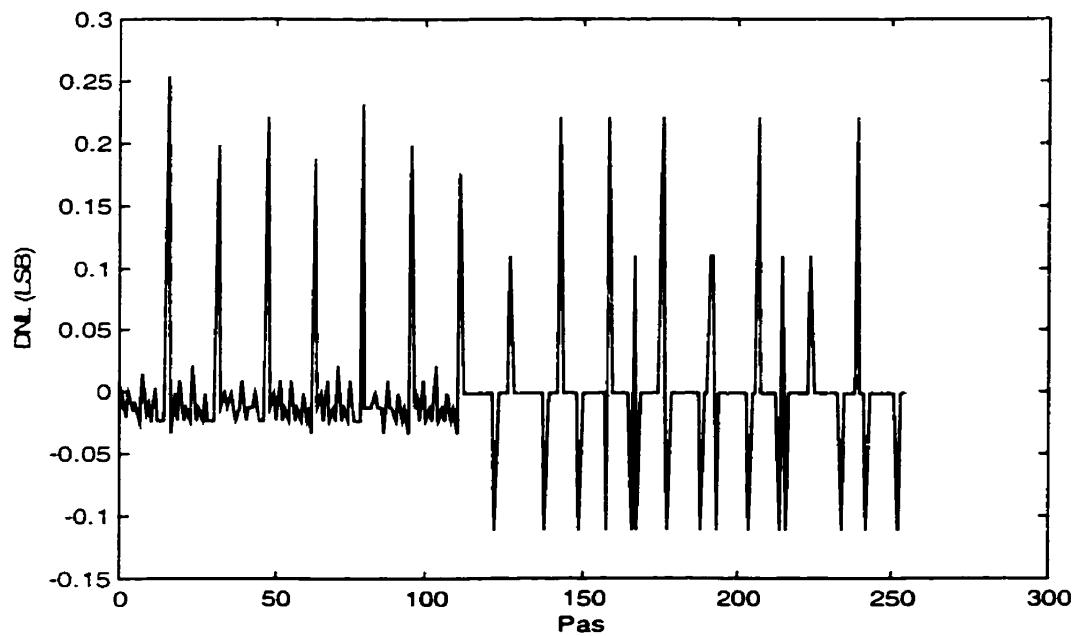

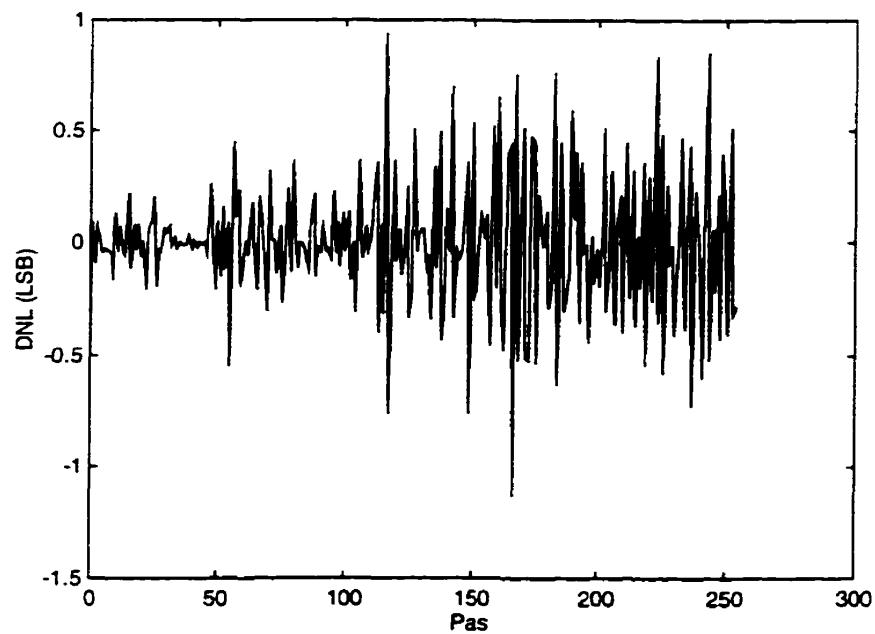

| Figure C.6 : Non-linéarité différentielle (DNL) du CNA .....                          | 143 |

| Figure C.7 : Réponse théorique (-) et simulé (..) du CNA avec miroir de courant ..... | 144 |

| Figure C.8 : Non-linéarité intégrale du CNA avec miroir de courant .....              | 144 |

| Figure C.9 : Non-linéarité différentielle du CNA avec miroir de courant .....         | 145 |

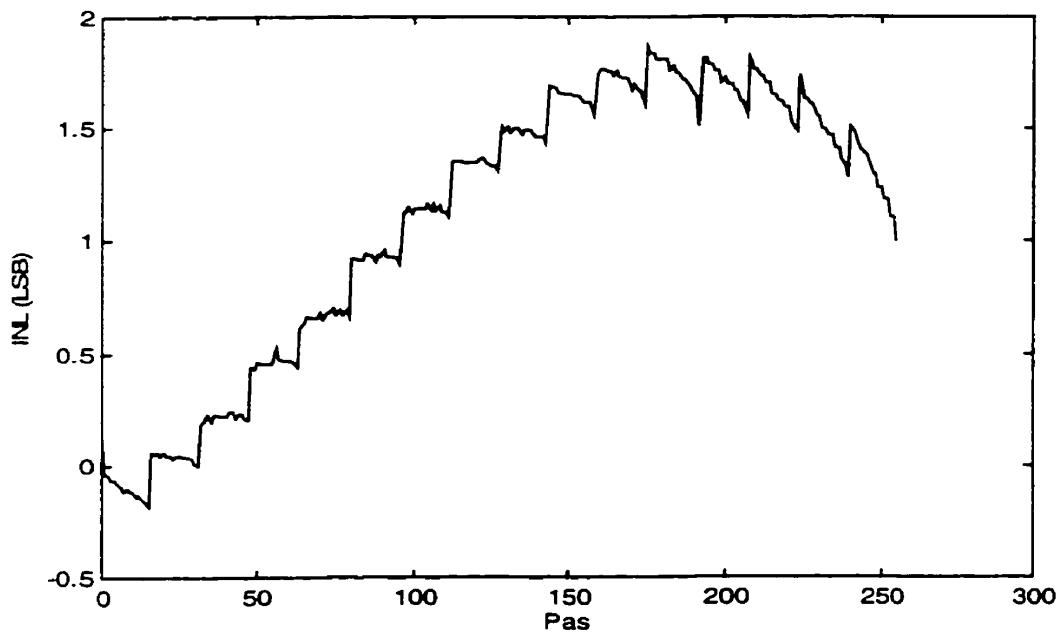

| Figure C.10 : INL du CEB au début du mode maintient .....                             | 145 |

| Figure C.11 : DNL du CEB au début du mode maintient .....                             | 146 |

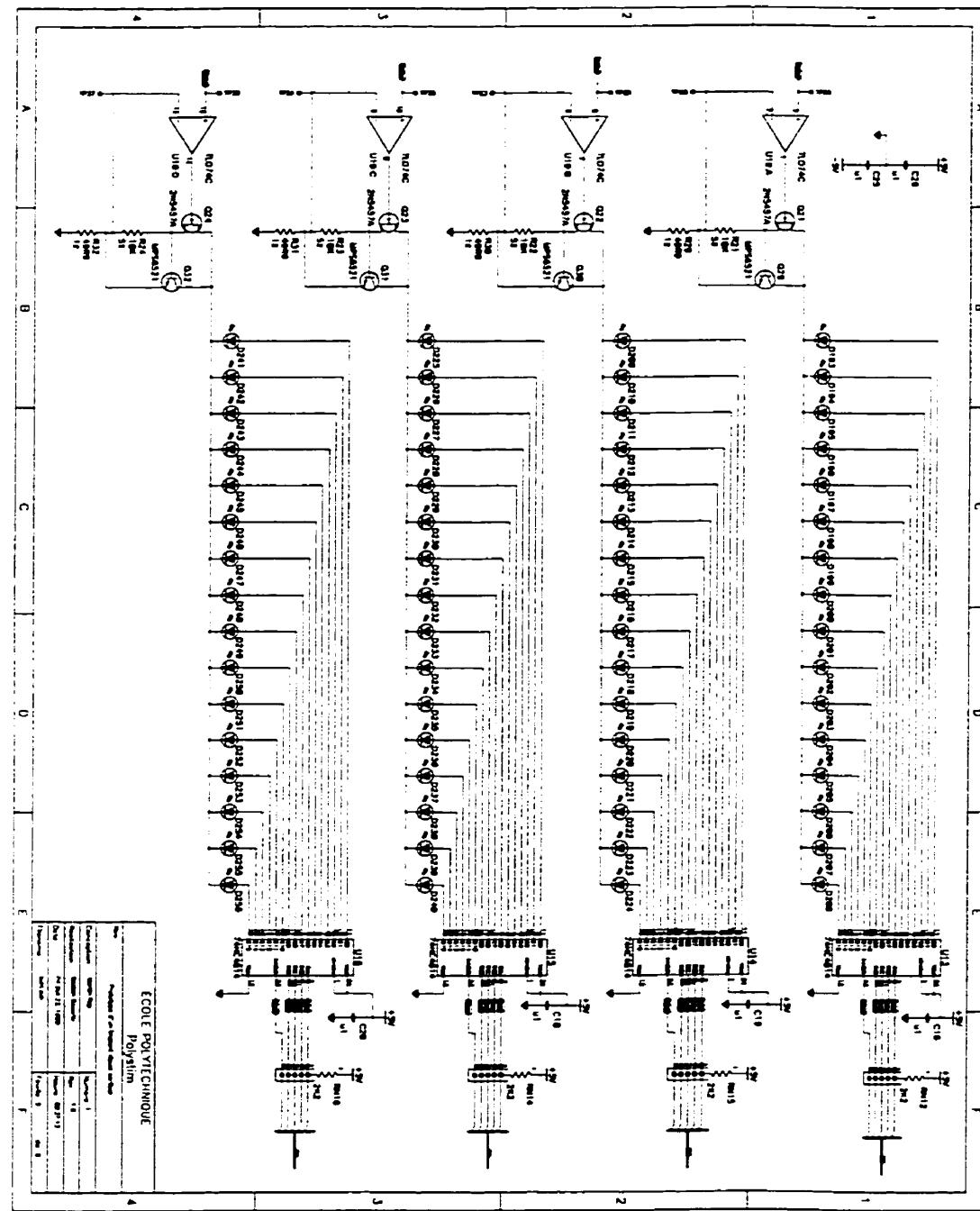

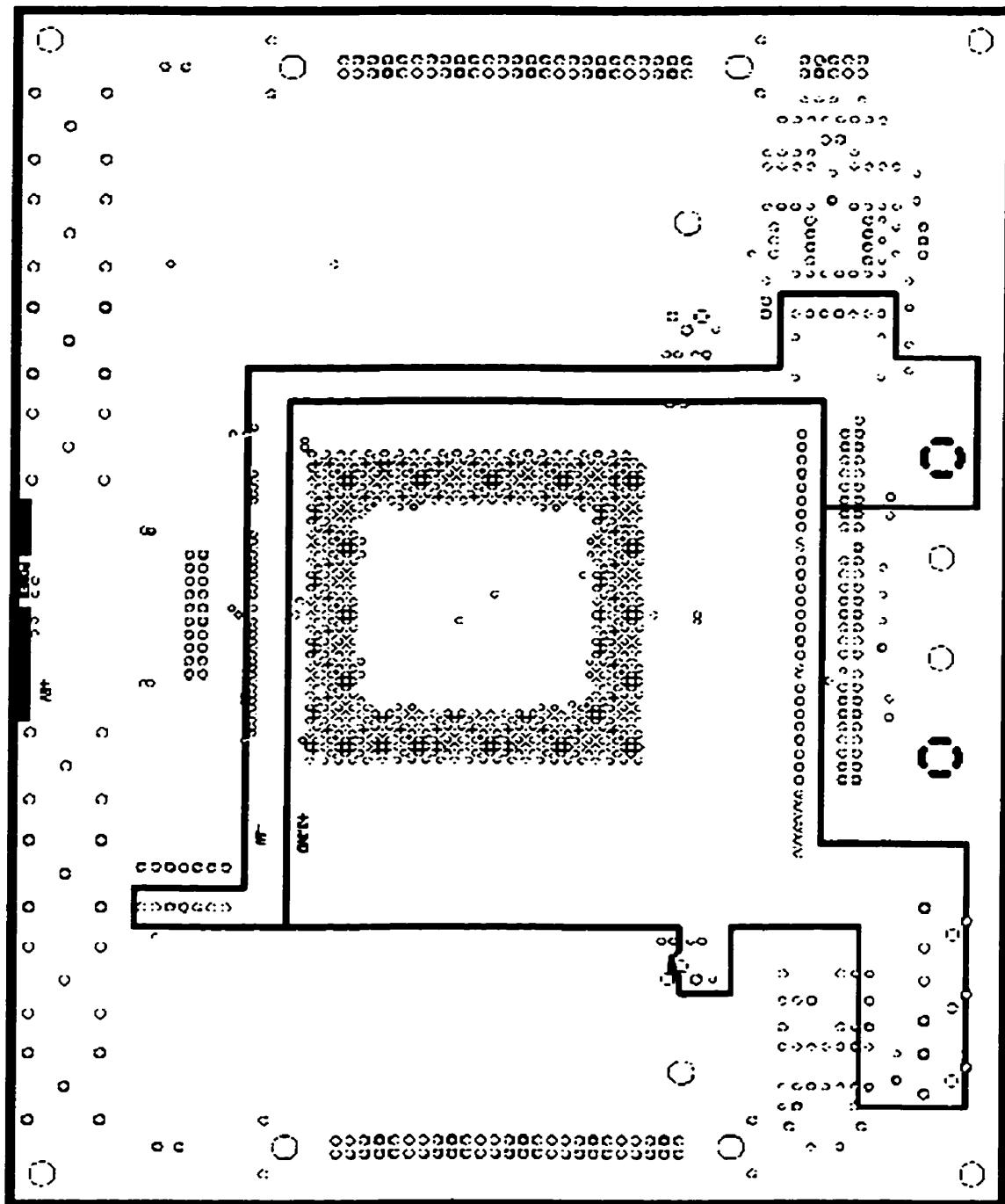

| Figure E.1 : Circuit imprimé de la carte maîtresse (1/6) .....                        | 195 |

| Figure E.2 : Circuit imprimé de la carte maîtresse (2/6) .....                        | 196 |

| Figure E.3 : Circuit imprimé de la carte maîtresse (3/6) .....                        | 197 |

| Figure E.4 : Circuit imprimé de la carte maîtresse (4/6) .....                        | 198 |

| Figure E.5 : Circuit imprimé de la carte maîtresse (5/6) .....                        | 199 |

| Figure E.6 : Circuit imprimé de la carte maîtresse (6/6) .....                        | 200 |

|                                                                                 |     |

|---------------------------------------------------------------------------------|-----|

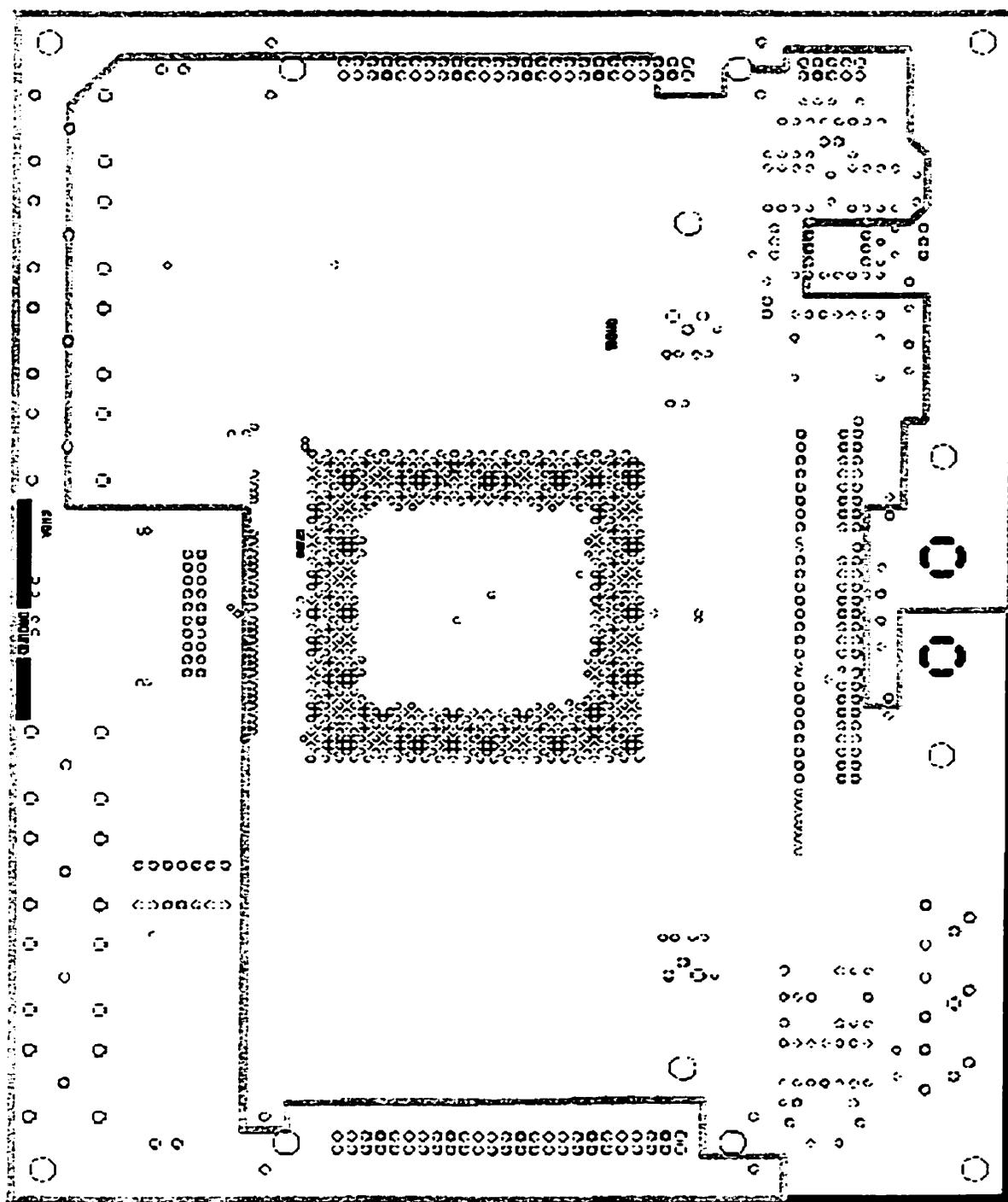

| Figure E.7 : Circuit imprimé de la carte affichage (1/3) .....                  | 201 |

| Figure E.8 : Circuit imprimé de la carte affichage (2/3) .....                  | 202 |

| Figure E.9 : Circuit imprimé de la carte affichage (3/3) .....                  | 203 |

| Figure F.1 : Simulation du correcteur de Hamming.....                           | 205 |

| Figure F.2 : Simulation du fonctionnement du CPIVC (1/4) .....                  | 206 |

| Figure F.3 : Simulation du fonctionnement du CPIVC (2/4) .....                  | 207 |

| Figure F.4 : Simulation du fonctionnement du CPIVC (3/4) .....                  | 208 |

| Figure F.5 : Simulation du fonctionnement du CPIVC (4/4) .....                  | 209 |

| Figure F.6 : Simulation du fonctionnement d'un canal de stimulation (1/2) ..... | 210 |

| Figure F.7 : Simulation du fonctionnement d'un canal de stimulation (2/2).....  | 211 |

## **LISTE DES ANNEXES**

|                                                             |     |

|-------------------------------------------------------------|-----|

| Annexe A : Détails de conception et circuit du PIVC .....   | 111 |

| Annexe B : Circuit complet du CEB .....                     | 130 |

| Annexe C : Résultats de simulation du CEB .....             | 141 |

| Annexe D : Description VHDL du contrôleur du PIVC .....     | 147 |

| Annexe E : Schémas des circuits imprimés du prototype ..... | 194 |

| Annexe F : Résultats de simulation du contrôleur .....      | 204 |

| Annexe G : Le banc de test .....                            | 212 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|        |                                             |

|--------|---------------------------------------------|

| ACS    | Adressage des canaux et des sites           |

| AM     | Amplitude Modulation                        |

| AMP    | Amplitude                                   |

| AMPC   | Amplitude commune                           |

| ASK    | Amplitude Shift Keying                      |

| BiCMOS | Bipolar and CMOS                            |

| BTHS   | Base de temps pour l'horloge de stimulation |

| CCD    | Charge Coupled Device                       |

| CE     | Contrôleur externe                          |

| CEB    | CNA et échantillonneur-bloqueur             |

| CI     | Circuit intégré                             |

| CMOS   | Complementary Metal Oxide Semiconductor     |

| CNA    | Convertisseur numérique-analogique          |

| CPLD   | Complex Programmable Logic Device           |

| DAC    | Digital to analog converter                 |

| DEL    | Diode électroluminescente                   |

| DIC    | Durée d'interphase commune                  |

| DIP    | Durée d'interphase                          |

| DIT    | Durée inter-train                           |

| DNL    | Differential Nonlinearity                   |

|       |                                                     |

|-------|-----------------------------------------------------|

| DP    | Durée de phase                                      |

| DPC   | Durée de phase commune                              |

| DT    | Durée d'un train                                    |

| EB    | Échantillonneur-Bloqueur                            |

| E/S   | Entrées/sorties                                     |

| FA    | Fanion amplitude                                    |

| FCS   | Fanion canal et site                                |

| FDI   | Fanion durée d'interphase                           |

| FDP   | Fanion durée de phase                               |

| FSK   | Frequency Shift Keying                              |

| INL   | Integral Nonlinearity                               |

| IVC   | Implant visuel cortical                             |

| LCMSP | Longueur d'une chaîne de mot de stimulation partiel |

| LSK   | Load Shift Keying                                   |

| MOS   | Metal Oxide Semiconductor                           |

| MSA   | Machine séquentielle algorithmique                  |

| NBA   | Nombre de bit d'amplitude                           |

| NBDI  | Nombre de bit de durée d'interphase                 |

| NBDP  | Nombre de bit de durée de phase                     |

| NMOS  | N-channel Metal Oxide Semiconductor                 |

| PIVC  | Prototype de l'implant visuel cortical              |

| PSK   | Phase Shift Keying                                  |

|       |                                                                |

|-------|----------------------------------------------------------------|

| PSVC  | <b>Prototype du stimulateur visuel cortical</b>                |

| RAM   | <b>Random Access Memory</b>                                    |

| RC1   | <b>Registre de configuration du PIVC #1</b>                    |

| RC2   | <b>Registre de configuration du PIVC #2</b>                    |

| RC3   | <b>Registre de configuration du PIVC #3</b>                    |

| RC4   | <b>Registre de configuration du PIVC #4</b>                    |

| RF    | <b>Radio fréquence</b>                                         |

| SIDNE | <b>Stimulation-Induced Depression of Neuronal Excitability</b> |

| SCM   | <b>Société canadienne de microélectronique</b>                 |

| SVC   | <b>Stimulateur visuel cortical</b>                             |

## INTRODUCTION

La dernière étude de Statistique Canada concernant le nombre de personnes souffrant d'une déficience visuelle au Canada remonte à 1986. On estimait alors ce nombre à 581110 personnes dont 51005 étaient légalement aveugles [1]. Une personne est légalement aveugle lorsque l'acuité de la vision centrale de son meilleur œil est égale ou inférieure à 20/200. Aux États-Unis, le nombre d'hommes et de femmes légalement aveugles, âgés de 40 ans et plus fut estimé à 775796 en 1990 [2]. La plupart des personnes atteintes d'une déficience visuelle conservent cependant une vision partielle. Aux États-Unis, environ 10% des personnes légalement aveugles ont une cécité totale c'est-à-dire qu'elles ne perçoivent aucune sensation de vision [2].

La génétique moléculaire devrait permettre un jour de limiter l'expansion de certaines maladies et même de restaurer en partie la vision, mais actuellement, la plupart de ces maladies sont irréversibles, donc lorsqu'une personne devient aveugle, elle le demeure pour le reste de sa vie [3]. Plusieurs moyens, comme le Braille pour la lecture ou bien l'utilisation d'un chien guide pour les déplacements, sont à la disposition des personnes non-voyantes afin d'augmenter leur indépendance. Par ailleurs, des systèmes de réhabilitation par substitution développés au cours des dernières années permettent de donner une certaine assistance à ces personnes. Ces dispositifs captent l'information visuelle, la traitent et finalement la dirigent vers un organe sensoriel qui est intact comme le système auditif par exemple [77]. Ces moyens et ces systèmes, bien qu'utiles, ne permettent cependant pas aux gens aveugles d'effectuer certaines fonctions aussi efficacement et rapidement que s'ils possédaient une certaine forme de vision. La prothèse visuelle (ou stimulateur visuel) constitue une nouvelle alternative qui devrait permettre dans un proche avenir à redonner une vision partielle à la majorité des non-voyants.

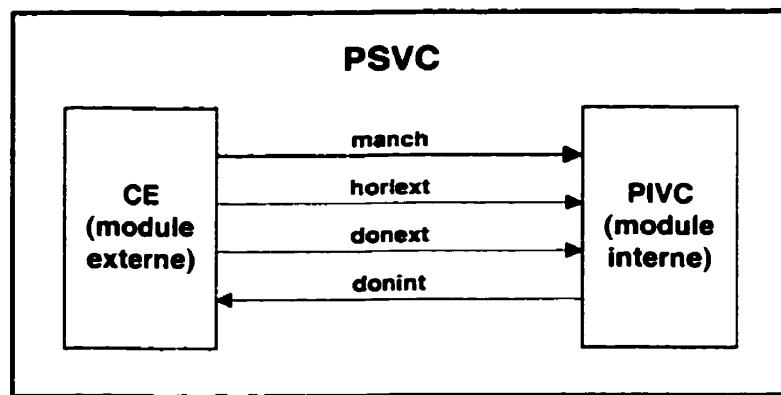

À ce jour, il existe essentiellement trois grandes avenues de recherche pour rétablir partiellement la vision chez un non-voyant : la stimulation de la rétine, la stimulation du nerf optique et la stimulation du cortex visuel. De façon très générale et quelle que soit l'approche utilisée, le système de stimulation doit comporter un module externe et un module interne (implanté dans le corps humain). Les principales tâches de la partie externe sont de capter des images et d'effectuer un certain traitement sur celles-ci. L'information résultante est alors envoyée à l'implant. Celui-ci est chargé d'injecter des courants de stimulation à un endroit particulier du système visuel humain (répine, nerf optique ou cortex visuel).

La stimulation du cortex visuel semble être l'approche la plus prometteuse à bien des égards. En effet, elle seule jusqu'à maintenant a fait l'objet d'expériences chez les humains. Les résultats sont encourageants et laissent entrevoir la possibilité que cette approche puisse être réalisable. L'injection de courants de stimulation dans le cortex visuel d'un non-voyant, produit de petits points lumineux (appelés phosphènes) dans son champ visuel. De plus, il semble y avoir un lien direct entre la position d'un phosphène dans le champ visuel et l'endroit où la stimulation est appliquée dans le cortex visuel [16,22,23]. L'activation de plusieurs phosphènes adjacents permettrait donc de créer une image. Chaque phosphène correspondant à un pixel de l'image.

Un des projets de l'équipe de recherche PolySTIM de l'École Polytechnique, consiste à concevoir et à réaliser un stimulateur visuel cortical (SVC). Le développement d'un système comme celui-ci demande un effort de recherche dans des directions qui touchent plusieurs disciplines comme le génie physique, le génie biomédical, le génie électrique et la médecine.

Quelques obstacles techniques doivent être franchis avant de pouvoir réaliser ce genre de système. Par exemple, pour des raisons de biocompatibilité, les liens physiques (fils) entre les deux modules doivent absolument être évités. Cette contrainte nécessite l'utilisation d'un lien inductif pour la transmission d'énergie et d'information du module externe vers l'implant, ce qui implique l'existence d'un seul et unique canal de

transmission série. L'implant doit alors être en mesure de récupérer l'information et ensuite d'effectuer des opérations d'aiguillages des données reçues vers les canaux de stimulation. Le circuit de l'implant possède donc implicitement une certaine complexité. De plus, le processus de développement de son architecture doit tenir compte de plusieurs autres éléments qui seront décrits dans les prochains chapitres. Il est ainsi préférable de passer par une étape de prototypage du système avant sa réalisation définitive [85].

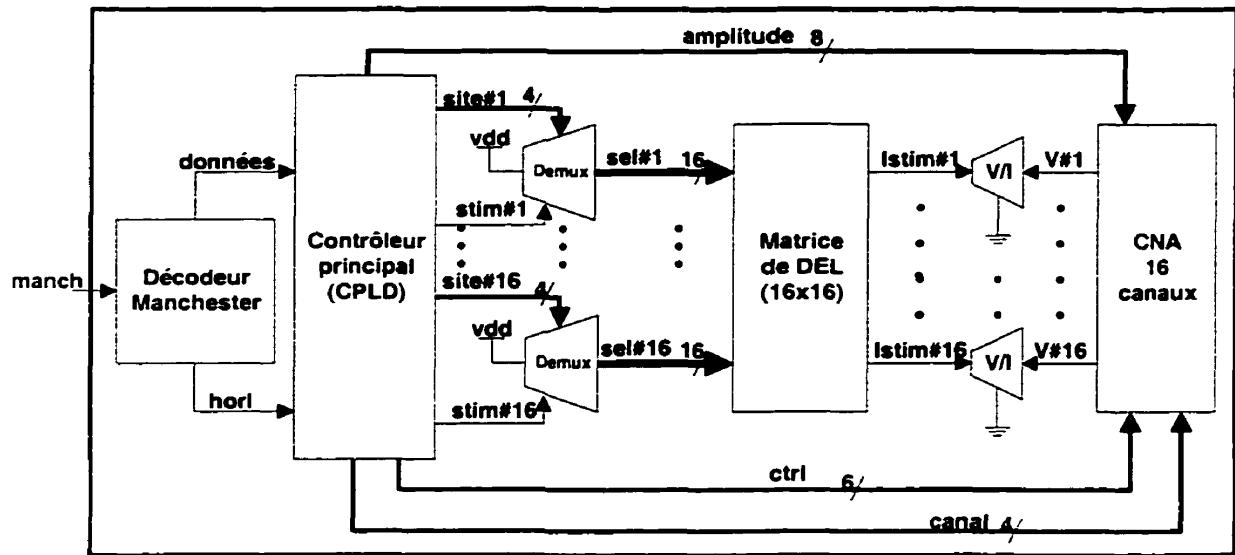

Le but du présent projet de maîtrise est de concevoir et réaliser un prototype d'un implant visuel cortical (PIVC), donc de la partie interne du stimulateur. Jumelé avec le contrôleur externe, la fonctionnalité du stimulateur visuel cortical en entier pourra être testée et vérifiée avant son intégration finale. Le but du prototype n'est pas de stimuler des cellules nerveuses, mais bien de donner un aperçu de ce qu'une personne non-voyante peut voir avec un stimulateur cortical. Pour ce faire, le prototype comporte une matrice de diodes électroluminescentes (DEL) qui permettent de simuler les sensations des phosphènes perçues par un non-voyant, suite à des opérations de stimulation.

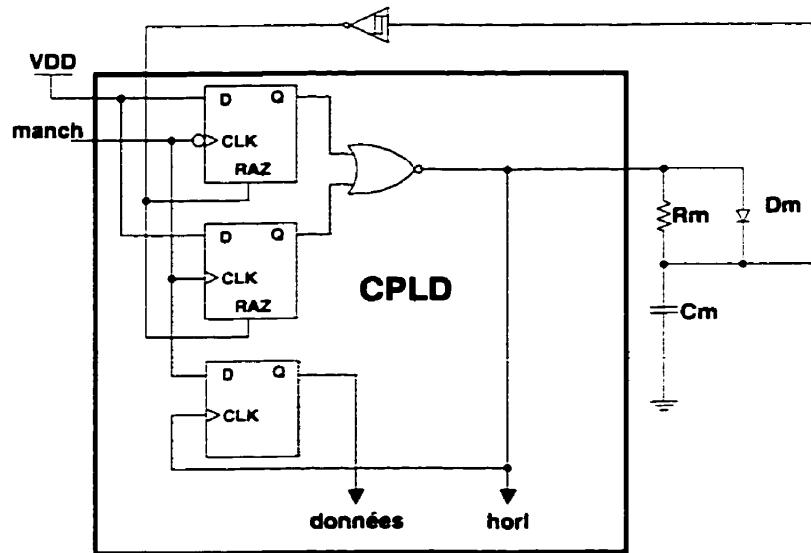

Un seul prototype est fabriqué mais nous proposons dans ce mémoire deux architectures permettant d'implanter la fonctionnalité d'un implant visuel cortical. La première (qui est fabriquée) est composée uniquement de composants et circuits intégrés commerciaux. La deuxième, semblable à la première, utilise également des composants et circuits intégrés commerciaux, mais possède en plus un circuit intégré prédiffusé qui contient une partie des circuits analogiques. La deuxième architecture n'a pu être fabriquée suite à un défaut de fabrication du circuit prédiffusé. Dans chaque cas, le circuit numérique de contrôle est implanté dans un circuit intégré programmable (CPLD). La partie numérique du prototype est donc facilement modifiable en partie ou en totalité.

La réalisation du prototype permet d'atteindre deux objectifs. Premièrement, il valide une nouvelle architecture d'implant visuel cortical qui favorise la flexibilité dans la communication des données avec le contrôleur externe. Deuxièmement, le prototype

peut servir d'outil de développement car sa partie numérique est entièrement reconfigurable. Ainsi, avenant une évolution des connaissances sur la stimulation corticale, un nouveau circuit numérique de contrôle pourra être testé rapidement grâce au prototype.

Le premier chapitre est une introduction aux stimulateurs physiologiques. On y retrouve principalement une description d'un système de classement des stimulateurs, ainsi que leurs principales caractéristiques physiques.

Le chapitre 2 traite des stimulateurs visuels et débute par une brève description du système visuel humain. Les trois approches de restauration de la vision sont ensuite approfondies. Finalement, on y présente les connaissances actuelles sur la stimulation du cortex visuel et de ses effets, ainsi que quelques architectures d'implant visuel cortical proposées par certains chercheurs.

Le chapitre 3 est consacré au développement des deux architectures. On y retrouve les éléments de leurs circuits analogiques et les interactions entre leurs différents modules. Les détails du circuit prédiffusé sont également traités.

Le chapitre 4 présente le circuit numérique de contrôle du prototype. Nous proposons d'abord un protocole de communication entre le contrôleur externe et le prototype. Ensuite nous développons le circuit numérique en entier.

Le chapitre 5 traite des résultats et de certains aspects par rapport aux réalisations du prototype et du prédiffusé. On approfondit notre compréhension du fonctionnement du prototype grâce notamment à des figures illustrant des résultats de simulation.

# CHAPITRE 1

## ÉTUDE DES STIMULATEURS PHYSIOLOGIQUES

### 1.1 Introduction

La stimulation physiologique est un sujet de recherche intéressant, car les progrès réalisés dans ce domaine ont un impact direct sur la qualité de vie de nombreuses personnes et les applications qui en découlent n'ont cessé de croître au fil des années. À ce jour, essentiellement trois méthodes existent pour créer un changement du comportement des cellules du système nerveux. La première méthode consiste à injecter une substance chimique à un groupe de cellules. Cette substance permet de modifier l'activité synaptique grâce à ses propriétés d'excitation ou d'inhibition [55]. La deuxième méthode utilise un stimulateur magnétique qui, par induction électromagnétique, permet de créer un champ électrique dans une fibre nerveuse dans le but de provoquer un potentiel d'action [27,28]. Un potentiel d'action correspond à une impulsion électrique qui se propage le long de l'axone d'une cellule nerveuse. La dernière méthode, la stimulation électrique, emploie des électrodes afin de transmettre un courant ionique à une fibre nerveuse et donc de produire un potentiel d'action [24].

Récemment, Chen et al. [55] ont développé et testé *in vivo* une sonde très compacte qui permet d'introduire une petite quantité de liquide à un endroit bien précis dans le corps. La méthode de stimulation recourant aux substances chimiques demeure au stade des activités de recherche dans le domaine de la neurobiologie. Aucune application permettant de récupérer une fonction chez l'humain n'utilise cette approche. Ceci est en partie dû au fait que l'injection d'un liquide est un processus plutôt lent.

La stimulation magnétique est surtout employée pour le diagnostic de maladie neuro-musculaire et pour la cartographie du cerveau [78]. Malgré le fait qu'au moins une étude

ait démontré des résultats encourageants, il n'y a, pour l'instant, aucune application qui permet de rétablir une fonction chez l'humain en utilisant cette approche [28]. Cette méthode offre comme avantage, par rapport à la stimulation électrique, une meilleure biocompatibilité, grâce à l'absence de contact métal-tissu (pas d'électrodes) [28]. La stimulation électrique reste néanmoins le meilleur moyen connu pour récupérer une quelconque fonction chez l'humain, car elle possède la précision requise par la majorité des applications.

Ce chapitre débute par une brève description de la cellule nerveuse, du phénomène du potentiel d'action et de l'interaction entre le stimulateur et la cellule. Dans un deuxième temps, on présente une classification des stimulateurs électriques permettant ainsi de cibler le type le plus convenable à la réalisation d'une prothèse visuelle. Ensuite, les technologies de fabrication de ces stimulateurs ainsi que quelques-unes de leurs caractéristiques techniques seront abordées. Les opérations de stimulation et leurs effets biologiques sont des facteurs qui doivent être absolument tenus en compte lors de la conception d'un implant. Ces particularités d'ordre biomédical seront donc considérées subséquemment.

## 1.2 La cellule nerveuse

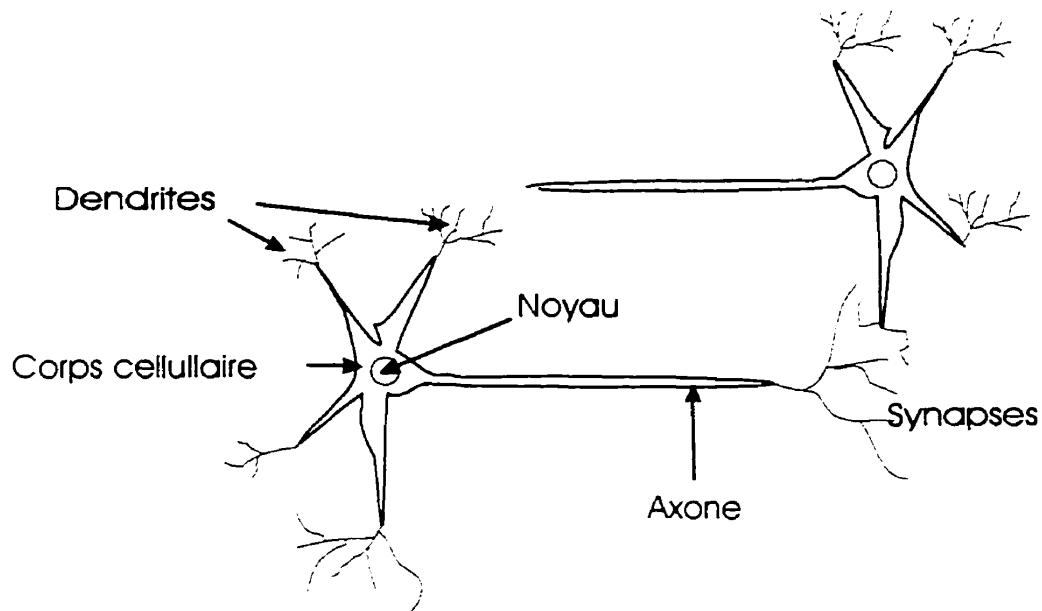

Le travail effectué par une cellule nerveuse consiste à intégrer l'information provenant des cellules qui lui sont rattachées et ensuite, d'envoyer le résultat (une fois l'information traitée) vers d'autres cellules sous forme d'impulsions électriques. La figure 1.1 montre la structure simplifiée d'une cellule nerveuse. Celle-ci est principalement composée de dendrites qui reçoivent les impulsions des cellules avoisinantes, d'un corps cellulaire, d'un noyau et finalement de l'axone [4]. La jonction entre l'axone d'une cellule et les dendrites d'une autre est appelée synapse.

Une impulsion électrique appelée potentiel d'action peut être transmise à travers l'axone d'une cellule nerveuse, grâce à la propriété électrochimique de la membrane nerveuse. Celle-ci possède des pompes ioniques qui lui permettent de maintenir une différence de potentiel d'environ  $-65$  mV entre le milieu intérieur et le milieu extérieur de la cellule.

Une dépolarisation de la membrane nerveuse se crée lors de l'arrivée de potentiels d'action de neurones voisins. Cette dépolarisation est obtenue grâce à un neuromédiateur (provenant des synapses) qui ouvre des canaux ioniques sur la membrane. Cette dépolarisation augmente la perméabilité de la membrane aux ions de sodium ce qui entraîne une rupture des équilibres ioniques et la création d'un potentiel d'action.

**Figure 1.1 : La cellule nerveuse**

La structure électrochimique des cellules des tissus humain peut donc répondre à l'application d'un courant ionique. Cette propriété permet d'influencer le comportement d'un groupe de cellules ou d'un muscle du corps à partir d'une source externe de courant. La stimulation électrique consiste donc à injecter un courant ionique sur une partie du corps humain, dans le but de lui « commander » un certain travail. Ce courant est injecté à l'aide d'électrodes ou d'un réseau d'électrodes selon l'application.

### 1.3 Classification des stimulateurs électriques

Des gammes complètes de stimulateurs électriques furent développées pour diverses applications durant les dernières décennies. Le stimulateur cardiaque est sans aucun doute le type le plus connu. Une classification possible des stimulateurs électriques est la suivante [24]:

- 1) les systèmes reliés par fils;

- 2) les systèmes externes;

- 3) les systèmes reliés par liens transcutanés ;

- 4) les systèmes totalement implantables.

Les stimulateurs de la classe #1 sont des systèmes où un implant est connecté à un contrôleur externe à l'aide de quelques fils qui traversent la peau (connexions percutanées). Ce genre de système est surtout utilisé pour effectuer des expériences en clinique, car il y a risque d'infection de la peau dû aux fils qui la traversent. Cependant, des applications non expérimentales entrent dans cette classe, comme par exemple le stimulateur cardiaque temporaire qui peut être introduit dans le cœur via une veine accessible et ensuite être enlevé lorsque le support cardiaque n'est plus requis [24]. Le professeur Wise et son équipe ont développé durant les dix dernières années une panoplie de stimulateurs et de sondes appartenants à cette classe [35,36,42,44,45].

Les stimulateurs de la classe #2 sont des systèmes où les stimulations sont appliquées directement sur la peau à l'aide d'électrodes de surface. Parmi les applications de cette classe, on retrouve le stimulateur électrique neuronal transcutanée (TENS) et la thérapie par choc électroconvulsif (ECT) [24]. Ces stimulateurs sont généralement employés dans un but thérapeutique et non comme moyen pour récupérer une fonction.

Les stimulateurs de la classe #3 utilisent un lien transcutané (aucune connexion physique) pour la transmission d'information et d'énergie entre un contrôleur externe et

un implant [37]. Le lien transcutané est généralement réalisé à l'aide d'un couplage inductif [24]. Plusieurs systèmes de stimulation de muscles paralysés [26], de la cochlée [43,54] et de la vessie [25] font partie de cette classe.

Les stimulateurs de la classe #4 ne comportent qu'un seul module qui est totalement implantable et indépendant. Ce genre de stimulateur doit donc contenir sa propre source d'énergie. Le stimulateur cardiaque appartient à la classe #4. Souvent, la pile utilisée dans cette application peut être rechargée à l'aide d'un lien inductif.

Généralement, c'est l'application qui détermine la classe de stimulateur à utiliser. Seuls les classes de stimulateur #1 et #3 peuvent être employées pour réaliser une prothèse visuelle. En effet, deux modules sont essentiels dans ce type d'application. Le module externe est nécessaire pour capter la lumière (les images) et pour la traiter. Le module interne (l'implant) est indispensable, car l'endroit à stimuler dans tous les cas (répine, nerf optique ou cortex) est situé à l'intérieur du corps humain.

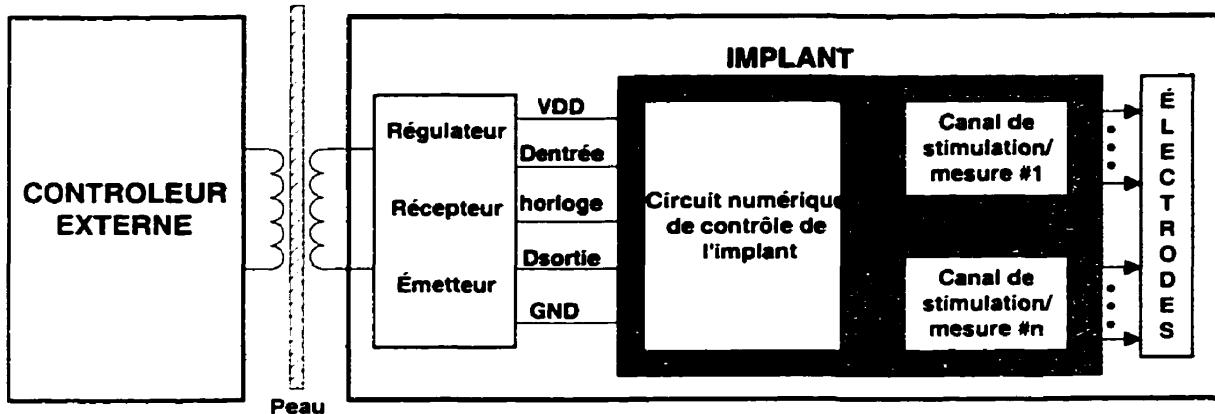

Deux sous-catégories existent dans les classes #1 et #3 : les systèmes possédant un seul canal de stimulation et les systèmes en possédant plusieurs. L'implant cortical comporte nécessairement plusieurs canaux car différents sites dans le cortex doivent être excités simultanément pour générer des patrons reconnaissables par le non-voyant. L'implant cortical n'est pas la seule application des stimulateurs multicanaux. L'implant rétinien [3], certains implants cochléaires [43], musculaires [26] et de la vessie [25] utilisent eux aussi plusieurs canaux de stimulation. Un schéma bloc typique d'un stimulateur multicanaux est montré à la figure 1.2.

La partie implantable du stimulateur possède généralement un premier bloc regroupant un récepteur, un émetteur et un régulateur. Ce bloc permet la réception de l'information et du signal d'horloge, ainsi que la transmission de données. C'est également ce module qui convertit l'énergie reçue du contrôleur externe en un ou plusieurs niveaux de tension utiles.

**Figure 1.2 :Schéma bloc typique d'un stimulateur multicanaux**

L'implant comporte aussi un circuit numérique qui selon les instructions du contrôleur externe, commande les opérations à effectuer à un ou plusieurs canaux de stimulation ou de mesure. Finalement une matrice d'électrodes est utilisée comme étage de sortie pour injecter les courants de stimulation aux cellules nerveuses.

Chaque canal de stimulation ou de mesure comprend un convertisseur numérique-analogique (CNA) et habituellement un système d'aiguillage des courants dans le cas où plusieurs sites (groupes de cellules) doivent être stimulés séquentiellement. Mise à part la stimulation de structure cellulaire, les implants peuvent également être utilisés pour enregistrer des signaux provenant de ces structures. Le système de mesure d'un canal est donc utile pour enregistrer ces signaux, mais aussi pour connaître l'état de l'interface tissu-électrode.

Les tâches effectuées par les implants peuvent être plus ou moins complexes. Certaines conceptions permettent la programmation de quelques paramètres de stimulation offrant la flexibilité requise pour les applications nouvelles ou pour celles qui risquent d'évoluer. Les prochaines sections donnent un aperçu des technologies utilisées ainsi que de quelques circuits existants permettant la réalisation de stimulateurs et autres implants de complexités diversifiées.

## 1.4 Les technologies

Les progrès réalisés dans le domaine des stimulateurs et autres implants en général sont étroitement reliés aux progrès effectués dans les procédés de fabrication des électrodes et réseaux d'électrodes ainsi que dans le domaine de la microélectronique. Généralement, le circuit numérique en entier et une bonne partie des circuits analogiques sont réalisés à l'intérieur d'un seul circuit intégré (CI) afin de réduire l'espace occupé par un implant.

De nos jours, la technologie CMOS est largement dominante en ce qui concerne le nombre des CI fabriqués. Un procédé de fabrication plus simple et moins coûteux est une première caractéristique qui avantage le transistor CMOS par rapport à son plus grand concurrent, le transistor bipolaire. Employés dans un circuit numérique, les transistors CMOS consomment très peu d'énergie lorsque la fréquence de commutation n'est pas trop élevée. Finalement, la grande impédance de grille de ces transistors en fait des composants idéaux pour l'étage d'entrée d'un circuit analogique.

Les transistors bipolaires ont cependant comme avantages de pouvoir fonctionner à des fréquences beaucoup plus élevées ainsi que de manipuler des courants plus importants que les transistors CMOS de même taille, ce qui est un atout certain lors de la conception de circuit analogique. Le procédé de fabrication BiCMOS intègre des transistors CMOS et bipolaires dans un seul et même CI. Cette technologie permet de prendre avantage de chacun des deux types de transistor. Toutefois, le procédé de fabrication d'un CI BiCMOS est considérablement plus coûteux car il nécessite plus de masques.

Une faible consommation de puissance et des petites dimensions sont les caractéristiques les plus souhaitables d'un CI incorporé dans un implant. De plus, la chaleur dissipée par l'implant et transmise au corps humain doit être réduite à son minimum. En effet, l'augmentation de température près des électrodes doit être inférieure à 1°C, sous peine d'endommager les tissus environnants [42]. De plus, dans le cas d'un stimulateur de classe #3, l'énergie fournie à l'implant par le contrôleur externe doit également être la

plus faible possible, afin de limiter les effets néfastes du champ magnétique créé par le lien inductif sur le cerveau.

Pour toutes les raisons mentionnées précédemment, la technologie CMOS est pour l'instant la technologie la plus utilisée afin de réaliser un CI incorporé dans un implant [25,26,35,36,45,54,57]. Toutefois, d'autres CI d'implants sont réalisés avec la technologie BiCMOS [42,56,59]. De meilleures performances, surtout avec les circuits analogiques, sont obtenues par ces implants.

L'équipe de Wise [35,36,42,44,45] a proposé quelques conceptions de stimulateurs et de sondes dont l'électronique est directement intégrée dans le même substrat utilisé pour fabriquer les électrodes de stimulation. Cette façon de faire à l'avantage de minimiser l'espace total occupé par l'implant. Par contre, des étapes additionnelles au procédé CMOS standard sont nécessaires pour fabriquer de tels implants.

## 1.5 Les techniques analogiques

Malgré le fait que les implants doivent dissiper le moins de puissance possible en plus d'être compacts, les nouvelles conceptions deviennent de plus en plus complexes et intègrent de plus en plus d'électronique au fil des ans. De nombreuses techniques analogiques développées au cours des dernières années permettent la réalisation de ces implants dont la complexité ne cesse d'augmenter.

Ces techniques sont axées principalement sur la réduction de la consommation de puissance et des dimensions du circuit plutôt que sur l'optimisation de leur vitesse et leur précision. Les circuits analogiques des implants se retrouvent la plupart du temps aux étages d'entrée et de sortie. Parmi ces circuits, on retrouve les circuits de transmission et de réception de données et d'énergie, les CNA, les circuits d'aiguillage des courants de stimulation et finalement les systèmes de mesure et de vérification de l'interface électrode-tissu. Les deux prochaines sections traitent de certains détails de conception des deux plus importants blocs analogiques, soit le système de transmission et de réception et les CNA.

### 1.5.1 Transmission et réception de données et d'énergie

Le type de système employé pour la transmission et la réception de données et d'énergie entre un implant et son contrôleur externe dépend largement de l'application. Le transfert peut être fait soit à l'aide de fils (connexion percutanées), d'un lien optique ou d'un lien inductif. Le transfert à l'aide de fils comporte un inconvénient majeur soit le risque d'infection de la peau par ces fils [58]. Le lien optique doit posséder un canal de transmission transparent, ce qui est difficilement réalisable dans le cas de l'implant cortical. Le lien inductif reste donc pour le moment le meilleur moyen pour effectuer ce travail.

Quatre fonctions doivent être accomplies par le bloc regroupant le transmetteur, le récepteur et le régulateur de l'implant cortical. Parmi ces fonctions, on retrouve :

- la régulation d'une ou plusieurs tensions pour alimenter le reste du circuit de l'implant;

- la détection des données (commandes de stimulation);

- la transmission de données (mesure ou état de l'implant);

- le recouvrement et la génération de l'horloge.

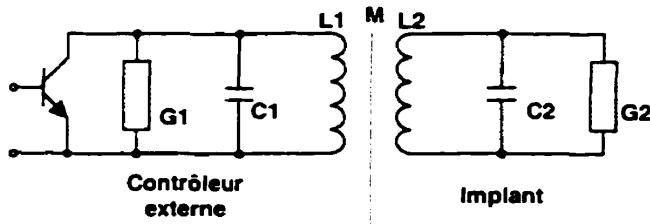

Quelques auteurs proposent divers moyens pour accomplir ces tâches à l'aide d'un implant comportant une seule [25,26,38,56-59,66] ou deux [65] bobines. La transmission d'énergie est rendue possible grâce au couplage inductif entre la bobine du contrôleur externe et celle de l'implant. Une configuration possible pour planter un lien inductif est présentée à la figure 1.3.

Figure 1.3 : Circuit simplifié d'un lien inductif

L'amplificateur de puissance du contrôleur externe et le circuit récepteur de l'implant forment tous les deux des filtres passe bande centrés sur une fréquence commune  $\omega_0$  où :

$$\omega_0 = \frac{1}{\sqrt{L_1 C_1}} = \frac{1}{\sqrt{L_2 C_2}} \quad (1.1)$$

Le choix de la fréquence  $\omega_0$  de la porteuse du signal dépend principalement de la capacité d'absorption des tissus et des dimensions de l'implant. Plus la fréquence est élevée, plus les grandeurs des bobines peuvent être réduites. Par contre, selon la puissance transmise par le contrôleur externe, la fréquence de transmission peut être limitée, car l'absorption des ondes électromagnétiques par les tissus humains augmente elle aussi avec la fréquence [69]. Plusieurs autres facteurs entrent en ligne de compte dans la conception d'un lien inductif comme par exemple la forme des bobines, la position de l'implant par rapport au contrôleur externe, la tolérance au déplacement et finalement les besoins en énergie, en tension régulée et en bande passante [60,65]. Le rendement du lien inductif, soit le rapport de la puissance consommée par l'implant sur la puissance totale qui lui est transmise est surtout fonction de la fréquence de la porteuse, du coefficient de couplage  $k$  entre les deux bobines et du type de régulateur utilisé.

La régulation de tension se fait à partir d'un redresseur à simple [54] ou double alternance [26]. Des condensateurs sont utilisés dans ces circuits pour emmagasiner l'énergie et réduire les rebonds. Une diode zener peut être employée pour fournir une meilleure régulation [43].

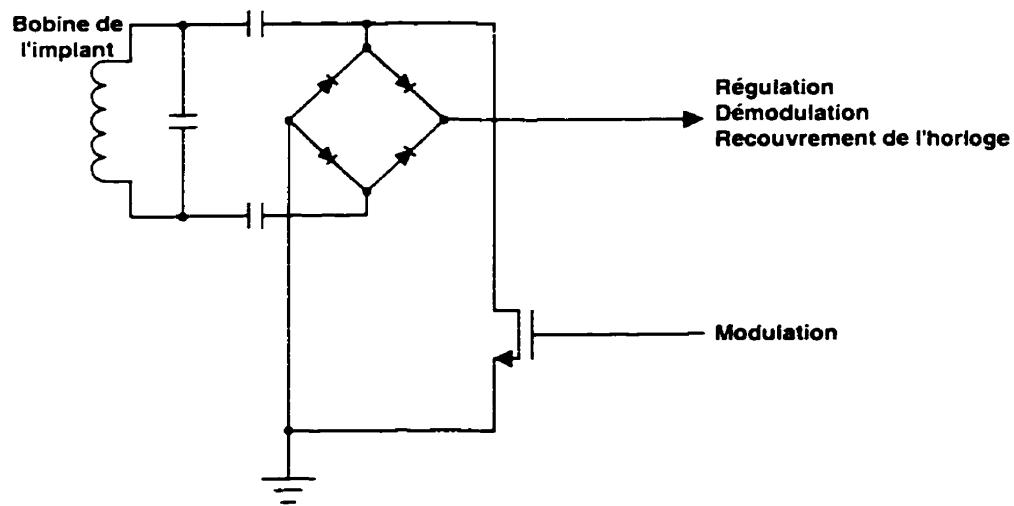

La plupart des systèmes implantables de biotélémétrie utilisent la modulation de fréquence pour la transmission des signaux [61]. Dans les systèmes dont la distance entre les bobines émettrice et réceptrice est petite, les signaux FM ne sont pas affectés par le mouvement continu de ces bobines. Ceci fait du FM la solution de choix pour la transmission de signal analogique. Toutefois, en ce qui concerne la transmission de signaux numériques, plusieurs types de modulation peuvent être employés comme le ASK (Amplitude Shift Keying), le FSK (Frequency Shift Keying) et le PSK (Phase Shift Keying). Le ASK a l'avantage d'avoir le circuit de modulation/démodulation le plus simple. Le LSK (Load-Shift Keying) est une nouvelle méthode qui semble très prometteuse, car elle permet une transmission de données de l'implant vers le module externe très efficace en terme de consommation de puissance. La figure 1.4 montre un exemple de circuit pour planter la modulation LSK.

**Figure 1.4 : Récepteur et modulateur LSK**

Le LSK utilise la propriété du couplage inductif qui implique qu'un changement dans la charge de la bobine secondaire se reflète par un changement dans l'impédance de la bobine primaire [61]. Ce changement d'impédance peut facilement être détecté par le contrôleur externe. Dans le circuit de la figure 1.4, c'est en activant le transistor NMOS que l'impédance peut être changée. Ce type de modulation consomme peu de puissance

par rapport à la plupart des autres méthodes de transmission où la génération d'une porteuse est nécessaire. Au moins deux systèmes utilisent ce type de modulation pour leur transfert de données [26,58].

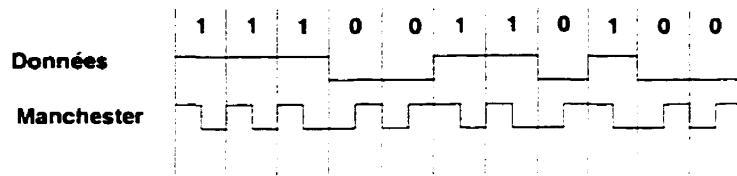

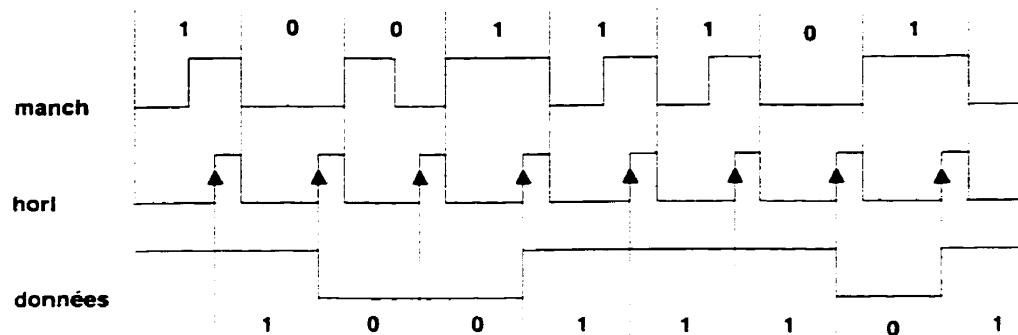

La fonction de recouvrement des données et la génération de l'horloge peuvent être accomplies de plusieurs façons. Une première méthode consiste à utiliser le code Manchester de façon à intégrer le signal d'horloge dans les données transmises du contrôleur externe vers l'implant. Avec ce type de codage, il y a toujours au moins une transition du signal par bit transmis ce qui permet de fournir un signal de synchronisation pour le générateur d'horloge. Comme illustré à la figure 1.5, un front montant indique qu'un « 0 » logique vient d'être transmis alors que les fronts descendant sont utilisés pour signaler les « 1 » logiques.

Figure 1.5 : Codage Manchester

Cette méthode à l'avantage d'être simple à planter. Cependant, la fréquence de transmission des données est deux fois moins élevée que la fréquence de l'horloge [25,52]. Une autre approche consiste à utiliser la porteuse du signal transmis pour générer une horloge synchronisé avec le contrôleur externe [58].

La plupart des implants emploient des composants discrets dans une bonne partie de la circuitrie du système de réception, de transmission et de régulation. Ceci est nécessaire car plusieurs composants comme les diodes zener et les bobines par exemple sont plus difficiles à intégrer. Récemment, Akin et al. [58] ont développé un implant dont la circuitrie de réception et de transmission, à l'exception de la bobine, est entièrement intégrée dans un seul et unique CI.

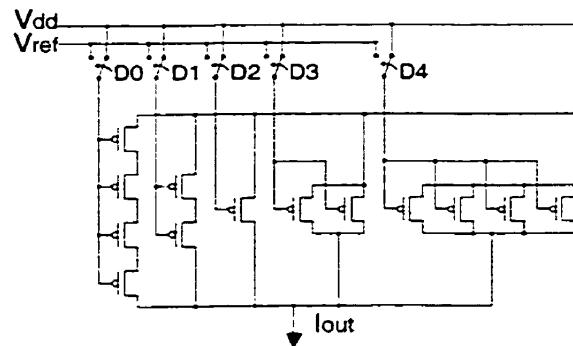

### 1.5.2 Convertisseur numérique analogique (CNA)

Le convertisseur numérique analogique est un étage critique dans les stimulateurs implantables. En effet, ce module doit produire un courant avec une bonne précision (jusqu'à 8 bits quelquefois), être compact et consommer peu d'énergie. Les deux dernières caractéristiques sont très importantes, car il y a le même nombre de convertisseurs que de canaux dans un stimulateur multicanaux. Par exemple, l'implant visuel proposé par Boyer [52] utilise 25 CNA. Quelques auteurs ont proposé des architectures intéressantes de CNA utilisés dans des implants [36,39,42,45,52,62].

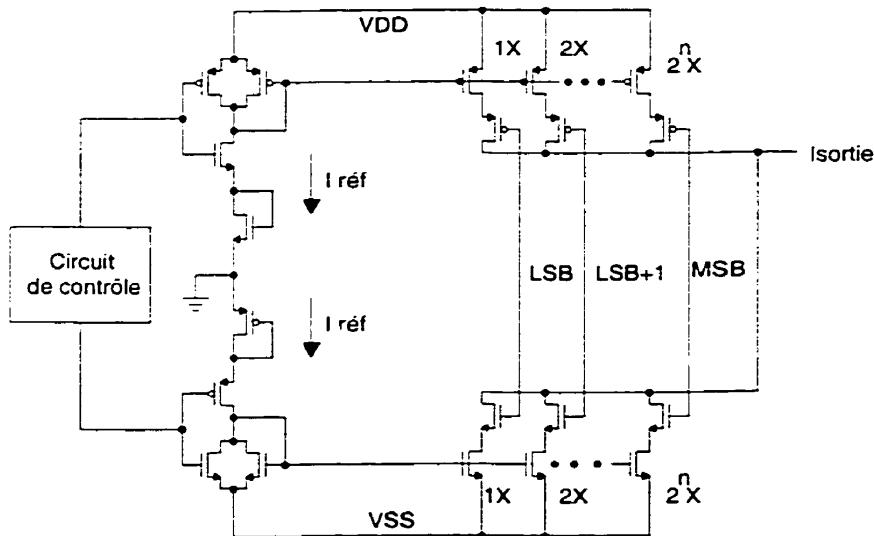

Un convertisseur simple employé par Kim [45] est présenté à la figure 1.6. Elle utilise des miroirs de courants dont le rapport W/L augmente d'un facteur deux pour chaque bit du mot d'entrée. Chaque bit est associé à un miroir de type N pour tirer un courant du nerf vers la source et un autre de type P pour envoyer un courant de la source vers le nerf. L'utilisation des deux types de miroir donne la possibilité d'effectuer des stimulations biphasiques.

Figure 1.6 : CNA à miroirs de courant simple

L'impédance de sortie de ce convertisseur peut être augmentée en utilisant des miroirs de courant de type cascode, tels qu'employés dans le CNA utilisé par Jones et Normann

[39]. Cependant, cette dernière source occupe environ le double de l'espace par rapport au CNA de Kim.

Une seconde topologie proposée par Kim [42] et réalisée à l'aide d'un procédé BiCMOS, utilise des interrupteurs MOS associés à chacun des bits pour contrôler le courant de base d'un transistor bipolaire et donc son courant au collecteur (figure 1.7).

**Figure 1.7 : CNA en BiCMOS**

Les dimensions de ce circuit sont réduites par rapport aux deux autres convertisseurs, car ici les transistors utilisés comme interrupteurs sont également employés pour contrôler le courant dans la base du transistor bipolaire.

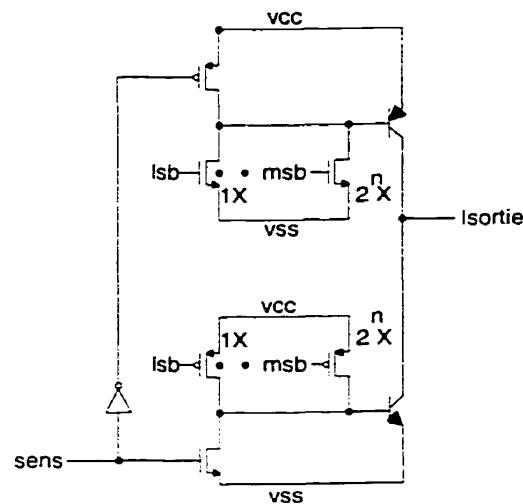

La figure 1.8 montre une dernière topologie dont la principale caractéristique est d'être très compacte. Le courant de référence généré par le CNA est réalisé à l'aide de transistors identiques placés en série ou en parallèle [62,63]. La direction du courant dans le nerf est contrôlée à l'aide d'une configuration en H, telle que montrée à la figure 1.9.

Figure 1.8 : CNA proposé par St-Amand [62]

Figure 1.9 :Contrôle du sens du courant

## 1.6 Électrodes et réseaux d'électrodes

Les électrodes et réseaux d'électrodes servent d'intermédiaire entre l'étage de sortie de l'électronique et les cellules nerveuses lors de l'injection des courants de stimulation. Depuis environ trois décennies, des techniques basées sur la lithographie ont fait leur apparition, permettant de réaliser des réseaux d'électrodes de faibles dimensions [29-33,64]. Le silicium s'est avéré comme étant un substrat très avantageux pour servir de base à une telle structure, car il offre une bonne précision, il est biocompatible et il permet l'intégration de circuits électroniques [32]. Ces progrès ont amené la réalisation de réseaux d'électrodes de grande densité (figure 1.10) qui pourraient éventuellement être utilisés dans des systèmes de stimulation corticale [32, 33].

**Figure 1.10 : Réseau d'électrodes (tiré de [33])**

Le choix du matériau qui recouvre la surface de stimulation des électrodes doit tenir compte de la biocompatibilité et de certains effets nuisibles comme la polarisation des électrodes. Le matériau doit être le plus inerte possible afin de prévenir son oxydation. Par contre, ce même type de matériau a généralement la propriété d'être facilement polarisable (accumulation de charge à l'interface électrode-tissu). Ce phénomène peut cependant être éliminé en effectuant des stimulations biphasiques.

### 1.6.1 Modélisation de l'interface électrode-tissu

Les recherches effectuées au niveau du comportement électrochimique de l'interface entre les électrodes de stimulation et les tissus humains ont démontré la grande complexité à modéliser cette interface [46,47,67,68]. Une bonne connaissance de ce phénomène est néanmoins nécessaire pour pouvoir garantir le fonctionnement efficace et sécuritaire de l'implant. Par exemple, la caractérisation de cette interface permet de connaître son impédance, un élément important dans la conception des sources de courant de l'implant. Un modèle très utilisé de cette interface est présenté à la figure 1.11. La source de tension  $E_{1/2}$  modélise le potentiel demi-cellule dont la valeur dépend principalement du type de métal de l'électrode, de la concentration de ses ions dans l'électrolyte et de la température [70]. Ce potentiel est dû à une séparation des charges à l'interface, produisant une double couche électrique où un type de charge est dominant sur la couche de l'électrode et le type de charge opposé est dominant sur l'autre couche. Ce phénomène est appelé la double couche de Helmholtz. Lorsque la densité de courant n'est pas trop élevée, les valeurs de la résistance  $R_w$  et du condensateur  $C_w$  (impédance

de Warburg) varient proportionnellement avec l'inverse de la racine carré de la fréquence. La valeur de  $R_w$  diminue et celle de  $C_w$  augmente de façon non-linéaire avec une augmentation dans la densité de courant.

**Figure 1.11 : Modèle de l'interface électrode-électrolyte**

La résistance de Faraday  $R_f$  doit nécessairement être incluse dans le modèle, car il est possible de faire passer un courant continu à travers l'interface. Cette résistance est composée en réalité de trois éléments, soit la résistance de transfert, la résistance de diffusion et finalement de la résistance de réaction [67]. Les détails de cette interface dépassent le cadre du présent projet maîtrise. Des explications plus approfondies sur ce sujet peuvent par contre être trouvées dans divers articles [46,47,67,68].

## 1.7 Considérations d'ordre biomédicales

Seuls quelques aspects techniques furent abordés jusqu'à présent dans ce chapitre. Toutefois, d'autres considérations doivent être tenues en compte lors de la conception d'un implant. Selon l'application, le stimulateur peut demeurer à l'intérieur du corps humain pendant plusieurs années. Celui-ci possède cependant des mécanismes qui le protègent contre l'intrusion de corps étrangers. L'implant doit donc être biocompatible. Par ailleurs, l'objectif premier d'un stimulateur est d'injecter un courant dans le tissu nerveux afin de provoquer une certaine réaction. L'injection de charges peut endommager les tissus nerveux. Des précautions doivent donc être prises pour éviter cela.

### 1.7.1 Biocompatibilité des implants

Les implants sont habituellement recouverts d'un polymère ou d'un verre quelconque qui ont comme fonction de bien protéger l'implant sans causer d'effets néfastes sur le corps humain. La biocompatibilité des implants est surtout critique au niveau des électrodes de stimulation. Celles-ci doivent être conçues de façon à minimiser les blessures causées aux tissus nerveux car ces blessures peuvent provoquer des inflammations [50]. L'injection d'un courant dans le corps à l'aide d'électrodes produit des réactions électrochimiques. Ces réactions peuvent changer de façon importante l'environnement des électrodes en changeant les concentrations d'ions et le PH et ainsi provoquer leur corrosion [50]. Le platine ou l'iridium sont couramment utilisés comme surface de stimulation [36,45,57,64] car ces matériaux sont presque inertes chimiquement. Outre les matériaux, la biocompatibilité des électrodes est fonction de leur géométrie, leur stérilisation, des paramètres de stimulation et finalement de la technique utilisée pour les insérer dans le cerveau [49,50,71].

### 1.7.2 Excitabilité et lésion neuronale

La stimulation prolongée d'une structure dans le système nerveux central ou sur une fibre nerveuse peut causer des lésions neuronales irréversibles. Habituellement, des stimulations biphasiques sont utilisées pour exciter un groupe de cellules nerveuses, c'est-à-dire qu'une opération de stimulation comporte deux phases, l'une positive et l'autre négative. Le courant de stimulation dans les cellules passe donc dans les deux directions.

Selon McCreery et al. [48], deux facteurs, soit la charge par phase et la densité de charge contribuent conjointement aux risques d'induire des lésions aux neurones. La charge par phase est définie comme étant l'intégrale du courant d'une phase (demi-cycle) de stimulation. La densité de charge est définie comme étant l'intégrale de la densité du courant de l'une ou l'autre des phases du stimulus. La densité de charge correspond également à la charge par phase divisée par la surface active des électrodes. Toujours selon McCreery et al., la densité de charge déterminerait la proportion des neurones près

de l'électrode qui sont excités et la charge par phase déterminerait le volume total de tissu dans lequel les neurones sont excités. Les risques de lésions peuvent donc être réduits en augmentant la surface active des électrodes et en diminuant la quantité de charge (donc le courant) injectée par phase. La surface de l'électrode doit par contre être limitée, car plus celle-ci est grande, plus les lésions « mécaniques » causées lors de son insertion sont importantes.

Une autre conséquence d'une stimulation prolongée d'un groupe de neurones consiste en une réduction de leur excitabilité [51]. Ce phénomène nommé SIDNE (Stimulation-Induced Depression of Neuronal Excitability) est beaucoup moins néfaste qu'une lésion, car il est réversible et serait dû à un mécanisme de protection contre les lésions neuronales [51]. La sévérité d'un SIDNE s'accentue avec l'augmentation de la durée et de la fréquence de la stimulation. Augmenter l'amplitude pour contrer un SIDNE ne fait qu'aggraver ce phénomène. Une façon possible pour éviter ce phénomène est de distribuer la stimulation sur plusieurs électrodes de façon séquentielle, pour ainsi réduire la durée d'activation par cycle de chaque électrode.

## 1.8 Conclusion

Ce chapitre a présenté une introduction aux stimulateurs sensoriels. Nous avons décrit et expliqué les différentes classes de stimulateurs, ainsi que les principaux aspects à considérer par rapport aux technologies, aux techniques analogiques et aux électrodes de stimulation. Finalement, nous avons fait état de certaines considérations d'ordre biomédical dont on doit tenir compte.

Un élément qui se démarque dans l'étude des implants c'est qu'ils doivent tous être optimisés en fonction de leur consommation d'énergie et de leur dimension. Ces caractéristiques sont également essentielles pour n'importe quel type d'implant visuel.

Le prochain chapitre traite des prothèses visuelles. C'est-à-dire des stimulateurs visuels en général (rétine, nerf optique et cortex) et de l'implant cortical en particulier.

## CHAPITRE 2

# LES PROTHÈSES VISUELLES

### 2.1 Introduction

Le chapitre précédent a exposé les principaux points touchant les stimulateurs physiologiques en général. Le présent chapitre approfondit le sujet de la récupération partielle de la vision.

La première section décrit le système visuel humain et les principales maladies de la vision. Ensuite, on présente et compare brièvement les trois grandes avenues de recherche pour rétablir la vision soit : la stimulation de la rétine, la stimulation du nerf optique et finalement la stimulation du cortex visuel.

Le type de prothèse visuelle en cours de réalisation par notre équipe de recherche (PolySTIM) est un stimulateur cortical. Le prototype développé dans le cadre de ce projet de maîtrise doit donc avoir la même fonctionnalité qu'un implant cortical. C'est pourquoi la section suivante traite des connaissances actuelles sur la stimulation du cortex visuel et de ses effets.

Finalement, nous présentons les principaux travaux de recherche sur le développement de l'implant cortical et sur l'efficacité de la vision que l'on projette obtenir à l'aide de celui-ci.

### 2.2 Le système visuel humain et les maladies de la vision

La figure 2.1 montre la structure de l'œil. La principale tâche de l'œil est de focaliser la lumière sur sa rétine, premier étage cellulaire du système visuel humain. La rétine est constituée entre autres de deux types de cellules photoréceptrices (qui détectent la lumière) soient les cônes et les bâtonnets. Les cônes, surtout concentrés près de la fovéa,

sont sensibles à de hauts niveaux d'intensité lumineuse et aussi à la couleur. Les 5.5 millions de ce type de cellule occupent une surface circulaire d'environ 0.5 mm de diamètre sur la rétine de chaque œil. Les bâtonnets, répartis sur toute la surface de la rétine, sont sensibles à de faibles niveaux d'intensité lumineuse et sont insensibles à la couleur. Il y a environ 120 millions bâtonnets dans la rétine de chaque œil. La rétine possède principalement deux autres étages cellulaires, soit les cellules bipolaires et horizontales et les cellules ganglionnaires. Ces étages de cellules effectuent quelques traitements avant d'envoyer l'information aux autres étages de cellules dans le système nerveux.

**Figure 2.1 : Vue en coupe d'un œil**

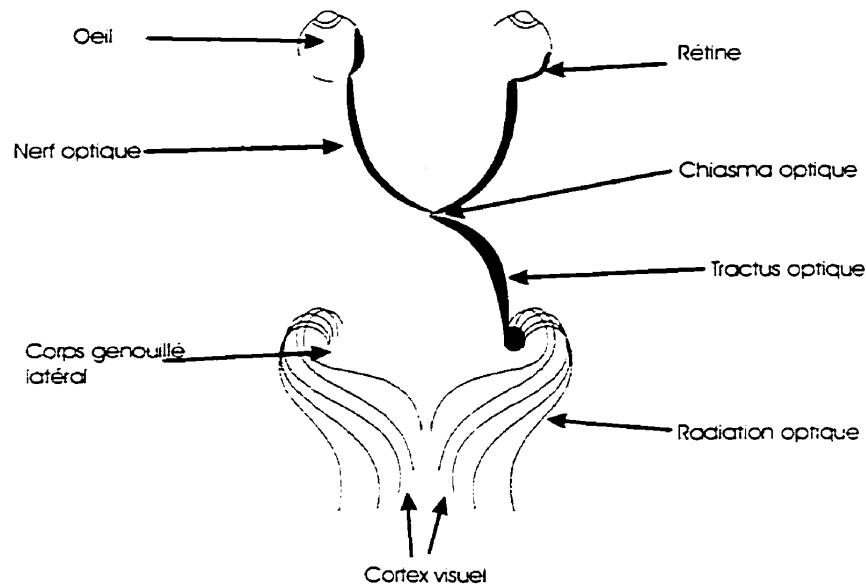

La figure 2.2 montre la structure du système visuel humain aussi appelé « voies visuelles ». Les deux nerfs optiques amènent l'information des cellules ganglionnaires de chaque rétine à un point de croisement appelé Chiasma optique. Ensuite, l'information passe par les tractus optiques vers une couche de cellules située de chaque côté du cerveau appelé corps genouillé latéral qui passera à son tour l'information au cortex visuel. Les nerfs optiques, le chiasma optique et les tractus optiques ne font pas ou font peu de traitement. Leur principale utilité est de joindre l'information des deux côtés du champ visuel provenant de chaque œil.

**Figure 2.2 : Le système visuel humain**