|                         | A fixed-point simd array processor and its applications to video compression coding                                                                                                                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Peijian Yuan                                                                                                                                                                                                                                                       |

| Date:                   | 2001                                                                                                                                                                                                                                                               |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                          |

| Référence:<br>Citation: | Yuan, P. (2001). A fixed-point simd array processor and its applications to video compression coding [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/8681/">https://publications.polymtl.ca/8681/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/8681/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Guy Bois                              |

| <b>Programme:</b><br>Program:            | Non spécifié                          |

## UNIVERSITÉ DE MONTRÉAL

# A FIXED-POINT SIMD ARRAY PROCESSOR AND ITS APPLICATIONS TO VIDEO COMPRESSION CODING

## Peijian YUAN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU GRADE DE MAÎTRIE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

March 2001

© Peijian YUAN, 2001.

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-65596-2

# <u>UNIVERSITÉ DE MONTRÉAL</u> ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thése intitulèe:

## A FIXED-POINT SIMD ARRAY PROCESSOR AND ITS APPLICATIONS TO VIDEO COMPRESSION CODING

présentée par: Peijian YUAN

en vue de l'obtention du diplôme de: Maîtrise ès Sciences Appliquées

a été dûment accepté par jury d'examen constitué de:

M. SAWAN Mohamad, Ph.D., président

M. BOIS Guy Ph.D., membre et directeur de recherche

M. SAVARIA Yvon Ph.D., membre et codirecteur de recherche

M. <u>ABOULHAMID Mostapha</u> Ph.D., membre

# **Dedication**

To my wife, Beisong

To my son, Max

## Acknowledgements

It is my great pleasure to express sincere gratitude to these who have contributed to the successful completion of this work.

I have a deep feeling of indebtedness to my supervisor, Dr. Guy Bois for his constant confidence, support, encouragement, guidance and providing me financial support. His suggestions and criticisms were appreciated, and more importantly, his invaluable friendship will never be forgotten.

I am also thankful to my co-supervisor Dr. Yvon Savaria for introducing the thesis topic to me and providing me financial support to work in the PULSE research group.

I would like to express my appreciation to my colleagues Ivan Kralijic and Claude Villeneuve for helping me with using the PULSE simulation tools.

Many thanks to all my friends for helping to establish a convivial environment in which to work and for providing needed moral support during the difficult stages of this work.

Finally, I would like to thank my wife, Beisong Liu, to whom I owe much for her unending patience, encouragement and understanding, without which I could hardly have completed this work. Special thanks are to my lovely son Max Yuan, for understanding me for not giving him full attention during his growing years.

## Résumé

Cette thèse traite de l'utilisation de PULSE, un processeur à instruction unique et données multiples (SIMD) pour le Traitement et la Compression d'Images en format MPEG-2. De nos jours, les équipements de conférences vidéo, de téléphonie vidéo, de stockage d'images vidéo numérique, de télévision haute-définition (HDTV) et les systèmes de télévision et de multémedia numériques utilisent ce genre de fonctionnalité. Le stockage ou la transmission de données d'image numérique impliquent des bandes passantes et des quantités de mémoire importantes.

L'objectif principal de cette thèse est d'étudier les systèmes de codage de compression d'image. Elle traite notamment de la conception de systèmes de haute performance et elle étudie les compromis entre la précision et la complexité afin de réaliser des systèmes efficaces.

1) Le mémoire propose un algorithme précis et efficace pour effectuer la détection du mouvement dans un flot d'images. La méthode de recherche complète est rapide et précise. Elle est cependant très coûteuse. Une méthode de recherche graduelle mais complète permet de trouver le meilleur appariement avec un effort moyen réduit pour des images simples.

- 2) Une architecture adaptée à l'algorithme proposé est analysée et sa réalisation est décrite. Nos résultats démontrent qu'une puce PULSE permet de réaliser des systèmes de compression d'images efficaces et flexibles, qui exploitent un haut degré de parallélisme. Combiné avec un processeur de traitement de signal commercialement disponible, le C40 de la société Texas Instruments, on peut réaliser efficacement des systèmes de compression d'images de haute performance. Une telle architecture hétérogène est efficace et flexible.

- 3) Nous proposons aussi une méthode efficace pour le calcul de la transformée cosinus (DCT et IDCT) avec une puce PULSE. Cette méthode exploite une table de cosinus chargée dans les mémoires internes de PULSE pour éviter des calculs qui exigent un grand nombre d'opérations.

Des développements additionnels permettraient d'optimiser encore plus les algorithmes proposés afin d'accélérer la compression d'image avec PULSE.

## **Abstract**

This thesis is concerned with applying a Fixed-point SIMD Array Processor PULSE to Image Compression with the MPEG-2 Standard. Video compressor is widely used in today's video conferences, videophone, digital video storage. Storage or transmission of digital images requires large memories and transmission bandwidth. This motivated research on this topic.

The main objective of this thesis is to study image compression coding systems. Several aspects of design for high-speed and high accuracy processing are considered. In order to realize a simple and effective image compression coding system, the following areas are investigated.

- 1) A high-speed and high accuracy algorithm for motion estimation is developed.

The Gradual Full search method (GFSM) algorithm reduces the time required to find matches and no possible solution is neglected in the search area. Although the program is slightly more complex than the Full Searching Method (FSM), it is three times faster than FSM when processing a simple image.

- 2) Different system architectures for image compression coding are discussed and designed.

The results obtained during the research conducted for this thesis will prove that a PULSE chip can be used to construct flexible multi DSP systems, to accelerate image compression. Using PULSE chips with a C40 DSP and a FPGA control unit, we can construct a hardware/software system for image compression. It will not only reduce the cost of an image compression coding systems, but also improve its flexibility.

3) A simple and effective method to calculate DCT or IDCT with cosine functions using the PULSE chip is developed.

A possible method to compute the cosine function uses exponential function.

Calculating cosine function is relatively expensive. Thus we propose using precomputed tables stored in PULSE's internal memory to accelerate computation of DCT or IDCT.

Further developments could improve the throughput of image compression on the PULSE chip.

# **Table of Contents**

| Dedication                                                 | iii  |

|------------------------------------------------------------|------|

| Acknowledgements                                           | iv   |

| Résumé                                                     | vi   |

| Abstract                                                   | viii |

| Table of Contents                                          | x    |

| List of Figures                                            | xv   |

| List of Tables                                             | xvi  |

| List of Appendix                                           | xvii |

| Chapter 1 Introduction                                     | 1    |

| Chapter 2 A Review of Image Compressing Algorithms and The | eir  |

| Processor Architectures                                    | 5    |

| 2.1 MPEG standard                                          | 5    |

| 2.1.1 Background                                           | 5    |

| 2.1.2 A brief overview of MPEG-2                           | 6    |

| 2.1.3 Convolution                                          | 15   |

| 2.2 Motion estimation algorithm                            | 15   |

| 2.2.1 FSM (full search method)                             | 16   |

|             | 2.2.2 CDS (conjugate direction searching)                   | 16 |

|-------------|-------------------------------------------------------------|----|

|             | 2.2.3 Three-step searching                                  | 18 |

|             | 2.2.4 CSA (cross-search algorithm)                          | 20 |

|             | 2.2.5 GFSM (gradual full search method)                     | 21 |

|             | 2.2.6 Comparison of the different algorithms                | 22 |

| 2.3 Pro     | ocessor architecture review                                 | 23 |

|             | 2.3.1 Custom chip set for MPEG-2 coding                     | 23 |

|             | 2.3.2 VLSI implementation for motion estimation             | 26 |

|             | 2.3.3 APC based image compression system                    | 27 |

| 2.4 SII     | MD architecture of the PULSE chip                           | 29 |

|             | 2.4.1 Introduction                                          | 29 |

|             | 2.4.2 Chip architecture                                     | 31 |

|             | 2.4.3 Processing element block diagram                      | 33 |

|             | 2.4.4 Instruction set                                       | 35 |

|             | 2.4.5 PULSE V1 assembler                                    | 37 |

|             | 2.4.6 PULSE applications                                    | 38 |

| Chapter 3 I | Implementing a Convolution on PULSE                         | 40 |

| 3.1 Th      | e convolution algorithm versus PULSE architectural features | 40 |

| 3.2 Str     | ucture of the convolution software                          | 44 |

| 3.3 Su      | mmary                                                       | 46 |

|             |                                                             |    |

| Chapter 4 Motion | <b>Estimation</b> | Algorithms | and |

|------------------|-------------------|------------|-----|

|                  |                   |            |     |

| Implementations4                                    | 17             |

|-----------------------------------------------------|----------------|

| 4.1 Motion estimation algorithm                     | <b>‡</b> 7     |

| 4.1.1 General description                           | 48             |

| 4.1.2 Data structure for motion estimation in PULSE | <del>1</del> 9 |

| 4.2 Gradual full search method and full search      |                |

| algorithm with the PULSE chip                       | 52             |

| 4.2.1 Speed of GFSM and FSM algorithms in PULSE     | 52             |

| 4.2.2 Motion estimation program for PULSE           | 53             |

| Chapter 5 DCT & IDCT Algorithms and                 |                |

| Implementations                                     | 60             |

| 5.1 DCT & IDCT algorithms                           | 60             |

| 5.1.1 DCT                                           | 60             |

| 5.1.2 IDCT                                          | 63             |

| 5.2 Implementation of DCT & IDCT on PULSE           | 64             |

| 5.2.1 Data structure of DCT on PULSE                | 54             |

| 5.2.2 Requirements and performance for DCT and      |                |

| IDCT on PULSE                                       | 67             |

| Chapter 6 Image Processing with PULSE Chips and     |                |

| a C40 Processor6                                    | 8              |

| 6.1 System architecture composed of one PULSE chip  |                |

| and a C40                               | 69         |

|-----------------------------------------|------------|

| 6.2 Improvement of the C40/PULSE system | 73         |

| Chapter 7 Conclusions                   | 77         |

| 7.1 Results                             | 77         |

| 7.2 Future work                         | 78         |

| References                              | <b>Q</b> 1 |

# List of Figures

| Figure 1-1  | MPEG system layer block diagram                                        |

|-------------|------------------------------------------------------------------------|

| Figure 1-2  | System layer pack and packet structure                                 |

| Figure 1-3  | Picture types                                                          |

| Figure 1-4  | Essential elements of coding system in MPEG standard                   |

| Figure 1-5  | Motion compensation                                                    |

| Figure 1-6  | Zigzag Scan                                                            |

| Figure 1-7  | MPEG cording system data flow block diagram                            |

| Figure 1-8  | PULSE chip VI logic symbol – subject to design review                  |

| Figure 1-9  | PULSE chip version 1 architecture                                      |

| Figure 1-10 | Architecture of PEs and communication chains                           |

| Figure 1-11 | PULSE V 1.3.f 16-bit processor architecture                            |

| Figure 1-12 | Pipeline structure instruction in four cycles of clock                 |

| Figure 2-1  | Function partitioning in MPEG-2 encoding                               |

| Figure 2-2  | Chip sets feature of flexible pipeline architecture based on RISC CPUs |

| Figure 2-3  | EST256 architecture                                                    |

| Figure 2-4  | Structure diagram for a video image compression system                 |

| Figure 2-5  | The current and previous frames in a search area (N=16,n=8)            |

| Figure 2-6  | CDS method                                                             |

| Figure 2-7  | Three steps method                                                     |

| Figure 2-8  | CSA method                                                             |

| Figure 2-9. | Gradually searching                                                    |

| Figure 3-1  | Splitting of 1K x 1K original image into four parts for processing on a |

|-------------|-------------------------------------------------------------------------|

|             | PULSE chip                                                              |

| Figure 3-2  | Distributed data structure for parallel computation of a convolution    |

| Figure 3-3  | Original picture data and result picture data (boundary effect)         |

| Figure 3-4  | Instruction pipelining in a convolution                                 |

| Figure 3-5  | Overlapping of calculation with exportation of output results           |

| Figure 4-1  | Position & relation between blocks & search areas in frameA & frameB    |

| Figure 4-2  | Data of blocks and data of search areas in current picture and previous |

|             | picturememA and memB                                                    |

| Figure 4-3. | Data structure in PEs                                                   |

| Figure 4-4. | FSM & GFSM program diagram and its instructions (one block)             |

| Figure 4-5. | Flowchart of a basic match unit                                         |

| Figure 4-6  | Data of block search in independent memory space                        |

| Figure 4-7  | Program t1                                                              |

| Figure 7-8  | Program t2                                                              |

| Figure 5-1  | Cosine table and input data stores in PEs memories                      |

| Figure 5-2  | DCT program diagram and instructions                                    |

| Figure 6-1  | The C40/PULSE system                                                    |

| Figure 6-2. | Program flowchart for the C40/PULSE system                              |

| Figure 6-3  | A C40/PULSE system implementation                                       |

| Figure 6-4  | The C40/4PULSE system                                                   |

## List of Tables

| Table 2-1 | Comparison of different algorithms                     | 23 |

|-----------|--------------------------------------------------------|----|

| Table 6-1 | Comparison searching results with different algorithms | 76 |

| List of App | pendix                                         | 85    |

|-------------|------------------------------------------------|-------|

| Appendix A  | PULSE V1 Competitive analysis                  | 85    |

| Appendix B  | PULSE V1 technical features                    | 89    |

| Appendix C  | PULSE V1 logic symbol-subject to design review | 91    |

| Appendix D  | The convolution program flowchart and program  | 92    |

| Appendix E  | Convolution program, data of source image      |       |

|             | and data of result image                       | 96    |

| Appendix F  | Program of Motion estimation                   | 101   |

| Appendix G  | Result of motion estimation                    | 123   |

| Appendix H  | DCT program for PULSE                          | 125   |

| Appendix I  | IDCT program for PULSE                         | 128   |

| Appendix J  | Cosine Table                                   | 131   |

| Appendix K  | DCT program in C++                             | 132   |

| Appendix L  | IDCT program in C++                            | 134   |

| Appendix M  | Cosine table generation program in C++         | 139   |

| Appendix N  | Data transfer programs for c40 and PULSE       | 140   |

| Appendix O  | PULSE vs Competitors                           | . 147 |

#### CHAPTER 1

#### INTRODUCTION

#### A General Presentation of the Problem

This thesis presents a Hardware Software Co-design with the PULSE(Parallel Ultra Large Scale Engine) chip used for image processing. It reports or research carried as part of the PULSE project that led to the development of the PULSE chip. Nowadays, moving image coding systems have a very promising application field: Videoconferencing, Videophone, Digital Video Storage, High-Definition Television (HDTV), Digital Television and Multimedia Systems. In moving image coding systems, data compression is needed for efficient management of large amounts of information. For example, a color image with a resolution of 1000 by 1000 pixels (picture elements) occupies 3 megabytes of storage in an uncompressed form. Data compression is especially useful for the transmission of such high data through transmission channels. For instance, bit-rate ranges from 10 Mb/s for broadcast-quality video to more than 100 Mb/s for HDTV signals.

In order to reduce the transmission rate, using prediction techniques based on motion estimation. This scheme increases the compression ratio to 50~200:1. Motion Estimation is the most demanding part in the coding algorithm. For example, in an image coding system in MPEG2 standard (Figure 2-3), the computational power required is approximately 1.2 GOPS; and around 50% of this effort is devoted to motion estimation.

At the decoder, motion estimation is not necessary, therefore lower computational power is required.

#### Main Objective and Methodology

The main objective of this thesis is to study image compression coding systems and some popular algorithms used for that purpose. Several aspects of design for high-speed and high accuracy processing are considered. In order to realize a simple and effective image compression coding system, the PULSE chip is considered as a potential platform.

The PULSE chip is a new ultra-high performance SIMD (Single Instruction Multiple Data) architecture DSP (Digital Signal Processing) for high-end video and related applications. It has one controller and four process elements with clock of 54MHZ and 4 ports, having an I/O capability as high as 216 Mega words/sec. Its I/O ports are designed to allow forming linearly connected chains of chips. With this system architecture and using PULSE assembly language, a real time image processing system can be implemented.

#### Originality

1) A high-speed and high accuracy algorithm for motion estimation is developed.

The Gradual Full search method (GFSM) algorithm reduces the time required to find matches and no possible solution is neglected in the search area. Although the

program is slightly more complex than the Full Searching Method (FSM), it is three times faster than FSM when processing a simple image.

2) A simple and effective method to calculate DCT or IDCT with cosine functions using the PULSE chip is developed.

A possible method to compute the cosine function uses the exponential function.

Calculating cosine function is relatively expensive. Thus we propose using precompute tables, stored in PULSE's internal memories, to accelerate computation of DCT or IDCT.

Further developments could improve the throughput of image compression on the PULSE chip.

Different system architectures for image compression coding are discussed and designed.

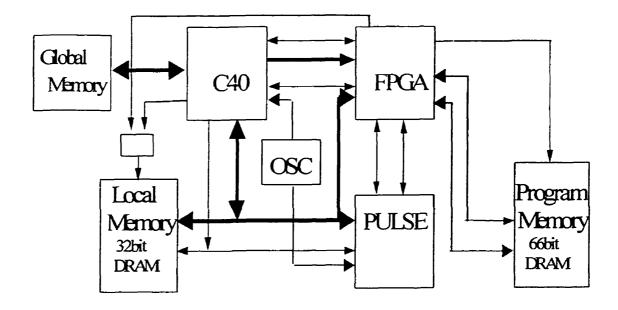

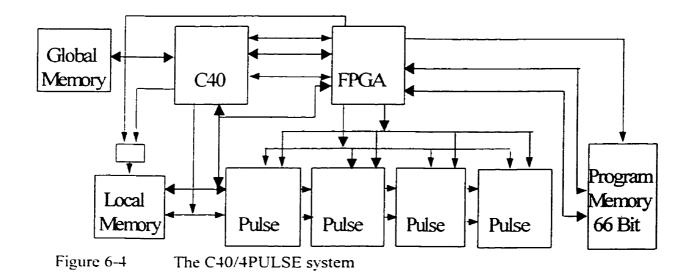

The results obtained during the research conducted for this thesis will prove that a PULSE chip can be used to construct flexible multi DSP systems, and to accelerate image compression. Using PULSE chips with a C40 DSP and a FPGA control unit, we can construct a hardware/software system for image compression. It will not only reduce the cost of image compression coding systems, but also improve their flexibility.

#### Organization of the Thesis

Chapter 2 will introduce the MPEG2 standard, the PULSE chip, and review some previous research work. I will also describe some proposed algorithms. Chapter 3 describes the implementation of the convolution algorithms on PULSE. Chapter 4, 5 and 6 are the main parts of this thesis. Chapter 4 and 5 include the processing of motion estimation and DCT algorithms using the PULSE chip. A hardware and software codesign system using a C40 chip & PULSE chips is discussed in chapter 6. Chapter 7 summarizes our conclusions.

#### **CHAPTER 2**

# A REVIEW OF IMAGE COMPRESSING ALGORITHMS AND THEIR PROCESSOR ARCHITECTURES

#### 2.1 MPEG Standard

In today's world, videoconferencing, videophone, digital video storage, high-definition television (HDTV), digital television and multimedia systems are widespread. Storage or transmission of these data requires large memories and high bit-rate. Therefore, data compression has been a subject of intensive research and development for the past few years.

#### 2.1.1 Background

MPEG is a video compression technology formulated by the Moving Pictures Experts Group, a joint committee of the International Standardization Organization (ISO). The first MPEG standard, known as MPEG-1, was formalized by the MPEG committee in January 1992.

MPEG-1 compression incorporates both audio and video. For NTSC video (United States and Japan) MPEG-1 uses the Standard Image Format (SIF) of 352x240 at 30 frames per second. Audio is 16-bit, stereo sampled at 44KHz. MPEG data rates are variable,

although MPEG-1 was designed to provide VHS video quality, and CD-ROM audio quality at a combined data rate of 1.2 megabits per second.

By resolution and data rate, MPEG-1 is targeted primarily at the computer and games markets. By contrast, MPEG-2, adopted in the spring of 1994, is a broadcast standard specifying 720x480 pixels resolution, playback at 60 fields per second and data rates ranging from two to 10 megabits per second. MPEG-2 is the core compression technology for DVD, the high-density CD-ROM standard that many fell will replace VHS tapes as the standard for consumer video.

MPEG-3 was dropped, and MPEG-4 is a very low-bit-rate codec targeting videoconferencing. Internet, and other low-bandwidth applications.

#### 2.1.2 A Brief Overview of MPEG-2

#### 1) What is MPEG-2

MPEG-2 is an audio/video compression/decompression standard. The audio/video inputs are compressed by an encoder, and decompressed by a decoder for playback.

The MPEG-2 standard is actually composed of three standards formulated by the Moving Pictures Experts Group, a working group of the International Organization for Standardization (ISO). ISO standard 13818-1 covers the MPEG-2 system stream, ISO standard 13818-2 addresses MPEG-2 video, and ISO standard 13818-3 describes MPEG-

2 audio. Work on MPEG-2 started back in 1988, and all three standards were finally approved in November 1994.

MPEG-2 video resolution can range from 720x480 to 1280x720, with the latter targeting high-definition television (HDTV) applications (cable 15.1). The most common resolution is 720x480, roughly the resolution of a full-screen NTSC (National Television Standards Committee) image. This contrasts with MPEG-1's maximum resolution of 352x240, or quarter-screen TV. While MPEG-1 is limited to 30 frames per second. MPEG-2 can operate at 60 fields, the scan rate of NTSC television, enhancing suitability for broadcast applications like HDTV, cable television, and broadcast satellite.

#### 2) Video Compression Technology

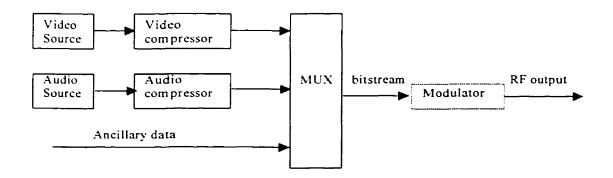

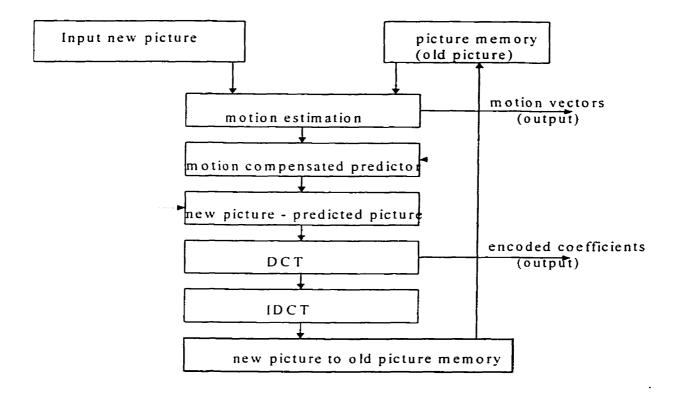

Since MPEG-2 includes both audio and video, all MPEG-2 codecs must address both formats. The block diagram of an MPEG-2 encoder system is shown in Figure 2-1.

Figure 2-1 The block diagram of MPEG-2 encoder system

This thesis is mainly focused on the implementation of the video compressor. MPEG video is specifically used in compression of video sequences which are simply a series of

pictures taken at closely spaced intervals in time. Except for the special case of a scene change, these pictures tend to be quite similar from one to the next. Intuitively, a compression system ought to be able to take advantage of this similarity.

The compression techniques (compression models) with MPEG take advantage of this similarity or predictability from one picture to the next in a sequence. Compression techniques that use information from other pictures in the sequence are usually called interframe techniques.

When a scene change occurs, interframe compression does not work and the compression model should be changed. In this case the compression model should be structured to take advantage of the similarity of a given region of a picture to immediately adjacent area in the same picture. Compression techniques that only use information from a single picture are usually called intraframe techniques. These two compression techniques, interframe and intraframe, are at the heart of the MPEG video compression algorithm.

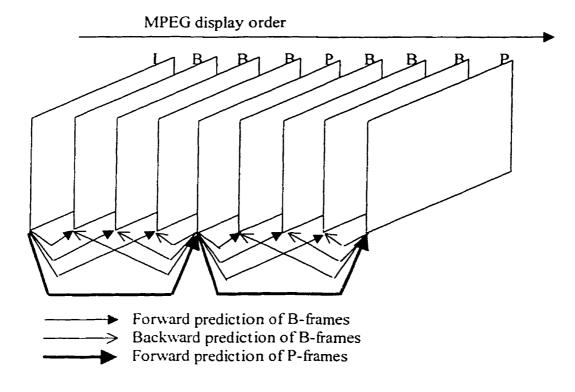

Each video sequence is divided into one or more groups of pictures, and each group of pictures is composed of one or more pictures of three different types, I, P, and B, as illustrated in Figure 2-2. I-pictures (intra-coded pictures) are coded independently, entirely without reference to other pictures. P and B-pictures are compressed by coding the differences between the picture and reference I or P-pictures, thereby exploiting the similarities from one picture to the next.

P-pictures (predictive-coded pictures) obtain predictions from temporally preceding I or P-pictures in the sequence, whereas B-pictures (bi-directionally predictive-coded pictures) obtain predictions from the nearest preceding and / or upcoming I or P-pictures in the sequence. Different regions of B-pictures may use different predictions, and may predict from preceding pictures, upcoming pictures, both, or neither. Similarly, P-pictures may also predict from preceding pictures or use no prediction. If no prediction is used, that region of the picture is coded by intraframe techniques.

In a closed group of pictures, P and B-pictures are predicted only from other pictures in that group of pictures; in an open group of pictures, the prediction may be from pictures outside of the group of pictures [MPG97].

Figure 2-2 Picture types

## 3) Video Encoder

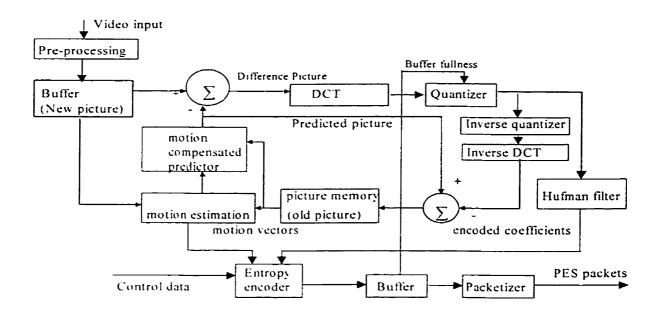

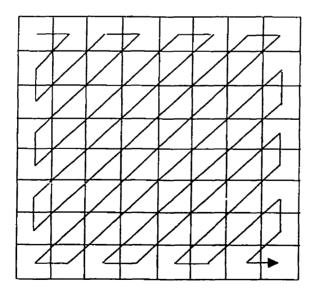

Figure 2-3 is a diagram showing the essential elements of a video coding system for MPEG -2 Standard. Temporal redundancy is reduced using the following process.

Figure 2-3 Essential elements of video coding system in MPEG –2 standard

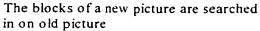

In the motion estimation section, an input video frame, called a new picture, is compared with a previously transmitted picture held in the picture memory. Pixel blocks (an area of 16-pixel wide and 16-pixel high) of the previous picture are examined to determine if a close match can be found in the new picture. First, the new picture buffer is divided into 8x8 pixel blocks, each 8x8 pixel block is searched in the old picture area of 16x16 pixels. The match algorithm of motion estimation is: [Eq.2.1]

$$M = \sum_{i=0}^{7} \sum_{i=0}^{7} |A(i,j) - B(i,j)|$$

(Eq.2.1)

Where *M* is the distortion value, *A[i,j]* and *B[i,j]* are the new and old images' pixel values respectively. If the value of M is less than a threshold value, then the vector coordinate of this block is called a close match. When a close match is found, a motion vector is produced describing the direction and distance the pixel block moved. A predicted picture is generated by the combination of all the close matches as shown in Figure 2-4. Finally, the new picture is compared with the predicted picture to produce a difference picture [MPG97].

The blocks of old picture predict the new picture

Figure 2-4 Motion compensation

The process of reducing spatial redundancy begin with a DCT (Discrete Cosine Transform) on the difference picture of an 8x8 pixel block. The first value in the DCT matrix (top left corner) represents the DC value of the 64 pixels of the 8x8 block. The other 63 values in the matrix represent the AC values of the DCT with higher horizontal

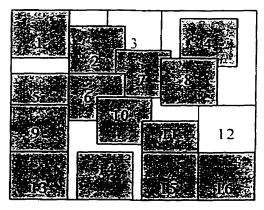

and vertical frequencies as one moves to the bottom right corner of the matrix. If there is little detail in the picture, these higher frequency values become very small. The DCT values are presented to a quantizer which, in an irreversible manner, can "round-off" the values. Quantization noise arises because coefficients are rounded-offs. It is important that the round off be done in a manner that maintains the highest possible picture quality. When quantizing the coefficients, the perceptual importance of the various coefficients can be exploited by allocating the bits to the perceptually more important areas. The quantizer coarseness is adaptive, and is coarsest (fewest bits) when the quantization errors are expected to be least noticeable. The DCT coefficients are transmitted in a zigzag order as shown in Figure 2-5. After rounding, the higher frequency coefficients often have a zero-value (See Chapter 5 The Algorithm of DCT and IDCT). This leads to frequent occurrence of several zero-value coefficients in sequence.

Figure 2-5 Zigzag Scan

The quantizer output is presented to an entropy encoder, which increases the coding efficiency, by assigning shorter codes to more frequently occurring code words. The entropy encoder bit stream is placed in a buffer at a variable input rate, but taken from the buffer at a constant output rate. This is done to match the capacity of the transmission channel and to protect the decoder buffer from overflow or underflow. If the encoder buffer is almost full, the quantizer is signaled to decrease the precision of coefficients to reduce the instantaneous bit rate. If the encoder buffer is almost empty, the quantizer is allowed to increase the precision of coefficients. The output of the buffer is packetized as a stream of PES packets. [DIG94]

In order to use the motion compensated picture for next prediction, the encoder requires the reconstruction of the picture contained in the transmitted bitstream. The quantizer output is presented to the inverse quantizer, then to the inverse DCT. IDCT output adds the predicted picture, and then place the result in the picture memory [MPG97].

The data flow coding system in MPEG standard is shown in Figure 2-6.

Figure 2-6 Data flow of coding system in MPEG standard

#### 2.1.3 Convolution

Most motion pictures need some pre-processing filter. This pre-processing enhances as perceived by human visual sense. Convolution is one of the popular algorithms used. It will be discussed in chapter 3.

#### 2.2 Motion Estimation Algorithm

Several algorithms for motion estimation have been proposed. A number of popular methods, as well as the one proposed in this thesis, are presented below.

#### 2.2.1 FSM (full search method)

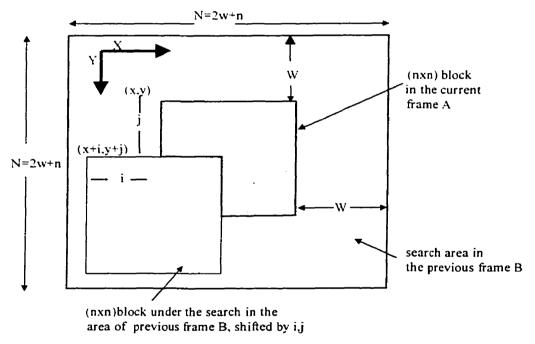

The search of a block frame A (current picture) starts at the upper-left corner of the area of frame B(previous picture). If the value of M in equation [Eq2.1] is less than the threshold value (zero means exact match), stop searching and output motion vector. Otherwise search from left to right and from top to bottom through frame B. The search is stopped when the right bottom corner is reached or when M is smaller than a threshold value. This search sequence is illustrated in figure 2-7. [MPG97]

Figure 2-7 The current and previous frames in a search area (N=16,n=8)

#### 2.2.2 CDS (conjugate direction searching)

The search progresses in the direction of the smaller distortion, until a minimum distortion is found (see figure 2-8)[MPG97]. Descriptions of the algorithms refer to points to express the shift between the reference positions in the two compared images. The algorithm is listed below:

M is the value in equation [Eq2.1]; threshold is a value selected by the designer according the allowed error; the left, right, up and down mean the direction of next compared center point from the current center point. [A]horizontal: compare center point; if (M<threshold) then stop search and output vector; else compare left and right point; if((right(2)<left(0)and(right>threshold))then let right be the new center point; elsif((right(2)>left(0)and(left>threshold))then let left be the new center point; endif: endif: repeat [A]horizontal until boundary or minimum point is found in horizontal direction: [B]vertical: compare center point (4)(produced by [A]horizontal); if (M<threshold) then stop search and output vector; else compare up and down point; if((up(7) < down(6) and(up(7) > threshold)))then let up(7) be the new center point; elsif((up(7)>down(6)and(down(6)>threshold))then let down be the new center point: endif: endif:

repeat [B]vertical until boundary or minimum point is found in vertical direction;

end:

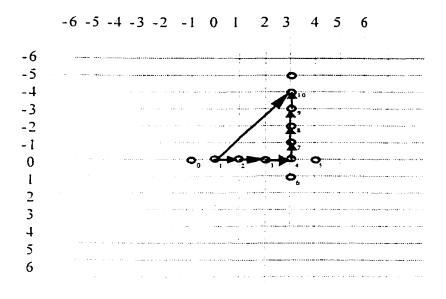

Figure 2-8 CDS method

# 2.2.3 Three-step searching

The three-step searching method looks for motion displacements. As it progresses through the steps, the search range is decreased. As shown in figure 2-9[MPG97]. The algorithm is listed below:

The definition of M and threshold are the same as with the CDS method. step(1): compare center point;

if(M<threshold)then stop search and output vector;

else compare four (a) point;

if ((minimum M(a)<threshold)then stop search and output vector; else compare two M(aa)points(in minimum (a) direction);

if (minimum M(aa)<threshold)then stop search and output vector;

else new center point = the position of minimum M((a) or (aa)); endif;

endif:

endif:

repeat step(1) three times:(minimum M(aa) be the center for b search),(minimum M(b) be the center for c search).

end:

From figure 2-9, the aa point (minimum (M(a) or M(aa))) is as the new center point in step(2) searching. Using a similar method, the b point (minimum (M(b) or M(bb))) is used as the new center point in step(3) searching.

Figure 2-9 Three steps method

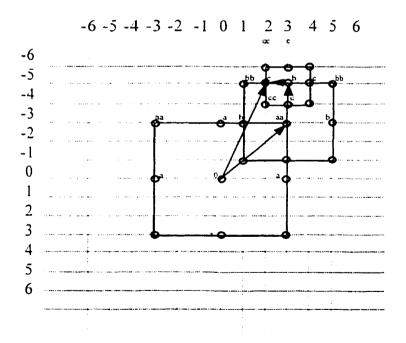

# 2.2.4 CSA (Cross-Search Algorithm)

This algorithm differs from other search methods in the final step. In reference to figure 2-10, the final searching can be either the (X) or (+) directions. This is determined by minimum point. If it is in left up corner or right down corner, the next searching point will choose (X) points. If it is in right up corner or left down corner, the next searching point will choose (+) points [CRO90].

Figure 2-10 CSA method

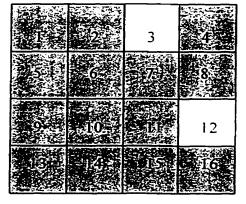

## 2.2.5 GFSM(Gradual Full Search Method)

The gradual full search algorithm is a new method proposed here. It begins at the center point and gradually increases the searching range around this point. The method is illustrated in figure 2-11. This method was developed for two reasons.

We analysed the fast algorithms and we found similar problems with most of them. The search direction is usually guided toward the minimum value of M (equation 1) by comparing 4 points at each step. Thus many points inside the search region are skipped. In some cases, moving by one pixel may give very different results. The search direction is controlled by the minimum M, which may lead to incorrect decisions. Fast algorithm are faster than FSM, but they may give incorrect results.

Also, when successive frames do not change much, the last motion sector is a short distance from the center.

The gradual full search method typically takes a short time to find the best match, and yet no point is ignored in the search area. Although the algorithm is slightly complex than FSM, it is much faster for most applications.

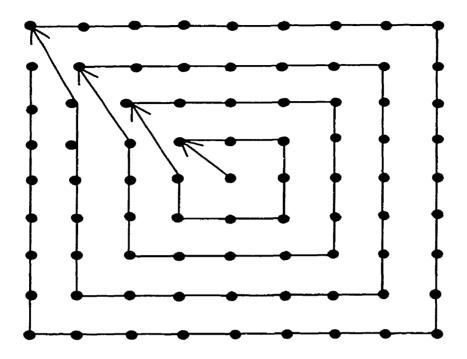

Figure 2-11. Gradual Full Search Method (GFSM)

# 2.2.6 Comparison of the different algorithms

Table 2-1 shows the maximum number of search points with the different algorithms. The fast algorithms (CDS, CSA and 3STEPS) are faster than FSM and GFSM. When w is large, this is more obvious. However, the fast algorithms sometimes produce incorrect results.

| Algorithm | Maximum number of search points | w  |     |      |

|-----------|---------------------------------|----|-----|------|

|           |                                 | 4  | 8   | 16   |

| FSM       | $(2w+1)^2$                      | 81 | 289 | 1089 |

| CDS       | 3+2w                            | 11 | 19  | 35   |

| CSA       | 5+4 log w                       | 13 | 17  | 21   |

| 3 step    | 25                              | 25 |     |      |

| Gradually | $(2w+1)^2$                      | 81 | 289 | 1089 |

W=(size of search area – size of block)/2

Table 2-1 Comparison of different algorithms

### 2.3 Processor Architecture Review

In order to implement a MPEG coding system, a powerful calculation engine is required.

A huge number of calculations are required to perform motion estimation, DCT, etc.

Therefore, some special purpose chips are often used to implement these functions. Three different MPEG-2 video encoders are discussed below.

# 2.3.1 Custom chip set for MPEG-2 coding

The paper "Two-chip MPEG-2 Video Encoding" [TWO96], describes a system composed of two chips that implements a MPEG-2 video encoder. The key features of these chips set are:

• The Enc-M chip mainly executes motion estimation and compensation steps.

• The Enc-C chip is the main coding and control chip. It executes not only coding operations like discrete cosine transformation (DCT), inverse discrete cosine transformation (IDCT), quantization (Q), inverse quantization (IQ), and variablelength coding (VLC), but also header generation, rate control, and output buffer control. It has an external output buffer (FIFO-structured desired from a 2-Mbit DRAM) to meet the requirements of the MPEG-2 algorithm.

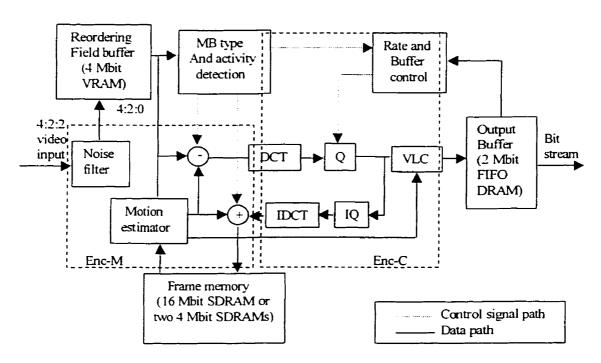

Figure 2-12 Function partitioning in MPEG-2 encoding

Figure 2-12 shows the partitioning of the MPEG-2 encoder. It uses two encoder chips (Enc-M and Enc-c), as well as three peripheral memories, a reordering field buffer, a frame memory, and an output buffer.

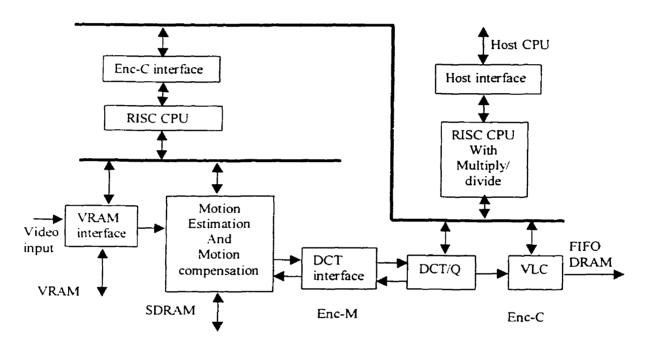

Since MPEG-2 is a complex algorithm that requires a flexible and efficient control structure, the pipeline architecture based on RISC CPUs (Figure 2-13) is used. Both the Enc-M and Enc-C have their own RISC CPU. For flexible pipeline operation, each functional unit has a CPU I/O device controlled by the CPU via the I/O port. Some units communicate with neighbouring units in a request-acknowledge manner.

Figure 2-13 Chip set feature of flexible pipeline architecture based on RISC CPUs

The encoder chip set can easily be used to develop a compact encoder system. The encoding algorithm is the MPEG-2 simple profile at main level with a variable frame size from 64 to 720 pixels (column) and 64 to 576 pixels (row). The chip set thus supports the conventional sizes of 720x480, 720x576 and 640x480 pixels required for NTSC, PAL

and VGA standards. Using a 4:2:2 video input format, the maximum frame rate is 30 frames per second for a 720x480 frame size. That means the system processes up to 40,500 macroclocks(16 by 16 pixel) every second for a maximum output of 15 Mbits per second.

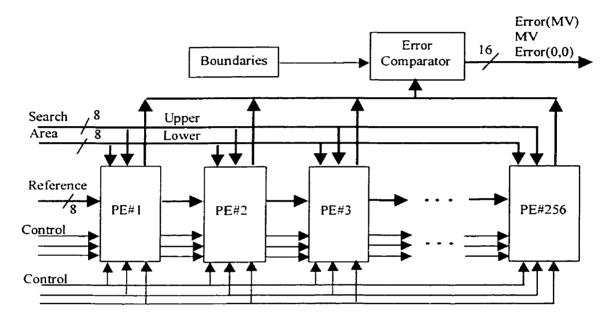

# 2.3.2 VLSI implementation for Motion Estimation

The paper "VLSI Architecture for Motion Estimation using the Block-Matching Algorithm" [VLS96] introduces the EST256 chip used for motion estimation. The architecture, EST256, which consists of 256 processing elements, deals with a search area(32x32 pixel) for block(16x16pixel) and performs 11GOPS at 44MHz clock (subtraction, absolute value determination, accumulation and comparison). Considering a 720x576 pixel image, the processing rate for motion estimation is 49 frames per second.

The number of PEs working concurrently is 256, and each single processor computes the cost function for one of the 256 possible locations of the reference block within the search area. The array outputs the motion vector corresponding to each reference block, 256 cycles after the last pixel of the block has been entered into the array. Figure 2-14 shows the structure of the 256 processors array. To reduce the required bandwidth, EST256 has three 8-bit input ports. After initial latency, the comparator block inputs one error computation in each cycle and compares it with the previous minimum, storing the lowest. The boundary block disables the comparator when its input value is not valid, this condition arises for some locations of the blocks located on the top, bottom, left and right

.

boundaries of the image. The architecture provides the minimum error value, the coordinates of the motion vector for this position and the error value for the (0,0) motion vector (no movement).

Figure 2-14 EST256 architecture

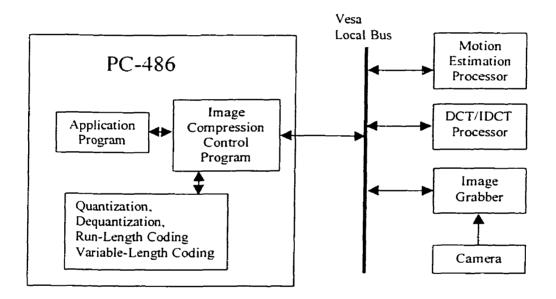

# 2.3.3 A PC based image compression system

The paper "A High-performance System for Real-time Video Image Compression Applications" [HIG95] introduces a PC based image compression system. As shown in Figure 2-15, the system consists of a PC-486, a motion estimation processor (MEP), a DCT/IDCT processor (DCT/IDCTP), an image grabber, and a camera. Meanwhile, both the MEP and DCT/IDCTP act as backend processors for PC-486 through its Vesa local-bus interface. The PC-486 handles all the computations except motion estimation, DCT, and Inverse DCT. Currently, by operating at 12.5MHz, the MEP takes around 100us to

compute the motion vector with tracking range 32x32 for each 16x16 block, and, the DCT/IDCT takes around 10us to compute the two dimensional DCT or inverse DCT for each 8x8 block. Also, overlapping data loading and processing can achieve the optimal performance. Therefore, for each 256x256 image frame, the system presented would take around 25.6ms and 10ms for computing motion vectors and two dimensional DCT or inverse DCT individually.

Figure 2-15 Structure Diagram for a Video Image Compression System

### **Conclusions**

As described above, in order to implement real time image processing, special processor or functional units are needed. As a general purpose DSP, single PULSE chip may not be very powerful. However, it is easy to connect multiple PULSE chips to implement real

time image processing. An array of PULSE chips can implement motion estimation, DCT, etc. Each chip also implements a control unit, and these chips can easily be interfaced with other processors. So, PULSE chips give us the ability to build different systems to implement various algorithms and applications.

# 2.4 SIMD Architecture of PULSE Chip

#### 2.4.1 Introduction

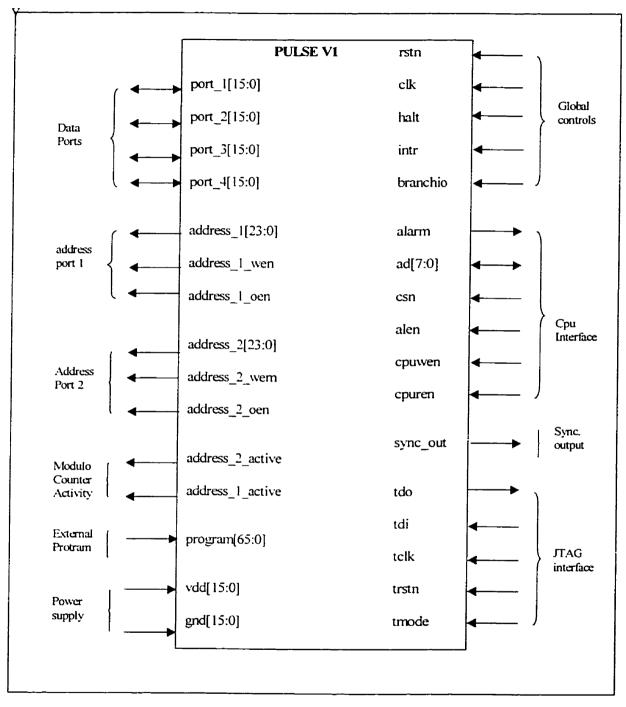

PULSE V1 is a 16 bit, fixed point SIMD array processor designed to operate at 54 MHz. It contains (on a single chip) one controller and four PEs (Processing Elements). The custom designed architecture and instruction set of the PULSE processor allow efficient implementation of all linear (multiply add accumulate etc.), nonlinear (maximum, minimum, medium, rank order, etc.) and hybrid operations, thus providing a complete solution for any fixed point DSP related applications.

PULSE V1 employs heavy parallel operations to handle data I/O. inter-processor communications, address generations, and computations. One parallel instruction could simultaneously provide multiple computations (such as multiply add accumulate, and 3-point rank order), multiple address generations and memory access, multiple data transfer within the PE and between the neighbor PEs. All these operations can be done at the rate of one per cycle however, PULSE data-path is a 4-stage pipeline. One PULSE instruction could perform more than 10 conventional operations. Effectively, the PULSE V1 chip can provide more than 2 Billion RISC like operations per second for linear processing.

Usually conditional execution on SIMD machines can become highly inefficient, since each PE might get different conditions, but the controller can only supply a Single Instruction based on a single condition. The usual way to solve this multi-condition problem is to turn some PEs off, thus wasting computation power. The innovative design of the PULSE V1 processor partly removes these conditional executions by supporting a rich set of nonlinear instructions. For example, each PE can implement a 3 point rank order (maximum, medium, and minimum) in a single cycle of PULSE V1. The implementation of this operation (rank order of 4 vectors, 3 data each) could require more than 60 operations on conventional processors such as Tl TMS320C40. In that specified case, the PULSE processor provides more than 4 Billion equivalent RISC like operations per second for nonlinear processing.

To handle real-time image and video processing. PULSE V1 provides up to 864 Mbytes/sec. of bandwidth for data I/O and 432 Mbytes/sec. for inter-processor communications. An innovative communication mechanism provides efficient use of the bandwidth and allows flexible algorithm mapping. Furthermore, the PULSE processor provides a rich set of parallel and vector instructions, which can be used to improve the application performance while reducing the program size.

PULSE V1 provides easy system integration for different classes of applications. It can be used as a stand-alone processor to replace some ASIC chips; it can be used as a coprocessor or accelerator to other processors of computer systems; it can have external programs and data memory for large kernel applications. The cascade of multiple PULSE chips is relatively straightforward, and it can be done without any additional glue-logic. A wide variety of architectures and related system applications can be obtained with suitably cascaded PULSE chips.

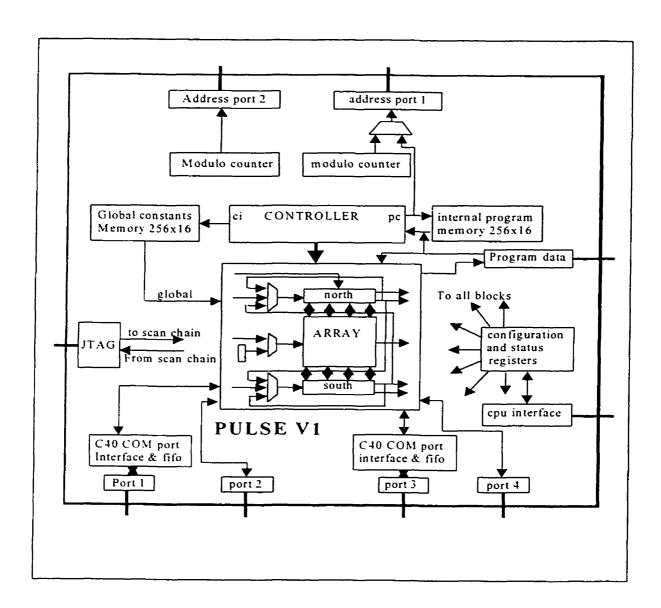

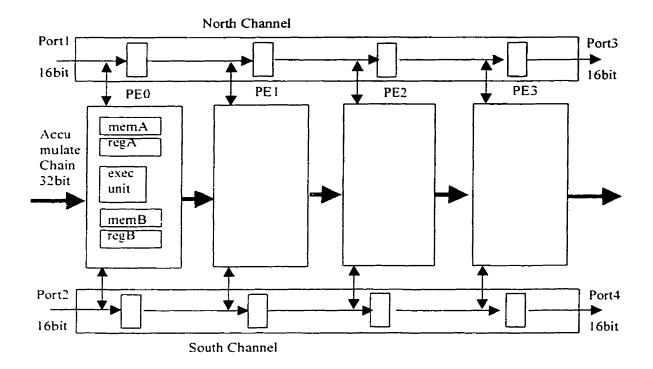

# 2.4.2 Chip Architecture

The PULSE chip version 1 is a PE array, with four data communication ports (two of them are compatible with C40), two address ports, global constant memory and internal program memory. The chip architecture is shown in Figure 2-16. The PE array is the core of the PULSE chip. Its architecture and communication chains are shown in Figure 2-17.

Figure 2-16 PULSE Chip Version 1 Architecture

Figure 2-17 Architecture of PEs and Communication Chains

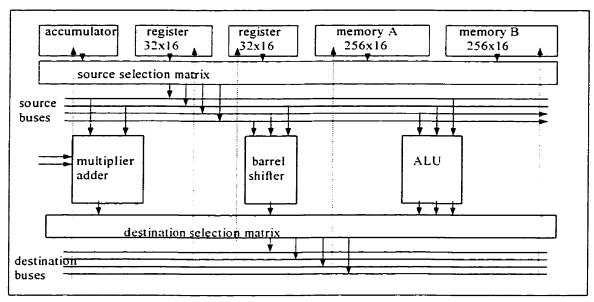

# 2.4.3 Processing element block diagram

Each of the four PULSE processing elements contains the following elements:

- 2 register files of 32, 16-bit words

- I read port, I write port gives optimal storage density/access

- 2 memories of 256, 16-bit words

- Single port 1 read/write with direct link to communication channels

- Addressing is direct, register indirect or via two modulo counters per memory for read and write addresses

- Memories are designed to store data with a longer lifetime than those stored in the register files

- 1 signed multiplier-adder of 16x16+32 bits with 32-bit signed result

- This is to implement MADD (multiply add)

- Direct connection of neighbor processors data sources into addend input of the multiplier-adder allows accumulation chain between processors to be built

- 1 accumulator of 32 bits

- Internal resolution is 33-bit signed with overflow detection

- Programmable saturation and clipping functions to 32-bit signed or 31-bit unsigned ranges

- Separate accumulator allows implementation of reduction algorithms it is possible to perform MADDACC – multiply-add-accumulate

- I full barrel shifter of 32 bits in, 32 bits out

- Supports full range of shift logical and arithmetic shift operations

- 1 multi-function 3-operand arithmetic-logic unit

- Allows single cycle rank, max, med, min, chip and cor functions on three operands

- Usual arithmetic and logic functions available

The functional units of each processing element are designed to operate in parallel so that a typical PULSE instruction will simultaneously perform a computation, data load and data communication operations. Also, the instruction set is designed to be as orthogonal

as possible so that any operation can be performed on any piece of data, regardless of where it resides. Figure 2-18 presents PULSE V 1.3.f 16-bit processor architecture.

Figure 2-18 PULSE V 1.3.f 16-bit processor architecture

#### 2.4.4 Instruction Set

PULSE employs highly parallel operations to handle data I/O, interprocessor communications, address generations, and computations. Some parallel instructions can simultaneously perform multiple computations, multiple address generations and memory access, multiple data transfer within the PE and between the neighbor PEs. All its operations can be executed at the rate of one per cycle.

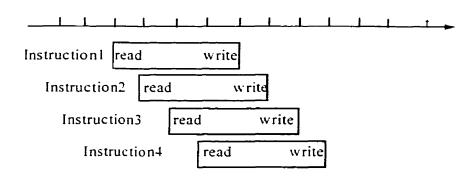

PULSE instructions, due to a 4-stage pipeline, generally require four clock cycles, except "stc", "fwd" and "io" instructions (one cycle). The pipeline operation is illustrated in

figure 2-19. At the first cycle, PULSE reads data from memory, register, or port. The second and third cycles execute the operation. The fourth cycle write the results back to memories, registers, or ports.

Figure 2-19 Pipeline Structure Instruction in Four Cycles of Clock

The PULSE instruction set is designed for both linear and non-linear digital signal processing, with an emphasis on image/video processing. It provides a rich set of instructions, including conventional instructions and extended non-conventional instructions.

The instruction set is organized into the following functional groups:

- PEs instruction set

- Miscellaneous

- Data movement

- Conventional arithmetic

- Special arithmetic

- Conventional logical

- Shift/rotate

- Transfer of control

- Shift register communication

- Controller instruction set

- Parallel instruction set

- Vector instruction set

Each of these groups is listed in the PULSE Technical Report Composite Document. [PUL96]

# 2.4.5 PULSE V1 Assembler

The assembler translates assembly-language source files into object files. These files are in common object file format (COFF). Source files can contain the following assembly language elements:

- Assembler directives

- Assembly language instructions

The assembler does the following:

- Process the source statements in a text file to produce an object file.

- Produce a source listing (if requested) and provide the user with control over this

listing

Define and reference global symbols and append a cross-reference listing to the source listing (if requested)

Each time the user uses the assembler, it processes one source program. The source program is composed of one or more files (The standard input is also a file.)

If no file name is provided, the assembler attempts to read one input file from the standard input, which is normally the terminal.

# 2.4.6 PULSE Applications

As mentioned earlier, the PULSE processor supports both linear and non-linear operations, and allows flexible algorithm mapping. These features make the PULSE processor ideal for a very wide range of applications. Some of them are listed below for reference:

- Filtering

- Transforms

- Image/video/graphics processing

- Image analysis and Machine Vision

- Neural networks

- Speech Processing

- Communications

- Instrumentation

A brief comparison between PULSE V1 and other competitive devices from adaptive solutions, Analog devices, Texas Instruments, and Oxford Computers is provided in appendix A. As can be seen from appendix A, PULSE v1 offers significant advantages in various aspects over the competitive devices, such as strong support for inter-processor communication, and strong support for linear, non-linear and hybrid processing.

The PULSE v1 technical features and the PULSE logic symbol are shown in appendix B and appendix C.

#### **CHAPTER 3**

## IMPLEMENTING A CONVOLUTION ON PULSE

# 3.1 The Convolution Algorithm Versus PULSE Architectural Features

The convolution algorithm plays an important role in image processing. For instance, it is used for noise reduction, edge sharpening and skeletonization. The generic convolution is adapted to perform these various functions by appropriately selecting the weights of its kernel. In general, odd size kernels are used.

For example, the 3 by 3 generic convolution algorithm is defined by equation [Eq.3.1].

$$R_{x,y} = \sum_{i=-1}^{1} \sum_{j=-1}^{1} P_{x+i,y+j} \bullet S_{i,j}$$

(Eq.3.1)

In this equation,  $R_{x,y}$  is the convoluted pixel, value  $P_{x,y}$  is the input image pixel value, and  $S_{i,j}$  is the convolution kernel weight. Equation 3.1 indicates that the 3 by 3 convolution  $P^*m.n$  (m by n pixel image) of each pixel  $P_{x,y}$  requires knowledge of the values of its 8 immediate neighbors. On the image boundary, a different algorithm is applied depending on the application.

The following discussion of a convolution applied to a 3 x 3 sample window on a 1K by 1K image will refer to a 2D FIR filter for brevity. These parameters are widely used for preprocessing of images.

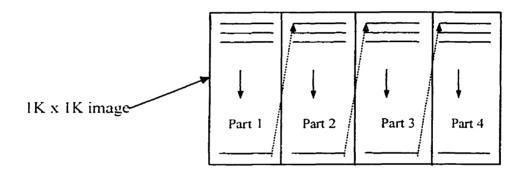

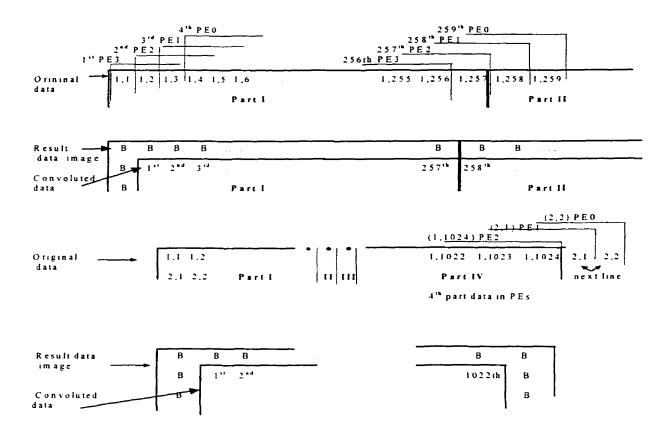

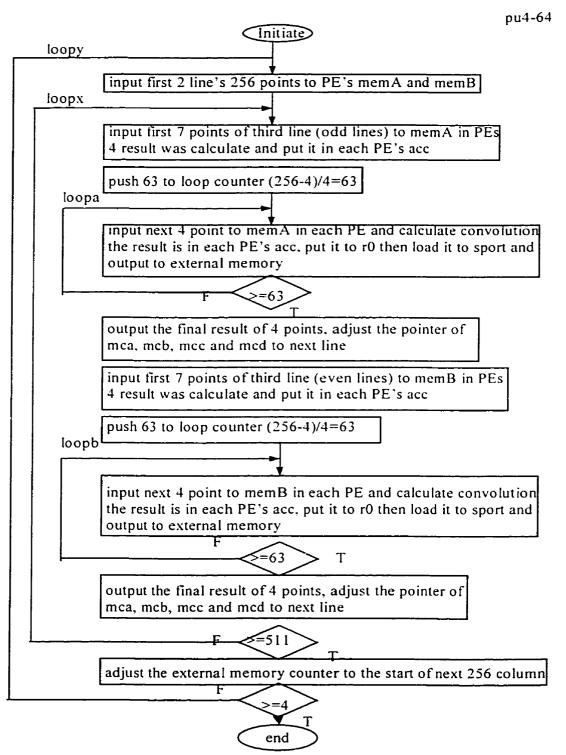

1) Each PE in a PULSE chip has two 256 words memory units. For processing 1K by 1K images, they must be partitioned. One possibility is to split the images in vertical bands. Thus we could calculate the 1024 lines of part one, then calculate part two, three and four, as shown in Figure 3-1.

Figure 3-1 Splitting of 1K x 1K original image into four parts for processing on a PULSE chip

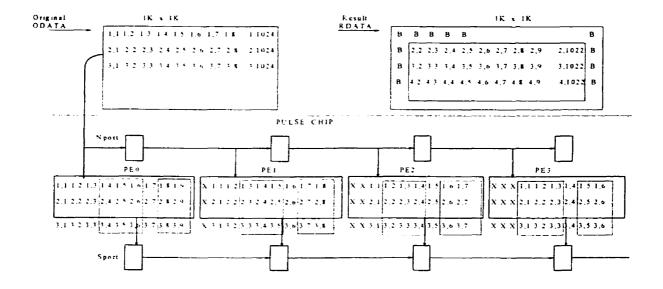

2) The processing of the convolution algorithm with a PULSE chip can be executed in parallel, because each chip has 4 PEs. The first data line (256 points) of part one is stored in "memA", the second line is stored in "memB". Data is brought into 4PEs in parallel through the "North Channel" (Figure 2-17). At the first instruction cycle, the data point 1.1 of the original image is stored in PE0, the unspecified data 'x' is stored in PE1, PE2 and PE3 individually. At the second instruction cycle, the point data 1,2 of the original image and the data point 1,1 are respectively stored in PE0 and PE1, while an unspecified

data 'x' is stored in PE2 and PE3. This progresses until the pipeline is full and each processor receives a pixel at each cycle. The resulting distributed data structure is shown in figure 3-2. Respective positions in the rectangle correspond to data stored at the same address of respective processor memories. The processing loop called "loopa" shown in figure 3-5, thus computes 4 pixels of the output image in parallel.

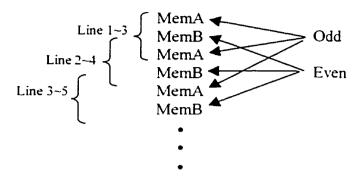

Figure 3-2 Distributed data structure for parallel computation of a convolution

3) Only two lines of data can be stored in memory, because each PE has only two 256 words memory units. The data in "memA" is first used while a third line of data is stored in "memA". When the processing of first data line is finished, the third line has replaced it in memory. The data in "memB" is then used and replaced by a fourth line of data. Thus, "memA" always holds data of odd numbered lines, and "memB" stores even numbered lines. Processing alternates from one to the other.

4) Convolution calculation results stored in external memory. Considering the erosion of image boundaries induced by the algorithm, the output image starts from the second line at the second point (2.2). Therefore, a result picture comprises 1022 by 1022 pixels and edge points "B" as shown in Figure 3-2. The edge points "B" of result image can be filled with the edge points of the original image at the same position. In this case, the edge points are not the result of a convolution. In order to overcome boundary effects between parts (see Figure 3-1), the edge parts are calculated by processing 257 columns. Vertical bands expansion is illustrated in figure 3-3. For part I, columns 1 to 258 (original image) are processed and columns 2 to 257 (result image) are produced. Part II, columns 257 to 514 (original image) are produced and columns 258 to 513 (result image) are produced. Part III, operates on pixels 512 to 770 (original image), and part IV operates on pixels 768 to 1024+2 (original image). Thus, only the edge of the 1K by 1K output picture exhibits boundary effects. There are no boundary effects between part I and part II, part II and part III, and part III and part IV.

Figure 3-3 Original picture data and result picture data (boundary effect)

#### 3.2 Structure of the Convolution Software

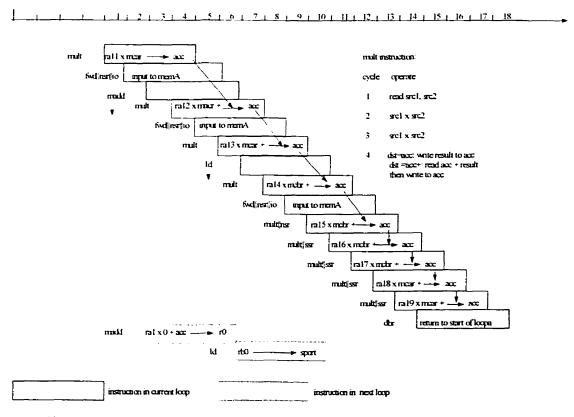

For a 3 x 3 convolution, nine multiplies are needed. The minimum theoretical processing time is 9 multiply instructions and 1 loop control instruction. However each instruction takes 4 cycles. Also, five additional instructions must be inserted with the 9 multiply instructions (three "fwd||nsr||io", one "madd" and one "ld"). Figure 3-4 shows the detail of a loop that computes a convolution.

More precisely, it shows that the result of the first multiply is available after the fifth cycle. Two wait cycles are needed before the second multiply. Then, the "fwd||nsr||io" and "madd" instructions are inserted to avoid waiting time due to processing latency. Using the same principle, two "fwd||nsr||io" and one "ld" instructions are inserted among the remaining instructions, thus, five additional instructions are inserted to fill up various waiting cycle, which reduces the loop execution time.

Figure 3-4 Instruction pipelining in a convolution

To process the basic 3 by 3 convolution, the output is first computed and then the result is sent out as shown in figure 3-5. The process of sending out the previously computed output line is overlapped with the calculation of the next to avoid wasting time.

figure 3-5 Overlapping of calculation with exportation of output results

### 3.3 Summary

An ideal processor with one multiplier requires at least 10 cycles to compute a 3 by 3 convolution. PULSE takes 15 instructions due to pipeline latencies and data dependencies. A PULSE chip computes 4 results at the same time. This corresponds to an average of 3.75 instructions (75ns) per 3x3 convolution. The program flow chart and listing are provided in appendix A. A sample image and the computed results are listed in appendix B.

## **CHAPTER 4**

## MOTION ESTIMATION ALGORITHMS AND

## **IMPLEMENTATIONS**

The principle of Motion Estimation is to perform a search that maximize the correlation or minimize error between a block in the new (current) picture and a corresponding area in the old (previous) picture. The search process tries to find the coordinate values of a block of already transmitted pixel values in the new picture and transmit them. Thus, if the search succeeds, the block in the new picture is not transmitted.

Motion estimation is a key component of an image processing system such as the MPEG2 standard, because it consumes most of the processing time. For this system, the data rate of 768x480x30x8bps can be reduced 100 times by motion estimation. Obviously, choosing a suitable processor and a good algorithm for motion estimation is key in an image processing system that supports the MPEG2 standard.

# 4.1 Motion Estimation Algorithm

The motion estimation algorithm that was implemented is given in section 4.1.1. Section 4.1.2 describes the data structure used in PULSE to implement it.

# 4.1.1 General Description

The mean Square Error (MSE) (Eq.4.1) and Mean Absolute Distortion (MAD) (Eq.4.2) are popular criterions used to measure the fit between data blocks. MAD is the simplest.

$$M = \sum_{i=0}^{7} \sum_{j=0}^{7} A^{2}(i,j) - B^{2}(i,j)$$

(Eq.4.1)

$$M = \sum_{j=0}^{\infty} \sum_{i=0}^{\infty} |A(i,j) - B(i,j)|$$

(Eq.4.2)

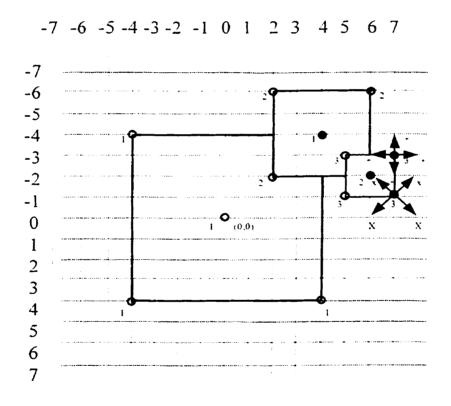

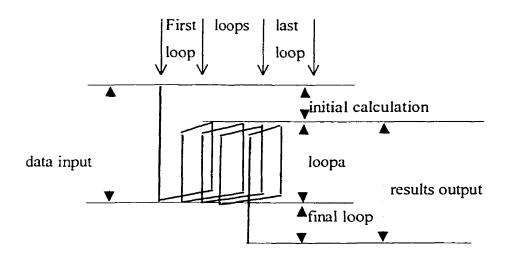

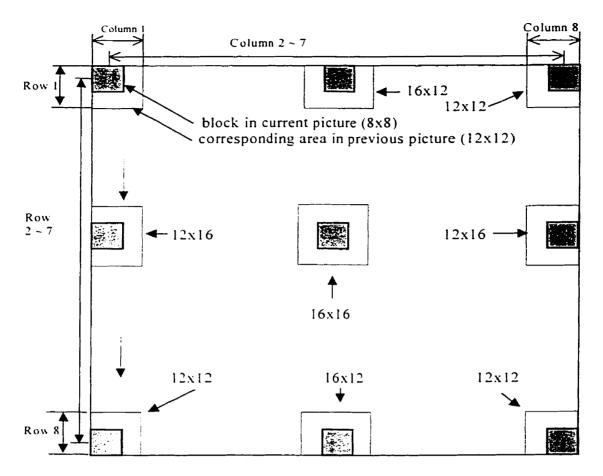

The method for choosing the corresponding area in the reference (old) picture is based on the estimation of the moving speed in the content of an image. If this speed is slow, a small area in the reference picture is chosen for searching, otherwise, it is necessary to choose a larger area. The larger the area in the reference picture is, the longer is the search time. Generally, if 8x8 or 16x16 data block in the new picture is chosen, then, 16x16 or 32x32 search area in the reference picture is chosen. Considering the boundary, according to Figure 4-1 and equation (Eq.4.2), there are nine cases of interest, where for each case, the block size is not changed (8x8), but the size of the corresponding area is changed (12 pixels x 12 lines, 16 pixels x 12 lines, 12 pixels x 16 lines and 16 pixels x 16 lines etc.). Thus, nine different programs have been created.

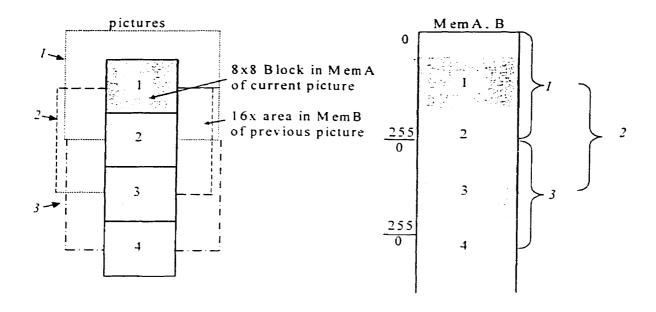

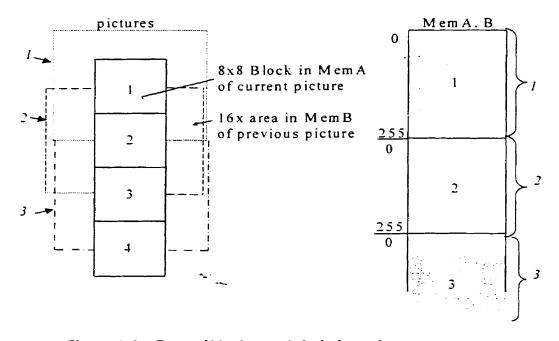

Figure 4-1 Position & relation between blocks & search areas in current picture and previous picture

### 4.1.2 Data Structure for Motion Estimation in PULSE

The blocks of data from the new picture search area and from the old picture are respectively loaded into memory A and memory B of each PE in PULSE. Each time 128 pixels are loaded. Figure 4-2 illustrates these data structures.

Figure 4-2 Data of blocks and data of search areas in memA and memB

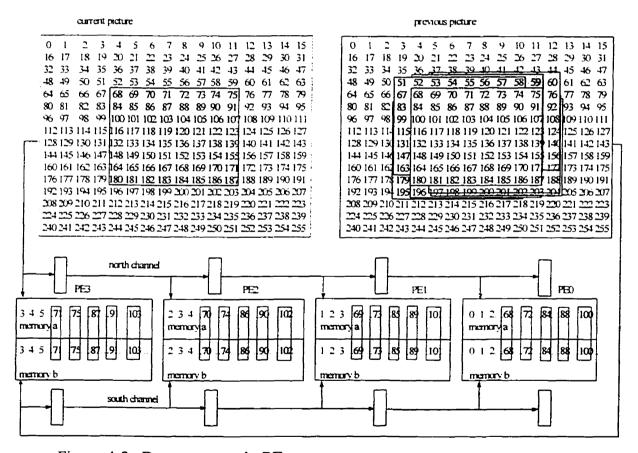

The data is distributed in 4 PEs as shown in Figure 4-3. The results for positions 68, 69, 70 and 71 are calculated in parallel with 4PEs in one processing phase. The next step computes elements 72 to 75. There is no new input data in memA and memB before finishing the block search in the correspond area.

Furthermore. Figure 4-3 illustrates the proposed method to perform a Gradual Full Search Method (GFSM). There are two address counters pointing memory A and B holding respectively a block of new picture and a corresponding area of an old picture. For each comparison, 4 pixel pointers are adjusted to point to the next 4 pixels. When the first search over 64 pixels is completed, the counter indexing memory A is returned to the first pixel unit of the new picture block and the counter indexing memory B is set to the next start pointer of correspond area in the old picture according the gradual search algorithm.

No matter whether a match is found or not, after 81 comparisons with these data sets, the new data of next block and next corresponding area are loaded in MemA and MemB. The next block searching then starts. The gradual search algorithm is somewhat more complex than FSM with respect to the order in which pointers are adjusted, but it is 3 times faster on average.

Figure 4-3. Data structure in PEs

### 4.2 Gradual Full Search Method and Full Search Algorithm with the PULSE Chip

In section 4.2.1, the speed of the GFSM and FSM algorithms (see chapter 2.2) are characterized. Moreover, the basic match program is presented in section 4.2.2.

## 4.2.1 Speed of GFSM and FSM Algorithms in PULSE

The MAD algorithm needs 192 operations (64 subtractions + 64 absolute value computations + 64 accumulate instructions). If this was spread ideally on 4 processors, a minimum of 48 instructions would be required.

In order to complete 81 block comparisons over one region, 3888 instructions (48 x 81) are needed. There are 5760 (768 x 480 / 64) blocks in one frame. In a real time system, pictures must be processed at the rate of 30 per second. A total of (5760 x 30 = 172800) blocks search must be done every second.

Assuming 54 MHz PULSE chips, (48 x 81 x 172800 / 54E6 = 12.4) 12.4 chips would be required. However, in practice, more resources are needed due to the overhead associated with data input, loop control, address counter setting and instructions that cannot be parallelized.

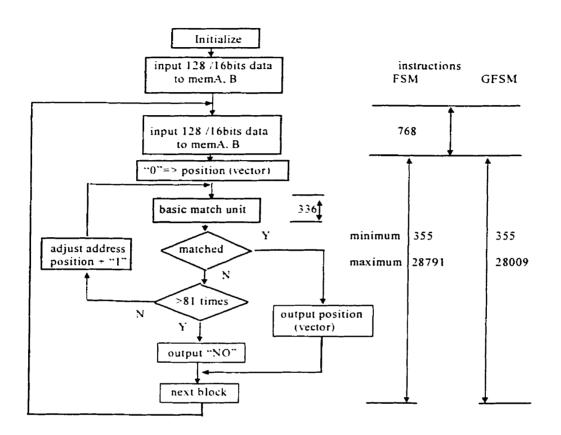

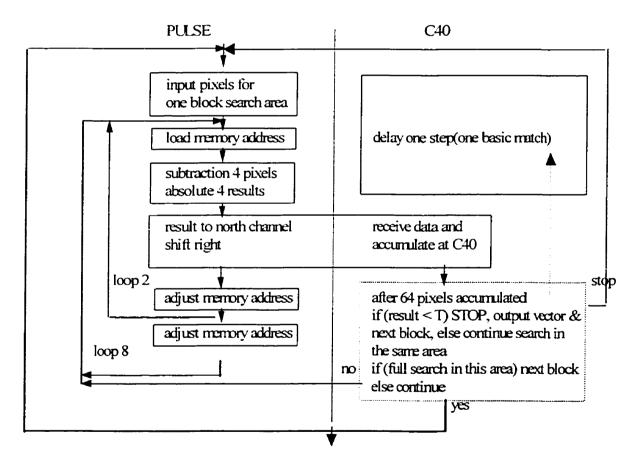

Figure 4-4 shows the program flow chart and its instructions with GFSM or FSM algorithms, for one block match. For a single search, it uses 768 input + 355 cal. = 1123 cycles or 17.7 cycles / pixel. For a full search, time is 768 input +28009 calculations = 28777 cycles or 449.6 cycles / pixels. Considering that: 1) one PULSE chip can run 54,000,000 instructions/second, 2) one 768x480 pixels image has 96x60=5760(8x8)

blocks to be processed out. 3) 30 frame pictures/ second are used, then 28777instructions  $\times$  30  $\times$  5760 / 54E6 = 92 PULSE chips are needed for GFSM.

Figure 4-4. FSM & GFSM program diagram and its instructions (one block)

# 4.2.2 Motion Estimation Program for PULSE

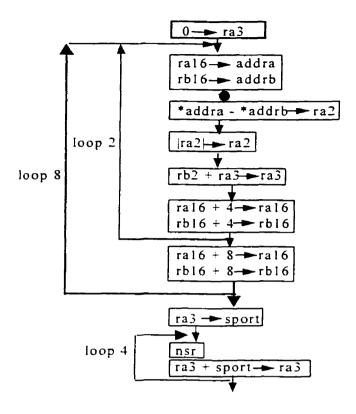

Figure 4-5 shows the instructions executed to perform one basic match program for the full search method (FSM) or the gradual full search method (GFSM). (corresponds to PULSE assembly language)

Figure 4-5. Flowchart of a basic match unit

As shown in figure 4-2, address pointer for memA and memB is 256. If the address pointer is over 255, it will return to 0. For the second block search, some data remains from the first block search, thus the start address in the new picture is 194 and the start address of area in the old picture is 128. In other words, each block search only needs to renew 128 pixels. In order to implement this behavior, mechanism to adjust address pointers are needed. In the basic match program, 72 instructions are required for this task. For one block search, 5832 instructions are needed, out of which a fifth are used to check and adjust address pointers. These instructions are identified in basic match program (Figures 4-7 and 4-8).

For each block search, Figure 4-6, if 256 memory locations are reserved, starting at address zero, then some instructions can be saved. In order to implement this idea, for each block search, 256 pixels (one search area) must be transferred from external memory. As shown in Figure 4-6, some instructions are added to adjust the start address of the pointer that accesses the external memory. 80 PULSE chips would be required to support real time processing of this algorithm.

Figure 4-6 Data of block search in independent memory space

In figure 4-7, the basic match program called 't1', contains some 'nop' instructions due to PULSE' s pipeline architecture. In order to reduce the number of 'nop' instruction, some instructions can be shifted without changing the result. In Figure 4-8, the program 't2' is an improved version exploiting this idea. It removes loop2 to save loop set instruction cycles. The marked instructions are moved into other places occupied by 'nop' in 't1'.

With this improved version 21300instructions x 172800/54E6 =  $\underline{68}$  PULSE chips are needed.

```

Program 'tl'-----

ld 0, ra3; clear accumulater ra3

ld rb6, rb1

push 8; accumulate 64 pixels

icop3:

push 2; accululate 1 line (8 pixels)

loop2:

#1 nop

ld ralé, addra

ld rb16, addrb

#3 nop

sub 'addra, 'addrb, rb2;ra2

#3 nop

abs rb2, rb2;

#3 nop

add rb2, ra3, ra3

add ral6, 4, ral6;

+4

Anciación de la lación de l

add rb16, 4, rb16;

ESTONIES AND THE PROPERTY OF THE PARTY OF TH

dbr loop2

add ra16, 8, ra16;

16-4x2=8

Brook and the second of the second

```

```

er edito our land

dbr loop3

ld ra3, sport

push 3

loop1:

add rai, sport, rai

ssr; add before ssr

dbr loopl

sub ral6, 128, ral6; -128 back to start point

iflt ral6, 0, 0; (if ral6<0, +256)

#3 nop

add ra16, 256, ra16

else

nop

restore

sub rb16, 128, rb16; -128 back to start point

64 (2016) 10 (2016) 10 (2016) 10 (2016) 10 (2016)

#3°nop

add_rb16, 256; rb16

else

nop

restore

** The "and ral6, coffh, ral6" instruction keeps the value of ral6 less

than 256, when increase 4.

add ral6, 4, ral6; +4

```

add rb16, 8, rb16:  $16-4\times2=8$

ret

```

and ral6, 00ffh, ral6; model 256

```

Figure 4-7 Program t1

```

program 't2'-----

ttl:

ld 0, ra3; clear accumulater ra3

ld rb6, rb1

push 8

;accumulate 64 pixels

;accululate 1 line (8 pixels)

lccp3:

ld ral6, addra

ld rbl6, addrb

nop

add rale, 4, rale, 4

add rb16, 4, rb16; + +4

sub *addra, *addrb, rb2;ra2

nop

ld ralé, addra

ld rb16, addrb

abs rb2, rb2;

#3 ncp

add rb2, ra3, ra3

sub *addra, *addrb, rb2;ra2

#3 nop

abs rb2, rb2;

多多年 "我们是这个一直是一个一直的是这个一个一个是是一种是

1.21

```

```

add rb2, ra3, ra3

dbr leop3

ld ra3, sport

push 3

lccpl:

add ra3, sport, ra3

ssr; add before ssr

dbr lcop1

sub ra16, 129, ra16; -128 back to start point

sub rb16, 129, rb16; -128 back to start point

```

Figure 4-8 Program t2

Sample programs and corresponding results are provided in appendix A. The simulation uses Mentor Graphic QHSIM tool. The source file includes two 64x64 pixel images. The 8x8 block FSM and Gradual Full Search Method (GFSM) are implemented with 16x16 matching area. The running time, matched pixels coordinate values in new picture and the coordinate values of corresponding area in old picture for first block searching are also provided in appendix A.

#### CHAPTER 5

#### DCT & IDCT ALGORITHMS AND IMPLEMENTATIONS

#### 5.1 DCT & IDCT Algorithms

In this section, a data compression algorithm, the Discrete Cosine transform (DCT)

[FAS87] and its inverse algorithm, the Inverse Discrete Cosine Transform (IDCT)

[IEE90] are described. These algorithms are widely used in image compression

programs. They implement a transform from the time domain to the frequency domain.

#### 5.1.1 DCT

DCT is an essential part of the MPEG data compression. There are two good reasons for using DCT in data compression. First, DCT coefficients have been shown to be relatively uncorrelated, and this makes it possible to construct relatively simple algorithms for compressing the coefficient values. Second, the DCT is a process for (approximately) decomposing the data into underlying spatial frequencies. This is very important in terms of compression, as it allows the precision of the DCT coefficients to be reduced in a manner consistent with the properties of the human visual system. [MPG97]

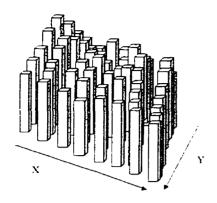

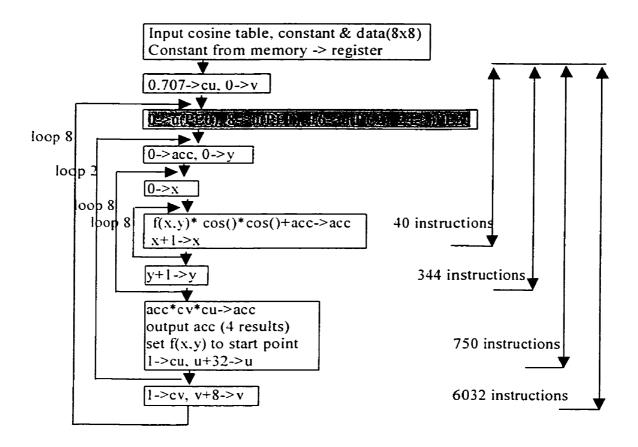

For data compression with the MPEG standard, two-dimensional array (2-D) of samples are considered. Arrays of eight points by eight points (8x8) are usually considered. Suppose that a 2-D array of sample, f(x,y), is to be transformed into a 2-D DCT. The equation is as below (Eq.5.1):

$$F(u,v) = C(u)C(v)/4\sum_{y=0}^{7}\sum_{x=0}^{7}f(x,y) \cdot \cos[(2x+1)u\pi/16] \cdot \cos[(2y+1)v\pi/16]$$

$$C(u) = 1/\sqrt{2}$$

if  $u = 0$ ;  $C(v) = 1/\sqrt{2}$  if  $v = 0$  (Eq.5.1)

$$C(u) = 1$$

if  $u > 0$ ;  $C(v) = 1$  if  $v > 0$

For example, the input value of matrix f(x,y) is:

120 108 90 75 69 73 82 89

127 115 97 81 75 79 88 95

134 122 105 89 83 87 96 103

137 125 107 92 86 90 99 106

131 119 101 86 80 83 93 100

117 105 87 72 65 69 78 85

100 88 70 55 49 53 62 69

89 77 59 54 48 42 51 58

Also, suppose '0' means black and '255' means white. The corresponding 8x8 bar diagram is represented below.

Then, the DCT transform calculated with equation (Eq.5.1), produces the following result:

700 90 100 0 0 0 0 0

90 0 000000

-89 0 0 0 0 0 0 0

$0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0$

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

It is remarkable that almost all values are equal to zero, the non-zero values are concentrated at the upper left corner of the matrix. These non-zero values are transferred to the receiver in zigzag scan order (see Chapter 2, Figure 2-5), which is 700 90 90 -89 0 100 0 0 0 ... 0. The zero values are not transferred. They are replaced by an 'end-of – block' symbol.

#### 5.1.2 IDCT

IDCT is a inverse algorithm of DCT. It is used to regenerate the data back to the time domain from frequency domain representation. The IDCT algorithm is expressed in equation (Eq. 5.2).

$$f(x,y) = \sum_{v=0}^{7} \sum_{u=0}^{7} C(u)C(v) / 4F(u,v) \cdot \cos[(2x+1)u\pi/16] \cdot \cos[(2y+1)v\pi/16]$$

$$C(u) = 1/\sqrt{2} \quad \text{if} \quad u = 0; \quad C(v) = 1/\sqrt{2} \quad \text{if} \quad v = 0$$

$$C(u) = 1 \quad \text{if} \quad u > 0; \quad C(v) = 1 \quad \text{if} \quad v > 0$$

$$(Eq.5.2)$$

In equation (Eq.5.2), the F(u,v) of DCT result with (Eq.5.1) will be transformed again, the result of matrix f'(x,y) is as below:

120 108 91 75 69 73 82 89

127 115 97 81 75 79 88 95

134 122 105 90 83 87 96 103

137 125 107 92 86 90 99 106

131 119 101 88 80 83 93 100

117 105 87 72 65 69 78 85

100 88 70 59 49 53 62 69

89 77 59 54 48 42 51 58

Comparing the original matrix f(x, y) and the inverse transfer matrix f'(x, y), there are few small differences between them. It caused by the calculation accuracy. In other word, it is limited by the word length of the processor. This error is generated by two times transfer calculation (DCT and IDCT). It means that the error is produced at remote decoder device. In order to limit error accumulation in the decoder, the IDCT can be used in encoding system to generate an 'old picture' (See Chapter 2, Figure 2-3).

#### 5.2 Implementation of DCT & IDCT on PULSE

This section deals with the storage of a cosine table and to the time required to compute it.

#### 5.2.1 Data Structure of DCT on PULSE