**Titre:** Développement d'une méthodologie de codesign matériel/logiciel

Title: pour des applications de communications à haute vitesse

**Auteur:** Isabelle Campagna

Author:

**Date:** 2000

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Campagna, I. (2000). Développement d'une méthodologie de codesign

matériel/logiciel pour des applications de communications à haute vitesse

Citation: [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

<https://publications.polymtl.ca/8679/>

**Document en libre accès dans PolyPublie**

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8679/>

PolyPublie URL:

**Directeurs de

recherche:** Guy Bois, & Jean-Louis Houle

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

DÉVELOPPEMENT D'UNE MÉTHODOLOGIE

DE CODESIGN MATÉRIEL/LOGICIEL POUR DES

APPLICATIONS DE COMMUNICATIONS

À HAUTE VITESSE.

ISABELLE CAMPAGNA

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

MARS 2000

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-53563-0

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

DÉVELOPPEMENT D'UNE MÉTHODOLOGIE

DE CODESIGN MATÉRIEL/LOGICIEL POUR DES

APPLICATIONS DE COMMUNICATIONS

À HAUTE VITESSE

Présenté par: CAMPAGNA Isabelle

En vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

A été dûment accepté par le jury d'examen constitué de:

M. Savaria Yvon, Ph.D., président

M. Aboulhamid Moustapha, Ph.D., membre

M. Bois Guy, Ph.D., membre et directeur de recherche

M. Houle Jean-Louis, Ph.D., membre et co-directeur de recherche

## Remerciements

Je tiens à remercier mon directeur de recherche Guy Bois, pour son soutien et ses encouragements tout au long de ce projet. Son enthousiasme est communicatif. Je voudrais également remercier mon codirecteur de recherche Jean-Louis Houle. Je ne peux passer sous silence les conseils et l'aide apportés par Moustapha Aboulhamid de l'Université de Montréal.

Deux compagnies ont subventionné notre projet de recherche, Mentor Graphics ainsi que Nortel. Je voudrais remercier ces deux compagnies, et plus particulièrement Jacques Baillargé de Mentor Graphics qui a plusieurs fois fait le lien entre notre groupe de recherche et les deux partenaires industriels. Il a été d'une aide précieuse pour l'installation et l'utilisation de plusieurs outils.

En terminant, je voudrais remercier Yannick Héneault et Geneviève Cyr qui ont partagé avec moi les hauts et les bas de la maîtrise. Et je ne voudrais surtout pas oublier ma famille et mes amis.

## Résumé

Les systèmes embarqués étant de plus en plus gros et complexes, des méthodologies de conception sont nécessaires afin d'obtenir le système le plus performant possible, tout en gardant les coûts de développement et de fabrication les plus bas possibles. Ce sont les raisons pour lesquelles, nous avons voulu développer une méthodologie de codesign matériel/logiciel. L'objectif de ce projet de recherche est de développer une méthodologie qui sera testée et validée sur une application de communications à haute vitesse.

Le codesign matériel/logiciel est en fait la conception d'un système en utilisant des techniques de conception matérielle et logicielle. Les développements du matériel et du logiciel sont intégrés dans une méthodologie commune. La plupart des systèmes numériques utilisés comme systèmes embarqués consistent en un processeur d'utilisation générale, d'une mémoire et d'un circuit spécifique fait en matériel. Ce matériel peut être des ASICs (Application-Specific Integrated Circuit) ou des FPGAs (Field Programmable Gate Array). Des exemples de tels systèmes se retrouvent dans des instruments médicaux, des véhicules, des réseaux automatisés et des systèmes de communications.

Nous avons développé trois applications, c'est-à-dire trois modems de la famille xDSL, pour tester et valider notre méthodologie. Ces trois modems sont le ADSL (Asymmetric Digital Subscriber Line), le Universal ADSL qui est une version légère du ADSL et finalement le VDSL (Very High Bit-Rate Digital Suscriber Line) qui est une version plus performante du ADSL. Ces trois modems utilisent la même technologie, appelés DMT (Discrete Multitone), mais façons différentes. Nous avons évalué quatre critères pour les modems qui sont le temps d'exécution, les temps de communications, la surface du matériel et finalement la dissipation de puissance. Pour

fusionner les valeurs de ces différents critères en une seule représentant la qualité du modèle, nous utilisons une fonction objectif. Puis, un algorithme de partitionnement nous permet de déterminer la qualité de plusieurs modèles différents.

Notre méthodologie nous a permis de trouver un partitionnement matériel/logiciel optimal pour un modem. La différence principale entre notre méthodologie et celles développées précédemment, est que nous avons essayé d'intégrer le plus possible, des outils commerciaux existants. Pour composer avec ces nouvelles réalités, chacun des blocs des modems est évalué une seule fois et cela avant d'utiliser l'algorithme de partitionnement. Notre méthodologie est efficace mais il aurait été plus facile de le démontrer en utilisant une application moins complexe ou un processeur plus performant. Cette méthodologie pourrait être utilisée dans le futur lors de la conception de systèmes embarqués pour vérifier les choix des concepteurs d'une façon structurée et efficace.

## Abstract

Embedded systems are becoming bigger and increasingly complex. Therefore, design methodologies are necessary in order to get the most effective system, while keeping development and manufacturing cost as low as possible. Consequently, the objective of this research project is to develop a methodology to test and validate hardware/software systems such as these used in high speed communications.

Hardware/software codesign is a methodology whose the goal is to integrate the hardware and the software parts of a system. Most of the digital systems are used as embedded systems. They consist of a general purpose processor, a memory and application specific circuits made in hardware. These circuits can be ASICs (Application-Specific Integrated Circuit) or FPGA (Field Programmable Gate Array). Examples of such systems can be found in medical instruments, transportation vehicles, automated networks, and communications systems.

We developed three related applications, selected from the xDSL family, to test and to validate our methodology. These three modems are the ADSL (Asymmetric Digital Subscriber Line), the Universal ADSL that is a light version of the ADSL and finally the VDSL (Very High Bit - Rate Digital Suscriber Line) which is the most effective version of the ADSL. These three modems use the same technology, called DMT (Discret Multitone), but in different ways. For the modem evaluation, we use four metrics: execution time, communications time, hardware area and power dissipation. We put the metrics values together in an cost fonction to find the model quality. Then a partitioning algorithm allows us to find the quality of different models.

Our methodology enabled us to find an optimal hardware/software partitioning for a modem. The difference between our methodology and those developed previously, is that we used as much as possible, existing tools. To compose with these new realities, each block of the modems are evaluated only once before using the partitioning algorithm. Our methodology is effective but it would have been easier to demonstrate it with less complex applications or with a more powerful processor. This methodology could be used in the future when designing embedded systems to validate the design made by the designers in a regular and effective way.

## Table des matières

|                                                             |          |

|-------------------------------------------------------------|----------|

| REMERCIEMENTS .....                                         | IV       |

| RÉSUMÉ .....                                                | V        |

| ABSTRACT .....                                              | VII      |

| TABLE DES MATIÈRES .....                                    | IX       |

| LISTE DES ANNEXES .....                                     | XVII     |

| LISTE DES ABRÉVIATIONS.....                                 | XVIII    |

| AVANT-PROPOS .....                                          | XX       |

| <b>CHAPITRE 1 INTRODUCTION .....</b>                        | <b>1</b> |

| 1.1 Définition du codesign .....                            | 1        |

| 1.2 But du projet de recherche .....                        | 3        |

| 1.3 Application utilisée pour valider la méthodologie ..... | 5        |

| 1.4 Plan du mémoire .....                                   | 6        |

| <b>CHAPITRE 2 INTRODUCTION AU CODESIGN.....</b>             | <b>7</b> |

| 2.1 Les différentes étapes du codesign.....                 | 7        |

| 2.2 Les différents composants du partitionnement .....      | 10       |

| 2.2.1 <i>Modèle d'estimation</i> .....                      | 10       |

| 2.2.2 <i>Algorithme de partitionnement</i> .....            | 12       |

| 2.2.3 <i>Estimateurs</i> .....                              | 13       |

| 2.2.4 <i>Fonction objectif</i> .....                        | 15       |

| 2.3 Description des estimateurs utilisés .....              | 15       |

| 2.4 Estimateurs pour la partie logicielle.....              | 15       |

|                                                                      |    |

|----------------------------------------------------------------------|----|

| 2.4.1 <i>Temps d'exécution</i> .....                                 | 15 |

| 2.4.1.1 Modèles d'estimation .....                                   | 16 |

| 2.4.1.2 Profilage des blocs du logiciel.....                         | 17 |

| 2.4.1.3 Ordonnancement.....                                          | 18 |

| 2.4.2 <i>Dissipation de puissance</i> .....                          | 19 |

| 2.4.2.1 Profilage .....                                              | 20 |

| 2.4.2.2 En utilisant un modèle matériel.....                         | 20 |

| 2.4.2.3 Modèles de puissance au niveau des instructions.....         | 21 |

| 2.4.2.4 Autres techniques .....                                      | 26 |

| 2.5 Estimateurs pour la partie matérielle.....                       | 26 |

| 2.5.1 <i>Surface du circuit intégré et temps d'exécution</i> .....   | 26 |

| 2.5.1.1 Représentation du comportement.....                          | 27 |

| 2.5.1.2 Allocation .....                                             | 29 |

| 2.5.1.3 Ordonnancement.....                                          | 30 |

| 2.5.1.4 Les algorithmes d'ordonnancement de base.....                | 31 |

| 2.5.1.5 Partage des ressources (binding) .....                       | 35 |

| 2.5.1.6 Calcul de la surface .....                                   | 38 |

| 2.5.2 <i>Dissipation de puissance pour le matériel</i> .....         | 38 |

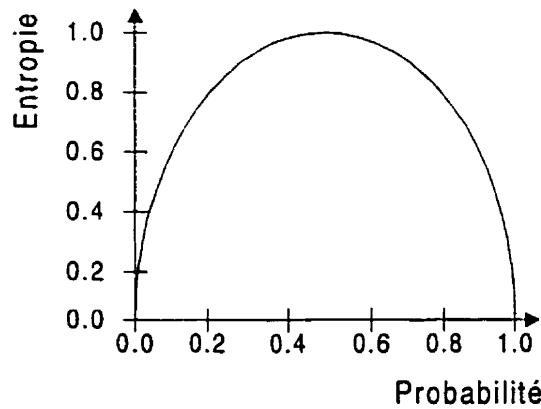

| 2.5.2.1 Modèles de théorie de l'information .....                    | 39 |

| 2.5.2.2 Modèles basés sur la complexité .....                        | 40 |

| 2.5.2.3 Modèles basés sur la synthèse .....                          | 42 |

| 2.6 Estimation et modèle de communications.....                      | 42 |

| 2.6.1 <i>Modèles de communications</i> .....                         | 42 |

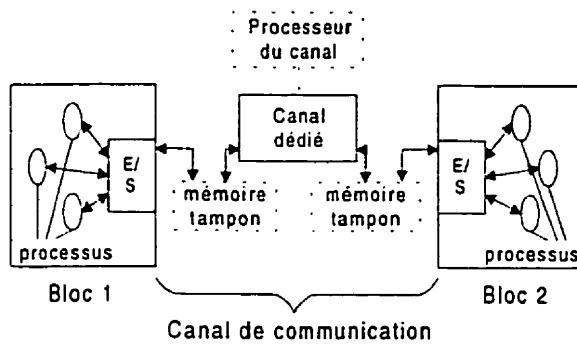

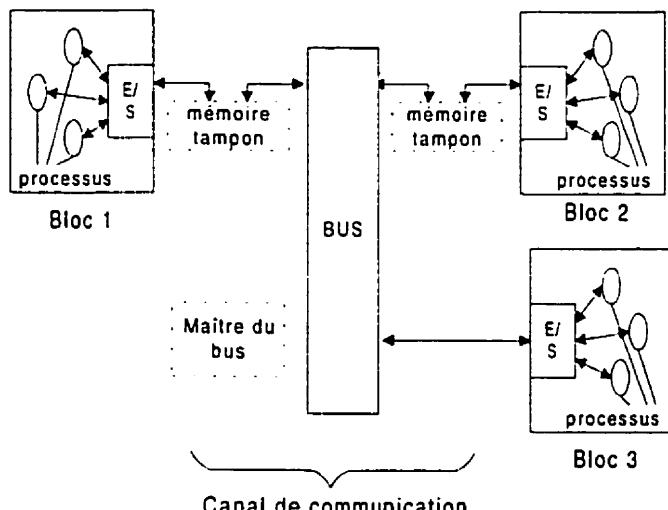

| 2.6.1.1 Passage de message .....                                     | 42 |

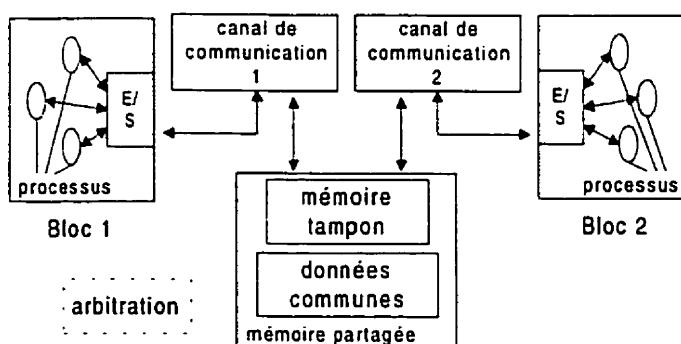

| 2.6.1.2 Mémoire partagée .....                                       | 44 |

| 2.6.2 <i>Canaux de communications</i> .....                          | 44 |

| 2.6.3 <i>Estimation du temps de communications</i> .....             | 48 |

| 2.6.4 <i>Modèle proposé par Ralf Niemann dans l'outil COOL</i> ..... | 51 |

| 2.6.4.1 Ajout au modèle .....                                        | 52 |

|                                                                               |           |

|-------------------------------------------------------------------------------|-----------|

| 2.7 La fonction objectif .....                                                | 53        |

| 2.7.1 <i>Calcul de la fonction avec des pondérations</i> .....                | 53        |

| 2.7.2 <i>Calcul de la fonction objectif avec contraintes</i> .....            | 54        |

| 2.7.3 <i>Calcul de la fonction objectif avec normalisation</i> .....          | 55        |

| 2.8 Les algorithmes de partitionnement .....                                  | 55        |

| 2.8.1 <i>Recherche « BRANCH-AND-BOUND »</i> .....                             | 55        |

| 2.8.2 <i>Algorithme vorace</i> .....                                          | 56        |

| 2.8.3 <i>Recuit simulé</i> .....                                              | 57        |

| 2.8.4 <i>Algorithme génétique</i> .....                                       | 57        |

| 2.8.5 <i>Recherche Tabu</i> .....                                             | 58        |

| <b>CHAPITRE 3 INTRODUCTION À LA TECHNOLOGIE xDSL .....</b>                    | <b>60</b> |

| 3.1 Qu'est-ce que les services xDSL? .....                                    | 60        |

| 3.2 Historique .....                                                          | 61        |

| 3.3 Les différents types de xDSL .....                                        | 62        |

| 3.3.1 <i>Asymmetric Digital Subscriber Line (ADSL)</i> .....                  | 63        |

| 3.3.2 <i>UADSL</i> .....                                                      | 64        |

| 3.3.3 <i>Very High Bit-Rate Digital Suscriber Line (VDSL)</i> .....           | 65        |

| 3.4 Les trois technologies sur le même modem .....                            | 65        |

| 3.5 Les schémas de modulation des xDSL.....                                   | 66        |

| 3.5.1 <i>CAP (Carrierless Amplitude/Phase)</i> .....                          | 66        |

| 3.5.2 <i>DMT (Discrete Multitone)</i> .....                                   | 67        |

| 3.5.3 <i>Les avantages et les inconvénients des deux technologies</i> .....   | 68        |

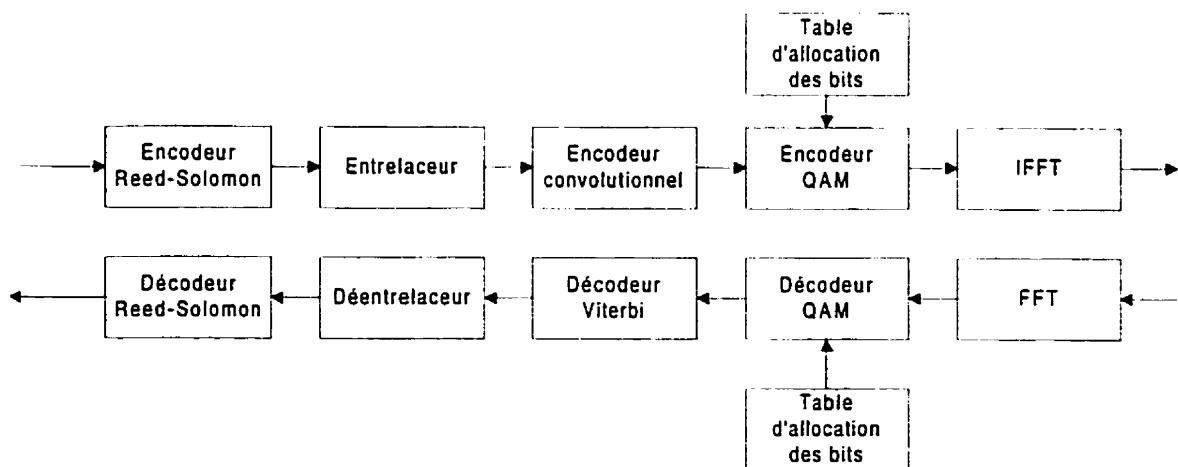

| 3.6 Description des différents blocs en utilisant de la technologie DMT ..... | 69        |

| 3.6.1 <i>Encodeur Reed-Solomon</i> .....                                      | 70        |

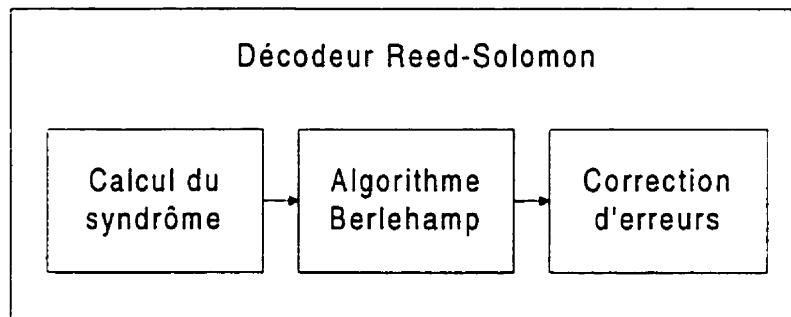

| 3.6.2 <i>Décodeur Reed-Solomon</i> .....                                      | 71        |

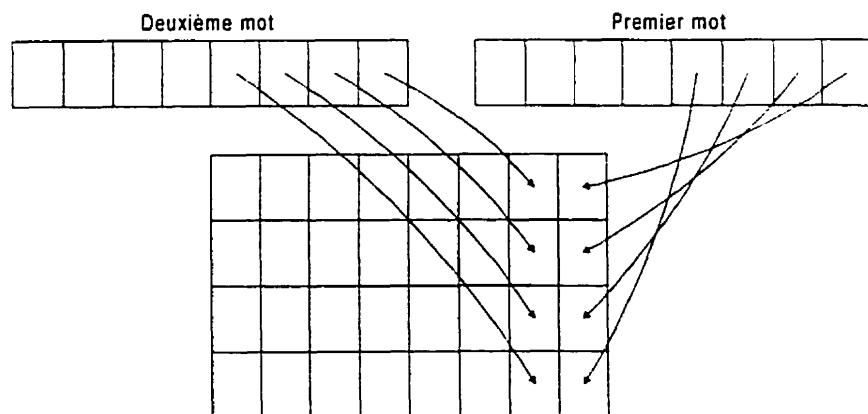

| 3.6.3 <i>Entrelaceur</i> .....                                                | 71        |

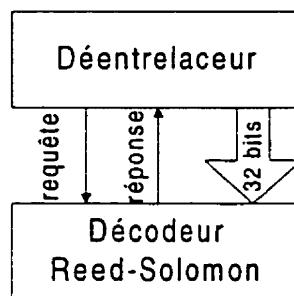

| 3.6.4 <i>Déentrelaceur</i> .....                                              | 72        |

| 3.6.5 <i>Encodeur Convolutionnel</i> .....                                    | 72        |

|                                                                              |           |

|------------------------------------------------------------------------------|-----------|

| 3.6.6 <i>Decodeur Viterbi</i> .....                                          | 73        |

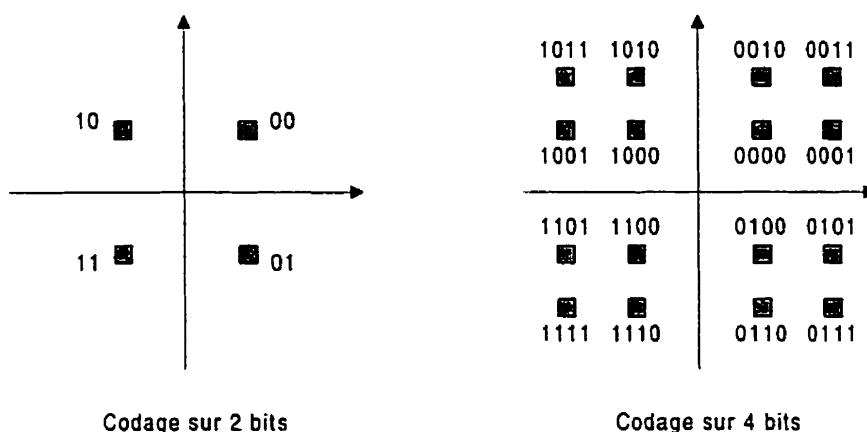

| 3.6.7 <i>Encodeur QAM</i> .....                                              | 74        |

| 3.6.8 <i>Decodeur QAM</i> .....                                              | 75        |

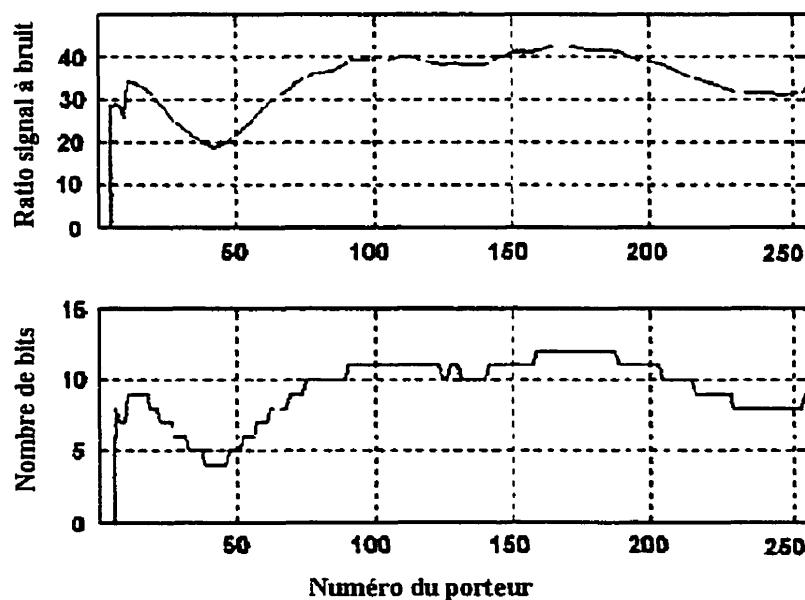

| 3.6.9 <i>Table de chargement des bits</i> .....                              | 76        |

| 3.6.10 <i>Transformée rapide de Fourier (FFT)</i> .....                      | 76        |

| 3.6.11 <i>Transformée rapide de Fourier inverse (IFFT)</i> .....             | 77        |

| 3.7 Spécifications des différents modems.....                                | 78        |

| <b>CHAPITRE 4 MÉTHODOLOGIE UTILISÉE ET RÉSULTATS .....</b>                   | <b>82</b> |

| 4.1 Description des outils utilisés .....                                    | 82        |

| 4.1.1 <i>Monet de Mentor Graphics</i> .....                                  | 82        |

| 4.1.2 <i>Description des outils de Synopsys</i> .....                        | 86        |

| 4.1.3 <i>Seamless de Mentor Graphics</i> .....                               | 89        |

| 4.2 Description de notre méthodologie .....                                  | 93        |

| 4.3 Spécifications du système et définition des blocs.....                   | 93        |

| 4.4 Description des blocs pour le logiciel et le matériel .....              | 93        |

| 4.5 Développement de la dissipation de puissance pour le logiciel.....       | 96        |

| 4.5.1 <i>Dissipation de puissance pour chacune des instructions</i> .....    | 97        |

| 4.5.2 <i>Les dépendances de la dissipation de puissance</i> .....            | 98        |

| 4.5.2.1 Dépendance vis-à-vis des données .....                               | 99        |

| 4.5.2.2 Dépendance inter-instructions .....                                  | 100       |

| 4.5.3 <i>Classes d'instructions</i> .....                                    | 100       |

| 4.5.4 <i>Vérification des résultats obtenus</i> .....                        | 102       |

| 4.6 Estimation du temps d'exécution logiciel .....                           | 106       |

| 4.7 Estimation de la surface et du temps d'exécution du matériel .....       | 109       |

| 4.8 Estimation de la dissipation de puissance pour la partie matérielle..... | 117       |

| 4.9 Estimation des communications.....                                       | 119       |

| 4.10 Fonction objectif .....                                                 | 122       |

| 4.11 Algorithme de partitionnement .....                                     | 124       |

|                                                              |            |

|--------------------------------------------------------------|------------|

| 4.12 Le meilleur partitionnement pour le Universal ADSL..... | 125        |

| 4.13 Implantation de mécanismes de communications.....       | 125        |

| 4.14 Implantation de canaux de communications .....          | 126        |

| 4.15 Co-simulation matérielle/logicielle.....                | 133        |

| <b>CHAPITRE 5 CONCLUSION.....</b>                            | <b>135</b> |

| <b>BIBLIOGRAPHIE .....</b>                                   | <b>187</b> |

## Liste des tableaux

|                                                                       |     |

|-----------------------------------------------------------------------|-----|

| Tableau 3.1 Taux de transmission et caractéristiques des modems ..... | 63  |

| Tableau 3.2 Les spécifications du UADSL .....                         | 79  |

| Tableau 3.3 Les spécifications du ADSL.....                           | 80  |

| Tableau 3.4 Les spécifications du VDSL.....                           | 81  |

| Tableau 4.1 Coût de base des instructions.....                        | 98  |

| Tableau 4.2 Dépendances des données des instructions .....            | 99  |

| Tableau 4.3 Les dépendances inter-instructions.....                   | 100 |

| Tableau 4.4 Comparaisons des résultats et des coûts de base .....     | 105 |

| Tableau 4.5 Temps d'exécution des blocs logiciels .....               | 109 |

| Tableau 4.6 La surface des blocs matériels .....                      | 114 |

| Tableau 4.7 Temps d'exécution des blocs matériels .....               | 116 |

| Tableau 4.8 Accélération des blocs placés en matériel .....           | 117 |

| Tableau 4.9 Puissance dissipée pour les blocs matériels.....          | 118 |

| Tableau 4.10 Temps de communication avec un bloc matériel .....       | 122 |

| Tableau 4.11 Temps de communication avec un bloc logiciel .....       | 122 |

| Tableau B.1 La machine à états.....                                   | 162 |

| Tableau E.1 Consommation de base des instructions .....               | 174 |

| Tableau E.2 Les effets inter-instructions.....                        | 176 |

## Liste des figures

|                                                                                            |     |

|--------------------------------------------------------------------------------------------|-----|

| Figure 2.1 Activités de conception matérielle/logicielle .....                             | 7   |

| Figure 2.2 Configuration typique d'un système de partitionnement .....                     | 11  |

| Figure 2.3 Graphe de flots de données .....                                                | 28  |

| Figure 2.4 Classification des algorithmes d'ordonnancement .....                           | 30  |

| Figure 2.5 Entropie d'une variable booléenne .....                                         | 40  |

| Figure 2.6 Représentation des canaux de communications .....                               | 47  |

| Figure 2.7 Modèle de communications sur un canal .....                                     | 48  |

| Figure 2.8 Modèle de communications modifié .....                                          | 52  |

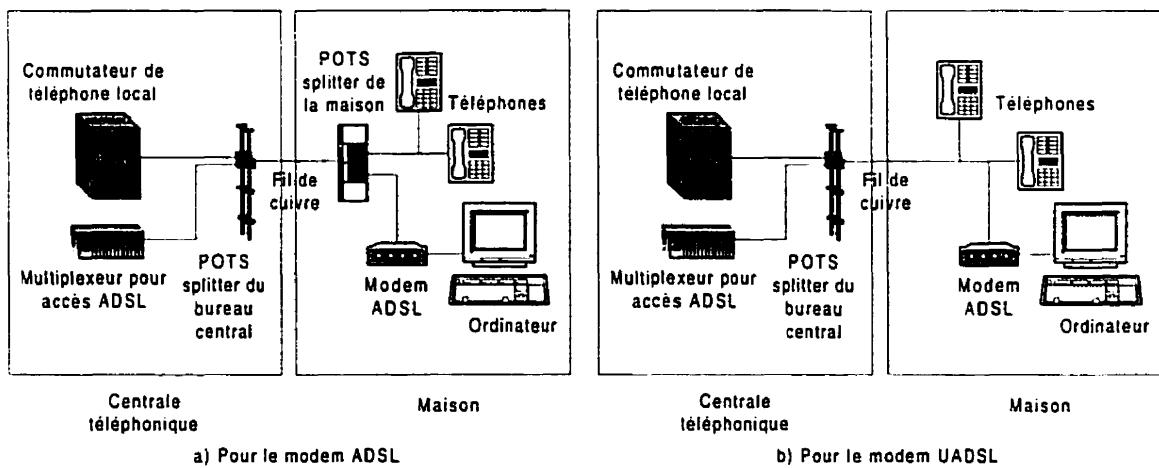

| Figure 3.1 Configuration d'un système pour le ADSL ou le UADSL .....                       | 64  |

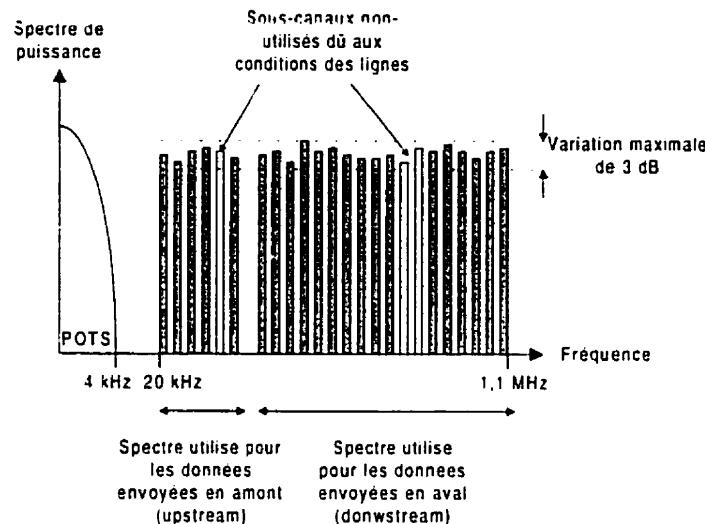

| Figure 3.2 La technologie DMT .....                                                        | 69  |

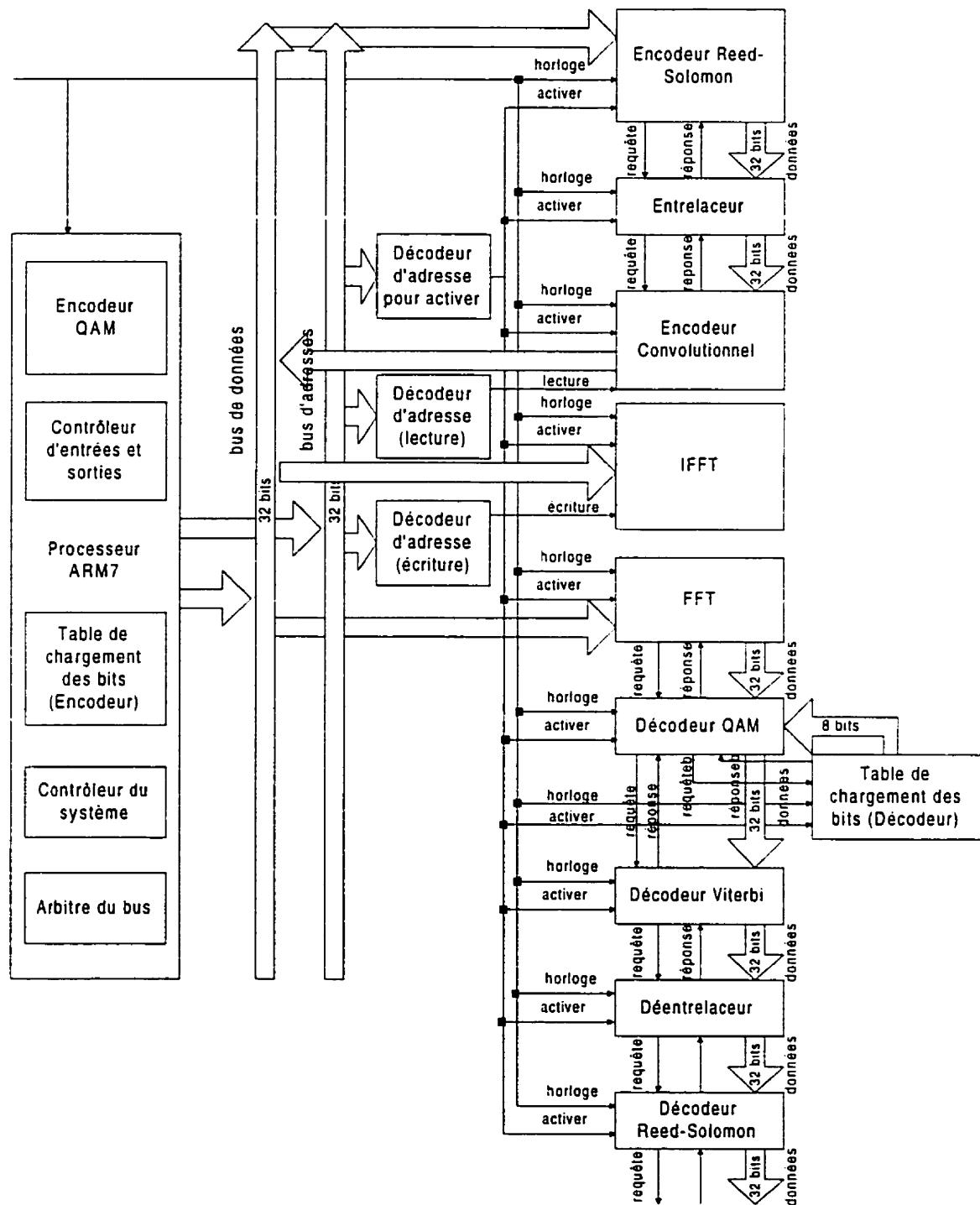

| Figure 3.3 Les différents blocs de la technologie DMT .....                                | 69  |

| Figure 3.4 L'entrelaceur .....                                                             | 72  |

| Figure 3.5 Encodeur QAM .....                                                              | 74  |

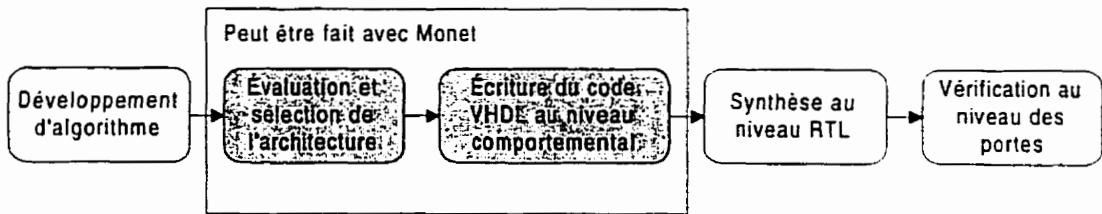

| Figure 4.1 Méthode de conception matérielle avec Monet .....                               | 83  |

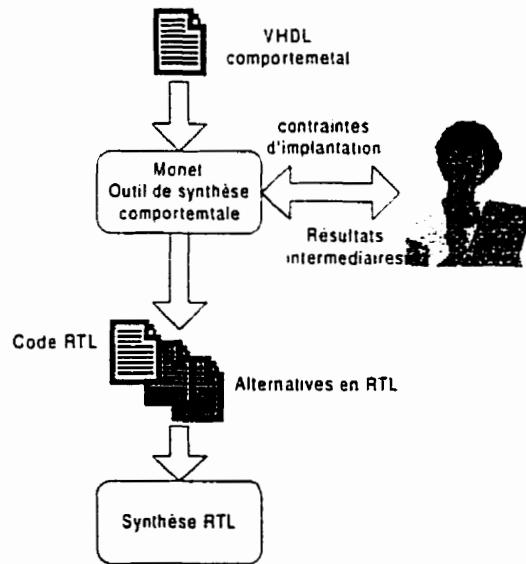

| Figure 4.2 Synthèse avec Monet .....                                                       | 84  |

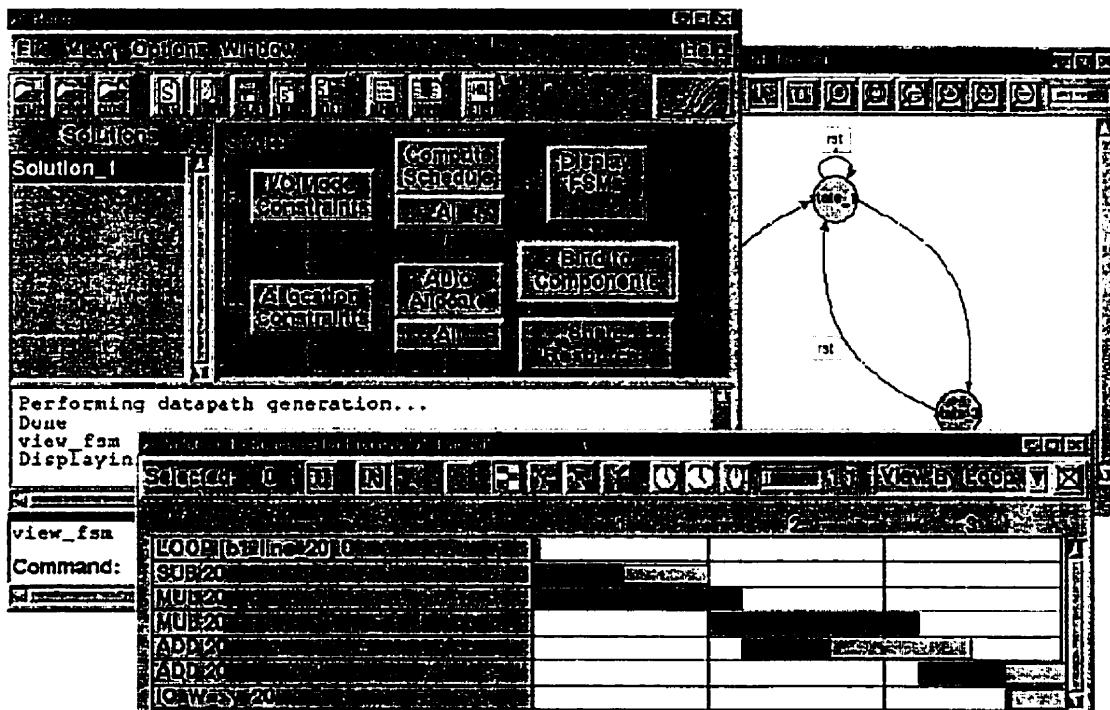

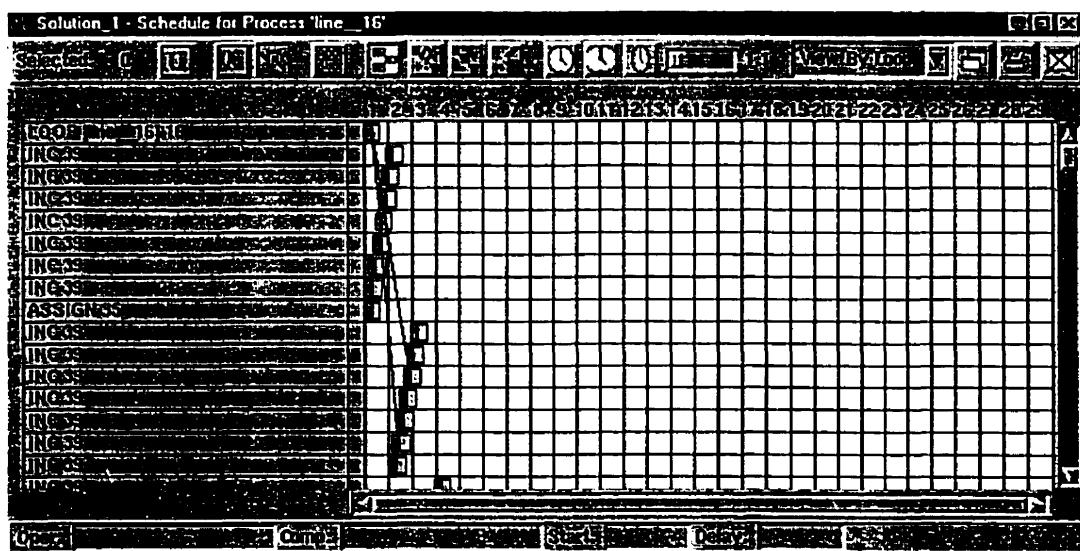

| Figure 4.3 Représentation des diagramme de Kantt et d'états dans Monet .....               | 86  |

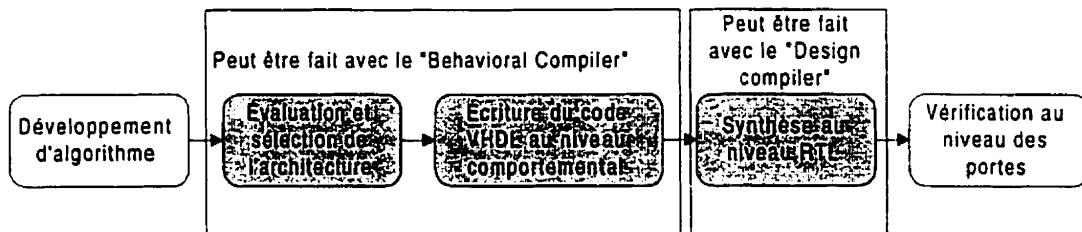

| Figure 4.4 Étapes de conception avec les outils de Synopsys .....                          | 87  |

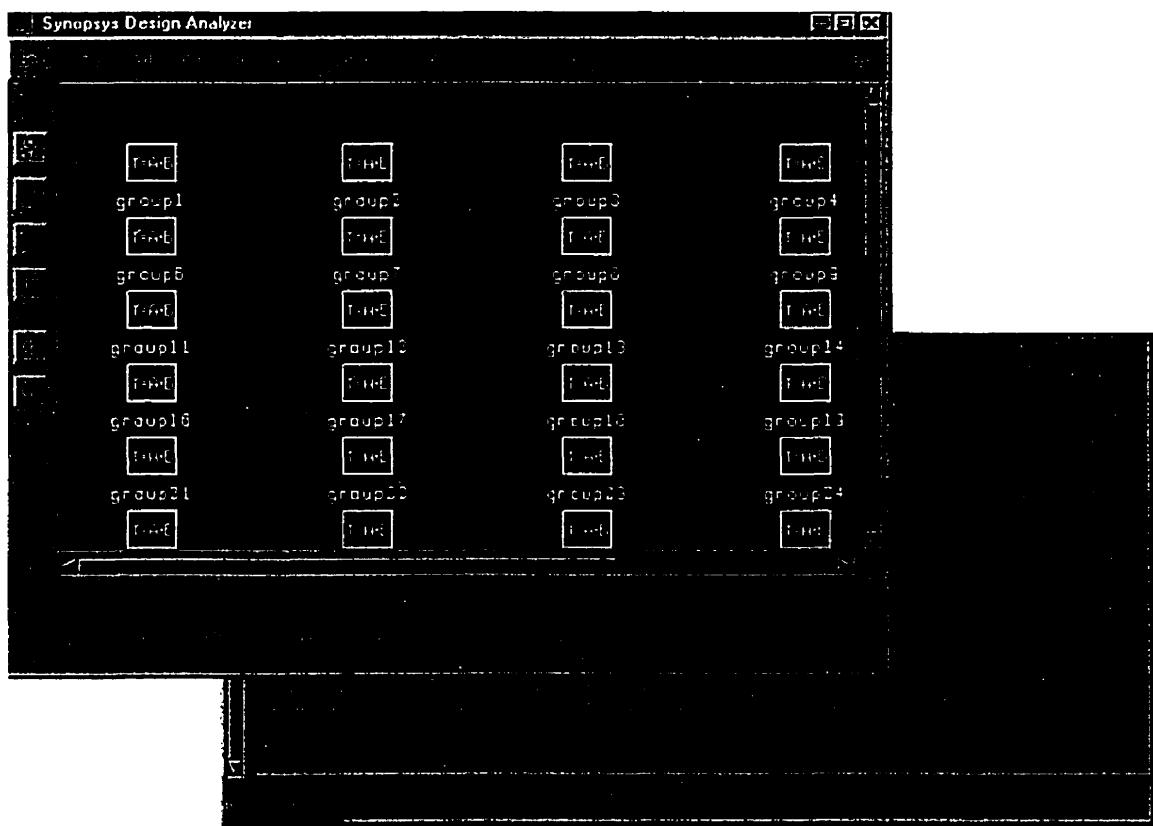

| Figure 4.5 L'interface du « Behavioral Compiler » de Synopsys .....                        | 89  |

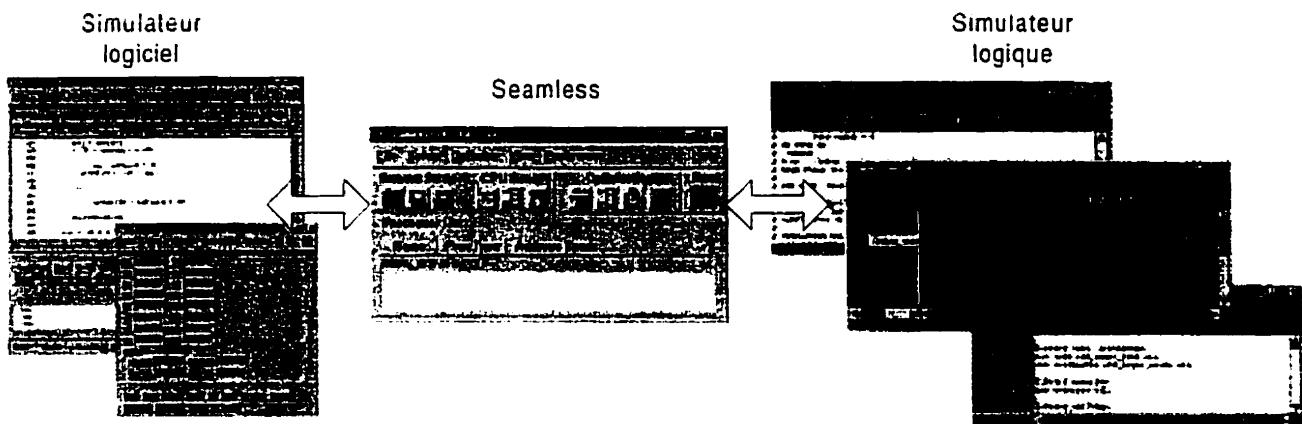

| Figure 4.6 Seamless CVE pour la cosimulation matérielle/logicielle .....                   | 91  |

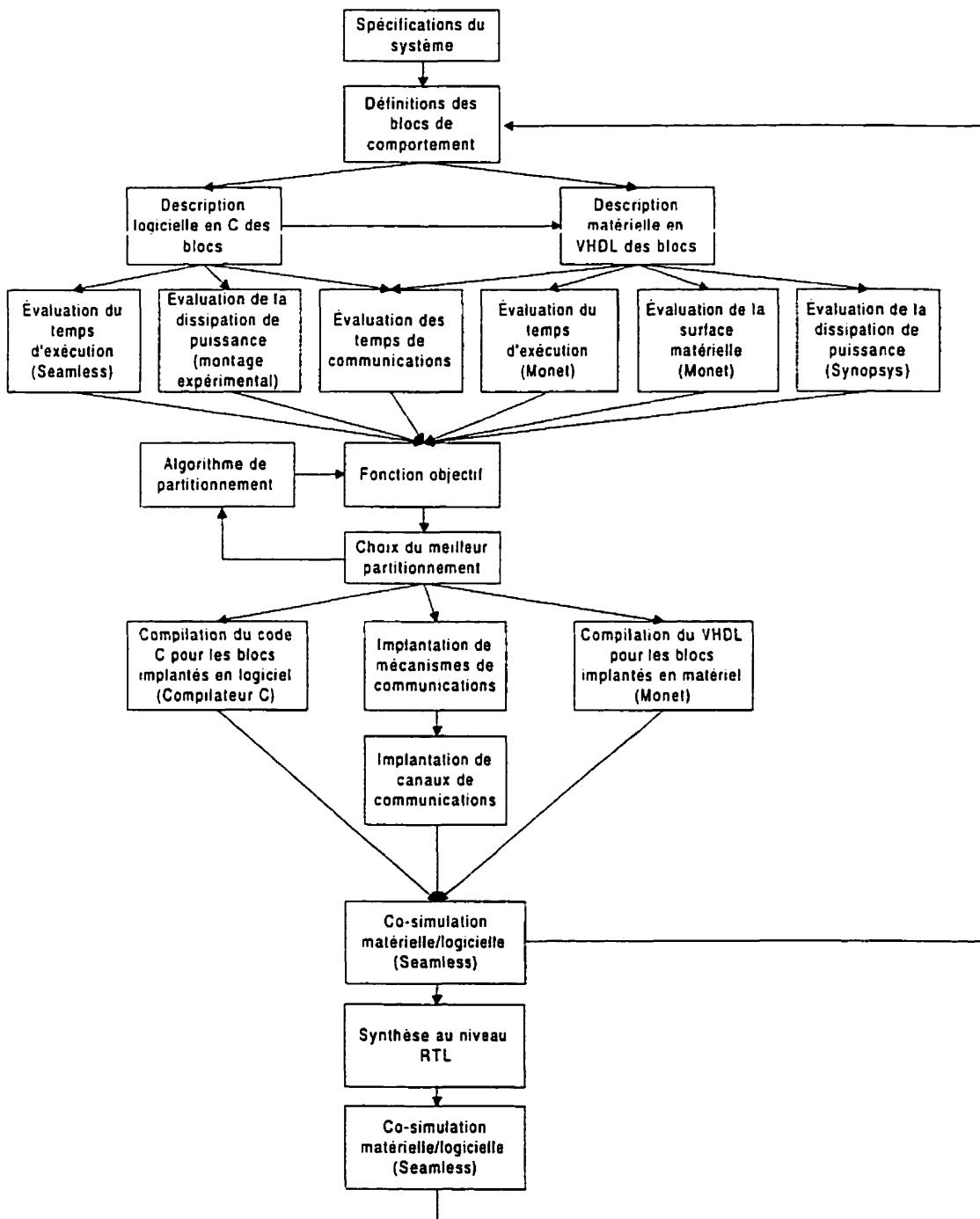

| Figure 4.7 Les étapes de notre méthodologie de codesign .....                              | 95  |

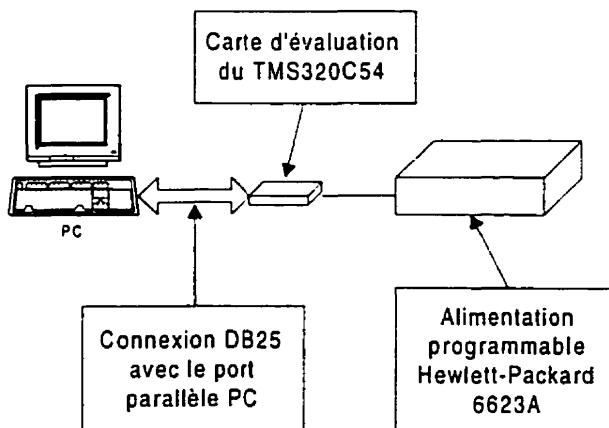

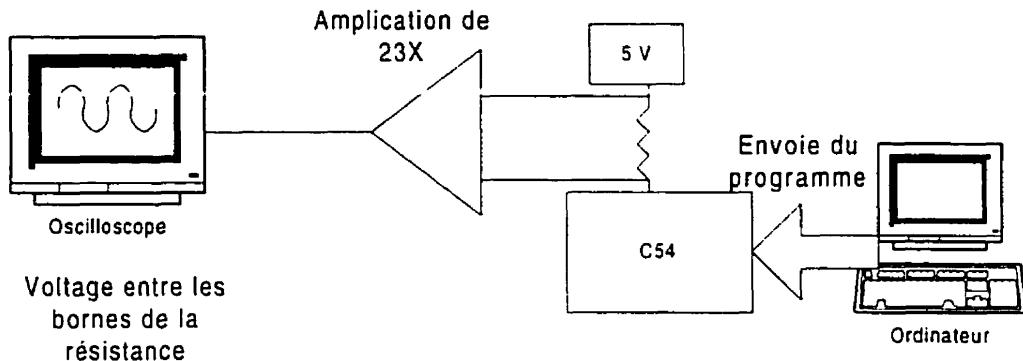

| Figure 4.8 Montage pour mesures expérimentales .....                                       | 97  |

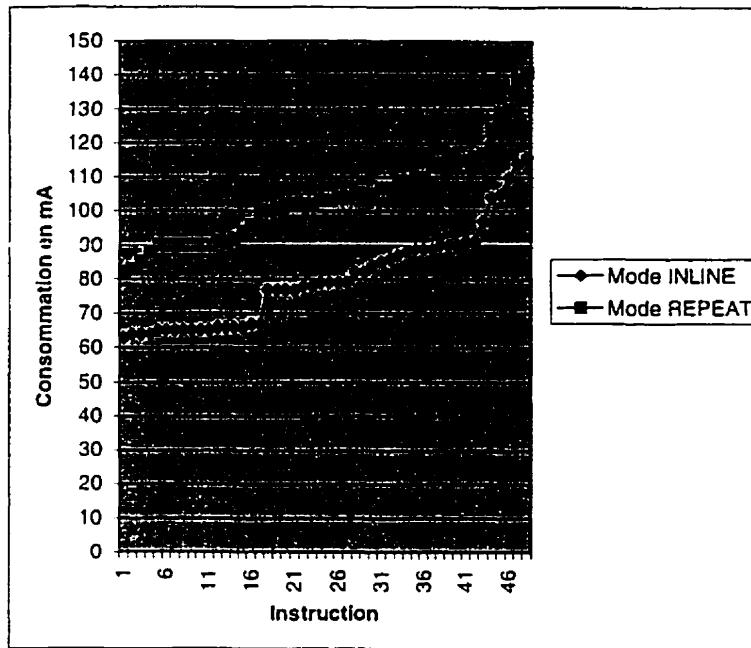

| Figure 4.9 Consommation de puissance des différentes instructions en ordre croissant ..... | 101 |

| Figure 4.10 Système de classes de consommation .....                                       | 102 |

| Figure 4.11 Montage pour le calcul de la dissipation de puissance .....                    | 103 |

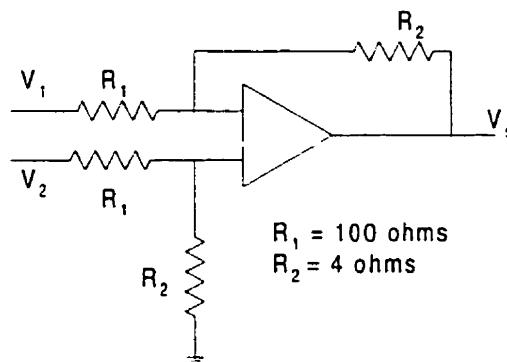

| Figure 4.12 Amplificateur 23 X du montage .....                                            | 104 |

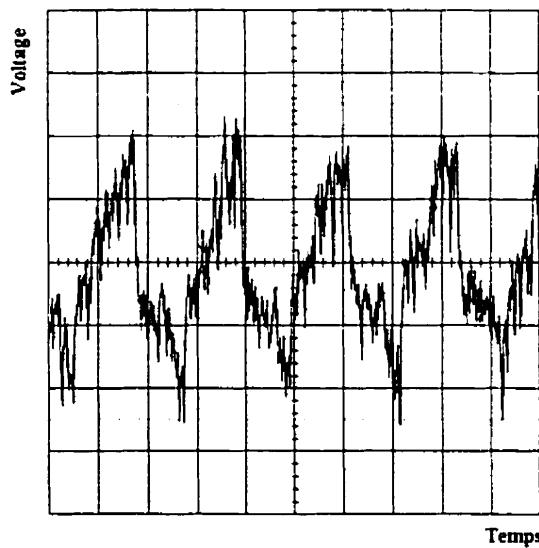

| Figure 4.13 FFT de 1024-points dans une boucle .....                                       | 105 |

|                                                                                                           |     |

|-----------------------------------------------------------------------------------------------------------|-----|

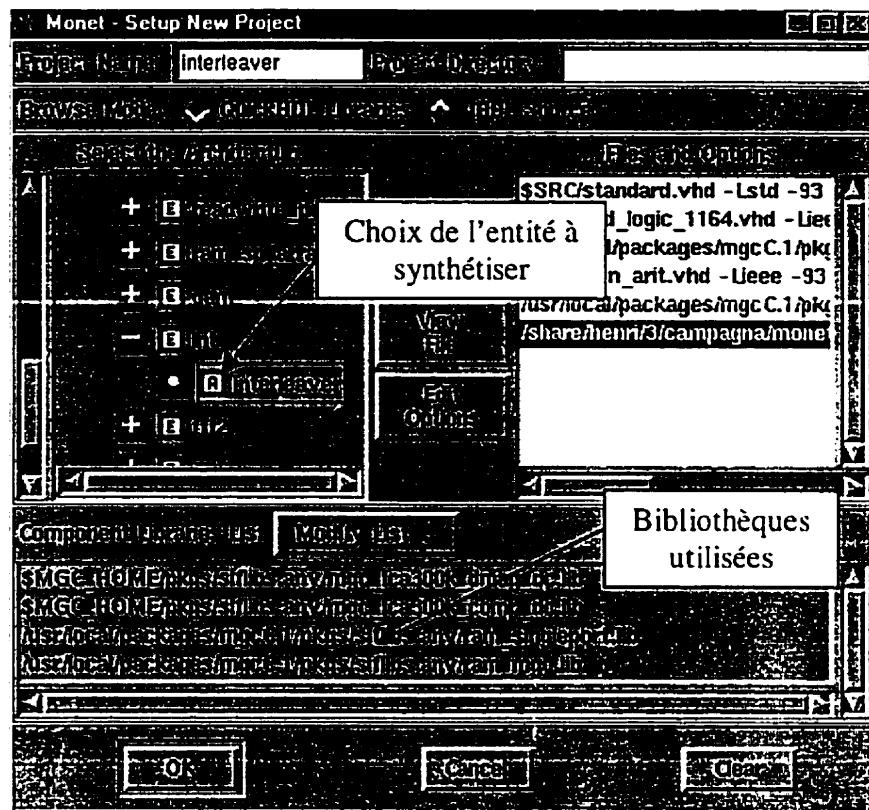

| Figure 4.14 Sélection du code à synthétiser et des bibliothèques. ....                                    | 110 |

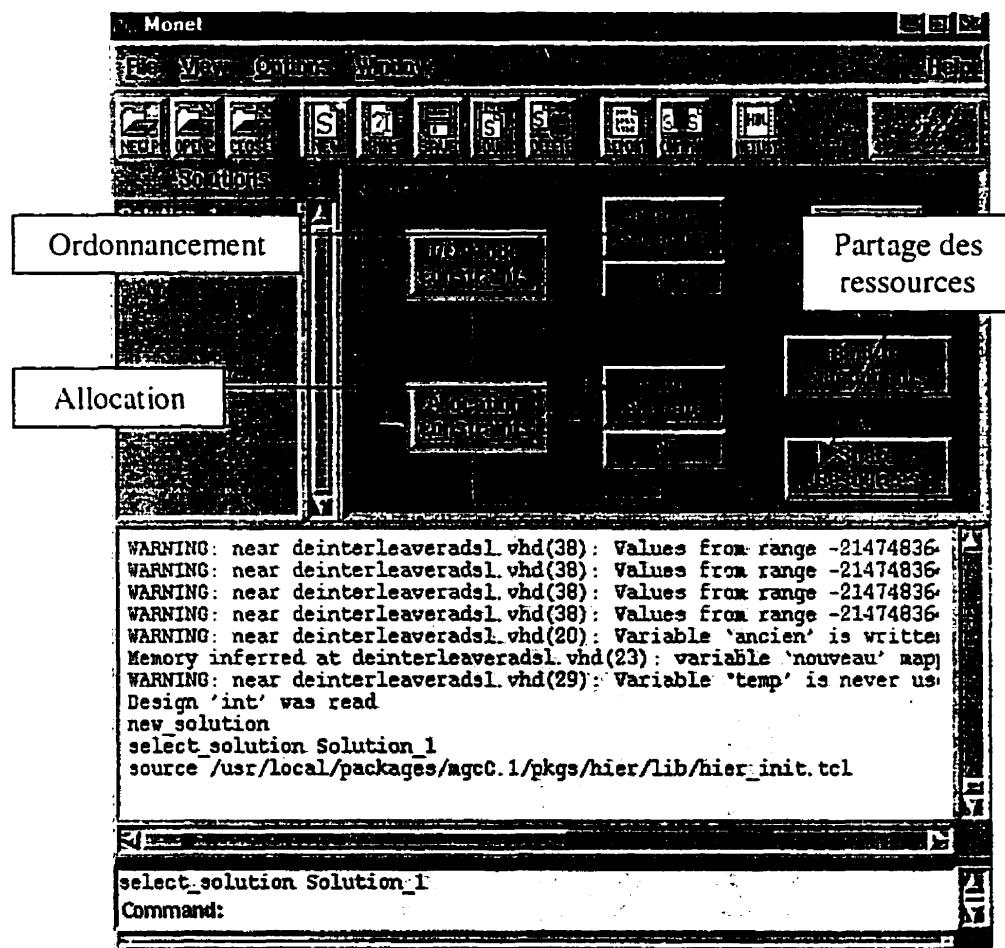

| Figure 4.15 Différentes étapes de la synthèse avec Monet .....                                            | 111 |

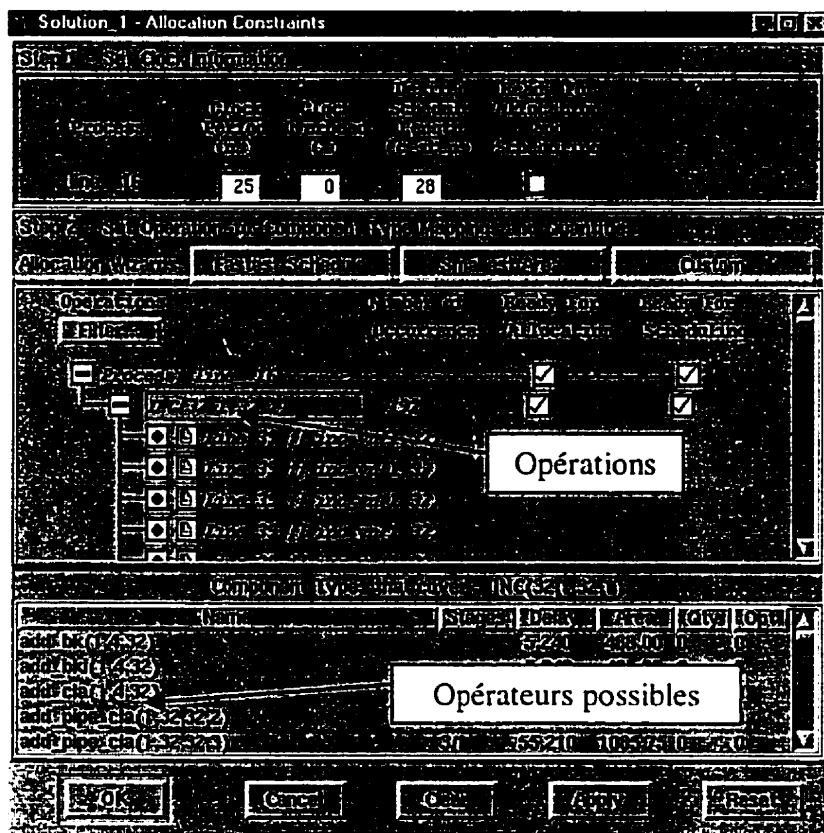

| Figure 4.16 Contraintes d'allocation .....                                                                | 111 |

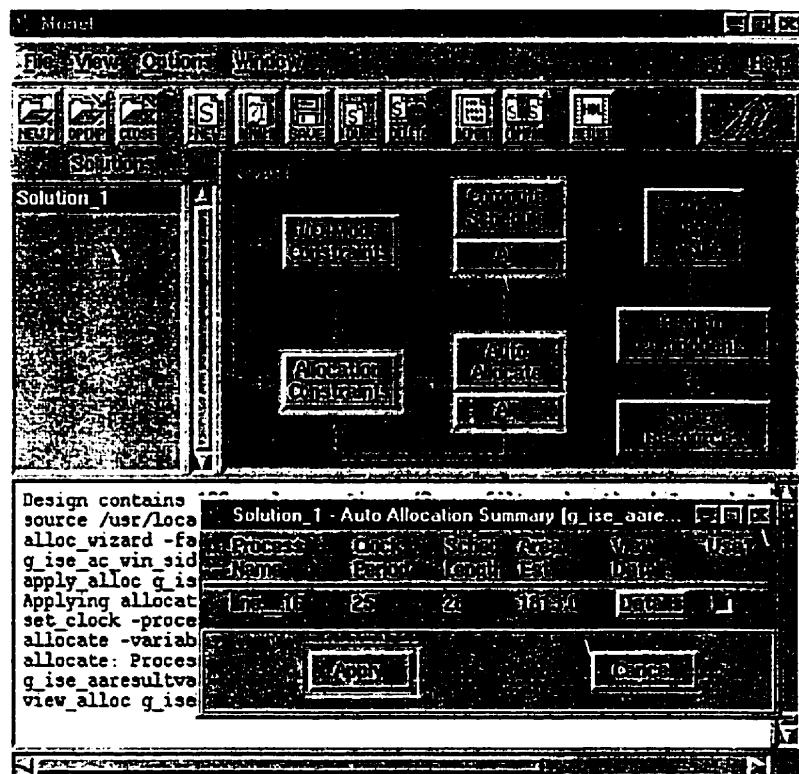

| Figure 4.17 Allocation avec Monet.....                                                                    | 112 |

| Figure 4.18 Diagramme de Kanttt pour visualiser l'ordonnancement .....                                    | 113 |

| Figure 4.19 Schéma du partitionnement de l'encodeur Reed-Solomon .....                                    | 116 |

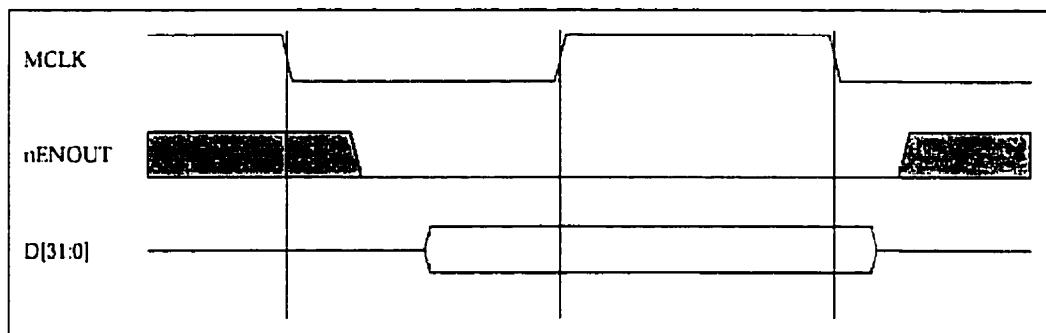

| Figure 4.20 Cycle pour écriture sur le bus bidirectionnel .....                                           | 120 |

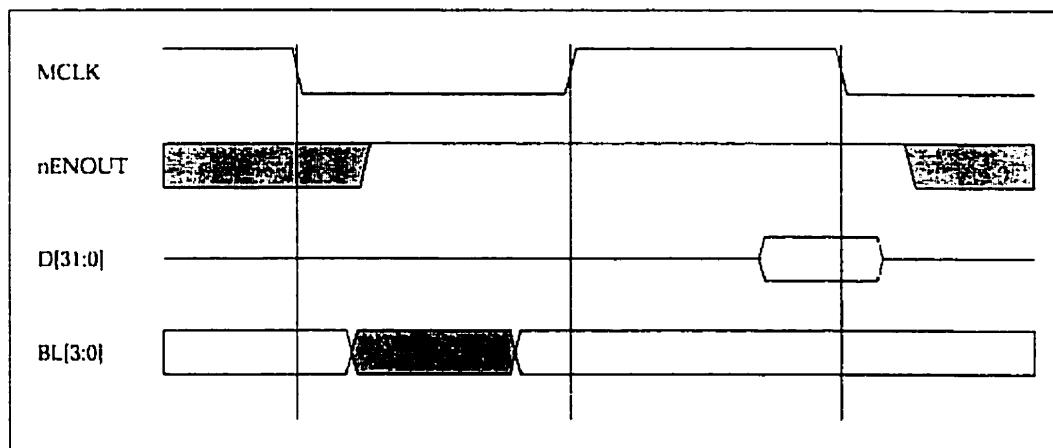

| Figure 4.21 Cycle pour lecture sur le bus bidirectionnel.....                                             | 121 |

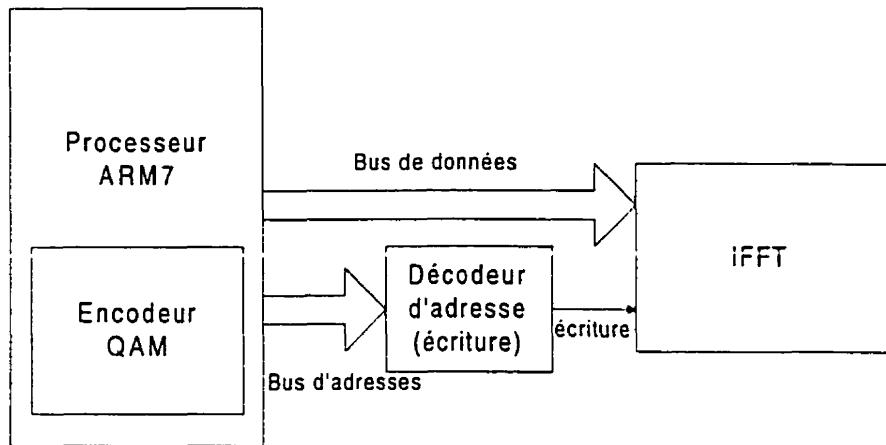

| Figure 4.22 Communication avec une architecture mémoire Harvard.....                                      | 127 |

| Figure 4.23 Communication avec broches pour co-processeur.....                                            | 127 |

| Figure 4.24 Communication directe sur le bus de données.....                                              | 128 |

| Figure 4.25 Communications utilisant les bus unidirectionnels.....                                        | 130 |

| Figure 4.26 Implantation du modem .....                                                                   | 131 |

| Figure 4.27 Communications entre deux blocs matériels .....                                               | 132 |

| Figure 4.28 Communications entre un bloc logiciel et un bloc matériel.....                                | 133 |

| Figure A.1 Le champs Galois de $2^4$ éléments ( $GF(2^4)$ ) $p(\alpha) = \alpha^4 + \alpha + 1 = 0$ ..... | 143 |

| Figure A.2 Les puissance de $\alpha^4$ de $GF(2^4)$ .....                                                 | 144 |

| Figure A.3 Les polynomes primitifs.....                                                                   | 145 |

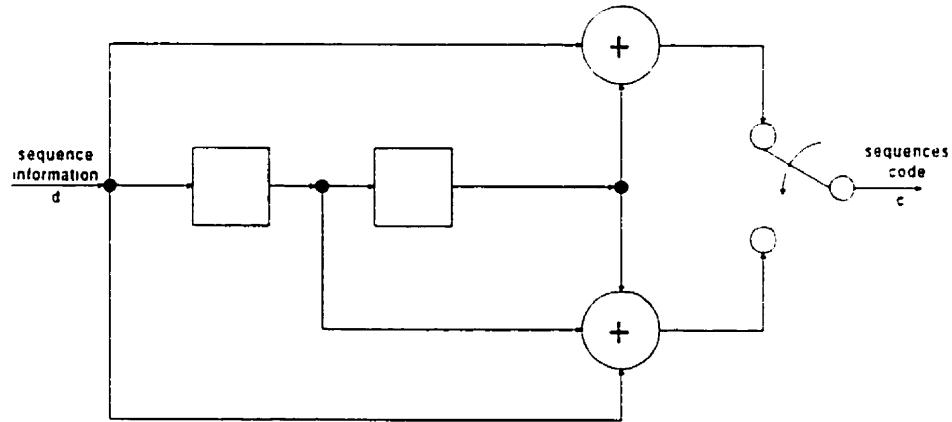

| Figure B.1 Encodeur pour un code convolutionnel (2,1) avec m=2 .....                                      | 160 |

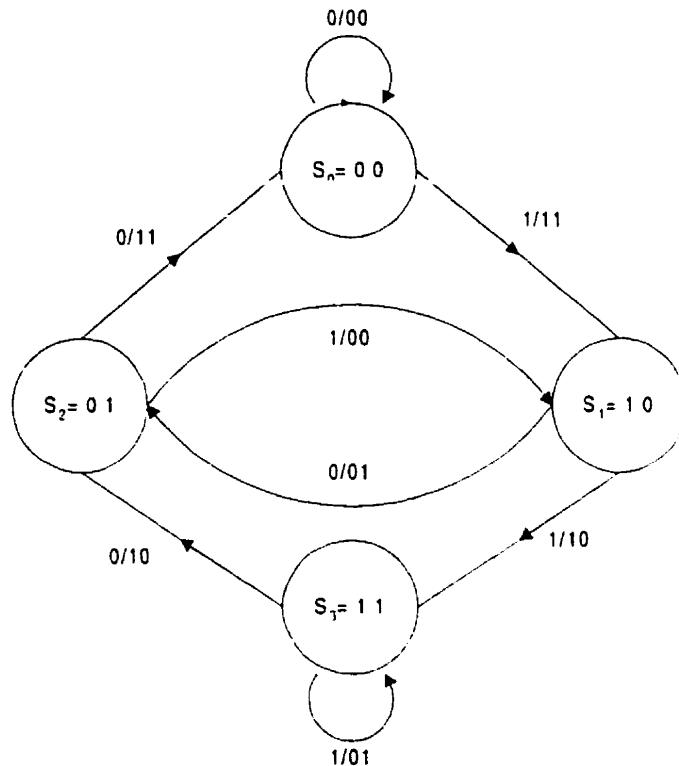

| Figure B.2 Encodeur du diagramme d'état pour la figure B.1 .....                                          | 163 |

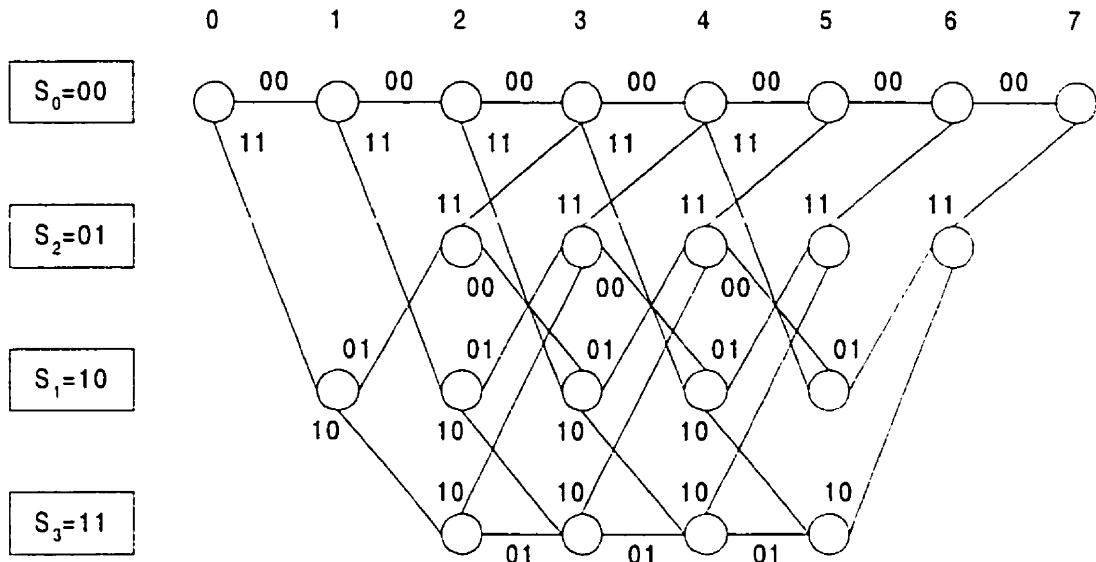

| Figure B.3 Diagramme treillis pour un code convolutionnel .....                                           | 164 |

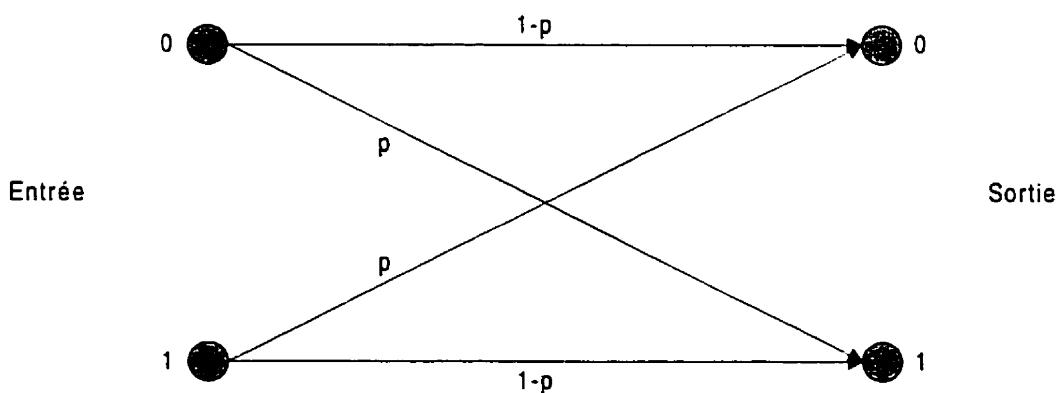

| Figure B.4 Représentation BSC .....                                                                       | 165 |

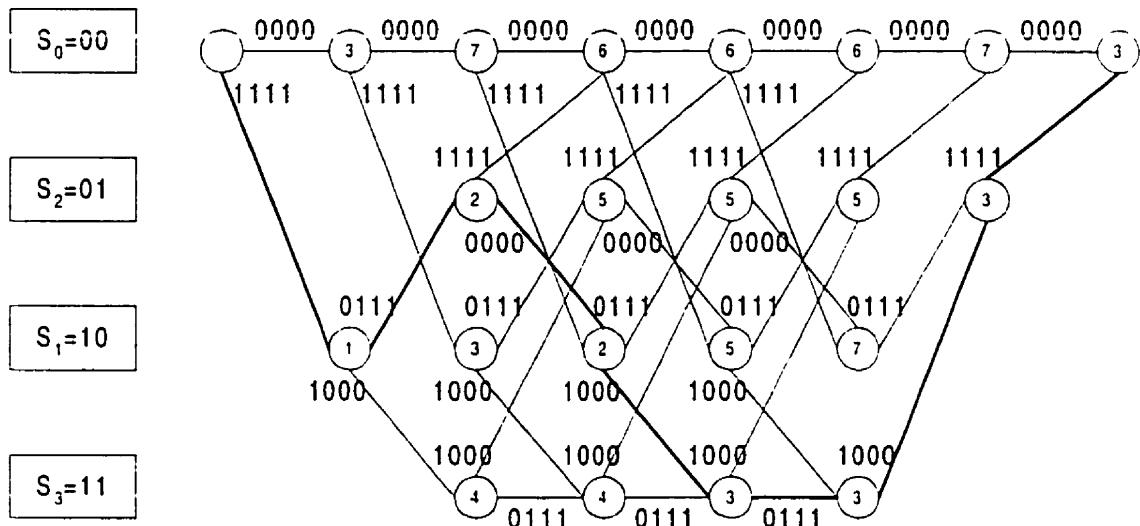

| Figure B.5 Décodage Viterbi pour BSC.....                                                                 | 166 |

## Liste des annexes

|                                                                              |     |

|------------------------------------------------------------------------------|-----|

| Annexe A: Champs Galois et encodeur et décodeur Reed-Solomon .....           | 142 |

| Annexe B: Un encodeur/decodeur Treillis utilisant l'algorithme Viterbi ..... | 157 |

| Annexe C: Table d'allocation des bits.....                                   | 167 |

| Annexe D: Résultats de dissipation pour le TMS320C54.....                    | 171 |

| Annexe E: Programmes de tests pour la dissipation de puissance du C54. ....  | 179 |

## Liste des abréviations

|             |                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>ADSL</b> | (Asymmetric Digital Subscriber Line) Ligne Numérique à Paire Asymétrique (LNPA)                                                                                                                                                                                                            |

| <b>ANSI</b> | (American Standard Institute) Organisme nord Americain de normalisation membre de l'ISO.                                                                                                                                                                                                   |

| <b>ASIC</b> | (Application-Specific Integrated Circuit) Circuit Intégré spécialisé. En général, ils sont produits en petites quantités, car c'est du sur-mesures.                                                                                                                                        |

| <b>CAD</b>  | (Computer Aided Design) Conception Assistée par Ordinateur, ou CAO en français.                                                                                                                                                                                                            |

| <b>CAP</b>  | (Carrierless Amplitude/Phase Modulation) Modulation Amplitude/Phase sans Porteuse. Technique de modulation développée par "Bell Labs". Première technologie de transmetteur ADSL à être déployée commerciallement, CAP est une variation de la modulation d'amplitude en quadrature (MAQ). |

| <b>FIFO</b> | (First In First Out) Premier entré, premier sorti. C'est-à-dire une queue, une file d'attente.                                                                                                                                                                                             |

| <b>HDSL</b> | (High bit/data rate Digital Subscriber Line/Loop) Technique de transmission. Elle permet l'utilisation des fils de cuivre à paires torsadées pour transmettre des signaux à des débits allant de 784 Kbps à 2 048 Kbps selon la technique de codage et le nombre de paires utilisées.      |

| <b>IEEE</b> | Institute of Electrical and Electronics Engineers                                                                                                                                                                                                                                          |

| <b>POTS</b> | (Plain Old Telephone Service) "Le Bon Vieux Téléphone" Service téléphonique de base sur paire torsadée. Le téléphone utilise la bande 300-3400 Hz, et tout service qui veut partager le médium                                                                                             |

avec le téléphone doit soit utiliser une bande de fréquence supérieure, soit la voix téléphonique doit être numérisée et être groupée(multiplexée) avec les autres signaux de données.

**QAM** (Quadrature Amplitude Modulation) voir Modulation d'Amplitude en Quadrature

**SDL** (Specification and Description Language) voir Langage de Spécification et de Description

## Avant-propos

Le codesign matériel/logiciel est de plus en plus utilisé dans l'industrie. Par contre, les concepteurs n'ont pas de méthodologie pour les guider lors de la conception de leurs systèmes. Ils utilisent plutôt leur instinct et leur expérience pour déterminer de bons partitionnements entre le matériel et le logiciel, sans vraiment vérifier et valider leurs choix. Les gens de Nortel nous ont donc demandé de développer une telle méthodologie. Après avoir fait la conception d'un modem Universal ADSL, nous devions valider et vérifier leurs choix lors du partitionnement matériel/logiciel. Nous avons également examiné d'autres modems de la même famille que le Universal ADSL, pour vérifier les possibilités de les planter en utilisant une méthodologie de codesign.

Notre projet était également subventionné par une autre compagnie, Mentor Graphics. Dans leur cas, ils étaient intéressés par une méthodologie de codesign qui utiliserait leurs outils de conception, de simulation et de synthèse. C'est la raison pour laquelle nous avons essayé le plus possible d'intégrer des outils conçus par Mentor Graphics à l'intérieur de notre méthodologie.

Nous avons donc associé les demandes de nos deux partenaires industriels pour en faire un seul projet qui est devenu comme son titre l'indique le développement d'une méthodologie de codesign matériel/logiciel pour des applications de communications à haute vitesse.

# Chapitre 1

## Introduction

### 1.1 *Définition du codesign*

Les systèmes sont de plus en plus gros et de plus en plus complexes. La complexité croissante des systèmes numériques ainsi que la disponibilité de différentes technologies pour leur implantation ont complètement révolutionné le processus de conception [AdTh96]. Plusieurs systèmes sont aujourd’hui faits d’un ensemble de matériel et de logiciel. Ce type d’implantation obtenu par un processus de partitionnement matériel/logiciel aussi appelé codesign, permet de tirer partie des avantages d’une implantation en logiciel tout autant que des avantages d’une implantation en matériel. En fait, le codesign matériel/logiciel essaie d’intégrer les techniques de conception du logiciel et du matériel dans le but de concevoir une méthode de conception unique pour la création d’un système.

La plupart des systèmes numériques qui sont utilisés pour des systèmes embarqués consistent en un processeur d’utilisation générale, d’une mémoire et de circuits spécifiques fait en matériel. Cela peut être des ASICs (Application-Specific Integrated Circuit) ou des FPGAs (Field Programmable Gate Array). Des exemples de tels systèmes se retrouvent dans des instruments médicaux, des véhicules, des réseaux automatisés et des systèmes de communications.

Il existe plusieurs avantages à combiner le développement matériel et logiciel dans une méthodologie commune [Axel97]. D’abord, des spécifications détaillées de haut niveau du comportement complet sont prises avant la sélection de l’architecture et du partitionnement. Donc, plus d’information est disponible au départ et les décisions

cruciales d'implantation peuvent alors être prises avec une plus grande précision. Les décisions importantes qui influencent la qualité du système se prennent généralement au début du processus de conception. La possibilité d'avoir déjà l'information en main diminue la probabilité de faire des erreurs coûteuses. De plus, une description uniforme des modules matériels et logiciels permet de déplacer des parties du système à n'importe quel stade de son développement. Des changements dynamiques sont alors possibles entre les différentes parties implantées en logiciel et celles implantées en matériel. Un autre avantage est que cela permet de faire une évaluation rapidement, à l'intérieur du processus de conception, des importantes caractéristiques du système. Cela évite de découvrir à un stade avancé de la conception de graves problèmes. Et finalement, une méthodologie de codesign est la meilleure façon de rapprocher le développement de logiciel et de matériel, réduisant ainsi les coûts finaux d'intégration entre les différents domaines technologiques.

Les avantages que nous venons de mentionner permettent de diminuer le temps et les coûts de l'implantation en plus d'en améliorer la qualité. Par exemple, Carolyn Kuttner [Kutt96] a estimé pour l'implantation d'une FFT dans un système embarqué, une réduction des coûts de 50% et de 35% pour le temps de conception de l'étude de cas, en utilisant une méthodologie de codesign matériel/logiciel.

Il est possible pour un concepteur de déterminer lui-même la façon d'implanter les différentes parties du système. C'est-à-dire, décider sur quels composants seront implantées les différentes parties du système. Mais, à cause de la complexité des systèmes d'aujourd'hui, il est de plus en plus difficile pour un concepteur de déterminer un partitionnement matériel/logiciel conduisant à des performances optimales.

Les concepteurs de systèmes embarqués ont donc présentement très peu d'aide lors des différentes tâches de conception d'un système. Plus précisément, il n'existe

aucune méthodologie largement répandue et adoptée comme norme ou d'outils disponibles commercialement pour aider les concepteurs à créer une spécification fonctionnelle et la transformer en une architecture au niveau système [GaVa95]. Cette lacune provient des multiples dimensions que peut prendre ce genre de conception. Chaque méthodologie développée peut avoir différentes hypothèses, comme par exemples des choix de composants (matériels ou logiciels) fixes pour certaines fonctionnalités, différents types de contraintes, différents critères lors du partitionnement, etc [AdTh96]. Par conséquent, une méthodologie est nécessaire pour arriver à vérifier différentes possibilités d'implantation d'une manière optimale et trouver un juste équilibre entre le matériel et le logiciel.

Différentes universités font de la recherche dans le développement d'outils pour l'automatisation de la conception de systèmes embarqués. Voici une brève énumération des outils développés auxquels certaines références seront faites ultérieurement: Chinook [Cob95][OrBo98], Comet [KnPa96], Cool [NiMa98], Cosmos [DMVJ97][DIMJ97], Cosyma [EHB93] [HHE94], Cosyn [HeSa97], Lycos [User99]. Specsyn [GaVa95], Polis et Ptolemy [poli99] et finalement Vulcan [GuDe93][GCM92][CLG96].

## **1.2 But du projet de recherche**

Le but de notre projet de recherche est de développer et de valider une méthodologie de codesign. En fait, nous allons nous concentrer davantage sur le partitionnement matériel/logiciel à l'intérieur de la méthodologie. Nous devons déterminer en étudiant une application particulière, son partitionnement optimal.

Pour y arriver différents éléments doivent être étudiés. Tout d'abord, nous devons déterminer quelles sont les contraintes du système étudié. Dans notre cas, qui est l'évaluation d'une application de communications à haute vitesse, les contraintes étudiées sont les **temps d'exécution**, les **temps de communications**, la **surface du matériel** et la **dissipation de puissance**. Ces contraintes doivent être évaluées à partir d'une description de haut niveau. Chacune de ces contraintes est évaluée, sauf pour la surface du matériel, du côté matériel ainsi que du côté logiciel. Ces différentes métriques doivent être ensuite fusionnées en une seule valeur qui estimera la qualité d'un modèle. Un algorithme de partitionnement est également utilisé pour déterminer les différents modèles à évaluer. Les différents éléments d'une méthodologie de codesign matériel/logiciel seront développés d'une façon plus détaillée dans le prochain chapitre.

Nous voulions également déterminer le potentiel des outils commerciaux pour l'estimation de gros circuits. Les outils de codesign développés par d'autres université antérieurement n'intégraient pas d'outils commerciaux pour faire des estimations. Nous voulons donc examiner jusqu'à quel point les outils existant peuvent être intégrés dans une méthodologie de codesign et être utilisés comme outils d'estimation. Nous avons principalement utilisé les outils de Mentor Graphics et de Synopsys dans notre méthodologie. De plus, pour les métriques ne pouvant être évaluées par des outils commerciaux, nous devons trouver et valider des techniques d'estimation.

Un autre critère que nous devons considérer est la possibilité d'utiliser cette méthodologie pour d'autres types d'application. Donc, même si des métriques sont éliminées ou ajoutées, nous devons pouvoir continuer à utiliser notre méthodologie.

Finalement, nous voulons évaluer les possibilités d'implanter les modems de la famille xDSL en utilisant une méthodologie de codesign. Nous voulons également déterminer s'il est avantageux pour ce type d'application d'utiliser une méthodologie de codesign matériel/logiciel.

### ***1.3 Application utilisée pour valider la méthodologie***

Pour valider notre méthodologie, nous avons décidé d'utiliser la partie numérique de trois modems de la famille xDSL, c'est-à-dire le ADSL (Asymmetric Digital Subscriber Line), le Universal ADSL qui est une version légère du ADSL et finalement le VDSL (Very High Bit-Rate Digital Suscriber Line) qui est une version plus performante du ADSL. Pour valider notre méthodologie, une modélisation des trois modems a été faite. Une description comportementale des différents blocs composant les modems a d'abord été faite en langage C. Cette modélisation nous permet alors, d'évaluer les aspects logiciels de nos modems. Puis, cette description comportementale a été reprise en VHDL, afin d'évaluer les aspects matériels de nos modems.

Les critères que nous évaluons pour les modems sont les temps d'exécution, les temps de communications, la surface du matériel et finalement la dissipation de puissance. Le chapitre 3 contient une explication plus détaillée des trois modems, de leurs contraintes et de leurs modélisations.

#### **1.4 Plan du mémoire**

Dans ce premier chapitre, une introduction au projet de recherche a été faite. Nous allons alors voir d'une manière plus détaillée les différents éléments présentés dans ce chapitre. Le chapitre 2 contient une description détaillée des éléments d'une méthodologie de codesign. Cela comprend les différentes métriques utilisées pour évaluer les modems, la fonction objectif regroupant ces métriques et l'algorithme de partitionnement utilisé pour déterminer les différents modèles à évaluer. Le chapitre 3 présente les trois modems que nous avons utilisés pour valider notre méthodologie. Le chapitre 4 explique les techniques utilisées pour estimer les aspects décrits dans le chapitre 2, ainsi que les résultats obtenus. Et finalement, le chapitre 5 contient les conclusions du projet.

## Chapitre 2

### Le codesign matériel/logiciel

Nous allons pour débuter présenter une méthodologie de codesign dans son ensemble. Puis nous irons plus en détails dans les parties qui nous intéressent. En particulier dans le développement de notre méthodologie pour le partitionnement matériel/logiciel.

#### ***2.1 Les différentes étapes du codesign***

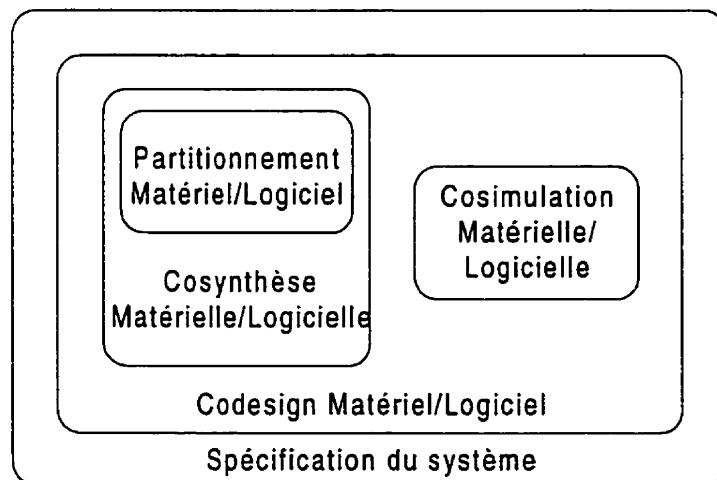

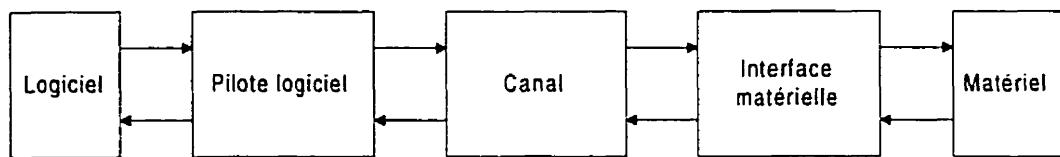

Chacune des activités de conception doit être faite en fonction du partitionnement logiciel et matériel. Que ce soit dans les spécifications du système, ou dans les simulations, tous les composants sont utilisés. Vous trouverez à la figure 2.1 les activités de conception logiciel/matériel [AdTh96].

**Figure 2.1 Activités de conception matérielle/logicielle**

Voici une brève description de ces différentes activités.

- Spécification du système: Une description du comportement ainsi que des contraintes (temps d'exécution, surface, dissipation de puissance, etc...) pour le système hétérogène au complet sont données. Cela peut être fait avec un programme dans un langage quelconque (C, C++, ADA, Java [YMS+98]), des ensembles d'instructions, des graphes de flots de données ou des langages spécifiques de description matérielle (VHDL, HardwareC, Lustre, Esterel, Verilog, Sillage) [GaRa94].

Les gens ont souvent tendance à choisir un langage de programmation couramment utilisé, car il a l'avantage d'être déjà connu [GuLi97]. Cela rend également possible la réutilisation de programmes déjà écrits. De plus, il est intéressant d'avoir une description qui peut être exécutable, car cela permet de vérifier si la fonctionnalité du système est bonne [DRG97].

Il y a plusieurs façons de représenter un système et cela à différents stades du processus de conception. Il peut y avoir des représentations comportementale, structurelle, physique et hybride [GVNG94]. Nous allons nous concentrer sur les descriptions comportementales, qui sont à un plus haut niveau d'abstraction. Une description comportementale d'un système ne contient pas d'informations structurelles tels le type de composants, leurs interconnexions, le nombre de pipelines et les phases de l'horloge [GaRa94]. C'est-à-dire que le comportement du système est décrit, mais il n'y a rien de mentionné au sujet de son implantation.

- Codesign logiciel/matériel: C'est dans cette étape que le système est partitionné et que ses différentes parties sont implantées soit en logiciel, soit en matériel. Puis le système est simulé pour en vérifier la fonctionnalité et le respect de ses

contraintes. Les différentes parties du codesign logiciel/matériel sont expliquées plus en détail dans les rubriques suivantes :

➤ *Partitionnement logiciel/matériel:* Dans cette partie de la conception, un algorithme est utilisé pour déterminer les parties du comportement qui seront implantées en logiciel et celles implantées en matériel. Un partitionnement particulier est appelé un modèle et consiste à une des représentations possibles du système. Un modèle est un prototype virtuel d'un système à évaluer. Il n'est pas implanté, mais contient toutes les informations pour le faire.

Afin d'utiliser un algorithme, les différentes parties du comportement doivent être décomposées en blocs. Plusieurs facteurs peuvent influencer la façon dont le partitionnement entre le logiciel et le matériel sera fait [Axel97] :

- Les performances globales du système.

- Le coût de l'implantation du système.

- La facilité à modifier les parties logicielles ou matérielles (avec par exemple des composants matériels interchangeables) du système.

- La nature des calculs, c'est-à-dire la façon dont le système traite les données.

- Le parallélisme entre les composants.

- Le temps de communications entre les composants.

➤ *Cosynthèse logicielle/matérielle:* En général, un outil de synthèse est utilisé pour ajouter des détails au niveau de l'implantation du système décrit avec

un plus haut niveau d'abstraction. Un compilateur peut être utilisé pour générer le langage machine du côté logiciel et un outil de synthèse de haut niveau pour obtenir les ASICs ou FPGAs du côté matériel à partir de la description comportementale.

- *Cosimulation logicielle/matérielle:* Une fois la synthèse du système faite, il est possible de vérifier le comportement de celui-ci en simulant la partie matérielle en même temps que la partie logicielle.

Nous allons maintenant examiner plus en détails une des activités de conception matérielle/logicielle, le partitionnement.

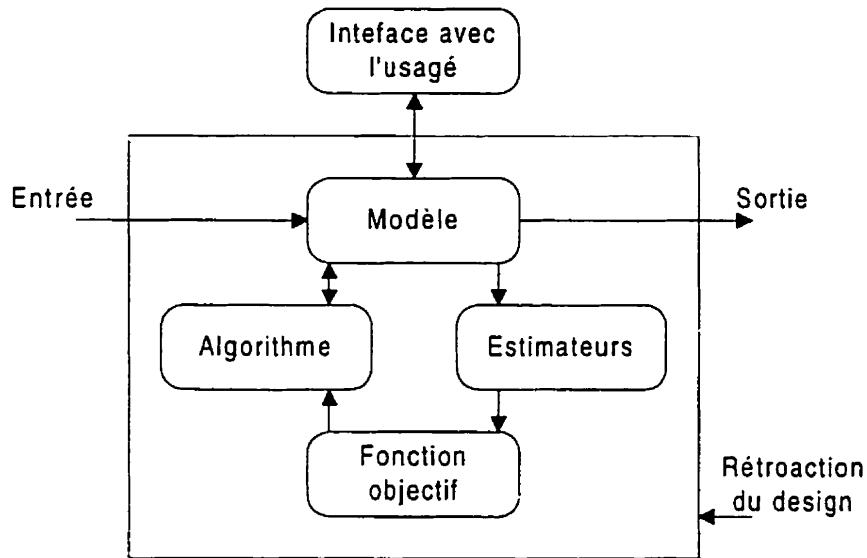

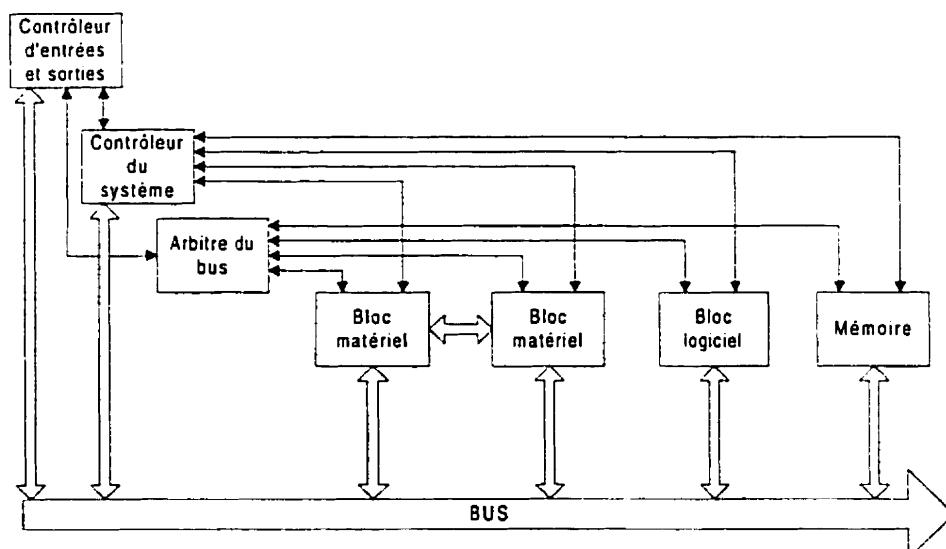

## 2.2 Les différents composants du partitionnement

Un bon partitionnement matériel/logiciel dépend de différents critères. Ces différents éléments interagissent les uns avec les autres influençant grandement les résultats qui seront obtenus. Par exemple, même si l'algorithme de partitionnement est bon, si les estimateurs ne sont pas précis, nous n'obtiendrons pas un système conçu de façon optimale. Vous pouvez voir les liens entre les différents éléments du partitionnement à la figure 2.2 [GaVa95]. La figure sera expliquée d'une manière plus détaillée dans les prochaines sous-sections.

### 2.2.1 Modèle d'estimation

Avant d'élaborer un modèle et de l'évaluer, il est important de déterminer la granularité de notre système. La granularité des objets est la dimension des parties qui

devront être implantées en logiciel ou en matériel. On peut appeler ces différentes parties des blocs.

**Figure 2.2 Configuration typique d'un système de partitionnement**

La taille de ceux-ci est déterminée selon l'application et les contraintes du système. La grosseur d'un bloc peut aller d'un bloc de base qui est en fait la plus petite unité possible, comme une instruction, jusqu'au système complet. Lorsque le partitionnement est à grains fins, c'est-à-dire qu'il y a un grand nombre de petits blocs, les résultats obtenus seront plus précis. Par contre, vu le nombre élevé de blocs à traiter et le grand nombre de combinaisons possibles entre le partitionnement logiciel et matériel, le temps de calcul sera beaucoup plus long. On doit donc trouver un juste milieu entre la taille des blocs et la durée du temps de calcul [HBKG98].

En général, nous allons appeler un partitionnement à grain fin, un partitionnement au niveau des blocs de base ou des instructions comme l'ont fait Ernst, Henkel et Brener dans Cosyma[EHB93] [HHE94], Gupta et De Micheli avec Vulcan [GuDe93], ainsi que Knudson et Madson avec Lycos [User99]. Tandis que Srivastana

et Brodersen [SrBr91] et Athanos et Silverman [AtSi93] ont utilisé une approche à gros grains, ce qui signifie un partitionnement au niveau des tâches ou des processus [HeEr97].

Un autre point à considérer est qu'il est plus avantageux pour le matériel d'avoir de petits blocs. Cela permet un plus grand parallélisme, car plusieurs blocs peuvent être exécutés en même temps. Par contre, du côté logiciel, plus il y a de blocs, plus il y a de changements de contextes. Il est donc avantageux pour une architecture ayant un seul processeur, d'avoir de plus gros blocs de façon à réduire le temps perdu lors des changements de contextes.

La principale question est de savoir comment unir les blocs de base de façon à former les blocs utilisés lors du partitionnement. Pour faire cela, il existe des estimateurs que l'on joint ensemble pour calculer une fonction de proximité. La fonction de proximité peut être formée de différents critères et est utilisée pour déterminer les blocs à unir de façon à atteindre un meilleur partitionnement. Par exemple, il sera plus profitable d'unir deux blocs qui ont une grande quantité de communications de l'un à l'autre [VaGa95a][VaGa95b][BGN97]. Après avoir déterminé les différents blocs, il est possible de passer au partitionnement et d'obtenir un modèle.

### 2.2.2 Algorithme de partitionnement

Dans la recherche du modèle qui satisfera les contraintes de façon optimale, plusieurs modèles devront être considérés. Il est donc important d'avoir un algorithme qui effectuera des itérations sur les modèles de façon à explorer différentes possibilités. Pour un système de  $n$  blocs pouvant être placés sur  $k$  éléments différents, il y a  $k^n$  possibilités de partitionnement. Si le nombre de blocs n'est pas très élevé, il est

possible d'utiliser un algorithme qui trouvera le meilleur partitionnement avec certitude. Par contre, s'il est élevé, un heuristique ne trouvant pas nécessairement le meilleur partitionnement, mais qui s'exécute dans un plus court laps de temps peut être utilisé. Un compromis doit donc être fait entre le temps d'exécution de l'algorithme et la qualité du partitionnement trouvé. Les différents modèles obtenus avec l'algorithme de partitionnement seront ensuite évalués à l'aide d'estimateurs.

### 2.2.3 Estimateurs

Certains critères de performance doivent être considérés pour un système embarqué. Souvent ces critères sont en conflits les uns avec les autres. Par exemple la performance est proportionnelle au coût, toutes choses étant égales par ailleurs. Il est très difficile de diminuer le coût et d'améliorer la performance d'un système en même temps.

Il est important de connaître les valeurs de ces différents critères de performance afin d'obtenir le meilleur système possible. Malheureusement, le temps nécessaire à l'implantation du système en entier pour tous les modèles utilisés est beaucoup trop élevé. Nous devons donc évaluer ces critères de performance à l'aide d'estimateurs [Axel97][GaVa95]. Voici les estimateurs les plus fréquemment utilisés. Ceux qui seront utilisés pour évaluer notre application seront traités avec plus de détails dans les sections 2.3, 2.4 et 2.5.

- Performance: Le but d'un grand nombre de systèmes embarqués est de trouver une implantation dont la performance est suffisante pour rencontrer les contraintes de temps. Cet aspect est très important pour les systèmes en temps réel ou les systèmes réactifs. Les données viennent de l'extérieur à un certain rythme et le système doit être capable de les analyser rapidement.

- Coût: L'utilisation d'ASICs ou de microprocesseurs programmables est dispendieuse. Il est important de garder les coûts les plus bas possible.

- Maintenance: Certaines parties du comportement auront peut-être besoin d'être modifiées lorsque le système sera en opération. Ces parties devront donc être implantées en logiciel de façon à pouvoir être facilement modifiable ou en matériel mais en utilisant un standard permettant facilement la réutilisation des blocs comme VSIA (Virtual Socket Interface Alliance) [CHB+99].

- Distribution: Certaines parties du système peuvent être implantées dans des endroits différents. Par exemple les parties nécessitant des données provenant de capteurs peuvent être placées près de ceux-ci. Donc, les blocs devront être divisés de manière à faire partie du composant dont la location correspond à la provenance des données dont ils ont besoin.

- Consommation de puissance: Certains systèmes embarqués peuvent être portables, utiliser une source d'énergie limitée ou être situés dans un espace limité, sans la possibilité d'y placer des ventilateurs. Dans de tels cas, il est important de diminuer la consommation de puissance.

- Poids: Encore une fois, cet aspect peut être très important pour des systèmes portables. Que ce soit pour un téléphone mobile ou une application aérospatiale, le poids peut être un élément important.

- Tolérance aux fautes: Si un certain système embarqué ne tolère aucune faute, il est important d'ajouter une façon de détecter les défaillances du système. Par exemple, la fonctionnalité pourrait être dupliquée.

#### 2.2.4 Fonction objectif

La fonction objectif utilise les valeurs obtenues des différents estimateurs pour créer une fonction unique qui quantifie la qualité du modèle. La plupart des algorithmes de partitionnement ont besoin d'un nombre unique pour comparer les différents modèles et ainsi garder celui qui rencontre de façon optimale les contraintes du système. Les façons de composer une fonction objectif seront décrites dans la section 2.7.

### 2.3 *Description des estimateurs utilisés*

Après avoir survolé rapidement les différents éléments du codesign, nous allons traiter d'une manière plus détaillée les parties que nous allons utiliser dans ce projet. Nous verrons donc les points décrits dans la section 2.2 d'une manière beaucoup plus précise et élaborée. Nous allons d'abord commencer par les estimateurs utilisés, puis la fonction objectif et finalement les algorithmes de partitionnement.

### 2.4 *Estimateurs pour la partie logicielle*

Nous allons maintenant voir la façon d'estimer ces différents critères du côté logiciel, puis du côté matériel.

#### 2.4.1 Temps d'exécution

La première chose à vérifier dans un système est sa fonctionnalité. Une fois le comportement vérifié, on doit s'assurer que ce comportement est exécuté dans les bons délais [DRG97].

Pour calculer le temps d'exécution des parties du système implantées en logiciel, nous devons tenir compte du temps d'exécution de chacun des blocs de base et de l'ordonnancement de ces blocs. Pour une implantation logicielle la description du comportement doit être compilée dans un ensemble d'instructions du processeur cible selon un des deux modèles qui seront présentés dans la sous-section 2.4.1.1. On suppose que les variables du comportement sont logées dans la mémoire du processeur. Donc, toutes les variables du comportement sont implantées avec les opérations écriture/lecture en mémoire [GVNG94].

#### 2.4.1.1 Modèles d'estimation

Il y a d'abord un modèle d'estimation avec un processeur spécifique. Le temps d'exécution peut être estimé de façon précise en compilant chacun des blocs dans un ensemble d'instructions pour un processeur particulier, en utilisant un compilateur spécifique à ce processeur. Une estimation à partir de ce modèle est très précise. Par contre, elle prend beaucoup de temps de calcul. De plus, l'estimation complète devra être faite pour chacun des processeurs faisant partie de la bibliothèque des composants avec des compilateurs différents.

Au lieu d'utiliser différents compilateurs et estimateurs, un modèle alternatif générique a été suggéré par Gajsky et al. [GVNG94]. Knieser et Papachristou l'utilisent également dans leur outil de conception pour le codesign Comet [KnPa96]. Le comportement est d'abord compilé dans un ensemble d'instructions génériques. Pour chaque processeur, un fichier technologique est disponible, contenant les informations au sujet du nombre de périodes d'horloge et le nombre d'octets de chacune des instructions génériques requises. Les estimations sont donc faites à partir des instructions génériques et des fichiers technologiques pour le processeur cible.

### 2.4.1.2 Profilage des blocs du logiciel

Il existe deux façons de déterminer le temps d'exécution d'un programme. Il y a d'abord une façon dynamique[GVNG94]. Une simulation dynamique exécute plusieurs fois les blocs du programme avec différentes données et enregistre le nombre de périodes d'horloge requises pour chacune des exécutions. Tout dépendant des données, le nombre de périodes d'horloge peut différer selon les branchements conditionnels et les boucles dépendantes des données. L'estimation dynamique demande un long temps de calcul, car l'exécution du programme doit être faite plusieurs fois. Il existe des outils qui peuvent être utilisés pour accomplir cette tâche comme QPT [Qpt99] et MIPS Pixie [Pixi99]. Ces deux programmes réécrivent le programme source en y ajoutant des instructions pour calculer la fréquence d'exécution de chaque bloc de base ou séquence de blocs de base. Un bloc de base contient des instructions étant exécutées le même nombre de fois et est en général borné par le début et la fin d'une boucle ou d'un branchement conditionnel.

Une autre façon de déterminer le temps d'exécution des blocs d'un programme est d'utiliser une méthode statique. Cette méthode ne tient pas compte des données utilisées et peut atteindre de très bons résultats si le nombre d'itérations des boucles est connu et que la probabilité des branchements conditionnels peut être prédite de façon précise. Pour le profilage statique, il existe un outil appelé Cinderella [Cind99], qui peut être utilisé pour profiler des programmes s'exécutant sur un processeur i960 d'Intel et les processeurs de la famille M68000 de Motorola. Cinderella lit le code exécutable des programmes et construit en séparant le programmes en blocs de base un graphe de flots de contrôle (CFG) et en déduit les contraintes structurelles. L'utilisateur doit fournir les bornes supérieures et inférieures de toutes les boucles. En utilisant les bornes supérieures des boucles, il est possible de déterminer le chemin le plus long dans

l'exécution du programme. On peut ensuite trouver le temps d'exécution maximal en ordonnançant les différents blocs de base.

#### 2.4.1.3 Ordonnancement

Le problème d'ordonnancement consiste à décider l'ordre et le temps d'exécution d'un ensemble de blocs de base ayant certaines caractéristiques connues par le concepteur (la durée déterminée avec le modèle, puis le nombre d'exécutions déterminé lors du profilage) [BLMS98] [OBE99]. L'ordonnancement est en général fait par le système d'exploitation utilisé par le processeur.

Vérifier si un ordonnancement permet de rencontrer les contraintes de temps est difficile à déterminer, même si le temps d'exécution des blocs est connu. Il existe différentes techniques d'ordonnancement pour le logiciel. Ces techniques sont en général statiques ou dynamiques. L'ordonnancement est dit statique lorsque les différentes tâches s'exécutent dans un ordre fixe et prédéterminé. Un ordonnancement statique ne demande pratiquement aucun temps CPU lors de l'exécution, ce qui implique un faible temps de service. Un ordonnancement statique est optimal lorsque les temps où les différentes tâches sont prêtes à être exécutées est bien connu à l'avance.

Dans certains cas, un ordonnancement statique n'arrive pas à rencontrer les contraintes de temps, alors un ordonnancement dynamique est nécessaire. Une exécution dynamique est basée sur la priorité. Les tâches prêtes à être exécutées sont choisies dynamiquement selon leur ordre de priorité. La priorité est la mesure de l'urgence avec laquelle une tâche doit être exécutée. De plus, une tâche peut être préemptive, c'est-à-dire qu'elle peut être suspendue lorsqu'une tâche qui a une priorité plus élevée est prête à être exécutée. Le principal désavantage est le temps de service

nécessaire à l'ordonnancement. Celui-ci est très élevé, car à chaque changement de contexte, des calculs élaborés doivent être faits, augmentant de façon significative le temps d'exécution [Axel97].

#### 2.4.2 Dissipation de puissance

L'estimation de la puissance pour un système matériel et logiciel est de plus en plus importante [HeLi98]. Lorsque l'espace est limité ou qu'il n'y a pas de possibilité d'y placer un ventilateur, cet aspect de la conception doit être pris en ligne de compte (un téléphone cellulaire avec un ventilateur ne serait pas un très bon produit...).

La dissipation de puissance peut différer de beaucoup, tout dépendant du système implanté. La tension d'alimentation d'une carte n'est pas très représentative en tant que métrique, car les activités à l'intérieur du processeur sont en général associées à ses périphériques. De plus en plus, le processeur n'est qu'une petite partie du système.

Le processeur est fait d'un circuit CMOS. Le changement de voltage sur une capacitance nécessite un transfert de charge, et par conséquent cause une consommation de puissance. Une fois la capacitance chargée, la porte logique peut maintenir un voltage DC sans mouvement de charge additionnel et ne consomme pas de courant. Pour cette raison, la circuitrie CMOS consomme de la puissance seulement en changeant d'état.

Il est important de souligner que la consommation d'énergie d'un microprocesseur dépend de ses stimulus déterminés par le logiciel et les entrées qu'il reçoit. Donc, faire une analyse de la dissipation de puissance sans tenir compte du logiciel impliqué peut mener à des estimations très loin de la réalité. Jusqu'à maintenant, lorsqu'un client veut choisir un microprocesseur pour un système

embarqué, il a seulement la possibilité de connaître une valeur moyenne, ou une échelle allant de la plus petite valeur à la plus grande, mais sans connaître le type d'application sur lequel ces valeurs ont été calculées [STA98].

Il existe trois principales façons de calculer la dissipation de puissance et nous allons les traiter dans ce document. Ces méthodes sont: le profilage, l'estimation à partir d'un modèle matériel et l'estimation à partir des instructions.

#### 2.4.2.1 Profilage

Il est possible d'utiliser une approche montante (bottom-up) pour déterminer la dissipation de puissance d'un processeur. On peut le faire sous forme de profilage. Il s'agit d'exécuter un programme plusieurs fois et à chaque fois en calculer la dissipation de puissance. Pour obtenir la dissipation de puissance, plusieurs techniques peuvent être utilisées. Il est possible de recouvrir le processeur et de mesurer la chaleur qui s'en dégage. Mais, une façon plus simple de procéder est de mesurer le courant utilisé ( $I_{LOG}$ ) à l'entrée du processeur lors de l'exécution du programme, pour ensuite en utilisant le voltage ( $V_{DD}$ ) fourni au processeur en déduire la puissance utilisée ( $P_{LOG}$ ), en utilisant la formule  $P_{LOG} = I_{LOG} * V_{DD}$ .

#### 2.4.2.2 En utilisant un modèle matériel

Il est possible également d'utiliser un modèle matériel du processeur pour estimer la dissipation de puissance de la partie logicielle. Pour un programme relativement simple, une façon de calculer la consommation de puissance est d'exécuter le programme sur un modèle comportemental ou RTL (Register Transfer Level) du

système et de mesurer la consommation de puissance en utilisant des techniques pour l'estimation de puissance au niveau du matériel.

Par contre, une application complexe consomme des millions de cycles machine, ce qui le rend très difficile à estimer en utilisant des techniques d'estimation pour le matériel au niveau comportemental ou RTL. Mais Hsieh et al. [MaPe98][HsPe98] ont quand même réussi à présenter une méthode basée sur cette technique, appelée *approche par synthèse de programme* pour calculer la dissipation de puissance d'un processeur. Ils utilisent un modèle transformé de celui-ci et appliquent une méthode d'évaluation de dissipation de puissance pour le matériel au niveau RTL. Les auteurs synthétisent un programme d'une telle façon que la trace résultante en terme de performance et de dissipation de puissance soit équivalente à la trace du programme originale. La nouvelle trace d'instructions est par contre beaucoup plus courte que la trace du programme originale et peut donc être simulée plus facilement par une description matérielle du processeur et donner des résultats rapidement au sujet de la dissipation de puissance.

Pour utiliser ce type d'estimation, le processeur doit être bien connu au niveau comportemental ou RTL. Souvent cette information n'est pas disponible et une autre technique doit être examinée.

#### 2.4.2.3 Modèles de puissance au niveau des instructions

Une alternative populaire à la simulation d'un modèle matériel du processeur est d'utiliser des modèles de puissance au niveau des instructions. Ces modèles sont reliés à la consommation de puissance d'un processeur pour chaque instruction ou séquence d'instructions qu'il peut exécuter. Des raffinements supplémentaires sont faits à cette

évaluation en utilisant des statistiques tels que le pourcentage de fautes de la mémoire cache, le taux de blocage des pipelines, etc.

L'environnement de conception assistée par ordinateur pour le co-design appelé TOSCA [FGS+98] utilise cette méthode pour calculer la métrique de puissance au niveau logiciel servant à guider le partitionnement du système. Nous allons nous attarder plus longuement à cette technique, car elle nous apparaît la plus intéressante. Un compilateur ou un simulateur d'ensemble d'instructions pour un processeur cible pourraient être améliorés en utilisant un tel modèle[LRD+99].

Pour certains processeurs, il est possible de calculer la dissipation de puissance en multipliant le nombre de cycles du programme par une valeur moyenne de dissipation de puissance par cycle. Russell et al. [RuJa99] ont étudié un processeur RISC embarqué de 32 bits, le i960 de Intel. Ce modèle de processeur n'est pas très complexe et il a été démontré par les auteurs qu'ils pouvaient prédire la consommation d'énergie à l'intérieur de 8% dans 99% des cas s'ils comparaient leurs estimations à des mesures physiques. Leurs conclusions démontrent que les variations de consommation de puissance à travers les instructions assembleurs n'ont aucune signification statistique pour le processeur i960. En fait, il n'y a aucun besoin de considérer les instructions assembleurs individuelles pour prédire la consommation d'énergie réelle correctement. La puissance fluctue pendant un cycle d'horloge, mais sa moyenne est stable. Les registres sources et destinations, ainsi que le code conditionnel n'ont aucun influence significative. Cette façon est rapide et facile, mais elle ne s'applique malheureusement pas à la plupart des processeurs.

Dans [TMW94] et [TTMF97] en se basant sur les mesures réelles de quelques processeurs, Tiwari et Al. présentent le modèle suivant de dissipation de puissance au niveau des instructions:

$$Energie_p = \sum_i (BC_i N_i) + \sum_{ij} (SC_{ij} N_{ij}) + \sum_k OC_k, \quad (2.1)$$

où  $Energie_p$  est la dissipation d'énergie totale du programme qui est divisé en trois parties. La première partie est l'addition du coût de l'énergie de base de chaque instruction (( $BC_i$  est le coût de l'énergie de base et  $N_i$  est le nombre de fois où l'instruction est exécutée). La deuxième partie de l'équation donne l'état du circuit ( $SC_{ij}$  est le coût d'énergie quand l'instruction  $i$  est suivie par  $j$  pendant l'exécution du programme et  $N_{ij}$  est le nombre de fois où ces instructions se suivent). La troisième partie de l'équation représente la contribution en énergie des autres effets d'instruction ( $OC_k$ ), tels les fautes de la mémoire cache et le blocage des pipelines pendant l'exécution du programme

Pour mesurer le coût de base d'une instruction, la même instruction ou un bloc d'instructions est exécuté plusieurs fois dans une boucle infinie. La puissance moyenne est ensuite mesurée pour plusieurs itérations de la boucle du programme. Basée sur ces essais, une estimation de la consommation de puissance moyenne est trouvée pour chacune des instructions. Puis, une table de puissance peut être pour chaque processeur, en rapportant la consommation d'énergie pour chaque instruction comprise dans l'ensemble d'instructions et pour tous les modes d'adresses associés à chaque type d'instruction. Il existe des moyens de minimiser la taille de ces tables en les plaçant dans des classes. Par exemple, si on prend les coûts de base des instructions, les instructions ayant des consommations de puissance similaires peuvent être placées dans la même classe. En utilisant cette méthode, Chunho et al. [CMP99] ont divisé les instructions d'un processeur DSP Fujitsu en six différentes classes.

En général, la puissance moyenne dissipée par un processeur en exécutant un programme est  $P_{LOG} = I_{MOY} * V_{DD}$ , où  $I_{MOY}$  est le courant moyen et  $V_{DD}$  est la tension

d'alimentation fournie au processeur. L'énergie est donnée par  $E_{LOG} = P_{LOG} * t_{LOG}$  où  $t_{LOG}$  est le temps d'exécution du programme sur le processeur qui est exprimé par:  $t_{LOG} = N_{HOR} * \tau_{HOR}$ , où  $N_{HOR}$  est le nombre de cycles de l'horloge pour exécuter le programme et  $\tau_{HOR}$  la période de l'horloge. Pour calculer le courant moyen utilisé pendant l'exécution de chaque instruction, il est nécessaire de prendre des mesures du coût en énergie pour chacune des instructions.

Pour certains processeurs, il est important de tenir compte des effets des instructions précédentes. Les contributions supplémentaires au calcul de la dissipation de puissance globale proviennent des effets inter-instructions, ce qui n'a pas été considéré dans le calcul du coût de base de chaque instruction. L'activité de permutation dans un circuit est en fonction de l'entrée présente et de l'état précédent du processeur. Donc, le coût en énergie d'une instruction peut être un peu différent de son coût de base. Cela est dû au fait que lors du calcul des coûts de base, l'état précédent du processeur pouvait ne pas être le même. Pour certains processeurs, il est possible de considérer cet effet inter-instructions comme étant constant sans affecter la qualité de l'estimation. Mais, dans d'autres cas, c'est un élément qui doit être considéré et qui peut parfois être difficile à faire. Pour réussir à bien comprendre les effets inter-instructions, l'architecture interne du processeur, ainsi que la façon dont les instructions sont microprogrammées, doivent être connus.

Les données utilisées pour chacune des instructions peuvent également influencer la dissipation de puissance d'une instruction. Selon [TTMF97][TTMF95], les données n'ont pas tellement d'influence si l'on utilise un processeur général. Par contre, lorsqu'un processeur DSP est utilisé, les données peuvent influencer la dissipation de puissance d'une manière assez significative pour devoir en tenir compte. L'équation doit donc être modifiée pour refléter cette réalité.

Pour d'autres processeurs, il est important de tenir compte des effets des contraintes de ressources et des fautes de cache sur le budget de puissance. Par contre, ces effets peuvent être négligés dans les programmes exécutés par certains processeurs simples comme le M68000, Intel 805, Z80, etc... où des caractéristiques aussi avancées peuvent ne pas exister et dans des processeurs plus sophistiqués où le taux de succès des caches peut atteindre 98% et procurer une exploitation maximale des différents niveaux du pipeline.

Il est important de mentionner que même si le processeur possède un pipeline, cette méthodologie tient toujours. La preuve a été faite par Tiwari et al. dans [TMW94] pour un processeur 486DX2CPU. Prenons  $E_{jIk}$  qui est l'énergie moyenne consommée par l'étape  $j$  du pipeline, lorsque l'instruction  $Ik$  s'exécute dans cet étape. Les étapes du pipeline sont séparées les uns des autres par des bascules. Donc, les consommations d'énergie des différentes étapes sont indépendantes les unes des autres. Prenons par exemple à un cycle donné, l'instruction  $II$  est exécutée par l'étape  $I_1$ ,  $I_2$  par l'étape 2 et ainsi de suite. L'énergie totale consommée par le processeur dans ce cycle sera :

$$E_{cycle} = E_{I_1 II} + E_{I_2 II} + E_{I_3 II} + E_{I_4 II} + E_{I_5 II}. \quad (2.2)$$

D'un autre côté, l'énergie totale consommée par l'instruction  $II$  lorsqu'elle se déplace à travers les étapes du pipeline est  $E_{ins} = \sum_j E_{jII}$ . Donc, en plaçant l'instruction  $II$  qui est à évaluer, dans une boucle d'instructions, cela donne comme résultat

$$E_{cycle} = E_{ins}, \quad (2.3)$$

puisque dans ce cas  $I_1 = I_2 = I_3 = I_4 = I_5$ .  $E_{cycle}$  représente l'énergie d'un cycle, c'est-à-dire des différentes étapes du pipeline et  $E_{ins}$  l'énergie d'une instruction. Dans ce cas, le courant moyen est :

$$\sum_j E_{jII} / (V_{CC} * temps), \quad (2.4)$$

ce qui a été vérifié expérimentalement par les auteurs.

Une fois l'analyse de puissance complétée pour toutes les instructions, elle est étendue à tous les modules du logiciel, en calculant la consommation de puissance selon leur fréquence d'appel[FGS+98].

#### 2.4.2.4 Autres techniques

Finalement, d'autres méthodes ont été brièvement mentionnées dans [MaPe98]. La première méthode estime la dissipation de puissance en utilisant la capacitance moyenne lorsque les modules du processeur, sont utilisés. C'est-à-dire que chaque fois qu'un module est utilisé, on ajoute sa dissipation de puissance à la puissance totale dissipée. Les activités de changement sur les bus (adresse, instruction, données) peuvent également être utilisées pour calculer la consommation de puissance d'un processeur.

### 2.5 Estimateurs pour la partie matérielle

Nous allons maintenant voir les différentes métriques utilisées pour évaluer le matériel.

#### 2.5.1 Surface du circuit intégré et temps d'exécution

Un autre point majeur dans le développement d'un système est son coût. Le principal composant de ce coût est la partie implantée en matériel. Le processeur commercial utilisé coûtera le même prix quel que soit le nombre de blocs implantés sur

celui-ci en logiciel. Par contre le nombre de blocs implantés en matériel a un lien étroit avec la quantité de matériel nécessaire à sa réalisation. Il est donc important d'être capable d'évaluer la quantité de matériel nécessaire afin d'être en mesure d'estimer le coût d'un système.

Pour déterminer le temps d'exécution, ainsi que la surface du circuit intégré utilisé, nous allons prendre une technique de synthèse. Une synthèse rapide est utilisée, en omettant des tâches qui consomment beaucoup de temps, comme par exemple les optimisations de la logique [VaGa95c].

Une synthèse de haut niveau utilise une séquence de tâches qui transforme une représentation comportementale en un modèle de bas niveau en utilisant des unités fonctionnelles comme des unités arithmétiques et logiques, ainsi que des unités d'entreposage des données et d'interconnexion [GaRa94]. Cela devient en fait la représentation interne du système.

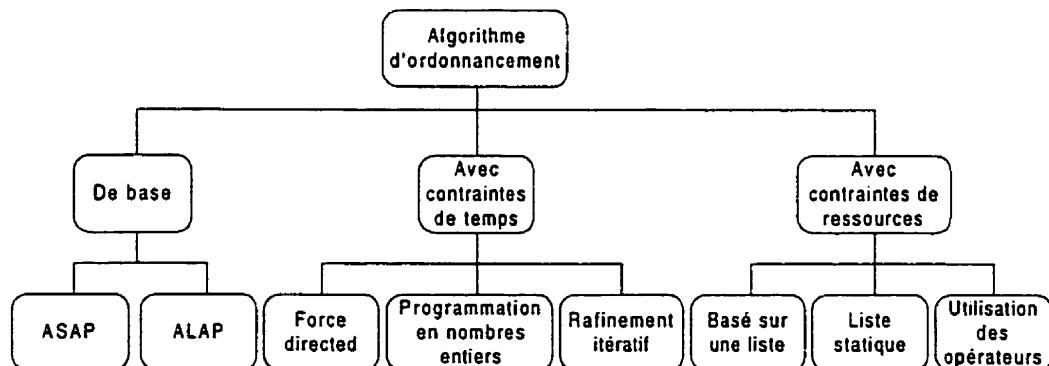

Une synthèse est effectuée en trois étapes. Il y a d'abord l'allocation, puis l'ordonnancement et finalement le partage des ressources (binding) [GaRa94]. Pour estimer la surface et le temps d'exécution, nous allons suivre les trois étapes de la synthèse qui seront décrites plus en détails dans les prochaines sections. Mais, nous allons tout d'abord présenter les façons de représenter le comportement d'un bloc pour son évaluation matérielle.

### 2.5.1.1 Représentation du comportement

En général, la meilleure façon de décrire le comportement d'un système est à l'aide d'un graphe de flots de données, car il permet de représenter les opérations arithmétiques et les dépendances de lecture et d'écriture qui définissent l'ordre

d'exécution. Donc, avant d'en faire la synthèse, une description matérielle, faite par exemple en VHDL, doit être transformée en graphe de flots de données ou en quelque chose d'équivalent.

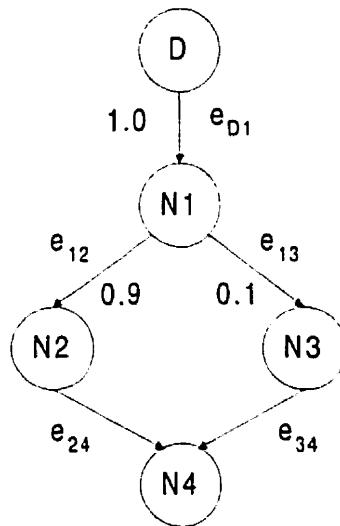

Un graphe de flots de données possède des nœuds  $v$  et des liens  $e$  entre les différents blocs. Le comportement est divisé en nœuds et les dépendances entre les nœuds sont représentées par des liens. Par exemple, le lien  $e_{ij}$  relie le nœud  $i$  au nœud  $j$ , comme nous pouvons le voir à la figure 2.3.

**Figure 2.3 Graphe de flots de données**

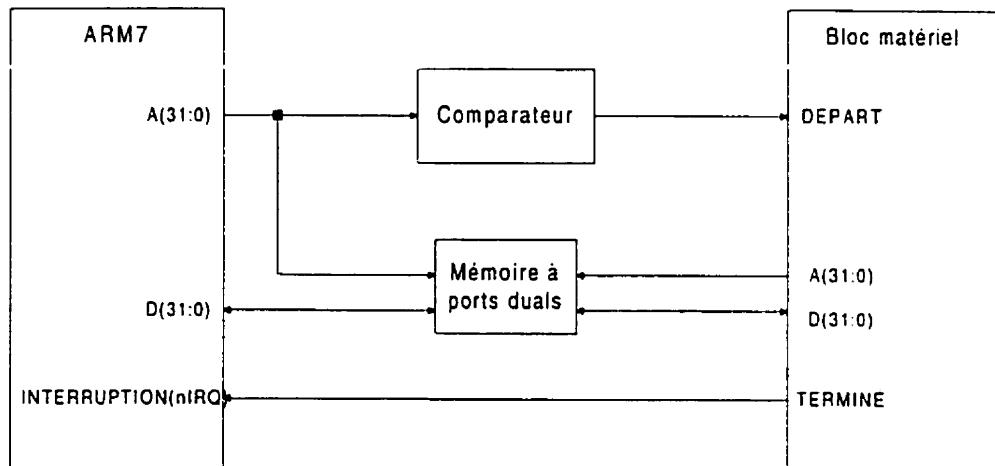

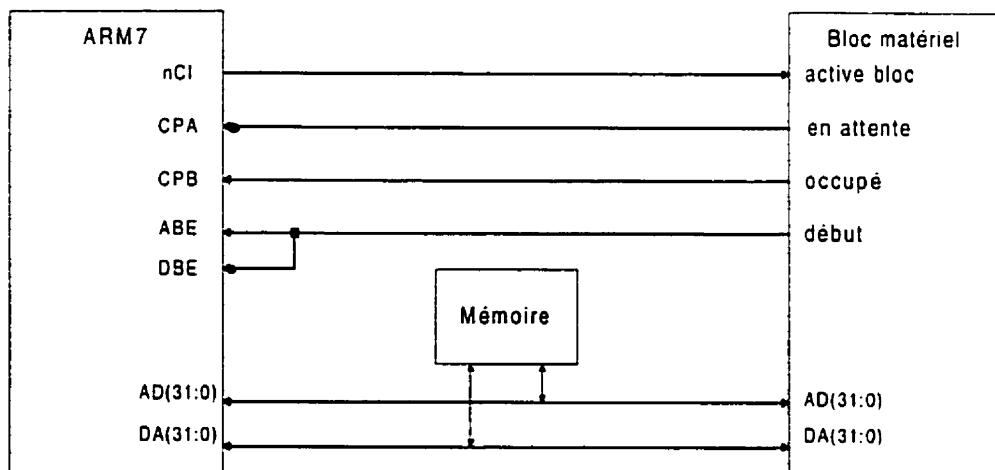

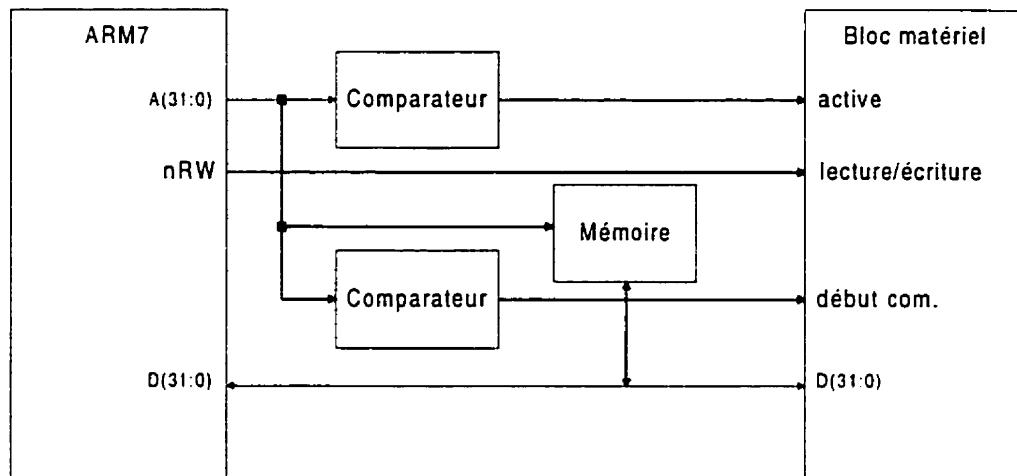

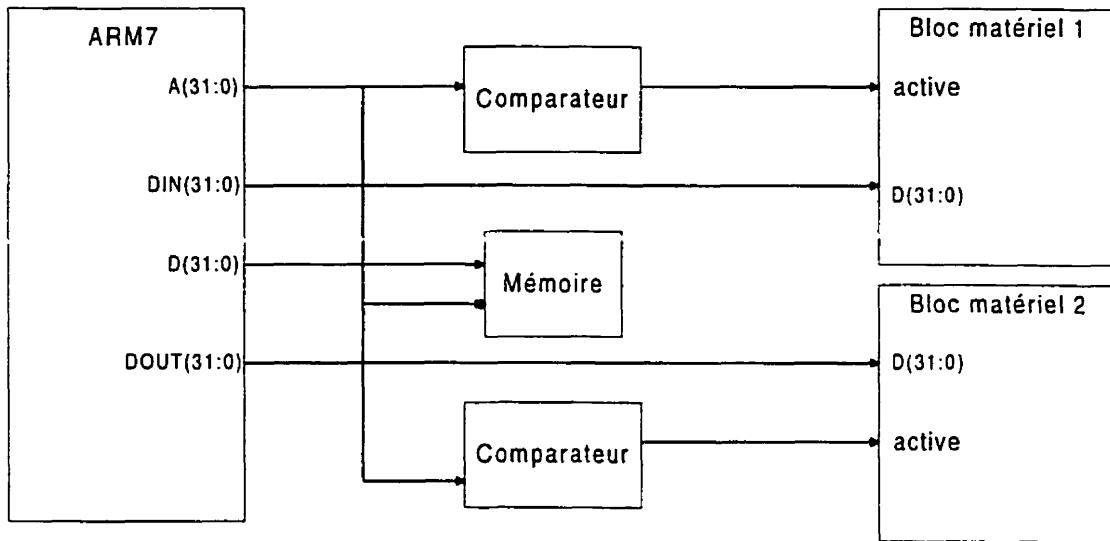

Il existe cinq différents types de nœuds de base : les nœuds de données, les nœuds conditionnels, les nœuds hiérarchiques, les nœuds d'emplacement et les nœuds de contrôle de boucle. Les nœuds de données représentent les opérations arithmétique et logique. Les nœuds conditionnels correspondent aux *if* et aux *case*. Les nœuds hiérarchiques contiennent les autres nœuds et liens qui correspondent aux boucles, aux fonctions et aux procédures. Les nœuds d'emplacement représentent parfois les sauts avant dans un graphe d'état ou simplement une connexion sur le graphe. Finalement les nœuds de contrôle de boucle dénotent les limites de la boucle [Knap96]. Lorsque nous