**Titre:** Validation de circuits numériques utilisant le principe du test par mutation

Title: mutation

**Auteur:** Patrice Vado

Author:

**Date:** 1999

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Vado, P. (1999). Validation de circuits numériques utilisant le principe du test par mutation [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/8635/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8635/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria

Advisors:

**Programme:** Non spécifié

Program:

**UNIVERSITÉ DE MONTREAL**

**VALIDATION DE CIRCUITS NUMÉRIQUES UTILISANT LE PRINCIPE DU TEST

PAR MUTATION**

**PATRICE VADO**

**DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

20 AOÛT 1999**

© PATRICE,VADO 1999.

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-48874-8

Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

VALIDATION DE CIRCUITS NUMÉRIQUES UTILISANT LE PRINCIPE DE TEST

PAR MUTATION

présenté par: VADO PATRICE

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. BOIS Guy, Ph. D., président

M SAVARIA Yvon, Ph. D., membre et directeur de recherche

M. SAWAN Mohamad, Ph. D., membre

## **REMERCIEMENTS**

Bien qu'il soit d'habitude établi de remercier en premier le directeur d'études, j'aimerais remercier mon père, celle qui est à mes cotés et mes frères pour leurs constants encouragements.

Je tiens à remercier Monsieur Savaria qui a guidé mes recherches et qui par ses nombreux conseils éclairés m'a permis d'achever mon travail. Il a été d'un grand soutien aussi bien professionnel que personnel. Je le remercie d'avoir trouvé le temps de suivre le déroulement de mes travaux et de les avoir orientés dans le bon sens.

Je tiens à remercier Monsieur Yannick Zocarrato ainsi que l'équipe VALSYS de Grenoble. Leur appui et leur compréhension tout au long de la collaboration m'a permis d'explorer de nouvelles voies.

Je remercie Monsieur Boukari Zahir avec qui j'ai travaillé sur le simulateur Pulse et qui m'a permis de découvrir un autre aspect de la validation.

Je remercie Monsieur Paul Marriot, Ivan Kraljic, Nicolas Contandriopoulos et toute l'équipe Pulse pour leur soutien constant durant mon séjour dans l'équipe.

Enfin, merci à toute l'équipe du GRM pour leur soutien...

## RESUME

Les systèmes numériques augmentent continuellement en taille et en complexité. La performance des circuits intégrés double tous les deux ans. En raison d'une trop grande complexité certaines fonctionnalités ne sont pas vérifiées, réduisant alors la confiance dans les circuits. La complexité actuelle des circuits révèle les limitations des méthodes traditionnelles de vérification par simulation. Afin de répondre à ces limitations, les méthodes formelles de vérification tentent d'utiliser la rigueur mathématique afin de prouver l'exactitude d'un circuit. Cependant, la rigueur du formalisme ainsi que le peu d'outils performants réduisent une utilisation industrielle fréquente.

Ce mémoire propose une méthodologie de validation et d'enrichissement de vecteurs de validation de circuits numériques basée sur le test par mutation consistant à insérer des fautes spécifiques dans un langage de description matériel tel que VHDL. Le programme contenant la faute spécifique est alors appelé mutant. La validation de la méthode proposée a été réalisée sur différents bancs d'essais décrits en langage VHDL et simulés à l'aide de Synopsys. Un algorithme d'enrichissement des vecteurs de validation ainsi qu'un générateur de mutants ont été écrits en langage C. L'utilisation de cette méthode a montré qu'il était nécessaire de disposer d'un espace disque important, puisque le nombre de mutants générés est grand. Un certain nombre de concepts, tel que la contrôlabilité et l'observabilité, provenant du domaine du test matériel ont été empruntés afin d'expliquer la réduction de la couverture des mutants. Par ailleurs, une métrique appelée score de mutation a été utilisée afin de quantifier la qualité d'un jeu de vecteurs de validation.

## ABSTRACT

Digital systems continuously grow in scale and functionality. In addition, the performance of integrated circuits (IC) doubles every two year. Due to the growing complexity, functionalities are not fully verified which reduce the confidence in designs. That growing complexity unravels the limitations of traditional verification methods based on functionnal simulation. To address these limitations, formal methods and tools for specifying and verifying such systems have been proposed. However, the complexity of formal notations and the practical limitations of available tools reduce their use in industry.

This master proposes a methodology based on mutation testing for validating and enriching a set of functional validation vectors for digital circuits. This methodology injects specific faults in a hardware description language description such as VHDL. A program which contains a fault is called a mutant. The validation of the proposed methodology was realized on VHDL benchmarks that were simulated with Synopsys. A mutant generator and a test suite enriching algorithm were written in the C programming language. Existing mutation testing tools were shown to require a lot of memory to analyze small functional descriptions. A metric called mutation score was used to quantify the quality of a vector set. Justification and observability concepts were applied to mutation testing to explain the reduction of the mutation score.

## TABLE DES MATIÈRES

|                                                  |             |

|--------------------------------------------------|-------------|

| <b>REMERCIEMENTS .....</b>                       | <b>IV</b>   |

| <b>RÉSUMÉ .....</b>                              | <b>V</b>    |

| <b>ABSTRACT .....</b>                            | <b>VI</b>   |

| <b>TABLE DES MATIÈRES .....</b>                  | <b>VII</b>  |

| <b>LISTE DES TABLEAUX.....</b>                   | <b>XII</b>  |

| <b>LISTE DES FIGURES .....</b>                   | <b>XIII</b> |

| <b>INTRODUCTION.....</b>                         | <b>1</b>    |

| <b>CHAPITRE 1 : METHODES DE VALIDATION .....</b> | <b>8</b>    |

| 1.1    Méthode Formelle.....                     | 8           |

| 1.1.1    Introduction .....                      | 8           |

| 1.1.2    Vérification du modèle .....            | 10          |

| 1.1.3    Démonstration de théorème.....          | 14          |

| 1.1.4    Conclusion.....                         | 15          |

| 1.2    Test par mutation .....                   | 15          |

| 1.2.1    Test logiciel .....                     | 16          |

| 1.2.2    Principe du test par mutation.....      | 17          |

| 1.2.2.1    Méthodologie. ....                    | 18          |

| 1.2.2.2    Génération des Mutants. ....          | 19          |

| 1.2.2.3    Les mutants équivalents .....         | 21          |

| 1.2.2.4    Évaluation du test.....               | 22          |

| 1.2.2.5    Le test par la mutation faible.....   | 23          |

|                                                                                             |           |

|---------------------------------------------------------------------------------------------|-----------|

| 1.2.2.6 mutation sélective .....                                                            | 26        |

| 1.2.2.7 La mutation N-sélective .....                                                       | 27        |

| 1.2.2.8 La mutation E-sélective .....                                                       | 29        |

| 1.2.2.9 Génération de test.....                                                             | 31        |

| <b>CHAPITRE 2 : APPLICATION DU TEST<br/>PAR MUTATION AUX CIRCUITS VLSI .....</b>            | <b>33</b> |

| 2.1    Introduction.....                                                                    | 33        |

| 2.2    Présentation de Mothra.....                                                          | 34        |

| 2.2.1    Génération de vecteurs de validation. ....                                         | 35        |

| 2.2.1.1    La représentation des contraintes. ....                                          | 38        |

| 2.2.1.2    L'analyseur de chemin. ....                                                      | 39        |

| 2.2.1.3    Le résolveur de contraintes .....                                                | 40        |

| 2.3    Opérateurs de mutation.....                                                          | 42        |

| 2.4    Chaine de validation .....                                                           | 43        |

| 2.5    Validation de la méthode .....                                                       | 45        |

| 2.5.1    Description des bancs d'essai.....                                                 | 45        |

| 2.5.2    Processus de validation .....                                                      | 46        |

| 2.6    Résultats.....                                                                       | 47        |

| 2.6.1    Le circuit sortie.....                                                             | 47        |

| 2.6.2    Le circuit d'entrée de l'edh .....                                                 | 50        |

| 2.6.3    Le circuit cla.....                                                                | 52        |

| 2.6.4    Complexité algorithmique.....                                                      | 53        |

| 2.6.5    Conclusion.....                                                                    | 56        |

| 2.6.5.1 étude de la puissance des mutants.....                                              | 57        |

| <b>CHAPITRE 3 : MÉTHODE SYSTÉMATIQUE D'ENRICHISSEMENT DE<br/>VECTEURS FONCTIONNELS.....</b> | <b>61</b> |

| 3.1    Introduction.....                                                                    | 61        |

| 3.1.1    Limitations de Mothra pour la validation.....                                      | 61        |

|                                                     |            |

|-----------------------------------------------------|------------|

| 3.1.2 Redéfinition de la méthode de validation..... | 62         |

| 3.2 Description du banc d'essai .....               | 63         |

| 3.2.1 Processeur ancillaire.....                    | 63         |

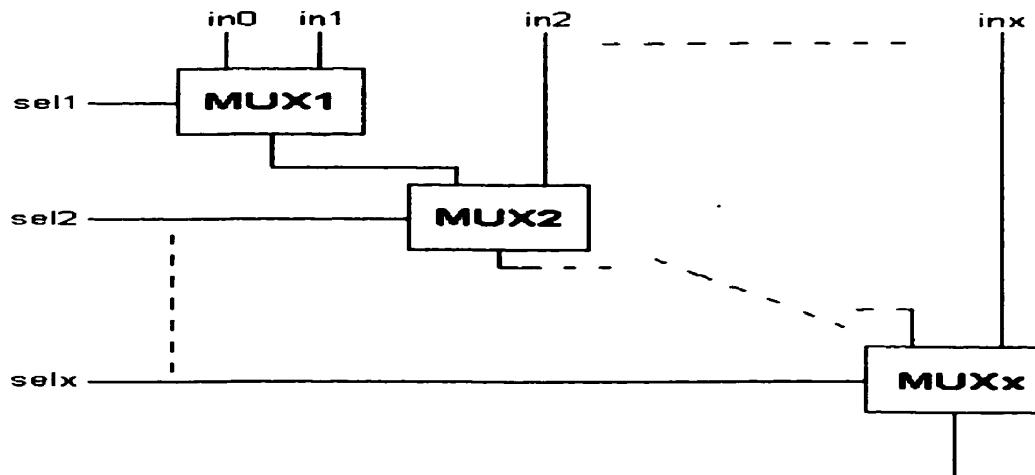

| 3.2.1.1 Module EDH .....                            | 65         |

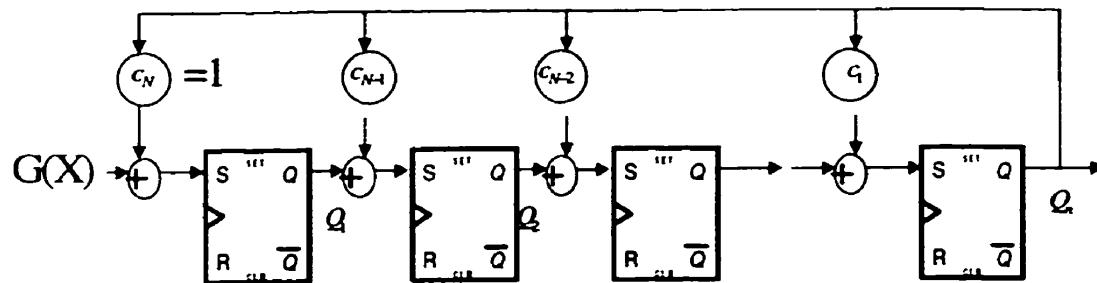

| 3.2.1.2 Implémentation du CRCCs .....               | 66         |

| 3.2.1.3 Implémentation du module EDH .....          | 66         |

| 3.3 Opérateurs de mutation.....                     | 68         |

| 3.3.0.1 Programmes de mutation .....                | 70         |

| 3.4 Implémentation des programmes de mutation.....  | 78         |

| 3.4.1 Algorithmes de mutation .....                 | 82         |

| 3.5 Implémentation C .....                          | 89         |

| 3.6 Algorithme final de mutation.....               | 93         |

| 3.7 Résultats.....                                  | 95         |

| <b>CONCLUSION .....</b>                             | <b>100</b> |

| <b>BIBLIOGRAPHIE.....</b>                           | <b>104</b> |

| <b>ANNEXE A .....</b>                               | <b>107</b> |

| <b>ANNEXE B : FONCTION MID .....</b>                | <b>111</b> |

| <b>ANNEXE C .....</b>                               | <b>112</b> |

## **LISTE DES TABLEAUX**

|                                                                          |    |

|--------------------------------------------------------------------------|----|

| Tableau 1.1 :Mutation E selective.....                                   | 31 |

| Tableau 2.1 :Opérateurs de mutation.....                                 | 42 |

| Tableau 2.2 :Circuit de sortie.....                                      | 50 |

| Tableau 2.3 :Résultats de sortie pour le circuit d'entrée de l'EDH.....  | 52 |

| Tableau 2.4 :Résultats de sortie pour le circuit cla.....                | 53 |

| Tableau 2.5 :Résultats obtenus pour la fonction MID.....                 | 54 |

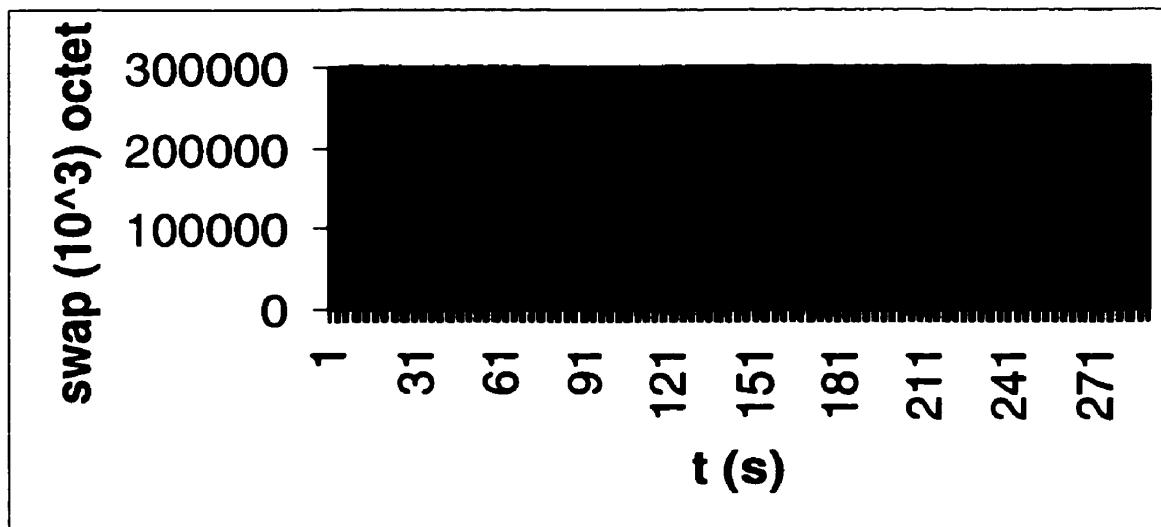

| Tableau 2.6 :Cascade de Multiplexeurs.....                               | 56 |

| Tableau 2.7 : Puissance des opérateurs.....                              | 58 |

| Tableau 3.1 :Opérateurs de mutation.....                                 | 70 |

| Tableau 3.2 :Codage des états pour la mutation AOR.....                  | 81 |

| Tableau 3.3 :Comparaison des algorithmes de validation par mutation..... | 96 |

## LISTE DES FIGURES

|                     |                                                                           |           |

|---------------------|---------------------------------------------------------------------------|-----------|

| <b>Figure 0.1:</b>  | <b>Méthodologie de conception .....</b>                                   | <b>1</b>  |

| <b>Figure 0.2:</b>  | <b>Processus de validation par simulation .....</b>                       | <b>2</b>  |

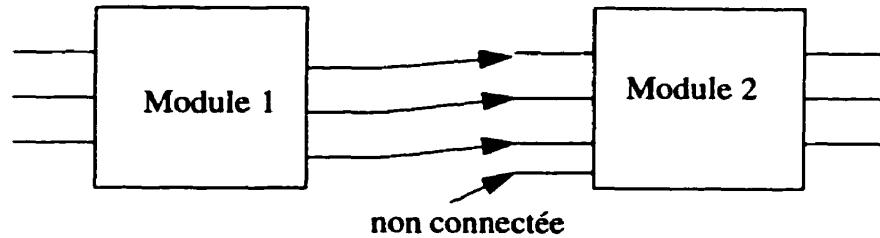

| <b>Figure 0.3:</b>  | <b>Architecture simplifiée de Pulse. ....</b>                             | <b>3</b>  |

| <b>Figure 0.4:</b>  | <b>Validation Fonctionnelle. ....</b>                                     | <b>4</b>  |

| <b>Figure 1.1:</b>  | <b>Construction d'un CTL à partir d'un automate.....</b>                  | <b>12</b> |

| <b>Figure 1.2:</b>  | <b>La fonction Max avec quatre mutants superposés .....</b>               | <b>21</b> |

| <b>Figure 2.1:</b>  | <b>Implémentation de Godzilla.....</b>                                    | <b>37</b> |

| <b>Figure 2.2:</b>  | <b>Méthode de validation de circuits numériques utilisant Mothra.....</b> | <b>44</b> |

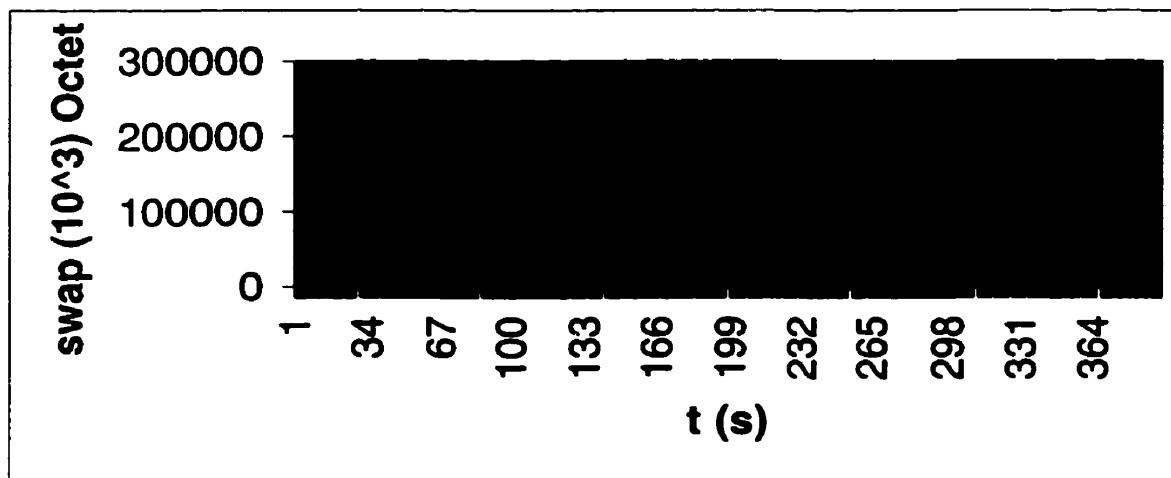

| <b>Figure 2.3:</b>  | <b>Consommation mémoire pour le circuit de sortie.....</b>                | <b>48</b> |

| <b>Figure 2.4:</b>  | <b>Consommation mémoire pour le circuit d'entrée .....</b>                | <b>51</b> |

| <b>Figure 2.5:</b>  | <b>Cascade de multiplexeurs .....</b>                                     | <b>55</b> |

| <b>Figure 3.1:</b>  | <b>Architecture de l'EDH .....</b>                                        | <b>68</b> |

| <b>Figure 3.2:</b>  | <b>Design de type structurel .....</b>                                    | <b>72</b> |

| <b>Figure 3.3:</b>  | <b>Simulation du fichier original à l'aide de Synopsys. ....</b>          | <b>73</b> |

| <b>Figure 3.4:</b>  | <b>Résultat de SUR.....</b>                                               | <b>73</b> |

| <b>Figure 3.5:</b>  | <b>Simulation obtenue sans VSAR.....</b>                                  | <b>74</b> |

| <b>Figure 3.6:</b>  | <b>Mutation avec VSAR.....</b>                                            | <b>75</b> |

| <b>Figure 3.7:</b>  | <b>Mutation avec SSR .....</b>                                            | <b>77</b> |

| <b>Figure 3.8:</b>  | <b>Diagramme d'état pour la mutation AOR.....</b>                         | <b>80</b> |

| <b>Figure 3.9:</b>  | <b>Pseudo code pour la mutation CLR .....</b>                             | <b>84</b> |

| <b>Figure 3.10:</b> | <b>Pseudo code pour la mutation CNR.....</b>                              | <b>85</b> |

| <b>Figure 3.11:</b> | <b>Pseudo code pour la mutation CSR .....</b>                             | <b>86</b> |

| <b>Figure 3.12:</b> | <b>Pseudo code pour la mutation SUR .....</b>                             | <b>87</b> |

| <b>Figure 3.13:</b> | <b>Pseudo code pour la mutation SSR .....</b>                             | <b>87</b> |

| <b>Figure 3.14:</b> | <b>Pseudo code pour la mutation LCR .....</b>                             | <b>88</b> |

| <b>Figure 3.15:</b> | <b>Pseudo code pour la mutation VSAR .....</b>                            | <b>89</b> |

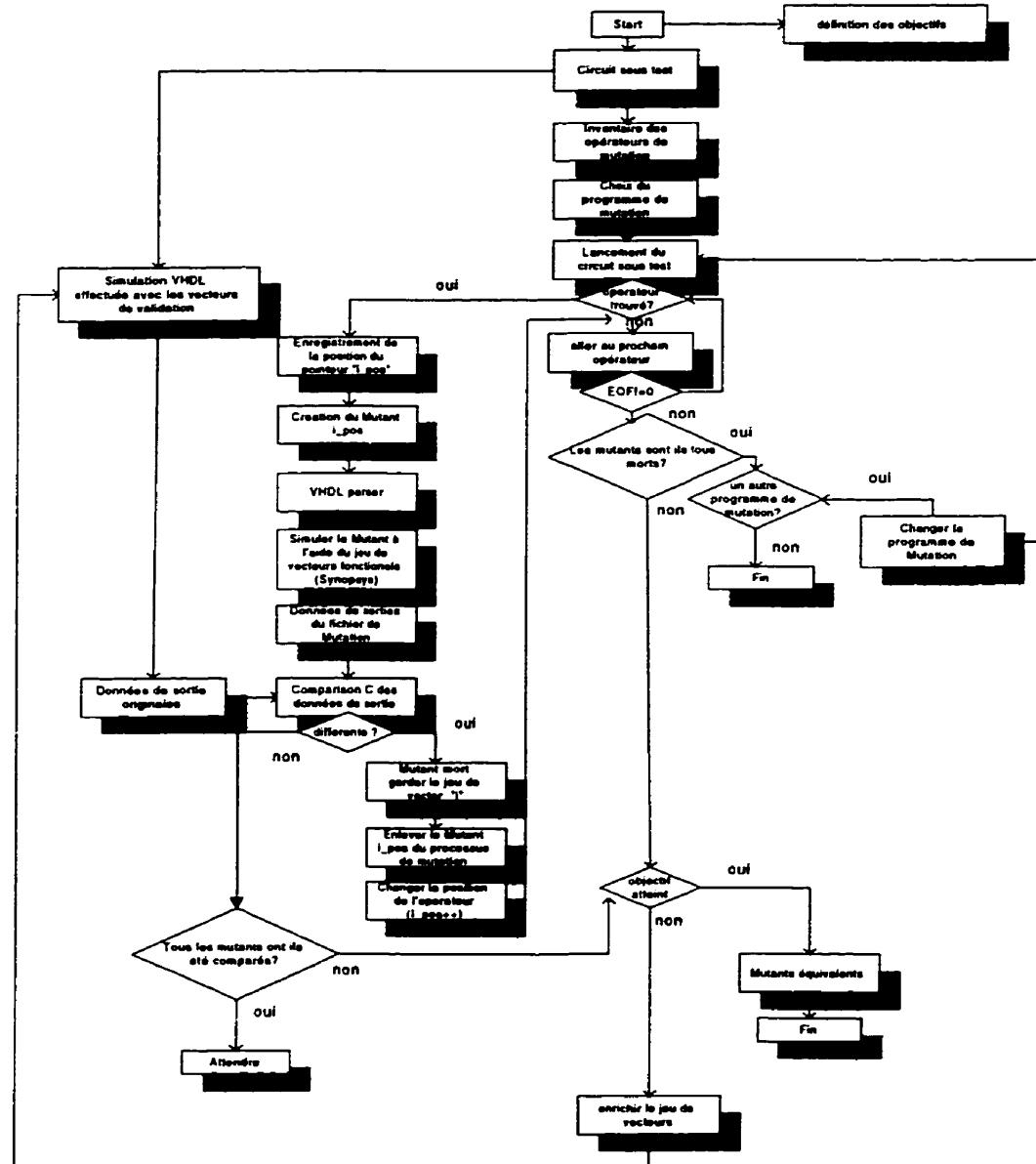

Figure 3.16: Test par mutation et génération de mutants ..... 93

## INTRODUCTION

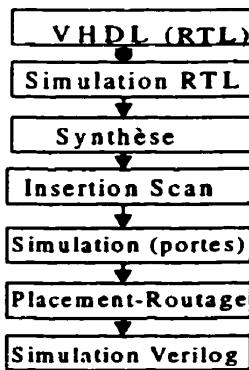

La vérification par la simulation est la méthode la plus largement répandue afin de vérifier qu'un design respecte bien les spécifications voulues. Elle fait partie intégrante de la méthodologie de conception VLSI selon la figure 0.1. La validation devient de nos jours un des goulots d'étranglement du processus de conception qui ralentit la mise en marché de puces électroniques dans un monde extrêmement compétitif et en perpétuel changement. D'autre part, certains composants défectueux ne sont découverts que chez le client, ce qui augmente considérablement les coûts de développement et entache la crédibilité des fournisseurs à qui cela arrive. En tout état de cause, tous s'accordent à dire que le processus de validation est primordial.

**Figure 0.1: Méthodologie de conception.**

Cependant, en raison de la complexité sans cesse croissante des circuits numériques, le processus de validation devient de plus en plus long et coûteux. Dans le processus traditionnel de test par simulation, le concepteur crée un jeu de test complet représentant

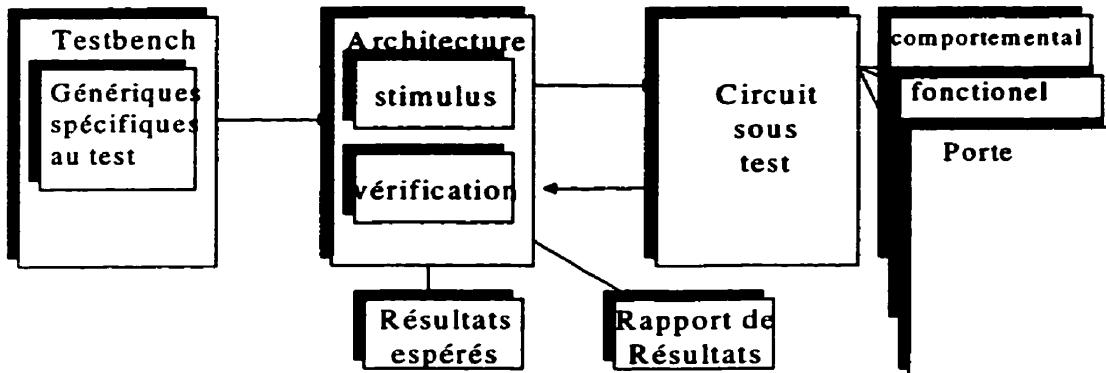

toutes les entrées possibles du circuit et en compare les résultats avec ceux prédicts. Selon la figure 0.2, l'environnement de test est inscrit dans ce que l'on appelle un banc d'essai ou un *test bench* dans la terminologie propre au VHDL.

Figure 0.2: Processus de validation par simulation.

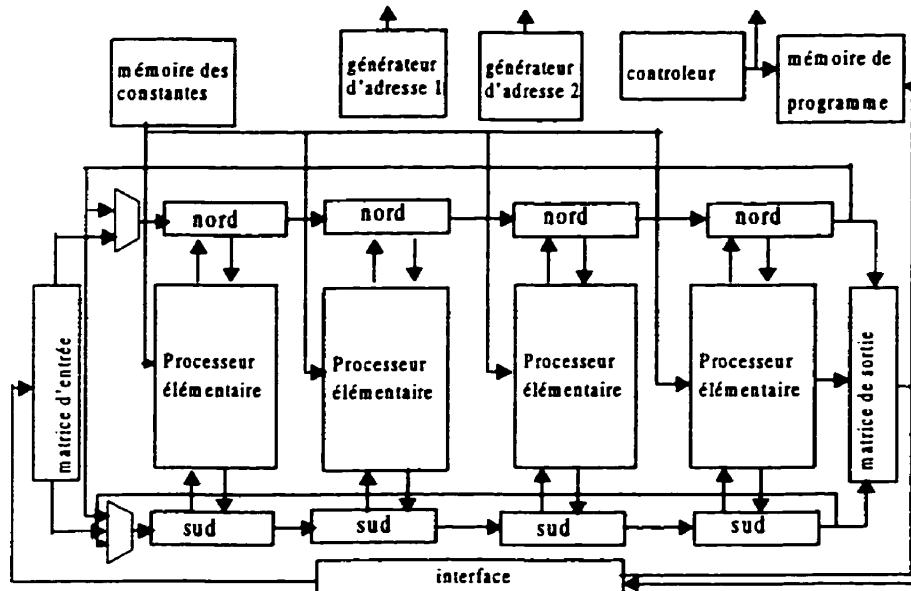

Dans le cadre de la validation de circuits industriels de plus en plus complexes, des variantes basées sur la définition de modèles de référence sont couramment préconisées. Une de ces variantes a été largement utilisée dans le cadre du projet PULSE[1] développé à l'École polytechnique. Afin de valider une puce conçue selon une architecture SIMD(single instruction multiple data), un simulateur décrivant l'architecture fonctionnelle du circuit a été développé. PULSE, dont l'architecture est présentée à la figure 0.3, est optimisé pour le traitement d'images en temps réel. Cette puce, dont la conception a été réalisée en langage VHDL, contient environ un million de transistors et a été validée à l'aide d'un simulateur écrit en langage C [2].

**Figure 0.3: Architecture simplifiée de Pulse.**

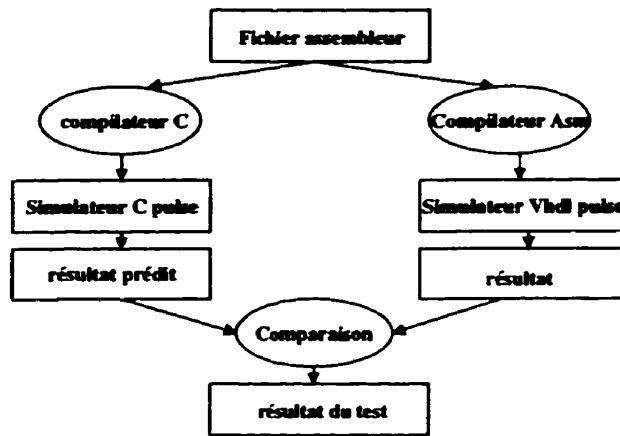

Dans le projet PULSE, le modèle C est une description fidèle de l'architecture qui représente la fonctionnalité de la puce, ainsi que les unités opératives tel que l'ALU, le décaleur et le multiplicateur additionneur. Le contrôleur avec ses différents compteurs, les registres, ainsi que les canaux de communication ont eux aussi été modélisés. Un des avantages d'une méthodologie utilisant un modèle de référence, c'est que ce modèle est sensiblement moins complexe que le design en VHDL. Nous avons, dans le cas du modèle C de Pulse, modélisé le jeu d'instruction de la puce. La méthodologie de validation adoptée était la suivante. Partant d'une même séquence de vecteurs de validation, le résultat de l'exécution du programme sur le modèle VHDL est comparé avec celui du simulateur C. L'avantage de ce genre de méthode est que la description du simulateur est indépendante de l'implantation du modèle VHDL. Elle dépend seulement d'un jeu

d'instructions défini lors de la spécification. La méthodologie de validation est schématisée à la figure 0.4.

**Figure 0.4: Validation Fonctionnelle.**

Un des gros problèmes de la méthode par validation est que pour des circuits ayant un grand nombre d'entrées, il est impossible de tester toutes les possibilités. En effet, pour être complète, la simulation doit étudier le comportement du circuit dans toutes les configurations possibles et pour toutes les séquences.

Par opposition à la simulation, la vérification formelle tente de prouver qu'une description structurelle possède un comportement équivalent à une description fonctionnelle à un niveau d'abstraction supérieur. Il s'agit donc de comparer des descriptions abstraites. Bien que cette méthode fasse de plus en plus d'émules, il ne faut pas oublier les problèmes qui en ralentissent une utilisation industrielle fréquente. Les principaux problèmes[3] sont au nombre de trois: d'une part l'extraction d'une description

du comportement, d'autre part la formulation d'une spécification de haut niveau et finalement, la comparaison entre la description extraite et la spécification.

Le premier problème nécessite la définition d'un modèle temporel et d'une description. Un circuit peut être décrit à différents niveaux d'abstraction, à savoir: électrique, commutateur, porte logique, registre... Le modèle temporel est continu au niveau électrique et, discret aux niveaux supérieurs. Dans ce dernier cas, un modèle de délai doit être défini: instantané pour l'étude des circuits combinatoires, unitaire correspondant à une période d'horloge pour les circuits synchrones.

Le second problème nécessite d'exprimer le comportement souhaité. La spécification correspond à la fois au but à atteindre et à la description abstraite du comportement en termes d'entrées-sorties. Cette spécification est alors exprimée sous la forme d'un automate de haut-niveau. Une spécification complète est parfois difficile à obtenir, en conséquence, seules certaines propriétés sont vérifiées. Citons par exemple la preuve qu'un système ne peut se bloquer, ou que certaines règles ou protocoles d'échange soient respectés. Cependant, le problème de complétude de la validation, ou le fait que les propriétés définies remplissent toutes les volontées du concepteur restent des questions ouvertes.

Bien que de nombreuses études et avancements aient été réalisées dans le domaine de la vérification formelle, l'utilisation de ces techniques lors de la validation amène un trop lourd formalisme mathématique pour bien des concepteurs. Par contre, la validation par la simulation traditionnelle ne permet souvent pas de valider pleinement de grands circuits.

Aussi diverses méthodes ont été proposées afin d'enrichir un jeu de vecteurs de validation amenant une meilleure confiance dans les circuits VLSI. Le test par mutation est une des techniques dérivées de la validation par simulation. Cette méthode permet d'enrichir la suite de vecteurs de validation. Il est à noter que d'autres techniques ont été proposées afin d'augmenter la confiance dans un design. Une manière valable de s'attaquer aujourd'hui aux défis inhérents à la vérification, c'est d'utiliser les analyses de couverture du code. La compagnie Summit Design inc propose un certain nombre d'outils permettant de chiffrer la couverture d'un programme HDL et la couverture des machines à états par des données de test. Ces outils permettent de montrer combien les vecteurs de validation ont pu exercer une région du circuit et en révéler les régions non testées. Par ailleurs, ils identifient les tests qui ont les plus grandes couvertures et permettent de réduire les tests redondants. Il est intéressant de remarquer que pour calculer une couverture du code, ces outils comptent combien de fois la suite de test exerce chaque ligne, chemin, expression, état et séquence. La mutation par contre ne compte pas combien de fois un vecteur a exercé une région, mais plutôt si toutes les régions ont été exercées au moins une fois.

Les différents objectifs de ce mémoire sont de trois types. Le premier consiste à étudier l'utilisation du test par mutation dans le cas de la validation de circuits numériques. Le second permet de définir un ensemble d'opérateurs de mutation permettant d'identifier d'éventuelles erreurs fonctionnelles survenant dans un langage de description matériel tel que le VHDL. Enfin, le troisième abouti à la proposition d'une nouvelle méthodologie de validation par mutation permettant l'enrichissement systématiquement d'un jeu de vecteurs de tests.

Le premier chapitre de ce mémoire consiste en une présentation des méthodes formelles ainsi que des difficultés rencontrées lors de l'utilisation de ces différentes techniques. Ce chapitre se poursuit par une revue de littérature dans le domaine du test logiciel et particulièrement sur le test par mutation.

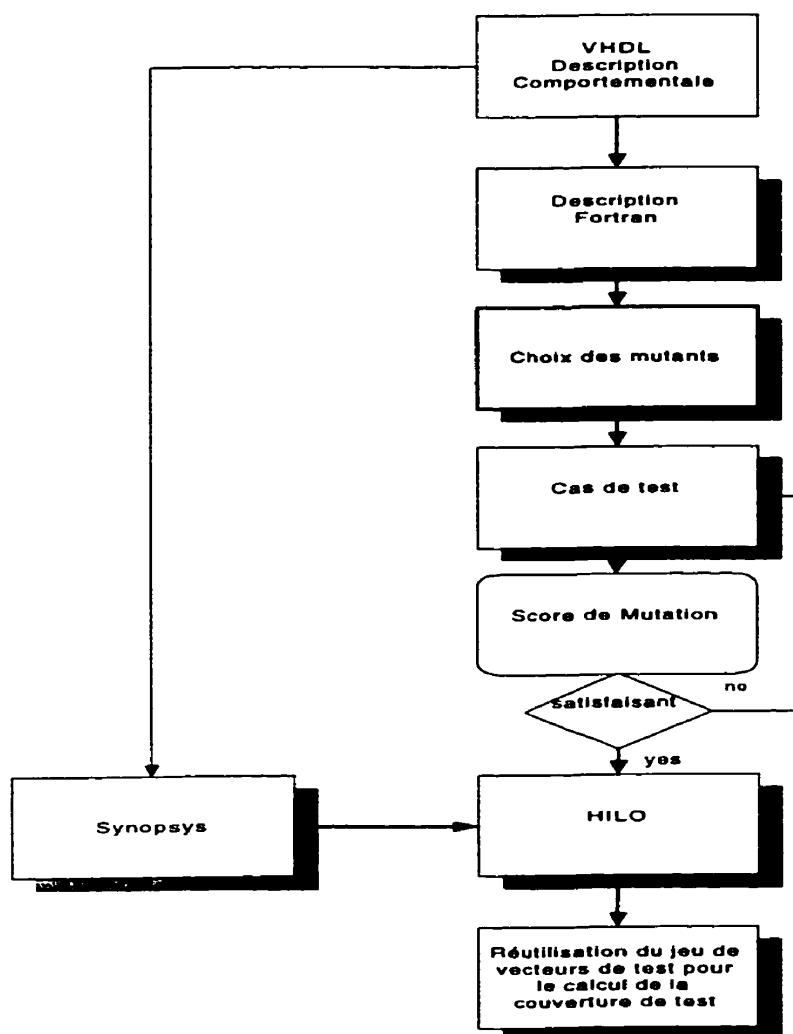

Le second chapitre propose une adaptation du test par mutation à la validation des circuits VLSI ainsi que les résultats obtenus sur différents bancs d'essais ainsi que les problèmes inhérents au test par mutation. Aussi nous présenterons une méthodologie systématique de test par mutation dans le cas de circuits VLSI.

Enfin, le troisième chapitre présente l'algorithme de génération de mutants et d'enrichissement de vecteurs de validation, ainsi que le banc d'essai qui a permis la définition des différents opérateurs de mutation. Ce chapitre commencera donc par une redéfinition des opérateurs de mutation dans le cas de circuits VLSI et se continuera par la proposition d'un algorithme systématique de validation de circuits numériques utilisant l'outil Synopsys.

# CHAPITRE 1

## METHODES DE VALIDATION

### 1.1 Méthode Formelle

#### 1.1.1 Introduction

Bien que la vérification par la simulation soit la méthode la plus largement utilisée dans le processus de validation de circuits VLSI, l'augmentation du niveau de complexité des circuits, ainsi que la difficulté à procéder à des tests exhaustifs, augmente le risque que certains aspects du design ne soient pas vérifiés. Une alternative basée sur des méthodes mathématiques rigoureuses a été proposée : la vérification formelle.

Cette méthode est basée sur des langages, des techniques et des outils mathématiques. La plupart de ces langages, techniques et outils, utilisent des représentations binaires plus connues sous le nom de diagrammes binaires de décision (BDD). Le BDD[4] est une simple représentation canonique de la logique binaire énumérant toutes les valeurs possibles pouvant se produire dans un circuit combinatoire. L'utilisation des méthodes formelles ne garantit pas, *a priori*, l'exactitude du design mais, elle augmente de manière significative la compréhension d'un système en y révélant les ambiguïtés et les inconsistances. Cependant, un problème majeur des méthodes formelles est l'utilisation abondante de la mémoire et du temps CPU, qui croissent parfois de manière exponentielle en fonction de la taille du circuit.

Les méthodes formelles s'appuient sur trois outils principaux afin de vérifier une spécification. On retrouve des outils de vérification d'équivalence, de vérification de modèle et des prouveurs de théorèmes. Les vérificateurs d'équivalence comparent la spécification avec un design de référence. Les vérificateurs de modèles prouvent la véracité des propriétés du design par rapport à la spécification. D'autre part, les prouveurs de théorèmes permettent à l'usager de bâtir une preuve montrant que le design respecte bien la fonction voulue.

Nous exposerons plus en détail dans la suite de ce paragraphe les vérificateurs du modèle et les prouveurs de théorèmes, deux types de vérification couramment utilisées.

Deux exigences importantes doivent être respectées dans le processus de vérification. La première est la définition d'un langage formel capable de décrire le comportement d'un système et l'expression de propositions(propriétés) bâties à partir de celui-ci. La seconde exigence est de disposer d'un calcul déductif capable de prouver toutes les propositions exprimées dans le langage. Les méthodes de vérification formelle utilisent l'approche générale suivante:

1. Écrire une spécification formelle S décrivant le comportement pour lequel le système doit être vérifié et est supposé exempt de défauts.

2. Écrire une spécification pour chaque type de primitive des composants utilisés dans la construction du système. Ces spécifications sont supposées décrire les comportements des composants réels du système.

3. Définir une expression  $D$  qui décrit le comportement du système que l'on désire prouver. La définition de  $D$  est de la forme suivante :  $D = P_1 + \dots + P_n$ ,

où  $P_1, \dots, P_n$  spécifient le comportement des parties constituantes du système et le  $+$  est l'opérateur de composition qui représente l'effet de lier les composants ensemble. Les expressions  $P_1, \dots, P_n$  utilisées ici sont des instances des spécifications des composants primitifs définis à l'étape 2.

4. Prouver alors que le circuit est décrit par l'expression  $D$ . Ceci se fait par une preuve d'un théorème de la forme :  $D$  satisfait  $S$

où *satisfait* est une relation de satisfaction des spécifications du comportement du système.

### 1.1.2 Vérification du modèle

La vérification du modèle est une technique qui consiste à construire un modèle fini d'un système et, à démontrer que les propriétés spécifiées sont bien respectées. En pratique, deux approches sont utilisées en vérification du modèle. La première, la vérification de modèles temporels est une technique développée dans les années 1980 par Clarke et Emerson d'une part et par Queille et Sifakis d'autre part. Dans cette approche que nous présenterons plus loin, les spécifications sont exprimées en logique temporelle (TL) et les systèmes sont modélisés comme des systèmes à états finis qui effectuent des transitions. Dans la seconde approche, la spécification est donnée sous la forme d'une machine à états. Dans ce cas, le système est lui aussi représenté par une machine à états et, est comparé à la spécification afin de déterminer si oui ou non ses comportements sont conformes à ceux de la spécification.

## Vérification de modèle temporel

Un système à états finis peut être représenté par un graphe de transition d'états étiquetés, où les étiquettes d'un état sont les valeurs des propositions atomiques de cet état (par exemple pour les valeurs des bascules). Les propriétés concernant le système sont exprimées comme des formules en logique temporelle pour lesquelles le système à transitions d'états doit être un modèle. La vérification du modèle consiste à parcourir la machine à états des transitions du système (FSM) et à vérifier s'il satisfait les formules représentant la propriété.

## Arbre de calcul logique

La logique temporelle exprime l'ordre des événements dans le temps par une spécification des propriétés des opérateurs tel que "*p aura éventuellement lieu*". Il y a plusieurs versions de logique temporelle, dont une concernant le CTL[5] pour laquelle celui-ci découle de l'arbre des transitions d'états.

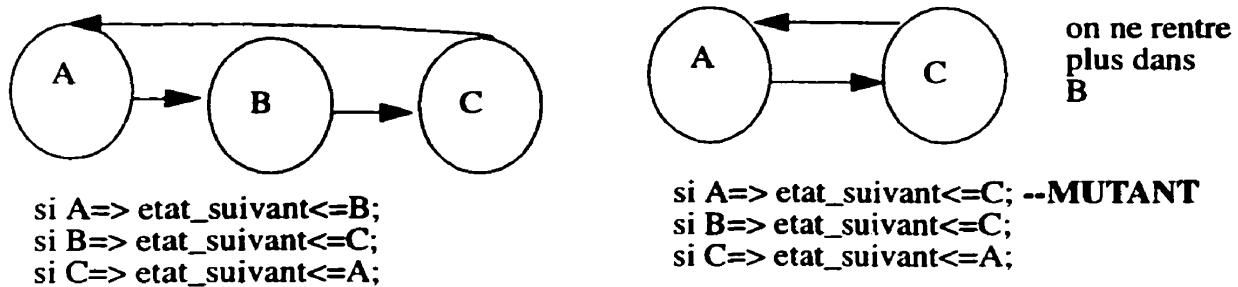

Donnons à titre d'explication l'exemple classique des feux de circulation (Figure 1.1).

**Figure 1.1: Construction d'un CTL à partir d'un automate.**

Les chemins dans l'arbre de la figure 1.1 représentent toutes les possibilités de calcul du système. Les formules en CTL font référence à l'arbre de calcul dérivé du modèle. La méthode CTL est classifiée comme une analyse des branchements logiques temporels, car ses opérateurs décrivent la structure de branchement de l'arbre. Les états du système sont des valeurs enregistrées dans des bascules. Chaque formule de la logique est soit vraie ou fausse pour un état donné. L'exactitude est évaluée à partir de l'exactitude de ces sous formules de manière récursive, jusqu'à ce qu'une proposition atomique soit vraie (1) ou fausse (0) pour un état donné. Une formule est satisfaite par un système si elle est vraie pour tous les états initiaux du système. Contrairement à la démonstration de théorèmes, la vérification du modèle est complètement automatique et relativement rapide. Cette méthode peut être utilisée afin de vérifier des spécifications partielles. Ainsi, elle peut

donner une information déterminante sur la validité d'un système, même si ce dernier n'est spécifié que partiellement. En tout état de cause, elle produit des contres exemples représentant des erreurs subtiles du design et peut ainsi être utilisé pour le déverminage. Le problème le plus important du modèle d'équivalence est l'explosion des états. En 1987 McMillan utilise les BDD et son extention MDD (Multi-valued Decision Diagram) afin de proposer une heuristique permettant de représenter les systèmes d'états de transition de manière efficace. D'autre part, il propose la minimisation de la sémantique afin d'éliminer les états non- nécessaires du modèle.

### **Les diagrammes de décision binaire**

Les diagrammes de décision binaires (BDD) sont des graphes acycliques orientés qui permettent de représenter des fonctions booléennes. Selon Bryant, les BDD sont une représentation canonique des fonctions qui constituent une technique complémentaire à la vérification de modèle. La taille des BDD est très sensible à l'ordonnancement des variables et à la taille des BDD intermédiaires. La meilleure représentation des fonctions booléennes représentant les équations des circuits numériques est dérivée du BDD. C'est le "*Ordered Binary Decision Diagram*" (OBDD). Bien que les BDD ont été utilisés avec succès dans la vérification des FSM, ils ne constituent pas une panacée dans le cas des FSM de grandes tailles:

- les BDD demandent trop de mémoire,

- leur manipulation est très coûteuse en temps de calcul.

### 1.1.3 Démonstration de théorème

La démonstration de théorème est une technique dans laquelle le système et ses propriétés sont exprimés comme des formules en logique mathématique. Cette logique est donnée par un système formel, qui définit l'ensemble des axiomes et des règles d'inférence. La démonstration de théorème est le processus permettant de trouver une preuve d'une propriété en partant des axiomes pour un système spécifié. Les étapes de la preuve font appel aux axiomes, aux règles d'inférences et à la dérivation de définitions et de lemmes intermédiaires. La démonstration de théorème comprend plusieurs techniques regroupées en deux classes principales :

1. La déduction automatique qui est utilisée comme procédure générale de recherche.

2. La déduction interactive qui est beaucoup plus intéressante pour des développements formels systématiques en mathématique.

Les techniques sont :

- Boyer-Moore[6] (First-Order Logic).

- HOL (High-Oder Logic): HOL[7] utilise les notions standards de la logique des prédicats.

En plus des notions standards de la logique des prédicats, HOL est caractérisée par le fait que les variables peuvent être utilisées à des degrés plus élevés que ceux des fonctions et des prédicats. Ce genre de variable est appelé HOV (Higher Order Variable) et peut être quantifiée. Contrairement au modèle d'équivalence, la démonstration de théorème peut traiter les espaces à états infinis. Elle se base sur des techniques comme l'induction

structurale pour prouver ces domaines infinis. Cependant, comme elle requiert la participation humaine, le temps nécessaire à la démonstration d'un théorème est généralement beaucoup plus long que le temps de calcul dans le cas de l'équivalence du modèle et les erreurs sont beaucoup plus fréquentes.

#### **1.1.4 Conclusion**

Bien que la vérification formelle s'avère être un outil très utile dans la spécification des propriétés des systèmes numériques, elle ne peut être que complémentaire aux méthodes traditionnelles de vérification par simulation. En effet, les outils de travail ne cachent aucunement aux usagers leurs caractères formels. Par ailleurs les notations basées sur les écritures mathématiques sont généralement très complexes. Les outils et les méthodes développées aujourd'hui ne sont accessibles qu'aux spécialistes de la vérification formelle.

#### **1.2 Test par mutation**

Le test par mutation est une technique de test logiciel originale proposée par Budd et al. 1978 [8]. Cette technique peut être décrite de la manière suivante: un grand nombre de fautes simples sont introduites, une à la fois, dans un programme sous test. Les versions modifiées, résultant de ces modifications, sont appelées mutants. Les données de test sont alors construites afin de détecter ces mutants. Lorsqu'une différence de comportement est détectée entre le mutant et la spécification de référence, le mutant est considéré tué et n'est plus réutilisé dans le processus de test. La mutation permet donc

d'élaborer un ensemble de vecteurs capables de détecter un ensemble fini et bien spécifié de fautes. Dans le but de faciliter la compréhension de cette méthode, il nous apparaît utile d'exposer les différents concepts du test logiciel.

### 1.2.1 Test logiciel

Le test logiciel consiste à appliquer un jeu de vecteurs de test sur un programme afin d'en révéler les défauts. Les stratégies de test se groupent en deux grandes catégories:

- structurelle(dites aussi stratégies de test boite-blanche) qui utilisent explicitement la structure du programme afin de générer les tests.

- fonctionnelle(dites aussi stratégies de test boite-noire) qui génèrent le test en n'ayant aucune information sur la structure du programme Dans ce dernier cas, on a recours à la spécification.

Le test fonctionnel examine les fonctions du programme depuis les entrées/sorties en vérifiant que pour des entrées légales on obtient des sorties correctes. Afin de quantifier la qualité du test, les stratégies structurelles cherchent à remplir certains critères relatifs à la structure du programme [9]:

- la couverture des énoncés : chacun des énoncés du programme doit être exécuté, au moins une fois.

- la couverture des branches: chaque condition de branchement binaire (IF-THEN-ELSE) doit être évaluée au moins une fois, aux valeurs booléennes VRAI et FAUX . Dans le cas

de branchement non-binaire (CASE) la condition doit être évaluée pour toutes les valeurs possibles.

- la couverture des conditions : si la condition est constituée de plusieurs conditions simples, le test des conditions consiste à évaluer toute condition simple alternativement à VRAI et FAUX.

- la couverture des chemins : tous les chemins possibles dans le programme doivent être exécutés(sensibilisés) au moins une fois.

Dans le test fonctionnel, le concepteur identifie les fonctions supposées être implémentées par le programme et teste ensuite la conformité du code avec la(les) spécification(s) de ces fonctions [10]. Malheureusement, au contraire du test structurel dans lequel beaucoup de méthodes basées en général sur la théorie des graphes ont été proposées , la majorité des méthodes de test fonctionnel sont des méthodes ad hoc et souvent manuelles.

### **1.2.2 Principe du test par mutation**

Comme il a été dit précédemment, le test par mutation permet de quantifier la capacité d'un jeu de vecteurs fonctionnels à tester différentes fonctions dans un programme. Durant le test par mutation, des fautes simples introduites dans le programme original génèrent une multitude de programmes défectueux. Chacun de ces programmes contient une seule faute et est appelé mutant. Le test par mutation est fondé sur quatre hypothèses:

1. Le programmeur est compétent. Cette hypothèse présuppose que le programmeur écrit des programmes presque "*corrects*". C'est-à-dire que bien qu'incorrects, les programmes écrits différeront de la "*bonne version*" par des fautes relativement simples.

2. Les fautes sont couplées [11]: on suppose ici qu'un jeu de test capable de détecter toutes les fautes simples est aussi capable de détecter les fautes plus complexes. Cette hypothèse a été justifiée à la fois de manière théorique [12] et expérimentale [13].

3. On dispose d'un ensemble valide d'opérateurs de mutation. Il s'agit d'un ensemble prédéfini d'opérateurs qui modélise toutes les fautes simples d'un programme. Ces opérateurs sont déterminés de manière tout à fait empirique et il n'existe toujours pas de méthode systématique afin de déterminer l'ensemble minimal relatif à un langage de programmation.

4. On possède un oracle : cette référence permet de vérifier systématiquement que le résultat du programme est conforme, pour un jeu de test donné.

#### 1.2.2.1 Méthodologie.

Etant donné un programme P et un jeu de vecteurs de test T, il s'agit d'exécuter T sur P. Supposons, par ailleurs, que le résultat de T sur P soit correct; i.e. P passe le test T. Plusieurs programmes générés en appliquant de petites modifications sur P, appelées mutants, sont exécutés avec T comme stimulation. Si le résultat d'un mutant est différent de celui de P, on dit que le mutant est tué (détecté). Dans le cas contraire, il est dit vivant

( $T$  est incapable de détecter le mutant). Si un mutant survit, le jeu de test  $T$  est insuffisant et doit être augmenté. Nous allons maintenant nous intéresser à la génération des mutants.

### 1.2.2.2 Génération des Mutants.

Plusieurs techniques ont été proposées afin de déterminer un jeu de vecteurs de test capable d'isoler des "fautes spécifiques". Une des plus difficiles et plus coûteuses tâches dans l'application de ces techniques est la génération de données de test qui est en général faite à la main. Une méthode [14] a été proposée afin de rendre la génération de ces tests, purement automatiques. Cette méthode est applicable de manière structurelle. Ces algorithmes utilisent le constraint based testing (CBT). Ces contraintes de test incluent des conditions qui permettent de tuer les programmes mutants et génèrent des données qui satisfont les contraintes. Le test de grands systèmes est composé de tests de sous-systèmes et de fonctions, si ces systèmes admettent la hiérarchie. Dans le cas d'énormes programmes non hiérarchiques, le processus de génération de vecteurs peut s'avérer intraitable.

Ces algorithmes sont assez performants s'ils sont applicables sur des "unités de programme". Une unité de programme est une sous-routine ou un ensemble de sous-routines ou de fonctions. La génération de jeu de test est en général une tâche laborieuse. En effet, afin de produire les vecteurs de test adéquats, le responsable du test est pratiquement obligé d'interagir avec le système de mutation en examinant de manière exhaustive les mutants survivants. Ce faisant, il doit ensuite construire manuellement un

jeu de vecteurs capables de les éliminer. Le processus de test par mutation commence par la construction de tous les mutants du programme. Les mutants sont générés à partir d'un jeu d'opérateurs de mutation. Les opérateurs utilisés représentent les fautes les plus répétitives faites par les concepteurs. Ces opérateurs suggèrent que les données de test couvrent tous les états, toutes les branches, les valeurs extrêmes, les domaines de perturbations et modélisent plusieurs types de fautes. Lorsque l'un de ces opérateurs est appliqué à un état, il effectue un changement simple (tout en gardant une bonne syntaxe). Le processus de test est le suivant: le programme original est testé par le jeu de test. Il en résulte des valeurs pour chacune des sorties. Un oracle (en général celui qui est en charge de la validation) se charge de vérifier que les sorties sont exactes. Si les sorties sont identiques, le programme doit être changé, puis le processus de test doit être réitéré. Dans le cas contraire, ces derniers tests sont appliqués à chacun des mutants survivants.

Après que ces derniers aient exécuté ces vecteurs avec succès, deux informations surgissent: la proportion des mutants tués, qui indique au concepteur dans quelle mesure le programme a été testé, et le nombre de mutants survivants, qui renseigne quant au nombre de fautes non testées, ou encore, quant à la faiblesse du jeu de test. A titre d'exemple, la Figure 1.2 montre le processus de mutation sur la fonction Max, qui donne le maximum de deux valeurs entières. Afin d'alléger la figure 1.2, tous les mutants sont portés sur la même figure. Autrement dit, chacune des instructions transformée par mutation représente un mutant séparé, dans lequel l'instruction mutée remplace l'instruction correspondante du programme initial. Dans le premier mutant, une valeur absolue a été injectée dans la première instruction. Le deuxième et le troisième mutants

sont les résultats d'injection de fautes dans l'opérateur relationnel de la seconde instruction. Le dernier mutant résulte de l'injection de fautes sur la variable de la troisième instruction .

```

Function Max(integer: m, n):integer;

begin

1      Max:= m;

--      Max := ABS(m);

2      if (n > m) then

--      if (n < m) then

--      if (n = m) then

3          Max:= n;

--      Max:= m;

```

**Figure 1.2:** la fonction Max avec quatre mutants superposés

Il est en général impossible de tuer tous les mutants, car certains changements n'ont aucun effet sur la fonctionnalité du programme original. En général, ces mutants équivalents sont identifiés soit par celui qui est en tâche de la validation soit par des heuristiques.

### 1.2.2.3 Les mutants équivalents

Un mutant est dit équivalent au programme original [12, 13, 15] s'il n'existe aucun vecteur de test permettant de révéler une différence de comportement entre les deux programmes. Il est en général très difficile de prouver qu'un mutant est équivalent. En effet, les raisons pour lesquelles un mutant peut être fonctionnellement identique sont:

1. Le mutant est fonctionnellement équivalent au programme original. Ce mutant produira toujours la même sortie que le programme initial et ceci quelque soit le test.

2. Le mutant peut être tué, mais le jeu de test est insuffisant.

Une manière de démontrer l'équivalence est de procéder à des tests exhaustifs, évidemment, ceci n'est pas pratique pour de gros programmes. Dans la pratique, c'est au programmeur qu'incombe la tâche de déclarer un mutant équivalent. Ce problème reste toutefois une difficulté pratique et théorique devant l'automatisation du test par mutation.

#### 1.2.2.4 Évaluation du test

Le test par mutation a été initialement proposé afin d'évaluer la capacité d'un jeu de test à exercer un programme. Les vecteurs de test peuvent être générés manuellement, aléatoirement, ou à l'aide d'un outil de génération de test. L'analyse de mutation associe une métrique (score de mutation) au jeu de test dans le but d'évaluer son efficacité. Ce score de mutation est le pourcentage de mutants non équivalents tués. Le score est donné par la formule suivante:

$$MS(P,T)=Mk / (Mt - Mq).$$

où  $P$  est le programme de test

$T$  le jeu de test

$Mk$  le nombre de mutant tué par  $T$

$Mt$  le nombre total de mutants générés par le programme

$Mq$  le nombre de mutants équivalents.

Plus le nombre de mutants détectés est grand, plus l'efficacité du jeu de test est importante. Étant donné un jeu de test  $T$ , le programme  $P$  est d'abord exécuté et vérifié sur chaque vecteur qui compose  $T$ . Si le résultat est incorrect, une faute est trouvée et le

programme doit être corrigé puis le processus est relancé. Si le résultat est correct ( $P$  passe le test  $T$ ), tous les vecteurs dans  $T$  sont exécutés pour tous les mutants vivants. Les mutants tués sont retirés du processus de test. Une fois tous les vecteurs de  $T$  exécutés, chacun des mutants encore vivant doit appartenir à une des deux catégories: le mutant est fonctionnellement équivalent au programme initial, ou il ne peut être tué par le jeu de test. Dans le premier cas, les deux programmes sont fonctionnellement équivalents et il n'existe aucune entrée permettant de révéler des résultats différents. Dans le deuxième cas, le jeu de test doit être renforcé par de nouveaux vecteurs. Notons que le coût du test par mutation tend à croître de façon importante, parce que chaque mutant est simulé avec l'ensemble de la suite de test et que le nombre de mutants peut devenir important. C'est pourquoi diverses techniques ont été utilisées afin de réduire le nombre de mutants générés tout en gardant un score de mutation satisfaisant. Les méthodes proposées ont été appelées **mutation faible** et **mutation sélective**.

#### **1.2.2.5 Le test par la mutation faible**

La mutation forte est une méthode très efficace, cependant elle génère une grande quantité de mutants. La méthode de test par mutation faible proposée par Howden[16,17], demande moins de tests. Elle ne considère ni l'hypothèse du programmeur compétent ni l'hypothèse du couplage des fautes. Les différences intervenant entre mutation faible et mutation forte sont que:

1. Les opérateurs de mutation dans la mutation forte sont dépendants du langage de programmation, tandis que dans la mutation faible, ils sont génériques et ne dépendent pas du langage.

2. Dans la mutation forte, il n'existe pas une méthode globale pour générer les tests qui révèlent les fautes prédefinies par les opérateurs de mutation. Il existe toutefois un compromis dans lequel les tests peuvent être générés, si et seulement si, leur capacité de détection des fautes a été affaiblie, d'où le terme mutation faible. Howden (dans la même référence) a défini le composant comme la structure élémentaire de calcul dans le programme. Les références aux variables, les expressions arithmétiques et logiques sont des exemples de composants. Cette méthode de mutation peut être décrite de la manière suivante: si P est un programme qui contient un composant C, il existe alors une mutation C' de C et P' de P où P' correspond à P contenant C'. Dans la mutation faible, un test t est construit de manière où C et C' ont au moins une valeur différente lors de l'exécution de t par P et P', sans garantir toutefois que les résultats de P et P' soient différents. Les changements (ou les mutations des composants) dans la mutation faible affectent les composants suivants :

1. les références à une variable: il s'agit de remplacer une référence à une variable par une autre. Pour détecter ce type de mutation, il faut exécuter le programme sur des entrées pour lesquelles la variable en question se verra attribuée des valeurs différentes de celles de toutes les autres variables compatibles dans le programme.

2. les affectations d'une variable : il s'agit ici d'affecter une valeur à la mauvaise variable. Pour détecter cette mutation, il est nécessaire d'affecter une valeur différente de la valeur actuelle de la variable.

Les deux types précédents sont des mutations primitives qui contribuent dans les types de mutation suivants:

3. transformations des expressions arithmétiques : l'expression est modifiée par l'addition d'une constante, la multiplication par une constante ou bien en modifiant les coefficients qu'elle contient. La détection de l'addition d'une constante ou de la multiplication par une constante demande un seul vecteur de test, tandis que la détection des coefficients modifiés est plus complexe et demande plus d'un vecteur(Howden82).

4. transformation des relations arithmétiques : l'expression est modifiée par un opérateur relationnel incorrect ou l'addition d'une constante. La détection d'un opérateur incorrect est effectuée par l'exécution de la relation sur des données qui distinguent l'opérateur correct de tous les autres opérateurs. La détection de l'addition d'une constante est effectuée par la sélection appropriée d'un point de test.

5. transformation des expressions booléennes: les expressions booléennes sont modifiées en utilisant les opérateurs précédents sur les sous-expressions. Pour détecter la mutation, l'expression doit être testée sur toutes les valeurs dans la table de vérité de l'expression. Howden a proposé des méthodes pour contrôler la taille du jeu de test dans le cas des expression booléennes. Le test par mutation faible a plusieurs avantages sur le test

par mutation (forte). Notamment, il n'est pas nécessaire d'effectuer une exécution des mutants pour sélectionner les données de test. De plus, le nombre de vecteurs de test est souvent petit (un seul) peut parfois suffire pour la plupart des mutations. Un autre avantage majeur est la possibilité de spécifier a priori les données de test nécessaires pour que la mutation donne une sortie incorrecte. Par contre, le test par mutation faible ne garantit pas que les données choisies pour détecter une mutation donne une sortie incorrecte pour le programme tout entier.

#### 1.2.2.6 mutation sélective

Cette méthode a été proposée par Offutt et al. afin de réduire le coût de la mutation en réduisant le nombre de mutants générés. Le coût du test par mutation est essentiellement lié au nombre de mutants. Afin d'estimer la complexité du test par mutation, de nombreuses techniques empiriques ont été proposées. La première l'a été par Acree [18]. Selon ce modèle, le nombre de mutants généré est proportionnel au nombre de lignes du programme au carré. Budd [19] a affiné cette relation en estimant que le nombre de mutants étant proportionnel à  $O(\text{Vals} * \text{Refs})$ , où Vals représente le nombre d'objets de données du programme (ex : déclaration des variables et des constantes) et Refs représente le nombre de références à ces objets. Une étude statistique récente effectuée par Offutt et Lee, [20] a montré que la relation proposée par Budd est la plus représentative de la complexité réelle du test par mutation. Afin de réduire la complexité du test, une réduction des opérateurs de mutation a été proposée afin de réduire le nombre de mutants du programme. Cette approche appelé la mutation sélective, s'effectue de deux manières.

Dans la première, au lieu de considérer tous les mutants pouvant être générés par un opérateur de mutation, on sélectionne, de façon aléatoire, une portion de ces mutants. Une étude réalisée par Wong et Mathur (1995) a montré qu'en appliquant seulement 10% des mutants, on pouvait atteindre des scores de mutation très proches de ceux atteints par la mutation originale. Dans la seconde, certains opérateurs de mutation sont éliminés du processus de génération de test.

#### **1.2.2.7 La mutation N-sélective**

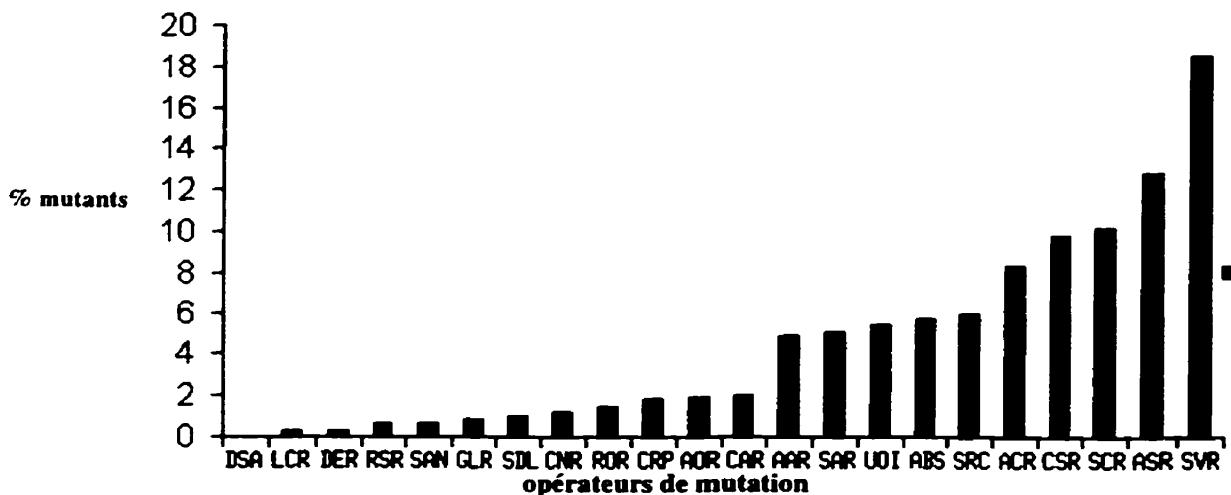

Dans un premier temps, il a été proposé de supprimer les opérateurs responsables de la génération du plus grand nombre de mutants [ 21]. Mathur[22] a proposé d'appliquer une méthode appelée la mutation 2-sélective, sur les deux opérateurs les plus coûteux (ASR et SVR). ASR consiste à remplacer chaque signal par un tableau alors que SVR consiste à remplacer chaque variable par un scalaire. L'expérience a débuté par une étape de comptage des mutants générés (à partir de 28 programmes différents). Les résultats obtenu sont présentés à la figure 1.2. Par la suite, une comparaison a été faite entre les deux méthodes de test (sélective et non-sélective). Pour effectuer cette comparaison, un jeu de vecteurs de test ayant un score de mutation de 100% (pour la mutation sélective) a été créé. Puis, dans un deuxième temps, ce même jeu de vecteurs a été appliqué à la mutation non sélective et son score a été de nouveau calculé.

Afin d'éviter au maximum les aléas (dûs au fait que l'on génère les vecteurs aléatoirement), 5 jeux de tests ont été générés pour chacun des dix programmes considérés. Les valeurs ci-après sont en fait la moyenne de tout cela. Le but de cette expérimentation est de montrer qu'un jeu de vecteurs capable d'obtenir un bon score de mutation lors de la mutation sélective est aussi capable d'obtenir un bon score pour la mutation forte.

mutation 2-sélective : 99.99% (score de mutation) et 23.98% (de mutants non générés).

mutation 4-sélective : 99.84% (score de mutation) et 41.36% (de mutants non générés).

mutation 6-sélective : 99.71% (score de mutation) et 60.56% (de mutants non générés).

Le but de cette expérimentation n'est pas de mettre à jour des mutants équivalents, mais de comparer les scores de mutation obtenus pour la méthode sélective avec ceux obtenus par la mutation forte.

#### 1.2.2.8 La mutation E-sélective

Cette nouvelle technique vise encore à diminuer le nombre de mutants générés en supprimant certains opérateurs. Les opérateurs sont classés en 3 grandes catégories:

- type R : remplacent chaque opérande du programme par toutes les autres opérandes compatibles.

- type E: modifient les expressions en remplaçant les opérateurs par d'autres de même nature (arithmétique, relationnelle ou booléenne).

- type S : modifient les tests conditionnels du programme.

L'objectif sous-jacent est de déterminer empiriquement un sous-ensemble suffisant d'opérateurs de mutation permettant une réduction de la complexité de test, tout en gardant une efficacité satisfaisante. Une étude empirique comparant les performances des mutations suivantes: ES, RE, RS, et E a été menée. Dans une mutation sélective de type XY ou de type X, on applique seulement les opérateurs de mutation compris dans le(s) type(s) mentionnés lors de la génération de test. Il a été montré que le type R génère un nombre de mutants de l'ordre de  $O(\text{Vals} * \text{Refs})$ , le type E de l'ordre de  $O(\text{Refs})$ , et le type S de l'ordre de  $O(\text{Lignes})$ . Il est à noter que le type R est le plus coûteux, car 70% des

mutants générés sont en général de ce type. Une des premières préoccupations lors de l'utilisation de la mutation sélective est de déterminer la possibilité d'éliminer le type R sans avoir à réduire l'efficacité du test généré. En d'autres mots, est-il possible de procéder au processus de mutation en n'utilisant que des types -ES ou -E. Une étude empirique effectuée par Offut et al. [21] a montré qu'un jeu de test 100% adéquat par rapport à la mutation sélective-ES est suffisamment adéquat (99.54% en moyenne) par rapport à une mutation non-sélective.

Il a aussi été proposé de supprimer les opérateurs de type S dans le souci de définir un ensemble minimal suffisant d'opérateurs de mutation. Le résultat de l'application de la mutation sélective à montré que le test généré est là encore quasi-adéquat (99.51 % en moyenne). Par conséquent, dans la pratique, on peut considérer que la mutation sélective -E est suffisante pour générer des tests efficaces.

A titre d'exemple, les résultats d'une expérience réalisée par Irene koo [16] sont donnés ci-dessous. Ces résultats ont été obtenus en appliquant un processus identique à celui appliqué pour la mutation sélective précédente :

mutation ES-sélective : 99.54% (score de mutation) et 71.52% (de mutants non générés)

mutation RS-sélective : 97.31% (score de mutation) et 22.44% (de mutants non générés).

**mutation RE-sélective : 99.97% (score de mutation) et 6.04% (de mutants non générés).**

**mutation E-sélective : 99.51% (score de mutation) et 77.56% (de mutants non générés).**

Pour la mutation E-sélective, le score de mutation va de 98.5% à 99.5% suivant le programme, pour un pourcentage de mutants non générés allant de 37.1% à 92.12%.

Par la suite, une étude a été menée dans le but de réduire encore plus le nombre de mutants générés, en supprimant un opérateur parmi les 5 (cf tableau 1.1).

**Tableau 1.1 : mutation E selective**

| Programme | Avec les 5 opérateurs | Sans UOI | Sans ROR | Sans LCR | Sans AOR | Sans ABS |

|-----------|-----------------------|----------|----------|----------|----------|----------|

| Banker    | 99.57                 | 98.57    | 99.57    | 99.57    | 91.57    | 91.57    |

| Bub       | 99.93                 | 98.93    | 99.93    | 99.93    | 99.93    | 97.93    |

| Cal       | 99.63                 | 95.63    | 99.63    | 99.63    | 99.63    | 99.63    |

| Euclid    | 99.00                 | 97.30    | 99.30    | 99.30    | 99.30    | 99.30    |

| Find      | 99.30                 | 98.70    | 99.70    | 99.70    | 99.70    | 99.70    |

| Insert    | 99.75                 | 98.95    | 99.95    | 99.95    | 99.95    | 97.95    |

| Mid       | 99.90                 | 98.00    | 100.0    | 100.0    | 100.0    | 94.00    |

| Quad      | 100.00                | 99.09    | 99.09    | 99.09    | 99.09    | 97.09    |

| Trytip    | 99.36                 | 98.36    | 98.36    | 99.36    | 99.36    | 98.36    |

| Warshall  | 99.67                 | 97.67    | 98.67    | 98.67    | 98.67    | 98.67    |

### 1.2.2.9 Génération de test

Dans le test par mutation, le but du concepteur est de trouver des vecteurs capables de révéler une différence de comportement. Un test est considéré efficace s'il tue au moins

un mutant. Un moyen largement utilisé dans le domaine du test par mutation afin de générer automatiquement des tests, c'est d'avoir recours à des contraintes mathématiques. En fait ces contraintes permettent de générer des vecteurs de test à partir des propriétés que les entrées du programme doivent avoir pour tuer les mutants. Ces contraintes permettent de rejeter les vecteurs inefficaces. Les contraintes doivent amener le mutant à révéler un comportement différent du programme original. Puisque le mutant est représenté par un seul changement dans le programme, l'état du mutant doit être différent de celui du programme original tout de suite après l'état muté. Cette caractéristique est une condition nécessaire afin de tuer le mutant. Cependant, cette condition n'est pas suffisante, car il peut très bien arriver que le changement de comportement ne parvienne pas à l'une des sorties du programme. Aussi, une condition suffisante est que le test cause une différence à l'une des sorties. Il est cependant très difficile de satisfaire les deux conditions, car cela demande de savoir à l'avance le chemin que va suivre le programme, ce qui est bien sûr un problème très difficile à résoudre. Pour être certain que le test tue le mutant, le mutant doit être exécuté en globalité et, sa réponse comparée avec la réponse du programme. En pratique, il est admis qu'un test remplit la condition nécessaire s'il remplit la condition suffisante sinon, le mutant produit le même résultat que le programme original et reste vivant.

## CHAPITRE 2

### APPLICATION DU TEST PAR MUTATION AUX CIRCUITS VLSI

#### 2.1 Introduction

Ce chapitre fait état des investigations effectuées par l'équipe Valsys de Grenoble et de Valence, ainsi que des résultats obtenus suite à une collaboration effectuée avec notre groupe. Ces travaux sont à la base d'une proposition d'un premier algorithme de validation par mutation de circuits numériques. Tout au long de ce chapitre, nous présenterons les raisons qui ont guidé le choix d'un outil de mutation spécifique ainsi que son architecture. Nous décrirons les différents bancs d'essai sur lesquels les mutations ont été réalisées. Enfin, nous décrirons un algorithme de validation et les problèmes sous-jacents à cette méthode de validation.

Bien que le test par mutation ait été originellement proposé afin de vérifier un programme, il a par la suite été proposé d'utiliser cette méthode afin de valider une description matérielle. En effet, tout comme pour le test des logiciels, cette méthode se révèle intéressante si on travaille à partir de langages de description matériel tels que VHDL(Very High speed integrated circuit Hardware Description Language) et VERILOG. Par ailleurs, les approches fonctionnelles sont indépendantes de l'implémentation matérielle du circuit, ce qui permet d'avoir recours à un haut niveau d'abstraction capable de traiter des circuits VLSI complexes. Il n'existe pas un ensemble de principes reconnus pour la validation de circuits VLSI, qui est en général réalisée de manière ad-hoc. Aussi, en se tournant vers le test logiciel, on peut, si on considère chaque description VHDL

comme un programme, utiliser les rudiments du test logiciel (voir section 1.2.1). Par ailleurs, le test par mutation se compare à bien des égards au test matériel, comme il sera démontré dans la suite de ce chapitre.

Afin de valider et d'établir les fondations de la méthode de validation par mutation de descriptions matérielles, nous avons eu recours à l'outil Mothra[23], qui est l'environnement le plus complet pour le test par mutation dans le domaine logiciel. Cet outil permet de tester des modules écrits en FORTRAN. Mothra génère automatiquement tous les mutants d'un programme en utilisant un ensemble défini d'opérateurs de mutation. L'architecture de Mothra ainsi que la définition de ces opérateurs sont présentés dans la section suivante.

## 2.2 Présentation de Mothra

Mothra utilise une technique de test qui est basée sur des contraintes, ce qui permet d'automatiser le processus de test par mutation en représentant sous la forme de contraintes mathématiques, les conditions pour lesquelles un mutant est tué. Mothra est constitué d'un ensemble d'outils qui permet à la fois de créer les mutants et de générer des vecteurs de test. La génération de ces vecteurs est réalisée par Godzilla. Les outils Mothra/Godzilla ont été implémentés en langage C.

### 2.2.1 Génération de vecteurs de validation.

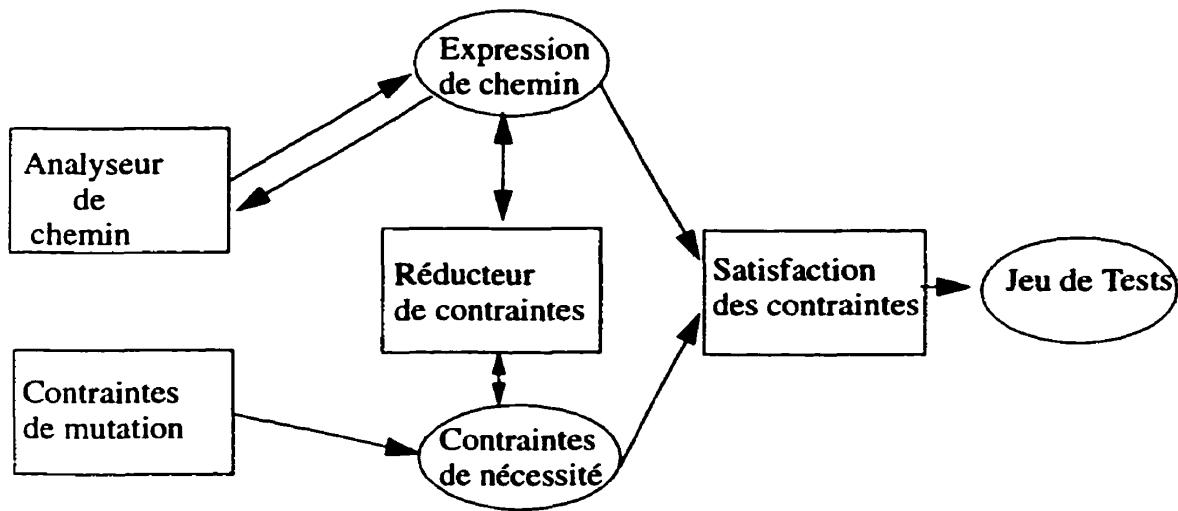

Godzilla génère des vecteurs de test en tentant de trouver les propriétés que doivent avoir les entrées du programme afin de tuer les mutants. Dans le chapitre 1, il a été montré qu'il fallait que le comportement suite à la mutation soit différent de celui du programme non muté. Aussi, dans la validation par mutation, il est nécessaire que les entrées du programme engendrent un état erroné directement après l'exécution de l'état mutant. Par analogie avec le test matériel, il faut au moins que le test stimule la panne à la source en produisant une différence de comportement observable à cet endroit (condition nécessaire). Ensuite, une fois la panne stimulée, cette différence doit se propager sur un résultat observable de l'extérieur.

Godzilla décrit ces conditions sous forme d'un système de contraintes mathématiques. La condition d'accessibilité est décrite par un système de contraintes appelé "expression de chemin". Si on représente le lieu où une panne est susceptible d'être introduite comme un état, chaque état du programme a une expression de chemin permettant de décrire la manière d'atteindre l'état mutant à partir de n'importe quel état. Une condition spécifique au type de faute modélisé par le mutant décrit à la fois la condition qui engendre le comportement défectueux du programme et la nécessité d'une exécution intermédiaire incorrecte. Ces deux critères constituent une condition nécessaire, car bien qu'un état intermédiaire incorrect soit nécessaire, il n'est pas suffisant pour tuer un mutant. Afin de tuer un mutant, il faut que le programme génère des sorties incorrectes de manière à ce que l'état final du programme soit différent de celui du programme

original. Cependant, bien qu'il soit nécessaire de satisfaire la condition de suffisance, elle est pratiquement irréalisable. En effet, déterminer complètement la condition de suffisance implique de connaître à l'avance le chemin que va prendre le programme. Grâce à ce système de contraintes, Godzilla intègre plusieurs techniques de test logiciel dont le détail est donné ci-dessous:

**La couverture des états :** Si on considère un état comme une combinaison des valeurs de toutes les variables dans le programme à un instant donné, chaque état du programme est exécuté au moins une fois. La couverture est réalisée directement à partir du système de contraintes appelé "l'expression de chemin".

**La couverture des branches :** technique qui requiert que toutes les branches du programme soient parcourues. Cette technique est respectée par le test par mutation, en effet les mutants ne peuvent être tués que si les prédictats prennent la valeur vraie puis fausse.

**Domaine de perturbation :** Cela consiste à partitionner les entrées du programme en domaines. Chaque vecteur compris dans un domaine suit le même chemin. La stratégie du domaine de perturbation sélectionne les vecteurs de manière à prendre les valeurs frontières du domaine. Les opérateurs de mutation forcent les vecteurs à satisfaire le domaine de perturbation en modifiant légèrement chaque expression (en ajoutant 1, en soustrayant 1 ou en prenant 10% de la valeur etc.) et en remplaçant chaque opérateur.

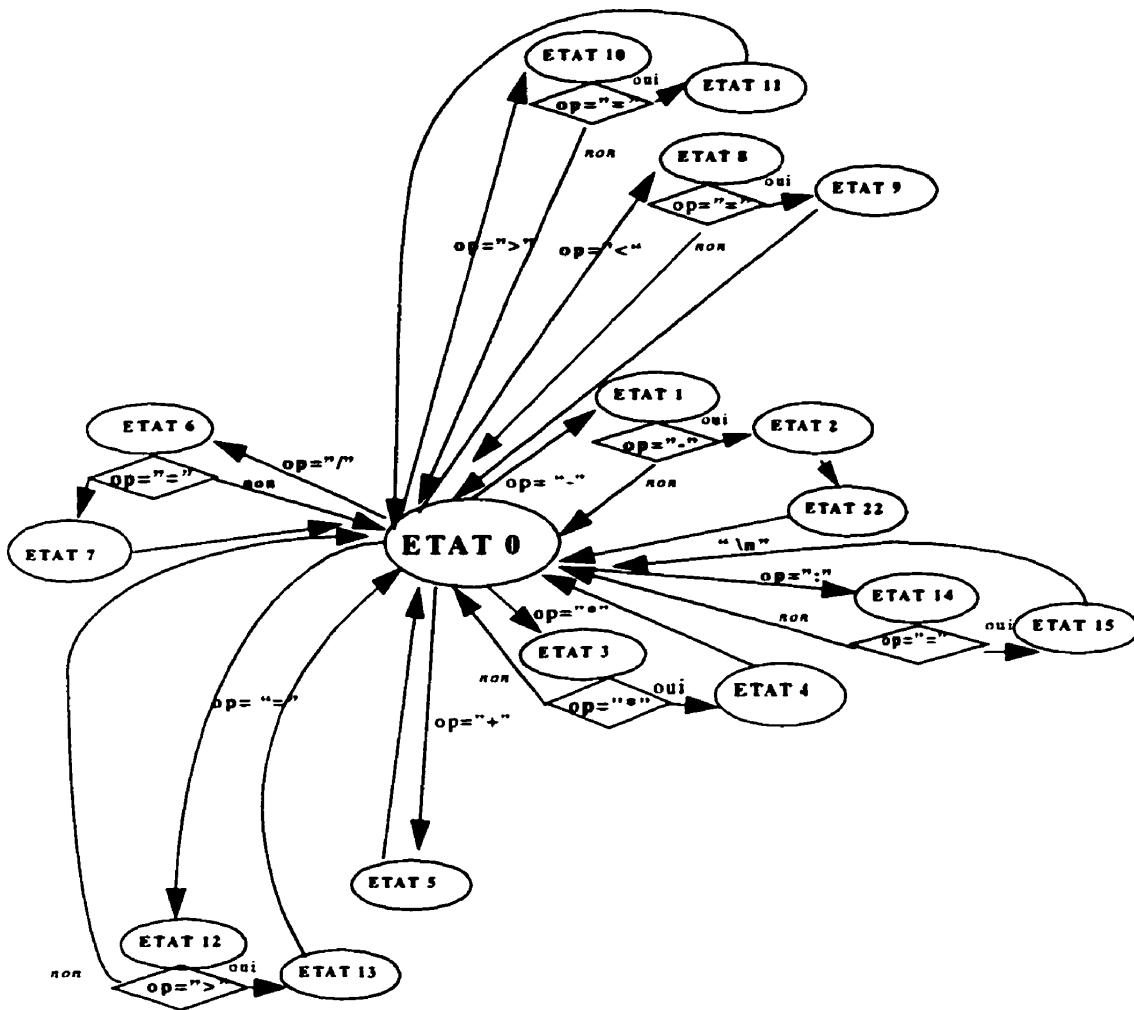

L'architecture de Godzilla est donnée à la figure 2.1

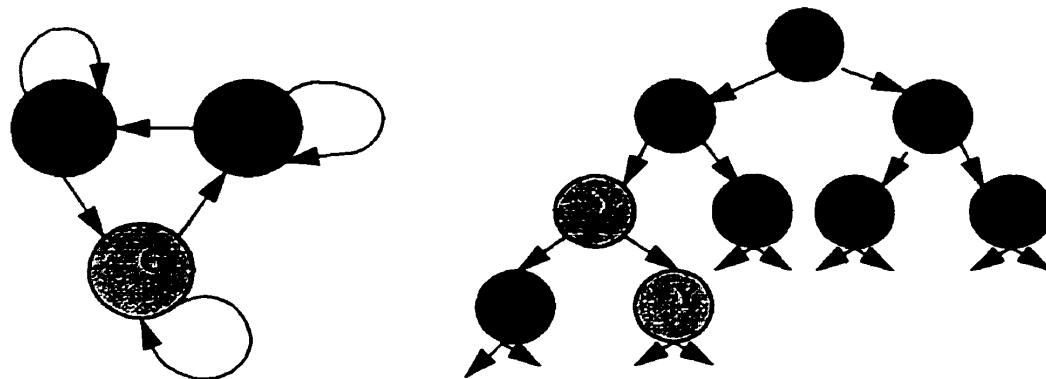

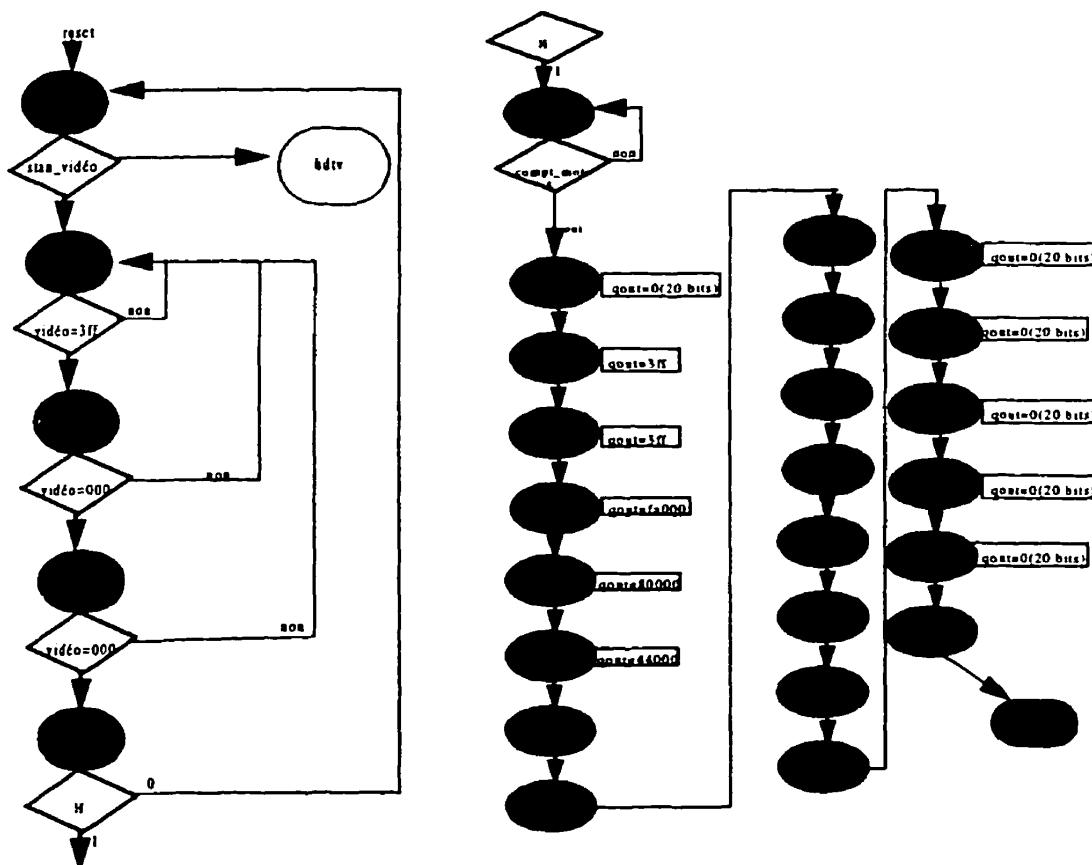

**Figure 2.1: Implémentation de Godzilla**

Les principales fonctions de Godzilla sont montrées ci-dessus. Cet outil intègre différentes fonctions, chacune d'entre elles a été implémentée dans différents programmes, ceux-ci communiquent par l'intermédiaire de fichiers qui sont représentés par des ellipses. Les flèches de la figure 2.1 indiquent les flots d'information du système Godzilla. Les fichiers sont accessibles par des routines communes à tous les outils, ils sont ainsi vus en faisant abstraction du type de données. Ce système permet une plus grande modularité et une plus grande extensibilité en donnant à chaque outil un accès uniforme aux routines qui créent, modifient, enregistrent et récupèrent les contraintes.

### 2.2.1.1 La représentation des contraintes.

Le système de contraintes de Godzilla a une structure hiérarchique composée de contraintes, d'expressions et de clauses arrangées de manière “disjonctive normale”. L'expression algébrique est l'élément de base du système de contrainte. Elle est composée de variables, de parenthèses et d'opérateurs spécifiques au FORTRAN. Une contrainte est une paire d'expression algébrique reliée par un des opérateurs suivants { $>$ ,  $<$ ,  $=$ ,  $\geq$ ,  $\leq$ ,  $\neq$ }. Les contraintes sont évaluées soit à la valeur binaire VRAI, soit à la valeur FAUSSE et elles peuvent être modifiées par l'opérateur de négation NOT ( $\neg$ ). Une *clause* est une liste de contraintes reliées par les opérateurs logiques ET ( $\wedge$ ) et OU ( $\vee$ ). Une *clause conjonctive* utilise seulement le ET logique et une *clause disjonctive* seulement le OU logique. Dans le système Godzilla, toutes les contraintes sont sous la forme *normal disjonctive* (DNF), qui est en fait une série de *clauses conjonctives* reliées par des opérateurs OU. La forme DNF est utilisée par commodité durant la génération des contraintes (en effet, il suffit de satisfaire une seule *conjonctive clause*). Godzilla considère le système de contrainte comme étant un ensemble de contraintes, qui prises collectivement forment un vecteur de test.

A titre d'exemple, considérons le système de contraintes de l'équation suivante:

$$((X + Y \geq Z) \wedge (X \leq Y)) \vee (X > Z)$$

$X+Y$  est une expression et  $(X+Y \geq Z)$  est une contrainte.  $((X+Y \geq Z) \wedge (X \leq Y))$  est une *clause conjonctive*, et l'expression entière est un système de contraintes. Des vecteurs de test tels que  $(X=3, Y=4, Z=2)$ ,  $(X=3, Y=4, Z=4)$  et  $(X=4, Y=1, Z=3)$  satisfont les con-

traintes.

### 2.2.1.2 L'analyseur de chemin.

L'analyseur de chemins utilise la technique de couverture des chemins parcourant ainsi tout le programme afin de construire des contraintes d'accessibilité. Pour chaque état du programme original, l'analyseur de chemins crée une contrainte telle que si le vecteur atteint cet état, la contrainte est vraie. Il faut noter qu'il vaudrait mieux avoir des contraintes inverses (si la contrainte est satisfaite, l'état est exécuté). Cependant, créer des contraintes qui garantissent l'accessibilité implique de trouver une réponse au problème de connaître à l'avance le chemin que pourrait prendre le programme. L'algorithme construisant les expressions de chemin partiel est présenté ci-dessous:

#### Générateur de contraintes

Variables: CPE est l'expression courante du chemin

```

PE [ ] contient l'expression courante de chaque état.

P est le programme.

S et S' sont des états du programme P.

ρ est l'expression d'un prédictat.

1 CPE = VRAI                                -- initialisation

2 pour chaque état S de P

3   PE [ S ] = FAUX                         -- initialisation (aucun état n'a été trouvé)

4   fin

5   pour chaque état de S de P

6     PE [ S ] = PE [ S ] V CPE            -- CPE(nouvelle manière d'atteindre S) est ajouté à l'état précédent

7     CPE = PE [ S ]                      -- le nouvel état devient l'état courant

8     Si S est un état de contrôle de flux alors

9       { ρ est le prédictat de S, S' est la cible de la branche. } -- condition préalable à l'évaluation de S

10      mise à jour de CPE selon le type de l'état.

11      PE [ S' ] = PE [ S' ] V ( PE [ S ] ∧ ρ )    -- ajout de l'expression du chemin et de la conjonction de

12                                    -- CPE et du contrôle de flux

13 end

```

L'expression du chemin courant CPE (Current Path Expression) est tout d'abord initialisée à la valeur VRAI, et chaque état à la valeur FAUSSE indiquant qu'aucun

chemin menant à cet état n'a été trouvé. Pour atteindre l'état S, plusieurs actions sont entreprises. Premièrement, Le CPE est ajouté à la liste des précédentes expressions de S. En effet, le CPE représente une nouvelle voie possible pour atteindre S (ligne 6). Chaque chemin susceptible d'atteindre S est enregistré comme une nouvelle *clause disjonctive* à l'expression des chemins. Ensuite, le nouveau PE de l'état S devient le CPE (ligne 7). Chaque *clause disjonctive* dans l'expression des chemins représente une exécution différente du chemin menant à l'état S. Enfin, si S est un état de contrôle de flux (représentant différentes possibilités, branches...), le CPE est mis à jour par une règle de modification qui dépend de S. La *clause disjonctive* et le prédicat de contrôle de flux(condition du choix multiple) sont finalement ajoutés à l'expression du chemin de l'état cible (ligne 9 et 10).

### 2.2.1.3 Le résolveur de contraintes

La dernière étape du processus de génération de vecteurs de tests est de trouver des valeurs qui satisfont le système de contraintes. Godzilla travaille avec des heuristiques, et produit rapidement des vecteurs de test quand les contraintes ont une forme simple et plus lentement lorsque leur forme est plus compliquée. Tout d'abord, un domaine de valeurs possible est assigné à chaque variable. Théoriquement, ce domaine de valeur dépend du type de variable et de la machine sur laquelle le programme est utilisé. En pratique, Godzilla permet de réduire ce domaine. Par défaut, les domaines de variation des variables sont initialisés arbitrairement aux valeurs (-100, 100). Cependant, ces valeurs peuvent être modifiées dans le cas où le besoin s'en fait sentir. Chaque contrainte dans un

système de contrainte réduit le domaine de variation d'une ou de plusieurs variables. Quand le domaine de variation d'une variable est réduit à une valeur, cette valeur fait partie du vecteur de test. La variable est alors remplacée par sa valeur dans toutes les autres contraintes. Si le domaine de variation est réduit à l'ensemble vide, la résolution de ce système de contrainte est alors impossible. Lorsque toutes les simplifications ont été faites, et qu'il reste un domaine de plusieurs valeurs, une valeur est choisie. Godzilla utilise une heuristique qui affecte la variable qui utilise le plus petit domaine de variation, en espérant que c'est cette variable qui a le moins de chance de rendre le système infaisable. Ce processus est répété jusqu'à ce que toutes les variables se soient vues assignées une valeur.

A chaque fois qu'une valeur est affectée à une variable, le domaine de variation des contraintes est réduit d'une dimension. Si la valeur est mal choisie, elle peut rendre le système infaisable. Lorsqu'un système de contraintes devient infaisable après une affectation, le processus recommence à partir du système de contraintes original. Les expériences ont montré qu'en moyenne, le processus de réduction de contrainte trouve une solution en 4 itérations (avec un maximum de 25). Dans le cas où l'objectif n'a pas été atteint après 25 essais, on considère que le système de contraintes ne possède pas de solutions. Toutefois ce dernier cas ne s'est pas encore produit.

### 2.3 Opérateurs de mutation

Les opérateurs constituent le noyau du test par mutation. Ces opérateurs sont au nombre de 22 et ils identifient les modifications syntaxiques responsables des programmes mutants. Les opérateurs qui sont implémentés dans Mothra sont énumérés au tableau 2.1.

**Tableau 2.1 : Opérateurs de mutation**

| Opérateurs de mutation | Description                                     |

|------------------------|-------------------------------------------------|

| AAR                    | Array reference for Array reference Replacement |

| ABS                    | ABSolute value insertion                        |

| ACR                    | Array reference for Constant Replacement        |

| AOR                    | Arithmetic Operator Replacement                 |

| ASR                    | Array reference for Scalar variable Replacement |

| CAR                    | Constant for Array reference Replacement        |

| CNR                    | Comparable array Name Replacement               |

| CRP                    | Constant RePlacement                            |

| CSR                    | Constant for Scalar variable Replacement        |

| DER                    | Do statement                                    |

| DSA                    | Data Statement Alteration                       |