**Titre:** Évaluation des entrelaceurs au sein des Codes Turbo par simulations

Title: simulations

**Auteur:** Grégory Bruno Ludevic Royer

Author:

**Date:** 2000

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Royer, G. B. L. (2000). Évaluation des entrelaceurs au sein des Codes Turbo par simulations [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/8597/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8597/>

PolyPublie URL:

**Directeurs de recherche:** David Haccoun

Advisors:

**Programme:** Non spécifié

Program:

**UNIVERSITÉ DE MONTRÉAL**

**Évaluation des entrelaceurs au sein des Codes Turbo par simulations**

**GRÉGORY ROYER**

**DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (M. Sc. A)

(GÉNIE ÉLECTRIQUE)

NOVEMBRE 2000**

**© Grégory Royer 2000.**

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-60915-4

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

Évaluation des entrelaceurs au sein des Codes Turbo par simulations

présenté par : Grégory Royer

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

Professeur Jean Conan, Ph. D., Président

Professeur David Haccoun, Ph. D., Directeur de recherche

Professeur François Gagnon, Ph. D., Membre du jury

**À MES PARENTS ET EMERIK**

## **Remerciements**

**Le travail présenté dans ce mémoire n'aurait pu être mené à terme sans l'aide et le soutien de nombreuses personnes.**

**Je tiens tout d'abord à exprimer toute ma gratitude à mon directeur de recherche, le professeur David Haccoun, pour son soutien constant et sa confiance qu'il m'a accordée pendant mes années de maîtrise. Je tiens aussi à le remercier pour son soutien financier.**

**Je tiens surtout à remercier mes parents sans qui je n'aurais pas atteint un tel niveau d'études. Ils ont réussi à me soutenir moralement et à m'aider dans les moments les plus difficiles. Ils ont réussi à me montrer le bon chemin à chaque fois que je dérivais. Enfin, c'est grâce aussi à leur soutien financier que j'ai pu profiter de mes années universitaires. Ma gratitude va également à mon frère et Guylaine qui ont toujours été là quand il le fallait.**

**Je tiens à émettre aussi une pensée à tous mes collègues de la section de communications, Afif, Mehdi, Mélita, Guillaume et Pierre-Frédéric. J'ai énormément apprécié travailler en compagnie d'Afif.**

**Je n'oublierai pas tous mes amis, Julien, Hervé, Richard, Marguerite, Thierry, Anne, Joan et tous les autres. Je remercie en particulier Julien pour la lecture et les corrections pertinentes de ce mémoire**

## Résumé

Le présent mémoire porte sur l'évaluation des performances des Codes Turbo. Ces derniers font partie des techniques les plus puissantes pour la correction des erreurs pour les transmissions numériques. L'encodage se fait à l'aide d'une concaténation parallèle de deux codeurs convolutionnels récursifs et systématiques à travers un entrelaceur.

C'est par le décodage que ces codes sont qualifiés de turbo. Le décodage est itératif et s'effectue à l'aide de deux décodeurs en série. Une information de fiabilité (information extrinsèque) est transmise entre les deux décodeurs permettant ainsi au décodeur suivant de corriger des erreurs que le précédent n'aurait pu modifier. Pour ce processus, l'algorithme MAP est utilisé. Ce dernier permet d'atteindre de très bonnes performances proches de la limite de Shanon.

L'analyse des performances des Codes Turbo est très complexe. En effet, pour ce faire, il faut considérer tous les éléments de cet encodage. Nous pouvons penser à différents paramètres comme ceux des codeurs convolutionnels qui constituent l'encodage. Nous pouvons également penser à l'algorithme de décodage qui modifie de façon conséquente les performances.

Les performances des Codes Turbo en fonction des entrelaceurs font le sujet de ce mémoire. Dans un premier temps, les entrelaceurs pseudo-aléatoires sont considérés. L'évaluation des performances des entrelaceurs aléatoires purs montrent qu'ils sont d'excellents systèmes. L'entrelacement symétrique est introduit en y ajoutant la notion d'aléatoire : la notion de séparation de distance après entrelacement est utilisée. Ceci permet d'imposer une séparation minimum entre les bits consécutifs après entrelacement. Les performances de cet entrelacement hybride sont meilleures que celles de l'aléatoire. Toutefois, une analyse de la complexité de l'entrelaceur symétrique S révèle qu'il est parfois difficile de générer un tel processus

Les entrelaceurs déterministes sont ensuite étudiés. Ils sont caractérisés par la connaissance à l'avance de la position des bits après entrelacement. L'entrelacement bloc est le premier étudié et montre de bonnes performances pour de petites tailles de bloc. Néanmoins, à mesure que la taille des blocs augmente, ces performances se détériorent. La complexité de cet entrelacement est moindre. L'entrelacement convolutionnel est ensuite considéré. Les performances obtenues avec ce type d'entrelacement ne sont pas excellentes, quelle que soit la taille de bloc utilisée.

Enfin, l'entrelacement de type bloc-hélicoïdal est présenté. Ce dernier présente des caractéristiques bien particulières car il permet d'obliger une certaine séparation entre les bits après entrelacement. De plus, sa simplicité est excellente car le processus inverse de l'entrelaceur est simple grâce à des symboles de synchronisation. Trois types d'entrelacement bloc-hélicoïdal sont présentés et les trois donnent de bonnes performances quelle que soit la taille de bloc considérée. Toutefois, le comportement est meilleur pour des faibles tailles de bloc.

## Abstract

This thesis evaluates the performances of Turbo Codes. These are among the best error correcting codes for digital communications. They are concatenated codes composed of two recursive and systematic convolutionnal codes. An interleaver is used to allow the two encoders to see different sequences of bits.

The decoding process is what gives to those codes the property of turbo. This process is iterative and is done with two decoders in serie. The extrinsec information links the two decoders and offers some reliability information for the second decoder. This allows the second decoder to correct errors the first one may have not modified. The MAP algorithm is used and allows the Turbo Codes to reach excellent performances.

Many factors have to be considered to analyze the performances of Turbo Codes. The parameters of the two convolutionnal encoders are among them. We may also consider the decoding algorithm.

Nevertheless, the interleavers are the sub-systems considered in this thesis. The pseudo-random interleavers are first studied. The pure random interleaver is evaluated and gives very good performances. We then introduce the symetric interleaver, to which we add the property of randomness. This allows to induce a separation between two consecutive bits after interleaving. Those interleavers give much better performances than the pure random ones. Nevertheless, the complexity may be high depending on the chosen parameters.

The deterministic interleavers are classical and of low complexity. The block interleaver is evaluated and gives very good performances for short block sizes. However, the performances decrease with the block size. The convolutional interleavers are more

complex because they induce some delay to the encoding process. Their performances are not excellent, whether the block size is large or not.

Finally, the block-helical interleaving process is introduced. It allows a certain separation after interleaving and its deinterleaving process is easy thanks to synchronization bits. There are three types of these interleavers, which gives same kind of good performances. Nevertheless, the behavior of such an interleaver seems better for short block sizes.

## Table des matières

|                                                              |              |

|--------------------------------------------------------------|--------------|

| <b>Résumé .....</b>                                          | <b>vi</b>    |

| <b>Abstract .....</b>                                        | <b>viii</b>  |

| <b>Table des matières .....</b>                              | <b>x</b>     |

| <b>Table des figures.....</b>                                | <b>xiv</b>   |

| <b>Liste des tableaux .....</b>                              | <b>xviii</b> |

| <b>Chapitre 1 - Introduction .....</b>                       | <b>1</b>     |

| 1.1 Théorie de l'information.....                            | 1            |

| 1.2 Les premiers usages des codes correcteurs d'erreur ..... | 2            |

| 1.3 L'avènement des Codes Turbo .....                        | 5            |

| 1.4 Composition du mémoire .....                             | 6            |

| <b>Chapitre 2 – Concaténation parallèle.....</b>             | <b>9</b>     |

| 2.1 Introduction .....                                       | 9            |

| 2.2 Systèmes de communication.....                           | 9            |

| 2.3 Codage Convolutionnel .....                              | 12           |

| 2.3.1 Codeurs convolutionnels non récursifs.....             | 13           |

| 2.3.2 Codeurs convolutionnels récursifs.....                 | 16           |

| 2.4 Concaténation parallèle .....                            | 19           |

| 2.5 Modulation BPSK .....                                    | 22           |

| 2.6 Les types de canaux.....                                 | 24           |

| 2.6.1 Canal AWGN (Additive White Gaussian Noise) .....       | 24           |

| 2.6.2 Canal de Rayleigh.....                                 | 25           |

| 2.7 Conclusion.....                                          | 26           |

| <b>Chapitre 3 - Algorithmes de décodage .....</b>            | <b>27</b>    |

| 3.1 Introduction .....                                       | 27           |

| 3.2 Probabilité a posteriori .....                           | 28           |

| 3.3 Maximum a posteriori .....                               | 29           |

| 3.4 Probabilité conjointe.....                               | 31           |

| 3.5 L'algorithme MAP .....                                   | 33           |

| 3.5.1 Définitions .....                                      | 33           |

| 3.5.2 Probabilité conjointe.....                             | 33           |

| 3.5.3 Métrique d'état en avant.....                          | 36           |

|                                                                  |    |

|------------------------------------------------------------------|----|

| 3.5.4 Métrique d'état en arrière .....                           | 38 |

| 3.5.5 Métrique de branche .....                                  | 39 |

| 3.6 L'algorithme MAP dans un canal AWGN .....                    | 40 |

| 3.7 Algorithme Log-MAP utilisé.....                              | 42 |

| 3.8 Autres versions de l'algorithme MAP .....                    | 46 |

| 3.8.1 Algorithme log-MAP.....                                    | 46 |

| 3.8.2 L'algorithme MAP sous optimal .....                        | 47 |

| 3.9 Comparaison de l'algorithme SOVA avec l'algorithme MAP ..... | 48 |

| 3.10 Conclusion .....                                            | 48 |

| Chapitre 4 – Décodage itératif et entrelacement.....             | 50 |

| 4.1 Introduction .....                                           | 50 |

| 4.2 Principe de décodage itératif .....                          | 51 |

| 4.3 Information extrinsèque.....                                 | 52 |

| 4.4 Décodeur turbo .....                                         | 55 |

| 4.5 Introduction aux entrelaceurs [26].....                      | 57 |

| 4.6 Méthodes d'entrelacement.....                                | 59 |

| 4.6.1 Entrelaceurs blocs.....                                    | 60 |

| 4.6.2 Entrelaceurs multiplexés.....                              | 61 |

| 4.7 Représentations et décomposition .....                       | 61 |

| 4.7.1 Décomposition.....                                         | 61 |

| 4.7.2 Notion d'équivalence.....                                  | 63 |

| 4.7.3 Notion de causalité .....                                  | 64 |

| 4.8 Paramètres d'un entrelaceur .....                            | 65 |

| 4.8.1 Le délai .....                                             | 65 |

| 4.8.2 Mémoire .....                                              | 66 |

| 4.8.3 Facteur d'étalement .....                                  | 67 |

| 4.9 Conclusion.....                                              | 69 |

| Chapitre 5 - Entrelaceurs pseudo-aléatoires .....                | 70 |

| 5.1 Les entrelaceurs pseudo-aléatoires .....                     | 70 |

| 5.1.1 Principe d'aléatoire.....                                  | 70 |

| 5.1.2 Résultats .....                                            | 71 |

| 5.1.2.1 Codes Turbo $R_t = 1/3$ et $K = 3$ .....                 | 71 |

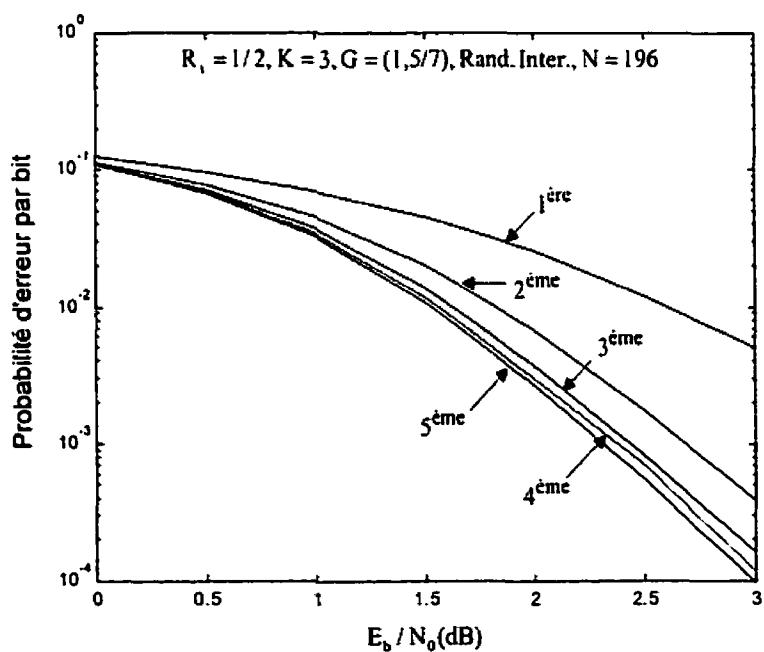

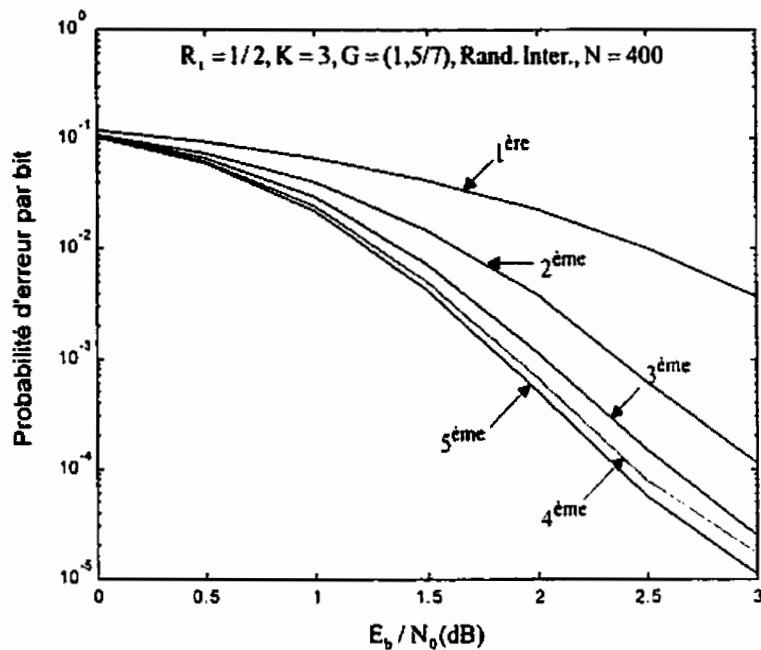

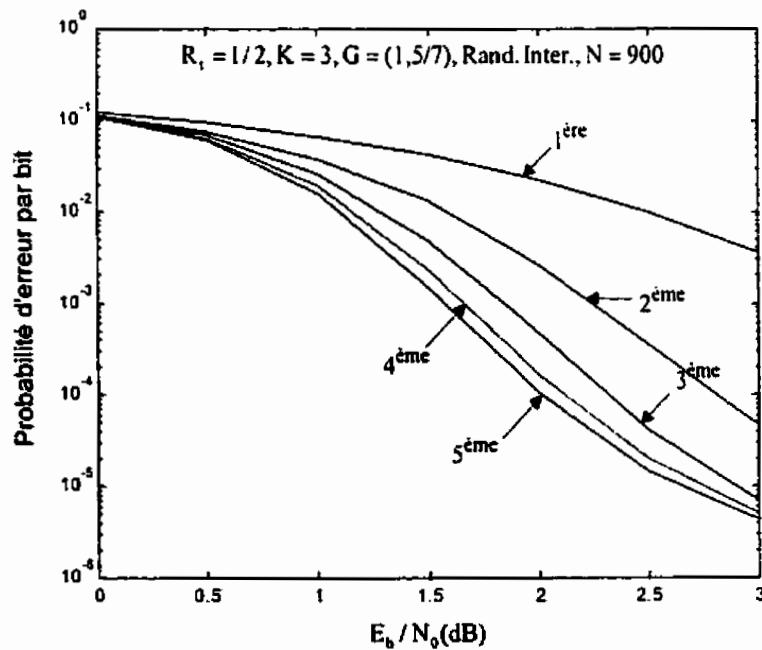

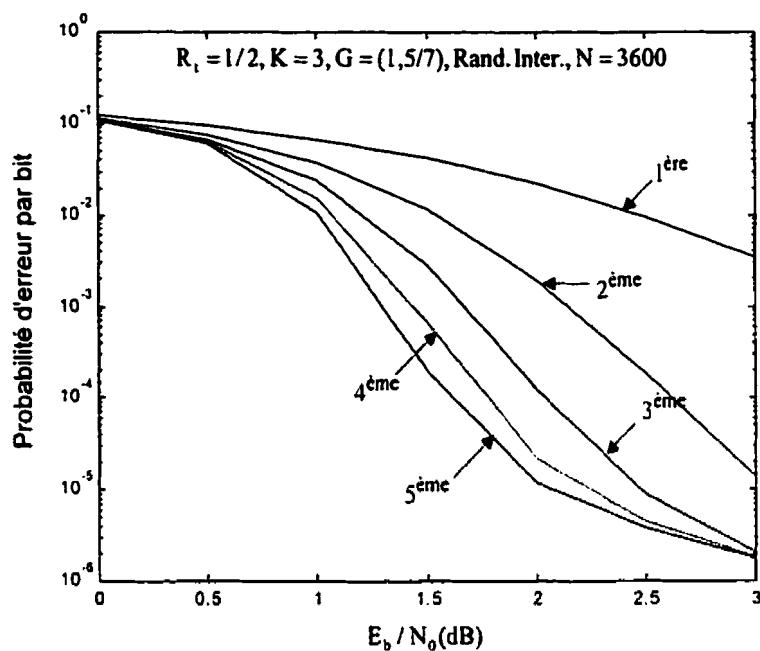

| 5.1.2.2 Codes Turbo $R_t = 1/2$ et $K = 3$ .....                 | 75 |

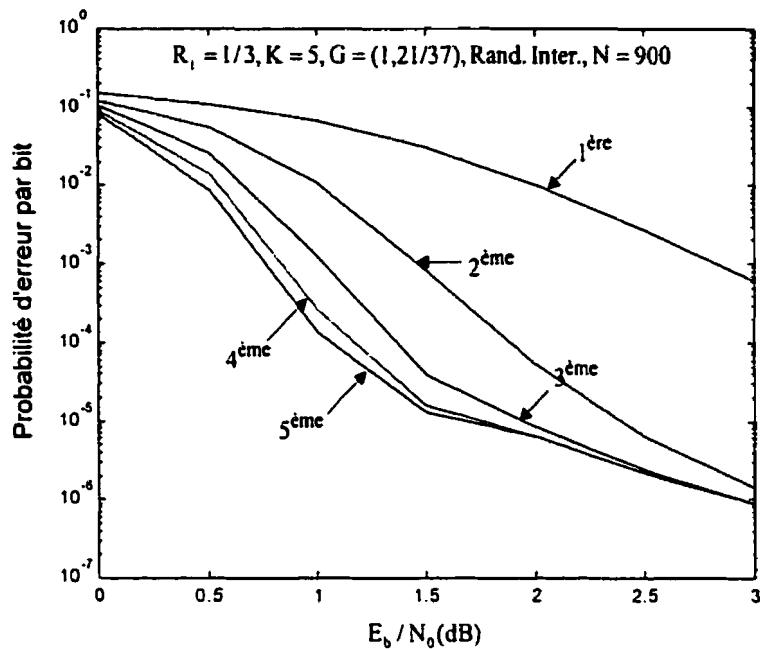

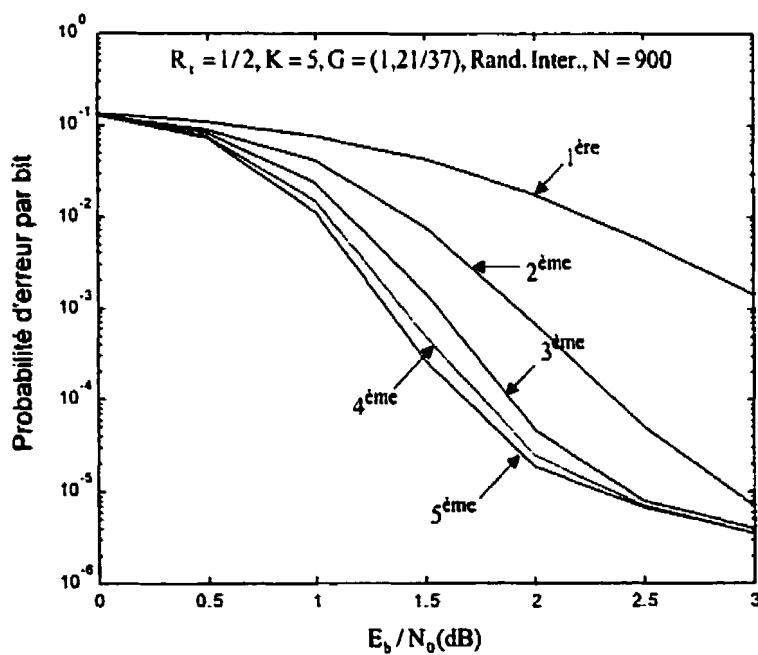

| 5.1.2.3 Codes Turbo $K = 5$ .....                                | 77 |

| 5.2 Les entrelaceurs symétriques S [28] .....                    | 79 |

|                                                                                        |            |

|----------------------------------------------------------------------------------------|------------|

|                                                                                        | xii        |

| <b>5.2.1 Les entrelaceurs symétriques .....</b>                                        | <b>79</b>  |

| <b>5.2.2 Les entrelaceurs symétriques S.....</b>                                       | <b>80</b>  |

| <b>5.2.3 Résultats .....</b>                                                           | <b>83</b>  |

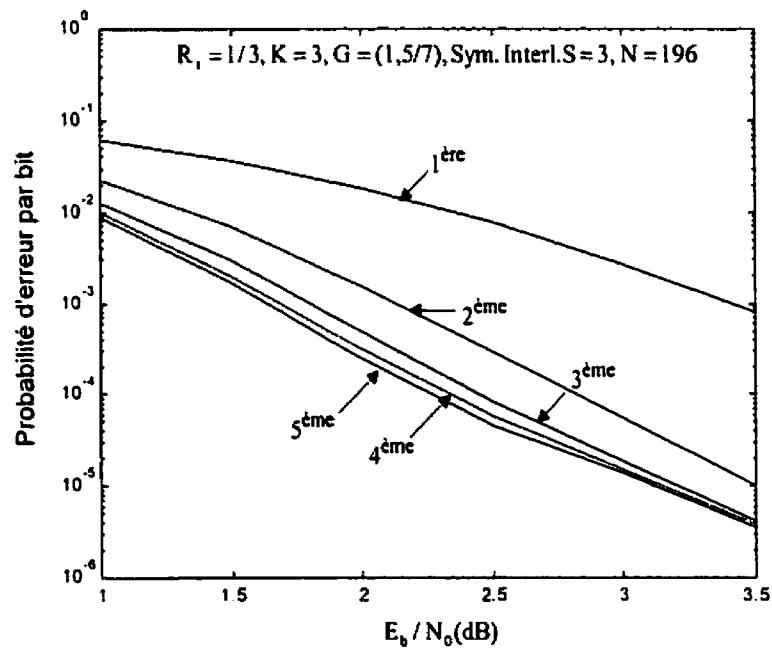

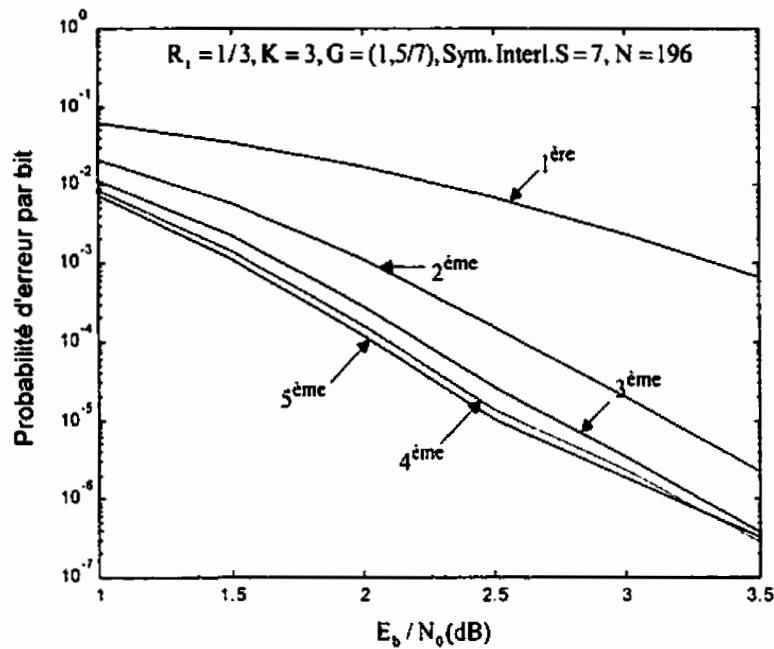

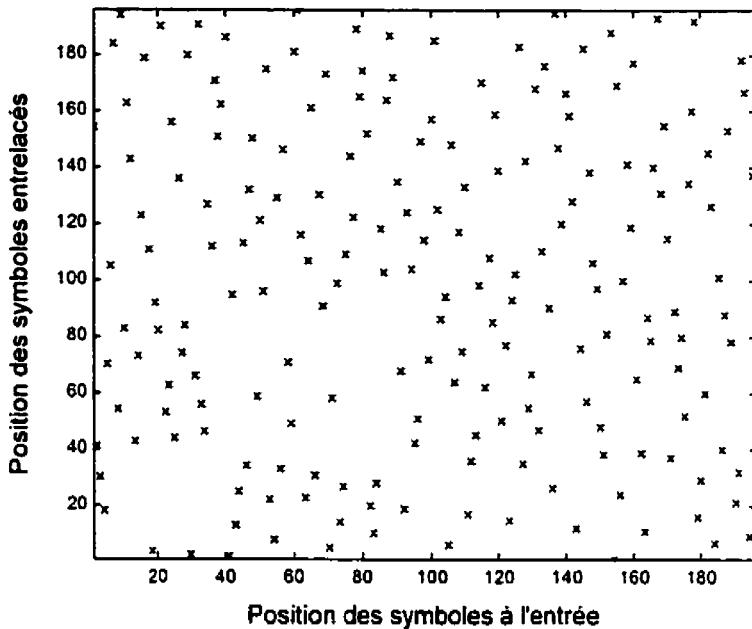

| <b>5.2.3.1 Entrelaceurs de longueur 196 bits.....</b>                                  | <b>83</b>  |

| <b>5.2.3.2 Entrelaceurs de longueur 400 bits.....</b>                                  | <b>87</b>  |

| <b>5.2.3.2 Entrelaceurs de longueur 900 bits.....</b>                                  | <b>90</b>  |

| <b>5.2.3.3 Influence du paramètre S .....</b>                                          | <b>93</b>  |

| <b>5.2.3.4 Délai .....</b>                                                             | <b>95</b>  |

| <b>Chapitre 6 - Entrelaceurs blocs et convolutionnels.....</b>                         | <b>98</b>  |

| <b>6.1 Les entrelaceurs blocs.....</b>                                                 | <b>98</b>  |

| <b>6.1.1 Principe.....</b>                                                             | <b>98</b>  |

| <b>6.1.2 Résultats .....</b>                                                           | <b>100</b> |

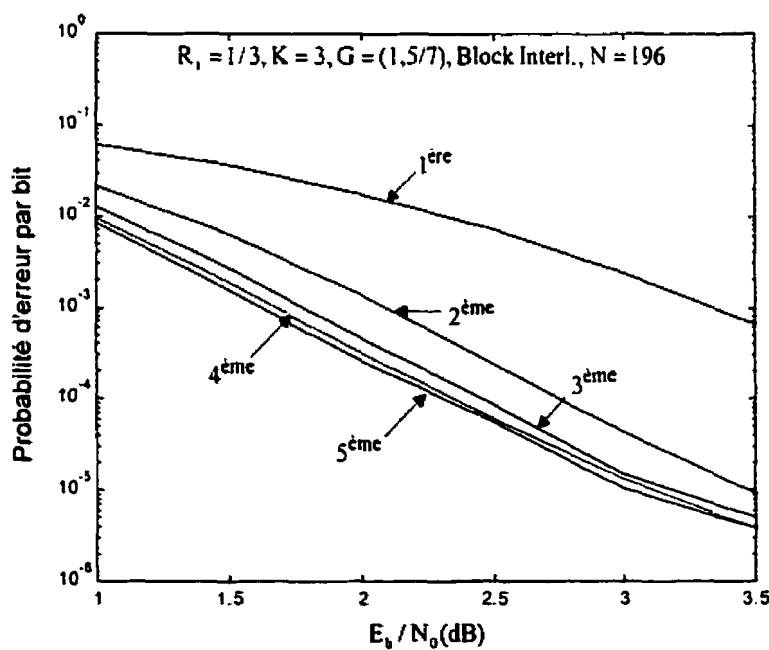

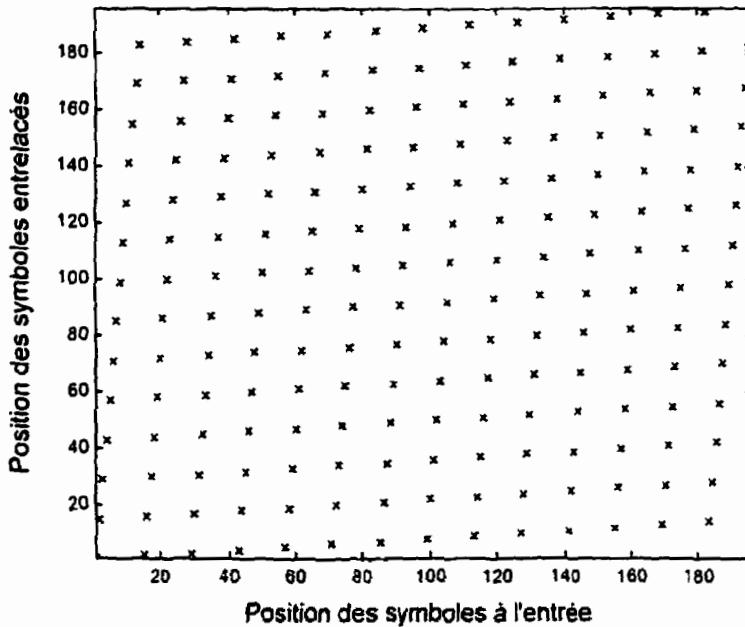

| <b>6.1.2.1 Entrelaceurs de longueur 196 bits.....</b>                                  | <b>100</b> |

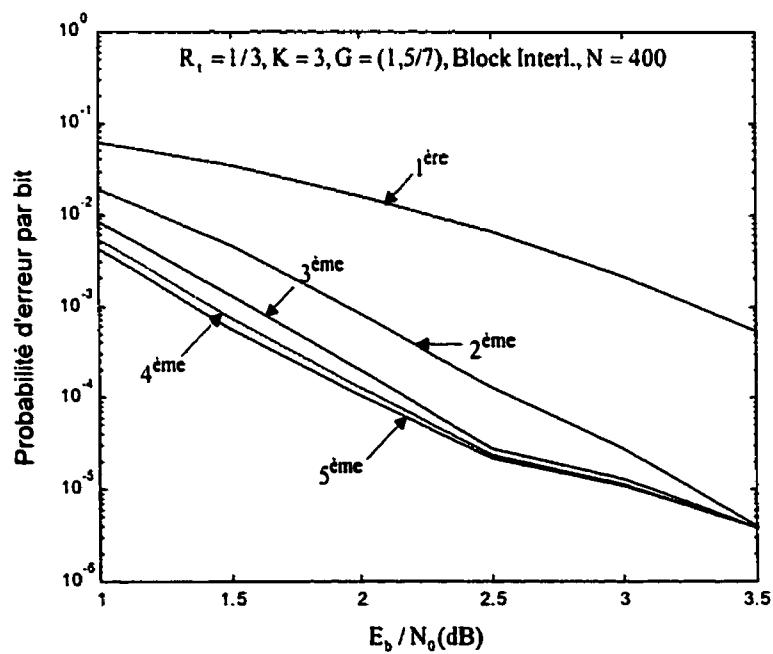

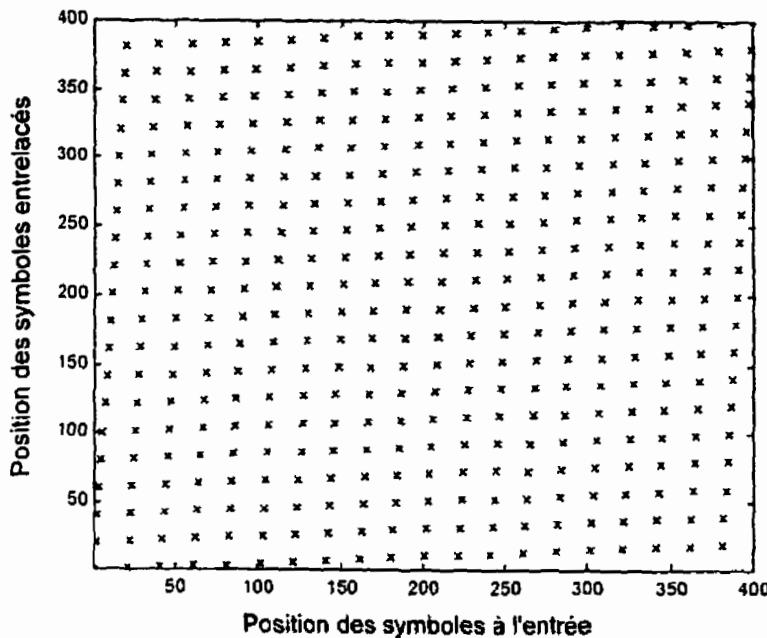

| <b>6.1.2.2 Entrelaceurs de longueur 400 bits.....</b>                                  | <b>102</b> |

| <b>6.1.2.2 Entrelaceurs de longueur 900 bits.....</b>                                  | <b>104</b> |

| <b>6.2 Les entrelaceurs convolutionnels.....</b>                                       | <b>106</b> |

| <b>6.2.1 Principe.....</b>                                                             | <b>106</b> |

| <b>6.2.2 Résultats .....</b>                                                           | <b>109</b> |

| <b>6.2.2.1 Entrelaceurs de longueur 196 bits.....</b>                                  | <b>109</b> |

| <b>6.2.2.1.1 Variation des paramètres m et D.....</b>                                  | <b>109</b> |

| <b>6.2.2.1.2 Évaluation des entrelaceurs convolutionnels de longueur 196 bits.....</b> | <b>112</b> |

| <b>6.2.2.2 Entrelaceurs de longueur 400 bits.....</b>                                  | <b>116</b> |

| <b>6.2.2.2.1 Variation des paramètres m et D.....</b>                                  | <b>116</b> |

| <b>6.2.2.2.2 Évaluation des entrelaceurs convolutionnels de longueur 400 bits.....</b> | <b>117</b> |

| <b>6.2.2.3 Entrelaceurs de longueur 900 bits.....</b>                                  | <b>121</b> |

| <b>6.2.2.3.1 Variation des paramètres m et D.....</b>                                  | <b>121</b> |

| <b>6.2.2.3.2 Évaluation des entrelaceurs convolutionnels de longueur 900 bits.....</b> | <b>122</b> |

| <b>6.3 Conclusion.....</b>                                                             | <b>125</b> |

| <b>Chapitre 7 - Entrelaceurs hélicoïdaux.....</b>                                      | <b>126</b> |

| <b>7.1 Entrelaceurs hélicoïdaux.....</b>                                               | <b>126</b> |

| <b>7.1.1 Entrelaceurs de profondeur (N-1).....</b>                                     | <b>126</b> |

| <b>7.1.2 Entrelaceurs hélicoïdaux de profondeur autre que (N-1).....</b>               | <b>129</b> |

| <b>7.2 Entrelaceurs bloc-hélicoïdaux (BH) [15].....</b>                                | <b>131</b> |

| <b>7.2.1 Notations.....</b>                                                            | <b>131</b> |

| <b>7.2.2 Introduction aux entrelaceurs BH.....</b>                                     | <b>131</b> |

|                                                                                                      |            |

|------------------------------------------------------------------------------------------------------|------------|

|                                                                                                      | xiii       |

| <b>7.3 Les nouveaux entrelaceurs BH .....</b>                                                        | <b>135</b> |

| <b>7.3.1 Les entrelaceurs BH – Aspect théorique.....</b>                                             | <b>135</b> |

| <b>7.3.1.1 Le processus de lecture lit bien les ND symboles une et une seule fois .....</b>          | <b>135</b> |

| <b>7.3.1.2 D symboles entrelacés qui se suivent appartiennent à des mots de code différents.....</b> | <b>137</b> |

| <b>7.3.1.2 Deux symboles de synchronisation sont séparés par N symboles .....</b>                    | <b>140</b> |

| <b>7.3.2 Les entrelaceurs BH de type I.....</b>                                                      | <b>140</b> |

| <b>7.3.3 Les entrelaceurs BH de type II .....</b>                                                    | <b>141</b> |

| <b>7.3.4 Les entrelaceurs BH de type III.....</b>                                                    | <b>144</b> |

| <b>7.4 Résultats .....</b>                                                                           | <b>147</b> |

| <b>7.4.1 Entrelaceurs de longueur 200 bits.....</b>                                                  | <b>148</b> |

| <b>7.4.2 Entrelaceurs de longueur 400 bits.....</b>                                                  | <b>152</b> |

| <b>7.4.3 Entrelaceurs de longueur 900 bits.....</b>                                                  | <b>156</b> |

| <b>7.5 Conclusion.....</b>                                                                           | <b>159</b> |

| <b>Chapitre 8 – Conclusion .....</b>                                                                 | <b>160</b> |

| <b>8.1 Comparaison des résultats .....</b>                                                           | <b>160</b> |

| <b>8.2 Conclusion et perspectives de recherche .....</b>                                             | <b>165</b> |

## Table des figures

|                                                                                                                                          |           |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Figure 2.1 – Système de communication.....</b>                                                                                        | <b>11</b> |

| <b>Figure 2.2 – Codeur convolutionnel non récursif et non systématique,.....</b>                                                         | <b>14</b> |

| $G(D) = [1 + D^2 \quad 1 + D + D^2].....$                                                                                                | 14        |

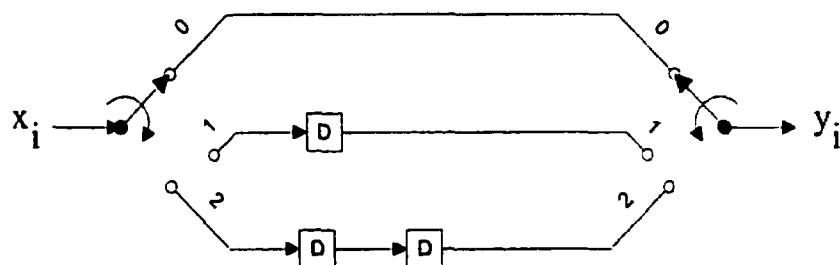

| <b>Figure 2.3 – Codeur convolutionnel récursif et systématique <math>K = 3</math>, <math>R = 1/2</math> .....</b>                        | <b>16</b> |

| <b>Figure 2.4 – Codeur convolutionnel récursif systématique <math>R = 1/2</math>, <math>K = 3</math>, <math>G = (1, 7/5)</math>.....</b> | <b>18</b> |

| <b>Figure 2.5 – Diagramme d'état d'un codeur convolutionnel.....</b>                                                                     | <b>19</b> |

| <b>Figure 2.6 – Codeur turbo.....</b>                                                                                                    | <b>21</b> |

| <b>Figure 2.7 - Modulateur BPSK.....</b>                                                                                                 | <b>23</b> |

| <b>Figure 2.8 – Modèle de canal de Rayleigh .....</b>                                                                                    | <b>25</b> |

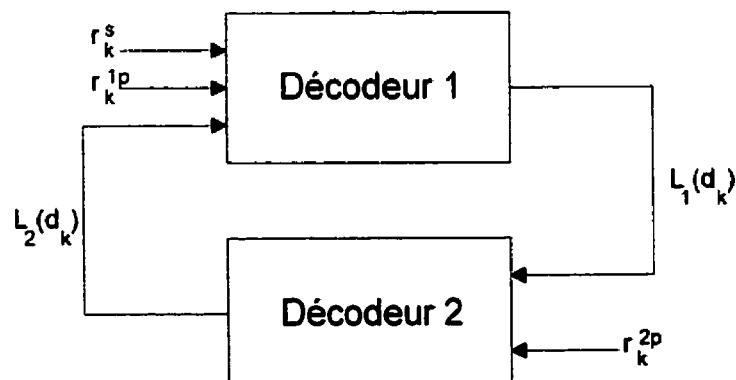

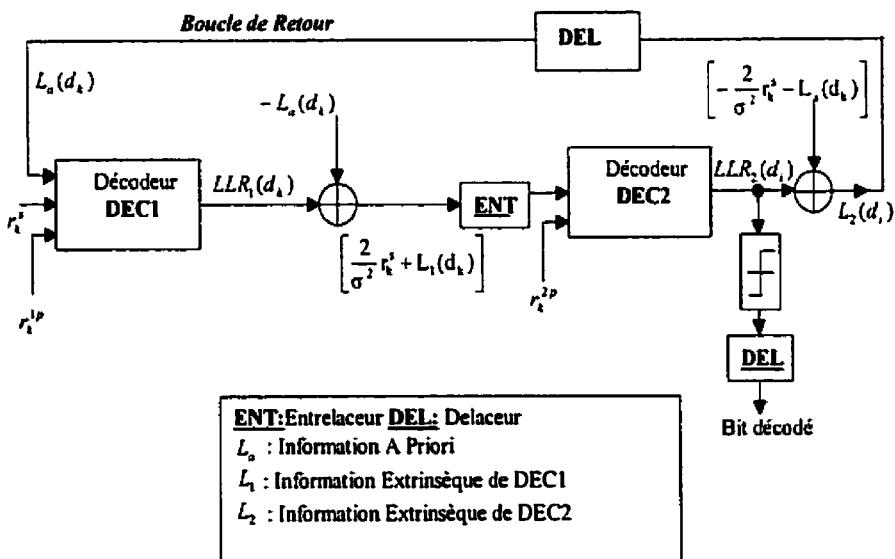

| <b>Figure 4.1 – Principe de décodage itératif.....</b>                                                                                   | <b>51</b> |

| <b>Figure 4.2 – Schéma d'un décodeur turbo.....</b>                                                                                      | <b>55</b> |

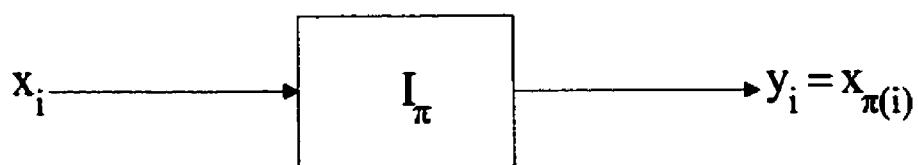

| <b>Figure 4.3 – Un entrelaceur .....</b>                                                                                                 | <b>57</b> |

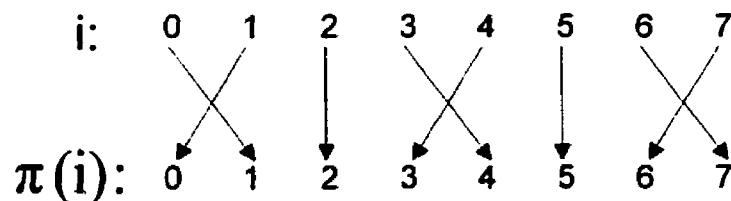

| <b>Figure 4.5 – Un entrelaceur de période 3.....</b>                                                                                     | <b>59</b> |

| <b>Figure 4.6 – Un exemple de processus bloc .....</b>                                                                                   | <b>60</b> |

| <b>Figure 4.6 – Un entrelaceur multiplexé .....</b>                                                                                      | <b>61</b> |

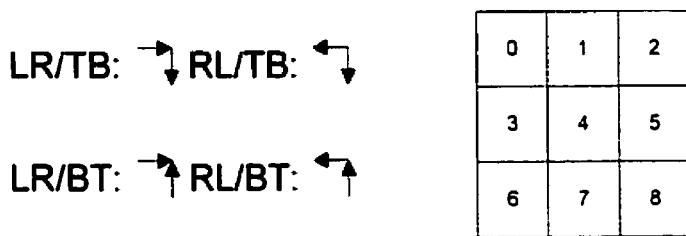

| <b>Figure 4.7 – Matrices génératrices <math>3 \times 3</math> d'entrelaceurs blocs.....</b>                                              | <b>62</b> |

| <b>Figure 4.8 – Un exemple de deux permutations équivalentes .....</b>                                                                   | <b>64</b> |

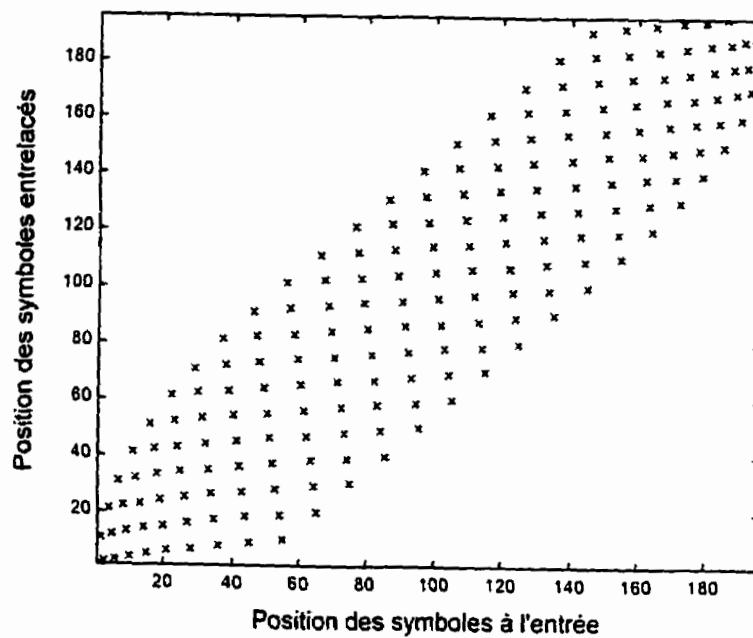

| <b>Figure 4.9 – Un entrelaceur dont le facteur d'étalement est mauvais.....</b>                                                          | <b>68</b> |

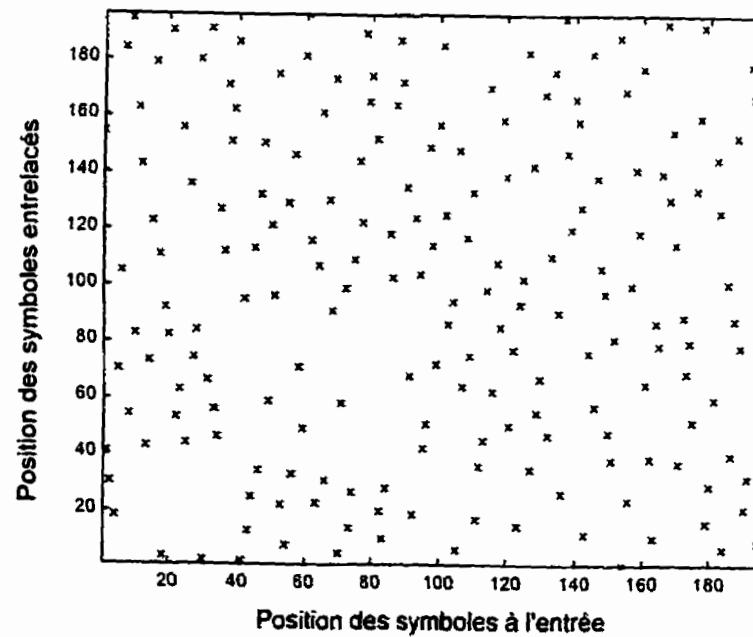

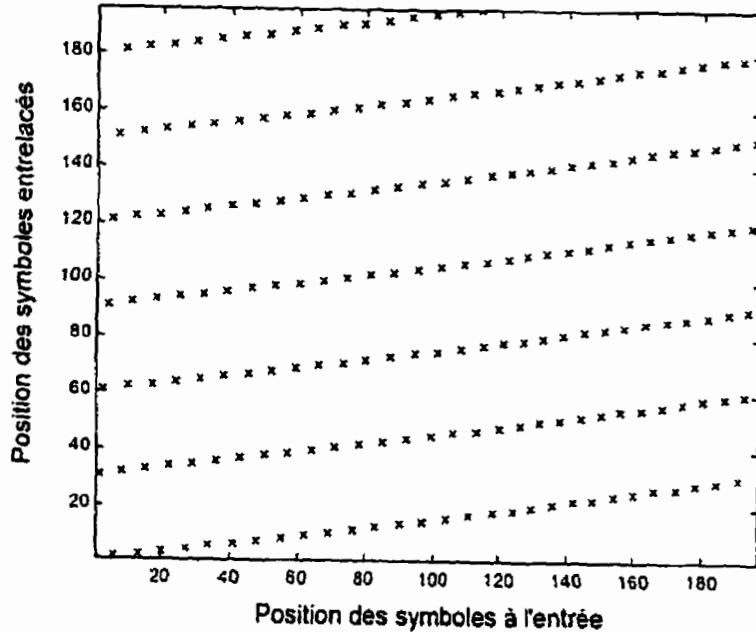

| <b>Figure 4.10 – Un entrelaceur dont le facteur d'étalement est bon .....</b>                                                            | <b>68</b> |

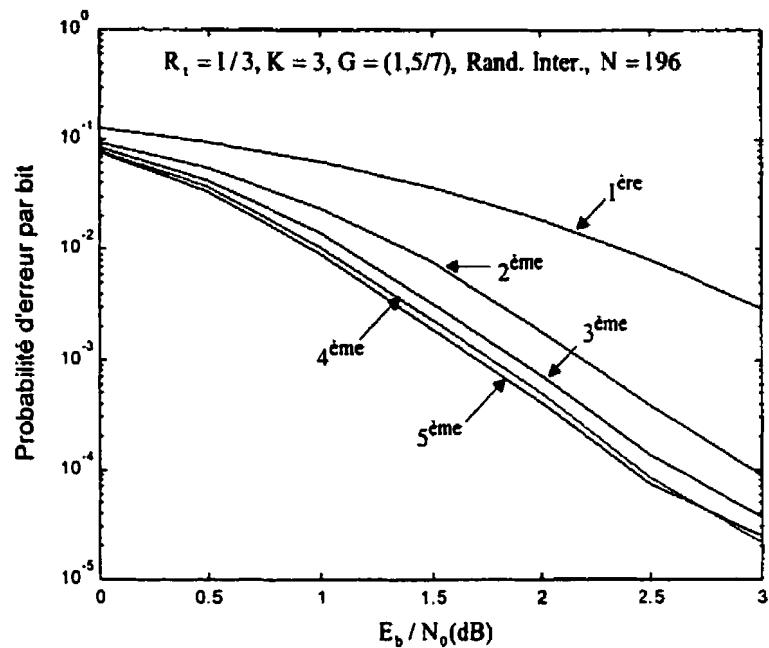

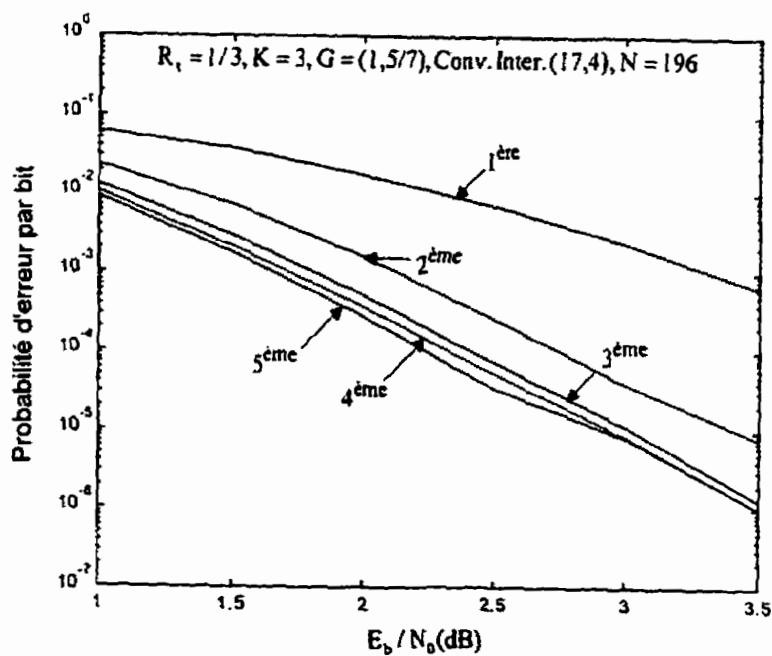

| <b>Figure 5.1 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur aléatoire, canal AWGN, <math>N = 196</math> .....</b>       | <b>73</b> |

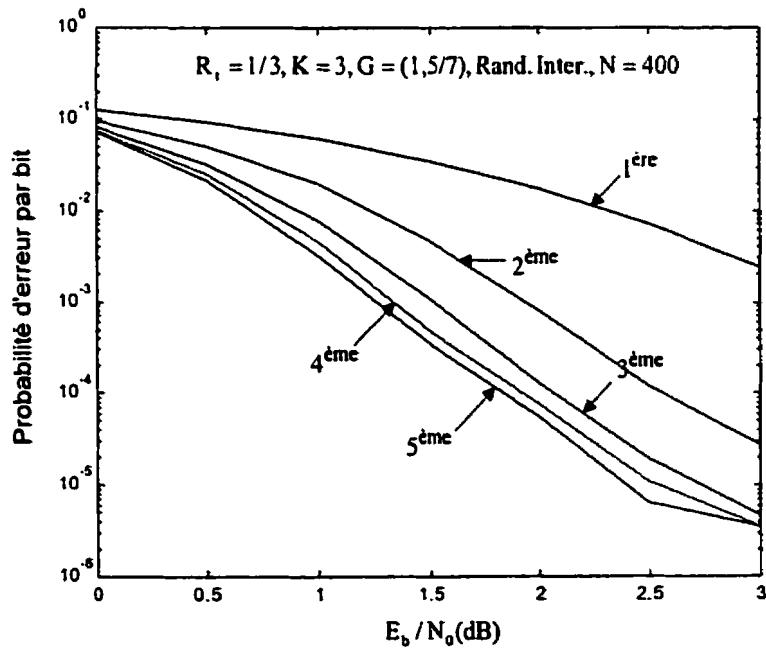

| <b>Figure 5.2 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur aléatoire, canal AWGN, <math>N = 400</math> .....</b>       | <b>73</b> |

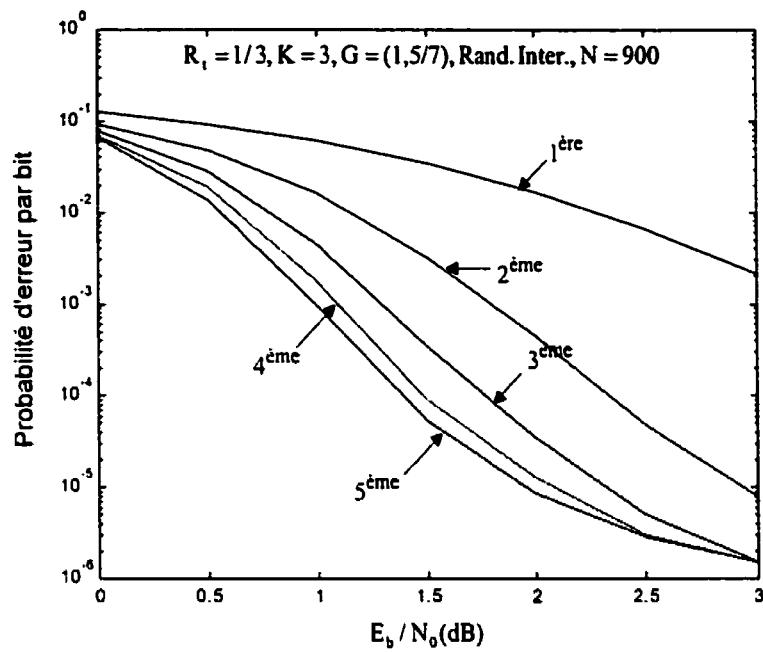

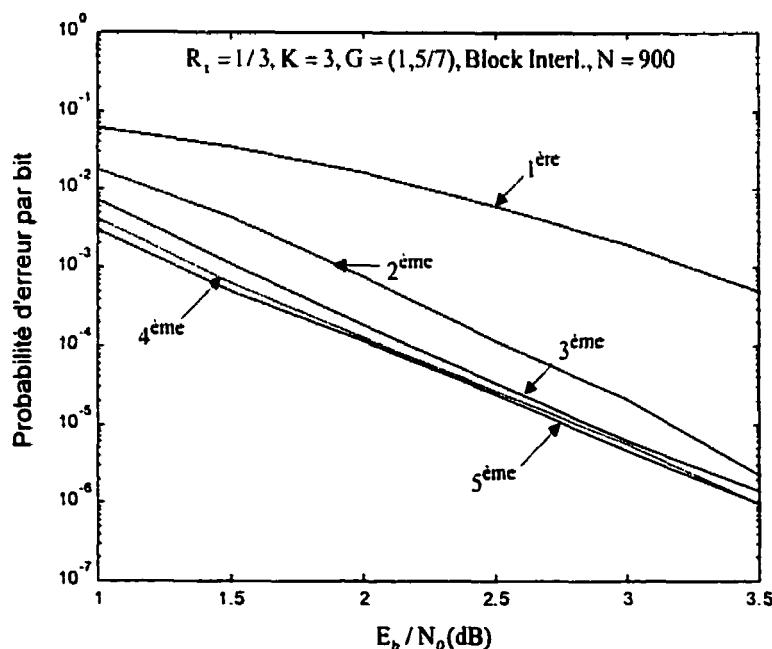

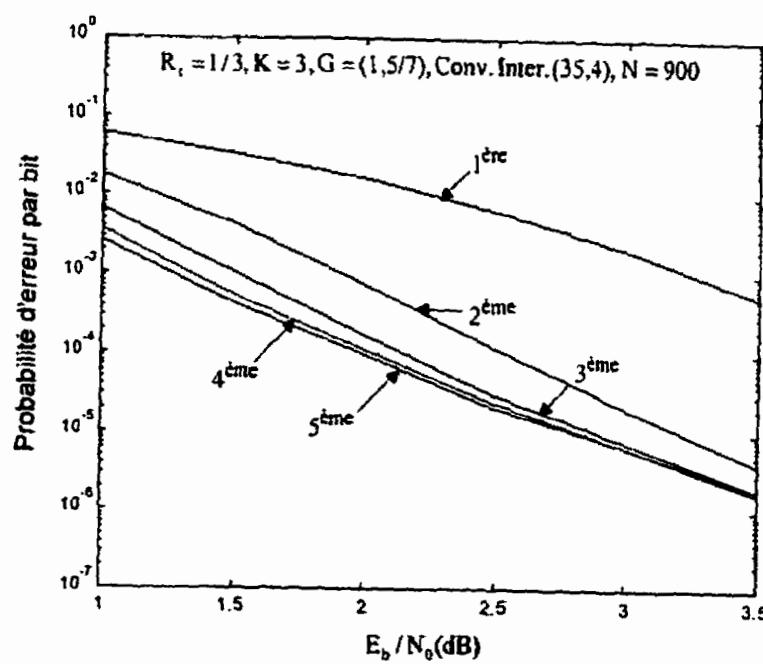

| <b>Figure 5.3 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur aléatoire, canal AWGN, <math>N = 900</math> .....</b>       | <b>74</b> |

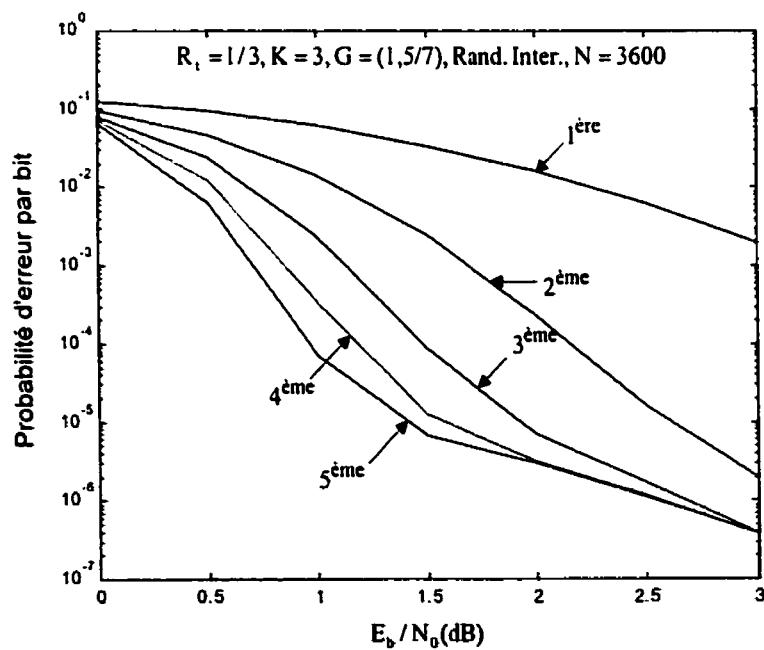

| <b>Figure 5.4 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur aléatoire, canal AWGN, <math>N = 3600</math> .....</b>      | <b>74</b> |

| <b>Figure 5.5 – BER, <math>R_t = 1/2</math>, <math>K = 3</math>, entrelaceur aléatoire, canal AWGN, <math>N = 196</math> .....</b>       | <b>75</b> |

| <b>Figure 5.6 – BER, <math>R_t = 1/2</math>, <math>K = 3</math>, entrelaceur aléatoire, canal AWGN, <math>N = 400</math> .....</b>       | <b>76</b> |

| <b>Figure 5.7 – BER, <math>R_t = 1/2</math>, <math>K = 3</math>, entrelaceur aléatoire, canal AWGN, <math>N = 900</math> .....</b>       | <b>76</b> |

| <b>Figure 5.8 – BER, <math>R_t = 1/2</math>, <math>K = 3</math>, entrelaceur aléatoire, canal AWGN, <math>N = 3600</math> .....</b>      | <b>77</b> |

| <b>Figure 5.9 – BER, <math>R_t = 1/3</math>, <math>K = 5</math>, entrelaceur aléatoire, canal AWGN, <math>N = 900</math> .....</b>       | <b>78</b> |

| <b>Figure 5.10 – BER, <math>R_t = 1/2</math>, <math>K = 5</math>, entrelaceur aléatoire, canal AWGN, <math>N = 900</math> .....</b>      | <b>78</b> |

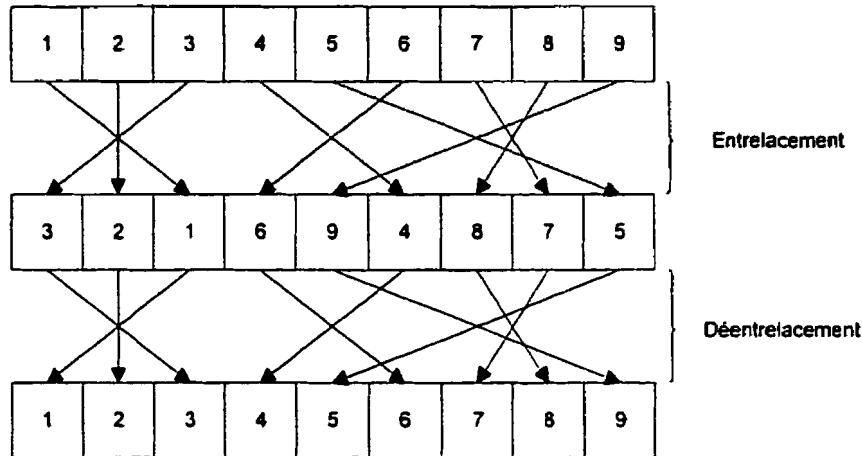

| <b>Figure 5.11 – Un processus d'entrelacement symétrique .....</b>                                                                       | <b>80</b> |

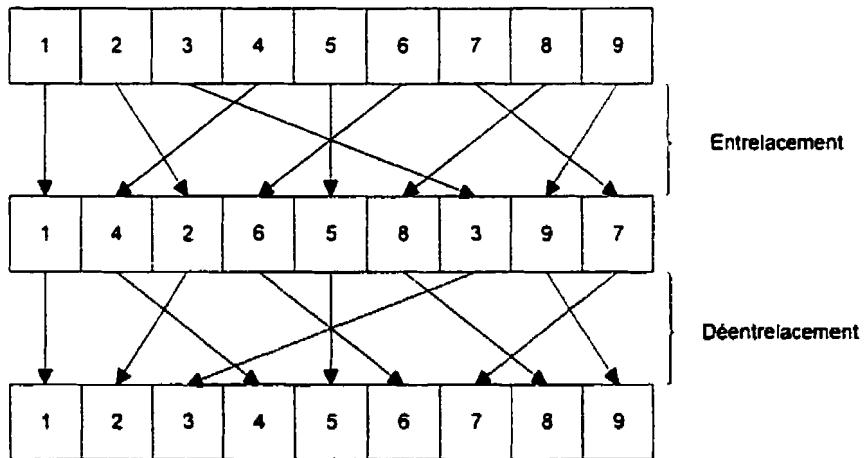

| <b>Figure 5.12 – Un processus d'entrelacement non symétrique .....</b>                                                                   | <b>80</b> |

|                                                                                                                                          |            |

|------------------------------------------------------------------------------------------------------------------------------------------|------------|

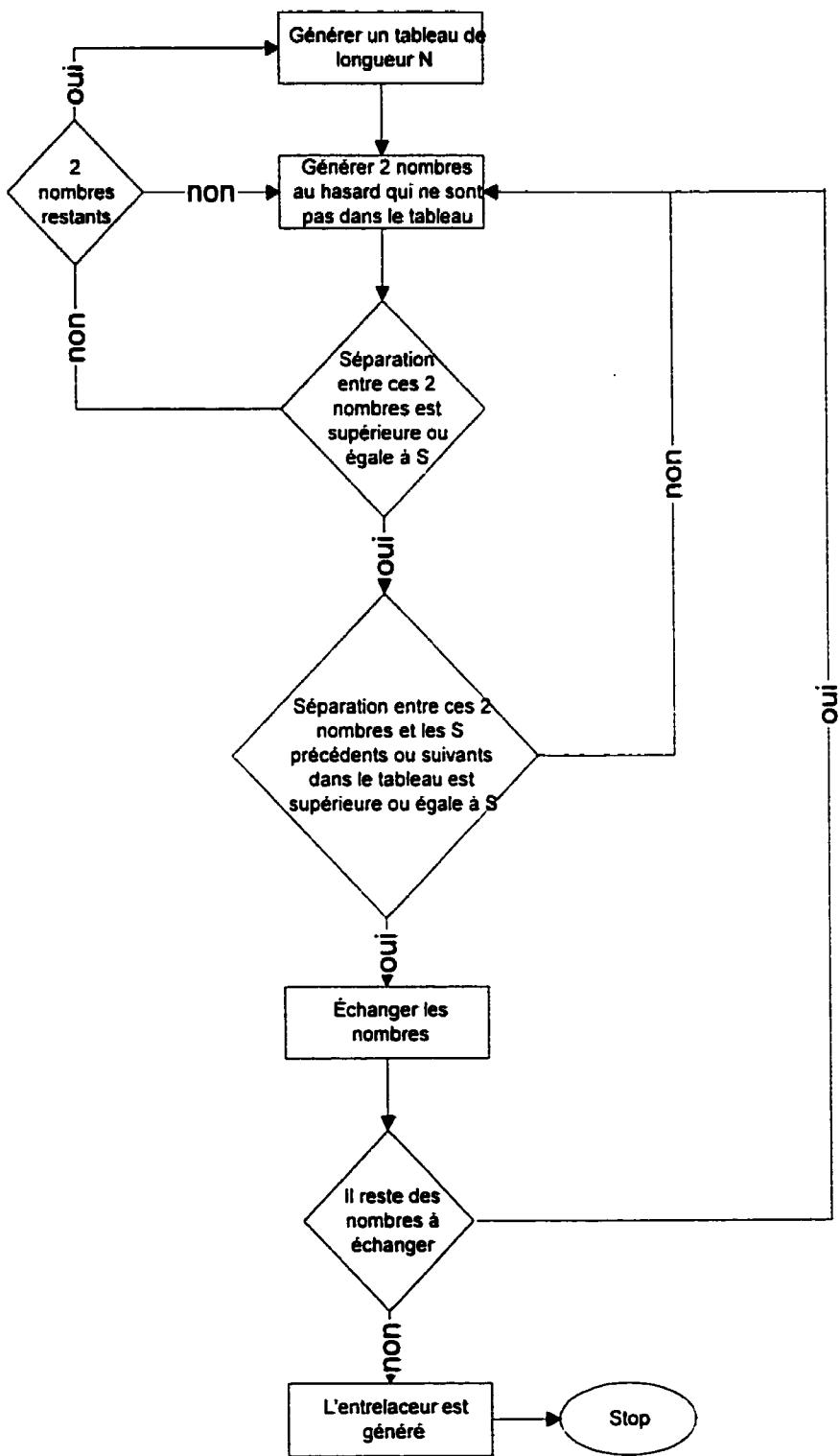

| <b>Figure 5.13 – Algorithme de l'entrelaceur symétrique S .....</b>                                                                      | <b>82</b>  |

| <b>Figure 5.14 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, ent. symétrique (3), canal AWGN, <math>N = 196</math> .....</b>        | <b>85</b>  |

| <b>Figure 5.15 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, ent. symétrique (7), canal AWGN, <math>N = 196</math> .....</b>        | <b>86</b>  |

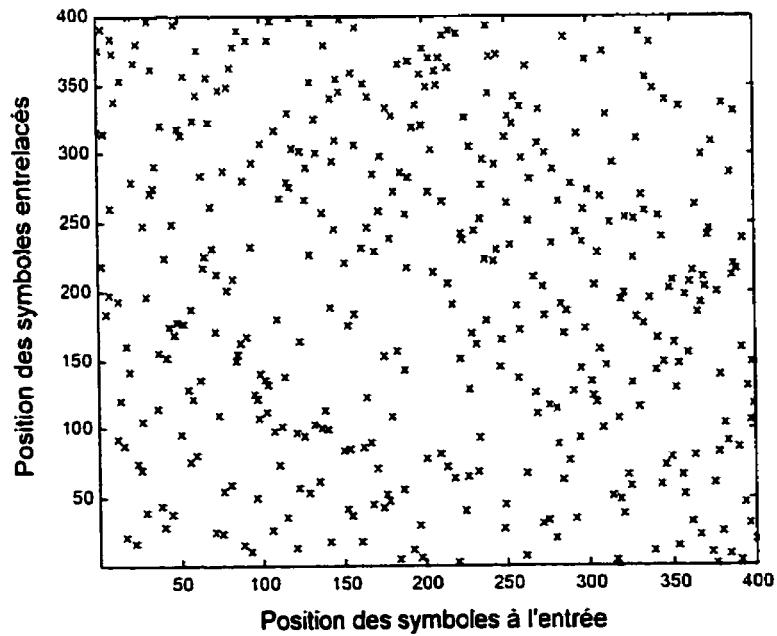

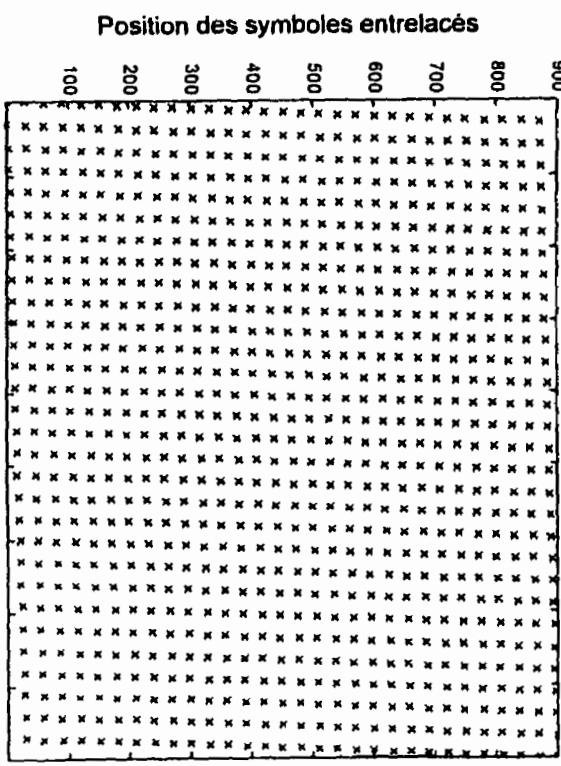

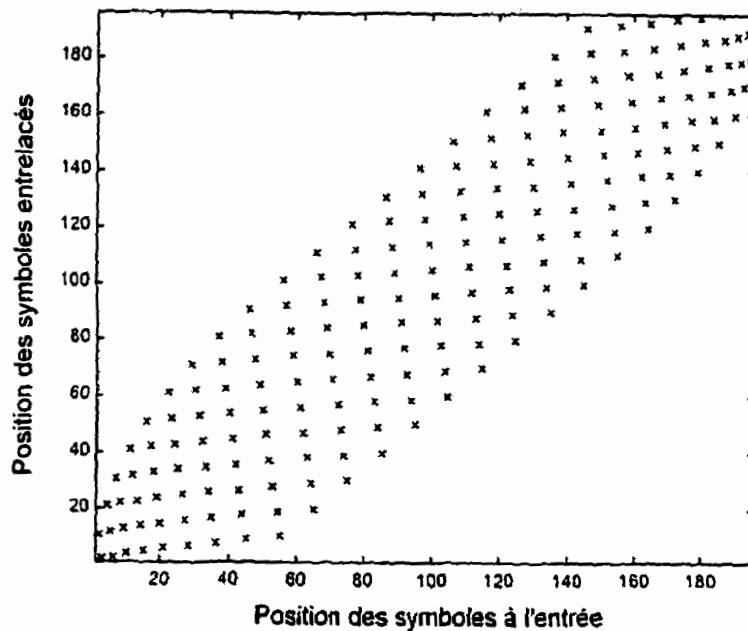

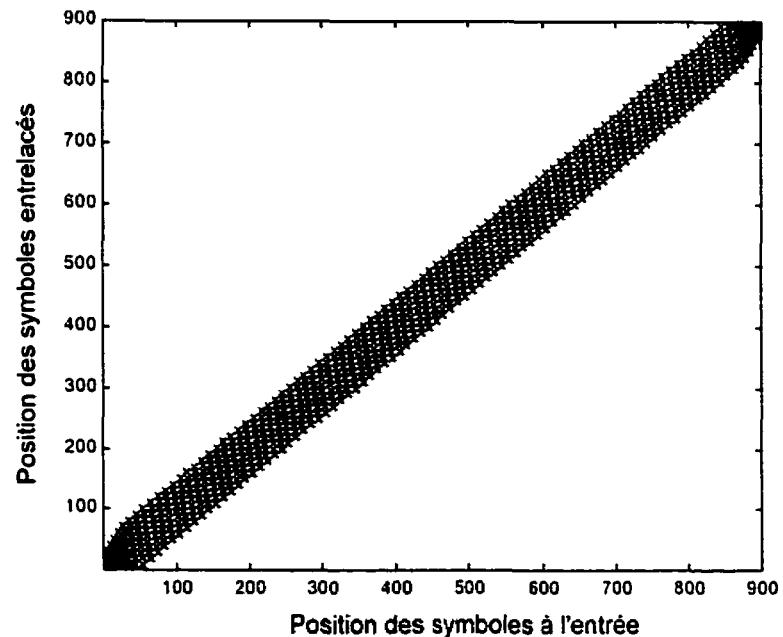

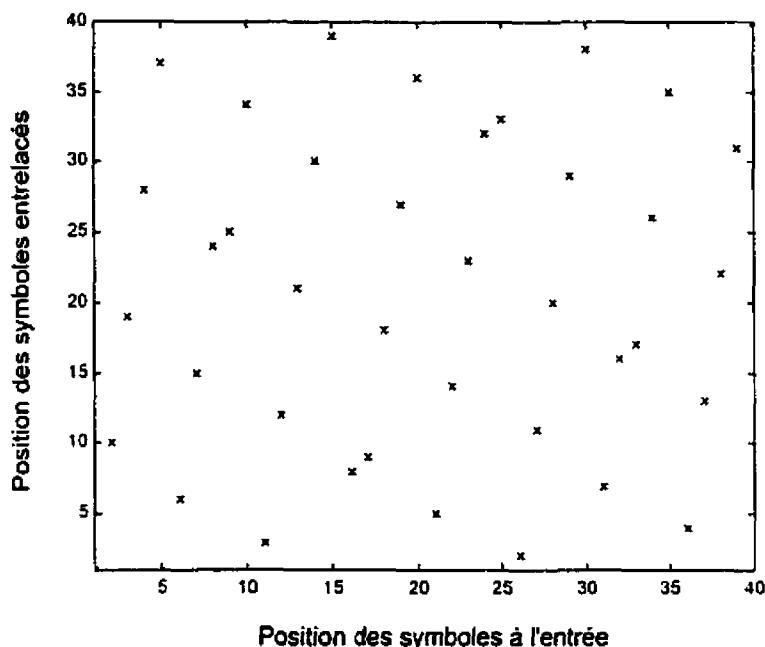

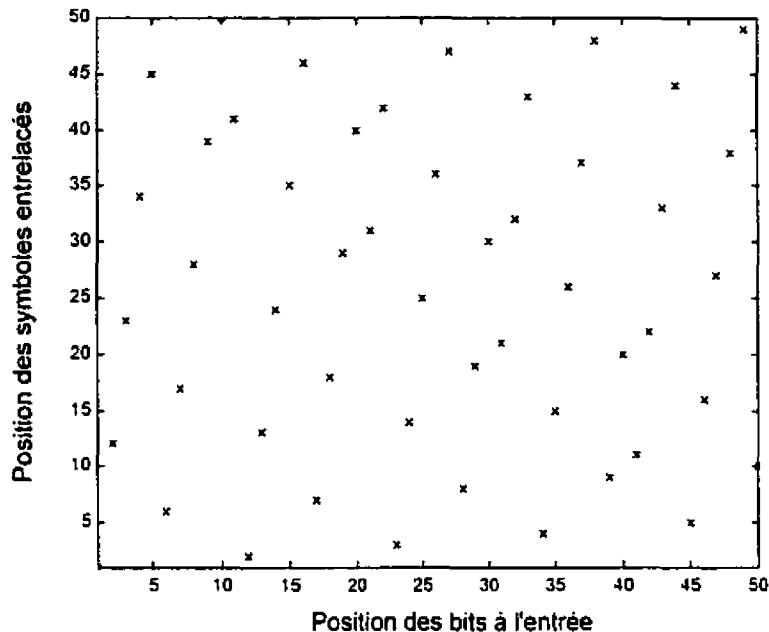

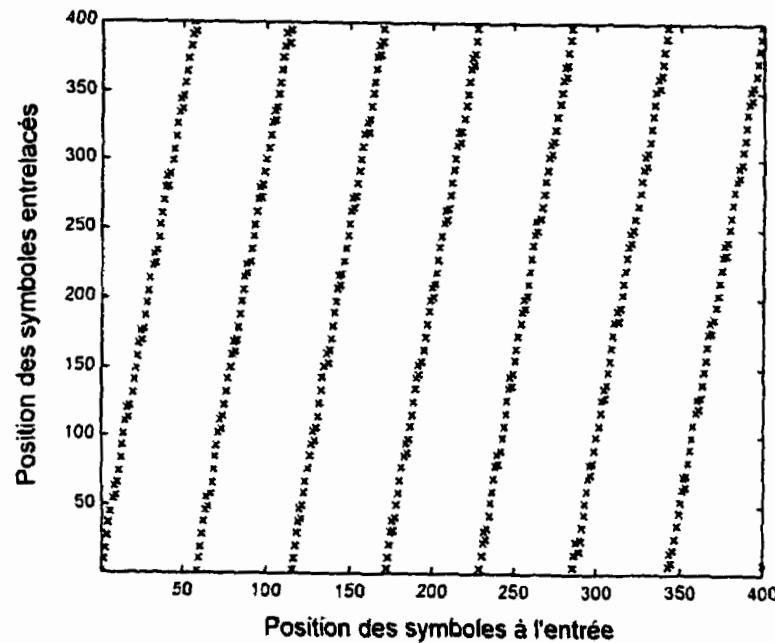

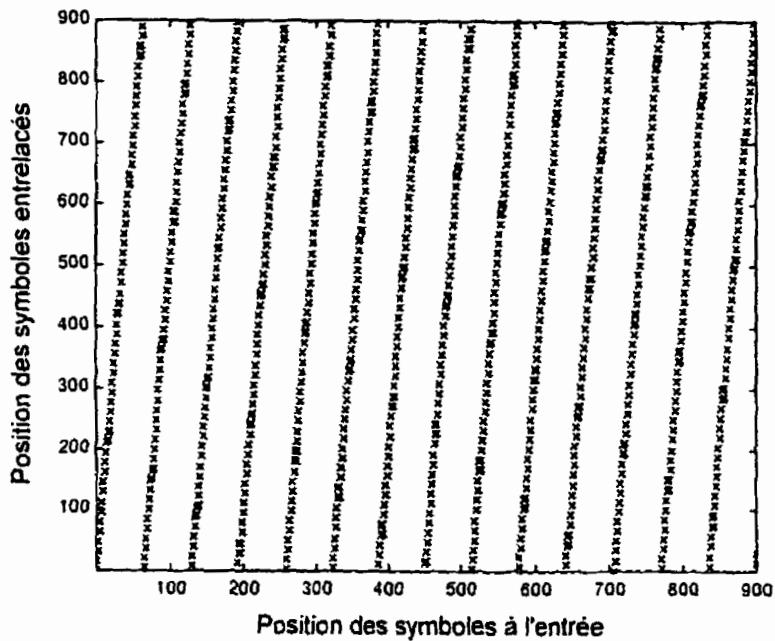

| <b>Figure 5.16 – Facteur d'étalement, entrelaceur symétrique <math>S = 3</math>, <math>N = 196</math> .....</b>                          | <b>86</b>  |

| <b>Figure 5.17 – Facteur d'étalement, entrelaceur symétrique <math>S = 7</math>, <math>N = 196</math> .....</b>                          | <b>87</b>  |

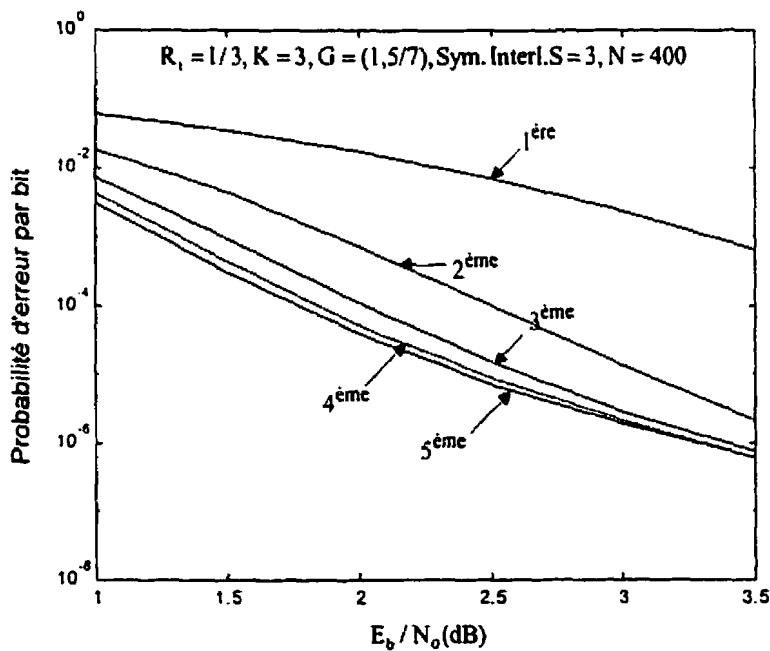

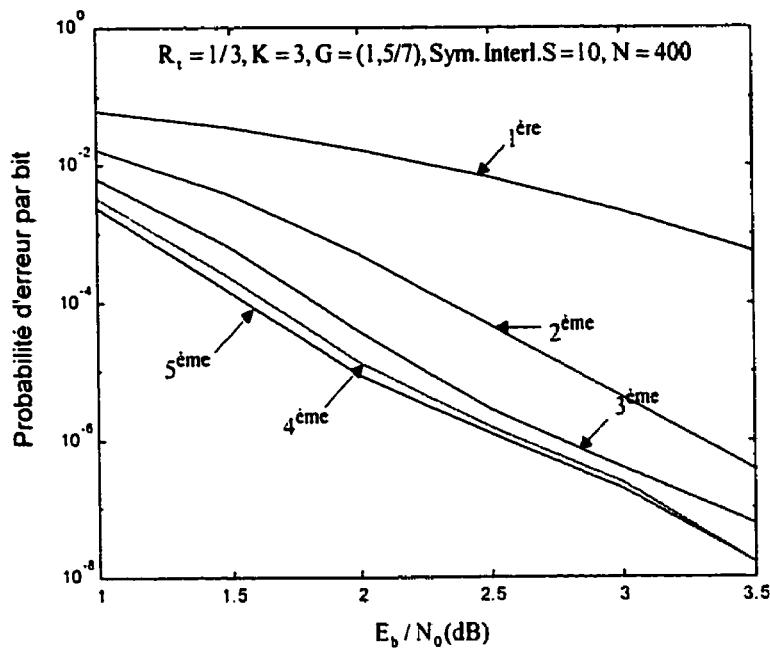

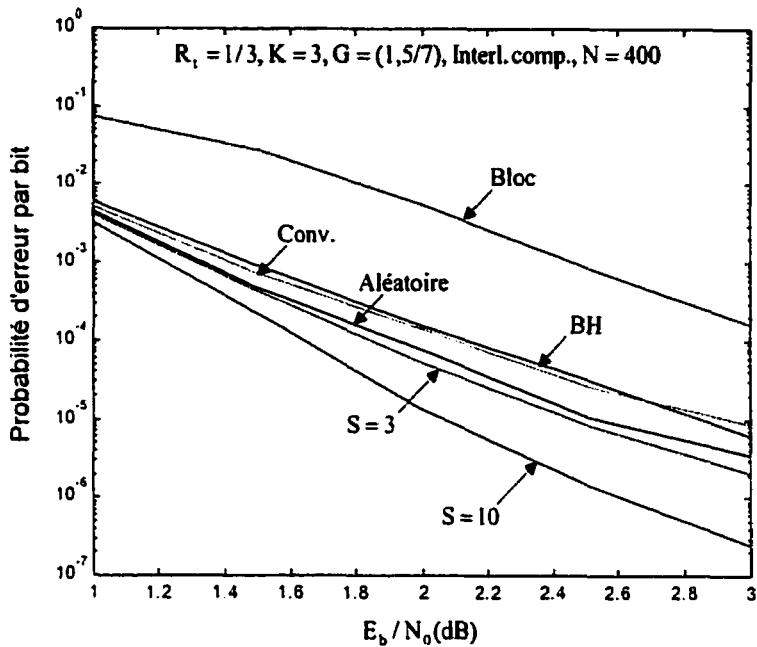

| <b>Figure 5.18 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, ent. symétrique (3), canal AWGN, <math>N = 400</math> .....</b>        | <b>88</b>  |

| <b>Figure 5.19 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, ent. symétrique (10), canal AWGN, <math>N = 400</math> .....</b>       | <b>89</b>  |

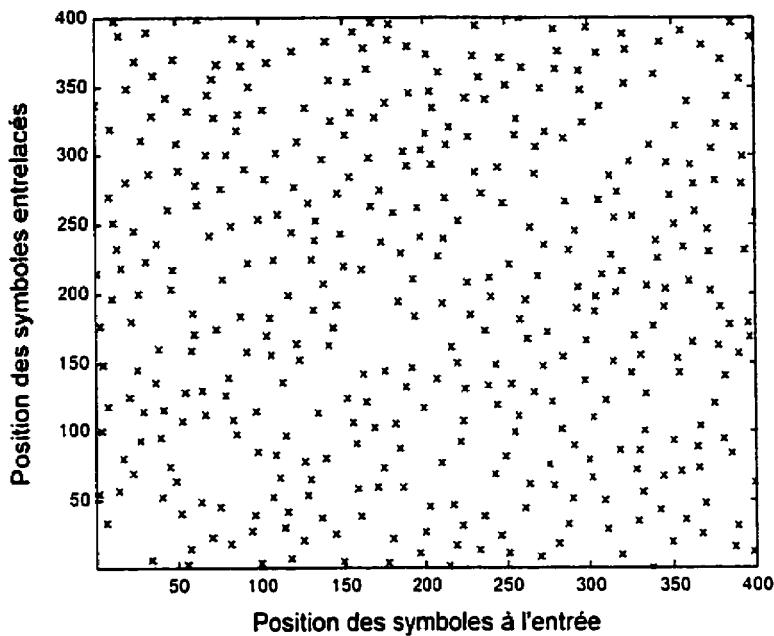

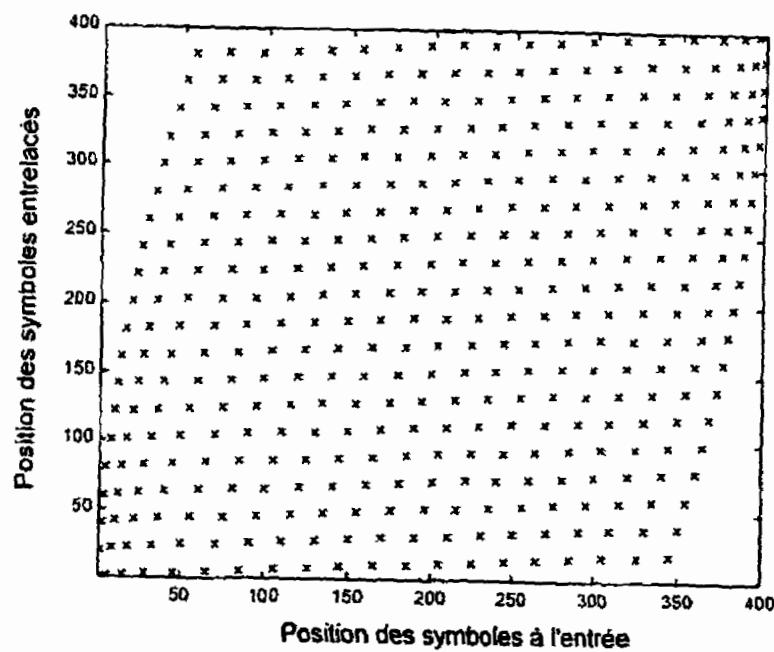

| <b>Figure 5.20 – Facteur d'étalement, entrelaceur symétrique <math>S = 3</math>, <math>N = 400</math> .....</b>                          | <b>89</b>  |

| <b>Figure 5.21 – Facteur d'étalement, entrelaceur symétrique <math>S = 10</math>, <math>N = 400</math> .....</b>                         | <b>90</b>  |

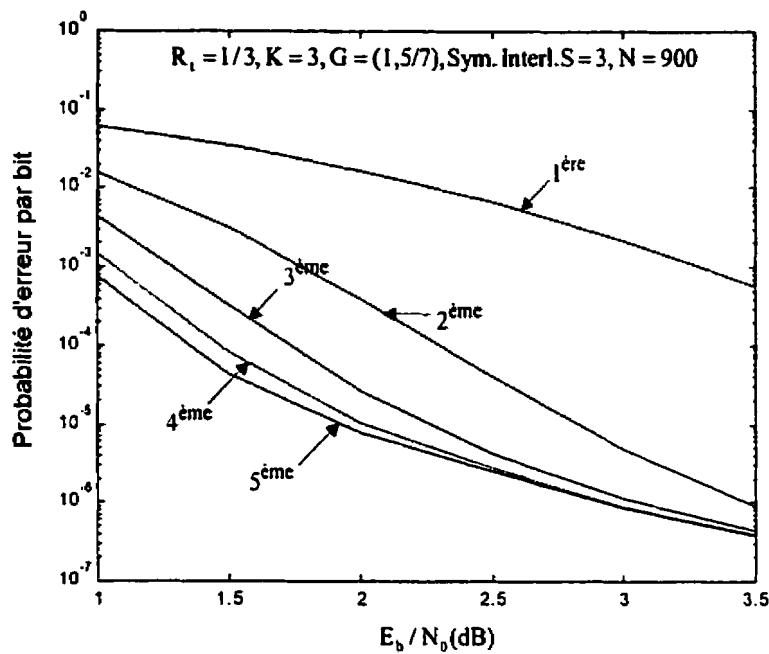

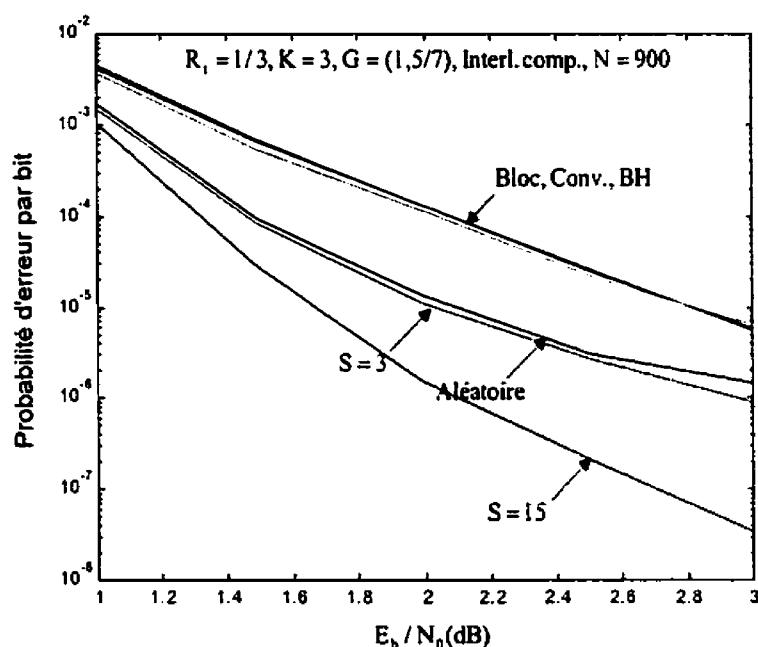

| <b>Figure 5.22 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, ent. symétrique (3), canal AWGN, <math>N = 900</math> .....</b>        | <b>91</b>  |

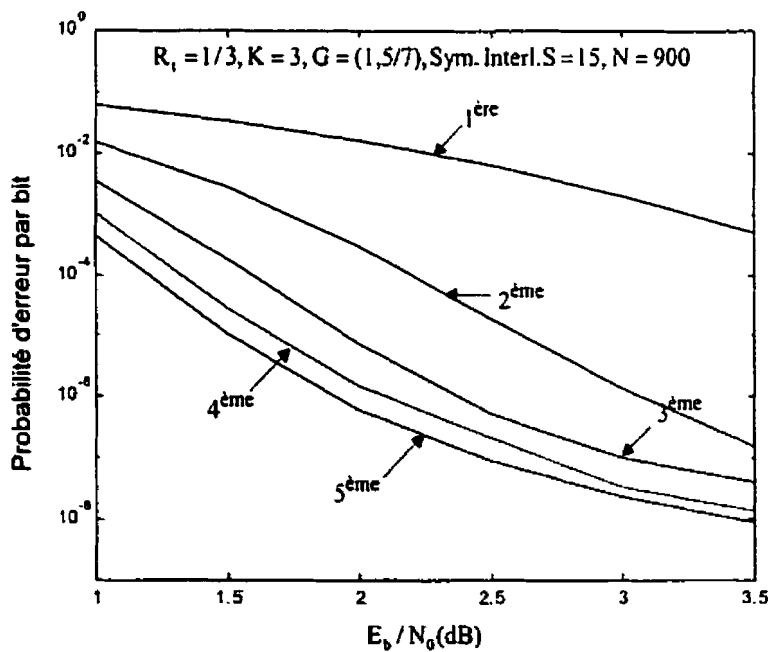

| <b>Figure 5.23 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, ent. symétrique (15), canal AWGN, <math>N = 900</math> .....</b>       | <b>91</b>  |

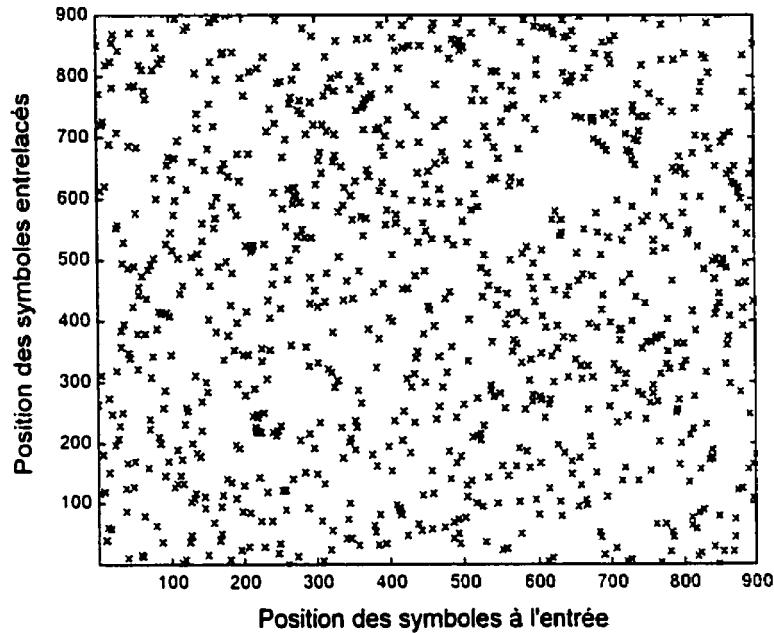

| <b>Figure 5.24 – Facteur d'étalement, entrelaceur symétrique <math>S = 3</math>, <math>N = 900</math> .....</b>                          | <b>92</b>  |

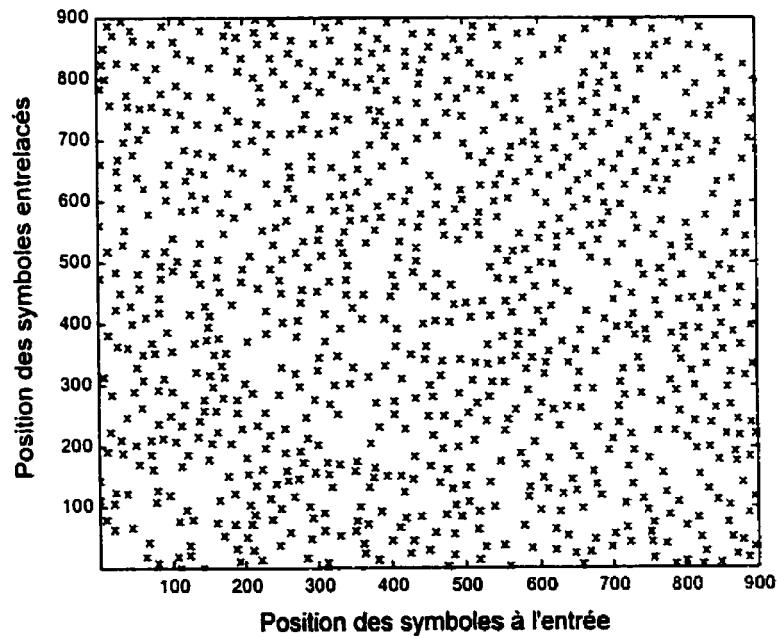

| <b>Figure 5.25 – Facteur d'étalement, entrelaceur symétrique <math>S = 15</math>, <math>N = 900</math> .....</b>                         | <b>92</b>  |

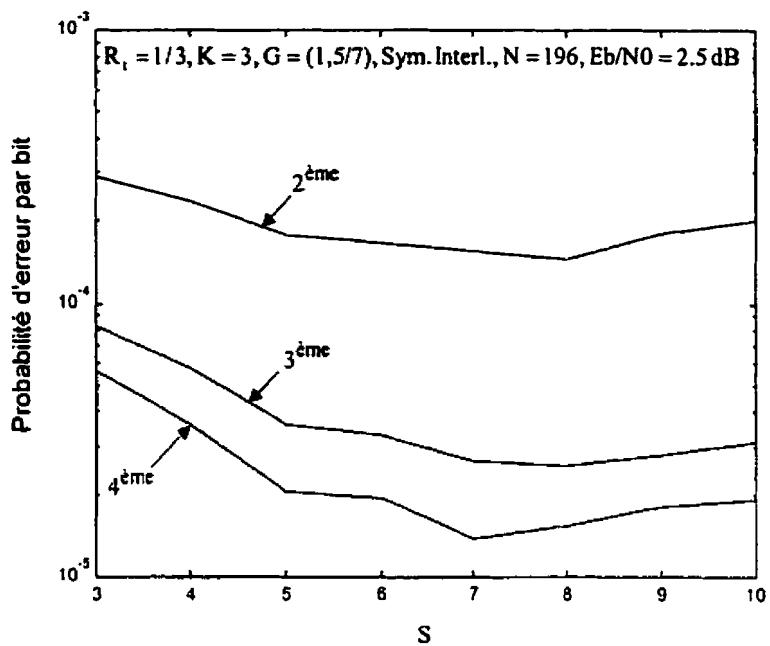

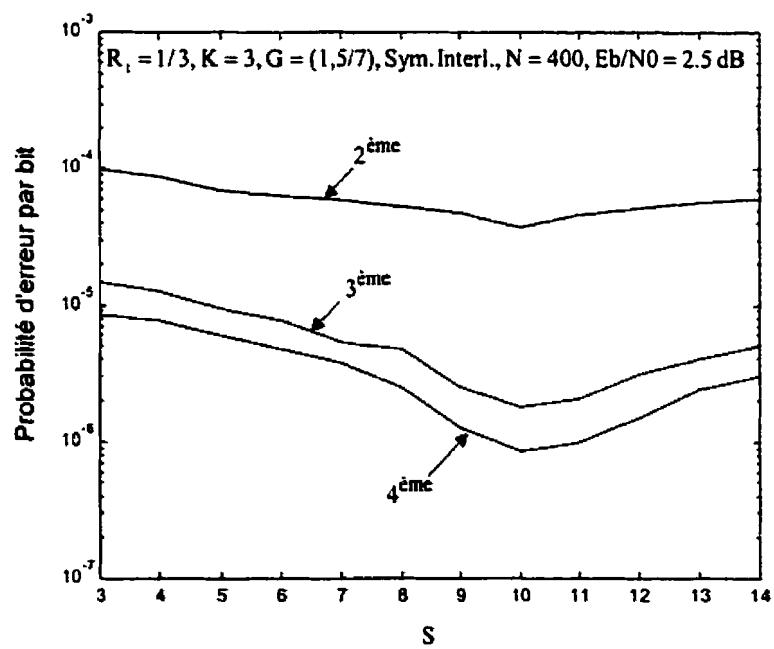

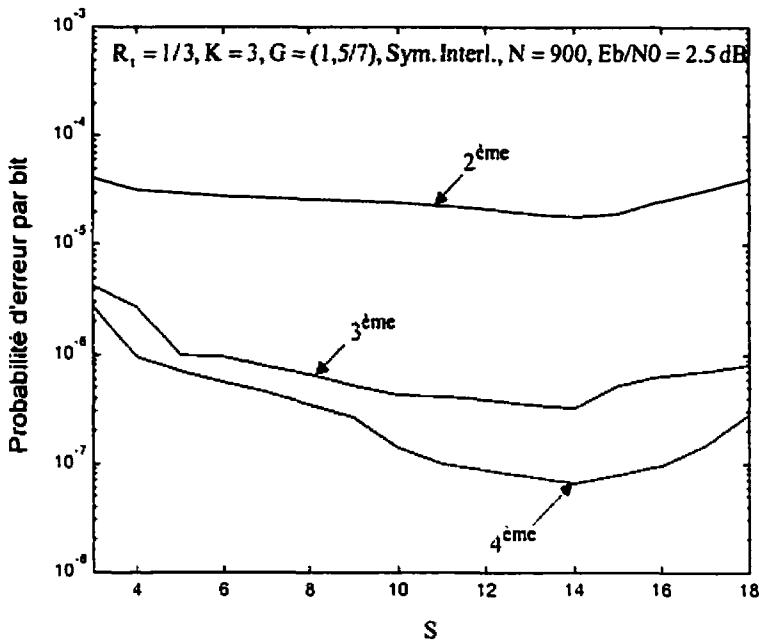

| <b>Figure 5.26 – Comparaison des entrelaceurs symétriques, <math>N = 196</math>, 2.5 dB .....</b>                                        | <b>94</b>  |

| <b>Figure 5.27 – Comparaison des entrelaceurs symétriques, <math>N = 400</math>, 2.5 dB .....</b>                                        | <b>94</b>  |

| <b>Figure 5.28 – Comparaison des entrelaceurs symétriques, <math>N = 900</math>, 2.5 dB .....</b>                                        | <b>95</b>  |

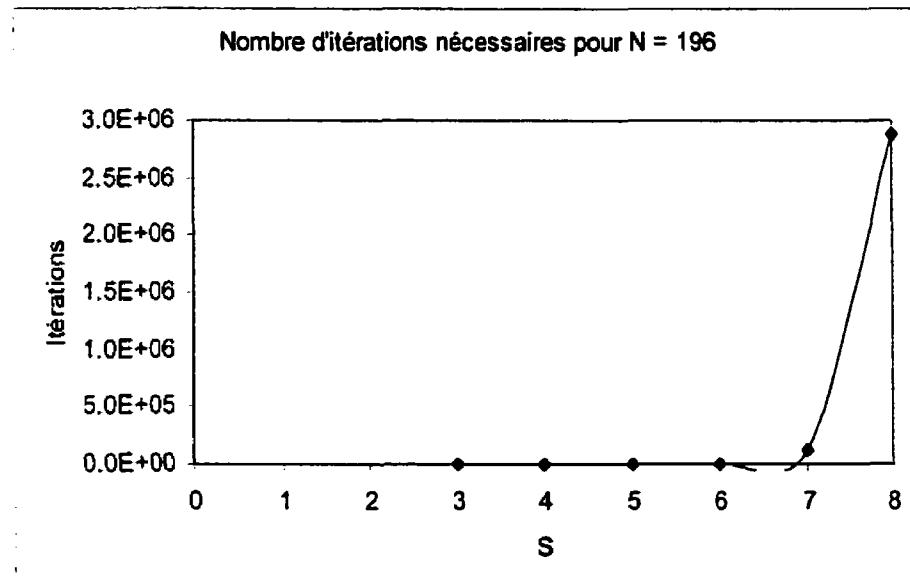

| <b>Figure 5.29 – Nombre d'itérations en fonction de <math>S</math> pour <math>N = 196</math> .....</b>                                   | <b>96</b>  |

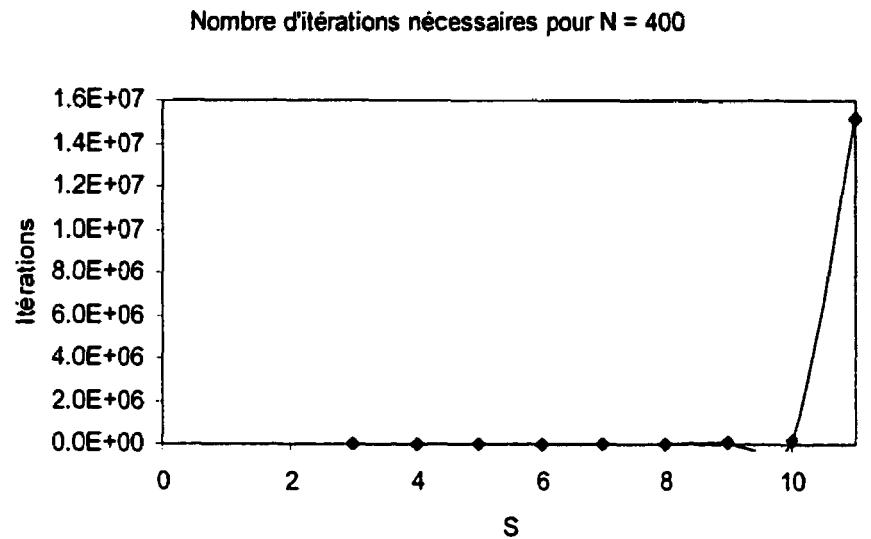

| <b>Figure 5.30 – Nombre d'itérations en fonction de <math>S</math> pour <math>N = 400</math> .....</b>                                   | <b>97</b>  |

| <b>Figure 5.31 – Nombre d'itérations en fonction de <math>S</math> pour <math>N = 900</math> .....</b>                                   | <b>97</b>  |

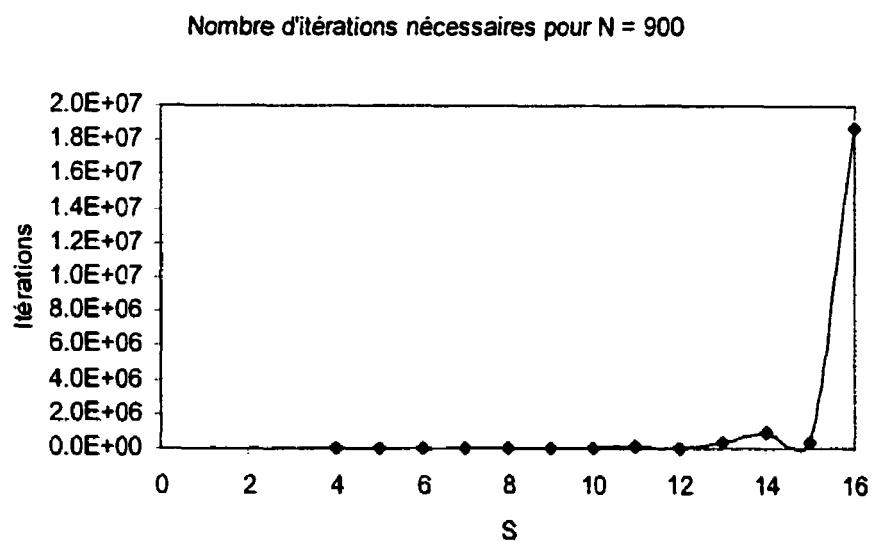

| <b>Figure 6.1 – Entrelacement bloc .....</b>                                                                                             | <b>99</b>  |

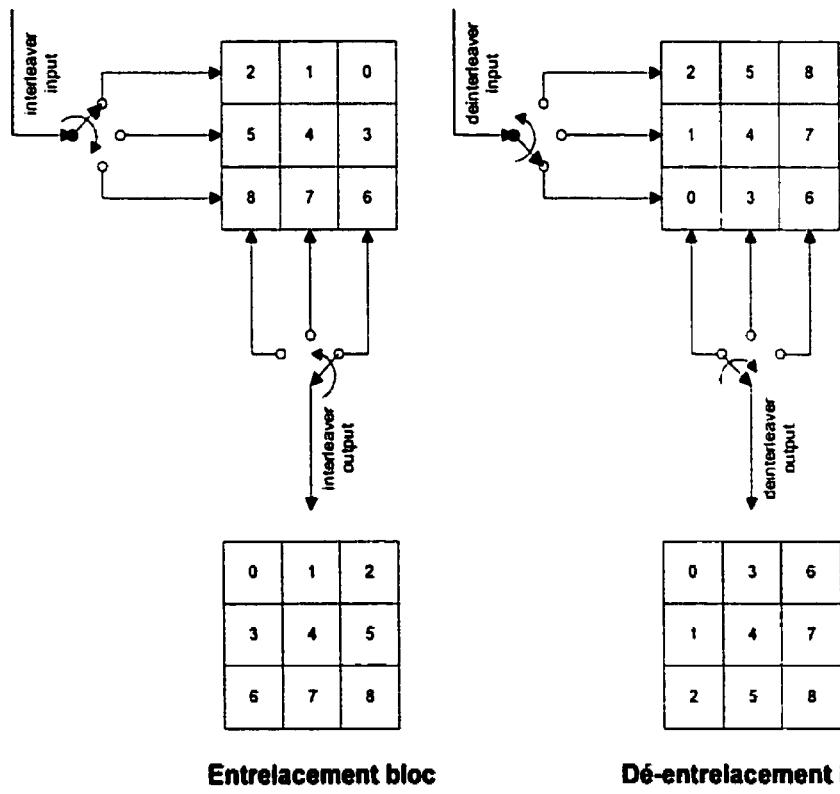

| <b>Figure 6.2 – Processus d'entrelacement bloc .....</b>                                                                                 | <b>100</b> |

| <b>Figure 6.3 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur bloc, canal AWGN, <math>N = 196</math> .....</b>            | <b>101</b> |

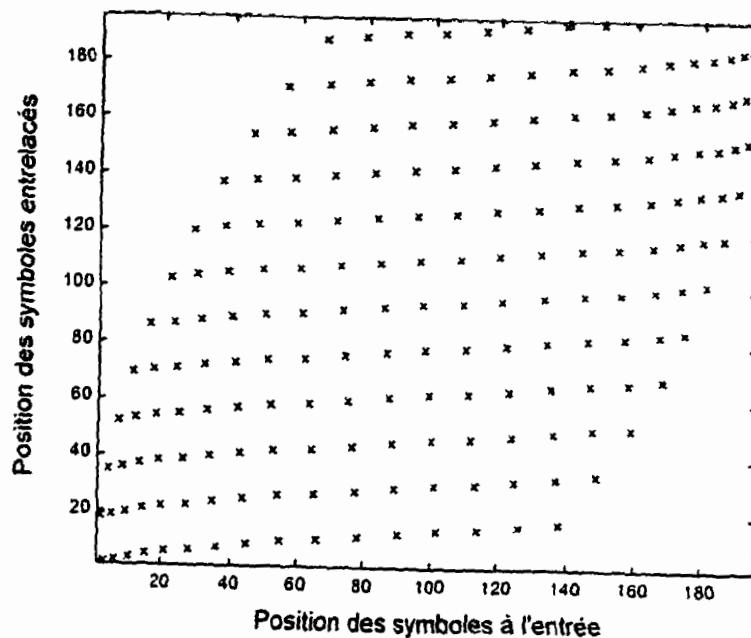

| <b>Figure 6.4 – Facteur d'étalement, entrelaceur bloc, <math>N = 196</math> .....</b>                                                    | <b>102</b> |

| <b>Figure 6.5 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur bloc, canal AWGN, <math>N = 400</math> .....</b>            | <b>103</b> |

| <b>Figure 6.6 – Facteur d'étalement, entrelaceur bloc, <math>N = 400</math> .....</b>                                                    | <b>104</b> |

| <b>Figure 6.7 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur bloc, canal AWGN, <math>N = 900</math> .....</b>            | <b>105</b> |

| <b>Figure 6.8 – Facteur d'étalement, entrelaceur bloc, <math>N = 900</math> .....</b>                                                    | <b>106</b> |

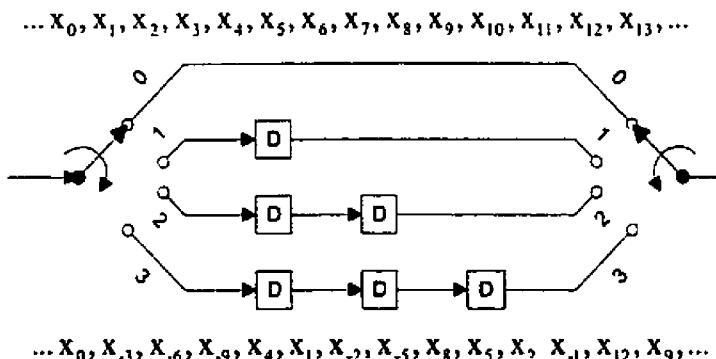

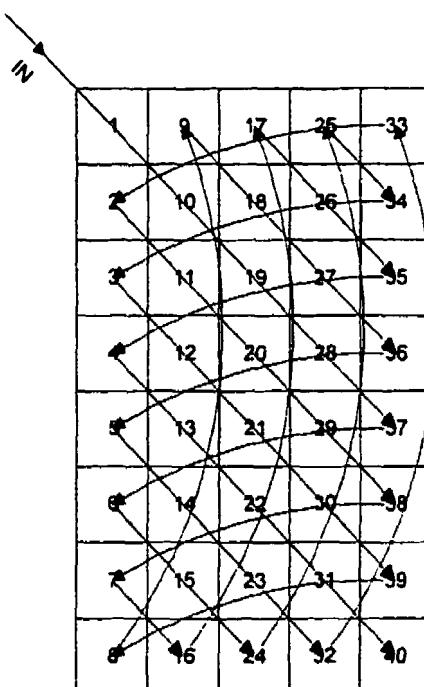

| <b>Figure 6.9 - Processus d'entrelacement convolutionnel (<math>m = 4</math>, <math>D = 1</math> bit) .....</b>                          | <b>107</b> |

| <b>Figure 6.10 - Matrice de l'entrelacement convolutionnel <math>m = 4</math>, <math>D = 1</math> .....</b>                              | <b>107</b> |

| <b>Figure 6.11 - Séquence de sortie de l'entrelacement convolutionnel <math>m = 4</math>, <math>D = 1</math> .....</b>                   | <b>108</b> |

| <b>Figure 6.12 - Matrice de l'entrelacement convolutionnel <math>m = 4</math>, <math>D = 2</math> .....</b>                              | <b>108</b> |

| <b>Figure 6.13 - Séquence de sortie de l'entrelacement convolutionnel <math>m = 4</math>, <math>D = 2</math> .....</b>                   | <b>108</b> |

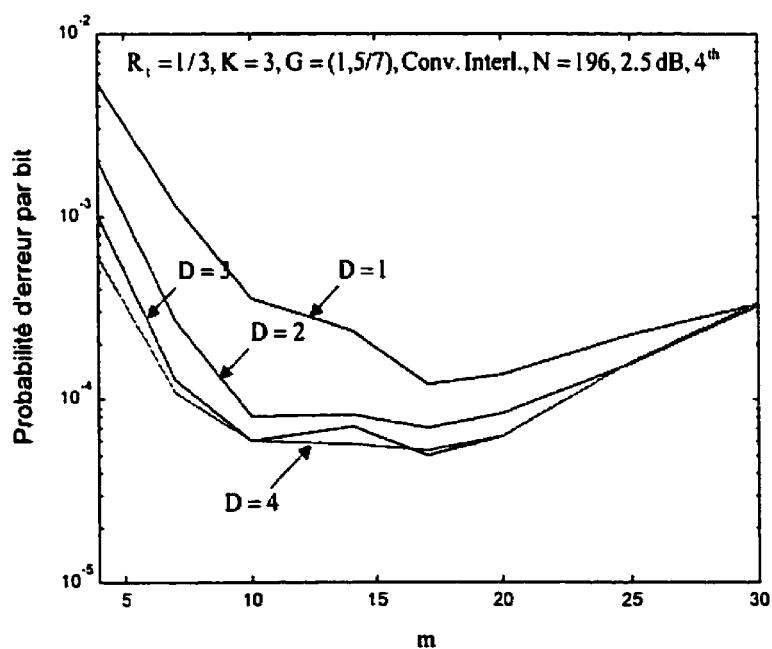

| <b>Figure 6.14 – BER de l'entrelaceur convolutionnel en fonction de <math>m</math> et <math>D</math> pour <math>N = 196</math> .....</b> | <b>111</b> |

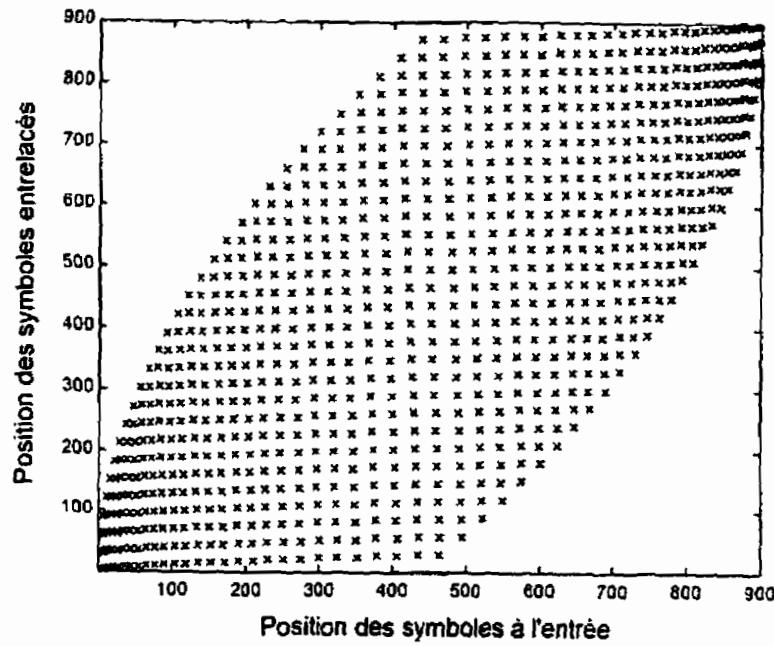

| <b>Figure 6.15 – Facteur d'étalement, entrelaceur convolutionnel (10,1), <math>N = 196</math> .....</b>                                  | <b>113</b> |

| <b>Figure 6.16 – Facteur d'étalement, entrelaceur convolutionnel (17,1), <math>N = 196</math> .....</b>                                  | <b>114</b> |

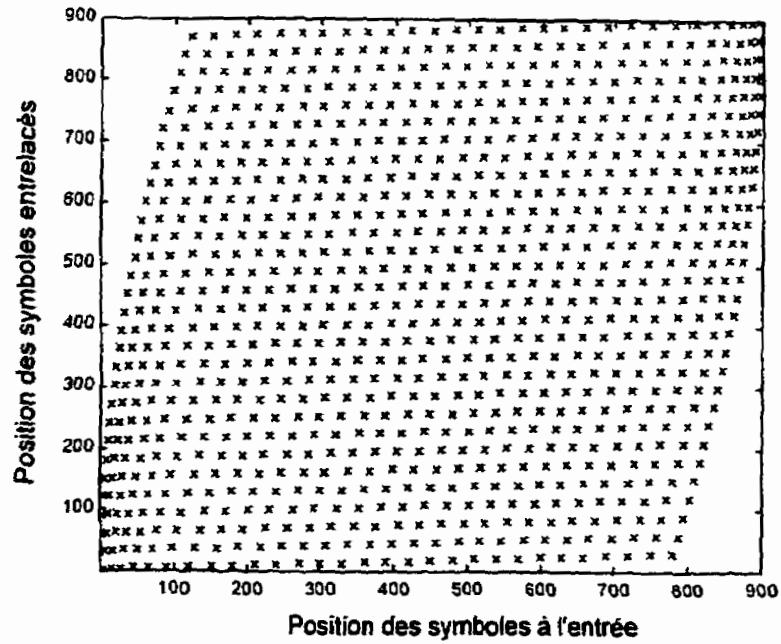

|                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------|-----|

| <b>Figure 6.17 – Facteur d'étalement, entrelaceur convolutionnel (17,4), N = 196 .....</b>                     | 114 |

| <b>Figure 6.18 – Facteur d'étalement, entrelaceur convolutionnel (30,4), N = 196 .....</b>                     | 115 |

| <b>Figure 6.19 – BER, <math>R_t = 1/3</math>, K = 3, ent. convolutionnel (17,4), canal AWGN, N = 196 .....</b> | 115 |

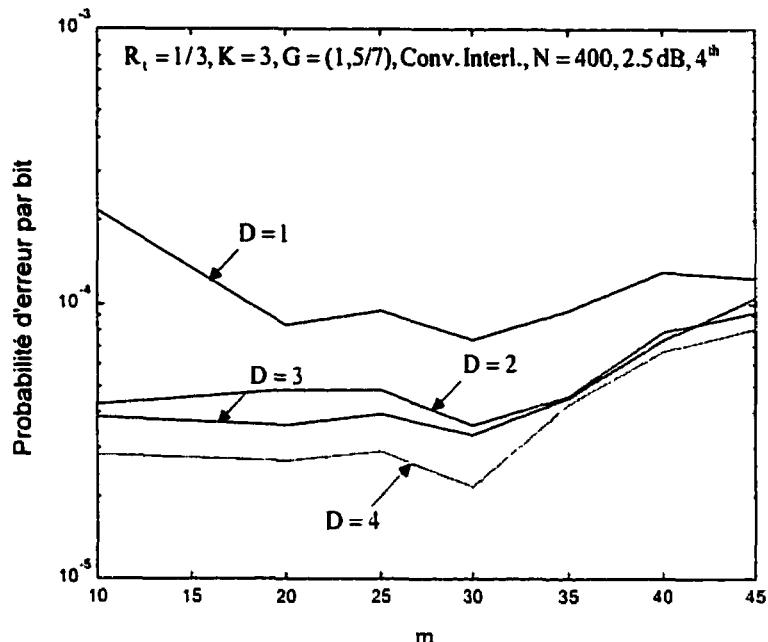

| <b>Figure 6.20 – BER de l'entrelaceur convolutionnel en fonction de m et D pour N = 400.....</b>               | 117 |

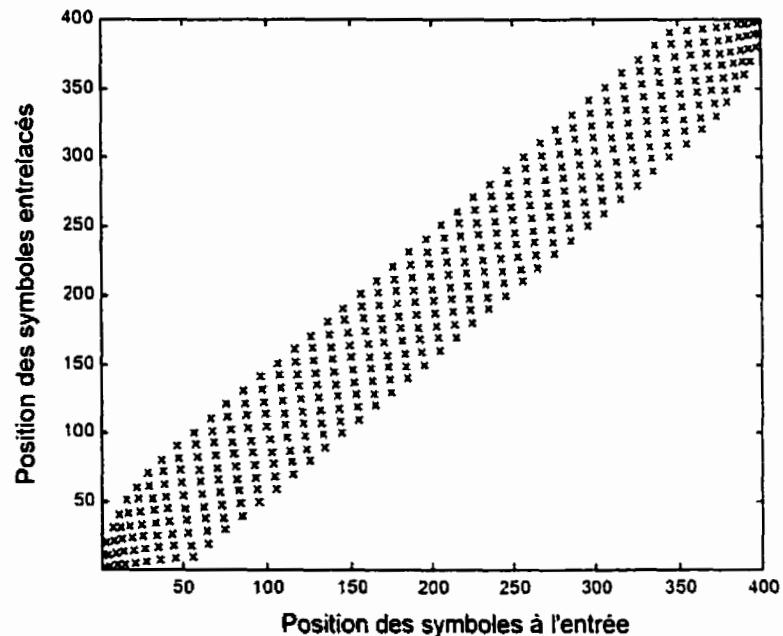

| <b>Figure 6.21 – Facteur d'étalement, entrelaceur convolutionnel (10,1), N = 400 .....</b>                     | 118 |

| <b>Figure 6.22 – Facteur d'étalement, entrelaceur convolutionnel (30,1), N = 400 .....</b>                     | 119 |

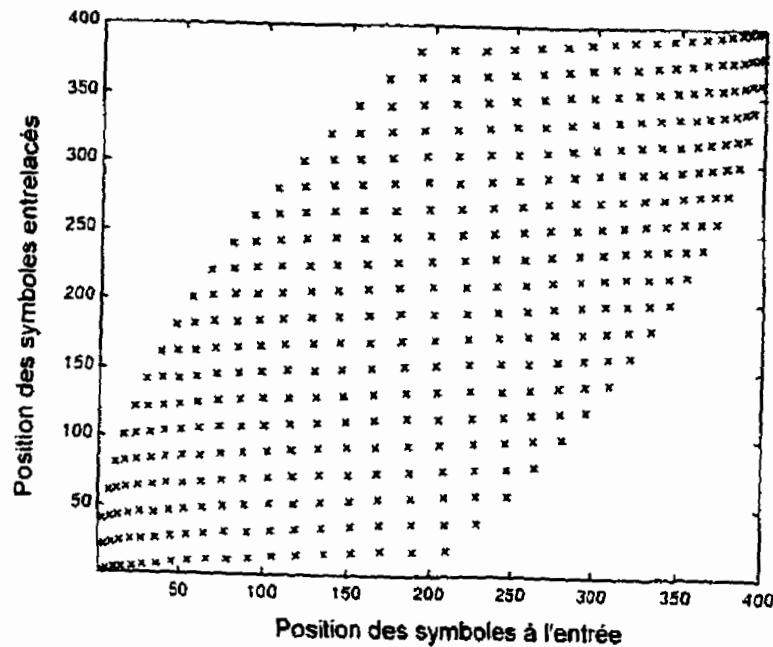

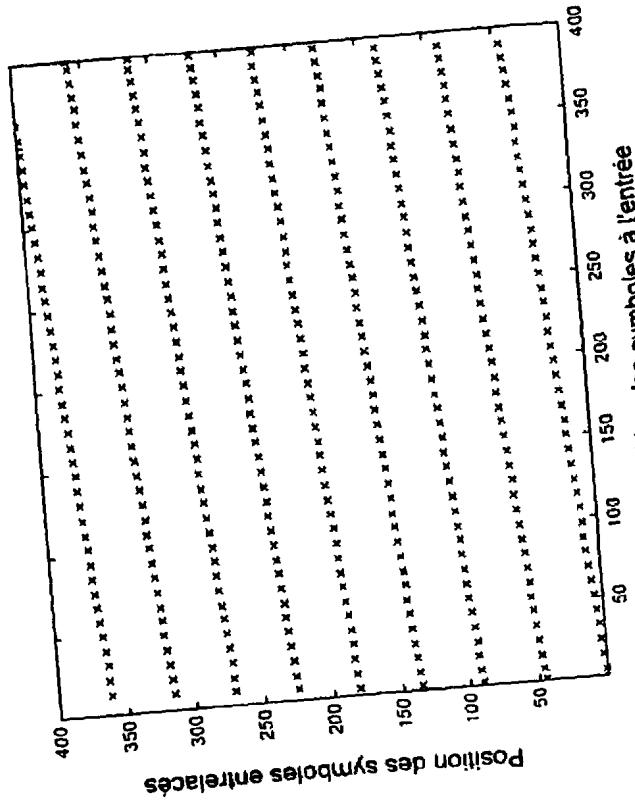

| <b>Figure 6.23 – Facteur d'étalement, entrelaceur convolutionnel (30,4), N = 400 .....</b>                     | 119 |

| <b>Figure 6.24 – Facteur d'étalement, entrelaceur convolutionnel (45,4), N = 400 .....</b>                     | 120 |

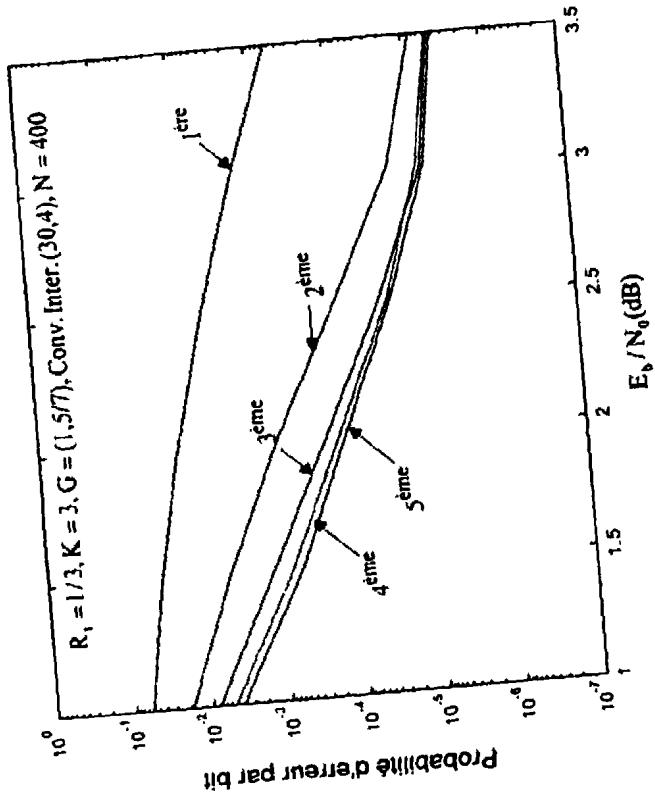

| <b>Figure 6.25 – BER, <math>R_t = 1/3</math>, K = 3, ent. convolutionnel (30,4), canal AWGN, N = 400 .....</b> | 120 |

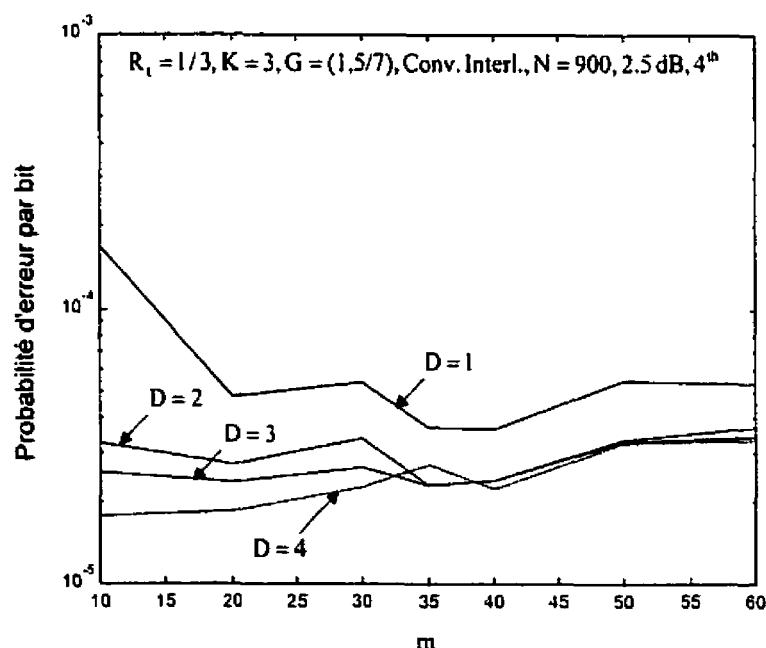

| <b>Figure 6.26 – BER de l'entrelaceur convolutionnel en fonction de m et D pour N = 900.....</b>               | 121 |

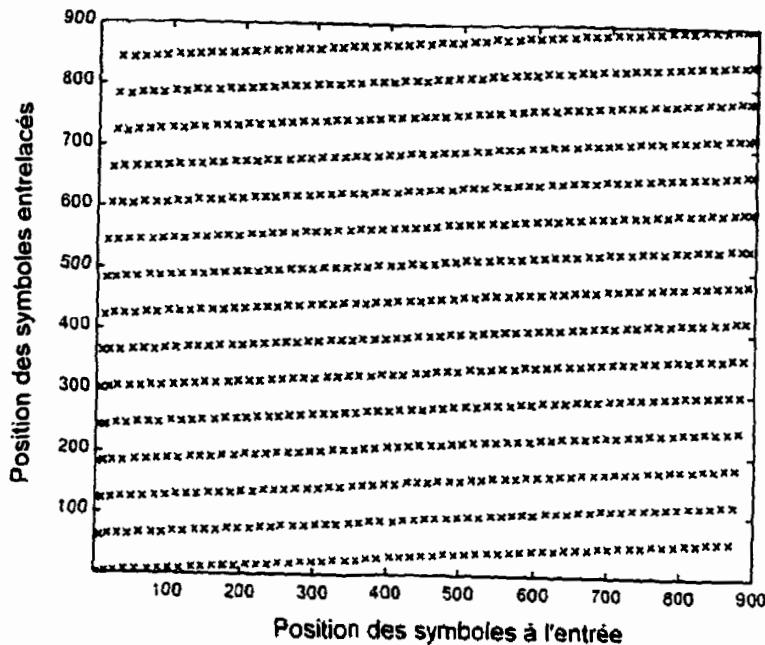

| <b>Figure 6.27 – Facteur d'étalement, entrelaceur convolutionnel (10,1), N = 900 .....</b>                     | 122 |

| <b>Figure 6.28 – Facteur d'étalement, entrelaceur convolutionnel (35,1), N = 900 .....</b>                     | 123 |

| <b>Figure 6.29 – Facteur d'étalement, entrelaceur convolutionnel (35,4), N = 900 .....</b>                     | 123 |

| <b>Figure 6.30 – Facteur d'étalement, entrelaceur convolutionnel (60,4), N = 900 .....</b>                     | 124 |

| <b>Figure 6.31 – BER, <math>R_t = 1/3</math>, K = 3, ent. convolutionnel (35,4), canal AWGN, N = 900 .....</b> | 124 |

| <b>Figure 7.1 – Matrice du processus d'entrelacement hélicoïdal H(4,3) .....</b>                               | 127 |

| <b>Figure 7.2 – Séquence de sortie de l'entrelaceur hélicoïdal H(4,3) .....</b>                                | 127 |

| <b>Figure 7.3 – Matrice du processus d'entrelacement hélicoïdal H(8,5) .....</b>                               | 129 |

| <b>Figure 7.4 – Séquence de sortie de l'entrelaceur hélicoïdal H(8,5) .....</b>                                | 130 |

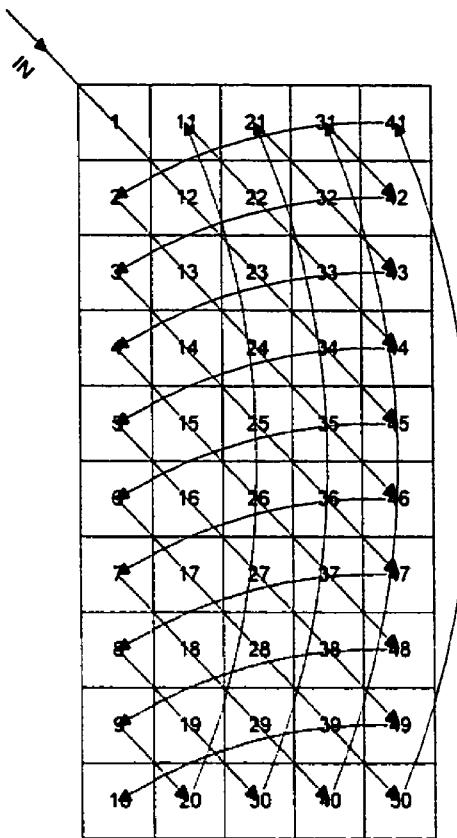

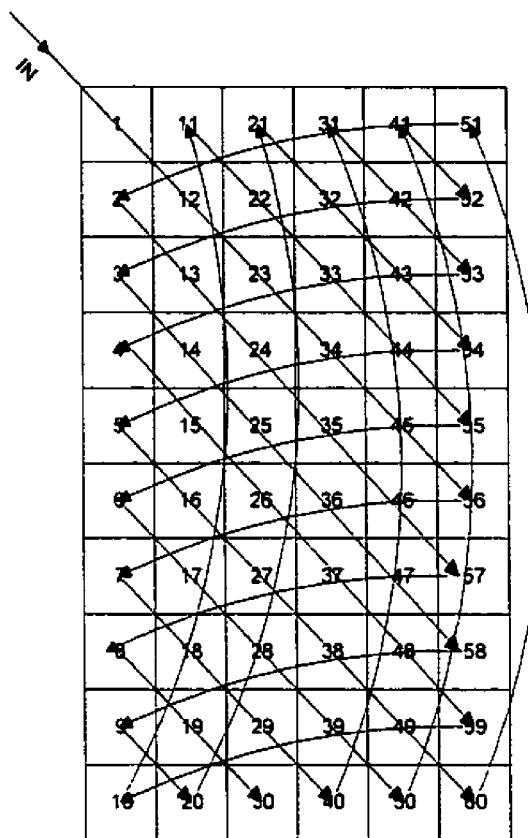

| <b>Figure 7.5 – Processus d'entrelacement BH(8,5) .....</b>                                                    | 133 |

| <b>Figure 7.6 – Séquence de sortie de l'entrelaceur BH(8,5) .....</b>                                          | 133 |

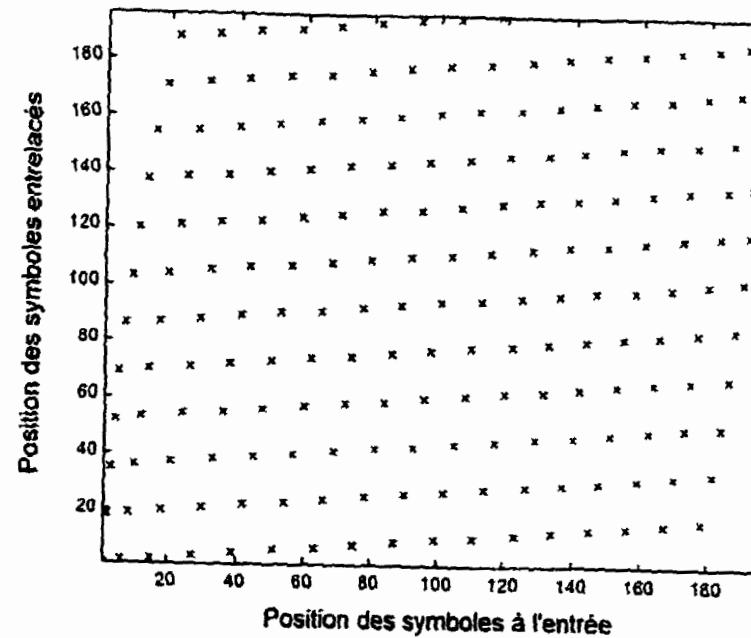

| <b>Figure 7.7 – Facteur d'étalement de l'entrelaceur BH(8,5) .....</b>                                         | 134 |

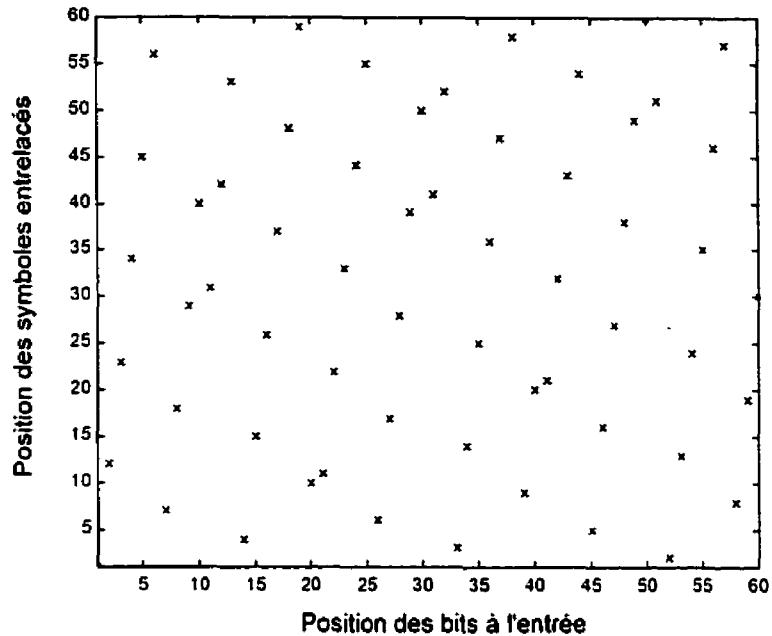

| <b>Figure 7.8 – Processus d'entrelacement BH(10,5) .....</b>                                                   | 143 |

| <b>Figure 7.9 – Séquence de sortie de l'entrelaceur BH(10,5) .....</b>                                         | 143 |

| <b>Figure 7.10 – Facteur d'étalement de l'entrelaceur BH(10,5) .....</b>                                       | 144 |

| <b>Figure 7.11 – Processus d'entrelacement BH(10,6) .....</b>                                                  | 146 |

| <b>Figure 7.12 – Séquence de sortie de l'entrelaceur BH(10,6) .....</b>                                        | 146 |

| <b>Figure 7.13 – Facteur d'étalement de l'entrelaceur BH(10,6) .....</b>                                       | 147 |

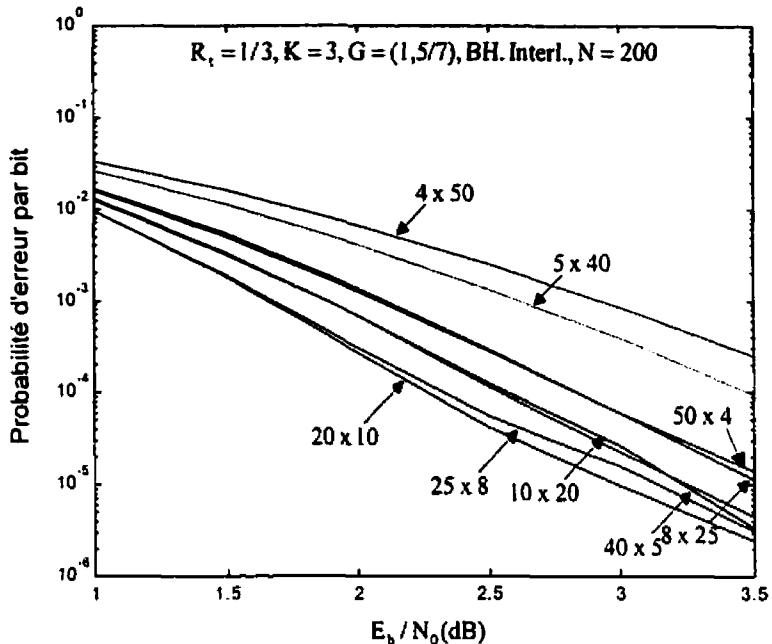

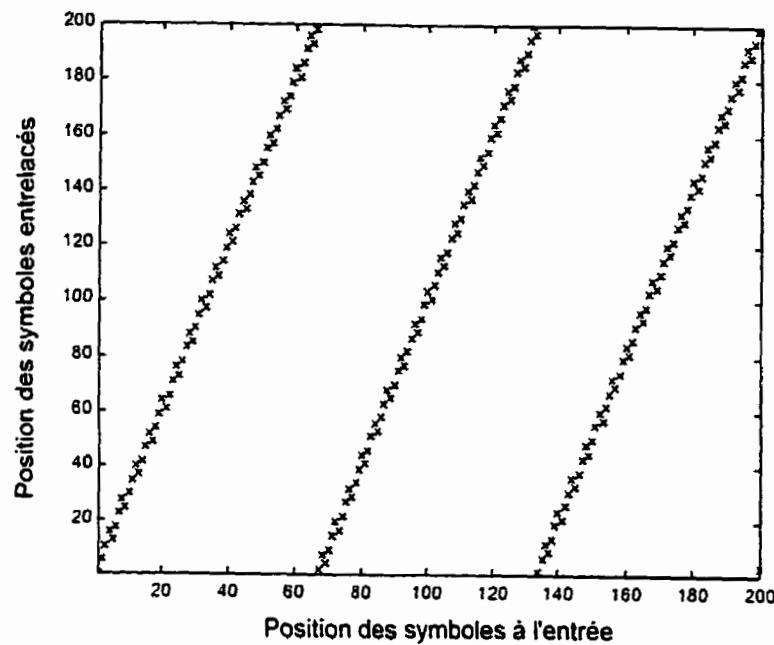

| <b>Figure 7.14 – Différentes performances des entrelaceurs BH N = 200 .....</b>                                | 150 |

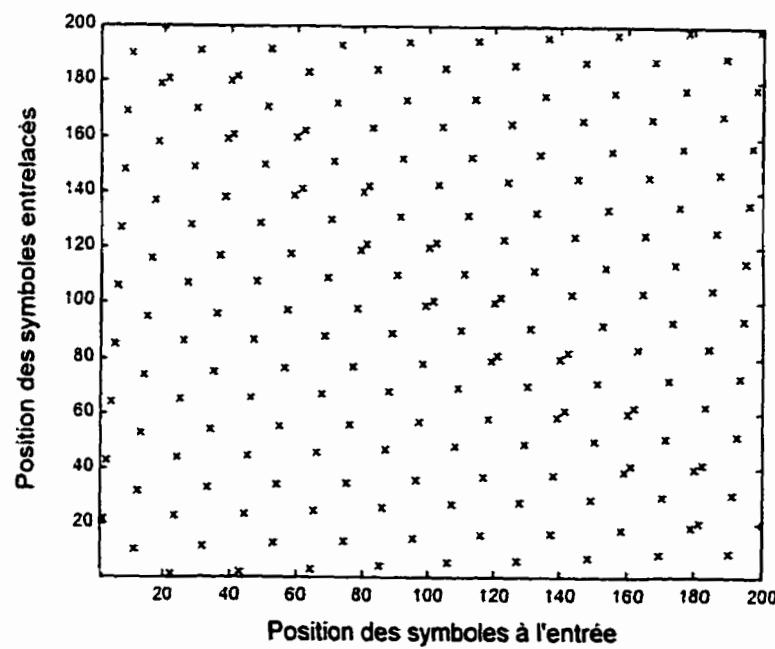

| <b>Figure 7.15 – Facteur d'étalement, entrelaceur BH 4 x 50, N = 200 .....</b>                                 | 151 |

| <b>Figure 7.16 – Facteur d'étalement, entrelaceur BH 20 x 10, N = 200 .....</b>                                | 151 |

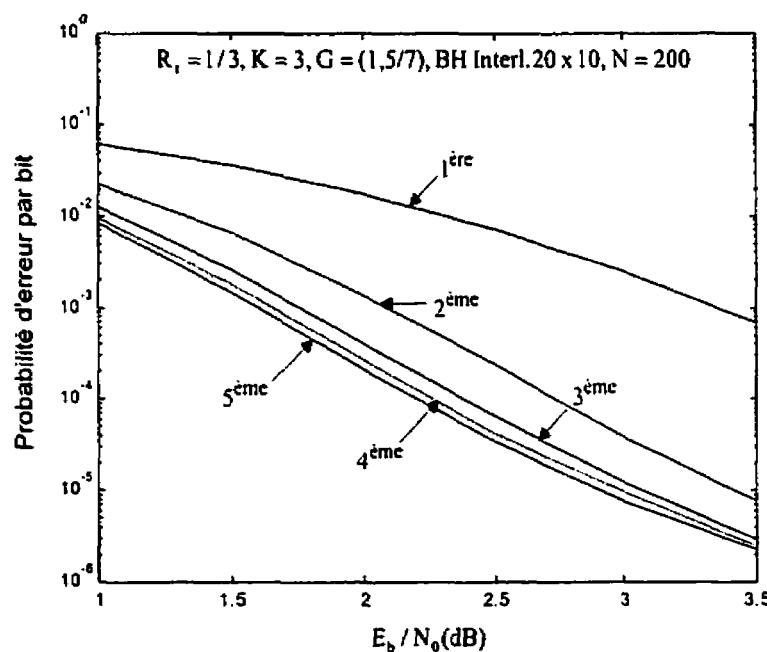

| <b>Figure 7.17 – BER, <math>R_t = 1/3</math>, K = 3, entrelaceur BH 20 x 10, canal AWGN, N = 200 .....</b>     | 152 |

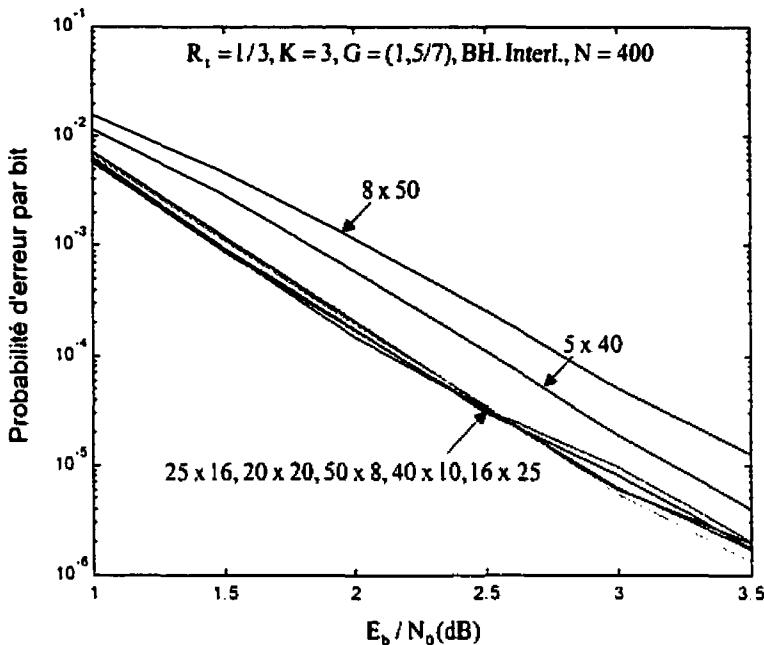

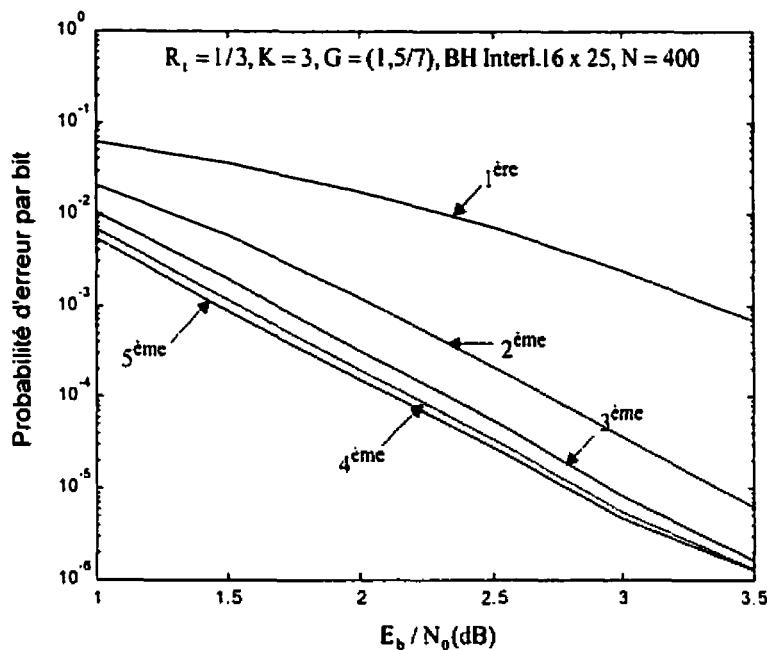

| <b>Figure 7.18 – Différentes performances des entrelaceurs BH N = 400 .....</b>                                | 154 |

| <b>Figure 7.19 – Facteur d'étalement, entrelaceur BH 8 x 50, N = 400 .....</b>                                 | 155 |

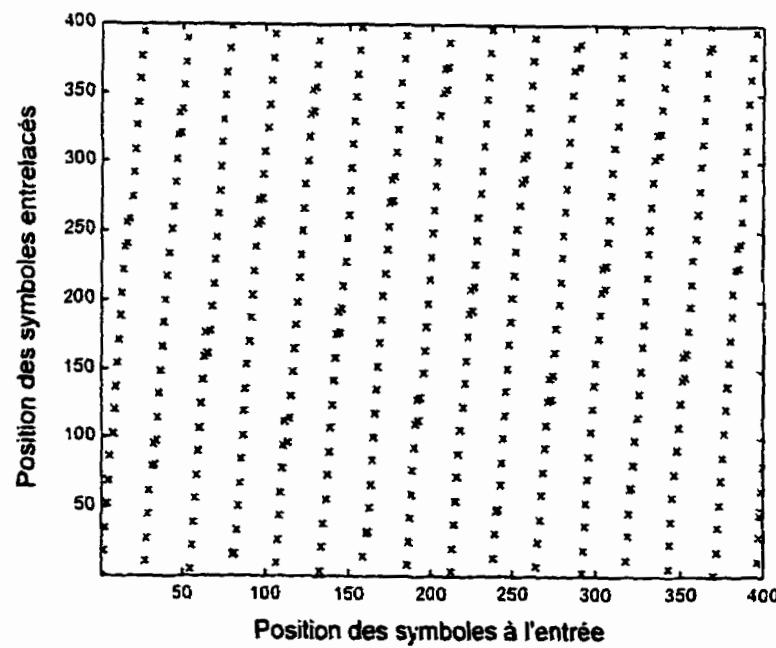

| <b>Figure 7.20 – Facteur d'étalement, entrelaceur BH 16 x 25, N = 400 .....</b>                                | 155 |

|                                                                                                                                      |            |

|--------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>Figure 7.21 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur BH 16 x 25, canal AWGN, <math>N = 400</math> .....</b> | <b>156</b> |

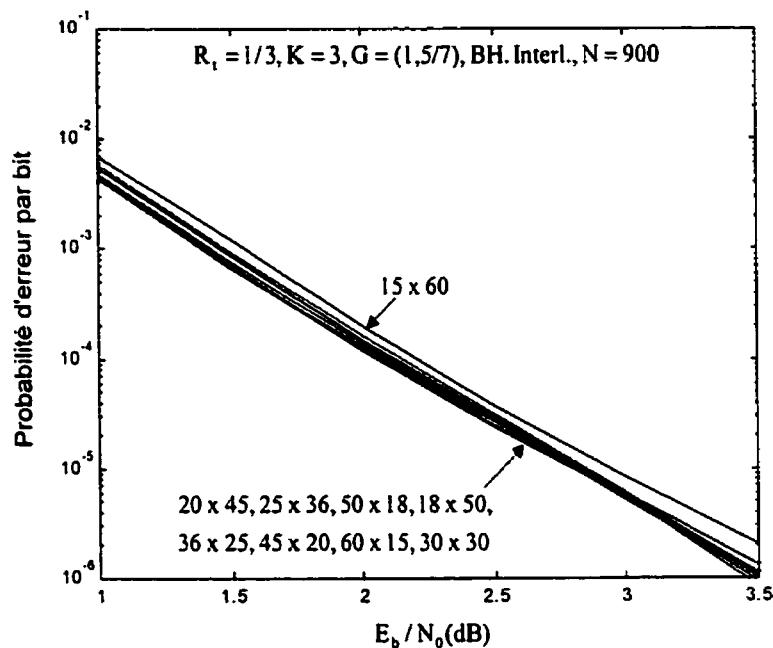

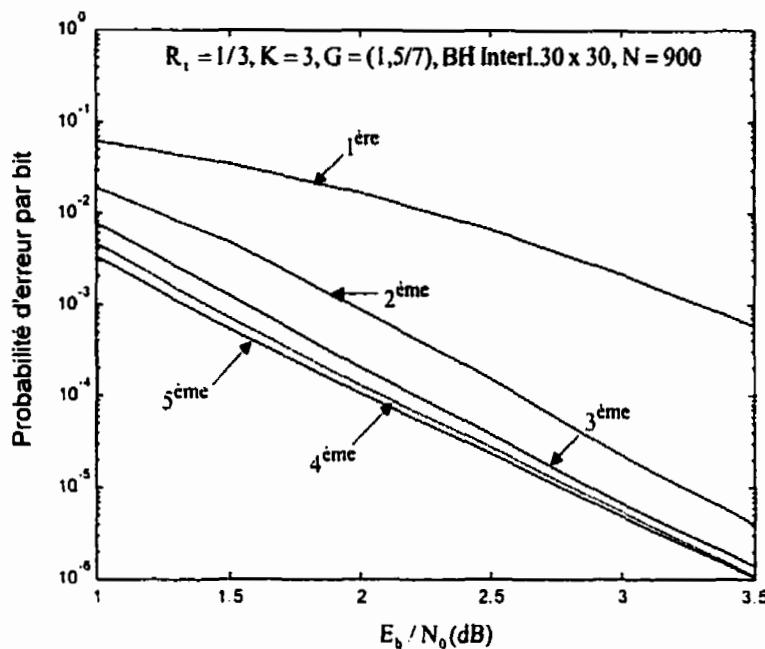

| <b>Figure 7.22 – Différentes performances des entrelaceurs BH <math>N = 900</math>, 4<sup>ème</sup> itération.....</b>               | <b>157</b> |

| <b>Figure 7.23 – Facteur d'étalement, entrelaceur BH 15 x 60, <math>N = 900</math>.....</b>                                          | <b>158</b> |

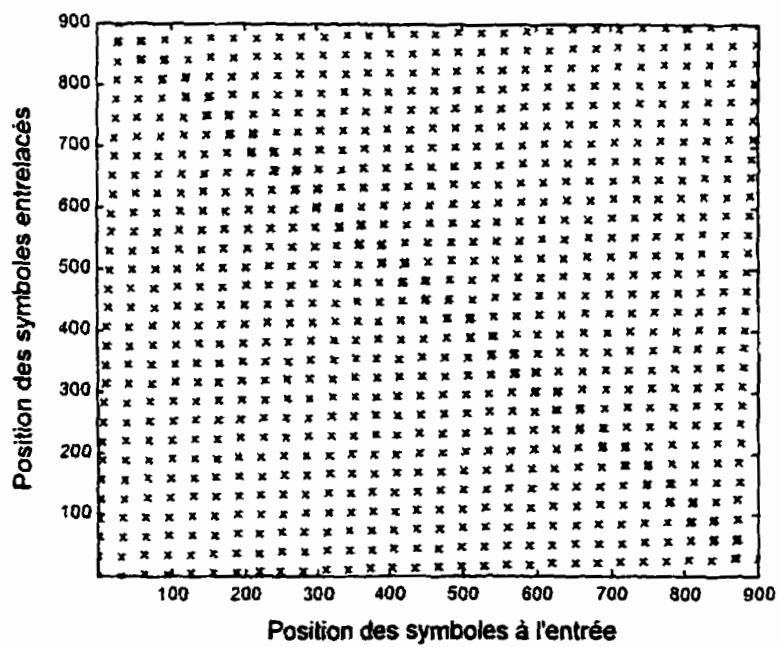

| <b>Figure 7.24 – Facteur d'étalement, entrelaceur BH 30 x 30, <math>N = 900</math>.....</b>                                          | <b>158</b> |

| <b>Figure 7.25 – BER, <math>R_t = 1/3</math>, <math>K = 3</math>, entrelaceur BH 30 x 30, canal AWGN, <math>N = 900</math> .....</b> | <b>159</b> |

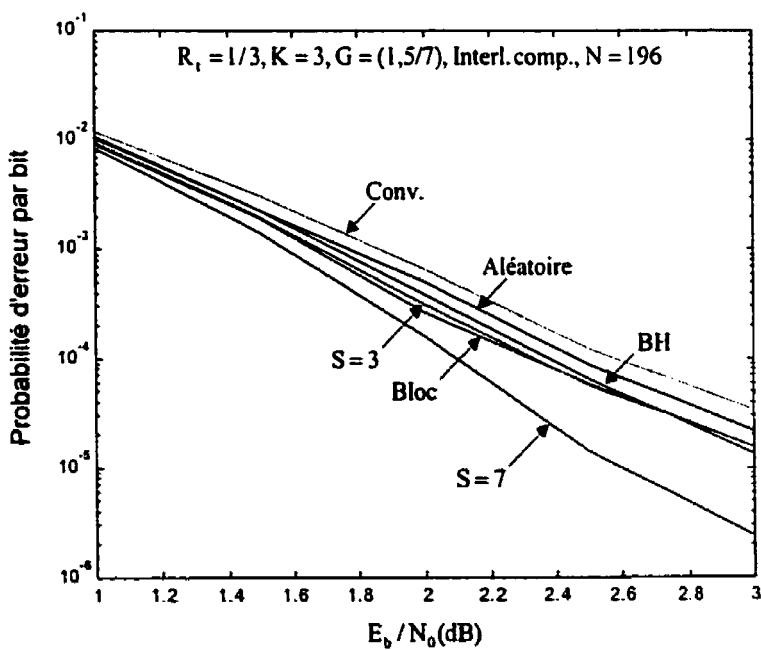

| <b>Figure 8.1 – Comparaison des entrelaceurs, <math>N = 196</math>, 4<sup>ème</sup> itération.....</b>                               | <b>161</b> |

| <b>Figure 8.2 – Comparaison des entrelaceurs, <math>N = 400</math>, 4<sup>ème</sup> itération.....</b>                               | <b>163</b> |

| <b>Figure 8.3 – Comparaison des entrelaceurs, <math>N = 900</math>, 4<sup>ème</sup> itération.....</b>                               | <b>164</b> |

## Liste des tableaux

|                                                                                     |            |

|-------------------------------------------------------------------------------------|------------|

| <b>Tableau 7.1 – Ordre de lecture des lignes et des colonnes pour BH(8,5).....</b>  | <b>132</b> |

| <b>Tableau 7.2 – Ordre de lecture des lignes et des colonnes pour BH(10,5).....</b> | <b>142</b> |

| <b>Tableau 7.3 – Ordre de lecture des lignes et des colonnes pour BH(10,6).....</b> | <b>145</b> |

| <b>Tableau 8.1 – Choix d'un entrelaceur pour une taille de bloc donnée .....</b>    | <b>165</b> |

## Chapitre 1 - Introduction

### 1.1 Théorie de l'information

Un système de communications numériques est un moyen de transport de l'information entre un utilisateur et un autre. Le terme numérique est relatif à la séquence de symboles qu'il utilise pour représenter l'information. En général, pour les communications numériques l'alphabet utilisé est binaire. Ce genre de transmission de données est très intéressant dans le sens où il permet l'utilisation de nombreuses techniques de manipulation de l'information. Parmi celles-ci, nous pouvons penser à la compression de l'information, à l'encryptage de cette dernière, mais aussi aux codes correcteurs d'erreurs. Ce sont ces derniers qui font l'objet de beaucoup de recherches actuellement.

En 1948, Shannon a publié un article intitulé "A Mathematical Theory of communication" dans le Bell Systems Technical Journal [48]. Par la suite, il publia un second article en 1949, toujours dans le même journal "Communication Theory of Secrecy Systems" [49]. Ces deux articles faisaient référence au travail sur le codage de l'information. Le premier de ces deux papiers définit la manière dont nous effectuons des transmissions numériques de nos jours. Il s'agit de la base de la théorie de l'information. Dans cet article, il introduit la métrique au travers de laquelle l'information peut être quantifiée. Cette métrique définit le nombre minimum de symboles nécessaires de façon à numériser un message sans faire d'erreur. À partir de ceci, un message qui contient la même information mais un nombre de symboles supérieur est redondant et ouvre la porte au codage de l'information et à la correction des erreurs grâce aux codes. C'est ainsi que trois types de codages ont pu être introduits :

- codage de source : ce dernier est utilisé pour supprimer la redondance dans les paquets d'information de la source;

- codage d'encryptage : seul le destinataire peut décoder l'information transmise grâce à ce type d'encodage;

- codage correcteur d'erreur : un tel codage sert à minimiser l'impact du bruit. Ceci est réalisé en introduisant de la redondance. Ce type de codage est aussi appelé codage de canal.

Finalement, il est important de relater le théorème de Shannon à la base des codes correcteurs d'erreur. Pour tout canal, il est possible d'associer une capacité de canal  $C$ . Il existe alors des codes de contrôle d'erreur de façon à ce que l'information puisse être transmise au travers du canal à des taux inférieurs à  $C$  avec une probabilité d'erreur par bits faible.

Shannon fut un des précurseurs des codes correcteurs d'erreur. Il y en a eu bien d'autres. Un autre nom que nous pouvons mentionner dans ce chapitre d'introduction est Hamming. Ce dernier était un contemporain de Shannon et travaillait pour les laboratoires Bell dans les années quarante. Beaucoup le considèrent comme le fondateur du sujet des codes correcteurs d'erreur grâce à son article "Error Detecting and Error Correcting Codes" paru dans le Bell System Technical Journal en 1950 [24]. Ce grand chercheur est très connu pour ses fameux codes de Hamming.

## 1.2 Les premiers usages des codes correcteurs d'erreur

C'est le domaine spatial qui a permis le développement de ces codes correcteurs d'erreur. En effet, les premières utilisations de ceux-ci en communication devaient permettre de surmonter la perte de puissance lors de la propagation entre le récepteur ou transmetteur de l'engin spatial et le transmetteur ou le récepteur de la station terrestre. Les engins envoyés dans l'espace, à l'origine, se devaient d'être assez petits pour des raisons économiques, mais aussi des raisons d'énergie, comme la poussée des moteurs. Par

conséquent, emporter une grande antenne, ou de grosses batteries, ou encore de grands panneaux solaires dans ces appareils était hors de question. Réduire la taille de l'antenne entraînait obligatoirement une perte de puissance à l'émission ou à la réception. Le signal transmis avait donc une puissance moindre. Néanmoins, le bruit est toujours le même. Ainsi, de nombreuses erreurs pouvaient facilement détériorer le signal.

L'idée des codes correcteur d'erreur est de gagner en terme de puissance (dB). En général, nous parlons de rapport signal sur bruit. Le gain de codage est la différence entre un rapport signal à bruit  $E_b/N_0$  requis pour atteindre une certaine performance d'erreur par bit (BER) avec un système codé et le  $E_b/N_0$  requis pour atteindre la même performance d'erreur avec un système non codé.

De façon plus spécifique, nous allons maintenant parler du choix de la modulation. En ce qui concerne les transmissions spatiales, la modulation binaire de phase BPSK est la plus sensée car elle offre une meilleure puissance par rapport aux autres modulations. Le gain de cette modulation par rapport à la modulation binaire de fréquence BFSK est de 3 dB [46] [52]. Une transmission BPSK non codée nécessite un  $E_b/N_0$  de 9.6 dB pour atteindre une performance de  $10^{-5}$ . En utilisant un codage de Reed-Solomon avec un code convolutionnel, de façon standard, il est possible d'atteindre la même performance à 2.2 dB. Ceci équivaut donc à un gain de codage de 9.6-2.2, soit 7.6 dB.

Nous venons de voir que les codes correcteurs d'erreur permettent de réduire la valeur du  $E_b/N_0$  nécessaire à l'entrée du démodulateur pour obtenir la même performance d'erreur sans codage. Ceci a un impact notamment sur les exigences requises vis-à-vis des paramètres de liaison. Grâce au codage, des communications seront fiables pour de plus grandes distances étant donné que la puissance d'émission peut être réduite. Il est également possible de réduire la taille des antennes, ce qui a, comme nous l'avons vu, un impact matériel et économique sur l'envoi d'engins spatiaux entre autres. Un gain de 1 dB est équivalent à une grande économie d'argent pour les concepteurs de systèmes de

communication. Actuellement, on évalue à 80 millions de dollars le gain de 1 dB [52], mais ceci n'est qu'une estimation.

Avec de tels chiffres, il serait possible de penser réduire au maximum le coût d'un appareil de transmissions numériques. Malheureusement, il en est tout autrement dans la vie de tous les jours. En effet, il existe une limite au codage. Shannon a ainsi défini la capacité de canal en considérant le cas du bruit blanc additif et gaussien (AWGN) comme :

$$C = W \log_2 \left( 1 + \frac{S}{N} \right) \text{ bits par seconde} \quad (1.1)$$

Dans cette équation,  $W$  est la largeur de bande du canal en Hertz,  $S$  est la puissance moyenne du signal et  $N$  la puissance du bruit dans le canal. À partir de cette équation, il est possible de développer une limite sur le gain de codage. L'efficacité spectrale  $\eta$  est introduite en bits par seconde par Hertz. Cette dernière représente le nombre moyen de bits d'information transmis par intervalle de signalisation. La valeur de  $E_b/N_0$  est alors :

$$\frac{E_b}{N_0} \phi \frac{2^\eta - 1}{\eta} \quad (1.2)$$

Jusqu'au début des années 90, les chercheurs ont été capables d'aller gagner jusqu'à 2 dB de cette limite. Néanmoins, il restait tout de même ces 2 dB à aller chercher. De nouveaux codes ont permis d'approcher davantage cette limite, à savoir les Codes Turbo qui ne sont qu'à 0.3 dB de la capacité.

### 1.3 L'avènement des Codes Turbo

Les codes correcteurs d'erreur peuvent être classifiés en deux catégories, à savoir les codes blocs et les codes convolutionnels. Tandis que les premiers requièrent la subdivision au préalable des bits d'information en paquets ou blocs d'information, les seconds sont plus intéressants puisqu'ils permettent un codage de l'information de façon continue.

Les codes convolutionnels sont parmi les plus utilisés dans les communications sans fil de par leur propriété de continuité dans la transmission de l'information. En effet, nous n'avons pas à attendre que le bloc de bits soit arrivé avant de transmettre. Leur performance est excellente et ceci grâce à la puissance des algorithmes de décodage disponibles. Entre autres, nous pouvons penser au décodage de Viterbi qui fut une révolution. Cet algorithme est à maximum de vraisemblance et donc optimal; il assure le minimum de probabilité d'erreur par séquence. Néanmoins, ces codes ont un désavantage de taille. En augmentant la longueur de contrainte, nous augmentons certes le gain de codage, mais également la complexité du décodage de façon exponentielle. Ceci est tel que les systèmes pratiques sont limités à une longueur de contrainte égale à 9

Les codes convolutionnels connaissant des limites, la recherche s'est concentrée sur la conception de codes correcteurs d'erreur plus puissants. L'idée de base était évidemment de conserver l'avantage des codes convolutionnels tout en se débarrassant de leur contrainte. De multiples tentatives ont aboutit aux codes produit [18], aux codes concaténés [20], aux codes multi-niveaux [31], mais aussi aux algorithmes sous-optimaux pour le décodage des codes convolutionnels avec de grandes longueurs de contraintes, comme le décodage séquentiel [10], le décodage de Viterbi adaptatif [13] et le décodage bidirectionnel [11].

En 1993, Berrou Glavieux et Thitimajshima ont développé une nouvelle approche aux codes correcteurs d'erreur : les Codes Turbo [8]. Il s'agit en fait de la concaténation parallèle de deux codeurs convolutionnels récursifs et systématiques de faible longueur de contrainte à travers un entrelaceur. Le décodage est effectué de façon itérative par deux décodeurs concaténés en série. Les auteurs cités ci-dessus ont montré que nous ne sommes plus qu'à 0.7 dB de la borne de Shannon. Étant donné qu'avec les codes correcteurs d'avant, nous étions à 2.2 dB, ceci veut dire que l'avènement des Codes Turbo apportait un gain de codage additionnel de 1.5 dB. Actuellement, les Codes Turbo se situent à 0.2 dB de cette fameuse limite [38].

Les performances des Codes Turbo sont fonction non seulement des codes convolutionnels utilisés, mais aussi de l'algorithme de décodage et des entrelaceurs. De nombreuses recherches ont porté sur les deux derniers points. Les Codes Turbo étant très complexes, une des méthodes utilisées pour leur étude est d'examiner l'effet de chacun des paramètres un à la fois. Dans ce mémoire, nous nous sommes concentrés sur l'effet des entrelaceurs sur la performance des Codes Turbo. Ces derniers font l'objet de beaucoup de recherche et de nombreux algorithmes ont été développés de façon à améliorer les performances des transmissions numériques. Une des utilités des entrelaceurs est de mélanger l'information de façon à annuler l'effet néfaste des canaux de transmission. Pour les Codes Turbo, ces entrelaceurs permettent surtout au décodeur de pouvoir corriger les erreurs de façon subséquente. Nous nous intéresserons à l'effet des entrelaceurs dans ce mémoire.

## 1.4 Composition du mémoire

Pour l'étude des entrelaceurs au sein des Codes Turbo, nous avons divisé notre recherche en plusieurs parties. Les premiers chapitres de ce mémoire portent sur l'aspect théorique des systèmes de communication et des Codes Turbo. Ainsi, dans le second chapitre, nous nous intéressons à ce que nous appelons la concaténation parallèle. Cette dernière est une

méthode utilisée de nos jours pour le codage de l'information que nous devons corriger à la réception. Il s'agit d'utiliser deux codeurs en parallèle qui reçoivent la même séquence d'information, mais dans un ordre différent. Dans ce chapitre, nous introduisons tout d'abord les systèmes de communication. Le codage convolutionnel qui est la base des Codes Turbo est aussi introduit de façon théorique. Nous en verrons deux types, à savoir le codage convolutionnel non récursif et le récursif. Par la suite, la concaténation parallèle est vue en détail et nous terminons ce chapitre par différents paramètres pertinents aux transmissions numériques : la modulation BPSK et les différents types de canaux disponibles.

Le troisième chapitre fait l'objet d'un des paramètres importants des Codes Turbo. En effet, sans l'algorithme de décodage, ces derniers ne sont plus d'excellents correcteurs d'erreur. Il existe de nombreux algorithmes de décodage et un des meilleurs pour les Codes Turbo s'avère être l'algorithme MAP. L'étude qui en sera faite sera de nature théorique. Nous voyons en particulier tous les paramètres nécessaires à cet algorithme comme les métriques d'états. Nous restreignons notre étude au canal AWGN et enfin présentons quelques variantes de cet algorithme.

L'algorithme de décodage étant présenté, nous pouvons nous intéresser aux Codes Turbo. Ces derniers font partie du chapitre suivant. Le principe de décodage itératif est présenté en premier lieu car il est à la base du décodage de ces codes. Les différents termes pertinents de l'information extrinsèque sont développés. Ces derniers sont nécessaires au bon fonctionnement du décodage. Enfin, le décodage turbo est introduit. Par la suite, dans ce chapitre, l'élément que nous allons étudier dans tout le reste du mémoire est présenté. Il s'agit de l'entrelaceur. Une grande partie de la théorie des entrelaceurs est faite à la fin du chapitre. Nous verrons, entre autres, le facteur d'étalement qui est un paramètre pertinent à l'étude des Codes Turbo.

Une fois les entrelaceurs introduits, il est possible de commencer l'étude qui fait l'objet de ce mémoire. en effet, dans le chapitre 5, les entrelaceurs pseudo-aléatoires sont étudiés. Tout d'abord, l'intérêt se porte sur les entrelaceurs purement aléatoires. Ces derniers nous servent de tremplin pour la description des performances des Codes Turbo en général. Par la suite, les entrelaceurs symétriques sont introduits pour enfin nous concentrer aux entrelaceurs symétriques S dont l'intérêt porte sur l'aspect d'aléatoire et de symétrie.

Le chapitre suivant porte sur des entrelaceurs plus classiques qui sont déterministes. Il s'agit tout d'abord des entrelaceurs blocs dont la simplicité est notoire. Les entrelaceurs convolutionnels font alors l'objet d'une étude assez poussée pour en comprendre le fonctionnement au sein des Codes Turbo. Ces deux types d'entrelaceur ont en commun la connaissance de la position des bits de sortie à l'avance.

L'objet du chapitre 7 porte sur les entrelaceurs hélicoïdaux. Ces derniers sont introduits dans leur plus grande généralité. Nous nous concentrons ensuite sur les tous nouveaux entrelaceurs bloc-hélicoïdaux dont il existe trois types. Nous effectuons l'étude des performances de ces entrelaceurs au sein des Codes Turbo.

Finalement, nous concluons à l'aide du chapitre 8. Mais avant de conclure sur tout le travail que nous avons effectué, nous comparons tous les entrelaceurs que nous avons présentés dans ce mémoire de façon à en faire ressortir les meilleurs dans chacun des cas considérés.

## Chapitre 2 – Concaténation parallèle

### 2.1 Introduction

Le domaine des télécommunications est un domaine en mouvement constant. Au tout début, on se souvient des téléphones résidentiels avec fils. Nous avons ensuite connu l'avènement des MODEMS pour les ordinateurs. Depuis une décennie, le monde des télécommunications découvre l'ère du sans fil ("wireless") et surtout des transmissions numériques. Ces dernières ont permis de connaître des échanges de données de plus en plus fiables. Elles sont à l'origine du développement de ce qu'on appelle le codage correcteur d'erreur (Error Correcting Codes). Nous avons déjà mentionné Hamming qui fut un des tous premiers à introduire ces codes, mais il y a aussi les codes de Reed Solomon, et bien d'autres noms que nous pourrions citer comme Viterbi et son fameux algorithme de décodage.

En 1993 ont été introduits les Codes Turbo. Mais avant de parler de ces codes très puissants, il nous faut faire une introduction générale sur les systèmes de communications et le codage correcteur d'erreur en particulier. C'est pourquoi, nous allons, dans un premier temps, décrire les systèmes de communication. Nous nous intéresserons par la suite au codage correcteur d'erreur et en particulier aux codes convolutionnels qui sont la base des Codes Turbo. Nous verrons également certaines notions nécessaires à la compréhension de la suite du mémoire comme différents types de canaux de transmission et modulation. Enfin, nous introduirons les Codes Turbo.

### 2.2 Systèmes de communication

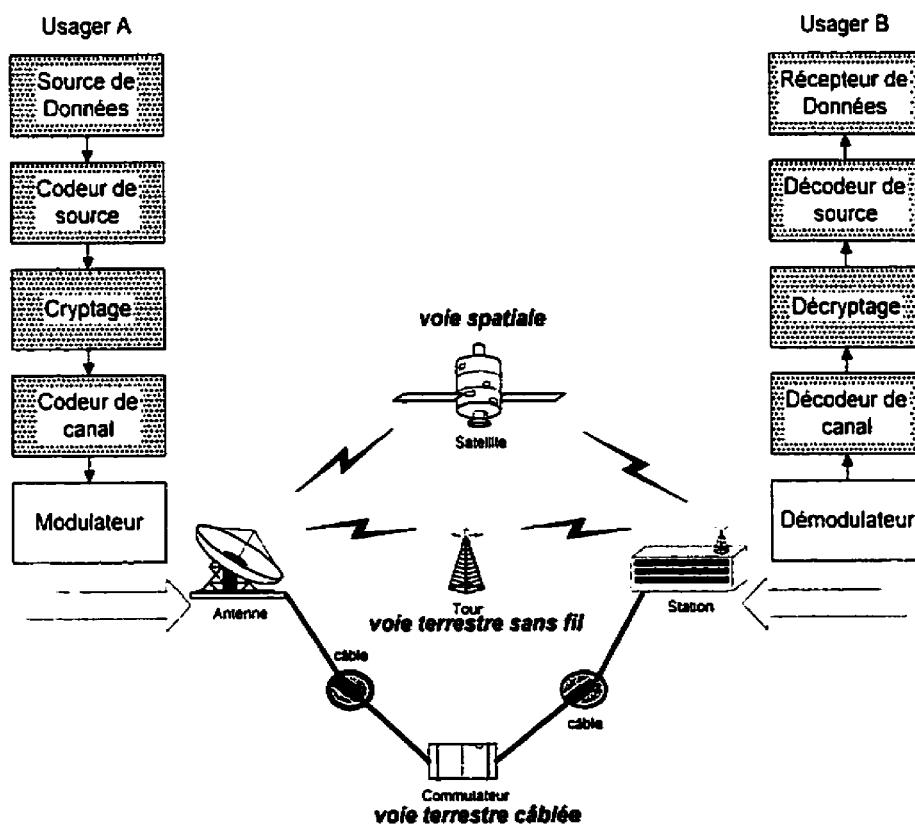

Un système de communication est un moyen de transport de l'information d'un usager à un autre, le plus souvent éloigné. Le système que nous considérons est numérique : une

séquence de symboles d'un alphabet est utilisée pour transmettre cette information. Dans notre cas, il s'agit de l'alphabet binaire. Comme nous l'avons déjà mentionné, utiliser les transmissions numériques permet en particulier de pouvoir corriger les erreurs. Les différents éléments d'un système de communication sont représentés à la figure 2.1. Différentes étapes y sont illustrées, comme le codage de source, le cryptage et le codage de canal. Nous allons présenter ces différentes étapes.

La première opération qui est effectuée sur la source de données est le codage de source [50]. Ce dernier est principalement utilisé pour réduire la redondance dans la séquence d'information. Il existe deux types de sources de données. Tout d'abord, la source de données la plus répandue est analogique. Il s'agit tout simplement de signaux électriques. Par exemple, pour un cellulaire, la source de données sera le microphone de l'appareil. En général, lorsque nous sommes confrontés à ce type de source de données, pour pouvoir effectuer du codage, il est nécessaire de numériser l'information d'origine. Ceci nous amène alors au deuxième type de données qui est tout simplement une source numérique. En effet, le numérique se retrouve en grande partie dans les ordinateurs. Lorsque nous parlons de transmissions à l'aide des ordinateurs, la source de données est directement numérique et n'a nullement besoin d'être numérisée. Dans ce cas, le codage de source s'applique directement à la source de données.

La plupart du temps, la source est analogique. Il faut donc la numériser. Le signal qui provient de la source doit, dans un premier temps, être échantillonné. Ensuite, il faut quantifier et enfin le transformer en une suite binaire de "0" et de "1". Cette transformation s'effectue à l'aide de techniques de conversion analogique-numérique comme la modulation à impulsion codée (PCM).

Après avoir codé la source, il s'agit de passer à l'étape de cryptage. Cette dernière a pour principal but d'empêcher les usagers non autorisés de comprendre le message transmis à l'aide de la source de données. Ensuite, le codage de canal est effectué. Ce dernier

consiste à ajouter de la redondance au message de façon à pouvoir corriger les erreurs qui pourraient se transmettre dans le canal. Ces erreurs sont le plus souvent introduites par du bruit qui pourrait faire passer un bit "0" à l'état de bit "1". Les trois étapes de codage que nous venons de décrire sont à effectuer dans l'ordre indiqué. Enfin, le modulateur joue le rôle d'adaptateur de canal. Son rôle est de faire en sorte que la séquence convienne au canal physique par lequel les données sont transmises.

Figure 2.1 – Système de communication

La source de données ainsi modifiée passe au travers d'un canal physique. Il existe trois types de canaux différents. Le premier canal est spatial. Le signal est émis par satellite via une station terrestre. Le deuxième type de canal est le genre de canaux que nous retrouvons dans les transmissions radiomobiles comme les cellulaires. Ce type de

transmission est aussi appelé "wireless". Enfin, un troisième type de canal existe. Il s'agit des liaisons par câble, le plus souvent via de la fibre optique. On peut penser aux liaisons téléphoniques mais aussi au tout nouveau mode de transmission de l'Internet qu'offre, par exemple, la compagnie montréalaise Vidéotron. Nous nous intéresserons plus loin dans ce mémoire à ces différents types de canaux.

Ainsi, le signal est transmis vers le récepteur. Néanmoins, nous avons effectué plusieurs opérations sur ce dernier, ce qui implique évidemment qu'à la réception, nous ne recevons pas le signal d'origine. Si une voix est transmise via un cellulaire, ce que nous obtenons pour le moment n'est qu'une séquence de "1" et de "0". Pour retrouver le signal d'origine, c'est-à-dire le message vocal transmis, il faut effectuer les étapes inverses de ce que nous avons décrit ci-dessus. Évidemment, ces étapes doivent être effectuées dans l'ordre inverse. Le signal est donc tout d'abord démodulé pour ensuite être décodé par le décodeur de canal. Le décodage est en général un algorithme bien particulier correspondant au codage d'origine qui va minimiser la probabilité d'erreur. Enfin, le signal sera décrypté et le décodage de source terminera le processus.

Ayant décrit un système de communication dans son ensemble, nous allons maintenant nous intéresser au codage de l'information et tout particulièrement au codage convolutionnel.

### 2.3 Codage Convolutionnel

Les codes convolutionnels font partie des codes correcteurs d'erreur et sont parmi les plus utilisés dans les communications sans fil où une probabilité d'erreur par bit faible est requise. Il existe deux types de codage, à savoir le bloc et le convolutionnel. Les codeurs blocs prennent une séquence d'entrée et la séparent en plusieurs blocs de  $N$  bits. Le codeur doit donc attendre d'avoir eu  $N$  bits à son entrée pour effectuer son opération

d'encodage et transmettre son bloc codé. Les codeurs convolutionnels ont une différente approche dans le sens où le flux de bits à l'entrée et à la sortie est continu. Il ne sépare pas les bits d'entrées en blocs. Quand un bit entre dans le codeur, un ou plusieurs symboles codés sont générés à la sortie. Les codes convolutionnels ont été introduits en 1955 par Elias [19]. Ce dernier montra qu'une certaine redondance peut être introduite à l'aide de registres à décalage.

Un codeur convolutionnel binaire  $(n,k)$  est un dispositif qui accepte des  $k$ -tuples binaires en entrée et produit des  $n$ -tuples binaires en sorties. Il existe deux types de codeurs convolutionnels. Tout d'abord, un codeur convolutionnel à réponse finie à une impulsion est aussi connu sous le nom de codeur convolutionnel non récursif. Il existe aussi les codeurs convolutionnels à réponse infinie à une impulsion, qu'on appelle aussi codeur récursif. Mentionnons aussi l'appellation de systématique qui décrit un codeur dont l'information présente à l'entrée est reproduite intégralement à la sortie. Les trois principaux paramètres qui caractérisent un codeur convolutionnel sont :

- Sa longueur de contrainte  $K$  : il s'agit du nombre de bits de cases de registre nécessaires à la génération d'un bit de sortie;

- Son taux de codage  $R$  : en général, il s'agit d'une fraction dont le numérateur correspond au nombre d'entrées pour un nombre de sorties correspondant au dénominateur;

- Ses générateurs  $G_1, \dots, G_v$  : ceux-ci caractérisent le code et sont les opérations binaires qui permettent d'obtenir les symboles codés de sortie.

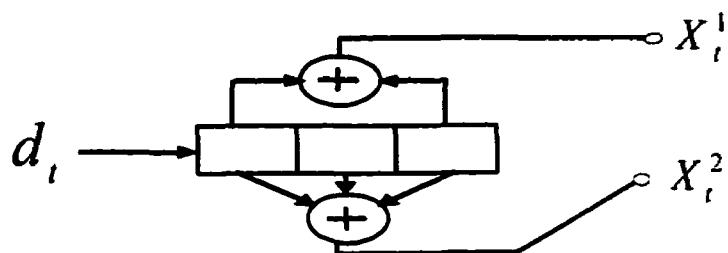

### **2.3.1 Codeurs convolutionnels non récursifs**

Intéressons-nous maintenant aux codeurs convolutionnels non récursifs. La figure 2.2 représente l'exemple simple d'un codeur convolutionnel de taux  $R = \frac{1}{2}$  et de longueur de contrainte  $K = 3$ . À l'entrée, les bits d'information  $d_t$  sont introduits un à la fois de façon

continuelle. Ils sont insérés dans un registre à décalage dont la longueur est égale à  $K$ . La mémoire du codeur ainsi défini est  $\mu = K - 1$ .

**Figure 2.2 – Codeur convolutionnel non récursif et non systématique,**

$$G(D) = [1 + D^2 \quad 1 + D + D^2]$$

À la sortie, comme nous avons un taux de codage de  $\frac{1}{2}$ , deux symboles de parité sont générés. Ces derniers sont définis par l'addition modulo 2 des bits d'information. Les additions sont définies par les générateurs du code. Qu'entendons-nous par vecteurs générateurs? Sur la figure 2.2, nous constatons qu'il y a des additionneurs. La connexion d'un additionneur  $i$  ( $i = 1, 2, \dots, V$ ) à une cellule  $j$  ( $j = 0, 1, \dots, K - 1$ ) est définie par le paramètre binaire  $g_{ij}$ . Ce paramètre est égal à 1 s'il y a une connexion et 0 s'il n'y en a pas. Pour un  $i$  donné, nous pouvons définir un vecteur générateur que nous noterons  $G_i$ . Dans le cas de notre figure, les vecteurs générateurs sont:

$$\begin{cases} G_1 = (101) \\ G_2 = (111) \end{cases} \quad (2.1)$$

Ceci est exprimé en base binaire. Néanmoins, ces vecteurs générateurs sont le plus souvent exprimés en base octale. Ainsi, dans notre cas, nous obtiendrons :

$$\begin{cases} G_1 = 5 \\ G_2 = 7 \end{cases} \quad (2.2)$$

De façon mathématique, soit  $d_t$  le bit d'information à l'entrée du codeur à l'instant  $t$ , nous pouvons écrire que le symbole codé correspondant  $X_t^i$  peut s'écrire :

$$X_t^i = \sum_{j=0}^{K-1} g_{ij} d_{t-j} \pmod{2} \quad i = 1, \dots, V \quad (2.3)$$

La séquence de sortie est donc une combinaison linéaire des entrées présentes et passées. Cette séquence peut s'exprimer sous la forme du produit de convolution de la séquence d'entrée et de la réponse impulsionale du codeur (réponse à l'entrée 1000...), d'où le nom de codes convolutionnels.

Il est possible d'écrire cette équation sous forme de matrice, plus facile à interpréter. En introduisant la variable  $D$  comme le délai séparant deux intervalles de temps successifs, il vient que :

$$\begin{aligned} \vec{X}(D) &= [X_1(D), X_2(D), \dots, X_n(D)] \\ \vec{d}(D) &= [d_1(D), d_2(D), \dots, d_k(D)] \begin{bmatrix} g_{1,1}(D) & g_{1,2}(D) & \dots & g_{1,n}(D) \\ g_{2,1}(D) & g_{2,2}(D) & \dots & g_{2,n}(D) \\ \vdots & \vdots & \ddots & \vdots \\ g_{k,1}(D) & g_{k,2}(D) & \dots & g_{k,n}(D) \end{bmatrix} \quad (2.4) \\ \vec{X}(D) &= \vec{d}(D)G(D) \end{aligned}$$

$$\text{où } d_u(D) = \sum_t d_t D^t$$

La matrice  $G(D)$  est la matrice génératrice du codeur. Dans l'exemple de la figure 2.2, nous obtenons :

$$G(D) = [1 + D^2 \ 1 + D + D^2] \quad (2.5)$$

Une représentation équivalente du codeur de la figure 2.2 est illustrée à la figure 2.3. Cette représentation permet de mettre en évidence l'aspect mémoire du code. Ce genre de codeur est appelé récursif et systématique.

**Figure 2.3 – Codeur convolutionnel récursif et systématique  $K = 3, R = 1/2$**

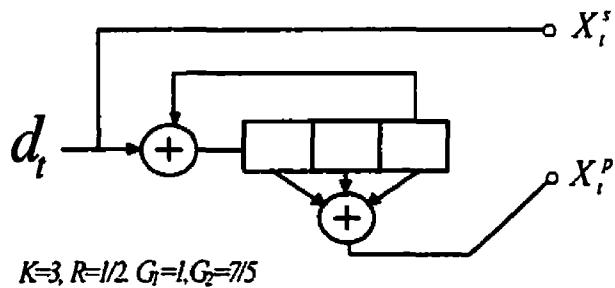

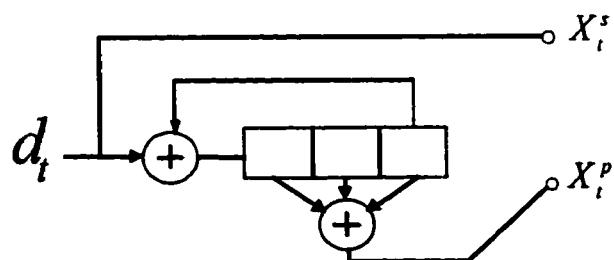

### 2.3.2 Codeurs convolutionnels récursifs

Il existe un autre type de codeur, à savoir les codeurs récursifs et systématiques. La récursivité est caractérisée par le fait que les  $n$  équations de sortie sont fonctions des entrées et sorties précédentes. Quant à l'aspect systématique, nous avons déjà mentionné qu'il s'agissait de transmettre les bits d'information dans les symboles codés. Selon Forney [21], il existe pour chaque code non systématique, un code systématique avec une boucle de contre-réaction, possédant les mêmes propriétés de distance. Pour montrer un tel processus, nous allons prendre l'exemple de la figure 2.2 et utiliser deux sorties. On a alors :

$$X^i(D) = G_i(D)d(D) \quad i = 1, 2 \quad (2.6)$$

Nous avons vu que pour avoir la propriété systématique, il faut qu'à l'une des sorties nous retrouvions exactement l'information. Nous devons donc avoir :

$$\begin{cases} \overline{X^1}(D) = d(D) = \overline{G_1}(D)d(D) \\ \overline{X^2}(D) = \frac{\overline{G_2}(D)}{\overline{G_1}(D)}d(D) = \overline{G_2}(D)d(D) \end{cases} \quad (2.7)$$

où  $\overline{G} = (\overline{G_1}, \overline{G_2})$  représente le vecteur de la version systématique. Nous savons de plus que :

$$\overline{X^i}(D) = \frac{X^i(D)}{G_i(D)} \quad (2.8)$$

Nous obtenons alors les générateurs du code systématique recherché :

$$\begin{cases} \overline{G_1}(D) = 1 \\ \overline{G_2}(D) = \frac{\overline{G_2}(D)}{\overline{G_1}(D)} \end{cases} \quad (2.9)$$

Les bits de sortie peuvent alors s'écrire :

$$\begin{cases} \overline{X^1}(D) = d(D) \\ \overline{X^2}(D) = d(D)A(D) \\ A(D) = \frac{d(D)}{G_1(D)} \end{cases} \quad (2.10)$$

ce que nous pouvons écrire dans l'espace temporel :

$$d_t = \sum_{j=0}^{K-t} g_{tj} a_{t-j} \quad (2.11)$$

En tenant compte du fait que toutes les opérations sont faites modulo 2, et en faisant l'hypothèse que  $g_{10} = 1$ , le symbole  $a_k$  peut s'exprimer récursivement en fonction des symboles  $a_{k-j}$  ( $j = 1, 2, \dots, K-1$ ) et du symbole  $d_k$ .

$$a_t = d_t + \sum_{j=1}^{K-1} g_{1j} a_{t-j} \quad (2.12)$$

Ainsi, dans le cas d'un codeur récursif et systématique, ce sont les symboles  $a_k$  qui sont contenus dans le registre à décalage du codeur. À partir des équations ci-dessus, nous pouvons alors construire les symboles de parité à la sortie du codeur, l'une de ces deux séquences étant les bits d'information :

$$\begin{cases} X_t^s = d_t = \sum_{j=0}^{K-1} g_{1j} a_{t-j} \\ X_t^p = \sum_{j=0}^{K-1} g_{2j} a_{t-j} \end{cases} \quad (2.13)$$

La figure 2.4 illustre un codeur convolutionnel récursif systématique correspondant au codeur de la figure 2.2:

Figure 2.4 – Codeur convolutionnel récursif systématique  $R = \frac{1}{2}$ ,  $K = 3$ ,  $G = (1, 7/5)$

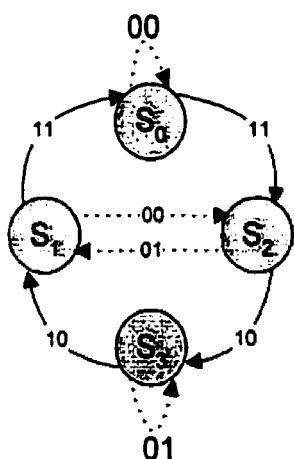

Enfin, mentionnons les méthodes graphiques pour représenter un code convolutionnel. Il en existe trois, à savoir l'arbre, le treillis et le diagramme d'état. Ce dernier très utilisé et il est une représentation de tous les états possibles du codeur ainsi que de toutes les transitions d'un état à un autre. À la figure 2.5, nous avons illustré un exemple de ce type de diagramme. Les  $S_i$ ,  $i = 0, 1, 2, 3$  représentent les états 00, 01, 10 et 11. Les lignes en gras indiquent que le bit 1 est transmis, les lignes en pointillées que le bit 0 est transmis.

**Figure 2.5 – Diagramme d'état d'un codeur convolutionnel**

## 2.4 Concaténation parallèle

C'est à partir des codes convolutionnels que nous venons de décrire que les Codes Turbo ont été découverts. La concaténation est à la base de ces derniers. Il existe deux sortes de concaténations, à savoir la concaténation série et la parallèle. La première à avoir été introduite fut la concaténation série par Forney en 1965 [20]. En effet, ce dernier eut l'idée de relier un codeur de Reed-Solomon à un codeur convolutionnel, le tout séparé d'un entrelaceur. Le terme série indique que les deux codeurs sont mis l'un après l'autre. Cette idée de concaténation série a permis d'améliorer la probabilité d'erreur par bit de façon exponentielle. Cependant, tout gain est accompagné d'un prix que nous nous

devons de payer. Dans ce cas, le prix à payer fut la complexité. Le gain obtenu en produisant ce système s'accompagnait d'une complexité accrue dans le décodage.

Il fallut attendre trente ans pour que Berrou, Glavieux et Thitimajshima [8] décrivent ce que nous appelons maintenant la concaténation parallèle. En fait, cette dernière fut le point partant des Codes Turbo. Elle fut introduite avec la notion de décodage itératif. La différence avec la concaténation série, c'est que cette fois, les codeurs utilisés sont en parallèle. Ces derniers opèrent donc sur le même ensemble de bits plutôt que l'un sur la sortie de l'autre comme c'est le cas dans la concaténation série. Il est à noter que, que ce soit pour la concaténation série ou la parallèle, le nombre de codeurs peut être de deux ou plus. En ce qui concerne les Codes Turbo, ils ont été introduits en mettant en parallèle deux codeurs convolutionnels identiques. Par ailleurs, ces codeurs étaient récursifs et systématiques. Néanmoins, il est important de noter qu'il est possible de concevoir des Codes Turbo possédant plus de deux codeurs convolutionnels. Les Codes Turbo que nous considérons dans ce mémoire sont constitués de deux codeurs identiques de type récursifs et systématiques séparés par un entrelaceur. Il va de soi que si nous prenions trois codeurs, nous aurons deux entrelaceurs et ainsi de suite. Nous avons représenté un codeur turbo classique à la figure ci-dessous.

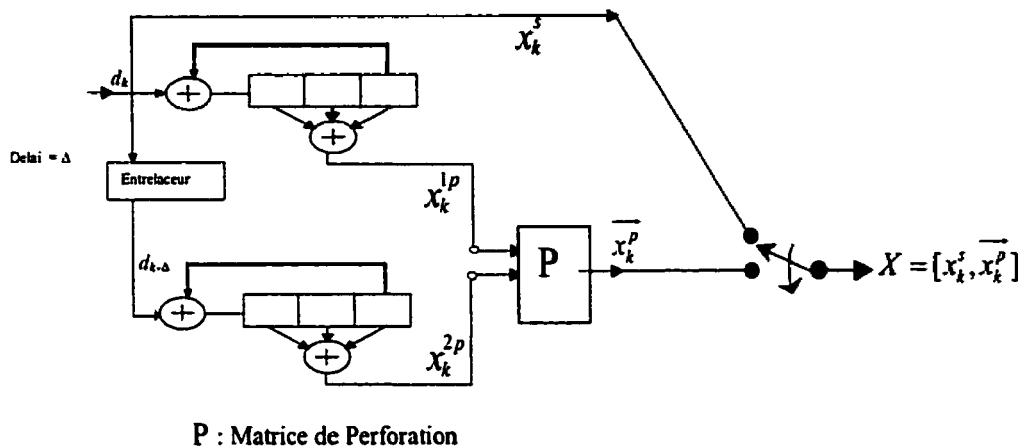

**Figure 2.6 – Codeur turbo**

Intéressons-nous maintenant au fonctionnement des Codes Turbo. Nous allons expliquer ces derniers à partir de la figure 2.6. Nous observons que ce codeur possède deux étages. Le premier étage correspond à la transmission de l'information d'entrée, c'est-à-dire que les bits sont transmis tels quel. Ce que nous appelons le deuxième étage correspond à la génération des symboles de parité permettant la correction des erreurs. Cet étage produit deux symboles de parité pour chaque symbole d'information transmis.

Lorsqu'une séquence de symboles  $d_k$  arrive au codeur, elle passe par deux étapes parallèles. La première correspond au premier codeur de l'étage supérieur. Cette étape est simplement le codage convolutionnel de cette séquence. Elle produit alors une séquence de symboles de parité  $x_k^{1p}$ . La séquence d'entrée passe en parallèle par le codeur inférieur après avoir été entrelacée. Ce deuxième codeur produit une séquence de symboles de parité  $x_k^{2p}$ . Une fois ces deux symboles de parité générés, ils peuvent être perforés ou non afin de produire la séquence ou le vecteur de parité  $\overline{x_k^p} = (x_k^{1p}, x_k^{2p})$  qui sera multiplexé avec les symboles d'information  $\overline{x_k^s}$ . Le but de la perforation, si perforation il y a, est de supprimer certains symboles de parité afin de faire varier le taux de codage.

Si nous considérons la concaténation parallèle de deux codeurs systématiques dont les taux de codage sont  $R_1 = \frac{b}{V_1}$  et  $R_2 = \frac{b}{V_2}$ , le taux global du codeur turbo est :

$$R = \frac{b}{V_1 + V_2 - b} = \frac{b}{\frac{b}{R_1} + \frac{b}{R_2} - b} \text{ bits/symboles} \quad (2.14)$$

La soustraction, au dénominateur, de  $b$  est due au fait que les symboles systématiques ne sont transmis qu'une seule fois. Cette dernière équation s'écrit aussi :

$$\frac{1}{R} = \frac{1}{R_1} + \frac{1}{R_2} - 1 \quad (2.15)$$

Dans notre cas de la figure 2.6, les taux de codage  $R_1$  et  $R_2$  sont tous deux de  $\frac{1}{2}$ . Le taux global de notre codeur turbo sans perforation est alors  $1/3$ .

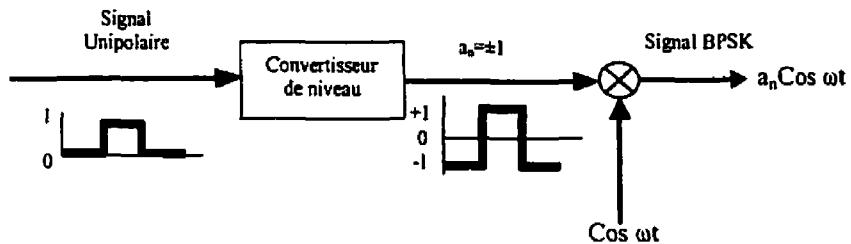

## 2.5 Modulation BPSK

Il existe de nombreux types de modulation pour les communications numériques. Néanmoins, pour notre recherche, nous n'en avons utilisé qu'une, à savoir la modulation BPSK (Binary Phase Shift Keying). Cette dernière est une modulation très utilisée dans l'étude théorique des communications numériques [37]. Effectivement, elle est caractérisée par une faible probabilité d'erreur par bit. Un modulateur BPSK est représenté à la figure ci-dessous.

**Figure 2.7 - Modulateur BPSK**

En appliquant les sorties  $X_k$  et  $Y_k$  du codeur turbo à l'entrée du modulateur, nous obtenons :

$$\begin{cases} \tilde{X}_k = 2X_k - 1 \\ \tilde{Y}_k = 2Y_k - 1 \end{cases} \quad (2.16)$$

En BPSK, les phases opposées de la porteuse ( $0$  et  $\pi$ ) sont transmises toutes les  $T$  secondes en considérant  $T$  la durée temporelle d'un bit. Ces phases sont aussi représentées par  $+1$  et  $-1$ . Ces derniers viennent des expressions  $\cos(\omega_c t)$  et  $\cos(\omega_c t + \pi)$ . Ceci se représente sous forme de constellation à deux points. Chaque bit entrant dans le modulateur BPSK se retrouvera en l'un de ces deux points de cette constellation. Ceci est alors une modulation par phase.

Étant donné que nous avons affaire à une modulation par phase, le problème du démodulateur est de récupérer la bonne phase pour démoduler. Ceci constitue la principale difficulté du récepteur BPSK. Enfin, écrivons l'expression de la probabilité d'erreur par bit d'un tel modulateur :

$$P_b = Q\left(\sqrt{\frac{2E_b}{N_0}}\right) \quad \text{avec} \quad Q(x) = \int_x^{\infty} \frac{1}{\sqrt{2\pi}} e^{-\frac{x^2}{2}} dx, x > 0 \quad (2.17)$$

## 2.6 Les types de canaux

Le canal est un véritable problème pour les transmissions de données. En effet, il est source de bruits de toutes sortes. Il existe des modèles pour identifier ce bruit et nous allons nous évertuer à en décrire quelques-uns.

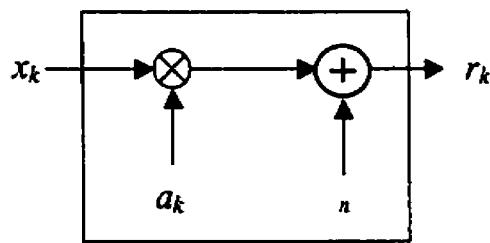

### 2.6.1 Canal AWGN (Additive White Gaussian Noise)

Le premier modèle est le plus utilisé en théorie. Il s'agit du bruit additif blanc et gaussien (AWGN). Il fournit un modèle presque parfait pour certains systèmes de communication et se prête à des calculs relativement faciles. Ce modèle implique que le bruit du canal est une variable aléatoire  $n$  qui s'additionne au signal modulé. Dans ce cas, la variable  $n$  est gaussienne, de moyenne nulle et de variance  $\sigma^2$ . Mathématiquement, nous pouvons écrire la densité de probabilité du bruit additif blanc gaussien :

$$p(n) = \frac{1}{\sqrt{2\pi\sigma^2}} e^{-\frac{n^2}{2\sigma^2}} \quad (2.18)$$

La densité spectrale unilatérale de ce type de bruit est constante de valeur  $N_0$ . Conséquemment, si nous considérons la variable du signal modulé  $x_k$ , il nous est possible de donner la sortie du canal comme :

$$r_k = x_k + n \quad (2.19)$$

Le modèle de bruit additif blanc gaussien est très simple et très pratique, comme nous l'avons dit, pour les calculs théoriques. Il reflète également très bien la réalité dans les communications spatiales. Néanmoins, si nous nous intéressons maintenant aux communications terrestres comme les communications radiomobiles, ce type de bruit ne reflète plus très bien la réalité. Il nous faut donc prendre un autre modèle.

### 2.6.2 Canal de Rayleigh

Sur la terre, les signaux sont en général soumis à une forte atténuation. Cette atténuation est le plus souvent reliée à la vitesse du récepteur, par exemple, lorsqu'on téléphone au moyen d'un cellulaire dans une voiture. Cette atténuation n'est pas modélisée par les bruit AWGN. Toutefois, il existe un modèle qui prend en compte cette atténuation. Il s'agit du modèle de canal de Rayleigh.

Le modèle de canal de Rayleigh est caractérisé par deux paramètres et est illustré à la figure 2.8. L'un de ces deux paramètres est une variable aléatoire  $n$  de distribution gaussienne. L'autre variable est l'enveloppe du signal,  $a_k$ .

Canal de Rayleigh

**Figure 2.8 – Modèle de canal de Rayleigh**

La sortie  $r_k$  du modèle de canal de Rayleigh est :

$$r_k = a_k x_k + n \quad (2.20)$$

La fonction de densité de  $a_k$  est :

$$p(a_k) = a_k e^{-\frac{a_k^2}{2}}, \quad a_k \geq 0 \quad (2.21)$$

Le modèle d'un canal de Rayleigh est schématisé à la figure 2.8, où  $r_k$  est la version bruitée du signal  $x_k$  à l'entrée du canal. La méthode la plus simple pour obtenir l'enveloppe dont la puissance moyenne est unitaire est de générer deux variables gaussiennes  $b_k$  et  $c_k$  de variance  $\frac{1}{2}$  et de moyenne nulle. En considérant que le processus d'évanouissement est décorrélé, l'enveloppe du signal sera alors donnée par :

$$a_k = \sqrt{b_k^2 + c_k^2} \quad (2.22)$$

## 2.7 Conclusion