**Titre:** Évaluation des performances de l'imagerie thermique par fluorescence pour l'analyse de défaillance des flip chips

Title: Evaluation of thermal imaging performance by fluorescence for flip chip failure analysis

**Auteur:** Nicolas Boyer

Author:

**Date:** 1999

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Boyer, N. (1999). Évaluation des performances de l'imagerie thermique par fluorescence pour l'analyse de défaillance des flip chips [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/8577/>

---

### Document en libre accès dans PolyPublie

Open Access document in PolyPublie

---

**URL de PolyPublie:** <https://publications.polymtl.ca/8577/>

PolyPublie URL:

**Directeurs de recherche:** Michel Meunier

Advisors:

**Programme:** Non spécifié

Program:

## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning

300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

**UNIVERSITÉ DE MONTRÉAL**

**MÉTHODES DE CONCEPTION ET DE PARTITIONNEMENT

LOGICIEL POUR DES ARCHITECTURES

PARALLÈLES SIMD LINÉAIRES**

**NICOLAS CONTANDRIOPoulos

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AUTOMNE 1998**

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-42901-6

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

MÉTHODES DE CONCEPTION ET DE PARTITIONNEMENT

LOGICIEL POUR DES ARCHITECTURES

PARALLÈLES SIMD LINÉAIRES

présenté par: Nicolas Contandriopoulos

en vue de l'obtention du diplôme de: Maîtrise ès Sciences Appliquées

a été dûment accepté par le jury d'examen constitué de:

M. BOIS Guy, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. BLAQUIÈRE Yves, Ph.D., membre et codirecteur de recherche

M. SAWAN Mohamad, Ph.D., membre

## REMERCIEMENTS

Même si le titre de maître n'est décerné qu'à un seul, même si cette gratification ne semble récompenser qu'un travail individuel, il est évident que jamais celui-ci n'aurait pu aboutir sans l'aide d'un grand nombre de personnes qui m'ont soutenu scientifiquement, administrativement et affectivement. À moins d'avoir confiance absolue en soi, le travail de chercheur est une perpétuelle remise en question, une succession de périodes d'enthousiasme et de périodes de doutes, de succès et de découragements aggravés par les tracas administratifs quotidiens. Ainsi ce n'est qu'avec le soutien de chercheurs aguerris, dans le cadre de travail purgé de contraintes non scientifiques et avec le soutien moral de mes proches que j'ai pu conclure mes études.

Mes premiers remerciements vont tout naturellement à M. Yvon Savaria qui m'a fait partager sa vision scientifique pour aborder les embûches rencontrées lors de mes recherches. Son appui et sa compréhension tout au long de mon programme m'ont permis de me sentir à l'aise pour discuter ouvertement de tout problème. Je tiens aussi à exprimer ma gratitude envers M. Yves Blaquièvre pour son appui et sa disponibilité malgré l'éloignement géographique. Je le remercie tout particulièrement pour sa grande contribution dans la rédaction et la mise au point de l'article réalisé durant mes études.

Je dois beaucoup également aux chercheurs de l'équipe PULSE avec qui j'ai travaillé. Ce sont entre autre et par ordre d'apparition (si mes souvenirs sont exacts) Qunshan Gu, Paul Marriott, Zahir Boukari et Ivan C. Kraljic, pour ne pas tous les citer.

Il m'est impossible de remercier tous les amis qui m'ont accompagné dans mon travail tant ils sont nombreux.

Enfin, je remercie ma famille qui a toujours été très présente même si l'éloignement géographique m'en a séparé.

## RÉSUMÉ

La demande toujours croissante d'intégration, de sophistication, de fiabilité, et surtout de performance pousse à concevoir des systèmes multiprocesseurs de plus en plus complexes ce qui rend leur conception et leur maîtrise plus difficile. De nouvelles méthodes d'aide à l'optimisation logiciel sont recherchées pour permettre d'accroître les performances, la fiabilité, et la portabilité des applications exécutées sur de tels systèmes.

Le présent mémoire s'inscrit dans ce contexte de recherche. Une revue de littérature des méthodes pertinentes est réalisée. L'une d'entre elles est identifiée selon nos besoins et adaptée pour être utilisée dans le cadre du projet PULSE (Parallel Ultra Large Scale Engine). Ce projet vise à développer et concevoir un multiprocesseur SIMD (Single Instruction Multiple Data) complexe dédié au traitement temps réel de signaux numériques de type vidéo. Une série d'exemples d'applications types sont optimisées suivant la méthode retenue. Les performances obtenues sont analysées et comparées avec des mises en œuvre manuelles, pour ainsi évaluer les gains obtenus et les limites de la méthode.

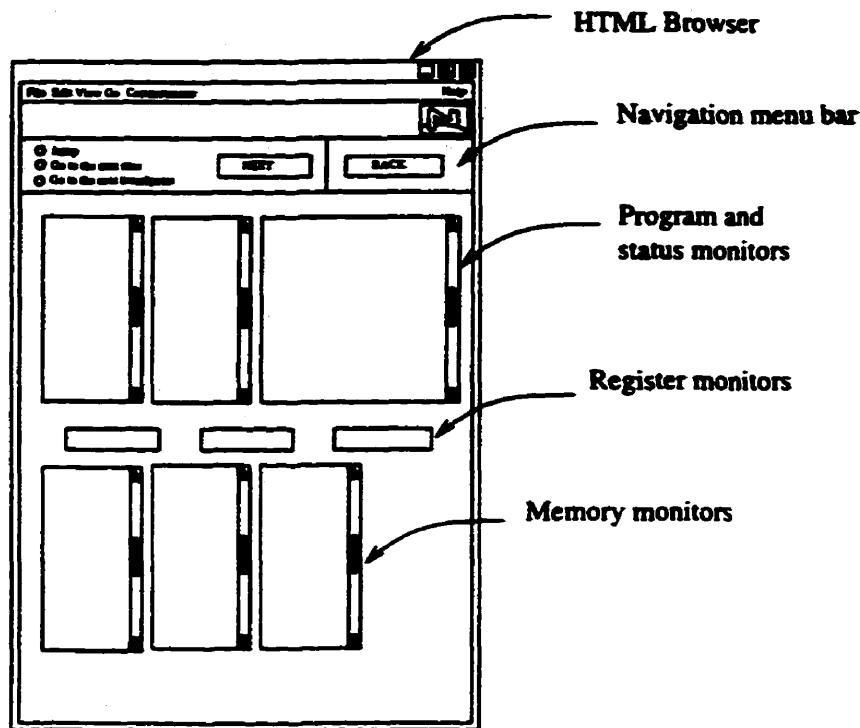

Un outil de simulation du système PULSE a été développé pour permettre l'analyse et l'estimation de performances dynamiques. De plus, cet outil permet de visualiser les états d'une simulation pas à pas. Utilisé par de nombreux membres de l'équipe de développement du projet PULSE, l'outil de simulation a permis la mise au point de nombreuses applications et facilité l'apprentissage du maniement du multiprocesseur PULSE.

Ces travaux ont permis d'adapter des méthodes d'optimisation manuelles, d'élaborer des heuristiques d'estimation de performances, et de développer un environnement de simulation.

## ABSTRACT

The growing demand for integration, sophistication, reliability and particularly performance, pushes to design microelectronics systems of increasing complexity which makes the development and the use of these systems more difficult. This motivates the need for new optimization methods allowing to increase the performances, reliability and applications portability on these systems. The search for such methods is the object of this thesis.

This thesis begins with a literature review of relevant methods. A suitable method is selected and adapted to be used in the framework of the PULSE project. This project was aimed at developing a SIMD multiprocessor dedicated to real time processing of digital signals, including video signals. A series of examples representative of typical applications are optimized according to the selected method. The obtained performances are analyzed and compared with manual practical applications, evaluating obtained gains and setting the method limits.

A tool for simulating the PULSE system was developed to allow the analysis and the estimation of dynamic performances. This tool also allows to visualize step by step, the simulation states. This characteristic was very much used by a wide number of development team members on the PULSE project. Which permitted the debugging of many applications and facilitated the training of users for the PULSE multiprocessor.

This thesis is a step toward the development of methods for optimizing and estimating performances. In spite of significant progress, the goal of developing an automatic parallelising compiler for PULSE remained elusive. Such a compiler, whose development appears feasible, but beyond the scope of this project, could handle the hard task of extracting and exploiting parallelism available in the applications.

## TABLE DES MATIÈRES

|                                                           | page       |

|-----------------------------------------------------------|------------|

| <b>Remerciements.....</b>                                 | <b>iv</b>  |

| <b>Résumé.....</b>                                        | <b>v</b>   |

| <b>Abstract .....</b>                                     | <b>vi</b>  |

| <b>Table des matières .....</b>                           | <b>vii</b> |

| <b>Liste des tableaux .....</b>                           | <b>ix</b>  |

| <b>Liste des figures .....</b>                            | <b>x</b>   |

| <b>Introduction .....</b>                                 | <b>1</b>   |

| <b>Chapitre I : À la recherche de performances.....</b>   | <b>7</b>   |

| 1.1. Le principe traditionnel de la parallélisation ..... | 10         |

| 1.1.1. Les fondations de la parallélisation .....         | 11         |

| 1.1.2. Notations et terminologies.....                    | 14         |

| 1.1.3. Histoire d'algorithmes.....                        | 18         |

| 1.2. Analyse des dépendances .....                        | 23         |

| 1.3. Transformations de boucles.....                      | 30         |

| 1.3.1. Technique générale.....                            | 32         |

| 1.3.2. La transformation sur mesure .....                 | 39         |

| 1.3.3. Remarques sur la règle du "owner compute" .....    | 41         |

| 1.4. Conclusion .....                                     | 42         |

| <b>Chapitre II : De la théorie à la pratique.....</b>     | <b>44</b>  |

| 2.1. Le filtre IIR 1D .....                               | 45         |

| 2.2. Le filtre FIR 2D .....                               | 51         |

| 2.3. Les vilains petits canards .....                     | 59         |

| 2.3.1. Le filtre de détection de contours .....           | 59         |

|                                                                        | page      |

|------------------------------------------------------------------------|-----------|

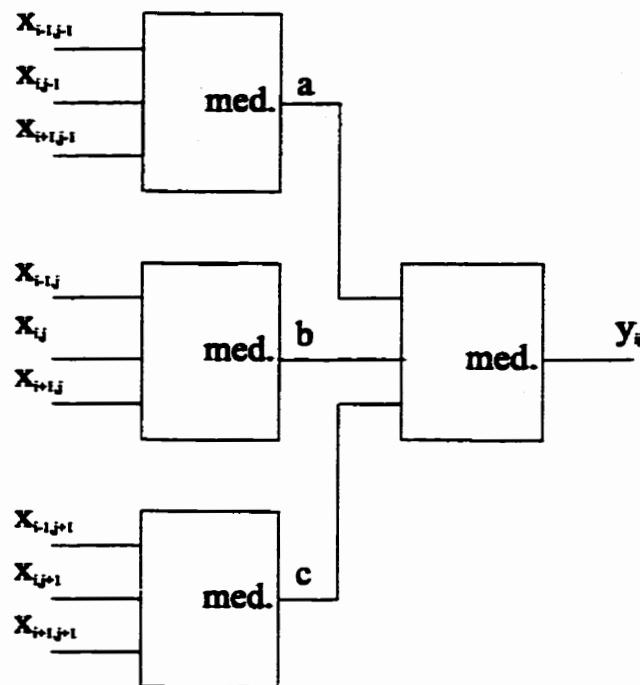

| <b>2.3.2. Le filtre médian .....</b>                                   | <b>61</b> |

| <b>2.4. Conclusion .....</b>                                           | <b>62</b> |

| <b>Chapitre III : Le simulateur SimPULSE .....</b>                     | <b>64</b> |

| <b>3.1. Pertinences et objectifs .....</b>                             | <b>66</b> |

| <b>3.2. Description sommaire de l'environnement de simulation.....</b> | <b>67</b> |

| <b>3.3. L'interface de l'environnement de simulation.....</b>          | <b>69</b> |

| <b>3.3.1. La première version : SimPULSE-CGI.....</b>                  | <b>72</b> |

| <b>3.3.2. La seconde version : SimPULSE-Java.....</b>                  | <b>75</b> |

| <b>3.4. Les estimations de performance .....</b>                       | <b>80</b> |

| <b>Chapitre IV : Conclusion.....</b>                                   | <b>84</b> |

| <b>Références.....</b>                                                 | <b>88</b> |

| <b>Annexe : I .....</b>                                                | <b>94</b> |

## LISTE DES TABLEAUX

|                                                                          | page |

|--------------------------------------------------------------------------|------|

| 1.1. Comparaison entre les différents algorithmes de parallélisation,... | 22   |

| 2.1. Filtre IIR 1D .....                                                 | 51   |

| 2.2. Filtre FIR 2D .....                                                 | 58   |

| 3.1. Estimateurs de performance disponibles .....                        | 82   |

## LISTE DES FIGURES

|                                                                                        | page |

|----------------------------------------------------------------------------------------|------|

| 1.1. Principe de la parallélisation .....                                              | 13   |

| 1.2. Le nid de boucles parfait .....                                                   | 15   |

| 1.3. Domaine d'itération vs. allocation et placement des données sur des processeurs.. | 16   |

| 1.4. Domaine d'itération du programme exemple 1.1,...                                  | 26   |

| 1.5. Domaine d'itération du programme exemple 1.1 possédant un parallélisme,...        | 29   |

| 1.6. Domaine d'itération de l'exemple 1.2.....                                         | 38   |

| 1.7. Dictionnaire de transformation primaire .....                                     | 39   |

| 1.8. Domaine d'itération de l'exemple 1.3 .....                                        | 41   |

| 2.1. Domaine d'itération du filtre IIR 1D .....                                        | 47   |

| 2.2. Domaine d'itération du filtre FIR 2D .....                                        | 54   |

| 2.3. Filtre médian 3x3.....                                                            | 61   |

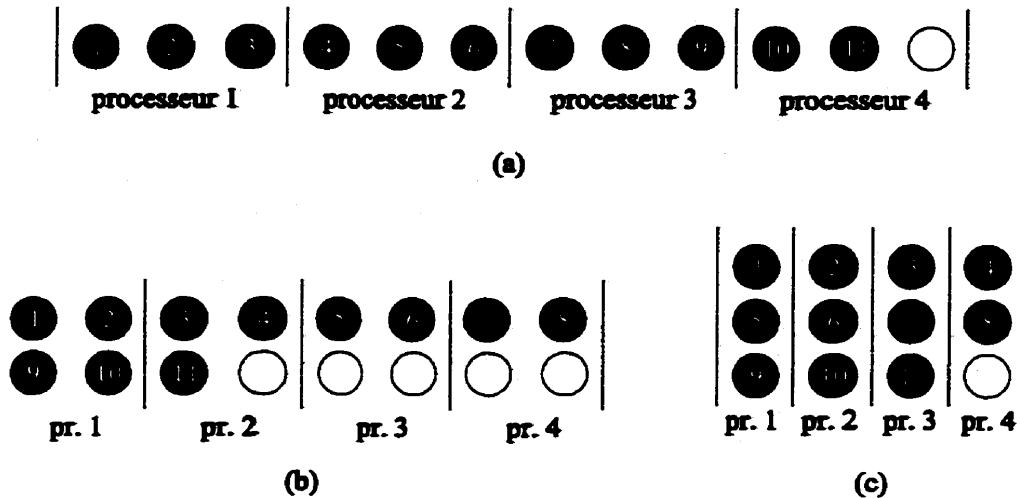

| 2.4. Différents types d'allocation,... .....                                           | 63   |

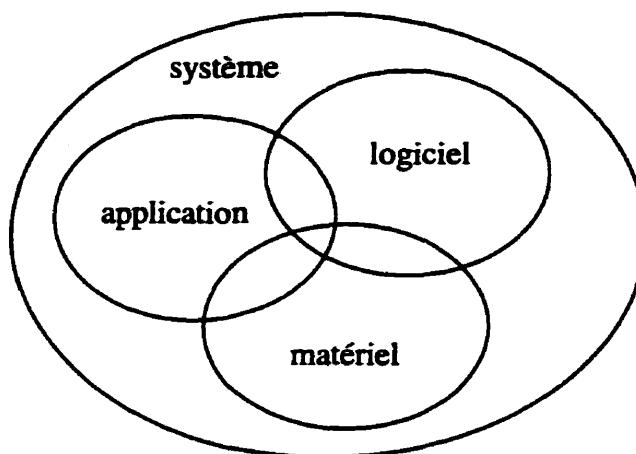

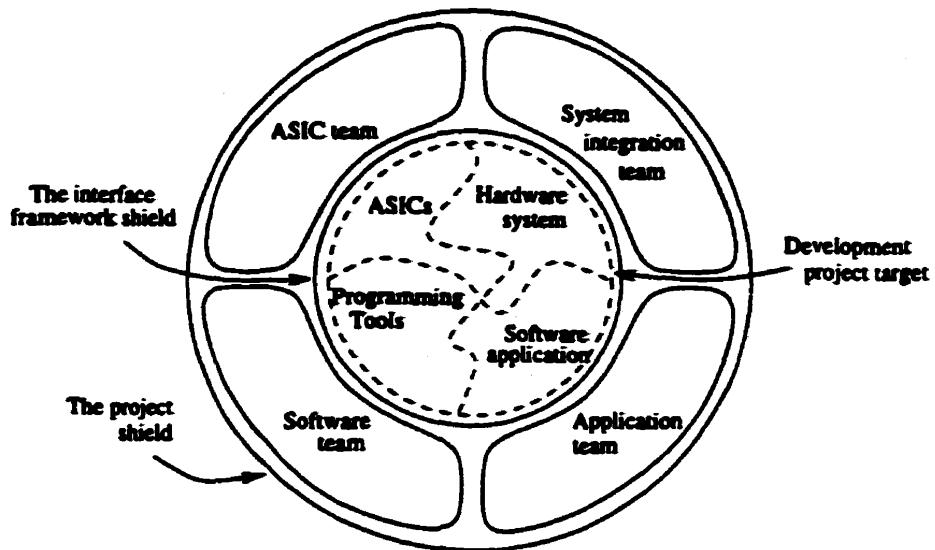

| 3.1. Représentation d'un système complet.....                                          | 65   |

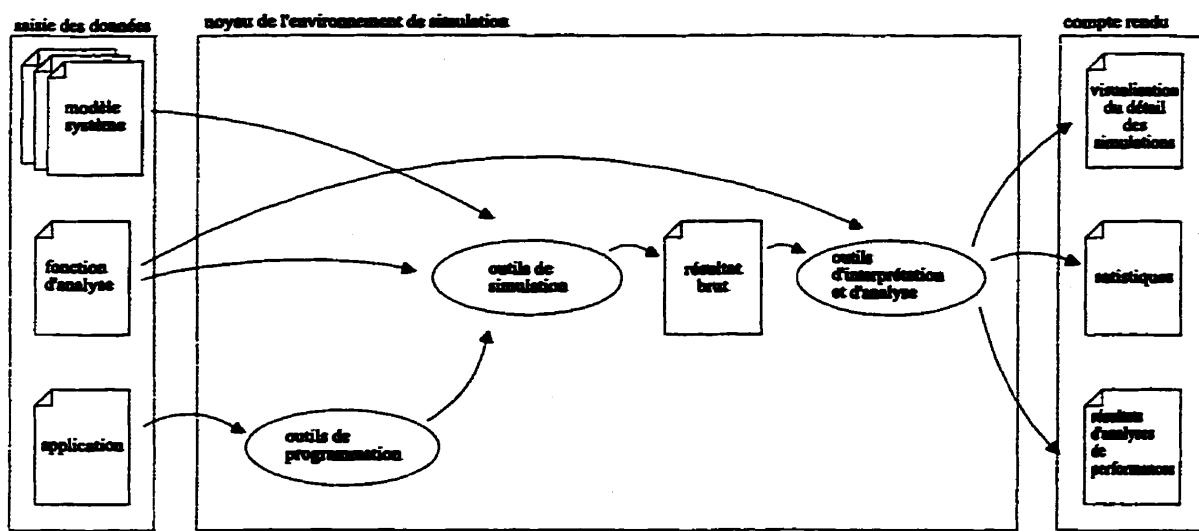

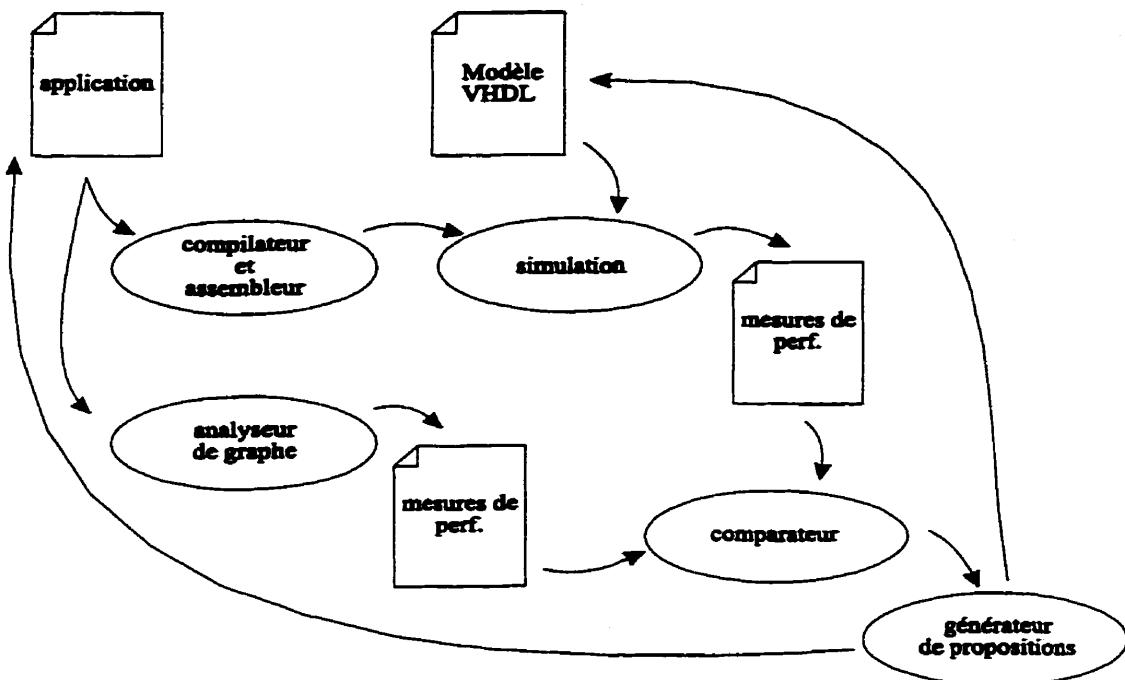

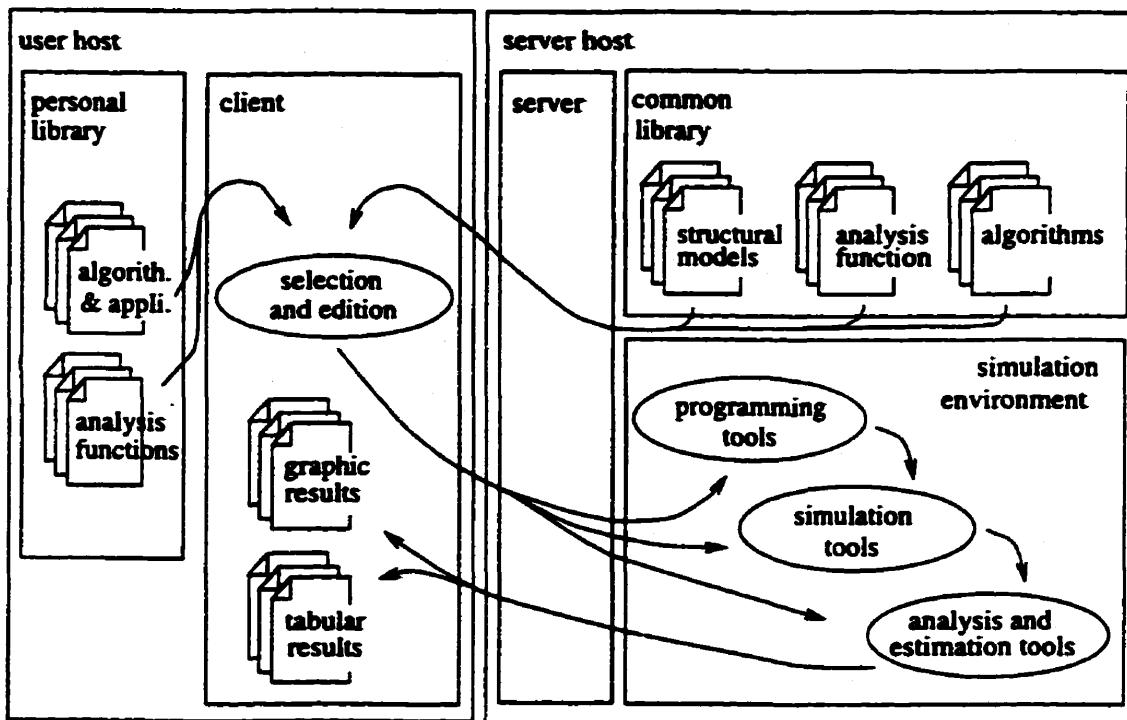

| 3.2. Flux d'information à travers l'environnement de simulation.....                   | 71   |

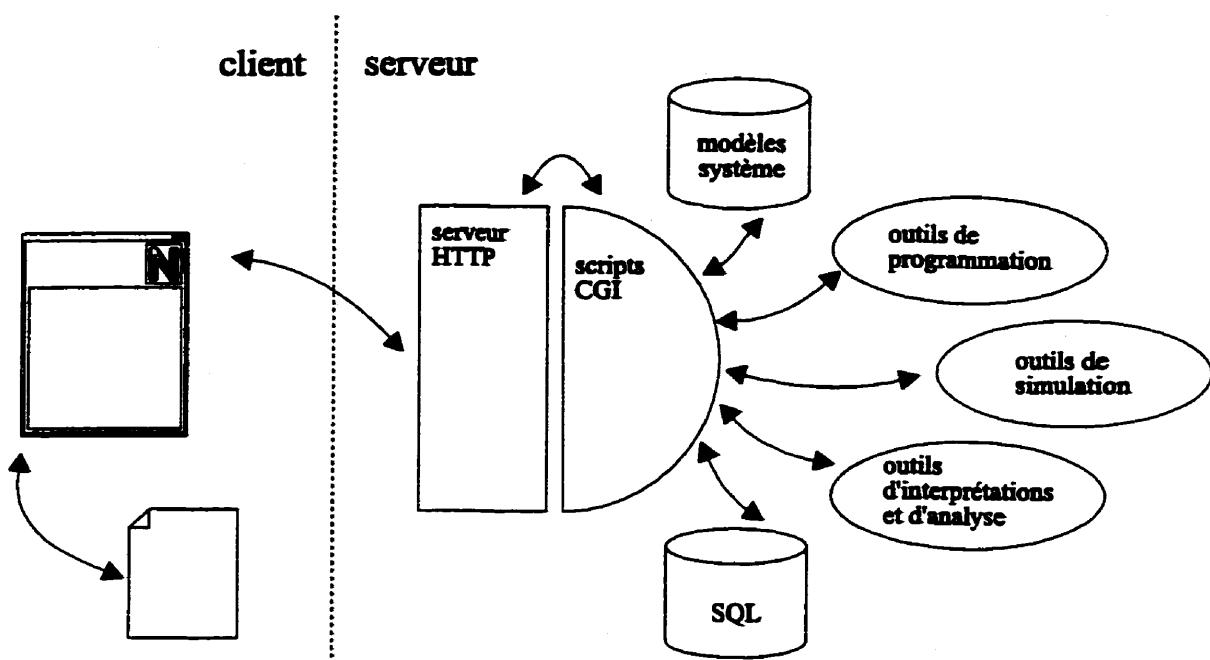

| 3.3. Modèle de fonctionnement du SimPULSE-CGI .....                                    | 72   |

| 3.4. L'interface SimPULSE-CGL.....                                                     | 73   |

| 3.5. Le moteur de recherche de SimPULSE-CGI.....                                       | 74   |

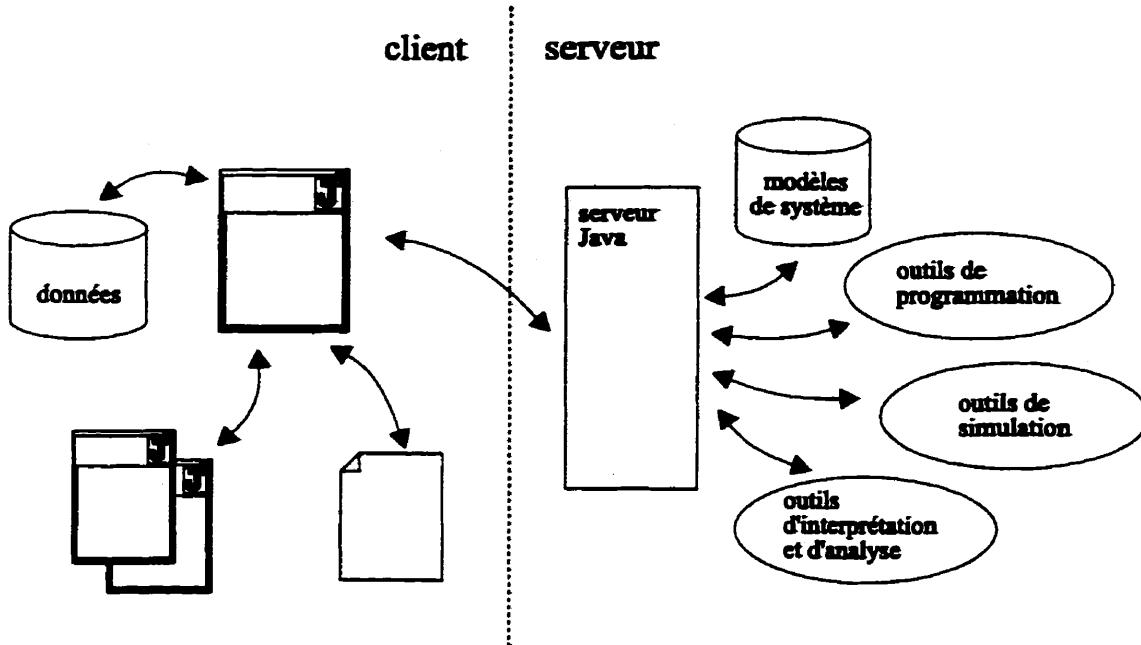

| 3.6. Modèle de fonctionnement du SimPULSE-Java.....                                    | 76   |

| 3.7. L'interface SimPULSE-Java: panneau de contrôle et moniteurs .....                 | 78   |

| 3.8. Le contenu d'un processeur PULSE visualisé par SimPULSE-Java .....                | 79   |

| 3.9. Le contenu d'une mémoire externe visualisé par SimPULSE-Java.....                 | 80   |

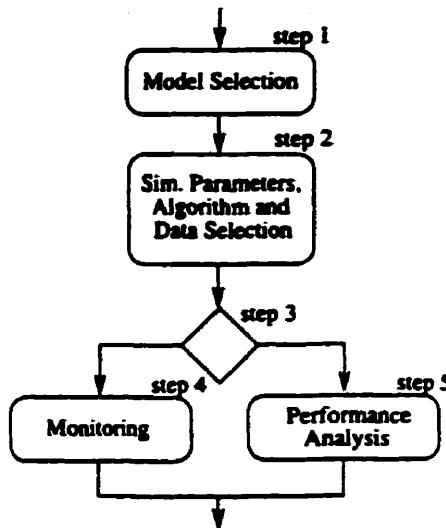

| c.1. La boucle générale d'optimisation.....                                            | 86   |

## INTRODUCTION

La demande croissante de fonctionnalités et de performances dans les applications des systèmes électroniques modernes pousse les concepteurs à réaliser des prouesses en termes de puissance de calcul et de rapidité d'exécution. Pour illustrer cette observation et ainsi justifier le fait qu'il faut trouver des méthodes pour accroître les performances des calculateurs, utilisons un domaine très en vogue, le multimédia, et plus précisément le traitement d'images.

Le traitement numérique d'images est un domaine particulièrement vaste. Les applications sont nombreuses et variées. Elles vont de la gestion de bases de données d'images, à la compression d'images fixes ou animées en vue de leur mémorisation ou de leur transmission, pour aller jusqu'à l'analyse et la compréhension d'images. Toute manipulation d'images met en jeu un volume considérable de données. Celui-ci est lié à la dimension des images manipulées par l'application et croît lorsque, pour fournir un élément d'interprétation, il s'agit d'avoir accès à plusieurs images consécutives d'une séquence.

Généralement, chaque image passe par plusieurs niveaux de traitement. D'une manière schématisée, ceux-ci sont habituellement qualifiés de bas niveau, de niveau intermédiaire et de haut niveau. Les traitements de bas niveau les plus classiques sont les opérations au niveau du pixel qui créent de nouvelles images (algorithmes de seuillage, égalisation d'histogrammes, etc.), ainsi que les opérations de voisinage (filtrages) et les opérations construisant une nouvelle image à partir de deux images initiales (addition, soustraction, produit d'images, opération logique, etc.). Les traitements de niveau intermédiaire partent d'images et aboutissent à des primitives, c'est-à-dire à des représentations condensées de l'information. Les traitements de haut

niveau exploitent les primitives résultant du niveau intermédiaire pour produire de nouvelles primitives et visent à fournir une interprétation de l'image. Il convient cependant de noter que la frontière entre traitement de bas niveau et traitement de niveau intermédiaire tend de plus en plus à disparaître. Dans les algorithmes d'analyse d'images, le terme traitement de bas niveau englobe toutes transformations d'une matrice de pixels en une matrice de primitives.

À chacun de ces niveaux et plus particulièrement au niveau le plus bas, le traitement est dispendieux en calculs. Aussi, le volume de calculs inhérents à de nombreuses applications de traitement d'images excède la capacité de traitement de toute machine séquentielle. Le problème est encore plus critique dans un contexte temps réel où une séquence d'images doit être traitée dans un intervalle de temps très court.

La structure de données couramment manipulée en traitement d'image est le tableau bidimensionnel qui représente la distribution spatiale des valeurs de luminance (niveaux de gris ou couleur). Dans de nombreux algorithmes, le traitement à réaliser consiste en l'application d'un ensemble d'opérations en chaque point de la structure de données image. Ces opérations peuvent aussi être réalisées en parallèle pour chaque élément du tableau.

Les systèmes matériels utilisés pour réaliser ce type d'opérations s'étendent de la simple carte (type carte PC) aux énormes super-calculateurs. Ils tirent parti d'une vaste gamme de composants allant du processeur commercial aux circuits intégrés VLSI (Very Large Scale Integration) spécifiques. En conséquence, les machines parallèles couramment employées pour le traitement des images sont aussi bien des architectures à usage général que des architectures dédiées. Les architectures parallèles à usage général sont intéressantes pour leur flexibilité ; elles supportent une large gamme d'algorithmes avec des performances intéressantes qui permettent de rencontrer les spécifications de l'application considérée. Quant aux architectures spécialisées ou dédiées, elles offrent généralement des performances supérieures en terme de vitesse de traitement, avec souvent comme objectif un traitement en temps réel, et elles disposent de mécanismes

d'entrées/sorties dédiées à leur environnement cible. Le champ d'application de ces machines reste dédié et leur flexibilité généralement limitée.

Plusieurs raisons militent en faveur d'une approche "architecture parallèle spécialisée" où le système est "taillé sur mesure" pour une classe de problèmes ; ce sont les caractéristiques du problème qui déterminent la structure et le contrôle du système.

Les principales raisons sont les suivantes :

- Il est souvent nécessaire d'atteindre une grande rapidité de traitement (système temps réel).

- Le système doit souvent être compact (matériel embarqué). Il est dans ce cas primordial d'optimiser l'architecture pour une classe de problèmes, afin d'en minimiser l'encombrement.

- Les progrès de la technologie des circuits intégrés VLSI ont rendu possible la réalisation de systèmes ayant un grand nombre de processeurs, où chaque processeur intègre des fonctionnalités de traitements minimales ou réalise une fonction particulière. Il est ainsi plus facile de dimensionner le système.

Une solution naturelle conduit à la réalisation de multiprocesseur approchant les performances des super-ordinateurs, tout en ayant le coût des monoprocesseurs. Les composants disponibles commercialement ne permettent généralement pas d'atteindre ce rapport prix/performance. Grâce à la conception de circuits intégrés dédiés (ASIC, *Application Specific Integrated Circuit*) et les nouvelles technologies, plusieurs processeurs peuvent être intégrés dans une puce pour augmenter la capacité de traitement. Parmi les architectures existantes, la structure SIMD<sup>1</sup> (Single Instruction stream, Multiple Data stream) est bien adapté aux problèmes du traitement d'images. Les traitements de bas et de moyen niveaux, qui sont caractérisés par l'application d'opérations identiques à tous les pixels, sont bien adaptés à cette classe d'architecture. Un parallélisme très fin peut-être exploité par ce type de configuration.

---

<sup>1</sup> D'après la classification de Flynn (1972).

Par ailleurs, l'idée de base qui consiste à associer un processeur élémentaire (PE) par pixel de l'image peut s'avérer trop coûteuse, surtout dans le cas de réseaux 2D. Le nombre de processeurs est aussi généralement inférieur à la dimension de l'image, ce qui implique un découpage en blocs et rend la mise en œuvre de l'application plus complexe. Dans ce cas, la parallélisation des applications est dirigée par les données.

C'est en suivant ces considérations que le projet PULSE (Parallel Ultra Large Scale Integration) a émergé (P. Mariott, 1998). Ce projet se propose de réaliser un système permettant des opérations en temps réel pour certaines classes d'applications de traitement des signaux numériques. Ce système possède une structure SIMD linéaire basée sur des processeurs complets, possédant des jeux d'instructions complets et des chemins de données complexes et divers. Ce projet va constituer une base de référence et d'expérimentation pour les sujets traités dans ce mémoire.

Cette architecture parallèle, bien que spécialisée, est programmable. En effet, la programmabilité permet une évolution rapide des fonctionnalités par le développement de nouvelles applications. Mais il est important que la maîtrise de cette programmation ait été prise en compte dès la conception de l'architecture, afin d'éviter que l'utilisation d'un langage évolué s'avère difficile et peut conduire à des mises en œuvre inefficaces.

L'objectif des recherches actuelles est donc, d'une part, d'élaborer un moyen d'exploiter efficacement ces machines, c'est-à-dire de se rapprocher, pour chaque application, de la puissance théorique maximale offerte par la machine, et d'autre part de pouvoir concevoir, vérifier et maintenir les programmes le plus facilement possible. Ces problèmes ont été étudiés dans le cadre du traitement séquentiel et, il est nécessaire d'y apporter également une réponse pour la programmation parallèle.

C'est dans cette optique qu'une adaptation des programmes doit être réalisée pour exploiter au maximum les performances potentielles de l'architecture. Cette *optimisation* des programmes est basée sur deux aspects : le problème du placement des données dans le temps (problème temporel, problème d'ordonnancement) ; et le problème du placement des données au sein des processeurs (problème spatial, problème

d'allocation). Une étude approfondie de ces deux aspects est nécessaire pour la mise en œuvre d'outils de parallélisation automatiques et c'est précisément l'objet de ce mémoire. Compte tenu de la complexité du problème, ce mémoire se limite à présenter une méthode de parallélisation manuelle systématique adaptée à l'architecture PULSE. Cette méthode pourra par la suite être automatisée lors d'une intégration dans un outil de compilation de haut niveau. Pour permettre de comparer, et d'analyser finement les performances obtenues par les méthodes de parcellisation un outil d'analyse a été développé. Cet outil a en plus subit de nombreuses évolutions qui lui ont permis d'accroître son champ d'action et ainsi devenir un outil de simulation et d'estimation de performances dans un milieu de conception de système VLSI.

Ce mémoire est composé de trois chapitres. Le premier (chapitre I) décrit la méthode de parallélisation de programmes appliquées au système PULSE. Il est lui-même découpé en deux parties : la première est une revue de littérature qui définit les concepts, l'état de l'art, et tente de différencier les approches existantes ; la seconde partie détaille une des approches, la mieux adaptée au système PULSE. Elle passe en revue les règles d'optimisation de cette méthode, appelées les stratégies de transformation. L'objectif de cette partie est de présenter quelques-unes de ces stratégies, en précisant les hypothèses sous-jacentes à leur utilisation.

Une fois les méthodes de parallélisation de programme assimilées, le chapitre suivant (chapitre II) traite plusieurs cas réels en insistant sur les performances atteintes avec le système PULSE. Chacun des cas étant unique, une comparaison peut-être réalisée entre eux et avec des applications réelles. Ce chapitre se termine sur une synthèse des performances obtenues et des améliorations à apporter aux méthodes de parallélisation définies au chapitre précédent.

Puisqu'il est question de performance, le dernier des trois chapitres (chapitre III) décrit la manière avec laquelle les performances ont été extraites. Un outil d'analyse a été développé à cette fin dans le cadre de ce mémoire. Cet outil permet de visualiser le fonctionnement des programmes pas à pas et d'estimer les performances dynamiques du

système PULSE. Deux versions de cet outil ont été réalisées. Ce chapitre décrit leur fonctionnement et leur utilisation.

Enfin, une conclusion clôture ce mémoire. Elle replace ce projet dans le contexte de la boucle d'optimisation globale de système imaginée lors de mon entrée à l'École Polytechnique. Nous y proposons une manière de fermer cette boucle qui reste ouverte jusqu'à présent.

## CHAPITRE I

### À LA RECHERCHE DE PERFORMANCES

C'est maintenant un lieu commun que de constater que les processeurs modernes font et vont faire de plus en plus appel au parallélisme pour améliorer leurs performances. Ceci est vrai dans toute la gamme des puissances, des monoprocesseurs jusqu'aux super-ordinateurs. Dans le cas des monoprocesseurs, le parallélisme exploitable est limité. Il se trouve essentiellement à l'intérieur d'une instruction ou d'une séquence de quelques dizaines d'instructions, si bien qu'il peut être caché au programmeur. Cela n'est pas suffisant pour les super-ordinateurs, surtout dans leurs variantes massivement parallèles. En apparence, ceci nécessite la collaboration de l'utilisateur, dû au fait que les interactions entre les traitements ne sont pas faciles à mettre en évidence, alors que le programmeur en a généralement une connaissance au moins intuitive.

La programmation d'une machine parallèle peut ainsi se faire à bas niveau, par exemple en ajoutant à un langage classique les instructions représentant les *opérations* caractéristiques de la programmation parallèle (i.e. création de tâches, synchronisation, communication) et en supprimant celles qui n'ont pas lieu d'exister dans ce contexte. Dans le cas du projet PULSE, ce niveau de programmation se situe dans le langage appelé Cpulse (M. Achim, C. Bonello et V. Van Dongen, 1997). Cette approche a le grand mérite de la transparence : le programmeur contrôle dans le détail l'implantation de son algorithme. Il s'agit donc de la méthode de choix pour le développement de nouveaux algorithmes nécessitant des mécanismes particuliers et précis.

En revanche, en tant que méthode de production générale d'applications, elle possède des défauts, tel que la difficulté de mise au point des applications, due essentiellement au caractère non-déterministe de nombreuses architectures parallèles. De plus, il y a des

cas où la manière d'exploiter le parallélisme présent dans l'application n'est perçue clairement que par le programmeur. Un grand nombre de chercheurs se sont préoccupés, depuis les travaux pionniers de David J. Kuck (1972), de développer des outils d'aide à la programmation parallèle.

Nous pouvons imaginer qu'un compilateur, plus sophistiqué que les compilateurs usuels (appelé *compilateur-paralléliseur*), se charge de rechercher dans les programmes le parallélisme implicite et de l'exploiter sur la machine cible. Ainsi, le programmeur pourrait définir son application en utilisant des langages sources sans séquencement (langage fonctionnel, à flot de données, logique, etc.) ou des langages de haut niveau beaucoup plus simples à utiliser, tel que HPCP dans le cas du projet PULSE (N. Belanger. 1997). Cette approche correspond à ce que nous appelons la parallélisation automatique au sens le plus courant du terme. La parallélisation automatique se donne ainsi trois objectifs :

- faciliter le développement de nouvelles applications,

- rechercher un optimum de performance pour une application sur une architecture parallèle cible,

- assurer la portabilité des programmes entre les architectures parallèles.

Au près des groupes de recherche les deux premiers objectifs sont très en vogue. Il est très tentant de développer un algorithme en version séquentielle, avec tous les moyens et environnements existants, et de ne passer à la version parallèle que lorsque l'essentiel de la mise au point a été fait, afin de laisser un compilateur-paralléliseur rechercher le meilleur partitionnement atteignant les performances souhaitées. De plus, ces objectifs permettent de rendre explicite des aspects parallèles d'un programme qui n'ont pas été décelés par le programmeur.

Bien qu'éloigné de nos objectifs immédiats, l'importance du troisième objectif croît avec l'apparition à cadence rapide de nouvelles architectures. Les ordinateurs séquentiels se ressemblent tous, au moins du point de vue conceptuel, et il est tout à fait concevable de mettre au point un algorithme sur un IBM-PC pour l'exécuter sur un IBM-3090. En

revanche, la portabilité d'un programme entre des architectures parallèles est très délicate et complexe.

Les techniques de parallélisation sont en pleine évolution<sup>2</sup>. Cependant, les méthodes utilisées ont un air de famille. Le travail se fait toujours en deux étapes principales. Une phase d'analyse permet de rassembler des informations globales sur la façon dont les diverses instructions interagissent entre elles. Nous parlons usuellement d'*analyse sémantique*, pour montrer que cette phase s'intéresse aux traitements exécutés par le programme et non pas seulement à la façon dont il est écrit.

La deuxième étape consiste à exploiter les résultats obtenus dans la phase d'analyse pour guider la génération du programme parallèle. Elle peut être vue comme l'identification dans le programme source des formes caractéristiques des opérations possédant un parallélisme implicite. Naturellement, la reconnaissance de ces formes est d'autant plus facile (i.e. il y a d'autant moins de modèles à considérer) que la phase d'analyse a fourni une représentation plus synthétique du programme original.

La suite du chapitre décrit des méthodes de parallélisation de programme. Une de ces méthodes est détaillée en profondeur en vue d'être appliquée dans le cadre du projet PULSE. Ce chapitre se répartit en quatre sections. La première (section 1.1) définit le principe traditionnel de la parallélisation de programmes et propose un diagramme de flot de ce processus, suivi d'une comparaison des différentes techniques. Les deux sections suivantes (sections 1.2 et 1.3) détaillent les différentes étapes de ce processus de parallélisation. Décrivant, pour la première, les mécanismes d'analyse des dépendances, et pour la seconde, la technique de transformation de boucles. Enfin, une conclusion clôture cette présentation des méthodes de parallélisation. Tout au long de ce chapitre, l'architecture soutenue par le projet PULSE guide nos critères de sélection.

---

<sup>2</sup> La parallélisation automatique est actuellement étudiée par de nombreux groupes de recherche et plusieurs outils de parallélisation ont été écrits: SUIF à l'université de Stanford en Californie, PIPS à l'École Nationale Supérieure des Mines de Paris, la bibliothèque Omega à l'université du Maryland, PooPo à l'université de Passau en Allemagne, le compilateur Paradigm à l'université de l'Illinois, PAF à l'université de Versailles, pour n'en citer que quelques-uns.

## 1.1. Le principe traditionnel de la parallélisation

L'analyse et l'interprétation d'un programme en vue de son exécution parallèle ne peut pas s'appuyer sur la notion d'instruction, parce que c'est entre les différentes répétitions d'une même instruction que nous espérons trouver le plus de parallélisme. Chaque exécution d'une instruction doit être considérée comme une entité distincte, une *opération*. Un programme doit être vu comme un ensemble d'opérations donné *a priori*, au moins conceptuellement. Mais un programme ne se réduit pas à l'ensemble de ses opérations, pas plus qu'une sonate ne peut se jouer en frappant simultanément l'ensemble des notes de la partition. Ici, comme en musique, l'ordre d'exécution des opérations est primordial. Un programme doit donc être représenté comme un ensemble ordonné d'opérations. L'ordre d'exécution est caractérisé par leur séquence caractérisée par des successions et imbriques de boucles et de conditions.

C'est pour cette raison que les emboîtements de boucles sont au cœur de la stratégie de parallélisation des compilateurs-paralléliseurs des ordinateurs parallèles contemporains. Leur importance, en termes d'applications, est claire : pour de nombreux programmes scientifiques, le temps passé dans quelques boucles constitue une grande fraction du temps d'exécution total, et le parallélisme potentiel en est souvent considérable (P. Boulet, A. Darté, G-A. Silber et F. Viven, 1997). D'une part, la restriction de l'analyse aux emboîtements de boucles ne constitue pas une limitation trop pénalisante. Cela permet de traiter une vaste classe d'applications (qui contient notamment la plupart des applications de traitement du signal ou d'algèbre linéaire numérique). La parallélisation des boucles a fait l'objet de nombreuses recherches (J.R. Allan et K. Kennedy, 1984 ; U. Banerjee, Fév. 1993 ; U. Banerjee, 1993, R. V. Hanxleden et K. Kennedy, 1992).

D'autre part, la structure régulière et répétitive des emboîtements de boucles facilite la mise en œuvre de techniques d'analyse des dépendances et la recherche de fonctions d'ordonnancement et d'allocation. Le problème général de l'ordonnancement optimal d'un système de tâches sur une machine parallèle est connu comme un problème difficile, du essentiellement aux communications, même s'il est supposé disposer d'un

nombre illimité de processeurs. Pourtant, dans le cas des boucles imbriquées, il est possible de définir des algorithmes d'ordonnancement efficaces et d'établir leur optimalité en utilisant des outils mathématiques. Les caractéristiques principales qui différencient les techniques d'ordonnancement des emboîtements de boucles par opposition aux systèmes généraux de tâches sont :

- *La cyclicité* : La structure régulière et répétitive d'un emboîtement de boucles permet de ne considérer que les dépendances pour la recherche d'un ordonnancement optimal.

- *La générericité* : Il est possible de trouver des ordonnancements génériques, valables pour toutes les valeurs des paramètres.

Par déduction, l'étude de la parallélisation des emboîtements de boucles attirera particulièrement notre attention dans ce mémoire.

### 1.1.1. Les fondations de la parallélisation

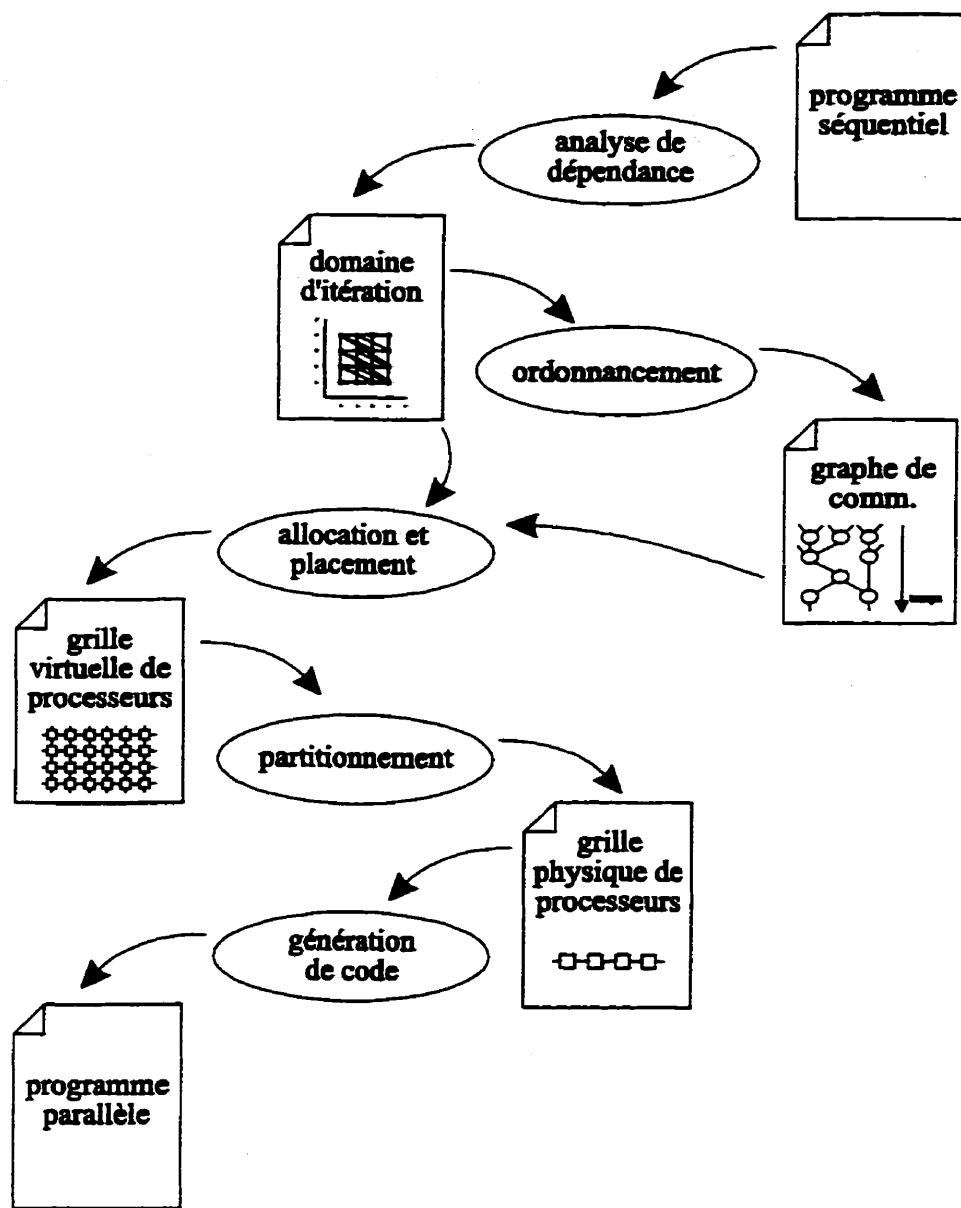

La figure 1.1 présente le processus de parallélisation d'un programme séquentiel effectué par un compilateur-paralléliseur contemporain. Ce processus peut-être décomposé comme suit, en plusieurs étapes interdépendantes :

- L'*analyse des dépendances* consiste à créer un graphe, appelé *domaine d'itérations*, représentant les contraintes sur l'ordre d'exécution des opérations déduites à partir des relations entre les données utilisées par chaque opération.

- L'étape d'*ordonnancement* utilise le domaine d'itérations pour construire un *graphe de communication* qui associe un temps d'exécution à chaque instance de chaque opération. Ainsi un moment d'exécution est assigné à chaque opération. Le but de cette étape est de minimiser la latence globale, qui se trouve être la concaténation des tout les temps d'exécutions de chacune des opérations ayant des interdépendances.

- L'étape d'*allocation et placement* cherche à répartir les données et calculs sur une *grille virtuelle de processeurs* de taille et de dimension infinie. Cette recherche se base sur le graphe de communication et le domaine d'itérations pour trouver une répartition où les communications inter-processeurs sont minimales.

- Le *partitionnement* a pour but de découper la grille virtuelle de processeurs et de répartir les morceaux sur la *grille physique de processeurs*. Cette tâche est effectuée en répartissant la charge de travail de chaque processeur le plus équitablement possible, et en respectant les travaux effectués lors des phases d'ordonnancement et d'allocation précédentes.

- La dernière étape est la *génération de code*. Cette dernière a pour but de réécrire, dans un langage de programmation donné, la nouvelle représentation des boucles et tableaux du programme initial pour chacun des processeurs physiques avec un **parallélisme explicite**.

Les étapes d'ordonnancement et d'allocation ne sont pas indépendantes et c'est le problème majeur que toute technique de compilation a à affronter. Deux tâches ordonnancées au même moment ne peuvent pas être allouées au même processeur sans perte de parallélisme.

Figure 1.1: Principe de la parallelisation

Il est à noter que la figure 1.1 n'est pas entièrement exacte. Dans un cas réel, des optimisations de code avant la première étape et après la dernière peuvent être réalisées. Ces optimisations sont de bas niveau et servent à éliminer le code mort, à normaliser les constantes et indices, et à supprimer les fausses dépendances.

### 1.1.2. Notations et terminologies

Avant de se lancer dans le vif du sujet, une identification et une définition des principaux termes et règles de notation utilisées est réalisée. Il est à noter que les restrictions énoncés lors des définitions ci-dessous ont pour but de restreindre le champ d'investigation et ainsi de permettre de proposer une méthode et d'exposer son déroulement dans le cadre d'un mémoire de maîtrise.

**Définition 1.1 - Type de données :** À tout moment, sauf si spécifié, lorsqu'il est question de données, il est sous-entendu que les données se trouvent sous une représentation de scalaires ou de tableaux multidimensionnels de scalaires. L'allocation de mémoire est supposée faite de façon unique (sans surnommage ou *aliasing*), c'est-à-dire que deux éléments d'un même tableau correspondent à la même adresse mémoire si et seulement si ce sont les éléments d'un même tableau et que les indices sont identiques.

**Définition 1.2 - Paramètres de structure :** Le programme peut dépendre de paramètres, définis une et une seule fois dans le programme par une instruction d'entrée/sortie ou par une relation avec d'autres paramètres de structure déjà définis.

**Définition 1.3 - Instructions :** Les instructions sont les opérations d'affectation portant sur un scalaire ou un élément d'un tableau et celles supportées implicitement par l'architecture matérielle cible. De la même façon que pour les compteurs de boucle, les fonctions d'accès aux tableaux sont restreintes aux fonctions affines composées par des paramètres de structure et les indices des boucles englobantes.

**Définition 1.4 - Boucle :** La notion de boucle est construite à partir des opérateurs du type `for` avec un compteur explicite  $i$ , dont les bornes inférieures  $L$  et supérieures  $U$  sont-elles aussi explicites. Le *corps* de la boucle, noter  $H$ , contient toutes les instructions effectuées par la boucle. Si le corps ne contient pas de branchement hors de la boucle et si le pas du compteur est 1, alors les bornes du compteur sont atteintes.

**Définition 1.5 - Nid de boucles :** Lorsque le corps d'une boucle contient lui-même une autre boucle, cet emboîtement est appelé un *nid*. Notons que cet emboîtement est nécessairement fini. Si le corps de toute boucle est une boucle ou une séquence d'assignments<sup>3</sup>, le nid est dit *parfait*. Un exemple de la structure d'un nid parfait est codé ci-dessous. Cette structure est reprise de celle utilisée par Uptal Banerjee (1988). Il est à noter que les bornes des boucles ne sont pas constantes dans ce modèle. Cette non-constance des bornes et des indices peut amener à avoir des vecteurs de *distance de dépendances* (voir définition 1.10 en page 29) non constants, ce qui rend le problème de la recherche de parallélisme dans les boucles NP-complet (M.L. Dowling, 1990). La *profondeur* d'un nid de boucles est le nombre de boucles emboîtées. De façon analogue, la profondeur d'une instruction est le nombre de boucles englobantes. Par abus de notation, les termes *nid* et *nid de boucles* seront utilisés indifféremment.

```

for i1=n1, N1 {

for i2=n2(i1), N2(i1) {

...

for in=nn(i1, i2, ..., in-1), Nn(i1, i2, ..., in-1) {

H(i1, i2, ..., in)

}

...

}

}

```

Figure 1.2: Le nid de boucles parfait

---

<sup>3</sup> Les assignments portent sur des scalaires ou des tableaux multidimensionnels de scalaires uniquement (définition 1.1).

**Définition 1.6 - Vecteur d'itération :** Le vecteur d'itération d'un nid est le vecteur formé par les compteurs englobants, du compteur de la boucle externe jusqu'au compteur de la boucle interne. Celui du nid précédent est donc  $i = (i_1, i_2)$ . Il est clair que la dimension du vecteur d'itération est égale à la profondeur du nid de boucles correspondant.

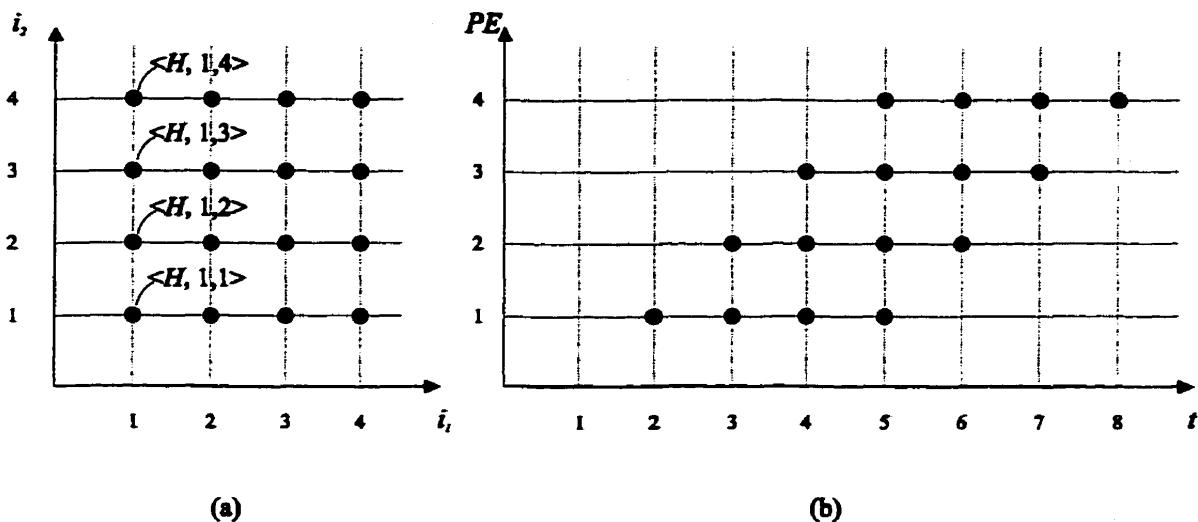

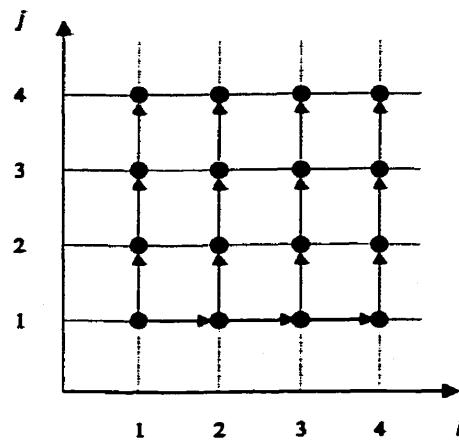

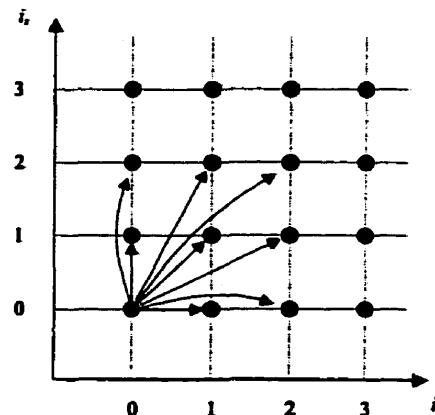

**Définition 1.7 - Domaine d'itération :** Nous appelons domaine d'itération (voir figure 1.3a)  $G$  d'un nid, l'ensemble des valeurs prises par le vecteur d'itération au cours de l'exécution, tel que

$$G = \{(i_1, \dots, i_n) \mid L_1 \leq i_1 \leq U_1, \dots, L_n(i_1, \dots, i_{n-1}) \leq i_n \leq U_n(i_1, \dots, i_{n-1})\} \quad (1.1)$$

Figure 1.3: Domaine d'itération vs. allocation et placement des données sur des processeurs pour un domaine à deux dimensions  $\langle H, i_1, i_2 \rangle$

L'exécution d'un nid donnera lieu à autant d'*instances* de  $H$ , ou d'opérations, qu'il y a de valeurs possibles pour le vecteur d'itération. Ainsi, chaque point du domaine d'itération peut être identifié avec une instance de  $H$ , et  $G(H)$  représente le domaine d'itération associé au corps de boucle  $H$ . Une opération peut alors être référencée sans ambiguïté

par le nom de l'instruction et par la valeur du vecteur d'itération ; la notation  $\langle H, i \rangle$  est utilisée pour désigner une instance de  $H$  pour une valeur  $i$  du vecteur d'itération. Par abus de notation,  $\langle H, i \rangle$  et  $\langle H, i_1, \dots, i_n \rangle$  seront utilisés indifféremment.

D'après la définition, le domaine d'itération est caractérisé par un ensemble d'inégalités linéaires et affines correspondant aux bornes des vecteurs d'itérations. Étant affines, ces équations peuvent être représentées sous une forme matricielle par les deux relations suivantes :  $S_L I \geq l$  et  $S_U I \leq u$ , où  $S_L$  et  $S_U$  sont des matrices triangulaires de taille  $n$  par  $n$  ;  $I$  est un vecteur d'itération de taille  $n$  par 1 ;  $l$  et  $u$  sont des vecteurs d'entiers de taille 1 par  $n$ . En les combinant, nous obtenons un système qui régit les limites haute et basse des vecteurs d'itération d'un nid de boucle

$$(S, c) = \left( \begin{bmatrix} S_L \\ -S_U \end{bmatrix}, \begin{bmatrix} l \\ -u \end{bmatrix} \right) \quad (1.2)$$

où  $(S, c)$  est la représentation complète des bornes du domaine d'itération.

**Définition 1.8 - Ordre lexicographique** (noté  $\prec$ ) : Les couples  $i = (i_1, \dots, i_n)$  et  $j = (j_1, \dots, j_n)$  satisfont  $i \prec j$  si et seulement si il existe un entier  $k$ , tel que  $1 \leq k \leq n$  et que  $i_1 = j_1, \dots, i_{k-1} = j_{k-1}$  et  $i_k < j_k$ .

**Définition 1.9 - Matrice de transformation** : Matrice qui permet de réaliser des transformations de boucles et les instructions contenues dans un nid de boucles.

La section 1.3. y est entièrement consacrée.

### 1.1.3. Histoire d'algorithmes

Cette section passe en revue les principaux algorithmes de détection du parallélisme : ceux de Lamport, d'Allen et Kennedy, de Wolf et Lam, de Feautrier, de Darté et Vivien, et de Lim et Lam. Cette liste permet de choisir la (ou les) méthode qui se rapproche le plus possible de nos préoccupations. Il est bien entendu que cette liste n'est pas exhaustive, seul les noms des personnes ayant apportés une contribution significative dans le domaine sont cités. Ensuite une synthèse sous forme d'un tableau de comparaison est présenté en guise de conclusion de cette sous-section.

**L'algorithme de Lamport (1974) :** Leslie Lamport est connu en parallélisation pour sa *méthode de l'hyperplan*. Cette méthode considère des nids de boucles parfaits avec des vecteurs de distances constantes. Il crée un hyperplan qui lui permet de constituer sa matrice unimodulaire de transformation. Cette méthode, qui repose sur la lexicopositivité des vecteurs de distance, est en fait un algorithme de construction d'ordonnancements linéaires représenté sous forme d'hyperplan fortement séparateur. Elle considère des nids dont les dépendances sont représentées par des vecteurs dirigés dont seul la première composante peut ne pas être constante. Il a également présenté une méthode généralisée qui s'appelle : la *méthode du plan* qui permet d'avoir des vecteurs de direction constants.

Leslie Lamport a remarqué que ses ordonnancements est un problème de programmation linéaire, mais il ne connaît pas de méthode pratique permettant de le résoudre dans un cas général. Son algorithme est optimal pour des nids de boucles dont les dépendances sont uniformes et dont les graphes et dépendances sont fortement connexes.

**L'algorithme de Allen et Kennedy (1987) :** Cet algorithme a été originellement proposé pour la vectorisation de boucles. Il a été ultérieurement étendu pour maximiser le nombre de boucles parallèles générées et pour minimiser le nombre de

synchronisations requises. Cet algorithme prend en entrée un *graphe de dépendances réduit par niveaux* (GDRN). Il repose sur les deux propriétés suivantes :

- Une boucle est parallèle si elle ne porte pas de dépendance, c'est-à-dire s'il n'existe pas de dépendance dont le niveau soit égal à la profondeur de cette boucle et concernant une instruction étant à l'intérieur de cette dernière.

- Toutes les itérations du corps de boucles  $H$  peuvent être exécutées avant que ne soit évaluée une seule instance de l'instruction  $H^*$ , si le graphe de dépendance réduit ne contient pas de dépendances de  $H^*$  vers  $H$ .

La première propriété permet de marquer les boucles : séquentielles ou parallèles. La seconde suggère que la détection du parallélisme puisse être menée indépendamment dans les différentes composantes du GDRN. L'extraction du parallélisme se fait au moyen d'une simple distribution de boucles déroulées. Cet algorithme détecte autant de boucles englobantes parallèles que possible pour chaque instruction du code original. Ceci le rend optimal pour générer du code parallélisé dans lequel les instances d'une instruction quelconque sont énumérées avec les mêmes boucles que dans le code initial. Autrement dit, aucun algorithme ne peut trouver plus de parallélisme dans un graphe de dépendance réduit par niveaux que n'en trouve cet algorithme.

**L'algorithme de Wolf et Lam (1991) :** Michael Wolf et Monica Lam ont proposé un algorithme qui accepte en entrée une approximation des dépendances par des vecteurs dirigés. Leurs travaux unifient les algorithmes antérieurs basés sur des opérations matricielles élémentaires, telles que des torsions (ang. *skew*), l'inversion (ang. *interchange*) et le renversement (ang. *reversal*) de boucles, en se plaçant dans le cadre unique des transformations unimodulaires valides. L'algorithme proposé généralise la méthode du plan de Lamport.

L'algorithme de Wolf et Lam a pour objectif de construire des ensembles de boucles totalement permutables. Ces boucles totalement permutables sont à la base de toutes les techniques de partitionnement (ang. *tiling*). Le partitionnement est utilisé pour exposer du parallélisme à grain moyen. Cependant, un ensemble de  $n$  boucles imbriquées

totallement permutables peut toujours être transformé en un ensemble de  $n-1$  boucles parallèles imbriquées entourées d'une boucle séquentielle. Les boucles permutables sont donc aussi liées à la parallélisation à grain fin.

Wolf et Lam cherchent, au moyen de transformations unimodulaires, le plus grand<sup>4</sup> ensemble de boucles externes totalement permutables<sup>5</sup>. Ils considèrent récursivement les dimensions restantes et les vecteurs non satisfaits par ces boucles. Pour que les boucles soient permutables, il faut qu'elles soient imbriquées. Wolf et Lam ne considèrent donc que des nids parfaitement imbriqués. Cet algorithme trouve un maximum de parallélisme à gros grain.

**L'algorithme de Feautrier (1992) :** Contrairement aux algorithmes précédents, Paul Feautrier n'a pas essayé de trouver du parallélisme dans une représentation approchée des dépendances : il ne s'occupe implicitement que de dépendances exactes. Dans le cadre des programmes à contrôle statique, il a d'abord décrit un algorithme de construction d'ordonnancements affines unidimensionnels, puis multidimensionnels. Ces algorithmes s'appuient sur une représentation des dépendances par des polyèdres. Cette représentation lui permet de paralléliser des nids parfaits et des nids débalancés contenant des dépendances affines, ce qui rend cet algorithme plus performant pour la recherche de dépendances exactes dans des nids de boucles. Les seuls résultats d'optimalité communs pour cet algorithme concernent les nids de boucles uniformes à une ou plusieurs instructions.

**L'algorithme de Darte et Vivien (1996) :** Alain Darte et Frédéric Vivien proposent une simplification de l'algorithme de Feautrier au niveau de la représentation des dépendances, ce qui leur permettent de réaliser des transformations affines sur les boucles. Elles possèdent toutefois des restrictions sur leurs formes. Cet algorithme est

<sup>4</sup> Nous pouvons compter sans risque le nombre de boucles du nid, car les transformations unimodulaires ne modifient pas ce nombre.

<sup>5</sup> Dans le cadre de boucles dont tous les incrément sont positifs, les  $k$  boucles externes sont totalement permutables si les  $k$  premières composantes de tous les vecteurs de directions sont positives.

optimal pour détecter un maximum de parallélisme si les dépendances peuvent être approximées par des polyèdres. Ceci résulte en un algorithme plus simple et plus performant que celui de Feautrier pour la permutation de boucles, la minimisation des synchronisations entre les boucles, et la génération de code. Des restrictions au niveau des boucles à paralléliser impliquent que cet algorithme est globalement moins exact sur la recherche de parallélisme.

**L'algorithme de Lim et Lam (1997) :** Les algorithmes précédemment décrits cherchaient tous à exhiber le maximum de parallélisme. Celui de Amy Lim et Monica Lam recherche plutôt le maximum de parallélisme exposable sans dépasser un volume donné de synchronisations. Cet algorithme travaille dans les mêmes conditions que celui de Feautrier et peut donc être considéré comme une extension : il s'intéresse aux dépendances exactes des nids à contrôle statique dont les fonctions d'accès sont affines. Il produit un placement des calculs et un ordonnancement de ceux-ci au moyen de fonctions affines. Plutôt que de résoudre des programmes linéaires comme l'algorithme présenté par Feautrier, celui de Lim et Lam calcule des noyaux de matrices. Cet algorithme recherche le parallélisme qui peut-être obtenu avec une qualité croissante de synchronisation : aucune synchronisation,  $O(1)$  synchronisations,  $O(N)$  synchronisations, etc., où  $N$  est le paramètre de taille du domaine d'itération. Lim et Lam affirment que leur algorithme explore le parallélisme de façon optimale : « L'algorithme trouve tous les degrés de parallélisme du programme étudié, tout le parallélisme étant à grain aussi gros que possible ». Il faut toutefois rajouter la condition suivante pour que cette affirmation soit valide : « parmi les algorithmes produisant des transformations affines ».

Tableau 1.1: Comparaison entre les différents algorithmes de parallélisation, adapté de P. Boulet (1997)

| Algorithm      | dépendance                    | transformation | parallélisme | synchronisation | génération de code | permute- |

|----------------|-------------------------------|----------------|--------------|-----------------|--------------------|----------|

| Lamport        | simple, imparfait             | unimodulaire   | optimal      | oui             | très simple        | oui      |

| Allen-Kennedy  | simple, imparfait             | distribution   | optimal      | oui             | très simple        | non      |

| Wolf-Lam       | vecteur de direction, parfait | unimodulaire   | optimal      | non             | simple             | oui      |

| Feautrier      | affine (exact), imparfait     | affine         | sub-optimal  | non             | compliqué          | non      |

| Darte-Viven    | polyèdre, parfait             | (shift linear) | optimal      | partiel         | un peut compliqué  | oui      |

| Lim-Lam        | affine (exacte), imparfait    | affine         | sub-optimal  |                 |                    | Oui      |

| Uptal Banerjee | simple, imparfait             | unimodulaire   | optimal      |                 | simple             | Oui      |

Le tableau 1.1 expose les différences majeures entre les six algorithmes discutés plus celui choisi dans le cadre de ce mémoire. Nous avons d'un côté des algorithmes utilisant des techniques puissantes sur une représentation exacte des dépendances mais sans garantie sur leur efficacité. De l'autre côté, nous avons des algorithmes plus simples travaillant sur une représentation approchée des dépendances et dont l'(in)efficacité est bien définie. Schématiquement, dans le contexte de ce mémoire, nous recherchons un algorithme travaillant sur une représentation approchée des dépendances afin de pouvoir traiter des programmes plus généraux que ceux étudiés par l'algorithme de Feautrier. Nous voudrions utiliser des techniques suffisamment puissantes pour extraire tout le parallélisme contenu dans la représentation des dépendances choisie. Cependant, nous

aimerions générer des codes aussi simples que faire se peut. Nous aimerais que cet algorithme idyllique trouve du parallélisme à chaque fois que Allen et Kennedy ou Wolf et Lam en trouvent. Pour ce faire et pour ne pas entrer dans des considérations mathématiques aussi complexes que celles qui soutiennent les algorithmes de Feautrier, Darte et Vivien, ou Lim et Lam, dans ce mémoire, la technique de Banerjee (1988), décrite en détail dans la prochaine section, va être utilisée pour l'analyse des dépendances. L'algorithme d'extraction du parallélisme jusqu'à la réécriture du code va être dérivé d'une symbiose des algorithmes de Wolf et Lam et de Banerjee (1993).

## 1.2. Analyse des dépendances

La connaissance des instructions et des domaines d'itération n'est pas suffisante pour définir complètement la sémantique d'un nid de boucles. Tel qu'énoncé dans la section précédente, l'analyse des dépendances est une part importante de la recherche de parallélisme d'une application (1993). Cette section décrit les mécanismes et processus qui régissent cette analyse.

L'exécution séquentielle attribue un ordre total aux opérations, appelé ordre lexicographique. Par contre, une description séquentielle est souvent inutilement rigide, et peut être partiellement désordonnée. En fait, deux opérations peuvent être effectuées dans n'importe quel ordre, y compris simultanément, si elles sont *indépendantes*. Une dépendance apparaît lorsque les deux opérations cherchent à utiliser une même ressource ou à modifier un même résultat.

Pour ce mémoire, nous nous restreindrons à un type bien particulier de conflits d'accès : les dépendances liées à l'utilisation de la mémoire et des unités de calcul. Ces dépendances sont représentatives de l'ensemble des facteurs spécifiques qui limitent l'exploitation du parallélisme dans l'architecture multiprocesseurs SIMD qu'est PULSE. En effet, le présent travail se concentre sur les noyaux<sup>6</sup> des programmes, ainsi que sur

---

<sup>6</sup> Ces noyaux sont essentiellement des nids de boucles.

les entrées/sorties aux périphériques, qui sont supposées avoir lieu avant et/ou après ces noyaux.

Ces dépendances décrivent parfaitement les liens qui existent entre les différents calculs. Une analyse exacte des dépendances est souvent impossible car trop d'information sur les zones mémoire affectées est analysée d'une manière statique. Une attitude pessimiste est généralement adoptée, consistant à dire qu'il existe une dépendance dans les cas où l'indépendance ne peut pas être certifiée. Ceci permet d'éviter d'autoriser des transformations qui pourraient mener à une perte de la sémantique du programme initial. Des algorithmes ont été proposés, comme le test de Banerjee, le *GCD test*, le *Lambda test*, le *Power test* et le *Omega test* pour trouver une solution satisfaisante à ce problème NP-complet (P. Feautrier, 1991).

Quels sont donc les conflits d'accès à la mémoire ? Si deux opérations successives doivent écrire dans une même cellule de la mémoire, il est clair qu'inverser l'ordre d'exécution de ces opérations aboutirait à un état différent de la mémoire. De même, si une des opérations lit et l'autre écrit dans une même case, la valeur lue par la première ne peut être préservée que si l'ordre initial est respecté. Trois conditions suffisantes ont été identifiées pour que deux opérations  $o_1$  et  $o_2$ , prescrites dans un ordre particulier dans le programme séquentiel, puissent être exécutées dans un ordre quelconque (U. Banerjee, 1988). Soient  $L(o_1), M(o_1)$  et  $L(o_2), M(o_2)$ , les ensembles des cellules mémoires lues et mises à jour par  $o_1$  et  $o_2$  respectivement. Les opérations  $o_1$  et  $o_2$  sont indépendantes si et seulement si

- C1:  $M(o_1) \cap L(o_2) = \emptyset, o_1 \delta^r o_2$

- C2:  $L(o_1) \cap M(o_2) = \emptyset, o_1 \bar{\delta} o_2$

- C3:  $M(o_1) \cap M(o_2) = \emptyset, o_1 \delta^o o_2$

Le non-respect de chacune de ces conditions provoque une *dépendance de données* :

- **Non-respect de C1 :** Le résultat d'une opération est sauvegardé en mémoire et utilisé ensuite par une autre opération. Cette dépendance est appelée

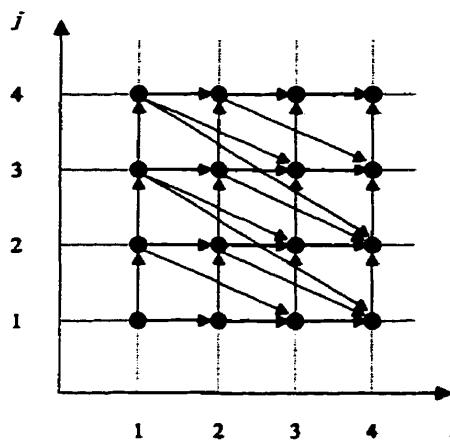

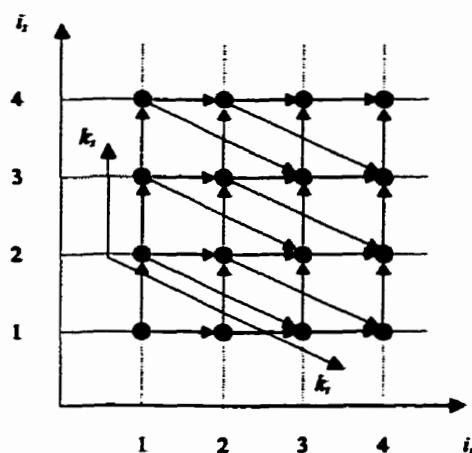

indifféremment *vraie dépendance* ou *dépendance producteur-consommateur* (PC). Nous noterons cette dépendance  $o_1 \delta^r o_2$ . Par exemple, soit les opérations  $\langle S,1,1 \rangle$  et  $\langle S,2,1 \rangle$  de l'exemple 1.1 où  $\langle S,a,b \rangle$  est l'opération réalisée lorsque les indices valent  $i=a$  et  $j=b$ . Ces opérations sont dépendantes suivant une dépendance PC, puisque la première écrit dans la cellule mémoire a(2) qui est lue par la seconde. L'ensemble des dépendances PC du programme exemple, pour  $n=4$ , sont représentées par des arcs dans le graphe de dépendance de la figure 1.4a.

- **Non-respect de C2 :** Le non-respect de C2 est une *anti-dépendance* ou une *dépendance consommateur-producteur* (CP), notée  $o_1 \bar{\delta} o_2$ . Une dépendance CP lie  $\langle S,1,3 \rangle$  à  $\langle S,2,1 \rangle$  puisque  $\langle S,1,3 \rangle$ , compte tenu de l'ordre lexicographique du programme, doit pouvoir lire dans a(3) avant que le contenu de cette case mémoire ne soit remplacé par  $\langle S,2,1 \rangle$ .

- **Non-respect de C3 :** De la même façon, le non-respect de C3 provoque une *dépendance de sortie* ou *dépendance producteur-producteur* (PP), notée  $o_1 \delta^o o_2$ . Ainsi les opérations  $\langle S,1,2 \rangle$  et  $\langle S,2,1 \rangle$  de l'exemple sont en dépendance de sortie puisque toutes deux écrivent dans a(3).

### **Exemple 1.1.**

```

for i=1, n {

for j=1, n{

a(i+j) = a(i+j-1);

}

}

```

Lorsqu'une dépendance de donnée PP, PC ou CP existe entre deux opérations  $o_1$  et  $o_2$ , nous écrirons  $o_1 \delta o_2$ . L'ensemble de toutes les dépendances de données de l'exemple 1.1, pour  $n=4$ , est représenté sur la figure 1.4b. Une dépendance d'une opération  $o_1$  à une

opération  $o_2$  est dite *respectée* si  $o_1$  est exécutée avant  $o_2$ . Une dépendance est donc une contrainte de précédence. La relation d'ordre  $\delta$  est un ordre inclus dans  $\prec$ , l'ensemble des relations d'ordre lexicographique ; si  $\delta$  est partielle, le programme *contient du parallélisme*. Le but de la parallélisation est donc d'exhiber un ordre partiel  $\prec_{\parallel}$  tel que

$$\delta \subseteq \prec_{\parallel} \subseteq \prec \quad (1.3)$$

et que  $\prec_{\parallel}$  soit évidemment le plus *proche* possible de  $\delta$ .

(a)

(b)

*Figure 1.4: Domaine d'itération de l'exemple 1.1 :*

*(a) dépendances PC, (b) ensemble des dépendances PC, CP et PP*

Une remarque peut ainsi être faite : de nombreuses dépendances sont redondantes car elles sont obtenues par transitivité.

- Deux dépendances PP sur une même cellule mémoire entraînent l'existence d'une troisième dépendance PP ; ces dépendances PP obtenues par transitivité ne sont pas montrées sur la figure 1.4a.

- Deux dépendances PP  $o_1\delta^o o_2$  et PC  $o_2\delta' o_3$  donnent par transitivité une dépendance PC  $o_1\delta' o_3$ . Cette nouvelle dépendance est artificielle, car si la cellule mémoire lue par  $o_3$  a été modifiée par  $o_1$  et  $o_2$ , l'effet de bord de  $o_1$  a été oblitéré (ang. *killed*) par l'effet de  $o_2$ . En fait, la valeur réellement lue par  $o_3$  est celle produite par  $o_2$ . Ce type particulier de dépendance PC, qui concerne une opération de lecture dans une cellule et la dernière opération écrivant dans cette cellule, est appelé *flot de donnée*. De façon imagée, la donnée *coule* de sa *source* (l'opération productrice  $o_2$ ) à son *puits* (l'opération  $o_3$ ). Cette dépendance sera notée  $o_1\Gamma o_3$ .

- Pour trois opérations  $o_1$ ,  $o_2$  et  $o_3$  exécutées dans cet ordre, deux dépendances PC  $o_1\delta' o_2$  et PP  $o_1\delta^o o_3$  impliquent l'existence d'une dépendance CP  $o_1\bar{\delta} o_3$ . En général, une dépendance CP est due à la succession d'une dépendance PC et d'une dépendance PP<sup>7</sup>.

Nous arrivons donc à la conclusion que supprimer tous les arcs PP entraîne la suppression de la plupart des arcs PC et CP dans le graphe de dépendances. En fait, les dépendances PP, CP, et PC autres que celles dues au flot de données sont des dépendances dues à une réutilisation de la mémoire (ang. *memory-based dependencies*). Par opposition, les dépendances dues au flot de données transportent les valeurs au cours de l'exécution et sont donc inhérentes à l'algorithme, et non plus au programme et/ou au langage de programmation.

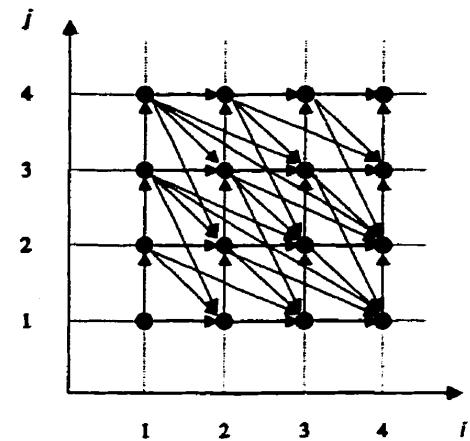

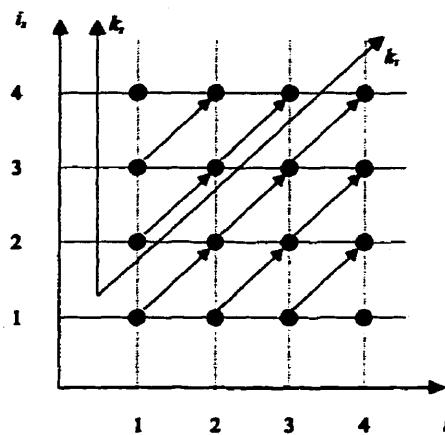

De plus, la coupure de ces arcs diminue le nombre de contraintes, donc nous pouvons accroître le parallélisme. Ce qui ce trouve être le but de la recherche du parallélisme maximal. Le graphe des flots de données dans l'exemple 1.1 apparaît en figure 1.5. En

---

<sup>7</sup> Ce n'est pas vrai si la lecture n'a pas de source dans le programme, par exemple si cette lecture est la première opération du programme.

terme d'ordre,  $\Gamma \subseteq \delta \subseteq \prec$ , ce qui nous incite à essayer de prendre en compte  $\Gamma$  au lieu de  $\delta$ , et de construire un ordre parallèle  $\prec_{\parallel}$  tel que

$$\Gamma \subseteq \prec_{\parallel} \subseteq \prec \quad (1.4)$$

et qui soit évidemment le plus *proche* possible de  $\Gamma$ . Comme nous venons de le discuter, ceci nécessite la coupure des arcs PP.

À partir de cette constatation, un mécanisme de parallélisation pourrait être *la mise en assignation unique*. Pour couper tous les arcs PP, il faut que toutes les opérations écrivent dans une cellule mémoire qui lui soit propre. Si toute cellule mémoire n'est écrite que par au plus une opération, alors le programme est en assignation unique. Deux objections viennent à l'esprit : un programme en assignation unique est extrêmement gourmand en espace mémoire, puisque le nombre de cellules est égal au nombre d'assignations. Deuxièmement, les programmes réels n'ont pas cette propriété. Mais, étant donné le parallélisme potentiel des programmes en assignation unique, un mécanisme de conversion automatique en assignation unique a été proposé par Paul Feautrier (1988). Ce mécanisme d'optimisation peut-être intéressant dans des cas bien spécifiques. Dans le cadre du projet PULSE, ce type de programme composé d'aucune dépendance PP est rare et trop lourd pour les petites mémoires de PULSE, donc pas vraiment intéressant.

Pour réaliser nos transformations de boucles telles que décrites dans la section suivante (section 1.3), nous n'avons pas besoin d'aller si loin dans la recherche car nous nous basons sur le *vecteur de distance de dépendance* (ang. *dependence distance vector*) et ce pour toutes les paires d'itérations.

Figure 1.5: Domaine d'itération de l'exemple 1.1 possédant un parallélisme accrut

**Définition 1.10 - Vecteur de distance de dépendance :** Pour une paire d'itérations  $i = (i_1, \dots, i_n)$  et  $j = (j_1, \dots, j_n)$  tel que  $i \delta j$ , le vecteur de distance de dépendance est  $j - i = (j_1 - i_1, \dots, j_n - i_n)$ .

Dorénavant, à moins d'exceptions clairement identifiées, les dépendances seront exprimées par un *vecteur de distance de dépendance*.

**Définition 1.11 - Direction de dépendance :** Pour une paire d'itération  $i = (i_1, \dots, i_n)$  et  $j = (j_1, \dots, j_n)$ , la direction de dépendance est :

$$\text{sign}(j - i) = (\text{sign}(j_1 - i_1), \dots, \text{sign}(j_n - i_n)), \text{ où } \text{sign}(a) \in \{1, 0, -1\}.$$

Un vecteur de dépendance  $(d_1, \dots, d_n)$  est dit *positif* si le premier élément non nul  $d_k$  est positif. Dans ce cas, nous parlons de dépendance portée par la  $k^{\text{ième}}$  boucle. La sémantique séquentielle des boucles suggère que le flux des dépendances est en tout temps positif<sup>8</sup>. La matrice de dépendance  $D$  est de taille  $n$  par  $m$ , où  $n$  est la profondeur

---

<sup>8</sup> Cette propriété détermine la validité des transformations effectuée sur un nid de boucles.

du nid de boucle et  $m$  est le nombre de dépendances non nulles que possède  $H(i_1, \dots, i_n)$ .

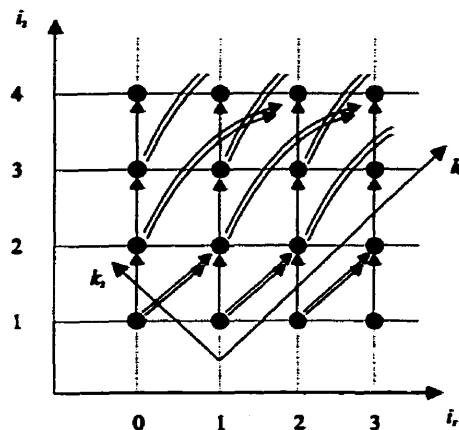

### 1.3. Transformations de boucles

Une fois l'analyse des dépendances effectuée, nous nous retrouvons avec un ordonnancement des opérations en fonction du temps contenu dans un graphe de communication guidé par le temps d'exécution. À partir de là, le temps total du programme est connu.

L'étape suivante a pour objectif de réordonner les opérations pour minimiser le temps total d'exécution en exploitant le parallélisme implicite du programme source (A. Darte, 1993). Cette étape est réalisée en essayant de supprimer le maximum de dépendances infligées par l'aspect séquentiel du programme source. Ceci permet par la suite d'attribuer les opérations et les données aux éléments d'une grille virtuelle de processeurs au cours de l'étape d'allocation. Cette grille est, dans cette étape, de taille et de dimension non bornée. Le but de cette allocation est de réaliser une répartition qui propose une minimisation du nombre de communications inter-processeurs, pour ainsi réduire la latence engendrée. Cette répartition doit prendre comme référence de départ le graphe de communications qui supporte l'ordonnancement total des opérations. D'une manière générale, la distribution des calculs est dirigée par celle des données suivant la règle du *owner computes* (U. Banerjee, 1993) (certains aspects de cette règle sont détaillés à la section 1.3.3). Cette règle stipule que le processus sur lequel est alloué la donnée résultante d'une opération exécute cette opération.

Une fois que sont connues les tâches que doivent réaliser chaque processeur virtuel, il suffit de réécrire le programme contenant : des boucles explicitement parallèles et une répartition des données qui est, elle aussi, explicite. Ce travail est le rôle de la génération de code, la dernière étape d'un compilateur-paralléliseur (voir figure 1.1). Cela peut paraître simpliste, mais un vaste travail reste cependant à effectuer pour produire une méthode de réécriture de boucles prenant en compte tous les décalages

d'indices entre les différentes instructions, tant du point de vue spatial que du point de vue temporel : une telle méthode devra permettre de réécrire automatiquement les nids de boucles en gérant les problèmes liés aux effet de bords, aux réenroulement des boucles, et à l'introduction de pas d'itération (ang. *step*) différents de 1. Conceptuellement, il n'y a pas de difficulté majeure à la complète automatisation de la réécriture et la génération d'un code correct. Par contre, la génération d'un code efficace dans lequel les expressions des bornes et les structures de contrôle sont simplifiées nécessite encore un travail important et difficile (A. Darte, 1993). Mais, ceci n'est qu'une partie du problème de la génération de code. Il faut également être capable de générer tous les transferts de données impliqués par une telle répartition : communications externes des données, gestion de la mémoire et réutilisation de données. Cette section se donne pour objectif de démystifier ces étapes d'ordonnancement d'allocation et de génération de code en proposant un algorithme basé sur la transformation de boucles. Le but de cet algorithme est de reconstruire un nouveau nid de boucles pouvant exploiter le parallélisme proposé par l'architecture matérielle ciblée, tout en générant les mêmes résultats que le nid original. Les objectifs de cette transformation sont d'accroître le parallélisme explicite du nid à un niveau donné, de minimiser la taille de la boucle séquentielle dominante, d'égaliser la charge de travail de chacune des unités de calculs, de réduire les distances entre les données et les unités de calculs, et enfin de regrouper les données réutilisées. Il existe plusieurs types de transformation applicables aux boucles :

- La *permutation* effectue une permutation de deux ou plusieurs boucles d'un même nid. Cette transformation peut-être utilisée dans le cas où nous souhaitons amener une boucle parallélisable à un niveau donné.

- L'*inversion* change le sens de l'incrément d'une boucle donnée. Tout en gardant un incrément positif et égal à 1 en accord avec la méthode.

- Le *front d'onde* (ang. *wavefront*) identifie un nombre d'itérations possédant des dépendances et restructure le nid de boucle pour les effectuer séquentiellement.

- Le *regroupement* combine des blocs d'itérations dans les boucles internes. Ce regroupement réduit la taille des boucles par un facteur donné. Plus la taille des boucles les plus internes est petite, plus les données ont la chance de tenir dans la mémoire locale du processeur ce qui réduit ainsi les communications externes.

Une transformation unimodulaire a l'effet de réaliser un changement de repère dans le domaine d'itération du nid source de boucles. Réaliser des transformations de boucle implique l'utilisation de règles strictes lors du changement de repère et des limites des bornes de boucle. Ces règles ont pour unique but de s'assurer que le nid de transformations résultant réalise le même traitement que le nid source. Pour ce faire (dans le cas de notre analyse), seules les transformations unimodulaires sont valides (M.L. Dowling, 1990). Pour exploiter au maximum la structure des architectures matérielles cibles, il est généralement nécessaire d'appliquer plusieurs transformations successives.

Dans la sous-section suivante, l'algorithme qui réalise des transformations unimodulaires proposé par U. Banerjee (1993) est développé. Ce ne sera pas avant la sous-section 1.3.2. que nous chercherons à obtenir une transformation efficace.

### 1.3.1. Technique générale

Une transformation unimodulaire est définie par une matrice unimodulaire<sup>9</sup> de nombres entiers  $U$  de taille  $n$  par  $n$ .  $U$  transforme un vecteur d'itération  $I$  en un nouveau vecteur d'itération  $K$ , tel que

$$UI = K \tag{1.5}$$

et ainsi transforme les dépendances du nid source  $D$  en de nouvelles  $D'$ , tel que

$$D' = UD \tag{1.6}$$

<sup>9</sup> Qui possède un déterminant égale à  $\pm 1$ .

Cette transformation est légale si et seulement si  $D'$  est lexicographiquement positif. La positivité des dépendances est une condition de la validité de la transformation. Il existe des cas où nous pouvons recourir à des valeurs négatives (M.L. Dowling, 1990), mais dans ce mémoire (pour ne pas surcharger la méthode de transformation), nous nous astreindrons à satisfaire ce critère de positivité.

Pour réaliser cette transformation, il faut substituer les indices de boucles (le vecteur d'itération) du nid source par les nouveaux, et les bornes des boucles par les nouvelles. Dans un premier cas, la substitution des indices de boucles et des références dans les instructions par les nouveaux est supportée par l'équation suivante

$$U^{-1}K = I \quad (1.7)$$

En revanche, déterminer les nouvelles bornes des boucles est moins évident. Partant de

$SI \geq c$

nous obtenons

$$SU^{-1}UI \geq c \quad (1.8)$$

d'où

$$SU^{-1}K \geq c \quad (1.10)$$

Cette inégalité décrit un polyèdre convexe, qui implique que les nouvelles bornes du nid de boucles soient des fonctions affines.

En partant de

$$S' = SU^{-1} \quad (1.11)$$

les nouvelles bornes du nid peuvent être directement obtenues à partir de la rangée de  $S'$ . En général, la technique d'élimination de variable proposée par Fourier-Motzkin en 1986 se base sur  $S'$  pour obtenir ces nouvelles bornes. Supposons que  $\alpha$  et  $\beta$  sont des

expressions linéaires dans  $k_1, \dots, k_{n-1}$ , et  $a$  et  $b$  sont des constantes. Les inégalités  $\beta \leq bk_n$  et  $ak_n \leq \alpha$  proviennent de la borne supérieure de  $k_n$ ,  $\max|a/b|$  et de la borne inférieure  $\min|\beta/b|$ . En éliminant  $k_n$ , cela nous donne l'inégalité  $a\beta \leq b\alpha$ , où  $k_n$  a disparu. En réarrangant ces nouvelles inégalités, nous obtenons  $k_{n-1}$  en fonction de  $(k_1, \dots, k_{n-2})$ . Si nous continuons de la même manière pour toutes les autres variables, nous arrivons à obtenir  $k_i$  constant. L'exemple suivant illustre ce concept.

Considérons le nid de boucles

```

for i1=n1, N1 {

for i2=n2, N2 {

H(i1, i2)

}

}

```

où  $(i_1, i_2)^T$  est le vecteur d'itération. Supposons la matrice unimodulaire suivante

$$U = \begin{bmatrix} u_{11} & u_{12} \\ u_{21} & u_{22} \end{bmatrix} \quad (1.12)$$

Le nid résultant de la transformation a la forme suivante

```

for k1=m1, M1 {

for k2=m2(k1), M2(k1) {

H(f(k1, k2), g(k1, k2))

}

}

```

où  $(k_1, k_2)^T$  est le nouveau vecteur d'itération, tel que

$$(k_1, k_2)^T = U(i_1, i_2)^T = (u_{11}i_1 + u_{12}i_2, u_{21}i_1 + u_{22}i_2)^T \quad (1.13)$$

et  $m_1$  et  $M_1$  sont constant,  $m_2()$  et  $M_2()$  sont des fonctions de  $k_1$ , et  $f()$  et  $g()$  sont des fonctions de  $k_1$  et  $k_2$ .

Il est à se rappeler que nous devons respecter l'unimodularité de la matrice de transformation et donc nous avons :  $\Delta = \det(U) = \pm 1$ . Si nous notons  $\Delta u_{ij}$  équivalant à  $\det(U) * u_{ij}$ , alors nous pouvons écrire

$$U^{-1} = \begin{bmatrix} \Delta u_{22} & -\Delta u_{12} \\ -\Delta u_{21} & \Delta u_{11} \end{bmatrix} \quad (1.14)$$

Ce qui donne

$$(i_1, i_2)^T = U^{-1}(k_1, k_2)^T = (\Delta u_{22}k_1 - \Delta u_{12}k_2, -\Delta u_{21}k_1 + \Delta u_{11}k_2)^T \quad (1.15)$$

Les bornes de  $k_1$  et  $k_2$  peuvent être obtenues comme suit. Les bornes de  $k_1$  sont constantes et dérivées de

$$k_1 = u_{11}i_1 + u_{12}i_2 \quad (1.16)$$

Ce qui donne

$$m_1 = \min(u_{11}i_1 + u_{12}i_2, n_1 \leq i_1 \leq N_1, n_2 \leq i_2 \leq N_2)$$

$$M_1 = \max(u_{11}i_1 + u_{12}i_2, n_1 \leq i_1 \leq N_1, n_2 \leq i_2 \leq N_2)$$

Pour alléger les notations nous introduisons la notation suivante :  $a^+ = \max(a, 0)$  et  $a^- = \max(-a, 0)$ . Ce qui permet d'écrire  $m_1$  et  $M_1$  tel que

$$m_1 = u_{11}^+n_1 - u_{11}^-N_1 + u_{12}^+n_2 - u_{12}^-N_2 \quad (1.17)$$