**Titre:** Étude de la défaillance des circuits bipolaires en mode courant et

Title: leur testabilité

**Auteur:** Bernard Antaki

Author:

**Date:** 1999

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Antaki, B. (1999). Étude de la défaillance des circuits bipolaires en mode courant et leur testabilité [Mémoire de maîtrise, École Polytechnique de Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/8540/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8540/>

PolyPublie URL:

**Directeurs de

recherche:** Yvon Savaria

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

ÉTUDE DE LA DÉFAILLANCE

DES CIRCUITS BIPOLAIRES EN MODE COURANT

ET LEUR TESTABILITÉ

BERNARD ANTAKI

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUILLET 1999

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-46643-4

Canadæ

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

**ÉTUDE DE LA DÉFAILLANCE

DES CIRCUITS BIPOLAIRES EN MODE COURANT

ET LEUR TESTABILITÉ**

présenté par: ANTAKI Bernard

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. SAWAN Mohamad, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. MEUNIER Michel, Ph.D., membre

## REMERCIEMENTS

Tout au long de ma maîtrise, j'ai eu l'assistance, le support moral et le support matériel de bien des amis, de collègues de travail, de mon directeur de projet ainsi que de Nortel Networks et de divers organismes.

En premier lieu, dois-je remercier Serge Patenaude pour sa présence tout au long du projet avec Nortel, en personne ou bien par téléphone, par courrier électronique ou par «talk». En faisant équipe à deux, nous avons eu la chance de nous motiver, alors que notre moral n'était pas toujours bien haut. Pendant plus de seize mois, nous avons dû communiquer de divers problèmes par l'entremise d'ordinateurs, alors que de telles discussions auraient été bien plus efficaces en personne. Dans un même élan de gratitude envers amis et collègues, j'aimerais soulever le grand apport technique que m'ont donné Sylvain Bourret et Mathieu Gagnon vis-à-vis les outils du laboratoire. Sans eux, non seulement les outils auraient été moins intéressants, mais aussi le temps écoulé durant ma maîtrise.

J'aimerais aussi remercier M. Yvon Savaria pour m'avoir permis de travailler avec lui sur divers projets, dont évidemment celui de maîtrise, et pour tous les conseils et suggestions pratiques qu'il ait pu me donner durant nos nombreuses réunions.

De plus, je me dois de remercier la Société canadienne de microélectronique (CMC) pour son support matériel et technique hors pairs à l'échelle nationale.

La bourse que m'a offerte le Conseil de recherches en sciences naturelles et génie du Canada (CRSNG) a été grandement appréciée et a su m'éviter bien des tracas financiers. Il faut aussi mentionner l'apport financier et tout le bagage d'expérience que m'a offerts Nortel Networks pour laquelle j'ai eu la chance d'y faire deux stages et de passer une semaine en Angleterre pour affaires. Grâce à l'effort soutenu de M. Saman Adham travaillant pour cette entreprise, il m'a été possible d'orienter ma maîtrise sur un projet lié aux besoins présents de l'industrie.

## RÉSUMÉ

La forte diminution des tailles des transistors bipolaires par rapport aux années 80' permet maintenant aux circuits logiques en mode courant (CML) de reprendre le terrain perdu aux circuits CMOS lorsqu'il s'agit de performance. Néanmoins, le développement des méthodes de test pour ces circuits n'a pas eu une grande attention au sein de la communauté scientifique. De plus, les auteurs qui se sont penchés sur la question ont observé que les méthodes développées pour les circuits CMOS numériques, fortement orientées sur les pannes de collage, n'ont pas une couverture suffisante des défectuosités possibles dans une famille logique CML. Par conséquent, ce mémoire présente une analyse détaillée des portes CML en présence de défectuosités et classe les pannes observées selon leur prépondérance. Ce travail est effectué par un outil automatique hautement flexible, développé dans le cadre du projet, qui permet d'analyser des portes CML de tout genre. L'analyse démontre que les pannes les plus courantes et dont les fréquences d'apparition dépassent les collages sont les marges de bruit réduites, les tables de vérité corrompues, les délais et les amplitudes excessives. Dans le but d'améliorer la couverture de pannes, une nouvelle technique de test est proposée et analysée. Cette technique permet de détecter les amplitudes excessives. Elle demande une faible augmentation de surface et la méthodologie de test est relativement simple. Enfin, une puce d'évaluation des méthodes de test développées est présentée. Cette puce permet d'évaluer le

fonctionnement et l'efficacité de deux méthodes de détection de marges de bruit réduites ainsi que la méthode de détection d'amplitudes excessives. Pour évaluer ces méthodes, la puce contient un ensemble de circuits simples, exploitant toutes les ressources d'une bibliothèque de portes CML, sur lesquels sont connectés les circuits de test. L'architecture de cette puce permet donc d'analyser tous les circuits indépendamment par toutes les méthodes implémentées. Bien que la puce n'est pas encore fabriquée et testée, nous avons une confiance élevée en ces méthodes. D'ailleurs, la méthode de détection d'amplitudes excessives est présentement en instance de brevet pour la compagnie Nortel Networks.

## ABSTRACT

During the last decade, bipolar transistors have reduced in size considerably, giving Current-Mode Logic (CML) circuits a chance to reclaim from CMOS the domain of high performance circuits. However, the development of test methods for CML was barely touched by the scientific community. Moreover, authors that did work in this field have shown that methods developed to detect faults in digital CMOS circuits, specifically stuck-at faults, are not able to cover a sufficient percentage of all possible defects in bipolar processes. Therefore, this thesis presents a detailed analysis of defective CML gates and classifies observed faults according to defect coverage. This job is performed by an automatic tool, developed for this project, which can analyse CML gates of any sort with highly flexible configuration options. The analysis performed with this tool allowed to characterize the frequency of occurrence of various fault types. It was observed, for instance, that the faults with the highest frequency of occurrence higher than stuck-ats, are reduced noise margins, truth table faults, delays and excessive amplitudes. Furthermore, to improve fault coverage, a new test technique to detect excessive amplitudes was developed and analysed. This technique requires a small area overhead and uses a simple test methodology. Finally, a test method evaluation chip that was developed is also presented. This chip will help evaluate the functionality and the efficiency of two reduced noise margin detection methods, as well as the excessive amplitude testing technique. To evaluate them, the

chip contains a number of simple circuits, making use of several CML library cells, surrounded by the testing apparatuses. The chip's architecture will help analyse independently all circuits according to all implemented methods. While the test chip has not yet been manufactured and tested, we have a high confidence that these methods will perform well. In fact, the excessive amplitude testing technique is currently being submitted as a patent for Nortel Networks.

## TABLE DES MATIÈRES

|                                                                      |              |

|----------------------------------------------------------------------|--------------|

| <b>REMERCIEMENTS .....</b>                                           | <b>.iv</b>   |

| <b>RÉSUMÉ .....</b>                                                  | <b>.vi</b>   |

| <b>ABSTRACT .....</b>                                                | <b>.viii</b> |

| <b>LISTE DES TABLEAUX .....</b>                                      | <b>.xiii</b> |

| <b>LISTE DES FIGURES .....</b>                                       | <b>.xiv</b>  |

| <b>LISTE DES SIGLES ET ABRÉVIATIONS .....</b>                        | <b>.xvii</b> |

| <b>INTRODUCTION .....</b>                                            | <b>1</b>     |

| <b>CHAPITRE I : NOTIONS DE BASE ET REVUE DE</b>                      |              |

| <b>LITTÉRATURE .....</b>                                             | <b>5</b>     |

| 1.1    Introduction .....                                            | 5            |

| 1.2    Principes de base de la conception de circuits CML .....      | 6            |

| 1.3    Conception des portes à niveaux multiples .....               | 11           |

| 1.4    Défauts rencontrés dans les technologies bipolaires .....     | 16           |

| 1.5    Pannes retrouvées dans les circuits CML .....                 | 19           |

| 1.5.1    Pannes à caractère logique .....                            | 21           |

| 1.5.2    Pannes de type analogique .....                             | 23           |

| 1.6    Méthodes de test marquantes sur la détection des pannes ..... | 26           |

| 1.6.1    Détection de pannes logiques .....                          | 27           |

| 1.6.2    Détection des pannes de complémentarité corrompue .....     | 29           |

|       |                                       |    |

|-------|---------------------------------------|----|

| 1.6.3 | Détection des pannes de délai         | 29 |

| 1.6.4 | Détection de marges de bruit réduites | 31 |

| 1.7   | Conclusion                            | 34 |

## **CHAPITRE II : OUTIL DE CARACTÉRISATION**

|       |                                                 |    |

|-------|-------------------------------------------------|----|

|       | <b>AUTOMATIQUE DE PANNE</b>                     | 36 |

| 2.1   | Introduction                                    | 36 |

| 2.2   | Engin de l'outil et principes de base           | 38 |

| 2.2.1 | Configuration des cellules                      | 38 |

| 2.2.2 | Défectuosités couvertes et méthode d'injection  | 40 |

| 2.2.3 | Banc de test                                    | 45 |

| 2.2.4 | Fonctions d'analyse des résultats de simulation | 45 |

| 2.2.5 | Fonctionnement de l'outil                       | 48 |

| 2.3   | Résultats d'analyse                             | 49 |

| 2.4   | Conclusion                                      | 56 |

## **CHAPITRE III : MÉTHODES DE TEST ADAPTÉES AUX**

|       |                                                                       |    |

|-------|-----------------------------------------------------------------------|----|

|       | <b>CIRCUITS CML</b>                                                   | 59 |

| 3.1   | Introduction                                                          | 59 |

| 3.2   | Injection de défectuosités et impact sur le comportement des circuits | 60 |

| 3.3   | Test d'amplitude                                                      | 66 |

| 3.3.1 | Variante 1 - détecteur unipolaire                                     | 67 |

| 3.3.2 | Variante 2 - détecteur bipolaire                                      | 72 |

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| 3.3.3 Conversion du signal de sortie du détecteur en valeur logique ..... | 76         |

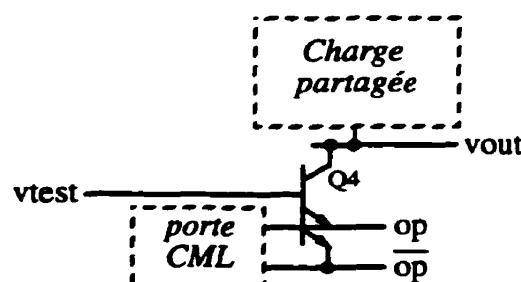

| 3.3.4 Partage du circuit de charge .....                                  | 80         |

| 3.3.5 Optimisation de surface .....                                       | 86         |

| 3.3.6 Approche pour le test .....                                         | 87         |

| 3.4 Conclusion .....                                                      | 88         |

| <b>CHAPITRE IV : PUCE D'ÉVALUATION DES MÉTHODES DE TEST .....</b>         | <b>90</b>  |

| 4.1 Introduction .....                                                    | 90         |

| 4.2 Méthodes de test évaluées par la puce .....                           | 91         |

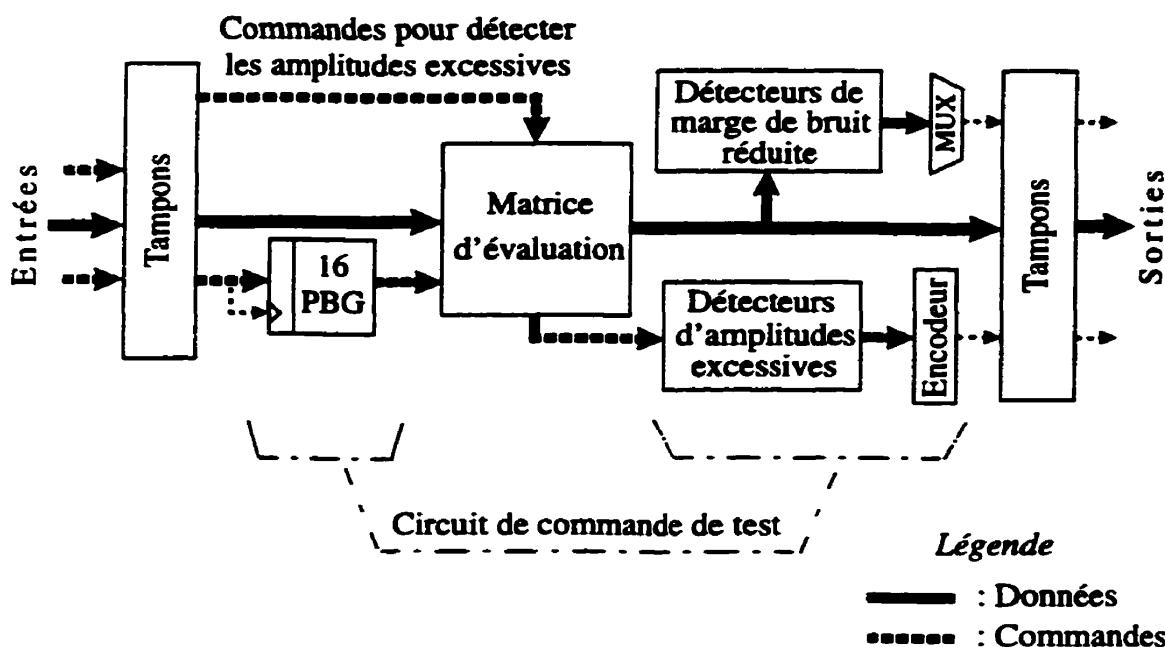

| 4.3 Architecture de la puce .....                                         | 92         |

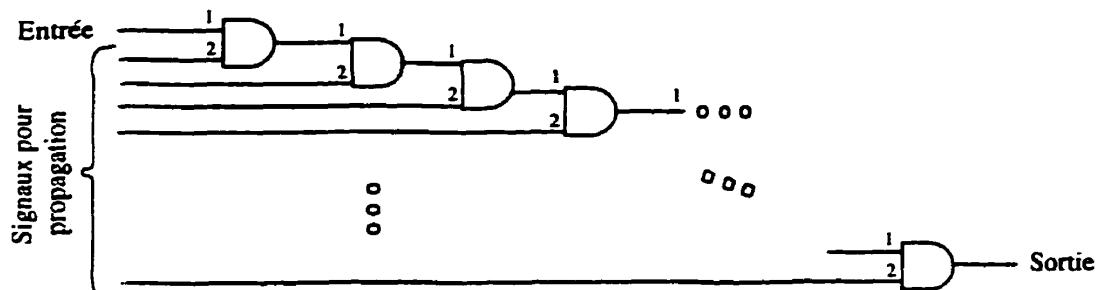

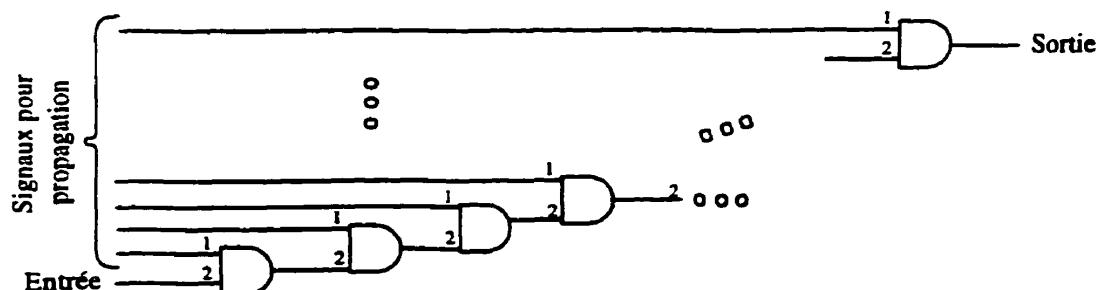

| 4.3.1 Circuits testés .....                                               | 96         |

| 4.3.2 Circuits pour la commande des tests .....                           | 102        |

| 4.4 Procédure de test .....                                               | 107        |

| 4.4.1 Étapes pour appliquer les tests .....                               | 108        |

| 4.5 Conclusion .....                                                      | 110        |

| <b>CONCLUSION .....</b>                                                   | <b>112</b> |

| <b>RÉFÉRENCES .....</b>                                                   | <b>117</b> |

| <b>BIBLIOGRAPHIE .....</b>                                                | <b>121</b> |

| <b>ANNEXE I : RÉSULTATS D'ANALYSE DE PORTES CML .....</b>                 | <b>123</b> |

**LISTE DES TABLEAUX**

|             |                                                                                  |     |

|-------------|----------------------------------------------------------------------------------|-----|

| Tableau 1.1 | <b>Équations des portes illustrées</b>                                           | 14  |

| Tableau 1.2 | <b>Pannes observées dans les portes ECL/CML</b>                                  | 20  |

| Tableau 2.1 | <b>Description des critères pour identifier les pannes</b>                       | 47  |

| Tableau 3.1 | <b>Temps de transition des signaux des chaînes avec et sans<br/>défectuosité</b> | 63  |

| Tableau 3.2 | <b>Temps de transition des sorties des chaînes avec et sans<br/>défectuosité</b> | 64  |

| Tableau 4.1 | <b>Méthodes de test retenues pour la puce d'évaluation</b>                       | 91  |

| Tableau 4.2 | <b>Modes de la machine à états reconfigurable</b>                                | 101 |

| Tableau 4.3 | <b>Adressage des PBG</b>                                                         | 105 |

| Tableau 4.4 | <b>Étapes d'application des tests pour une rangée</b>                            | 109 |

| Tableau I.1 | <b>Résistances utilisées pour modéliser les défectuosités</b>                    | 123 |

## LISTE DES FIGURES

|            |                                                                                                          |    |

|------------|----------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 | Porte tampon pour les circuits CML de Nortel .....                                                       | 6  |

| Figure 1.2 | Portes CML à deux étages .....                                                                           | 8  |

| Figure 1.3 | Différentes portes logiques à deux niveaux .....                                                         | 15 |

| Figure 1.4 | Une panne collé-à typique .....                                                                          | 22 |

| Figure 1.5 | Panne de marge de bruit typique .....                                                                    | 24 |

| Figure 1.6 | Panne extrême de marge de bruit pour un circuit CML .....                                                | 25 |

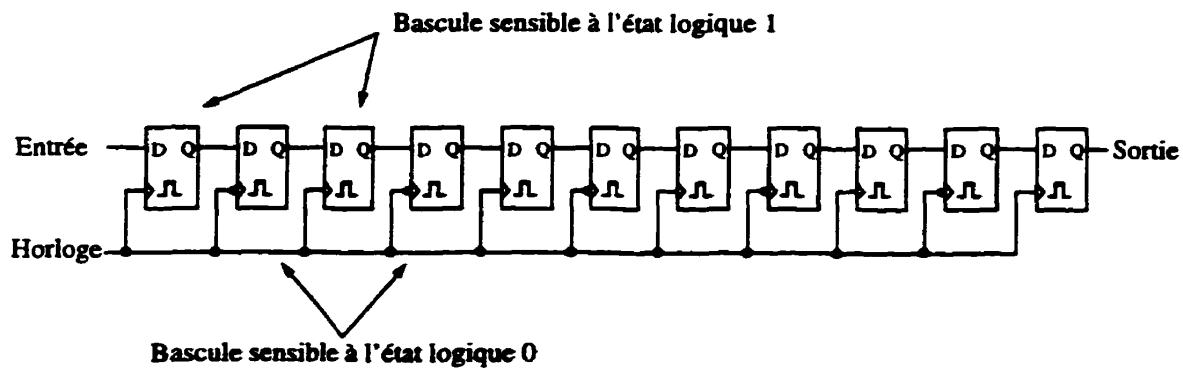

| Figure 1.7 | Bascule sensible à l'état du signal d'horloge avec mode de transparence (tirée de Patenaude, 1998) ..... | 28 |

| Figure 1.8 | Porte OU modifiée pour le test de débalancement (tirée de Anderson, 1988) .....                          | 32 |

| Figure 1.9 | Détecteur de marge de bruit réduite (tirée de Patenaude, 1998) .....                                     | 34 |

| Figure 2.1 | Exemples de traitement de ponts .....                                                                    | 43 |

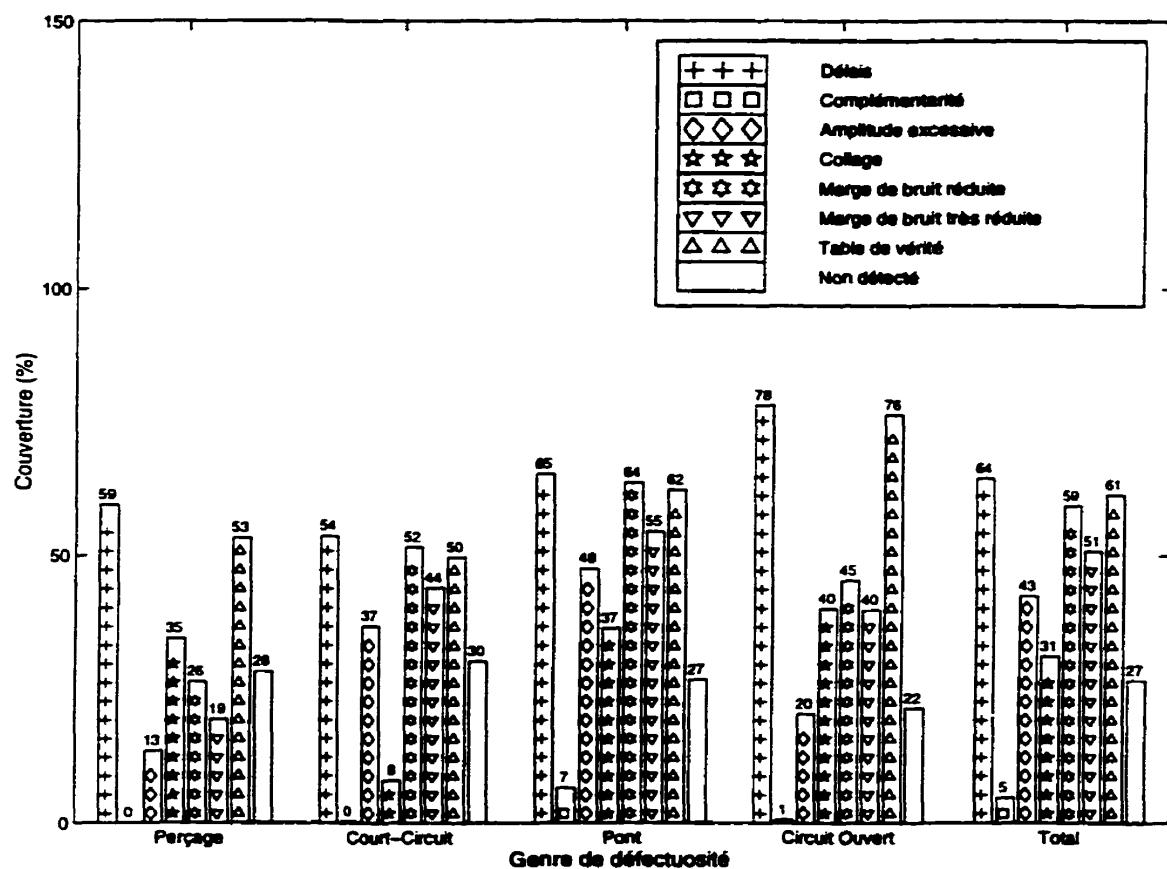

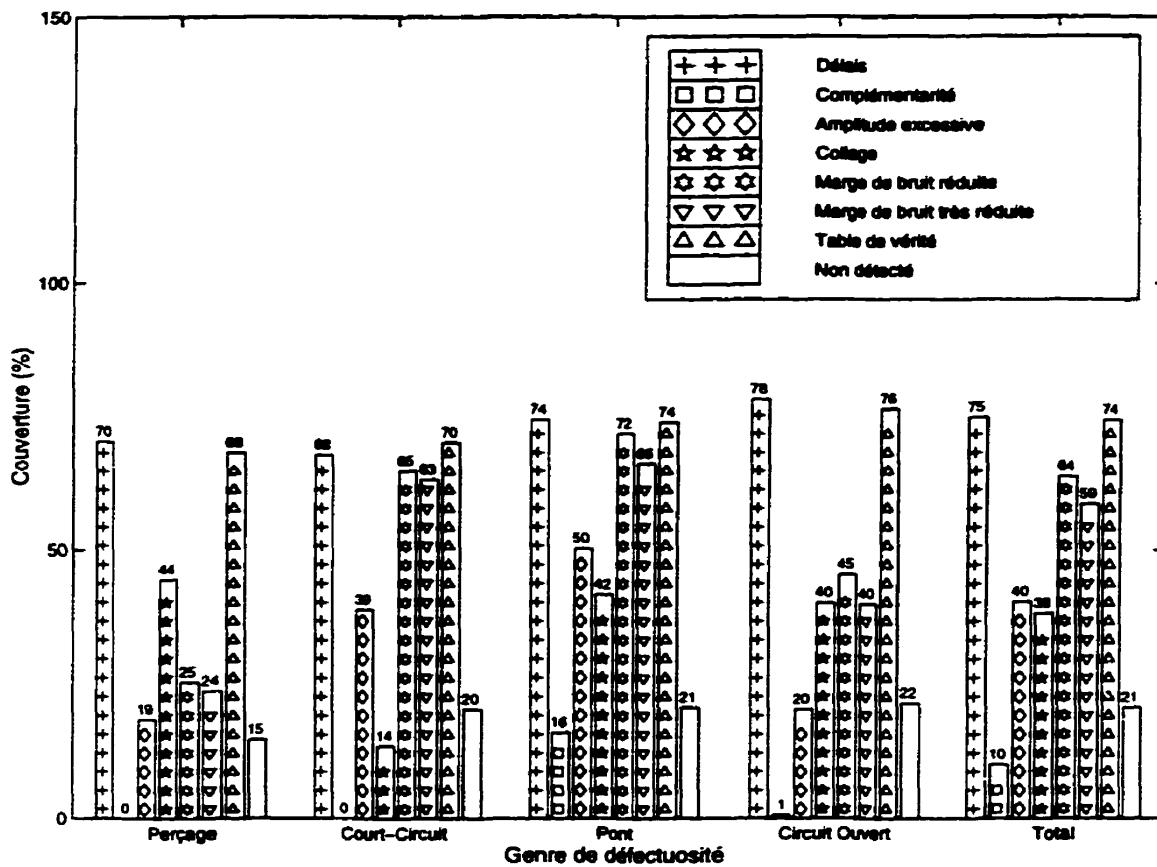

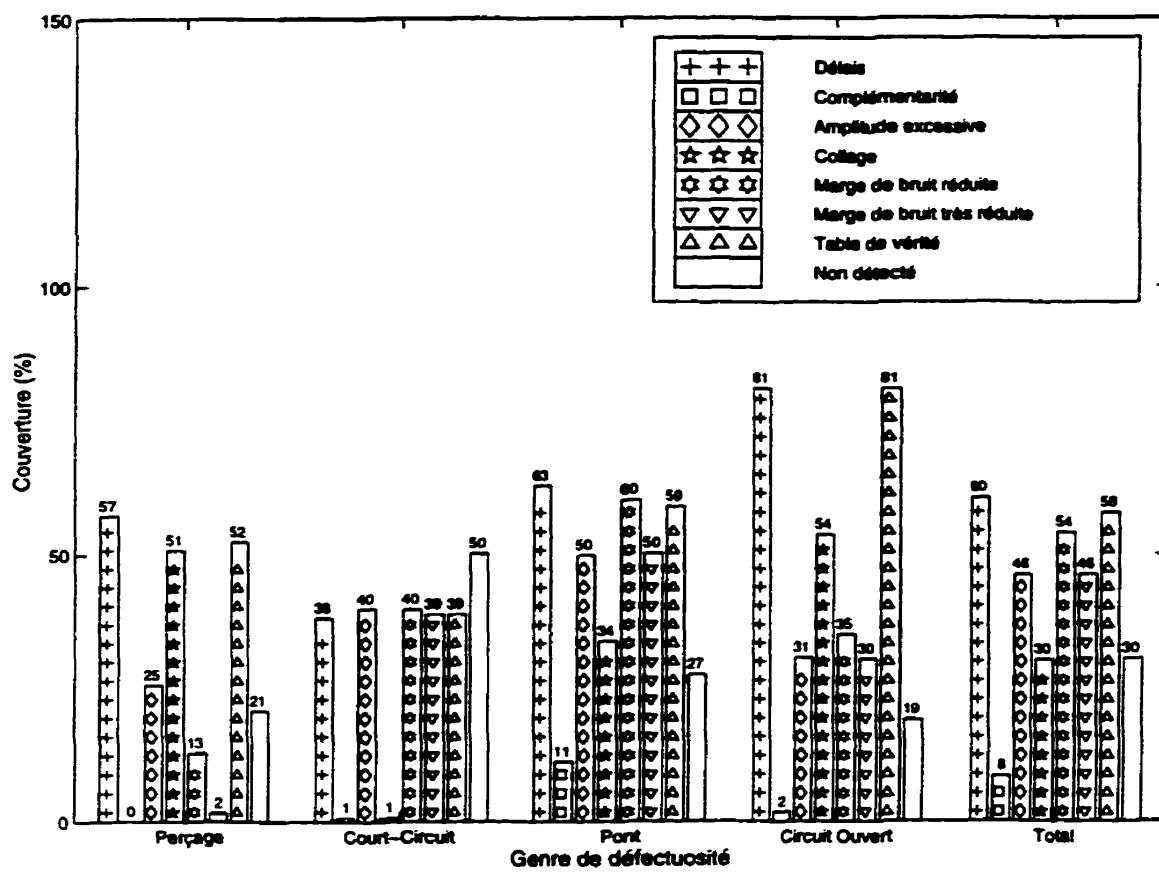

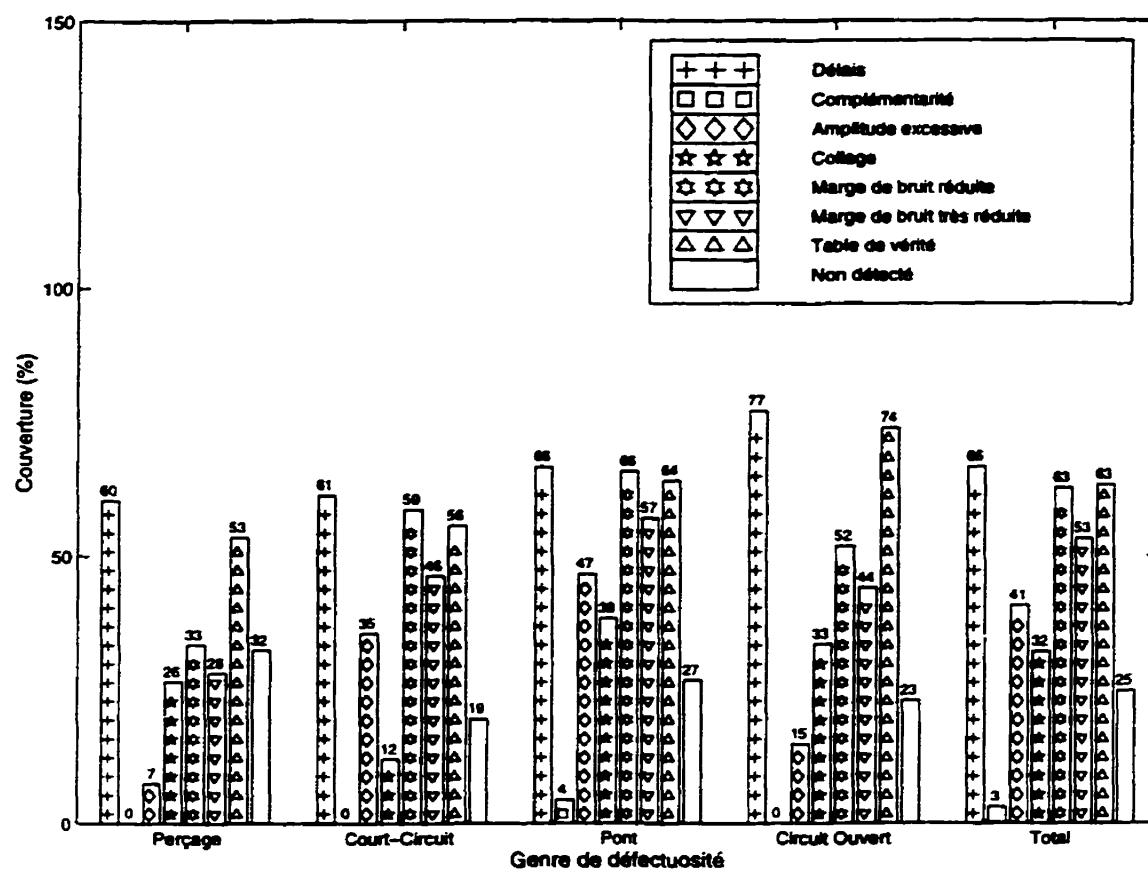

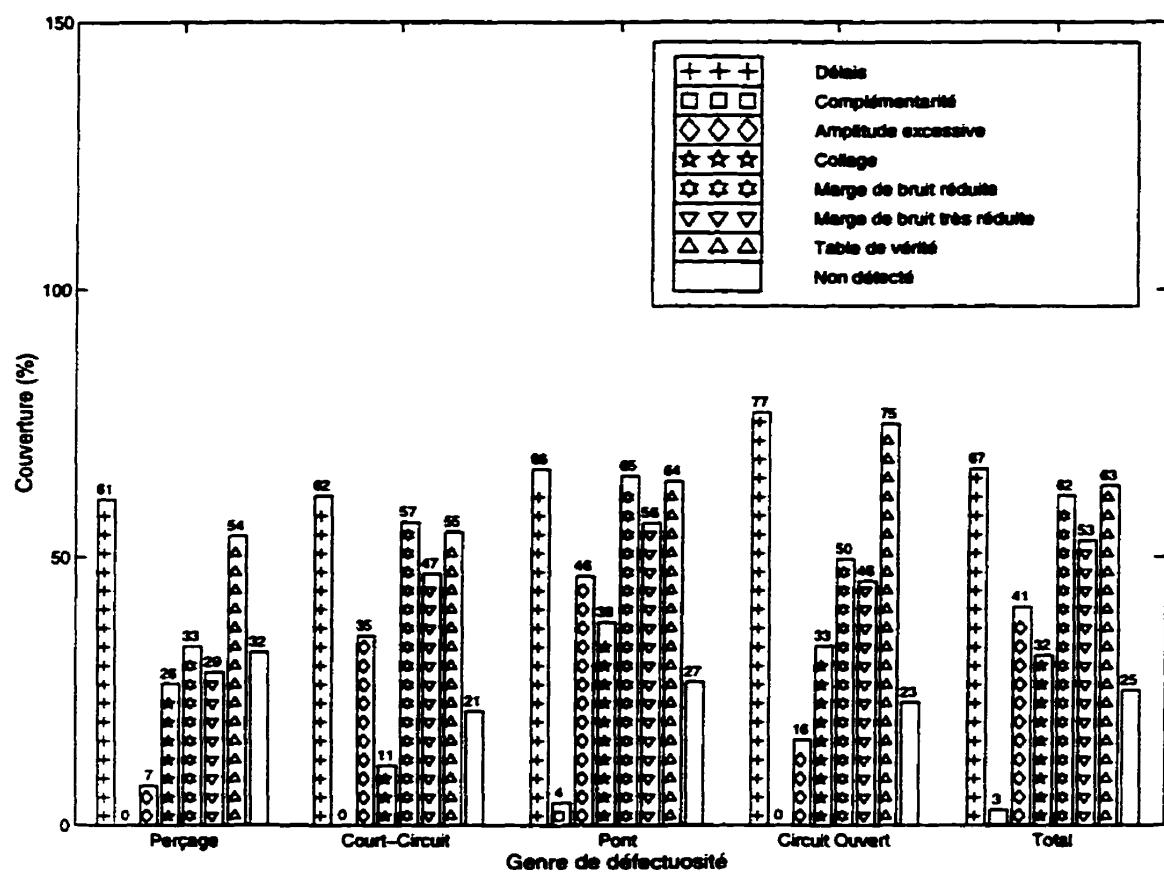

| Figure 2.2 | Couvertures moyennes des défectuosités des trois portes analysées .....                                  | 50 |

| Figure 2.3 | Couvertures moyennes des plus fortes défectuosités des portes analysées .....                            | 53 |

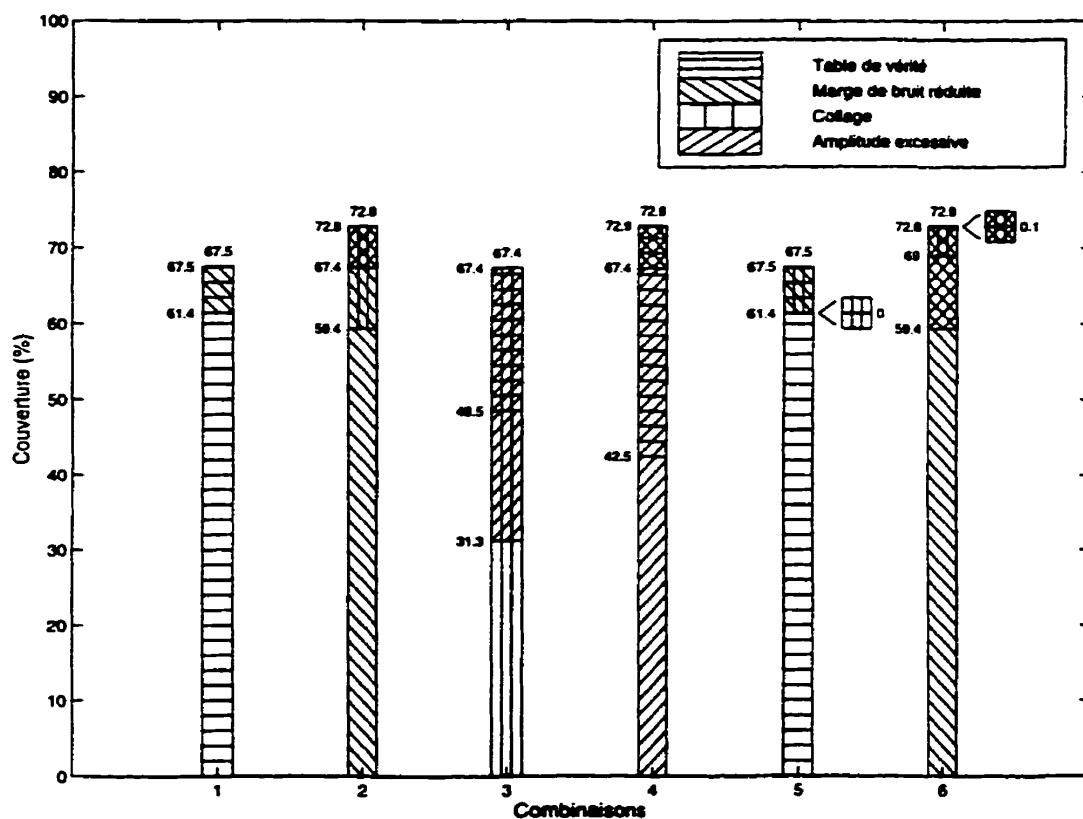

| Figure 2.4 | Couvertures de défectuosités selon les meilleures combinaisons .....                                     | 55 |

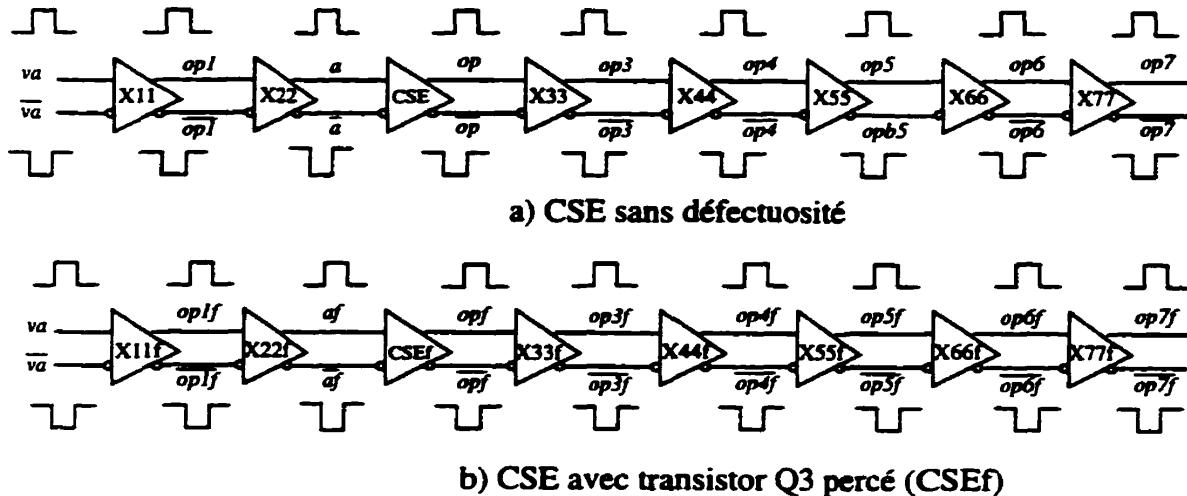

| Figure 3.1 | Circuit test (chaîne de 8 portes tampon) .....                                                           | 61 |

|                                                                                                                                              |    |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

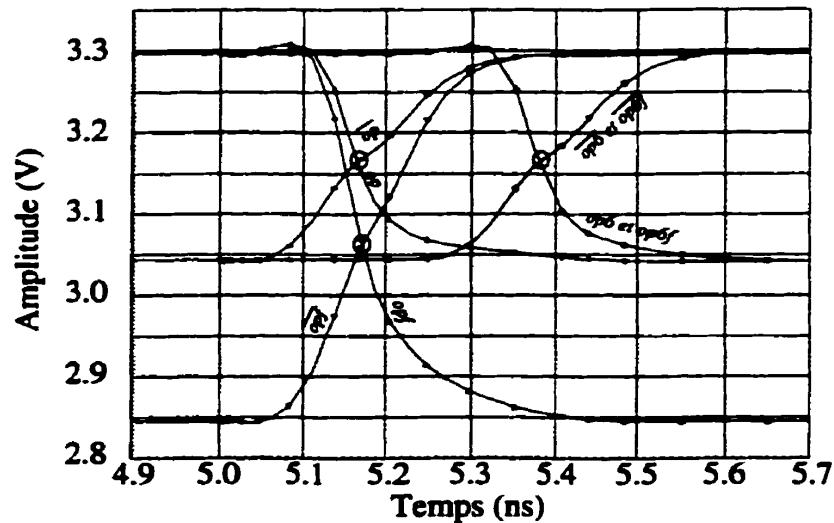

| Figure 3.2 Signaux de sortie de CSE (op et $\overline{op}$ ) et de X66 (op6 et $\overline{op6}$ ) avec et sans perçage de 4 K $\Omega$ ..... | 62 |

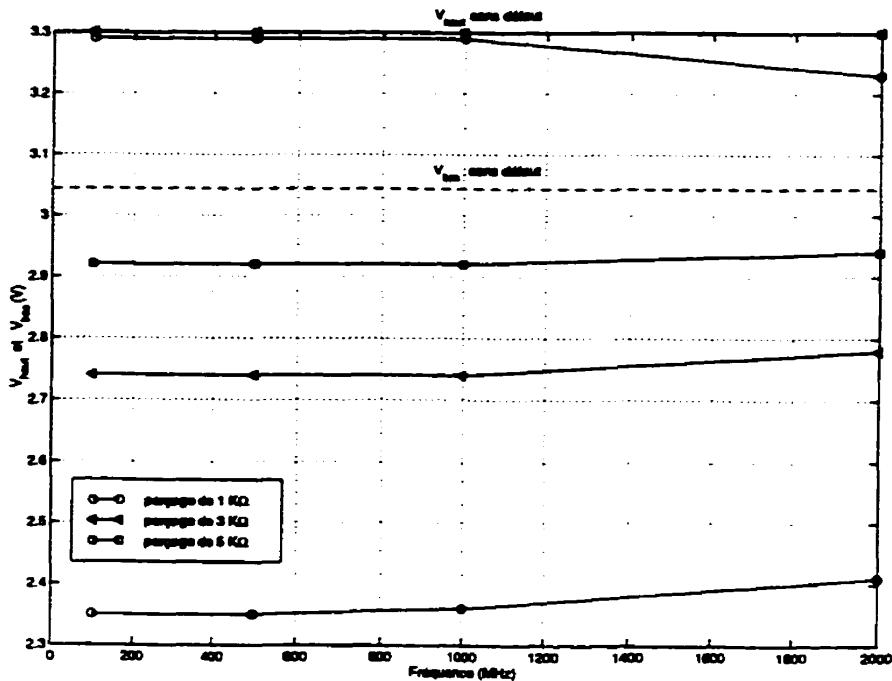

| Figure 3.3 $V_{\text{bas}}$ et $V_{\text{haut}}$ vs des valeurs de perçage et de fréquence de stimulation .....                              | 66 |

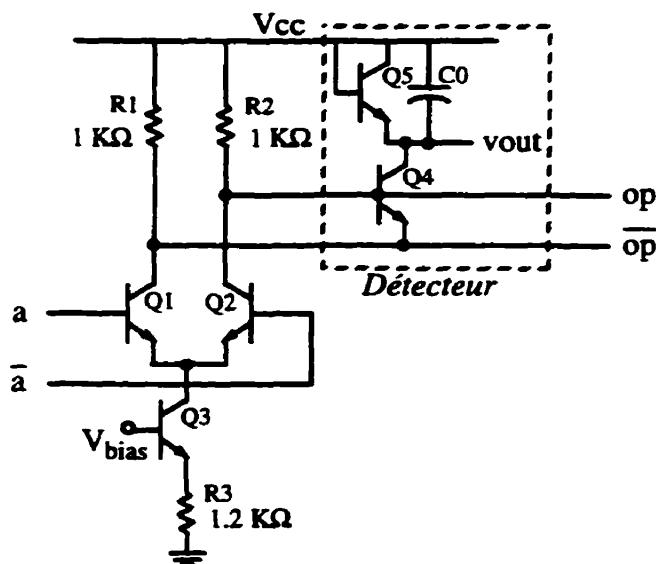

| Figure 3.4 DéTECTEUR intégré proposé (variante 1) .....                                                                                      | 67 |

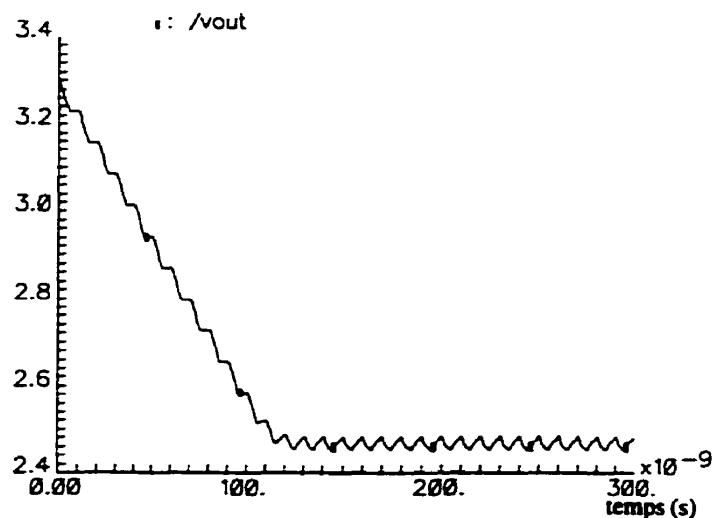

| Figure 3.5 Réponse du détECTEUR (perçage de 1 K $\Omega$ et charge de 10 pF à 100 MHz) .....                                                 | 69 |

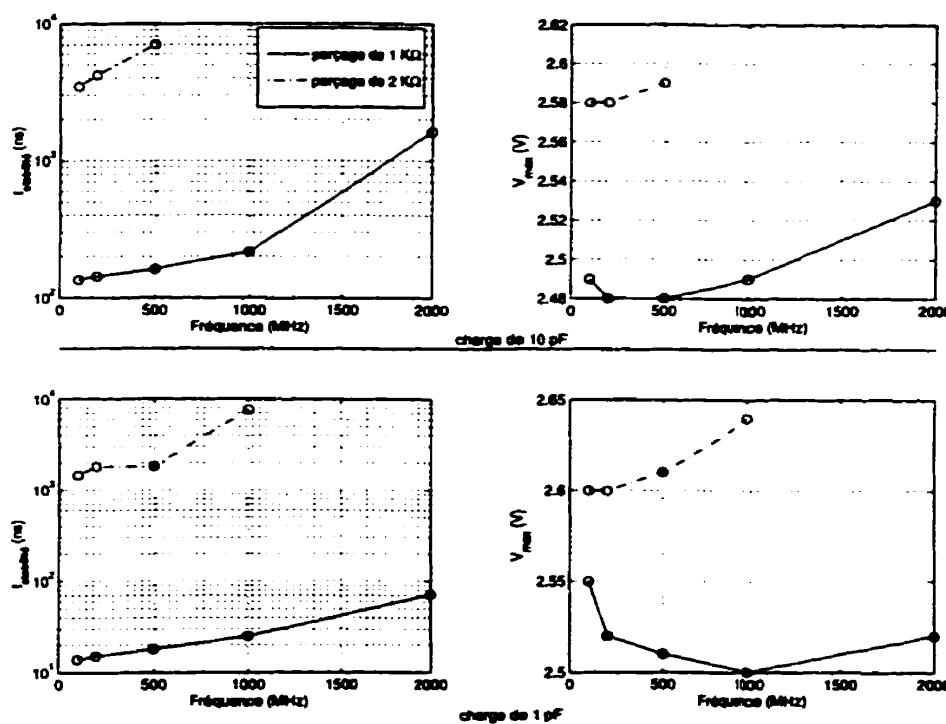

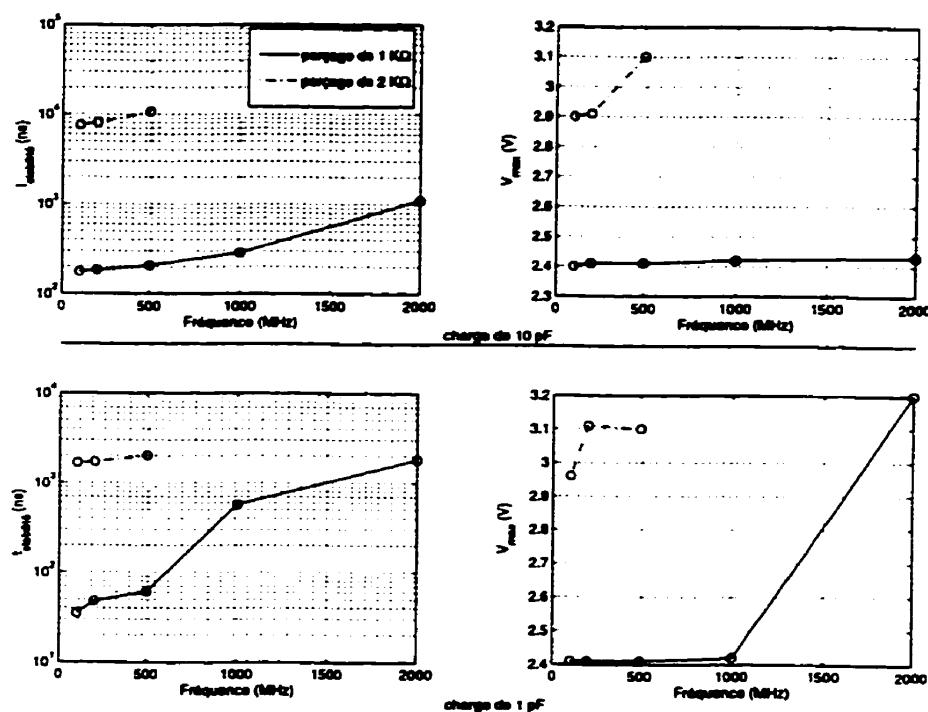

| Figure 3.6 $t_{\text{stabilité}}$ et $V_{\text{max}}$ vs fréquence, perçage et charge (variante 1, diode) .....                              | 70 |

| Figure 3.7 $t_{\text{stabilité}}$ et $V_{\text{max}}$ vs fréquence, perçage et charge (variante 1, 160 K $\Omega$ ) .....                    | 71 |

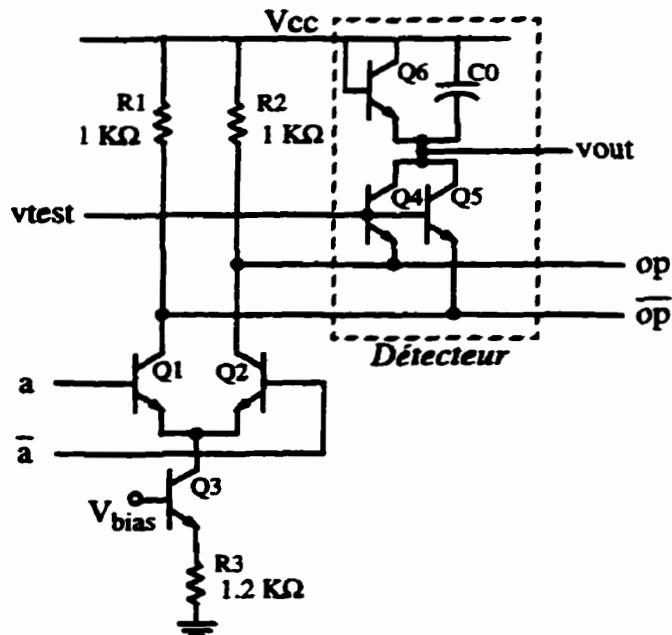

| Figure 3.8 détECTEUR intégré proposé (variante 2) .....                                                                                      | 73 |

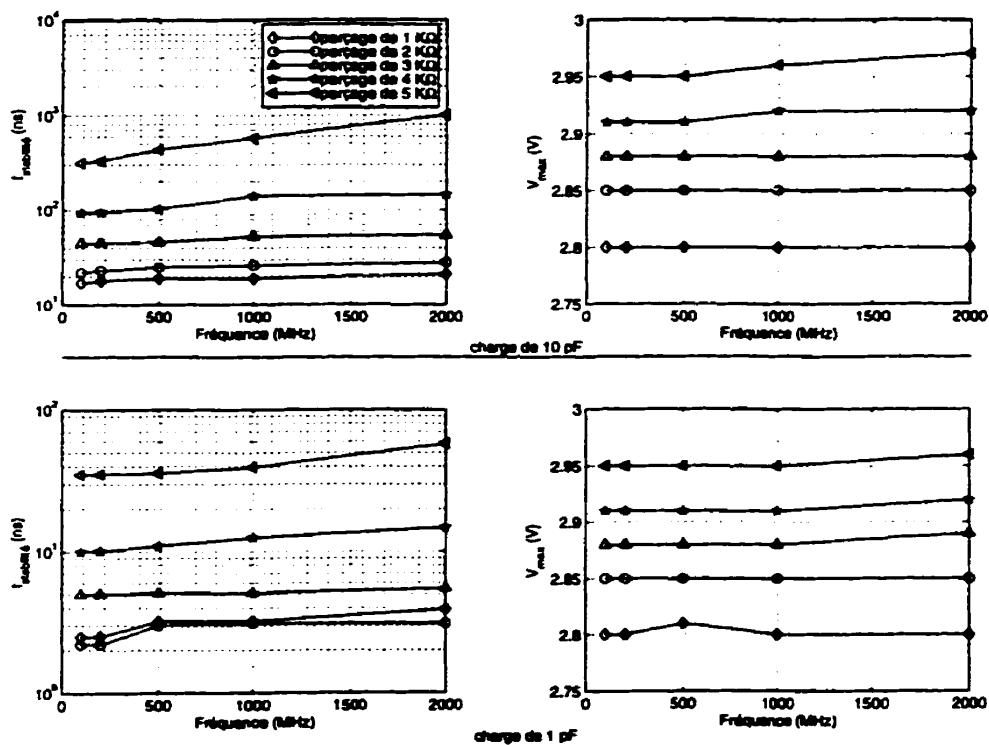

| Figure 3.9 $t_{\text{stabilité}}$ et $V_{\text{max}}$ vs fréquence, perçage et charge (variante 2) .....                                     | 75 |

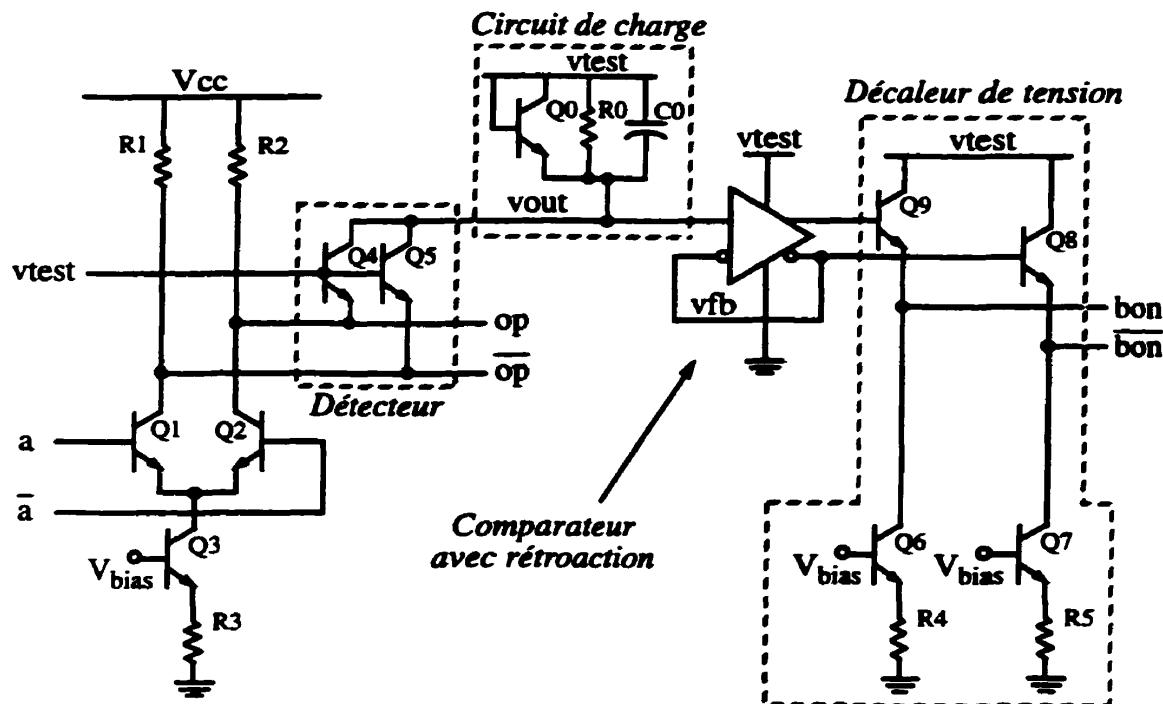

| Figure 3.10 DéTECTEUR d'amplitude amélioré (variante 3) .....                                                                                | 77 |

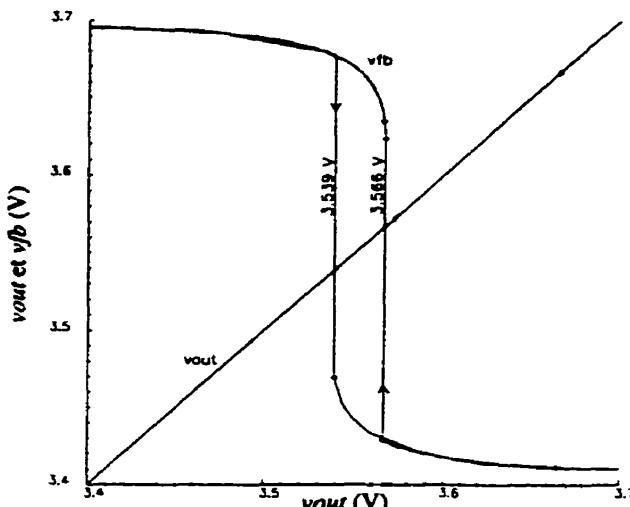

| Figure 3.11 Caractéristique d'hystérésis du comparateur .....                                                                                | 79 |

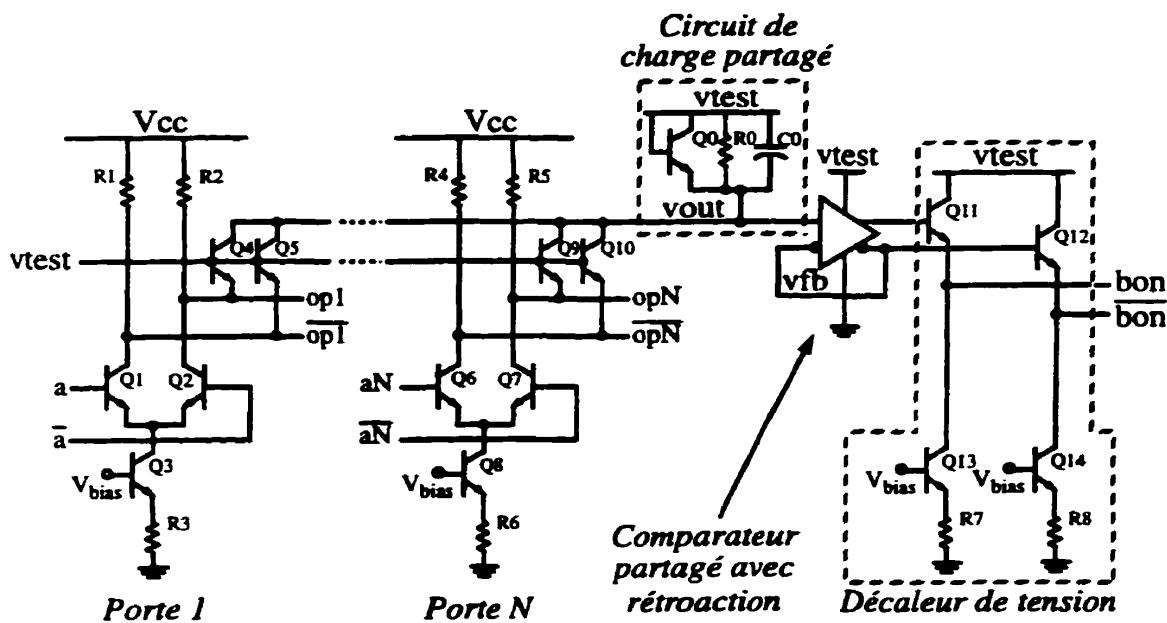

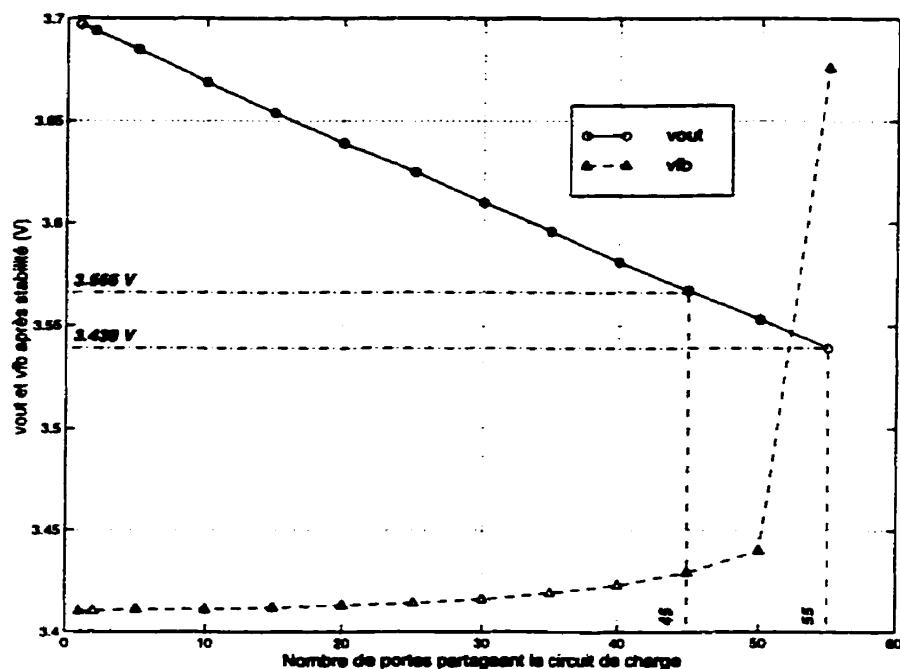

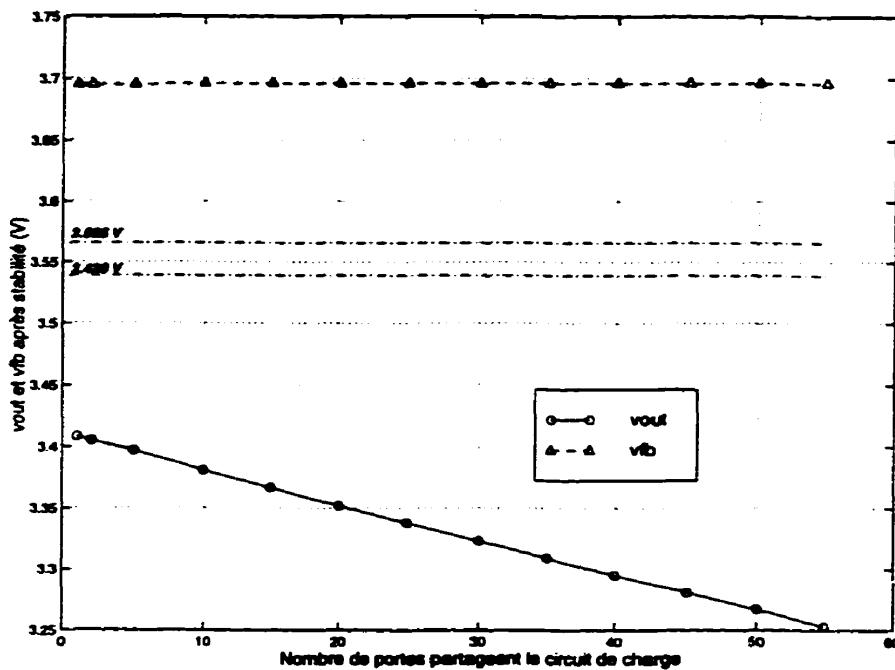

| Figure 3.12 Partage du circuit de charge pour la variante 3 .....                                                                            | 80 |

| Figure 3.13 Réponse du comparateur pour une chaîne sans défectuosité .....                                                                   | 81 |

| Figure 3.14 Réponse du comparateur avec une chaîne où une des portes tampon a un perçage de 5 K $\Omega$ .....                               | 84 |

| Figure 3.15 Optimisation de surface avec un transistor à émetteurs multiples .....                                                           | 86 |

|            |                                                                          |     |

|------------|--------------------------------------------------------------------------|-----|

| Figure 4.1 | Diagramme bloc de la puce d'évaluation .....                             | 93  |

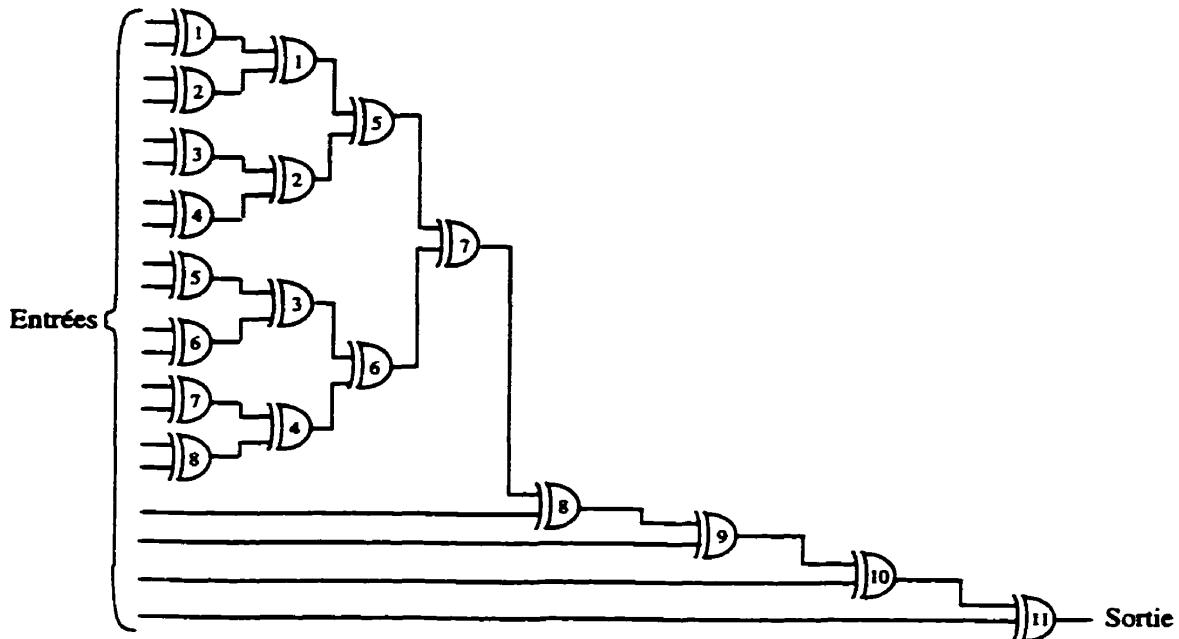

| Figure 4.2 | Mise en cascade des portes ET (rangées 4 à 7) .....                      | 97  |

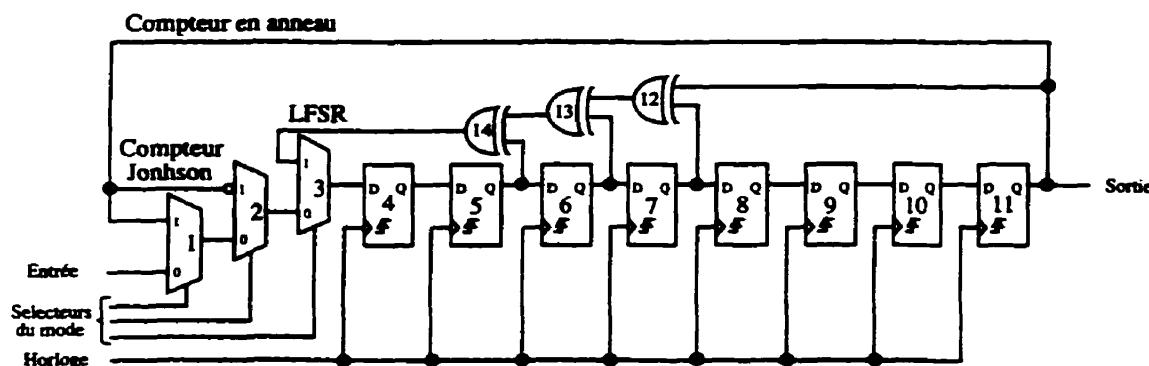

| Figure 4.3 | Registre à décalage (rangées 8 et 9) .....                               | 99  |

| Figure 4.4 | Arbre binaire convergeant de portes OU-exclusif (rangées 10 et 11) ..... | 100 |

| Figure 4.5 | Machine à états reconfigurable (rangées 12 et 13) .....                  | 102 |

| Figure I.1 | Couvertures de défectuosités pour les portes tampon .....                | 124 |

| Figure I.2 | Couvertures de défectuosités pour les portes ET .....                    | 125 |

| Figure I.3 | Couvertures de défectuosités pour les portes OU .....                    | 126 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|      |                                                                                   |

|------|-----------------------------------------------------------------------------------|

| ATPG | Automatic Test Pattern Generation (génération de patrons de test automatique)     |

| BIST | Built-in Self Test (auto-évaluation intégré)                                      |

| CSE  | Cellule sous évaluation                                                           |

| CML  | Current Mode Logic (logique en mode courant)                                      |

| CMOS | Complementary Metal-Oxyde Semiconductor (semiconducteur à oxyde de métal)         |

| DFT  | Design For Testability (conception adaptée au test)                               |

| ECL  | Emitter Coupled Logic (logique à émetteurs couplés)                               |

| IFA  | Inductive Fault Analysis (analyse de défauts par induction)                       |

| LFSR | Linear Feedback Shift Register (registres à décalage à rétroaction linéaire)      |

| NPN  | Transistor bipolaire de type N                                                    |

| OCAP | Outil de caractérisation automatique de pannes                                    |

| PBG  | Programmable Bias Generator (générateur de tensions de polarisation programmable) |

| RAM  | Random Access Memory (mémoire vive d'un ordinateur)                               |

## INTRODUCTION

Au fil des années, l'évolution de la technologie a permis à des méthodes de conception autrefois mises de côté, telles que les CML et ECL, de revenir à la mode. Auparavant, dues à la grande consommation de puissance des transistors bipolaires, les circuits utilisant ces architectures devaient être limités en taille. Toutefois, avec le développement des technologies, la taille des dispositifs microélectroniques a diminué rapidement et a entraîné une chute dans la dissipation de puissance de circuits qui en font l'usage. Par exemple, les circuits à transistors bipolaires rapportés par Rein et al. ([15], 1996) présentent des portes logiques ayant des délais bien en-dessous de 1 ns et des taux de transfert de données aux alentours de 50 Gbits/s, où la puissance dissipée, quoique importante, n'est plus un aspect critique. En effet, à ces vitesses d'opération, les circuits CMOS peuvent dissiper autant, sinon plus. De plus, les circuits numériques bipolaires ECL/CML ont montré un avantage certain vis-à-vis les CMOS lorsqu'il s'agit de vitesse. Citons Gu et al. ([6], 1996) qui exposent des architectures de dispositifs d'émission et de réception radio fonctionnant dans les Gbits/s conçus à l'aide de circuits CML et ECL.

Avec la popularité croissante des circuits CML, il devient important d'étudier en détail leur testabilité. Toutefois, un regard rapide sur la littérature montre une étude clairsemée sur cet aspect. Évidemment, lorsque l'on considère la grande emprise des

circuits CMOS dans le marché, il n'est guère surprenant que l'attention de l'industrie et de la communauté scientifique y soit rivée. Or, comme le sera montré au chapitre I, certaines études ont prouvé que les méthodes de test développées pour les circuits numériques CMOS ne sont pas à la hauteur pour les circuits CML. En effet, elles ne peuvent détecter un suffisamment grand nombre de défectuosités. Par conséquent, la fonctionnalité et même la fiabilité à long terme de ces circuits ne sont plus assurées.

Ainsi, le projet entrepris par notre équipe de travail, comprenant aussi Serge Patenaude ([14], 1998), se veut un pas vers l'avant dans le domaine sur plusieurs aspects. N'ayant pas *a priori* de connaissances sur les portes CML, le premier objectif de notre recherche consiste à comprendre les notions de base et la structure de leurs portes logiques complexes. Puis, compte tenu de la pauvreté de la littérature spécifique au test des circuits CML, notre recherche doit se pencher sur une synthèse de ce qui s'est fait dans un horizon plus large pour avoir une vue d'ensemble du travail à accomplir. Pour la même raison, l'étendue de la recherche doit aussi s'étendre aux types de circuits dont l'architecture ou les dispositifs utilisés s'apparentent à ceux des CML. Par la suite, il faut analyser les circuits CML en présence de défectuosités pour identifier tous les comportements anormaux exhibés. Puis, ayant pris connaissance de ces comportements, il devient possible de développer des techniques de détection adaptées particulièrement aux pannes les plus courantes. Ceci nous amène alors à chercher des combinaisons de ces techniques pour maximiser la détection des défectuosités. Puis, il

reste à valider les méthodes développées pour assurer leur efficacité dans de vrais circuits.

Ainsi, le premier chapitre de ce mémoire présente les notions de base de l'architecture de circuits CML ainsi qu'une technique pour concevoir des portes logiques complexes. De plus, il fait un tour d'horizon sur les différents aspects du test de ces circuits. Il couvre donc les différentes défectuosités qui peuvent apparaître dans un procédé à transistors bipolaires, les pannes qui découlent de ces défectuosités dans des portes CML et les méthodes développées jusqu'à présent pour détecter certaines de ces pannes.

Le deuxième chapitre présente un outil de caractérisation automatique de pannes. Cet outil permet d'analyser les comportements de portes logiques en présence de défectuosités. Par ces analyses, il devient alors possible d'identifier les pannes les plus fréquentes et ainsi, orienter les développements de méthodes de test sur ces pannes. Les résultats d'analyse de quelques portes sont aussi présentés.

Au troisième chapitre, une nouvelle technique de conception pour la testabilité est présentée. Cette technique a été développée suite à des recherches préliminaires cherchant à identifier les pannes les plus courantes. Le chapitre montre ainsi la force de cette technique vis-à-vis l'art antérieur dans le domaine de la détection de pannes pour

des circuits CML. De plus, cette technique évite les problèmes liés aux approches nécessitant un test à la pleine vitesse de fonctionnement.

Finalement, le quatrième chapitre présente la structure de la puce conçue pour évaluer les méthodes de test développées par l'équipe de travail. Il décrit les circuits à tester ainsi que les circuits nécessaires pour faire ces tests. De plus, il fait rapport de la méthodologie d'application des tests.

# CHAPITRE I

## NOTIONS DE BASE ET REVUE DE LITTÉRATURE

### 1.1 Introduction

L'objectif principal de ce projet est de développer des méthodes de test appliquées à des circuits logiques en mode courant (CML). Toutefois, pour mieux cerner la testabilité de ces circuits, il nous fallait en comprendre l'architecture. Ainsi, nos recherches initiales ont couvert autant le test que la conception des circuits CML. D'autre part, la littérature étant pauvre dans ces domaines, il a fallu étendre nos recherches aux circuits ECL (une architecture soeur des CML) pour la conception et le test ainsi qu'aux CMOS et BiCMOS pour le test. Ce mémoire se veut concis et dans cette optique, les discussions présentées se résument aux points importants retenus ou qui risquent d'être nécessaires dans la poursuite du projet.

Ainsi, cette revue de littérature couvre la conception des circuits CML, la modélisation des défectuosités pour les technologies bipolaires, les pannes qui découlent de ces défectuosités dans les circuits CML bipolaires et les méthodes de test pour les détecter.

## 1.2 Principes de base de la conception de circuits CML

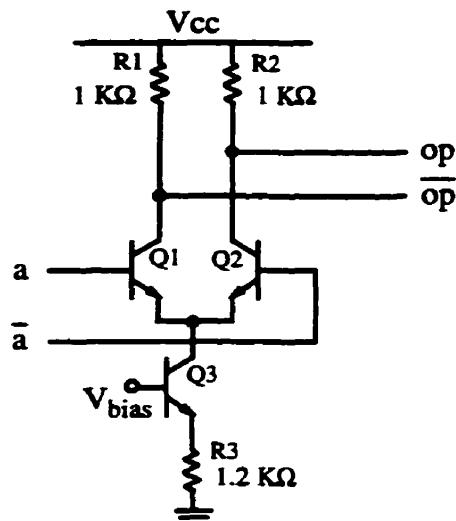

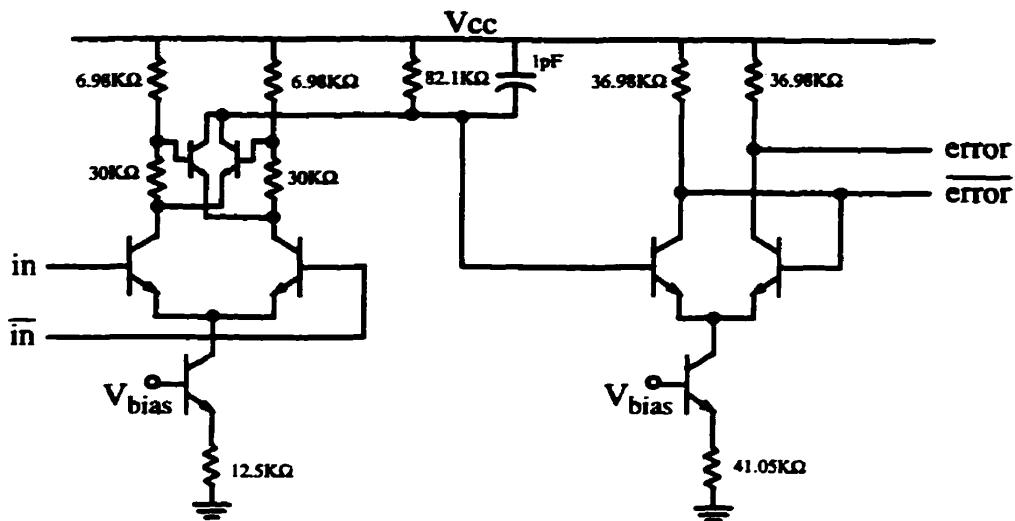

L'architecture CML est un style de conception bien adapté pour développer des bibliothèques de portes numériques rapides dans une technologie à transistors bipolaires. Elle est basée sur un simple amplificateur différentiel comme le montre la figure 1.1. Cette figure illustre une porte logique tampon d'où découlent toutes les autres portes CML. Cette porte provient de la bibliothèque VersArray25 de Nortel.

Figure 1.1 Porte tampon pour les circuits CML de Nortel <sup>1</sup>

L'amplificateur est pourvu d'une source de courant stable réalisée par le transistor Q3. La stabilité de cette source est obtenue par une source de tension fixe, indépendante de l'environnement, appliquée à la base du transistor Q3 pour ainsi le polariser. La puissance de cette approche réside dans sa simplicité. Les transistors Q1 et Q2

1. Pour la librairie de Nortel,  $V_{cc} = 3.3$  V ou 5 V.

aiguillent ce courant stable à travers une seule des deux branches formées par ces transistors, lorsque l'un ou l'autre est activé par la combinaison des signaux d'entrée  $a$  et  $\bar{a}$ . Pour activer un transistor, il suffit que la tension du signal appliquée à sa base soit plus élevée que celle du signal appliquée à celle du transistor homologue. Le courant de la branche sélectionnée crée une chute de potentiel aux bornes de sa résistance, alors que dans la seconde branche où un très faible courant circule, la tension aux bornes de sa résistance est tenue à  $V_{cc}$ . Les collecteurs des transistors Q1 et Q2 constituent une paire indissociable et forment les sorties de la porte logique (voir signaux  $op$  et  $\bar{op}$ ). En conception CML, chaque signal numérique est ainsi représenté par la différence de tension entre deux noeuds. Puisque les sorties sont toujours complémentaires, la marge de bruit d'une porte est accrue. De plus, cette tension différentielle est suffisante pour qu'une fois appliquée aux entrées d'une porte de même nature, elle puisse aiguiller tout le courant de cette autre porte dans l'une ou l'autre de ses deux branches.

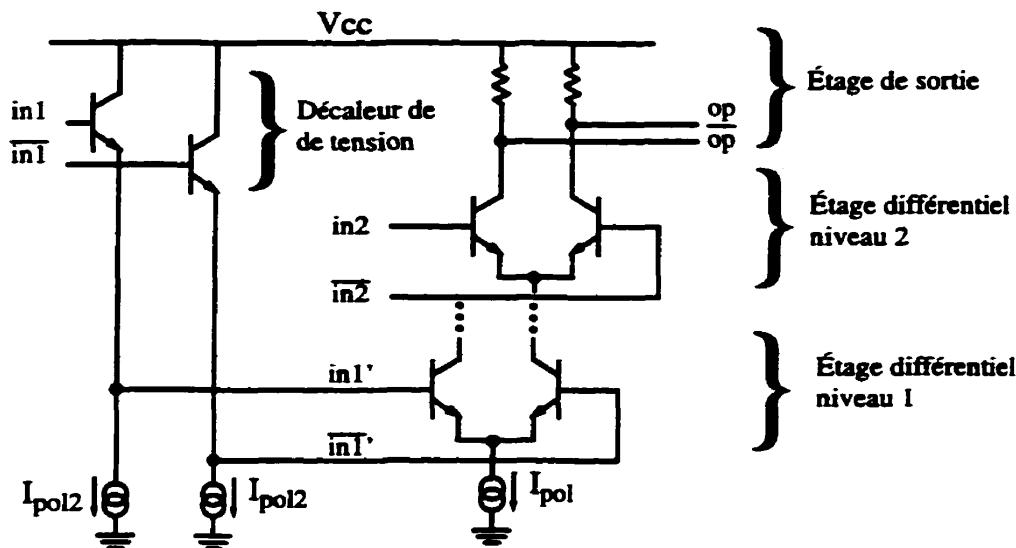

Pour implémenter des portes logiques plus complexes que la porte tampon, des étages différentiels sont ajoutés en série de manière verticale, comme le montre la figure 1.2. Pour créer la fonction logique désirée, les étages différentiels de niveaux supérieurs se servent aussi de la méthode d'aiguillage du courant de polarisation. Bien entendu, chaque étage différentiel ne compare que des signaux complémentaires et le courant de polarisation doit toujours être aiguillé pour passer à travers l'une ou l'autre des résistances de sortie.

Figure 1.2 Portes CML à deux étages

Notons qu'il ne peut y avoir qu'un seul courant de polarisation qui soit aiguillé vers ces résistances. Aussi, compte tenu de la valeur fixe de la source d'alimentation  $V_{cc}$ , le nombre d'étages qu'on peut mettre en série est limité. En effet, il faut tenir compte de la tension nécessaire pour empêcher la saturation du transistor de la source de courant en plus d'allouer au moins un  $V_{BE}^2$  à chaque niveau pour assurer que les transistors ne limitent pas le courant qui les traversent. Ainsi, pour deux niveaux d'étages différentiels, une tension de 3.3 V est suffisante, alors qu'avec 5 V, le nombre d'étages maximum se limite à 3 pour une technologie à 0.7 V d'après Embabi et al. ([4], 1993) et Jalali et al. ([8], 1995)<sup>3</sup>. Pour éviter d'obtenir une polarisation directe de la jonction

-

2. La technologie bipolaire de Nortel offre des transistors dont la tension d'activation se situe près de 0.85 V.

3. D'après leurs équations, même avec la technologie NT25 de Nortel où  $V_{BE} = 0.85$  V, il devrait être possible d'avoir 4 niveaux d'étage différentiel avec une alimentation de 5 V, tout en allouant une tension satisfaisante de 1.6 V au collecteur de la source de courant.

base-collecteur des transistors des étages différentiels inférieurs, les tensions des niveaux standards doivent être abaissées par un décaleur d'un  $V_{BE}$  avant de les commander. La section 1.3 présente plus de détails sur une méthode pour concevoir des portes logiques CML.

Les performances des familles logiques CML sont liées à leur architecture originale ainsi qu'à une conception minutieuse. Au point de vue de l'architecture, plusieurs avantages se démarquent. Grâce au principe d'aiguillage de courant qui limite le  $dI/dt$  dans les rails d'alimentation, la puissance de consommation statique est conservée à une valeur fixe, indépendante de l'activité du circuit. Aussi, la nature différentielle des CML permet aux champs magnétiques indépendants des signaux pairés de s'annuler et ainsi de réduire l'interférence entre les signaux. De plus, en utilisant une source de courant fixe, les transistors de l'étage différentiel ne peuvent entrer en saturation, ce qui permet des commutations à hautes vitesses. Il faut aussi mentionner que les portes CML offrent toujours un signal et son complément, simplifiant ainsi les circuits et réduisant la profondeur logique quand l'inverse des signaux est régulièrement nécessaire.

Au point de vue de conception, les circuits CML fonctionnent correctement avec des amplitudes de signaux différentiels très petites, de l'ordre de 250 mV. En effet, un des grands avantages de la nature différentielle des CML est leur grand rapport signal à

bruit, puisqu'il n'y a plus de tension intermédiaire de référence pour établir l'état d'un signal. De plus, cette petite amplitude permet une réduction considérable de la consommation de la puissance dynamique, car elle dépend du carré de l'amplitude. D'autre part, elle contribue aussi à obtenir des fonctionnements à hautes vitesses. En effet, le taux de montée maximum ne variant pas avec l'amplitude, plus celle-ci est petite, moins long seront les temps de commutations.

Bien entendu, une amplitude fixe ne limite qu'en partie les valeurs des résistances de sortie et du courant de la source. La marge de manoeuvre qui reste permet des combinaisons assez avantageuses pour un concepteur. Avec des courants de source plus élevés et donc des résistances de sortie plus faibles, il est possible d'augmenter la vitesse de commutation des portes ainsi que la puissance de sortie<sup>4</sup>. En effet, un plus grand courant et de plus faibles résistances de sortie permettent de charger plus rapidement les condensateurs parasites. À l'inverse, un faible courant de source diminue la puissance nécessaire pour entretenir une cellule plus lente ou qui ne fournit pas de signaux à un grand nombre de cellules. Par exemple, Nortel offre une famille de portes comportant 7 différents grades de vitesse/puissance pour être utilisées selon les besoins. Bien entendu, une cellule de faible puissance doit passer par une série d'amplificateurs pour transmettre un signal à une cellule de haute puissance, mais les

---

4. Une plus grande puissance de sortie d'une porte permet un plus gros «fanout».

mélanges de grade sont peu fréquents. Ils permettent néanmoins d'améliorer de manière significative les performances dans bien des cas.

### 1.3 Conception des portes à niveaux multiples

À force de travailler avec l'architecture CML, nous avons développé une certaine expertise dans la conception de portes logiques CML<sup>5</sup>. Voici donc une technique pour obtenir le circuit associé à une fonction logique. En premier lieu, il est de mise d'établir la plus simple équation en algèbre de Boole de la fonction logique à implémenter sous la forme d'une somme de produits. Sachant qu'une porte CML génère deux sorties (le signal en logique positive et son complément), il faut aussi établir l'équation booléenne simplifiée de l'inverse de cette fonction.

Deuxièmement, il faut établir le niveau que prendra l'étage différentiel de chaque paire de signaux dont dépend la fonction. Évidemment, les choix faits ne sont qu'à titre de repères et pourront changer aux étapes subséquentes. Pour faciliter la décision, il est préférable de tenir compte de certaines propriétés de l'architecture CML. Une transition aux entrées d'un étage différentiel se propage vers ses sorties avec un délai non-négligeable. Donc, plus l'étage différentiel est à un niveau bas, plus une transition à ses entrées prendra du temps à se propager vers les sorties de la cellule. Ainsi, il est

---

5. Jalali et al. ([8], 1995) est une bonne référence montrant plusieurs portes logiques CML.

préférable de placer les variables les moins susceptibles de changer aux niveaux inférieurs. Aussi, sachant que l'architecture CML est à l'image d'un arbre dichotomique dont le tronc part de la source de courant, les niveaux inférieurs sont limités en étages différentiels. Ainsi, il est préférable de placer les variables les plus présentes dans les produits des équations booléennes aux niveaux inférieurs. La règle va jusqu'à devoir modifier les deux équations booléennes lorsque celles-ci ne comportent pas dans tous leurs produits l'un ou l'autre des signaux complémentaires de niveau 1. Cette règle sera justifiée à la troisième étape.

Une fois les niveaux choisis pour chaque variable, la troisième étape consiste à établir les connexions entre les étages différentiels. Pour construire un produit partiel d'une équation, il suffit de mettre en série les transistors (de différents niveaux) dont les bases sont connectées aux signaux qui le forment. Pour construire la somme d'une équation, il suffit de créer un OU-câblé avec les sorties qui réalisent ses produits partiels. Notons que chaque transistor d'une série fait parti d'un étage différentiel où le transistor homologue reçoit le signal complémentaire à sa base. Notons encore que tout transistor d'étage différentiel doit être utilisé dans une série. Autrement, le courant ne pourrait que passer dans le transistor homologue et fausser la fonction à implémenter. D'autre part, il est très possible que certains produits soient indépendants de certains signaux. Dans ces cas, il ne suffit que de sauter les niveaux qui y sont associés. L'exception à cette règle revient à la paire de signaux de niveau 1, où il est impossible de faire le saut.

En effet, l'étage différentiel de niveau 1 est directement relié à la source de courant et sauter ce signal serait avoir un produit fonctionnant sans courant. Pour pallier au problème, il faut modifier les équations, comme mentionné ci-haut, pour que tous les produits dépendent de l'un ou l'autre signal de la paire.

En CMOS, toutes les portes statiques simples inversent car la conduction d'un réseau N activé par des variables logiques d'entrée produit un 0 en sortie. En CML, c'est le même principe. Par contre, la logique CML comporte toujours le complément d'un signal. Ainsi, il n'est guère difficile d'inverser les connexions des OU-câblés aux sorties pour retourner en logique positive.

En dernière étape, il ne reste qu'à faire les connexions à la source de courant et à l'étage de sortie ainsi que les branchements aux décaleurs de tensions qui abaissent les niveaux logiques de un ou plusieurs  $V_{BE}$ . La source de courant doit se brancher aux émetteurs des transistors de l'étage différentiel de niveau 1, comme le montre la figure 1.2. Quant à l'étage de sortie, chacune des deux résistances se branche au complément du OU-câblé associé à son équation. Pour les décaleurs de tension<sup>6</sup>, ils sont placés aux entrées pour amener les signaux de tension standards à des tensions adaptées aux niveaux inférieurs. Lorsque le nombre de niveaux dépasse deux, il faut ajouter des diodes pour accroître la chute de potentiel.

---

6. Voir la figure 1.2 pour un circuit de décalage de tension. Mentionnons aussi que l'entrée et la sortie d'un décaleur de tension sont des variables logiques équivalentes.

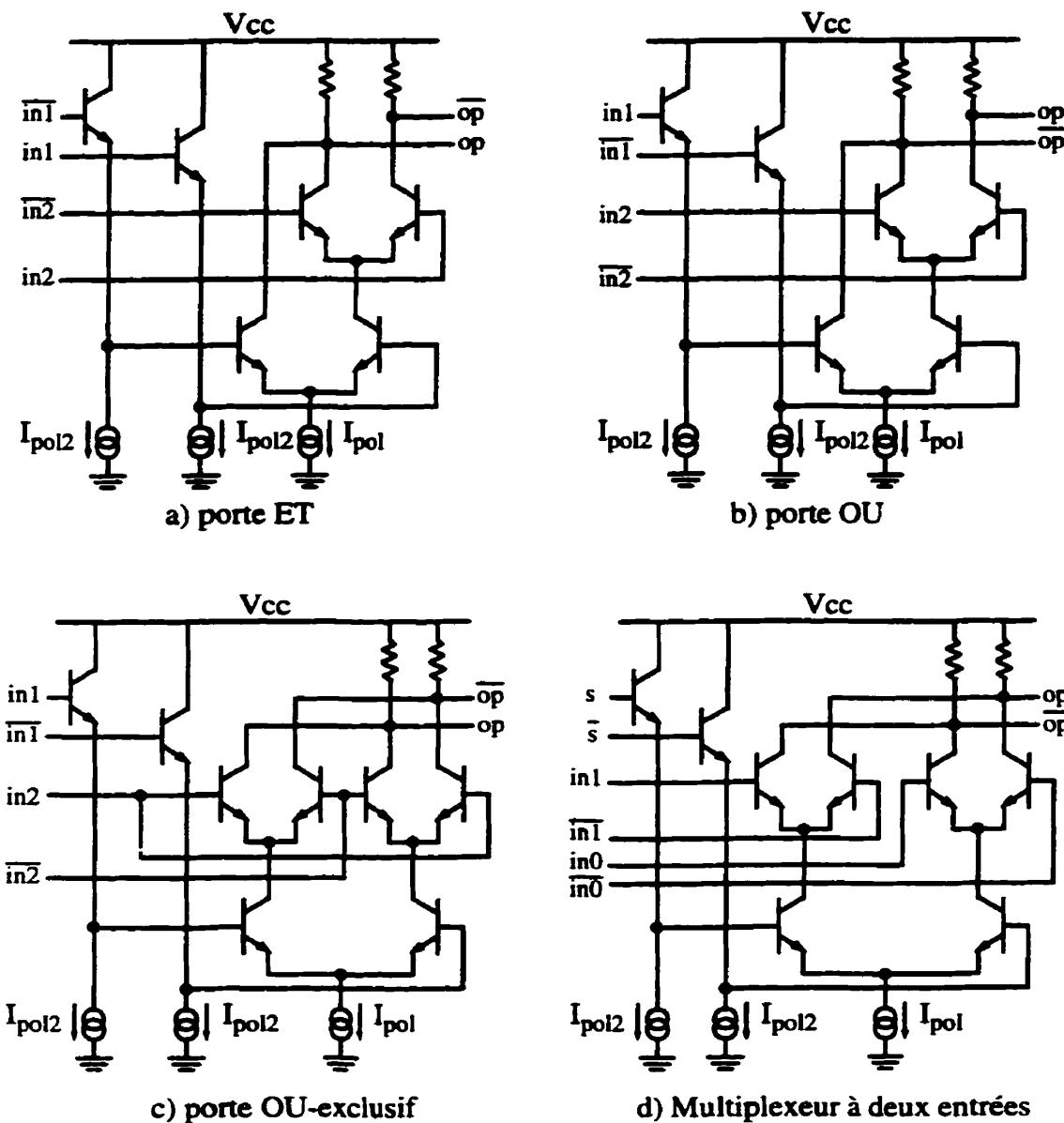

La figure 1.3 montre quelques configurations de portes logiques à deux niveaux, et le tableau 1.1 présente les équations booléennes des fonctions implémentées.

Tableau 1.1 Équations des portes illustrées

| Porte                                    | Sortie          | Équation normale                                        | Équation ajustée                                        |

|------------------------------------------|-----------------|---------------------------------------------------------|---------------------------------------------------------|

| ET                                       | $op$            | $in1 \cdot in2$                                         | $in1 \cdot in2$                                         |

|                                          | $\overline{op}$ | $\overline{in1} + \overline{in2}$                       | $\overline{in1} + in1 \cdot \overline{in2}$             |

| OU                                       | $op$            | $in1 + in2$                                             | $in1 + in1 \cdot in2$                                   |

|                                          | $\overline{op}$ | $\overline{in1} \cdot \overline{in2}$                   | $\overline{in1} \cdot \overline{in2}$                   |

| OU-exclusif                              | $op$            | $in1 \cdot \overline{in2} + \overline{in1} \cdot in2$   | $in1 \cdot \overline{in2} + \overline{in1} \cdot in2$   |

|                                          | $\overline{op}$ | $in1 \cdot in2 + \overline{in1} \cdot \overline{in2}$   | $in1 \cdot in2 + \overline{in1} \cdot \overline{in2}$   |

| Multiplexeur à deux entrées <sup>a</sup> | $op$            | $s \cdot in1 + \bar{s} \cdot in0$                       | $s \cdot in1 + \bar{s} \cdot in0$                       |

|                                          | $\overline{op}$ | $s \cdot \overline{in1} + \bar{s} \cdot \overline{in0}$ | $s \cdot \overline{in1} + \bar{s} \cdot \overline{in0}$ |

a. Lorsque  $s = 0$ ,  $in0$  est transmis vers  $op$  et pour  $s = 1$ ,  $in1$  est transmis.

Un point important à remarquer est la ressemblance des portes ET et OU. En effet, l'algèbre de Boole montre qu'il est possible d'inverser entrées et sorties pour passer d'une porte OU à une porte ET, et vice-versa. Un autre fait à remarquer pour ces deux portes est le saut du niveau 2 pour passer directement à la sortie. Le produit ne tenant compte que du signal de niveau 1, le contact peut se faire directement à la résistance de sortie puisque c'est le courant qui fixe la tension de sortie.

Figure 1.3 Différentes portes logiques à deux niveaux

Quant aux portes OU-exclusif et multiplexeur à deux entrées, elles partagent aussi des caractéristiques semblables. En effet, une façon différente de percevoir une porte OU-exclusif est de considérer qu'elle transmet le signal  $in2$  lorsque  $in1 = 1$  et elle transmet

un autre signal (il s'agit ici du complément de  $in2$ ), lorsque  $in1 = 0$ . Ainsi, avec le multiplexeur, le signal  $in1$  change pour devenir  $s$  et les signaux à transmettre sont  $in0$  et  $in1$ . Une autre porte qui partage la même construction est la bascule sensible à l'état du signal d'horloge<sup>7</sup>. Le signal  $s$  est remplacé par l'horloge, le signal  $in1$  par l'entrée  $d$  et le signal  $in0$  est remplacé par la sortie<sup>8</sup>.

#### 1.4 Défauts rencontrés dans les technologies bipolaires

À travers la littérature, différents types de défectuosités ont été exposés pour les procédés bipolaires. Cette section révise rapidement les types de défectuosités les plus communs et la façon dont ils sont modélisés.

Les procédés de fabrication de circuits semiconducteurs sont sujets à diverses imperfections et variations paramétriques. Celles-ci peuvent engendrer des connexions entre segments d'une même couche, des discontinuités dans des segments ou même des modifications dans l'épaisseur de certaines couches ou oxydes (Esonu et al. [5], 1994; Jorczyk et al. [9], 1995; Menon et al. [12], 1996). Par exemple, si une couche métallique est bien plus mince que la normale dans une région localisée, cette région pourrait fondre par électromigration. Avec le temps, il est possible que le segment devienne interrompu sur toute sa largeur et donc que le courant ne passe plus. Un

7. Contrairement aux bascules sensibles à la transition du signal d'horloge, communément appelées «flip-flop».

8. Lorsque l'horloge est à l'état 0, la porte devient une boucle fermée où la sortie se conserve.

auteur (Cecchi [2], 1988) mentionne même que la couche «contact» est souvent vulnérable aux défectuosités, au point où les contacts ne font plus leur travail de joindre ensemble des couches de différents niveaux.

Une classe toute particulière de défectuosités s'associe directement aux dispositifs bipolaires. Les transistors bipolaires sont caractérisés par un gain de courant déterminé par l'épaisseur de leur base. Cette épaisseur peut être modulée par divers phénomènes. Par exemple, la dislocation de la couche active du semiconducteur est une imperfection physique qui joue sur l'épaisseur effective de la base lorsqu'elle se manifeste à l'intérieur de celle-ci. Ceci crée généralement un point à très grand gain et à courant de fuite excessif (Stewart et al. [17], 1991). Ce comportement est communément connu sous le nom de transistor percé. Les transistors verticaux (NPN, généralement) sont plus vulnérables au perçage.

Les segments interrompus, ou plus communément circuits ouverts, sont couramment observés aux alentours des bornes de transistors, aux métallisations et dans les éléments résistifs. Quant aux connexions indésirables, la littérature les divise en deux parties: celles liées aux dispositifs et celles liées aux couches de métallisation. Celles liées aux dispositifs sont tout simplement appelées courts-circuits et elles sont retrouvées entre les bornes des transistors et les bornes des résistances. D'autre part, les connexions indésirables liées aux métallisations sont appelées ponts et elles sont

définies comme des connexions entre deux segments d'une même couche de métallisation, formant des «ponts» entre les signaux.

Les classes de défectuosités vues ci-haut peuvent être modélisés avec une bonne précision au niveau des dispositifs (e.g. transistors et résistances). De tels modèles incluent des courts-circuits, des ponts, des circuits ouverts ou des transistors percées (Stewart et al. [17], 1991). Ainsi, dans un simulateur de type Spice, une résistance de faible valeur ( $\sim 1 \Omega$ ) peut être utilisée pour modéliser un court-circuit ou un pont. Pour simuler un circuit ouvert, les éléments normalement connectés peuvent être isolés à l'aide d'une résistance de plus de  $100 \text{ M}\Omega$  en parallèle avec un condensateur parasite de  $1 \text{ fF}$ . Un transistor percé est normalement modélisé par un transistor avec une résistance de quelques  $\text{K}\Omega$  entre son collecteur et son émetteur.

Si l'objectif est d'obtenir une évaluation exacte de la proportion des défectuosités qui sont détectées<sup>9</sup>, il faut tenir compte de la distribution de la taille de ces défectuosités, soit la probabilité d'apparition de chaque type de défectuosités. Une telle information est habituellement inaccessible vue le côté confidentiel de son contenu et il est donc commun de traiter toutes les défectuosités comme si elles étaient équiprobales.

---

9. Cette proportion correspond à la définition de la couverture de défectuosités.

## 1.5 Pannes retrouvées dans les circuits CML

Une modélisation au niveau des dispositifs est le moyen le plus précis pour simuler les effets d'une défectuosité. Toutefois, il devient trop complexe d'étudier un circuit complet à l'aide de ce type de modèle et d'ailleurs, ces modèles sont rarement complets ou accessibles. De même, la tâche d'analyser toutes les pannes d'un circuit et de trouver les défectuosités qui les causeraient est d'une grande complexité et elle n'est réalisée que de façon exceptionnelle sur de petits nombres d'échantillons défectueux. Une voie plus adéquate pour étudier le problème consiste à analyser les conséquences de chaque défectuosité sur le comportement électrique des portes de base d'une bibliothèque, pour ensuite les traduire comme une panne dont les conséquences peuvent être propagées à l'intérieur du circuit jusqu'aux broches. Il est donc de mise de passer à un modèle de pannes. Bien sûr, pour valider une liste de pannes probables, celles-ci doivent être observées dans des circuits défectueux.

Des travaux récents sur la testabilité des ECL/CML ont démontré que ces circuits ont de nombreuses pannes à caractère unique et que les méthodes de détection de pannes collées ne donnent pas une couverture satisfaisante de ces pannes (Anderson [1], 1988; Esonu et al. [5], 1994; Jorczyk et al. [9], 1995; Menon et al. [12], 1996). De plus, il a été prouvé que les circuits combinatoires ECL ont une tendance à masquer des pannes

qui se manifestent dans les premiers étages de circuits ayant une certaine profondeur logique (Anderson [1], 1988).

Le tableau 1.2 présente les pannes les plus fréquemment considérées, accompagnées d'une liste de références qui en traitent. Chaque panne sera définie par après.

Tableau 1.2 Pannes observées dans les portes ECL/CML

| Pannes                              | Références                                        |

|-------------------------------------|---------------------------------------------------|

| Ligne collée                        | Esonu et al. [5], 1994; Morandi et al. [13], 1988 |

| Table de vérité corrompue           | Esonu et al. [5], 1994                            |

| Comportement séquentiel             | Menon et al. [11], 1993                           |

| OU-câblé                            | Menon et al. [11], 1993                           |

| Complémentarité corrompue           | Menon et al. [12], 1996                           |

| Panne byzantine                     | Anderson [1], 1988                                |

| Marge de bruit réduite              | Anderson [1], 1988; Esonu et al. [5], 1994        |

| Niveau logique indéfini             | Jorczyk et al. [9], 1995; Menon et al. [11], 1993 |

| Panne de délai                      | Esonu et al. [5], 1994; Jorczyk et al. [9], 1995  |

| Oscillation par rétroaction         | Menon et al. [11], 1993                           |

| Courant de fuite excessif $I_{ddq}$ | Esonu et al. [5], 1994                            |

La section 1.5.1 présente les pannes de type logique et la section 1.5.2, les pannes de type analogique. Il est à mentionner que ces pannes ne sont pas mutuellement exclusives et peuvent très bien apparaître en même temps peu importe le groupe.

### 1.5.1 Pannes à caractère logique

Dans ce document, une panne est considérée de type logique lorsque son comportement affecte la logique de la cellule. Dans ce cas, les signaux continuent à être interprétés comme des valeurs logiques plus ou moins conformes aux signaux logiques normaux pour la technologie considérée. De plus, bien que cela ne soit pas toujours aisé, il est possible de détecter ce type de pannes par des méthodes de test numériques. De la liste des pannes énumérées ci-haut, les collé-à, table de vérité corrompue, comportement séquentiel et OU-câblé font partie des pannes à caractère logique.

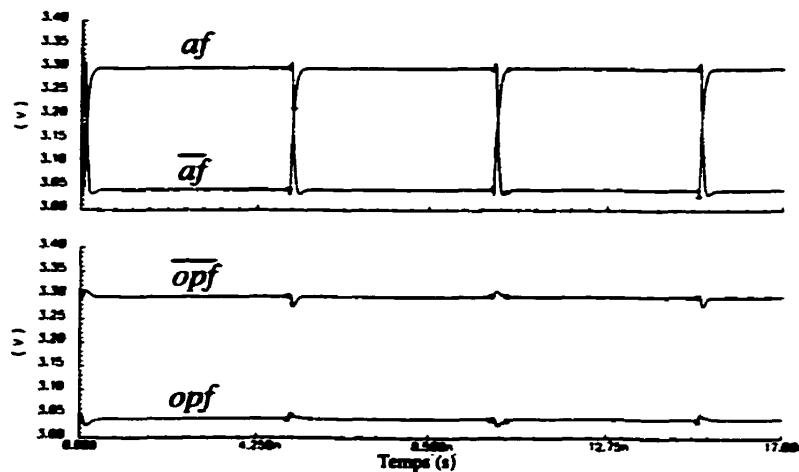

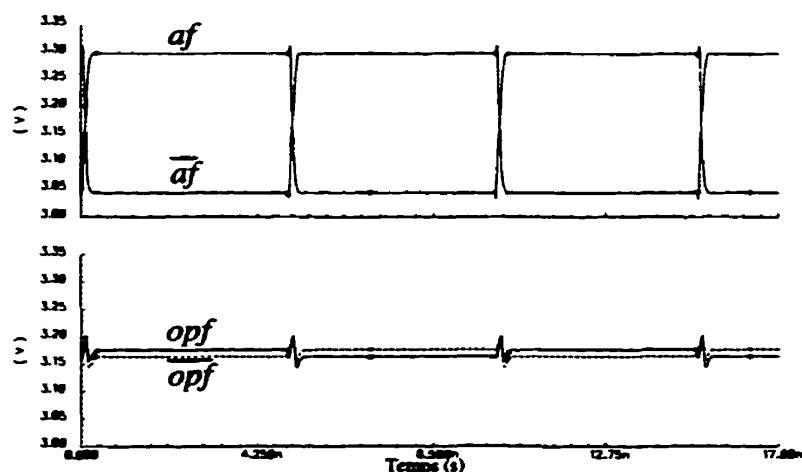

Tout comme les circuits CMOS, certaines défectuosités engendrent des pannes de type collé (aussi connue comme des collages). Une cellule ayant une panne de collage s'observe par un comportement où une de ses entrées ou de ses sorties reste collée au même état logique. Un signal numérique peut donc être collé à l'état 1 ou 0. La figure 1.4 montre les effets d'un court-circuit entre l'émetteur et le collecteur du transistor Q2 d'une porte tampon (voir figure 1.1) générant un collage à 0 à la sortie. La paire de signaux d'entrée est définie par  $af$  et  $\bar{af}$  et la paire de signaux de sortie est définie par  $opf$  et  $\bar{opf}$ .

Figure 1.4 Une panne collé-à typique

De plus, il a été observé que pour plusieurs défauts possibles, un seul signal de la paire est collé, alors que son complément continu à fonctionner normalement. Ceci amène un sous-modèle de pannes: les lignes collées.

Un autre modèle de panne observé auprès des circuits ECL se manifeste pour une ou plusieurs combinaisons déterminées des valeurs logiques aux entrées. Dans ce cas, on obtient une réponse anormale du signal de sortie et il est alors question de table de vérité corrompue. Certaines pannes de table de vérité corrompue peuvent être interprétées par des pannes de collage, toutefois, d'autres ne peuvent être représentées que par ce modèle. De surcroît, la littérature mentionne que certaines portes combinatoires défectueuses ont un comportement séquentiel, donnant ainsi un effet de mémoire à la porte, sans pour autant la rendre collée à une valeur logique.

Aussi, il est connu que certaines défectuosités dans les circuits ECL peuvent donner des OU-câblés de sorties court-circuitées. Ces pannes sont reliées au fait qu'en ECL les signaux d'entrée ne sont pas différentiels et que l'étage de sortie des portes ECL est fréquemment réalisé sous la forme d'un émetteur-suiveur, étage que l'on ne retrouve pas dans les portes CML. Ainsi, ce type de pannes ne semble pas possible dans les circuits CML.

### 1.5.2 Pannes de type analogique

Une panne de type analogique est définie ici par un comportement anormal d'une cellule observable par une réponse hors de ses spécifications paramétriques. Il faut encore mentionner qu'une défectuosité engendrant une panne de ce groupe peut aussi bien engendrer des pannes d'ordre logique. Dans ce groupe de pannes, on retrouve les pannes de délai, de complémentarité corrompue, byzantine, à marge de bruit réduite, de niveau logique indéfini, d'oscillation par rétroaction et de courant de fuite excessif  $I_{ddq}$ .

Une panne de délai est obtenue lorsqu'une différence significative est observée dans le délai de propagation d'un signal. Cette différence peut soit être un accroissement, soit une diminution du délai accepté comme normal. Il peut sembler étonnant et sans conséquence qu'une défectuosité améliore le temps de réponse d'une cellule, toutefois,

il est fort probable qu'une telle défectuosité engendre d'autres pannes en même temps ou qu'elle puisse nuire sur d'autres plans de la performance de cette cellule (dissipation, fiabilité).

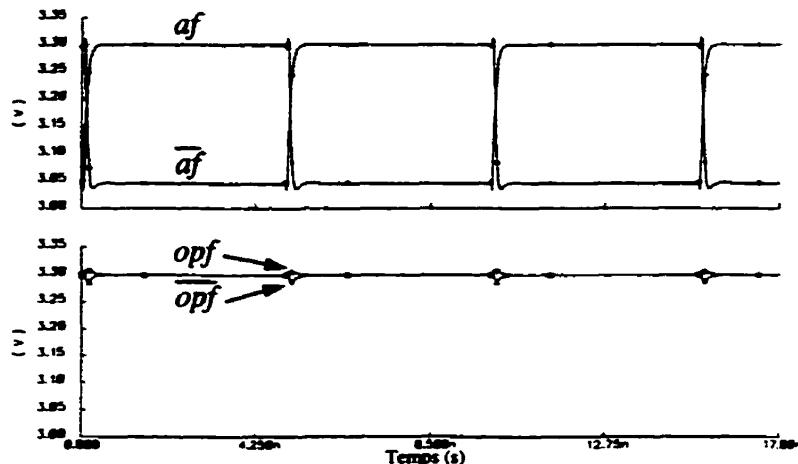

Notre étude qui visait à identifier les comportements possibles nous a permis d'observer de nombreux cas où une défectuosité se manifeste par une amplitude différentielle réduite qui diminue la marge de bruit. En effet, moins grande est la différence entre les signaux complémentaires, plus le signal est susceptible d'être compromis par des bruits dans la puce. Toutefois, la fonctionnalité de la porte reste souvent intègre et si le bruit reste en deçà du point critique, la panne ne se propagera pas et le circuit pourrait sembler parfaitement correct. Un exemple typique de panne de marge de bruit est présenté à la figure 1.5, où un pont faible a été simulé entre les signaux de sortie  $opf$  et  $\overline{opf}$ . Le résultat donne une amplitude de sortie de 10 mV qui est inacceptable pour des puces mises sur le marché.

Figure 1.5 Panne de marge de bruit typique

À l'extrême, comme le démontre la figure 1.6 où le transistor fournissant la source de courant comporte un circuit ouvert à son collecteur, la marge de bruit est réduite dramatiquement et seules de faibles excursions sont visibles aux transitions d'états aux signaux d'entrée.

Figure 1.6 Panne extrême de marge de bruit pour un circuit CML

De cette défectuosité découlent une panne de niveau logique indéfini ou pire, une différente interprétation du niveau logique des signaux de sortie (panne byzantine) par les portes recevant cette paire de signaux.

Aussi, des cas de perte de complémentarité entre deux signaux pairés ont déjà été rapportés pour des circuits ECL, connu sous le nom de panne à complémentarité corrompue. Puisque ces pannes sont liées à l'étage typique émetteur-suiveur des portes ECL, ces pannes ne sont pas possibles en CML.

De plus, il a été observé des cas où une défectuosité ajoute une rétroaction interne dans une cellule, générant de manière aléatoire une oscillation indésirable du signal de sortie.

Enfin, certains circuits ECL présentent un accroissement dans le courant de repos ( $I_{ddq}$ ) où les sources de courant des cellules demandent un courant d'alimentation supérieur à la normale. L'idée d'en faire un modèle de panne provient d'études poussées pour les circuits CMOS où un courant de repos anormal est bien plus critique.

### 1.6 Méthodes de test marquantes sur la détection des pannes

Pour la plupart des cas de défectuosités qui engendrent des pannes de type logique, la fonctionnalité des circuits est corrompue. Toutefois, pour un bon nombre de défectuosités qui n'engendrent que des pannes de type analogique, seules les caractéristiques des cellules sont compromises. Dans plusieurs cas, il n'y a pas d'effet sur la fonctionnalité d'une puce. Or, souvent, les défectuosités peuvent se dégrader avec le temps. Dans ce cas, la défectuosité ne deviendrait une panne que chez le client où l'environnement n'est pas nécessairement aussi stable que sur les bancs de test. Pour simplifier le problème du test face à la grande variété des pannes possibles, différentes méthodes de tests ont été proposées dans la littérature.

### 1.6.1 Détection de pannes logiques

Un circuit d'auto-évaluation intégré (BIST) fonctionnant à la vitesse d'opération normale du circuit a été proposé par Jorczyk et al. ([10], 1996) pour tester des circuits intégrés ECL. Cette méthode permet de couvrir des pannes qui échappent aux tests à vitesse réduite. Le BIST proposé se compose d'une série de registres à décalage à rétroaction linéaire (LFSR) et la méthode de vérification prônée est d'observer le diagramme en oeil des sorties de la puce. Néanmoins, cette technique demande un effort important de conception et de test, et peut devenir gourmand au niveau surface.

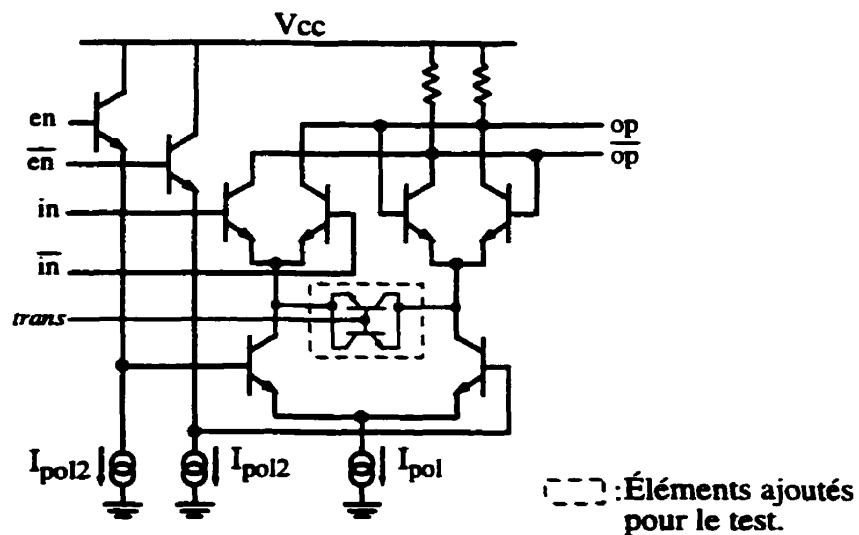

Une méthode simple de propagation des pannes logiques à travers des portes séquentielles ou des multiplexeurs a été développée par Patenaude ([14], 1998). Cette technique de la transparence permet en mode test de rendre ces portes transparentes au signal de commande (qu'il soit le signal d'horloge ou de sélection). Somme toute, la technique transforme ces portes en simples tampons. L'intérêt de cette méthode découle du besoin d'insérer des chaînes de balayage dans un circuit séquentiel pour appliquer des patrons de test ATPG. Le circuit de test, comme le montre la figure 1.7, ajoute deux transistors et un signal de commande (*trans*) à chaque porte nécessitant un mode test de transparence. L'idée principale est de forcer le courant de polarisation à passer aux deux étages différentiels du niveau supérieur en appliquant à *trans* une tension de l'ordre de  $V_{cc}$ . Ainsi, le courant sera divisé dans les deux étages

différentiels de deuxième niveau. L'étage de gauche reçoit l'entrée alors que l'étage de droite donne une rétroaction positive (à faible gain) de la sortie. Le signal d'entrée ayant une impédance plus faible que la rétroaction, le signal de sortie le suit et la rétroaction accélère le gain. Cette méthode conduit à une faible baisse en performance et une variation dans l'amplitude différentielle négligeable. Toutefois, l'auteur mentionne que la méthode possède un désavantage qui peut être contourné, mais qui demande un effort de plus pour y remédier. Il mentionne qu'un circuit similaire à une machine à état qui comporte des rétroactions pourrait entrer en oscillation si toutes les bascules devaient transparentes en mode test. Pour une bonne couverture de pannes où tous les sous-circuits sont testés, il faudrait plusieurs signaux de commande de transparence. Chaque signal serait donc relié à différentes portes séquentielles sélectionnées pour éviter toute oscillation involontaire.

Figure 1.7 Bascule sensible à l'état du signal d'horloge avec mode de transparence

(tirée de Patenaude, 1998)

### 1.6.2 Détection des pannes de complémentarité corrompue

Pour tester la corruption des signaux complémentaires (aux sorties de chaque porte) des circuits ECL, Menon et al. ([12], 1996) ont proposé une technique simple. La technique utilise une porte OU-exclusif à polarité simple pour vérifier que tous les signaux complémentaires soient de niveaux logiques opposés. Toutefois, cette technique demande une grande surface pour la portion de test (une porte de test pour chaque porte du circuit) et ceci n'améliore que la couverture d'un seul type de panne qui n'est pas observé dans les circuits CML.

### 1.6.3 Détection des pannes de délai

Higeta et al. ([7], 1995) ont développé des techniques pour vérifier les délais des chemins de données de modules de mémoire RAM ECL-CMOS. En utilisant des bascules ECL aux entrées et sorties de ces modules et en stimulant le circuit à l'aide d'un générateur de patrons, ils ont établi le délai des chemins de données en nombre de cycle de l'horloge de test. Bien que cette technique puisse être utilisée pour des circuits CML, elle a en général un défaut qui fait que même certaines pannes évidentes ne peuvent pas être détectées. En considérant qu'un circuit puisse avoir une variation modeste de 10% vis-à-vis les paramètres nominaux du procédé, le délai d'une porte défectueuse deux fois plus lente que la normale ne pourra pas être détecté si la donnée

se propage dans un circuit de profondeur logique de plus de 10 portes de même nature, si les neuf autres portes possèdent un comportement nominal. En effet, la variation permise de 10% dans le délai total du chemin de donnée dans l'exemple est équivalente à une porte en plus. Or, la panne non-négligeable sus-mentionnée apporte exactement un délai de cette envergure. Ainsi, dans ce contexte, ce type de panne ne peut pas être détectée.

Cecchi ([2], 1988) a breveté une technique originale pour palier à certaines pannes de délai difficilement observables dans une bibliothèque de cellules. La cause de ces pannes provenait d'une défectuosité possible dans leur technologie, soit un circuit ouvert dans la couche «contact»<sup>10</sup>. Après modification du dessin des masques des cellules standards de la bibliothèque, Cecchi a pu veiller à ce qu'un défaut dans la couche «contact» au noeud sensible considéré ne puisse se manifester que sous la forme d'un collage. Au point de vue performance des cellules, rien n'a changé et la surface totale des cellules n'a pas été compromise. Ainsi, il évite le temps de développement et la surface nécessaire pour des dispositifs de test pour détecter des pannes difficiles à détecter. Cette technique peut très bien s'appliquer à d'autres types de panne; la seule différence réside dans une compréhension parfaite des conséquences de chaque défectuosité dans la conception au niveau des masques.

---

10. Couche métallique donnant accès à la première couche de métallisation aux dispositifs.

Une autre technique développée dans l'optique de détecter des pannes de délai qui peut très bien servir à d'autres fins de détection a été proposée par Chang et McCluskey ([3], 1996) pour des circuits CMOS. Leur méthode consiste à abaisser la tension d'alimentation d'une puce aux alentours de 2 à 2.5 fois la tension de seuil  $V_t$  des transistors. Dans cette région, le délai des portes défectueuses augmente de manière significative par rapport à la normale. Ceci implique que les pannes de délai s'amplifient au point d'être plus facilement détectées. Les auteurs mentionnent que la technique a aussi prouvé son efficacité pour détecter des pannes logiques de fonctionnalité, de synchronisation et de courant de fuite  $I_{ddq}$ . Il est vrai que la méthode visait les technologies CMOS, mais le principe pourrait bien s'appliquer aux CML en considérant le stress qu'elle apporte sur la marge de bruit.

#### 1.6.4 Détection de marges de bruit réduites

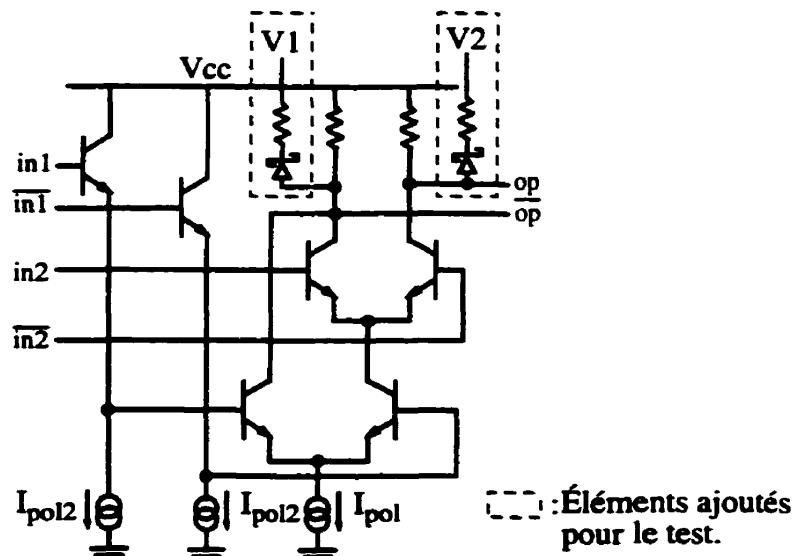

Pour détecter les pannes à marge de bruit réduite qui sont souvent difficiles à détecter, Anderson ([1], 1988) a présenté une technique brevetée par IBM qui empêche un circuit de récupérer des effets d'une panne, la forçant à se manifester sous forme d'un collage. La figure 1.8 présente une porte OU modifiée pour intégrer cette technique de test. La technique utilise deux sources d'alimentation additionnelles ( $V1$  et  $V2$ ) en mode test pour déséquilibrer dans les deux sens l'étage différentiel de toutes les portes d'un circuit. En effet, en appliquant une tension suffisamment inférieure à  $Vcc$  sur

l'une ou l'autre des alimentations additionnelles, il est possible de jouer sur la plage de tension d'une des branches de l'étage différentiel. Puisque l'autre branche conserve la plage de tension non-modifiée, il est possible de générer un collage en empêchant les signaux de se croiser. Avec des tensions de test bien calculées, un collage pourrait n'être induit que pour les cas où la marge de bruit est réduite. Si en mode normal un signal ne comporte pas de panne de marge de bruit, l'amplitude différentielle du signal serait diminuée, mais pourrait quand même se propager. De plus, pour isoler en mode normal le circuit de toute perturbation provenant des alimentations additionnelles, de petits dispositifs sont ajoutés à chacune des deux sorties des portes, soit une diode Schottky<sup>11</sup> et une résistance (voir encadrés de la figure 1.8). Dans ce cas, les tensions  $V1$  et  $V2$  seraient amenées à prendre la même tension que  $Vcc$ .

Figure 1.8 Porte OU modifiée pour le test de débalancement (tirée de Anderson, 1988)

11. La diode Schottky possède une capacité parasite plus faible qu'une jonction PN normale. Ceci permet ainsi de diminuer les pertes de performance qu'apporte l'inclusion du circuit de test.

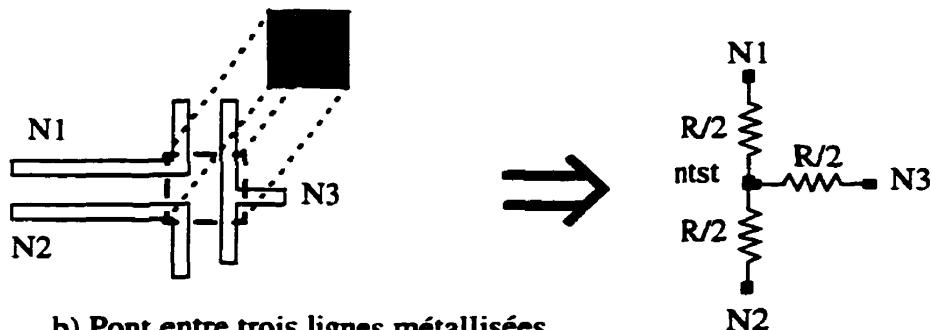

Patenaude ([14], 1998) a développé une combinaison de techniques pour la détection de pannes de marges de bruit réduites. Sachant que les portes CML ont un gain supérieur à l'unité, une panne de marge de bruit réduite peut être cachée par les portes recevant le signal en panne. La première technique part du principe que le courant de polarisation d'une porte CML influence son gain. En abaissant ce courant, il devient possible de réduire le gain de la porte. La technique consiste donc à utiliser en mode test un courant de polarisation qui donne un gain très près de l'unité. Ainsi, les portes sans pannes peuvent très bien propager des signaux sans perte de fonctionnalité, mais le signal anormalement petit d'une porte ayant une panne de marge de bruit réduite sera propagé vers les sorties en conservant une amplitude réduite. Ceci permet alors d'observer la panne. Néanmoins, l'auteur rencontre une difficulté à ajuster le gain avec grande précision, puisqu'il doit passer par la tension de polarisation du transistor qui agit comme source de courant. De plus, il a dû composer avec une grande variété de portes dont les gains changent sensiblement de l'une à l'autre. Ainsi, avec une tension de test fixe, il n'a pas pu obtenir un gain unitaire pour toutes les portes. Pour palier au problème, il s'agit de trouver une tension moyenne pour que toutes les portes aient approximativement un gain unitaire pour ensuite compenser la perte en ajoutant des détecteurs de marge de bruit réduite à intervalles réguliers à travers le circuit. Ce deuxième élément de test permet de détecter toute amplitude différentielle de moins de 70 mV aux sorties d'une porte, peu importe l'état logique et hors des périodes de transition. La figure 1.9 présente ce détecteur. Le condensateur du détecteur permet

d'ignorer l'amplitude différentielle pendant les transitions puisqu'elles sont trop courtes. Sa fréquence de coupure a été choisie pour assurer une bonne discrimination, et donc, les meilleurs résultats sont obtenus à des fréquences d'application de vecteurs de test aux alentours de quelques MHz.

Figure 1.9 Détecteur de marge de bruit réduite (tirée de Patenaude, 1998)

### 1.7 Conclusion

Nous avons présenté dans ce chapitre une base pour comprendre les concepts de l'architecture CML. De plus, nous avons couvert les défauts possibles qui peuvent se glisser dans un procédé bipolaire, ainsi que les pannes qui peuvent en découler dans les circuits CML. Aussi, nous avons présenté quelques méthodes de test existantes permettant de détecter ces pannes.

Au prochain chapitre, il sera question d'un outil permettant de quantifier la distribution des pannes lorsqu'on considère une liste exhaustive de défectuosités probables. De plus, quelques résultats prometteurs pour orienter le développement de méthodes de test sont présentés.

## CHAPITRE II

### OUTIL DE CARACTÉRISATION AUTOMATIQUE DE PANNES

#### 2.1 Introduction

L'outil de caractérisation automatique de pannes (OCAP) a été développé pour caractériser le comportement des cellules de la bibliothèque VersArray25 lorsqu'elles sont défectueuses. Combiné à l'outil Inductive Fault Analysis (IFA) développé par Patenaude ([14], 1998), l'OCAP donne à l'utilisateur la possibilité de configurer plusieurs aspects de l'analyse d'une cellule. Par souci de flexibilité, la majorité des fonctions de l'outil sont reconfigurables, donnant à l'utilisateur la possibilité d'ajuster les paramètres de caractérisation. De plus, pour simplifier le travail de l'utilisateur, toute configuration se fait par de simples fichiers textes.

Ainsi, pour configurer l'environnement de test, il est possible de définir pour chaque cellule, ses terminaux, ses connexions aux alimentations à de quelconques valeurs, les stimuli de test, le circuit de source de polarisation ainsi que le type de portes tampons à utiliser pour simuler l'environnement. De plus, un circuit personnel peut être attaché à la cellule sous évaluation (CSE) pour augmenter sa fonctionnalité (par exemple, un circuit intégré au CSE qui permet d'améliorer sa testabilité).

Avec l'environnement de test défini, l'outil peut caractériser les cellules en présence de différentes défectuosités et analyser les résultats après simulations. Tout comme l'environnement, l'analyse des simulations est aussi configurable. Si de nouveaux outils d'analyse sont nécessaires, un brin de programmation est requis, mais l'engin de l'OCAP reste indemne. Cette combine est possible grâce à l'édition de liens dynamique. Pendant l'exécution de l'engin de l'outil, celui-ci peut éditer les liens d'une bibliothèque et exécuter des fonctions d'analyse de cette bibliothèque en suivant un protocole bien défini. À travers la configuration des analyses, l'utilisateur peut choisir les bibliothèques d'analyse à utiliser et les tests à appliquer pour identifier les pannes. Grâce à cette flexibilité, l'utilisateur peut intégrer un circuit de test à sa cellule, créer une bibliothèque de fonctions pour analyser les sorties du circuit de test et en évaluer l'efficacité.

De plus, après la caractérisation complète d'une cellule, l'OCAP présente une analyse statistique sous forme de tableau des couvertures de défectuosités d'après les types de pannes. En utilisant une version améliorée de l'analyseur statistique, l'utilisateur peut obtenir des couvertures plus précises qui considèrent les fréquences de chaque défectuosité. De plus, comme les types de pannes ne sont pas orthogonaux, la version améliorée permet de les combiner pour créer des super-types et ensuite évaluer leur couverture de défectuosités.

## 2.2 Engin de l'outil et principes de base

Comme mentionné précédemment, cet outil a été conçu pour automatiser la caractérisation par simulation de cellules soumises à des défectuosités. Pour simuler un environnement normal, chaque cellule est insérée dans un banc de test stimulé par des vecteurs définis par l'utilisateur. Après chaque simulation, un ensemble de mesures est effectué pour évaluer le comportement de la cellule défectueuse. Notons que pour chaque cellule, une version sans défectuosité du banc de test est simulée et son comportement est enregistré. Ces données sont conservées pour ensuite servir de référence lors de l'analyse de la cellule lorsqu'en présence d'une défectuosité.

### 2.2.1 Configuration des cellules

Pour faciliter l'analyse des différents types de cellules à étudier, l'OCAP permet à l'utilisateur de décrire ses caractéristiques, son environnement de simulation ainsi que les types d'analyse à lui appliquer.

Les caractéristiques possibles sont les noms des terminaux de la cellule ainsi que les tensions d'alimentation et la source de tension de polarisation qu'il faut lui appliquer. Les terminaux sont séparés par catégories, qu'ils soient d'entrée, de sortie, d'alimentation, de test ou de tout autre type qui puisse être d'intérêt. Quant aux

tensions d'alimentation, il s'agit d'associer aux terminaux qui ont besoin d'alimentations stables, les valeurs de tension<sup>1</sup> à appliquer. Pour la source de tension de polarisation, contrairement aux alimentations stables idéales, il a été préféré d'incorporer dans le banc de test le circuit choisi par l'utilisateur qui va produire cette tension. En effet, la tension étant appliquée à la base du transistor de source, une petite variation de tension due à une charge supplémentaire aura un effet significatif sur le courant et donc sur le comportement de la cellule. Par conséquent, c'est un phénomène qui doit être intégré dans le banc de test pour reproduire correctement un vrai circuit. D'ailleurs, ayant un circuit de génération de tension adapté aux cellules, il serait inapproprié de ne pas l'utiliser. Il faut mentionner que le circuit de la source de tension de polarisation possède aussi des caractéristiques à configurer et pour cela, il faut le définir comme une cellule indépendante.

Pour définir l'environnement d'analyse de la cellule, il existe 3 éléments configurables. Il y a la définition de la cellule tampon à utiliser pour reproduire les caractéristiques électriques normales des signaux, les stimuli à appliquer au banc de test pour évaluer le comportement de la cellule et le circuit à attacher à la cellule. Le choix de la cellule tampon à utiliser pour reproduire l'environnement de test repose dans les mains de l'utilisateur. Ceci permet de tenir compte des différents grades de vitesse de la bibliothèque de cellules VersArray25 de Nortel ainsi que des ajouts d'éléments

---

1. Les tensions sont obtenues par des sources de tension idéales.

spéciaux pour toutes les cellules de certains bancs de test. De plus, l'OCAP permet de choisir le nombre de portes tampons à utiliser avant et après la CSE <sup>2</sup>. Quant aux stimuli, l'utilisateur doit premièrement créer des circuits de génération de vecteurs de test à l'aide de sources de tensions génériques. Puis, dans la configuration de chaque cellule, il fait référence au circuit de stimuli approprié. Le côté générique permet de réutiliser un même circuit de stimuli par des cellules de différents grades de vitesse. En effet, l'outil permet de changer l'échelle de temps des signaux selon les demandes de l'utilisateur pour les adapter aux différentes cellules. Enfin, pour le circuit attaché, il s'agit simplement d'indiquer où se trouve son fichier et quels sont les signaux auxquels il doit s'attacher.

Pour définir les types d'analyse des résultats de simulation, il suffit de mentionner les noms des bibliothèques de fonctions d'analyse à utiliser, ainsi que les noms des tests d'évaluation de pannes de chacune de ces bibliothèques à appliquer. La section 2.2.4 décrit en plus de détails le fonctionnement de ces fonctions d'analyse.

### **2.2.2 Défectuosités couvertes et méthode d'injection**

L'engin de l'outil traite 4 genres de défectuosités qui peuvent être injectées à l'intérieur d'une cellule. Il traite des courts-circuits, des perçages de transistors, des ponts et des

---

2. Voir section 2.2.3 pour l'utilisation de ses portes tampons.

circuits ouverts. Il est à mentionner que pour chaque genre de défectuosités, une approche différente est prise pour l'injecter.

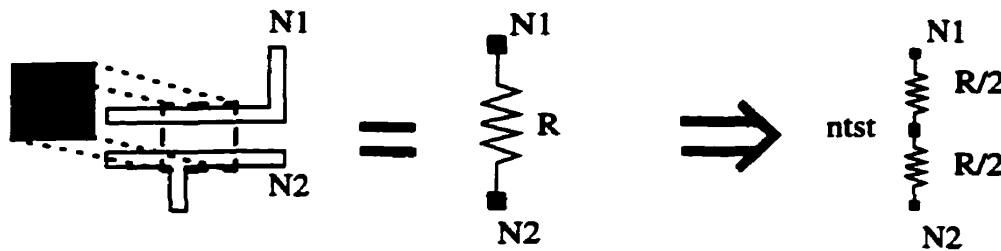

Pour l'injection d'un court-circuit, d'un perçage ou d'un pont, des résistances de valeurs modifiables sont insérées aux noeuds impliqués dans le listage de type SPICE de la cellule. Pour une même défectuosité des trois genres sus-mentionnés, l'OCAP permet d'appliquer différentes valeurs de résistances, suivant une liste de valeurs définies par l'utilisateur. Ainsi, il devient possible de couvrir différentes intensités d'un même genre de défectuosité.