**Titre:** Une enveloppe pour la norme P1500 incorporant des structures de test intégré pour les systèmes sur puces

Title: test intégré pour les systèmes sur puces

**Auteur:** Abdelaziz Larab

Author:

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Larab, A. (2006). Une enveloppe pour la norme P1500 incorporant des structures de test intégré pour les systèmes sur puces [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/8515/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8515/>

PolyPublie URL:

**Directeurs de recherche:** Abdelhakim Khouas

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

UNE ENVELOPPE POUR LA NORME P1500 INCORPORANT DES

STRUCTURES DE TEST INTÉGRÉ POUR LES SYSTÈMES SUR

PUCES

ABDELAZIZ LARAB

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU

DIPLÔME DE MAÎTRISE EN SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUILLET 2006

Library and

Archives Canada

Bibliothèque et

Archives Canada

Published Heritage

Branch

Direction du

Patrimoine de l'édition

395 Wellington Street

Ottawa ON K1A 0N4

Canada

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-19310-5

*Our file* *Notre référence*

ISBN: 978-0-494-19310-5

**NOTICE:**

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

**AVIS:**

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

**Canada**

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire est intitulé :

UNE ENVELOPPE POUR LA NORME P1500 INCORPORANT DES

STRUCTURES DE TEST INTÉGRÉ POUR LES SYSTÈMES SUR

PUCES

Présenté par : LARAB Abdelaziz

En vue de l'obtention du diplôme : Maîtrise ès sciences appliquées

A été dûment accepté par le jury d'examen constitué de :

M. SAVARIA Yvon, Ph. D., président

M. BOIS Guy, Ph. D., membre

M. KHOUAS Abdelhakim, Ph. D., membre et directeur de recherche

## DÉDICACE

À la mémoire de mon père Mohamed Saïd et mon beau-père Saleh.

À ma mère et ma belle-mère.

À ma femme et mes enfants.

À toute ma famille et ma belle-famille.

## REMERCIEMENTS

J'aimerai remercier d'abord, Monsieur Abdelhakim Khouas, qui m'a accueilli au sein de son équipe de recherche au département de génie électrique de l'école Polytechnique de Montréal et qui m'a fait bénéficier de ses compétences scientifiques, ses qualités humaines et sa constante disponibilité. Je tiens particulièrement à lui exprimer ici ma profonde et amicale reconnaissance pour m'avoir soutenu financièrement. J'ai été très touché par la confiance qu'il m'a témoignée tout au long de mon travail.

Je tiens à exprimer mes plus sincères remerciements à Monsieur Yvon Savaria, Directeur du Groupe de Recherche en Microélectronique (GRM) de l'école Polytechnique de Montréal, qui me fait l'honneur de juger ce travail et d'en être le président du jury. J'adresse également mes remerciements à Monsieur Guy Bois, Professeur au département génie informatique et membre du GRM, pour avoir accepté de juger ce travail et d'en être membre du jury.

Je tiens à exprimer ma reconnaissance à ma femme et à mes enfants, pour leur patience inconditionnelle face à mon humeur ponctuée des hauts et bas durant ces années d'études. Je remercie également mes parents et tous mes proches qui m'ont encouragé tout au long de mes études.

Finalement, mes remerciements vont à Ghyslaine Ethier-Carrier pour son aide et à l'ensemble du personnel de soutien administratif et informatique du GRM qui n'ont aménagé aucun effort pour rendre agréable notre passage au sein du groupe.

## RÉSUMÉ

Les systèmes sur puces « Systems On Chip » (SOC) deviennent de plus en plus complexes et leurs tests difficiles à réaliser. Ces dernières années, plusieurs architectures de test ont été proposées pour ces systèmes afin de leur garantir une bonne qualité de test avec un coût raisonnable. Mais, ces architectures engendrent une augmentation de la surface des SOC ainsi qu'une importante dégradation des délais internes de propagation.

L'objectif principal de ce travail est de réduire la surface additionnelle engendrée par l'insertion des architectures de test dans les SOC. C'est pourquoi, nous avons proposé une nouvelle architecture de test pour les modules des SOC et pour les interconnexions entre ces modules. Cette nouvelle architecture est une interface matérielle dans laquelle, les modules du SOC sont encapsulés. En mode normal, l'interface devient transparente pour permettre le fonctionnement normal des modules. En mode test, l'interface est configurable en registre à décalage et en structure du test intégré pour réaliser le test des modules et des interconnexions à partir de l'extérieur et à l'interne du SOC. Le registre à décalage sert à transférer les données de test à appliquer aux entrées des modules et aux interconnexions à partir d'équipements de test externes aux SOC. Ce registre est également utilisé pour l'acheminement des réponses de test vers les testeurs externes pour analyse. La structure du test intégré sert à générer les données de test à appliquer aux entrées des modules et aux interconnexions ainsi que l'analyse des réponses de test à l'interne du SOC.

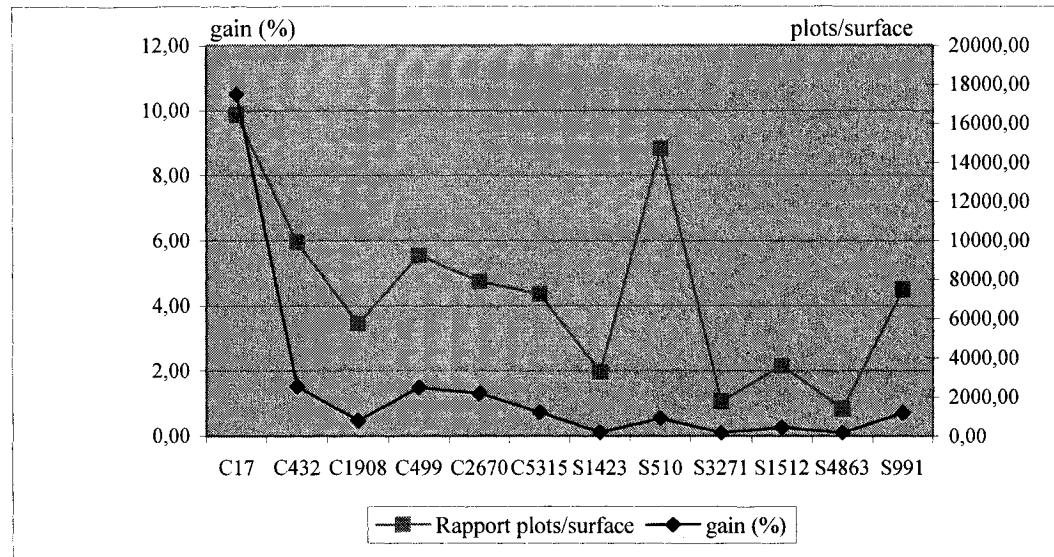

Les résultats de validation de l'architecture de test proposée ont été obtenus par simulation sur des circuits d'essai. Ces résultats ont montré que l'architecture de test proposée permet une réduction de la surface du semi-conducteur. Cette réduction peut dépasser les 9% avec les circuits qui présentent un rapport plots/surface initiale élevé.

## ABSTRACT

Systems On Chip (SOC) are getting more complex and their tests become difficult to perform. During the last few years, several test architectures were suggested to these systems to guarantee higher levels of test quality and reduce the costs. The principal disadvantages of these architectures are the area overhead and the internal delay degradations.

The main objective of this work is to reduce the overhead area caused by the test architectures insertion. Therefore, we suggest a new architecture that can be used to test SOC modules and the interconnections between the modules. This architecture is a wrapper in which SOC modules can be encapsulated. In normal mode, this wrapper becomes transparent to allow a normal operation of the modules. In test mode, the wrapper can be configured as a shift register and as an integrated test structure. The shift register is used to transfer test data to be applied to the input signals of modules and to interconnects from external test equipments. This shift register is also used to transport test responses to external test equipments for analysis. The integrated test structure is used to generate and apply test data to the input signals of the modules and to the interconnects, and also to analyze the responses in side SOC. The validation results of the new test architecture are obtained by simulation using benchmarks circuits.

These results show that with the proposed test architecture the area overhead reduction can exceed 9% when the circuits have a higher ratio pins/initial area.

# TABLE DES MATIÉRES

|                                                       |       |

|-------------------------------------------------------|-------|

| DÉDICACE.....                                         | IV    |

| REMERCIEMENTS.....                                    | V     |

| RÉSUMÉ.....                                           | VI    |

| ABSTRACT.....                                         | VIII  |

| TABLE DES MATIÉRES .....                              | X     |

| LISTE DES FIGURES.....                                | XV    |

| LISTE DES TABLEAUX.....                               | XVIII |

| LISTE DES SIGLES ET ABRÉVIATIONS .....                | XIX   |

| INTRODUCTION GÉNÉRALE .....                           | 1     |

| I.1 Motivation.....                                   | 1     |

| I.2 Organisation du mémoire.....                      | 5     |

| CHAPITRE 1 CONCEPTS DE BASE.....                      | 7     |

| 1.1 Introduction.....                                 | 7     |

| 1.2 Système sur puce et les modules IP .....          | 7     |

| 1.3 Structure de test du module IP .....              | 10    |

| 1.4 Génération de vecteurs de test pour les SOC ..... | 12    |

| 1.4.1 Génération déterministe .....                   | 12    |

|                                                       |                                                                          |    |

|-------------------------------------------------------|--------------------------------------------------------------------------|----|

| 1.4.2                                                 | Génération pseudo-aléatoire.....                                         | 13 |

| 1.5                                                   | Conception en vue de test .....                                          | 14 |

| 1.6                                                   | Test intégré (BIST) .....                                                | 16 |

| 1.6.1                                                 | Architecture BIST .....                                                  | 17 |

| 1.6.1.1                                               | Générateur de vecteurs de test .....                                     | 17 |

| 1.6.1.2                                               | Analyseur des réponses .....                                             | 19 |

| 1.7                                                   | Norme IEEE P1500.....                                                    | 20 |

| 1.7.1                                                 | Enveloppe P1500 .....                                                    | 21 |

| 1.7.2                                                 | Langage de test « Core Test Language » (CTL).....                        | 23 |

| 1.8                                                   | Conclusion .....                                                         | 23 |

| CHAPITRE 2 REVUE DES TECHNIQUES DE TEST DES SOC ..... |                                                                          | 24 |

| 2.1                                                   | Introduction.....                                                        | 24 |

| 2.2                                                   | Architectures de test des modules IP .....                               | 24 |

| 2.2.1                                                 | Architectures du test externe pour les modules IP .....                  | 25 |

| 2.2.2                                                 | Architectures de test intégré pour les modules IP .....                  | 27 |

| 2.2.2.1                                               | Conversion des vecteurs de test aléatoires en vecteurs déterministes ... | 28 |

| 2.2.2.2                                               | BIST associé aux chaînes de balayage de l'IP .....                       | 29 |

| 2.2.2.3                                               | Conversion des vecteurs de test déterministes en vecteurs aléatoires ... | 30 |

| 2.3                                                   | Architectures de test des interconnexions entre les modules IP .....     | 31 |

| 2.4                                                   | Conclusion .....                                                         | 34 |

| CHAPITRE 3 ARCHITECTURE DE TEST PROPOSÉE .....        |                                                                          | 35 |

|         |                                                                   |    |

|---------|-------------------------------------------------------------------|----|

| 3.1     | Introduction .....                                                | 35 |

| 3.2     | Présentation de la nouvelle architecture de test .....            | 36 |

| 3.3     | Architecture de la nouvelle enveloppe .....                       | 37 |

| 3.4     | Cellules de l'enveloppe .....                                     | 39 |

| 3.4.1   | Cellule à deux états de l'enveloppe.....                          | 41 |

| 3.4.2   | Modes de fonctionnement de WBC .....                              | 43 |

| 3.4.3   | Cellule à trois états de l'enveloppe .....                        | 45 |

| 3.4.4   | Cellule bidirectionnelle de l'enveloppe .....                     | 47 |

| 3.4.5   | Autres variantes des cellules de l'enveloppe .....                | 48 |

| 3.5     | Registres de l'enveloppe .....                                    | 49 |

| 3.5.1   | Registre d'instruction WIR .....                                  | 49 |

| 3.5.2   | Registre de données WBR .....                                     | 52 |

| 3.5.3   | Registre de données WBY .....                                     | 54 |

| 3.6     | Contrôleur de test .....                                          | 55 |

| 3.7     | Instructions de test implémentées par la nouvelle enveloppe ..... | 57 |

| 3.7.1   | Instructions de test sans fonctionnalité BIST .....               | 58 |

| 3.7.1.1 | Instruction WBYPASS .....                                         | 59 |

| 3.7.1.2 | Instruction WEXTESTS .....                                        | 60 |

| 3.7.1.3 | Instruction WCORETESTS .....                                      | 61 |

| 3.7.1.4 | Instruction WPRELOADS.....                                        | 62 |

| 3.7.1.5 | Instruction WCLAMP.....                                           | 64 |

| 3.7.2   | Instructions de test avec fonctionnalité BIST .....               | 65 |

|                                              |                                                                   |    |

|----------------------------------------------|-------------------------------------------------------------------|----|

| 3.7.2.1                                      | Instruction WEXBIST .....                                         | 65 |

| 3.7.2.2                                      | Instruction WCOREBIST .....                                       | 67 |

| 3.7.2.3                                      | Instruction de test WOPMISR .....                                 | 68 |

| 3.8                                          | Conclusion .....                                                  | 70 |

| CHAPITRE 4 IMPLÉMENTATION ET RÉSULTATS ..... |                                                                   | 71 |

| 4.1                                          | Introduction .....                                                | 71 |

| 4.2                                          | Insertion de l'architecture de test .....                         | 72 |

| 4.3                                          | Simulation fonctionnelle de l'architecture de test proposée ..... | 73 |

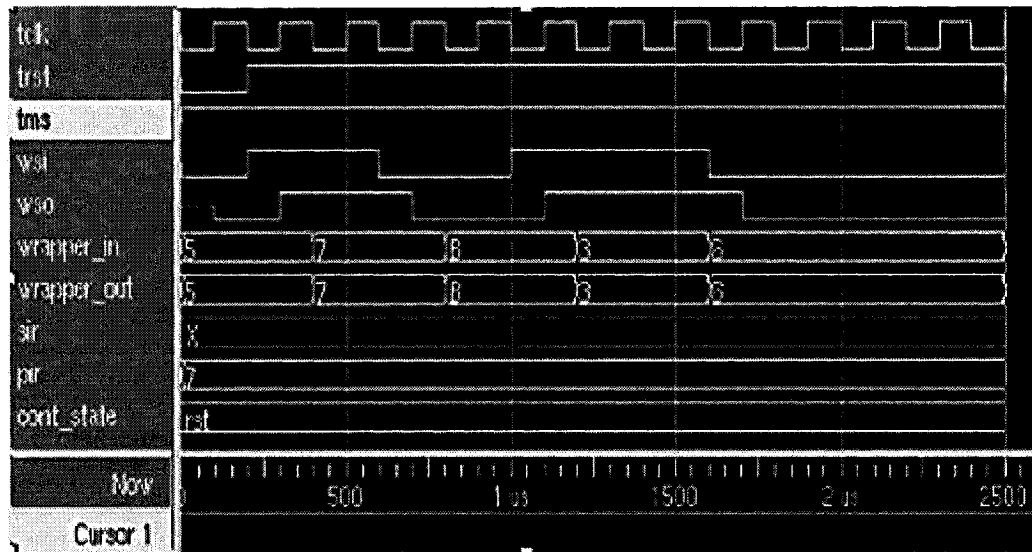

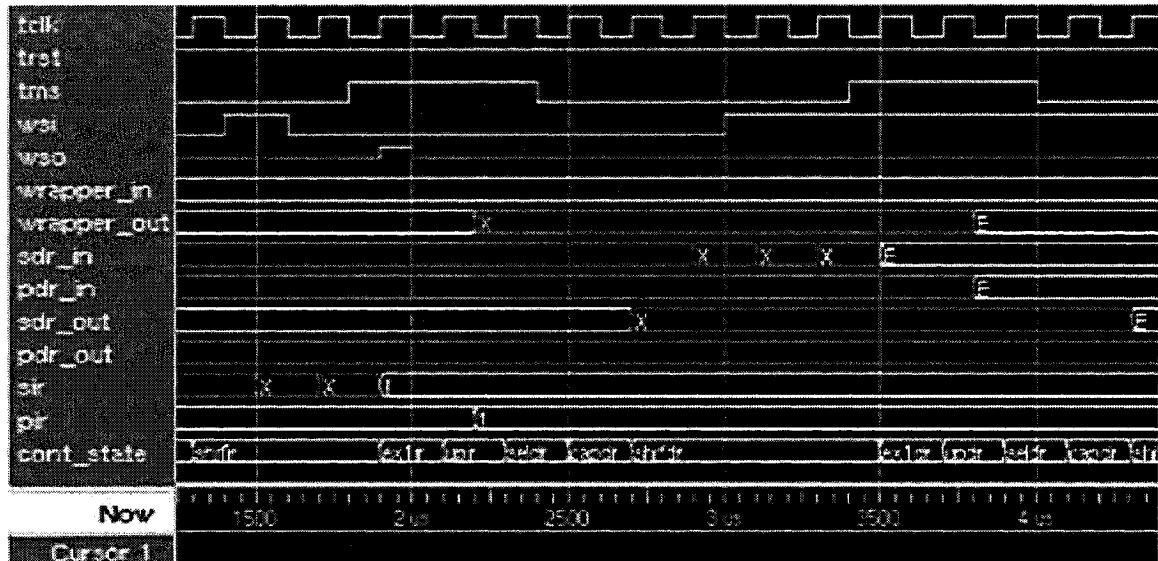

| 4.4                                          | Chronogrammes des instructions de test sans BIST .....            | 74 |

| 4.4.1                                        | Instruction de test WBAYPASS .....                                | 75 |

| 4.4.2                                        | Instruction de test WEXTESTS .....                                | 76 |

| 4.4.3                                        | Instruction de test WCORETESTS .....                              | 77 |

| 4.4.4                                        | Instruction de test WPRELOADS .....                               | 78 |

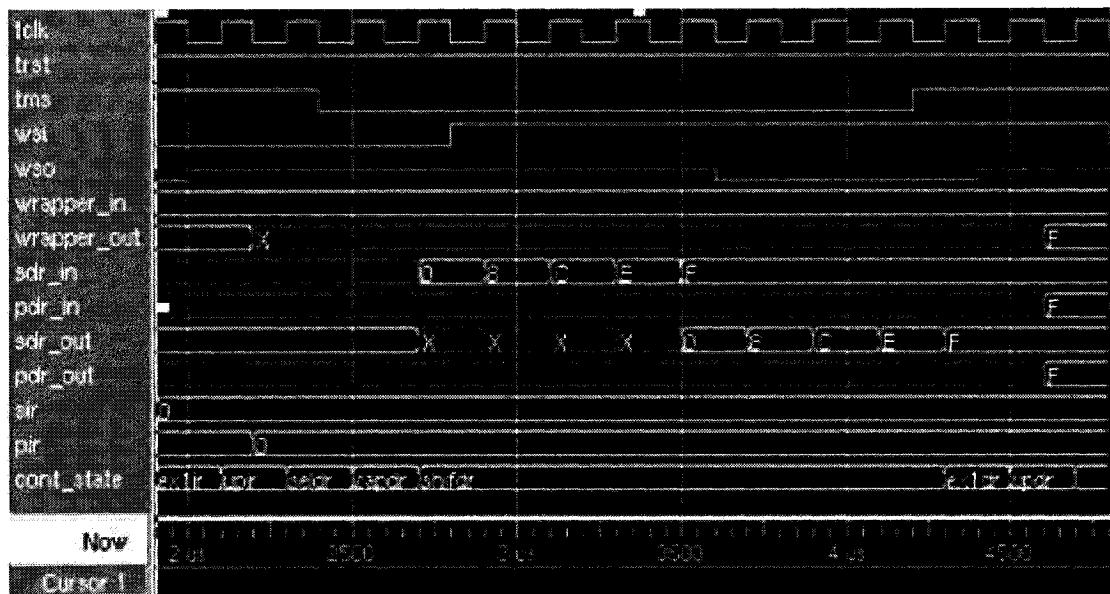

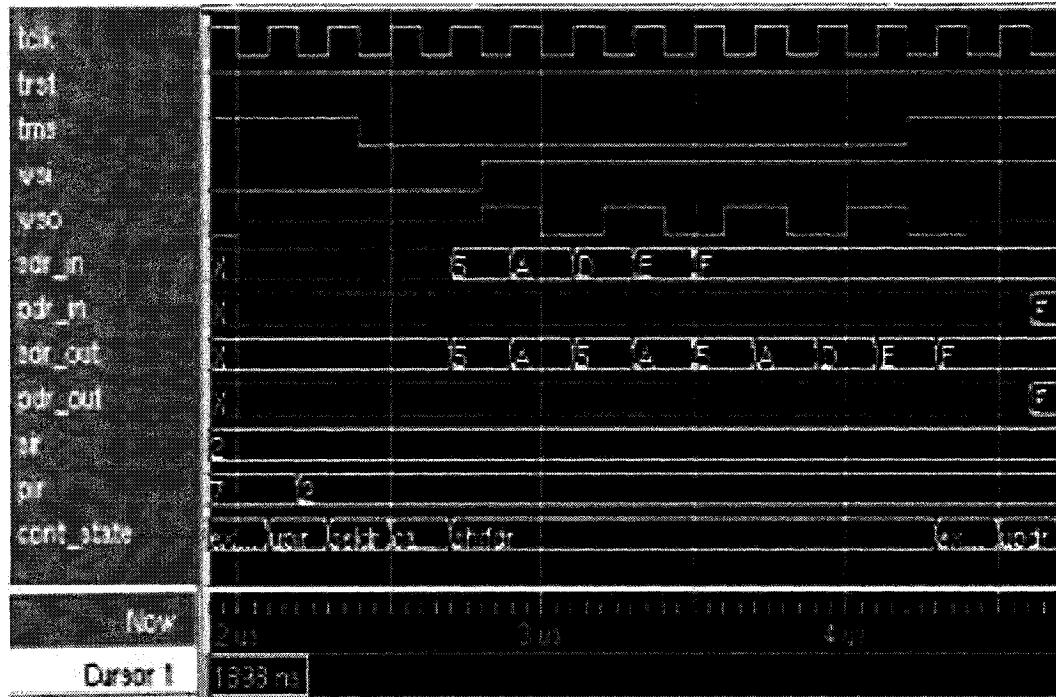

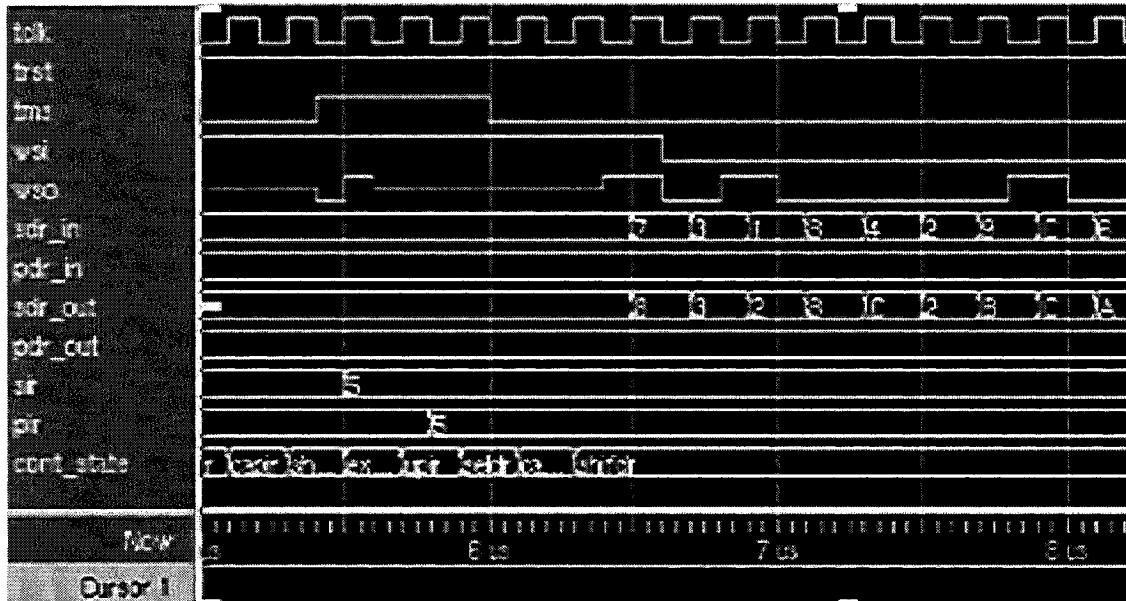

| 4.5                                          | Chronogrammes des instructions de test avec BIST .....            | 79 |

| 4.5.1                                        | Instruction de test WEXBIST .....                                 | 79 |

| 4.5.2                                        | Instruction de test WCOREBIST .....                               | 82 |

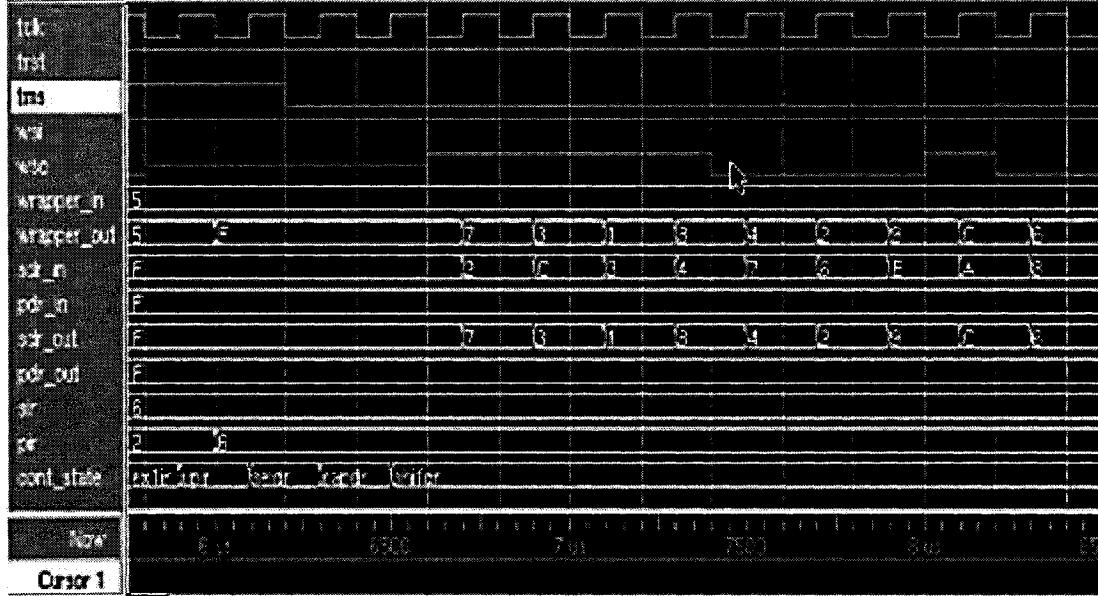

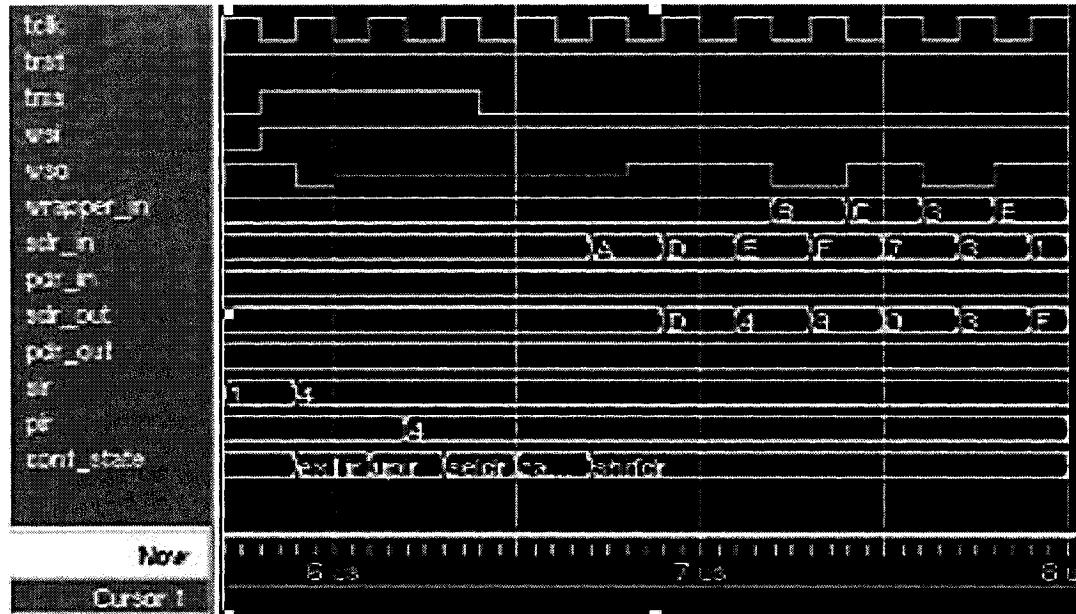

| 4.5.3                                        | Instruction de test WOPMISR .....                                 | 83 |

| 4.6                                          | Délais de propagation .....                                       | 85 |

| 4.7                                          | Estimation du gain en surface .....                               | 86 |

| 4.7.1                                        | Présentation des circuits d'essai .....                           | 87 |

| 4.7.2                                        | Résultats du gain en surface .....                                | 88 |

| 4.8                                          | Réduction du nombre de vecteurs de test déterministes .....       | 90 |

|                                                 |     |

|-------------------------------------------------|-----|

| 4.9      Conclusion .....                       | 92  |

| CHAPITRE 5   CONCLUSION ET TRAVAUX FUTURS ..... | 93  |

| 5.1      Conclusion générale.....               | 93  |

| 5.2      Travaux futurs .....                   | 95  |

| RÉFÉRENCES.....                                 | 97  |

| ANNEXE.....                                     | 103 |

# LISTE DES FIGURES

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Figure 1.1: Modules IP qui peuvent composer un SOC .....                                          | 8  |

| Figure 1.2: Flot de conception du système sur puce [44] .....                                     | 9  |

| Figure 1.3: Structure de test pour un IP du SOC [41].....                                         | 10 |

| Figure 1.4: Circuit séquentiel (a) avant insertion chaîne de balayage, .....                      | 15 |

| Figure 1.5: Architecture du test intégré. ....                                                    | 17 |

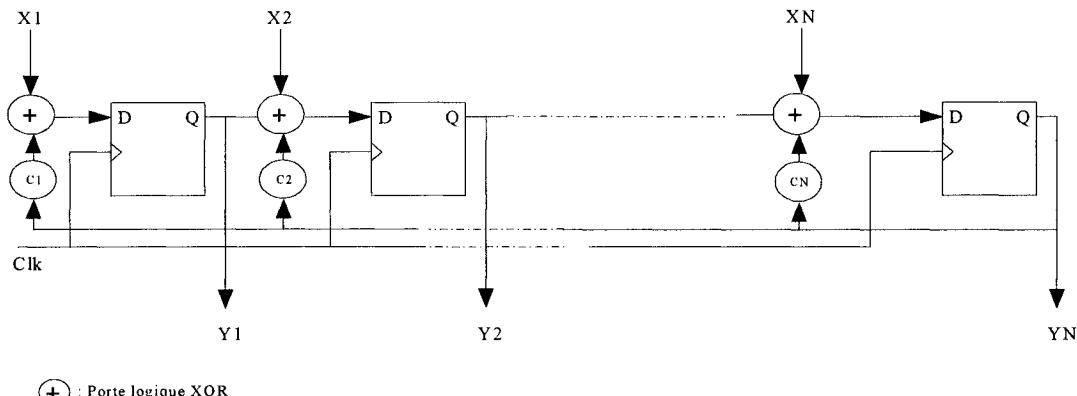

| Figure 1.6: Architecture d'un LFSR générique d'ordre N et à XOR externe.....                      | 18 |

| Figure 1.7: Analyseur de réponses de test.....                                                    | 19 |

| Figure 1.8: Architecture d'un MISR générique à XOR internes d'ordre N.....                        | 20 |

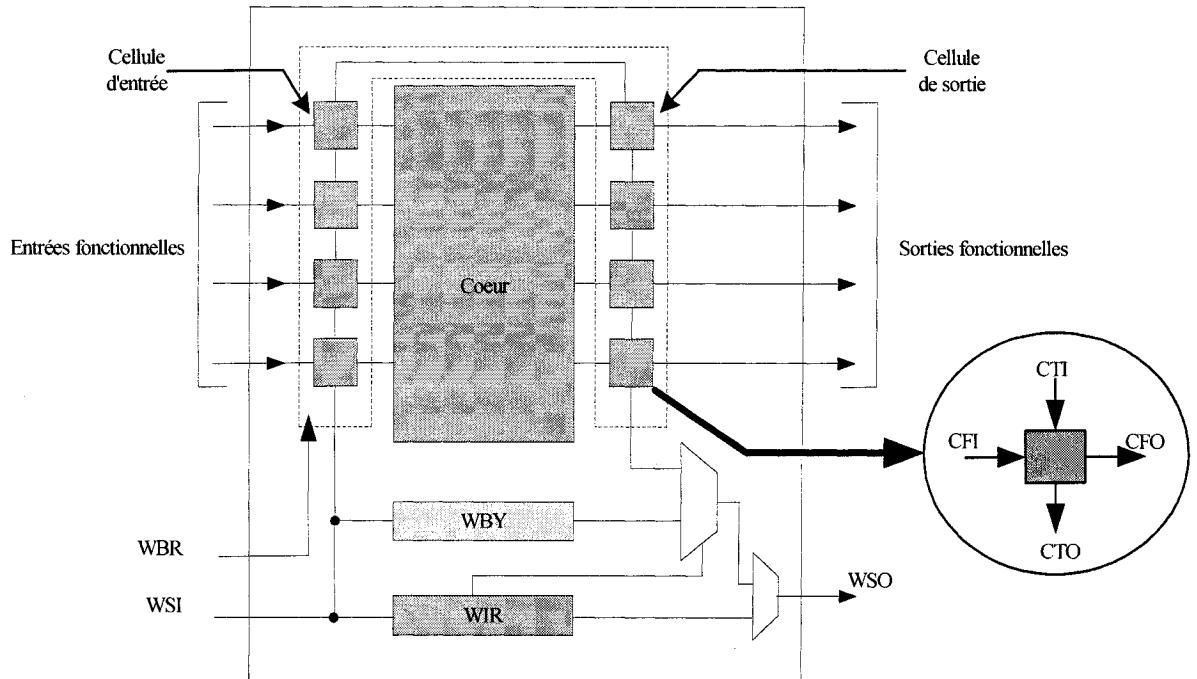

| Figure 1.9: Architecture de l'enveloppe IEEE P1500.....                                           | 21 |

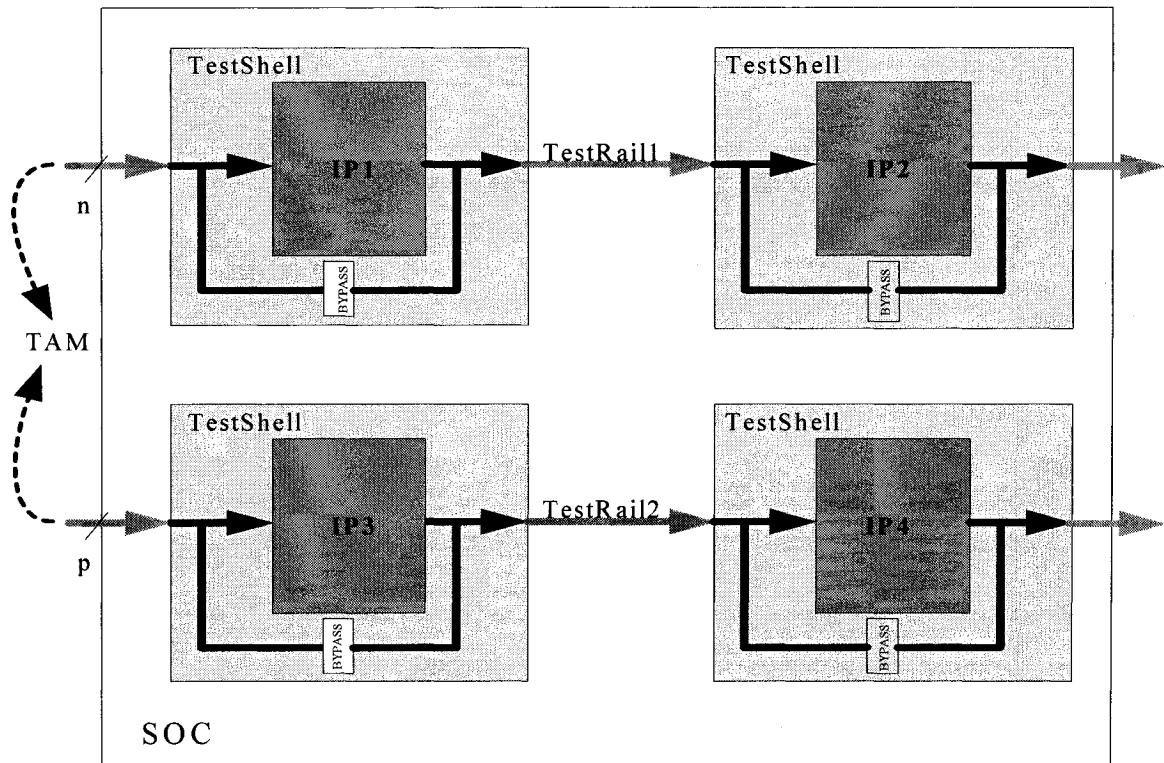

| Figure 2.1: Architecture du bus de test TestRail [31]. ....                                       | 25 |

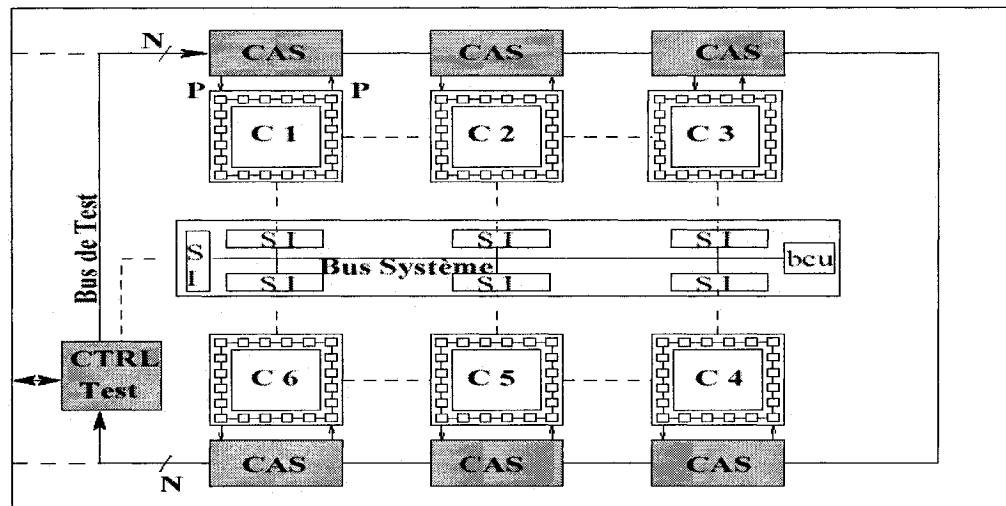

| Figure 2.2: Architecture de test Cas-Bus [7].....                                                 | 27 |

| Figure 2.3: Exemple de la logique de génération de séquence de test [25]. ....                    | 30 |

| Figure 2.4: Combinaison du BIST et du Boundary Scan pour le test des interconnexions<br>[5]. .... | 31 |

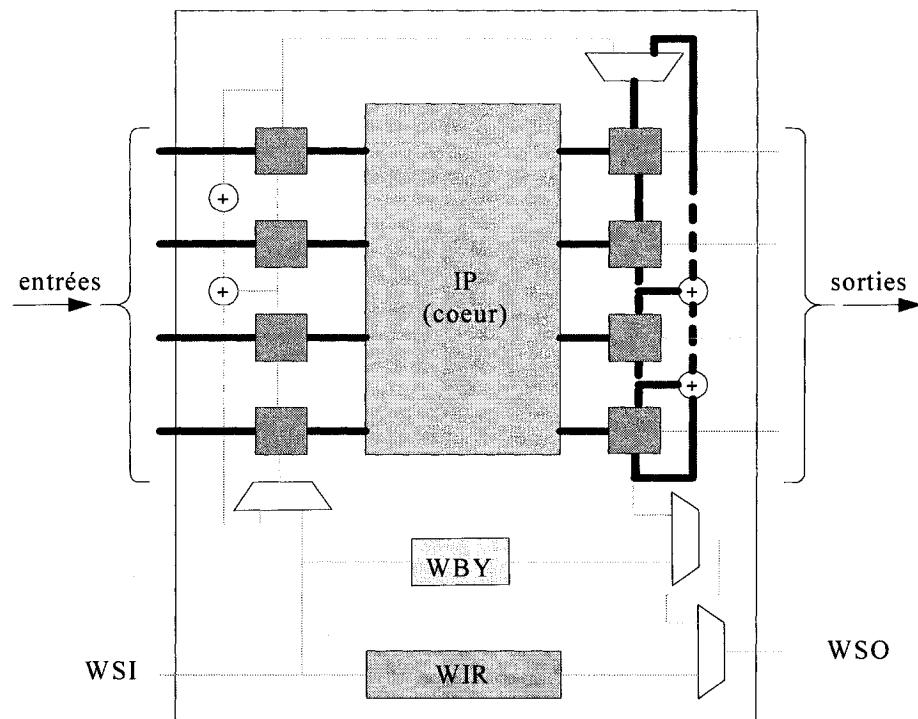

| Figure 3.1: Architecture de test proposée. ....                                                   | 36 |

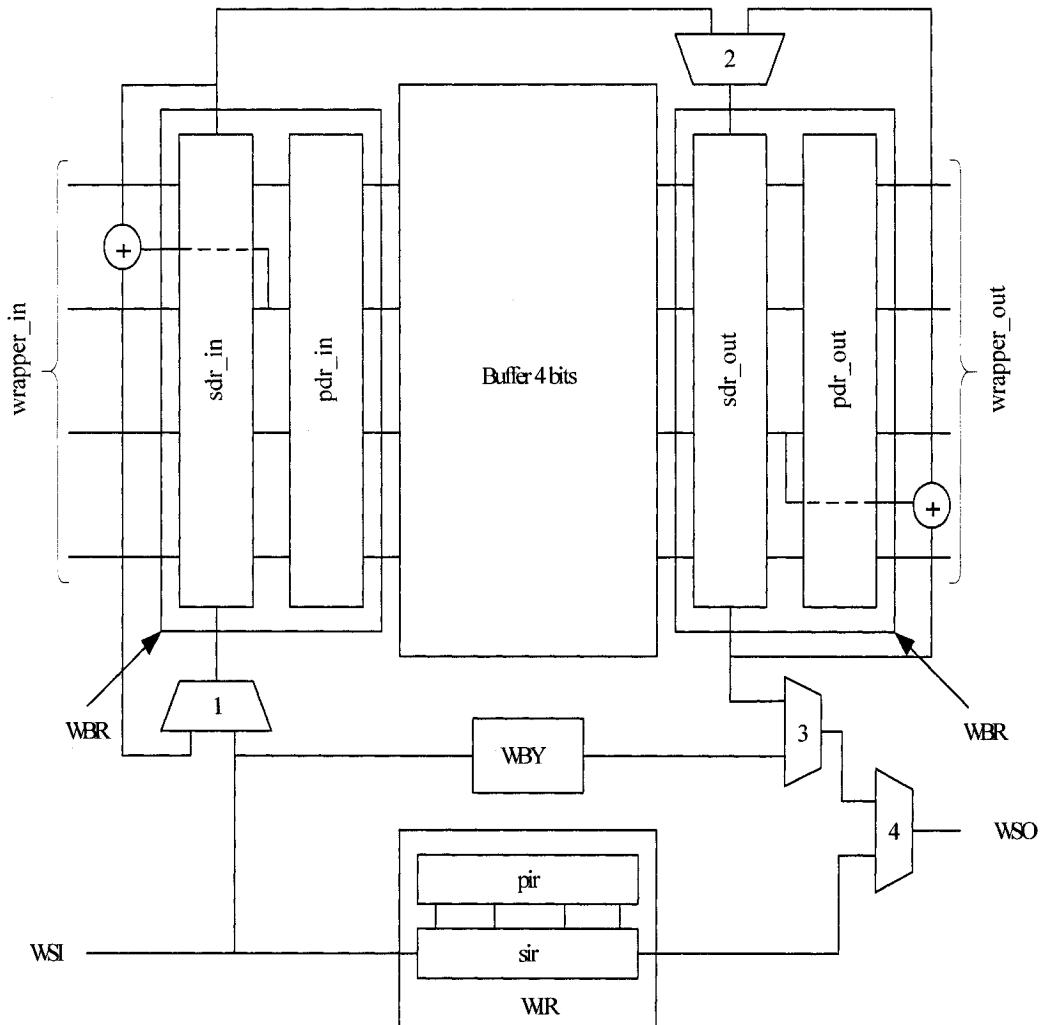

| Figure 3.2: Architecture de l'enveloppe proposée. ....                                            | 38 |

| Figure 3.3: Cellule à deux états WBC.....                                                         | 42 |

| Figure 3.4: Cellule de sortie à 3 états (WBOC3) . ....                                            | 45 |

| Figure 3.5: Cellule de contrôle de la sortie de la cellule WBC3.....                              | 46 |

| Figure 3.6: Cellule bidirectionnelle.....                                                         | 47 |

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

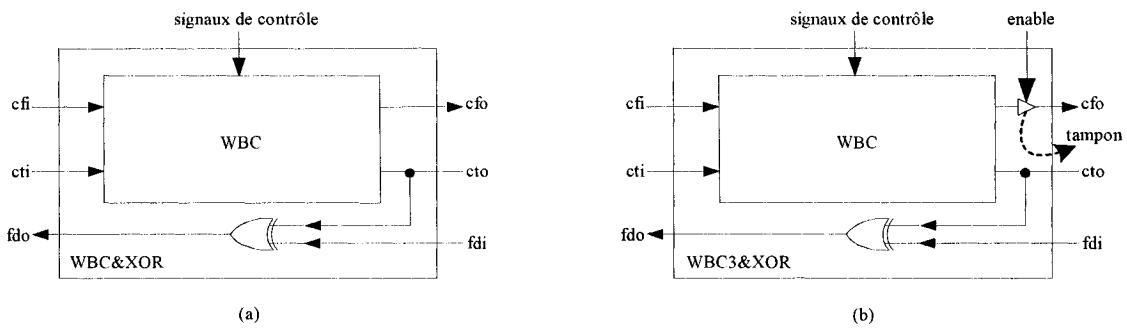

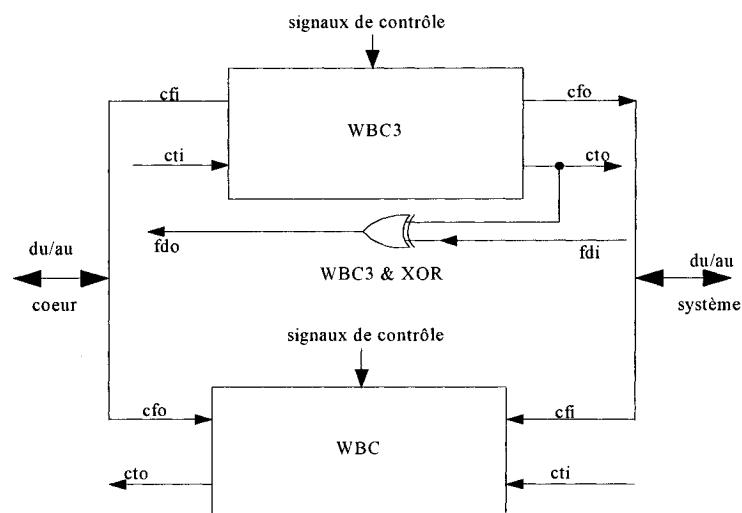

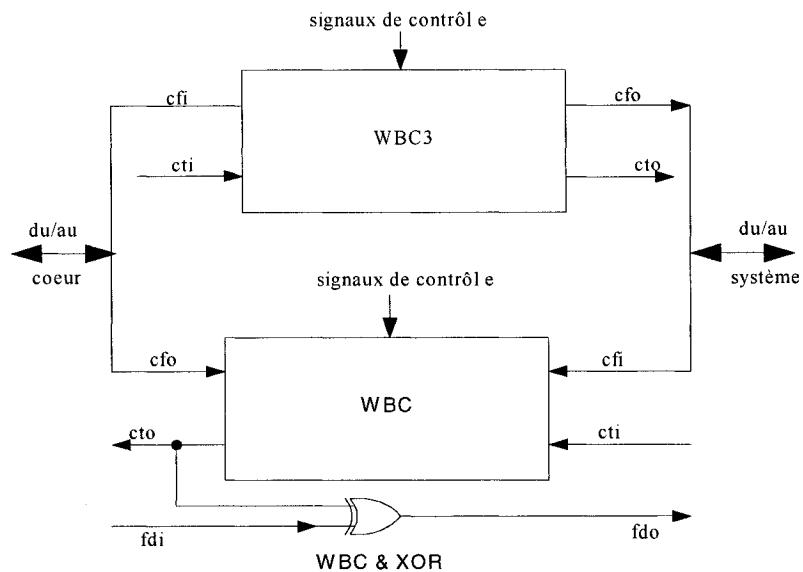

| Figure 3.7: Schéma synoptique des cellules : (a) WBC&XOR ; (b) WBC3&XOR.....        | 49 |

| Figure 3.8: Registre d'instruction WIR [19].....                                    | 51 |

| Figure 3.9: Registre à décalage WBR .....                                           | 52 |

| Figure 3.10: Architecture du registre de court-circuit [19].....                    | 55 |

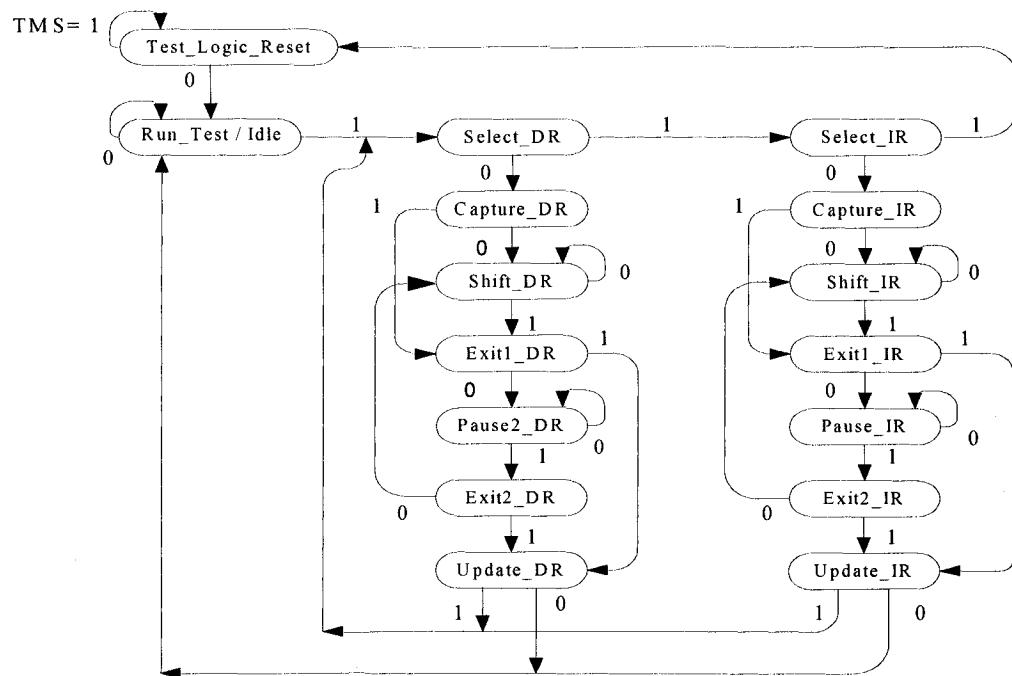

| Figure 3.11: Diagramme de transition du contrôleur TAP [19].....                    | 55 |

| Figure 3.12: Instruction WBYPASS.....                                               | 59 |

| Figure 3.13: Instruction WEXTESTS.....                                              | 60 |

| Figure 3.14: Instruction WCORETESTS.....                                            | 61 |

| Figure 3.15: Instruction WPRELOADS .....                                            | 63 |

| Figure 3.16: Instruction WCLAMP. ....                                               | 64 |

| Figure 3.17: Instruction WEXBIST. ....                                              | 66 |

| Figure 3.18: Instruction WCOREBIST.....                                             | 67 |

| Figure 3.19: Instruction WOPMISR. ....                                              | 68 |

| Figure 4.1: Tampon 4 bits encapsulé dans l'enveloppe de test proposée. ....         | 74 |

| Figure 4.2: Chronogramme de l'instruction de test WBYPASS.....                      | 75 |

| Figure 4.3: Chronogramme de l'instruction de test WEXTESTS.....                     | 76 |

| Figure 4.4: Chronogramme de l'instruction de test WCORETESTS.....                   | 77 |

| Figure 4.5: Chronogramme de l'instruction de test WPRELOADS.....                    | 78 |

| Figure 4.6: Chronogramme de l'instruction de test WEXBIST.....                      | 80 |

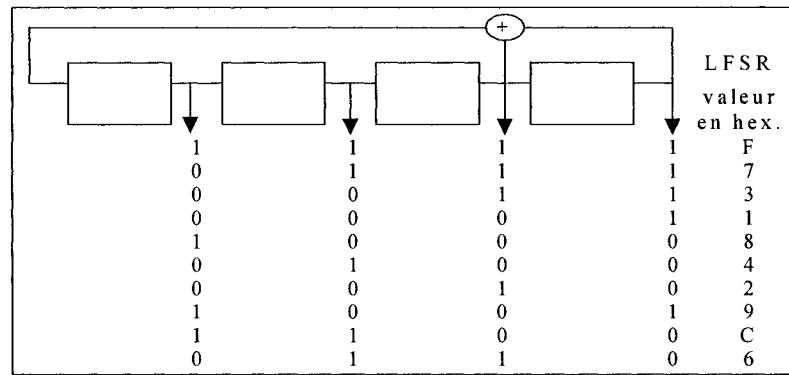

| Figure 4.7: Séquence complète générée par un LFSR d'ordre 4 et $P=1+x^3+x^4$ . .... | 81 |

| Figure 4.8: MISR à XOR externe initialisé à F.....                                  | 81 |

| Figure 4.9: Chronogramme de l'instruction de test WCOREBIST.....                    | 82 |

|                                                                                       |    |

|---------------------------------------------------------------------------------------|----|

| Figure 4.10: Génération des vecteurs de test et le compactage des réponses. ....      | 83 |

| Figure 4.11: Chronogramme de l'instruction de test WOPMISR. ....                      | 84 |

| Figure 4.12: Illustration de l'instruction de test WOPMISR. ....                      | 85 |

| Figure 4.13: Cellule du registre WBR: a) enveloppe proposée; b) enveloppe P1500. .... | 86 |

| Figure 4.14: Gain en surface versus le rapport (plots/surface) du circuit. ....       | 90 |

## LISTE DES TABLEAUX

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

| Tableau 3.1: Différents modes de configuration de WBC.....                                 | 43 |

| Tableau 3.2: Valeurs des signaux de contrôle pour les instructions de test.....            | 57 |

| Tableau 4.1: Circuits utilisés pour la validation de l'architecture de test proposée. .... | 88 |

| Tableau 4.2: Résultats du gain en surface. ....                                            | 89 |

| Tableau 4.3: Réduction du nombre de vecteurs de test déterministes. ....                   | 91 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|             |                                   |

|-------------|-----------------------------------|

| <b>ATE</b>  | Automated Test Equipment          |

| <b>ATPG</b> | Automated Test Patterns Generator |

| <b>BIST</b> | Built-In Self-Test                |

| <b>BSC</b>  | Boundary Scan Cell                |

| <b>bc</b>   | BIST cell                         |

| <b>CTL</b>  | Core Test Language                |

| <b>CAS</b>  | Core Access Switch                |

| <b>CST</b>  | Circuit Sous Test                 |

| <b>CI</b>   | Circuit Intégré                   |

| <b>cfi</b>  | Cell functional in                |

| <b>cfo</b>  | Cell functional out               |

| <b>cti</b>  | Cell test in                      |

| <b>cto</b>  | Cell test out                     |

| <b>DFT</b>  | Design For Testability            |

| <b>fdi</b>  | Feedback in                       |

| <b>fdo</b>  | Feedback out                      |

| <b>HDL</b>  | Hardware Description Language     |

| <b>IP</b>   | Intellectual Properties           |

| <b>LFSR</b> | Linear Feedback Shift Register    |

| <b>MISR</b> | Multi In Put Shift Register       |

|                |                                                                  |

|----------------|------------------------------------------------------------------|

| <b>OPMISR</b>  | On Product MISR                                                  |

| <b>PRPG</b>    | Pseudo Random Patterns Generator                                 |

| <b>PR</b>      | Parallel Register                                                |

| <b>pdr_in</b>  | Parallel data register in                                        |

| <b>pdr_out</b> | Parallel data register out                                       |

| <b>pir</b>     | Parallel instruction register                                    |

| <b>SIA</b>     | Semiconductor International Association                          |

| <b>SOC</b>     | System On Chip                                                   |

| <b>SOB</b>     | System On Board                                                  |

| <b>SR</b>      | Serial Register                                                  |

| <b>sdr_in</b>  | Serial data register in                                          |

| <b>sdr_out</b> | Serial data register out                                         |

| <b>sir</b>     | Serial instruction register                                      |

| <b>TAM</b>     | Test Access Mecanism                                             |

| <b>TMS</b>     | Test Mode Select                                                 |

| <b>TC</b>      | Taux de Couverture                                               |

| <b>VHDL</b>    | Very High Speed Integrated Circuit Hardware Descreption Language |

| <b>WIR</b>     | Wrapper Instruction Register                                     |

| <b>WBR</b>     | Wrapper Boundary Register                                        |

| <b>WBY</b>     | Wrapper Bypass Register                                          |

| <b>WSI</b>     | Wrapper Scan In                                                  |

| <b>WSO</b>     | Wrapper Scan Out                                                 |

|             |                                   |

|-------------|-----------------------------------|

| <b>WBC</b>  | Wrapper Boundary Cell             |

| <b>WBC3</b> | Three State Wrapper Boundary Cell |

| <b>wrck</b> | Wrapper clock                     |

| <b>wc</b>   | Wrapper cell                      |

# INTRODUCTION GÉNÉRALE

## I.1 Motivation

Les différentes applications de l'électronique dans divers domaines scientifiques et techniques exigent de nouvelles générations de circuits intégrés (CI). Ces circuits doivent posséder plusieurs fonctionnalités et doivent être : rapides, compacts, peu coûteux et fiables. Grâce à l'évolution de la microélectronique et des outils d'aide à la conception, il est désormais possible de répondre favorablement à ces exigences. Actuellement, l'industrie des semi-conducteurs est capable de fabriquer de nouveaux circuits qui sont fortement intégrés. Ces nouveaux circuits sont connus sous le nom de système sur puce « System on Chip » (SOC). À cause de la forte concurrence qui règne dans cette industrie, ce secteur fait face à des défis importants. D'une part, il faut développer rapidement des composants complexes et d'autre part, il faut les produire à moindre coût. Comme solution à ces défis, les industriels ont adopté un nouveau flot de production pour les SOC en se basant sur le principe de la réutilisation « reuse » des modules préconçus. Ces modules sont nommés « Intellectual Properties » (IP) ou « cores » [45].

Les IP permettent de concevoir des SOC très complexes en un temps court, mais ils rendent le test de ces systèmes difficiles et coûteux à accomplir. Ces difficultés sont

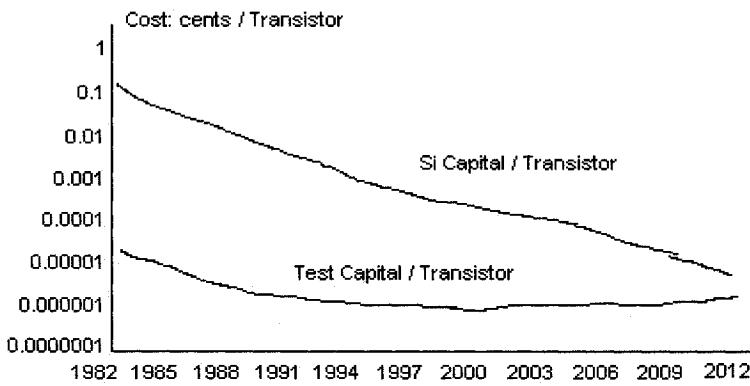

dues à: 1) l'inaccessibilité aux plots d'entrée/sortie primaires des IP à partir de ceux du SOC; 2) la diversité des sources de provenance des IP qui fait que chaque module peut avoir une stratégie de test différente de celle des autres IP. La figure I.1 illustre les résultats de l'étude réalisée par la « Semiconductor International Association » (SIA) [42] qui prédit que dans un futur proche, le coût de test des SOC risque de dépasser le coût de leur fabrication.

**Figure I.1: Coût de production par transistor versus coût de test par transistor [38].**

À partir de cette étude, on peut donc conclure que, dans le futur, le principe de la réutilisation des IP ne pourra pas assurer la réduction du coût de production des SOC. Pour réduire le coût de production de ces systèmes, il faut également penser à minimiser le coût de leur test.

Les techniques de test développées pour les systèmes électroniques sur cartes « System On Board » (SOB) ne peuvent être appliquées aux SOC. En effet, les SOB sont conçus à partir de CI qui ont déjà été fabriqués et testés. De ce fait, le test de ces systèmes est

limité au test des interconnexions entre les CI. La réduction du coût de test des SOC n'est possible que par l'utilisation de nouvelles approches de test développées spécifiquement pour eux. Dans cette optique, plusieurs architectures de test ont été proposées, mais elles sont destinées soit aux IP soit aux interconnexions entre les IP. Il n'existe pas de technique qui permette de tester efficacement les IP et les interconnexions avec une même structure de test. Pour un test complet d'un SOC, il faut donc insérer des architectures pour le test des IP et d'autres pour le test des interconnexions. Ceci engendre une dégradation des délais internes et un accroissement important de la surface. Parmi les techniques de test développées pour améliorer la testabilité des SOC, on peut mentionner les deux plus importantes qui sont le test intégré « Built-In Self-Test » (BIST) et la norme IEEE P1500.

La technique BIST offre des structures de test peu coûteuses qui permettent la génération et l'application des données de test au cœur des IP et aux interconnexions, ainsi que l'analyse des réponses à l'interne du SOC. En général, le BIST n'assure pas une bonne qualité de test, ceci est dû à la nature aléatoire de ses vecteurs de test qui ne permettent pas de vérifier efficacement la présence ou l'absence des pannes difficiles.

La norme IEEE P1500 permet d'accéder aux signaux d'entrée/sortie des IP à partir de l'extérieur. Cette norme, qui utilise des vecteurs de test déterministes, permet de tester les IP et les interconnexions du SOC avec des équipements de test externes. Les vecteurs de test déterministes sont générés à l'externe du SOC par des générateurs

automatiques « Automated Test Patterns Generator » (ATPG). L'inconvénient majeur de la norme IEEE P1500 est l'utilisation prolongée des équipements de test externes « Automated Test Equipment » (ATE) qui sont généralement très dispendieux. Le temps d'utilisation d'ATE dépend de la longueur de la séquence de test et de la longueur du registre à décalage à travers lequel les valeurs de test sont appliquées aux IP et aux interconnexions.

À cause de l'augmentation rapide de la complexité des SOC et de leur vitesse, les ATE deviennent dépassés en termes d'espace mémoire et de vitesse. Afin d'assurer une bonne qualité de test pour les SOC et de réduire le temps d'application des vecteurs, les manufacturiers sont appelés à remplacer plus souvent leurs ATE. Ceci nécessite des investissements additionnels, qui font augmenter le coût de test des SOC.

L'objectif de notre travail est de proposer une architecture de test qui permet de vérifier les IP et les interconnexions des SOC avec une même structure de test. Ceci a pour but la réduction de la surface additionnelle et la minimisation des dégradations des délais internes qui sont engendrées par l'insertion des architectures de test dans les SOC. La nouvelle architecture doit être aussi configurable en structure BIST et en enveloppe P1500 pour permettre à l'intégrateur des IP de réaliser des bons compromis entre la qualité de test et le temps d'utilisation des ATE.

## I.2 Organisation du mémoire

Ce mémoire est principalement structuré en quatre chapitres :

Le premier chapitre est consacré aux concepts de base du test des SOC. Nous y exposons un rappel sur les SOC et les différentes catégories d'IP qui rentrent dans leur conception. Nous abordons également les spécificités du test des SOC et finalement, les techniques de conception en vue de test conçues pour améliorer la testabilité des SOC.

Le deuxième chapitre est un survol des architectures existantes développées pour le test des SOC. Dans ce chapitre, nous présentons différentes architectures de test proposées pour les IP et les interconnexions des SOC. En premier lieu, nous exposons les techniques de test externe et celles qui sont intégrables qui ont été développées pour les IP. En dernier, nous présentons les techniques de test externe et les techniques BIST qui ont été conçues pour les interconnexions.

Le troisième chapitre est relatif à l'architecture de test proposée. Nous y présentons l'architecture et le fonctionnement des cellules d'entrée/sortie à deux états, à trois états, bidirectionnelles et des différents registres qui composent la structure de test proposée. Dans ce chapitre, nous parlons également du contrôleur de test qui gère le fonctionnement de la nouvelle architecture de test. À la fin de ce chapitre, nous illustrons et expliquons les différentes instructions de test que l'architecture proposée implémente, pour le test des IP et des interconnexions, à partir de l'extérieur et à l'interne du SOC.

Le quatrième chapitre présente les résultats de la validation de l'architecture de test proposée qui ont été obtenus par simulation sur des circuits d'essai. Ces résultats se rapportent au gain en surface et à la réduction du temps d'application des vecteurs de test. Ce chapitre est suivi par la conclusion générale et les perspectives pour des travaux futurs.

# CHAPITRE 1

## CONCEPTS DE BASE

### 1.1 Introduction

Dans ce chapitre, nous présentons les concepts de base concernant le test des SOC.

Parmi ces concepts, nous abordons les spécificités du test du SOC et les types de vecteurs de test qui peuvent être appliqués aux SOC. Nous parlons également du BIST qui est la technique « Design For Testability » (DFT) la plus utilisée pour le test des SOC et de la norme IEEE P1500 développée pour standardiser le test des SOC. Pour mieux comprendre d'où vient la difficulté à tester un SOC, nous commençons par un rappel sur ces systèmes et sur les différentes catégories d'IP qui entrent dans leur conception.

### 1.2 Système sur puce et les modules IP

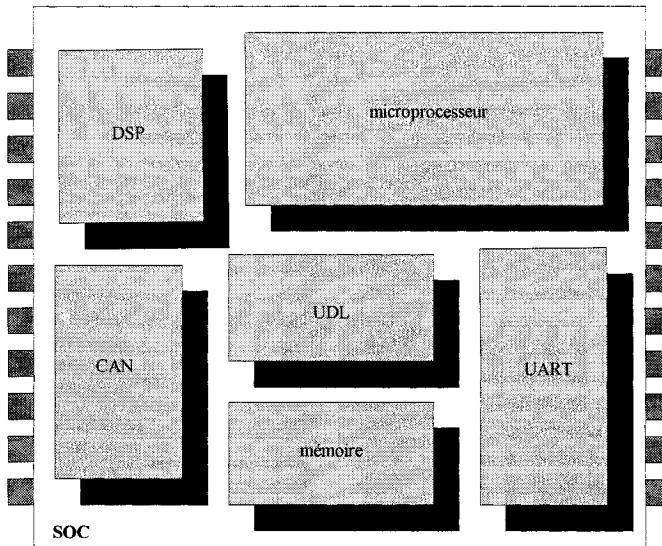

Le SOC est un circuit intégré très complexe, qui peut contenir plusieurs millions de transistors. Ce circuit peut remplacer tout un système électronique composé de plusieurs cartes. La figure 1.1 montre que le SOC est conçu par l'intégration de différents modules IP : numérique, analogique, mémoire, microprocesseur, module RF, etc. Ces modules IP sont classés en trois catégories [16].

**Figure 1.1: Modules IP qui peuvent composer un SOC.**

La première catégorie est celle des IP matériels « Hard Core » qui sont des modules placés et routés suivant une bibliothèque technologique spécifique. Ces IP qui sont prêts à l'usage, sont livrés à l'utilisateur sous forme de boîtes noires avec des performances optimisées (puissance, délais, etc.). La portabilité de ces modules d'une technologie à une autre est faible mais la propriété intellectuelle associée à ces modules est bien protégée et leurs performances finales sont prévisibles.

La deuxième catégorie est celle des IP logiciels « Soft Core » qui sont livrés sous forme de code source synthétisable d'un niveau d'abstraction élevé. Ceci procure pour ce type d'IP une bonne portabilité d'une technologie à une autre. Par contre, la propriété intellectuelle associée à ces modules est non protégée et leurs performances finales dépendent de la technologie utilisée pour leur implémentation.

La troisième catégorie est celle des IP dits « Firm Core » qui se situe entre les IP câblés (Hard Core) et ceux qui sont entièrement logiciel (Soft Core). Ces IP sont décrits en « Hardware Description Language » (HDL) structurel en utilisant des composants élémentaires d'une bibliothèque générique. Les IP « Firm Core » sont livrés à l'intégrateur, placés et optimisés en surface et en vitesse mais non routés. Les performances de ces IP et leurs tailles sont prévisibles mais la protection de leur propriété intellectuelle n'est pas assurée.

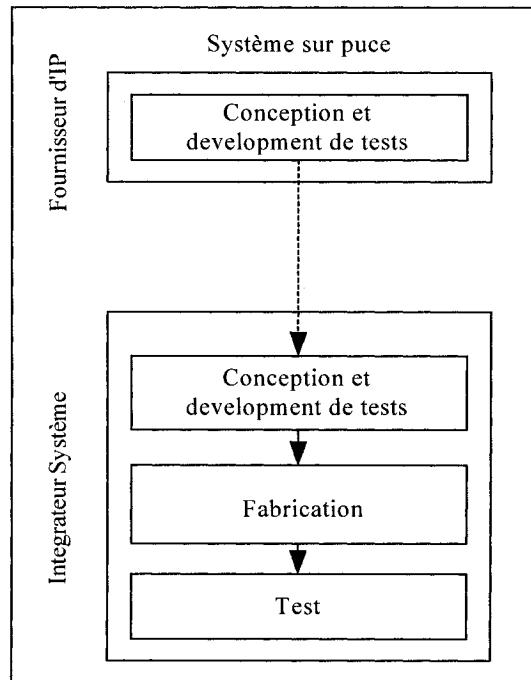

**Figure 1.2: Flot de conception du système sur puce [45].**

D'après le flot de conception des SOC présenté à la figure 1.2, nous distinguons deux types d'intervenants dans cette industrie. Il y a les fournisseurs qui conçoivent les IP et élaborent leurs stratégies de test, et les intégrateurs qui combinent les IP pour concevoir

des SOC. Les intégrateurs assurent la vérification de ces systèmes à la sortie du procédé de fabrication en réutilisant les vecteurs de test livrés avec les IP. Ces vecteurs de test, qui peuvent être déterministes ou aléatoires, tel que discuté à la section 1.4, permettent de détecter les défauts physiques qui peuvent affecter le bon fonctionnement du SOC. Les défauts physiques sont provoqués notamment par les imperfections des tranches du semi-conducteur « wafer » (dislocations, impuretés, etc.), l'instabilité du processus de fabrication, l'opérateur humain etc. [34]. L'application des vecteurs de test aux IP à la dernière étape de la fabrication du SOC n'est pas une opération facile à réaliser. Cette difficulté est due à l'inaccessibilité aux signaux d'entrée/sortie des IP à partir des plots primaires du SOC. Il faut donc que l'intégrateur prévoie des structures de test pour les IP dès le début de la conception du SOC.

### 1.3 Structure de test du module IP

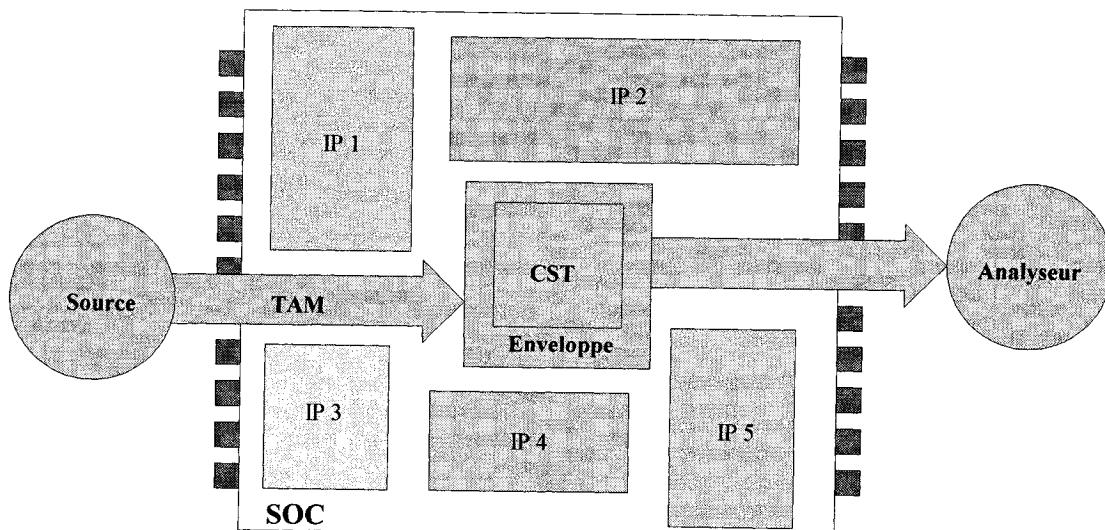

Figure 1.3: Structure de test pour un IP du SOC [41].

La figure 1.3 illustre le schéma de principe de la structure de test de l'IP que doit prévoir l'intégrateur dès le début de la conception du SOC. Cette structure est composée de trois éléments [45] : source/analyseur, mécanisme d'accès au test et enveloppe.

La source est l'élément à partir duquel, les vecteurs de test sont appliqués au circuit sous test (CST). L'analyseur est l'élément qui collecte les réponses du test du CST et les compare aux réponses du circuit correct. La source et l'analyseur peuvent être intégrés ou non dans le SOC.

Le « Test Access Mecanism » (TAM) est le chemin d'accès aux tests qui sert à transporter les vecteurs, de la source au CST et les réponses, du CST à l'analyseur. Les TAM peuvent être réalisés selon trois principes : 1) la possibilité de propager les données de test à travers les IP sans perdre d'information [11] [12], ce que nous appelons la transparence des IP; 2) utilisation des bus fonctionnels du système pour acheminer les données de test vers les IP [4]; 3) insertion des bus supplémentaires dédiés aux tests [44].

Le troisième et dernier élément de cette structure est l'enveloppe qui est une interface matérielle insérée entre l'IP et le reste du SOC. Cette interface permet d'accéder aux entrées et aux sorties de l'IP à partir de l'extérieur du SOC. En mode normal, l'enveloppe connecte l'IP aux autres modules du SOC, alors qu'en mode test, elle isole l'IP du reste du SOC et relie ses signaux d'entrée/sortie à un ATE externe à travers le TAM.

## 1.4 Génération de vecteurs de test pour les SOC

De nos jours, il existe des SOC avec plusieurs dizaines de plots d'entrée. Le test exhaustif de ces SOC nécessite de longues séquences de test dont le temps d'application peut accéder plusieurs heures ou jours. Ceci n'est pas réaliste dans l'industrie des semi-conducteurs qui exige de faibles coûts de production. Pour détecter le maximum de pannes en un temps court, l'une des trois approches de test citées ci-après peut être adoptée: 1) l'approche pseudo-exhaustive [45] qui propose de décomposer un réseau de portes logiques en une série de petits réseaux et de tester chacun d'eux exhaustivement. Cette approche pseudo-exhaustive garantit une bonne qualité de test et réduit le nombre de vecteurs à appliquer. Mais, la décomposition d'une structure logique en sous circuits n'est pas toujours faisable ; 2) l'approche déterministe qui utilise des vecteurs de test spécifiques pour détecter des pannes spécifiques ; 3) l'approche pseudo aléatoire qui permet de détecter un bon nombre de pannes en utilisant uniquement des vecteurs de test générés aléatoirement à faible coût. Dans cette section, nous exposons seulement les deux dernières approches de test parmi celles présentées ci-dessus. En effet, l'approche déterministe et la pseudo aléatoire sont les plus efficaces et les plus utilisées dans l'industrie des semi-conducteurs.

### 1.4.1 Génération déterministe

Dans toute séquence de test exhaustif ou pseudo exhaustif, seul un nombre restreint de vecteurs sont efficaces pour la détection de pannes. Il est donc profitable de générer

uniquement les vecteurs de test utiles à la détection des pannes en se basant sur la génération déterministe. Ce type de génération, qui est orienté pannes, garantit un vecteur de test, s'il en existe un bien sûr [45]. Les vecteurs de test déterministes sont générés par des ATPG suivant des modèles de pannes. Parmi ces modèles de pannes, les plus utilisés sont le modèle de collage [33] et le modèle de court-circuit [41]. La génération des vecteurs de test déterministes est un problème NP complet. C'est pourquoi, les ATPG qui génèrent ces vecteurs, utilisent des Algorithmes tels que l'Algorithm D [37], PODEM [14] ou FAN [10]. Ces algorithmes fournissent des séquences de test efficaces mais qui ne sont pas forcément optimales. L'inconvénient majeur de la génération déterministe est le temps de génération qui augmente rapidement avec la complexité des IP. Malgré cet inconvénient, le test déterministe reste largement utilisé dans l'industrie de la microélectronique, parce qu'il assure une bonne qualité de test.

#### 1.4.2 Génération pseudo aléatoire

Le test pseudo aléatoire consiste à utiliser des vecteurs de test générés aléatoirement. L'idée d'utiliser des vecteurs aléatoires est venue de l'application des vecteurs de test déterministes qui souvent détectent d'autres pannes en plus de celles pour lesquelles ils ont été développés [41]. Les vecteurs de test aléatoires peuvent être générés et appliqués à l'interne du circuit en utilisant un module de génération comme le registre linéaire à décalage rebouclé « Linear Feedback Shift Register » (LFSR) qui est présenté à la

section 1.6. Les vecteurs aléatoires peuvent également être générés par un programme informatique et appliqués à partir de l'extérieur du circuit en utilisant des ATE. Le test aléatoire permet d'atteindre une certaine qualité de test pour les SOC à moindre coût, mais il ne permet pas de détecter certaines pannes difficiles à détecter. La génération pseudo aléatoire est habituellement utilisée dans les techniques de test intégré et par les ATPG avant de passer au mode déterministe pour réduire le temps de génération des séquences de test.

## 1.5 Conception en vue de test

Les SOC sont des circuits intégrés complexes qui peuvent contenir plusieurs millions de portes logiques par puce, ce qui conduit à un rapport portes logiques/plots très élevé. Ceci rend la contrôlabilité et l'observabilité des signaux internes du SOC à partir des plots d'entrée/sortie très difficile à réaliser. Pour améliorer la testabilité des SOC, plusieurs techniques de conception en vue du test (DFT) ont vu le jour. La DFT consiste à insérer du matériel dédié au test dans un circuit à condition de ne pas changer sa fonctionnalité. Les techniques de DFT permettent de mieux contrôler et d'observer les noeuds internes du circuit à partir de l'extérieur et à l'interne du circuit. Parmi ces techniques, nous pouvons énumérer l'insertion des points de test et des chaînes de scan. Ces deux techniques sont les premières techniques DFT à être utilisées par les concepteurs. Nous pouvons également citer le BIST et la norme IEEE P1500 que nous détaillons dans les prochaines sections 1.6 et 1.7.

La technique d'insertion de points de test [40] propose d'ajouter du matériel à certains nœuds internes du circuit qui sont difficiles à tester. Cette technique nous permet d'imposer des valeurs externes aux nœuds internes et d'observer les réponses aux sorties du circuit. L'inconvénient de cette technique est le nombre élevé de plots supplémentaires à ajouter au circuit. Cette technique d'insertion des points de test ne peut pas être appliquée aux SOC limités en nombre de plots.

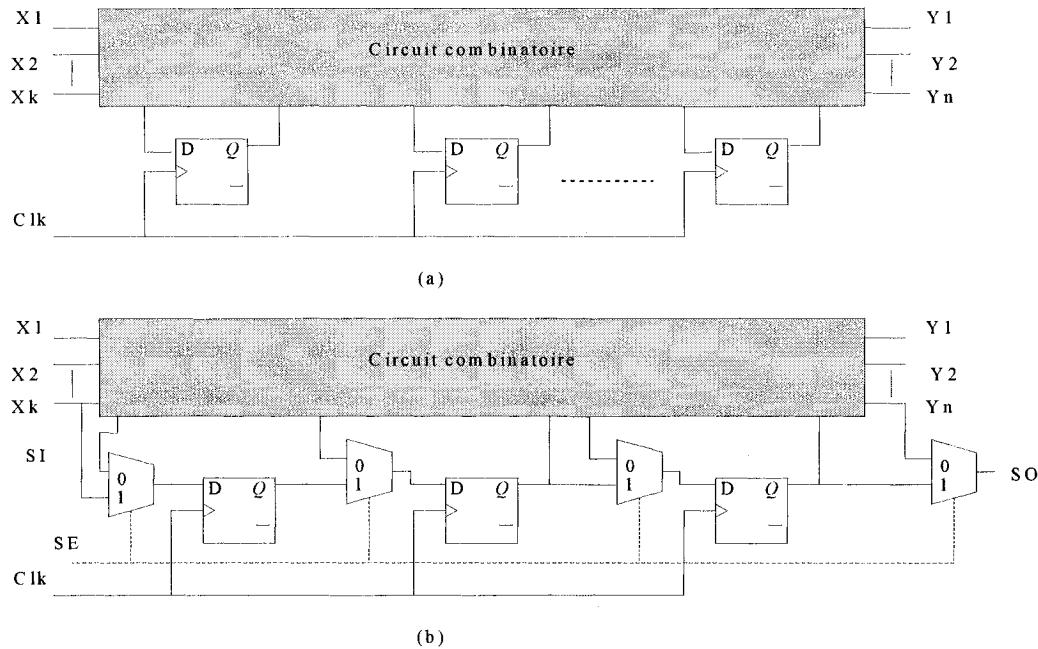

**Figure 1.4: Circuit séquentiel (a) avant insertion chaîne de balayage, (b) après insertion chaîne de balayage.**

La figure 1.4 montre le principe de la technique chaînes de balayage [34] qui consiste à remplacer tous les éléments mémoires d'un circuit séquentiel par des éléments mémoires contrôlés. Cette technique de test permet d'imposer des valeurs aux bascules

d'un IP séquentiel à partir de l'extérieur. En mode normal, les éléments mémoires agissent en tant que bascule normale. En mode test, les éléments mémoires sont connectés en série et forment un long registre à décalage. Ce registre sert à transporter en série les valeurs de test à appliquer aux entrées de la partie combinatoire et à récupérer les réponses de test de la partie combinatoire pour les transmettre vers un ATE externe pour analyse. Les inconvénients de la technique chaîne de balayage sont : 1) la surface additionnelle nécessaire pour l'implémentation des éléments mémoires contrôlés; 2) le temps de test qui dépend de la longueur de la chaîne de balayage et du nombre de vecteurs de test à appliquer.

## 1.6 Test intégré (BIST)

Le BIST [1] [2] [26] qui est une technique d'autotest, est l'une des méthodes DFT les plus utilisées. Cette technique permet de générer et d'appliquer des vecteurs de test ainsi que d'analyser des réponses de test à l'interne du SOC. L'usage de cette technique de test s'est généralisé suite aux problèmes de testabilité des CI rencontrés vers le début des années 90 [38]. Ces problèmes sont: 1) l'impossibilité de tester les CI à leur vitesse nominale, parce que les ATE externes sont généralement moins rapides que les circuits à tester; 2) l'augmentation du temps de génération des vecteurs de test et du temps de leur application; 3) l'augmentation du nombre de vecteurs de test à appliquer à partir d'ATE externes. Le BIST offre certains avantages comparativement aux techniques de test qui utilisent des ATE externes [22]. Premièrement, les vecteurs de test sont générés de façon pseudo aléatoirement à faible coût. Deuxièmement, l'application des vecteurs de test et

l'analyse des réponses de test se font à l'interne du SOC. Ceci donne la possibilité de tester les IP et les interconnexions à la vitesse nominale des SOC, ce qui réduit la durée d'application des vecteurs de test. Malgré ces avantages, l'utilisation du BIST engendre certains inconvénients comme l'augmentation de la surface et les dégradations des délais internes du circuit.

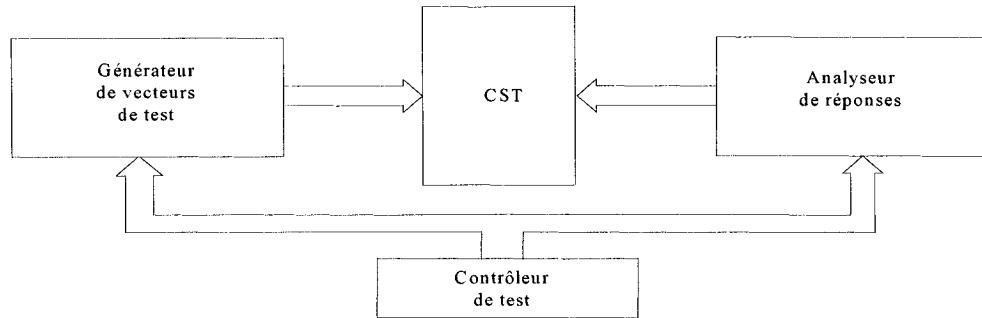

### 1.6.1 Architecture BIST

La figure 1.5 montre le schéma de principe d'une structure BIST pour le test du CST à l'interne. Cette structure BIST est composée d'un générateur de vecteurs de test, d'un analyseur de réponses et d'un contrôle de test qui sert à gérer le fonctionnement de la structure BIST.

**Figure 1.5: Architecture du test intégré.**

#### 1.6.1.1 Générateur de vecteurs de test

Le générateur est la source à partir de laquelle proviennent les vecteurs de test qui sont appliqués au CST. Plusieurs techniques peuvent être utilisées pour générer à l'interne les vecteurs de test [9], parmi elles, nous citons: les ROM et les LFSR.

Une mémoire ROM permet de stocker des vecteurs de test déterministes générés par un ATPG externe. Ces vecteurs qui garantissent une bonne qualité de test sont emmagasinés pour être appliqués au CST. Mais la taille de la mémoire dans laquelle ces vecteurs sont emmagasinés peut être importante, ce qui peut engendrer une augmentation importante de la surface du circuit.

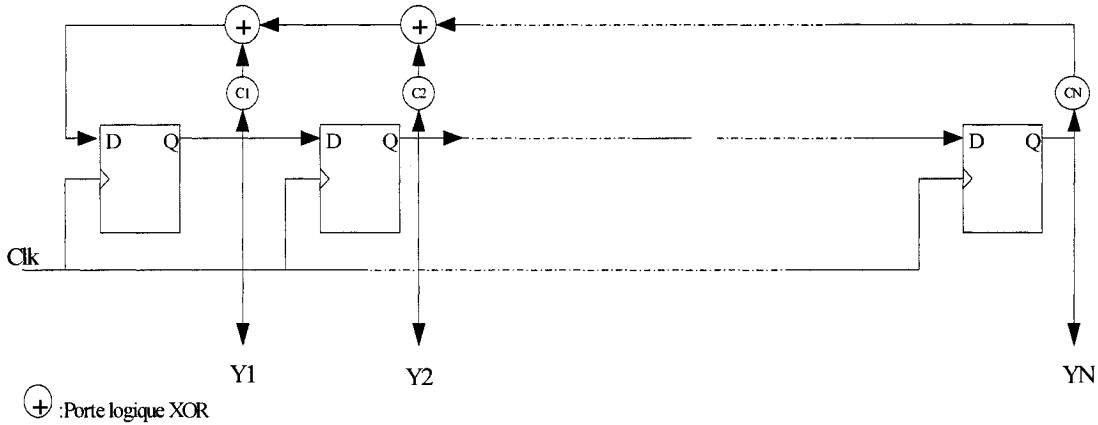

**Figure 1.6: Architecture d'un LFSR générique d'ordre N et à XOR externe.**

Le LFSR [40] est le moyen le plus utilisé pour la génération des vecteurs de test à l'intérieur d'un circuit. La figure 1.6 représente le schéma d'un LFSR générique d'ordre N (N : nombre de bascules) à XOR externe. Ce registre est qualifié de registre autonome, parce qu'il n'a aucune autre entrée à part celle de l'horloge. Chaque fois que le coefficient  $C_i$  ( $1 \leq i \leq N$ ) est à 1, l'étage du LFSR qui lui correspond est rebouclé vers l'entrée de la première bascule du LFSR à travers une porte XOR. À chaque front montant de l'horloge, la bascule suivante prend la valeur de la bascule précédente, sauf la première bascule qui prend le résultat de l'opération XOR réalisée entre tous les rebouclages. Les sorties des différentes bascules constituent les bits du vecteur de test.

généré. Le LFSR initialisé à une valeur autre que 00...0, génère  $2^N - 1$  vecteurs de test avant de recommencer la même séquence.

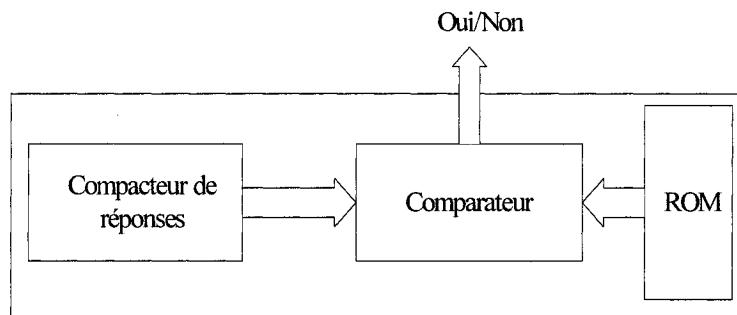

### 1.6.1.2 Analyseur des réponses

L'analyseur sert à compacter les réponses de test du CST pour calculer la signature de test et à comparer cette signature à celle du circuit correct. La Figure 1.7 montre le schéma de principe d'un analyseur des réponses qui est composé d'un compacteur, d'un comparateur et d'une mémoire ROM. Dans certains cas, l'analyseur peut uniquement être formé d'un compacteur si la comparaison de la signature de test à celle du circuit correct est faite à l'extérieur du circuit.

**Figure 1.7: Analyseur de réponses de test.**

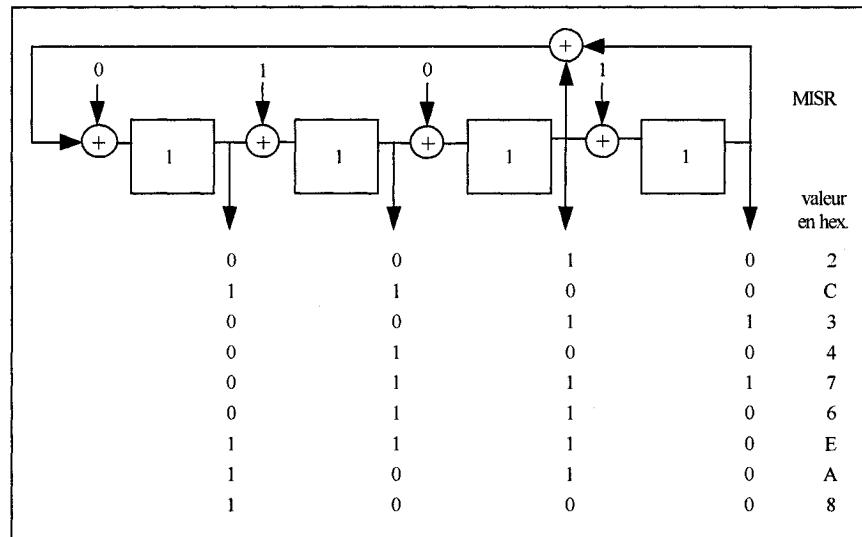

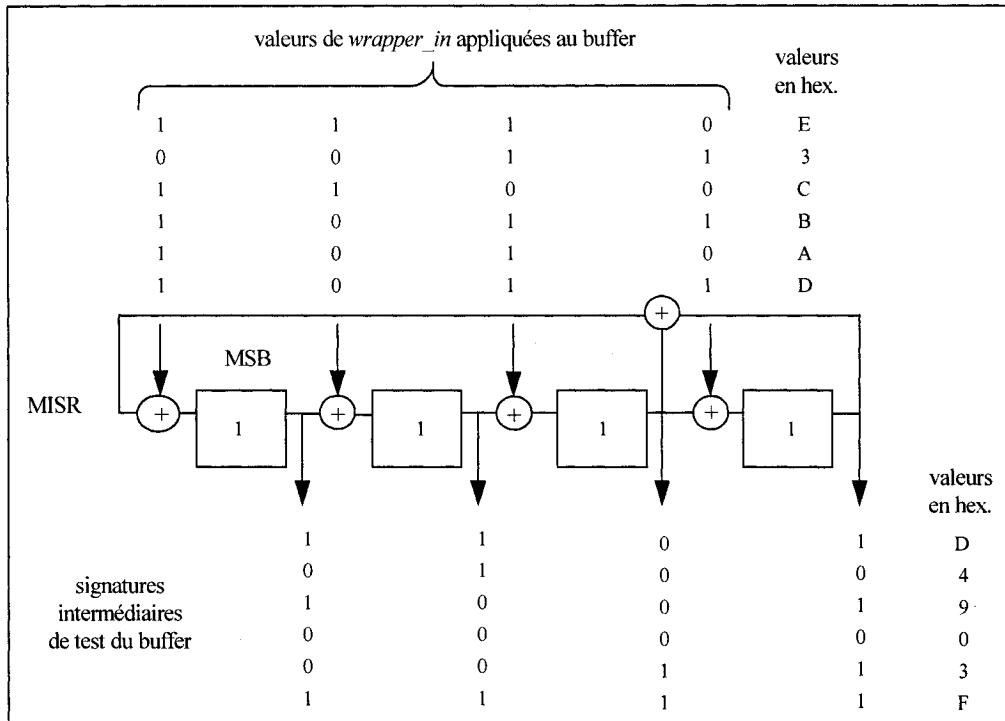

Le compactage des réponses de test peut être réalisé par plusieurs techniques comme le comptage de transition de 0 à 1 et de 1 à 0 et le comptage des 1 [34]. Mais, le compactage des réponses de test avec le registre à décalage à plusieurs entrées « Multi Input Shift Register » (MISR) [9] reste la méthode la plus utilisée dans la technique BIST. La figure 1.8 représente le schéma d'un MISR générique d'ordre N à XOR

interne. La porte XOR du premier étage du MISR est contrôlée par le signal d'entrée et le signal de rebouclage. Les autres portes XOR du MISR sont contrôlées par le signal d'entrée, la sortie de la bascule précédente et le signal de rebouclage. À chaque front montant de l'horloge, le résultat de la porte XOR est emmagasiné dans la bascule suivante. Les valeurs finales des sorties des bascules du MISR constituent la signature du CST. L'inconvénient majeur du compactage des réponses avec le MISR est le masquage d'erreur. Le masquage est la possibilité qu'une erreur masque une autre erreur, ce qui permet au circuit fautif d'avoir la même signature que celle du circuit correct. Pour minimiser ce problème, nous pouvons utiliser des MISR d'ordre N élevé ou bien prendre des signatures intermédiaires avant la signature finale du test.

Figure 1.8: Architecture d'un MISR générique à XOR internes d'ordre N.

## 1.7 Norme IEEE P1500

Dans l'industrie des SOC, le test de ces systèmes est une opération partagée entre les fournisseurs des IP et les intégrateurs de ces IP. Les fournisseurs insèrent les structures de test dans les IP et génèrent les vecteurs de test pour ces modules. Les intégrateurs

élaborent des stratégies de test pour les SOC conçus en réutilisant les vecteurs de test fournis avec les IP. Pour réussir le test des IP qui sont généralement livrés à l'intégrateur sous forme de boîtes noires, il faut transmettre du concepteur à l'intégrateur toutes les informations concernant le test de ces modules. Dans cette optique, un groupe constitué d'universitaires et d'industriels, travaille depuis septembre 1995 pour élaborer la norme IEEE P1500 destinée au test des SOC [20] [32] [39]. Cette norme a été inspirée de la norme IEEE 1149.1 [19] qui a été développée pour le test des SOB. Ce groupe de travail a proposé une structure de test nommée enveloppe P1500 et un langage de test appelé « Core Test Language » (CTL).

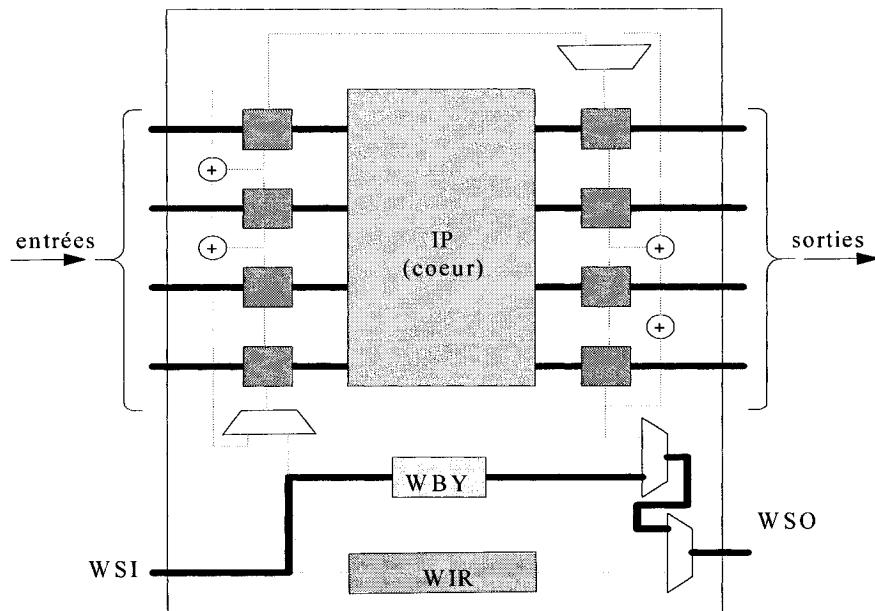

### 1.7.1 Enveloppe P1500

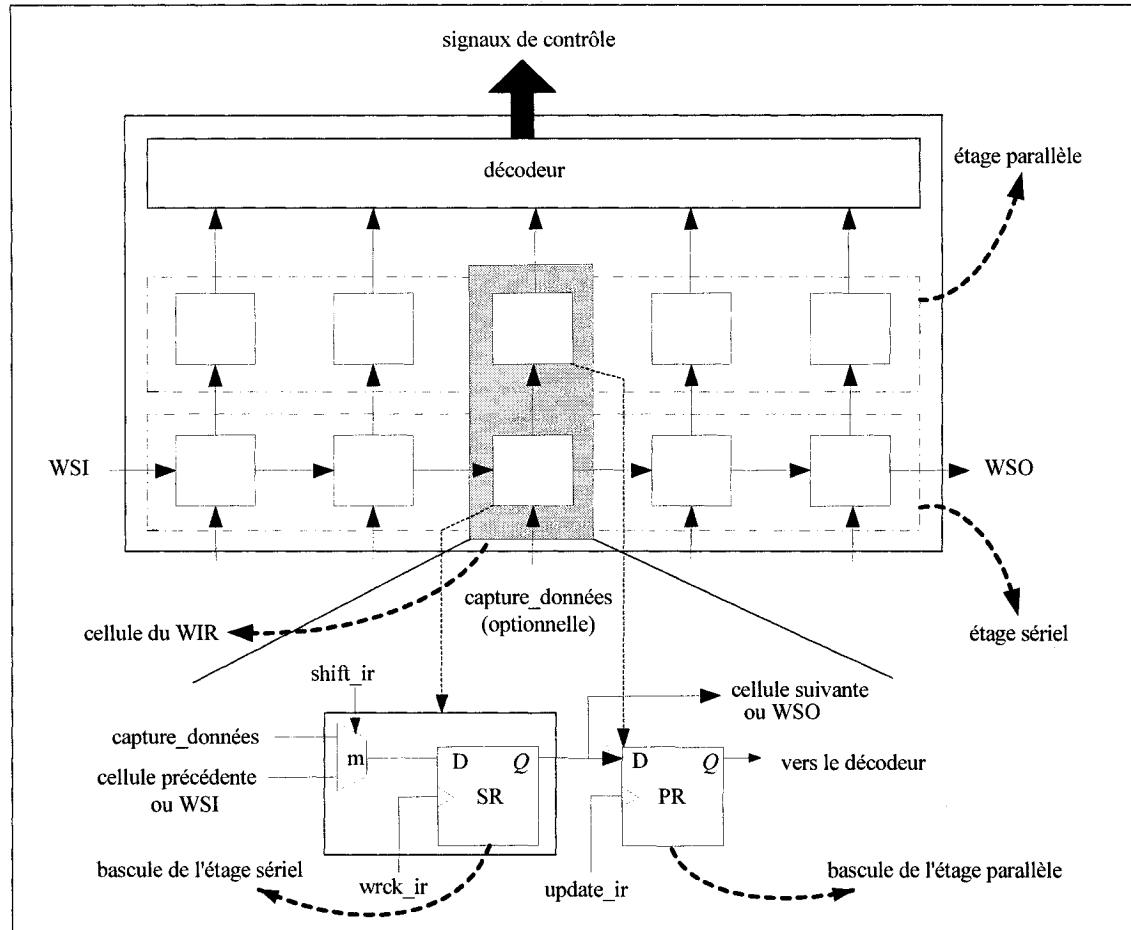

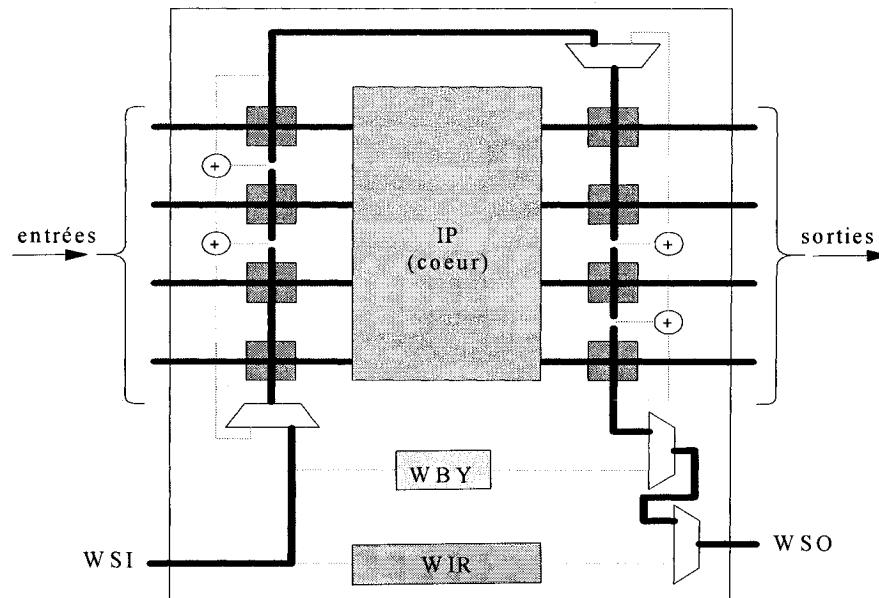

Figure 1.9: Architecture de l'enveloppe IEEE P1500.

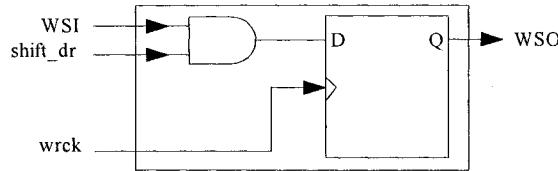

L'enveloppe P1500 est l'ensemble des registres et des multiplexeurs insérés autour de l'IP. Cette interface de test offre l'accès aux plots d'entrée/sortie de l'IP à partir de quelques plots supplémentaires ajoutés au SOC. La figure 1.9 représente la structure de l'enveloppe P1500 qui est essentiellement composée de trois registres [20] [29]. Le premier est le registre d'instruction de l'enveloppe « Wrapper Instruction Register » (WIR). Dans ce registre, les codes opérations des instructions de test sont chargés en série et décodés pour configurer l'enveloppe P1500 dans le mode de fonctionnement approprié. Le deuxième est le registre à décalage de l'enveloppe « Wrapper Boundary Register » (WBR). Ce registre est formé par la concaténation en série de toutes les cellules de l'enveloppe P1500 associées aux signaux d'entrée/sortie du cœur de l'IP. En mode normal, WBR devient transparent pour ne pas altérer le fonctionnement normal des IP. En mode test, WBR agit comme un registre à décalage pour acheminer en série les valeurs de l'entrée serielle de l'enveloppe « Wrapper Scan Input » (WSI) à appliquer aux signaux d'entrée de cœur de l'IP. Le registre WBR sert aussi à capturer les valeurs des signaux de sortie du cœur de l'IP. Par la suite, ces valeurs sont transmises en série vers un ATE via la sortie serielle de l'enveloppe « Wrapper Scan Output » (WSO) pour analyse. Le troisième et dernier registre de l'enveloppe P1500 est le registre de court-circuit « Wrapper Bypass Register » (WBY). Ce registre est prévu pour court-circuiter WBR de l'IP non concerné par une procédure de test. WBY permet de raccourcir la longueur du chemin de balayage entre l'entrée WSI et la sortie WSO de l'enveloppe P1500. En plus de ces trois registres obligatoires, d'autres registres optionnels peuvent

être ajoutés à l'enveloppe P1500, tel que le registre d'identification utilisé par les fabricants pour identifier leurs produits.

### **1.7.2 Langage de test « Core Test Language » (CTL)**

À cause de la diversité des sources de provenance des IP, le langage de test CTL [30] a été développé par le groupe P1500 pour uniformiser la manière dont les informations relatives aux tests des IP sont transférées du fournisseur à l'intégrateur. Parmi les informations que nous pouvons trouver dans un CTL, nous avons le type de DFT insérée dans l'IP, les différentes instructions de test et leurs codes opérations, les vecteurs de test à appliquer, les longueurs des chaînes de balayage et leurs nombres, les modèles de pannes utilisés, etc.

## **1.8 Conclusion**

Le test est une opération fondamentale qui est réalisée à la sortie de tout procédé de fabrication du SOC afin de détecter les composants défectueux. Dans ce chapitre, nous avons exposé les raisons qui ont rendu le test du SOC très difficile à accomplir et les spécificités du test de ces systèmes comparativement aux SOB. Pour mieux comprendre le test des SOC, certaines notions de base ont été exposées telles que les défauts physiques, la génération des vecteurs de test et leur application. Nous avons également présenté la technique BIST et la norme IEEE P1500 qui ont été développées pour l'amélioration de la testabilité du SOC.

# CHAPITRE 2

## REVUE DES TECHNIQUES

### DE TEST DES SOC

#### 2.1 Introduction

Ces dernières années, plusieurs travaux de recherche ont été menés dans le milieu académique et industriel pour améliorer la testabilité des SOC. L'objectif de ces travaux est de développer de nouvelles architectures qui assurent une bonne qualité de test pour les SOC tout en diminuant le coût. Les différentes architectures de test proposées, peuvent être classées en deux groupes: 1) les architectures de test des IP; 2) les architectures de test des interconnexions entre les IP. Dans ce chapitre, nous exposons les avantages et les inconvénients de certaines de ces architectures afin de positionner notre travail par rapport à ce qui a été déjà réalisé dans le domaine du test des SOC.

#### 2.2 Architectures de test des modules IP

Plusieurs architectures de test ont été proposées pour les IP du SOC. Parmi celles-ci, il y a celles qui utilisent des ATE externes pour tester les IP à partir de l'extérieur du SOC. Alors que d'autres architectures de test des IP ont été développées en se basant sur le test intégré présenté à la section 1.6. Les architectures de test intégré permettent de

contourner la problématique de l'accessibilité aux signaux d'entrée/sortie des IP à partir des plots des SOC.

### 2.2.1 Architectures du test externe pour les modules IP

Les architectures de test externe des IP sont des interfaces matérielles insérées autour de ces modules. En mode normal, ces interfaces deviennent transparentes pour ne pas gêner le fonctionnement normal des IP. En mode test, ces interfaces connectent les IP aux ATE externes à travers des TAM.

Figure 2.1: Architecture du bus de test TestRail [32].

Marinissen et Arendsen [32] ont proposé une architecture de test extensible appelée TestRail. Cette architecture simplifie l'accès aux signaux d'entrée/sortie des IP à partir de quelques plots supplémentaires ajoutés au SOC. La figure 2.1 présente le principe de cette architecture où les IP sont encapsulés dans des structures de test nommées TestShells. Le TestShell est l'interface qui connecte l'IP au TAM lorsque le SOC est en mode test et aux autres modules quand le SOC est en mode normal. Cette interface est composée de cellules associées aux signaux fonctionnels d'entrée/sortie de l'IP, de multiplexeurs et d'un registre de court-circuit. Dans cette solution de test que propose Marinissen et Arendsen, les IP peuvent être regroupés en petit nombre et leurs TestShells reliés en série. Les vecteurs de test sont appliqués aux signaux d'entrée des IP à partir d'ATE externe à travers les TAM et les Testshells. Les réponses de test sont transmises en série de l'IP à l'ATE pour analyse via les TestShells et les TAM. L'architecture TestRail permet de tester plusieurs IP en parallèle et de leur assurer une bonne qualité de test. Cependant l'usage du TestRail nécessite une étude préliminaire afin de déterminer l'impact de cette architecture sur la surface et les performances du SOC. Le coût relatif à cette architecture dépend de la complexité des IP à tester.

Benabdenbi et al. [7] ont proposé l'architecture de test CAS-BUS qui est présentée à la figure 2.2. Cette architecture offre un accès direct aux signaux d'entrée/sortie des IP du SOC à partir d'un nombre réduit de plots supplémentaires ajoutés au SOC. Les auteurs proposent d'associer à chaque IP un multiplexeur configurable appelé « Core Access Switch » (CAS). Selon le code opération de l'instruction chargée dans le registre de

configuration du multiplexeur, un CAS connecte au bus de test ou court-circuite les IP encapsulés dans des enveloppes. Cette architecture permet de tester plusieurs IP en parallèle, ce qui minimise le temps d'application des vecteurs de test. La bande passante du bus de test à insérer dans le SOC dépend du compromis à réaliser entre le temps d'application des vecteurs de test et la surface additionnelle. Cette contrainte peut limiter l'utilisation de l'architecture de test CAS-BUS aux IP qui ne nécessitent pas une grande bande passante.

Figure 2.2: Architecture de test Cas-Bus [7].

## 2.2.2 Architectures de test intégré pour les modules IP

Pour réduire le coût de test des SOC, d'autres architectures de test basées sur la technique BIST ont été proposées pour les IP. Ces architectures permettent la génération et l'application des vecteurs de test ainsi que l'analyse des réponses de test à l'interne du SOC. Certaines de ces approches de test sont décrites ci-après.

### 2.2.2.1 Conversion des vecteurs de test aléatoires en vecteurs déterministes

Le BIST offre des structures de test peu coûteuses mais il n'assure pas une très bonne qualité de test à cause de la nature pseudo aléatoire de ses vecteurs qui ne détectent pas certaines pannes difficiles. Pour améliorer la qualité de test du BIST, certains chercheurs ont proposé de convertir les vecteurs aléatoires en vecteurs plus efficaces.

Akers [3] a proposé une architecture de test pour les IP du SOC qui est composée d'un compteur et d'un réseau de portes logiques XOR. Les vecteurs de test aléatoires générés par le compteur, sont modifiés par un réseau de portes logiques XOR en vecteurs déterministes. Selon l'auteur, cette architecture de test réduit la surface additionnelle par un facteur de 1,5 à 6 par rapport à celle qui utilise une mémoire pour stocker jusqu'à 65536 vecteurs déterministes. Les inconvénients de cette architecture de test sont l'augmentation de la surface qui est proportionnelle à la taille du réseau de portes XOR ainsi que les dégradations des délais internes.

Touba [43] a proposé une architecture de test qui consiste à insérer de la circuiterie combinatoire entre le LFSR et les entrées de l'IP. Le rôle de cette circuiterie est de transformer les vecteurs de test aléatoires qui ne détectent aucune panne en vecteurs efficaces. Selon Touba, cette architecture nécessite peu de portes logiques à insérer entre le LFSR et l'IP comparativement à d'autres architectures de test qui proposent la même approche. L'architecture proposée par Touba n'est pas extensible, ce qui nous conduit à analyser chacune des séquences de test originales des IP pour déterminer la circuiterie

combinatoire à insérer entre le LFSR et l'IP. Le temps d'analyse de ces séquences de test risque d'être long pour les IP complexes.

Kagaris et al. [23] ont proposé une nouvelle architecture de test qui génère des vecteurs déterministes à faible coût. L'idée est de générer une séquence de test déterministe pour chacun des IP du SOC et de l'analyser pour identifier les colonnes constantes et celles qui sont semblables ou complémentaires. Les signaux d'entrée de l'IP sous test qui correspondent aux colonnes constantes, sont reliés à Vcc ou à Vss. Les signaux d'entrée de l'IP qui correspondent aux colonnes identiques ou complémentaires, sont connectés aux même sorties du compteur qui génère le reste des bits des vecteurs de test. Cette architecture réduit la surface additionnelle, mais le temps de génération et d'analyse des vecteurs de test déterministes de chaque IP peut être important.

### **2.2.2.2 BIST associé aux chaînes de balayage de l'IP**

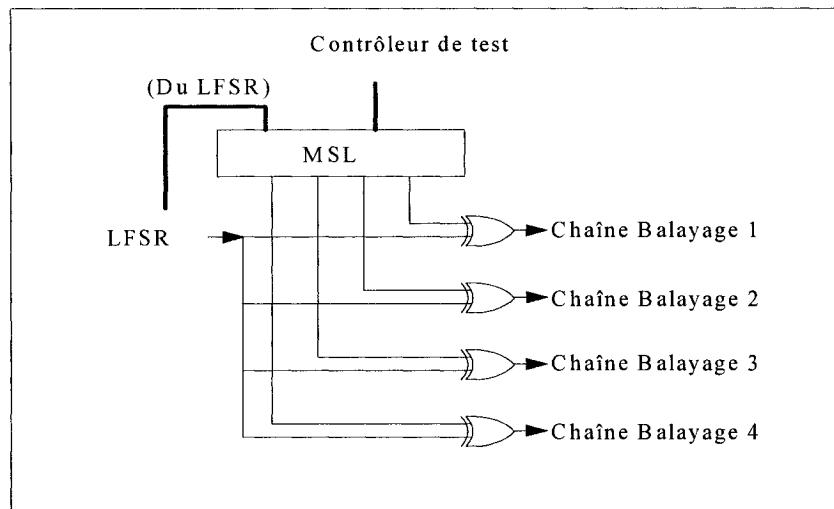

L'utilisation de vecteurs déterministes pour tester les IP séquentiels ne garantit pas forcément une bonne qualité de test. Ceci est dû à certains noeuds internes de l'IP qui sont difficiles à contrôler et à observer à partir des signaux d'entrée/sortie primaires de l'IP. Pour résoudre ce problème, Kiefer et Wunderlich [25] ont proposé l'architecture de test nommée BIST déterministe. Cette architecture associée à une multitude de chaînes de balayage, est présentée à la figure 2.3. L'architecture de test proposée par les deux auteurs, est composée d'un LFSR, d'un contrôleur de test, d'un module de modification

des vecteurs de test aléatoires en vecteurs déterministes nommé Modificateur de Séquence Logique (MSL) et d'un ensemble de portes XOR. Dans un premier temps, les vecteurs de test générés par LFSR sont convertis en vecteurs déterministes par un MSL. Ensuite, ces vecteurs déterministes sont décalés dans les chaînes de balayage de l'IP à travers les portes XOR. L'inconvénient que nous pouvons rencontrer avec cette architecture est le temps d'application des vecteurs de test. Ce temps d'application dépend de la longueur des chaînes de balayage et du nombre de vecteurs de test à appliquer.

**Figure 2.3: Exemple de la logique de génération de séquence de test [25].**

### 2.2.2.3 Conversion des vecteurs de test déterministes en vecteurs aléatoires

Les vecteurs déterministes assurent une bonne qualité de test mais leur stockage dans le SOC nécessite une mémoire de taille importante, ce qui augmente la surface du SOC.

Comme solution à cette contrainte, Kunzmann [27] a proposé une architecture de test qui utilise des vecteurs déterministes pour détecter les pannes difficiles et des vecteurs aléatoires pour détecter les pannes faciles. Les vecteurs aléatoires sont générés en perturbant les vecteurs de test déterministes (inversion, rotation, etc.). Avec cette approche de test, l'auteur a réussi à réduire de 90% la longueur de la séquence de test déterministe qui devait être emmagasinée dans la mémoire insérée dans le SOC. Malgré la diminution considérable du nombre de vecteurs de test, la taille de la mémoire peut être importante pour les SOC complexes, ce qui demande une surface additionnelle importante.

### 2.3 Architectures de test des interconnexions entre les modules IP

Figure 2.4: Combinaison du BIST et du Boundary Scan pour le test des interconnexions [5].

Les techniques de test développées pour le test des interconnexions entre les circuits intégrés (CI) des SOB, ont été réutilisées pour le test des interconnexions entre les IP du SOC. Parmi ces architectures, nous pouvons mentionner la norme IEEE 1149.1 [19] qui est connue sous le nom du Boundary Scan. Cette norme propose d'encapsuler chacun des CI du SOB dans une enveloppe dans laquelle, les signaux d'entrée/sortie du CI sont associés aux cellules. En mode test, les cellules du Boundary Scan forment un registre à décalage qui relie l'entrée serielle à la sortie serielle de l'enveloppe. À travers ce registre à décalage, les données de test à appliquer aux signaux d'entrée du CI à partir d'un ATE externe sont transférées en série. Le registre à décalage sert aussi à l'acheminement en série des réponses de test du CI vers un ATE externe pour analyse. La technique Boundary Scan ajoute peu de plots supplémentaires au SOB, mais sa bande passante est limitée à un bit. La limitation de la bande passante du Boundary Scan prolonge le temps d'application des vecteurs de test. Pour réduire le temps d'application des vecteurs de test, d'autres architectures de test basées sur le BIST ont été développées pour les interconnexions.

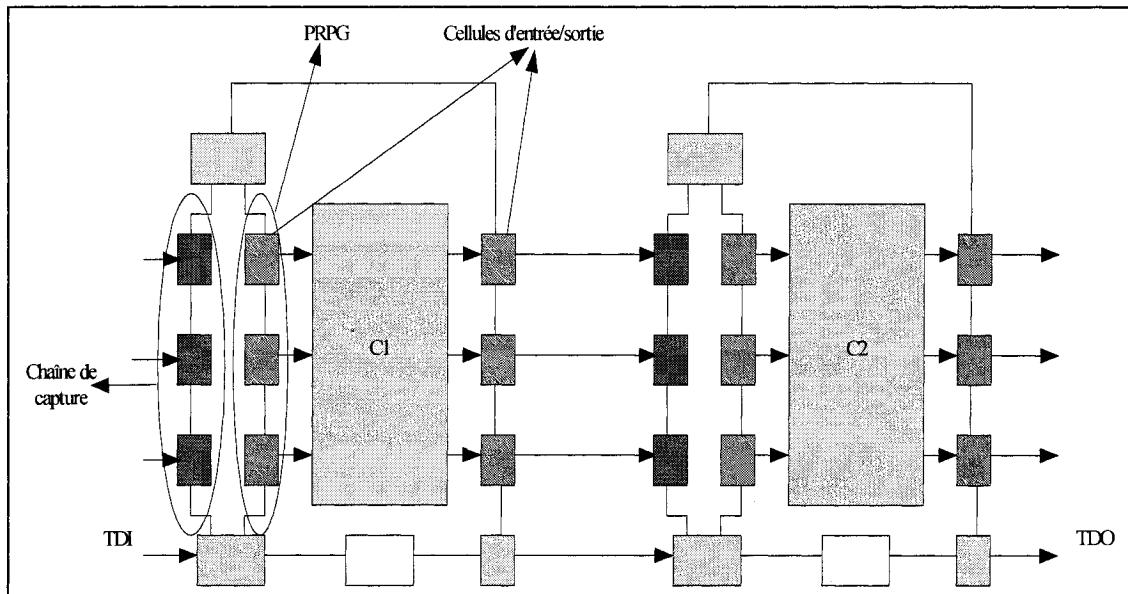

Ashok et Harold [5] ont proposé pour le test des interconnexions l'architecture représentée à la figure 2.4, qui combine le BIST avec le Boundary Scan. Ces deux auteurs proposent de doubler le nombre de cellules d'entrée de l'enveloppe Boundary Scan pour former deux chaînes à décalage connectées en parallèle. Les cellules associées aux signaux d'entrée du circuit fonctionnent comme un générateur de vecteurs de test aléatoires « Pseudo Random Pattern Generator » (PRPG). Par contre, les cellules

connectées en parallèles au PRPG forment un registre parallèle/série, appelé chaîne de capture. Ce registre parallèle/série capture les réponses des interconnexions sous test et les transmet en série vers un ATE externe. À titre d'exemple, pour le test des interconnexions entre les circuits C1 et C2 de la figure 2.4, les vecteurs sont générés par le PRPG formé par les cellules associées aux signaux d'entrée du circuit C1. Les vecteurs de test sont appliqués en parallèle aux interconnexions à travers C1. Les réponses de test des interconnexions sont récupérées par la chaîne de capture du circuit C2 et transférées en série vers un ATE externe pour analyse. Cette architecture de test exige des CI transparents pour permettre le transfert des données de test sans perte d'information.

Pendurkar [36] a présenté l'architecture du BIST distribué pour le test des interconnexions entre les CI d'un SOB. Cette solution propose d'ajouter du matériel au niveau des cellules du Boundary Scan associées aux signaux d'entrée/sortie des CI. En mode test des interconnexions, les cellules du Boundary Scan connectées aux signaux de sortie des CI, forment un LFSR qui génère les vecteurs de test. Par contre, les cellules du Boundary Scan reliées aux signaux de sortie des CI, agissent en MISR pour compacter les réponses de test. L'implantation de cette architecture de test nécessite une surface additionnelle importante et cause des dégradations des délais internes de propagation.

## 2.4 Conclusion

Le test des SOC peut être accompli par des approches de test externe ou par des approches de test intégré. Les approches du test externe requièrent des ATPG pour générer les vecteurs de test et des ATE pour leur application. Ces approches nécessitent aussi du matériel dédié au test à insérer dans le SOC pour rendre les signaux d'entrée/sortie des IP accessibles à partir de l'extérieur. Les architectures de test externe assurent une bonne qualité de test mais le coût de test est généralement élevé. Le coût dépend du surcoût en surface, du prix des ATE et du temps de génération des vecteurs de test. Les approches de test intégré offrent des structures peu coûteuses pour le test des IP et des interconnexions. Toutefois, l'insertion de ces architectures dans le SOC engendre une augmentation de la surface et la dégradation des délais internes de propagation. Malgré cela, les architectures de test intégré représentent une bonne solution pour les SOC, parce qu'elles réduisent le temps d'application des vecteurs de test et ne nécessitent pas d'outils externes pour générer les vecteurs de test.

## CHAPITRE 3

# ARCHITECTURE DE TEST PROPOSÉE

### 3.1 Introduction

Il est difficile d'avoir une seule architecture de test applicable à tous les SOC, parce que chacun de ces systèmes a ses propres contraintes de conception. Il est donc indispensable de diversifier les architectures afin de permettre aux intégrateurs de réaliser des compromis entre la qualité et le coût de test. Dans cette optique, nous avons développé une nouvelle architecture de test, que nous présentons dans ce chapitre. Cette architecture peut être utilisée pour vérifier les IP et les interconnexions du SOC avec ou sans la fonctionnalité BIST. Cette approche de test permet de réduire le nombre d'architectures à insérer dans le SOC, ce qui permet de minimiser la surface additionnelle et la dégradation des performances du SOC.

Dans ce chapitre, nous commençons notre présentation par un aperçu global sur l'architecture de test proposée. Nous exposons par la suite en détail la structure matérielle de la nouvelle architecture de test. À la fin du chapitre, nous décrivons les différentes instructions de test, que l'architecture proposée implémente pour le test des IP et des interconnexions du SOC avec ou sans fonctionnalité BIST.

### 3.2 Présentation de la nouvelle architecture de test

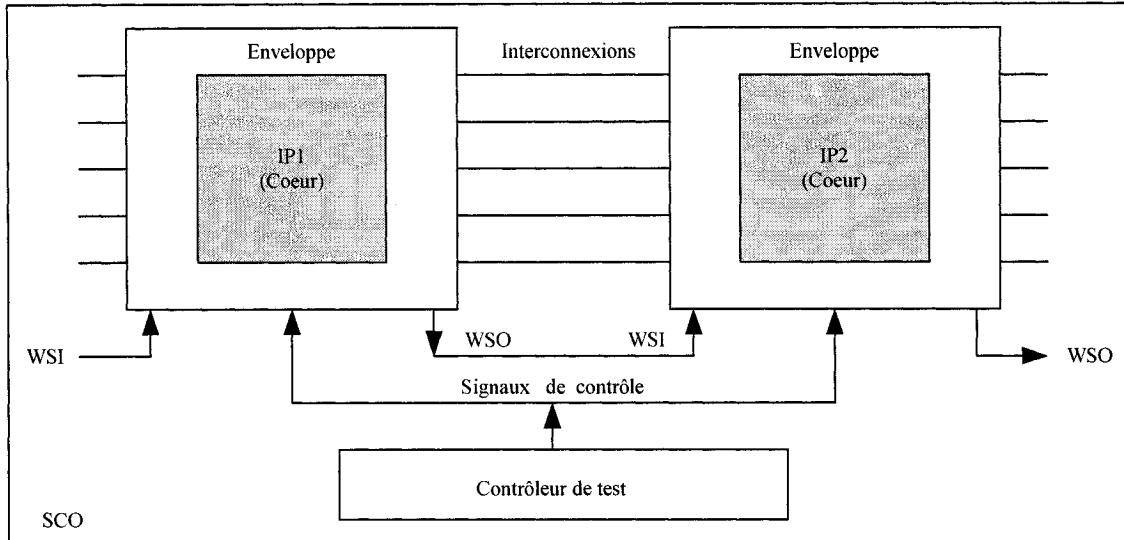

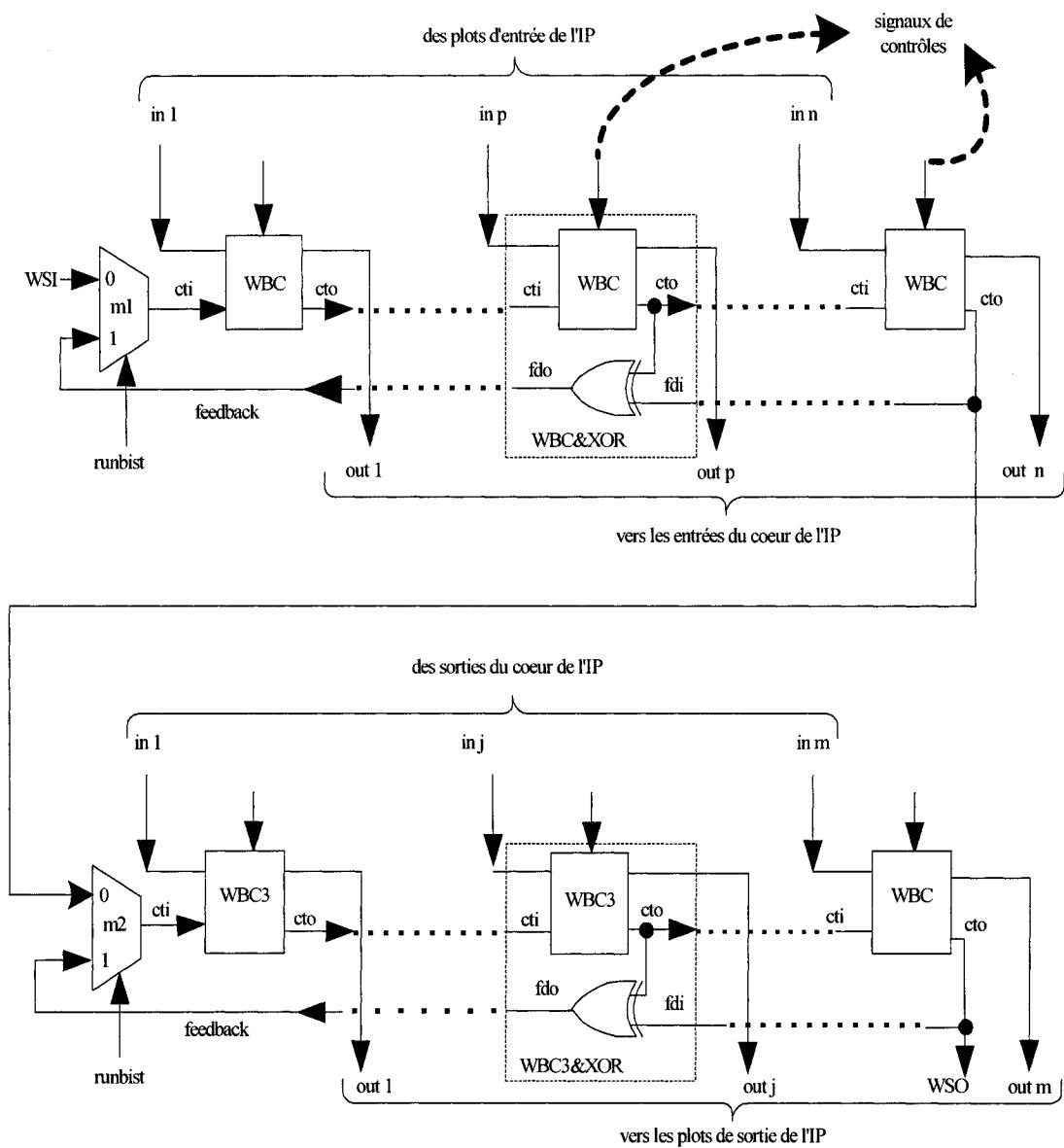

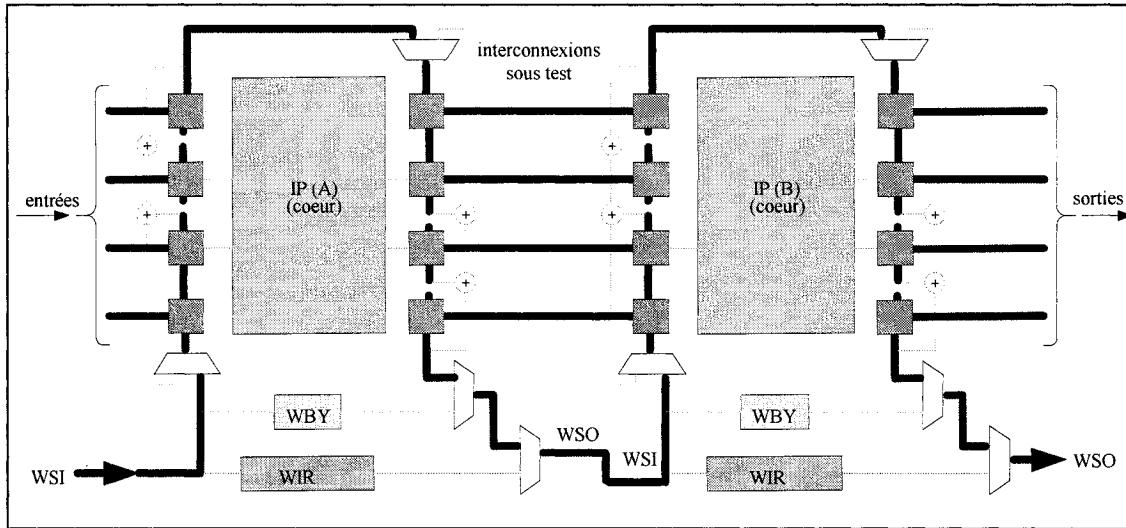

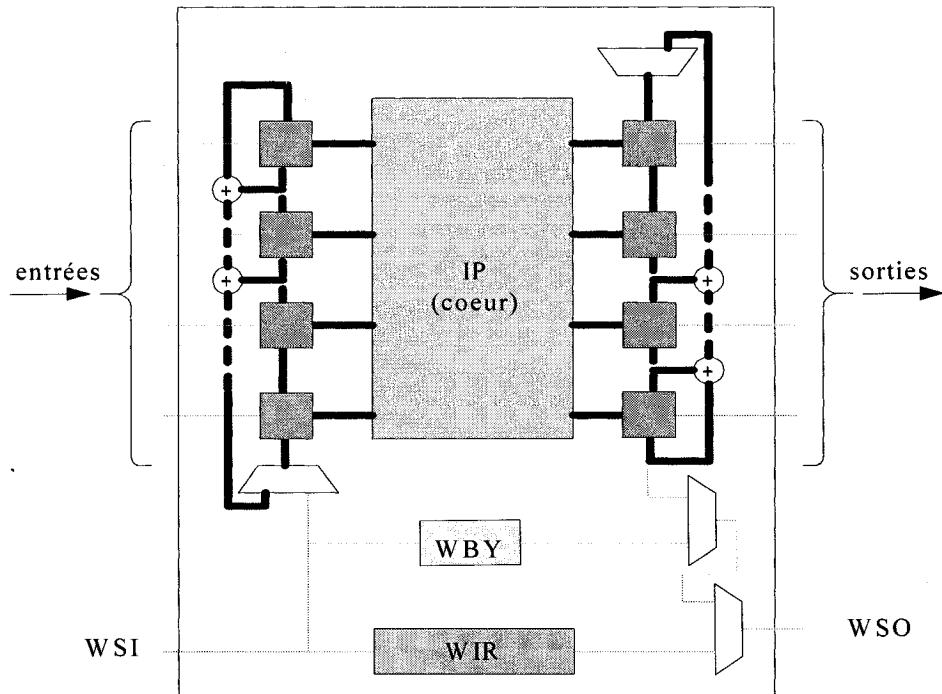

**Figure 3.1: Architecture de test proposée.**

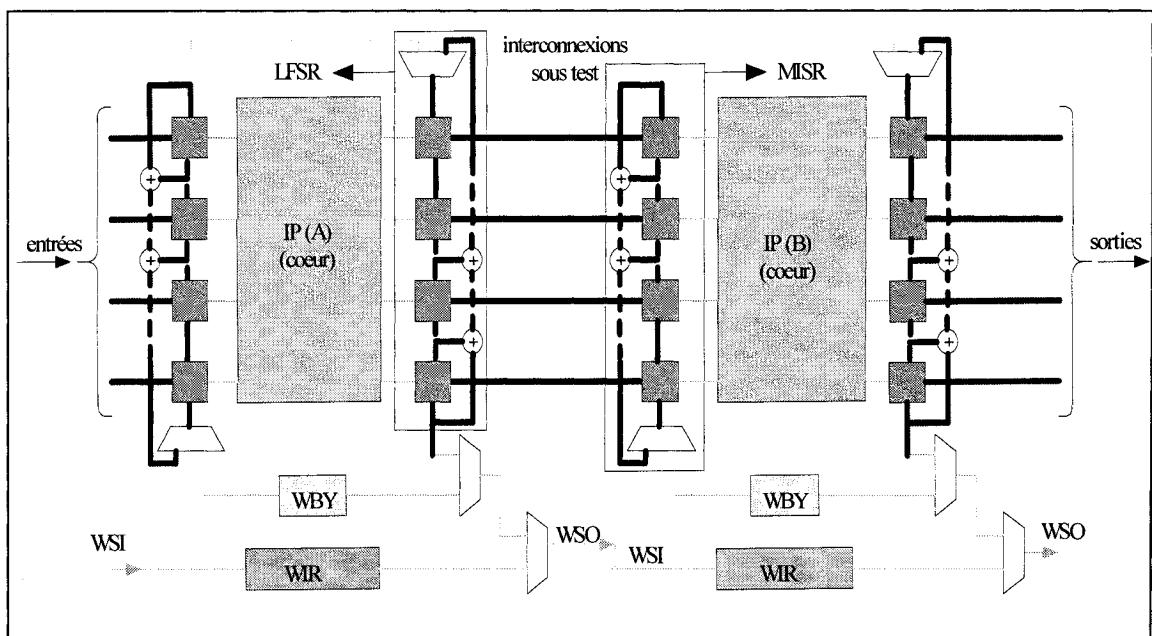

La figure 3.1 illustre le schéma de principe de la nouvelle architecture proposée pour le test des IP et des interconnexions. Cette architecture est composée d'une enveloppe dans laquelle, les IP sont encapsulés et d'un contrôleur qui gère les opérations de test. En mode normal, l'enveloppe agit en tant qu'interface qui relie l'IP aux autres modules du SOC. En mode test, l'enveloppe agit en structure de test qui permet de vérifier les IP et les interconnexions avec et sans la fonctionnalité BIST.

À titre d'exemple, lors du test du cœur de l'IP1 et de celui de l'IP2 ainsi que des interconnexions entre ces deux IP sans la fonctionnalité BIST, l'enveloppe de l'IP1 et celui de l'IP2 agissent en tant qu'enveloppe P1500 tel que présentée à la section 1.8. Dans ce mode de test, les enveloppes sont connectées en série et forment un registre à

décalage qui relie le signal d'entrée de l'enveloppe « Wrapper Scan In » (WSI) de l'IP1 au signal de sortie de l'enveloppe « Wrapper Scan Out » (WSO) de l'IP2. Ce registre sert à transférer en série les valeurs de WSI à appliquer aux signaux d'entrée du cœur de l'IP1 et à ceux du cœur de l'IP2 ainsi qu'aux interconnexions entre les IP. Ce registre est également utilisé pour récupérer et transmettre en série les réponses des IP et des interconnexions vers un testeur externe via WSO pour analyse.

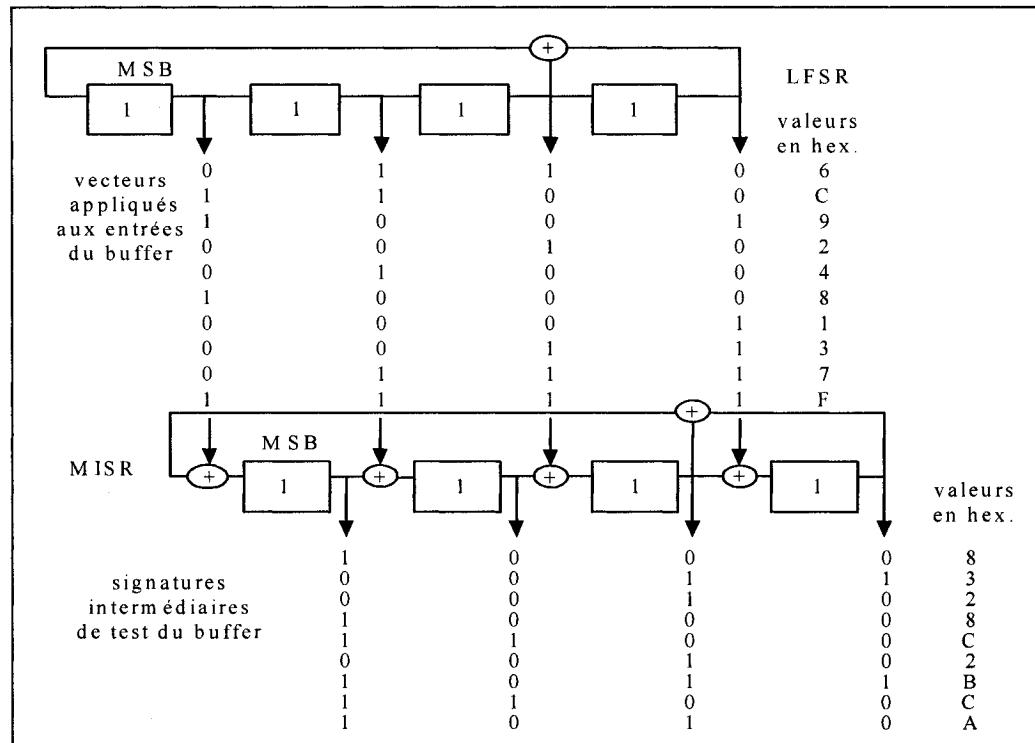

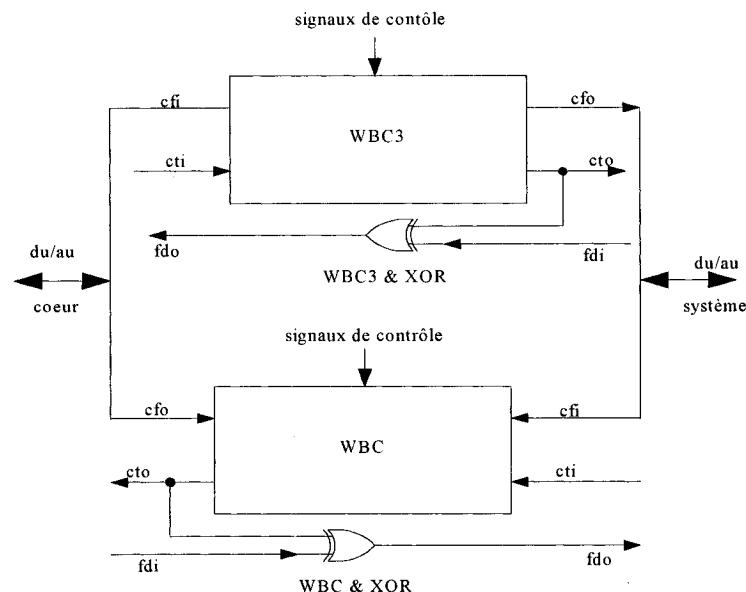

Pour tester le cœur de l'IP1 et celui de l'IP2 ainsi que les interconnexions entre ces deux IP avec la fonctionnalité BIST, les enveloppes des IP sont configurées en structures BIST dont le principe a été présenté précédemment à la section 1.7. Lors du test du cœur de l'IP, les cellules de l'enveloppe connectées aux entrées du cœur, agissent en LFSR pour générer et appliquer les vecteurs de test. Les réponses du cœur de l'IP sont compactées par le MISR formé par les cellules de l'enveloppe connectées aux sorties du cœur de l'IP. Par contre, lors du test des interconnexions entre l'IP1 et l'IP2, les vecteurs de test à appliquer aux interconnexions sont générés par les cellules de sortie de l'enveloppe de l'IP1 qui forment un LFSR. Les réponses de test des interconnexions sont compactées par les cellules d'entrée de l'enveloppe de l'IP2 qui agissent en MISR.

### 3.3 Architecture de la nouvelle enveloppe

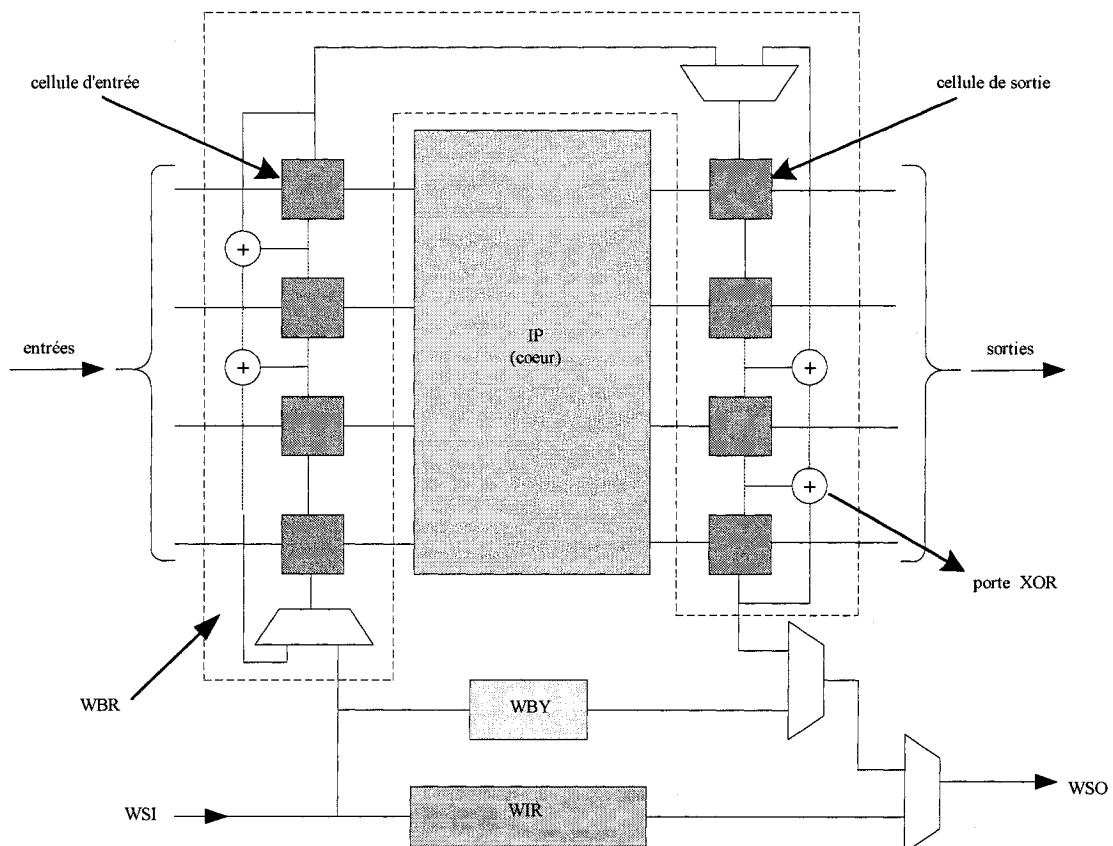

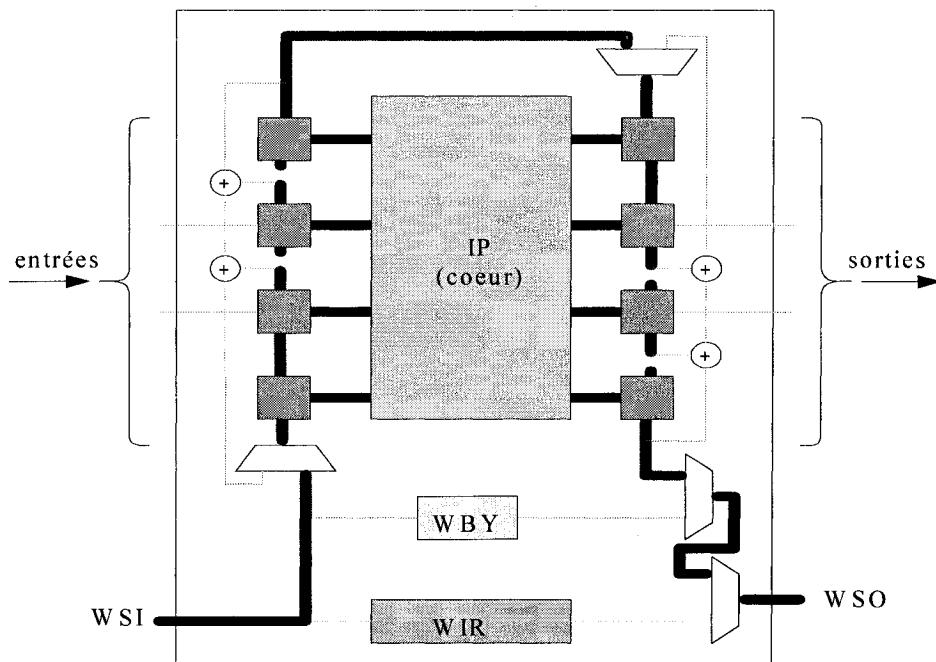

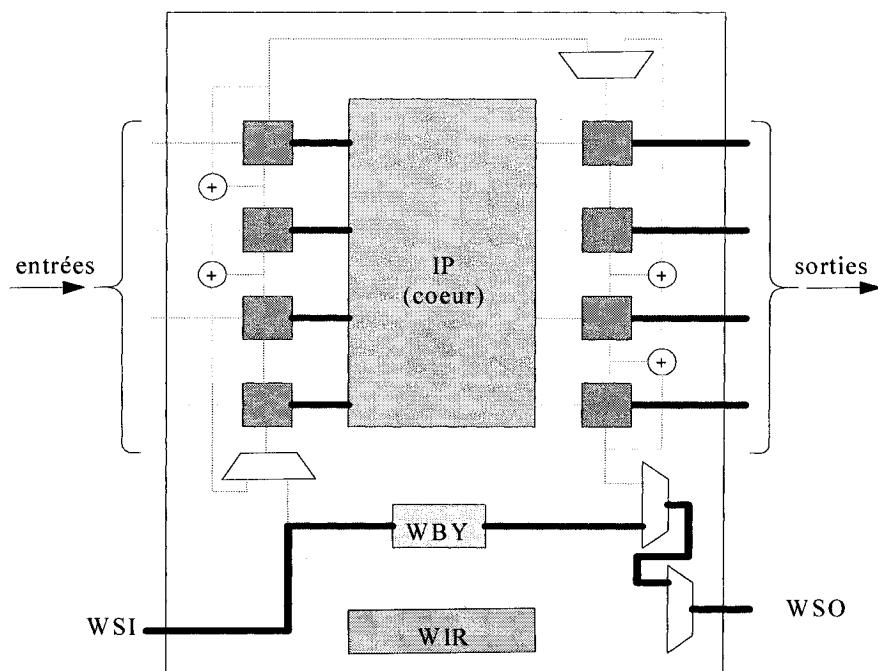

La figure 3.2 représente l'architecture de l'enveloppe proposée, que nous définissons comme une enveloppe P1500 dans laquelle la fonctionnalité BIST est incorporée [28]. La différence entre l'enveloppe proposée et celle que propose la norme IEEE P1500

résidé dans le comportement de leurs cellules qui sont associées aux entrées/sorties du cœur de l'IP. La nouvelle enveloppe est composée de quatre multiplexeurs et de trois registres à décalage obligatoires. La structure de l'enveloppe proposée peut également contenir d'autres registres optionnels propres à l'intégrateur. Les registres à décalage, que nous présentons ci-après, portent les mêmes noms que ceux de l'enveloppe P1500.

Figure 3.2: Architecture de l'enveloppe proposée.

Le premier registre obligatoire est le registre d'instruction « Wrapper Instruction Register » (WIR). Dans ce registre l'instruction de test est chargée en série et décodée pour générer les signaux de contrôles nécessaires au fonctionnement de l'enveloppe.

Le deuxième registre obligatoire est le registre à décalage de l'enveloppe « Wrapper Boundary Register » (WBR). Ce registre est inséré entre les signaux d'entrée/sortie du cœur de l'IP et les plots d'entrée/sortie de l'IP. En mode normal, les cellules de WBR relient en parallèle les signaux d'entrée/sortie du cœur de l'IP aux plots d'entrée/sortie de l'IP. En mode test sans BIST, le WBR est configuré en registre à décalage entre WSI et WSO. Ce registre offre un accès aux signaux d'entrée/sortie du cœur de l'IP à partir de l'extérieur du SOC. En mode test avec BIST, le WBR agit en structure BIST pour assurer le test des coeurs des IP et des interconnexions entre les IP à l'interne du SOC.

Le dernier registre obligatoire de l'enveloppe proposée est le registre de court-circuit « Wrapper Bypass Register » (WBY). Ce registre sert à court-circuiter WBR de l'IP qui ne participe pas dans une procédure de test. Ceci raccourcit la longueur du chemin de balayage, ce qui permet de réduire le temps d'application des vecteurs de test aux autres IP et interconnexions du SOC.

Avant de décrire l'architecture et le fonctionnement des registres énumérés ci-dessus, nous présentons en premier lieu l'architecture et le fonctionnement des différentes cellules de la nouvelle architecture de test.

### 3.4 Cellules de l'enveloppe

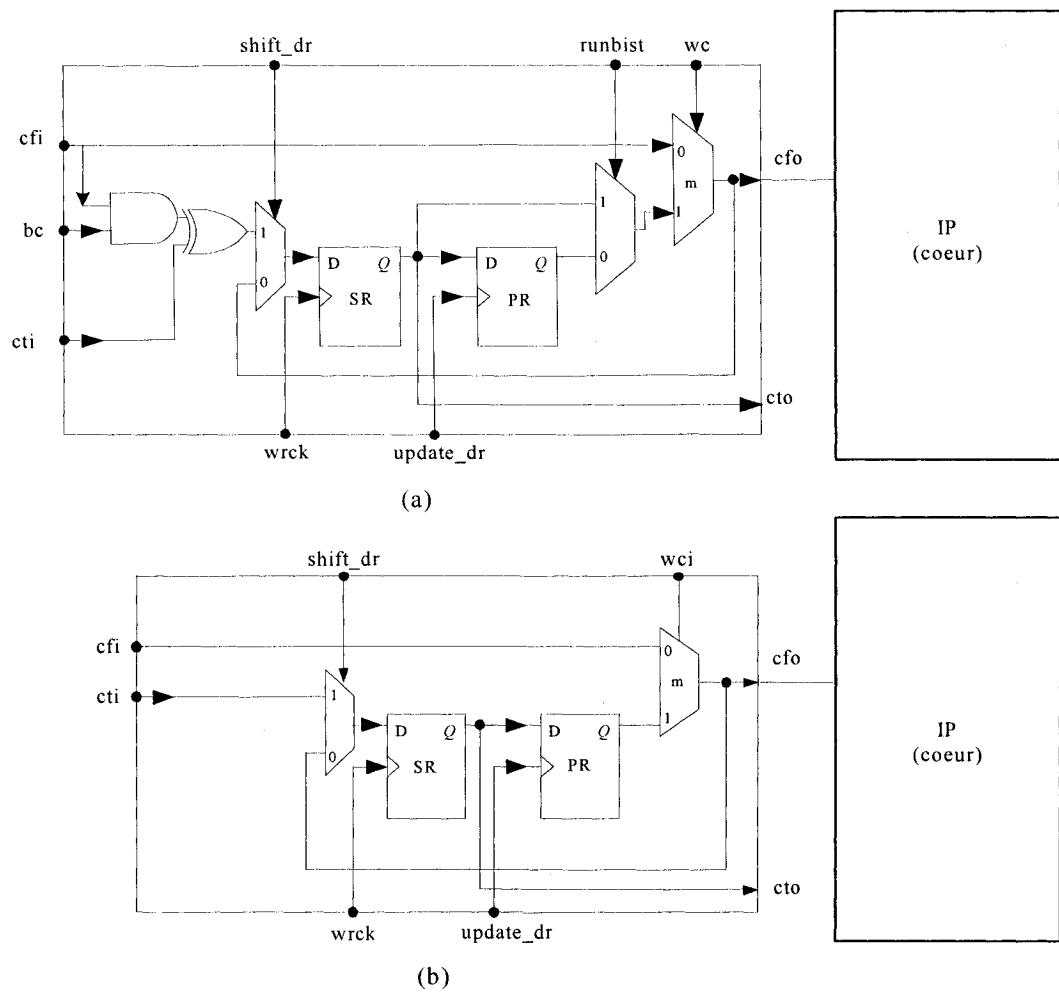

Dans cette section, nous présentons les cellules à deux états, à trois états et bidirectionnelles, que nous avons développé pour l'enveloppe proposée. Ces cellules ont

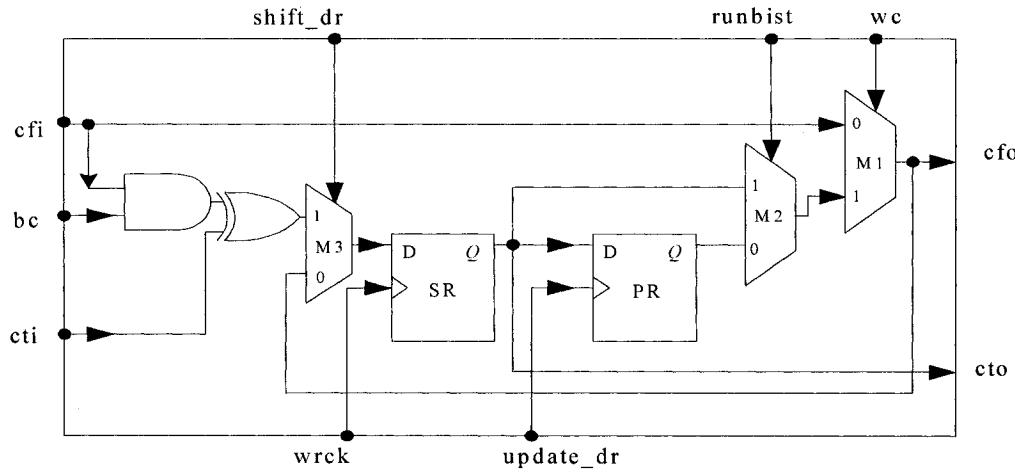

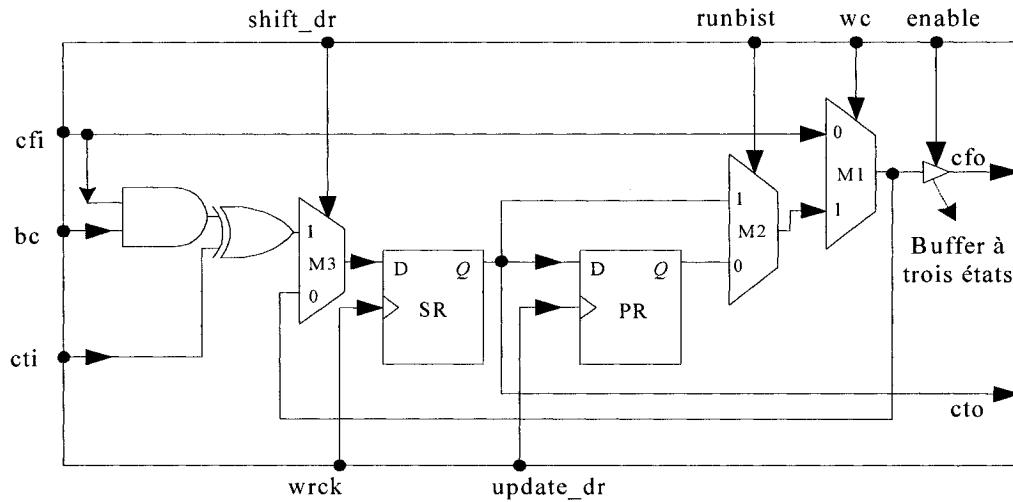

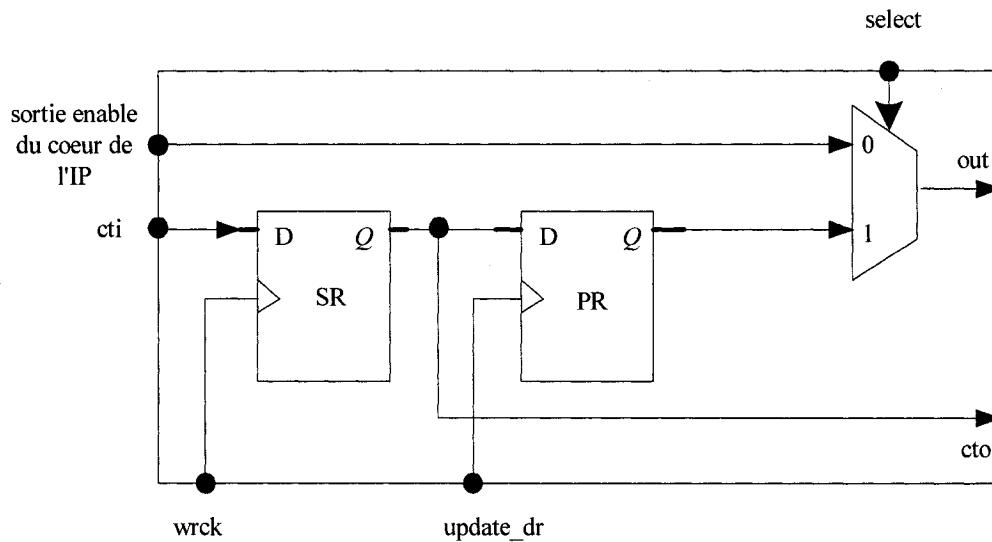

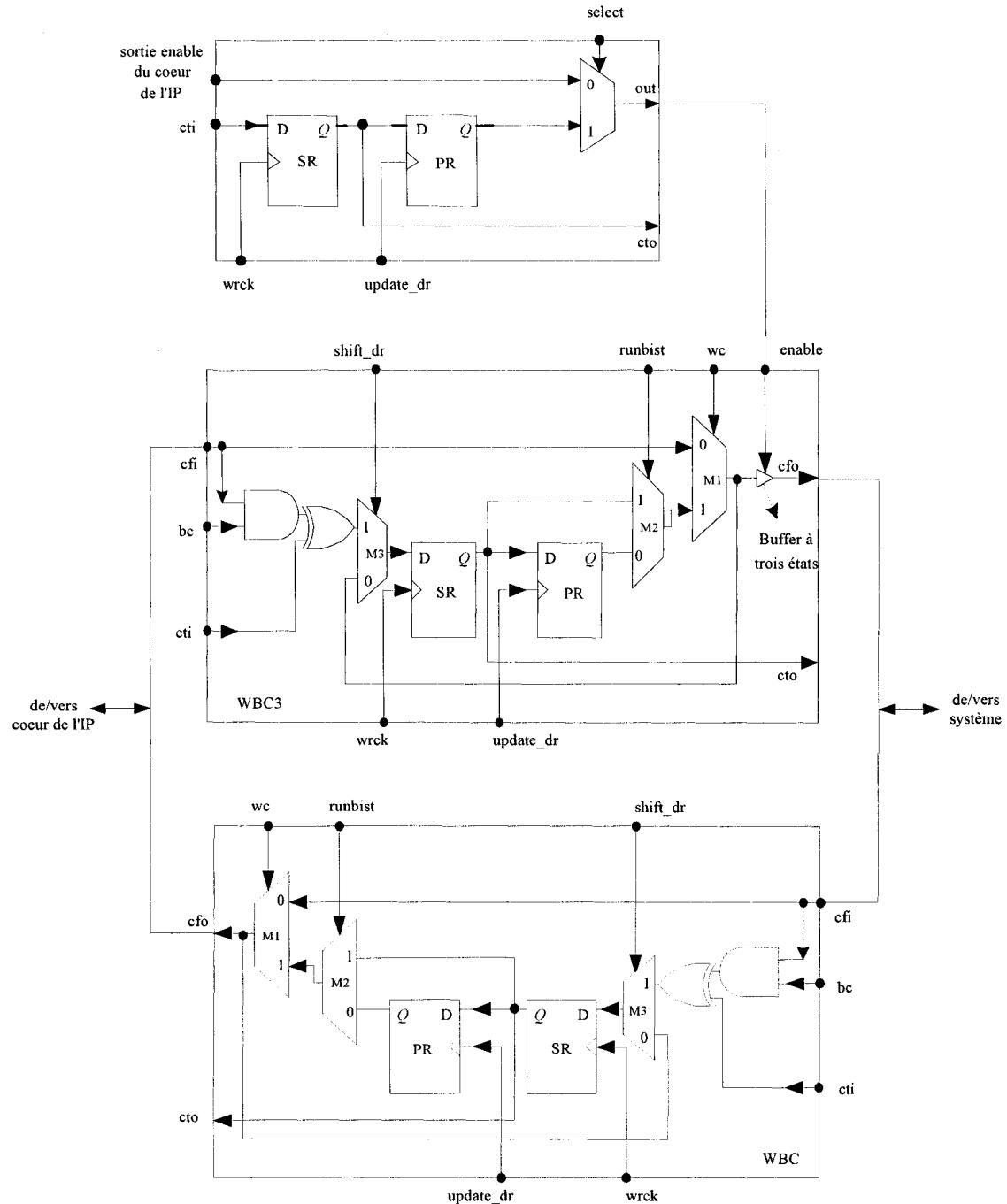

étaient conçues en modifiant l'architecture interne de la cellule « Boundary Scan Cell » (BSC) de la norme IEEE 1149.1 [19]. En mode normal, les cellules deviennent transparentes pour ne pas nuire au fonctionnement normal du cœur de l'IP. En mode test sans fonctionnalité BIST du cœur de l'IP et des interconnexions, les cellules assurent les opérations *Capture*, *Shift* et *Update* qui sont définies par la norme IEEE P1500 [20].