|                         | Dynamic pupil reacting to incident light dedicated to ocular implants                                                                                                                             |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Mohamad Wehbe                                                                                                                                                                                     |

| Date:                   | 2009                                                                                                                                                                                              |

| Туре:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                         |

| Référence:<br>Citation: | Wehbe, M. (2009). Dynamic pupil reacting to incident light dedicated to ocular implants [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. https://publications.polymtl.ca/8497/ |

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/8497/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Mohamad Sawan                         |

| <b>Programme:</b><br>Program:            | Non spécifié                          |

### NOTE TO USERS

This reproduction is the best copy available.

**UMI**°

#### UNIVERSITÉ DE MONTRÉAL

# DYNAMIC PUPIL REACTING TO INCIDENT LIGHT DEDICATED TO OCULAR IMPLANTS

# MOHAMAD WEHBE INSTITUT DE GÉNIE BIOMÉDICAL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE BIOMÉDICAL)

AOÛT 2009

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-57263-4 Our file Notre référence ISBN: 978-0-494-57263-4

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### UNIVERSITÉ DE MONTRÉAL

#### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

## DYNAMIC PUPIL REACTING TO INCIDENT LIGHT DEDICATED TO OCULAR IMPLANTS

présenté par: <u>WEHBE Mohamad</u>

en vue de l'obtention du diplôme de: <u>Maîtrise ès sciences appliquées</u>

a été dûment accepté par le jury d'examen constitué de:

- M. LESAGE Frédéric, Ph.D., président

- M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

- M. KASHYAP Raman, Ph.D., membre

"Human subtlety will never devise an invention more beautiful, more simple or more direct than does nature because in her inventions nothing is lacking, and nothing is superfluous."

Leonardo da Vinci

1452 - 1519

To my loving parents,

Raëf and Ghada

#### ACKNOWLEDGMENTS

Foremost, I would like to express my sincere gratitude to my supervisor, Professor Mohamad Sawan for his continuous support and guidance, and for the freedom he has granted me throughout the period of my study.

I would like to thank also M. Frédéric Lesage and M. Raman Kashyap for accepting to be a part of the jury and evaluating this work.

I would also like to thank my fellow labmates in the Polystim neurotechnologies research group for their support and technical advice as well as providing me with a great environment to work in. These thanks go in particular to everyone who has passed by the room M5304.

I would like to thank Mustapha Yakoub for his support for the ADC part of this work.

Thanks also go to Marise Duquette for her support and her help in the french translation of the abstract and the condensé en français.

I would like also to thank my parents for their unconditional support throughout my Master's thesis.

Finally I would like to thank the Canadian Microelectronic Corporation for fabricating the chip and the NSERC for the financial support.

#### RÉSUMÉ

Une des fonctions de contrôle autonome de l'œil est d'adapter la luminosité aux différentes conditions extérieures pour une meilleure acuité visuelle. Ceci est fait en changeant la taille de la pupille.

La perte d'un œil est traumatisante peu importe l'âge. Elle a un grand impact sur l'image et l'estime de soi, ainsi que sur la confiance en soi. Bien que des solutions d'œil artificiel existent, elles ne sont qu'une amélioration esthétique et psychologique pour le patient, mais ne restaurent en aucune façon la vision. De plus un défaut d'anisocorie post-prothèse, c.à.d., la taille de la pupille qui ne change pas peu importe l'éclairage, apparaît avec un œil artificiel, ce qui produit un effet néfaste sur le patient.

Dans ce projet de maîtrise nous proposons de réduire le défaut d'anisocorie post-prothèse. Pour ce faire nous avons développé une pupille dynamique dédiée aux yeux artificiels. La pupille artificielle va en premier lieu capter la lumière ambiante à travers une photodiode, puis convertir le signal capté en un signal numérique pour déduire l'intensité lumineuse et finalement contrôler l'afficheur en conséquence. Ce système remplacera ainsi la pupille statique des yeux artificiels. Les résultats des simulations post-layout et expérimentaux nous ont permis de valider le bon fonctionnement du système. La partie principale du système a été implementée en utilisant la technologie CMOS  $0.18~\mu m$  avec une superficie totale de  $1.3~mm^2$ .

Un convertisseur analogique/numérique a été intégré au système, le rendant plus compact. En réalisant un convertisseur tension/courant, nous étions capable d'intégrer à notre système un convertisseur analogique/numérique ayant une entrée courant développé par une équipe du laboratoire de neurotechnologies Polystim.

#### ABSTRACT

One of the autonomous control functions of the eye is to regulate light input to suit the conditions for best visual acuity. This is done by changing the size of the pupil. Losing an eye is devastating at any age. It has great impact on one's self image, self confidence and self esteem causing physical as well as psychological distress. A person who has lost an eye will replace the latter with an ocular implant. Standard ocular implants will attempt to faithfully reproduce the physical features of a natural eye, however the prosthetic pupil is fixed all the time giving a poor cosmetic appearance.

In this master's thesis we propose an artificial human pupil, which is composed of a dedicated controller and a miniaturized display. The purpose of this system is to overcome the problem of post-prosthesis anisocoria for people with ocular implants, by creating iris diaphragm in the prosthetic eye with photosensitive receptors responding to light so as to work in symmetry with the normal eye. The proposed artificial pupil would acquire ambient light through a photosensor, convert the acquired signal to digital data, transform this data to light intensity and finally control the display accordingly. This system would replace the static iris of a prosthetic eye. Experimental results from developed prototype, and post-layout simulation results from the integrated controller faithfully reproduce the expected performance, which is in the form of a dilating and contracting pupil. The main part of the system is implemented in  $0.18~\mu m$  CMOS process and has a total area of  $1.3~mm^2$ .

An analog-to-digital converter (ADC) has been integrated to the system, making it more compact. By developing a voltage-to-current converter we were able to use a current input ADC developed by a team of the Polystim neurotechnologies laboratory.

#### CONDENSÉ EN FRANÇAIS

#### Introduction

La majorité des déformations oculaires résultent de traumas, bien que dans 28.5% des cas, les tumeurs exigent l'énucléation de l'œil (Cheng et al. (2008)). Dans ces situations, les gens sont laissés avec un seul œil. Suite à la perte d'un œil, un implant est placé dans le globe oculaire pour faciliter la construction de la prothèse oculaire. Ceci est fait pour empêcher l'affaissement de l'orbite après l'énucléation.

Les implants oculaires ont subi des améliorations durant plusieurs décennies afin de fournir un remplacement esthétique pour l'œil énuclée (Beumer et al. (1979)). Malheureusement, les résultats esthétiques optimaux sont compromis quand la taille de la pupille choisie a un diamètre fixe peu importe les conditions d'éclairage.

Le diamètre de la pupille est très sensible à l'intensité lumineuse, et peut ainsi varier entre 2 mm et 8 mm. Ce phénomène est appelé l'anisocorie post-prothèse.

Des études ont été faites pour décrire la relation entre la taille de la pupille humaine et la densité de la lumière présente à la rétine (Spring and Stiles (1948), Groot and Gebhard (1952), Bergamin et al. (1998)). Groot and Gebhard (1952) ont dérivé une équation qui décrit cette relation :

$$\log d = 0.8558 - 0.0004(\log B + 8.1000)^3,\tag{1}$$

où d est le diamètre de la pupille en mm, et B est la luminosité en milliLamberts.

Dans ce projet de maîtrise, nous proposons de réduire le défaut d'anisocorie postprothèse. Pour ce faire, nous avons développé une pupille dynamique dédiée aux yeux artificiels.

#### La pupille dynamique

#### Le prototype

Un prototype a été développé en vue de valider notre design avant la conception du système intégré. Ce prototype a été conçu avec des composantes électroniques discrètes.

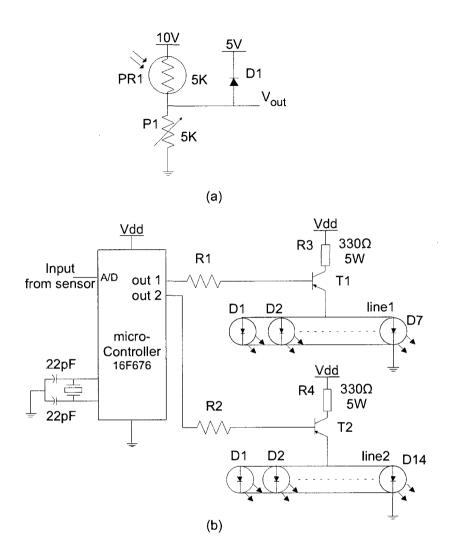

Ce design peut être divisé en deux parties, soit une partie analogique et une partie numérique. La partie analogique est dédiée à la détection de la lumière. Elle comprend une photorésistance qui joue le rôle du capteur et une résistance variable pour ajuster la tension de sortie de cette partie.

La partie numérique est un contrôleur qui est basé sur un microcontrôleur (PIC 16F676) représentant un convertisseur analogique à numérique et effectuant trois fonctions essentielles, soit de convertir le signal analogique provenant du capteur en un signal numérique de 8 bits représentant la luminosité, puis de comparer cette valeur numérique à des valeurs mises en mémoire et finalement, de contrôler l'afficheur-simulant la pupille humaine.

#### La version intégrée

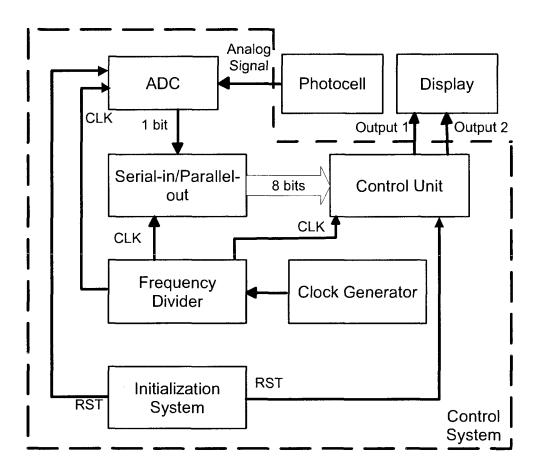

Ce système est constitué d'une photodiode, d'un contrôleur et d'un afficheur. Il peut être divisé en deux parties : la partie électronique de traitement de signal et la partie affichage reflétant le niveau de lumière reçu.

#### Partie électronique

Cette partie comprend un générateur d'horloge sur puce, un circuit de délai pour initialiser le système au démarrage, une unité de contrôle et finalement un convertisseur analogique/numérique.

#### • Générateur d'horloge

Nous avons choisi l'architecture d'oscillateur en anneau à 7 étages pour générer le signal d'horloge requis. La fréquence d'oscillation est donnée par l'équation suivante :

$$f_{osc} = \frac{1}{2N_{osc}\tau_{inv}} \tag{2}$$

où  $N_{osc}$  est le nombre d'étages et  $\tau_{inv}$  est le délai d'inversion pour chaque étage. Avec un délai d'inversion de  $\tau_{inv} = 79.3$  ps, on obtient une fréquence d'oscillation de  $f_{osc} = 900.9 \times MHz$ .

Un diviseur de fréquence comprenant des bascules D en série est utilisé pour ramener la fréquence à 100 kHz, la fréquence d'opération du convertisseur analogique/numérique.

#### • Le circuit d'initialisation

Ce circuit est utilisé pour initialiser le contrôleur au démarrage. Pour ce faire, ce circuit force un '0' logique sur le "reset" du contrôleur pour une certaine durée, pendant laquelle le système est remis à zéro.

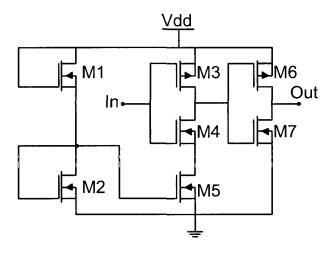

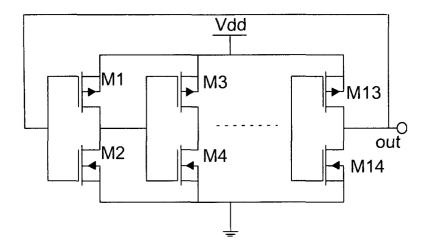

Le circuit d'initialisation utilisé est un circuit de délai, illustré dans la figure 1.

FIGURE 1: Le circuit de délai

L'unité principale de ce circuit est le tampon "current-starved" formé par les transistors M3 à M7. Le courant de chargement et de déchargement de la capacité de sortie est contrôlé par le miroir de courant constitué des transistors M2 et M5. Dès que le transistor M4 devient en état passant, sa capacité de sortie commence à décharger. Le courant de déchargement est contrôlé par M5 qui agit comme source de courant. Le courant passant dans ce dernier est contrôlé à son tour par la tension à la grille de M2. Cette tension est déterminée par le courant passant à travers le drain de M2. Le transistor M1 contrôle le courant passant par M2. Le ratio W/L de M1 a donc été conçu pour obtenir le délai voulu.

#### Convertisseur analogique/numérique

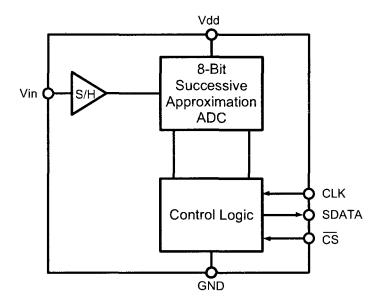

Après avoir exploré les différentes architectures de CAN disponibles, nous avons jugé que le CAN à approximation successive est le meilleur choix pour notre système.

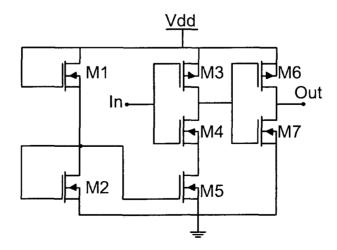

Ce CAN 8-bit de "Analog Devices" (figure 2) mesure de longueur 2.9 mm, de largeur 1.9 mm et une épaisseur de 0.9 mm, et peut donc être facilement intégré au prototype dy système.

FIGURE 2: Diagramme bloc du CAN utilisé dans le premier prototype du système

Ce CAN est connecté directement à la photodiode, convertissant la sortie analogique de cette dernière en un signal numérique compatible avec le circuit numérique de contrôle.

L'acquisition des données et la conversion sont contrôlées par le signal  $\overline{CS}$  et par l'horloge. Le signal d'entrée est échantillonné sur le front descendant de  $\overline{CS}$ , et la conversion est également initiée au même moment. La tension de référence est prise directement de  $V_{DD}$ , permettant une plage d'entrée plus grande. Par conséquent, la plage d'entrée analogique est de 0 V à  $V_{DD}$ .

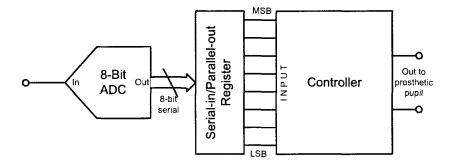

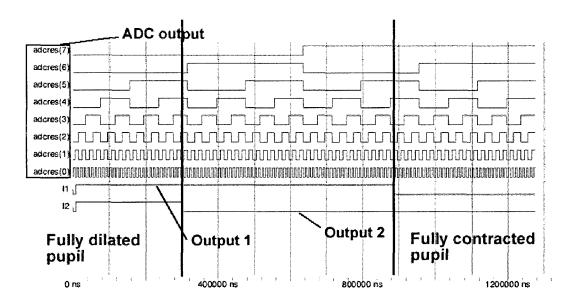

#### • Le contrôleur

Le contrôleur est le module principal du présent système électronique. Celui-ci contrôle la contraction et la dilatation de la pupille prothétique. L'entrée de ce module provient de la sortie à 8 bits du CAN. Puisque la sortie du CAN est sérielle, un registre "serial-in/parallel-out" a été conçu pour connecter le contrôleur au CAN. Par la suite, le contrôleur transforme le signal numérique en intensité lumineuse, en se basant sur les données présentées au tableau 1.1. Ce module fournit trois niveaux d'animation pour la pupille prothétique, allant de complètement contractée à complètement dilatée. Pour atteindre une telle résolution, le contrôleur génère deux sorties codées en binaire.

Le contrôleur a été implémenté et testé en VHDL. L'algorithme implémenté compare l'entrée à des valeurs équivalentes à la luminosité dans le tableau 1.1, et, par la suite contrôle l'afficheur (pupille prothétique) en conséquence. L'algorithme a été synthétisé avec Design Vision (Synopsys, Inc.) pour générer un "netlist" du circuit. Le circuit physique a été créé par l'outil de placement-et-routage Soc-Encounter (Cadence).

L'algorithme utilisé dans le design du contrôleur est :

```

if (IN > 316 lux) then

OUT1 = 0

OUT2 = 0

elsif (1 lux < IN < 316 lux) then

OUT1 = 1

OUT2 = 0

else

OUT1 = 1</pre>

```

0UT2 = 1

endif;

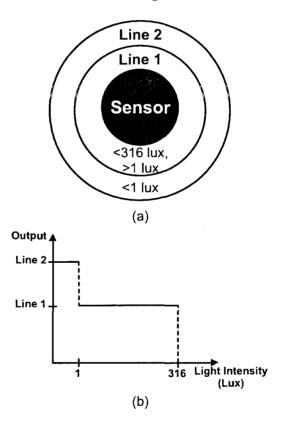

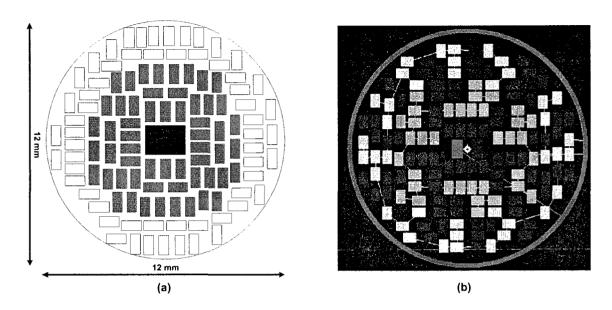

#### L'afficheur

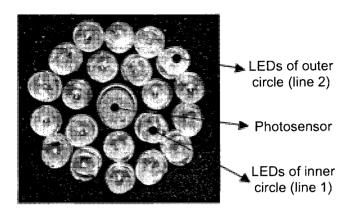

Avec la technologie d'aujourd'hui, le développement d'un afficheur à cristaux liquides ayant la taille de l'iris humain serait très dispendieux. Un compromis a donc été fait et l'afficheur simulant la pupille humaine a été développé en utilisant des diodes électroluminescentes (DEL). Les DELs utilisées ont une taille de  $1.0~\rm mm \times 0.5~\rm mm$ . Elles sont assemblées d'une manière circulaire, formant un afficheur ayant un diamètre de  $12~\rm mm$ , taille de l'iris humain. Une surface fixe de  $4~\rm mm^2$  n'est pas influencée par la quantité de lumière; le capteur de lumière est installé dans cette région. La surface variable selon la lumière est un anneau ayant un diamètre intérieur de  $2~\rm mm$  et un diamètre total de  $12~\rm mm$ . Ainsi, selon la quantité de lumière, le diamètre de la pupille varie entre  $2~\rm mm$  et  $12~\rm mm$ .

La photodiode utilisée est une photodiode commerciale (TDK, Garden City, NY) ayant une taille de  $1.5 \text{ mm} \times 2 \text{ mm}$ , une sensibilité spectrale entre 350 et 750 nm et une plage de luminosité entre 0 et 75,000 Lux.

Les DELs forment deux cercles indépendants, fournissant trois niveaux d'animation. Ces deux cercles sont contrôlés par les deux sorties du contrôleur.

#### Résultats

#### Validation expérimentale du prototype

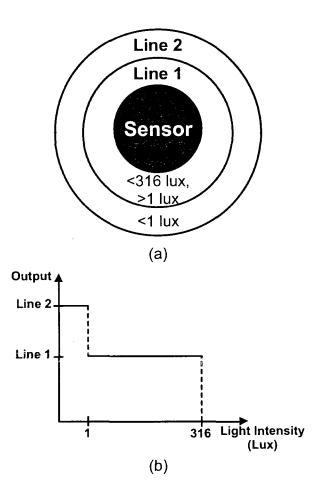

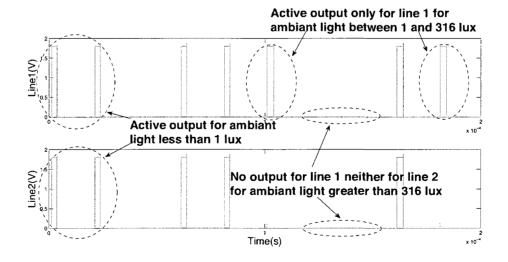

Le prototype a été assemblé sur un PCB utilisant des composantes discrètes, soit un microcontrôleur, une photorésistance, des transistors et des DELs. Le circuit schématique du circuit est illustré dans la figure 3.1 (chapitre 3). Le prototype a été testé dans différentes conditions d'éclairage, soit de l'éclairage faible à l'éclairage fort. Les résultats du test sont illustrés dans la figure 3.

FIGURE 3: Résultats du test du prototype : (a) Diagramme d'intensité (b) Graphique illustrant la sortie du prototype

Lorsque la lumière est vive, les deux lignes sont désactivées. Lorsque l'éclairage est normal, seule la ligne 1 est active, tandis que les deux lignes sont actives lorsque l'éclairage est faible.

#### Dessins de masques

Une fois la conception schématique terminée, arrive l'étape du dessin de masques. En faisant le dessin de masques, on prend en considération l'apparition des résistances et des capacités parasites, les mésappariements et la capture du bruit provenant du substrat.

#### Résultats des simulations post-layout

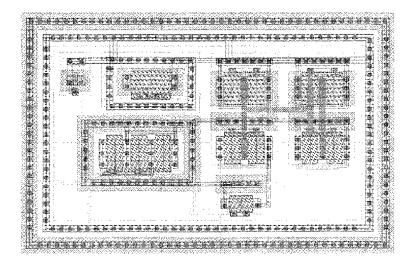

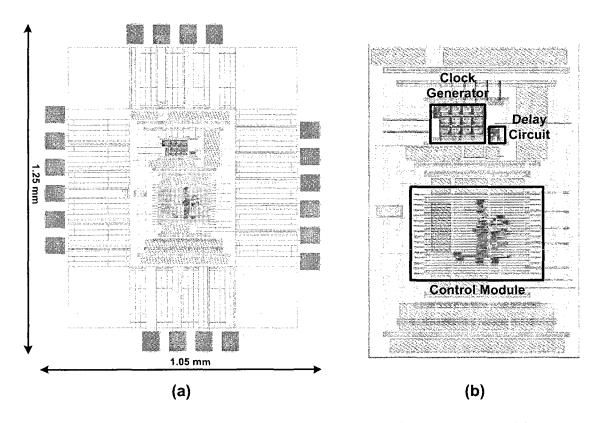

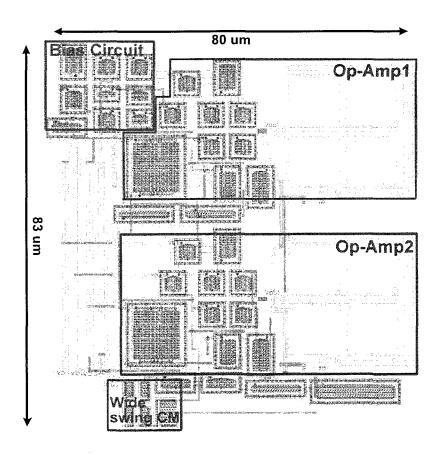

Le circuit intégré a été conçu et fabriqué en utilisant la technologie CMOS 0.18  $\mu$ m à puits n de la Taiwan (TSMC), ayant une superficie totale de 1.25 mm × 1.05 mm.

La première étape, lors de la vérification d'un circuit, est de valider son fonctionnement module par module, puis de vérifier la chaîne complète.

#### Le générateur d'horloge

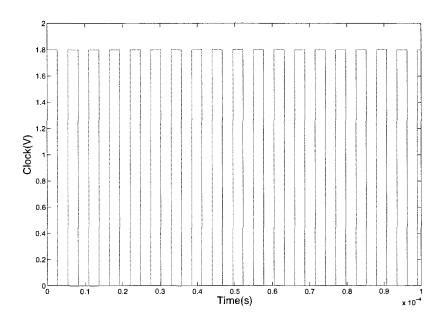

La taille de ce module est de 95  $\mu m \times 57 \mu m$ . Ce dessin de masques comprend le "layout" de l'oscillateur en anneau avec le diviseur de fréquence. Tous les blocs sont entourés par deux anneaux de garde connectés respectivement à  $V_{DD}$  et  $V_{SS}$ . Les simulations post-layout de ce module ont donné un signal carré ayant une fréquence de 180 kHz.

#### Le circuit de délai

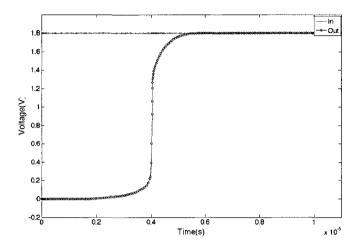

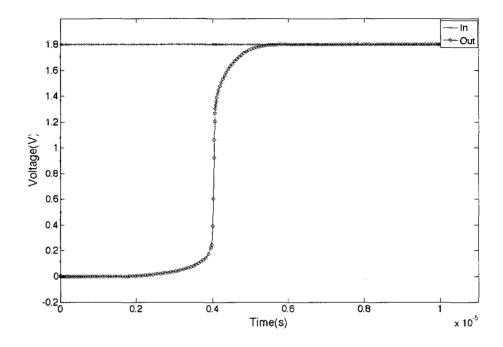

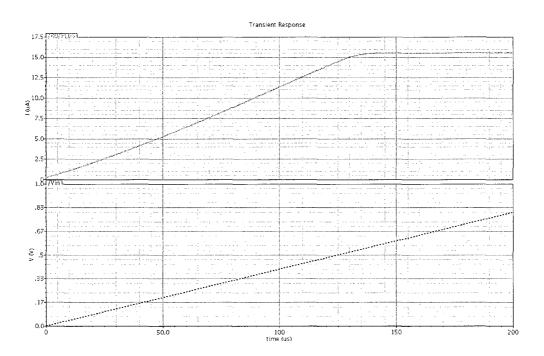

Ce module a été utilisé pour initialiser le système au démarrage, en appliquant un '0' au "reset" du contrôleur pour une période de 4  $\mu s$ , après laquelle un '1' logique (1.8 V) est appliqué pour activer le circuit. À l'entrée de ce circuit, le signal  $V_{DD}$  est connecté.

FIGURE 4: Résultats des simulations post-layout du circuit de délai

#### Le circuit de contrôle

Ce module est un contrôleur entièrement numérique, utilisant les blocs numériques fournis par la librairie "artisan" de la TSMC.

Le signal numérique provenant du CAN est appliqué à l'entrée de ce circuit. Ce signal contient de l'information sur l'intensité lumineuse. La sortie de ce circuit consiste en un mot de 2 bits contrôlant l'afficheur, tout comme dans le prototype.

#### Le circuit intégré

Après avoir validé le fonctionnement de chaque module seul, nous avons connecté tous les modules ensemble et testé la chaîne complète. Après la connection des différents modules, nous avons ajouté des pads et des plots de la librairie "tpz973g".

Le système a été simulé avec une tension d'alimentation de 1.8 V. Les résultats correspondent à nos attentes. Par la suite, le circuit a été testé avec différentes charges capacitives et résistives à la sortie.

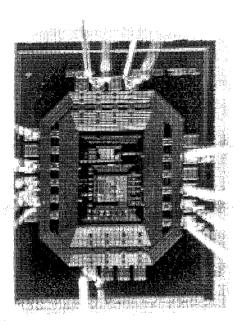

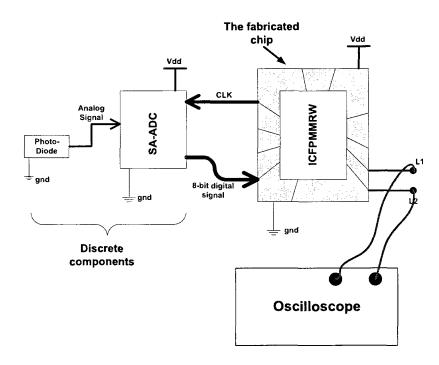

#### Résultats expérimentaux

Un banc d'essai a été réalisé pour récupérer le signal d'horloge et les deux sorties du contrôleur. Le banc d'essai consistait en la mise à l'essai du CAN à approximation successive, de notre puce mentionnée ci-dessus, d'un capteur de lumière (photodiode), d'une source d'alimentation et d'un oscilloscope.

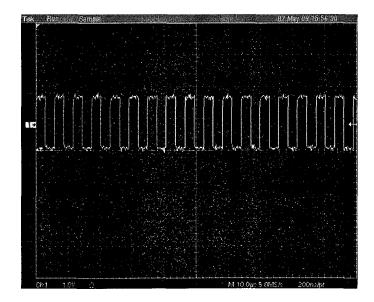

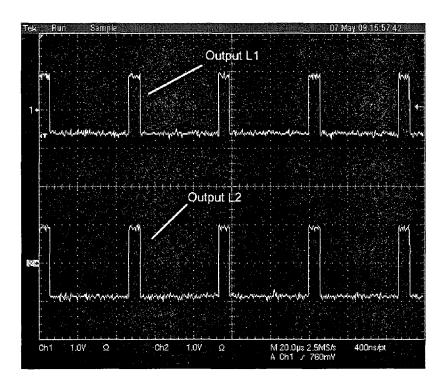

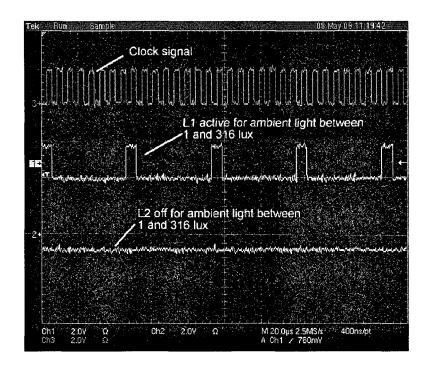

Premièrement, nous avons mesuré le signal d'horloge. Nous avons visualisé un signal ayant une amplitude de 1.76 V et une fréquence de 172 kHz. La puce a été testée comme montré dans la figure 4.11, et les résultats étaient identiques à ceux des simulations post-layout. Nous avons commencé le test avec une luminosité réduite, c'est-à-dire, une tension d'entrée près de 0 V, et les deux signaux de sortie étaient actifs, indiquant une pupille complètement dilatée. Par la suite, nous avons poursuivi le test avec une lumière vive, et les deux sorties du contrôleur étaient désactivées.

Le tableau 1 compare nos simulations post-layout avec les résultats expérimentaux.

Table 1: Paramètres simulés vs. paramètres mesurés

| Paramètre                   | Simulé  | Mesuré  | Erreur % |

|-----------------------------|---------|---------|----------|

| Tension d'alimentation      | 1.8 V   | 1.8 V   | N/A      |

| Tension d'horloge           | 1.8 V   | 1.76 V  | 2.2 %    |

| $F_{CLK}$                   | 180 kHz | 172 kHz | 4.4~%    |

| Tension de sortie           | 1.8 V   | 1.76 V  | 2.2 %    |

| $F_{OUT}$                   | 20 kHz  | 21 kHz  | 5 %      |

| Rapport cyclique (sortie) % | 20 %    | 13.5 %  | 32.5 %   |

#### Intégration du CAN

Une lacune de ce système était que le CAN n'était pas intégré dans la même puce que le reste des modules et qu'il occupait ainsi un espace important et augmentait la consommation de la puissance. Pour combler cette lacune, nous avons entrepris l'étape d'intégration d'un CAN basse consommation d'énergie.

#### Le CAN intégré

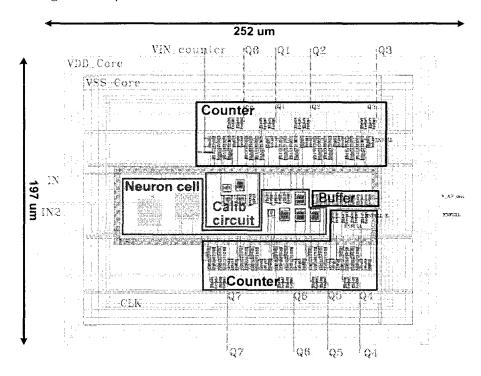

Le CAN que nous avons intégré à notre puce est un CAN neuromimétique de 8 bits, qui a été développé par Yakoub (Yakoub et al. (2009)), membre de notre équipe de technologie Polystim. L'opération de ce CAN est inspirée de l'opération du neurone humain.

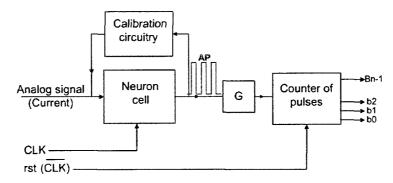

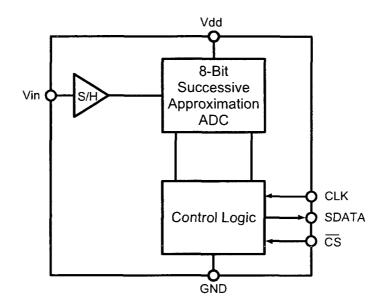

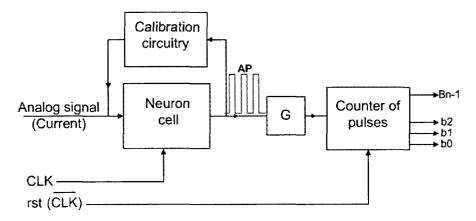

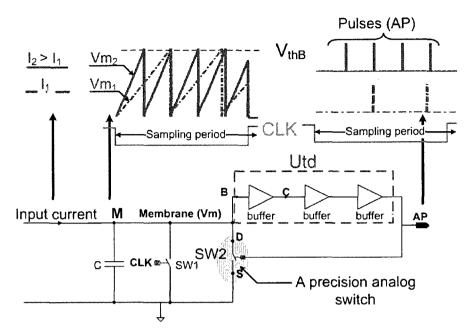

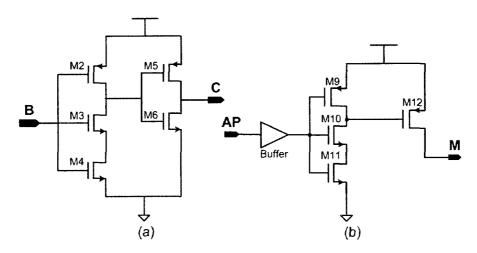

La figure 5 illustre le diagramme bloc de ce CAN.

FIGURE 5: Diagramme bloc du CAN neuromimétique (Tiré de Yakoub et al. (2009))

Les blocs principaux qui constituent ce CAN sont la cellule neuronale, le circuit de calibration et le compteur.

L'entrée en courant de ce CAN est au niveau de la cellule neuronale. Cette dernière génère des impulsions en tension ayant une magnitude identique et une fréquence directement proportionnelle au courant d'entrée. Le circuit de calibration a pour fonction de satisfaire la proportionnalité entre le nombre d'impulsions et le courant d'entrée. Finalement, le compteur compte le nombre d'impulsions par une période de temps prédéfinie.

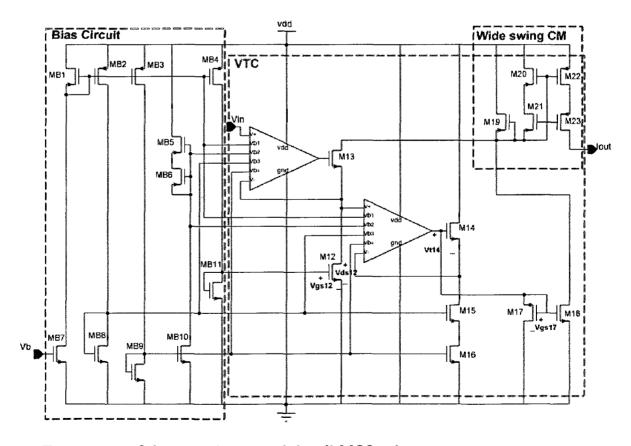

#### Convertisseur tension-courant

Étant donné que le CAN utilisé a une entrée en courant et que la photodiode a une sortie en tension, nous avons eu recours à un convertisseur tension-courant pour pouvoir faire la jonction entre ces deux modules. Le convertisseur tension-courant est un circuit "all-MOS" sans résistance (Fotouhi (2001)).

Ce convertisseur produit une sortie de courant qui est la somme des courants passant dans deux transistors opérant dans la zone linéaire et la zone de saturation. Un circuit schématique de ce convertisseur est montré dans la figure 5.4 (chapitre 5).

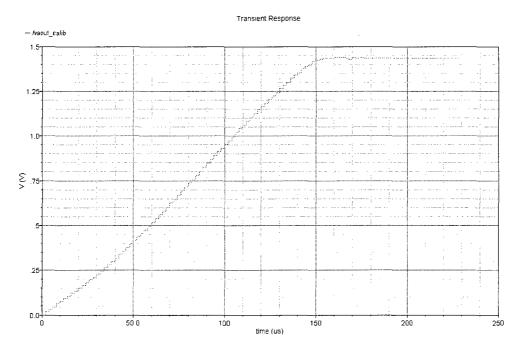

#### Résultats des simulations post-layout

Le convertisseur tension-courant et le CAN ont été conçus en utilisant la technologie CMOS 0.18  $\mu m$ .

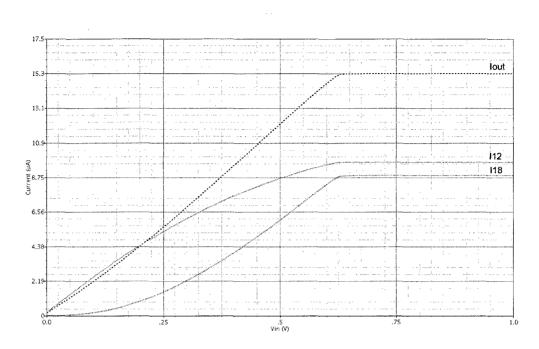

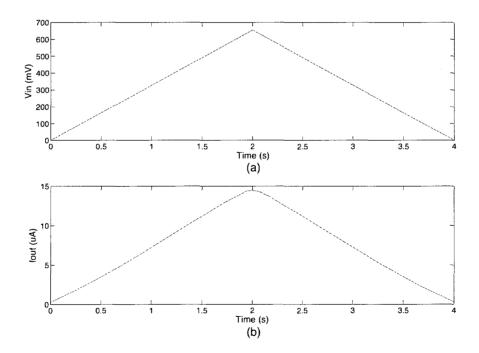

Nous avons simulé le convertisseur tension-courant avec une rampe allant de 0 V à 660 mV. Le courant de sortie de ce circuit  $(I_{out})$  est directement proportionnel à cette rampe d'entrée  $(V_{in})$ . Cette relation est donnée par l'équation :  $I_{out} = 2.65 \times 10^{-5} \ V_{in}$ . Le convertisseur tension-courant atteint la saturation pour une entrée dépassant 660 mV, ce qui convient à notre application, la photodiode ayant une sortie entre 0 V et 650 mV.

Le courant de sortie de ce module varie entre 285 nA et 15.3  $\mu A$ , également compatible à notre système, le CAN ayant une plage d'entrée entre 100 nA et 16  $\mu A$ .

À la suite de la simulation du convertisseur tension-courant, nous avons couplé ce dernier avec le CAN. Nous avons connecté les 8 bits de sortie du CAN à un convertisseur numérique-analogique (CNA) idéal conçu en **veriloga**. Finalement, nous avons simulé la sortie du CNA qui représente une rampe reproduisant l'entrée.

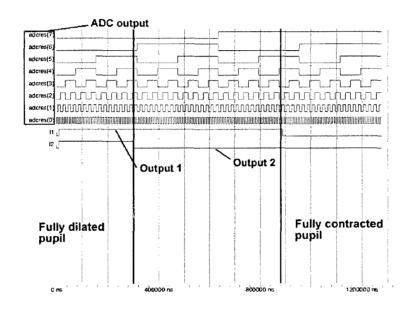

À la suite de la simulation du convertisseur tension-courant et du CAN, nous avons testé le contrôleur couplé avec ces derniers. La figure 6 montre les résultats de simulation de l'ensemble du système. Ces résultats sont identiques aux résultats obtenus avec un CAN externe.

FIGURE 6: Résultats de simulation du système (contrôleur et du CAN)

#### Conclusion

Nous avons présenté, dans ce mémoire, un système d'implants oculaire pour les personnes ayant perdu un œil et qui désirent le remplacer par un œil artificiel qui ressemble à un œil normal. Ce système consiste en une pupille dynamique réagissant à la lumière incidente. Les résultats de simulation post-layout ainsi que les résultats expérimentaux ont montré le bon fonctionnement du système. Nous avons entre autres, proposé une version complètement intégrée du système qui regroupe un convertisseur analogique-numérique, mode courant et un convertisseur tension-courant pour diminuer la consommation de puissance et la taille occupée du système.

#### TABLE OF CONTENTS

| DEDIC  | ATION  | T                              | V                |

|--------|--------|--------------------------------|------------------|

| ACKNO  | OWLED  | DGMENTS                        | vi               |

| RÉSUM  | ſÉ     |                                | vii              |

| ABSTR  | ACT    |                                | ix               |

| CONDE  | ENSÉ E | EN FRANÇAIS                    | Х                |

| TABLE  | OF C   | ONTENTS                        | ιiν              |

| LIST O | F TAB  | LES                            | vii              |

| LIST O | F FIGU | URES                           | <sup>,</sup> iii |

| LIST O | F ABB  | REVIATIONS AND SYMBOLS         | ciii             |

| LIST O | F APP  | ENDICES                        | χv               |

| INTRO  | DUCTI  | ION                            | 1                |

| СНАРТ  | TER 1  | BACKGROUND                     | 3                |

| 1.1    | Introd | luction                        | 3                |

| 1.2    | Physic | ological Background            | 3                |

|        | 1.2.1  | The Human Eye                  | 3                |

|        | 1.2.2  | Pathologies                    | 6                |

|        | 1.2.3  | Pupil Size vs. Ambient Light   | 7                |

| 1.3    | Ocular | r Prosthetics                  | 8                |

|        | 1.3.1  | Types of Ocular Implants       | 10               |

|        | 1.3.2  | Advances in Ocular Prosthetics | 11               |

| 1.4   | Technical Background                                 | 12 |

|-------|------------------------------------------------------|----|

|       | 1.4.1 Optical Detectors and Receivers                | 12 |

|       | 1.4.2 Main Types of Oscillators                      | 15 |

|       | 1.4.3 Main Types of Analog-to-Digital Converters     | 20 |

| 1.5   | Recapitulation                                       | 25 |

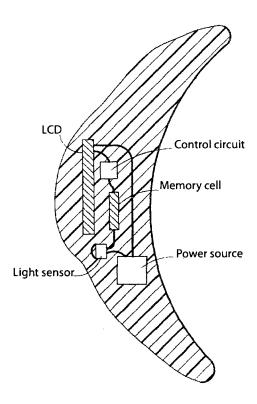

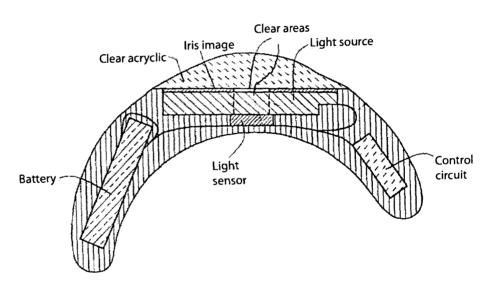

| СНАРТ | TER 2 INTELLIGENT OCULAR IMPLANTS                    | 27 |

| 2.1   | Introduction                                         | 27 |

| 2.2   | Robotic Prosthetic Eye                               | 27 |

| 2.3   | Prosthetic Eye with Polarized Pupil                  | 29 |

| 2.4   | Photochromatic Dilating Pupil for Ocular Prosthetics | 30 |

| 2.5   | Ocular Prosthesis displaying iris and pupil on a LCD | 31 |

| 2.6   | Dilating Ocular Prosthesis                           | 33 |

| 2.7   | Recapitulation                                       | 34 |

| СНАРТ | TER 3 A NEW PROSTHETIC DYNAMIC PUPIL                 | 35 |

| 3.1   | Introduction                                         | 35 |

| 3.2   | Discrete-Component Prototype                         | 35 |

| 3.3   | Integrated Version                                   | 38 |

|       | 3.3.1 The Circuits                                   | 39 |

| 3.4   | Power Consumption                                    | 49 |

| 3.5   | Recapitulation                                       | 49 |

| СНАРТ | ΓER 4 RESULTS                                        | 51 |

| 4.1   | Introduction                                         | 51 |

| 4.2   | Prototype Experimental Validation                    | 51 |

| 4.3   | FPGA Prototyping Board                               | 52 |

| 4.4   | Implementation of the Full Custom Version            | 54 |

|       | 4.4.1 Post-Layout Simulation                         | 54 |

|       | 4.4.2 Precautions to Minimize Parasitic Elements     | 60 |

|       | 4.4.3 Precautions to Minimize Noise                     | 61 |

|-------|---------------------------------------------------------|----|

| 4.5   | Experimental Results                                    | 62 |

| 4.6   | Comparison Between Experimental and Post-Layout Results | 65 |

| 4.7   | Recapitulation                                          | 66 |

| СНАРТ | TER 5 LOW POWER ADC FOR BETTER INTEGRATION              | 67 |

| 5.1   | Introduction                                            | 67 |

| 5.2   | The Integrated ADC                                      | 67 |

|       | 5.2.1 Characteristics                                   | 70 |

| 5.3   | Voltage-to-Current Converter                            | 71 |

| 5.4   | Post-Layout Simulation Results                          | 74 |

|       | 5.4.1 The Voltage-to-Current Converter                  | 74 |

|       | 5.4.2 NC-ADC                                            | 75 |

|       | 5.4.3 Controller                                        | 79 |

| 5.5   | Recapitulation                                          | 79 |

| CONCI | LUSION                                                  | 81 |

| BEFER | RENCES                                                  | 83 |

#### LIST OF TABLES

| Table 1   | Paramètres simulés vs. paramètres mesurés             | XΣ |

|-----------|-------------------------------------------------------|----|

| Table 1.1 | Pupil size with respect to light intensity            | 8  |

| TABLE 1.2 | Characteristics of the main topologies of oscillators | 20 |

| Table 1.3 | Characteristics of the main topologies of ADCs        | 25 |

| Table 4.1 | Simulated vs. measured parameters                     | 65 |

| Table 5.1 | Specifications of the NC-ADC (Yakoub et al. (2009))   | 71 |

#### LIST OF FIGURES

| Figure 1   | Le circuit de délai xiii                                                                                                       | į   |

|------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2   | Diagramme bloc du CAN utilisé dans le premier prototype du système                                                             | ,   |

| Figure 3   | Résultats du test du prototype : (a) Diagramme d'intensité (b)  Graphique illustrant la sortie du prototype xvii               | i   |

| Figure 4   | Résultats des simulations post-layout du circuit de délai xix                                                                  | :   |

| FIGURE 5   | Diagramme bloc du CAN neuromimétique (Tiré de Yakoub et al. (2009))                                                            | i   |

| FIGURE 6   | Résultats de simulation du système (contrôleur et du CAN) . xxii                                                               | ii  |

| Figure 1.1 | A cross-sectional view of the human eye                                                                                        | Į   |

| FIGURE 1.2 | A frontal view of the human iris (adapted from: Gray (1918)) 5                                                                 | )   |

| Figure 1.3 | A drawing of the ocular implant with the prosthesis (adapted from Erickson's Artificial Eyes: http://www.ericksons-eyes.com) 9 | )   |

| FIGURE 1.4 | Full artificial eye prosthesis: (a) a bio-ceramic orbital implant, (b) the eye prosthesis                                      | )   |

| Figure 1.5 | Scleral shell prosthesis                                                                                                       |     |

| FIGURE 1.6 | Photocathodes band model (Adapted from Dakin and Brown (2006)                                                                  | į   |

| FIGURE 1.7 | Photodiode cross-section (Adapted from Dakin and Brown (2006) 14                                                               | E . |

| FIGURE 1.8  | LC oscillator: (a) ideal model and (b) real model                                                                              | 16 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.9  | Relaxation oscillator based on Schmitt Trigger                                                                                 | 18 |

| FIGURE 1.10 | Ring oscillator: (a) N-stage ring oscillator (b) circuit of one inverter                                                       | 19 |

| Figure 1.11 | Block diagram of a parallel ADC                                                                                                | 21 |

| Figure 1.12 | Architecture of a successive approximation converter                                                                           | 22 |

| Figure 1.13 | Analog module of a basic 1st order sigma-delta ADC                                                                             | 24 |

| FIGURE 2.1  | The robotic eye: (a) electrode configuration (second generation), (b) the artificial eye model (adapted from Gu et al. (2001)) | 28 |

| FIGURE 2.2  | Cross sectional view of the prosthetic eye proposed by Young (adapted from Young (2007))                                       | 29 |

| Figure 2.3  | Side view of the ocular prosthetic proposed by Friel (adapted from Friel (1991))                                               | 30 |

| Figure 2.4  | Cross sectional view of the eye prosthesis proposed by Budman et al. (adapted from Budman and Stack (2003))                    | 32 |

| Figure 2.5  | Sectional view of the ocular prosthetic proposed by Schleipman et al. (adapted from Schleipman et al. (2000))                  | 33 |

| Figure 3.1  | The electrical diagram of the prototype of the proposed system:  (a) the analog part, (b) the digital part                     | 36 |

| Figure 3.2  | The prosthetic pupil developed for the prototype                                                                               | 38 |

| Figure 3.3  | Drawing of the described system                                                                                                | 39 |

| FIGURE 3.4  | Block diagram of the proposed integrated system                                                         | 40 |

|-------------|---------------------------------------------------------------------------------------------------------|----|

| FIGURE 3.5  | Schematic of the seven-stage ring oscillator                                                            | 41 |

| FIGURE 3.6  | The delay element                                                                                       | 42 |

| FIGURE 3.7  | Block diagram of the utililised ADC                                                                     | 44 |

| FIGURE 3.8  | The controller and ADC                                                                                  | 45 |

| FIGURE 3.9  | The controller and two comparators replacing the ADC                                                    | 45 |

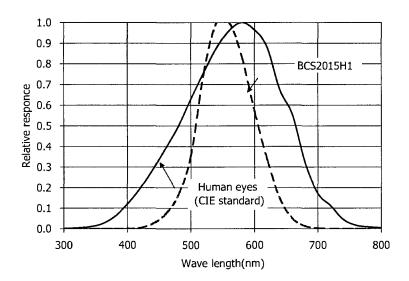

| FIGURE 3.10 | Comparison of the spectral responses of the human eye and the used photodiode (From Digikey datasheets) | 48 |

| Figure 3.11 | The integrated version display: (a) a drawing of the display, and (b) its layout                        | 49 |

| Figure 4.1  | The prototype test results: a diagram (a) and a graph (b) illustrating the prototype output             | 52 |

| FIGURE 4.2  | The Fusion development kit (Source: www.actel.com)                                                      | 53 |

| FIGURE 4.3  | Layout of the clock generator                                                                           | 55 |

| FIGURE 4.4  | Post-layout simulation results of the clock generator                                                   | 56 |

| FIGURE 4.5  | Layout of the delay circuit                                                                             | 56 |

| FIGURE 4.6  | Post-layout simulation results of the delay unit                                                        | 57 |

| FIGURE 4.7  | Layout of the control module                                                                            | 58 |

| Figure 4.8  | Post-layout simulation results of the control module                                                    | 58 |

| FIGURE 4.9  | Layout of the complete integrated circuit (ICFPMMRW): (a)                                                      |    |

|-------------|----------------------------------------------------------------------------------------------------------------|----|

|             | the complete layout with pads, and (b) detailed different modules                                              | 60 |

| FIGURE 4.10 | Microphotograph of the fabricated chip                                                                         | 62 |

| FIGURE 4.11 | Testbench configuration                                                                                        | 63 |

| FIGURE 4.12 | Measured clock signal (the frequency of the signal is 172 kHz)                                                 | 63 |

| FIGURE 4.13 | Measured outputs for dim light: L1 and L2                                                                      | 64 |

| FIGURE 4.14 | Measured outputs for room light: clock signal, L1 and L2                                                       | 65 |

| FIGURE 5.1  | Block diagram of the neuromimetic ADC (Adapted from Yakoub et al. (2009))                                      | 68 |

| FIGURE 5.2  | Neuron cell circuit, showing the waveforms at various nodes in the circuit (Adapted from Yakoub et al. (2009)) | 69 |

| FIGURE 5.3  | (a) The buffer circuit, and (b) the calibration circuit (Adapted from Yakoub et al. (2009))                    | 70 |

| FIGURE 5.4  | Schematic diagram of the all-MOS voltage-to-current converter                                                  | 73 |

| FIGURE 5.5  | Layout of the VCC                                                                                              | 75 |

| FIGURE 5.6  | The VCC output current versus the input voltage                                                                | 76 |

| FIGURE 5.7  | Post-layout simulation results of the VCC: (a) input voltage, (b) output current                               | 76 |

| FIGURE 5.8  | Layout of the NC-ADC                                                                                           | 77 |

| FIGURE 5.9  | Voltage input of the system, and current input of the ADC                                                      | 78 |

| Figure 5.10 | Voltage output of the DAC representing the digital output of      |    |

|-------------|-------------------------------------------------------------------|----|

|             | the NC-ADC                                                        | 78 |

| FIGURE 5.11 | Simulation results of the controller with the parallel-output ADC | 79 |

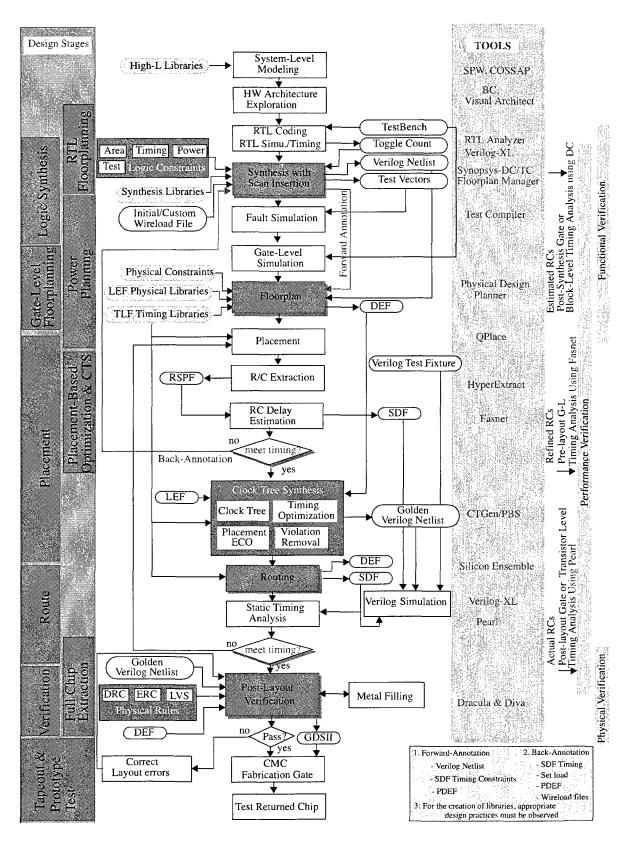

| Figure I.1  | The digital design flow provided by CMC (Used with permission)    | 89 |

#### LIST OF ABBREVIATIONS AND SYMBOLS

#### Abbreviations

ADC Analog-to-Digital Converter

DAC Digital-To-Analog Converter

DFF D Fip-Fop

DNL Differential Nonlinearity

DSP Digital Signal Processing

EOG Electro-oculograph

FPGA Field-Prgrammable Gate Array

INL Integral Nonlinearity

IR Infra-Red

LCD Liquid Crystal Display

LED Light Emitting Diode

LSB Least Significant Bit

MSB Most Significant Bit

NC-ADC Neuron Cell Analog-to-Digital Controller

OTA Operational Transconductance Amplifier

PCB Perforated Circuit Board

SAR Successive Approximation Register

S/H Sampling-and-Hold

UV Ultra-Violet

VCC Voltage-To-Current Converter

VST

Virtual Silicon Technology

WHO

World Health Organization

# Symbols

h 6.626069 ×  $10^{-34}Js$  (Planck's constant)

$\nu$   $c/\lambda$

## LIST OF APPENDICES

| APPENDIX I | DIGITAL DESIGN FLOW |  | 88 |

|------------|---------------------|--|----|

|------------|---------------------|--|----|

#### INTRODUCTION

The majority of ocular defects result from traumas, although in 28.5% of the cases, tumors require the removal of the eye (Cheng et al. (2008)). So in these cases, people are left with one eye only. This is devastating at any age, having great impact on one's self image, self confidence and self esteem causing physical as well as psychological distress.

Frequently an implant is placed in the tissue bed to facilitate construction of the ocular prosthesis. This is done to prevent the eye socket from collapsing after enucleation. The art and science of ocular prosthetics has been refined over many decades to provide a cosmetic replacement for the enucleated or eviscerated eye (Beumer et al. (1979)). Unfortunately, cosmetic results are often compromised by the fixed pupil size. The pupil diameter is very sensitive to incident light intensity, and can vary from 2 mm to 8 mm in diameter depending on the light intensity. In ocular implants the fixed pupil is very noticeable. This is called post-prosthesis anisocoria.

Attempts have been made to simulate human pupil that adjusts to light level so as to dilate or contract with respect to ambient light. Several patents pertaining to developments in the field of ocular implants have been published (Young (2007), Budman and Stack (2003), Schleipman et al. (2000)).

The present master project deals with a dynamic prosthetic pupil to replace the static pupil that present-day ocular prosthesis have. This system would require a display that simulates the iris, a photodiode to measure the light quatity and a control system in order to be automated. In this master thesis a solution to overcome the problem of

post-prosthesis anisocoria is proposed; a prototype to validate the proposed solution is developed and tested. An integrated version is then designed, having an integrated circuit implemented and fabricated in the 0.18  $\mu$ m CMOS technology.

Chapter 1 introduces some anatomical and physiological notion about the human eye and the pupil. We also introduce the ocular prosthesis, talk about the different types that exist, and the advances in the field.

Chapter 2 will be dealing with intelligent ocular implants, i.e., the kind of implants that render the eye prosthesis more realistic. Along this chapter we are going to describe work done in this field going from prosthetic eye movement to pupil size control.

Details of the development of the light controlled pupil are the subject of chapter 3. This chapter will discuss the different modules constituting the system. In this chapter a digital solution is proposed, the main purpose behind choosing such an approach is the ability to generate a square wave output with a controlled duty cycle in order to reduce the display activation time, therefore its energy consumption. This will be detailed in chapter 3.

Chapter 4 is devoted to the presentation of the results, from prototype results, analog layout techniques used, to the integrated circuit post-layout simulation results. The last chapter deals with improvements that we considered useful for the integration of the system and the reduction of power consumption.

#### CHAPTER 1

#### **BACKGROUND**

#### 1.1 Introduction

In this chapter we give the necessary background information needed to understand the development of ocular implants and prosthetics, as well as some theory we were based on to develop the system.

This chapter is divided to three sections, namely: physiological background, ocular implants, and technical background.

## 1.2 Physiological Background

## 1.2.1 The Human Eye

The human eye is a complex anatomical organ. The eye is able to refract light and produce a focused image that can stimulate neural responses and enable the ability to see.

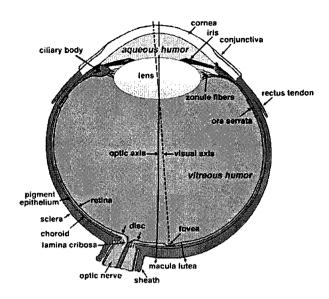

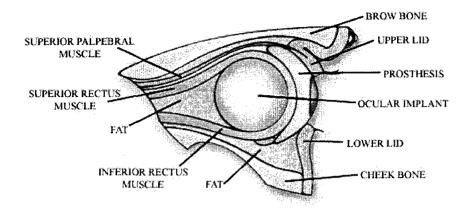

The eyeball is a slightly asymmetrical sphere, with an approximate sagittal diameter of 24 to 25 mm and a transverse diameter of 24 mm. A cross-sectional view of the eye shows three different layers, as illustrated in figure 1.1:

- The outer layer formed by the sclera and cornea

- The intermediate layer formed by the choroid

FIGURE 1.1: A cross-sectional view of the human eye

• The inner layer formed by the retina

Three chambers of fluid are also found in the eye:

- The anterior chamber found between the cornea and the iris

- The posterior chamber found between the iris, zonule fibers and the lens

- The vitreous chamber found between the lens and the retina

The first two chambers are filled with aqueous humor whereas the vitreous chamber is filled with a more viscous fluid, the vitreous humor.

After giving a brief description of the gross anatomy of the eye, now we are interested in a closer description of the pupil and its function.

## 1.2.1.1 The Pupil

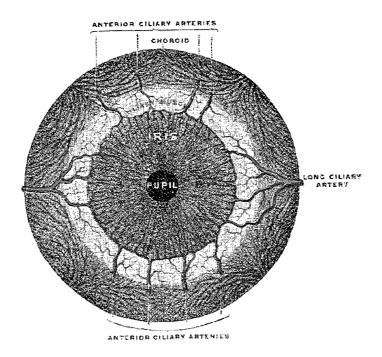

The pupil is the sphere that is located in the center of the iris of the eye, as shown in figure 1.2. When functioning normally, the pupil is linked with a feedback-mechanism in the central nervous system, which controls the quantity of light crossing the lens and reaching the retina (Zinn (1972)). The size of the pupil influences also the depth of focus.

The iris controls the amount of light entering the eye. Irises are pigmented with melanin, and their dimensions vary slightly between individuals, but on average they are 12 mm in diameter. Due to its heavy pigmentation, light can only pass through the iris via the pupil (Lefohn *et al.* (2003)).

FIGURE 1.2: A frontal view of the human iris (adapted from: Gray (1918))

The aperture of the eye is controlled by the iris that behaves as a diaphragm, either contracting or dilating as a result of the opposing actions of two ectodermal muscles (Davson (1972)).

In general the pupil size varies approximately from 2 to 8 mm in diameter. A pupil of varying size performs three main functions:

- Modifying the amount of light entering the eye, thus permittimg useful vision over a wide range of luminance levels.

- Adapting the depth of focus for near and far objects.

- Minimizing abberations.

The factors that affect the size of the pupil are grouped into mechanical, extrinsic and intrinsic factors. Given that the mechanical and the intrinsic factors are purely physiological and congenital factors, hence of no interest to this work, we will only discuss the extrinsic factors.

Extrinsic factors cause what is known as pupillary light reflex. Pupillary light reflex is an innervation reflex that controls the size of the pupil in response to light intensity falling on the retina of the eye (Purves et al. (2008)). Greater light intensity causes the pupil to become smaller, allowing less light in, whereas lower light intensity causes the pupil to become larger, allowing more light in. In other words, the pupillary light reflex regulates the light quantity entering the eye.

#### 1.2.2 Pathologies

A list containing every known eye disease and disorder is published by the World Health Organization (WHO) in the International Statistical Classification of Diseases and Related Health Problems (ICD-10), however we are only interested in a disorder called anisocoria.

Anisocoria is a condition characterized by an unequal size of pupils. Causes of anisocoria are varied, it could be pathophysiologic, pharmacologic, mechanical, self induced

etc. According to the Merck manual of diagnosis, about 20 % of people have physiologic anisocoria. Self induced anisocoria also known as post-prosthesis anisocoria is present in persons who have lost an eye, and replaced the latter with an ocular implant. The ocular implant has a fixed pupil size all the time, while the natural eye has a normal pupil, this causes a difference in the size of the pupils.

## 1.2.3 Pupil Size vs. Ambient Light

Studies have been made to describe the relationship between the size of the human pupil and the density of the incident light on the retina (Spring and Stiles (1948), Groot and Gebhard (1952), Bergamin *et al.* (1998)). De Groot and Gebhard have derived a relation between the diameter of the human pupil and the intensity of the incident light. This relation is illustrated by

$$\log d = 0.8558 - 0.0004(\log B + 8.1000)^3, \tag{1.1}$$

where d is the diameter of the pupil in millimeters and B is the luminance of the visual field in millilamberts. This relation was used in the development of our system. Table 1.1 summarizes the values we got from equation (1.1). In table 1.1 we converted the millilamberts to lux, since the lux is the SI unit of illuminance (NIST (2000)). For a better understanding of these values some explanations should be given. A 3,000 lux intensity is the luminance our eyes experience in the outdoor morning light (Figueiro  $et\ al.\ (2007)$ ). Looking directly to bright sun our eyes experience a luminance of  $100,000\ lux$ . However an intensity like this could damage the human eye. Buildings interior and bright offices have a typical intensity between  $100\ and\ 500\ lux$ , and a dim room has a light density of less than  $1\ lux$ .

Luminance Pupil Luminance Pupil (Lux)diameter (mm)(Lux)diameter (mm) $10.00\overline{000}$ 0.0000107.12 4.39 0.000100 3.996.9831.62278 0.001000 6.73 100.0000 3.59 316.2277 1.000000 5.15 3.17 3.162278 4.78 19952.62 1.87

TABLE 1.1: Pupil size with respect to light intensity

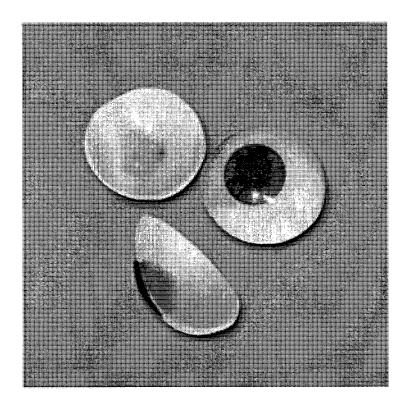

#### 1.3 Ocular Prosthetics

An ocular prosthesis or artificial eye replaces an absent natural eye following an enucleation, or evisceration (Beumer et al. (1979)). Enucleation is the surgical removal of the eye ball, leaving the eye muscles and remaining orbital contents intact; while evisceration is the surgical evacuation of the entire contents of the eye ball including the cornea. An artificial eye does not provide sight, it fills the cavity of the eye socket and serves only as a cosmetic enhancement with psychological impact on the patient.

The objectives behind fitting a prosthesis after one has lost an eye could be as follows (Prince (1946)):

- To maintain the shape of the eyelid

- To re-establish full lid movement

- To prevent fluid accumulation in the cavity

- For Cosmetic purposes.

The last reason is the most important one as far as the patient is concerned, unless a detailed explanation about the other reasons is added.

FIGURE 1.3: A drawing of the ocular implant with the prosthesis (adapted from Erickson's Artificial Eyes: http://www.ericksons-eyes.com)

In most cases an ocular implant, or orbital implant, is used to fill the area in the orbit that was occupied by the natural eye as shown in figure 1.3. This spherical implant will maintain the natural structure of the orbit and will provide support for the artificial eye. The ocular implant itself is not visible.

An ocular prosthesis, or artificial eye, is the element that is seen by the outside world, and it is used to restore the natural appearance of the eye and surrounding tissues. Ocular implants are usually made of acrylic or glass.

More natural appearances were achieved by the developpement of hydroxyapatite for ocular implants. Hydroxyapatite is a bioceramic having mineral components similar to bones of the human body, and has the ability to chemically interact with it (Hench (1991), Gittings *et al.* (2009)). Thus, once implanted, the tissues of the eye orbit will grow into the hydroxyapatite implants, which will become a part of the body.

Different types of implants have existed, and can be categorized based on the implant material (porous or nonporous, alloplastic or autogenous) and its relationship to the overlying prosthesis (integrated or non-integrated, buried or exposed) (Rubin *et al.* (1998)). In the following section we will discuss some of the main types of ocular implants.

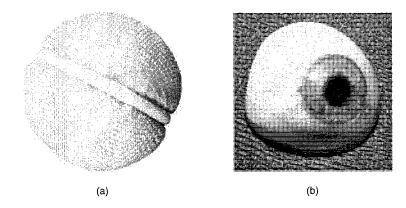

FIGURE 1.4: Full artificial eye prosthesis: (a) a bio-ceramic orbital implant, (b) the eye prosthesis

## 1.3.1 Types of Ocular Implants

## 1.3.1.1 Full Artificial Eye Prosthesis

When an eye is removed (after enucleation), surgeons typically place a small round implant (figure 1.4 (a)) into the orbit and connect it to the eye muscles around it to hold it in place (Adkinsson (2006)). This implant takes the place of the eye in the orbit. Against this implant, a prosthesis resembling the natural eye (figure 1.4 (b)) will fit.

The implants are usually made from acrylic, or glass. Other implants made from materials such as coral, hydroxyapatite or perforated plastic exist, with the idea that the muscles will grow into them allowing the implant to move, mimicking the natural eye. These implants typically have a titanium peg protruding forward from the implant upon which the prosthesis rests.

#### 1.3.1.2 Scleral Shell

Many people lose the sight in one eye, without losing the eye itself. Following sight loss, the eye will start to shrink, discolor, or move erratically. In these situations a

FIGURE 1.5: Scleral shell prosthesis

scleral shell is proposed.

The scleral shell (figure 1.5) is a custom-made, thin hard acrylic shell-like eye prosthesis fitted directly over a discolored and/or disfigured eye. It includes the iris and the sclera (Anonymous (2009)). This prosthesis will help restore volume loss, and will assist the upper lid to return to normal position, matching the natural eye. Good motility is obtained usually with scleral shells.

#### 1.3.2 Advances in Ocular Prosthetics

Artificial eyes have seen little change over the years. Originally made from glass, ocularists started using synthetic materials in the 1940s. Although several improvements have been reported in the manufacturing of ocular prosthesis, the fabrication methods currently in use are based on obsolete technologies, lack high degree of precision and

are time-consuming (Shah and Aeran (2008)). Examples of advances in the field of ocular prosthesis include a magnetically coupled implant and prosthesis as described by Garonzik (2001). The orbital implant is inserted in the empty eye socket, and the eye prosthesis is coupled magnetically to the implant overcoming problems associated with the use of a coupling post such as the extrusion of the implant and conjunctival erosion. Furthermore, a self-lubricating ocular prosthesis has been designed that releases a lubricant continuously on the surface of the prosthesis, eliminating dry eye syndrome, burning and itching (Kelley (1992)). Recent development in the ocular prosthesis fabrication include the use of specially developed biomaterials to reduce any allergic reaction. Development in this field also includes realistic modelling and rendering in iris synthesis (Lefohn et al. (2003)).

## 1.4 Technical Background

## 1.4.1 Optical Detectors and Receivers

This section describes the operating principles of optical detectors. Optical detectors can be classified by their principle of light detection: physical or chemical changes, solid or gas ionization, scintillation, and photoelectric effect (Dakin and Brown (2006)). Detectors utilizing physical or chemical changes are photographic films, and are rarely used nowadays in photometric applications. Methods utilising solid or gas ionization and scintillation are usually limited to x-ray applications.

Photodetectors with photoelectric effects are widely used as Ultra-Violet (UV) to Infra-Red (IR) sensors in application including communication devices and measurement instruments.

Because of space restrictions, we will only discuss the photoelectric effects.

#### 1.4.1.1 Photoelectric Effects

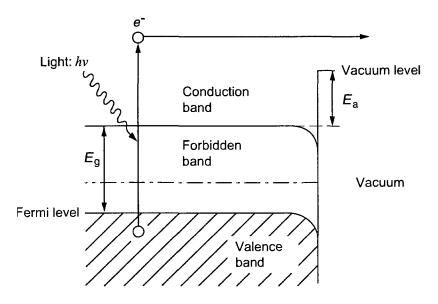

Optical detectors utilizing these effects can be further divided into two groups: one group using external photoelectric effects by which bound electrons inside a semi-conductor thin film are released into vacuum when light hits the semiconductor, and the other one using internal photoelectric effects where photoelectrons are generated inside the semiconductor by light and excited into the conduction band (Sommer (1980), Bube (1992)).

## 1.4.1.1.1 External Photoelectric Effect

Optical detectors utilizing external photoelectric effects include phototubes, photomultiplier tubes and image intensifiers (Dakin and Brown (2006)).

Semiconductor thin films with a photoemissive surface are usually referred to as "photocathodes" (Sommer (1980)). A general band model of photocathodes is illustrated in figure 1.6. Inside a semiconductor there is what is known as a valence band which is occupied by electrons, a forbidden band where electrons connot occupy, and a conduction band where electron have the freedom to move.

When photons hit a photocathode, electrons in the valence band absorb the photon energy  $h\nu$ , become excited into the conduction band, and diffuse toward the surface. When a diffused electron has enough energy to overcome the vacuum level, it is emitted into the vacuum as photoelectron.

#### 1.4.1.1.2 Internal Photoelectric Effect

Photodetectors using internal photoelectric effects include photodiodes, phototransistors, and photoconductive cells. Photoelectric effect include both photoconductive effect, and photovoltaic effect (Dakin and Brown (2006)). However, we will focus on

FIGURE 1.6: Photocathodes band model (Adapted from Dakin and Brown (2006) the photovoltaic effect in this section.

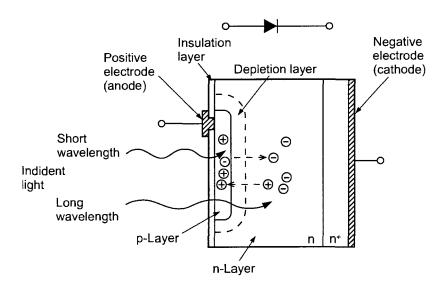

The photovoltaic effect will be explained using a photodiode example. Figure 1.7 shows a cross-section of a photodiode.

FIGURE 1.7: Photodiode cross-section (Adapted from Dakin and Brown (2006)

A p-n junction serving as a photoelectric converter is formed by the p-layer at the

light sensitive surface and the n-layer at the substrate. The photodiode's spectral and frequency responses can be controlled by varying the thickness of the outer p-layer, substrate n-layer and bottom  $N^+$  layer as well as the doping concentration.

When light striking the photodiode has an energy greater than the band gap energy, electrons in the valence band are excited into the conduction band, leaving holes in their place in the valence band. The electron-hole pairs are generated in the p-layer, depletion layer and n-layer. The electric field in the p-layer and depletion layer accelerates the holes toward the p-layer, and the electrons toward the n-layer. In the n-layer, of the electron-hole pairs generated, the electrons are left in the n-layer along with electrons coming from the p-layer, and the holes are collected in the p-layer. This way, electron-hole pairs generated proportionally to the amount of incident light are stored in the p-layer and n-layer, creating a positive charge in the p-layer and a negative charge in the n-layer. So by connecting a circuit between the p-layer and the n-layer, holes will flow from the p-layer and electrons from the n-layer toward the opposite electrode.

## 1.4.2 Main Types of Oscillators

The characteristics we are looking for in an oscillator for the proposed device are low output noise, low power consumption and integrability. Different types of oscillators exist in the literature, here we are going to describe the most appropriate for the proposed device.

#### 1.4.2.1 LC Oscillator

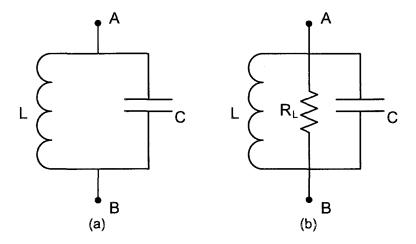

In an LC circuit, the frequency  $f_{lc}$  at which the circuit resonates is given by the following equation (Mansour et al. (2004), Sadat et al. (2005)):

$$f_{lc} = \frac{1}{2\pi\sqrt{LC}}\tag{1.2}$$

The LC oscillator is shown in the circuit illustrated in figure 1.8.

FIGURE 1.8: LC oscillator: (a) ideal model and (b) real model

In the real model, the inductance L has a small parasitic resistance  $R_L$  as shown in the figure 1.8 (b). Due to this resistance, some energy stored in the reactive element will be dissipated in  $R_L$  as heat, and as a result, the oscillation dies. Now if we connect a negative resistance to the LC tank, the energy lost in  $R_L$  will be compensated for by the energy supplied by the negative resistance, thus the circuit oscillates. This negative resistance is usually synthesized by a differential pair.

An LC oscillator could be divided into three different parts: the RLC circuit, a differential pair and a variable capacitor.

- The RLC circuit is the core of the oscillator since it defines the resonance frequency.

- The differential pair allows the system to oscillate by generating a negative resistance.

• The variable capacitor allows for the oscillator to have a certain excursion range in the frequency.

The advantage of using such oscillators is the signal quality. In fact their output signal has low phase noise compared to other types of oscillators. However, two main drawbacks may prevent, sometimes, from choosing this type of oscillators (Fouzar (2005)). These drawbacks are their limited excursion range and their cost.

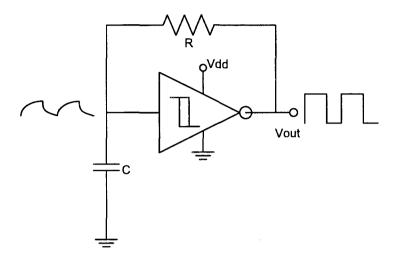

#### 1.4.2.2 Relaxation Oscillator

This type of oscillators contains usually two essential parts: a comparator with hysteresis (schmitt inverter) and a capacitor, as shown in figure 1.9. The principle of operation consists of charging and discharging a capacitor in a voltage interval defined by the threshold voltages of the comparator. At startup, the voltage across C is zero, and the output of the inverter is high. The capacitor then starts charging up via R. When the capacitor's voltage reaches the high voltage threshold of the inverter,  $V_H$ , the output of the inverter goes low. With the output low, C starts discharging toward 0V. When the capacitor's voltage drops below the low voltage threshold of the inverter,  $V_L$ , the output goes high. The cycle repeats. The half-period of the oscillations is defined by the time the capacitor's voltage takes to go from  $V_L$  to  $V_H$ . The other half depends on the time needed to go from  $V_H$  to  $V_L$ .

As a result, the frequency of oscillations  $(f_{osc})$  is determined by the high-going and low-going threshold voltages and the RC time constant. This relation is defined by the following equation (Wokhlu *et al.* (1998)):

$$f_{osc} = \frac{1}{T_{osc}} = \frac{1}{RC \ln([\frac{V_H}{V_I}][\frac{V_{dd} - V_L}{V_{dd} - V_H}])}$$

(1.3)

FIGURE 1.9: Relaxation oscillator based on Schmitt Trigger

where C is the capacitor, R is the resistor, and  $V_{t-l}$  and  $V_{t-h}$  are the minimal and maximal voltage thresholds, respectively.

Compared to LC oscillators, the relaxation oscillators offer a larger frequency excursion range, and could be easily integrated on a chip (Fouzar (2005)). However, they do suffer from output phase noise, which could limit their use in some applications.

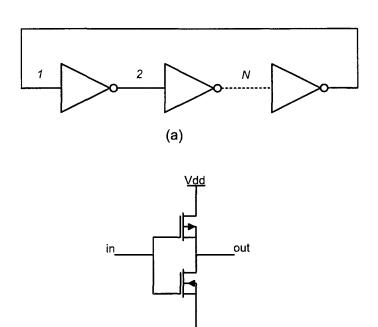

## 1.4.2.3 Ring Oscillator

This type of oscillators is formed by a finite number of inverters,  $N_{osc}$ , in cascade, forming a reaction loop. The ring oscillator requires an odd number of inverters in its loop to generate oscillations. This type of oscillators uses the principle of charging and discharching its intrinsic capacitances to generate oscillations at its output. Figure 1.10 (a) illustrates this type of circuits.

In the loop forming this circuit, the phase of each inverter is shifted relatively to neighboring inverters. During each half period,  $T_{osc}/2$ , a signal is propagated through

FIGURE 1.10: Ring oscillator: (a) N-stage ring oscillator (b) circuit of one inverter

(b)

the loop and will change its polarity. Supposingly that the input 1 in figure 1.10 (a) is initialized to logic '0', this value will propagate through the N inverters of the loop in  $T_{osc}/2$ , in which time the input 1 will change value to '1'. After another half period,  $T_{osc}/2$ , the value at 1 will return to '0', giving a complete period of oscillation,  $T_{osc}$ . Assuming the delay for each inverter is  $\tau_{inv}$ , the duration of a half period could be determined by:

$$\frac{T_{osc}}{2} = N_{osc}\tau_{inv} \tag{1.4}$$

With this relation we could determine the frequency of oscillations given by:

$$f_{osc} = \frac{1}{2N_{osc}\tau_{inv}} \tag{1.5}$$

In general, ring oscillators are among the most used in the majority of applications (Fouzar (2005)). This is due to the fact that they are easy to integrate and they have a larger excursion range.

## 1.4.2.4 Comparison of the Described Oscillators

Table 1.2 compares the three different oscillators described above with respect to three characteristics: integrability, output noise and power consumption. A rank of 4 in a performance category indicates that the architecture is inherently better than the others for that category. As can be seen from this table, the LC and the ring oscillators have the lowest output noise, the relaxation and the ring oscillators are easily integrable, and the relaxation oscillator has the lowest power consumption.

Table 1.2: Characteristics of the main topologies of oscillators

| Characteristic<br>Oscillator | Integrability | Low output noise | Low power consumption |  |

|------------------------------|---------------|------------------|-----------------------|--|

| LC oscillator                | 1             | 4                | 1                     |  |

| Relaxation oscillator        | 4             | 1                | 3                     |  |

| Ring oscillator              | 4             | 4                | 2                     |  |

## 1.4.3 Main Types of Analog-to-Digital Converters

The most important characteristics in an analog-to-digital converter (ADC) for the present application are low power consumption, conversion of non-periodic signals and small size (integrability). Many types of ADCs have been developed for different applications. Some are adapted for applications of high sampling rate, others for application requiring low power consumption, and in other cases the precision of the ADC is the most important factor.

Here is a summary of the main topologies.

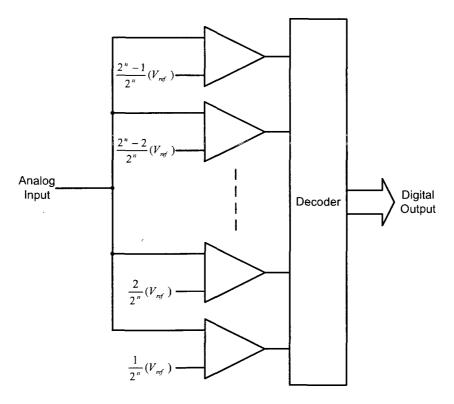

## 1.4.3.1 Parallel ADC

This type of converters work by comparing the input analog voltage to a series of different reference voltages using several comparators placed in parallel. For a resolution of n bits, there are  $2^{n-1}$  comparators. One input of the comparator is connected

FIGURE 1.11: Block diagram of a parallel ADC

to the input signal and the other input is connected to a reference voltage as shown in figure 1.11. This reference is generated using a network of resistors acting as a voltage divider. Thus at each comparator there is a different reference voltage  $V_{ref(N)}$ . The output of every comparator where the input signal is greater than the reference voltage will be logic '1', while the other outputs will be at logic '0'. A decoder is connected to the output of the comparators. This decoder will convert the  $2^{n-1}$  comparators'

outputs to a binary word of n bits.

The inconvenience of such converters are the space they occupy on a chip to obtain high resolutions, and they require identical replicas for all the comparators (Miled (2007)).

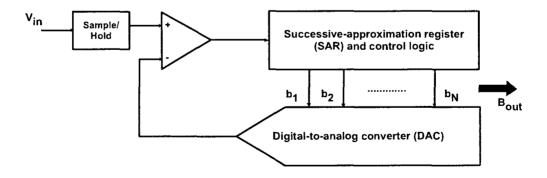

## 1.4.3.2 Successive Approximation ADC

SAR ADCs are known for their low speed of operation versus a low power consumption, since their architecture relies on the operation of only one comparator. In addition they are well suited for applications having non periodic inputs (Black (1999)).

The technique used here consists of approximating the analog input to binary values. An n bit successive approximation register (SAR) contains originally an initial value '0'. After that the most significant bit (MSB) takes the value of '1', and the contents of the SAR are sent to a digital-to-analog converter (DAC) that converts them to an analog value. The analog signal obtained will be compared to the input voltage. If

FIGURE 1.12: Architecture of a successive approximation converter

the latter is inferior to the value provided by the DAC, the bit that have taken the value of '1' will take the value of '0', and the following bit will take the value of '1'

and we redo the comparison over until we reach the least significant bit (LSB). So a given bit cannot keep the value of '1' unless the value given by the DAC is inferior to the input. As a result, we need a comparison of n stages to generate the digital value of the analog input. These types of ADCs are precise and provide often an output of parallel n-bit, and sometimes in series starting by the MSB. The architecture of successive approximation ADC is shown in figure 1.12 (Troadec (2004)).

## 1.4.3.3 Pipelined ADC

This architecture is adapted for high frequency circuits. Pipelining allows doing several operations at the same time. This converter is composed of several stages. The analog signal  $V_{in}$  first reaches the first stage where it is sampled and held by a sample-and-hold (S/H), while the ADC of stage 1 quantizes it to n bits, this forms the MSBs of the digital output; the n bits output is then fed to a DAC and the DAC's output is subtracted from the input and the "residue" obtained is then fed to stage 2 while stage 1 continues the same process for the following sample, and so forth until we reach stage N, for an  $N \times n$  ADC. So once the latency time is achieved at the beginning, which lasts for N cycles of conversion, at every cycle we have a new digital value that corresponds to the analog input.

The major problem of this ADC is the need of a sampler/holder at each stage for which the realization is somewhat delicate, which presents the principal limitation of this architecture (Troadec (2004)).

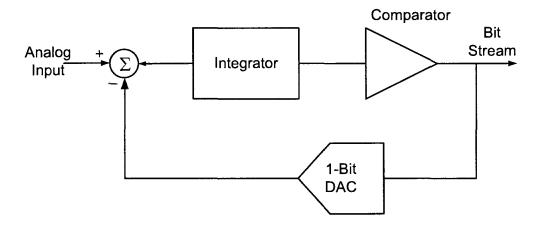

## 1.4.3.4 Sigma-Delta Converter

In its basic form a sigma-delta converter consists of two modules: a mixed-signal analog/digital module that converts the analog signal into a bit stream, and a digital

filter that converts this bit stream into an n bits digital value. The mixed-signal module consists of an integrator a comparator and a single bit DAC as shown in figure 1.13.

FIGURE 1.13: Analog module of a basic 1st order sigma-delta ADC

The output of the DAC is subtracted from the input signal; the resulting value is then integrated, and converted to a single bit digital value through the comparator. The resulting bit becomes the input to the DAC and goes through the loop again. This closed loop is carried out at a very high rate, in what is called "oversampling" (Black (1999)). The bit stream data is then fed to the digital filter that results in a binary digital output. The digital filter consequently has the following functions:

- Bringing the frequency of oversampling to Nyquist frequency, an operation known as decimation

- Eliminating the noise caused by the quantization.

So in other words, this filter calculates the average of the input bit stream. A limitation of this architecture is its latency, which is substantially greater than that of the other types (Black (1999)). They are not often used in multiplexed signal applications. Sigma-delta converters are not suited for high frequency signals; the

major drawback is the size of the decoder part (digital filter) which is done either by an FPGA, DSP, or a computer, so a sigma-delta converter could not be used in applications where small size is critical.

## 1.4.3.5 Comparison of the ADCs

At this point, we find it useful to compare the ADCs presented in this section. Table 1.3 summarizes the main characteristics of these ADCs. Also in this table a rank of 4 in a performance category indicates that the architecture is inherently better than the others for that category.

Table 1.3: Characteristics of the main topologies of ADCs

| ADC Topology Characteristic       | Parallel | SAR | Pipelined | Sigma-<br>Delta |

|-----------------------------------|----------|-----|-----------|-----------------|

| Sampling Frequency                | 4        | 2   | 3         | 1               |

| Resolution                        | 1        | 3   | 2         | 4               |

| Conversion of non-periodic signal | 4        | 4   | 3         | 2               |

## 1.5 Recapitulation

This chapter deals with the anatomy and physiology of the human eye, and more specifically the iris and pupil. In this chapter we treat as well pathologies relevant to our work such as anisocoria; an overview about pupil size vs. ambient light is also given. Following that, an aperçu about ocular implants and prosthesis, and their development is provided. A notion about optical detectors is given. Finally, we illustrated different architectures of oscillators and analog-to-digital converters to justify our choice for the architectures.

However before proceeding to describe our work, it is important to investigate some

of the works of other laboratories working in this field, which will make the subject of our next chapter.

,

#### CHAPTER 2

#### INTELLIGENT OCULAR IMPLANTS

#### 2.1 Introduction

Following the discussion about physiology and pathologies of the human eye, and the presentation of different types of ocular implants in chapter 1, we are now interested in intelligent ocular implants. The latter gives patients the ability to have a natural looking prosthetic eye, boosting their confidence.

Along this chapter we are going to describe work done in this field going from prosthetic eye movement to pupil size control.

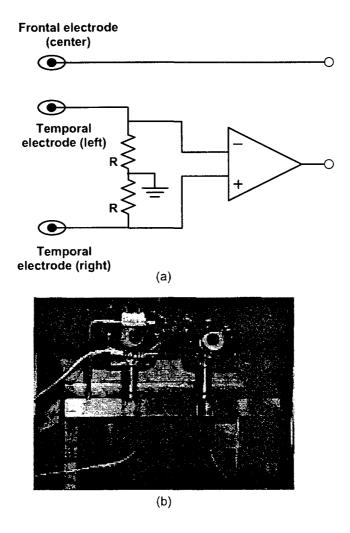

#### 2.2 Robotic Prosthetic Eye

Gu (2001), from the University of Alberta, have designed a robotic prosthetic eye that moves horizontally in synchronization with the movement of the natural eye. This is done by sensing the movement of the natural eye and then controlling the prosthetic eye accordingly.

They developed two generations of robotic prosthetic eye models. The first generation uses an external infrared sensor array that is mounted on the frame of a pair of eyeglasses. This sensor array is used to detect the natural eye movement and to feed the control system so to drive the artificial eye to move in synchronism with the natural one. The second generation model removes the external sensor array, and gets rid of the eyeglasses frame and uses instead the electrooculograph (EOG) signal picked up by electrodes placed on the side of one's head, carrying out the same eye

FIGURE 2.1: The robotic eye: (a) electrode configuration (second generation), (b) the artificial eye model (adapted from Gu et al. (2001))

movement detection and control as mentioned before.

The artificial eye is mounted onto a small servomotor to gain the movement function (Gu et al. (2001)). Detection of the natural eye movement is done in horizontal direction only, in both generations. Then, the motor is controlled to drive the artificial eyeball to move correspondingly, matching the horizontal movement of the natural eye. the system is depicted in fig 2.1.

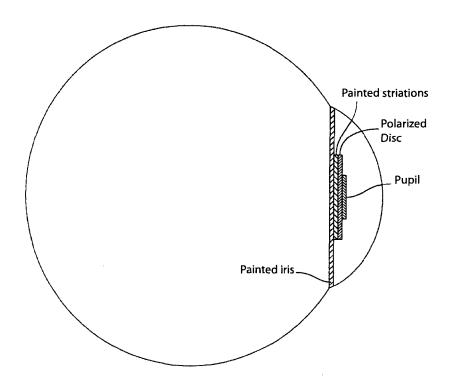

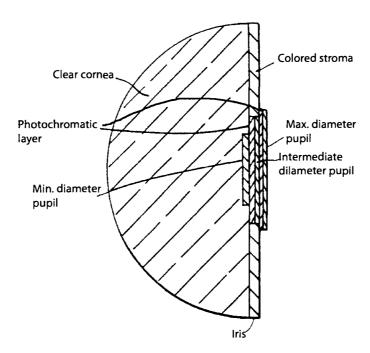

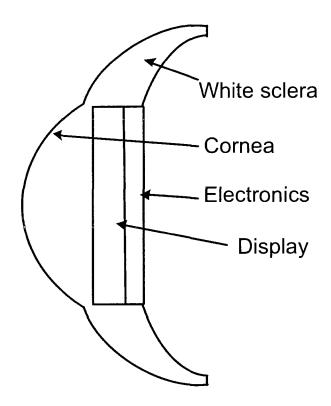

## 2.3 Prosthetic Eye with Polarized Pupil

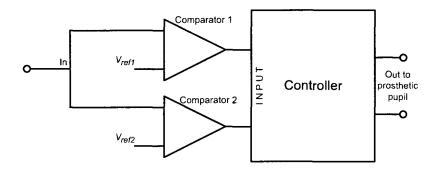

Young have investigated a prosthetic eye with a simulated iris painted on the front and a horizontal polarized disc at the center of the iris (Young (2007)). The center of the polarized disc is dark to simulate a pupil with a small diameter. The polarized disc is transparent, and striations are painted on its back to blend with the iris. This prosthetic eye is used in conjunction with a special pair of eyeglasses, having polarized lenses. When the eyeglasses are used, the pupil appears dilated, because they cause the entire polarized disc to be blackened. Figure 2.2 illustrates the proposed system by Young.