**Titre:** Réalisation d'un système de communications sans-fil sur une plateforme de prototypage rapide

Title: Realization of a wireless communication system on a rapid prototyping platform

**Auteur:** Yony Kevin Ah-Koon

Author:

**Date:** 2009

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Ah-Koon, Y. K. (2009). Réalisation d'un système de communications sans-fil sur une plateforme de prototypage rapide [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/8490/>

Citation:

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8490/>

PolyPublie URL:

**Directeurs de recherche:** Jean-François Frigon

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

RÉALISATION D'UN SYSTÈME DE COMMUNICATIONS SANS-FIL SUR UNE

PLATEFORME DE PROTOTYPAGE RAPIDE

YONY KEVIN AH-KIOON

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUIN 2009

Library and Archives

Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

ISBN: 978-0-494-57239-9

*Our file Notre référence*

ISBN: 978-0-494-57239-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

RÉALISATION D'UN SYSTÈME DE COMMUNICATIONS SANS-FIL SUR UNE

PLATEFORME DE PROTOTYPAGE RAPIDE

présenté par: AH-KIOON Yony Kevin

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. CARDINAL Christian, Ph.D., président

M. FRIGON Jean-François, Ph.D., membre et directeur de recherche

M. DAVID Jean-Pierre, Ph.D., membre

À ceux qui m'ont aidé.

## **REMERCIEMENTS**

Je tiens à exprimer ma reconnaissance envers mon directeur de recherche, Dr. Jean-François Frigon, pour sa collaboration, ses précieux conseils et ses commentaires dans la réalisation de ce travail.

Je remercie aussi mes collègues pour leur contribution au niveau de suggestions et d'échanges d'idées dans le développement de ce projet.

J'aimerais exprimer ma gratitude envers mon père, ma mère, Steve, Keith et Cindy pour leur présence et leur encouragement. Un merci spécial à mon frère pour me fournir ses conseils et me faire part de ses expériences de recherche.

Je remercie Marie-France Nguyen et sa famille pour leur support au courant de mes années d'études au Canada.

Je remercie Quan Yim pour m'aider à garder patience et calme dans les moments les plus difficiles.

Finalement, j'aimerais remercier les membres du comité du jury, Dr. Christian Cardinal et Dr. Jean-Pierre David pour prendre le temps de lire et de commenter ce mémoire.

## RÉSUMÉ

L'industrie des télécommunications sans-fil connaît une grande croissance depuis quelques années. Plusieurs nouveaux produits sont proposés aux consommateurs chaque année. La décision de permettre l'utilisation non-licenciée de certaines bandes de fréquences a aussi favorisé le développement d'une multitude d'équipements sans-fil personnels, tels que les réseaux locaux sans-fil (WLAN) à courte portée ou encore les écouteurs sans-fil. Parallèlement, les avancées dans les techniques de prototypage rapide ont contribué à faciliter la validation et l'évaluation de divers algorithmes de communications en augmentant la performance des composantes électroniques utilisées et en réduisant le coût associé. Dans le cadre de ce mémoire, nous faisons la conception théorique et matérielle d'un système de communications sans-fil à bande étroite. Le projet décrit dans ce document est divisé en deux parties.

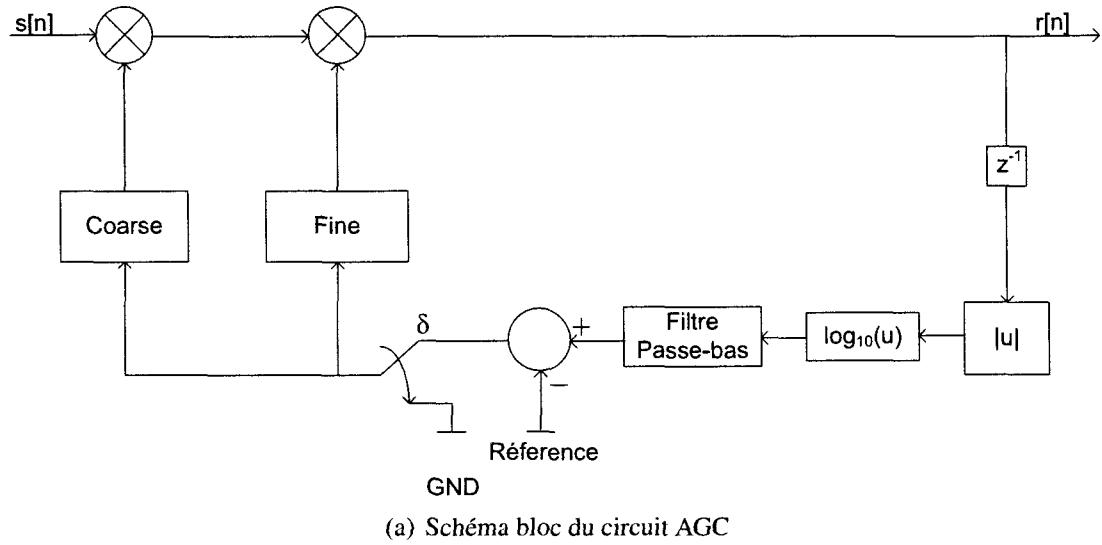

Dans la première partie, un système complet de communications est développé et simulé à l'aide de l'outil de simulation Simulink. Le canal considéré est à évanouissement lent et non-sélectif en fréquence. Grâce à un contrôleur de gain automatique (AGC), l'amplitude du signal reçu est maintenue dans une plage permettant une utilisation efficace des convertisseurs analogique-numérique. Un algorithme de détection de trames est utilisé pour détecter l'arrivée des paquets et déclencher les boucles de synchronisation. La phase et l'amplitude du signal reçu sont corrigées avec un filtre adaptatif de type *Least Mean Square* (LMS). L'algorithme de recouvrement d'horloge utilise les transitions entre symboles pour estimer le temps d'échantillonnage idéal. La boucle PLL requise pour la synchronisation de fréquence est basée sur un algorithme utilisant l'erreur de phase entre le symbole reçu et le point de la constellation le plus proche.

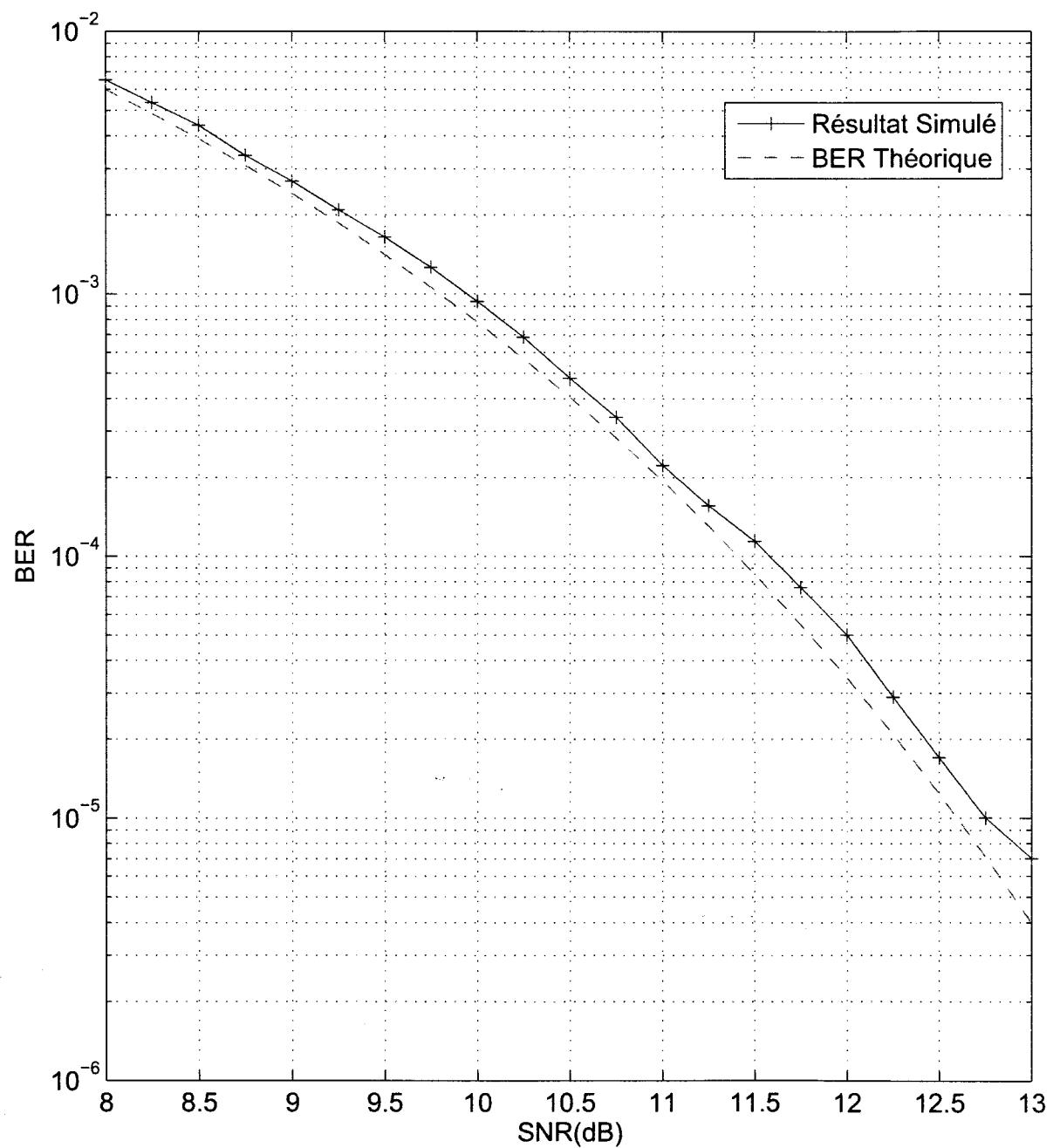

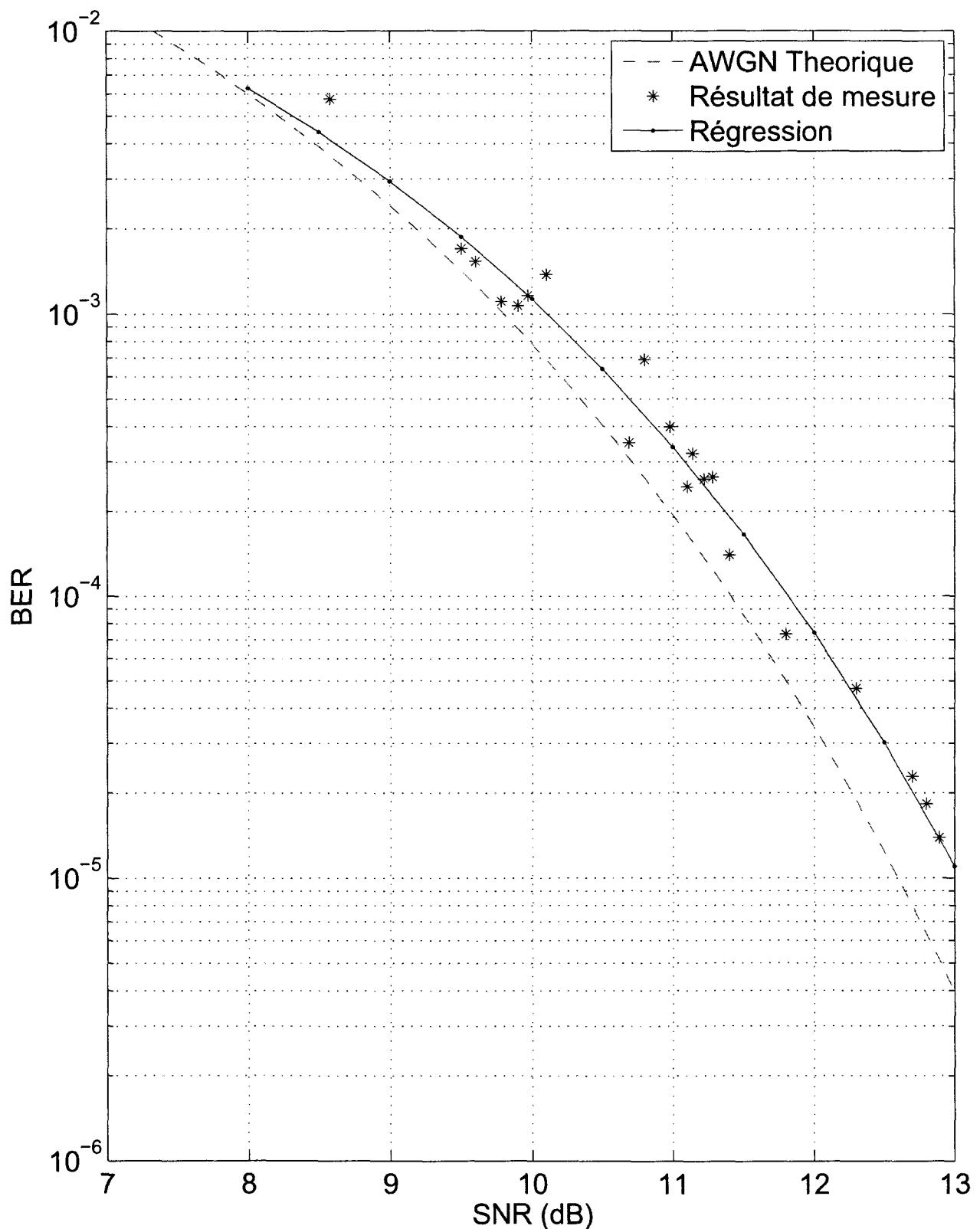

Ainsi, ces différents algorithmes sont tout d'abord vérifiés et validés à l'aide de l'outil Simulink. La performance est évaluée en vérifiant le taux d'erreurs binaires pour différents niveaux de rapport signal à bruit (SNR). En comparant la performance simulée avec celle d'un système idéal, nous observons une dégradation maximale de 0.3 dB pour des SNR allant de 8 dB à 13 dB.

Par la suite, ce système est implémenté en partie sur une plateforme de prototypage rapide de la compagnie Lyrtech Inc. L'implémentation effectuée constitue la partie bande de base du système de communications. Elle permet d'obtenir une idée de la faisabilité et de la performance du système. Le transmetteur et l'algorithme de recouvrement d'horloge ainsi que le filtre LMS et le bloc de détection de trame ont été programmés sur la plateforme. La calibration des paramètres utilisés est faite de façon heuristique. En général, nous avons utilisé les valeurs obtenues dans la partie simulation comme point de départ. Les résultats obtenus montrent une perte de 0.8 dB par rapport à la courbe théorique et de 0.5 dB par rapport à la courbe obtenue par simulation. Des améliorations pouvant être apportées au système sont finalement proposées.

## ABSTRACT

The telecommunications industry is growing fast with several new services being proposed to customers every year. Unlicensed use of part of the frequency spectrum has certainly helped in the development of various additional personal communications services, ranging from home wireless Local Area Networks (WLAN) to wireless headsets. At the same time, hardware prototyping and implementation are increasingly converging towards a reasonably affordable reach as well as an improved performance. In this thesis, we present the development of a broadband wireless communications system. The document is mainly divided in two sections.

In the first part, a full broadband communications system is developed and simulated using Simulink for a slow fading non-selective channel. An automatic gain control (AGC) loop is used for power control at the input of the receiver in order to ensure efficient utilization of the dynamic range of analog to digital converters. A frame detection algorithm ensures the detection of incoming packets so as to trigger synchronization loops. The phase and the amplitude errors of the received signal are fine tuned with a Least Mean Square (LMS) filter. In addition to this, we have identified timing and frequency inconsistencies as the main potential sources of error. An algorithm based on the sign of the half-baud symbol is used for timing recovery. Frequency synchronization is accomplished using an algorithm based on the sign of the imaginary part of the projection of the incoming data symbols on their respective closest constellation points.

These different algorithms are implemented and simulated for validation. Finally, the performance of the system as a whole is evaluated through the Bit Error Rate (BER) for different levels of Signal to Noise Ratio (SNR). Comparison of the achieved performance shows that a maximum 0.3 dB power loss compared to Shannon's theoretical limit is observed for a signal to noise ratio range from 8 dB to 13 dB.

This system is meant to be implemented on a rapid prototyping platform solution proposed by Lyrtech Inc. Part of the baseband implementation of the communications system follows in order to give a general idea of the feasibility of the project as well as the perfor-

mance characteristics that can be expected from the communications systems. The clock synchronization algorithm together with the LMS filter and frame detection block are integrated. Their parameters are heuristically calibrated, usually starting with initial values obtained from simulation parameters. Results show that there is a 0.8 dB power loss compared to Shannon's theoretical limit and a 0.5 dB power loss compared to simulated results. Finally, potential improvement and future works are proposed.

**TABLE DES MATIÈRES**

|                                               |      |

|-----------------------------------------------|------|

| DÉDICACE . . . . .                            | iv   |

| REMERCIEMENTS . . . . .                       | v    |

| RÉSUMÉ . . . . .                              | vi   |

| ABSTRACT . . . . .                            | viii |

| TABLE DES MATIÈRES . . . . .                  | x    |

| LISTE DES FIGURES . . . . .                   | xii  |

| LISTE DES ACRONYMES . . . . .                 | xiii |

| LISTE DES TABLEAUX . . . . .                  | xv   |

| LISTE DES ANNEXES . . . . .                   | xvi  |

| INTRODUCTION . . . . .                        | 1    |

| CHAPITRE 1 CONCEPTS DE BASE . . . . .         | 5    |

| 1.1 Le canal sans-fil . . . . .               | 5    |

| 1.1.1 Bruit additif . . . . .                 | 6    |

| 1.1.2 Atténuation . . . . .                   | 8    |

| 1.1.3 Multi-trajets . . . . .                 | 9    |

| 1.1.4 Interférences . . . . .                 | 12   |

| 1.2 La modulation . . . . .                   | 13   |

| 1.3 La conversion en bande passante . . . . . | 14   |

| 1.4 La période d'un symbole . . . . .         | 16   |

| 1.5 Détection optimale . . . . .              | 17   |

| 1.6 L'horloge . . . . .                       | 18   |

|                                                                                                |                                                          |           |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------|

| 1.7                                                                                            | Oscillateurs . . . . .                                   | 20        |

| 1.8                                                                                            | Système global . . . . .                                 | 21        |

| <b>CHAPITRE 2 SURVOL DES TECHNIQUES DE PROTOTYPAGE DE SYSTÈMES DE COMMUNICATIONS . . . . .</b> |                                                          | <b>23</b> |

| 2.1                                                                                            | Critères de développement . . . . .                      | 23        |

| 2.2                                                                                            | La radio logicielle . . . . .                            | 24        |

| 2.3                                                                                            | Traitement hors ligne . . . . .                          | 25        |

| 2.4                                                                                            | DSP . . . . .                                            | 26        |

| 2.5                                                                                            | ASIC . . . . .                                           | 27        |

| 2.6                                                                                            | FPGA . . . . .                                           | 28        |

| 2.7                                                                                            | Prototypes hybrides . . . . .                            | 29        |

| <b>CHAPITRE 3 LES ÉLÉMENTS DU MODÈLE DE SIMULATION . . . . .</b>                               |                                                          | <b>30</b> |

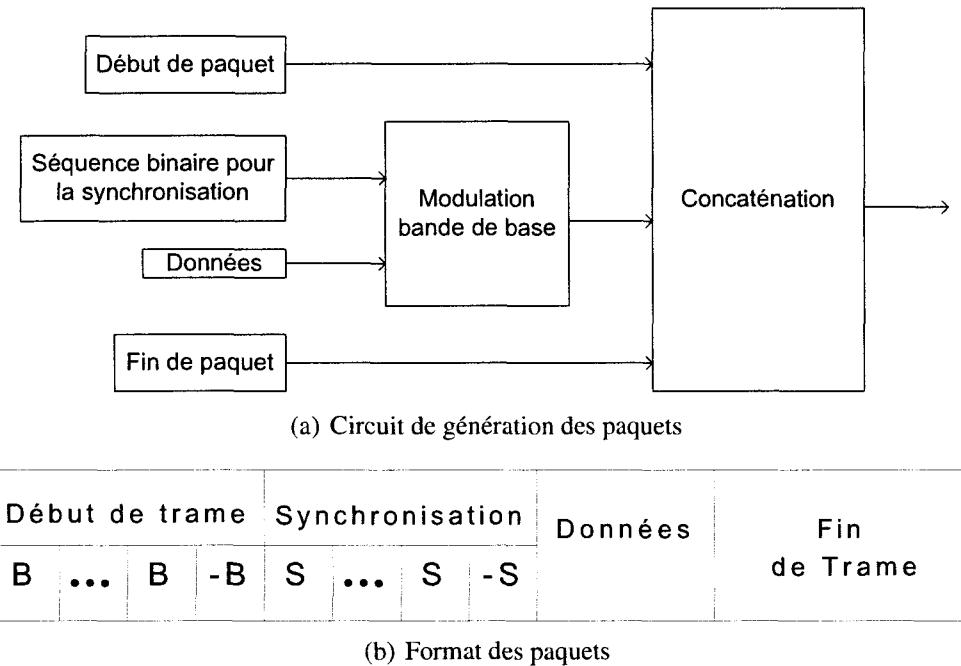

| 3.1                                                                                            | Format des paquets transmis . . . . .                    | 31        |

| 3.1.1                                                                                          | Séquence de début des trames . . . . .                   | 33        |

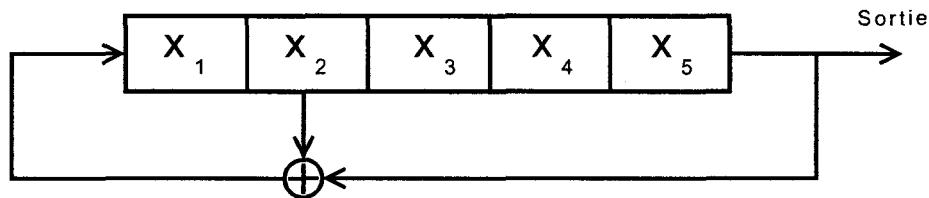

| 3.1.2                                                                                          | Séquence de synchronization . . . . .                    | 34        |

| 3.1.3                                                                                          | Séquence de fin des trames . . . . .                     | 35        |

| 3.2                                                                                            | Le modulateur et le démodulateur . . . . .               | 35        |

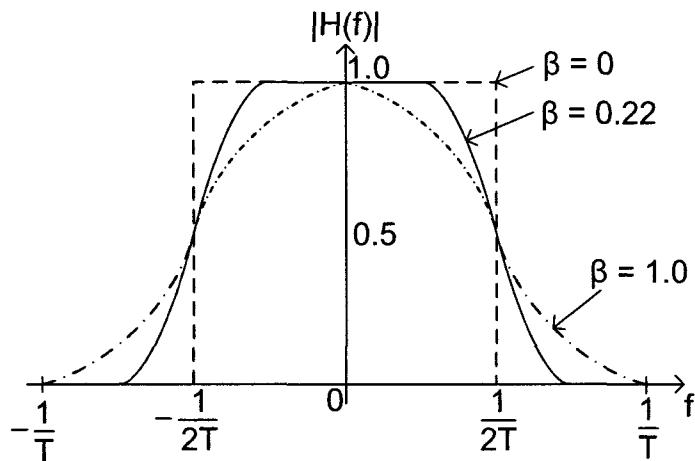

| 3.3                                                                                            | Filtres de Nyquist . . . . .                             | 36        |

| 3.4                                                                                            | Filtre d'égalisation . . . . .                           | 41        |

| 3.5                                                                                            | Circuit d'ajustement initial de puissance . . . . .      | 45        |

| 3.5.1                                                                                          | Circuit utilisé . . . . .                                | 45        |

| 3.5.2                                                                                          | Tests de performance . . . . .                           | 48        |

| 3.6                                                                                            | Détection de début de trame de synchronisation . . . . . | 48        |

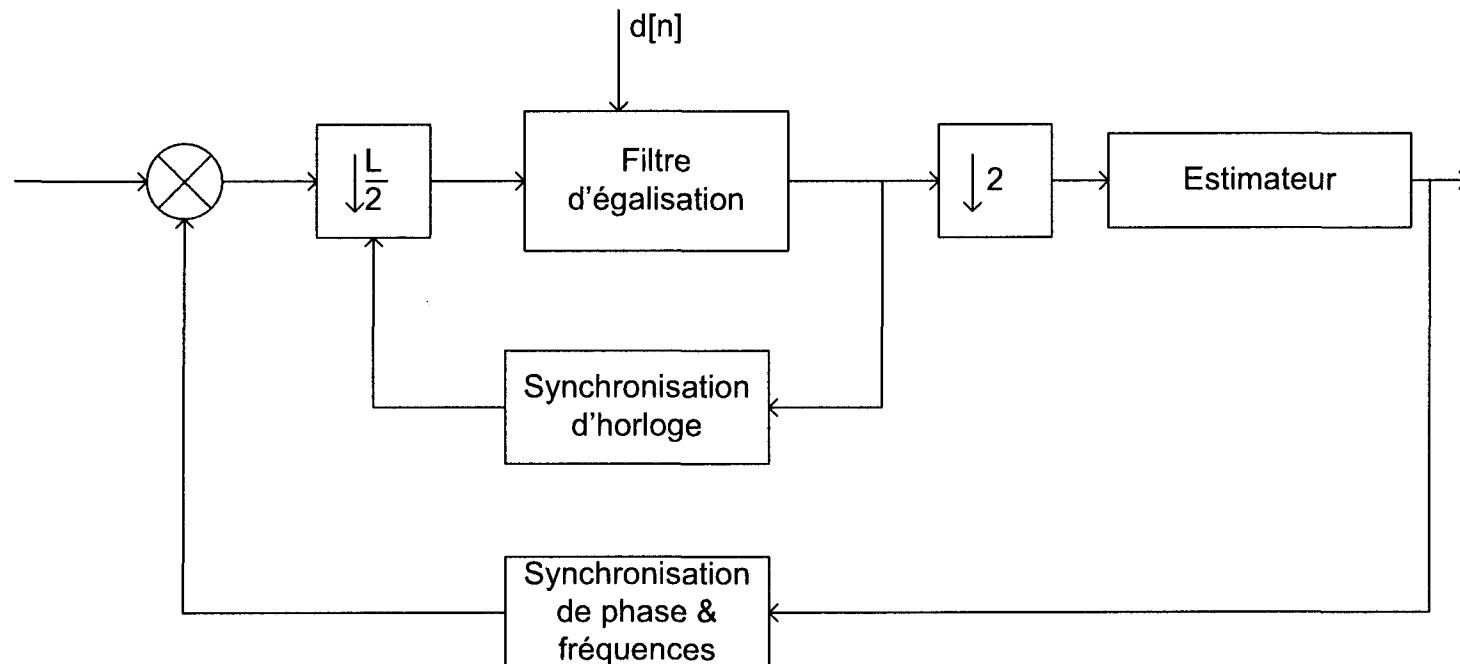

| 3.7                                                                                            | Synchronisation du récepteur . . . . .                   | 51        |

| 3.7.1                                                                                          | Synchronisation de phase et de fréquence . . . . .       | 53        |

| 3.7.2                                                                                          | Recouvrement d'horloge . . . . .                         | 56        |

| 3.8                                                                                            | Simulations et résultats . . . . .                       | 62        |

|                                                                  |            |

|------------------------------------------------------------------|------------|

| <b>CHAPITRE 4      LES APPAREILS DE PROTOTYPAGE . . . . .</b>    | <b>65</b>  |

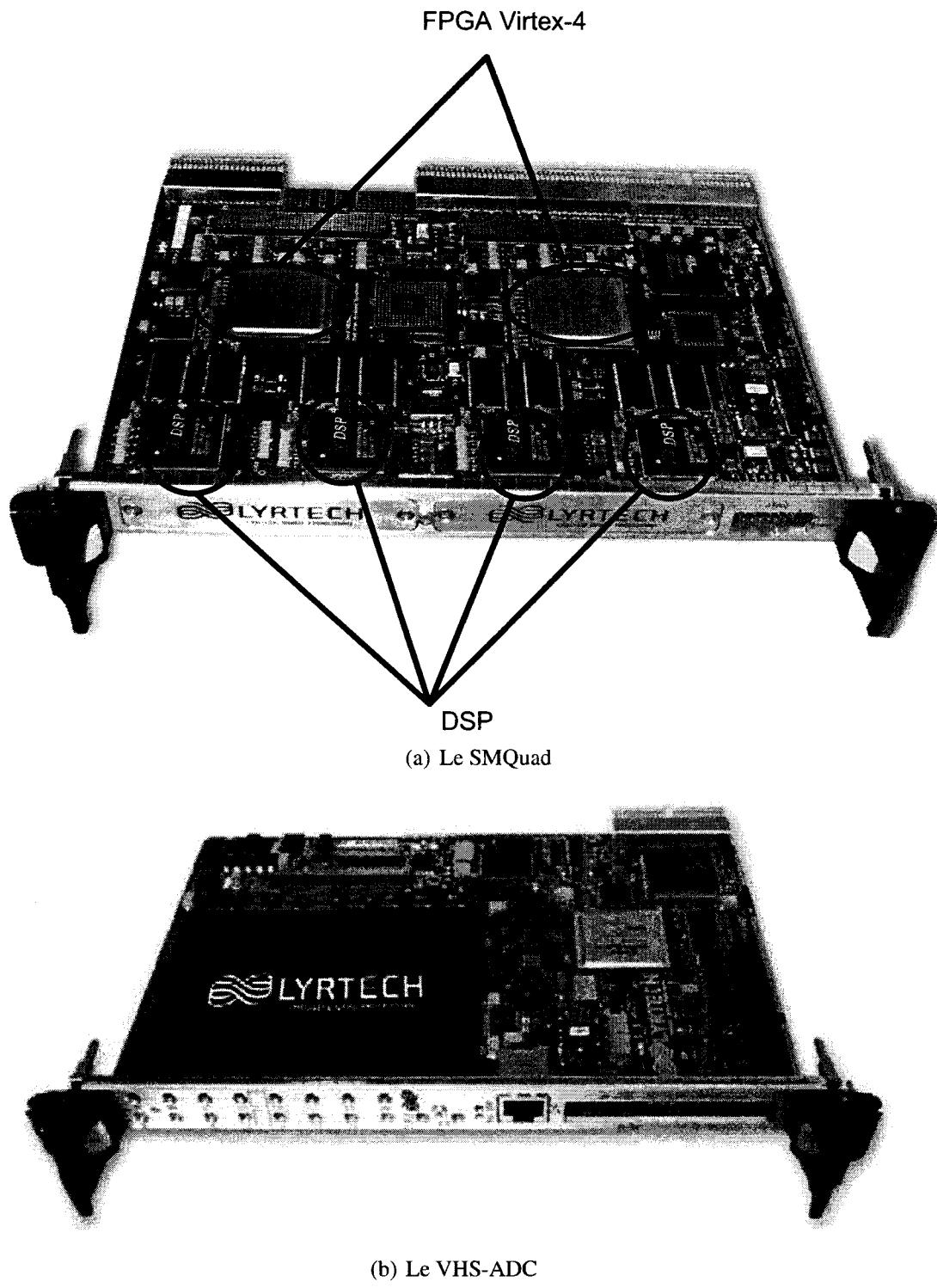

| 4.1   Vue d'ensemble du matériel . . . . .                       | 65         |

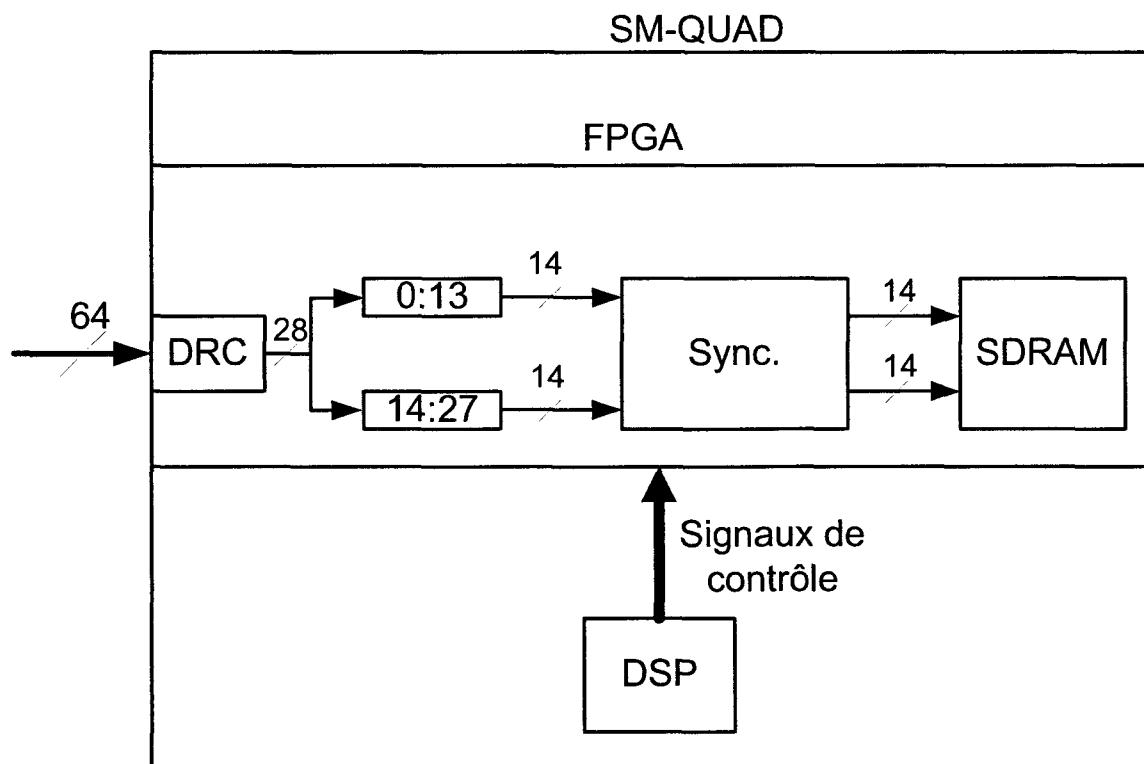

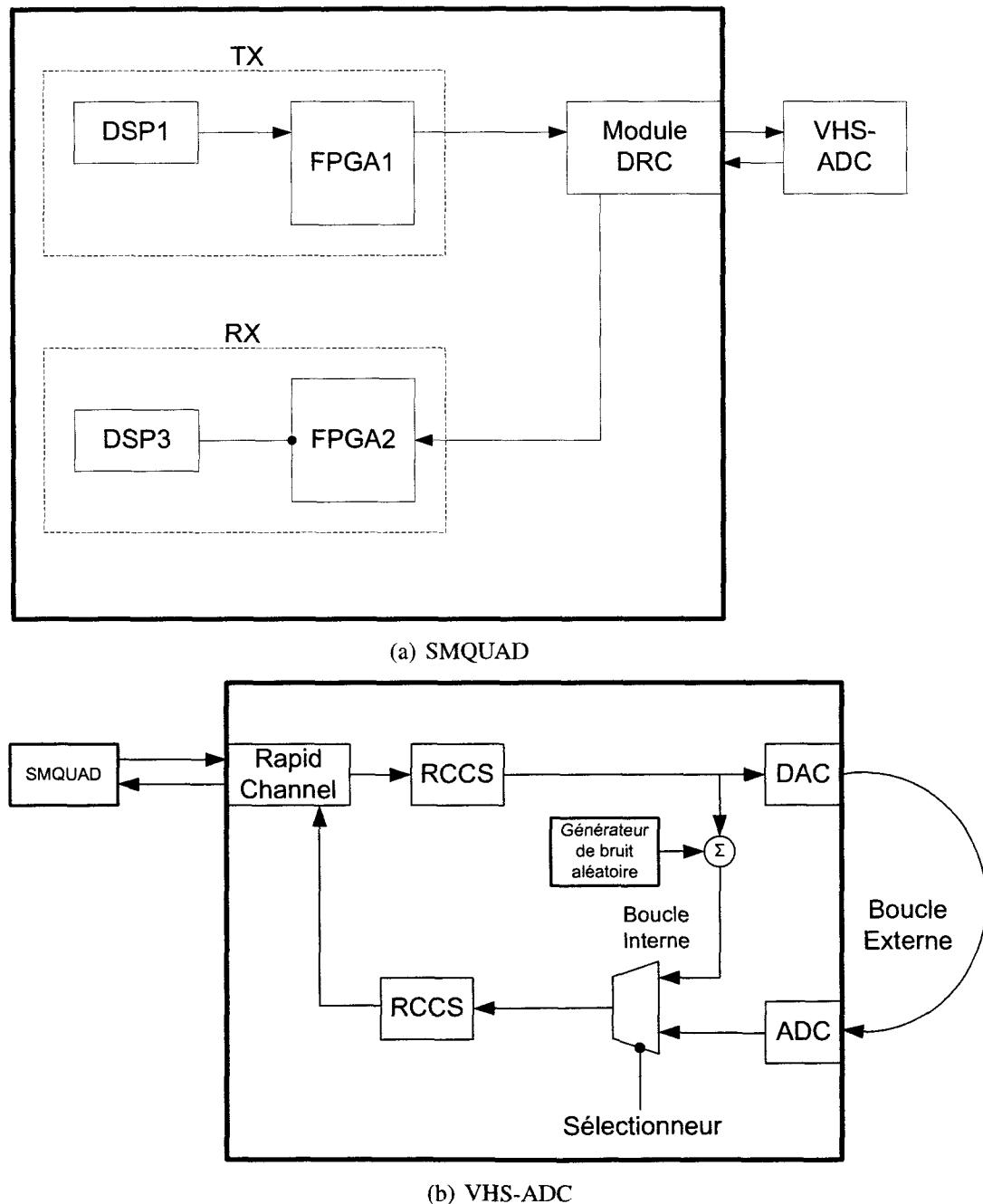

| 4.2   Description hardware du Signal Master QUAD . . . . .       | 67         |

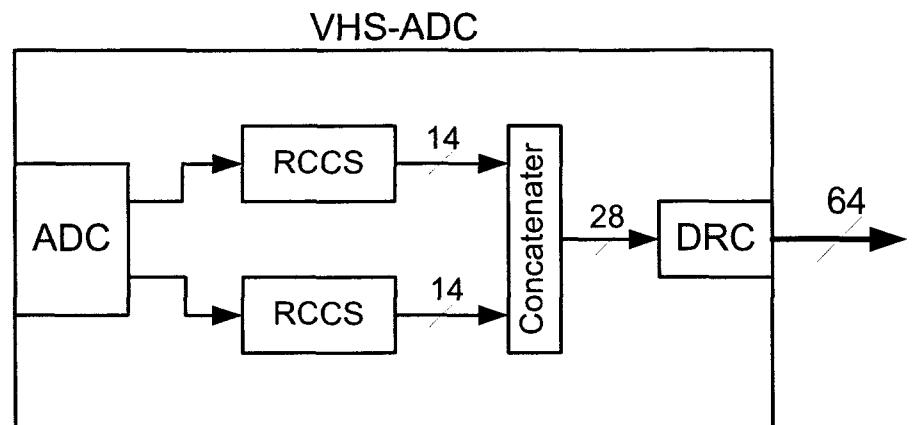

| 4.3   Description hardware du VHS-ADC . . . . .                  | 75         |

| 4.4   Description software . . . . .                             | 76         |

| 4.5   Outils nécessaires au développement . . . . .              | 82         |

| <br>                                                             |            |

| <b>CHAPITRE 5      RÉALISATION ET PERFORMANCE . . . . .</b>      | <b>86</b>  |

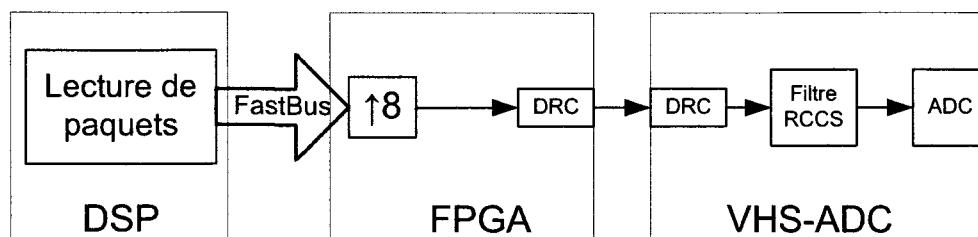

| 5.1   Le transmetteur . . . . .                                  | 86         |

| 5.2   Le récepteur . . . . .                                     | 90         |

| 5.2.1   Circuit utilisé au VHS-ADC . . . . .                     | 94         |

| 5.2.2   Détection de début de paquet . . . . .                   | 94         |

| 5.2.3   Algorithme de recouvrement d'horloge . . . . .           | 95         |

| 5.2.4   Filtre d'égalisation . . . . .                           | 99         |

| 5.2.5   Enregistrement des données reçues . . . . .              | 100        |

| 5.2.6   Blocs DSP . . . . .                                      | 103        |

| 5.3   Performances . . . . .                                     | 104        |

| 5.3.1   Caractérisation du transmetteur . . . . .                | 105        |

| 5.3.2   Vérification de la fonctionnalité du récepteur . . . . . | 109        |

| 5.3.3   Performance du récepteur . . . . .                       | 109        |

| <br>                                                             |            |

| <b>CHAPITRE 6      DISCUSSIONS ET CONCLUSION . . . . .</b>       | <b>116</b> |

| 6.1   Conclusion . . . . .                                       | 116        |

| 6.2   Améliorations . . . . .                                    | 116        |

| 6.3   Perspectives . . . . .                                     | 118        |

| <br>                                                             |            |

| <b>RÉFÉRENCES . . . . .</b>                                      | <b>120</b> |

| <br>                                                             |            |

| <b>ANNEXES . . . . .</b>                                         | <b>125</b> |

## LISTE DES FIGURES

|             |                                                                                                                             |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|----|

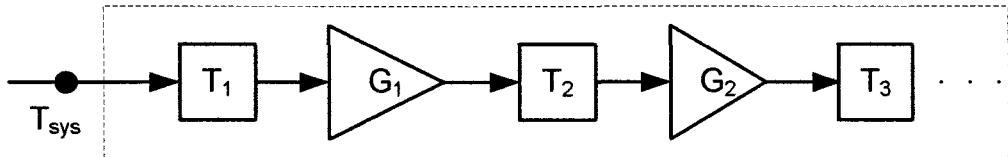

| FIGURE 1.1  | Température du bruit pour un système en cascade . . . . .                                                                   | 6  |

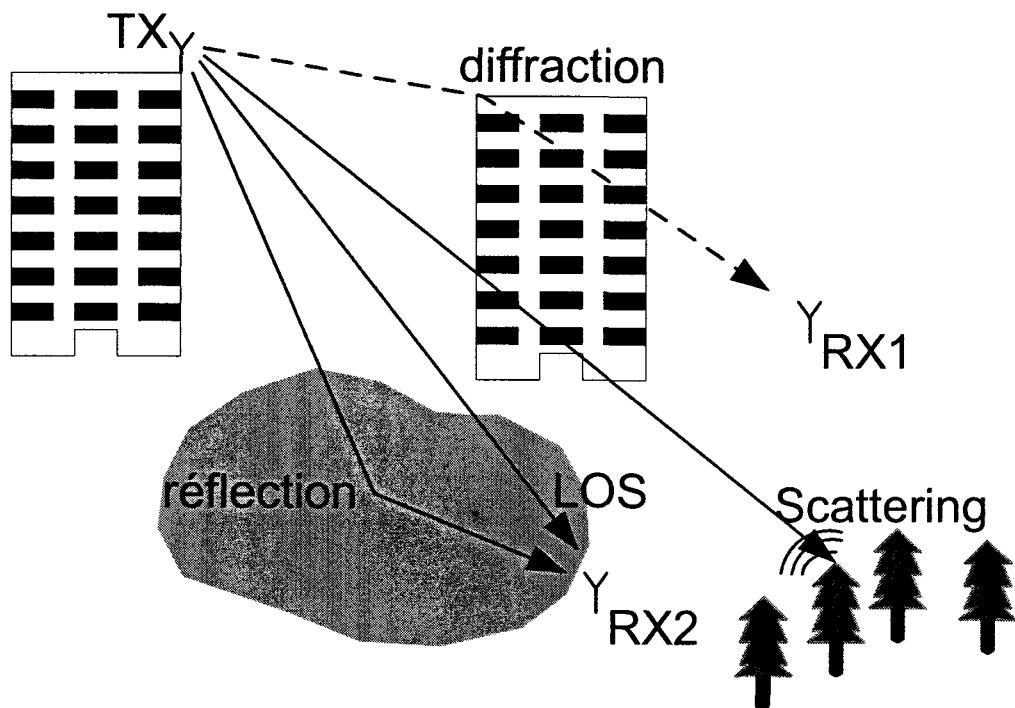

| FIGURE 1.2  | Les causes de multi-traj ectoires . . . . .                                                                                 | 10 |

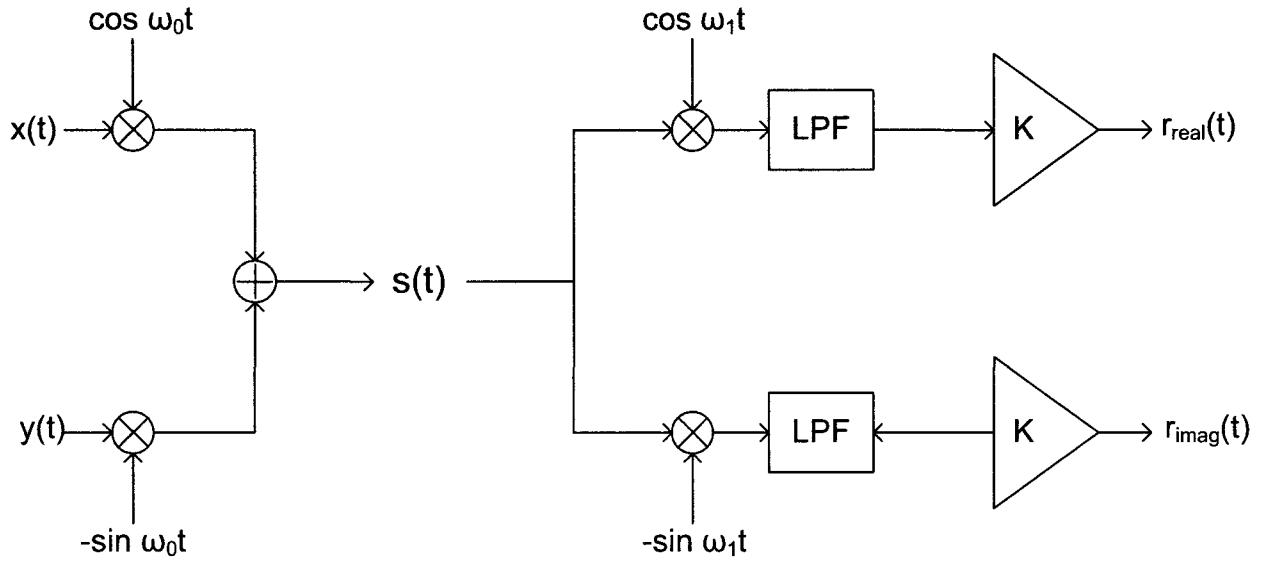

| FIGURE 1.3  | Conversion de bande de base à bande passante au transmetteur et<br>de bande passante à bande de base au récepteur . . . . . | 16 |

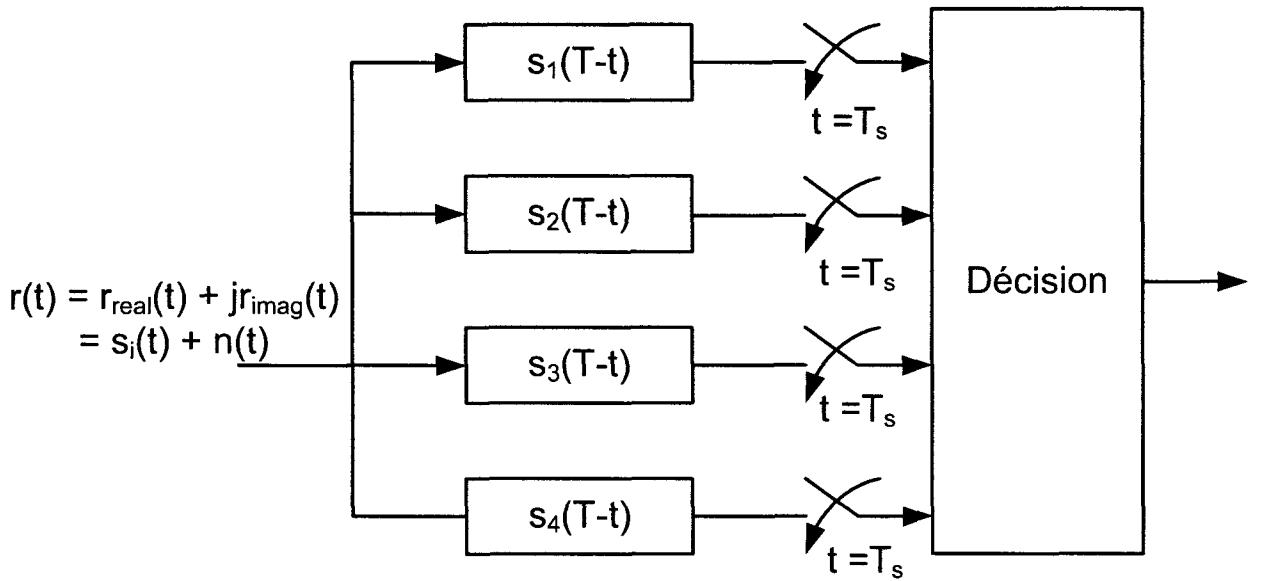

| FIGURE 1.4  | Structure d'un récepteur optimal . . . . .                                                                                  | 17 |

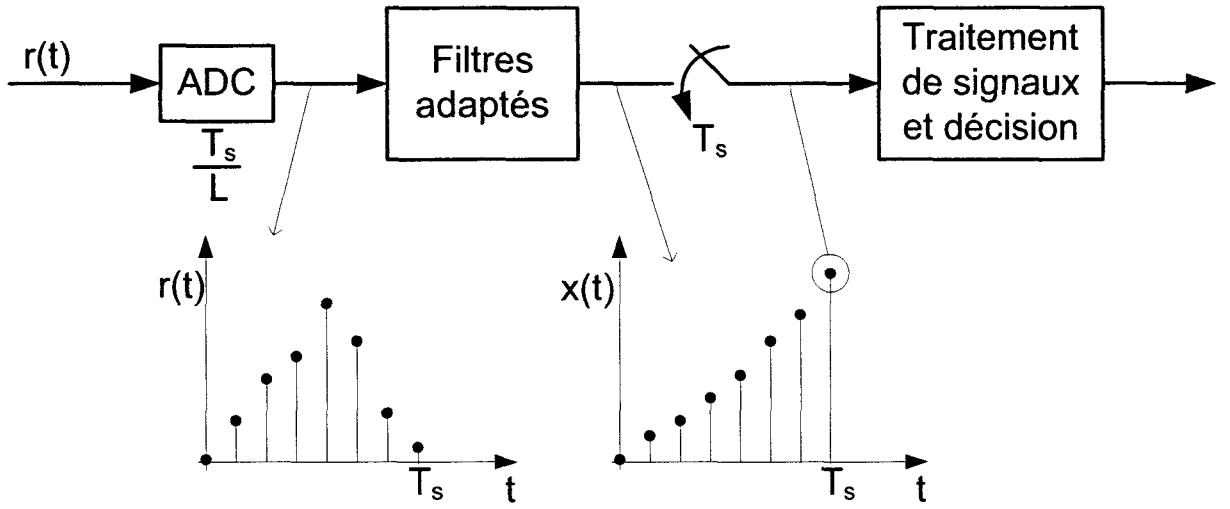

| FIGURE 1.5  | Discrétisation du filtre adapté . . . . .                                                                                   | 18 |

| FIGURE 1.6  | Effet du délai de canal sur le moment d'échantillonage . . . . .                                                            | 19 |

| FIGURE 1.7  | Une vue de haut niveau du système de communications . . . . .                                                               | 22 |

| FIGURE 2.1  | Plateforme pour un SDR sur DSP [Stuber G.L. et al, 2004] . . .                                                              | 27 |

| FIGURE 2.2  | Modèle d'un système FPGA [Barbero, L.G. & Thompson, J.S., 2005]                                                             | 28 |

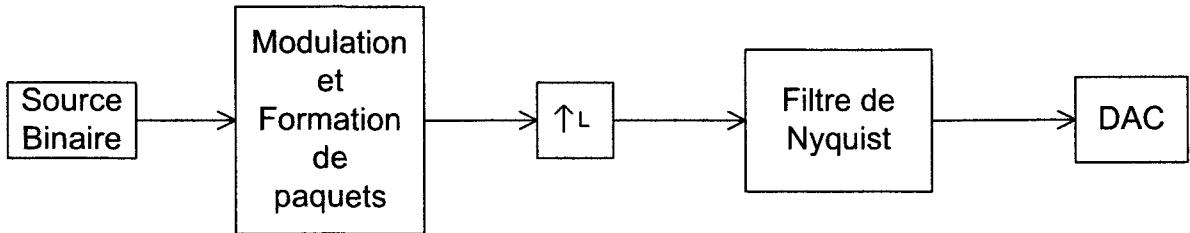

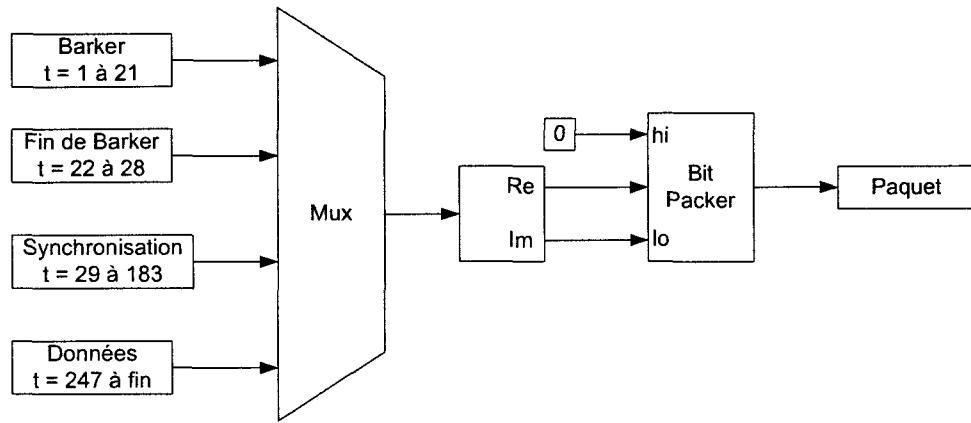

| FIGURE 3.1  | Schéma bloc du transmetteur . . . . .                                                                                       | 31 |

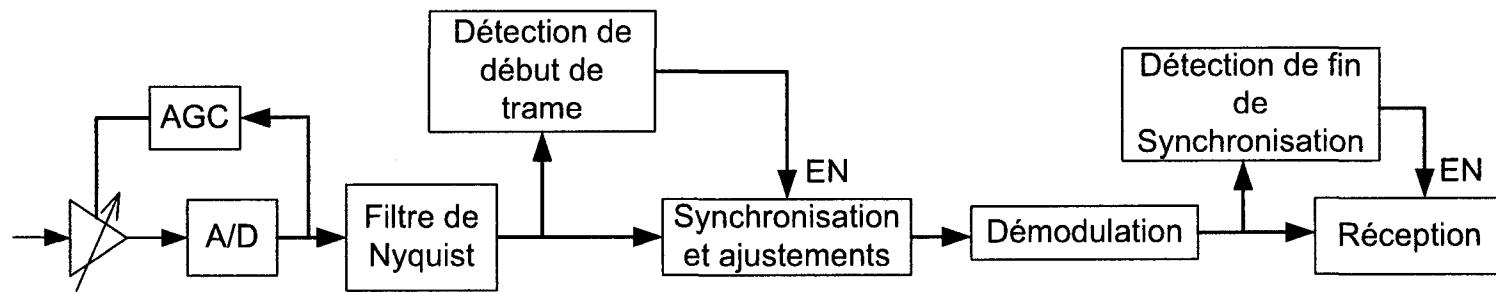

| FIGURE 3.2  | Structure du récepteur modélisé . . . . .                                                                                   | 32 |

| FIGURE 3.3  | Vue générale des paquets . . . . .                                                                                          | 33 |

| FIGURE 3.4  | Génération d'un PBRS avec un registre à décalage. . . . .                                                                   | 34 |

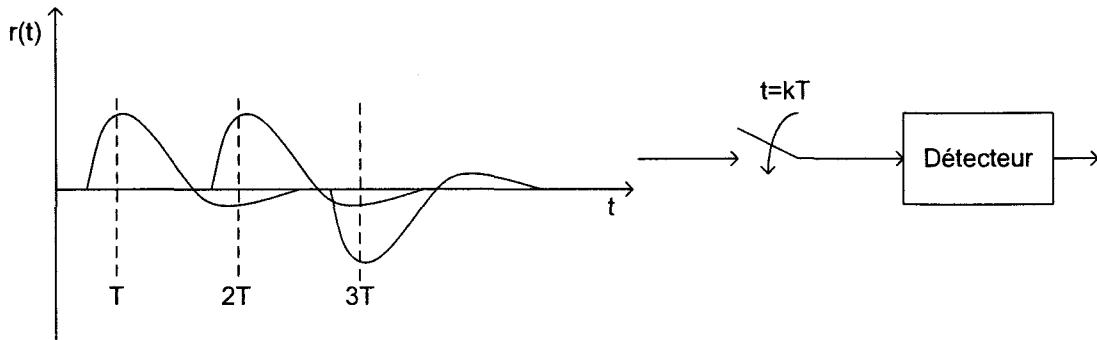

| FIGURE 3.5  | Interférences entre symboles. . . . .                                                                                       | 36 |

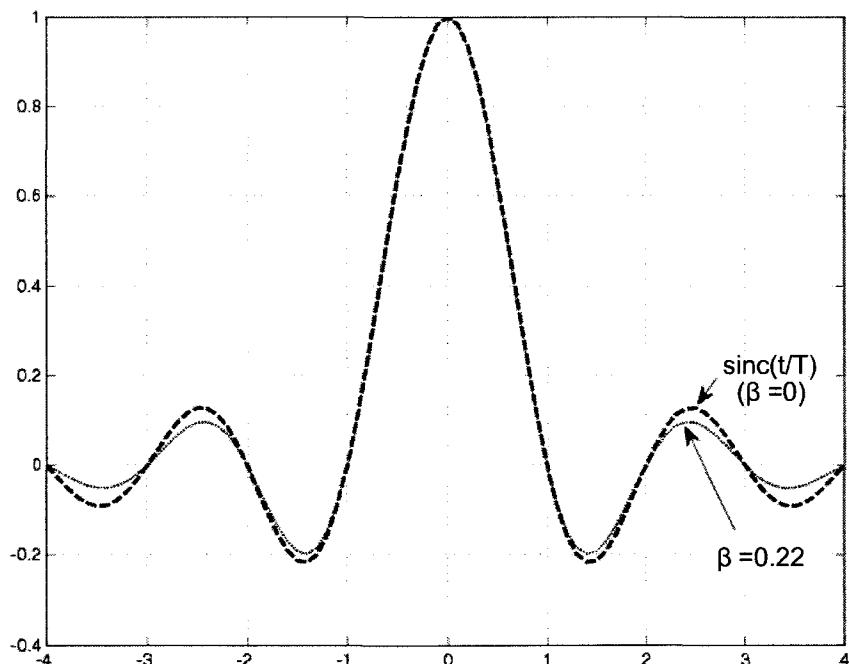

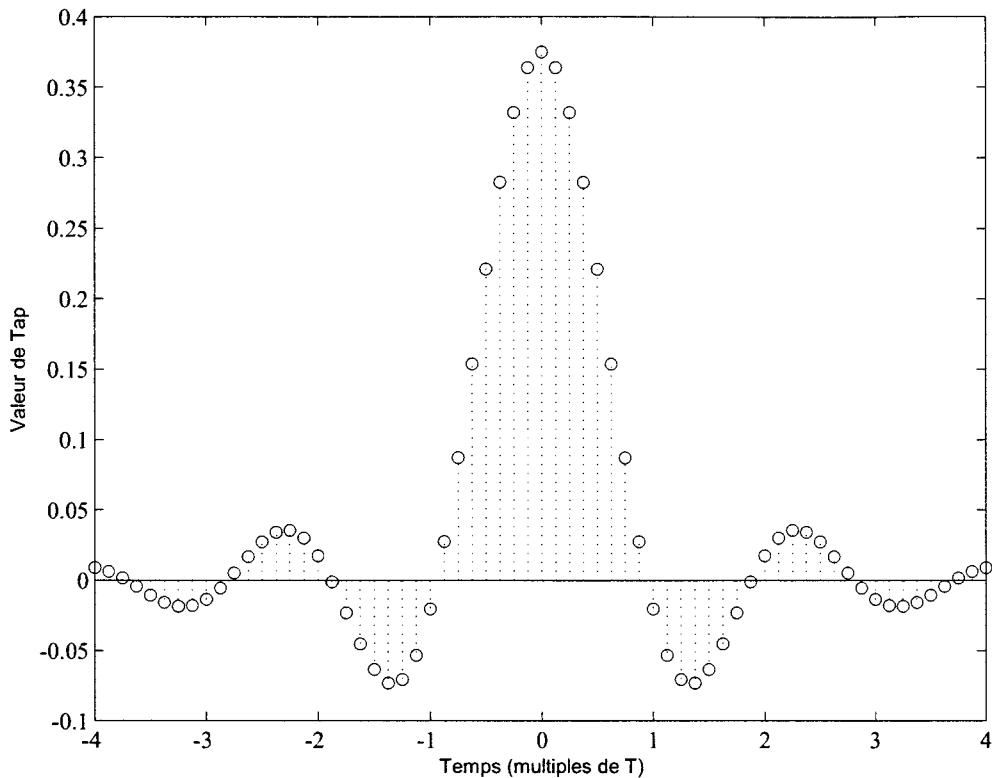

| FIGURE 3.6  | Réponses des filtres en cosinus surélevés. . . . .                                                                          | 38 |

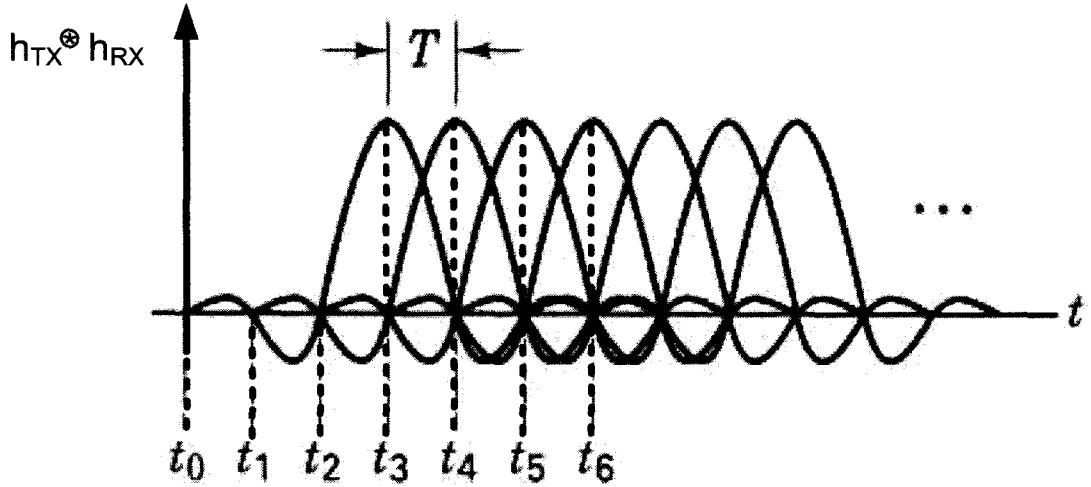

| FIGURE 3.7  | Réponse impulsionnelle du filtre en racine cosinus surélevé pour<br>mise en forme d'impulsions. . . . .                     | 40 |

| FIGURE 3.8  | Symboles à la sortie du filtre adapté. . . . .                                                                              | 41 |

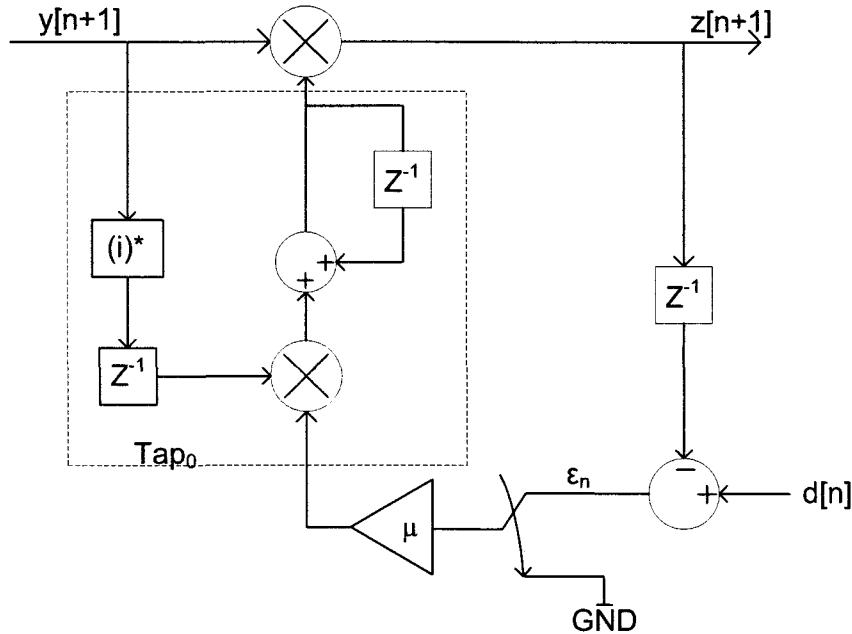

| FIGURE 3.9  | Filtre LMS à 1 tap. . . . .                                                                                                 | 43 |

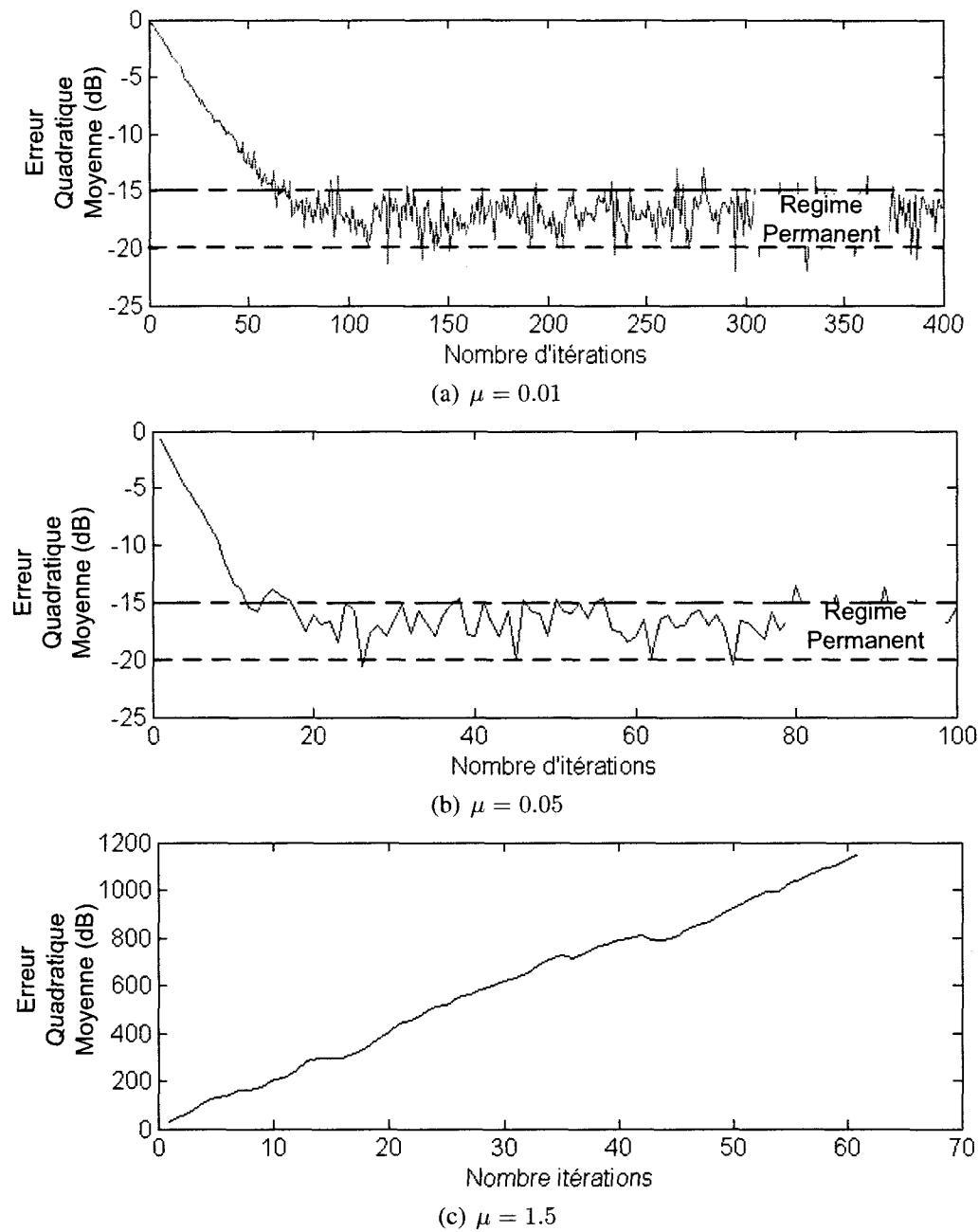

| FIGURE 3.10 | Taux de convergence de l'algorithme LMS pour différentes va-<br>leurs de $\mu$ . . . . .                                    | 44 |

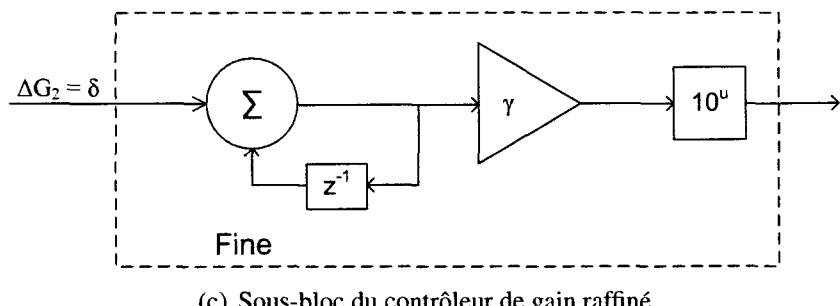

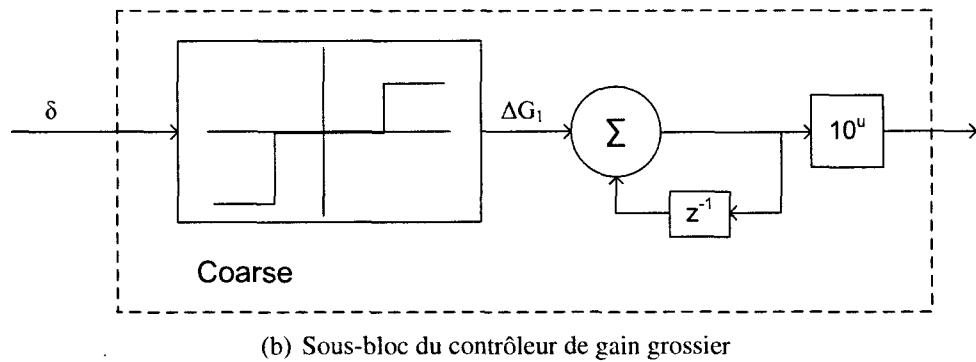

| FIGURE 3.11 | Contrôleur de gain automatique. . . . .                                                                                     | 47 |

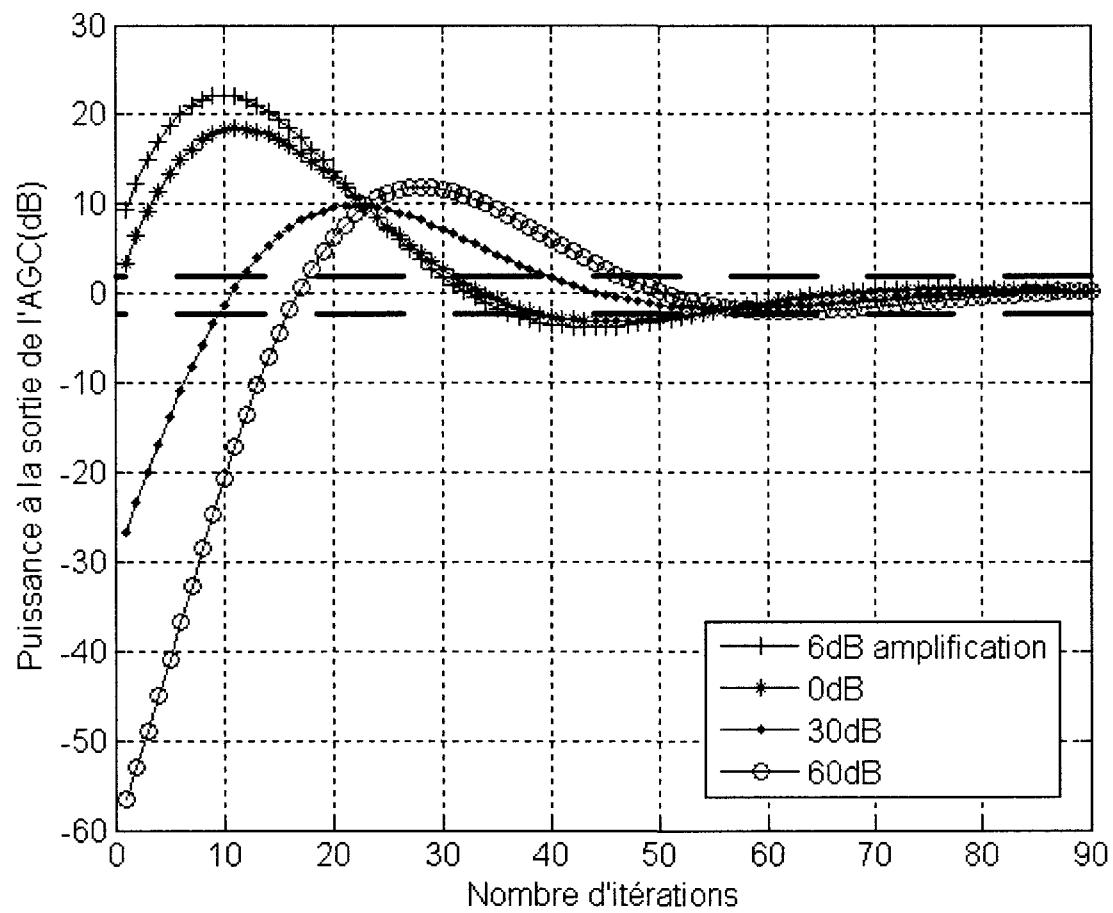

| FIGURE 3.12 | Résultat des tests effectués sur le contrôleur de puissance. . . . .                                                        | 49 |

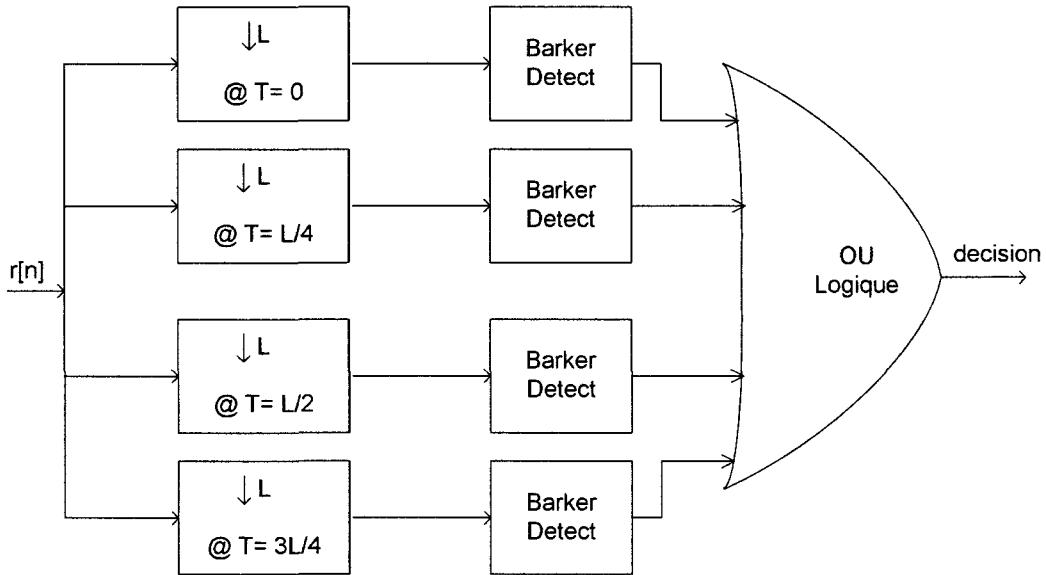

| FIGURE 3.13 | Circuit de détection de début de trame. . . . .                                                                             | 50 |

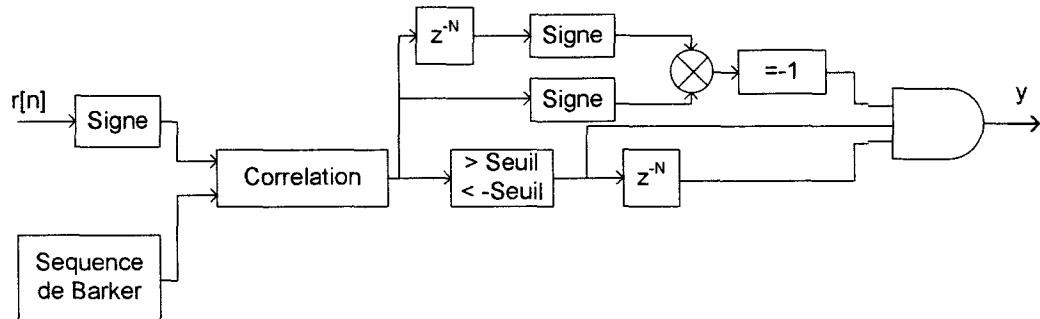

| FIGURE 3.14 | Circuit de détection de séquence de Barker. . . . .                                                                         | 51 |

|             |                                                                                                     |    |

|-------------|-----------------------------------------------------------------------------------------------------|----|

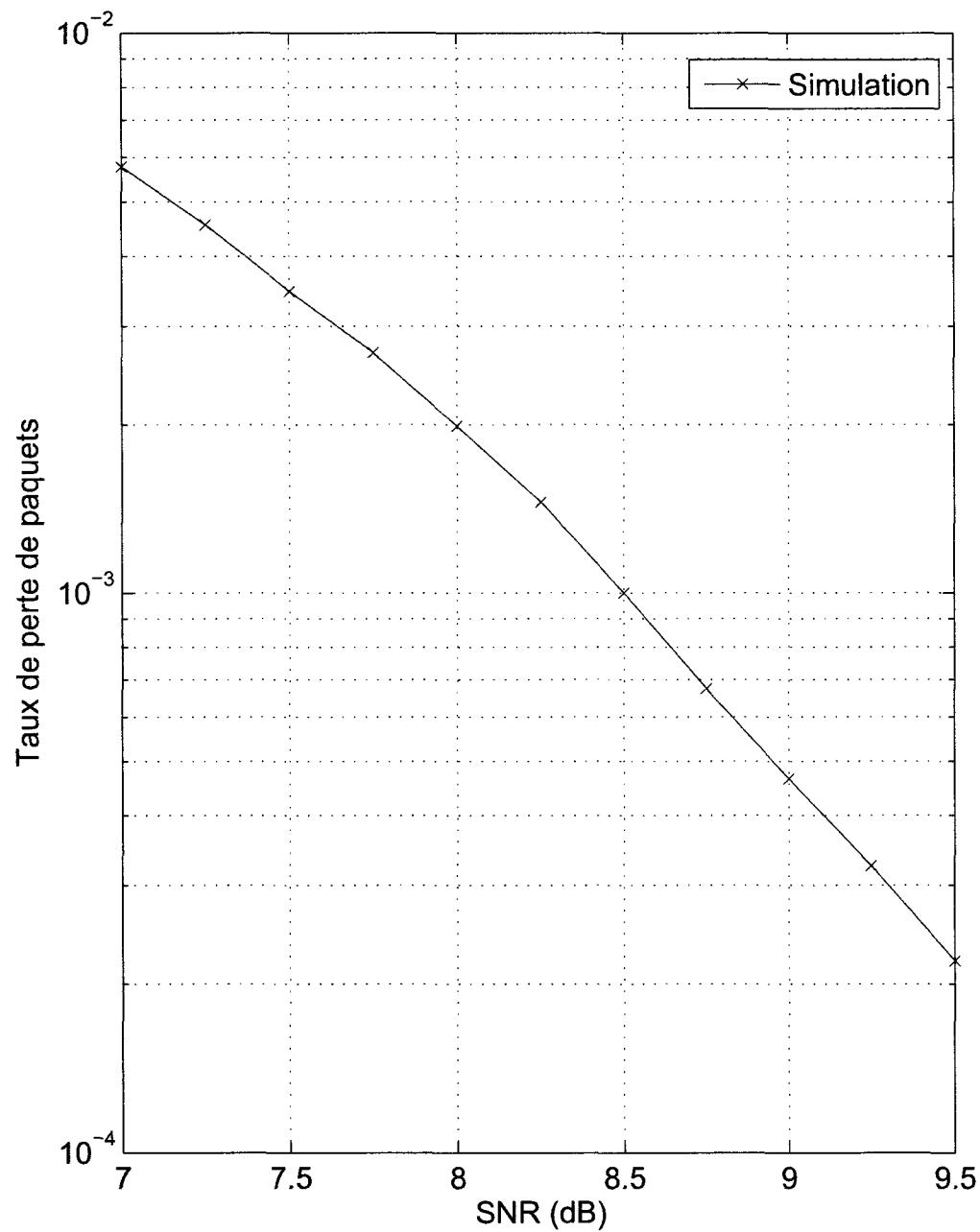

| FIGURE 3.15 | Taux de pertes de paquets pour différents niveaux de SNR avec un seuil de détection à 6 . . . . .   | 52 |

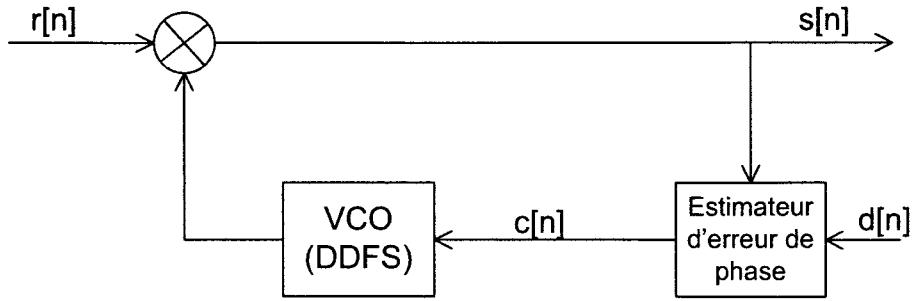

| FIGURE 3.16 | Schéma bloc de la boucle de correction de phase. . . . .                                            | 53 |

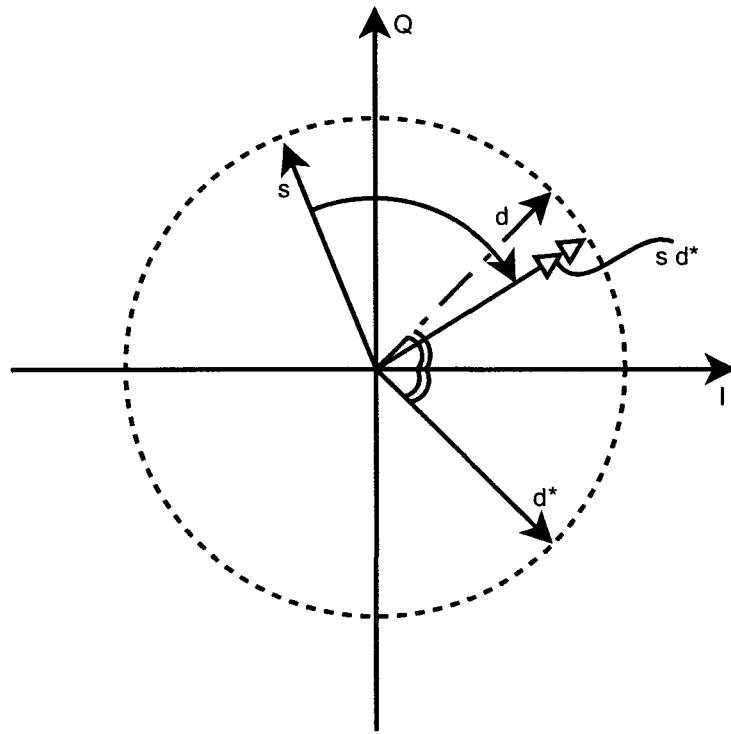

| FIGURE 3.17 | Comparaison de phases du signal de réception et de la référence dans le plan I-Q . . . . .          | 55 |

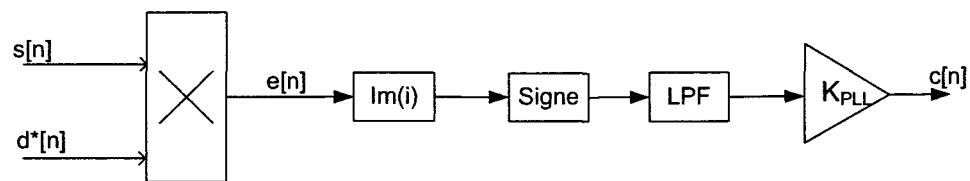

| FIGURE 3.18 | Estimation d'erreur de phase. . . . .                                                               | 55 |

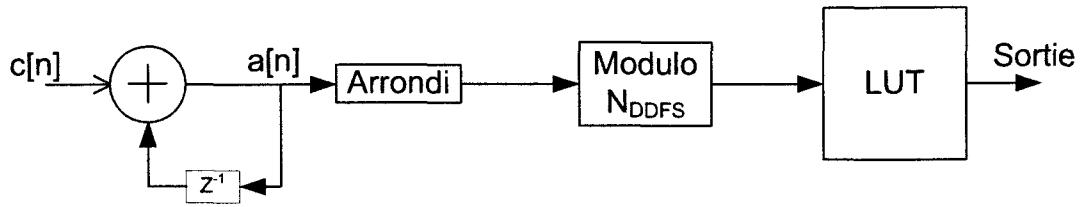

| FIGURE 3.19 | Circuit d'un DDFS. . . . .                                                                          | 56 |

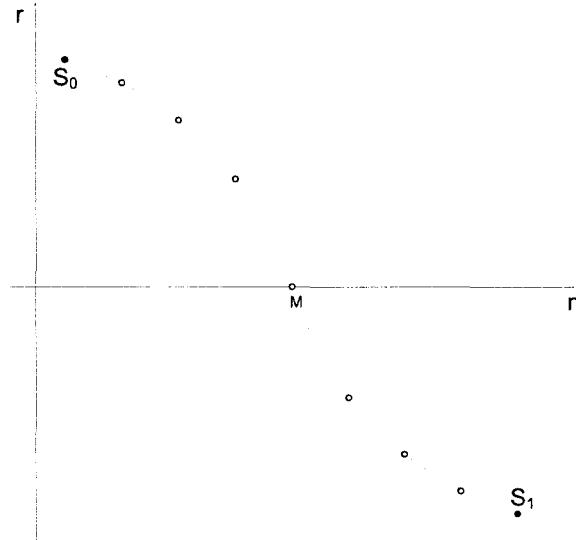

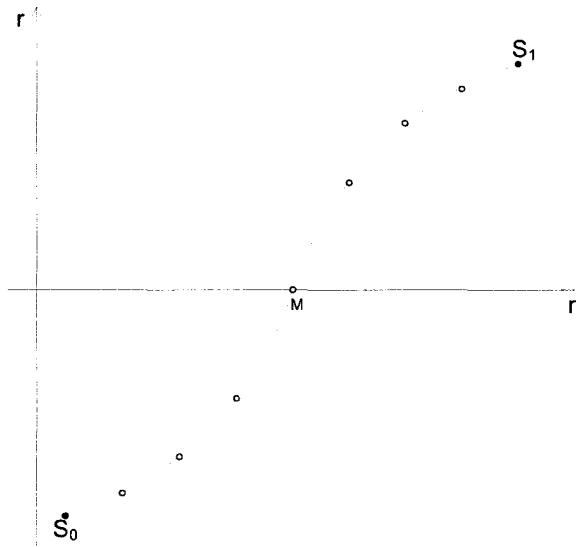

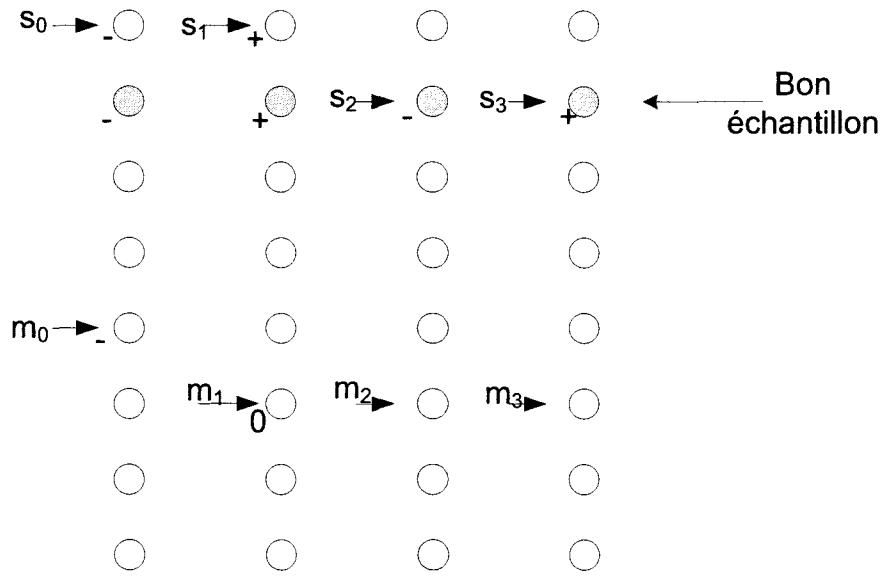

| FIGURE 3.20 | Illustration simplifiée des transitions possibles lors de la transmission d'un signal BPSK. . . . . | 58 |

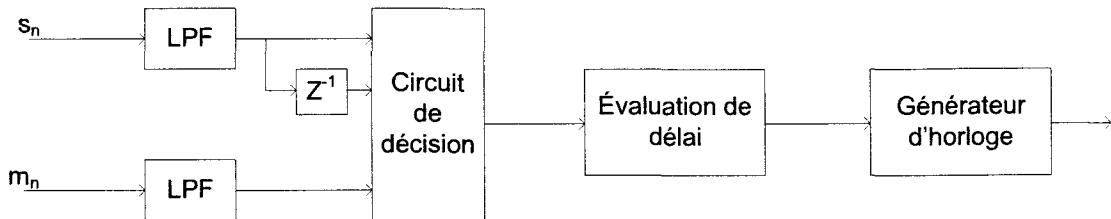

| FIGURE 3.21 | Circuit de recouvrement d'horloge . . . . .                                                         | 59 |

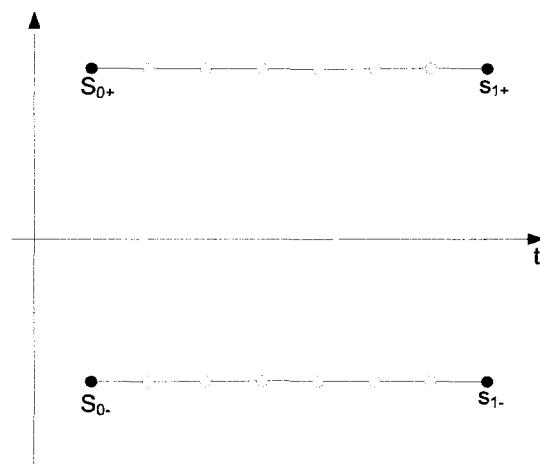

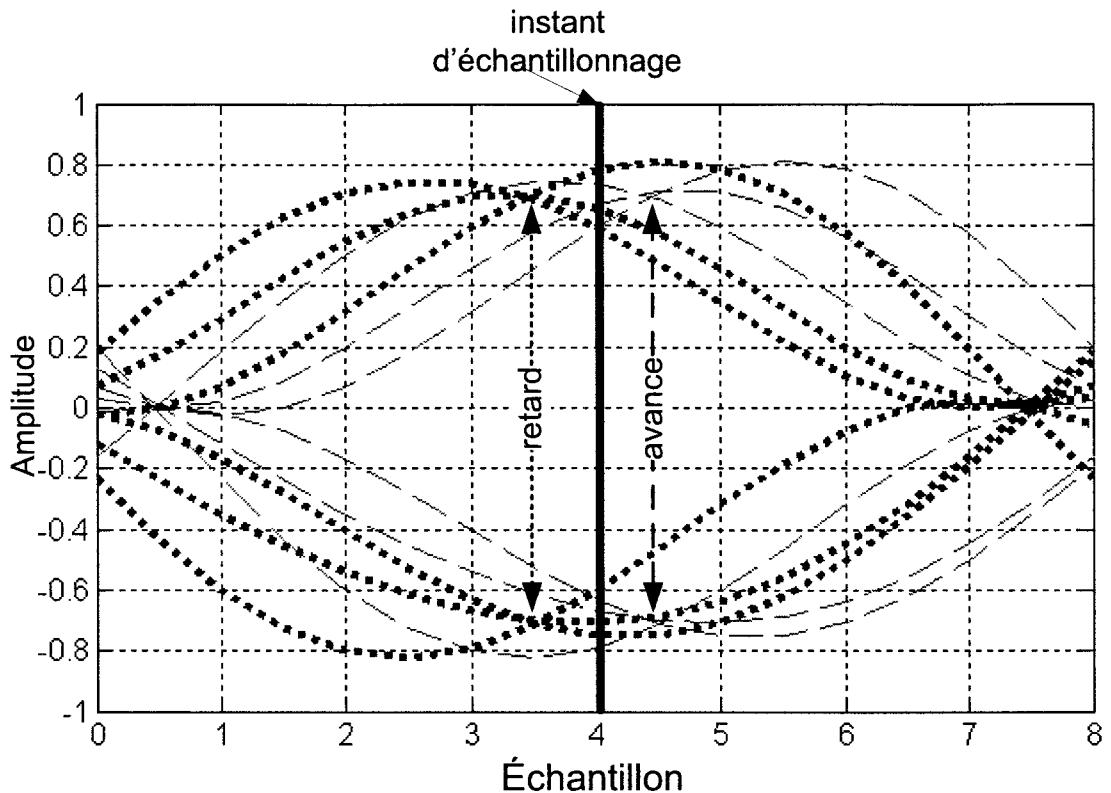

| FIGURE 3.22 | Exemple de synchronisation d'horloge . . . . .                                                      | 60 |

| FIGURE 3.23 | Effet d'un décalage d'un demi échantillon . . . . .                                                 | 62 |

| FIGURE 3.24 | Résultat de simulation sur Simulink . . . . .                                                       | 64 |

| FIGURE 4.1  | Photos des plateformes de développement . . . . .                                                   | 66 |

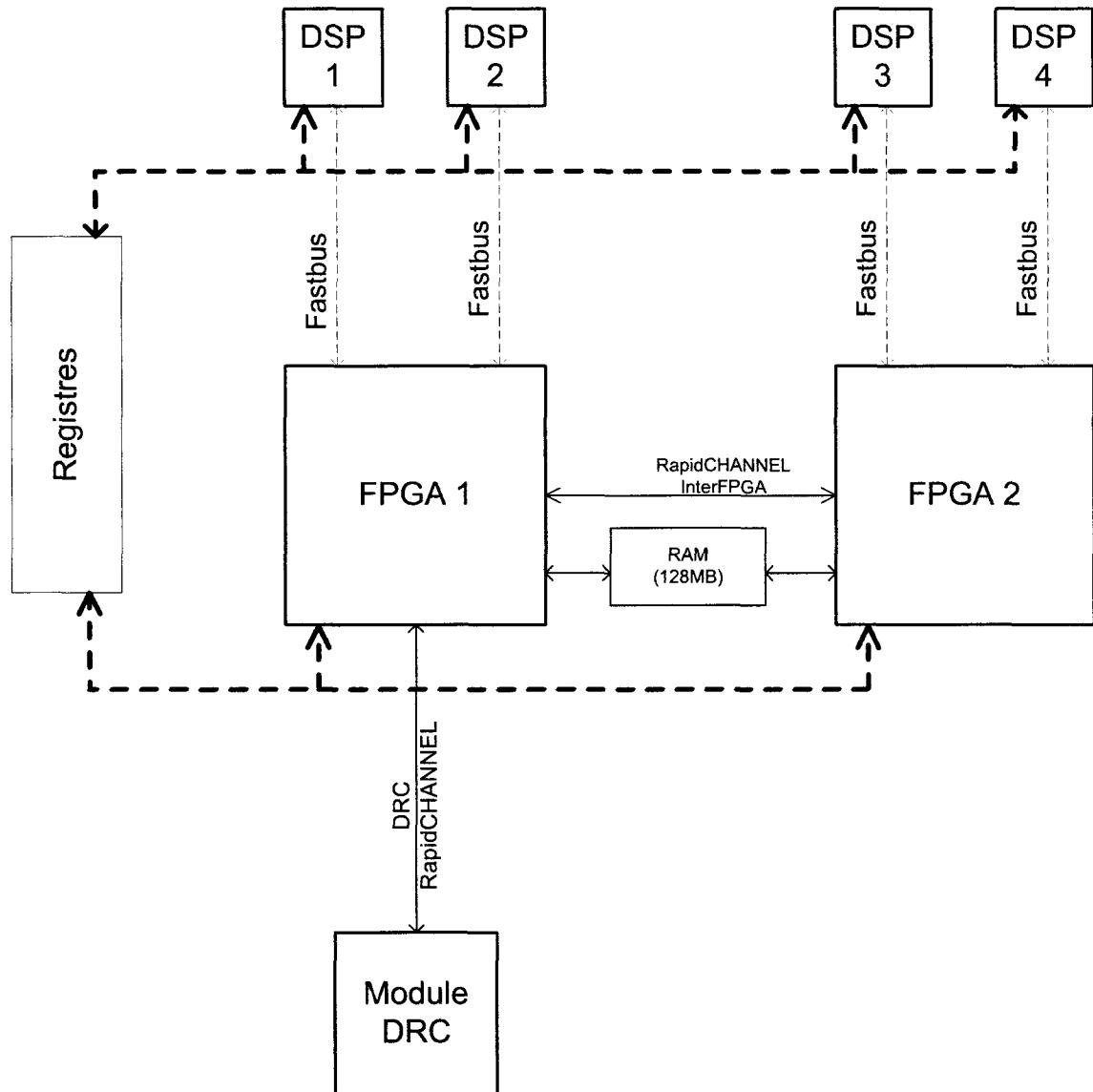

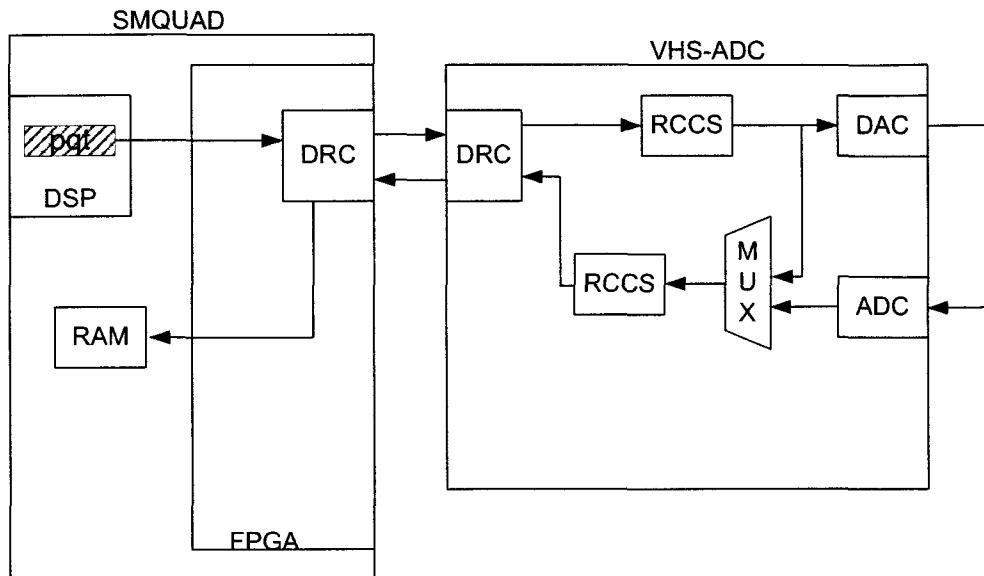

| FIGURE 4.2  | Composantes du SMQUAD et leurs interconnexions . . . . .                                            | 68 |

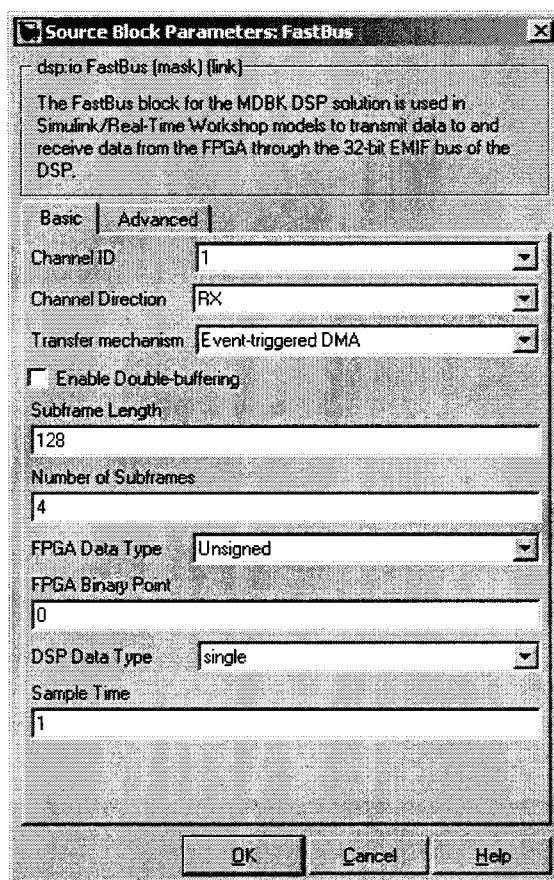

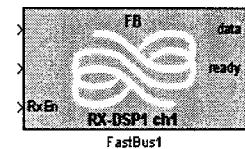

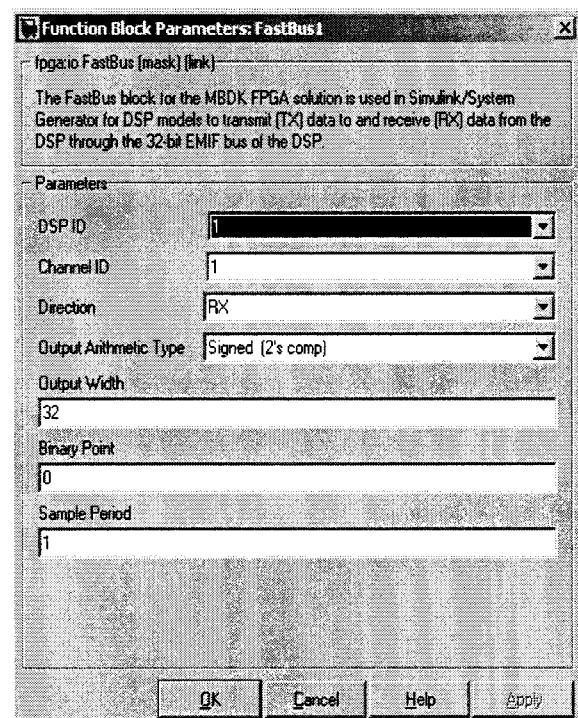

| FIGURE 4.3  | Les blocs FastBus . . . . .                                                                         | 69 |

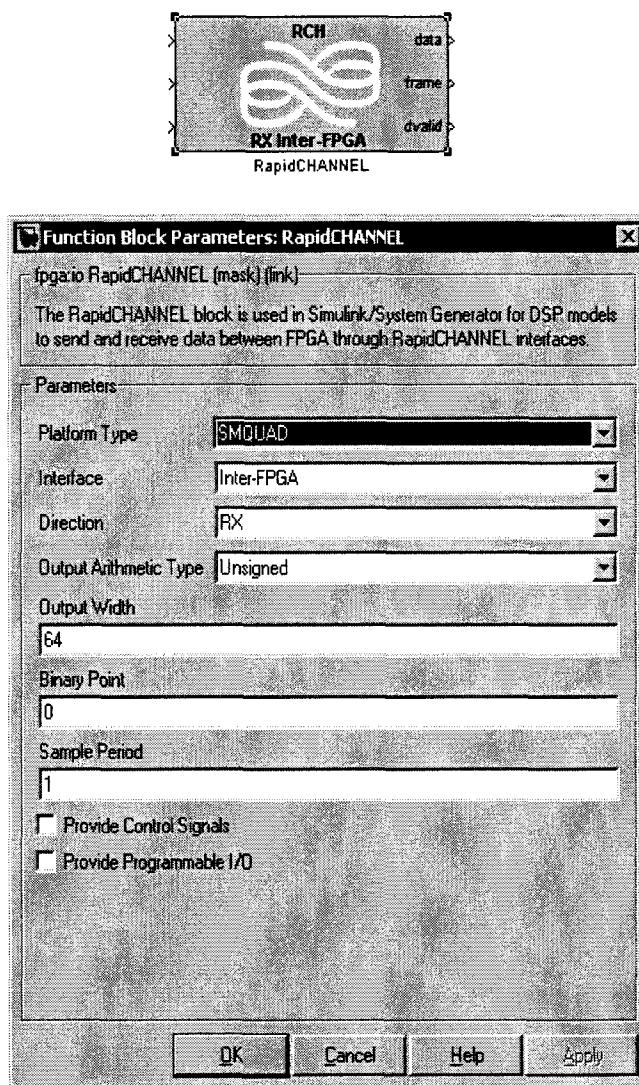

| FIGURE 4.4  | Interface Simulink du bloc RapidChannel. . . . .                                                    | 72 |

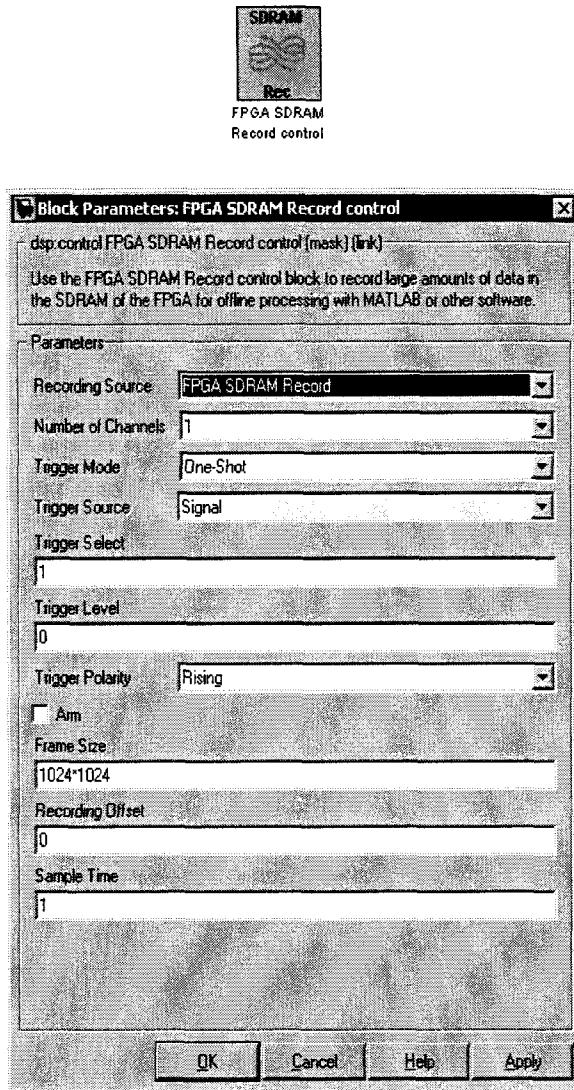

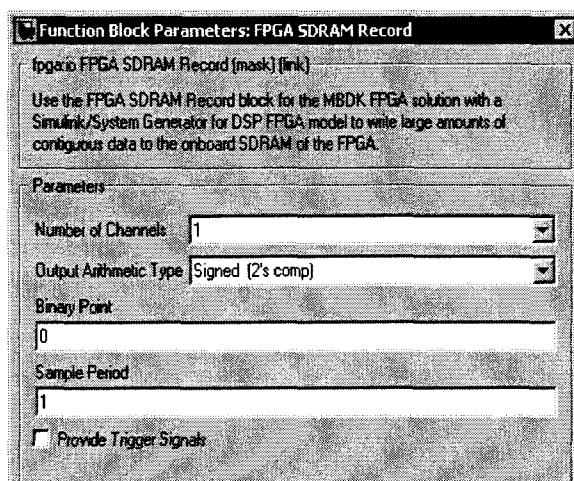

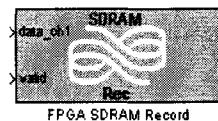

| FIGURE 4.5  | Les blocs utilisés pour l'enregistrement de données . . . . .                                       | 74 |

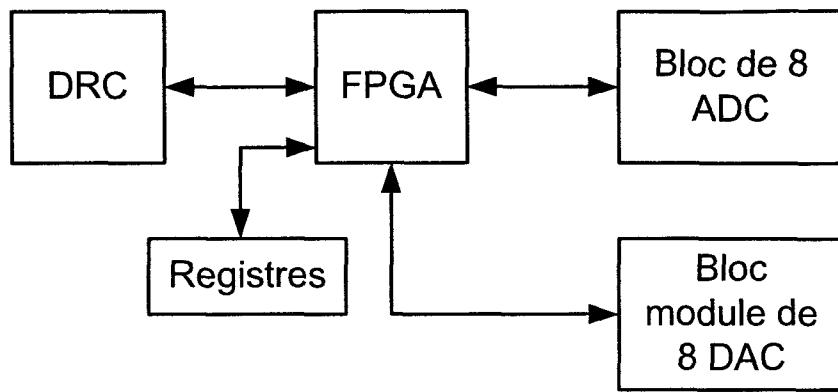

| FIGURE 4.6  | Diagramme bloc des principales composantes du VHS-ADC . . . . .                                     | 75 |

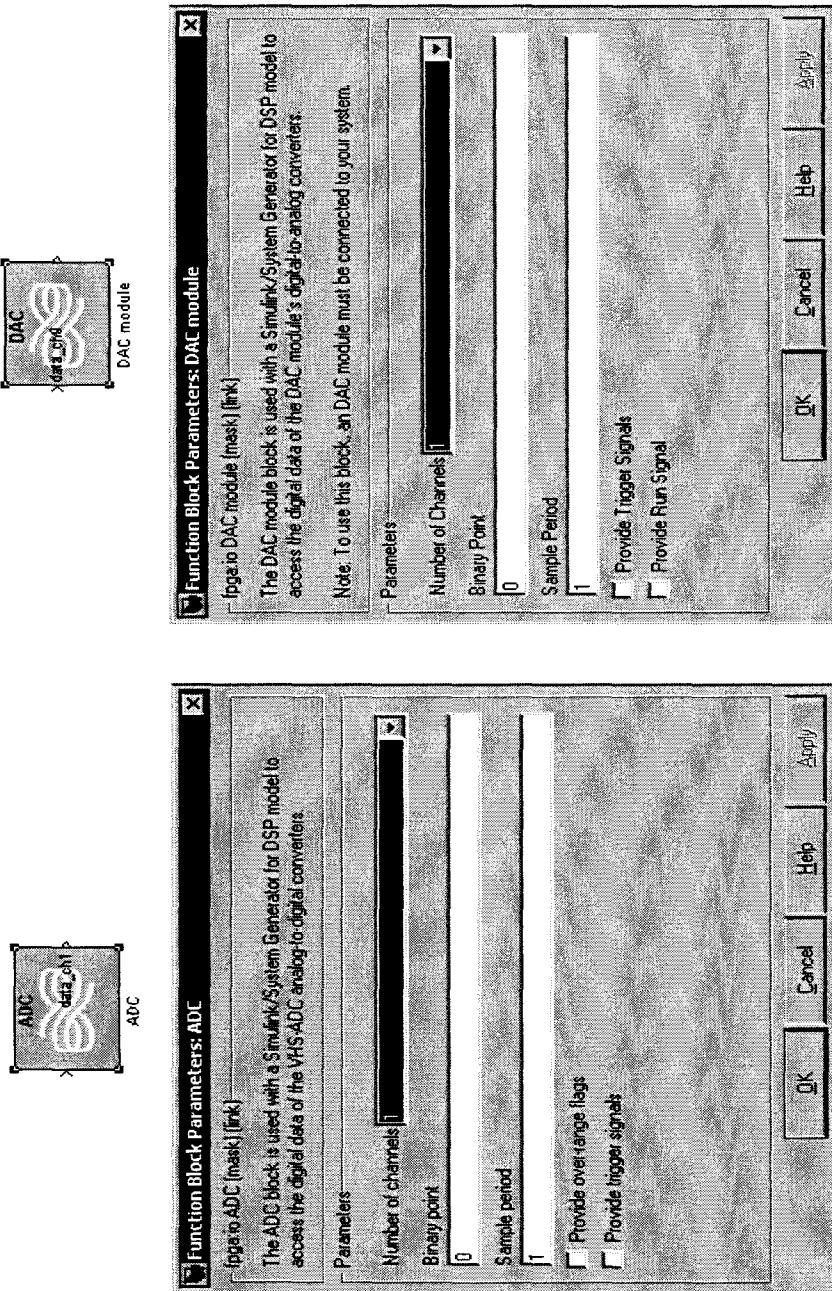

| FIGURE 4.7  | Les convertisseurs et leurs paramètres . . . . .                                                    | 77 |

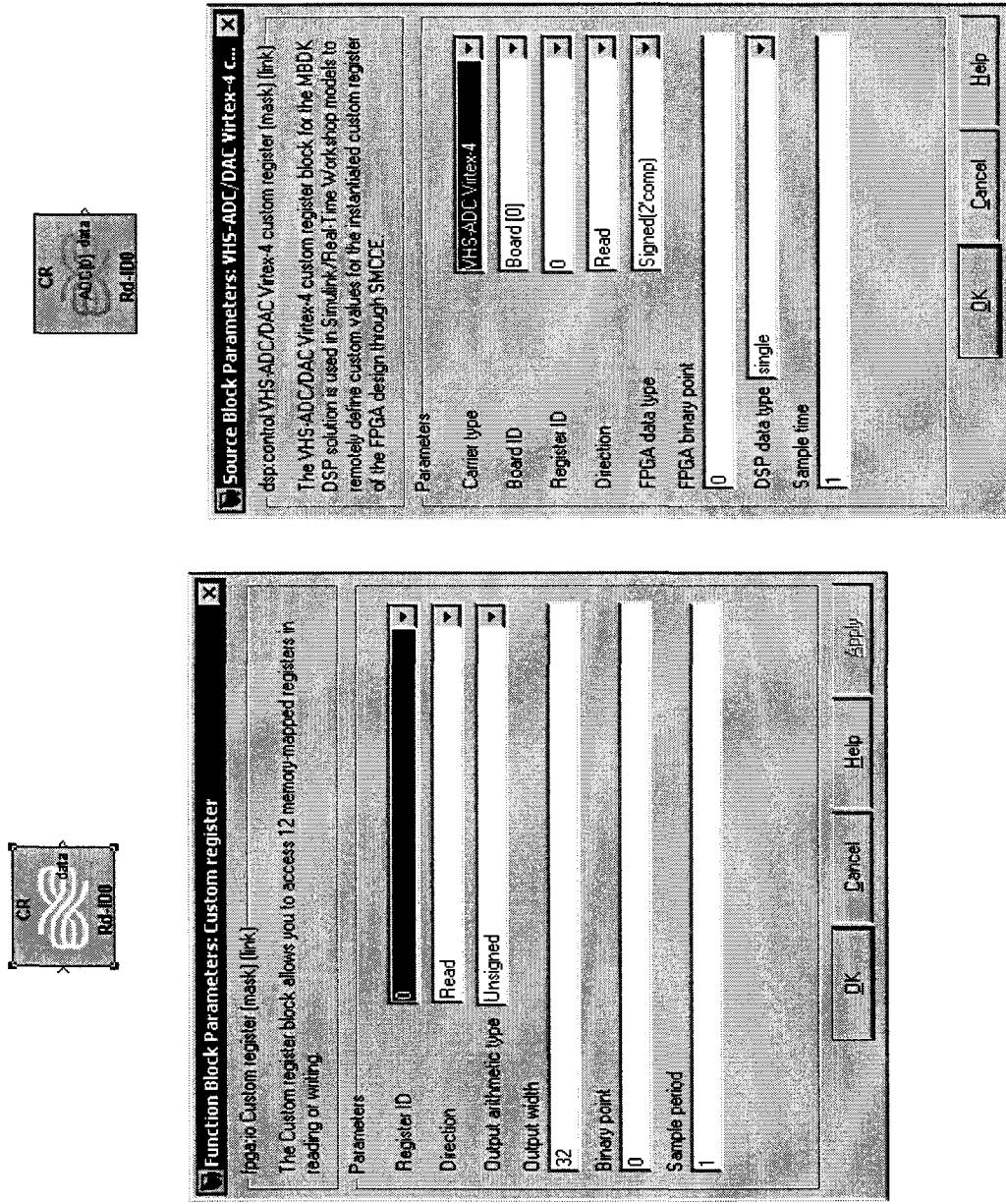

| FIGURE 4.8  | Blocs des Registres du VHS-ADC . . . . .                                                            | 78 |

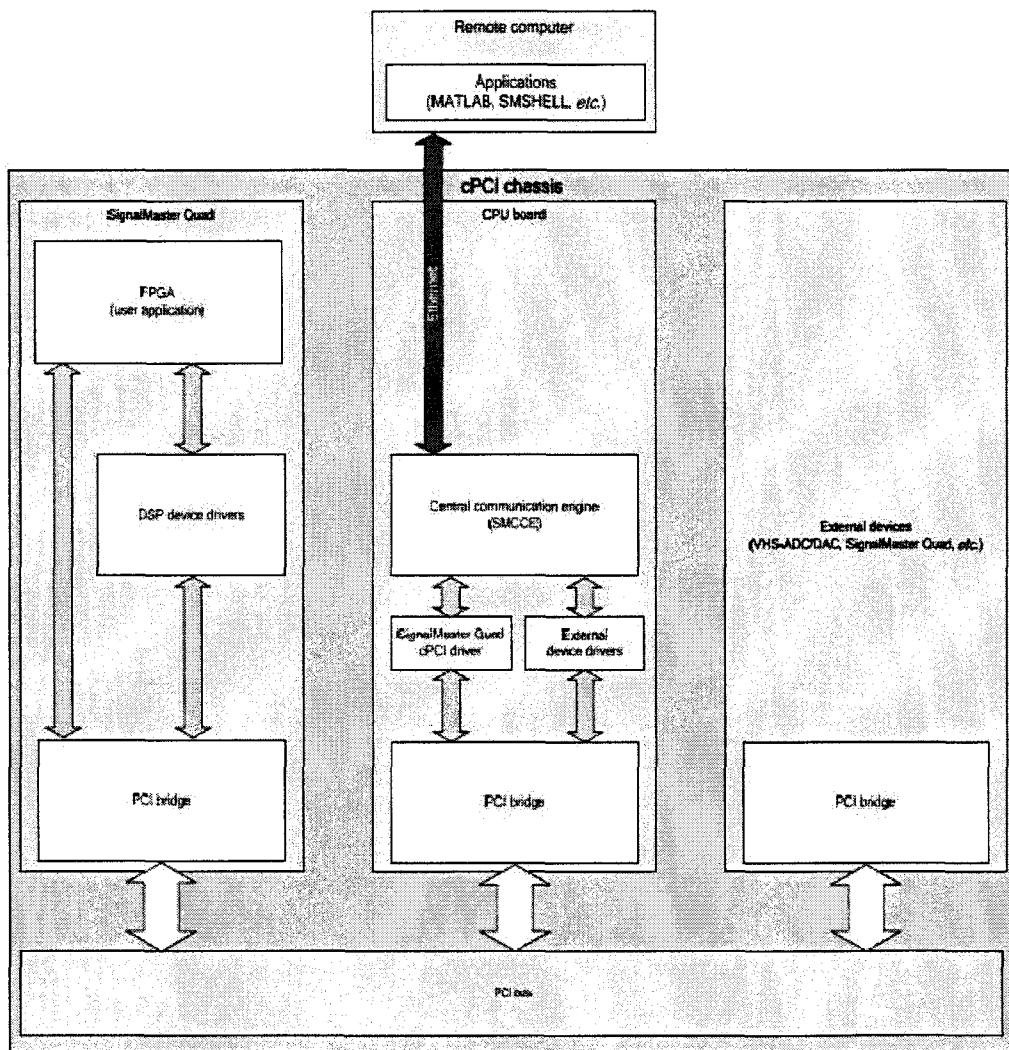

| FIGURE 4.9  | Le SMCCE comme un pont de communications . . . . .                                                  | 80 |

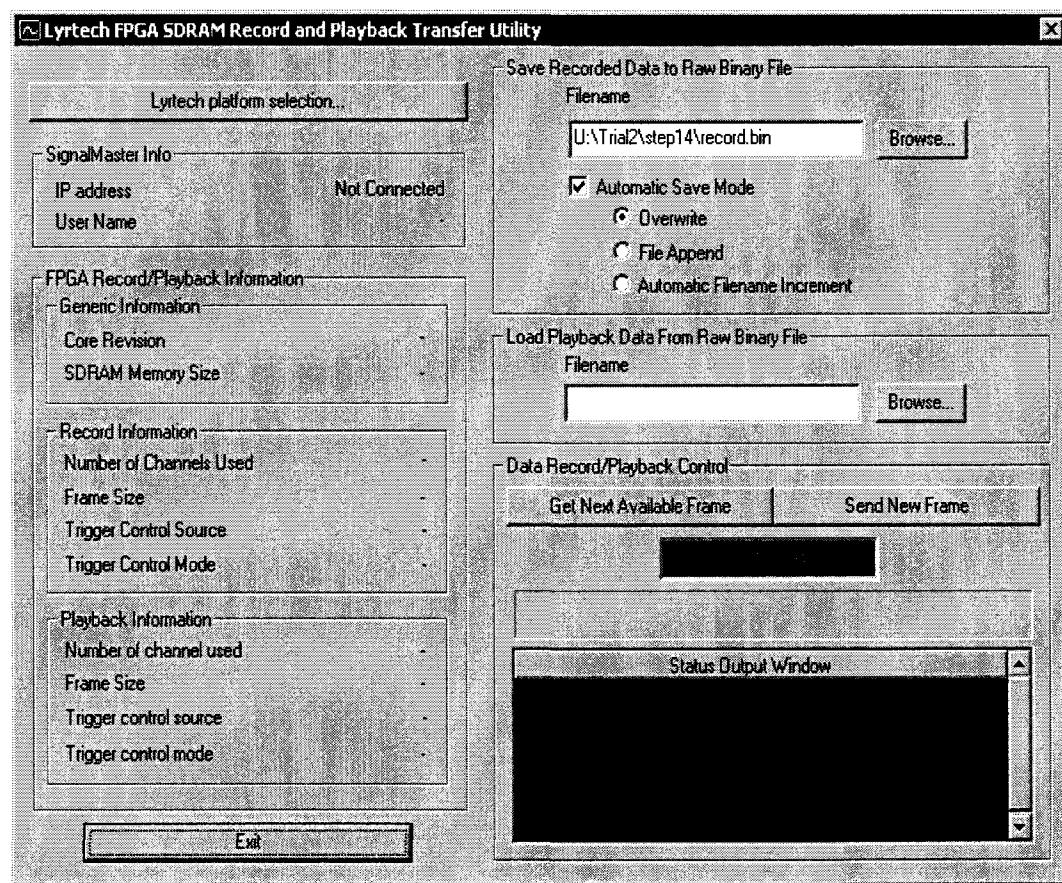

| FIGURE 4.10 | Interface Graphique du Record and Playback Utility . . . . .                                        | 81 |

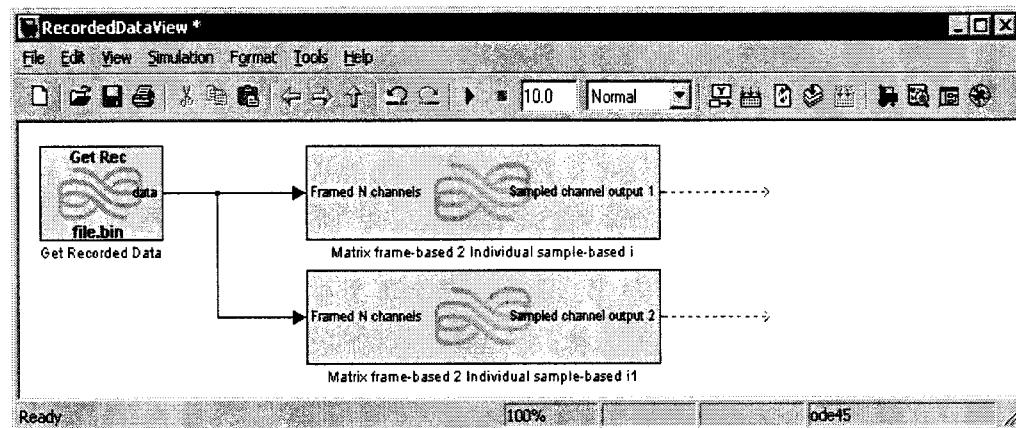

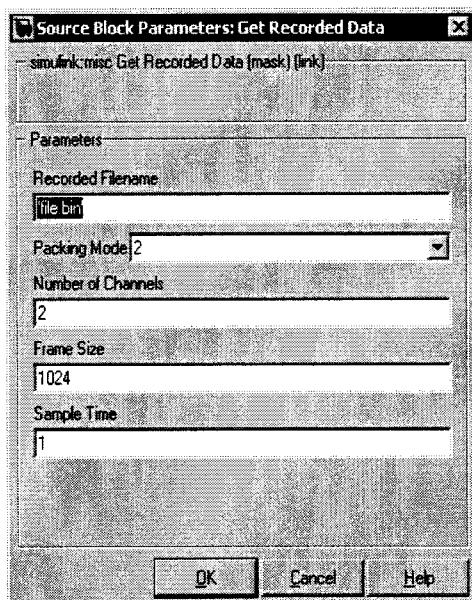

| FIGURE 4.11 | Lecture des données enregistrées à partir d'un fichier binaire . . . . .                            | 83 |

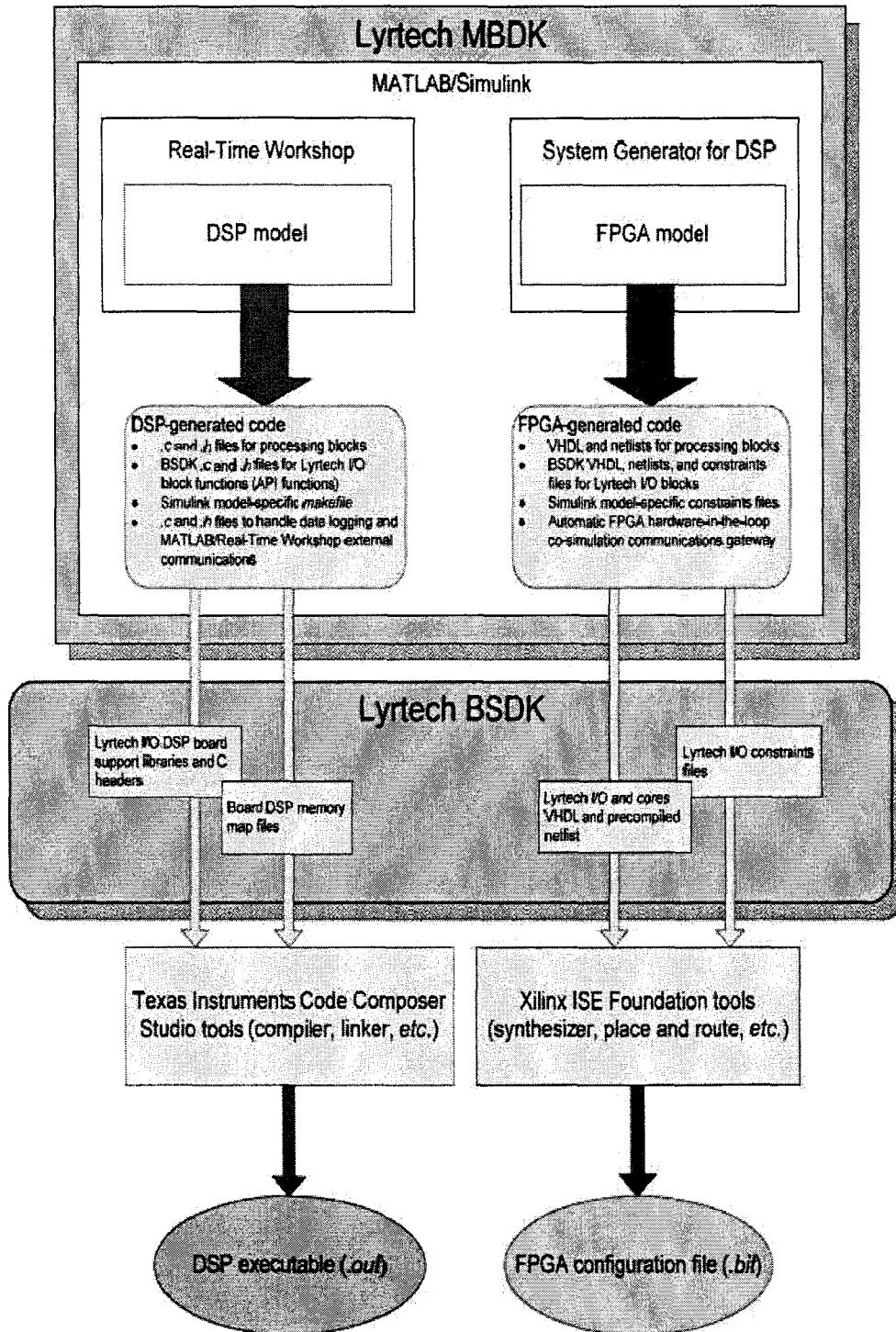

| FIGURE 4.12 | Étapes de développement [Lyrtech SMQ DesignGuide]. . . . .                                          | 84 |

| FIGURE 5.1  | Diagramme bloc du transmetteur . . . . .                                                            | 86 |

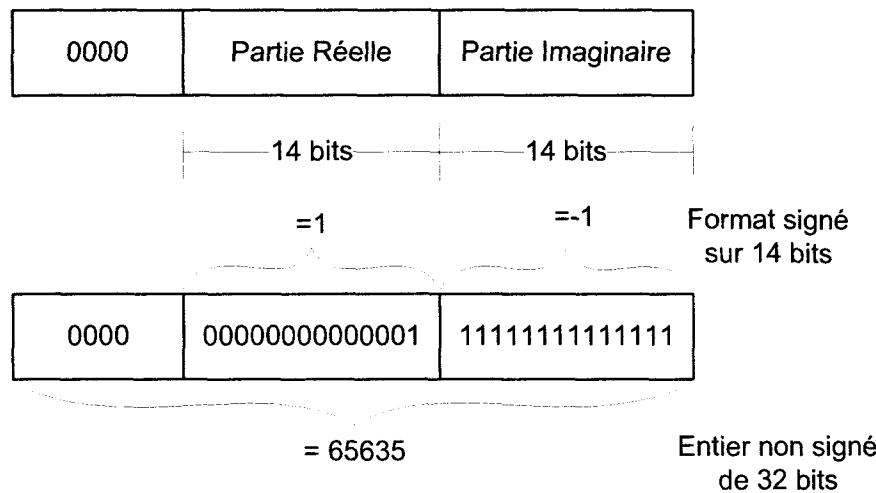

| FIGURE 5.2  | Représentation et interprétation de chaque symbole . . . . .                                        | 87 |

| FIGURE 5.3  | Circuit utilisé pour générer les paquets . . . . .                                                  | 88 |

|             |                                                                                            |     |

|-------------|--------------------------------------------------------------------------------------------|-----|

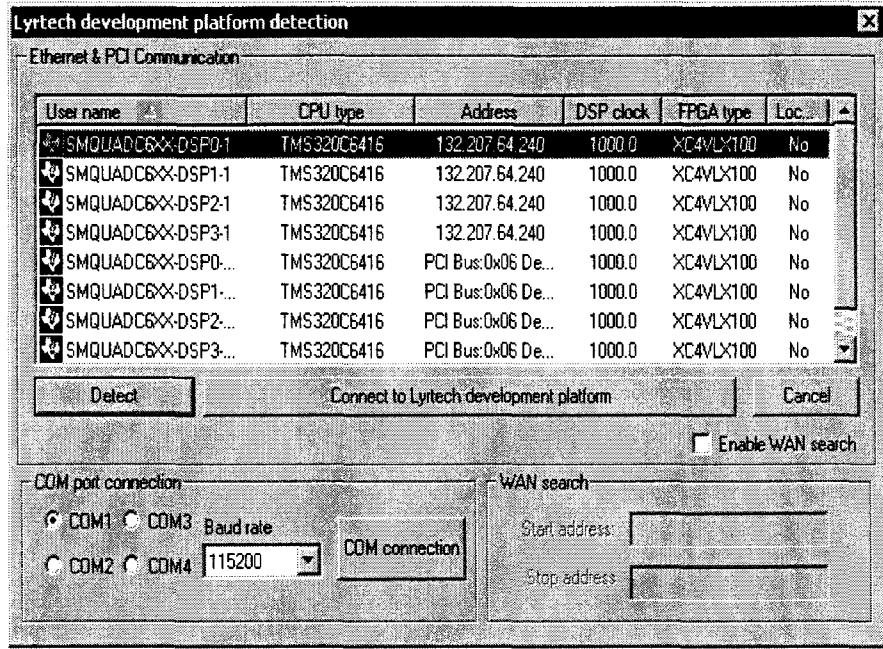

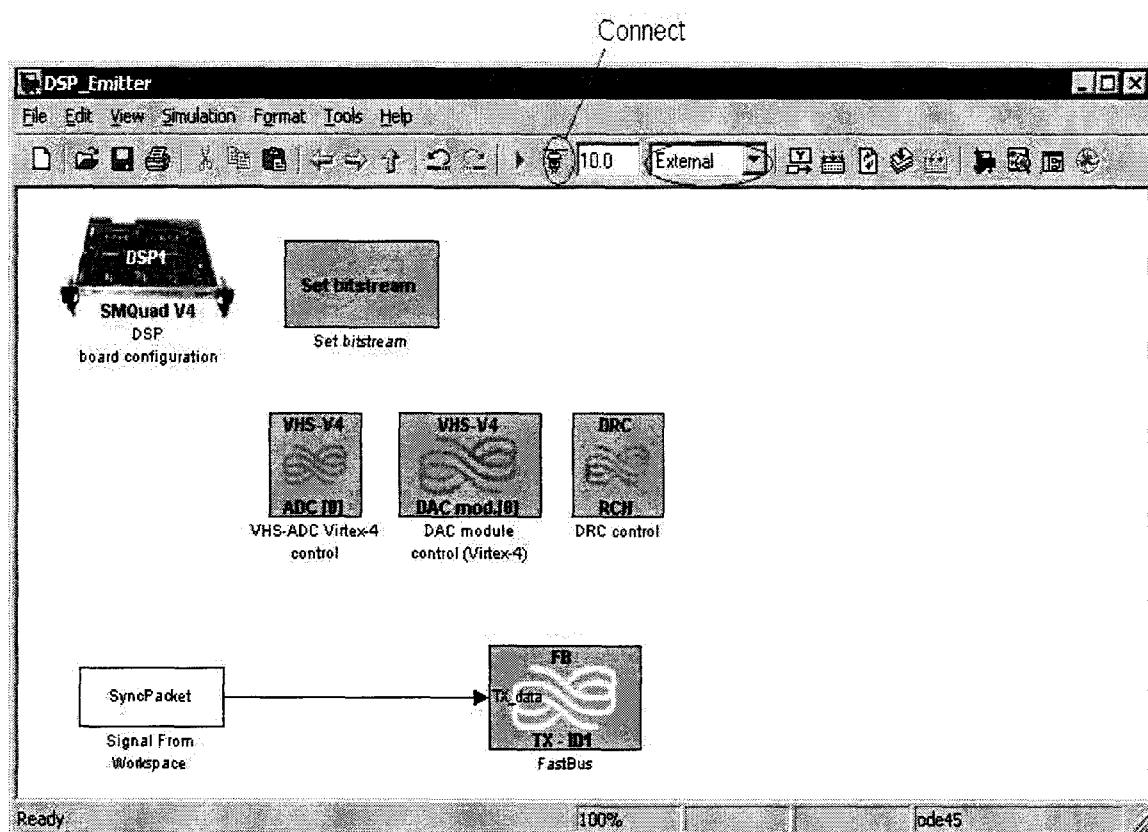

| FIGURE 5.4  | Interface utilisateur pour la connexion . . . . .                                          | 90  |

| FIGURE 5.5  | Architecture du récepteur . . . . .                                                        | 91  |

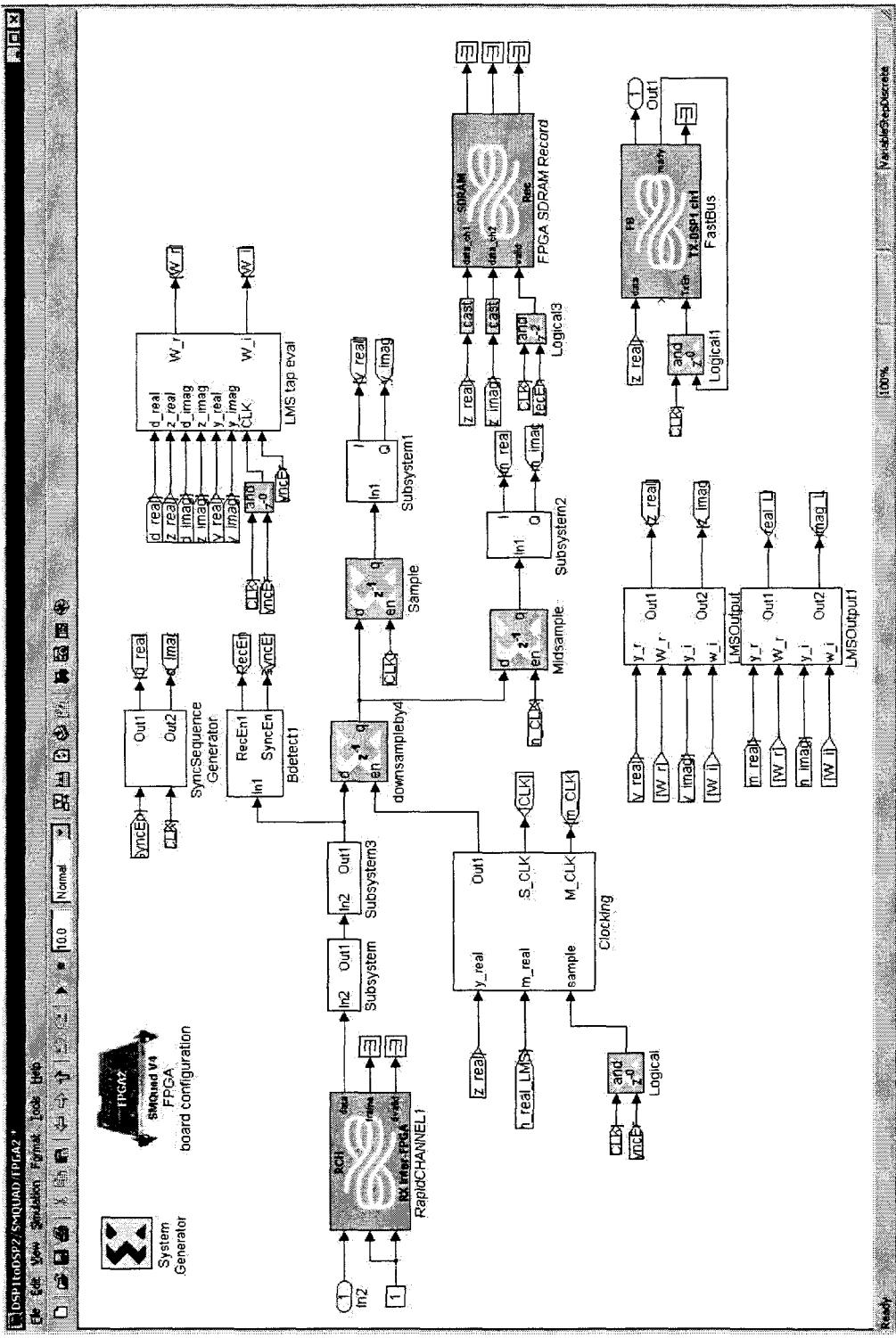

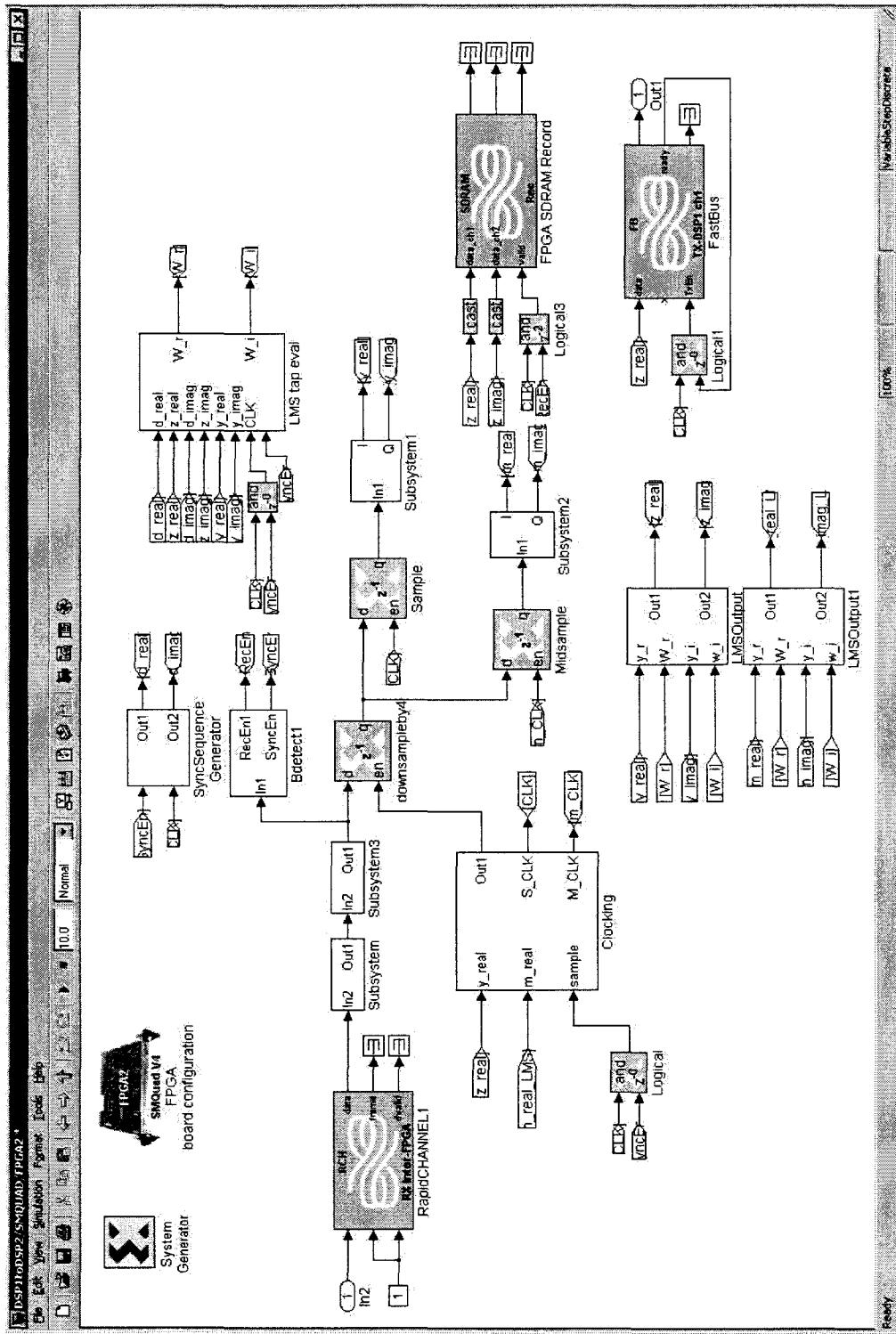

| FIGURE 5.6  | Modèle Simulink du FPGA du récepteur sur le VHS-ADC . . . . .                              | 92  |

| FIGURE 5.7  | Modèle Simulink du FPGA du récepteur sur le SMQuad . . . . .                               | 93  |

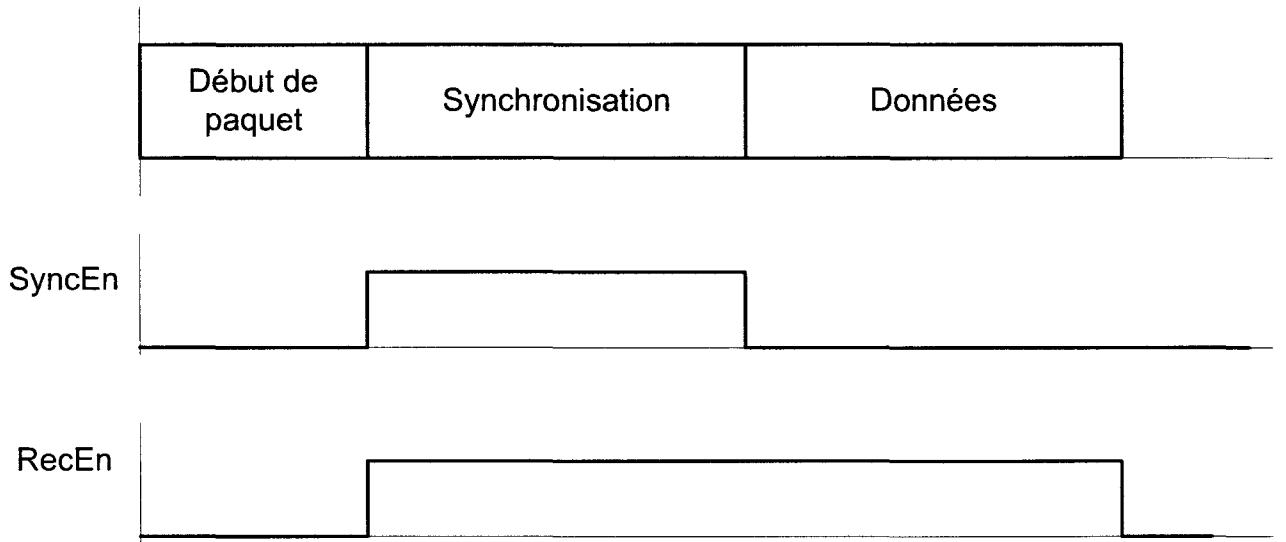

| FIGURE 5.8  | Diagramme temporel des états de RecEn et de SyncEn . . . . .                               | 95  |

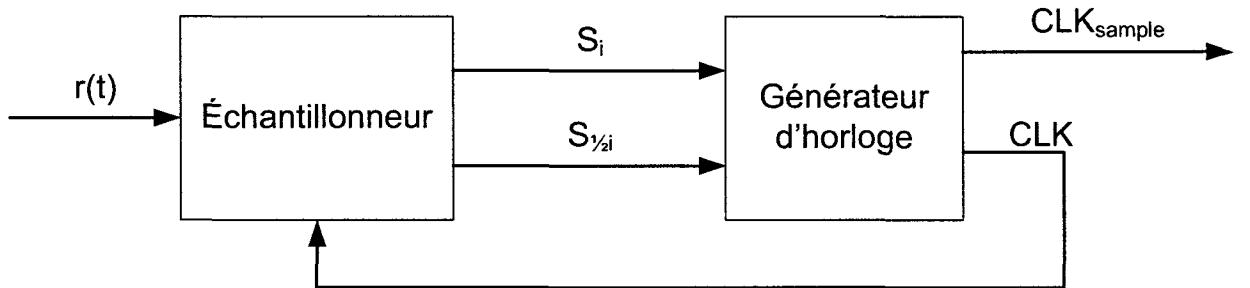

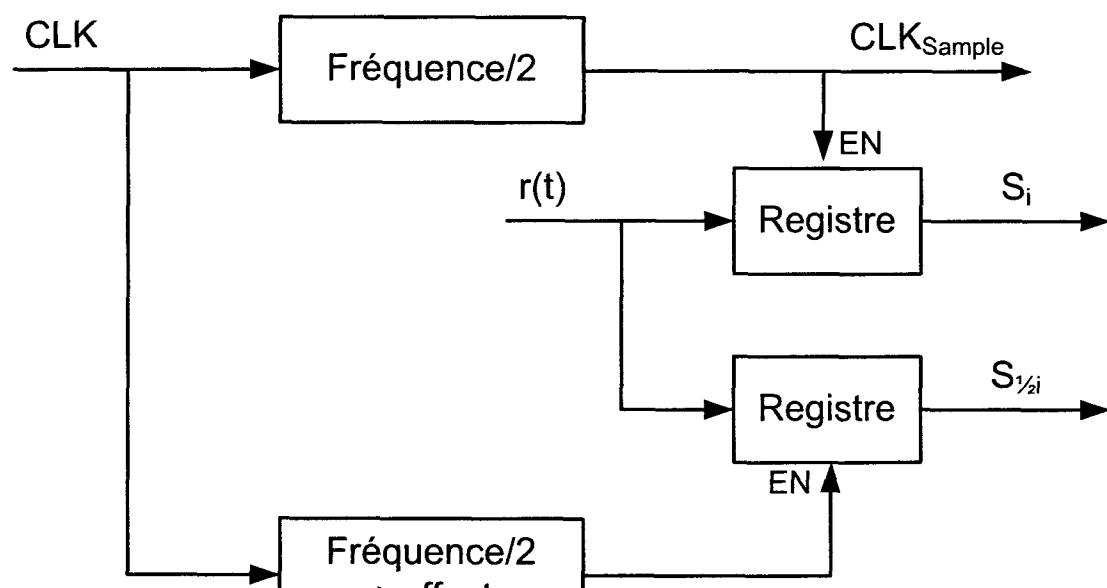

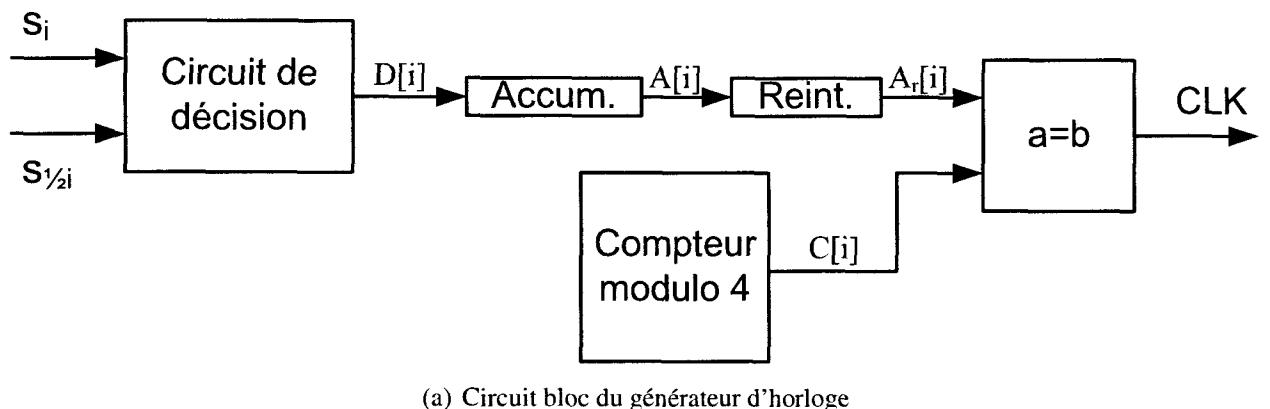

| FIGURE 5.9  | Schéma bloc du circuit de recouvrement d'horloge . . . . .                                 | 95  |

| FIGURE 5.10 | Détail bloc des circuits de recouvrement d'horloge . . . . .                               | 96  |

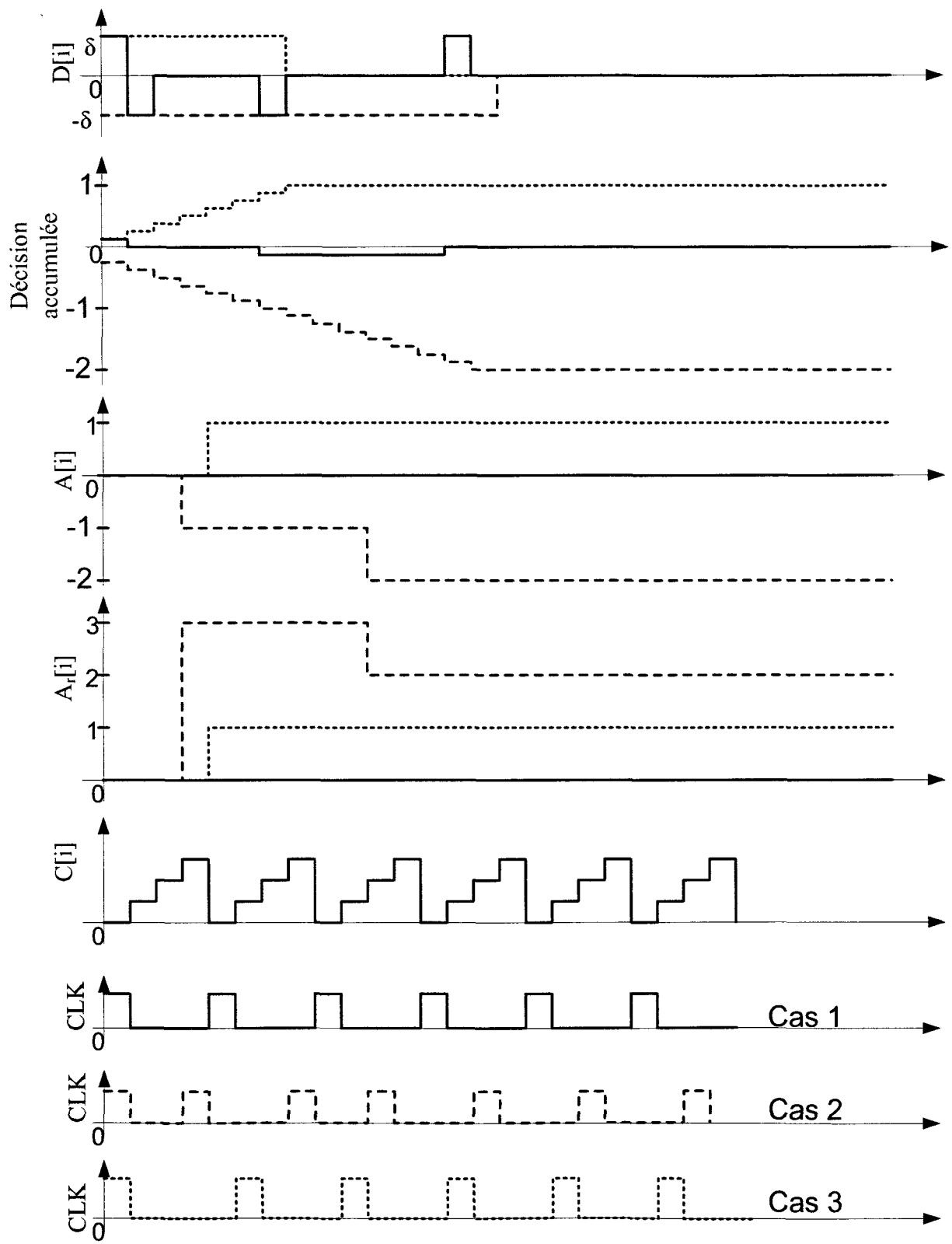

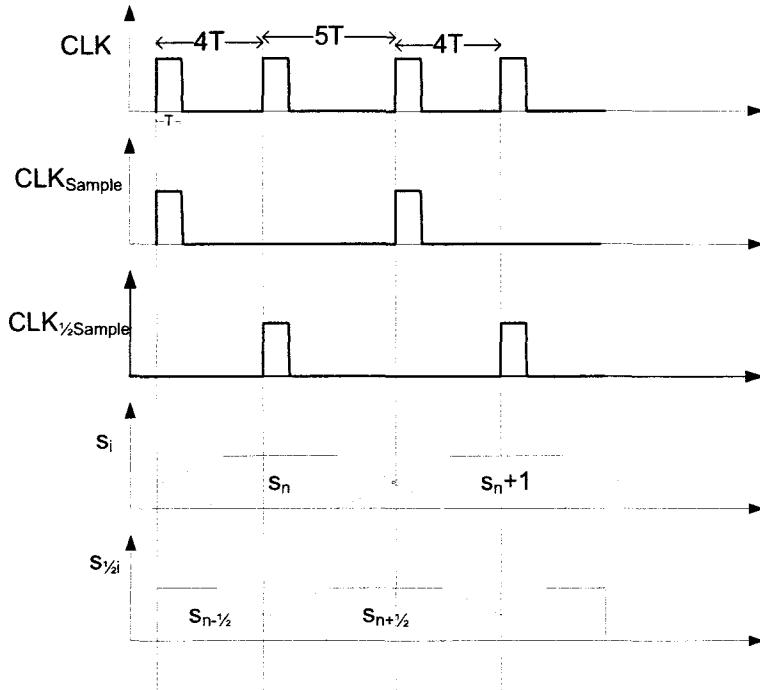

| FIGURE 5.11 | Diagramme temporel de la génération d'horloge . . . . .                                    | 98  |

| FIGURE 5.12 | Dynamique de l'échantillonnage . . . . .                                                   | 99  |

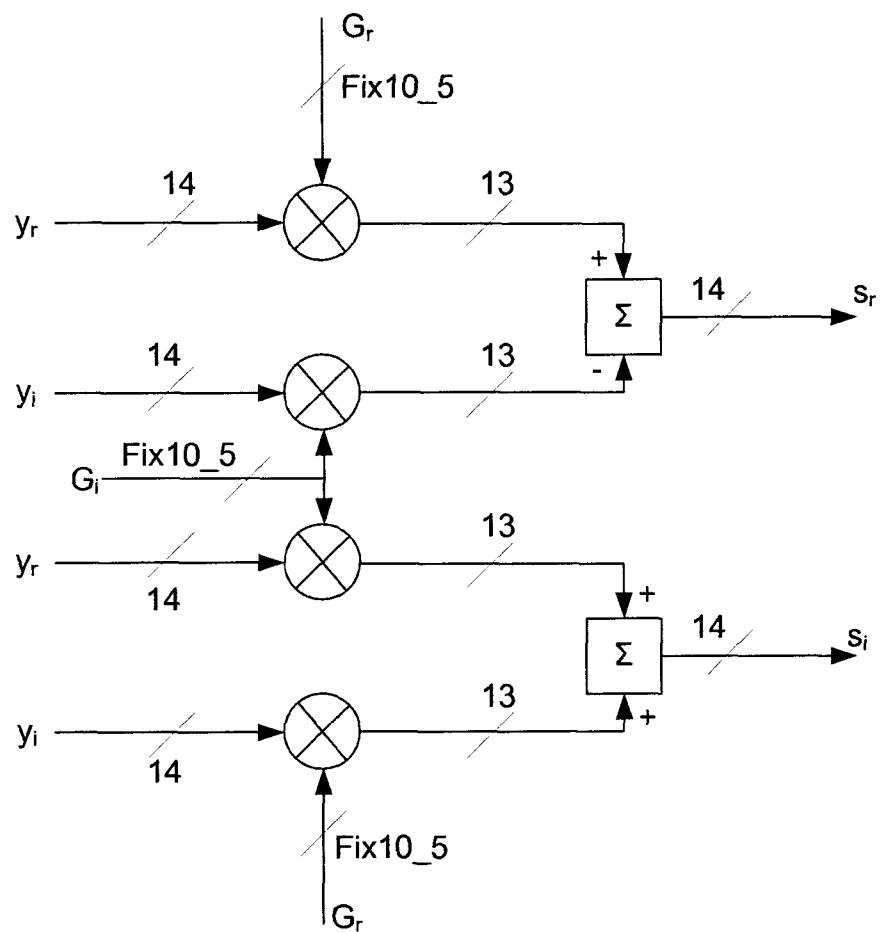

| FIGURE 5.13 | Circuit de multiplication complexe . . . . .                                               | 101 |

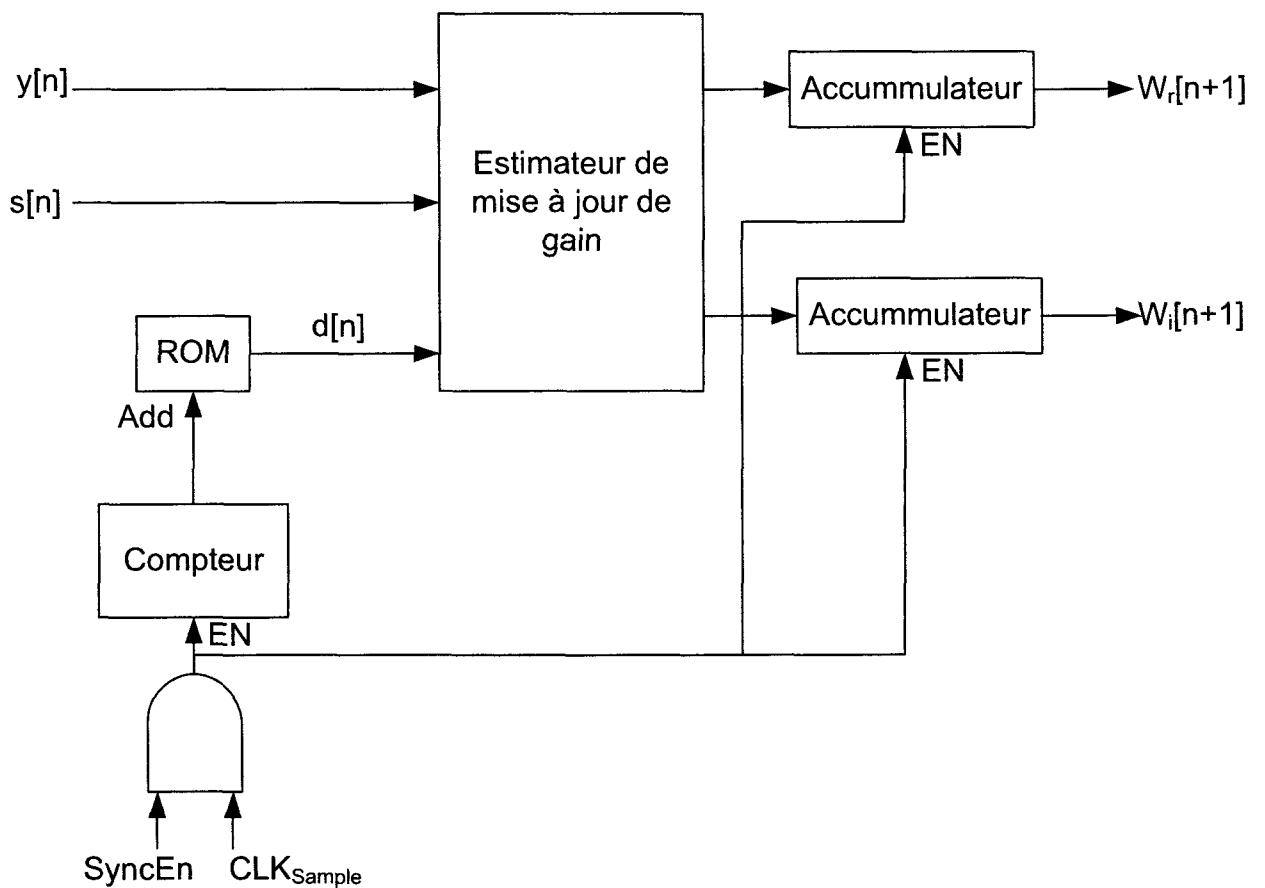

| FIGURE 5.14 | Circuit d'ajustement du gain du filtre LMS . . . . .                                       | 102 |

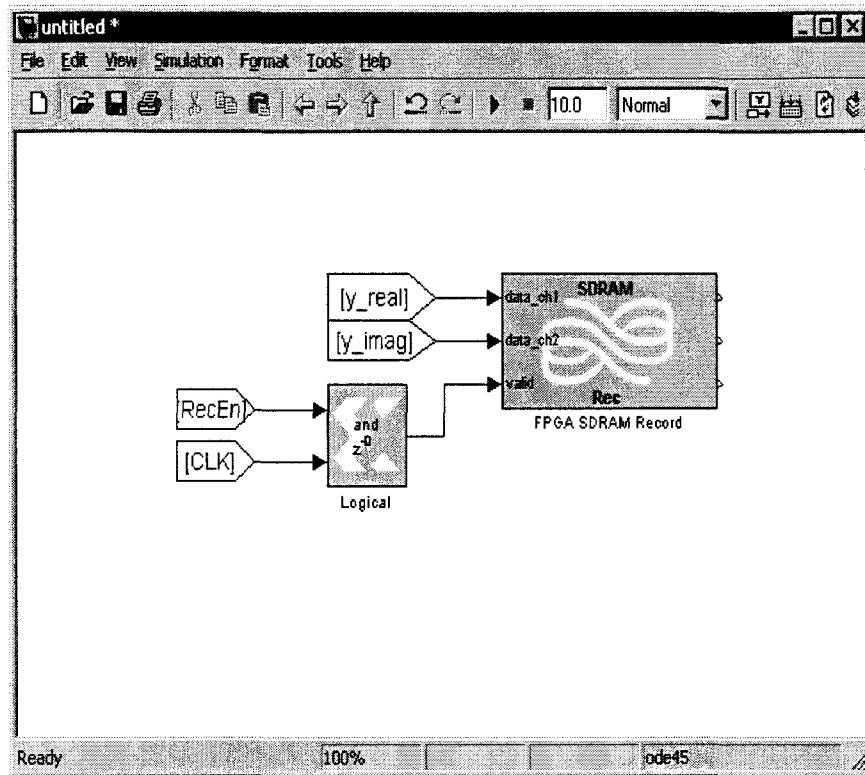

| FIGURE 5.15 | Logique de sélection des données enregistrées . . . . .                                    | 103 |

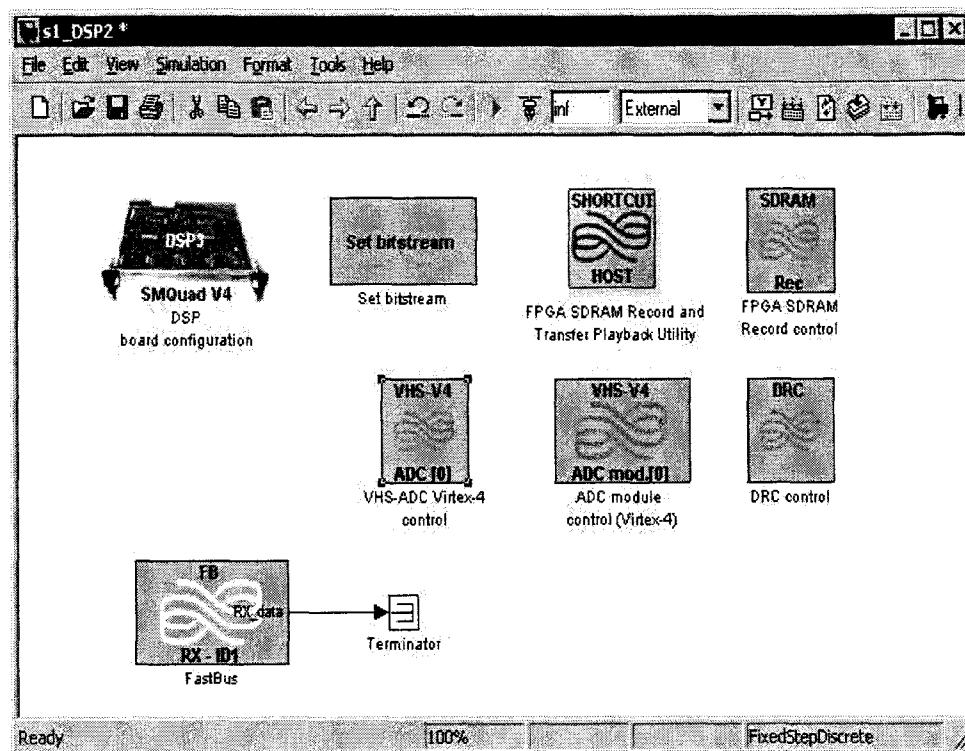

| FIGURE 5.16 | Blocs utilisés au DSP du récepteur . . . . .                                               | 104 |

| FIGURE 5.17 | Circuit pour la caractérisation du transmetteur . . . . .                                  | 105 |

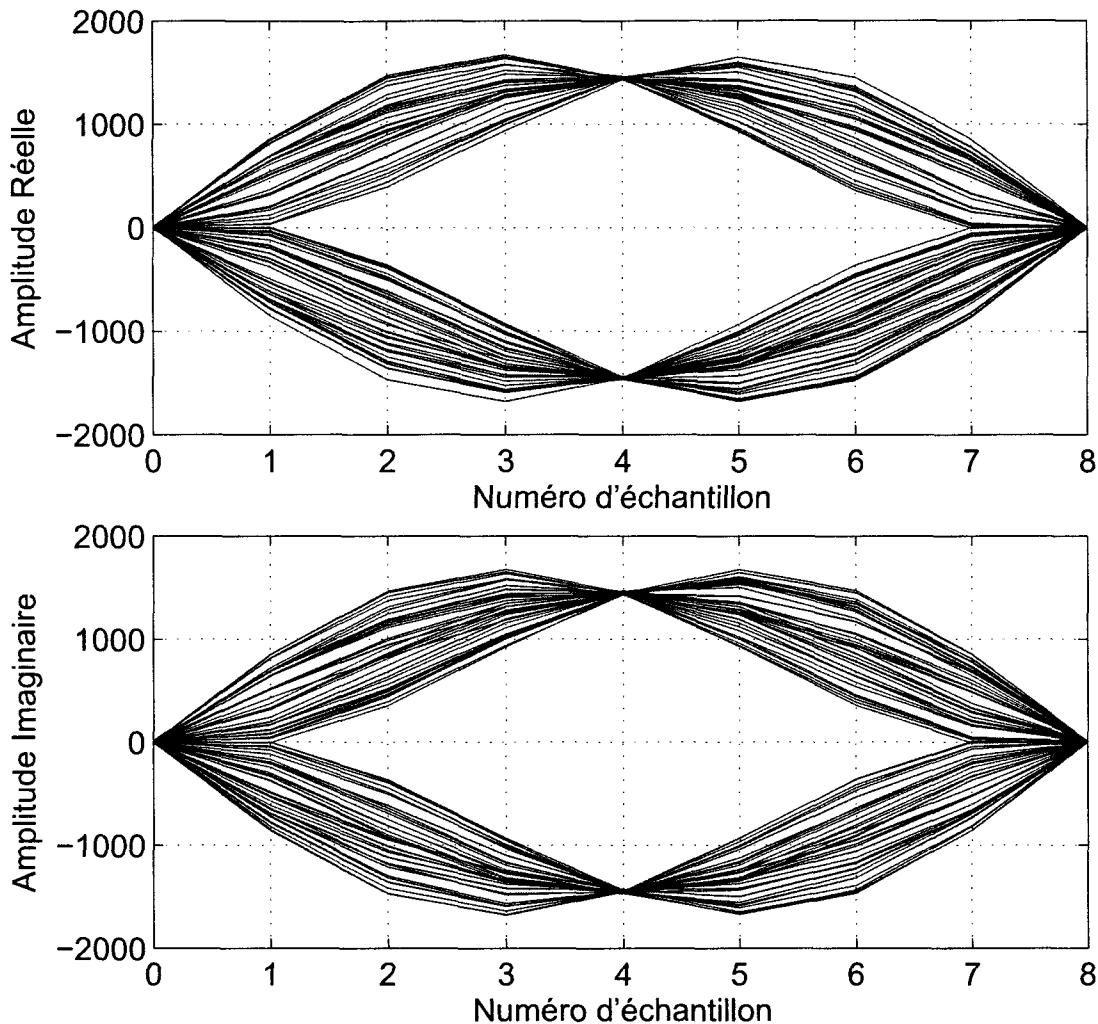

| FIGURE 5.18 | Diagrammes d'oeil pour une boucle interne . . . . .                                        | 106 |

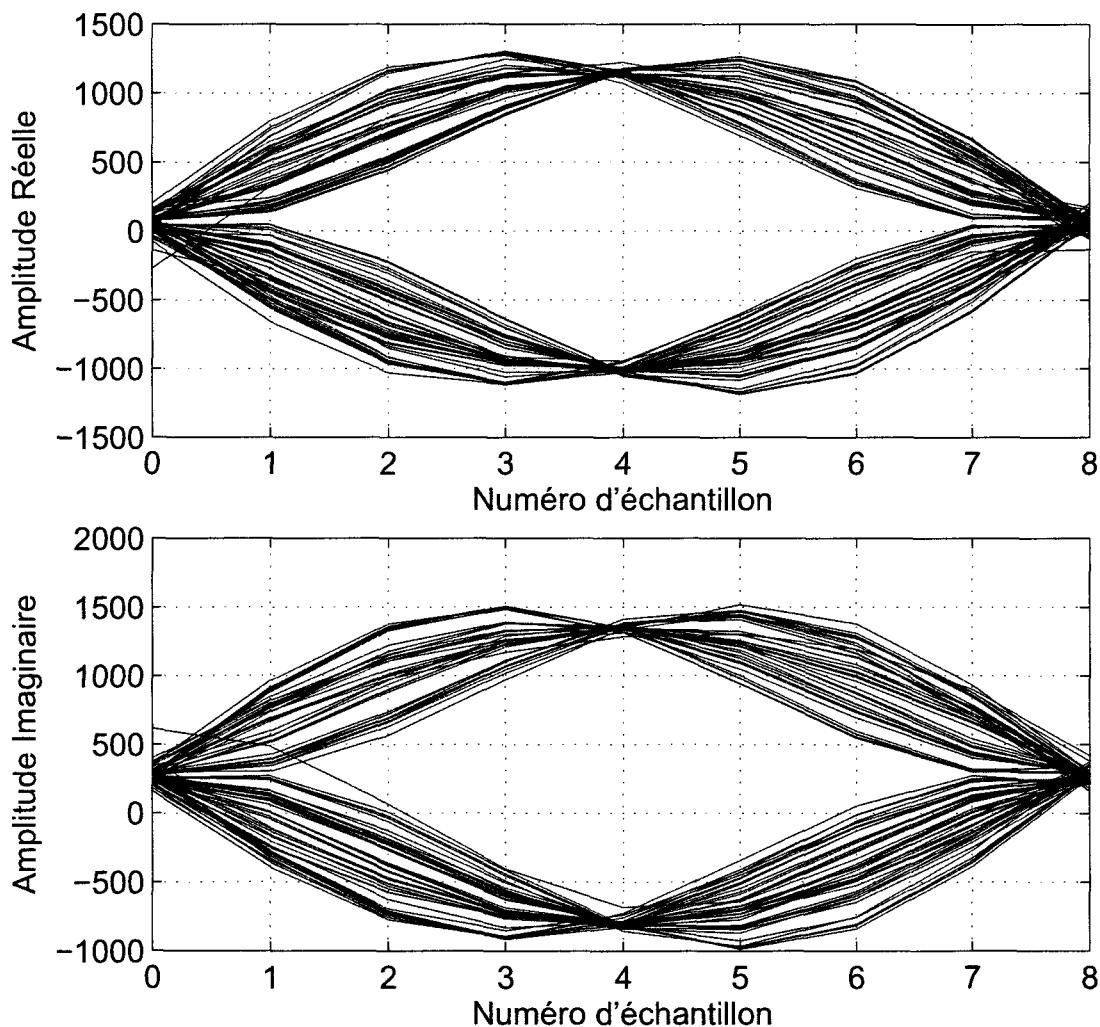

| FIGURE 5.19 | Diagrammes d'oeil pour une boucle externe . . . . .                                        | 108 |

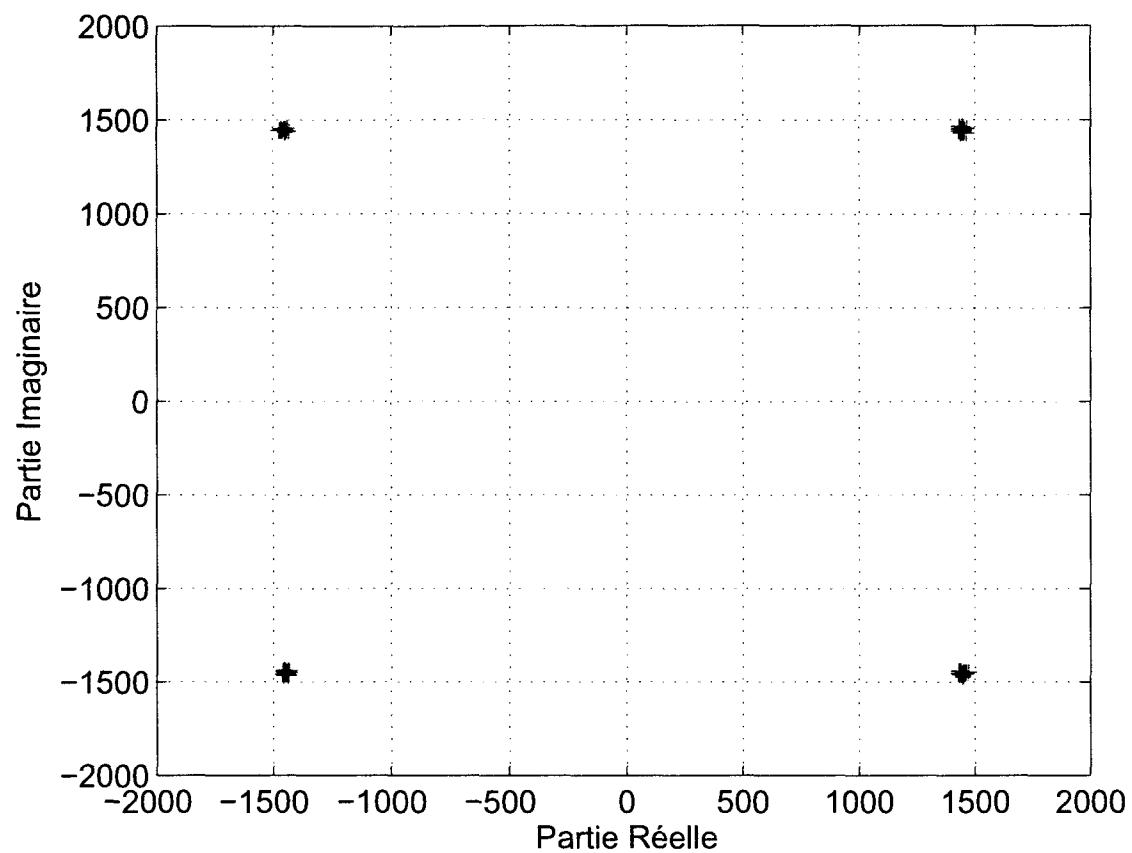

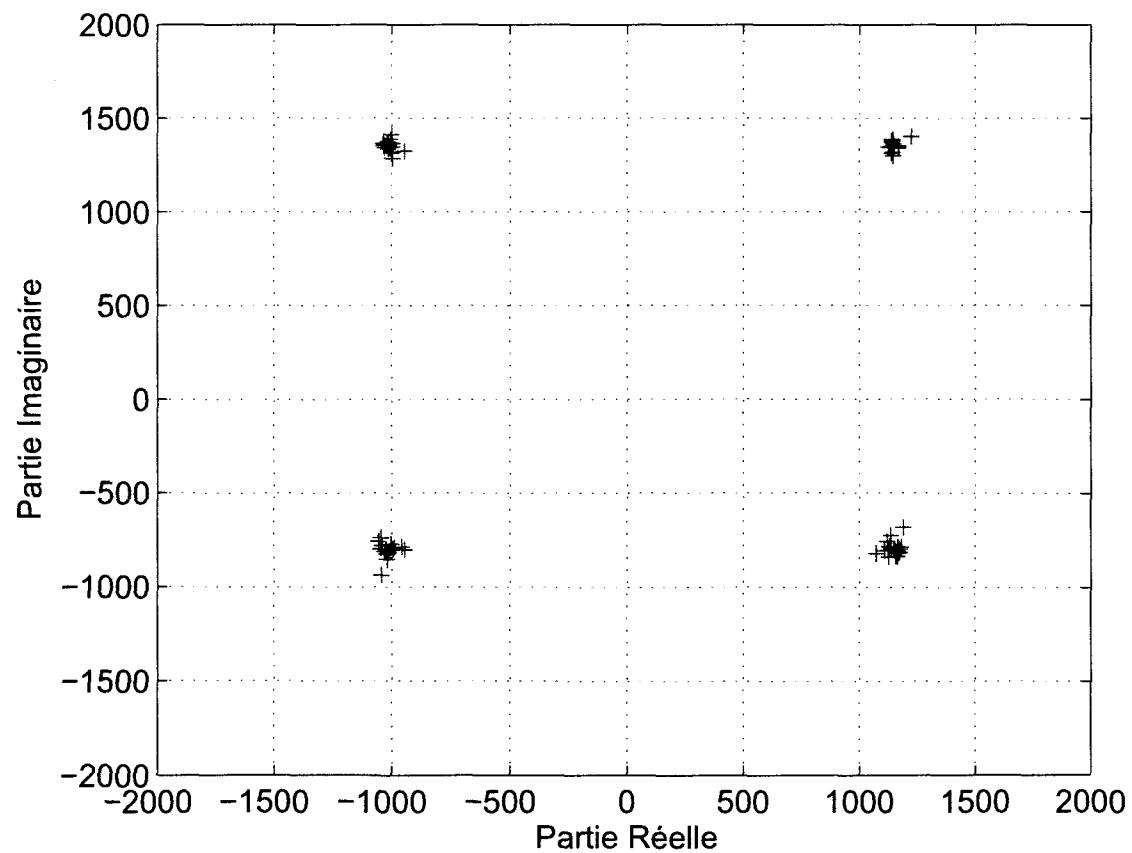

| FIGURE 5.20 | Constellations des signaux de réception dans le cas d'une transmission en boucle . . . . . | 110 |

| FIGURE 5.21 | Architecture utilisée pour la vérification du récepteur . . . . .                          | 111 |

| FIGURE 5.22 | Courbe de BER vs SNR . . . . .                                                             | 114 |

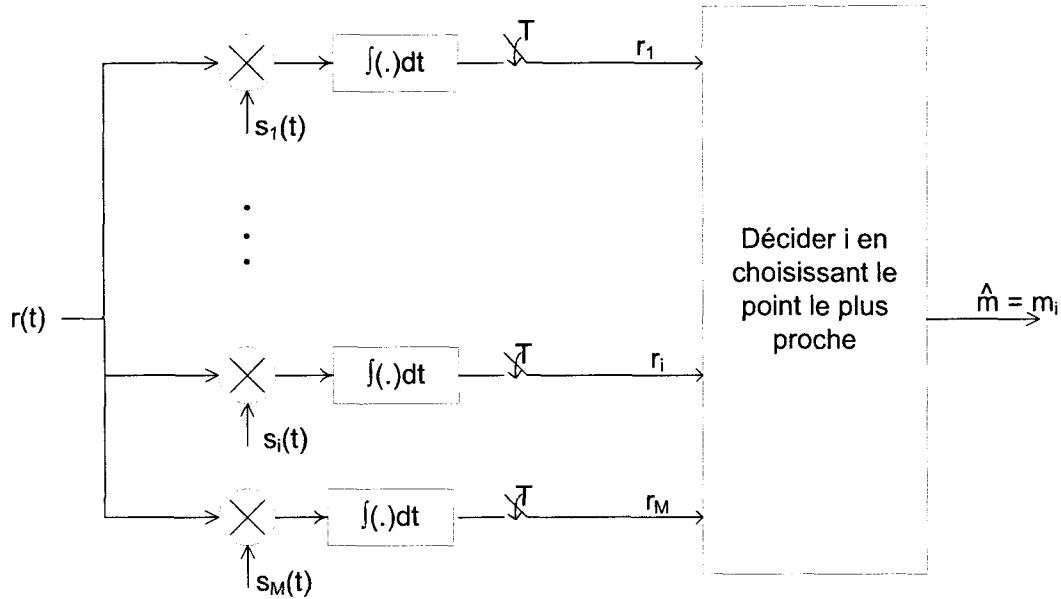

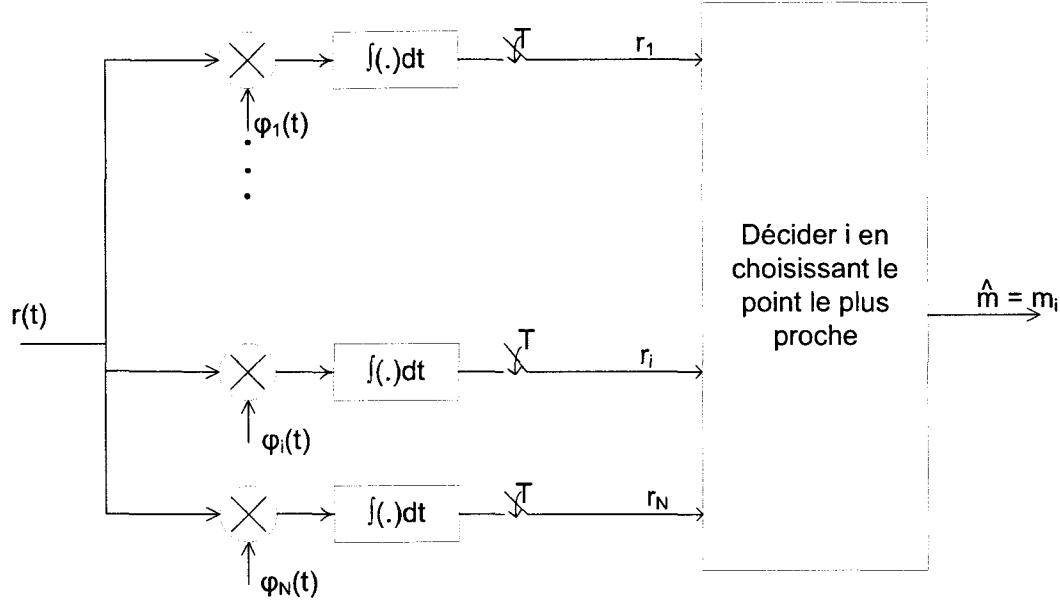

| FIGURE I.1  | Récepteur à correlation . . . . .                                                          | 126 |

| FIGURE I.2  | Structure d'un récepteur pour la détection d'un signal dans le bruit AWGN . . . . .        | 127 |

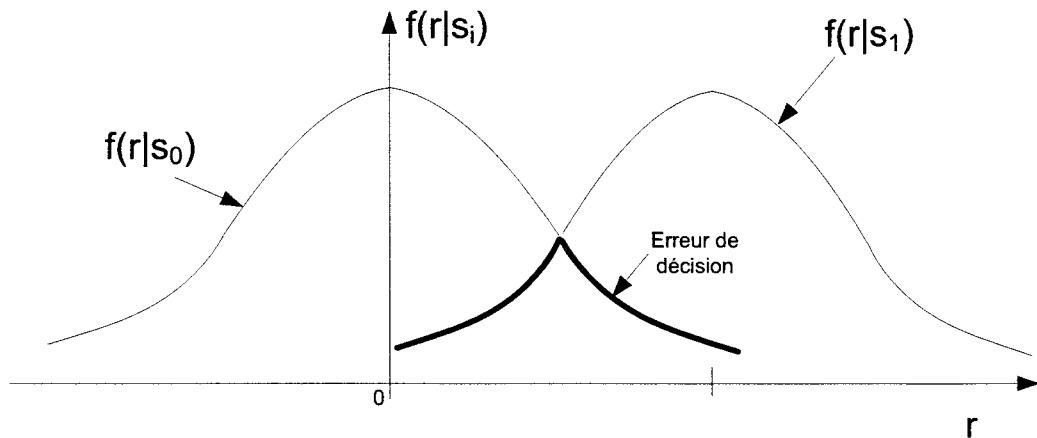

| FIGURE I.3  | Fonctions de densité de probabilité conditionnelles dans un canal AWGN . . . . .           | 129 |

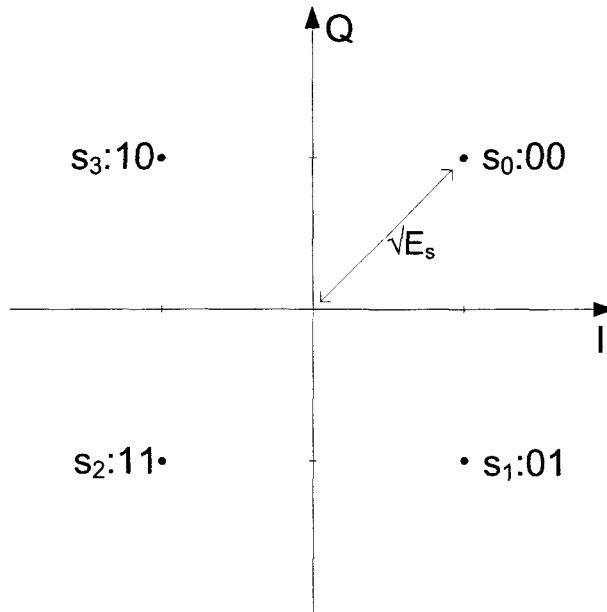

| FIGURE I.4  | Constellation QPSK . . . . .                                                               | 130 |

| FIGURE I.5  | Estimation linéaire d'une source à partir d'un signal de réception .                       | 132 |

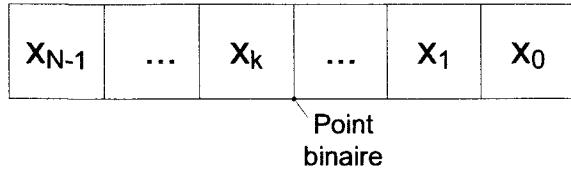

| FIGURE I.6  | Nombre en format binaire . . . . .                                                         | 134 |

|             |                                              |     |

|-------------|----------------------------------------------|-----|

| FIGURE II.1 | DSP de l'émetteur . . . . .                  | 137 |

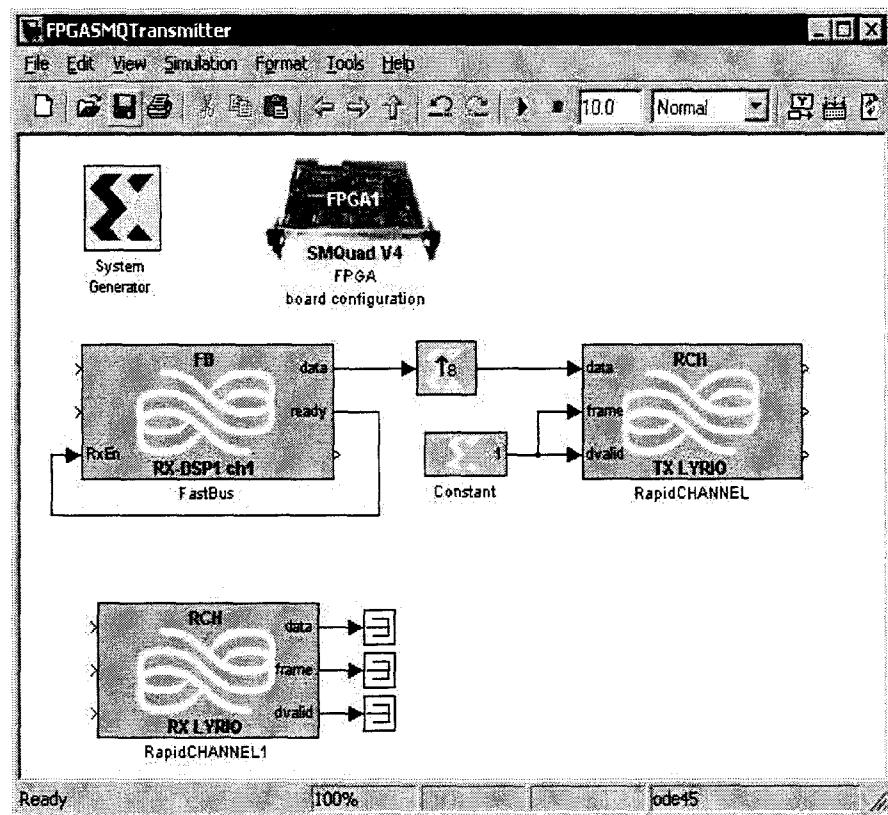

| FIGURE II.2 | FPGA sur le SMQuad au transmetteur . . . . . | 142 |

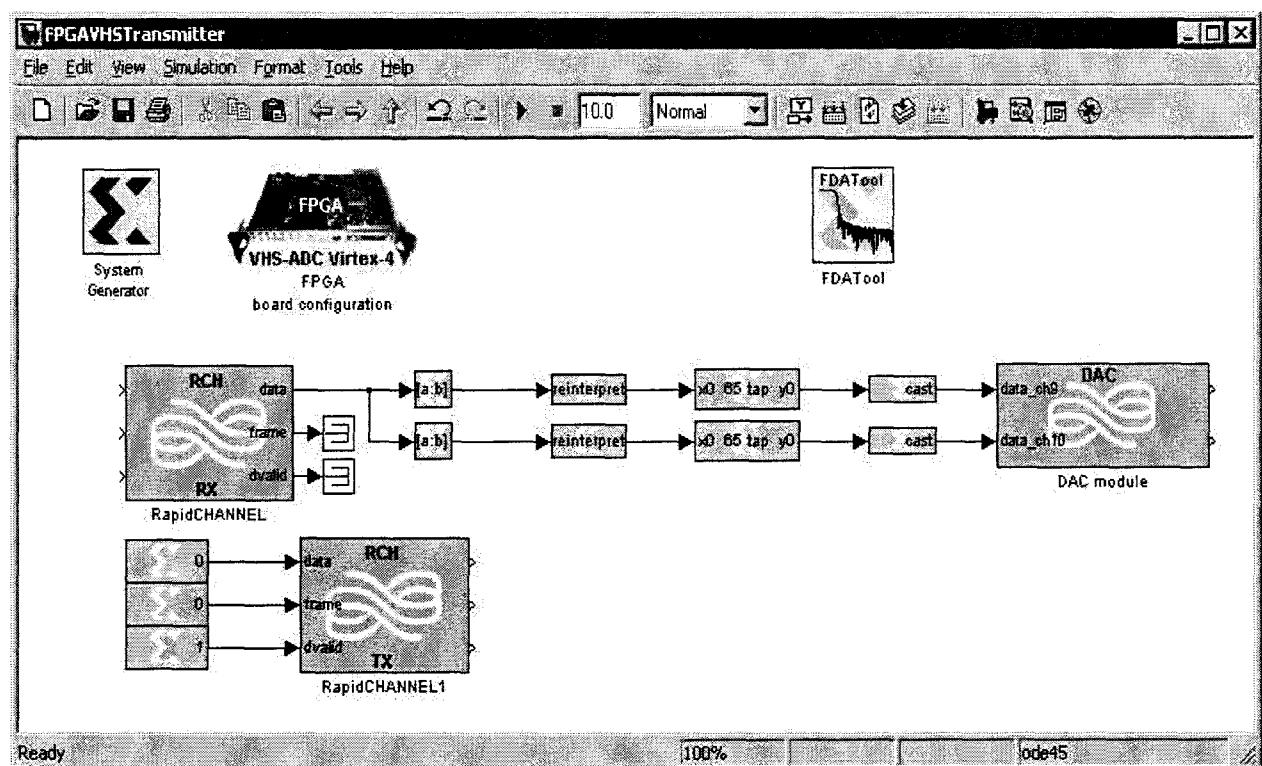

| FIGURE II.3 | FPGA sur le VHS du transmetteur . . . . .    | 145 |

## LISTE DES ACRONYMES

### **ABBREVIATIONS**

|                  |                                      |

|------------------|--------------------------------------|

| ADC :            | Convertisseur analogique-numérique   |

| AGC :            | Contrôleur de Gain Automatique       |

| AWGN :           | Bruit Blanc Gaussien Additif         |

| BER :            | Taux d'erreurs binaires              |

| CLK :            | Signal d'horloge                     |

| $CLK_{Sample}$ : | Signal d'horloge d'un échantillon    |

| DAC :            | Convertisseur numérique à analogique |

| EMIF :           | <i>External Mode Interface</i>       |

| ISI :            | Interférence Entre Symboles          |

| LPF :            | Filtre Passe-bas                     |

| MB :             | MégaOctets                           |

| pdf :            | Fonction de Densité de probabilité   |

| PLL :            | Phase-Locked Loop                    |

| PRBS :           | Séquence binaire pseudo-aléatoire    |

| QPSK :           | Quadrature Phase Shift Keying        |

| SDRAM :          | Mémoire Vive                         |

| SMQUAD :         | Plateforme Signal Master Quad        |

| SNR :            | Rapport Signal à bruit               |

### **FONCTIONS DÉFINIES**

|             |                                                                                 |

|-------------|---------------------------------------------------------------------------------|

| $e^x$ :     | Exponentiel                                                                     |

| $\log(x)$ : | Logarithme base 10                                                              |

| $Q(x)$ :    | Intégrale de la fonction de densité de probabilité Gaussienne de $x$ à $\infty$ |

| $\Re$ :     | Partie réelle                                                                   |

| $\Im$ :     | Partie imaginaire                                                               |

| $z^{-N}$ :  | Total de N délais                                                               |

## INDICES

|             |                                                      |

|-------------|------------------------------------------------------|

| $dB$ :      | Décibels                                             |

| $h$ :       | Constante de Plank ( $6.625 \times 10^{-34} J - s$ ) |

| $k$ :       | Contante de Boltzmann ( $1.38 \times 10^{-23} J/K$ ) |

| $T$ :       | Température (K)                                      |

| $T$ :       | Période                                              |

| $\phi$ :    | Angle ou phase                                       |

| $f$ :       | Fréquence (Hz)                                       |

| framesize : | Longueur d'une trame (Nombre de symboles)            |

| $G, K$ :    | Gain d'amplification                                 |

| $L$ :       | Taux de suréchantillonnage                           |

| $P$ :       | Puissance                                            |

| $\Gamma$ :  | Coefficient de réflexion de Fresnel                  |

| $N_0$ :     | Puissance de bruit                                   |

| $r(t)$ :    | Signal de réception                                  |

| $n(t)$ :    | Bruit à la réception                                 |

| $S_i$ :     | $i^{me}$ symbole                                     |

| $\tau$ :    | Délai                                                |

| $V$ :       | Tension                                              |

| $W$ :       | Largeur de bande                                     |

**LISTE DES TABLEAUX**

|           |                                                                                                                    |    |

|-----------|--------------------------------------------------------------------------------------------------------------------|----|

| TABLE 1.1 | Résumé des types de canaux sans-fil . . . . .                                                                      | 12 |

| TABLE 1.2 | Comparaison du BER et de l'efficacité spectrale pour différentes modulations avec une détection cohérente. . . . . | 14 |

| TABLE 3.1 | Les séquences de Barker connues. . . . .                                                                           | 34 |

| TABLE 3.2 | Liste des paramètres du système utilisés lors de la simulation . . .                                               | 63 |

**LISTE DES ANNEXES**

|                  |                                                               |     |

|------------------|---------------------------------------------------------------|-----|

| <b>ANNEXE I</b>  | <b>QUELQUES BASES THÉORIQUES</b>                              | 125 |

| I.1              | Les récepteurs à maximum de vraisemblance [Proakis, J., 2000] | 125 |

| I.1.1            | Structure du récepteur                                        | 125 |

| I.1.2            | Correspondance dans un espace vectoriel                       | 125 |

| I.2              | Performances d'une modulation                                 | 128 |

| I.2.1            | Puissance de transmission et le SNR                           | 128 |

| I.2.2            | Taux d'erreurs dans un canal AWGN                             | 129 |

| I.2.3            | Efficacité spectrale                                          | 132 |

| I.3              | Calcul de SNR à partir du MMSE                                | 132 |

| I.4              | Représentation de nombres binaires                            | 134 |

| <b>ANNEXE II</b> | <b>DETAILS D'IMPLÉMENTATION SUR SIMULINK</b>                  | 136 |

| II.1             | Design du DSP                                                 | 136 |

| II.2             | Détails du FPGA du SMQUAD                                     | 140 |

| II.3             | Détails du VHS-ADC en transmission                            | 144 |

## INTRODUCTION

La vision du sans-fil a beaucoup changé depuis le premier déploiement des systèmes de téléphonie cellulaire au début des années 1980. Une utilisation fractionnée du spectre de fréquences avait alors été considérée comme étant primordiale pour permettre une communication entre utilisateurs avec un minimum d'interférences. De nos jours, plusieurs organisations travaillent sur l'allocation et la réglementation du spectre des fréquences. Au Canada et aux États-Unis, Industrie Canada et la Federal Communications Commission en sont respectivement responsables. Au niveau global, l'International Telecommunications Union (ITU) est une agence des Nations Unies qui aide à coordonner l'utilisation du spectre des radiofréquences. Ces organismes ont dégagé certaines bandes de fréquence pouvant être utilisées sans licence. Cette initiative qui avait pour but de permettre l'innovation et les implémentations à faible coûts a connu un grand succès. De nos jours, plusieurs systèmes de communications sans-fil opèrent à l'intérieur de ces bandes de fréquence. Ces technologies sont vastes, allant du réseau local sans-fil (WLAN) aux instruments Bluetooth et téléphones sans-fil.

L'industrie des semiconducteurs a aussi été en développement constant. En effet, l'implémentation d'algorithmes de haute complexité est de nos jours plus facilement atteignable avec les composantes matérielles (hardware) disponibles. Les composantes électroniques reprogrammables tels que les FPGA et les DSP utilisent une description logicielle (VHDL ou C++ embarqué) pour configurer aisément les algorithmes qu'ils réalisent. L'amélioration de ces outils de prototypage rapide a permis d'atteindre les objectifs majeurs suivants [Wakerly, J.F, 2001] :

- Limiter le temps de développement des produits. La configuration des composantes se fait à partir de la logique du design et ne requiert pas nécessairement des considérations au niveau de l'opération des transistors ou autres composantes analogiques.

- Diminuer les coûts associés à l'implémentation des solutions. Comme le comporte-

ment des circuits digitaux sont décrits par leur logique d'opération, la reproduction des circuits peut se faire de façon répétitive pour fournir des résultats similaires.

- Fournir des mesures préliminaires à l'étape de la faisabilité, limitant ainsi le risque associé au développement des produits complexes.

- Augmenter la vitesse de traitement des données. Plusieurs algorithmes nécessitent une grande vitesse de traitement des données offerte par les circuits intégrés pour atteindre de bonnes performances.

Cependant, avec cette croissance d'utilisation d'équipements sans-fil dans les bandes de fréquences sans license, une des craintes soulevées est le niveau des interférences générées et subies par les transmissions radio. Ces liens fonctionnent normalement à une puissance de transmission relativement basse et sont conçus pour fonctionner à courte portée. Cependant, dans une même zone plusieurs équipements sans-fil peuvent être en utilisation dans la même bande. Par exemple, l'utilisation des routeurs sans-fil pour l'accès à un réseau local et à Internet devient de plus en plus courant. Dans un même bâtiment résidentiel, plusieurs d'entre eux peuvent souvent être détectés. Comme l'interférence ainsi produite peut être non-négligeable, une dégradation du signal de réception pourrait s'en suivre, ce qui peut détériorer la qualité de la transmission et de la performance du système de communications.

## Objectifs

Pour caractériser le type de dégradation selon différents environnements de propagation, des mesures de performance d'un lien sans-fil doivent être effectuées. Dans le cadre de ce projet, nous faisons le développement de la partie bande de base d'un système de communications sans-fil sur des plateformes de prototypage rapide de la compagnie Lyrtech Inc. Le projet est une étape préliminaire à l'élaboration d'un système de communications sans-fil avancé. Les objectifs que nous nous sommes fixés ici sont les suivants :

- Élaborer un modèle de communications sans-fil en bande de base de complexité moyenne.

- Vérifier la fonctionnalité du modèle à l'aide d'un outil de simulation et comparer sa performance par rapport aux résultats théoriques.

- Comprendre et documenter l'outil de développement fourni par Lyrtech Inc.

- Passer au premier stade de prototypage du système de communications sans-fil et en évaluer la performance.

Cette plateforme a été récemment acquise par le département de génie électrique de l'École Polytechnique de Montréal. Plusieurs autres universités à travers le monde ont développé leur prototype d'essai. Dans ce contexte, le projet marque donc le début de la conception du premier prototype d'un système de communications sans-fil pour le groupe de télécommunications du département. Il s'agit principalement de comprendre la programmation des composantes de la plateforme et l'utilisation des outils fournis dans le contexte de la communication sans-fil.

## **Organisation du mémoire**

Ce document décrit les étapes que nous avons suivies dans le cadre de ce projet. L'organisation de ce mémoire est comme suit. Au chapitre 1, nous faisons un rappel de certains concepts de base utilisés dans le cadre de ce projet. Ceci devrait permettre au lecteur d'avoir un bref aperçu des défis liés à la conception des systèmes de communications sans-fil.

Au chapitre 2, nous faisons une brève revue des techniques de prototypage de systèmes de communications utilisées et des systèmes réalisés à travers le monde scientifique.

Au chapitre 3, nous présentons le modèle du système et les différents algorithmes utilisés ainsi que les résultats obtenus par simulation. Nous décrivons les différents blocs élaborés et intégrés tant au transmetteur qu'au récepteur. Cette étape permettra de valider le système conçu ainsi que de prévoir les limites en terme de performance à laquelle s'attendre.

L'outil de prototypage rapide proposé par Lyrtech Inc est introduit au chapitre 4. Nous y décrivons les principales composantes matérielles et logicielles qui sont utilisées dans le cadre de ce projet.

Les parties implémentées sur la plateforme de prototypage sont décrites au chapitre 5. L'implémentation du transmetteur est détaillée. En ce qui a trait au récepteur, nous fournissons les démarches et concepts utilisés dans le design. Le filtre d'égalisation LMS ainsi que les algorithmes de synchronisation de phase et de recouvrement d'horloge sont implémentés. La méthodologie pour la collecte des données est décrite et l'analyse des mesures obtenues est aussi présentée dans ce chapitre. Ces résultats permettent la caractérisation du système et de valider sa fonctionnalité au niveau matériel.

Nous fournissons finalement des idées d'améliorations et des propositions pour des développements potentiels au chapitre 6.

## CHAPITRE 1

### CONCEPTS DE BASE

Les systèmes de communications point à point sont tous constitués de trois composantes : le transmetteur, le canal de transmission et le récepteur. Il existe plusieurs critères de performance pour un lien de communications. Pour les systèmes de communications numériques, l'objectif visé est de minimiser le taux d'erreurs binaires et de maximiser le taux de transmission sujet à la bande passante du canal et à la puissance de transmission. Dans ce chapitre, nous présentons les concepts de base nécessaires concernant les éléments affectant la performance d'un système de communications sans-fil.

Afin d'assurer une bonne fonctionnalité d'un système, il est utile de préalablement le simuler en intégrant les différents algorithmes utilisés. Ceci permettra d'avoir une bonne perspective sur les performances réalisables du système. Dans ce chapitre, nous mentionnons donc aussi les modèles utilisés pour caractériser chacun des éléments importants.

#### 1.1 Le canal sans-fil

Un canal de communications peut être défini comme la liaison entre le transmetteur et le récepteur. De manière générale, il est perçu comme la source de plusieurs types de distortion du signal transmis. Ces distorsions peuvent être caractérisées par les paramètres décrits dans les prochaines sections. De plus, un même canal peut être vu sous différentes perspectives selon le type de communication effectué, ce qui influencera le modèle utilisé pour évaluer la performance simulée du système conçu.

FIGURE 1.1 Température du bruit pour un système en cascade

### 1.1.1 Bruit additif

Le bruit présent au récepteur est un des principaux facteurs qui influencent la performance d'un système de communications. De façon générale, le bruit additif est considéré comme étant la somme de plusieurs sources de distortion. Le bruit thermique et le bruit de quantification en sont deux exemples classiques.

Le bruit thermique est généré par l'excitation des électrons provenant des composantes électroniques. La mécanique quantique suggère que la densité spectrale du bruit thermique est donnée par l'équation 1.1 [Alexander S. B, 1997].

$$S(f) = \frac{hf}{e^{\left(\frac{hf}{kT}\right)} - 1} \frac{\text{watts}}{\text{Hz}} \quad (1.1)$$

où  $h$  est la constante de Plank,  $f$  est la fréquence (Hz),  $k$  est la constante de Boltzmann et  $T$  est la température (Kelvin). Comme les systèmes de communications opèrent à des fréquences de l'ordre de quelques Gigahertz au plus et que la largeur de bande est relativement petite, nous pouvons, en utilisant la règle de l'Hopital, poser l'hypothèse que le bruit thermique est blanc, c'est-à-dire que la densité spectrale de puissance est uniforme [Alexander S. B, 1997].

$$S(f) \approx kT = N_0 \quad (1.2)$$

Un des paramètres utile pour le caractériser est la température effective de bruit. Pour les systèmes en cascade (figure 1.1), la température  $T_{sys}$  globale du bruit thermique peut être évaluée à partir des températures  $T_i$  individuelles de chacune des composantes ainsi que de leur gain  $G_i$ .

En appliquant l'équation 1.3, il sera donc possible d'avoir une bonne estimation du niveau de bruit au récepteur [Rappaport, T.S., 2002].

$$T_{sys} = T_1 + \frac{T_2}{G_1} + \frac{T_3}{G_1 G_2} + \dots \quad (1.3)$$

Le bruit de quantification est une autre source de distortion du signal qui provient de l'arrondissement de la valeur ou de la troncation des bits de données lors de la numérisation des calculs en points fixes. Le convertisseur analogique-numérique (ADC) est un des blocs où s'effectue l'arrondissement numérique des données. Pour un signal avec une tension crête de  $V_p$  quantifié sur  $b$  bits, la variance du bruit de quantification qui s'ajoute au système est donnée selon l'équation 1.4. Nous pouvons considérer que l'erreur de quantification suit une distribution uniforme [Sklar, B., 2001].

$$\sigma^2 = \frac{1}{3} \cdot \left( \frac{V_p}{2^b} \right)^2 \quad (1.4)$$

### Modélisation

Puisque le bruit additif provient de plusieurs sources, il est raisonnable d'utiliser le théorème Central Limite pour affirmer que la fonction de densité de probabilité du bruit suivra une distribution Gaussienne de moyenne nulle. Sa variance  $N_0$  équivaudra à la puissance du bruit. Par ailleurs, pour modéliser le bruit en bande de base, nous utilisons une variable aléatoire Gaussienne complexe circulaire,  $N$ . Ceci implique que la matrice de covariance  $K = N_0 I$  est nécessaire et suffisante pour complètement décrire les statistiques de  $N$  [Tse D. & Viswanath, P., 2005].

$$N \sim \mathcal{CN}(0, K) \quad (1.5)$$

Donc, selon la définition d'une statistique Gaussienne complexe circulaire, nous pouvons affirmer que  $N = N_x + jN_y$  avec  $N_x$  et  $N_y$  indépendants et définis par l'équation 1.6.

$$N_x \text{ et } N_y \sim \mathcal{N}(0, \frac{N_0}{2}) \quad (1.6)$$

La variable aléatoire  $X \sim \mathcal{N}(\mu, \sigma^2)$  est définie par la fonction de densité de probabilité fournie par l'équation 1.7.

$$f(x) = \frac{1}{\sqrt{2\pi\sigma^2}} \exp\left(-\frac{(x-\mu)^2}{2\sigma^2}\right), \quad x \in \Re \quad (1.7)$$

Par ailleurs, la densité spectrale du bruit varie selon le type de système conçu. Pour des systèmes de communications à bande étroite, il est raisonnable de considérer que la densité spectrale est constante puisque la largeur de bande est trop petite pour que les fluctuations dans le spectre puissent être observables. En d'autres mots, un modèle de bruit additif blanc Gaussien (AWGN) est convenable.

### 1.1.2 Atténuation

La propagation dans l'espace libre est utile pour estimer le niveau de puissance du signal reçu au récepteur en absence d'obstacles. Dans le cas général, nous pouvons affirmer que

$$P_r \propto d^{-n} \quad (1.8)$$

avec  $P_r$  la puissance du signal au récepteur,  $d$  la distance, et  $n$  un facteur indiquant le taux de décroissance de la puissance [Rappaport, T.S., 2002]. Pour une source isotropique se trouvant dans l'espace libre,  $n$  est égal à 2. En effet, la puissance est distribuée à une distance  $d$  sur une sphère de surface  $4\pi d^2$ , ce qui implique qu'avec un récepteur de surface

$A$ , la puissance capturée est de

$$P_r = \frac{P_t A}{4\pi d^2} \quad (1.9)$$

où  $P_t$  est la puissance transmise.

Dans d'autres situations,  $n$  peut varier de 1 à 6 selon l'environnement de propagation. Par exemple, des mesures effectuées dans [Saleh, A. & Valenzuela, R., 1987] mentionnent la valeur  $n = 3.9$  pour un bâtiment commercial avec le transmetteur et le récepteur se situant sur le même étage.

### Modélisation

L'atténuation peut être modélisée par un facteur de gain ou être incorporée dans le niveau de bruit relatif à la puissance du signal reçu. Son niveau dépend alors du type d'application projeté. Comme nous tentons de valider la performance du système, la pire atténuation possible sera utilisée. Elle sera l'atténuation provenant d'une source isotrope avec un récepteur se trouvant à la distance maximale désirable pour l'application.

#### **1.1.3 Multi-trajets**

Dans des systèmes de communications sans-fil, le signal transmis peut parcourir plusieurs trajectoires distinctes pour atteindre le récepteur tel qu'ilustré à la figure 1.2. Plusieurs sources de multi-trajets sont décrites dans la littérature [Hashemi, H., 1993, Rappaport, T.S., 2002].

Lorsque le signal est réfléchi, l'énergie transmise est reliée au coefficient de réflexion de Fresnel,  $\Gamma$ . Celui-ci est fonction de plusieurs paramètres, notamment la polarisation de l'onde, l'angle d'incidence, la fréquence de l'onde, et les propriétés du matériel.

FIGURE 1.2 Les causes de multi-traj ectoires

La diffraction permet à l'onde de se propager à travers des parcours obstrués. Même si la puissance du signal peut chuter de façon significative, elle peut être suffisante pour être utile au récepteur. Les études de l'effet de la diffraction peuvent être réalisées à travers différents modèles, notamment les zones de Fresnels et le *Knife-edge Diffraction model*.

Finalement, lorsque le signal est réfléchi sur une surface rugueuse, elle est dispersée dans toutes les directions, incluant vers le récepteur. Même si la puissance ainsi transmise est une fraction du signal incident sur la surface, elle est une cause non-négligeable de multi-trajets. Ce phénomène est souvent référencé dans la littérature par la terminologie *scattering*.

Les trajets multiples sont la cause d'interférences constructives ou destructives. Ceci mène au phénomène d'évanouissement dans les systèmes de communications sans-fil.

## **Modélisation**

La variation temporelle et aléatoire de l'environnement de propagation rend l'analyse de l'effet des multi-trajets complexe. En effet, le signal de réception est la somme des différentes composantes du signal atténuees, déphasées et retardées. Une des méthodes proposées pour modéliser ce phénomène est de considérer le canal comme un filtre linéaire [Hashemi, H., 1993]. Grâce à celui-ci, pour un signal de transmission en bande de base  $s(t)$ , le signal reçu sera donné par l'équation 1.10.

$$r(t) = \Re \left[ \sum_{k=0}^{N-1} a_k s(t - \tau_k) e^{j(\omega_0 t + \theta_k)} \right] \quad (1.10)$$

où  $a_k$ ,  $\tau_k$  et  $\theta_k$  sont l'atténuation le délai subi et la phase respectivement de la  $k^{ime}$  composante,  $\omega_0$  est la fréquence angulaire de la porteuse et N est le nombre de multi-trajets. Une analyse de la dynamique du système [Tse D. & Viswanath, P., 2005] permet de définir les métriques suivantes :

### Temps de cohérence, $T_c$

Il définit la durée pour laquelle les paramètres du canal ne changent pas significativement.

### Étalement de Doppler, $D_s$

L'étalement de Doppler indique le taux auquel le patron d'interférence change. Il est inversement proportionnel au temps de cohérence.

### Étalement de délai, $T_D$

Ce paramètre est défini comme étant la différence maximale entre les temps de propagation du signal. Comme il n'est pas toujours pratique de le mesurer, d'autres paramètres, tel que l'étalement de délai rms (rms delay spread),  $\tau_{rms}$ , peuvent être utilisés.

| Type de Canal         | Caractéristique     |

|-----------------------|---------------------|

| Non-sélectif          | $W \ll W_c$         |

| Sélectif en fréquence | $W \gg W_c$         |

| Évanouissement lent   | $T_{trame} \ll T_D$ |

| Évanouissement rapide | $T_{trame} \gg T_D$ |

TABLE 1.1 Résumé des types de canaux sans-fil

Bande de Cohérence,  $W_c$

Elle définit la largeur de la bande de fréquence pour laquelle le gain du canal reste quasi-mérit constant. Elle est reliée à l'étalement de délai par la formule 1.11 :

$$W_c \propto \frac{1}{2T_d} \quad (1.11)$$

Le tableau 1.1 décrit la classification des canaux sans-fil en fonction de ces quatre paramètres.  $T_{trame}$  est la durée d'une trame de données alors que  $W$  est la largeur de bande occupée par le signal transmis. Comme nous le constatons au tableau 1.1, les caractéristiques du canal dépendent de la relation entre les propriétés du signal transmis par rapport aux paramètres du canal. Par exemple, le même canal peut être sélectif en fréquences pour des techniques de transmission utilisant de larges bandes de fréquences mais être non-sélectif pour les transmissions à bande étroite. À noter qu'un canal non-sélectif en fréquence peut être modélisé par un canal avec une seule composante de multi-trajet (i.e  $N = 1$ ) [Tse D. & Viswanath, P., 2005].

#### 1.1.4 Interférences

Les deux principales sources d'interférences sont l'interférence entre symboles (ISI) et l'interférences provenant des liens externes. L'ISI provient des effets de filtrage existant dans les systèmes de communications. Par exemple, les canaux sans-fil sont souvent caractérisés par une fonction de transfert, c'est-à-dire qu'ils agissent comme des filtres. Ny-

quist a étudié le problème de la communication sans ISI dans les canaux à bande limitée (Nous en discuterons davantage à la section 3.3).

Par ailleurs, il est possible qu'un système de communications avoisinant opère dans la même bande de fréquence (co-channel interference) ou proche (adjacent channel interference). Ces types d'interférences peuvent être limités à travers une bonne planification du réseau sans-fil [Sklar, B., 2001]. D'un point de vue pratique, il est raisonnable dans la plupart des cas de considérer les interférences externes comme étant des sources de bruit additif.

## 1.2 La modulation

La modulation consiste à effectuer l'encodage des données binaires selon un signal ou une combinaison d'un ensemble de signaux de base. Cet ensemble de signaux de base est habituellement orthonormal. Ainsi les signaux de transmission possibles pourront être modélisés comme des vecteurs dans un espace vectoriel où chaque axe correspondra à une des fonctions orthonormales. Chaque séquence binaire possible est alors assignée à un point de la constellation.

Le démodulateur au récepteur doit estimer la séquence transmise. Une des techniques utilisées est de décider selon le point de la constellation le plus proche du vecteur reçu. En d'autres termes, ce récepteur, défini comme le récepteur à maximum de vraisemblance (Maximum Likelihood Receiver), décide de la combinaison des signaux transmis en faisant une comparaison avec ceux auxquels il s'attend. Le récepteur à maximum de vraisemblance est davantage détaillé dans l'annexe I.1.

Le choix de la technique de modulation utilisée est principalement basé sur les considérations suivantes [Goldsmith A., 2005] :

- le taux de transfert ;

| Modulation | BER                                                                 | Efficacité Spectrale (bits/s/Hz) |

|------------|---------------------------------------------------------------------|----------------------------------|

| BPSK       | $Q(\sqrt{2SNR})$                                                    | 1                                |

| QPSK       | $Q(\sqrt{SNR})$                                                     | 2                                |

| M-PSK      | $\frac{2}{\log_2 M} Q(\sqrt{2SNR} \sin(\pi/M))$                     | $\log_2(M)$                      |

| M-QAM      | $\frac{4(\sqrt{M}-1)}{\sqrt{M}\log_2 M} Q(\sqrt{\frac{3SNR}{M-1}})$ | $\log_2(M)$                      |

TABLE 1.2 Comparaison du BER et de l'efficacité spectrale pour différentes modulations avec une détection cohérente.

- l'efficacité spectrale ;

- l'efficacité de puissance ;

- le taux d'erreurs ;

- le coût d'implémentation.

Par exemple, tel qu'indiqué dans le tableau 1.2, le taux d'erreurs binaires obtenu par une modulation BPSK est inférieur à celui d'une modulation QPSK. Il y a une perte de 3dB en termes de rapport signal à bruit ( $SNR = \frac{E_s}{N_0}$ ) requis pour atteindre le même taux d'erreurs. Cependant, l'efficacité spectrale est meilleure pour une modulation QPSK. Le choix de la modulation nécessite donc clairement un compromis entre les divers facteurs mentionnés.

À noter que dans le calcul du taux d'erreurs binaires (BER), nous avons assumé qu'un ordonnancement de Gray est utilisé. Dans un ordonnancement de Gray, la correspondance binaire de chaque symbole de la constellation est assignée de sorte à ce que chaque symbole se distingue de son voisin le plus proche par au plus 1 bit.

### 1.3 La conversion en bande passante

Avant la transmission des données à travers le canal sans-fil, une modulation vers des radio-fréquences est généralement effectuée. Une des justifications pour cette opération est que la dimension requise des antennes de transmission et de réception est proportionnelle à la longueur d'onde du signal. Par exemple, en assumant que la dimension de

l'antenne doit être de  $\lambda/4$ , pour transmettre une longueur d'onde de 30kHz, une antenne irréaliste de 2500m serait nécessaire. À 600MHz, elle sera de 12.5cm.

Il est cependant désirable d'effectuer l'analyse et le traitement des signaux en bande de base car le coût du matériel requis ainsi que la complexité de calculs sont ainsi considérablement réduits. La représentation en quadrature est alors utile. Elle établit une équivalence entre les signaux bande de base et bande-passante facilitant ainsi l'analyse et le traitement de données en bande de base.

### Représentation en quadrature

Soit un signal bande de base  $m(t) = x(t) + jy(t)$  de largeur de bande limitée à  $W$ . La modulation en quadrature peut être vue comme étant la multiplication de  $m(t)$  par  $e^{j2\pi f_0 t}$  suivi de la transmission de la partie réelle du signal. En écrivant  $m(t)$  comme  $x(t) + jy(t)$ , la relation mathématique suivante peut être établie.

$$\begin{aligned} s(t) &= \operatorname{Re}\{m(t)e^{j2\pi f_0 t}\} \\ &= \operatorname{Re}\{(x(t) + jy(t))(\cos 2\pi f_0 t + j \sin 2\pi f_0 t)\} \quad (1.12) \\ &= x(t)\cos 2\pi f_0 t - y(t)\sin 2\pi f_0 t \end{aligned}$$

Au récepteur, les multiplications de  $s(t)$  par  $\cos 2\pi f_0 t$  et  $-\sin 2\pi f_0 t$  suivi d'un filtre passe-bas génèrent respectivement la partie réelle et imaginaire de  $m(t)$ .

$$\begin{aligned} r_{real}(t) &= s(t) \cos 2\pi f_0 t|_{passe-bas} & r_{imag}(t) &= s(t) (-\sin 2\pi f_0 t)|_{passe-bas} \\ &= \frac{x(t)}{2}(1 + \cos 4\pi f_0 t) & &= \frac{y(t)}{2}(1 - \cos 4\pi f_0 t) \\ &- \frac{y(t)}{2}\sin 4\pi f_0 t|_{passe-bas} & & - \frac{x(t)}{2}\sin 4\pi f_0 t|_{passe-bas} \\ &= \frac{x(t)}{2} & &= \frac{y(t)}{2} \quad (1.13) \end{aligned}$$

FIGURE 1.3 Conversion de bande de base à bande passante au transmetteur et de bande passante à bande de base au récepteur

La figure 1.3 illustre les étapes décrites ci-haut. À noter que même si le signal de réception  $r(t)$  a été atténué, il n'y a pas de perte d'information et donc la capacité n'est pas affectée. En effet, il est toujours possible d'amplifier le signal par un facteur de deux pour compenser ces atténuations.

#### 1.4 La période d'un symbole

Combiné avec le type de modulation utilisé, la période d'un symbole  $T_s$  détermine le taux de transfert des informations binaires. Pour une modulation QPSK, deux bits de données sont représentés par symbole. Donc, pour une période  $T_s$  secondes, le taux de transfert est de  $2/T_s$  bits/s. Par contre, pour une constellation M-QAM,  $\log_2 M$  bits de données sont représentés par symbole. Le taux de transfert est alors de  $(\log_2 M)/T_s$  bits/s.

FIGURE 1.4 Structure d'un récepteur optimal

### 1.5 Détection optimale

Au transmetteur, le modulateur se base sur la combinaison des données binaires pour envoyer un des  $M$  signaux possibles. Au récepteur, le défi est de faire la meilleure estimation du signal transmis pour décider du message. Un récepteur qui permet de maximiser le rapport signal à bruit permettra de faire la meilleure décision. La probabilité d'erreurs sera alors minimisée. Ce récepteur optimal comprend un ensemble de filtres linéaires adaptés aux signaux transmis (voir figure 1.4). Comme chacun de ces filtres est équivalent à un corrélateur, le récepteur optimal est aussi un récepteur à maximum de vraisemblance tel que décrit à l'Annexe I.1 [Wozencraft, J.M & Jacobs, I.M., 1965].

À la figure 1.4, nous observons que la sortie du filtre doit être échantillonnée à une période  $T_s$  correspondant à la durée d'un symbole. Un des critères importants pour la détection optimale est de faire l'échantillonnage des filtres adaptées au bon instant. Comme nous l'observons à la figure 1.5, dans un système de communication numérique, le convertisseur analogique-numérique effectue la discréttisation du signal reçu. De façon générale, ce convertisseur échantillonne le signal de réception à un facteur  $L$  de la période  $T_s$ . Le fac-

FIGURE 1.5 Discréétisation du filtre adapté

teur  $L$  est le taux de suréchantillonnage. Chaque suréchantillon à la sortie du convertisseur passe à travers le filtre adapté. Le bon échantillon de chaque groupe de  $L$  suréchantillons devra alors être choisi. Dans l'exemple de la figure 1.5, un signal BPSK est transmis et le signal reçu  $r(t)$  est suréchantillonné par le convertisseur analogique numérique. Un corrélateur effectue la corrélation des suréchantillons avec la fonction de base utilisée et à sa sortie, l'instant optimal d'échantillonnage est lorsque  $t = T_s$ . Il est important de sélectionner le bon échantillon à la sortie des filtres adaptés pour maximiser le rapport signal à bruit et donc minimiser le taux d'erreurs.

## 1.6 L'horloge

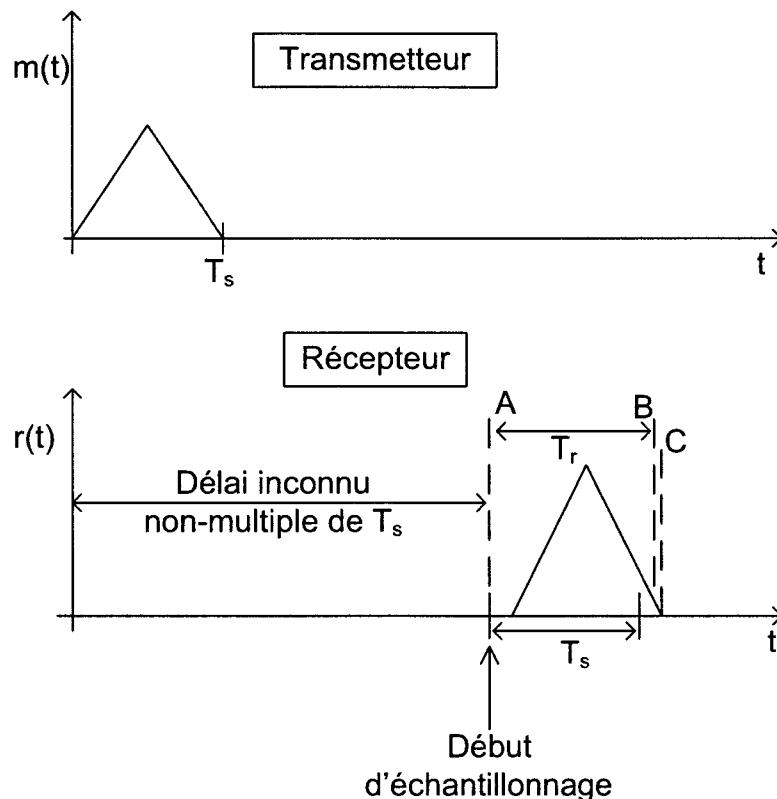

Dans les systèmes de communications numériques, les données sont transmises par des symboles de durée  $T_s$  secondes. Cependant, le délai subi par le signal à travers le canal n'est pas nécessairement un multiple de  $T_s$ . Ainsi, l'échantillonnage du signal reçu ne sera pas effectué de façon synchrone. La figure 1.6 illustre ce phénomène. Plusieurs blocs au récepteur requièrent l'échantillonnage à des instants  $kT$ , pour des valeurs de  $k$  entières, du signal de réception. La démodulation optimale en est un exemple. De plus, si

FIGURE 1.6 Effet du délai de canal sur le moment d'échantillonage

l'instant d'échantillonnage du signal de réception est inexact, il y aura de l'interférence inter-symboles pour un canal à bande limitée [Sklar, B., 2001]. À priori, nous pouvons affirmer que le récepteur n'a pas de notion du moment exact auquel l'échantillonnage être effectuée. Dans le cas présenté à la figure 1.6, celui-ci se passe en avance (au point A) par rapport au bon instant (Point C).

De plus, la durée d'une période d'une symbole au récepteur  $T_r$  peut être légèrement différente de celle au transmetteur dû aux imperfections des oscillateurs. À la figure 1.6, le récepteur considère qu'un symbole dure pendant une période  $T_r$  qui est supérieure à la vrai durée  $T_s$  d'un symbole. À long terme, cette erreur peut s'accumuler et nécessite donc d'être corrigée.

## Modélisation

En insérant un nombre aléatoire de délais de période équivalent à  $T_s/L$  dans le modèle de canal (avec  $T_s$  la période d'un symbole et L le facteur de suréchantillonnage), nous pouvons considérer que le récepteur aura perdu la notion du temps d'arrivée exact des données. Ainsi, cela pourra servir de test pour vérifier la validité d'un algorithme de recouvrement d'horloge.

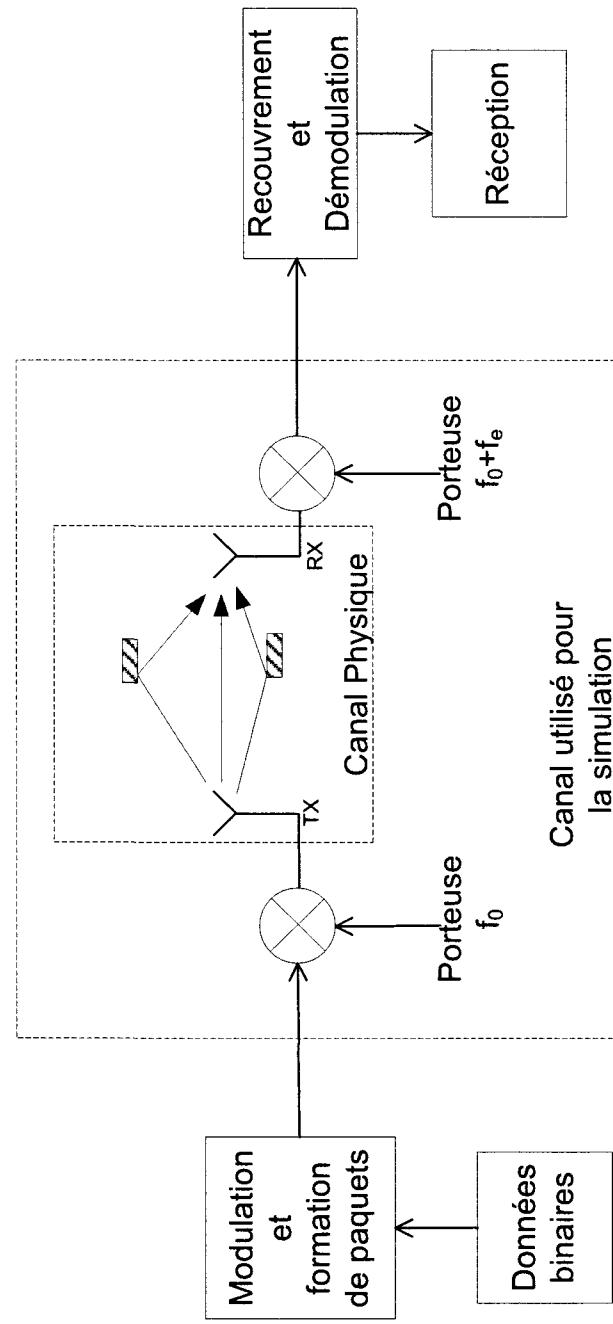

## 1.7 Oscillateurs

La génération des fonctions cycliques tels que l'horloge électronique et les sinusoïdaux se fait souvent à partir d'un cristal. Cependant, comme ceci n'est pas parfait, il existe une déviation entre sa fréquence nominale et réelle. Ceci fait que les cristaux au transmetteur et au récepteur oscilleront à des fréquences légèrement différentes. En conséquence, il existera une différence entre la fréquence de la porteuse reçue et de la sinusoïdale de référence (voir figure 1.3). Le passage des radio-fréquences en basse fréquence comportera donc une erreur, ce qui devra être compensée par un algorithme de synchronisation de fréquence.

## Modélisation

Afin d'inclure cette disparité, nous avons considéré que la différence entre les fréquences équivaut à une sinusoïdale d'erreur de fréquence  $f_e$  modulant le signal dans le canal, la fréquence  $f_e$  étant égale à  $(f_{transmetteur} - f_{récepteur})$ , où  $f_{transmetteur}$  est la fréquence au transmetteur et  $f_{récepteur}$  est la fréquence au récepteur.

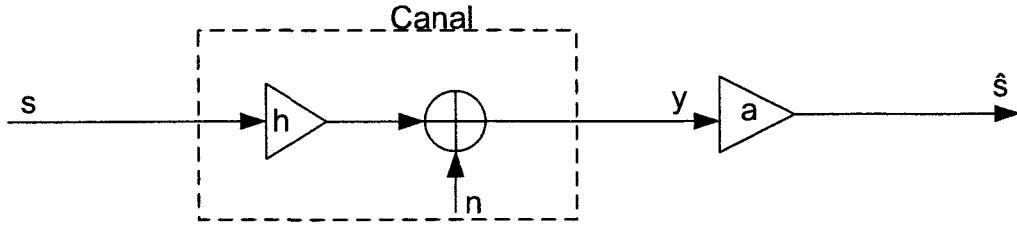

## 1.8 Système global

La figure 1.7 permet de résumer le système de communications. Au transmetteur, les données binaires sont traitées pour former des paquets qui seront transmis. Le canal de transmission réel est constitué de plusieurs facteurs mais la simulation d'un système ne requiert qu'une modélisation partielle mais suffisante du système.

FIGURE 1.7 Une vue de haut niveau du système de communications

## CHAPITRE 2

### SURVOL DES TECHNIQUES DE PROTOTYPAGE DE SYSTÈMES DE COMMUNICATIONS

La conception des systèmes de communications sans-fil fait face à plusieurs défis. Au courant de ces dernières années plusieurs nouveaux concepts ont été élaborés. Par exemple, les études sur les systèmes à multiples antennes (MIMO) sont très répandues. Une bonne étude théorique fournit une base solide à partir de laquelle plusieurs idées peuvent être développées. La simulation des systèmes conçus fournit la possibilité de vérifier leurs fonctionnalités et les performances prévues en se basant sur des modèles avant de passer à l'implémentation matérielle. Dans ce chapitre, nous faisons un bref aperçu de quelques systèmes de prototypage qui ont été réalisés au cours de ces dernières années.

#### 2.1 Critères de développement

La réalisation matérielle d'un système de communications requiert un certain niveau d'ingénierie qui pouvait être ignorée lors des études théoriques. Ainsi, elle est assujettie à plusieurs contraintes qui influencent la faisabilité du produit. Quelques critères de décision sont les suivants [Raghu M.R. et al, 2004, Safadi M.S. & Ndzi D.L., 2006] :

- **Coût.** Ce coût peut être mesuré en argent, en temps de développement ou en termes de consommation de puissance.

- **Flexibilité.** Aux stades préliminaires de développement, une bonne configurabilité est importante pour différentes raisons. Par exemple, cela permettra de valider aisément certains algorithmes. De plus, un vaste choix de fonctionnalités est désirable.

- **Débit binaire.** Le débit qui peut être atteint est classé selon deux catégories : le transfert

temps-réel et non temps-réel. Un transfert en temps réel est beaucoup plus demandant en termes de besoin de traitement et de développement qu'un transfert non temps réel, mais il est plus représentatif des différentes applications de systèmes de communications existants.

## 2.2 La radio logicielle

Il est clair que les besoins en termes de communications sans-fil ont beaucoup évolué au courant de ces dernières années. De nos jours, les produits sans-fil sont utilisés pour une panoplie d'activités, notamment les communications voix et vidéo, les transferts de données et le contrôle à distance. La radio logicielle (Software Defined Radio, SDR) est définie comme tout système qui permet d'avoir une communication sans-fil et qui contient au moins une fonction de la couche physique définie par une composante logicielle [SDR Forum]. Elles sont attrayantes pour les raisons suivantes [Nakajima, N. et al, 2001] :

- **Reconfigurabilité.**

Présentement, les logiciels utilisés sur les stations mobiles sont principalement utilisés dans la couche application (Jeux, etc.). Un des objectifs futurs est de permettre la configuration de certaines autres fonctions. Par exemple, à une station de base, l'allocation des horaires de transmission (time slots) peut être modifiée sans avoir à faire des changements matériels.

- **Opération Multimode.**

Les systèmes sans-fil de troisième (3G) et de quatrième (4G) génération sont présentement en déploiement à travers la planète. Il est essentiel d'être en mesure de fournir du service aux utilisateurs qui font beaucoup de déplacements indépendamment de leur emplacement. Dans certains cas, l'utilisateur pourrait même se retrouver en mode roaming à un endroit où seulement le 2G est supporté. Donc, les terminaux multi-modes sont désirables.

### – Déverminage et mise à jour logicielle.

Beaucoup de terminaux mobiles sont déployés de nos jours. Lorsque la correction d'un bug est trouvée, il peut être coûteux de passer à son application tant au niveau de la station de base qu'au niveau du mobile si des changements matérielles sont nécessaires. Avec les SDR, le matériel d'une station de base peut être reprogrammable. Cela implique alors une diminution des coûts de réparation et du temps d'indisponibilité. Le problème survient surtout au niveau des stations mobiles où la quantité déployée peut être énorme. Un rappel de ces équipements pour effectuer le changement matériel peut être alors coûteux. Le remplacement à distance du logiciel (lorsque possible) devient ainsi une option intéressante.

Plusieurs approches ont été utilisées pour le développement des radios logicielles. Dans les sections suivantes, nous faisons un bref aperçu des méthodes proposées dans la littérature.

## 2.3 Traitement hors ligne

Dans les phases initiales de développement de nouveaux systèmes, le traitement hors ligne des données permet de valider des résultats théoriques et de simulation pour des environnement réalistes. Ceci offre la possibilité de faire études de performance et ajustements nécessaires préalables à l'intégration matérielle [Raghu M.R. et al, 2004].

Le système de [Lang, S. et al., 2004] est une plateforme destinée à concevoir un système SISO-OFDM. Le système réalisé est une première phase de développement et permettait d'avoir un système non-temps réel. Dans une phase subséquente, des systèmes MIMO sont prévus.

Le système fonctionne avec une porteuse de 5,25 GHz. Au niveau du transmetteur, les données ont été transmises dans la mémoire vive et transmises en paquets vers des conver-

tiseurs analogiques-numériques puis la section RF. Au niveau du récepteur, les données sont gardées en mémoire pour être traitées hors-ligne.

Le traitement de données se fait hors ligne avec différents algorithmes. Un tel système permet d'activer/désactiver certains blocs et de réajuster certains paramètres avec un temps de développement minimal. Le coût de développement est relativement faible. Cependant, il peut être utilisé seulement pour des mesures de systèmes à bande étroite. De plus, le traitement de données n'est pas effectué en temps réel.

## 2.4 DSP

Dans plusieurs situations, le développement d'un système dans un environnement temps réel est requis pour l'étude de performances. Une plateforme avec un DSP (Digital Signal Processor) permet d'atteindre cet objectif.

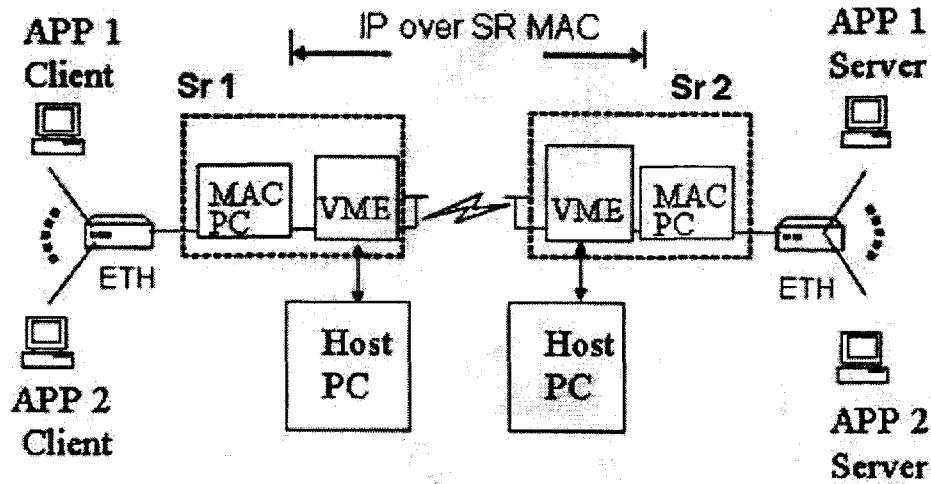

Un des systèmes réalisés sur DSP est présenté par [Stuber G.L. et al, 2004]. La configuration utilisée est présentée à la figure 2.1. L'utilisateur communique à chacun des deux cartes de développement à travers une interface VME à PCI. L'architecture avait été proposée par [Mitola, J., 1995]. Un système MIMO-OFDM  $2 \times 2$  est réalisé avec un codage d'Alamouti. Au récepteur, les différentes opérations à réaliser (synchronization temporelle et fréquentielle, estimation et compensation de canal & démodulation) sont distribuées aux quatre processeurs présents sur la plateforme.

L'auteur mentionne que la prochaine phase de développement est l'utilisation des FPGA disponible pour effectuer du FEC (Forward Error Correction).

FIGURE 2.1 Plateforme pour un SDR sur DSP [Stuber G.L. et al, 2004]

## 2.5 ASIC

Un circuit ASIC (Application Specific Integrated Circuit) est un circuit intégré spécialisé pour effectuer certaines fonctions. Le coût de développement et la complexité associés avec ce type de produit sont élevés [Safadi M.S. & Ndzi D.L., 2006]. Les meilleures performances des puces ASIC offrent la possibilité d'effectuer des opérations temps réel pour des systèmes très demandant [Raghu M.R. et al, 2004]. De plus, le coût de production par échantillon est réduit par la suite.

L'article [Frigon J.-F. & Daneshrad, B., 2002] présente un système qui utilise la technologie ASIC. Au transmetteur, le signal est modulé à une fréquence IF de 43,75 MHz. La fréquence de la porteuse utilisée est de 2,44GHz. Au récepteur, une série de quatre antennes de réception espacées de  $\frac{1}{2}\lambda$  est utilisée. Le récepteur est configuré de sorte à avoir une série d'antennes intelligente. Toutes les fonctions du récepteur (traitement de signaux spatio-temporel, filtrage et synchronisation) ont été implémentées dans un seul ASIC. Les auteurs ont pris un total de 59 262 mesures pour un environnement de propagation intérieur et une communication point à point. Plusieurs résultats ont été déduits à partir de ces mesures. Par exemple, avec une puissance de transmission de 10 mW, le

FIGURE 2.2 Modèle d'un système FPGA [Barbero, L.G. & Thompson, J.S., 2005]

Le système était en mesure de fournir un taux de transfert de 30 Mbps avec un taux d'erreurs binaires de  $10^{-3}$ , une probabilité de blocage de 5% sur un rayon de couverture de 20 m.

## 2.6 FPGA

L'utilisation d'un FPGA (Field Programmable Gate Array) utilise les avantages des systèmes ASIC tout en limitant le coût de développement. De plus, le FPGA offre une bonne réadaptabilité car il peut être reprogrammé pour faire des modifications au design.

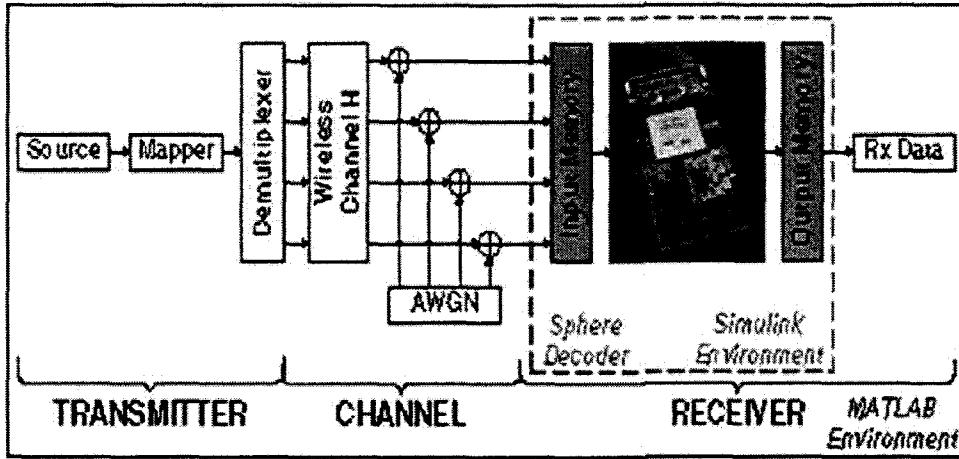

Un tel système est présenté dans [Barbero, L.G. & Thompson, J.S., 2005]. L'objectif est d'implémenter et de faire l'analyse de plusieurs algorithmes pour des systèmes à multiples antennes (MIMO). Un schéma bloc du système utilisé est illustré à la figure 2.2.

L'outil Xilinx DSP System Generator est utilisé pour faire l'implémentation à partir d'un environnement Simulink de Matlab. Après avoir identifié la partie utile du modèle Simulink, cette dernière est isolée et compilée pour générer un bitstream. Le modèle FPGA est alors simulé comme un système embarqué sous un environnement Simulink. Cette technique est surnommé le Hardware in the Loop. Elle permet de simuler un morceau du

système et de changer son entrée selon les besoins à travers un interface usager (GUI) de Simulink. Les résultats correspondent aux données obtenues suite à un traitement en temps réel.

Une des reproches des FPGAs est l'utilisation inefficace de la logique disponible, ce qui implique une consommation excessive de puissance [Safadi M.S. & Ndzi D.L., 2006].

## 2.7 Prototypes hybrides

Les prochaines générations de SDR utilisent des architectures hybrides en combinant les différentes technologies disponibles. Comme mentionné à la section 2.4, une plateforme utilisant quatre DSP et deux FPGA est envisagée pour effectuer du MIMO-OFDM avec FEC.

Une architecture utilisant des FPGA et DSP est aussi mentionnée sous l'acronyme BEE (Berkeley Emulation Engine) par [Takai, M. et al, 2005]. Un environnement Simulink est utilisé pour développer les modèles. Ils peuvent ensuite être exécutés et la réalisation de la radio se fait par du prototypage rapide.

Il existe d'autres bancs d'essai en développement ou sur lesquels des systèmes ont été implantés. Un banc d'essai utilisant une combinaison d'ASICs avec plusieurs FPGA de haute vitesse est en développement selon ce qui est mentionné par [Takai, M. et al, 2005]. Le but est de créer un système pouvant supporter des configurations MIMO  $4 \times 4$  pour un signal ayant une bande passante de 25 MHz et du traitement en temps réel.

Nous avons utilisé une plateforme de prototypage hybride. La plateforme est constituée de deux FPGA et de quatre DSP. Elle est davantage décrite au chapitre 4.

## CHAPITRE 3

### LES ÉLÉMENTS DU MODÈLE DE SIMULATION