**Titre:** Élaboration d'un modèle d'abstraction des communications point-à-point pour une plateforme (SOC) multiprocesseur hétérogène

Title: [Élaboration d'un modèle d'abstraction des communications point-à-point pour une plateforme \(SOC\) multiprocesseur hétérogène](#)

**Auteur:** Sylvain Goyette

Author: [Sylvain Goyette](#)

**Date:** 2008

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Goyette, S. (2008). Élaboration d'un modèle d'abstraction des communications point-à-point pour une plateforme (SOC) multiprocesseur hétérogène [Master's thesis, Ecole Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/8483/>

**Document en libre accès dans PolyPublie**

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8483/>

PolyPublie URL: <https://publications.polymtl.ca/8483/>

**Directeurs de recherche:** Guy Bois, & El Mostapha Aboulhamid

Advisors: [Guy Bois](#), [El Mostapha Aboulhamid](#)

**Programme:** Unspecified

Program: [Unspecified](#)

UNIVERSITÉ DE MONTRÉAL

ÉLABORATION D'UN MODÈLE D'ABSTRACTION DES

COMMUNICATIONS POINT-À-POINT POUR UNE PLATEFORME (SOC)

MULTIPROCESSEUR HÉTÉROGÈNE

SYLVAIN GOYETTE

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

AVRIL 2008

Library and Archives

Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

ISBN: 978-0-494-57252-8

*Our file Notre référence*

ISBN: 978-0-494-57252-8

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

ÉLABORATION D'UN MODÈLE D'ABSTRACTION DES

COMMUNICATIONS POINT-À-POINT POUR UNE PLATEFORME (SOC)

MULTIPROCESSEUR HÉTÉROGÈNE

présenté par : GOYETTE Sylvain

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. LANGLOIS J.M. Pierre, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. ABOULHAMID El Mostapha, Ph.D., membre et codirecteur de recherche

M. BOLAND Jean-François, Ph.D., membre

« All truths are easy to understand once they are discovered; the point is to discover them. »

- Galileo Galilei

« A man's errors are his portals of discovery. »

- James Joyce

« New ideas pass through three periods: 1) It can't be done. 2) It probably can be done, but it's not worth doing. 3) I knew it was a good idea all along! »

- Arthur C. Clarke

## REMERCIEMENTS

Je tiens à remercier M. Bois, mon directeur de maîtrise pour ses conseils, sa disponibilité et son analyse qui furent indispensables pour réaliser l'ensemble de mes travaux de recherche.

Je voudrais aussi souligner le support financier du CRNSG et du ReSMIQ qui me permit de me consacrer entièrement à ce projet. De plus, je remercie les membres du groupe de recherche en codesign CIRCUS de l'École Polytechnique, Cédric, Sébastien, Laurent, Luc, Maxime, Marc-André et Benoît, pour leur collaboration, leur soutien et les précieuses discussions.

Finalement, je tiens à remercier mes amis, mes parents et ma fiancée Trinh qui m'ont soutenu moralement tout au long de ces six longues années à Polytechnique.

## RÉSUMÉ

Le domaine des systèmes embarqués fait face depuis quelques temps aux difficultés posées par leur complexité, l'écart de productivité entre la technologie et les outils de conception ainsi que les temps de commercialisation toujours plus courts. L'apparition des systèmes multiprocesseurs sur puce (MPSoC), où coexistent sur un même circuit différents composants logiciels et matériels, pose de nouveaux défis au niveau des communications inter-composants et de l'hétérogénéité des composants.

Un des aspects importants de la complexité inhérente des MPSoC est le choix de la topologie de l'architecture de communication. Plusieurs groupes de recherche dans le domaine travaillent au développement de langages, de plateformes et de modèles permettant d'augmenter le niveau d'abstraction des mécanismes de communication.

La symbiose compliquée du logiciel et du matériel impose une revue des méthodologies de conception. Le « Electronic System Level », ou ESL, propose un processus de conception et de vérification ciblant une abstraction à haut niveau qui permet d'améliorer la compréhensibilité et la facilité d'implémentation des systèmes. S'inscrivant dans cette pensée, la technologie de Space Codesign™, basée sur SystemC, assure une spécification unique et homogène des systèmes ainsi qu'un raffinement progressif vers des partitions logicielles et matérielles. Elle maintient la transparence des mécanismes de communication peu importe la technologie sous-jacente utilisée.

La recherche effectuée se base sur la technologie de Space Codesign™ et cible l'élaboration d'un modèle d'abstraction des communications point-à-point faisant bon usage des nouvelles avenues qu'offrent les processeurs embarqués (canaux haut-débit, extensibilité du jeu d'instruction, etc.). Ceci passe par la consolidation de la plateforme SPACE autour d'une architecture hétérogène basée sur le standard CoreConnect d'IBM

et des processeurs embarqués µBlaze et PowerPC 405 FX offert sur les FPGA Virtex-4 de la compagnie Xilinx.

Le paradigme résultant est le DirectLink qui augmente les fonctionnalités de la plateforme SPACE en étendant les services de communication existants basés sur la transmission de messages. DirectLink offre une interface unique tant pour les composants logiciels que matériels et diminue ainsi la complexité de la conception d'une topologie de système de communication.

DirectLink aide à améliorer les performances de l'architecture de communication et reste indépendant de la plateforme matérielle cible. Il peut diminuer les délais induits par les protocoles standards SPACE d'environ 90% et accélérer l'exécution d'une application complexe d'un facteur de 5. Le paradigme peut même s'étendre vers d'autres plateformes comme le Xtensa de Tensilica ou le NIOS-II d'Altera.

## ABSTRACT

The field of embedded systems has been facing for some time now difficulties posed by an increasing gap of productivity between technology and design tools, an unprecedented complexity as well as increasingly short time to market. The apparition of multiprocessor systems-on-chip (MPSoC), in which software and hardware components coexist on the same circuit, poses new challenges in terms of inter-components communications and heterogeneity of components.

One of the important aspects of the inherent complexity of MPSoC is the choice of a topology for the communication architecture. Several research groups in the area are working on the development of languages, platforms and models to increase the level of abstraction of these communication mechanisms.

The intricate symbiosis between software and hardware requires a rethinking of design methodologies. ESL design and verification proposes a high-level abstraction that improves the understandability and ease of implementation of systems. In line with this thinking, the Space Codesign™ technology, based on SystemC, provides a unique and homogeneous system specification and a progressive refinement to software and hardware partitions. It maintains transparency of communication mechanisms regardless of the underlying technology.

This research is based on the Space Codesign™ technology and aims to develop of a model of abstraction for point-to-point communications making good use of new opportunities offered by embedded processors (high-speed channels, ISA extensibility, and so on.). This requires a consolidation of the SPACE platform around a heterogeneous architecture based on IBM CoreConnect standard and embedded

processors such as µBlaze and PowerPC 405 FX, all available on Virtex-4 Fogs manufactured by Xilinx.

The resulting paradigm is called DirectLink which increases the functionality of the platform by extending existing SPACE communication services based on message passing mechanisms. DirectLink offers a single interface for both software and hardware that reduces the complexity of communication system design.

DirectLink improves performances of the communication architecture and remains independent of the targeted hardware platform. It can reduce by approximately 90% delays induced by standard SPACE protocols and accelerate the execution of a complex application by a factor of 5. The paradigm may even extend to other platforms such as the Tensilica Xtensa or Altera NIOS-II.

## TABLE DES MATIÈRES

|                                                             |      |

|-------------------------------------------------------------|------|

| REMERCIEMENTS .....                                         | V    |

| RÉSUMÉ .....                                                | VI   |

| ABSTRACT.....                                               | VIII |

| TABLE DES MATIÈRES.....                                     | X    |

| LISTE DES FIGURES .....                                     | XIV  |

| LISTE DES TABLEAUX.....                                     | XVI  |

| LISTE DES ACRONYMES .....                                   | XVII |

| LISTE DES ANNEXES .....                                     | XIX  |

| CHAPITRE 1 INTRODUCTION .....                               | 1    |

| 1.1.    Les systèmes embarqués modernes.....                | 1    |

| 1.2.    Problématique .....                                 | 2    |

| 1.3.    Objectif.....                                       | 4    |

| 1.4.    Méthodologie .....                                  | 5    |

| 1.5.    Contributions.....                                  | 6    |

| 1.6.    Organisation du mémoire.....                        | 7    |

| CHAPITRE 2 LES COMMUNICATIONS DANS UN SYSTÈME-SUR-PUCE..... | 8    |

| 2.1.    Les modèles de communication pour MPSoC.....        | 8    |

| 2.1.1.    Communication inter logiciel.....                 | 8    |

| 2.1.2.    Communication inter matériel .....                | 9    |

| 2.1.3.    Communication logiciel/matériel.....              | 9    |

| 2.2.    Les architectures de communication.....             | 10   |

| 2.2.1.    Bus de communication.....                         | 10   |

| 2.2.2.    Liens point à point et communication ad hoc ..... | 12   |

| 2.2.3.    GALS .....                                        | 12   |

|                                                                                                                     |                                                              |           |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|

| 2.3.                                                                                                                | Abstraction des communications à haut niveau .....           | 14        |

| 2.3.1.                                                                                                              | Le modèle SPACE .....                                        | 14        |

| 2.3.2.                                                                                                              | Le modèle ImpulseC .....                                     | 21        |

| 2.3.3.                                                                                                              | Le modèle d'interface matériel/logiciel unifié.....          | 22        |

| 2.4.                                                                                                                | Génération des interfaces logiciel-matériel.....             | 25        |

| 2.4.1.                                                                                                              | L'approche des composants basés service .....                | 25        |

| 2.4.2.                                                                                                              | L'approche des adaptateurs de communication .....            | 26        |

| 2.4.3.                                                                                                              | L'approche coprocesseur .....                                | 26        |

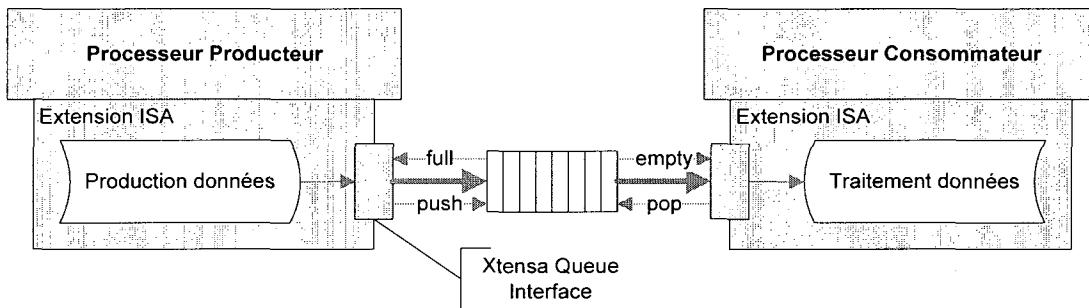

| 2.4.4.                                                                                                              | L'approche du Tensilica Xtensa.....                          | 27        |

| <b>CHAPITRE 3 UNE PLATEFORME VIRTUELLE HÉTÉROGÈNE ET EXTENSIBLE POUR SPACE ..</b>                                   |                                                              | <b>29</b> |

| 3.1.                                                                                                                | La plateforme CoreConnect d'IBM implémentée par Xilinx ..... | 29        |

| 3.1.1.                                                                                                              | Le bus PLB.....                                              | 30        |

| 3.1.2.                                                                                                              | Le bus OPB .....                                             | 30        |

| 3.1.3.                                                                                                              | Le bus FCB .....                                             | 30        |

| 3.1.4.                                                                                                              | Le bus FSL .....                                             | 31        |

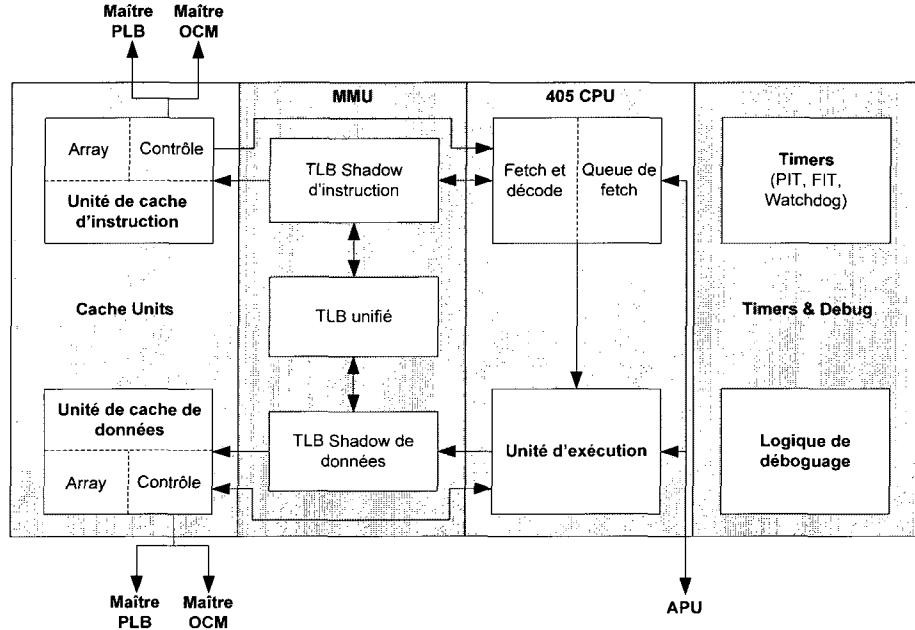

| 3.2.                                                                                                                | Le PowerPC405FX .....                                        | 31        |

| 3.2.1.                                                                                                              | Architecture.....                                            | 31        |

| 3.2.2.                                                                                                              | Les composants APU et FCB.....                               | 33        |

| 3.2.3.                                                                                                              | Instructions spécialisées .....                              | 34        |

| 3.3.                                                                                                                | Intégration de l'ISS du PowerPC à SpaceLib .....             | 35        |

| 3.3.1.                                                                                                              | Le simulateur PSIM .....                                     | 36        |

| 3.3.2.                                                                                                              | Méthodologie d'intégration et interface avec SPACE .....     | 41        |

| 3.3.3.                                                                                                              | Modélisation de l'APU et du FCB .....                        | 49        |

| <b>CHAPITRE 4 DIRECTLINK : ABSTRACTION DES COMMUNICATIONS POINT-À-POINT DANS LA PLATEFORME VIRTUELLE SPACE.....</b> |                                                              | <b>53</b> |

| 4.1.                                                                                                                | Paradigme du DirectLink .....                                | 53        |

| 4.2.                                                                                                                | Méthodologie .....                                           | 54        |

| 4.3.                                                                                                                | Spécification des interfaces.....                            | 56        |

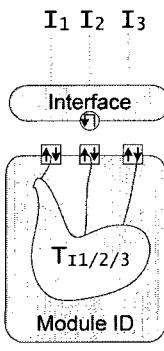

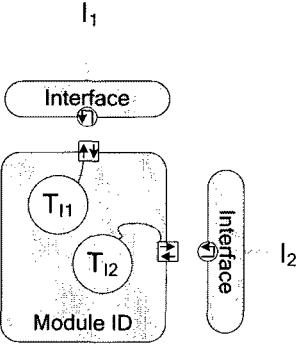

| 4.3.1.                                                                                                              | Constitution du module.....                                  | 56        |

|                                                     |                                                   |    |

|-----------------------------------------------------|---------------------------------------------------|----|

| 4.3.2.                                              | Disponibilité des interfaces .....                | 57 |

| 4.3.3.                                              | Évaluation du problème interface/contrôle .....   | 58 |

| 4.4.                                                | Connexions module/module HW-HW .....              | 59 |

| 4.5.                                                | Connexions module/module HW/SW ou SW/HW .....     | 60 |

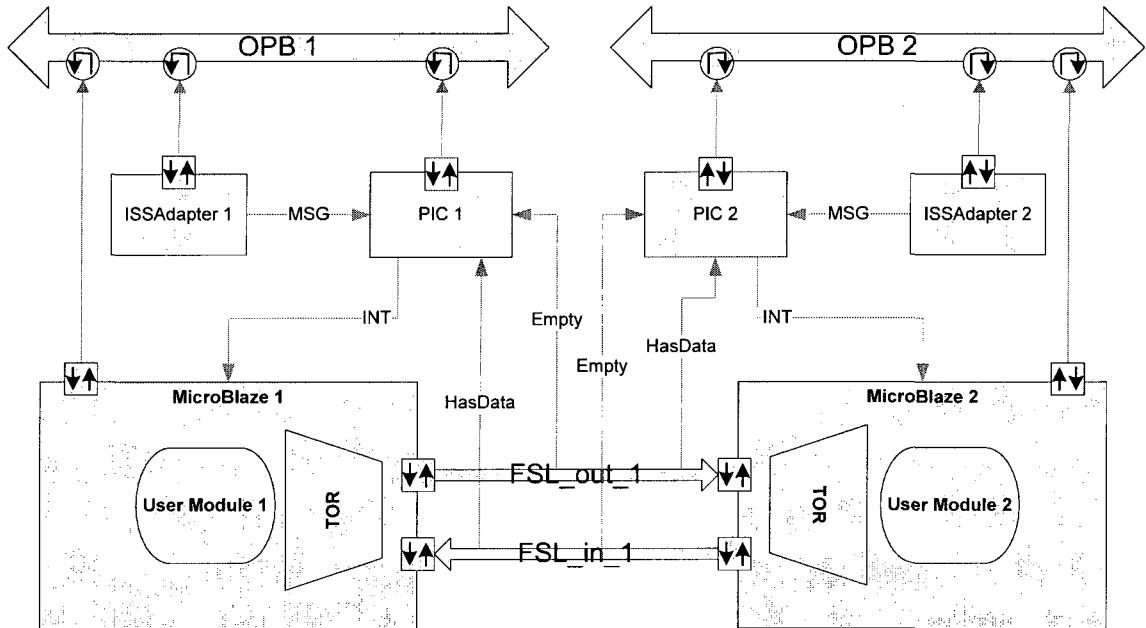

| 4.5.1.                                              | Cas du µBlaze .....                               | 60 |

| 4.5.2.                                              | Particularités du µBlaze .....                    | 63 |

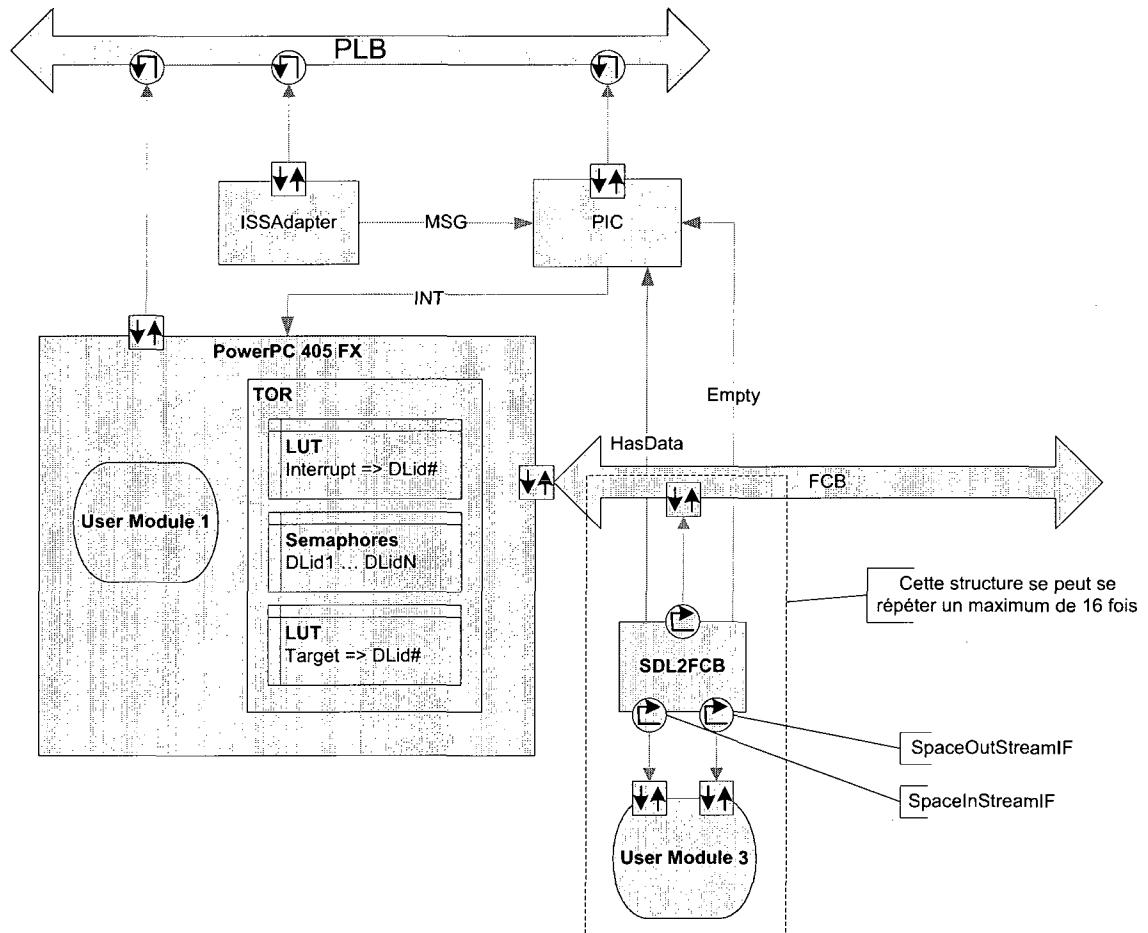

| 4.5.3.                                              | Cas du PowerPC405.....                            | 63 |

| 4.5.4.                                              | Particularités du PowerPC405.....                 | 66 |

| 4.6.                                                | Connexions module/module SW/SW .....              | 67 |

| 4.6.1.                                              | Architecture homogène µBlaze.....                 | 67 |

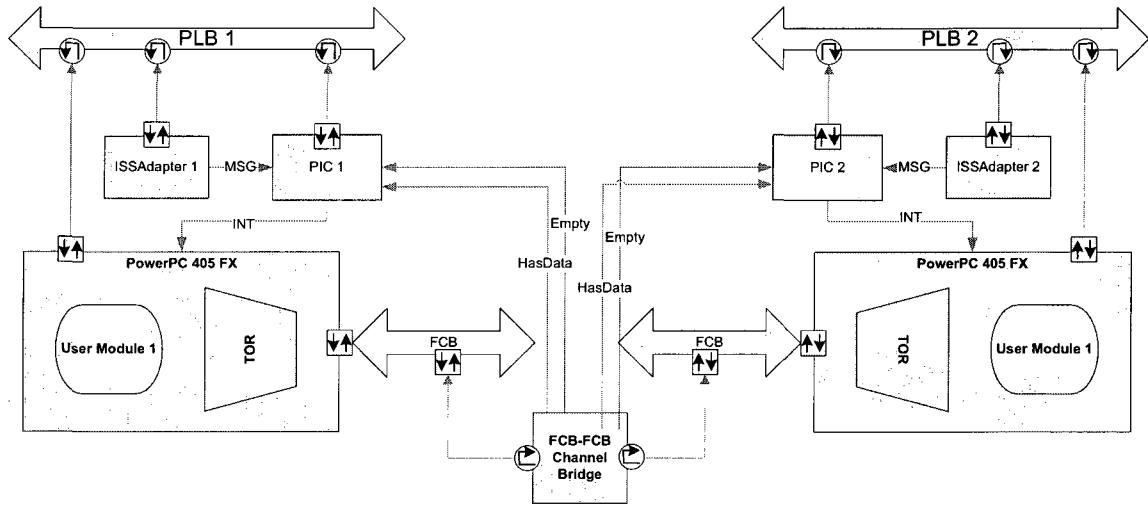

| 4.6.2.                                              | Architecture homogène PowerPC405 .....            | 68 |

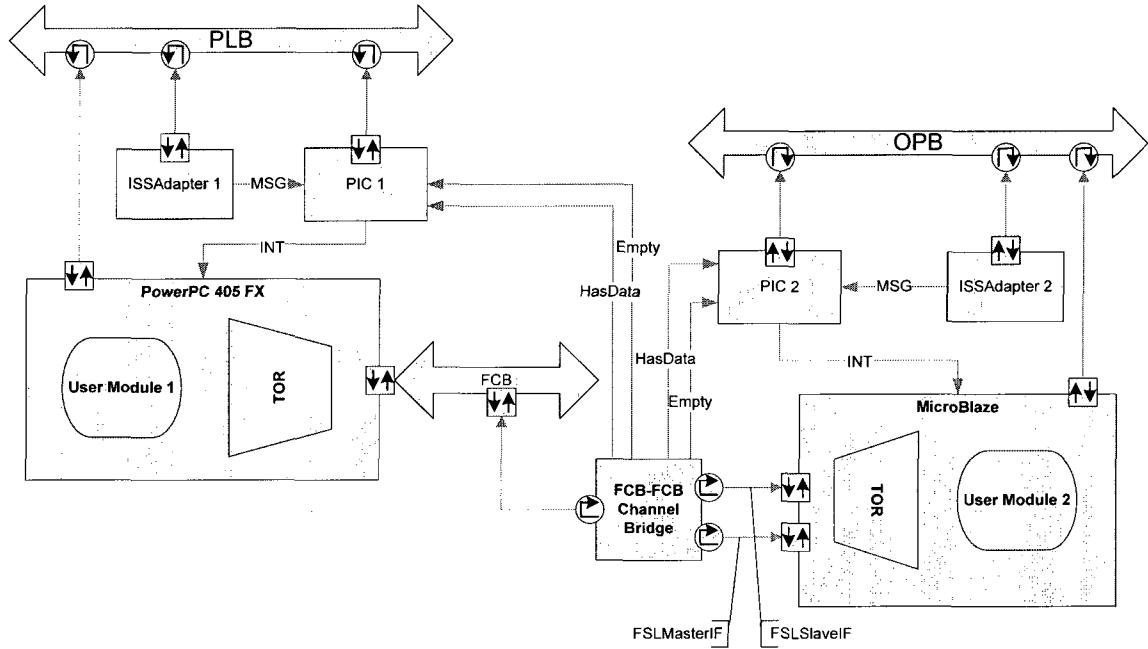

| 4.6.3.                                              | Architecture hétérogène µBlaze-PowerPC405 .....   | 69 |

| 4.7.                                                | Design des composants SpaceLib .....              | 70 |

| 4.7.1.                                              | Interfaces .....                                  | 70 |

| 4.7.2.                                              | SDLShiftRegister .....                            | 71 |

| 4.7.3.                                              | SDLToFSLAdapter .....                             | 72 |

| 4.7.4.                                              | SDLToFSBAdapter.....                              | 73 |

| 4.7.5.                                              | FCBFCBChannelBridge .....                         | 76 |

| 4.7.6.                                              | FCBFSLChannelBridge .....                         | 76 |

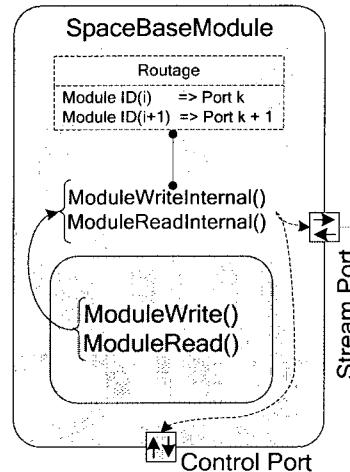

| 4.7.7.                                              | SpaceBaseModule .....                             | 76 |

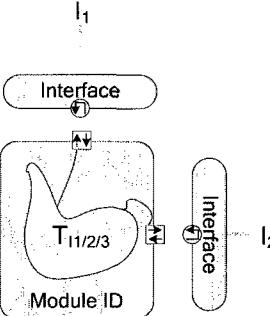

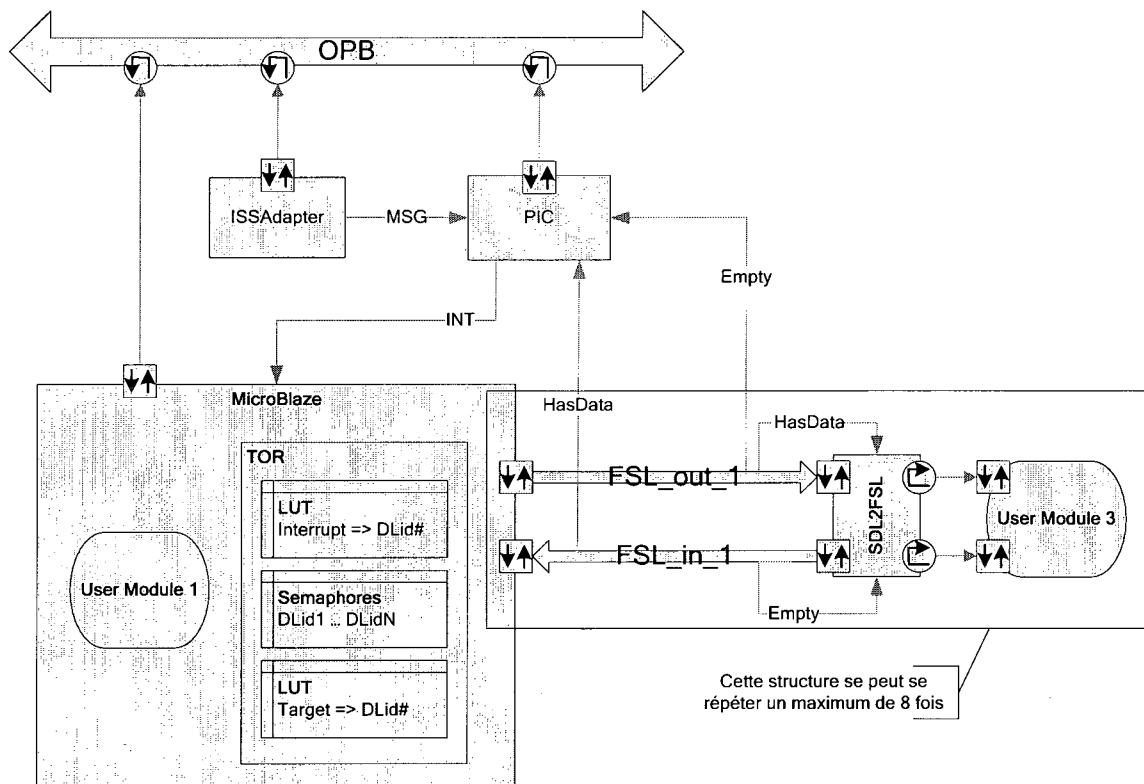

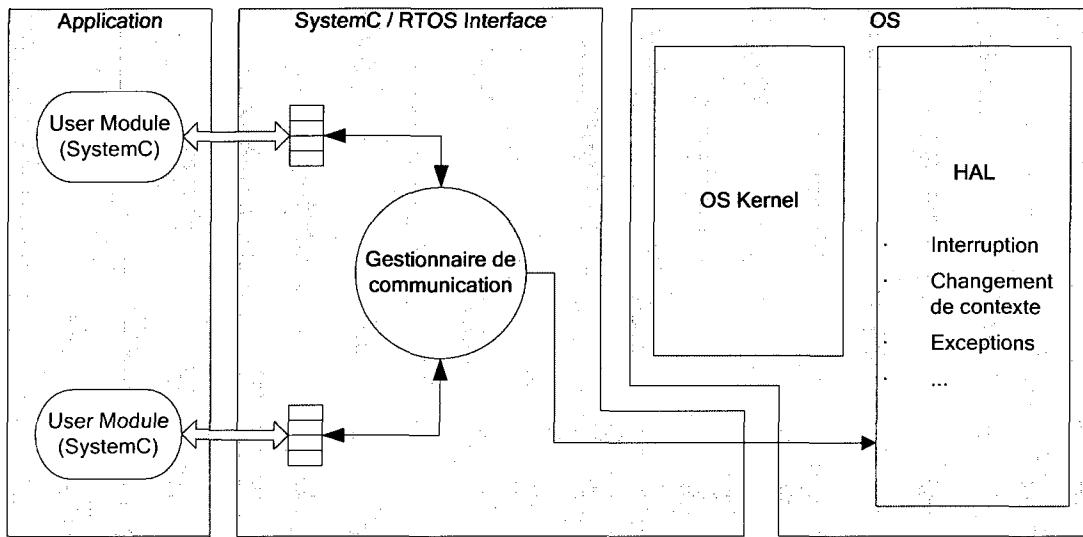

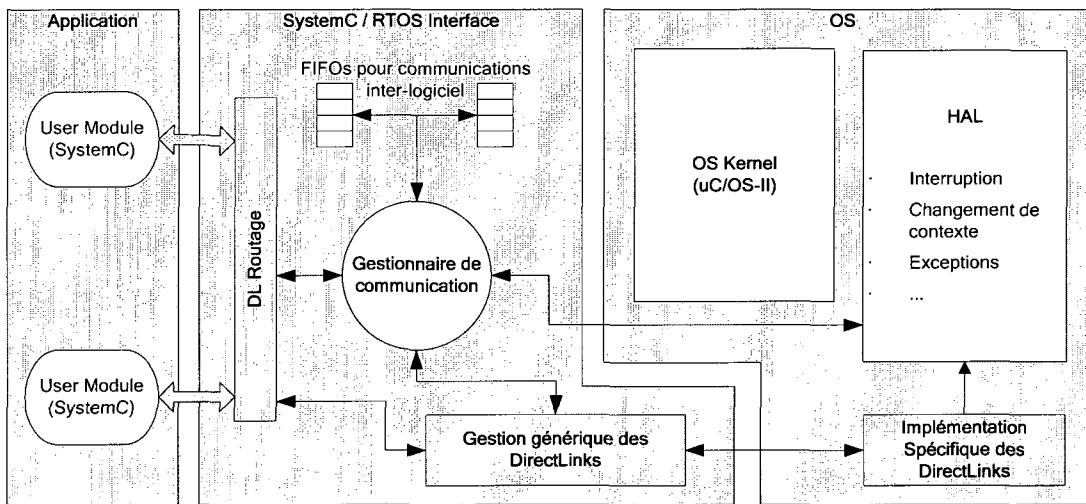

| 4.8.                                                | Implications au niveau de la pile logicielle..... | 78 |

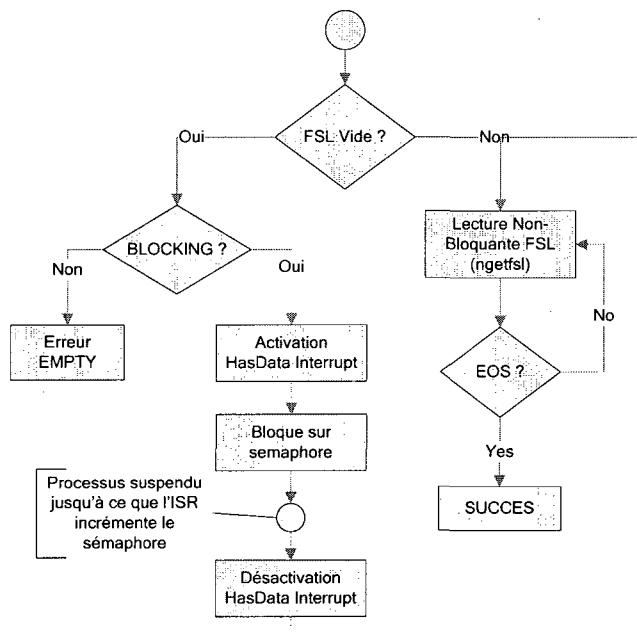

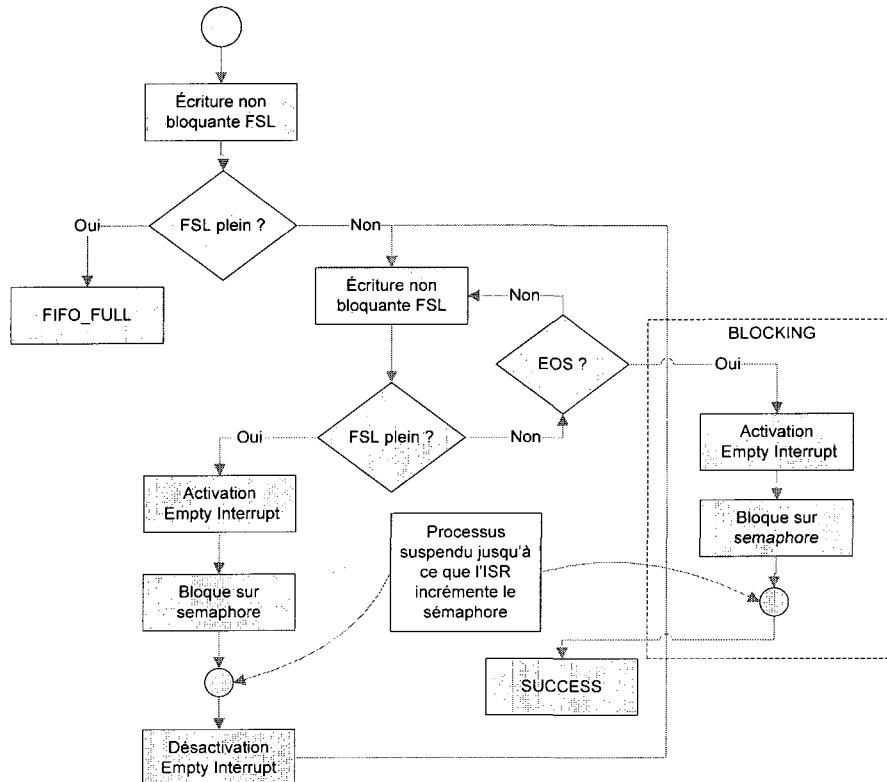

| 4.8.1.                                              | Protocoles µBlaze .....                           | 81 |

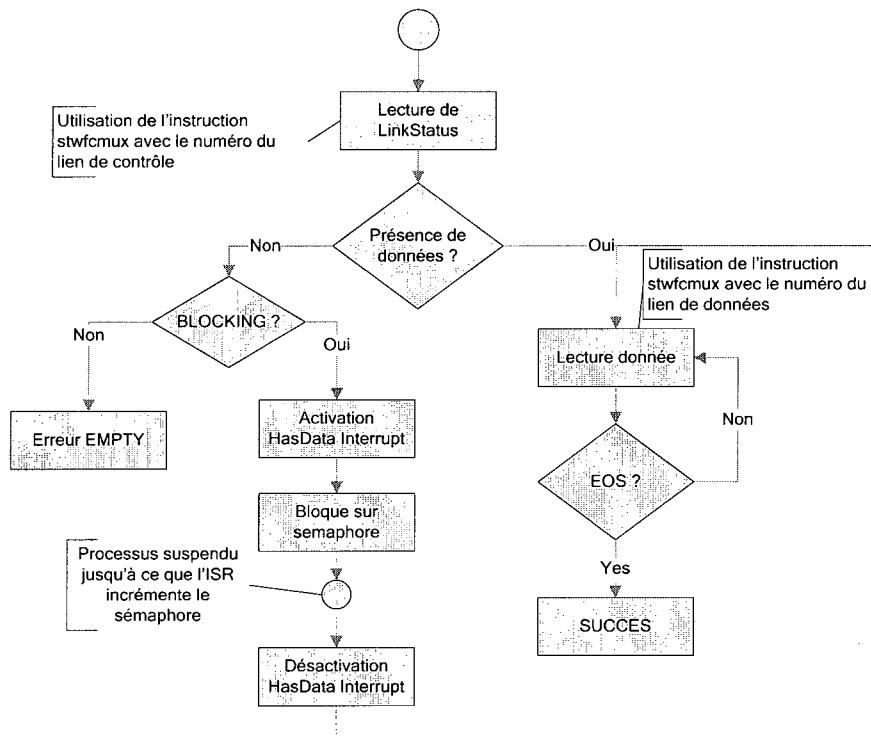

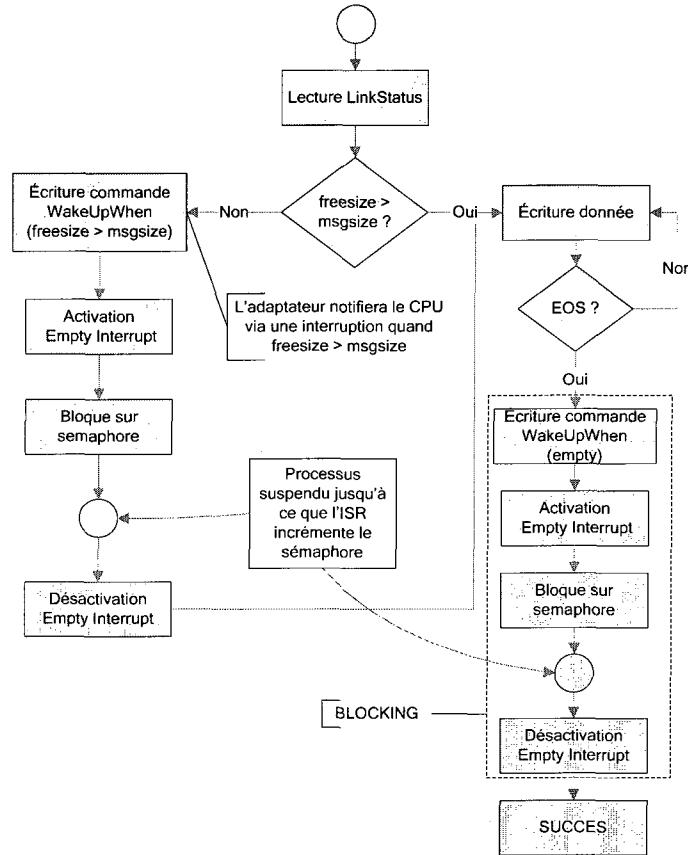

| 4.8.2.                                              | Protocoles PowerPC405.....                        | 83 |

| 4.9.                                                | Abstraction du DirectLink dans SPACE.....         | 86 |

| 4.9.1.                                              | Modélisation.....                                 | 86 |

| 4.9.2.                                              | Implémentation dans SpaceLib .....                | 88 |

| CHAPITRE 5 ANALYSE, PERFORMANCES ET DISCUSSION..... |                                                   | 90 |

| 5.1.                                                | Validation du paradigme DirectLink .....          | 90 |

| 5.2.                                                | Technique d'analyse des performances .....        | 93 |

|        |                                                                      |     |

|--------|----------------------------------------------------------------------|-----|

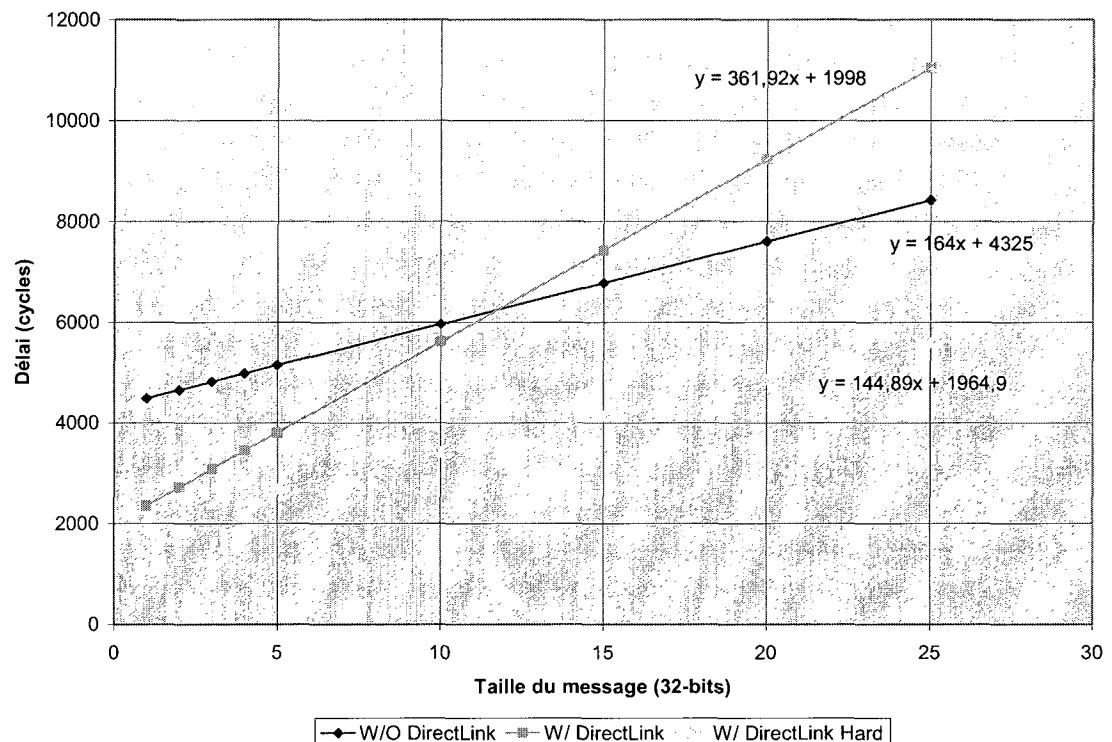

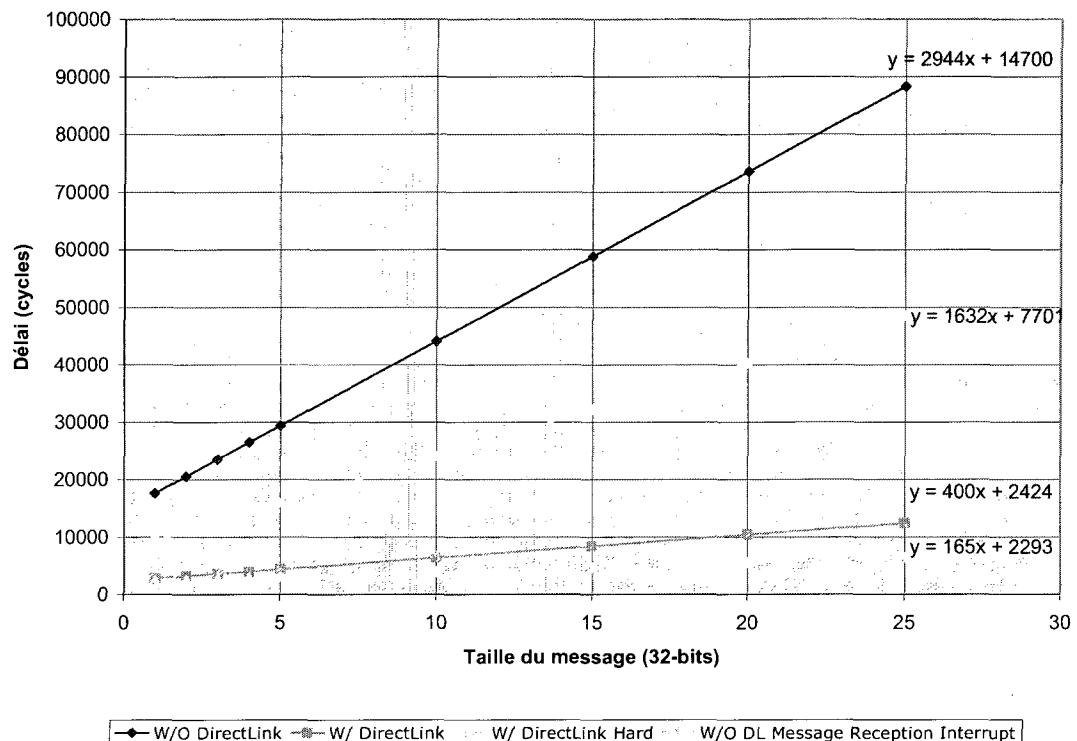

| 5.3.   | Performances du DirectLink .....                                     | 94  |

| 5.3.1. | Latences matérielles .....                                           | 95  |

| 5.3.2. | Latences logicielles .....                                           | 99  |

| 5.4.   | Impact sur l'utilisation des ressources matérielles.....             | 105 |

| 5.5.   | Accélération d'une application dans SPACE avec le DirectLink.....    | 108 |

| 5.6.   | Extensibilité du paradigme à d'autres plateformes .....              | 110 |

| 5.6.1. | Tensilica XTensa.....                                                | 110 |

| 5.6.2. | Altera NIOS-II .....                                                 | 111 |

| 5.7.   | Comparaison avec d'autres travaux .....                              | 112 |

| 5.8.   | Améliorations suggérées à l'architecture de communication SPACE..... | 114 |

|        | CONCLUSION ET TRAVAUX FUTURS .....                                   | 117 |

|        | RÉFÉRENCES .....                                                     | 120 |

|        | ANNEXES .....                                                        | 128 |

## LISTE DES FIGURES

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

| Figure 2.1 – Taxonomie des architectures communication pour SoC .....             | 10 |

| Figure 2.2 – Schéma de haut niveau d'un système GALS .....                        | 13 |

| Figure 2.3 – Interconnexion asynchrone de sous-systèmes uniprocesseur.....        | 14 |

| Figure 2.4 – Modèle d'application ImpulseC utilisant le paradigme CSP .....       | 21 |

| Figure 2.5 – Interface logicielle/matérielle unifiée.....                         | 23 |

| Figure 2.6 – Outil de génération des interfaces logicielles/matérielles .....     | 26 |

| Figure 2.7 – Extension du Xtensa pour communication par queue de données .....    | 27 |

| Figure 3.1 – Architecture simplifiée du PowerPC405 .....                          | 32 |

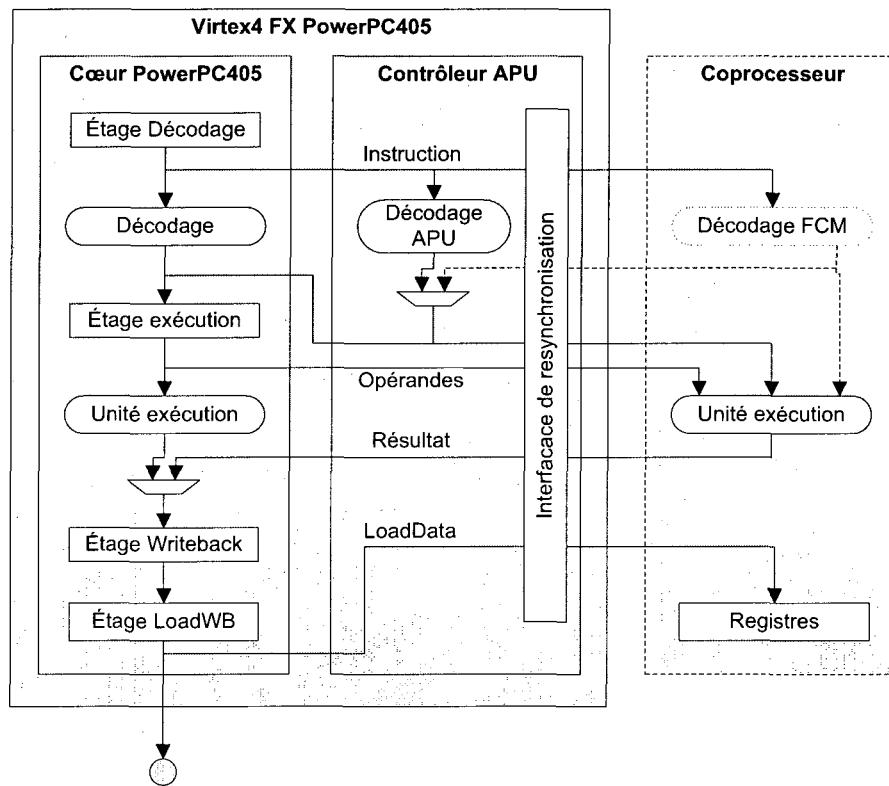

| Figure 3.2 – Relation entre le contrôleur APU et le pipeline du PowerPC405 .....  | 34 |

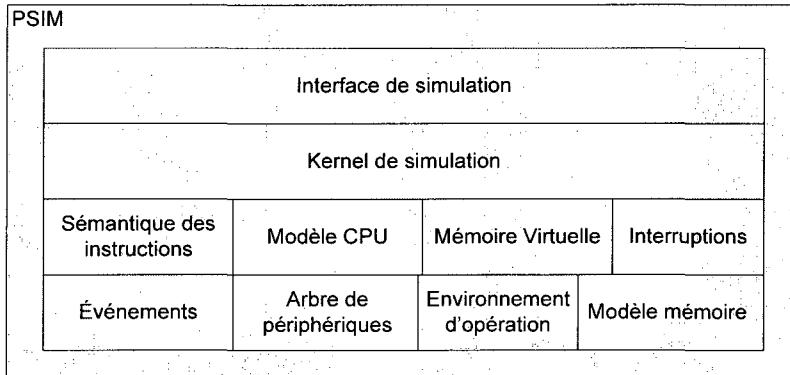

| Figure 3.3 – Schématisation de l'architecture de PSIM .....                       | 37 |

| Figure 3.4 – Exemple de sémantique d'instruction .....                            | 39 |

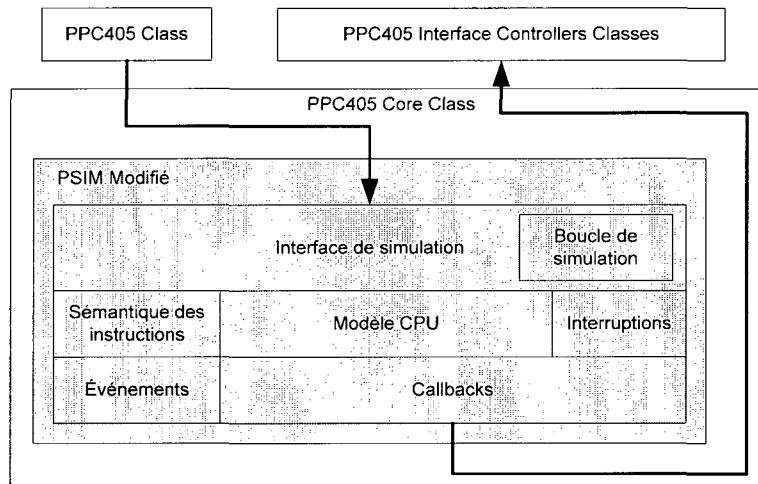

| Figure 3.5 – Schématisation de l'intégration de PSIM à SPACE.....                 | 42 |

| Figure 3.6 – Exemple de structure de callback .....                               | 43 |

| Figure 3.7 – Exemple de fonction de registration.....                             | 44 |

| Figure 3.8 – Exemple de fonction callback et utilisation.....                     | 44 |

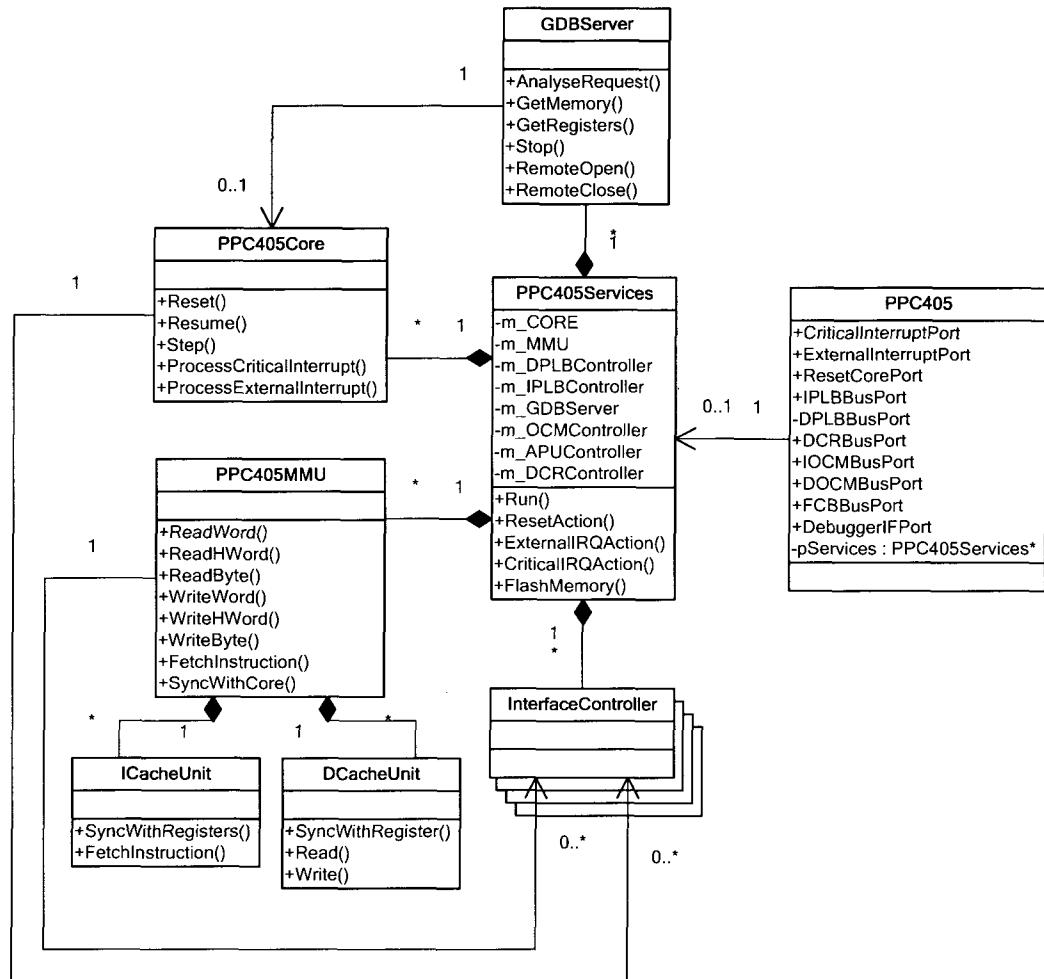

| Figure 3.9 – Diagramme de classe simplifié du PowerPC405.....                     | 46 |

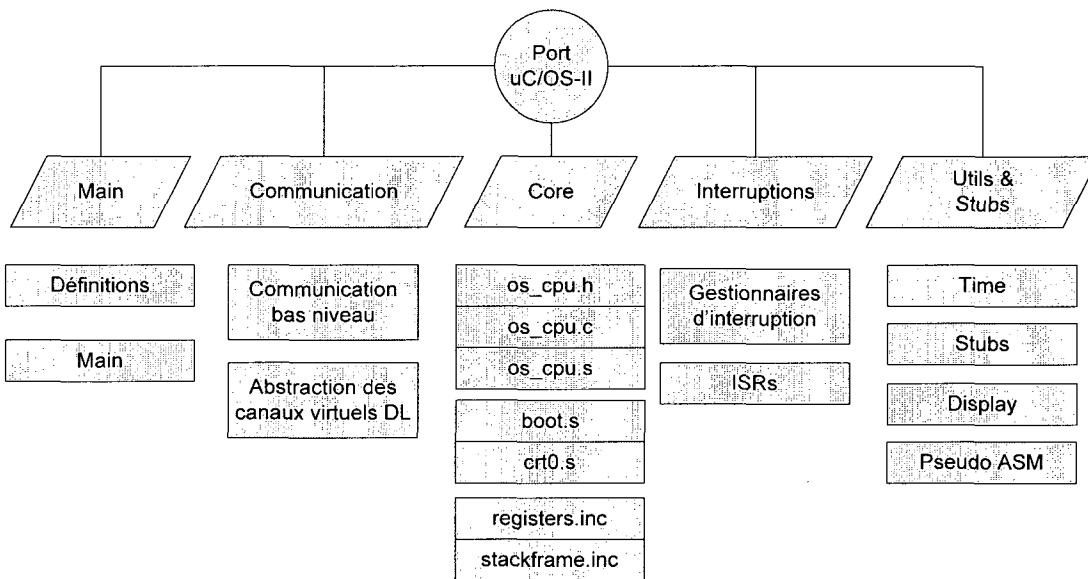

| Figure 3.10 – Structure du port d'µC/OS-II pour le PowerPC405 .....               | 47 |

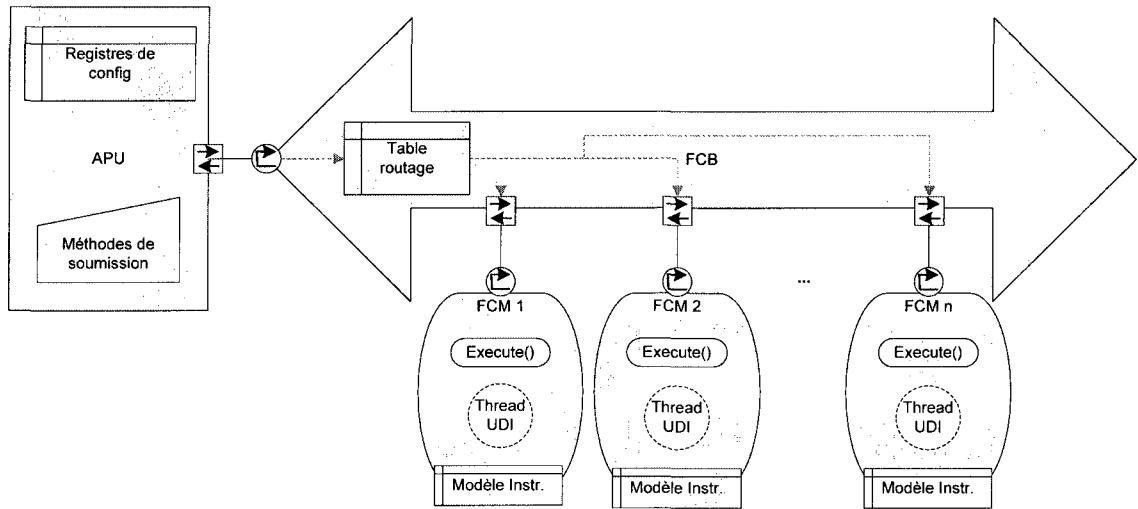

| Figure 3.11 – Architecture de l'APU et du FCB .....                               | 50 |

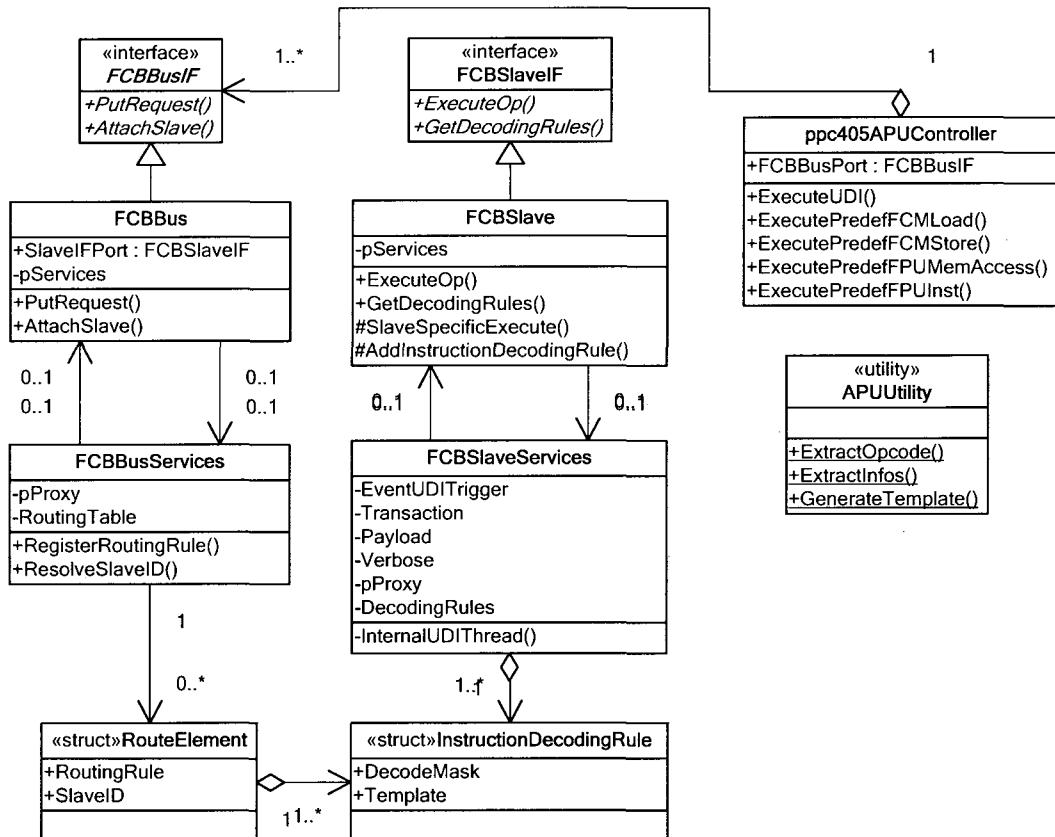

| Figure 3.12 – Diagramme de classe simplifié de l'APU .....                        | 51 |

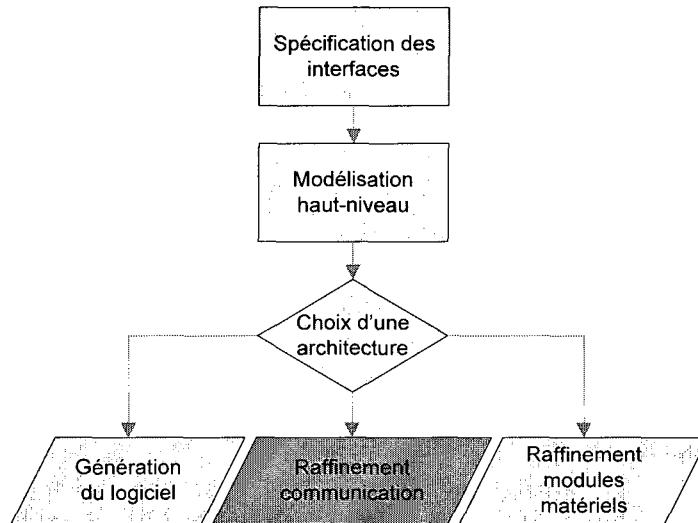

| Figure 4.1 – Méthodologie d'implémentation du DirectLink à une architecture cible | 55 |

| Figure 4.2 – Lien de contrôle et lien de données .....                            | 57 |

| Figure 4.3 – Exemple 1 : Lien direct SDL style pipeline .....                     | 57 |

| Figure 4.4 – Exemple 2 : Lien direct pour des échanges rapides inter modules..... | 58 |

| Figure 4.5 – Schématisation du raffinement DirectLink pour µBlaze.....            | 61 |

| Figure 4.6 – Schématisation du raffinement DirectLink pour PowerPC405 FX.....     | 64 |

| Figure 4.7 – Interconnexion de deux µBlaze par DirectLink .....                   | 68 |

| Figure 4.8 – Interconnexion de deux PowerPC405 par DirectLink.....                | 69 |

|                                                                              |     |

|------------------------------------------------------------------------------|-----|

| Figure 4.9 – Interconnexion d'un µBlaze et d'un PPC405 par DirectLink .....  | 70  |

| Figure 4.10 – Code des interfaces In/Out Stream .....                        | 71  |

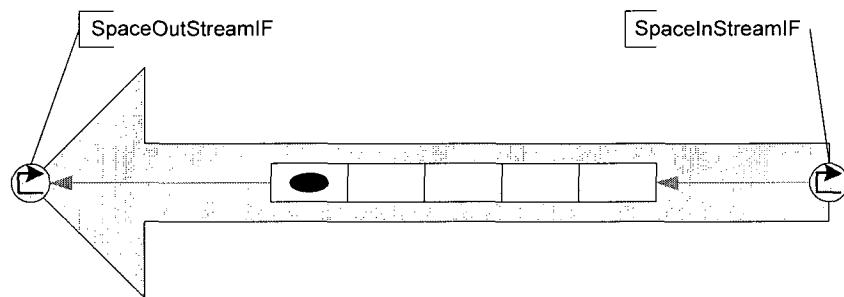

| Figure 4.11 – Architecture du SDLShiftRegister .....                         | 71  |

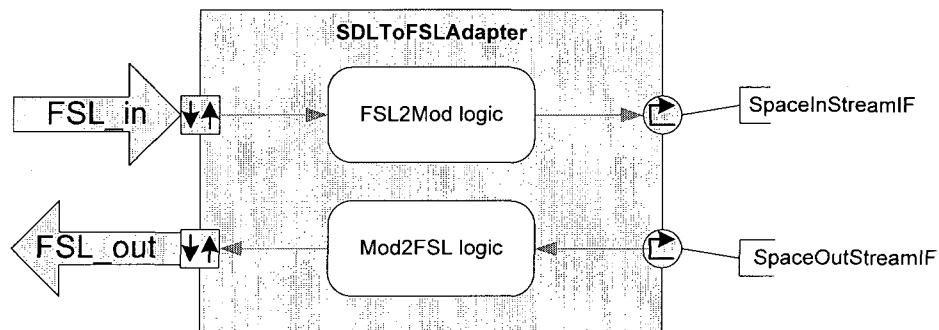

| Figure 4.12 – Architecture du composant SDLToFSLAdapter .....                | 72  |

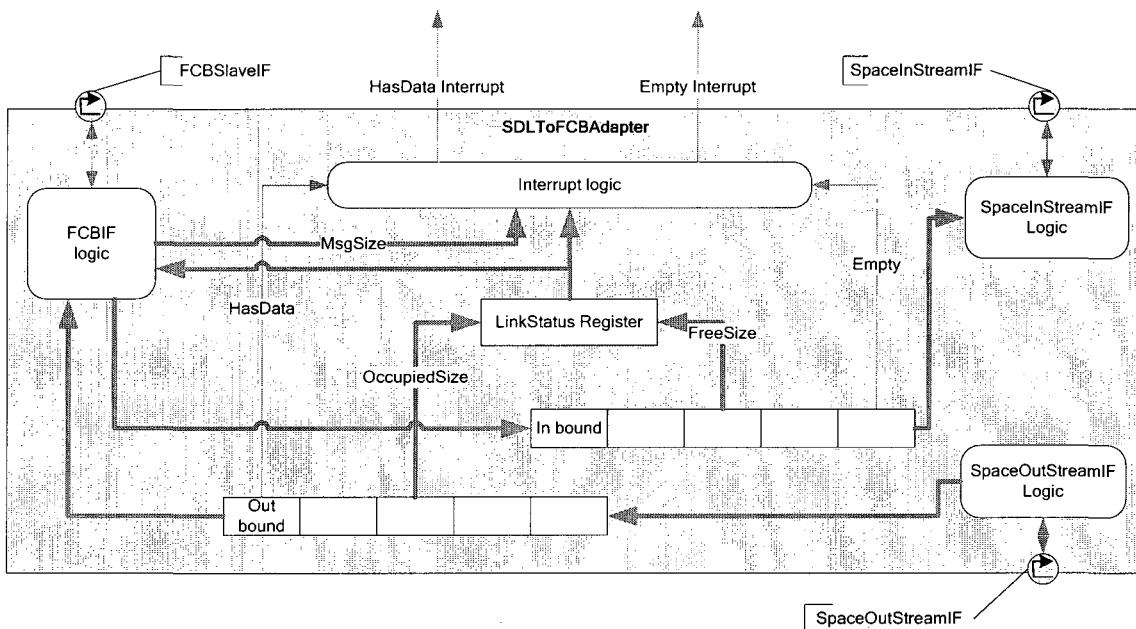

| Figure 4.13 – Architecture du composant SDLToFCBAdapter .....                | 73  |

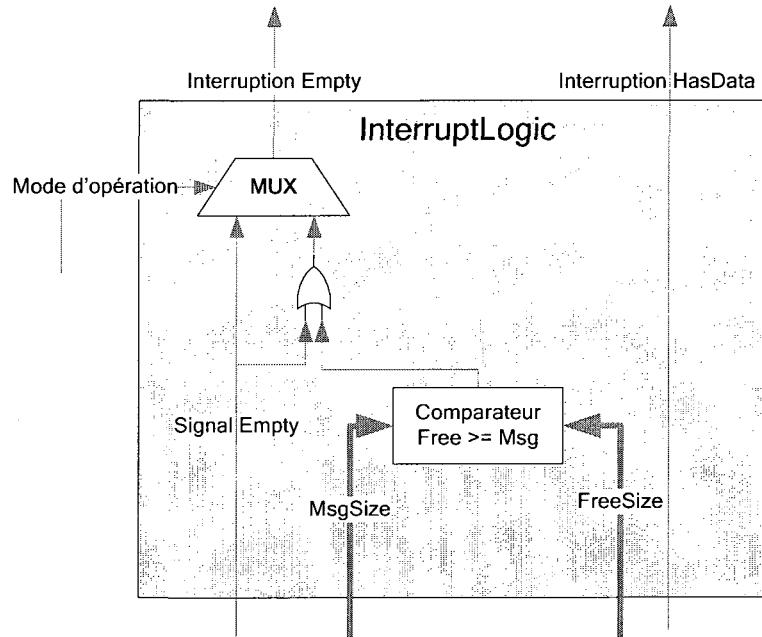

| Figure 4.14 – Logique d'interruption pour le composant SDLToFCB .....        | 74  |

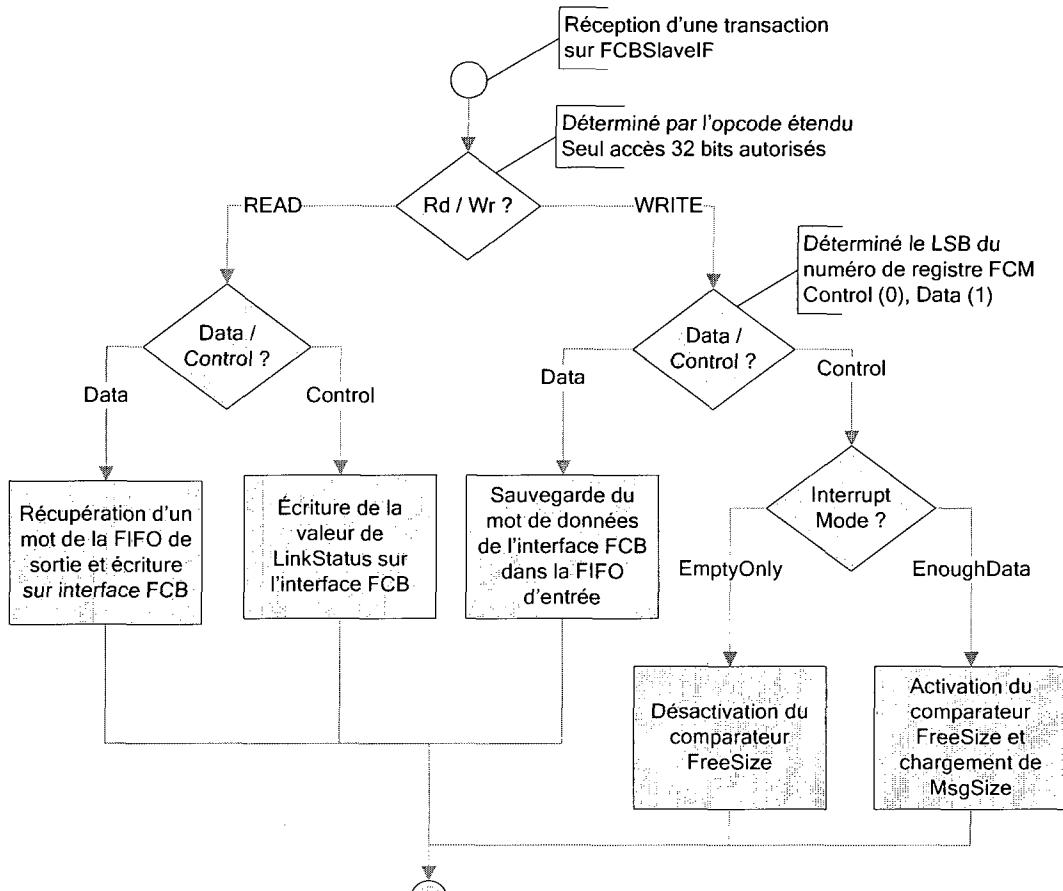

| Figure 4.15 – Arbre de décision du FCBIF logic .....                         | 75  |

| Figure 4.16 – SpaceBaseModule amélioré .....                                 | 77  |

| Figure 4.17 – Architecture logicielle SPACE pré-DirectLink .....             | 79  |

| Figure 4.18 – Architecture logicielle SPACE post-DirectLink .....            | 79  |

| Figure 4.19 – Diagramme de décision pour les lectures via FSL .....          | 81  |

| Figure 4.20 – Diagramme de décision pour les écritures via FSL .....         | 83  |

| Figure 4.21 – Diagramme de décision pour les lectures via FCB .....          | 84  |

| Figure 4.22 – Diagramme de décision pour les écritures via FCB .....         | 86  |

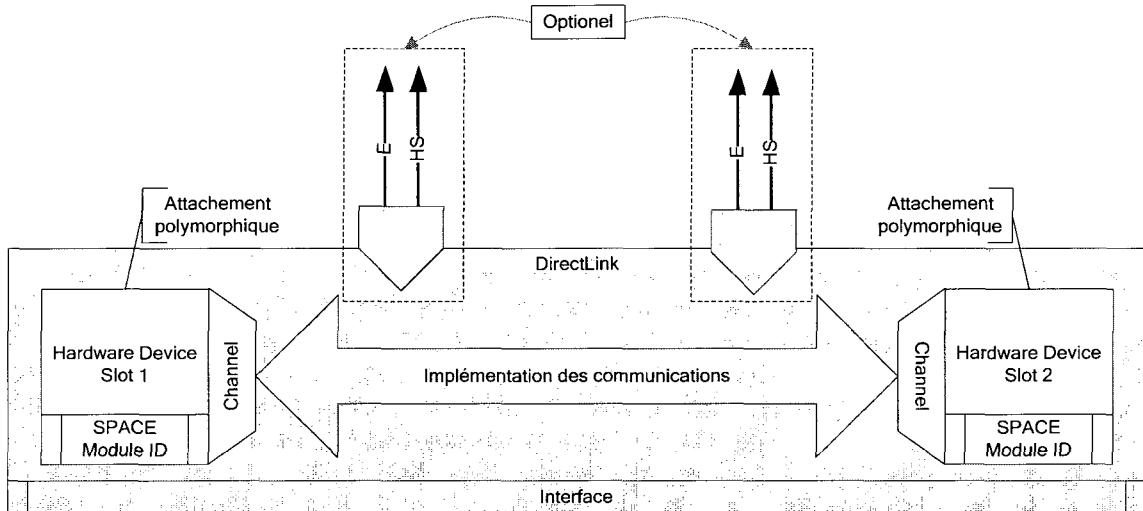

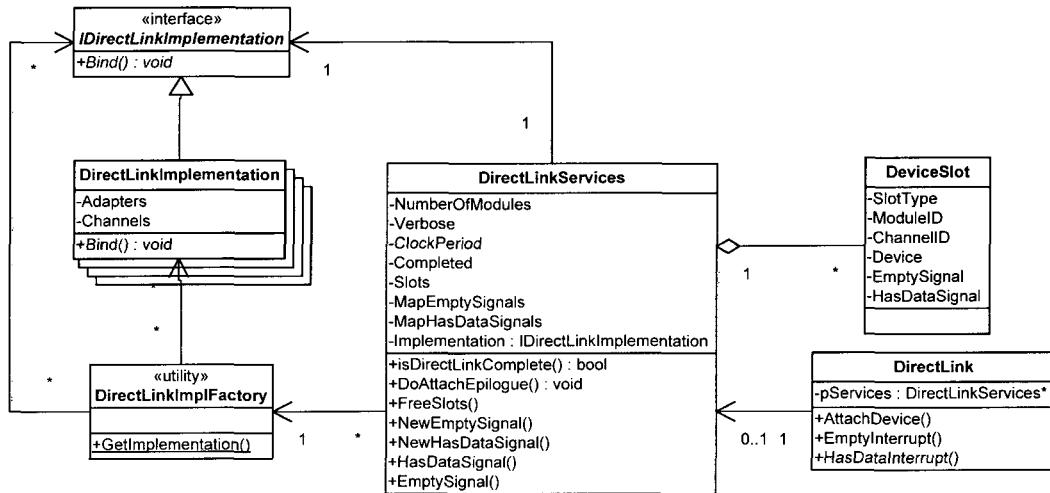

| Figure 4.23 – Schématisation de l'abstraction DirectLink .....               | 87  |

| Figure 4.24 – Diagramme de classe simplifié du DirectLink .....              | 89  |

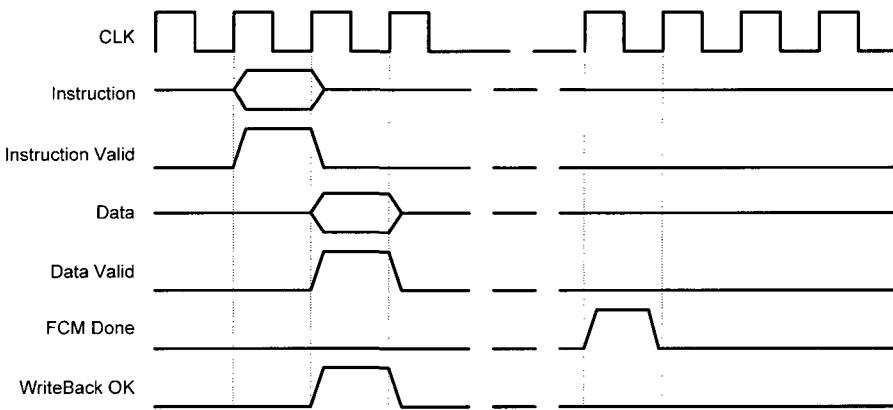

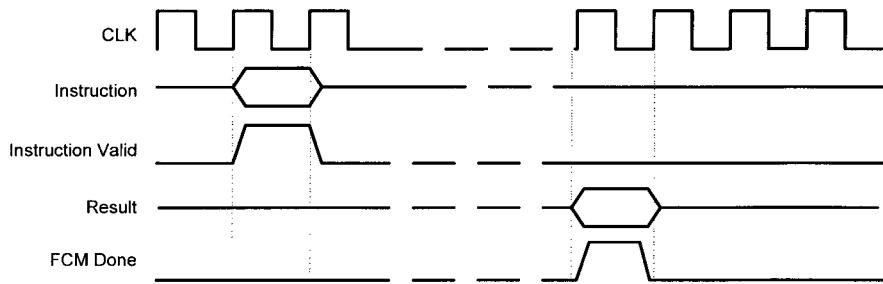

| Figure 5.1 – Chronogramme d'une instruction FCM Load 32 bits .....           | 97  |

| Figure 5.2 – Chronogramme d'une instruction FCM Store 32 bits .....          | 98  |

| Figure 5.3 – Implémentation du DirectLink pour Tensilica Xtensa .....        | 110 |

| Figure 5.4 – Illustration du problème d'atomicité des transferts SPACE ..... | 114 |

| Figure 5.5 – Résolution du problème d'atomicité des transferts .....         | 116 |

## LISTE DES TABLEAUX

|                                                                                                                                                          |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 1.1 – Marché des systèmes embarqués jusqu'en 2009 (Millions de \$) .....                                                                         | 2   |

| Tableau 2.1 – Paramètres des primitives de communication .....                                                                                           | 16  |

| Tableau 2.2 – Exemples de conversions d'appels SystemC en appels µC/OS-II .....                                                                          | 19  |

| Tableau 2.3 – Structure d'une adresse dans SPACE.....                                                                                                    | 20  |

| Tableau 3.1 – Instructions ajoutées à PSIM .....                                                                                                         | 39  |

| Tableau 3.2 – Modifications au vecteur d'interruption.....                                                                                               | 40  |

| Tableau 4.1 – Comparaison des méthodes de contrôle des interfaces .....                                                                                  | 59  |

| Tableau 4.2 – Format des instructions prédéfinis STWFCMUX et LWFCMUX.....                                                                                | 66  |

| Tableau 5.1 – Augmentation de la bande passante utile selon l'interface DirectLink et<br>l'opération effectuée .....                                     | 99  |

| Tableau 5.2 – Temps d'exécution pour écriture sur µBlaze .....                                                                                           | 101 |

| Tableau 5.3 – Temps d'exécution pour écriture sur PowerPC405 .....                                                                                       | 102 |

| Tableau 5.4 – Temps d'exécution pour lecture sur µBlaze.....                                                                                             | 103 |

| Tableau 5.5 – Temps d'exécution pour lecture sur PowerPC405 .....                                                                                        | 104 |

| Tableau 5.6 – Utilisation des ressources matérielles par un lien FSL (VIRTEX-2 Pro<br>VP30).....                                                         | 106 |

| Tableau 5.7 – Utilisation des ressources matérielles par un adaptateur de module<br>(VIRTEX-2 Pro VP30).....                                             | 106 |

| Tableau 5.8 – Utilisation des ressources matérielles par un adaptateur de module en<br>fonction du nombre de FIFO de réception (VIRTEX-2 Pro VP30) ..... | 107 |

| Tableau 5.9 – Accélération d'une application JPEG avec DirectLink sur µBlaze .....                                                                       | 109 |

## LISTE DES ACRONYMES

|      |                                           |

|------|-------------------------------------------|

| AMBA | Advanced Microcontroller Bus Architecture |

| API  | Application Programming Interface         |

| APU  | Auxiliary Processor Unit                  |

| ASIC | Application Specific Integrated Circuit   |

| BA   | Bit Accurate                              |

| BCA  | Bus Cycle Accurate                        |

| BRAM | Block RAM                                 |

| CPLD | Complex Programmable Logic Device         |

| DMA  | Direct Memory Access                      |

| DCR  | Device Control Register                   |

| EIC  | External Interrupt Controller             |

| ESL  | Electronic System Level                   |

| FCB  | Fabric Coprocessor Bus                    |

| FCM  | Fabric Coprocessor Module                 |

| FIFO | First-In First-Out                        |

| FIT  | Fixed Interval Timer                      |

| FPGA | Field Programmable Gate Array             |

| FPU  | Floating Point Unit                       |

| FSL  | Fast Serial Link                          |

| GALS | Globally Asynchronous Locally Synchronous |

| GDB  | GNU Debugger                              |

| HAL  | Hardware Abstraction Layer                |

| HDL  | Hardware Description Language             |

| ISA  | Instruction Set Architecture              |

| ISR  | Interrupt Service Routine                 |

|       |                                                          |

|-------|----------------------------------------------------------|

| ISS   | Instruction Set Simulator                                |

| MMU   | Memory Management Unit                                   |

| MPSoC | Multi-Processor System-on-Chip                           |

| OCM   | On-Chip Memory                                           |

| OEA   | Operating Environment Architecture                       |

| OPB   | On-chip Peripheral Bus                                   |

| PIC   | Programmable Interrupt Controller                        |

| PIT   | Programmable Interval Timer                              |

| PLB   | Processor Local Bus                                      |

| PPC   | PowerPC                                                  |

| RAM   | Random Access Memory                                     |

| RTL   | Register Transfer Level                                  |

| RTOS  | Real Time Operating System                               |

| SDL   | Space Direct Link                                        |

| SISDL | Space In-Stream Direct Link                              |

| SOSDL | Space Out-Stream Direct Link                             |

| SPACE | SystemC Partitioning Aspects of Codesign and Exploration |

| SoC   | System-on-chip                                           |

| TLB   | Translation Look-aside Buffer                            |

| TLM   | Transaction-Level Modeling                               |

| TF    | Timed Functional                                         |

| UART  | Universal Asynchronous Receiver/Transmitter              |

| UDI   | User-Defined Instruction                                 |

| UEA   | User Environment Architecture                            |

| UTF   | Un-Timed Functional                                      |

| VEA   | Virtual Environment Architecture                         |

## **LISTE DES ANNEXES**

|                                                                  |     |

|------------------------------------------------------------------|-----|

| ANNEXE A : MPSOC : DÉFINITION, PROBLÉMATIQUE ET CONCEPTION ..... | 128 |

| ANNEXE B : SYSTEMC : LANGAGE DE DESIGN AU NIVEAU SYSTÈME.....    | 134 |

| ANNEXE C : ISS : OUTIL DE COSIMULATION .....                     | 137 |

| ANNEXE D : SPACE : UNE PLATEFORME DE DÉVELOPPEMENT ESL .....     | 140 |

| ANNEXE E : LE PROCESSEUR : BLOC DE BASE DE LA CONCEPTION .....   | 144 |

| ANNEXE F : LA PILE LOGICIELLE.....                               | 146 |

| ANNEXE G : LATENCES LOGICIELLES AVEC DIRECTLINK.....             | 148 |

# CHAPITRE 1

## INTRODUCTION

Cette section introduit le concept de systèmes sur puce (SoC), élément central de ce mémoire. Elle traite de maints aspects de leur conception, des méthodes de design et des architectures de communications utilisées.

### 1.1. Les systèmes embarqués modernes

Les systèmes embarqués sont de nos jours rendus omniprésents. L'environnement technologique dans lequel l'homme moderne baigne en est submergé. Leurs domaines applicatifs sont extrêmement variés, allant de l'appareil d'usage quotidien – téléphone cellulaire, montre digitale, four micro-onde – jusqu'aux gadgets technologiques et moyens de transports – iPod, système GPS, anti-patinage sur les voitures de luxe.

Considérant cela, il n'est pas surprenant d'apprendre que moins de 2% des 9 milliards de microprocesseurs et microcontrôleurs fabriqués en 2005 fassent partie des ordinateurs personnels et des stations de travail. Les systèmes embarqués ont utilisés les 8.8 autres milliards [1]. L'architecture d'un système embarqué peut varier du simple microcontrôleur exécutant son code d'une ROM jusqu'aux microprocesseurs roulant de complexes tâches en temps réel. Les variantes sont aussi nombreuses que sont les problèmes qu'elles ciblent.

Il ne serait pas faux d'affirmer que pratiquement tous les appareils électroniques actuellement produits sont des systèmes embarqués et que tous et chacun les utilisent dans son quotidien. En 2002, on estimait qu'une voiture contenait entre 40 et 50 microprocesseurs embarqués [2].

Comme la pression du marché continue de pousser le développement à des niveaux d'intégration de plus en plus élevés tout en tentant de réduire les coûts de productions, la taille des circuits et la consommation de puissance, l'innovation devient primordiale. Le Tableau 1.1 montre la croissance des marché et les prévisions jusqu'en 2009 [3]. Pour accommoder la croissance exponentielle de la demande pour des circuits de plus en plus gros, les concepteurs ont sans cesse poussé les limites des contraintes de la technologie et du design. Les systèmes embarqués sont le résultat de ce processus.

**Tableau 1.1 – Marché des systèmes embarqués jusqu'en 2009 (Millions de \$)**

|                             | 2003   | 2004   | 2009   | AAGR% <sup>†</sup> |

|-----------------------------|--------|--------|--------|--------------------|

| Logiciels embarqués         | 1 401  | 1 641  | 3 448  | 16.0               |

| Circuits intégrés embarqués | 34 681 | 40 539 | 78 746 | 14.2               |

| Cartes embarquées           | 3 401  | 3 693  | 5 950  | 10.0               |

| Total                       | 39 483 | 45 873 | 88 144 | 14.0               |

<sup>†</sup>Taux de croissance annuel moyen (Average Annual Growth Rate)

Comme mentionné précédemment, poussés par la demande, ces systèmes deviennent de plus en plus complexes. La technologie disponible permet l'accroissement de cette complexité car la quantité de transistors sur une puce suit une progression géométrique, doublant à tous les 18 mois selon la loi de Moore.

## 1.2. Problématique

La conception de systèmes embarqués devient une tâche de plus en plus ardue et les ingénieurs doivent résoudre d'imposants problèmes. Poussée par la forte pression du marché et la part toujours grandissante du contenu logiciel des architectures, la complexité des systèmes croît à chaque nouvelle génération. Ceci met à rude épreuve l'ingéniosité des concepteurs qui doivent souvent se battre avec des outils de design n'offrant pas des méthodologies à la productivité adéquate pour la tâche à réaliser.

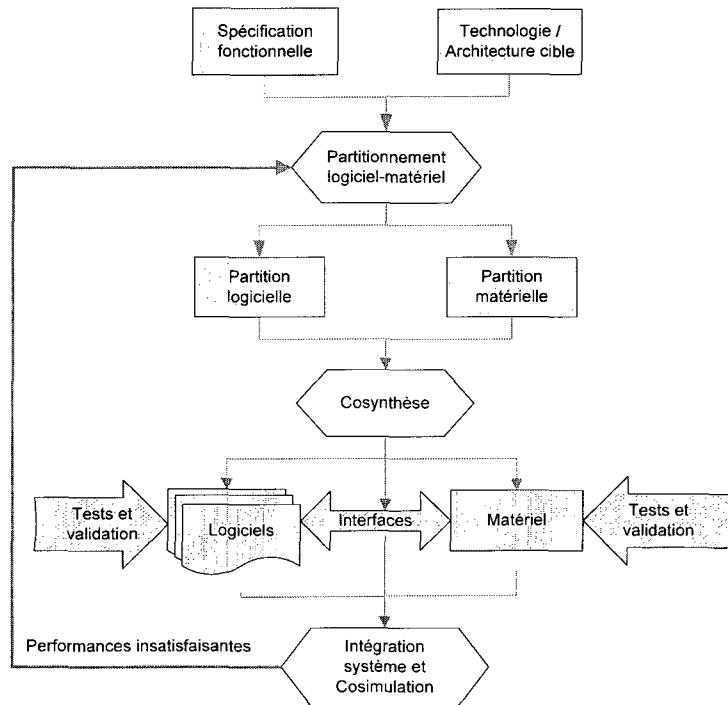

Un problème important des systèmes embarqués est celui de l'exploration architecturale et plus particulièrement celui du partitionnement matériel-logiciel qui vise la

décomposition d'une spécification au niveau transactionnel. Le résultat du processus est une partition. Le but principal du concepteur d'un système est de trouver la partition qui requiert le moins de matériel pour rencontrer les critères de performance. Un aspect important de l'exploration architecturale et du partitionnement est le système de communication qui affecte grandement les performances d'un système donné.

Il est aujourd'hui devenu essentiel d'offrir aux concepteurs des outils qui accélèrent et facilitent la conception de tels systèmes embarqués, surtout dans le contexte très complexe des systèmes multiprocesseurs hétérogènes sur puces. Les environnements de développements actuels parviennent avec beaucoup de difficultés à offrir des solutions acceptables à ces obstacles.

La conception à bas niveau d'abstraction, tant sur le plan logiciel que matériel, demande trop de temps et d'efforts. Avoir à prendre en compte tous les détails d'implémentation d'une application C comportant plusieurs dizaines de milliers de lignes de code en même temps que la conception au niveau RTL d'une architecture matérielle pouvant contenir des millions de transistors devient un obstacle grandissant.

Les processus de conception doivent donc abstraire l'implémentation finale lors de la spécification et la conception du système. Les dépendances vers les détails de bas niveau doivent être éliminées ou réduites au maximum tout en laissant au concepteur un degré de liberté acceptable. De plus, la validation de cette spécification et de cette conception doit pouvoir commencer à être faite dès le début du processus en fournissant au concepteur des méthodologies et des abstractions qui fonctionneront correctement lors du raffinement à bas niveau.

De plus, du moment où la quantité de composants d'un MPSoC augmente, la largeur de bande de l'architecture de communication devient un facteur fondamental à considérer pour les performances globales. Il en résulte un besoin d'architectures de

communication à haut débit et extensibles. Cependant, la tendance de progression technologique indique que la performance et la consommation d'énergie des réseaux d'interconnexion se dégradent rapidement par rapport aux composants logiques [4]. Ceci résulte en un écart de performance significatif entre les réseaux de communication et la logique qui continuera à s'agrandir même en la présence de nouveaux modèles ou d'optimisations agressives desdits réseaux de communication..

L'environnement d'exploration architecturale et de conception SPACE [5], se basant sur la bibliothèque de classes SystemC, a pour but à résoudre ces nombreux problèmes. Il permet une abstraction complète des détails d'implémentation des systèmes-sur-puce lors des phases de design tout en réduisant les temps de conception et de validation. De plus, il facilite l'optimisation des performances.

### **1.3. Objectif**

Le principal objectif de ce travail consiste à augmenter les fonctionnalités de la plateforme de conception SPACE en développant de nouveaux mécanismes de communications point-à-point propices aux architectures multiprocesseurs hétérogènes. Ces nouveaux mécanismes doivent tirer avantage de la présence de canaux de communication dédiés sur les processeurs embarqués ou la possibilité de configurer ces processeurs et se présenter sous la forme d'une abstraction complète des implémentations possibles.

Le paradigme choisi doit étendre les services de communication existants qui se basent sur la transmission de messages et aider à améliorer les performances de l'architecture de communication tout en restant générique et indépendant de la plateforme matérielle choisie. Le mécanisme doit être configurable afin d'offrir une certaine liberté de conception et offrir un compromis entre flexibilité et performances.

Afin de respecter la philosophie de SPACE, le lien point-à-point doit être offert pour des modules pré-partitionnés en matériel et en logiciel. Un lien direct point-à-point peut être aisément visualisé en matériel, mais ce n'est pas le cas pour un lien matériel/logiciel ou logiciel/logiciel multiprocesseur, pour lequel il faut prendre en compte les spécificités du processeur.

Toutes les prémisses de SPACE doivent être respectées, notamment concilier la souplesse du concept de glisser-déposer des modules dans SPACE aux caractéristiques d'une communication point-à-point.

#### 1.4. Méthodologie

La réalisation de ces objectifs passe par maintes étapes :

1. Pour débuter, une familiarisation avec la librairie **SystemC** et l'environnement **SPACE** est nécessaire. Le concept du **TLM**, i.e. la modélisation au niveau système et transactionnelle, doit aussi être approfondi car c'est sur lui que repose la méthodologie de SPACE.

2. Par la suite sera définie une plateforme au niveau TLM qui peut recevoir un ou plusieurs processeurs configurables de types différents. L'environnement SPACE sera donc consolidé autour de l'architecture de communication CoreConnect d'IBM. La création et l'ajout d'un simulateur d'instruction du processeur configurable PowerPC405 FX sera l'étape logique subséquente afin d'avoir un environnement de conception complet couvrant l'ensemble des technologies disponibles par Xilinx. Cette plateforme permettra de prouver que le paradigme du lien point-à-point à haut niveau est valide et applicable sur différentes technologies.

3. Viendra ensuite la conception de l'interface de programmation à travers laquelle le nouveau mécanisme de communication sera disponible. Tel que requis par

SPACE, cette interface développée avec SystemC devra être utilisable à la fois par les tâches logicielles et matérielles.

4. L'étape subséquente consistera à développer des composants architecturaux nécessaires à l'implantation du nouveau mécanisme utilisant les différentes technologies disponibles sous la plateforme de simulation (actuellement les FPGA de Xilinx). Ces blocs matériels seront conçus au niveau transactionnel tout en gardant en tête que des versions synthétisables, décrites en VHDL, doivent être réalisables. La couche logicielle d'abstraction du matériel des différents processeurs sera modifiée pour tenir compte du nouveau mécanisme de communication point-à-point.

5. Une classe basée sur le patron de conception *Abstract Factory* sera ensuite développée afin de générer l'implantation du lien de communication point-à-point selon les blocs matériels ou logiciels qui y sont attachés. Cette classe abstraira le nouveau mécanisme peut importe la technologie utilisée et cachera la complexité de l'implémentation. Elle représentera un nouveau paradigme de communication dans SPACE peut importe le niveau d'abstraction du modèle.

## 1.5. Contributions

Ce travail a offert trois principales contributions :

1. D'abord, ce travail a permis une exploration de la littérature scientifique sur les méthodes de conception d'architectures de communication développées pour les systèmes multiprocesseurs sur puce, dans le contexte d'utilisation de processeurs configurables et extensibles.

2. Une nouvelle interface de programmation est désormais disponible dans l'environnement SPACE afin d'établir des communications point-à-point entre les différents modules logiciel et matériel dans une architecture multiprocesseur hétérogène. Un modèle d'abstraction de ces liens point-à-point est disponible

pour cacher les différentes implémentations possibles selon les technologies offertes dans SPACE. Ce modèle est générique et extensible à toute nouvelle technologie qui pourrait être introduite dans SPACE. Ces nouveaux mécanismes permettent d'améliorer l'utilisation de la bande passante disponible et d'accélérer les performances des applications.

3. De plus, la plateforme CoreConnect d'IBM est entièrement intégrée et consolidée dans l'environnement SPACE, augmentant ses capacités, son potentiel commercial et permettant de nouvelles possibilités lors de la conception de systèmes multiprocesseurs hétérogènes. Avec l'introduction dans SPACE d'un simulateur d'instruction du PowerPC405, la porte est ouverte pour des travaux futurs sur la modélisation et l'analyse de plateformes hétérogènes.

## 1.6. Organisation du mémoire

Ce mémoire est constitué de **cinq chapitres**. Le présent chapitre est une introduction aux systèmes embarqués ainsi qu'à la méthodologie et les objectifs de recherche. Le **deuxième chapitre** est une revue des différentes architectures de communication et des techniques utilisées pour déterminer l'architecture appropriée pour une plateforme multiprocesseur. Le **chapitre 3** constitue une description de l'intégration et de la consolidation d'une plateforme multiprocesseur hétérogène extensible dans un environnement de codesign logiciel/matériel. Le **chapitre 4** présente les objectifs et la conception du paradigme du DirectLink au niveau système dans la plateforme SPACE ainsi que les mécanismes utilisés dans les différentes technologies offertes dans cette plateforme. Le **dernier chapitre** présente les performances du DirectLink dans différentes technologies et des exemples de gains dans des applications. Enfin, la conclusion résume le travail de recherche qui a été accompli et suggère de futurs travaux. Afin de maintenir la concision de ce mémoire et puisque beaucoup de projets de recherche du laboratoire CIRCUS ont déjà abordé maintes fois certains thèmes et sujets, plusieurs sections sont présentées en annexe.

## CHAPITRE 2

### LES COMMUNICATIONS DANS UN SYSTÈME-SUR-PUCE

Avec l'apparition d'année en année de circuits intégrés offrant des centaines de millions de transistors, les systèmes multiprocesseurs sur puce gagnent en intérêt. Le concept de système-sur-puce (SoC), apparu au tournant du millénaire, se veut la réunion complexe sur une seule puce de différents composants hétérogènes dans le but de répondre aux besoins croissants de performance du marché dans des domaines d'application spécialisés comme le multimédia, des télécommunications, de l'automatisation, etc.

Ce chapitre présente dans un premier temps les différents modèles et architectures de communication pour les MPSoC. Par la suite, un survol de quelques paradigmes d'abstraction des communications à haut niveau et des méthodologies de génération d'interfaces logicielles/matérielles est présenté.

#### 2.1. Les modèles de communication pour MPSoC

Les communications dans un MPSoC se classifient en 3 catégories distinctes selon les partitions impliquées.

##### 2.1.1. Communication inter logiciel

Dans les MPSoC, les communications logiciel/logiciel peuvent se produire entre deux tâches qui se retrouvent sur un même processeur ou sur deux processeurs différents. De plus, les communications peuvent être implicites ou explicites [32]:

- **Communication implicite** : s'effectue par un mécanisme de mémoire partagée et visible par plusieurs tâches ou plusieurs microprocesseurs. Des mécanismes de

synchronisation sont donc nécessaire afin d'assurer la cohérence et l'intégrité des données partagées.

- **Communication explicite** : s'effectue par des appels à des méthodes du type écriture ou lecture, bloquantes ou non bloquantes. Ce mécanisme se base sur le concept de passation de messages et implique donc l'utilisation d'un FIFO logiciel ou matériel.

### 2.1.2. **Communication inter matériel**

L'architecture de communication pour la partition matérielle a un impact significatif sur les performances, la taille du circuit, la dissipation de puissance et le coût global. De plus, les mêmes mécanismes de communication explicite et implicite mentionnés en 2.1.1 peuvent être utilisés pour les échanges inter matériel.

### 2.1.3. **Communication logiciel/matériel**

Dans les MPSoC, ce type de communication représente les échanges de données entre une tâche logicielle s'exécutant sur un processeur et un module du reste de la plateforme matérielle. Les données peuvent transiger à travers les mêmes mécanismes que pour les communications inter matérielles. Cependant, la liaison entre la tâche logicielle et l'interface matérielle n'est pas directe car les données seront souvent traitées par des fonctions de la pile logicielle qui abstraient le protocole de communication matériel utilisé.

De plus, il peut y avoir des mécanismes de communication directs, propres au microprocesseur utilisé, qui permettent d'établir un lien dédié entre le processeur et un module matériel. Le processeur peut aussi offrir une interface pour connecter un coprocesseur directement au cœur du processeur. Dans le cas des données qui transigent du matériel vers le logiciel, i.e. une tâche s'exécutant sur un processeur, deux

mécanismes peuvent être utilisés : les interruptions ou l'attente active (de l'anglais *polling*).

## 2.2. Les architectures de communication

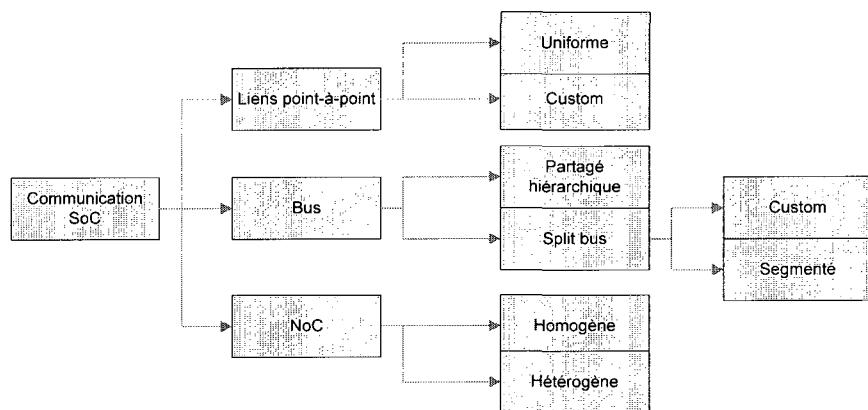

Selon [33] la taxonomie des réseaux d'interconnexion de SoC s'opère selon une classification en arbre – tel qu'illustré à la Figure 2.1 – basée sur leur structure physique, les protocoles de communications et les interfaces utilisées. L'emphase sera ici mise sur les bus, les connections point à point et le concept de GALS. Le domaine des NoC (ou *Network on Chip*, réseau sur puce) ne sera pas exploré ici puisqu'il n'intervient pas dans la compréhension des thèmes qui seront abordés ultérieurement.

**Figure 2.1 – Taxonomie des architectures communication pour SoC**

### 2.2.1. Bus de communication

Dans un bus, les connexions physiques (fils) sont groupés pour former un seul canal de communication physique qui est partagé entre différents canaux logiques. Cette architecture diminue la longueur totale de fils nécessaire et diminue la surface requise pour les interfaces. Cependant, avec la réduction d'échelle continue des circuits, plus il y a de blocs attachés au bus, plus il est difficile de gérer la longueur des fils lors du

placement et routage [33]. Les bus permettent la communication entre différents blocs matériels d'une architecture qui sont séparés en deux catégories : maîtres (qui initient les transactions) et les esclaves (qui exécutent les transactions).

La bande passante d'un bus peut être améliorée en utilisant un bus matriciel (ou *cross-bar switch*) où chaque composant maître est connecté à tous les composants esclaves et dans lequel plusieurs canaux parallèles sont disponibles pour supporter des transmissions concurrentes de données, e.g. le bus Avalon d'Altera [9] ou AMBA de ARM [34]. L'architecture d'un bus se base sur 3 paramètres [32] visant à répondre aux objectifs systémiques :

- **Arbitrage** : Puisque plusieurs maîtres peuvent initier des transactions sur un bus, un mécanisme d'arbitrage utilisant une méthode appropriée est nécessaire. Le mécanisme affecte le taux d'utilisation et la latence. Les méthodes *First-In-First-Out*, *Round-Robin* – chances égales d'obtenir le bus – ou basés sur les priorités sont souvent utilisées.

- **Fréquence et largeur du bus** : Déterminent le débit des transferts et influencent la consommation d'énergie, la surface requise et le coût.

- **Types de transferts** : Un bus peut implanter des mécanismes de transfert plus complexes que les simples lectures et écritures de mots de donnée :

- Blocs fixes : transfert de bloc dont la taille est une puissance de 2, souvent utilisé pour les mémoires caches.

- Différés (*split transaction*) : un transfert peut être interrompu par une requête d'un autre maître puis reprendre lorsqu'elle est complétée.

- Atomique : un mécanisme de réservation du bus (*bus lock*) assure à un maître l'obtention ininterrompue du bus pour des transferts en rafale.

### 2.2.2. Liens point à point et communication ad hoc

Dans un lien point à point, ou direct, une paire de blocs de calcul communiquent directement à travers des connections (fils) physiquement dédiées. Cette simplicité est l'avantage majeur de cette architecture. Il en existe certaines topologies uniformes comme les réseaux de neurones [33]

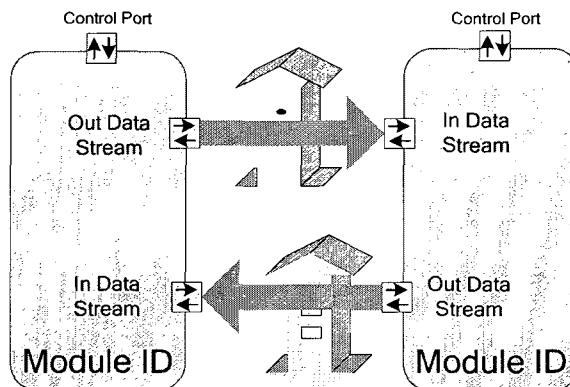

Il permet de diminuer la latence de communication entre deux modules matériels et réduire la puissance utilisée. La latence et la performance deviennent déterministes. Le transfert de données se fait directement d'un module à un autre sans passer par un canal partagé. On élimine donc la complexité et la latence induite par l'arbitrage et les signaux de contrôle d'un bus. Un désavantage flagrant est qu'il limite la réutilisation de l'architecture en impliquant un design spécifique à l'application. De plus, il devient difficile de concevoir la topologie d'un système où les modules communiquent avec plusieurs autres composants si uniquement des liens directs sont utilisés. Le taux d'utilisation des connections physiques est bas dans le cas d'application à faible bande passante et une interface dédiée est requise pour chaque canal de communication.

Les données transmises peuvent être tamponnées ou non. Dans le cas d'utilisation d'un tampon (FIFO), le mécanisme permet la lecture/écriture bloquante et non bloquante selon l'état du FIFO (vide ou plein). Il est donc possible d'établir un système de communication de passation de message avec rendez-vous. Dans le cas de communication bidirectionnelle, il est nécessaire d'avoir 2 liens directs.

### 2.2.3. GALS

Le concept des GALS (*Globally Asynchronous Locally Synchronous*) a été proposé par Chapiro en 1984 [35]. Ce paradigme permet la réduction de l'effort de conception du réseau de distribution d'horloge, une diminution de la consommation de puissance et la

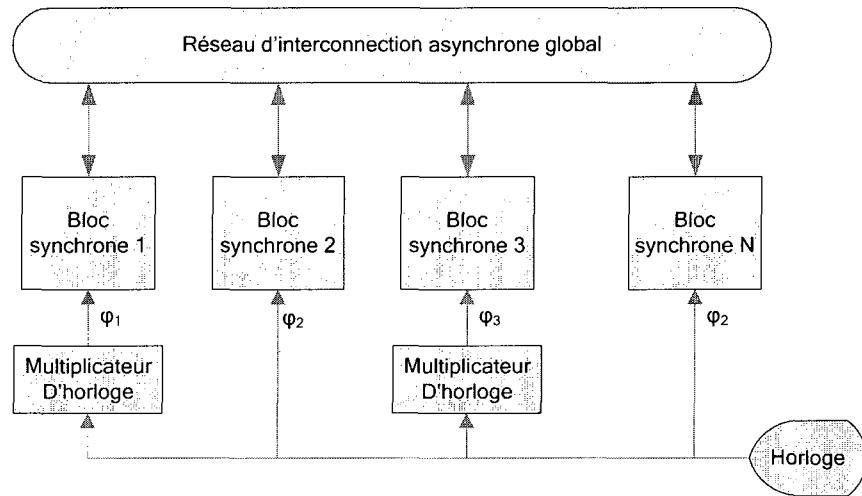

réutilisation de blocs IP conçus et optimisés pour fonctionner à une fréquence spécifique [36]. La Figure 2.2 illustre l'organisation globale d'un système GALS qui relie différents domaines d'horloge via un mécanisme d'interconnexion asynchrone [37] et qui sera selon [38] l'implémentation de la prochaine génération de SoC pour atteindre les requis de contrainte de puissance.

**Figure 2.2 – Schéma de haut niveau d'un système GALS**

Une méthodologie de partitionnement a été développée dans [39] pour optimiser la consommation de puissance d'une architecture en se basant sur les quatre modes de communication possible des GALS : FIFO, handshake, strobe, ou send and forget.

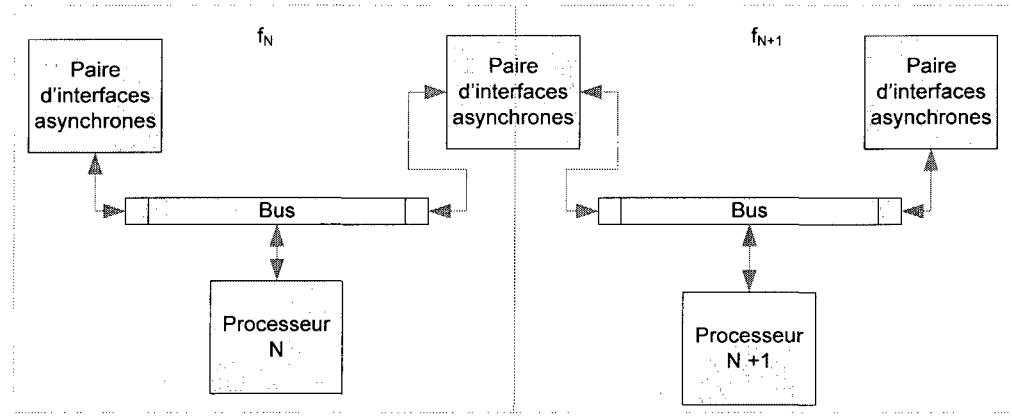

Dans [40], les auteurs proposent une interface GALS à basse latence et ne requérant pas d'altérer les signaux d'horloges, qui se base sur des FIFOs asynchrones dans un contexte multiprocesseur et de communication avec un coprocesseur. Chaque sous-système uniprocesseur est connecté aux autres par des ponts asynchrones tels qu'illustré à la Figure 2.3.

**Figure 2.3 – Interconnexion asynchrone de sous-systèmes uniprocesseur**

La méthodologie de [41] adresse le problème de l'analyse de performance et de puissance des systèmes GALS en utilisant une modélisation au niveau transactionnel basée sur SystemC. Les processus de calcul y sont décrits dans un langage procédural (comme le C) et interfacent un canal de communication BCA modélisant une FIFO asynchrone.

### 2.3. Abstraction des communications à haut niveau

L'abstraction des architectures de communication à haut niveau est un des avantages de la méthodologie TLM. Quelques modèles existant sont ici décrits.

#### 2.3.1. Le modèle SPACE

La plateforme SPACE (ANNEXE D) offre un modèle d'abstraction qui permet d'assurer la communication entre les modules logiciels et matériels d'une architecture par un mécanisme de passation de messages.

### 2.3.1.1. *Paradigme de communication*

SPACE utilise un paradigme de communication asynchrone par passage de message. Les messages envoyés sont stockés dans des FIFO jusqu'à la leur lecture. Chaque message comporte deux parties : un en-tête de quatre octets contenant des drapeaux, la taille du message et les identificateurs numériques des modules source et destination, ainsi que la charge utile du message, soit les données. La taille du message peut être de 4 à 256 octets. Les envois sont sérialisés par les adaptateurs afin de pouvoir transiger sur le bus partagé.

Ces mécanismes sont assurés par la présence de primitives de communications accessible par les processus légers des modules SPACE aussi bien logiciels que matériels. La complexité de l'implémentation est donc abstraite et indépendante de la fonctionnalité d'un module. Il faut toujours respecter le modèle de communication par rendez-vous, e.g. si un module *A* écrit un message à *B*, il doit utiliser une primitive de lecture et vice versa.

### 2.3.1.2. *Les primitives de communication*

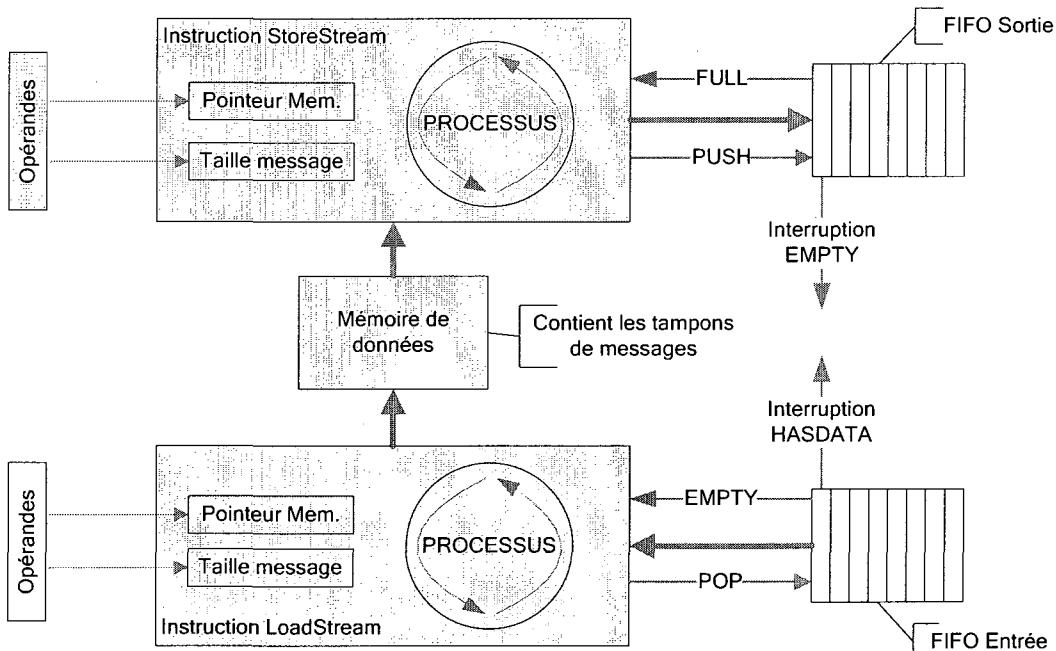

SPACE fournit quatre fonctions de base pour communiquer avec un autre module ou un périphérique de SpaceLib. L'implémentation utilise le bus partagé, les adaptateurs matériels et une couche spéciale de la pile logicielle. Ces fonctions sont les suivantes :

- **ModuleWrite** : Permet l'écriture d'un message d'un module vers un module. Les messages transigent par le bus et sont stockés dans des FIFO matérielles ou logicielles jusqu'à ce que le destinataire le consomme. Les messages provenant du matériel vers le logiciel sont stockés dans l'ISSAdapter qui notifie le processeur par interruption de leurs arrivées.

- **ModuleRead** : Permet la lecture d'un message qui a été stockée dans une FIFO logicielle (ex. : liste chaînée en mémoire) ou matérielle (ex. : lien FSL). C'est une opération locale entre un module et son adaptateur ne nécessitant pas d'opération sur le bus partagé.

- **DeviceWrite** : Écriture à un périphérique par le bus.

- **DeviceRead** : Lecture d'un périphérique par le bus.

Les champs OrgID et DestID sont inclus dans les en-têtes de message (Tableau 2.1) et permettent d'effectuer le routage des messages dans l'architecture de communication. L'origine sert à stocker le message dans la FIFO appropriée quand un module de destination peut recevoir des messages de plusieurs sources. Aussi, le champ Timeout est encodé dans la portion *flags* de l'en-tête du message.

**Tableau 2.1 – Paramètres des primitives de communication**

| Paramètre | Signification                                                     |

|-----------|-------------------------------------------------------------------|

| OrgID     | Identificateur numérique du module source                         |

| DestID    | Identificateur numérique du module de destination                 |

| Priority  | Priorité du message                                               |

| *pData    | Pointeur sur le tampon de mémoire contenant le message            |

| DataSize  | Taille du message                                                 |

| TimeOut   | Paramètre indiquant si l'opération est bloquante ou non bloquante |

### 2.3.1.3. *Les types de communication*

SPACE support quatre types de communication en fonction de la valeur du paramètre *TimeOut* qui peut être SPACE\_WAIT\_FOREVER (bloquant) ou SPACE\_NO\_WAIT (non bloquant). Les opérations avec expiration dans un délai de temps spécifié ne sont pas supportées pour le moment.

- **Lecture non bloquante :** Le module effectuant la lecture n'attend pas que des données soit présentes dans la FIFO avant de poursuivre son exécution.

- **Lecture bloquante :** Le module effectuant la lecture attend la présence d'un message dans la FIFO avant de poursuivre son exécution.

- **Écriture non bloquante :** Le module effectuant l'écriture poursuit son exécution immédiatement après avoir complété la transmission de son message.

- **Écriture bloquante :** Le module effectuant l'écriture attend que le message soit lu par la destination avant de poursuivre son exécution. Le module attend donc la réception d'un acquittement (*ACK*) en provenance du module de destination.

De plus, après la complétion d'une lecture (bloquante ou non bloquante), le module doit absolument envoyé un ACK à la source si le message a été envoyé par une écriture bloquante. Si une opération échoue, un code d'erreur sera retourné par la primitive de communication.

#### *2.3.1.4. Les classes de communication*

Selon les partitions impliquées dans un transfert de données au niveau Simtek, il existe quatre classes de communication se rapprochant des trois modèles de la section 2.1. Au niveau Elix, toutes les communications sont de la classe matériel/matériel.

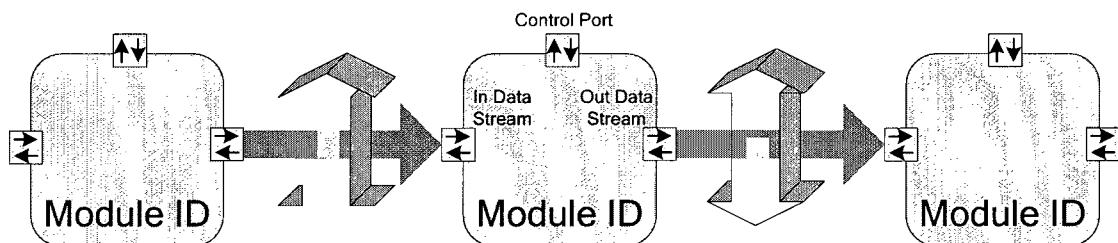

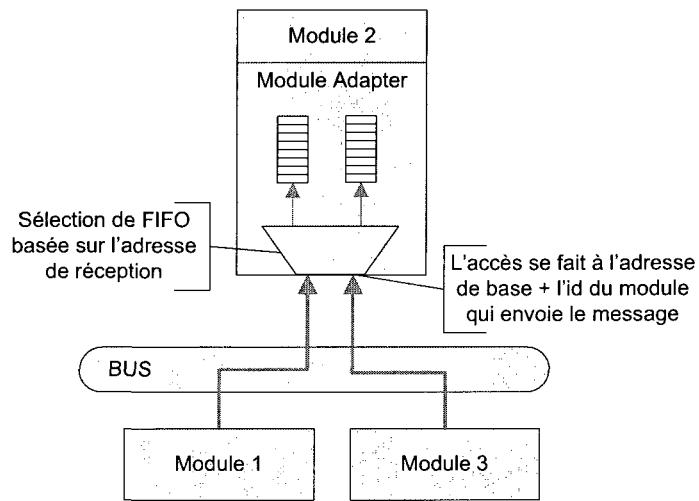

- **Classe matériel/matériel :** Le message transige d'un module de la partition matériel vers un autre module de la même partition. Le transfert se produit en deux étapes :

- Le module M1 appelle la primitive ModuleWrite. Le message est passé à l'adaptateur de communication A1 qui sérialise le message afin de le transférer sur le bus. L'adaptateur A2 réceptionne le message et le stocke dans une FIFO interne.

- Le module M2 appelle la primitive ModuleRead. Le message est lu directement dans la FIFO de l'adaptateur A2 via son interface. Il est à noter que M2 peut renvoyer un ACK à M1 si le ModuleWrite était bloquant. Le mécanisme de transmission est le même.

- **Classe logiciel/logiciel :** Le message transige d'un module logiciel vers un autre module de la même partition. Il y a deux cas de figure possibles :

- Cas uniprocesseur : Les modules sont sur le même processeur, le mécanisme est donc interne au logiciel applicatif de ce processeur et fait intervenir un mécanisme de communication explicite interprocessus habituel (voir section 2.1.1) utilisant une FIFO logicielle. Les mécanismes du RTOS sont utilisés par les primitives de communication.

- Cas multiprocesseur : Les modules sont sur des processeurs distincts. Ce cas revient à la classe logiciel/matériel. Le matériel est ici l'ISSAdapter associé au processeur contenant le module de destination.

- **Classe logiciel/matériel :** Un module logiciel écrit un message vers un module matériel. Le message transige directement à travers le bus via l'interface du processeur contenant le module logiciel M1 et est stocké dans la FIFO de l'adaptateur A2 du module matériel M2. Le module M2 lit localement le message dans la FIFO de son adaptateur. La primitive de communication ModuleWrite est définie dans une couche d'abstraction des communications de la pile logicielle.

- **Classe matériel/logiciel :** Un module matériel écrit un message à un module logiciel. Le processus se déroule en quatre étapes :

- Le module M1 envoie le message à l'ISSAdapter du processeur (ISS) contenant le module M2 via son adaptateur et le bus partagé. L'ISSAdapter stocke le message dans une FIFO interne.

- L'ISSAdapter notifie par interruption (section 2.1.3) le processeur contenant M2.

- Une routine de service d'interruption (ISR) s'exécute et récupère le message pour le stocker dans une FIFO logicielle propre aux mécanismes de communication interprocessus (section 2.1.1).

- Le module M2 récupère le message dans sa FIFO logicielle.

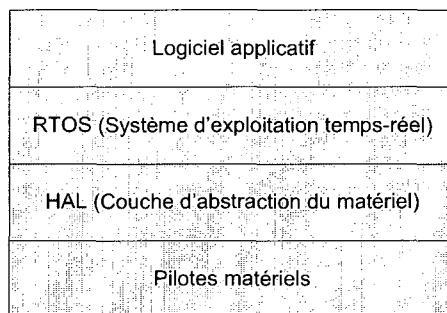

#### *2.3.1.5. Fonctionnement de la pile logicielle*

Sous SPACE, le logiciel applicatif est composé des modules de la partition logicielle initialement décrits en SystemC avec les ajouts de SPACE pour les primitives de communication.

Ces modules sont interprétés comme étant des tâches logicielles s'exécutant sur un RTOS, ici µC/OS-II. Une API (*Application Programming Interface*) spécifiquement développée pour ce RTOS permet la conversion des appels de fonction SystemC en appels compris par le système d'exploitation (Tableau 2.2). Cet API se nomme **Tor** dans SPACE. Ceci permet de supporter, sans modifications aux modules logiciels, l'ordonnancement préemptif et la gestion multitâche sur un processeur exécutant plusieurs modules SPACE. Le Tor comporte aussi l'implémentation générique des mécanismes de communication SPACE.

**Tableau 2.2 – Exemples de conversions d'appels SystemC en appels µC/OS-II**

| <b>Fonction<br/>SystemC</b> | <b>Fonction<br/>MicroC/OS-II</b> | <b>Description</b>                                      |

|-----------------------------|----------------------------------|---------------------------------------------------------|

| wait()                      | OSTaskDelay()                    | Attente d'un délai d'un nombre de cycles spécifié       |

| sc_start()                  | OSStartScheduler()               | Lancement de la simulation ou de l'ordonnanceur du RTOS |

| sc_stop()                   | OSStopScheduler()                | Arrêt de la simulation ou de l'ordonnanceur du RTOS     |

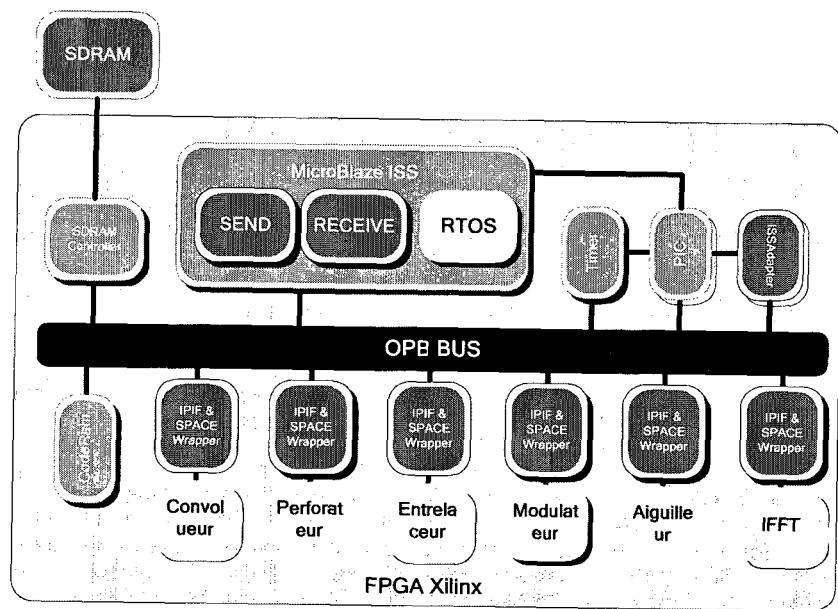

### 2.3.1.6. Raffinement BCA actuel dans SPACE

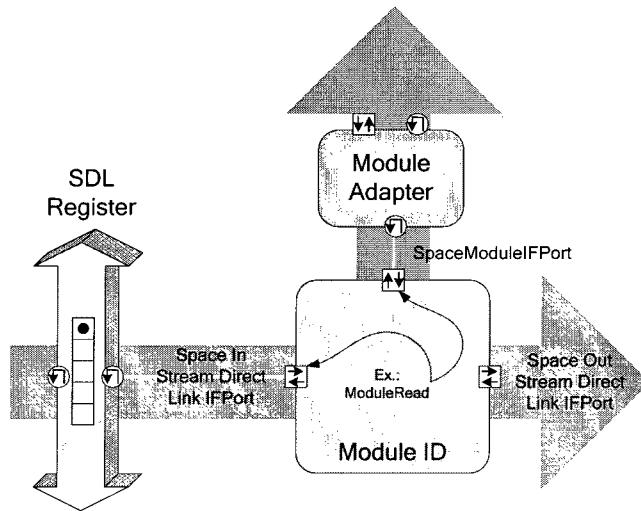

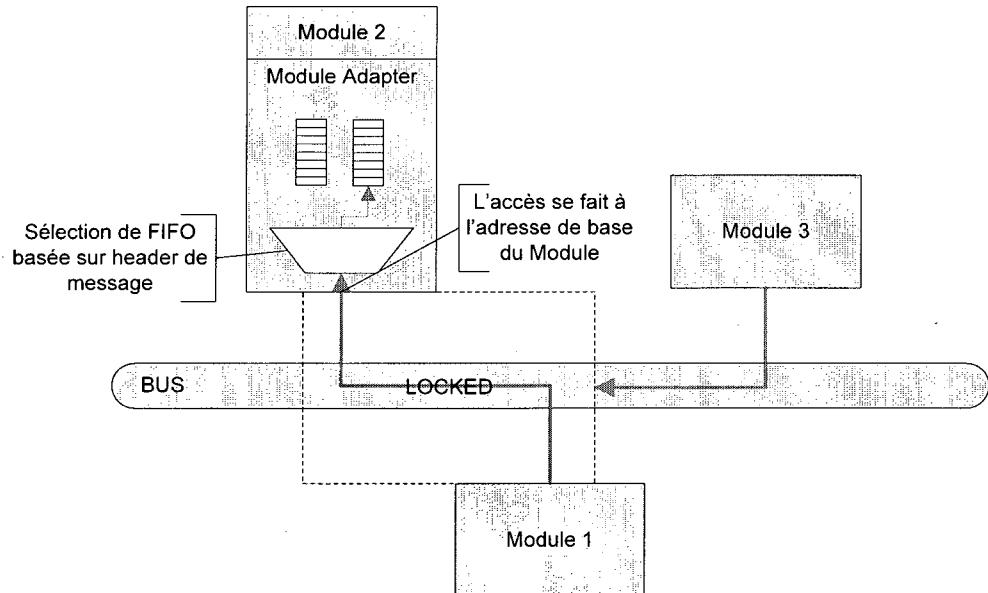

Les adaptateurs de communications des modules ont à la fois une interface maîtresse et esclave sur le bus. Ainsi, ils peuvent initier des transactions et répondre aux requêtes des autres modules. Tous les adaptateurs implémentent la même interface unique (SpaceModuleIF) qui permet de les connecter sur le port de communication du module utilisateur. Puisque le bus utilise des adresses de 32 bits pour identifier les esclaves connectés, les adaptateurs de communication doivent effectuer une conversion des identificateurs numériques des modules. Une fonction permet de dynamiquement générer les adresses en décalant de 22 bits l'identificateur numérique stocké sur un octet (Tableau 2.3).

**Tableau 2.3 – Structure d'une adresse dans SPACE**

| Bits 30-31                           | Bits 22-29                         | Bits 0-14                                            |

|--------------------------------------|------------------------------------|------------------------------------------------------|

| Bits prévus pour la gestion multibus | Identificateur numérique du module | Espace mémoire réservé pour le module (4 mégaoctets) |

Cette méthode de conversion des identificateurs en adresses permet 3 choses :

- Abstraire le mode d'adressage des modules ;

- Réduire la taille des en-têtes des messages ;

- Rendre homogène l'identification des modules matériels et logiciels.

L'architecture de communication doit aussi assurer l'atomicité des transferts des messages afin d'éviter qu'un transfert vers un module soit interrompu par un autre transfert vers le même module. Ceci violerait l'intégrité du premier message en cours de transmission. Pour ce faire, les modules matériels activent physiquement le *bus lock* (voir section 2.2.1) pendant une communication. Les modules logiciels doivent quant à eux utiliser une instruction spéciale du processeur afin d'indiquer aux contrôleurs de bus d'activer le *bus lock*.

### 2.3.2. Le modèle ImpulseC

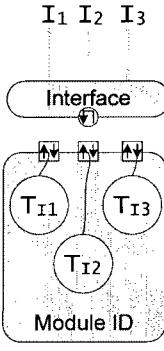

ImpulseC [15] étend, à la manière de SystemC, le langage ANSI C avec des librairies supportant la création d'applications basées sur les processus de communication séquentiels [42] (ou *Communication Sequential Processes, CSP*), i.e. un paradigme de programmation similaire au modèle flot de données. ImpulseC vise le développement d'**applications parallèles** qui peuvent aisément être converties en VHDL. Il permet que la description d'une application logicielle puisse être appliquée directement sur une plateforme matériel/logiciel.

Le paradigme de programmation est basé sur le transfert tamponné de données entre des processus via des flux (ou flots de données) gérés comme des FIFOs. Ceci permet l'écriture d'applications parallèles à haut niveau d'abstraction sans besoin de mécanismes de synchronisation entre les processus. Les différentes portions d'une application sont exécutées de manière concurrente et indépendamment synchronisés par des processus. Ils opèrent en acceptant des données en entrée, en opérant des calculs sur celles-ci et en générant des résultats en sortie. Ils sont persistants, invoqués qu'une seule fois et s'exécutant tant et aussi longtemps qu'il y a des données à traiter. Les données transitent de processus en processus le long des flux.

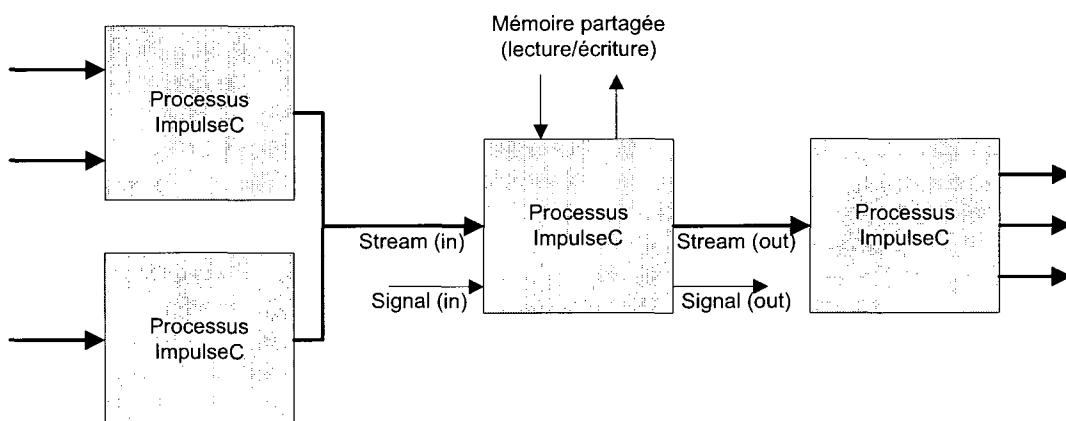

Figure 2.4 – Modèle d'application ImpulseC utilisant le paradigme CSP

L'API d'ImpulseC fournit des méthodes de communication incluant les *streams*, la mémoire partagée et les signaux (Figure 2.4). Les *streams* représentent des canaux de communication unidirectionnelle reliant des processus matériels ou logiciels. Ils sont définis par la largeur des mots de données qu'ils acceptent (de 8 bits à 128 bits) et la profondeur du tampon. On peut y effectuer des opérations de lecture/écriture via les fonctions `co_stream_read` et `co_stream_write`. Chaque flot de données est manipulé explicitement par les fonctions. La lecture bloque tant qu'il n'y a pas de données dans le canal et l'écriture bloque tant que le canal est plein. En matériel, les *streams* sont implémentés comme des FIFO qui peuvent avoir une ou deux horloges si les processus s'exécutent à des fréquences différentes. Le *stream* abstrait les détails des communications logicielles/matérielles pour les différents types de plateformes et rend l'application portable.

CoDeveloper est un environnement de développement supportant le modèle ImpulseC. Il permet le partitionnement logiciel/matériel des processus ImpulseC. CoDeveloper supporte une large variété de plateformes matérielles (Xilinx, Altera, etc.). Il génère automatiquement les modules VHDL, les interfaces matérielles et l'HAL en se basant sur une librairie de composants. Sur le Virtex-4 de Xilinx, les *streams* connectés aux processus s'exécutant sur le PowerPC405 Fx utilisent l'interface APU ou le PLB [43][44].

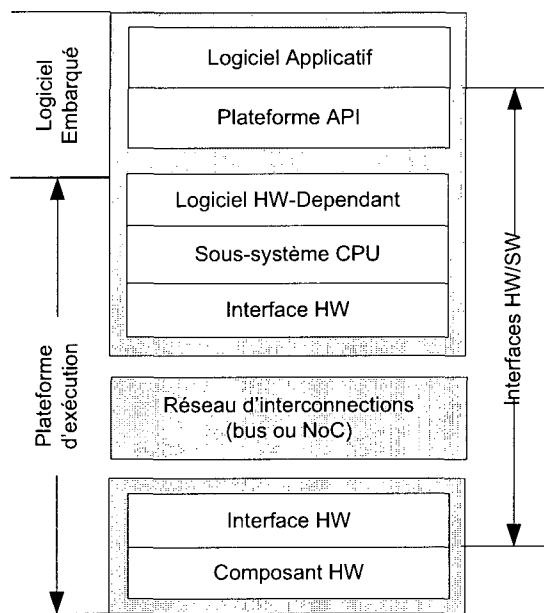

### 2.3.3. Le modèle d'interface matériel/logiciel unifié

Dans [11], les auteurs proposent une interface unifiée qui abstrait, du côté logiciel, le CPU sous une couche implémentant des pilotes de bases, des fonctionnalités I/O et des systèmes d'exploitation. Du côté matériel, cette interface abstrait les détails du bus du CPU. À la différence de SPACE, cette approche n'utilise pas deux modèles compilés séparément de l'interface, soit un pour le logiciel et un pour le matériel.

L'API (Figure 2.5) cache les détails matériels comme les contrôleurs d'interruption, la mémoire et les systèmes I/O. Le logiciel *hardware-dependant* support l'API et l'adapte au sous-système CPU. Ce sous-système élimine l'architecture complexe généralement présente dans un simulateur de jeu d'instruction (ou ISS, voir ANNEXE C) pour atteindre les performances de simulation requises. L'objectif est d'être capable de concevoir le matériel et le logiciel à tous les niveaux d'abstraction.

Figure 2.5 – Interface logicielle/matérielle unifiée

À haut niveau, un système est représenté par un ensemble de processus qui peuvent communiquer à travers une multitude de canaux abstraits. Un processus désirant communiquer à travers un canal précis doit appeler la primitive de communication (*send* ou *receive*) de ce canal. Chaque application peut posséder son propre ensemble de primitives (*send\_short*, *send\_atm*, *send\_int*, etc.). Chaque canal se base sur des unités de communication sélectionnées d'une librairie. D'un point de vue conceptuel, une unité de communication est un objet qui peut exécuter une ou plusieurs primitives de communication avec un protocole spécifique [45] et à différents niveaux d'abstractions [46].

### 2.3.3.1. Modèle de simulation

Comparativement à une approche traditionnelle basée ISS, le sous-système CPU du modèle de simulation, utilisant SystemC, fournit un environnement où les composants logiciels peuvent s'exécuter nativement sur la machine hôte de simulation [47]. Le sous-système CPU implémente à la fois l'interface matérielle sous la forme de services fournis (ports SystemC slave) et de services requis (ports SystemC master), ainsi que l'API logiciel. Au lieu de définir en détail toute la mécanique interne d'un processeur (comme dans un ISS), le sous-système CPU implémente les concepts abstraits suivants dans un méta-modèle de processeur :

- **Unité d'exécution** : Fil d'exécution logiciel (thread) et les méthodes pour manipuler son exécution (changement de contexte) ;

- **Unité de données** : Emplacement pour le stockage de données et abstraction d'une entité physique comme la mémoire. Permet la lecture/écriture par adresse via des méthodes ;

- **Unité d'accès** : Abstraction de la projection en mémoire (*memory map*) d'une unité d'exécution. Pourrait implémenter des mécanismes de MMU tel la mémoire virtuelle ;

- **Unité de synchronisation** : Permet l'abstraction des interruptions et l'attachement d'ISR.

Le logiciel devant s'exécuter sur le processeur n'est pas interprété mais exécuté nativement. Puisque le logiciel est indépendant du matériel, il peut être compilé pour la machine hôte et manipuler la librairie de HAL (interface unifiée) correspondant au processeur à modéliser [48]. L'inconvénient est que le code logiciel doit être modifié par l'ajout d'annotations temporelles permettant de conserver la précision du temps de simulation tout en effectuant une simulation comportementale.

## 2.4. Génération des interfaces logiciel-matériel

Il existe différentes manières d'établir les interfaces de communication entre les partitions logicielles et matérielles.

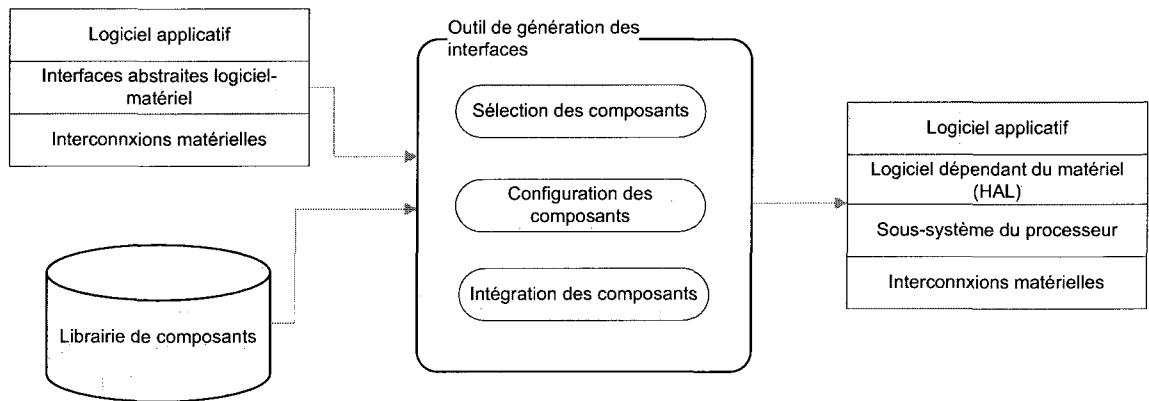

### 2.4.1. L'approche des composants basés service

Dans [49] et [50], les auteurs proposent un modèle unifié qui généralise l'approche de composants basés service pour englober l'interface logiciel/matériel. Cette méthode permet une fine composition de l'implémentation de l'interface, un partitionnement flexible et une génération automatique de l'architecture basée sur une librairie de composantes. L'abstraction de cette interface est définie en spécifiant deux ensembles de services : (1) les services reliés au logiciel applicatif (API) et (2) les services reliés au réseau d'interconnexion (services de communication)

Chaque composant est modélisé par la déclaration d'une interface qui définit les services offerts et la manière de le connecter aux autres composants, et un arbre d'implémentation qui décrit le comportement du composant en utilisant du macrocode qui sera utilisé pour générer le logiciel, le modèle matériel ou le modèle de simulation fonctionnel. L'utilisation de ce modèle vise un flot de conception en 2 étapes:

- Conception et partitionnement de l'architecture à haut-niveau résultant en une abstraction du système comportant des modules logiciels, matériels et des interfaces abstraites de communication;

- Implémentation de chaque élément décrit dans le modèle abstrait.

L'outil de génération prend la spécification de l'interface et le modèle de composant en entrée afin de sélectionner un ensemble de composants nécessaire à l'implantation et

d'en créer des instances en les paramétrant selon la valeur des paramètres fournis à l'interface abstraite. La Figure 2.6 illustre cette méthode.

**Figure 2.6 – Outil de génération des interfaces logicielles/matérielles**

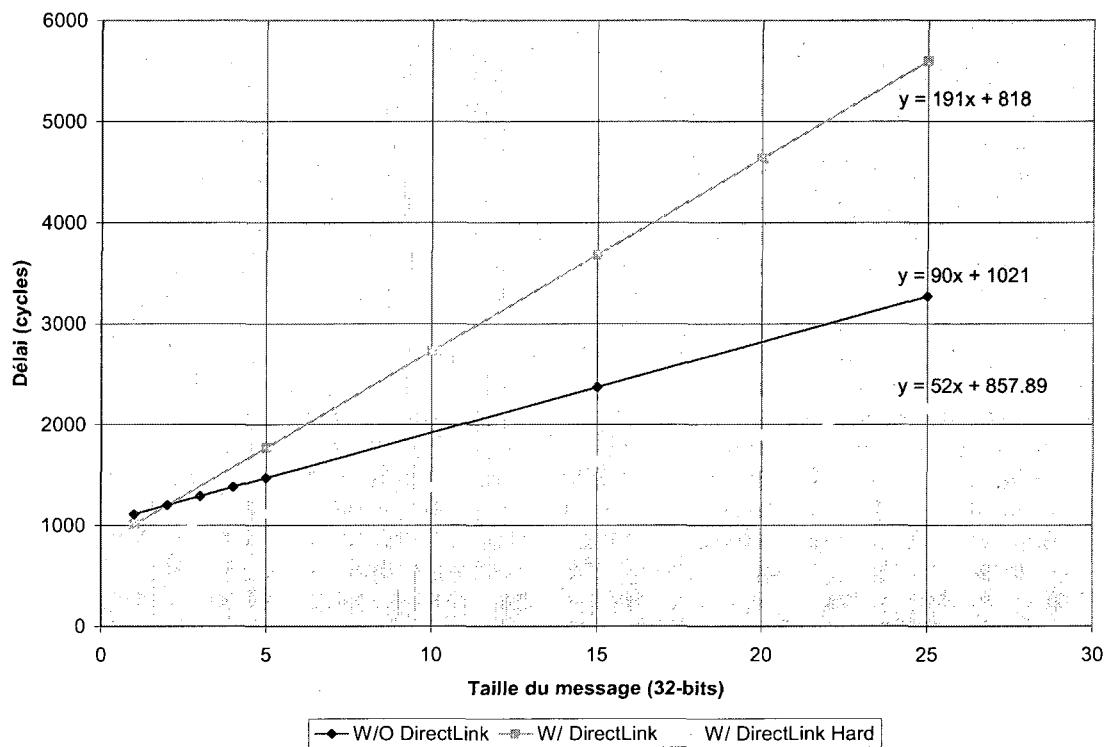

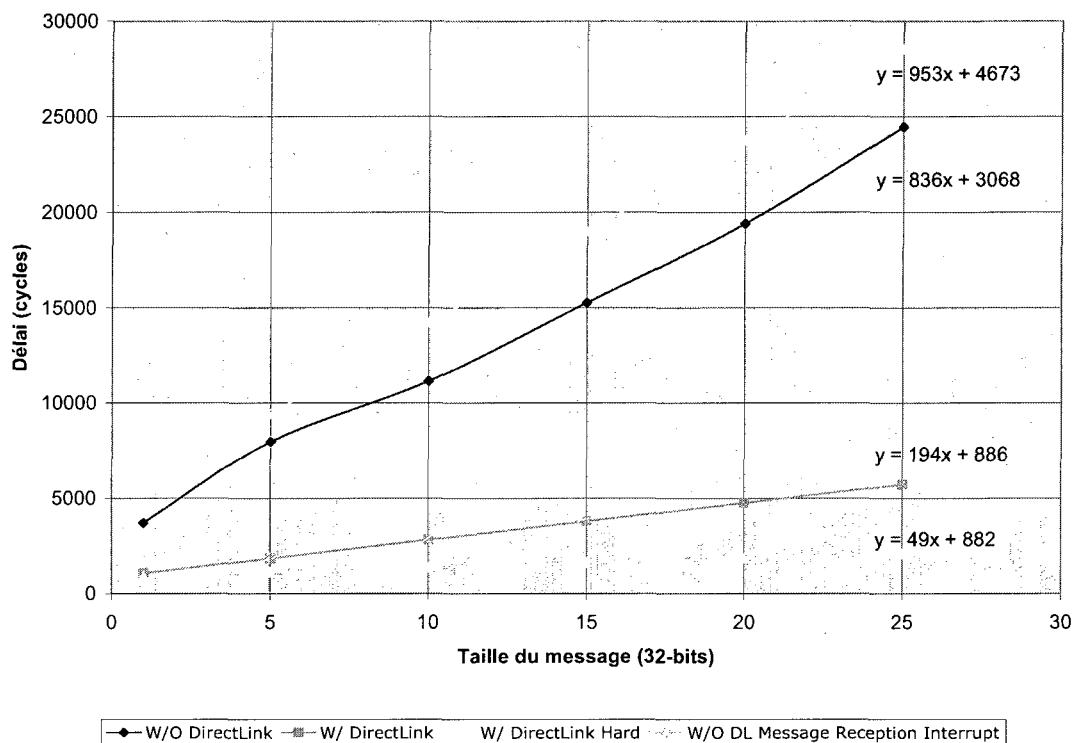

#### 2.4.2. L'approche des adaptateurs de communication