|                   |                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Titre:</b>     | Conception et réalisation d'un outil d'exploration architecturale de la hiérarchie de mémoire d'un système sur puce afin d'optimiser la performance de la plateforme logicielle                                                                                                                                                                                    |

| <b>Auteur:</b>    | Sébastien Fontaine                                                                                                                                                                                                                                                                                                                                                 |

| <b>Date:</b>      | 2008                                                                                                                                                                                                                                                                                                                                                               |

| <b>Type:</b>      | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                                                                                          |

| <b>Référence:</b> | Fontaine, S. (2008). Conception et réalisation d'un outil d'exploration architecturale de la hiérarchie de mémoire d'un système sur puce afin d'optimiser la performance de la plateforme logicielle [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/8479/">https://publications.polymtl.ca/8479/</a> |

| <b>Citation:</b>  | Fontaine, S. (2008). Conception et réalisation d'un outil d'exploration architecturale de la hiérarchie de mémoire d'un système sur puce afin d'optimiser la performance de la plateforme logicielle [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/8479/">https://publications.polymtl.ca/8479/</a> |

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8479/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois

Advisors:

**Programme:** Non spécifié

Program:

## **NOTE TO USERS**

**This reproduction is the best copy available.**

**UMI<sup>®</sup>**

UNIVERSITÉ DE MONTRÉAL

CONCEPTION ET RÉALISATION D'UN OUTIL D'EXPLORATION

ARCHITECTURALE DE LA HIÉRARCHIE DE MÉMOIRE D'UN SYSTÈME SUR

PUCE AFIN D'OPTIMISER LA PERFORMANCE DE LA PLATEFORME

LOGICIELLE

SÉBASTIEN FONTAINE

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

DÉCEMBRE 2008

Library and Archives

Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

ISBN: 978-0-494-57246-7

*Our file Notre référence*

ISBN: 978-0-494-57246-7

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

■■■

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

CONCEPTION ET RÉALISATION D'UN OUTIL D'EXPLORATION

ARCHITECTURALE DE LA HIÉRARCHIE DE MÉMOIRE D'UN SYSTÈME SUR

PUCE AFIN D'OPTIMISER LA PERFORMANCE DE LA PLATEFORME

LOGICIELLE

présenté par : FONTAINE Sébastien

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. LANGLOIS J.M. Pierre, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. DAVID Jean-Pierre, Ph.D., membre

## DÉDICACE

640 KB ought to be enough for everybody – citation attribuée à Bill Gates

## **REMERCIEMENTS**

Je tiens d'abord à remercier M. Bois, mon directeur de maîtrise pour ses idées, ses conseils et sa disponibilité qui m'ont permis de mener à bien mes travaux de recherche.

Je tiens également à remercier les membres du groupe de recherche CIRCUS de l'École Polytechnique : Benoît Pilote, Laurent Moss, Luc Filion, Marc-André Cantin, Maxime De Nanclas et Sylvain Goyette pour leur précieuse collaboration et leur soutien.

Je tiens plus particulièrement à remercier Carole Vézina, ma mère, pour m'avoir aidé à corriger le texte et Louis-Mathieu Houle pour ses commentaires constructifs.

En dernier lieu, je tiens à remercier mes parents et amis qui m'ont soutenu moralement durant mes 6 années et demie à l'École Polytechnique.

## RÉSUMÉ

Avec la croissance continue du nombre de transistors par puce grâce aux récents progrès en lithographie, il devient maintenant possible d'intégrer un grand nombre de composants complexes sur un même circuit intégré. Afin de tirer avantage de ce nombre de transistors, les concepteurs se tournent vers les systèmes multiprocesseurs sur puce (MPSoC) où plusieurs processeurs coexistent sur la même puce et travaillent de pair afin de produire un système performant et efficace. Ce nombre croissant de processeurs sur une même puce pose alors de nouveaux défis aux concepteurs pour l'utilisation de la mémoire intégrée à ces MPSoC.

Un de ces défis est l'utilisation efficace de la mémoire intégrée disponible sur la puce afin de maximiser la performance des logiciels s'exécutants sur les processeurs. Dans le cas de petits programmes, il est possible de stocker ceux-ci totalement sur cette mémoire intégrée (mémoire locale au processeur) afin de maximiser leur performance. Par contre, avec la complexification des applications et la monté en popularité des systèmes multiprocesseurs, la taille limitée de la mémoire intégrée devient un problème. Il est alors nécessaire de stocker le programme dans une mémoire plus volumineuse mais aussi plus lente et externe à la puce. Deux solutions se présentent alors : le partitionnement de mémoire qui vise à morceler le programme et à le répartir entre la mémoire intégrée et la mémoire externe et l'utilisation de la mémoire intégrée en tant que mémoire cache qui vise alors à accélérer la latence moyenne d'accès à la mémoire externe.

Plusieurs travaux se sont penchés sur l'amélioration de la performance de tels systèmes en tentant d'optimiser la hiérarchie de la mémoire. Certains travaux se concentrent uniquement sur l'utilisation de la mémoire locale, d'autres sur la configuration optimale de la mémoire cache. Par contre, peu de travaux se sont penchés sur l'utilisation et l'optimisation commune de la mémoire locale et de la mémoire cache.

Un outil, MemoryOptimizer, a donc été conçu dans l'optique d'effectuer l'exploration architecturale de la hiérarchie mémoire d'un système sur puce en utilisant une combinaison de mémoire locale et de mémoire cache. De plus, afin d'assurer des résultats précis en simulation, un modèle du MicroBlaze a été développé pour l'environnement de conception de systèmes sur puce SPACE. Finalement, un outil de recueil de la trace d'exécution, permettant à MemoryOptimizer d'amasser les métriques nécessaires à l'analyse du comportement du programme à optimiser, a été conçu et intégré au modèle de simulation.

À l'aide de MemoryOptimizer, il est maintenant possible de déterminer automatiquement le contenu et la taille de la mémoire locale ainsi que de déterminer les tailles optimales des mémoires cache. Il en résulte un système où la minorité du programme, demandant le plus grand nombre d'accès à la mémoire est contenu en mémoire locale et le reste, stocké en mémoire externe, est accéléré par l'utilisation des mémoires cache. De plus, l'outil permet de suggérer une taille minimale pour la pile et le tas du programme, ce qui permet de réduire davantage l'utilisation de la mémoire.

Les expériences menées démontrent que MemoryOptimizer permet d'améliorer grandement les performances d'un système basé sur la mémoire externe en plus de diminuer l'utilisation de la mémoire intégrée. Il est ainsi possible de réduire par un facteur de 6 la taille de la mémoire intégrée tout en maintenant la performance d'un programme situé uniquement en mémoire locale. L'intégration d'un grand nombre de processeurs sur une même puce est donc aisément réalisable sans qu'il soit nécessaire de faire des compromis en termes de performance. De plus, la méthodologie présentée n'est pas limitée seulement au MicroBlaze et à SPACE mais peut être adaptée à d'autres processeurs ainsi qu'à d'autres plateformes de simulation.

## ABSTRACT

As the quantity of transistors per single chip steadily increases due to recent advances in lithography, it becomes possible to integrate a number of complex components on an integrated circuit. In order to maximize the use of these transistors, designers now concentrate on multi-processor systems on chip (MPSoC) on which many processors coexist and work together to produce a fast and efficient system. This increasing number of processors on a single chip thus poses new challenges in term of integrated memory utilization.

In order to perform optimally, a program executed by a processor is generally contained in a small memory integrated on the chip and directly connected to this processor. This type of memory is called local memory. Because this memory is limited in a given chip, the presence of multiple processors, every one of them striving to provide the best performance, severely limits the amount of local memory available to each processor. Using the integrated memory to store all these programs becomes impossible and mandates the use of an external memory which is much larger but also much slower than the integrated memory.

Previous works dealing with the performance enhancement of such systems by optimizing the memory hierarchy are numerous. Some works focus on effectively using the local memory while others focus on finding the optimal cache configuration. On the other hand, few works focus on the use and optimization of both the local memory and cache.

A tool, MemoryOptimizer, was thus designed to resolve this gap, by presenting a method of design space exploration of the memory hierarchy of a SoC, by using a combination of local memory and cache memory. In order to provide accurate simulation results, a model of the MicroBlaze processor has been implemented in the

SPACE simulation platform. Lastly, an execution-tracing tool has been designed and integrated into the MicroBlaze model to provide the metrics necessary for MemoryOptimizer to analyze the behavior of the program executed on the processor.

With MemoryOptimizer, it is now possible to automatically establish the content and the minimal size of the local memory but also the optimal configurations of the caches. The result of this optimization is a system where a small but memory intensive part of the program is relocated in local memory and where the remaining of the program is stored in external memory and access to this memory is accelerated by cache memories. Moreover, the tool can evaluate the minimal size of the stack and the heap to further reduce the memory footprint.

MemoryOptimizer can greatly enhance the performance of a system based on an external memory while also reducing the size of the required integrated memory. Thus, it is possible to reduce the size of the integrated memory by a factor of 6 while maintaining the same performance level than the same program completely stored in local memory. More processors can now be integrated in a single chip without compromising the execution speed of the programs. Furthermore, the proposed methodology is not limited only to the MicroBlaze and SPACE but can also be adapted to other processors and simulation platforms.

## TABLE DES MATIÈRES

|                                                                                     |       |

|-------------------------------------------------------------------------------------|-------|

| DÉDICACE.....                                                                       | IV    |

| REMERCIEMENTS .....                                                                 | V     |

| RÉSUMÉ.....                                                                         | VI    |

| ABSTRACT .....                                                                      | VIII  |

| TABLE DES MATIÈRES .....                                                            | X     |

| LISTE DES FIGURES.....                                                              | XIII  |

| LISTE DES TABLEAUX.....                                                             | XV    |

| LISTE DES ANNEXES.....                                                              | XVII  |

| LISTE DES ACRONYMES .....                                                           | XVIII |

| CHAPITRE 1 INTRODUCTION .....                                                       | 1     |

| 1.1.    Les systèmes embarqués d'aujourd'hui .....                                  | 1     |

| 1.2.    Problématique .....                                                         | 2     |

| 1.3.    Objectif.....                                                               | 4     |

| 1.4.    Méthodologie .....                                                          | 5     |

| 1.5.    Contributions.....                                                          | 6     |

| 1.6.    Organisation du mémoire .....                                               | 7     |

| CHAPITRE 2 SYSTÈMES SUR PUCE: HIÉRARCHIE MÉMOIRE, LOGICIEL<br>ET OPTIMISATION ..... | 8     |

| 2.1.    Hiérarchie mémoire.....                                                     | 8     |

| 2.1.1.    Mémoire principale .....                                                  | 11    |

| 2.1.2.    Mémoire locale .....                                                      | 11    |

| 2.1.3.    Mémoire cache .....                                                       | 12    |

| 2.2.    Structure d'un logiciel compilé.....                                        | 16    |

| 2.2.1.    Compilation.....                                                          | 17    |

|                                              |    |

|----------------------------------------------|----|

| 2.2.2. Édition des liens .....               | 19 |

| 2.2.3. Profilage .....                       | 19 |

| 2.3. Optimisation de la hiérarchie .....     | 20 |

| 2.3.1. Mémoire locale .....                  | 21 |

| 2.3.2. Mémoire cache .....                   | 23 |

| 2.4. Environnement de simulation SPACE ..... | 25 |

## CHAPITRE 3 MISE À JOUR DE LA PLATEFORME DE SIMULATION

|                                                              |    |

|--------------------------------------------------------------|----|

| SPACE .....                                                  | 27 |

| 3.1. Plateforme MicroBlaze .....                             | 27 |

| 3.1.1. Architecture Xilinx .....                             | 28 |

| 3.1.2. Processeur MicroBlaze .....                           | 30 |

| 3.1.3. Contrôleur de mémoire MCH OPB SDRAM .....             | 35 |

| 3.2. Environnement de simulation SPACE .....                 | 36 |

| 3.2.1. ISS du MicroBlaze .....                               | 36 |

| 3.2.2. Contrôleur OPB SDRAM .....                            | 38 |

| 3.3. Mise à jour des composantes .....                       | 38 |

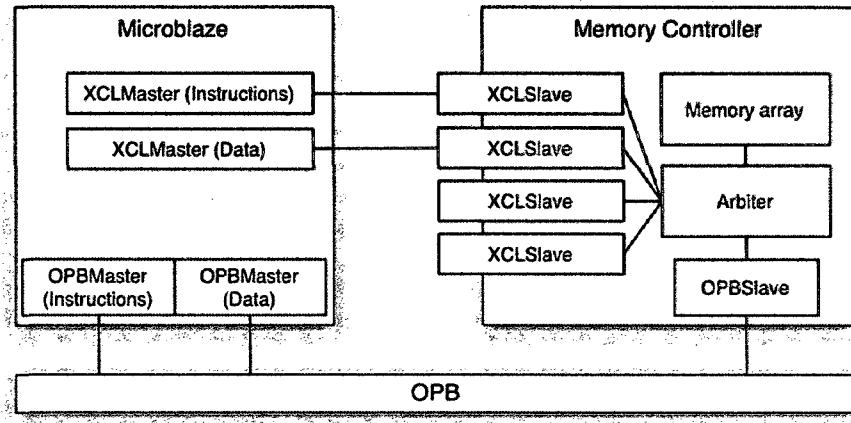

| 3.3.1. Implémentation du lien XCL .....                      | 38 |

| 3.3.2. Implémentation du MicroBlaze version 6 .....          | 40 |

| 3.3.3. Implémentation du contrôleur MCH OPB SDRAM .....      | 49 |

| 3.4. Outil de traçage d'exécution .....                      | 50 |

| 3.4.1. Interface de la classe uBlazeV6Tracer .....           | 51 |

| 3.4.2. Fichier de trace .....                                | 51 |

| 3.4.3. Intégration du traceur dans l'ISS du MicroBlaze ..... | 54 |

## CHAPITRE 4 MEMORYOPTIMIZER : OPTIMISATION DE LA HIÉRARCHIE

|                                                        |    |

|--------------------------------------------------------|----|

| MÉMOIRE .....                                          | 57 |

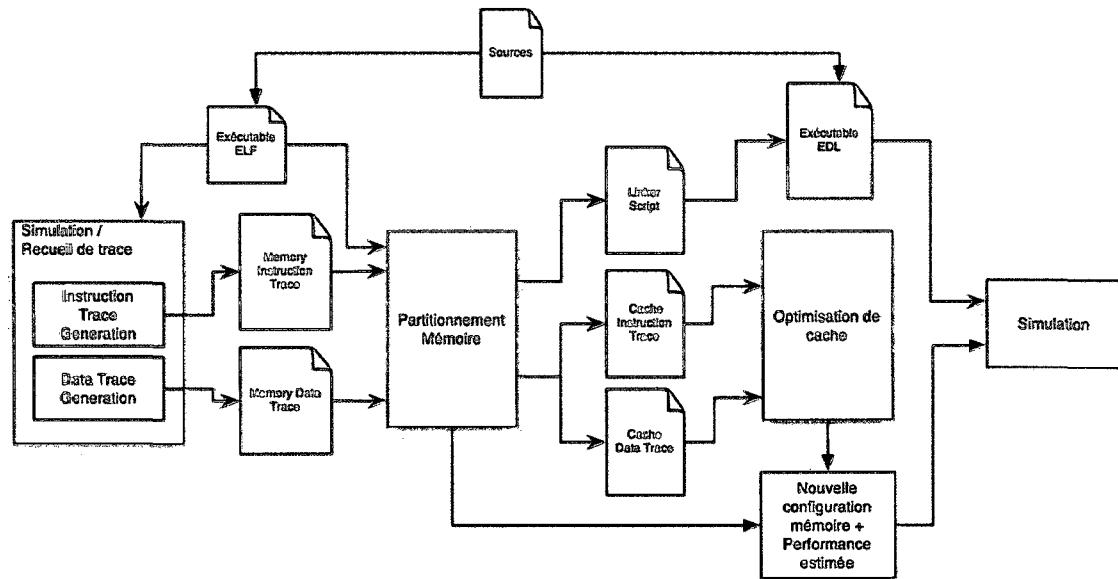

| 4.1. Flot d'exécution .....                            | 57 |

| 4.2. Partitionnement de mémoire .....                  | 59 |

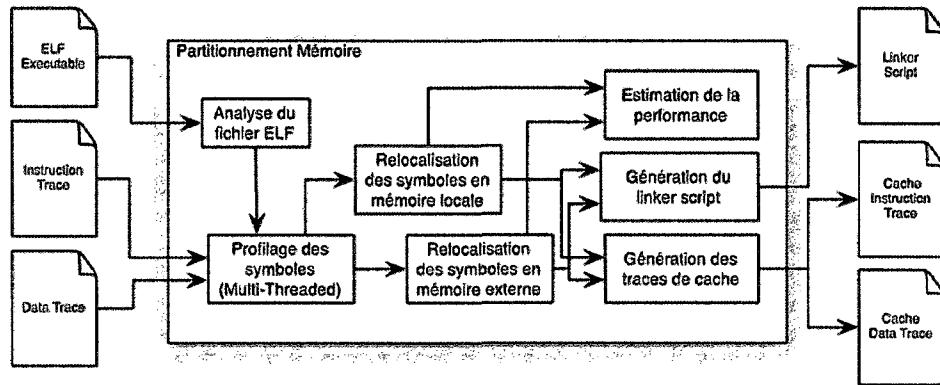

| 4.2.1. Architecture .....                              | 60 |

| 4.2.2. Récupération des symboles et des sections ..... | 63 |

| 4.2.3. Lecture de la trace .....                       | 65 |

|                                                                          |     |

|--------------------------------------------------------------------------|-----|

| 4.2.4. Profilage .....                                                   | 66  |

| 4.2.5. Algorithme de relocalisation des symboles .....                   | 69  |

| 4.2.6. Algorithme d'estimation de la performance .....                   | 73  |

| 4.2.7. Génération du script de l'éditeur de liens .....                  | 74  |

| 4.2.8. Génération de la trace de cache.....                              | 75  |

| 4.3. Optimisation de la mémoire cache.....                               | 77  |

| 4.3.1. Architecture.....                                                 | 77  |

| 4.3.2. Simulation des configurations de cache.....                       | 78  |

| 4.3.3. Estimation de la performance.....                                 | 80  |

| 4.3.4. Sélection de la configuration optimale.....                       | 81  |

| CHAPITRE 5 ANALYSE, PERFORMANCES ET DISCUSSION .....                     | 83  |

| 5.1. Méthodologie d'analyse des performances.....                        | 83  |

| 5.1.1. Méthodologie .....                                                | 84  |

| 5.1.2. Dhrystone .....                                                   | 86  |

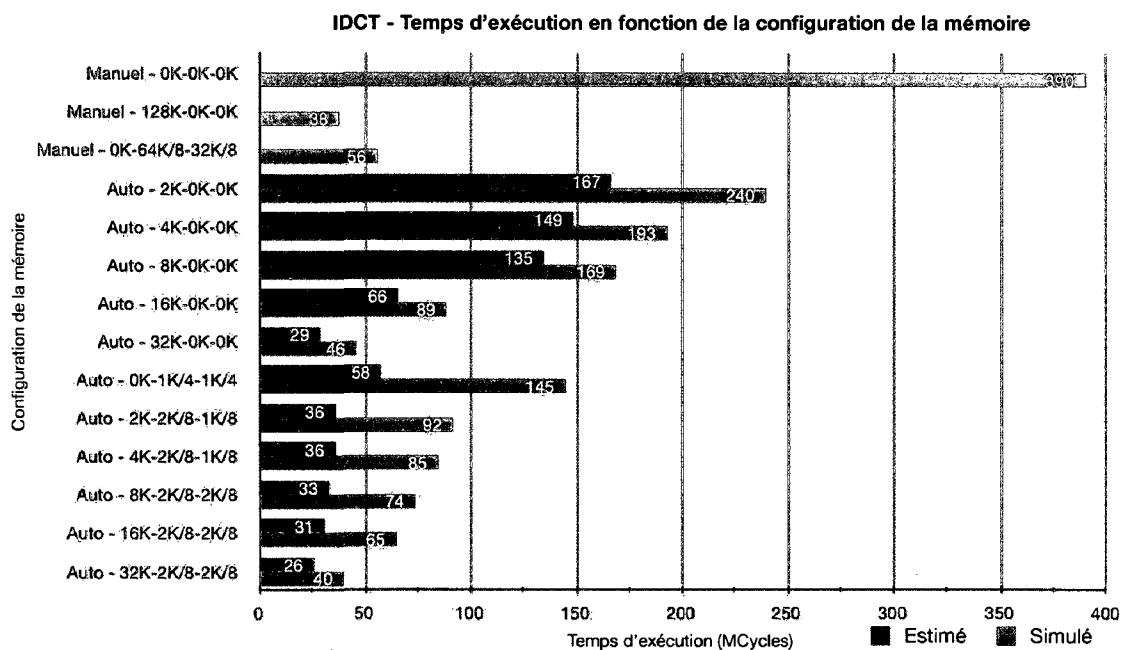

| 5.1.3. IDCT .....                                                        | 87  |

| 5.2. Résultats de l'exploration architecturale.....                      | 88  |

| 5.2.1. Dhrystone .....                                                   | 89  |

| 5.2.2. IDCT .....                                                        | 92  |

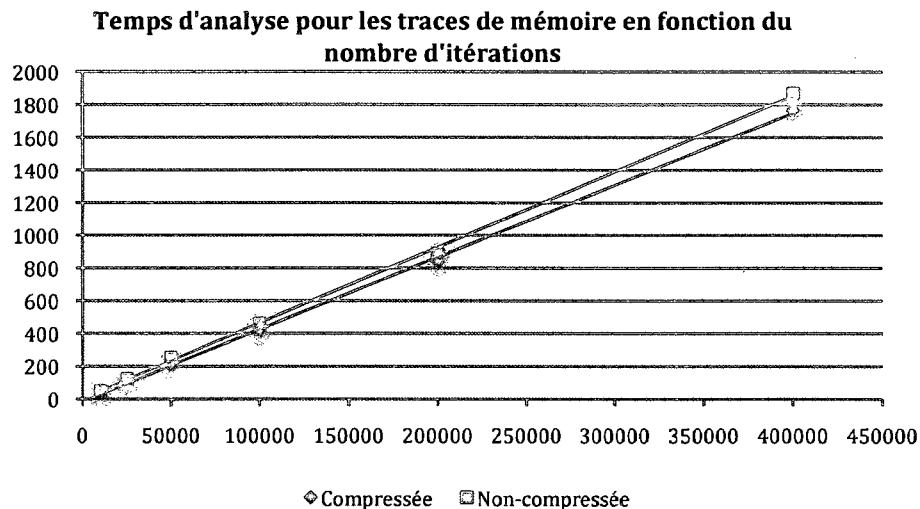

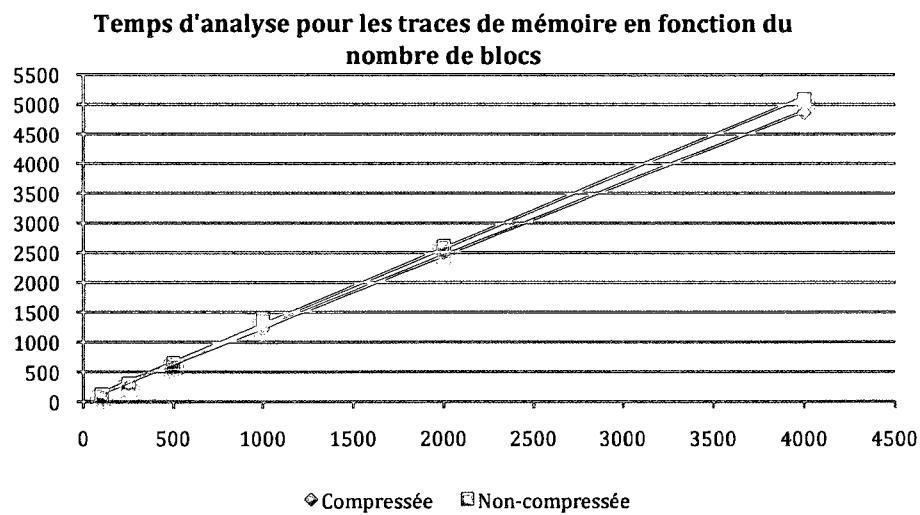

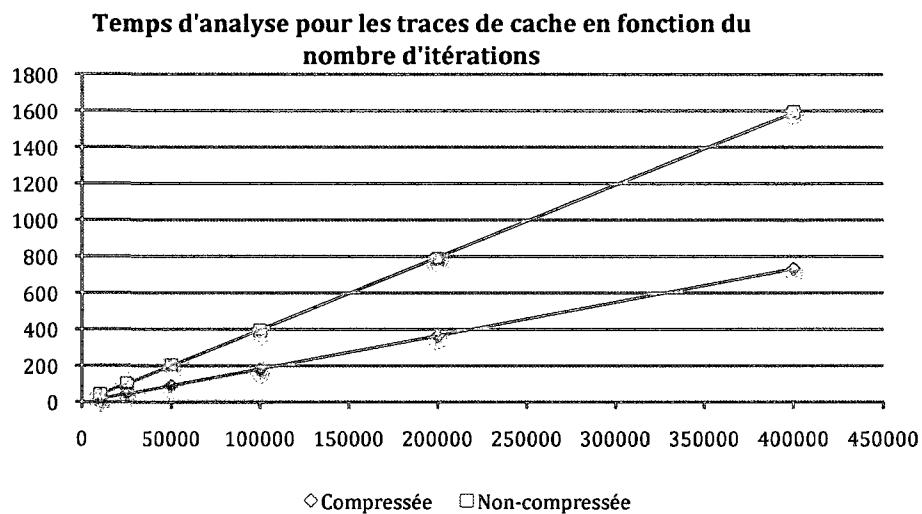

| 5.3. Efficacité des algorithmes de compression de trace .....            | 94  |

| 5.3.1. Efficacité de la compression sur la taille des traces .....       | 94  |

| 5.3.2. Efficacité de la compression sur le temps d'exécution .....       | 95  |

| 5.4. Extensibilité à d'autres processeurs/plateformes de simulation..... | 98  |

| 5.5. Comparaison avec d'autres travaux .....                             | 100 |

| 5.6. Rencontre des requis .....                                          | 101 |

| CONCLUSION ET TRAVAUX FUTURS .....                                       | 104 |

| RÉFÉRENCES.....                                                          | 108 |

| ANNEXES .....                                                            | 114 |

## LISTE DES FIGURES

|             |                                                                                         |    |

|-------------|-----------------------------------------------------------------------------------------|----|

| Figure 2.1  | Architecture d'un SoC.....                                                              | 9  |

| Figure 2.2  | Hiérarchie de mémoire .....                                                             | 10 |

| Figure 2.3  | Comparaison de la performance des processeurs et de la mémoire<br>DRAM.....             | 11 |

| Figure 2.4  | Mémoire cache à accès direct .....                                                      | 14 |

| Figure 2.5  | Fonctionnement d'une mémoire cache à accès direct.....                                  | 15 |

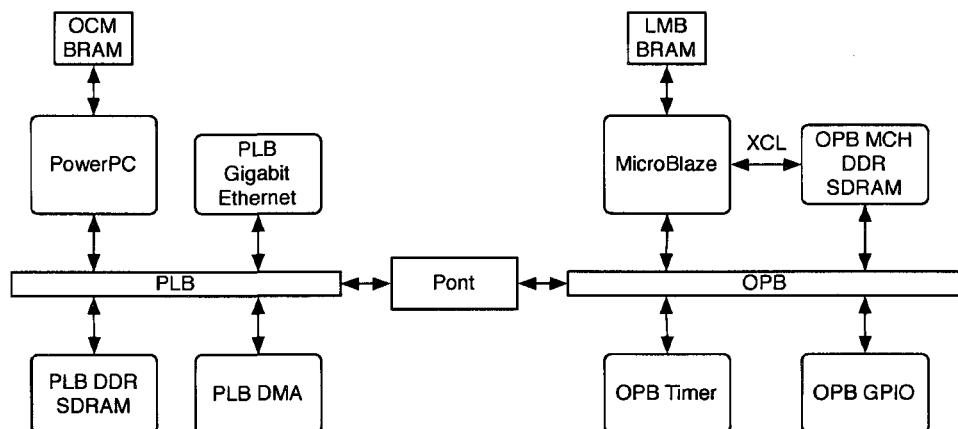

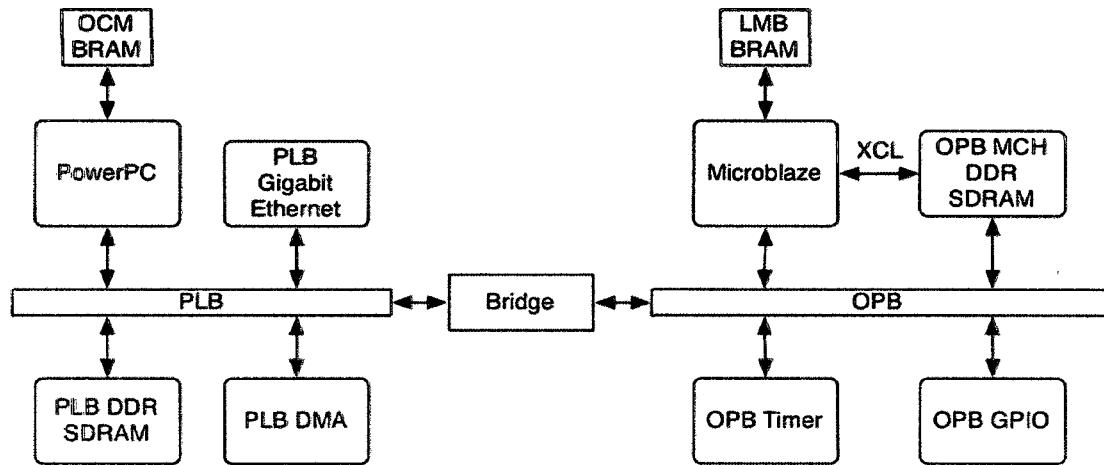

| Figure 3.1  | Exemple d'une plateforme Xilinx .....                                                   | 28 |

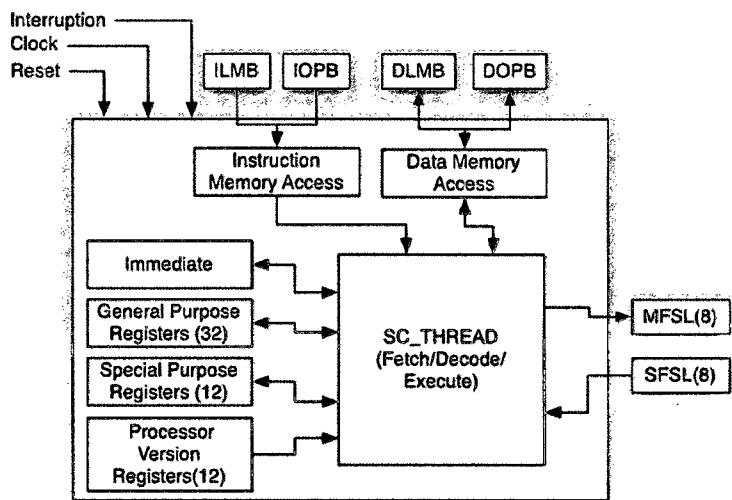

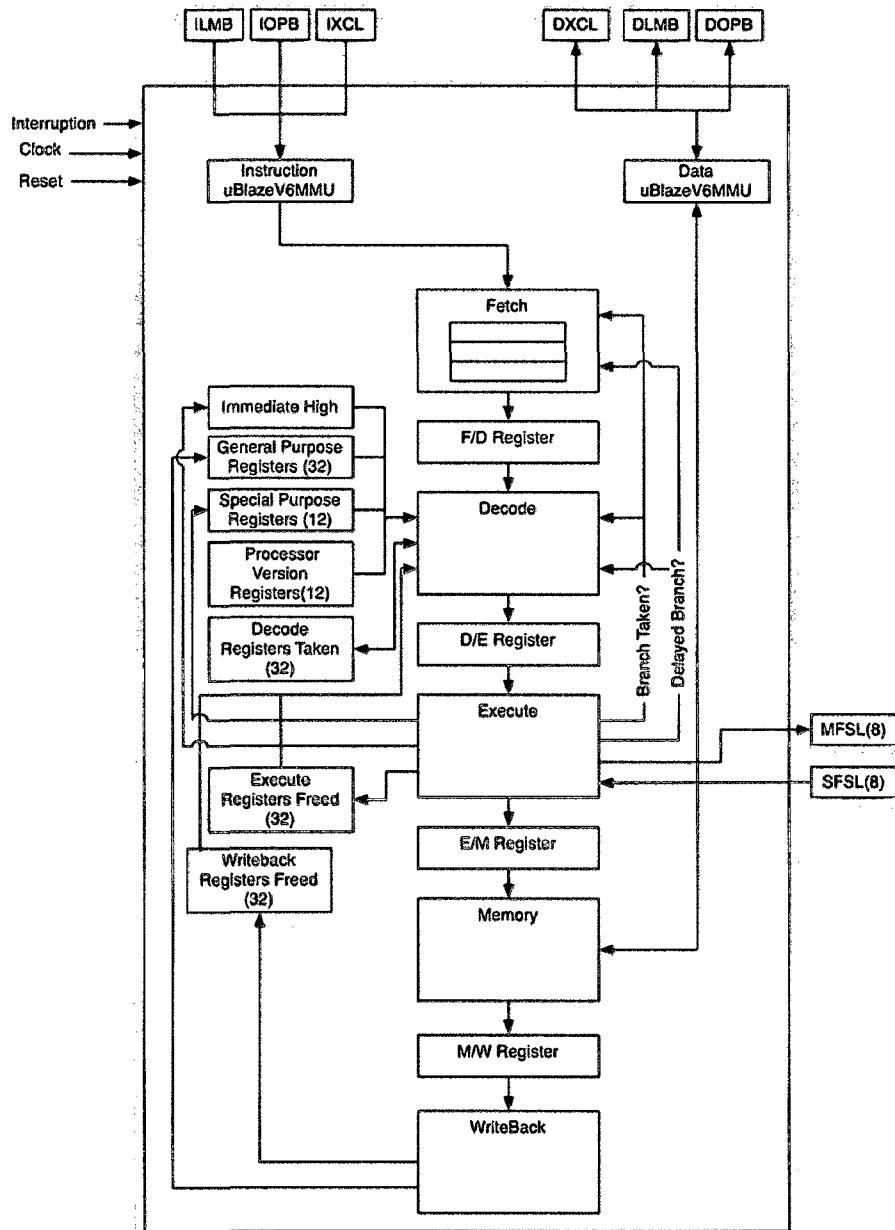

| Figure 3.2  | Schéma bloc du MicroBlaze.....                                                          | 31 |

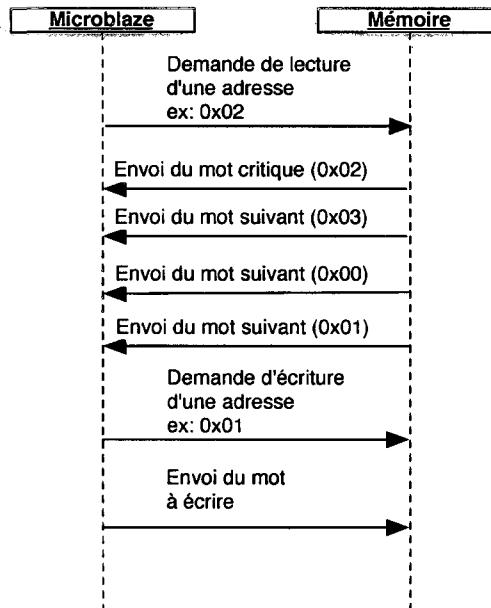

| Figure 3.3  | Diagramme de séquence du protocole XCL .....                                            | 34 |

| Figure 3.4  | Architecture de l'ISS initial du MicroBlaze .....                                       | 37 |

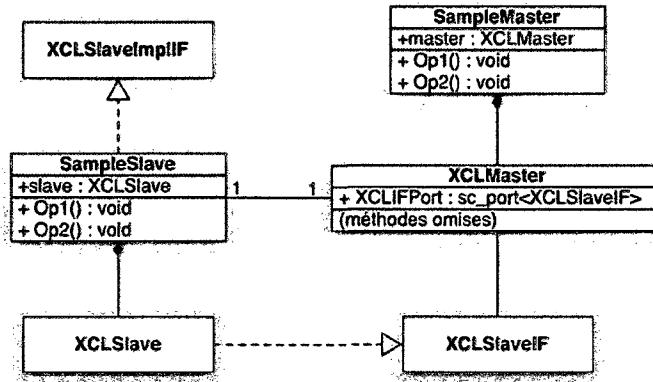

| Figure 3.5  | Exemple d'utilisation d'un lien XCL en simulation.....                                  | 40 |

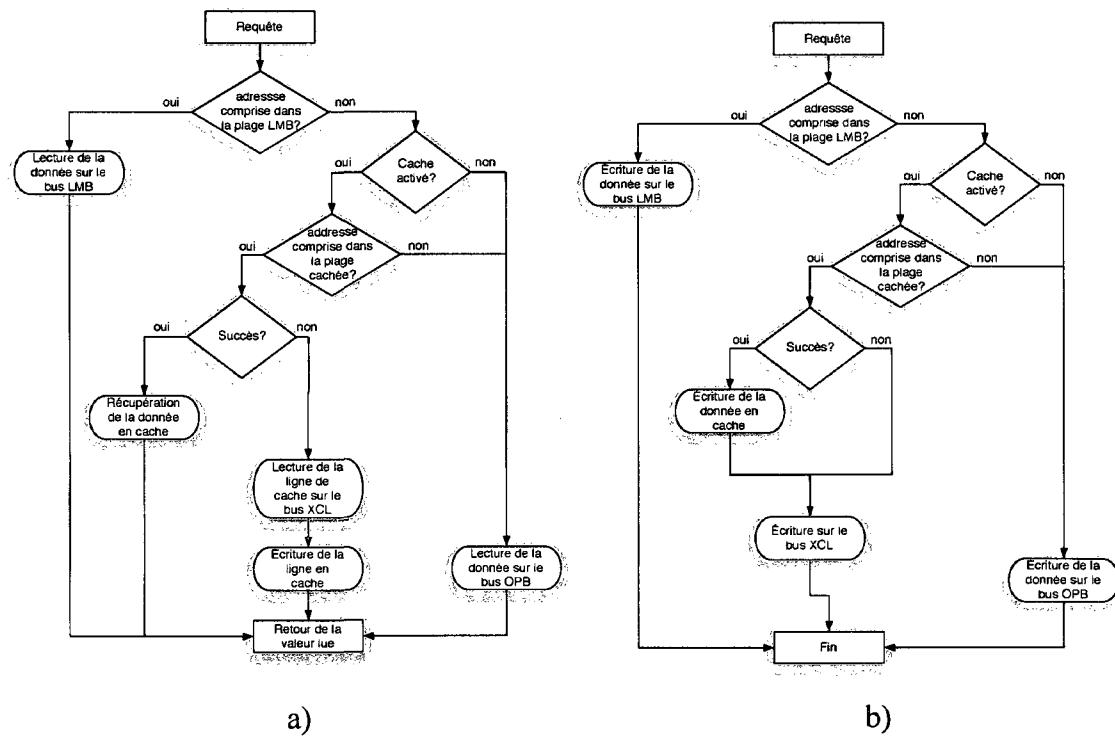

| Figure 3.6  | Logique de décision de la méthode d'accès .....                                         | 41 |

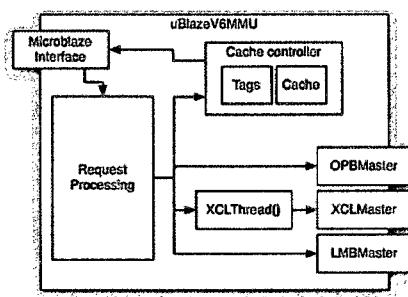

| Figure 3.7  | Schéma bloc du composant uBlazeV6MMU .....                                              | 42 |

| Figure 3.8  | Architecture de l'ISS modifié du MicroBlaze .....                                       | 44 |

| Figure 3.9  | Connexions entre le MicroBlaze et le contrôleur MCH OPB SDRAM .....                     | 50 |

| Figure 3.10 | Algorithme de compression de la trace de mémoire .....                                  | 53 |

| Figure 3.11 | Algorithme de compression de la trace de cache.....                                     | 54 |

| Figure 3.12 | Ajout de la trace dans l'ISS .....                                                      | 56 |

| Figure 4.1  | Flot d'exécution de MemoryOptimizer.....                                                | 58 |

| Figure 4.2  | Diagramme de flux de données du partitionnement de mémoire .....                        | 61 |

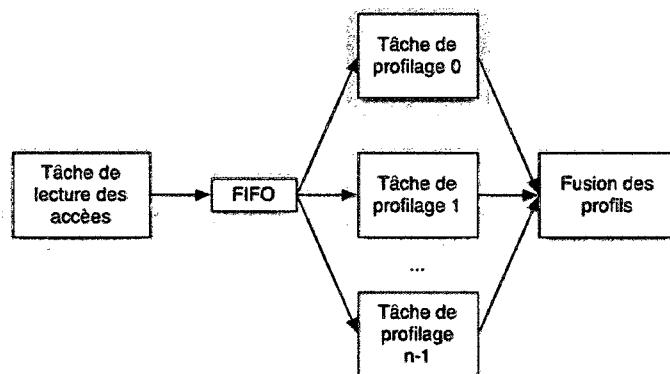

| Figure 4.3  | Modèle de multithreading pour le profilage .....                                        | 67 |

| Figure 4.4  | Algorithme d'évaluation de l'utilisation de la pile et du tas.....                      | 68 |

| Figure 4.5  | Algorithme d'ajout des sections en mémoire locale .....                                 | 75 |

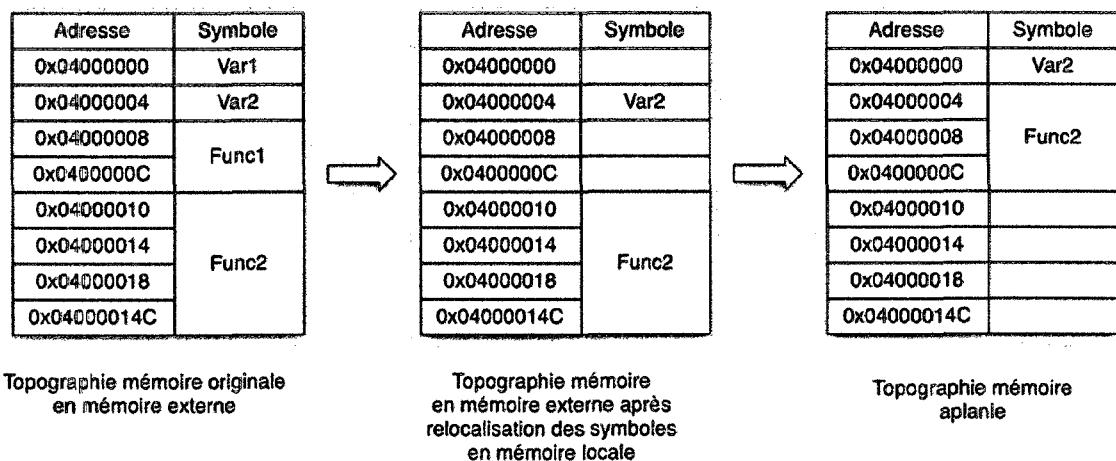

| Figure 4.6  | Aplanissement de la topographie mémoire.....                                            | 76 |

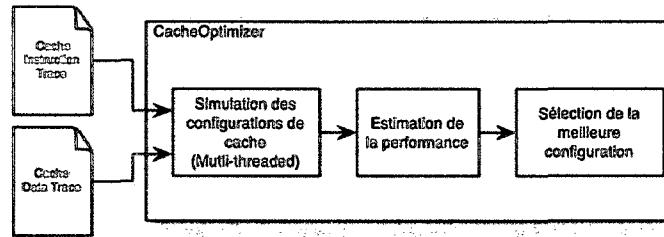

| Figure 4.7  | Diagramme de flux de données de l'optimisation de mémoire cache.....                    | 78 |

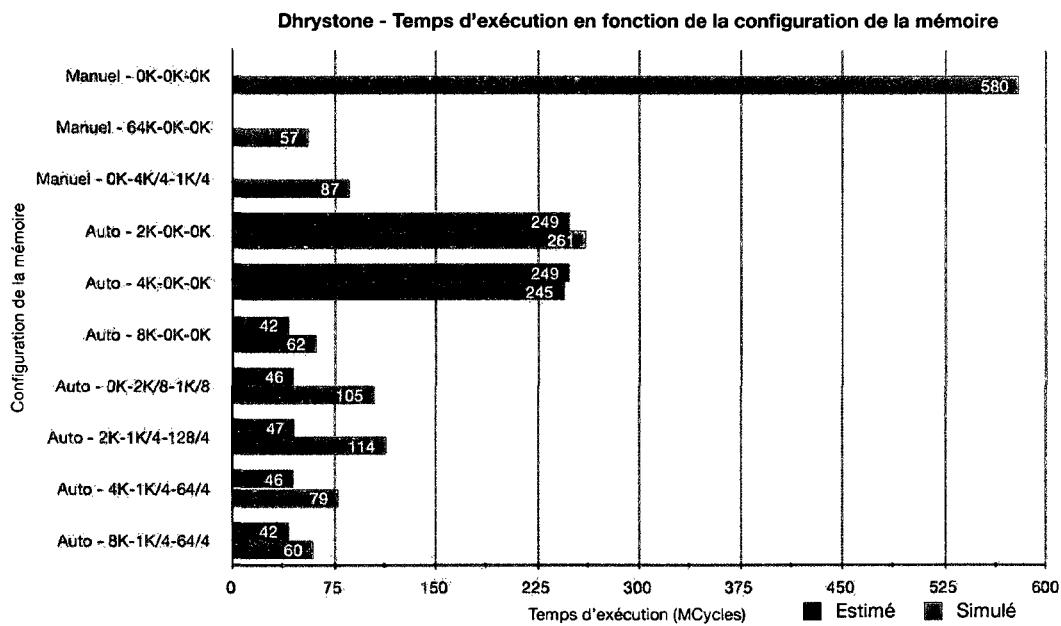

| Figure 5.1  | Temps d'exécution en fonction de la configuration de la mémoire pour<br>Dhrystone ..... | 89 |

|                                                                                                             |     |

|-------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.2 Temps d'exécution en fonction de la configuration de la mémoire pour IDCT .....                  | 92  |

| Figure 5.3 Temps d'analyse pour la trace de mémoire en fonction du nombre d'itérations pour Dhrystone ..... | 96  |

| Figure 5.4 Temps d'analyse pour la trace de mémoire en fonction du nombre de blocs.....                     | 96  |

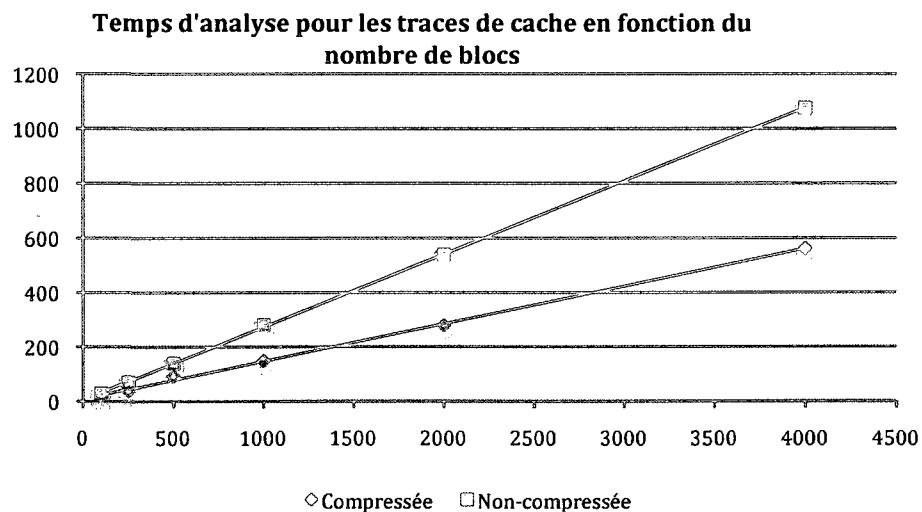

| Figure 5.5 Temps d'analyse pour la trace de cache en fonction du nombre d'itérations .....                  | 97  |

| Figure 5.6 Temps d'analyse pour la trace de cache en fonction du nombre de blocs pour IDCT .....            | 97  |

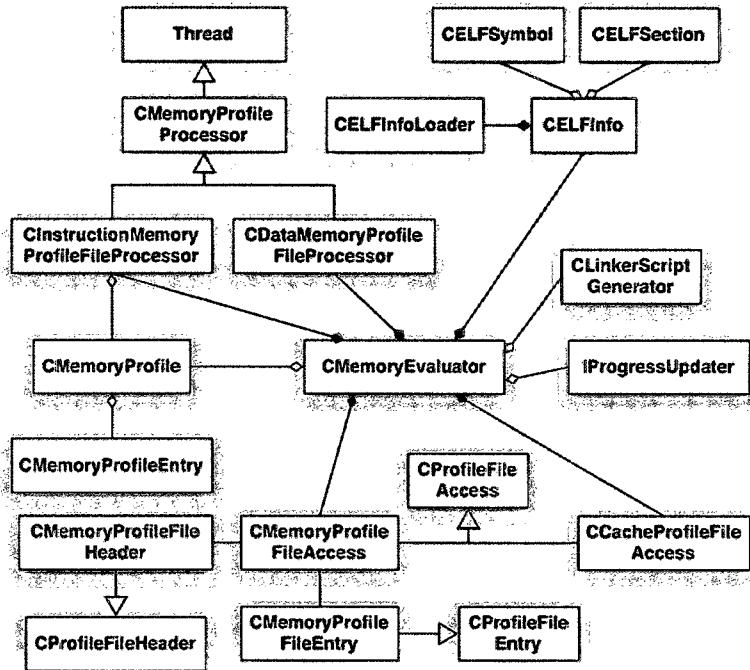

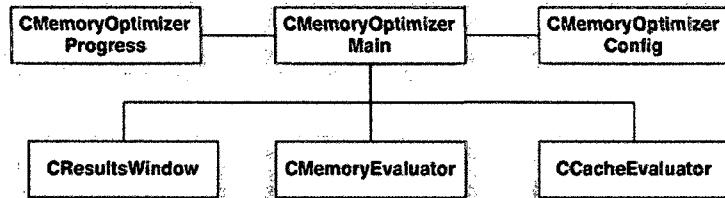

| Figure 5.7 Diagramme de classes simplifié du partitionnement de mémoire .....                               | 115 |

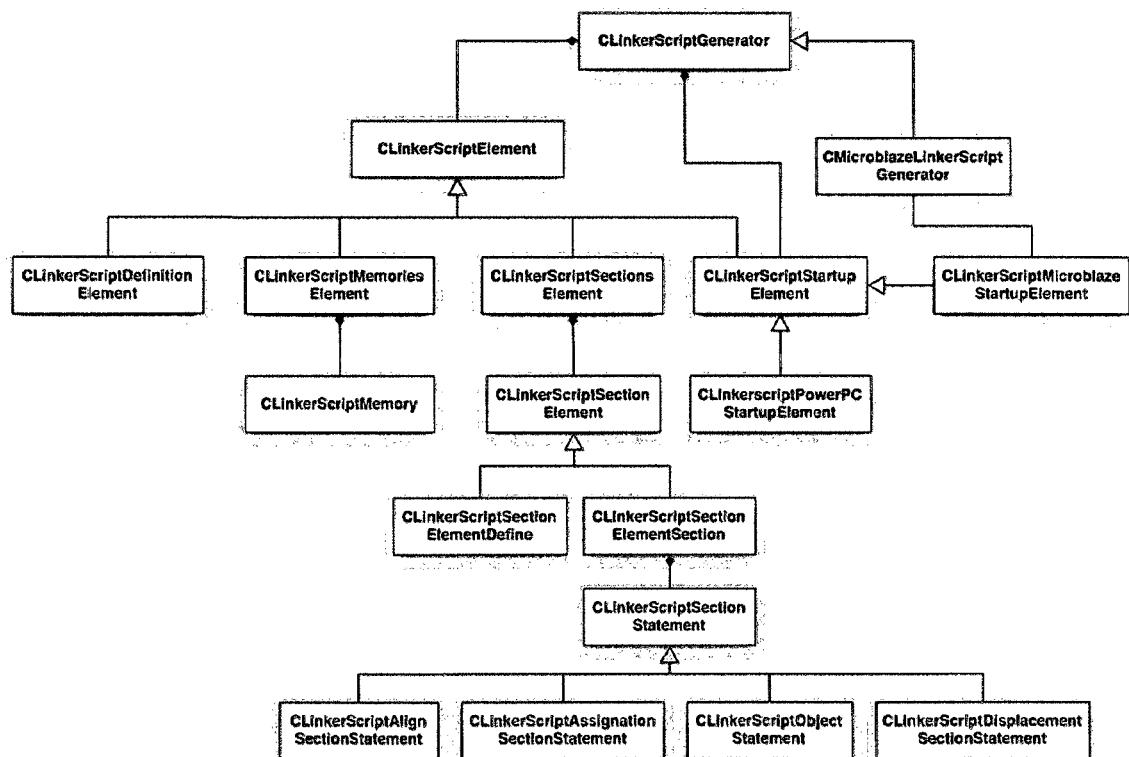

| Figure 5.8 Diagramme de classes du générateur de scripts de l'éditeur de liens.....                         | 117 |

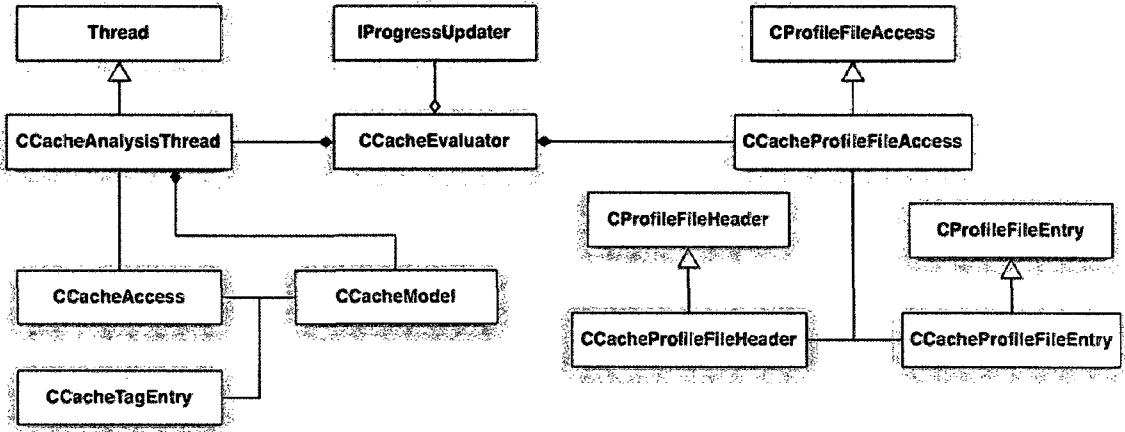

| Figure 5.9 Diagramme de classes simplifié de l'optimisation de mémoire cache.....                           | 119 |

| Figure 5.10 Création d'une nouvelle session d'optimisation .....                                            | 121 |

| Figure 5.11 Fenêtre de configuration .....                                                                  | 122 |

| Figure 5.12 Fenêtre indiquant la progression de l'optimisation .....                                        | 123 |

| Figure 5.13 Fenêtre des résultats – Survol .....                                                            | 124 |

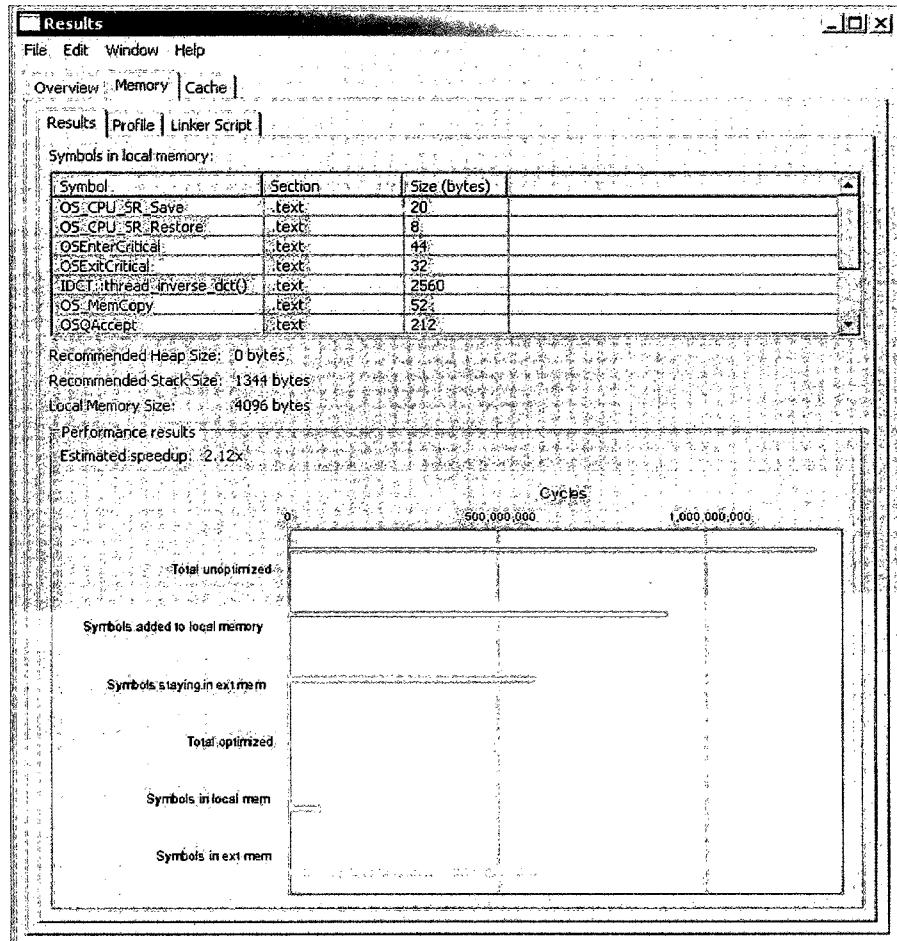

| Figure 5.14 Sous-onglet des résultats de partitionnement .....                                              | 125 |

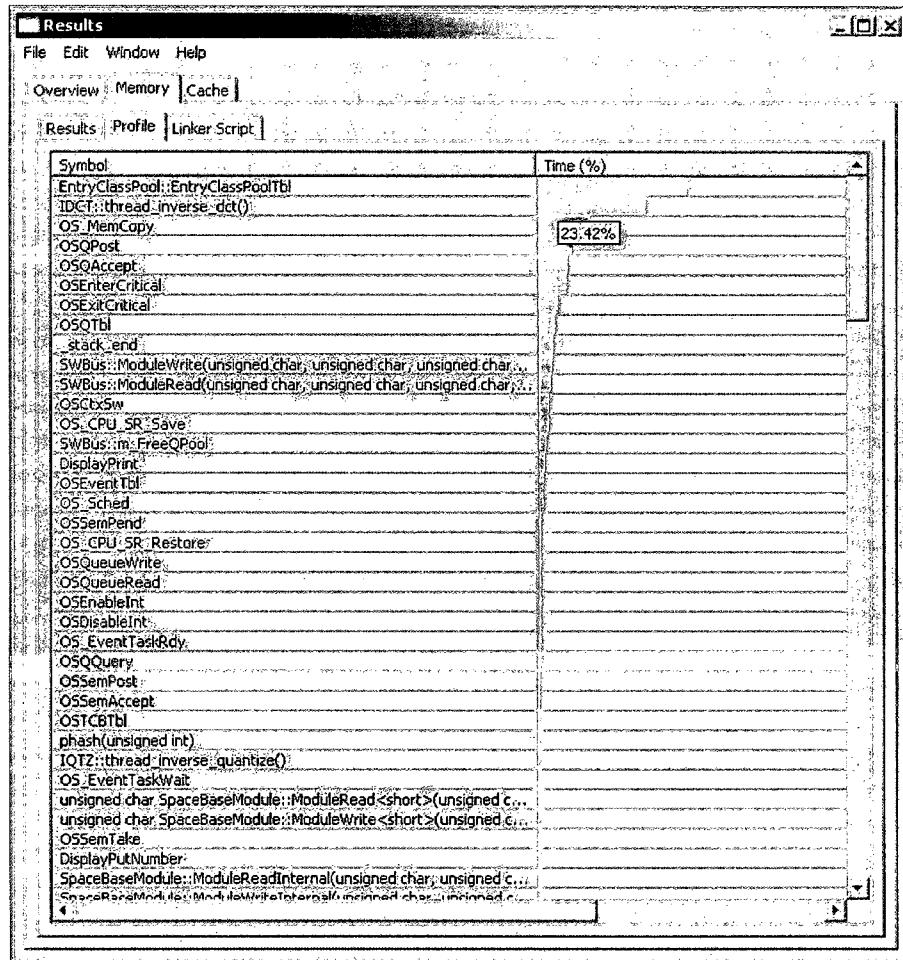

| Figure 5.15 Sous-onglet de profilage des symboles.....                                                      | 126 |

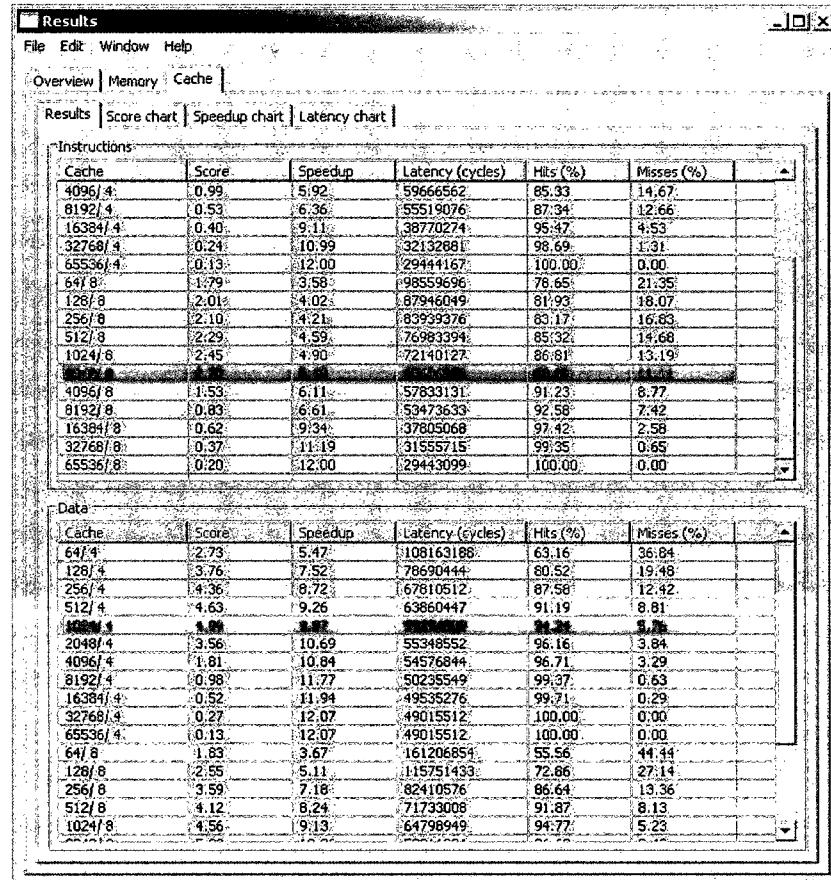

| Figure 5.16 Onglet de résultats de l'optimisation des mémoires cache .....                                  | 127 |

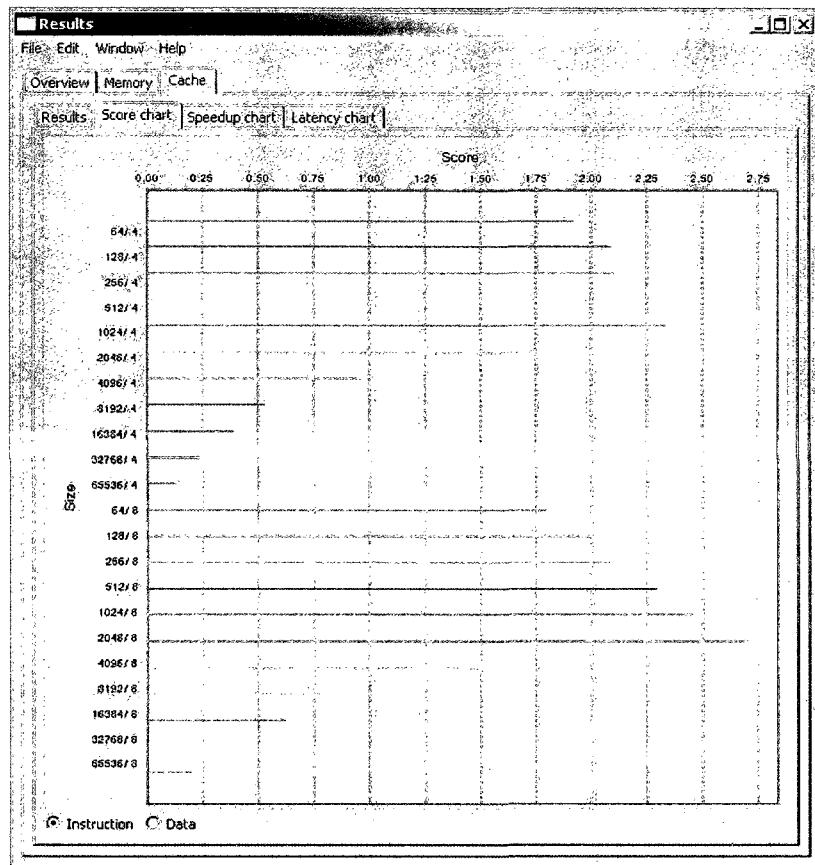

| Figure 5.17 Sous-onglet des résultats des configurations de cache .....                                     | 128 |

| Figure 5.18 Diagramme de classe des classes principales du GUI .....                                        | 129 |

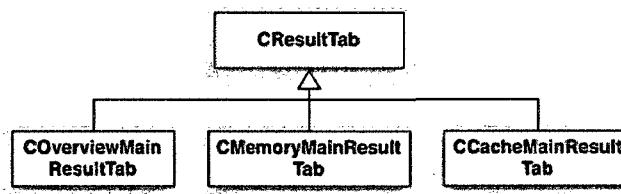

| Figure 5.19 Diagramme de classe de la fenêtre de résultats .....                                            | 129 |

| Figure 5.20 Diagramme de classe des onglets .....                                                           | 129 |

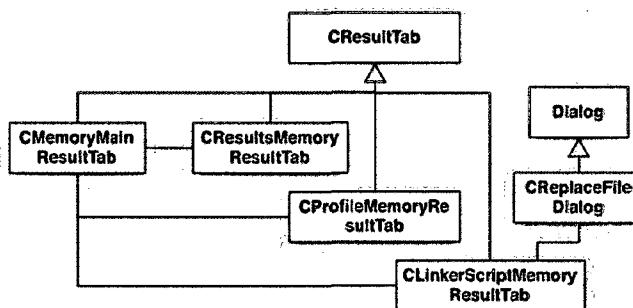

| Figure 5.21 Diagramme de classe des sous-onglets de partitionnement de mémoire....                          | 130 |

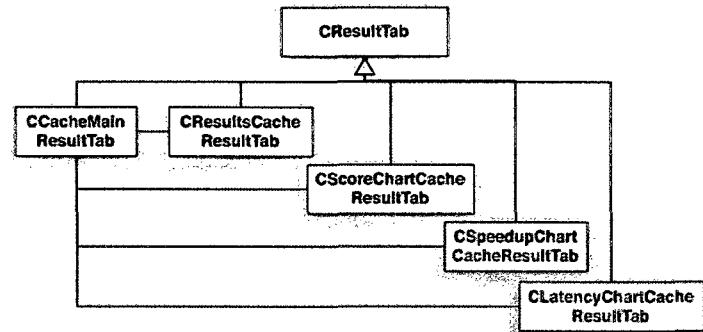

| Figure 5.22 Diagramme de classe des sous-onglets d'optimisation de cache .....                              | 131 |

## LISTE DES TABLEAUX

|                                                                                                            |     |

|------------------------------------------------------------------------------------------------------------|-----|

| Tableau 3.1 Structure des registres de pipeline.....                                                       | 45  |

| Tableau 3.2 En-tête de fichier de trace.....                                                               | 52  |

| Tableau 3.3 Entrées du fichier de trace .....                                                              | 52  |

| Tableau 4.1 Format de la sortie de l'outil mb-objdump .....                                                | 63  |

| Tableau 4.2 Exemple de sortie de l'outil mb-objdump .....                                                  | 64  |

| Tableau 5.1 Tailles suggérées du tas et de la pile pour Dhrystone .....                                    | 92  |

| Tableau 5.2 Tailles suggérées du tas et de la pile pour IDCT.....                                          | 94  |

| Tableau 5.3 Taille moyenne relative des traces compressées par rapport aux traces<br>non-compressées ..... | 95  |

| Tableau 5.4 Temps de simulation et d'exploration pour Dhrystone .....                                      | 102 |

| Tableau 5.5 Résultats de profilage pour Dhrystone .....                                                    | 132 |

| Tableau 5.6 Symboles en mémoire locale pour Dhrystone – 2K-1K/4-128/4 .....                                | 134 |

| Tableau 5.7 Symboles en mémoire locale pour Dhrystone – 4K-1K/4-64/4 .....                                 | 134 |

| Tableau 5.8 Symboles en mémoire locale pour Dhrystone – 8K-1K/4-64/4 .....                                 | 135 |

| Tableau 5.9 Résultats de profilage pour IDCT .....                                                         | 136 |

| Tableau 5.10 Symboles en mémoire locale pour IDCT – 2K-2K/8-1K/8 .....                                     | 139 |

| Tableau 5.11 Symboles en mémoire locale pour IDCT – 4K-2K/8-1K/8 .....                                     | 140 |

| Tableau 5.12 Symboles en mémoire locale pour IDCT – 8K-2K/8-2K/8 .....                                     | 140 |

| Tableau 5.13 Symboles en mémoire locale pour IDCT – 16K-2K/8-2K/8 .....                                    | 141 |

| Tableau 5.14 Symboles en mémoire locale pour IDCT – 32K-2K/8-1K/8 .....                                    | 141 |

| Tableau 5.15 Résultats de la cache d'instructions pour Dhrystone - 0K-2K/8-1K/8 ....                       | 143 |

| Tableau 5.16 Résultats de la cache de données pour Dhrystone - 0K-2K/8-1K8.....                            | 143 |

| Tableau 5.17 Résultats de la cache d'instructions pour Dhrystone - 2K-1K/4-128/4 ....                      | 144 |

| Tableau 5.18 Résultats de la cache de données pour Dhrystone - 2K-1K/4-128/4.....                          | 144 |

| Tableau 5.19 Résultats de la cache d'instructions pour Dhrystone - 4K-1K/4-64/4 .....                      | 145 |

| Tableau 5.20 Résultats de la cache de données pour Dhrystone - 4K-1K/4-64/4.....                           | 145 |

| Tableau 5.21 Résultats de la cache d'instructionss pour Dhrystone - 8K-1K/4-64/4 ....                      | 146 |

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| Tableau 5.22 Résultats de la cache de données pour Dhystone - 8K-1K/4-64/4.....   | 146 |

| Tableau 5.23 Résultats de la cache d'instructions pour IDCT - 0K-1K/4-1K/4 .....  | 147 |

| Tableau 5.24 Résultats de la cache de données pour IDCT - 0K-1K/4-1K/4 .....      | 148 |

| Tableau 5.25 Résultats de la cache d'instructions pour IDCT - 2K-2K/8-1K/8 .....  | 148 |

| Tableau 5.26 Résultats de la cache de données pour IDCT - 2K-2K/8-1K/8 .....      | 149 |

| Tableau 5.27 Résultats de la cache d'instructions pour IDCT - 4K-2K/8-1K/8 .....  | 149 |

| Tableau 5.28 Résultats de la cache de données pour IDCT - 4K-2K/8-1K/8 .....      | 150 |

| Tableau 5.29 Résultats de la cache d'instructions pour IDCT - 8K-2K/8-2K/8 .....  | 150 |

| Tableau 5.30 Résultats de la cache de données pour IDCT - 8K-2K/8-2K/8 .....      | 151 |

| Tableau 5.31 Résultats de la cache d'instructions pour IDCT - 16K-2K/8-2K/8 ..... | 151 |

| Tableau 5.32 Résultats de la cache de données pour IDCT - 16K-2K/8-2K/8 .....     | 152 |

| Tableau 5.33 Résultats de la cache d'instructions pour IDCT - 32K-2K/8-2K/8 ..... | 152 |

| Tableau 5.34 Résultats de la cache de données pour IDCT - 32K-2K/8-2K/8 .....     | 153 |

## LISTE DES ANNEXES

|                                                   |     |

|---------------------------------------------------|-----|

| ANNEXE A : DIAGRAMMES DE CLASSES .....            | 114 |

| ANNEXE B : INTERFACE GRAPHIQUE .....              | 120 |

| ANNEXE C : RÉSULTATS DE PROFILAGE .....           | 132 |

| ANNEXE D : RÉSULTATS DE SIMULATION DE CACHE ..... | 143 |

## LISTE DES ACRONYMES

|      |                                         |

|------|-----------------------------------------|

| ALU  | Arithmetic-Logic Unit                   |

| API  | Application Programming Interface       |

| APU  | Auxiliary Processing Unit               |

| ASIC | Application Specific Integrated Circuit |

| AST  | Abstract Syntax Tree                    |

| CA   | Cycle Accurate                          |

| CWF  | Critical Word First                     |

| BRAM | Block RAM                               |

| DDR  | Dual Data Rate                          |

| DMA  | Direct Memory Access                    |

| DRAM | Dynamic Random Access Memory            |

| DSP  | Digital Signal Processor                |

| ELF  | Executable and Linkable Format          |

| EMC  | External Memory Controller              |

| FIFO | First In First Out                      |

| FPGA | Field Programmable Gate Array           |

| FPU  | Floating Point Unit                     |

| FSL  | Fast Serial Link                        |

| GDB  | GNU Debugger                            |

| GUI  | Graphical User Interface                |

| HDL  | Hardware Description Language           |

| IDCT | Inverse Discrete Cosine Transform       |

| IF   | Interface                               |

| ISA  | Instruction Set Architecture            |

| ISS  | Instruction Set Simulator               |

|       |                                                                  |

|-------|------------------------------------------------------------------|

| LMB   | Local Memory Bus                                                 |

| LUT   | Look Up Table                                                    |

| MCH   | Multi Channel                                                    |

| MIPS  | Million of Instructions Per Second                               |

| MMU   | Memory Management Unit                                           |

| MPSoC | Multi-Processor System-on-Chip                                   |

| MSR   | Machine State Register                                           |

| OCM   | On-Chip Memory                                                   |

| OPB   | On-chip Peripheral Bus                                           |

| PC    | Program Counter                                                  |

| PIC   | Programmable Interrupt Controller                                |

| PLB   | Processor Local Bus                                              |

| RAM   | Random Access Memory                                             |

| RISC  | Reduced Instruction Set Computer                                 |

| RTL   | Register Transfer Level                                          |

| RTOS  | Real Time Operating System                                       |

| SDRAM | Synchronous DRAM                                                 |

| SPACE | SystemC Partitioning Aspects of Codesign and Exploration         |

| SRAM  | Static RAM                                                       |

| SoC   | System-on-chip                                                   |

| SWT   | Standard Widget Toolkit (Eclipse)                                |

| TLM   | Transaction-Level Modeling                                       |

| TTM   | Time-To-Market                                                   |

| TF    | Timed Functional                                                 |

| UART  | Universal Asynchronous Receiver/Transmitter                      |

| UTF   | Un-Timed Functional                                              |

| VHDL  | Very high speed integrated circuit Hardware Description Language |

| XCL   | Xilinx Cache Link                                                |

# CHAPITRE 1

## INTRODUCTION

Cette section introduit le concept de systèmes sur puce (SoC), concept central à ce mémoire. Elle traite des aspects de conception, méthodes de design, des hiérarchies de mémoire utilisées ainsi que des problèmes reliés à ces hiérarchies.

### 1.1. Les systèmes embarqués d'aujourd'hui

Au cours des dernières années, les systèmes embarqués sont devenus omniprésents. Ils sont utilisés dans une multitude de domaines d'application : télécommunication, divertissement, transport, équipement médical. Certains instruments de musique utilisent même des systèmes embarqués afin d'étendre leurs fonctionnalités [1].

Certains produits n'utilisent qu'un seul processeur et d'autres en utilisent plusieurs ce qui permet d'améliorer les performances ou encore la fiabilité du système. Un exemple extrême est l'automobile de la série 7 de BMW qui contient plus de 100 processeurs [2]. Vu la quantité de voitures et de cellulaires vendus chaque année, il n'est donc pas étonnant d'apprendre que le marché des processeurs embarqués représentait 98% des ventes de processeurs [3] en 2005.

Bien qu'il n'ait été question jusqu'ici strictement que de processeurs embarqués, un système embarqué ne se résume pas seulement à un processeur. Un système embarqué se définit également par les accélérateurs matériels, la mémoire et les entrées-sorties. Bref, un système embarqué est bien souvent similaire à un ordinateur de bureau avec une différence majeure : il n'est en général conçu que pour exécuter un nombre limité de tâches [4], il est souvent conçu de la manière la plus performante et la moins coûteuse possible et avec un budget de puissance limité. Par contre, avec la miniaturisation des

transistors, il est maintenant possible de concevoir des systèmes embarqués très complexes sur une seule puce (SoC) et capables d'effectuer une variété grandissante de tâches comme les téléphones cellulaires dits « intelligents ».

## 1.2. Problématique

La complexification continue des SoCs et des systèmes multiprocesseurs sur puce (MPSoC) est en partie possible grâce à la célèbre loi de Moore. Cette loi, formulée originellement en 1965 par Gordon Moore [5] et révisée en 1975 [6], stipule que le nombre de transistors sur les puces double chaque 24 mois. Cette complexification des systèmes engendre un écart de productivité entre les ressources disponibles sur les puces (tant sur les ASIC que les FPGA) et la difficulté de concevoir du matériel utilisant ces ressources. Ce problème de productivité peut être atténué par l'utilisation des processeurs embarqués dans les SoC. L'utilisation de ces processeurs permet de diminuer le temps de développement du circuit [7] puisque l'on utilise des blocs déjà conçus et permet de diminuer le temps de conception du système puisque le comportement du système peut maintenant être codé en langage de plus haut niveau (en C par exemple) par opposition au VHDL. Afin de simplifier davantage la conception des programmes, un système d'exploitation peut être utilisé afin de fournir des mécanismes de synchronisation, d'exécution de tâches multiple et d'abstraction de matériel.

L'environnement d'exploration architecturale et de conception SPACE [44], basé sur la bibliothèque SystemC, vise à simplifier davantage ce processus de développement en proposant entre autres un mécanisme d'abstraction des détails d'implémentation des SoC. À l'aide de SPACE, il est possible d'effectuer des partitionnements logiciel-matériel et de créer facilement des systèmes multiprocesseurs. Les systèmes peuvent ensuite être simulés et optimisés à l'aide d'une suite d'outils de monitoring. Ceci permet donc de réduire significativement les temps de conception et de validation.

En général, le concepteur tente de stocker le programme à exécuter dans une mémoire intégrée au SoC très rapide. Puisque la technologie des mémoires ne progresse pas au même rythme que la technologie des processeurs, la taille de ces mémoires est limitée. Dans le cas des FPGA de Xilinx, la mémoire intégrée BRAM est d'une taille de quelques centaines de kilo-octets. Bien que cette mémoire soit de petite taille, elle est très rapide et peut exécuter jusqu'à 2 transferts par cycle ce qui permet d'exécuter le programme à pleine vitesse [14] lorsqu'elle est connectée directement à un processeur (mémoire locale au processeur). Un problème survient lorsque la taille des programmes dépasse la taille de la mémoire intégrée. Le concepteur est alors forcé d'utiliser une mémoire externe, plus volumineuse, mais aussi beaucoup plus lente. Le temps d'accès à une donnée passe donc de 1 cycle à plus de 10 cycles. De plus, dans un système multi processeur, les processeurs doivent alors se faire compétition pour obtenir l'accès à la mémoire, ce qui augmente encore une fois le temps d'accès moyen. Ce problème ne se pose généralement pas avec des mémoires locales puisque l'on peut dédier une mémoire à chaque processeur.

Il existe quelques méthodes afin d'augmenter la performance du système dans ces situations. Ici, deux méthodes seront discutées. Premièrement, il est possible d'utiliser des mémoires cache [13] qui permettent alors de stocker dynamiquement les instructions et les données récemment utilisées dans une mémoire rapide. Cette approche est simple et permet d'obtenir de très bonnes performances. Par contre, il reste difficile de déterminer la taille optimale de la mémoire cache afin de maximiser la performance. Également, dans certains cas la taille optimale de la mémoire cache peut se révéler trop importante et donc difficile à implémenter.

La deuxième méthode consiste à stocker une petite partie du code et des données dans une mémoire locale au processeur et de stocker le reste dans la mémoire externe. Encore une fois, cette solution n'est pas parfaite puisqu'il reste difficile de déterminer les portions du programme à stocker dans cette mémoire locale. De plus, les outils

disponibles permettent rarement de morceler un programme et d'en stocker des portions dans des mémoires arbitraires. Finalement, il est toujours possible de tenter de diminuer la taille du programme en coupant dans le code ou en utilisant des bibliothèques plus légères, mais cette approche n'est pas toujours réalisable en pratique.

### **1.3. Objectif**

L'objectif de ce travail consiste à développer un outil qui permettra de tirer profit de la hiérarchie mémoire disponible sur un système sur puce afin d'améliorer la performance d'un programme s'exécutant sur un microprocesseur embarqué (ici le MicroBlaze). Une plateforme de simulation de système sur puce doit être utilisée afin de générer des métriques qui seront ensuite analysées par l'outil qui déterminera la meilleure combinaison de mémoire locale et de mémoire cache.

L'outil développé doit automatiquement minimiser la taille de la mémoire locale utilisée de même que la taille de la mémoire cache tout en tentant de maximiser la performance du programme à exécuter. Cet outil doit être plus rapide que les méthodes manuelles et ne doit être minimalement dépendant de la plateforme de simulation. Seul le mécanisme de génération de métriques doit dépendre de la plateforme de simulation. L'outil doit ensuite analyser les métriques d'exécution récoltées afin de proposer une configuration à l'utilisateur. L'outil d'analyse doit présenter à l'utilisateur certaines options de configuration comme la taille maximale de mémoire locale à utiliser. Finalement, les résultats doivent être présentés dans une interface graphique à titre d'application autonome, mais l'outil doit également avoir la possibilité d'être intégré dans d'autres environnements et doit donc posséder des interfaces de programmation simples à utiliser.

## 1.4. Méthodologie

Afin de réaliser l'objectif décrit ci-haut, plusieurs étapes sont requises. Premièrement, une familiarisation avec SystemC et l'environnement SPACE est nécessaire. De plus, une étude des concepts de modélisation de haut niveau comme par exemple le Transaction Level Modeling (TLM) est de mise. Ceci permettra de réaliser les étapes suivantes qui reposent sur la plateforme SPACE.

Ensuite, le simulateur de processeur MicroBlaze, disponible sur la plateforme SPACE, devra être étendu et amélioré afin de le mettre à niveau avec la dernière mouture disponible en matériel, notamment la présence de mémoire cache. L'implémentation de ce simulateur doit également être modifiée afin d'améliorer l'exactitude de la simulation en termes de cycles d'exécution. De plus, afin de connecter le processeur directement avec la mémoire comme il est possible en matériel, un contrôleur de mémoire SDRAM supportant le protocole XCL sera implémenté.

L'étape subséquente sera la définition et l'implémentation du mécanisme de récolte des métriques. Ce mécanisme fournira à l'outil d'analyse toute l'information nécessaire afin d'optimiser la configuration de la hiérarchie mémoire sous la forme de fichiers de trace d'exécution.

Par la suite, une méthode d'optimisation doit être développée afin de produire les résultats désirés. Le problème sera abordé en deux volets : le partitionnement de mémoire et l'optimisation de la mémoire cache. Le partitionnement de mémoire cible la relocalisation des instructions et données les plus utilisées dans la mémoire locale du processeur. L'optimisation de la mémoire cache vise, quant à elle, à minimiser la taille des mémoires cache d'instructions et de données et d'obtenir une bonne accélération. Pour chacun de ces volets, la littérature reliée devra être étudiée afin de recenser les différentes approches possibles.

Le partitionnement de la mémoire utilisera un profil d'accès mémoire pour lequel chaque fonction et donnée se voit attribuer un pourcentage d'utilisation du temps processeur. Les fonctions et données présentant un grand pourcentage seront alors relocalisées en mémoire locale. Viendra ensuite l'optimisation de la mémoire cache qui se fera en simulant les différentes configurations de cache possibles. Pour chaque configuration simulée, la performance de cette configuration sera estimée, ce qui permettra de déterminer la configuration de mémoire cache la plus appropriée.

L'étape finale consistera du développement de l'interface graphique qui permettra de démarrer l'analyse et de visualiser les configurations et les résultats obtenus. Les résultats seront visibles sous une forme textuelle et sous forme de graphiques. L'interface graphique doit être simple d'utilisation tout en restant flexible.

### **1.5. Contributions**

Ce travail apporte deux contributions. Premièrement, de nouveaux composants exhibant les fonctionnalités disponibles en matériel, de même qu'un comportement temporel plus précis sont maintenant disponibles dans la plateforme SPACE, une plateforme de conception haut niveau de systèmes sur puce. Avec ces nouveaux composants, il est désormais possible d'obtenir des métriques de performance plus précises pour le processeur, mais également pour l'ensemble du système. Il est également possible d'obtenir une trace d'exécution qui peut être utilisée à d'autres fins que celles prévues lors de la conception.

Finalement, un outil complet de partitionnement et d'optimisation de la mémoire a été développé. Cet outil permet au concepteur de connaître la configuration mémoire avec laquelle sa plateforme produira la meilleure performance tout en tentant de minimiser le coût en matériel. Le concepteur n'a plus à tenter de réduire la taille du programme afin de le placer entièrement dans la mémoire locale ou d'effectuer des dizaines de

simulations afin de connaître la taille optimale de la mémoire cache. Avec l'outil de partitionnement et d'optimisation, le concepteur n'a qu'à simuler une fois son système pour générer les traces d'exécution, démarrer l'outil d'analyse et reconfigurer son système avec la configuration suggérée. Le concepteur peut ensuite simuler le système et comparer la performance du système en simulation avec la performance estimée par l'outil. Comparativement aux méthodes existantes, la méthode proposée permet d'optimiser à la fois la mémoire locale et la mémoire cache en plus de générer le fichier script de l'éditeur de liens (*linker script*) à l'aide d'un seul outil. L'outil permet également de visualiser les résultats dans une interface graphique, ce qui n'est pas possible dans les autres travaux existants.

## 1.6. Organisation du mémoire

Ce mémoire est organisé en cinq chapitres. Le présent chapitre sert d'introduction aux systèmes embarqués et aux méthodes de conception de ces systèmes. Le deuxième chapitre présente une revue des différents concepts d'architecture de mémoire et des méthodes développées dans le passé afin de tirer profit de ces architectures. Le troisième chapitre décrit le développement et l'intégration de composants additionnels à l'environnement SPACE qui permettront de générer les données nécessaires à l'outil de partitionnement de la hiérarchie mémoire développé. Le chapitre 4 présente les objectifs et la conception de l'outil de même que les différents mécanismes utilisés par l'outil. Le dernier chapitre présente les gains de performance obtenus avec deux applications et présente des comparaisons entre les performances estimées par l'outil et les performances en simulation. Finalement, la conclusion résume le travail de recherche qui a été accompli et suggère des améliorations et des travaux futurs.

## CHAPITRE 2

# SYSTÈMES SUR PUCE: HIÉRARCHIE MÉMOIRE, LOGICIEL ET OPTIMISATION

L'avancement constant des procédés lithographiques permet aujourd'hui d'intégrer près de deux milliards de transistors sur une seule puce [8]. Ce nombre impressionnant de transistors signifie qu'il est maintenant possible de concevoir des systèmes multiprocesseurs sur puce contenant jusqu'à 8 processeurs ou même plus. Cette nouvelle réalité permet aux SoC de suivre une évolution similaire à celle des logiciels d'ordinateurs de bureau. Le développement peut maintenant s'effectuer à un niveau d'abstraction plus élevé et ainsi diminuer le délai de développement et de commercialisation d'un produit (TTM). Le développement passe donc du design de matériel dédié complexe au design de logiciel s'exécutant sur microprocesseur.

Ce chapitre introduit tout d'abord l'architecture mémoire des systèmes sur puce centrés sur un processeur. Par la suite, un survol du processus de compilation de la plateforme logicielle est effectué. Les différentes approches utilisées pour améliorer la performance de la plateforme logicielle à l'aide de la hiérarchie de mémoire sont ensuite discutées. Ensuite, la librairie SPACE qui servira à la simulation est introduite et est suivie d'une brève comparaison de l'approche utilisée avec les travaux antérieurs est présentée. Finalement, un bref retour sur les concepts vus au cours de ce chapitre est effectué.

### 2.1. Hiérarchie mémoire

L'exécution d'un logiciel sur un processeur implique la présence de différents composants. Une mémoire doit ensuite être présente afin de stocker le logiciel qui sera exécuté. Lorsque le logiciel devient volumineux, il devient nécessaire d'utiliser une

mémoire externe à la puce. L'utilisation d'une hiérarchie de mémoire devient alors inévitable afin d'assurer la performance du système. En effet, si la mémoire ne peut fournir le processeur en données, ce dernier se retrouve sous-utilisé et sous-performant.

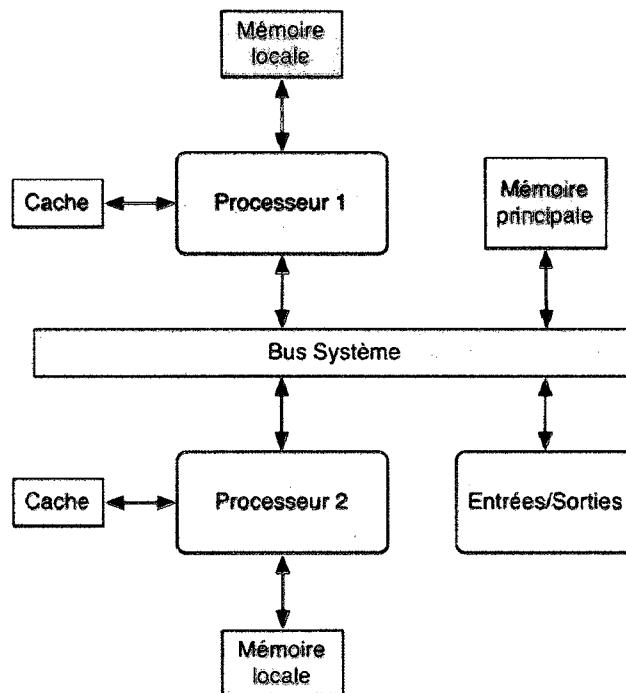

La Figure 2.1 illustre l'architecture simplifiée d'un SoC. Ce SoC pourrait par exemple être un système sur FPGA basé sur les cœurs de processeurs logiciels MicroBlaze (de l'anglais *softcore*). Dans cette architecture, chaque processeur est connecté directement à une mémoire locale ainsi qu'à une mémoire cache. De plus, les processeurs sont reliés par l'entremise du bus système à une mémoire principale externe à la puce.

**Figure 2.1 Architecture d'un SoC**

Dans une telle situation, la hiérarchie de mémoire prend alors tout son sens. Si chaque processeur doit sans cesse utiliser le bus pour récupérer les instructions qu'il doit exécuter ainsi que les données à lire et à écrire, la bande passante disponible à chaque processeur sera divisée au mieux par deux. Lorsque les autres composants sur le bus entrent en jeu tel que les accélérateurs matériels, interfaces d'entrées/sorties ou encore

des modules DMA, la situation s'empire. Non seulement la mémoire ne peut suffire à la demande, mais le bus non plus. Une hiérarchie de mémoire est donc nécessaire afin d'alléger le trafic et de permettre aux processeurs de réaliser leur plein potentiel.

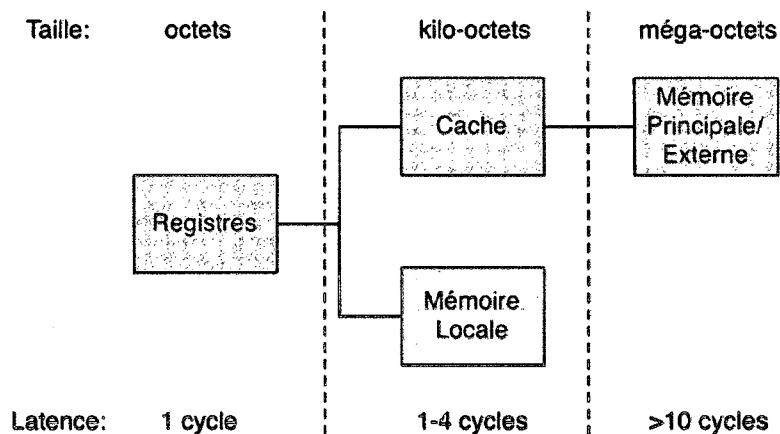

Une hiérarchie de mémoire se compose de mémoires petites et rapides en allant vers des mémoires de plus en plus volumineuses et lentes (Figure 2.2).

Figure 2.2 Hiérarchie de mémoire

Les registres sont internes au processeur et sont généralement de taille avoisinant les 100 octets. Ils sont généralement implantés sous la forme de bascules et sont donc très rapides d'accès. La mémoire locale et la mémoire cache quant à elles sont plus volumineuses et peuvent aller jusqu'à plusieurs centaines de kilo-octets. Elles peuvent par contre être légèrement plus lentes que les registres avec une latence de quelques cycles. Finalement, la mémoire externe peut atteindre des tailles de quelques mégaoctets à quelques giga-octets selon les besoins. Évidemment, ces tailles apportent un important coût en terme de performance. Par conséquent, le temps d'accès de ces mémoires peut être très grand, de l'ordre des dizaines de cycles et pouvant aller même à des centaines de cycles. Dans les sections suivantes, les mémoires principales, mémoires caches et mémoires locales seront discutées plus en détail.

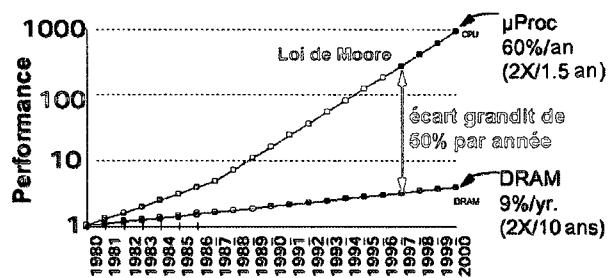

### 2.1.1. Mémoire principale

La mémoire principale d'un SoC est généralement présente sous forme de mémoire DRAM et est externe au SoC. Cette technologie permet de produire de la mémoire volumineuse à un faible coût comparativement à la technologie utilisée pour les registres et la mémoire cache. Bien que cette technologie permette de stocker une grande quantité de mémoire sur une seule barrette (des barrettes de 4 Go sont maintenant disponibles sur le marché), le temps d'accès s'en trouve grandement affecté. En effet, il n'est pas rare de voir le processeur attendre 10 ou même 100 cycles pour accéder à une seule donnée.

Figure 2.3 Comparaison de la performance des processeurs et de la mémoire DRAM

L'utilisation de la mémoire principale est souvent inévitable pour des systèmes relativement complexes mais a comme effet de ralentir considérablement le programme exécuté. Dans ce cas, il devient donc approprié d'ajouter au système une mémoire cache ou une mémoire locale afin d'accélérer la performance.

### 2.1.2. Mémoire locale

Certains systèmes, par exemple le MicroBlaze, disposent d'une connexion dédiée à de la mémoire intégrée sur le SoC. Sur d'autres systèmes, comme dans le cas d'un système basé sur le processeur PowerPC, cette mémoire est connectée au bus principal. Ce type de mémoire se nomme «mémoire locale» puisqu'elle est intégrée au SoC et connectée au

processeur. Son emplacement et sa technologie d'implémentation (souvent de la SRAM) lui permettent d'offrir des temps d'accès très rapides dans les environs de 1 à 2 cycles d'horloge.

La mémoire locale opère de façon identique à la mémoire principale, c'est-à-dire qu'elle doit être gérée de façon explicite. Il est donc du ressort du programmeur ou du compilateur de stocker les données dans cette mémoire. Son utilisation est donc bien différente de la mémoire cache qui est transparente au programme. L'avantage de cette approche est que le programmeur peut lui-même déterminer le contenu de cette mémoire et donc peut donner priorité à certaines données ou certaines fonctions. Ceci, couplé au temps d'accès constant, permet à la mémoire locale d'assurer le déterminisme. Cela contraste avec la mémoire cache qui ne peut offrir ce déterminisme puisque le cache tente de minimiser le temps d'accès moyen et non de garantir un temps d'accès minimal.

Les mémoire locales sont déjà très utilisées dans les processeurs DSP [9] et gagnent en popularité dans les processeurs conventionnels. Un exemple de processeur commercial utilisant plusieurs mémoires locales, de façon à permettre aux différentes unités de fonctionner à leur performance maximale, est le processeur Cell [10] de Sony, Toshiba et IBM. Ce processeur contient 8 co-processeurs vectoriels contenant chacun 256 Ko de mémoire locale. Chaque mémoire locale peut être accédée par les autres co-processeurs via un DMA (et moyennant un coût en latence d'accès) ce qui permet, par exemple, de réaliser une architecture multi processeurs pipelinée en minimisant les accès à la mémoire principale externe.

### 2.1.3. Mémoire cache

La mémoire cache [13] a pour but de diminuer le temps d'accès moyen aux instructions et aux données. C'est une mémoire rapide dont le contenu est modifié dynamiquement selon le comportement du programme exécuté. La mémoire cache tire profit des

principes de localité : elle met à profit le principe de localité temporelle et de localité spatiale.

Le principe de localité temporelle est le principe selon lequel une donnée récemment utilisée a de bonnes chances d'être réutilisée dans le futur. Les mémoires caches permettent donc de stocker dans une mémoire rapide les instructions et les données récemment utilisées dans l'espoir qu'elles seront réutilisées dans le futur. Ceci permet donc d'éviter d'accéder à la mémoire principale.

Le principe de localité spatiale quant à lui est le principe selon lequel la donnée qui suit (dans la mémoire) la donnée accédée a de bonnes chances d'être accédée dans le futur. En règle générale, les mémoires caches ne transfèrent donc pas uniquement la donnée nécessaire mais aussi les quelques données qui la suivent. Ceci est particulièrement utile lors de l'exécution d'une boucle, par exemple, où la même séquence d'instructions est exécutée à répétition.

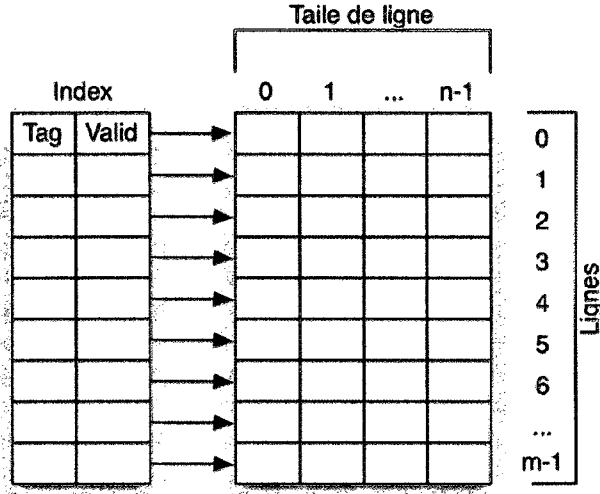

L'implémentation d'un cache simple peut être conceptualisée sous la forme de 2 tableaux (Figure 2.4). Le premier tableau agit à titre d'index et le deuxième tableau agit sous forme de conteneur des données (la mémoire cache proprement dite).

Une mémoire cache simple de type à accès direct (*direct-mapped*) est tout d'abord divisée en  $m$  lignes de cache. La ligne de cache représente l'unité élémentaire manipulée par le contrôleur de cache. La taille d'une ligne de cache ( $n$ ) se compte généralement en mots. Pour un processeur 32 bits, un mot représente une donnée de 32-bits. À chaque ligne de cache est associée une entrée dans l'index. Cette entrée indique si les données dans la ligne de cache sont valides ou non et contient également l'étiquette (*tag*) qui est le complément de l'adresse. À l'aide de l'étiquette et du numéro de ligne de cache, il est possible de reconstruire l'adresse de la donnée stockée en cache et donc de déterminer si

l'adresse de l'accès correspond à l'adresse de la donnée contenue en cache (succès ou *hit*).

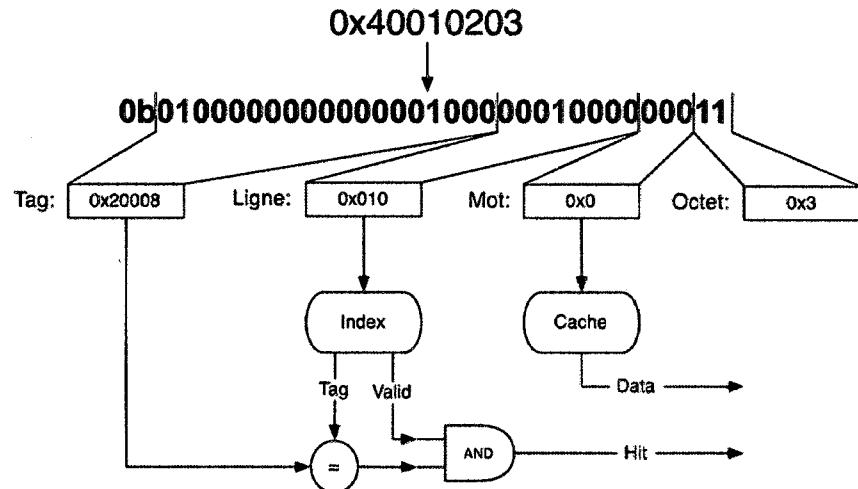

Figure 2.4 Mémoire cache à accès direct

Lorsque le processeur effectue une lecture, le contrôleur de cache doit déterminer si la donnée est présente ou non dans le cache. Si la donnée n'est pas présente, il doit lire la donnée de la mémoire principale et stocker cette donnée dans le cache. Dans le cas d'une mémoire cache à accès direct l'adresse d'une donnée est séparée en sections *étiquette*, *adresse de ligne* et *adresse de mot*. Selon la taille de l'espace d'adressage du processeur et la configuration du cache, chaque section englobera un nombre de bits différent. Considérons la situation suivante : un processeur avec un espace d'adressage de 32 bits, une taille de mots de 32 bits, un cache de 8 Ko et une taille de ligne de 8 mots. L'étiquette comprendra alors 19 bits, l'adresse de ligne comprendra 8 bits, l'adresse de mot 3 bits, les 2 bits les moins significatifs restants sont ignorés par le contrôleur de cache. Pour déterminer si une donnée est présente en cache, le contrôleur détermine d'abord à quelle ligne de cache correspond la requête. Ensuite, l'étiquette présente dans l'index est comparée avec celle de l'adresse de la requête et le bit de validité est vérifié. Si les étiquettes correspondent et que la ligne est valide, la ligne est récupérée dans la mémoire cache et le mot désiré est retourné. La Figure 2.5 (inspirée de [14]) illustre ce fonctionnement.

Figure 2.5 Fonctionnement d'une mémoire cache à accès direct

Lorsque la donnée demandée n'est pas disponible en cache, elle est alors récupérée et remplace la donnée déjà présente en cache. On parle alors d'échec (*cache miss*), dans le cas contraire, on parle de succès (*cache hit*). Ces concepts, de même que les métriques de performances des mémoires cache sont décrits dans [11] où l'auteur définit entre autres les trois types d'échecs: capacité, obligatoire et conflit.

Lorsqu'une donnée doit être écrite, deux approches sont fréquemment utilisées [12]. La première est d'écrire la valeur dans la mémoire principale peu importe si la donnée est présente en cache ou non, cette méthode porte le nom de politique d'écriture immédiate (*write-through policy*). La deuxième approche est de n'écrire la donnée que dans le cache et porte le nom de politique d'écriture différée (*write-back policy*). La première approche est simple à gérer. Lorsqu'une donnée doit prendre la place d'une autre dans le cache, la cohérence entre l'état du cache et la mémoire principale est assurée. Ceci n'est pas le cas pour la politique *write-back*. En effet, puisque la donnée n'est écrite que dans le cache, il y a discordance entre la donnée présente en cache et en mémoire. Le contrôleur doit donc utiliser un drapeau supplémentaire pour chaque ligne de cache afin de signifier qu'elle a été modifiée, le *dirty bit*. Si un remplacement de ligne doit être

effectué, le contrôleur vérifie si la ligne a été modifiée et si oui, l'écrit d'abord dans la mémoire principale pour ensuite aller récupérer la nouvelle ligne. Le *write-back* implique donc une logique supplémentaire par rapport au *write-through* mais elle permet de diminuer les accès à la mémoire principale.

Bien qu'un cache à *accès direct* soit simple à implémenter, il n'est pas adapté à tous les scénarios. Plusieurs concepts entrent donc en jeu afin d'améliorer la performance des caches dans ces conditions. L'associativité est un concept permettant d'éviter des remplacements inutiles de lignes. En relation avec l'associativité, la politique de remplacement permet de déterminer quelle ligne remplacer. L'utilisation de niveaux multiples de cache permet également d'améliorer la performance. Puisque la méthode présentée ne touche pas à ces concepts, le lecteur désireux d'en apprendre plus peut se référer à [13], [15] et [16].

## 2.2. Structure d'un logiciel compilé

Pour qu'un code source soit converti en un programme exécutable, une série d'opérations doit être effectuée sur ce code afin de le rendre compréhensible au processeur cible [18]. Les deux étapes majeures de ce processus sont la compilation du code et l'édition des liens. Lorsque ces étapes sont terminées, un fichier exécutable est généralement créé selon un format spécifique. Dans le cas du processeur MicroBlaze, ce fichier exécutable est au format ELF. Finalement, une dernière étape (souvent optionnelle) consiste à profiler le logiciel afin de déterminer les points chauds de celui-ci et donc de réduire l'impact de ces points chauds sur le temps d'exécution de ce dernier.

### 2.2.1. Compilation

Compiler un code source (ici du C) est un processus complexe qui peut se diviser en trois étapes [17] :

1. Frontale

2. Optimisation

3. Finale

L'étape frontale se charge de traduire le code source en une représentation intermédiaire plus facile à comprendre pour le compilateur : l'arbre syntaxique abstrait ou *Abstract Syntax Tree* (AST). Lorsque cette étape est terminée, l'étape d'optimisation prend la relève et optimise le programme en effectuant des simplifications et des optimisations de boucles. Finalement, à la troisième étape, la représentation intermédiaire est convertie en code machine spécifique à l'architecture ciblée.

Le processus de compilation ne fait pas que compiler du code, il sert également à séparer le programme en différentes sections. Ceci permet de compartimenter un programme et devient utile lors de la phase d'édition des liens. Un programme est normalement constitué de quelques sections de base [19] :

- .data

- .bss

- .text

- .stack

- .heap

La section `.data` contient des données initialisées, la section `.bss` contient des données non-initialisées et finalement, la section `.text` contient le code lui-même ainsi que des

données qui sont en lecture seulement. Finalement, les sections `.stack` et `.heap` contiennent respectivement les données locales aux fonctions (pile) et les données allouées dynamiquement (tas). Fait à noter : la pile croît dans le sens négatif des adresses en mémoire tandis que le tas croît dans le sens positif.

Il est par contre possible de spécifier des sections additionnelles en plus des sections prédéfinies. Ceci est fait à l'aide d'un attribut pouvant être spécifié à la fin de la déclaration d'une variable, classe, structure ou fonction [20]. La syntaxe pour spécifier une section est la suivante :

```

type_var nom_var __attribute__ ((section("nom_section")));

```

Une autre méthode proposée par le compilateur GCC est d'utiliser deux options lors de la compilation :

- `-ffunction-sections`

- `-fdata-sections`

Ces options de compilation permettent d'assigner une section à chaque fonction (`-ffunction-sections`) et à chaque variable globale (`-fdata-sections`). Le nom des sections ainsi créées dépend de la section dans laquelle la variable ou la fonction se trouve et de son nom. À titre d'exemple, pour la fonction :

```

void Func_1(char a, char b)

```

qui réside dans la section `.text` par défaut, le compilateur lui assignera la section :

```

.text._Z6Func_1cc

```

Cette nouvelle section peut ensuite être utilisée par l'éditeur de liens pour spécifier un emplacement mémoire pour cette fonction. Si l'option n'est pas utilisée lors de la compilation, il n'est pas possible de déplacer manuellement la fonction en mémoire et le compilateur s'occupe de déterminer l'emplacement le plus approprié.

### 2.2.2. Édition des liens

Suite à la compilation, le fichier objet créé ne contient aucune référence à des adresses en mémoire. Les références se font à l'aide des noms des fonctions et des variables (symboles). L'édition des liens est l'étape qui permet de remplacer ces symboles par leur adresse définitive dans la mémoire. Ce processus permet également d'intégrer le code provenant de librairies statiques au programme final ou de lier le programme à des librairies partagées [21]. Le résultat sera un exécutable ou une librairie, souvent sous le format ELF [24].

Une fonction importante de l'éditeur de liens est la possibilité de spécifier manuellement l'adresse désirée des différentes sections d'un programme [22]. Ceci peut être effectué à l'aide d'un script qui sera ensuite passé en paramètre à l'éditeur de liens. À l'aide de cette fonctionnalité, il est possible de placer des sections à n'importe quelle adresse dans n'importe quelle mémoire disponible sur le système [23].

### 2.2.3. Profilage

Le profilage d'un programme est le processus selon lequel de l'information sur le temps d'exécution et la fréquence d'exécution des fonctions d'un programme est recueillie. Profiler un programme suggère généralement que le développeur désire connaître les points chauds de son application afin de pouvoir accélérer ces points chauds. En effet, selon la loi du 90/10, un programme passe environ 90% de son temps à exécuter 10% du code [13]. Il est donc payant d'optimiser ce 10%.

Le profilage implique généralement l'ajout d'instructions qui comptent le nombre de cycles passés dans une fonction. Cette approche est utile lorsque le programmeur ne peut que compiler et exécuter son programme sur un processeur existant. Un fichier peut alors être généré et peut servir à un outil d'interprétation graphique. L'inconvénient de cette approche est qu'elle peut avoir un impact non négligeable sur le temps d'exécution du programme et peut biaiser les résultats. Par contre, elle ne nécessite généralement aucune modification manuelle au programme de la part du développeur puisque les outils existants se chargent eux-mêmes d'instrumenter le code [25].

Une deuxième approche est d'utiliser un simulateur d'instructions (ISS) qui peut alors intercepter les instructions exécutées par le processeur simulé [26]. Dans ce cas, le code original peut être exécuté sans insertion de code d'instrumentation. Cette approche a l'avantage de n'avoir aucun impact sur le temps d'exécution simulé du programme et par conséquent ne biaise pas les résultats. Par contre, il est nécessaire de disposer d'une plateforme de simulation et le fait de simuler l'exécution ralentit sensiblement la vitesse d'exécution.

### 2.3. Optimisation de la hiérarchie

L'ajout d'une certaine hiérarchie mémoire implique qu'il devient nécessaire d'effectuer une certaine exploration architecturale afin d'obtenir les meilleures performances possibles. Bien entendu, il est possible d'effectuer ces explorations manuellement lorsque les configurations offertes sont limitées. Par contre, lorsque l'on a affaire à un SoC hautement configurable, l'utilisation d'une méthode automatique devient alors incontournable. Dans cette section, les méthodes de partitionnement de mémoire ainsi que les méthodes d'optimisation de la configuration de la mémoire cache sont présentées.

### 2.3.1. Mémoire locale

Avec l'utilisation croissante de la mémoire locale à l'intérieur de processeurs et des SoC, plusieurs techniques d'optimisation de l'utilisation de la mémoire locale ont été développées. Lorsqu'aucune technique d'optimisation n'est employée, l'utilisation de la mémoire locale se résume à:

- Contenir les vecteurs d'interruption du programme,

- Contenir le programme en entier, ou

- À titre de mémoire tampon[28].

Lorsque la mémoire locale ne contient que les vecteurs d'interruption, le programme est contenu dans une mémoire externe de taille plus importante. Ceci permet d'avoir des programmes de grande taille mais induit un délai significatif.

Si le programme est de taille inférieure à la taille de la mémoire locale, il est possible de le placer entièrement dans la mémoire locale. Ceci permet une rapidité d'accès optimale aux instructions et aux données, mais impose une contrainte de taille significative à l'application développée. En effet, il suffit d'exécuter une application basée sur le RTOS µC pour observer que même ce système d'exploitation simple dépasse la taille maximale de 64 Ko pour un contrôleur de mémoire locale. Il va sans dire qu'il est donc très facile d'être limité par la taille pour des systèmes complexes.

Finalement, la mémoire locale peut être utilisée comme tampon (*scratchpad*). Une mémoire tampon est une mémoire qui sert à stocker temporairement des données ou des instructions lorsque le programmeur désire accéder rapidement ou de façon déterministe à ces données. Ceci est un avantage de la mémoire tampon par rapport au cache: le temps d'accès est déterministe. Par contre, c'est au programmeur de s'assurer que les bonnes données seront présentes lorsqu'elles seront nécessaires.

Afin de remédier aux limites et à la difficulté pour le programmeur de manipuler manuellement le contenu de la mémoire locale, plusieurs techniques ont été développées. Ces techniques se divisent en deux catégories : statiques ou dynamiques. Pour les méthodes d'optimisations statiques, le contenu de la mémoire locale est déterminé à l'aide d'analyse de traces [27] ou d'analyse de code. Le contenu de la mémoire locale restera alors fixe durant l'exécution du programme. Dans le cas des méthodes d'optimisation dynamiques, un sous-système, semblable à de la mémoire virtuelle, charge les données et les instructions dynamiquement dans la mémoire locale durant l'exécution du programme. L'avantage de cette approche est la plus grande flexibilité du contenu de la mémoire locale mais elle impose des coûts de gestion de la mémoire.

Parmi les méthodes statiques notons tout d'abord la solution proposée par [29] qui présente une méthode d'optimisation de la performance d'un système embarqué utilisant une combinaison de mémoire tampon et de cache. Bien que la méthode proposée permette de déterminer automatiquement ce qui devrait être placé dans la mémoire tampon, elle ne propose pas de méthode pour effectuer l'allocation. De plus, les tailles des caches ne sont pas déterminées automatiquement. Par contre, la conclusion des auteurs est qu'il est important d'utiliser judicieusement la mémoire locale et la mémoire cache afin d'obtenir la meilleure performance possible, ce qui valide le travail présenté dans ce mémoire.

Dans [30], la méthode présentée, plus complète, utilise tout d'abord une trace d'exécution afin de recueillir la fréquence d'utilisation de chaque adresse. Ensuite, un algorithme analyse les entrées dans le profil créé précédemment et détermine la solution optimale selon la taille fixée de la mémoire locale, le gain de performance engendré pour chaque entrée et le coût de partitionnement de cette entrée. Finalement, un outil modifie directement le code exécutable afin de relocaliser les blocs dans la mémoire locale. Cette méthode permet d'améliorer la performance de 20% par rapport à la performance obtenue lorsque le système utilise uniquement la mémoire cache.

Plusieurs travaux [31] [32] et [33] ont abordés les méthodes de partitionnement dynamiques. La méthode proposée par [33] est particulièrement intéressante puisqu'elle utilise le MMU du processeur afin de permettre la gestion du contenu de la mémoire locale. Pour utiliser cette fonctionnalité du processeur, les auteurs ont développé un algorithme d'analyse ainsi qu'un moteur d'exécution (*runtime*). Afin de permettre le fonctionnement de ce moteur d'exécution, un profil de l'application est tout d'abord généré par l'exécution du programme à optimiser. Ensuite, un outil analyse ce profil et détermine les dépendances entre les blocs de base [34]. L'outil modifie ensuite le programme afin d'inclure ces données d'analyse et d'intégrer le moteur d'exécution dans le fichier binaire. L'approche permet donc d'utiliser la mémoire locale et la mémoire externe comme mécanisme de mémoire virtuelle. Ce mécanisme est ensuite combiné à de la mémoire cache pour améliorer davantage les performances. Des gains de performance de 12% sont atteints par rapport à un système utilisant uniquement de la mémoire cache.

Il existe nombre de systèmes développés utilisant des mémoires locales afin d'améliorer la performance. Un exemple d'un tel système mettant à contribution des mémoires tampons ainsi que des mémoires cache est proposé dans [35]. Cette approche, combinée à une architecture utilisant trois processeurs configurables permet d'obtenir un gain de performance de 22,3x par rapport à une architecture monoprocesseur conventionnelle.

### 2.3.2. Mémoire cache

L'optimisation de la configuration des caches a suscité beaucoup d'intérêt dans les dernières années et les outils d'exploration architecturale sont nombreux. Les méthodes sont toutes centrées sur l'utilisation d'une trace d'exécution et d'un simulateur de cache. Par contre, les approches diffèrent sur la méthode utilisée pour simuler et également sur la méthode utilisée pour recueillir la trace d'exécution.

L'avantage d'utiliser une trace d'exécution est qu'il devient possible d'effectuer l'optimisation en différé mais surtout de diminuer le temps de simulation du cache en compactant la trace. En effet, une trace d'exécution peut devenir rapidement très volumineuse. Par exemple, la trace d'une seule seconde d'exécution d'un processeur cadencé à 100MHz peut occuper jusqu'à 500 Mo d'espace disque.

Dans [37], les auteurs présentent une méthode d'évaluation de la performance d'un cache en utilisant une approche basée sur l'échantillonnage de la trace d'exécution. Puisqu'un échantillonnage est utilisé, l'ensemble de la trace d'exécution n'a pas à être gardé en mémoire et un gain significatif de vitesse de simulation peut être observé.

La méthode proposée dans [38] est une méthode itérative qui réduit la taille de la trace à simuler à chaque itération. Ceci permet de simuler rapidement un grand nombre de configurations de cache. Par contre, ce modèle ne peut garantir l'exactitude des résultats.

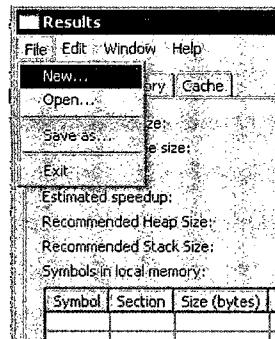

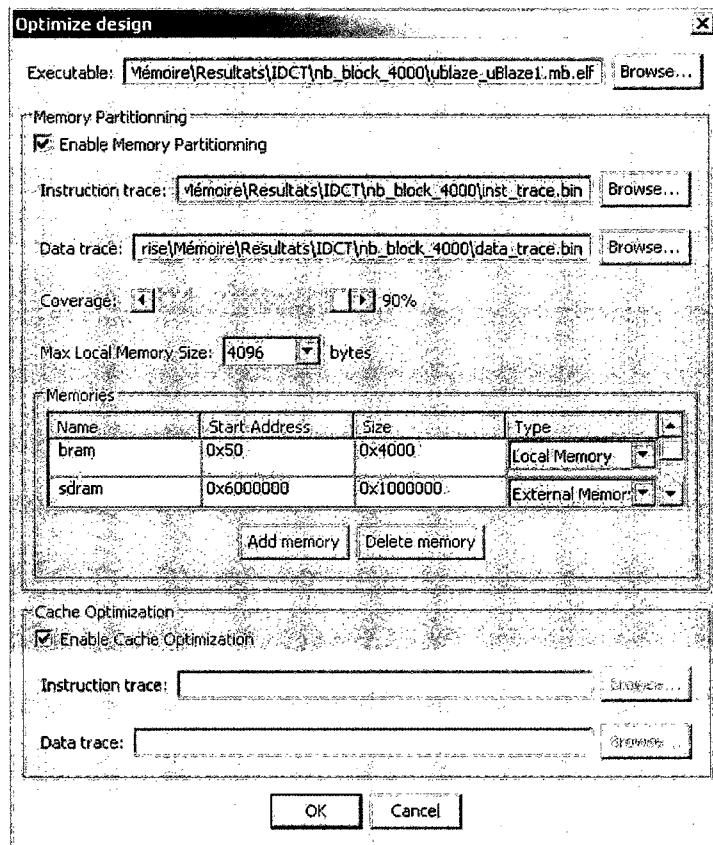

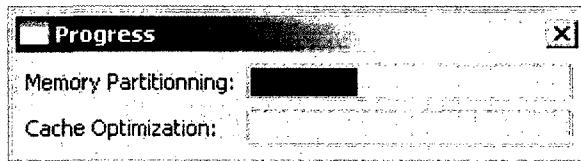

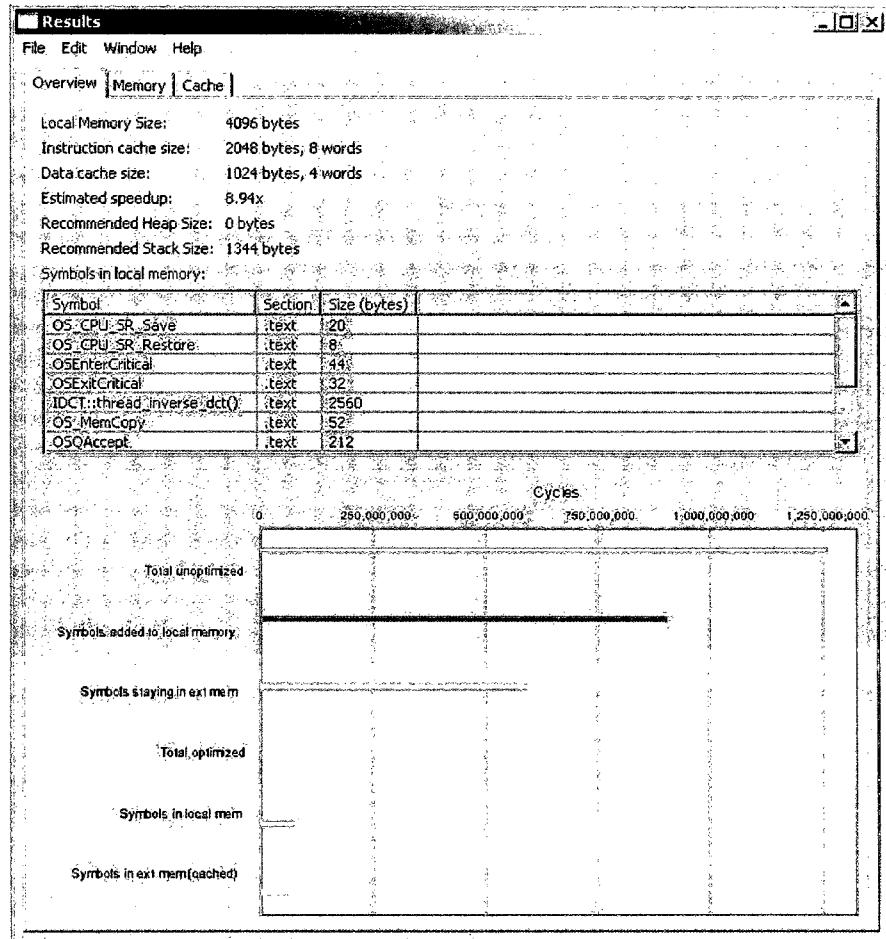

W.-H. Wang et J.-L. Baer [39] proposent quant à eux de réduire dès le départ la trace en utilisant un algorithme de compression. Leur méthode simule un cache associatif mais, afin de compresser la trace, ils simulent d'abord un cache à accès direct et ne gardent que les instructions qui causent un échec ou une écriture. Ceci leur permet d'obtenir une trace réduite et d'utiliser cette dernière pour simuler l'ensemble des configurations de cache associatif qui sont plus coûteuses en termes de temps à simuler.