**Titre:** Vérification fonctionnelle et validation de performance

Title: architecturale pour des tissus d'interconnexion

**Auteur:** Dany Lebel

Author:

**Date:** 2009

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Lebel, D. (2009). Vérification fonctionnelle et validation de performance

architecturale pour des tissus d'interconnexion [Mémoire de maîtrise, École

Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/8475/>

Citation:

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8475/>

PolyPublie URL:

**Directeurs de

recherche:** Yvon Savaria, & Gabriela Nicolescu

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

VÉRIFICATION FONCTIONNELLE ET VALIDATION DE PERFORMANCE

ARCHITECTURALE POUR DES TISSUS D'INTERCONNEXION

DANY LEBEL

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

Août 2009

Library and Archives

Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

ISBN: 978-0-494-57256-6

*Our file Notre référence*

ISBN: 978-0-494-57256-6

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des theses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

■■■

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

VÉRIFICATION FONCTIONNELLE ET VALIDATION DE PERFORMANCE

ARCHITECTURALE POUR DES TISSUS D'INTERCONNEXION

présenté par: LEBEL Dany

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. DAVID Jean-Pierre, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

Mme. NICOLESCU Gabriela, Doct., membre et codirectrice de recherche

M. LANGLOIS Pierre, Ph.D., membre

## DÉDICACE

*À mes parents*

## REMERCIEMENTS

Plusieurs personnes ont contribué à ce que cette maîtrise soit un succès et que l'expérience acquise tant au niveau personnel que technique soit des plus enrichissante.

Pour commencer, merci à Yvon Savaria de m'avoir confié ce projet des plus intéressants et pertinents dans mon cheminement de carrière. Il a su m'épauler tout au long de la progression de mes travaux. Les qualités d'interlocuteur technique et de présentateur exceptionnel de ce dernier ne peuvent que me servir d'exemple.

Merci à Gabriela Nicolescu d'avoir permis à ce projet de se concrétiser. Son expertise logicielle et réseautique a contribué à son succès.

Merci également à Normand Bélanger pour son implication importante dans le projet. Ses conseils démontrant pleinement sa grande expérience dans le domaine ont souvent servi d'inspiration à l'évolution du projet. Sa grande disponibilité et les discussions reliées ou non au domaine furent très appréciées.

Un merci tout particulier à Maria Mbaye et Nicolas Beucher, mes voisins de bureau les plus présents. Maria a été d'une grande aide lors de mes débuts à collaborer avec Monsieur Savaria. Ses conseils, son savoir faire ainsi que les quelques heures passées ensemble sur les laboratoires de VLSI furent appréciés. Quant à Nicolas, sans contredit le plus fidèle au poste dans le bureau, ses commentaires d'un œil externe furent toujours pertinents. La réalisation d'un système qui intègre nos deux projets fut une belle expérience d'intégration. Il ne faut pas passer sous silence les nombreuses parties de badminton en compagnie de Nicolas et Mohamed qui nous ont permis de s'aérer l'esprit. Merci à Mohamed Rouatbi pour ses suggestions occasionnelles ainsi que pour les séances de « gym extrême » et sorties forts agréables.

Merci à Rahul, Gilbert, Vincent et tous les autres que j'ai côtoyés, d'avoir rendu cette expérience encore plus agréable.

Merci à mes parents de m'avoir encouragé et soutenu durant toutes mes études. Un merci fort mérité à Henriette pour son soutien quotidien et son amour.

## RÉSUMÉ

L'exploration architecturale, la validation et la vérification sont parmi les défis les plus ardu斯 en conception de circuits intégrés. Le développement d'un environnement adéquat pour toutes les phases d'un projet reste un défi de taille malgré l'avènement d'outils, langages et bibliothèques tel que le SystemC. Un tel environnement, qui s'intègre bien à la méthode de conception, est présenté dans ce mémoire. L'environnement inclut deux niveaux d'abstraction dans le but d'intégrer l'exploration architecturale et la vérification d'un design. Afin d'être flexible et complet, l'environnement inclut trois types de génération de données : pseudo-aléatoire constraint, synthétique et réelle, avec une application exécutée sur un processeur. Il est montré que la productivité est potentiellement accrue pour l'exploration architecturale et les phases ultérieures du développement. Ce projet traite de la validation de tissus d'interconnexion et implante, pour des fins de démonstration, deux types d'ordonnanceurs : « Weighted Round-Robin » et « Wrapped Wave Front Arbiter ». L'environnement est aisément modifiable pour d'autres contextes et besoins. Le but premier est de démontrer la pertinence de l'environnement et non de prouver l'efficacité d'une architecture en particulier. L'évaluation de l'équité sous un trafic non-uniforme pour les deux ordonneurs est, entre autres, utilisée comme exemple d'évaluation de performance.

## ABSTRACT

Architectural exploration, validation, and design verification are currently among the toughest challenges in ASIC design. Devising an ASIC development environment to meet those needs remains a challenge even with current tools, languages, and libraries such as SystemC. In this document, such an environment, which integrates well to the design methodology, is presented. This environment supports two abstraction levels in order to allow smooth transition from architectural exploration and validation to design verification. In order to enable complete and flexible architecture validation, it also includes three types of data generation: constrained pseudo-random, synthetic, and traffic produced by a real application running on a processor. It is shown that the productivity is potentially increased when performing architectural exploration. The created environment focuses on validating switch fabric architectures and, in order to demonstrate its usage, two types of schedulers are implemented: Weighted Round-Robin and Wrapped Wave Front Arbiter. The environment can easily be modified for other contexts and needs. The primary goal is to show the usefulness of the ideas behind the environment instead of showing the performance of a specific architecture. Fairness evaluation under non-uniform traffic for two types of scheduler is used as one of the examples of performance evaluation.

## TABLE DES MATIÈRES

|                                                                                 |              |

|---------------------------------------------------------------------------------|--------------|

| <b>DÉDICACE .....</b>                                                           | <b>iv</b>    |

| <b>REMERCIEMENTS .....</b>                                                      | <b>v</b>     |

| <b>RÉSUMÉ .....</b>                                                             | <b>vii</b>   |

| <b>ABSTRACT .....</b>                                                           | <b>viii</b>  |

| <b>TABLE DES MATIÈRES.....</b>                                                  | <b>ix</b>    |

| <b>LISTE DES TABLEAUX.....</b>                                                  | <b>xii</b>   |

| <b>LISTE DES FIGURES .....</b>                                                  | <b>xv</b>    |

| <b>LISTE DES SIGLES ET ABRÉVIATIONS .....</b>                                   | <b>xvi</b>   |

| <b>LISTE DES ANNEXES.....</b>                                                   | <b>xviii</b> |

| <b>INTRODUCTION.....</b>                                                        | <b>1</b>     |

| <b>CHAPITRE 1. CONTEXTE ET GÉNÉRALITÉS.....</b>                                 | <b>5</b>     |

| 1.1    Vérification .....                                                       | 5            |

| 1.2    Validation de performance.....                                           | 14           |

| 1.3    Tissu d'interconnexion.....                                              | 15           |

| 1.4    Statistiques pertinentes aux tissus d'interconnexion.....                | 21           |

| 1.5    XTSC de Tensilica.....                                                   | 23           |

| 1.6    Conclusion .....                                                         | 24           |

| <b>CHAPITRE 2. ENVIRONNEMENT DE VALIDATION/VÉRIFICATION À HAUT NIVEAU .....</b> | <b>25</b>    |

| 2.1    Concepts et description de l'environnement de validation .....           | 25           |

| 2.1.1    Généralités .....                                                      | 25           |

| 2.1.2    Description du modèle de paquets et des opérateurs de paquets .....    | 29           |

| 2.1.3    Description des paramètres de configuration architecturale du TI ..... | 31           |

| 2.1.4    Description modulaire.....                                             | 32           |

| 2.2    Concepts et description de l'environnement de vérification.....          | 41           |

| 2.2.1    Généralités .....                                                      | 41           |

|                                                                          |                                                                                            |           |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------|

| 2.2.2                                                                    | Description du modèle de paquets .....                                                     | 42        |

| 2.2.3                                                                    | Description modulaire.....                                                                 | 43        |

| 2.2.4                                                                    | Fonctions de vérification utiles.....                                                      | 51        |

| 2.3                                                                      | Dualité de l'environnement de vérification et validation de performance et simulation..... | 51        |

| 2.4                                                                      | Collecte de données et calculs de statistiques.....                                        | 53        |

| 2.4.1                                                                    | Collecte de données .....                                                                  | 53        |

| 2.4.2                                                                    | Calculs statistiques.....                                                                  | 55        |

| 2.5                                                                      | Conclusion .....                                                                           | 59        |

| <b>CHAPITRE 3. INTÉGRATION DE MODELES DE TRAFIC COMPLÉMENTAIRES.....</b> |                                                                                            | <b>60</b> |

| 3.1                                                                      | Intégration d'une application complète matériel-logiciel .....                             | 60        |

| 3.1.1                                                                    | Concepts et description de l'environnement avec XTSC .....                                 | 60        |

| 3.1.2                                                                    | Collecte de données et calculs de statistiques.....                                        | 68        |

| 3.1.3                                                                    | Synthèse sur l'intégration d'une application concrète .....                                | 68        |

| 3.2                                                                      | Intégration d'un modèle de trafic synthétique à l'environnement .....                      | 68        |

| 3.2.1                                                                    | Concepts pour l'intégration d'un modèle de trafic synthétique.....                         | 69        |

| 3.2.2                                                                    | Module de conversion réalisé (if. non-bloquante) .....                                     | 71        |

| 3.2.3                                                                    | Synthèse sur l'intégration d'un modèle de trafic synthétique.....                          | 71        |

| 3.3                                                                      | Conclusion .....                                                                           | 72        |

| <b>CHAPITRE 4. RÉSULTATS.....</b>                                        |                                                                                            | <b>73</b> |

| 4.1                                                                      | Méthode de conception qui englobe la validation .....                                      | 73        |

| 4.2                                                                      | Résultats obtenus avec l'environnement à haut niveau .....                                 | 75        |

| 4.2.1                                                                    | Aspect commun aux simulations : modèle de paquet.....                                      | 75        |

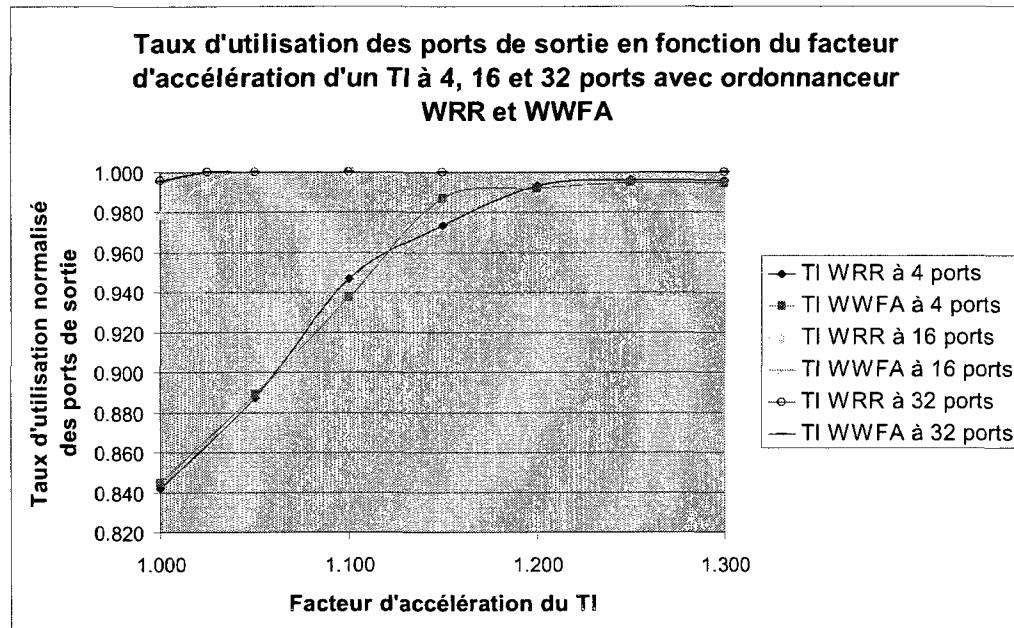

| 4.2.2                                                                    | Détermination du facteur d'accélération et analyse pour un trafic symétrique .....         | 76        |

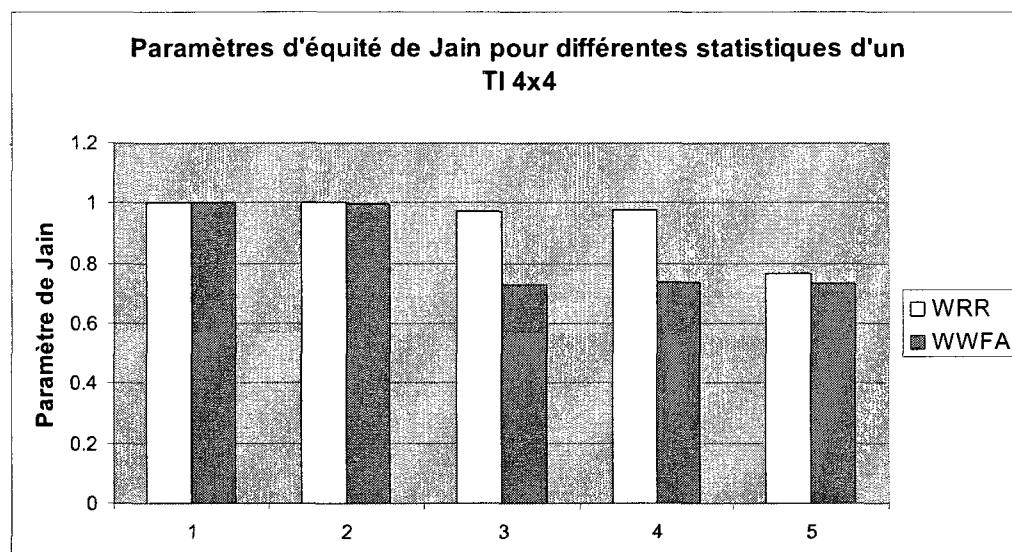

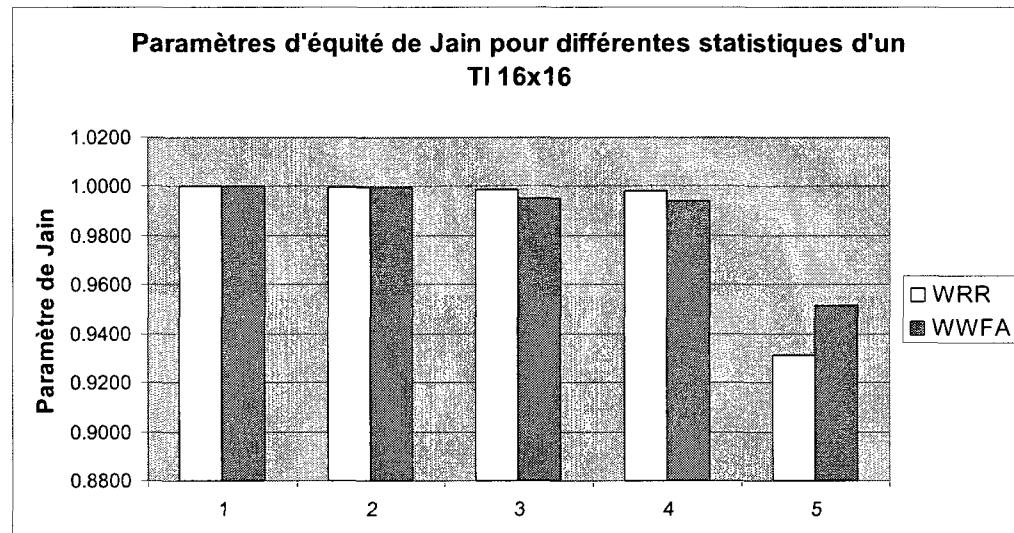

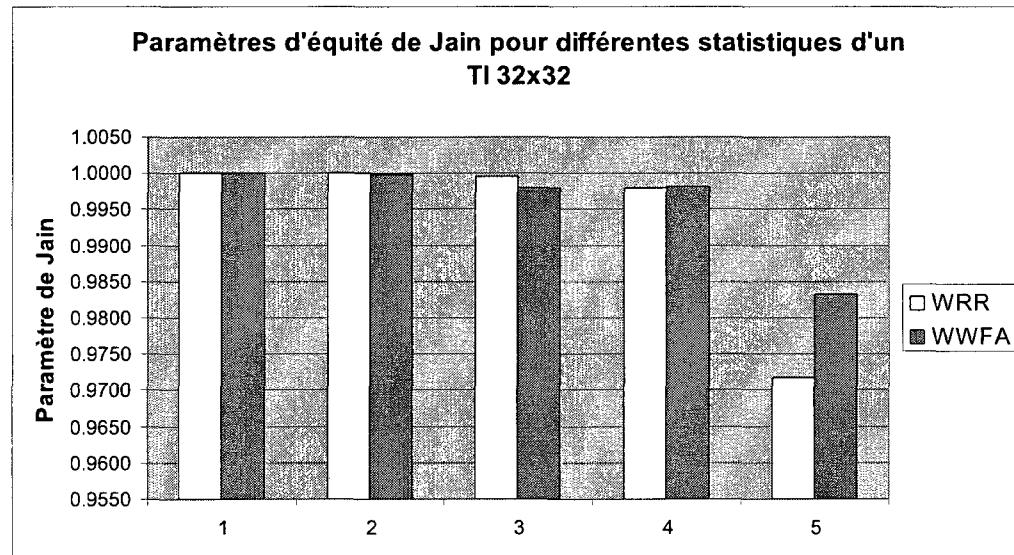

| 4.2.3                                                                    | Analyse de l'équité pour un trafic asymétrique .....                                       | 88        |

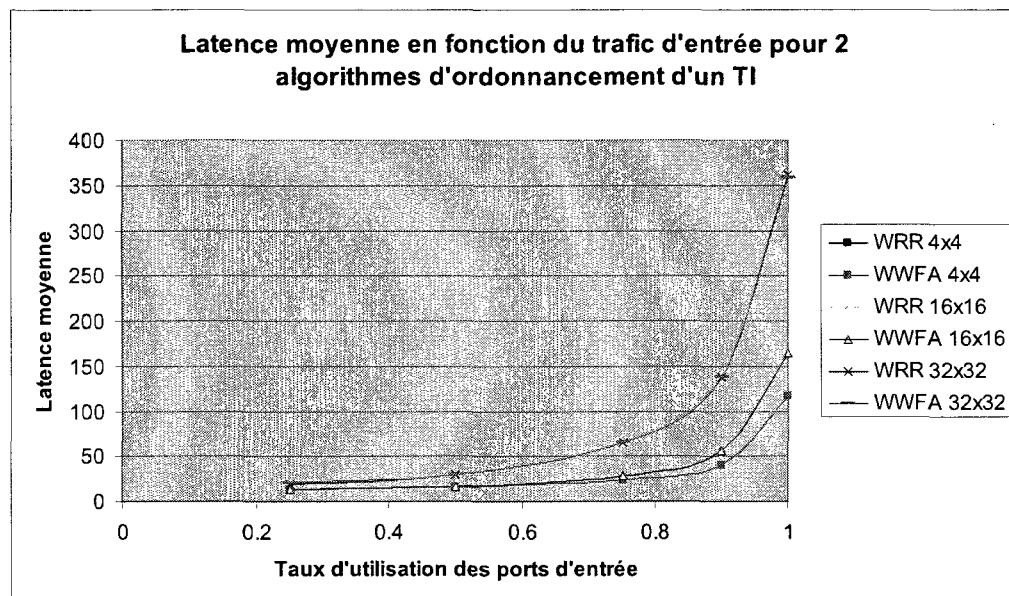

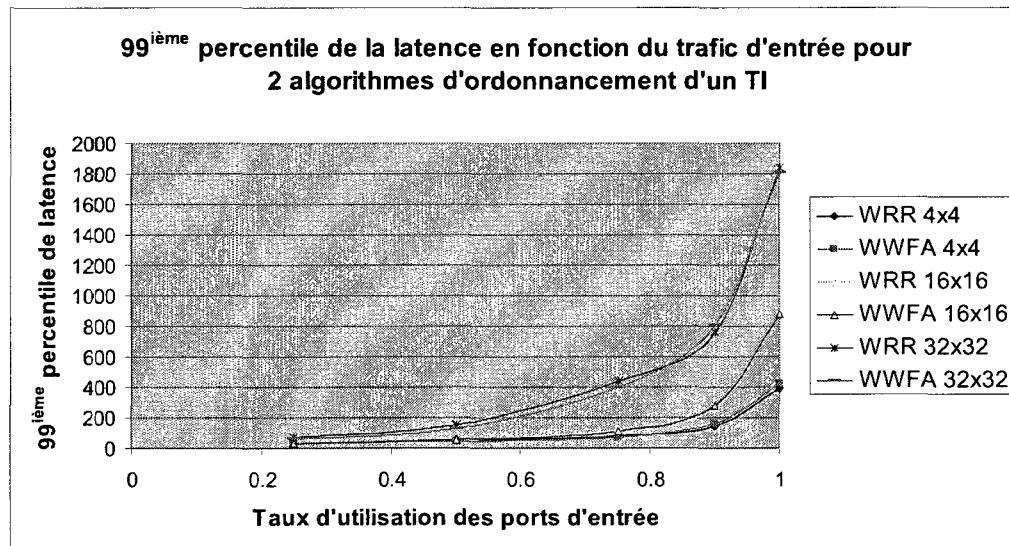

| 4.2.4                                                                    | Caractérisation d'un TI en fonction du trafic d'entrée.....                                | 101       |

| 4.3                                                                      | Conclusion .....                                                                           | 106       |

|                                 |            |

|---------------------------------|------------|

| <b>CONCLUSION .....</b>         | <b>107</b> |

| <b>RÉFÉRENCES.....</b>          | <b>109</b> |

| <b>CONTENU DES ANNEXES.....</b> | <b>114</b> |

## LISTE DES TABLEAUX

|                                                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 1.1 Avantages et inconvénients de différents types de tests .....                                                                           | 11 |

| Tableau 2.1 Description du paquet .....                                                                                                             | 29 |

| Tableau 2.2 Description de configuration du TI SystemC (haut niveau) .....                                                                          | 31 |

| Tableau 2.3 Paramètres utilisés par le module de test pour générer le trafic.....                                                                   | 37 |

| Tableau 2.4 Liste des paramètres génériques du TI.....                                                                                              | 47 |

| Tableau 2.5 Description des ports du TI matériel.....                                                                                               | 48 |

| Tableau 2.6 Description des ports matériels du module de conversion.....                                                                            | 50 |

| Tableau 2.7 Paramètres calculés par le script d'analyse statistique.....                                                                            | 56 |

| Tableau 3.1 Définition des opérations possibles.....                                                                                                | 64 |

| Tableau 4.1 Définition des dimensions du paquet .....                                                                                               | 75 |

| Tableau 4.2 Configuration du TI utilisé pour déterminer le facteur d'accélération .....                                                             | 77 |

| Tableau 4.3 Paramètres de la génération du trafic pour déterminer le facteur<br>d'accélération.....                                                 | 78 |

| Tableau 4.4 Paramètres de l'analyse statistique pour déterminer le facteur d'accélération<br>.....                                                  | 78 |

| Tableau 4.5 Taux d'utilisation des ports de sortie pour un TI à 4 ports .....                                                                       | 79 |

| Tableau 4.6 Taux d'utilisation des ports de sortie pour un TI à 16 ports .....                                                                      | 79 |

| Tableau 4.7 Taux d'utilisation des ports de sortie pour un TI à 32 ports .....                                                                      | 79 |

| Tableau 4.8 Statistiques de simulation d'un trafic symétrique sur un TI 4x4 avec<br>ordonnanceur WRR et un facteur d'accélération de 1.2 .....      | 83 |

| Tableau 4.9 Statistiques de simulation d'un trafic symétrique sur un TI 4x4 avec<br>ordonnanceur WWFA et un facteur d'accélération de 1.2 .....     | 83 |

| Tableau 4.10 Statistiques de simulation d'un trafic symétrique sur un TI 16x16 avec<br>ordonnanceur WRR et un facteur d'accélération de 1.05 .....  | 84 |

| Tableau 4.11 Statistiques de simulation d'un trafic symétrique sur un TI 16x16 avec<br>ordonnanceur WWFA et un facteur d'accélération de 1.05 ..... | 85 |

|                                                                                                                                                 |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 4.12 Statistiques de simulation d'un trafic symétrique sur un TI 32x32 avec ordonnanceur WRR et un facteur d'accélération de 1.2 .....  | 86  |

| Tableau 4.13 Statistiques de simulation d'un trafic symétrique sur un TI 32x32 avec ordonnanceur WWFA et un facteur d'accélération de 1.2 ..... | 87  |

| Tableau 4.14 Paramètres de l'analyse statistique pour l'évaluation d'équité .....                                                               | 89  |

| Tableau 4.15 Configuration du TI utilisé pour l'évaluation d'équité .....                                                                       | 90  |

| Tableau 4.16 Paramètres de la génération du trafic pour l'évaluation d'équité .....                                                             | 90  |

| Tableau 4.17 Statistiques de l'analyse à trafic asymétrique d'un TI 4x4 avec ordonnanceur WRR et un facteur d'accélération de 1.2 .....         | 91  |

| Tableau 4.18 Statistiques de l'analyse à trafic asymétrique d'un TI 4x4 avec ordonnanceur WWFA et un facteur d'accélération de 1.2 .....        | 92  |

| Tableau 4.19 Statistiques de l'analyse à trafic asymétrique d'un TI 16x16 avec ordonnanceur WRR et un facteur d'accélération de 1.05 .....      | 93  |

| Tableau 4.20 Statistiques de l'analyse à trafic asymétrique d'un TI 16x16 avec ordonnanceur WWFA et un facteur d'accélération de 1.05 .....     | 94  |

| Tableau 4.21 Statistiques de l'analyse à trafic asymétrique d'un TI 32x32 avec ordonnanceur WRR et un facteur d'accélération de 1.025 .....     | 95  |

| Tableau 4.22 Statistiques de l'analyse à trafic asymétrique d'un TI 32x32 avec ordonnanceur WWFA et un facteur d'accélération de 1.025 .....    | 96  |

| Tableau 4.23 Configuration du TI utilisé pour l'évaluation d'équité .....                                                                       | 102 |

| Tableau 4.24 Paramètres de la génération du trafic pour l'évaluation d'équité .....                                                             | 103 |

| Tableau 4.25 Paramètres de l'analyse statistique pour l'évaluation d'équité .....                                                               | 103 |

| Tableau 4.26 Latence et 99 <sup>ième</sup> percentile de la latence .....                                                                       | 104 |

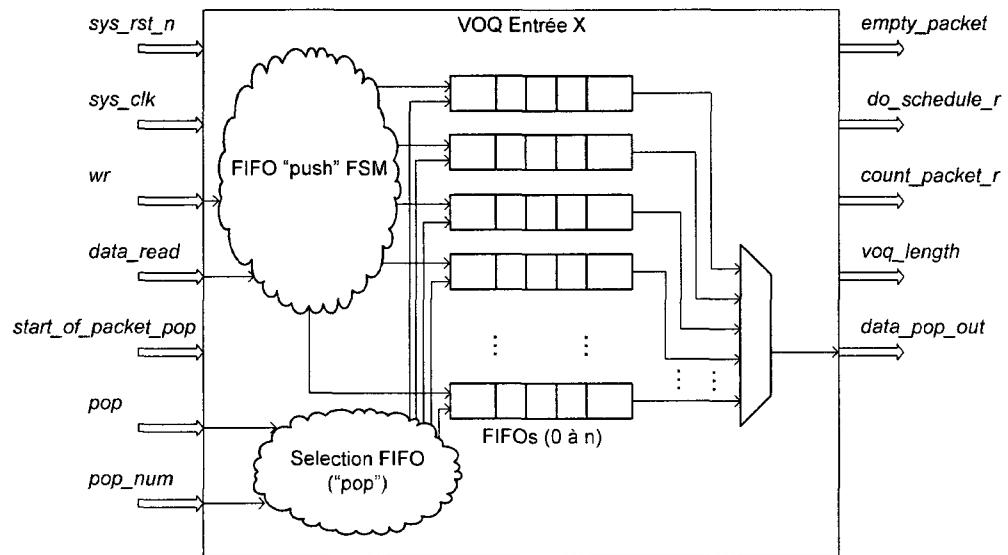

| Tableau A.1 Liste des paramètres génériques du VOQ .....                                                                                        | 117 |

| Tableau A.2 Description des ports du VOQ .....                                                                                                  | 118 |

| Tableau A.3 Description des paramètres génériques de l'ordonnanceur .....                                                                       | 119 |

| Tableau A.4 Description des ports de l'ordonnanceur .....                                                                                       | 119 |

| Tableau A.5 Description des paramètres génériques du module « send_pkt_ctrl » .....                                                             | 122 |

| Tableau A.6 Description des ports du « send_pkt_ctrl » .....                                                                                    | 122 |

|                                                                                 |     |

|---------------------------------------------------------------------------------|-----|

| Tableau A.7 Description des paramètres génériques du commutateur crossbar ..... | 125 |

| Tableau A.8 Description des ports du commutateur crossbar .....                 | 126 |

## LISTE DES FIGURES

|                                                                                                                                 |     |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1.1 Schéma détaillé d'un banc d'essai transactionnel en SystemC .....                                                    | 8   |

| Figure 1.2 Banc d'essai VHDL simple .....                                                                                       | 9   |

| Figure 1.3 Représentation de base d'un tissu d'interconnexion .....                                                             | 16  |

| Figure 1.4 Architecture de base d'un tissu d'interconnexion de type commutateur crossbar à files de sortie virtuelles .....     | 17  |

| Figure 1.5 Algorithme d'ordonnanceur WWFA ("Wrapped Wave Front Arbiter") .....                                                  | 20  |

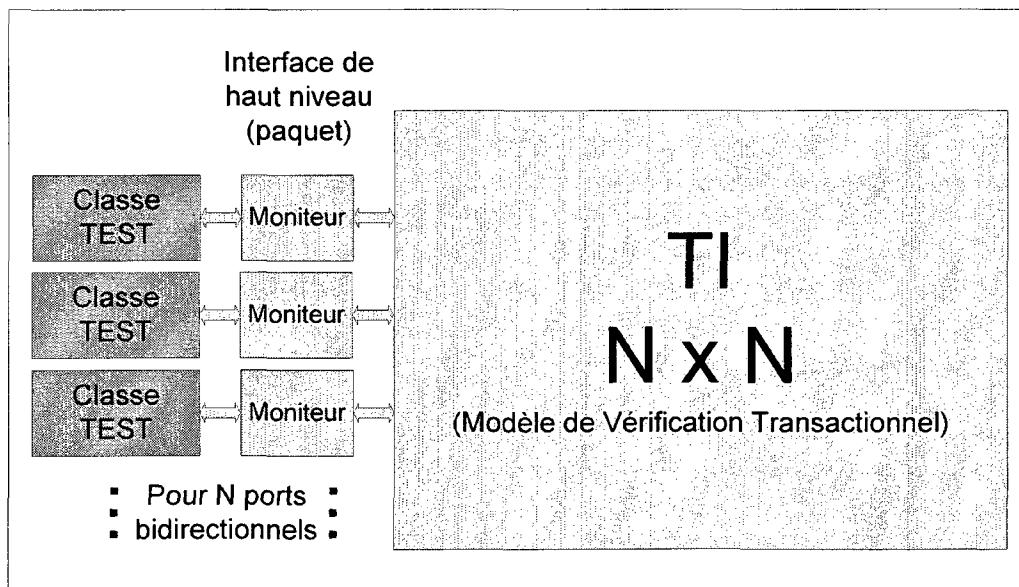

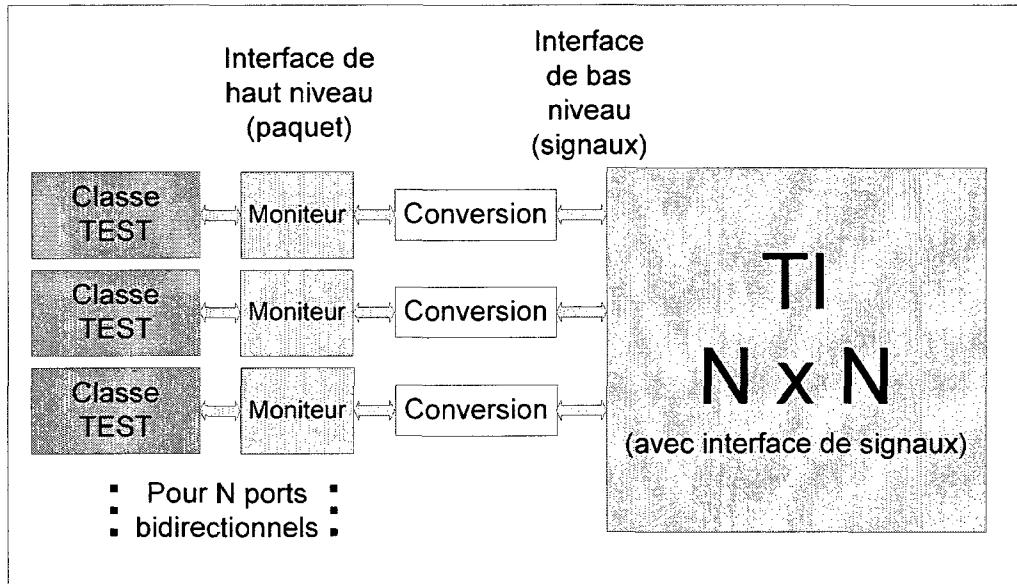

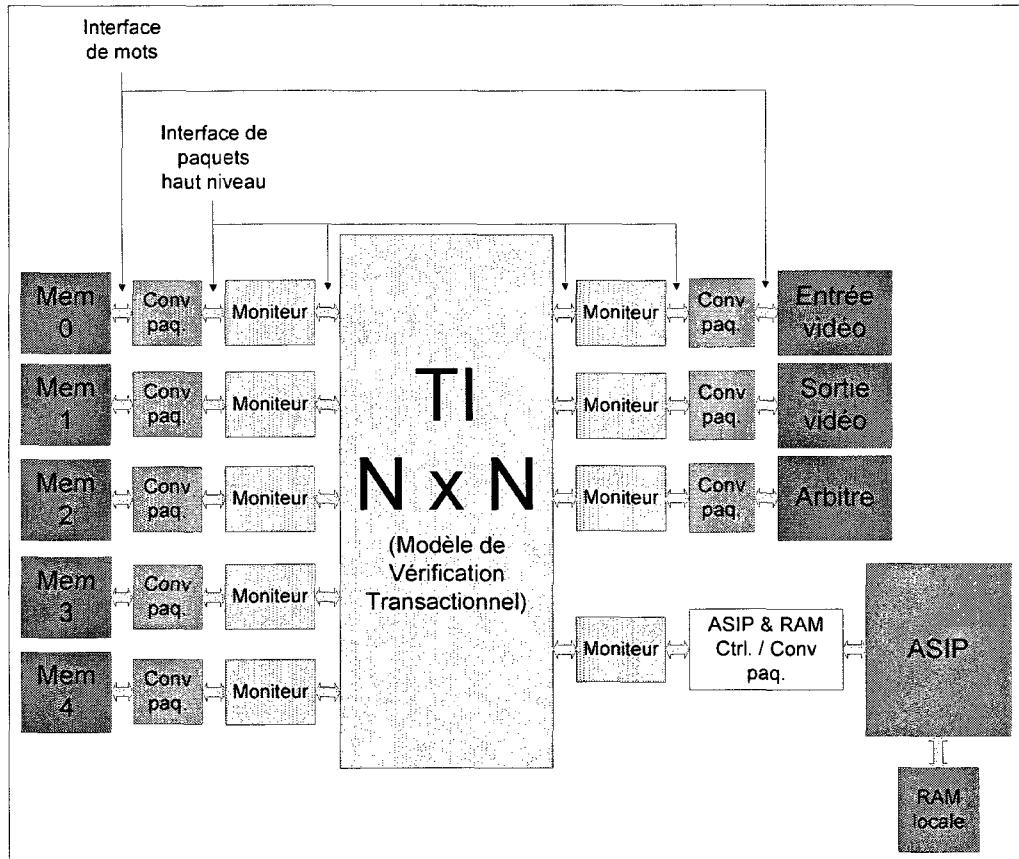

| Figure 2.1 Vue d'ensemble de l'environnement de validation de performance .....                                                 | 28  |

| Figure 2.2 Vue d'ensemble de l'environnement de vérification.....                                                               | 42  |

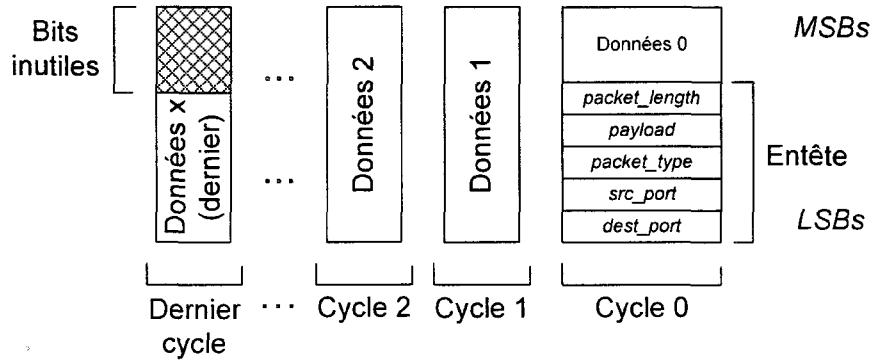

| Figure 2.3 Structure d'un paquet divisé en plusieurs cycles.....                                                                | 43  |

| Figure 2.4 Schéma bloc du tissu d'interconnexion matériel.....                                                                  | 45  |

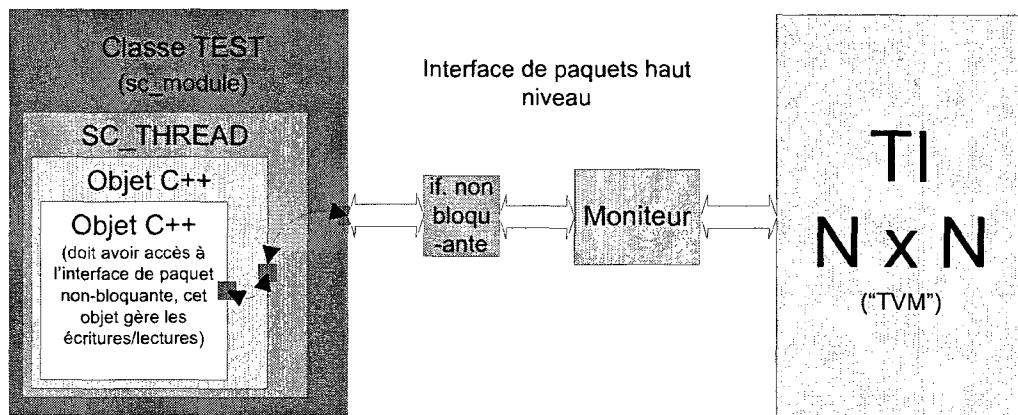

| Figure 2.5 Vue d'ensemble de l'environnement de vérification et validation intégré.....                                         | 52  |

| Figure 3.1 Architecture qui utilise un TI pour un calcul de compensation de mouvement fait avec un ASIP .....                   | 62  |

| Figure 3.2 Environnement de vérification/validation avec modèle de trafic externe intégré .....                                 | 70  |

| Figure 4.1 Taux d'utilisation des ports de sortie en fonction du facteur d'accélération....                                     | 80  |

| Figure 4.2 Comparaison des paramètres de Jain pour différentes statistiques pour l'ordonnanceur WRR et WWFA d'un TI 4x4 .....   | 97  |

| Figure 4.3 Comparaison des paramètres de Jain pour différentes statistiques pour l'ordonnanceur WRR et WWFA d'un TI 16x16 ..... | 98  |

| Figure 4.4 Comparaison des paramètres de Jain pour différentes statistiques pour l'ordonnanceur WRR et WWFA d'un TI 32x32 ..... | 98  |

| Figure 4.5 Latence en fonction du trafic d'entrée.....                                                                          | 105 |

| Figure 4.6 99 <sup>ième</sup> percentile de la latence en fonction du trafic d'entrée .....                                     | 105 |

| Figure A.1 Schéma bloc du VOQ .....                                                                                             | 116 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|        |                                                                                                                             |

|--------|-----------------------------------------------------------------------------------------------------------------------------|

| ASIC   | “Application-Specific Integrated Circuit », circuit intégré dédié à une application spécifique                              |

| ASIP   | “Application-Specific Instruction-set Processor », processeur à jeu d’instructions spécialisé                               |

| AVM    | “Advanced Verification Methodology”, une méthode de vérification proposée par Mentor Graphics.                              |

| CI     | Circuit intégré                                                                                                             |

| DUV    | “Design Under Verification”, module sous vérification                                                                       |

| FIFO   | “First In, First Out”, une organisation de mémoire sous forme de file qui préserve l’ordre d’entrée.                        |

| FS     | File de Sortie.                                                                                                             |

| FSM    | “Finite State Machine”, machine à états                                                                                     |

| HDL    | “Hardware Description Language”, langage de description matériel                                                            |

| MC-FRC | “Motion Compensated Frame Rate Conversion”, augmentation du taux de trames par compensation de mouvement                    |

| OSCI   | “Open SystemC Initiative”, version gratuite de SystemC                                                                      |

| PIM    | “Platform Independent Model”. Il s’agit de l’interface externe fournie par Tensilica pour communiquer avec leur processeur. |

| RTL    | “Register Transfer Language”, langage de transfert de registre tel que VHDL et Verilog                                      |

| SCV    | “SystemC Verification library”, bibliothèque de vérification de SystemC                                                     |

|      |                                                                                        |

|------|----------------------------------------------------------------------------------------|

| SoC  | “System On Chip”, Systèmes sur puce                                                    |

| TI   | Tissu d’interconnexion                                                                 |

| TLM  | “Transaction Level Model”, modèle transactionnel                                       |

| TVM  | ”Transaction-Based Verification Model”, modèle de vérification transactionnel          |

| VIP  | “Verification Intellectual Property”, un module de vérification standard réutilisable. |

| UVM  | “Unified Verification Methodology”, Méthode de Vérification Unifiée de Cadence         |

| VOQ  | “Virtual Output Queues”, Files de sortie virtuelles                                    |

| WRR  | “Weighted Round-Robin”, un type d’arbitre                                              |

| WWFA | “Wrapped Wave Front Arbiter”, un type d’arbitre                                        |

| XTSC | XTensa SystemC                                                                         |

## **LISTE DES ANNEXES**

|           |                                        |     |

|-----------|----------------------------------------|-----|

| ANNEXE A. | IMPLEMENTATION DU TI MATERIEL .....    | 115 |

| ANNEXE B. | FORMAT DES DONNEES DE SIMULATION ..... | 127 |

## INTRODUCTION

Les tissus d’interconnexion (TI) sont largement utilisés pour les communications. Avec la complexité des circuits intégrés qui ne cesse d’augmenter, les TI augmentent en popularité dans les systèmes embarqués. Le protocole *rapid-io* est exploité dans une classe de TI populaire pour la réalisation des systèmes embarqués. Les TI peuvent, par exemple, être utilisés pour connecter plusieurs processeurs ou modules matériels dédiés avec des mémoires externes. Ce type d’architecture pourrait être amené à remplacer l’architecture basée sur un « bus », qui est bien connue mais qui possède un désavantage majeur : lorsque le bus est utilisé, le milieu de transmission est bloqué pour les autres communications qui n’ont possiblement aucun lien logique avec la communication active [37]. Les TI [28] ont l’avantage majeur de permettre plusieurs communications indépendantes en parallèle, tout en permettant d’avoir accès à n’importe quelle ressource à partir de n’importe quelle autre ressource. Le coût principal de cette approche est la surface de silicium. Les TI *rapid-io* actuels offerts par *Tundra Semiconductor* [36] possèdent jusqu'à 16 ports et ils supportent un nombre limité de protocoles de communication. Les prochaines générations vont impliquer plus de ports et de protocoles, ce qui entraîne un goulot d’étranglement plus significatif pour l’ordonnanceur qui décide des connexions et le chemin de transfert des données. D’ailleurs, il est souhaité que l’ordonnanceur prenne sa décision en un faible nombre de cycles afin que des petits paquets hautement prioritaires soient traités rapidement. Des valeurs ajoutées aux TI sont également anticipées comme des fonctionnalités de calculs programmables intégrées.

Dans un tel contexte et avec des défis architecturaux multiples, il est d'une grande importance d'assurer que le TI se comporte de la façon anticipée et qu'il atteint les performances requises avant son implémentation RTL. Pour atteindre ces objectifs, une approche intéressante est la création d'un environnement de validation de performance. Idéalement, cet environnement se doit d'être conçu rapidement en abstrayant certains

éléments d'implémentation non-nécessaires. Cela permet d'éviter l'introduction de délais supplémentaires dans le projet. Il se doit également d'être facilement configurable pour permettre de valider divers scénarios. Il est de plus souhaitable que cet environnement serve de base à la vérification et ainsi permettre la réutilisation du design (« design-reuse » [4], [20]). Les multiples niveaux d'abstraction, la notion de concurrence et les types de données de SystemC, ainsi que toutes les possibilités qu'offre le C++ et les diverses bibliothèques C++ standards, sont d'un grand attrait pour atteindre un tel objectif. Plus le niveau d'abstraction est élevé, plus il est aisément d'abstraire les détails d'implémentation. Cela permet d'avoir un meilleur focus sur l'architecture lors de l'implémentation. La modélisation doit inclure une notion de temps (en termes de cycle) pour bien représenter l'architecture. Ceci est significatif puisque la latence est un des paramètres importants qui permet d'assurer une performance adéquate. Le modèle transactionnel de SystemC (TLM) [30] permet d'atteindre le niveau d'abstraction élevé voulu. Dans le cadre de notre application, le système peut envoyer et recevoir un paquet sous forme de simples transactions. La bibliothèque de SystemC pour la vérification (SCV) permet de rendre disponible des techniques avancées de vérification basées sur les concepts à haut niveau d'abstraction du SystemC et de modéliser divers scénarios [31]. Ces bibliothèques permettent d'obtenir un modèle de haut niveau aisément configurable, ce qui facilite grandement la validation des choix architecturaux. Ils permettent également d'obtenir un environnement qui supporte la vérification.

Il existe des travaux reflétant l'état de l'art pour la validation de TI. Pour la validation de leur propre architecture incluant leur ordonneur, Mandiwalla et Tzeng ont effectué des simulations d'implémentations matérielles [21]. Bien que précis, ce type de validation peut nécessiter un effort considérable sans garantir les résultats escomptés. La création d'un modèle adéquat peut améliorer considérablement plusieurs aspects dont le temps de développement, la rapidité d'exécution et la flexibilité de la validation. Dans cette optique de modélisation, on retrouve dans la littérature un environnement qui a été développé à partir de *ns2*, un simulateur de réseau dont le code source est disponible [41].

Bien que *ns2* donne accès à des scénarios de trafic et des statistiques intéressantes sans effort ajouté, il ne permet pas l'aisance de modéliser une architecture au cycle près puisqu'il est axé sur la réseautique. Il n'est également pas aisément intégrable à d'autres étapes de la méthode de conception d'un CI, telle que la vérification. L'environnement développé pour ce projet applique plusieurs concepts d'actualité présentés dans une méthode de vérification avancée d'actualité (« Open Verification Methodology » ou OVM) développée conjointement par Cadence et Mentor Graphics [25]. Ces concepts sont également appliqués pour la validation de performance. Également, XTSC de Tensilica [35] permet d'intégrer un modèle de TI SystemC utilisé dans l'environnement présenté à un système réel incluant un processeur et exécutant une application réelle, ce qui permet une validation et une vérification dans un contexte réel.

La principale contribution espérée du présent projet est de développer une plateforme de validation de performance efficace pour le développement d'un TI. Une des contributions secondaires espérées est d'obtenir une méthode de conception de CI qui, en plus d'intégrer les aspects de la méthode de conception usuelle, telle que la vérification, intègre de façon efficace les concepts de validation de performance développés avec l'environnement créé. Les étapes de validation et de vérification ont potentiellement des éléments communs et ce projet se permet de les exploiter.

L'élément le plus complexe et critique d'un TI est l'ordonnanceur. Il doit rendre la meilleure décision de routage des paquets possible à l'intérieur d'un nombre de cycles petit et souvent fixe qui se doit d'être à une fréquence d'opération la plus élevée possible. Pour atteindre une performance optimale, le TI doit assurer l'équité de ses décisions et une latence faible sur les paquets. L'algorithme d'ordonnancement WRR (« Weighted Round-robin ») [40] est utilisé comme modèle théorique de référence dans ce document, alors que le WWFA (« Wrapped Wave Front Arbiter ») [11] est présenté comme étant une solution intéressante pour une implémentation matérielle. La performance de ces algorithmes est quantifiée pour quelques scénarios de trafic.

Ce mémoire présente, dans le premier chapitre, le contexte et les aspects généraux relatifs au projet. La vérification et validation de performance y sont introduites. L'architecture générale d'un TI ainsi qu'un exemple de banc d'essai simple pour un TI sont aussi présentés. Les diverses statistiques pertinentes au projet suivent. Enfin, ce chapitre aborde les concepts supportés par XTSC (Xtensa SystemC) [35]. Le deuxième chapitre discute de l'environnement de validation de performance et de vérification aisément configurable avec trafic aléatoire constraint réalisé avec SystemC et SCV. Cet environnement permet de rapidement valider des idées architecturales avec un modèle de trafic aléatoire constraint ou spécifique à un comportement particulier. Le troisième chapitre de ce mémoire présente l'ajout de modèles de trafic complémentaires et plus complexes. Une application complète et réaliste y est d'abord présentée. Cette application est sous une forme matériel-logiciel et elle inclut un TI intégré avec XTSC. Il s'agit d'une application réelle de compensation de mouvement [38] qui est exécutée avec un ASIP [2], [3], [18]. Ce même chapitre présente les concepts à utiliser pour incorporer un modèle de trafic existant C++ à notre environnement SystemC, ce qui permet de potentiellement réutiliser des modèles de trafic existants. Cela peut s'avérer important pour une entreprise avec des modèles de trafic existants qui désirent réutiliser les éléments disponibles et éprouvés. Finalement, des résultats de simulation obtenus avec l'environnement décrit au chapitre 2 sont présentés et discutés dans le dernier chapitre. Les trois types de trafic supportés par l'environnement qui sont abordés aux chapitres 2 et 3 sont complémentaires et ils permettent une validation de performance complète et efficace à différents niveaux. Ils s'intègrent bien à une méthode de conception complète, telle que montré au chapitre 4. Le tout est suivi d'une conclusion qui passe en revue les points majeurs de ce mémoire et aborde brièvement les travaux qui pourraient donner suite au projet.

# CHAPITRE 1. CONTEXTE ET GÉNÉRALITÉS

Ce chapitre présente divers concepts qui servent de base aux travaux de ce mémoire. Il sert de référence pour le contenu des chapitres suivants. Il traite d'abord divers aspects de la vérification et de la validation de performance. Ensuite, les TI et les statistiques pertinentes aux TI sont discutés. XTSC de Tensilica est également présenté. Finalement, une brève conclusion termine le chapitre.

## 1.1 Vérification

La vérification se fait en comparant un modèle matériel ou logiciel avec une spécification [4], [27]. Le but est de garantir que le comportement obtenu est bien celui spécifié. Il s'agit d'un aspect important de la conception et il est pertinent si la spécification est adéquate.

Dans un cas réel, comparer un modèle à une spécification est peu pratique. Ainsi, idéalement, une équipe indépendante crée un modèle logiciel à partir de la spécification afin de vérifier un modèle matériel créé par une autre équipe. En ayant deux interprétations de la spécification, cela permet de vérifier une implémentation matérielle. En cas de divergence d'opinion, on doit réviser la spécification pour en retirer l'ambiguïté [4].

La vérification peut se faire de façon formelle [4] ou via simulation. Dans ce dernier cas, un banc d'essai doit être conçu. Il s'agit en fait de l'outil principal pour la vérification. Il existe plusieurs langages pour la vérification et le choix d'un langage influence l'architecture du banc d'essai. L'approche la plus connue et simple est l'utilisation d'un langage de description de matériel, tels que le VHDL et le Verilog. Une autre option est l'utilisation d'un langage de description de matériel étendu.

SystemVerilog est un exemple d'extension du Verilog qui peut être utilisé pour la vérification [29]. Une approche plus classique peut également être réalisée avec des langages logiciels comme le C++ et le Java. Une telle réalisation est présentée à titre d'exemple concret plus loin dans ce chapitre. Enfin, il existe même des langages dédiés à la vérification matérielle, tels qu'OpenVera [4] et SystemC accompagné de SCV [12]. Il s'agit de langages modernes avec un grand potentiel dont la popularité est croissante. L'État de l'art montre que des librairies C++ supplémentaires ont même été créées afin de compléter les fonctionnalités de vérification offertes par SystemC/SCV [26].

Un type de vérification efficace, qui a également servi de base aux travaux de ce mémoire, est l'utilisation d'un langage de vérification de matériel, en l'occurrence SystemC/SCV. SystemC est une bibliothèque de description de matériel et SCV, une bibliothèque de vérification qui s'ajoute à SystemC. Le tout est écrit en C++. Les travaux courants servent d'exploration de ces bibliothèques pour la vérification. SystemC/SCV est une norme établie afin d'uniformiser la vérification et de la rendre portable à plusieurs environnements (C++).

L'un des principaux avantages d'utiliser SystemC/SCV est que cela permet de créer des bancs d'essai à haut niveau d'abstraction rapidement tout en utilisant une bibliothèque C++, donc un langage connu et répandu. Toutes les fonctionnalités du C++ sont donc disponibles, telles que la notion d'orienté-objet, les structures, les chaînes de caractères et la surcharge d'opérateurs. Étant du C++, l'exécution est rapide. La rapidité à créer de nouveaux scénarios de test est également un aspect important.

SystemC intègre à ce langage connu la possibilité de travailler avec des types similaires à ceux disponibles dans un langage de description de matériel et il supporte la concurrence d'exécution avec les « sc\_module ». Le module est en quelque sorte un composant VHDL. Les « sc\_module » s'exécutent en concurrence et communiquent par des ports (« sc\_port »). Divers canaux de communication sont disponibles, tels que des

signaux, FIFO, mutex et sémaphores. Les ports des modules utilisent des canaux pour communiquer. La synchronisation des modules est faite soit par événements ou soit par une liste de sensibilité. SystemC possède également les notions de temps et d'horloge.

SCV amène quelques aspects intéressants à la bibliothèque SystemC. Le support de la vérification transactionnelle (TVM [6]) est, sans contredit, l'aspect le plus important. Cela permet d'abstraire, au niveau des transactions, les entrées/sorties du banc d'essai. L'envoi d'un paquet constitue un exemple de transaction. L'abstraction de détails d'implémentation constitue un avantage majeur en vérification, puisque cela permet au concepteur de se focaliser davantage sur la tâche à accomplir, ce qui rend le processus plus efficace. SCV intègre aussi comme éléments majeurs : un générateur aléatoire, des contraintes et poids de génération aléatoire et une fonctionnalité d'observation de variables et transactions.

SCV OSCI est disponible gratuitement. Cependant, la version OSCI permet de simuler du C++ seulement. Donc, elle est parfaite pour vérifier un module SystemC mais sans plus. Cependant, SCV est disponible avec plusieurs simulateurs HDL, tels que NC-Sim et Modelsim, ce qui permet d'effectuer une simulation multi-langage. SCV permet donc d'intégrer des parties de codes diverses écrites en C++ ou VHDL, par exemple. Modelsim impose, par contre, certaines contraintes à l'utilisateur de SCV. Certaines seront discutées au chapitre 2. Modelsim fournit également un ensemble d'outils comme « scgenmod » qui permet de créer de façon automatisée une classe C++ à partir du module HDL. Cette classe inclut la fonction d'accès au module VHDL.

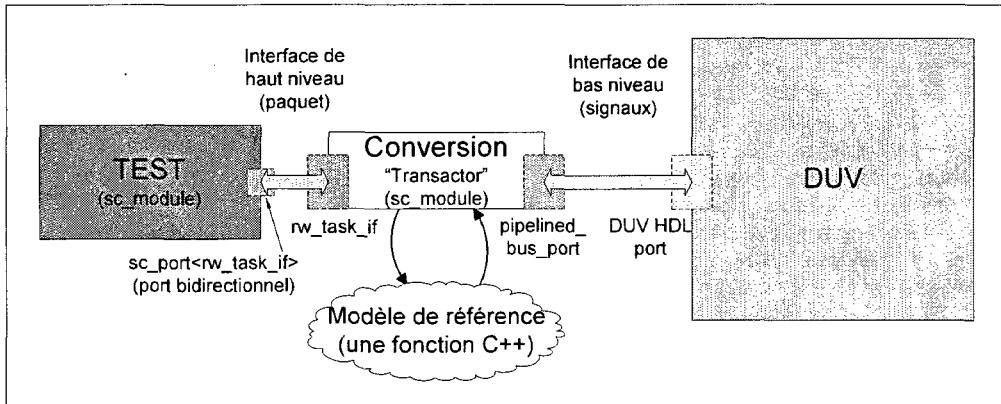

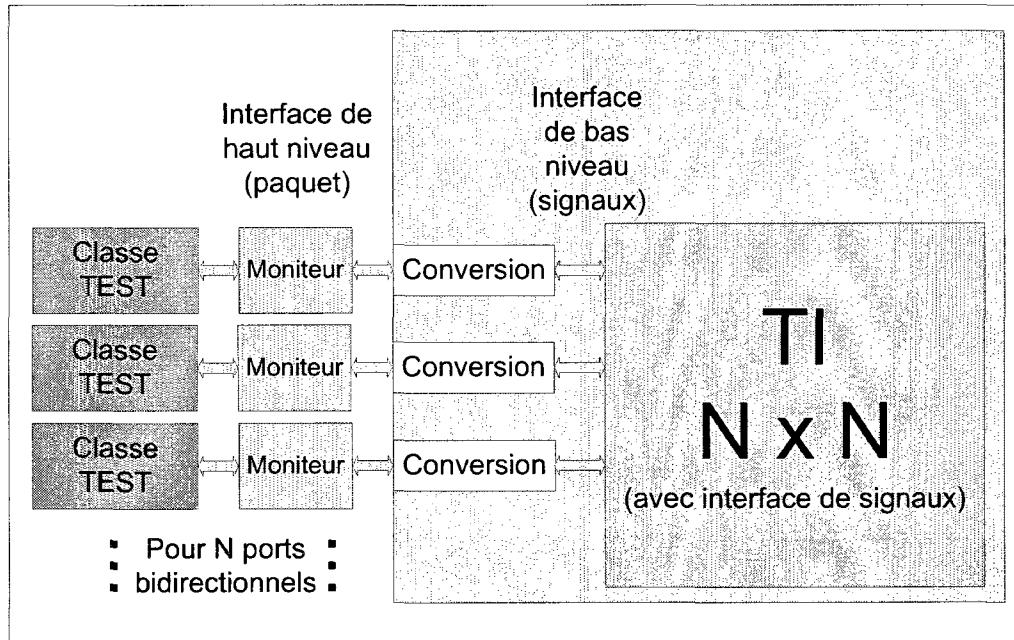

La figure 1.1 montre le modèle transactionnel proposé par SCV pour la vérification. Il est à noter que l'appel au modèle de référence n'est pas spécifié par SCV, mais une implémentation possible est incluse au schéma.

Figure 1.1 Schéma détaillé d'un banc d'essai transactionnel en SystemC

Le banc d'essai contient principalement trois modules : le module de génération de vecteurs de test, le module de conversion de transactions (« transactor ») et le module RTL testé (« Design Under Verification » – DUV). Le module de génération de vecteurs de test contient du code de haut niveau qui génère des transactions en entrées/sorties avec, généralement, des contraintes aléatoires. La conversion sert d'adaptateur entre les transactions du module de test et l'interface matérielle du DUV. Il permet d'abstraire ce détail d'implémentation du module de génération de vecteurs de test. Donc, deux interfaces ont été créées. L'une d'entre elles (« `rw_task_if` » – voir figure 1.1) définit la structure de l'information transmise (paquet) et les fonctions de lecture/écriture pour l'interface à haut niveau d'abstraction. Cette interface hérite de la classe « `sc_interface` » de SystemC. La deuxième interface (« `pipelined_bus_port` ») définit les signaux de l'interface matérielle. Une transaction générée par le module de test serait, par exemple, l'envoi d'un paquet. Le module de conversion de transactions est ensuite en charge de convertir ce paquet, et ce, en plusieurs cycles si nécessaire. Il peut également être utilisé pour abstraire l'appel du modèle de référence du test en temps réel, ce qui permet de cacher cette fonctionnalité au test tout en comparant les sorties au fur et à mesure. Le résultat du modèle de référence peut soit être écrit dans un fichier de sortie pour comparaison ultérieure et/ou comparé en temps réel. Dans les deux cas, il est possible de

produire un résultat global de succès ou échec du test (« pass » ou « fail »). Cela permet de savoir rapidement, après l'exécution du test, si des erreurs sont survenues.

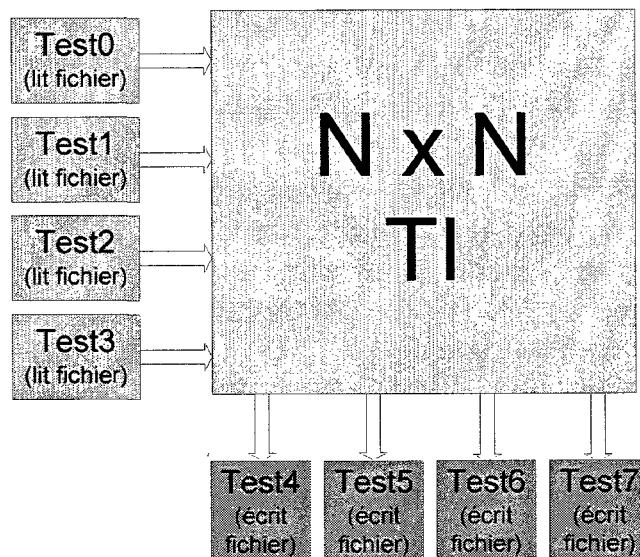

Afin d'illustrer la différence entre la méthode de vérification appliquée avec SCV/SystemC et une méthode plus simple, un banc d'essai écrit complètement en VHDL a été réalisé pour ce projet. Il est présenté à la figure 1.2. Cet exercice permet, entre autres, d'observer les limitations d'une telle approche et d'observer les avantages qu'offre un environnement plus évolué.

Figure 1.2 Banc d'essai VHDL simple

Il y a un module de lecture des fichiers d'entrée par port. Chacun des modules accède à son fichier propre et se charge de la transmission des données sur les ports d'entrée. Le format du fichier est un ensemble de lignes contenant chacune un mot à envoyer sur le port indiqué sur cette même ligne, suivi d'une autre ligne indiquant si le mot/paquet courant doit être écrit sur le port ou non. Cela permet de modéliser un certain pourcentage d'utilisation de la bande passante de façon simplifiée. Il y a également un

module équivalent pour chaque port de sortie qui produit un fichier de sortie contenant tous les mots transmis du TI avec leur temps spécifique pour chacun des ports.

Bien que la quantité de travail requise pour la création du banc d'essai soit faible, on remarque que celui-ci offre des possibilités très limitées. En effet, il permet de tester rapidement le fonctionnement, mais il est ardu d'obtenir des scénarios de tests spécifiques sans y ajouter des éléments. Avec seulement ce banc d'essai simple, l'usager doit produire manuellement les fichiers qui déterminent les trafics aux entrées, ce qui devient lourd lorsqu'on veut tester plusieurs scénarios de test spécifiques de complexité variable. On voit clairement un besoin pour une architecture plus avancée. Une approche classique pour résoudre cette problématique serait d'ajouter un programme C++ pour la création des fichiers d'entrée lus par le banc d'essai VHDL réalisé. Ce programme, étant en C++, peut utiliser des éléments plus avancés, tels que les objets (un objet complexe de type paquet par exemple), la surcharge d'opérateurs, les pointeurs et les bibliothèques de fonctions qui permettent la génération de nombres aléatoires. Cela permet de rendre le banc d'essai de la figure 1.2 plus efficace et bien plus aisés à configurer avec le niveau d'abstraction plus élevé qu'amène le C++. La simulation d'un test particulier a le désavantage de s'effectuer en deux étapes. Cependant, ce projet amène la méthode de développement d'un circuit à un autre niveau en éliminant ce processus à deux étapes et en y intégrant l'aspect validation de performance. En effet, comme on le verra au chapitre 2, en utilisant une approche basée sur des modules SystemC qui s'exécutent en concurrence, on peut intégrer des modèles de circuits plus avancés. Ceci vient intégrer l'aspect validation de performance du début de projet au processus de conception. Cette validation doit être réalisée pour être efficace de toute manière.

Tel que mentionné, SCV permet de générer des cas de test aléatoires contraints en plus des tests plus conventionnels dirigés et aléatoires. Un test dirigé vérifie un cas particulier. Un test aléatoire vérifie toutes les entrées de façon aléatoire. Un quatrième type pertinent s'ajoute et sera décrit plus en détail au chapitre 3 de ce document; il s'agit

du test appliqué. Nous verrons au chapitre 3 que ce type est également réalisable avec un environnement SystemC/SCV, ce qui en fait un environnement complet. Le tableau 1.1 montre les avantages et inconvénients de chaque type de test.

**Tableau 1.1 Avantages et inconvénients de différents types de tests**

| Type de test                | Avantages                                                                                                                                                                                                                                                | Inconvénients                                                                                                                            |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Tests dirigés               | <ul style="list-style-type: none"> <li>- Précis</li> <li>- Utile pour le déverminage ou les cas particuliers</li> </ul>                                                                                                                                  | <ul style="list-style-type: none"> <li>- Long à développer</li> <li>- Laborieux de parcourir un éventail de cas de tests</li> </ul>      |

| Tests aléatoires            | <ul style="list-style-type: none"> <li>- Rapidité de développement</li> <li>- Teste rapidement plusieurs bits sur les entrées</li> </ul>                                                                                                                 | <ul style="list-style-type: none"> <li>- Ne teste pas l'architecture en profondeur</li> <li>- Redondant</li> <li>- Inefficace</li> </ul> |

| Tests aléatoires contraints | <ul style="list-style-type: none"> <li>- Teste rapidement un grand éventail de cas de test</li> <li>- Adaptation des contraintes de cas de test facilement modifiables</li> <li>- Meilleure couverture</li> <li>- Pas exhaustif mais efficace</li> </ul> | <ul style="list-style-type: none"> <li>- Dans certains cas, on veut tester un cas précis</li> </ul>                                      |

| Tests appliqués             | <ul style="list-style-type: none"> <li>- Permet de tester un cas tiré d'une application réelle</li> </ul>                                                                                                                                                | <ul style="list-style-type: none"> <li>- Environnement plus lourd et moins flexible.</li> </ul>                                          |

En vérification, plusieurs éléments sont désirables. L'approche SCV en intègre plusieurs. En effet, SCV permet d'avoir un haut niveau d'abstraction ainsi qu'un environnement hautement configurable et auto-vérifiant. De plus, un simulateur comme Modelsim intègre l'aspect couverture (de code, fonctionnelle ou autre [23]) à l'environnement. SCV permet également de séparer l'environnement de vérification des tests. Une approche orientée-objet, telle qu'utilisée en C++, étant modulaire, cela favorise la réutilisation. En effet, on peut facilement s'imaginer créer une bibliothèque de classes

de tests et modules de conversion divers par exemple. Finalement, tout étant codé en C++, il est aisément d'effectuer les comparaisons avec une référence et de produire un résultat de type succès ou échec (« pass » ou « fail »).

Cadence et Mentor Graphics ont maintenant conjointement développé une méthode de vérification moderne, OVM (« Open Verification Methodology ») [25]. Cette dernière provient en fait d'une méthode unifiée de vérification de Cadence (Universal Reuse Methodology (URM) [7], [8]) combinée à des idées de la méthode de vérification avancée (AVM) développée par Mentor Graphics [13]. OVM est disponible avec les simulateurs Incisive® de Cadence et Questa de Mentor Graphics. OVM va plus loin que les standards SystemC et SCV. Il s'agit d'un standard disponible gratuitement qui vise d'abord l'utilisation standard avec n'importe quel simulateur du SystemVerilog pour la vérification. Il propose une bibliothèque normalisée et une méthode de développement éprouvée. Il rend plus aisément la création et l'utilisation de IP préconstruits pour la vérification. Bien que le standard ait été créé principalement pour le SystemVerilog, ces modules VIP (« Verification Intellectual Property ») peuvent être codés en SystemVerilog, SystemC et langage *e*, trois des langages de vérification avancés les plus populaires. L'approche proposée par OVM est disponible depuis 2008 et est une bonne approche à suivre pour un nouveau projet. Le projet courant n'utilise pas cette méthode puisque le standard n'était pas encore diffusé ni disponible au début du projet. Par contre, la plupart des concepts avancés de vérification qui sont inclus dans OVM se retrouvent dans ce projet. Un des éléments concrets que cette méthode aurait apporté au présent projet est d'avoir un environnement indifférent par rapport au simulateur utilisé. Ce projet a été réalisé en suivant les directives de Mentor Graphics non-standardisées pour l'intégration du SystemC. Il s'agit d'un avantage considérable pour OVM, considérant qu'il est souhaitable d'avoir divers modules VIP disponibles ouvertement pour accélérer le processus de vérification et, par le fait même, la validation de performance en appliquant la méthode présentée dans ce mémoire.

OVM se base sur un modèle de vérification transactionnel, tout comme les travaux courants. OVM permet également de modifier aisément des bancs d'essais à l'exécution et d'écrire plusieurs tests à partir de l'environnement de base avec des changements de codes minimaux. Il permet de créer rapidement des tests abstraits du module testé qui peuvent même générer des stimuli aléatoires contraints, aléatoires ou dirigés. Une séquence ainsi créée peut être réutilisée aisément. Il rend disponible également une interface d'écriture de test simple et une méthode d'affichage des messages standardisée.

La Méthode de Vérification Unifiée de Cadence (UVM) [8] présente des concepts intéressants pour la vérification. Ces éléments ne sont pas primordiaux pour ce projet puisqu'ils n'ont aucun impact sur l'aspect le plus important pour ces travaux, la validation de performance. Également, ils ne sont pas pertinents pour le niveau de détail de vérification exploré dans le cadre de ce projet de maîtrise. Par contre, il est intéressant de pouvoir appliquer ces éléments disponibles avec la plupart des simulateurs avancés à une phase ultérieure de vérification. Il s'agit, entre autres, du concept de couverture autant du code, que structurel, ainsi que de l'application et des interfaces. La réutilisation des éléments d'un banc d'essai est également primordiale pour améliorer le temps de développement. La méthode d'interface transactionnelle présentée s'applique également au niveau modulaire. En effet, une bonne approche modulaire consiste à créer plusieurs modules du design avec une interface transactionnelle. Au départ, tous ces modules communiquent directement au niveau de la modélisation transactionnelle. En cours de projet, des modules matériels peuvent être intégrés graduellement avec les modules de conversion des transactions adéquats (« transactor »). L'aspect rapidité d'exécution avec une méthode d'accélération est également un aspect important. Le prototypage FPGA ou l'utilisation d'un émulateur matériel permet d'accélérer les simulations. D'ailleurs, cette accélération peut se faire de façon modulaire en intégrant un modèle matériel avec d'autres modèles logiciels à haut niveau et les modules de conversion adéquats

(« transactor »). Il n'est donc pas nécessaire d'avoir un système entier pour réaliser une simulation matérielle rapide.

## 1.2 Validation de performance

La validation de performance se fait en comparant un modèle avec les requis. Il permet d'évaluer si le modèle atteint les performances voulues. Cela peut se traduire en une évaluation de la performance d'une architecture avec un modèle sommaire qui inclut les caractéristiques importantes pour permettre une validation. Cette évaluation est comparée aux requis selon certains critères établis. Il s'agit d'un paramètre distinct de la vérification qui a pour but de vérifier que le comportement obtenu correspond bien à la description contenue dans la spécification. La validation doit idéalement être faite en début de projet sur un modèle en cas d'incertitude sur les performances, et, également, une fois l'implémentation matérielle complète pour confirmer l'atteinte des performances recherchées. On voit que, théoriquement, il est possible d'avoir un seul environnement qui applique les stimuli sur un modèle et sur une implémentation matérielle. Le chapitre 2 développe cette idée.

La validation en début de projet est un aspect à prioriser en cas d'incertitude pour le projet. Le coût du temps passé à faire cette validation est nettement inférieur au coût d'un projet complété qui n'atteint pas les performances désirées. Par contre, trop de temps passé à la validation peut avoir un impact sur l'échéancier du projet. Il faut par conséquent bien doser le temps passé à réaliser des tâches de validation. Il est donc essentiel d'avoir une méthode de validation efficace.

La littérature propose diverses méthodes pour valider la performance. Des travaux publiés par Armstrong, Gray et Vuppala montrent une méthode de validation qui se base sur la création d'une modélisation simplifiée en VHDL [1]. La littérature prouve également qu'une simulation SystemC s'avère significativement plus rapide qu'une

simulation RTL [9]. En plus du haut niveau d'abstraction que le SystemC offre, cette constatation en fait un candidat idéal pour modéliser une architecture dans le but d'analyser sa performance. On s'attend ainsi d'obtenir un temps de conception du modèle et de simulation amélioré. L'état de l'art montre quelques exemples qui utilisent cette approche afin de créer un environnement de validation pour l'exploration architecturale de CI divers [22].

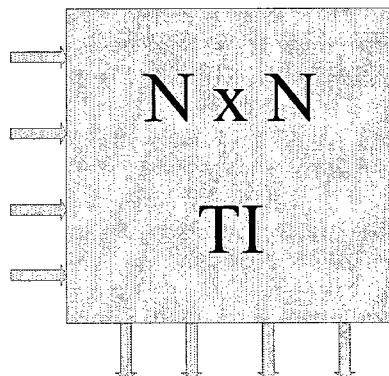

### 1.3 Tissu d'interconnexion

Un tissu d'interconnexion (TI) [28] peut se définir, de façon générale, comme étant une structure de communication qui reçoit des paquets sur des ports d'entrée et les transfère vers les ports de sortie. Un modèle de base est présenté à la figure 1.3. Le tissu d'interconnexion est surtout utilisé pour faire la communication entre divers modules passifs et actifs dans un système embarqué. Les modules peuvent être un processeur avec jeu d'instruction spécifique (ASIP) ou un FPGA/ASIC dédié qui accède à plusieurs mémoires ou ports de communication, comme un port Ethernet. D'autres unités de calculs peuvent opérer en parallèle et accéder aux mêmes mémoires au travers du tissu d'interconnexion. Les paquets transmis pour ces applications sont de tailles variables contrairement aux TI utilisés pour le routage de cellules (« cell based routing »), comme celles utilisées dans les systèmes ATM. Ce dernier type de communication n'est pas traité dans le présent ouvrage. Il est à noter que l'interconnexion à granularité de cellule est un cas particulier qui peut aisément être couvert par ces travaux en supposant des paquets de tailles égales, que ce soit en convertissant le protocole en entrée/sortie du medium ou en ne supportant qu'un protocole de paquet à tailles fixes de façon native. Une architecture de type TI permet d'avoir plusieurs communications indépendantes en parallèle, contrairement à une architecture de type « bus », qui ne permet pas les communications simultanées. En effet, pendant une communication, le medium est bloqué pour toutes les autres transmissions et ce, même si les communications sont totalement indépendantes

[37]. Cela constitue l'avantage principal du TI au prix d'un médium d'interconnexion plus complexe et couteux en termes de surface de silicium.

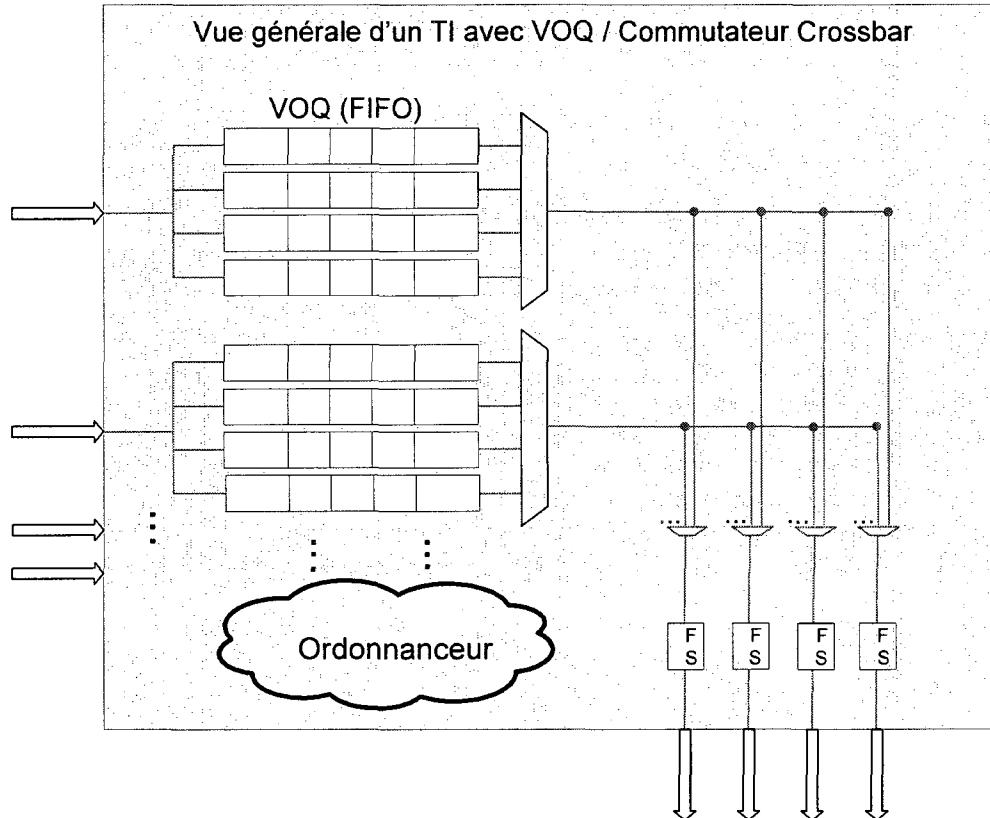

**Figure 1.3 Représentation de base d'un tissu d'interconnexion**

Il existe plusieurs types d'architectures qui ont chacun leurs avantages respectifs selon le type de protocole de communication utilisé. Pour les travaux courants, une architecture connue pour son efficacité dans des systèmes embarqués a été utilisée. Il s'agit d'une architecture de type commutateur crossbar [28], [37] qui utilise des files de sortie virtuelles (« Virtual Output Queuing » – VOQ) [34]. Les files sont utilisées en entrée. Pour chaque entrée, il existe une file par sortie. Dépendamment de la destination du paquet en entrée, celui-ci est placé dans la file de sortie virtuelle correspondante. Cette architecture permet de faire une classification des paquets dès leur arrivée dans le TI. Cela permet aussi de préserver l'ordre des paquets et d'éviter le blocage de file par le premier élément (« head of line blocking »). Ce dernier événement se produit lorsqu'un paquet à la tête de la file bloque un autre paquet de cette file qui serait en mesure d'être transmis dans le TI. Puisque les paquets sont classifiés dans des files virtuelles séparées, cela ne peut se produire avec une architecture qui utilise des VOQ. La figure 1.4 montre l'idée de base de ce type d'architecture.

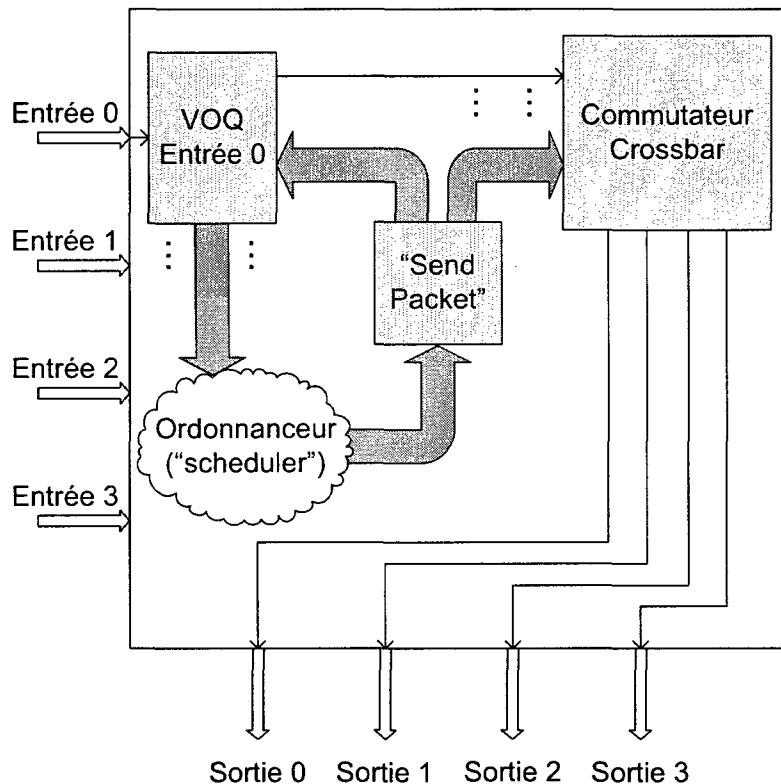

**Figure 1.4 Architecture de base d'un tissu d'interconnexion de type commutateur crossbar à files de sortie virtuelles**

Chaque port d'entrée possède son propre ensemble de files de sortie virtuelles. Ces files sont dites virtuelles car, ayant besoin d'un seul port d'écriture/lecture au FIFO par port d'entrée du TI, l'implémentation est habituellement faite avec une seule mémoire qui est gérée avec des pointeurs. Pour des profondeurs de files considérables, cela devient avantageux en termes de surface de silicium parce que la mémoire est utilisée de façon plus efficace. Une fois le paquet dans une des files virtuelles, sa destination étant connue, il ne reste qu'à arbitrer les diverses files s'adressant à la même sortie. Les files de sortie virtuelles font ensuite suivre les paquets vers le commutateur crossbar un à la fois. Le commutateur crossbar [28] se définit comme étant le chemin de données qui route les

paquets vers les sorties. Il suit les files dans le chemin de données. Il s'agit souvent d'un agencement de multiplexeurs (tels que montrés à la figure 1.4) et de fils habituellement longs puisqu'ils doivent parcourir physiquement presque toute la hauteur ou la largeur de la puce de silicium. Avec un commutateur crossbar, une entrée peut envoyer un seul paquet à une seule sortie à la fois. Cela constitue un compromis afin de simplifier la circuiterie et les contraintes. Un commutateur crossbar peut être accéléré par rapport aux ports d'entrée/sortie en ayant un débit plus important. Le rapport de bande passante entre les chemins de données du commutateur crossbar et ceux des ports d'entrée/sortie est défini comme le facteur d'accélération. Habituellement, il existe un étage de files de sortie (FS) qui contient une quantité minimale de mémoire tampon avant que le paquet ne soit envoyé à la sortie du tissu. Cela permet, entre autres, d'ajuster la largeur des données à la largeur du port de sortie et d'absorber les irrégularités de débit du TI. Combiné au facteur d'accélération du commutateur crossbar, la mémoire tampon en sortie permet d'améliorer les performances du TI en diminuant les contraintes sur le matériel. L'ordonnanceur est, en quelque sorte le chef d'orchestre qui choisit quels paquets sont envoyés au commutateur crossbar et à quel moment. Il utilise habituellement une forme de logique pour prioriser les divers paquets à partir des informations des diverses files. Par exemple, si aucune des files n'est vide, alors toutes les entrées tentent de transmettre un paquet vers toutes les sorties. Différents mécanismes pour la gestion des priorités peuvent être utilisés en fonction de paramètres comme : le temps que le paquet a passé dans la file, la longueur et le type des paquets, leur priorité. Tous ces facteurs tendent à rendre l'ordonnanceur plus complexe, mais aussi plus efficace. Cependant, il faut tout de même définir un mécanisme de priorité dans le cas où chaque connexion entrée/sortie a un poids équivalent. Cette priorité se doit d'être variable dans le temps afin d'assurer une décision équitable. Chaque connexion entrée/sortie doit avoir la même chance d'être sélectionné. La priorité est donnée par l'algorithme à chaque appel de l'ordonnanceur, mais en moyenne, après un certains temps, la décision se doit d'être équitable pour être efficace. Un algorithme efficace demeure équitable même si les paquets d'entrée ne sont pas de tailles égales entre les ports.

Une version simple et efficace d'ordonnanceur est le « weighted round-robin » (WRR) [28], [40]. Le WRR étant un algorithme théorique, cela en fait une référence intéressante pour ce projet. Pour cet algorithme, la priorité est donnée en alternance à la manière d'un « round-robin » entre les files. À chaque décision, la plus haute priorité est donnée à un port de sortie et une alternance « round-robin » est appliquée sur le port prioritaire pour la décision suivante. La priorité est initialement, et sans perte de généralité, donnée au port 0. Il en est de même pour le port d'entrée prioritaire mais la priorité passe au port d'entrée suivant seulement après que tous les ports de sortie aient reçus la plus haute priorité pour un port d'entrée donné. L'algorithme inclut également une notion de poids qui se doit d'être fixe et de refléter le trafic en entrée. Pour un ordonnancement, l'entrée qui nécessite une plus grande bande passante (en termes de paquets) selon ce poids se voit assigner plusieurs paquets. Par exemple, un port d'entrée qui reçoit des paquets deux fois plus petits transmettrait deux paquets lorsqu'il est choisi et que ces deux paquets sont disponibles. Étant donné que le trafic est défini dans notre environnement et que le trafic à chaque entrée est connu, il est facile de configurer le poids de chaque entrée. Ce n'est généralement pas le cas dans un système réel, mais cela donne un avantage lors d'une analyse. Cet algorithme sert en fait de référence pour une analyse de performance avec n'importe quelle architecture d'ordonnanceur. L'algorithme est théoriquement efficace mais n'est pas réalisable physiquement si le nombre de ports est élevé. Ceci vient du fait que le nombre de connexions potentielles à analyser en un nombre de cycles fixe croît en fonction du carré du nombre de ports du TI. Donc, avec un grand nombre de connexions à analyser en un nombre de cycles faible, le nombre de niveaux logiques nécessaires à l'analyse décisionnelle devient trop élevé, ce qui rend la fréquence d'opération du circuit peu intéressante. Le nombre de cycles pour la décision se doit par ailleurs d'être faible afin d'éviter de dégrader la performance pour les petits paquets. Ces derniers sont reçus rapidement et ils doivent donc idéalement être transmis rapidement. Une autre approche doit être envisagée pour l'implémentation.

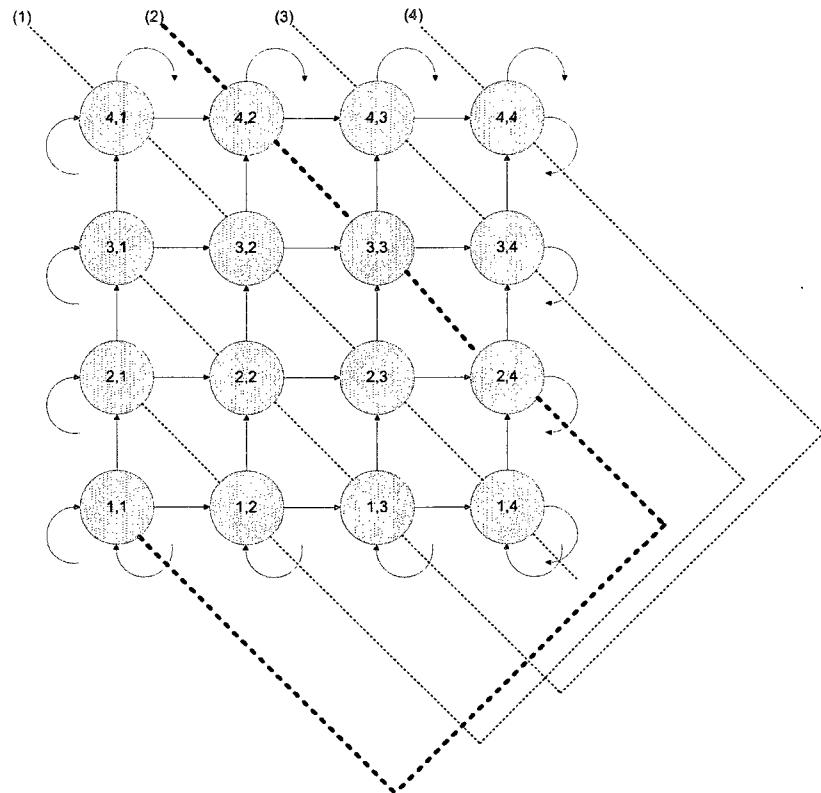

Le WWFA (« Wrapped Wave Front Arbiter ») [11], en plus d'avoir un potentiel de performance intéressant, est beaucoup plus adapté à une implémentation matérielle. Il se prête bien au contexte de ce projet puisqu'on s'y intéresse pour d'autres travaux avec *Tundra Semiconductor* [36]. Cet arbitre permet d'améliorer la fréquence d'opération du circuit en distribuant la décision parmi les nœuds du TI. La figure 1.5 montre les quatre vagues diagonales utilisées par l'algorithme pour un TI à quatre ports. Chaque diagonale contient une seule fois chacun des ports de sortie. Il en est de même pour les ports d'entrée. Ceci est l'élément qui permet de distribuer la décision. À chaque décision, la diagonale prioritaire est alternée. Chacun des nœuds communique à ses nœuds voisins si la connexion est établie ou non. Donc, chaque nœud de la diagonale prioritaire influence les autres nœuds en propageant sa décision. Il en est de même pour les nœuds voisins.

**Figure 1.5 Algorithme d'ordonnanceur WWFA (“Wrapped Wave Front Arbiter”)**

#### 1.4 Statistiques pertinentes aux tissus d'interconnexion

Un des paramètres de base de toute interface de données en matériel est le débit de données, soit la bande passante. Ce paramètre peut être quantifié de diverses façons. La plus commune est de présenter le débit en bits par seconde. Une abstraction plus élevée de ce paramètre est le pourcentage d'utilisation d'un lien. Celui-ci abstrait le nombre de bits passés, mais est valable lorsqu'on compare deux liens de même largeur par exemple. Ces deux descriptifs du débit permettent de quantifier les débits de divers ports d'un TI.

La latence est un autre paramètre important de tout système matériel. Dans le cas d'un TI, on parle de latence d'un paquet dans le TI. Il s'agit du temps qu'un paquet a passé dans un TI avant d'en être sorti. Pour obtenir une comparaison juste, on considère pour ce projet que la latence se calcule entre le moment où le paquet est complètement arrivé dans le TI et le moment où il en est complètement sorti. Avec cette convention, la latence minimale obtenue est le nombre de cycles que prend le paquet sur le lien d'un port. La latence moyenne sur un nombre significatif de paquets est évidemment influencée par les débits aux entrées et l'architecture du TI.

L'équité de l'ordonnanceur est un paramètre pertinent aux TI. L'ordonnanceur décide, en cas de conflit, à quel port donner la priorité. L'équité définit une mesure de la qualité de l'arbitrage entre les divers ports d'un TI. Il existe plusieurs publications [15], [19], [33] qui comparent ou évaluent l'équité de différents ordonnanceurs avec différentes métriques. L'analyse peut être pour un trafic équilibré ou non. Plusieurs scénarios sont possibles. En fait, contrairement à la latence ou au débit, ce paramètre n'a pas de formule prétablie. Plusieurs mesures d'équité sont utilisées pour ces travaux et elles sont décrites ici. Selon quelques sources, il peut être calculé en évaluant le 99<sup>ième</sup> percentile de la latence [32], [33]. Pour un même trafic global, un TI plus équitable devrait donner un 99<sup>ième</sup> percentile de latence plus petit. Une autre façon de le mesurer est de comparer les latences moyennes pour les divers ports pour un certain trafic connu

[15]. Il y aussi la comparaison du nombre de paquets perdus par port et du taux d'utilisation des files VOQ par port qui permet d'indiquer l'équité d'un TI suite à une simulation. On s'attend à ce que ces trois derniers paramètres discutés soient équivalents pour tous les ports d'entrée en présence d'un ordonnanceur équitable. Pour des fins d'analyse, une métrique non-standard a également été utilisée. Il s'agit de l'équité de connexion. Elle se définit comme étant le rapport du nombre de cycles d'envoi de paquets pour une entrée donnée alors qu'il y a au moins un paquet à envoyer de cette entrée. Les cycles pour lesquels aucune donnée n'est à transmettre sont ainsi éliminés de l'analyse. Ce rapport peut être comparé pour les diverses entrées.

Puisque ces mesures d'équité mènent à une analyse d'uniformité, il est intéressant d'avoir une métrique qui évalue cette uniformité pour un certain nombre de valeurs. On peut vouloir, par exemple, calculer l'uniformité de la latence par port pour un TI. Une façon intéressante de le calculer est avec le critère d'équité établie par Jain [17]. Voici le calcul théorique pour ce paramètre de Jain.

$$F = \frac{\left(\sum_{i=1}^n y_i\right)^2}{n \sum_{i=1}^n (y_i)^2}$$

Où, dans notre cas,  $y_i$  est l'un des paramètres d'équité décrit ci-haut pour le port  $i$ ,  $n$  représente le nombre de ports et  $F$  représente le facteur de Jain pour le paramètre choisi. Ce facteur peut prendre des valeurs entre 0 et 1, 1 représentant une grande équité. Pour un trafic non-équilibré, dans le cas où on connaît les trafics en entrée, on s'attend à ce que certaines entrées, pour certains paramètres, aient un poids plus ou moins élevé. Ainsi, pour un algorithme juste, un port avec une taille moyenne des paquets deux fois plus grands qu'un autre port avec trafic similaire devrait perdre deux fois moins de paquets, ce qui correspond à une même quantité de données. Une équation proposée par Jain qui mesure l'équilibre en tenant compte de poids par port  $w_i$  s'énonce comme suit:

$$F = \frac{(\sum_{i=1}^n w_i y_i)^2}{n \sum_{i=1}^n (w_i y_i)}$$

Pour notre exemple de paquets perdus précédent, on pourrait choisir  $w_i$  à 1 pour un port qui a des paquets deux fois gros qu'un autre port avec  $w_i$  à 2. Une autre publication présente un concept similaire pour une application différente (TCP) [24].

## 1.5 XTSC de Tensilica

La compagnie Tensilica offre des ASIP qui sont des processeurs génériques que l'usager peut configurer afin d'ajouter de nouvelles instructions spécialisées pour une application donnée [2], [3], [18]. Ceci se fait par la description de la fonctionnalité des instructions ajoutées dans un langage matériel propre à Tensilica, le TIE. Cela permet de créer un processeur qui, en plus de posséder tous les atouts d'un processeur générique incluant la stabilité des divers modules fixes, intègre une partie configurable pour spécialiser le processeur. Tensilica fournit un simulateur pour ce processeur configuré et peut également fournir une version matérielle du processeur. Un code C s'exécutant sur le processeur spécialisé fait un appel explicite à l'instruction ajoutée pour en tirer profit. Étant un environnement réel permettant d'exécuter une application tout aussi réelle et étant disponible dans une version SystemC (XTSC), cet environnement devient pertinent dans le cadre d'un projet de vérification et validation avec SystemC/SCV. Il permet d'avoir des scénarios d'entrée/sortie tirés d'une application réelle sans avoir à créer à partir de zéro un nouveau système pour chaque nouvelle application.

XTSC inclut des modules de Tensilica contenus dans des « sc\_module ». Entre autres, `xtsc_core` est un module SystemC qui inclut le simulateur d'instructions de

Tensilica. Il inclut des méthodes qui permettent l'accès aux divers ports : les ports de la mémoire locale, l'interface de la mémoire locale de Xtensa (XLMI), l'interface processeur (PIF), l'interface d'instruction TIE et certains ports d'entrée/sortie du système. Cet objet permet de charger un programme à exécuter et plusieurs autres paramètres de configuration et fonctionnalités. Le fonctionnement des interfaces XTSC TLM sont décrites en détail à la section 3.1 du guide de l'usager XTSC [35]. Tensilica fournit son propre jeu d'outils. Il inclut, entre autres, un outil de simulation (xtsc\_run) et un outil de déverminage (xt-gdb).

Il est donc possible pour l'usager d'interfacer n'importe quel module SystemC avec le processeur Tensilica via diverses connexions par des appels de fonctions. On peut ainsi simuler ce module SystemC avec l'environnement fourni par Tensilica.

## 1.6 Conclusion

Ce chapitre permet de prendre connaissance des aspects généraux de la vérification, de ce qu'amène un langage pour la vérification avancée, des principaux aspects architecturaux d'un TI, des statistiques de performance pertinentes aux TI et de la possibilité d'intégrer un trafic tiré d'une application réelle qui s'exécute sur un processeur. Tous les éléments sont maintenant en place pour présenter un environnement efficace qui intègre la validation de performance et la vérification pour un TI.

## CHAPITRE 2. ENVIRONNEMENT DE VALIDATION/VÉRIFICATION À HAUT NIVEAU