|                   |                                                                                                                                                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Titre:</b>     | Conception et prototypage de décodeurs à seuil itératif à haut débit                                                                                      |

| Title:            |                                                                                                                                                           |

| <b>Auteur:</b>    | Abbas Nemr                                                                                                                                                |

| Author:           |                                                                                                                                                           |

| <b>Date:</b>      | 2009                                                                                                                                                      |

| <b>Type:</b>      | Mémoire ou thèse / Dissertation or Thesis                                                                                                                 |

| <b>Référence:</b> | Nemr, A. (2009). Conception et prototypage de décodeurs à seuil itératif à haut débit [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. |

| Citation:         | <a href="https://publications.polymtl.ca/8439/">https://publications.polymtl.ca/8439/</a>                                                                 |

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

|                           |                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------|

| <b>URL de PolyPublie:</b> | <a href="https://publications.polymtl.ca/8439/">https://publications.polymtl.ca/8439/</a> |

| PolyPublie URL:           |                                                                                           |

|                                 |                                     |

|---------------------------------|-------------------------------------|

| <b>Directeurs de recherche:</b> | Mohamad Sawan, & Christian Cardinal |

| Advisors:                       |                                     |

|                   |              |

|-------------------|--------------|

| <b>Programme:</b> | Non spécifié |

| Program:          |              |

UNIVERSITÉ DE MONTRÉAL

CONCEPTION ET PROTOTYPAGE DE DÉCODEURS À SEUIL ITÉRATIF À

HAUT DÉBIT

ABBAS NEMR

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AOÛT 2009

Library and Archives

Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

ISBN: 978-0-494-53915-6

*Our file Notre référence*

ISBN: 978-0-494-53915-6

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

CONCEPTION ET PROTOTYPAGE DE DÉCODEURS À SEUIL ITÉRATIF À

HAUT DÉBIT

présenté par: NEMR Abbas

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. DAVID Jean-Pierre, Ph.D., président

M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

M. CARDINAL Christian, Ph.D., membre et codirecteur de recherche

M. HACCOUN David, Ph.D., membre

À celui que tout le monde attend...

## **REMERCIEMENTS**

Je tiens à remercier par ces quelques lignes les personnes qui m'ont permis de mener à bien cette recherche.

J'aimerais au début remercier mon directeur de recherche, le Dr. Mohamad Sawan, ainsi que mon co-directeur de recherche, le Dr. Christian Cardinal, dont leurs précieux conseils m'ont aidé tout au long de mon travail. Je tiens à remercier aussi le Dr. David Haccoun ainsi que mes directeurs pour l'aide financière qu'ils m'ont accordée.

Je tiens aussi à remercier tous mes collègues du laboratoire pour toutes ces discussions quotidiennes enrichissantes. Je pense particulièrement à Saeid, Amine, Mostapha, Mohamad, Éric et Bassam.

Finalement, je tiens à remercier ma famille et en particulier mon père, ma mère et ma femme ainsi que mes amis pour leur soutien.

## RÉSUMÉ

Le travail de recherche effectué dans ce mémoire concerne la conception et le prototypage sur FPGA de décodeurs à seuil itératif à haut débit.

Le décodage à seuil itératif utilisé conjointement avec des codes convolutionnels doublément orthogonaux (CDO) constitue un nouvel algorithme performant de correction d'erreurs. Cependant, les implémentations de ce type de décodeur qui ont été réalisées à ce jour n'atteignent que 42 Mbps de débit et ne supportent qu'un seul taux de codage  $R = 1/2$ . Afin de satisfaire les critères de communication tels que, par exemple, ceux spécifiés pour des systèmes WiMAX mobiles (IEEE 802.16e), le débit binaire à la sortie du décodeur des codes CDO doit être augmenté. En outre, les codeurs/décodeurs utilisés doivent avoir la capacité de fonctionner à plusieurs taux de codages.

Dans la première partie de ce travail, l'architecture du décodeur à seuil itératif a été détaillée. Ainsi, les composants qui limitent le débit du décodeur ont été améliorés. De plus, une technique efficace de pipelinage a été développée et appliquée à l'architecture du décodeur à seuil afin d'en augmenter son débit. Les modules de perforation ont été développés et intégrés dans le codeur CDO et le décodeur à seuil itératif. Par conséquent, le décodeur à seuil itératif qui a été développé et implanté sur FPGA est capable de supporter les taux de codages allant de  $R = 1/2$  à  $R = 8/9$  à un débit qui peut atteindre 269 Mbps.

Dans la deuxième partie de ce travail, une autre approche qui consiste à étudier les codes CDO à multi-registres à décalage (M-CDO) a été utilisée afin d'augmenter le débit du décodeur. Les codes M-CDO sont générés par un codeur à  $M$  registres à décalage et offrent un décodage à architecture parallèle. Par conséquent, le débit du décodeur est  $M$  fois plus grand qu'un décodeur des codes CDO. Cependant, la complexité du décodeur

est  $M$  fois plus grande ce qui a été compromis par la simplification des codes M-CDO. Le prototype du décodeur à seuil itératif des codes M-CDO implémenté est capable d'atteindre des très hauts débits allant jusqu'à 1.3 Gbps pour certains codes.

Au cours de ces étapes, plusieurs nouveaux générateurs de codes CDO et M-CDO ont été introduits. De plus, les résultats expérimentaux des décodeurs ont été exposés. Ces résultats ont montré que les codes M-CDO simplifiés offrent un compromis attrayant entre débit, complexité et performances d'erreur au décodage.

## ABSTRACT

The research presented in this master's thesis deals with the design and prototyping on FPGA of very high throughput iterative threshold decoders.

The iterative threshold decoding used in conjunction with convolutional doubly orthogonal (CDO) codes constitutes a new powerful error correcting algorithm. However, the implementations of this type of decoder that have been completed to date can reach a low throughput of 42 Mbps and support only one coding rate  $R = 1/2$ . In order to meet the communication systems criteria, such as those specific to mobile WiMAX systems (IEEE 802.16e), the throughput at the output of the decoder of CDO codes must be increased. In addition, the used encoders/decoders must have the capacity to operate at multiple coding rates.

In the first part of this work, the architecture and the main components of the iterative decoder threshold are presented. Later, the cited components that limit the throughput of the decoder have been improved. In addition, an effective pipelining technique was developed and applied to the architecture in order to increase its throughput. The new design which was implemented on FPGA is able to handle coding rates ranging from  $R = 1/2$  to  $R = 8/9$  at a throughput that can reach up to 269 Mbps.

In the second part of this work, another approach that consists of studying multi-shift registers CDO (M-CDO) encoders was used to increase the throughput of the decoder. M-CDO codes are generated by a  $M$ -shift registers coder and decoded using a parallel architecture. Thus, the throughput of the decoder is  $M$  times larger than that of the decoder of CDO codes. However, the new decoder suffers from complexity ( $M$  times) which could be reduced by simplifying M-CDO codes. The new pipelined parallel decoder achieves a very high throughput of 1.3 Gbps for specific codes.

In this work, several new generators of CDO and M-CDO codes have been introduced. Moreover, experimental results of the implemented decoders are presented. These results prove that the simplified M-CDO codes offer attractive trade-off between throughput, complexity and error performances at decoding.

**TABLE DES MATIÈRES**

|                                                        |       |

|--------------------------------------------------------|-------|

| DÉDICACE . . . . .                                     | iv    |

| REMERCIEMENTS . . . . .                                | v     |

| RÉSUMÉ . . . . .                                       | vi    |

| ABSTRACT . . . . .                                     | viii  |

| TABLE DES MATIÈRES . . . . .                           | x     |

| LISTE DES FIGURES . . . . .                            | xiv   |

| LISTE DES TABLEAUX . . . . .                           | xx    |

| LISTE DES ANNEXES . . . . .                            | xxiii |

| LISTE DES SIGLES ET DES SYMBOLES . . . . .             | xxiv  |

| CHAPITRE 1      INTRODUCTION . . . . .                 | 1     |

| 1.1 Motivation . . . . .                               | 1     |

| 1.2 Contributions . . . . .                            | 2     |

| 1.3 Organisation du mémoire . . . . .                  | 3     |

| CHAPITRE 2      NOTIONS PRÉLIMINAIRES . . . . .        | 5     |

| 2.1 Introduction . . . . .                             | 5     |

| 2.2 Codage de canal . . . . .                          | 5     |

| 2.2.1 Système de communication numérique . . . . .     | 5     |

| 2.2.2 Principe du codage correcteur d'erreur . . . . . | 7     |

| 2.2.3 Les codes LDPC . . . . .                         | 8     |

| 2.2.4 Les codes Turbo . . . . .                        | 11    |

|                                                                        |                                                                                                        |    |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----|

| 2.2.5                                                                  | Les codes CDO . . . . .                                                                                | 13 |

| 2.3                                                                    | Notions matérielles . . . . .                                                                          | 22 |

| 2.3.1                                                                  | La technologie FPGA . . . . .                                                                          | 22 |

| 2.3.2                                                                  | Les FPGA de la famille Virtex-II Pro de Xilinx . . . . .                                               | 23 |

| 2.3.3                                                                  | Délai critique d'un circuit numérique . . . . .                                                        | 25 |

| 2.3.4                                                                  | Stratégie de resynchronisation d'un circuit numérique . . . . .                                        | 26 |

| 2.3.5                                                                  | Environnement d'évaluation des performances d'erreur du DS1 .                                          | 27 |

| 2.4                                                                    | Conclusion . . . . .                                                                                   | 29 |

| <br>CHAPITRE 3        DÉCODEUR À SEUIL ITÉRATIF À HAUT DÉBIT DES CODES |                                                                                                        |    |

|                                                                        | CDO . . . . .                                                                                          | 30 |

| 3.1                                                                    | Introduction . . . . .                                                                                 | 30 |

| 3.2                                                                    | Architecture du décodeur à seuil . . . . .                                                             | 30 |

| 3.2.1                                                                  | Le pondérateur . . . . .                                                                               | 32 |

| 3.2.2                                                                  | Les registres à décalage . . . . .                                                                     | 34 |

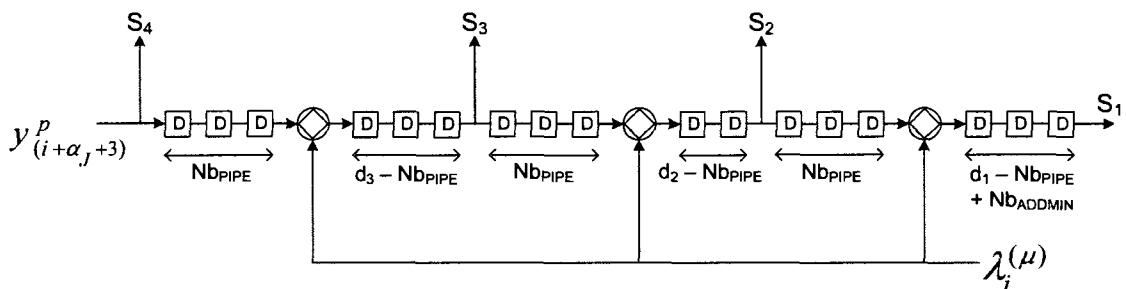

| 3.3                                                                    | Technique de pipelinage du décodeur . . . . .                                                          | 39 |

| 3.3.1                                                                  | Stratégie de resynchronisation du décodeur . . . . .                                                   | 40 |

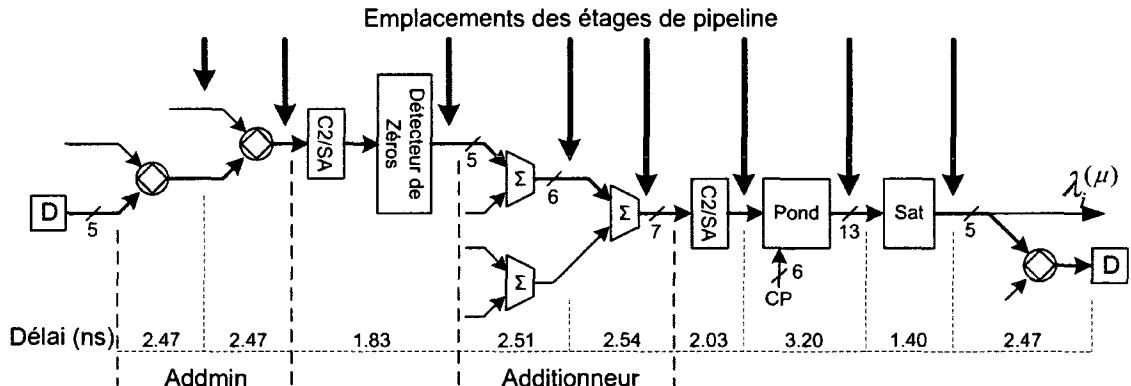

| 3.3.2                                                                  | Emplacements des étages de pipeline . . . . .                                                          | 41 |

| 3.3.3                                                                  | Capacité de pipelinage d'un codeur CDO . . . . .                                                       | 43 |

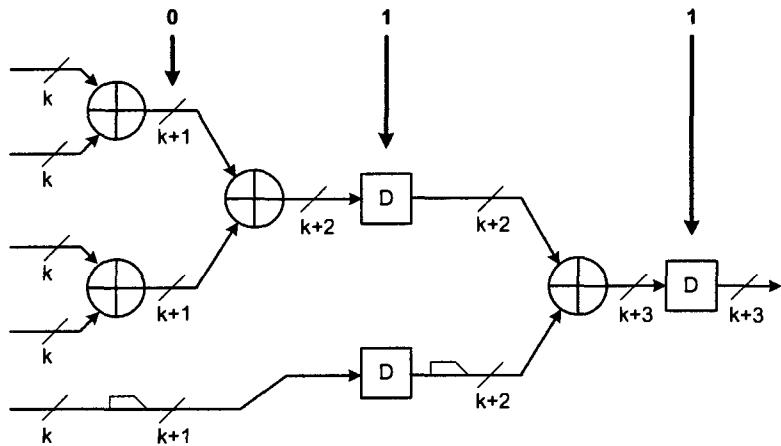

| 3.3.4                                                                  | Implémentation des composants pipelinés . . . . .                                                      | 45 |

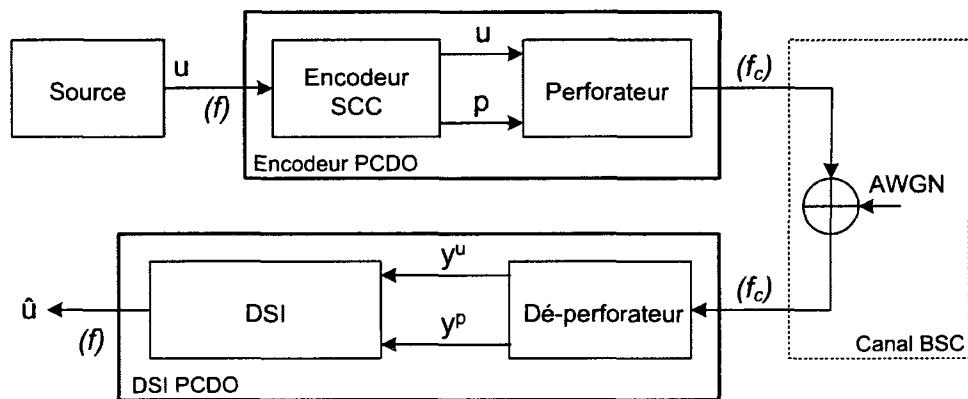

| 3.4                                                                    | Système de communication adapté aux codes perforés . . . . .                                           | 48 |

| 3.4.1                                                                  | Introduction . . . . .                                                                                 | 48 |

| 3.4.2                                                                  | Gestionnaire d'horloge . . . . .                                                                       | 50 |

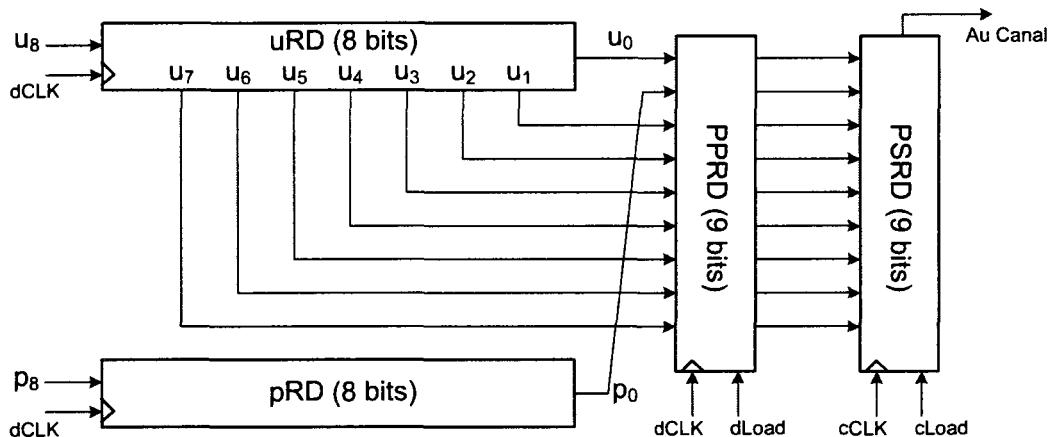

| 3.4.3                                                                  | Encodeur perforé . . . . .                                                                             | 52 |

| 3.4.4                                                                  | Décodeur à seuil itératif adapté aux codes perforés . . . . .                                          | 54 |

| 3.5                                                                    | Recherche de générateurs des codes PCDO à taux compatibles et à haute capacité de pipelinage . . . . . | 55 |

| 3.6                                                                    | Conclusion . . . . .                                                                                   | 56 |

|                                                                                                              |           |

|--------------------------------------------------------------------------------------------------------------|-----------|

| <b>CHAPITRE 4        CODES CONVOLUTIONNELS DOUBLEMENT ORTHOGONaux À MULTI-REGISTRES À DÉCALAGE . . . . .</b> | <b>58</b> |

| 4.1   Introduction . . . . .                                                                                 | 58        |

| 4.2   Définition des codes M-CDO . . . . .                                                                   | 59        |

| 4.3   Simplification des codes M-CDO . . . . .                                                               | 64        |

| 4.3.1   Représentation vectorielle des différences simples et doubles . .                                    | 65        |

| 4.3.2   Simplification des conditions de la définition des codes M-CDO                                       | 67        |

| 4.4   Décodeur à seuil itératif à haut débit de codes M-CDO . . . . .                                        | 69        |

| 4.4.1   Les registres à décalage . . . . .                                                                   | 70        |

| 4.4.2   Le noyau de logique combinatoire . . . . .                                                           | 76        |

| 4.5   Pipelining du décodeur à seuil des codes M-CDO . . . . .                                               | 77        |

| 4.5.1   Nombre d'emplacements des étages de pipeline . . . . .                                               | 78        |

| 4.5.2   Capacité de pipelining d'un générateur de codes M-CDO . . .                                          | 79        |

| 4.6   Recherche des meilleurs générateurs de codes M-CDO . . . . .                                           | 79        |

| 4.7   Conclusion . . . . .                                                                                   | 80        |

| <b>CHAPITRE 5        RÉSULTATS EXPÉRIMENTAUX . . . . .</b>                                                   | <b>84</b> |

| 5.1   Introduction . . . . .                                                                                 | 84        |

| 5.2   Notations utilisées . . . . .                                                                          | 85        |

| 5.3   Comparaison des délais des deux architectures du pondérateur . . . .                                   | 87        |

| 5.4   Choix de la résolution interne du décodeur . . . . .                                                   | 89        |

| 5.5   Pipelining du décodeur à seuil . . . . .                                                               | 90        |

| 5.5.1   Influence de l'architecture du registre à décalage élémentaire .                                     | 91        |

| 5.5.2   Exemple de pipelining d'un décodeur à seuil des codes M-CPDO                                         | 93        |

| 5.6   Prototypage du DS1 des codes PCDO à taux compatibles . . . . .                                         | 94        |

| 5.6.1   Simulation du gestionnaire d'horloge . . . . .                                                       | 94        |

| 5.6.2   Résultats expérimentaux du DS1 des codes PCDO à taux compatibles . . . . .                           | 95        |

|                                        |                                                                       |            |

|----------------------------------------|-----------------------------------------------------------------------|------------|

| 5.6.3                                  | Influence de la protection quasi-EEP sur les performances . . . . .   | 95         |

| 5.7                                    | Comparaison des codes doublement orthogonaux . . . . .                | 97         |

| 5.7.1                                  | Comparaison des codes doublement orthogonaux pour $R = 1/2$ . . . . . | 97         |

| 5.7.2                                  | Comparaison des codes doublement orthogonaux pour $R = 2/3$ . . . . . | 99         |

| 5.8                                    | Conclusion . . . . .                                                  | 101        |

| <b>CHAPITRE 6 CONCLUSION . . . . .</b> |                                                                       | <b>102</b> |

| 6.1                                    | Bilan de la recherche réalisée . . . . .                              | 102        |

| 6.2                                    | Améliorations envisageables . . . . .                                 | 103        |

| 6.3                                    | Ouverture . . . . .                                                   | 104        |

| <b>RÉFÉRENCES . . . . .</b>            |                                                                       | <b>105</b> |

| <b>ANNEXES . . . . .</b>               |                                                                       | <b>110</b> |

## LISTE DES FIGURES

|             |                                                                                                  |    |

|-------------|--------------------------------------------------------------------------------------------------|----|

| Figure 2.1  | Modèle du système de communication numérique . . . . .                                           | 6  |

| Figure 2.2  | Schéma bloc du codeur <i>Turbo</i> , $R = 1/3$ . . . . .                                         | 12 |

| Figure 2.3  | Schéma bloc du décodeur itératif <i>Turbo</i> , $R = 1/3$ . . . . .                              | 12 |

| Figure 2.4  | Codeur convolutionnel systématique, $R = 1/2$ , $\alpha_J = 4$ , $A = \{0, 1, 4\}$ . . . . .     | 14 |

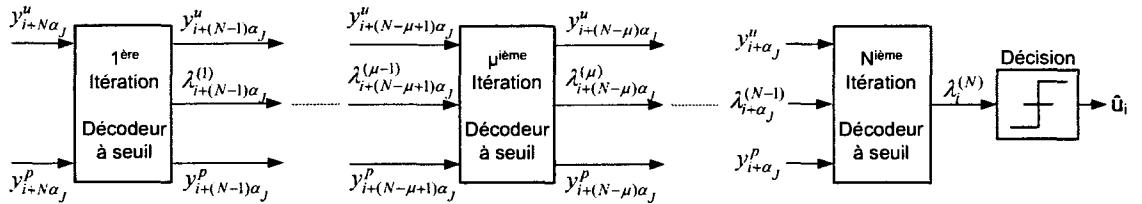

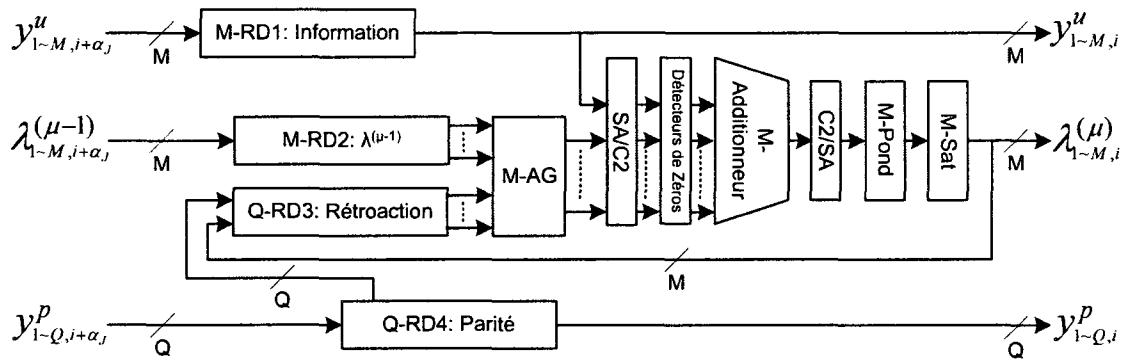

| Figure 2.5  | Schéma bloc du décodeur à seuil itératif . . . . .                                               | 16 |

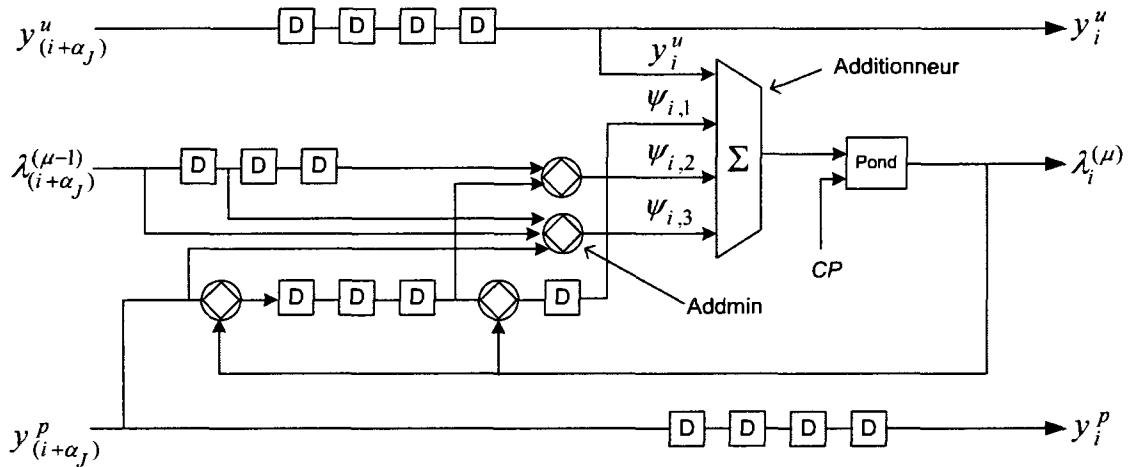

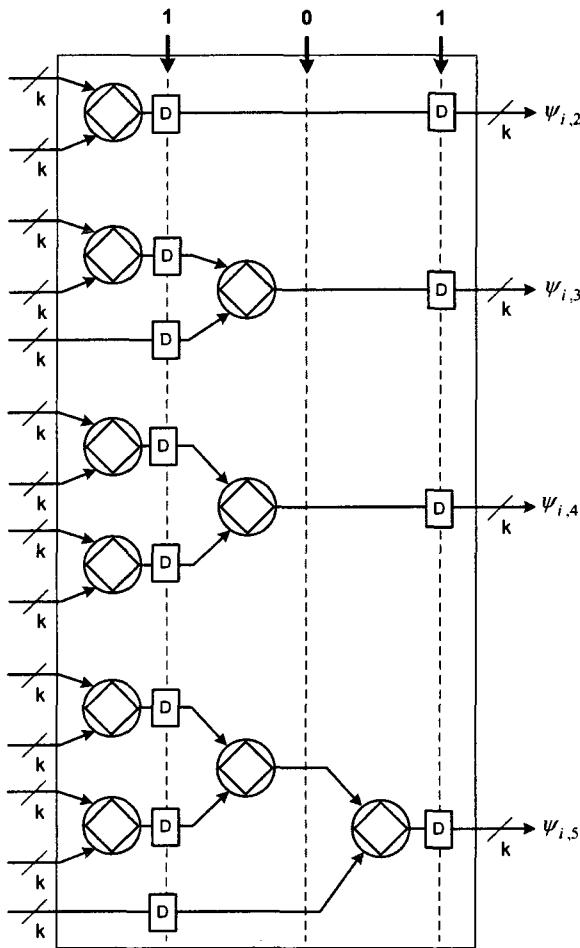

| Figure 2.6  | Architecture du décodeur à seuil correspondant au générateur $A = \{0, 1, 4\}$ . . . . .         | 17 |

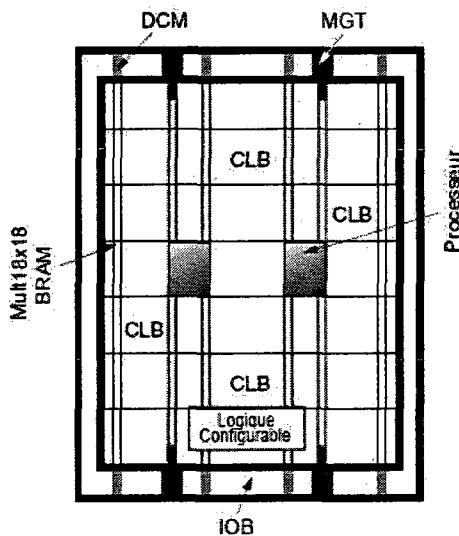

| Figure 2.7  | Architecture générique des FPGA de la famille Virtex-II Pro . .                                  | 23 |

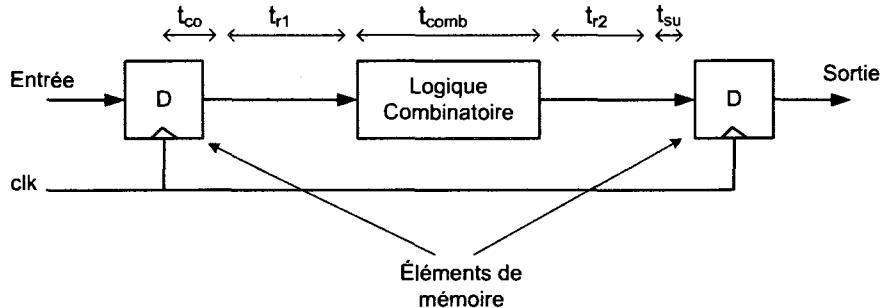

| Figure 2.8  | Délais de propagation dans un système numérique . . . . .                                        | 26 |

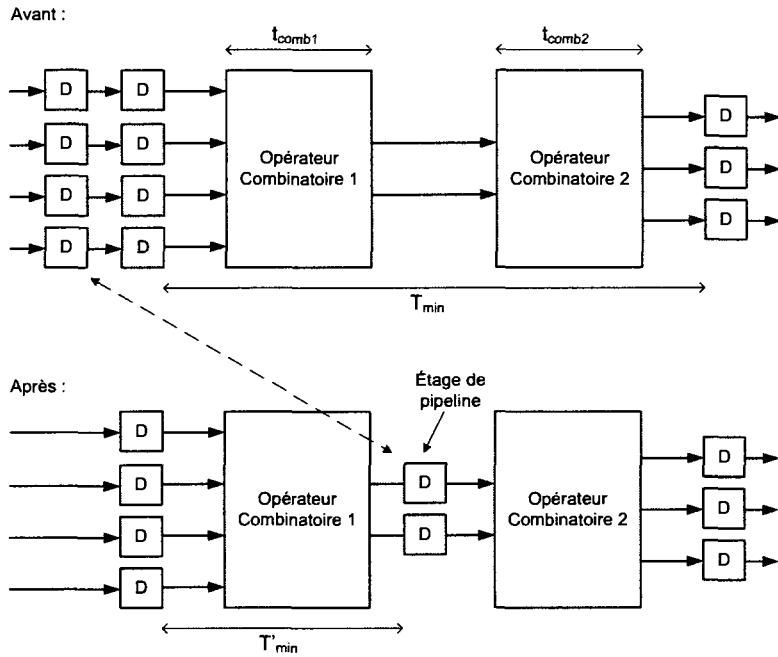

| Figure 2.9  | Exemple de resynchronisation d'un circuit numérique . . . . .                                    | 27 |

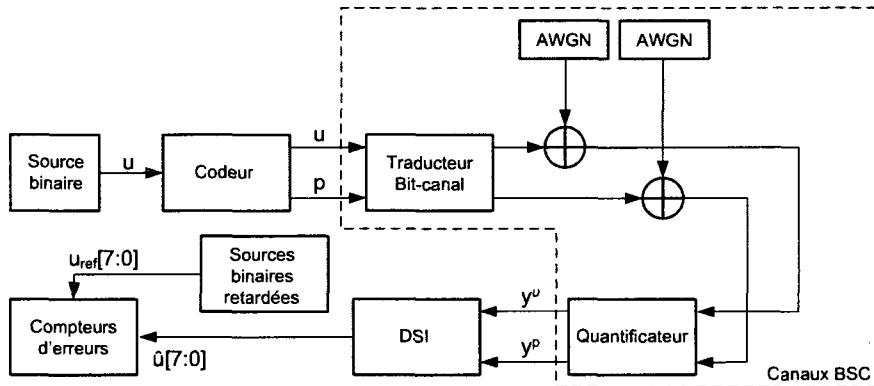

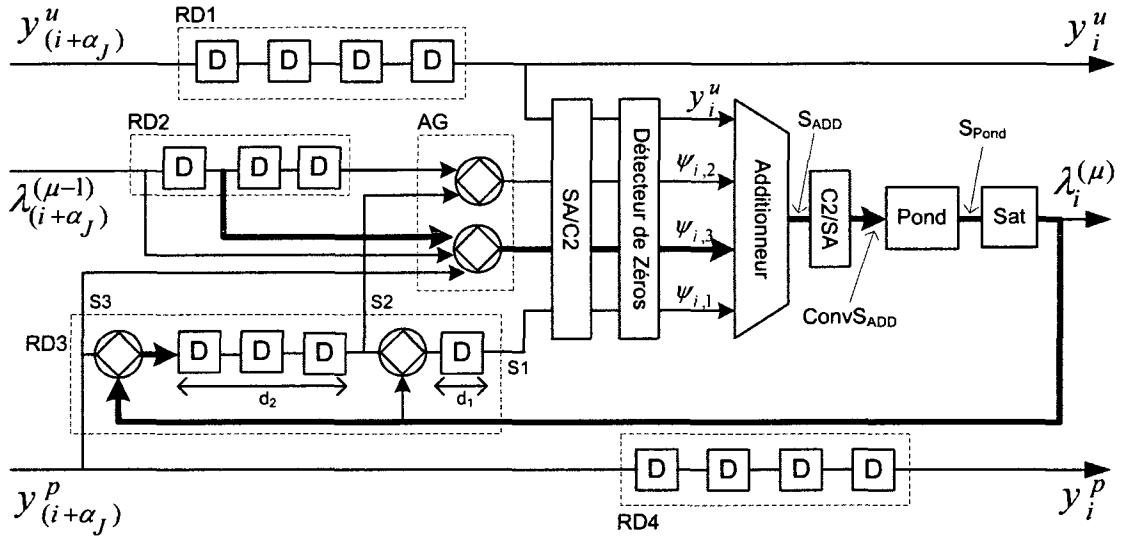

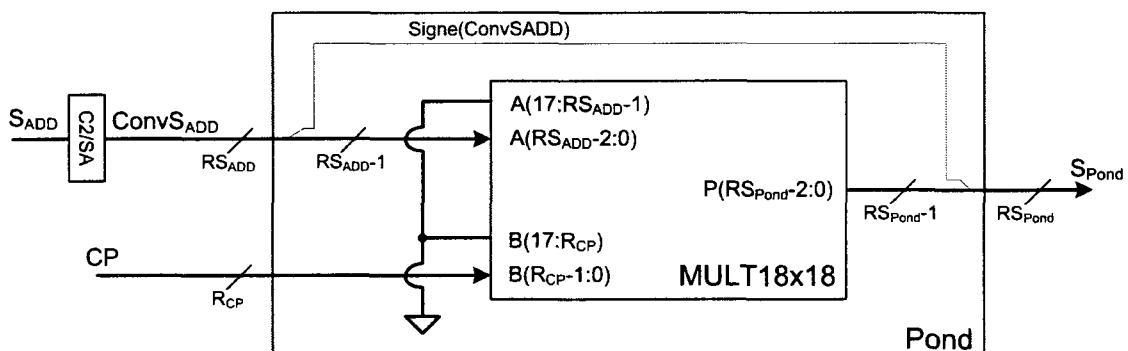

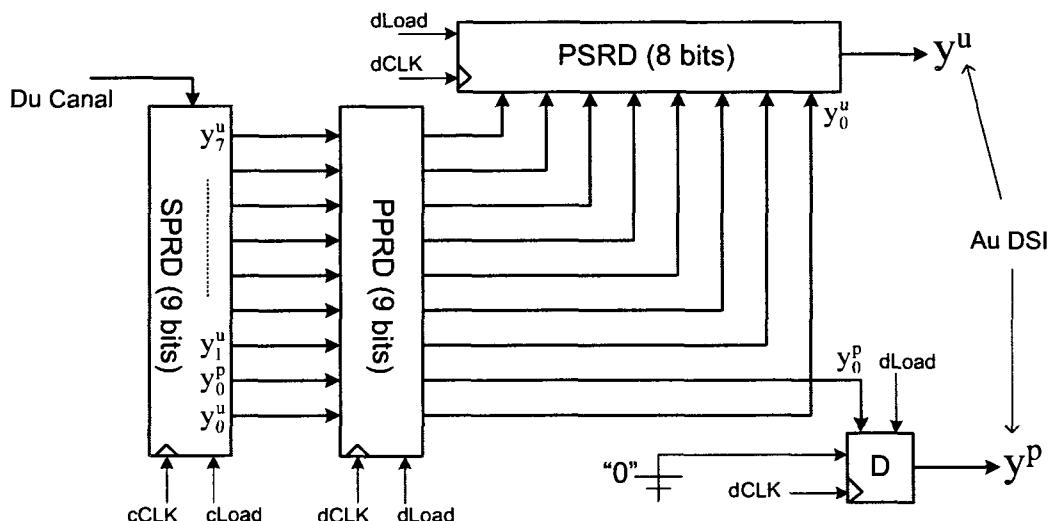

| Figure 2.10 | Schéma bloc de l'environnement d'évaluation des performances d'erreur . . . . .                  | 28 |

| Figure 3.1  | Architecture du décodeur à seuil des codes CDO générés par le codeur $A = \{0, 1, 4\}$ . . . . . | 31 |

| Figure 3.2  | Nouvelle architecture du pondérateur exploitant le format binaire SA . . . . .                   | 33 |

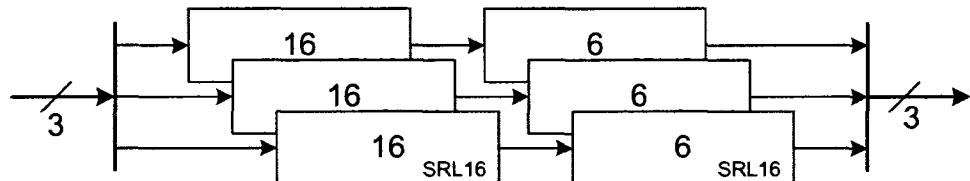

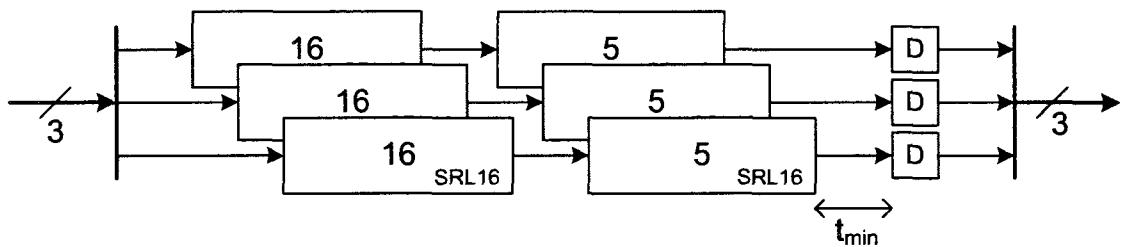

| Figure 3.3  | Implémentation du registre à décalage élémentaire à partir de SRL16s . . . . .                   | 35 |

| Figure 3.4  | Nouvelle architecture du registre à décalage élémentaire . . . .                                 | 36 |

| Figure 3.5  | Implémentation du registre à décalage de rétroaction . . . . .                                   | 38 |

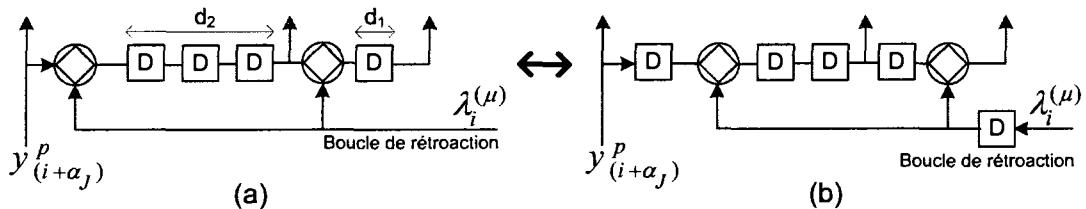

| Figure 3.6  | Resynchronisation de RD3, Avant (a) et Après (b) . . . . .                                       | 40 |

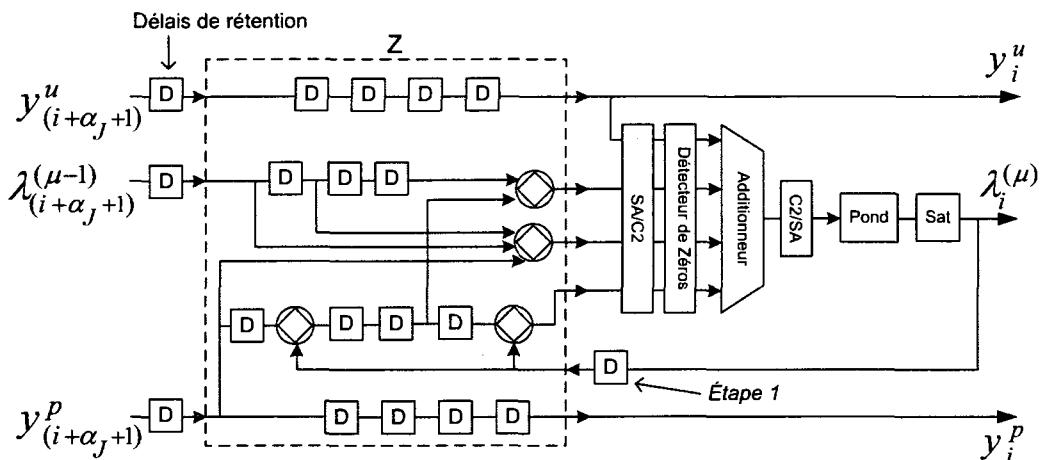

| Figure 3.7  | <i>Étape 2</i> , Bloc Z et ajout des délais de rétention . . . . .                               | 40 |

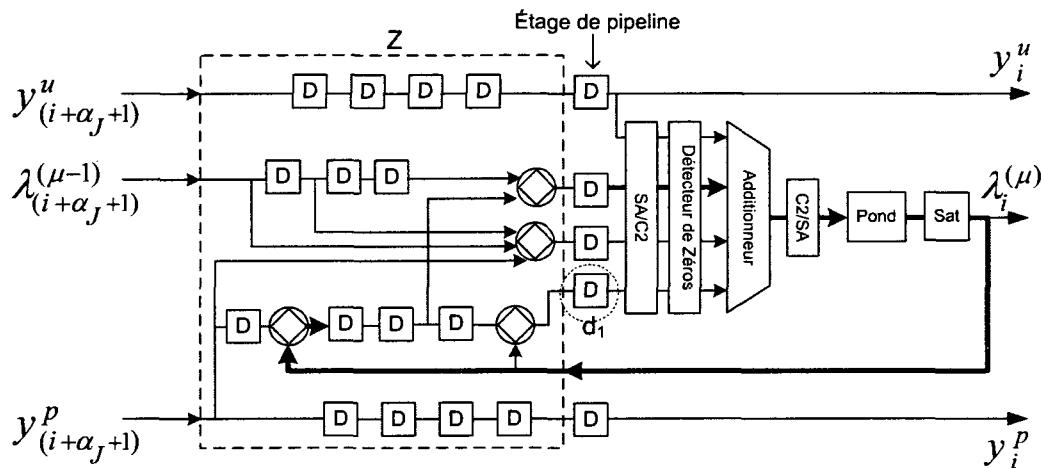

| Figure 3.8  | <i>Étape 3</i> , insertion de l'étage de pipeline . . . . .                                      | 41 |

| Figure 3.9  | Emplacements des étages de pipeline dans le chemin critique du design . . . . .                  | 42 |

|             |                                                                                                                                            |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.10 | Architecture de l'additionneur, $J = 4$ , PIPE\_ADDER = (0,1,1) .                                                                          | 46 |

| Figure 3.11 | Architecture de l'opérateur AG, $J = 5$ , PIPE\_ADDMIN = (1,0,1)                                                                           | 47 |

| Figure 3.12 | Architecture pipelinée de RD3, $A = \{0, 4, 9, 15\}$ , $J = 4$ , $P_c = 4$ , $Nb_{PIPE} = 3$ et $Nb_{ADDMIN} = 2$ . . . . .                | 48 |

| Figure 3.13 | Schéma bloc d'un système de communication adapté aux codes perforés . . . . .                                                              | 49 |

| Figure 3.14 | Architecture du gestionnaire d'horloge . . . . .                                                                                           | 51 |

| Figure 3.15 | Architecture du perforateur . . . . .                                                                                                      | 52 |

| Figure 3.16 | Architecture du dé-perforateur . . . . .                                                                                                   | 54 |

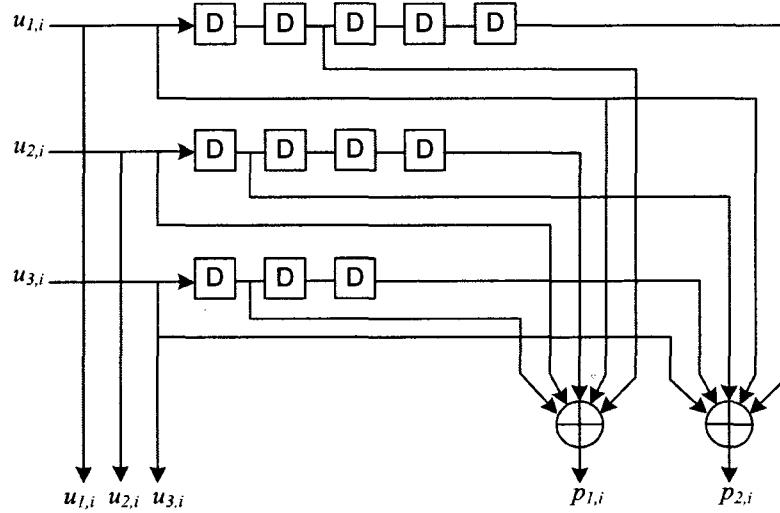

| Figure 4.1  | Exemple d'un encodeur 3-CDO, $R = 3/5$ . . . . .                                                                                           | 61 |

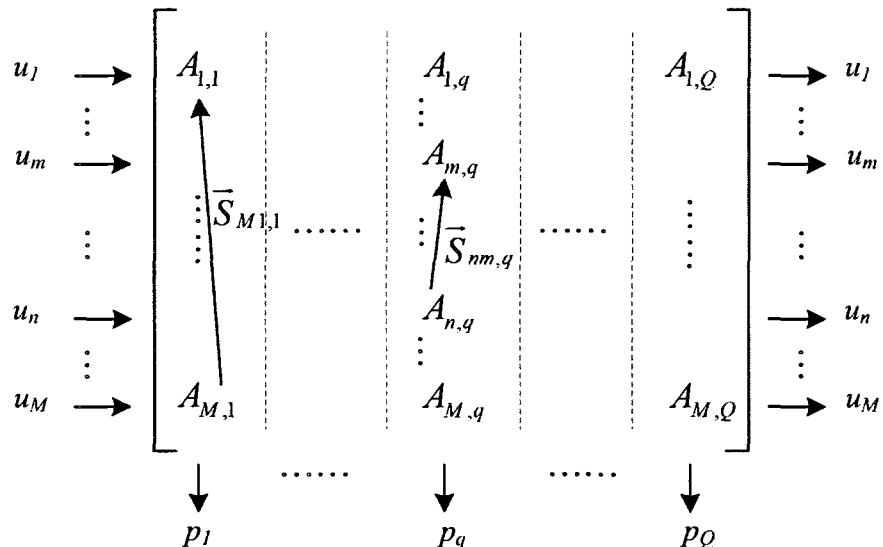

| Figure 4.2  | Exemples de la matrice $\mathcal{A}$ et du vecteur $\vec{S}$ . . . . .                                                                     | 65 |

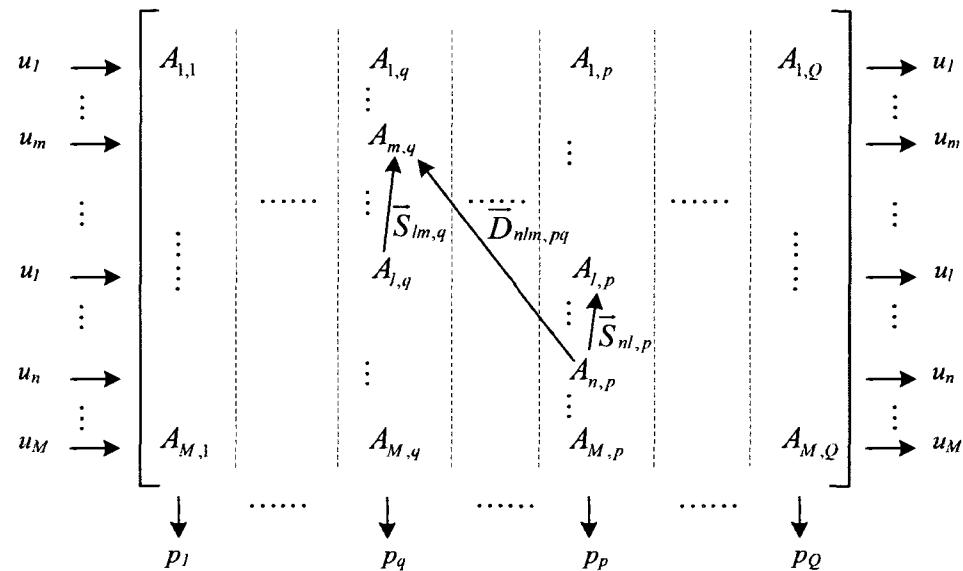

| Figure 4.3  | Exemple du vecteur $\vec{D}_{nlm,pq}$ . . . . .                                                                                            | 67 |

| Figure 4.4  | Schéma bloc du décodeur à seuil des codes M-CDO . . . . .                                                                                  | 70 |

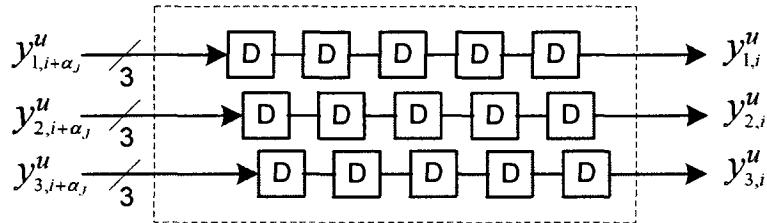

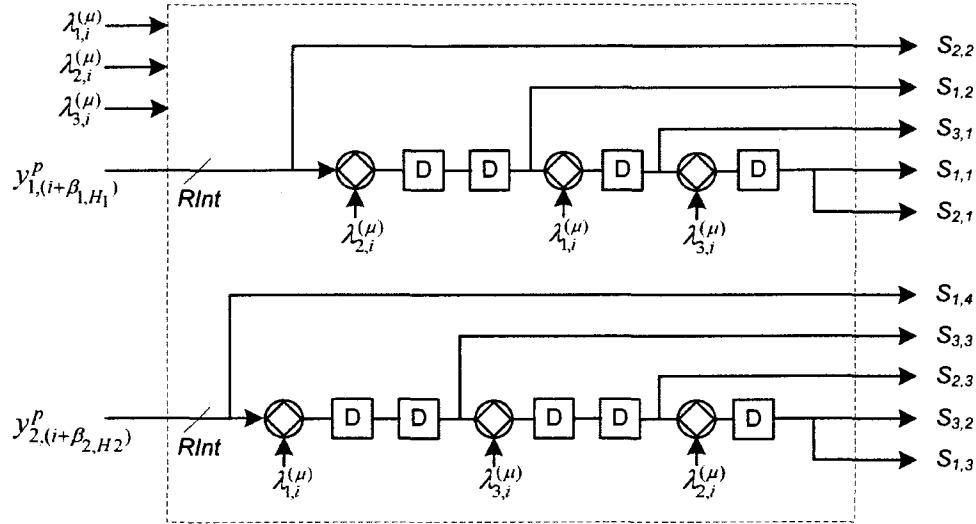

| Figure 4.5  | Structure de 3-RD1, $M = 3$ et $\alpha_J = 5$ . . . . .                                                                                    | 71 |

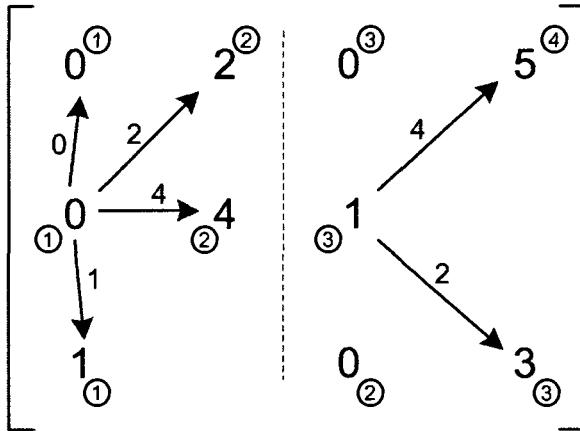

| Figure 4.6  | Identification des différences simples positives, $\vec{S}_{2m}^+$ , $1 \leq m \leq 3$                                                     | 72 |

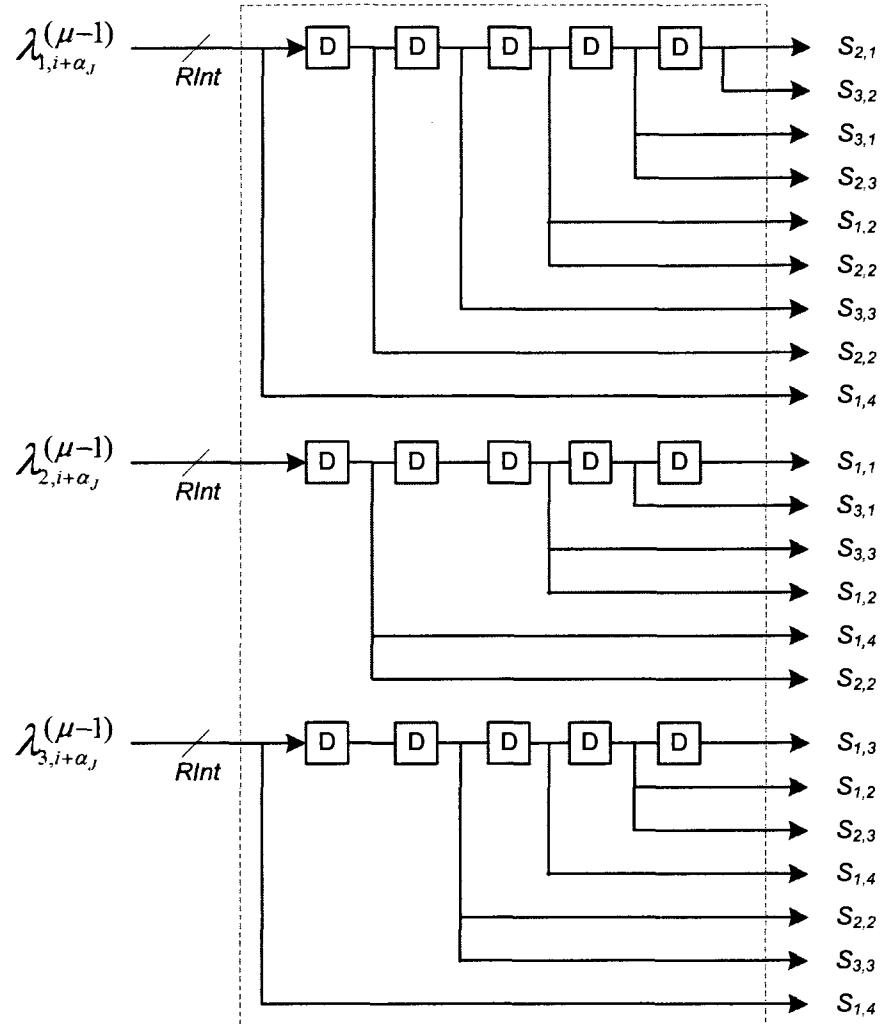

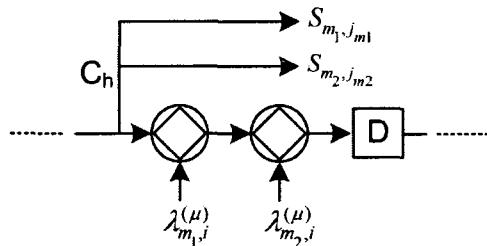

| Figure 4.7  | Architecture du registre à décalage de $\lambda^{(\mu-1)}$ (3-RD2), $M = 3$ et $\alpha_J = 5$ . . . . .                                    | 73 |

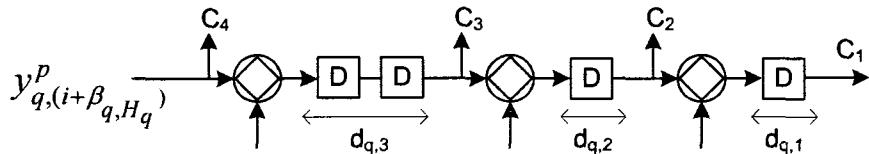

| Figure 4.8  | Implémentation de q-RD3 à partir de $B_q$ , $\beta_{q,H_q} = 4$ . . . . .                                                                  | 74 |

| Figure 4.9  | Implémentation de q-RD3 : 2 triplets ont la même valeur de $\alpha_{m,q,j}$                                                                | 75 |

| Figure 4.10 | Architecture de 2-RD3, $Q = 2$ , $\beta_{1,H_1} = 4$ et $\beta_{2,H_2} = 5$ . . . . .                                                      | 76 |

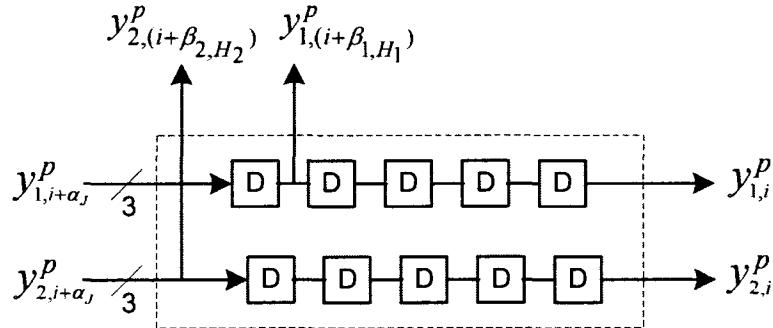

| Figure 4.11 | Registre à décalage de parité (2-RD4), $Q = 2$ , $\alpha_J = 5$ , $\beta_{1,H_1} = 4$ et $\beta_{2,H_2} = 5$ . . . . .                     | 76 |

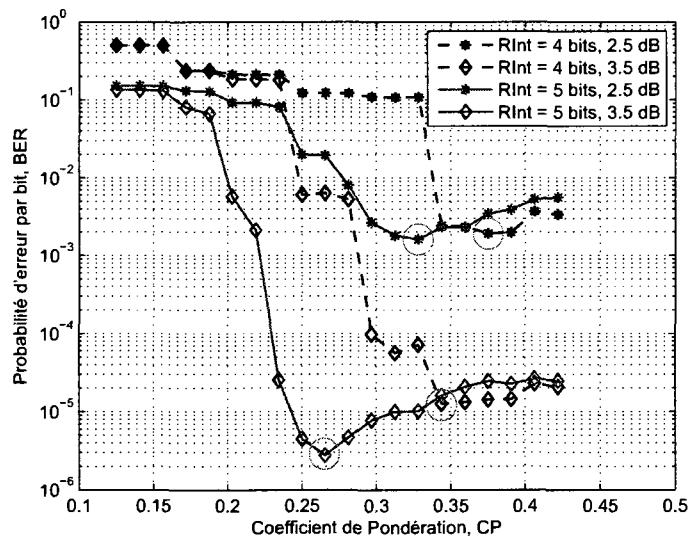

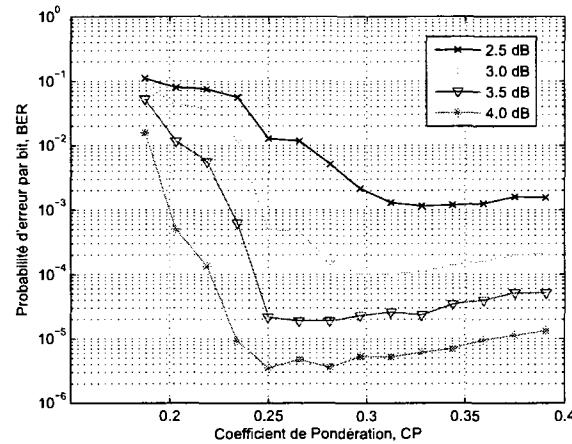

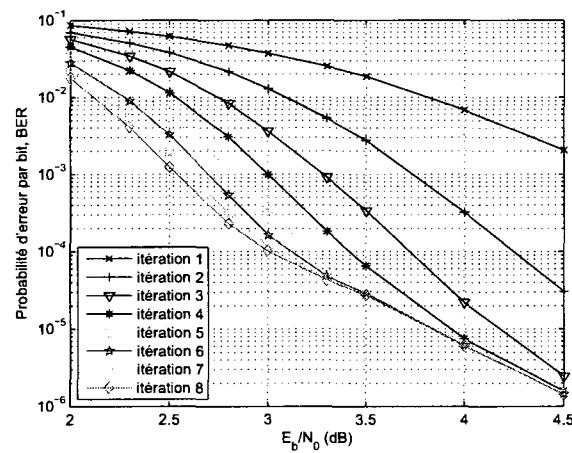

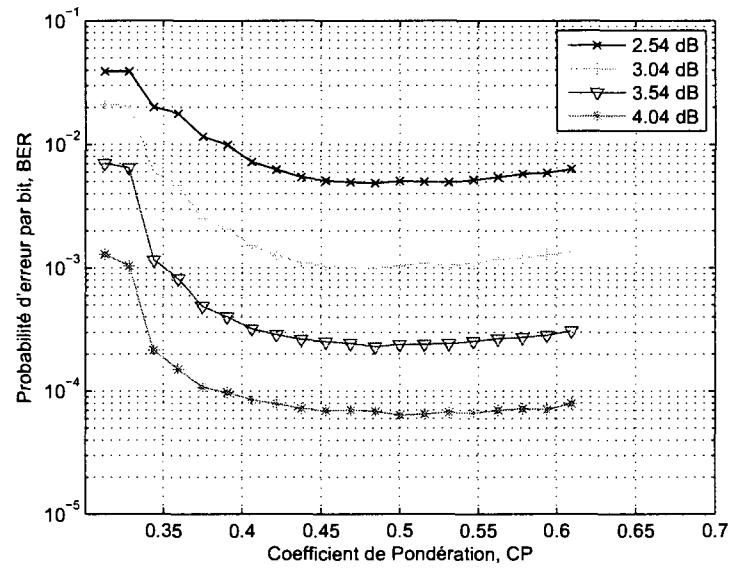

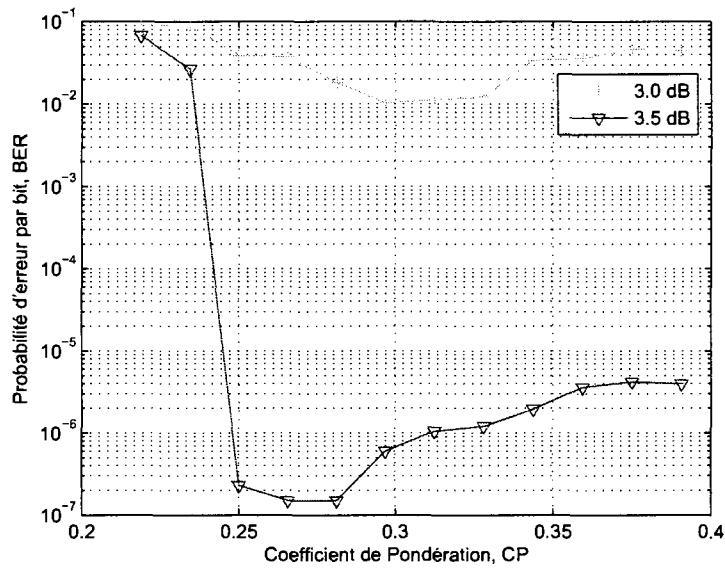

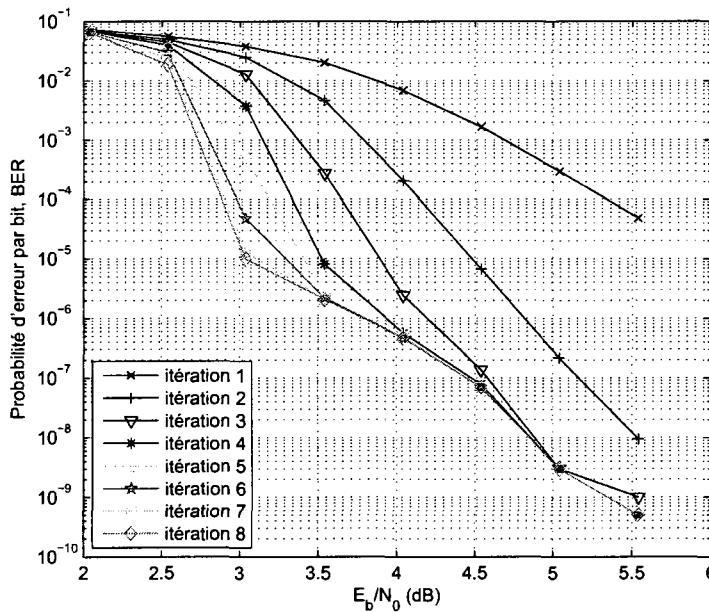

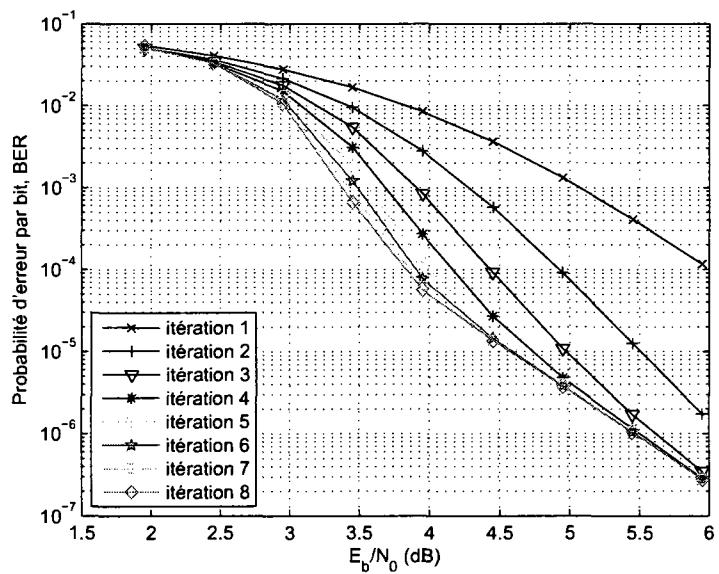

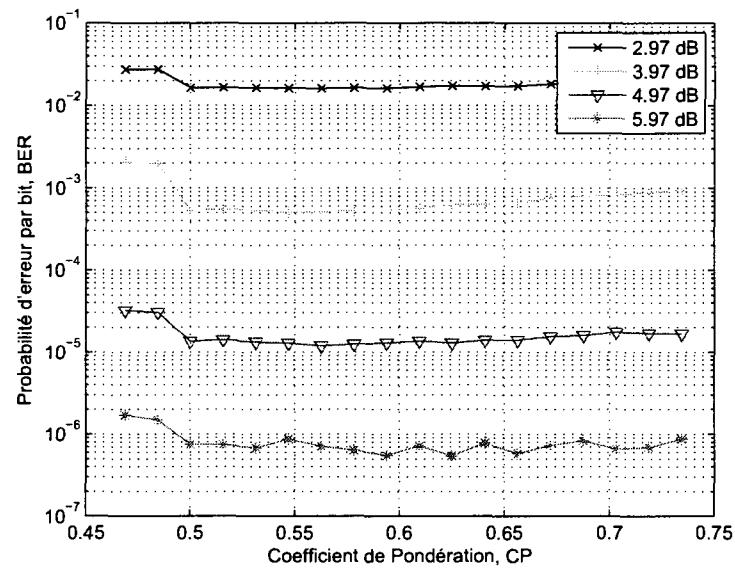

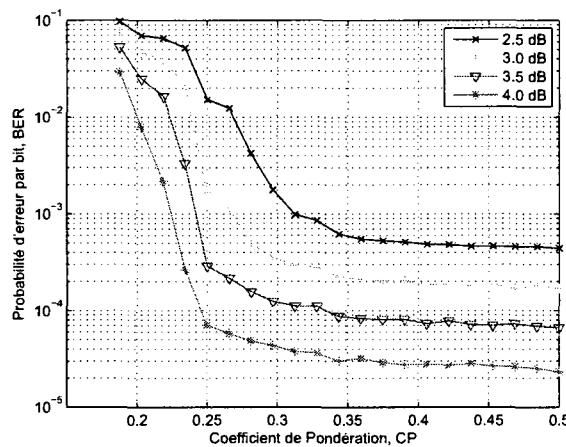

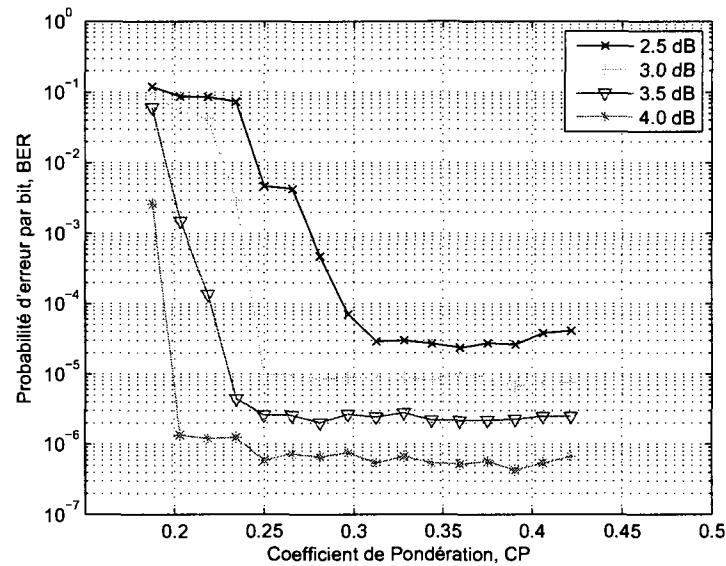

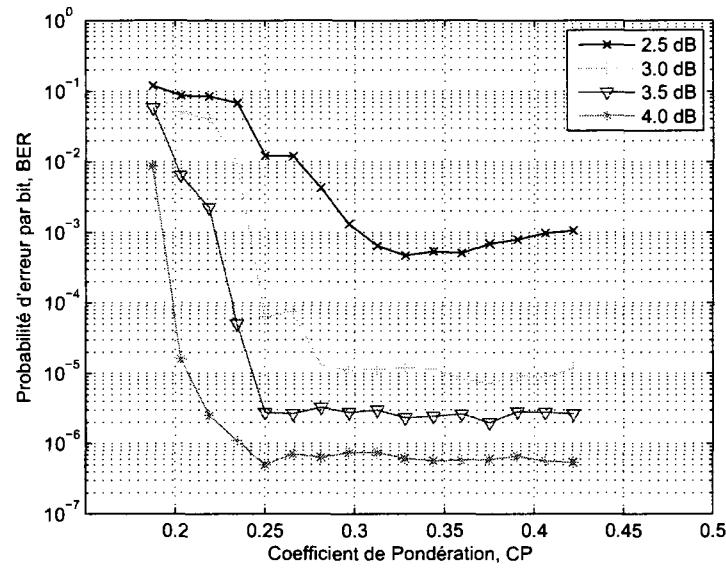

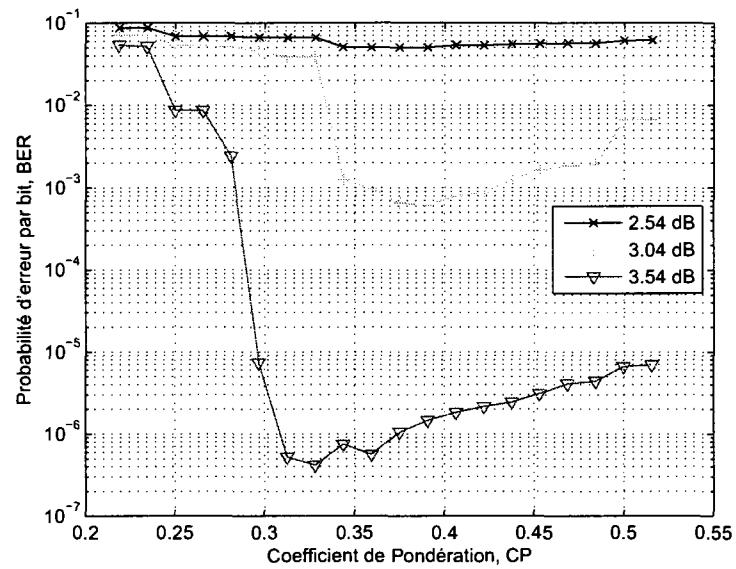

| Figure 5.1  | BER en fonction de $CP$ , Codes CDO $\{J = 10, \alpha_J = 366\}$ , $R = 1/2$ , 8 itérations . . . . .                                      | 86 |

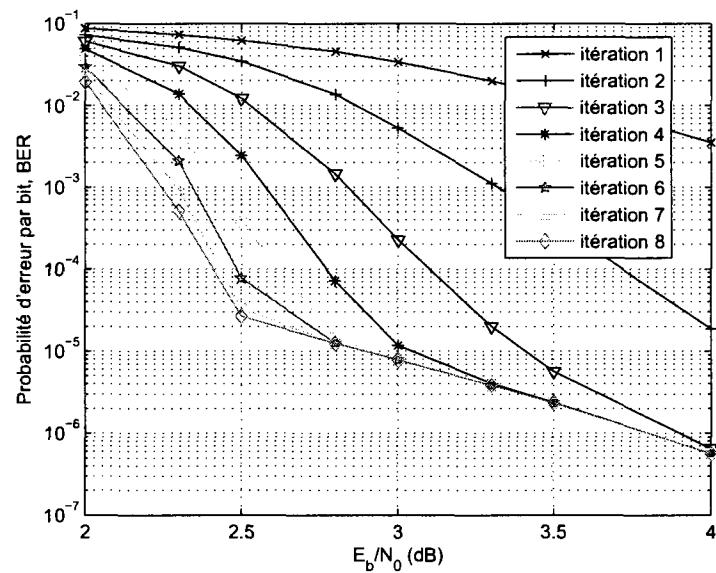

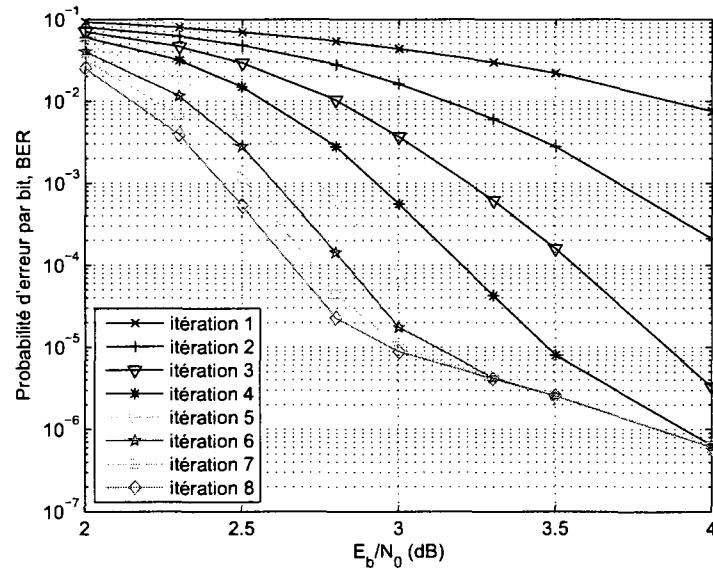

| Figure 5.2  | BER à meilleurs CPs, Codes CDO $\{J = 10, \alpha_J = 366\}$ , $R = 1/2$ , 8 itérations . . . . .                                           | 87 |

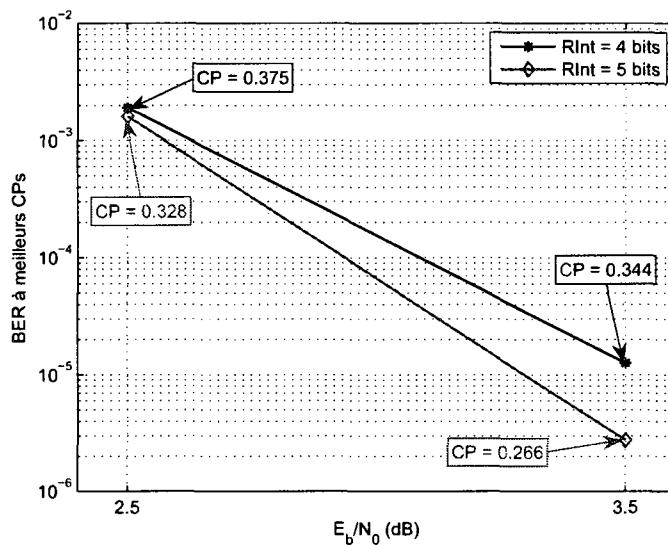

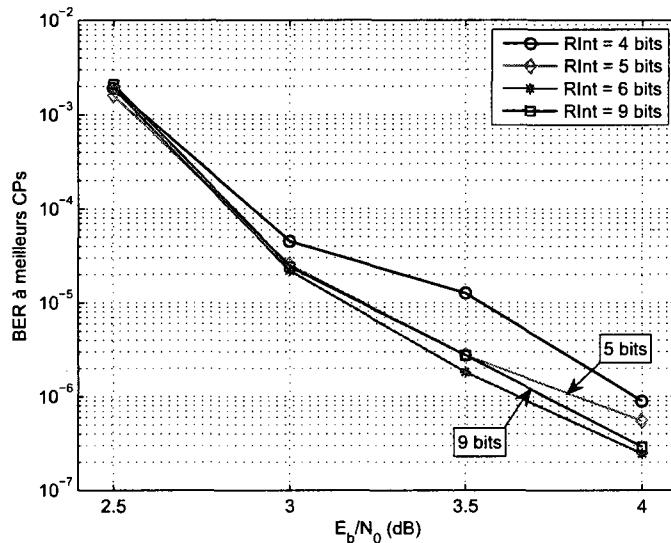

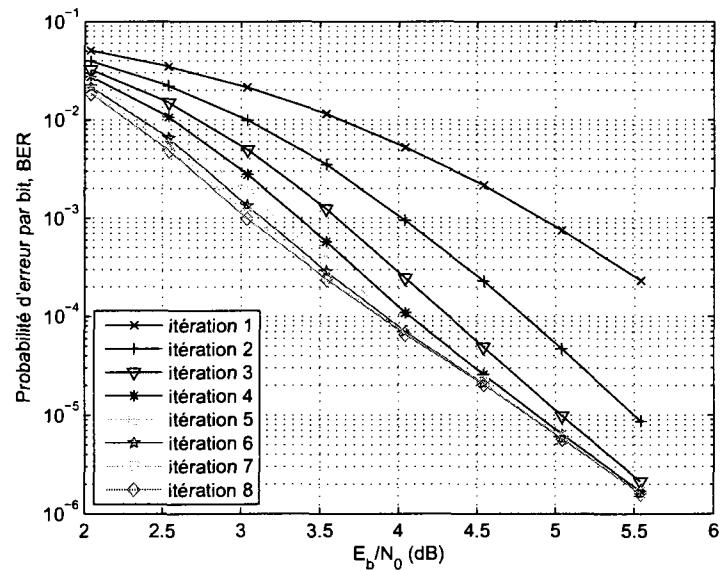

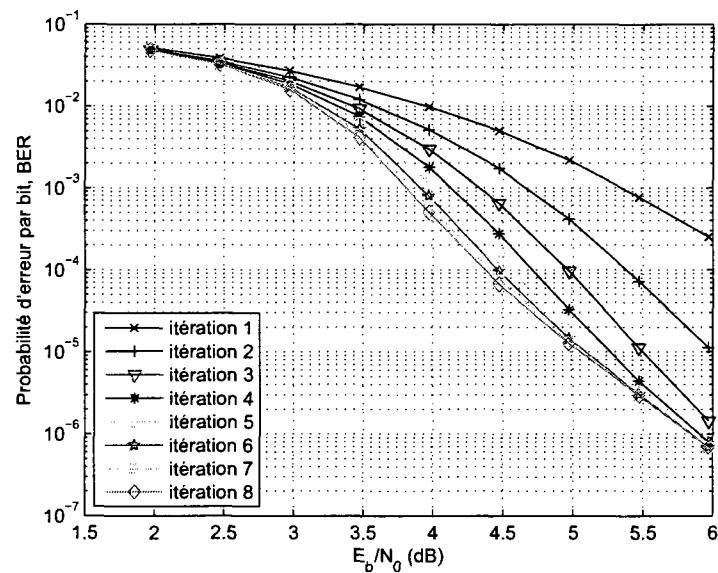

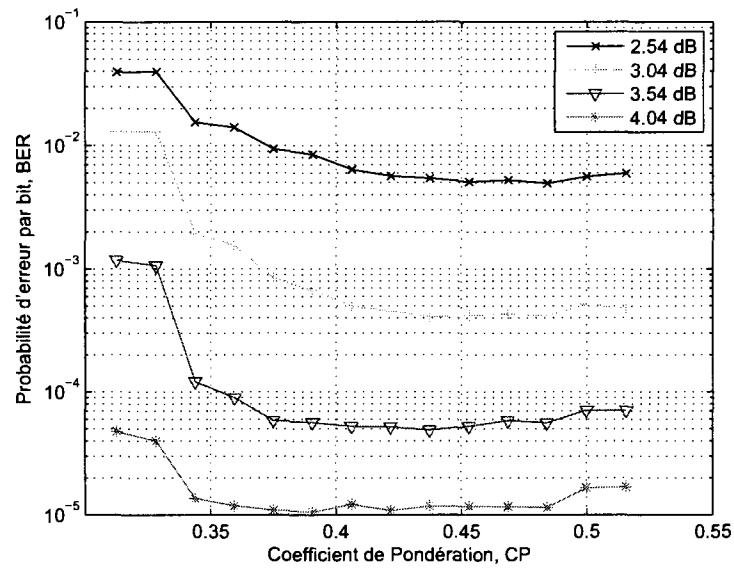

| Figure 5.3  | BER à meilleurs CPs, PCDO à taux compatibles $\{J = 10, \alpha_J = 366\}$ , $R = 1/2$ , $RInt = 4, 5, 6$ et 9 bits, 8 itérations . . . . . | 90 |

|             |                                                                                                                                                                                                                                    |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.4  | Extrait du rapport de synchronisme post placement et routage, architecture du registre à décalage élémentaire sans FF utilisée .                                                                                                   | 91  |

| Figure 5.5  | Extrait du rapport de synchronisme post placement et routage, architecture du registre à décalage élémentaire avec FF utilisée .                                                                                                   | 93  |

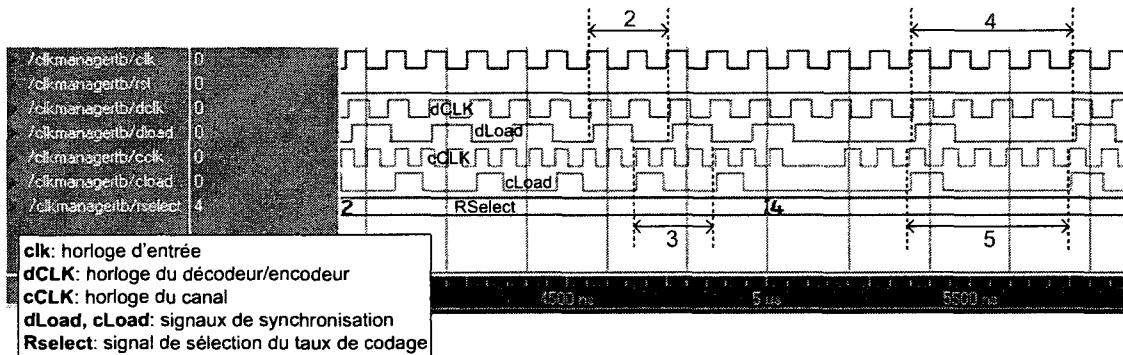

| Figure 5.6  | Simulation post placement et routage du gestionnaire d'horloge                                                                                                                                                                     | 94  |

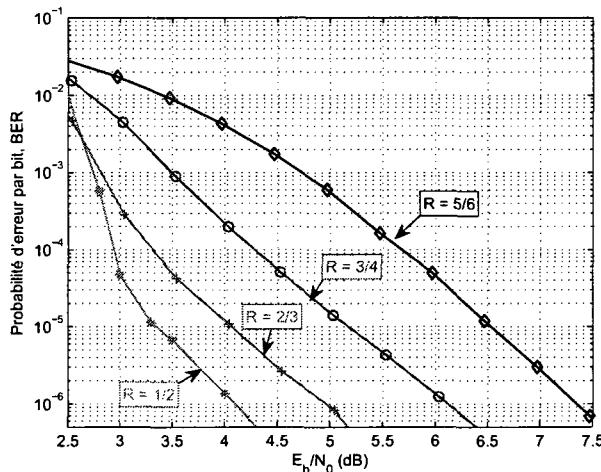

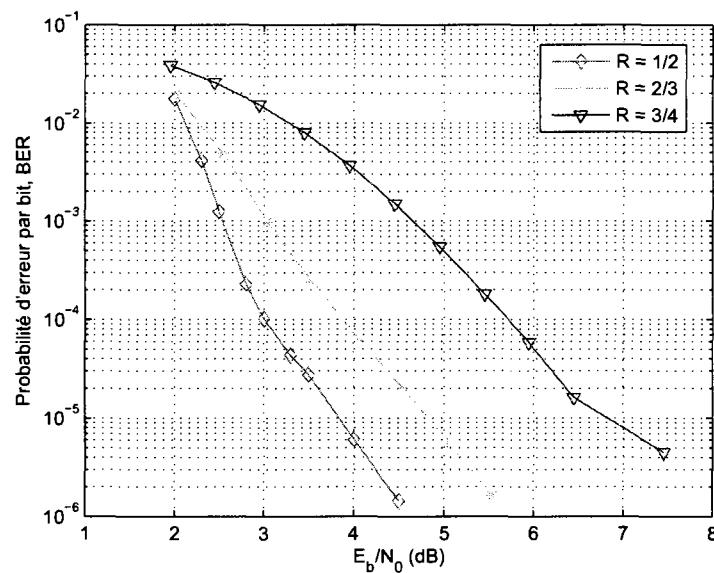

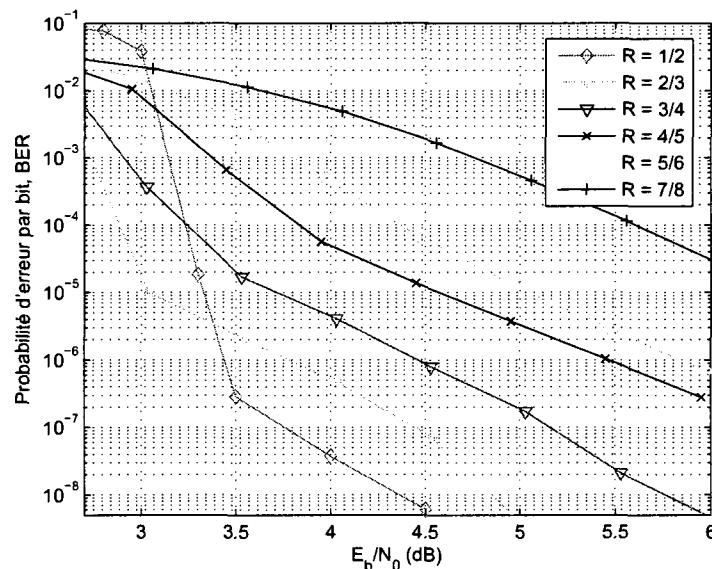

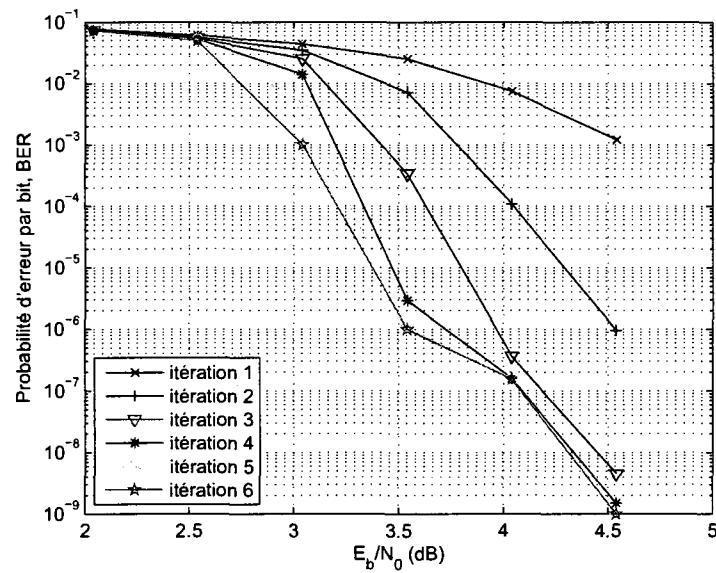

| Figure 5.7  | Résultats expérimentaux du DSI des codes PCDO à taux compatibles $\{J = 10, \alpha_J = 366\}$ , $RInt = 5$ bits, 6 itérations, $CP_{R=1/2} = 0.297$ , $CP_{R=2/3} = 0.422$ , $CP_{R=3/4} = 0.547$ et $CP_{R=5/6} = 0.75$ . . . . . | 95  |

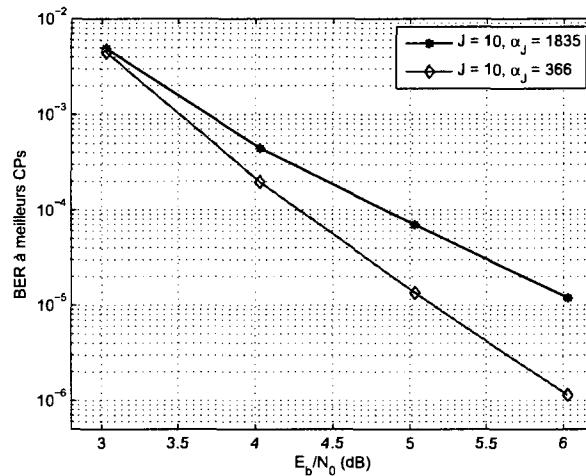

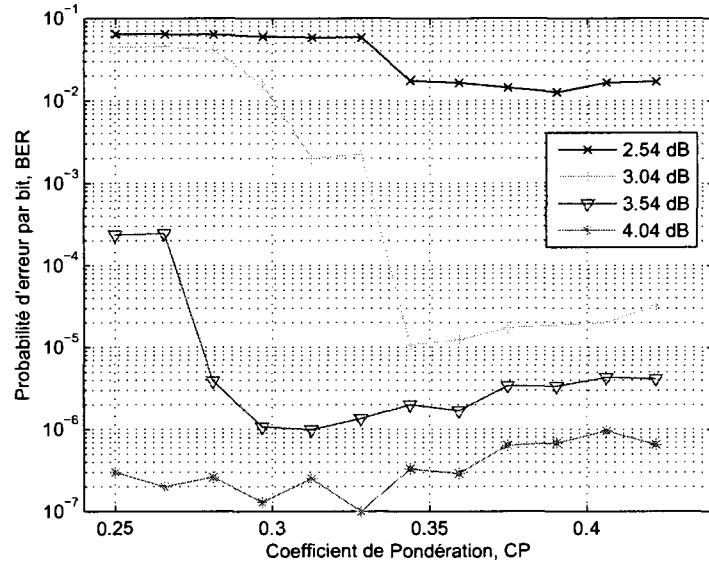

| Figure 5.8  | Comparaison de performances des codes PCDO de type quasi-EEP $\{J = 10, \alpha_J = 366\}$ avec les codes PCDO de type UEP $\{J = 10, \alpha_J = 1835\}$ , 6 itérations, $R = 3/4$ , $RInt = 5$ bits . . . . .                      | 96  |

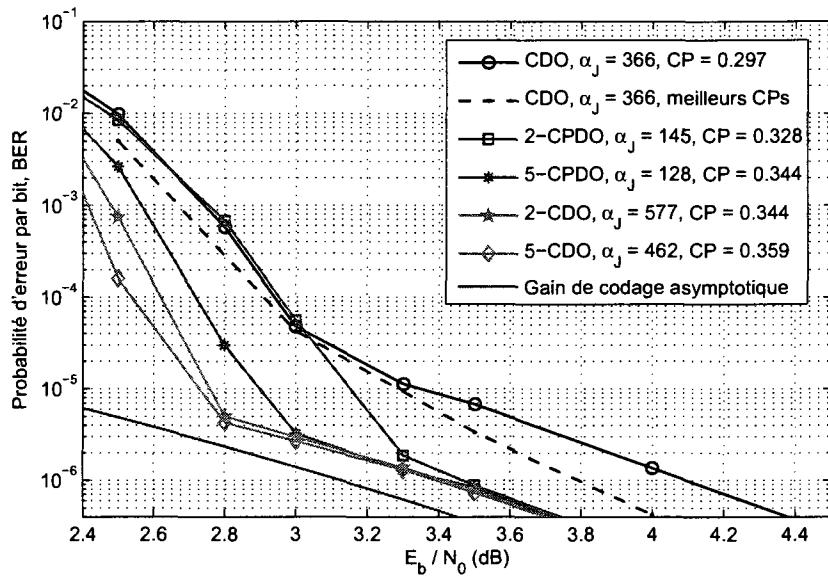

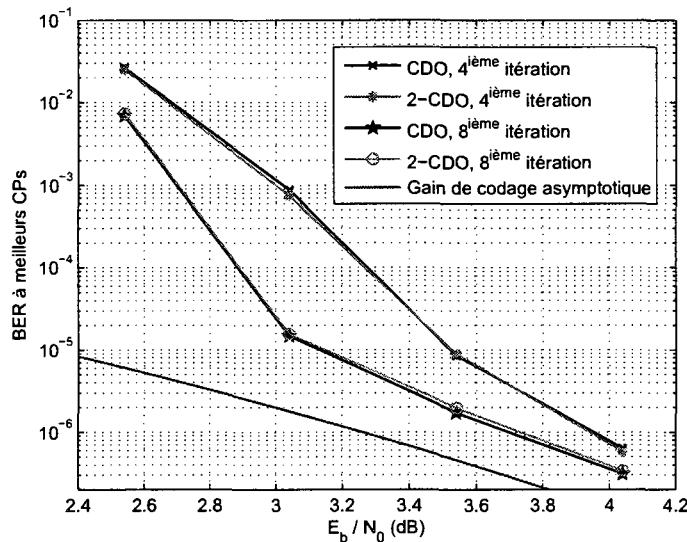

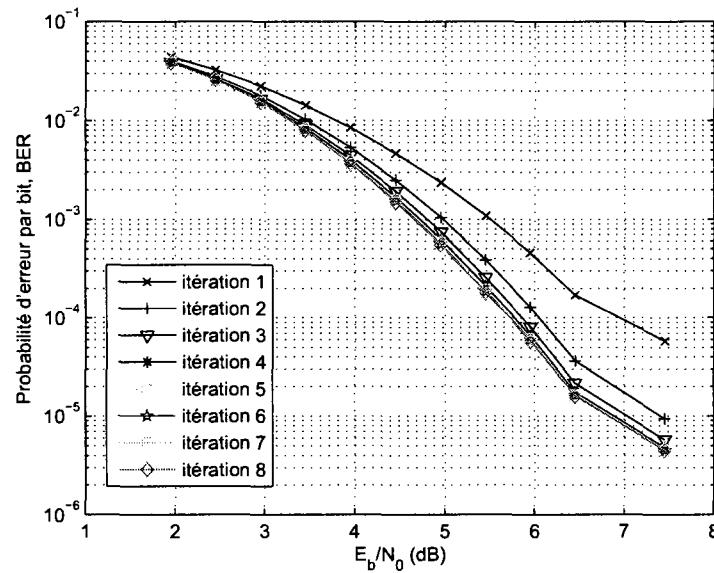

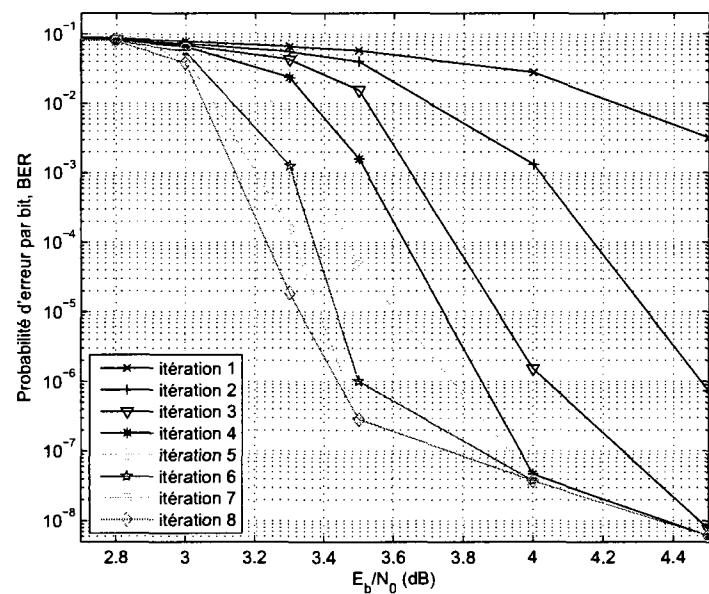

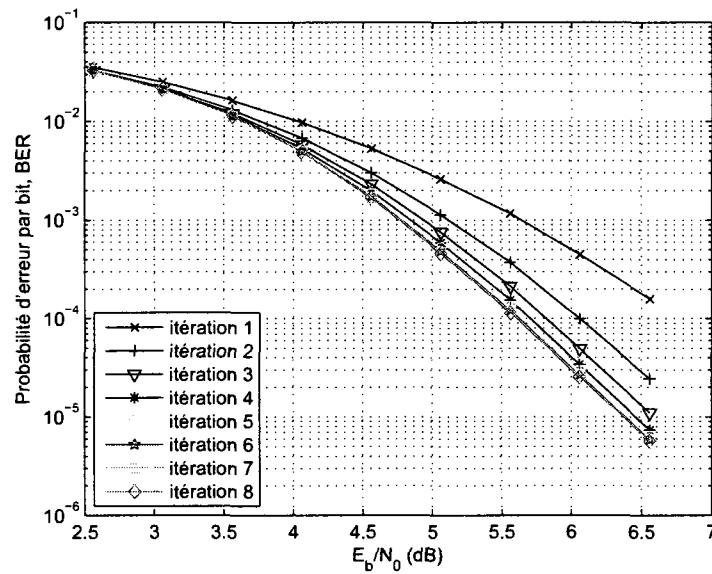

| Figure 5.9  | Comparaison de performances des codes doublement orthogonaux, 6 itérations, $J = 10, R = 1/2, RInt = 5$ bits . . . . .                                                                                                             | 98  |

| Figure 5.10 | Comparaison de performances des codes PCDO $\{J = 14, \alpha_J = 1359\}$ avec les codes 2-CDO $\{R = 2/3, J = 7, \alpha_J = 613\}$ , $R = 2/3$ et $RInt = 5$ bits . . . . .                                                        | 100 |

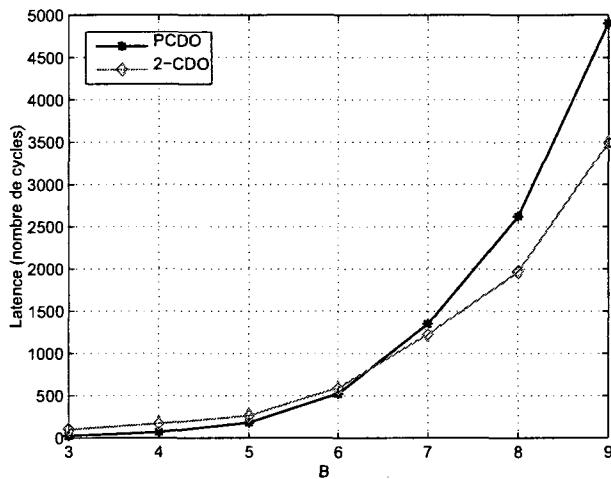

| Figure 5.11 | Comparaison de la latence de décodeurs à seuil des codes 2-CDO et PCDO, $R = 2/3$ . . . . .                                                                                                                                        | 101 |

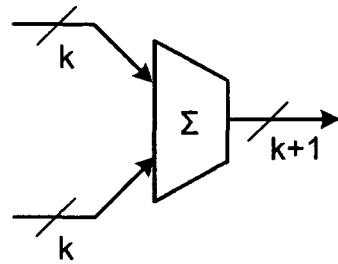

| Figure I.1  | Additionneur à deux entrées . . . . .                                                                                                                                                                                              | 111 |

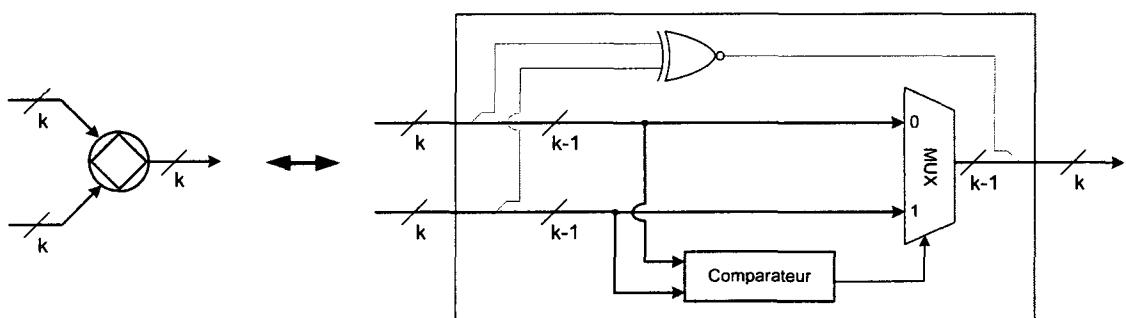

| Figure I.2  | Architecture de l'opérateur Addmin à deux entrées . . . . .                                                                                                                                                                        | 111 |

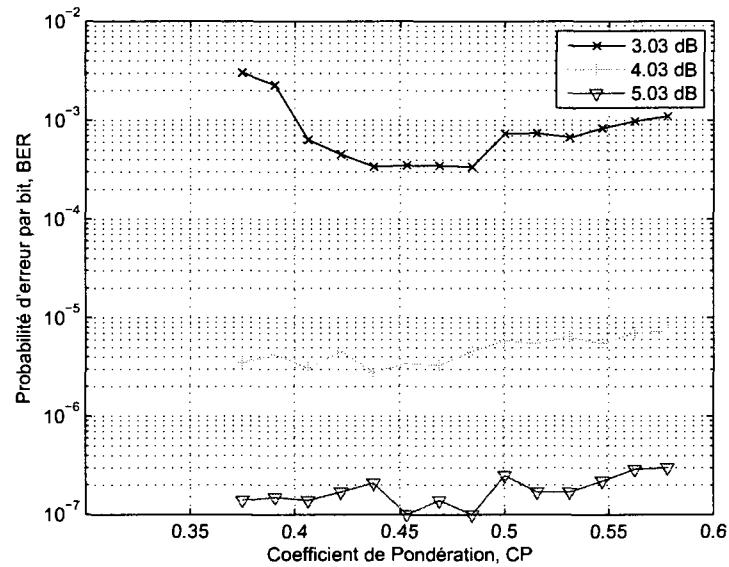

| Figure V.1  | BER en fonction de $CP$ , CDO $\{J = 8, \alpha_J = 139\}$ , $R = 1/2$ , $RInt = 5$ bits, 8 itérations . . . . .                                                                                                                    | 145 |

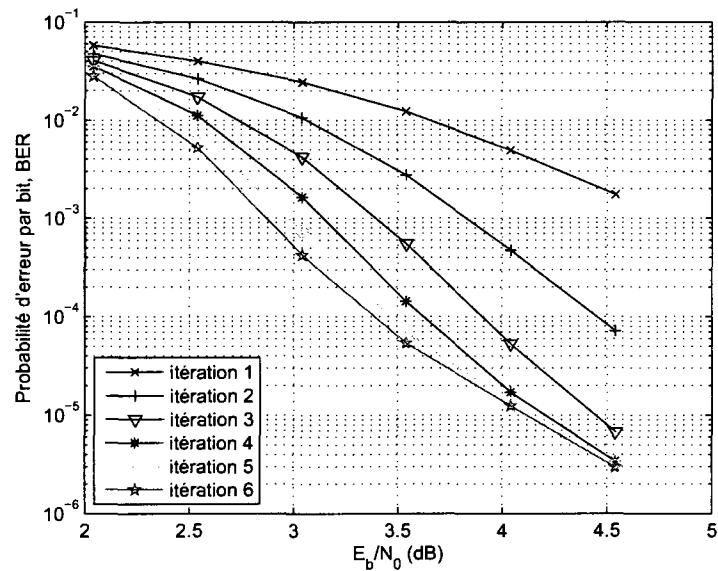

| Figure V.2  | BER en fonction de $E_b/N_0$ , CDO $\{J = 8, \alpha_J = 139\}$ , $R = 1/2$ , $CP = 0.3125$ , $RInt = 5$ bits, 8 itérations . . . . .                                                                                               | 145 |

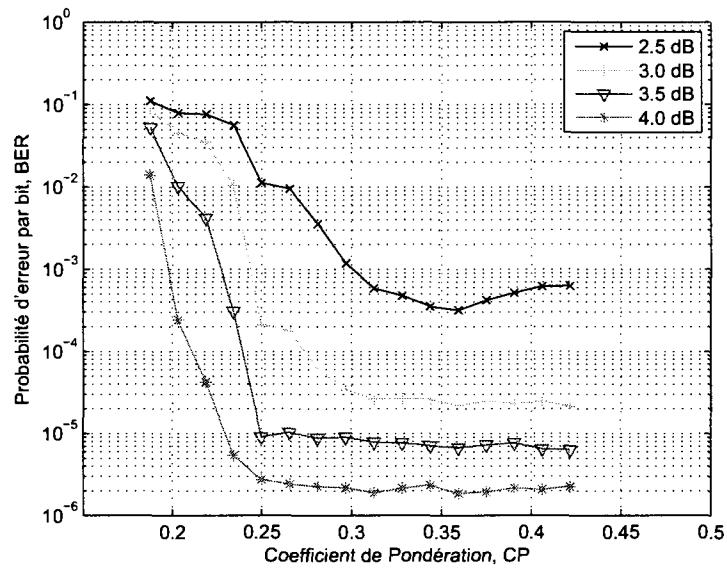

| Figure V.3  | BER en fonction de $CP$ , PCDO $\{J = 8, \alpha_J = 139\}$ , $R = 2/3$ , $RInt = 5$ bits, 8 itérations . . . . .                                                                                                                   | 146 |

|             |                                                                                                                                                       |     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

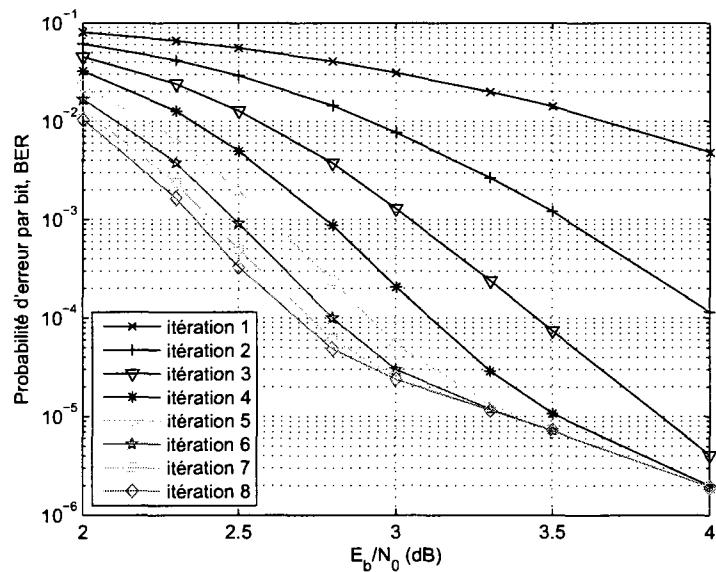

| Figure V.4  | BER en fonction de $E_b/N_0$ , PCDO $\{J = 8, \alpha_J = 139\}$ , $R = 2/3, CP = 0.484375, RInt = 5$ bits, 8 itérations . . . . .                     | 146 |

| Figure V.5  | BER en fonction de $E_b/N_0$ , PCDO $\{J = 8, \alpha_J = 139\}$ , $R = 4/5, CP = 0.75, RInt = 5$ bits, 8 itérations . . . . .                         | 147 |

| Figure V.6  | BER en fonction de $E_b/N_0$ , PCDO à taux compatibles $\{J = 8, \alpha_J = 139\}$ , $R = 1/2, 2/3$ et $4/5, RInt = 5$ bits, 8 itérations . . . . .   | 147 |

| Figure V.7  | BER en fonction de $CP$ , CDO $\{J = 15, \alpha_J = 2932\}$ , $R = 1/2, RInt = 5$ bits, 8 itérations . . . . .                                        | 148 |

| Figure V.8  | BER en fonction de $E_b/N_0$ , CDO $\{J = 15, \alpha_J = 2932\}$ , $R = 1/2, CP = 0.25, RInt = 5$ bits, 8 itérations . . . . .                        | 148 |

| Figure V.9  | BER en fonction de $CP$ , PCDO $\{J = 15, \alpha_J = 2932\}$ , $R = 2/3, RInt = 5$ bits, 8 itérations . . . . .                                       | 149 |

| Figure V.10 | BER en fonction de $E_b/N_0$ , PCDO $\{J = 15, \alpha_J = 2932\}$ , $R = 2/3, CP = 0.34375, RInt = 5$ bits, 8 itérations, 10 Gbits simulés . . . . .  | 149 |

| Figure V.11 | BER en fonction de $CP$ , PCDO $\{J = 15, \alpha_J = 2932\}$ , $R = 3/4, RInt = 5$ bits, 8 itérations . . . . .                                       | 150 |

| Figure V.12 | BER en fonction de $E_b/N_0$ , PCDO $\{J = 15, \alpha_J = 2932\}$ , $R = 3/4, CP = 0.453125, RInt = 5$ bits, 8 itérations, 10 Gbits simulés . . . . . | 150 |

| Figure V.13 | BER en fonction de $CP$ , PCDO $\{J = 15, \alpha_J = 2932\}$ , $R = 4/5, RInt = 5$ bits, 8 itérations . . . . .                                       | 151 |

| Figure V.14 | BER en fonction de $E_b/N_0$ , PCDO $\{J = 15, \alpha_J = 2932\}$ , $R = 4/5, CP = 0.546875, RInt = 5$ bits, 8 itérations . . . . .                   | 151 |

| Figure V.15 | BER en fonction de $CP$ , PCDO $\{J = 15, \alpha_J = 2932\}$ , $R = 5/6, RInt = 5$ bits, 8 itérations . . . . .                                       | 152 |

| Figure V.16 | BER en fonction de $E_b/N_0$ , PCDO $\{J = 15, \alpha_J = 2932\}$ , $R = 5/6, CP = 0.546875, RInt = 5$ bits, 8 itérations . . . . .                   | 152 |

|              |                                                                                                                                                                              |     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure V.17  | BER en fonction de $E_b/N_0$ , PCDO { $J = 15, \alpha_J = 2932\}$ ,<br>$R = 7/8, CP = 0.75, RInt = 5$ bits, 8 itérations . . . . .                                           | 153 |

| Figure V.18  | BER en fonction de $E_b/N_0$ , PCDO à taux compatibles { $J = 15,$<br>$\alpha_J = 2932\}$ , $R = 1/2, 2/3, 3/4, 4/5, 5/6$ et $7/8, RInt = 5$ bits,<br>8 itérations . . . . . | 153 |

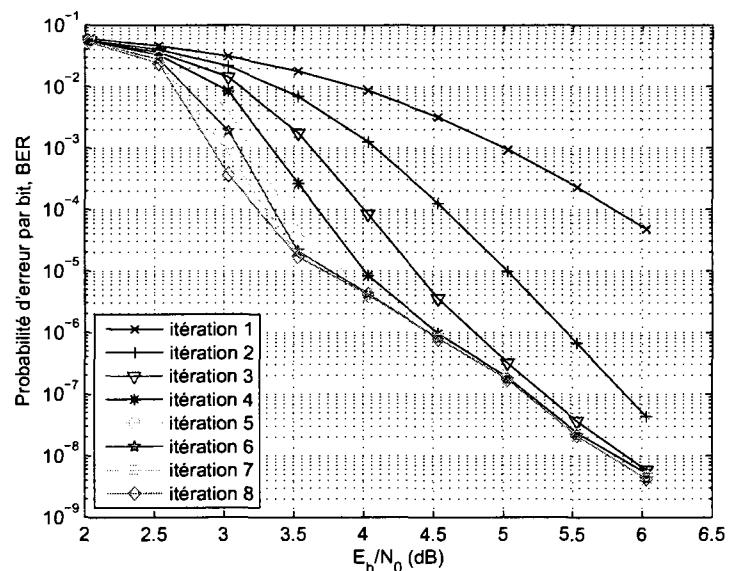

| Figure VI.1  | BER en fonction de $CP$ , 3-CDO { $R = 3/6, J = 6, \alpha_J = 67\}$ ,<br>$RInt = 5$ bits, 8 itérations . . . . .                                                             | 154 |

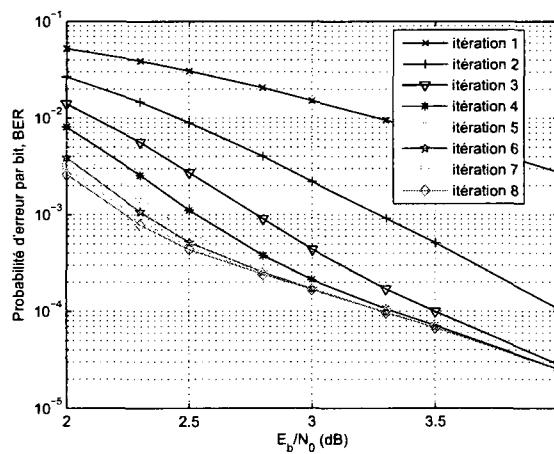

| Figure VI.2  | BER en fonction de $E_b/N_0$ , 3-CDO { $R = 3/6, J = 6, \alpha_J =$<br>$67\}$ , $CP = 0.5, RInt = 5$ bits, 8 itérations . . . . .                                            | 154 |

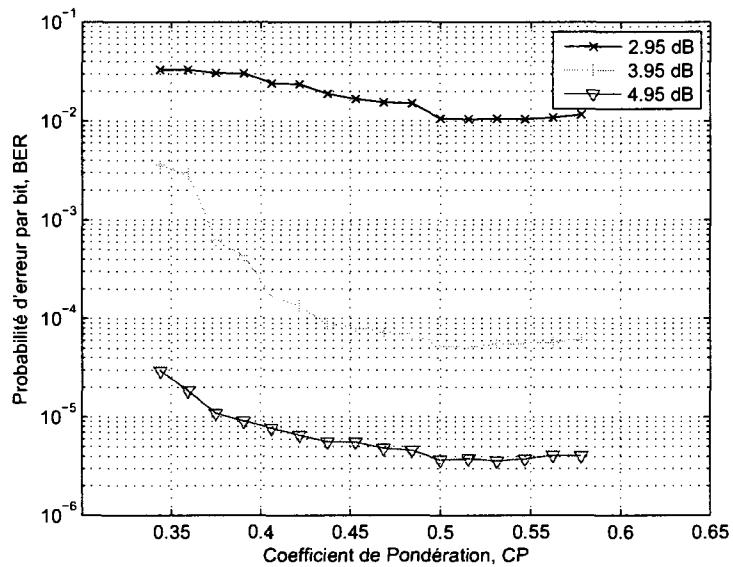

| Figure VI.3  | BER en fonction de $CP$ , 2-CDO { $R = 2/4, J = 8, \alpha_J = 256\}$ ,<br>$RInt = 5$ bits, 8 itérations . . . . .                                                            | 155 |

| Figure VI.4  | BER en fonction de $E_b/N_0$ , 2-CDO { $R = 2/4, J = 8, \alpha_J =$<br>$256\}$ , $CP = 0.375, RInt = 5$ bits, 8 itérations . . . . .                                         | 155 |

| Figure VI.5  | BER en fonction de $CP$ , 2-CDO { $R = 2/4, J = 9, \alpha_J = 383\}$ ,<br>$RInt = 5$ bits, 8 itérations . . . . .                                                            | 156 |

| Figure VI.6  | BER en fonction de $E_b/N_0$ , 2-CDO { $R = 2/4, J = 9, \alpha_J =$<br>$383\}$ , $CP = 0.375, RInt = 5$ bits, 8 itérations . . . . .                                         | 156 |

| Figure VI.7  | BER en fonction de $CP$ , 2-CPDO { $R = 2/4, J = 8, \alpha_J =$<br>$100\}$ , $RInt = 5$ bits, 8 itérations . . . . .                                                         | 157 |

| Figure VI.8  | BER en fonction de $E_b/N_0$ , 2-CPDO { $R = 2/4, J = 8, \alpha_J =$<br>$100\}$ , $CP = 0.359375, RInt = 5$ bits, 8 itérations . . . . .                                     | 157 |

| Figure VI.9  | BER en fonction de $CP$ , 3-CPDO { $R = 3/6, J = 9, \alpha_J =$<br>$107\}$ , $RInt = 5$ bits, 8 itérations . . . . .                                                         | 158 |

| Figure VI.10 | BER en fonction de $E_b/N_0$ , 3-CPDO { $R = 3/6, J = 9, \alpha_J =$<br>$107\}$ , $CP = 0.34375, RInt = 5$ bits, 8 itérations . . . . .                                      | 158 |

| Figure VI.11 | BER en fonction de $CP$ , 2-CDO { $R = 2/3, J = 5, \alpha_J = 132\}$ ,<br>$RInt = 5$ bits, 6 itérations . . . . .                                                            | 159 |

|              |                                                                                                                                                               |     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure VI.12 | BER en fonction de $E_b/N_0$ , 2-CDO { $R = 2/3$ , $J = 5$ , $\alpha_J = 132$ }, $CP = 0.453125$ , $RInt = 5$ bits, 6 itérations . . . . .                    | 159 |

| Figure VI.13 | BER en fonction de $CP$ , 2-CDO { $R = 2/3$ , $J = 9$ , $\alpha_J = 1746$ }, $RInt = 5$ bits, 6 itérations . . . . .                                          | 160 |

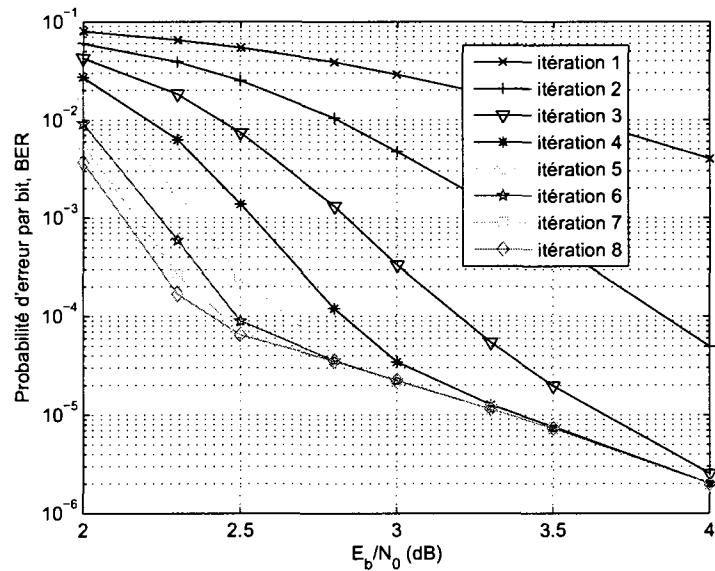

| Figure VI.14 | BER en fonction de $E_b/N_0$ , 2-CDO { $R = 2/3$ , $J = 9$ , $\alpha_J = 1746$ }, $CP = 0.359375$ , $RInt = 5$ bits, 6 itérations, 10 Gbits simulés . . . . . | 160 |

## **LISTE DES TABLEAUX**

|             |                                                                                                                                                                                                                                                                                                                                            |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 2.1 | Exemples de générateurs des codes CDO, $J = 10, R = 1/2$                                                                                                                                                                                                                                                                                   | 19 |

| Tableau 2.2 | Ressources matérielles du FPGA Virtex-II Pro XC2VP70-7                                                                                                                                                                                                                                                                                     | 24 |

| Tableau 3.1 | Nombre total des emplacements des étages de pipeline en fonction de $J$                                                                                                                                                                                                                                                                    | 43 |

| Tableau 3.2 | Ensemble des meilleurs connexions $\alpha_j \in \mathcal{A}$ pour les codes PCDO à taux compatibles : Nombre de connexions $J$ , Capacité de pipelinage $P_c$ , Taux de codage supportés $R$ , Facteur de simplification pour chaque taux supporté $\delta_{max}$ et Ensemble des connexions $\{\alpha_j\}$                                | 57 |

| Tableau 4.1 | Ensemble de meilleurs connexions $\alpha_{m,g,j} \in \mathcal{A}$ pour les codes M-CDO où $M = Q, R = 1/2$ : Nombre minimal des équations de parité $J$ , nombre de registres à décalage $M$ , Span $\alpha_J$ , Capacité de pipelinage $P_{cM}$ , Facteur de simplification $\delta_{max}$ et Ensemble des connexions $[\alpha_{m,g,j}]$  | 81 |

| Tableau 4.2 | Ensemble de meilleurs connexions $\alpha_{m,g,j} \in \mathcal{A}$ pour les codes M-CPDO où $M = Q, R = 1/2$ : Nombre minimal des équations de parité $J$ , nombre de registres à décalage $M$ , Span $\alpha_J$ , Capacité de pipelinage $P_{cM}$ , Facteur de simplification $\delta_{max}$ et Ensemble des connexions $[\alpha_{m,g,j}]$ | 82 |

| Tableau 4.3 | Ensemble de meilleurs connexions $\alpha_{m,g,j} \in \mathcal{A}$ pour les codes M-CDO où $Q = 1, M = 2, R = M/(M + 1) = 2/3$ : Nombre minimal des équations de parité $J$ , Span $\alpha_J$ , Capacité de pipelinage $P_{cM}$ , Facteur de simplification $\delta_{max}$ et Ensemble des connexions $[\alpha_{m,g,j}]$                    | 83 |

| Tableau 5.1 | Comparaison de délais des deux architectures du pondérateur                                                                                                                                                                                                                                                                                | 88 |

|              |                                                                                                                                                                                                                                                     |     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 5.2  | Délai du pondérateur (SA) pour $R_{CP} = 4, 6$ et $8$ bits, $RS_{ADD} = 9$ bits . . . . .                                                                                                                                                           | 88  |

| Tableau 5.3  | Comparaison de la complexité et du débit par itération du décodeur à seuil des codes PCDO $\{J = 10, \alpha_J = 366\}$ pour $RInt = 4, 5, 6$ et $9$ bits . . . . .                                                                                  | 89  |

| Tableau 5.4  | Comparaison de la complexité et du débit par itération du décodeur à seuil des codes PCDO $\{J = 10, \alpha_J = 366\}$ avant et après l'application de la technique de pipelinage, $RInt = 5$ bits . . . . .                                        | 91  |

| Tableau 5.5  | Comparaison de la complexité et du débit par itération du décodeur à seuil des codes PCDO $\{J = 10, \alpha_J = 366\}$ pour les deux architectures du registre à décalage élémentaire, $RInt = 5$ bits, 12 étages de pipeline insérés . . . . .     | 92  |

| Tableau 5.6  | Comparaison de la complexité et du débit par itération du décodeur à seuil des codes 5-CPDO $\{R = 5/10, J = 10, \alpha_J = 128\}$ avant et après l'application de la technique de pipelinage, $RInt = 5$ bits . . . . .                            | 93  |

| Tableau 5.7  | Codes PCDO de types quasi-EEP et UEP, $J = 10, R = 3/4$ . . . . .                                                                                                                                                                                   | 96  |

| Tableau 5.8  | Comparaison de la complexité et du débit par itération des décodeurs à seuil des codes doublement orthogonaux, 12 étages de pipeline insérés, $R = 1/2, J = 10$ et $RInt = 5$ bits . . . . .                                                        | 97  |

| Tableau 5.9  | Comparaison du décodeur des codes PCDO $\{J = 14, \alpha_J = 1359\}$ , 12 étages de pipeline insérés, avec le décodeur des codes 2-CDO $\{R = 2/3, J = 7, \alpha_J = 613\}$ , 11 étages de pipeline insérés, $R = 2/3$ et $RInt = 5$ bits . . . . . | 99  |

| Tableau IV.1 | Complexité et débit par itération du décodeur à seuil des codes PCDO $\{J = 8, \alpha_J = 139\}$ , $RInt = 5$ bits, 11 étages de pipeline insérés . . . . .                                                                                         | 142 |

|              |                                                                                                                                                                        |     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau IV.2 | Complexité et débit par itération du décodeur à seuil des codes PCDO { $J = 15, \alpha_J = 2932\}$ , $RInt = 5$ bits, 12 étages de pipeline insérés . . . . .          | 142 |

| Tableau IV.3 | Complexité et débit par itération du décodeur à seuil des codes 3-CDO { $R = 3/6, J = 6, \alpha_J = 67\}$ , $RInt = 5$ bits, 10 étages de pipeline insérés . . . . .   | 142 |

| Tableau IV.4 | Complexité et débit par itération du décodeur à seuil des codes 2-CDO { $R = 2/4, J = 8, \alpha_J = 256\}$ , $RInt = 5$ bits, 11 étages de pipeline insérés . . . . .  | 143 |

| Tableau IV.5 | Complexité et débit par itération du décodeur à seuil des codes 2-CPDO { $R = 2/4, J = 9, \alpha_J = 383\}$ , $RInt = 5$ bits, 12 étages de pipeline insérés . . . . . | 143 |

| Tableau IV.6 | Complexité et débit par itération du décodeur à seuil des codes 2-CPDO { $R = 2/4, J = 8, \alpha_J = 100\}$ , $RInt = 5$ bits, 11 étages de pipeline insérés . . . . . | 143 |

| Tableau IV.7 | Complexité et débit par itération du décodeur à seuil des codes 3-CPDO { $R = 3/6, J = 9, \alpha_J = 107\}$ , $RInt = 5$ bits, 12 étages de pipeline insérés . . . . . | 144 |

| Tableau IV.8 | Complexité et débit par itération du décodeur à seuil des codes 2-CDO { $R = 2/3, J = 5, \alpha_J = 132\}$ , $RInt = 5$ bits, 11 étages de pipeline insérés . . . . .  | 144 |

| Tableau IV.9 | Complexité et débit par itération du décodeur à seuil des codes 2-CDO { $R = 2/3, J = 9, \alpha_J = 1746\}$ , $RInt = 5$ bits, 13 étages de pipeline insérés . . . . . | 144 |

## LISTE DES ANNEXES

|            |                                                                                |     |

|------------|--------------------------------------------------------------------------------|-----|

| ANNEXE I   | ARCHITECTURE DES COMPOSANTS DU DÉCODEUR À<br>SEUIL DES CODES CDO . . . . .     | 110 |

| I.1        | Opérateurs élémentaires . . . . .                                              | 110 |

| I.1.1      | Additionneur à deux entrées . . . . .                                          | 110 |

| I.1.2      | Opérateur Addmin à deux entrées . . . . .                                      | 111 |

| I.2        | Opérateur de conversion binaire . . . . .                                      | 112 |

| I.3        | Le détecteur de zéros . . . . .                                                | 113 |

| I.4        | Registres à décalage . . . . .                                                 | 114 |

| I.4.1      | Registres à décalage de l'information et de parité . . . . .                   | 114 |

| I.4.2      | Registre à décalage de $\lambda^{(\mu-1)}$ . . . . .                           | 114 |

| I.5        | Le saturateur . . . . .                                                        | 115 |

| ANNEXE II  | NOMBRE DE DIFFÉRENCES DOUBLES INÉVITABLES EN<br>FONCTION DE $J_{RA}$ . . . . . | 116 |

| II.1       | Cas où $(m, q) = (l, p) = (n, p)$ : . . . . .                                  | 116 |

| II.2       | Cas où $(m, q) = (l, p) \neq (n, p)$ : . . . . .                               | 117 |

| ANNEXE III | CODE VHDL DU GESTIONNAIRE D'HORLOGE . . . . .                                  | 118 |

| ANNEXE IV  | COMPLEXITÉ ET DÉBIT DES DÉCODEURS À SEUIL . .                                  | 142 |

| ANNEXE V   | PERFORMANCES D'ERREUR DE DSI DES CODES PCDO                                    | 145 |

| ANNEXE VI  | PERFORMANCES D'ERREUR DE DSI DES CODES M-CDO<br>ET M-CPDO . . . . .            | 154 |

## LISTE DES SIGLES ET DES SYMBOLES

### Sigles

|               |                                                                 |

|---------------|-----------------------------------------------------------------|

| <b>ASIC</b>   | Application-Specific Integrated Circuit                         |

| <b>AWGN</b>   | Additive White Gaussian Noise                                   |

| <b>BER</b>    | Bit Error Rate                                                  |

| <b>BPSK</b>   | Binary Phase Shift Keying                                       |

| <b>BSC</b>    | Binary Symmetric Channel                                        |

| <b>C2</b>     | format binaire Complètement à 2                                 |

| <b>CDO</b>    | Convolutional Doubly Orthogonal                                 |

| <b>CP</b>     | coefficient de ponderation                                      |

| <b>DCM</b>    | Digital Clock Manager                                           |

| <b>DSI</b>    | Décodeur à Seuil Itératif                                       |

| <b>EEP</b>    | Equal Error Protection                                          |

| <b>FF</b>     | Flip-Flop                                                       |

| <b>FPGA</b>   | Field Programmable Gate Array                                   |

| <b>LDPC</b>   | Low Density Parity Check code                                   |

| <b>LSB</b>    | Low Significant Bit                                             |

| <b>LUT</b>    | Look-Up Table                                                   |

| <b>M-CDO</b>  | Multi-shift registers Convolutional Doubly Orthogonal           |

| <b>M-CPDO</b> | Multi-shift registers Convolutional Partially Doubly Orthogonal |

| <b>MSB</b>    | Most Significant Bit                                            |

| <b>PCDO</b>   | Punctured Convolutional Doubly Orthogonal                       |

| <b>SA</b>     | format binaire Signe-Amplitude                                  |

| <b>SRL16</b>  | Shift Registre Look-Up Table                                    |

| <b>UEP</b>    | Unequal Error Protection                                        |

## Symboles

|                |                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| $\alpha_J$     | Span ou mémoire du codeur convolutionnel                                                                                          |

| $C_{it}$       | Complexité par itération                                                                                                          |

| $D$            | Débit du décodeur                                                                                                                 |

| $D_{it}$       | Débit par itération                                                                                                               |

| $E_b$          | Énergie du symbole binaire $u_i$                                                                                                  |

| $f$            | fréquence d'opération du décodeur                                                                                                 |

| $J$            | Nombre minimal des équations de parité utilisées pour décoder un bit d'information à l'intérieur du décodeur (codes non perforés) |

| $J_{RA}$       | Nombre maximal de connexions existant entre un registre à décalage et un additionneur modulo 2 dans le codeur                     |

| $M$            | Nombre de registres à décalage du codeur                                                                                          |

| $N$            | Nombre d'itérations du décodeur                                                                                                   |

| $R$            | Taux de codage                                                                                                                    |

| $R_{CP}$       | Résolution binaire du coefficient de ponderation                                                                                  |

| $RDC_{it}$     | Rapport débit sur complexité par itération                                                                                        |

| $RInt$         | Résolution interne du décodeur                                                                                                    |

| $t_{co}$       | Clock to out time                                                                                                                 |

| $t_r$          | Route time                                                                                                                        |

| $t_{su}$       | Setup time                                                                                                                        |

| $\oplus$       | Somme modulo 2                                                                                                                    |

| $\diamond$     | Opérateur addmin                                                                                                                  |

| $\binom{n}{k}$ | Combinaison $C_n^k$ , choisir $k$ objets parmi $n$ objets                                                                         |

| $[x]$          | Le plus grand entier supérieur à $x$                                                                                              |

## CHAPITRE 1

### INTRODUCTION

#### 1.1 Motivation

Depuis plusieurs années, les communications électroniques sont devenues un besoin essentiel dans notre société moderne. Grâce à de grandes avancées technologiques dans le domaine du micro-électronique, nous sommes aujourd’hui témoin de l’utilisation grandissante des ordinateurs portables et des téléphones cellulaires intelligents. La diversité des applications dont ces technologies peuvent supporter (Internet, Voix, Video, MP3...) a encouragé les consommateurs ”mobiles” ou fixes à explorer les nouveaux horizons de services offerts. Cependant, les fournisseurs de services doivent innover en permanence pour rester attrayants, et afin de répondre aux exigences qui en découlent. Ils ont donc besoin de transmettre avec grande efficacité les informations demandées par les clients, sans erreurs et à des débits remarquablement élevés. Pour atteindre l’efficacité requise, un des moyens utilisés consiste à considérer le codage correcteur d’erreur.

L’année 1993 a été marquée par la découverte des codes correcteurs d’erreur ”Turbo” [1] qui ont permis, grâce à leur décodage itératif Turbo, de s’approcher de très près des limites théoriques de transmission prédictes par Shannon [2]. En 1995, les codes LDPC ont été redécouverts [3]. Le processus du décodage itératif des codes LDPC ainsi introduits a permis d’atteindre des performances d’erreurs aussi importantes que celles des codes Turbo. Toutefois, la complexité matérielle engendrée par les décodeurs itératifs des codes Turbo et LDPC a constitué un désavantage qui s’avère limiter l’utilisation à grande échelle de ces algorithmes dans les systèmes de communication à hauts débits.

Le décodage à seuil itératif de codes convolutionnels doublement orthogonaux (CDO) a été introduit récemment par Cardinal *et al.* [4] comme un nouvel algorithme performant de correction d'erreurs. Bien que beaucoup d'efforts aient été déployés pour implémenter et améliorer cet algorithme, les implémentations de ce type de décodeur qui ont été réalisées à ce jour ne sont pas suffisamment rapides pour les applications actuelles en télécommunications. En effet, le débit binaire à l'entrée/sortie du décodeur doit être augmenté afin de satisfaire les critères de communication tels que, par exemple, ceux spécifiés par la norme Wimax [5]. Dans le cadre de ce projet, les objectifs concernent la conception et le prototypage de décodeurs à seuil itératifs à hauts débits. Les différents facteurs qui limitent le débit des décodeurs ont été identifiés. De plus, une nouvelle architecture parallèle qui permet d'augmenter le débit du décodeur à seuil itératif sans exploser sa complexité a été introduite.

## 1.2 Contributions

Plusieurs contributions ont été apportées dans ce mémoire.

1. Conception de nouvelles architectures de pondérateur et du registre à décalage élémentaire ce qui a abouti à améliorer le débit du décodeur.

2. Élaboration de la technique de pipelinage du décodeur à seuil itératif et introduction de la "capacité de pipelinage" comme un nouveau critère de sélection de générateurs des codes CDO qui permettent un décodage à hauts débits dans le cas où cette capacité est élevée.

3. Conception et prototypage du décodeur à seuil itératif (DSI) à hauts débits des codes CDO.

4. Conception des modules de perforation qui permettent au DSI de fonctionner à

plusieurs taux de codage et prototypage de la première version du DSİ à hauts débits des codes CDO perforés à taux compatibles.

5. Réalisation de la recherche d'un ensemble de générateurs des codes CDO perforés à taux compatibles ayant une capacité de pipelinage élevée.

6. Introduction d'un nouveau type des codes CDO à multi-registres à décalage (M-CDO) qui permet un décodage parallèle à haut débit. Ainsi, la simplification de ces codes a été étudiée et la recherche d'un ensemble de générateurs a été effectuée.

7. Conception et prototypage du DSİ à hauts débits des codes M-CDO.

8. Génération et comparaison des résultats expérimentaux des codes CDO et M-CDO.

### 1.3 Organisation du mémoire

Ce mémoire comporte six chapitres. À la suite du présent chapitre, le document se subdivise de la façon suivante.

- Le chapitre 2 présente les notions préliminaires en matière de télécommunication ainsi que celles de la technologie FPGA. Les codes LDPC et les codes Turbo sont exposés brièvement. Ensuite les codes convolutionnels doublement orthogonaux et leur processus de décodage à seuil itératif sont présentés. La technologie FPGA et quelques notions matérielles associées sont également rapportées dans ce chapitre.

- Le chapitre 3 présente l'architecture du décodeur à seuil itératif à hauts débits. Ainsi, la nouvelle technique de pipelinage est décrite. Les modules de perforation sont illustrés et l'architecture du décodeur à seuil itératif qui fonctionne à plusieurs

taux de codage est exposée. Enfin, un ensemble des nouveaux générateurs des codes convolutionnels doublement orthogonaux à taux compatible et qui permettent un décodage à haut débit est présenté.

- Le chapitre 4 définit un nouveau type des codes convolutionnels doublement orthogonaux à mutli-registres à décalage. La simplification de ces codes est étudiée et l'architecture parallèle du décodeur à seuil est exposée. Un ensemble de générateurs des codes convolutionnels doublement orthogonaux à mutli-registres à décalage est fourni à la fin du chapitre.

- Le chapitre 5 présente les résultats expérimentaux des codes convolutionnels doublement orthogonaux. Le débit, la complexité et les performances d'erreur du décodeur sont étudiés et les résultats expérimentaux sont comparés pour les différents codes.

- Finalement, le chapitre 6 résume l'ensemble des travaux effectués et propose certaines idées à étudier dans le futur.

## CHAPITRE 2

### NOTIONS PRÉLIMINAIRES

#### 2.1 Introduction

Dans ce chapitre, les différents notions et concepts reliés au codage de canal dans un système de communication numérique sont abordés. De plus, les notions matérielles qui concernent le prototypage d'un système numérique sur FPGA sont également présentées. Nous nous intéressons seulement aux codes correcteurs d'erreurs utilisés conjointement avec des décodeurs itératifs tels que, les codes à faible densité de parité (LDPC, en anglais Low Density Parity Check), les codes Turbo et les codes convolutionnels doublément orthogonaux (CDO). Ces derniers sont décodés par un algorithme de décodage à seuil itératif dont l'architecture du décodeur est abordée en détail aux chapitres 3 et 4.

#### 2.2 Codage de canal

##### 2.2.1 Système de communication numérique

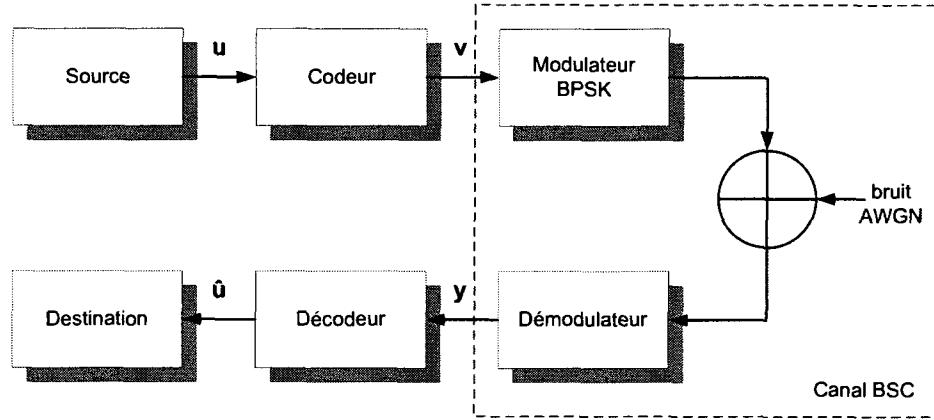

Le modèle du système de communication numérique utilisé dans ce mémoire est présenté à la figure 2.1. Une séquence de symboles binaires  $\mathbf{u} = (u_0, u_1, \dots)$  où chaque bit  $u_i$  est d'énergie  $E_b$ , est émise par une source d'information vers un codeur de taux de codage  $R$ . Le codeur ajoute selon certaines règles des symboles de redondance pour former la séquence binaire codée ou tout simplement les codes,  $\mathbf{v} = (v_0, v_1, \dots)$ . Les codes sont ensuite envoyés vers un modulateur BPSK (modulation antipodale) qui traduit les symboles codés sous forme analogique avant de les transmettre dans le canal.

Figure 2.1: Modèle du système de communication numérique

Le canal considéré est binaire symétrique (BSC, en anglais Binary Symmetric Channel) sans mémoire à bruit blanc additif et gaussien (AWGN). Ce bruit AWGN est un processus aléatoire gaussien de moyenne nulle et de densité de puissance spectrale bilatérale égale à  $N_0/2$  (Watt/Hz). À la sortie du démodulateur, la séquence reçue  $\mathbf{y} = (y_0, y_1, \dots)$  est quantifiée sur 3 bits (quantification douce), puis fournie au décodeur qui utilise les symboles redondants insérés par le codeur afin de calculer une estimation  $\hat{\mathbf{u}}$  sur les symboles d'information.

Pour un canal BSC, la capacité du canal,  $\mathcal{C}$ , qui représente le débit maximum permis a été établie par Shannon. Elle est donnée par la relation suivante [2] :

$$\mathcal{C} = W \log_2 \left( 1 + \frac{P_{moy}}{WN_0} \right) (\text{bits/s}) \quad (2.1)$$

où  $W$  (Hz) est la largeur de bande utilisée et  $P_{moy}$  est la puissance moyenne d'émission. Cette relation montre que si le débit d'information à la sortie de la source est inférieur à la capacité du canal  $\mathcal{C}$ , alors il est théoriquement possible d'effectuer une transmission sans erreur en utilisant un code correcteur d'erreur approprié. Sachant (2.1), le rapport signal sur bruit minimal,  $(E_b/N_0)_{min}$ , à partir duquel il est théoriquement possible de faire une transmission fiable de l'information peut être calculé, et pour un canal à bruit

AWGN, il est exprimé par :

$$(E_b/N_0)_{min} \geq -1.6 \text{ dB} \quad (2.2)$$

En d'autres termes, il n'existe aucune technique de codage correcteur d'erreurs qui assure une transmission fiable si le canal est très bruité où  $(E_b/N_0) < -1.6 \text{ dB}$  [2].

### 2.2.2 Principe du codage correcteur d'erreur

Le codage correcteur d'erreur permet, comme son nom l'indique, de corriger les erreurs de la transmission en intégrant selon certaines règles des symboles de redondance dans la séquence transmise dans le canal. Nous pouvons distinguer deux catégories principales du codage correcteur d'erreur : le codage bloc et le codage convolutionnel. Le codage bloc consiste à utiliser un bloc de bits de taille prédéfinie afin de produire un nombre déterminé de symboles de parité. Cependant, le codage convolutionnel consiste à calculer les symboles de parité au fur et à mesure que les bits d'information sont acheminés au codeur. Cette propriété découle du fait que le codeur convolutionnel utilise une fenêtre temporelle fixe où certaines données sont utilisées pour calculer chaque symbole de parité. Ainsi, le taux de codage,  $R$ ,  $R < 1$ , d'un codeur (bloc ou convolutionnel) qui associe  $Q$  symboles de parité à  $M$  symboles d'information est défini par :

$$R = M/(M + Q) \quad (2.3)$$

## 2.2.3 Les codes LDPC

### 2.2.3.1 Définition des codes bloc

Les codes bloc ont été découverts par Hamming [6] dans les années 50. Un code bloc  $(n, k), n > k$ , est spécifié par une matrice génératrice,  $\mathbf{G}$ , de dimensions  $k \times n$ . Chaque mot de code est représenté par un des  $2^k$  vecteurs de dimension  $n$  qui représente la longueur du code. Ainsi, à partir de  $\mathbf{G}$ , le codeur fait correspondre chaque mot d'information de la source  $\mathbf{u} = (u_1, \dots, u_k)$  à un mot de code  $\mathbf{v} = (v_1, \dots, v_n)$  de la façon suivante :

$$\mathbf{v} = \mathbf{u} \cdot \mathbf{G} \quad (2.4)$$

Le taux de codage ainsi obtenu à la sortie du codeur est donné par :

$$R = k/n \quad (2.5)$$

La matrice  $\mathbf{G}$  est construite de façon à ce que toute combinaison linéaire des mots de code donne un autre mot de code. Par conséquent, le code est linéaire. Un exemple de la matrice génératrice  $\mathbf{G}$  linéaire est celle du code de Hamming (7,4) :

$$\mathbf{G} = \begin{bmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix} \quad (2.6)$$

À toute matrice génératrice  $\mathbf{G}$  d'un code en bloc, une matrice de parité  $\mathbf{H}$  de dimensions  $(n - k) \times n$  intervenant pour le décodage est calculée telle que :

$$\mathbf{G} \cdot \mathbf{H}^T = 0 \quad (2.7)$$

Soit pour la matrice  $\mathbf{G}$  de (2.6) :

$$\mathbf{H} = \begin{bmatrix} 1 & 1 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 1 & 0 & 0 & 1 \end{bmatrix} \quad (2.8)$$

La matrice  $\mathbf{H}$  sert au niveau du décodeur à détecter et corriger les erreurs en vérifiant si la séquence reçue,  $\mathbf{y}$ , est valide. Pour cela, il faut satisfaire :

$$\mathbf{y} \cdot \mathbf{H}^T = \mathbf{u} \cdot \mathbf{G} \cdot \mathbf{H}^T = 0 \quad (2.9)$$

### 2.2.3.2 Les codes bloc à faible densité de parité

Les codes à faible densité de parité, LDPC, sont des longs codes linéaires bloc définis par l'ensemble de  $(n - k)$  équations de parité,  $\mathbf{v} \cdot \mathbf{H}^T = 0$ .  $\mathbf{H}$  est la matrice de parité de dimensions  $(n - k) \times n$  dont un exemple est montré par :

$$\mathbf{H} = \left[ \begin{array}{ccccccccc|cc} 1 & 1 & 0 & 0 & 0 & 0 & 0 & \dots & \dots & \dots & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 1 & 0 & \dots & \dots & \dots & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 1 & \dots & \dots & \dots & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & \dots & \dots & \dots & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 1 & 0 & \dots & \dots & \dots & 0 & 0 \\ 1 & 0 & 0 & 1 & 0 & 0 & 0 & \dots & \dots & \dots & 0 & 1 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 & \dots & \dots & \dots & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 & 0 & \dots & \dots & \dots & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & \dots & \dots & \dots & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 1 & 0 & \dots & \dots & \dots & 0 & 1 \end{array} \right] \quad (2.10)$$

Les codes LDPC ont été découverts par Gallager en 1962 [7]. Pour que les codes LDPC soient performants, la matrice de parité de ces codes doit être très creuse ou à faible densité de 1's ce qui explique leur appellation. Gallager a proposé une méthode de décodage itératif pour ses codes. Toutefois, la nécessité d'une grande complexité de calculs pour le codeur et le décodeur n'a pas permis d'exploiter les codes LDPC pendant plusieurs années.

Ce n'est qu'en 1995 que Mackay et Neal ont redécouvert les codes LDPC [3, 8, 9]. Ils ont effectué le décodage des codes LDPC en utilisant l'algorithme de décodage itératif "*belief propagation*" (BP) de Pearl [10] qui n'est qu'une version itérative de l'algorithme "*somme-produit*" [11]. À chaque itération, l'algorithme BP consiste à affiner davantage les probabilités a posteriori  $\{P(\mathbf{v}/\mathbf{y})\}$  où  $\mathbf{v}$  est un mot du code et  $\mathbf{y}$  est la séquence reçue du canal. Pour ce faire, le décodeur calcule les probabilités correspondantes aux équations de contrôle de parité dans une première étape, puis dans une deuxième étape, il propage les probabilités et fait la mise à jour des symboles à décoder. Cette dernière étape se fait de façon à ce que les équations de parité qui contiennent le symbole courant à décoder ne soient pas incluses.

Les premiers codes LDPC développés par Gallager étaient des codes réguliers. Les codes LDPC réguliers sont construits de façon à ce que la matrice  $\mathbf{H}$  ait un nombre constant de 1's sur les lignes ainsi que sur les colonnes. En contrepartie, les codes LDPC irréguliers [12] ne respectent pas cette propriété de régularité.

## 2.2.4 Les codes Turbo

En 1993, Berrou, Glavieux et Thitimajshima ont introduit une nouvelle technique du décodage itératif baptisée *Turbo* [1]. Cette technique qui utilise un codage concaténé en parallèle permet d'atteindre de très bonnes performances d'erreur s'approchant étroitement de la limite théorique de Shannon [2]. Dans les deux sous-sections suivantes, les processus de codage et de décodage turbo sont décrits brièvement.

### 2.2.4.1 Principe du codage Turbo

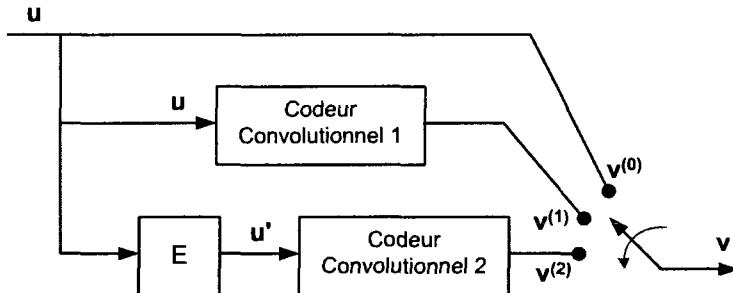

Un codeur turbo de taux de codage  $R = 1/3$  est illustré à la figure 2.2. Ce codeur est composé de deux codeurs convolutionnels montés en parallèle et séparés par un entrelaceur (E) qui permute les symboles d'information de sorte que les deux codeurs n'encodent pas la même séquence d'information,  $\mathbf{u} \neq \mathbf{u}'$ . La taille de l'entrelaceur peut être très élevée, de l'ordre de plusieurs milliers de bits, ce qui permet de minimiser la probabilité d'erreurs au décodage [13]. En effet, l'amélioration des performances d'erreur des codes Turbo est quasi proportionnelle à la taille de l'entrelacement [14]. Les taux de codage  $R > 1/3$  peuvent être obtenus par l'application de la technique de perforation au codeur turbo [15].

Figure 2.2: Schéma bloc du codeur Turbo,  $R = 1/3$

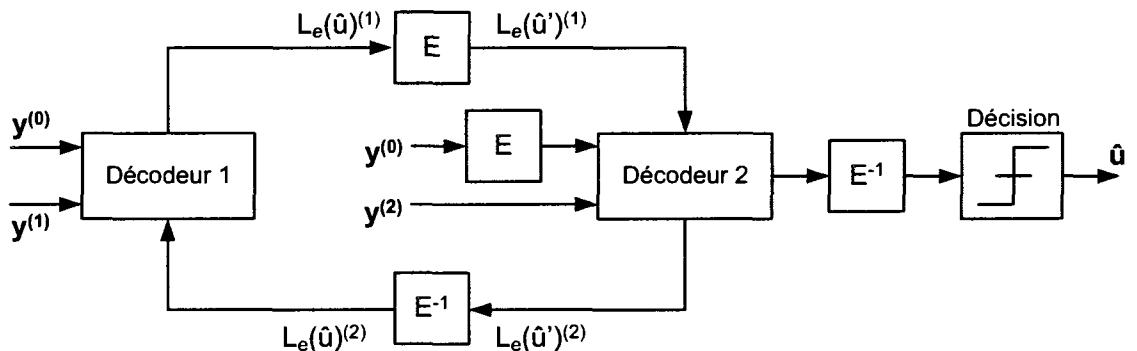

#### 2.2.4.2 Décodeur itératif Turbo

Le schéma bloc du décodeur turbo est montré à la figure 2.3. Le décodeur turbo se compose de deux décodeurs, des entrelaceurs identiques à celui utilisé par le codeur turbo et d'un délaveur ( $E^{-1}$ ) qui effectue l'opération inverse de l'entrelaceur.

Figure 2.3: Schéma bloc du décodeur itératif Turbo,  $R = 1/3$

Le principe du décodage turbo repose sur l'échange d'information entre les deux décodeurs qui utilisent généralement les algorithmes SOVA (en anglais Soft Output Viterbi Algorithm) [16] ou BCJR [17]. À la première itération, le premier décodeur génère la valeur extrinsèque  $L_e(\hat{u}_i)^{(1)}$  à partir des sorties du canal  $y_i^{(0)}$  et  $y_i^{(1)}$  associées à  $v_i^{(0)}$  et  $v_i^{(1)}$  du codeur. Le deuxième décodeur utilise  $L_e(\hat{u}_i)^{(1)}$  entrelacé, soit  $L_e(\hat{u}'_i)^{(1)}$ , ainsi que  $y_i^{(0)}$  et  $y_i^{(2)}$  comme informations a priori afin de calculer  $L_e(\hat{u}'_i)^{(2)}$  qui sera retourné au premier décodeur en passant par le délaveur à l'itération suivante. Le premier décodeur

turbo proposé dans [1] utilise un entrelaceur pseudo-aléatoire de taille 64 kbits et deux décodeurs BJCR. Ce décodeur a été capable d'atteindre une probabilité d'erreur de  $10^{-5}$  à 0.7 dB de la capacité du canal après 18 itérations.

### 2.2.5 Les codes CDO

Les performances remarquables de deux techniques des codage du canal, LDPC et Turbo, présentées dans les sections précédentes sont associées à une complexité matérielle au décodage itératif qui pourrait compromettre leurs avantages. En effet, afin de minimiser la probabilité d'erreur, les codes LDPC doivent avoir une longueur de code importante ainsi qu'un très grand nombre d'itérations, tandis que les codes Turbo ont besoin d'un entrelaceur ayant une grande taille, conduisant ainsi à une complexité très élevée du décodeur itératif.

Une des solutions à ce problème de complexité consiste à réitérer les codes plusieurs fois sur un petit nombre d'itérations implémentées physiquement. Cependant, le débit à la sortie du décodeur sera diminué, comme dans [18] où le débit a été réduit à 9 Mbps seulement dans certains cas. Ces compromis entre complexité/débit/performance du décodeur a motivé les chercheurs à réaliser plusieurs travaux sur cette problématique [19–22].

Dans le but d'offrir un meilleur compromis, les auteurs de [23], [24] et [25] ont proposé une nouvelle technique de codage du canal inspirée par le décodage itératif Turbo et basée sur le concept du décodage à seuil des codes convolutionnels simplement orthogonaux (CSO) de Massey [26]. Les nouveaux codes ainsi introduits doivent respecter certaines conditions de double orthogonalité afin de permettre un décodage à seuil itératif sans entrelacement à la réception. La description de ces codes convolutionnels doublement orthogonaux (CDO) ainsi que leur décodage à seuil itératif, est présentée dans les

sous-sections suivantes.

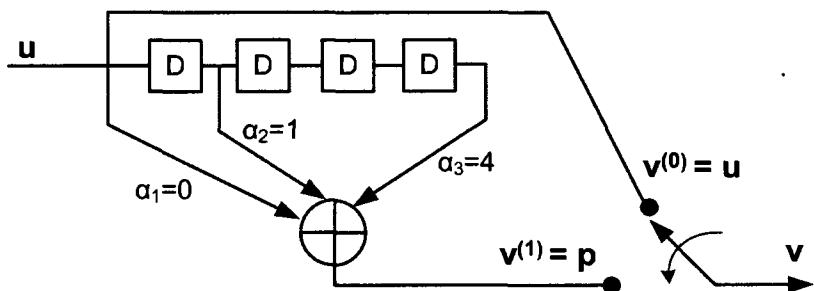

### 2.2.5.1 Définition des codes CDO

En principe, un codeur convolutionnel utilise les symboles d'information courants et passés afin de calculer un nouveau symbole de parité. Les symboles d'information sont préservés dans un registre à décalage qui agit comme fenêtre temporelle. Un codeur convolutionnel est dit systématique si l'information présente à l'entrée du codeur est retenue dans la séquence codée à sa sortie sans être modifiée. La figure 2.4 montre un exemple d'un codeur convolutionnel systématique de taux de codage  $R = 1/2$ . Un tel codeur peut être décrit en utilisant l'ensemble des positions de connexions  $A = \{\alpha_1, \dots, \alpha_J\}$  où  $J$  représente le nombre de ces connexions. Chaque élément  $\alpha_j$ ,  $1 \leq j \leq J$ , représente la position sur le registre à décalage du codeur où une connexion le relie au sommateur modulo 2 qui calcule le symbole de parité. La longueur du registre à décalage correspond alors à  $\alpha_J$  qui représente la longueur de la mémoire ou le "Span" du codeur.

Figure 2.4: Codeur convolutionnel systématique,  $R = 1/2$ ,  $\alpha_J = 4$ ,  $A = \{0, 1, 4\}$

Par convention, l'ensemble des positions de connexions  $A$  est appelé le générateur du code. Ainsi, les codes CDO sont définis comme suit [24] :

**Définition 1** *Un encodeur convolutionnel systématique de taux de codage  $R = 1/2$  est dit doublement orthogonal (CDO) si son générateur  $A = \{\alpha_j : j = 1, \dots, J\}$ , satisfait aux conditions suivantes :*

1. *Les différences simples,  $(\alpha_j - \alpha_k) : j \neq k$ , sont distinctes.*

2. *Les différences doubles,  $(\alpha_j - \alpha_k) - (\alpha_n - \alpha_m) : j \neq k, j \neq n, m \neq k, m \neq n$ , sont distinctes à l'exception des répétitions inévitables provenant des permutations des indices  $j$  avec  $m$  et  $k$  avec  $n$ .*

3. *Les différences doubles sont distinctes des différences simples.*

### 2.2.5.2 Décodage à seuil itératif des codes CDO

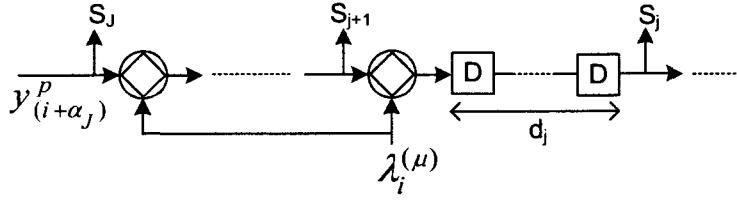

À la réception, les codes CDO sont décodés par un décodeur à seuil itératif (DSI) [24] qui est composé d'un ensemble de  $N$  itérations élémentaires où chaque itération est un décodeur à seuil tel qu'illustré à la figure 2.5. L'algorithme du décodage à seuil itératif est décrit par les deux équations suivantes [24] :

À la première itération :

$$\lambda_i^{(1)} = y_i^u + \sum_{j=1}^J \psi_{i,j}^{(1)} = y_i^u + \sum_{j=1}^J \left( y_{(i+\alpha_j)}^p \diamond \sum_{k=1}^{j-1} \diamond y_{(i+\alpha_j-\alpha_k)}^u \diamond \sum_{k=j+1}^J \lambda_{(i+\alpha_j-\alpha_k)}^{(\mu)} \right) \quad (2.11)$$

Et à chaque itération  $\mu$ , ( $1 < \mu \leq N$ ) :

$$\lambda_i^{(\mu)} = y_i^u + \sum_{j=1}^J \psi_{i,j}^{(\mu)} = y_i^u + \sum_{j=1}^J \left( y_{(i+\alpha_j)}^p \diamond \sum_{k=1}^{j-1} \lambda_{(i+\alpha_j-\alpha_k)}^{(\mu-1)} \diamond \sum_{k=j+1}^J \lambda_{(i+\alpha_j-\alpha_k)}^{(\mu)} \right) \quad (2.12)$$

où  $\psi_{i,j}$  représente les équations de parité :

$$\psi_{i,j}^{(\mu)} = y_{(i+\alpha_j)}^p \diamond \sum_{k=1}^{j-1} \lambda_{(i+\alpha_j-\alpha_k)}^{(\mu-1)} \diamond \sum_{k=j+1}^J \lambda_{(i+\alpha_j-\alpha_k)}^{(\mu)} \quad (2.13)$$