**Titre:** Méthodes de raffinement des communications pour passer d'une plate-forme systemc à un système reprogrammable

Title: Methods of refinement of communications to pass from a systemc platform to a programmable system

**Auteur:** Ahmed Faiz

Author:

**Date:** 2007

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Faiz, A. (2007). Méthodes de raffinement des communications pour passer d'une plate-forme systemc à un système reprogrammable [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/8431/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8431/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

**MÉTHODES DE RAFFINEMENT DES

COMMUNICATIONS POUR PASSER D'UNE

PLATE-FORME SYSTEMC À UN SYSTÈME

REPROGRAMMABLE**

AHMED FAIZ

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

AOÛT 2007

Library and Archives

Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

ISBN: 978-0-494-53901-9

*Our file Notre référence*

ISBN: 978-0-494-53901-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

**MÉTHODES DE RAFFINEMENT DES

COMMUNICATIONS POUR PASSER D'UNE

PLATE-FORME SYSTEMC À UN SYSTÈME

REPROGRAMMABLE**

présenté par : FAIZ Ahmed

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. LANGLOIS Pierre, J.M., Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. ABOULHAMID El Mostapha, Ph.D., membre

## Remerciements

Je tiens d'abord à remercier chaleureusement mon directeur de recherche, M. Guy Bois, pour sa compréhension, son support technique et financier, et ses conseils précieux durant toute la période de ma maîtrise.

Je remercie les membres du jury, M. Mostapha Aboulhamid et M. Pierre Langlois, pour avoir pris de leur temps afin d'assister à la soutenance de mes travaux.

Je remercie également mes collègues du laboratoire Circus de l'École Polytechnique de Montréal pour leur aide et leur fraternité.

Je profite de cette occasion pour remercier mon épouse Hassnaa pour son aide morale et pour sa patience.

## Résumé

Le temps de commercialisation et la productivité sont parmi les critères les plus importants de l'industrie des systèmes numériques et des systèmes embarqués. Auparavant, ces systèmes étaient totalement conçus en matériel. Or, l'introduction des processeurs embarqués a changé la donne, et les systèmes embarqués sont présentement composés dans la majorité des cas d'une partie logicielle et d'une autre matérielle. Ils sont donc devenus des systèmes sur puce, ou *system-on-chips* (SoC).

Cette coexistence entre le logiciel et le matériel nécessite la mise à jour des méthodologies de conception et deux solutions sont possibles : 1) séparer les spécifications du logiciel et du matériel dès le départ, 2) travailler sur une seule spécification et raffiner le système au fur et à mesure jusqu'à ce qu'il faille diviser le système en deux partitions : une logicielle et une matérielle.

La nature de l'application est un facteur important dans les décisions de partitionnement en logiciel et en matériel d'un architecte système. Le logiciel, par sa flexibilité, convient parfaitement aux parties de l'application nécessitant du contrôle informatique, tandis que le matériel (généralement plus ardu à implémenter que le logiciel) convient mieux aux parties de l'application orientées flot de données.

Plusieurs groupes de recherche et sociétés dans le domaine des SoC travaillent sur la mise en œuvre de langages de programmation et de plates-formes afin d'augmenter le niveau d'abstraction des spécifications lors de la phase de conception, et de pouvoir travailler sur une spécification commune au logiciel et au matériel. Parmi ces langages, nous nous intéressons particulièrement à SystemC [2] qui sera présenté au deuxième chapitre.

L'utilisation des langages de haut niveau tels que le C ou le C++ pour concevoir des applications destinées à l'implantation sur puce amène des questions telles que le choix

du partitionnement logiciel/matériel, le passage d'une spécification haut niveau vers l'implémentation physique et la synthèse des communications entre le logiciel et le matériel.

Notre travail se base sur la plate-forme Space Codesign™, un environnement SystemC servant à la simulation et à la validation de systèmes décrits à haut niveau d'abstraction. Nous proposons d'abord, dans une méthodologie, le raffinement des communications logicielles/matérielles pour les systèmes orientés bus, pour ensuite effectuer le passage de façon semi automatique d'une spécification haut niveau vers une implémentation physique de type FPGA. Pour atteindre cet objectif, nous concevons en VHDL des adaptateurs pour assurer la communication matériel-matériel, matériel-logiciel et logiciel-matériel. Ces adaptateurs permettent la conversion du protocole de communication utilisé à haut niveau vers le protocole de communication de l'architecture cible au niveau implémentation.

## Abstract

Time-to-market and productivity are amongst the most important criteria when speaking of digital and embedded systems. Originally, these systems were designed in hardware only. Nowadays, the introduction of embedded processors changed this situation, and embedded systems are most of the time composed of a software part and a hardware part, which have now become systems-on-chips.

This coexistence between software and hardware requires the adaptation of design methodologies. In this case, two solutions are possible: 1) to separate software and hardware specifications at the early stages of the design cycle, 2) to work out from a unique specification and to progressively refine it until it becomes necessary to divide the system into two partitions: software and hardware.

Also, the nature of the embedded application is an important factor in the software/hardware partitioning decision. Because of its flexibility, software is appropriate for the parts of the application requiring control, while hardware (generally more difficult to implement than the software) is appropriate for the parts of the application processing enormous quantity of data.

In the most specified field of system-on-chips, several research groups and companies work on the implementation of platforms and new programming languages to increase the level of abstraction in the early design stages. One advantageous outcome of these implementations work led to use a common specification to describe both software and hardware. Among these languages is SystemC [2] on which we focused, which will be presented in the Second Chapter.

The use of high level languages such as C or C++ to design applications intended for on-chip implementations comes with many questions such as making decisions on software/hardware partitioning, the migration from a high level specification to a physical implementation and the synthesis of the communications between software and hardware. Starting with the SystemC-based Space Codesign™ platform we used for simulating and validating high level systems, our work consisted in proposing a bus-based, hardware/software communication refinement methodology, then in carrying out in by an automated technique the transfer from a high level specification to an FPGA physical implementation.

## Table des matières

|                                                                                |       |

|--------------------------------------------------------------------------------|-------|

| Remerciements.....                                                             | iv    |

| Résumé .....                                                                   | v     |

| Abstract .....                                                                 | vii   |

| Table des matières.....                                                        | ix    |

| Liste des tableaux.....                                                        | xii   |

| Liste des figures .....                                                        | xiv   |

| Liste des acronymes.....                                                       | xvi   |

| Liste des Annexes .....                                                        | xviii |

| Introduction .....                                                             | 1     |

| Chapitre 1 Revue du raffinement des communications pour systèmes sur puce..... | 6     |

| 1.1 Le modèle TLM .....                                                        | 6     |

| 1.2 Les systèmes sur puce .....                                                | 8     |

| 1.2.1 Évolution.....                                                           | 8     |

| 1.2.2 Approche de conception par codesign .....                                | 9     |

| 1.2.3 Langages de programmation à haut niveau et les SoC .....                 | 12    |

| 1.3 Modèles de communication pour un SoC .....                                 | 13    |

| 1.3.1 La communication inter logiciel .....                                    | 13    |

| 1.3.2 La communication inter matériel .....                                    | 14    |

| 1.3.3 La communication entre le logiciel et le matériel.....                   | 16    |

| 1.4 Éléments du raffinement de SoC .....                                       | 17    |

| 1.4.1 L'architecture cible .....                                               | 17    |

| 1.4.2 Les différentes synthèses .....                                          | 19    |

| 1.5 Revue des travaux sur le raffinement.....                                  | 20    |

| 1.5.1 Raffinement par l'utilisation d'adaptateurs de communication.....        | 21    |

| 1.5.2 Raffinement par processeur / coprocesseur .....                          | 26    |

| Chapitre 2 La plateforme Space .....                                           | 27    |

| 2.1 La librairie SystemC .....                                                 | 27    |

|            |                                                                             |    |

|------------|-----------------------------------------------------------------------------|----|

| 2.1.1      | Introduction.....                                                           | 27 |

| 2.1.2      | Architecture générale de SystemC.....                                       | 28 |

| 2.1.3      | Les niveaux de raffinement de SystemC .....                                 | 32 |

| 2.1.4      | Exemple d'une bascule avec SystemC .....                                    | 33 |

| 2.2        | La plateforme Space .....                                                   | 34 |

| 2.2.1      | Vue d'ensemble .....                                                        | 35 |

| 2.2.2      | Les niveaux de raffinement dans Space.....                                  | 39 |

| 2.2.3      | Le protocole de communication dans Space.....                               | 42 |

| Chapitre 3 | Raffinement des communications de Space .....                               | 50 |

| 3.1        | Les outils de développement.....                                            | 51 |

| 3.1.1      | EDK .....                                                                   | 51 |

| 3.1.2      | FPGA Virtex-II de Xilinx .....                                              | 52 |

| 3.2        | Méthodologie .....                                                          | 53 |

| 3.3        | Implémentation au niveau RTL .....                                          | 56 |

| 3.3.1      | Interface d'un module matériel .....                                        | 56 |

| 3.3.2      | Fonctionnement d'un module matériel au niveau RTL .....                     | 60 |

| 3.3.3      | Adaptateur d'un module matériel .....                                       | 62 |

| 3.3.4      | Adaptateur des communications entre le matériel et le logiciel .....        | 70 |

| 3.4        | Comparaison avec les autres travaux de recherche.....                       | 71 |

| Chapitre 4 | Résultats, discussions et améliorations .....                               | 73 |

| 4.1        | Quelques restrictions de fonctionnement de l'IPIF .....                     | 73 |

| 4.2        | Latences des communications matériel-matiel .....                           | 75 |

| 4.2.1      | Présentation de l'application.....                                          | 75 |

| 4.2.2      | Latences des communications de l'adaptateur version no 1 .....              | 79 |

| 4.2.3      | Illustration du calcul de la latence .....                                  | 83 |

| 4.2.4      | Latences de communication de l'adaptateur version no 2 .....                | 85 |

| 4.2.5      | Latence de l'adaptateur par rapport à l'utilisation directe de l'IPIF ..... | 87 |

| 4.3        | Latence des communications entre le matériel et le logiciel .....           | 87 |

| 4.3.1      | Considération sur la taille des mémoires .....                              | 88 |

|       |                                                                                     |     |

|-------|-------------------------------------------------------------------------------------|-----|

| 4.3.2 | Méthode de mesure du temps d'exécution en logiciel.....                             | 88  |

| 4.3.3 | Communication du matériel vers le logiciel .....                                    | 89  |

| 4.3.4 | Communication du logiciel vers le matériel .....                                    | 95  |

| 4.3.5 | Communication du logiciel vers le logiciel .....                                    | 97  |

| 4.3.6 | Proposition d'un nouveau concept pour les communications<br>matériel-logiciel ..... | 99  |

| 4.4   | La profondeur des FIFO d'envoi et de réception.....                                 | 104 |

| 4.5   | Utilisation des ressources et fréquence maximale .....                              | 105 |

| 4.5.1 | Cas de l'adaptateur d'un module matériel .....                                      | 105 |

| 4.6   | Remarques générales .....                                                           | 109 |

|       | Conclusion et travaux futurs .....                                                  | 112 |

|       | Références.....                                                                     | 115 |

|       | ANNEXES .....                                                                       | 120 |

## Liste des tableaux

|               |                                                                                                                                 |     |

|---------------|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 2. 1  | Correspondances entre les appels SystemC et ceux de MicroC-OS II .....                                                          | 39  |

| Tableau 2. 2  | Arguments des fonctions de communications .....                                                                                 | 43  |

| Tableau 2. 3  | Génération d'une adresse à partir d'un identificateur.....                                                                      | 49  |

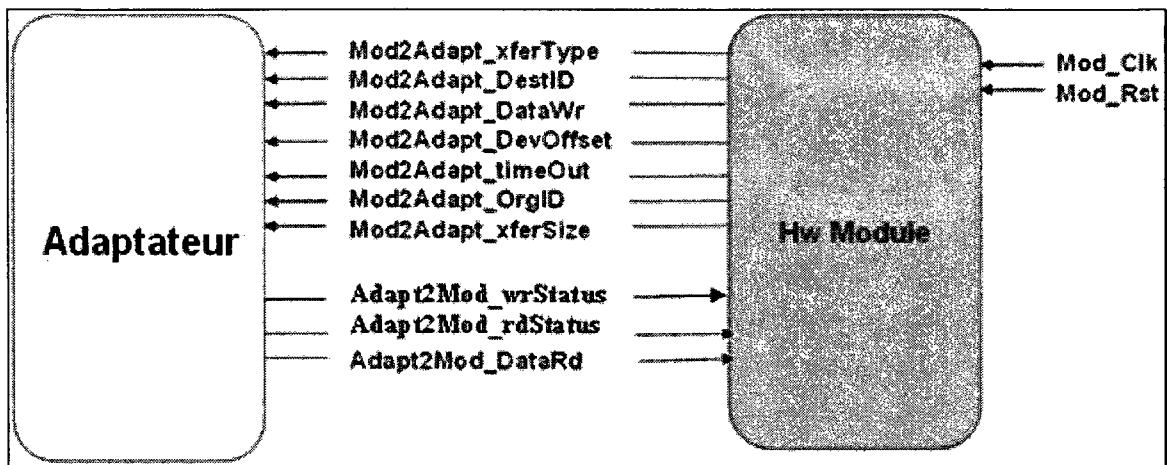

| Tableau 3. 1  | Description des signaux de l'interface d'un module matériel.....                                                                | 57  |

| Tableau 3. 2  | Types de requêtes d'un module matériel au niveau RTL .....                                                                      | 59  |

| Tableau 3. 3  | Statut d'une requête d'un module matériel au niveau RTL.....                                                                    | 59  |

| Tableau 3. 4  | Encodage de l'adresse de lecture locale de l'IPIF .....                                                                         | 66  |

| Tableau 4. 1  | Sommaire des latences de communication de l'adaptateur version 1.....                                                           | 84  |

| Tableau 4. 2  | Sommaire des latences de communication de l'adaptateur version no 2..                                                           | 86  |

| Tableau 4. 3  | Latences de communication entre le matériel et le logiciel, composante<br>HwSwCom version 1, adaptateur matériel version 1..... | 92  |

| Tableau 4. 4  | Latences de communication entre le matériel et le logiciel, composante<br>HwSwCom version 2, adaptateur matériel version 1..... | 94  |

| Tableau 4. 5  | Latences des communications logiciel- matériel avec utilisation de Space<br>.....                                               | 97  |

| Tableau 4. 6  | Latences des communications logiciel- matériel sans utilisation de Space<br>.....                                               | 97  |

| Tableau 4. 7  | Latences des communications logiciel-logiciel .....                                                                             | 98  |

| Tableau 4. 8  | Sommaire des latences de transfert des données entre la composante<br>HwSwCom et le logiciel .....                              | 103 |

| Tableau 4. 9  | Latences de lecture d'un message à partir de la composante HwSwCom,<br>version améliorée .....                                  | 103 |

| Tableau 4. 10 | Utilisation des ressources et fréquence maximale pour l'adaptateur<br>matériel (Virtex 2P VP30) .....                           | 106 |

| Tableau 4. 11 | Ressources utilisées par l'adaptateur matériel en fonction de la profondeur<br>de la FIFO de réception (Virtex 2P VP30) .....   | 107 |

|                                                                                                                                |     |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 4. 12 Ressources utilisées par l'adaptateur matériel en fonction du nombre de FIFO de réception (Virtex 2P VP30) ..... | 108 |

| Tableau C. 1 Encodage de l'adresse de destination par l'IPIF .....                                                             | 126 |

## Liste des figures

|              |                                                                                              |    |

|--------------|----------------------------------------------------------------------------------------------|----|

| Figure 1. 1  | Les différents niveaux de raffinement d'un modèle TLM .....                                  | 7  |

| Figure 1. 2  | Transaction de lecture par un DMA vers une mémoire au niveau TLM.....                        | 8  |

| Figure 1. 3  | Flot de conception classique de SoC .....                                                    | 11 |

| Figure 1. 4  | Flot de conception de SoC au niveau système .....                                            | 13 |

| Figure 1. 5  | Architecture type d'un bus pour un SoC .....                                                 | 18 |

| Figure 1. 6  | Canal, ports et interfaces du modèle SHIP .....                                              | 22 |

| Figure 1. 7  | Flot de conception proposé dans [3].....                                                     | 23 |

| Figure 1. 8  | Le modèle raffiné proposé dans [3].....                                                      | 23 |

| Figure 1. 9  | Architecture d'un wrapper tel que proposé dans [3] .....                                     | 24 |

| Figure 1. 10 | Hw/Sw adaptateur tel que proposé par [3] .....                                               | 25 |

| Figure 1. 11 | Le modèle obtenu après synthèse tel que proposé par [3].....                                 | 25 |

| Figure 1. 12 | Architecture de SoC, composée d'un processeur principal et des processeurs spécialisés ..... | 26 |

| Figure 2. 1  | Architecture de la librairie SystemC .....                                                   | 29 |

| Figure 2. 2  | Exemple simple d'une bascule D en SystemC .....                                              | 34 |

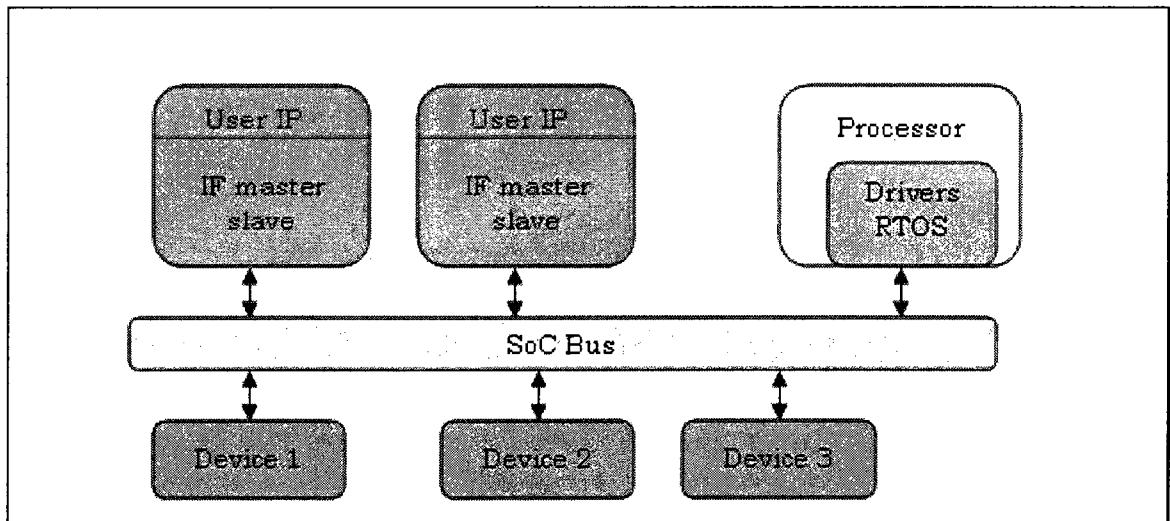

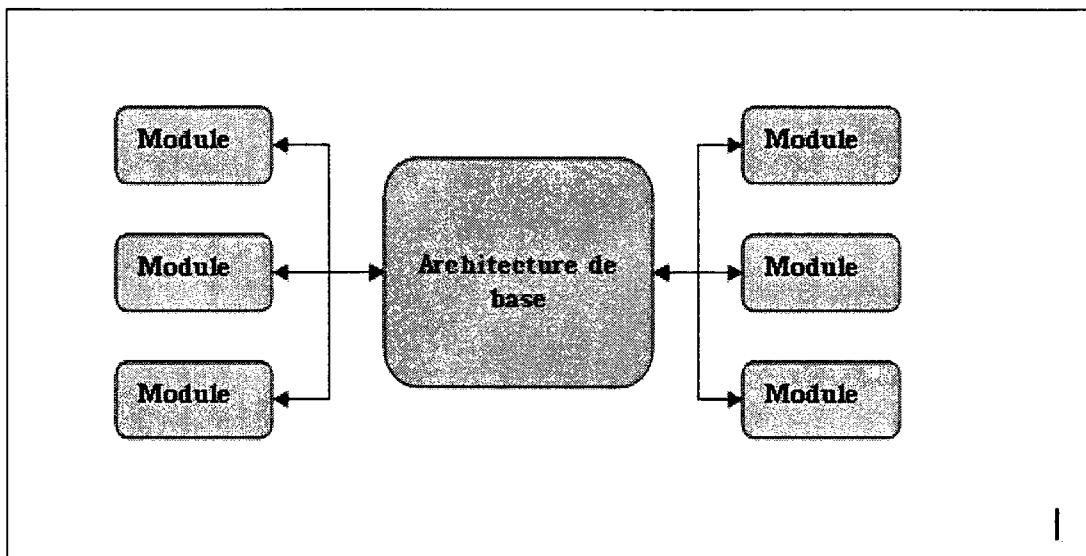

| Figure 2. 3  | Vue d'ensemble d'un système conçu avec Space .....                                           | 36 |

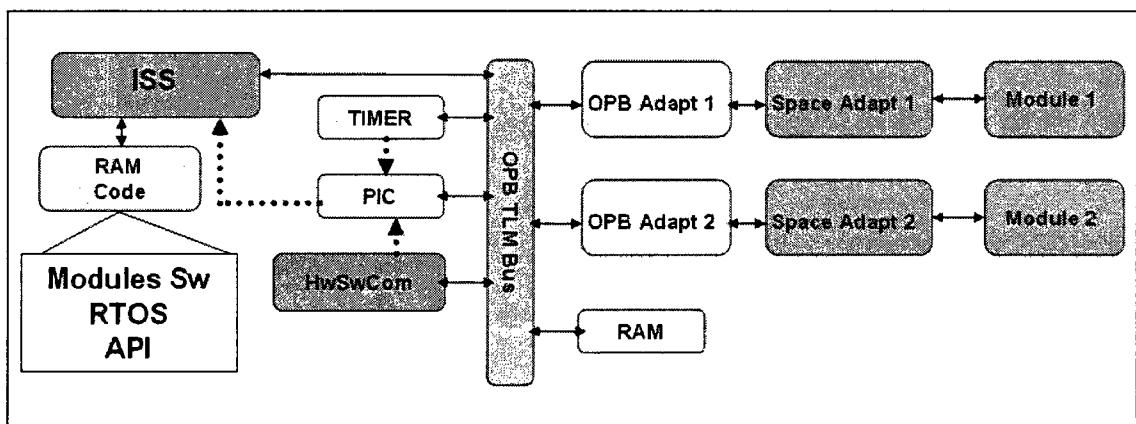

| Figure 2. 4  | Architecture de base au niveau de raffinement BCA de Space.....                              | 38 |

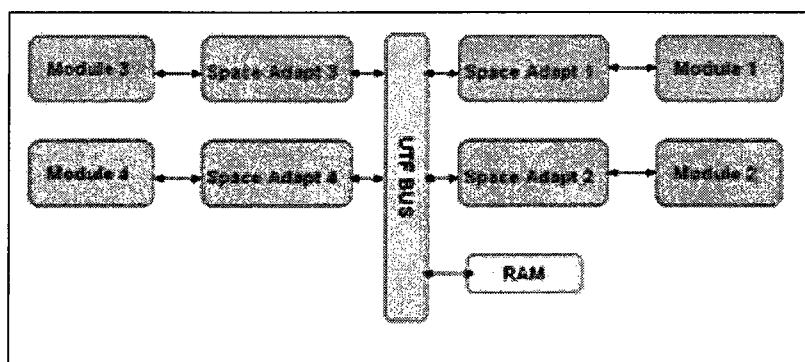

| Figure 2. 5  | Un système composé de quatre modules au niveau UTF.....                                      | 41 |

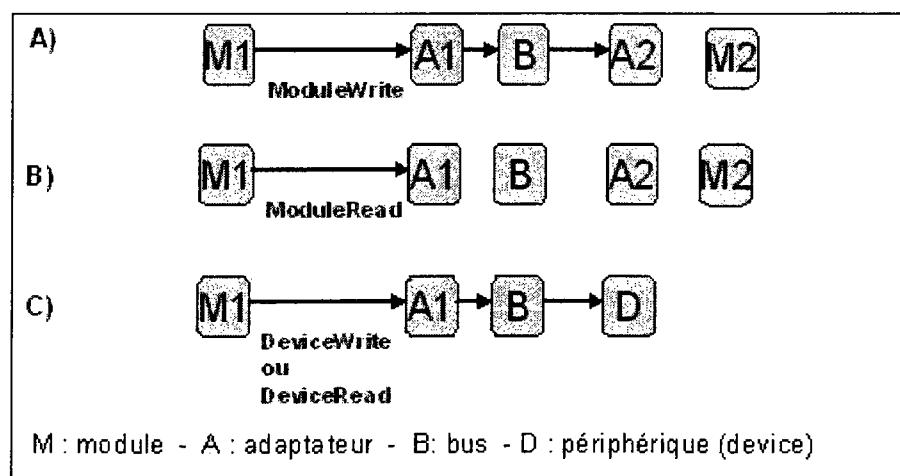

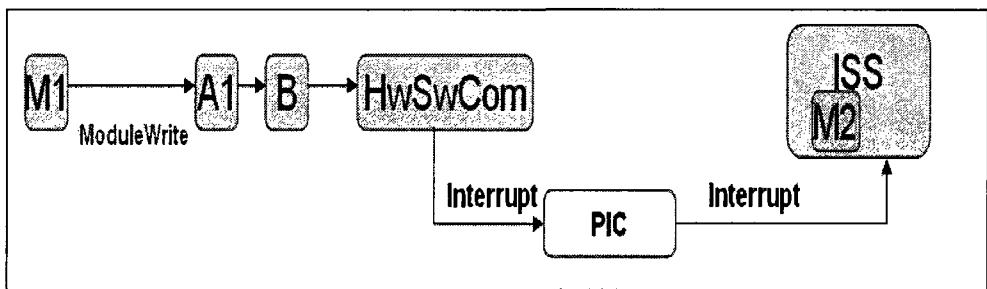

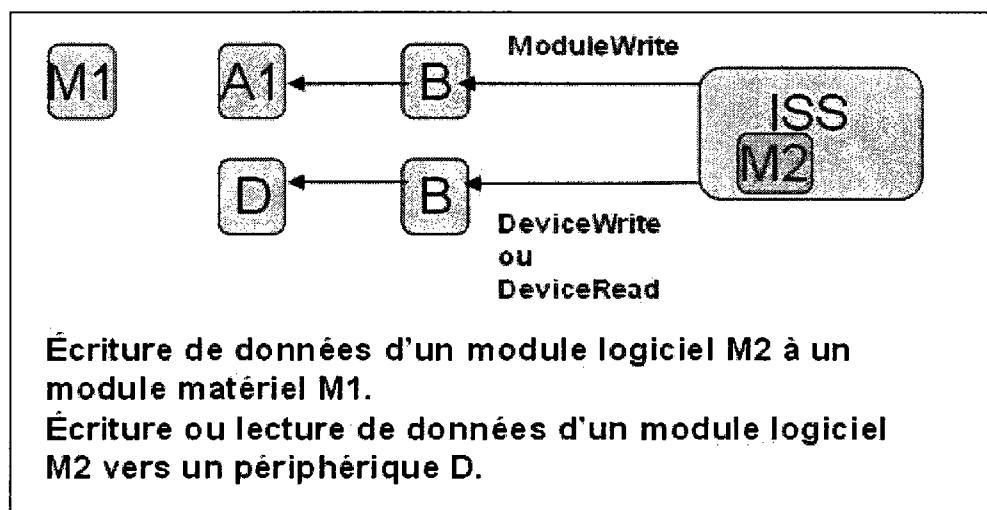

| Figure 2. 6  | Illustration de la communication de matériel à matériel .....                                | 44 |

| Figure 2. 7  | Illustration de la communication de matériel à logiciel .....                                | 45 |

| Figure 2. 8  | Illustration de la communication du logiciel au matériel .....                               | 46 |

| Figure 2. 9  | Format de l'en-tête d'un message.....                                                        | 48 |

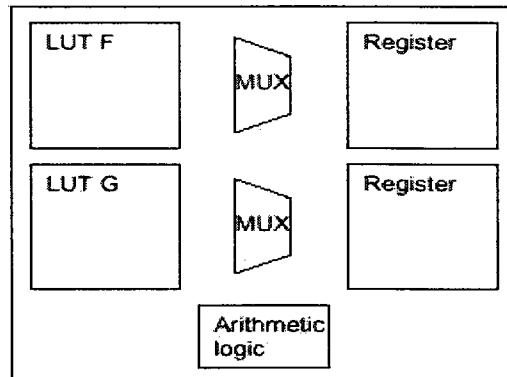

| Figure 3. 1  | Slice d'un CLB. FPGA Virtex-II.....                                                          | 53 |

| Figure 3. 2  | Méthodologie de raffinement d'un système conçu avec Space.....                               | 54 |

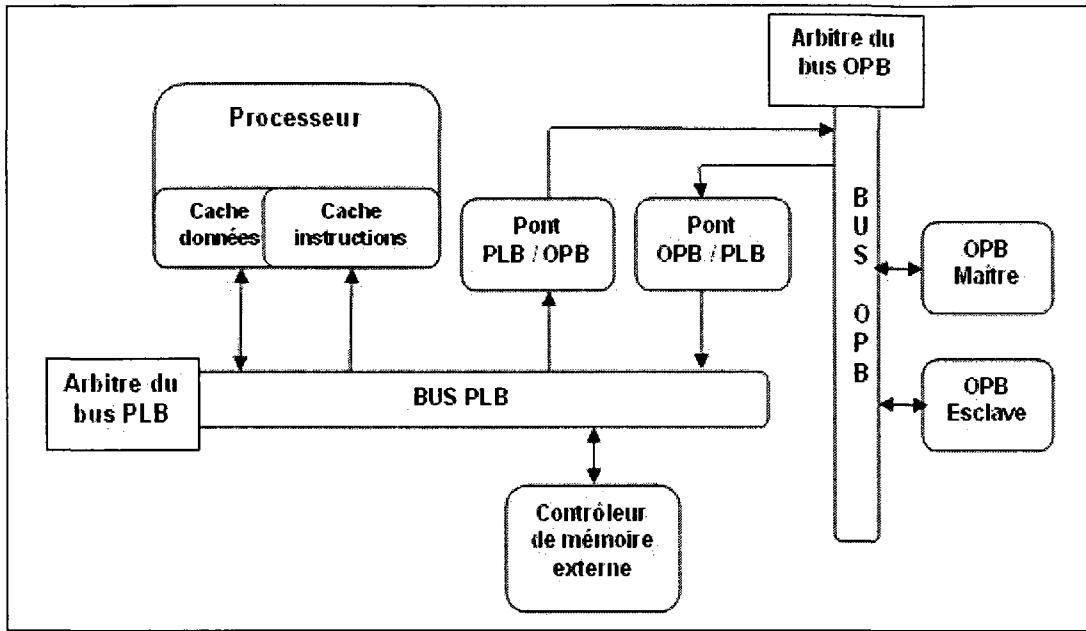

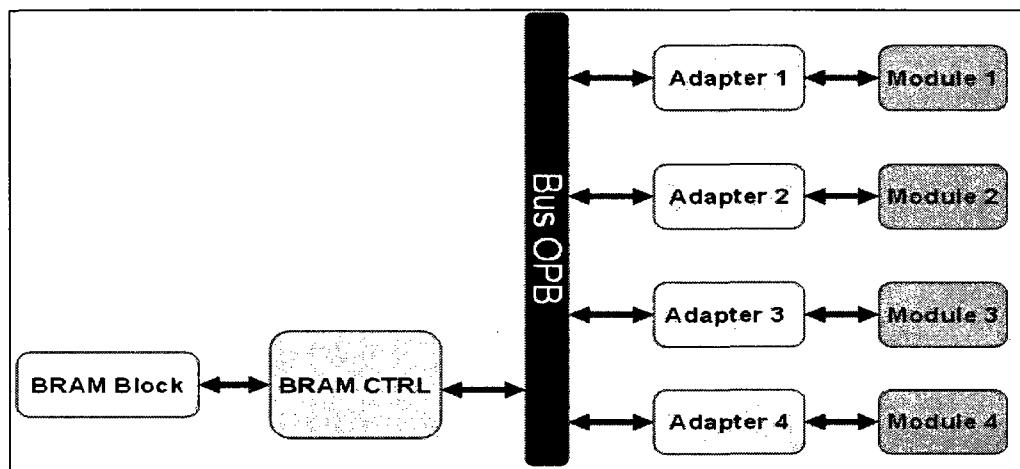

| Figure 3. 3  | Architecture type basée sur le standard CoreConnect de IBM.....                              | 55 |

| Figure 3. 4  | Interface entre un module matériel et son adaptateur au niveau RTL.....                      | 57 |

|                                                                                                      |     |

|------------------------------------------------------------------------------------------------------|-----|

| Figure 3. 5 Écriture d'un module matériel à un autre module au niveau RTL .....                      | 61  |

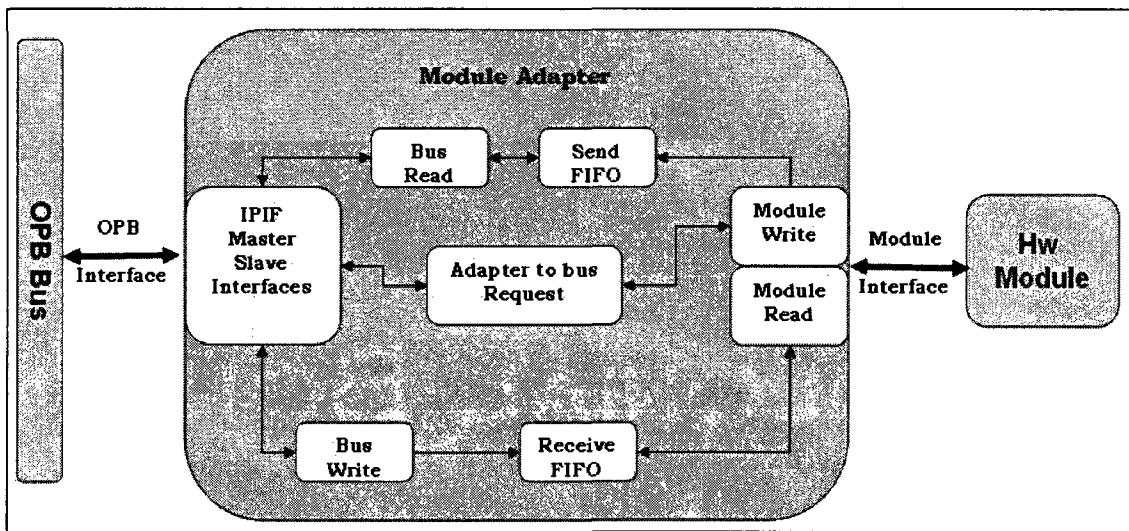

| Figure 3. 6 Schéma de principe d'un adaptateur pour un module matériel .....                         | 62  |

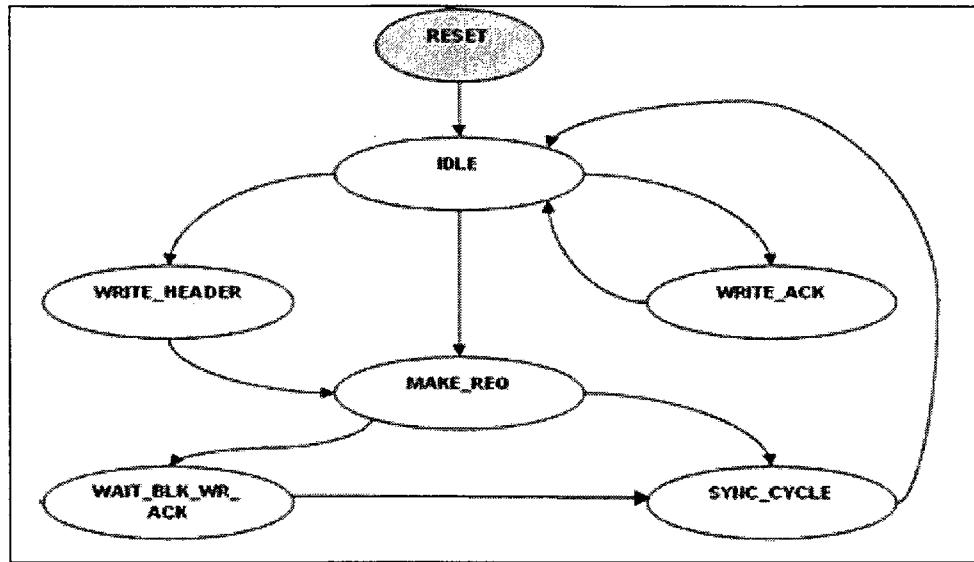

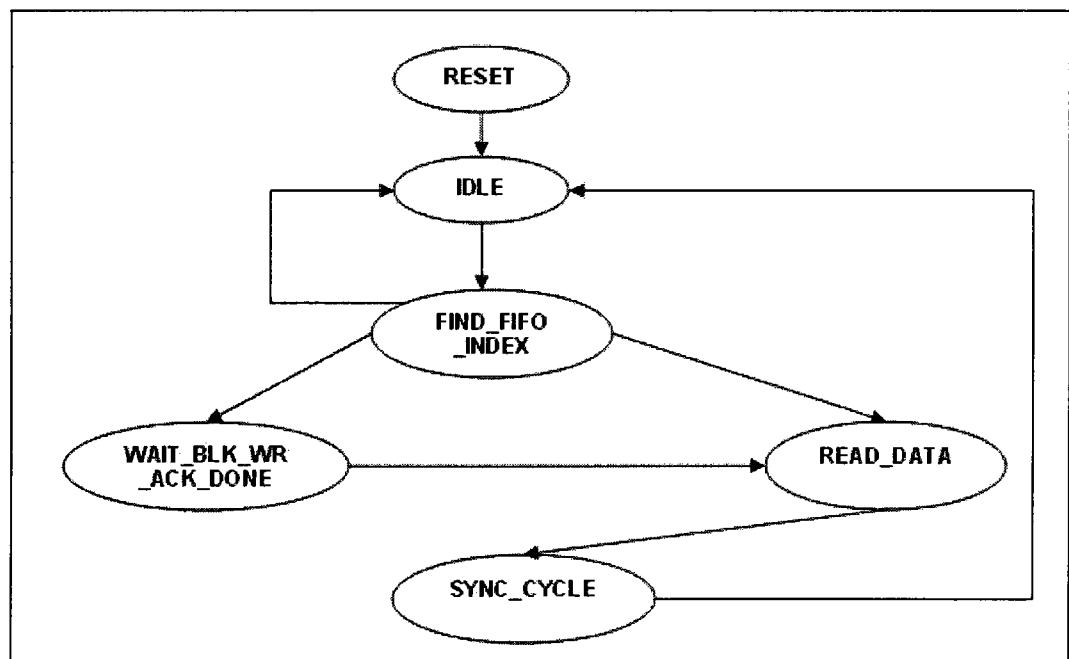

| Figure 3. 7 Diagramme d'états simplifié de l'entité « Adapter to bus Request ».....                  | 64  |

| Figure 3. 8 Pseudo-code pour allouer une FIFO.....                                                   | 67  |

| Figure 3. 9 Diagramme d'états simplifié de l'entité « Module Read ».....                             | 69  |

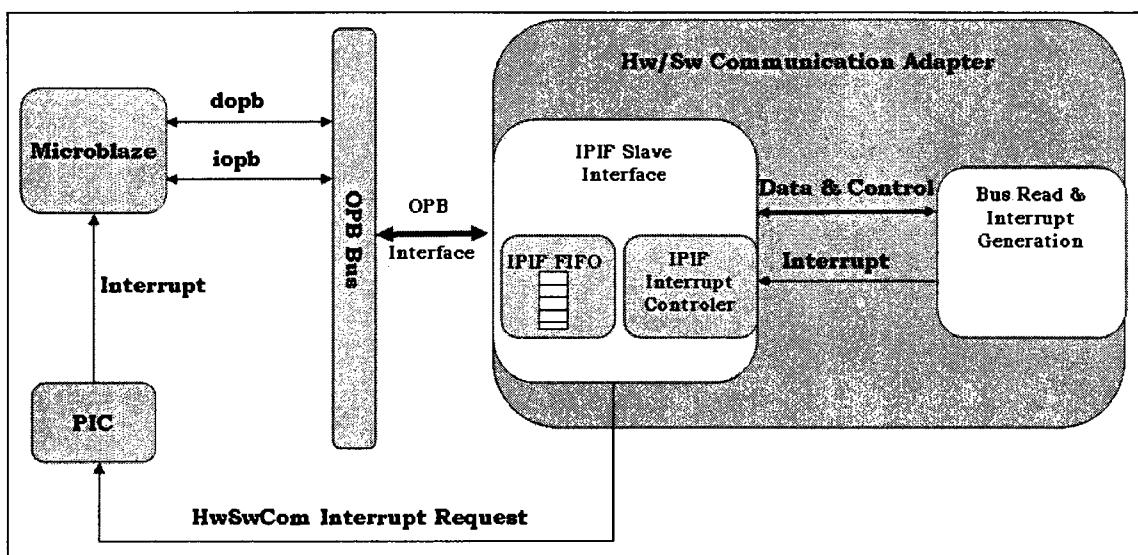

| Figure 3. 10 Schéma bloc de l'adaptateur des communications matériel/logiciel.....                   | 70  |

| Figure 4. 1 Modification de l'IPIF de Xilinx (cas du transfert en rafale).....                       | 75  |

| Figure 4. 2 Application d'illustration des latences de communication matérielle.....                 | 76  |

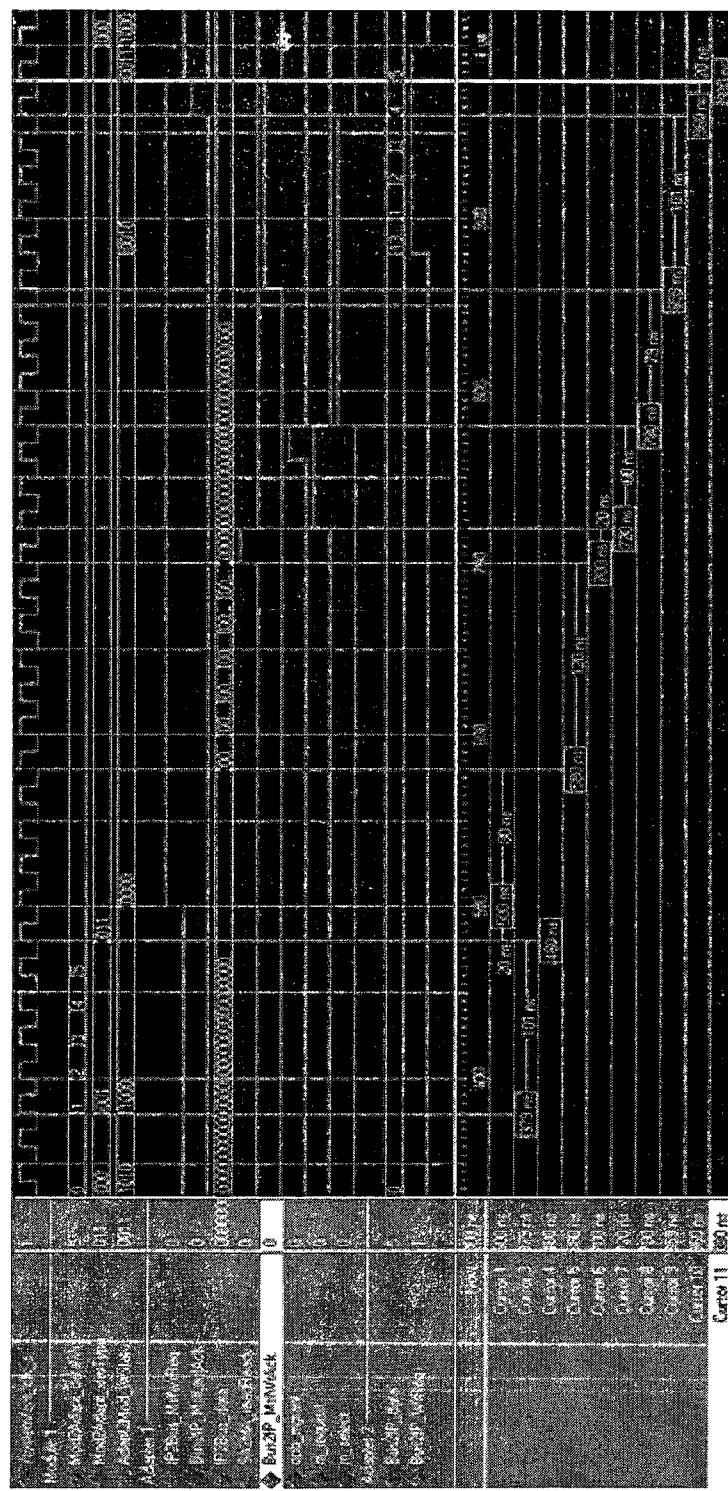

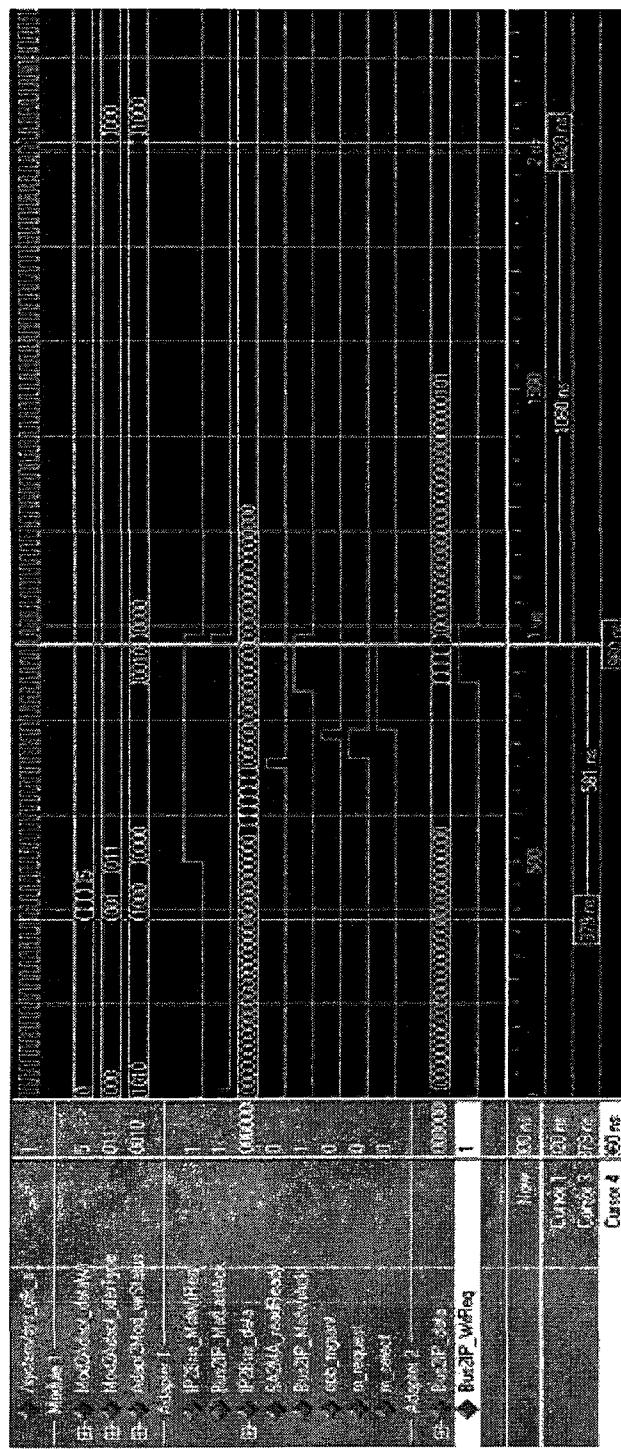

| Figure 4. 3 Trace de simulation de l'écriture non bloquante ... .....                                | 77  |

| Figure 4. 4 Trace de simulation de l'écriture bloquante ... .....                                    | 78  |

| Figure 4. 5 Mesure du temps d'exécution d'une section de code logiciel.....                          | 89  |

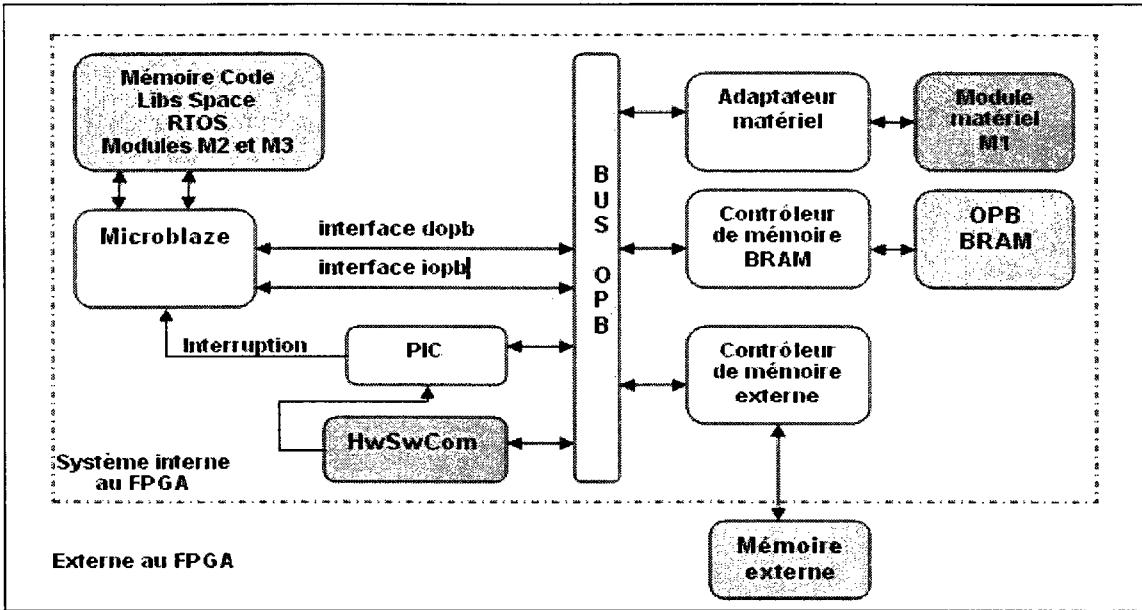

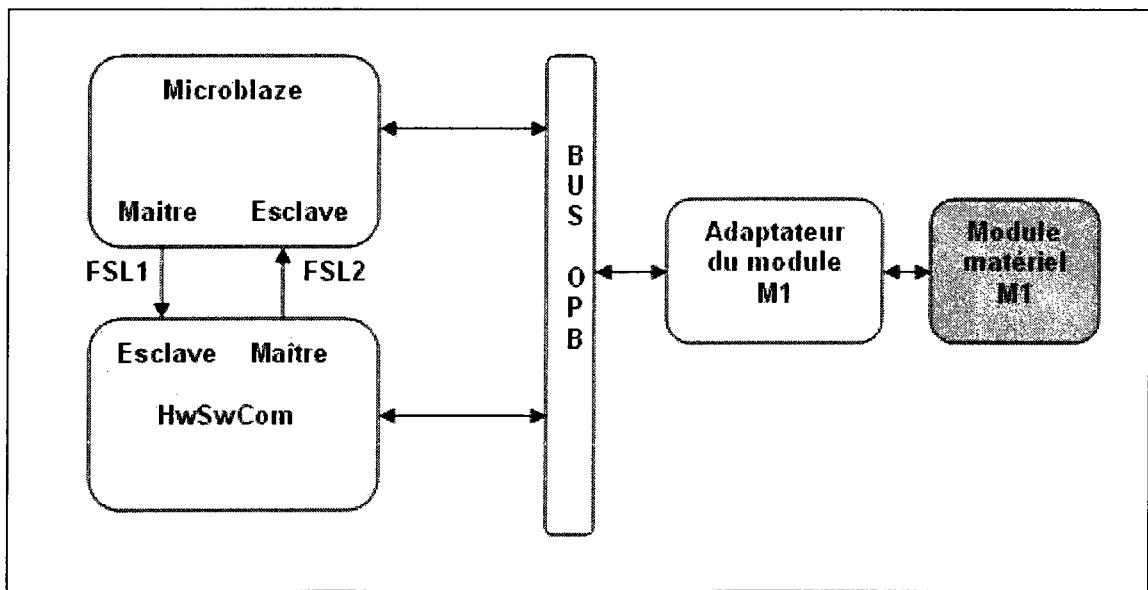

| Figure 4. 6 Système utilisé pour déterminer les latences de communication<br>matériel-logiciel ..... | 91  |

| Figure 4. 7 Adaptateur des communications matériel-logiciel, version FSL .....                       | 100 |

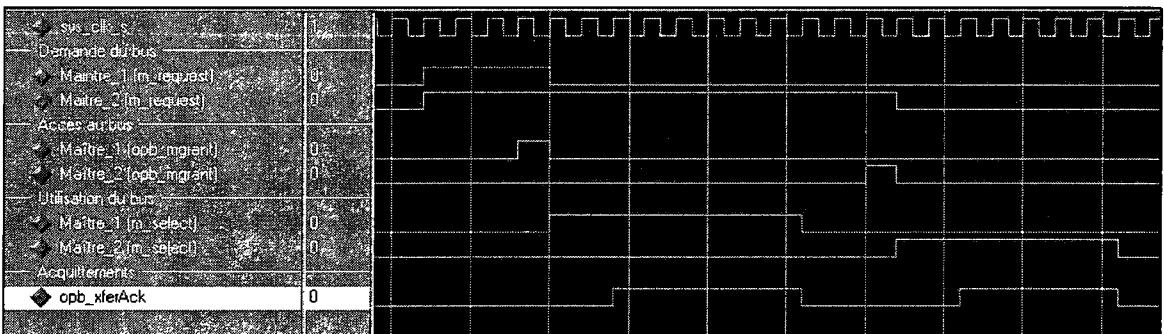

| Figure A. 1 Illustration de la demande d'accès au bus OPB par deux maîtres.....                      | 122 |

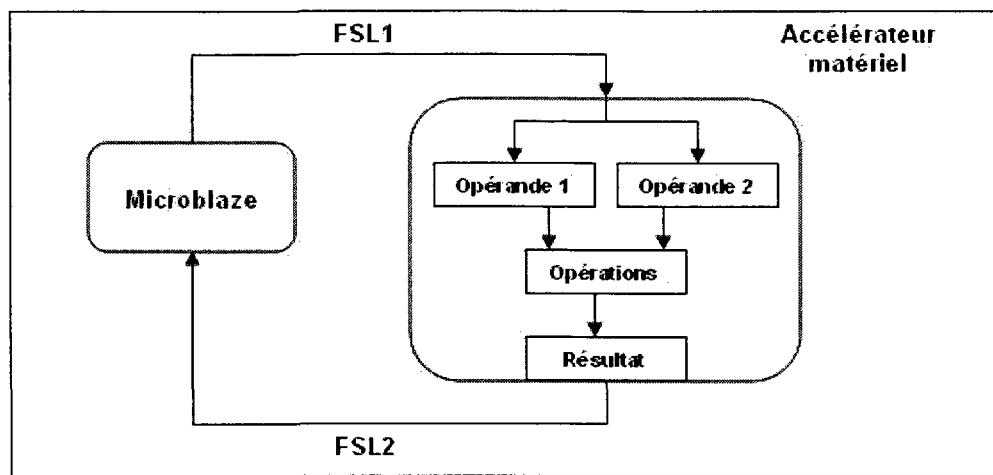

| Figure B. 1 Exemple d'accélérateur matériel connecté au Microblaze par FSL .....                     | 124 |

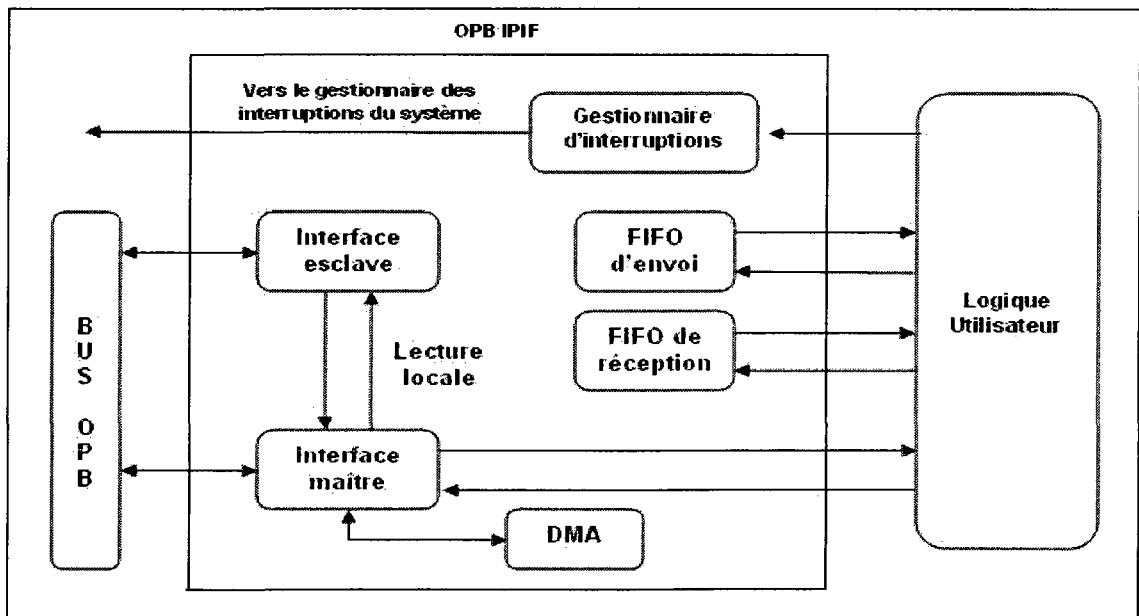

| Figure C. 1 Schéma bloc de l'IPIF maître/esclave .....                                               | 125 |

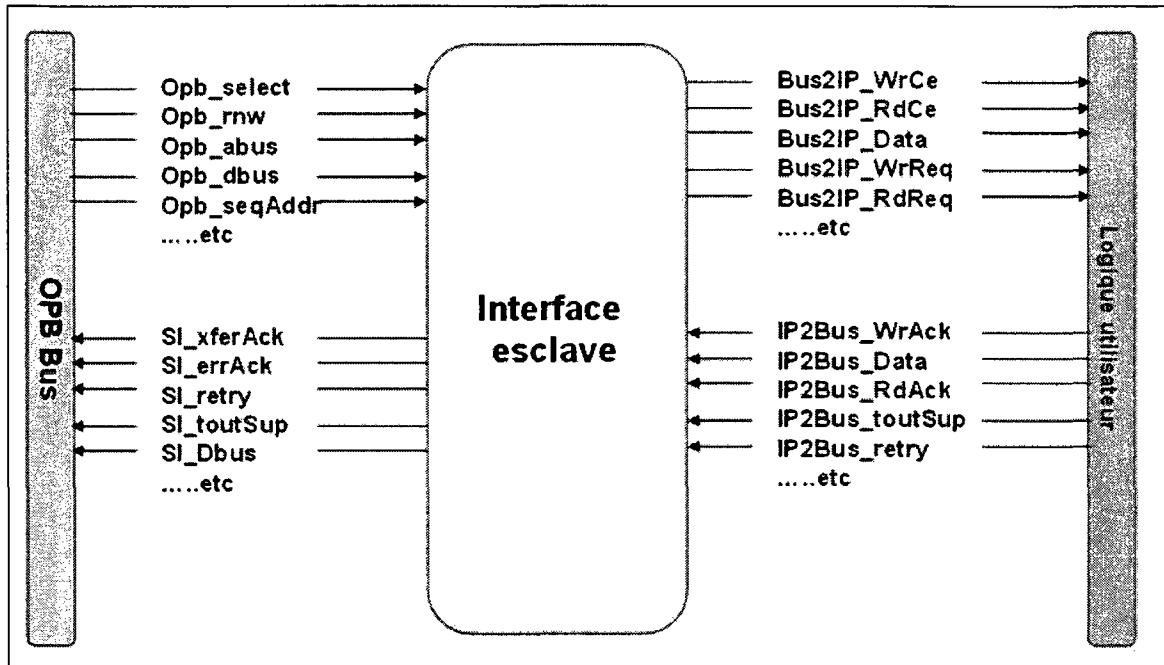

| Figure C. 2 Interface esclave de l'IPIF .....                                                        | 127 |

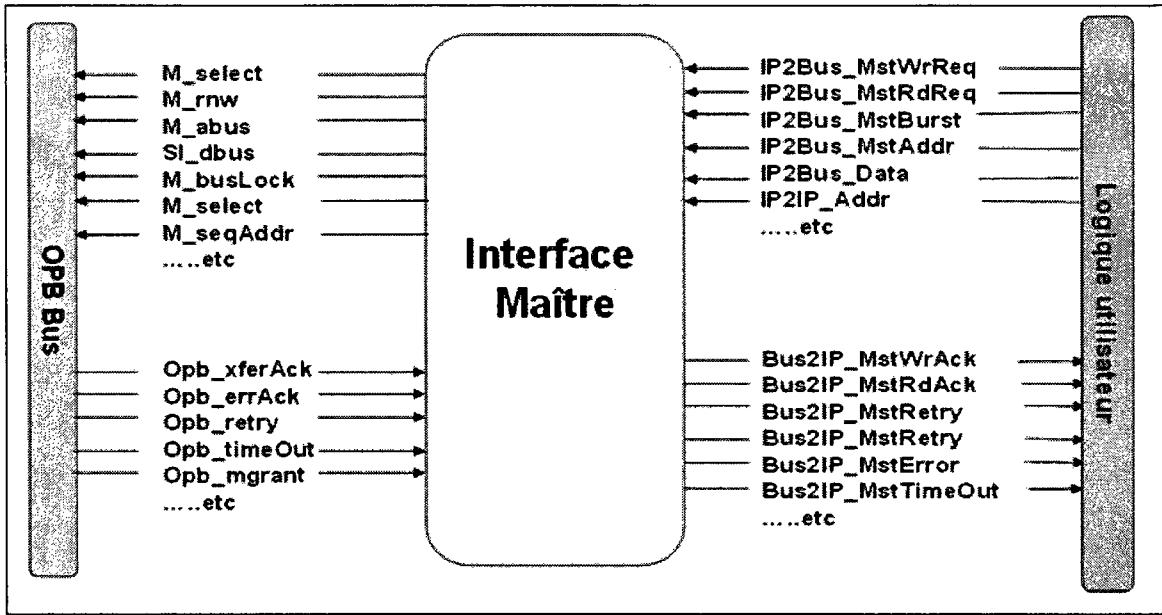

| Figure C. 3 Interface maître de l'IPIF.....                                                          | 128 |

## Liste des acronymes

|              |                                           |

|--------------|-------------------------------------------|

| <b>AHB</b>   | Advanced High-performance Bus             |

| <b>AMBA</b>  | Advanced Microcontroller Bus Architecture |

| <b>API</b>   | Application Programming Interface         |

| <b>BCA</b>   | Bus Cycle Accurate                        |

| <b>BRAM</b>  | Block RAM                                 |

| <b>DDR</b>   | Double Data Rate                          |

| <b>DMA</b>   | Direct Memory Access                      |

| <b>DSOCM</b> | Data Side OCM                             |

| <b>EDK</b>   | Embedded Development Kit                  |

| <b>ESL</b>   | Electronic System Level                   |

| <b>FIFO</b>  | First In First Out                        |

| <b>FPGA</b>  | Field Programmable Gate Array             |

| <b>IP</b>    | Intellectual Property                     |

| <b>IPIF</b>  | IP InterFace                              |

| <b>ISS</b>   | Instruction Set Simulator                 |

| <b>LUT</b>   | Look Up Table                             |

| <b>OCM</b>   | On Chip Memory                            |

| <b>OCP</b>   | Open Core Protocol                        |

| <b>OPB</b>   | On Chip Periphal Bus                      |

| <b>OSCI</b>  | Open SystemC Initiative                   |

| <b>PIC</b>   | Programmable Interrupt Controller         |

| <b>PLB</b>   | Processor Local Bus                       |

| <b>RAM</b>   | Random Access Memory                      |

| <b>RTL</b>   | Register Transfer Level                   |

| <b>RTOS</b>  | Real-Time Operating System                |

| <b>SDRAM</b> | Synchronous Dynamic RAM                   |

| <b>SHIP</b>  | SystemC High-Level Interface Protocol     |

|             |                                                                         |

|-------------|-------------------------------------------------------------------------|

| <b>SoC</b>  | <b>System On Chip</b>                                                   |

| <b>SRAM</b> | <b>Static RAM</b>                                                       |

| <b>TF</b>   | <b>Timed Functional</b>                                                 |

| <b>TLM</b>  | <b>Transactional Level Modeling</b>                                     |

| <b>UART</b> | <b>Universal Asynchronous Receiver Transmitter</b>                      |

| <b>UTF</b>  | <b>Untimed Functional</b>                                               |

| <b>VHDL</b> | <b>Very High Speed Integrated Circuit Hardware Description Language</b> |

| <b>XPS</b>  | <b>Xilinx Platform Studio</b>                                           |

| <b>ZBT</b>  | <b>Zero-Bus Turnaround</b>                                              |

## Liste des Annexes

|                 |                                             |     |

|-----------------|---------------------------------------------|-----|

| <b>ANNEXE A</b> | Description de l'interface du bus OPB ..... | 119 |

| <b>ANNEXE B</b> | Description du processeur Microblaze .....  | 122 |

| <b>ANNEXE C</b> | Description de l'IPIF maître/esclave .....  | 124 |

## Introduction

La complexité des circuits à concevoir, en particulier pour les SoC augmente rapidement avec l'augmentation de la densité d'intégration [1]. Les données à traiter au niveau RTL augmentent de manière exponentielle, d'où la nécessité d'élever le niveau d'abstraction lors de la conception de tels circuits.

Une récente étude [1] menée par la Société du marché Internationale Business Stratégies auprès des ingénieurs de conception des SoC, montre que le développement du logiciel prend une part de plus en plus importante dans l'effort global de conception des SoC. Il devient donc important de démarrer le développement du logiciel en même temps que celui du matériel.

Le TLM (Transaction Level Modeling) permet d'augmenter le niveau d'abstraction de la conception des SoC. Il consiste à modéliser uniquement les échanges de données entre les différents modules d'une architecture du système à concevoir. À ce niveau le système peut être divisé en partitions logicielles et /ou matérielles et simulé sur une plate-forme au sein de laquelle les différentes composantes du système échangent des données via des médiums de communication (e.g. de type bus).

L'objectif principal du TLM est de représenter le comportement global du système à concevoir, en mettant l'accent sur l'échange de données et en ne se souciant pas des détails au niveau signaux.

De plus en plus de compagnies dans le domaine de conception des systèmes numériques et des systèmes embarqués, développent des outils de conception [1], de vérification et même de synthèse pour la conception au niveau système. Toutefois, de nos jours il existe encore des réticences [1] vis-à-vis ces outils. Les raisons sont prétendument techniques, liées à la maturité de ces outils, ou encore dues à la résistance au changement et à la protection d'un savoir faire accumulé depuis plusieurs années.

## Problématique

L'utilisation des langages de programmation et de plates-formes à haut niveau d'abstraction pour la conception d'un système destiné à l'implémentation sur une puce permettent au concepteur de valider son système et ses choix architecturaux de manière plus rapide que de travailler directement au niveau RTL. Contrairement à l'approche traditionnelle qui consistait à concevoir un prototype RTL et à démarrer ensuite la conception du logiciel, désormais les concepteurs peuvent travailler sur une spécification commune du logiciel et du matériel.

Une fois le système validé à haut niveau, il faut l'implémenter physiquement. Idéalement, le concepteur devra disposer d'outils qui lui permettent de passer automatiquement d'une spécification de haut niveau vers la synthèse de son application sur l'architecture cible. Or, plusieurs plates-formes de conception à haut niveau utilisent des spécifications basées sur des langages (e.g. SystemC TLM et System Verilog) qui ne peuvent pas être synthétisées totalement.

La plate-forme Space Codesign™ (abrégé par Space) est une plate-forme basée sur SystemC. Elle est développée au sein du laboratoire de codesign de l'École Polytechnique de Montréal. Elle permet la conception et la simulation des systèmes à haut niveau, fournit plusieurs IP standards en SystemC afin d'augmenter la réutilisation, fournit le support d'un RTOS au niveau du logiciel d'un simulateur de niveau jeu d'instructions (ISS) pour simuler le logiciel, et fournit un modèle TLM pour une architecture de bus standard à savoir le bus OPB.

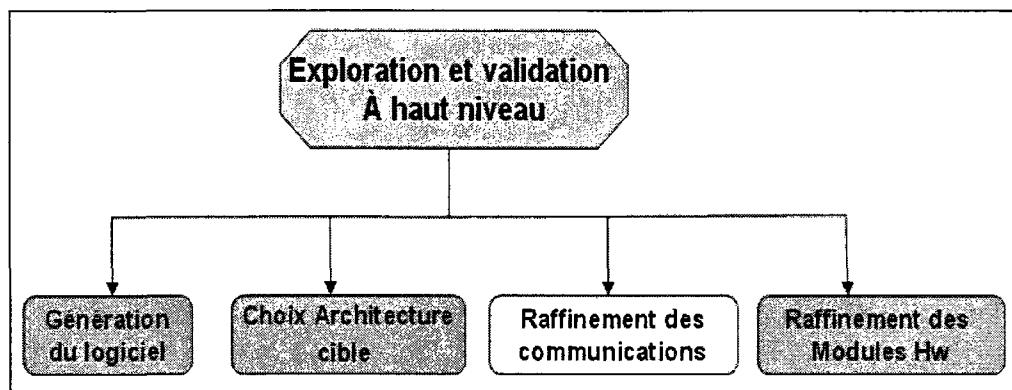

Toutefois, pour étendre la méthodologie de conception de Space jusqu'à l'implémentation physique, il faut pouvoir assurer une génération (semi-automatique) des composantes suivantes : exécutable du logiciel sur le processeur embarqué, architecture cible au niveau de la puce, modules matériels de l'application, et interfaces de communication entre le logiciel et le matériel.

## Objectif du travail

Nous travail consiste à proposer une méthode pour passer d'une spécification basée sur le niveau TLM vers l'implémentation physique sur puce en utilisant l'architecture cible. Cet objectif se divise à son tour en 3 objectifs secondaires :

- 1) Conception d'un adaptateur d'un module matériel lui permettant de connecter à un bus d'une architecture standard.

- 2) Conception d'un adaptateur pour assurer les communications entre le matériel et le logiciel.

- 3) Génération du code exécutable pour la partition logicielle.

## Méthodologie

Nous utiliserons deux technologies pour réaliser nos objectifs :

- 1) La technologie Space qui inclut un niveau TLM et un mécanisme de communication par échanges de messages, à partir desquels nous procéderons au raffinement.

- 2) La technologie Virtex2 Pro de Xilinx qui inclut le processeur MicroBlaze et le standard de bus OPB de CoreConnect.

Par conséquent, nous procéderons à la conception et à l'implémentation : 1) d'un adaptateur pour un module matériel et 2) d'un adaptateur pour la communication entre partitions. Ceci permettra d'une part d'envoyer et recevoir des données à travers le bus OPB en utilisant le protocole de communication et ainsi d'assurer les différents types de communication requis : 1) communication logiciel/logiciel (e.g. deux partitions logicielles sur un même processeur), 2) logiciel/matériel (e.g. entre un processeur et un coprocesseur) et 3) matériel/matériel (e.g. entre deux coprocesseurs distincts)<sup>1</sup>. Finalement, nous procéderons à la génération du logiciel qui sera compilé et exécuté à bas niveau par le processeur embarqué, avec le minimum voire aucune modification par rapport au logiciel exécuté sur l'ISS du processeur au niveau TLM. Notez que la

---

<sup>1</sup> La communication matériel/matériel sur un même coprocesseur est pour l'instant impossible dans Space, puisque l'on suppose un processus par coprocesseur.

génération matérielle à partir d'une description comportementale ne fait pas l'objet de ce travail. Nous supposerons que cette génération se fait manuellement ou se fait à l'aide d'un outil d'un tiers. C'est d'ailleurs pour cette raison que nous utiliserons dans ce travail le terme *génération semi-automatique* plutôt que *génération automatique*.

## Contribution

Trois niveaux de spécification d'un système sont actuellement possible dans Space. Ces niveaux vont de la vérification fonctionnelle jusqu'à la validation au cycle près (BCA de l'anglais *Bus Cycle Accurate*) du système à concevoir. Notre travail permettra l'ajout d'un niveau d'abstraction qui est celui du RTL et d'une passerelle semi-automatique pour passer du niveau BCA au niveau RTL. Ce dernier étant beaucoup plus proche de l'implémentation que le niveau BCA, nous pourrons aussi valider la précision de notre modèle TLM (e.g. au niveau des latences prises en compte).

Enfin, notre travail permet de définir les bases d'un travail futur de passage complètement automatique d'une spécification TLM vers une implémentation physique et la possibilité d'utiliser des outils commerciaux capables de synthétiser du SystemC TLM, ou d'effectuer une conversion vers un langage HDL synthétisable.

## Distribution des chapitres

Ce travail est organisé en quatre chapitres. Le chapitre 1 présente quelques concepts de la méthodologie de codesign, ainsi que la revue des travaux de raffinement des systèmes numériques conçus à haut niveau. Le chapitre 2 introduit brièvement SystemC, puis décrit les niveaux de raffinements et le protocole de communication de la plate-forme Space. Le chapitre 3 présente en détail l'implémentation à bas niveau de l'adaptateur d'un module matériel, l'implémentation de l'adaptateur qui gère les communications entre le matériel et le logiciel, et l'interface entre un module matériel et son adaptateur. Le chapitre 4 présente les résultats obtenus des latences de communications (permettant du même coup de valider l'exactitude du modèle TLM), des ressources matérielles

utilisées par les adaptateurs de communication, et un exemple de vérification du fonctionnement du protocole de communication de Space à bas niveau.

# Chapitre 1      Revue du raffinement des communications pour systèmes sur puce

Un système embarqué peut être composé de partitions logicielles et/ou matérielles. La méthodologie de conception employée devrait assurer des mécanismes de communications entre les différentes composantes du système. Plusieurs modèles pour la communication sont possibles, et vont d'une communication point à point, jusqu'à une communication basée sur un réseau d'interconnexions (en anglais Network on chip). Ce chapitre présente l'approche de conception codesign. Nous nous intéressons aux étapes de génération d'un modèle du système au niveau RTL à partir d'un modèle conçu au niveau système. Plusieurs mécanismes de communication entre les parties logicielle et matérielle d'un SoC seront présentés. Par conséquent, nous parcourons quelques travaux de recherche et leurs approches pour le raffinement d'un système conçu à haut niveau vers une implémentation physique, en particulier nous mettons l'accent sur les techniques utilisées pour générer les interfaces de communication.

## 1.1 Le modèle TLM

Le modèle TLM décrit un système numérique complexe à un haut niveau d'abstraction. Il permet aux concepteurs d'explorer différentes architectures du système avant d'atteindre l'étape détaillée de l'implémentation finale du système sur une puce [32]. La vérification fonctionnelle est effectuée par des bancs d'essais (*testbenches*) basés sur les transactions de données.

Une transaction réfère à un échange d'une donnée entre deux composantes du système. Cette donnée peut être représentée par un mot, une série de mots, ou par une structure plus complexe [32]. Le modèle TLM, contrairement à d'autres modèles (e.g le modèle RTL) ne s'intéresse pas aux détails du protocole qui a permis d'effectuer la transaction.

Dans un modèle TLM, les détails de la communication sont séparés des détails de calcul. Les communications sont modélisées par des canaux, et les transactions ont lieu par l'appel des fonctions offertes par l'interface du canal en question [42].

Le modèle TLM est rapide à réaliser et à valider puisqu'il est moins détaillé qu'une réalisation complète du système au niveau RTL. Une fois ce modèle est finalisé, il pourra être raffiné progressivement vers le niveau RTL en y ajoutant plus de détails à chaque niveau de raffinement.

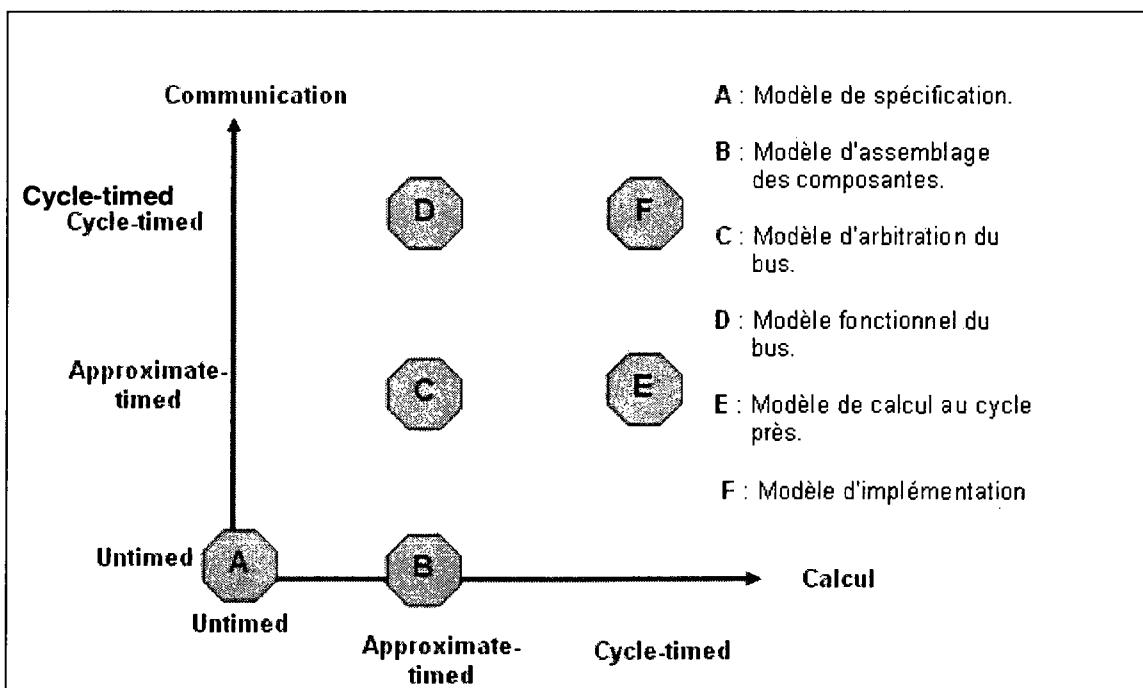

Selon la littérature, les niveaux d'abstraction diffèrent légèrement les uns des autres, mais en général, le premier niveau d'un modèle TLM permet de valider la fonctionnalité du système sans aucun détail sur la notion de temps, le deuxième niveau intègre la notion de temps pour simuler les délais que peuvent avoir certaines composantes du système durant une transaction, et un troisième niveau est détaillé au cycle près.

La figure 1.1 présente différents niveaux de raffinement d'un modèle TML tel que défini dans [42].

Figure 1.1 Les différents niveaux de raffinement d'un modèle TLM

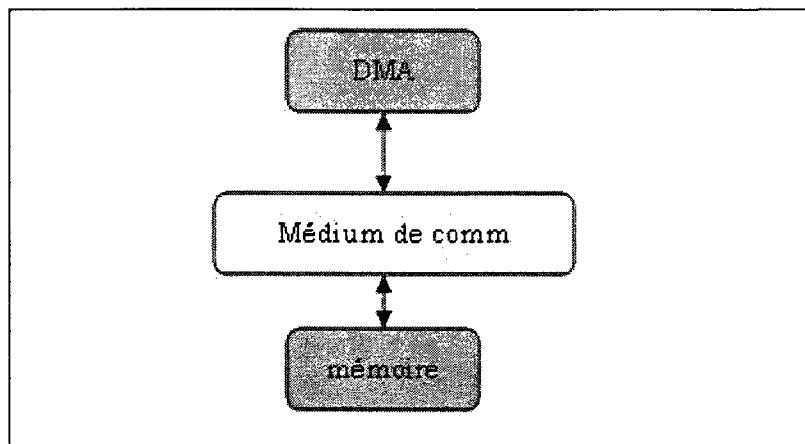

La figure 1.2 représente une requête de lecture d'une mémoire faite par un DMA dans un niveau d'abstraction TLM, elle pourra être vue comme une transaction de lecture en précisant simplement l'adresse de la mémoire à lire. Le DMA appelle une fonction *read* que le médium de communication implémente.

Figure 1.2 Transaction de lecture par un DMA vers une mémoire au niveau TLM

## 1.2 Les systèmes sur puce

### 1.2.1 Évolution

Les dernières années ont connu de grandes avancées en ce qui concerne la vitesse, la puissance et la complexité des circuits intégrés tels que les mémoires (RAM), les microprocesseurs et autres. L'évolution de la densité d'intégration a rendu possible la mise en œuvre des systèmes sur puce (SoC). Ces derniers sont construits en utilisant des modèles pré-conçus de fonctions complexes connues sous le nom de IP utilisées dans diverses applications. Un SoC intègre donc sur une même puce une combinaison de composantes IP de différentes fonctions telles des microprocesseurs, des mémoires, des contrôleurs de vidéo, modem, des contrôleurs 2D, des fonctions de DSP, etc.

L'avancement de la technologie des FPGA a permis de construire des SoC basés sur cette technologie dont la flexibilité de re-programmation permet de reconfigurer la puce avec l'ensemble de IP sélectionnées pour obtenir la fonctionnalité désirée.

La présence d'un processeur et de différentes composantes IP sur la même puce a permis le développement d'applications dont une partie est implémenté en matériel, et l'autre partie en logiciel. Le pourcentage d'utilisation du logiciel dans de telles applications dépend la nature de l'application, et ce pourcentage frôle les 35 % dans certains cas [1]. Certains noyaux de systèmes d'exploitation en temps réel ont été portés pour rouler sur les processeurs embarqués des SoC, permettant d'avoir un système multitâches en logiciel. Ceci permet donc de concevoir et d'implémenter des applications à temps réel pour des systèmes embarqués.

### 1.2.2 Approche de conception par codesign

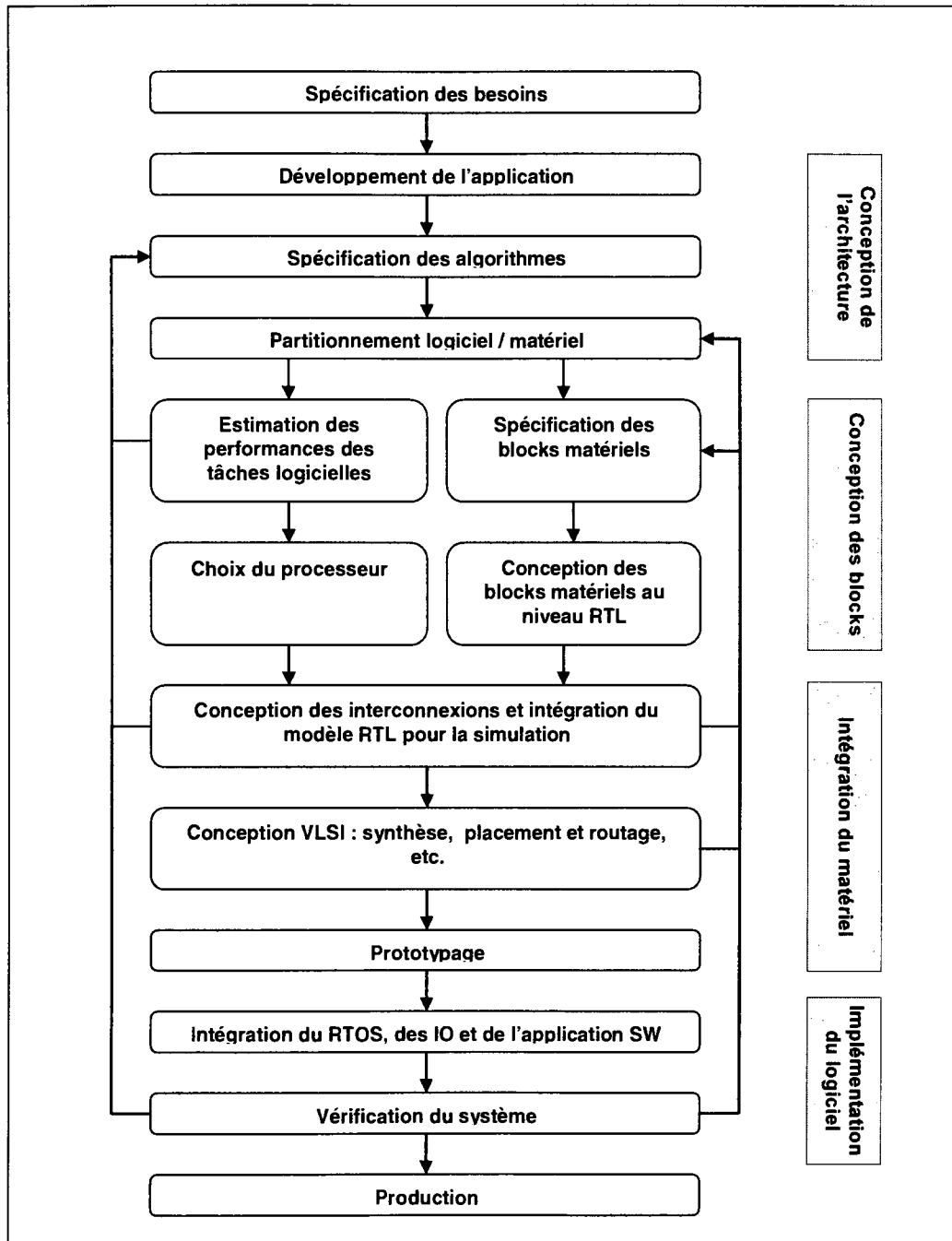

La méthode classique de conception des SoC, telle que présentée à la figure 1.3 [24], consiste à séparer le développement du logiciel et celui du matériel. Les partitions logicielles et matérielles sont décidées à l'avance, et des équipes de concepteurs travaillent séparément sur la spécification logicielle ou matérielle selon leurs spécialités.

Cette approche souffre des faiblesses suivantes

- Manque d'une spécification permettant une représentation unifiée du matériel et du logiciel, ce qui introduit des difficultés pour vérifier le système en entier.

- La complexité croissante des applications entraîne une augmentation considérable de la durée de développement.

- Possibles incompatibilités entre les frontières du logiciel et du matériel (interfaces).

- La configuration logicielle / matérielle choisie dès le début du flot de conception n'est pas toujours la plus optimale.

- Manque d'un flot de conception bien défini qui rend les spécifications (logicielle et matérielle) difficiles à réviser et peut augmenter le temps de mise en marché.

Pour pallier à ces faiblesses, de nouvelles méthodologies de conception sont recherchées. La conception au niveau système appelée conception conjointe logiciel/matériel (de l'anglais *codesign*) essaie de répondre à ce problème. Son but est de couvrir tout le cycle de conception de la spécification jusqu'au prototype de l'application à réaliser.

Le codesign propose une nouvelle méthodologie. Dans la littérature, cette dernière varie selon les besoins de l'application, mais tous les chercheurs s'entendent sur le principe du développement conjoint du logiciel et du matériel devenu essentiel.

La spécification du système à haut niveau est une des techniques utilisées par la méthodologie de codesign, elle permet au concepteur de spécifier les fonctionnalités du système dans un langage haut niveau tel que C, C++ ou SystemC. La simulation du système à haut niveau est plus rapide par rapport à une simulation au niveau RTL. Plusieurs variantes de la méthodologie de codesign intègrent le modèle TLM dès les premières phases de la conception.

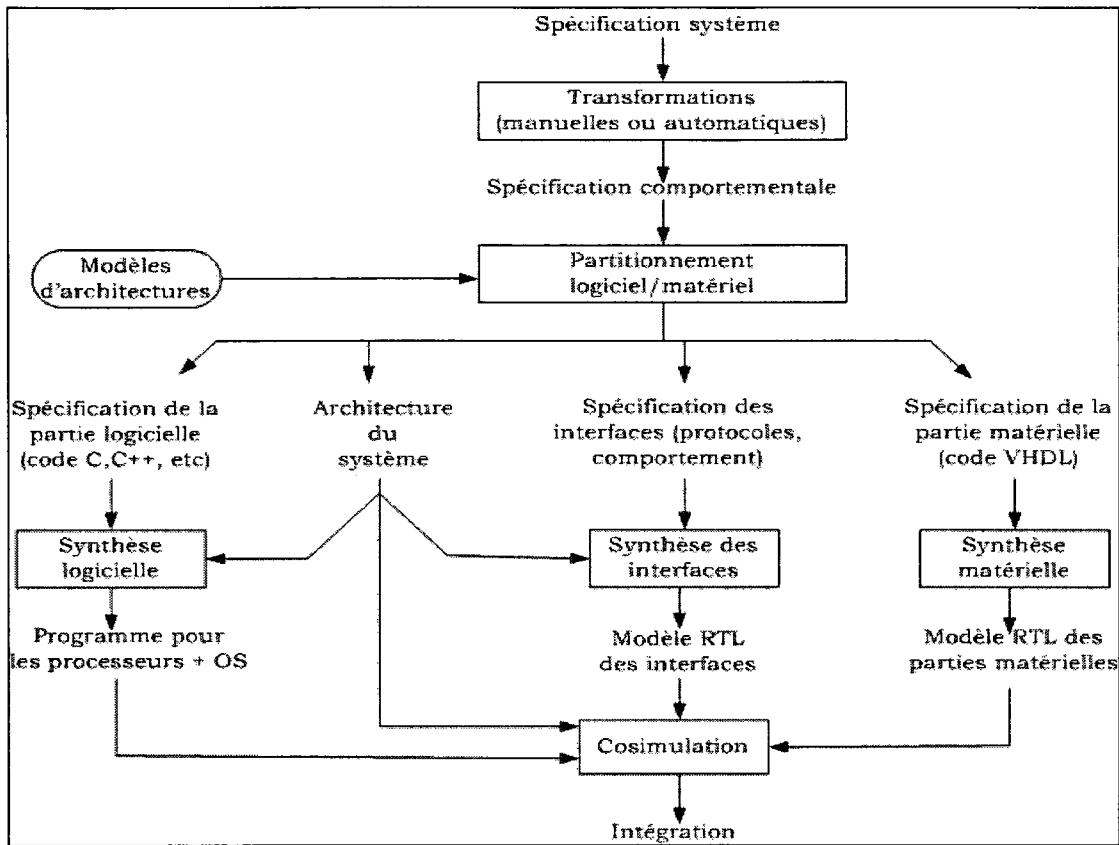

La figure 1.4 [8] représente les différentes étapes de la conception conjointe d'un système.

Figure 1. 3 Flot de conception classique de SoC

### 1.2.3 Langages de programmation à haut niveau et les SoC

Les langages de programmation utilisés durant le flot de conception peuvent être classifiés selon l'étape de conception à laquelle ils sont utilisés [24]. Une manière générale est de les classifier en langages de description du matériel et en langages de description du logiciel.

La majorité des langages de programmation ont été utilisé pour la description des systèmes, spécialement le langage C avec des extensions pour la gestion de la concurrence et du temps. HardwareC [19], HandelC [20], SpecC [21], et SystemC [2] (qui sera décrit plus en détail au chapitre 2) sont les langages les plus connus. Ils dérivent du C ou du C++ et ils sont utilisés pour la spécification au niveau système.

SystemC utilise le même modèle de calcul celui des langages VHDL et Verilog. Il est basé sur les événements discrets et sa force réside dans son support pour la modélisation des systèmes au niveau TLM, afin de faciliter l'exploration architectural et la validation d'un système à haut niveau. L'objectif n'est pas que SystemC remplace VHDL ou Verilog, mais plutôt de fournir un nouvel environnement pour la simulation au niveau système.

D'autre part, il existe également des langages synchrones tels que Esterel, Lustre, StateCharts, et Signal sont utilisés pour décrire des systèmes réactifs qui interagissent avec leurs environnements à temps réel. Le langage Esterel est utilisé pour la spécification et la validation d'un système [22,23].

Figure 1.4 Flot de conception de SoC au niveau système

### 1.3 Modèles de communication pour un SoC

Les mécanismes de communication dans un SoC dépendent des parties du système mises en jeu. On distingue la communication inter logiciel, la communication inter matériel, et la communication entre le logiciel et le matériel.

#### 1.3.1 La communication inter logiciel

Dans [9], les modèles de communication entre les différentes tâches d'un système logiciel sont classés en deux catégories : la communication explicite dans laquelle le transfert des données entre les tâches est effectué par des méthodes du type *send* et *receive*, et la communication implicite dans laquelle le transfert des données est effectué à travers un mécanisme de mémoire partagée.

La communication explicite entre les tâches est modélisée par un mécanisme de passage de messages. Ce modèle implique l'utilisation des mémoires de type queue ou FIFO, et la communication peut être bloquante ou non.

La communication implicite entre les tâches est modélisée par un mécanisme de mémoire partagée. Dans ce mode une partie de la mémoire, allouée pour les données, est visible à une ou plusieurs tâches. Un arbitrage est donc requis pour accéder à cette mémoire partagée. Les opérations de lecture et d'écriture vers cette mémoire devront être gérées de façon à assurer la cohérence des données. Les langages de programmation du logiciel embarqué sont munis d'extensions pour faciliter l'utilisation de la mémoire partagée. Par exemple, en langage C une variable dans une mémoire partagée se verra attribuée le mot clé *volatile*.

L'utilisation de la mémoire partagée, généralement utilisée pour assurer l'échange de données dans un système multi-processeur [15], nécessite d'autres mécanismes pour assurer la cohérence des données. Par exemple, un mécanisme de synchronisation est utilisé dans le cas d'accès simultanés à la mémoire partagée par plusieurs tâches.

Toutefois, les architectures multi-processeurs de SoC dépassent le cadre de notre travail et ne seront pas abordées.

### 1.3.2 La communication inter matériel

Le choix d'un mécanisme de communication pour une partition matérielle a un impact sur la performance, et sur le coût de la puce. Les modèles de communication par passage de messages ou par mémoire partagée utilisés pour le logiciel, peuvent aussi être modélisés pour les communications entre les différentes composantes matérielles du système en utilisant un des trois types de communication suivant : ..par bus, point à point et par réseaux de connexions (de l'anglais *network on chip*). À l'exception des réseaux de connexions qui dépassent le cadre de ce travail, dans ce qui suit nous présentons les deux premiers types de communication.

## Communication par bus

Le bus permet la communication entre plusieurs blocs matériels du système, ces blocs peuvent être des maîtres (tels que les processeurs) ou des esclaves (telles que les mémoires). Un bus est en général muni d'un mécanisme d'arbitrage basé sur différentes politiques telles que l'arbitrage en mode FIFO et l'arbitrage basé sur les priorités.

La conception d'un bus utilise plusieurs stratégies afin de répondre aux objectifs générales de l'architecture dans laquelle le bus sera utilisé. Les décisions de conception du bus sont basées sur trois paramètres [9]:

- Largeur du bus et fréquence: ces paramètres déterminent la fréquence de transfert de données à travers le bus, et ont un impact sur le coût, la consommation d'énergie, et sur les requis de la technologie.

- Arbitrage: la politique d'arbitrage affecte directement le taux d'utilisation du bus et la latence de chaque maître du bus. *L'arbitrage de type FIFO ou Round-robin* en anglais permet aux maîtres d'avoir des chances égales d'accéder au bus, mais présente l'inconvénient de faire attendre une requête de plus haute priorité. *L'arbitrage basé sur la priorité* donne accès au bus au maître qui a la plus haute priorité.

- Type de transfert : un bus simple implémente juste quelques types de transfert tels que des lectures et des écritures de données pouvant aller de 8 à 32 bits de taille. Par contre, des bus plus complexes implémentent d'autres types de transfert plus avancés tels que :

- Transfert de blocs fixes: en général des blocs de données dont la taille est une puissance de deux. Ce type de transfert est utilisé par exemple pour les mémoires caches.

- Transfert de type différé : dans ce mode de transfert (en anglais *split transaction*), l'accès au bus peut passer à un autre maître en attendant que la requête du maître qui avait le bus soit complétée. Ce type de transfert est particulièrement intéressant dans le cas de mémoires lentes.

- Transfert atomique : ce type de transfert est utilisé dans le cas où plusieurs maîtres accèdent à une mémoire partagée. Il renforce la politique d'arbitrage utilisée par *un mécanisme de réservation du bus* (en anglais *bus lock*). Un maître peut se servir de ce mécanisme afin de transférer plusieurs données successivement sans avoir à redemander le bus fréquemment, c'est ce qu'on appelle le transfert en rafale (en anglais *burst*).

### **La connexion point à point**

La connexion point à point (aussi appelée *directe*) entre les blocs matériels réduit les coûts et la latence de communication. Elle permet l'envoi direct des données d'un bloc à un autre. Ce type de communication se trouve rapidement limité dans le cas de composantes devant communiquer avec plusieurs composantes, de même il ne permet pas la réutilisation de l'architecture de base, et reste spécifique au type de l'application.

Dans un système de type un producteur et plusieurs consommateurs, le producteur envoie la donnée qui est acheminée vers la FIFO de réception du consommateur concerné. Un mécanisme de décodage d'adresses pourra être utilisé afin de choisir la bonne FIFO parmi celles des blocs consommateurs.

Ce mécanisme permet la lecture et l'écriture bloquantes de manière implicite, le bloc effectuant l'écriture bloque si la FIFO de réception est pleine, le bloc effectuant la lecture bloque si sa FIFO de réception est vide. Il est aussi possible de réaliser ces opérations de manière non bloquante, chaque bloc devra vérifier de son côté si la FIFO est pleine, ou s'elle est vide.

#### **1.3.3 La communication entre le logiciel et le matériel**

La communication entre le logiciel et le matériel est une communication entre le processeur qui exécute le logiciel et le reste de la plateforme matériel. Pour les SoC basés sur une architecture de bus, le processeur communique avec les autres composantes matérielles à travers le bus commun. Il peut y avoir une communication

directe entre le processeur et une composante du système et ce à travers une liaison dédiée basée en général sur le mécanisme de FIFO telle que la liaison FSL [25] sur un processeur Microblaze [26].

Pour assurer le transfert des données d'un bloc matériel vers système logiciel multitâches, le mécanisme d'interruption est souvent utilisé pour éviter l'attente active (de l'anglais *polling*) [3].

## 1.4 Éléments du raffinement de SoC

La figure 1.4 présente le flot de conception d'un SoC au niveau système. Nous nous intéressons dans cette section aux étapes de choix de l'architecture du système et aux différentes synthèses effectuées afin de transformer les spécifications vers un niveau plus bas, généralement le niveau RTL.

### 1.4.1 L'architecture cible

L'architecture cible définit le support du système [8]. Elle peut être déduite après partitionnement ou imposée avant le partitionnement. Pour cet architecture, il faut déterminer le type de processeur (général, DSP, spécifique) qui convient le mieux à l'application. Il faut aussi décider de la structure de l'ensemble : nombre de bus, mémoires, entrées/sorties, etc.

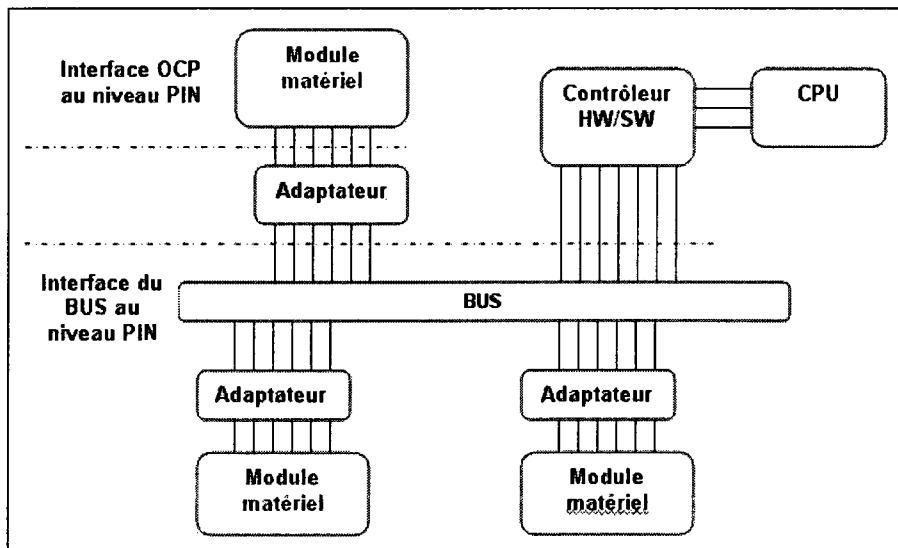

Pour faire le lien avec l'architecture cible, on utilise en général l'approche dite *plateforme*, dans laquelle la correspondance est faite entre l'architecture à haut niveau et une architecture standard cible constituée en général d'un standard de bus et de ses périphériques principales. La figure 1.5 représente une architecture type d'un bus pour un SoC.

Lors du raffinement de l'approche plate-forme, les blocs du système partitionnés en logiciel et en matériel devront être respectivement compilés et synthétisés. Le bus de l'architecture choisie assure la communication entre les blocs. Des interfaces de communication entre le logiciel et le matériel peuvent s'avérer nécessaires dans le cas de

protocoles spécifiques. Et enfin, une couche d'adaptateurs est aussi nécessaire afin de réduire la complexité de connexion des blocs matériels du système sur le bus.

Les architectures standards de bus utilisées par les SoC telles que CoreConnect de IBM [10], Avalon de Altera [12], et AMBA de ARM [11], peuvent représenter une solution pour une approche de raffinement plateforme. Elles fournissent aussi des solutions partielles à la génération des interfaces de communication entre les différentes composantes de la plateforme. Par exemple, les librairies de IP fournies avec les outils de la compagnie Xilinx incluent une composante appelée IPIF [29]. D'une part, cette dernière permet de normaliser l'interface de connexion de chaque composante du système (uart, timer, mémoire) sur le bus (OPB ou PLB) et d'autre part elle facilite l'ajout de blocs matériels par l'utilisateur en lui fournissant l'interface de connexion sur le bus en question.

Figure 1. 5 Architecture type d'un bus pour un SoC

### 1.4.2 Les différentes synthèses

L'étape de synthèse dans un flot de conception de SoC (figure 1.4) est effectuée après les décisions de partitionnement. Elle comporte trois phases de synthèse: logicielle, matérielle et communications.

#### Synthèse logicielle

Elle consiste à générer le code binaire qui sera exécuté par le processeur de l'architecture cible. L'idéal est d'utiliser le même code source que celui utilisé à haut niveau dans lequel la partie logicielle du système est généralement validée sur un émulateur de processeur. En effet, des compagnies telles que IBM et ARM ont développé des ISS pour leurs processeurs embarqués respectifs (respectivement PowerPC et ARM).

Également, un système d'exploitation temps réel est généralement associé avec la partie logicielle dans le cas où plusieurs tâches doivent être exécutées sur le même processeur.

#### Synthèse matérielle

Elle consiste à transformer la spécification de la partie matérielle du système en un circuit électronique. C'est aussi la possibilité de réutiliser des fonctions existantes (IP). Cette synthèse débute habituellement avec une spécification au niveau RTL décrite dans un langage HDL tel VHDL ou Verilog. Elle peut aussi débuter à un plus haut niveau d'abstraction, c'est-à-dire au niveau comportemental. Selon le langage utilisé à haut niveau (e.g. SystemC, C/C++), plusieurs cas de figures sont possibles pour le passage de la spécification à haut niveau vers le niveau RTL ou vers le niveau portes logiques:

- Passage du haut niveau vers le niveau des portes logiques, se traduisant par la génération d'une liste d'interconnexions (en anglais *netlist*).

- Translation de la spécification haut niveau vers une spécification au niveau RTL. Des exemples d'outils commerciaux sont Synthesizer de Fortes Design et Catapult de Mentor Graphics.

- Translation manuelle de la spécification du langage haut niveau vers un langage HDL synthétisable. À priori, on peut penser que cette manière engendre un double effort durant le cycle de développement, mais le facteur de facilité de modélisation à haut niveau dans un langage tel que C ou SystemC est important.

### **Synthèse des communications**

La synthèse des communications est la réalisation des interfaces de communication entre les différentes composantes du système. Nous avons mentionné que le choix de l'architecture cible impose un certain protocole de communication auquel les blocs matériels de l'application, ainsi que les tâches logicielles, devront être adaptés. En considérant les différents types de communication, quatre possibilités doivent être considérées:

- La communication entre les tâches du logiciel dans le cas d'un système multitâches.

- La communication entre les blocs matériels.

- La communication du logiciel vers le matériel.

- La communication du matériel vers le logiciel.

### **1.5 Revue des travaux sur le raffinement**

La conception des SoC au niveau système est une approche récente, plusieurs groupes de recherche et compagnies du domaine EDA s'y intéressent. La majeure partie des travaux de recherche se limite à la validation du système à haut niveau [6, 13, 14, 27, 28] ou traite une partie de la problématique à savoir comment effectuer le raffinement final qui produira une spécification synthétisable à partir des spécifications haut niveau. Les compagnies quand à elles proposent des outils pour automatiser le flot de conception au complet en partant d'une spécification de haut niveau jusqu'à l'implémentation du système sur puce.

Pour des systèmes monoprocesseurs, les étapes d'exploration et de validation diffèrent principalement au niveau des termes utilisés pour décrire les étapes de raffinement et

des langages de programmation utilisés pour la spécification du système (SystemC, System Verilog, Esterelle, C/C++, SpecC, etc.).

On distingue principalement deux approches pour passer d'un modèle niveau système à un prototype au niveau RTL synthétisable. La première approche [3, 4, 7, 16, 17, 18] utilise des adaptateurs pour les blocs matériels pour des fins de compatibilité avec le protocole de communication de l'architecture cible à bas niveau et utilise une interface matériel entre le processeur embarqué et le reste de l'architecture cible afin de gérer les communications entre la partie logicielle et la partie matérielle. Cette interface que l'on peut nommer adaptateur de processeur peut être directement connectée au processeur via des liaisons rapides ou à travers le bus de l'architecture cible.

Dans la deuxième approche [5, 30], la partie logicielle du système est exécutée par le processeur de l'architecture cible, tandis que la partie matérielle est divisé en plusieurs fonctionnalités que chacune est implémentée comme étant un coprocesseur directement connecté au processeur.

Dans ce qui suit nous examinons plus en détail un exemple de chacune des deux approches.

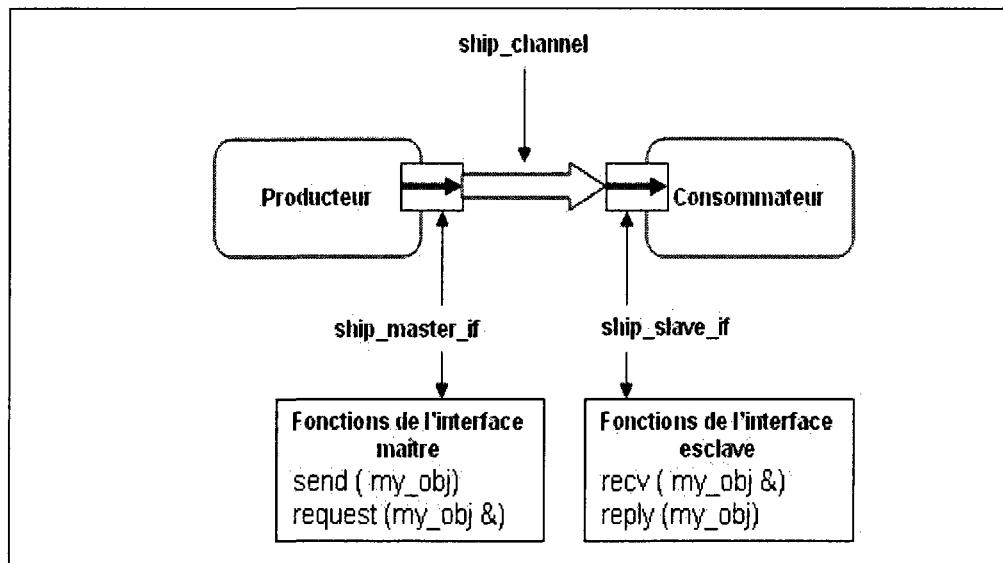

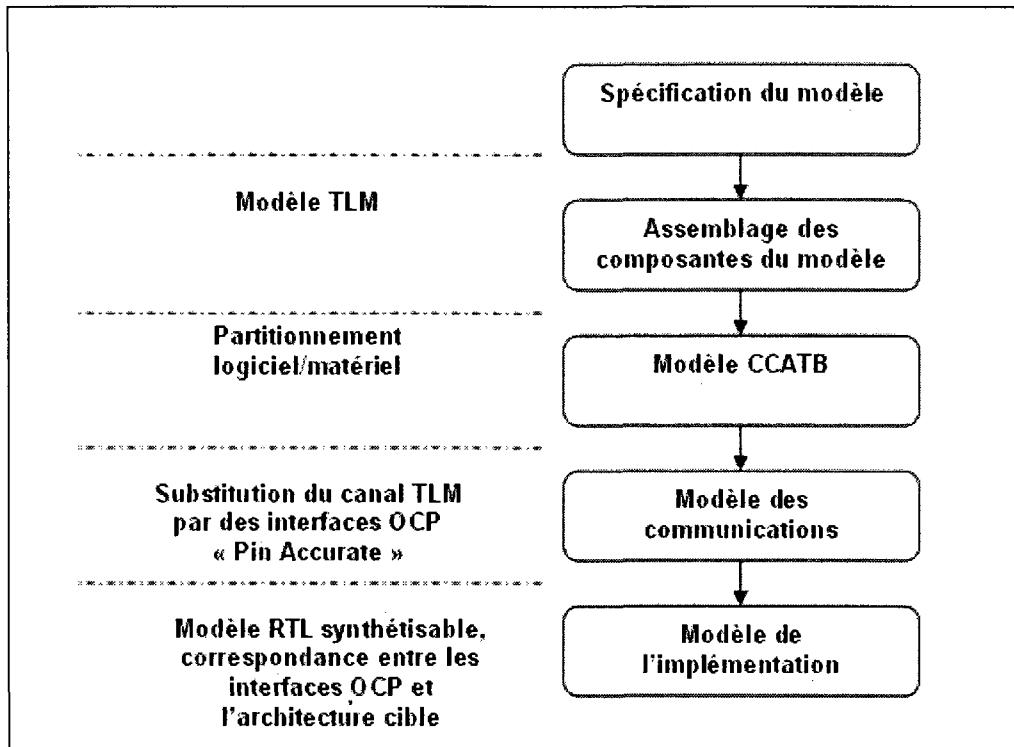

### 1.5.1 Raffinement par l'utilisation d'adaptateurs de communication

Dans [3] on propose une méthodologie de raffinement des communications d'un modèle TLM vers un modèle RTL. Dans cette méthodologie, le protocole de communication, appelé SHIP (de l'anglais *SystemC High-Level Interface Protocol*), est basé sur SystemC et défini un canal de communication point à point pour le passage des messages entre les entités du système. Une entité peut être soit maître, soit esclave. La communication est définie en termes de fonctions *send/request* pour un maître, et *recv/reply* pour un esclave. La figure 1.6 présente le modèle de communication à haut niveau tel que présenté dans [3]. Le flot de conception proposé dans [3] et représenté à la figure 1.7. Il est composé de plusieurs niveaux d'abstractions pour obtenir à la dernière étape un modèle raffiné au niveau RTL synthétisable. Le flot en question est considéré le

point d'entrée pour la génération d'un prototype du système qui pourra être implémenté sur une puce. Les étapes de raffinement proposées se résument à :

- Validation du système au niveau fonctionnel en utilisant l'architecture basée sur un canal SHIP (figure 1.6).

- Remplacement du canal SHIP par un mécanisme de communication précis au niveau cycle appelé CASM (communication architecture simulation model en anglais).

- Partitionnement du système en logiciel et matériel.

- Connexion du module en logiciel au CASM par un mécanisme appelé *HwSwChannel* afin d'assurer la communication entre le matériel et le logiciel.

- Raffinement des ports SHIP d'un module matériel vers un niveau d'abstraction plus bas niveau, basé sur le protocole OCP [33].

Figure 1.6 Canal, ports et interfaces du modèle SHIP

Figure 1. 7 Flot de conception proposé dans [3]

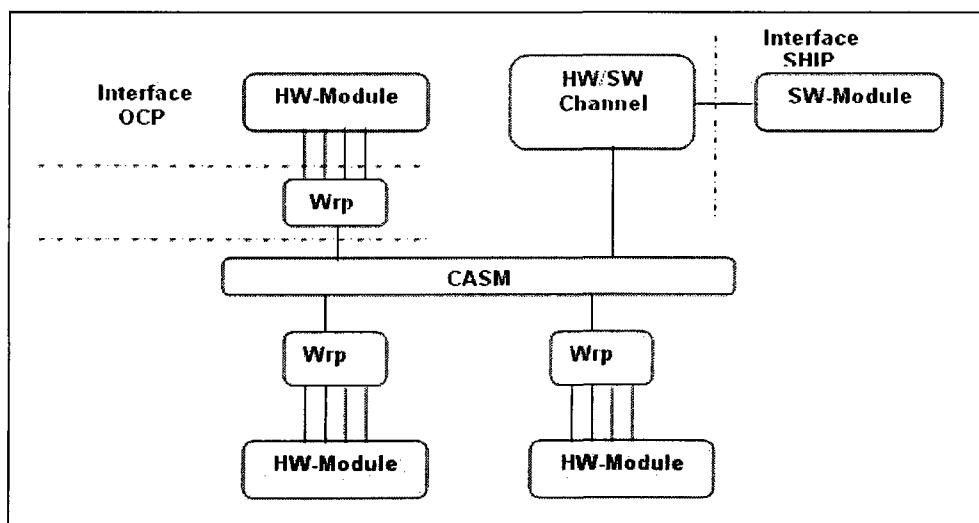

Un exemple de système raffiné est représenté à la figure 1.8

Figure 1. 8 Le modèle raffiné proposé dans [3]

D'autre part, les phases de la synthèse proposées sont :

- Choix de l'architecture de communication: bus ou réseau de connexion sur puce.

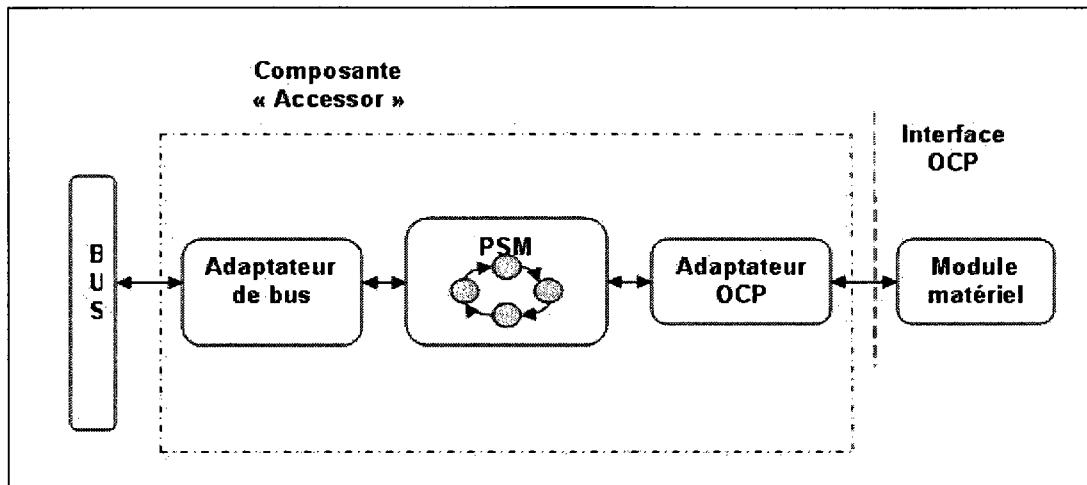

- Connexion d'un module matériel à l'architecture de communication par un mécanisme de *wrapper* appelé *Accessor* (figure 1.9), implémenté au niveau RTL, qui effectue la correspondance entre le protocole OCP et le protocole de l'architecture de communication via un mécanisme appelé PSM (Protocol State Machine).

Figure 1.9 Architecture d'un wrapper tel que proposé dans [3]

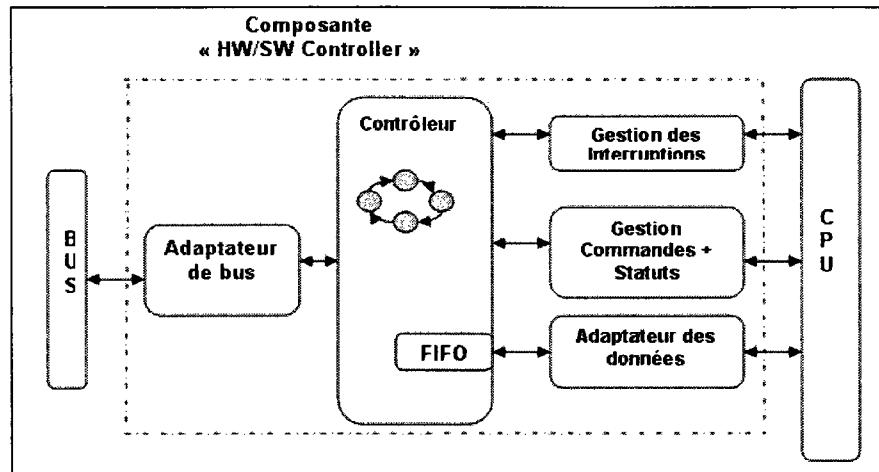

- Utilisation d'un adaptateur appelé *HW/SW-Controller* (figure 1.10) qui assure la communication entre le logiciel et le matériel. Ce contrôleur s'occupe de l'envoi des données du logiciel vers les autres composantes du système, il s'occupe aussi de la réception des données destinées au logiciel. Le contrôleur est connecté au processeur via les interfaces rapides disponibles pour certains processeurs telles que les interfaces DSOCM du PowerPC405 [34]. Un mécanisme d'interruption est utilisé entre le contrôleur et le processeur afin de traiter les requêtes destinées au logiciel. Enfin, le contrôleur est connecté sur l'architecture de communication (un bus en général) et dispose d'une FIFO pour y stocker les données en attendant d'avoir fini le traitement de la requête en cours.

La figure 1.11 représente le modèle d'implémentation obtenu à la fin des étapes de synthèse.

Figure 1. 10 Hw/Sw adaptateur tel que proposé par [3]

Figure 1. 11 Le modèle obtenu après synthèse tel que proposé par [3]

### 1.5.2 Raffinement par processeur / coprocesseur

La méthodologie proposée dans [5] part d'une spécification du système à haut niveau basée sur le langage C. Les fonctions en C qui exigent des calculs intenses sont implémentées en matériel et le reste du système est implémenté en logiciel.

Pour implémenter le système en logiciel et en matériel, l'approche processeur et coprocesseur est utilisée. Chaque fonction partitionnée en matériel sera implémentée en VHDL sur un coprocesseur. Les fonctions identifiées pour être implémentées en matériel sont converties en VHDL, et liées aux coprocesseurs.

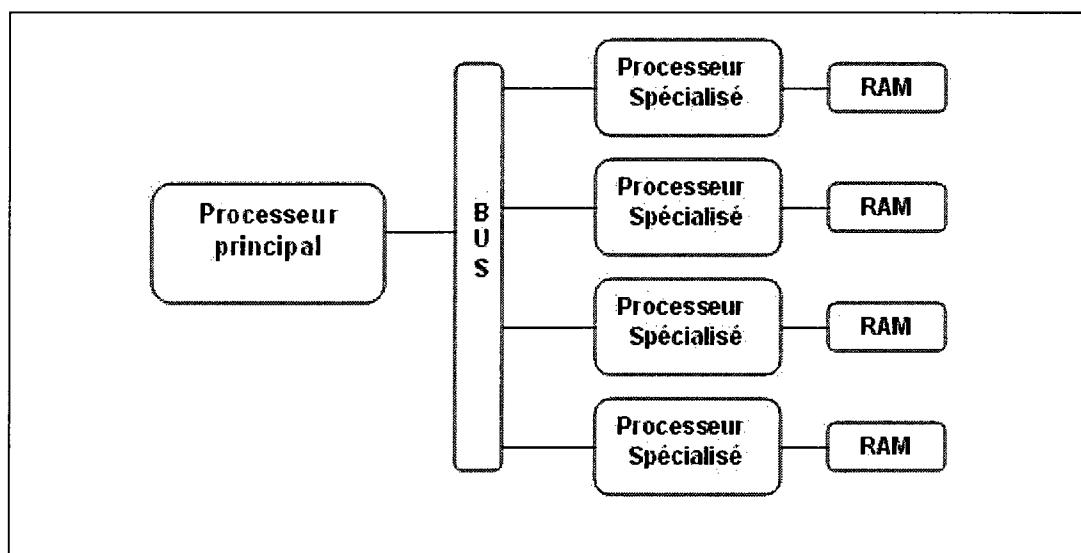

Notons également une approche proposée dans [31], comparable à [5], qui consiste à spécifier le système en C/C++. Le système est ensuite partitionné en logiciel et en matériel. La partie matérielle contient les fonctions nécessitant une accélération matérielle. Chacune de ces fonctions est mappée sur un petit processeur spécialisé (figure 1.12) conçu en SystemC RTL synthétisable.

Figure 1.12 Architecture de SoC, composée d'un processeur principal et des processeurs spécialisés

## Chapitre 2      La plateforme Space

La plateforme Space est le résultat du travail de plusieurs étudiants, elle a été développée au laboratoire de codesign de l'École Polytechnique de Montréal. La plateforme est bâtie autour de SystemC et permet de concevoir des applications au niveau système. Dans une approche de haut vers le bas, la méthodologie de conception, basée sur Space, offre trois niveaux de raffinement progressif incluant un processus de partitionnement logiciel/matériel.

Ce chapitre est divisé en deux parties. La première partie propose une description non exhaustive de la librairie SystemC, alors que la deuxième présente une description de l'architecture et la philosophie de la plateforme Space. Nous mettons l'accent sur le protocole de communication entre les différentes composantes d'un système développé dans Space afin d'établir le lien avec notre travail à savoir le raffinement des communications de la plateforme vers un système reprogrammable de type FPGA.

### 2.1 La librairie SystemC

#### 2.1.1 Introduction

SystemC est une librairie basée sur le langage de programmation orienté objet C++. On désigne généralement SystemC comme étant un langage pour la modélisation à haut niveau d'abstraction du comportement matériel des composantes d'un système. SystemC est souvent comparé aux langages HDL tels que VHDL et Verilog. L'extrait suivant tiré de [35] résume bien l'origine de SystemC :

« En 1989, Synopsys met son outil commercial Scenic dans le domaine libre, et crée la version 0.9 de SystemC. Une première contribution de Frontier Design donne lieu à la version 1.0, et une autre de CoWare aboutit en 2000 à la version 1.1, première version officielle de SystemC. L'OSCI (Open SystemC Initiative) est alors créé, rassemblant une

multitude de sociétés et laboratoires de recherche. Cette organisation est responsable de diffuser, promouvoir et rédiger les spécifications de SystemC

Les spécifications de SystemC ont été étendues en 2001 à la modélisation de systèmes abstraits (de très haut niveau, avant partitionnement matériel/logiciel), aboutissant à la version 2.0 ».

En 2005, SystemC a été standardisé IEEE 1666-2005. La version courante étant 2.2, on parle déjà de la version 3.0 qui devrait supporter la modélisation de logiciel embarqué.

L'objectif principal de SystemC consiste à éléver le niveau d'abstraction durant la modélisation d'un système. Au lieu de démarrer la conception à un niveau bas tel que le niveau RTL, SystemC permet de valider la spécification au niveau transactionnel sans se soucier de tous les détails de l'implémentation finale.

Malgré qu'on parle de SystemC comme étant un langage pour la modélisation d'un système composé de matériel et/ou logiciel, à la base SystemC est beaucoup plus orienté pour la modélisation du comportement matériel. En effet, les versions actuelles et antérieures, de SystemC ne fournissent pas un support complet pour la modélisation du comportement logiciel.

### 2.1.2 Architecture générale de SystemC

La figure 2.1 présente l'architecture générale de la librairie SystemC. Elle est basée sur le langage C++ et fournit une collection de classes représentant des modèles en matériel, des mécanismes de communication, des éléments de synchronisation et le support de plusieurs types de données. Ces classes de base permettent la modélisation d'un système. La librairie inclut aussi un simulateur événementiel.

Dans ce qui suit, nous décrirons brièvement dans ce qui suit les éléments de chaque couche. Notez que la première couche (couche du haut sur la Figure 2.1) ne fait pas partie des éléments de base de la librairie SystemC. Elle n'est donc pas présentée dans ce qui suit, toutefois le lecteur peut référer à [2] pour plus de détails.

|                                                                            |                                                                                                                 |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| <b>Librairies Spécifiques</b><br>Librairie Maître/esclave, etc.            | <b>Couches de librairies</b><br>Librairie de vérification<br>Librairie TLM, etc                                 |

| <b>Canaux primitifs</b><br>Signal, FIFO, Mutex, Semaphore, etc.            |                                                                                                                 |

| <b>Éléments structuraux</b><br>Modules.<br>Ports.<br>Interfaces<br>Canaux. | <b>Types de données</b><br>Type bit et vecteur de bits.<br>Entier à précision arbitraire.<br>Types à point fixe |

| <b>Simulation Événementiel</b><br>Événements, processus                    |                                                                                                                 |

| <b>Langage C++ Standard</b>                                                |                                                                                                                 |

Figure 2. 1 Architecture de la librairie SystemC

### Canaux primitifs

Les canaux primitifs sont des éléments de communication ou de synchronisation. Ils sont élémentaires et font partie de la construction de base d'un modèle de système basé sur SystemC. Selon le type du canal primitif, ce dernier se prête à une utilisation en matériel ou en logiciel. Par exemple, un signal est plus utilisé en matériel, et une correspondance directe peut être faite avec un signal décrit en VHDL. Par contre, les types mutex et sémaphore sont plus utilisés pour représenter un comportement en logiciel.

## Éléments structuraux

### Module

Un système est généralement divisé en plusieurs blocs, chaque bloc réalisant une fonctionnalité donnée. Un bloc est représenté en SystemC par un module qui est une classe décrivant le comportement d'un tel bloc. En général, un module contient :

- Un ou plusieurs ports à travers lesquels communique le module avec le reste du système.

- Un ou plusieurs processus où chaque processus décrit un comportement

- Des données et canaux primitifs internes afin d'assurer la communication et la synchronisation entre les processus du module.

- D'autres (sous) modules à travers une hiérarchie.

### Interface

Une interface est un ensemble des fonctions (ou méthodes) qui peuvent être utilisées à travers un port. Une interface ne contient pas de code, ce n'est qu'une déclaration de fonctions. Les fonctions de ces interfaces sont implémentées dans les canaux.

Toutes les interfaces en SystemC dérivent de la classe de base *sc\_interface*

### Canaux

Les canaux assurent la communication entre les différents modules d'un système à travers le port. Ils ne sont pas limités à une communication point à point comme c'est le cas d'un signal ou d'une FIFO. Les interfaces déclarent les fonctions disponibles pour la communication à travers un port. L'utilisation des interfaces permet donc d'implémenter différemment les fonctions de communications dans différents canaux.

On distingue les canaux primitifs qui sont atomiques et les canaux hiérarchiques avec lesquels il est possible de modéliser le comportement d'un médium de communication plus complexe tel qu'un bus dans un système sur puce.

## Ports

En SystemC, les ports sont des objets qui permettent aux composantes d'un modèle de communiquer entre elles par l'intermédiaire des fonctions de l'interface implémentées par le canal.. Chaque port est spécifié avec le type d'interface auquel il correspond. La composante qui hérite de l'interface spécifiée par un port, devra donc implémenter les fonctions de l'interface correspondante au port en question.

Un port est spécifié par la déclaration `sc_port <interface_type>`.

## Moteur de simulation événementiel

### Processus

Un processus est l'unité de base pour représenter une fonctionnalité donnée. Un module SystemC peut avoir un ou plusieurs processus pour modéliser le comportement global du module en question. Contrairement aux langages de programmation séquentiels, SystemC permet la simulation d'un comportement concurrentiel grâce aux processus.

Les processus ont une liste de sensibilité sur un ou plusieurs paramètres tels que l'horloge ou d'autres signaux.

SystemC fournit trois types de processus : `SC_METHOD`, `SC_THREAD` et `SC_CTHREAD`. Le **SC\_METHOD** s'exécute entièrement du début à la fin de son code suite à un changement dans sa liste de sensibilité et ne peut pas être suspendue explicitement par un appel à la fonction `wait()`. Le **SC\_THREAD** peut être interrompu à n'importe quel endroit de son code et quand son exécution reprend il peut restituer l'état juste avant la suspension et continuer l'exécution à partir de cet état. Finalement, le processus **SC\_CTHREAD** est identique au `SC_THREAD`, mais sensible uniquement sur les fronts de l'horloge.

## Événements

Un événement est un objet de la classe `sc_event`. Il représente en général une certaine condition sous laquelle l'exécution d'un processus s'arrête ou redémarre. Il maintient une liste de processus dont la liste de sensibilité contient l'événement en question. Le

changement d'une certaine condition est notifié à travers l'événement, ce qui permet de réordonner les processus sensibles à cet événement.

Un événement pourra être directement utilisé par un processus pour contrôler un autre processus en particulier si les deux processus en question ont besoin de synchroniser leurs exécutions sur une certaine condition.

### **Le non-déterminisme**

Le non-déterminisme du comportement d'un système en SystemC lors de la simulation est un facteur important à prendre en considération [37]. En effet, l'ordre d'exécution des processus n'est pas spécifié particulièrement au démarrage ou au cours de la simulation quand plusieurs processus sont prêts simultanément.

Malgré cet aspect de non-déterminisme de SystemC, globalement un système se comporte de la même manière entre deux simulations effectuées sur une même machine et avec les mêmes entrées, puisque l'Ordonnanceur effectue le même choix du processus à exécuter entre deux simulations [36].

#### **2.1.3 Les niveaux de raffinement de SystemC**

SystemC offre plusieurs niveaux de raffinement pour le système à concevoir. Ces niveaux diffèrent principalement au niveau de la granularité des détails liés au fonctionnement du système. Ainsi d'un niveau à l'autre, des latences liées à la communication ou au calcul pourront être ajoutées à différentes composantes du système et en particulier au médium de communication. SystemC permet donc de passer d'une spécification purement transactionnelle (niveau TLM), à une spécification plus proche du niveau RTL (au niveau des signaux).

Les niveaux de raffinement supportés par SystemC sont comme suit [35] :

- **UTF (Untimed Functional)** : le modèle ne comporte aucune notion de durée d'exécution, mais seulement un ordre éventuel dans l'exécution des événements. Chaque requête s'exécute en un temps nul. Seul compte l'ordonnancement des événements.

- **TF (Time Functional)** Le modèle comporte des notions de durée d'exécution (e.g. temps d'exécution des processus et latence des communications).

- **BCA (Bus Cycle Accurate)** Ce niveau signifie que la modélisation des transactions sur l'interface est précise au cycle près. Un modèle BCA n'apporte aucune information sur les bits (signaux) de l'interface.

- **BA (Bit Accurate)** Ce niveau signifie que la modélisation des transactions sur l'interface est de niveau BCA et considère aussi sur les signaux de l'interface. La modélisation est donc précise au bit près. On désigne souvent ce niveau par le terme CABA (cycle accurate / bit accurate).

- **RTL (Register Transfert Level)** Chaque bit, chaque cycle et chaque registre du système sont modélisés.

#### 2.1.4 Exemple d'une bascule avec SystemC

Pour illustrer la syntaxe de SystemC, nous présentons à la figure 2.2 un exemple simple d'une bascule D avec un signal de remise à zéro (*reset*) asynchrone.

Dans cet exemple, **SC\_MODULE** est une macro qui déclare un module dont le nom est **diffa** et qui a trois ports d'entrées (*clock*, *reset*, et *din*) et un port de sortie (*dout*). Le module a un processus de type **SC\_METHOD** qui est sensible au front montant de l'horloge *clock*, et sur le niveau du signal *Reset*.

```

#include "systemc.h"

SC_MODULE (dff)

{

sc_in<bool> clock , reset, din;

sc_out<bool> dout;

void do_ff()

{

if (reset) {

dout = false;

} else if (clock.event()) {

dout = din;

}

};

SC_CTOR(dff)

{

SC_METHOD (do_ff);

sensitive (reset);

sensitive_pos (clock);

}

};

```

Figure 2. 2 Exemple simple d'une bascule D en SystemC

## 2.2 La plateforme Space