**Titre:** Intégration d'un tomographe d'impédance électrique dans un

Title: réseau de portes programmables (FPGA)

**Auteur:** Pierre-Luc Dazé

Author:

**Date:** 2004

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Dazé, P.-L. (2004). Intégration d'un tomographe d'impédance électrique dans un

réseau de portes programmables (FPGA) [Mémoire de maîtrise, École

Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/8406/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8406/>

PolyPublie URL:

**Directeurs de

recherche:** Robert Guardo

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

Intégration d'un tomographe d'impédance électrique dans un

réseau de portes programmables (FPGA)

Pierre-Luc Dazé

INSTITUT DE GÉNIE BIOMÉDICAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE BIOMÉDICAL)

Août 2004

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-47658-1

*Our file* *Notre référence*

ISBN: 978-0-494-47658-1

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE

Ce mémoire intitulé:

Intégration d'un tomographe d'impédance électrique

dans un réseau de portes programmables (FPGA)

présenté par: DAZÉ Pierre-Luc

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. MATHIEU Pierre A., D.Sc.A., président

M. GUARDO Robert, Ph.D., membre et directeur de recherche

M. LAFORTUNE Michel, B.Sc.A., membre

Maintenant je sais, je sais qu'on ne sait jamais !

...

C'est tout c'que j'sais ! Mais ça, j'le sais... !

Jean Gabin (Maintenant je sais)

# Remerciements

J'aimerais tout d'abord remercier mon directeur de recherche, Dr Robert Guardo, pour ses conseils, sa grande disponibilité, et son appui financier tout au long de la réalisation de ce projet. Je le remercie également pour m'avoir initié, il y a sept ans de cela, au domaine du génie biomédical.

Je tiens également à remercier Dr Hervé Gagnon pour sa grande aide à la réalisation de ce projet et pour son support sans lesquels la réalisation de ce projet aurait été plus que compromise.

Je ne peux passer sous silence l'aide et l'appui de tous les étudiants du laboratoire d'instrumentation biomédicale: Chang, Dominic, Élizabeth, Eva, Isabelle, Louis-Francois, Lucie, Nassiri, Nicolas Coulombe, Nicolas Robitaille et Warsama. Ils ont tous contribué à créer une atmosphère de travail agréable qui a facilité la réalisation de ce projet. Il faut également mentionner l'aide de madame Diane Giroux pour tout les aspects administratifs reliés à la réalisation d'études au deuxième cycle. De plus, bien qu'ils soient trop nombreux pour être nommés, je tiens à remercier tous mes amis pour tous ces moments qui m'ont permis de garder un certain équilibre entre ma vie sociale et mes études.

Enfin, je tiens à remercier ma famille: Yves, Louise, et Jean-François pour leur soutien indéfectible et leur réconfort dans les moments les plus difficiles.

# Résumé

La tomographie d'impédance électrique (TIE) est une technique non invasive qui permet d'obtenir des images des changements de conductivité d'une section du corps à partir de mesures de potentiel et de courant obtenues à l'aide d'électrodes placées à sa surface. L'Institut de génie biomédical (IGB) de l'École Polytechnique de Montréal participe au développement de la TIE depuis 1987. Les travaux récents du groupe portent principalement sur la réalisation de systèmes (matériel, algorithme de traitement de données et d'images, etc) destinés au monitorage de la ventilation chez les patients sous assistance respiratoire. Le projet décrit dans le présent mémoire s'inscrit dans le cadre de ce programme de recherche.

Quatre générations de systèmes de TIE ont été développées par l'IGB. La dernière génération est représentée par le système TIE4-USB qui est décrit en détail dans ce mémoire. Cet instrument rencontre les exigences minimales, en termes de précision, de sécurité, et d'encombrement physique, pour être utilisé dans des essais cliniques. Toutefois, il comporte des lacunes importantes qui découlent d'une conception basée sur des composants électroniques mal assortis aux caractéristiques des signaux de TIE. En effet, la chaîne de traitement de signal dans un système de TIE comprend essentiellement deux unités: 1) un synthétiseur qui génère la porteuse de référence contrôlant le courant appliqué au corps par une paire d'électrodes, et 2) un démodulateur synchrone qui détermine la différence de potentiel mesurée par une

seconde paire d'électrodes à la fréquence désirée. Dans le système TIE4-USB, ces fonctions de synthèse et de démodulation sont réalisées par des circuits intégrés conçus pour le domaine des télécommunications. Les caractéristiques des signaux traités dans ce domaine (notamment, la plage de fréquences) sont assez différentes de celles de la TIE imposant ainsi des compromis qui affectent la précision des mesures de TIE. De plus, il n'est pas possible avec les circuits intégrés utilisés dans le système TIE4-USB de maintenir un synchronisme absolu entre le synthétiseur et le démodulateur, ce qui se traduit également par une perte de précision dans les mesures.

L'objectif du présent projet de maîtrise est d'éliminer les principales lacunes du système TIE4-USB par une restructuration complète de la chaîne de traitement de signal. Ceci a été réalisé en intégrant dans un réseau de portes programmables de type FPGA l'ensemble des circuits numériques faisant partie de cette chaîne. Ainsi, le synthétiseur de la porteuse de référence, le démodulateur synchrone, les circuits de contrôle des convertisseurs analogique-numérique et numérique-analogique, la mémoire tampon des données provenant du démodulateur, l'interface au micro-contrôleur USB qui effectue le transfert des données à un ordinateur, de même que divers circuits auxiliaires, sont maintenant regroupés dans un FPGA.

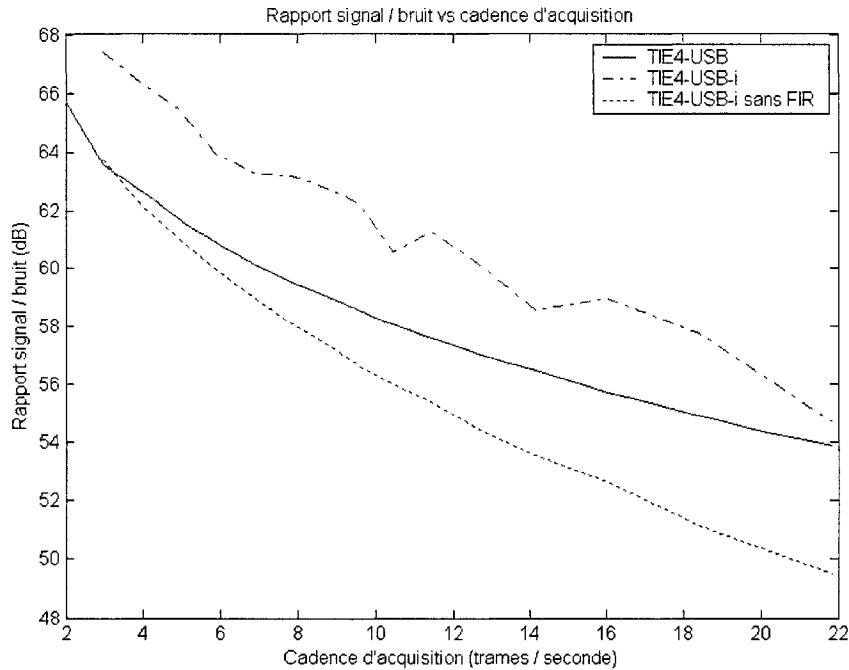

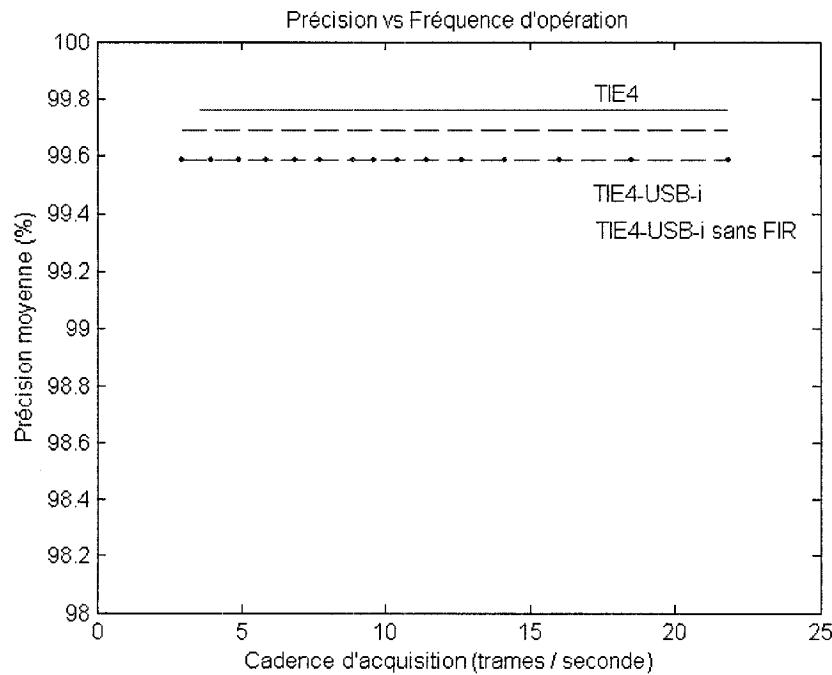

Un circuit imprimé de ce nouveau design a été réalisé et un système complet, appelé TIE4-USB-i, a été construit. Des essais ont été effectués sur un *fantôme* composé de 340 résistances de précision comme substitut du thorax. Des essais comparatifs entre les deux systèmes révèlent une légère amélioration des performances. Ainsi, le rapport signal sur bruit du système TIE4-USB-i est approximativement 4 dB supérieur à celui du TIE4-USB pour toutes les cadences d'images comprises entre 3 et 22 trames par seconde. Le rapport signal sur bruit maximal atteignable passe

donc de 63.5 dB à 67.5 dB. Du point de vue de la précision des données recueillies, une faible diminution a été observée passant de 99.76 % à 99.69 %. D'autres avantages découlent de l'utilisation d'un FPGA. Comme la totalité des opérations de traitement du signal sont maintenant définies par le code de configuration du FPGA, celles-ci peuvent être modifiées à volonté sans aucun changement matériel au système.

# Abstract

Electrical impedance tomography (EIT) is a non-invasive imaging technique that produces images of conductivity changes in a section of the body using potential and current measurements made with electrodes on the body surface. The biomedical engineering institute (Institut de génie biomédical) of École Polytechnique de Montréal participates in the development of EIT since 1987. Recent work at the IGB focuses on developing systems (hardware, algorithms, etc) for monitoring lung ventilation of patients under respiratory assistance. The project described in this thesis is part of this research program.

Four generations of EIT systems have been developed by the IGB. The last generation is represented by the TIE4-USB system. This instrument meets the minimal requirements in terms of precision, patient safety, and physical dimensions for use in clinical studies. However, it has significant limitations that originate from a system design based on electronic components not best suited for processing EIT signals. Indeed, the signal processing chain of an EIT system is made up of two main units: 1) a synthesizer which generates the reference carrier that controls the current applied to the patient by a pair of electrodes, and 2) a synchronous demodulator which determines the potential difference measured by a second pair of electrodes at a specified frequency. In the TIE4-USB system, carrier synthesis and demodulation are performed by Integrated Circuits (ICs) designed for telecommunication applications.

The characteristics of the signals used in this field of application (the frequency range in particular) are quite different from those of EIT leading to some compromises affecting the precision of the EIT measurements. Furthermore, it is not possible, given the ICs used in the TIE4-USB system, to maintain a perfect synchronism between the synthesizer and the demodulator; this also reduces measurement precision.

The objective of this master's project is to eliminate the main limitations of the TIE4-USB system by completely restructuring the signal processing chain. This has been done by integrating all the digital circuits of the processing chain into a single Field Programmable Gate Array (FPGA) IC. Thus, the synthesizer, the synchronous demodulator, the control circuits for the analog-to-digital and digital-to-analog converters, the buffer memory which stores the output data from the demodulator, the interface to the USB microcontroller which transfers this data to the computer, as well as other auxiliary circuits are now grouped together inside an FPGA.

A printed circuit board of this new design has been realized and a complete system, named TIE4-USB-i, has been built. Tests have been performed on a *phantom* composed of 340 precision resistors to simulate the thorax. Comparative tests of the two systems showed a slight improvement in performance. The signal to noise ratio (SNR) of the TIE4-USB-i system is approximately 4 dB higher than that of the TIE4-USB system, for all frame rates between 3 and 22 frames / second. The maximum SNR increased from 63.5dB to 67.5dB. A slight decrease was observed in measurement precision, from 99.76% to 99.69%. The use of an FPGA for signal processing yields other advantages. Given that all processing are now defined by the configuration code of the FPGA, those operations can be modified at will with no hardware changes.

# Table des matières

|                                                                   |      |

|-------------------------------------------------------------------|------|

| Dédicace . . . . .                                                | iv   |

| Remerciements . . . . .                                           | v    |

| Résumé . . . . .                                                  | vi   |

| Abstract . . . . .                                                | ix   |

| Table des matières . . . . .                                      | xi   |

| Liste des tableaux . . . . .                                      | xiii |

| Liste des figures . . . . .                                       | xiv  |

| Liste des sigles et abréviations . . . . .                        | xvi  |

| Introduction . . . . .                                            | 1    |

| Chapitre 1 Revue de la littérature . . . . .                      | 5    |

| 1.1 Historique et applications médicales . . . . .                | 5    |

| 1.1.1 Applications pulmonaires . . . . .                          | 6    |

| 1.1.2 Vidange gastrique . . . . .                                 | 8    |

| 1.1.3 Imagerie cérébrale . . . . .                                | 9    |

| 1.1.4 Détection de tumeurs du sein . . . . .                      | 10   |

| 1.2 Instrumentation . . . . .                                     | 12   |

| 1.2.1 Disposition des électrodes actives . . . . .                | 13   |

| 1.2.1.1 Électrodes actives distribuées . . . . .                  | 13   |

| 1.2.1.2 Électrodes actives regroupées . . . . .                   | 15   |

| 1.2.2 Générateur de porteuse . . . . .                            | 15   |

| 1.2.3 Démodulation . . . . .                                      | 17   |

| 1.2.3.1 Démodulation d'amplitude . . . . .                        | 18   |

| 1.2.3.2 Démodulation sensible à la phase . . . . .                | 19   |

| Démodulation synchrone au moyen de circuits analogiques . . . . . | 20   |

| Démodulation par des systèmes numériques . . . . .                | 26   |

|                                |                                                                            |            |

|--------------------------------|----------------------------------------------------------------------------|------------|

| 1.2.4                          | Résumé des techniques de synthèse et de démodulation des signaux . . . . . | 32         |

| 1.2.5                          | Discussion . . . . .                                                       | 34         |

| <b>Chapitre 2</b>              | <b>Méthodes et instrumentation . . . . .</b>                               | <b>35</b>  |

| 2.1                            | Analyse du système TIE4-USB . . . . .                                      | 35         |

| 2.1.1                          | Module de synthèse et de démodulation (MSD) . . . . .                      | 38         |

| 2.2                            | Conception du système TIE4-USB-i . . . . .                                 | 42         |

| 2.2.1                          | Architecture . . . . .                                                     | 43         |

| 2.2.1.1                        | Générateur de porteuse . . . . .                                           | 46         |

| 2.2.1.2                        | Démodulateur . . . . .                                                     | 49         |

| 2.2.1.3                        | Filtre de décimation . . . . .                                             | 50         |

| 2.2.1.4                        | Filtre FIR . . . . .                                                       | 55         |

| 2.2.1.5                        | Registres et logique de contrôle . . . . .                                 | 56         |

| 2.2.1.6                        | FIFO . . . . .                                                             | 60         |

| 2.2.1.7                        | Contrôle du MEA . . . . .                                                  | 60         |

| 2.2.2                          | Programmation du FPGA . . . . .                                            | 64         |

| 2.2.3                          | Choix des convertisseurs A/N et N/A . . . . .                              | 70         |

| 2.2.3.1                        | Convertisseur analogique-numérique . . . . .                               | 70         |

| 2.2.3.2                        | Convertisseur numérique-analogique . . . . .                               | 72         |

| 2.3                            | Discussion . . . . .                                                       | 73         |

| <b>Chapitre 3</b>              | <b>Résultats . . . . .</b>                                                 | <b>75</b>  |

| 3.1                            | Vérification du fonctionnement du système . . . . .                        | 75         |

| 3.2                            | Pureté de la porteuse générée . . . . .                                    | 77         |

| 3.3                            | Rapport signal sur bruit des données . . . . .                             | 78         |

| 3.3.1                          | Saisie des données . . . . .                                               | 79         |

| 3.3.2                          | Dépendance du RSB . . . . .                                                | 80         |

| 3.3.3                          | Comparaison des systèmes . . . . .                                         | 85         |

| 3.4                            | Précision des données . . . . .                                            | 87         |

| <b>Chapitre 4</b>              | <b>Discussion et travaux futurs . . . . .</b>                              | <b>91</b>  |

| 4.1                            | Atteinte des objectifs du projet . . . . .                                 | 91         |

| 4.2                            | Travaux futurs . . . . .                                                   | 92         |

| 4.2.1                          | Intégration matérielle . . . . .                                           | 92         |

| 4.2.2                          | Optimisation de la chaîne de démodulation . . . . .                        | 95         |

| 4.2.3                          | Imagerie quasi-statique . . . . .                                          | 95         |

| <b>Conclusion . . . . .</b>    |                                                                            | <b>97</b>  |

| <b>Bibliographie . . . . .</b> |                                                                            | <b>100</b> |

# Liste des tableaux

|     |                                                                                                                        |    |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Comparaison des résultats des différents tests de dépistage du cancer du sein par rapport à la biopsie . . . . .       | 11 |

| 1.2 | Comparaison des générateurs d'onde et des méthodes de démodulation utilisées dans différents systèmes de TIE . . . . . | 33 |

| 2.1 | Table des registres du FPGA dans le système TIE4-USB-i . . . . .                                                       | 61 |

| 2.2 | Avantages et inconvénients de chaque méthode de programmation . .                                                      | 68 |

| 2.3 | Comparaison des blocs fonctionnels des systèmes TIE4-USB et TIE4-USB-i . . . . .                                       | 73 |

| 3.1 | Mesure de la plage dynamique exempte de parasite (SFDR) pour les systèmes TIE4-USB et TIE4-USB-i . . . . .             | 78 |

| 4.1 | Valeur de $\sigma$ et de $\epsilon$ pour différents tissus à différentes fréquences . . .                              | 96 |

# Liste des figures

|      |                                                                                                          |    |

|------|----------------------------------------------------------------------------------------------------------|----|

| 1.1  | Architecture typique d'un système de TIE . . . . .                                                       | 13 |

| 1.2  | Module d'électrodes actives distribuées posé sur un patient . . . . .                                    | 14 |

| 1.3  | Module d'électrodes actives regroupées posé sur un patient . . . . .                                     | 16 |

| 1.4  | Démodulation d'amplitude par détection d'enveloppe . . . . .                                             | 19 |

| 1.5  | Démodulation cohérente par démodulation synchrone . . . . .                                              | 20 |

| 1.6  | Démodulation cohérente par détection synchrone . . . . .                                                 | 23 |

| 1.7  | Démodulation cohérente par échantillonnage synchronisé de la porteuse AM . . . . .                       | 25 |

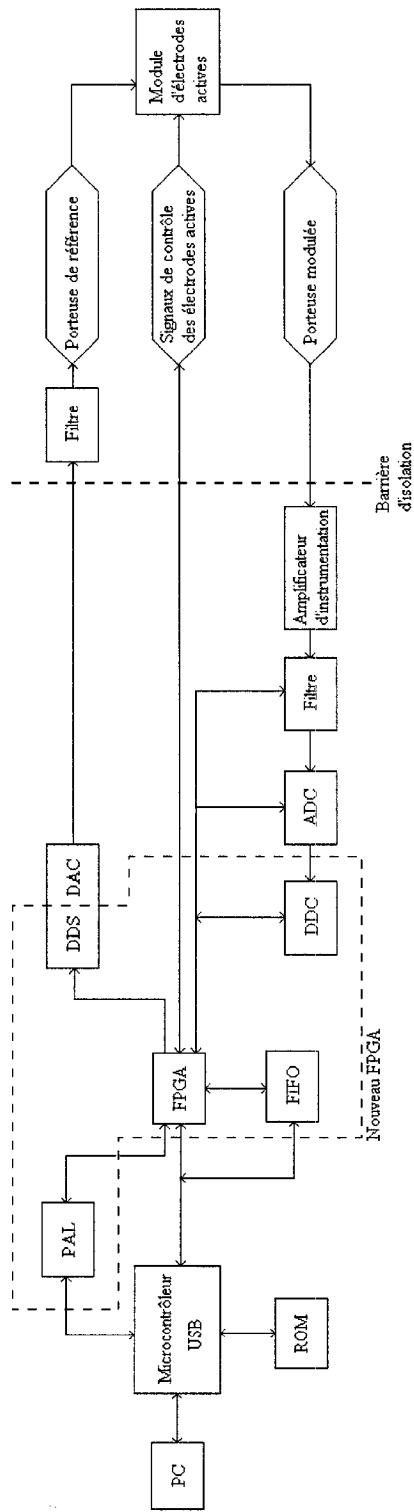

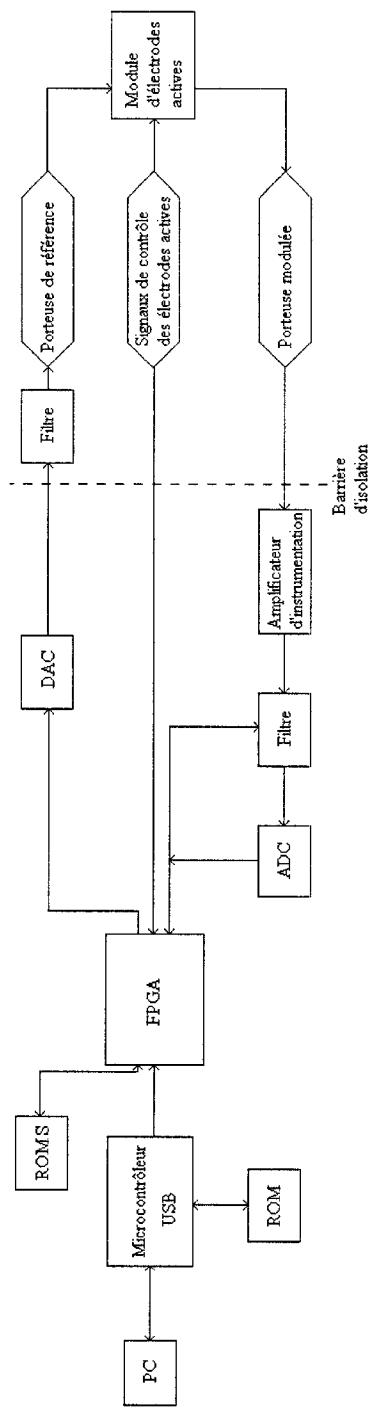

| 2.1  | Architecture du système TIE4-USB . . . . .                                                               | 36 |

| 2.2  | Système TIE4-USB . . . . .                                                                               | 36 |

| 2.3  | Architecture du MSD du système TIE4-USB . . . . .                                                        | 39 |

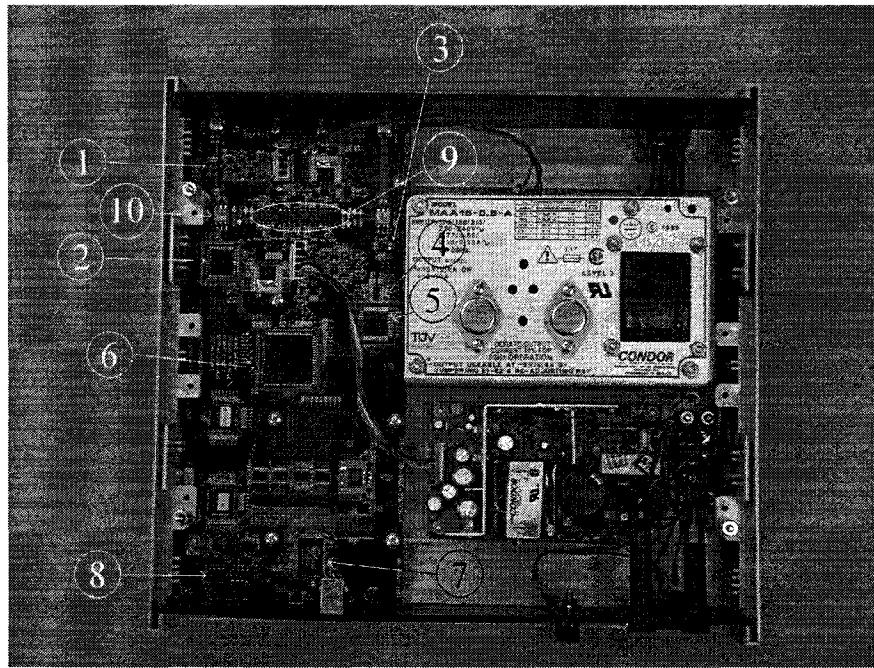

| 2.4  | Vue interne du système TIE4-USB . . . . .                                                                | 41 |

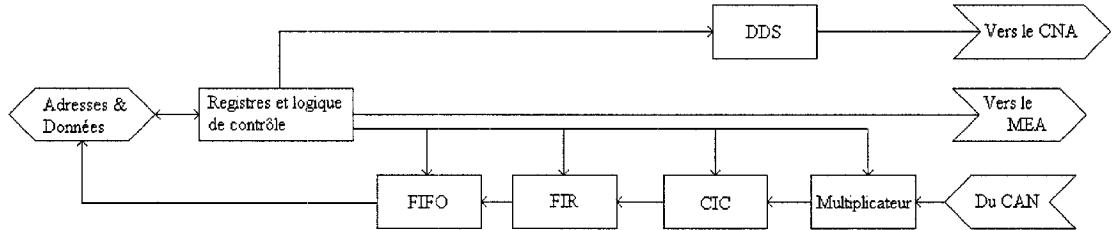

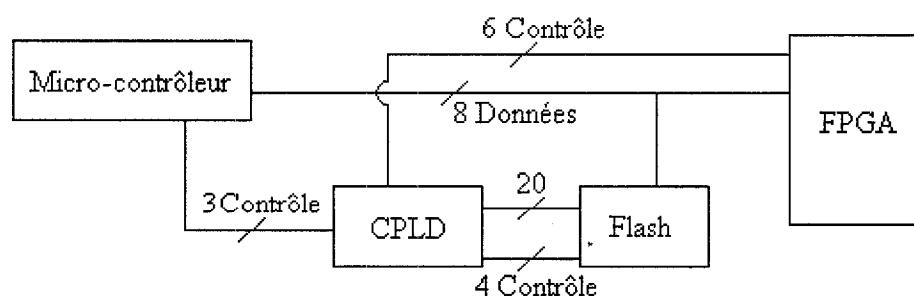

| 2.5  | Architecture du MSD du nouveau système TIE4-USB-i . . . . .                                              | 44 |

| 2.6  | Architecture du FPGA du système TIE4-USB-i . . . . .                                                     | 46 |

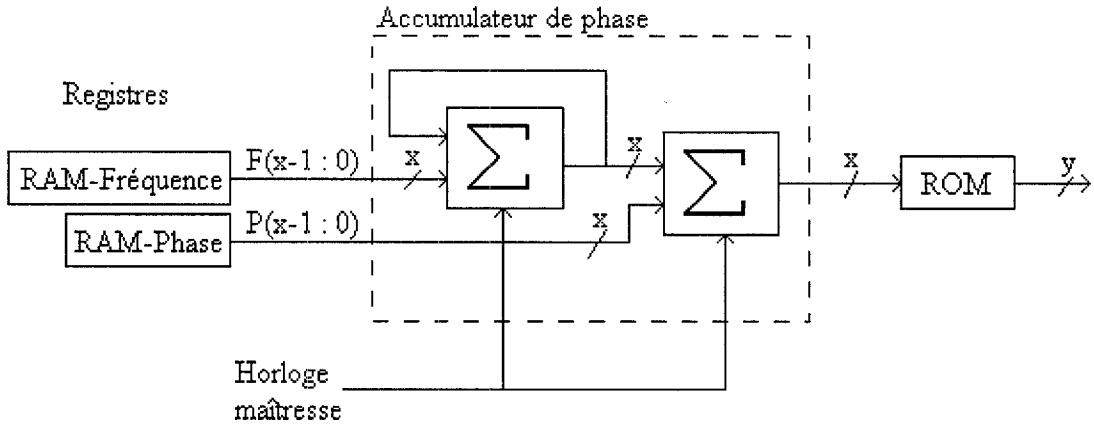

| 2.7  | Structure du DDS . . . . .                                                                               | 47 |

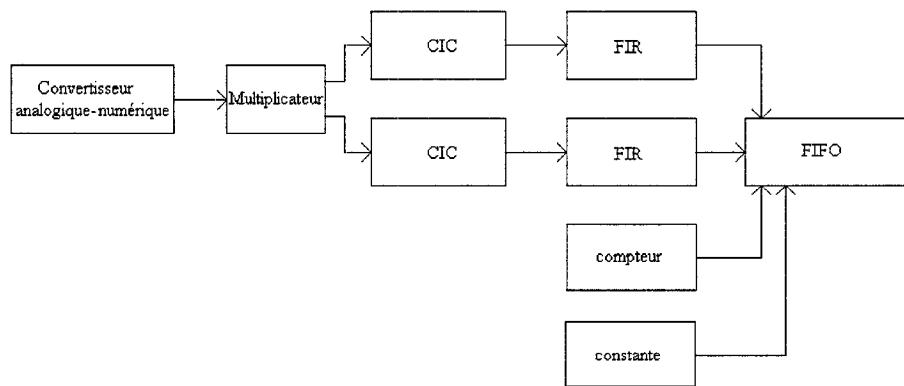

| 2.8  | Circuit de démodulation du système TIE4-USB-i . . . . .                                                  | 49 |

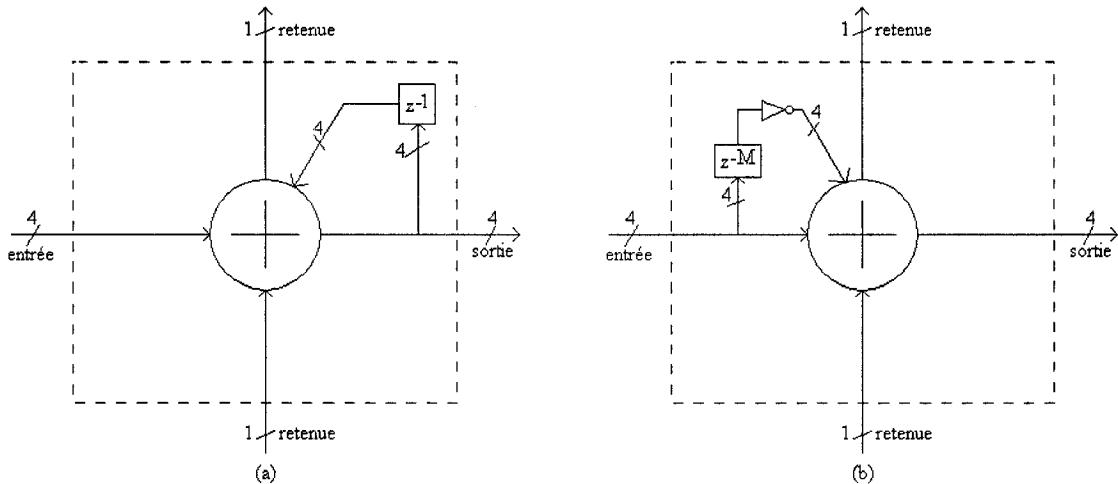

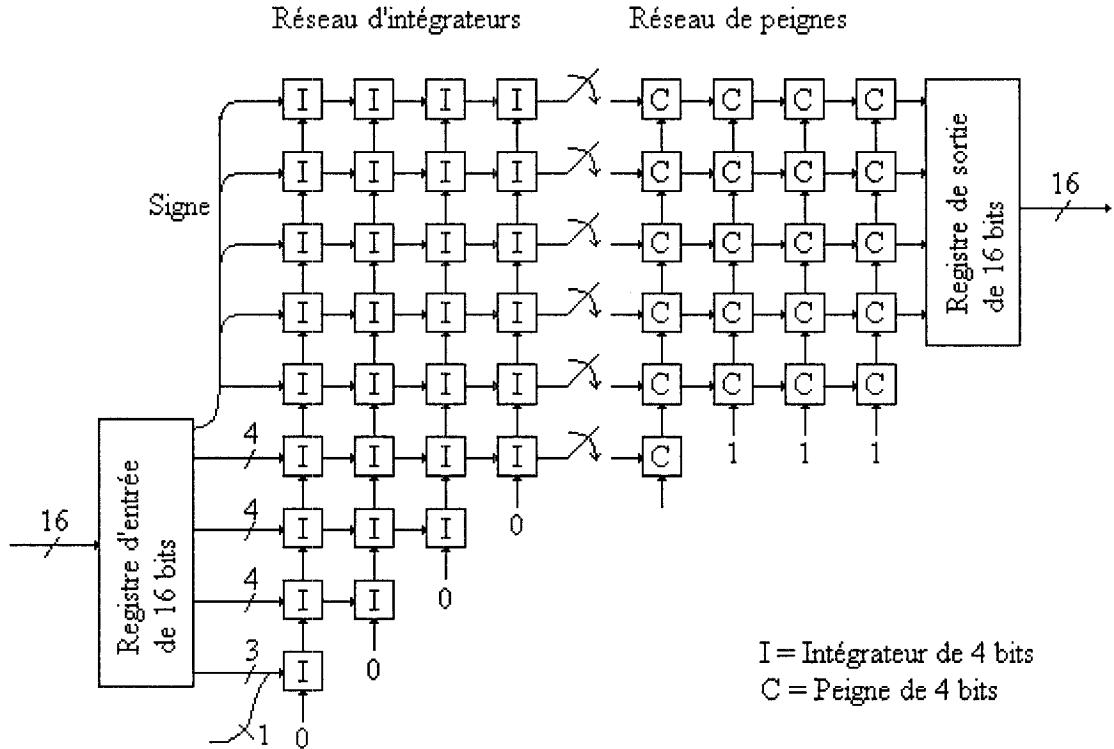

| 2.9  | Schéma des éléments d'un CIC . . . . .                                                                   | 51 |

| 2.10 | Structure d'un filtre de décimation CIC . . . . .                                                        | 52 |

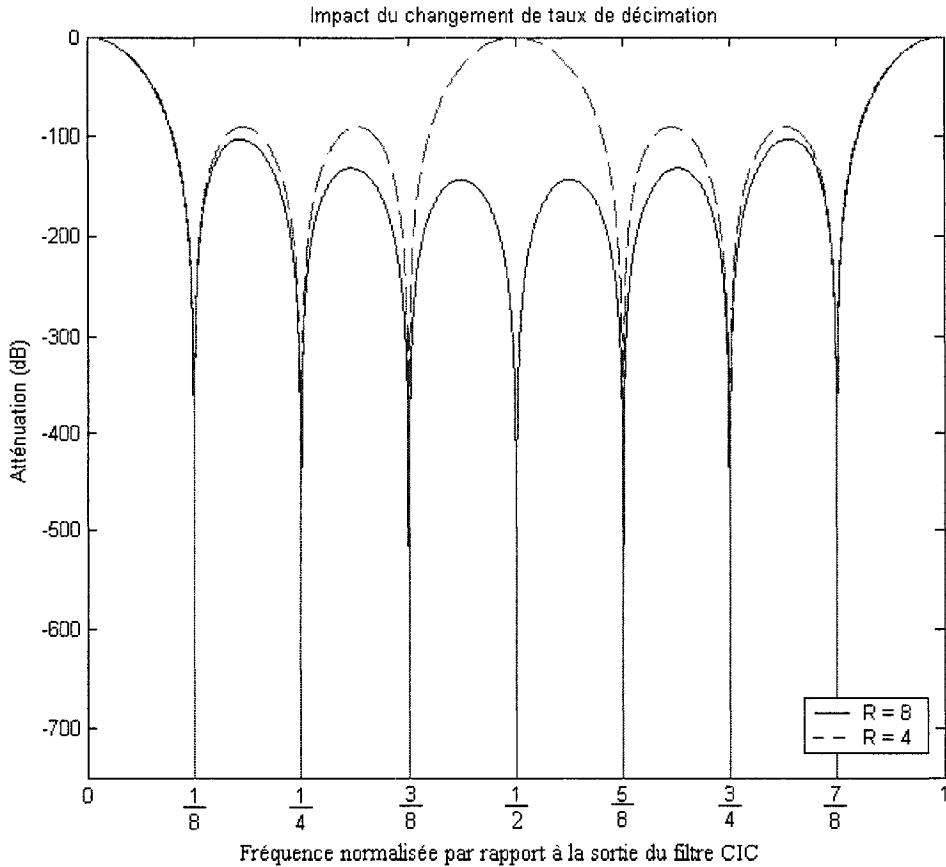

| 2.11 | Impact du taux de décimation (R) sur la réponse en fréquence d'un filtre CIC . . . . .                   | 53 |

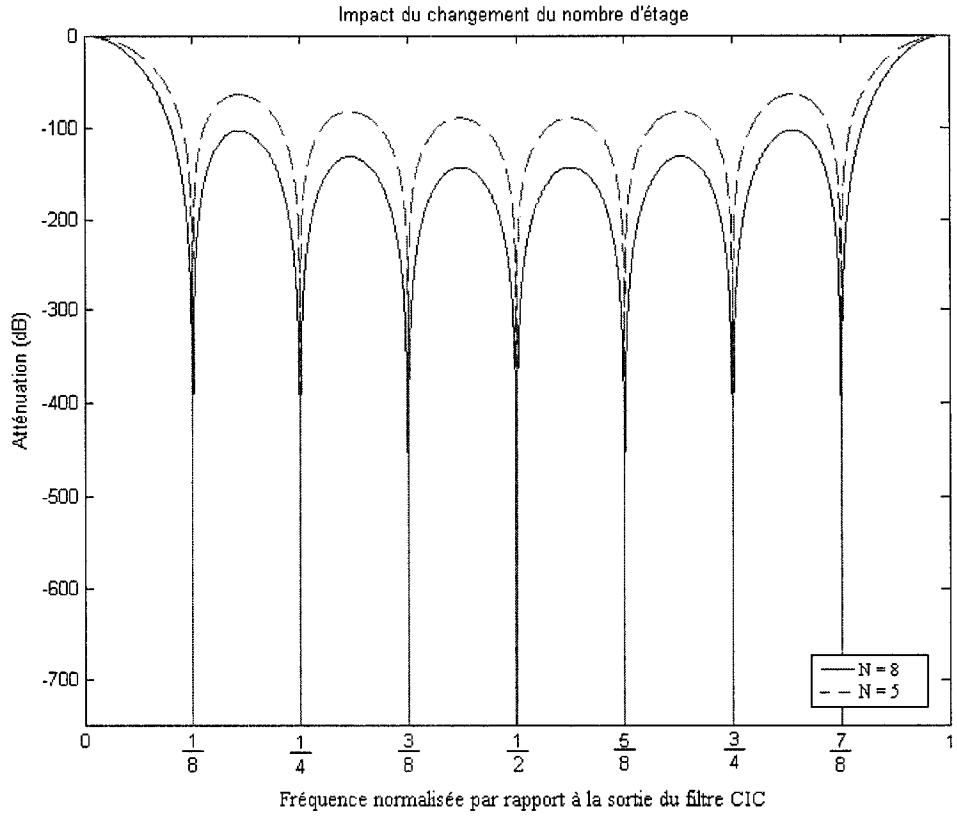

| 2.12 | Impact du nombre d'étages (N) sur la réponse en fréquence d'un filtre CIC . . . . .                      | 54 |

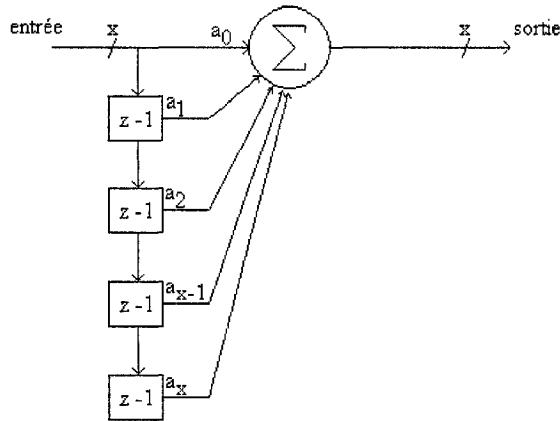

| 2.13 | Structure d'un filtre numérique de type FIR . . . . .                                                    | 56 |

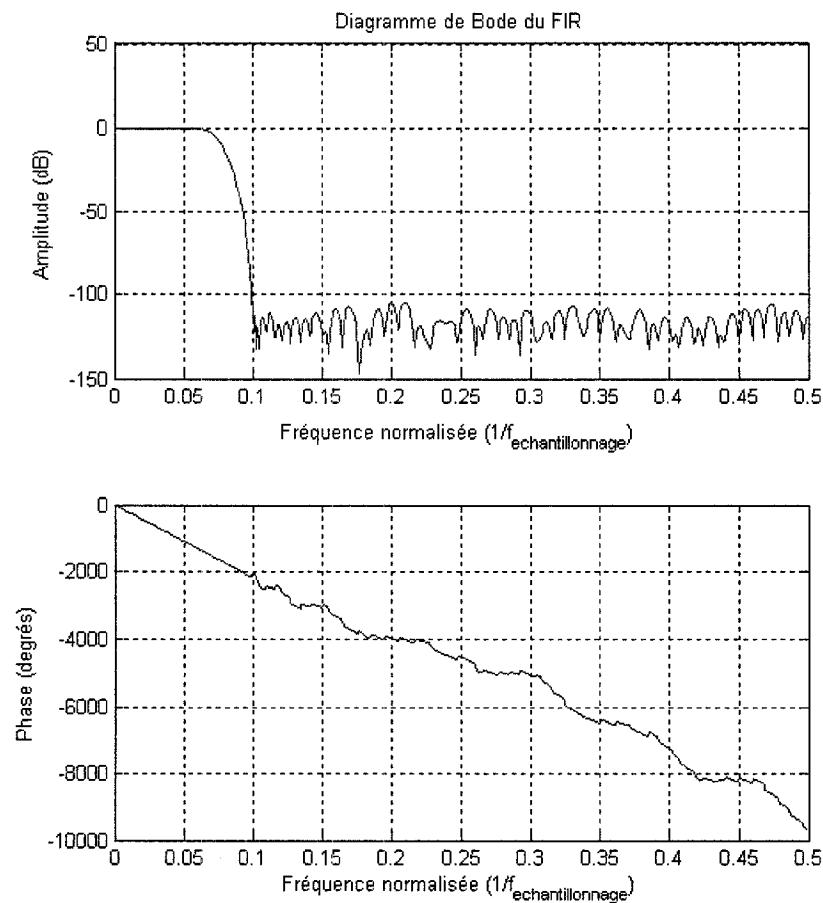

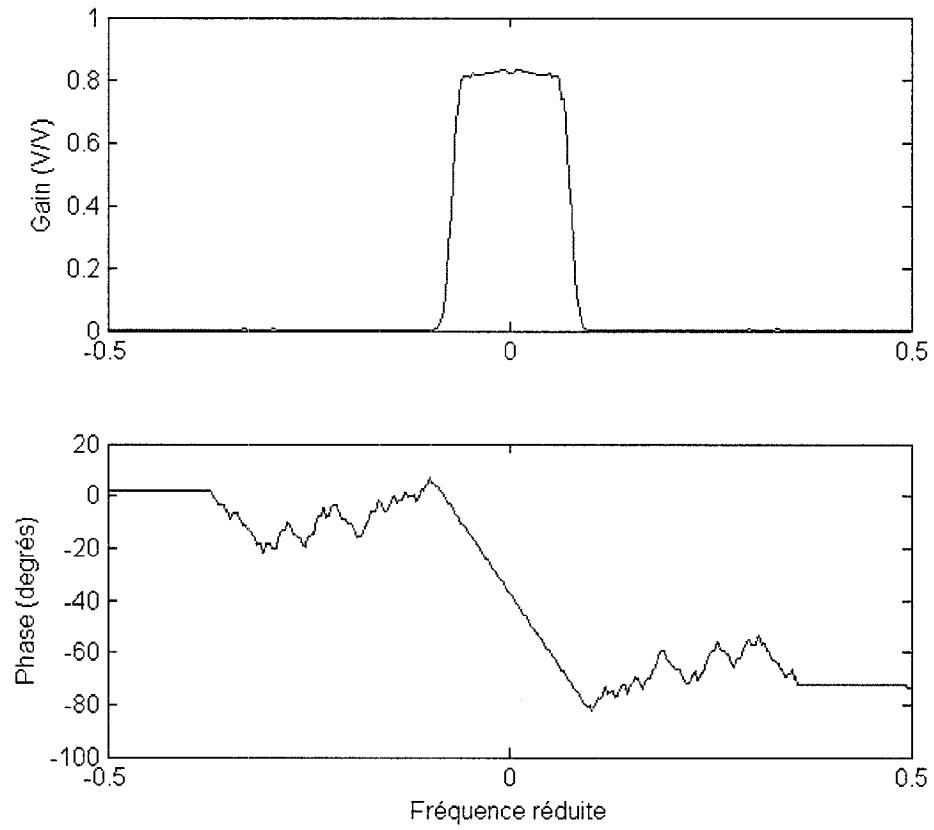

| 2.14 | Diagrammes de Bode des filtres FIR des systèmes TIE4-USB et TIE4-USB-i . . . . .                         | 57 |

| 2.15 | Réponse en fréquence du filtre FIR . . . . .                                                             | 58 |

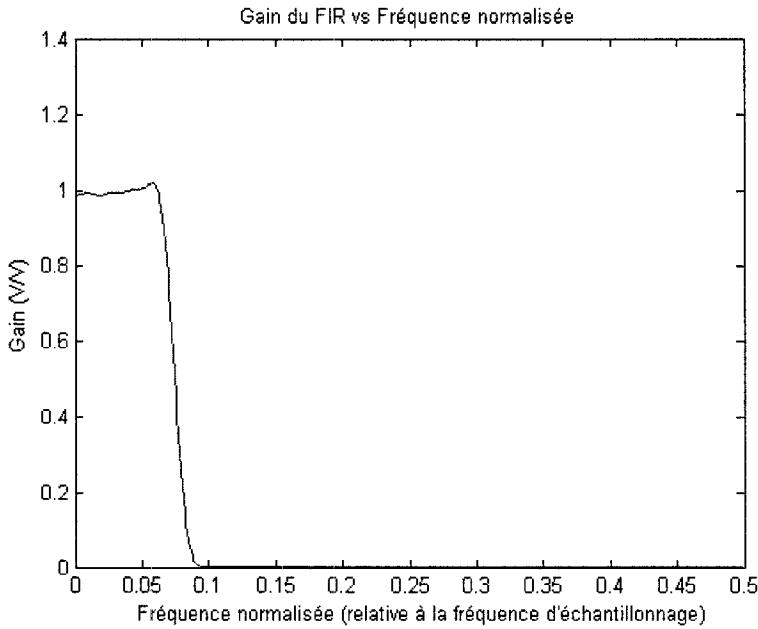

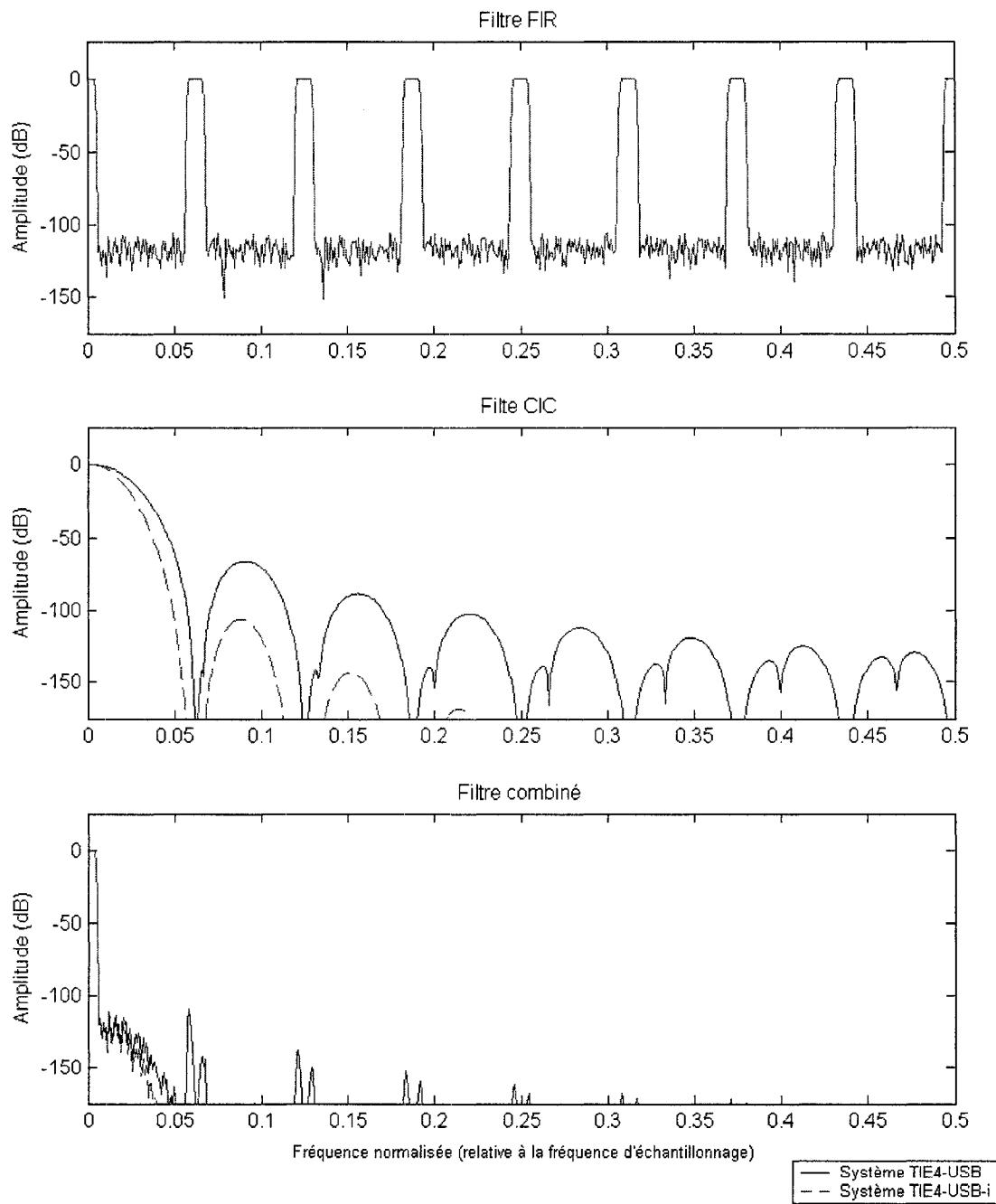

| 2.16 | Réponse en fréquence de la chaîne de démodulation du système TIE4-USB et du système TIE4-USB-i . . . . . | 59 |

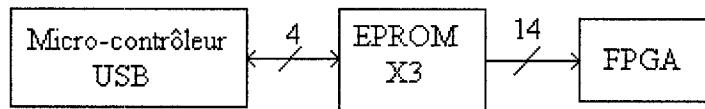

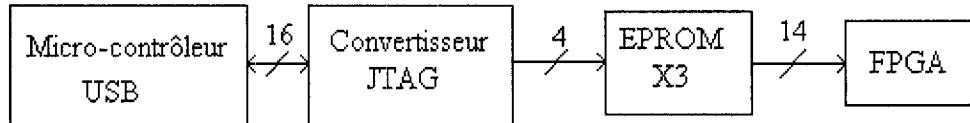

| 2.17 | Utilisation du EEPROM de Xilinx avec émulation du protocole JTAG par le microcontrôleur . . . . .        | 65 |

| 2.18 | Utilisation du EEPROM de Xilinx avec convertisseur JTAG spécialisé .                                     | 66 |

|                                                                                               |    |

|-----------------------------------------------------------------------------------------------|----|

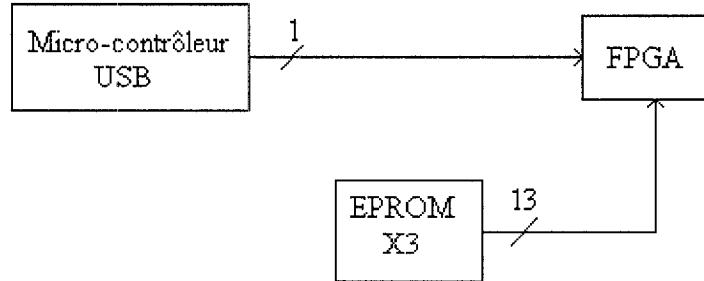

| 2.19 Utilisation du EPROM de Xilinx sans reprogrammabilité en cours d'utilisation . . . . .   | 66 |

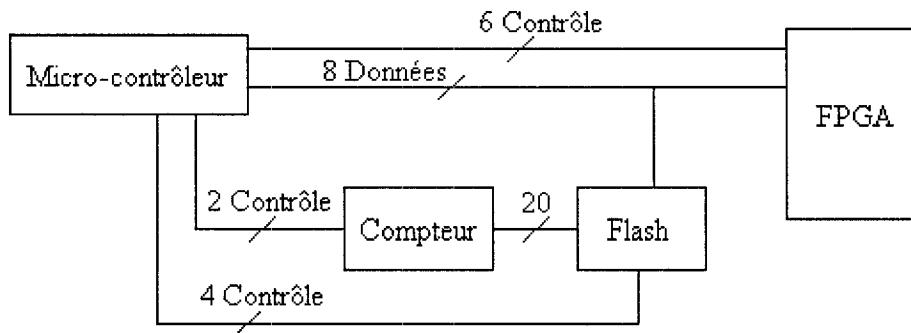

| 2.20 Utilisation d'une mémoire Flash avec compteur . . . . .                                  | 67 |

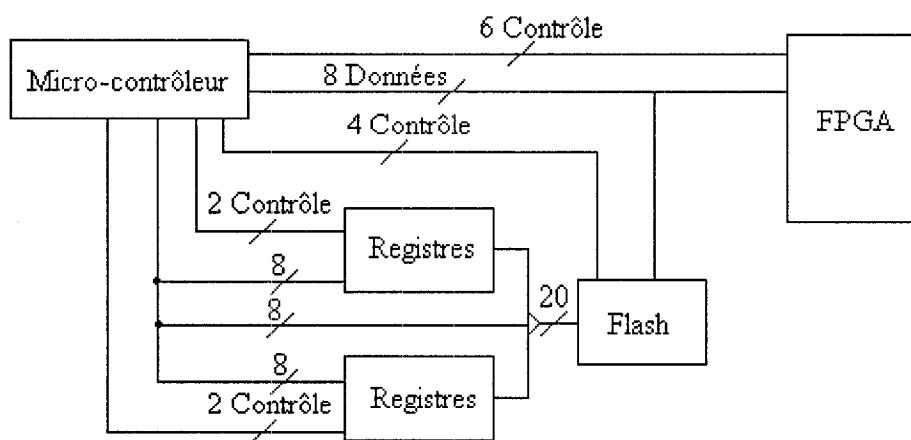

| 2.21 Utilisation d'une mémoire Flash avec bascules . . . . .                                  | 67 |

| 2.22 Utilisation d'une mémoire Flash avec un CPLD . . . . .                                   | 67 |

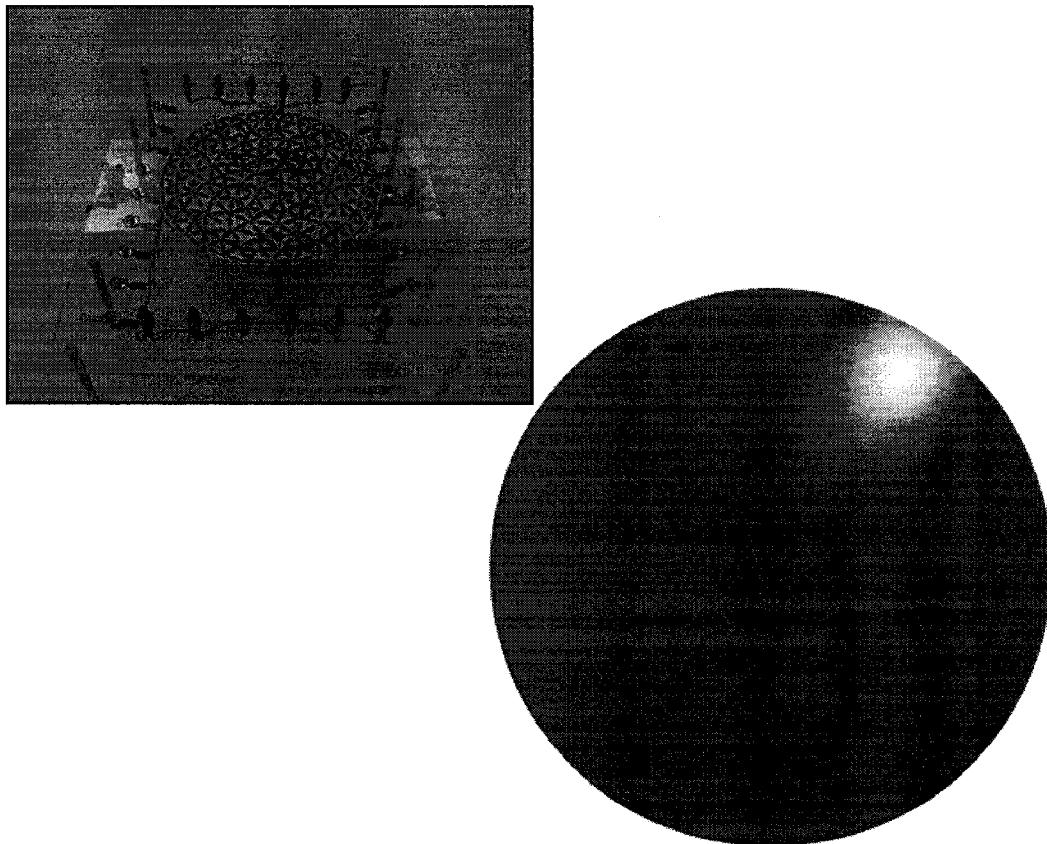

| 3.1 Image générée par le système TIE4-USB-i . . . . .                                         | 76 |

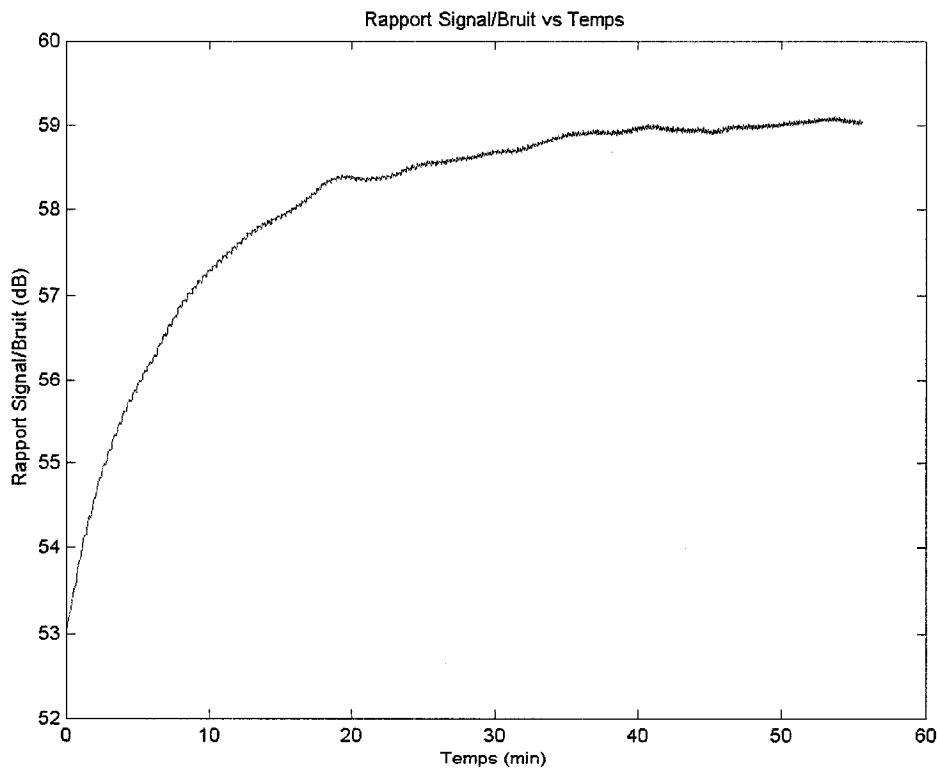

| 3.2 Évolution du RSB dans le temps pour un système initialement au repos                      | 79 |

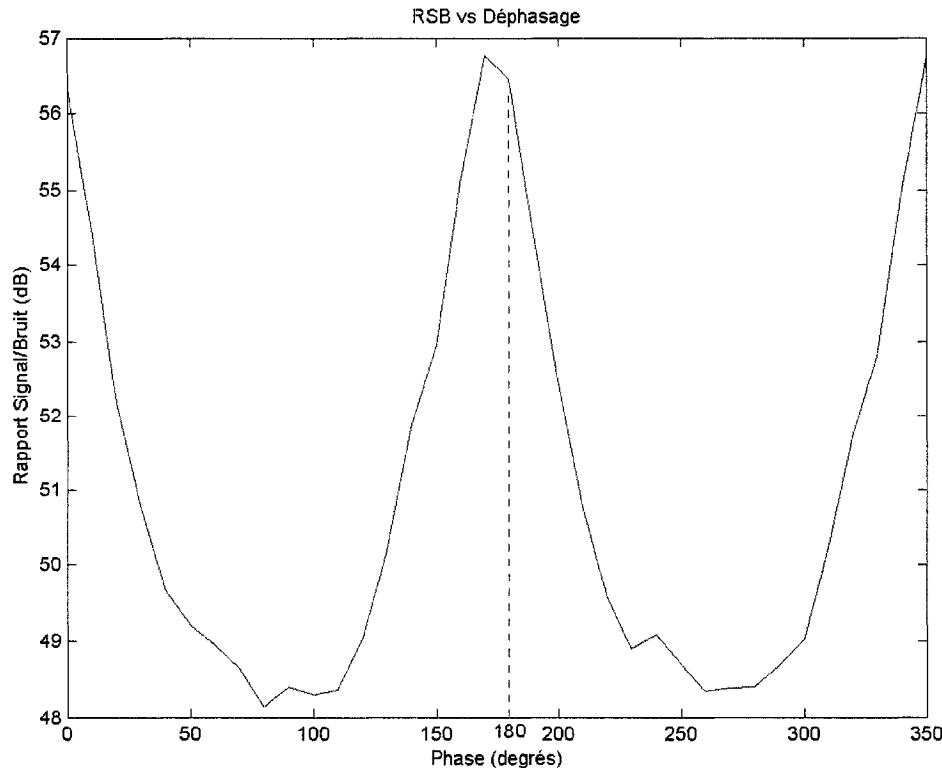

| 3.3 Impact du déphasage entre la porteuse de référence et la porteuse AM sur le RSB . . . . . | 81 |

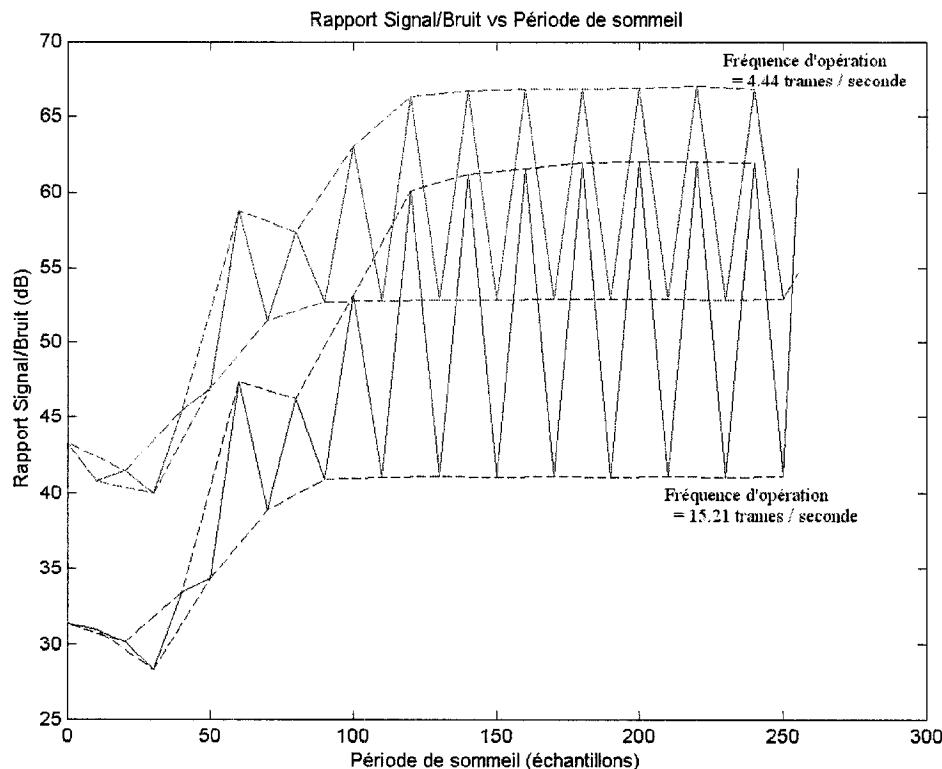

| 3.4 Relation entre la période de sommeil et le RSB pour deux fréquences d'opération . . . . . | 82 |

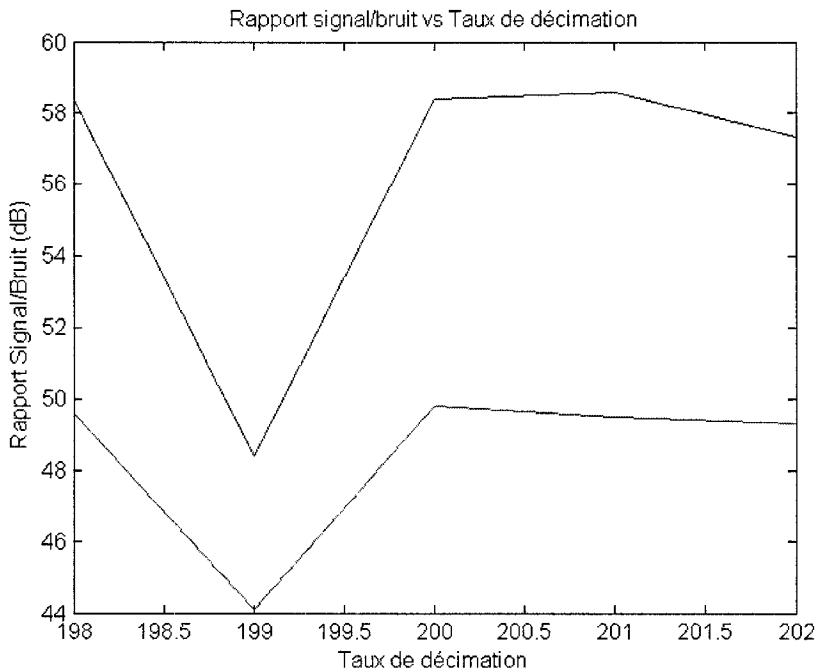

| 3.5 Effet d'un passage par un multiple de 20 du taux de décimation du CIC                     | 85 |

| 3.6 RSB en fonction de la fréquence d'opération . . . . .                                     | 86 |

| 3.7 Réponse en fréquence des filtres du MSD . . . . .                                         | 88 |

| 3.8 Précision moyenne de chaque système pour différentes cadences d'acquisition . . . . .     | 90 |

# Liste des sigles et abréviations

|             |                                                               |

|-------------|---------------------------------------------------------------|

| $\sigma$    | Conductivité (S)                                              |

| $\omega$    | Fréquence angulaire (radians/seconde)                         |

| $\epsilon$  | Permitivité (Farad/mètre)                                     |

| $\nabla$    | Gradient                                                      |

| $\theta$    | Phase (degrés ou radians)                                     |

| ASIC        | Application Specific Integrated Circuit                       |

| CAN (ADC)   | Convertisseur analogique-numérique (Analog-Digital Converter) |

| CNA (DAC)   | Convertisseur numérique-analogique (Digital-Analog Converter) |

| CIC         | Cascaded Integrator Comb                                      |

| CLB         | Combinatory Logic Block (bloc de logique combinatoire)        |

| CPLD        | Complex Programmable Logic Device                             |

| dB          | DéciBel                                                       |

| DC          | Direct Current                                                |

| DDC         | Digital Down Converter                                        |

| DDS         | Direct Digital Synthesizer                                    |

| DLL         | Dynamic Linked Library                                        |

| DNL         | Differential Nonlinearity                                     |

| DSP         | Digital Signal Processing                                     |

| (E)PROM     | (Electrically) Programmable Read-Only Memory                  |

| $\vec{E}$   | Champ électrique (V/m)                                        |

| $f$         | Fréquence ou fréquence réduite                                |

| FFT         | Fast Fourier Transform                                        |

| FIFO        | First-In, First-Out                                           |

| FIR         | Finite Impulse Response                                       |

| FPGA        | Field Programmable Gate Array                                 |

| IGB         | Institut de Génie Biomédical                                  |

| $\vec{J}$   | Densité de courant ( $A/m^2$ )                                |

| $\vec{J}_c$ | Densité de courant de conduction ( $A/m^2$ )                  |

| $\vec{J}_d$ | Densité de courant de déplacement ( $A/m^2$ )                 |

| LSB         | Least Significant Bit                                         |

| (M)DAC      | (Multiplying) Digital-Analog Converter                        |

|            |                                                                   |

|------------|-------------------------------------------------------------------|

| MEA        | Module d'Électrodes Actives                                       |

| MSB        | Most Significant Bit                                              |

| MSD        | Module de Synthèse et de Démodulation                             |

| PC         | Personal Computer                                                 |

| PSD        | Phase Sensitive Detector                                          |

| RSB        | Rapport Signal sur Bruit                                          |

| SFDR       | Spurious Free Dynamic Range (plage dynamique exempte de parasite) |

| TIE        | Tomographie d'impédance électrique                                |

| TIE4-USB   | Système de TIE version 4 avec protocole USB                       |

| TIE4-USB-i | Système de TIE version 4 intégré, avec protocole USB              |

| USB        | Universal Serial Bus                                              |

| $X_I$      | Composante en phase de X                                          |

| $X_Q$      | Composante en quadrature de X                                     |

# Introduction

## Généralités

La tomographie d'impédance électrique (TIE) utilise des électrodes placées à la surface d'un volume conducteur pour effectuer des mesures de tension et/ou de courant à partir desquelles on pourra reconstruire la distribution de conductivité qui caractérise ce volume. Des électrodes, habituellement 16, sont disposées uniformément sur le périmètre d'une section du corps à étudier. À tour de rôle, chaque paire d'électrodes applique un courant électrique sinusoïdal et chacune des autres paires effectue la mesure d'une différence de potentiel. Un algorithme de reconstruction utilise l'ensemble de ces mesures pour former une image de la distribution de conductivité électrique du corps étudié.

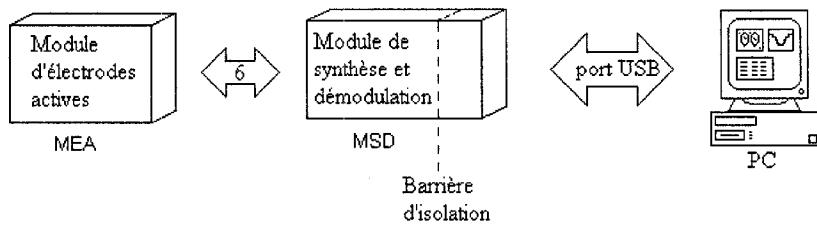

Le système TIE4-USB, développé à l'Institut de génie biomédical (IGB) de l'École Polytechnique de Montréal, comprend trois unités : le module d'électrodes actives (MEA), le module de synthèse et de démodulation (MSD), et l'ordinateur personnel (PC). Le PC sert d'interface graphique pour l'usager et traite les données recueillies par le MSD pour reconstruire l'image de variation de conductivité. Le module d'électrodes actives contient les circuits analogiques qui permettent d'appliquer un courant sinusoïdal entre des paires d'électrodes et à mesurer des différences de po-

tentiel entre d'autres paires d'électrodes. Il contient également des circuits logiques qui déterminent l'ordre d'utilisation des électrodes pendant l'acquisition. Le module de synthèse et de démodulation contient les circuits qui synthétisent la porteuse de référence contrôlant les sources de courant ainsi que les circuits de démodulation de la porteuse retournée par le MEA. Les communications entre le système TIE4-USB et le PC s'effectuent par un port USB.

Bien que l'utilité de la TIE s'étende à plusieurs domaines, le programme de recherches en TIE de l'IGB porte exclusivement sur les applications médicales de cette technique, et tout particulièrement sur le monitorage respiratoire. Plusieurs techniques permettent d'évaluer la ventilation pulmonaire. Les principales techniques utilisées sont la scintigraphie et la tomodensitométrie (CT-Scan) Coulombe (2003). Comme ces techniques utilisent des substances radioactives et des rayons X, elles ne peuvent être employées de façon continue. De plus, les appareils nécessaires sont volumineux et extrêmement coûteux. La TIE, quant à elle, peut être employée sur de longues périodes sans effets néfastes pour la santé. L'instrumentation requise est très compacte (occupant un volume comparable à un ordinateur portable) et son coût est suffisamment bas pour que l'on puisse dédier un système à chaque patient.

## Objectifs du projet

Le système de TIE actuellement utilisé à l'IGB rencontre les exigences pour d'éventuelles applications cliniques. Toutefois, les composants électroniques utilisés pour effectuer la synthèse et la démodulation des signaux sont des puces conçues pour des applications en télécommunication et sont optimisés pour un fonctionnement à hautes

fréquences (plusieurs MHz). Le système de TIE actuel applique un courant sinusoïdal de 50kHz. Les composants sont donc mal assortis à notre domaine d'application. De plus, il n'est pas possible avec les circuits intégrés utilisés dans le système TIE4-USB de maintenir un synchronisme absolu entre le synthétiseur et le démodulateur, ce qui se traduit par une perte de précision dans les mesures. Finalement, le grand nombre de puces spécialisées rend la gestion de l'obsolescence complexe. C'est-à-dire qu'au fur et à mesure que ces puces ne seront plus disponibles, des modifications majeures à l'architecture du système devront être faites. Le principal objectif du présent projet est de s'affranchir des diverses contraintes en regroupant les fonctions réalisées par plusieurs puces en un seul réseau de portes programmables.

Les objectifs secondaires du projet sont d'améliorer la précision des mesures et, si possible, de réduire les dimensions et les coûts du système. Cependant, des performances minimalement comparables à celles du système TIE4-USB sont exigées.

## Approche

Ce projet de maîtrise porte exclusivement sur le module de synthèse et de démodulation (MSD) du système de TIE. Afin de réduire le nombre de composants, toute la section numérique du module de synthèse et de démodulation sera intégrée dans une seule puce programmable de type FPGA. En réduisant le nombre de composants spécialisés, on facilite grandement la gestion de l'obsolescence de ces derniers. De plus, étant donné que toutes les étapes de traitement du signal sont programmées, il est possible de les adapter au contexte de la TIE et par conséquent, d'améliorer la précision des mesures. Cette intégration devrait aussi contribuer à réduire la taille du système.

Comme le projet est basé sur le système TIE4-USB, il était important dans un premier temps d'analyser le fonctionnement de ce dernier. Une architecture pour le nouveau système a ensuite été proposée. L'étape suivante a été d'implanter les fonctions désirées dans le FPGA. Finalement, le circuit imprimé a été adapté pour fonctionner avec le nouveau FPGA.

## Contenu du mémoire

Ce mémoire se compose de quatre chapitres. Le premier est une revue de la littérature. Les principales applications médicales de la TIE y sont décrites. On y traite également des différentes techniques de génération de signal et de démodulation. Les différentes approches concernant l'application du courant au patient y sont aussi abordées. Le second chapitre explore le fonctionnement du système TIE4-USB et décrit la conception du système TIE4-USB-i, développé dans le cadre de ce projet. Le troisième chapitre présente les mesures de performance effectuées pour comparer ces deux systèmes. Finalement, le chapitre quatre évalue la réussite de ce projet et propose des avenues de développement rendues possibles grâce à la réalisation de ce projet.

# Chapitre 1

## Revue de la littérature

Ce chapitre se divise en deux sections. La première donne un bref aperçu des origines de la TIE et décrit les principales applications médicales de cette technique. La deuxième section traite de l'instrumentation utilisée en TIE. Les différentes approches pour effectuer les mesures d'impédance y sont abordées. De plus, les techniques employées dans plusieurs systèmes de TIE pour synthétiser la porteuse de référence et démoduler le signal mesuré sont décrites. Les avantages et inconvénients de chacune d'entre elles sont également présentés.

### 1.1 Historique et applications médicales

Un des pionniers du développement de la tomographie d'impédance électrique, le professeur Brian Brown de l'Université de Sheffield (Royaume-Uni), estime que l'idée d'obtenir des images de l'impédance des tissus vivants remonte au début des années 70 Brown (2003). Il admet cependant que celle-ci aurait pu être formulée bien avant cela. Brown et son collègue, le professeur David Barber, ont été les premiers à publier,

en 1982, une image tomographique d'une section de l'avant-bras. Ceci survient quatre ans après que Henderson et Webster aient publié une image d'impédance transpulmonaire Brown (2003).

L'Institut de génie biomédical (IGB) a commencé à s'intéresser à la TIE en tant que domaine de recherche vers 1985. Au cours des 10 années qui ont suivi, trois systèmes différents ont été développés à l'École Polytechnique et de nombreux travaux de simulation, des essais avec des fantômes et des études *in-vivo* ont été réalisés [Guardo *et al.*, 1993, Adler et Guardo, 1994, Guardo *et al.*, 1994, Adler, 1995, Adler *et al.*, 1995, Adler et Guardo, 1995, Trudelle, 1995]. En 1996, un quatrième système, désigné TIE4, est mis au point. Il est ensuite amélioré pour donner naissance au système TIE4-USB en 2000 Robitaille (2000); Gagnon (2003). Ce système est actuellement le système de référence autour duquel sont articulés plusieurs projets de recherche à l'IGB.

Plusieurs applications médicales ont été proposées pour la TIE. Bon nombre de celles-ci ont fait l'objet d'études *in-vivo* chez l'animal ou d'essais cliniques à petite échelle. Les principales applications sont présentées ci-dessous.

### 1.1.1 Applications pulmonaires

Plusieurs applications de la TIE sont liées à l'étude du système respiratoire. Il est établi que les tissus du poumon ont une conductivité bien inférieure aux tissus environnants. De plus, la conductivité de ces tissus varie de façon significative durant le cycle respiratoire Brown (2003). La TIE peut donc être employée pour des fins de monitor-

age respiratoire. Deux études de Harris *et al.* (1987, 1988) concluent que les volumes pulmonaires obtenus par traitement d'images de TIE sont différentes d'environ 10% de ceux obtenus par spiromètre. Ils ont également effectué une étude sur cinq sujets soumis à un test à l'effort utilisant une bicyclette-ergomètre, suivi d'une période de repos Harris *et al.* (1992). Cette étude a démontré que la précision de la TIE pour la mesure du volume pulmonaire était comparable à celle du spiromètre dans ces conditions. Brown *et al.* (1994) ont démontré que la perfusion pulmonaire pouvait être observée à l'aide de la TIE. L'IGB s'est également intéressée au problème de quantification de la ventilation pulmonaire par TIE Coulombe (2003). Lors d'une étude impliquant 22 sujets normaux, une forte corrélation a été observée entre le changement de conductivité moyenne thoracique et le changement de volume d'air pulmonaire mesuré avec un spiromètre. Une relation de type quadratique a été trouvée entre ces deux variables et les coefficients de l'équation semblent influencés par certains paramètres, comme le sexe, le pli cutané et la circonférence thoracique mesurée au niveau des électrodes.

Dans un poumon normal, on retrouve environ 80% d'air et 5% de liquide physiologique. Le reste étant constitué de tissus biologique. Une proportion supérieure à 5% de liquide est habituellement un signe de la présence d'oedème pulmonaire. Comme la différence de conductivité entre l'air et le liquide est très grande, il est possible de monitorer l'évolution de cette pathologie. Une étude menée par Campbell *et al.* (1994) auprès de huit sujets chez qui un oedème a été volontairement provoqué par infusion de salin a révélé une baisse de la résistivité thoracique de 22%, 24%, et 11% respectivement à capacité pulmonaire totale, au volume respiratoire et au volume résiduel. La détection de l'oedème pulmonaire par TIE a également été étudiée à l'IGB. Adler (1995) a effectué une série d'expériences sur six chiens visant à mesurer

le volume respiratoire et la quantité de liquide présent. Après avoir anesthésié les chiens, une solution saline était instillée dans un poumon à l'aide d'un cathéter. Des mesures de TIE étaient prises à intervalles réguliers pour monitorer la réabsorption du fluide. Une bonne corrélation ( $r=0.975$  à  $0.998$ ) a été obtenue entre le changement de conductivité estimé par TIE et la quantité de liquide instillée.

### 1.1.2 Vidange gastrique

La vitesse à laquelle l'estomac se vide après l'ingestion d'un repas (vidange gastrique) dépend de plusieurs facteurs dont la pression entre l'estomac et le duodénum, la température du repas, son acidité, et son contenu énergétique. Plusieurs pathologies du système digestif se manifestent par une vidange gastrique atypique. Par exemple, une vidange gastrique particulièrement lente peut indiquer la présence de sténose du pylore Trudelle (1995), la valve fermant l'accès au duodénum (début de l'intestin) à partir de l'estomac. À l'opposé, une vidange très rapide peut indiquer un ulcère duodénal ou le syndrome de Zollinger-Ellison Trudelle (1995). La scintigraphie ou la dilution de marqueurs sont employées en clinique pour évaluer la vidange gastrique. Toutefois, ces techniques sont considérées semi-invasives. La scintigraphie utilise un isotope radioactif dans un repas test. Ce repas test est habituellement constitué de foie de poulet auquel du technétium ( $^{99m}Tc$ ) a été injecté. La dilution de marqueurs utilise une sonde endoscopique pour suivre l'évolution de la concentration du marqueur (habituellement du rouge de phénol). Si un repas ayant une résistance électrique significativement différente des tissus de l'estomac est ingéré, son cheminement peut être monitoré par TIE Avill *et al.* (1987); Magnall *et al.* (1987). Dans la plupart des études, un tel repas est composé de purée de pommes de terre salée.

Une étude clinique sur 28 enfants, dont 21 souffraient de symptômes de sténose du pylore, a été menée en 1988 Lamont *et al.* (1988). Cette étude n'a pas permis de conclure que la TIE peut détecter la présence de sténose du pylore. Toutefois, les données obtenues par TIE, conjointement à d'autres tests cliniques, ont été jugées utiles pour poser un diagnostic. Une étude menée en 1995 à l'IGB Trudelle (1995) portait sur quatre sujets sains. Les temps de vidange à 50% ont été évalués à la fois par scintigraphie et par TIE pour chaque sujet. Cette étude fut menée avec un des premiers systèmes de TIE développés par l'IGB. Les performances de ce système n'étaient malheureusement pas suffisantes pour que l'on puisse conclure que la TIE permet d'évaluer la vidange gastrique avec la même précision que la scintigraphie.

### 1.1.3 Imagerie cérébrale

L'impédance des tissus cérébraux varie en fonction de leur activité et des pathologies qui les affectent. Il a été démontré que lors de crises d'épilepsie, d'accidents vasculaires cérébraux, ou en présence d'ischémie cérébrale, la conductivité de ces tissus augmente d'environ 10% Holder (2001). Cette variation s'expliquerait par un apport sanguin plus important aux tissus et par le gonflement des cellules. La TIE pourrait donc être employée pour évaluer la gravité de la pathologie. D'autre part, des chercheurs de l'université de Londres (University College) ont réussi à détecter un changement d'impédance lié à des stimuli externes, tels des flashes lumineux, à l'aide de la TIE. Cette découverte laisse entrevoir la possibilité d'études fonctionnelles semblables à celles réalisées présentement à l'aide d'imagerie par résonance magnétique (IRM) ou de tomographie par émission de positrons (PET). La principale difficulté est que le

système de TIE présentement employé par ces chercheurs ne fournit pas de résultats reproductibles quant à la localisation du changement de conductivité Tidswell *et al.* (2001).

#### 1.1.4 Détection de tumeurs du sein

Selon Statistique Canada, environ 18 700 femmes sont diagnostiquées chaque année d'un cancer du sein et 5 400 autres en meurent<sup>1</sup>. L'importance de tests de dépistage fiables et peu coûteux est donc évidente. Les examens actuellement utilisés incluent la mammographie, les ultrasons, la thermographie, et la palpation. Il a été établi que la présence d'une tumeur affecte la circulation sanguine, modifiant ainsi la conductivité locale Jongschaap *et al.* (1994). La compagnie TransScan Medical Ltée (Israël) a mis au point un appareil, le TS2000, qui est utilisé comme complément à la mammographie pour la détection du cancer du sein. Une sonde composée d'une grille de 256 électrodes est appliquée sur le sein de la patiente. Celle-ci tient dans sa main un cylindre métallique qui sert d'électrode de référence. Chacune des 256 électrodes de la grille est reliée à la masse virtuelle d'un amplificateur opérationnel monté en amplificateur à transconductance (i.e. un courant d'entrée est transformé en tension à la sortie de l'amplificateur). Un signal de tension, dont l'amplitude et la fréquence peuvent être variées, est appliqué entre l'électrode de référence et la masse du système. En analysant les 256 signaux obtenus des 256 amplificateurs opérationnels, on peut tracer une carte de conductivité des tissus du sein. Cette carte permettrait, selon les concepteurs de cet appareil, de détecter certains types de tumeurs Florestal (2001). Cet appareil a été approuvé pour commercialisation par le *Food and Drug Administration* en 1999 FDA (1999). Des essais cliniques multicentre ont eu lieu au cours des

---

<sup>1</sup>Données estimées pour 1999, Statistique Canada

années suivantes. Les résultats définitifs de ces essais n'ont pas encore été publiés. Par contre, une étude clinique menée à l'hôpital de Pistoia (Italie) auprès de 6000 femmes a démontré que le dépistage du cancer du sein peut se faire au moyen de données d'impédance électrique Piperno *et al.* (1990). Dans cette étude, un système semblable à celui développé par la compagnie TransScan Medical Ltée était utilisé. Le système avait cependant une matrice de 64 électrodes. Les patientes subissaient un examen clinique régulier incluant la palpation, la thermographie, l'ultrasonographie, la radiographie, et la diaphanoscopie avant d'être examinées à l'aide du système à impédance. Lorsqu'un des examens indiquait une possibilité de cancer, une biopsie était pratiquée. Un total de 745 biopsies ont été effectuées. La table 1.1.4 indique les conclusions de chaque test de dépistage par rapport à la biopsie (celle-ci est considérée comme étant la référence).

Tableau 1.1: Comparaison des résultats des différents tests de dépistage du cancer du sein par rapport à la biopsie. Adapté de Piperno *et al.* (1990)

| Méthode de dépistage | Résultats confirmés | Résultats ambigus | Résultats divergents |

|----------------------|---------------------|-------------------|----------------------|

| Système à impédance  | 454                 | 172               | 119                  |

| Palpation            | 349                 | 220               | 176                  |

| Thermographie        | 388                 | 130               | 227                  |

| Ultrasonographie     | 334                 | 264               | 147                  |

| Radiographie         | 395                 | 196               | 154                  |

| Diaphanoscopie       | 269                 | 245               | 231                  |

Comme le fonctionnement de ces appareils est basé sur les différences de conductivité entre les tissus, la TIE est toute indiquée pour effectuer des tests de dépistage. Un projet de maîtrise réalisé à l'IGB en 2000-2001 visait à vérifier si la TIE multi-fréquence pouvait permettre de détecter des tumeurs du sein Florestal (2001). Des

simulations et des essais sur un fantôme d'Agar ont été réalisés avec un système multifréquence prototype. Cette étude visait principalement à identifier les spécifications essentielles du système de mesure multifréquence. Parmi celles-ci, l'importance d'une réponse en fréquence uniforme sur une bande de fréquence allant de quelques kilohertz à un mégahertz ou plus a été identifiée. L'architecture du module d'électrodes actives a aussi été définie. Tel que mentionné précédemment, ce module est responsable de l'application du courant d'excitation. Le courant appliqué est affecté par l'impédance de contact des électrodes et l'impédance du milieu biologique qui sont toutes deux inconnues. Devant la difficulté de réaliser une source de courant idéale pour une aussi grande largeur de bande, Florestal recommande d'implanter un mécanisme permettant de mesurer l'amplitude réelle du courant appliqué par chaque électrode.

## 1.2 Instrumentation

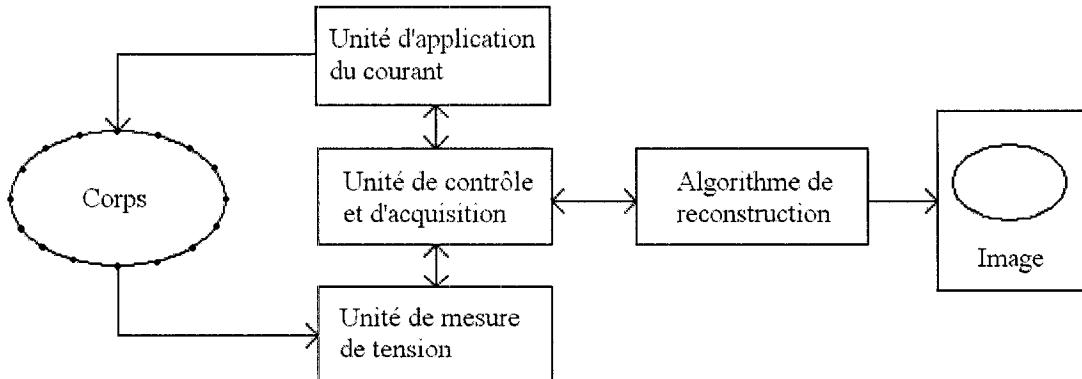

La description d'un système de TIE est grandement facilitée si on le subdivise en modules. L'architecture type d'un système de TIE est présentée à la figure 1.1. Chaque système possède une organisation qui lui est propre, mais tous les modules présentés à la figure 1.1 sont présents sous une forme ou une autre. Dans le cas du système TIE4-USB, développé à l'IGB, l'unité d'application de courant et l'unité de mesure de tension sont toutes deux situées dans le module d'électrodes actives (MEA). Une partie de l'unité de contrôle et d'acquisition est aussi située dans le MEA alors que la plus grande partie est située dans le module de synthèse et de démodulation (MSD). Le traitement des données par un algorithme de reconstruction d'images s'effectue dans le PC.

Figure 1.1: Architecture typique d'un système de TIE

Adapté de Bourne (1996)

### 1.2.1 Disposition des électrodes actives

Deux des problèmes les plus importants affectant la précision des données recueillies par un système de TIE sont 1) les capacités parasites entre les fils reliant les électrodes à l'unité de contrôle et d'acquisition, et 2) la diaphonie (*cross-talk*) entre ces mêmes fils Rigaud *et al.* (1993). Une solution à ces problèmes consiste à réduire le plus possible la longueur de ces fils.

#### 1.2.1.1 Électrodes actives distribuées

Une première façon de réduire la longueur des fils d'interconnexion consiste à munir chaque électrode de son propre circuit de contrôle [Anah *et al.*, 1988, Rigaud *et al.*, 1993]. Dans cette approche, un module de contrôle est physiquement construit sur chaque électrode et ces modules sont reliés entre eux par un faisceau de fils permettant de synchroniser l'action de l'ensemble des électrodes. On est donc en présence

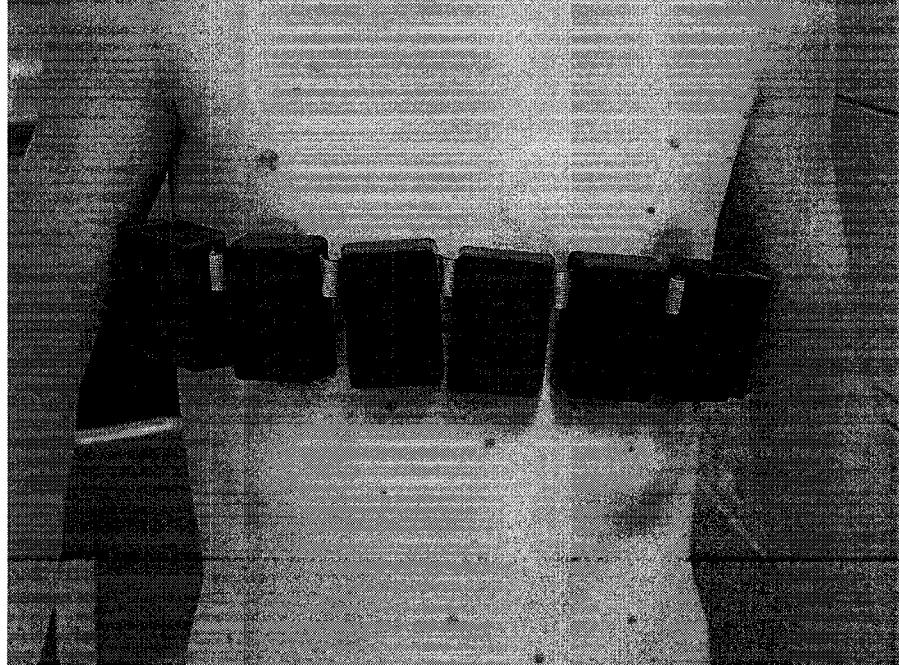

d'*électrodes actives distribuées*. Cette approche a été reprise à l'IGB Guardo *et al.* (1994) où un micro-contrôleur était employé pour chaque électrode, ce qui a permis de réduire le nombre d'interconnexions entre les modules. Il est à noter qu'avec cette approche, chacune des électrodes actives est fonctionnellement identique. Le déplacement de certaines opérations d'acquisition près du site de mesure permet de réduire les capacités parasites et la diaphonie. Un impact majeur de cette approche est d'augmenter la fréquence maximale atteignable par le système Record (1994). Il s'agit donc d'un avantage indéniable pour les systèmes multifréquences. Malgré ces avantages, l'approche par électrodes actives distribuées rend le système très inconfortable Robitaille (2000). Par exemple, le premier prototype d'électrodes actives réalisé à l'IGB mesurait 6 cm x 8 cm x 2 cm. Comme le montre la figure 1.2 ce réseau d'électrodes actives est inutilisable pour des enregistrements en position couchée.

Figure 1.2: Module d'électrodes actives distribuées posé sur un patient

### 1.2.1.2 Électrodes actives regroupées

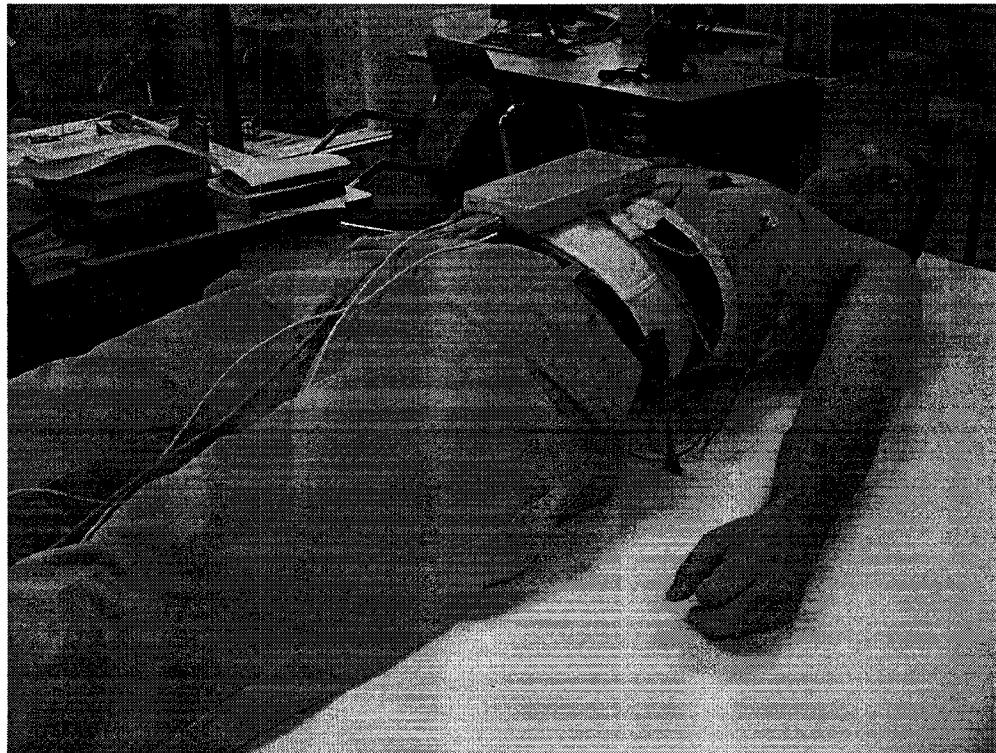

Pour régler le problème de dimension des électrodes actives distribuées, l'IGB a conçu un système hybride exploitant à la fois les avantages du système à électrodes actives distribuées et du système à électrodes distantes (i.e. les électrodes sont directement reliées au module d'acquisition à l'aide de long fils). Dans ce système hybride, tous les circuits servant à appliquer le courant, mesurer des tensions, et contrôler les 16 électrodes actives se retrouvent dans un module placé sur le thorax du patient. Les fils partant de ce module et allant aux électrodes ont tout au plus 30 cm Robitaille (2000). On appelle cette architecture *électrodes actives regroupées*. Une approche semblable a été employée par le groupe de recherche de Lyon Jossinet *et al.* (1994). Comme seules les électrodes sont physiquement reliées au patient, ce système peut être utilisé en position couchée. La figure 1.3 montre un réseau d'électrodes actives regroupées posé sur un patient en position couchée.

### 1.2.2 Générateur de porteuse

Le signal qui contrôle les sources de courant, appelé *porteuse de référence* est une onde sinusoïdale. Plusieurs moyens peuvent être utilisés pour générer ce signal. Bien que quelques groupes de TIE utilisent encore des circuits analogiques, par exemple un oscillateur à pont de Wien, la grande majorité synthétise numériquement ce signal pour ensuite le convertir en signal analogique Rigaud *et al.* (1994b).

Le générateur numérique utilise souvent une mémoire contenant un ou plusieurs cycles de la sinusoïde (lookup table). La vitesse et la manière auxquelles cette mémoire est parcourue permettent de générer des signaux de fréquences et de phases variables.

Figure 1.3: Module d'électrodes actives regroupées posé sur un patient

Pour contrôler l'amplitude de la porteuse, les valeurs binaires lues de la mémoire sont multipliées par une variable contenue dans un registre. Puisque la valeur à la sortie du générateur change brusquement lors de chaque mise à jour de la valeur du signal, ce dernier a une forme d'escalier. Pour adoucir ces transitions, la sortie du générateur est acheminée à un filtre passe-bas qui élimine les composantes spectrales indésirables. Tous les circuits numériques (multiplicateurs, registres,etc...) permettant d'effectuer ces opérations, de même que la mémoire de la table de sinus et un convertisseur numérique/analogique sont contenus dans une puce électronique appelée DDS (Direct Digital Synthesiser). Le fonctionnement d'un DDS sera expliqué à la section 2.2.1.1

### 1.2.3 Démodulation

Les tissus sont caractérisés par deux propriétés électriques: la conductivité ( $\sigma$ ) et la permittivité ( $\epsilon$ ). La densité du courant ( $\vec{J}$ ), exprimée par l'équation 1.1, qui est appliquée au patient contient deux composantes: la densité de courant de conduction ( $\vec{J}_c$ ) et la densité de courant de déplacement ( $\vec{J}_d$ ). Les courants de conduction et de déplacement sont respectivement liés à la conductivité  $\sigma$  et à la permittivité  $\epsilon$  selon les expressions 1.2 et 1.3.

$$\vec{J} = \vec{J}_c + \vec{J}_d \quad (1.1)$$

$$\vec{J}_c = \sigma \vec{E} \quad (1.2)$$

$$\vec{J}_d = j\omega\epsilon \vec{E} \quad (1.3)$$

où  $\omega$  représente la fréquence angulaire.

Si on considère l'hypothèse que le champ magnétique ne varie pas dans le temps, le champ électrique ( $E$ ) s'exprime comme:

$$\vec{E} = \nabla V \quad (1.4)$$

En substituant 1.2, 1.3, et 1.4 dans 1.1, on obtient une relation liant le gradient de potentiel ( $\nabla V$ ) et la densité de courant (eq. 1.5).

$$\vec{J} = (\sigma + j\omega\epsilon) \nabla V \quad (1.5)$$

Pour évaluer à la fois la conductivité et la permittivité, il est nécessaire de connaître

la composante réelle et imaginaire des valeurs de tension mesurées. Dans cette optique, on peut diviser les méthodes de démodulation en deux grandes catégories: celles qui sont sensibles à la phase et celles qui ne le sont pas. Les démodulateurs qui ne sont pas sensibles à la phase permettent d'évaluer l'amplitude du signal modulant mais ne donnent aucune indication quant à sa phase. Ainsi, un démodulateur d'amplitude permet d'évaluer la norme du terme  $\sigma + j\omega\epsilon$  alors qu'un démodulateur sensible à la phase permet d'évaluer à la fois  $\sigma$  et  $\epsilon$ .

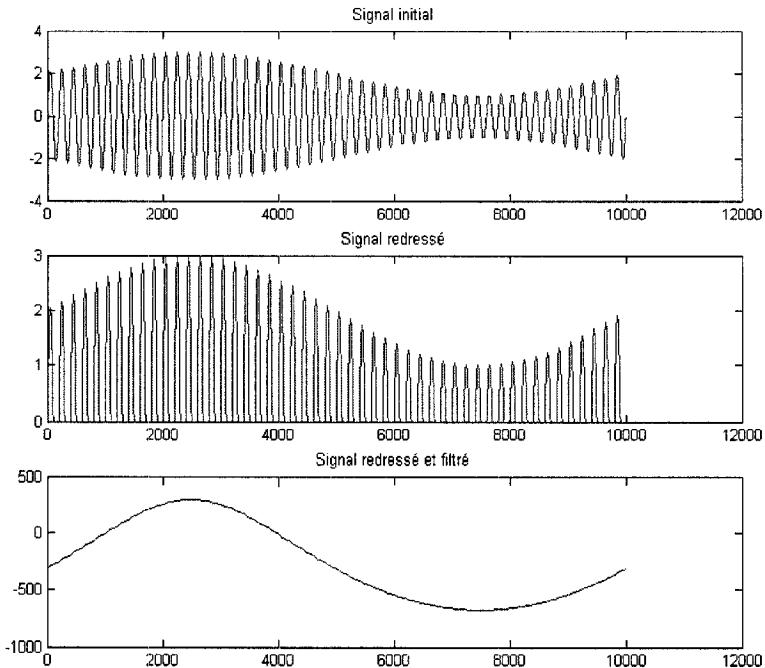

### 1.2.3.1 Démodulation d'amplitude

On recense principalement deux techniques de démodulation d'amplitude (ou non sensible à la phase). La première, utilisée par les groupes de l'Université de Tucumán (Argentine) et celui de l'Hôpital Général de Bristol (Royaume-Uni), est un démodulateur à détection d'enveloppe (ce type de démodulation est utilisé pour la réception de signaux radio AM). Le signal est d'abord redressé pour ensuite être filtré passe-bas. Les différentes étapes du traitement de signal sont illustrées à la figure 1.4.

Le principal inconvénient de ce type de démodulation est que le bruit présent dans la porteuse est également redressé et contribue au signal de sortie.

La seconde technique, utilisée dans le système de TIE développé par le groupe de l'Université de Louvain (Belgique) consiste à détecter les crêtes du signal à démoduler à l'aide d'un suiveur de crête (*peak-follower*) Bourne (1996). Les crêtes sont ensuite filtrées ou reliées entre elles par un échantillonneur-bloqueur pour retrouver le signal modulant.

Figure 1.4: Démodulation d'amplitude par détection d'enveloppe

Comme les circuits analogiques réalisant ce genre de démodulation sont très simples et peu coûteux, on peut en utiliser un par paire d'électrodes. On obtient donc un système parallèle ou semi-parallèle, ce qui permet d'atteindre des cadences d'acquisition de données plus élevées. En contrepartie, ce circuit ne permet pas de distinguer le signal d'intérêt qui se trouve à la fréquence de la porteuse des autres composantes fréquentielles du signal. On démodule l'ensemble du signal ce qui nuit à la précision des mesures.

#### 1.2.3.2 Démodulation sensible à la phase

La majorité des systèmes de TIE décrits dans la littérature utilisent des techniques de démodulation sensibles à la phase. Ces techniques permettent d'évaluer à la fois la composante réelle (en phase) et la composante imaginaire (en quadrature)

de l'impédance. On peut mettre en oeuvre ces techniques au moyen de circuits analogiques ou numériques.

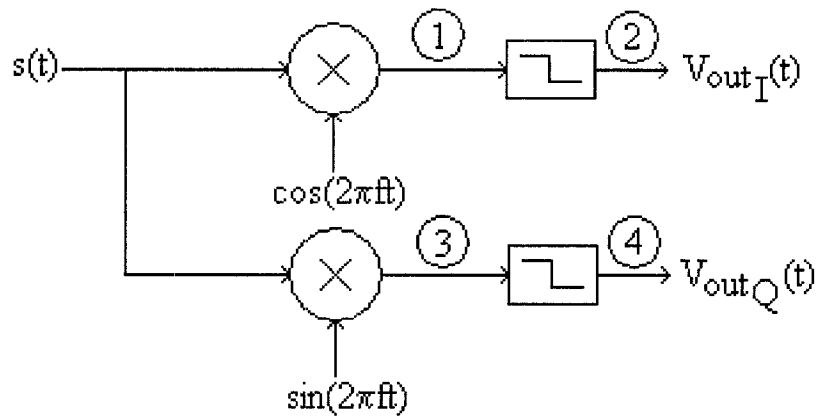

**Démodulation synchrone au moyen de circuits analogiques** Il existe principalement deux façons de réaliser un système analogique de démodulation sensible à la phase Blair et Sydenham (1975). La première approche, illustrée à la figure 1.5, utilise des multiplicateurs et des filtres passe-bas. Le signal à démoduler  $s(t)$  est multiplié par une sinusoïde de même fréquence et en phase avec la porteuse. Cette multiplication dans le domaine du temps est équivalente à une convolution dans le domaine fréquentiel; le signal produit comporte par conséquent un terme spectral centré autour de 0 Hz, et un second terme spectral centré autour du double de la fréquence de la porteuse. Ce second terme est éliminé par un filtre passe-bas situé à la sortie du multiplicateur. Le terme spectral centré autour de zéro est la composante réelle (en phase) du signal  $s(t)$ . La composante en quadrature est obtenue de la même façon mais le signal à démoduler est multiplié par une sinusoïde déphasée de  $90^\circ$ .

Figure 1.5: Démodulation cohérente par démodulation synchrone

Une démonstration mathématique de ce procédé de démodulation est donnée ci-dessous. Le signal d'entrée  $s(t)$  est une sinusoïde de fréquence  $f$  dont l'amplitude  $m(t)$  et la phase  $\theta(t)$  sont fonction du temps (éq. 1.6). Ce signal peut être exprimé comme la somme d'une composante en phase  $m_I(t)$  et d'une composante en quadrature  $m_Q(t)$  (éq. 1.8).

$$s(t) = m(t) \cdot \cos(2\pi ft + \theta(t)) \quad (1.6)$$

$$s(t) = m(t) \sin(\theta(t)) \cos(2\pi ft) + m(t) \cos(\theta(t)) \sin(2\pi ft) \quad (1.7)$$

$$s(t) = m_I(t) \cos(2\pi ft) + m_Q(t) \sin(2\pi ft) \quad (1.8)$$

$$\text{avec } m_I(t) = m(t) \sin(\theta(t)) \text{ et } m_Q(t) = m(t) \cos \theta(t) \quad (1.9)$$

Au point 1 du circuit de la figure 1.5 on a donc,

$$s(t) = m_I(t) \cos^2(2\pi ft) + m_Q(t) \sin(2\pi ft) \cos(2\pi ft) \quad (1.10)$$

$$= m_I(t) \cdot \frac{1 + \sin(2\pi(2f)t)}{2} + m_Q(t) \cdot \frac{\sin(2\pi(2f)t)}{2} \quad (1.11)$$

En supposant un filtre passe-bas idéal de fréquence de coupure inférieure à  $2f$ , les composantes à  $2f$  sont éliminées et on obtient au point 2:

$$V_{out_I}(t) = \frac{m_I(t)}{2} = \frac{m(t) \cdot \sin(\theta(t))}{2} \quad (1.12)$$

Par un raisonnement similaire, on obtient au point 3:

$$m_I(t) \cdot \frac{\sin(2\pi(2f)t)}{2} + m_Q(t) \cdot \frac{1 + \cos(2\pi(2f)t)}{2} \quad (1.13)$$

et au point 4

$$V_{out_Q}(t) = \frac{m_Q(t)}{2} = \frac{m(t) \cdot \cos(\theta(t))}{2} \quad (1.14)$$

Des signaux  $V_{out_I}$  et  $V_{out_Q}$ , on peut déterminer la fonction  $m(t)$  qui module la porteuse et la fonction  $\theta(t)$  qui représente le déphasage du signal modulé par rapport à la porteuse de référence. Les fonctions  $m(t)$  et  $\theta(t)$  sont utilisées dans la reconstruction d'images de TIE. Comme la distinction entre les composantes en phase et en quadrature est basée sur le déphasage entre le signal mesuré et celui de référence, il est primordial de garder un signal de référence synchronisé avec celui qui est appliqué.

Cette technique de démodulation permet de bien isoler le signal d'intérêt du reste du signal à démoduler. Comme il s'agit d'un circuit sensible à la phase, il permet également d'extraire les composantes réelle et imaginaire du signal modulé. Il est cependant difficile de réaliser un circuit analogique qui agisse comme un vrai multiplicateur. Ceux-ci possèdent en général une erreur de l'ordre de 5% sur toute leur plage dynamique. La réalisation de filtres passe-bas d'ordre élevé qui présentent à la fois une grande uniformité dans la bande passante et une phase très linéaire représente l'autre grand défi lors de la conception de ce circuit de démodulation. Compte tenu du coût de ce circuit de démodulation, il est généralement utilisé dans un système sériel. Le signal  $s(t)$  provient donc d'un multiplexeur. Le taux de multiplexage dépend du taux de rafraîchissement d'images désiré. Plus cette fréquence est grande, plus le nombre de mesures par unité de temps le sera. Ces changements fréquents étant riches en hautes fréquences, le spectre de  $s(t)$  s'en trouvera élargi ayant pour effet de compliquer encore plus la conception de filtres passe-bas adéquats. Le deuxième système de TIE réalisé à l'IGB au début des années 90 utilisait cette technique de

démodulation.

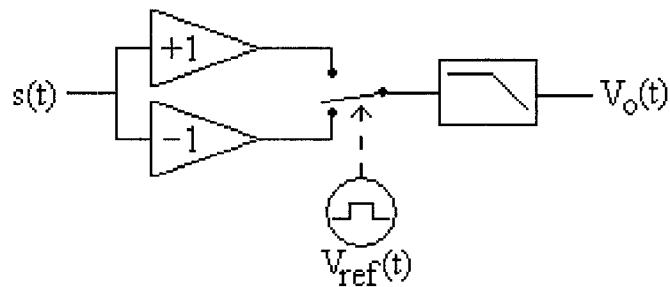

La seconde réalisation par circuits analogiques de la démodulation synchrone consiste à multiplier le signal à démoduler par une onde carrée symétrique d'amplitude crête unitaire synchronisée avec la porteuse de référence. On parle alors de détection synchrone ou de détection sensible à la phase. Ce procédé de démodulation est illustré à la figure 1.6.

Figure 1.6: Démodulation cohérente par détection synchrone

Le signal  $s(t)$  est appliqué simultanément à un suiveur et à un inverseur de gain unitaire. Un commutateur électronique (réalisé avec des portes linéaires) sélectionne alternativement la sortie du suiveur et de l'inverseur. Si le signal  $V_{ref}(t)$  qui commande le commutateur est synchronisé avec le passage à zéro de la porteuse de référence, alors le signal à la sortie du commutateur sera une version redressée du signal  $s(t)$ . Le procédé de démodulation peut être décrit mathématiquement en considérant le produit entre le signal  $s(t)$  (eq. 1.15) et les termes de la série de Fourier qui représente l'onde carrée  $V_{ref}(t)$  (eq. 1.16)

$$V_{ref}(t) = \frac{4V}{\pi} \left[ \cos(2\pi ft) - \frac{\cos(3(2\pi f)t)}{3} + \frac{\cos(5(2\pi f)t)}{5} \dots \right] \quad (1.15)$$

$$s(t) = m(t) \cdot \cos((2\pi f)t + \theta(t)) \quad (1.16)$$

Après la multiplication de  $s(t)$  par  $V_{ref}(t)$ , on a:

$$\begin{aligned} V_{ref}(t) \cdot V_i(t) &= \frac{4Vm(t)}{2\pi} \{ \sin(2(2\pi f)t + \theta(t)) + \sin(\theta(t)) \\ &\quad - \frac{\sin((2\pi f + 3(2\pi f))t + \theta(t))}{3} - \frac{\sin((2\pi f - 3(2\pi f))t + \theta(t))}{3} \\ &\quad + \frac{\sin((2\pi f + 5(2\pi f))t + \theta(t))}{5} + \frac{\sin((2\pi f - 5(2\pi f))t + \theta(t))}{5} + \dots \} \end{aligned} \quad (1.17)$$

Encore une fois, si on suppose que le filtre passe-bas est idéal et que sa fréquence de coupure est inférieure à  $2f$ , les termes de fréquence  $2f$  et plus sont éliminés.

$$V_o(t) = \frac{2Vm(t) \sin(\theta(t))}{\pi} \quad (1.18)$$

On peut obtenir la composante en quadrature en utilisant un signal  $V'_{ref}(t)$  déphasé de  $90^\circ$  relativement au signal  $V_{ref}(t)$  ci-dessus. C'est-à-dire en effectuant la commutation entre les sorties du suiveur et de l'inverseur aux crêtes de la porteuse de référence plutôt que lors de ses passages à zéro.

En pratique, cette technique de démodulation donne de meilleurs résultats que la précédente puisqu'il est plus facile de réaliser un commutateur quasi-idéal qu'un multiplicateur analogique. Cependant, lors de la commutation, le signal est entaché par quelques pics provenant d'un transfert de charge dans le commutateur électronique. Bien que les composantes en hautes fréquences de ces pics soient facilement éliminées par le filtre passe-bas, il existe également une partie DC qui reste présente à la sor-

tie du filtre. Cette partie DC est due au fait que les pics ne sont pas équilibrés. Les problèmes liés à la conception des filtres passe-bas qui étaient présents dans la méthode précédente se retrouvent également dans cette technique. Cette technique de démodulation a été employée dans le premier système de TIE de l'IGB.

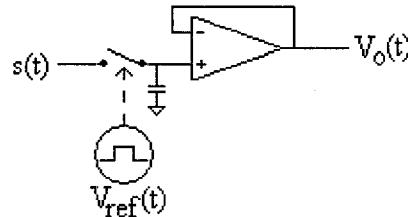

Une autre forme de démodulation analogique a été utilisée dans un système de TIE développé par le groupe de Xanthi (Grèce). Il s'agit d'échantillonner la porteuse modulée AM de manière à obtenir directement la composante réelle et imaginaire. Selon l'équation 1.8, si le signal est échantillonné alors que le signal de référence ( $\cos 2\pi ft$ ) passe par zéro, alors la partie en phase du signal est nulle. La composante imaginaire est donc obtenue. Pour obtenir la partie en phase, il suffit d'échantillonner alors que le signal de référence est à un maximum Koukourlis *et al.* (1992). Cette méthode est illustrée à la figure 1.7.

Figure 1.7: Démodulation cohérente par échantillonnage synchronisé de la porteuse AM

Une variante de la méthode présentée à la figure 1.5 a été employée dans un système développé à l'IGB (TIE-3) Guardo *et al.* (1993). Il s'agit d'une technique superhétérodyne. On effectue une première multiplication du signal à démoduler. Cette opération décale le spectre du signal à démoduler autour d'une fréquence intermédiaire ( $f_{IF}$ ). Un filtre analogique passif de grande précision optimisé pour fonc-

tionner à cette fréquence est utilisé pour rejeter les termes indésirables du produit. Le signal centré à  $f_{IF}$  est ensuite démodulé par des circuits semblables à ceux de la figure 1.5. Cette technique est particulièrement utile dans un système multifréquence puisque, peu importe la fréquence de la porteuse, le signal à démoduler est ramené à la même fréquence intermédiaire. Il est donc plus facile d'optimiser le processus de démodulation.

**Démodulation par des systèmes numériques** Le traitement numérique de signaux permet d'effectuer certaines opérations qui sont difficilement réalisables par des circuits analogiques. La première technique consiste à démoduler le signal de façon cohérente tel que démontré à la section 1.2.3.2. Une multiplication numérique est donc effectuée suivie d'un filtrage du signal. Ce type de démodulation peut être effectué à l'aide d'une unité de traitement numérique spécialisée nommée *changeur abaisseur de fréquence* (digital down converter - DDC). Cette approche est employée dans les systèmes TIE4 et TIE4-USB Robitaille (2000); Gagnon *et al.* (2003).

Les systèmes numériques permettent de réaliser des muplificateurs et des filtres passe-bas qui se rapprochent de l'idéal. En fait, la seule limite à la précision de la démodulation est le nombre de bits utilisés pour représenter  $s(t)$ . Cependant, l'augmentation des coûts et de la complexité fait que cette technique est principalement utilisée dans des systèmes sériels. La contrepartie de l'augmentation de précision dans les mesures est donc une réduction du taux de rafraîchissement de l'image.

Le système de TIE développé par le groupe de Stoke-on-Trent (Royaume-Uni) utilise une technique de démodulation basée sur la transformée discrète de Fourier.

La démonstration mathématique qui suit est adaptée de l'article de Jain *et al.*(1979).

Soit un signal à démoduler:

$$s(t) = \sum_{m=1}^M A_m \sin 2\pi f_m t + \phi_m \quad (1.19)$$

Dans cette expression,  $A_m$  et  $\phi_m$  sont fonction du temps. Toutefois, pour simplifier l'écriture, on omet les  $(t)$ . La transformée de Fourier discrète (TFD) du signal donne:

$$S(i) = \sum_{k=0}^{N-1} x(k) \cdot e^{-j \cdot \frac{2\pi}{N} ik} = \sum_{k=0}^{N-1} \sum_{m=1}^M A_m \sin 2\pi f_m t + \phi_m \cdot e^{-j \cdot \frac{2\pi}{N} ik} \quad (1.20)$$

La sommation étant un opérateur linéaire, la transformée de Fourier d'une somme de signaux est égale à la somme des transformées de Fourier de chaque signal. Ainsi:

$$S(i) = \sum_{m=1}^M \sum_{k=0}^{N-1} A_m \sin 2\pi f_m t + \phi_m \cdot e^{-j \cdot \frac{2\pi}{N} ik} = \sum_{m=1}^M \text{TFD}(A_m \sin 2\pi f_m t + \phi_m) \quad (1.21)$$

Le sinus peut être réexprimé en utilisant la relation d'Euler.

$$\sin \theta = -j \frac{e^{\theta} - e^{-\theta}}{2} \quad (1.22)$$

$$S(i) = \sum_{m=1}^M A_m \text{TFD}\left(\frac{-j}{2} e^{2\pi f_m t + \phi_m} - e^{-(2\pi f_m t + \phi_m)}\right) \quad (1.23)$$

Si on évalue la TFD, on a:

$$S(i) = \sum_{m=1}^M \frac{-j \cdot A_m}{2}$$

$$\left[ e^{-j\pi(i-f_m)\frac{N-1}{N}} \frac{\sin \pi(i-f_m)}{\sin \frac{\pi(i-f_m)}{N}} e^{j\phi_m} - e^{-j\pi(i+f_m)\frac{N-1}{N}} \frac{\sin \pi(i+f_m)}{\sin \frac{\pi(i+f_m)}{N}} e^{-j\phi_m} \right] \quad (1.24)$$

En substituant  $a = \pi \frac{N-1}{N}$  et  $f_m = \lambda_m f_0$ , on obtient, en fréquence réduite,

$$S(i) = \sum_{m=1}^M \frac{-j \cdot A_m}{2} \left[ e^{j(a(\lambda_m-i)+\phi_m)} \frac{\sin \pi(\lambda_m-i)}{\sin \pi \frac{\lambda_m-i}{N}} - e^{-j(a(\lambda_m+i)+\phi_m)} \frac{\sin \pi(i+\lambda_m)}{\sin \pi \frac{i+\lambda_m}{N}} \right] \quad (1.25)$$

À partir de cette transformée de Fourier discrète, il est possible d'évaluer l'amplitude et la phase à une fréquence d'intérêt ( $f_1$ ). On définit  $f_1$  par le produit de la fréquence d'échantillonnage ( $f_0$ ) par une constante ( $\lambda$ ).

$$f_1 = f_0 \cdot \lambda \quad (1.26)$$

La constante  $\lambda$  obtenue est composée d'une partie entière ( $l$ ) et d'une partie fractionnaire ( $\delta$ ). On définit alors la composante de fréquence  $f_1$ .

$$s_1(t) = A_1 \sin 2\pi f_1 t + \phi_1 \quad (1.27)$$

La transformée de Fourier discrète de ce signal est:

$$S(i) = -\frac{jA_1}{2} \left( e^{j(a(\lambda_1-i)+\phi_1)} \frac{\sin \pi(\lambda_1-i)}{\sin \pi \frac{\lambda_1-i}{N}} - e^{-j(a(\lambda_1+i)+\phi_1)} \frac{\sin \pi(\lambda_1+i)}{\sin \pi \frac{\lambda_1+i}{N}} \right) \quad (1.28)$$

Puisque la fréquence d'intérêt correspond à la fondamentale, il suffit de chercher les plus grandes lignes du spectre. On notera ces lignes  $S(l)$  et  $S(l+1)$ . Lorsque  $\lambda$  et  $N$  sont grands, le fait d'ignorer la seconde partie de l'équation 1.28 ne contribue

qu'à 0.04% de l'erreur totale Jain *et al.* (1979). L'équation 1.28 évaluée à  $l$  et à  $l + 1$  devient:

$$S(l) = \frac{-jA_1}{2} e^{j(a\delta+\phi_1)} \frac{\sin \pi\delta}{\sin \frac{\pi\delta}{N}} \quad (1.29)$$

$$S(l + 1) = \frac{-jA_1}{2} e^{j(a(\delta-1)+\phi_1)} \frac{\sin \pi(\delta-1)}{\sin \frac{\pi(\delta-1)}{N}} \quad (1.30)$$

De plus, comme  $N$  est grand, le sinus au dénominateur peut être approximé par son argument.

$$S(l) = \frac{-jA_1}{2} e^{j(a\delta+\phi_1)} \frac{\sin \pi\delta}{\frac{\pi\delta}{N}} \quad (1.31)$$

$$S(l + 1) = \frac{-jA_1}{2} e^{j(a(\delta-1)+\phi_1)} \frac{\sin \pi(\delta-1)}{\frac{\pi(\delta-1)}{N}} \quad (1.32)$$

En isolant l'amplitude dans 1.31 on obtient l'amplitude du signal d'intérêt démodulé.

$$A = \frac{2\pi\delta}{N} \frac{|S(l)|}{|\sin \pi\delta|} \quad (1.33)$$

ou

$$A = \frac{2\pi(1-\delta)}{N} \frac{|S(l+1)|}{|\sin \pi(1-\delta)|} \quad (1.34)$$

Jain *et al.* (1979) recommande cependant d'utiliser l'équation 1.33 sauf si  $|S(l+1)| > |S(l)|$ . Similairement, on évalue la phase avec

$$\phi = \text{Phase}\{S(l)\} - a\delta + \frac{\pi}{2} \quad (1.35)$$

ou

$$\phi = \text{Phase}\{S(l+1)\} - a(\delta-1) + \frac{\pi}{2} \quad (1.36)$$

Selon les auteurs, cette technique est principalement utile lorsqu'employée pour un système multifréquence. En effet, en choisissant comme signal d'excitation une somme de sinusoïdes dont les fréquences sont des nombres premiers et dont la phase est aléatoire, on peut démoduler l'ensemble des fréquences en une seule opération.

La dernière méthode présentée dans ce chapitre porte le nom de *méthode de démodulation de Prony*. Cette méthode a été développée par le groupe de Toulouse. Il s'agit d'une méthode paramétrique basée sur les travaux de Gaspard Riche, baron de Prony qui lui a donné son nom. On considère que le signal à démoduler  $x$  peut être exprimé sous la forme d'une somme de  $p$  exponentielles ( $b_m$ ) Chaveau *et al.* (1996). Avec  $p < \frac{N}{2}$  si  $N$  échantillons sont pris.

$$x[n] = \sum_{m=1}^p b_m z_m^n \quad (1.37)$$

Si on considère que le signal à la forme d'une sinusoïde à laquelle une valeur constante est ajoutée (éq. 1.38), on peut assumer que la fonction nécessitera trois exponentielles complexes (notées  $z_i$ ). En effet, deux exponentielles conjuguées-complexes représentent la sinusoïde alors que la troisième sert à introduire le décalage.

$$x[n] = a + 2A \cos\left(2\pi n \frac{f}{f_s} + \varphi\right) = b_1 \cdot Z_1 + b_2 \cdot Z_2 + b_3 \cdot Z_3 \quad (1.38)$$

Les paramètres sont donc définis comme étant:

$$b_1 = A e^{j\varphi}$$

$$b_2 = b_1^*$$

$$b_3 = a$$

$$\begin{aligned}

Z_1 &= e^{j\pi \frac{f}{f_s}} \\

Z_2 &= Z_1^* \\

Z_3 &= e^{j\pi \frac{0}{f_s}} = 1

\end{aligned}

\tag{1.39}$$

Si on écrit les p équations sous forme matricielle, on obtient:

$$\begin{aligned}

\hat{x} &= \vec{b}V \\

\text{avec } b = [b_1 b_2 b_3] \quad x = & \begin{bmatrix} x_0 \\ x_1 \\ x_2 \\ \vdots \\ x_n \end{bmatrix} \quad V = \begin{bmatrix} Z_0^0 & Z_0^1 & \dots & Z_0^n \\ Z_1^0 & Z_1^1 & \dots & Z_1^n \\ Z_2^0 & Z_2^1 & \dots & Z_2^n \end{bmatrix}

\end{aligned}

\tag{1.40}$$

Comme la matrice de Van der Monde  $V$  n'est pas inversible, on résout en servant d'une technique de moindres carrés

$$b = A^{-1}V^H\hat{x} \tag{1.41}$$

avec  $A = V^H V$ .

Selon Chaveau *et al.* (1996), le principal avantage de cette technique est la simplicité de son implantation. Cette simplicité est cependant compensée par un traitement très lent des données (1.5 min/trame à 10 kHz pour 128 échantillons / mesure).

#### **1.2.4 Résumé des techniques de synthèse et de démodulation des signaux**

Le tableau 1.2 présente différentes approches adoptées par des groupes de recherche pour générer la porteuse de référence et pour démoduler le signal provenant des électrodes. Les données présentées dans cette table sont tirées d'un sondage effectué par Rigaud *et al.* (1994b). Dans la majorité des cas, seule une indication générale sur la technique employée est donnée sans précision sur la méthode exacte.

Tableau 1.2: Méthodes de générations de porteuse et de démodulation utilisées en TIE. Adapté de Bourne (1996)

| Système         | Pays        | Générateur de porteuse de référence        | démodulation                                                |

|-----------------|-------------|--------------------------------------------|-------------------------------------------------------------|

| Aberdeen        | Royaume-Uni | Sinus numérique (EPROM + DAC)              | démodulation sensible à la phase (logiciel)                 |

| Ankara          | Turquie     | Générateur analogique                      | Démodulateur sensible à la phase (Quadrature)               |

| Barcelone       | Espagne     | Oscillateur contrôlé par voltage ou DDS    | démodulation sensible à la phase                            |

| Cardiff         | Royaume-Uni | Numérique                                  | démodulation sensible à la phase                            |

| Gdansk          | Pologne     | Générateur d'onde sinusoïdale (hétérodyne) | DSP + hétérodyne                                            |

| Göttingen       | Allemagne   | DDS                                        | Corrélation numérique                                       |

| Kuopio          | Finlande    | Composant générateur de fonction           | Numérique                                                   |

| Londres         | Royaume-Uni | PROM                                       | démodulation sensible à la phase                            |

| Lund            | Suède       | Interpolation linéaire avec MDAC           | démodulation sensible à la phase                            |

| Lyon            | France      | Non donnée                                 | démodulation sensible à la phase                            |

| Montréal        | Canada      | DDS                                        | démodulation sensible à la phase                            |

| Moscou          | Russie      | Pulsations de courant                      | Détecteur synchrone                                         |

| Oxford          | Royaume-Uni | Onde sinusoïdale                           | Sur-échantillonnage non uniforme                            |

| Sheffield       | Royaume-Uni | DAC + PROM                                 | Démodulateur analogique                                     |

| Stroke-on-Trent | Royaume-Uni | Numérique                                  | FFT + Filtre                                                |

| Stuttgart       | Allemagne   | EPROM + DAC                                | démodulation sensible à la phase                            |