**Titre:** Gestion générique et raffinement de systèmes électroniques à haut niveau

Title: high level

**Auteur:** Nicolas Laug

Author:

**Date:** 2008

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Laug, N. (2008). Gestion générique et raffinement de systèmes électroniques à haut niveau [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/8222/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8222/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

GESTION GÉNÉRIQUE ET RAFFINEMENT DE SYSTÈMES ÉLECTRONIQUES À

HAUT NIVEAU

NICOLAS LAUG

DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

DÉCEMBRE 2008

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file Votre référence*

*ISBN: 978-0-494-48927-7*

*Our file Notre référence*

*ISBN: 978-0-494-48927-7*

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

GESTION GÉNÉRIQUE ET RAFFINEMENT DE SYSTÈMES ÉLECTRONIQUES À

HAUT NIVEAU

présenté par : LAUG Nicolas

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

Mme. NICOLESCU Gabriela, Doct., présidente

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. GAGNON Michel, Ph.D., membre

## REMERCIEMENTS

Mes premiers remerciements s'adressent à mon directeur de recherche, M. Guy Bois pour son encadrement de mon travail de maîtrise, et qui a développé mon intérêt pour la conception de systèmes électroniques à haut niveau.

Je tiens également à remercier vivement Mme Gabriela Nicolescu et M. Michel Gagnon pour avoir accepté d'être présidente et membre du jury de cette maîtrise. Le temps qu'ils ont consacré à l'évaluation de ce travail est grandement apprécié.

Je salue aussi les membres du laboratoire CIRCUS, présents et passés, que j'ai rencontrés au cours de ma maîtrise. En particulier, merci à Marc-André pour son aide précieuse sur l'implémentation bas niveau, et à Benoit qui m'a grandement aidé à définir les contraintes des plateformes haut niveau. Merci aussi à Luc et Maxime pour leurs bons conseils. Sans oublier mes collègues de bureau, Fatoumata, Sébastien et Karim, ainsi que les autres membres du CIRCUS, Lam, Michel, Laurent, ...

Merci aussi au personnel de Polytechnique pour son aide lors des démarches administratives que j'ai eu à faire.

Merci enfin à ceux qui accepté mon départ de France, et tous ceux qui m'ont fait aimer le Québec.

## RÉSUMÉ

La complexité des systèmes sur puce augmente exponentiellement avec le temps. Ajoutée à une forte contrainte sur les temps de mise sur le marché (*time-to-market*), cette constatation aboutit à un besoin important de productivité. L'émergence récente des techniques de conception niveau système (*ESL*) apporte de nombreux avantages, dont la finalité est de répondre à ce besoin.

Pour réduire le temps de développement, il est également important de favoriser la réutilisation. L'échange de composants ne peut se faire que par un format de données standard. Le format IP-XACT, qui supporte l'*ESL* depuis sa dernière version 1.4, répond à ce besoin.

Le travail présenté dans ce mémoire de maîtrise est le cœur d'un environnement de conception *ESL* fondé sur IP-XACT. Il repose sur une bibliothèque de composants et est conçu de manière totalement générique. Autrement dit, le programme est entièrement indépendant des composants qu'il manipule.

Il est capable de manipuler des *designs* afin de générer des simulations. Mais il est surtout accompagné, et cela constitue la contribution essentielle du travail, d'un ensemble d'outils génériques. L'utilisation de ces outils nécessite des extensions au format IP-XACT, qui sont proposées dans ce mémoire.

L'utilisation de la plateforme suit la démarche de conception selon l'*ESL*. Les premières étapes sont consacrées à la spécification de l'application du système à concevoir. Puis, en utilisant des niveaux d'abstraction de plus en plus bas et précis, l'architecture finale est définie. La mise en œuvre réelle du système constitue la dernière étape.

Les outils permettent d'automatiser les tâches de création et de modification des modèles tout au long de ce flot de conception. Ils permettent en outre à l'utilisateur de faire abstraction des détails d'implémentation et d'être assisté lors des étapes de raffinement du système, jusqu'à son implantation sur carte à FPGA.

Le bon fonctionnement de la plateforme et des outils a été validé par différents essais unitaires. Dans ce mémoire, un cas d'utilisation est présenté. Il utilise la plateforme tout le

long du flot de conception d'un système, ce qui valide la fonctionnalité globale.

## ABSTRACT

Complexity of system on chips increases exponentially with time. Added to the pressure of time-to-market constraint, that situation leads to a great need of productivity.

Recent rise of electronic system level (ESL) techniques brings various advantages, aiming to answer that need.

To reduce development time, it is also important to foster reuse. Component exchange is possible only with a standard data format. IP-XACT standard, which supports ESL since its last 1.4 version meets that requirement.

The work presented in this report is the core of an ESL design environment based on IP-XACT. It uses a component library and it is design in a totally generic way. In other words, the software program is totally independent from the component it deals with. It is able to handle designs to generate simulations. Moreover, it embeds a set of generic tools, which are the main contribution of this work. Those tools need to add extensions to IP-XACT, which are proposed in this report.

The platform use follows the ESL design flow. The first steps are dedicated to specification of the application of the system to make. Then, using lower and more precise abstraction levels, the final architecture is defined. The last step is the real implementation of the system.

Tools automate model creation and modification tasks, in the ESL design flow. They also let the user make abstraction of implementation details, and be assisted in the refinement steps, down to an FPGA implementation.

Various unit tests have been run to validate the platform and its tools. In this report, a use case is presented. It uses the platform all along the design flow of a system, which validates its global functionality.

**TABLE DES MATIÈRES**

|                                                               |       |

|---------------------------------------------------------------|-------|

| REMERCIEMENTS . . . . .                                       | iv    |

| RÉSUMÉ . . . . .                                              | v     |

| ABSTRACT . . . . .                                            | vii   |

| TABLE DES MATIÈRES . . . . .                                  | viii  |

| LISTE DES FIGURES . . . . .                                   | xii   |

| LISTE DES ACRONYMES . . . . .                                 | xiv   |

| LISTE DES TABLEAUX . . . . .                                  | xvi   |

| LISTE DES ALGORITHMES . . . . .                               | xvii  |

| LISTE DES ANNEXES . . . . .                                   | xviii |

| INTRODUCTION . . . . .                                        | 1     |

| CHAPITRE 1 REVUE DE LITTÉRATURE . . . . .                     | 6     |

| 1.1 Hauts niveaux d'abstraction . . . . .                     | 6     |

| 1.1.1 Première étape : du niveau portes vers le RTL . . . . . | 6     |

| 1.1.2 Du RTL au TLM . . . . .                                 | 7     |

| 1.1.3 Les avantages du TLM . . . . .                          | 8     |

| 1.1.4 Les sous-niveaux transactionnels . . . . .              | 10    |

| 1.2 Réutilisation . . . . .                                   | 12    |

| 1.3 Automatisation et assistance de la conception . . . . .   | 14    |

| 1.4 SpaceCodesign . . . . .                                   | 16    |

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>CHAPITRE 2 IP-XACT . . . . .</b>                                | <b>21</b> |

| 2.1 Introduction . . . . .                                         | 21        |

| 2.2 Mode de connexion . . . . .                                    | 24        |

| 2.2.1 Ports . . . . .                                              | 24        |

| 2.2.2 Interfaces . . . . .                                         | 28        |

| 2.3 Composants et designs . . . . .                                | 30        |

| 2.3.1 Composants . . . . .                                         | 30        |

| 2.3.2 Designs . . . . .                                            | 31        |

| 2.3.3 Composants hiérarchiques . . . . .                           | 32        |

| 2.4 Extensions . . . . .                                           | 32        |

| 2.4.1 Ajout d'informations : les <i>vendorExtensions</i> . . . . . | 32        |

| 2.4.2 Générateurs . . . . .                                        | 33        |

| <b>CHAPITRE 3 STRUCTURE LOGICIELLE . . . . .</b>                   | <b>38</b> |

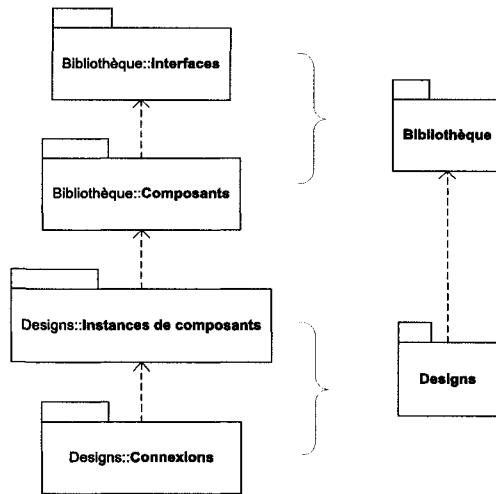

| 3.1 Gestion de la bibliothèque . . . . .                           | 40        |

| 3.1.1 Définition des interfaces de bus . . . . .                   | 40        |

| 3.1.2 Composants . . . . .                                         | 41        |

| 3.2 Designs . . . . .                                              | 43        |

| 3.2.1 Instances de composants . . . . .                            | 43        |

| 3.2.2 Connexions . . . . .                                         | 47        |

| 3.3 Projets . . . . .                                              | 51        |

| <b>CHAPITRE 4 OUTILS DE LA PLATEFORME . . . . .</b>                | <b>54</b> |

| 4.1 Introduction . . . . .                                         | 54        |

| 4.2 Signaux obligatoires . . . . .                                 | 55        |

| 4.3 Importation de paramètres . . . . .                            | 59        |

| 4.4 Génération d'adaptateurs . . . . .                             | 60        |

| 4.5 Automatisation du raffinement . . . . .                        | 64        |

| 4.5.1 Introduction . . . . .                                       | 64        |

|                   |                                                                         |           |

|-------------------|-------------------------------------------------------------------------|-----------|

| 4.5.2             | Spécification des équivalences de composants . . . . .                  | 65        |

| 4.5.3             | Exploration des choix de design . . . . .                               | 67        |

| 4.5.4             | Création du design raffiné . . . . .                                    | 69        |

| 4.5.5             | Support des cas particuliers : utilisation des générateurs . . . . .    | 71        |

| 4.5.6             | Composants hiérarchiques . . . . .                                      | 73        |

| 4.6               | Composants utilisateur . . . . .                                        | 75        |

| 4.7               | Exploration du partitionnement logiciel-matériel . . . . .              | 76        |

| 4.8               | Liens directs . . . . .                                                 | 80        |

| 4.8.1             | Liens matériel-matériel . . . . .                                       | 81        |

| 4.8.2             | Liens matériel-logiciel et logiciel-logiciel . . . . .                  | 83        |

| <b>CHAPITRE 5</b> | <b>VERS L'IMPLÉMENTATION MATÉRIELLE</b> . . . . .                       | <b>85</b> |

| 5.1               | Introduction . . . . .                                                  | 85        |

| 5.2               | Contraintes et spécifications dans les fichiers IP-XACT . . . . .       | 86        |

| 5.2.1             | Blocs IP . . . . .                                                      | 86        |

| 5.2.2             | Description des cartes . . . . .                                        | 87        |

| 5.3               | Méthode . . . . .                                                       | 89        |

| 5.3.1             | Différences avec la méthode haut niveau . . . . .                       | 89        |

| 5.3.2             | Génération du projet XPS . . . . .                                      | 90        |

| 5.4               | Cas particuliers et générateurs . . . . .                               | 90        |

| 5.4.1             | Composants utilisateur . . . . .                                        | 91        |

| 5.4.2             | Horloges . . . . .                                                      | 92        |

| 5.4.3             | Signal de réinitialisation . . . . .                                    | 93        |

| 5.4.4             | Processeur . . . . .                                                    | 93        |

| 5.5               | Outils supplémentaires pour la génération de fichiers IP-XACT . . . . . | 94        |

| 5.5.1             | Lecteur de MPD . . . . .                                                | 94        |

| 5.5.2             | Lecteur de XBD . . . . .                                                | 95        |

| 5.5.3             | Lecteur de sc_main . . . . .                                            | 95        |

|                                                |            |

|------------------------------------------------|------------|

| <b>CHAPITRE 6        APPLICATION . . . . .</b> | <b>98</b>  |

| 6.1 Présentation du système . . . . .          | 98         |

| 6.2 Création du premier design . . . . .       | 100        |

| 6.3 Second design et partitionnement . . . . . | 103        |

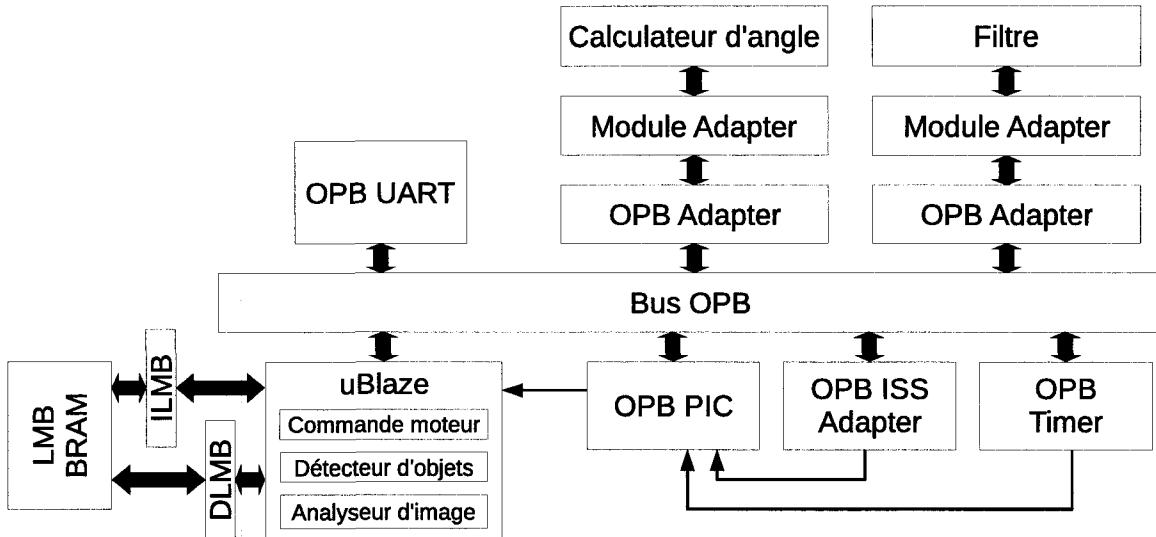

| 6.4 Génération bas niveau . . . . .            | 105        |

| <b>CHAPITRE 7        CONCLUSION . . . . .</b>  | <b>107</b> |

| <b>RÉFÉRENCES . . . . .</b>                    | <b>110</b> |

| <b>ANNEXES . . . . .</b>                       | <b>114</b> |

## LISTE DES FIGURES

|             |                                                                                     |    |

|-------------|-------------------------------------------------------------------------------------|----|

| Figure 1    | Le fossé de productivité . . . . .                                                  | 2  |

| Figure 1.1  | Simple communication transactionnelle entre deux modules . . .                      | 8  |

| Figure 1.2  | Modification du flot de conception en utilisant le TLM . . . . .                    | 8  |

| Figure 1.3  | Découpage des niveaux transactionnels selon deux axes . . . . .                     | 10 |

| Figure 1.4  | Modèle en couches . . . . .                                                         | 11 |

| Figure 1.5  | Vue globale de SpaceStudio . . . . .                                                | 17 |

| Figure 1.6  | Vue globale de la plateforme . . . . .                                              | 20 |

| Figure 2.1  | Exemple de fichier IP-XACT . . . . .                                                | 23 |

| Figure 2.2  | Communication port-module . . . . .                                                 | 25 |

| Figure 2.3  | Communication port-export . . . . .                                                 | 26 |

| Figure 2.4  | Cas d'utilisation des exports . . . . .                                             | 27 |

| Figure 2.5  | Architecture de communication selon la TGI . . . . .                                | 35 |

| Figure 3.1  | Dépendances globales de la plateforme . . . . .                                     | 39 |

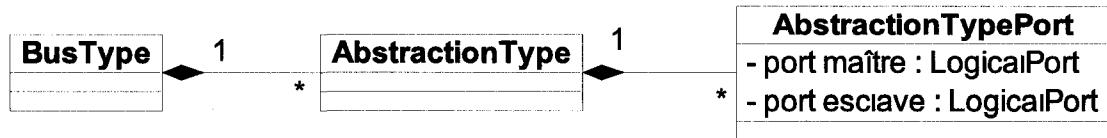

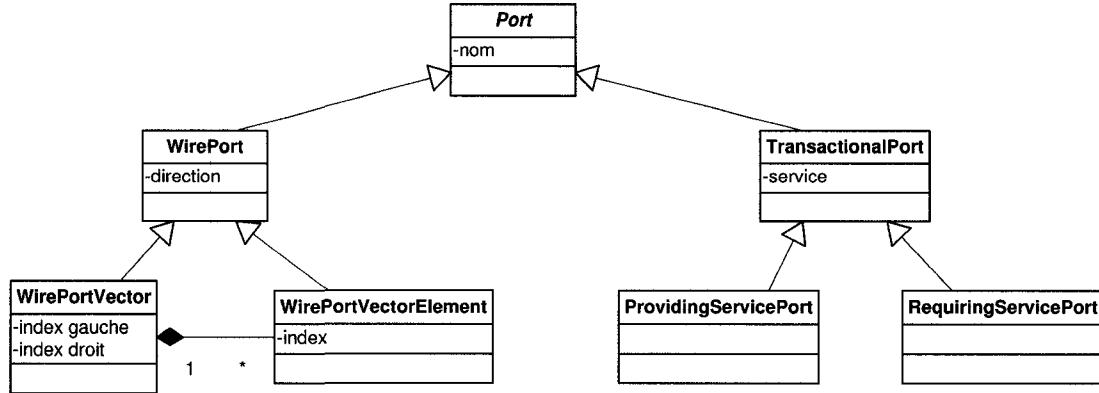

| Figure 3.2  | Relations de composition dans la définition des interfaces . . .                    | 41 |

| Figure 3.3  | Diagramme de classes pour la gestion des ports de composant .                       | 41 |

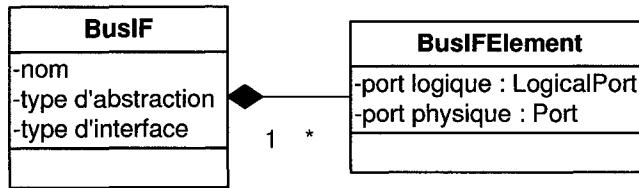

| Figure 3.4  | Interfaces de bus dans les composants . . . . .                                     | 42 |

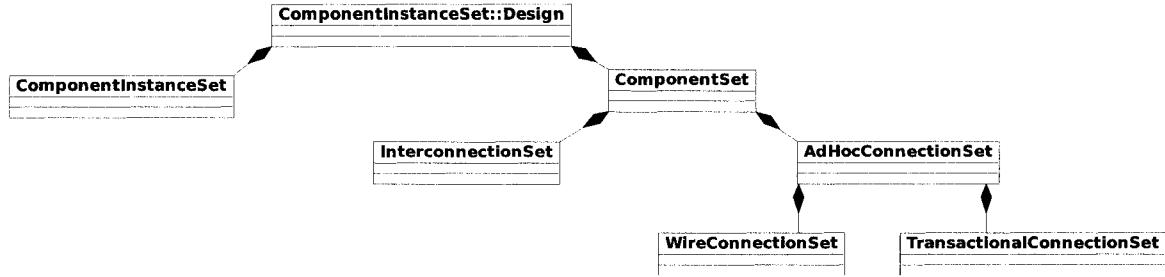

| Figure 3.5  | Gestionnaires des éléments de design . . . . .                                      | 43 |

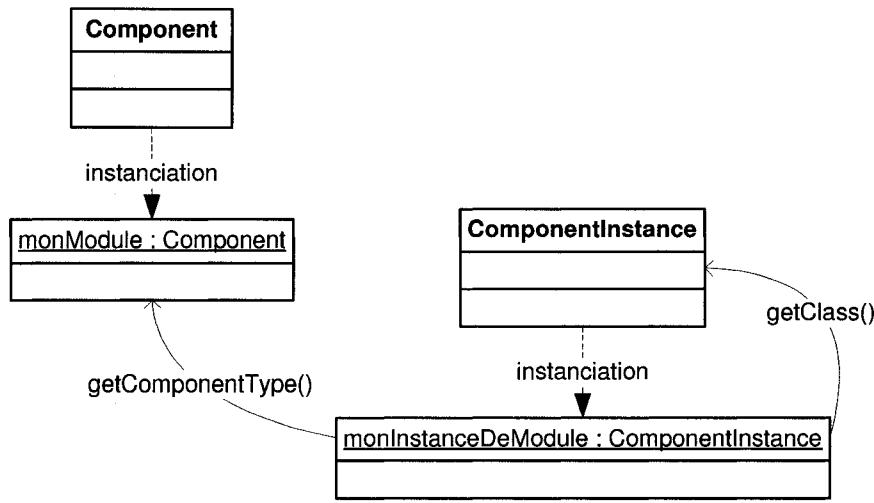

| Figure 3.6  | « Métaclasse » pour les composants . . . . .                                        | 44 |

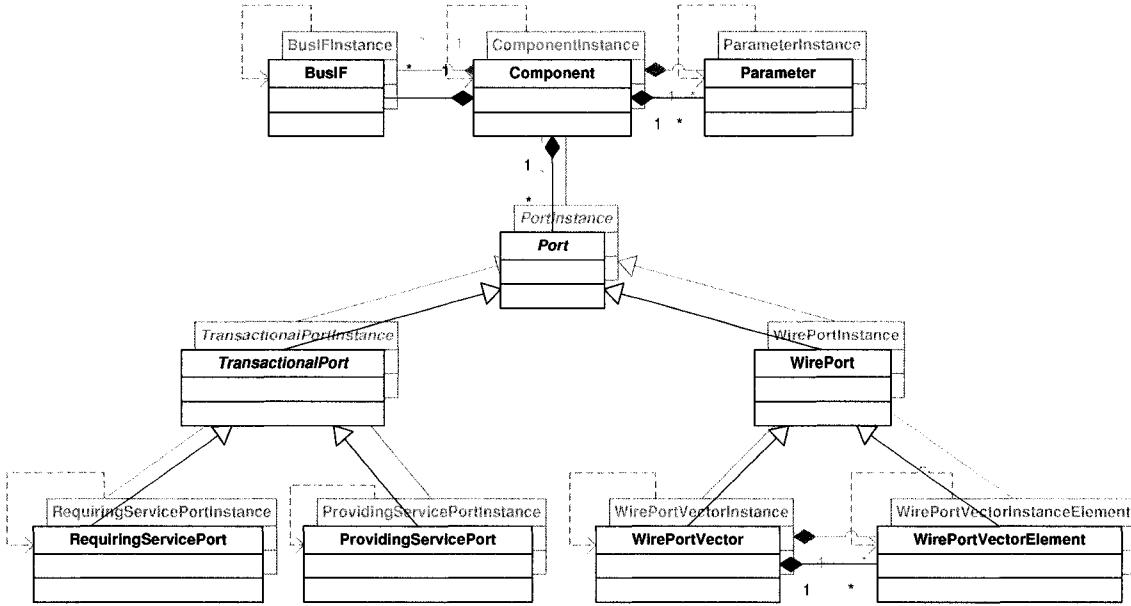

| Figure 3.7  | Diagrammes de classes de description des instances et types de composants . . . . . | 45 |

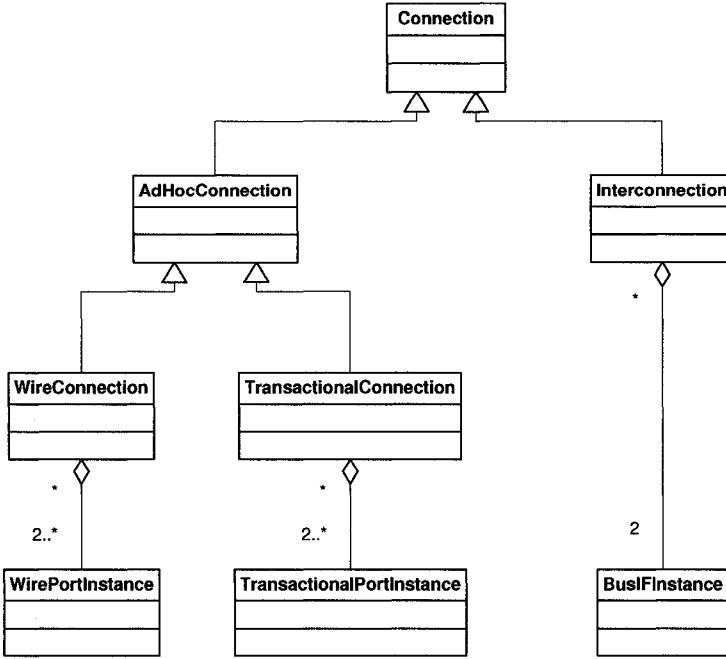

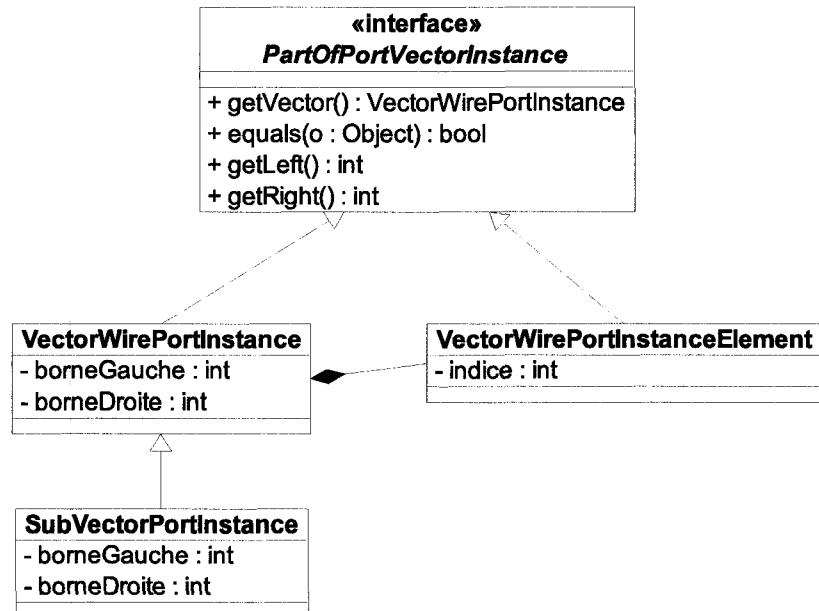

| Figure 3.8  | Relations d'héritage et de d'agrégation des classes de connexion .                  | 48 |

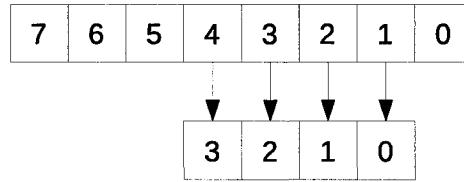

| Figure 3.9  | Connexion d'une partie de vecteur . . . . .                                         | 49 |

| Figure 3.10 | Interface <i>PartOfPortVectorInstance</i> . . . . .                                 | 50 |

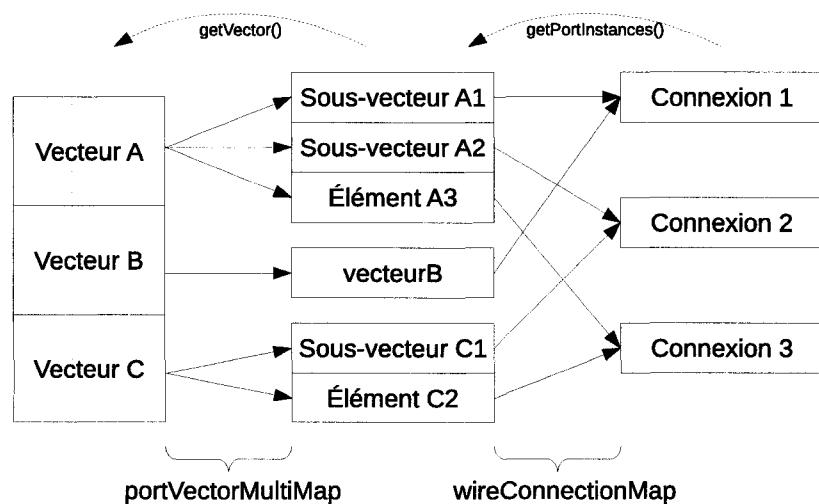

| Figure 3.11 | Tables de hachage du gestionnaire de connexions <i>wire</i> . . . . .               | 50 |

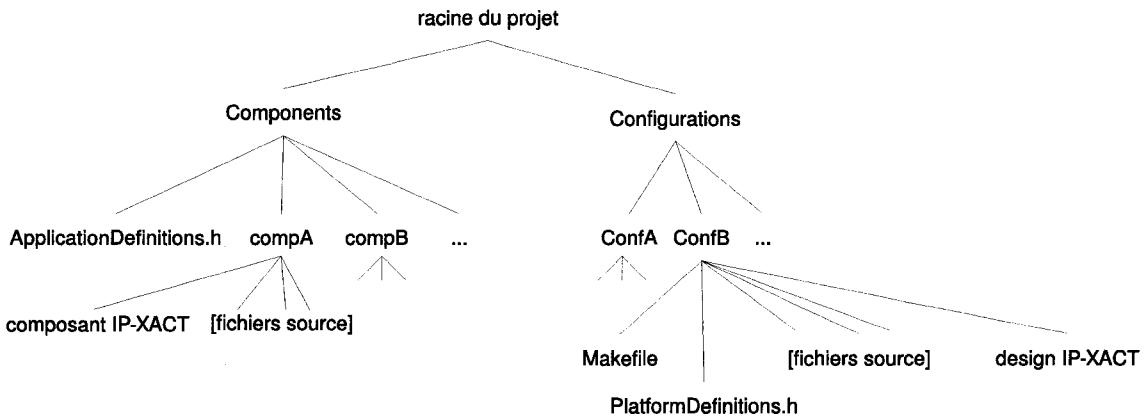

| Figure 3.12 | Structure de répertoire d'un projet SystemC . . . . .                               | 52 |

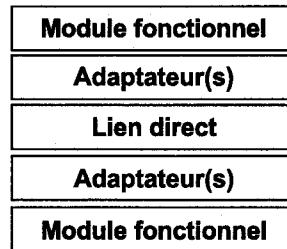

| Figure 4.1  | Exemple de chaîne de deux adaptateurs . . . . .                                     | 61 |

|            |                                                                          |     |

|------------|--------------------------------------------------------------------------|-----|

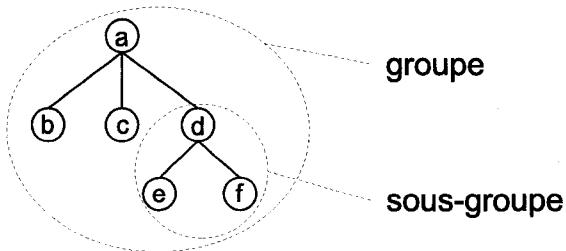

| Figure 4.2 | Définition de groupes et sous-groupes par relations d'héritage . . . . . | 66  |

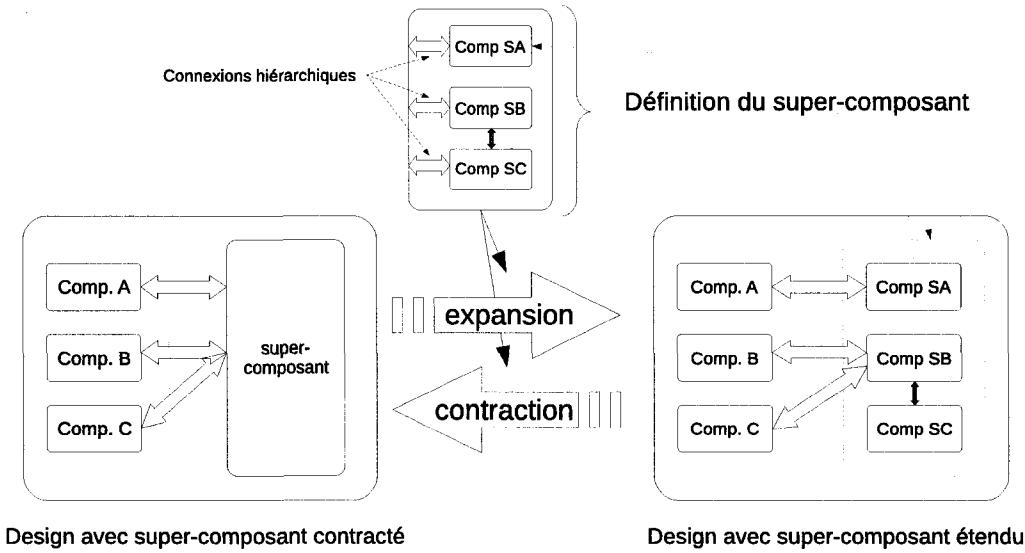

| Figure 4.3 | Expansion et contraction de composants hiérarchiques . . . . .           | 74  |

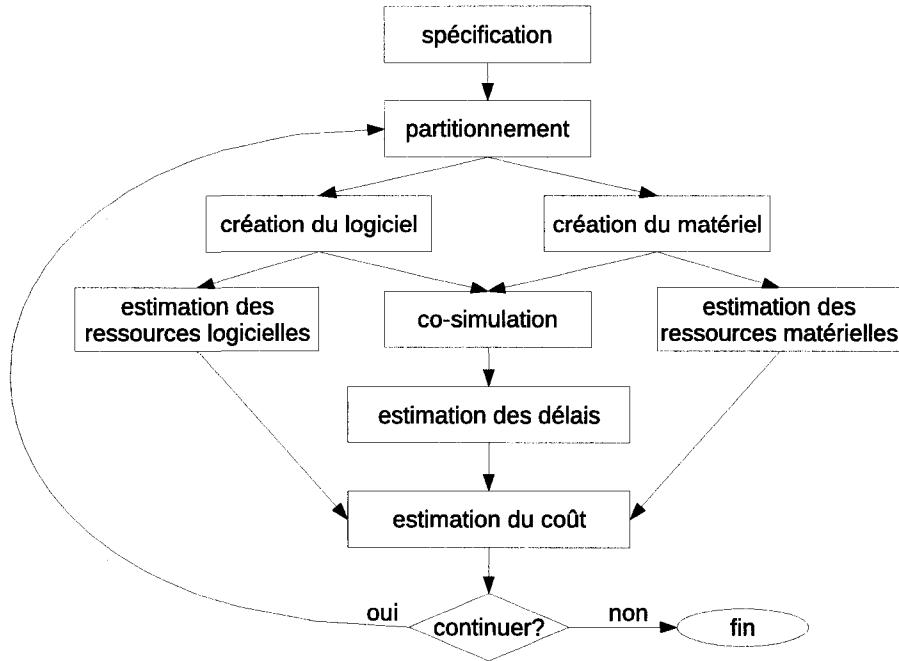

| Figure 4.4 | Principe général des méthodes de partitionnement . . . . .               | 77  |

| Figure 4.5 | Structure générée pour réaliser des liens directs matériels . . . . .    | 81  |

| Figure 4.6 | Classes utilisées pour la génération de liens directs . . . . .          | 81  |

| Figure 4.7 | Utilisation des générateurs dans les liens directs avec logiciel . .     | 83  |

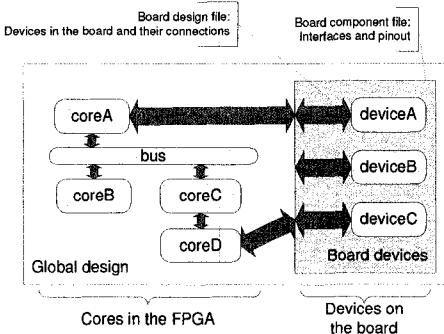

| Figure 5.1 | Représentation habituelle des cartes . . . . .                           | 87  |

| Figure 5.2 | Représentation des cartes pour l'outil de raffinement à bas niveau       | 88  |

| Figure 5.3 | Chaînes de DCM avec signaux d'horloge et reset . . . . .                 | 93  |

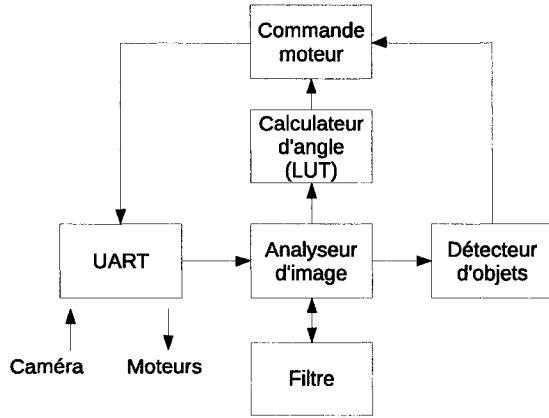

| Figure 6.1 | Principe de fonctionnement du rover . . . . .                            | 99  |

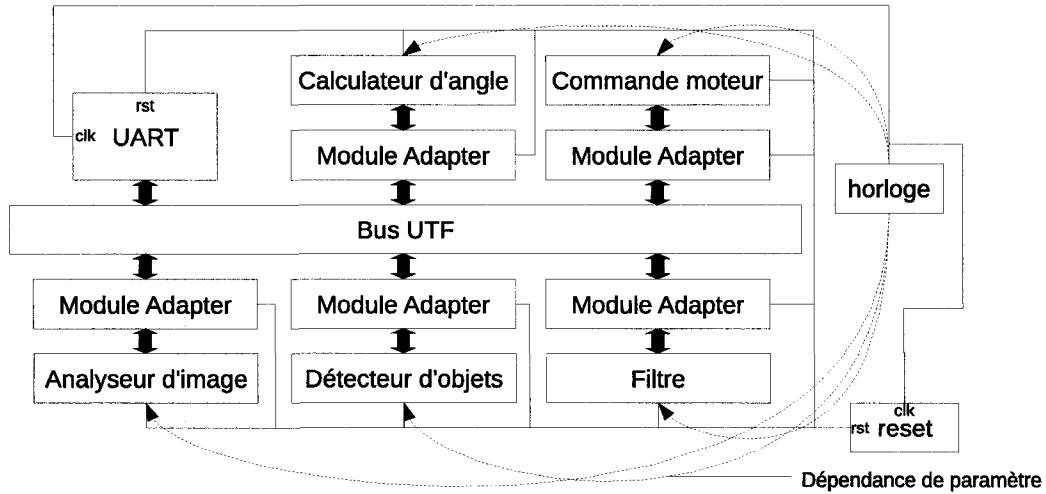

| Figure 6.2 | Premier design du rover . . . . .                                        | 102 |

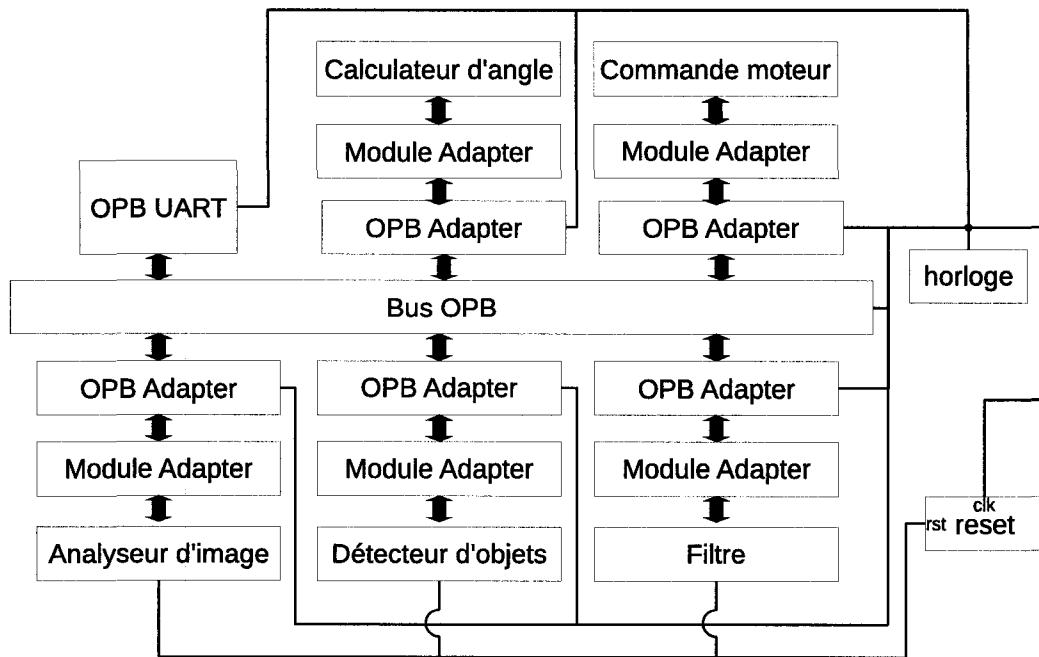

| Figure 6.3 | Design après raffinement . . . . .                                       | 104 |

| Figure 6.4 | Design avec un modèle de processeur . . . . .                            | 105 |

## LISTE DES ACRONYMES

|        |                                       |

|--------|---------------------------------------|

| BRAM : | Block Random Access Memory            |

| DCM :  | Digital Clock Manager                 |

| EDA :  | Electronic Design Automation          |

| ESL :  | Electronic System Level               |

| FCB :  | Fabric Coprocessor Bus                |

| FIFO : | First In First Out                    |

| FPGA : | Field Programmable Gate Array         |

| FSL :  | Fast Simplex Link                     |

| HDL :  | Hardware Description Language         |

| HTML : | HyperText Markup Language             |

| HTTP : | HyperText Transfer Protocol           |

| IP :   | Intellectual Property                 |

| ISBN : | International Standard Book Number    |

| ISS :  | Instruction Set Simulator             |

| JAR :  | Java Archive                          |

| JTAG : | Joint Test Action Group               |

| LMB :  | Local Memory Bus                      |

| LUT :  | Look-Up Table                         |

| MHS :  | Microprocessor Hardware Specification |

| MoML : | Modeling Markup Language              |

| MPD :  | Microprocessor Peripheral Definition  |

| MSS :  | Microprocessor Software Specification |

| MVC :  | Modèle, Vue, Contrôleur               |

| OCP :  | Open Core Protocol                    |

| OPB :  | On-chip Peripheral Bus                |

| PAO :  | Peripheral Analyze Order              |

|          |                                                                                    |

|----------|------------------------------------------------------------------------------------|

| PIC :    | Programmable Interrupt Controller                                                  |

| RTL :    | Register Transfer Level                                                            |

| SDRAM :  | Synchronous Dynamic Random Access Memory                                           |

| SPIRIT : | Standard Structure for Packaging, Integrating and Re-using IP within<br>Tool-flows |

| TGI :    | Tight Generator Interface                                                          |

| TLM :    | Transaction Level Modeling                                                         |

| UART :   | Universal Asynchronous Receiver-Transmitter                                        |

| UCF :    | User Constraints File                                                              |

| UML :    | Unified Modeling Language                                                          |

| URI :    | Uniform Resource Identifier                                                        |

| URL :    | Uniform Resource Locator                                                           |

| UTF :    | Untimed Functional                                                                 |

| VHDL :   | VHSIC Hardware Description Language                                                |

| VHSIC :  | Very High Speed Integrated Circuit                                                 |

| VLVN :   | Vendor, Library, Name, Version                                                     |

| W3C :    | World Wide Web Consortium                                                          |

| XBD :    | Xilinx Board Definition                                                            |

| XML :    | Extensible Markup Language                                                         |

| XMP :    | Xilinx Microprocessor Project                                                      |

| XPS :    | Xilinx Platform Studio                                                             |

| XSD :    | XML Schema Definition                                                              |

**LISTE DES TABLEAUX**

|             |                                                                                                 |     |

|-------------|-------------------------------------------------------------------------------------------------|-----|

| Tableau 2.1 | Connexion de deux vecteurs . . . . .                                                            | 28  |

| Tableau 3.1 | Statistiques du projet Java . . . . .                                                           | 39  |

| Tableau 3.2 | Équivalences entre éléments IP-XACT et classes Java pour la définition des interfaces . . . . . | 40  |

| Tableau 5.1 | Emplacement des informations pour la génération des fichiers XPS                                | 91  |

| Tableau 6.1 | Ressources utilisées sur le FPGA . . . . .                                                      | 106 |

**LISTE DES ALGORITHMES**

|                 |                                                                |    |

|-----------------|----------------------------------------------------------------|----|

| Algorithme 4.1  | Fonction domaine ( <i>instComp, ifType</i> ) . . . . .         | 57 |

| Algorithme 4.2  | Fonction domaineSurVoisins ( <i>instComp, ifType</i> ) . . . . | 58 |

| Algorithme 4.3  | Connexion automatique des signaux obligatoires . . . . .       | 59 |

| Algorithme 4.4  | Principe de la recherche d'adaptateurs . . . . .               | 62 |

| Algorithme 4.5  | Principe de la méthode de raffinement . . . . .                | 67 |

| Algorithme 4.6  | Fonction trouvConnAbstraites ( <i>componentInstance</i> ) .    | 68 |

| Algorithme 4.7  | Fonction répercuterSurVoisins ( <i>componentInstance</i> ) .   | 69 |

| Algorithme 4.8  | Importation de paramètres lors du raffinement . . . . .        | 70 |

| Algorithme 4.9  | Recréation des interconnexions lors du raffinement . . . . .   | 71 |

| Algorithme 4.10 | Principe de la génération de liens directs . . . . .           | 82 |

**LISTE DES ANNEXES**

|            |                                                                                                  |     |

|------------|--------------------------------------------------------------------------------------------------|-----|

| ANNEXE I   | EXTRAITS DE FICHIERS IP-XACT . . . . .                                                           | 114 |

| ANNEXE II  | TYPES DE COMPOSANTS . . . . .                                                                    | 126 |

| ANNEXE III | FICHIERS RENCONTRÉS POUR LA GÉNÉRATION DE FICHIERS<br>BAS NIVEAU . . . . .                       | 127 |

| ANNEXE IV  | COMMANDES DE LA PLATEFORME . . . . .                                                             | 131 |

| ANNEXE V   | ASSISTED CREATION AND REFINEMENT OF TRANSAC-<br>TIONAL LEVEL SPECIFICATIONS BASED ON IP-XACT . . | 133 |

## INTRODUCTION

En 1965, Gordon Moore a énoncé le célèbre principe connu désormais sous le nom de *loi de Moore* [1]. Cette prévision, vérifiée jusqu'à présent, indique que la complexité des circuits électroniques augmente exponentiellement en fonction du temps. La conséquence de cette tendance est l'augmentation constante de l'utilisation de l'électronique, celle-ci ayant des capacités toujours plus importantes à des coûts qui diminuent. À cause de l'évolution rapide des systèmes électroniques, la priorité de l'industrie est de mettre le plus tôt possible les nouveaux produits sur le marché. Cette contrainte se nomme le *time-to-market*, c'est à dire la durée séparant le lancement d'un projet à sa mise sur la marché.

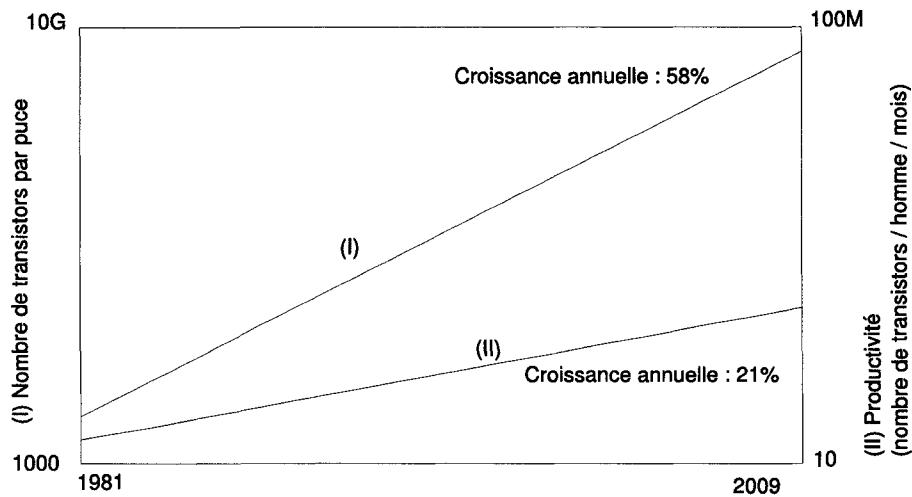

Ainsi, les capacités des circuits augmentent, le temps de développement doit être le plus court possible, et sans augmenter le coût de la conception. La productivité de la conception de systèmes électroniques est donc le premier objectif pour l'industrie. L'amélioration des techniques de conception a permis de l'augmenter considérablement. Cependant, cette augmentation de productivité (en nombre de transistors par rapport à la quantité de travail) ne suffit pas à compenser la complexification des circuits sur puce. Autrement dit, produire un nouveau système sur puce coûte de plus en plus cher en développement. Ce phénomène est connu sous le terme de fossé de productivité (*productivity gap*), figure 1<sup>1</sup>.

Il existe principalement trois directions pour augmenter la productivité.

La réutilisation est la plus évidente. En effet, tout système sur puce contient des éléments préexistants. Il peut s'agir d'entités de taille relativement petite, comme des additionneurs ou beaucoup plus gros, comme des calculateurs de transformée de Fourier, voire des processeurs. Pour favoriser la réutilisation, les plateformes de conception de systèmes sur puce intègrent généralement une bibliothèque de composants. Il est également possible pour

---

<sup>1</sup>Principe énoncé lors de l'édition 1999 de l'*International Technology Roadmap for Semiconductors*. Il a été cité de nombreuses fois par la suite, en particulier dans [2].

Figure 1: Le fossé de productivité

les concepteurs de systèmes d'acheter spécialement des composants à des fournisseurs. La réutilisation permet évidemment de gagner du temps de développement en évitant de réinventer la roue à chaque fois. Les composants réutilisables apportent aussi fiabilité et performance. D'abord, les développeurs peuvent être spécialisés dans le domaine concerné. De plus, comme le module pourra être vendu un grand nombre de fois, il est possible économiquement de consacrer un travail conséquent à son optimisation : diminution des temps de latence et des ressources utilisées, tests intensifs... Pour des raisons de rentabilité, un tel travail n'aurait peut-être pas été possible pour une utilisation unique.

Une autre voie pour augmenter la productivité est l'utilisation de niveaux d'abstraction plus élevés. La première étape importante fut le passage des descriptions physiques (portes logiques) au niveau des transferts de registres (RTL, *Register Transfer Level*). La simulation d'un système RTL est plus rapide que celle d'une description des portes. Il est donc possible de valider la description RTL avant de passer aux niveaux d'abstraction plus précis. De plus la synthèse de ces descriptions peut être automatisée, ce qui permet de supprimer les erreurs humaines tout en faisant gagner du temps. Enfin, une spécification RTL peut se synthétiser vers plusieurs types de matériel, ce qui favorise donc aussi la réutilisation. S'il est indiqué pour le développement de blocs matériels donnés, le RTL possède néanmoins ses limites.

En effet, il exige que l'architecture du système soit préalablement définie, au moins partiellement. C'est pourquoi des niveaux d'abstraction plus élevés, dits transactionnels, sont apparus. Kai et Gajski [3], et Ghenassia et Clouard [4] détaillent le flot de conception à mettre en œuvre. Ce flot se fait selon une approche *top-down*, c'est à dire partant des hauts niveaux d'abstraction pour aller vers les bas niveaux.

Le développement commence à partir des spécifications du produit. La première étape consiste à diviser l'application en modules fonctionnels communiquant entre eux. Ce haut niveau est nommé selon les cas TL3 (*transaction level 3*) ou UTF (*untimed functional*). Le temps de calcul n'est pas considéré. Seule la fonctionnalité globale est prise en compte. Puis, par raffinements successifs, la précision des calculs et des communication augmente, jusqu'à arriver à l'implémentation finale. Au fur et à mesure des raffinements, des choix architecturaux sont réalisés. Les plus importants sont le partitionnement logiciel/matériel et l'architecture des communications (par exemple : simple bus, bus multiples, réseau sur puce).

La troisième solution est d'automatiser les tâches qui peuvent l'être tout au long du flot de conception. La synthèse a déjà été évoquée, mais d'autres fonctions peuvent être aussi créées, par exemple pour simplifier l'implémentation des communications inter-modules.

**Problématique** Ces trois voies (réutilisation, hauts niveaux d'abstraction et automation) peuvent être combinées dans une plateforme de développement. Comme nous le verrons dans le chapitre 1, certaines solutions existantes répondent partiellement à ce problème en se focalisant sur une partie du problème. Cependant, il n'existe pas à ce jour de solution connue combinant les trois voies.

La réutilisation, pour qu'elle soit efficace, exige que de nouveaux blocs puissent être ajoutés facilement. Il est donc nécessaire que la plateforme de conception soit générique, c'est à dire qu'elle puisse traiter des nouveaux modules sans modifier le programme lui-même.

Le support des hauts niveaux passe par celui d'un langage approprié. Enfin, des outils automatisant certaines tâches s'ajoutent pour libérer l'utilisateur d'opérations fastidieuses.

**Objectif** L'objectif du travail de maîtrise présenté dans ce mémoire est de mettre en œuvre le cœur d'une plateforme de conception tirant parti de ces trois axes : réutilisation, hauts niveaux et automatisation. Tout d'abord, elle est conçue de manière à être entièrement générique. Elle est ainsi facilement extensible, puisque le programme en lui-même est totalement indépendant des composants utilisés. Les caractéristiques propres aux composants sont documentées dans des fichiers de données distincts du programme. Pour favoriser la réutilisation, un format de fichier standard est utilisé pour décrire les composants : IP-XACT. De plus, il s'agit d'une plateforme à haut niveau ; bien que facilement extensible à d'autres langages, elle est axée sur SystemC. Enfin, pour que cette plateforme ait un intérêt à l'utilisation, elle intègre différents outils qui facilitent la création des modèles de systèmes.

**Contributions** Les contributions de ce travail peuvent être vues selon deux aspects. Bien que distincts, ils sont liés et reposent tous deux sur une base logicielle présentée dans le chapitre 3. Le premier aspect est l'ensemble d'outils génériques présenté aux chapitres 4 et 5, en particulier :

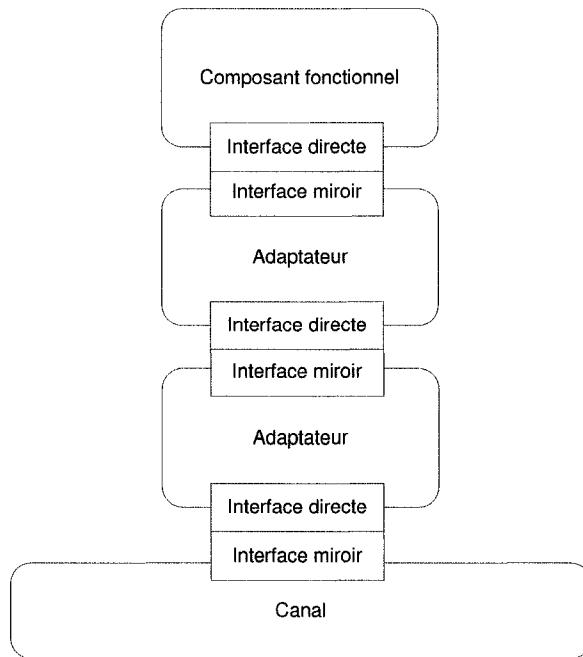

- la sélection et l'insertion automatiques de chaînes d'adaptateurs entre un composant fonctionnel et un canal (sec. 4.4),

- la sélection et l'insertion automatiques de lien direct entre deux composants fonctionnels matériels (sec. 4.8.1),

- le raffinement fondé sur une bibliothèque de composants à hauts et bas niveaux (sec. 4.5, chap. 5).

Le second ensemble de contributions est constitué des propositions d'extensions au format IP-XACT. En plus de celles dépendant des outils énumérés ci-dessus, on trouve :

- l'utilisation de nouveaux types de générateurs (sec. 2.4.2),

- la description du logiciel reposant sur des instances de composants (sec. 4.7),

- un type de connexion supplémentaire correspondant aux liens directs abstraits (sec. 4.8.2),

- l'application de la notion d'héritage à des composants matériels afin de définir des équivalences (sec. 4.5.2),

- l'ajout d'informations propres à la disponibilité des composants pour une architecture cible bas niveau (sec. 5.2).

**Structure** Ce document se divise en sept parties. Le chapitre 1 effectue une revue plus en profondeur des techniques de conception de systèmes sur puce visant à augmenter la productivité. Il introduit ainsi les principaux concepts qui seront utilisés dans la plateforme. Le chapitre 2 a pour objet le format de données IP-XACT, utilisé pour décrire des composants, leurs interfaces et leurs mises en œuvre dans des *designs*. Le chapitre 3 expose la structure générale du logiciel, qui repose grandement sur les paradigmes de IP-XACT. Les outils simplifiant l'utilisation du logiciel se greffent sur cette structure. Les principaux sont détaillés dans le chapitre 4. Le chapitre 5 se concentre sur la génération d'une implémentation basée sur une carte à FPGA. Cela implique des contraintes et descriptions d'objets supplémentaires. Enfin, une utilisation de la plateforme est présentée dans le chapitre 6, et la conclusion se trouve dans le chapitre 7.

Les principes généraux de la plateforme ont fait l'objet d'un article [5], qui a été accepté et qui sera présenté lors de la conférence IP08. Cet article se trouve dans l'annexe V.

## CHAPITRE 1

### REVUE DE LITTÉRATURE

#### 1.1 Hauts niveaux d'abstraction

Comme il l'a été mentionné dans l'introduction, l'utilisation de hauts niveaux d'abstraction est un des moyens pour concevoir rapidement et efficacement des systèmes sur puce. Le premier stade fut l'utilisation du niveau de transfert des registres (RTL), plus élevé que le niveau portes. Plus récemment, l'introduction des niveaux transactionnels (TLM), encore plus hauts, permet de modifier avantageusement le flot de conception.

##### 1.1.1 Première étape : du niveau portes vers le RTL

Face à la complexité croissante des systèmes sur puce, l'utilisation de hauts niveaux d'abstraction se révèle indispensable. La première transition importante a lieu dans les années 1980, avec l'apparition des langages modernes de description du matériel, en particulier Verilog et VHDL. Il est ainsi désormais possible de décrire des systèmes sur puce au niveau RTL (*Register Transfer Level*). Le RTL spécifie l'évolution de l'état des registres, sans nécessairement détailler toute l'architecture matérielle implémentant ces fonctions logiques. Le niveau d'abstraction est donc plus élevé qu'une description structurelle des portes logiques, ce qui présente plusieurs avantages. D'abord, pouvoir abstraire les détails de mise en œuvre permet de créer des descriptions plus simplement et rapidement. La simulation est également plus rapide qu'au niveau des portes. On peut donc valider la fonctionnalité d'un module à ce niveau avant de la transformer vers des descriptions plus précises. De plus, des outils de synthèse logique permettent d'automatiser cette opération de raffinement. Le cycle de développement est donc plus rapide, et les

erreurs humaines sont réduites. Enfin, le niveau RTL est suffisamment abstrait pour ne pas être entièrement lié au matériel sur lequel le système sera implanté. La réutilisation est ainsi favorisée.

### 1.1.2 Du RTL au TLM

Le RTL présente cependant certaines limitations. Tout d'abord, les langages HDL, comme leur nom l'indique, sont dédiés à la description du matériel, et non du logiciel. De plus, le développement de composants RTL exige un travail important en amont, afin de définir précisément les spécifications. C'est pourquoi des niveaux d'abstraction plus élevés sont apparus. Il s'agit des niveaux transactionnels (*TLM, Transaction Level Modeling*), qui font partie du domaine plus large de l'ESL (modélisation niveau système). Bien que le TLM regroupe en fait tout un ensemble de niveaux, il est possible d'établir des principes communs.

Pour commencer, les modèles transactionnels utilisent un découpage du système en blocs qui communiquent entre eux. Selon les sources, ces blocs sont nommés composants (*components*), éléments de traitement (*processing elements*) ou modules. Cette division montre que les modèles transactionnels se trouvent à un niveau plus précis que la spécification globale du système.

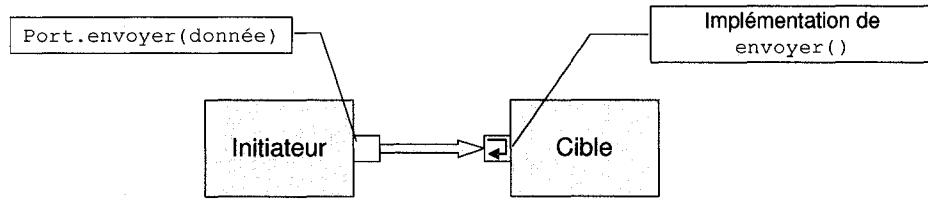

Le second point réside dans le mode de communication choisi : les *transactions*. Chaque transaction implique deux modules : un *initiateur* et une *cible*. L'initiateur est à l'origine de la requête. La cible la reçoit, et éventuellement y répond. Contrairement au niveau RTL, où les communications reproduisent la réalité physique (un signal porté par un ou plusieurs fils), les communications TLM se font par des appels de fonction. L'initiateur appelle donc une fonction, et cet appel est transmis à la cible. Des canaux intermédiaires peuvent assurer le lien entre les deux modules. La figure 1.1 montre un exemple grandement simplifié d'une communication entre deux modules. Dans ce cas, la communication se fait directement,

Figure 1.1: Simple communication transactionnelle entre deux modules

Figure 1.2: Modification du flux de conception en utilisant le TLM

sans canal intermédiaire. On trouve ce type de communication dans le plus haut des niveaux transactionnels.

### 1.1.3 Les avantages du TLM

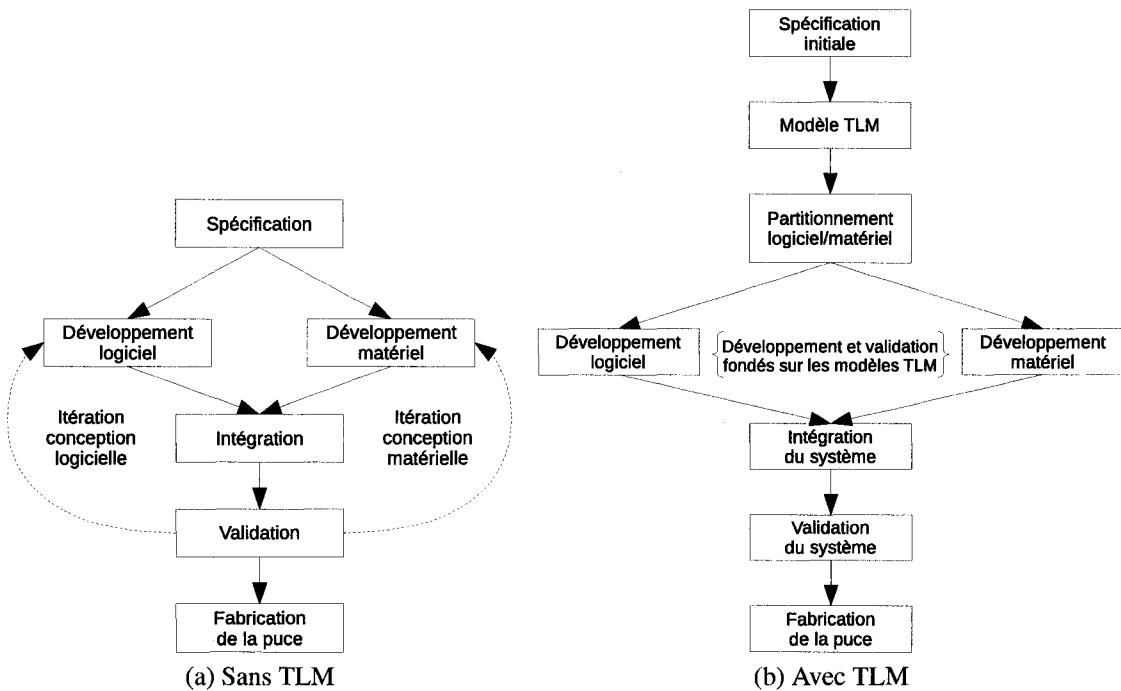

Disposer d'un modèle à haut niveau exécutable dès les premières étapes de développement du système est un atout certain. Il est ainsi possible de modifier le lot de conception en tenant compte [4]. La figure 1.2 montre les conséquences positives du TLM sur

la conception d'un système. Dans les deux cas, la première étape consiste à spécifier la fonctionnalité du système, ou *application*. L'objectif est de parvenir à une *implémentation* qui réalise cette application. L'implémentation finale est souvent divisée en une partie logicielle, exécutée par un processeur, et des blocs matériels qui mettent en œuvre une partie de l'application.

La figure 1.2a représente le cycle de développement classique. La séparation entre le logiciel et le matériel se fait très tôt. Les deux équipes de développement ne disposent donc que des documents de spécification comme base de travail. En outre, il n'est possible de valider le système qu'après intégration. Chaque itération est donc coûteuse en temps et implique à la fois les développeurs du logiciel et du matériel.

En revanche, le TLM apporte une solution à ces problèmes (figure 1.2b). Les modèles transactionnels réalisés avant la séparation permettent d'explorer les possibilités de partitionnement. De plus, le modèle transactionnel des éléments de traitement constitue une référence qui peut être utilisée par les deux parties pour tester et valider leurs composants. Cette validation peut se faire d'au moins deux manières : 1) en comparant les sorties des deux implémentations (transactionnelle et bas niveau) pour des entrées identiques, et 2) en réalisant des simulations transactionnelles du système entier dans lesquelles le composant à tester est intégré (en utilisant des adaptateurs pour permettre les communications).

Pour récapituler, les avantages du transactionnel sont les suivants :

- modélisation du matériel et du logiciel

- exploration architecturale

- rapidité d'exécution des simulations

- création de modèles de référence pour valider les implémentations à bas niveau

De plus, les outils de synthèse comportementale tels que Forte Cynthesizer sont capables de raffiner des modèles transactionnels vers le RTL.

Figure 1.3: Découpage des niveaux transactionnels selon deux axes

#### 1.1.4 Les sous-niveaux transactionnels

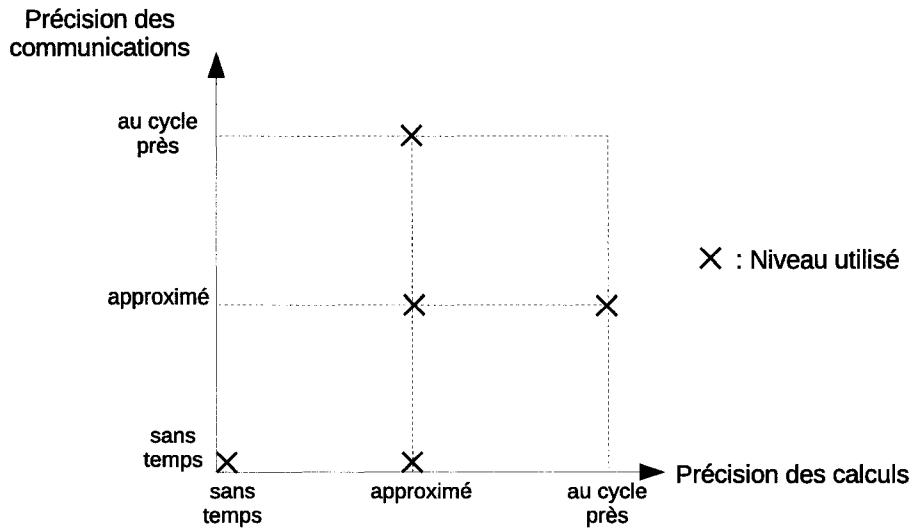

Les modèles transactionnels sont conçus selon le principe d'orthogonalité des modèles du calcul et des communications. Il est ainsi possible de modifier la mise en œuvre des communications sans modifier celle des calculs, et réciproquement. À partir de ce principe, Kai et Gajski [3] classent les sous-niveaux du TLM en deux dimensions, tel que représenté dans la figure 1.3. Tous les niveaux possibles ne sont pas présents sur ce graphique. En effet, les auteurs considèrent par exemple qu'il n'est pas pertinent de réaliser un modèle dans lequel les calculs sont modélisés sans notion de temps avec un modèle de communications précis au cycle d'horloge près.

L'orthogonalité communication/calculs implique que les éléments de traitement et les canaux ne partagent pas les mêmes interfaces de communication. Les interfaces des canaux sont en effet nécessairement liées à la granularité des communications dans le modèle choisi. Si les modules étaient directement connectés aux canaux, il devraient donc adapter leurs interfaces au modèle de communication, ce qui s'oppose au principe d'orthogonalité.

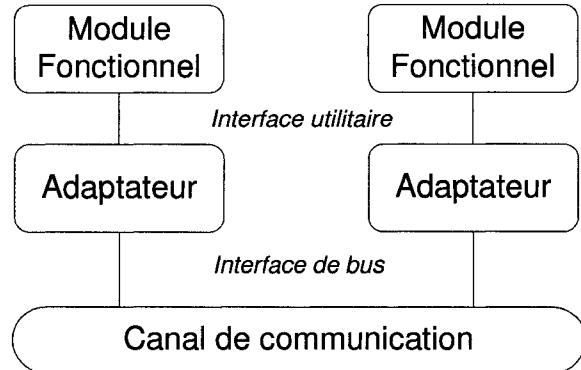

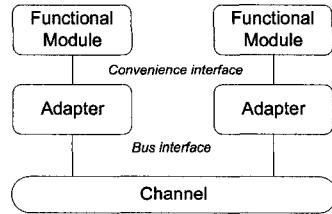

Figure 1.4: Modèle en couches

L'approche retenue est donc la suivante : les éléments de traitement disposent d'une interface simple, tandis que celle des canaux est adaptée à leur modèle. On arrive ainsi à un modèle en couches (figure 1.4), tel que présenté dans [6] et [7]. La première couche est celle des composants fonctionnels, avec une interface simple dont les fonctions sont appelées par le traitement à l'intérieur des modules. Ces composants sont connectés à des adaptateurs. Ceux-ci effectuent le lien entre les communications sur l'interface des modules fonctionnels et celle des canaux, eux aussi connectés aux adaptateurs.

Il existe un très grand nombre de niveaux utilisés, chacun se focalisant sur tel ou tel aspect de la conception du système. On peut néanmoins en dégager trois groupes principaux.

**TL3** Aussi appelé PV (*Programmer's View*) ou UTF (*Untimed Functional*), il n'a pas pour but d'estimer les temps d'exécution. Son rôle est d'établir une spécification fonctionnelle des éléments de calcul, et d'observer leur ordonnancement.

**TL2** Ce niveau porte aussi les noms de PVT (*Programmer's View with Time*), TF (*Timed Functional*) ou AV (*Architect's View*). Il apporte une dimension temporelle aux communications entre les modules du système. Il offre un bon compromis entre la précision des simulations d'une part, et la rapidité de simulation et de développement d'autre part.

On peut alors explorer différentes architectures, que ce soit pour les communications (architectures multibus, réseaux sur puce, liens directs), ou pour le partitionnement logiciel/matériel, en introduisant des modèles de processeurs.

**TL1** Dans ce niveau, les communications et les calculs sont estimés au cycle près. Chaque transaction de ce cycle correspond à une transaction du bus. Ce niveau est très proche du RTL ; la principale différence se situe dans les interfaces de communications : le TL1 est transactionnel, tandis qu'en RTL les interfaces sont un ensemble de ports de signaux. Son avantage par rapport au RTL est dans la rapidité de simulation, pour une précision quasi identique. Il peut aussi être utilisé pour tester un module RTL : on le simule pour cela dans une configuration où les autres modules sont transactionnels. Les sorties du module RTL peuvent également être comparées à son modèle transactionnel (considéré comme modèle de référence). On peut ainsi valider le module, pour une simulation relativement rapide. Cela peut aussi se faire pour les plus hauts niveaux, mais la proximité du TL1 avec le RTL en fait le niveau privilégié pour ce type d'utilisation.

## 1.2 Réutilisation

Dans la conception de systèmes sur puce, la réutilisation est un domaine complexe. Il faut en effet que les composants puissent communiquer avec le reste du système. Ils doivent en outre être paramétrables pour s'adapter aux différentes situations de mise en œuvre possibles. De nombreuses autres contraintes viennent s'ajouter, telles que les temps d'exécution, le matériel disponible et la protection de la propriété intellectuelle.

Pour pouvoir établir les connexions, il est nécessaire d'adopter des interfaces standard. Il s'agit en général d'interfaces de bus sur puce, comme OPB ou AMBA. Avec cette technique, l'utilisateur commence par choisir un type de bus. Dans le cas où le système possède au moins un processeur, celui-ci constraint fortement le choix du bus. Une fois le

bus choisi, il est possible de sélectionner les composants pouvant s'y connecter.

Cette technique présente un inconvénient majeur : le fournisseur du composant doit choisir son type d'interface lors de la conception. Si un utilisateur a besoin d'un autre type, il faut modifier le composant.

Le standard OCP [8] résout ce problème. Il définit une interface standard, indépendante du bus utilisé. Cette interface est très complète, mais aussi fortement configurable, de manière à éviter d'implémenter des fonctions inutiles. Des adaptateurs pour différents bus courants sont disponibles. Ainsi, tout composant conforme à l'interface OCP peut se connecter à différents bus et réseaux sur puce. L'inconvénient de cette solution se situe dans les ressources supplémentaires utilisées par les adaptateurs.

Au niveau transactionnel, la réutilisation de composants pose également le problème des interfaces. L'organisation qui développe le protocole OCP, l'OCP-IP propose des modèles transactionnel en SystemC des canaux de communication OCP. Ces modèles sont disponibles à trois niveaux d'abstraction différents.

Le standard TLM 2.0 proposé par l'OSCI [9] a pour but d'unifier les interfaces de communication transactionnelles. Il définit à la fois des interfaces proprement dites et la « charge utile » (*payload*) qui y transite. Les interfaces correspondent aux fonctions de communication appelées ou implémentées par les modules. Elles peuvent être bloquantes ou non bloquantes, avec possibilité d'indiquer les temps de communication. La charge utile correspond aux objets qui sont communiqués lors des transactions. La première version de la norme ne définissait pas de charge utile générique. Les utilisateurs devaient donc créer leur propres structures de données, ce qui nuisait fortement à l'interopérabilité et la réutilisation.

Le projet GreenSocs est aussi orienté vers l'interopérabilité. Il propose pour cela différents outils et interfaces à code source ouvert. Parmi ses projets, GreenBus était un environ-

nement définissant des interfaces de communication, à différents niveaux d'abstraction. GreenSocs ayant participé à l'élaboration de la norme OSCI TLM 2.0, ces concepts y ont été intégrés, et le développement de GreenBus est donc arrêté.

En permettant la portabilité des composants entre différentes architectures de communication, ces solutions favorisent donc la réutilisation. Cependant, un outil de gestion s'appuyant uniquement sur une de ces interfaces est fortement limité. En effet il présuppose que tous les composants soient conçus conformément à l'interface. Cela constitue une contrainte importante, et la gestion d'une grande bibliothèque de composants implique nécessairement de devoir manipuler plusieurs types d'interfaces, y compris des interfaces *a priori* inconnues. Pour cela, la plateforme doit être totalement générique vis-à-vis des interfaces et des composants. Il s'agit là du principal atout du travail présenté dans ce mémoire.

La norme IP-XACT est utile pour répondre à ce problème. Elle est dédiée aux métadonnées. Autrement dit, il ne s'agit pas de descriptions exhaustives des composants, mais d'informations qui permettent de les utiliser et des intégrer dans un système. En particulier, les fichiers IP-XACT décrivent les interfaces afin de les connecter. Ce format sera étudié plus longuement dans le chapitre 2.

### 1.3 Automatisation et assistance de la conception

Pour diminuer le temps de conception, les développeurs peuvent également profiter d'un ensemble d'outils. Ces outils permettent d'automatiser des étapes que la complexité actuelle des systèmes a rendu impossible à réaliser manuellement pour un coût raisonnable. Nous avons abordé les outils de synthèse dans la section 1.1. Il en existe de nombreux autres, que ce soit pour la vérification, le placement, le routage, ou la compilation du logiciel.

Les environnement de développement intégrés facilitent aussi la conception des systèmes sur puce. Tout d'abord, ils fournissent en général un moyen graphique et aisément visualiser et de modifier les architectures. Ensuite, ils sont capables d'accéder à un ensemble d'outils, tels ceux précédemment abordés. Parmi ces environnements, citons notamment Xilinx Platform Studio (XPS) [10] et Quartus de Altera [11]. Par exemple, XPS donne entre autres accès à :

- la génération de simulations (pour les environnements ModelSim et NCSim)

- une bibliothèque de composants et de cartes

- une vue graphique et modifiable de l'architecture

- un outil de synthèse

- des outils de génération de la mise en œuvre sur FPGA

- un compilateur et un éditeur de liens (gcc et ld)

- un débogueur

Cependant, les outils fournis par ces environnements sont basés sur les bas niveaux, à la différence de la plateforme proposée ici qui se concentre sur les hauts niveaux (sans y être exclusive).

Les outils présentés dans [12, 13] ont les mêmes objectifs que la plateforme : ils permettent à l'utilisateur de créer une implémentation à partir d'une spécification à haut niveau. Ils sont fondés sur la génération de adaptateurs et de canaux permettant aux éléments du système de communiquer à partir de primitives simples. Cependant, ils restent dépendants de l'interface de communication *get/set* sur les composants et leur généricité est donc moindre. L'utilisation d'une interface de communication simple du côté des composants est à rapprocher des travaux de SpaceCodesign, présentés dans la section suivante.

## 1.4 SpaceCodesign

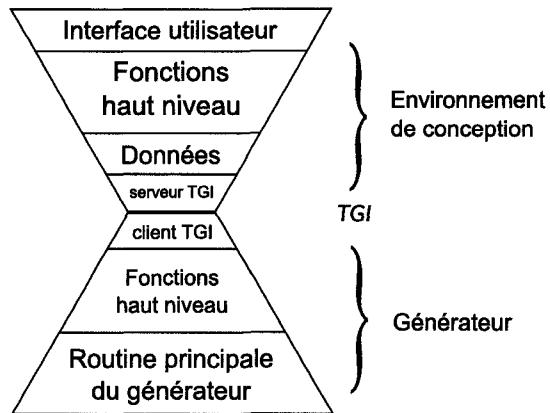

SpaceCodesign [14] est une plateforme de conception à haut niveau. Elle repose sur le langage de spécification SystemC [15].

**SystemC** Plus qu'un langage à proprement parler, SystemC est en fait un ensemble de classes, fonctions et macros de C++. Il présente plusieurs avantages, qui en ont fait le langage principal pour la modélisation à haut niveau. En particulier, le fait qu'il repose sur C++ permet de disposer des nombreux compilateurs déjà existants. Le code source du moteur de simulation est disponible, ce qui permet d'en créer des variantes répondant à des besoins spécifiques, telle que la co-simulation continu/discret [16]. De plus, SystemC permet de modéliser des composants selon une vue fonctionnelle ou une implémentation logicielle ou matérielle. Enfin, il supporte les ports transactionnels, ce qui est fondamental pour le TLM.

**SpaceLib** La plateforme SpaceCodesign peut se diviser en deux parties : SpaceLib et SpaceStudio. SpaceLib est un ensemble de composants SystemC qui sont utilisables selon la méthodologie suivante. Tout d'abord l'utilisateur crée la vue applicative de son système. Autrement dit, il conçoit les modules qui constituent la fonctionnalité. Il s'agit des éléments de traitement, que nous avons présentés lors de l'introduction du TLM (section 1.1.2). Ces modules dérivent de SpaceBaseModule, ce qui leur donne accès à des primitives de communication très simples pour envoyer des données ou en demander à d'autres modules.

À partir de ces éléments, il est possible de créer des configurations, en les connectant avec des composants de SpaceLib. Parmi ces composants, on trouve des canaux de communications (bus, liens point à point), des composants d'architecture (mémoires, processeurs), et des adaptateurs. On distingue deux niveaux d'abstraction. Le premier, Elix, permet de valider la fonctionnalité. Il repose sur les bus UTF (sans modélisation du temps)

Figure 1.5: Vue globale de SpaceStudio

et TF (modélisation approchée du temps). Ces bus modélisent un bus abstrait, qui n'a pas pour but de représenter une implémentation de bus particulière. Le second niveau, Simtek, est plus bas, il permet d'explorer l'espace des architectures possibles. Les modèles des bus sont plus précis, ils correspondent à des bus réels (OPB, PLB). C'est également à ce niveau que le partitionnement logiciel/matériel est réalisé. En effet, SpaceLib intègre des modèles de processeurs sous forme de simulateurs de jeu d'instructions. De plus, les primitives de communication pour les modules de l'application ont été implémentées sous forme logicielle. Ainsi, il est possible de faire passer un élément de l'application du domaine logiciel au matériel très facilement, sans changer le code du composant.

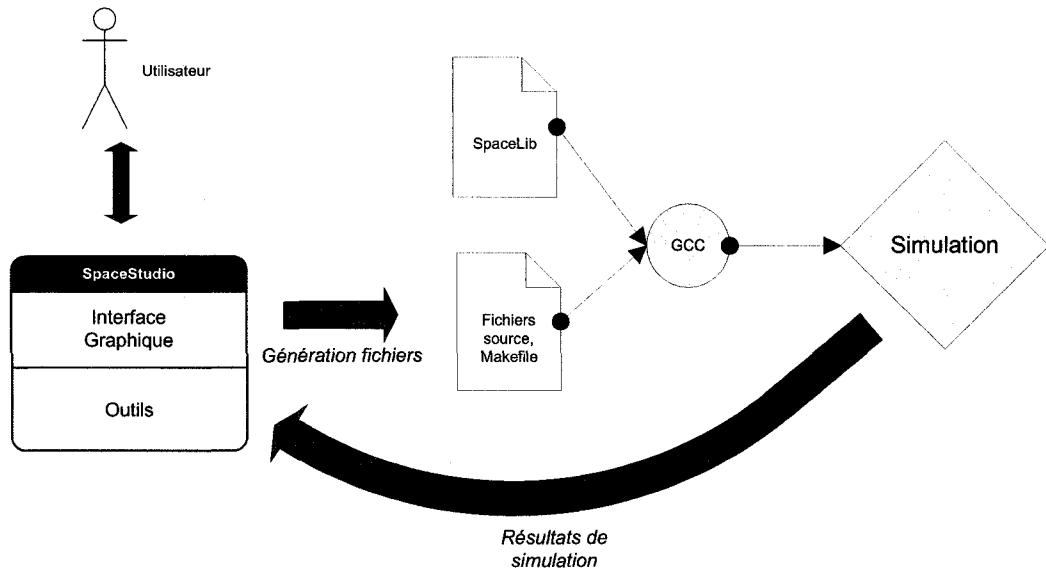

**SpaceStudio** SpaceStudio est l'environnement de développement de SpaceCodesign. Fondé sur l'environnement Eclipse, il facilite l'utilisation de SpaceLib. Son fonctionnement global est présenté figure 1.5. D'abord il offre une représentation graphique des configurations de simulation, utilisable pour les visualiser et les modifier. Ensuite, il apporte de nombreux outils, tels que la gestion des identifiants des composants et la génération d'adaptateurs de communication. À partir des configurations créées par l'utilisateur, il

génère des fichiers SystemC qui sont compilés et exécutés pour simuler le système. SpaceStudio peut aussi automatiser le passage d'une configuration Elix vers Simtek. Enfin il intègre Gen-X, qui est capable de générer un projet XPS à partir d'un modèle Simtek, en vue d'une implémentation sur FPGA.

**Extensibilité et généricité** SpaceStudio est donc orienté entièrement vers une utilisation de SpaceLib. Ce lien lui permet de profiter d'une connaissance complète du fonctionnement des composants de la bibliothèque. Ceux-ci sont donc correctement configurés dans les modèles qu'il crée, sans que l'utilisateur n'ait besoin de beaucoup de connaissances de Space.

Ce point fort induit un inconvénient important : le code de SpaceStudio est fortement lié au contenu de SpaceLib. Le code comporte de nombreux tests pour effectuer des actions spéciales en fonction du type des composants. Le besoin de fichiers de description indépendants du code s'est néanmoins fait sentir. Il existe donc de tels fichiers, qui permettent de définir les ports, les paramètres et des dépendances des composants. Cependant, le contenu de ces fichiers reste très lié à la plateforme Space. En particulier, l'insertion des adaptateurs pour connecter les modules de l'application aux bus est codée en dur. De plus il est conçu en fonction du paradigme « parent-enfant », qui représente les architectures sous forme d'arbres dans lesquels les bus sont les parents des modules qui y sont connectés. Cette conception, propre à SpaceStudio, lui permet d'afficher une vue en arbre facile à comprendre et à visualiser pour les utilisateurs. Cependant, elle n'est pas faite pour pouvoir s'appliquer à n'importe quel type de composant, possédant un nombre quelconque de ports. Pour résumer, les fichiers de données utilisés par SpaceStudio sont utiles pour éviter d'enregistrer des données sous forme de chaînes de caractères dans le code du programme. Mais ils restent profondément liés au paradigmes et fonctionnalités de SpaceStudio et par conséquent sont peu portables à d'autres environnements de développement.

Pour qu'une plateforme soit extensible, elle se doit d'être générique. Autrement dit elle doit être conçue de manière à pouvoir supporter tout nouveau type de composant. Les informations propres aux composants figurent alors dans des fichiers de données, distincts du code du logiciel. Ainsi pour ajouter (ou enlever) un élément de la bibliothèque, il suffit de modifier le contenu du dossier des données. Il n'est pas nécessaire de mettre à jour le programme ou de le recompiler pour qu'il intègre les changements.

Tel qu'indiqué précédemment, la plateforme développée dans le cadre de cette maîtrise est conçue selon ce principe de générnicité. C'est son principal apport par rapport à Space Studio. Il existe de plus d'autres plateformes génériques supportant le haut niveau, telles que Magillem Platform Assembly [17]. Cependant, elles ne fournissent pas des outils simplifiant la manipulation des modèles tels que ceux présentés dans le chapitre 4.

Le format des fichiers décrivant les composants, leurs interfaces et les *designs*<sup>1</sup> est le standard IP-XACT. Il possède en effet les avantages d'être conçu spécifiquement décrire ces objets, et ne nécessite pas l'ajout de sémantique. De plus, pour favoriser l'interopérabilité, il est important de s'appuyer sur un standard déjà répandu dans l'industrie, ce qui est le cas de IP-XACT.

MoML [18] est un autre format de données, dont le but est de décrire des composants abstraits, paramétrés, et leurs interconnexions. Ces composants peuvent correspondre aussi bien à des processus qu'à des objets logiciels ou des blocs matériels, il est nécessaire de leur ajouter une sémantique pour que la plateforme puisse les manipuler. De nombreuses extensions auraient été nécessaires pour ajouter l'information dont la plateforme a besoin. IP-XACT a donc été choisi comme format pour décrire les composants, interfaces et designs.

---

<sup>1</sup>Selon la terminologie de IP-XACT, ce terme anglais désigne une configuration d'instances de composants interconnectées (cf. sec. 2.3.2). Afin de conserver le lien avec la norme, il est laissé dans sa version anglaise dans ce mémoire.

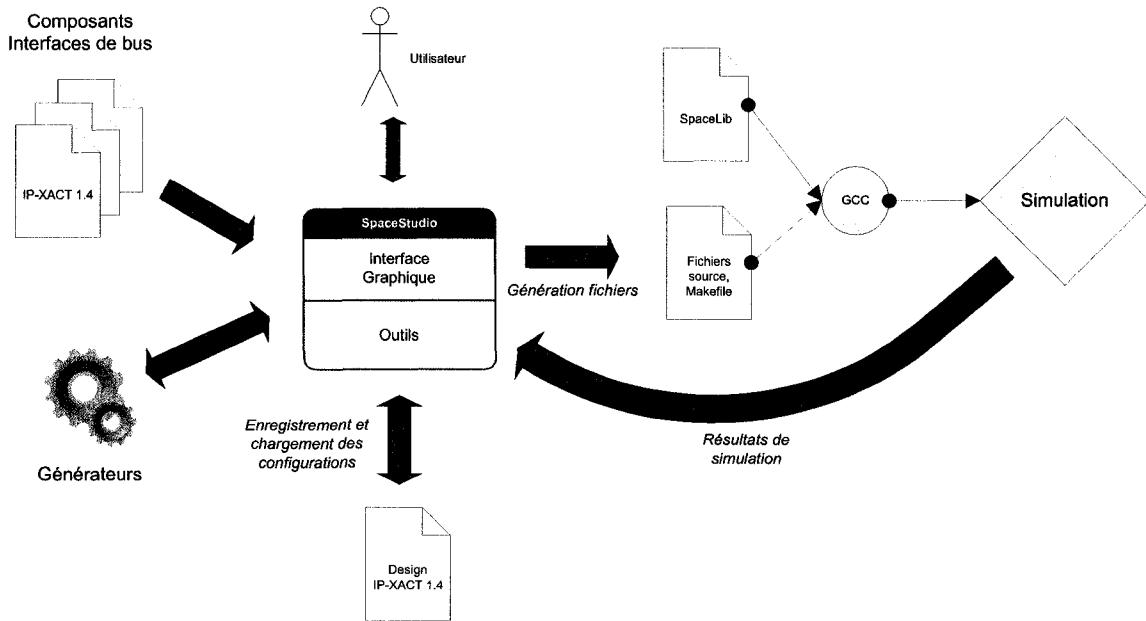

Figure 1.6: Vue globale de la plateforme

Une vue globale de la plateforme est proposée figure 1.6. Le chapitre suivant présente le standard, dont les paradigmes ont fortement influencé la conception du logiciel.

## CHAPITRE 2

### IP-XACT

#### 2.1 Introduction

Tel que mentionné dans la section 1.3, l'industrie des systèmes sur puce est constituée de nombreux acteurs, jouant des rôles différents :

- Les créateurs d'IP ;

- les fournisseurs d'outils de conception (simulation, vérification, synthèse, placement et routage, etc.) ;

- les créateurs d'environnements de conception, qui offrent une interface utilisateur à ces outils ;

- les concepteurs de systèmes.

Dans le cas typique, ces derniers assemblent des IP pour créer des systèmes. Ils font pour cela appel à des outils de conception, par l'intermédiaire d'un environnement de conception.

Cette multiplicité des acteurs pose un problème important : comment échanger l'information ?

Les outils de simulation et de synthèse (entre autres) nécessitent une description du comportement des éléments à traiter. Il existe pour cela différents langages, comme VHDL et Verilog pour une description matérielle à bas niveau ou SystemC pour des niveaux d'abstraction plus élevés.

Ainsi, chaque composant peut exister sous différents formats simultanément : un modèle à haut niveau en SystemC, un assemblage d'entités VHDL, et une version synthétisée sous

forme de liste de nœuds (*netlist*). De plus, il est possible de créer des modèles mixtes, qui mélangeant plusieurs formats de composants. Ce type de modèle est particulièrement utile pour valider un module à bas niveau, en le simulant avec des modèles à haut niveau. On profite ainsi de la rapidité d'exécution des modèles à haut niveau.

Il est donc nécessaire de disposer d'un format de données regroupant ces informations : identification du composant, interfaces de connexion, paramètres et référence vers des descriptions internes. Ces informations sont appelées *métadonnées*, car elles se situent « au dessus » des descriptions vues précédemment. Autrement dit, elles offrent un point de vue plus global.

La norme IP-XACT [19] répond à ce besoin de métadonnées. Elle a pour but de documenter de façon standard les composants, de manière à pouvoir les assembler dans des systèmes. IP-XACT est développé par un consortium d'industriels de l'EDA, le Spirit Consortium. Elle compte parmi ses membres les principaux acteurs du marché, en particulier dans son conseil d'administration (ARM, ST Microelectronics, Synopsys, Texas Instruments, etc.)

La première version de la norme est parue en 2004 et se nommait SPIRIT (*Standard Structure for Packaging, Integrating and Re-using IP within Tool-flows* — structure standard pour l'empaquetage, l'intégration et la réutilisation des IP dans la circulation entre les outils). Depuis la version 1.2, le format se nomme IP-XACT pour éviter la confusion entre le nom de du standard et celui du consortium qui le publie. La version 1.4, sortie en mars 2008 apporte une nouveauté importante : le support des modèles à haut niveau, et en particulier des ports transactionnels.

La documentation des composants repose sur le format XML (*extensible markup language*). Il est normalisé par le W3C (*World Wide Web Consortium*). Un document XML contient des balises, qui peuvent elles-mêmes contenir d'autres balises, des attributs et des données (textuelles ou numérales). Il est en outre généraliste et extensible, c'est-à-dire que les utilisateurs peuvent définir leur propres balises pour correspondre à leurs

```

<?xml version="1.0" encoding="UTF-8"?>

<!--

// Description : interrupt.xml

// Author : SPIRIT Schema Working Group

// Version: 1.0

-->

<spirit:busDefinition

xmlns:spirit="http://www.spiritconsortium.org/XMLSchema/SPIRIT/1.4">

<spirit:vendor>spiritconsortium.org</spirit:vendor>

<spirit:library>busdef.interrupt</spirit:library>

<spirit:name>interrupt</spirit:name>

<spirit:version>1.0</spirit:version>

<spirit:directConnection>true</spirit:directConnection>

<spirit:isAddressable>false</spirit:isAddressable>

</spirit:busDefinition>

```

Figure 2.1: Exemple de fichier IP-XACT

besoins de représentation des données. Par conséquent, il est utilisé pour un très grand nombre d'applications (formatage de texte, services web, localisation géographique, etc.). De nombreuses bibliothèques logicielles conformes au standard sont disponibles, ce qui rend l'analyse de fichiers XML simple, robuste et conforme au standard. De plus, bien que XML soit conçu pour que ses fichiers soient analysés par les ordinateurs, il présente l'avantage d'être lisible par l'homme, ce qui facilite son utilisation.

Pour chaque domaine d'utilisation du XML, il est possible de créer des fichiers décrivant la syntaxe des documents. Ces fichiers indiquent notamment comment les balises peuvent se succéder et s'imbriquer, et quelles données elles contiennent. Il existe plusieurs types de ces fichiers de syntaxe. IP-XACT utilise des fichiers XSD (*XML Shema Definition*), qui sont eux-mêmes des fichiers XML. En disposant d'une description formelle de la syntaxe, il est possible de vérifier de manière automatique qu'un fichier donné respecte bien cette syntaxe ; on parle alors de *validation*. Ainsi, lorsque l'analyse du contenu XML débute réellement, on sait qu'il respecte la syntaxe définie par le XSD.

Parmi les sept types de documents définis par la norme, nous utiliserons les quatre principaux :

**busDefinition** pour les informations générales sur un type de bus ;

**abstractionDefinition** pour décrire les mises en œuvre d'une interface à un niveau donné ;

**component** décrit un type de composant, qui possède notamment des interfaces, des ports et des paramètres ;

**design** instancie des composants, les paramètre et les connecte.

Chaque objet IP-XACT décrit par ces fichiers possède un identifiant unique nommé VLNV (Vendor, Library, Name, Version).

Les sections suivantes de ce chapitre présentent les paradigmes utilisés par IP-XACT pour décrire les composants et les designs. La section 2.2 présente comment sont spécifiées les connexions, la section 2.3 détaille comment les composants sont décrits, puis leur instantiation dans les fichiers design. Enfin, la section 2.4 offre un aperçu des possibilités laissées par la norme pour étendre sa fonctionnalité de base ; possibilités qui seront largement utilisées dans les chapitres 4 et 5.

## 2.2 Mode de connexion

### 2.2.1 Ports

Les ports peuvent être de deux types : *wire* pour les ports transportant un signal, comme les ports physiques ou *transactional* pour les ports transactionnels.

#### 2.2.1.1 Ports transactionnels

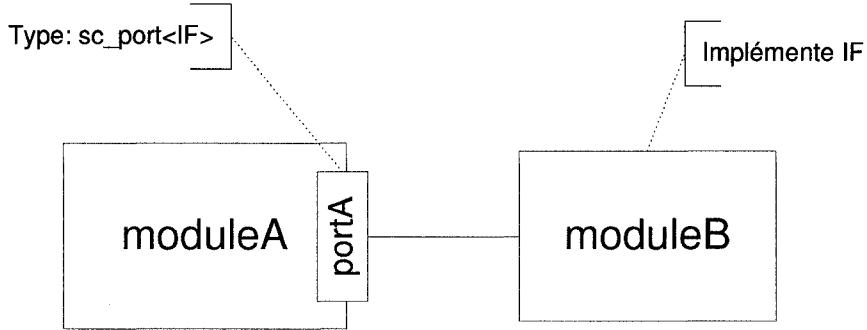

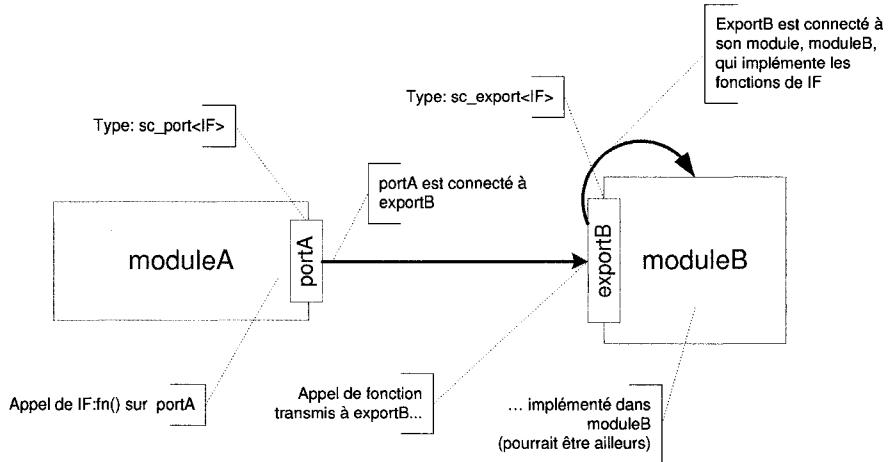

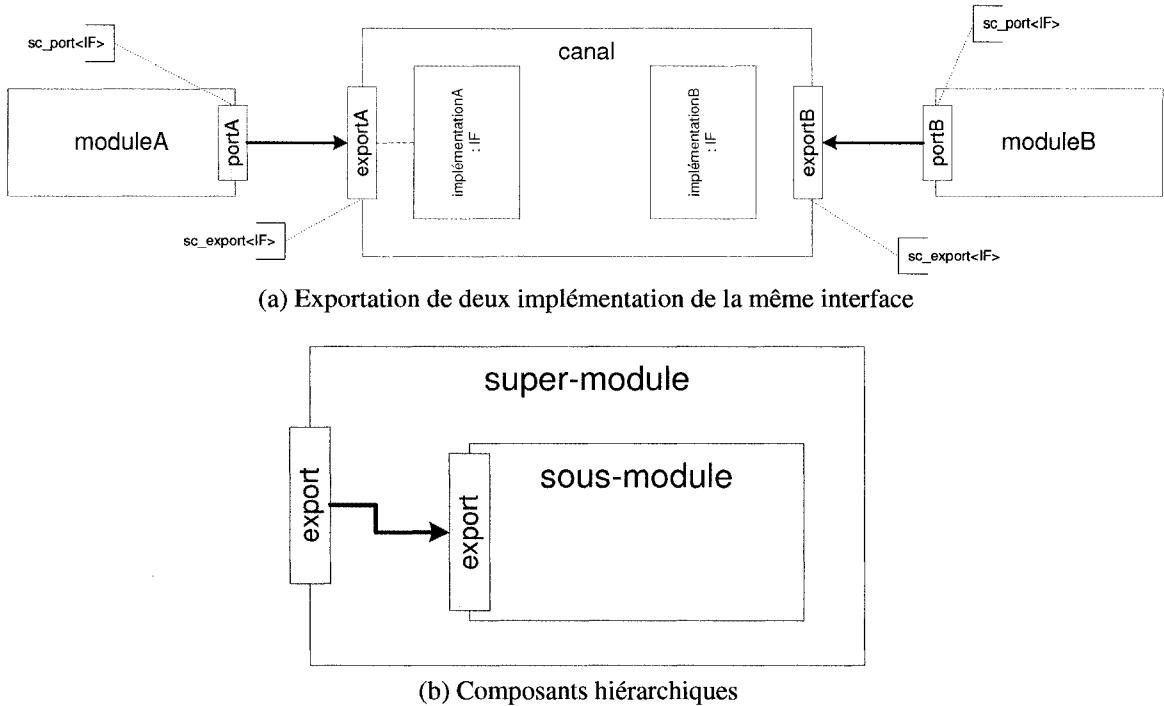

Comme indiqué dans la section 1.1.2, les communications transactionnelles sont fondées sur des appels de fonctions inter-modules. En SystemC, avant la version 2.1, la méthode courante était la suivante : Une interface *IF* est définie sous forme de classe abstraite dérivant de *sc\_interface*. Un module *B* implémente cette interface, la classe qui le définit dérive pour cela de *IF*. Un autre module *A* requiert cette interface : il possède pour cela un port de type *sc\_port<IF>*.

Figure 2.2: Communication port-module

Considérons une configuration possédant une instance de chacun de ces deux modules : *moduleA* et *moduleB* (voir figure 2.2). Pour qu'ils communiquent, le port de *moduleA* est connecté à *moduleB*. Ainsi *moduleA* peut faire des appels de fonctions par l'intermédiaire de son port, qui seront transmis à *moduleB*.

IP-XACT ne gère pas ce genre de connexion « port-à-module ». Il utilise plutôt un type de port apparu dans la version 2.1 de SystemC : *sc\_export*. Le principe est de fournir le dual des *sc\_port*. Alors que les ports requièrent une interface et doivent être connectés à une implémentation de l'interface, les exports déclarent qu'ils fournissent l'interface et reçoivent les appels de fonctions. On peut facilement faire une analogie, bien qu'imparfaite, avec les ports bas niveau, qui communiquent par signaux. Les *sc\_port* correspondraient alors à des ports de sortie, les *sc\_export* à des ports d'entrée, et les signaux seraient des appels de fonctions.

La figure 2.3 représente une communication dans laquelle l'interface est implémentée dans le module qui possède l'export. Dans cette situation précise, l'avantage des exports est loin d'être évident. Leur intérêt devient visible dans des cas plus complexes. Dans l'annexe A de [7], on trouve deux de ces situations. Le premier cas est celui où un composant fournit deux implémentations de la même interface (fig. 2.4a). Sans les exports, cela est impossible : on ne pourrait pas distinguer les deux implémentations de l'interface. Pour faire cette distinction, il suffit d'ajouter deux exports au module. Chacun est relié à une

Figure 2.3: Communication port-export

implémentation de l’interface. Ainsi, lors de la connexion au module, avec des liens « port-à-export », on peut choisir l’export, et donc l’implémentation à utiliser. Le second cas est celui des modules hiérarchiques. Les exports permettent de transmettre directement les appels à un sous-module avec une connexion « export-à-export » (fig. 2.4b). Sans cela, il aurait fallu créer pour le super-module une implémentation de l’interface dans laquelle chaque méthode appelle la méthode correspondante dans le sous-module, ce qui est bien plus fastidieux.

IP-XACT n’étant pas spécifique à SystemC, il utilise un vocabulaire différent pour décrire ces ports. Les ports transactionnels sont définis par deux informations :

**l’initiative** peut être *provides* (fournit) ou *requires* (requiert). Un *sc\_port* requiert un service, un *sc\_export* le fournit.

**le service** est l’interface fournie ou requise par le port.

### 2.2.1.2 Ports wire

Ces ports sont plus simples, cependant il est nécessaire de détailler la manière dont IP-XACT les représente. En effet, la particularité de la norme est que tous les ports de ce type

Figure 2.4: Cas d'utilisation des exports

ont une largeur unitaire.

Pour les ports de largeur supérieure, on utilise des ports de type *vecteur*. Ils correspondent aux ports dont la déclaration SystemC est du type suivant :

```

sc_in< sc_lv<16> > port;

```

La largeur du port doit être connue et fixe. En particulier les ports *sc\_in<int>* ne sont pas autorisés, le type *int* n'ayant pas de largeur fixée en C++ (voir [20], section 2.3.1). De façon plus générale, tous les ports doivent être connus dans la définition des composants. Il n'est donc pas possible de déclarer un port conditionnel en utilisant une macro. Dans ce cas, il faut décrire autant de composants qu'il y a de possibilités.

Les ports peuvent donc porter un vecteur. Par contre, il n'est pas possible de déclarer les vecteurs et tableaux de ports comme *sc\_in<bool>[16]* directement. Il faut alors les détailler un à un.

|                         |                                                                          |                                                                          |

|-------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|

| valeurs des bornes      | $g_a = 7, d_a = 4,$<br>$g_b = 5, d_b = 2$                                | $g_a = 7, d_a = 4,$<br>$g_b = 2, d_b = 5$                                |

| connexions des éléments | va [7] – vb [5]<br>va [6] – vb [4]<br>va [5] – vb [3]<br>va [4] – vb [2] | va [7] – vb [2]<br>va [6] – vb [3]<br>va [5] – vb [4]<br>va [4] – vb [5] |

Tableau 2.1: Connexion de deux vecteurs  $va$  et  $vb$ , avec pour bornes gauche et droite respectivement  $(g_a, d_a)$  et  $(g_b, d_b)$

Ces limitations peuvent apparaître contraignantes. Mais il faut garder à l'esprit que le but de la norme est de se situer au dessus des langages de description. Elle se focalise donc sur le plus grand diviseur commun, en évitant les spécificités propres à tel ou tel langage.

Plus précisément, ce n'est pas la taille qui est mentionnée dans les fichiers IP-XACT mais l'intervalle des indices des éléments du vecteur. Cet intervalle est défini par ses bornes gauche et droite. Il n'y a pas de contrainte quant à l'ordre des limites : la borne gauche peut être indifféremment plus grande ou plus petite que la borne droite. L'ordre des bornes sera important lors de la connexion du vecteur de ports avec un autre vecteur de même taille. Lorsqu'on connecte deux vecteurs  $va$  et  $vb$  aux bornes  $(g_a, d_a)$  et  $(g_b, d_b)$ , les éléments  $va[g_a]$  et  $vb[g_b]$  sont connectés, de même que  $va[d_a]$  et  $vb[d_b]$ . Les autres éléments sont reliés en fonction de l'ordre des bornes, comme le montre l'exemple de la table 2.1.

### 2.2.2 Interfaces

Les interfaces sont un moyen commode de regrouper les ensembles de ports sur un composant. Ainsi, on peut spécifier une connexion de deux groupes de ports en une connexion « interface-à-interface », plutôt que détailler toutes les connexions « port-à-port ». En plus de cette fonction de regroupement, les interfaces permettent de préciser le rôle des ports en y ajoutant un identifiant. Par exemple, c'est de cette façon que l'on distingue un port d'horloge d'un port *reset*, qui sont par ailleurs en tout point identiques.

Cette possibilité sera détaillée dans le chapitre 4, en particulier dans les sections 4.2 et 4.4.

Sur les composants, les interfaces peuvent appartenir à différents modes. Nous nous limiterons aux quatre principaux qui sont : maître, esclave, maître miroir et esclave miroir. Les interfaces miroir sont les « reflets » de leurs équivalents directs. Plus précisément, elles sont identiques, sauf que les directions des ports *wire* sont inversées, de même que les initiatives des ports transactionnels. Typiquement, les interfaces miroir sont présentes sur les canaux de communication, tandis que les modules fonctionnels possèdent des interfaces directes. Dans le cas normal, seules les connexions maître – maître miroir et esclave – esclave miroir sont autorisées.

La description des types d’interfaces que les composants peuvent utiliser se trouve dans deux fichiers distincts. D’abord, chaque fichier *busDefinition* correspond à un type de bus. Seules des informations d’ordre général sur le bus y figurent. En particulier, il y est mentionné si le bus est adressable et si les connexions directes sont autorisées. Dans ce dernier cas, il est possible de connecter directement une interface maître à une interface esclave (sans interface miroir). Par exemple, le type de bus pour les interfaces d’interruptions est non adressable et direct (celui qui émet l’interruption est le maître, et il est connecté directement à celui qui la reçoit — l’esclave). Les bus courants (par exemple OPB, LMB) sont adressables (à chaque transaction est associée une adresse), et non directs (les modules maîtres et esclaves doivent être connectés au bus, et non directement l’un à l’autre).

La liste des ports à utiliser pour implémenter une interface dépend de son niveau d’abstraction. Elle figure donc dans le fichier *abstractionDefinition* correspondant. Chaque fichier de ce type est associé à un type de bus ; on y trouve donc en premier lieu l’identifiant VLNV du fichier *busDefinition* correspondant. Puis les ports à utiliser pour cette abstraction du bus sont listés. Chaque port est nommé, puis son type (transactionnel ou *wire*) est spécifié. Ensuite, pour les modes maître et esclave, si le port est présent sur ce mode, ses

caractéristiques sont données. Dans le cas d'un port transactionnel, il s'agit de son service et son initiative ; et pour un port *wire*, de sa direction et éventuellement sa largeur.

## 2.3 Composants et designs

### 2.3.1 Composants

Chaque modèle de composant est décrit dans un fichier *component*. Les informations essentielles qu'il contient sont ses ports et des interfaces, ainsi que ses paramètres.

Les ports du composant sont appelés ports *physiques*, par opposition aux ports *logiques* présents dans les définitions des abstractions d'interface. Ports physiques et ports logiques sont décrits d'après les mêmes informations : selon les cas, direction et largeur ou service et initiative.

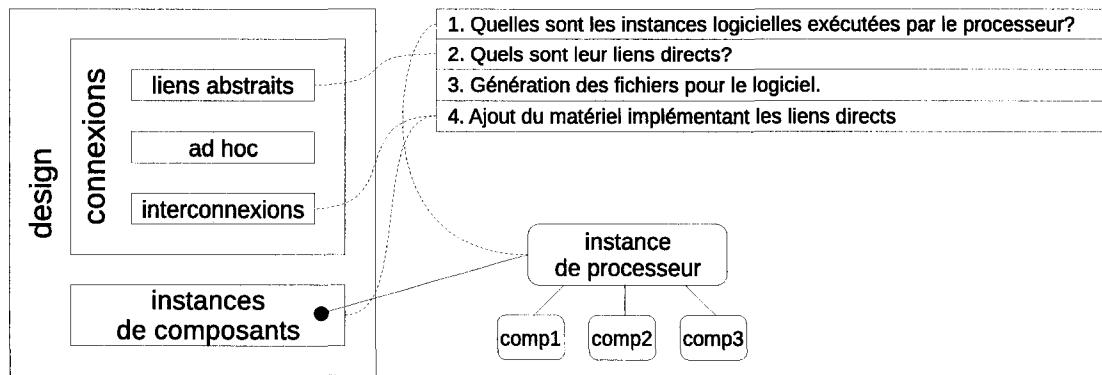

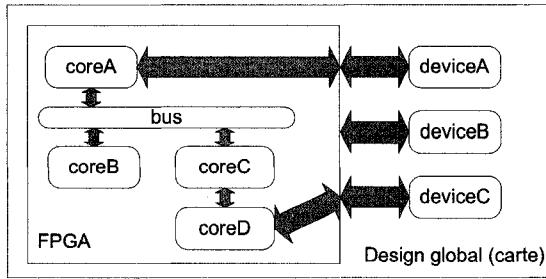

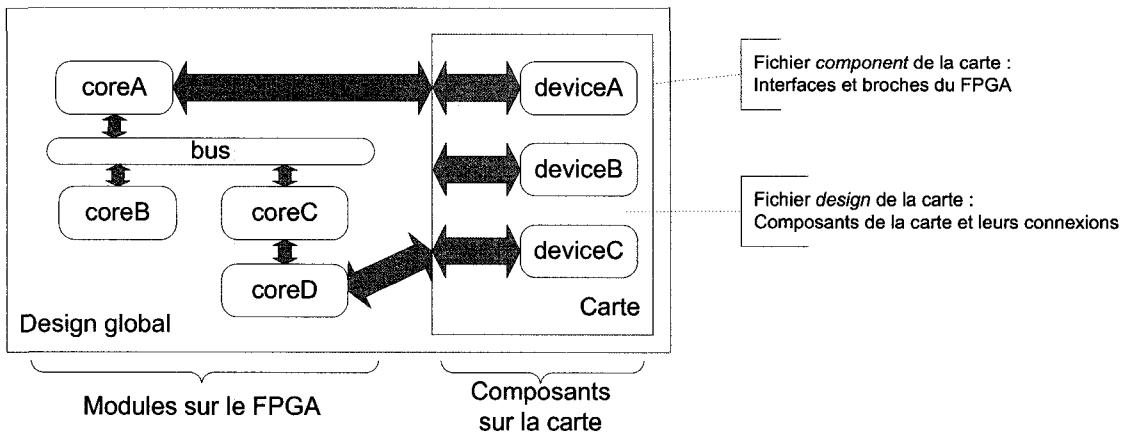

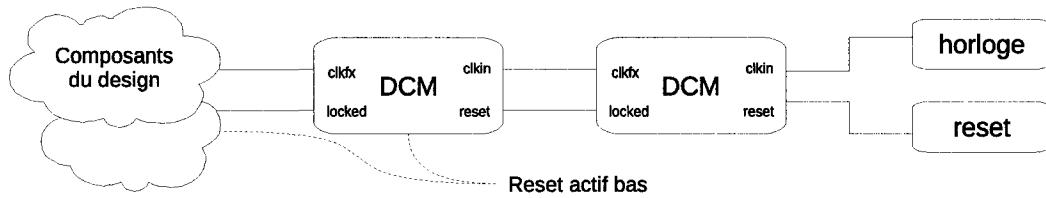

Dans les déclarations d'une interface du composant, on trouve en premier lieu son nom, les identifiants de la définition de bus et d'abstraction, puis son mode. Ensuite la section *portMaps* (facultative) indique les équivalences entre les ports physiques du composant et les ports logiques de la définition de l'abstraction.