|                         | Control systems for experiments in quantum communication and computing on optical fibres                                                                                                                                                                                 |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | David Alfonso Guzman                                                                                                                                                                                                                                                     |

| Date:                   | 2008                                                                                                                                                                                                                                                                     |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                |

| Référence:<br>Citation: | Guzman, D. A. (2008). Control systems for experiments in quantum communication and computing on optical fibres [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/8217/">https://publications.polymtl.ca/8217/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/8217/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Nicolas Godbout, & Jean Pierre David  |

| <b>Programme:</b><br>Program:            | Unspecified                           |

# UNIVERSITÉ DE MONTRÉAL

# CONTROL SYSTEMS FOR EXPERIMENTS IN QUANTUM COMMUNICATION AND COMPUTING ON OPTICAL FIBRES

# DAVID ALFONSO GUZMÁN DÉPARTEMENT DE GÉNIE PHYSIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE PHYSIQUE)

DÉCEMBRE 2008

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-48920-8 Our file Notre référence ISBN: 978-0-494-48920-8

## NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

# AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

# Ce mémoire intitulé:

# CONTROL SYSTEMS FOR EXPERIMENTS IN QUANTUM COMMUNICATION AND COMPUTING ON OPTICAL FIBRES

présenté par: <u>GUZMÁN David Alfonso</u>

en vue de l'obtention du diplôme de: <u>Maîtrise ès sciences appliquées</u>

a été dûment accepté par le jury d'examen constitué de:

- M. FRANCOEUR Sébastien, Ph.D., président

- M. GODBOUT Nicolas, Ph.D., membre et directeur de recherche

- M. DAVID Jean-Pierre, Ph.D., membre et codirecteur de recherche

- M. AZAÑA José, Ph.D., membre

#### **ACKNOWLEDGMENTS**

I would like to thank my research director, Nicolas Godbout at the Physics engineering department (génie physique) for letting me work on the quantum experiments of the Fibre optics Laboratory in a way that I put both physics and electronics knowledge in practice; for his interest in experimental applications of quantum communication and computing; for his financial support.

At the same time, I would like to thank my research co-director, Jean-Pierre David at the Electric engineering department (génie électrique) for his great support and dedication; for opening his door and mind to other domains in science; for making this project possible.

For allowing me to get involved in their experiments, I thank also Yasaman Soudagar and Guido Berlín, for sharing their knowledge and for several discussions. Their experience in the domain was really valuable to me.

To Mikaël Leduc for his technical experience, his help and advice. To François Busque, Stéphane Virally and Suzanne Lacroix who permittes me to work on their laser stability measurement project. Also to Stéphane Virally for both professional and personal talks. To everyone who received me in this land. For their lessons, patience and interest. Among them Jean-Simon Corbeil deserves here a special mention.

To my parents for their trust and support, unconditional as usual.

# RÉSUMÉ

Un système électronique utilisable pour une certaine catégorie d'expériences en information quantique est réalisé. Les spécifications du système lui permettent de répondre aux besoins particuliers de certaines protocoles (expériences de pile ou face et génération d'états « *cluster* »).

Le système réalisé au cours de ce projet est flexible et permet une adaptation à d'autres expériences par simple reprogrammation. Il permet en particulier d'accomplir des tâches utiles à la détection de photons uniques, aux comptes de coïncidences, à la détection d'événements, à la génération de nombres aléatoires, et au contrôle de phase et d'amplitude de signaux optiques.

Le cœur du système est constitué d'un circuit logique programmable (field-programmable gate array en anglais), qui communique avec un ordinateur via USB. Les ports externes d'entrée-sortie servent à faire la liaison entre l'unité de traitement et les périphériques. Les signaux de sortie de détecteurs de photons et d'autres périphériques sont gérés par un circuit imprimé dont l'architecture a été dessinée au cours du projet, et qui a été réalisé sur commande. Un second circuit imprimé, permettant la gestion de modulateurs électro-optiques, a également été réalisé.

Le système peut être géré par l'intermédiaire d'interfaces graphiques simples ; certaines ont été programmées à titre d'exemple. La modification du code du système se fait par l'intermédiaire de fichiers dll standards, dont la programmation en langage C est relativement aisée.

#### **ABSTRACT**

An electronic system enabling certain classes of quantum information processing experiments is designed and assembled. Requirements for the development of this system were obtained by studying particular quantum optical experiments, such as the implementation of coin tossing protocols, and cluster state generation.

This project provides a flexible, reprogrammable electronic system. It addresses required utilities such as single and coincident photon detection, time stamping of events, random number generation, and optical phase and amplitude control.

The processing takes part in a field-programmable gate array, which has a USB communication channel for connection to any computer. External input/output ports serve to link the processing unit and peripheral devices. Outputs from different kinds of photon detectors and similar devices are processed by a custom designed printed circuit. Electro-optic modulators require signals that change their voltage levels during a single experience; a second printed circuit was designed to deal with this situation.

Graphical user interfaces are possible with the current system; some of them were done. Generation of dll libraries that contains C code instructions suffices to program the card, send and receive both instructions and data during an execution of the loaded program.

# CONDENSÉ EN FRANÇAIS

#### Introduction

La technologie en informatique quantique se développe en permettant aujourd'hui d'avoir des implémentations physiques réalisables. Elle promet des systèmes de cryptographie sécuritaires et des solutions à des problèmes computationnels que les ordinateurs classiques ne sont pas capables de résoudre, ou qu'ils peuvent résoudre de façon moins efficace. Grâce à ces promesses le sujet de recherche est devenu intéressant et actif.

Les systèmes électroniques sont une partie incontournable de ce type d'expériences; ils permettent l'enregistrement d'un grand nombre de mesures et le contrôle d'appareils.

Typiquement, on affronte les besoins en électronique en utilisant des appareils de type « boîte noire », capables de remplir une seule fonction spécifique. En plus, il est possible que ce type d'appareils fonctionne avec un signal d'entrée très spécifique et pas nécessairement conventionnel. L'alternative est de créer des systèmes électroniques au besoin.

L'intérêt de concevoir des systèmes d'information quantique et les défis que les systèmes électroniques posent à leur fabrication forment la principale motivation de ce projet. L'absence de systèmes commerciaux qui fonctionnent avec différent sortes de détecteurs et leurs signaux, et l'incompatibilité entre les étages d'acquisition, traitement et d'exécution des expériences ont encouragé la réalisation de ce projet.

L'objectif de cette recherche est donc de réaliser un système électronique pour contrôler les appareils de mesure et de contrôle utilisés en expériences d'informatique quantique basées sur fibres optiques. Les implémentations optiques sont au centre du projet. On désire une solution flexible qui marche dans le plus grand nombre de scénarios.

Parmi les exigences du système, on doit acquérir et enregistrer les données provenant des détecteurs de photons. La détection de coïncidences entre détecteurs est requise pour observer et exploiter l'intrication, propriété donnée par la mécanique quantique. Par ailleurs, le contrôle de modulateurs électro-optiques de phase et d'amplitude est important pour générer l'information encodée optiquement. Il nous permet d'utiliser la superposition, une deuxième propriété offerte par la mécanique quantique.

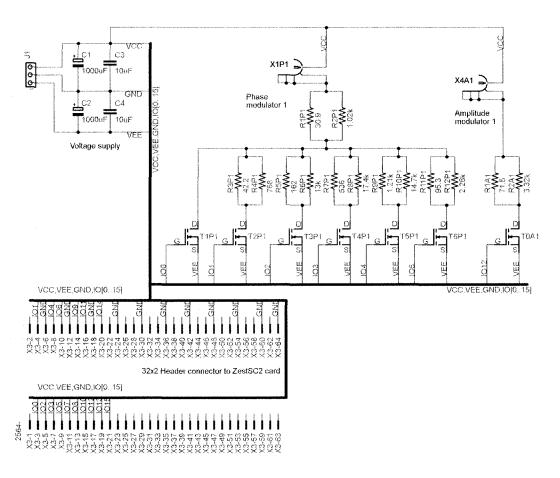

La solution proposée remplit ces exigences. Il est conçu sur une carte électronique reprogrammable, un FPGA (« field-programmable gate array »), qui peut communiquer avec un ordinateur pendant l'exécution d'une routine en temps réel. La standardisation des signaux d'entrée est faite par un circuit imprimé fait sur mesure. L'amplification de quelques signaux de sortie est requise, et est réalisée par un deuxième circuit imprimé fait sur mesure.

Des tests des applications programmées sont présentés et analysés. Ils démontrent l'utilité, la flexibilité et la performance du produit ici développé.

#### Contenu

Dans ce projet, l'information quantique est encodée sur des photons. Leur information peut être encodée sur des états de polarisation, où la base habituelle est  $|\phi\rangle=\alpha|H\rangle+\beta|V\rangle$  (horizontal et vertical). Également, elle peut être encodée sur des états d'encodage temporel (time-bin encoding), avec la base  $|\phi\rangle=\alpha|s\rangle+\beta|l\rangle$  qui correspond aux chemins court  $|s\rangle$  (short en anglais) et long  $|l\rangle$  d'un interféromètre de Mach-Zender.

L'information temporelle de la génération des photons (signal de synchronisation du laser), et leur détection (détecteurs de photons individuels) peut être utilisée pour synchroniser l'expérience, processus utile pour déterminer la corrélation entre les photons

émis et mesurés. Ceci impose la réception de différents types de signaux électriques, et leur traitement sur un pied d'égalité. Un module de conversion analogique-digital est réalisé.

Pour déterminer l'état quantique, on fait des mesures sur différentes bases. La détection des coïncidences et anti-coïncidences est requise pour faire cette discrimination.

La démonstration des protocoles de pile ou face quantique ou de cryptographie quantique nécessitent la génération de nombres aléatoires classiques. Il est possible de les générer à partir d'un système électronique produisant des séquences de bits pseudo-aléatoires.

L'utilisation d'un interféromètre pour l'encodage et le décodage temporel des photons nécessite le contrôle d'un modulateur de phase. Ce modulateur accepte un signal électrique périodique, laquelle détermine avec son amplitude la phase qui sera appliqué sur le signal optique.

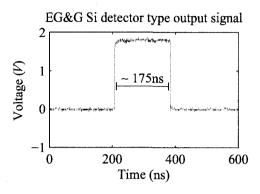

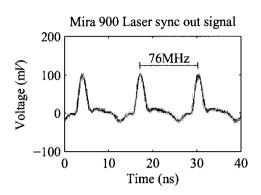

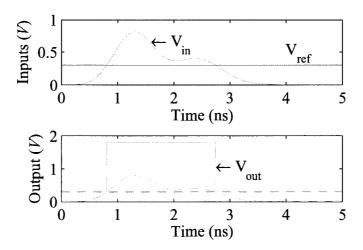

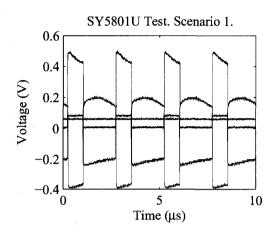

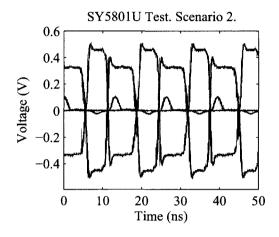

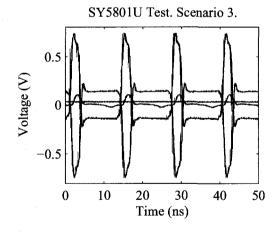

L'implémentation des protocoles quantiques nécessite l'acquisition de différents types de signaux électriques. Le système d'acquisition développé dans cet objectif permet d'acquérir aussi bien des signaux TTL de 1,8 V d'une durée d'environ 150 ns que des impulsions irrégulières autour de 100 mV d'amplitude et de durées de l'ordre de 3 ns. Ces signaux sont typiques des sorties de détecteurs de photon (Si ou InGaAs) et des impulsions de synchronisation de laser pulsés.

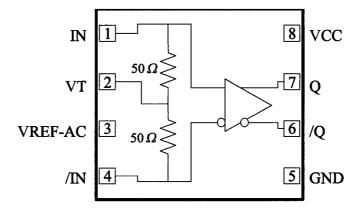

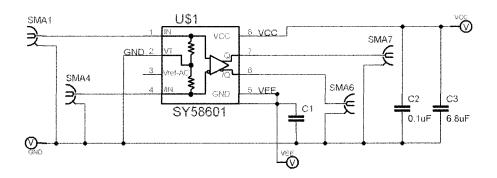

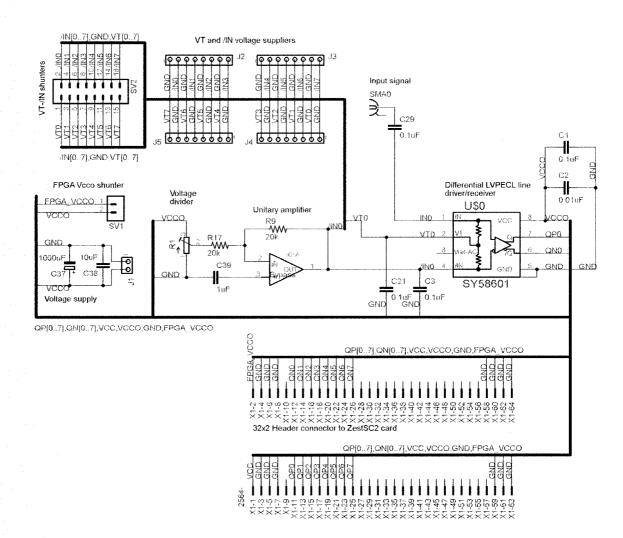

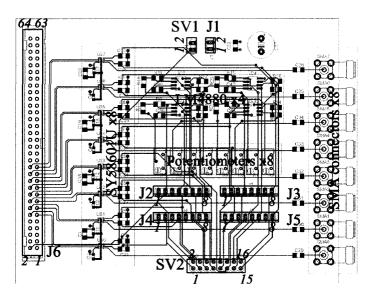

Le composant choisi pour réaliser la conversion des signaux est un Micrel SY58601U (ultra-precision differential 800 mV LVPECL line driver/receiver with internal termination). Il permet de générer un signal différentiel qui peut être lu par un FPGA. Un PCB (circuit imprimé) capable de réaliser la conversion de 8 canaux a été développé. Les signaux produits par le PCB sont ensuite acheminés vers la carte FPGA qui les traite.

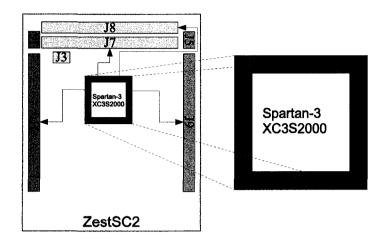

Le FPGA utilisé est un Spartan-3 de Xilinx, intégré à une carte électronique ZestSC2

d'Orange Tree Technologies. En plus du FPGA, la carte intègre un système de communications USB, une mémoire SDRAM, une mémoire flash, et des diodes électro-luminescentes (DELs). La carte est programmable en C, et des exemples de configuration en VHDL et verilog, un fichier ucf pour configurer le FPGA et quelques applications exécutables, sont fournis.

Plusieurs applications ont été réalisées pour répondre aux besoins particuliers des expériences d'information quantique. En particulier, la mesure de compte d'évènements, la détection de coïncidences, et l'enregistrement d'information temporelle ajoutée aux données issues de l'acquisition ont été développées au cours du projet.

La génération de numéros aléatoires et la génération de signaux périodiques sont permettent d'offrir un signal de sortie, qui peut gérer des modulateurs électro-optiques. Le FPGA peut générer la porteuse pour ces signaux. Mais il est nécessaire de moduler l'amplitude du signal pour gérer les modulateurs également.

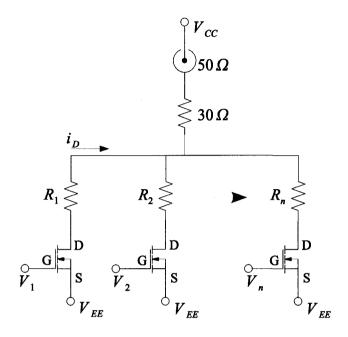

Un deuxième circuit imprimé est fabriqué pour amplifier des signaux périodiques. Une modulation de phase quelconque  $\phi$  s'obtient avec un voltage appliqué sur le modulateur de phase de  $V_{\phi} = \phi V_{\pi}/\pi$ , où  $V_{\pi}$  détermine le voltage nécessaire pour avoir une phase optique de  $\pi$ ; une valeur typique est  $V_{\pi} = 5$  V.

Les amplificateurs opérationnels ne possèdent pas la bande-passante adéquate pour amplifier les signaux aux fréquences désirées. Pour le cas où il faut travailler à quelques centaines de MHz, l'utilisation de transistors comme interrupteurs est nécessaire. Le transistor choisi est le PD57002-E (*RF power transistor* de STMicroelectronics). Il est conçu pour fonctionner à haute fréquence jusqu'à 1 GHz.

Les protocoles de communication quantique requérant un encodage temporel (*time-bin*), utilisent des valeurs discrètes et prédéterminées de modulation de phase. Les valeurs typiques pour ce genre d'application sont des multiples de  $\pi/4$ , mais d'autres valeurs

peuvent être requises pour des applications particulières.

La solution implémentée pour obtenir plusieurs valeurs de modulation consiste à des branches partagées par un connecteur. Chaque branche possède une résistance différente et un transistor qui gère le courant dans la branche. Les sorties logiques (0 ou 1) du FPGA déterminent quelles branches s'activent, ce qui permet de moduler la tension de sortie.

Le circuit imprimé possède 4 sorties : deux d'entre elles génèrent 6 niveaux de tension différent; les deux autres ne délivrent qu'un seul niveau de tension Les modulateurs de phase sont gérés par les deux premières et les modulateurs d'amplitude par les deux autres. Le même circuit peut être reproduit sur deux ports de la carte ZestSC2, ce qui permet de gérer jusqu'à huit appareils simultanément : quatre modulateurs de phase et quatre modulateurs d'amplitude.

#### Conclusion

Un système de traitement de données d'expériences en communication et calcul quantique a été réalisé. Le système développé offre une solution flexible et adaptable à de nombreuses situations grâce au circuit imprimé conçu, réalisé et testé au cours du projet.

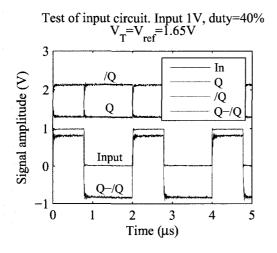

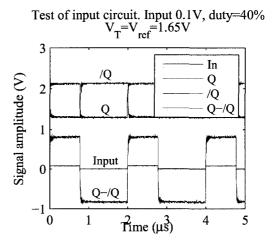

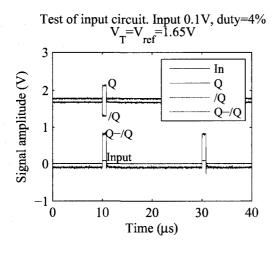

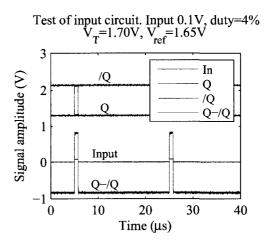

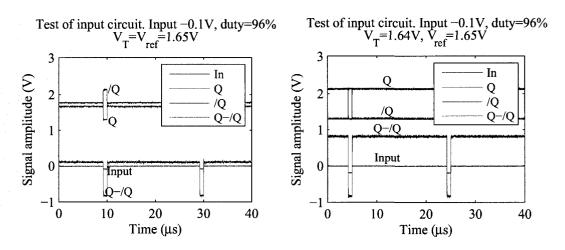

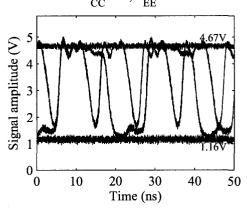

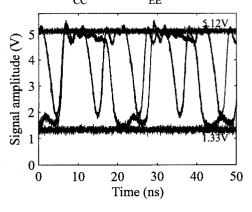

Le circuit d'entrée gérant la standardisation des signaux a été testé dans des conditions variant en amplitude de 100 mV à 1 V et en cycle d'utilisation de 4 à 96%. La sortie du circuit fournit un signal différentiel de  $\pm 800 \text{ mV}$  dont la fréquence suit celle du signal d'entrée.

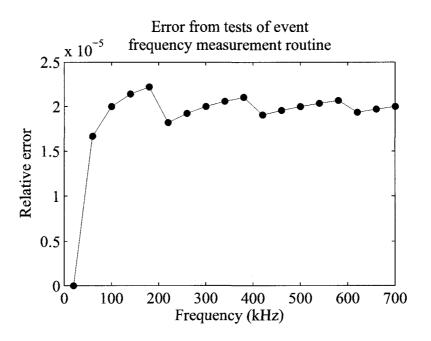

Des applications particulières ont été réalisées, comme la mesure de compte d'évènements, la détection de coïncidences, l'enregistrement d'information temporelle, la génération de nombres pseudo-aléatoires, et la génération de signaux périodiques. La routine de compte d'évènements performe de manière exceptionnelle, avec un taux d'erreur sur la fréquence mesurée ne dépassant pas 0,002 5%.

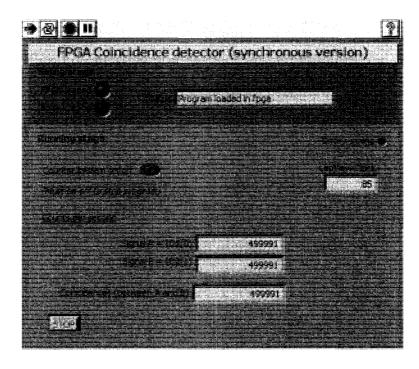

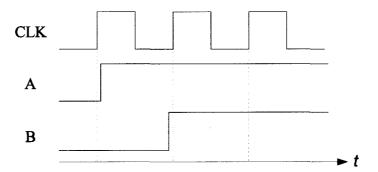

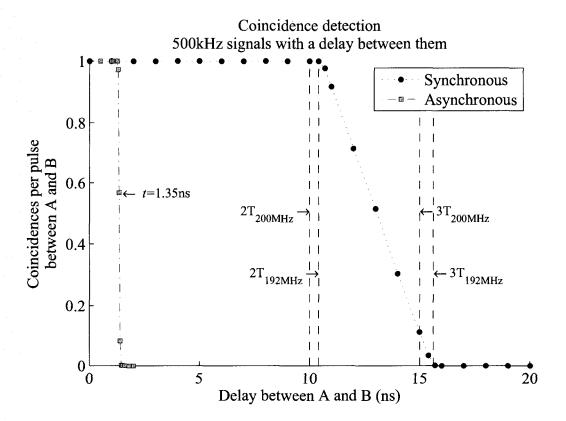

La détection de coïncidences a été réalisée de deux manières : synchrone et asynchrone. Les deux méthodes sont capables de correctement distinguer entre des scenarios avec et sans coïncidences. Pour la version asynchrone, la fenêtre de coïncidence a une durée de 1,35 ns. Une version synchrone équivalente aurait besoin d'une horloge nterne proche de 4 GHz. Pour la version synchrone, la fenêtre de coïncidence dépends de l'horloge du système ; avec  $T_{\rm CLK}=200$  MHz la durée d'ouverture de la fenêtre et comprise entre 10 ns et 15 ns.

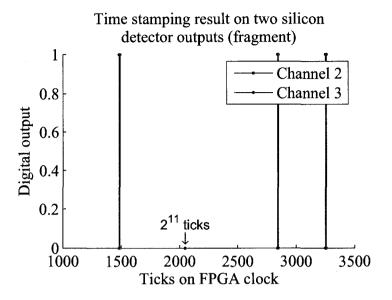

L'application d'enregistrement d'information temporelle permet de reconstruire jusqu'à 5 signaux numériques. Le nombre de signaux enregistrés peut être modifié, ce qui entraîne un changement dans le temps de débordement. L'information temporelle ajoutée est requise pour la détection de coïncidences, l'étude de la corrélation entre les signaux et les statistiques d'arrivées. Cela est fondamental pour les expériences de communication quantique, où le taux de comptes est entre 100 et 10 000 comptes par seconde.

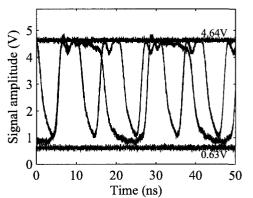

Pour contrôler des modulateurs de phase et d'amplitude, des signaux périodiques ont été générées à 45 MHz et 96 MHz. Leur amplitude est amplifiée (ou réduite) en utilisant le circuit imprimé conçu et fabriqué dans ce but. Ce circuit a été testé dans des conditions prouvant que ses caractéristiques sont suffisantes pour obtenir la modulation de phase et d'amplitude requises. Pour un fonctionnement nominal entre 0 V et 5 V, les tensions de sortie étaient de 0,63 V et 4,67 V respectivement. La réponse en fréquence a été également testée avec succès.

Une séquence de nombres pseudo-aléatoires a été générée à l'aide d'un LFSR Galois. Une telle séquence peut être utilisée dans un générateur de pile ou face et dans les protocoles de communication quantique nécessitant d'une sélection aléatoire d'éventements.

Le système développé présente plusieurs avantages. En particulier, sa flexibilité, sa capacité de reprogrammation, son adaptation facile à d'autres sujets permettent une expansion facile du projet. En plus, il offre des interfaces graphiques faciles à gérer, comme celles qu'ont été réalisées avec LabView.

Le codage utilisé pour programmer le FPGA est spécifique à la carte électronique Zest-SC2. Mais grâce au design par bloc, il est possible de l'adapter pour d'autres cartes électroniques, y compris celles provenant de manufacturiers différents.

La principale barrière technologique de ce travail est la vitesse de traitement. L'horloge du système fonctionne normalement à 48 MHz. L'utilisation d'autres fréquences peut impliquer des modifications importantes. De plus, la plage des fréquences pouvant être générées par le FPGA est limitée, et la carte électronique utilisée dans ce projet ne supporte pas de fréquences plus élevées que 210 MHz.

Quand on l'utilise avec des systèmes de fibres optiques utilisant un encodage temporel (*time-bin encoding*), la vitesse maximale devient une limitation de taille pour l'interféromètre optique. Par exemple une horloge à 200 MHz (5 ns) provoque un retard de 1,5 m dans l'interféromètre.

Il est recommandable de prolonger ce projet. Des nouvelles applications et fonctions peuvent être ajoutées et intégrées, de telle façon que le produit final soit plus avantageux. Le produit pourrait être utilisé pour différents sujets de recherche.

Un chercheur qui voudrait continuer avec ce projet devrait partir des applications ici déjà développées, les exécuter et comprendre leur codage dans les différents langages de programmation (VHDL, C, LabView). Comme premier tâche, je suggère d'améliorer la détection de coïncidences en réglant les temps de délai internes du FPGA.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS                                        |

|--------------------------------------------------------|

| RÉSUMÉ                                                 |

| ABSTRACT                                               |

| CONDENSÉ EN FRANÇAIS                                   |

| TABLE OF CONTENTS                                      |

| LIST OF FIGURES                                        |

| LIST OF NOTATIONS AND SYMBOLS                          |

| LIST OF TABLES                                         |

| LIST OF APPENDICES                                     |

| INTRODUCTION                                           |

| CHAPTER 1. BASICS IN QUANTUM COMMUNICATION AND COMPUT- |

| ING                                                    |

| 1.1. Quantum information                               |

| 1.1.1. Entangled states                                |

| 1.2. Quantum communication                             |

| 1.2.1. Polarization encoding                           |

| 1.2.2. Time-bin encoding                               |

| 1.3. Quantum Protocols                                 |

| 1.3.1. BB84 protocol                                   |

| 1.3.2. Quantum teleportation                           |

|    |                      |                                                                            | 1.3.2.1. Quantum circuits                                                                                                                                                                                                                                                | 12                                                       |

|----|----------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|    |                      |                                                                            | 1.3.2.2. Quantum teleportation procedure                                                                                                                                                                                                                                 | 14                                                       |

|    |                      | 1.3.3.                                                                     | Quantum coin tossing                                                                                                                                                                                                                                                     | 15                                                       |

|    | 1.4.                 | Experi                                                                     | mental electronic requirements                                                                                                                                                                                                                                           | 16                                                       |

| CF | IAPT]                | ER 2.                                                                      | PHOTON DETECTION                                                                                                                                                                                                                                                         | 18                                                       |

|    | 2.1.                 | Photon                                                                     | detection mechanisms                                                                                                                                                                                                                                                     | 19                                                       |

|    |                      | 2.1.1.                                                                     | Used photodetectors: Avalanche Photodiodes                                                                                                                                                                                                                               | 20                                                       |

|    | 2.2.                 | Signal                                                                     | conversion and standardization                                                                                                                                                                                                                                           | 22                                                       |

|    |                      | 2.2.1.                                                                     | Test results with evaluation board                                                                                                                                                                                                                                       | 25                                                       |

|    | 2.3.                 | The inj                                                                    | put circuit                                                                                                                                                                                                                                                              | 26                                                       |

|    |                      | 2.3.1.                                                                     | PCB schematic                                                                                                                                                                                                                                                            | 28                                                       |

|    |                      | 2.3.2.                                                                     | PCB layout                                                                                                                                                                                                                                                               | 30                                                       |

|    | 2.4.                 | Chapte                                                                     | er summary                                                                                                                                                                                                                                                               | 31                                                       |

|    |                      |                                                                            |                                                                                                                                                                                                                                                                          |                                                          |

| CH | IAPT                 | ER 3.                                                                      | INFORMATION PROCESSOR AND APPLICATIONS: THE                                                                                                                                                                                                                              | ,                                                        |

| CH | IAPT                 | ER 3.                                                                      | INFORMATION PROCESSOR AND APPLICATIONS: THE                                                                                                                                                                                                                              | 33                                                       |

| CH | 3.1.                 |                                                                            |                                                                                                                                                                                                                                                                          | 33                                                       |

| CH |                      |                                                                            | FPGA                                                                                                                                                                                                                                                                     | 33<br>34                                                 |

| CH |                      | Spartar                                                                    | FPGA                                                                                                                                                                                                                                                                     | 33<br>34<br>35                                           |

| CH |                      | Spartar                                                                    | FPGA                                                                                                                                                                                                                                                                     | 33<br>34<br>35<br>36                                     |

| CH |                      | Spartar 3.1.1. 3.1.2. 3.1.3.                                               | FPGA                                                                                                                                                                                                                                                                     |                                                          |

| CH | 3.1.                 | Spartar 3.1.1. 3.1.2. 3.1.3. Other of                                      | FPGA                                                                                                                                                                                                                                                                     | 33<br>34<br>35<br>36<br>37                               |

| CH | 3.1.<br>3.2.         | Spartar 3.1.1. 3.1.2. 3.1.3. Other of                                      | FPGA                                                                                                                                                                                                                                                                     | 33<br>34<br>35<br>36<br>37<br>38                         |

| CH | 3.1.<br>3.2.         | Spartar 3.1.1. 3.1.2. 3.1.3. Other of Software                             | FPGA  n-3 FPGA characteristics  Configurable logic blocks  Digital clock managers  Regular and differential input/output ports  characteristics of ZestSC2 card  re used                                                                                                 | 33<br>34<br>35<br>36<br>37<br>38                         |

| CH | 3.1.<br>3.2.         | Spartar 3.1.1. 3.1.2. 3.1.3. Other 6 Softwar 3.3.1. 3.3.2.                 | FPGA  n-3 FPGA characteristics  Configurable logic blocks  Digital clock managers  Regular and differential input/output ports  characteristics of ZestSC2 card  re used  Xilinx ISE and VHDL code                                                                       | 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41       |

| CH | 3.1.<br>3.2.         | Spartar 3.1.1. 3.1.2. 3.1.3. Other 6 Softwar 3.3.1. 3.3.2. 3.3.3.          | FPGA  n-3 FPGA characteristics  Configurable logic blocks  Digital clock managers  Regular and differential input/output ports  characteristics of ZestSC2 card  re used  Xilinx ISE and VHDL code  FPGA configuration load and Visual studio                            | 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>43 |

| CH | 3.1.<br>3.2.<br>3.3. | Spartar 3.1.1. 3.1.2. 3.1.3. Other of Softwar 3.3.1. 3.3.2. 3.3.3. Built a | FPGA  n-3 FPGA characteristics  Configurable logic blocks  Digital clock managers  Regular and differential input/output ports  characteristics of ZestSC2 card  re used  Xilinx ISE and VHDL code  FPGA configuration load and Visual studio  Labview and DLL libraries | 333<br>344<br>355<br>366<br>377<br>388<br>399<br>400     |

|        |         |                                            | XVI |

|--------|---------|--------------------------------------------|-----|

|        | 3.4.2.  | Coincidence detection                      | 48  |

|        |         | 3.4.2.1. Asynchronous solution's principle | 51  |

|        |         | 3.4.2.2. Synchronous solution's principle  | 52  |

|        | 3.4.3.  | Time stamping                              | 54  |

|        | 3.4.4.  | Pseudo-random number generator             | 56  |

|        | 3.4.5.  | Periodic signal generator                  | 59  |

| 3.5.   | Chapte  | er summary                                 | 62  |

| CHAPT: | ER 4.   | OUTPUTS AND CONTROL                        | 63  |

| 4.1.   | Electro | o-optic modulators                         | 63  |

|        | 4.1.1.  | Phase modulators                           | 64  |

|        | 4.1.2.  | Amplitude modulators                       | 66  |

| 4.2.   | Electri | c signal amplification                     | 66  |

| 4.3.   |         | tput circuit                               | 68  |

|        | 4.3.1.  |                                            | 69  |

|        | 4.3.2.  | PCB layout                                 | 71  |

| 4.4.   |         | er summary                                 | 73  |

|        | 1       |                                            |     |

| CHAPT  | ER 5.   | RESULTS AND ANALYSIS                       | 74  |

| 5.1.   | Input c | pircuit                                    | 74  |

|        | 5.1.1.  | Analysis                                   | 76  |

| 5.2.   | Event   | frequency measurement                      | 77  |

|        | 5.2.1.  | Analysis                                   | 77  |

| 5.3.   | Coinci  | dence detection                            | 78  |

|        | 5.3.1.  | Synchronous solution                       | 79  |

|        | 5.3.2.  | Asynchoronous solution                     | 82  |

|        | 533     | Analysis                                   | 82  |

|        |                           |  | 4 | XVII |

|--------|---------------------------|--|---|------|

| 5.5.   | Periodic signal generator |  |   | 86   |

|        | 5.5.1. Analysis           |  |   | 86   |

| 5.6.   | Output circuit            |  |   | 88   |

| CONCL  | JSION                     |  |   | 92   |

| REFERE | NCES                      |  |   | 95   |

| APPENI | DICES                     |  |   | 98   |

# LIST OF FIGURES

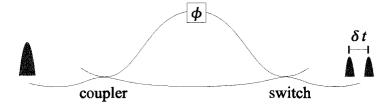

| Figure 1.1.  | fibre interferometer for time-bin encoding                                      | ģ  |

|--------------|---------------------------------------------------------------------------------|----|

| Figure 1.2.  | Arbitrary unitary gate                                                          | 13 |

| Figure 1.3.  | Hadamard gate                                                                   | 13 |

| Figure 1.4.  | C-not gate.                                                                     | 14 |

| Figure 1.5.  | Quantum teleportation circuit                                                   | 15 |

| Figure 2.1.  | Avalanche process in APDs                                                       | 21 |

| Figure 2.2.  | Examples of input signals for the electronic system                             | 23 |

| Figure 2.3.  | Principle of operation for the conversion of signals to TTL                     | 24 |

| Figure 2.4.  | Micrel SY58601U internal schematic                                              | 24 |

| Figure 2.5.  | Schematic of Micrel SY58601U evaluation board. DC-coupled                       |    |

|              | configuration                                                                   | 25 |

| Figure 2.6.  | Micrel SY58601U DC-coupled evaluation board tests                               | 27 |

| Figure 2.7.  | Schematic of designed input PCB                                                 | 29 |

| Figure 3.1.  | Input/output banks in XC3S2000 FPGA and their distribution in                   |    |

|              | ZestSC2 card                                                                    | 37 |

| Figure 3.2.  | Xilinx ISE processes window                                                     | 41 |

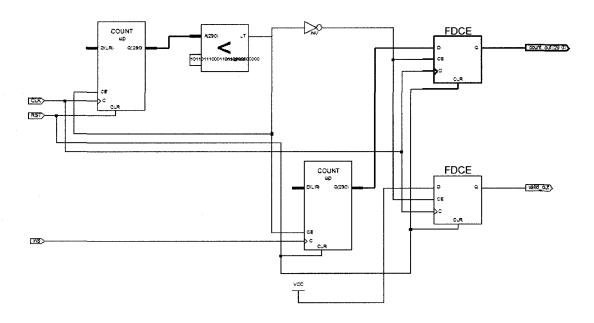

| Figure 3.3.  | RTL of main block for event frequency measurement                               | 46 |

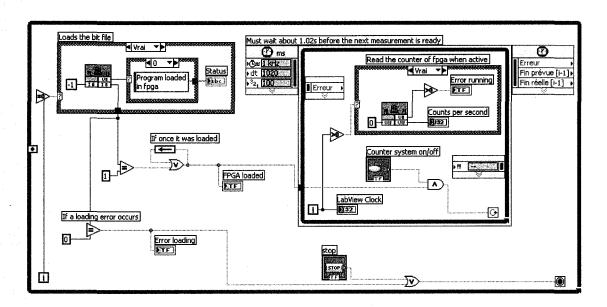

| Figure 3.4.  | LabVIEW block diagram for event frequency measurement rou-                      |    |

|              | tine                                                                            | 4  |

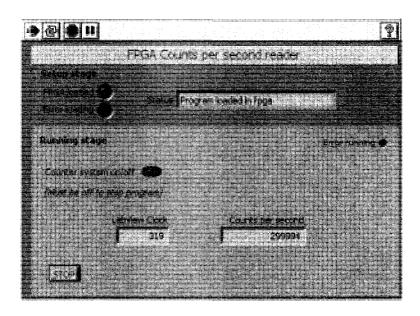

| Figure 3.5.  | LabVIEW front panel for event frequency measurement routine.                    | 48 |

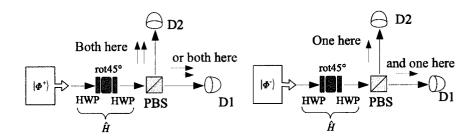

| Figure 3.6.  | Experimental setup to distinguish between $ \Phi^+\rangle$ and $ \Phi^-\rangle$ | 49 |

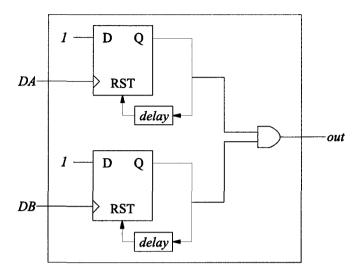

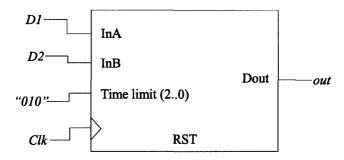

| Figure 3.7.  | Architecture for asynchronous coincidence detection                             | 52 |

| Figure 3.8.  | Architecture block for synchronous coincidence detection                        | 53 |

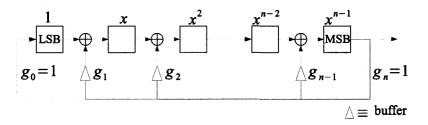

| Figure 3.9.  | LFSR Galois general scheme                                                      | 57 |

| Figure 3.10. | LFSR Galois example                                                             | 58 |

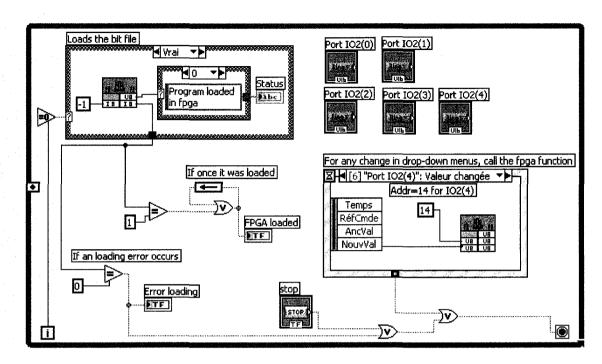

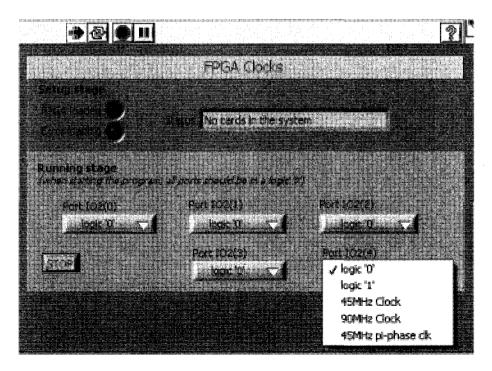

| Figure 3.11. | LabVIEW block diagram for periodic signal generator routine                     | 6  |

| Figure 3.12. | LabVIEW front panel for periodic signal generator routine                       | 61  |

|--------------|---------------------------------------------------------------------------------|-----|

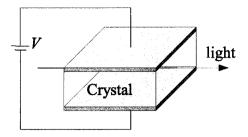

| Figure 4.1.  | Phase modulator made with a non-linear crystal inside a capacitor.              | 64  |

| Figure 4.2.  | Phase modulator driver circuit scheme, with $n$ possible phase                  |     |

|              | values                                                                          | 67  |

| Figure 4.3.  | Schematic of designed output PCB                                                | 70  |

| Figure 5.1.  | Test results of designed input circuit, with $40\%$ duty cycle input.           | 75  |

| Figure 5.2.  | Test results of designed input circuit, with $4\%$ duty cycle $100\mathrm{mV}$  |     |

|              | amplitude input                                                                 | 75  |

| Figure 5.3.  | Test results of designed input circuit, with $96\%$ duty cycle $100\mathrm{mV}$ |     |

|              | amplitude input                                                                 | 76  |

| Figure 5.4.  | Relative error obtained on event frequency measurement appli-                   |     |

|              | cation tests                                                                    | 78  |

| Figure 5.5.  | Front panel of coincidence detection application in LabView                     | 80  |

| Figure 5.6.  | Synchronous systems cannot distinguish between signals that ar-                 |     |

|              | rive within the same $T_{\mathrm{CLK}}$                                         | 80  |

| Figure 5.7.  | Coincidence detection results                                                   | 81  |

| Figure 5.8.  | Time stamping. Reconstruction of two single photon detectors                    |     |

|              | signals                                                                         | 84  |

| Figure 5.9.  | Periodic signal generator output waveforms for the three pro-                   |     |

|              | gramed values                                                                   | 87  |

| Figure 5.10. | Results from tests on custom built output circuit, at a single am-              |     |

|              | plitude modulator output                                                        | 90  |

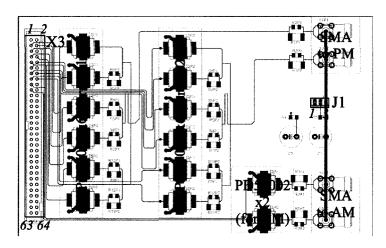

| Figure I.1.  | Layout of PCB for signal conversion                                             | 98  |

| Figure I.2.  | Layout of PCB for signal conversion                                             | 102 |

#### LIST OF NOTATIONS AND SYMBOLS

⊕: Addition modulo 2

⊕: Controlled-not quantum operator

$\otimes$ : Tensor product

: Parallel to (resistances or capacitors)

$\mathbb{C}$ : Complex numbers

N: Natural numbers

$\hat{U}$ : Quantum operator

$\hat{U}^{\dagger}$ : Hermitian conjugate of a quantum operator

$\eta$ : Quantum efficiency

$\lambda$ : Wavelength

f: Frequency

I: Current

n: Refractive index

P: Power

Q: Positive signal of differential pair output

/Q: Negative signal of differential pair output

R: Resistance

t: Time

T: Period

V: Voltage

x: Distance

Z: Impedance

# Acronyms and abbreviations

AC: Alternating current

APD: Avalanche Photodiode

BNC: Bayonet Neill Concelman

CLB: Configurable Logic Block

CLK: Clock

DC: Direct current

DCM: Digital Clock Manager

DLL: Dynamic Link Library

FIFO: First In, First Out

FPGA: Field-programmable gate array

GND: Ground

GUI: Graphical User Interface

I/O: Input/output

IOB: Input/Output Block

LED: Light-emitting-diode

LFSR: Linear feedback shift register

LSB: Least significant bit

LUT: Look-Up Table

LVCMOS: Low Voltage Complementary Metal Oxide Semiconductor

LVPECL: Low-voltage positive emitter-coupled logic

LVTTL: Low Voltage Transistor-transistor logic

MLF: MicroLeadFrame

MSB: Most significant bit

PCB: Printed circuit board

PBS: Polarization beam splitter

PRNG: Pseudo-random number generator

RAM: Random Access Memory

RF: Radio frequency

RNG: Random number generator

RTL: Register Transfer Level

SDRAM: Synchronous dynamic random access memory

SMA: SubMiniature version A

SMD: Surface-mount device

TTL: Transistor-transistor logic

UCF: User constraints file

USB: Universal Serial Bus

VHDL: VHSIC hardware description language

VHSIC: Very-High-Speed Integrated Circuits

XST: Xilinx Synthesis Technology

# LIST OF TABLES

| Table 1.1.  | Jones' matrices for some polarization elements                       |

|-------------|----------------------------------------------------------------------|

| Table 2.1.  | Configuration cases for Micrel SY58601U DC-coupled evalua-           |

|             | tion board tests                                                     |

| Table 2.2.  | Components in the input circuit PCB                                  |

| Table 3.1.  | Xilinx Spartan-3 XC3S2000-4 FG676 block components 35                |

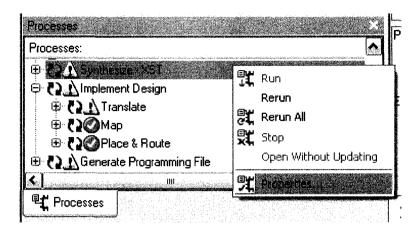

| Table 3.2.  | Property changes in Xilinx ISE for a ZestSC2 card                    |

| Table 3.3.  | Behaviour of coincidence detection with synchronous approach. 53     |

| Table 3.4.  | Encoded output value for periodic signal generator application. 60   |

| Table 4.1.  | Resistance values to obtain some phase modulation values 70          |

| Table 4.2.  | Components in the output circuit PCB                                 |

| Table 5.1.  | Event frequency measurement application tests                        |

| Table 5.2.  | Periodic signal generator. Measured output characteristics 86        |

| Table I.1.  | Pins for J1 in input PCB: JTAG header for voltage supply 99          |

| Table I.2.  | Pins for J2 in input PCB: JTAG header for $V_{\rm ref}(03)$ 99       |

| Table I.3.  | Pins for J3 in input PCB: JTAG header for $V_{\rm ref}(47)$ 99       |

| Table I.4.  | Pins for J4 in input PCB: JTAG header for $V_T(03)$ 100              |

| Table I.5.  | Pins for J5 in input PCB: JTAG header for $V_T(47)$ 100              |

| Table I.6.  | Pins for J6 in input PCB: JTAG header to be connected with FPGA. 101 |

| Table I.7.  | Pins for SV1 in input PCB: JTAG header to shunt supply voltages 101  |

| Table I.8.  | Pins for SV2 in input PCB: JTAG header to shunt reference volt-      |

|             | ages                                                                 |

| Table I.9.  | SMA connectors in input PCB                                          |

| Table I.10. | Pins for J1 in output PCB: JTAG header for voltage supply 103        |

| Table I.11. | Pins for X3 in output PCB: JTAG header to be connected with          |

|             | FPGA                                                                 |

| Table I.12. | SMA connectors in output PCB                                         |

# LIST OF APPENDICES

| APPENI | OIX I.      | PCB PIN CONN     | ١E | EC | ŢΙ | ON | 1S | ٠ |  | • | • |  |  |  |  |  |  | 98  |

|--------|-------------|------------------|----|----|----|----|----|---|--|---|---|--|--|--|--|--|--|-----|

| I.1.   | Input circu | it connections   |    |    |    |    |    |   |  |   |   |  |  |  |  |  |  | 98  |

| I.2.   | Output circ | cuit connections |    |    |    |    |    |   |  |   |   |  |  |  |  |  |  | 102 |

#### INTRODUCTION

Quantum information theory and technology have developed in such a way that, nowadays, its practical implementation is starting to arise. It promises unconditionally secure cryptographic systems and solutions to computational problems that current classical computers solve either inefficiently of not at all, reasons that make it an attractive and active research subject.

Electronic systems are unavoidably involved in this process; they are tied to measurement devices and external controllers, regardless of the experiments' quantum nature. The most common existing approach is to deal with electronic systems using specific function black-boxes, where each of them serves a single purpose; most of the time they may only work with a determined non-conventional type of signal. A second approach is to make custom solutions when required.

This project born moved by the interest in making quantum information systems feasible, and due to the diversity of challenges that electronic systems offer to such implementations. The lack of commercial systems that work for different type of detector signals, and the disconnection between acquisition, processing and action stages are among the reasons that encouraged the realization of this project.

Hence, the purpose of the present investigation is to develop an electronic system to control the action and measurements devices used in quantum information experiments based on optical fibres. Optical schemes being the focus of this project, are specifically targeted. A flexible solution, which works in as many contexts as possible, is pursued.

Electronic requirements for running quantum information experiments on optical schemes are identified and addressed. They require acquisition and recording of data coming from photon detectors. Recognition of coincidences between detectors is required to detect

and exploit a quantum mechanical property named entanglement. Controlling phase and amplitude electro-optical modulators is relevant in order to manipulate the information on optical systems; this enables harnessing superposition, a second property provided by quantum mechanics. For experiments with more than one party, providing a classical communication channel is necessary. Finally, it is important to synchronize the whole system.

The proposed solution takes into account these requirements. It is based on a reprogrammable electronic device, a field-programmable gate array, which can communicate with a computer while executing a routine in real time. Standardization of incoming signals is done by a custom designed printed circuit. Amplification of some outgoing signals is required, and is done by a second custom designed printed circuit.

Tests of programmed applications are presented and analysed. They demonstrate the utility, flexibility and performance of the product here developed.

## **CHAPTER 1**

# BASICS IN QUANTUM COMMUNICATION AND COMPUTING

To operate experimentally either a quantum communication or a quantum computing system, many electronic tasks are required. The purpose of this project is to provide an electronic system as general as possible for these situations. The quantum information domain is treated before entering the electronics domain, to illustrate the requirements and relevance of the developed system.

Quantum information offers characteristics that are not available in its classical counterpart, and makes possible solving some problems for which current algorithms are either innefficient or inexistant. Superposition and entanglement properties allow quantum schemes be differentiated from classical ones. The theory behind this statement is presented in this chapter, along with the experimental optical implementation schemes that enclose this project.

Of particular interest is the one way quantum computing scheme proposed by Raussendorf and Briegel [Raussendorf and Briegel, 2001] as well as quantum communication problems, like the quantum key distribution intended for cryptography purposes and the quantum coin tossing protocol [Bennett and Brassard, 1984].

#### 1.1. Quantum information

This scheme of computing is based on the quantum mechanical properties provided by its minimal information unit, known as a qubit (quantum bit). They can be obtained by any quantum system of two levels, which are represented as  $|0\rangle$  and  $|1\rangle$ .

While a classic bit can only take one of the values, 0 or 1, a quantum state is able to be in a *superposition* of both basic states  $|0\rangle$  and  $|1\rangle$ . This means that in a quantum system it is possible to be in both values at the same time, each of them with a certain probability. The sum of these probabilities must be as usual 1. In other words

$$|\psi\rangle = \alpha|0\rangle + \beta|1\rangle \tag{1.1}$$

where  $|\psi\rangle$  represent the qubit state, and  $\alpha, \beta \in \mathbb{C}$  are the probability amplitudes, that must satisfy the normalization condition  $|\alpha|^2 + |\beta|^2 = 1$ . The qubits can be represented as vectors in an abstract vector space, called Hilbert space. One possible basis in this space is

$$|0\rangle = \begin{pmatrix} 1\\0 \end{pmatrix} \qquad |1\rangle = \begin{pmatrix} 0\\1 \end{pmatrix} \tag{1.2}$$

and then a superposition in this basis, namely  $|\psi\rangle=\alpha|0\rangle+\beta|1\rangle$ , would be represented as

$$|\psi\rangle = \begin{pmatrix} \alpha \\ \beta \end{pmatrix} \tag{1.3}$$

Obtaining information from these states is possible via measurements. However, it is impossible to obtain enough information from the state in order to be able of reconstructing it, or in other words both values  $\alpha$  and  $\beta$  cannot be acquired. After measuring the state  $\phi$ , it will collapse into one of the states  $|0\rangle$  or  $|1\rangle$ . The result of this measurement will be  $|0\rangle$  with probability  $|\alpha|^2$ , or  $|1\rangle$  with probability  $|\beta|^2$ . Is important to state that because a measurement implies an interaction with the system, the quantum state prior to a measurement will be lost, and the new state will be determined by the results of the measurement.

An important property of quantum systems is the no cloning theorem, first demonstrated

by Wooters and Zurek [Wootters and Zurek, 1982]. This says that is impossible to copy a quantum state. This property that in principle appears as inconvenient since the classical view uses typically the resource of duplicating information, becomes a powerful tool if properly exploited, because you can avoid with certitude that the information in such a system could be ever fully copied.

# 1.1.1. Entangled states

It is possible to have systems of several qubits. For example two qubits, let's say  $|\psi_1\rangle, |\psi_2\rangle$  can be in their corresponding 'ground' state  $|0\rangle$ . This can be represented as, in different equivalent representations,

$$|\psi_1\rangle \otimes |\psi_2\rangle = |0\rangle \otimes |0\rangle \tag{1.4}$$

$$|\psi_1\rangle|\psi_2\rangle = |0\rangle|0\rangle \tag{1.5}$$

$$|\psi_1 \psi_2\rangle = |00\rangle \tag{1.6}$$

They could also be each one in a superposition state  $\frac{|0+1\rangle}{\sqrt{2}}$ . Here the state of the system is

$$|\psi_1\rangle \otimes |\psi_2\rangle = \frac{|0+1\rangle}{\sqrt{2}} \otimes \frac{|0+1\rangle}{\sqrt{2}}$$

(1.7)

$$|\psi_1\psi_2\rangle = \frac{1}{2}(|00\rangle + |01\rangle + |10\rangle + |11\rangle)$$

(1.8)

This kind of states, that can be rewritten as a tensor product of n qubits for a system of n elements (in the previous examples n=2) is known as *separable state*. On the other hand some quantum states cannot be separated in such a way. They are called *entangled states*.

For the particular case of a two qubit system  $|\Gamma\rangle = a|00\rangle + b|01\rangle + c|10\rangle + d|11\rangle$ , where  $\{a,b,c,d\} \in \mathbb{C}$  and  $|a|^2 + |b|^2 + |c|^2 + |d|^2 = 1$ , it can be proved that if  $ad \neq bc$ , then  $|\Gamma\rangle$  is an entangled state.

Some examples of entangled states are the Bell states,

$$|\Phi^{+}\rangle = \frac{|00\rangle + |11\rangle}{\sqrt{2}} \qquad |\Psi^{+}\rangle = \frac{|01\rangle + |10\rangle}{\sqrt{2}}$$

(1.9)

$$|\Phi^{-}\rangle = \frac{|00\rangle - |11\rangle}{\sqrt{2}} \qquad |\Psi^{-}\rangle = \frac{|01\rangle - |10\rangle}{\sqrt{2}}$$

(1.10)

the GHZ state of n qubits (standing for Greenberger, Horne and Zeilinger),

$$|GHZ_n\rangle = \frac{1}{\sqrt{2}} (|0\rangle_1 \dots |0\rangle_n + |1\rangle_1 \dots |1\rangle_n)$$

(1.11)

and the W state of n qubits

$$|W_n\rangle = \frac{1}{\sqrt{n}} (|1\rangle_1 |0\rangle_2 \dots |0\rangle_n + |0\rangle_1 |1\rangle_2 \dots |0\rangle_n + \dots + |0\rangle_1 |0\rangle_2 \dots |1\rangle_n). \tag{1.12}$$

# 1.2. Quantum communication

The exploitation of quantum systems by two (or more) parties for information transfer purposes is called *quantum communication*. Entanglement in particular could be exploited by them. Given that they share the qubits from an entangled state, when one of them, let's say Alice, measures its corresponding qubit, the result that the other party(ies) will obtain is correlated with Alice's measurement. There are also some applications that don't require a shared entanglement source, like the BB84 protocol exposed in section 1.3.1.

To implement quantum communication applications as well as quantum circuits, an opti-

cal approach was selected due to the experience of the research group where this project was developed.

For the production of the raw qubit material in the optical approach (the photons), a laser is typically used. Critical characteristics at the moment of selecting one laser are the output wavelength and repetition rate, if it's not from the continuous wave type. The wavelength will determine constraints on all the elements that follow the laser: mirrors, crystals, fibres, detectors.

The repetition rate determines how fast experiments can be performed. In spite of this, the control of these experiences becomes unmanageable when the repetition rate is too high. Another related issue is that detectors typically have a period of time where they are unable to detect a new photon after detection; this period is known as *dead time*. The detection systems will be discussed in chapter 2. Even more critical, the electronics that process all the information put a limit on how fast the experiments can run. This is the subject of chapter 3.

To keep track of a photon, it is handy to work with the *sync out* signal provided by some lasers. It provides the starting time of a single experience. So it is desirable to have a *sync out* signal from the photon source to be used, if some type of control or time processing is wanted.

Because qubits are realized by single photons in conventional schemes, weak pulses from lasers are often used. By attenuating the power of a laser, a single photon source can in principle be obtained. Because of its probabilistic nature, it can also generate several photons at the same time, or none of them with a certain probability.

Parametric down conversion is another method used to generate single photons. This process occurs in non-linear crystals and converts a photon of one wavelength to two photons with different wavelengths, conserving energy and momentum. Because both

output photons are entangled, when one of them is detected the other has been certainly created.

# 1.2.1. Polarization encoding

A photon property easily used for quantum information tasks is its polarization. Polarizers block one component of the electric field and transmit the other. From an observer's coordinate system, the output polarization can be horizontal, vertical, or any other position. It can represent the quantum state of single photons, where  $|H\rangle$ ,  $|V\rangle$  correspond to the preferred orthogonal positions, the so-called computational basis. One state can be represented as

$$|\psi\rangle = \alpha |H\rangle + \beta |V\rangle \tag{1.13}$$

where  $|\alpha|^2 + |\beta|^2 = 1$ . Polarizer beam splitters can separate these two polarizations in different paths. Actually they can separate any two orthogonal polarizations depending on its alignment. To modify the polarization state of photons, wave plates are used.

These elements and their behaviour are described by matrices, representing their transformations. This description is known as Jones formalism or calculus. Some examples are shown in table 1.1 [Saleh and Teich, 1991]. Thanks to the case of operating over a polarization qubit, this encoding type is mainly favoured for quantum computation experiences.

# 1.2.2. Time-bin encoding

When a photon enters a Mach-Zender interferometer, it can go through the short arm or the long arm, from a probabilistic point of view. In a quantum scale description, the photon goes by both arms at the same time. It is necessary to have a photon generated

Table 1.1 Jones' matrices for some polarization elements

Linear polarizer along

$$x$$

$$\begin{pmatrix} 1 & 0 \\ 0 & 0 \end{pmatrix}$$

Linear polarizer at angle  $\theta$

$$\begin{pmatrix} \cos^2 \theta & \sin \theta \cos \theta \\ \sin \theta \cos \theta & \sin^2 \theta \end{pmatrix}$$

Wave retarder

$$\begin{pmatrix} \text{Quarter wave plate: } \Gamma = \frac{\pi}{2} \\ \text{Half wave plate: } \Gamma = \pi \end{pmatrix}$$

$$\begin{pmatrix} 1 & 0 \\ 0 & e^{-i\Gamma} \end{pmatrix}$$

Polarization rotator

$$\begin{pmatrix} \cos \theta & -\sin \theta \\ \sin \theta & \cos \theta \end{pmatrix}$$

Figure 1.1 fibre interferometer for time-bin encoding, as introduced by [Brendel et al., 1999].

with a short pulse duration compared to the length difference between the arms of the interferometer [Brendel et al., 1999].

The basis used is such that when the photon passes by the short arm, it is in the  $|s\rangle$  state, and for the long case its state is  $|l\rangle$ . Then, a qubit state in time-bin encoding is

$$|\psi\rangle = \alpha|s\rangle + \beta|l\rangle \tag{1.14}$$

Because fibres affect the polarization of photons on it, polarization encoding is not ideal for communication experiments. As an alternative time-bin can be implemented over fibres, since the interferometer can be fabricated with them. However, making computations in time-bin is currently unpractical, as there is no easy way to perform arbitrary unitary transforms on such a basis.

# 1.3. Quantum Protocols

A protocol is a set of rules that have to be followed in a certain order to achieve a defined goal. For example, to get money from an ATM a protocol between the machine and the user has to be followed: insert the card, type the password, etc. To register the executed transaction, the ATM has a protocol to communicate with a central database in a secure way.

Quantum protocols are a set of rules applied on quantum states, requiring a qubit source or even an entanglement source in some cases. These protocols become of interest when they can make something better than a classical version of them; more efficient answers, or eventually an answer that classically cannot be found.

When quantum cryptography is mentioned, the promise of a secure cryptography scheme comes to mind. Actually, what quantum mechanical properties offer is a way to create random keys and share them securely between two parties (Alice and Bob). This private random bit sequence can then be used to encrypt a classical message to be sent between them. One example of this type of protocol is exposed in section 1.3.1.

In cases two users prefer (or need) to transfer quantum information securely instead of classical information, they can use *quantum teleportation* [Gisin et al., 2002], provided that they share a prior entangled state, as explained in section 1.3.2.

#### 1.3.1. BB84 protocol

The first quantum key distribution protocol is known as BB84, as the authors' initials and its publication year [Bennett and Brassard, 1984]. This requires the capability of creating a qubit, encoding it, sending it (Alice's side), receive it, measure it (Bob's side) and a classical communication channel for post-processing tasks between both parties.

The feasibility of each step depends highly on the implementation scheme and the type of encoding chosen.

The protocol goes as follows. Alice has to generate a couple of random classical bits: the first one will be the bit sent to Bob (x), and the second determines the basis in which Alice will encode the bit (b). The choice for the encoding basis can be anyone agreed between the two parties, with the condition that the two bases are orthogonal between them. For example, they can choose the rectangular and diagonal basis; for the rectangular basis a classical 0 is encoded in a  $|0\rangle$  state and classical 1 in  $|1\rangle$ ; for the diagonal basis a classical 0 is encoded in a  $|+\rangle = \frac{1}{\sqrt{2}}(|0\rangle + |1\rangle)$  state, while a classical 1 is in a  $|-\rangle = \frac{1}{\sqrt{2}}(|0\rangle - |1\rangle)$  state.

Alice prepares and sends to Bob the state corresponding to her random pair of bits according to the previous rules. Bob then measures the received state in one of the basis (rectangular or diagonal, for example) in a random way, independent of Alice behaviour. Notice that if Bob chooses the same basis that Alice selected to encode the bit, the measured value will be the bit sent by Alice. If the opposite occurs, i.e. both choose a different but orthogonal basis, Bob will learn nothing about the state. This happens because he will measure 0 or 1 with probability 1/2 in those cases.

To complete the protocol, Bob talks to Alice using a classical communication channel, and asks for each of the selected bases. If they have selected the same one, they keep the corresponding bit as part of their key. If they didn't, the bit is just discarded. They repeat this procedure as many times as they want, until they obtain the desired amount of shared bits.

There exist some variations of this protocol to make sure that a possible eavesdropper hadn't access to their quantum channel. One typical procedure includes the verification that some of the bits they claim to share are equal. This assures that nobody had modified

the information, since a third party in order to obtain information has to measure in one random basis (possibly a different one from the two chosen by Alice and Bob) and then resend the data, biased on its own selection of a basis. Remember the no-cloning theorem [Wootters and Zurek, 1982] that prevents a third party to copy the state, save a copy for himself and measure it after hearing the classical conversation.

### 1.3.2. Quantum teleportation

Thanks to entanglement, Alice and Bob can transfer between them a quantum state. Their interest could be to exchange the result of a quantum operation that only Alice is able to make, but Bob is the one who is interested in its output. The procedure known as *quantum teleportation* [Bennett et al., 1993] will permit them to achieve this. To do it they need 3 qubits, where two of them are entangled and shared between them, and the third one contains the quantum state to be transferred.

Before entering on the schematic description of the quantum teleportation procedure (section 1.3.2.2), is helpful to introduce the concept of quantum circuits (section 1.3.2.1).

#### 1.3.2.1. Quantum circuits

Qubits can be altered. The second postulate of quantum mechanics states that:

"The evolution of a closed quantum system is described by a unitary transformation" [Nielsen and Chuang, 2000]

Then, a modification to these states can only be done by unitary transformations  $\hat{U}$  (where  $\hat{U}^{-1} = \hat{U}^{\dagger}$ ) in the Hilbert space. Qubits can also be transferred and measured. The joint of these actions on qubits form what is called a *quantum circuit*.

An arbitrary transformation  $\hat{U}$  applied to a state  $|\psi_1\rangle$ , such that its output  $|\psi_2\rangle = \hat{U}|\psi_1\rangle$  is represented as

$$|\Psi_1

angle ---- |\Psi_2

angle$$

Figure 1.2 Arbitrary unitary gate.

The Walsh-Hadamard transformation  $\hat{H}$ , usually referred only as Hadamard, converts a  $|0\rangle$  into a  $\frac{|0\rangle+|1\rangle}{\sqrt{2}}$  and a  $|1\rangle$  into a  $\frac{|0\rangle-|1\rangle}{\sqrt{2}}$ . Using the basis from equation (1.2), the  $\hat{H}$  transform is represented as

$$\hat{H} = \begin{pmatrix} \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \\ \frac{1}{\sqrt{2}} & -\frac{1}{\sqrt{2}} \end{pmatrix}$$

(1.15)

Its circuit application is represented as

$$|\Psi_1

angle ----- |\Psi_2

angle$$

Figure 1.3 Hadamard gate.

Other useful one qubit gates are the negation  $\hat{N}$  and the phase flip  $\hat{P}$ . They are given by

$$\hat{N} = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix} \qquad \hat{P} = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix} \tag{1.16}$$

where for the negation gate  $\hat{N}|0\rangle = |1\rangle$ ,  $\hat{N}|1\rangle = |0\rangle$ , and for the phase flip gate  $\hat{P}|0\rangle = |0\rangle$ ,  $\hat{P}|1\rangle = -|1\rangle$ .

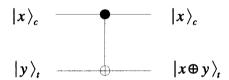

Another important transformation is the controlled-not gate, or just c-not, noted by  $\hat{\oplus}$ . It is a two qubit gate which changes the state of the second qubit (target qubit) from

$|0\rangle$  to  $|1\rangle$  or from  $|1\rangle$  to  $|0\rangle$  only if the first qubit (control qubit) is in the state  $|1\rangle$ . Or, if  $\{x,y\} \in \{0,1\}$  then  $\hat{\oplus}(|x\rangle_c|y\rangle_t) = |x\rangle_c|x \oplus y\rangle_t$ . The corresponding matrix to this transformation in the  $|00\rangle$ ,  $|01\rangle$ ,  $|10\rangle$ ,  $|11\rangle$  basis is

$$\hat{\oplus} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix} \tag{1.17}$$

and the diagram which represents it is

Figure 1.4 C-not gate.

# 1.3.2.2. Quantum teleportation procedure

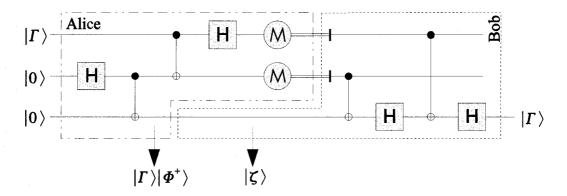

The two interested parties, Alice and Bob, start by generating a pair of entangled qubits, a  $|\Phi^+\rangle = \frac{|00\rangle + |11\rangle}{\sqrt{2}}$ , one of the Bell states from equation (1.9). Alice and Bob each keep one of these qubits, and therefore share entanglement. This state can be made from two qubits at  $|0\rangle$ , an  $\hat{H}$  gate followed by a c-not, as shown in the first part of figure 1.5.

Then, Alice takes the state to be transferred  $|\Gamma\rangle$  and applies the next transformation between  $|\Gamma\rangle$  and her part of the entangled state as indicated in figure 1.5.

At this moment, the state of the circuit is the following

$$|\zeta\rangle = \frac{1}{2}|00\rangle|\Gamma\rangle + \frac{1}{2}|01\rangle\hat{N}|\Gamma\rangle + \frac{1}{2}|10\rangle\hat{P}|\Gamma\rangle + \frac{1}{2}|11\rangle\hat{N}\hat{P}|\Gamma\rangle \tag{1.18}$$

Figure 1.5 Quantum teleportation circuit. Alice and Bob share an entangled state  $|\Phi^+\rangle$ , which allows them to transfer the  $|\Gamma\rangle$  state from Alice to Bob.

where Bob's state, the third qubit, is related to the transferred state  $|\Gamma\rangle$  except for  $\hat{N}$  and/or  $\hat{P}$  transformations; they were defined in equation (1.16). Alice then measures her qubits, immediatly collapsing Bob's state to one of the four options. She communicates via a classical channel the result of the measurement, so Bob can apply the correct transformation to recover  $|\Gamma\rangle$  on his side.

### 1.3.3. Quantum coin tossing

Alice and Bob want to throw a coin and decide on a winner from this result. They are not in the same place. If one of them wants to cheat, he or she will succeed in a classical scenario every time. Nevertheless, in the quantum scenario protocols have been proposed to avoid that the cheater wins all the time. It has been demonstrated [Kitaev, 2002] that in the best case (from the honest person point of view) the cheater will succeed with a probability of about 71%.

One of these protocols was introduced in the same paper as the quantum key distribution scheme presented in section 1.3.1 [Bennett and Brassard, 1984]. Here is exposed the simplified version described recently [Berlín et al., 2008b]. Alice prepares one of four states at random, corresponding to two random bits like in the key distribution protocol:

$|0\rangle, |1\rangle$  for b=0 or  $|+\rangle, |-\rangle$  for b=1. Then she sends this qubit to Bob.

Bob replies to Alice with a random bit g. Then he measures the received qubit in a random basis, namely Bob's  $\tilde{b}$  with the same convention as Alice's b. His result will be  $\tilde{x}$ .

Alice declares her values for b and x. In the case that Bob guessed the basis  $(b = \tilde{b})$  and the value measured doesn't correspond to the one sent by Alice  $(x \neq \tilde{x})$ , Bob recognizes that Alice is cheating. If Bob continues with the protocol, the coin value will be  $b \oplus g$ .

For this protocol Bob cannot cheat. Alice could cheat by lying over the value of b she used, or by sending a different state from the agreed four possibilities.

A newer version of the protocol [Berlín et al., 2008a] does not require a quantum memory. For the experimental implementation of this protocol, random numbers are required. If time-bin encoding is selected, depending on the selected basis a phase has to be applied in one of an interferometer's arm; this happens at encoding and decoding stages. Consequently, driving phase modulators is required. Single photon measurement at the end of the process is also required. All the above tasks can be done, with the support of the products of this project.

### 1.4. Experimental electronic requirements

Now that the fundations behind this work are explained, it is possible to talk about experimental requirements that can be addressed from the electronics.

Timing information of photon generation (laser fast photo diodes) and photon detection (single photon detectors) can be used to synchronize the process chain, which is useful to determine correlations between emitted photons and their measured counterparts. This

requires that the system receives different kind of analog signals and treats them equally. An analog to digital conversion stage scheme is presented at section 2.2.

For timing issues, an external clock is employed as a master clock for the whole system. It can be provided also by an electronic system. Recording this type of events with the timing information is used for this task. This procedure is presented in section 3.4.3.

To determine the actual state of a quantum state, measurements in different basis are done. Frequently coincidence (or anticoincidence) detection is required. This is discussed in section 3.4.2.

Coin tossing protocols even in its quantum version require the generation of classical random bits (section 1.3.3). Typically quantum communication protocols make use of this randomness source. This is possible to address with an electronic system, which creates a pseudo-random sequence of bits following a procedure exposed in section 3.4.4.

For the implementation of an interferometer designed for time-bin encoding (see section 1.2.2), it is necessary to control a phase modulator. This modulator, as discussed in section 4.1.1, is gated via a periodic electrical signal which depending on its voltage level indicates the phase that has to be applied to the optical signal.

### **CHAPTER 2**

### PHOTON DETECTION

As stated, detection of photons is a key step in experiments in optical quantum information, whatever encoding is been used. Even more critical, at the quantum level it is important to be able to detect a single photon. In some cases it is desirable to determine how many photons arrive, to facilitate distinction between the arrival of a single photon or a two or three photons event.

A wide variety of single photon detectors exist in the market. Each of them is designed to function for a certain wavelength range. Hence the choice of photon detectors is relevant when designing an optical experiment. This implies that for different setups, the detectors used are usually different.

This difference between detectors lies not only on its design, but also in its working principle and then, in the output that can be acquired for collecting data. There are several characteristics that differ, depending on the selection, such as efficiency, cost, temperature range operation and portability.

In section 2.1 several photon detection mechanisms are explored, putting a special emphasis on *avalanche photodiodes* (APDs), being the choice for our experiments. Dealing with the outputs of these detectors is considered in section 2.2. The proposal of a circuit which unifies the diversity of electrical signal types is exhibited in section 2.3, closing this chapter.

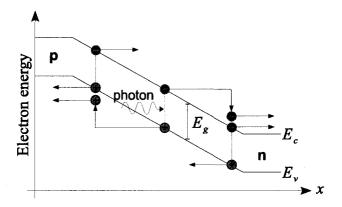

## 2.1. Photon detection mechanisms