|                         | Design and Architecture of a Hardware Platform to Support the Development of an Avionic Network Prototype                                                                                                                                                                                 |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Davide Trentin                                                                                                                                                                                                                                                                            |

| Date:                   | 2012                                                                                                                                                                                                                                                                                      |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                                 |

| Référence:<br>Citation: | Trentin, D. (2012). Design and Architecture of a Hardware Platform to Support the Development of an Avionic Network Prototype [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/808/">https://publications.polymtl.ca/808/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/808/ |

|------------------------------------------|--------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Yvon Savaria, & Guchuan Zhu          |

| Programme: Program:                      | Génie Électrique                     |

# UNIVERSITÉ DE MONTRÉAL

# DESIGN AND ARCHITECTURE OF A HARDWARE PLATFORM TO SUPPORT THE DEVELOPMENT OF AN AVIONIC NETWORK PROTOTYPE

# DAVIDE TRENTIN DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (GÉNIE ÉLECTRIQUE) AVRIL 2012

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

# DESIGN AND ARCHITECTURE OF A HARDWARE PLATFORM TO SUPPORT THE DEVELOPMENT OF AN AVIONIC NETWORK PROTOTYPE

présenté par: <u>TRENTIN</u>, <u>Davide</u> en vue de l'obtention du diplôme de: <u>Maîtrise ès Sciences Appliquées</u> a été dûment accepté par le jury d'examen constitué de:

- M. DAVID, Jean-Pierre, Ph.D., président.

- M. SAVARIA, Yvon, Ph.D., membre et directeur de recherche.

- M. ZHU, Guchuan, Doct., membre et codirecteur de recherche.

- M.  $\underline{\text{LIU}}$ , Xue, Ph.D., membre.

À mes parents, Carmen et Claudio, et à mon frère Stefano qui m'ont toujours supporté même si ça voulait dire me voir partir.

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my research directors Prof. Yvon Savaria at École Polytechnique de Montréal, and Prof. Cristiana Bolchini at Politecnico di Milano, and to my research codirector Prof. Guchuan Zhu at École Polytechnique de Montréal for their suggestions, guidance, and encouragement, that helped me completing this thesis.

I also want to thank Bombardier Aerospace and Thales Canada Inc., as well as CRIAQ, NSERC/CRSNG, and MITACS, for funding the AVIO 402 Project, allowing me to explore the world of embedded avionic systems and networks, and to get in contact with professionals and experts of this domain.

Leaving Italy to study in Montreal has not been easy, but it was definitely an experience worth having, not only for what I learned in school, but also for what I learned about myself and for the great people I met. Thanks to my university colleagues José-Philippe, Talal, and Safwen, who shared with me problems and achievements during the entire project, and to Normand, who always had precious suggestions ready when I needed them. Thanks to the people who are living the same amazing international experience, Sergio, Mauro, Giuseppe, Francesca, Giovanni, Andrea, and the rest of the Italian gang for the nice moments spent together. Thanks to those who lived great adventures with me and to the greatest roommates I have ever had: Danai, Massimo, Ilaria, Sarah, and Jon.

Thank you Marie for always supporting me, for being at my side in the best and in the worst moments of the last year, and for being so special. And yes, thank you for revising my french! Most importantly, a great thank you to my beloved family, Stefano, Carmen, and Claudio, who always supported, loved, and encouraged me, even if this meant watching me go far away for two years and a half.

## RÉSUMÉ EN FRANÇAIS

La récente évolution des architectures des systèmes avioniques a permis la création de réseaux avioniques modulaire embarqués (IMA) et l'augmentation du nombre de systèmes embarqués numériques dans chaque avion. Cette transition vers une nouvelle génération d'avions plus électriques permet une réduction du poids et de la consommation énergétique des aéronefs et aussi des couts de production et d'entretien. Pour atteindre une réduction du poids encore plus poussée et une amélioration de la bande passante des réseaux utilisés, des technologies innovatrices ont récemment été adoptées : ARINC 825 et AFDX qui permettent en fait une réduction du câblage nécessaire pour réaliser le réseau embarqué.

Dans le cadre du projet AVIO 402, qui inclut plusieurs sujets de recherche qui concernent aussi les capteurs et leur interface avec le système IMA, une nouvelle architecture a été proposée pour la réalisation du réseau utilisé pour le système de contrôle de vol. Cette architecture est basée sur des bus ARINC 825 locaux, connectés entre eux en utilisant un réseau AFDX qui offre une meilleure bande passante ; les ponts entre les deux protocoles et les modules qui connectent les nœuds au réseau ont une structure générique pour supporter des protocoles différents et aussi plusieurs types des capteurs et actionneurs. Pour une évaluation des performances et une analyse des défis de son implémentation, la réalisation d'un prototype du réseau proposé est requise par le projet.

Dans ce mémoire, le développement d'une plateforme matérielle pour soutenir la réalisation de ce prototype est traité et trois modules fondamentaux du prototype ont été conçus sous forme de "IP core" pour être subséquemment intégrés dans l'architecture du réseau qui sera implémenté en utilisant des FPGA. Les trois systèmes sont le contrôleur du bus CAN, utilisé comme base pour l'implémentation du protocole ARINC 825, le "End System" AFDX et le commutateur nécessaires pour la réalisation d'un réseau AFDX. Dans la première partie de ce mémoire, les objectifs visés sont présentés et une analyse des spécifications des protocoles considérés est fournie, cela permet d'identifier les fonctionnalités qui doivent être incluses dans chaque système et de déterminer si des solutions pour leur implémentation ont déjà été publiées et peuvent être réutilisées. Ensuite, le développement de chaque système est présenté et les choix de conception sont expliqués afin de montrer comment les fonctionnalités requises par les spécifications des deux protocoles peuvent être implémentées pour mieux répondre aux nécessités du projet AVIO 402.

Au début du projet AVIO 402, CAN, CANaerospace et ARINC 825 étaient considérés comme des solutions acceptables pour la réalisation des bus locaux, donc un contrôleur CAN facilement reconfigurable a été développé pour supporter ces trois technologies différentes, en

profitant des leurs grandes similitudes. Dans un deuxième temps, il a été préféré d'inclure le seul ARINC 825 dans le prototype et le système conçu a été adapté à cette solution. La plupart des architectures pour des contrôleurs CAN publiées dans les dernières années proposent une structure basée sur deux modules de traitement séparés pour les trames entrant et sortant du nœud. Pour rendre le IP plus facilement adaptable au bus ARINC 825, où les trames de surcharge ne sont pas permises, un gestionnaire central a été ajouté à ce type de système. Puisqu'il est responsable de toutes les fonctionnalités qui différencient un protocole de l'autre, ce gestionnaire est la seule partie du contrôleur qui nécessite une modification. Le système conçu garantit une occupation de seulement 3% des ressources du FPGA Spartan-6 utilisées pour la réalisation du prototype.

Pour le développement du "End System" (ES), une approche logiciel a été préférée à la réalisation d'un IP matériel à cause des interconnexions avec les applications du NCAP, le pont entre le bus local et le réseau principal, qui seraient exécutées par un processeur embarqué. Pour profiter des similitudes avec Ethernet et pour garantir une meilleure portabilité du code développé, le protocole AFDX est implémenté à partir de fonctionnalités de réseautage du noyau Linux exécuté par le processeur Microblaze. Cette solution permet de réutiliser l'interface API généralement utilisée pour Ethernet, basée sur les sockets, et les protocoles UDP et IP fournis par Linux, et aussi de rendre le "End System" indépendant du materiel. Pour émuler un environnement ARINC 653, requis par le projet AVIO 402, le système embarqué a été abandonné et un ordinateur a été utilisé pour continuer la modification des fonctions de réseautage du noyau Linux ; cette migration a permis d'apprécier la bonne portabilité du design conçu, puisque le code développé est indépendant du processeur utilisé.

Le dernier système réalisé est le commutateur du réseau AFDX. Pour minimiser la latence maximale des trames, ce module a été complètement implémenté en VHDL pour implémenter un traitement matériel parallèle des trames reçues. Une architecture à routage en parallèle, souvent utilisées dans des switch Ethernet, a été adoptée pour effectuer aussi le filtrage requis par la norme AFDX en parallèle. Un algorithme "token bucket" est exécuté par le module de gestion, qui détermine aussi la destination des paquets reçus, pour éliminer tous ceux qui ne respectent pas la bande passante allouée pour leur lien virtuel. L'ordonnancement des trames vers les destinations correspondantes tient compte des deux niveaux de priorité prévus par la norme. Un double tampon a été utilisé pour le stockage de trames en entrée pour séparer le traffic critique du traffic non critique, et conséquemment réduire encore plus la latence des premières ; la présence d'un tampon supplémentaire permet aussi de créer un système redondant où le deuxième tampon peut gérer les trames critiques quand l'autre est en panne. Le commutateur réalisé peut gérer un traffic à la vitesse maximale que le

réseau peut supporter (100 Mbit/s) sur chaque port et éviter l'accumulation des paquets dans les mémoires internes. Le module de routage est non bloquant, il peut donc transmettre plusieurs paquets simultanément quand ils n'ont pas la même destination et donc éviter toute congestion dans cette situation.

Le travail effectué dans ce mémoire sera utile non seulement pour la production du prototype en profitant des modules développés, mais aussi pour les leçons apprises et les solutions identifiées pour leur implémentation. L'architecture du commutateur AFDX en particulier est une contribution originale; en effet, la littérature concernée est très limitée et donc le système de filtrage des paquets et de ségrégation de trafics critiques et non critiques de ce type de système n'a jamais été étudié.

#### **ABSTRACT**

The objective of the present project is to design three modules for a hardware platform that will support the implementation of an avionic network prototype based on the FPGA technology. The considered network has been conceived to reduce cabling weight and to improve the available bandwidth, and it exploits the recently introduced ARINC 825 and AFDX protocols. In order to support the implementation of both these protocols, a CAN bus controller, an AFDX End System, and an AFDX Switch have been designed. After an extensive review of the existing literature about the two related avionic protocols, a study of the existing solutions for CAN and Ethernet protocols, on which they are based, has been done as well to identify what knowledge and technology could be reused.

Because they are very similar, a flexible CAN controller has been implemented in hardware instead of an ARINC 825 one in order to support both these technologies and in order to reduce the IP core size. A combined HW/SW approach has been preferred for the AFDX End System architecture to leverage an existing UDP/IP protocol stack and the Ethernet layer included in the Linux kernel has been modified to create a portable and configurable implementation of AFDX. Since various problems have been encountered to reproduce an ARINC 653 compliant environment on the embedded system, the suggested design has been ported in a PC. Finally, an original solution for the implementation of the AFDX switch fabric has been finally presented; a space-division switching architecture has been chosen and tailored to meet the AFDX specification. Hardware parallelism is exploited to reduce the latency introduced on each frame by filtering them concurrently. Input buffers have been duplicated to separate high from low priority traffics, further reducing latency of critical frames and creating a redundancy that reduce the possibility of packet loss. Packet scheduling and double queuing guarantee that all critical frames are forwarded before low priority ones.

**Keywords:** Avionic Full-Duplex Switched Ethernet, AFDX, ARINC 664, ARINC 825, CAN, Avionic Data Networks, Ethernet Switch, FPGA.

## TABLE OF CONTENTS

| DEDIC  | ATION   | ·                                   | . iii  |

|--------|---------|-------------------------------------|--------|

| ACKNO  | OWLED   | OGEMENTS                            | . iv   |

| RÉSUM  | MÉ EN I | FRANÇAIS                            | . v    |

| ABSTR  | CACT    |                                     | . viii |

| TABLE  | OF CO   | ONTENTS                             | . ix   |

| LIST O | F TAB   | BLES                                | . xii  |

| LIST O | F FIGU  | URES                                | . xiii |

| LISTE  | DES Al  | NNEXES                              | . xv   |

| LIST O | F ABB   | BREVIATIONS                         | . xvi  |

| INTRO  | DUCTI   | ION                                 | . 1    |

| СНАРІ  | TRE 1   | CONTEXT AND OBJECTIVES              | . 3    |

| 1.1    | The A   | AVIO 402 project                    | . 4    |

| 1.2    | Projec  | ct objectives                       | . 8    |

| 1.3    | Hardw   | vare platform                       | . 9    |

|        | 1.3.1   | Development environment             | . 9    |

|        | 1.3.2   | IP modules                          | . 10   |

| CHAPI  | TRE 2   | AVIONIC DATA COMMUNICATION NETWORKS | . 12   |

| 2.1    | Overvi  | riew of avionic protocols           | . 12   |

|        | 2.1.1   | The CAN protocol                    | . 13   |

|        | 2.1.2   | The AFDX protocol                   | . 17   |

| 2.2    | Litera  | ture review                         | . 20   |

|        | 2.2.1   | CAN bus controller                  |        |

|        | 2.2.2   | AFDX End System                     |        |

|        | 2.2.3   | AFDX Switch                         |        |

| CHAPI' | TRE 3   | CAN BUS CONTROLLER                                                                                                               |

|--------|---------|----------------------------------------------------------------------------------------------------------------------------------|

| 3.1    | Specifi | cation and requirements                                                                                                          |

| 3.2    | Design  | 30                                                                                                                               |

|        | 3.2.1   | Hardware vs. Software considerations                                                                                             |

|        | 3.2.2   | Architecture                                                                                                                     |

| 3.3    | Impler  | nentation                                                                                                                        |

|        | 3.3.1   | Functional verification                                                                                                          |

|        | 3.3.2   | Migration towards ARINC 825                                                                                                      |

| CHAPI' | TRE 4   | AFDX END SYSTEM                                                                                                                  |

| 4.1    | Specifi | cations                                                                                                                          |

| 4.2    | Propos  | sed solution $\dots \dots \dots$ |

|        | 4.2.1   | The Linux Ethernet protocol stack                                                                                                |

|        | 4.2.2   | End System design                                                                                                                |

| 4.3    | End S   | ystem development                                                                                                                |

|        | 4.3.1   | Hardware embedded system                                                                                                         |

|        | 4.3.2   | Software implementation                                                                                                          |

| 4.4    | Practio | cal Problems and Lesson Learned                                                                                                  |

| CHAPI' | TRE 5   | AFDX SWITCH                                                                                                                      |

| 5.1    | Specifi | cation and requirements                                                                                                          |

|        | 5.1.1   | ADFX switch specification                                                                                                        |

|        | 5.1.2   | Switch Fabric                                                                                                                    |

|        | 5.1.3   | AVIO 402 requirements                                                                                                            |

| 5.2    | Core I  | Design                                                                                                                           |

|        | 5.2.1   | Hardware advantages                                                                                                              |

|        | 5.2.2   | Switch Architecture                                                                                                              |

| 5.3    | Synthe  | esis results                                                                                                                     |

|        | 5.3.1   | System size                                                                                                                      |

|        | 5.3.2   | Timing                                                                                                                           |

|        | 5.3.3   | Considerations on the implementation                                                                                             |

| 5.4    | Test a  | nd validation                                                                                                                    |

|        | 5.4.1   | Testbenches                                                                                                                      |

|        | 5.4.2   | System behaviour                                                                                                                 |

|        | 5.4.3   | Performance measurement                                                                                                          |

| CHAPI' | TRE 6   | CONCLUSION AND FUTURE WORK                                                                                                       |

| BIBLIO | GRAPI    | IY 8               | 87 |

|--------|----------|--------------------|----|

| APPEN  | DICES    |                    | 90 |

| FSM    | I implen | nentation          | 90 |

| B.1    | Queue    | implementation     | 98 |

| B.2    | Manag    | er implementation  | 07 |

| B.3    | Schedu   | ler implementation | 12 |

| B.4    | Filter i | mplementation      | 15 |

| C.1    | Switch   | Fabric test cases  | 21 |

|        | C.1.1    | Test test case 1   | 21 |

|        | C.1.2    | Test test case 2   | 22 |

|        | C.1.3    | Test test case 3   | 23 |

|        | C.1.4    | Test test case 4   | 23 |

|        | C.1.5    | Test test case 5   | 24 |

|        | C.1.6    | Test test case 6   | 25 |

|        | C.1.7    | Test test case 7   | 26 |

|        | C.1.8    | Test test case 8   | 28 |

|        | C.1.9    | Test case 9        | 28 |

|        | C.1.10   | Test case 10       | 29 |

|        |          |                    | 29 |

# LIST OF TABLES

| Table 3.1 | Size of the CAN controller modules                                                  | 36  |

|-----------|-------------------------------------------------------------------------------------|-----|

| Table 3.2 | Hexa<br>decimal value of each state of the reception branch of the<br>${\rm FSM}$ . | 38  |

| Table 3.3 | List of the scenarios used to validate the $Manager$ behaviour                      | 39  |

| Table 3.4 | Size of the ARINC 825 controller                                                    | 41  |

| Table 5.1 | System size for 10 and 20 ports                                                     | 72  |

| Table 5.2 | Size of single modules                                                              | 72  |

| Table 5.3 | After synthesis operating frequence                                                 | 74  |

| Table 5.4 | List of the most significant tests                                                  | 77  |

| Table 5.5 | Technological latency for frames of minimum and maximum length   .                  | 79  |

| Table 5.6 | Output FIFO overflow                                                                | 81  |

| Table C.1 | Test 3: VLs and their destinations                                                  | 124 |

| Table C.2 | Test 4: VLs and their destinations                                                  | 125 |

| Table C.3 | Test 7: Output FIFO overflow                                                        | 127 |

| Table C.4 | Test 10: Frame sizes                                                                | 130 |

### LIST OF FIGURES

| Figure 1.1  | Avio 402 network overview                                                   |

|-------------|-----------------------------------------------------------------------------|

| Figure 1.2  | Network architecture                                                        |

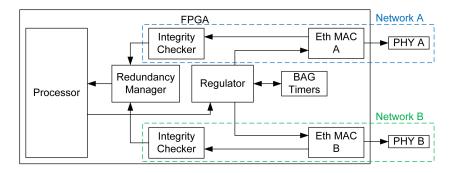

| Figure 1.3  | NCAP structure                                                              |

| Figure 1.4  | Prototype overview                                                          |

| Figure 2.1  | CAN extended data frame structure                                           |

| Figure 2.2  | AFDX network example                                                        |

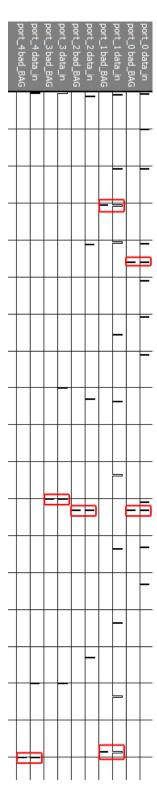

| Figure 2.3  | BAG and Jitter in ES transmission                                           |

| Figure 2.4  | AFDX frame structure                                                        |

| Figure 2.5  | HW implementation of the ES                                                 |

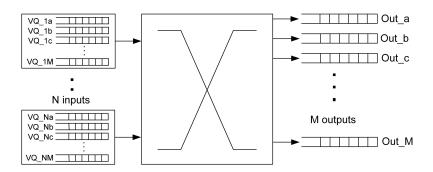

| Figure 2.6  | Combined input/output buffering structure                                   |

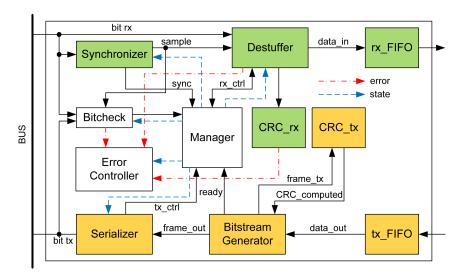

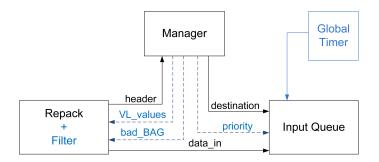

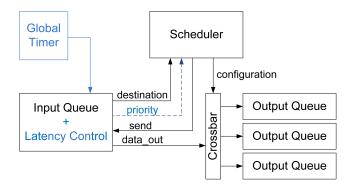

| Figure 3.1  | CAN controller internal architecture                                        |

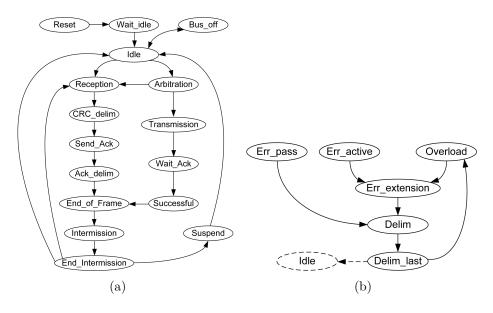

| Figure 3.2  | FSM execution flow                                                          |

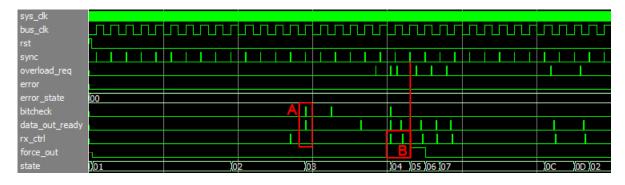

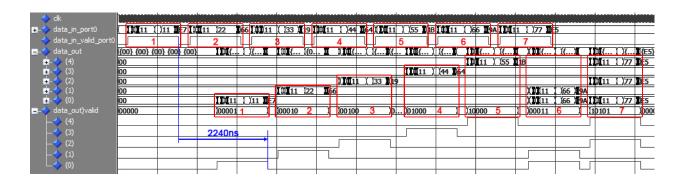

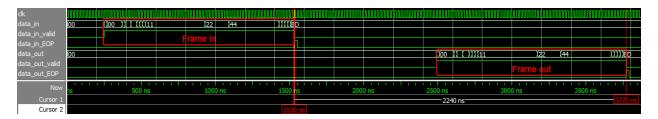

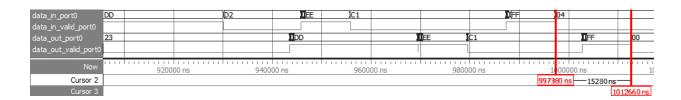

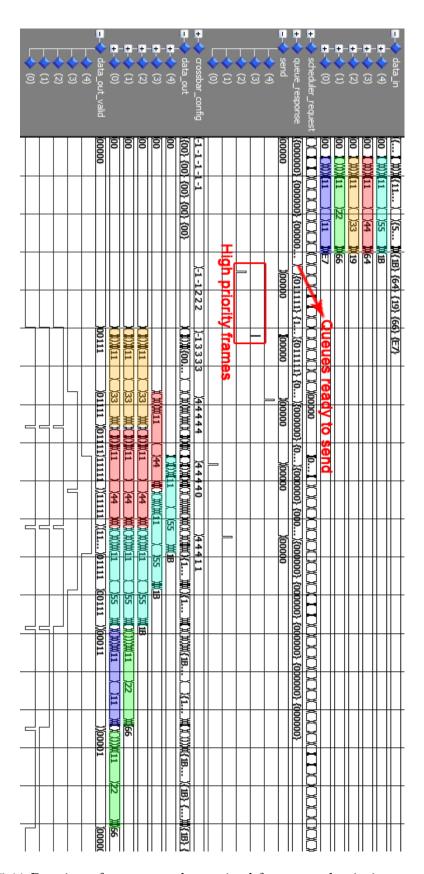

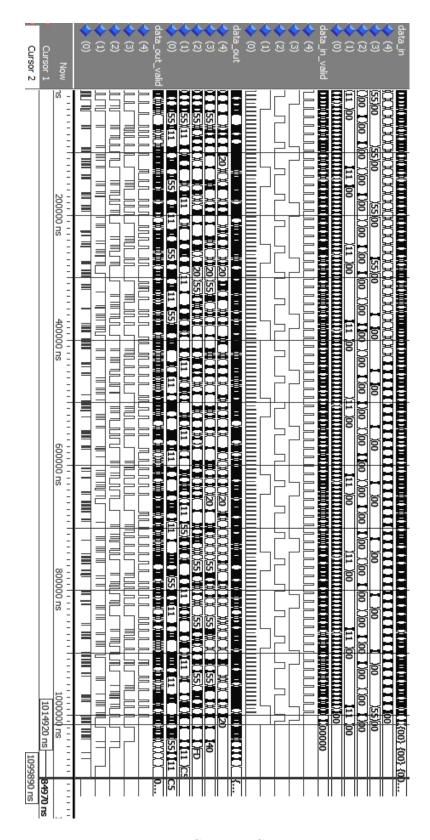

| Figure 3.3  | Simulation example: FSM reception reception flow                            |

| Figure 4.1  | SW architecture overview                                                    |

| Figure 4.2  | ES hardware architecture                                                    |

| Figure 4.3  | SW architecture overview                                                    |

| Figure 4.4  | Modified prototype structure                                                |

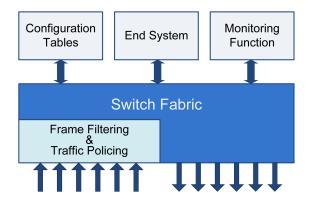

| Figure 5.1  | Representation of the modules of the Switch taken from the specification 57 |

| Figure 5.2  | Example of frame-based leaky bucket algorithm application 59                |

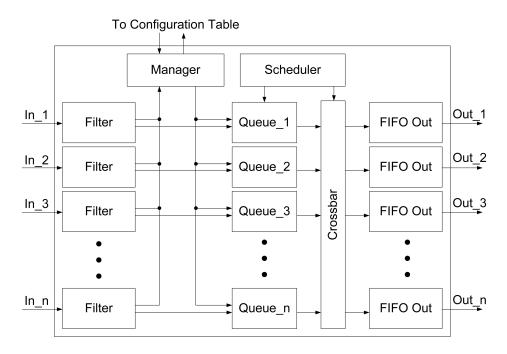

| Figure 5.3  | Architecture of the Switch                                                  |

| Figure 5.4  | Reception modules                                                           |

| Figure 5.5  | Transmission modules                                                        |

| Figure 5.6  | Head of Line Blocking                                                       |

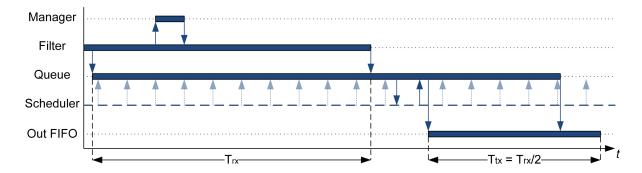

| Figure 5.7  | Frame treatment by the core functional modules                              |

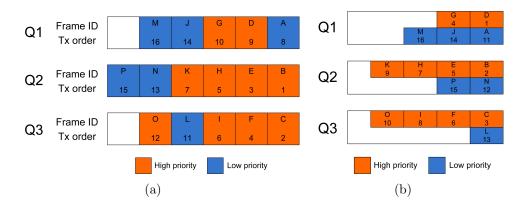

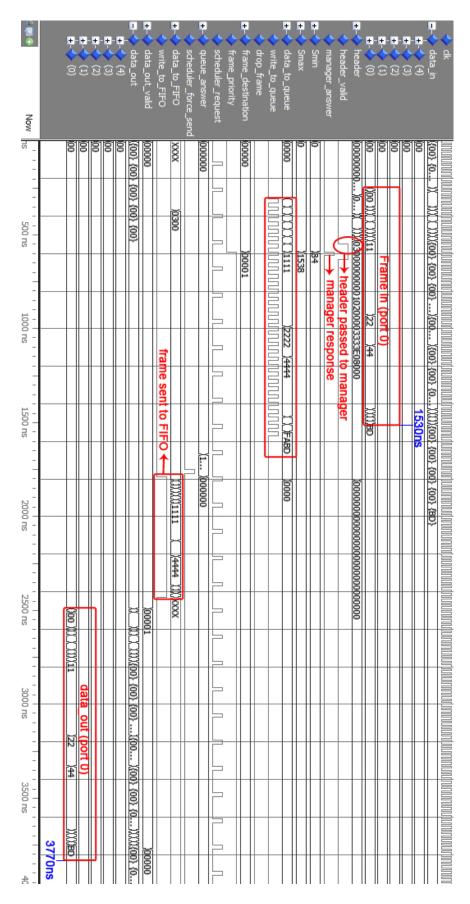

| Figure 5.8  | Basic routing functionalities                                               |

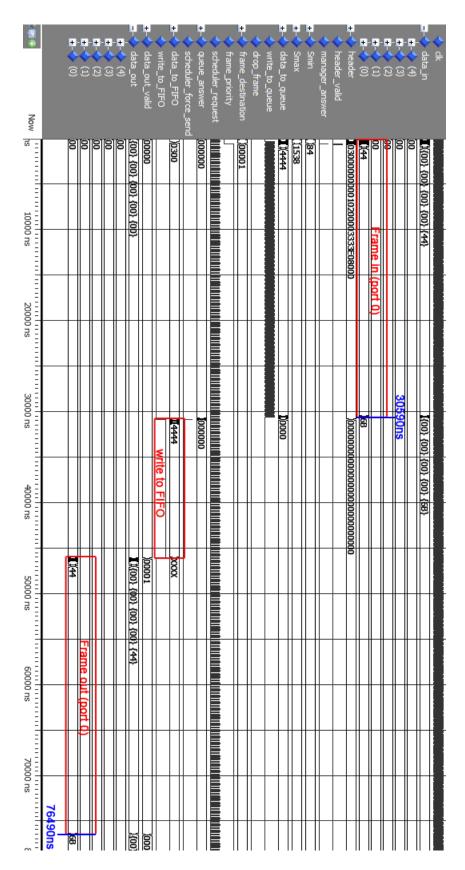

| Figure 5.9  | Minimal technological latency measure                                       |

| Figure 5.10 | Latency of the last byte for a 1ms single-port burst 80                     |

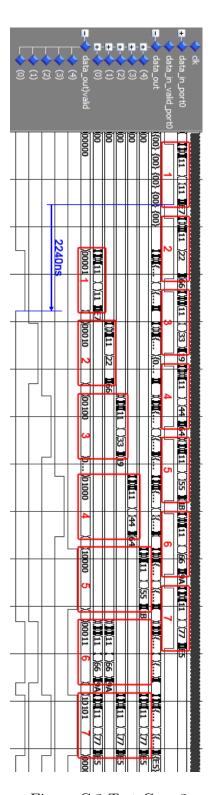

| Figure 5.11 | Routing of concurrently received frames and priority management 82          |

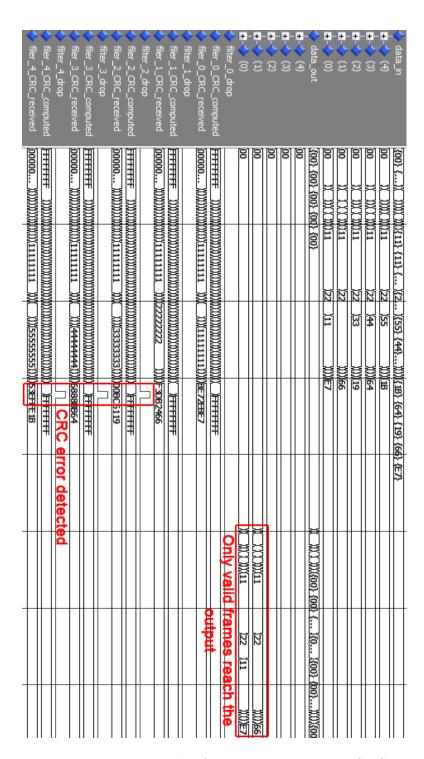

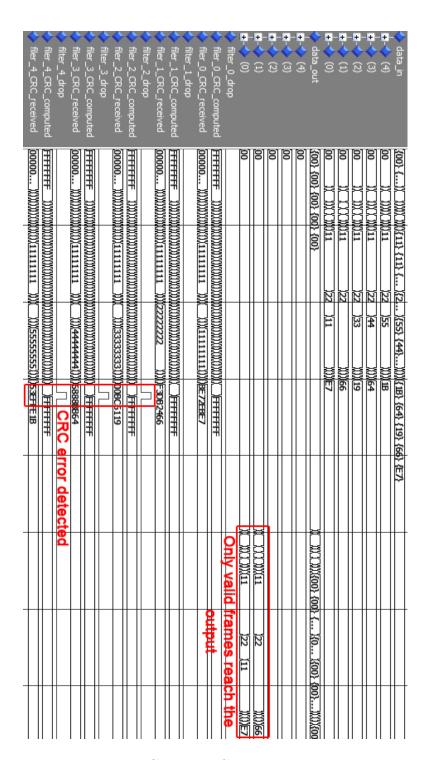

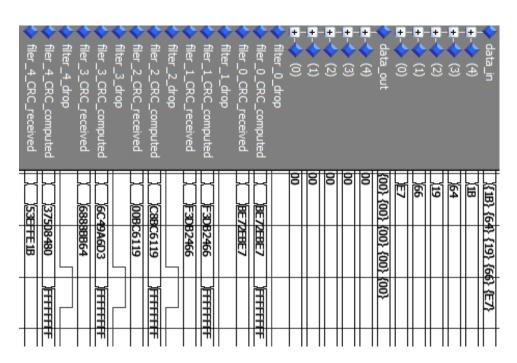

| Figure 5.12 | Example of error detection: bad CRC                                         |

| Figure C.1  | Test Case 1                                                                 |

| Figure C.2  | Test Case 2                                                                 |

| Figure C.3  | Test Case 3                                                                 |

| Figure C.4  | Test Case 4                                                                 |

| Figure C.5  | Test Case 5 - first example  | 135 |

|-------------|------------------------------|-----|

| Figure C.6  | Test Case 5 - second example | 136 |

| Figure C.7  | Test Case 6                  | 137 |

| Figure C.8  | Test Case 7                  | 138 |

| Figure C.9  | Test Case 8                  | 139 |

| Figure C.10 | Test Case 9 - overview       | 140 |

| Figure C.11 | Test Case 9 - CRC control    | 141 |

| Figure C.12 | Test Case 10                 | 142 |

| Figure C.13 | Test Case 11                 | 143 |

## LISTE DES ANNEXES

| Annexe A | IMPLEMENTATION OF THE MANAGER OF THE CAN CORE . | 90  |

|----------|-------------------------------------------------|-----|

| Annexe B | IMPLEMENTATION OF THE AFDX SWITCH               | 98  |

| Annexe C | SWITCH FABRIC TEST VERIFICATION                 | 121 |

#### LIST OF ABBREVIATIONS

AFDX Avionic Full-Duplex Switched Ethernet

AMP Arbitration based on Message Priority

BAG Bandwidth Allocation Gap

COTS Component Off The Shelf

CRC Cyclic Redundancy Check

CSMA Carrier Sense Multiple Access

ES End system

FCC Flight Control Computer

FCS Frame Control Sequence

IMA Integrated Modular Avionics

LRM Line Replaceable Module

LRU Line-replaceable Unit

MAC Media Access Controller

MEA More Electric Aircaft

MTU Maximum Transmission Unit

NCAP Network Capable Application Processor

NIC Network Interface Controller

QoS Quality of Service

SOF Start of Frame

TIM Transducer Interface Module

VL Virtual Link

#### INTRODUCTION

The aerospace industry has historically been reluctant to introduce significant innovations to replace old, well known, reliable systems. In recent years though, the market has been pushing toward the realization of more efficient and easily maintainable aircrafts to reduce production and maintenance costs. These needs allowed the introduction not only of new electronic technologies in the avionic environment, but also a general reorganization of the aircraft support structure. Integrated Modular Avionics (IMA) is slowly replacing the traditional federated architecture and the fly-by-wire philosophy is being applied more and more instead of the old mechanical and hydraulic control used in airborne systems, resulting in a general trend towards a More Electrical generation of Aircrafts (MEA).

All these innovations involve a significant increase in the complexity of electronic controls, and number of actuators, and sensors; therefore, the volume of digital data exchanged between avionic systems is growing and becoming harder to handle. Because of this transitions old and mature technologies exploited so far for the communication of electronic data, such as ARINC 429, are now showing their limits and problems, especially for what concerns their low bandwidth and the extremely large bundle of wiring they require. This is why new interesting solutions are finally finding place in avionic networks. For instance, AFDX and ARINC 825 are two of the most promising technologies available for the aerospace industry to solve the aforementioned problems.

The work presented in this thesis concerns the development of three IP cores to realize a hardware platform that will support the implementation of an avionic network prototype. Such a prototype will support verification as well as testing of reliability and performance of a new network architecture proposed as a part of the AVIO 402 CRIAQ project, which aims at helping the industrial partners migrate towards a greener, less costly, and more energy-efficient generation of aircrafts. ARINC 825, one of the considered protocols, is used for the communication between sensors and actuators grouped in local clusters. By contrast, AFDX provides a connection between these local networks and the central Flight Control Computers (FCCs) and other IMA systems. This architecture offers not only high bandwidth and reliability, but also a significant reduction of the required cabling, and consequently of the overall weight of the system.

With this thesis work, a development environment has been set for the prototype implementation and three fundamental modules of the network have been studied and conceived: a CAN bus controller to support ARINC 825 connectivity, an AFDX End System, and an AFDX switch fabric. Each module has been analysed to determine the best approach for its

implementation and to propose a design for its architecture considering the needs concerning performance and system size required by the protocol specification and by the AVIO 402 project. An implementation of their fundamental functionalities has been done as well to determine if the selected solutions can provide the necessary performance and to provide the starting point for the realization of the final prototype. The contribution of this work is not limited to the development of this hardware platform, but also to the identification of critical aspects of the implementation of these recently introduced technologies to propose possible design solutions that would help improving their Technology Readiness Level.

#### Outline of the Thesis

More precise information about the objectives of this work can be found in chapter 1, together with a description of its context and of the AVIO 402 project. In chapter 2, the ARINC 825 and AFDX protocols are introduced to highlight their peculiarities and their innovative features, and the state of the art concerning their implementation is presented together with a review of the existing literature. The following three chapters focus on the three developed systems, presenting the conceived design, the implemented features, and some obtained results. In chapter 3, the design of the CAN bus controller is described and the synthesis results are provided as well. The AFDX End System is treated in chapter 4, where the proposed solution is explained and its advantages and problems are discussed. Chapter 5 presents the design and implementation of the AFDX switch, describing how the conceived design can reduce frame latency and reduce the impact of the head-of-line blocking. Final considerations on the obtained results, on the lesson learned, and on the perspective opened by this work are included in chapter 6, where future work is discussed as well.

#### **CHAPITRE 1**

#### CONTEXT AND OBJECTIVES

The main trend of the aerospace industry in recent years has been directed towards the development of greener, less costly, and easily maintainable aircrafts. These goals are being achieved by making airplanes "more electrical", replacing mechanical controls with electrical fly-by-wire controls, and adopting Integrated Modular Avionic (IMA) architectures. All these aspects are closely interconnected with each other.

The idea of More Electrical Aircraft (MEA) became interesting thanks to advances in solid-state power-related electronics, that can now provide the necessary electrical power to replace heavy an expensive hydraulic parts, as explained by Rosero et al. [1]. More and more mechanical and hydraulic systems are now being eliminated from airplanes and electrical motors and actuators are taking their place. These are usually lighter and more energy-efficient than their predecessors, and they can also be easily digitally controlled. This last aspect made also possible the transition from mechanical controls to electrical ones, that brought to the development of fly-by-wire systems. MEA and fly-by-wire largely contributed to the reduction of aircraft weight and consequently of the overall fuel consumption, also reducing components wear out and maintenance costs of the machine.

A classic aircraft is based on a federated architecture, where each of its systems is developed as a Line Replaceable Unit (LRU) that can be easily changed or replaced, and that provides a single peculiar functionality in order to guarantee segregation of faults occurring in one of them and to avoid their propagation. Digital control of engines and actuators made possible the development of IMA architectures, where embedded systems are exploited to handle more than one task, thus reducing the number of sub-systems on board, and consequently of the overall weight and power consumption. This concept has been studied in the 90s and it has been finally standardized at the end of the 2000s, with the production of the Airbus A380 and the Boeing 787. The new sub-systems of the network are often called Line Replaceable Modules (LRMs) and they must ensure logical and physical segregation of the various tasks in order to keep each one of them independent from anything else and to prevent fault propagation. LRMs often exploit commercial off-the-shelf (COTS) components in order to reduce production costs and, when they are processor based, they usually rely on the ARINC 653 compliant operating systems to ensure time and spatial independence of the various applications running on it. The IMA architecture offers other important advantages such as reduction of inventories in Airline Maintenance Centres and reduction of cost for

version upgrades and functional enhancements.

All these became popular in the last decade and they brought a significant increase in the volume of digital data that needs to be exchanged on board, exposing limitations and disadvantages of old technologies usually adopted for data communications: traditional avionic technologies offer limited bandwidth, and they also involve bulky wiring bundles when the number of connected systems increases, leading to serious problems related to wiring weight. The need for a more efficient, highly-reliable network to transmit all this digital data across the aircraft is consequently becoming a priority. Recently developed protocols such as ARINC 825 or Avionic Full-Duplex Switched Ethernet (AFDX) aim at solving these problems providing large bandwidth and a network structure that allows wiring reduction while guaranteeing high reliability.

#### 1.1 The AVIO 402 project

This project has been proposed and is supervised by two industrial partners, Bombardier Aerospace Inc. and Thales Group, and it is supported by CRIAQ, NSERC-CRSNG, and MITACS as well. Not only École Polytechnique de Montreal, but also ETS and McGill University are involved in various aspects of the project. The project has multiple complementary goals, all intended to push the avionic industry towards a greener generation of aircrafts: the development of new MEMS, optical sensors, and of a universal smart sensors interface, and the frequency selection for on board wireless communications, are some of the other topics covered in this project along with the design of a reliable communication network.

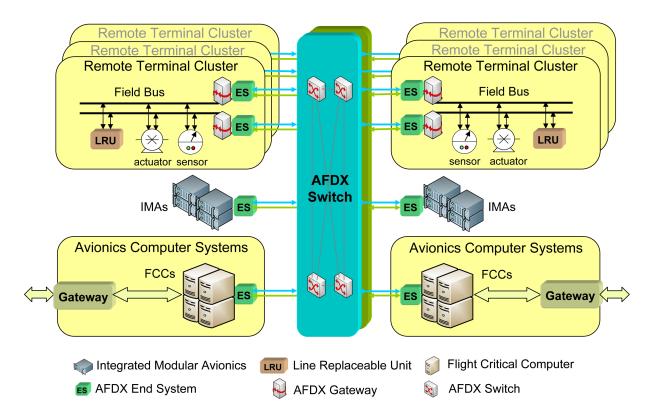

In parallel with the studies on AFDX performance, end-to-end latency, and optimization and of the reliability of the proposed network architecture, the development of a prototype of this network is required as well: the objective is to explore practical implementation issues, and to provide a platform, or test-bed, for practical testing and verification of the achievable performance and potential limitations. To understand the test-bed structure, what needs to be included in it, and which modules will be examined in this thesis, a description of the proposed network architecture is given in the following section. A high-level overview of the general architecture of the network that is being developed is shown in Figure 1.1: the system includes some local clusters relying on a local field bus, generic IMA modules, a main backbone AFDX network, and redundant Flight Control Computers (FCC). Each remote cluster can rely on a variety of possible technologies, such as CAN, ARINC 825, but also legacy systems that use traditional protocols such as ARINC 429, and the ES (End Systems) that connect these clusters with the main network must provide a gateway between these protocols and AFDX. In particular, ARINC 825 has been chosen for the prototype realization

Figure 1.1 Network overview directly taken from the internal documentation of the Avio 402 project

in order to explore this fairly recent technology.

#### System overview

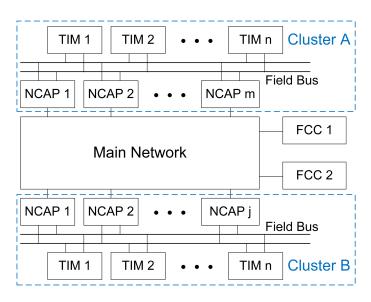

A refinement of the network architecture has been proposed by J.-P. Tremblay and it has been conceived to provide high bandwidth and wiring reduction while maintaining a high overall reliability. As shown in Figure 1.2, sensors and actuators present across the aircraft are grouped into local clusters, as specified by the AVIO 402 project, which rely on the ARINC 825 protocol. This CAN based protocol is an enhanced version of CANAerospace, which has known a wide diffusion in recent years, and it is a promising solution for small avionic networks based on the LRU concept, thanks to its high reliability and its efficient networking capability. This bus links all the sensors and actuators of the local group together and with multiple Network Capable Application Processors (NCAPs) as well. The bus is not directly connected to the peripherals, in fact Transducer Interface Modules (TIMs) are exploited to provide actuator control, or sensor management, while dealing with commands coming from the central control unit and with communications with other peripherals. On the other side,

the NCAP module realizes the bridge between the local and the main networks, providing a gateway between the two different adopted protocols and some additional services to handle data flow, to wrap packets together, and to determine data destination. The generic structure of this network, as well as the terminology and the acronyms that have been adopted are taken from the IEEE 1451 standard [2] for a smart transducer interface for sensors and actuators, that has been used as guideline but that had to be adapted to the avionic environment since it was not originally intended for it. The main network is based on the AFDX technology because it must provide a higher bandwidth than the local networks since multiple clusters will exploit it simultaneously. AFDX allows a reduction of the cabling thanks to the concept of virtual links and it is one of the most promising technologies for next generations of aircrafts.

Figure 1.2 Network architecture as specified by J.-P. Tremblay in the internal documentation of the Avio 402 project

Figure 1.2 shows two clusters, one on the top and one on the bottom, connected to the main network through multiple NCAPs, their number can change from one cluster to the other. Each NCAP is connected to the field bus that put it in communication with all the TIMs that are connected to the sensors and actuators of the local cluster. Redundant paths are used inside each TIM and NCAP module as well to provide even more possible routes for transmitted data: when one of the modules stop working correctly, an alternate path can be used to guarantee data delivery, but the price to pay is that more resources are required.

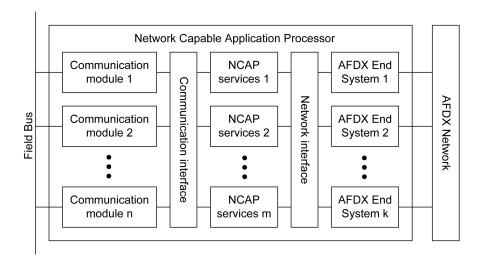

The NCAP constitutes a sort of bridge between the local network and the main one, realising a gateway that must be able to communicate with the two protocols it is interfaced with, but also to provide additional services for the control of the peripherals, for traffic flow

Figure 1.3 NCAP structure as designed by J.-P. Tremblay for the Avio 402 project

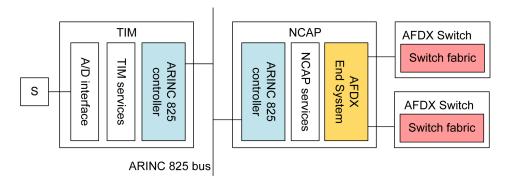

control, and for the identification of the nature of the information that is passing through it. As shown in Figure 1.3, the interface with each network is realized via a dedicated controller that must handle the corresponding protocol. In both directions, crossbars can redirect received packets towards any of the available service modules, and to any of the output interfaces, thereby reducing the introduced latency and avoiding the loss of frames in case of failure of one of the modules of the system. NCAP services are still not precisely determined, thus flexible interfaces must be considered to communicate with them. The TIM internal structure is not described here since it is not strictly related to this thesis, but it is important to know that a communication module identical to the one instantiated in the NCAP as interface with the field bus is present in the TIM as well to reproduce the same function. The AFDX network is based on the star topology typical of switched Ethernet, therefore it requires switches to handle frame routing and traffic control. These routing modules are mostly similar to a standard Ethernet switch but they must also provide some additional features required by the AFDX protocol.

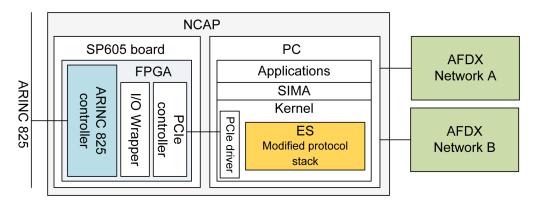

With the development of the prototype, it will be possible to test the overall functionality of this proposed network architecture and its performance. The experimental results will also be useful to validate the models developed to evaluate end-to-end delay, AFDX jitter, and system reliability. A first implementation of the prototype will not include the redundant paths included in the general structure previously presented; the overall structure of the system that should be included in the prototype is shown in Figure 1.4 where the modules conceived in this work are highlighted.

Figure 1.4 Prototype overview

#### 1.2 Project objectives

The goal of this thesis is to contribute to the development of a hardware platform by developing three Intellectual Properties (IPs) modules to support the realization on FPGA of the network prototype required by the AVIO 402 project. These modules will constitute the starting point of the implementation of an ARINC 825 controller, an AFDX End System (ES), and an AFDX Switch. It can be observed in Figure 1.4 that these subsystems constitute the fundamental blocks of the basic implementation of the network included in the prototype. An analysis of the considered modules is required to identify which approach is the most suitable in each case to reach the best results considering the context this modules need to be used in; a fully hardware implementation in VHDL, that could be optimal for certain systems, may not be advantageous when developing other parts of the network. The parameters used to select the preferable solution (between all those that can meet the performance required by the corresponding specification) are different for the three cases: while the size is critical for the ARINC 825, and reconfiguration capabilities are important for the AFDX End System, processing time and frame latency must be minimized in the AFDX switch fabric.

The first objective is to realize the three subsystems that meet the functionalities and performance required by the corresponding specification, but this must be done considering their future integration in the prototype and the tasks included in the AVIO 402 project. Interfaces need to be compatible with those defined for adjacent modules of the prototype, and the internal structure of each IP must support potential future modifications that could become necessary to integrate solutions proposed by other colleagues to improve the network performance. In order to develop a solution that can be exploited also in a commercial product (i.e. not only a test-bed for network analysis, design reuse must be addressed as far as possible; this will also help increase the technology readiness level of the exploited

protocols.

Although ARINC 825 has been adopted in the final network architecture, this solution was not initially confirmed, and CANaerospace and CAN were considered viable choices as well. Thanks to the very close similarity between these technologies, it has been decided to initially develop a standard CAN controller, that would be easily configurable to support the two avionic protocols if necessary. The other two systems needed for the prototype, the ES and the Switch, are really different from each other even if they realize the same protocol. The ES requires the development of the protocol on multiple layers, it must in fact communicate with the physical layer, encapsulate data following the ARINC 664 specification, meet the traffic control requirements described in the same documentation, and it also has to work in close relation with the NCAP services and Gateway functionalities integrated in the NCAP. The AFDX switch fabric has a similar role in the network to the one used in Ethernet switches, it must in fact route frames towards their destination but also filter them to discard the ones that do not respect the AFDX requirements.

#### 1.3 Hardware platform

Because of the flexibility required in a prototyping stage, the whole system will be implemented on FPGA. This solution allows easy modifications and testing even after the network development is completed, and it also provides the possibility of exploiting a mixed HW/SW approach for the realization of each subsystem. A description of the chosen development environment is given here before passing to a presentation of the three modules that will be discussed in this thesis.

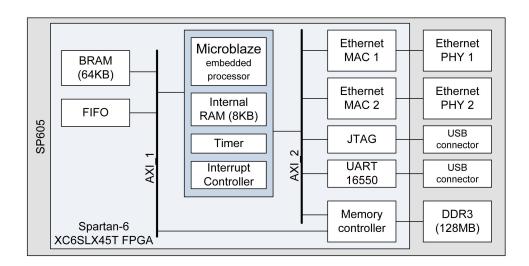

#### 1.3.1 Development environment

The FPGA development board has been chosen in function of the provided peripherals, of the FPGA size, and of its cost. Because of costs and development time, the same board should host all the various systems composing the network; the chosen device must consequently satisfy the needs of both the TIM and the NCAP modules, as well as of the AFDX switches. This solution facilitates portability of the developed modules from one system to another, for example, the CAN controller could be used on both the TIM and the NCAP with no modification at all.

The chosen board is the SP605 by Xilinx, expanded with the ISM networking FMC module by Avnet: this entry level board is an inexpensive solution that can host the whole NCAP, while the expansion FMC card provides additional communication ports. The SP605 board [3] is based on a Spartan-6 XC6SLX45T FPGA and it provides, among other features,

general I/O and UART connectors, one tri-mode Ethernet PHY, a DDR3 memory, a 1-lane PCI Express connector, and an FMC LPC (Low Pin Count) connector. This last connector is used to plug the ISMNET LPC extension card [4] that provides two additional Ethernet PHY as well as two CAN bus connectors required for the ARINC 825 communication into the board.

This generic development board provides an inexpensive and easy solution for the realization of the whole prototype. The two CAN bus ports provided by the FMC card are required for the field bus implementation, and the two Ethernet ports for the AFDX End system connection on the main network. The presence of three Ethernet PHYs overall allows the realization of a minimal switch on the same board as well.

#### 1.3.2 IP modules

The design and development of three fundamental Intellectual Properties is discussed in this thesis, these modules are conceived according to the selected FPGA development environment and to the objectives of the AVIO 402 project.

#### CAN bus controller

In the description of the network proposed for the AVIO 402 project, the CAN bus was not mentioned, but, as explained above, at the time this project started, the adoption of the ARINC 825 protocol was not confirmed yet. Because of the strong analogies between CAN, CANaerospace, and ARINC 825 protocols, it was planned to initially develop a standard CAN bus controller that would support potential future modifications if necessary; the smaller the required changes for this transition the better. A detailed analysis of the two avionic standards is required to identify their differences from CAN, and to determine how they could affect the implementation of its controller. Even if inspiration can be taken from already existing designs and solutions for a CAN controller's architecture, attention must be paid to ensure a complete compliance with these avionic technologies. Unfortunately, while an extensive literature is available for the implementation of a CAN core, the same cannot be said for ARINC 825 and CANaerospace bus controllers, and even if commercial products are available, no internal description of these systems has been found in the literature. This controller constitutes the communication module included in both the TIM and in the NCAP systems for the communication with the field bus, and, as depicted in Figure 1.3, it needs to be instantiated multiple times to guarantee better reliability; as a consequence the IP size can become a critical parameter depending on the number of instantiations required, and it must be considered as a key feature when designing this system.

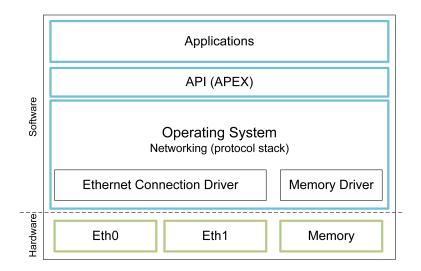

#### AFDX End System

The second module that must be designed is the front end of the NCAP module towards the AFDX network, which is included in the switches as well, and it is called an End System. The role of this system is to provide data encapsulation/decapsulation, traffic flow control, and transmission/reception of frames over the network. Data that is managed by higher level applications (that can implement NCAP services, or the Gateway towards the ARINC 825 field bus, or again the switch's health manager) is passed to the ES for transmission over the network. The strict relationship of the ES with these other required functionalities makes it impossible to develop them completely independently, therefore the design of this system must take the others into consideration and be as flexible as possible because of the provisional nature of those in this prototyping stage. Active research is in progress about optimal scheduling and other techniques aimed at minimizing frame latency and jitter in AFDX networks, and the final prototype should support and facilitate their potential implementation for testing. Key features of this IP must consequently be ease of integration and interaction with the aforementioned functionalities, and reconfigurability, to test this system with different scheduling algorithms and with different configurations of the supported Virtual Links.

#### **AFDX Switch**

The last system considered in this thesis is the routing module, that represents the heart of the AFDX switch. The AFDX network is based on the same switched topology as a standard switched Ethernet network, but the nodes that are responsible for the routing of the frames, although they share multiple identical features with their IEEE 802.3 counterpart, are different under various aspects such as frame filtering, traffic policing, latency and priority management. There are no publications in the current literature concerning the implementation of this system, thus a theoretical study of how techniques and architectures developed for ATM Ethernet switches can be applied in an AFDX environment becomes necessary to determine the most suitable approach for its development. The goal is to identify advantages and problems of existing solutions when applied to airborne networks, to successively identify the most suitable for the current application and implement it as an IP core that will be instantiated in the switches of the prototype. While many ATM switches are designed to optimize the average Quality of Service (QoS) and the average delay introduced, in AFDX switches, it is the maximum latency that must be limited, and a mandatory differentiated services (DiffServ) processing is required to handle separately high and low priority traffics.

#### CHAPITRE 2

#### AVIONIC DATA COMMUNICATION NETWORKS

In this chapter, essential information about the considered protocols is given, as well as an overview of the existing literature about the current state of the art concerning the architectures and implementations of the three systems considered in this thesis. Since a basic knowledge of the most important aspects of the studied technologies is fundamental to fully understand the architectural choices made throughout this work, a general overview of these features is depicted in Sections 2.1.1 and 2.1.2, while their detailed description can be found in the provided references. An exploration of the existing solutions for the implementation of these three systems is done afterwards in Section 2.2, together with a review of the publications concerning the considered technologies.

#### 2.1 Overview of avionic protocols

Classical Aircraft Data Networks (ADN) primarily utilize the ARINC 429 standard. This standard, developed over thirty years ago and still widely used today on a variety of aircrafts from different companies, has proven to be highly reliable in safety critical applications and to provide the necessary performance for avionic applications. ARINC 429 networks rely on a unidirectional bus with a single transmitter and up to twenty receivers. A data word consists of 32 bits communicated over a twisted-pair cable. There are two speeds of transmission: high speed operates at 100 Kbit/s and low speed operates at 12.5 Kbit/s. ARINC 429 operates in such a way that its single transmitter communicates in a point-to-point connection with its receivers, thus requiring a significant amount of wiring overhead since every new connection requires additional cables, significantly increasing overall aircraft weight. Although it is nowadays a popular standard in civil aerospace applications, ARINC 429 requires custom hardware, which can increase aircraft cost and development time.

Apart from ARINC 429, which remains the most popular and most widely used technology for digital on board communications, other technologies can be found on most airplanes. ARINC 629 for example, firstly introduced by Boeing for its 777 aircraft, provides a higher data speed, up to 2Mbit/s, and does not require the presence of a bus master, thereby increasing reliability of the network architecture. Its major drawback though is the need for custom hardware that can make its development time and costs excessive. Another common protocol is the MIL-STD-1553, mostly used in military avionics and spacecraft for on board

data handling. It provides very high reliability but it is expensive and its bandwidth is limited.

ARINC 825 and AFDX have been conceived to solve the bandwidth, wiring weight, and costs problems of the above mentioned protocols: the important cabling reduction, together with the good reliability they guarantee, makes them two of the most promising technologies for the development of lighter, greener, and less costly aircrafts. The interest in these technologies is attested by the rich literature that is being produced, especially on AFDX: various researches are being done on multiple aspects, such as worst-case end-to-end delay analysis, ES and Switch algorithms, or guaranteed reliability [5, 6, 7]. More details on the literature available on AFDX and CAN-based technologies are given in Section 2.2.

#### 2.1.1 The CAN protocol

The Controller Area Network (CAN) data bus is a serial communication protocol that supports distributed real-time control with a high level of security. It is designed to allow microcontrollers and devices to communicate with each other without the need for a master host computer. It was designed in the 80s by Robert Bosh GmbH [8] for automotive applications, but its success, reliability, and versatility attracted the attention of manufacturers in other industries, including process control, medical equipment, and recently Avionics. It was Airbus that first introduced it in this field during the development of the A380.

All the devices of a CAN network are connected to a single twisted-pair of wires that they must share as communication medium, but optical fibre can be used as well. The CAN bus operates at data rates up to 1Mbit/s for cable lengths less than 40m, but it is necessary to reduce the data rate for longer cables; it usually falls to 125Kb/s when the length is around 500m. Maximum speed must be decreased also when the number of LRUs connected to the bus increases. The International Standards Organisation (ISO) has formalized this protocol in the ISO 11898 (High-Speed CAN bus, up to 1Mbit/s) and ISO 11519 (Low-Speed CAN bus, up to 125Kb/s) specifications. Two version of the CAN protocol are specified: CAN 2.0 A and CAN 2.0 B, the first uses the standard or base frame format, that supports an 11-bit identifier, while the second uses an extended frame format in which the identifier is composed by 18 additional bits (for a total of 29 bits).

Controllers connected to the CAN bus must transmit and receive data while avoiding collision using the CSMA/AMP technique. With Carrier Sense Multiple Access (CSMA), a bus controller can start a new transmission only when the bus is idle, and if two nodes try to transmit at the same time an arbitration logic allows the transmission only of the message with the highest priority (Arbitration based on Message Priority or AMP).

CAN is a broadcast-type bus since each transmission is received by all the terminals

connected to it; it is each node's responsibility to determine if the received frame is relevant to that particular system or not, and to drop packets that were not addressed to it. Frames do not include source nor destination addresses, and their header is the only information the receiving terminal can use to identify relevant frames. This structure makes this bus really effective and versatile when working with LRUs.

#### Message arbitration

The bus can have two logic values, dominant and recessive, and whenever two terminals attempt a simultaneous transmission of a dominant bit and a recessive bit, a dominant logic value will result on the bus. In a typical implementation of a wired connection 0 is the dominant value, and consequently this is often called an "AND" implementation. The first controller that lose a contention, sending a recessive bit and reading a dominant value resulting on the bus, must immediately stop its transmission. The result is an arbitration technique based on the message header, which determines the communication priority.

#### Frame structure

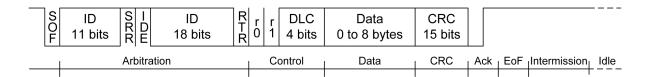

Figure 2.1 CAN extended data frame structure

CAN data frames consists of seven bit fields: Start Of Frame (SOF), Arbitration, Control, Data, CRC, ACK, and End Of Frame (EOF). At the end of a transmission there is an Intermission period where no other communication can start. SoF is always a dominant bit marking the beginning of a transmission, and it is followed by the Arbitration field, composed by the Identifier, the Remote Transmission Request (RTR) for a standard frame, or the Substitute Remote Request (SRR) for an extended frame, and finally the Extension bit IDE, that determines if the frame is standard or extended. r0 an r1 are reserved bits that are always dominant, and compose the Control field together with the Data Length Code of 4 bits, which specifies how many bytes are present in the Data field. The Data field contains the actual information, while the CRC is used to guarantee data integrity. During the recessive bit transmitted in the Acknowledgement field a dominant value must be received on the bus to ensure that the frame has been correctly received. In Figure 2.1, a data frame with extended identifier is shown, since it is the only one used by CANaerospace and ARINC

825: SRR and IDE equal to '1' signal the presence of the additional 18 bits Identifier, and RTR is '0' because this is a data frame. To ensure a strong synchronisation, the protocol avoids the presence of more than 5 consecutive bits of the same value in the transmitted frame by adding a stuffing bit after them in order to have a transition of the bus value that will let all the bus nodes readjust their sampling time.

#### **Error detection**

CAN bus is a technology that guarantees high reliability. Each terminal is in fact responsible for auto-supervision and faulty controllers are automatically disconnected from the bus, without the need for a global supervisor. Whenever an error occurs, the controller that identified the problem must generate an error frame to make all the other nodes connected to the bus aware of that. There are five different error types:

- Bit Error: the bus must be monitored during transmission to verify that, once the arbitration is won, the monitored bit value corresponds to the bit value that is sent;

- Stuff Error: it occurs whenever six consecutive equal bit values are detected in the received frame, thus violating the mandatory stuffing rule;

- CRC Error: it is detected if the computed CRC is not the same as the received one;

- Form Error: all the fixed-form fields of any received frame must have the expected structure;

- Acknowledgement Error: it must be flagged by the transmitter if no dominant bit is monitored during the corresponding acknowledgement slot.

A supervising module is required in any bus controller to disconnect the corresponding terminal if proven faulty multiple times, in order to keep the bus available for all the LRUs that are working correctly. A transmit error count and a receive error count are incremented whenever an error occurs following a precise algorithm, specified in [8], to give a suitable weight to each type of error, and the node is disconnected when its counter gets higher than a predetermined limit. If no error is detected, these counters are decremented and the node might eventually be reconnected to the bus. In normal working conditions, the controller is Error Active, meaning that, since everything is working correctly, it can participate in error detection generating error frames. If the transmit or the receive error count reaches a value of 128 the controller must be set in an Error Passive condition, in which it can still interact with the bus but it can only generate passive error frames, composed only by recessive bits and that consequently does not perturb the operation of other nodes. If further problems occur the controller is set as Bus Off so that it cannot interact with the bus any more.

#### **Overload Frame**

Another feature included in the CAN specification is the Overload Frame: whenever a node is not in condition to perform a new reception or whenever the bus is too busy, this kind of frame can be generated to reduce bus usage and let all the controllers be ready for the next communication. An overload situation can occur also if a dominant bit is monitored on the bus at the first or second bit of an *Intermission*, or in the delimiter of an error or overload frame. If the controller or the system connected to it need more time before being available for a new reception, they can start an Overload frame at the end of an *Intermission* or when the bus is *Idle*.

#### CANaerospace and ARINC 825: analogies and differences with standard CAN

The avionic industry opened its doors to CAN thanks to the reduction of cabling it allows, to its efficiency when working with LRUs, and its reliability. Although this technology already gave satisfying performance, some modifications were identified to fully adapt this protocol to airborne systems, bringing to the development of CANaerospace and ARINC 825. Both these avionic adaptations of CAN are based on the ISO 11898 to ensure interoperability between them and CAN as well.

CANaerospace defines additional ISO/OSI layers 3, 4, and 6 functions, i.e. in the composition of the frame header, to support node addressing, and it also introduces Time Triggered Bus Scheduling. This last feature reduces the maximum bandwidth available for each terminal, forcing it to transmit only in predetermined time slots where no other controller can use the bus. Thanks to this solution data collision is eliminated and the arrival time of each packet becomes deterministic, but inefficient bandwidth utilization is the price to pay. It must be noticed that none of these differences affects the physical layer, nor the data link layer, and consequently a CAN bus controller is compatible with CANaerospace without any modification.

The ARINC 825 specification [9] is a general standardization of CAN for airborne use. Since CAN physical layer already provides error recovery and protection mechanism necessary in avionic systems, no additional functions have been added at this level. Like CANaerospace, ARINC 825 is entirely based on the extended frame CAN 2.0B version. The 29 bits of the extended frame identifier allow the division of the identifier into sub-fields required for the creation of a standardized application layer. 11-bit identifiers may coexist on ARINC 825 buses but they are not required. The communication mechanism is derived from CANaerospace, and similar functions are added to ISO/OSI layers 3, 4, and 6 to support logical communication channels (LCCs), one-to-many/peer-to-peer communications, and station addressing.

Time Triggered Bus Scheduling is adopted in this protocol as well to improve determinism. Because of the extreme similarity with CANaerospace, ARINC 825 does not seem to require modification in the actual bus controller either, there is one difference though: since the time triggered bus scheduling prevents any terminal from starting a transmission during an intermission frame, no overload frame should occur when all the terminals are working correctly. To reduce network loading, overload frames are prohibited by ARINC 825, and situations that would cause their generation are to be considered erroneous.

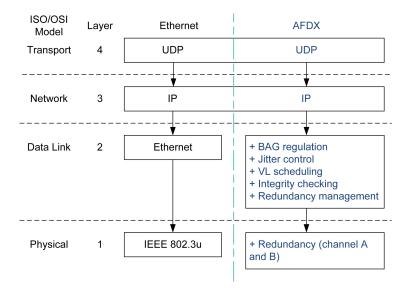

#### 2.1.2 The AFDX protocol

While presenting the network architecture proposed for the Avio 402 project, it has been stated that AFDX has been chosen to realize the central network of the system because of its two main advantages over other avionic protocols: high bandwidth and the low amount of cabling required. This technology is strongly based on the IEEE 802.3 Ethernet, thus making it possible to benefit from commercial-off-the-shelf (COTS) components, and from all the expertise and knowledge developed for it over the years, consequently reducing overall costs, making system development faster, and maintenance less costly as well. The following description of its features will make clear why this protocol is so promising and will highlight the differences and analogies with the IEEE 802.3 specification. It is important to remember that AFDX was designed to exploit Ethernet COTS components and functionalities, but following the ARINC 429 philosophy, i.e. implying point-to-point communication, known bandwidth, redundancy, and prioritized quality of service, in order to meet the reliability and determinism required in any avionic system. The official ARINC 664 (Part 7) specification [10] relies on many concept taken directly from UDP, IP, and Ethernet protocols.

#### Virtual Links

The first, and maybe the biggest, difference between AFDX and Ethernet is the concept of Virtual Link (VL): Virtual Links are independent virtual connections that share the same physical medium. They are point-to-point communications, but while in ARINC 429 each one of these requires a physical wire to connect its source with all the destinations, in this case they all coexist on the same star topology network, with a consequent reduction of the amount of required wiring. The virtual point-to-point communication channels are emulated on the network by allocating a limited bandwidth for each one of them: each node can transmit packets corresponding to a certain VL only in a predefined temporal window dedicated to that precise connection. This transmission window is called Bandwidth Allocation Gap (BAG) and allows various VLs to coexist on the same network without interfering with each other. In

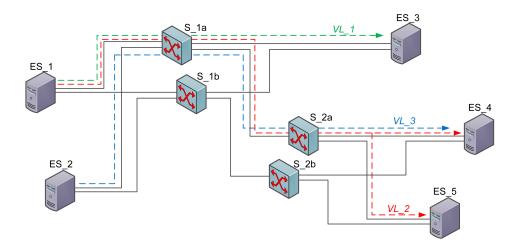

Figure 2.2 AFDX network example

Section 2.2, an example of a small AFDX network is given, showing how different VLs coexist and how redundancy is used to increase overall network reliability. Each ES communicates with two separate and redundant network in order to ensure data delivery, even when a critical problem makes one of them dysfunctional. Switch S\_1b and S\_2b constitute the redundant network B, that can have a different topology, but that must support the same VLs included in network A.

#### Flow/Traffic control

The BAG concept introduced by AFDX ensures guaranteed bandwidth and allows end-to-end delay reduction. In absence of Jitter, this parameter is defined as

...the BAG represents the minimum time interval between the first bits of two consecutive frames from the same VL.

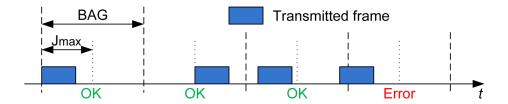

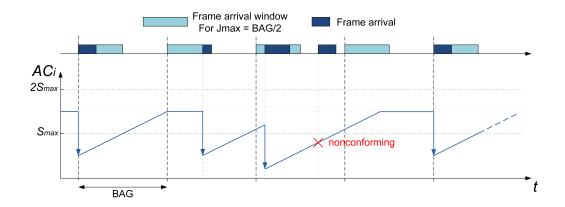

The BAG value is expressed in milliseconds and it must be 2<sup>n</sup>ms, with a minimal value of 1ms and a maximal one of 128ms. Whenever the scheduling of multiple VLs introduces jitter on their transmission, the BAG windown is always referred to the beginning of the transmission of the first frame, as shown in Figure 2.3.

In addition to the Bandwidth Allocation Gap each VL is assigned also another parameter, called  $L_{max}$ , that represents the maximum frame length, in bytes, that can be transmitted on that VL. In the official ARINC 664 documentation the maximum frame size  $S_{max}$  is often used instead of the length, and it corresponds to  $L_{max}$  plus the intermission and preamble fields, i.e. it is equal to  $L_{max}$  plus 20 bytes. This upper bound on the frame size limit the time taken for its transmission on the medium, and together with the BAG it determines the

Figure 2.3 BAG and Jitter in ES transmission

resulting maximum bandwidth allocated to the VL. A lower bound  $S_{min}$  is specified also. By limiting the rate at which frames can be transmitted on a virtual link and the size of these frames, a sort of isolation mechanism is created, to prevent any VL to interfere with other Virtual Links managed by the same source node. Non-optimal bandwidth usage decreases switches load thus reducing the jitter and delay added by them to the communication.

The last parameter that characterize the flow of frames at the output of the End System is the Jitter, which is the deviation, introduced by the scheduler, from the expected transmission time. A maximum value for this parameter must be guaranteed since it is hazardous for determinism, this upper bound is determined by the following equation.

$$\begin{cases}

max\_jitter \leq 40\mu s + \frac{\sum_{i \in setofVLs} (20bytes + L_{max}bytes) \times 8bits/bytes}{Nbwbits/s} \\

max\_jitter \leq 500\mu s

\end{cases} (2.1)$$

In Figure 2.3, an example is shown where various frames are sent respecting and not respecting the maximum Jitter defined for their VL; a situation like the one represented by the fourth frame must be avoided.

#### Frame structure

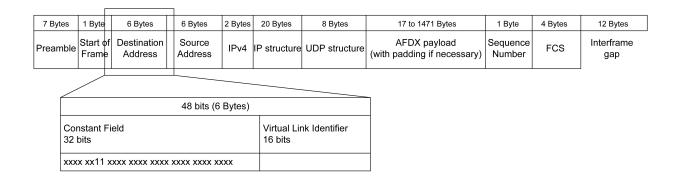

The structure of the AFDX frames, shown in Figure 2.4, is mostly identical to the one defined in IEEE 802.3 for Ethernet frames, in order to keep these two protocols as compatible as possible. The biggest differences relies in how the MAC addresses are composed and used and in an additional field at the end of the payload that contains the frame Sequence Number.

The Sequence Number is used to guarantee data integrity: the ARINC 664 specifications determines that data order for each VL must be respected, i.e. packets must be sent and received in the correct order. To ensure protocol compatibility and make the sequence number "invisible" for a standard Ethernet network, it is added at the end of the payload field, as if it were part of it.

Figure 2.4 AFDX frame structure

The MAC addresses structure, both for the source and the destination, includes information about the type of data contained in the frame and the VL on which the data must be sent. The peculiarity of the destination MAC address is that it is always defined as multicast (the 8th bit of the constant field is set to 1), and the last 16 bits determine the VL the packet must be sent on, as shown in Figure 2.4. In the source address, with some constant bits, there are also an interface identifier and a used-defined ID as well.

More information about how these features can be translated in a physical implementation of an ES is given in Chapter 4, while, in Chapter 5, the peculiar functionalities that must be provided by the AFDX switch, and that have not been discussed in this overview, are presented.

#### 2.2 Literature review

As mentioned before, various aspects of the two considered technologies have been explored in the last few years, confirming the attention that grows around them. Studies are being performed to identify the potential for CAN-based protocols in avionic networks, and Young et al. [11] underline how these technologies are suited for legacy line replaceable modules. The work presented by Zhang et al. [12] identifies CAN-based protocols as the ideal choice for unmanned helicopter systems. Even more promising is AFDX, whose innovative features opened multiple research perspectives: some examples are the analysis of the worst-case end-to-end delay [5, 13], the identification of the most performing scheduling algorithm for ES and Switches [6], or again the network modelling and its reliability analysis [7].

While a lot of attention is reserved to these topics, which are also explored in the Avio 402 project, only limited studies have been published concerning the physical implementation of these two protocols. In the following sections, a review of the proposed design and solutions for the system developed in this thesis is provided, but because of the lack of existing material,

especially on ARINC 825 controllers and AFDX switches, attention has been paid also to designs conceived for CAN and Ethernet. Since the considered systems are significantly different from each other, the review of the existing literature is being done separately for each one of them.

#### 2.2.1 CAN bus controller

The CAN protocol has been widely used for several years now and many implementations can be found in the existing literature. Unfortunately, no adaptation of these designs has been made to port them in an avionic environment, and no ARINC 825 nor CANaerospace controller has been published so far. As a consequence an analysis of these two avionic protocols and of related commercial products has been done in parallel with a review of available designs conceived for CAN bus controllers, to understand what knowledge can be reused and what should be added to a CAN design to adapt it for an airborne use.

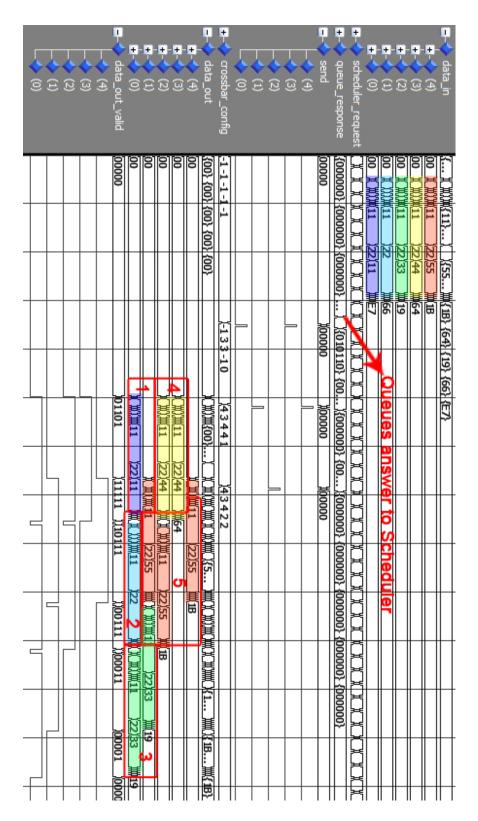

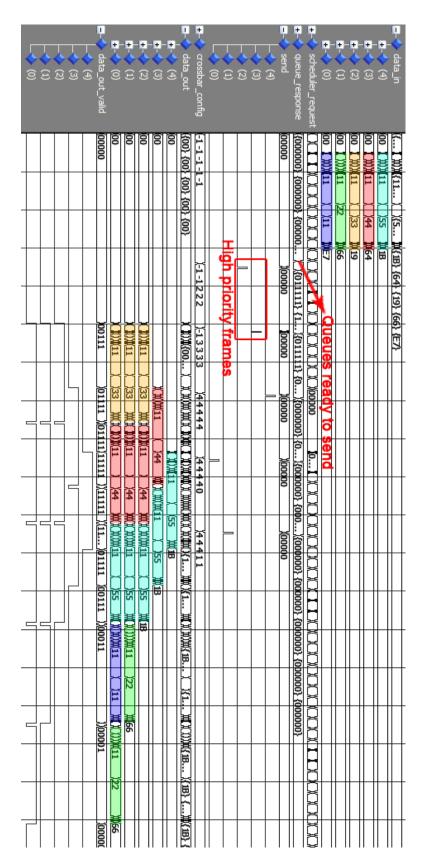

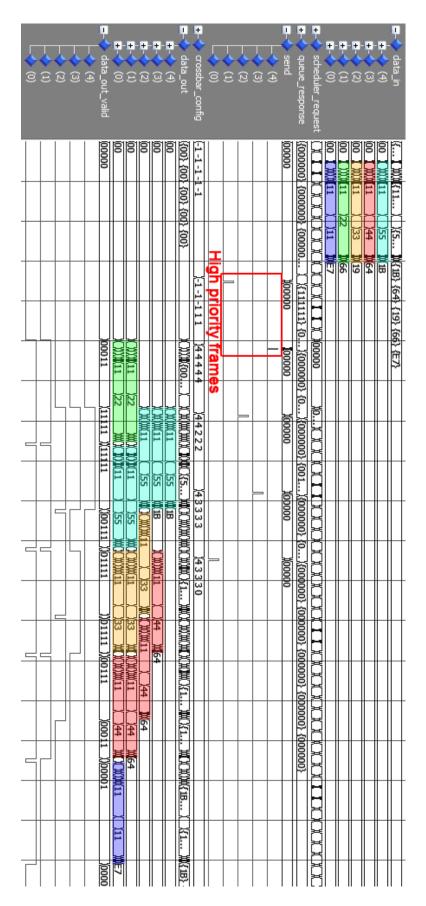

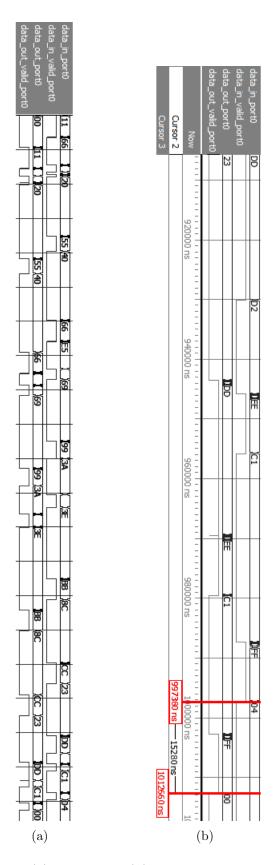

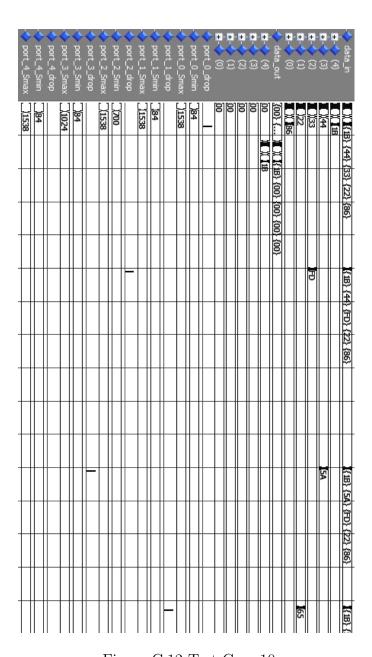

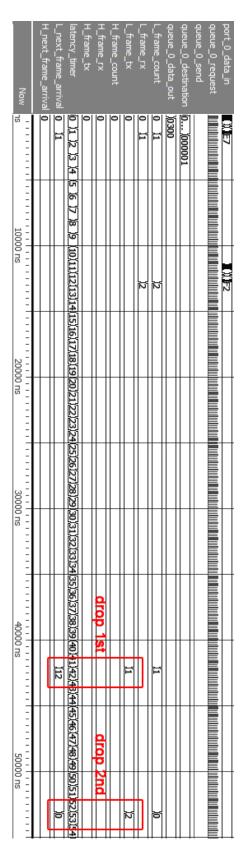

While describing the differences between these two avionic protocols and the standard CAN protocol in Section 2.1.1, it has been highlighted how most of the new features have been added in ISO/OSI layers that do not affect directly the design of the bus controller (layers 3, 4, and 6). Nevertheless, some of these alterations are reflected in a possible optimization of this controller since some functionalities usually necessary in a standard CAN bus are not needed any more.