**Titre:** Modélisation électrique du couplage et de l'injection de bruit dans le substrat

Title: substrat

**Auteur:** Vincent Binet

Author:

**Date:** 2007

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Binet, V. (2007). Modélisation électrique du couplage et de l'injection de bruit dans le substrat [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/8035/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8035/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Michel Meunier

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

MODÉLISATION ÉLECTRIQUE DU COUPLAGE ET DE L'INJECTION DE

BRUIT DANS LE SUBSTRAT

VINCENT BINET

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUIN 2007

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-35667-8

*Our file* *Notre référence*

ISBN: 978-0-494-35667-8

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

MODÉLISATION ÉLECTRIQUE DU COUPLAGE ET DE L'INJECTION DE

BRUIT DANS LE SUBSTRAT

présenté par: BINET Vincent

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. AUDET Yves, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. MEUNIER Michel, Ph.D., membre et codirecteur de recherche

M. VALORGE Olivier, Ph.D., membre

*Un seul être vous manque, et tout est dépeuplé.*

Alphonse de Lamartine

## REMERCIEMENTS

Tout d'abord, je tiens à remercier mon directeur de recherche Yvon Savaria et mon co-directeur Michel Meunier, pour m'avoir donné l'opportunité et les moyens de découvrir le monde de la recherche. Leur expérience et compétence dans leurs domaines respectifs, ainsi que leur complémentarité ont largement contribué à la réalisation de ce projet et ont permis de le rendre à la fois motivant et agréable.

Par la suite, j'aimerais remercier chaleureusement Etienne Boulais, Iliasse Benamrane et Rahul Singh, sans qui cette maîtrise n'aurait pas été possible et avec qui j'ai apprécié travailler. Je n'oublie pas également tous les membres du GRM que j'ai pu cotôyer pendant mes études, et notamment Gilbert pour sa verve et sa bonne humeur constante. Je remercie également Yves Gagnon pour ses conseils avisés, et Olivier Valorge pour son aide et ses conseils pertinents.

Je voudrais remercier tous mes colocataires Raphaël, Julien, Guitou, Sylvain, Hélène et Mathilde durant ces 3 années dans la belle Province, et plus particulièrement sa grandeur Raphaël, pour son talent d'acteur incontestable et pour avoir ramer avec moi sur la galère.

J'ai une pensée toute particulière à Elise, avec qui j'ai passé les meilleurs moments de ma vie, qui a su être compréhensive et a su me remonter le moral dans les moments difficiles.

Je remercie mes parents et mes frères, ainsi que toute ma famille pour m'avoir supporté et encouragé durant cette maîtrise, ainsi que pour m'avoir toujours soutenu dans mes choix et donné l'opportunité de réaliser ce que je voulais faire.

Finalement, j'aimerais remercier Anne-Marie pour le soleil qu'elle a apporté dans ma vie.

Et sans oublier les blagues de Polo....

## RÉSUMÉ

Les dernières années ont été marquées par l'arrivée massive sur le marché de l'électronique grand public de produits intégrant de nombreuses fonctionnalités autrefois propres à plusieurs appareils différents. L'exemple du téléphone cellulaire pour ne citer que lui est révélateur : "téléphoner" n'est qu'une option parmi tant d'autres telles que naviguer sur internet, écouter de la musique, regarder la télévision, communiquer par visioconférence, prendre des photos.... Cette course effrénée à la réduction d'échelle technologique qui en permet le développement et la pluridisciplinarité des produits impose de combiner des spécialités autrefois distinctes. Les Systèmes sur Puces ou "Systems On Chips" (SoC) ont permis de relever le défi de la conception de systèmes toujours plus complexes et multifonctions.

Cependant l'intégration sur un même substrat de circuits sensibles (analogiques de précision, convertisseur numérique / analogique et analogique / numérique ) et bruyants (convertisseur de puissance, Radio-Fréquence, utilisation de dispositifs ajustables par laser) pose des problèmes d'intégrité des signaux. Le substrat est alors un lieu de transport du bruit dans toute la puce que ce bruit soit généré par un laser ou un convertisseur de puissance. Sa modélisation est par conséquent un enjeu crucial dans la conception et le développement de circuits intégrés. Prévoir le niveau de bruit très tôt dans la conception et anticiper les problèmes d'interférences entre les circuits permet en effet de réduire les coûts de production et le temps de mise sur le marché des produits.

L'objectif de cette étude est donc de modéliser les couplages au substrat et l'injection de bruit dans le substrat pour deux applications comportant des systèmes bruyants : un convertisseur DC-DC et l'injection de charges dans le substrat due à la création d'une résistance diffusée par laser. Des modélisations résistives et capacitatives du substrat ont déjà été largement traitées dans la littérature et appliquées à l'étude du bruit injecté par de larges circuits numériques. Du fait des

larges variations de potentiel du substrat et des différents puits dans le cas de nos deux applications, de tels modèles ne peuvent être utilisés, car leurs hypothèses de départ sont violées. Dans ce projet, un modèle optimisé du substrat est proposé. Ce modèle inclut des éléments parasites tels que les transistors bipolaires verticaux non pris en compte par les modèles classiques mais pourtant bien présents physiquement.

L'analyse du bruit injecté par un convertisseur DC-DC a montré qu'en utilisant une modélisation optimisé du substrat, le potentiel du substrat à 15  $\mu\text{m}$  présente des pics d'une hauteur de 6 mV. Alors que pour un modèle purement résistif et capacitif, ce même potentiel était seulement de l'ordre de 100  $\mu\text{V}$ . L'étude a révélé que les chemins de courants offerts par les transistors bipolaires jouent un rôle primordial dans l'injection de bruit dans le substrat et les alimentations. L'isolation offerte par les puits profonds N et puits N s'est alors révélée beaucoup moins performante que ce qui était attendu. Des résultats expérimentaux menés sur une puce fabriquées au travers de la *CMC Microsystèmes* appuient les résultats obtenus en simulation. Au niveau de l'injection de charges par laser, des simulations "mixtes" ont été utilisées couplant des simulations par éléments finis et des simulations électriques. La modélisation par éléments finis développée par Boulais permet de quantifier les charges injectées dans le substrat par un laser focalisé. Le résultat obtenu est ensuite intégré comme une source de courant aux bornes des jonctions PN dans les simulations électriques prenant en compte le modèle optimisé du substrat relié à l'oscillateur en anneaux. Grâce à ce modèle optimisé du substrat comportant une modélisation des transistors bipolaires et des jonctions puits - substrat, l'impact des charges sur le potentiel du substrat est bien pris en compte et permet d'observer une modification de la fréquence de fonctionnement de l'oscillateur. Les larges variations des potentiels induites par les charges affectent par effet de substrat le fonctionnement des transistors des inverseurs de l'oscillateur. Les résultats expérimentaux ont confirmé le comportement obtenu en simulation et ont permis de

valider notre compréhension de l'impact des charges sur un circuit.

## ABSTRACT

Over the past several years, electronic products have offered on the market multifunction systems, previously available as separate devices. Nowadays, cellular phones can not only be used as a classical phone, but people can now surf on the internet, listen to music, watch TV, communicate by video... Recently System on Chip (SoC) integration has offered this high integration of complex systems. Because sensitive analog circuits need to share a common substrate with noisy circuits (RF designs, large digital circuits, power switches modules, laser trimmed devices), significant noise injection can degrade the global system performance. This is an important issue in the design of mixed signal SoCs. Thus to reduce the SoC development costs and time to market, accurate substrate model has to be developed and appears to be the key solution to predict coupling noise and ensure that it remains at an acceptable level.

This project aims to model noise substrate coupling and noise substrate injection in two different applications : DC-DC converter and charges injection caused by a focused laser beam on a laser diffused resistor. Existing literature deals with the case where large digital circuits comprising several thousand gates that switch simultaneously inject noise in the substrate by resistive and capacitive coupling. Unusual voltage variations occurring in power switches can activate parasitic vertical bipolar transistors. Such resistive and capacitive model can not be used for this application, because its basic assumptions are violated. This project proposes a custom substrate model which includes these parasitic devices.

Analysis of the substrate noise injected by a DC-DC converter shows an important impact on victim circuits in the neighbourhood of the noise source. Simulations with the proposed model predict a 6 mV noise in the substrate, whereas only resistive and capacitive model gives around 100  $\mu$ V for the same setup. Experimental results show that parasitic bipolar transistors play an important role in the injected

current, and have to be included to correctly estimate noise injected by a power converter. Our results also demonstrate that n-well and deep n-well isolations are much less effective than what it was predicted by classical model.

Mixed simulation methods have been used to analyze the impact on a ring oscillator of charges injected in a substrate by a focused laser. Such simulations have used finite element model elaborated by Boulais to quantify charges injected in the substrate. The result is then used as a current source across PN junctions into an electrical model of the ring oscillator linked to a custom substrate model. With this custom model, large potential variations induced by charges injection are now taken into account as "body effect" phenomenon affecting the ring oscillator frequency. Simulation results have shown good agreement with experimental results and validate our understanding of observed frequency changes.

## TABLE DES MATIÈRES

|                                                                                     |       |

|-------------------------------------------------------------------------------------|-------|

| DÉDICACE . . . . .                                                                  | iv    |

| REMERCIEMENTS . . . . .                                                             | v     |

| RÉSUMÉ . . . . .                                                                    | vi    |

| ABSTRACT . . . . .                                                                  | ix    |

| TABLE DES MATIÈRES . . . . .                                                        | xi    |

| LISTE DES FIGURES . . . . .                                                         | xvi   |

| LISTE DES NOTATIONS ET DES SYMBOLES . . . . .                                       | xxii  |

| LISTE DES ANNEXES . . . . .                                                         | xxiii |

| INTRODUCTION . . . . .                                                              | 1     |

| CHAPITRE 1 REVUE DE LA LITTÉRATURE : BRUIT DE SUBSTRAT<br>ET MODÉLISATION . . . . . | 5     |

| 1.1 Caractérisation du substrat . . . . .                                           | 6     |

| 1.1.1 Type de substrat . . . . .                                                    | 6     |

| 1.1.2 Modélisation physique du substrat . . . . .                                   | 7     |

| 1.1.3 Modèle capacitif et résistif du substrat . . . . .                            | 9     |

| 1.2 Source "classique" du bruit de substrat . . . . .                               | 11    |

| 1.2.1 Ionisation par impact . . . . .                                               | 12    |

| 1.2.2 Courant induit par des photons . . . . .                                      | 13    |

| 1.2.3 Couplage capacitif . . . . .                                                  | 13    |

| 1.2.4 Courant de fuite de la grille . . . . .                                       | 14    |

| 1.2.5 Courant de fuite de la diode . . . . .                                        | 14    |

|                                                                            |                                                                |    |

|----------------------------------------------------------------------------|----------------------------------------------------------------|----|

| 1.2.6                                                                      | Bruit présent sur les alimentations                            | 14 |

| 1.3                                                                        | Nouvelles sources de bruit                                     | 16 |

| 1.3.1                                                                      | Convertisseur DC-DC : une nouvelle source de bruit             | 16 |

| 1.3.2                                                                      | Injection de bruit dans le substrat par un laser               | 18 |

| 1.4                                                                        | Impact sur les circuits                                        | 20 |

| 1.4.1                                                                      | Mécanismes de transmission du bruit aux circuits sensibles     | 21 |

| 1.4.2                                                                      | Répercussions du bruit de substrat sur l'intégrité des signaux | 22 |

| 1.5                                                                        | Outils                                                         | 25 |

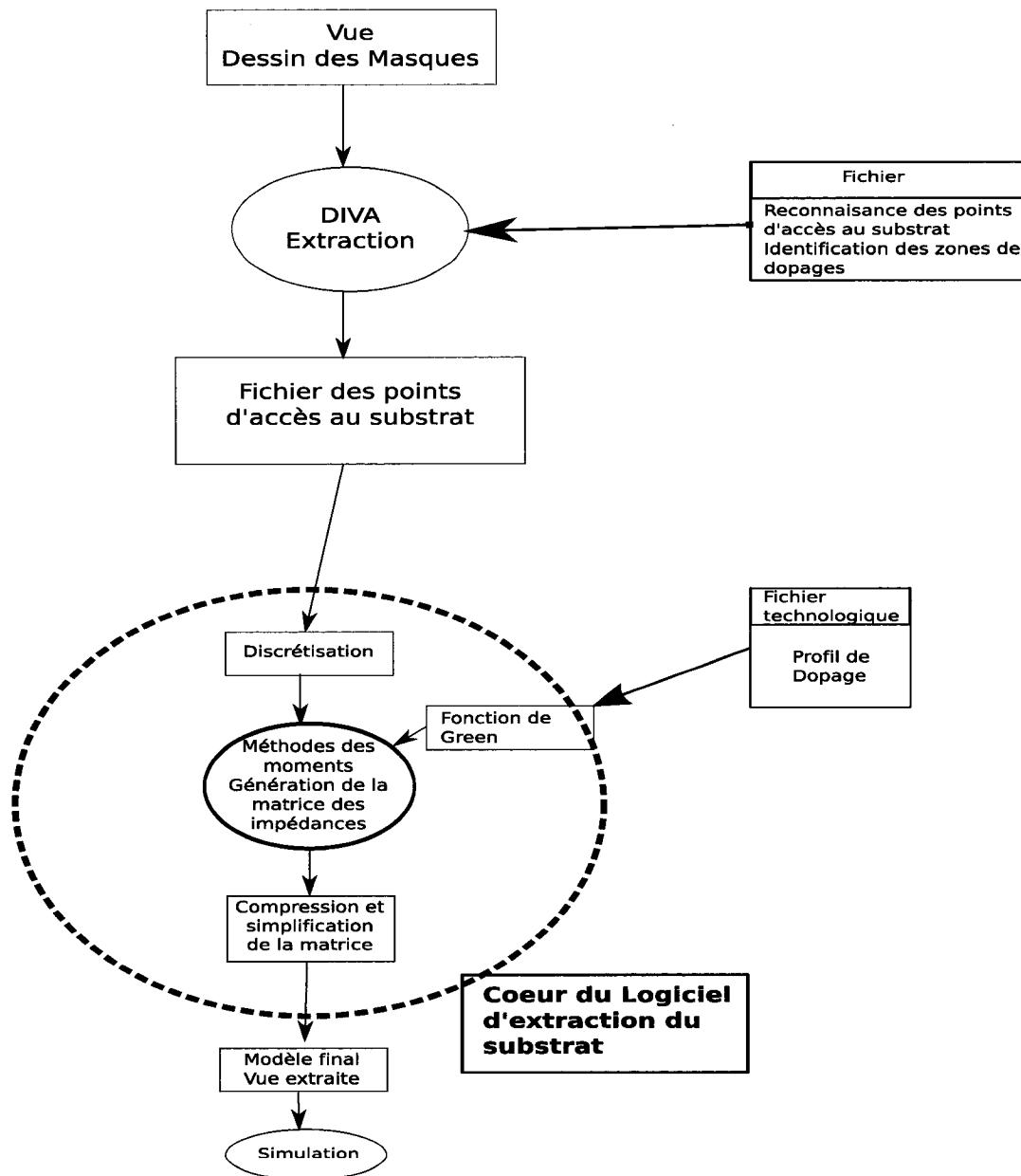

| 1.5.1                                                                      | Flot de conception                                             | 25 |

| 1.5.1.1                                                                    | Fichiers nécessaires                                           | 27 |

| 1.5.1.2                                                                    | Étapes de création d'un modèle                                 | 29 |

| 1.5.2                                                                      | Logiciels commerciaux existants                                | 31 |

| 1.5.3                                                                      | Utilisation de macro-modèles                                   | 32 |

| 1.6                                                                        | Limites                                                        | 33 |

| 1.6.1                                                                      | Insuffisance du couplage seulement capacitif et résistif       | 33 |

| 1.6.2                                                                      | Temps de calcul                                                | 33 |

| <b>CHAPITRE 2 MODÉLISATION DU BRUIT INJECTÉ PAR UN CONVERTISSEUR DC-DC</b> |                                                                | 35 |

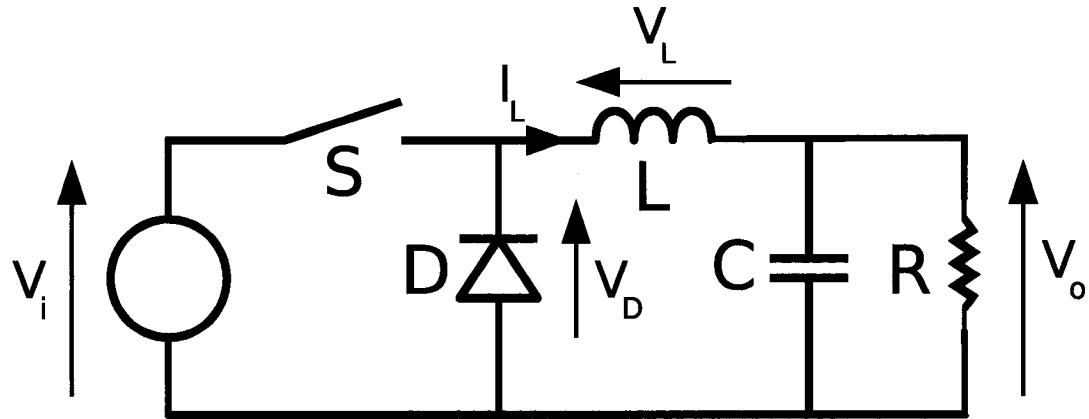

| 2.1                                                                        | Les convertisseurs DC-DC                                       | 35 |

| 2.1.1                                                                      | Présentation générale                                          | 35 |

| 2.2                                                                        | Circuit analysé                                                | 37 |

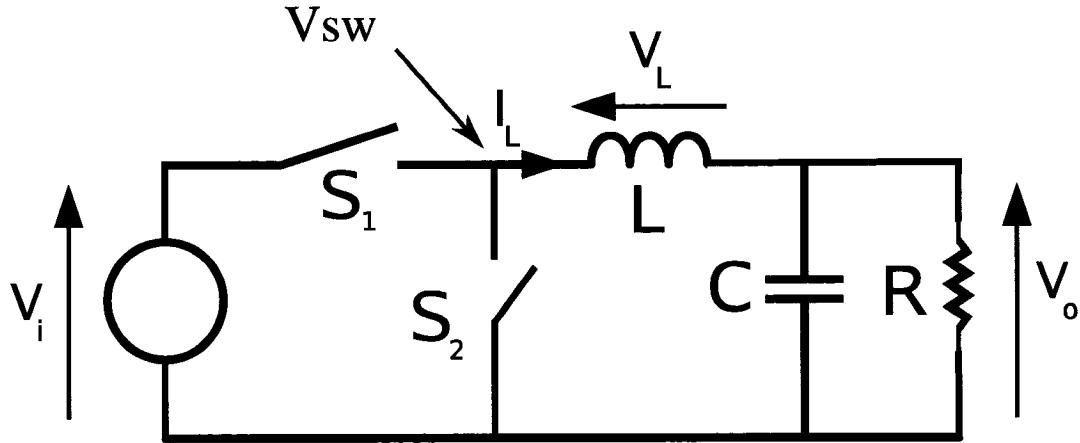

| 2.2.1                                                                      | Architecture proposée                                          | 38 |

| 2.2.2                                                                      | Fonctionnement idéal                                           | 38 |

| 2.2.3                                                                      | Fonctionnement réel                                            | 40 |

| 2.2.4                                                                      | Rendement                                                      | 42 |

| 2.2.5                                                                      | Design étudié                                                  | 43 |

| 2.3                                                                        | Étude du bruit de substrat à l'aide d'un modèle RC             | 48 |

|                                                                                          |                                                                    |     |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|

| 2.3.1                                                                                    | Modèle RC produit par SubstrateStorm                               | 48  |

| 2.3.2                                                                                    | Résultats de simulation avec SubstrateStorm                        | 48  |

| 2.3.3                                                                                    | Insuffisance du couplage seulement résistif et capacitif           | 54  |

| 2.4                                                                                      | Etude du bruit à l'aide d'un modèle personnalisé                   | 54  |

| 2.4.1                                                                                    | Modèle optimisé avec Substrate Coupling Analysis                   | 55  |

| 2.4.2                                                                                    | Résultats de simulations sans modélisation du boîtier              | 59  |

| 2.4.2.1                                                                                  | Cas (a) : PMOS "ON" -> "OFF" alors que NMOS<br>reste "OFF"         | 60  |

| 2.4.2.2                                                                                  | Cas (b) : NMOS "ON" -> "OFF" alors que PMOS<br>reste "OFF"         | 66  |

| 2.4.3                                                                                    | Résultats de simulations avec modélisation du boîtier              | 68  |

| 2.4.4                                                                                    | Résultats de simulations avec modélisation du boîtier et du<br>PCB | 78  |

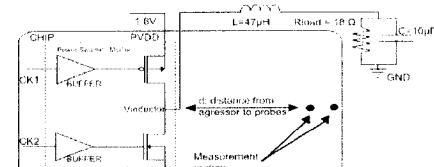

| 2.5                                                                                      | Résultats expérimentaux                                            | 86  |

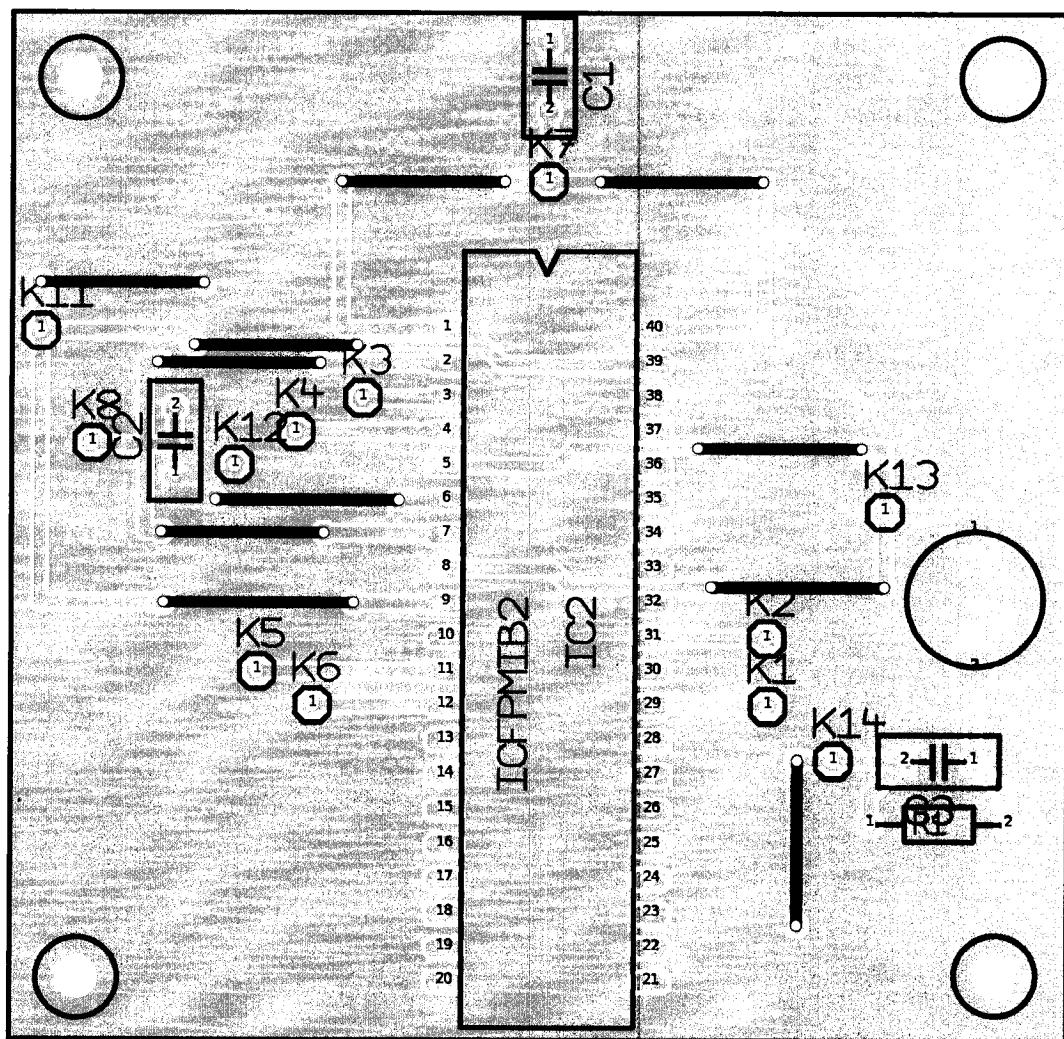

| 2.5.1                                                                                    | Puces fabriquées                                                   | 87  |

| 2.5.2                                                                                    | Résultats expérimentaux                                            | 87  |

| 2.5.2.1                                                                                  | Description du mode opératoire                                     | 88  |

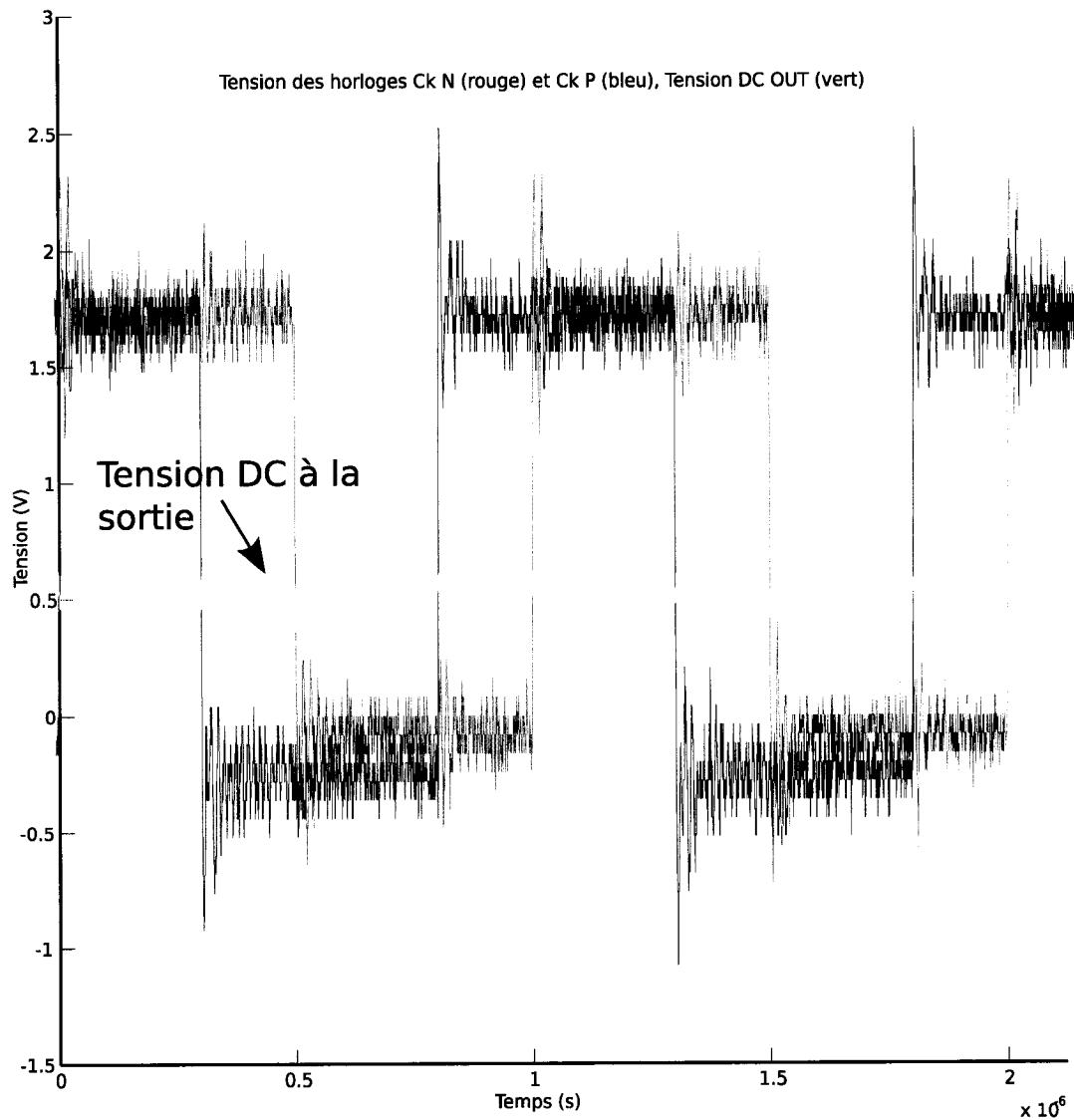

| 2.5.2.2                                                                                  | Fonctionnement                                                     | 88  |

| 2.5.2.3                                                                                  | Courants injectés dans les alimentations et le substrat            | 95  |

| 2.5.2.4                                                                                  | Bruit du substrat                                                  | 99  |

| 2.5.2.5                                                                                  | Etude fréquentielle                                                | 99  |

| 2.5.3                                                                                    | Discussion sur les résultats expérimentaux et les simulations      | 102 |

| <b>CHAPITRE 3 MODÉLISATION DE L'INJECTION DE BRUIT DANS LE<br/>SUBSTRAT PAR UN LASER</b> |                                                                    | 104 |

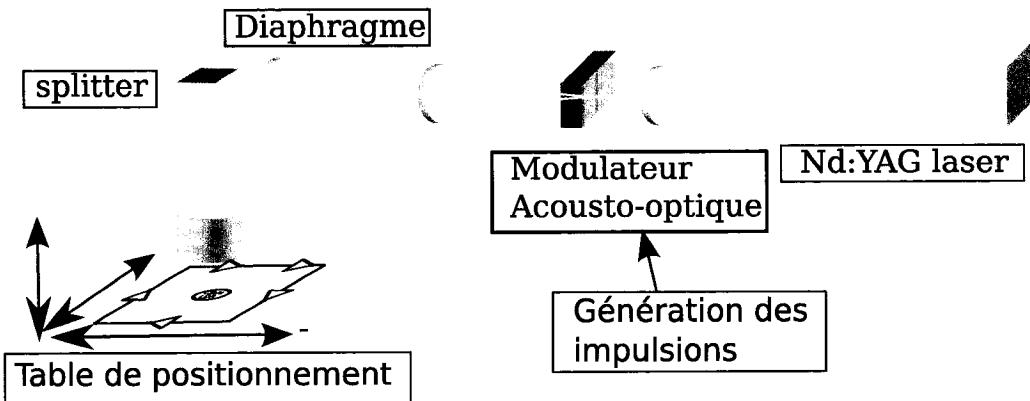

| 3.1                                                                                      | Système laser et montage optique                                   | 104 |

| 3.1.1                                                                                    | Montage laser                                                      | 105 |

| 3.1.2                                                                                    | Résistance diffusée par laser (LDR)                                | 106 |

|       |                                                                                                    |     |

|-------|----------------------------------------------------------------------------------------------------|-----|

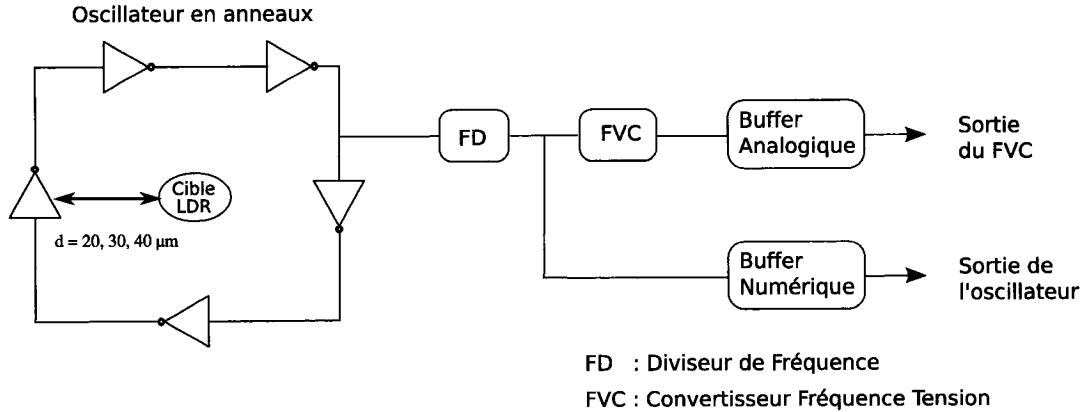

| 3.2   | Circuit Sensible : Oscillateur en Anneaux . . . . .                                                | 107 |

| 3.3   | Résultats expérimentaux . . . . .                                                                  | 108 |

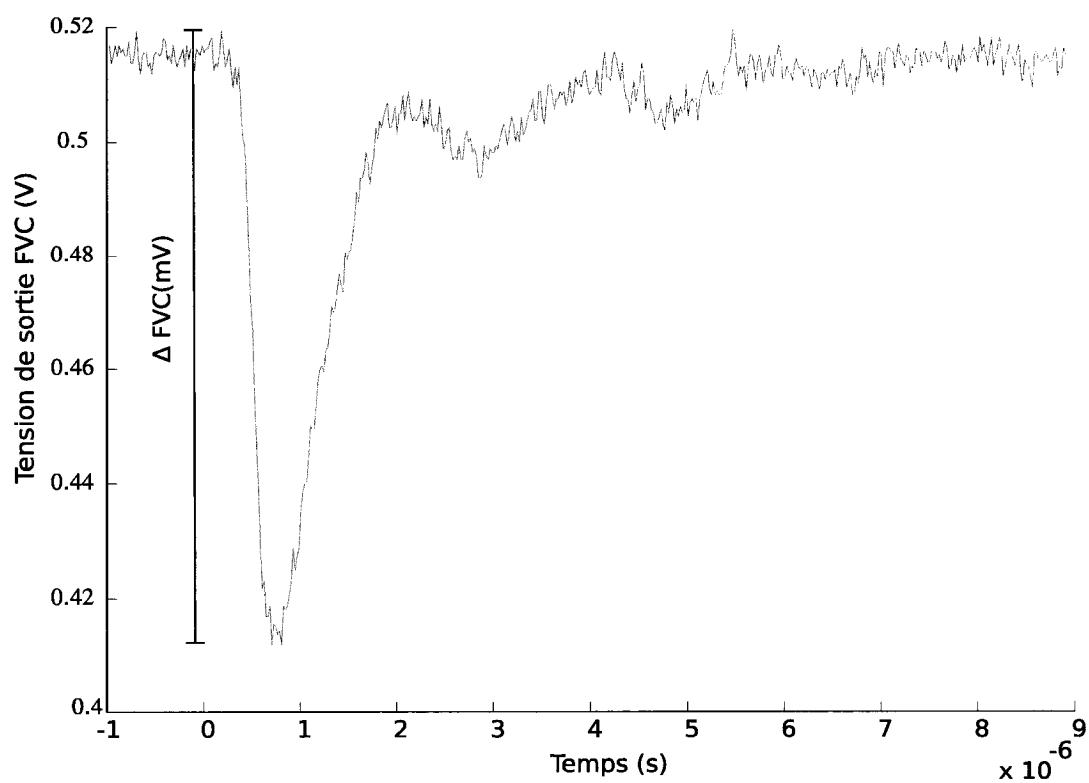

| 3.3.1 | Calibration du circuit de mesures électriques . . . . .                                            | 108 |

| 3.3.2 | Estimation de la puissance . . . . .                                                               | 111 |

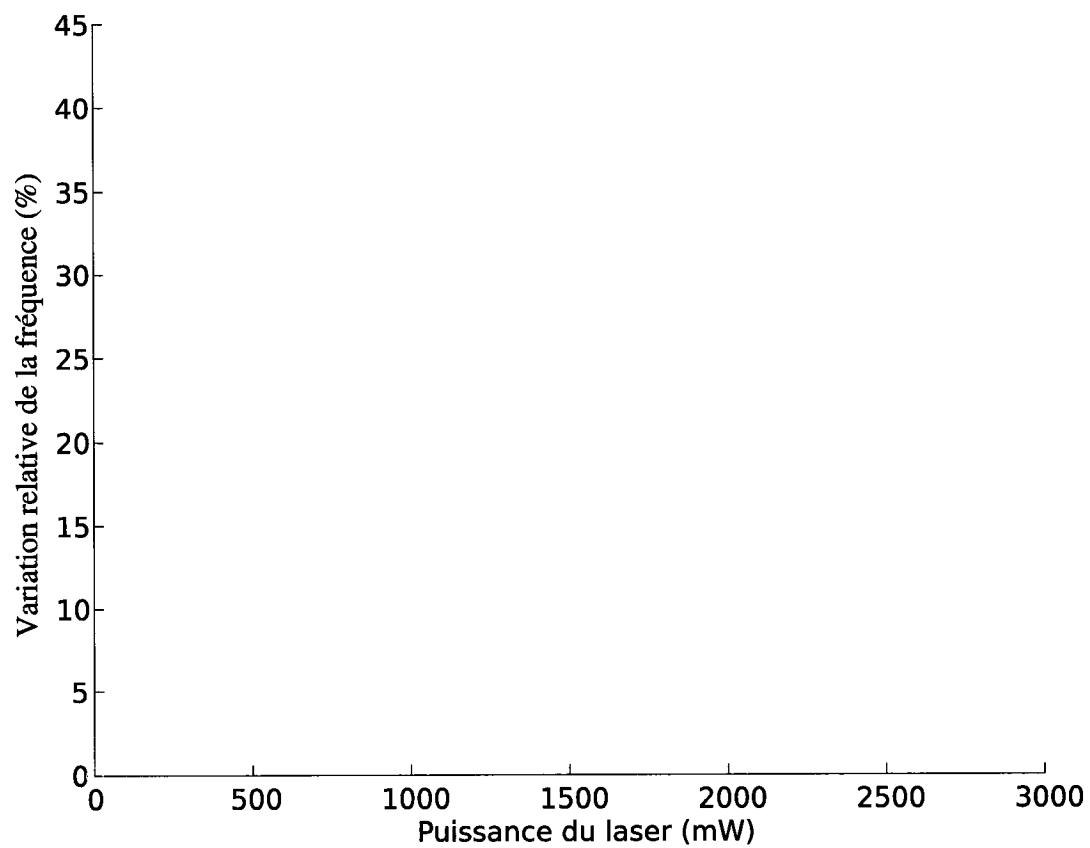

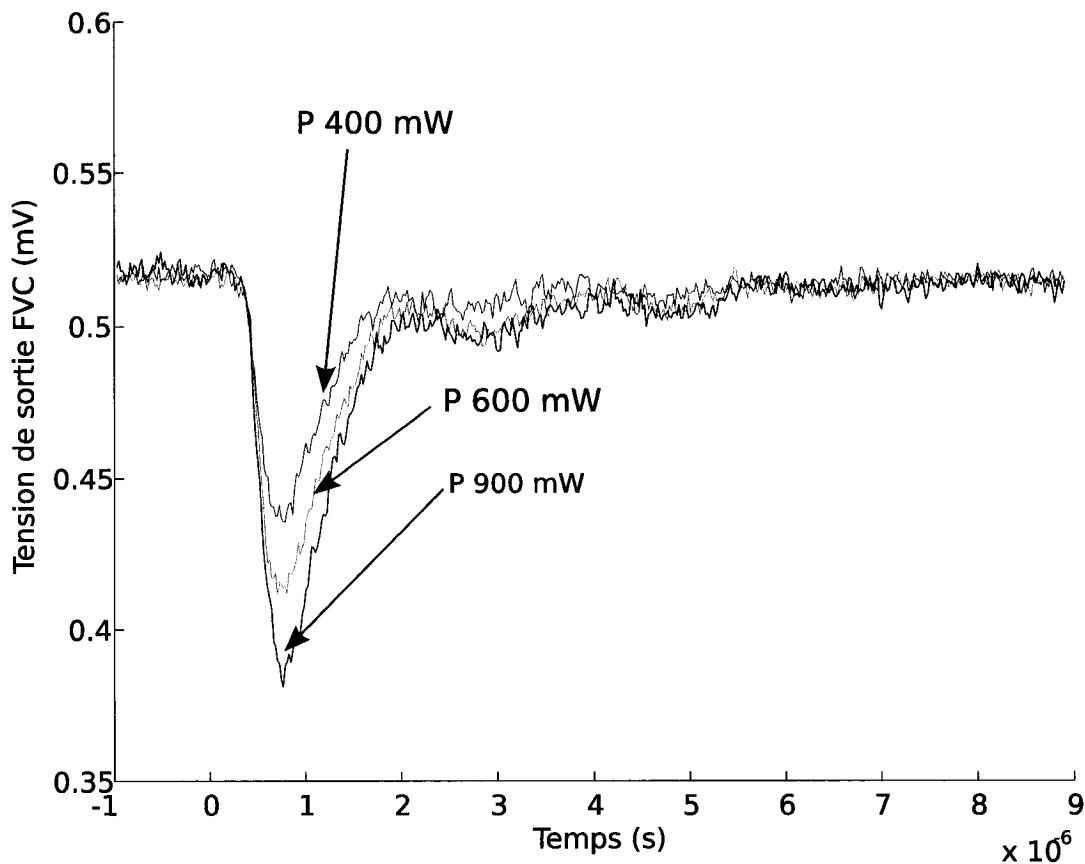

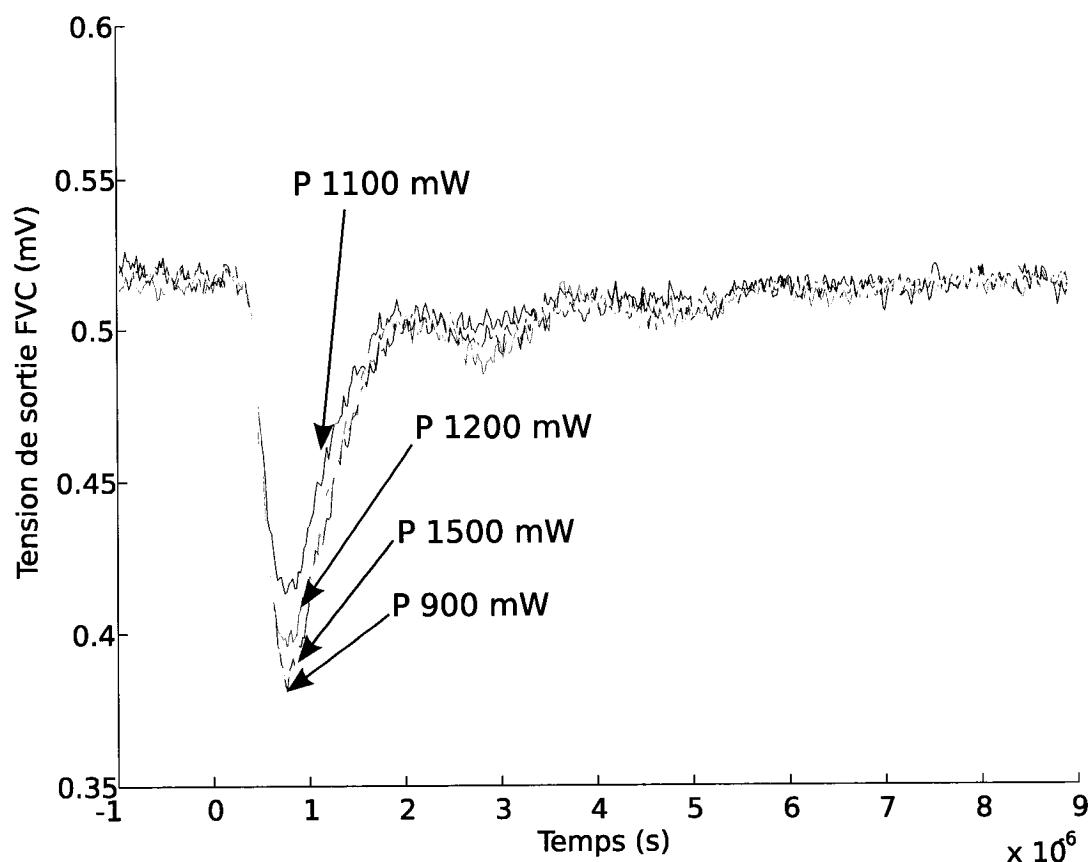

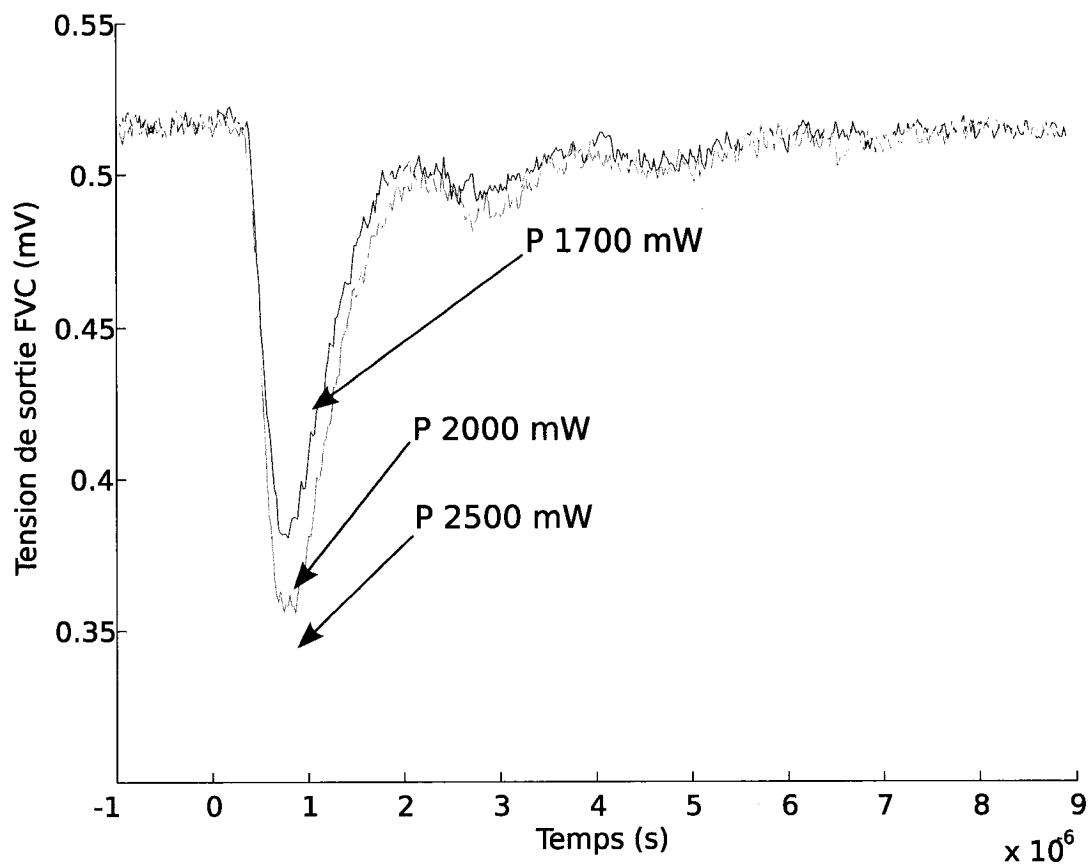

| 3.3.3 | Variation de la fréquence en fonction de la puissance . . . . .                                    | 111 |

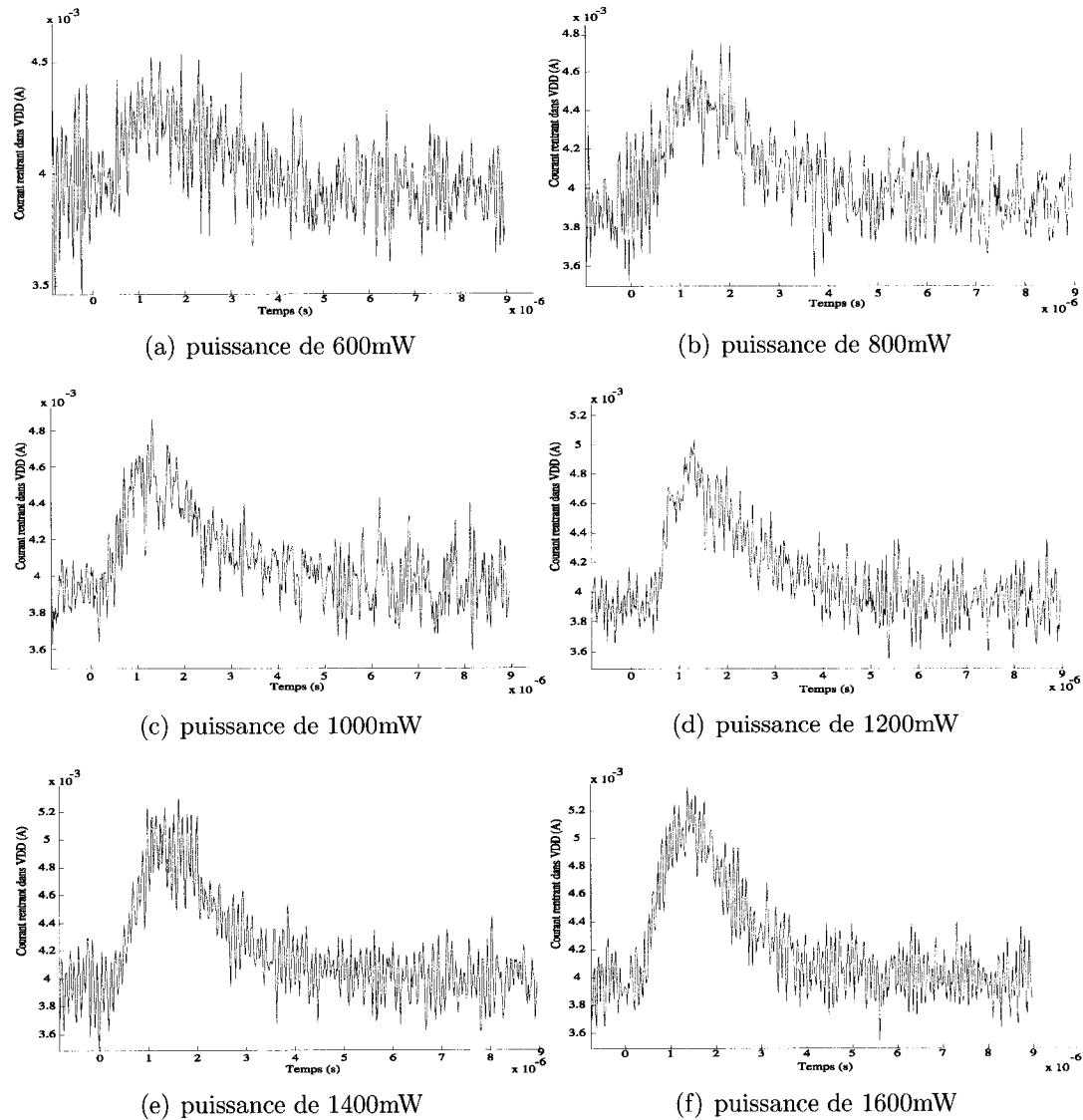

| 3.3.4 | Courant collecté au niveau des alimentations . . . . .                                             | 116 |

| 3.4   | Explication des phénomènes responsables de la modification de la fréquence d'oscillation . . . . . | 119 |

| 3.4.1 | Modélisation d'un inverseur . . . . .                                                              | 119 |

| 3.4.2 | Modélisation de l'impact de charges sur une jonction . . . . .                                     | 121 |

| 3.5   | Modélisation adaptée du substrat . . . . .                                                         | 126 |

| 3.5.1 | Nécessité d'un modèle du substrat . . . . .                                                        | 126 |

| 3.5.2 | Modèle capacitif et résistif inadéquat . . . . .                                                   | 126 |

| 3.5.3 | Modèle augmenté incorporant des composants parasites . . . . .                                     | 127 |

| 3.6   | Résultats de simulations . . . . .                                                                 | 128 |

| 3.6.1 | Fonctionnement normal non soumis à une illumination . . . . .                                      | 128 |

| 3.6.2 | Impact d'une impulsion laser sur le fonctionnement . . . . .                                       | 128 |

| 3.6.3 | Ajustement des paramètres du modèle aux résultats expérimentaux . . . . .                          | 131 |

| 3.7   | Confrontation des résultats de simulation et expérimentaux . . . . .                               | 137 |

| 3.7.1 | Robustesse du modèle . . . . .                                                                     | 137 |

| 3.7.2 | Variation de la fréquence en fonction de la puissance . . . . .                                    | 137 |

| 3.7.3 | Courant collecté par les alimentations . . . . .                                                   | 141 |

| 3.7.4 | Conclusion et limites du modèle . . . . .                                                          | 142 |

|       | CONCLUSION . . . . .                                                                               | 145 |

|       | RÉFÉRENCES . . . . .                                                                               | 148 |

## LISTE DES FIGURES

|                  |                                                                                                                                            |    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>FIG. 1.1</b>  | Structure d'un substrat de type épitaxial . . . . .                                                                                        | 6  |

| <b>FIG. 1.2</b>  | Modélisation d'un cube de substrat . . . . .                                                                                               | 8  |

| <b>FIG. 1.3</b>  | Modélisation du substrat pour un inverseur CMOS dans le cas d'un substrat faiblement dopé P . . . . .                                      | 10 |

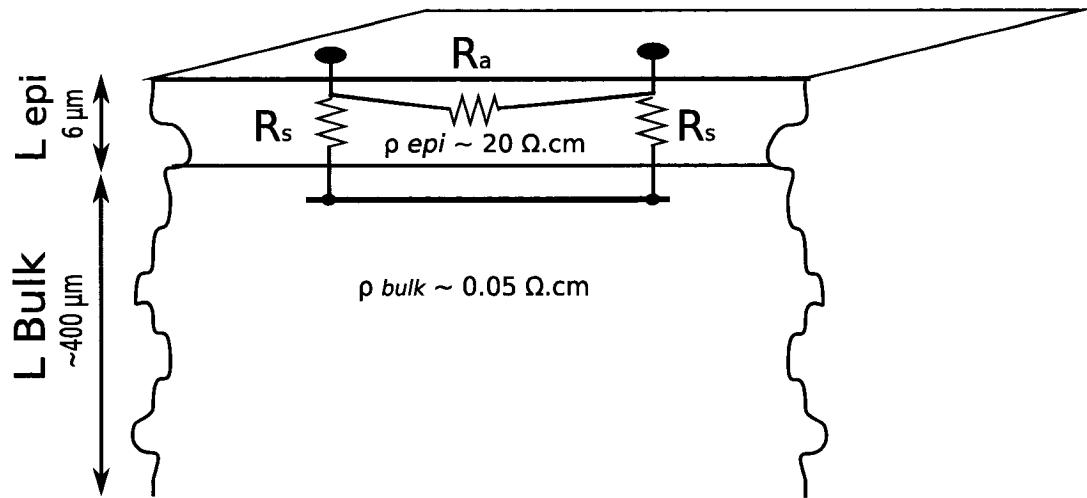

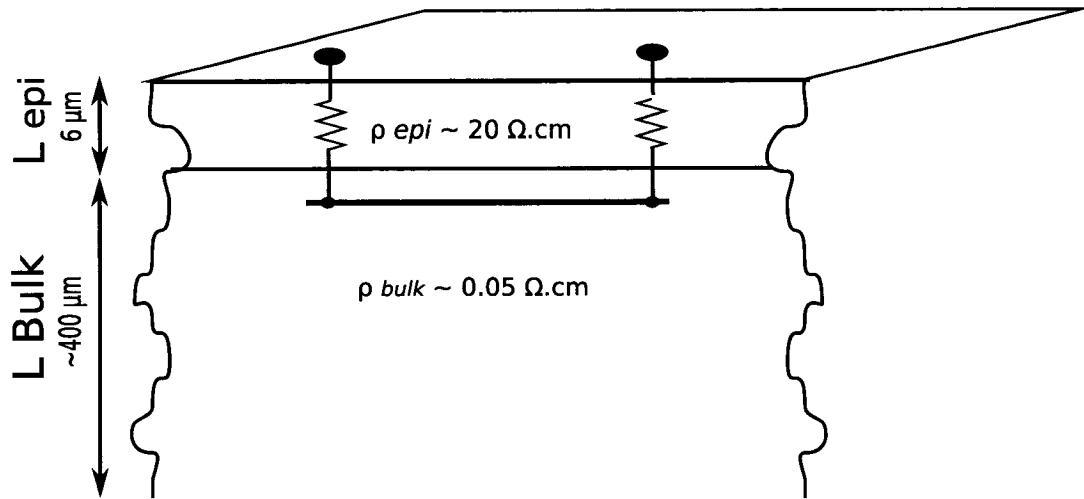

| <b>FIG. 1.4</b>  | Model résistif simple entre deux contacts proches (distance $< 4$ Lepi) pour un substrat épitaxial . . . . .                               | 11 |

| <b>FIG. 1.5</b>  | Modèle résistif simple pour deux contacts éloignés (distance $> 4$ Lepi) pour un substrat épitaxial . . . . .                              | 12 |

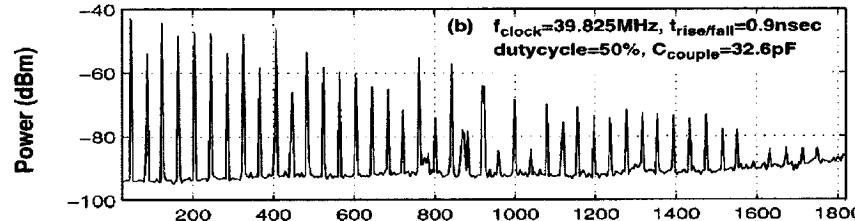

| <b>FIG. 1.6</b>  | Résistance diffusée par laser . . . . .                                                                                                    | 19 |

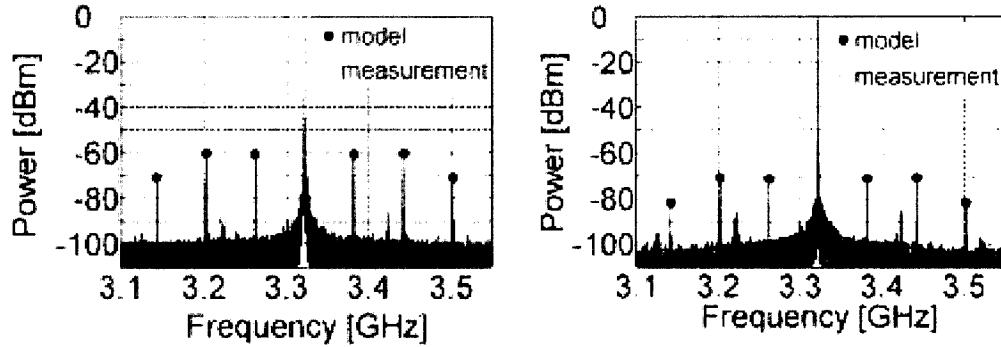

| <b>FIG. 1.7</b>  | Spectre de puissance du signal de sortie d'un VCO a) sans anneau de garde b) avec anneau de garde (tiré de (Soens et al., 2006)) . . . . . | 23 |

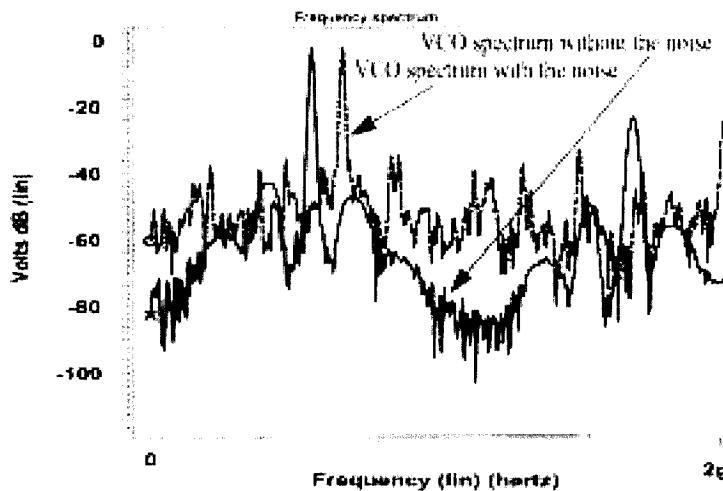

| <b>FIG. 1.8</b>  | Sortie du VCO en fonction de la fréquence avec ou sans la prise en compte du bruit de substrat (tiré de (Heydari, 2004))                   | 24 |

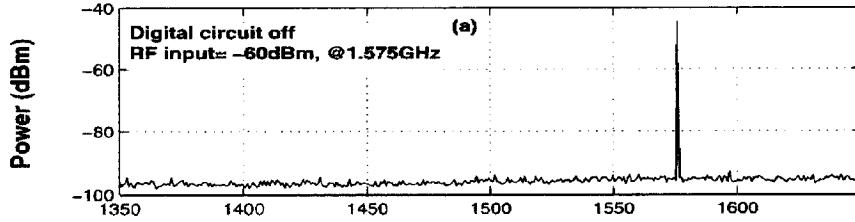

| <b>FIG. 1.9</b>  | Spectre de puissance de la sortie du LNA (tiré de (Xu et al., 2001)) . . . . .                                                             | 26 |

| <b>FIG. 1.10</b> | Fichiers nécessaires à l'élaboration d'un modèle du substrat                                                                               | 28 |

| <b>FIG. 1.11</b> | Flot d'extraction d'un modèle du substrat . . . . .                                                                                        | 30 |

| <b>FIG. 1.12</b> | Modèle complet du circuit électrique associé au modèle du substrat . . . . .                                                               | 31 |

| <b>FIG. 2.1</b>  | Hacheur série . . . . .                                                                                                                    | 37 |

| <b>FIG. 2.2</b>  | Hacheur série à redressement synchrone . . . . .                                                                                           | 38 |

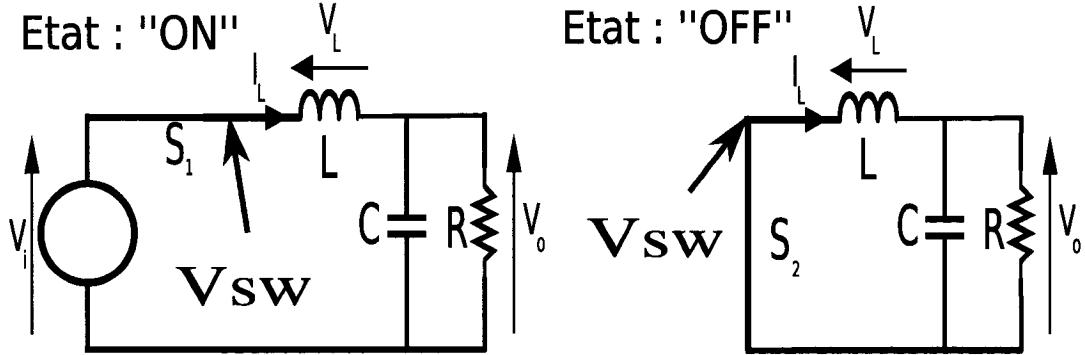

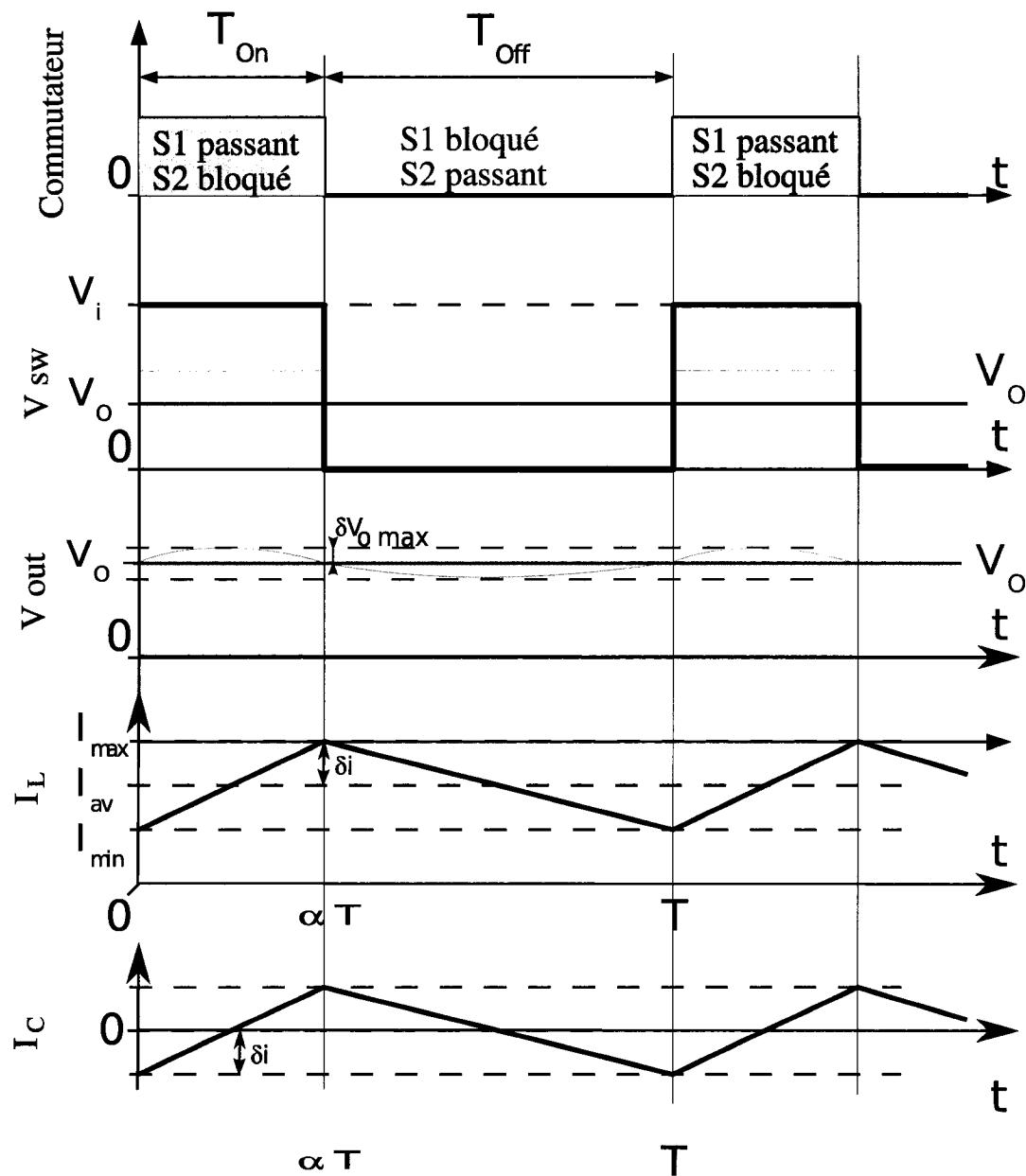

| <b>FIG. 2.3</b>  | Présentation des deux modes d'opération à gauche "ON", à droite "OFF" . . . . .                                                            | 39 |

| <b>FIG. 2.4</b>  | Chronogramme du fonctionnement du convertisseur . . . . .                                                                                  | 41 |

| <b>FIG. 2.5</b>  | Schéma du hacheur série à redressement synchrone . . . . .                                                                                 | 45 |

|           |                                                                                                                              |    |

|-----------|------------------------------------------------------------------------------------------------------------------------------|----|

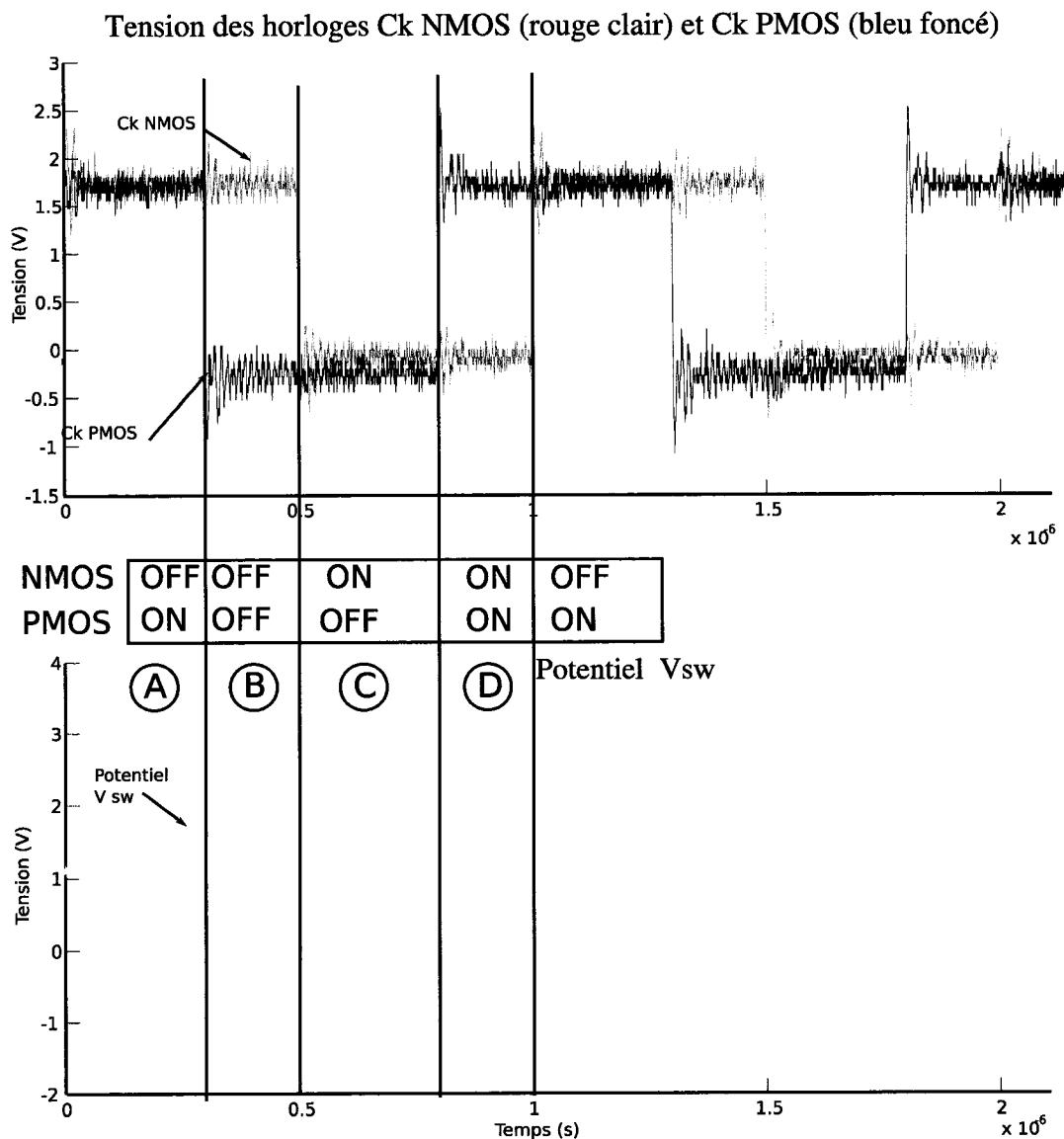

| FIG. 2.6  | Tension des signaux Ck PMOS, Ck NMOS et Vsw . . . . .                                                                        | 46 |

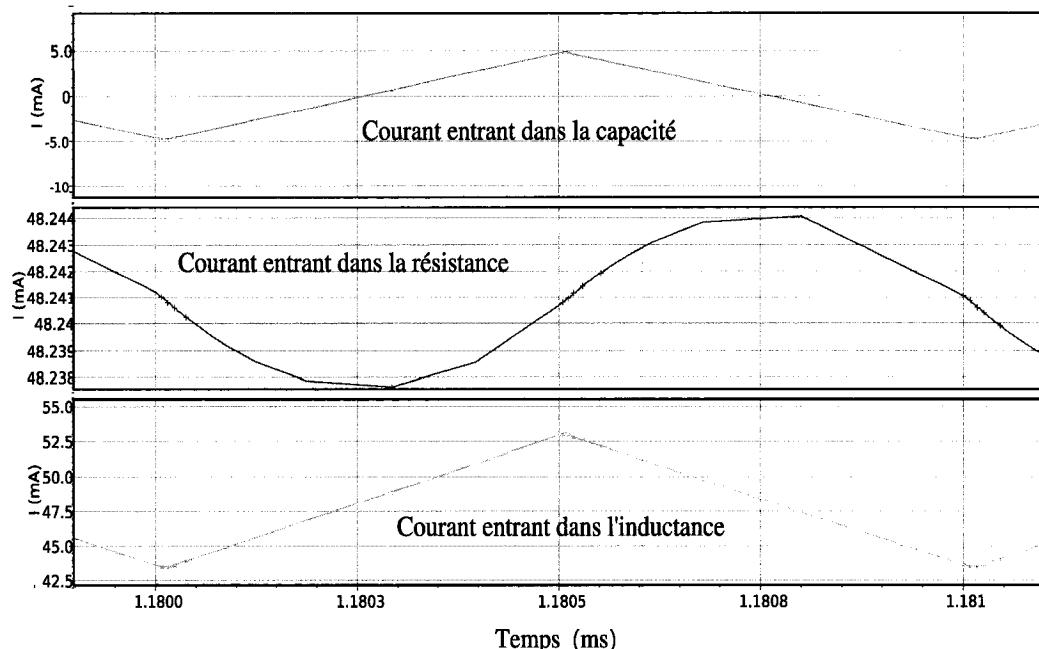

| FIG. 2.7  | Courant traversant l'inductance, la capacité et la résistance                                                                | 47 |

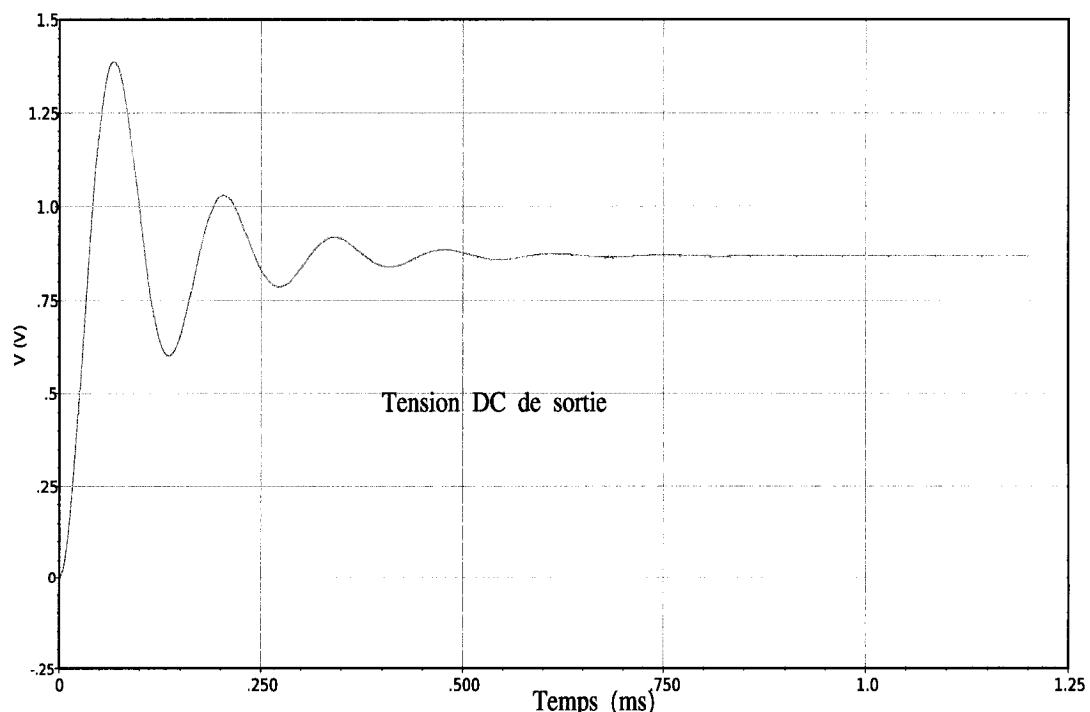

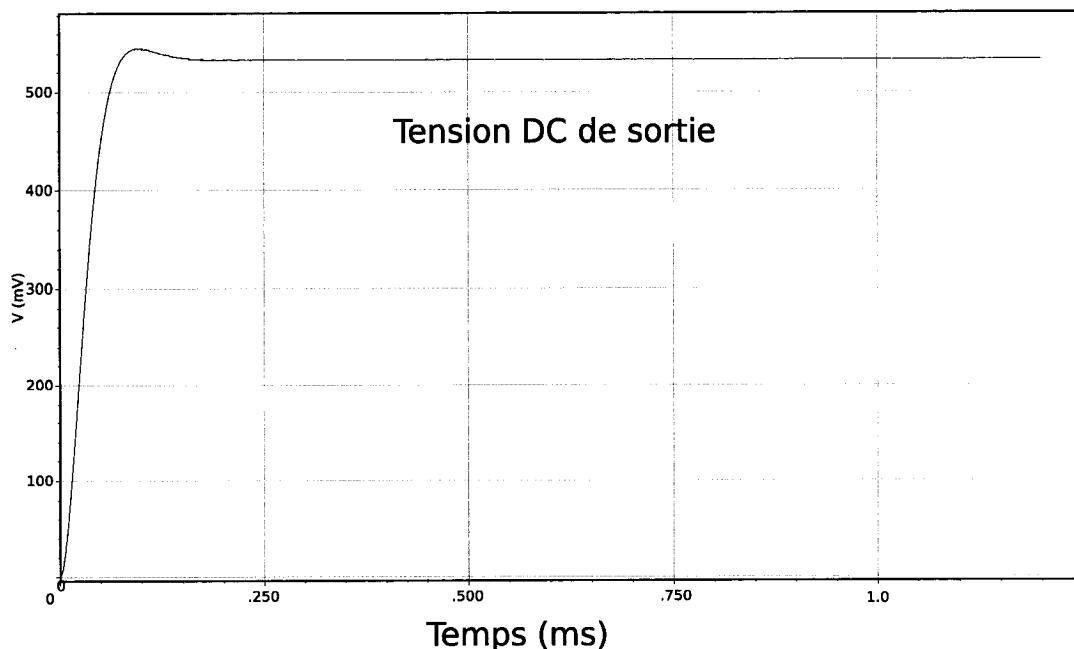

| FIG. 2.8  | Tension DC en sortie du convertisseur (au niveau de la charge résistive) . . . . .                                           | 47 |

| FIG. 2.9  | Tensions et courants principaux pour le modèle du substrat obtenu avec SubstrateStorm . . . . .                              | 52 |

| FIG. 2.10 | Courants de polarisation des puits P et N, courants entrant dans l'électrode "Bulk" des transistors . . . . .                | 53 |

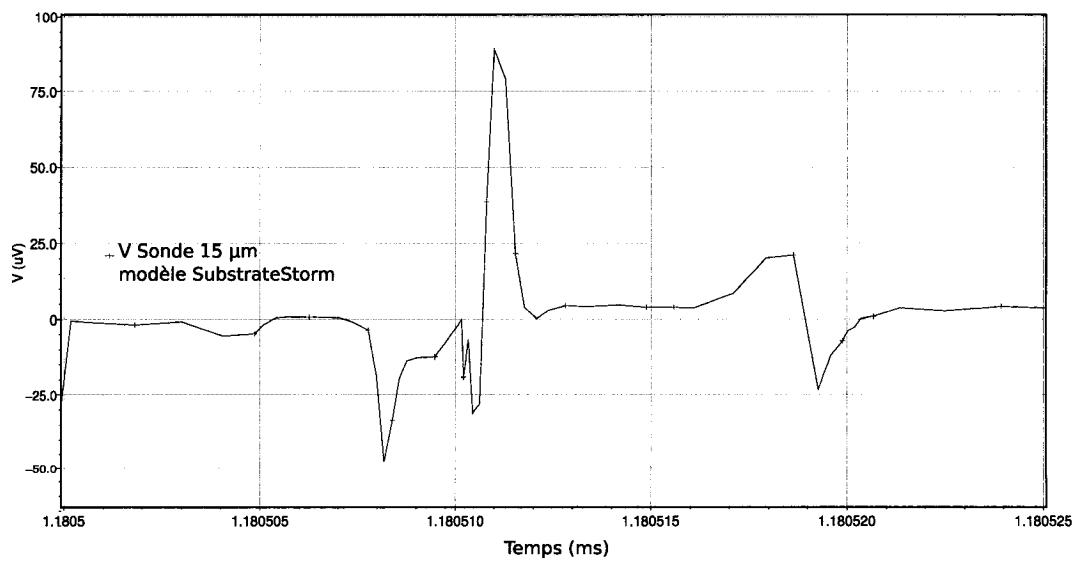

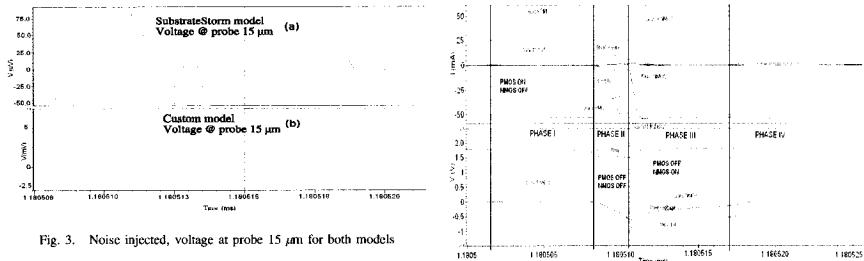

| FIG. 2.11 | Potentiel du substrat au niveau de la sonde 15 $\mu\text{m}$ . . . . .                                                       | 53 |

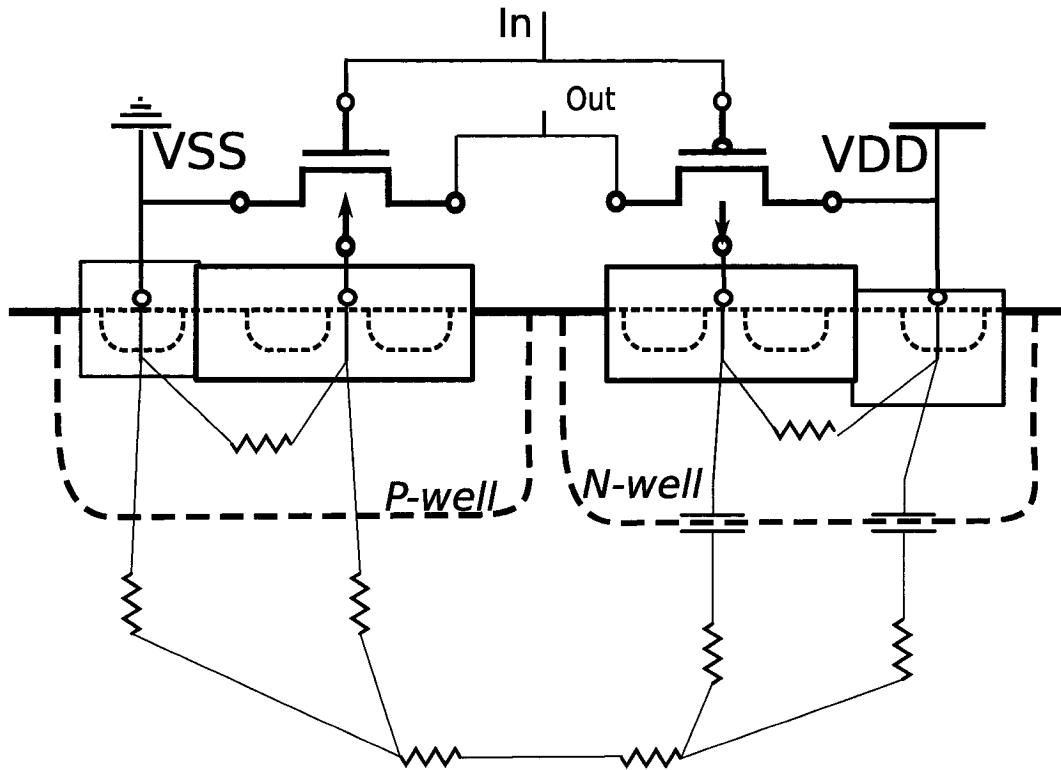

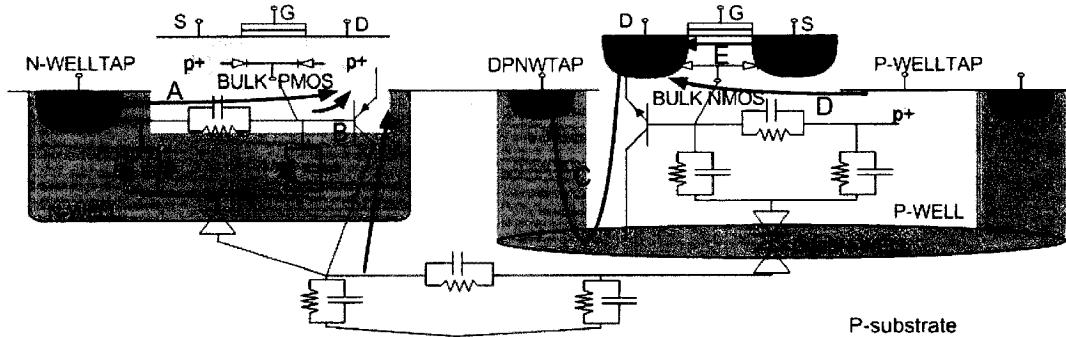

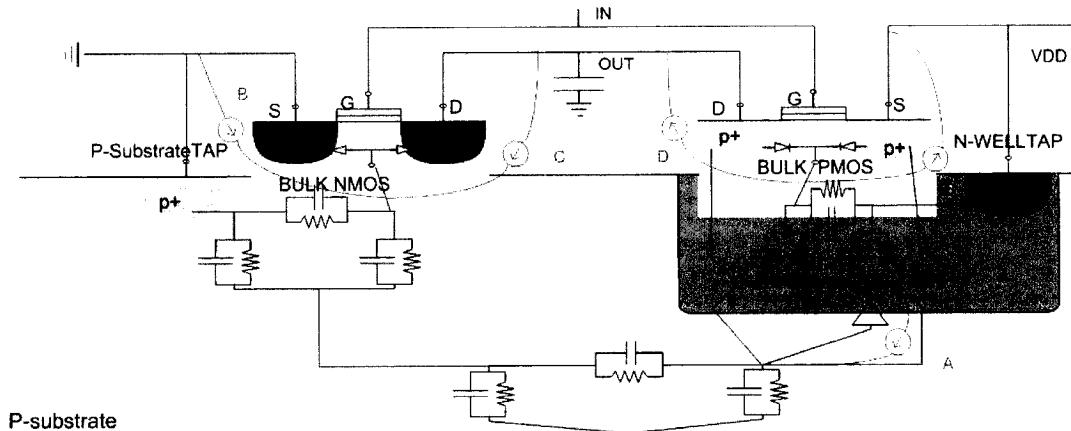

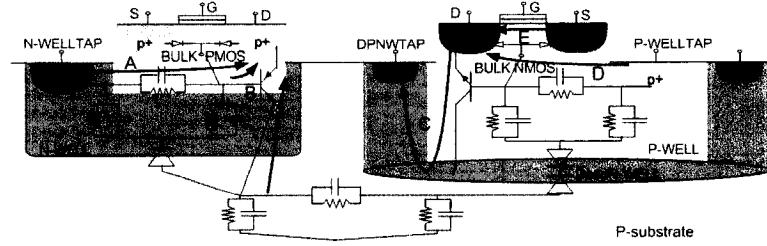

| FIG. 2.12 | Modélisation personnalisée du substrat et chemins de courant                                                                 | 56 |

| FIG. 2.13 | Comparaison des tensions entre les deux modèles SCA et SubstrateStorm . . . . .                                              | 57 |

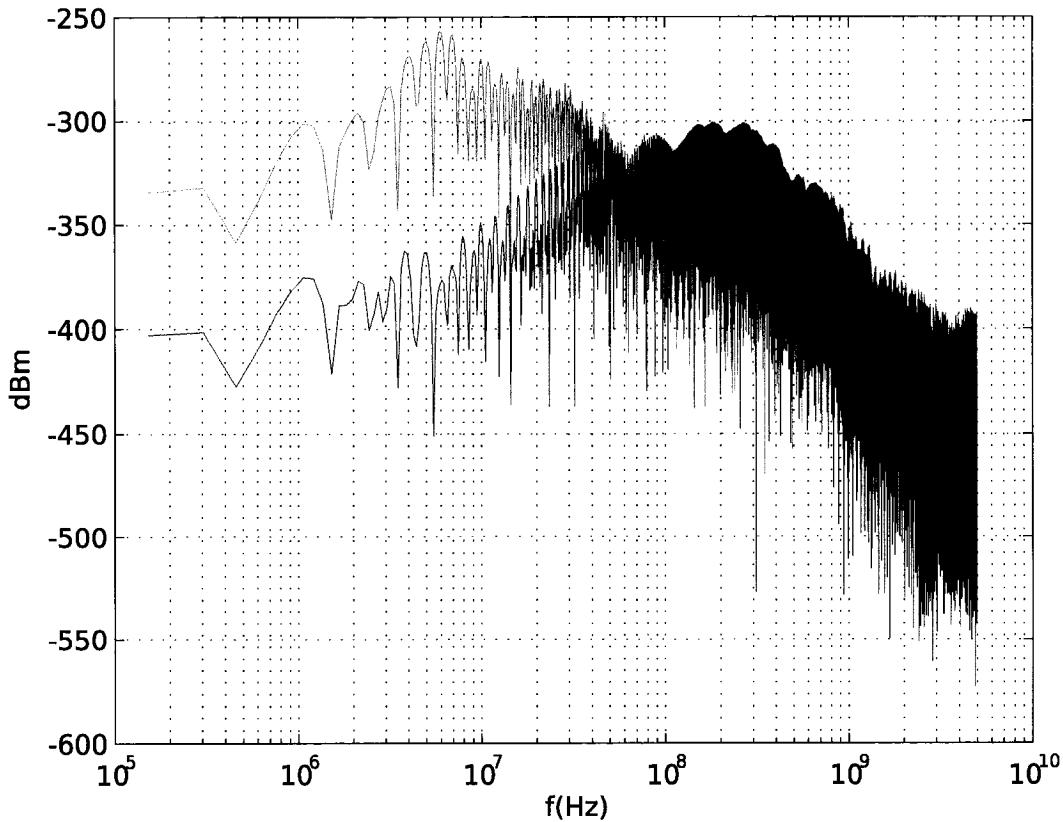

| FIG. 2.14 | Comparaison des spectres en puissances pour les 2 modèles (SCA en bleu (foncé) et SubstrateStorm en rouge(clair)) . .        | 58 |

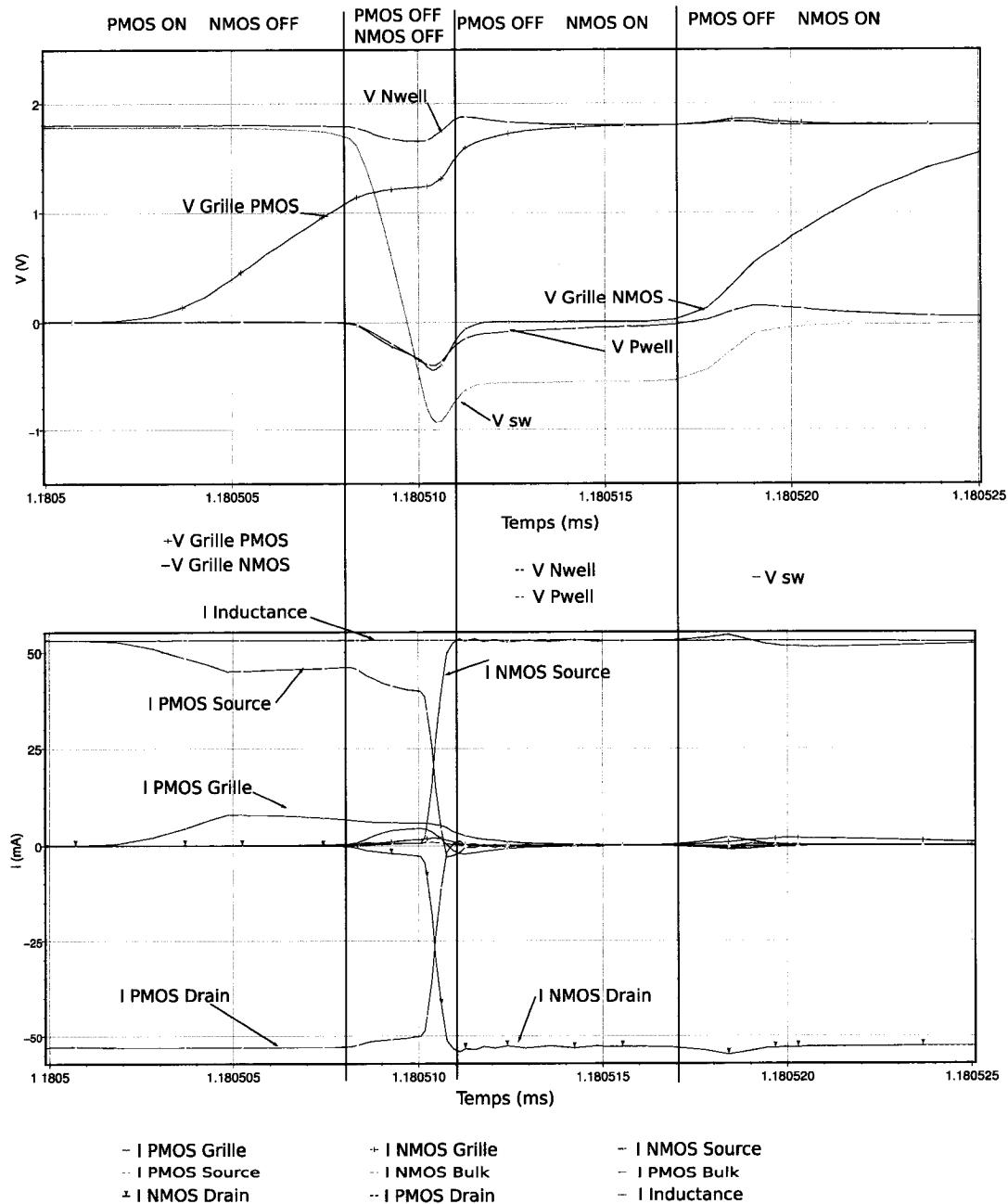

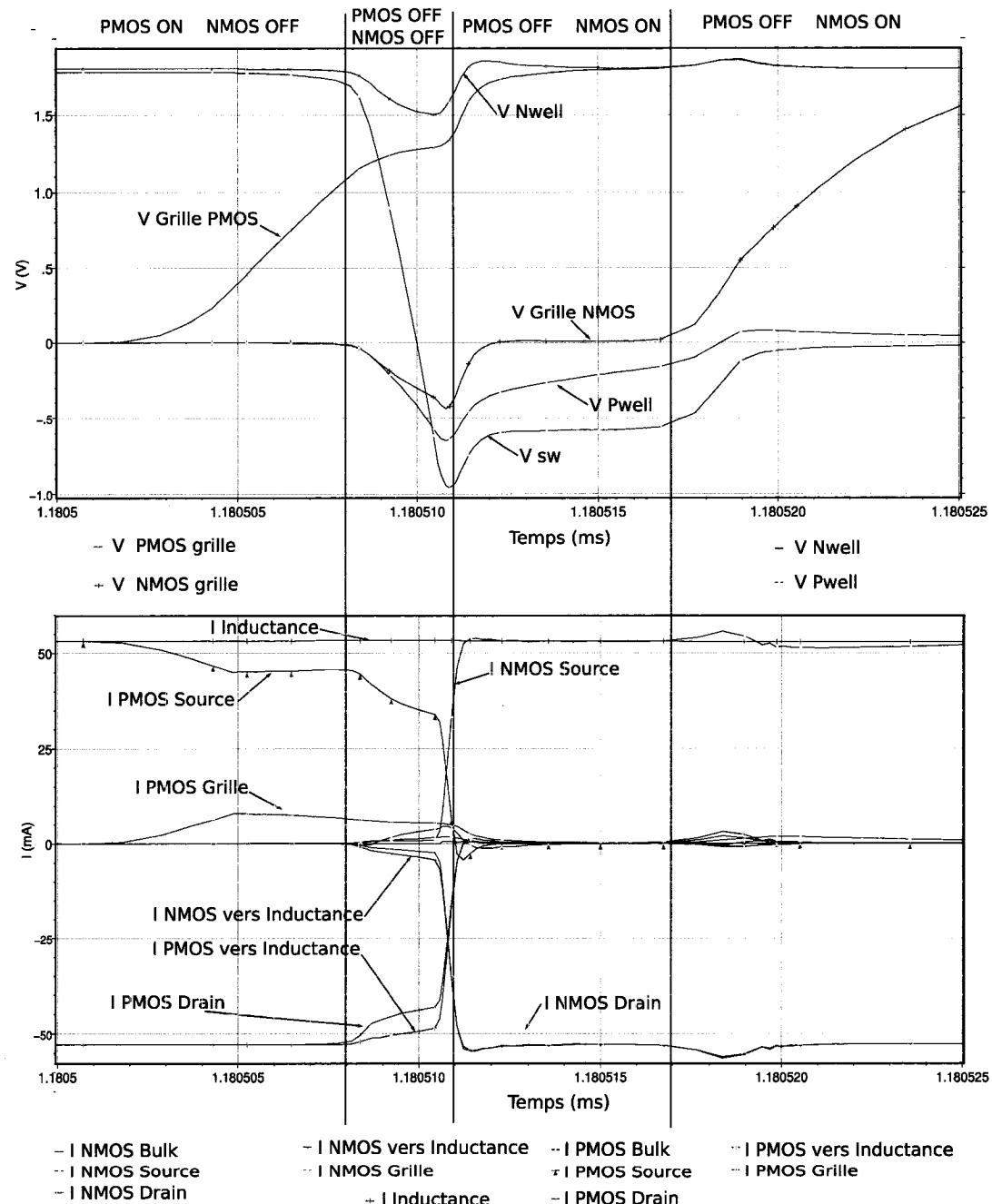

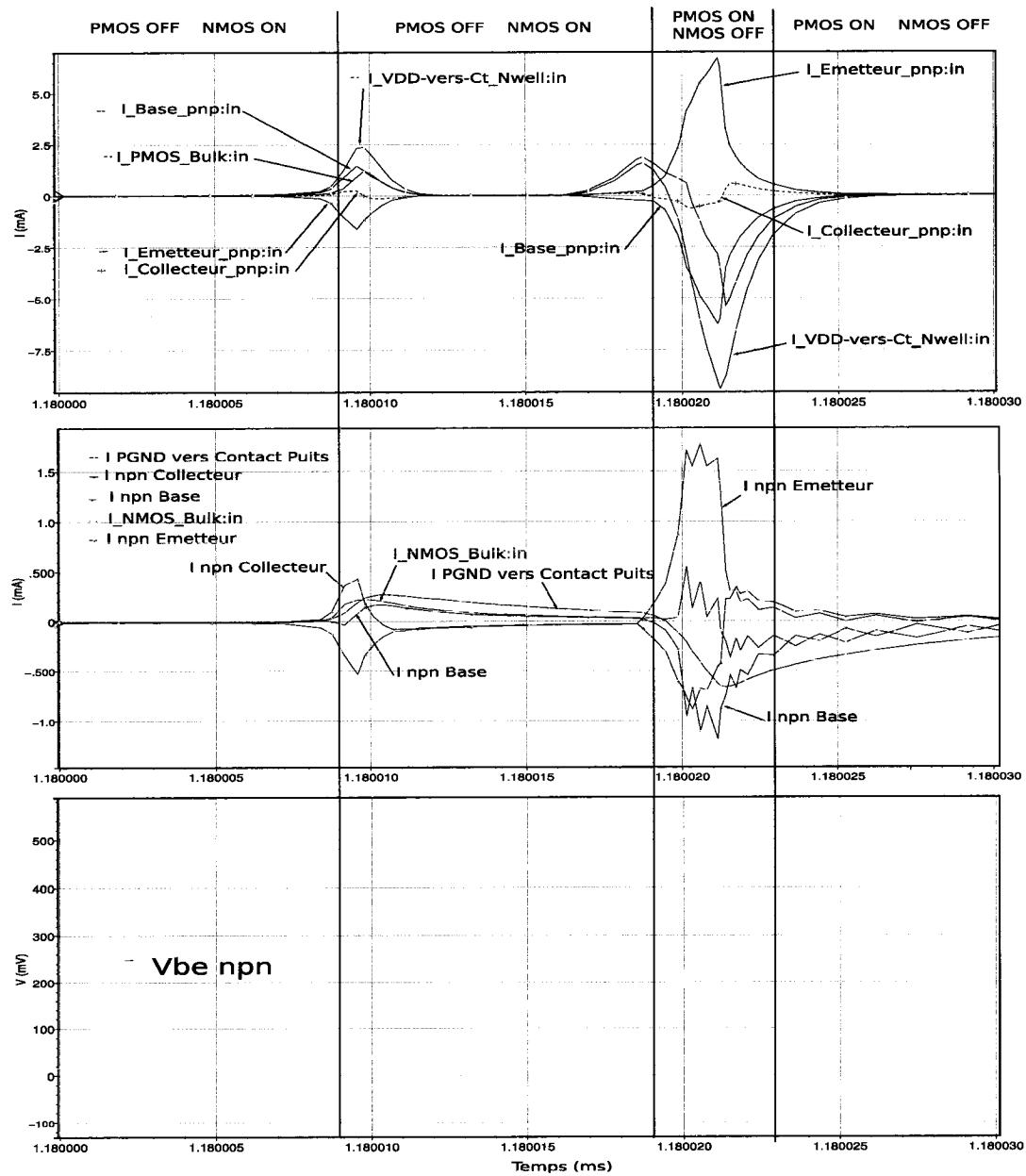

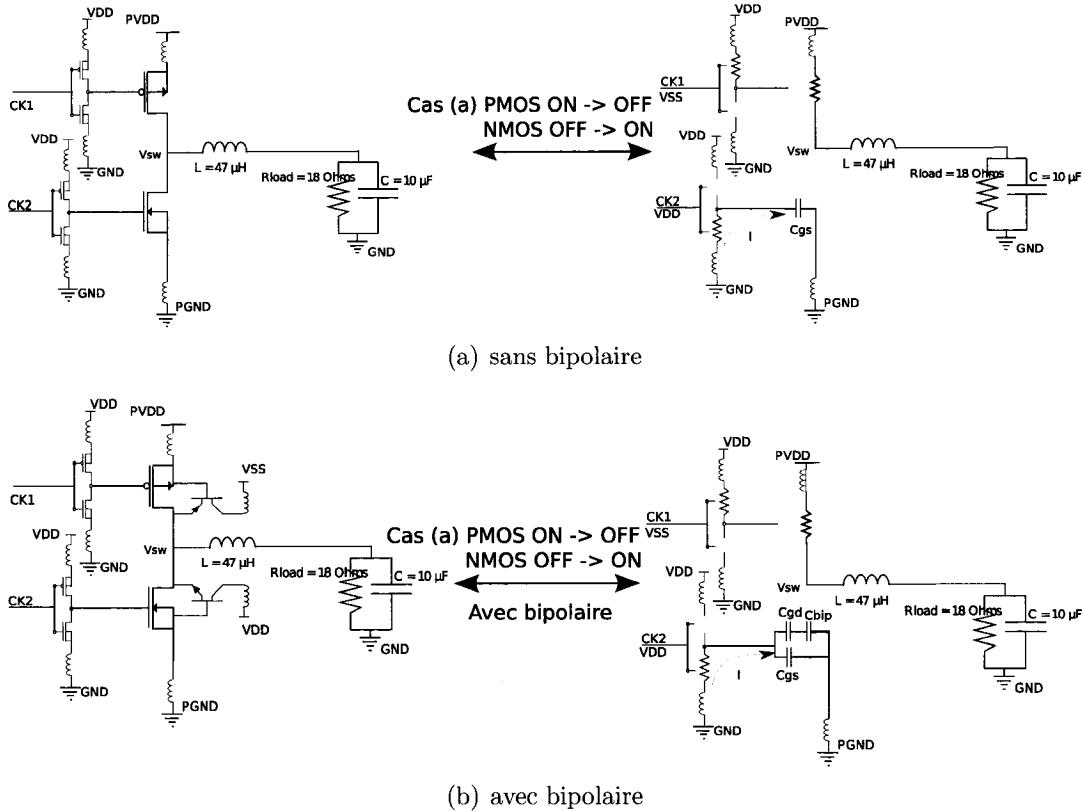

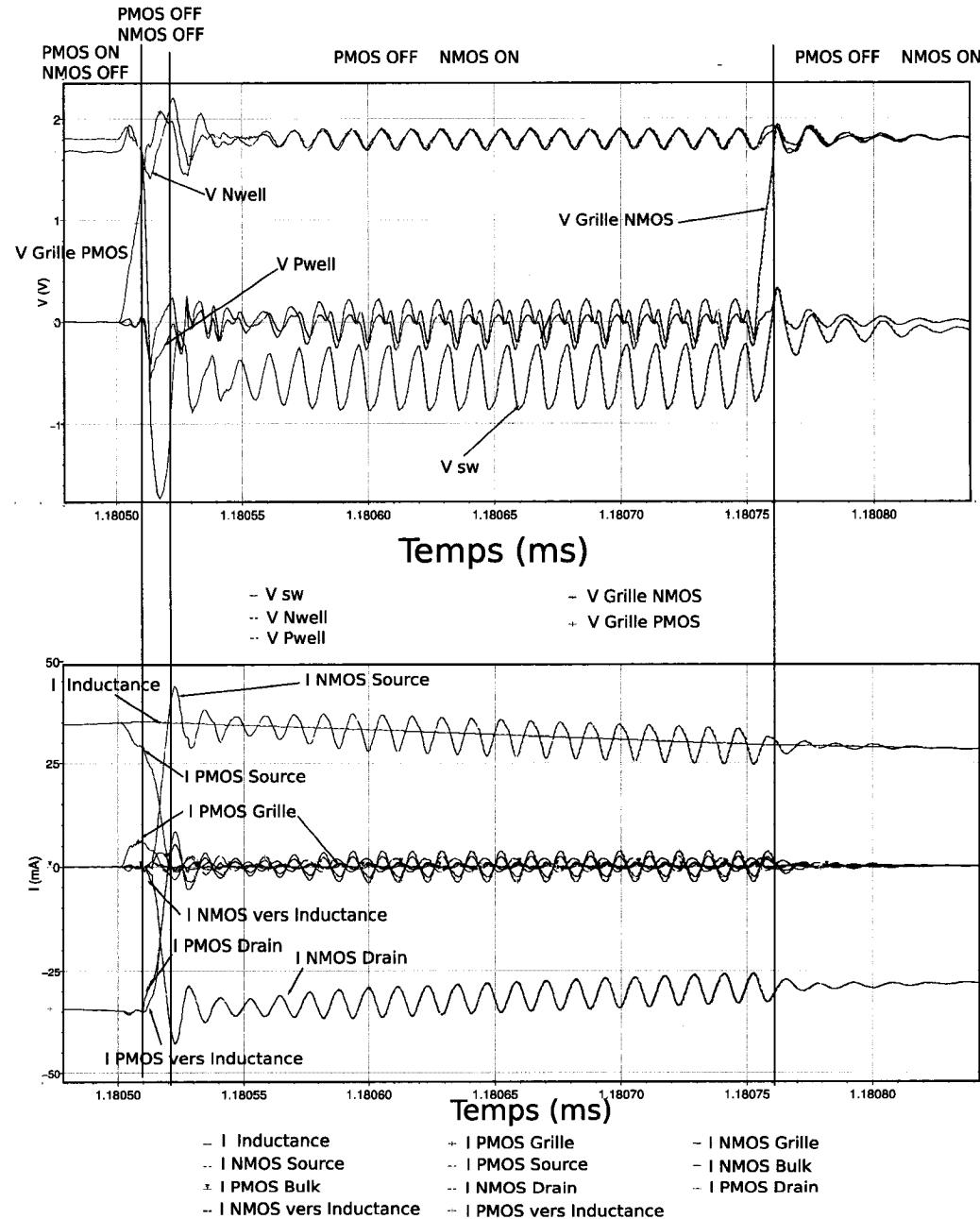

| FIG. 2.15 | Tensions principales et courants des transistors pour la transition de type (a) . . . . .                                    | 61 |

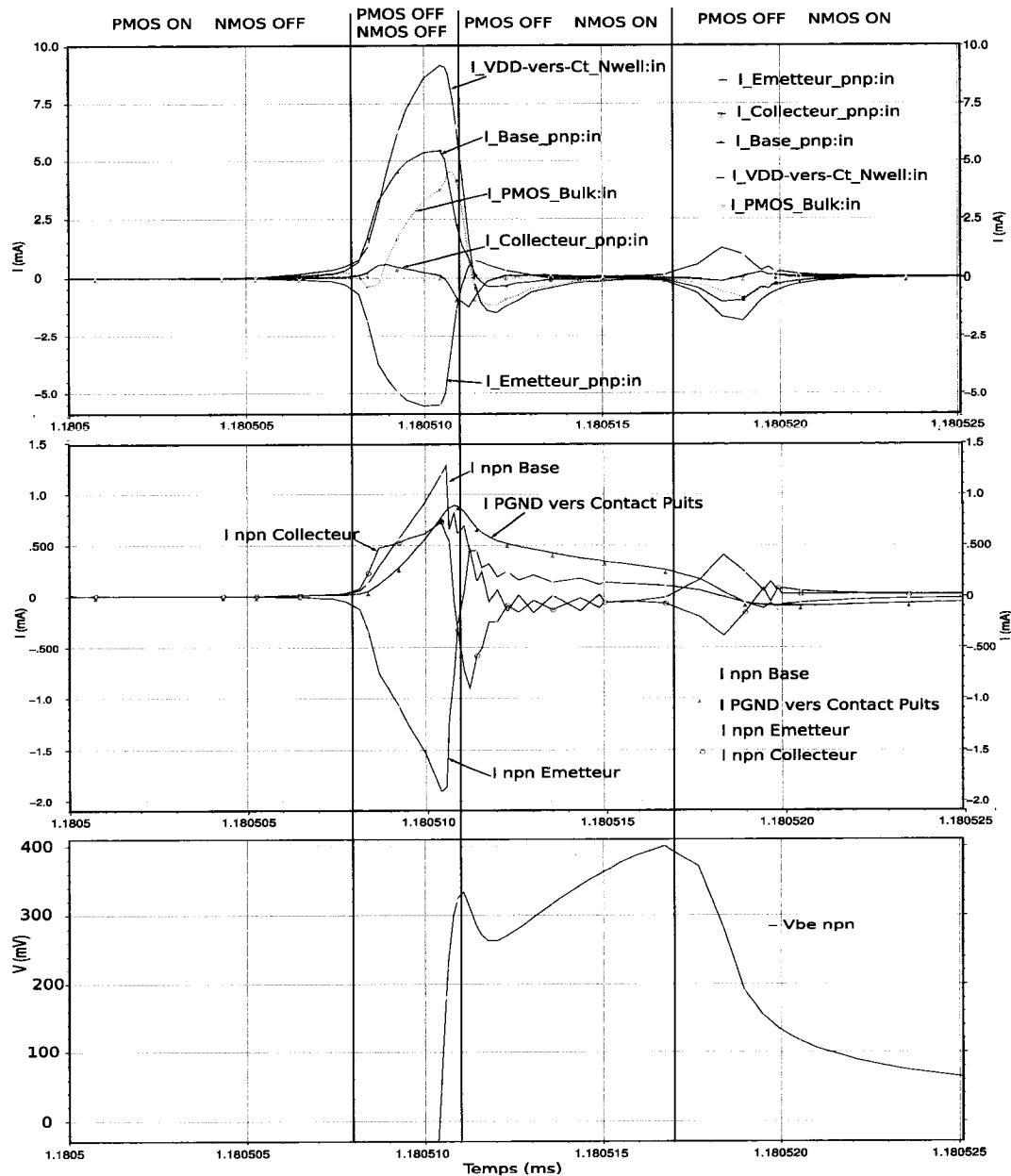

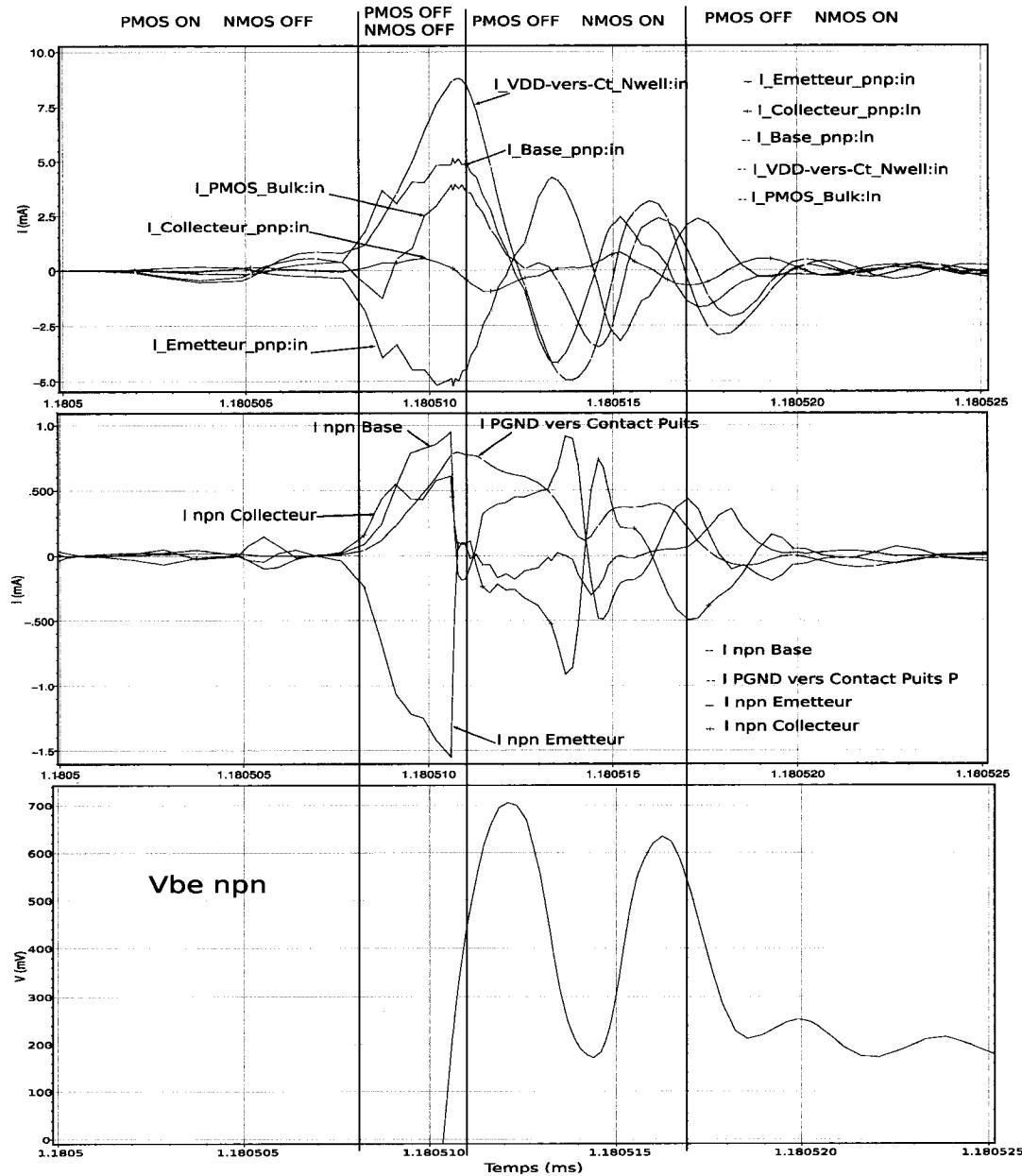

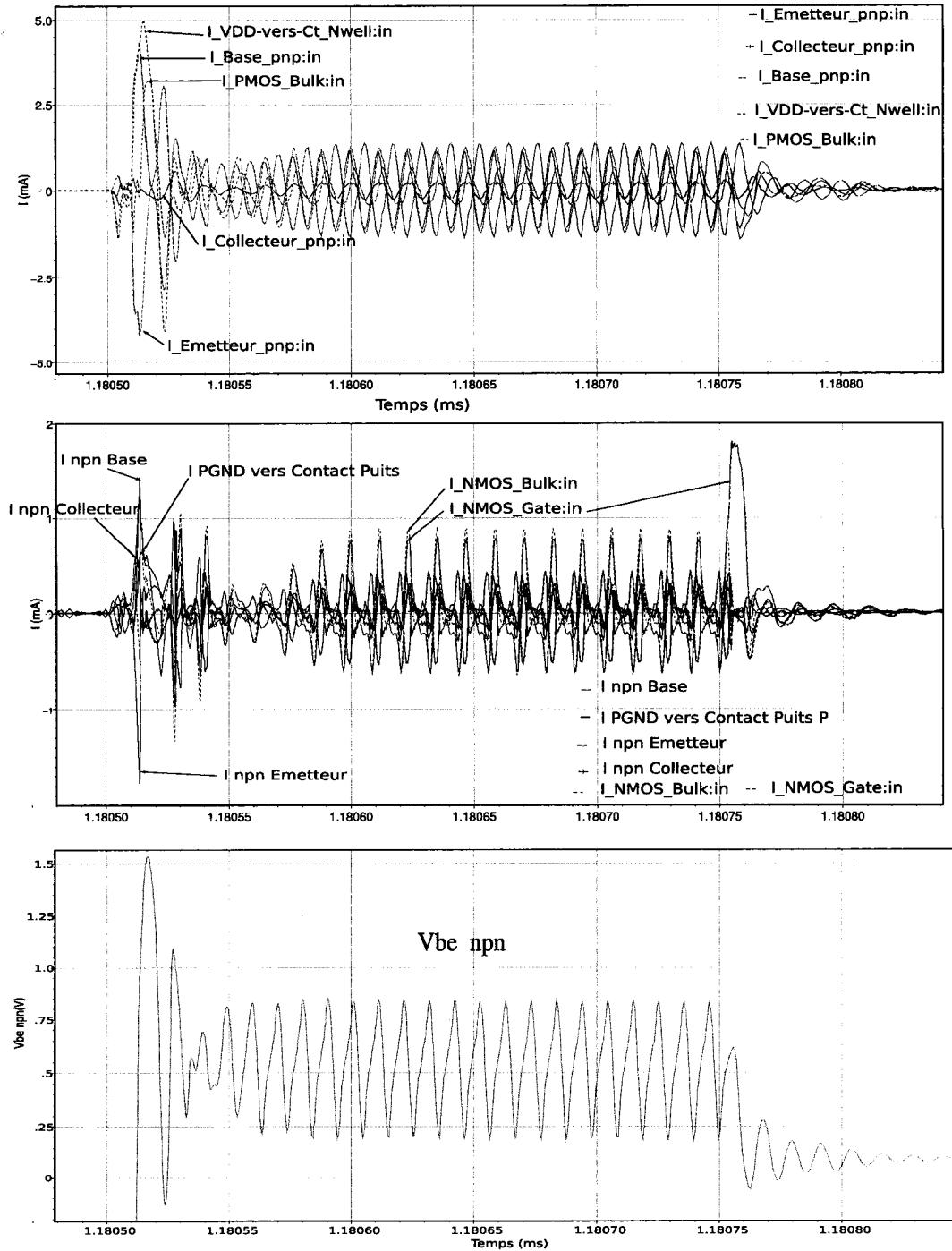

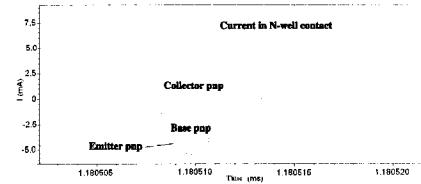

| FIG. 2.16 | Courants pnp, npn et tension base émetteur pour la transition de type (a) . . . . .                                          | 62 |

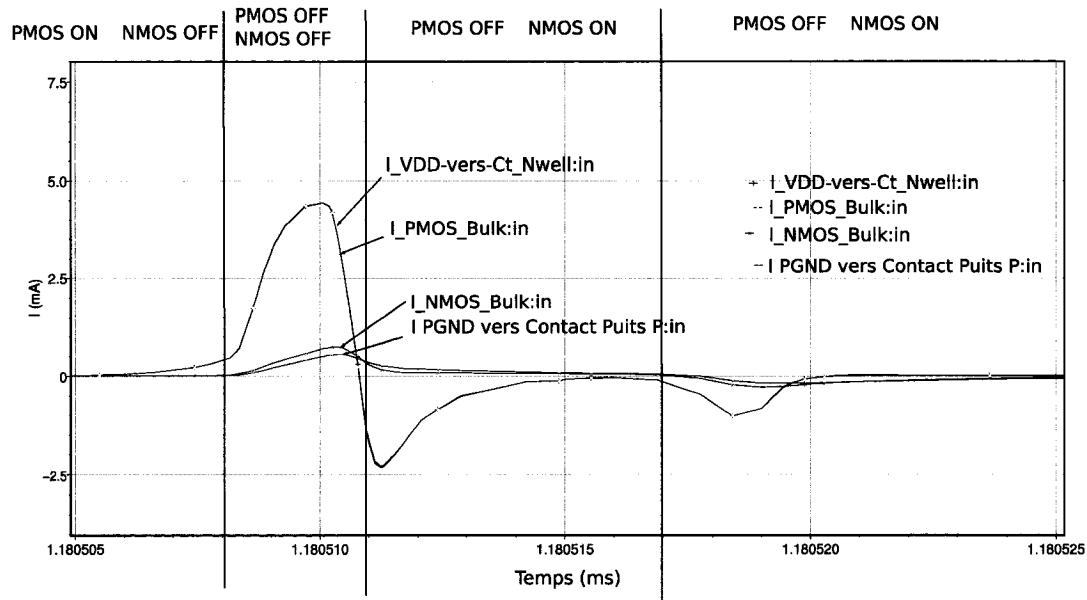

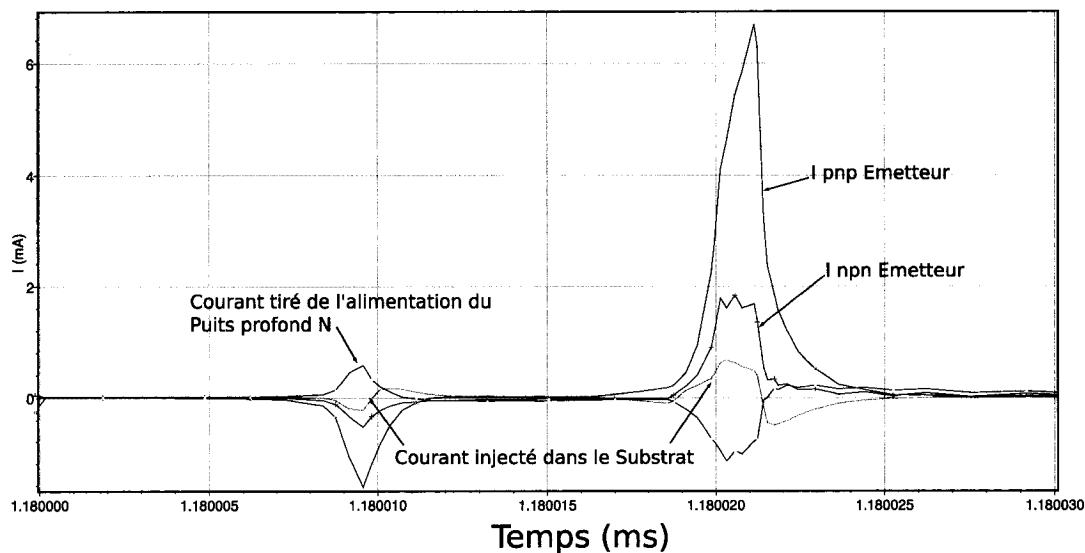

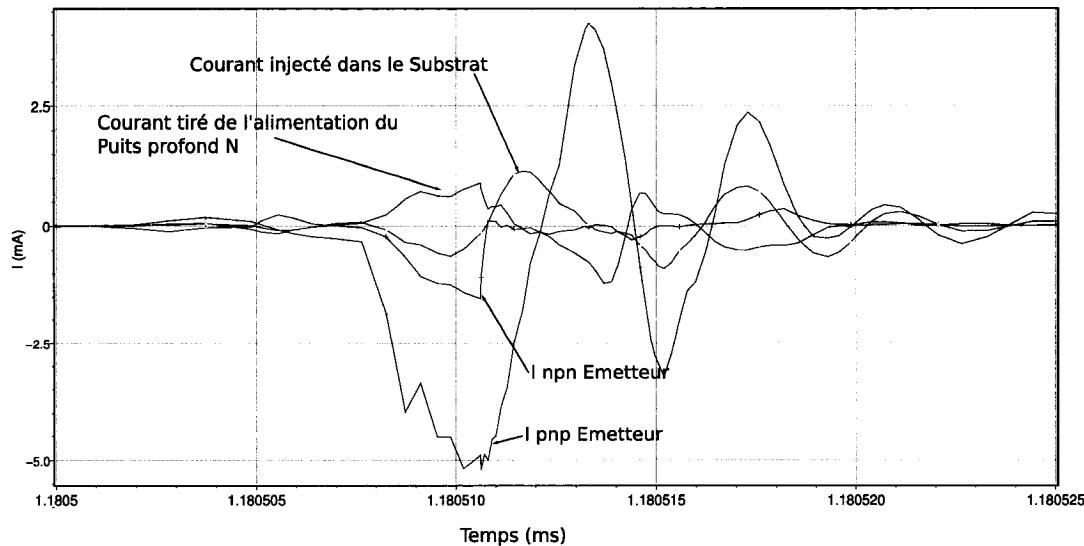

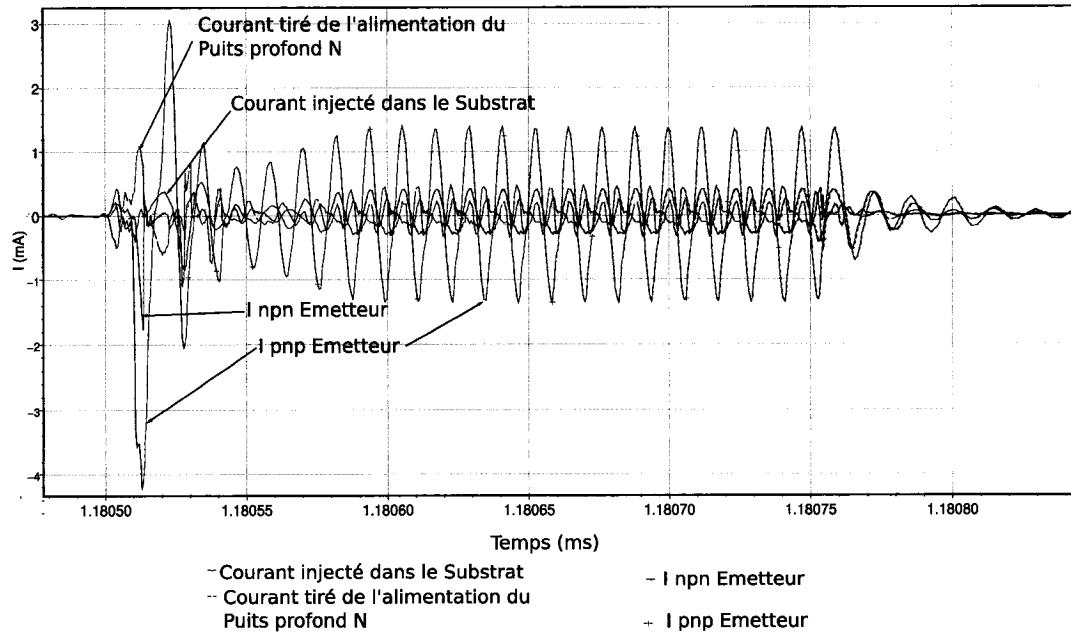

| FIG. 2.17 | Courants injectés dans le substrat et les alimentations pour la transition de type (a) . . . . .                             | 63 |

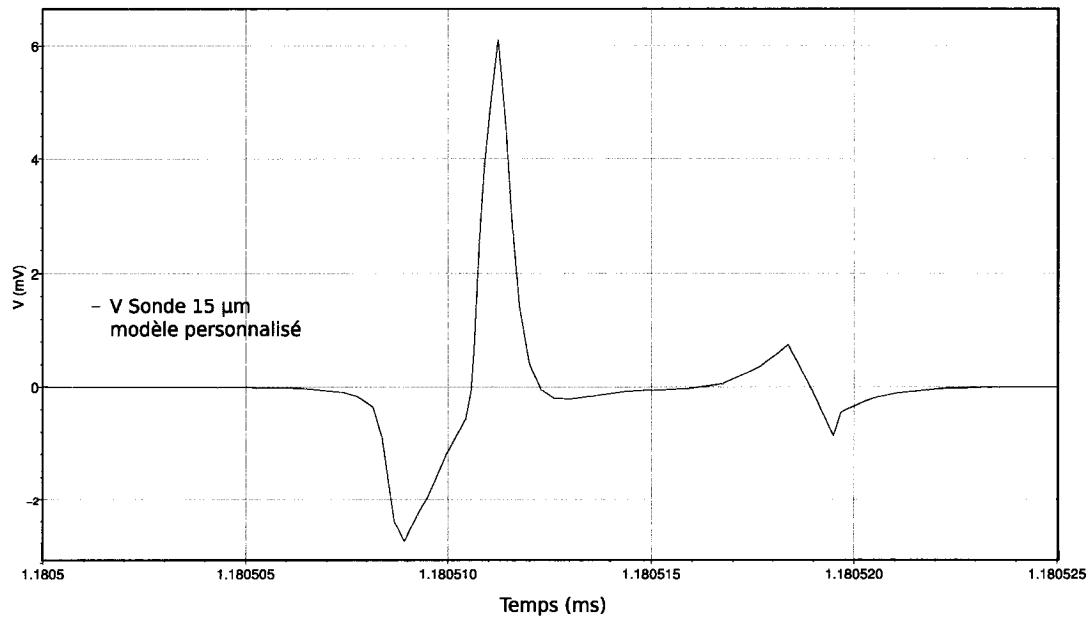

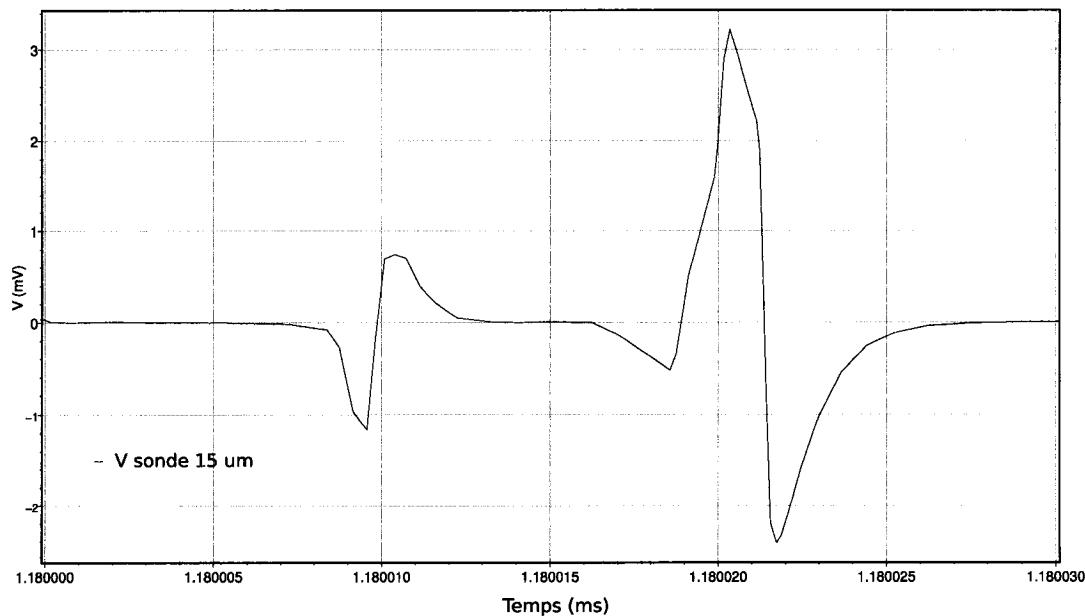

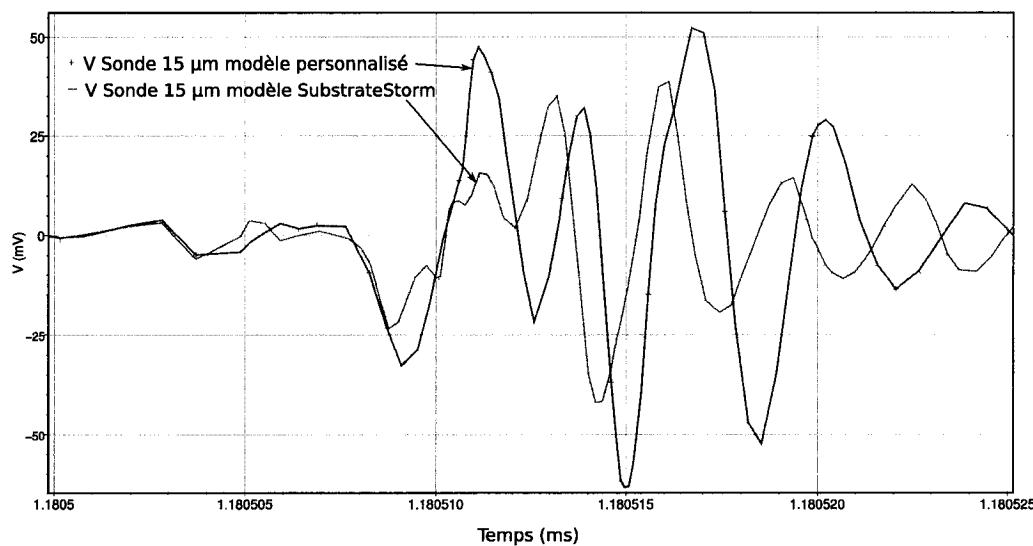

| FIG. 2.18 | Potentiel du substrat à 15 $\mu\text{m}$ de l'agresseur pour le modèle personnalisé pour la transition de type (a) . . . . . | 63 |

| FIG. 2.19 | Tensions principales et Courants des transistors pour la transition de type (b) . . . . .                                    | 69 |

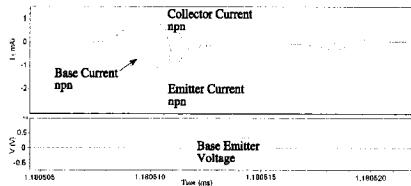

| FIG. 2.20 | Courants pnp, npn et tension base émetteur pour la transition de type (b) . . . . .                                          | 70 |

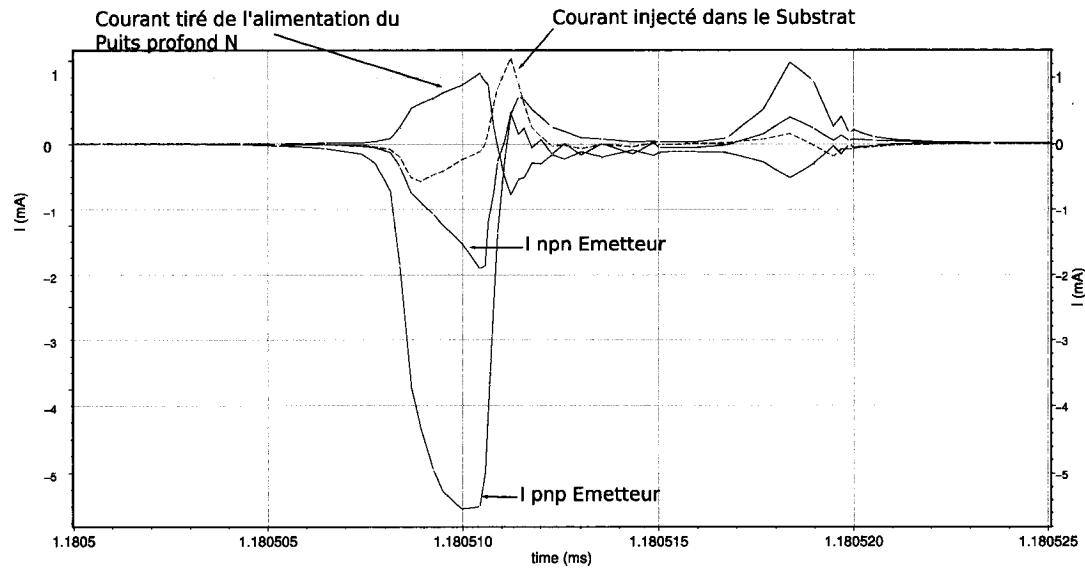

| FIG. 2.21 | Courants injectés dans le substrat et les alimentations pour la transition de type (b) . . . . .                             | 71 |

|           |                                                                                                                                                                                |    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIG. 2.22 | Potentiel du substrat à 15 µm de l'agresseur pour le modèle personnalisé pour la transition de type (b) . . . . .                                                              | 71 |

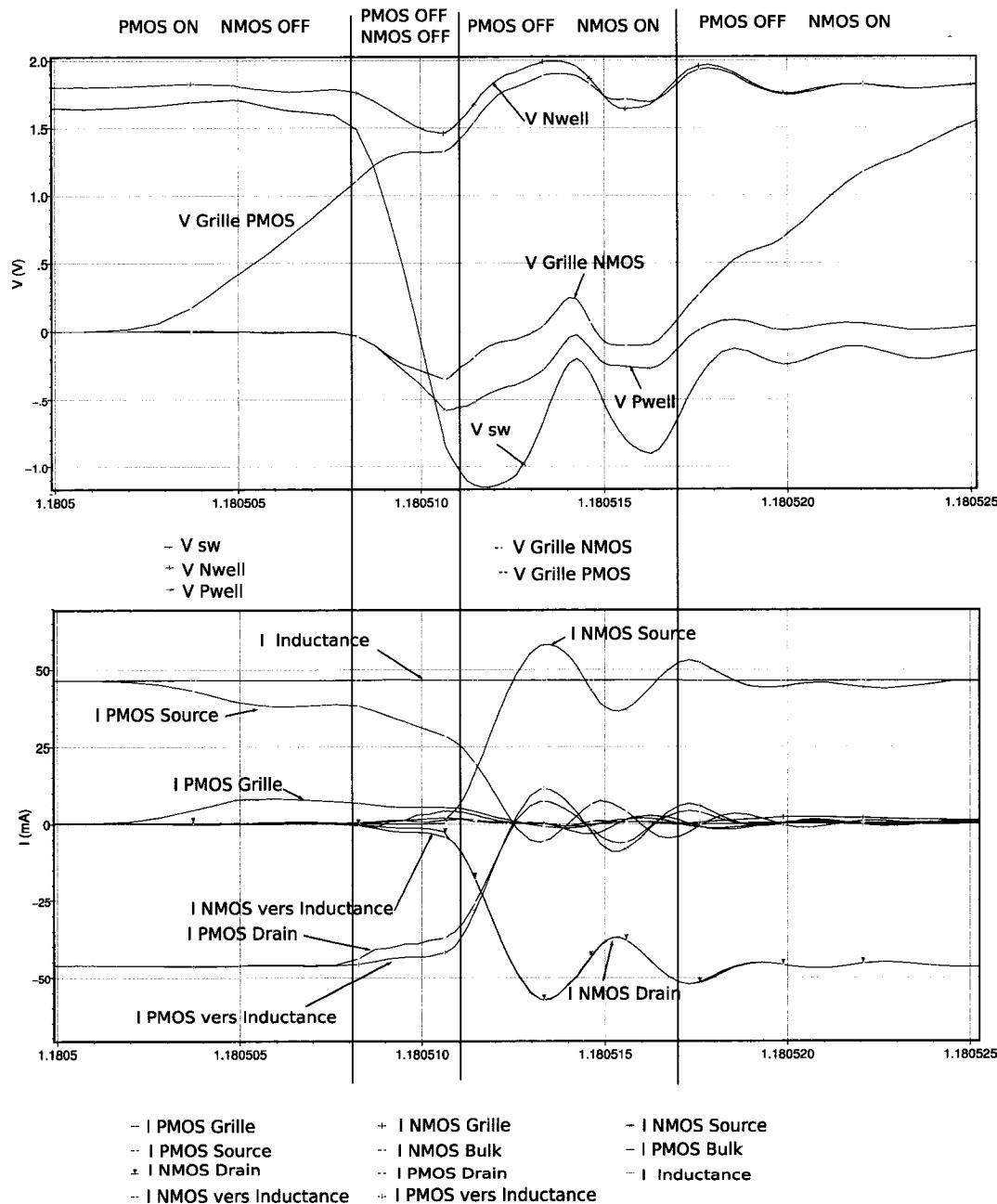

| FIG. 2.23 | Tensions principales et Courants des transistors pour la transition de type (a) prenant en compte le modèle du boîtier . .                                                     | 73 |

| FIG. 2.24 | Courants pnp, npn et tension base émetteur pour la transition de type (a) prenant en compte le modèle du boîtier . .                                                           | 74 |

| FIG. 2.25 | Courants injectés dans le substrat et les alimentations pour la transition de type (a) prenant en compte le modèle du boîtier .                                                | 75 |

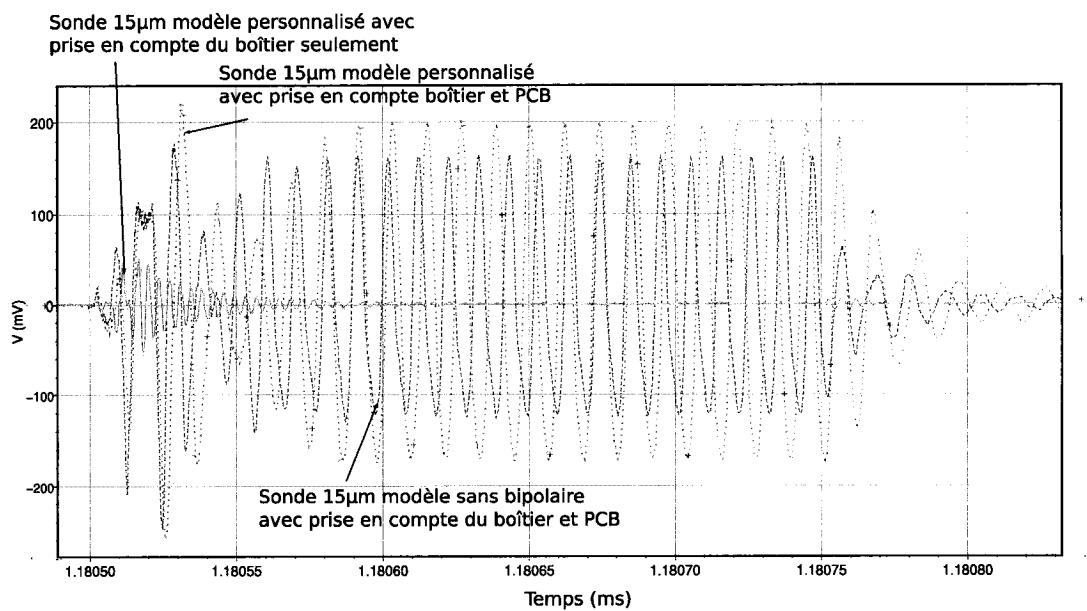

| FIG. 2.26 | Comparaison des potentiels du substrat à 15 µm pour le modèle optimisé et pour un modèle sans bipolaire lors d'une transition de type (a) . . . . .                            | 75 |

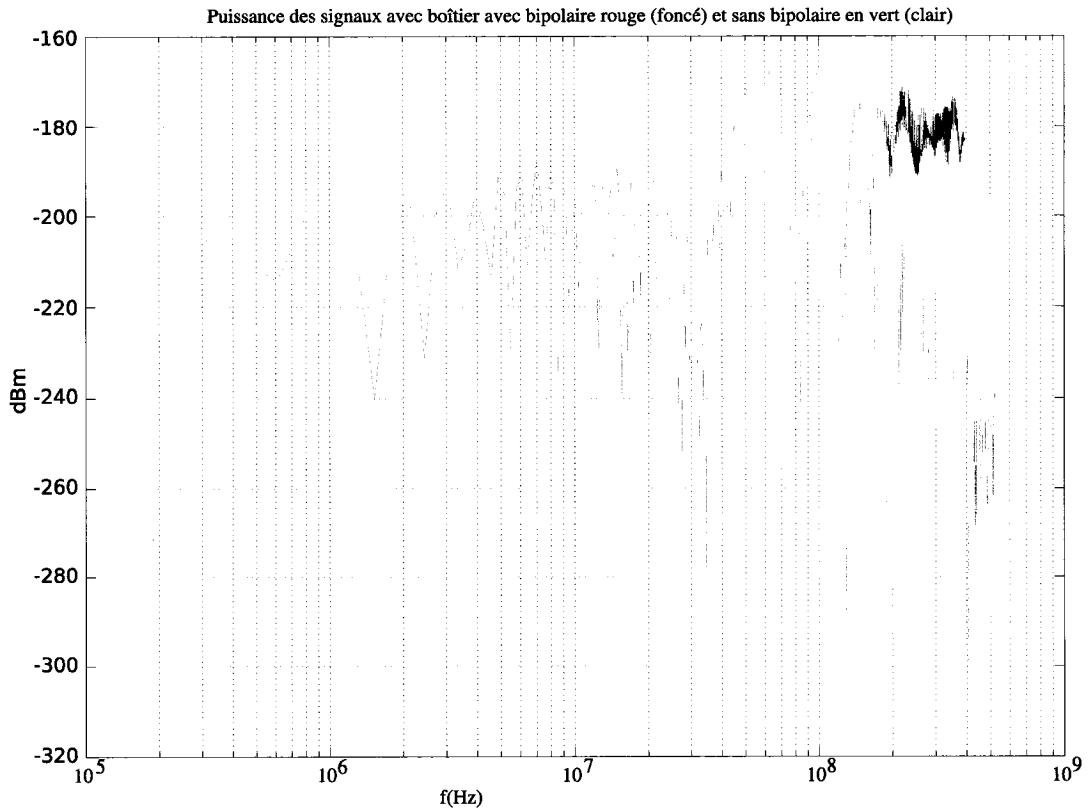

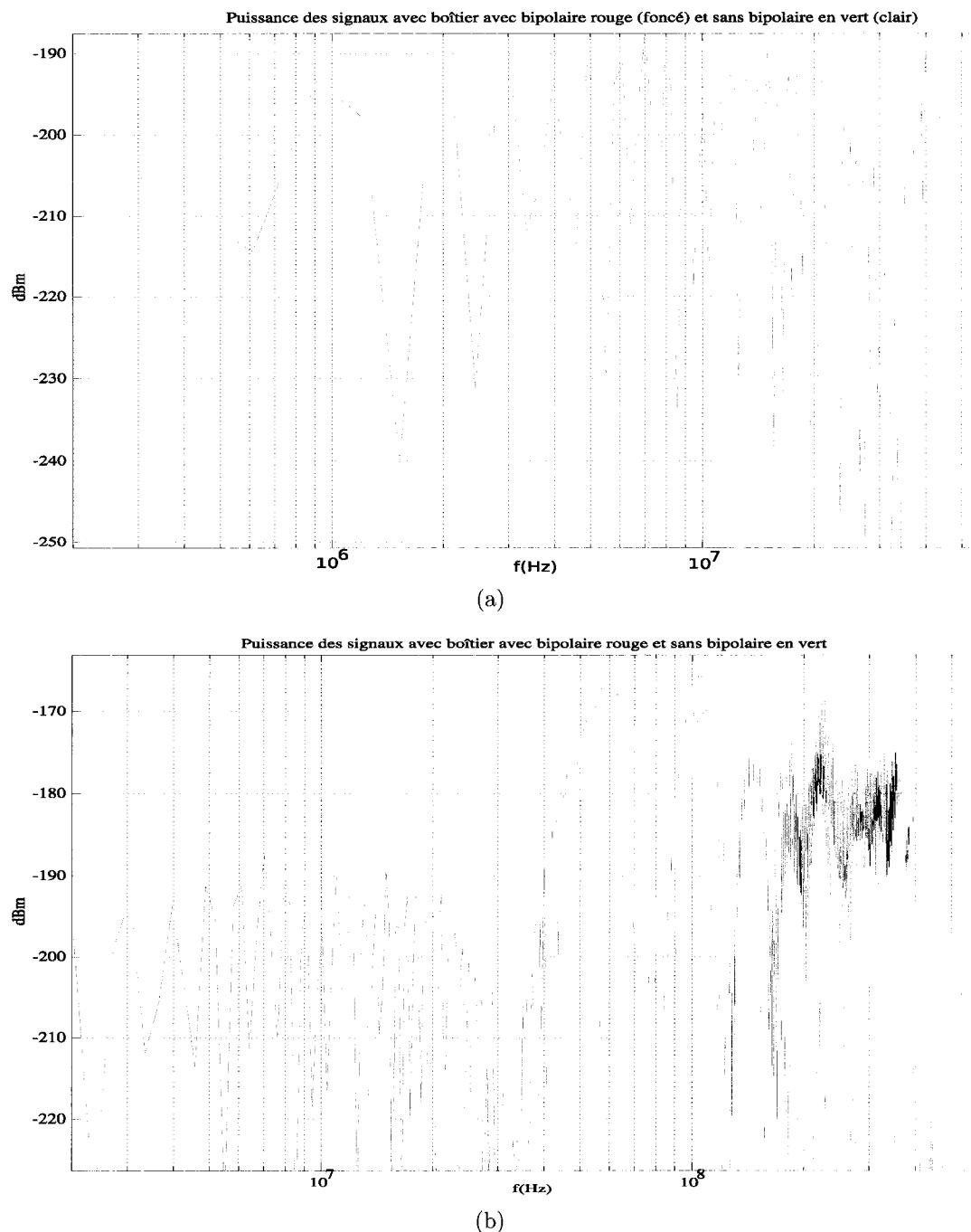

| FIG. 2.27 | Transformée de Fourier du potentiel de la sonde 15 µm pour les deux modèles (rouge (foncé) : modèle personnalisé) (vert (clair) : modèle sans bipolaire) . . . . .             | 76 |

| FIG. 2.28 | Zoom sur la Transformée de Fourier du potentiel de la sonde 15 µm pour les deux modèles (rouge (foncé) : modèle personnalisé) (vert (clair) : modèle sans bipolaire) . . . . . | 77 |

| FIG. 2.29 | Réseau RLC responsable de l'oscillation . . . . .                                                                                                                              | 79 |

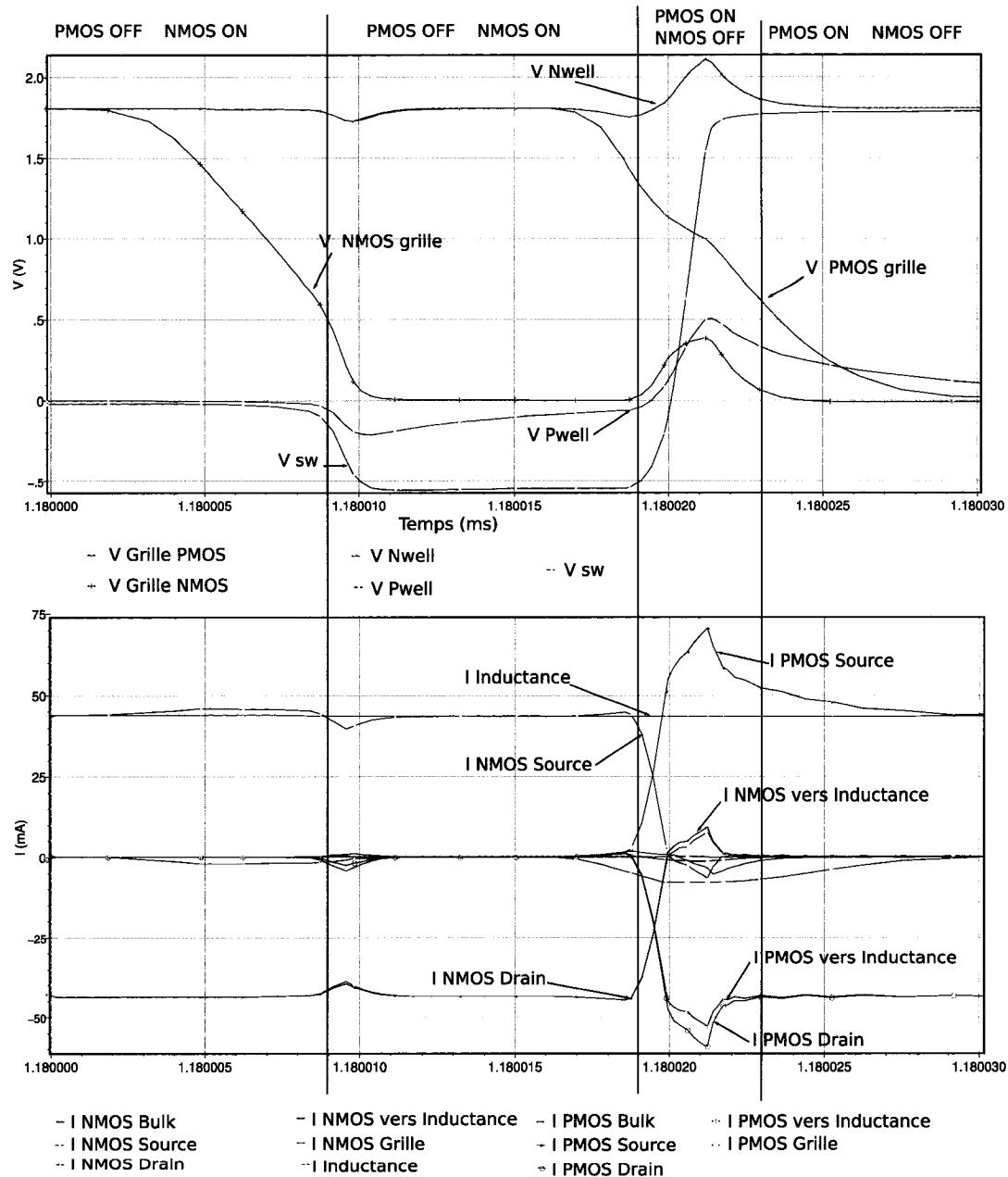

| FIG. 2.30 | Tensions principales et Courants des transistors pour la transition de type (a) prenant en compte le modèle du boîtier et du PCB . . . . .                                     | 81 |

| FIG. 2.31 | Courants pnp, npn et la tension V <sub>be</sub> du npn pour la transition de type (a) en prenant en compte le modèle du boîtier et du PCB . . . . .                            | 83 |

| FIG. 2.32 | Courants injectés dans le substrat et les alimentations pour la transition de type (a) en prenant en compte le modèle du boîtier et du PCB . . . . .                           | 84 |

|           |                                                                                                                                                                                                                                                                                                                                      |     |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| FIG. 2.33 | Comparaison du potentiel du substrat à 15 µm de l'agresseur pour le modèle personnalisé prenant en compte le modèle du boîtier et du PCB (rouge), le modèle sans les bipolaires en prenant en compte le modèle du boîtier et du PCB (bleu), le modèle personnalisé prenant en compte seulement le modèle du boîtier (rose) . . . . . | 85  |

| FIG. 2.34 | Tension de sortie DC en tenant compte du boîtier et du PCB                                                                                                                                                                                                                                                                           | 86  |

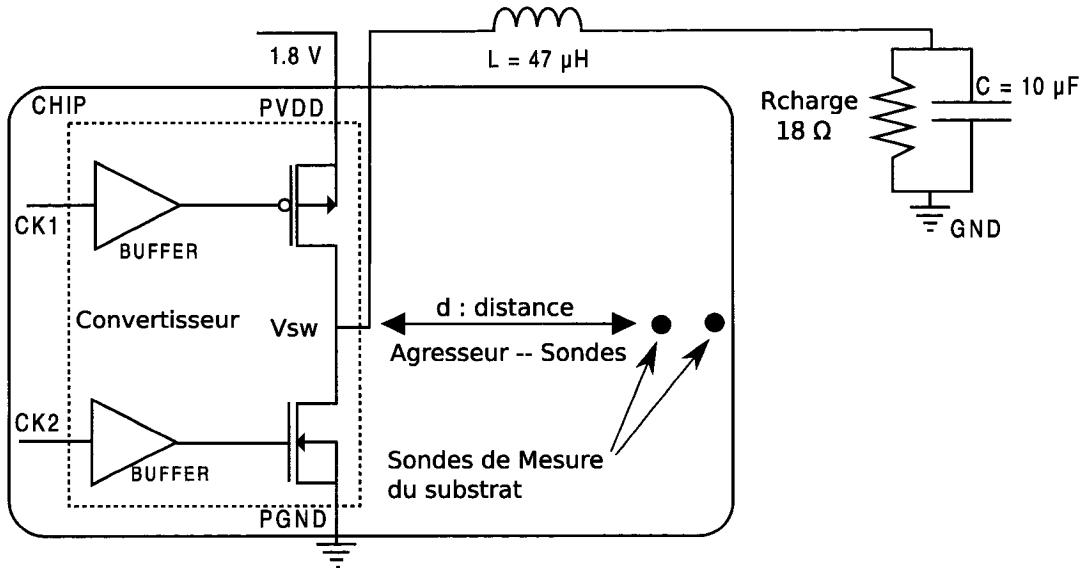

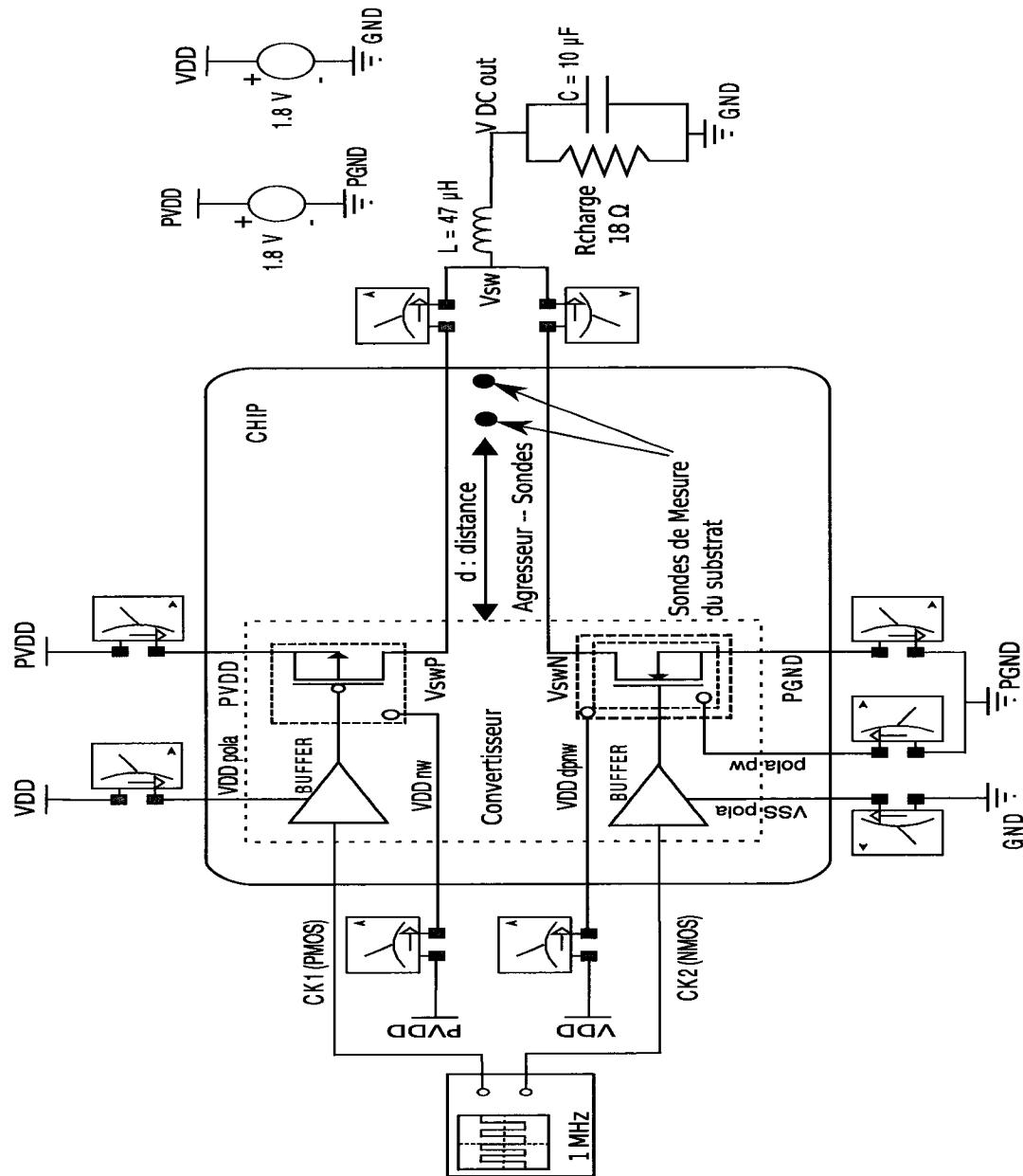

| FIG. 2.35 | Circuit de test du convertisseur . . . . .                                                                                                                                                                                                                                                                                           | 89  |

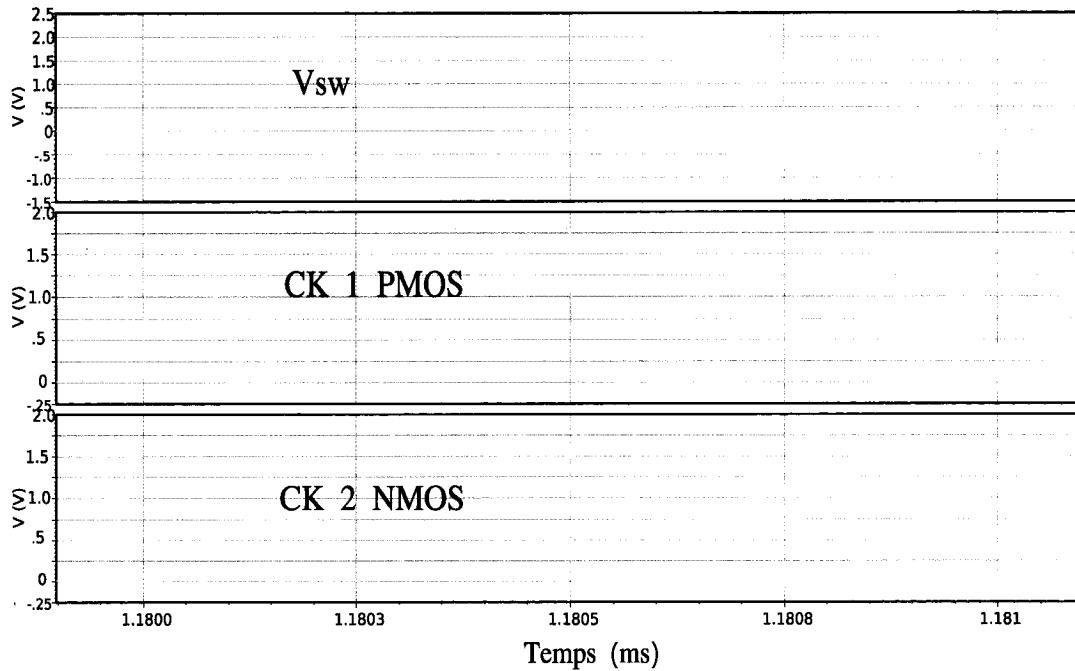

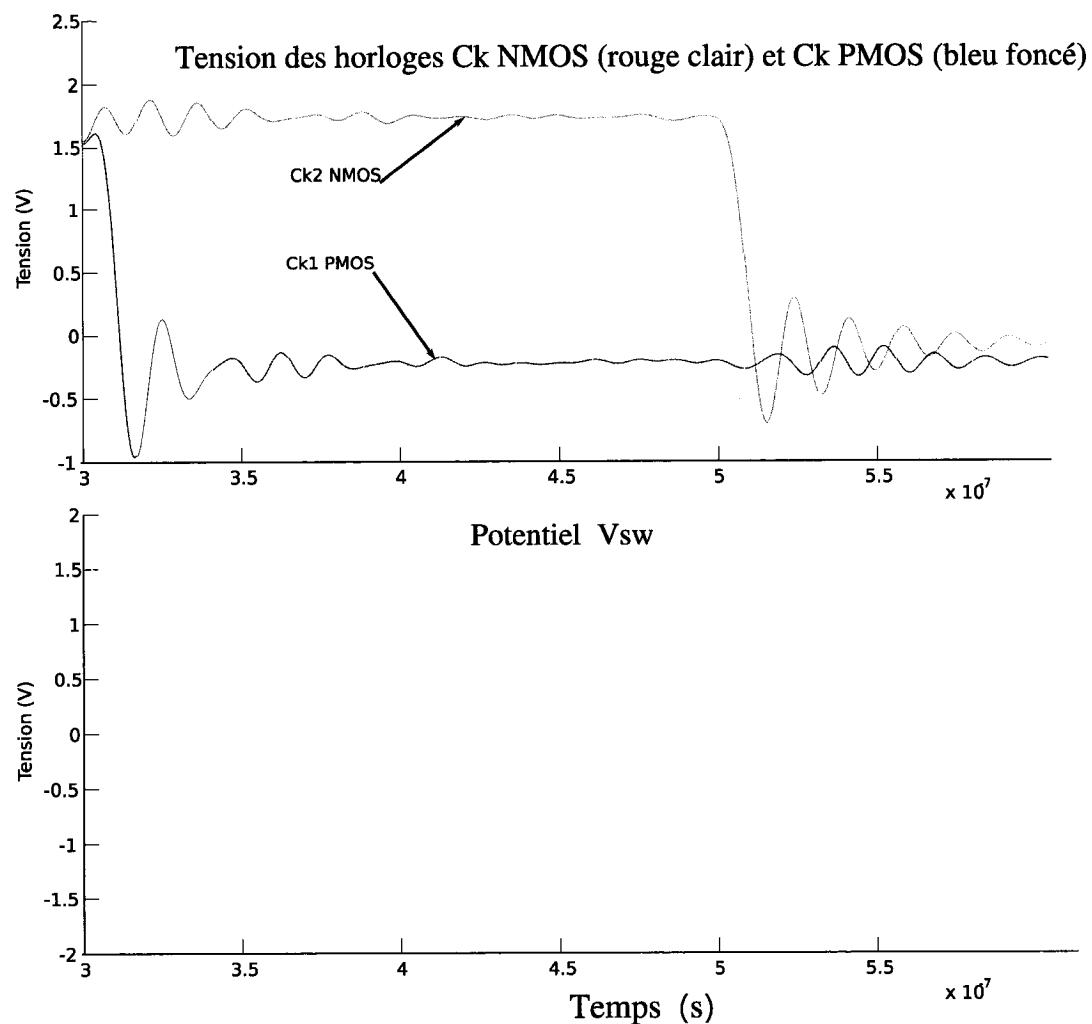

| FIG. 2.36 | Signaux expérimentaux des horloges de contrôles ck PMOS et ck NMOS, ainsi que du potentiel Vsw . . . . .                                                                                                                                                                                                                             | 92  |

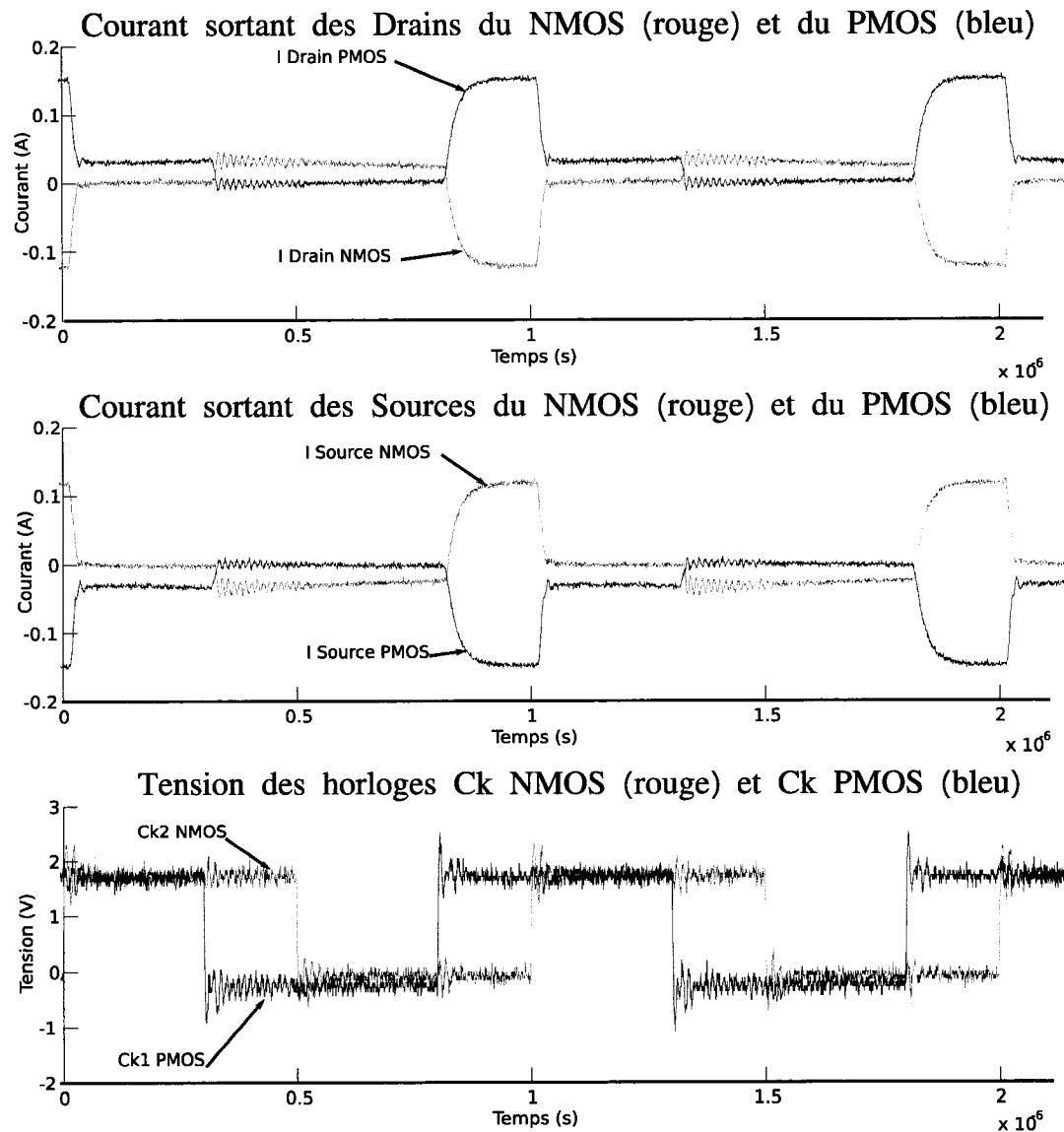

| FIG. 2.37 | Courants entrant dans les transistors NMOS et PMOS . . . . .                                                                                                                                                                                                                                                                         | 93  |

| FIG. 2.38 | Tension expérimentale Vout DC et les signaux d'horloges Ck PMOS et Ck NMOS . . . . .                                                                                                                                                                                                                                                 | 94  |

| FIG. 2.39 | Zoom sur les signaux expérimentaux des horloges de contrôles ck PMOS et ck NMOS, ainsi que du potentiel Vsw . . . . .                                                                                                                                                                                                                | 96  |

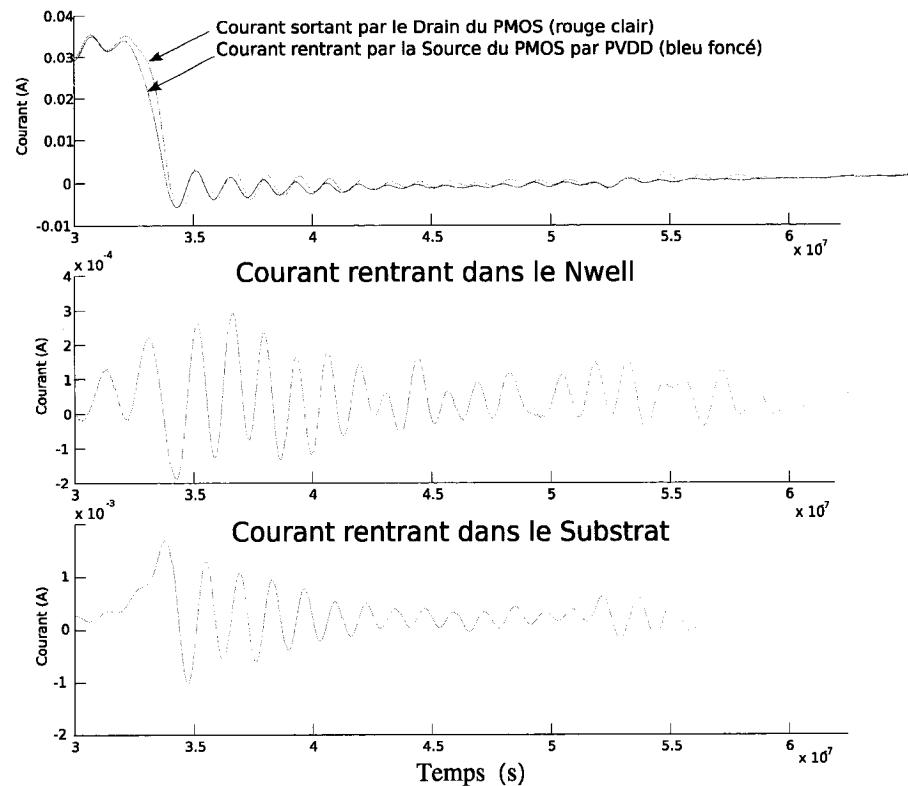

| FIG. 2.40 | Zoom sur les courants entrant et Sortant du PMOS, sur les courants entrant dans le substrat et dans le puits N . . . . .                                                                                                                                                                                                             | 98  |

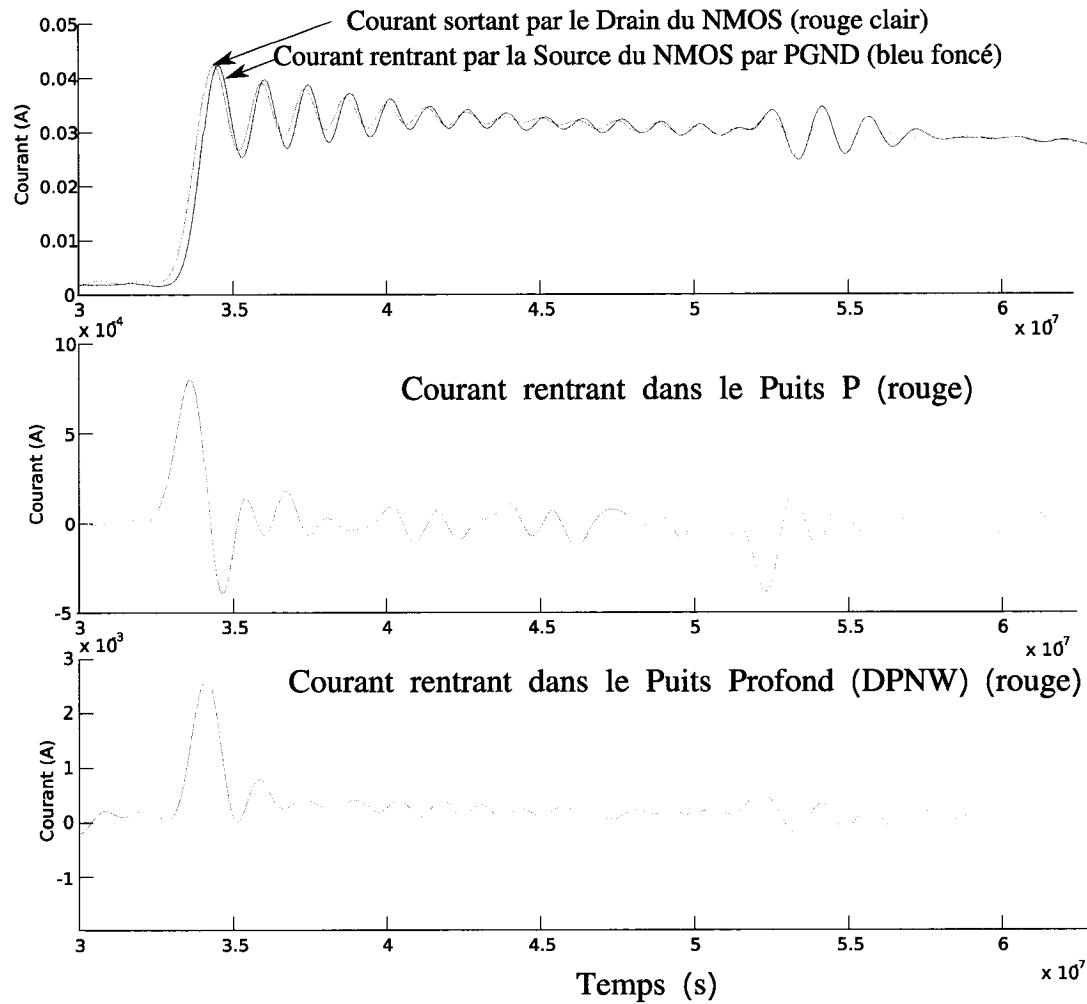

| FIG. 2.41 | Zoom sur les courants entrant et Sortant du NMOS, sur les courants entrant dans le puits P et dans le puits profond N .                                                                                                                                                                                                              | 100 |

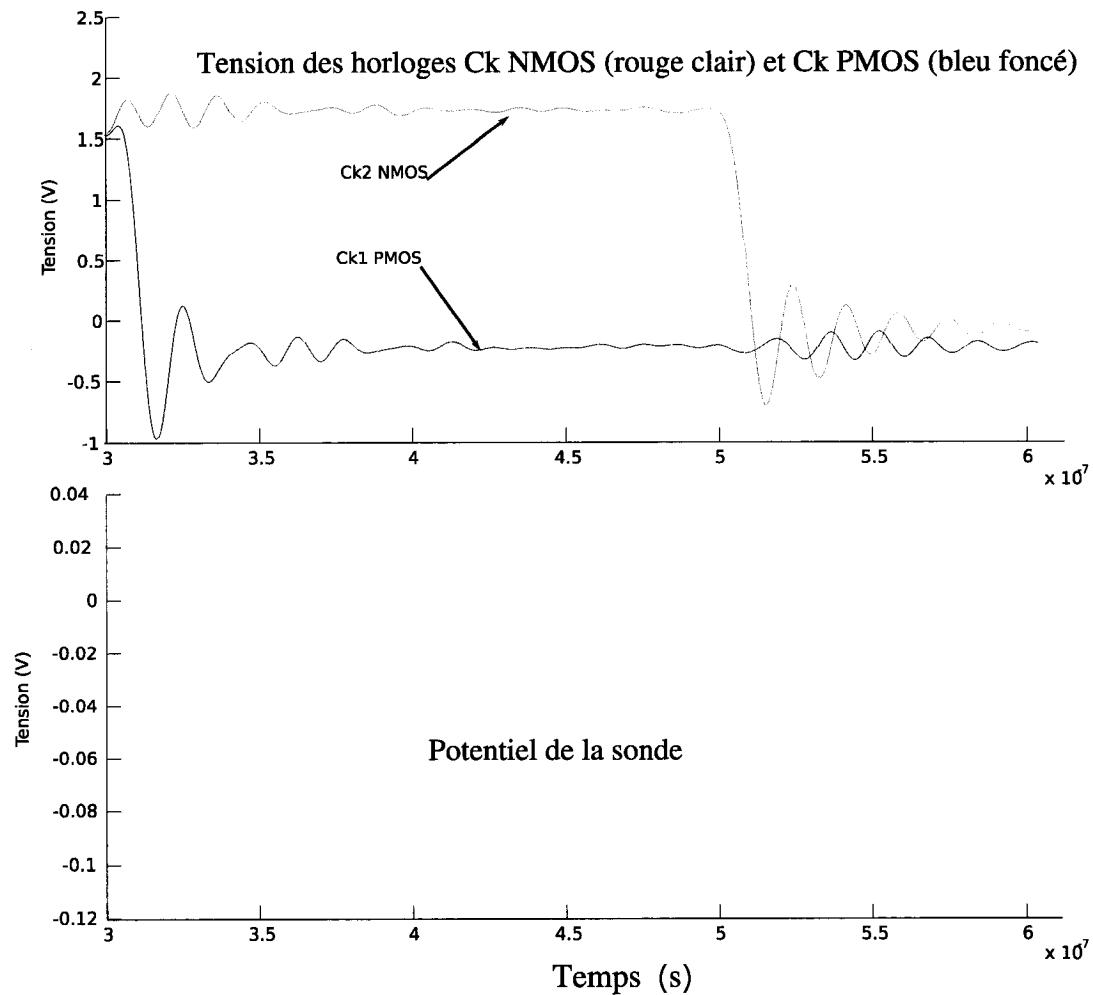

| FIG. 2.42 | Potentiel de la sonde . . . . .                                                                                                                                                                                                                                                                                                      | 101 |

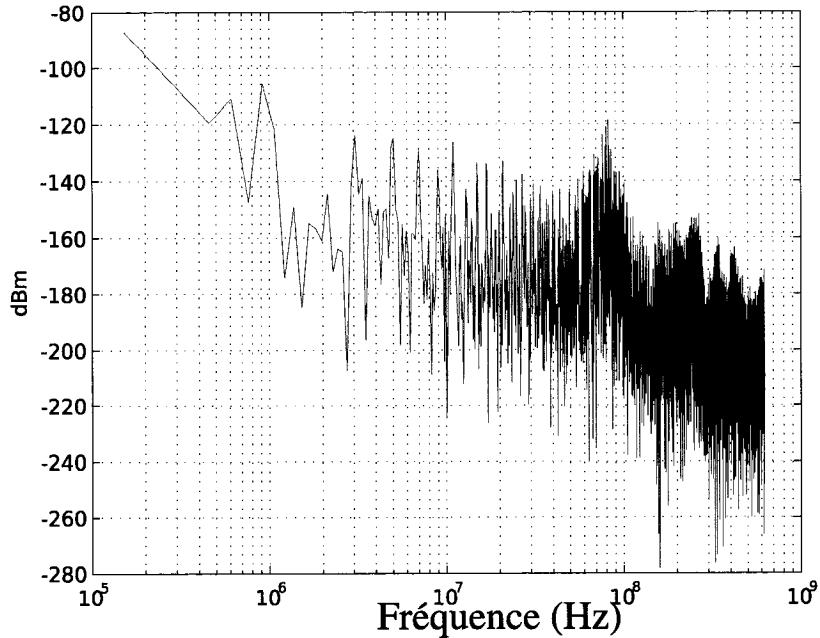

| FIG. 2.43 | Transformée de Fourier rapide du potentiel (FFT) de la sonde                                                                                                                                                                                                                                                                         | 102 |

| FIG. 3.1  | Montage optique . . . . .                                                                                                                                                                                                                                                                                                            | 106 |

| FIG. 3.2  | Schéma bloc du système permettant d'observer les modifications de la fréquence d'oscillation . . . . .                                                                                                                                                                                                                               | 108 |

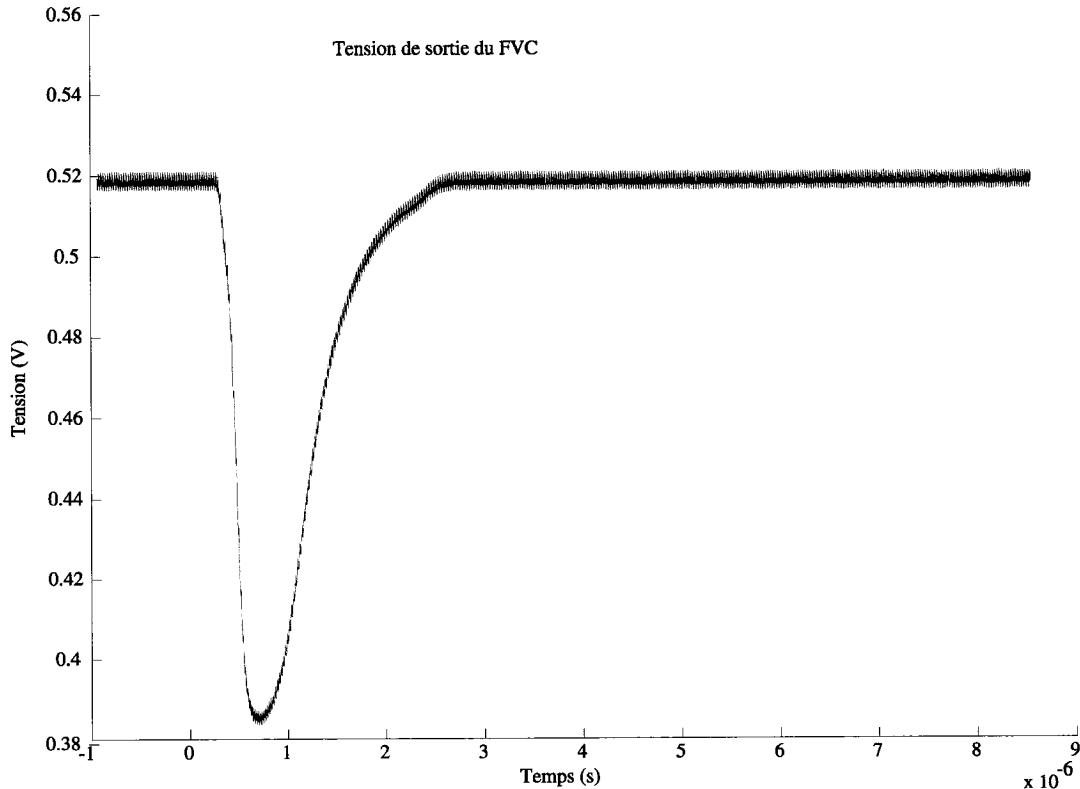

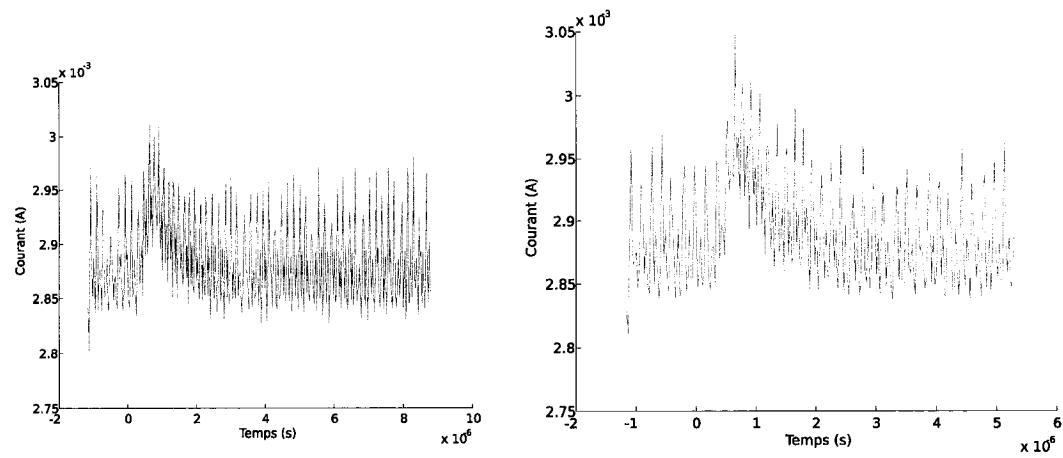

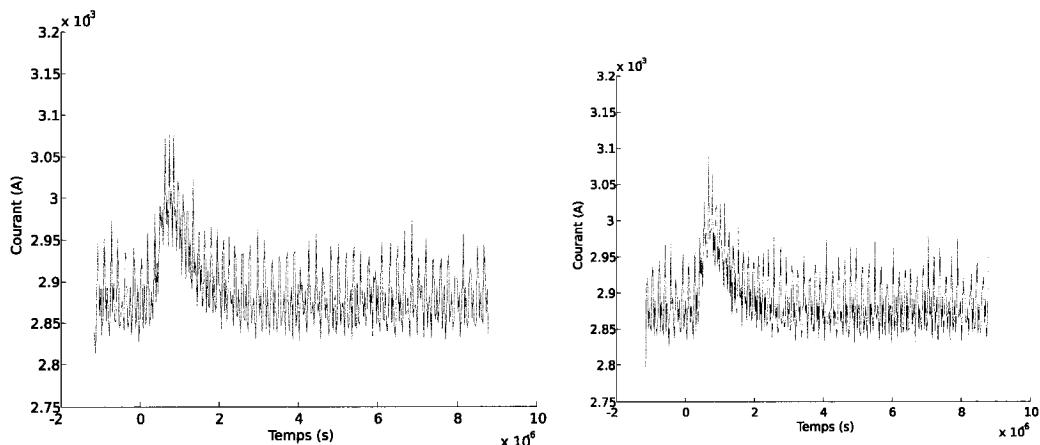

| FIG. 3.3  | Variation de la sortie du FVC pour une impulsion laser de durée 100 ns et de puissance 600 mW. . . . .                                                                                                                                                                                                                               | 110 |

| FIG. 3.4  | Variation relative de la sortie maximale du FVC en fonction de la puissance de l'impulsion laser de durée 100 ns . . . . .                                                                                                                                                                                                           | 112 |

|           |                                                                                                                                                                                   |     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| FIG. 3.5  | Variation relative de la sortie maximale du FVC en fonction de la puissance de l'impulsion laser de durée 100 ns . . . . .                                                        | 113 |

| FIG. 3.6  | Variation relative de la sortie maximale du FVC en fonction de la puissance de l'impulsion laser de durée 100 ns . . . . .                                                        | 114 |

| FIG. 3.7  | Variation relative de la sortie maximale du FVC en fonction de la puissance de l'impulsion laser de durée 100 ns . . . . .                                                        | 115 |

| FIG. 3.8  | Variation du courant entrant dans l'alimentation VDD pour des impulsions laser d'une durée de 100 ns et de puissance variant de 600 mW à 1600 mW. . . . .                         | 117 |

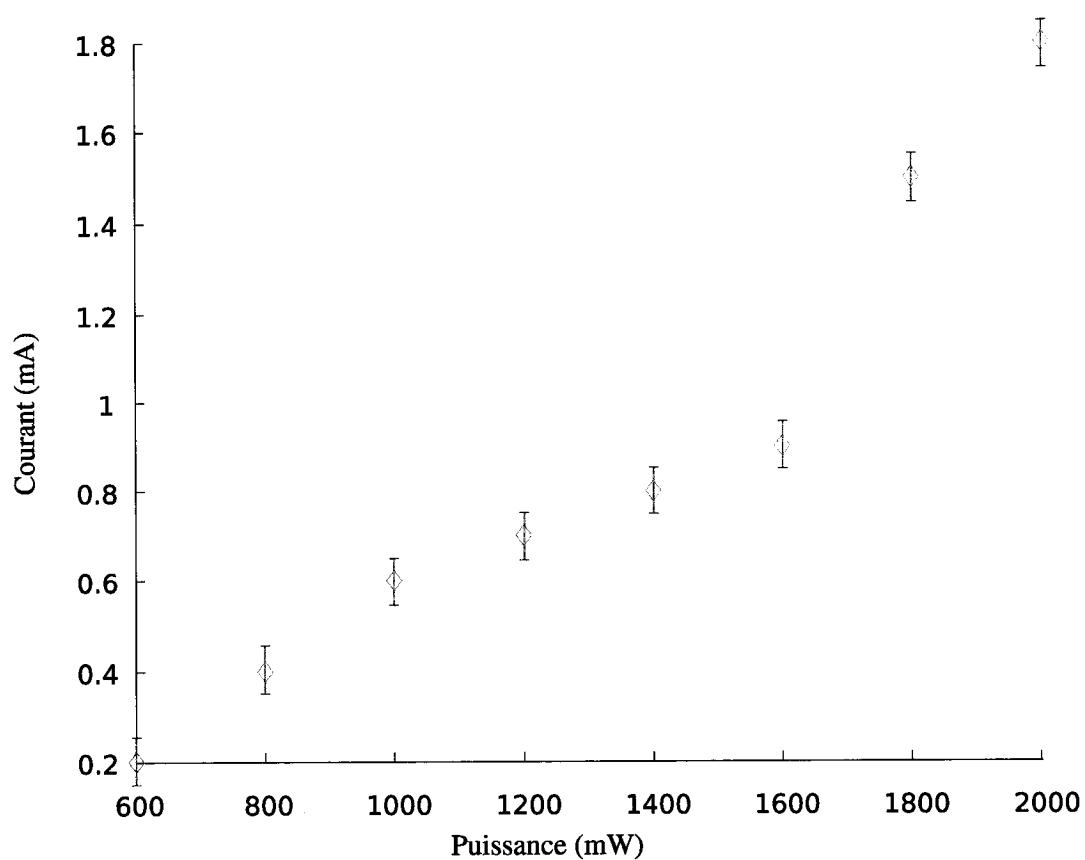

| FIG. 3.9  | Courant collecté par les alimentations en fonction de la puissance du laser . . . . .                                                                                             | 118 |

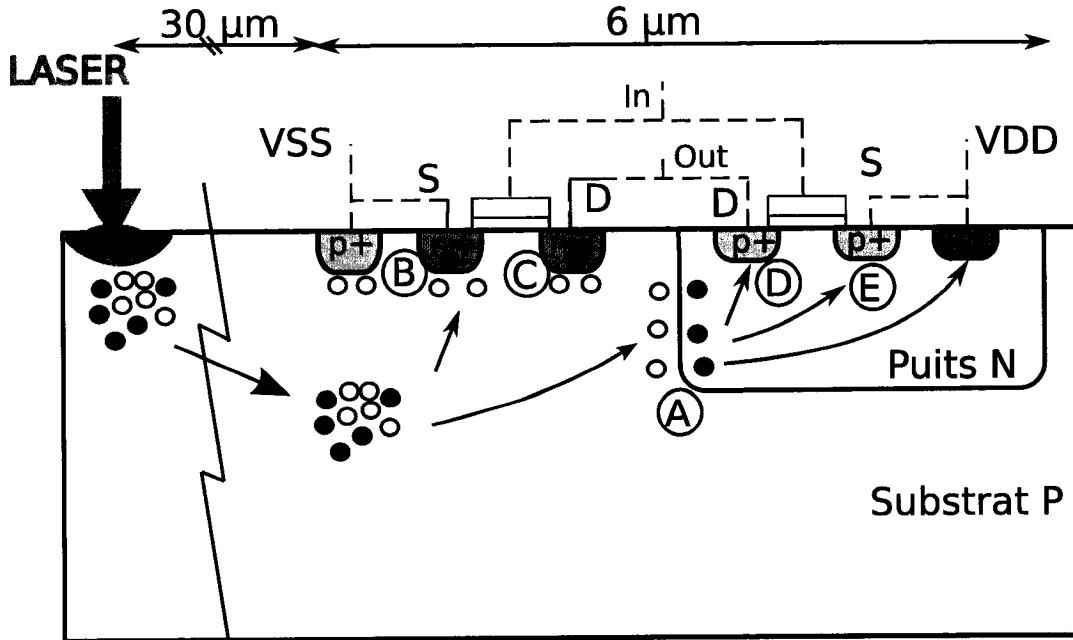

| FIG. 3.10 | Injection de charges par le laser et migration des charges . .                                                                                                                    | 122 |

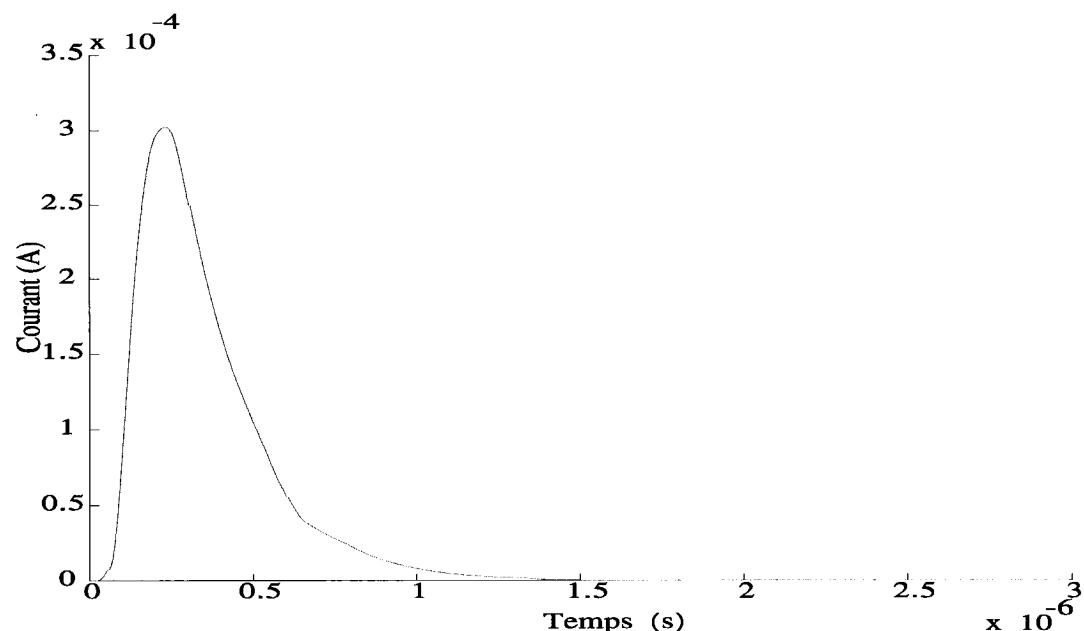

| FIG. 3.11 | Courants entrant dans le puits N pour différentes puissances laser simulées (tiré de (Boulais et al., 2007)) . . . . .                                                            | 125 |

| FIG. 3.12 | Modèle personnalisé du substrat . . . . .                                                                                                                                         | 127 |

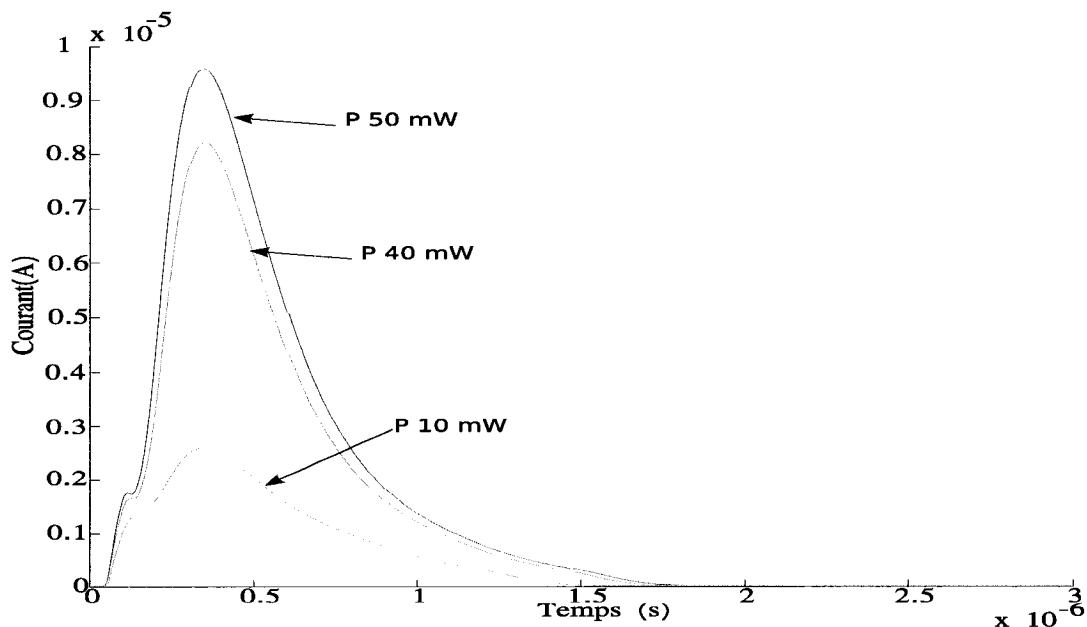

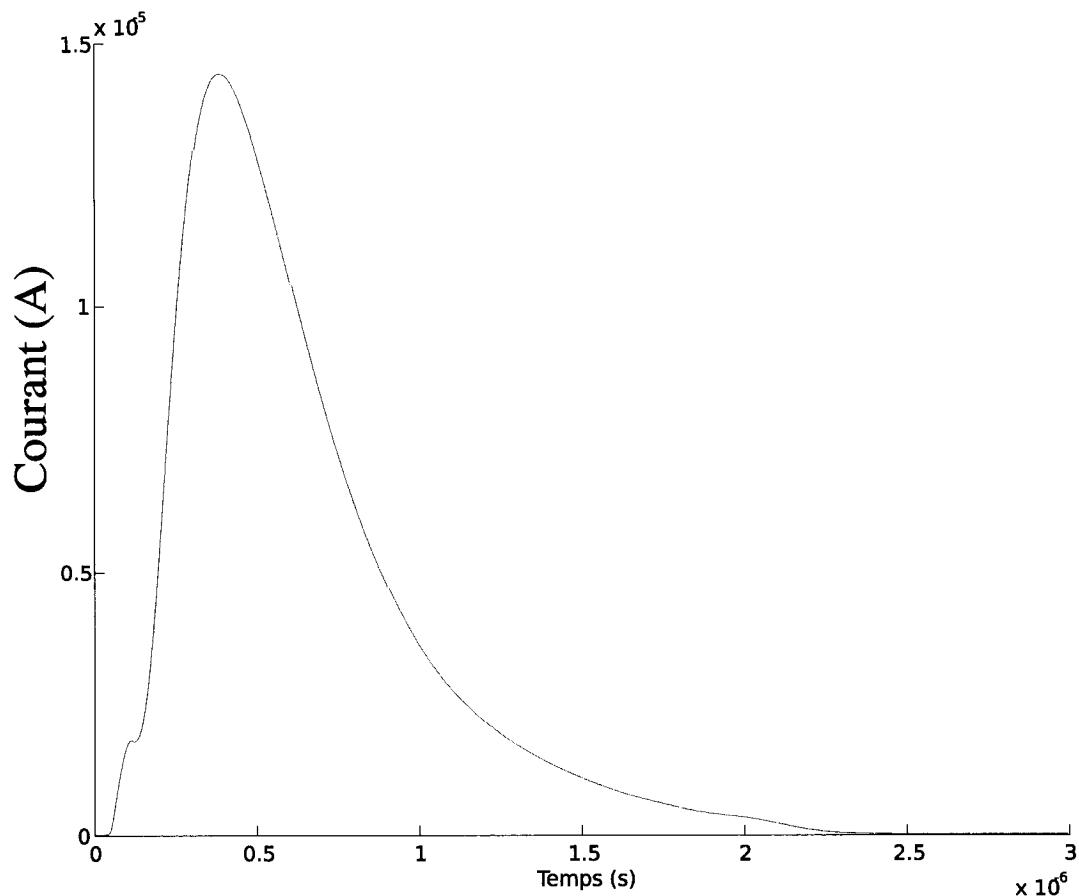

| FIG. 3.13 | Courant injecté dans le puits N pour une puissance laser simulée de 50 mW . . . . .                                                                                               | 129 |

| FIG. 3.14 | Simulation de la tension du FVC soumis à une impulsion laser associé au courant injecté de la figure 3.13 . . . . .                                                               | 130 |

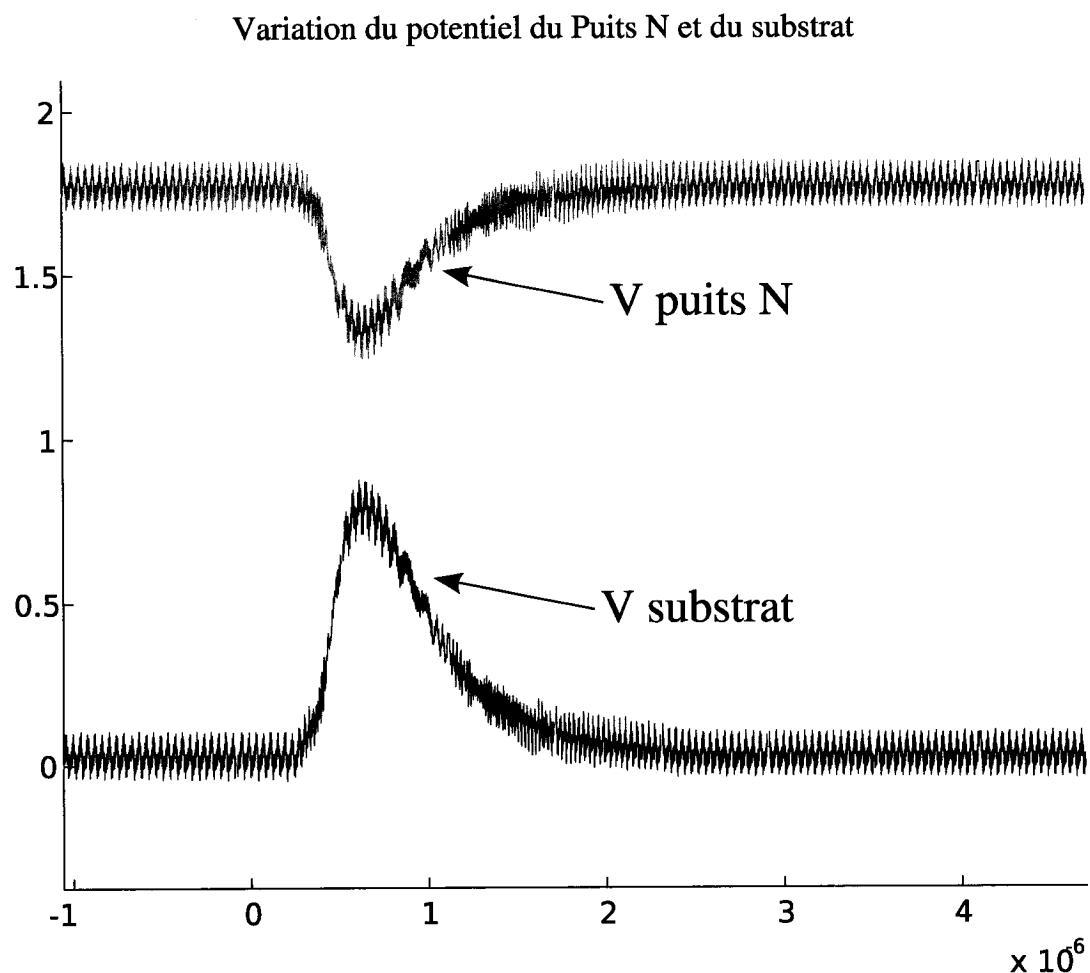

| FIG. 3.15 | Variation des potentiels du substrat et du puits N pour une injection de courant correspondant à une puissance laser de $P=50$ mW avec $\beta = 0.2$ et $\tau = 150$ ns . . . . . | 132 |

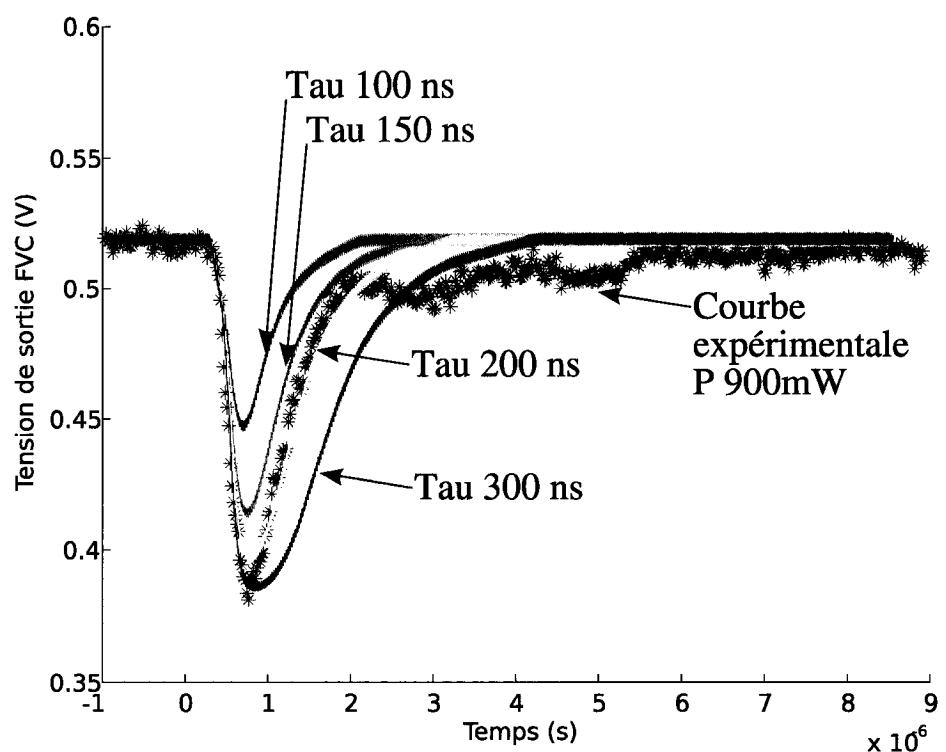

| FIG. 3.16 | Influence du paramètre $\tau$ sur la variation du FVC, $P=50$ mW et $\beta = 0.15$ . . . . .                                                                                      | 134 |

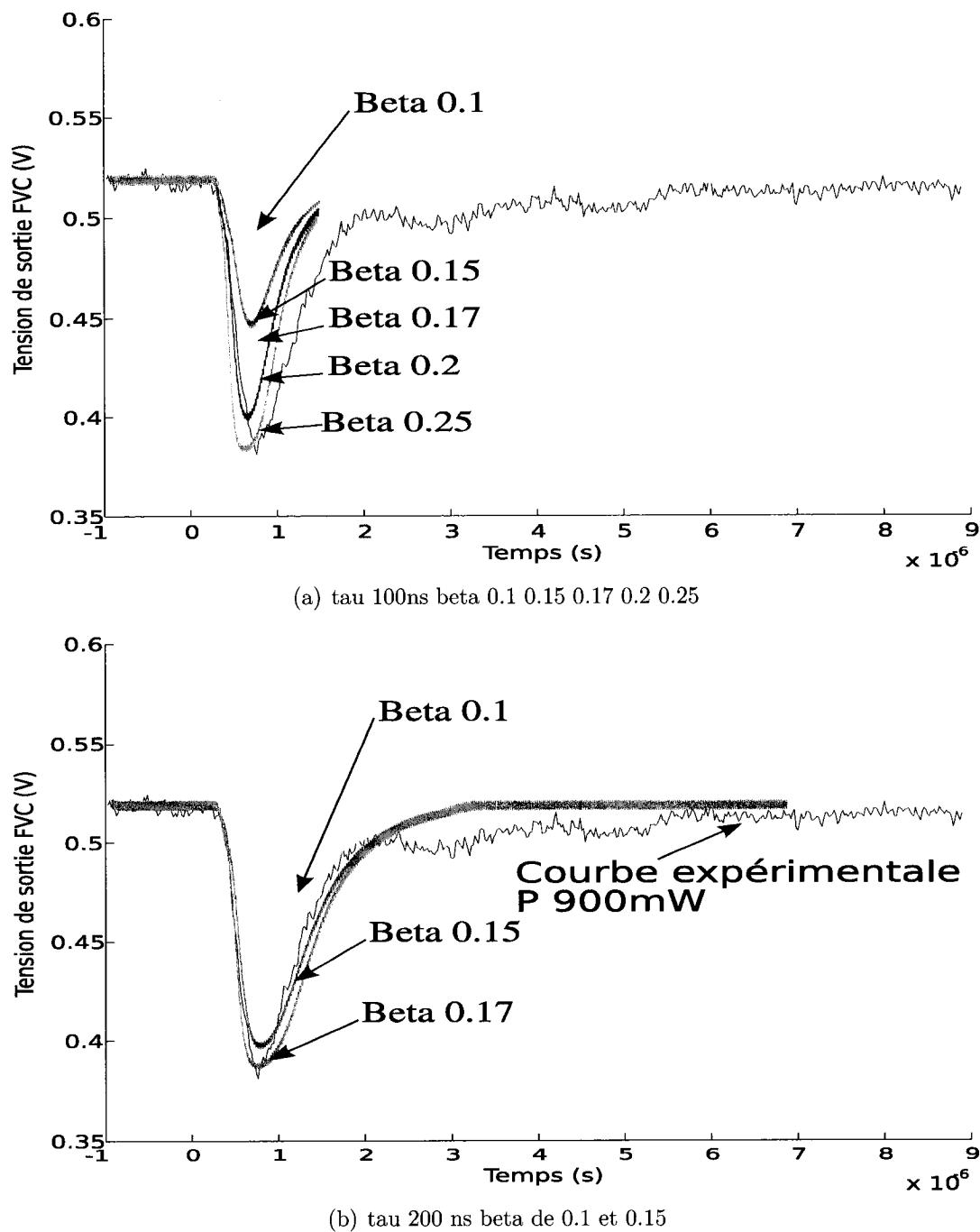

| FIG. 3.17 | Influence du paramètre $\beta$ sur la variation du FVC, $P=50$ mW                                                                                                                 | 136 |

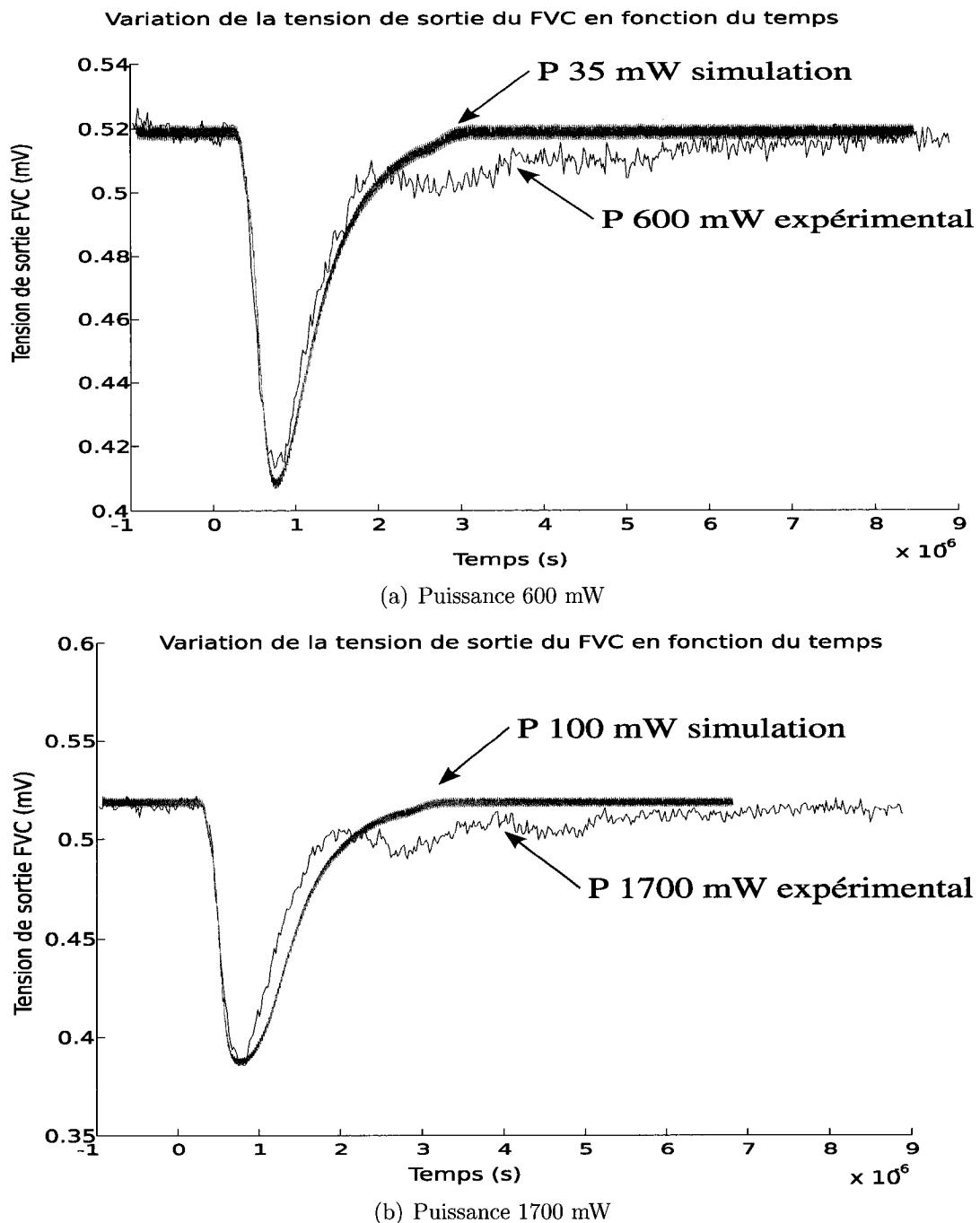

| FIG. 3.18 | Robustesse du modèle pour deux puissances . . . . .                                                                                                                               | 138 |

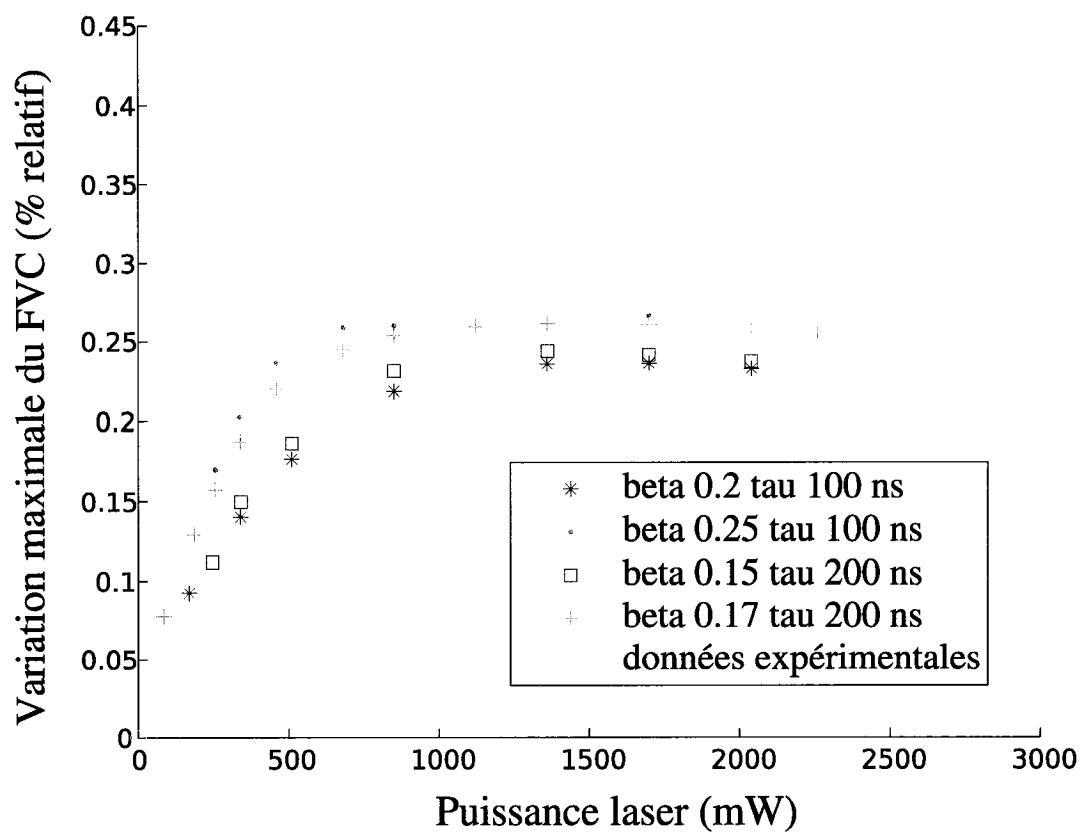

| FIG. 3.19 | Variation du maximum de variation du FVC en fonction de la puissance : simulation versus expérimentation . . . . .                                                                | 139 |

|           |                                                                                              |     |

|-----------|----------------------------------------------------------------------------------------------|-----|

| FIG. 3.20 | Structure géométrique responsable des multiple réflexions (figure non à l'échelle) . . . . . | 140 |

| FIG. 3.21 | Courant collecté par l'alimentation VDD obtenu par simulation . . . . .                      | 143 |

## LISTE DES NOTATIONS ET DES SYMBOLES

---

|              |                                          |

|--------------|------------------------------------------|

| <i>AC</i>    | Alternative Current                      |

| <i>BEM</i>   | Boundary Element Modelisation            |

| <i>CMOS</i>  | Complementary Metal Oxyde Semiconductor  |

| <i>DC</i>    | Direct Current                           |

| $\epsilon_0$ | Permitivité du vide                      |

| <i>FD</i>    | Frequency Divider                        |

| <i>FEM</i>   | Finite Element Modelisation              |

| <i>FVC</i>   | Frequency Voltage Converter              |

| <i>GRM</i>   | Groupe de Recherche en Microélectronique |

| <i>LDR</i>   | Laser Diffused Resistor                  |

| $\mu_n$      | Mobilité d'un électron                   |

| $\mu_p$      | Mobilité d'un trou                       |

| $n$          | Concentration des porteurs : électrons   |

| $p$          | Concentration des porteurs : trous       |

| $\rho$       | Résistivité du substrat                  |

| <i>SCA</i>   | Substrate Coupling Analysis              |

---

**LISTE DES ANNEXES**

|           |                              |     |

|-----------|------------------------------|-----|

| ANNEXE I  | ARTICLE ISCAS 2007 . . . . . | 154 |

| ANNEXE II | PCB . . . . .                | 158 |

## INTRODUCTION

Depuis une dizaine d'années, les applications de la microélectronique ont pris une part de plus en plus importante dans notre vie de tous les jours, que ce soit dans nos modes de communications avec les téléphones cellulaires, dans notre vie professionnelle avec les ordinateurs portables, ou bien plus encore dans nos divertissements notamment à travers les appareils photos numériques, les baladeurs MP3. Ces appareils, devenus des biens de consommation à part entière, se sont miniaturisés et complexifiés dans le même temps, intégrant désormais de nombreuses fonctionnalités autrefois propres à plusieurs appareils différents. C'est ainsi que les téléphones cellulaires ne permettent aujourd'hui plus seulement de téléphoner, mais l'utilisateur peut également écouter de la musique, regarder la télévision, se connecter à l'internet. Ces véritables ordinateurs portatifs deviennent de plus en plus puissants sans pour autant perdre en autonomie.

La course effrénée à la réduction d'échelle technologique qui en permet le développement et la pluridisciplinarité des compétences requises par l'industrie de la microélectronique impose de combiner des spécialités qui étaient autrefois bien distinctes. Avec le développement des Systèmes sur Puces ou "Systems On Chips" (SoC), l'industrie de la microélectronique a su relever le défi de la conception de systèmes complexes et pluridisciplinaires, ainsi que leur intégration sur le même substrat. En effet, une puce de téléphone portable peut regrouper des circuits d'horizons différents autrefois indépendants, tels que des circuits numériques, des convertisseurs de puissance, des circuits Radio-Fréquence (RF) et des circuits analogiques de haute précision. Cependant la sensibilité au bruit de tous ces circuits n'est pas la même, tout comme le niveau de bruit injecté. En effet les circuits analogiques nécessitent pour fonctionner correctement un niveau de bruit très faible en comparaison aux autres types de circuits et donc leur intégration au cœur d'un système peut poser

des problèmes d'intégrité des signaux. En outre, les circuits numériques contribuent à la création de bruit dans le substrat du fait des nombreuses portes qui commutent lors du fonctionnement. Les circuits analogiques de haute précision, tout aussi bien que les circuits RF oscillant à une fréquence qui doit être stable sont très sensibles aux agressions produites par un circuit numérique. Ce type d'agression a déjà largement été couvert par la littérature (Donnay and Gielen, 2003), cependant d'autres types d'agresseurs sont apparus du fait de l'intégration toujours plus grande des systèmes, mais également du fait de l'utilisation de nouvelles techniques de calibration par laser des circuits analogiques de haute précision. En plus des puces classiques intégrant déjà des circuits analogiques et une partie RF, l'utilisation de convertisseurs de puissance, également implantés sur la même puce, est apparue, afin de minimiser les pertes d'énergie. Du fait des forts courants mis en jeu et des larges variations de tensions, le bruit généré par ces modules de puissance peut tout aussi bien perturber des circuits analogiques que numériques. D'autre part, l'utilisation de dispositifs ajustables par laser après fabrication (Meunier et al., 2001), palliant aux mésappariements dus aux variations de procédés lors de la fabrication a permis d'atteindre des niveaux de précision plus élevés, élément critique pour les circuits de haute performance. Cependant l'utilisation d'un laser pour ajuster des résistances diffusées par laser injecte de nombreuses charges dans le substrat qui vont migrer vers les circuits sensibles présents dans le voisinage. Ces charges peuvent alors perturber le fonctionnement des circuits.

Tous ces circuits et ces dispositifs implantés sur une même puce ont un point en commun : ils partagent le même substrat, lieu possible de transport du bruit dans toute la puce, que ce bruit soit généré par un convertisseur de puissance ou un laser. L'enjeu principal est donc de modéliser avec précision et exactitude le substrat pour pouvoir estimer très tôt dans la conception le niveau de bruit injecté afin de développer des protections adéquates. Il est donc nécessaire d'analyser,

de comprendre les phénomènes de création et de transport du bruit, ainsi que l'interaction avec les circuits sensibles. Les travaux de recherche décrits dans ce mémoire trouvent leur source dans les besoins de la société LTRIM qui devait caractériser et maîtriser le bruit injecté par divers dispositifs (convertisseurs de puissance, dispositifs ajustables par laser).

*Objectifs :*

Les objectifs de cette recherche sont multiples. Il s'agit tout d'abord de comprendre et de modéliser les phénomènes mis en cause lors de l'injection de bruit dans le substrat, que ce bruit soit généré par un convertisseur de puissance ou par l'injection de charges suite à une calibration par laser. Deux types de modélisation ont été effectuées au cours de ce travail. Une première étude concerne l'impact de l'injection de charges par un laser focalisé sur un circuit sensible : un oscillateur en anneau. La deuxième étude traite des phénomènes d'injection de bruit par un convertisseur de puissance DC-DC, lors de son fonctionnement. Ces deux études s'appuient sur une modélisation précise et adaptée du substrat. Fort de ces modélisations, nous pourrons simuler le comportement des circuits et observer le bruit généré et leur sensibilité face au bruit. L'objectif de ces simulations est double, avoir une bonne compréhension des phénomènes pour concevoir des circuits de test adaptés, et confronter les simulations avec les observations expérimentales. En dernier lieu, ces études permettront de développer des protections adéquates afin de réduire le niveau de bruit dans le substrat. L'efficacité de ces protections pourra directement être évaluée en simulation, raccourcissant ainsi le temps de développement et de conception des circuits.

*Organisation du mémoire :*

Le mémoire s'articule autour de deux études principales : une analyse des perturbations induites par un laser, et l'étude du bruit injecté par un convertisseur DC-DC, l'idée directrice et fondatrice étant la modélisation du substrat. L'ensemble du travail s'organise comme suit.

- Le premier chapitre suivant l'introduction positionne le projet dans la littérature. Une revue de littérature sur ce qui a été fait en matière de couplage au substrat, de modélisation du substrat et de l'injection de bruit par un laser ou un convertisseur DC-DC est exposée dans ce chapitre.

- Le deuxième chapitre expose l'étude du bruit injecté par un convertisseur DC-DC. Une modélisation électrique des phénomènes est présentée ainsi que des résultats expérimentaux venant confirmer les simulations.

- Le troisième chapitre consiste en une modélisation électrique des phénomènes d'interactions entre les charges induites par le laser et un circuit oscillant. Des comparaisons entre les simulations obtenues et les résultats expérimentaux produits sont apportés pour justifier les modèles avancés.

- Enfin le dernier chapitre est une conclusion dressant le bilan du travail accompli.

## CHAPITRE 1

### REVUE DE LA LITTÉRATURE : BRUIT DE SUBSTRAT ET MODÉLISATION

Les dernières années ont été marquées par l'arrivée d'une multitude de circuits mixtes, systèmes comportant à la fois un design numérique et un design analogique. Leur conception est devenue de plus en plus complexe, car ils sont implantés sur des technologies de fabrication avancées. Caractériser le couplage parasite au substrat devient donc un enjeu principal dans la réalisation de circuits opérationnels, car estimer correctement le comportement réel du circuit permet d'anticiper les problèmes d'interférences liés à son utilisation et donc de raccourcir le cycle de développement et le temps requis pour la mise en marché du produit. Les réductions d'échelle toujours en vigueur (de 180 nm jusqu'à 45 nm) auxquelles sont constamment soumises les différentes technologies de fabrication proposées (CMOS pour Complementary Metal Oxyde Semiconductor, bipolaire, RF, mixte) complexifient grandement l'identification des sources de bruit et la modélisation du substrat. L'industrie de la microélectronique s'est alors dotée d'outils adaptés pour extraire les paramètres parasites du substrat, pour pouvoir estimer les perturbations induites par le bruit de substrat et développer des protections assurant l'intégrité des signaux.

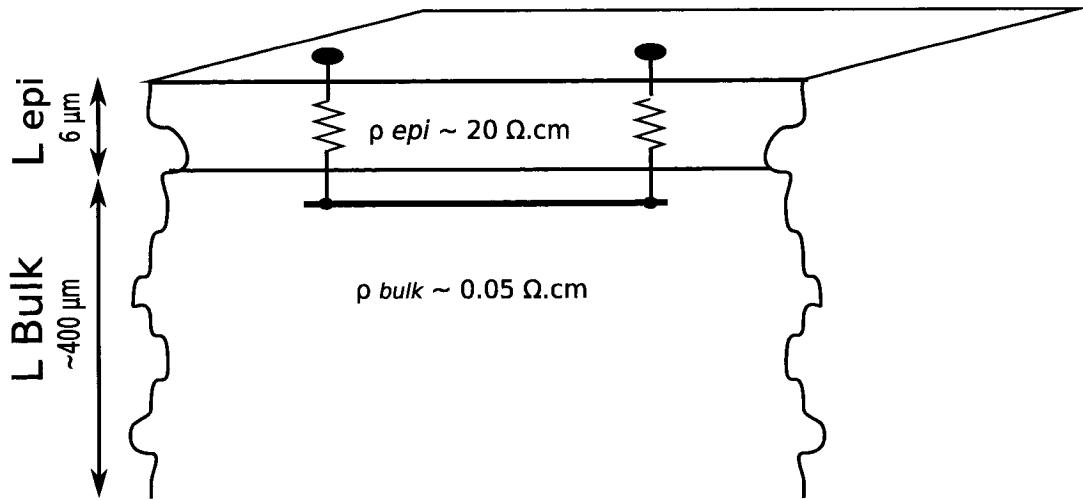

FIG. 1.1 Structure d'un substrat de type épitaxial

## 1.1 Caractérisation du substrat

### 1.1.1 Type de substrat

La fabrication de circuits intégrés (CI) est un processus long et coûteux, où une succession d'étapes est nécessaire pour obtenir le comportement électrique voulu. Le support initial, ou substrat (bulk en anglais), est le silicium, celui-ci peut être légèrement dopé (i.e. concentration de dopage de l'ordre de  $10^{15} \text{ cm}^{-3}$  d'où une résistivité de l'ordre de 10 à 50  $\Omega \cdot \text{cm}$ ) ou bien dit de type épitaxial, comme exposé à la figure 1.1 (i.e. une couche légèrement dopée au dessus d'un silicium fortement dopé de concentration environ de  $10^{19} \text{ cm}^{-3}$ ). Ce dernier est plus largement utilisé en conception numérique pour sa capacité à limiter les effets de thyristor parasite aussi appelé latchup. Le type de substrat le plus utilisé pour les circuits mixtes comportant une partie analogique et une partie numérique est un substrat légèrement dopé P.

Ce substrat subit ensuite de nombreuses altérations par des dopages successifs,

la formation de tranchées profondes isolantes et la croissance d'oxyde pour isoler entre elles certaines régions dopées du circuit. Le résultat de toutes ces étapes est un substrat où sont implantés de nombreuses jonctions, de nombreux puits dopés N (n-well en anglais) et de nombreux puits profonds dopés N (appelés en anglais deep n-well). Cette complexité s'est accrue davantage avec l'arrivée de technologies de fabrication à des échelles submicroniques (130 nm, 90 nm), où les règles de fabrication encore plus rigoureuses imposent de nombreuses tranchées d'isolation. Il est donc devenu difficile et coûteux d'obtenir un profil de dopage précis du substrat pour toute une puce, car il dépend à la fois du dessin des masques et des étapes de procédés utilisées pour la fabrication. En effet, le dessin de masque donne des informations sur la position des différentes zones dopées et des tranchées d'isolations dans le domaine (x,y). De plus, le profil de dopage sur l'axe des (z) est déterminé non seulement par le dessin des masques mais également par le processus de fabrication. Les concentrations des dopages et la profondeur des différentes zones dopées diffèrent selon le type de technologie utilisée (mixte, RF, analogique, numérique), la fonderie (TSMC, IBM ...), les masques utilisés, le type de gaufre utilisé (wafer).

### 1.1.2 Modélisation physique du substrat

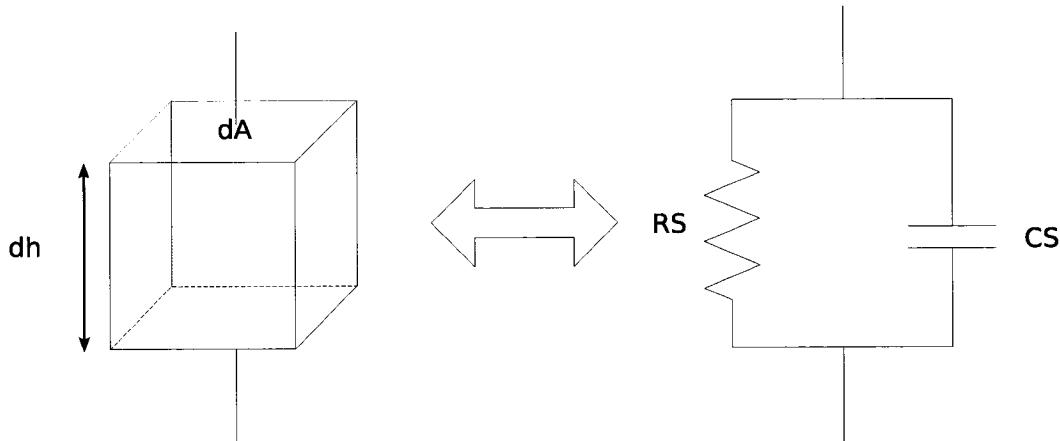

#### Modèle d'un cube de substrat

Considérons un cube de substrat de côté égal à  $dh$  et dont l'aire  $dA$  d'une face est égale à  $dh^2$ . En considérant les mobilités des porteurs comme constantes par rapport au champ électrique (hypothèse valide lors d'un fonctionnement normal), le cube de substrat peut être modélisé à l'aide d'une résistance et d'une capacité en parallèle (Cf. Figure 1.2).

Dans un semi-conducteur, la résistivité peut s'écrire  $\rho = 1/[q(p\mu_p + n\mu_n)]$ , où q est

FIG. 1.2 Modélisation d'un cube de substrat

la charge de l'électron, et  $\mu_n$  et  $\mu_p$  les mobilités respectives des porteurs électrons (n) et des trous (p), et n et p les concentrations de ces porteurs. La résistance du cube de substrat s'écrit donc  $R = \rho dh/dA$ . Quant à l'effet capacitif de ce cube, il est obtenu à partir de la constante diélectrique du silicium  $\epsilon_s$ . La capacité du cube est alors égale à  $C_s = (\epsilon_s dA)/dh$  avec  $\epsilon_s = 1.035 \text{ pF/cm}$ . En plus de la modélisation du substrat P, il faut également tenir compte des jonctions PN, des puits N et des puits N profonds. Une modélisation précise de ces composants pour l'ensemble du substrat peut s'avérer fastidieuse et coûteuse. Dans un fonctionnement "normal", i.e. pour des plages de tension en accord avec la technologie, une modélisation si précise s'avère inutile et des simplifications sont alors appliquées.

L'ajout d'hypothèses simplificatrices est nécessaire pour simplifier grandement la caractérisation électrique du substrat (Donnay and Gielen, 2003). Dans un fonctionnement "normal", ces hypothèses sont justifiées :

- (A) **Les jonctions puits substrat sont polarisées en inverse** : si cette hypothèse est violée, la diode est en polarisation directe, ce qui entraîne un court-circuit entre les alimentations. Lors d'un fonctionnement "normal" les puits et le substrat sont correctement polarisés et les tensions sont stables. Il est donc

évident de considérer la diode en polarisation inverse. La modélisation de jonction PN par sa capacité de jonction en polarisation inverse s'impose tout naturellement. Ce modèle capacitif est beaucoup moins coûteux en temps de calcul que le modèle d'une diode.

- **(B) Aucun phénomène de latchup n'apparaît durant le fonctionnement :** ce phénomène et son activation sont maintenant bien connus (Troutman, 1986) et des règles de design strictes permettent de les éviter.

- **(C) Le couplage inductif est négligé :** cette hypothèse est justifiée par le fait que la longueur d'onde maximale du champ magnétique est bien supérieure aux dimensions de la puce.

- **(D) Fréquence de coupure :** considérons le modèle capacitif et résistif du cube de substrat vu plus haut. La constante de temps de ce morceau est alors  $T_{coupure} = 1/(2\pi f_{coupure}) = RC$ . Pour des fréquences basses (inférieures à  $f_{coupure}$ ), l'effet résistif est prédominant, tandis que pour des fréquences élevées, l'effet capacitif domine. Ainsi selon la bande passante d'étude du circuit, on peut simplifier le modèle du substrat.

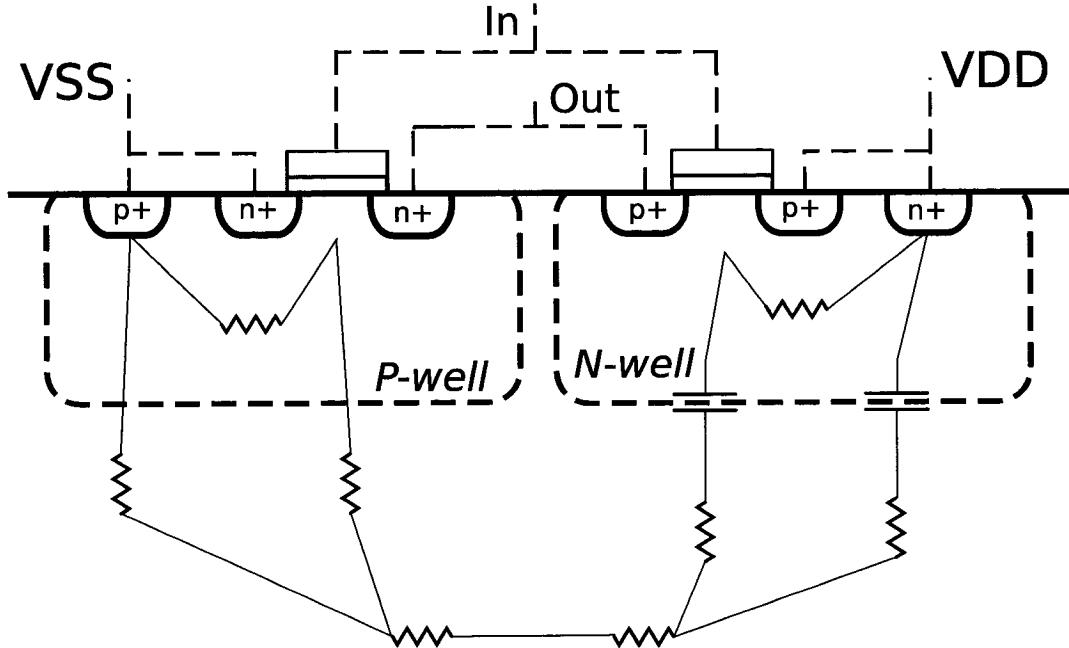

### 1.1.3 Modèle capacitif et résistif du substrat

A partir de toutes ces hypothèses et des modèles des composants du substrat, une représentation du substrat peut alors être élaborée. Cette modélisation s'apparente alors à un réseau résistif et capacitif tenant compte à la fois des dimensions physiques du dessin des masques et de la localisation des différents éléments du circuit. Le substrat peut se modéliser par une toile résistive et capacitive reliant les différentes parties de la puce. La figure 1.3 donne un exemple simple de la modélisation du substrat pour un inverseur.

Selon le type de substrat utilisé (épitaxial ou légèrement dopé), la modélisation

FIG. 1.3 Modélisation du substrat pour un inverseur CMOS dans le cas d'un substrat faiblement dopé P

est bien sûr différente, mais surtout ce sont les chemins utilisés par le bruit pour se propager qui diffèrent (Yeung et al., 1997). Pour un substrat légèrement dopé, la résistivité du lien entre deux contacts augmente linéairement avec la distance les séparant. Cela est vrai pour une distance entre les deux contacts supérieure à l'épaisseur de la gaufre. Pour des distances inférieures, le comportement n'est pas linéaire à cause des effets de bords, et un maillage plus précis est nécessaire pour extraire l'impédance entre deux contacts (Donnay and Gielen, 2003). Pour un substrat avec une couche épitaxiale, la couche inférieure du substrat est considérée comme une équipotentielle du fait de sa légère résistivité (0.05 Ohms.cm). Ainsi d'après (Donnay and Gielen, 2003), pour des distances inférieures à quatre fois l'épaisseur de la couche épitaxiale ( $L_{epi}$ ), le modèle résistif simple est exposé à la figure 1.4. Une grande partie du bruit passe par la résistance  $R_a$  car la résistivité de ce chemin est inférieure à celle de l'autre chemin possible ( $2.R_S$ ). Lorsque la

FIG. 1.4 Model résistif simple entre deux contacts proches (distance  $< 4 \text{ Lepi}$ ) pour un substrat épitaxial

distance entre les deux contacts augmente, la résistance  $R_a$  augmente de façon linéaire. Ainsi le chemin le moins résistif est celui formé par les deux résistances  $R_s$  (Cf. figure 1.5). En conclusion, le substrat avec une couche épitaxiale isole très mal du bruit les circuits sensibles des sources de bruit pourtant éloignées. Il est donc généralement préférable pour les circuits mixtes d'utiliser un substrat légèrement dopé.

## 1.2 Source "classique" du bruit de substrat

Dans les parties précédentes, nous avons mis en évidence le rôle joué par le substrat comme support de transmission pour le bruit. Cependant deux autres mécanismes étroitement liés au substrat sont tout aussi importants dans le processus d'interférences entre les circuits : la création des interférences et leur réception par les circuits. Les mécanismes de création de bruit vont être rappelés dans cette partie, tout comme l'impact de ces perturbations sur les circuits sensibles.

FIG. 1.5 Modèle résistif simple pour deux contacts éloignés (distance  $> 4$   $L_{\text{epi}}$ ) pour un substrat épitaxial

De nombreuses études ont répertorié et caractérisé les mécanismes injectant des perturbations dans le substrat (Charbon et al., 2001). Ces phénomènes induisent dans le substrat des courants qui ont été pris en compte dans les modèles classiques lors de l'analyse du bruit.

### 1.2.1 Ionisation par impact

De nombreux efforts de modélisation ont été accomplis pour décrire correctement ce phénomène (Briaire and Krisch, 2000). L'ionisation par impact est la création de paires électron-trou par dissipation de l'excès d'énergie des électrons «chauds». Ceux ci sont créés dans le canal des transistors en saturation lorsque le champ électrique au niveau de la zone de pincement du canal (au Drain) dépasse un certain seuil. Les trous créés lors de la désexcitation des porteurs chauds sont collectés par le substrat et contribuent au bruit de substrat par couplage résistif. Ce courant d'ionisation est fortement lié au champ électrique présent dans le canal. Des transistors à canal court présentent des champs électriques plus élevés, ainsi le développement

des technologies submicroniques pose de sérieux problèmes d'injection de bruit. En outre la modélisation de ces transistors à canal court est une chose plus complexe, rendant la modélisation du bruit injecté dans le substrat plus délicate. Du fait de leur isolation par le puits N, les transistors PMOS injectent moins de bruit dans le substrat que les NMOS.

### 1.2.2 Courant induit par des photons

Au phénomène d'ionisation par impact s'ajoute, dans une plus faible proportion, l'émission de photon lors de la désexcitation des électrons chauds (Toriumi et al., 1987) . Ces photons peuvent parcourir des centaines de  $\mu\text{m}$  avant d'être absorbés par le silicium et créer des paires électron-trou qui peuvent constituer une source de bruit.

### 1.2.3 Couplage capacitif

Lors du fonctionnement des circuits numériques, les portes réalisant les fonctions booléennes commutent au cours du temps. Les tensions aux bornes des transistors MOSFETs (Grille et Drain) alternent entre un état logique haut et bas. Par couplage capacitif au niveau des jonctions Drain/Substrat et Grille/Substrat, ces alternances de tension injectent du bruit dans le substrat. Les mêmes fluctuations de potentiels présentes aux bornes du transistor se retrouvent ensuite au niveau du substrat. Cette transmission dépend fortement des paramètres physiques du transistors et des fréquences de fonctionnement de ces transistors. Toutes ces dépendances sont incluses dans les modèles électriques du MOS : BSIM3v3 de Berkeley.

#### 1.2.4 Courant de fuite de la grille

Le courant de fuite au niveau du drain induit par la grille est un phénomène comparable à l'ionisation par impact qui se produit lorsqu'un champ électrique élevé est appliqué entre le drain et la grille (Chan et al., 1987). Ces conditions peuvent être réunies lorsque par exemple on applique au drain d'un transistor NMOS dont le canal est fermé ( $V_{GS} = 0$ ) une tension élevée (par exemple  $V_{DS} = VDD$ ). Une zone appauvrie, ou déplétée, est ainsi formée au niveau du recouvrement entre la grille et le drain. A partir d'un certain potentiel, la courbure de bande est suffisante pour entraîner le franchissement bande à bande des électrons de valence et par conséquent la création de paires électron-trou. Les trous migrent ensuite dans le substrat. Cependant ce phénomène injecte du bruit dans une proportion beaucoup plus faible que l'ionisation par impact.

#### 1.2.5 Courant de fuite de la diode

Les diodes polarisées en inverse des jonctions avec le substrat ( Source ou Drain avec le Substrat, Puits N avec le substrat) présentent un courant de fuite. Ce courant est dû à la génération thermique de paires électron-trou dans la zone de déplétion. Celles-ci sont ensuite expulsées hors de la jonction par le champ électrique : les trous sont injectés dans la région dopée P et les électrons sont inversement injectés dans la région dopée N.

#### 1.2.6 Bruit présent sur les alimentations

L'activité des portes lors du fonctionnement du circuit implique l'acheminement sur toute la puce d'un important courant. Ce courant d'alimentation présente de

nombreux pics, du fait de la consommation transitoire des portes lors de leurs commutations. La présence d'inductances sur ce large réseau de distribution de l'alimentation, dû principalement aux connexions reliant la puce au boîtier, génère de larges variations de tensions au niveau du substrat : "ground bounce", ou oscillation de la masse. En effet, l'inductance s'oppose aux variations brutales du courant en imposant une tension à ses bornes ( $V = L \frac{di}{dt}$ ). Ainsi, cette variation est répercutee directement sur le substrat par un couplage résistif au niveau de la masse VSS, ou bien par un couplage capacitif au niveau de la connexion à un puits N. En effet, l'alimentation positive VDD polarisant les puits N est également touchée par ces fluctuations. La variation des tensions d'alimentation est proportionnelle au ratio entre la somme des capacités commutantes sur la somme des capacités non commutantes (comprenant les capacités de découplage et les capacités d'entrées des portes qui ne commutent pas) (Badaroglu et al., 2006).

Dans (Badaroglu et al., 2006), une comparaison de ces différentes sources de bruit est réalisée. Les sources de bruit telles que l'ionisation par impact, le courant de fuite de la grille, le courant photo-induit peuvent être négligées par rapport au bruit injecté par les alimentations ou par couplage capacitif. Pour des circuits numériques dont le nombre de portes excèdent 1K, le bruit dû à l'activité sur les alimentations prédomine sur le bruit généré par couplage capacitif. Ceci lorsque le substrat est directement polarisé par la masse utilisée par la partie numérique. Lorsque le substrat est polarisé par une masse dédiée, l'injection de bruit par couplage capacitif devient primordiale. Par ailleurs, Baradoglu et al. se base sur la feuille de route divulguée par l'ITRS (ITRS, 2004) concernant les technologies futures afin d'estimer les prochaines sources de bruit dominantes auxquelles vont être confrontées les futures réductions d'échelle. Pour des technologies inférieures à 130 nm, les courants de fuite lorsque le transistor est dans son état fermé sont une source importante de bruit et limitent donc la course effrénée à la réduction des tensions d'alimen-

tations. Lorsque le substrat est polarisé directement avec la masse numérique, le bruit dû au couplage des alimentations avec le substrat devient le problème majeur. Ainsi, le ratio entre le courant dû au couplage par les alimentations et la tension d'alimentation est multiplié par 4.5 en passant de la technologie 90 nm à 22 nm.

### 1.3 Nouvelles sources de bruit :

#### 1.3.1 Convertisseur DC-DC : une nouvelle source de bruit

Les convertisseurs DC-DC sont largement utilisés au sein des circuits intégrés pour fournir, à partir des sources d'alimentations externes, un large éventail de faibles tensions d'alimentations avec un courant élevé au cœur des circuits (Choi et al., 2005). L'engouement récent pour des produits dits "nomades" (téléphones et ordinateurs portables, baladeurs MP3) exigeants en termes d'autonomie et de consommation de puissance a constraint les concepteurs à concevoir des convertisseurs de tension d'une efficacité croissante afin d'augmenter l'autonomie des produits (Kursun et al., 2003). Par ailleurs, le développement des Systèmes sur Puces (SoCs) intégrant toujours plus de fonctionnalités et de plus en plus complexes s'est vu confronté aux problèmes de pertes de puissance (Kursun et al., 2004; Kursun et al., 2003). En effet, de forts courants d'alimentation sont nécessaires pour subvenir aux besoins des nombreuses portes présentes dans les SoCs ou bien pour satisfaire la gourmandise des microprocesseurs quant aux courants dynamiques demandés en pleine charge. Ces courants doivent traverser de nombreux composants parasites présents sur la carte électronique qui permettent de relier les sources d'alimentation aux circuits de la puce (Kursun et al., 2003). Tous ces composants dissipent beaucoup de puissance lorsqu'ils sont réalisés sous forme discrète, et la minimisation des pertes qui y sont associées est primordiale et passe nécessairement par

leur intégration sur la puce (Kursun et al., 2003). Les éléments parasites sont en effet réduits grâce à la miniaturisation et une intégration plus dense. Par souci d'efficacité, les convertisseurs ont été directement implantés sur le SoC. Cette intégration est devenue un élément crucial pour lutter contre les pertes de puissance et améliorer l'autonomie des appareils mobiles. Cependant l'intégration de ces convertisseurs sur le même substrat que des circuits sensibles tels que le sont les parties analogiques ou RF pose de nombreux problèmes en terme d'intégrité des signaux et donc de dégradation des performances. Considérons par exemple un Convertisseur Numérique Analogique (DAC) de 10 bits, celui-ci a besoin pour fonctionner sans erreur d'un niveau de bruit sur ses signaux inférieur au pas de quantification de  $1/2^{10}V$  soit environ 1.75 mV pour un circuit alimenté à 1.8 V. Ainsi une modification de plus de 2 mV de la tension du substrat qui est prise comme la référence stable pour la partie analogique peut avoir des conséquences désastreuses sur le fonctionnement du DAC. Peu d'études traitent de l'injection de bruit dans le substrat par un convertisseur DC-DC. Dans (Vinella and Antonicelli, 2006), une première approche à l'aide de logiciels commerciaux (voir 1.5.2) a évalué ce bruit et l'efficacité de certaines protections comme des anneaux de garde. D'autres études (Secareanu et al., 2001; Secareanu et al., 2004) se concentrent sur les effets des convertisseurs de puissance sur des circuits numériques. Secareanu et al. étudie les mécanismes de transmission par le substrat du bruit injecté par des transistors de puissance. Une modélisation RC du substrat est utilisée pour analyser l'immunité des circuits numériques face au bruit. Des résultats expérimentaux ont montré que l'information stockée par des registres pouvait être affectée par des convertisseurs de puissance en fonctionnement.

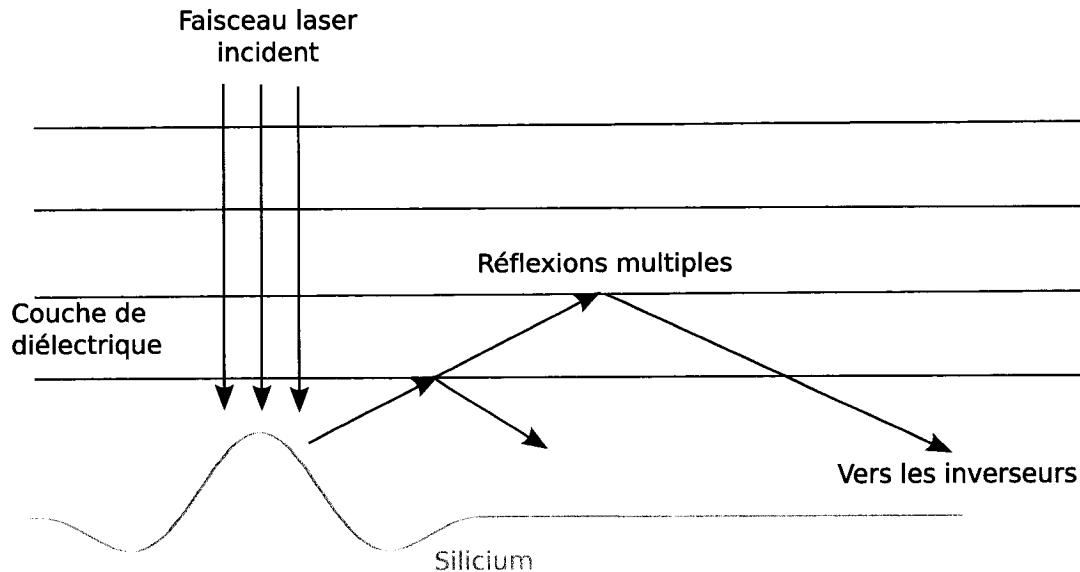

### 1.3.2 Injection de bruit dans le substrat par un laser

Depuis une vingtaine d'années, l'utilisation du laser en microélectronique s'est largement répandue, notamment pour l'ajustement de résistances par laser. Une autre application importante a été l'utilisation de lasers femtosecondes afin de reproduire et d'analyser l'impact de particules ionisantes sur des circuits de haute précision fonctionnant dans l'espace. Toutes ces techniques utilisant des lasers peuvent perturber les circuits à proximité de l'impact de la source lumineuse.

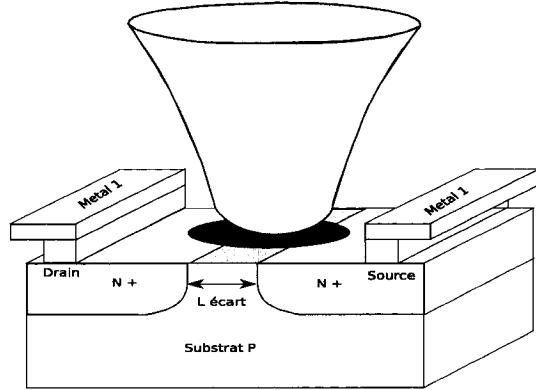

#### – Résistance Diffusée par laser (LDR : Laser diffused Resistor)

Les techniques d'ajustement de composants par laser sont employées depuis plusieurs années dans les technologies CMOS traditionnelles afin de compenser les mésappariements entre les composants dus aux variations de procédés durant la fabrication (Cohen et al., 1988; Kestenbaum and Baer, 1980; Chapman, 1992). Une nouvelle technique a été développée par Meunier et al. (Meunier et al., 2001) afin de créer des liens résistifs avec une précision de 50 ppm par l'application itérative d'impulsions laser sur un transistor MOS sans grille. Ces résistances appelées Laser Diffused Resistor (LDR), pour résistance diffusée par laser sont composées de deux régions fortement dopées séparées par une zone de dopage différent (d'où le transistor sans grille présenté à la figure 1.6). Initialement le dispositif est équivalent à deux jonctions PN têtes bêches, constituant un circuit ouvert. L'envoi d'un faisceau laser (de type Nd :YAG doublé en fréquence à  $\lambda = 532 \text{ nm}$ ) focalisé sur la zone d'écart non dopée permet de faire fondre le silicium et de provoquer la diffusion des dopants des régions les plus dopées vers la région la moins dopée (l'écart). Ainsi un canal résistif est formé.

L'injection de charges (électrons et trous) par effet photoélectrique est un phénomène bien connu depuis longtemps. Ces charges migrent dans le substrat et affectent

FIG. 1.6 Résistance diffusée par laser

les circuits environnants (Wild et al., 2005). Une augmentation de la fréquence de fonctionnement d'un oscillateur en anneau a été observée lorsqu'une impulsion laser d'énergie supérieure à 1 W et de longueur d'impulsion de l'ordre de la centaine de nanosecondes atteint le centre de l'oscillateur. L'utilisation de composants ajustables par laser afin d'augmenter les performances des circuits analogiques (Singh et al., 2007) peut donc s'avérer une source de bruit pour les circuits aux alentours. Il est donc important de modéliser l'impact de ces charges sur les circuits sensibles, afin de mieux comprendre les phénomènes d'interaction laser-circuit.

– **Perturbations des circuits dues à une particule isolée (Single Event Effects)**

Une application directe des perturbations induites par une impulsion laser est l'utilisation dans le but de reproduire et d'observer les interactions entre des circuits intégrés et des particules ionisantes. Cette utilisation particulière a pour but de tester la fiabilité des circuits dédiés à des applications spatiales face aux conditions brutales qu'ils vont rencontrer lors de leur mise en service. Les lasers utilisés sont principalement de type femtoseconde ou picoseconde avec des impulsions de faible puissance. Leur but est de reproduire le comportement d'une particule ionisante. Dans (Douin et al., 2006), une impulsion laser directement focalisée sur le drain

d'un transistor d'une cellule de mémoire SRAM a modifié l'information stockée par la mémoire. L'impact du laser sur un circuit peut même être utilisé pour injecter des fautes dans un convertisseur Analogique Numérique (ADC) (Pouget et al., 2004). Dans ces différents travaux (Boughassoul et al., 2004) (Pouget et al., 2004) (Douin et al., 2006), le faisceau laser utilisé est de puissance plus faible et de durée plus courte que celui utilisé pour créer des résistances diffusées par laser. Les phénomènes d'interaction entre le substrat et le laser, et par conséquent les processus d'injection de charges sont différents. En effet, l'impulsion laser nécessaire afin de créer le lien résistif doit avoir une puissance et une durée suffisante pour faire fondre le silicium et provoquer la diffusion des porteurs.

#### **– Modélisation électrique de l'injection de charges**