**Titre:** Conception et mise en oeuvre de processeurs configurables pour la conversion de taux de trames vidéos avec compensation de mouvement

Title:

**Auteur:** Nicolas Beucher

Author:

**Date:** 2007

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Beucher, N. (2007). Conception et mise en oeuvre de processeurs configurables pour la conversion de taux de trames vidéos avec compensation de mouvement

Citation: [Master's thesis, École Polytechnique de Montréal]. PolyPublie.

<https://publications.polymtl.ca/8034/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8034/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Guy Bois

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

CONCEPTION ET MISE EN OEUVRE DE PROCESSEURS CONFIGURABLES

POUR LA CONVERSION DE TAUX DE TRAMES VIDÉOS AVEC

COMPENSATION DE MOUVEMENT

NICOLAS BEUCHER

DÉPARTEMENT DE GÉNIE ELECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUILLET 2007

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-35665-4

*Our file* *Notre référence*

ISBN: 978-0-494-35665-4

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

CONCEPTION ET MISE EN OEUVRE DE PROCESSEURS CONFIGURABLES

POUR LA CONVERSION DE TAUX DE TRAMES VIDÉOS AVEC

COMPENSATION DE MOUVEMENT

présenté par: BEUCHER Nicolas

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. DAVID Jean-Pierre, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. BOIS Guy, Ph.D., membre et codirecteur de recherche

M. LANGLOIS Pierre, Ph.D., membre

À ma famille

## REMERCIEMENTS

Plusieurs personnes ont permis la réalisation de ce travail tant par leur soutien technique qu'humain. Ils ont su prodiguer conseils et encouragements qui ont permis à mon travail de progresser rapidement dans la bonne direction.

En premier lieu un grand merci à Yvon Savaria pour avoir accepté de diriger ma maîtrise et m'avoir proposé un sujet aussi intéressant. Il a su donné de la valeur à mes travaux en les dirigeant sur le bon chemin et en offrant conseils et suggestions pour progresser.

Merci également à Guy Bois dont les conseils et la vision ont été d'excellentes sources d'inspiration. Ses précieuses relectures de mes articles ont également permis d'en améliorer la qualité.

Un remerciement tout particulier à Normand Bélanger qui par son support technique appuyé par ses grandes connaissances, sa disponibilité et sa gentillesse m'ont permis d'avancer à grands pas. Merci à lui aussi pour toutes les discussions légèrement hors-sujet mais si intéressantes ;-).

Merci également à Maria et Dany qui ont permis par leurs patientes explications de faire démarrer cette maîtrise dans les meilleures conditions.

Enfin merci à Gilbert, Iliasse, Vincent, Rafael, Ali, Mohamed, Rahul et bien d'autres pour avoir fait de ces deux années au GRM un agréable séjour.

## RÉSUMÉ

Ce mémoire présente les travaux réalisés pour accélérer l'implémentation d'algorithmes d'augmentation de taux de trames par compensation de mouvement (Motion Compensated Frame Rate Conversion - MC-FRC) à l'aide de jeux d'instructions spécialisés. Différentes classes existent parmi ces algorithmes ; les travaux présentés ici s'intéressent aux algorithmes basés sur la division en blocs des images. Deux algorithmes sont implementés afin de déterminer leurs caractéristiques. Le premier, considéré comme simple, n'est en fait que le noyau de ce type d'algorithme et il permet de se faire une bonne idée des enjeux découlant de leur utilisation. Le second est une version plus complexe qui fait appel à plusieurs techniques pour obtenir un meilleur résultat. Dans les deux cas, les algorithmes réclament une grande puissance de calcul. Le déroulement des algorithmes est donc accéléré à travers la conception de jeux d'instructions spécialisés. Ces derniers permettent des accélérations de plus de 100 fois pour l'algorithme simple et d'environ 50 fois pour l'algorithme complexe. Les travaux présentés s'intéressent aussi à l'efficacité énergétique des processeurs spécialisés. Une méthodologie a donc été mise en place afin de comparer la consommation d'énergie d'un processeur standard avec celle d'un processeur spécialisé. Les résultats basés sur l'algorithme simple montrent que le processeur étendu est énergétiquement 50 fois plus efficace que le processeur standard. Une extension de ces travaux montre qu'une règle simple, liant l'accélération de performance, le rapport des surfaces entre les deux processeurs et le ratio d'énergie entre ces derniers peut prédire ce résultat. Cette règle est validée par trois cas de test décrits dans ce mémoire. Enfin, la description de travaux permettant la mise en oeuvre de ce type de processeurs dans des environnements multiprocesseurs ainsi qu'une discussion sur les algorithmes d'augmentation de taux de trames par compensation de mouvement terminent ce document.

## ABSTRACT

This document presents the work done to accelerate Motion Compensated Frame Rate Conversion (MC-FRC) algorithms using application specific instruction-sets. Many classes of MC-FRC algorithms exist ; here only the block motion estimation (BME) techniques are studied. Two algorithms are implemented to evaluate their characteristics. The first one, referred to as the simple one, is the main core of all MC-FRC algorithms based on BME. Its implementation gives a good idea of the work to do to accelerate such algorithms. The second algorithm, referred to as the complex one, is embedding more advanced techniques to increase the quality of the output. Both algorithms require a lot of computational effort and thus the need to develop specific instruction-sets to accelerate their execution. The acceleration reached range from more than 100-fold for the simple algorithm to about 50-fold for the complex one. The energy efficiency of extended processors is also of interest in the span of this work. Consequently, methodology to compare the energy consumption of the extended processor with the energy consumption of the standard processor has been built. The results show that, in the case of the simple algorithm, the extended processor is about 50 times more energy-efficient than the standard processor. An extension of this work also proves that this result could have been forecasted by a simple equation using the acceleration factor and the area overhead to deduce the energy saved. This simple model was validated by three test cases. To conclude, a description of the work done to allow simulation of these processors in more complex environnements (i.e. multiprocessors with network on chip systems) and a short discussion regarding MC-FRC algorithms close this document.

**TABLE DES MATIÈRES**

|                                                                                   |      |

|-----------------------------------------------------------------------------------|------|

| DÉDICACE . . . . .                                                                | iv   |

| REMERCIEMENTS . . . . .                                                           | v    |

| RÉSUMÉ . . . . .                                                                  | vi   |

| ABSTRACT . . . . .                                                                | vii  |

| TABLE DES MATIÈRES . . . . .                                                      | viii |

| LISTE DES FIGURES . . . . .                                                       | xi   |

| LISTE DES TABLEAUX . . . . .                                                      | xiii |

| LISTE DES NOTATIONS ET DES SYMBOLES . . . . .                                     | xiv  |

| INTRODUCTION . . . . .                                                            | 1    |

| CHAPITRE 1      TECHNOLOGIE DES ASIP : INTÉRÊT ET POSSIBILITÉS                    | 4    |

| 1.1    Généralités . . . . .                                                      | 4    |

| 1.2    Xtensa LX . . . . .                                                        | 6    |

| 1.3    Méthodologie pour la création d'un jeu d'instructions spécialisé . . . . . | 8    |

| CHAPITRE 2      ALGORITHMES DE MC-FRC . . . . .                                   | 11   |

| 2.1    Revue de littérature . . . . .                                             | 11   |

| 2.2    Algorithme simple . . . . .                                                | 18   |

| 2.3    Algorithme complexe . . . . .                                              | 21   |

| 2.4    Problématique . . . . .                                                    | 25   |

|                   |                                                                                        |           |

|-------------------|----------------------------------------------------------------------------------------|-----------|

| <b>CHAPITRE 3</b> | <b>CRÉATION D'UN JEU D'INSTRUCTIONS SPÉCIALISÉ</b>                                     | <b>27</b> |

| 3.1               | Le jeu d'instructions créé pour l'algorithme simple                                    | 27        |

| 3.1.1             | Registres pour la réutilisation : blocs et paramètres de l'algorithme                  | 28        |

| 3.1.2             | Liste des instructions                                                                 | 28        |

| 3.1.3             | Description complète des instructions                                                  | 30        |

| 3.1.3.1           | Instructions de chargement                                                             | 30        |

| 3.1.3.2           | Instructions de calcul                                                                 | 32        |

| 3.1.3.3           | Autres instructions                                                                    | 33        |

| 3.2               | Le jeu d'instructions créé pour l'algorithme complexe                                  | 35        |

| 3.2.1             | Liste des instructions                                                                 | 35        |

| 3.2.2             | Approche retenue pour l'optimisation de la réutilisation des données                   | 37        |

| 3.2.3             | Le problème des frontières de l'image                                                  | 38        |

| 3.2.4             | Machine à états, contrôle et autres instructions                                       | 40        |

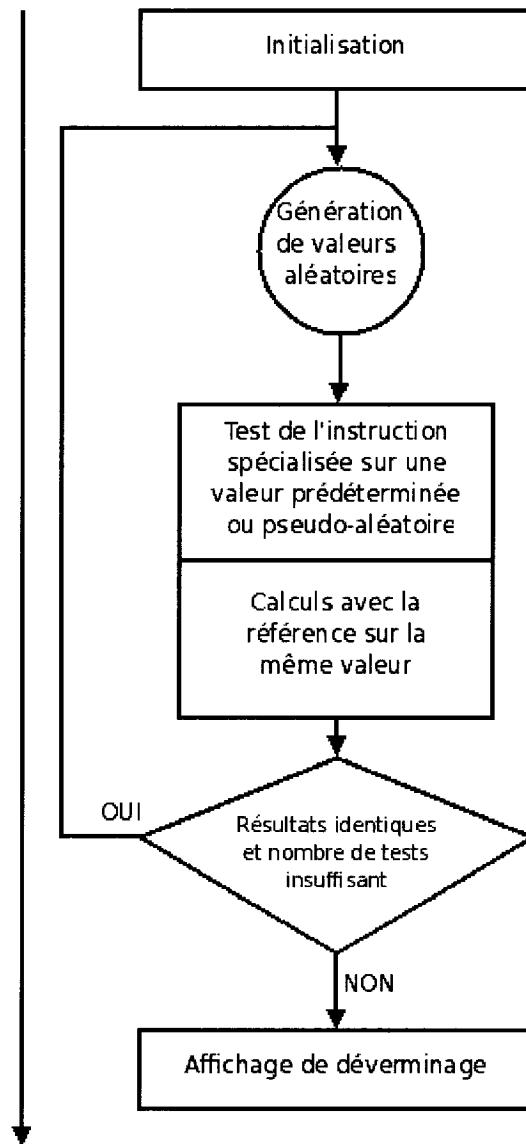

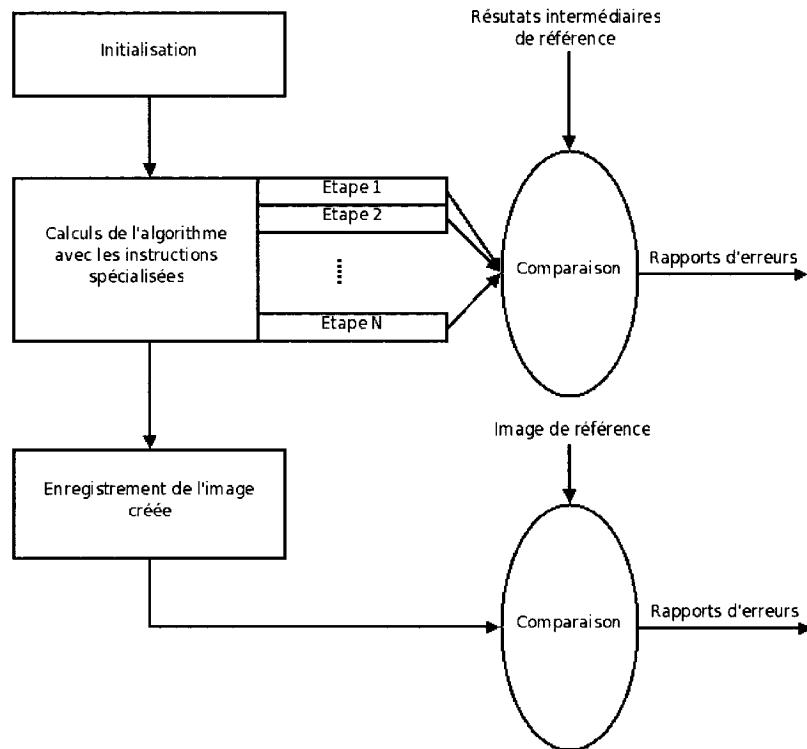

| 3.3               | Vérification fonctionnelle des instructions spécialisées et déverminage                | 41        |

| 3.4               | Modifications apportées aux programmes C                                               | 44        |

| 3.4.1             | Programmes C créés                                                                     | 44        |

| 3.4.2             | Exemple de modifications                                                               | 46        |

| <b>CHAPITRE 4</b> | <b>RÉSULTATS DE PERFORMANCE</b>                                                        | <b>49</b> |

| 4.1               | Pour l'algorithme simple                                                               | 49        |

| 4.1.1             | Superficie supplémentaire et fréquence d'horloge maximum du nouveau jeu d'instructions | 49        |

| 4.1.2             | Accélération : FS et ODFS                                                              | 50        |

| 4.1.3             | Impact de la taille de la cache et des délais mémoire                                  | 51        |

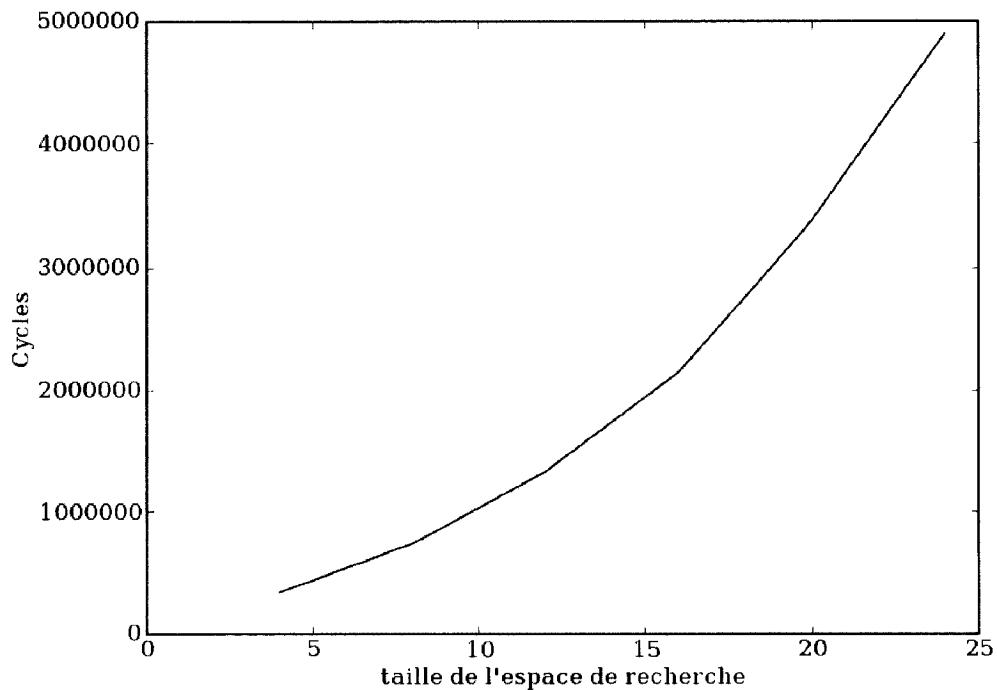

| 4.1.4             | Impact des paramètres de l'algorithme                                                  | 52        |

| 4.2               | Pour l'algorithme complexe                                                             | 54        |

|                                                                   |                                                                                                  |           |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------|

| 4.2.1                                                             | Superficie supplémentaire et fréquence d'horloge maximum du nouveau jeu d'instructions . . . . . | 54        |

| 4.2.2                                                             | Accélération . . . . .                                                                           | 54        |

| 4.3                                                               | Comparaisons de performance et de qualité . . . . .                                              | 55        |

| 4.3.1                                                             | Génération d'images . . . . .                                                                    | 55        |

| 4.3.2                                                             | Qualité . . . . .                                                                                | 56        |

| 4.4                                                               | Discussion sur la performance et les accélérations obtenues . . . . .                            | 57        |

| 4.4.1                                                             | Poids des calculs et impact de l'usage d'instructions spécialisées sur ces derniers . . . . .    | 57        |

| 4.4.2                                                             | Réutilisation des données . . . . .                                                              | 58        |

| 4.4.3                                                             | Contrôle et limitations . . . . .                                                                | 63        |

| 4.4.4                                                             | Accélération globale : loi d'Amdhal . . . . .                                                    | 64        |

| <b>CHAPITRE 5 ÉNERGIE ET ASIP . . . . .</b>                       |                                                                                                  | <b>66</b> |

| 5.1                                                               | Travaux antérieurs relatifs à la consommation d'énergie des ASIP . . . . .                       | 66        |

| 5.2                                                               | Méthodologie . . . . .                                                                           | 68        |

| 5.3                                                               | Résultats . . . . .                                                                              | 72        |

| 5.4                                                               | Discussion . . . . .                                                                             | 79        |

| 5.5                                                               | Validation de l'équation simplifiée . . . . .                                                    | 81        |

| 5.5.1                                                             | La suite de Fibonacci . . . . .                                                                  | 82        |

| 5.5.2                                                             | <i>Magnitude Coder</i> du JPEG2000 . . . . .                                                     | 88        |

| 5.5.3                                                             | Conclusion sur l'équation simplifiée . . . . .                                                   | 88        |

| <b>CHAPITRE 6 TRAVAUX ANNEXES ET EXTENSIONS FUTURES . . . . .</b> |                                                                                                  | <b>91</b> |

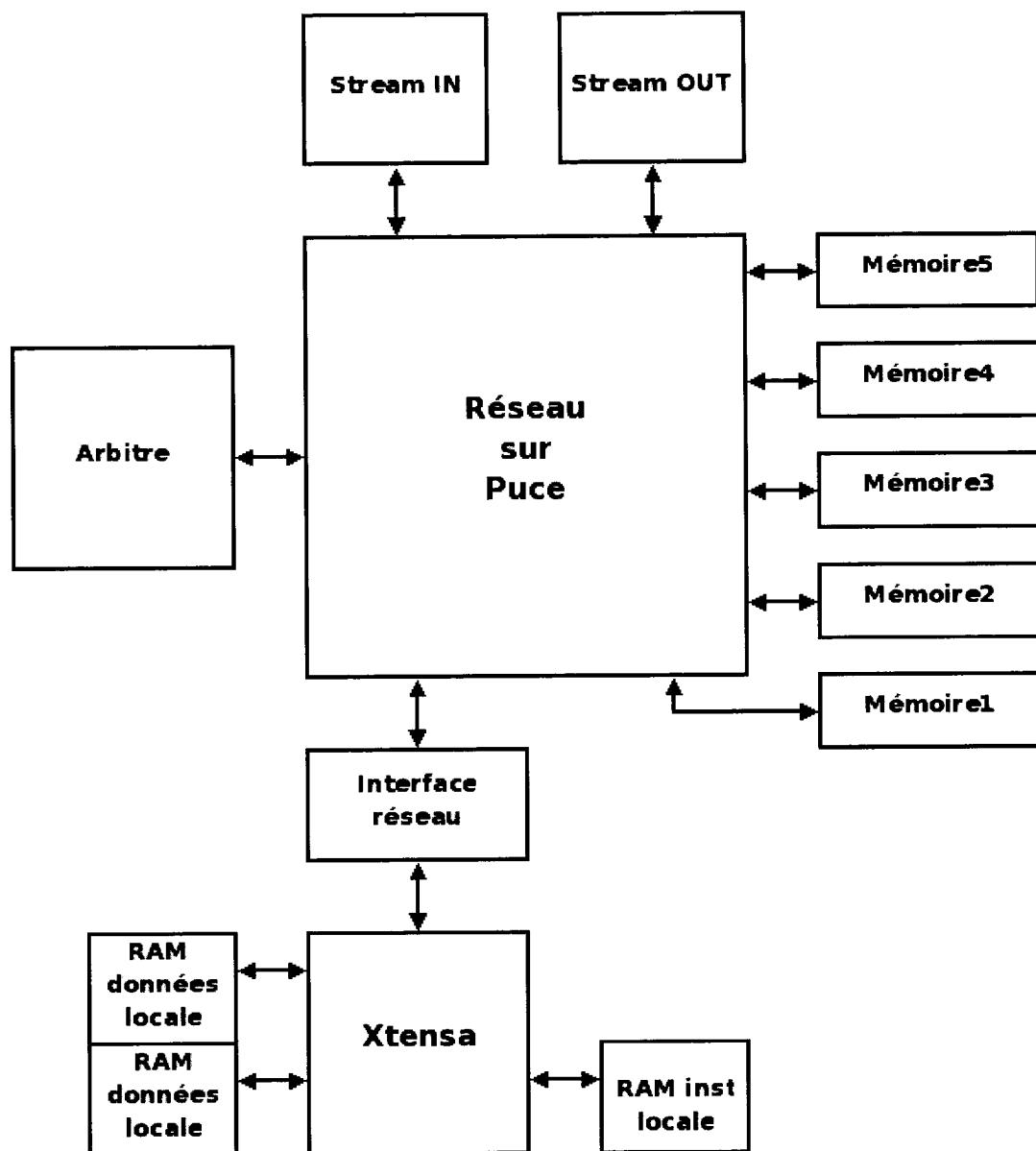

| 6.1                                                               | ASIP et Réseau sur puce . . . . .                                                                | 91        |

| 6.2                                                               | Optimisation des algorithmes de compensation de mouvement . . . . .                              | 93        |

| <b>CONCLUSION . . . . .</b>                                       |                                                                                                  | <b>95</b> |

| <b>RÉFÉRENCES . . . . .</b>                                       |                                                                                                  | <b>97</b> |

## LISTE DES FIGURES

|                 |                                                                                                |    |

|-----------------|------------------------------------------------------------------------------------------------|----|

| <b>FIG. 1.1</b> | Méthodologie de création d'un jeu d'instruction spécifique . . . . .                           | 10 |

| <b>FIG. 2.1</b> | Conversion de débit de 24 fps vers 30 fps, deux solutions possibles                            | 17 |

| <b>FIG. 2.2</b> | Schéma de l'algorithme simple . . . . .                                                        | 19 |

| <b>FIG. 2.3</b> | Exemple de résultat obtenu avec l'algorithme simple . . . . .                                  | 19 |

| <b>FIG. 2.4</b> | Résultat de l'interpolation avec la version optimisée de l'algorithme simple . . . . .         | 20 |

| <b>FIG. 2.5</b> | Schéma de l'algorithme complexe . . . . .                                                      | 21 |

| <b>FIG. 2.6</b> | Détails de l'estimation bidirectionnelle de mouvement . . . . .                                | 22 |

| <b>FIG. 2.7</b> | Résultat de l'interpolation avec l'algorithme complexe comparé à l'algorithme simple . . . . . | 23 |

| <b>FIG. 2.8</b> | Résultats avec défauts de l'algorithme complexe . . . . .                                      | 24 |

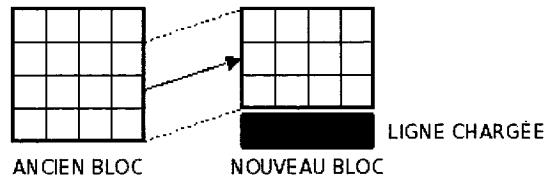

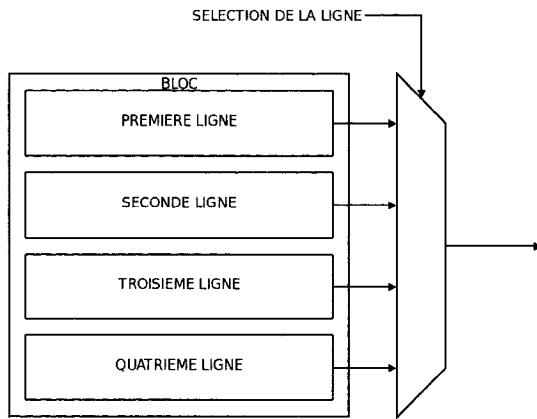

| <b>FIG. 3.1</b> | Méthode de chargement d'une ligne dans un bloc . . . . .                                       | 32 |

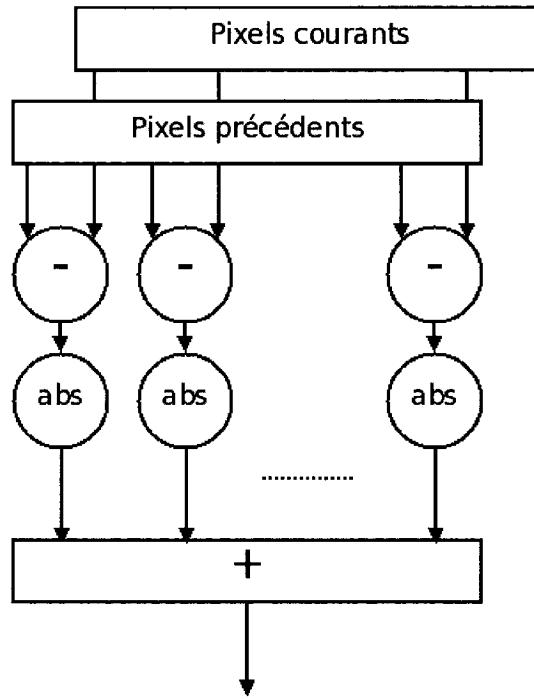

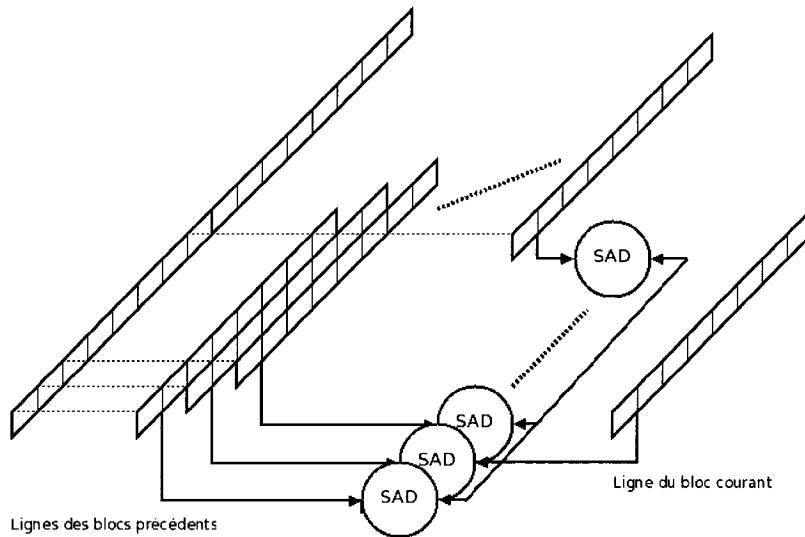

| <b>FIG. 3.2</b> | Calcul de la distance SAD . . . . .                                                            | 33 |

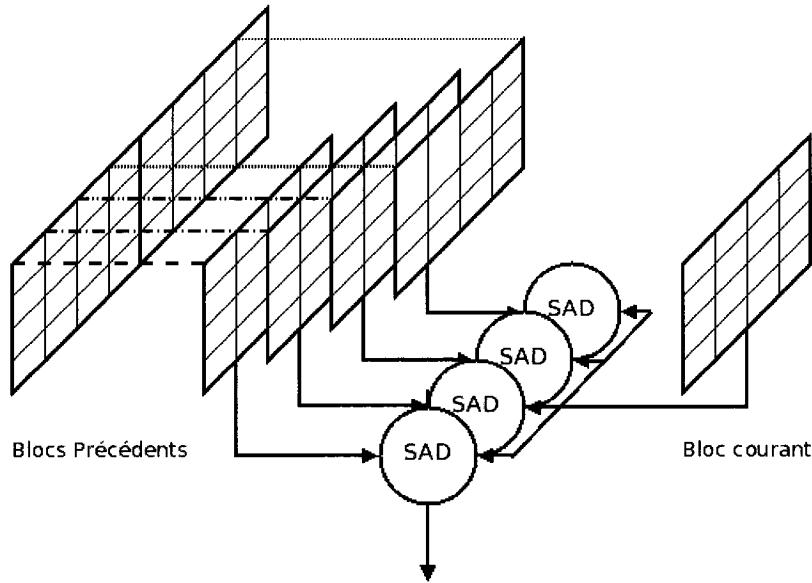

| <b>FIG. 3.3</b> | Fonctionnement de l'instruction <i>dist</i> . . . . .                                          | 34 |

| <b>FIG. 3.4</b> | Fonctionnement de l'instruction <i>movblr</i> . . . . .                                        | 35 |

| <b>FIG. 3.5</b> | Distance SAD sur les 8 lignes . . . . .                                                        | 39 |

| <b>FIG. 3.6</b> | Programme d'essai d'une instruction autovérifiant . . . . .                                    | 42 |

| <b>FIG. 3.7</b> | Vérification fonctionnelle d'un programme utilisant des instructions spécialisées . . . . .    | 43 |

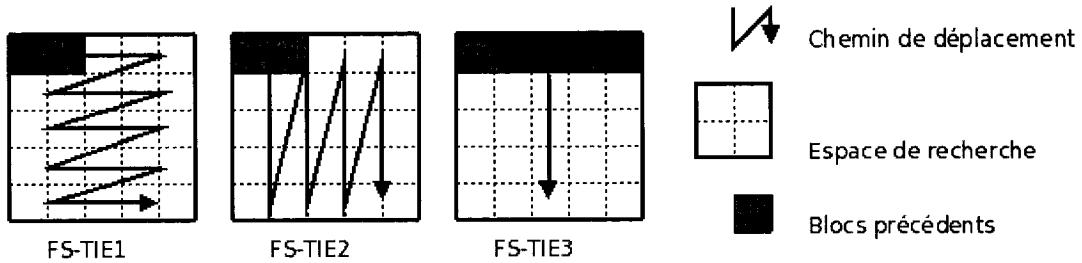

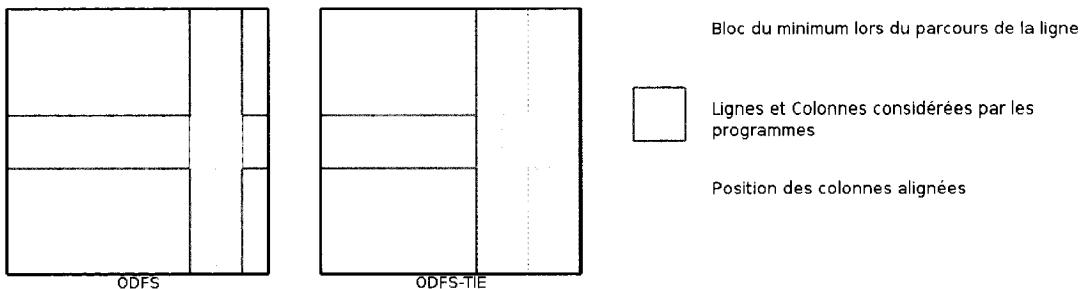

| <b>FIG. 3.8</b> | Parcours de l'espace de recherche par le programmes FS-TIE .                                   | 45 |

| <b>FIG. 3.9</b> | différence entre ODFS et ODFS-TIE . . . . .                                                    | 46 |

| <b>FIG. 4.1</b> | Impact de l'espace de recherche sur la performance . . . . .                                   | 53 |

| <b>FIG. 4.2</b> | Champs de l'adresse . . . . .                                                                  | 60 |

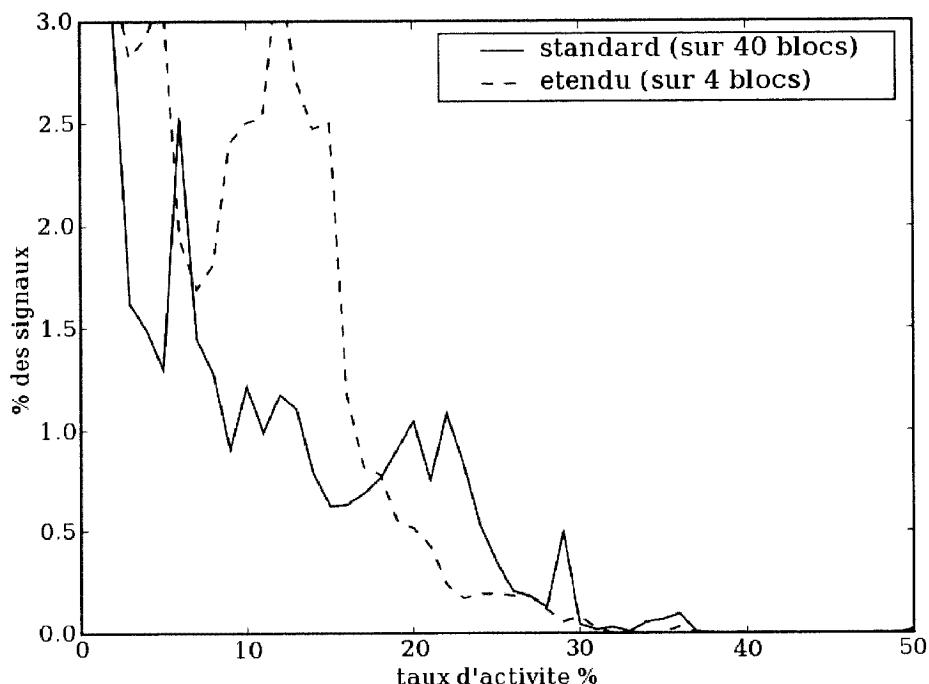

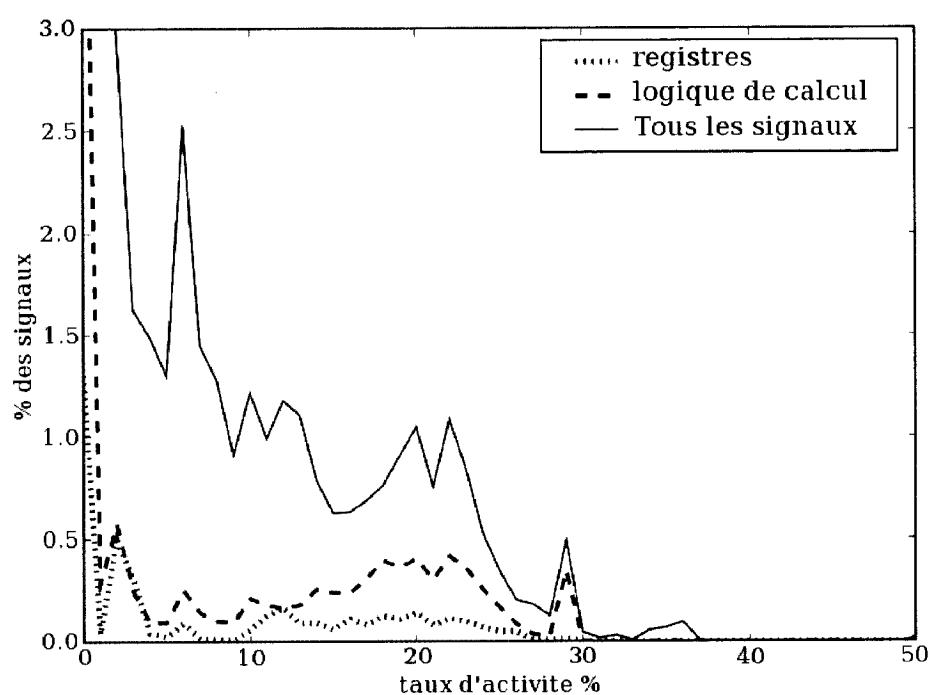

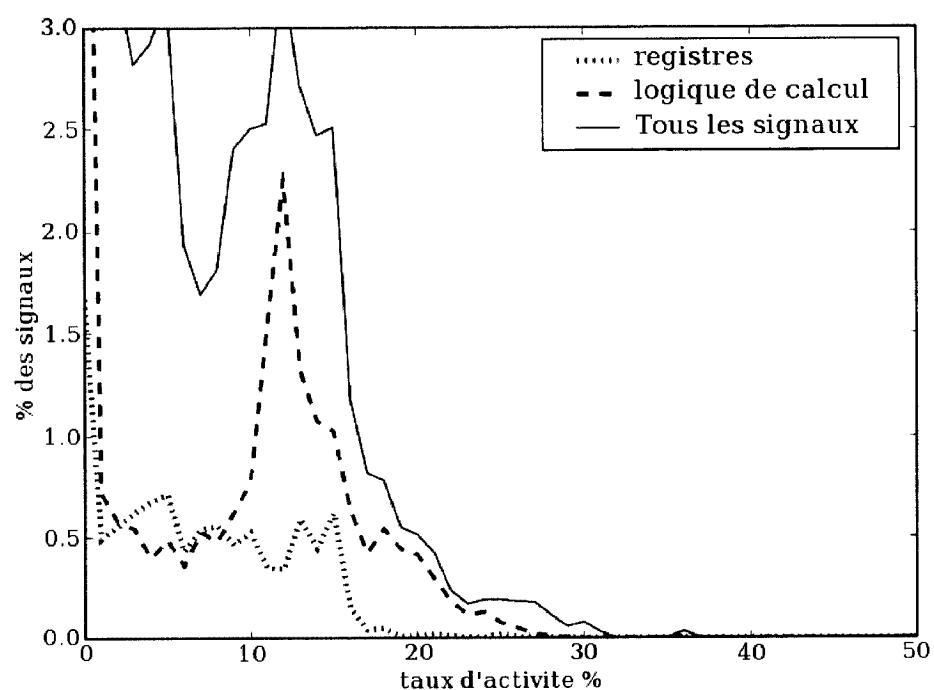

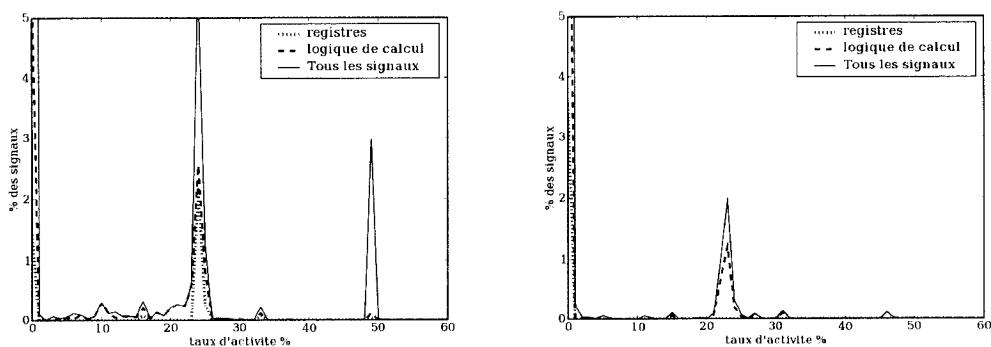

| <b>FIG. 5.1</b> | Histogramme de l'activité des signaux à l'intérieur des deux processeurs . . . . .             | 76 |

|                 |                                                                                                                                                               |    |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>FIG. 5.2</b> | Histogramme de l'activité des registres et de unités de traitement dans le processeur standard . . . . .                                                      | 77 |

| <b>FIG. 5.3</b> | Histogramme de l'activité des registres et unités de traitement au sein du processeur spécialisé . . . . .                                                    | 78 |

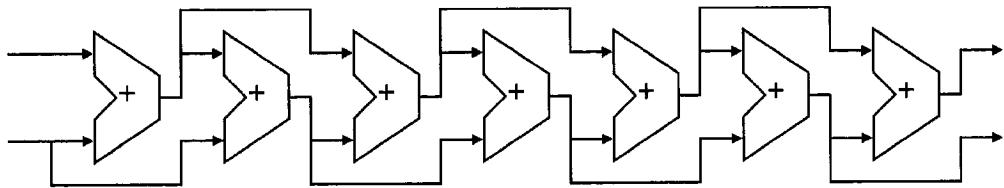

| <b>FIG. 5.4</b> | Instruction pour calculer la suite de Fibonacci . . . . .                                                                                                     | 83 |

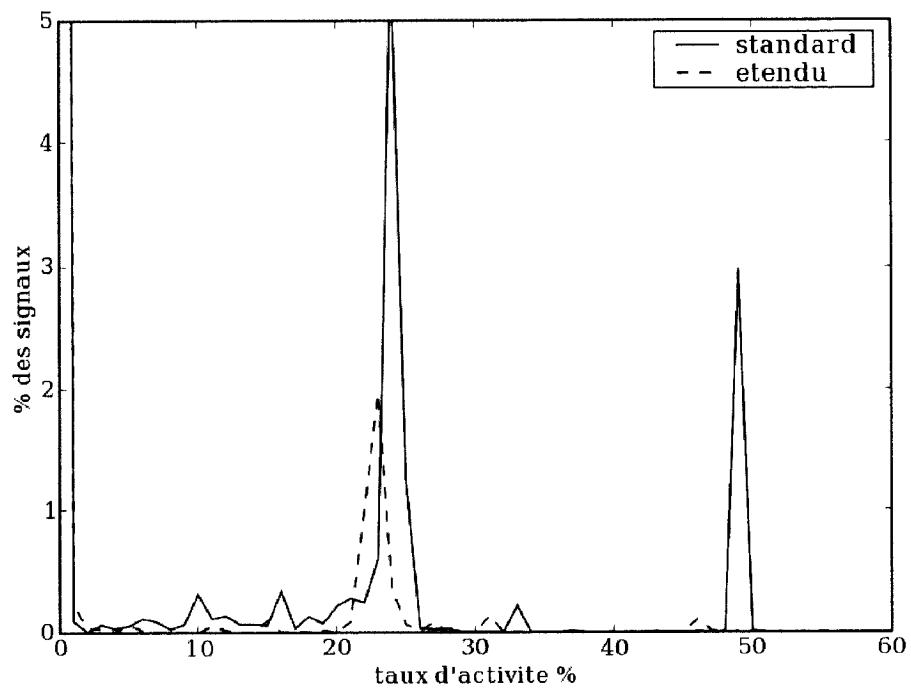

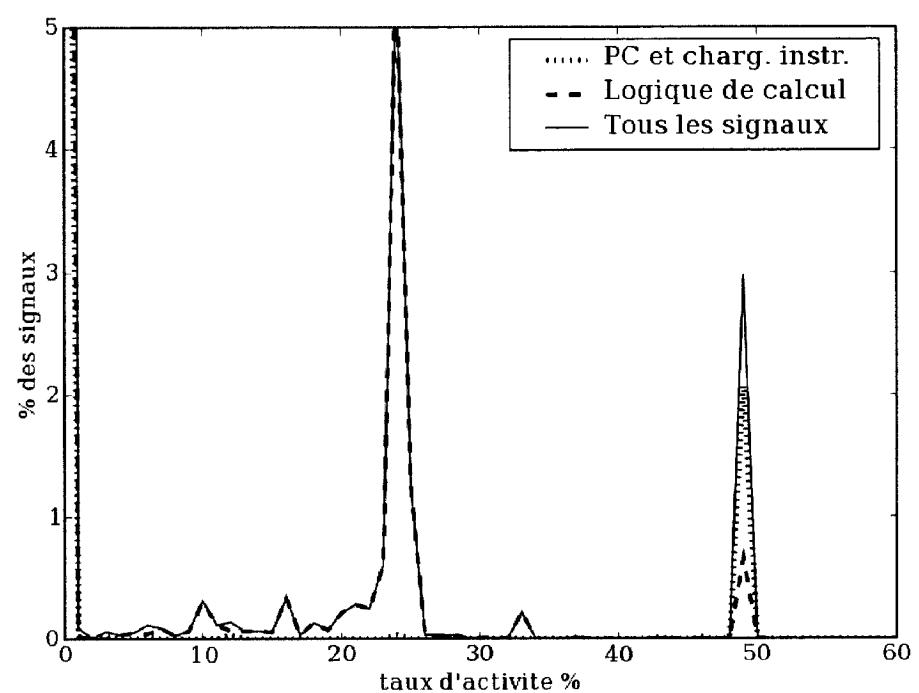

| <b>FIG. 5.5</b> | Histogramme de l'activité dans les processeurs réalisant la suite de Fibonacci . . . . .                                                                      | 85 |

| <b>FIG. 5.6</b> | Activité dans les registres et les ALU pour la suite de Fibonacci (standard à gauche) . . . . .                                                               | 85 |

| <b>FIG. 5.7</b> | Activité dans le module de chargement d'instructions et de la sémantique (logique de calcul) dans le processeur standard pour la suite de Fibonacci . . . . . | 86 |

| <b>FIG. 6.1</b> | Schéma du système Réseau sur Puce - Xtensa . . . . .                                                                                                          | 92 |

## LISTE DES TABLEAUX

|          |                                                                       |    |

|----------|-----------------------------------------------------------------------|----|

| TAB. 3.1 | Listes des instructions pour l'algorithme simple . . . . .            | 29 |

| TAB. 3.2 | Liste des instructions pour l'algorithme complexe . . . . .           | 36 |

| TAB. 4.1 | Accélération de l'algorithme simple : cas FS . . . . .                | 50 |

| TAB. 4.2 | Accélération de l'algorithme simple : cas ODFS . . . . .              | 50 |

| TAB. 4.3 | Impact de la politique et de la taille de la cache sur la performance | 51 |

| TAB. 4.4 | Impact de la latence de la mémoire en lecture sur la performance      | 52 |

| TAB. 4.5 | Impact de la taille de l'image sur la performance . . . . .           | 53 |

| TAB. 4.6 | Accélération de l'algorithme complexe . . . . .                       | 55 |

| TAB. 5.1 | Résultats de consommation (mW) pour le processeur standard .          | 73 |

| TAB. 5.2 | Résultats de consommation (mW) pour le processeur spécialisé          | 74 |

| TAB. 5.3 | Ratios de consommation d'énergie . . . . .                            | 75 |

| TAB. 5.4 | Consommation de puissance (mW) pour la suite de Fibonacci .           | 84 |

| TAB. 5.5 | Ratios de consommation d'énergie pour la suite de Fibonacci .         | 84 |

| TAB. 5.6 | Consommation de puissance (mW) pour le <i>Magnitude Coding</i> .      | 88 |

| TAB. 5.7 | Ratios de consommation d'énergie pour le <i>Magnitude Coding</i> .    | 89 |

| TAB. 5.8 | Résultat attendus et observés sur l'énergie . . . . .                 | 89 |

## LISTE DES NOTATIONS ET DES SYMBOLES

|                   |                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------|

| <i>ASIC</i> :     | Application Specific Integrated Circuit, circuit intégré dédié à une application spécifique            |

| <i>ASIP</i> :     | Application Specific Instruction-set Processor, processor à jeu d'instructions spécialisé              |

| <i>FPGA</i> :     | Field Programmable Gate Array, réseau prédiffusé programmable                                          |

| <i>DSP</i> :      | Digital Signal Processor, processeur de signal numérique                                               |

| <i>MC – FRC</i> : | Motion Compensated Frame Rate Conversion, augmentation de taux de trames par compensation de mouvement |

| <i>BME</i> :      | Block Motion Estimation, estimation du mouvement par bloc                                              |

| <i>BMA</i> :      | Block Matching Algorithm, algorithme de correspondance de bloc                                         |

| <i>FS</i> :       | Full Search, recherche complète                                                                        |

| <i>ODFS</i> :     | One-Dimensional Full Search, recherche complète sur une dimension                                      |

| <i>HD</i> :       | Haute-Définition                                                                                       |

| <i>ALU</i> :      | Arithmetic and Logic Unit, unité arithmétique et logique                                               |

| <i>JPEG</i> :     | Joint Photographic Experts Group                                                                       |

## INTRODUCTION

La vidéo constitue l'un des marchés les plus foisonnantes de la micro-électronique de loisir à l'heure actuelle. Avec la banalisation des appareils vidéos portables, l'essor de la télévision haute définition (HD) et le succès des sites web de partage de vidéo, les applications vidéos sont de plus en plus courantes et la demande très importante. L'enjeu est de créer des systèmes performants, adaptables et économiques pour répondre à cette demande. Les problèmes sont nombreux et concernent des domaines très larges de micro-électronique, d'informatique et d'algorithmique. Un des grands enjeux est de pouvoir faire face à la multiplication des sources disponibles, bien souvent dans des formats différents. La taille de l'image, le taux de trames ou encore l'encodage utilisé sont autant de variables auxquelles il faut faire face. Cette diversité impose le développement de longue chaînes de traitement afin d'être capable de supporter un vaste nombre de situations. Dans le présent mémoire de maîtrise, on s'intéresse à la conversion du taux de trames.

Le taux de trames, ou débit d'images, est une caractéristique essentielle d'une vidéo. En général, ce taux est supérieur à 10 images par seconde afin d'obtenir l'illusion du mouvement. En deçà de ce seuil, l'oeil humain est capable de discerner la séquence des images. En réalité pourtant, les vidéos auront tendance à utiliser des taux bien supérieurs (au moins le double) car ce taux est un élément important du confort de vision et les variations de perceptions entre individus imposent de s'assurer que l'on présente une bonne qualité pour tous. Seules les vidéos de basse qualité utilisent des taux de l'ordre de la dizaine. Au cinéma, le débit d'images est de 24 images par seconde. Les télévisions NTSC affichent 30 images par seconde. Dans ce dernier cas, cela s'explique historiquement par la fréquence des alimentations électriques en Amérique du Nord qui est fixée à 60 Hz. Les télévisions affichent les lignes paires puis les lignes impaires avec une fréquence de balayage vertical de 60 Hz. Les télévisions PAL, concernant l'Europe

notamment, utilisent un débit d'images de 25 par seconde pour des raisons similaires. Le taux de trames peut également prendre des valeurs bien plus élevées, jusqu'à 100, dans le cas de la télévision HD. Ceci impose donc d'être capable de convertir les différentes normes entre elles. C'est la tâche des algorithmes de conversion de taux de trames. Il existe plusieurs types d'algorithmes pour réaliser cette conversion, mais, dans le cadre de ce projet, seuls les algorithmes à compensation de mouvement seront étudiés (Motion Compensated Frame Rate Conversion - MC-FRC). Ils sont réputés offrir la meilleure qualité d'image au prix cependant d'efforts de calcul importants.

Une conséquence directe du coût en calcul de ces algorithmes est qu'ils réclament d'importants moyens matériels pour être mis en oeuvre. La technologie des processeurs configurables, aussi appelés processeurs à jeu d'instructions spécialisé (Application Specific Instruction-set Processor - ASIP), présente de nombreux intérêts pour ce type d'applications. Elle est rapide et aisée à utiliser et ne requiert pas autant d'efforts que la conception d'une puce spécialisée. Elle peut offrir des performances suffisantes pour faire les traitements requis. Enfin, sa grande réutilisabilité et son adaptativité sont des atouts certains pour ce type d'application puisqu'on peut ainsi concevoir une puce générique qui pourra être utilisée aussi bien dans des applications embarquées que sur des systèmes fixes.

Les travaux présentés dans ce mémoire portent sur la mise en oeuvre de la technologie des processeurs configurables dans le cadre des algorithmes d'augmentation de taux de trames par compensation de mouvement. Les travaux s'intéressent particulièrement à la création d'un jeu d'instructions spécialisé pour ce type d'application en vue d'augmenter la performance. Deux algorithmes issus de la littérature ont été implantés afin de servir de base de départ. Les jeux d'instructions créés permettent d'augmenter significativement la performance par des facteurs pouvant aller jusqu'à plus de 100 fois. Les travaux s'intéressent aussi à la consommation d'énergie engendrée par l'utilisation d'instructions spécifiques. Les résultats montrent que la spécialisation diminue la

consommation énergétique dans le même ordre de grandeur que l'accélération. Enfin, une partie des travaux porte sur le développement d'une architecture centrée autour d'un processeur spécialisé pour mettre en oeuvre l'algorithme de façon efficace.

Le présent mémoire est constitué de 7 chapitres en plus de l'introduction. Le chapitre 1 présente en détails la technologie des processeurs spécialisés (ASIP). Les forces et les faiblesses de cette technologie sont présentées ainsi que la méthodologie associée à leur utilisation. Le chapitre 2 présente les algorithmes de MC-FRC de façon générale. Leur intérêt et leurs particularités sont discutés. Ce chapitre présente également les deux algorithmes retenus pour ce projet. Le chapitre 3 présente les jeux d'instructions spécialisés créés pour accélérer le traitement des algorithmes de MC-FRC retenus. Les instructions sont décrites et expliquées. Le chapitre présente également les méthodes utilisées pour la vérification des instructions ainsi que les modifications apportées aux programmes C pour que ces derniers utilisent le nouveau jeu d'instructions. Le chapitre 4 présente les résultats obtenus avec les nouveaux jeux d'instructions et notamment l'accélération qu'ils ont permis. Ce chapitre discute également ces résultats. Le chapitre 5 présente la méthodologie développée pour estimer la consommation de puissance du jeu d'instructions étendu. Les résultats obtenus sont également présentés et discutés. Ce chapitre présente également une discussion sur le rapport entre l'énergie, l'accélération et la superficie. Deux cas, différents du MC-FRC, sont présentés. Le chapitre 6 présente les travaux annexes à ce projet et les extensions futures. Les travaux concernant l'interconnexion entre un processeur spécialisé et un réseau sur puce sont notamment présentés dans ce chapitre. Le dernier chapitre conclut ce mémoire.

## CHAPITRE 1

### TECHNOLOGIE DES ASIP : INTÉRÊT ET POSSIBILITÉS

#### 1.1 Généralités

Le terme ASIP, qui signifie Application Specific Instruction-set Processor, est utilisé pour désigner un grand nombre de processeurs ; les processeurs spécialisés qui possèdent un jeu d'instructions très spécifique qui les rend capables de réaliser des opérations particulières (par exemple les DSP), les processeurs configurables dont on peut modifier les caractéristiques internes comme la quantité de registres ou la nature de la mémoire cache (comme, par exemple, Nios de Altera) et les processeurs standards pour lesquels on peut aisément ajouter un jeu d'instruction supplémentaire dits processeurs extensibles(Xtensa de Tensilica[27]).

Les ASIP conservent la programmabilité des processeurs standards et permettent d'augmenter les performances de façon suffisante pour rivaliser avec des ASIC (Application Specific Integrated Circuits). Lorsqu'on les compare avec ces derniers, les ASIP sont plus faciles à mettre en oeuvre, à vérifier et finalement à réutiliser que les ASIC mais ils ne sont pas toujours suffisamment performants et sont bien moins efficaces en terme d'énergie qu'une puce spécialisée. Comparés aux processeurs standards, ils sont par contre bien plus performants (pour une application donnée) et consomment moins. Il perdent toutefois en partie la généralité de ces derniers car leur jeu d'instructions impose des contraintes plus fortes.

Toutefois, dans le cas des processeurs extensibles (Xtensa), on conserve la généralité du processeur standard tout en accédant à la performance d'un ASIP simple. Cela

implique toutefois un processeur plus grand en superficie et sans doute moins efficace en termes d'énergie, mais cette voie peut être une bonne solution pour les systèmes électroniques complexes qui peuvent embarquer plusieurs processeurs et structures spécialisées au sein d'une même puce. De tels systèmes sont relativement fréquents de nos jours. Un téléphone cellulaire classique possède généralement plusieurs DSP, pour le traitement de la voix et du signal, un processeur standard qui se charge de l'interface avec l'utilisateur et plusieurs autres éléments selon les capacités de l'appareil (vidéo, audio MP3, etc ...). Les ASIP basés sur l'extension peuvent alors être utiles pour remplacer efficacement plusieurs de ces modules tout en conservant la puissance de calcul nécessaire. Ils réduisent ainsi la complexité du système. Malgré tout les processeurs extensibles sont limités par leur base qui restreint les possibilités du concepteur. Certains ASIP peuvent être créés à partir de rien évitant ainsi le surplus dû à la base standard présente dans les processeurs extensibles. Par exemple, la technologie Lisatek de la compagnie Coware [10] permet de créer l'intégralité du processeur selon les besoins en performance. Ce type de technologie est donc plus souple que la technologie des processeurs extensibles mais elle exige davantage d'efforts de la part des concepteurs.

Leur grande généralité ainsi que leur performance générale a permis aux ASIP d'être utilisés dans de nombreux domaines tels que les traitements vidéos [18, 20, 22], le traitement du signal [1] ou encore la conception de puces pour les réseaux [23].

Des travaux complémentaires se consacrent à l'automatisation de la création des jeux d'instructions spécifiques. Le but étant de développer des outils qui analysent le code source de l'application, cherchent les goulots d'étranglement et créent les instructions permettant d'accélérer le traitement sans intervention humaine [2, 25].

## 1.2 Xtensa LX

Le Xtensa LX[28] est un processeur produit par la compagnie Tensilica. C'est un processeur configurable auquel on peut rajouter un jeu d'instructions spécialisé.

Le concepteur utilisant le Xtensa LX a donc la possibilité de créer un processeur standard selon ses spécifications en termes de performance, de superficie et de consommation énergétique. S'il souhaite obtenir plus de performance, il a également la possibilité d'ajouter, en suivant certaines règles, un jeu d'instructions supplémentaire qui ciblera un éventuel goulot d'étranglement de son algorithme.

Plus spécifiquement, la compagnie Tensilica met à la disposition du concepteur une interface de création de processeur, XPG (Xtensa Processor Generator), qui permet de créer et de configurer un processeur basé sur leur architecture de processeur 32 bits, Xtensa LX. Le concepteur peut modifier un certain nombre de paramètres internes comme l'ajout de certaines instructions (multiplieur 32 bits ou MAC), le nombre de registres, l'ordre mémoire des octets (gros ou petit boutiste (endian)), ou encore la taille et l'associativité des caches d'instructions et de données. Il peut également, s'il le souhaite, attacher directement au processeur des mémoires RAM ou ROM. L'outil XPG affiche tout au long de ses choix des estimations sur la puissance consommée, la superficie et la fréquence d'horloge maximale à laquelle le processeur sera capable de fonctionner.

Lorsque le concepteur est sûr de ses choix, il peut télécharger une gamme d'outils ciblés pour le processeur créé. Ces outils contiennent entre autres un compilateur C (xt-xcc), un simulateur (xt-run) et un outil de profilage (xt-gprof). Ils permettent de compiler et de simuler un programme C et d'obtenir des statistiques de performance. Le simulateur retourne le nombre exact de cycles qu'il a fallu pour compléter le programme ainsi que des statistiques sur l'utilisation de la cache. Le profileur permet de détailler les résultats obtenus pour chaque fonction du programme afin de cerner les goulets d'étranglement.

glement de l'application.

Si la performance souhaitée n'est pas atteinte, le concepteur peut alors, à l'aide d'une autre gamme d'outils, créer et intégrer un jeu d'instructions spécialisé pour accélérer le traitement des points chauds de l'algorithme. La création d'instructions spécialisées se fait à l'aide du langage TIE (Tensilica Instruction Extension). Le langage TIE est très proche du Verilog. Un certain nombre de mots clés supplémentaires permettent de créer de nouveaux fichiers de registres, des registres d'état ou encore des instructions spécifiques. Une fois le fichier TIE créé, il doit ensuite être compilé avec un compilateur spécial (tc) qui retourne un certain nombre de fichiers résultats. En premier lieu, le compilateur retourne un fichier Verilog décrivant les nouvelles instructions. Ce fichier peut être attaché aux fichiers HDL décrivant le processeur standard. Les nouvelles instructions sont donc directement intégrées au chemin de données du processeur. Le compilateur retourne également des scripts pour synthétiser les instructions spécialisées. Ceci permet d'obtenir la superficie supplémentaire ajoutée par le jeu d'instructions étendu et aussi de connaître la fréquence maximale de fonctionnement autorisée par ce dernier. Enfin, le compilateur retourne un certain nombre de fichiers qui permettent au concepteur d'utiliser ce nouveau jeu d'instructions dans son programme, de le compiler et de le simuler en tenant compte des nouvelles instructions.

Comme on peut le voir, les outils fournis par Tensilica permettent au concepteur de réaliser un processeur spécialisé et de le tester de façon relativement simple et rapide.

Les outils utilisés pour établir les résultats présentés dans ce document utilisent tous la version RA2006.6. Le processeur de base utilisé est donc un Xtensa LX qui possède les instructions standards ainsi qu'un multiplicateur 32-bit. Ce processeur embarque également une cache de données de 2 Ko configurée en ensemble associatif à 2 voies ainsi qu'un cache d'instruction de 1 Ko à accès direct. Le processeur peut communiquer avec des composants externes (bus, mémoires, DMA...) via une interface supportant des

mots de 128 bits. Ce processeur requiert un équivalent de quelques 64348 portes en superficie et fonctionne à une fréquence de 268 MHz d'après les indications fournies par l'outil de création XPG.

### **1.3 Méthodologie pour la création d'un jeu d'instructions spécialisé**

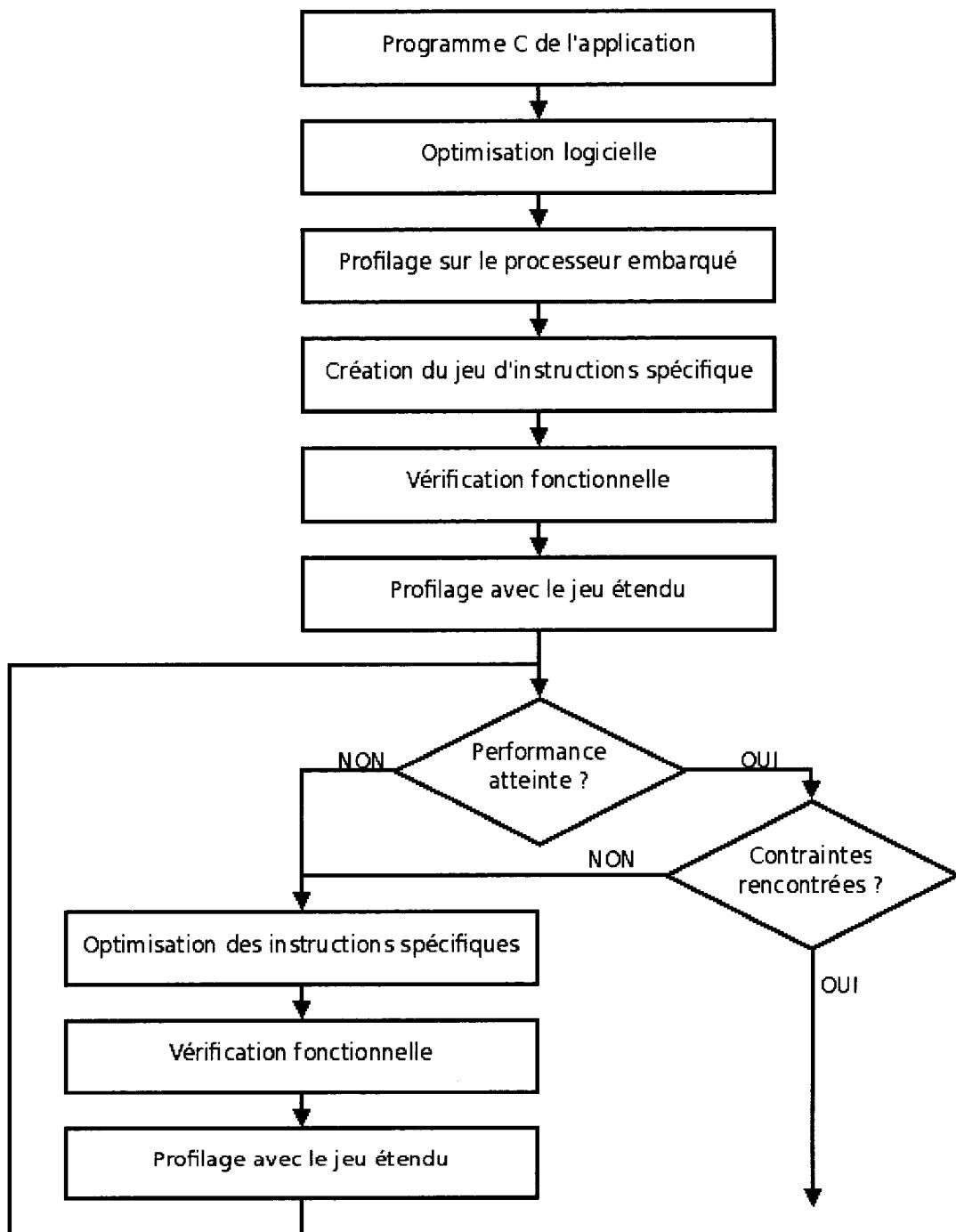

Créer un jeu d'instructions spécialisé se fait par étapes successives. La création s'appuie sur une implantation logicielle de l'algorithme ou de l'application que l'on souhaite accélérer à l'aide d'instructions spécifiques. Cette implantation est créée sur un ordinateur classique et optimisée pour être la plus rapide et la plus efficace possible. On peut ensuite profiler l'application sur le processeur embarqué à l'aide d'outils comme un simulateur et un profileur. Cela permet de déterminer les goulots d'étranglement de l'application. Cette version logicielle va donc servir de référence fonctionnelle mais aussi de référence de performance pour évaluer l'impact des nouvelles instructions sur les goulots d'étranglement. La création du nouveau jeu d'instructions aura donc pour but de réduire ces goulots. Chaque instruction créée doit être vérifiée afin de s'assurer qu'elle remplit correctement sa tâche. Une fois qu'un premier exemplaire du jeu d'instructions est créé et fonctionnel, le concepteur doit s'assurer de ses performances en réalisant un nouveau profilage de l'application, qui cette fois-ci, utilise le jeu étendu. Si la performance atteinte n'est pas suffisante, le concepteur doit améliorer le jeu d'instructions créé, en concevant des instructions supplémentaires ou en optimisant celles qui existent déjà, et répéter ce processus autant de fois que nécessaire afin d'atteindre le but fixé. Lorsque la performance atteinte est satisfaisante, le concepteur doit vérifier que l'ajout du nouveau jeu d'instructions remplit bien les contraintes temporelles (fréquences de l'horloge) et de superficie fixées. Là encore, si ces contraintes ne sont pas rencontrées, le concepteur doit retourner à sa table à dessin afin de modifier les instructions pour qu'elles puissent rencontrer ces contraintes. Bien entendu, chaque modification doit être faite en vérifiant

que la performance nécessaire est toujours atteinte. Le processus est ainsi répété jusqu'à ce que le jeu d'instructions créé satisfasse toutes les contraintes : performance, superficie, fréquence d'horloge. La figure 1.1 schématise ce processus. C'est le processus qui a été appliqué au cours de ces travaux pour créer les diverses instructions spécialisées.

FIG. 1.1 Méthodologie de création d'un jeu d'instruction spécifique

## CHAPITRE 2

### ALGORITHMES DE MC-FRC

Dans ce chapitre, le principe des algorithmes d'augmentation de taux de trames avec compensation de mouvement (Motion Compensated Frame Rate Conversion - MC-FRC) est présenté. Ce chapitre présente également les deux algorithmes utilisés pour établir les résultats présentés dans ce document.

#### 2.1 Revue de littérature

Les algorithmes de Frame Rate Conversion (FRC), parfois appelés Frame Rate-up Conversion, sont utilisés pour augmenter le taux d'images par seconde (frame per second - fps) d'un flux vidéo.

Tous les types de flux vidéo possèdent un débit d'images propre. Ainsi, dans les salles de cinéma, on diffuse les films avec un taux d'images par seconde de 24. Sur les télévisions nord-américaines, qui suivent la norme NTSC, ce taux est de 30 images par seconde alors que les télévisions européennes fonctionnent sur du 25 images par seconde. Le problème se complique encore si l'on considère les flux vidéo internet, la vidéo mobile (téléphone cellulaire et autres ipod vidéo) ou encore la télévision Haute Définition HD) qui étendent les possibilités en matière de taux d'images. L'existence d'un grand nombre possible de taux de trames impose la nécessité d'un algorithme de conversion. Le problème ne se posant réellement que dans le cas de l'augmentation du taux qui est bien plus complexe à réaliser que la simple diminution souvent réalisée en retirant des images du flux.

Il existe un certain nombre d'algorithmes pour réaliser cette conversion qui fournissent des résultats de qualité et de simplicité variables. L'exemple de la conversion cinéma vers télévision est assez frappant. Pour la conversion du cinéma vers les téléviseurs européens, le choix qui a été fait a été de simplement augmenter la vitesse du film. Ainsi le film passe 25 images par seconde au lieu des 24 initiales. La durée du film est donc réduite lorsque le film est diffusé à la télévision. Pour les téléviseurs nord-américain on utilise l'algorithme de 3 :2 pulldown [15]. Cet algorithme permet de passer de 24 images par seconde à 30 images par secondes, il lui faut donc générer 6 images par secondes pour compléter le flux vidéo originel. Cette augmentation revient donc à créer une cinquième image pour chaque lot de 4 images d'origine. L'algorithme de 3 :2 pulldown réalise cette tâche en entrelaçant les lignes paires de la troisième image d'origine avec les lignes impaires de la quatrième pour former une cinquième image qui sera diffusée entre les troisième et quatrième d'origine. Cet algorithme est très efficace pour les télévisions car il ne nécessite pas de calculs et il s'appuie sur le fonctionnement des téléviseurs qui affichent les lignes paires puis les lignes impaires mais il ne convient qu'à un seul et unique type de conversion. Il existe des algorithmes qui permettent de convertir n'importe quel débit d'image en un autre.

Parmi ces algorithmes, on compte les algorithmes à répétition d'images, les algorithmes à interpolation temporelle et les algorithmes à compensation de mouvement. La répétition d'image est la méthode la plus simple pour compléter un flux vidéo dans lequel il manque des images. Ainsi, pour passer d'un flux de 24 images par seconde à un flux de 30 images par seconde, on répéterait la dernière image de chaque lot de 4 pour en créer une cinquième. Cette méthode est très simple et ne nécessite aucun calcul mais elle dégrade la qualité de la vidéo en introduisant une impression de mouvement saccadé peu agréable à l'oeil. L'interpolation temporelle consiste à moyenner dans le temps les images originelles afin de créer les images manquantes. Bien que cette méthode ne produise pas de mouvements saccadés, elle introduit du flou dans l'image qui peut s'avé-

rer gênant pour le spectateur. Comme on le voit, ces deux méthodes sont simples mais elles ne répondent pas aux exigences en matière de qualité d'image et de confort visuel. Sur des téléviseurs HD, il est important de disposer de méthodes plus performantes qui maintiennent un haut niveau de qualité.

Les algorithmes à compensation de mouvement (Motion Compensated Frame Rate Conversion - MC-FRC) sont réputés offrir une bonne qualité d'image[6, 16, 9]. L'idée est d'analyser les mouvements entre les images au sein du flux vidéo et d'en déduire l'image qu'il faut ajouter pour augmenter le taux d'images par seconde sans briser la chaîne du mouvement, ce qui donnerait l'impression d'une saccade, et en évitant d'introduire du flou. L'algorithme est donc mathématiquement plus complexe puisqu'il faut d'abord calculer et estimer les mouvements au sein de l'image. Pour ce faire, de multiples méthodes existent [19, 11], parmi lesquelles on compte : l'estimation de mouvement global (Global Motion Estimation - GME), l'estimation de mouvement de blocs (Block Motion Estimation - BME), l'estimation de mouvement de blocs avec recouvrement (Overlapped Block Motion Estimation - OBME) [14], l'estimation par gradient et l'estimation par récursivité (pel-recursive). L'estimation de mouvement global permet de suivre les mouvements larges de la caméra mais est complètement aveugle aux objets se déplaçant à l'intérieur du champ visuel, ce qui la rend très mauvaise pour réaliser du MC-FRC. Toutefois, il peut être utile de connaître le mouvement général de la caméra pour augmenter la qualité des résultats. L'estimation par mouvement de blocs consiste à découper les images en blocs et à analyser le mouvement de chacun d'entre eux pour obtenir un champ de vecteurs de déplacement au sein de l'image. Ces méthodes proviennent du domaine de la compression vidéo (famille des encodeurs vidéos MPEG) où elles ont été utilisées avec succès. Toutefois, ces méthodes possèdent l'inconvénient de ne pas capter tous les types de mouvements (notamment la dilatation et la rotation qui, du fait de la nature rigide des blocs, ne sont pas détectables). De plus, elles présentent des défauts dits *d'artéfacts de blocs* qui surviennent lorsque le mouvement estimé d'un bloc

ne correspond pas au mouvement réel, le bloc est alors déplacé de façon incorrecte et sa position provoque une discontinuité dans l'image. Ces discontinuités sont très visibles pour l'observateur car elles présentent un gradient de luminosité élevé auquel l'oeil est très sensible. Pour remédier à ce problème, des techniques d'estimation de mouvement de bloc avec recouvrement ont été suggérées. Ces techniques utilisent des blocs plus larges qui se recouvrent les uns sur les autres. Cela permet de corriger les problèmes de discontinuité car les parties qui se recouvrent sont moyennées, atténuant ainsi les erreurs dues au mauvais déplacement d'un bloc. Elles présentent toutefois le même inconvénient que la simple BME car elles ne permettent pas de détecter des rotations ou des dilatations. Les techniques de gradient et de récursivité travaillent pixel par pixel et cherchent à trouver le mouvement par des techniques de descente de gradient sur la luminosité d'un pixel. Ces techniques sont encore plus coûteuse que les techniques de blocs car elles travaillent pixel par pixel et nécessitent plusieurs passes par pixel pour obtenir un résultat et elles sont également plus sensibles au bruit sur l'image. Toutefois, elles n'ont pas de limitations intrinsèques sur le type de mouvement dans l'image.

Comme on le voit, il existe plusieurs méthodes pour réaliser l'estimation de mouvement. Elles ne possèdent pas toutes les mêmes caractéristiques et ont chacune leurs avantages et désavantages. Les méthodes les plus couramment observées dans la littérature se basent sur des méthodes de BME. En premier lieu, ces méthodes sont simples à comprendre et à mettre en oeuvre. De plus, elles sont bien connues car exploitées dans l'encodage vidéo. Les diverses recherches ont conduit à la création de multiples techniques visant à réduire l'effort de calcul et à augmenter la qualité de l'estimation. Toutefois, les techniques de BME sont toutes basées sur les mêmes principes. La première étape consiste à diviser l'image courante en blocs d'une certaine taille, dans certains cas, ces blocs sont contigus les uns aux autres et dans d'autres cas ils se juxtaposent. Afin de déterminer le mouvement suivi par un bloc, on cherche à déterminer sa position dans une ou plusieurs images précédentes. Cette recherche est effectuée par des algorithmes

de correspondance de blocs (Block-matching algorithms - BMA). Afin de ne pas parcourir inutilement l'intégralité de l'image précédente, on limite la recherche à une portion de cette image centrée autour de la position du bloc dans l'image courante. Dans cet espace, on cherche la position qu'occupait le bloc dans l'image précédente en le comparant avec un certain nombre de blocs de cet espace. La comparaison, qui est en réalité une distance mathématique sur la valeurs des pixels des deux blocs considérés, est une simple somme des valeurs absolues des différences des pixels des blocs (Sum of Absolute Difference - SAD). L'équation 2.1 montre le calcul de la SAD pour un bloc de taille  $N$  situé à la position  $(x,y)$  dans l'image courante ( $t$ ) avec le bloc situé à la position  $(x,y)$  décalée de  $(u,v)$  dans l'image précédente ( $t-1$ ).  $F$  représente la valeur du pixel à la position considérée.

$$SAD_{(x,y)}(u, v) = \sum_{i=0}^N \sum_{j=0}^N |F_t(x+i, y+j) - F_{t-1}(x+i+u, y+j+v)| \quad (2.1)$$

L'ancienne position du bloc est considérée trouvée lorsque la somme rencontre son minimum. Il peut bien sûr exister plusieurs minimums, dans ce cas seul le premier sera conservé comme la position précédente. Avec l'ancienne position et la position actuelle du bloc, on peut calculer un vecteur de déplacement qui représente l'estimation du mouvement.

Le parcours de l'espace de recherche peut se faire selon diverses méthodes [31]. La plus simple et la plus gourmande en calcul est appelée Full Search (FS) ou encore Two-Dimensional Full Search (2DFS). Elle consiste à calculer la SAD pour tous les blocs de l'espace de recherche. Avec cette méthode, on est donc certain de trouver le minimum dans l'espace de recherche. Une autre méthode parcourt l'espace de recherche selon une dimension à la fois. Cette méthode, appelée One-Dimensional Full Search (ODFS) [8], teste d'abord toutes les blocs sur la ligne puis, à partir de la position du minimum sur

cette ligne, teste la colonne correspondante. Ce processus est répété une seconde fois sur un espace de recherche plus petit centré sur la position minimum trouvée lors de la première passe. Avec cette méthode, on réduit le nombre de calcul de SAD à effectuer. Il existe d'autres méthodes telles que le Three-Step-Search[7] ou encore le Four-Step-Search[26]. Ces méthodes utilisent toutes une procédure de recherche particulière pour trouver le minimum à l'intérieur de l'espace de recherche sans avoir à le parcourir en intégralité. Toutes ces méthodes permettent de réduire le coût de calculs de l'algorithme de BME.

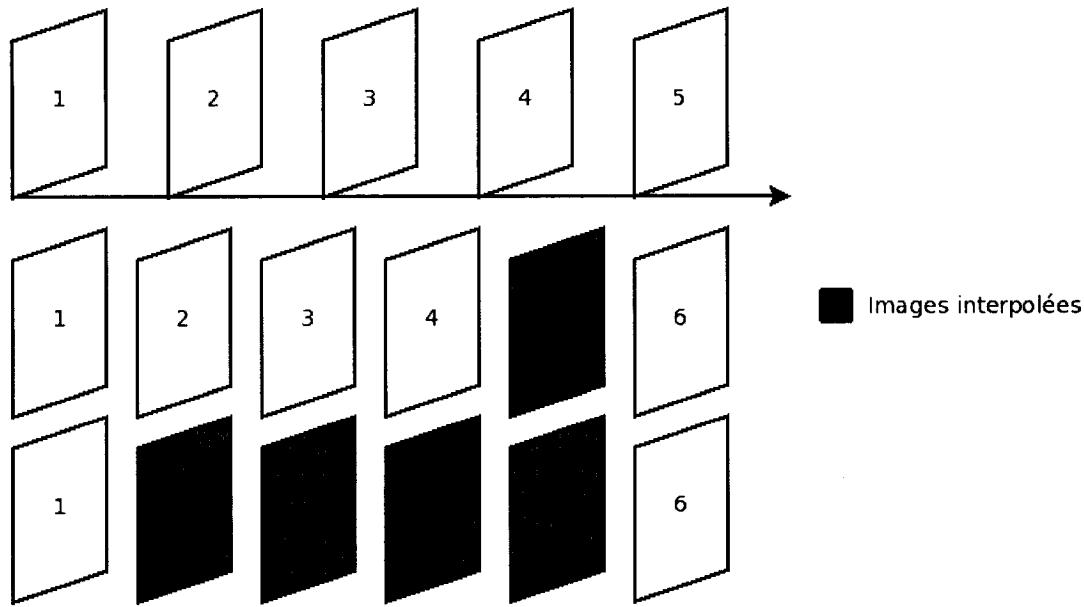

Pour conclure sur cette revue de littérature, il convient de noter ici un point important. Jusqu'ici nous avons considéré que l'augmentation du débit d'image consistait à simplement générer le bon nombre d'images supplémentaires pour compléter un flux vidéo. En théorie, la conversion d'un flux vidéo en un autre est plus complexe que le simple ajout d'un nombre fixé d'images. Dans un flux vidéo normal, chaque image est séparée de la suivante par un temps fixe. Au cinéma par exemple, il s'écoule  $1/24$  de seconde entre deux images. Les mouvements que l'on voit à l'écran sont donc le résultat de l'intégration de la vitesse des objets durant ce laps de temps. En reprenant la séquence de quatre images issues d'un film de cinéma et en considérant qu'on lui ajoute afin d'être en mesure de diffuser le film à la télévision une cinquième image, si l'on regarde les temps des mouvements entre les images on observe ceci : de 1 à 2 les mouvements correspondent à  $1/24$  de seconde, de même pour 2 vers 3 et pour 3 vers 4. Entre 4 et l'image créée, la 5, le temps du mouvement n'est de  $1/48$  et il est également de  $1/48$  entre cette image et la 6. Les temps de diffusion sont par contre de  $1/30$  entre chaque image. Les temps de diffusion ne correspondent donc plus aux temps des mouvements sur les images. Il faudrait alors recréer intégralement la séquence d'image pour faire correspondre les deux temps (diffusion et mouvement). Or, cela requiert d'importants efforts de calculs. De nombreux travaux [6, 15] se contentent de créer une cinquième image et de distordre les temps en essayant toutefois de limiter au maximum l'impact

FIG. 2.1 Conversion de débit de 24 fps vers 30 fps, deux solutions possibles

visuel de cette distortion. La figure 2.1 montre les deux solutions possibles pour convertir le débit d'un film de cinéma vers un film adapté à une diffusion télévisée (NTSC). La première solution présente de nombreux avantages :

- On conserve les données d'origine, lesquelles sont en général de meilleures qualité que ce que peut faire un algorithme de MC-FRC.

- L'effort de calcul est moins important puisqu'il ne faut créer qu'une seule image (au lieu de trois dans l'exemple).

- L'interpolation du mouvement est plus simple à implanter en matériel car elle s'obtient par une division par deux. On réduit ainsi la logique de calcul.

## 2.2 Algorithme simple

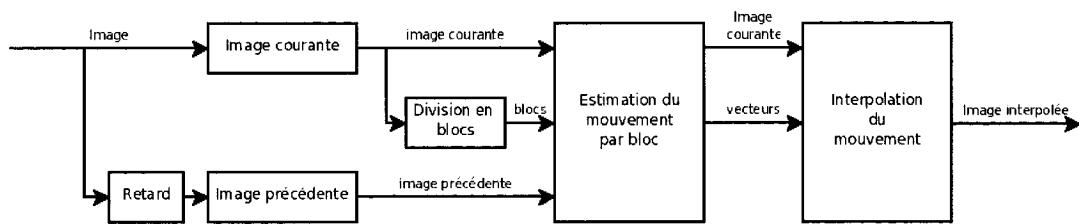

L'algorithme simple se base sur de l'estimation de mouvements de blocs. Il travaille avec 2 images référencées comme l'image courante et l'image précédente. L'image courante est divisée en blocs carrés de taille  $n$  ( $n$  peut prendre des valeurs entières variables mais qui doivent toutefois être des diviseurs de la hauteur et de la largeur de l'image). Les blocs sont contigus. Ensuite, pour chaque bloc de l'image, on cherche la position qu'il occupait dans l'image précédente à l'intérieur d'un espace de recherche de taille  $m$  centré autour de la position du bloc dans l'image courante. Le paramètre  $m$  indique que l'on va pouvoir tester toutes les positions allant de  $(-m, -m)$  à  $(m, m)$  relativement à la position du bloc considéré. La recherche dans cet espace peut se faire selon la méthode de Full Search (FS) ou selon ODFS, évoquées en 2.1. Une fois l'espace de recherche parcouru, on obtient la position estimée du bloc dans l'image précédente qui nous permet de calculer le vecteur de déplacement estimé. Ce vecteur est ensuite divisé par 2, puisqu'on cherche à générer une image située au milieu des images courante et précédente, pour obtenir la position qu'aurait le bloc dans l'image interpolée. Le bloc est ensuite déplacé selon ce vecteur pour générer l'image interpolée. La figure 2.2 présente un schéma du fonctionnement de cet algorithme. Un algorithme aussi simple ne donne pas des résultats de très grande qualité et, notamment, il arrive souvent que des pixels à l'intérieur de l'image interpolée soient orphelins, i.e s'ils n'ont pas été recouverts par un bloc déplacé. Ils restent donc nuls et se caractérisent par des rectangles noirs de tailles diverses dans l'image. Ces rectangles sont très visibles. Une correction simple consiste à copier à la place de ces pixels les valeurs des pixels à la même position dans l'image courante. Toutefois, même ainsi, le nombre d'artéfacts de blocs reste important et ces derniers sont visibles.

Les résultats de cet algorithme, dont on peut avoir un aperçu dans la figure 2.3, peuvent être améliorés de façon significative en procédant à plusieurs passes. Dans un

FIG. 2.2 Schéma de l'algorithme simple

FIG. 2.3 Exemple de résultat obtenu avec l'algorithme simple

FIG. 2.4 Résultat de l'interpolation avec la version optimisée de l'algorithme simple

premier temps, on calcule l'image interpolée en considérant les vecteurs de mouvement des blocs issus de l'image courante. On calcule ensuite une deuxième image où les mouvements considérés sont ceux des blocs de l'image précédente. On fusionne ensuite les deux images en procédant de la façon suivante : l'image issue des mouvements des blocs de l'image courante sert de base. Les pixels laissés intacts sur cette image (en noir donc) sont remplacés par les pixels de la deuxième image. La figure 2.4 montre un exemple de résultat obtenu en utilisant un tel algorithme. Bien entendu, la qualité est meilleure puisque les rectangles sombres sont effacés mais un certain nombre d'artefacts restent visibles sur l'image.

En réalité, l'algorithme simple est davantage une base commune à tous les algorithmes de MC-FRC basés sur des techniques d'estimation de mouvements par blocs (BME). En effet, il faut d'abord estimer le mouvement des blocs. Une fois les vecteurs de déplacements obtenus, l'algorithme doit s'assurer, d'une part, de leur validité et, d'autre part, de la façon de les utiliser correctement afin d'obtenir un résultat convainquant. S'assurer de la validité d'un vecteur est une tâche complexe puisqu'elle requiert de posséder

FIG. 2.5 Schéma de l'algorithme complexe

une métrique d'erreur. C'est cette difficulté qui différencie le fonctionnement d'un codec vidéo avec un algorithme de MC-FRC. Dans le cas des encodeurs vidéos, les erreurs éventuelles sur les vecteurs de mouvement sont corrigées par l'ajout d'une image représentant l'erreur entre l'image estimée par le mouvement et l'image réelle. Dans le cas de l'augmentation du débit, on ne possède pas l'image réelle et il est donc impossible de connaître l'erreur entre les deux images. Pour s'assurer de l'exactitude des vecteurs, on doit alors procéder à des raffinements ou bien introduire une mesure qui vise à détecter les vecteurs erronés. Ces deux solutions ajoutent en complexité et en temps à l'algorithme. L'utilisation des vecteurs est aussi une étape importante. Une utilisation simple (qui consiste à déplacer les blocs selon le vecteur estimé) présente beaucoup d'inconvénients dont le plus flagrant est la discontinuité observée dans l'image interpolée. Il faut donc opter pour des solutions plus évoluées comme le recouvrement des blocs. Tout ceci ajoute encore à la complexité globale de l'algorithme.

### 2.3 Algorithme complexe

L'algorithme complexe utilisé au cours des travaux présentés dans ce mémoire est basé sur l'algorithme présenté dans les travaux de Choi et al [9]. Cet algorithme utilise également une technique d'estimation de mouvement de bloc (BME) mais il cherche à affiner le résultat en appliquant un certain nombre de traitements supplémentaires.

FIG. 2.6 Détails de l'estimation bidirectionnelle de mouvement

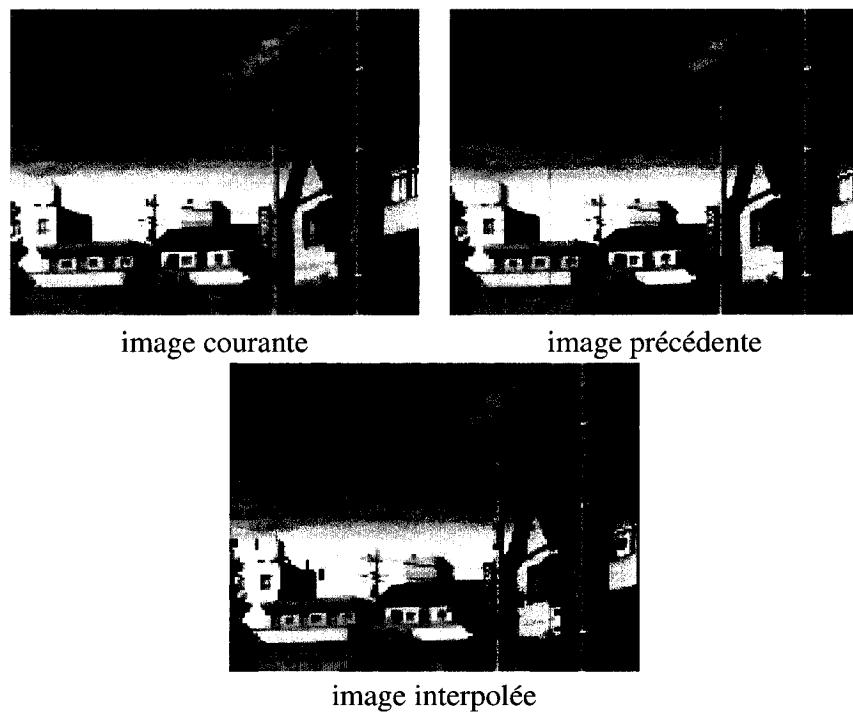

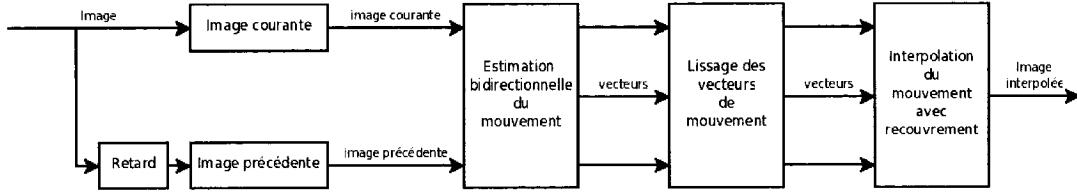

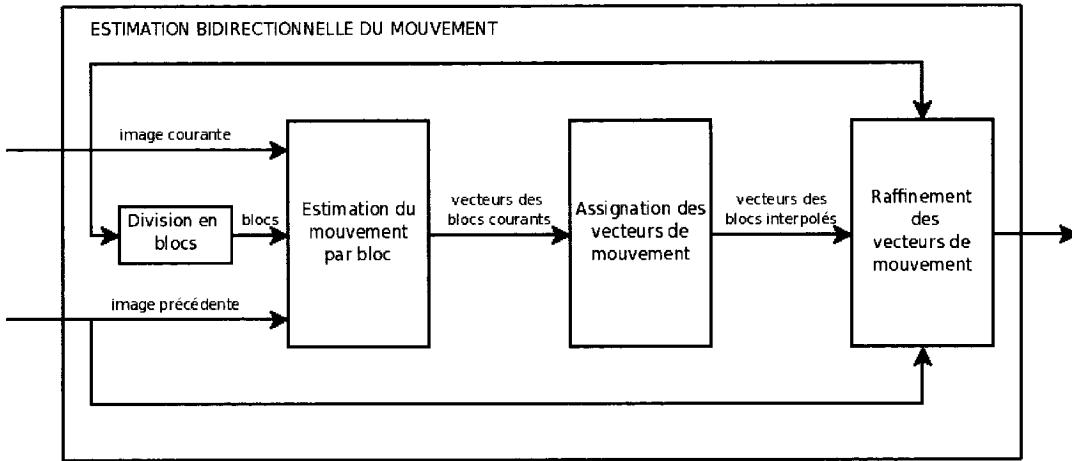

L'algorithme fonctionne en trois grandes étapes, comme montré dans la figure 2.5 : estimation de mouvements bidirectionnels, lissage des vecteurs de mouvement et interpolation par recouvrement de blocs. La première étape consiste donc à évaluer le mouvement des blocs. Toutefois, dans le cas de cet algorithme, on ne cherche plus à évaluer le mouvement des blocs de l'image courante ni de ceux de l'image précédente, mais bien de ceux de l'image qui sera interpolée. Pour cela, on crée une image vide qui deviendra l'image interpolée et on la découpe en blocs. On associe ensuite à chaque bloc un vecteur de mouvement qu'on a estimé en assignant des vecteurs issus de l'estimation du mouvement de l'image courante vers l'image précédente. L'assignation se fait en regardant quel bloc courant et le plus susceptible de correspondre au bloc de l'image interpolée considérée. Pour cela il suffit de regarder quel bloc de l'image courante, lorsqu'il est déplacé de la moitié de son vecteur de mouvement, recouvre le mieux le bloc de l'image interpolée. Le terme bidirectionnel provient donc du fait que les vecteurs trouvés permettent de déterminer la position du bloc de l'image interpolée dans l'image précédente ainsi que dans l'image courante. Le vecteur ainsi trouvé est ensuite raffiné pour offrir une meilleure qualité. Le raffinement consiste à faire tourner légèrement le

FIG. 2.7 Résultat de l'interpolation avec l'algorithme complexe comparé à l'algorithme simple

vecteur sur lui même et à conserver le meilleur vecteur. Ce dernier étant déterminé par un calcul de distance entre les blocs courants et précédents qui pointent à un endroit donné, le meilleur étant celui dont la distance est minimale. Cette partie de l'algorithme est détaillée dans le schéma de la figure 2.6. La seconde étape de l'algorithme, le lissage, consiste à comparer le vecteur de déplacement d'un bloc avec ceux de ses voisins afin d'éviter des erreurs de discontinuité. Enfin, la dernière étape consiste à créer l'image en utilisant ces vecteurs. La création de cette image utilise des techniques de recouvrement de blocs. On agrandit artificiellement la taille d'un bloc. Chaque pixel qui se retrouve dans une zone où plusieurs blocs se recouvrent est une moyenne des pixels issus de chacun des mouvements associés aux blocs. Ce procédé permet également d'éviter les discontinuités.

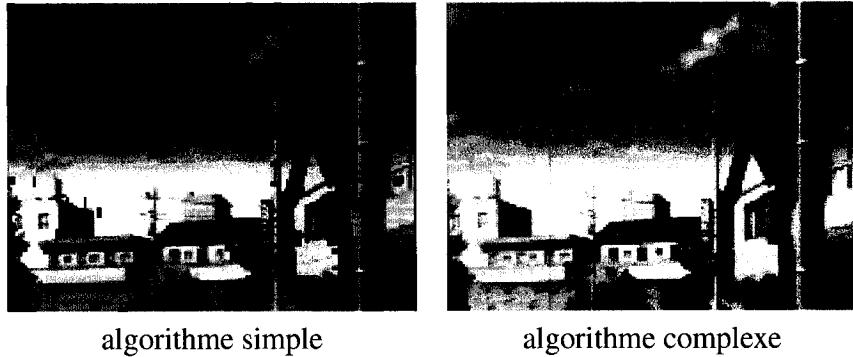

La figure 2.7 montre que les résultats de cet algorithme sont bien meilleurs que ceux de l'algorithme simple. Les images créées avec cet algorithme présente également un effet de flou qui provient de l'utilisation du recouvrement. Ce flou peut être aisément désactivé de façon logicielle, mais il permet également de corriger des défauts d'artéfacts trop visibles. Une fois intégrée à une vidéo, l'image apparaîtra sans défauts car le flou ne sera pas perçu étant, dans ce cas, un flou de mouvement classique, tandis que les

FIG. 2.8 Résultats avec défauts de l'algorithme complexe

défauts que le recouvrement permet de corriger pourraient être perçus. Toutefois, lorsque cet algorithme est confronté à des vidéos dans lesquelles les mouvements sont plus complexes, on observe toujours des défauts comme le montre la figure 2.8 avec notamment la raquette de tennis de table, ainsi que la main qui la tient, qui a disparu pour laisser la place à un ensemble informe de pixels.

En effet, bien que des efforts importants soient consentis pour améliorer la qualité de l'algorithme et de ses résultats, un certain nombre de défauts, inhérents à la technique utilisée, sont toujours visibles. Parmi les causes de ces défauts, on peut citer les objets invisibles (car beaucoup plus petits que la taille d'un bloc et dont l'influence sur les calculs de distance et donc sur la détermination des vecteurs de déplacement est très faible voire nulle), les collisions ou encore les mouvements trop amples. Le problème des objets invisibles est que la taille des blocs utilisée ne permet pas à l'algorithme de les repérer dans l'image et donc d'en tenir compte, ils risquent donc, entre autre, de disparaître de l'image interpolée. Une solution consiste à réduire la taille des blocs, mais elle est limitée par un aspect important de bruit. En effet, un bloc de petite taille est

plus susceptible d'être influencé par le bruit dans l'image. De plus, une petite taille ne permet pas de discriminer de manière efficace les blocs entre eux ; on risque donc de se retrouver avec plus d'erreurs d'estimation lorsqu'une petite taille est utilisée. Les collisions surviennent lorsqu'un objet est caché par un autre. Imaginons deux trains roulant en sens inverse, le train sur la voie la plus éloignée est caché par le second train lorsque ces derniers se croisent. Dans ce cas-ci, l'algorithme risque d'introduire des erreurs dans la zone de l'image où les deux trains se rejoignent car un des blocs disparaît. C'est ce qu'on observe sur la figure 2.8 avec la raquette qui passe devant l'épaule du joueur. Le problème des mouvements trop amples quant à lui concerne davantage la taille de l'espace de recherche dans l'image. Ce dernier est le résultat de l'hypothèse que le mouvement dans l'image n'excède pas une valeur déterminée. Ainsi, pour que cela fonctionne, aucun objet ne doit se déplacer plus rapidement que la limite fixée. Bien entendu, une telle supposition est irréalisable dans une situation normale. Il suffit pour s'en convaincre d'imaginer un match de tennis au cours duquel les balles peuvent atteindre une vitesse de plus de 200 km/h qui peut se traduire par des vitesses à l'écran (mesurées en pixel par seconde) très importante selon la position de la caméra.

## 2.4 Problématique

Les deux algorithmes, le simple et le complexe, réalisent beaucoup de calculs de distance entre des blocs de pixels pour déterminer le mouvement dans l'image ainsi que pour améliorer cette estimation (dans le cas du complexe). Ils nécessitent donc un grand effort de calculs pour être réalisés. Dans le cas de l'algorithme simple, le coût des calculs peut être réduit en utilisant un algorithme de parcours de l'espace de recherche plus intelligent pour le BMA. Cependant, le nombre de calculs et la bande passante mémoire nécessaire restent élevés. Pour l'algorithme complexe, les différentes étapes effectuées requièrent davantage de calculs, surtout si l'on considère les divisions réalisées dans le

BMA.

C'est une grosse difficulté reliée à ces algorithmes. En effet cela empêche de les exécuter en temps réel sur un processeur RISC de faible complexité lorsque des flux vidéos de taille normale ou en Haute-Définition sont considérés. Le but étant de réaliser l'algorithme de MC-FRC en temps réel, on ne peut donc pas utiliser ce type de processeur. Les processeurs de grandes complexité sont généralement contre-indiqués pour une application embarquée, à cause de leur coût et de la puissance qu'ils consomment.

Pour se donner une idée de l'ampleur de la tâche à réaliser, considérons le cas de l'algorithme simple utilisant la méthode FS pour le BMA. Lorsque ce dernier est lancé sur un processeur Xtensa à architecture RISC (des chiffres très semblables seraient obtenus sur d'autres types de processeurs RISC 32 bits), il requiert 67 millions de cycles d'horloge pour interpoler une seule trame en travaillant sur des images de taille réduite (160 par 120 pixels). Si on considère une horloge de 300MHz pour ce processeur, il peut générer 4.4 images par seconde. C'est clairement insuffisant puisque par exemple passer de 50 Hz à 60 Hz impose de créer au moins 10 images par seconde.

La solution retenue pour ce projet est la création d'un jeu d'instructions spécialisé pour compléter le jeu standard. Le chapitre suivant présente les jeux d'instructions créés pour les deux algorithmes.

## CHAPITRE 3

### CRÉATION D'UN JEU D'INSTRUCTIONS SPÉCIALISÉ

Dans ce chapitre, les méthodes et solutions retenues lors de la création des jeux d'instructions spécialisés sont présentées. Ce chapitre présente également les jeux d'instructions créés et fait l'analyse de leur impact sur les algorithmes. Il débute par la section 3.1 qui présente le cas de l'algorithme simple. La section 3.2 présente ensuite le cas de l'algorithme complexe. Les sections 3.3 et 3.4 présentent respectivement les approches pour vérifier les instructions et pour les utiliser dans les programmes C.

Pour faciliter la compréhension de ce chapitre, il convient de présenter ici certaines des conventions adoptées pour décrire les jeux d'instructions. Pour se référer dans l'image, on utilise le pixel en haut à gauche comme base de départ. L'axe des abscisses est croissant de la gauche vers la droite, celui des ordonnées croit vers le bas. En d'autres termes, le pixel en haut à gauche est situé en (0,0) et celui en bas à droite en (w-1,h-1) où w et h sont respectivement la largeur et la hauteur de l'image. La position (x,y) d'un bloc dans une image est la position (x,y) de leur pixel en haut à gauche. Tous les blocs sont considérés carrés.

#### 3.1 Le jeu d'instructions créé pour l'algorithme simple

Le jeu d'instructions créé pour l'algorithme simple et les résultats obtenus avec ce dernier ont fait l'objet d'une publication à la conférence SIPS2006 [3] ainsi qu'une soumission au Journal of DSP Technologies [4].

### 3.1.1 Registres pour la réutilisation : blocs et paramètres de l'algorithme

Pour l'algorithme simple, le jeu d'instructions a été créé en suivant un principe simple. Dans l'algorithme, on constate en effet que l'unité de base est le bloc d'une image. Les calculs sont faits entre les blocs et on s'intéresse au mouvement d'un bloc. Le jeu d'instructions spécialisé cherche donc à reproduire cet aspect de l'algorithme en intégrant ce module de base, le bloc, dans le processeur. Un bloc représente une surface carrée de pixels de l'image, ce sont donc des données sur lesquelles on réalise des calculs comme la somme des valeurs absolues des différences (SAD). Pour tirer parti de ce fait, des registres sont créés afin de contenir l'ensemble des pixels d'un bloc. Dans le cas du jeu d'instruction créé, ces registres sont larges de 128 bits et peuvent contenir des blocs de taille 4x4 pixels, où chaque pixel est représenté sur une valeur de 8 bits. Ce choix impose une limitation sur l'algorithme car la taille des blocs, originellement un paramètre de l'algorithme, est bloquée. Ces nouveaux registres sont créés dans un fichier de registre. Ceci permet une utilisation moins limitative que des registres d'état. Ces registres spécifiques seront appelés registres-bloc dans la suite de ce document.

Les registres d'états sont utilisés pour contenir les paramètres de l'algorithme ainsi que des données auxquelles les calculs font souvent appel. Notamment, les adresses mémoire des images traitées sont stockées dans des registres d'état spécifiques. Ces registres possèdent également l'avantage de permettre aux instructions de fonctionner avec plus de données que la limite architecturale (due à l'encodage des instructions) de trois valeurs.

### 3.1.2 Liste des instructions

Le tableau 3.1 présente une liste des instructions créées rangées par catégorie. Chaque instruction est décrite sommairement et le tableau indique également le nombre

TAB. 3.1 Listes des instructions pour l'algorithme simple

| Catégorie     | Nom               | Description                                                                                                                                                                      | T   | HK | Net | Cyc |

|---------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|-----|-----|

| Chargements   | <i>cloadline</i>  | Charge une ligne (4 pixels) du bloc de l'image courante selon la position (x,y) du premier pixel.                                                                                | 4   | 0  | 4   | 2   |

|               | <i>ploadline</i>  | Idem mais pour l'image précédente.                                                                                                                                               | 4   | 0  | 4   | 2   |

| Calculs       | <i>dist</i>       | Calcule la distance SAD entre un bloc courant et quatre blocs précédents.                                                                                                        | 192 | 0  | 192 | 2   |

|               |                   |                                                                                                                                                                                  |     |    |     |     |

| Paramétriques | <i>indexc</i>     | Calcule l'index d'un pixel dans le tableau à partir de sa position (x,y).                                                                                                        | 14  | 0  | 14  | 2   |

|               | <i>wprecxy</i>    | Place dans un registre d'état la position du bloc précédent considéré.                                                                                                           | 2   | 2  | 0   | 1   |

|               | <i>wcurxy</i>     | Idem mais pour le bloc courant.                                                                                                                                                  | 6   | 6  | 0   | 1   |

|               | <i>min_sas1</i>   | Calcule la taille de l'espace de recherche et ses limites en fonction de la position du bloc et des paramètres.                                                                  | 3   | 0  | 3   | 1   |

|               | <i>min_sas2</i>   |                                                                                                                                                                                  | 3   | 0  | 3   | 1   |

|               | <i>max_sas</i>    |                                                                                                                                                                                  | 3   | 0  | 3   | 1   |

|               | <i>multi</i>      | Multiplicateur 16 bits pour calculer y.w.                                                                                                                                        | 1   | 0  | 1   | 2   |

|               | <i>movblr</i>     | Extrait les lignes d'un registre bloc et les place dans un registre normal                                                                                                       | 4   | 4  | 0   | 1   |

| Automatiques  | <i>ld.bloc128</i> | Instructions pour charger, sauvegarder et déplacer les registres bloc. Crées automatiquement par les outils pour que le compilateur C puisse gérer le nouveau banc de registres. | 1   | 0  | 1   | 1   |

|               | <i>st.bloc128</i> |                                                                                                                                                                                  | 1   | 0  | 1   | 1   |

|               | <i>mv.bloc128</i> |                                                                                                                                                                                  | 1   | 0  | 1   | 1   |

d'opérations effectuées dans l'instruction ainsi que la nature de ces opérations. Les opérations équivalentes que réalise l'instruction peuvent en effet être de deux natures différentes : elles peuvent être nettes (colonne Net), c'est à dire qu'elles participent au déroulement de l'algorithme comme par exemple les opérations réalisées par l'instruction *dist*, ou elles sont présentes pour permettre le fonctionnement du jeu d'instructions et ne découlent pas de l'algorithme. Dans ce dernier cas, elles sont dites de maintenance (colonne HK pour House-Keeping) comme par exemple pour l'instruction *wcurxy*. Le total du nombre d'opérations effectuées par une instruction est indiqué dans la colonne T. Le nombre de cycles nécessaires pour réaliser l'instruction est fourni dans la colonne Cyc.