**Titre:** Caractérisation de la gigue et de l'étalement spectral du circuit

Title: DDPS

**Auteur:** Max-Élie Salomon

Author:

**Date:** 2007

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Salomon, M.-É. (2007). Caractérisation de la gigue et de l'étalement spectral du circuit DDPS [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/8022/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/8022/>

PolyPublie URL:

**Directeurs de recherche:** Abdelhakim Khouas, & Yvon Savaria

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

CARACTÉRISATION DE LA GIGUE ET DE L'ÉTALEMENT

SPECTRAL DU CIRCUIT DDPS

MAX-ÉLIE SALOMON

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(MICRO-ÉLECTRONIQUE)

JUILLET 2007

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-35698-2

*Our file* *Notre référence*

ISBN: 978-0-494-35698-2

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

CARACTÉRISATION DE LA GIGUE ET DE L'ÉTALEMENT

SPECTRAL DU CIRCUIT DDPS

Présenté par : SALOMON Max-Elie

En vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

A été dûment accepté par le jury d'examen constitué de :

M. BOYER François-R., PhD, président

M. KHOUAS Abdelhakim, PhD, membre et directeur de recherche

M. SAVARIA Yvon, PhD, membre et codirecteur de recherche

M. LANGLOIS Pierre, PhD, membre

## Remerciements

J'aimerais remercier M. Abdelhakim Khouas pour m'avoir au départ accueilli au sein du Groupe de Recherche en Microélectronique (GRM) en me proposant de travailler sur le sujet de cette recherche, en collaboration avec Yvon Savaria. Le support financier obtenu de la part de ce dernier, ainsi que par la compagnie Gennum, fut indispensable à la poursuite de mes travaux de recherche. La patience dont ont fait preuve mes directeurs de recherche, ainsi que les nombreux conseils et suggestions obtenus lors de l'écriture d'articles ou lors de l'interprétation de résultats sont grandement appréciés.

Je tiens également à remercier Nathalie Lévesque, commis aux affaires étudiantes au sein du département de génie électrique, pour sa bonne humeur et son empressement à m'aider à m'y retrouver dans le processus administratif de mes études. Un grand merci également à Ghyslaine Éthier-Carrier, secrétaire du GRM, pour sa gestion des activités du GRM.

## Résumé

Cet ouvrage présente un algorithme automatisé pouvant prédire à la fois la position et l'amplitude des raies spectrales causées par les diverses sources de gigue affectant de façon périodique le signal produit par synthèse directe numérique de phase (DDPS). L'algorithme présenté a permis de réduire de plusieurs minutes à une fraction de seconde le temps de requis pour calculer de façon précise le contenu spectral du signal de sortie. Ceci a par la suite permis d'effectuer des analyses plus approfondies en automatisant le calcul de la variation des performances spectrales selon les paramètres d'opération. Il en ressort des principes généraux guidant le design du circuit en fonction des contraintes à respecter.

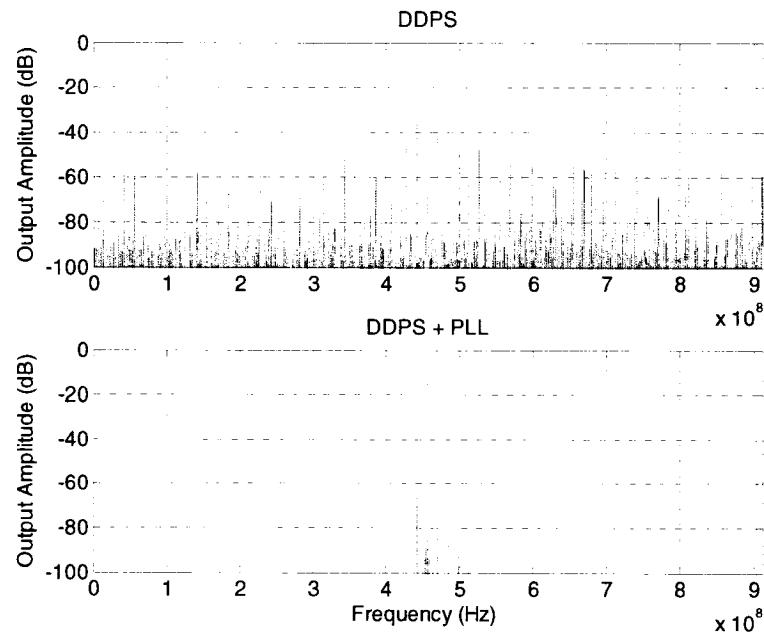

Certaines applications du DDPS (communications) nécessitent un contenu spectral propre. Cette nouvelle connaissance du lien entre le mode de fonctionnement du circuit et ses performances spectrales, qui découle de la possibilité d'effectuer des calculs sur des centaines de configurations, nous mène à explorer des modifications au circuit DDPS. Celles-ci améliorent les performances en réduisant l'amplitude du niveau de bruit, et en modifiant le profil spectral du signal produit. Finalement, une architecture hybride alliant le DDPS à une boucle de verrouillage de phase est également explorée. Elle permet à toutes fins pratiques d'éliminer les raies hors-bande. Les résultats sont issus de simulations et la comparaison de l'allure du spectre avec et sans les améliorations proposées dénote une atténuation de l'amplitude des raies spectrales nuisibles, aussi connues sous le terme de « spurs ». Par exemple, pour l'une des techniques explorées,

une réduction de 20dB l'amplitude du bruit entourant la fréquence d'horloge générée a été obtenue.

## Abstract

This thesis presents an automated algorithm for predicting both the position and the magnitude of spurs generated by different sources of jitter on a periodic signal. The case being studied here is the Direct Digital Period Synthesis (DDPS), a relatively new frequency synthesis architecture. An algorithm is presented that allows to reduce the computation time needed to accurately compute the spectrum of the signal and its spurious frequencies content from several minutes to a fraction of a second. This is a process that took a long time when it had to be performed by simulation. This improvement has in turn allowed performing deeper analyses when automating computation of spectral performance related to DDPS operating conditions. Some general principles are deduced that help guide circuit design according to various constraints.

Some DDPS applications (communications) require a clean spectral output. The new knowledge of the link between DDPS operation and its spectral performance, spurred by the possibility to compute the spectrum for hundreds of configurations, leads us to explore modifications to the circuit. These improve the performance by reducing the magnitude of the noise level, and by modifying the spectral profile of the DDPS output. Finally, a hybrid architecture combining a DDPS to a phase-locked loop is also explored. It basically allows removing out of band spurs. The results from simulations comparing the spectra of the proposed improvements with the regular DDPS show a decrease in the magnitude of unwanted spurs. For example, for one of the techniques explored, an

example shows a reduction of 20 dB in the magnitude of noise surrounding the generated clock frequency.

## Table des matières

|                                                |      |

|------------------------------------------------|------|

| Remerciements.....                             | iv   |

| Résumé.....                                    | v    |

| Abstract .....                                 | vii  |

| Table des matières.....                        | ix   |

| Liste des tableaux.....                        | xii  |

| Liste des figures .....                        | xiii |

| Liste des sigles et abréviations.....          | xv   |

| 1 Introduction.....                            | 1    |

| 1.1 Les circuits de synthèse de fréquence..... | 1    |

| 1.2 Applications .....                         | 2    |

| 1.2.1 Télécommunications .....                 | 2    |

| 1.2.2 Audio/Video.....                         | 4    |

| 1.3 Objectifs de cette recherche .....         | 6    |

| 1.4 Organisation du mémoire.....               | 8    |

| 2 Revue de la littérature pertinente .....     | 10   |

| 2.1 Concepts utiles.....                       | 11   |

| 2.1.1 Gigue.....                               | 11   |

| 2.1.2 Quantification .....                     | 12   |

| 2.1.3 Spectre fréquentiel .....                | 12   |

| 2.1.4 Circuit LFSR.....                        | 16   |

|       |                                                       |    |

|-------|-------------------------------------------------------|----|

| 2.1.5 | Circuit de modulation delta sigma .....               | 17 |

| 2.2   | Circuits de Synthèse de fréquence .....               | 20 |

| 2.2.1 | Circuits de synthèse indirecte .....                  | 20 |

| 2.2.2 | Synthèse directe .....                                | 24 |

| 2.3   | Fonctionnement du DDPS .....                          | 27 |

| 2.3.1 | Générateur de transitions .....                       | 28 |

| 2.3.2 | Accumulateur .....                                    | 32 |

| 2.3.3 | Sélection des transitions.....                        | 33 |

| 2.3.4 | Exemple de fonctionnement .....                       | 34 |

| 2.3.5 | Synthèse de fractions non binaires.....               | 34 |

| 2.4   | Synthèse de fréquence et modélisation spectrale.....  | 36 |

| 2.5   | Synthèse de fréquence et amélioration spectrale ..... | 39 |

| 3     | Simulation et observation du spectre du DDPS .....    | 41 |

| 3.1   | Distinction entre les niveaux de périodicité .....    | 42 |

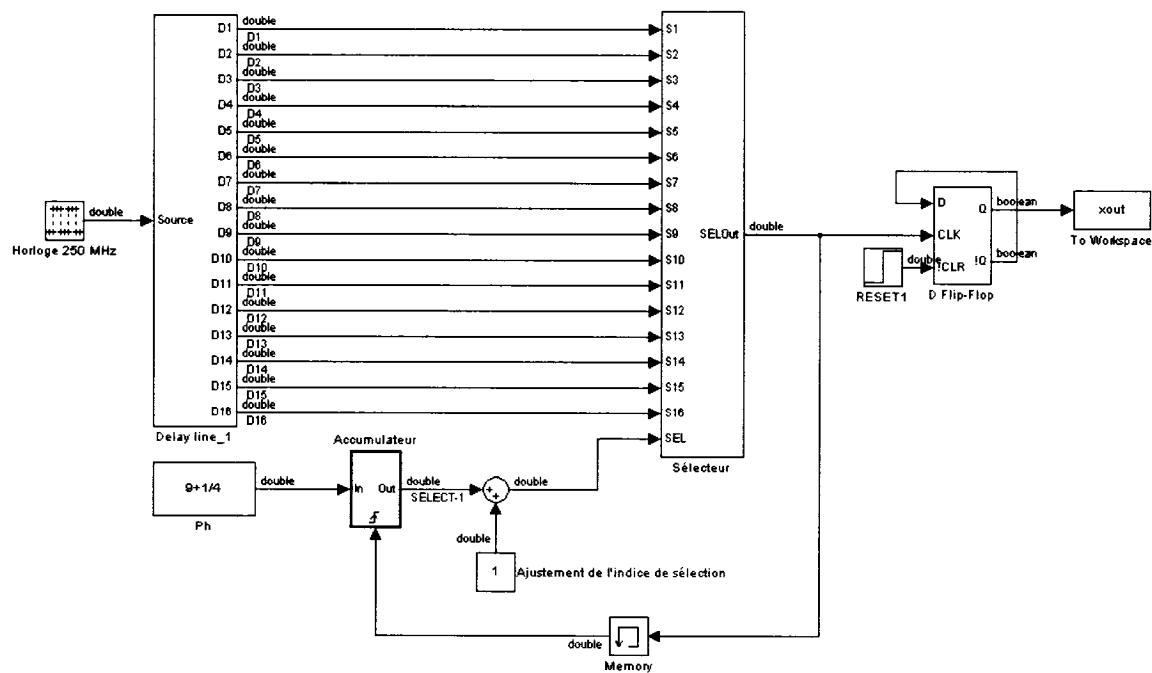

| 3.2   | Modèle de simulation.....                             | 43 |

| 3.3   | Utilisation du modèle de simulation .....             | 45 |

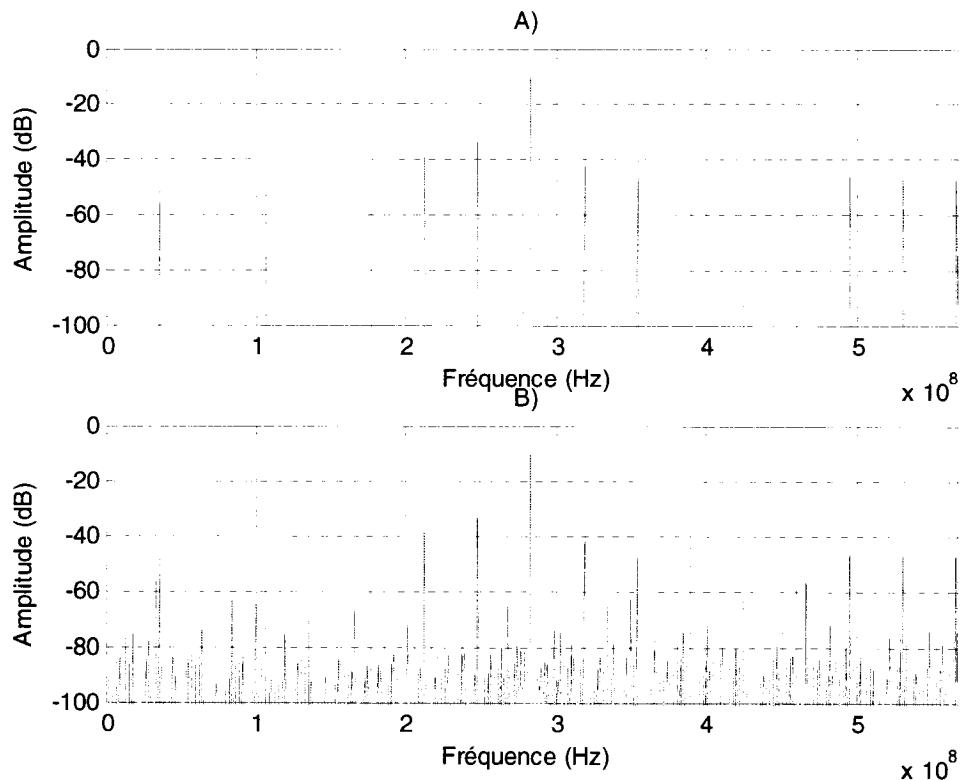

| 3.4   | Liens entre les périodicités et le spectre .....      | 46 |

| 4     | Modèle de prédiction spectrale du DDPS .....          | 48 |

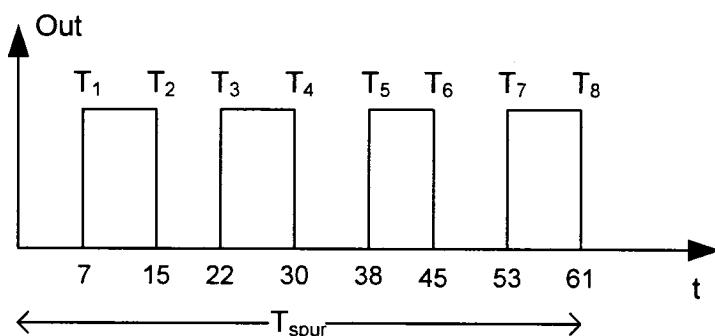

| 4.1   | Étude du cycle réel du signal de sortie.....          | 48 |

| 4.2   | Positions des spurs .....                             | 54 |

| 4.3   | Analyse de Fourier basée sur l'étude du cycle .....   | 55 |

| 4.4   | Algorithme .....                                      | 58 |

|       |                                                                                 |    |

|-------|---------------------------------------------------------------------------------|----|

| 4.5   | Formule analytique compacte pour les raies dues uniquement à la troncature..... | 59 |

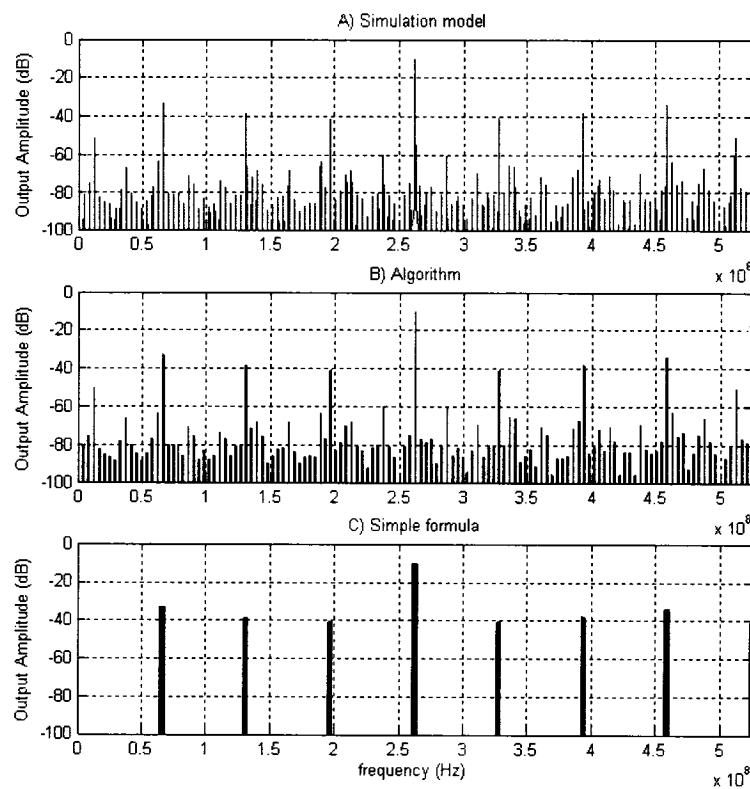

| 4.6   | validation de l'algorithme.....                                                 | 62 |

| 4.6.1 | Méthodologie de validation .....                                                | 63 |

| 4.6.2 | Observation des résultats .....                                                 | 64 |

| 4.7   | Étude des effets du mésappariement.....                                         | 67 |

| 4.7.1 | Paramètres de l'étude .....                                                     | 67 |

| 4.7.2 | Interprétation des résultats .....                                              | 69 |

| 5     | Paramètres de design et amélioration des performances du DDPS .....             | 73 |

| 5.1   | Choix des paramètres d'opération .....                                          | 74 |

| 5.1.1 | Choix du nombre de phases .....                                                 | 74 |

| 5.1.2 | Choix de la fréquence de référence.....                                         | 76 |

| 5.1.3 | Taille de l'accumulateur .....                                                  | 77 |

| 5.1.4 | Généralisation sur le choix de la valeur Ph.....                                | 78 |

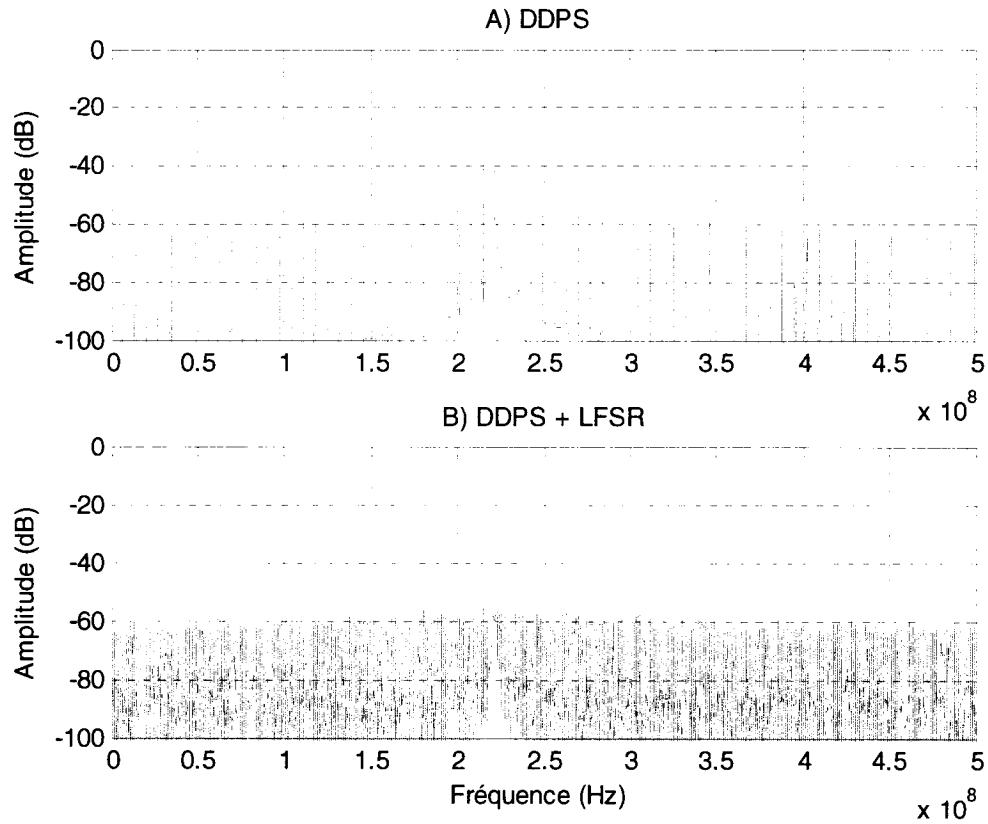

| 5.2   | Ajout de bruit à l'aide d'un LFSR.....                                          | 79 |

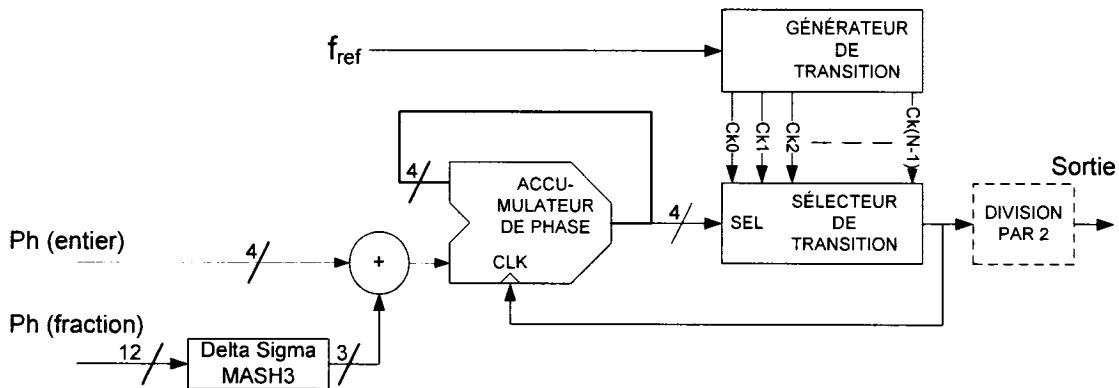

| 5.3   | Ajout de bruit par Modulation delta sigma.....                                  | 82 |

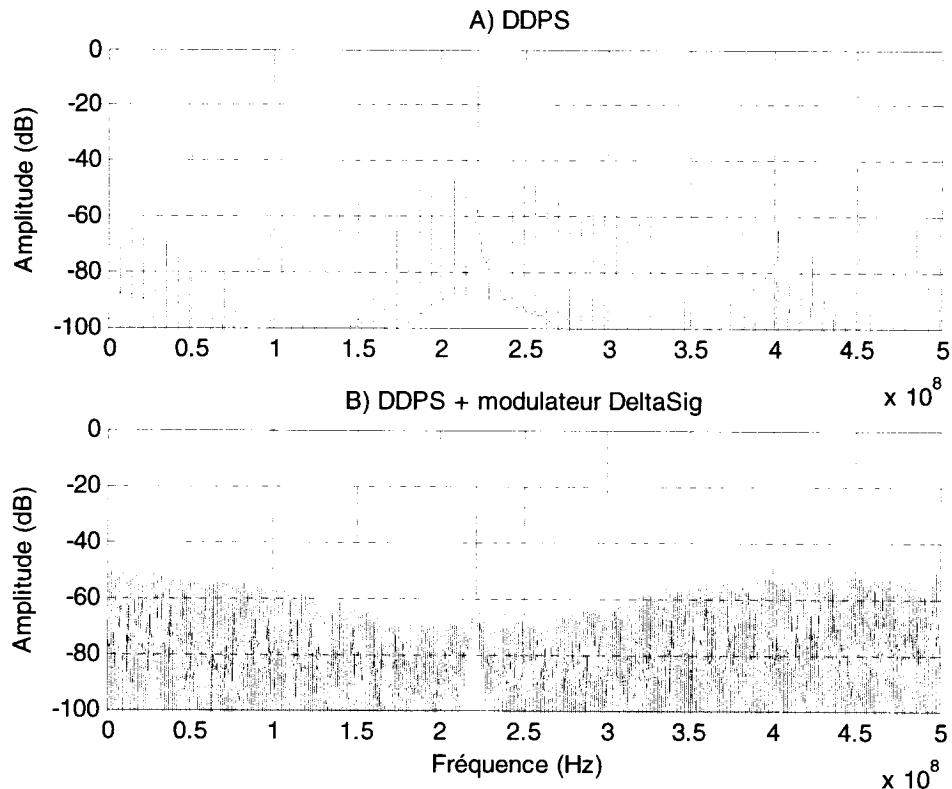

| 5.4   | Filtrage par la méthode de PLL .....                                            | 85 |

| 5.4.1 | Principe et application au DDPS.....                                            | 85 |

| 5.4.2 | Résultats de simulation .....                                                   | 87 |

| 6     | Conclusion .....                                                                | 89 |

|       | Références .....                                                                | 93 |

## Liste des tableaux

|                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------|----|

| Tableau 1 – Fréquences de réception et d'émission d'un appareil portable GSM.....                     | 3  |

| Tableau 2 – Échantillonnage requis par diverses applications .....                                    | 5  |

| Tableau 3 – Synchronisation Audio/Vidéo.....                                                          | 6  |

| Tableau 4 – Contenu de l'accumulateur et selection des phases ( $Ph = 9 + \frac{1}{4}, 2^M = 16$ ) .. | 34 |

| Tableau 5 – Exemple des niveaux de cyclicité du DDPS.....                                             | 50 |

| Tableau 6 – Exemple où $R = 2$ .....                                                                  | 52 |

| Tableau 7 – Sous groupes de selection de cellules .....                                               | 53 |

| Tableau 8 – Séquence du résidu dans l'accumulateur.....                                               | 61 |

| Tableau 9 – Résultats de comparaison des raies.....                                                   | 66 |

| Tableau 10 – Temps de simulation .....                                                                | 67 |

| Tableau 11 – Exemples de vecteurs de mésappariement selon la valeur crête en %.....                   | 68 |

| Tableau 12 – Résultats du SNR pour diverses conditions de mésappariement et valeurs de Ph .....       | 69 |

| Tableau 13 - Comparaison de DDPS opérant au même Ph .....                                             | 77 |

## Liste des figures

|                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------|----|

| Figure 1 – Spectre: a) d'une sinusoïde et b) d'une onde carrée .....                                        | 13 |

| Figure 2 – Sommes des sinusoïdes d'une onde carrée (1, 2 et 3 premiers termes) .....                        | 14 |

| Figure 3 – Spectre d'une onde carrée additionnée de bruit blanc .....                                       | 15 |

| Figure 4 – LFSR correspondant au polynôme $x^{11} + x^{13} + x^{14} + x^{16} + 1$ .....                     | 16 |

| Figure 5 – Modulateur delta sigma de type MASH3 .....                                                       | 18 |

| Figure 6 –MASH3 avec la logique de correction .....                                                         | 19 |

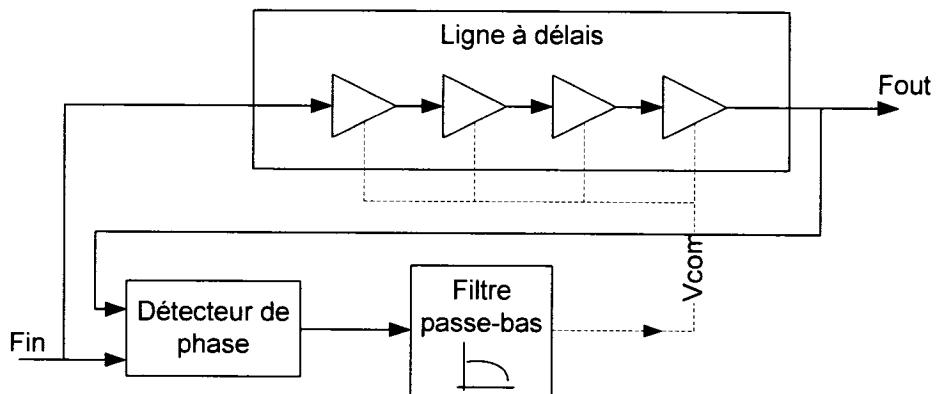

| Figure 7 – Architecture d'un "Phase-Locked Loop" (PLL).....                                                 | 21 |

| Figure 8 – PLL de type "fractional-N".....                                                                  | 22 |

| Figure 9 – "Delay-Locked Loop" .....                                                                        | 23 |

| Figure 10 – Synthèse Numérique Directe (DDS) .....                                                          | 24 |

| Figure 11 – Principe de fonctionnement du DDPS.....                                                         | 26 |

| Figure 12 – Schéma du DDPS .....                                                                            | 28 |

| Figure 13 – Phases générées par une boucle de délais.....                                                   | 30 |

| Figure 14 – Signaux Ck0 à Ck7 générés par 4 inverseurs en paire différentielle.....                         | 31 |

| Figure 15 – Circuit de sélection des transitions.....                                                       | 33 |

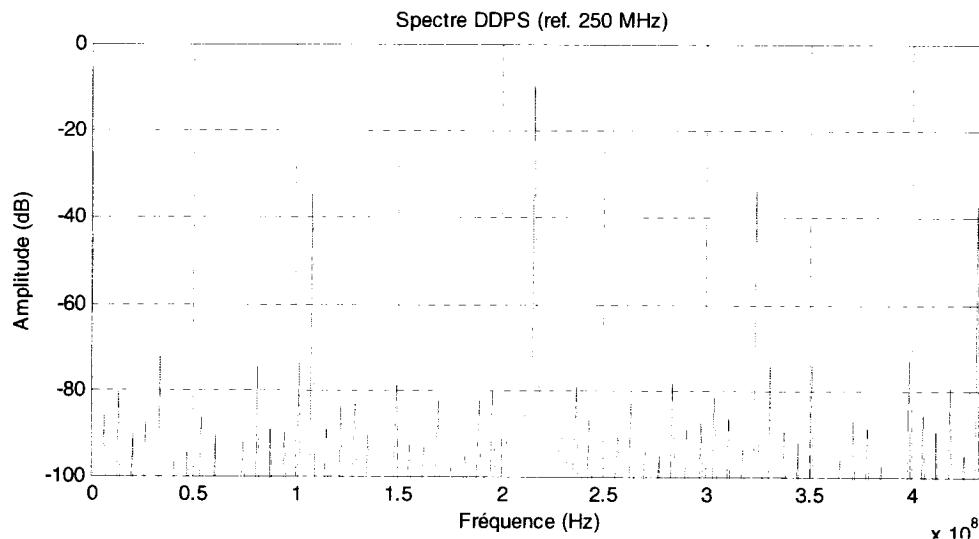

| Figure 16 – Contenu spectral de l'horloge générée par le DDPS.....                                          | 41 |

| Figure 17 – Modèle de simulation du DDPS dans Simulink .....                                                | 43 |

| Figure 18 – Spectres pour l'exemple choisi a) absence de mésappariement b) présence de mésappariement ..... | 46 |

| Figure 19 - Exemple lié aux instants de transition Ti .....                                                 | 57 |

|                                                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 20 – Comparaison des résultats spectraux .....                                                                             | 64 |

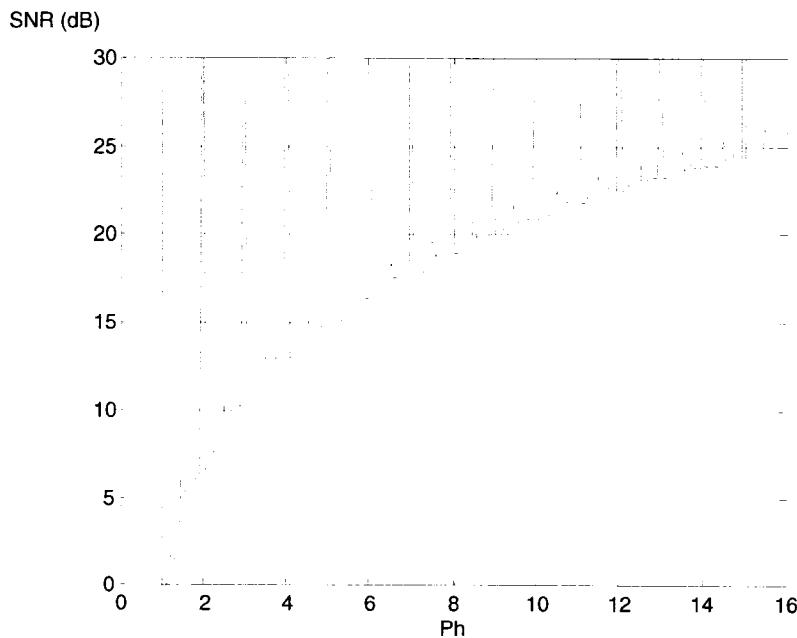

| Figure 21 – Valeurs en dB du SNR pour Ph allant de 1 à 16 .....                                                                   | 70 |

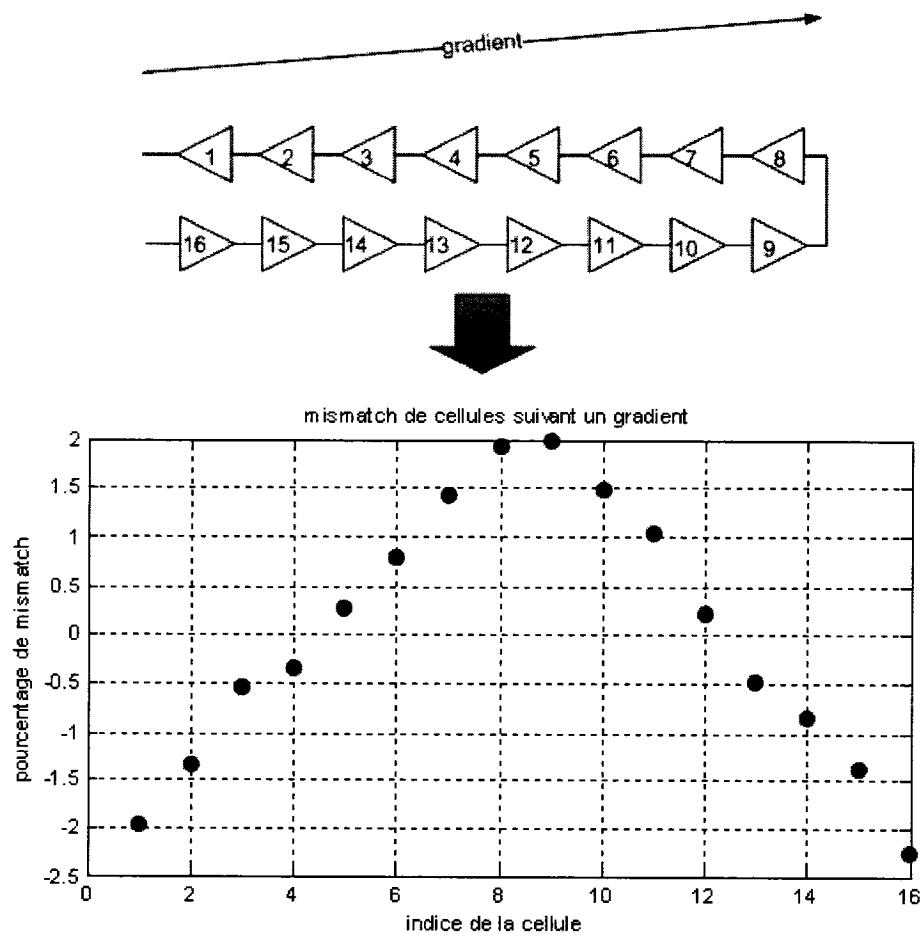

| Figure 22 – Mésappariement suivant une distribution en gradient.....                                                              | 72 |

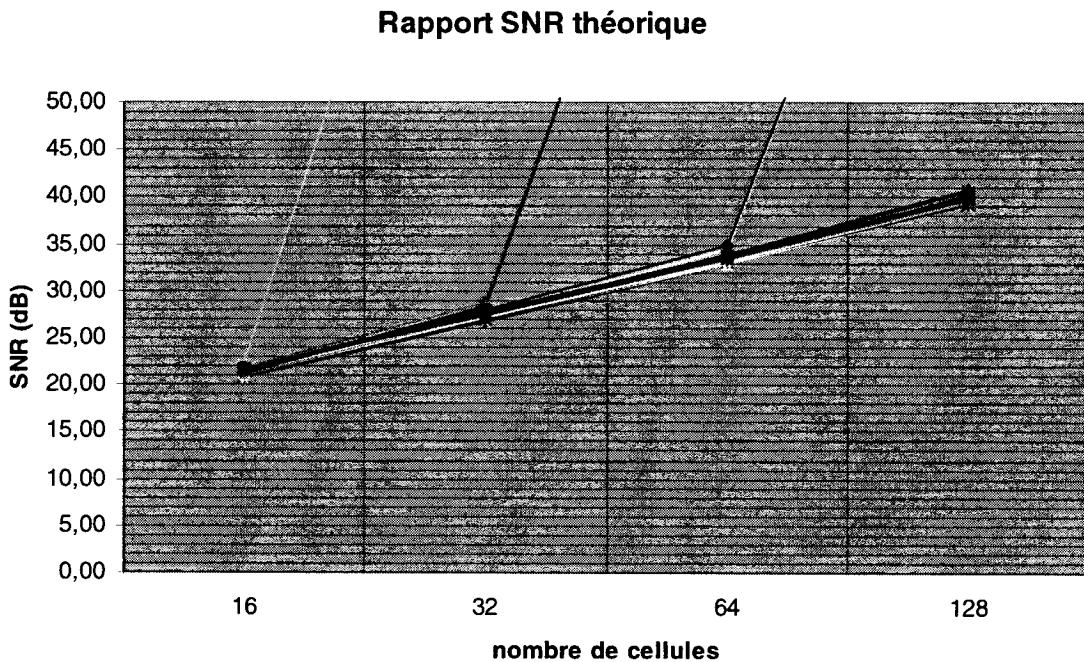

| Figure 23 - Rapport SNR théorique selon le nombre de cellules (courbes servant<br>uniquement à relier les points calculés) .....  | 75 |

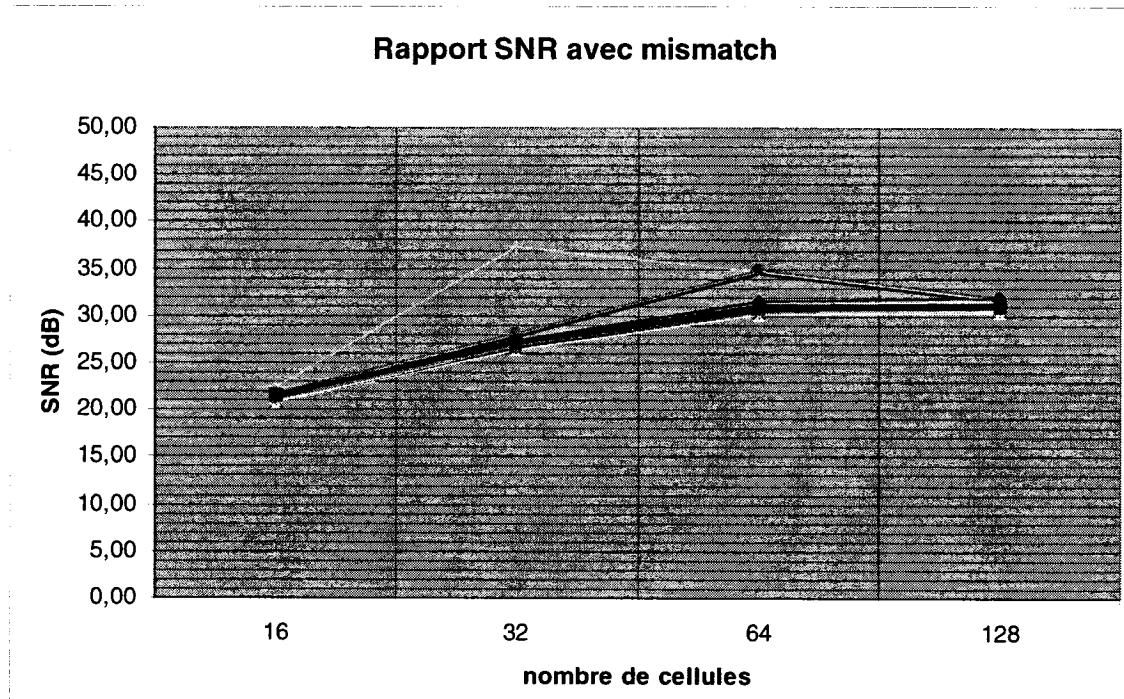

| Figure 24 - Rapport SNR en intégrant l'effet du mésappariement (courbes servant<br>uniquement à relier les points calculés) ..... | 76 |

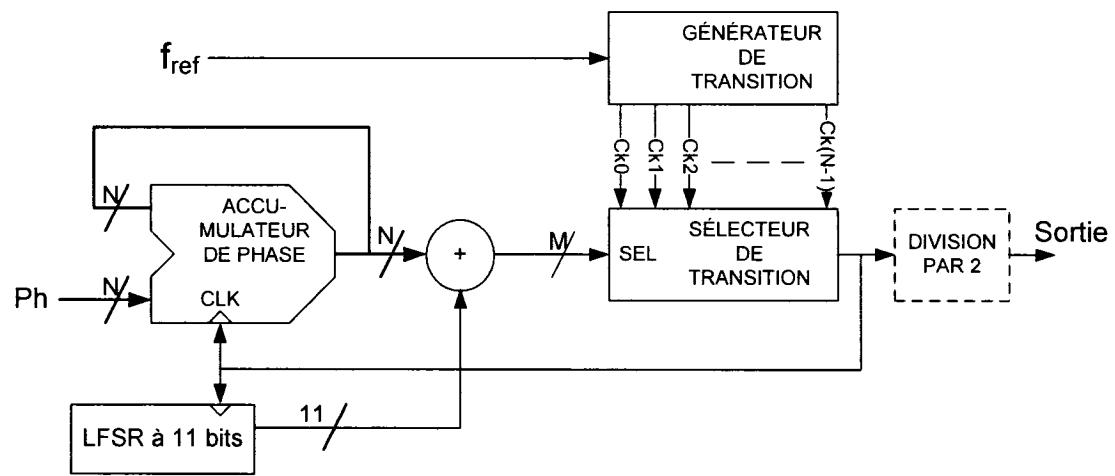

| Figure 25 – Circuit issu du jumelage entre un LFSR et le DDPS .....                                                               | 80 |

| Figure 26 - Amélioration spectrale suite à l'ajout de bruit avec un LFSR .....                                                    | 81 |

| Figure 27 – Jumelage entre le DDPS et un modulateur delta sigma .....                                                             | 83 |

| Figure 28 - Amélioration spectrale suite à l'ajout d'un modulateur Delta Sigma .....                                              | 83 |

| Figure 29 – PLL synchronisé au circuit DDPS.....                                                                                  | 86 |

| Figure 30 – Amélioration du spectre par la technique du PLL.....                                                                  | 88 |

## Liste des sigles et abréviations

ADC : Analog to Digital Converter

DAC : Digital to Analog Converter

DCDL : Digitally Controlled Delay Line

DDPS : Direct Digital Period Synthesizer

DDS : Direct Digital Synthesizer

DFT: Discrete Fourier Transform

DLL: Delay-Locked Loop

FFT: Fast Fourier Transform

GSM: Global System for Mobile Communications

LAN: Local Area Network

LFSR: Linear Feedback Shift Register

LUT: Look-up Table

LSB: Least Significant Bit

NTSC: National Television Standards Committee (norme de télévision américaine)

PAL: Phase Alternated Line (norme de télévision européenne)

PDA: Personal Digital Assistant

PLL: Phase-Locked Loop

RMS: Root Mean Square

SNR: Signal to Noise Ratio

UMTS: Universal Mobile Telecommunications System

VCO: Voltage Controlled Oscillator

W-CDMA: Wideband Code Division Multiple Access

# 1 Introduction

## 1.1 LES CIRCUITS DE SYNTHÈSE DE FRÉQUENCE

Les circuits et systèmes numériques utilisés en microélectronique, qu'il s'agisse d'un processeur, d'un circuit à application spécifique ou de tout autre type de circuit, se classent soit dans la catégorie des systèmes asynchrones, soit dans celle des systèmes synchrones. La plupart des circuits numériques utilisés de nos jours sont de type synchrone; ils requièrent la présence d'une horloge pour synchroniser à l'aide de registres les opérations effectuées par les transistors constituant la logique interne.

Cette horloge est un signal périodique dont la fréquence de répétition s'exprime généralement en Hertz, une unité qui signifie le nombre de répétitions par seconde. La fréquence à laquelle opère un circuit donné dépend de plusieurs facteurs liés à son utilisation prévue. Cependant, un circuit est tout de même soumis à des limites de fréquence imposées par ses caractéristiques physiques.

D'autre part, et c'est particulièrement le cas lorsqu'un circuit doit respecter un protocole de communication de données, une série de normes et de standards peut dicter la ou les fréquences d'opération. Dans un tel cas, il importe de disposer d'un signal ayant une fréquence précise et stable, ou même d'un signal pouvant alterner entre plusieurs valeurs de fréquence prédéterminées. Les circuits de synthèse de fréquence, dont celui à l'étude dans ce mémoire, visent à produire de tels signaux.

## 1.2 APPLICATIONS

### 1.2.1 Télécommunications

Les progrès dans le domaine des télécommunications ont engendré une quantité croissante de produits et applications disponibles au public. Par exemple, la technologie Bluetooth (ROGERS, G.S., 2003) est utilisée pour la synchronisation entre ordinateurs, organisateurs personnels (PDA) et téléphones cellulaires. Elle permet aussi l'utilisation d'appareils sans fils tels que microphones, écouteurs, claviers, etc. On dit que la gamme d'applications est appelée à s'accroître. Pour ce qui est de la plage de fréquences utilisée, ce système opère dans une bande non attribuée se situant au-dessus de 2.4 GHz. Pour la plupart des pays, la plage allouée est de 2.4 - 2.4835 GHz et elle est séparée en canaux d'une largeur de 1MHz.

Un second exemple d'application des circuits de synthèse de fréquence se situe au niveau de la téléphonie cellulaire (POOLE, I., 2006). Parmi les technologies dites de deuxième génération (2G), on retrouve la norme GSM (la plus importante, ayant dépassé le milliard d'utilisateurs mondialement en Février 2004). Cette norme utilise des bandes autour de 900MHz, 1800MHz ou 1900MHz, selon le système appliqué par le pays d'utilisation. En Amérique du Nord, la bande de 1900MHz est utilisée, bien que les appareils soient habituellement tri bande. Au niveau de la synthèse de fréquence, un appareil tri bande doit être en mesure de pouvoir émettre les fréquences incluses dans les plages contenues dans le tableau 1. L'espacement entre les différents canaux au sein d'une plage de fréquence est de 200 kHz.

**Tableau 1 – Fréquences de réception et d'émission d'un appareil portable GSM**

| <b>Bande</b> | <b>Réception</b> | <b>Émission</b> |

|--------------|------------------|-----------------|

| 900 MHz      | 935-960 MHz      | 890-915 MHz     |

| 1800 MHz     | 1805-1880 MHz    | 1710-1785 MHz   |

| 1900 MHz     | 1930-1990 MHz    | 1850-1910 MHz   |

Présentement, la transition est imminente vers une technologie de troisième génération (3G). Permettant de bénéficier d'un échange accru de données et images, le passage vers la 3G a pour prétention de révolutionner l'usage du téléphone portable. Une technologie candidate probable est la Universal Mobile Telephone Service (UMTS). Cette norme utilise la norme W-CDMA, qui fixe des exigences plus strictes au niveau de la pureté spectrale. Il s'agit donc d'un secteur où il y aura des efforts dans le développement et la recherche de circuits de synthèse de fréquence permettant à faible coût de respecter les nouvelles normes.

Finalement, un dernier exemple d'application de la synthèse de fréquence au domaine des télécommunications est au niveau de la couche physique des réseaux LAN sans fils (DRURY, G., 2001). Ces réseaux sont de plus en plus omniprésents dans les écoles, hôtels, cafés ainsi que dans les domiciles. La tendance est vers l'accroissement du débit, ainsi que l'intégration dans le processeur des ordinateurs portables. Ils utilisent en général la bande 2.4 GHz comme pour Bluetooth, mais s'en distinguent par leur plus haut débit de données et leur distance d'opération accrue.

### 1.2.2 Audio/Video

Au niveau des applications audio et vidéo, il existe une variété de formats numériques nécessitant des fréquences d'horloge différentes (FISCHER, W., 2004). Le format vidéo 4:2:2, par exemple, est un format représentant l'image par sa décomposition en trois signaux. L'un de ces signaux véhicule l'information correspondant à la luminance (Y) et les deux autres l'information correspondant à la chrominance (Cr et Cb). Comme le nom du format l'implique, le rapport entre le taux d'échantillonnage du signal Y (13,5 MHz) est le double de celui des signaux Cr et Cb (6,75 MHz). Lorsque l'on souhaite multiplexer ces signaux, pour les combiner sur une seule interface, l'horloge dont on doit disposer doit fonctionner à une cadence qui correspond à la somme totale, soit 27 MHz. Il s'agit aussi de la fréquence utilisée au sein d'applications faisant appel au format de compression mpeg-2, comme c'est le cas pour les DVD. Suivant la même logique, la version « widescreen » du format 4:2:2 widescreen, avec ses pixels additionnels par ligne, nécessite une horloge de 36 MHz.

Il est plausible qu'un appareil soit conçu pour traiter des images vidéo numériques respectant les formats numériques 4:2:2 (aussi bien régulier que widescreen), mais également des images numérisées à partir des formats analogiques NTSC et PAL (dont les fréquences porteuses se situent à 3,579545 MHz et 4,43361875 MHz respectivement). Suite à la numérisation de ces signaux NTSC ou PAL, la fréquence des signaux numériques est forcément un multiple de la porteuse du signal analogique. Ce multiple correspond en fait au taux d'échantillonnage appliqué, soit le nombre d'échantillons par cycle. Par exemple, un sur-échantillonnage par un facteur de 8 signifie que l'appareil en

question doit également contenir les fréquences de référence 28,63636 MHz et 35,46895 MHz.

Supposons ensuite que cet appareil soit conçu pour synchroniser une des sources vidéo numériques décrites au paragraphe précédent avec une trame audio numérique. Cette trame audio est habituellement issue de l'échantillonnage d'un signal analogique selon un taux de 32 kHz, 44,1 kHz ou de 48 kHz, selon la norme utilisée par l'application:

**Tableau 2 – Échantillonnage requis par diverses applications**

| Application                 | Échantillonnage Audio |

|-----------------------------|-----------------------|

| Caméscope miniDV            | 32 kHz                |

| CD audio, mp3               | 44,1 kHz              |

| Télé numérique, DVD, cinéma | 48 kHz                |

Lorsqu'un signal ainsi numérisé est ensuite recomposé en signal audio, on a habituellement recours à la technique du sur échantillonnage. Celle-ci vise à réduire la complexité du convertisseur numérique à analogique. En effet, pour une précision de conversion donnée, il est possible de réduire la complexité du convertisseur en l'opérant à plus haute fréquence. À titre d'exemple, on peut augmenter la précision d'un convertisseur de 20 bits en utilisant la moyenne de plusieurs échantillons consécutifs. En travaillant avec la moyenne de 128 échantillons, on peut ainsi espérer augmenter la précision d'une valeur de 7 bits additionnels. Les échantillons additionnels sont reconstruits par interpolation, et un modelage du bruit est effectué sur les bits additionnels. Après une multiplication par 128 de la vitesse du convertisseur par rapport

au signal qu'il doit traiter, les fréquences nécessaires pour le signal audio deviennent donc 4,096 MHz, 5,6448 MHz et 6,1440 MHz.

**Tableau 3 – Synchronisation Audio/Vidéo**

|                 |              | Fréquence Audio        |                         |                         |

|-----------------|--------------|------------------------|-------------------------|-------------------------|

|                 |              | 4,0960 MHz             | 5,6448 MHz              | 6,1440 MHz              |

| Fréquence vidéo | 27,00000 MHz | $\frac{512}{4475}$     | $\frac{392}{1875}$      | $\frac{256}{1125}$      |

|                 | 28,63636 MHz | $\frac{5632}{39375}$   | $\frac{616}{3125}$      | $\frac{2816}{13125}$    |

|                 | 35,46895 MHz | $\frac{81920}{709379}$ | $\frac{112896}{709379}$ | $\frac{122880}{709379}$ |

|                 | 36,00000 MHz | $\frac{128}{1125}$     | $\frac{98}{625}$        | $\frac{64}{375}$        |

Lors du montage entre l'une des sources vidéo avec l'une des sources audio, il est important de ne pas perdre la synchronisation entre l'image et le son. Par conséquent, le circuit de synthèse de fréquence de cet appareil doit être en mesure de générer les rapports de fréquence exacts contenus au tableau 3, issu de (CALBAZA, D.E., & SAVARIA, Y., 2000b), car autrement une certaine accumulation de l'erreur entre l'image et le son se fera avec le temps.

### **1.3 OBJECTIFS DE CETTE RECHERCHE**

Le développement de la microélectronique, notamment dans le domaine des réseaux sans fil et de la télévision numérique, entraîne une forte demande pour des circuits de synthèse d'horloge de haute performance, entièrement intégrés sur une puce et de faible coût. L'horloge servant à synchroniser ces circuits doit souvent être produite à

partir de la multiplication par un rapport fractionnaire exact d'une horloge globale de référence. Diverses techniques de synthèse de fréquence sont en mesure d'établir ce rapport fractionnaire. Elles introduisent néanmoins des imperfections découlant de leur principe de fonctionnement qui nuisent aux performances, tant au niveau temporel qu'au niveau du spectre fréquentiel.

Une des imperfections du circuit de synthèse numérique directe de phase DDPS (CALBAZA, D.E., & SAVARIA, Y., 2000) et (CALBAZA, D.E., & SAVARIA, Y., 2002), objet de cette étude, est son spectre fréquentiel impur. Préalablement à ce travail de recherche, la visualisation de ce spectre fréquentiel nécessitait une simulation temporelle à partir d'une modélisation utilisant un outil tel que SIMULINK, suivie d'une analyse fréquentielle avec la fonction de transformée rapide de Fourier. Cette technique demande un temps de calcul très élevé. Suite à certains travaux, une formule semi-empirique, mais fonctionnant pour tous les cas testés, fut disponible pour le calcul direct de la position et de l'emplacement des raies spectrales (IZZOUGHAGEN, B., & KHOUAS, A., & SAVARIA, Y., 2004). Elle a permis une économie de temps de modélisation, mais elle ne tient compte que d'une seule des deux sources majeures de raies spectrales indésirables, communément appelées spurs.

Cette étude a donc pour objet de mettre au point un modèle analytique permettant de prédire la position ainsi que l'amplitude des raies spectrales indésirables dues aux deux causes majeures de bruit du circuit DDPS, soit la troncature de l'accumulateur de phase et le mésappariement entre les phases choisies. De plus, à partir de ce modèle, nous

avons souhaité faire l'étude des performances lors de différentes conditions d'utilisation, pour ensuite suggérer le choix optimal des paramètres et/ou des modifications au circuit.

## 1.4 ORGANISATION DU MÉMOIRE

Ce premier chapitre a eu pour but de mieux comprendre les domaines d'application du circuit à l'étude. Les circuits de synthèse de fréquence sont donc utiles entre autres pour des applications de télécommunication, d'audio et de vidéo numérique.

Le prochain chapitre consiste en une revue de littérature. Nous aborderons certaines notions de base à propos de la synthèse de fréquence. Nous y verrons la distinction entre les circuits de synthèse indirecte et les circuits de synthèse directe en observant des exemples de circuits répandus, tout en s'attardant plus longuement sur le circuit DDPS et à son principe de fonctionnement. Nous aborderons le concept de la gigue, une forme de bruit affectant les signaux d'horloge et nous observerons des exemples de spectre dans le domaine fréquentiel, un outil très important pour la visualisation de la pureté spectrale des circuits de synthèse de fréquence. De plus, nous effectuerons un bref survol des travaux d'autres auteurs ayant fait des recherches sur des notions similaires à celles qui sont présentées dans le présent ouvrage.

On entre dans le vif du sujet à partir du troisième chapitre, où nous proposons un modèle de simulation du circuit DDPS qui permet d'obtenir l'allure du spectre du signal de sortie. Ce modèle permet de tirer quelques conclusions par rapport aux sources de raies spectrales, à la lumière du fonctionnement du circuit et de l'observation du spectre.

Au quatrième chapitre, nous présentons l'analyse menant à une modélisation algorithmique du spectre du circuit DDPS. Cette modélisation a fait l'objet d'un article de conférence (SALOMON, M.-E., KHOUAS, A, SAVARIA, Y., 2005). Une analyse du signal, comme nous le verrons en détails, mène à l'élaboration d'un algorithme calculant l'allure de la réponse fréquentielle du circuit en fonction des paramètres d'opération. On retrouve également une confirmation de l'équivalence entre les résultats obtenus par l'algorithme et ceux issus d'une simulation.

Au chapitre 5, nous voyons comment l'algorithme peut être utilisé pour évaluer rapidement différentes conditions d'opération du DDPS, à des fins d'optimisation du circuit. Finalement, diverses modifications à l'architecture du circuit sont proposées. Les résultats de calculs permettent de voir l'influence des divers degrés de liberté dont on dispose lors de la conception du circuit.

Le sixième chapitre vise à proposer des améliorations ou modifications au circuit DDPS. Ces modifications cherchent surtout à modifier le profil spectral du signal de sortie, dans le but de diminuer la quantité de bruit nuisible.

La conclusion permettra de faire le point sur les progrès effectués dans ce domaine de recherche et de les placer dans le contexte plus global des circuits de synthèse de fréquence.

## 2 Revue de la littérature pertinente

Nous ferons référence au long de cet ouvrage à quelques concepts qu'il est bon de présenter ici. La section 2.1 porte sur les notions de gigue, de quantification et de spectre fréquentiel qu'il est bon de clarifier avant d'entrer davantage dans le sujet. À la section 2.2, nous observerons les circuits de synthèse de fréquence les plus répandus, ainsi qu'un résumé sommaire du fonctionnement de ces circuits.

L'un des aboutissements du présent travail de recherche est la mise au point d'un algorithme de calcul permettant de calculer rapidement l'allure du spectre fréquentiel du signal émis par un circuit de type DDPS. Au niveau de la littérature existante, il s'agit d'une nouveauté, ce qui est en partie du au fait que l'utilisation du circuit DDPS n'est pas très répandue. À la section 2.3, nous nous pencherons sur le détail du circuit DDPS tel qu'on le retrouve dans la littérature.

Certains auteurs se sont déjà penchés sur la question de la modélisation spectrale des circuits de synthèse de fréquence. Ils ont travaillé sur les circuits de synthèse de fréquence que nous verrons, et leur approche est quelque fois similaire à celle qui est proposée ici pour le circuit DDPS. À la section 2.4, nous survolons les résultats de leurs travaux, en précisant les similarités avec le cas à l'étude ainsi que les différences justifiant une nouvelle approche.

De plus, un autre objectif des travaux présentés dans ce mémoire est de proposer des suggestions de modification au circuit DDPS, dans le but d'en améliorer les performances au niveau spectral et/ou au niveau de la gigue. Il est donc intéressant de se

pencher sur ce que d'autres auteurs ont eu à dire sur le sujet, concernant les autres circuits de synthèse de fréquence sur lesquels ils ont travaillé. Ceci fera l'objet de la section 2.5.

## 2.1 CONCEPTS UTILES

### 2.1.1 Gigue

La gigue est une forme de bruit affectant les signaux d'horloge (VAN DE BEEK, R.C.H., & KLUMPERINK, E.A.M., & VAUCHER, C.S., & NAUTA, B., 2002). Elle se résume comme étant une variation indésirable des intervalles entre fronts d'horloge successifs, alors que dans un cas idéal ces intervalles seraient tous égaux. Par rapport à une période de longueur idéale, les transitions d'une horloge où on retrouve de la gigue comportent donc une certaine erreur dans le temps; elles ont lieu soit un peu avant, soit un peu après l'instant idéal.

Il existe deux types principaux de gigue. La première est une variation rapide au niveau de la phase, résultant dans le raccourcissement ou l'allongement intermittent de la période. Elle peut être aléatoire ou cyclique. La gigue crête à crête est donc une métrique représentant la différence entre la phase maximale et la phase minimale du signal d'horloge dans le temps. Afin de déterminer la variation entre des périodes adjacentes, toutes les périodes consécutives doivent être mesurées. La gigue de période crête à crête correspond au pire cas de gigue de cycle à cycle (i.e. la plus grande différence entre deux périodes consécutives).

Le deuxième type de gigue est une accumulation de l'erreur de phase dans le temps; c'est donc la différence entre le moment où a lieu le front d'horloge et le moment idéal pour ce même front d'horloge. Il est possible qu'une faible gigue de cycle à cycle

engendre après un certain temps une gigue de phase élevée. La gigue de phase RMS correspond à l'écart-type de la gigue de phase. Cette valeur peut être exprimée en degrés, en radians ou en secondes.

### 2.1.2 Quantification

Le phénomène de quantification réfère à l'erreur causée par la précision limitée des éléments de circuits numériques. Nous verrons avec l'exemple du circuit DDS (2.2.2), qu'une quantification se produit lorsqu'on ignore les bits les moins significatifs de la phase (exprimée sur  $M$  bits) de façon à n'utiliser que les  $P$  bits les plus significatifs pour accéder aux valeurs de la table de conversion. Par conséquent, une partie de la précision contenue dans l'information de la phase n'est pas représentée par la table de conversion.

On observe à nouveau une quantification due à la précision limitée sur les valeurs contenues dans une mémoire servant de table de conversion. La table de conversion du circuit DDS contient les valeurs du signal sinusoïdal en fonction de la phase, mais une certaine erreur existe, compte tenu du nombre de bits utilisés pour représenter le signal, ce qui limite la précision des valeurs stockées. Il est donc probable que la valeur sur la courbe sinusoïdale ne puisse être exprimée en utilisant le nombre de bits disponibles dans l'emplacement alloué en mémoire, causant ainsi une erreur de quantification.

### 2.1.3 Spectre fréquentiel

Nous introduisons dans cette sous-section le concept de spectre fréquentiel. Selon la théorie de Fourier, tout signal réel peut être considéré comme composé d'une somme

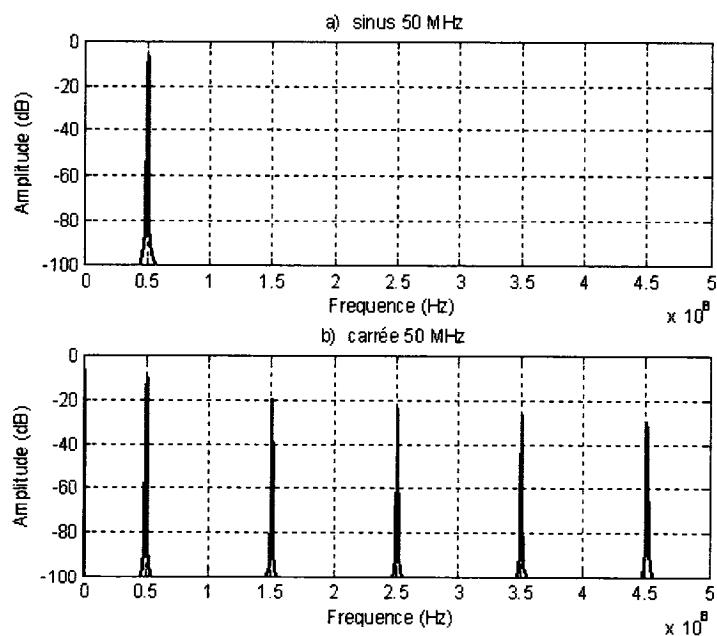

de signaux sinusoïdaux (en nombre infini si nécessaire) à des fréquences différentes (KREYSIG, E., 1999). Le graphe du spectre d'un signal est gradué selon la fréquence en abscisse, et selon l'amplitude en ordonnée. C'est donc l'amplitude de cette décomposition en signaux sinusoïdaux que nous observons. Par exemple, si un signal consiste en une sinusoïde pure, alors son spectre ne sera composé que d'une raie à la fréquence d'oscillation de cette sinusoïde. De plus, l'amplitude de cette raie sera celle de l'amplitude d'oscillation. Cet exemple est illustré à la figure 1a), où on retrouve le spectre d'un signal sinusoïdal de 50 MHz. Il est à noter que la raie spectrale, qui devrait être une raie discrète à 50 MHz, prend une forme légèrement évasée en raison de la numérisation du signal sinusoïdal utilisé pour tracer la courbe.

Figure 1 – Spectre: a) d'une sinusoïde et b) d'une onde carrée

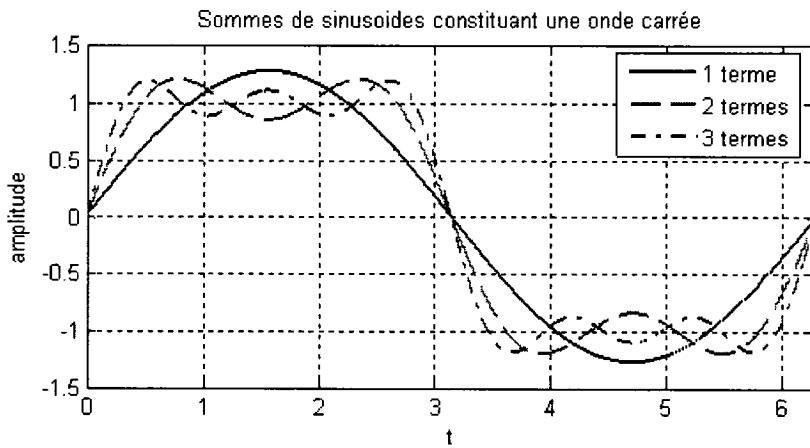

Ensuite, pour illustrer la théorie de Fourier énoncée au paragraphe précédent, prenons un signal formé d'une somme de sinusoïdes. Les signaux d'horloge prennent souvent la forme d'une onde carrée. Selon la théorie de Fourier, une onde carrée de période  $2\pi$  se compose de la somme de sinusoïdes suivante :

$$\sum_{n=1}^{\infty} b_n \cdot \sin(n \cdot x), \quad \text{où } b_n = \frac{2}{n\pi} (1 - \cos n\pi) \quad (1)$$

La figure suivante montre comment l'addition de termes à la somme permet de s'approcher progressivement d'une onde carrée.

Figure 2 – Sommes des sinusoïdes d'une onde carrée (1, 2 et 3 premiers termes)

Si nous observons le spectre d'un tel signal dans le domaine fréquentiel, nous verrons apparaître des raies aux endroits déterminés par les fréquences d'oscillation des sinusoïdes qui composent le signal d'onde carrée, comme à la figure 1 b) pour une onde carrée de 50 MHz.

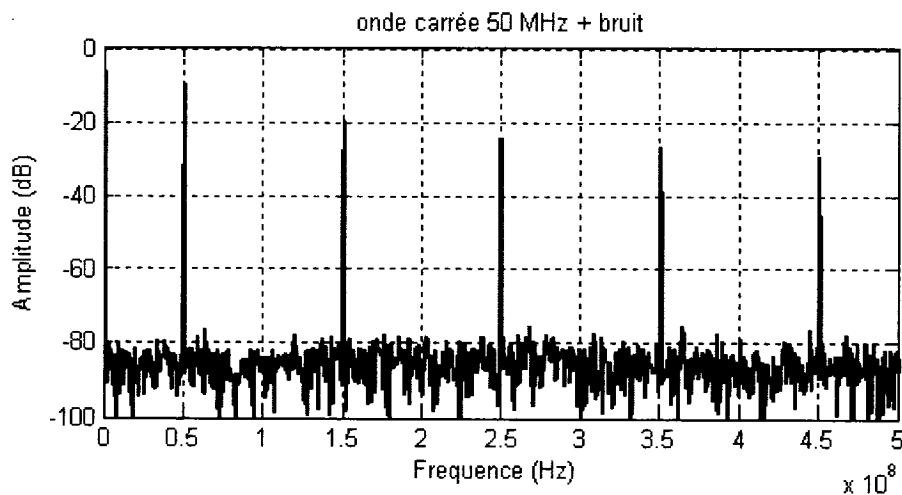

Pour terminer cette brève discussion sur le spectre des signaux, notons que les signaux observables, comme par exemple un signal d'horloge, ne correspondent pas à une sinusoïde idéale, ou à une onde carrée idéale. Une quantité plus ou moins importante

de bruit s'ajoute généralement au signal désiré. Ce bruit peut avoir diverses causes, liées aux paramètres du circuit utilisé pour produire le signal. À titre d'exemple, citons les fluctuations dans la source d'alimentation, ou les interférences électromagnétiques. Un type particulier de bruit qui serait distribué de façon uniforme le long de l'axe des fréquences porte le nom de bruit blanc. La figure 3 représente notre signal carré de la figure 1 b), auquel se rajoute maintenant une certaine quantité de bruit blanc.

**Figure 3 – Spectre d'une onde carrée additionnée de bruit blanc**

Nous voyons donc comment un bruit dans le circuit peut s'additionner au signal. Dans le circuit DDPS à l'étude, la cause majeure d'imperfection du contenu spectral consiste en une erreur périodique. Celle-ci est liée de façon intrinsèque au fonctionnement normal du circuit. La distribution du bruit n'est pas uniforme comme dans le cas d'un bruit blanc. Il restera donc au cours de cet ouvrage à caractériser la distribution de ce bruit, dans le but d'observer l'allure du spectre et de guider les paramètres de conception.

### 2.1.4 Circuit LFSR

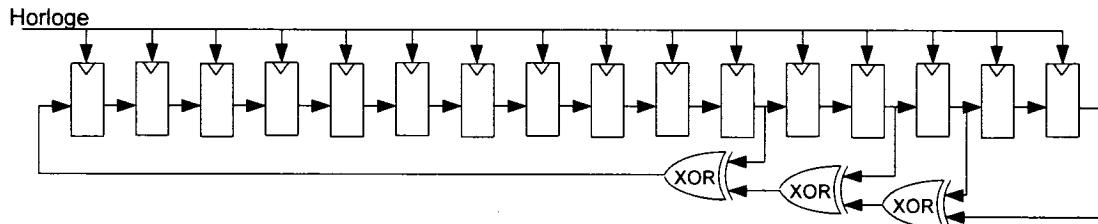

Figure 4 – LFSR correspondant au polynôme  $x^{11} + x^{13} + x^{14} + x^{16} + 1$

Le LFSR (Linear Feedback Shift Register), dont l'architecture est schématisée à la figure 4, est fréquemment utilisé comme générateur de nombres pseudo aléatoire (JOHN, M., & SMITH, S., 1997). Il s'agit en fait d'un simple registre à décalage où le bit d'entrée est une fonction linéaire des bits composant son état. La fonction utilisée est le XOR. Comme ce circuit comporte un nombre fini d'états, il entre éventuellement dans un cycle de répétition. Si cette fonction de rétroaction est bien choisie, on obtient une séquence avec un temps de répétition très long et qui semble par conséquent aléatoire. Les propriétés du LFSR, c'est à dire le fait que la valeur représentée par l'ensemble de ses bits varie d'un cycle à l'autre de façon équiprobable entre 0 et 1 avec une valeur moyenne de 0,5, jumelé au fait que le cycle de répétition soit très long, font en sorte qu'il soit parfois utilisé comme générateur de nombres aléatoires.

À partir d'un contenu initial nommé la semence (seed), la séquence des valeurs produites est entièrement déterministe. La longueur de la séquence d'un LFSR comportant un certain nombre de registres est influencée par le choix de sa fonction de rétroaction. En effet, on peut choisir lesquels parmi les bits de la chaîne seront ceux qui serviront à déterminer la prochaine valeur. Dans le cas de la figure 4, la fonction de

rétroaction correspond au polynôme  $x^{11} + x^{13} + x^{14} + x^{16} + 1$ . Les exposants correspondent à la position des bits de rétroaction, et le terme 1 ne correspond pas à un bit en tant que tel. Lorsque ce polynôme correspond à un LFSR maximal, la longueur de la séquence est alors de  $2^{N-1}$ , où N est le nombre de registres de la chaîne. On appelle alors cette séquence une MLS (maximal length sequence). Pour aider les concepteurs de LFSR, des tables ont été compilées pour indiquer quels bits font partie de la fonction de rétroaction pour une longueur de registre donnée (ALFKE, P., 1996).

### 2.1.5 Circuit de modulation delta sigma

La modulation delta sigma est une technique mise au point à l'origine pour être utilisée dans les circuits de conversion analogique à numérique (ADC) ou numérique à analogique (DAC). Dans ces circuits, on retrouve une quantité finie de niveaux de conversion, variant selon le nombre de bits du circuit. Par conséquent, une certaine erreur de conversion due à la quantification (section 2.1.2) est inévitable lors de la conversion.

Le principe à la base de l'architecture delta sigma consiste à mesurer l'erreur de quantification afin de l'intégrer, pour ensuite compenser cette erreur. La modulation delta sigma retire à la gigue du circuit son caractère déterministe. De plus, elle module le bruit pour que celui-ci se retrouve surtout vers les hautes fréquences (ZARKESHVARI, F., & NOEL, P., & KWANIEWSKI, T., 2005). En raison du fait que les variations entre les incrément de phase contenus dans la séquence de sélection varient de façon aléatoire et par des valeurs plus élevées que la distance entre deux niveaux de quantification, les raies spectrales résultant d'une périodicité des erreurs de phase sont évitées.

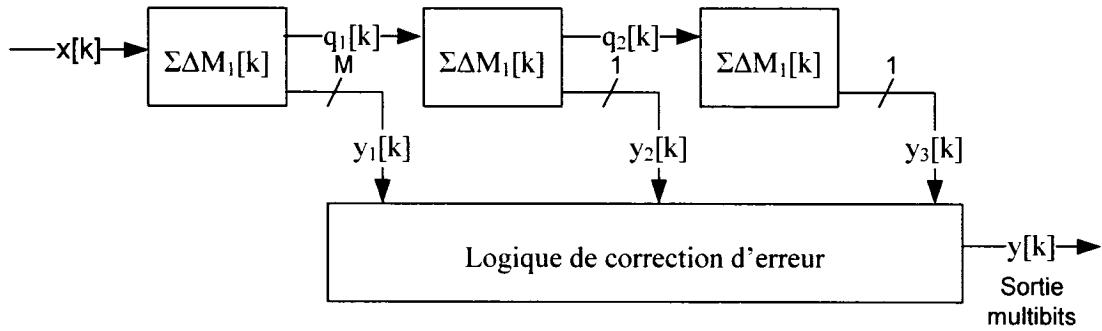

Figure 5 – Modulateur delta sigma de type MASH3

Plusieurs types de modulateurs delta sigma se retrouvent dans la littérature. En général, on peut les distinguer selon qu'ils soient linéaires ou en cascade (ZARKESHVARI, F. et al., 2005). De plus, ils sont caractérisés par leur ordre, qui correspond au nombre d'accumulateurs. Nous nous intéresserons plus tard dans cet ouvrage au modulateur en cascade d'ordre 3, présenté à la figure 5. Nous le choisissons car un modulateur dit linéaire est instable lorsqu'il s'agit de représenter les fractions proche de 0 ou de 1. Un modulateur en cascade comme celui choisi ne pose pas ce problème.

Pour présenter les équations régissant le fonctionnement du modulateur de la figure 5, utilisons la notation en  $z$ , où  $z^{-1}$  symbolise une unité de temps d'échantillonnage.

Pour un simple accumulateur, l'équation de la sortie est de:

$$y_1(z) = x(z) + z^{-1}r_1(z) - r_1(z), \text{ ou}$$

$$y_1(z) = x(z) - (1-z^{-1})r_1(z)$$

Lorsque trois accumulateurs sont disposés en cascade, comme c'est le cas ici, les équations pour les sorties des trois accumulateurs sont respectivement :

$$y_1(z) = x(z) - (1-z^{-1})r_1(z)$$

$$y_2(z) = r_1(z) - (1-z^{-1})r_2(z)$$

$$y_3(z) = r_2(z) - (1-z^{-1})r_3(z)$$

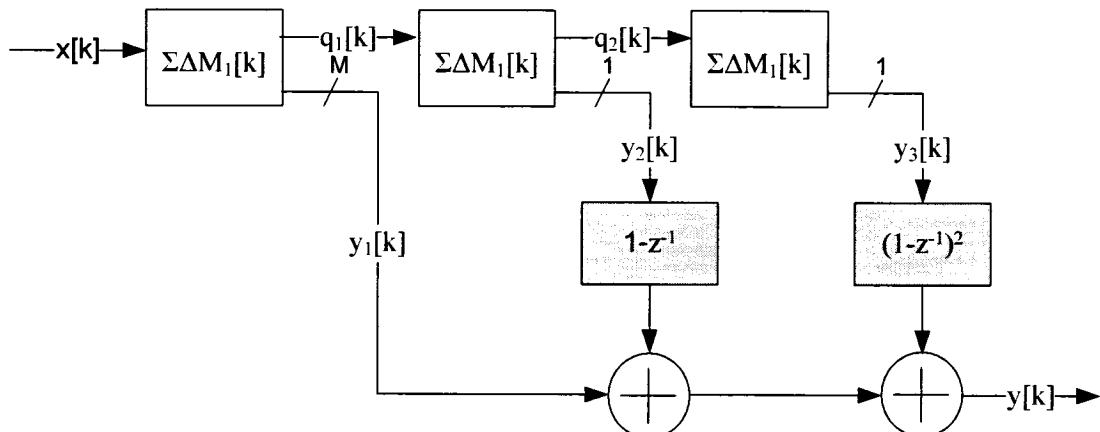

Comme telle, la somme de ces équations cumulerait une certaine erreur qu'il est facile d'annuler en ajoutant des fonctions logiques additionnelles, dont les équations sont représentées à la figure 6. Après le passage à travers les blocs ombragés de cette figure, nous aboutissons avec les termes qui suivent :

$$y_1(z) = x(z) - (1-z^{-1})r_1(z)$$

$$y_2(z) * (1-z^{-1}) = (1-z^{-1})r_1(z) - (1-z^{-1})^2r_2(z)$$

$$y_3(z) * (1-z^{-1})^2 = (1-z^{-1})^2r_2(z) - (1-z^{-1})^3r_3(z)$$

Figure 6 –MASH3 avec la logique de correction

L'équation en  $z$  du terme de sortie, soit la somme des signaux  $y_1$ ,  $y_2$  et  $y_3$ , est donc de:

$$Y(z) = x(z) - (1-z^{-1})^3r_3(z).$$

Elle est donc similaire à l'équation d'un accumulateur à un étage, mais le terme en  $z$  modulant le reste de l'addition est d'ordre 3.

## 2.2 CIRCUITS DE SYNTHÈSE DE FRÉQUENCE

Les circuits de synthèse de fréquence (KROUPA, V.F., 2003) peuvent être classés dans l'une des deux catégories suivantes: la synthèse directe ou la synthèse indirecte. Les circuits de synthèse indirecte se basent habituellement sur la présence d'une boucle de rétroaction. Un oscillateur, ou une ligne à délais, est ajusté en mesurant un signal correspondant à l'erreur entre la fréquence de son oscillation en comparaison à celle désirée. Le signal de sortie est donc produit par un élément de circuit dont on ajuste la fréquence. L'exemple le plus connu de ce type de circuit est la boucle à verrouillage de phase, ou PLL. Pour ce qui est des circuits à synthèse directe, le signal de sortie est reconstruit de toutes pièces; il appartient au domaine numérique du traitement de signal. Les sections 2.2.1 et 2.2.2 présentent des exemples courants de circuits de synthèse de fréquence, en démontrant sommairement leur fonctionnement.

### 2.2.1 Circuits de synthèse indirecte

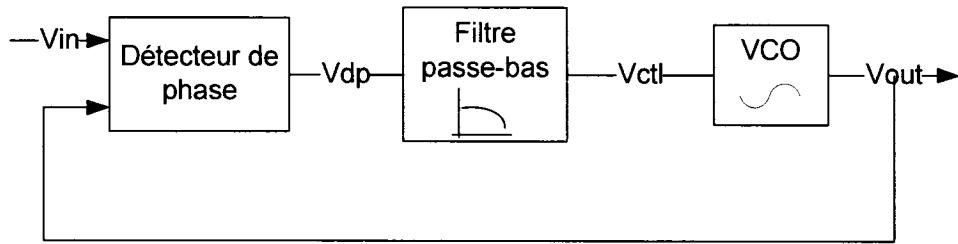

#### 2.2.1.1 Le PLL

Le PLL (GARDNER, F.M., 1980, BEST, R.E., 1984) est le plus ancien des circuits de synthèse de fréquence indirecte. Il s'agit d'une boucle d'asservissement où un oscillateur est contrôlé de façon à ce que sa période et sa phase se verrouillent à celles d'un signal d'entrée. La figure 7 représente schématiquement l'allure générale d'un PLL.

Figure 7 – Architecture d'un "Phase-Locked Loop" (PLL)

Le détecteur de phase reçoit les signaux Vin et Vout et émet un signal haut ou bas, selon que la phase du signal issu de l'oscillateur (Vout) est en retard ou en avance sur celle de la référence Vin. Ce signal Vdp, en moyenne égal à la différence de phase, servira à contrôler l'asservissement de l'oscillateur, mais passe d'abord à travers un filtre passe-bas. À la sortie de ce filtre, le signal stabilisé Vctl sert au contrôle d'un oscillateur dont la fréquence d'oscillation est contrôlée par une tension (Voltage Controlled Oscillator, ou VCO). Le PLL illustré aura pour effet de générer un signal de sortie ayant la même fréquence que celle de l'entrée, de façon à maintenir l'égalité  $F_{out} = F_{in}$ . Par contre, en insérant un diviseur par N dans la boucle, la boucle cherchera plutôt à maintenir l'égalité  $F_{out}/N = F_{in}$ , donc une fréquence de sortie  $F_{out} = N \cdot F_{in}$ .

Par conséquent, la valeur de la fréquence de sortie peut être ajustée en variant le rapport de division N. Comme la résolution sur le contrôle de la fréquence de sortie est égale à la valeur de la fréquence d'entrée Fin, on peut également ajouter un diviseur à l'entrée pour bénéficier d'une résolution plus élevée. Cependant, plus on utilise une valeur petite comme référence, plus la largeur de bande du PLL devra être petite (BEST, R.E., 1984). Or une bande étroite nuira à l'acquisition de fréquence en augmentant le temps requis.

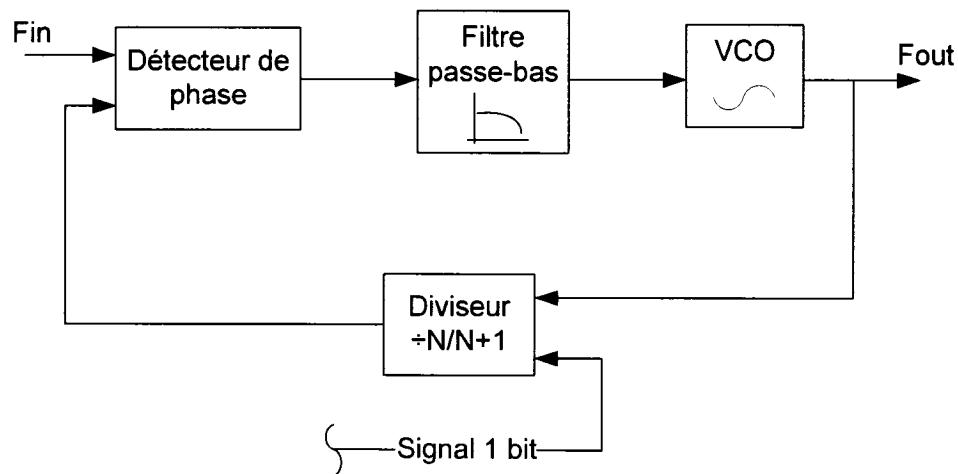

### 2.2.1.2 Synthèse Fractionnaire

Le circuit Frac-N (MUER, B., 2003) est un circuit de synthèse fractionnaire indirecte basé sur le PLL de la section précédente. Il permet de générer des signaux dont la fréquence est un multiple fractionnaire de l'horloge de référence. L'avantage majeur par rapport au PLL classique est que pour une résolution donnée dans le choix de la fréquence de sortie, le Frac-N permet d'utiliser une fréquence de référence élevée. Avec la largeur de bande plus élevée que celle-ci permet, il en résulte un temps d'acquisition nettement plus favorable.

Figure 8 – PLL de type "fractional-N"

Observons à la figure 8 une particularité de ce circuit en ce qui a trait au rapport de division. Celui-ci est variable et alterne entre  $N$  et  $N+1$ . Le rapport de division effectif du circuit correspond à la valeur moyenne du diviseur dans le temps. Par exemple, alterner successivement entre 2 et 3 résulte en une division par 2,5.

### 2.2.1.3 Delay Locked Loop

Le Delay Locked Loop, ou DLL, est un circuit qui permet, tout comme le PLL, de générer un signal de sortie verrouillé sur un signal de référence reçu en entrée (STEPHENS, D.R., 2002). Au lieu de contenir un oscillateur, celui-ci est remplacé par une ligne à délais. Cette ligne à délais est constituée de cellules dont la valeur du délai peut être ajustée en y appliquant une tension de commande plus ou moins élevée. Cette topologie est représentée à la figure 9.

Figure 9 – "Delay-Locked Loop"

Un front sur l'horloge de référence traverse et atteint la sortie de la ligne à délais après un temps équivalent à la somme du délai des cellules. L'objectif du DLL est d'égaliser le délai des cellules avec la période de l'horloge. Pour y arriver, les fronts sortant de la ligne à délais sont comparés avec ceux de l'horloge de référence. Si nécessaire, le délai total est augmenté ou diminué.

Un circuit de type DLL est utile pour récupérer un signal d'horloge à partir d'une référence bruitée. Son filtre lui confère une stabilité qui diminue la quantité de gigue, cette variation erronée de la position temporelle d'un front d'horloge présentée à la section 2.1.1. De plus, le signal sortant de la ligne à délais n'est pas influencé par celui des

périodes précédentes comme c'est le cas avec un oscillateur en boucle dans lequel le signal est re-circulé. Cependant, il est moins évident d'obtenir une sortie dont la fréquence soit un multiple de celle de l'horloge de référence. En effet, comme le signal ne traverse qu'une fois la ligne à délais, on ne peut pas insérer dans la boucle un compteur de périodes comme dans le cas du PLL. Il faut pour multiplier la fréquence recourir à une technique de sélection de phases.

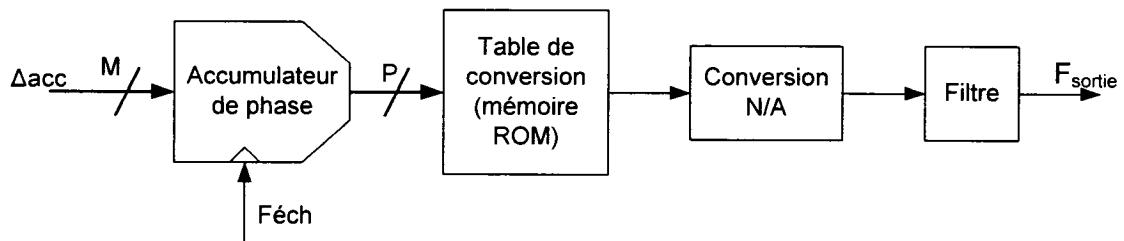

## 2.2.2 Synthèse directe

### 2.2.2.1 Direct Digital Synthesis

La synthèse numérique directe (DDS) est une méthode issue du domaine du traitement de signal (GOLDBERG, B., 1996, KROUPA, V.F. 1998); à partir d'une base de temps discrète, un signal périodique est généré avec une fréquence choisie. On cherche habituellement à générer un signal sinusoïdal, mais il est possible de générer un signal triangulaire, carré, ou toute autre forme périodique.

Figure 10 – Synthèse Numérique Directe (DDS)

La partie numérique d'une implémentation du circuit DDS est divisée en deux parties distinctes montrées à la figure 10 : un générateur de phase (l'accumulateur) et un convertisseur de phase à signal. Dans un premier temps, l'accumulateur de phase génère la séquence de phase à partir de la fréquence d'échantillonnage et d'une valeur

d'incrément de phase  $\Delta_{acc}$ . Cet accumulateur est constitué de  $N$  bits et peut donc accumuler jusqu'à une valeur de  $2^N-1$  avant de déborder et de recommencer à 0. Cette plage de 0 à  $2^N-1$  correspond à un cycle complet, soit une durée de  $2\pi$  rad. En dénotant par  $\Delta_{ACC}$  la valeur d'incrément de phase qui sera ajoutée à chaque échantillon de l'horloge d'entrée, le rapport entre la période d'échantillonnage et la période du signal produit est équivalent au rapport entre la valeur de l'incrément  $\Delta_{ACC}$  et le cycle de l'accumulateur  $2^N$ :

$$\frac{T_{éch}}{T_{sortie}} = \frac{\Delta_{ACC}}{2^N} \quad (2)$$

Par conséquent, l'équation pour la fréquence de sortie devient :

$$F_{sortie} = \frac{F_{éch} \cdot \Delta_{ACC}}{2^N} \quad (3)$$

À la sortie de l'accumulateur, la phase est encodée sur  $N$  bits. Pour chacune des valeurs que peut prendre cette phase, il est possible d'attribuer une valeur correspondante pour l'amplitude. Typiquement, ces valeurs sont stockées dans une table de conversion (*lookup table* : LUT). Il est donc possible qu'une LUT de  $2^N$  valeurs soit trop grande pour être implantée de façon réaliste. Dans ce cas, nous notons par  $2^P$  le nombre de valeurs dans la LUT, où  $P$  est un nombre de bits inférieur ou égal à  $N$ .

À la sortie de la LUT, on retrouve la valeur numérique de l'amplitude du signal. Un DAC convertit cette valeur en valeur analogique. Le signal ainsi obtenu est ensuite filtré.

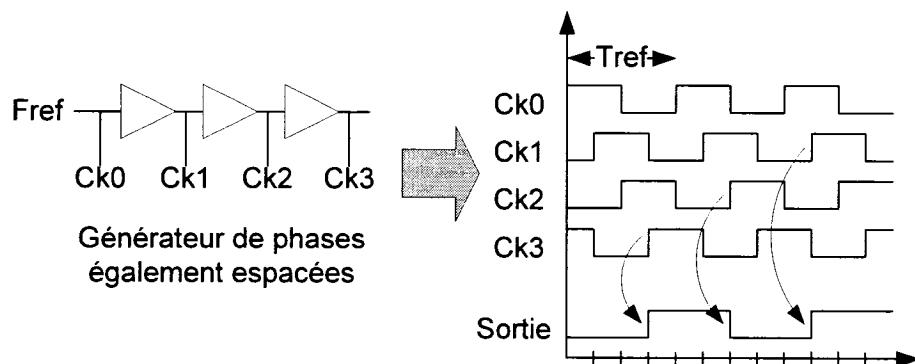

### 2.2.2.2 Direct Digital Period Synthesizer (DDPS)

Le principe d'opération du DDPS (CALBAZA, D.E., & SAVARIA, Y., 2000) est illustré à la Figure 11. On y suppose premièrement la présence de différents signaux de même période, mais ayant différentes phases. La partie de droite de la figure 11, représente ces signaux, numérotés Ck0 à Ck3 :

Figure 11 – Principe de fonctionnement du DDPS

Les phases des signaux Ck0 à Ck3 sont également réparties au sein de la période d'horloge  $T_{ref}$ . Ce sont des signaux qui peuvent être obtenus par exemple en verrouillant une ligne à délais soigneusement balancée à un signal d'horloge de référence ayant une fréquence stable. Une telle ligne à délais, représentée de façon schématique par la partie de gauche de la Figure 11, sera présentée plus en détails à la section 2.3.1, ou nous y verrons notamment les détails de son implantation. Pour l'instant, il suffit de remarquer que ces signaux sont répartis de façon équidistante dans le temps à l'intérieur de leur même période.

Ces signaux sont ensuite choisis dans un ordre approprié. La sélection d'un signal a pour effet de générer une transition sur le signal de sortie. L'exemple de la figure 11 montre un signal de sortie obtenu par le choix de chaque troisième transition. Ce nombre

de sauts de phase séparant deux transitions de sortie prend ici une valeur entière. Il est toutefois possible d'avoir des rapports intermédiaires lorsque l'on permet au circuit d'alterner entre deux nombres de transition consécutifs.

Par exemple, en alternant successivement entre un saut de 3 phases et un saut de 4 phases, on obtiendrait un délai effectif de 3,5 phases. L'avantage majeur d'utiliser une technique à sélection de phases est qu'elle augmente la résolution d'un oscillateur. En effet, par rapport à un oscillateur qui ne serait pas constitué de cellules dont les signaux sont individuellement accessibles, un oscillateur à phases multiples génère des transitions de sortie situées à des instants qui seraient inaccessibles. Par le fait même, cette résolution accrue a pour effet de préserver la gigue du signal de sortie à une valeur plus faible. Intuitivement, ceci s'explique par le fait qu'une transition ne s'éloigne pas de son instant idéal par un délai plus important que la distance entre deux phases consécutives.

D'autre part, en cherchant à reproduire des ratios fractionnaires nécessitant une alternance dans le nombre de saut de phases, la période du signal de sortie fluctue de façon régulière. Nous observerons plus en profondeur au chapitre 3 comment ceci résulte en une diminution de la pureté spectrale.

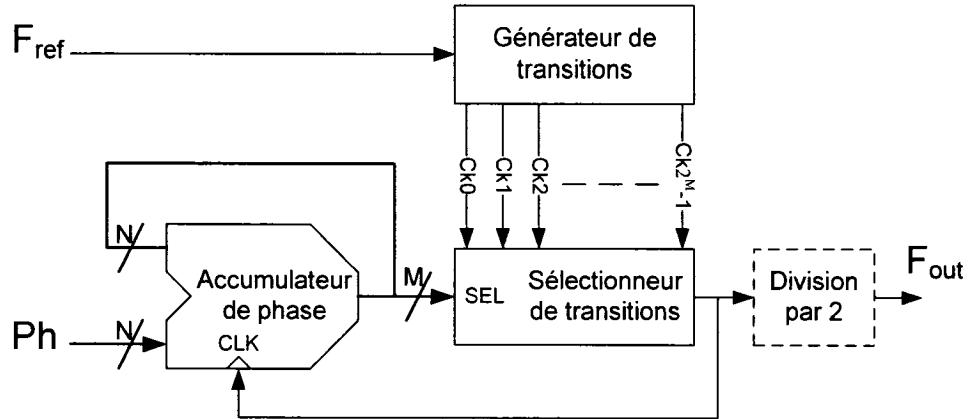

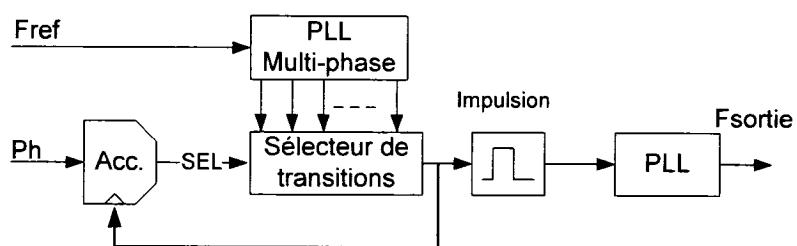

## 2.3 FONCTIONNEMENT DU DDPS

La figure 12 montre la structure du DDPS. Ce dernier est constitué de trois blocs principaux : un accumulateur de phase, un sélecteur de transitions ainsi qu'un générateur de transitions. Les prochaines sous-sections décriront un par un chacun de ces blocs. On

peut également se référer aux articles de CALBAZA, D.E. et SAVARIA, Y. (2000a, 2002).

Figure 12 – Schéma du DDPS

### 2.3.1 Générateur de transitions

Le générateur de transitions a pour fonction de générer une série de versions décalées dans le temps du signal de référence, comme nous l'avons vu à la figure 11 (section 2.2.2). Le DDPS de la figure 12 comporte un générateur fournissant  $2^M$  phases distinctes, dénotées ici par les signaux  $Ck_0$  à  $Ck_{2^M-1}$ . Idéalement, les transitions des signaux produits par le générateur de transitions sont uniformément distribuées à l'intérieur de la période de référence  $T_{ref}$ . En réalité cependant, des variations dans le procédé de fabrication font en sorte que chaque cellule n'a pas précisément la même valeur de délai. Par conséquent, il existe des fluctuations autour de la valeur nominale de l'espacement entre les phases que nous attribuons au mésappariement, un léger déséquilibre entre les cellules constituant la ligne à délais (EL SHEIKH, M., HAFEZ, A., 2003).

Parmi les diverses façons d'implanter le générateur de transitions, citons l'utilisation d'un synthétiseur de type DLL (Section 2.2.1), une option intéressante pour la génération des phases du DDPS. Également, l'utilisation d'un oscillateur à phases multiples, verrouillé selon le principe du PLL (Section 2.2.1) est également très intéressante, en raison du rapport de multiplication qu'on peut fixer entre la fréquence d'oscillation et la fréquence de référence. Dans un tel cas, l'oscillateur du PLL est utilisé comme générateur de transitions et doit être en mesure de générer plusieurs phases.

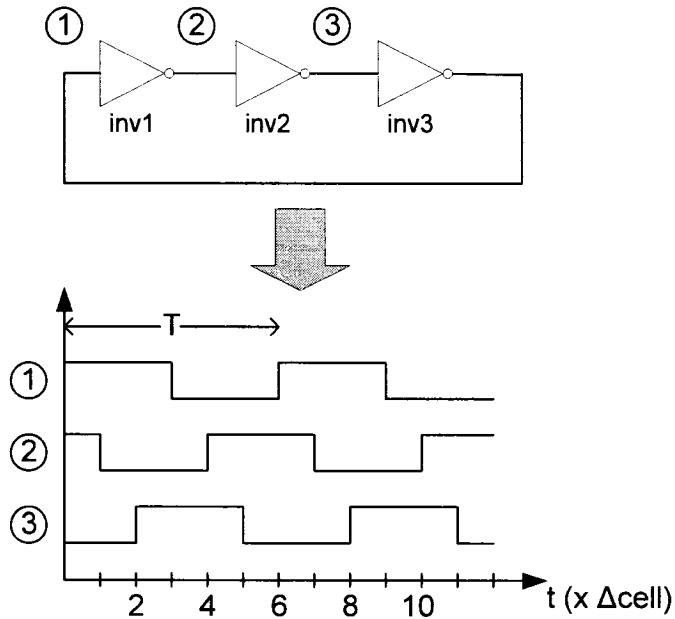

Pour obtenir cet oscillateur à multiples phases, une façon simple est de boucler un nombre impair d'inverseurs (JOHNS, D.A., MARTIN, K., 1997). En effet, un inverseur qui reçoit à son entrée un signal haut ou bas produit en sortie l'inverse de ce signal. Par conséquent, cette boucle n'a pas d'état stable; les signaux entre les cellules d'inversion chercheront continuellement à osciller entre les états haut et bas. Le délai de propagation à travers ces cellules d'inversion (le temps requis pour transmettre un changement d'état) déterminera la fréquence d'oscillation de la boucle.

Figure 13 – Phases générées par une boucle de délais

La figure 13 illustre l'opération de ce type d'oscillateur; un front montant sur un signal engendre un front descendant sur le signal suivant, après un délai correspondant à  $\Delta_{cell}$ , soit le délai de propagation à travers une cellule d'inversion. Par conséquent, une période complète est donnée par  $2 \cdot n_{cell} \cdot \Delta_{cell}$ , où  $n_{cell}$  est le nombre (impair) de cellules dans la boucle. Les signaux 1, 2 et 3 de la figure 10 sont donc également répartis au sein d'une période globale de  $6 \cdot \Delta_{cell}$ , où  $\Delta_{cell}$  est le délai de propagation à travers une cellule d'inversion.

Pour ajuster la fréquence d'oscillation de la boucle d'inverseurs, on module la quantité de courant alimentant ces cellules, de façon à influencer leur temps de réaction à un changement d'état. Cet ajustement se fait en variant la tension sur un transistor qui permettra à plus ou moins de courant d'alimenter la cellule. De cette façon, la fréquence

d'oscillation de la boucle est contrôlée par une tension, d'où l'expression "Voltage Controlled Oscillator".

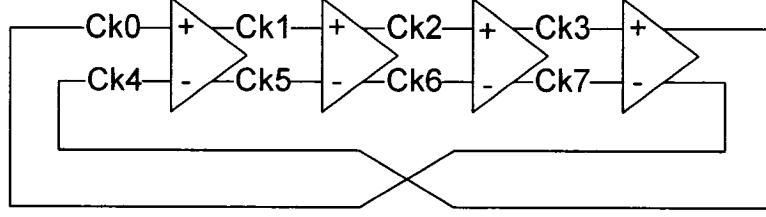

Une deuxième façon de réaliser un VCO est par l'utilisation d'inverseurs différentiels (JOHNS, D.A., MARTIN, K., 1997). Cette méthode offre l'avantage de pouvoir utiliser un nombre pair de cellules d'inversion. En effet, comme les cellules utilisent une paire de signaux, il suffit d'introduire un croisement dans les signaux de la boucle pour qu'elle soit instable et oscille, et ce même avec un nombre pair de cellules. Cette situation est schématisée à la figure 14.

Figure 14 – Signaux Ck0 à Ck7 générés par 4 inverseurs en paire différentielle

L'avantage d'utiliser une telle boucle est l'obtention d'un nombre de phases égal au double du nombre de cellules,  $n_{cell}$ . Il est donc possible de générer un nombre de phases qui soit une puissance de deux ( $2^{M+1}$ , car  $n_{cell} = 2^M$ ), ce qui facilite la conception des autres composantes du circuit DDPS. En sachant la période  $T_{ref}$  du signal auquel la boucle est verrouillée, ainsi que le nombre de phases dans le générateur de transitions, on peut déterminer l'espacement temporel entre deux phases,  $\Delta_{phase}$ , qui nous sera utile lors d'équations subséquentes:

$$\Delta_{phase} = \frac{T_{ref}}{2^{M+1}} \quad (4)$$

### 2.3.2 Accumulateur

L'accumulateur de phase du DDPS détermine la séquence de sélection des transitions. Cette séquence est produite par l'accumulation d'un incrément de phase Ph à chaque cycle. Cet incrément de phase représente le nombre de phases séparant deux transitions consécutives du signal de sortie et fixe par le fait même le rapport entre les fréquences d'entrée et de sortie du DDPS. Soit un nombre de phases égal à  $2^M$ , des formules peuvent être déduites pour exprimer les rapports entre les périodes et les fréquences d'entrée versus sortie. Les formules suivantes tiennent également compte de la division finale par 2 qui fait partie du circuit DDPS comme on le voit à la figure 12 :

$$T_{out} = \frac{T_{ref}}{2^M} \cdot Ph \cdot 2 \quad (5)$$

$$f_{out} = \frac{f_{ref} \cdot 2^{M-1}}{Ph} \quad (6)$$

L'incrément de phase Ph se représente sur N bits, où le nombre N de bits est supérieur au nombre M de bits servant à adresser la ligne à délais. Ainsi, les  $N - M$  bits les moins significatifs de l'accumulateur de phase représentent une fraction de phase qui s'accumule de cycle en cycle. Lorsqu'il y a débordement, cette fraction se manifeste sur la sélection de phase comme un délai de phase additionnel. Nous adoptons la notation suivante, dans laquelle W est le nombre entier de phases dans Ph et X/Y la partie fractionnaire :

$$Ph = W + X / Y \quad (7)$$

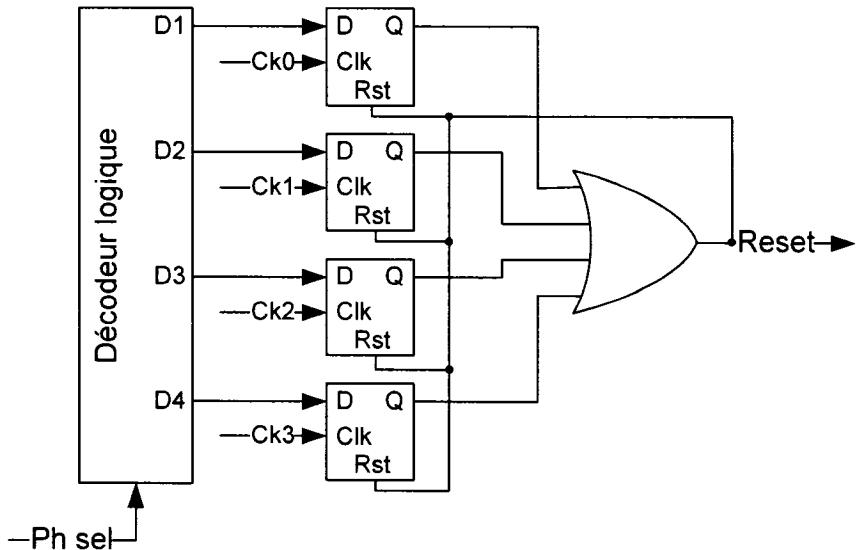

### 2.3.3 Sélection des transitions

Figure 15 – Circuit de sélection des transitions

Le sélecteur de transitions, représenté à la figure 15 agit en quelque sorte comme un multiplexeur qui serait à l'épreuve des aléas, ces signaux parasites qui influencent le fonctionnement des circuits asynchrones. Il permet à la phase choisie par l'accumulateur d'être vers la sortie lors d'un cycle donné. Une fois le sélecteur déclenché par le front montant de la phase choisie, il envoie une impulsion. Cette impulsion est utilisée d'une part pour mettre à jour le contenu de l'accumulateur de phase et d'autre part pour générer une transition sur le signal de sortie, en inversant l'état d'une bascule bistable qui convertit ainsi le train d'impulsions en une onde quasi-carrée. Le fait que la mise à jour de la sélection de phase soit déclenchée par son propre signal de sortie permet au DDPS de produire des périodes de sortie plus courtes que celle obtenue en référence. C'est une particularité qui distingue le DDPS des architectures à contrôle de ligne à délais DCDL comme celles proposées par NIEZNANSKI, J. (1998) ou McCUNE, E. (1993).

### 2.3.4 Exemple de fonctionnement

Le tableau 4 présente un exemple montrant l'accumulation d'une valeur d'incrément de phase  $Ph$  égale à  $9 + \frac{1}{4}$ . La colonne b) montre le contenu de l'accumulateur pour les 8 premiers cycles. La troncation de ces valeurs résulte en la sélection des transitions montrées à la colonne c). Finalement, la colonne d) montre que les sauts de phase, exprimés en termes de nombre de cellules, alternent périodiquement entre  $W$  et  $W+1$ . Bien que les transitions ne soient pas en leurs positions temporelles idéales, après un certain nombre de cycles, la période devient en moyenne celle désirée.

Tableau 4 – Contenu de l'accumulateur et sélection des phases ( $Ph = 9 + \frac{1}{4}$ ,  $2^M = 16$ )

| a)    | b)                 | c)            | d)                                       |

|-------|--------------------|---------------|------------------------------------------|

| Cycle | Phase accumulée    | Phase choisie | Saut de phase ( $\times \Delta_{cell}$ ) |

| 1     | $9 + \frac{1}{4}$  | Ck9           | 9                                        |

| 2     | $2 + \frac{1}{2}$  | Ck2           | 9                                        |

| 3     | $11 + \frac{3}{4}$ | Ck11          | 9                                        |

| 4     | 5                  | Ck5           | 10                                       |

| 5     | $14 + \frac{1}{4}$ | Ck14          | 9                                        |

| 6     | $7 + \frac{1}{2}$  | Ck7           | 9                                        |

| 7     | $0 + \frac{3}{4}$  | Ck0           | 9                                        |

| 8     | 10                 | Ck10          | 10                                       |

### 2.3.5 Synthèse de fractions non binaires

Le nombre  $N$  de bits dans l'accumulateur de phases d'un DDPS peut restreindre la capacité du circuit à exprimer de façon exacte certaines valeurs d'incrément de phase  $Ph$ . Certaines valeurs de  $Ph$  doivent être approximées par la plus proche valeur possible. À titre d'exemple, supposons qu'un circuit DDPS donné comporte un accumulateur de 12

bits et que la fréquence que l'on cherche à générer nécessite une valeur de Ph de  $9 + 2/5 = 9,4$ . Compte tenu de la précision de 12 bits, cette valeur devra obligatoirement être approximée par 9,39990234375 ou par 9,400146484375, les deux valeurs les plus proches. L'emploi de l'une ou l'autre de ces valeurs causera une accumulation de gigue dans le temps, ce qui peut être particulièrement néfaste lorsque l'horloge produite doit servir à des fins de synchronisation.

Une solution à ce problème (CALBAZA, D.E., & SAVARIA, Y., 2000b) consiste à alterner entre deux valeurs d'incrément de phase Ph0 et Ph1, qui sont respectivement des valeurs d'approximation immédiatement supérieure et immédiatement inférieure de la valeur d'incrément de phase Ph, mentionnées dans l'exemple du paragraphe précédent. Sans perte de généralité, sur un total de Y périodes d'horloge, Ph0 est présenté à l'accumulateur A fois, et Ph1 est présenté B fois. Les valeurs A et B peuvent être choisies de telle sorte que A + B soit égal à Y, respectant ainsi l'équation :

$$A \cdot Ph0 + B \cdot Ph1 = Y \cdot Ph \quad (8)$$

Cette approche permet de se prémunir contre l'accumulation de l'erreur d'approximation. Une façon simple d'alterner entre les valeurs Ph0 et Ph1 consiste en la modulation du bit « carry-in » de l'accumulateur. Un circuit faisant usage de cette solution est proposé et décrit dans (CALBAZA, D.E., & SAVARIA, Y., 2000b).

## 2.4 SYNTHÈSE DE FRÉQUENCE ET MODÉLISATION SPECTRALE

Le but du présent travail est d'analyser et d'interpréter le contenu spectral du signal de sortie du circuit DDPS, afin d'en arriver à des conclusions permettant d'optimiser les paramètres de conception ou de suggérer des modifications à apporter au circuit. Une première étape consiste à modéliser le spectre produit. Ceci permet, à l'aide d'un ensemble de formules mathématiques, de prévoir l'allure du spectre en fonction des paramètres d'opération du circuit. Ce genre d'analyse fut effectué pour des circuits de synthèse de fréquence plus connus. Comme il peut exister des similitudes au niveau de l'approche utilisée, il est intéressant de se pencher ici sur les travaux existants, pour voir dans quelle mesure ils s'appliquent ou non au cas du DDPS.

Comme nous l'avons vu dans la section précédente, la séquence de sélection des phases dans un circuit DDPS est générée par un accumulateur. Cette caractéristique de fonctionnement le rend similaire au DDS (section 2.2.2), où un accumulateur est utilisé pour adresser une LUT contenant la valeur des amplitudes du signal pour chaque phase correspondant à une adresse mémoire. Plusieurs articles se sont penchés sur le phénomène de la présence de raies dans le spectre fréquentiel du signal produit par le circuit DDS. Comme nous le verrons au chapitre 3, ce phénomène s'observe également dans le cas du circuit présentement à l'étude. C'est pourquoi on doit s'intéresser aux modèles simples et efficaces ayant été mis au point pour prédire la position et l'amplitude des raies spectrales d'un circuit similaire à celui à l'étude.

Une première technique visant à estimer les raies retrouvées dans le spectre du circuit DDS fut présentée par NICHOLAS, H.T., & SAMUELI, H. (1987). Dans cet

article, les auteurs se penchent sur un algorithme de calcul du spectre du DDS tenant compte de l'effet de la troncature des bits les moins significatifs de l'accumulateur de phase. Ils en arrivent à une expression pour l'amplitude, le nombre, et la position des raies spectrales additionnelles communément appelées *spurs* en fonction de la taille de la LUT, de la quantité de troncature et du mot de commande. Ils abordent brièvement le fait qu'il existe également un bruit causé par la précision de la LUT ainsi que par les non-linéarités du convertisseur DAC.

Peu de temps après parut un article (JENQ, Y.C., 1988) où l'auteur se penche davantage sur l'approximation de la sinusoïde emmagasinée dans la LUT, une autre source d'impureté spectrale. Selon l'auteur, « La méthode numérique avec LUT présente plusieurs caractéristiques désirables, telles que la stabilité à haute fréquence ainsi qu'un contrôle précis de la fréquence et de la phase du signal sinusoïdal produit. Cependant, des harmoniques indésirables sont générées lorsqu'on tente de syntoniser différentes fréquences en manipulant le mécanisme d'adressage mémoire au lieu de charger un nouvel échantillon de signal dans la mémoire, ce qui prend du temps et est parfois infaisable. »

KROUPA, V.F. (1993) V.F. fit paraître un modèle pour unifier l'approximation du spectre du DDS. Cependant, son algorithme se base sur des formulations mathématiques plutôt complexes, de sorte que d'autres auteurs se sont penchés par la suite sur des modèles plus simples d'approximations du spectre du DDS. Parmi ceux-ci, il est important de mentionner les travaux de TOROSYAN, A., & WILSON Jr., A. (2001) ainsi que de PIPAY, Z. (2001). Ces auteurs ont présenté des analyses fondées sur

les propriétés de la transformée discrète de Fourier afin de simplifier l'estimation des raies spectrales du DDS. Finalement, une technique pour déterminer ces raies de façon exacte et non par estimation fut récemment présentée par CURTICAPEAN, E., & NIITTYLAHTI, J. (2003).

D'autres travaux de modélisation du profil spectral existent certainement pour les autres circuits de synthèse de fréquence comme le PLL ou encore le Frac-N (Section 2.2.1). Par contre, comme il s'agit de circuits de synthèse analogiques et/ou indirects, les analyses que l'on retrouve concernant leur profil spectral ne s'appliquent pas au DDPS. En effet, bien qu'un PLL soit utilisé pour générer les phases du DDPS, nous verrons plus loin que les effets les plus importants sur la forme du spectre généré par ce circuit seront ceux qui causent une élongation de la périodicité réelle du signal de sortie. Les travaux présentés ici cependant sont basés sur un fondement similaire à ce qui servira à approfondir la modélisation spectrale du DDPS. Il existe non seulement une similitude vis-à-vis le mode de construction du signal (avec un accumulateur de phase) mais on peut également argumenter que l'erreur sur la précision des délais dans un DDPS est assimilable à l'imprécision sur les valeurs stockées dans la LUT pour les amplitudes du signal produit par le DDS, phénomène traité dans les références mentionnées. Cependant, il n'est pas exact de dire qu'il s'agit de phénomènes équivalents. La précision des délais du DDPS est un phénomène temporel. On ne peut donc utiliser les analyses du DDS qui sont basées sur une base de temps que l'on suppose discrète et uniforme. Ce que nous retiendrons de ces travaux, c'est qu'une approche en transformée de Fourier peut simplifier le processus d'analyse, mais que nous devrons nous ajuster au fait que l'on ne

dispose pas ici d'une base de temps discrète à proprement parler, puisque l'on ne peut pas considérer le délai d'une cellule de la ligne à délais du DDPS comme un élément temporel discret. En plus de ne pas être un élément discret, le délai d'une cellule n'est pas tout à fait constant. En effet, de légères fluctuations du milieu (température, bruit...) influent sur la valeur du délai. Par contre, comme il s'agit d'une boucle asservie, on considère dans notre analyse que ces phénomènes sont à long terme par rapport à l'intervalle entre un cycle et le prochain où les délais seront presque le même.

## 2.5 SYNTÈSE DE FRÉQUENCE ET AMÉLIORATION SPECTRALE

Après avoir présenté à la section précédente les travaux de modélisation de spectre qui servent d'inspiration à l'algorithme qui a été développé au cours des travaux de recherche présentés dans ce mémoire, nous nous penchons ici sur les améliorations aux circuits de synthèse de fréquences qui furent proposés dans le but d'en améliorer le profil spectral, ce que nous cherchons également à faire avec le DDPS.

En ce qui concerne le DDS, le circuit qui présente le plus de similarités avec le DDPS, notons que NICHOLAS, H.T., & SAMUELI, H. , & KIM, B. (1988) suggèrent une technique de compression de la taille de la LUT, pour une précision donnée. Dans le cas du DDPS, où il n'y a pas de LUT mais des phases générées par une ligne à délais, on cherchera plutôt à augmenter la précision de la valeur du délai des cellules de la ligne à délais. À ce sujet, un article de PARK, C., & KIM, O., & KIM, B. (2001) présente un oscillateur à phases multiples opérant à 1,8 GHz et muni d'un circuit d'auto-calibration

lui permettant d'ajuster le mésappariement entre ses cellules. Son utilisation comme générateur de phases au sein du circuit DDPS est donc très prometteuse.

VANKKA, J. (1996) proposa une revue de techniques de réduction des raies spectrales indésirables. Pour plus de détails concernant les propriétés ainsi que leurs avantages et inconvénients, il est intéressant de consulter son article. Il est à noter que son analyse est restreinte aux erreurs de quantification de la phase ainsi que de l'amplitude, phénomènes mentionnés précédemment. Parmi les solutions qu'il propose, notons l'ajout de bruit aléatoire pour appliquer la méthode dite de « *dithering* ». Qu'elle soit appliquée par l'ajout de bruit aléatoire, ou par modulation selon la technique delta-sigma comme proposé dans cet article pour le circuit DDS, nous verrons à l'aide de résultats de simulation comment ces techniques peuvent être intégrées à la conception de circuits DDPS présentant des profils spectraux différents.