|                         | Hybrid microfluidic CMOS capacitive sensors for lab-on-chip applications                                                                                                                                         |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Ebrahim Ghafar-Zadeh                                                                                                                                                                                             |

| Date:                   | 2007                                                                                                                                                                                                             |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                        |

| Référence:<br>Citation: | Ghafar-Zadeh, E. (2007). Hybrid microfluidic CMOS capacitive sensors for lab-on-<br>chip applications [Thèse de doctorat, École Polytechnique de Montréal].<br>PolyPublie. https://publications.polymtl.ca/7996/ |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/7996/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Mohamad Sawan, & Daniel Therriault    |

| <b>Programme:</b><br>Program:            | Non spécifié                          |

#### UNIVERSITÉ DE MONTRÉAL

# HYBRID MICROFLUIDIC CMOS CAPACITIVE SENSORS FOR LAB-ON-CHIP APPLICATIONS

Ebrahim Ghafar-Zadeh

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÉSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR (PH.D.)

(GÉNIE ÉLECTRIQUE)

Décembre 2007

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-37126-8 Our file Notre référence ISBN: 978-0-494-37126-8

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# UNIVERSITÉ DE MONTRÉAL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée

# HYBRID MICROFLUIDIC/CMOS CAPACITIVE SENSORS FOR LAB-ON-CHIP APPLICATIONS

Présentée par: Ebrahim Ghafar-Zadeh

en vue de l'obtention du diplôme de Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de :

- M. SAVARIA Yvon, Ph.D. président

- M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

- M. THERRIAULT Daniel, Ph.D., membre et co-directeur de recherche

- M. PETER Yves-Alain, Ph.D., membre

- M. CHODAVARAPU Vamsy, PhD, membre externe

Dedicated to my wife

Masoomeh

#### **ACKNOWLEDGEMENTS**

I would like to thank God for giving me strength and guidance to learn and share new knowledge. I would like to thank my advisor Professor Mohamad Sawan for all his help and guidance during my PhD studies in Polystim Neurotechnology laboratory. I thank my co-advisor Professor Daniel Therriault for his valuable comments on using direct-write microfluidic fabrication process. I would also like to thank all staff, faculty and graduate students who helped me during my research and education in Ecole Polytechnique de Montreal. I would like to express my deepest gratitude to my family for their love and their encouragements. Finally I would like to thanks, NSERC, CMC Microsystems and IMRST for their financial and technical supports and scholarship respectively.

#### **ABSTRACT**

The recent advances in lab-on-chip (LoC) technology offer the prospect of rapid, automated biological assays or procedures in analytical chemistry through miniaturized devices. The rapid response, portability, and ease-of-use make LoCs suitable for operation in real-world conditions, spanning a wide array of health and life science applications such as the diagnosis of genetic disorders or the testing of food and water supplies for contamination. The development of biochips is a major thrust of the rapidly growing biotechnology industry, and involves a multidisciplinary research effort encompassing microfluidics, microelectronics and biochemistry.

CMOS based capacitive sensors have recently received significant attention for biochemical testing applications such as DNA detection, antibody-antigen recognition and cell monitoring. In this thesis, we address this challenging issue by proposing hybrid microfluidic/CMOS capacitive sensor suitable for the aforementioned applications. A new high-precision charge-based sensor system is presented to detect the minute capacitance variations resulting from the presence of biochemical solutions/solvents in microchannel. We also propose a low temperature and low complexity direct-write microfluidic packaging procedure to implement the microfluidic channels on the top of CMOS sensor chip. The implementation and experimental results are demonstrated using organic solvents with known dielectric constants in order to reveal the viability of the proposed hybrid LoC platform for capacitive detection.

It is recognized by the researchers in the field that the custom design of a generic capacitive sensor system should be taken into account for LoC applications. Of course, this new multidisciplinary approach is in its early stage of development and it needs huge effort to transition from this level of research to the optimum design and implementation of fully automated sensor systems.

### **RÉSUMÉ**

Les développements récents de la technologie de laboratoire-sur-puce (Laboratory-on-Chip: LoC) proposent des analyses ou des procédés biologiques rapides et automatiques en chimie analytique à travers des dispositifs miniaturisés. Leur réponse rapide, portabilité, et facilité d'utilisation rendent les LoCs convenables pour opérer dans des conditions réelles, pour beaucoup d'applications de santé et de sciences de la vie comme le dépistage de maladies génétiques ou les tests de contamination de nourriture et d'eau. Le développement des biopuces est un immense défi dans l'industrie de la biotechnologie en expansion rapide. Ceci comprend un effort de recherche multidisciplinaire incluant la microfluidique, la microélectronique et la biochimie. Dans cette thèse, notre intérêt se porte sur l'aspect d'ingénierie des LoCs, et en particulier sur le développement d'un capteur hybride microfluidique/CMOS comme premier pas vers un LoC complètement intégré. Cependant, plusieurs LoCs basés sur la technologie CMOS ont été proposés récemment pour diverses applications, mais la technologie de laboratoire-sur-puce elle-même est encore dans sa phase préliminaire. Ce travail concerne l'intégration de structures microfluidiques avec de la microélectronique. Les composants microfluidiques sont requis pour injecter l'analyte vers les sites de détection. Nous relevons ce défi avec un procédé microfluidique d'écriture directe qui est utilisé pour la première fois sur une puce CMOS. Nous proposons aussi un capteur capacitif basé sur la charge pour détecter les petits changements de capacité induits par la présence de bioparticules dans le canal. Bien que beaucoup de capteurs capacitifs aient été publiés pour maintes applications, peu d'intérêts ont été accordés envers un système dédié à la détection capacitive d'un liquide sur la surface d'une puce CMOS. Pour cela, nous proposons trois architectures de puces avec des niveaux de complexité différents en CMOS 0.18 μm. Chaque puce capteur est incorporée avec de la microfluidique pour la détection d'analytes. Nous démontrons la viabilité du système proposé pour les applications de LoC pour différents solvants organiques avec différentes constantes diélectriques.

Le capteur capacitif proposé, ainsi que la structure microfluidique faite par d'écriture directe, offrent les avantages d'une basse complexité et d'une grande flexibilité pour différents types d'applications de LoC comme la détection d'ADN, la reconnaissance de virus et l'analyse de cellules.

# CONDENSÉ EN FRANÇAIS

#### I. INTRODUCTION

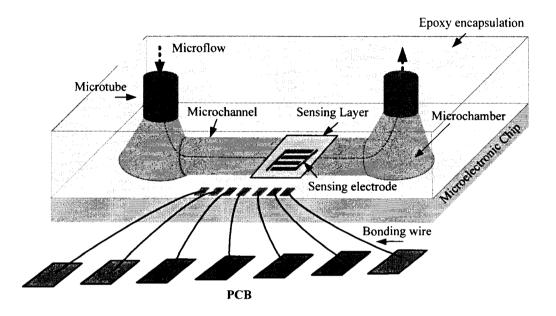

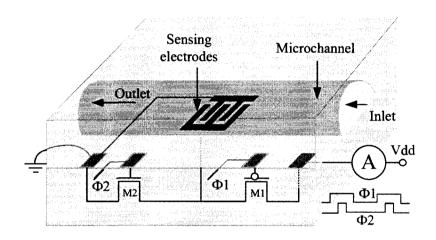

Les LoCs semblent avoir un avenir prometteur en tant que capteurs miniaturisés pour la mesure et la détection rapides et automatiques d'une gamme diversifiée d'analytes cliniques et environnementales. Une plateforme de LoC comprend de la microfluidique, des électrodes de détection et des interfaces microélectroniques (voir Fig. 4.1). Les composantes microfluidiques, tel que les canaux, les valves et les pompes dirigent et manipulent des fluides biologiques ou biochimiques. La fine pointe de la recherche sur l'intégration des microfluidiques en microélectronique est de nos jours, centralisée sur la fabrication de composants microfluidiques en tant que partie du procédé de fabrication microélectronique sur tranches plutôt que sur des puces encapsulées électriquement [PAL04]. Rasmussen et al, à titre d'exemple, ont réalisé des canaux microfluidiques sur une puce fabriquée en se basant sur des procédés conventionnels de micro-usinage de surfaces [RAS01]. D'autres efforts de la part de Masteranglo et al montrent le microusinage de surfaces polymères pour fabriquer les canaux microfluidiques sur la surface d'un circuit intégré CMOS [MAN97]. Chartier et al ont publié une méthode de fabrication d'une structure microfluidique intégrée sur une puce CMOS basée sur les polymères avec une technique de gaufrage à chaud [ICH03]. En effet, un LoC basé sur la technologie CMOS requiert un boîtier microfluidique efficace pour protéger la circuiterie des analytes biologiques et biochimiques. Cet aspect, qui est souvent négligé par les applications de LoC CMOS, est incontournable pour diriger les fluides vers les capteurs pour être analysés. Idéalement, l'encapsulation microfluidique doit être le résultat d'un procédé à basse température avec soudure fiable et hermétique. La fuite des analytes des composants microfluidiques risque d'augmenter les résistances et capacités parasites, modifiant alors les caractéristiques du circuit. Nous traitons ce problème aussi en proposant un procédé de fabrication microfluidique d'écriture directe [GHA07g]. Ce procédé fiable et robotisé est utilisé pour implémenter les microcanaux sur une puce de capteurs capacitifs.

Les capteurs capacitifs CMOS ont récemment attiré l'attention des chercheurs œuvrant dans le domaine de LoC pour tests biochimiques, tel que la détection d'antigènes par liaison d'anticorps (ex. la détection de virus [BAL05], l'analyse cellulaire [ROM05], la reconnaissance d'ADN [SON06] ainsi que la détection chimique). Les applications de LoC complètement intégrés de la sorte exigent un capteur microfluidique/CMOS-capacitif hybride. Dans cette thèse, nous relevons ce défi en proposant une matrice de capteurs capacitifs implémentée avec le procédé CMOS et intégrée avec des canaux microfluidiques (voir Fig. 4.1). Une couche de détection biofonctionnalisée spécifique à chaque application pourrait être formée sur les sites de détection pour des fins de détection sélective – mais ceci n'est pas le cas pour le présent travail.

Jusqu'à maintenant, plusieurs techniques de lecture de données employant des stratégies différentes ont été publiées pour des systèmes de capteurs capacitifs autonomes (ex. accéléromètre basé sur les systèmes microélectromécaniques). Par contre, la littérature ne parle pas trop de la conception sur mesure de LoC à capteurs capacitifs. Les capteurs capacitifs pour les applications de LoC n'exigent pas la détermination d'une seule valeur pour la capacité de détection, mais toutefois de pouvoir distinguer le comportement du dispositif plutôt en présence qu'en absence d'analyte dans le canal microfluidique. Les valeurs des capacités statiques avant et après l'injection d'analyte sont extraites à partir de mesures dynamiques de capacités pour la plupart des applications [VAK06]. Pour cela, les techniques basées sur la moyenne peuvent être employées de façon simple et efficace. Cette complexité réduite se révèle être un atout pour la conception et l'implémentation de grandes matrices de capteurs capacitifs [PRA07]. En effet, l'implémentation d'une grande matrice de capteurs sur une seule puce implique une petite empreinte de plots pour le circuit. Ceci écarte l'option d'utiliser une approche basée sur les amplificateurs opérationnels qui occuperaient une grande surface.

La mesure de capacité basée sur la charge (MCBC) est une méthode simple proposée pour la première fois en 1998 pour les mesures de capacités d'interconnexions inférieures à un femto-Farad dans les puces CMOS [SYL98]. À cause de la basse complexité, de la surface réduite, et de la haute précision, cette méthode de mesure statique s'est avérée être la préférée pour satisfaire les exigences des capteurs capacitifs

de LoC. Parmi les rares travaux sur la mesure de capacité basée sur la charge pour les capteurs capacitifs, Guiducci et al ont réussi à détecter l'ADN par le biais de circuiterie externe à la puce et d'électrodes intégrées [GUI04]-[STA07].

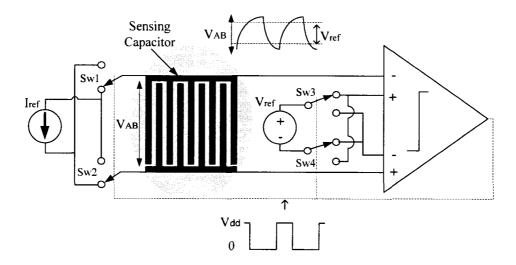

Cet thèse se concentre sur les noyaux-MCBC complètement intégrés, pour applications de LoC. Pour montrer l'applicabilité de la MCBC pour les capteurs capacitifs, une puce de test (PT1) a été implémentée initialement avec une grosse électrode interdigitée connectée à une seule paire n/pMOS (Fig. 4.1). Puisque la mesure de capacité basée sur la charge utilise l'instrumentation externe, elle ne peut pas être appliquée directement aux capteurs intégrés. Pour cela, un circuit complémentaire (PT2) a été conçu est implémenté dans un procédé CMOS. Cette puce comprend une électrode interdigitée et des circuits d'interface pour convertir la capacité en tension. Par la suite, une matrice d'électrodes interdigitées et d'autres circuits de calibration ont été implémentés dans une puce PT3. Nous avons également conçu et développé d'autres circuits pour incorporer tout le système de capteurs sur une puce.

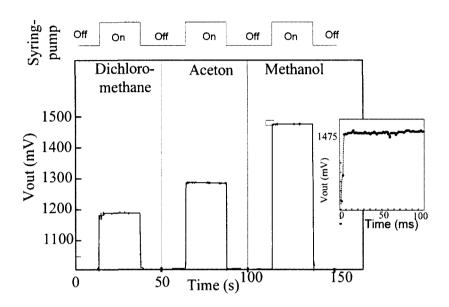

Les solvants organiques avec des constantes diélectriques connues offrent une bonne alternative pour modéliser la variation de capacité suite à un changement diélectrique à proximité de sites de détection. Nous caractérisons le capteur hybride proposé et montrons sa viabilité pour les applications de LoC en utilisant des substances chimiques contenant le la dichlorométhane, de l'acétone et du méthanol.

Le reste de ce condensé est organisé comme tel. La section II décrit l'analyse et la conception de circuits d'interface pour les noyaux-MCBC. La section III décrit le

procédé de fabrication microfluidique d'écriture directe. Les procédures d'expérimentation et les résultats se trouvent dans la section IV. Cette section est suivie d'un résumé qui fait l'objet de la section VI.

#### II. CIRCUIT D'INTERFACE À NOYAU- MCBC

Trois architectures de puces avec différents niveaux de complexité sont discutées dans cette section.

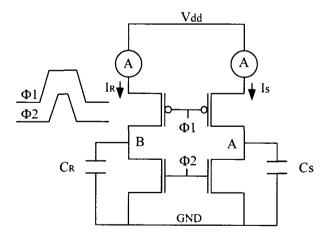

#### A. Banc d'essai de caractérisation capacitive

La structure MCBC est utilisée dans PT1 pour mesurer le changement de capacité en deux étapes. La Fig. 4.1 montre une électrode connectée à la masse et une autre connectée aux drains de la paire n/pMOS. La première étape consiste à enregistrer le courant de charge  $I_I$  à travers un ampèremètre CC (A) pour un canal vide. Par la suite, le total des capacités parasites ( $C_0$ ) associées aux transistors MOS et aux électrodes peut être représenté par l'équation suivante.

$$I_1 = f \cdot V_{dd} \cdot C_0 \tag{1}$$

où f et  $V_{dd}$  sont la fréquence des signaux à impulsions et la tension d'alimentation respectivement. Pour la seconde étape, une solution est injectée dans le microcanal et le courant de charge  $(I_2)$  est enregistré. Comme le montre l'Eq. 2, ce courant est proportionnel à la sommation de  $C_0$  avec la variation de capacité  $\Delta C$ .

$$I_2 = f \cdot V_{dd} \cdot (C_0 + \Delta C). \tag{2}$$

$C_0$  et  $\Delta C$  peuvent alors être déduits des Eqs. (1) et (2) pour une valeur particulière de f.

Il est important de mentionner que cette puce peut servir de méthode simple pour la caractérisation capacitive de capteurs de laboratoires-sur-puce. Cette procédure de caractérisation sert à extraire les changements de capacité ainsi que les capacités parasites générées. Les données extraites pourraient alors servir de modèle simplifié pour la conception et l'optimisation de circuits intégrés dédiés à des applications de laboratoire-sur-puce. Des outils de CAO basés sur les éléments finis, tel que FEMLab, sont typiquement utilisés pour l'analyse de telles variations de capacité. Cependant, en plus des dimensions physiques, la modélisation d'applications de la sorte nécessite beaucoup de données préliminaires, tel que des données physicochimiques et des traitements qui sont rarement disponibles. Donc, une méthode de caractérisation expérimentale qui pourrait établir des analyses précises en se basant sur des données préexistantes serait un atout.

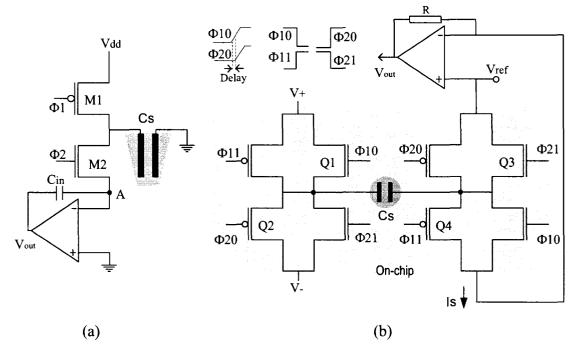

#### B. Capteur capacitif intégré

Pour remplacer le dispositif de mesure externe (A dans la Fig. 4.1) avec des circuits intégrés, la première étape a été d'implémenter un capteur capacitif et de concevoir un circuit d'interface dans PT2.

#### Analyse

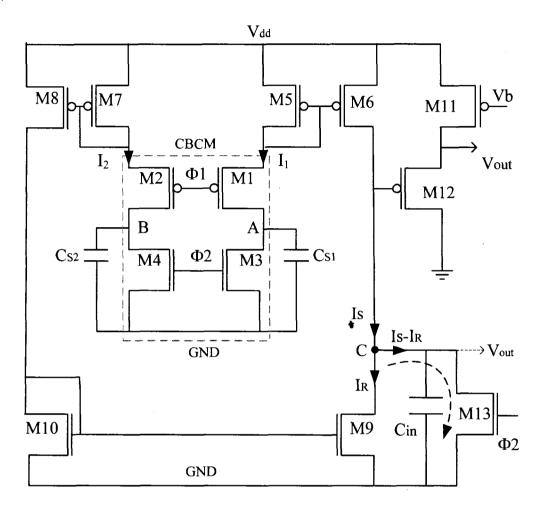

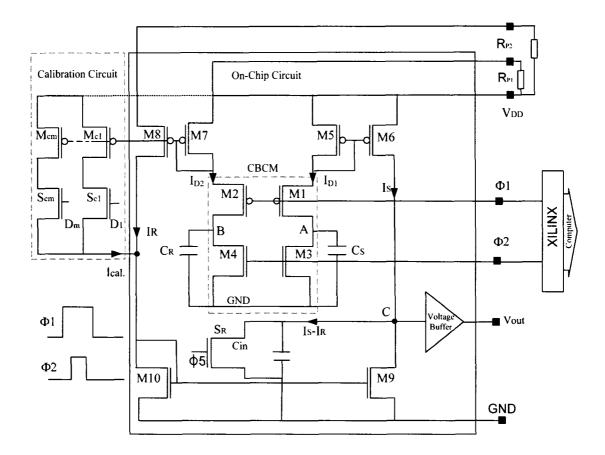

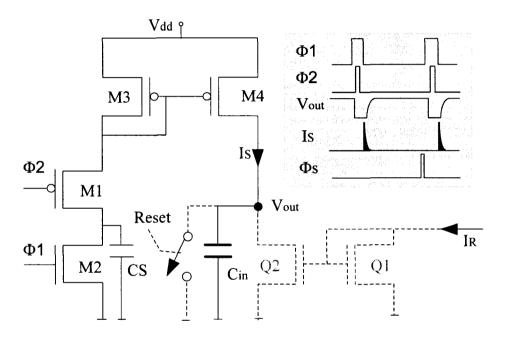

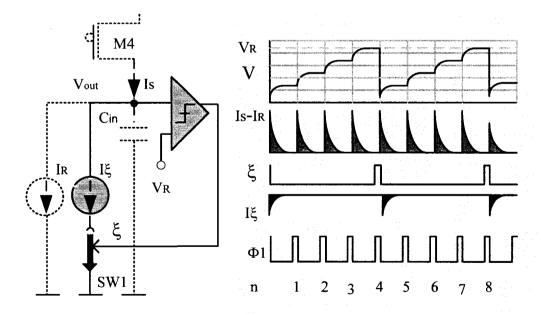

L'unité de base du circuit d'interface proposé (UCI) est illustrée dans la Fig. 4.2. Dans ce circuit, un miroir de courant composé de M<sub>3</sub> et M<sub>4</sub> est utilisé pour détecter et amplifier le courant de charge (I<sub>S</sub>), qui est converti en tension dans le condensateur

d'intégration ( $C_{in}$ ). Une fois que le signal  $\phi 1$  est bas, la tension sur  $C_S$  ( $V_S$ ) commence à augmenter en suivant l'Eq. (3).

$$C_S \frac{dV_S}{dt} = K_x \cdot (V_{gs} - V_{TP})^2 \tag{3}$$

où  $K_x$  dépends des paramètres du procédé, et  $V_{gs}$  et  $V_{TP}$  sont la tension entre la grille et la source et la tension de seuil d'un transistor à effet de champ à canal p respectivement. Aussi, les résistances d'activation de  $M_1$  et  $M_2$  ont été négligées. En remplaçant  $V_{gs}$  par  $V_{dd}$  – $V_S$  dans (3), et en considérant  $V_S$  = 0 à t = 0 (décharge) quand  $\phi 1$  et  $\phi 2$  sont hauts,  $V_S$  est donné par l'Eq. 4

$$V_S = (V_{dd} - V_{TP}) - \frac{(V_{dd} - V_{TP})C_S}{K_x (V_{dd} - V_{TP})t + C_S}.$$

(4)

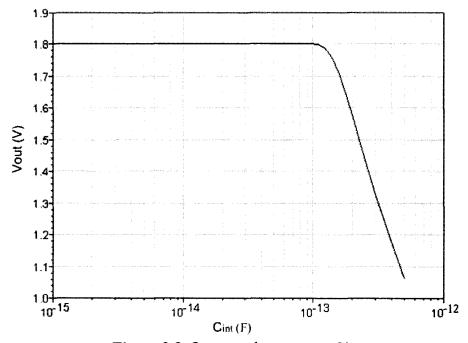

Tel que montré par cette équation et par la Fig. 4.2, et en supposant que les courants de charge transitoires auraient assez de temps pour s'établir durant la période de l'onde carrée, V<sub>S</sub> augmentera en conséquence jusqu'à une valeur d'une tension de seuil à court de la tension d'alimentation. À ce point, M4 est bloqué. Dans ce cas, la tension à travers le condensateur d'intégration est

$$V_{out} = \frac{W_4 / L_4}{W_3 / L_3} \cdot \frac{(\Delta C + C_0)}{C_{in}} \cdot V_S.$$

(5)

où  $W_4/L_4$  et  $W_3/L_3$  sont les rapports largeur/longueur de  $M_4$  et  $M_3$  respectivement. Il est clair que la gamme dynamique de  $V_{out}$  reste limitée puisque  $Co>>\Delta C$ . Pour cela, une empreinte du circuit d'interface est utilisée pour générer un courant de référence  $I_R$ . Comme le montre la Fig. 4.2, ce courant est reflété au nœud de sortie à travers un autre

miroir de courant et soustrait I<sub>s</sub>. À cause de sa symétrie et de son opération différentielle, V<sub>out</sub> est exprimé par l'Eq. 6

$$V_{out} = \frac{\Delta C}{C_{in}} (V_{dd} - V_{TP}) + V_{off}. \tag{6}$$

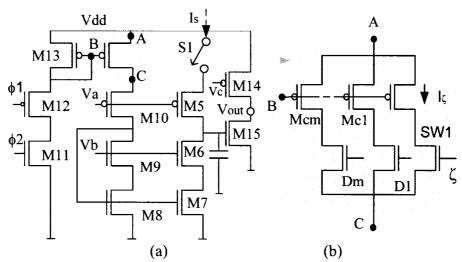

La tension de décalage résiduelle  $V_{off}$  est en principe due au défaut d'appariement des miroirs de courant et des circuits de MCBC. Pour réduire l'effet de cette erreur, un miroir de courant ajustable est utilisé, tel que montré dans les Figs. 4.3a et 4.3b. Pour chaque entrée numérique D1-Dm ( $D_{1-m}$ ) montrées dans la Fig. 4.3b, un certain courant ( $I_R$ ) est tiré de  $M_{C1}$ - $M_{Cm}$  qui ont des rapports largeur/longueur donnés par l'Eq. 7.

$$\frac{W_{13}}{L_{13}} = 2 \cdot \frac{W_{C1}}{L_{C1}} = 2^2 \cdot \frac{W_{C2}}{L_{C2}} \dots = 2^m \cdot \frac{W_{Cm}}{L_{Cm}}$$

(7)

Pour cette architecture, les données de l'entrée numérique sont générées à partir d'un circuit externe à la puce qui sera décrit dans la section suivante. Aussi, tel que montré dans la Fig. 4.3a, pour améliorer l'excursion de tension de la sortie V<sub>out</sub> et pour réduire la fuite de C<sub>in</sub>, notamment pour les impulsions d'horloge à basse fréquence, un miroir de courant à large excursion de tension, wide-swing, (M<sub>5</sub>-M<sub>10</sub>) est utilisé à la place du simple miroir de courant dessiné avec des lignes découpées dans la Fig. 4.3a. D'un autre côté, M<sub>14</sub> et M<sub>15</sub> forment un amplificateur à source chargée qui isole le nœud d'intégration des capacités parasites des étages subséquents. Il faut signaler que la tension V<sub>off</sub> est éliminée automatiquement par la soustraction de deux mesures consécutives précédant et suivant l'injection d'analyte. Par la suite, elle n'a aucun effet important sur la précision de la détection capacitive.

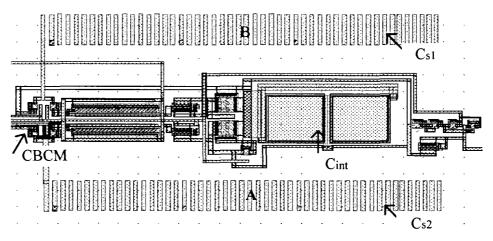

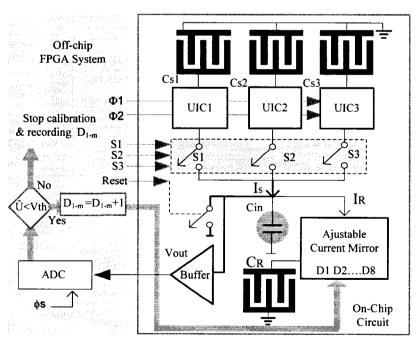

#### C. Système de détection capacitif

Tel que montré par la Fig. 4.4, un système de détection a été conçu et incorporé dans PT3 ayant quatre électrodes interdigitées comme condensateurs de détection ( $C_{S1}$ - $C_{S3}$ ) et de référence ( $C_R$ ), trois UCIs, un miroir de courant ajustable (voir Fig. 4.3), et un simple ampli-tampon à gain unitaire. Cette puce nécessite des signaux d'entrée-sortie analogiques ( $V_{out}$ ,  $V_a$ ,  $V_b$  and  $V_c$ ) et numériques ( $D_{1-m}$ ). Pour cette architecture, les électrodes de détection sont sélectionnées par des lignes d'adressage numérique  $S_1$ ,  $S_2$  et  $S_3$  ( $\check{S}$ ), tandis que la logique de contrôle englobe la réinitialisation et les signaux d'horloges  $\phi 1$ - $\phi 2$ .

Une procédure de calibration est préalablement nécessaire à l'injection d'analyte en repérant la valeur optimale des données d'entrée  $D_{1-m}$ . Pour cela, un module externe à la puce est commandé pour commencer la calibration du capteur avant la prise d'une mesure. Ce module est implémenté dans une plateforme FPGA comprenant un convertisseur analogique-numérique (CAN). La sortie numérique du CAN ( $\tilde{U}$ ) est employée comme critère de décision dans l'algorithme de calibration exécuté par le module externe à la puce. Pour chaque période de l'horloge  $\phi 1$ , si  $V_{out}$  dépasse une tension de seuil ( $V_{th}$ ),  $D_{1-m}$  est incrémenté jusqu'à ce que la valeur requise soit atteinte. Les rapports largeur/longueur de  $M_{C1}$ - $M_{C8}$  indiquent qu' $I_R$  est initialement inférieur à  $I_S$ , ce qui implique que le procédé de calibration commence toujours avec une valeur de  $V_{out}$  supérieure à  $V_{th}$ . La Fig. 4.4 montre que  $D_{1-m}$ ,  $\tilde{S}$  et les horloges ( $\phi 1$  and  $\phi 2$ ) sont fournis par en module externe à la puce implémenté dans un FPGA (AFS600, Actel). Le

signal numérique (Ũ) est finalement capté et mémorisé dans l'ordinateur.

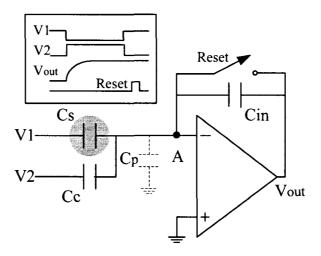

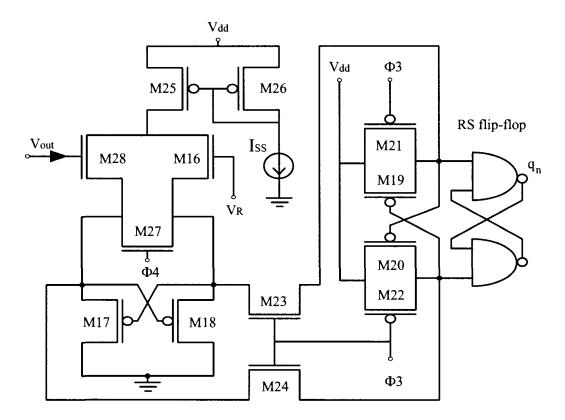

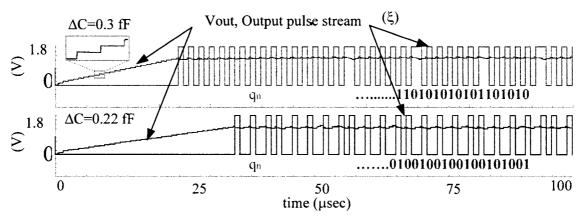

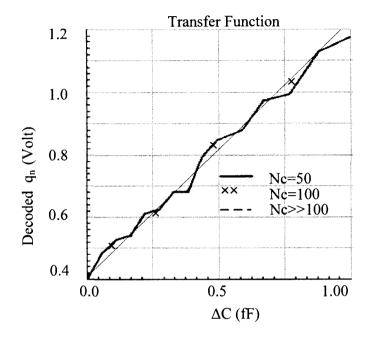

#### D. CAN dédié et efficace

Pour un capteur complètement intégré, il est nécessaire de concevoir un circuit de lecture de données pour l'enregistrement et pour des traitements plus poussés. Dans cette section, suite à notre circuit à noyau-MCBC, nous présentons un CAN simple et efficace conçu en ajoutant quelques dispositifs additionnels au circuit d'interface. Ôtons la réinitialisation (Reset) de la Fig. 4.2 et laissons V<sub>out</sub> s'élever à chaque période, tel que montré par la Fig. 4.6. Vout est comparé à une tension de référence (VR) et la sortie du comparateur (ζ) est utilisée pour commander l'interrupteur Sw1 qui est placé en série avec une source de courant I $_{\zeta}$  (voir Fig. 4.2 et Fig. 4.3b). Cette configuration met en vedette un simple CAN de premier ordre avec une entrée CC d'un-bit. Ce circuit numérique de lecture de données est implémenté avec un procédé CMOS utilisant un comparateur de tensions track and latch [VAK06] relié au circuit d'interface déjà expliqué. Les simulations suivant le dessin des masques (post-layout) montrent des flux d'impulsions différents pour différentes valeurs de  $\Delta C$  (Fig. 4.8). Tel que montré par la Fig. 4.8, la moyenne de chaque séquence (le nombre de uns par le nombre d'impulsions dans chaque séquence) est proportionnel à  $\Delta C$ . Suite à ces résultats, nous pouvons déduire que le CAN à bas coût proposé est similaire à un convertisseur sigma-delta conventionnel à entrée CC.

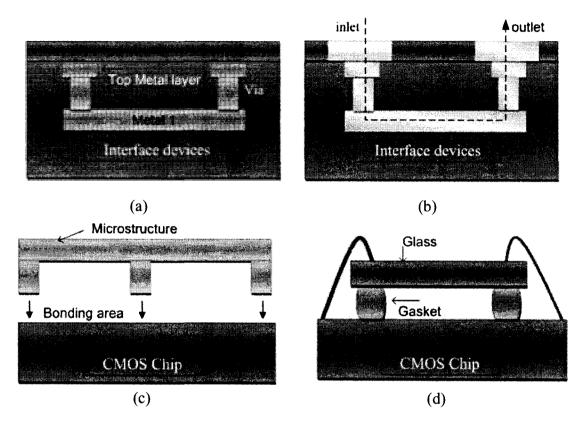

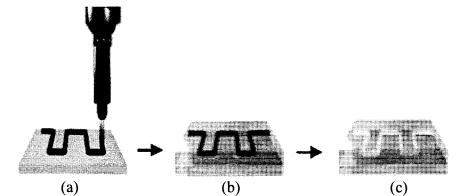

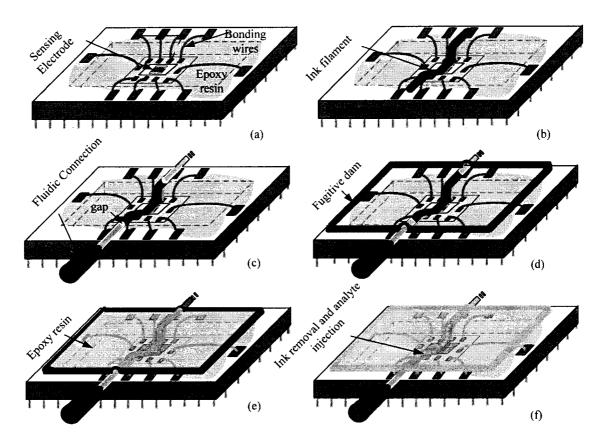

#### III. PROCÉDÉ DE FABRICATION MICROFLUIDIQUE PAR ÉCRITURE DIRECTE

Nous détaillons dans cette section l'encapsulation microfluidique proposée. Le procédé comprend six étapes décrites dans le texte suivant et illustrées dans la Fig. 4.1.

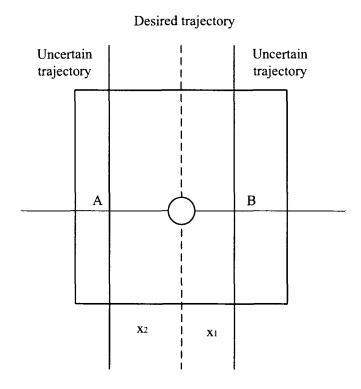

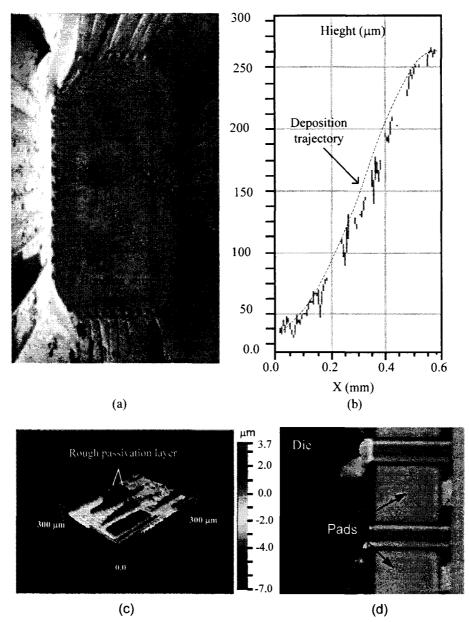

#### A. L'encapsulation des plots de connexion et des fils

Préalablement au début des trois étapes du procédé de fabrication microfluidique par écriture directe, les conducteurs doivent être couverts pour éviter le contact direct avec les fluides dans les canaux. Pour cela, une résine d'époxy partiellement polymérisée (Epon 828, Shell Chemical) est dispensée (Champion 8200 dispenser, Creative Automation Co.) sur la puce encapsulée pour encapsuler les fils de connexion. À cause de la tension superficielle et de la haute viscosité de l'époxy mi-polymérisé, celui-ci coule aisément autour des fils de connexion mais s'arrête prêt des pastilles (pads). La puce sans boîtier reste alors découverte – ce qui est nécessaire pour la détection. Les points de la trajectoire (x,y,z) de déposition d'encre doivent être initialement mesurés et programmés dans le système dispensateur commandé par un robot.

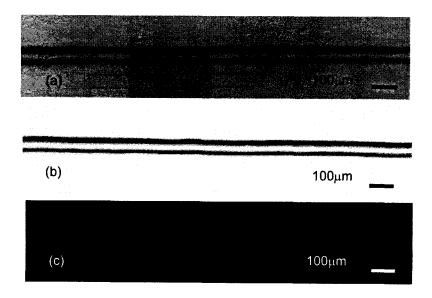

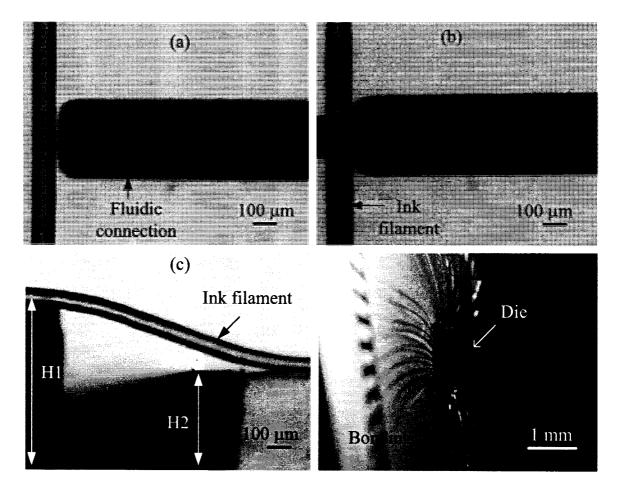

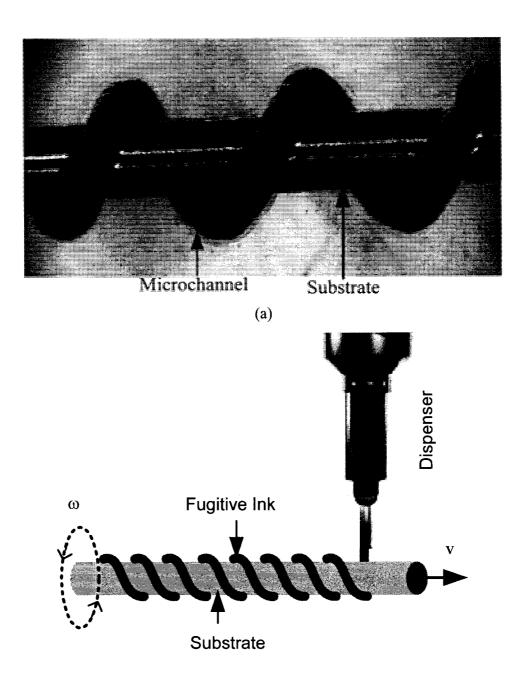

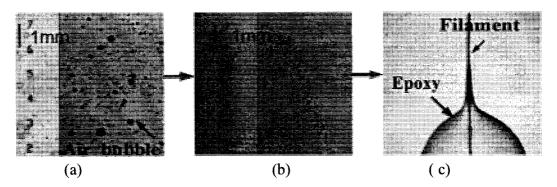

#### B. Déposition d'encre

De l'encre organique ayant une consistance de pâte (un mélange de vaseline et de cire microcristalline [GHA07i]) est extrudée (Ultra® 2400, EFD Inc.) à travers une microbuse pour être ensuite déposée sur le substrat. Pendant l'extrusion, un robot de micro-positionnement (Model I&J 2200, I&J FISNAR Inc.) déplace la buse à travers la trajectoire désirée (partie A, section II). Cette structure d'encre sacrificielle (Fig. 5.1b montre un filament d'encre) garde sa forme durant l'encapsulation d'époxy de la section

E. Les paramètres suivant doivent être modulés pour contrôler ce procédé : la pression d'air (P) appliquée pour extruder l'encre à travers la microbuse, la vélocité de la microbuse en mouvement sur la trajectoire (v), la hauteur relative entre la buse et le substrat (H) et la fraction microcristalline du mélange d'encre organique (M).

#### C. Connexion fluidique

À la suite du procédé de déposition d'encre, les armatures fluidiques à micro-échelle sont placées et fixées aux endroits requis près de l'encre déposée sur la puce avec quelques gouttes de colle thermofusible. Une déposition additionnelle d'encre fugitive de l'armature est nécessaire pour remplir l'espace entre le filament d'encre et la connexion fluidique, ainsi que pour prévenir l'infiltration de l'époxy dans l'armature durant le procédé d'encapsulation (voir "gap" dans la Fig. 5.1c).

#### D. Barrage fugitif

Un autre procédé de déposition d'encre est entrepris dans la surface de contour prédéfinie de l'encapsulation d'époxy. Ce barrage fugitif peut être retiré facilement pendant l'étape d'enlèvement de l'encre (f).

#### E. Procédé d'encapsulation et de remplissage d'encre

Dans cette étape, une résine d'époxy à basse viscosité est dispensée sur l'encre déposée à l'intérieur de la surface de contour d'encapsulation. La polymérisation de la résine s'effectue à température ambiante, en 24 heures. Ce procédé d'encapsulation d'époxy crée un lien puissant et hermétique sur la surface irrégulière de la puce sans boîtier. Il est aussi possible qu'un canal découvert peut être créé en utilisant un volume réduit

d'époxy. Ce type de canaux est nécessaire pour la déposition des couches de postdétection sélective et pourrait être recouvert plus tard.

#### F. Enlèvement d'encre et injection d'analyte

L'encre fugitive est fondue à ~75°C et propulsée sous une faible dépression ou sous la pression de l'air. Ensuite, de l'eau chaude est injectée dans le canal pour enlever les résidus d'encre. Suite à cette étape, une solution analyte peut être injectée directement dans le microcanal fabriqué sur la puce microélectronique pour des fins de détection.

#### IV. MONTAGE DE MESURE, FABRICATION DE PUCE ET MICROFLUIDIQUE

Dans cette section, nous décrivons la fabrication des puces, le montage de mesure et l'encapsulation microfluidique.

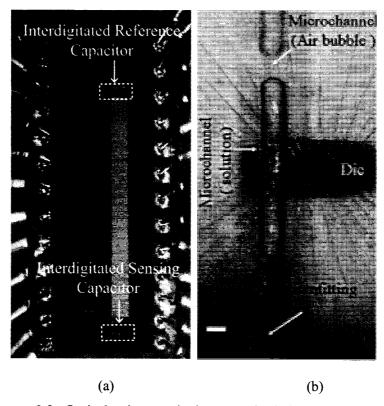

#### A. Fabrication de puces

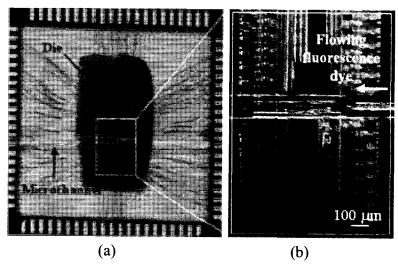

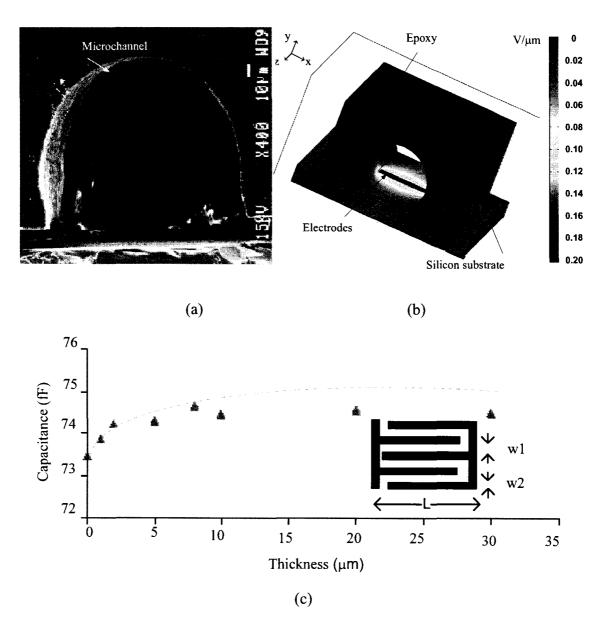

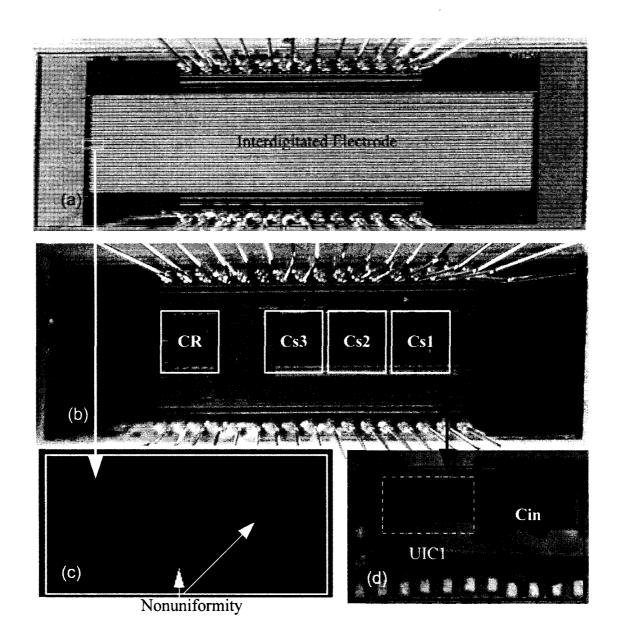

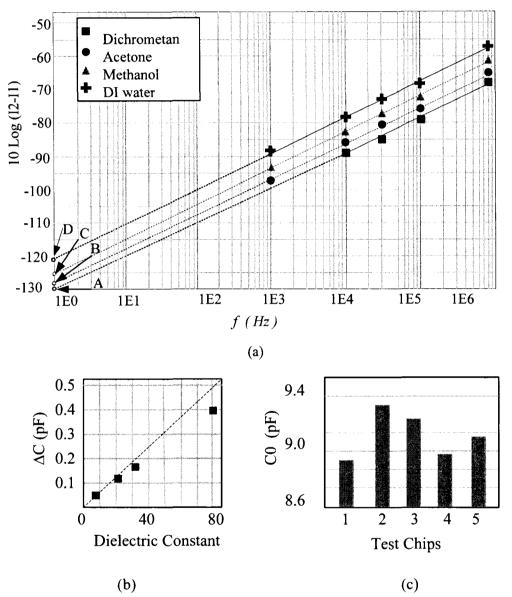

Les puces microélectroniques de capteurs (PT1, PT2, PT3) ont été fabriquées par la Taiwan Semiconductor Manufacturing Company (TSMC) avec le procédé CMOS 0,18 micron. Les Figs. 3.9a et 4.10a et 4.10b montrent les microphotographies des deux puces. Il faut mentionner que la technique de gravure de pastilles dans le procédé CMOS a été utilisée pour enlever les couches de passivation entre les doigts des électrodes pour augmenter la sensibilité [GHA07g]. Nous pouvons observer cela ainsi que le manque d'uniformité du à cette technique de gravure dans l'image MEB (Fig. 4.10d). Tel que vu dans la Fig. 4.10d, le condensateur d'intégration C<sub>in</sub> et le miroir de courant ajustable occupent la moitié de la surface du circuit d'interface; cependant, il n'est pas nécessaire de les répliquer si nous avons une matrice de capteurs capacitifs. De plus, les dimensions

des électrodes de détection  $C_S$  dans PT1 et PT2, ainsi que les électrodes de détection et de référence ( $C_R$ ,  $C_{S1}$ ,  $C_{S2}$  and  $C_{S3}$ ) dans TP3 sont montrées dans le Tableau 4.1 (TP2 dans ce Tableau) pour  $W_1=W_2=W$ .

#### B. Procédé de fabrication microfluidique par écriture directe (PFED)

Suite à ce procédé (PFED), les canaux fluidiques sont construits sur les puces de capteurs (PT1, PT2 et PT3). L'image obtenue avec le microscope optique des microcanaux sur PT2 et sur la plateforme hybride microfluidique/PT1 sont l'objet des Figs. 3.9b et 5.4.

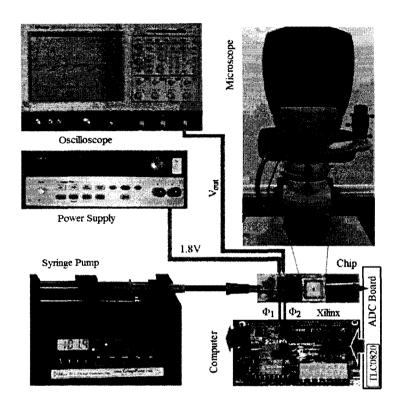

#### C. Montage de mesure multidisciplinaire

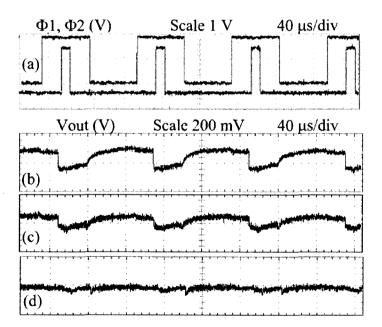

Tel que montré par la Fig. 3.12, un microscope stéréoscopique est utilisé pour observer la solution qui est injectée par une pompe seringue dans l'orifice d'entrée du canal microfluidique. Simultanément, l'oscilloscope (Digital Phosphor Oscilloscope, TD57154, Tektronix) surveille le V<sub>out</sub> périodique. Il a déjà été évoqué qu'une plateforme FPGA soutient la puce de capteur pour l'enregistrement de données et pour aider à trouver les conditions de mesure optimales.

#### V. RÉSULTATS DE MESURE

Les simulations suivant le dessin des masques (post-layout), les caractéristiques électriques, ainsi que les résultats des tests chimiques sont présentés dans cette section.

#### A. Simulations

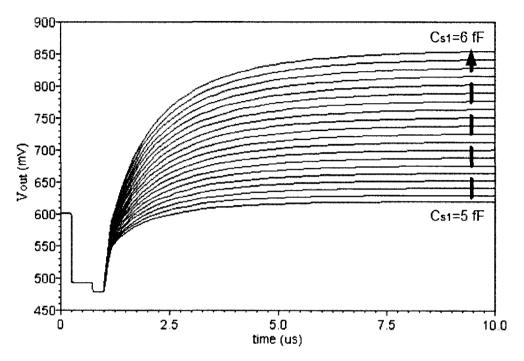

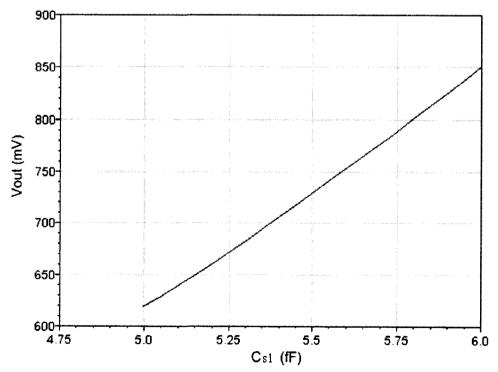

Des simulations post-layout avec SpectreS ont été utilisées pour valider l'architecture

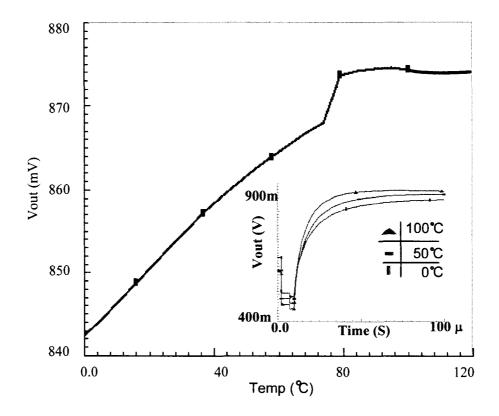

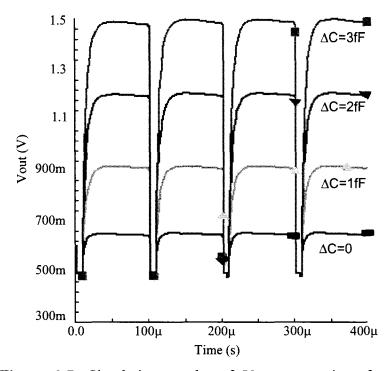

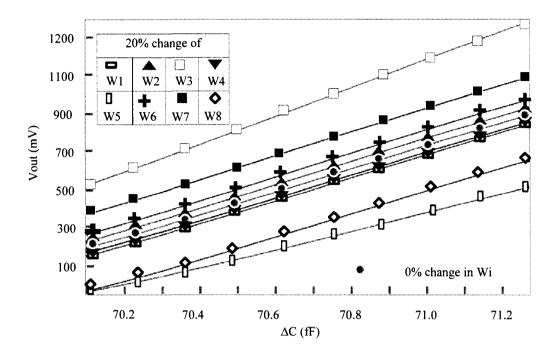

présentée dans cette section (voir Fig. 4.2) et pour atteindre la performance optimale. La Fig. 3.7a montre la forme d'onde de la tension de sortie de l'intégrateur  $C_{in}$  durant le cycle d'horloge pour plusieurs  $\Delta C_{s}$ . Tel que prévu,  $V_{out}$  augmente rapidement à une valeur proportionnelle à  $\Delta C_{s}$ . La linéarité de la variation de  $V_{out}$  ( $\Delta V_{out}$ ) par rapport à  $\Delta C_{s}$  est soulignée dans la Fig. 4.5 qui est en accord avec l'Eq. (6). Il faut signaler que l'extraction des capacités post-layout donne  $C_{0} \approx 70.2 \, \mathrm{fF}$  pour chaque électrode de référence et de détection ( $C_{R}$  et  $C_{S1}$ - $C_{S3}$ ).

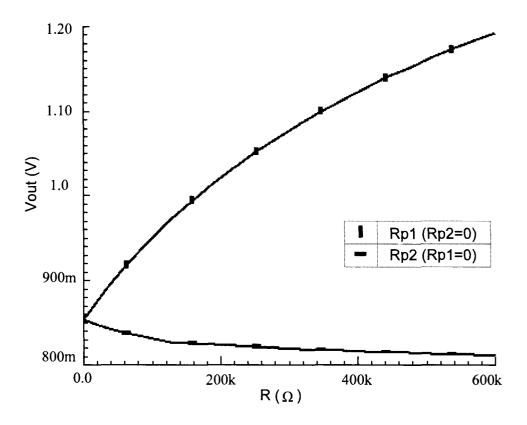

Cette figure montre qu'un changement de 20%  $W_1$ ,  $W_2$  et  $W_5$ - $W_8$  affecte de façon substantielle  $V_{\rm off}$  avec aucun changement dans la sensibilité. Cependant, il est prévisible que les défauts d'appariement de  $W_3$  et  $W_4$ , affectent  $V_{\rm off}$ , ainsi que la sensibilité. Bien sûr une configuration similaire à la calibration peut être utilisée pour compenser cette erreur en ajustant le gain de courant ( $M_3$ - $M_4$ ). Ces simulations considèrent un gain de courant de 10 avec un condensateur d'intégration de 1,2 pF. D'ailleurs, d'après les résultats de simulation, pour  $C_{\rm in} < 250 {\rm fF}$ ,  $V_{\rm out}$  ne suit pas l'Eq. (6) [GHA05a]. Ceci peut être possiblement attribué à des capacités parasites sur ce nœud. Les résultats de simulation dans la Fig. 4.5 montrent l'importance de l'annulation du décalage pour obtenir une gamme dynamique pleine gamme pour la sortie. Ils montrent aussi que la sensibilité du circuit d'interface est d'environ  $530 {\rm mV/fF}$ , à  $C_0$ =70 fF.

#### B. Caractérisation d'électrode de détection

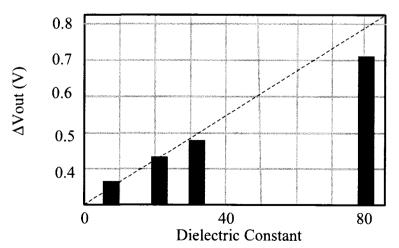

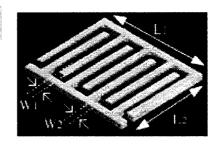

Suite à la discussion dans la section II-A et aux étapes de mesure de PT1, le courant de charge différentiel (I<sub>1</sub>-I<sub>2</sub>) par rapport à la fréquence pour quatre trois solutions est donné

dans la Fig. 4.11a. Ces solutions sont utilisées pour mesurer les variations de capacité. Ces solvants sont le dichlorométhane, l'acétone, le méthanol et l'eau déionisée. Les constantes diélectriques des ces solutions sont 9,1, 20,7, 30,4 et 80,4 respectivement à 69°F. Il faut dire que la conductivité du dichlorométhane comme solvant non-polaire est presque nulle et les basses conductivités de l'eau DI (0.04 μS/cm) et de l'acétone (0.02 μS/cm) peuvent être négligées. Dans ce travail, V<sub>dd</sub> garde sa valeur maximale (1,8V) et la fréquence est variée jusqu'à quatre décades pour montrer la linéarité de l'Eq. (1) pour la caractérisation de capacité dynamique. Pour cette large gamme de fréquences, les résultats de mesures sont montrés sur des échelles logarithmiques. Les droites parallèles dans la Fig. 4.11b sont en accord avec l'Eq. (8) qui est déduite des Eqs. (1) et (2).

$$\log(I_2 - I_1) = \log f + \log(V_{dd} \cdot \Delta C) \tag{8}$$

Alors, le changement de capacité ( $\Delta$ C) associé à chaque solution peut être extrait de la continuation de ces courbes. D'ailleurs, dans cette représentation logarithmique, pour les différentes solutions, la largeur de l'origine (A, B, C et D) est différente tandis que la pente de ces courbes est la même. La Fig. 4.11b montre le  $\Delta$ C extrait par rapport à la constante diélectrique. Chacune des valeurs mesurées dans la Fig. 4.11b est obtenue par le moyennage des cinq mesures répétées de suite suivies par une procédure de nettoyage (voir la section IV-B).

Des mesures similaires sont prises pour extraire C<sub>0</sub> pour cinq échantillons de puces avec aucune solution introduite sur les électrodes (Fig. 4.11c). La différence entre les C<sub>0</sub> extraites des différentes puces peut être le résultat de l'irrégularité de la gravure de

pastilles (pad-etching) (voir Fig. 4.10d.) et/ou la tolérance du procédé CMOS. Ces résultats témoignent que PT1 peut être utilisée comme capteur à complexité réduite pour laboratoires-sur-puce.

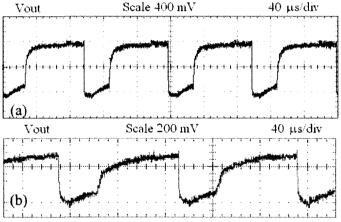

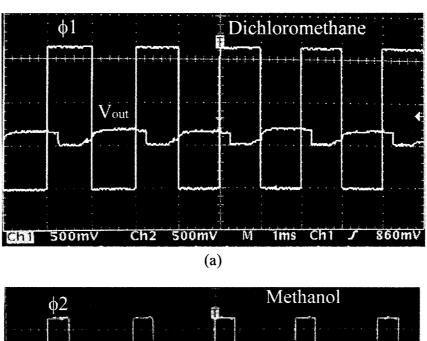

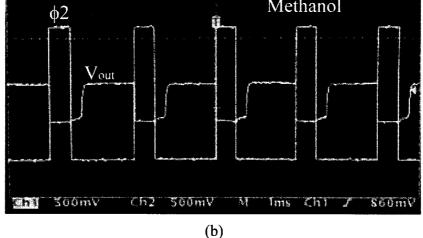

#### B. Tests chimiques

Suite à la procédure de calibration établie dans la section II-B avec un microcanal vide,  $V_{\rm off}$  est minimisé. Bien sûr, pour un  $V_{\rm off}$  plus bas plus que huit bits de calibration (D1-D8) doivent être considérés dans la conception de circuit. Tel que prévu,  $V_{\rm out}$  augmente (f=1kHz) quand les électrodes interdigitées sont exposées à des solutions diélectriques (dichlorométhane et méthanol) et diminue pendant la période de décharge (voir Figs. 4.12a-b). La tension CC de  $V_{\rm out}$  peut être réglée à travers  $V_{\rm c}$  (voir Fig. 4.2b).

Un procédé de nettoyage avec eau chaude, insufflation d'air et traitement de température est fait entre les mesures avant la réinjection de solution. Pour évaluer le temps de réponse du capteur, la moyenne des données enregistrées de trois électrodes est enregistrée pendant 50 secondes. Cette procédure est répétée pour différentes solutions avec des procédures de nettoyage entre les mesures. La Fig. 4.13 montre qu'une fois l'analyte est introduit dans l'électrode de détection, la tension correspondante apparait à la sortie du capteur aussi vite que permis par le circuit d'interface. Dans ce travail, la variation brusque de la sortie du capteur dans la Fig. 4.13 est due à la mesure directe de l'analyte sans ajouter une couche de détection sur les électrodes de détection. Par exemple, l'utilisation d'une couche de détection PEUT pour la détection chimique dans

la phase gazeuse cause une sensibilité linéaire pour une gamme dynamique plus large de concentrations d'analytes et donc une réponse plus lente du capteur [HAG02]. Alors, avec une couche de détection additionnelle, le temps de réponse peut dépasser celui des résultats montrés dans cette section.

Dans un autre test,  $\Delta V_{out}$  correspondant à  $C_{S1}$  devient 650mV et 800mW pour l'injection de DW et d'eau saline conductrice respectivement. Au fait, pour les constantes diélectriques plus élevées (constante diélectrique de DW  $\approx$  80.5), nous prévoyons un  $\Delta V_{out}$  plus élevé. Mais pour le cas de l'eau saline injectée, le  $\Delta V_{out}$  élevé est du à l'effet d'une grosse capacité parasite à travers la couche de passivation [GHA07h].

Il est important d'évoquer que la plupart des solutions biologiques sont ioniquement conductrices; cependant, pour les applications mentionnées plus tôt (ex. reconnaissance d'anticorps-antigènes, détection d'hybridation, etc.), après les réactions biologiques correspondantes, un nettoyage avec une solution non-conductrice (ex. Méthanol [STA06]) et parfois un traitement de température [BAL05], sont effectués pour préparer le capteur pour une mesure purement capacitive. Il peut être utile de prendre avantage du comportement de ce capteur envers les solutions conductrices pour surveiller si le procédé de rinçage est performé parfaitement et donc si le capteur est prêt pour une mesure capacitive, ou bien si quelques ions existent encore – ce qui nécessiterait plus de préparation.

#### VI. CONCLUSION

Nous avons décrit quelques circuits d'interface pour des capteurs capacitifs statiques utilisés pour la détection avec laboratoire-sur-puce. Une MCBC à complexité réduite et haute précision a été utilisée pour un capteur capacitif CMOS laboratoire-sur-puce. Les capteurs capacitifs basés sur la MCBC ont été implémentés dans le procédé CMOS 0.18µm pour la détection de liquide dans un microcanal. De plus, nous avons démontré avec succès les résultats expérimentaux utilisant des solutions chimiques standards pour montrer la viabilité du capteur hybride Circuit Intégré/Microfluidique proposé pour maintes applications tel que la surveillance d'analyte dans le canal, la microfluidique numérique, la détection cellulaire par analyses anticorps-antigènes, les micromatrices d'ADN complètement électroniques, ainsi que la détection de gaz chimique et de solvant organique pour la surveillance environnementale. Les circuits d'interface à bas coût proposés offrent de bonnes alternatives aux matrices de capteurs capacitifs complètement intégrées qui sont indispensables pour les laboratoires-sur-puce. Nous avons aussi présenté d'autres circuits (actuellement en étape de fabrication) fondés sur cette méthode basée sur la charge pour encapsuler le système capteur entier dans la même puce.

# TABLE OF CONTENTS

| DEDICATION                              | iv                                |

|-----------------------------------------|-----------------------------------|

| ACKNOWLEDGMENTS                         | v                                 |

| ABSTRACT                                | vi                                |

| RÉSUMÉ                                  | viii                              |

| CONDENSÉ EN FRAÇAIS                     | x                                 |

| TABLE OF CONTENT                        | xxix                              |

| LIST OF FIGURES                         | xxxi                              |

| LIST OF TABLES                          | xxxvi                             |

| LIST OF ABBREVIATIONS                   | xxxvii                            |

| LIST OF SYMBOLS                         | xxxix                             |

| THESIS ORGANISATION AND CONTRIB         | BUTIONSxli                        |

| CHAPTER 1: METHODS AND APPLICAT         | ΓΙΟΝS OF CMOS-BASED LOCS          |

| 1.1 Introduction                        | 1                                 |

| 1.2 Paper#1-A Multidisciplinary Approac | h to CMOS-Based Lab-on-Chip: Case |

| Study of Capacitive Sensors for Bioch   | nemical Applications1             |

| CHAPTER 2: HYBRID MICROFLUIDIC          | CMOS PLATFORM                     |

| 2.1 Introduction                        | 28                                |

| 2.2    | Paper#2  | 2-Novel Direct-Write CMOS based Lab-on-Chip: Design, Assembly as | nd  |

|--------|----------|------------------------------------------------------------------|-----|

|        | Experi   | mental Results                                                   | 28  |

| CHAPT  | TER 3:   | CMOS BASED CAPACITIVE SENSORS FOR LOCS                           |     |

| 3.1    | Introdu  | ction                                                            | 57  |

| 3.2    | Paper#3  | 3-A 0.18μm CMOS-Based Capacitive Sensor Lab-on-Chip              | 57  |

| CHAP   | ΓER 4:   | DIRECT-WRITE MICROFLUIDIC PACKAGING PROCEDURE                    |     |

| 4.1    | Introdu  | ction                                                            | 33  |

| 4.2    | Paper#4  | 4-A Hybrid Microfluidic/CMOS Capacitive Sensor Dedicated to La   | ıb- |

| on-    | Chip App | olications                                                       | 83  |

| CHAP   | ΓER 5:   | CORE-CBCM CAPACITIVE SENSOR ARRAY FOR LOCS                       |     |

| 5.1    | Introduc | ction                                                            | 10  |

| 5.2    | Paper#:  | 5- A Microfluidic Packaging Technique for LoC Applications1      | 10  |

| CHAP   | ΓER 6:   | CONCLUSION                                                       |     |

| 6.1    | Contrib  | outions                                                          | 29  |

| 6.2    | Recom    | mendations for future work12                                     | 30  |

| BIBLIC | OGRAPH   | IY13                                                             | 32  |

# LIST OF FIGURES

| Figure 1.1 | An illustration of hybrid microfluidic/ CMOS capacitive sensor for LoC       |

|------------|------------------------------------------------------------------------------|

|            | applications5                                                                |

| Figure 1.2 | Simplified diagram of sequential steps in a genetic diagnostic system7       |

| Figure 1.3 | Capacitive sensor LoCs: (a) DNA detection, (b) antibody-antigen              |

|            | recognition, (c) cell monitoring and (d) quasi interdigitated electrodes for |

|            | chemical sensing8                                                            |

| Figure 1.4 | Schematic of a basic capacitive readout circuit                              |

| Figure 1.5 | Schematic of CBCM structure                                                  |

| Figure 1.6 | Schematic of a simple capacitive DNA detection using CBCM: (a) Off           |

|            | chip realization, (b) on chip realization16                                  |

| Figure 1.7 | Schematic of capacitive cell detection with inputs and output                |

|            | waveforms                                                                    |

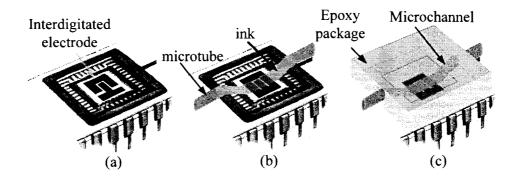

| Figure 1.8 | On-Chip CMOS/microfluidic techniques: microchannel realization               |

| C          | through CMOS process (a) before etching and (b) after etching along with     |

|            | (c) an adhesive microfluidic process and (d) a rapid prototyping             |

|            | method                                                                       |

| Figure 1.9 | Illustration of an on-chip microfluidic packaging procedure using direct-    |

| riguic 1.7 | write assembly technique: (a) before packaging, (b) ink deposition, (c)      |

|            |                                                                              |

| E' 0.1     | after epoxy encapsulation and ink removal                                    |

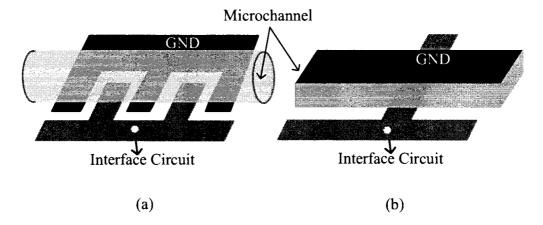

| Figure 2.1 | Schematic representation of sensing electrodes incorporated with a           |

|            | microchannel: (a) interdigitated electrode, (b) configuration presented in   |

|            | [5]35                                                                        |

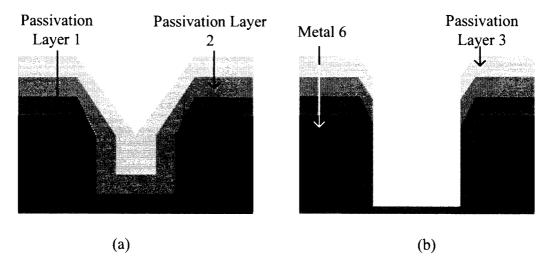

| Figure 2.2 | Passivation layers: (a) onto CMOSP18 (TSMSC), (b) after using removal        |

|            | through pad-etch technique                                                   |

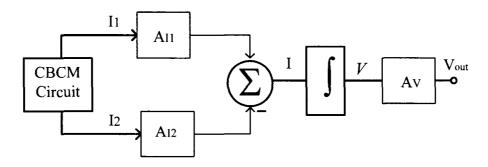

| Figure 2.3 | Simplified block diagram of proposed capacitive sensor                       |

| Figure 2.4  | Proposed capacitive interface circuit topology38                                  |

|-------------|-----------------------------------------------------------------------------------|

| Figure 2.5  | Schematic representation of DWFP technique: (a) ink deposition, (b)               |

|             | encapsulation in epoxy, (c) ink extraction42                                      |

| Figure 2.6  | Output voltage versus time for different values of C <sub>S1</sub>                |

| Figure 2.7  | Output voltage versus C <sub>S1</sub>                                             |

| Figure 2.8  | Output voltage versus C <sub>int</sub>                                            |

| Figure 2.9  | Layout of proposed circuit                                                        |

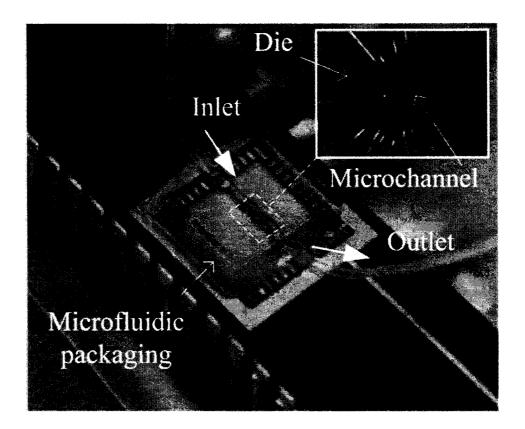

| Figure 2.10 | Microscopic images of 100 µm microchannel: (a) filament ink, (b)                  |

|             | filament ink inside epoxy, (c) UV image of fluorescent dye filled in              |

|             | microchannel                                                                      |

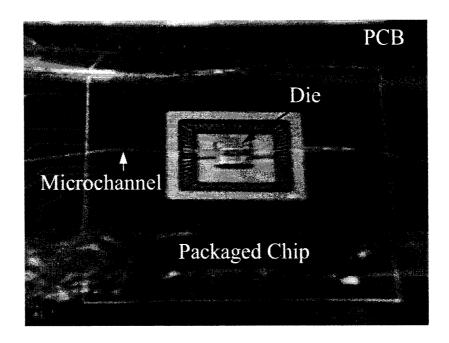

| Figure 2.11 | Microfluidic fabrication on electrical packaged chip (a) over view, (b)           |

|             | close-up view of die                                                              |

| Figure 2.12 | Schematic representation of full integration and packaging of LoC                 |

|             | system                                                                            |

| Figure 2.13 | Optical microscope images of (a) the fugitive ink and fitting, (b)                |

|             | deposited ink from fitting, (c) ink deposition between two substrates in          |

|             | different heights, (d) epoxy resin surrounding the die51                          |

| Figure 2.14 | Estimation of alignment error53                                                   |

| Figure 3.1  | Schematic of a conventional capacitive interface circuitSee Fig. 1.7              |

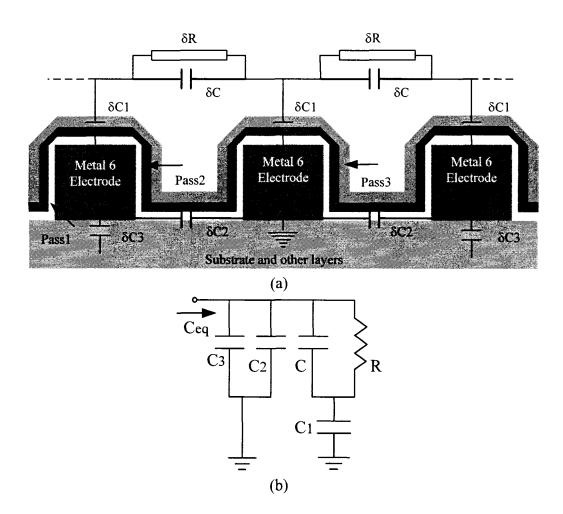

| Figure 3.2  | Fig. 3. Illustration of (a) parasitics generated on top of CMOS chip (δC          |

|             | and $\delta R$ are the partial parasitic capacitance and resistance respectively) |

|             | and (b) its equivalent circuit62                                                  |

| Figure 3.3  | A schematic of fabricated interface circuit, external connections and a           |

|             | switching calibration circuit                                                     |

| Figure 3.4  | Simulation and modeling results of interdigitated capacitive electrodes:          |

|             | (a) SEM image of microchannel fabricated through direct-write process,            |

|             | (b) the FEMLAB model of microchannel and (c) the simulation results               |

|             | of extracted capacitance in between the electrodes for different thickness        |

|             | value of thin layer of liquid in channel                                               |

|-------------|----------------------------------------------------------------------------------------|

| Figure 3.5  | Simulation results of Vout variations versus temperature. The transient                |

|             | responses for 0, 50 and 100°C are shown in the inset69                                 |

| Figure 3.6  | Simulation results of V <sub>out</sub> variations versus Rp1 and Rp270                 |

| Figure 3.7  | results of $V_{out}$ versus time for different values of $\Delta C$ 71                 |

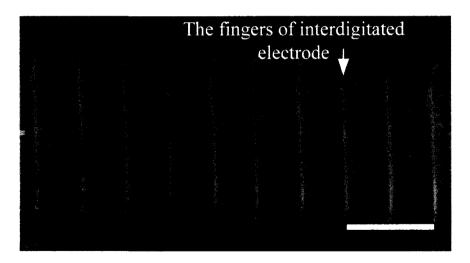

| Figure 3.8  | Chip fabrication results: (a) SEM image of interdigited electrode realized             |

|             | on CMOS chip, (b) SEM image of a patterned passivation layers on                       |

|             | CMOS chip (scale bar, 20 µm)72                                                         |

| Figure 3.9  | Optical microscopic images of (a) loose die including interdigitated                   |

|             | sensing and reference electrodes and (b) microfluidic channel with                     |

|             | interdigitated sensor (scale bar 150 µm)72                                             |

| Figure 3.10 | Measurements of V <sub>out</sub> for different values of Rp1                           |

| Figure 3.11 | Measurements of Vout for (a) a model analyte (polyelectrolyte) and (b)                 |

|             | dichloromethane solution in microchannel                                               |

| Figure 3.12 | Measurement set-up of proposed capacitive sensor LoC                                   |

| Figure 3.13 | Sensor's response for different solution                                               |

| Figure 4.1  | Schematic of a hybrid Microfluidic/CMOS capacitive sensor using                        |

|             | CBCM method86                                                                          |

| Figure 4.2  | Illustration of the proposed BIC along with the waveform of clock pulses,              |

|             | sensing current Is and sensor response Vout (As discussed in section II-B,             |

|             | Φs is the sampling clock pulse)90                                                      |

| Figure 4.3  | Adjustable current mirror: (a) wide swing current mirror and I <sub>R</sub> generator, |

|             | (b) digital current trimming91                                                         |

| Figure 4.4  | On-chip and off-chip architecture circuitries: TC2 and supporting FPGA                 |

|             | system for calibration92                                                               |

| Figure 4.5  | Variation of simulated $V_{out}$ versus $\Delta C$ for different mismatch errors (20%) |

|             | change of a transistor's width)94                                                      |

| Figure 4.6  | Proposed charge based sigma delta capacitive sensor and corresponding                   |

|-------------|-----------------------------------------------------------------------------------------|

|             | waveforms95                                                                             |

| Figure 4.7  | Implemented voltage comparator incorporated with $\Sigma\Delta$ modulator96             |

| Figure 4.8  | Simulation results of proposed sigma delta capacitive sensor97                          |

| Figure 4.9  | Simulation results of the proposed $\Sigma\Delta$ : (a) output bit stream for different |

|             | capacitance variations (b) sensitivity of decoded output sequence versus                |

|             | input $\Delta C$                                                                        |

| Figure 4.10 | Chip fabrication results: optical microscope images of (a) TC1 and (b)                  |

|             | TC2 along with (c) SEM images of interdigitated electrode, and (d)                      |

|             | optical microscopic image of interface circuit layout (UCI1 is the first                |

|             | unit of capacitive interface circuit, see section II-B)99                               |

| Figure 4.11 | Measurement results: (a) differential current versus frequency for four                 |

|             | different solutions, (b) the capacitance variation of chip versus dielectric            |

|             | constant and (c) the parasitic capacitance of 5 different                               |

|             | chips                                                                                   |

| Figure 4.12 | Measurement results: Vout when a channel is filled with (a)                             |

|             | Dichloromethane, and (b) Methanol104                                                    |

| Figure 4.13 | Testing results: recorded Vout when the channel is, empty (after                        |

|             | calibration), filled with dichloromethane, acetone and methanol                         |

|             | (Dielectric constant of methanolis is nearly 32.4 at 77 °F)105                          |

| Figure 5.1  | Microfluidic packaging procedure: (a) wire bonding encapsulation, (b) ink               |

|             | deposition, (c) fluidic connection, (d) fugitive dam, (e) fugitive ink                  |

|             | encapsulation and (f) ink removal and analyte injection114                              |

| Figure 5.2  | Trajectory recognition for ink deposition: (a) top view SEM image of a                  |

|             | chip after wire bonding encapsulation, (b) height measurements starting                 |

|             | from the mark x on the chip (a), (c) laser profiler image of the chip                   |

|             | (rectangle in the middle)shown in (a) and laser profiler image of bonding               |

|            | pads which stpoed the flowing epoxy resin                                    |

|------------|------------------------------------------------------------------------------|

| Figure 5.3 | SEM image of interdigited electrode realized on CMOS chip from top           |

|            | view of 45° Angle116                                                         |

| Figure 5.4 | Microhotograph of hybrid test structure including CMOS chip and              |

|            | microfluidic packaging120                                                    |

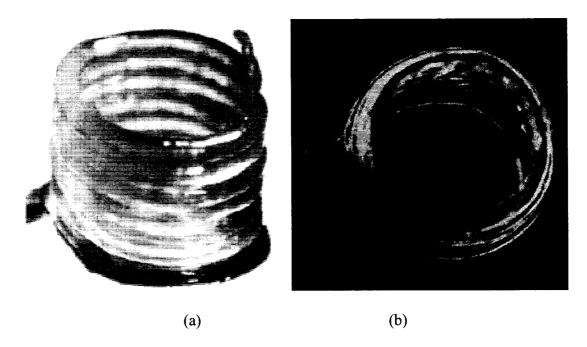

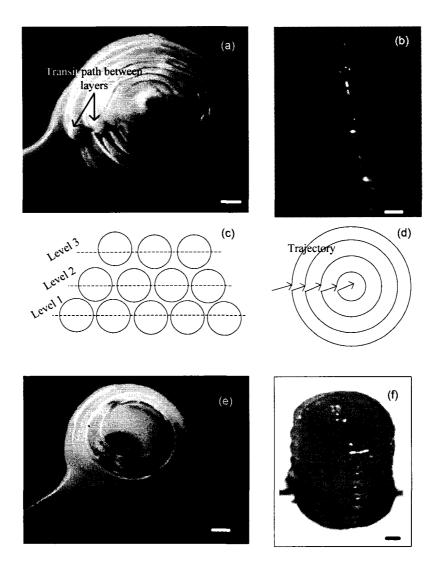

| Figure 5.6 | Helical microchannel embedded in side a clear epoxy: (a) optical             |

|            | microscope image of microchannel filled with a coloured liquid, (b)          |

|            | schematic of deposition set-up (scale bar, 100 µm)121                        |

| Figure 5.6 | Optical microscope images of (a) cylindrical ink architecture and (b)        |

|            | corresponding microchamber filled with fluorescent dye (Outer diameter       |

|            | of cylinder, 2mm)                                                            |

| Figure 5.7 | Conic and cylindrical microreservoir: (a) conic microfluidic chamber, (b)    |

|            | conic ink architecture, (c) stacked layers (b) trajectory of ink deposition, |

|            | (e) conic microfluidic chamber with less epoxy and (d) filled in             |

|            | cylindrical ink architecture                                                 |

| Figure 5.8 | Optical microscope images of a microchannel implemented through the          |

|            | proposed technique in an transparent epoxy on a package and printed          |

|            | circuit board and filled with a coloured liquid for better visualization124  |

| Figure 5.9 | Epoxy prepration and deposition (a) before degassing, (b) after degassing    |

|            | and (c) during deposition125                                                 |

# LIST OF TABLES

| Table 1.1: A summary of CMOS based capacitive sensor LoCs reported in recent | t the |

|------------------------------------------------------------------------------|-------|

| years                                                                        | 6     |

| Table 3.1: Sensor response against dichloromethane in microchannel for sev   | veral |

| iterations                                                                   | 76    |

| Table 3.2: A summary of chip specifications                                  | 77    |

| Table 4.1: Dimensions of interdigitated electrode in both fabricated chips   | 100   |

## LIST OF ABBREVIATIONS

ADC Analog to Digital Converter

CBCM Charge Based Capacitance Measurement

CE Electrophoresis

CIEF Charge-Injection-Induced Error-Free

CMOS Complementary metal—oxide—semiconductor

CVC Capacitance to Voltage Converter

DAC Digital to Analog Converter

DEP Dielectrophoresis

DNA Deoxyribonucleic Acid

DWFP Direct Write Fabrication Process

ESD Electrostatic Discharge

ELISA Enzyme Linked Immunosorbant Assay

FPGA Field Programmable Gate Array

ISFET Ion-Sensitive Field Effect Transistor

ITO Indium Tin Oxide

LoC Laboratory-on-Chip

MEMS Micro-Electro-Mechanical Systems

MOSFET Metal-Oxide-Semiconductor-FET

PCR Polymerase Chain Reaction

PEUT Polyetherurethane SC Switch Capacitor

SEM Scanning Electron Microscope

SPRS Surface Plasmon Resonance Sensor

TC Test Chip

TSMC Taiwan Semiconductor Manufacturing Company

UIC Unit of Interface Circuit

# LIST OF SYMBOLS

| μт                          | Micrometer                                      |

|-----------------------------|-------------------------------------------------|

| ξ                           | One-bit DAC input bit                           |

| εr                          | Dielectric constant                             |

| $\Phi_i$ ( $i=1,2,3,4$ )    | Clock pulses                                    |

| $S_{\Delta V\!/\!\Delta C}$ | Sensitivity of output voltage versus $\Delta C$ |

| $\Delta V_{out}$            | Output voltage variation                        |

| $\Delta C$                  | Capacitance variation                           |

| $A_I$                       | Current gain                                    |

| $A_V$                       | Voltage gain                                    |

| C                           | Capacitance                                     |

| $C_{in}$                    | Integrating capacitance                         |

| $C_R$                       | Reference capacitor                             |

| $C_{\mathcal{S}}$           | Sensing capacitor                               |

| $D_i (i=0,1,)$              | Calibration bits $(D_{I-m})$                    |

| f                           | Clock pulse frequency                           |

| I                           | Current                                         |

| $I_R$                       | Reference current                               |

| $I_{\mathcal{S}}$           | Sensing current                                 |

| $I_{\xi}$                   | One-bit DAC current                             |

| $K\Omega$                   | Kilo-ohm                                        |

| $L_i(i=1,2,)$               | Channel length                                  |

| MHz                         | Megahertz                                       |

| $M_i$ (i=1, 2)              | Transistors                                     |

| ms                          | millisecond                                     |

| N                           | Period of output sequence                       |

| P             | Performance factor of sensor |

|---------------|------------------------------|

| $q_n$         | Output sequence              |

| R             | Resistance                   |

| $\check{U}$   | Decoded output sequence      |

| V             | Volt                         |

| $V_R$         | Reference voltage            |

| $V_{out}$     | Output voltage               |

| $V_{th}$      | Threshold voltage            |

| $V_{o\!f\!f}$ | Offset voltage               |

| $V_{dd}$      | Power supply voltage         |

| $W_i$ (i=1,2) | Channel width                |

|               |                              |

#### THESIS ORGANISATION AND CONTRIBUTIONS

#### 1.1 Overview

The growing number of chronic diseases such as cancer, the absence of specific and efficient treatments for several viral and bacterial diseases and the absence of efficient and fast method of environmental monitoring has created the need of rapid identification and diagnosis. Lab-on-Chip is a sophisticated method to produce real-time, multiple and highly sensitive analysis at the point-of-care, while providing for doctors and patients. This multidisciplinary research approach calls for a convergence of microelectronic and microfluidic technologies with conventional techniques in biochemistry. Standard CMOS process is a technological platform to realize such LoC systems offering the advantages of well studied circuits and embedded sensors/actuators. The research work in this thesis is focused on a CMOS capacitive sensor integrated with microfluidic channels for LoC applications.

#### 1.2 Research contributions

The main contributions on this thesis have already been reported in several peer-reviwed scientific journals and international conferences. In this section a summary of these contributions is put forward.

We presented in [GHA05a] and [GHA05d] new design methodologies for charge based capacitive sensors. Based on the discussions reported in these papers, the charge based capacitance measurement can be used for LoC applications and the process mismatch error is not a limitating factor in detecting minute capacitance variation resulting for the

biochemicals in proximity of sensing electrodes. Of course this error should be cancelled using a calibration procedure to improve the dynamic range of sensor's output as discussed in [GHA06b]. Also, in [GHA07g], an array of capacitive sensors was reported using CBCM structure. The measurement results of our proposed core-CBCM sensor circuit were also reported in [GHA07b]. We have already reported a complete capacitive sensor system design including a simple ADC for LoCs in [GHA07b].

A new microfluidic packaging method was presented in [GHA05b], [GHA06a]. We reported the direct-write assembly as an efficient method for the fabrication of microfluidic structure on CMOS chip. In the later report, the advantages of DWFP for creating of three dimensional microfluidic components have been discussed.

Since this thesis is organised based on the published or submitted journal papers, we will provide the details of these articles in chapter 1-5. A complete list of our contributions in this thesis can also be seen in our references [GHA05]-[GHA07].

#### 1.3 Thesis organisation

In chapter 1, we put forward a comprehensive literature review of CMOS based sensors/actuators, in particular on-chip capacitive sensors for LoC applications. The main objective of this review is to highlight the engineering aspects of LoC applications by exploiting the advantages of CMOS process, microfluidic fabrication techniques and classical biochemistry. We present the main methodology of our approach using direct-write microfluidic fabrication process and the primary design of our proposed CMOS capacitive sensor in Chapter 2.

Chapter 3 reports the analysis of the proposed sensor chip for conductive and non-conductive solutions. We demonstrate the experimental results of implemented sensor chip using different chemical solvents in this chapter. In chapter 4, we put forward on the design, implementation and testing of two sensor chips with different levels of complexity. The first chip is a capacitive test-bed suitable for on-chip characterization purposes where the second chip features an array of capacitive sensors along with required calibration circuitries. In chapter 5, the six-step direct-write microfluidic packaging procedure is described. We demonstrate the experimental results and introduce unique advantages of DWFP for LoC applications in this chapter. Finally, the conclusion of this thesis is presented in chapter 6.

# Chapter 1

#### METHODS AND APPLICATIONS OF CMOS-BASED LOCS

#### 1.1 Introduction

The recent advances in CMOS based LoCs with a focus on capacitive sensors for biochemical diagnostics and environmental monitoring are reviewed in this section. The CMOS-based capacitive sensors consisting of interface circuits and microfluidic components along with functionalized sensing electrodes are detailed for the most important LoC applications. This literature review submitted to the "Journal of Analog Integrated Circuit and Signal Processing, Springer". This paper is reproduced as follows.

# 1.2 CMOS Based Capacitive Sensor Laboratory-on-Chip:

# A Multidisciplinary Approach

Ebrahim Ghafar-Zadeh<sup>1</sup>, Mohamad Sawan<sup>1</sup>, Fellow, IEEE and Daniel Therriault<sup>2</sup>

<sup>1</sup>Polystim Neurotechnologies Laboratory (Polystim), Department of Electrical Engineering, Ecole Polytechnique de Montreal.

<sup>2</sup>Center for applied research on polymers and composites (CREPEC), Department of Mechanical Engineering, Ecole Polytechnique de Montreal.

Submitted to: Analog Integrated Circuits and Signal Processing, December 2007.

#### **ABSTRACT**

In this paper, we review the recent advances of CMOS-based capacitive sensors for Labon-chip (LoC) applications. LoC design is a multidisciplinary approach of adapting classical biochemical assays to a miniaturized platform by exploiting advances in microelectronic and microfluidic technologies. By offering low cost and integrated devices, CMOS based LoCs could be amenable to a large number of biological and biochemical assays for disease diagnostics and biotechnology in the near future. While an exhaustive, all-encompassing review of CMOS-based LoCs is beyond the scope of this review, we have focused on the design and implementation of CMOS-based capacitive sensor LoCs for the most important biochemical applications. For each application, the corresponding biochemical sensing layer, interface circuit and microfluidic packaging technique are discussed based on the recent literature studies.

Keywords: CMOS, Capacitive Sensor, Lab-on-Chip, Bio-functionalized sensing layer, Microfluidic Packaging.

#### I. INTRODUCTION

A holistic system-based approach to LoC design seamlessly integrates microfluidic, microelectronic with biochemical reagents and reaction on a miniaturized platform. LoCs have attracted the attention of researchers for the miniaturization of biological assays for several applications such as point of care, disease diagnostics and in-situ environmental monitoring [1]. Fully automated LoCs would allow the advantages of rapid, low cost, portability, easy handling and low sample consumption. Additionally, standard CMOS

process offers the advantage of highly precise on-chip active circuits, embedded sensors/actuators and, as such, is a good alternative to play essential roles for the sensing of bioparticles. Owing to the exponential shrinkage of minimum feature sizes, today it is possible to design complex integrated circuits of the size of a cell to readout the output signals of capacitive sensors.

Many efforts have been made on implementation of biochips with a massive parallelism for DNA detection. The first DNA chip or so-called microarray commercialized by Affymetrix (GeneChip® Technology) in the late 1980s could be considered the first applicable Lab-on-chip for diagnostic purposes. An optical scanner is usually used to readout the microarrays. Nowadays, in addition to DNA microarrays, several types of microarrays such protein and antibody microarrays are in the market today and being used for diagnostics or clinical researches. A labelling procedure is frequently performed to bind a suitable fluorescence molecule to the fragment of DNA strand for visualization. As the scanner and relevant processing steps for labelling are expensive, a large effort is devoted to the development of electrical read-out devices which avoid tagging of the DNA target molecules [2]. Such fully electronic DNA detection would significantly enhance portability, as well as on-site sensing, and data processing. Capacitive sensor is recognized as the best alternative for such label free DNA detection [3]. In addition to DNA detection application with huge market potential, capacitive sensors have successfully been used for other LoC applications such as cellular monitoring, chemical sensing and antibody-antigen recognition [4-6].

To date, several capacitive readout techniques with different levels of complexity have been reported for autonomous MEMS based capacitive sensor (MBCS) systems (e.g. accelerometer [7]) but there is a little published literature on the custom design of an on-chip capacitive sensor for LoC applications. Indeed, the design strategy for LoC capacitive sensors differs from that of many other well established MBCS. As an example, for long term and continues sensing in a MBCS, a built-in self calibration module should be incorporated to correct the accumulating errors, whereas LoC capacitive sensors neither suffer from such a problem, nor need such a built-in module. Actually, in these applications, the sensing capacitances in the presence rather than in the absence of analyte are extracted through a differential procedure. For this, a capacitive sensor for LoC applications can be implemented through a simple architecture. This simplicity is an important issue for the design and implementation of a large capacitive sensor array [8] which is not the case of a MBCS application with only one single sensing capacitor.

Until now, several papers presented the fabrication of different types of microfluidic components for LoC applications using surface and bulk micromaching procedures on silicon and glass [9]. But, in this review, the emphasis is placed on low temperature microfabrication processes to build microflouidic devices on CMOS chips without any additional corrosive chemical solutions to damage the underlying circuits. A CMOS-compatible microfluidic fabrication process should be performed on dedicated chip in order to direct biological analyte toward sensing/actuating sites and also to protect the

remaining circuitry and pads from direct contact to solution. It should be mentioned that this protection is necessary to avoid superfluous parasitic capacitance and resistances which might convert the circuit design characteristics.

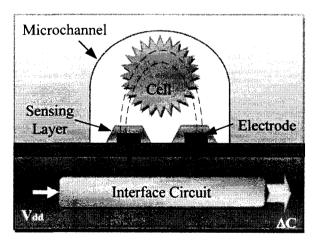

A generic hybrid IC/microfluidic capacitive sensor is illustrated in Fig. 1.1 including microfluidic components to direct the fluid toward sensing sites, functionalized sensing electrode to transduce the biological quantities into capacitance changes and finally microelectronic devices to detect the minute capacitance changes. Table I presents a summary of published articles on CMOS-based capacitive sensors for LoC applications. Of course, in the recent years, a variety of capacitive techniques have been put forward for the detection of bioparticles, but only a few articles reported the fully design and implementation of CMOS-based capacitive sensors for bio-particle detection purposes. More details about this table are given in the next sections.

Figure 1.1. An illustration of hybrid microfluidic/ CMOS capacitive sensor for LoC applications (Vdd and  $\Delta$ C are the power supply and sensing capacitance variation respectively).

Table I: A summary of CMOS based capacitive sensor LoCs reported in the recent years

| Application               | Sensing Electrode                                                                  | Circuit                      | Microfluidie          |        | <u> </u> | e Pagile     |

|---------------------------|------------------------------------------------------------------------------------|------------------------------|-----------------------|--------|----------|--------------|

| Cell Monitoring           | Top Most metal layer,<br>passivation layer                                         | Switch<br>Capacitor          | Adhesive<br>technique | 0.5µm  | 2007     | [19]         |

| Cell<br>localization      | Top Most metal layer, passivation layer                                            | Switch<br>Capacitor          | Adhesive<br>technique | 0.35µm | 2004     | [8],<br>[33] |

| Virus detection           | Thick metal layer,<br>silicon oxide insulation<br>layer, antibody<br>immoblization | <sup>1</sup> DRAM<br>Method  | Rapid<br>Prototyping  | 1.5µm  | 2005     | [17]         |

| DNA detection             | Gold electrode,<br>DNA immobilization                                              | Core<br>CBCM                 | Rapid<br>Prototyping  | 0.5μm  | 2006     | [15]         |

| DNA detection             | Gold electrode,<br>DNA immobilization                                              | <sup>3</sup> Basic<br>Method | Rapid<br>Prototyping  | 0.18µm | 2007     | [22]         |

| Organic solvent<br>sensor | Top Most metal layer, pad-<br>etched passivation layer,<br>PEUT layer              | Switch<br>Capacitor          | Adhesive<br>technique | 1.2 µm | 2002     | [20]         |

| Organic solvent sensor    | Top Most metal layer, pad-<br>etched passivation layer                             | Core<br>CBCM                 | <sup>2</sup> DWFP     | 0.18µm | 2007     | [21]         |

<sup>1</sup> Random Access Memory, 2 Direct-Write Microfluidic Fabrication Process

The remainder of this paper is organised as follows. In section II, the formation of biochemo-functionalized coatings on sensing electrodes is discussed for four important applications. The recent published design methodologies of capacitive interface circuits for LoC applications are put forward in section III. A review of microfluidic packaging techniques for CMOS sensors ia presented in section IV. This section is followed by a brief summary in section VII.

#### II. DIRECT BIO- CHEMICAL FUNCTIONALIZED SENSING ELECTRODES

In this section four different types of capacitive affinity biosensors are discussed. For

each instance, the biological/chemical principle, practical considerations and limiting factors on CMOS process are put forward.

#### A. Hybridization Detection

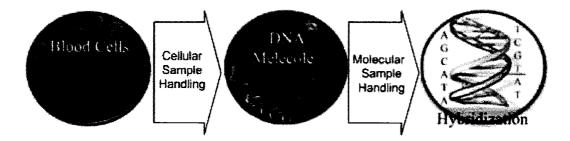

The genetic information is stored in DNA double-helical molecules confined in cell nuclei. A DNA code is a long and detailed message that instructs the cell how to make its vital proteins. Each code consists of sequences of four building blocks (A, G, C, T). Prior to reading out the DNA codes, several biological procedures should be accomplished to prepare the DNA sample from the cells as shown in Fig. 1.2. These procedures include cell pre-filtering, fractionation, and focusing in order to separate rare cells (e.g., cancer [10]) from a blood sample and make them ready for bursting. Thereafter, the DNA strands are extracted from the cells (cell lysis) followed by other molecular procedures (e.g. amplification, fragmentation and labelling [11]) to make the sample ready for DNA hybridization.

Figure 1.2. Simplified diagram of sequential steps of a genetic diagnostic system.

The hydrogen bonding of two complementary single strands of DNA such as AGCATA and TCGTAT is called hybridization. Thus, a double-stranded DNA or so-called renaturation process occurs at specific temperature and salinity conditions. In this

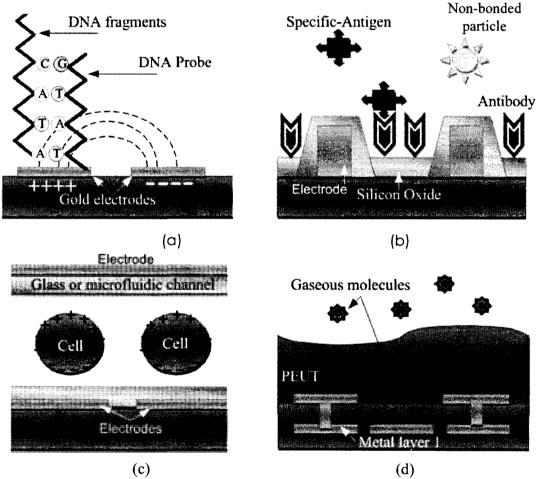

process, the known strands are immobilized on a substrate (also called DNA probe) and the unknown strands wander up and down in the sample solution until stopping beside the according probes. The hybridization bond is specific hence hybridization serves as a sequence detection mechanism (see Fig. 1.3a).

**Figure 1.3.** Capacitive sensor LoCs: (a) DNA detection, (b) antibody-antigen recognition, (c) cell monitoring and (d) quasi interdigitated electrodes for chemical sensing.