| <b>Titre:</b> Title:    | Undersampling bandpass modulator architectures                                                                                                                                                                                |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Ali Naderi                                                                                                                                                                                                                    |

| Date:                   | 2007                                                                                                                                                                                                                          |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                     |

| Référence:<br>Citation: | Naderi, A. (2007). Undersampling bandpass modulator architectures [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7991/">https://publications.polymtl.ca/7991/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| <b>URL de PolyPublie:</b> PolyPublie URL: | https://publications.polymtl.ca/7991/ |

|-------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors:  | Mohamad Sawan, & Yvon Savaria         |

| <b>Programme:</b> Program:                | Non spécifié                          |

## UNIVERSITÉ DE MONTRÉAL

#### UNDERSAMPLING BANDPASS MODULATOR ARCHITECTURES

# ALI NADERI DÉPARTEMENT DE GÉNIE ELECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR (Ph.D.)

(GÉNIE ELECTRIQUE)

OCTOBRE 2007

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-37133-6 Our file Notre référence ISBN: 978-0-494-37133-6

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# UNIVERSITÉ DE MONTRÉAL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

#### UNDERSAMPLING BANDPASS MODULATOR ARCHITECTURES

présentée par: NADERI Ali

en vue de l'obtention du diplôme de: Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de:

- M. AUDET Yves, Ph.D., président

- M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

- M. SAVARIA Yvon, Ph.D., membre et co-directeur de recherche

- M. KHOUAS Abdelhakim, Ph.D., membre

- M. HAMOUI Anas, Ph.D., membre externe

# **DEDICATION**

To the memory of my grand parents.

To my parents.

## REMERCIEMENTS

First and foremost, I would like to thank my research supervisors, Professor Mohamad Sawan and Professor Yvon Savaria who supported me technically and financially through all these years. There was much for me to learn from them, both in and beyond the technical realm.

My orals committee, Professor Yves Audet, Professor Anas Hamoui, and Professor Abdelhakim Khouas, deserve sincere thanks for their time and efforts. I am honoured to have them in the committee.

I am grateful for the guidance and the technical feedback that I received from my friends in GRM and Polystim, and thanks to all my friends, who enriched my years in Polytechnique. I would also like to thanks Mrs. Ghyslaine Carrier and Mrs. Claudine Ouellet for their great office support.

I am very grateful to my brother, Ghasem, for his helps and supports during all these years.

It is impossible to find appropriate words with which to thank my parents. This thesis is dedicated to them.

# **RÉSUMÉ**

Cette thèse présente des approches et des techniques de conception pour réaliser un convertisseur analogique à numérique (ADC) pour les récepteurs radiofréquence consacrés aux applications de radio configurable par logiciel. Elle propose des techniques architecturales et de niveau circuit pour réaliser une conception efficace pour une telle application. Les avantages des modulateurs de type sigma delta en comparaison à d'autres types d'ADC sont discutées. Les défis de conception des modulateurs à signaux continus dans le temps sont expliqués pour des fréquences d'entrée de l'ordre de 2GHz. L'approche retenue est également soutenue par une revue de la littérature qui fait le point sur la situation actuelle. On propose un modulateur de type delta sigma basé sur le sous échantillonnage applicable à des fréquences d'entrée aussi élevées que 1.8GHz, une fréquence populaire dans les systèmes de communication sans fil. On montre par simulation que l'approche et les circuits proposés pour la mettre en oeuvre peuvent convertir le signal d'entrée en données numériques avec une gamme dynamique (DR) de 46 dB à une fréquence d'échantillonnage de 810.1 MHz, lorsque la tension d'alimentation est de 1.2V, pour un circuit mis en œuvre avec une technologie CMOS de 0.13µm. Un nouveau modulateur delta (DM) est proposé. Ce circuit conçu pour recevoir un éventail de fréquences d'entrée assez large (2 GHz) a une architecture qui facilite la conception de son filtre passe-bande. Une simulation d'un modèle circuit extrait du dessin des masques réalisé montre un SFDR (Spurious Free Dynamic Range) de 41dB pour une tension d'alimentation de 1.2V. Ce modulateur delta a été fabriqué et des résultats

expérimentaux sont présentés. Ce circuit consomme une puissance totale de 37.2mW mesurée pour une fréquence d'échantillonnage de 500MHz. Un SFDR de 25dB a été mesuré pour une gamme de fréquences d'entrée allant de 500MHz à 2.6GHz quand la largeur de bande du modulateur est ajustée à 1MHz. Le facteur de qualité et la fréquence centrale du filtre actif-RC passe-bande sont réglables et les caractéristiques mesurées de ce filtre sont conformes aux résultats de simulation.

#### **ABSTRACT**

This thesis presents design approaches and techniques to realize an analog-digitalconverter (ADC) for radio-frequency receivers dedicated to software-defined-radio applications. It proposes architectural and circuit-level techniques to achieve an efficient design for such applications. Advantages of the delta sigma modulators over other types of ADCs are discussed. The design challenges associated with continuous time modulators are explained for input frequencies of the order of 2GHz. A proposed approach to address these challenges is also supported by a literature survey of the state of the art. A novel delta sigma modulator based on undersampling is proposed. It is applicable to input frequencies of the order of 1.8GHz, a popular frequency with wireless telecommunication standards. It is shown by simulations that the proposed design can convert the input signal into digital data with a dynamic range (DR) of 46 dB at a sampling frequency of 810.1 MHz and a low supply voltage of 1.2V using a 0.13µm CMOS technology. This design is then applied into a new delta modulator (DM) to receive a wide range of input frequencies and to reduce the design effort in its bandpass filter block. Post-layout simulation of the proposed DM shows a Spurious Free Dynamic Range (SFDR) of 41dB at a low supply voltage of 1.2V. The delta modulator is fabricated and experimental results are presented. The total power consumption is measured at 37.2mW for a clock frequency of 500MHz. The maximum measured postsilicon SFDR is 25dB for input frequencies ranging from 500MHz to 2.6GHz when the bandwidth of the modulator is set to 1MHz. The Q-factor and the center frequency of the

tunable bandpass active-RC filter were measured and are shown to be in agreement with simulation results.

## **CONDENSÉ**

L'emploi de systèmes électroniques devient de plus en plus répandu dans notre vie quotidienne, pour augmenter notre efficacité dans différentes tâches, et pour améliorer la qualité de vie. De tels systèmes exigent le traitement le plus rapide possible de quantités de données toujours croissantes. Pour cela, des systèmes numériques sont développés pour réaliser de tels objectifs. Cependant, la communication des données entre les différentes parties d'un système exige des systèmes analogiques et mixtes qui devraient être programmables et compatibles avec différentes normes. Aussi, une basse puissance de consommation est essentielle pour les applications portables. Par conséquent, les convertisseurs de données à haute vitesse et basse puissance (convertisseur analogique numérique (CAN) / convertisseur numérique analogique (CNA)) sont nécessaires dans les émetteurs-récepteurs des systèmes de communication et entre les parties analogiques et numériques des systèmes portatifs.

Les radiofréquences présentement utilisées dans les normes de communication sont plus élevées que 1 GHz, alors qu'elles portent une largeur de bande de signal plus étroite que 5 MHz. Afin d'acquérir de tels signaux, la porteuse est habituellement enlevée par au moins un ensemble de mélangeur et de filtre passe-bas, et un CNA est alors employé pour la numérisation. Cette méthode peut être améliorée si le CNA pourrait numériser le signal RF directement avec la même consommation de puissance. L'amélioration est attribuée à l'élimination des composantes analogiques et à

l'implantation d'un système programmable. Notre motivation dans cette recherche est d'explorer diverses idées et de proposer de nouvelles architectures de CAN. La programmabilité des émetteurs-récepteurs peut relier un utilisateur à tous les services de communication disponibles de manière continue, alors que ces services sont offerts à travers différents liens. Bien qu'un tel avantage soit partiellement accessible pour les téléphones cellulaires tri-bandes modernes, il exige du matériel additionnel qui augmente le coût final. De plus, le matériel additionnel est basé sur les normes connues, car l'emploi de nouvelles normes ferait que les vieux téléphones cellulaires ne seraient plus utilisables. Une telle requête pour obtenir toutes les normes possibles, qui était fondamentalement une demande militaire, a été présentée dans les années 90 pour des radios logicielles. La bande primaire de fréquences pour un tel récepteur se situait entre 2 MHz et 2000 MHz – ce qui n'est pas trivial même avec les technologies d'aujourd'hui. Cependant, cela introduit des avantages qui font que ça vaille le coup. De tels récepteurs se composent idéalement d'une antenne, d'un CNA, et d'un processeur de signaux numériques équipé de mémoire. En chargeant le logiciel dans la mémoire du processeur, le récepteur entier pourrait être contrôlé et adapté à une nouvelle norme. Ce logiciel pourrait même être automatiquement téléchargé dans les téléphones des utilisateurs comme une rustine (patch) venant du fournisseur de service. Mais a priori, quelques questions doivent être résolues, en commençant par la conception d'un CNA à basse puissance et haute résolution.

Le but de cette recherche est de concevoir et d'implémenter un modulateur deltasigma (MDS) dédié aux radios logicielles qui pourraient recevoir des signaux à bande étroite modulant une porteuse atteignant des fréquences qui peuvent excéder 2 GHz. Cette thèse propose des techniques aux niveaux circuit et architecture afin de parvenir à une solution efficace.

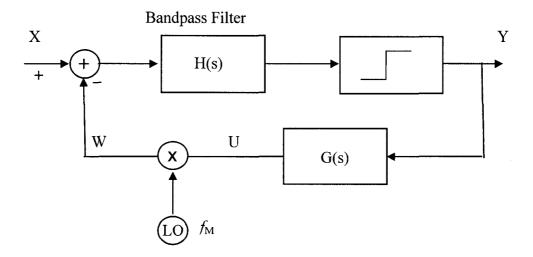

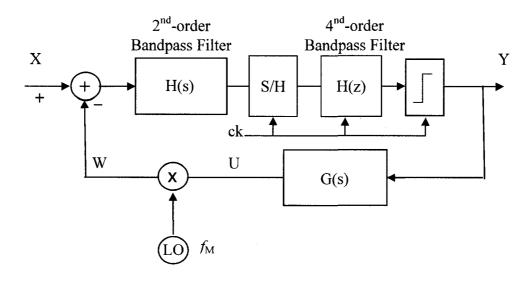

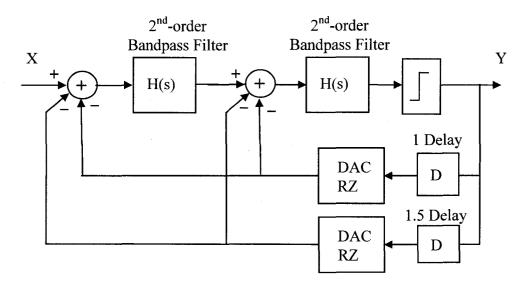

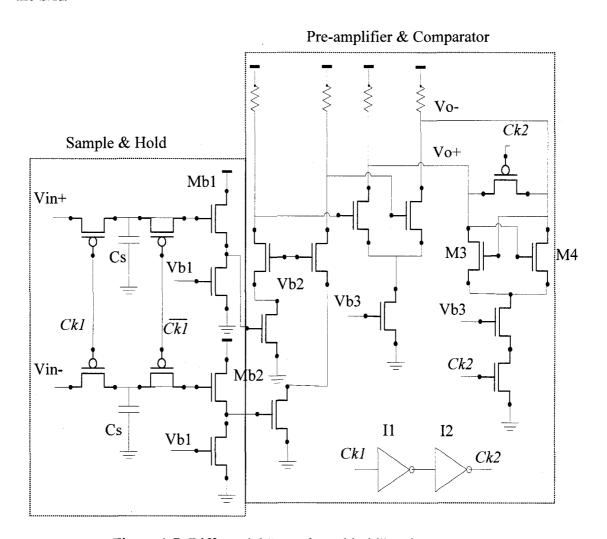

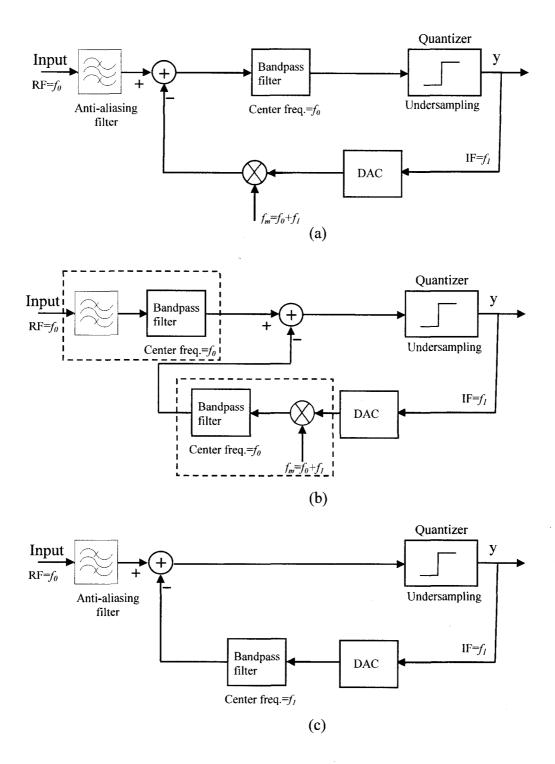

Avant de proposer la classe de solutions envisagées, nous discutons de diverses méthodes de conception et des techniques de pointe applicables aux radios logicielles. Les limites des techniques existantes nous amènent à proposer un nouveau modulateur delta-sigma passe-bande à sous-échantillonnage et à temps continu (Figure 4-1). L'architecture proposée convient à la numérisation RF, sans mélangeur analogique dans le chemin de rétroaction. Les équations de conception correspondantes sont dérivées et appliquées pour optimiser le point de fonctionnement pour un signal d'entrée de 1.8 GHz. L'architecture fondamentale proposée peut recevoir des porteuses à haute fréquence modulées par des signaux de largeurs de bande aussi grandes que 10 MHz. Nous démontrons que l'architecture proposée peut convertir le signal d'entrée en données numériques avec une plage dynamique sans bruit (Spurious Free Dynamic Range; SFDR) de 46 dB à une fréquence d'échantillonnage de 810.1 MHz en utilisant la technologie CMOS 0.13 µm. La consommation de puissance totale a été estimée à moins de 22 mW avec une tension d'alimentation de 1.3V. La méthode de conception qui a conduit à ce modulateur peut être appliquée pour développer des modulateurs d'ordre plus élevé qui produiraient un rapport signal à bruit plus élevé. L'adaptation entre les fréquences intermédiaires des côtés numériques et analogiques est effectuée en faisant du suréchantillonnage du côté numérique. Le modulateur proposé ne présente aucun délai de boucle supplémentaire attribué au réglage du taux d'échantillonnage. Le suréchantillonnage augmente le taux d'échantillonnage et la largeur de bande du CNA. Par conséquent, les images à haute fréquence ne seront pas trop atténuées par le CNA. Une telle technique réduit également l'effet des images du signal et améliore le rapport signal à bruit. Le MDS passe-bande proposé offre une performance sensiblement supérieure pour les hautes fréquences lorsqu'il est comparé aux convertisseurs  $\Delta\Sigma$  existants dans la littérature.

L'architecture proposée a été validée en utilisant MATLAB (**Figure 4-4**). Quelques circuits ont été proposés et conçus avec la technologie CMOS 0.13µm d'IBM. Les résultats de simulation au niveau circuit confirment également le concept proposé (**Figure 4-8**). Les effets des non-idéalités sont discutés et quelques solutions ont été proposées.

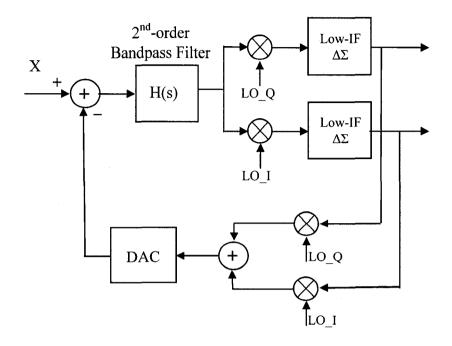

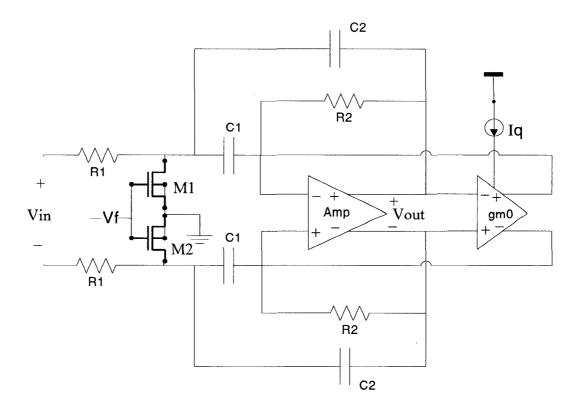

Un des effets reliés à cette architecture est qu'en augmentant la fréquence centrale du modulateur delta-sigma (MDS) à plusieurs GHz, les caractéristiques du filtre passebande du chemin direct dans le modulateur delta-sigma ne sont plus pratiques dans la technologie CMOS commerciale, sinon nous devrions avoir recours à des marges de tolérance excessive pour la conception. Compte tenu des considérations pratiques décrites ci-dessus, un modulateur delta à temps continu est proposé (Figure 5-2). Ce modulateur fonctionne avec la même performance que le modulateur delta-sigma et il est capable de recevoir des signaux à haute fréquence. En outre, la fréquence centrale n'est pas identique à la fréquence d'entrée de la porteuse, ce qui permet de relaxer les contraintes reliées à sa valeur élevée. Comme discuté plus tôt, le mélangeur dans la boucle de rétroaction et le réglage du filtre passe-bande sont deux limitations importantes des modulateurs delta-

sigma. Nous pouvons gérer les deux en considérant le fait que le but principal du filtre passe-bande est de former le spectre du bruit de quantification. Nous supposons que le signal d'entrée est déjà filtré par un filtre d'anti-recouvrement. Par conséquent, un filtre passe-bande dans le chemin direct ne change pas le spectre du signal d'entrée. Il n'a également aucun effet sur le signal de rétroaction si le gain passe-bande est unitaire. En conséquence, le filtre passe-bande dans le chemin direct peut être déplacé au chemin de rétroaction s'il est centré à la fréquence intermédiaire (FI) au lieu de la fréquence d'entrée. Dans ce cas, nous pouvons enlever le mélangeur ainsi que l'effet de toutes ses imperfections. D'ailleurs, la fréquence du signal d'entrée n'est pas limitée par la fréquence centrale du modulateur delta-sigma.

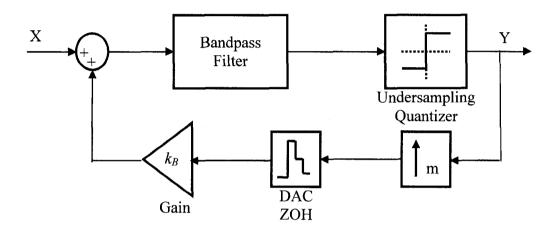

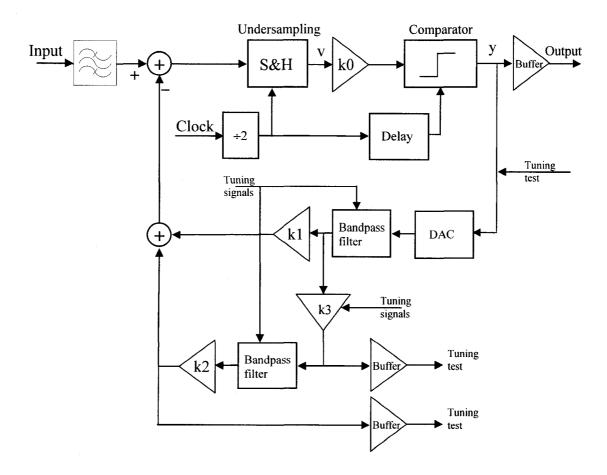

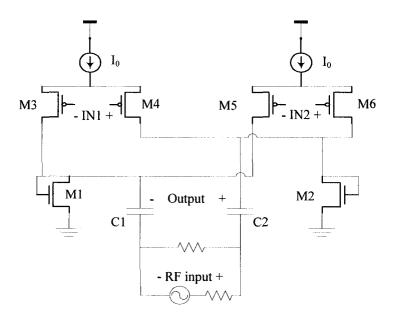

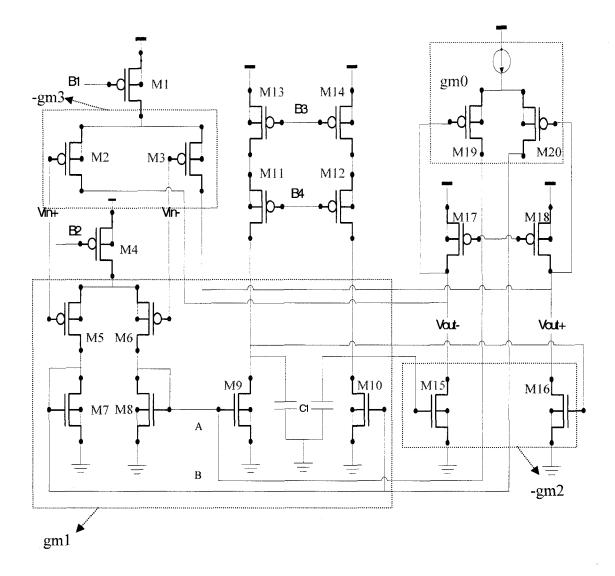

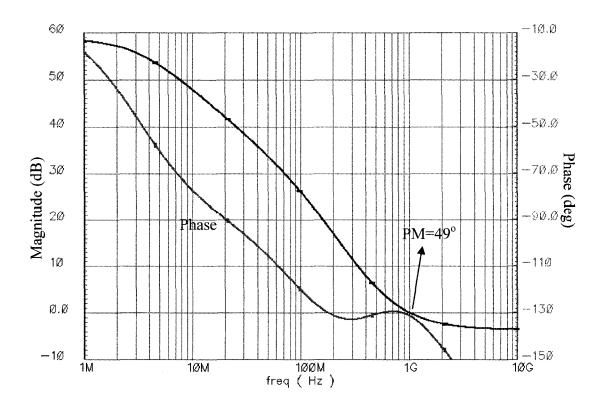

Le modulateur que nous avons conçu est un modulateur du quatrième-ordre qui a une architecture à double-boucle avec deux filtres passe-bandes de second ordre. Le filtre passe-bande utilisé dans le chemin de rétroaction est un filtre actif-RC de second ordre. Sa fréquence centrale et son facteur de qualité sont ajustables pour obtenir la performance désirée après la fabrication. Par conséquent, une entrée et une sortie sont disponibles pour le réglage pendant les périodes inactives. En outre, le système peut également être accordé en utilisant le signal de sortie du modulateur quand une porteuse de référence est disponible. Un échantillonneur bloqueur à bande ultra-large dans le chemin direct acquiert des signaux avec une fréquence maximale de 2 GHz. Des fréquences plus élevées peuvent également être capturées par cette architecture, mais cela dépend de la technologie et de l'implémentation du circuit. La fréquence d'échantillonnage suit la porteuse d'entrée. Dans ce cas-ci, un taux d'échantillonnage de 495 MHz est nécessaire

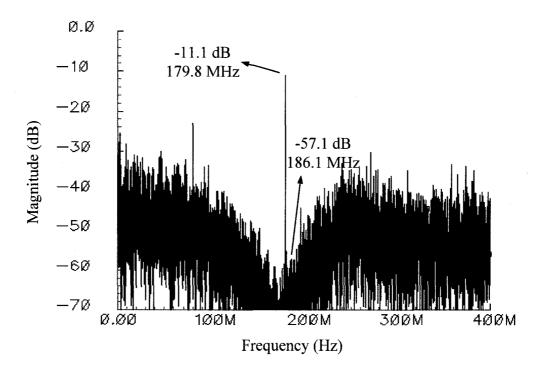

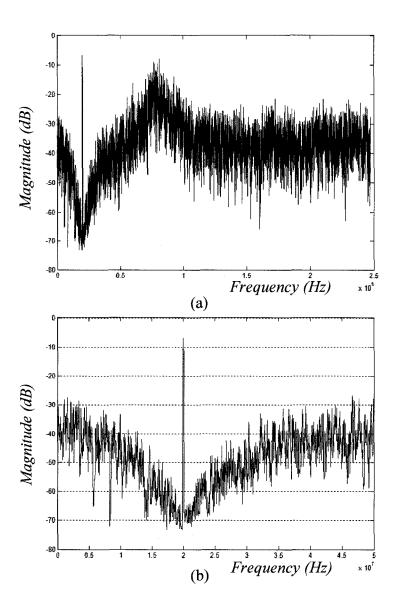

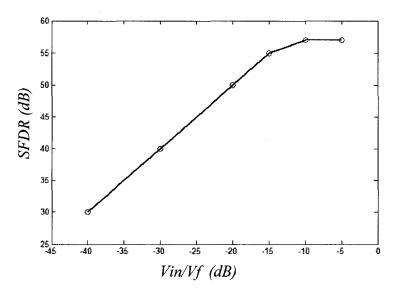

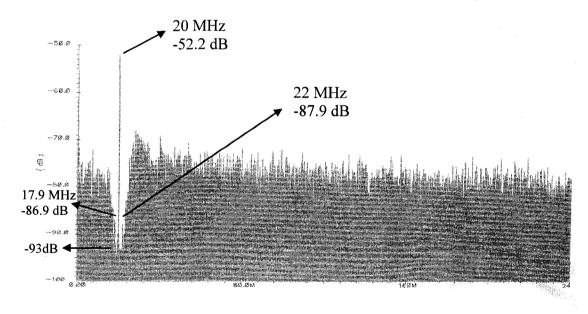

pour avoir une FI numérique à 20 MHz. La fréquence de l'horloge est deux fois plus élevée que la fréquence d'échantillonnage. En utilisant un diviseur de fréquence, la fréquence diminue et donc réduit la gigue et réalise un facteur d'utilisation (duty cycle) de 50%. Le quantificateur est un comparateur d'un bit et conduit un tampon (buffer) et un CNA. Les résultats des simulations après les dessins de masques donnent une gamme dynamique de 41dB pour une bande passante de 1 MHz (**Figure 5-11**). Le modulateur a été fabriqué et testé. Il absorbe un courant de 31mA pour une tension d'alimentation de 1.2V (37mW). Le rapport signal à bruit maximal mesuré est de 30dB pour une largeur de bande de 1MHz.

#### **Contributions**

Plusieurs contributions ont été apportées par cette recherche et elles sont résumées cidessous :

- Conception d'un modulateur delta-sigma à 1.8GHz. Une nouvelle architecture a

été proposée au niveau du schéma fonctionnel et des équations mathématiques ont

été développées. Le modulateur a été également conçu au niveau circuit et des

résultats de simulation ont été présentés en utilisant la technologie CMOS 0.13μm

d'IBM.

- 2. Conception, fabrication et test d'un modulateur delta à 2GHz. Une nouvelle architecture a été développée basée sur la technique de sous-échantillonnage pour acquérir des signaux d'entrée de 2GHz. L'architecture a été vérifiée en utilisant la technologie CMOS 0.13μm d'IBM et des résultats expérimentaux ont été présentés.

- 3. Conception, fabrication et test d'un filtre actif-RC passe-bande réglable convenable au modulateur delta.

- 4. Conception d'un filtre passe-bande réglable RF pour le modulateur delta-sigma.

- 5. Conception d'un filtre à 2GHz réglable pour l'antirecouvrement.

#### **Conclusion**

Dans cette thèse, plusieurs idées originales ont été présentées afin d'aider à améliorer la conception de DSM et de DM dans des récepteurs de radiofréquences. Des contributions ont été apportées au niveau système et circuit. Nous avons proposé

l'utilisation de sur-échantillonnage dans la rétroaction de le modulateur an chapitre 4. Des équations de conception applicables à cette architecture ont été développées aussi bien que des techniques de mise en œuvre au niveau circuit. L'adaptation entre les fréquences intermédiaires des côtés numériques et analogiques est effectuée en faisant du sur-échantillonnage du côté numérique. Le modulateur proposé ne présente aucun délai de boucle supplémentaire attribué au réglage du taux d'échantillonnage. Le sur-échantillonnage augmente le taux d'échantillonnage et la largeur de bande du CNA. Nous démontrons que l'architecture proposée peut convertir le signal d'entrée en données numériques avec une plage dynamique sans bruit (Spurious Free Dynamic Range; SFDR) de 46 dB à une fréquence d'échantillonnage de 810.1 MHz en utilisant la technologie CMOS 0.13μm. La consommation de puissance totale a été estimée à moins de 22mW avec une tension d'alimentation de 1.3V.

Cette approche de conception a été encore développée pour permettre la mise en œuvre d'un nouveau modulateur delta capable de recevoir un éventail de fréquences d'entrée afin de faciliter la conception du bloc de filtre passe-bande. Basé sur l'application présentée au chapitre 2, qui vise la numérisation de signaux RF, nous avons proposé un DM qui utilise le sous échantillonnage. Ce modulateur est réalisé sous la forme d'un schéma fonctionnel ainsi qu'au niveau circuit. Il est conçu pour s'intégrer dans des récepteurs radiofréquences. En utilisant le sous échantillonnage dans le chemin direct, il produit une deuxième fréquence intermédiaire (IF) à 20MHz. Le modulateur delta utilise un filtre passe-bande du 4ième ordre dans le chemin de rétroaction. Ce filtre a une fréquence centrale à 20MHz. Le quantificateur est un comparateur d'un bit qui

conduit un tampon (buffer) et un CNA. Les résultats des simulations après les dessins de masques donnent une gamme dynamique de 41dB pour une bande passante de 1 MHz. Le modulateur a été fabriqué et testé. Il absorbe un courant de 31mA pour une tension d'alimentation de 1.2V. Le rapport signal à bruit maximal mesuré est de 30dB pour une largeur de bande de 1MHz.

# TABLE OF CONTENTS

| DEDICATION                                        | iv    |

|---------------------------------------------------|-------|

| REMERCIEMENTS                                     | v     |

| RÉSUMÉ                                            | vi    |

| ABSTRACT                                          | viii  |

| CONDENSÉ                                          | x     |

| TABLE OF CONTENTS                                 | xix   |

| LIST OF TABLES                                    | xxii  |

| LIST OF FIGURES                                   | xxiii |

| LIST OF ABBREVIATIONS                             | xxvii |

| LIST OF APPENDICES                                | XXX   |

| Chapter 1: Introduction                           | 1     |

| 1.1. Motivation                                   | 1     |

| 1.2. Thesis Organization                          | 3     |

| 1.3. Contributions                                | 4     |

| Chapter 2: Continuous-Time Delta Sigma Modulators | 5     |

| 2.1. Basic Theory                                 | 5     |

| 2.2. Design Variations in Delta-Sigma             | 11    |

| 2.3. Continuous-Time vs Discrete-Time Design      | 15    |

| 2.4. Delta-Sigma vs Delta Modulator                                 | 16 |

|---------------------------------------------------------------------|----|

| 2.5. Conclusion                                                     | 21 |

| Chapter 3: Undersampling Delta-Sigma Modulators for Radio Receivers | 22 |

| 3.1. Introduction                                                   | 22 |

| 3.2. Delta Sigma Modulators in Receiver's Architectures             | 23 |

| 3.3. LC Bandpass Filter                                             | 26 |

| 3.3.1 Noise Analysis                                                | 36 |

| 3.4. Design Consideration                                           | 39 |

| 3.5. Noise Analysis                                                 | 45 |

| 3.6. High Frequency Modulators                                      | 49 |

| 3.7. Conclusion                                                     | 51 |

| Chapter 4: A Novel Continuous-Time Delta Sigma Modulator            | 53 |

| 4.1. Introduction                                                   | 53 |

| 4.2. Proposed Bandpass Delta Sigma Modulator Based on Undersampling | 54 |

| 4.3. Effect of Nonidealities                                        | 67 |

| 4.3.1 Clock Jitter                                                  | 67 |

| 4.3.2 Excess Loop Delay                                             | 69 |

| 4.3.3 Filter Noise Analysis                                         | 73 |

| 4.4. Conclusion                                                     | 75 |

| Chapter 5: New Delta Modulator Based on Undersampling               | 77 |

| 5.1. Introduction                                                   | 77 |

| 5.2. Proposed Undersampling Delta Modulator                         | 79 |

| 5.3. Bandpass Active-RC Filter                 | 95  |

|------------------------------------------------|-----|

| 5.4. Experimental Results                      |     |

| 5.5. Conclusion                                | 113 |

| Chapter 6: General Conclusion and Future Works | 114 |

| 6.1. Future Work                               | 116 |

| References:                                    | 118 |

# LIST OF TABLES

| Table 3.1: Performance summary of RF filters in the literature.                    | . 27 |

|------------------------------------------------------------------------------------|------|

| Table 3.2: Performance summary of high frequency modulators in the literature      | . 49 |

| Table 5.1: Simulated results of proposed delta modulator compared with other works | . 89 |

| Table 5.2: Simulated characteristic performance of the amplifier and comparison    | 100  |

| Table 5.3: Sizes of the transistors used in the active-RC filter                   | 101  |

| Table 5.4: Simulated characteristic performance of the filter and comparison       | 105  |

| Table 5.5: Summary of measured results in the filter                               | 111  |

| Table 5.6: Summary of measured results in Delta modulator.                         | 111  |

# LIST OF FIGURES

| Figure 2-1: Block diagram of a typical delta-sigma ADC5                                     |

|---------------------------------------------------------------------------------------------|

| Figure 2-2: Block diagram of a first-order Delta Sigma modulator                            |

| Figure 2-3: Spectral density of noise (N(f)), and quantization noise of 1-bit ADC (E(f)) in |

| a first-order Delta Sigma modulator                                                         |

| Figure 2-4: Delta sigma modulator variations                                                |

| Figure 2-5: A distributed feedback/feed-forward architecture in delta sigma modulator. 13   |

| Figure 2-6: A cascade (1-1-1) architecture in delta sigma modulator                         |

| Figure 2-7: Exponential delta modulator                                                     |

| Figure 2-8: Stream of one and zero at the output due to large quantization step             |

| Figure 2-9: Slope overload condition.                                                       |

| Figure 2-10: Main variations in delta modulator [99]                                        |

| Figure 3-1: Receiver block diagram of (a) Direct conversion, (b) Superheterodyne, (c)       |

| Superheterodyne using band-pass delta sigma modulator                                       |

| Figure 3-2: Negative conductance (-Y) generator. 28                                         |

| Figure 3-3: Proposed bandpass filter: (a) Circuit implementation. (b) Model of filter 29    |

| Figure 3-4: On-chip transformer structure                                                   |

| Figure 3-5: Filter responses for different center frequencies when Q=10034                  |

| Figure 3-6: Filter responses for various Qs when center frequency is 2 GHz34                |

| Figure 3-7: One-tone simulation results (solid line) and reference (dash line)       | . 35 |

|--------------------------------------------------------------------------------------|------|

| Figure 3-8: AC models of the bandpass LC filters.                                    | . 37 |

| Figure 3-9: Receiver architecture using undersampling in S/H and low-pass/band-pass  | ΔΣ   |

| modulator.                                                                           | . 42 |

| Figure 3-10: Two-path implementation of the filter.                                  | . 42 |

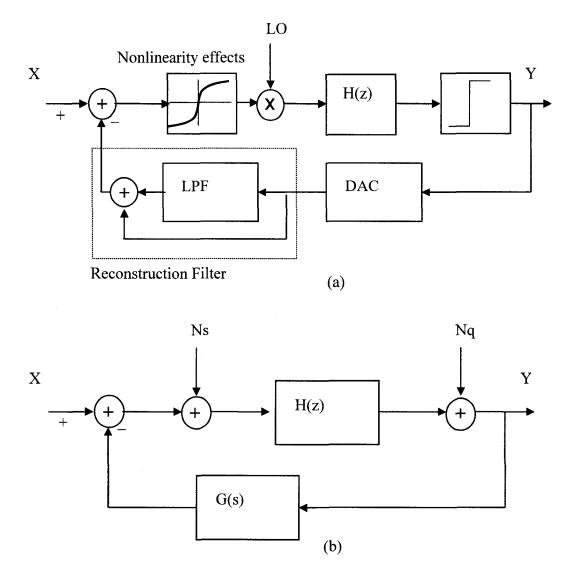

| Figure 3-11: Undersampling delta sigma modulator using sampling in the loop: a)      |      |

| architecture, b) modeling.                                                           | . 43 |

| Figure 3-12: Delta modulator for signal timing measurement [41].                     | . 44 |

| Figure 3-13: A continuous-time undersampling bandpass modulator [36]                 | . 47 |

| Figure 3-14: Block diagram of an undesampling modulator with a mixed continuous ar   | nd   |

| discrete-time filter [17].                                                           | . 48 |

| Figure 3-15: Block diagram of a multi-feedback modulator [20]                        | . 50 |

| Figure 3-16: Block diagram of a complex frequency translation [103]                  | . 51 |

| Figure 4-1: Proposed bandpass delta sigma modulator.                                 | . 55 |

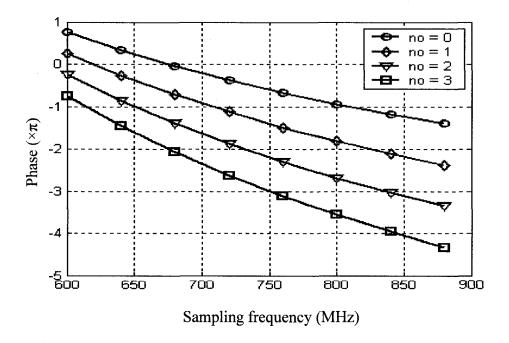

| Figure 4-2: Phase delay due to quantizer, up-sampling, and DAC (m=4, D=1,            |      |

| fi=1.8GHz)                                                                           | . 58 |

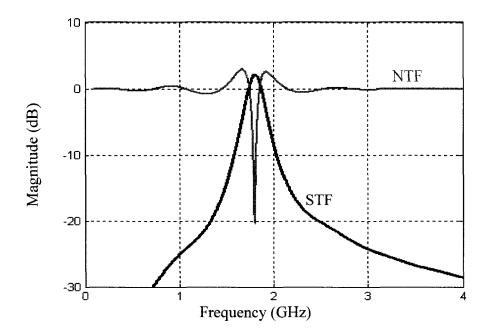

| Figure 4-3: NTF and STF of the proposed delta sigma modulator                        | . 59 |

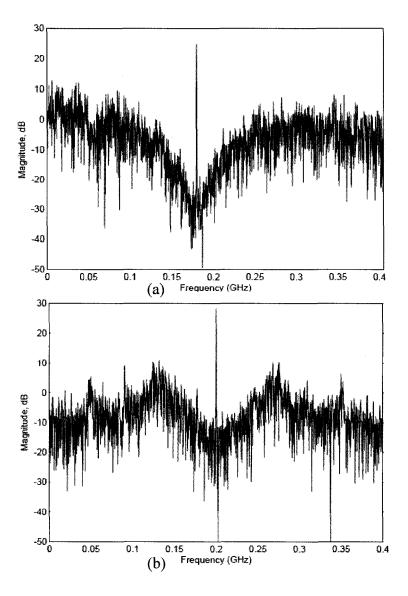

| Figure 4-4: Output power spectrum of (a) proposed modulator, (b) modulator using     |      |

| analog mixer                                                                         | . 60 |

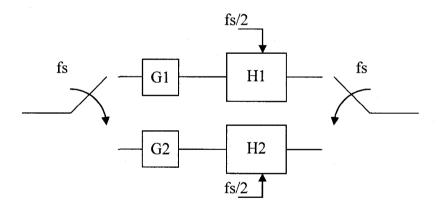

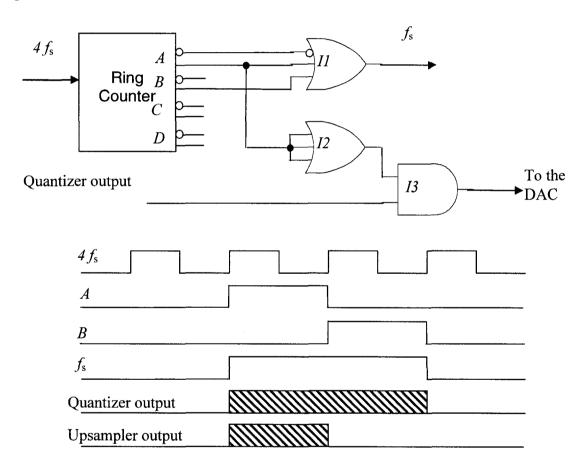

| Figure 4-5: Upsampling of modulator output: a) block diagram, b) its timing diagram. | . 63 |

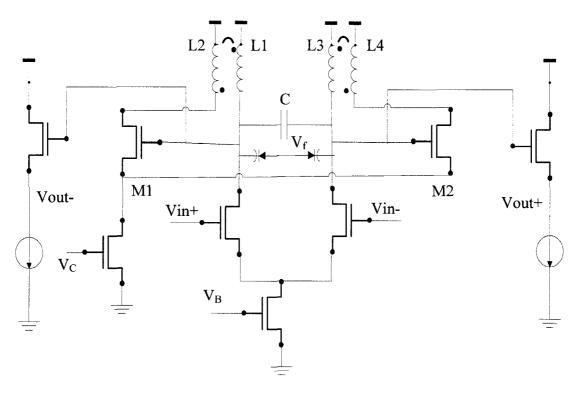

| Figure 4-6: Q-enhanced LC band-pass filter.                                          | . 64 |

| Figure 4-7: Differential "sample and hold" and comparator.                           | . 65 |

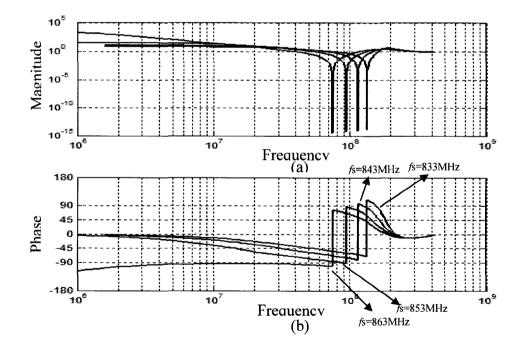

| Figure 4-8: Simulated output spectrum of the proposed modulator.                                       | 56         |

|--------------------------------------------------------------------------------------------------------|------------|

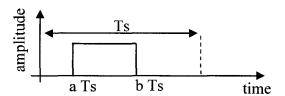

| Figure 4-9: DAC pulse used in the modulator.                                                           | 59         |

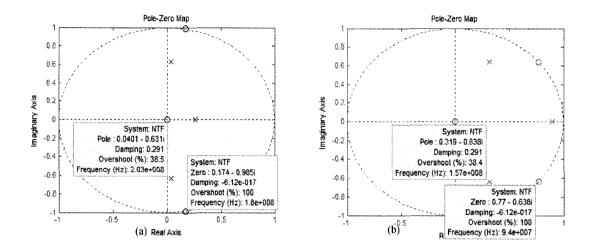

| Figure 4-10: Pole-zero map of NTF when (a) $fs$ =810MHz, $\Delta$ =0, (b) $fs$ =853MHz, $\Delta$ =0.06 | ś.         |

|                                                                                                        | 72         |

| Figure 4-11: NTF of the modulator for different sampling frequencies (a) magnitude, (b)                | )          |

| phase.                                                                                                 | 72         |

| Figure 4-12: Ac models of the bandpass LC filters.                                                     | 73         |

| Figure 5-1: Block diagram of the modulator: (a) proposed in [36], (b) intermediate step,               |            |

| (c) proposed in this work.                                                                             | 31         |

| Figure 5-2: Block diagram of the proposed delta modulator                                              | 32         |

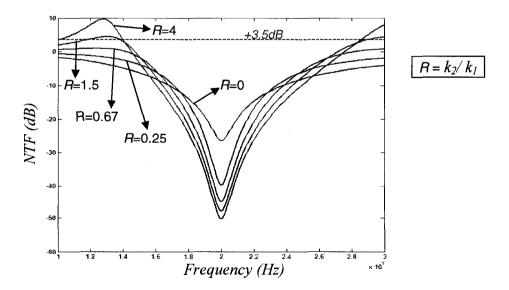

| Figure 5-3: NTF magnitude for different $k_1$ and $k_2$ .                                              | 36         |

| Figure 5-4: (a) Output power spectrum of the proposed modulator. (b) Magnified                         | 37         |

| Figure 5-5: Output SFDR versus ratio of input signal over feedback signal                              | 38         |

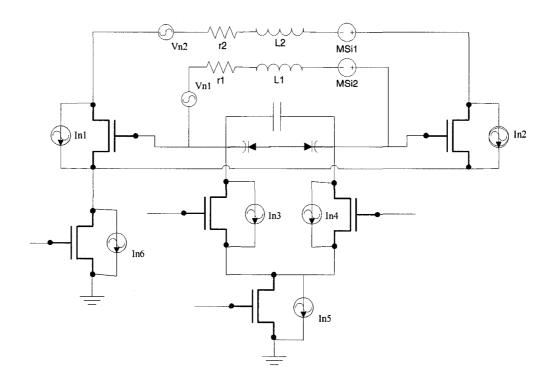

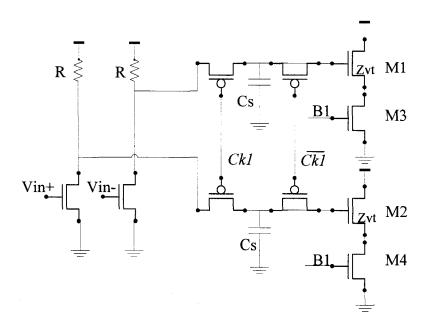

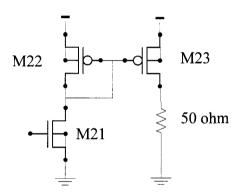

| Figure 5-6: Transistor level of the subtractor.                                                        | <b>)</b> ( |

| Figure 5-7: Buffer and S&H circuits.                                                                   | <b>)</b> 2 |

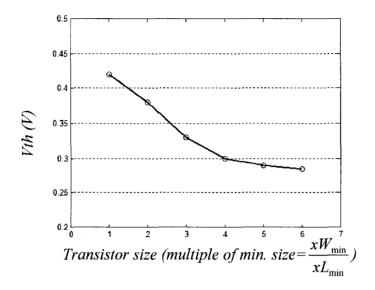

| Figure 5-8: Threshold voltage of an NMOS transistor versus size of transistor                          | <b>)</b> 3 |

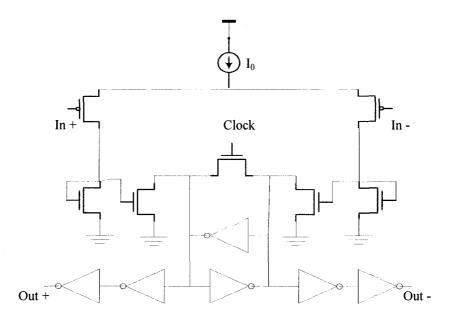

| Figure 5-9: Circuit level of the comparator employed in the delta modulator                            | <b>)</b> 4 |

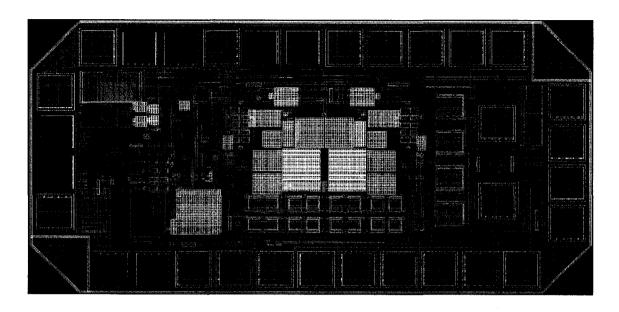

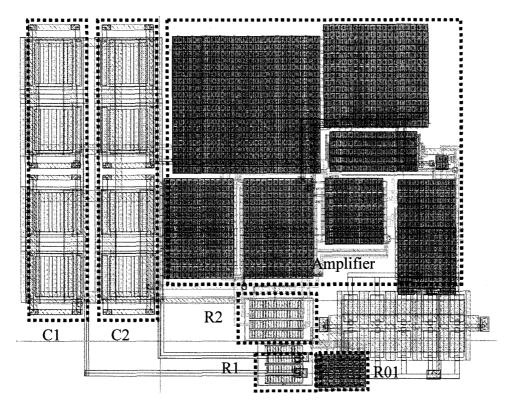

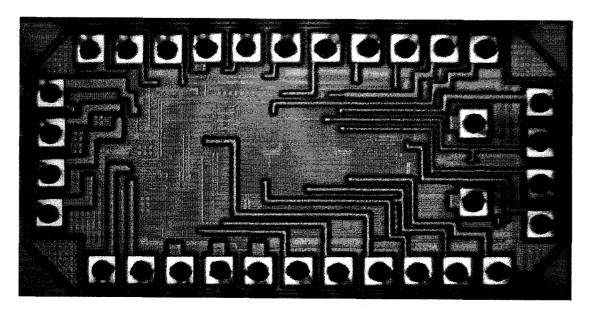

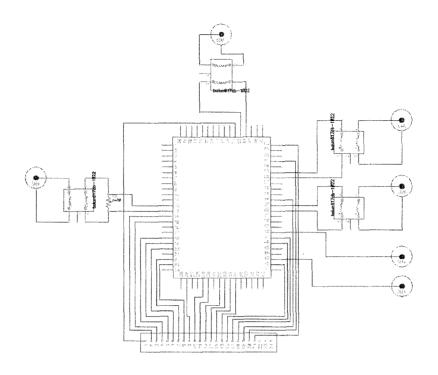

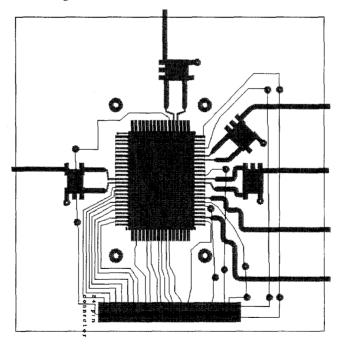

| Figure 5-10: Layout of the delta modulator in CMOS 0.13μm.                                             | €          |

| Figure 5-11: Simulated power spectrum of the modulator output                                          | )5         |

| Figure 5-12: Differential architecture of the bandpass filter.                                         | 98         |

| Figure 5-13: The amplifier with positive feedback to control Q-factor of the filter                    | <b>)</b> 9 |

| Figure 5-14: Frequency response of the amplifier                                                       | )1         |

| Figure 5-15: Output buffer in the active-RC filter                                      | . 102 |

|-----------------------------------------------------------------------------------------|-------|

| Figure 5-16: Layout of the active-RC filter in CMOS 0.13μm.                             | . 103 |

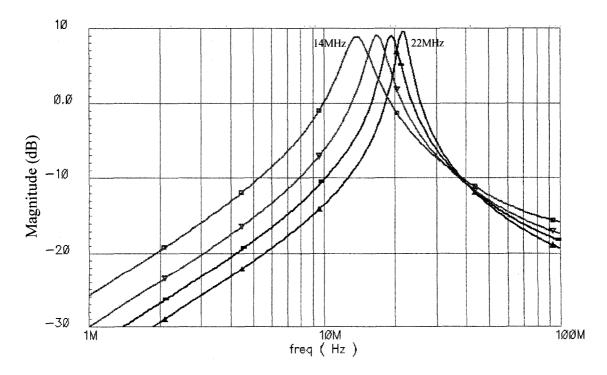

| Figure 5-17: Frequency response of the active-RC filter for various center-frequencie   | es.   |

|                                                                                         | . 103 |

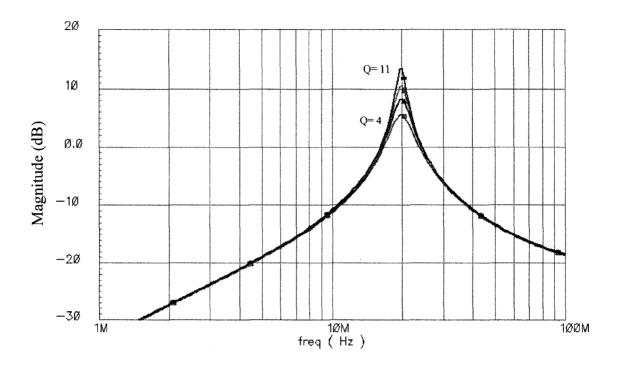

| Figure 5-18: Frequency response of the active-RC filter for various Q-factors           | . 104 |

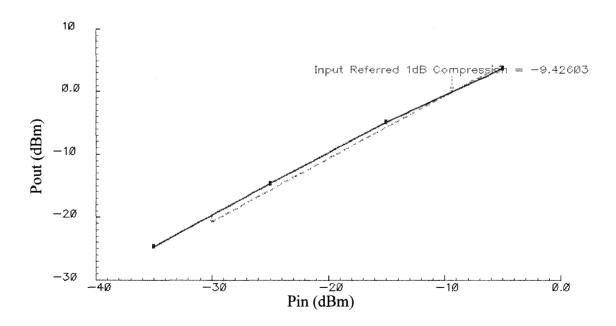

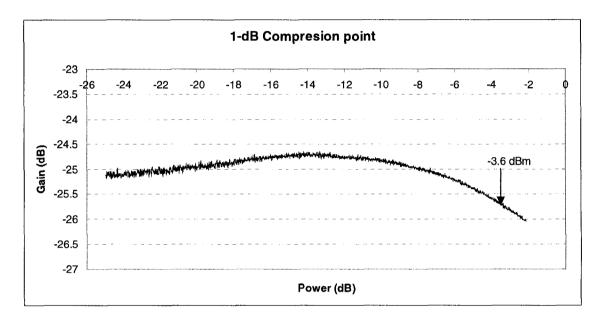

| Figure 5-19: Simulation result for 1-dB compression point in the active-RC filter       | . 104 |

| Figure 5-20: Microphotograph of the delta modulator.                                    | . 106 |

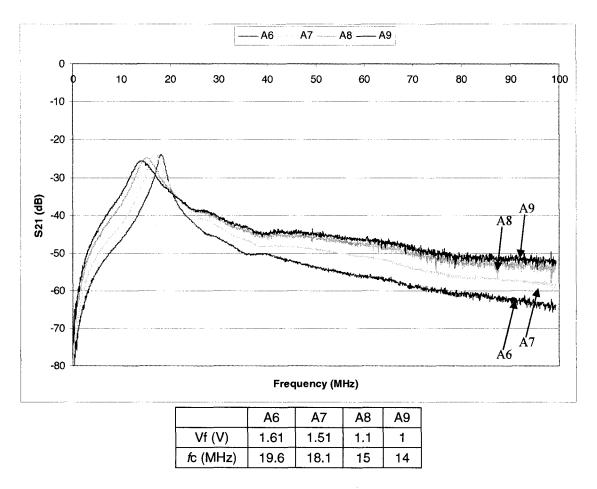

| Figure 5-21: Q-factor tuning measurements of the 2 <sup>nd</sup> -order filter          | . 107 |

| Figure 5-22 : Center frequency tuning measurements of the 2 <sup>nd</sup> -order filter | . 108 |

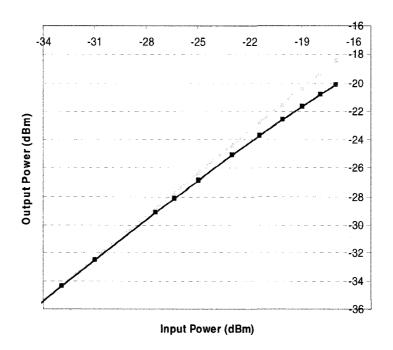

| Figure 5-23: Input 1-dB compression point measurement.                                  | . 109 |

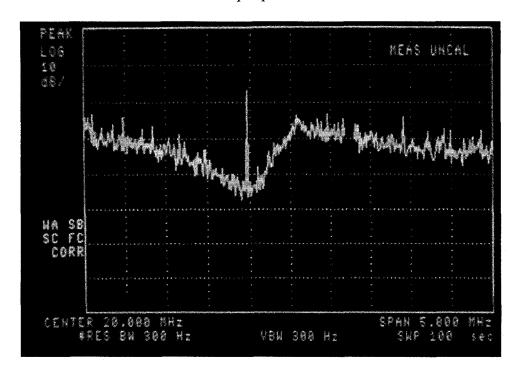

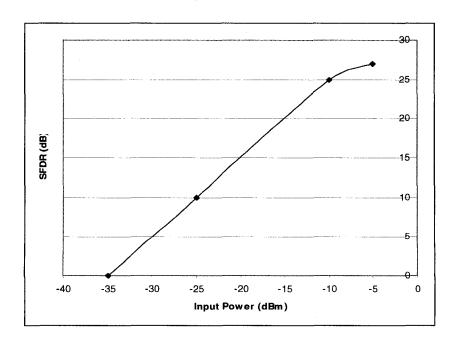

| Figure 5-24: Output power spectrum of the modulator.                                    | . 110 |

| Figure 5-25: the SFDR versus input power.                                               | . 110 |

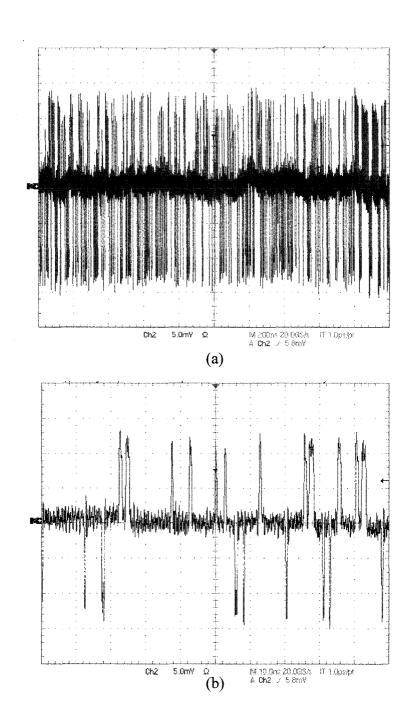

| Figure 5-26: (a) The modulator output signal in time domain. (b) Magnified              | . 112 |

| Figure A-1: Q-enhanced LC band-pass filter                                              | . 136 |

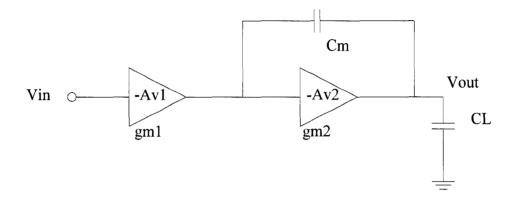

| Figure B-1: Simple miller compensation.                                                 | . 138 |

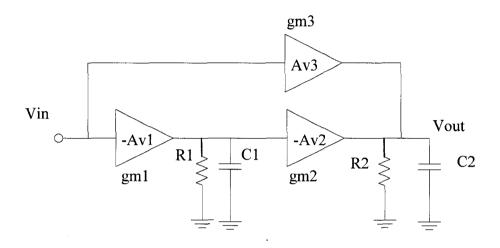

| Figure B-2: Multi-path compensation topology.                                           | . 139 |

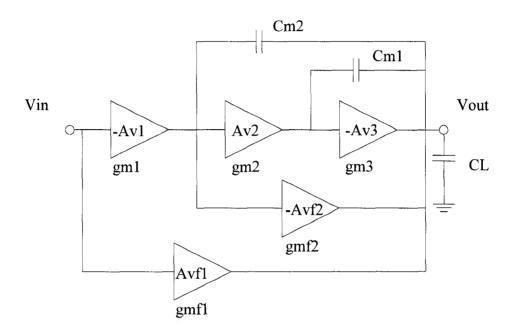

| Figure B-3: Nested Gm-C compensation topology.                                          | . 140 |

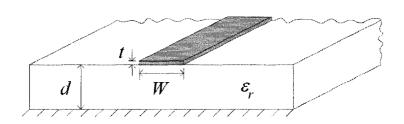

| Figure C-1: Microstrip line.                                                            | . 142 |

| Figure C-2: Schematic of the testboard.                                                 | . 143 |

| Figure C-3: Layout of the testboard.                                                    | 143   |

# LIST OF ABBREVIATIONS

AC Alternating Current

ADC Analog Digital Converter

ADM Asynchronous Delta Modulator

APDM Asynchronous Pulse Delta Modulator

ARWDM Asynchronous Rectangular Wave Delta Modulator

CIC Cascaded Integrator-Comb

CMOS Complementary Metal Oxide Semiconductor

CT Continuous Time

DAC Digital Analog Converter

DC Direct Current

DE Delayed Encoding

DEM Dynamic-Element-Matching

DFF D Flip-Flop

DM Delta Modulator

DR Dynamic Range

DSM Delta Sigma Modulator

DSP Digital Signal Processing

DT Discrete Time

ECDM Externally Companded Delta Modulator

ET Element-Trimming

FET Field-Effect Transistor

IC Integrated Circuit

ICDM Instantaneously Companded Delta Modulator

IF Intermediate Frequency

LHP Left-Half-Plane

LNA Low Noise Amplifier

LO Local Oscillator

MOS Metal Oxide Semiconductor

NMOS MOS transistor having electrons as majority carriers (N-type)

NTF Noise Transfer Function

OSR Over Sampling Ratio

PCM Pulse-Code Modulation

PLL Phase Locked Loop

PM Phase Margin

PMOS MOS transistor having holes as majority carriers (P-type)

PPM Parts Per Million

RF Radio Frequency

RHP Right-Half-Plane

rms root mean square

S/H Sample and Hold

SCALE Syllabically Companded All Logic Encoder

SCDM Syllabically Companded DM

SFDR Spurious Free Dynamic Range

SiGe Silicon Germanium

SMC Simple Miller Compensation

SNDR Signal to Noise Distortion Ratio

SNR Signal to Noise Ratio

STF Signal Transfer Function

UGBW Unity Gain Bandwidth

USR Undersampling Ratio

Vth Threshold Voltage of a Transistor

# LIST OF APPENDICES

| Appendix A: LC Bandpass filter                                      | 135            |

|---------------------------------------------------------------------|----------------|

| Appendix B: Amplifier Design and Compensation Methods for Continuou | s-Time Filters |

|                                                                     | 137            |

| Appendix C: Test board                                              | 141            |

## Chapter 1

## Introduction

#### 1.1. Motivation

Electronic systems are increasingly being used in our everyday life, to boost our performance in various tasks, and to enhance quality of life. Such systems need to process ever increasing volume of data as fast as possible. Digital implementations are increasingly popular for such purposes. However, communications of data between modules composing such systems are often performed by analog and mixed-mode subsystems. Ideally, these modules should be programmable and compatible with different communication standards. Furthermore, low power consumption is essential in portable applications. Hence, high speed and low-power data converters are needed in transceivers and portable systems linking analog and digital parts.

The radio frequencies used in communication standards are currently higher than 1 GHz, while they carry a signal bandwidth narrower than 5 MHz. In order to recover such signals, the carrier is usually removed by at least one set of mixers and lowpass filters, and then an ADC is used for digitization. This method can be improved if the ADC could digitize the RF signal directly with the same power consumption. The improvement is due to removing the analog components and having a programmable system. Our motivation for this research is to propose new ADCs for radio frequency

applications. Programmability of the transceivers could allow connecting a user to multiple available communication services seamlessly, even if those services are offered over different links. Although such advantage is partly accessible in modern tri-band cellular phones, it requires additional hardware that increases their final price. Furthermore, introducing new communication standards usually makes old cellular phones unusable if they are based on separate dedicated hardware for each software. The demand to support all possible standards is partly rooted in military requirements, which led in the 1990s to the concept of software defined radios. The primary frequency frame for such a receiver was between 2 MHz to 2000 MHz, which is considerable even with today's technologies. However, its benefits are worthwhile. Such receivers are ideally composed of an antenna, ADC, and then a digital signal processor with memory. By loading software into the memory of the processor, the whole receiver could be controlled and adapted to a new standard. This software may even be automatically downloaded into the users' phones via a patch by the service provider. To make this possible, we first need a low-power and high resolution ADC.

The goal of this research is to design and implement a delta sigma modulator dedicated to software-defined radios that could receive narrow-band signals modulated over carrier frequencies up to 2 GHz. This thesis proposes architectural and circuit-level techniques to achieve this goal. It also validates the proposal with analytical models, circuit simulation, chip layouts and prototype integrated circuits.

## 1.2. Thesis Organization

Chapter 2 reviews the fundamental concepts in the design of delta sigma modulators. It begins with basic theory and design variations in delta-sigma modulators. We discuss about continuous-time and discrete-time modulators. Then it presents design methods and trade-offs in the delta modulators. The chapter ends by review of receiver's architectures as an application of  $\Delta\Sigma M$  (delta sigma modulators) and conclusion.

Chapter 3 investigates design issues and factors limiting performance in the undersampling delta sigma modulators. Effect of undersampling in continuous-time modulators are considered in term of noise and aliasing. Such effect is formulated for some existing architectures. The information presented in this chapter is a reference for the work presented in the next chapters.

Chapter 4 describes a new undersampling CT (continuous time) band-pass  $\Delta\Sigma M$  and its circuit implementation. The proposed architecture is suitable for RF digitization, without an analog mixer in the feedback path. Related design equations are derived and applied to the optimization of its operating point for a 1.8 GHz input signal. Practical issues due to non-idealities are also discussed.

Based on the design trend in the previous chapters, which aims at RF signal digitization, Chapter 5 presents the proposed delta modulator suitable for radio frequency applications dealing with a carrier frequency of the order of 2 GHz. Stability of the modulator is analyzed and associated relations are developed. Simulation and

experimental results are given for IBM 0.13µm CMOS technology. Conclusions and future works are discussed in Chapter 6.

#### 1.3. Contributions

This research makes the following contributions:

- Design of a 1.8GHz delta sigma modulator[71][75]. A new architecture was

proposed at the block diagram level and mathematical relations were developed.

The modulator was also designed at the circuit level and simulation results were

presented using IBM 0.13μm CMOS technology.

- 2. Design, fabrication and test of a 2GHz delta modulator[73]. A new design was developed based on the undersampling technique to capture 2GHz input signals. The design was verified by IBM 0.13μm CMOS technology and experimental results were presented.

- 3. Design, fabrication and test of a tunable bandpass active-RC filter dedicated to the delta modulator [74].

- 4. Design of a tunable RF bandpass filter for delta sigma modulator [75].

- 5. Design of a tunable 2 GHz filter for anti-aliasing purposes [72].

# Chapter 2

## Continuous-Time Delta Sigma Modulators

In this chapter, we review basic theory of the delta sigma modulators. Then we move on to design methods applicable to  $\Delta\Sigma M$  that cover discrete and continuous time implementations. Then design issues and factors limiting performance in the design of delta sigma modulators and delta modulators are compared and discussed.

## 2.1. Basic Theory

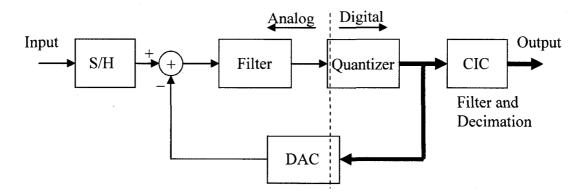

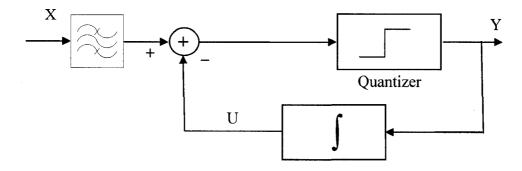

Delta sigma modulators are a class of circuits that allow quantizing while providing an excellent trade-off between power, speed, and resolution. **Figure 2-1** shows a general form of the modulator and required post-processing to digitize an analog signal.

Figure 2-1: Block diagram of a typical delta-sigma ADC.

The input is sampled at a rate higher than Nyquist rate. The quantizer works at the same rate with a low resolution. The output error is fed back and shaped spectrally using the characteristics of the filter. The system, therefore, shapes quantization error and pushes most of its power out of band. The out of band signals are removed using a digital filter, and a pure digital signal remains. Then the data rate is reduced by decimation to reach the Nyquist rate. This is the general form of any delta sigma ADC and all variations are about the modulator section rather than the digital filtering and decimation sections.

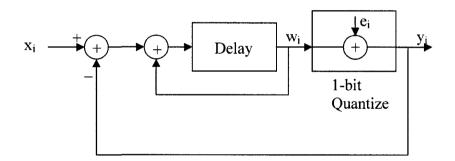

**Figure 2-2** shows a block diagram of a first order delta sigma modulator where a single-bit ADC is used as the main quantizer.

Figure 2-2: Block diagram of a first-order Delta Sigma modulator.

By considering a linear model for the components, a transfer function for input and output of the modulator can be derived as follows [79]:

$$w_{i} = x_{i-1} - e_{i-1}$$

$$y_{i-1} = w_{i-1} + e_{i-1}$$

(2-1)

$$y_i = x_{i-1} + e_i - e_{i-1} = x_{i-1} + n_i$$

(2-2)

$$N(z) = E(z)(1-z^{-1}), \quad z = e^{j\omega T}$$

(2-3)

$$N(\omega) = 2e_{rms}\sqrt{2T}\sin\left(\frac{\omega T}{2}\right) \tag{2-4}$$

$$e_{rms}^2 = \frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} e^2 de = \frac{\Delta^2}{12}$$

(2-5)

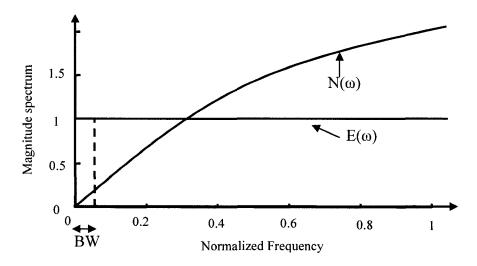

in which T is the sampling period,  $\Delta$  is quantization step, and  $\omega = 2\pi f$ . The N( $\omega$ ) is the overall output noise that presents effect of feedback on attenuation of quantization noise as shown in Figure 2-3. As a result, there is a part of the signal that can pass through the system with much less noise than the rest of the frequency band.

Figure 2-3: Spectral density of noise (N(f)), and quantization noise of 1-bit ADC (E(f)) in a first-order Delta Sigma modulator.

The power of the noise in that bandwidth can be expressed as follows[79]:

$$n^{2} = \int_{0}^{f_{0}} |N(f)|^{2} df$$

$$n^{2} = e_{rms}^{2} \frac{\pi^{2}}{3} OSR^{-3}$$

(2-6)

$$n^2 = e_{rms}^2 \frac{\pi^2}{3} OSR^{-3}$$

(2-7)

$$OSR = \frac{1}{2f_0T} \tag{2-8}$$

in which  $f_0$  is the signal bandwidth. By increasing OSR the noise power decreases. The above system is a first-order system because it contains a first-order lowpass filter in the loop. The noise power also decreases when a higher order filter is used in the loop. In a system with order L loop, if it is not over-loaded, the rms noise in the signal band is given by [79]:

$$n = e_{rms} \frac{\pi^L}{\sqrt{2L+1}} OSR^{-(L+0.5)}$$

(2-9)

And, in a general case, if the loop filter is expressed by H(z), the signal-transfer-function (STF) and noise-transfer-function (NTF) are given as:

$$STF = \frac{H(z)}{1 + H(z)} \tag{2-10}$$

$$NTF = \frac{1}{1 + H(z)} \tag{2-11}$$

Wherever there is a pole in H(z), the signal passes through the system while quantization noise does not. Therefore, in high order systems, poles are separated over the band of interest to get maximum signal-to-noise ratio (SNR). All the above relations were explained in the discrete-time domain. The system, however, can be implemented in a continuous-time form by using a continuous-time filter. In order to apply discrete-time rules to such a system, an equivalent discrete-time system is obtained using inverse Laplace transform. But matching of the equivalent system with the rules to get high SNR may be somewhat difficult, or needs pure and accurate continuous-time components.

Hence, usually, discrete-time systems have higher performance than continuous-time ones. On the other hand, discrete-time systems are limited to low frequency operation.

As loop filters can also be designed to get a bandpass architecture, we can derive results for bandpass sigma delta modulators that are similar to those obtained for lowpass modulators. This is useful when the input signal is modulated over a carrier frequency much higher than the signal bandwidth. Nevertheless, the sampling frequency must be high enough according to Nyquist theorem. Therefore, when the input carrier frequency is at radio frequency range, such as 1 GHz, in an oversampling architecture, the sampling frequency must be of the order of 4 GHz. Such high operation frequency creates many practical issues, such as power consumption and fabrication cost [32][48][49][27][19][9]. A bandpass system has the following advantages in comparison to a lowpass system [79][53][101][67][33].

- A) Band-pass converters are immune to 1/f noise.

- B) Conversion to digital at either Intermediate frequency (IF) or Radio frequency (RF) provides opportunities for dealing with the multiple standards present in commercial broadcasting and telecommunications.

- C) There is no need to introduce an extra multiplier and local oscillator to convert RF to base-band.

- D) Because of digital nature of the implementation, matching between I and Q channels can be obtained with no special effort.

- E) A decimator section is not necessary when conversion rate is not higher than the carrier frequency.

Some advantages in comparison to other video rate ADCs are:

- A) Inherent linearity (for single-bit systems).

- B) Reduced anti-aliasing filter complexity. They can even be eliminated when it is not necessary to design the filter for a very sharp cut-off.

- C) Band-pass converters are immune to 1/f noise.

- D) The smaller structure consumes smaller on-chip area and lower power.

- E) Sample-and-Hold can be omitted when a Continuous-Time filter is used.

However, there are some disadvantages in comparison to the lowpass modulators. These are:

- A) A typical bandpass (BP) converter consumes larger power than a typical lowpass (LP) one.

- B) A 2Nth order BP converter has a SNR as high as an Nth order LP converter.

- C) In LP converters, achieving an accuracy as high as 28-bit is feasible, while the best reported BP converters present an accuracy lower than 16-bit for IF < 10MHz and 12-bit for IF > 10MHz.

## 2.2. Design Variations in Delta-Sigma

Delta sigma modulators are very challenging in terms of having mixed analog and digital parts. In addition, the quantizer is a nonlinear component that makes modeling of the system extremely difficult, especially when the system is using continuous-time RF filters. Hence, practical realization of the system is not a trivial task. We will discuss later in this chapter non-idealities of the implementations and modeling, but here we review useful general design methodologies regardless of circuit level challenges.

As we have already mentioned, there is a significant trade-off between power, and speed/resolution of the quantizer. Processing higher speed signals usually means using higher oversampling-ratio (OSR), and therefore higher power consumption. By having higher resolution in the quantizer, the accuracy improves at the cost of higher power consumption. The accuracy of a modulator can also be increased by increasing the order of the loop filter, which puts more power of the quantization noise out of the signal band. Therefore, we can generally divide design methods to achieve high accuracy into two categories in terms of filter order and resolution of the quantizer; 1-high-order and single-bit, 2- high-order and multi-bit. When we deal with very high accuracy in the modulator, linearity of the conversion is a big concern. A single-bit quantizer is inherently linear and ideally suited for very high accuracy modulators, while a multi-bit quantizer requires a linearization algorithm to fix this issue. The order of the modulator sets the number of system poles. When the modulator order exceeds the second-order, like in any feedback system, instability is expected. Hence, stability is the main issue with high-order

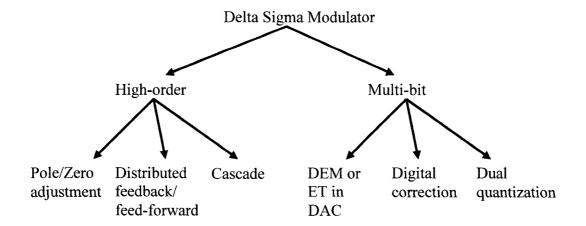

modulators, and linearity is the main problem of a multi-bit quantizer. All design methods are turning around some solutions for such issues. **Figure 2-4** shows some variations of the delta-sigma modulator based on the above discussion.

When the order of the system is higher than two, stability can be obtained, either by controlling the out-of-band noise power or splitting the high-order loop into several low-order loops. In the first method, the out-of-band noise power is controlled by having a few zeros in the transfer function of the system distributed over the signal bandwidth. The new zeros can reduce out-of-band power, and, consequently, stabilize the whole system. In the second method, the high order loop is converted into several low order loops by making multi-feedback or feed-forward ("Distributed feedback/feed-forward"), or by making several single loops in series (Cascade) as shown in **Figure 2-5**, and **Figure 2-6** [29].

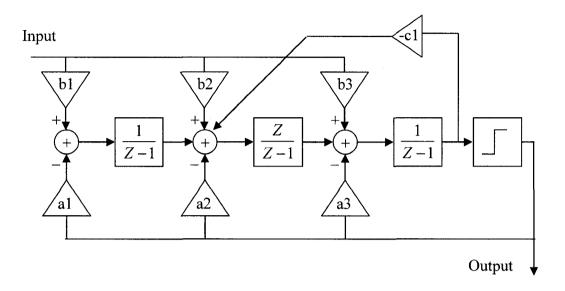

Figure 2-4: Delta sigma modulator variations.

Figure 2-5: A distributed feedback/feed-forward architecture in delta sigma modulator.

Figure 2-6: A cascade (1-1-1) architecture in delta sigma modulator.

Delta sigma modulators with multi-bit converters are more stable than single bit converters. The converted signal also has much higher SNR in the multi-bit systems. However, a notable limitation is that the output signal in a multi-bit modulator is not as linear as that in the single-bit modulator, while linear conversion is a must in many applications. The mismatches in a practical implementation of a modulator exacerbate nonlinearity issues, and require some solutions in the high level design. In a multi-bit modulator both ADC and DAC are multi-bit. However, the nonlinearity in the DAC makes the whole system nonlinear, and its error and nonlinearity must be less than the ultimate nonlinearity of the modulator. For example, in order to get 16-bit linearity in a modulator, the internal DAC should have accuracy better than 16-bit. This level of accuracy needs an almost perfect element matching that can be obtained by element-trimming (ET) after fabrication, which costs a lot [79], or by some circuit methods in the design step, such as dynamic-element-matching (DEM) [12][11].

Another method to increase the linearity of the multi-bit modulator is post-processing of the data. This correction is carried out by a memory block that contains all possible outputs and is placed after the modulator. Therefore, it can correct all errors by assigning each output to a right value [93]. The last method for improving the linearity is having a single bit DAC, instead of multi-bit, in the feedback, even though the ADC can still quantize signal multi-bit. This reduces the overall SNR and stability in the original multi-bit modulator, but it still has better performance than single-bit and enjoys inherent linearity.

## 2.3. Continuous-Time vs Discrete-Time Design

A delta sigma modulator is continuous-time when the loop filter is continuous-time. In this case, the system is a mixture of discrete and continuous time parts that make the analysis complex. As most techniques of linearization and stabilization are easier to develop in discrete-time, we can replace an equivalent discrete-time filter in the loop and assume the whole system is discrete-time. There are some tools such as MATLAB [65] which provide such one-to-one discrete-continuous transforms. For example, a first-order loop filter in a discrete-time modulator is mapped to continuous as follows:

$$H(z) = \frac{-z^{-1}}{1 - z^{-1}} \Leftrightarrow H(s) = \frac{-1}{s}$$

(2-12)

The above technique is the main technique used in the analysis of continuous time modulators. However, there is another option, in which by converting the discrete time part into continuous time, the system is seen to be purely continuous. This method is ostensibly easier, because we need only to replace a quantizer with a delay, and the DAC with a lowpass filter. The quantizer and the DAC are the common parts in all modulators and they are not dependent on the architecture of the loop filter of the modulator. Although a unique transfer function can be obtained in Laplace domain by this method, it is not a linear model due to nonlinear behaviour of the DAC. Therefore, finding the poles and zeros of the system is not trivial, and it requires very sophisticated mathematical tools for nonlinear equations. Hence, it may not be suitable for optimization analysis.

## 2.4. Delta-Sigma vs Delta Modulator

The main difference between DM and DSM is which one of the filter or quantizer is placed first in the forward path. All basic rules explained in the previous section for the delta sigma modulator (DSM) are also valid for the delta modulator (DM), a variation of oversampling modulators. However, there are a few concerns with the delta modulator and some solutions that make it more suitable for some applications such as voice, adaptive modulators and signal timing measurements [36][99].

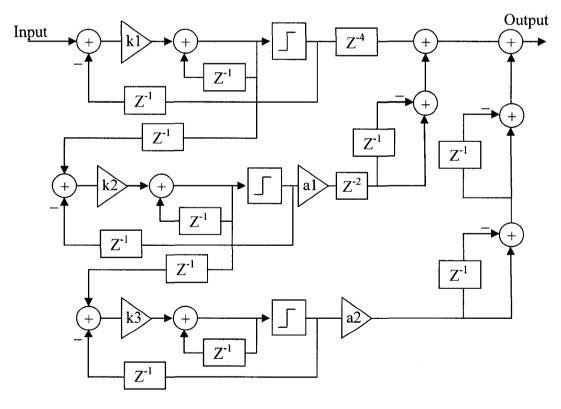

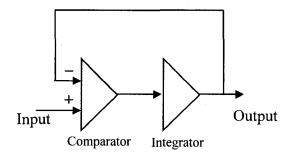

Delta modulators were developed mostly based on applications, which were often related to voice or video processing. By improving integrated circuit technology and having more complex filters on the chip, most of the designs were delta sigma modulators. Although the design method and results in DM and DSM are similar, signals at each point of a DM contain different information from those in a DSM. Hence, there are some trade-offs that differ from those explained for DSM. **Figure 2-7** shows a linear DM that is also called an exponential DM.

Figure 2-7: Exponential delta modulator.

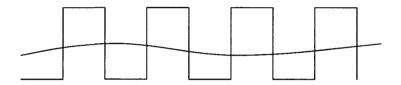

The signal U shown in **Figure 2-7** is actually a copy input signal, X, reproduced by the system. Therefore, U should always track the input signal with good accuracy. The digital output signal, Y, is the difference between the U and input signal. Hence, the quantizer's steps and rate of quantization are key points in which to have minimum error. In a similar fashion, DSM idling tones appear at the output when the step size in the quantizer is larger than the input amplitude or its variations. This issue is shown in **Figure 2-8**.

Figure 2-8: Stream of one and zero at the output due to large quantization step.

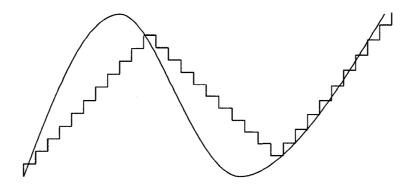

Having very small quantization steps could also prevent the modulator tracking input signals properly. This issue, which is called slope overload, may occur even when the input signal changes quickly. As shown in **Figure 2-9**, the maximum swing at the output is a variable of the quantization rate and step.

One of the main differences between DM and DSM is position of the filter in the loop, and the issues discussed here are the consequences of such a difference. If a signal is filtered first, and then quantized, the modulator is a DSM. As far as the DM and DSM are used for analog-to-digital-conversion, the output of the modulator is always probed at

the output of the quantizer. Hence, in a DM the filter is seen in the feedback path. However, in some applications like signal timing measurement [41], output of the filter is required as the modulator is not intended for analog to digital conversion.

Figure 2-9: Slope overload condition.

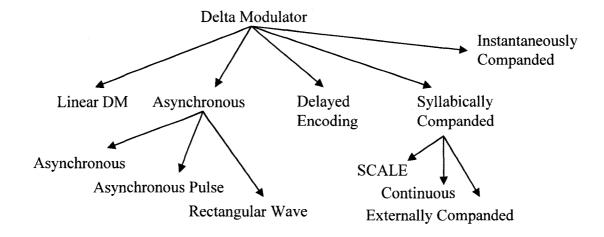

Figure 2-10 shows the main variations of DM as a solution for different applications [99]. Asynchronous DMs (ADMs) use a quantizer to digitize the magnitude of the signal without sampling or synchronization with a clock. The output of the modulator is a stream of pulses based on the output of the quantizer. The idle tones, which are due to sampling clock frequency, would not appear in this modulator when there is no sampling block. However, this version is not usable for digitization of an analog signal.

As we discussed, when the digital signal cannot follow the input analog signal, the modulator is overloaded. In order to predict overload conditions, the system may need to know about the future of the signal. If the signal is delayed enough before being entered into the modulator, then the current signal can be used to predict that the overload

condition may appear in the near future and then allow the system to be prepared for that condition. A DM based on this idea is said to use delayed encoding (DE).

Figure 2-10: Main variations in delta modulator [99].

In all described variations, there is a minimum level for input signal amplitude that produces the maximum SNR in the modulator. The modulator does not have the highest performance for small input amplitudes. One solution to address this issue is to use a compressor and expander in the transmitter and receiver. By compressing the signal prior to the modulator, a large-amplitude signal becomes closer to the smaller one, and the performance of the modulator for the whole range is improved. The combination of a compressor and an expander is called a compander. The distortion introduced by the compressor is removed by the expander after digitization. Another method to mitigate the issue is to adjust automatically the feedback signal amplitude, and to keep the ratio

between them constant. This solution requires less effort and has fewer drawbacks than the use of a compander, (companded delta modulator or SCDM).

Another method to adapt the feedback signal with the input one is to use some recent samples of the modulator output, which needs a short memory to store the samples. This method is known as instantaneously companded delta modulator (ICDM) and in comparison with the linear DM, an ICDM has a DR about 10 dB higher.

All methods to design better delta modulators briefly described in this section are suitable usually for very low frequencies depending on the technology of fabrication. Although design methods in DM and DSM are very similar, the design concerns in the above methods are far from those covered in the previous section. However, there are many other approaches in both system and circuit levels which could ease issues in some applications. In the next chapter, we focus on the issue associated with reaching high input frequencies and the proposed design is presented at system and circuit levels.

### 2.5. Conclusion

The basic theory of the oversampling modulators was introduced and design variations of the DSM and DM were briefly discussed. We discussed possible applications of the modulators for wireless receivers, where high dynamic range is needed over the bandwidth of the signal. However, with most existing architectures, the mandatory high oversampling-ratio severely limits their application to low frequencies when implemented in CMOS technology. Consequently, undersampling modulators were proposed to enable applications up to multigigahertz frequencies using standard CMOS. Aliasing that is the main issue in undersampling modulators needs to be controlled, as will be discussed in the next chapter.

# Chapter 3

# Undersampling Delta-Sigma Modulators for Radio Receivers

#### 3.1. Introduction

Advanced communication standards are demanding higher carrier frequencies, while the growing demand for portable devices creates a strong need for low power and low cost devices implementing these standards. This creates a strong need for alternative architectures and design methods. Band-pass delta sigma modulators are ideally suited for wireless receivers, where high dynamic range is needed over the bandwidth of the signal. However, with most existing architectures, the mandatory high oversampling-ratio severely limits their application to low frequencies when implemented in CMOS technology. Undersampling is an alternative to the well-known oversampling approach in delta sigma modulators. It enables applications up to multigigahertz frequencies using standard CMOS technologies by mixing a signal's carrier down to lower IF (Intermediate Frequency) and mitigating imperfections of analog mixers. However, for undersampling to be used successfully, the aliasing it causes should be controlled, which introduces variations into the design.

In this chapter, receiver's architectures as an application of  $\Delta\Sigma M$  (delta sigma modulators) are introduced. We present an LC bandpass filter as an essential RF block in receivers. Then we move on the main part of the receiver and the design consideration in

undersampling modulators is discussed and advantages and disadvantages of exiting structures are investigated. Noise analyses are presented for existing architectures and accordingly some solutions are proposed.

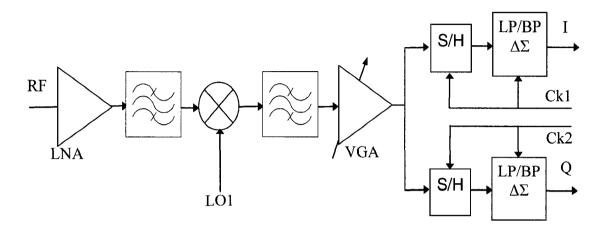

## 3.2. Delta Sigma Modulators in Receiver's Architectures

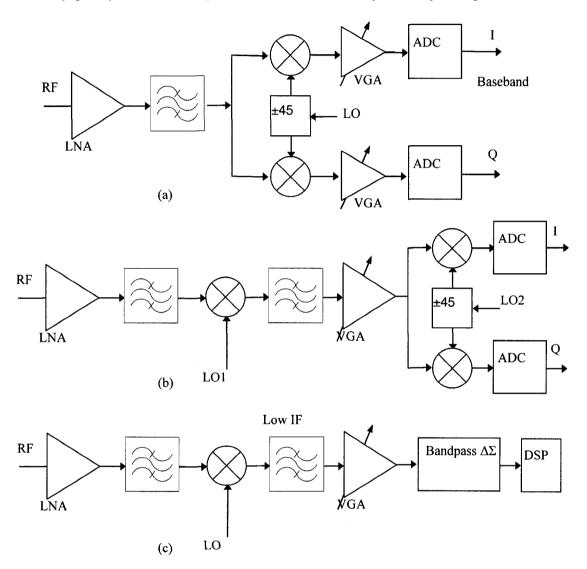

In order to clarify possibilities of  $\Delta\Sigma$ Ms in receiver's architectures, we briefly review existing receiver architectures. In the most common direct-conversion receivers, RF signals are down-converted directly to baseband using a mixer and they are filtered by a low-pass filter. In the case of I/Q modulation, the filtered signal is duplicated into two branches, and mixers driven by sine and cosine quadrature versions of a local oscillator frequency (**Figure 3-1a**) are used to recover the signal. This topology is very cost-effective and requires a small number of analog components. However, DC-offset, Flicker noise, and I/Q mismatches are among the critical issues associated with this architecture [1], [88].

It is of interest that DC-offsets due to the fact that the local oscillator (LO) and input signal have similar frequencies can be eliminated by introducing an intermediate frequency stage in super-heterodyne receivers, as shown in **Figure 3-1b**. In this architecture, after amplification of the input signal by a low noise amplifier (LNA), LO1 can convert the RF signal into an IF in the first stage, and then LO2 can bring that signal into the base band. In contrast to the direct-conversion approach, an image rejection filter

is required on the RF side of the heterodyne receiver. Image rejection and channel filtering quality define the IF parameters or the necessity of using multiple IFs.

Figure 3-1: Receiver block diagram of (a) Direct conversion, (b) Superheterodyne, (c) Superheterodyne using band-pass delta sigma modulator.

The heterodyne receivers have some known limitations, such as analog mismatches in the I/Q channels, as well as imperfections and parasitics due to the use of

analog off-chip components [89]. As the receiver is implemented by analog components, device mismatches are inevitable. Furthermore, programmability of the receiver is poor, while compatibility with multiple standards in communication systems is highly desired.

An architecture of growing popularity employs an analog to digital converter (ADC) feeding some digital signal processor (DSP), implementing the IF stage that extracts the I/Q channels (**Figure 3-1c**). Hence, demodulation of the signal is no more degraded by analog imperfections [110][110][94]. In theory, extensions to this scheme can even eliminate the analog mixer, and digitize signals directly after the LNA. The feasibility of architectures for which analog-digital conversion is performed directly on the RF signal depends on the conversion speed of ADCs and processing speed of digital signal processors (DSPs).

As current communication standards use carriers at frequencies larger than one gigahertz, direct digitization of a signal at those frequencies is extremely challenging. The challenge increases when considering the typical requirements for low power consumption, high resolution, and large bandwidth. Hence, in most cases, a low IF is still required to relax constraints on the ADC. However, when compared with a classical heterodyne receiver, the second mixer and filtering are often performed on the digital side to improve immunity to analog mismatches.

There is clearly a trade off in adopting a low IF as it imposes high Q-factor in the anti-aliasing filter, but adopting a high IF requires faster ADCs and DSPs. In addition, a Nyquist-rate ADC digitizes very wide bandwidth, which is not necessary when the signals of interest are in fact narrow-band. By contrast, band-pass delta-sigma modulators

are appealing when a narrow-band signal is modulated over an IF carrier. The main limitation for this architecture is the power consumption of the modulator that increases with the frequency of the IF signal [52][106]. Furthermore, the receiver can be enhanced and realized even without an IF stage if an undersampling band-pass  $\Delta\Sigma$ M is used after the RF filter. The undersampling process works basically as a mixer that converts the RF signal down in frequency to a digitized IF signal. This helps to keep the power dissipation of the ADC relatively low.

# 3.3. LC Bandpass Filter

An analog RF filter is an essential block in most transceivers and RF bandpass sigma-delta modulators, and its characteristics directly affect the final received signal. On-chip implementation of filters decreases performance in terms of dynamic range, power consumption, and quality factor (Q). Communication systems are, however, demanding fully integrated and programmable transceivers compatible with multiple RF standards. Active implementations of bandpass filters, Gm-C and active-inductors are usually limited to low frequencies and require high power [40]. Q-enhanced LC technique is the most appropriate method adopted by IC designers [26]. A summary of representative published results is given in **Table 3.1**.

Table 3.1: Performance summary of RF filters in the literature.

| Reference<br>Parameter | [26]           | [63]             | [70]          | [54]             | [6]            |

|------------------------|----------------|------------------|---------------|------------------|----------------|

| Filter order           | 2              | 4                | 4             | 2                | 2              |

| f <sub>O</sub> (GHz)   | 2.1            | 1.88             | 1.8           | 0.9              | 1.04           |

| Q                      | 20-170         | 5-20             | 22.5          | 45               | 5-180          |

| Vdd (V)                | 1.3            | 2.7              | 2.7           | 3                | 2.7            |

| Power consumption (mW) | 5.2            | 48.6ª            | 43.2          | 39               | 11.4-<br>15.5  |

| DR (dB)                | 34             | 63               | 42            | 78               | 80             |

| Technology             | 0.35μm<br>CMOS | 0.25µm<br>BiCMOS | 0.5μm<br>CMOS | Not<br>available | 0.35μm<br>CMOS |

a Excluding automatic tuning.

Dynamic range and power consumption generally decrease with the supply voltage. However, high Q filters are desired while tuning of Q and center frequency is still an open problem. On-chip automatic tuning using master-slave method has been investigated in [63]. This technique doubles the power and silicon area requirements. On-chip transformers were employed in [63][55] to get a fourth-order LC filter while poles of each stage of the filter never meet each other due to the loading effect of the transformer. Unfortunately the pass-band characteristics are variable unless the coupling factor, k, is as small as 0.005 - 0.04. This choice severely reduces the filter gain and increases noise and distortion due to coupling with bond-wires. Moreover, the coupled inductors must be sufficiently separated to produce low k, which consumes more area. Also, on-chip inductors suffer from high series resistance in CMOS technology and their Q-factor is usually very low. In addition, maximum Q may happen at a frequency higher than

desired. Optimization of Q at operating frequency requires more die area which leads to higher fabrication cost.

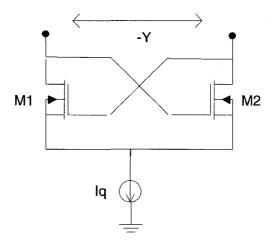

In a LC tank, energy is lost due to series resistance of inductor and eddy currents in the substrate. A loss compensation mechanism is necessary to increase the quality of the tank. This can be provided by a negative resistance in series with the inductor's resistance. As shown in **Figure 3-2**, positive feedback by two transistors presents a negative conductance equals to -gm/2. This leads to frequency dependent inductance values [98], but resulting distortion in narrow-band signals is often negligible. Moreover, this negative resistance can be used in many configurations. When positive feedback is used as a negative resistance, large swings become another source of distortion.

Figure 3-2: Negative conductance (-Y) generator.

If output swing is large enough, the value of such negative resistance varies and provokes distortion. Also, when the DC biasing makes the circuit operation close to Vdd [26], the dynamic range decreases significantly. In the proposed filter, the output DC

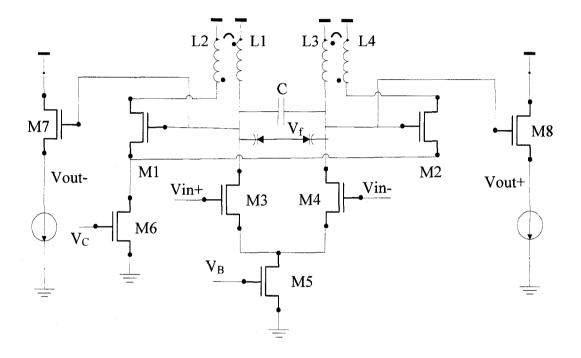

voltage is set around Vdd/2. Employing a transformer allows adjusting the output DC voltage with a DC current. Hence, a high dynamic range is expected from a low supply voltage. **Figure 3-3**(a) shows the proposed Q-enhanced LC bandpass filter.

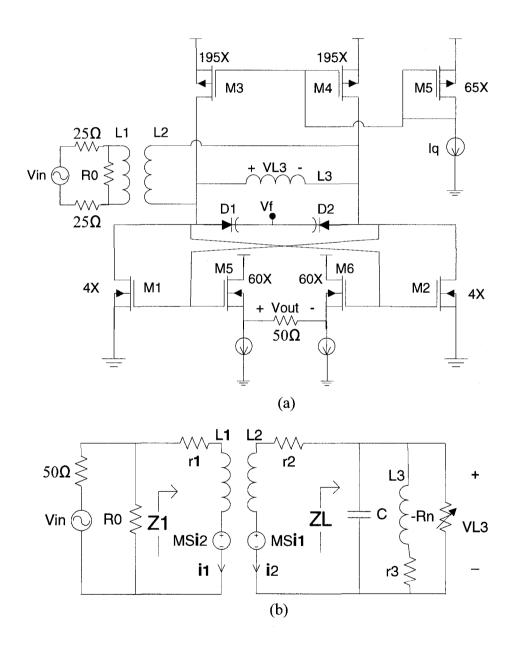

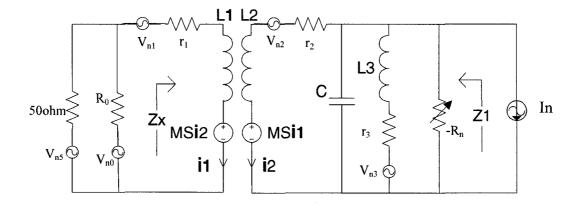

Figure 3-3: Proposed bandpass filter: (a) Circuit implementation. (b) Model of filter.

The input signal is fed to the filter using an on-chip transformer. The filter's center frequency is tuned by changing the varactors' differential capacitance. Negative resistance due to NMOS transistors helps to increase the Q-factor of the filter. DC voltage of output signals is approximately set to Vdd/2 by a DC current, which flows through NMOS transistors (M1 and M2). Output voltage swing increases to maximum possible value at this operating point. While minimum output swing is limited by the system's noise floor, increasing the output swing improves the dynamic range of the filter. The output signal can be buffered to allow driving a  $50\Omega$  load using M5 and M6. In our application, no buffer is necessary because an integrated comparator will be driven by this filter when embedded in its target application.

Nevertheless, effects of output matching and buffer transistors were considered in the simulations. High DC currents in most RF circuits are necessary to obtain good linearity. In this filter, the input stage consumes no DC current; consequently, the corresponding power consumption is low. An AC Model of the proposed circuit is shown in **Figure 3-3**(b). Series resistances in the transformer are significant due to on-chip implementation of inductors. Although low-Q varactors decrease the main performances of the filter, parasitics of the inductors are dominant. The transfer function of this filter is derived as:

$$H(s) = \frac{V_{L3}}{V_{in}} = \frac{Ms}{(r_1 + L_1 s) + \frac{(r_1 + L_1 s)(r_2 + L_2 s)}{Z_L} - \frac{M^2 s^2}{Z_L}}$$

(3-1)

In which,  $Z_L$  is expressed by:

$$Z_{L} = \frac{1}{Cs - \frac{1}{R_{n}} + \frac{1}{r_{3} + L_{3}s}}$$

(3-2)

where L1 and L2 are inductances of primary and secondary transformers respectively, M is the mutual inductance between them, and -Rn is the negative resistance due to the positive feedback. Therefore, the transfer function of the filter can be rewritten as:

$$H(s) = \frac{\frac{1}{k_0 k_2}}{L_3 C s^2 + (r_3 C - \frac{L_3}{Rn}) s + 1 - \frac{r_3}{Rn} + \frac{k_1}{k_0 k_2}}$$

(3-3)

where,

$$k_0 = \frac{(r_1 + L_1 s)(r_2 + L_2 s)}{M^2 s^2} - 1 \tag{3-4}$$

$$k_1 = \frac{\left(r_1 + L_1 s\right)}{M s} \tag{3-5}$$

$$k_2 = \frac{Ms}{(r_3 + L_3 s)} ag{3-6}$$

By choosing proper values for  $L_1$  and  $L_2$ , the transfer function of the filter shows second-order properties. Magnitudes of  $k_0$ ,  $k_1$  and  $k_2$  converge to constant values at high frequencies. Frequency dependence of series resistances may increase the order of the system in equation (3.3) for frequencies higher than the operating frequency. Center frequency of the filter can be derived as

$$\omega_0^2 = \frac{1 - \frac{r_3}{R_n} + \frac{k_1}{k_0 k_2}}{L_3 C} \tag{3-7}$$

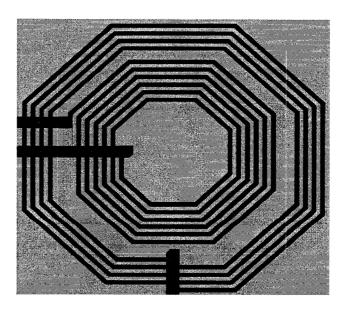

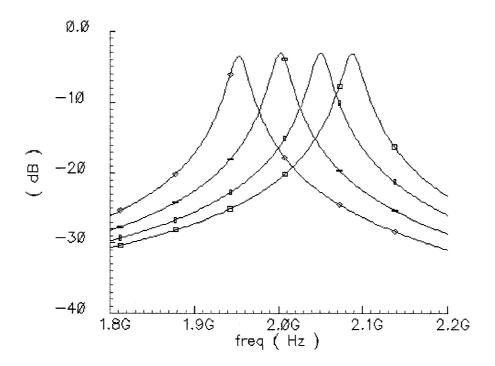

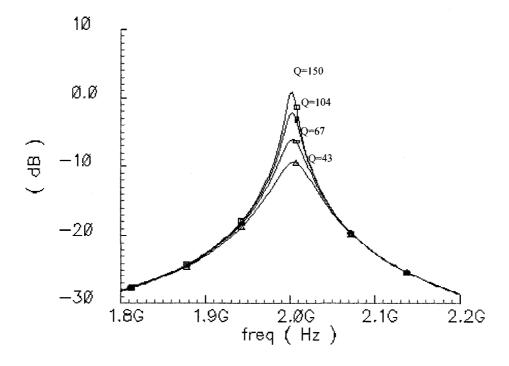

From equation (3.3), a relation between M and the maximum of H(s) can be found by  $\partial H/\partial M=0$ , which guides toward a suitable value for the coupling factor of the transformer. Numerical analysis shows the filter has the highest Q at coupling factor, k, equal to 0.45, which can be provided by a compact transformer structure. In addition, weak couplings with other elements are negligible at this value of k. Circuit level simulations also confirm filter gain is the highest at this point. **Figure 3-4** shows a transformer structure, designed with ASITIC [78]. Outer diameter of the primary inductor is 350 µm, and the secondary is laid out inside with a diameter of 240 µm. All inductors use the last layer of metal with 5 µm width. There is also 5 µm distance between lines. A BFMOAT ground plane has been used to obtain a low noise implementation.

Figure 3-4: On-chip transformer structure.

Input impedance of transformer, Z1, is given by

$$Z_1 = r_1 + L_1 s - \frac{M^2 s^2}{r_2 + L_2 s + Z_L}$$

(3-8)