**Titre:** Design and implementation of a high resolution, multi-hit time-to-digital converter (TDC) on FPGA

Title: Design and implementation of a high resolution, multi-hit time-to-digital converter (TDC) on FPGA

**Auteur:** Amir Mohammad Amiri

Author:

**Date:** 2007

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Amiri, A. M. (2007). Design and implementation of a high resolution, multi-hit time-to-digital converter (TDC) on FPGA [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7955/>

Citation:

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7955/>

PolyPublie URL:

**Directeurs de recherche:** Abdelhakim Khouas, & Mounir Boukadoum

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

**DESIGN AND IMPLEMENTATION OF

A HIGH RESOLUTION, MULTI-HIT TIME-TO-DIGITAL CONVERTER (TDC)

ON FPGA**

**AMIR MOHAMMAD AMIRI**

**DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

**MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME MAÎTRISE ÈS SCIENCES APPLIQUÉES**

**GÉNIE ÉLECTRIQUE**

**AVRIL 2007**

Library and

Archives Canada

Bibliothèque et

Archives Canada

Published Heritage

Branch

Direction du

Patrimoine de l'édition

395 Wellington Street

Ottawa ON K1A 0N4

Canada

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-29210-5

*Our file* *Notre référence*

ISBN: 978-0-494-29210-5

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

**UNIVERSITÉ DE MONTRÉAL**

**ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

Ce mémoire intitulé :

**DESIGN AND IMPLEMENTATION OF

A HIGH RESOLUTION, MULTI-HIT TIME-TO-DIGITAL CONVERTER (TDC)

ON FPGA**

Présenté par: AMIRI, Amir Mohammad

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. DAVID Jean-Pierre, Ph.D., président

M. KHOUAS Abdelhakim, Ph.D., membre et Directeur

M. BOUKADOUM Mounir, Ph.D., membre et Codirecteur

M. LANGLOIS Pierre, Ph.D., Membre

To My Parents

& All Family Members and Friends

## ACKNOWLEDGEMENT

I would like to say special thanks and offer special gratitude to professors Mounir Boukadoum and Abdelhakim Khouas for their excellent technical and moral support and guidance as my supervisors throughout the time that this research project was being carried out.

I would like to also pay my gratitude and appreciations to my parents, and all family members and friends that have been of enormous help for the duration of this research work. My success in carrying out and completion of this project would certainly not have been possible without their generous support.

I would like to also thank École Polytechnique de Montréal, the GRM (Groupe de Recherche en Microélectronique), L'université du Québec à Montréal (UQÀM), the Regroupement Stratégique en Microsystèmes du Québec (RESMIQ), and the National Science and Engineering Research Council of Canada (NSERC) for making it possible for me to carry out this research activity.

Further special appreciations are also offered to my friend, Mr. Jacque L. Athow, for his support in our mutual technical discussions related to FPGA architectures and associated issues.

And finally, my special thanks and appreciations go to all the staff members of the Department of Electrical Engineering, and the GRM personnel for their excellent assistance and services in providing an excellent working environment for research students.

## RESUMÉ

La notion et la mesure du temps ont leurs significations importantes dans divers domaines de la science et de l'ingénierie. Un intervalle de temps est défini comme le temps écoulé entre les occurrences de deux événements physiques, soit le retard de propagation d'un bloc logique dans les circuits électroniques numériques, ou les fluctuations entre les périodes consécutives d'un signal périodique tel que l'horloge du système, ou bien la distance dans le temps entre deux particules adjacentes libérées du point de collision dans les expériences de temps de vol (Time Of Flight). Un Convertisseur temps-numérique (Time-to-Digital Converter ou TDC) est un circuit électronique conçu pour mesurer le délai entre deux événements temporels. En général, un circuit TDC se compose d'un interpolateur grossier notamment un compteur binaire avec une résolution de mesure égale à la période de l'horloge de référence ( $T_{REF}$ ) du système et d'un autre interpolateur divisant  $T_{REF}$  en plusieurs plus petits pas. Les différents paramètres caractéristiques d'un circuit TDC incluent la résolution de la mesure, la précision/exactitude des mesures, la gamme dynamique, les erreurs de non linéarité, le temps mort, ainsi que la *réolution paire d'impulsion* (Pulse-Pair-Resolution ou PPR) pour les circuits TDC capable de mesurer plus qu'un intervalle de temps dans une seule phase de mesure. Les méthodes d'interpolation du temps comprennent des architectures analogiques et numériques.

Ce projet de recherche propose un circuit TDC basé sur un nouvel interpolateur de temps utilisant le principe de Vernier afin d'atteindre une haute résolution de mesure. L'architecture de l'interpolator est un tableau de lignes à délais de Vernier (VDL) utilisant des éléments tampon et des bascules à verrouillage D (*D-Latch*) comme élément à délai des lignes de propagation. Le tableau de lignes à délais peut aussi être vu comme une matrice à cellules de retard Vernier avec l'interconnexion entre les rangs successifs accomplis par les premières cellules de retard de chacune des lignes. Toutes les lignes du tableau partagent une horloge de référence commune. La matrice de retard mesure la distance dans le temps entre le front montant du signal de donnée et celui de l'horloge

appliqués aux entrées respectives de la matrice. L'interconnexion verticale de la matrice fournit un chemin de propagation avec le plus grand pas temporel  $\tau_Y$  tandis que la résolution élevée  $\tau_X$  de mesure est atteinte par la propagation horizontale à travers les lignes de retard de Vernier. Le circuit TDC mesure un intervalle de temps entre deux impulsions entrantes en prenant la différence des temps d'arrivée correspondants par rapport à un point de référence. En incorporant deux matrices de retard fonctionnant en parallèle dans les deux phases d'une période d'horloge, le temps morts du circuit est amélioré. Ainsi, le temps de mesure/interpolation du circuit est minimisé grâce au chemin de propagation vertical. Le TDC proposé est aussi capable de mesurer plus qu'un intervalle de temps dans une seule phase de mesure. Pour exploiter la portabilité et les aspects faible coût de conception et de fabrication, le prototype du circuit TDC a été implémenté sur la plateforme peu coûteuse de SPARTAN<sup>TM</sup>-3 FPGA de la famille SPARTAN<sup>TM</sup> de XILINX. En simulation, la résolution de mesure atteinte est de  $\tau_X = 113\text{ps}$ , alors que les résultats expérimentaux donnent  $\tau_X \sim 75\text{ps}$ , avec un PPR de l'ordre de 7.5ns. La déviation moyenne d'un intervalle mesuré par rapport à sa valeur idéale est de l'ordre de  $\sim 1.5\%$  pour les intervalles plus grands que 12.0ns. Cependant, cette déviation augmente à 3.5 % pour les intervalles dont les longueurs sont inférieurs à 12.0ns. Les sources principales d'erreur de mesure sont attribuées à l'existence du biais sur les lignes de l'horloge, à des variations dans les paramètres d'horloge de référence telles que les fluctuations périodiques (Jitter), l'erreur de phase et du cycle, la non uniformité du retard des cellules dû à la non uniformité de l'interconnexion des cellules adjacentes, ainsi qu'aux problèmes de mésappariement entre les éléments logiques identiques sur la surface du FPGA.

## ABSTRACT

The notion of timing and time measurement has its significance in many areas of science and engineering. A time interval is defined as the time elapsed between occurrences of two physical events, be it the propagation delay of a logic block in digital electronic circuits from an input to the output, the jitter in a periodic signal such as the system clock, or the distance in time between two or more adjacent particles liberated from the collision point in Time-Of-Flight experiments. A Time-to-Digital Converter (TDC), also referred as Time Interval Meter (TIM), is the electronic circuit designed to measure the time elapsed between two timing events/pulses. A TDC circuit usually consists of two time interpolating modules namely the fine time interpolator module used to slice the period of the reference clock into smaller time steps, and the coarse interpolator (binary counter) used to achieve coarse measurement of time with a resolution equal to the reference clock period. The various characteristic parameters of a TDC circuit include the resolution of the measurement, the precision/accuracy of the measurements, the maximum measurable interval (dynamic range), non-linearity of the conversion process, and the dead time. For multi-hit TDC circuits capable of measuring more than one time interval sequentially, pulse pair resolution is another parameter of importance.

Over the years, a lot of research efforts have been devoted to come up with new or more improved TDC structures. The many TDC solutions proposed by researchers involve design methods that vary from the early analog-based solutions to the recent partial or fully digital ones. The time-to-amplitude conversion and the time interval stretching are the famous analog-based time interpolation methods used in many TDC circuits. On the digital side, the interpolation solutions are mainly achieved by means of delay lines with resolutions proportional to single gate delay or the variants of delay lines such as the Vernier principle with sub-gate delay resolutions. Other complex structures with improved characteristics have also been proposed.

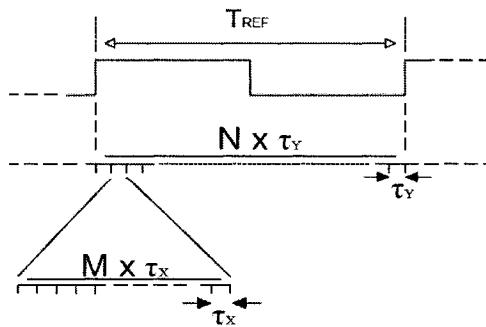

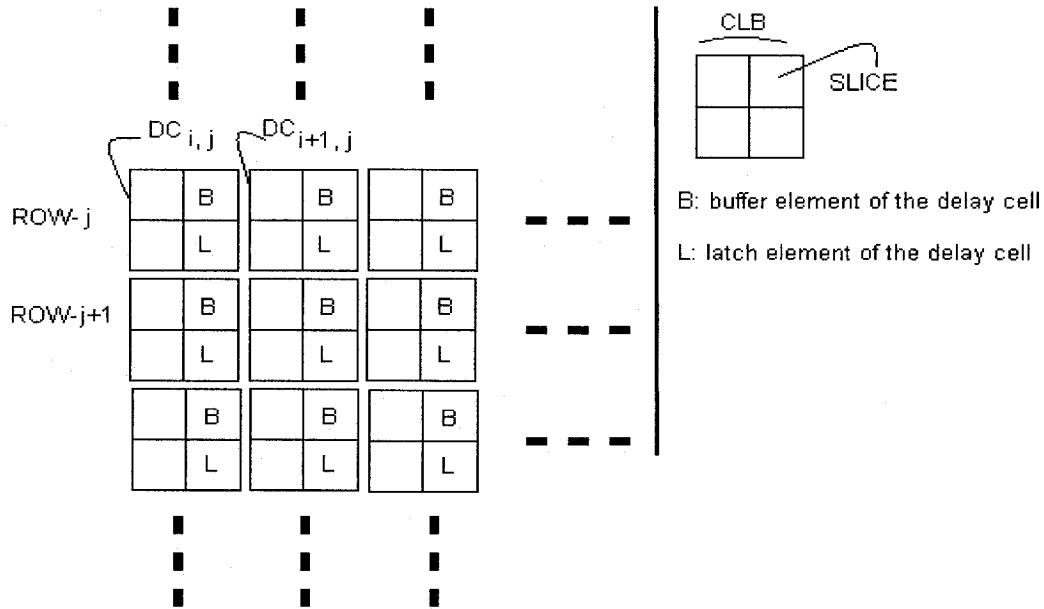

The proposed TDC circuit in this research work is based on a new time interpolator utilizing the Vernier principle in order to achieve the high measurement resolution. The time interpolator is an array of Vernier delay lines (VDL), also seen as matrix of Vernier delay cells, with the interconnection between successive rows achieved through the first delay cells of each line with a common reference clock line shared among all. The delay matrix measures the distance in time between the rising edges of the data and the subsequent clock signals applied at the respective data and clock inputs of the matrix. The matrix structure breaks this interval into two-level time bins of  $\tau_Y = t_L$  and  $\tau_X = t_L - t_B$  with  $t_B$  and  $t_L$  as the propagation delays of the buffer and latch elements of the matrix delay cells. The vertical interconnection provides a propagation path with larger time bin  $\tau_Y$  whereas the single-shot measurement resolution  $\tau_X$  is achieved by horizontal propagation throughout the Vernier delay lines. The TDC circuit measures an interval of time between two incoming pulses by taking the difference in corresponding arrival times with respect to some reference point.

The TDC circuit is implemented on a low-cost SPARTAN-3 FPGA from the SPARTAN<sup>TM</sup> family by XILINX in an attempt to exploit the recent advances in programmable logic devices. The measurement resolution attained is  $\tau_X = 113\text{ps}$  in simulation, whereas the experimental results give  $\tau_X \sim 75\text{ps}$ . The TDC circuit is capable of measuring multiple sequential intervals with a PPR  $\sim 7.5$  ns. The average deviation of a measured time interval  $T$  from its ideal value is  $\sim 1.5\%$  for intervals larger than 12.0 ns and 3.5% for intervals with ideal lengths less than 12.0ns. The main sources of measurement error are attributed to existence of clock skew on clock lines in the delay matrices, variations in reference clock parameters in forms of jitter, phase and duty cycle, non-uniformity of cell delays due to existence of non-uniform routings, and the on-chip delay mismatch among identical logic elements on FPGA surface.

## CONDENSÉ EN FRANÇAIS

### 0.1 Introduction

Un convertisseur temps-numérique (Time-to-Digital Converter ou TDC) est un circuit électronique conçu pour mesurer le délai entre deux événements (impulsions) détectés à l'entrée du TDC. En utilisant un circuit TDC, l'intervalle de temps est converti en un mot binaire pour le traitement numérique. Avec l'évolution rapide du monde numérique, comme plusieurs systèmes électroniques, le circuit TDC a migré d'une implémentation analogique vers une implémentation numérique.

Les applications nécessitant la mesure d'intervalles de temps se retrouvent dans divers domaines scientifiques et d'ingénierie. Dans un circuit électronique, l'intervalle de temps à mesurer pourrait représenter le retard de propagation d'un bloc logique entre le front montant/descendant d'un signal de test à l'entrée du circuit et le front correspondant à la sortie. De même, les fluctuations entre les périodes consécutives (Jitter) d'un signal périodique tel que l'horloge d'un système est un autre exemple concret pour lequel une mesure d'intervalle est utile. Dans les expériences de temps de vol (Time-of-Flight) et de spectrométrie massive, la distance dans le temps entre deux particules adjacentes déchargées du point de collision est mesurée pour trouver la masse moléculaire des particules relâchées. Dans l'instrumentation, les oscilloscopes numériques et les analyseurs logiques à haute résolution exigent la mesure précise d'intervalles de temps pour échantillonner les formes d'onde numériques. Parmi les autres applications de mesure d'intervalle de temps, on retrouve la spectroscopie de vie de positron et les appareils de viseur laser utilisés pour trouver la distance entre l'objet et le point de référence (position d'appareil), où la mesure du temps est un des éléments clés du système général.

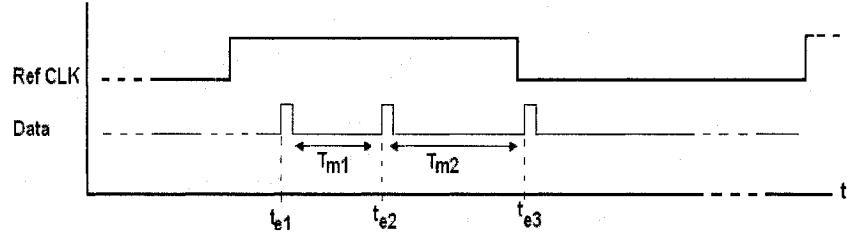

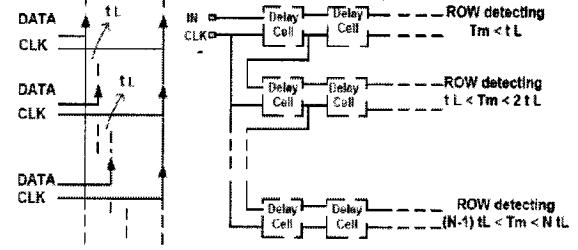

Un intervalle de temps à mesurer ( $T_m$ ) est défini entre les fronts montants de deux impulsions ordinairement nommées comme START et STOP. Étant plus grand que la

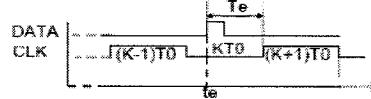

période d'horloge de référence,  $T_m$  peut être divisé en sous intervalles fins et grossiers. La section grossière de  $T_m$  est divisible par la période d'horloge du système, donc mesurable par un compteur avec une résolution de  $T_{REF\_CLK}$ . Cependant, pour mesurer les sections fines de  $T_m$ , il est nécessaire d'interpoler l'horloge du système en divisant la période d'horloge du système en plusieurs plus petits pas (voir Figure 1.2).

Les diverses métriques de performance d'un circuit TDC incluent la *résolution de mesure*, la *précision de mesure*, la *gamme dynamique*, le *temps de mesure*, le *temps mort*, le *multi-hit*, la *résolution paire d'impulsion* (pulse-pair resolution ou *PPR*), et la *non linéarité de conversion*. La *résolution de mesure* est le plus petit pas de temps qui peut être discriminé pour une mesure de temps, elle représente la finesse ou la granularité de la mesure. La *précision de mesure* représente le degré d'exactitude de la valeur mesurée par rapport à la véritable valeur. La *gamme dynamique* est l'intervalle maximal de temps mesurable par un circuit TDC. Le *temps de conversion/mesure* peut être défini comme le temps de traitement de l'intervalle à mesurer, c'est-à-dire de la détection de l'impulsion STOP jusqu'à l'obtention du mot binaire correspondant. L'appellation *temps de mesure* est également utilisée. Le *temps mort* est l'intervalle de temps le plus court qu'un TDC peut exiger entre la fin d'une mesure et la possibilité de démarrer la mesure suivante. Le *multi-hit* est la capacité d'un circuit de TDC de mesurer plus qu'un intervalle de temps dans une seule phase de mesure sans retourner à un état initial. La *résolution paire d'impulsion (PPR)* est la distance minimale dans le temps entre deux impulsions reçues qui peut être mesurée par un circuit TDC à multi-hit. La déviation de la réponse du convertisseur par rapport aux valeurs prévues est due aux erreurs de non linéarité intégrale et différentielle.

En prenant en considération les diverses caractéristiques des circuits TDC, le travail actuel vise l'amélioration de la résolution de mesure, du temps mort, et de la capacité de multi-hit, et une résolution paire d'impulsion (*PPR*) raisonnable. De plus, inspirés par les avancements récents dans les circuits logiques programmables tels que les FPGA, nous avons choisi de nous concentrer sur la portabilité et sur les aspects faible coût de

conception et de fabrication. Nous avons donc ciblé la technologie FPGA en implémentant notre prototype sur la plateforme peu coûteuse de SPARTAN<sup>TM</sup>-3 FPGA de la famille SPARTAN<sup>TM</sup> de XILINX.

## 0.2 Revue de littérature des méthodes d'interpolation de temps existantes

Au cours des dernières années, des efforts de recherche énormes ont été consentis dans le but de proposer des structures nouvelles et plus robustes pour les méthodes de mesure des intervalles de temps. L'objectif est de surmonter les diverses limitations affectant le comportement des circuits existants. Les solutions proposées comprennent des méthodes de conception analogiques et numériques.

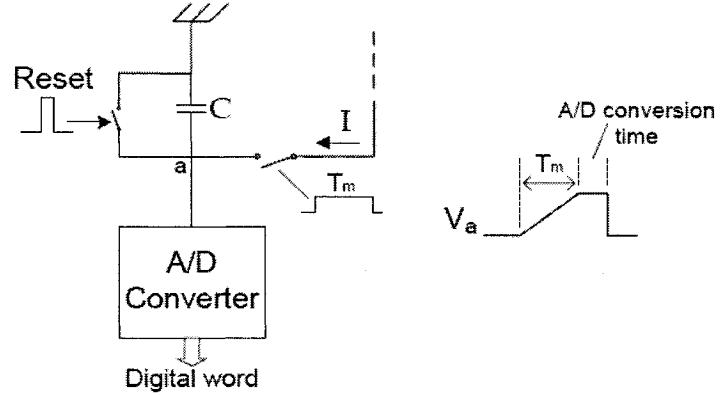

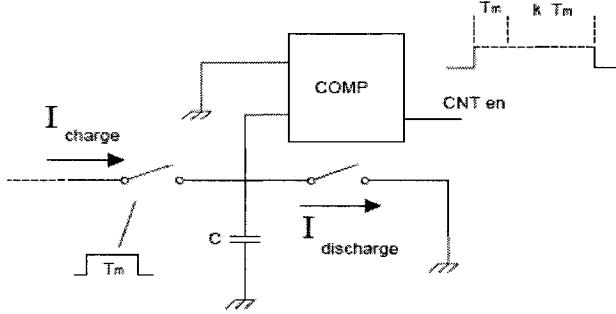

Les fameuses techniques d'interpolation analogique incluent la conversion temp-à-amplitude (Time-to-Amplitude or TAC) et la méthode d'allongement d'intervalle (Time Interval Stretching or TIS). Avec la technique du TAC, l'intervalle de temps à mesurer ( $T_m$ ) est transformé en une amplitude de tension  $V$  par chargement/déchargement d'un condensateur à l'aide d'un courant constant  $I$  pour une durée de  $T_m$ . Par la suite,  $V$  est converti en un mot binaire numérique utilisant un convertisseur analogique-numérique (CAN). Avec cette méthode, l'intervalle de temps à mesurer dépend linéairement de l'amplitude de la tension aux bornes du condensateur. La tension  $V$  aux bornes du condensateur devrait être maintenue jusqu'à ce que le mot binaire correspondant soit obtenu à la sortie du CAN. Le temps de conversion du TAC dépend principalement du temps requis par le CAN pour convertir la tension  $V$ , alors que la résolution de mesure du TAC dépend de la résolution de conversion du CAN utilisé.

TIS est une autre méthode analogique d'interpolation d'intervalle de temps. Ici, le petit pas de mesure est obtenu en convertissant  $T_m$  en un intervalle plus grand  $T$  donné par  $T = T_m + T_{str}$ . Cet intervalle est obtenu en additionnant  $T_m$  avec une version tendue de  $T_m$  par un facteur  $k$  ( $T_{str} = kT_m$ ). Par la suite,  $T$  peut être mesuré par un compteur avec une

horloge de fréquence  $f_0 = 1/T_0$  menant à  $T = T_m + T_{str} = (k + 1) T_m = N T_0$ . Donc, l'intervalle  $T_m$  à mesurer peut être calculé comme:  $T_m = NT_0 / (k + 1)$  avec une résolution de mesure de  $T_0 / (k + 1)$ . Avec la méthode TIS, une résolution de mesure de l'ordre de 10 ps a été rapportée [11]. Malgré sa haute résolution de mesure, TIS souffre d'un temps de conversion élevé dû au temps d'allongement  $kT_m$ .

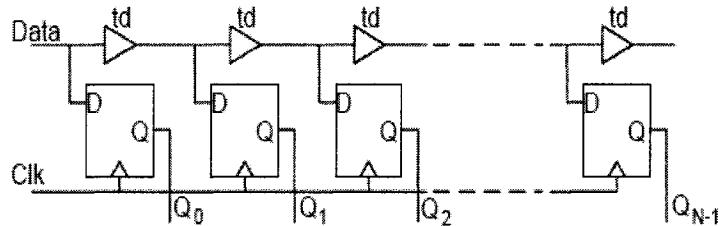

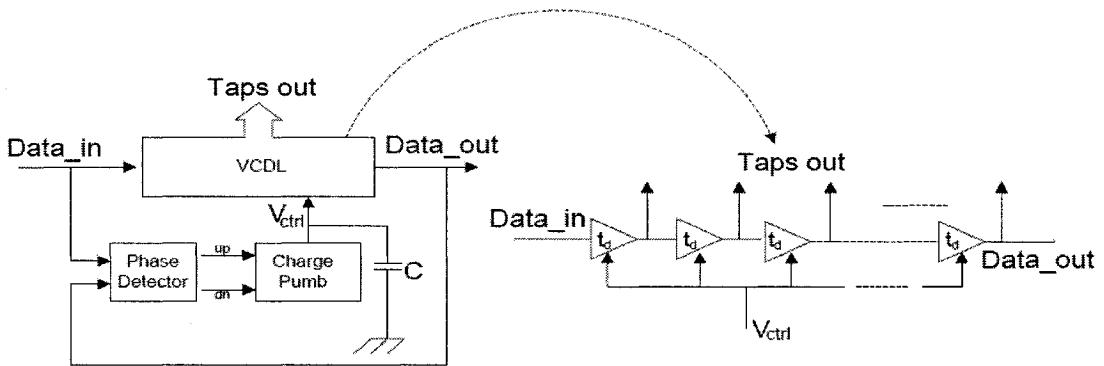

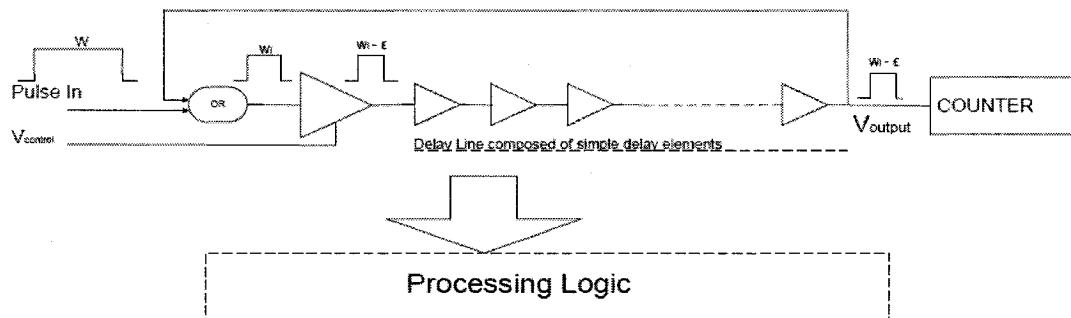

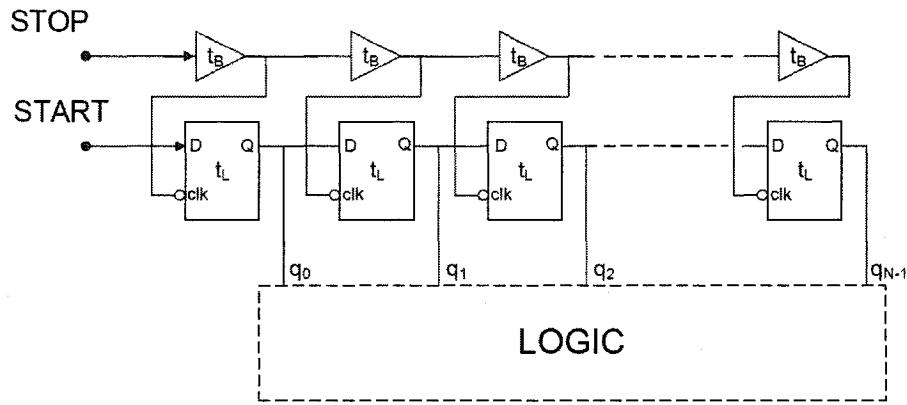

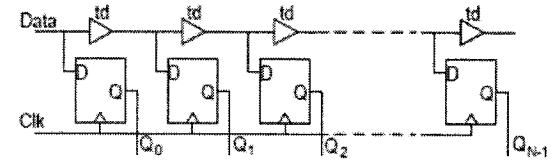

Dans le domaine numérique, il existe plusieurs solutions TDC incorporant différentes méthodes d'interpolation de temps. Une des techniques numériques les plus simples pour atteindre une grande résolution est l'interpolateur de ligne de retard qui utilise une chaîne d'éléments de retard [17][18] (voir Figure 2.3). Conduite par un signal  $s$ , une chaîne de retard à  $N$ -éléments avec un délai de propagation  $t_d$  pour chacun des éléments de retard retardera le front principal de  $s$  par  $t_d$  lorsque le signal traversera la chaîne. En calculant le nombre d'étages propagés par  $s$ , l'intervalle ( $T_m$ ) peut être mesuré avec une résolution de mesure de  $t_d$ . La gamme dynamique pour un interpolateur de ligne de retard dépend du nombre d'éléments de retard utilisés dans la chaîne. Cependant, la gamme dynamique peut être augmentée à l'aide d'un compteur binaire incorporé dans le système en parallèle. En remplaçant la chaîne à délai par une chaîne à délai d'un DLL (Delay-Locked-Loop), une interpolation plus efficace est obtenue [20][21][22]. Le DLL peut être verrouillé à un retard fixe avec les subdivisions égales au délai du retard configurable  $t_d$  des éléments de la chaîne à délai du DLL. L'utilisation d'un DLL pour l'interpolation de temps est une méthode efficace du point de vue de la stabilité, cependant, la résolution de mesure est toujours limitée au retard minimum d'un élément de délai.

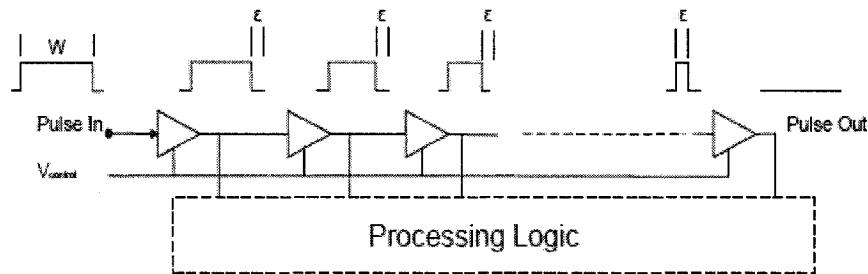

Pulse Shrinking (PS) est une autre technique utilisée dans la mesure d'intervalle de temps [17][23][24][25][26]. Elle consiste à mesurer une largeur  $W$  d'une impulsion par la réduction successive de  $W$  par une valeur constante  $\varepsilon$ , jusqu'à la disparition complète de l'impulsion lorsque elle traverse la chaîne d'éléments à délai (voir Figure 2.6). Les éléments de retard de la ligne à délai sont contrôlés par une tension avec les temps de montée et de descente variables qui raccourciront la largeur d'une impulsion d'entrée au

noeud de la sortie par la valeur constante de  $\varepsilon$  (voir Figure 2.8). De cette façon, la largeur d'impulsion est mesurée avec une résolution de mesure égale à la valeur de réduction  $\varepsilon$ . Le rétrécissement de l'impulsion dans la mesure d'intervalle de temps impliquant les impulsions START et STOP exige une conversion à deux niveaux. Premièrement, l'intervalle de temps  $T_m$  est transformé en une largeur  $W$  d'impulsion suivie d'une conversion subséquente de  $W$  dans le mot binaire. Bien que la résolution de mesure des solutions TDC précédentes à base de PS était dans la gamme de centaines de picosecondes [17][25], les nouvelles méthodes améliorées de réduction d'impulsion (Cyclic Pulse Shrinking) ont atteint des résolutions de mesure dans la gamme de 20 ps à 70 ps [23][24][26].

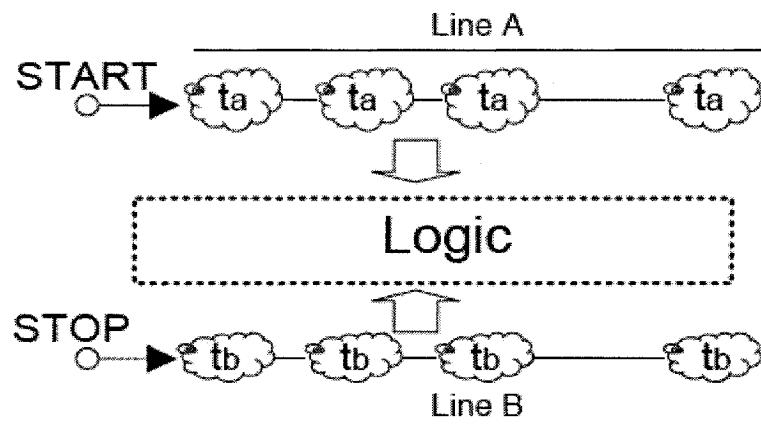

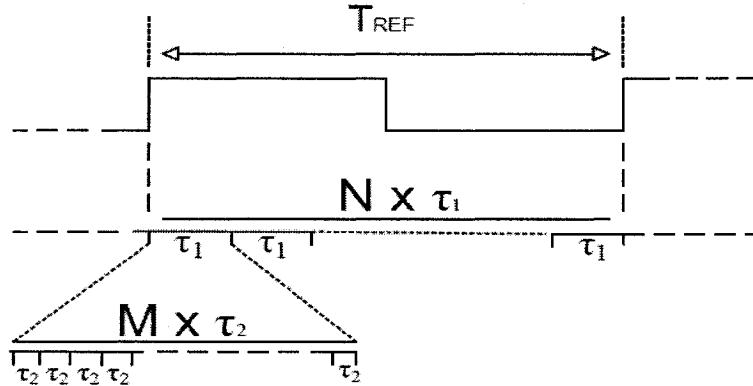

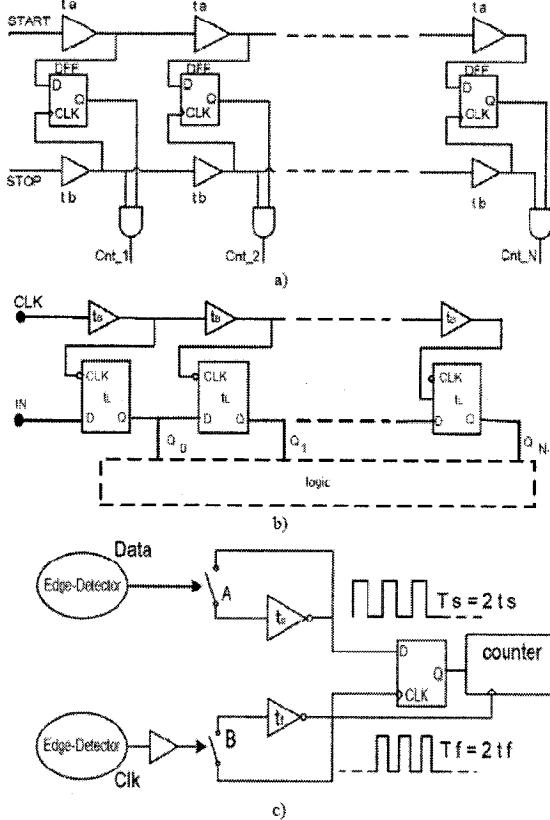

Avec les avancements récents dans la technologie rendant des systèmes fonctionnels à haute fréquence, les circuits TDC à basse résolution, notamment les TDC utilisant des chaînes à délai qui ont une résolution de mesure de l'ordre du délai des éléments de délai, pratiquement inutilisable. De nouvelles méthodes de conception visant à atteindre des résolutions de temps beaucoup plus élevées devaient être développées. Une des méthodes largement utilisées pour atteindre une résolution plus élevée est basée sur le principe de Vernier [27] (voir Figure 2.9). Le petit pas de temps par le principe de Vernier est atteint par une petite différence entre les périodes de deux signaux périodiques produits par deux oscillateurs en anneau (Ring Oscillator). Les deux oscillateurs sont déclenchés par les signaux de START et STOP et produisent des signaux périodiques de périodes  $T_1$  et  $T_2$ , respectivement avec  $T_1 > T_2$ . Les deux oscillateurs sont remis à l'état initial dès que la coïncidence entre les fronts de START et STOP est détectée à l'aide d'un circuit de détection de front (Edge Detector). L'intervalle  $T_m = t_{START} - t_{STOP}$  est mesuré en considérant la différence entre le nombre cumulatif des périodes produites par les deux oscillateurs, comptées par leurs compteurs respectifs. De cette façon, la plus petite unité de temps qui peut être discriminée pour trouver  $T_m$  est  $t_r = T_1 - T_2$  [11].

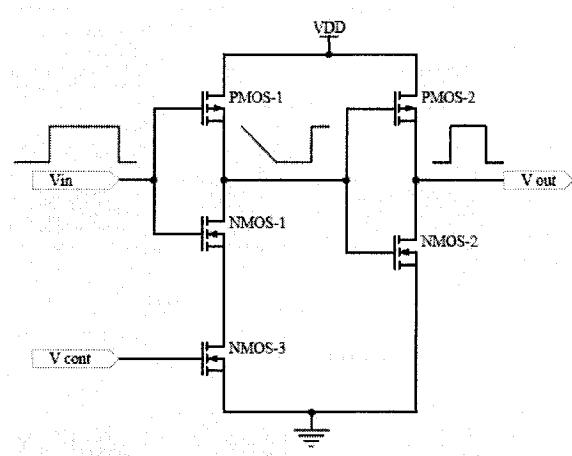

D'autres variantes de la méthode de Vernier permettent d'atteindre une résolution de mesure élevée en exploitant la différence dans les délais de propagation des éléments

logiques [27][29]. Pour de telles méthodes, les signaux concernés sont propagés à travers deux chaînes à délai différentes  $A$  et  $B$  contenant des éléments logiques identiques. Dépendamment de la méthode de conception, les chaînes  $A$  et  $B$  peuvent être composées d'éléments tampon, de bascules, ou d'autres éléments logiques. Par défaut, les délais des éléments dans une des deux chaînes, par exemple  $A$ , sont légèrement plus élevés que ceux de l'autre chaîne  $B$ . La plus petite unité de temps discriminable est donnée par la différence de retard  $\Delta t = t_a - t_b$ , où  $t_a$  et  $t_b$  sont les délais de propagation des éléments dans les lignes  $A$  et  $B$  respectivement.

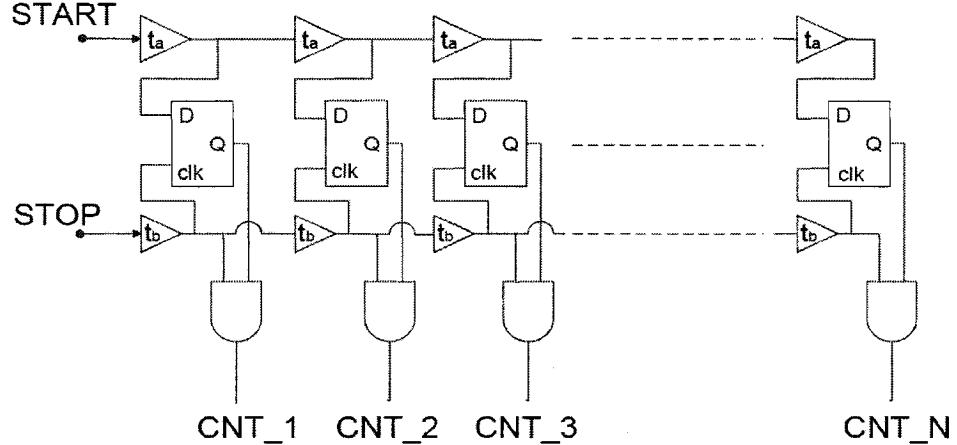

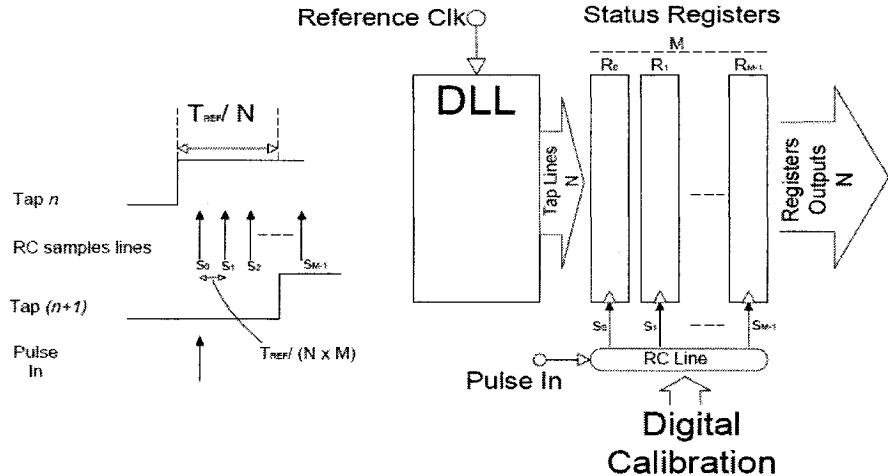

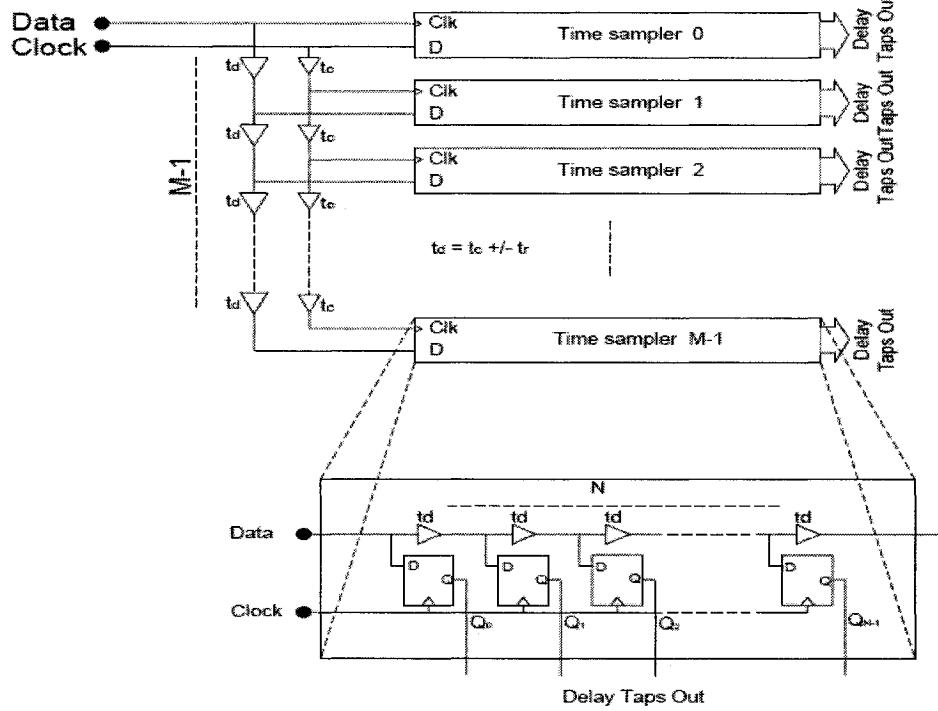

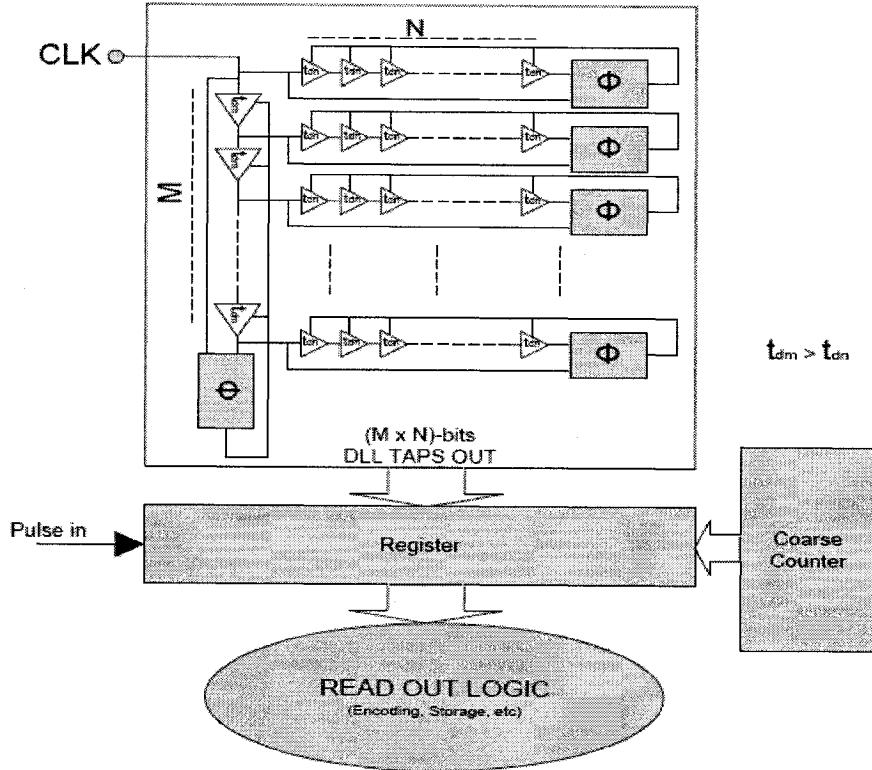

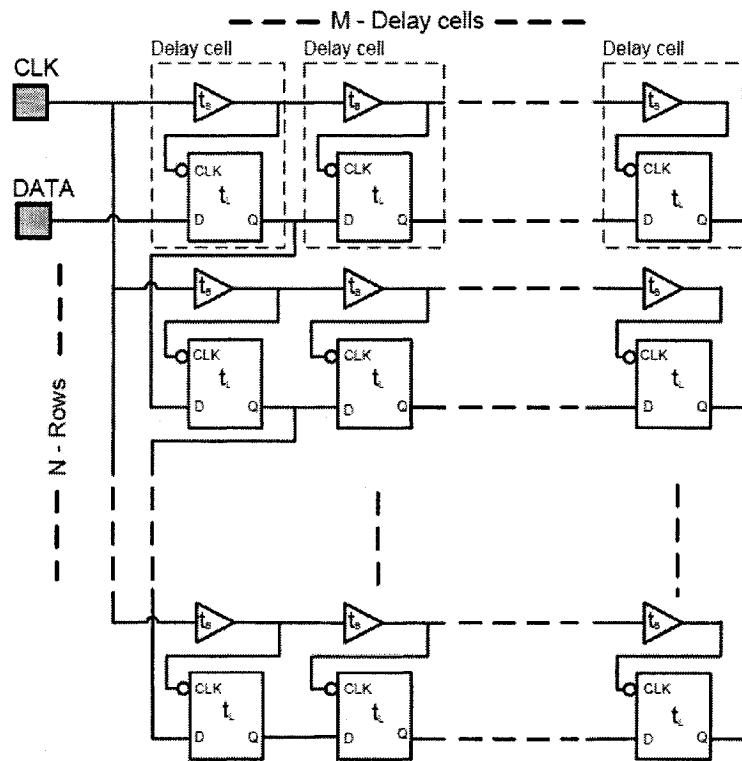

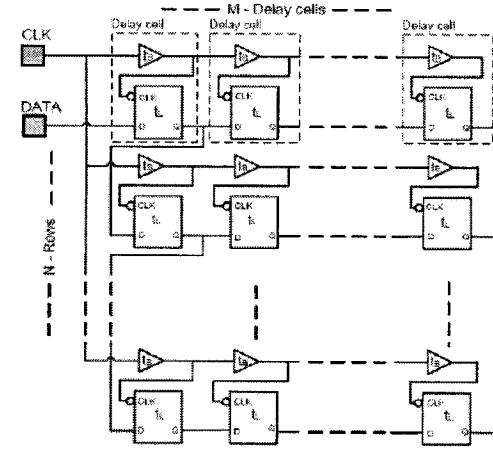

Afin d'augmenter la résolution de mesure, d'autres circuits TDC combinent plusieurs chaînes d'interpolation de temps dans des topologies plus complexes. Une telle structure combine  $M$  lignes de retard à  $N$  étages dans une topologie de tableau [18] (voir Figure 2.13). Dans cette topologie, les signaux de données sont propagés à travers  $M$  échantillonneurs de temps. Les entrées de données et d'horloge des échantillonneurs adjacents sont retardés par les petits retards respectifs de  $t_d$  et de  $t_c$ , par lesquels la résolution simple d'interpolateur  $t_d$  est divisée en  $M$ , donnant une résolution finale de  $\Delta t_r = t_d/M$ . Dans le même ordre d'idée, une autre solution de TDC combine des circuits DLL multiples dans une structure de tableau pour fournir une résolution de mesure améliorée [voir section 2.7]. Avec cette méthode, une résolution RMS de 34,3 ps, une gamme dynamique de 3,2 ns, et un LSB de 89,3 ps ont été obtenus avec une fréquence d'horloge de référence de 80 MHz [32].

### 0.3 Architecture TDC proposée

L'objectif principal de ce projet de recherche consiste à réaliser un circuit TDC permettant de surmonter certaines limitations de performance qui affectent les solutions TDC précédentes. En particulier, les objectifs initiaux de ce projet comprennent la réduction du temps de mesure, la capacité de mesurer plusieurs intervalles de temps dans une seule phase de mesure, l'obtention d'une résolution de mesure améliorée et la réalisation du circuit sur une plateforme peu coûteuse de FPGA. D'après le travail de

conception cité dans [29], une résolution de mesure acceptable de 100 à 200 ps est atteignable par la méthode de VDL proposée. Pour une ligne de VDL à  $M$  étages divisant un intervalle de temps  $T$  en  $N$  petits pas  $t_r$  ( $t_r = t_a - t_b$  où  $t_a$  et  $t_b$  sont les délais des éléments de logique dans les deux lignes à délai de VDL  $A$  et  $B$  et  $t_a > t_b$ ), l'intervalle maximale à mesurer est donné par  $T_{max} = M t_r$ . Le temps requis pour mesurer  $T_{max}$  est donné par le nombre d'étages propagé multiplié par le plus grand délai des élément dans la ligne VDL notamment  $t_a$ . C'est-à-dire, pour mesurer  $T_{max} = M t_r$ , il faut que les impulsions concernées propagent  $M$  étages avec un délai cumulatif de  $M t_a$ . Dans ce cas, le temps perdu est donné par  $(M t_a - M t_r) = M t_b$ . Si l'intervalle d'intérêt est grand et qu'il exige une ligne de VDL avec beaucoup plus d'étages, le temps supplémentaire de mesure requis peut devenir un défi de la conception. La topologie proposée est basée sur la technique de VDL présenté dans [29]. Pour réduire le temps de mesure, la méthode proposée utilise deux chemins de propagations pour les impulsions d'entrée dont le délai de propagation  $\tau_Y$  dans le premier chemin est plus grand que le délai  $\tau_X$  du deuxième chemin. En utilisant des pas plus grands, plusieurs propagations coûteuses de l'impulsion sont évitées. Ceci réduit significativement le nombre d'étapes de VDL exigées et, par conséquent, réduit considérablement le temps de mesure supplémentaire. Pour atteindre la détection et le traitement continus des données de mesure, le travail actuel utilise le parallélisme. En incorporant plus d'un interpolateur de temps en parallèle, le temps mort du circuit est amélioré. La plate-forme visée pour la réalisation du circuit TDC est basée sur le FPGA faible coût SPARTAN<sup>TM</sup>-3 de XILINX.

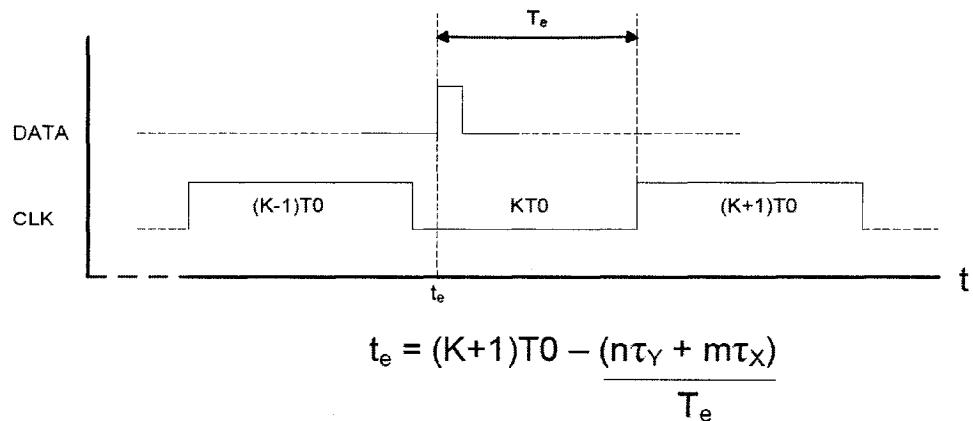

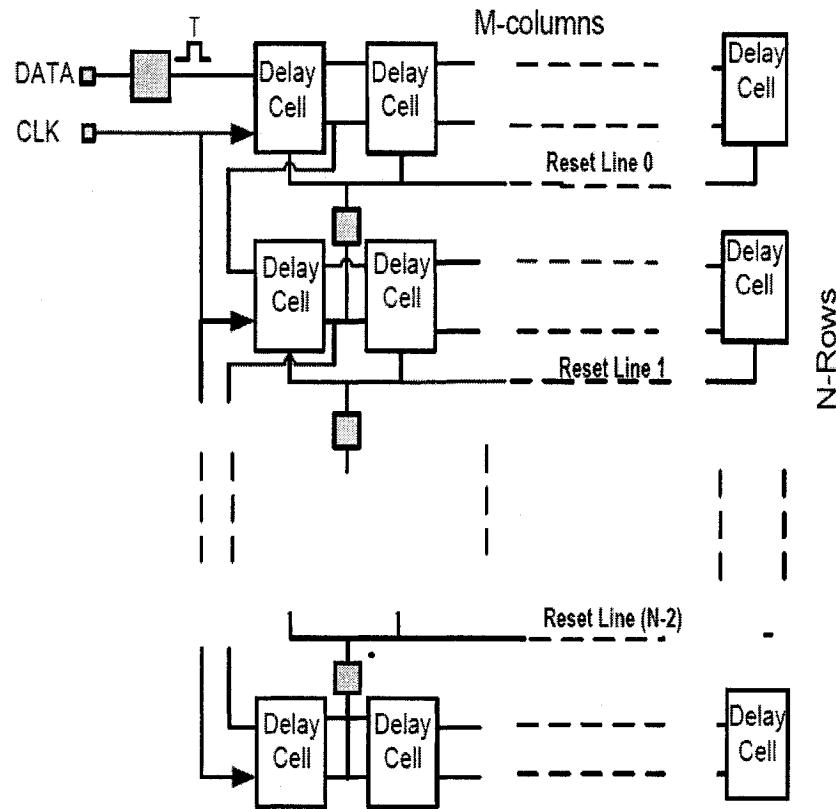

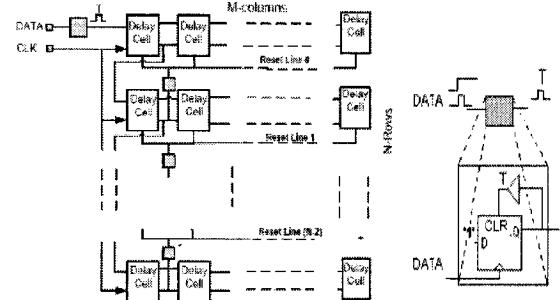

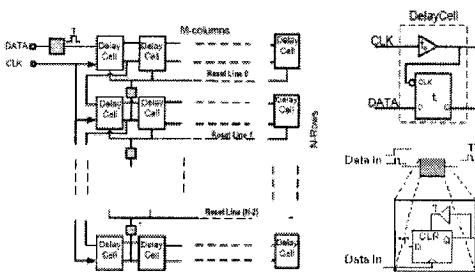

Tel que mentionnée ci-haut, le circuit TDC proposé est basé sur un interpolateur de temps utilisant le principe de Vernier afin d'atteindre une grande résolution de mesure. L'interpolator de temps est un tableau de lignes à délai de Vernier (VDL) utilisant des éléments tampon et des bascules à verrouillage D (D-Latch) comme élément à délai des lignes de propagation (voir Figure 4.2). L'interconnexion verticale entre deux rangs successifs est fournie par les premières cellules de retard de chacune des lignes. Toutes les lignes du tableau partagent une seule horloge de référence commune. L'architecture proposée peut aussi être vu comme une matrice de cellules à retard. La matrice de retard

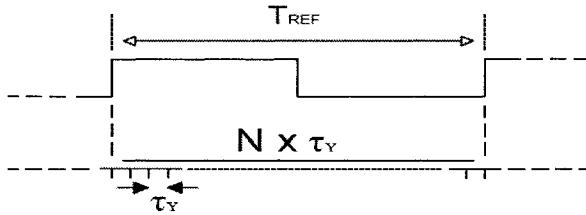

mesure la distance dans le temps entre les fronts montants des signaux de données et d'horloge subséquentes provenant des entrées respectives de la matrice. Cet intervalle est brisé en petits pas de temps à deux niveaux, notamment  $\tau_X = t_L - t_B$  et  $\tau_Y = t_L$  avec  $t_B$  et  $t_L$  étant les délais de propagation des éléments tampon et des loquet-D, respectivement. L'interconnexion verticale de la matrice fournit un chemin de propagation avec le plus grand pas de temps tandis que la résolution élevée de mesure est atteinte par la propagation horizontale à travers les lignes de retard de Vernier.

Le circuit TDC mesure un intervalle de temps entre deux impulsions entrantes en prenant la différence des temps d'arrivée correspondants par rapport à un point de référence. La matrice de cellules de retard sert donc à mesurer le temps d'arrivée des impulsions par rapport à l'horloge de référence qui, par la suite, sont utilisées pour déterminer la distance dans le temps entre deux impulsions consécutives.

À chaque saut vertical effectué par l'impulsion de donnée qui se propage, la distance dans le temps entre l'impulsion et le front d'horloge suivant est réduit par  $\tau_Y$ . Ce décalage continue jusqu'au moment où le sous intervalle résultant est plus court que  $\tau_Y$ . À ce moment, l'impulsion commence à propager horizontalement avec des pas de temps plus petits.

L'intervalle mesurable maximal obtenu en utilisant la matrice de retard est donné par les délais de propagation de  $N-1$  Loquet-D verticaux et de  $M$  délais différentiels horizontaux. C'est-à-dire :  $T_{max} = (N-1) \tau_Y + M \tau_X$ . Pour mesurer  $T_{max}$ , l'impulsion en question doit se propager à travers  $(N+M-1)$  Loquet-D, correspondant aux coordonnées  $(N-1, M)$ , ce qui exige un temps de mesure total de  $T_{total} = (N + M - 1) t_L$ . Pour mesurer  $T_{max}$ , le temps perdu maximal  $T_{ex}$  est donnée par  $T_{ex} = T_{total} - T_{max} = (N + M - 1) t_L - [(N-1) \tau_Y + M \tau_X] = M t_B$ .

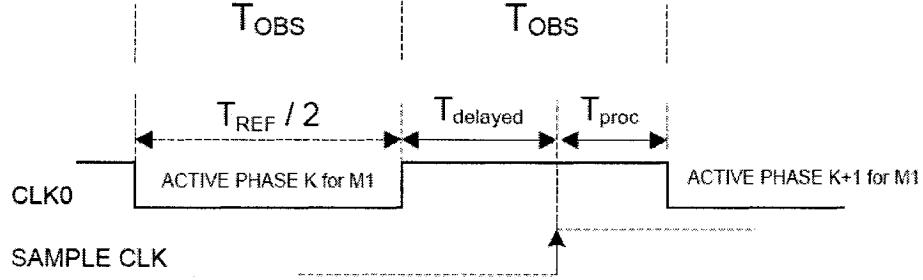

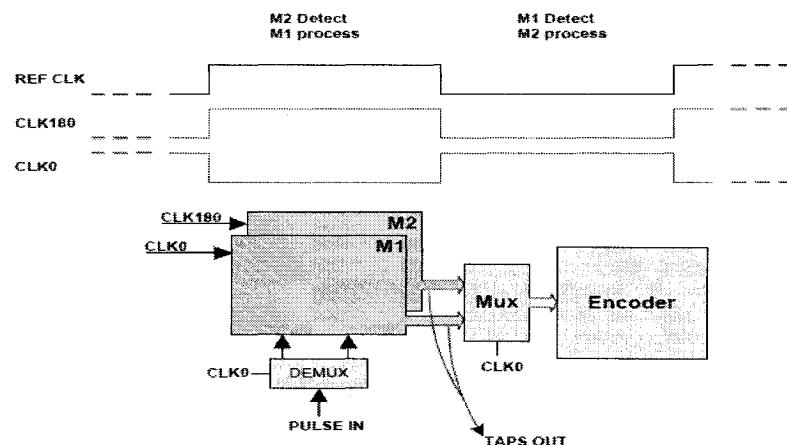

Une autre caractéristique importante est l'implémentation de deux matrices fonctionnant en parallèle, avec deux signaux d'horloge qui sont déphasés de 180 degrés. La présence de deux matrices de retard fonctionnant chacune dans une phase d'une

période d'horloge permet la détection et le traitement continu d'impulsions successives, tout en subissant un PPR minimal. Ceci réduit considérablement le temps mort requis pour réactiver le système pour les prochaines mesures.

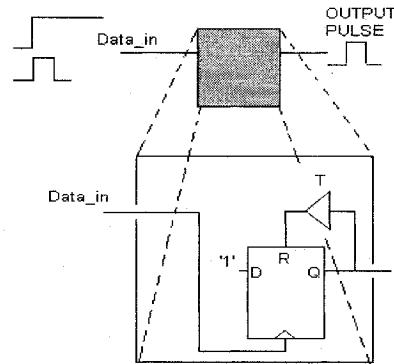

Idéalement, quand une impulsion fait un saut d'une rangée à l'autre, elle ne devrait exister nulle part dans la rangée précédente. Pour éviter la problématique de multi détection des mêmes impulsions sur plus d'un rang, chaque rangée de la matrice, à l'exception de la première, est équipée d'un circuit de réinitialisation qui, lors de la détection d'une nouvelle impulsion, génère un signal RESET d'une largeur constante, ce qui remet toutes les cellules de retard dans la rangée précédente à l'état initial. De plus, un générateur d'impulsions interne générant des impulsions d'une largeur constante est incorporé pour éviter la re-propagation d'une impulsion d'une largeur plus grande que la phase de l'horloge de référence à la phase active prochaine, ce qui autrement produirait des lectures erronées.

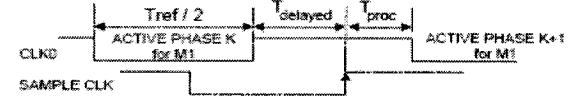

Le choix de taille de la matrice dépend principalement de la fenêtre de temps d'observation  $T_{OBS}$  ciblé et de la résolution verticale  $\tau_Y$ . Avec  $T_{OBS}$  et  $\tau_Y$  donnés, le nombre  $N$  de rangées à cellules de retard est donné par  $N \geq (T_{OBS} / \tau_Y)$  où  $\tau_Y = t_L$  et  $T_{OBS} = T_{REF}/2$ . De même, le nombre  $M$  d'étages est donné par  $M \geq (\tau_Y / \tau_X)$ . La valeur de la fenêtre de temps d'observation  $T_{OBS}$  dépend du temps requis pour qu'une impulsion se propage à travers la matrice au complet ainsi que de l'intervalle minimal de temps entre l'arrivée du front du signal d'échantillonnage et le prochain front d'horloge indiquant la prochaine phase de détection. Ce dernier garantit le temps requis par les processus d'encodage et de sauvegarde temporaire des données acquises avant le début d'une nouvelle phase active de détection.

Donc, la taille de la matrice de retard dépend de la résolution de mesure recherchée, des délais des éléments tampon et des Loquet-D utilisés, ainsi que de la valeur de  $T_{OBS}$ . Une taille minimale de matrice est obtenue si la résolution  $\tau_X$  est atteinte avec des éléments de tampon et de Loquet-D ayant un délai de propagation minime, ce qui amène une petite fenêtre d'observation et, par conséquent, une petite taille de la matrice.

## 0.4 Résultats

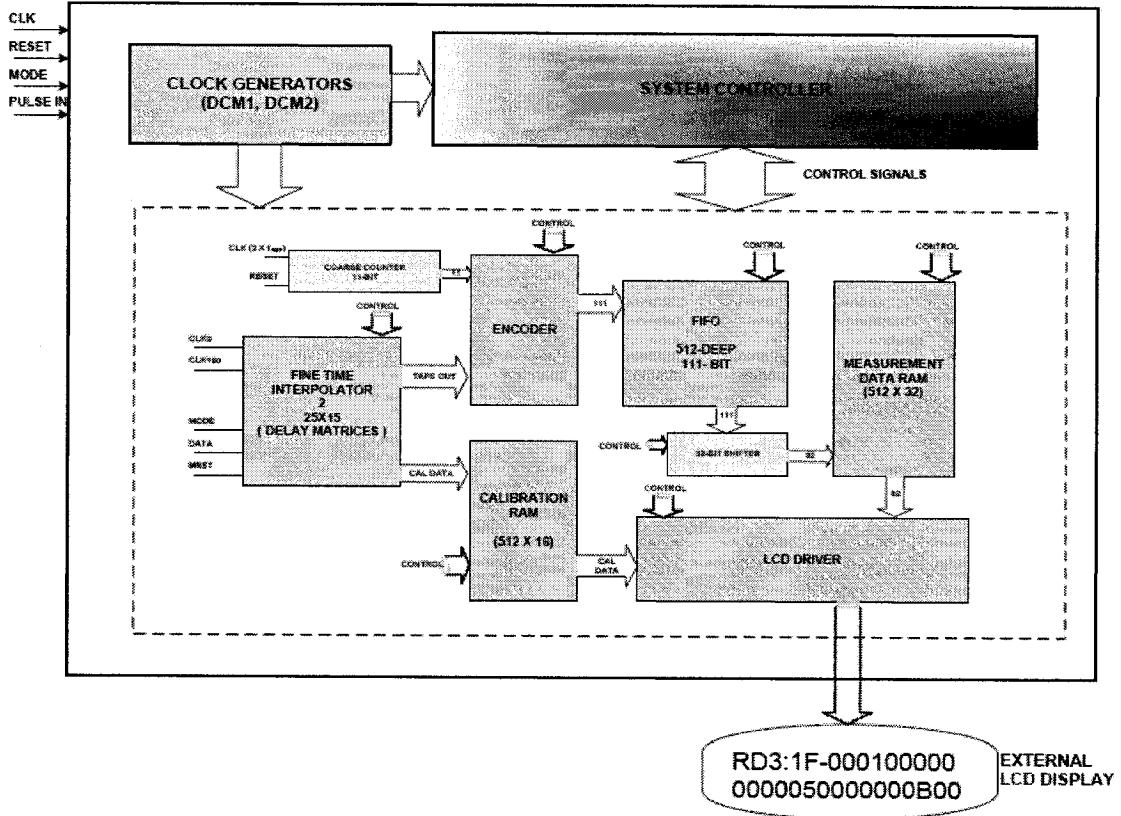

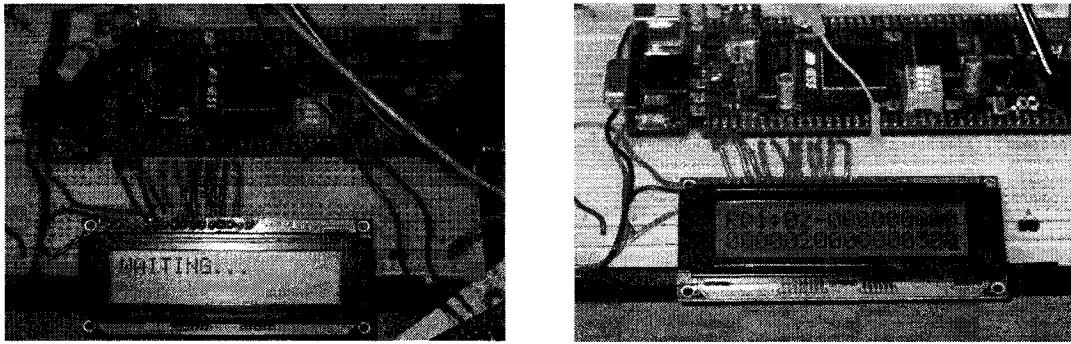

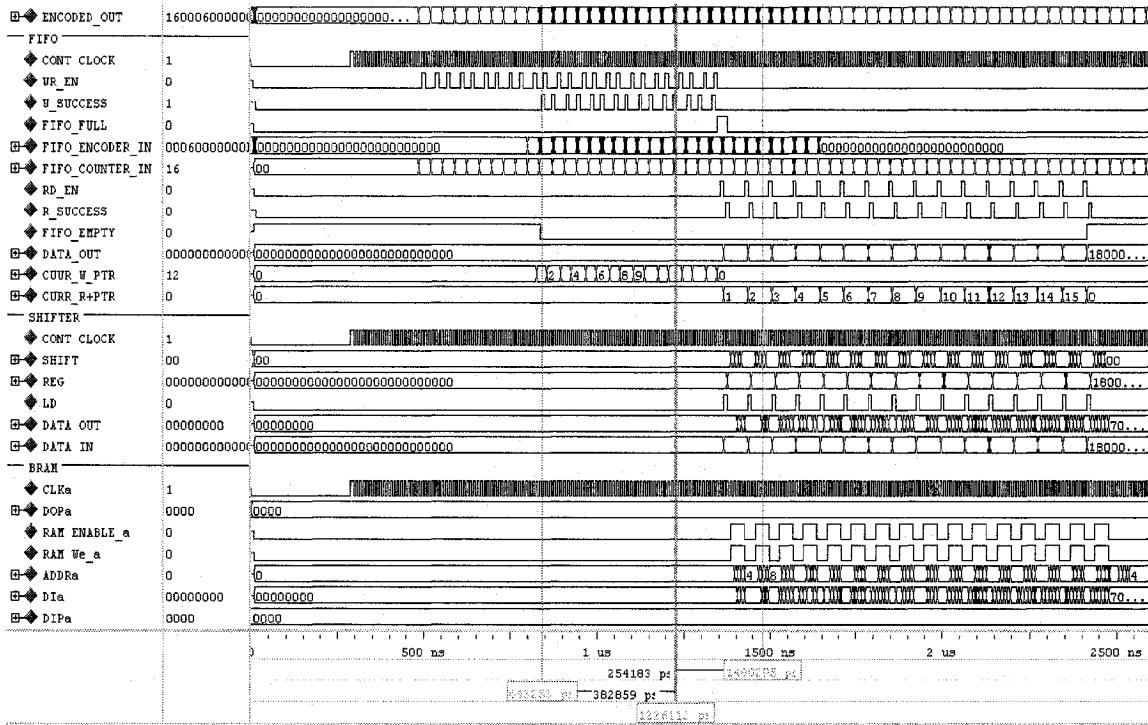

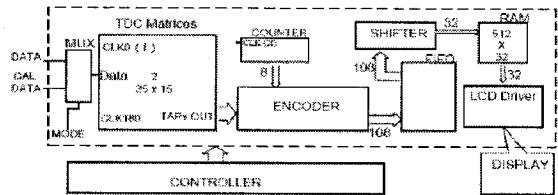

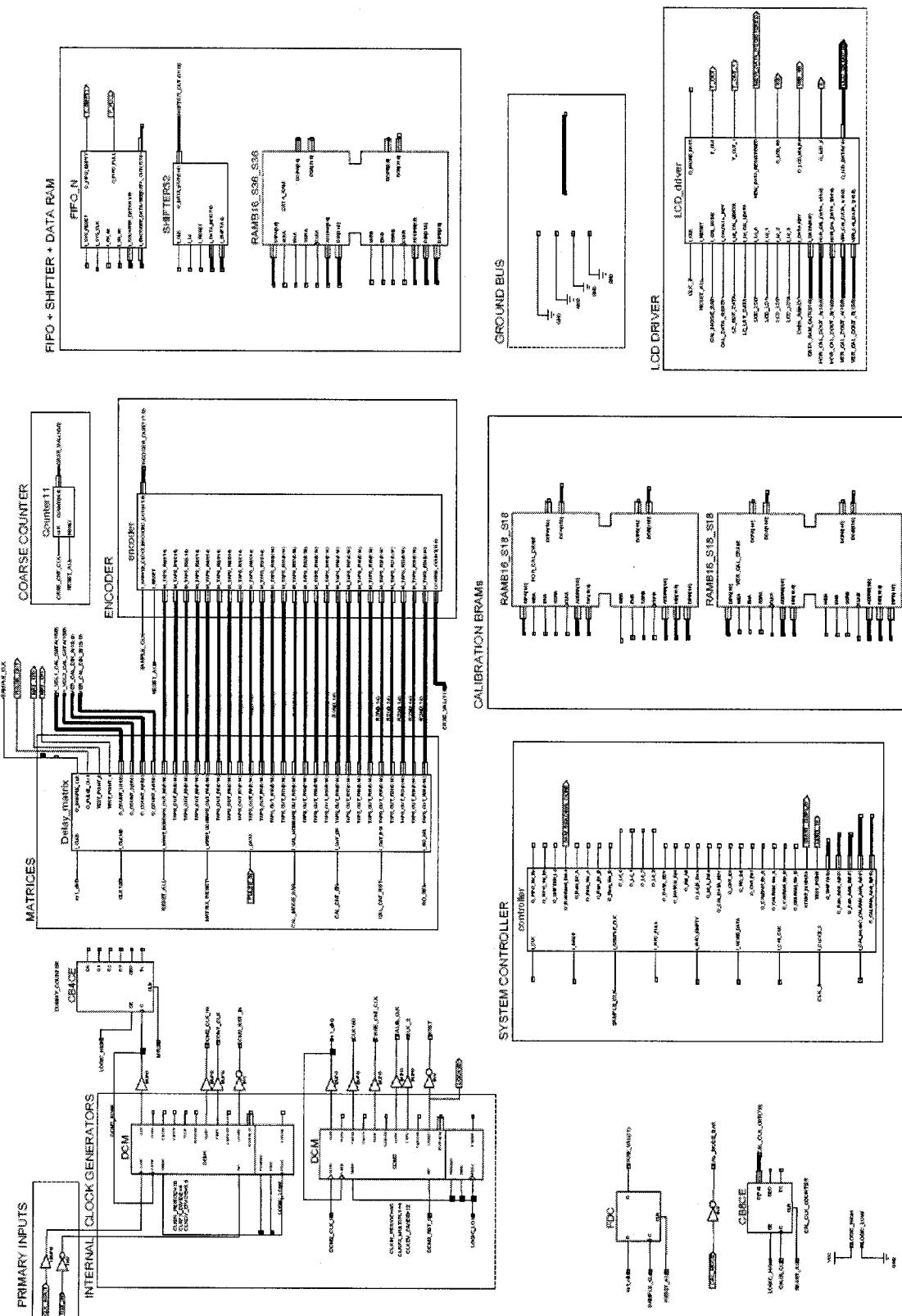

Le circuit de test est composé de deux matrices de retard fonctionnant en parallèle, une unité mémoire temporaire FIFO (First-In-First-Out), un encodeur permettant d'encoder les données détectées, un contrôleur basé sur des machines à états finis (FSM), un décaleur (Shifter), une mémoire de taille 512 X 32 octets, et un contrôleur d'affichage (LCD driver) pour l'affichage des données sur l'afficheur LCD (Liquid Crystal Display) (voir Figure 4.12). Le système a été implémenté sur une plateforme de prototypage utilisant un circuit FPGA de type SPARTAN<sup>TM</sup>-3 de XILINX. Les matrices de retard, synchronisées par deux horloges déphasées de 180 degrés, génèrent les données à chacune des phases de l'horloge de référence.

Pour atteindre l'uniformité exigée des délais et des retards des éléments tampon et des loquet-D, chaque cellule de retard des matrices a été manuellement placée. Les résultats de simulation de ModelSim et de l'outil d'analyse de temps de ISE de XILINX (Timing Analyser) donnent des valeurs moyennes de  $\tau_Y \sim 1.4$  ns et de  $\tau_X \sim 100$  ps. La taille de chaque matrice de retard a été définie à 25 x 15 ( $N=25$  et  $M = 15$ ).

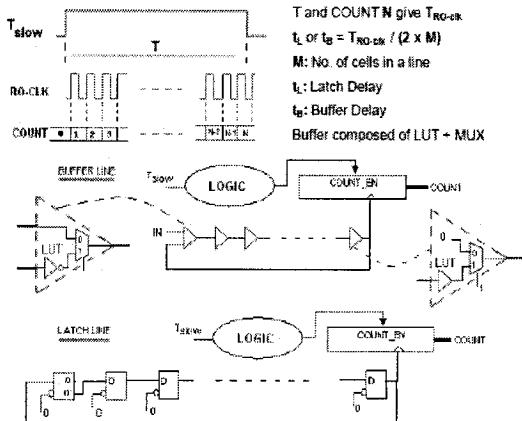

Les résultats expérimentaux donnent des délais de propagation qui sont légèrement différents de ceux obtenus en simulation. Afin d'estimer les valeurs des délais exactes des lignes de propagation verticales et horizontales, des lignes de calibration à base d'un oscillateur en anneau (Ring Oscillator ou RO) ont été implémentées. Pour les délais de propagation verticaux, le retard est estimé par la différence entre les périodes d'un RO de référence et d'un RO contenant trois cellules supplémentaires placées et connectées de façon identiques aux connexions de cellules verticales dans les matrices. De même, les lignes de calibration horizontales ont été placées et connectées comme les lignes de VDL horizontales des matrices. Les résultats de ces lignes de calibration donnent une résolution verticale d'une valeur de  $\sim 1.0$  ns, et la résolution horizontale varie entre 80 et 120 ps. Ainsi, le circuit est capable de détecter les impulsions séquentielle avec une PPR de 8.0 ns. La détection continue des impulsions d'une façon séquentielle élimine le

temps mort associé à un circuit TDC conventionnel. Le circuit a été aussi testé avec différentes valeurs d'intervalles. Les résultats mesurés montrent une erreur de mesure moyenne de l'ordre de  $\sim 1.5\%$  pour les intervalles plus grands que 12.0ns. Cependant, cette déviation augmente à 3.5 % pour les intervalles dont les longueurs sont inférieurs à 12.0ns. La valeur du skew maximal dans les lignes de l'horloge a été estimée de l'ordre de 400 ps.

## 0.5 Contraintes de performance

Pendant la réalisation et l'implémentation du circuit TDC proposé, plusieurs contraintes ont dû être respectées. Les contraintes les plus importantes sont : le placement manuel des éléments logiques, le routage identique des cellules de la matrice dans le but d'obtenir des délais uniformes, la minimisation du biais des lignes d'horloge, la limitation de la surface occupée par la structure symétrique de la matrice, et l'obtention d'un routage identique pour le chemin de données à partir de l'entrée principale du circuit jusqu'aux entrées de données respectives des matrices correspondantes. Au cours de la réalisation du projet et afin de respecter les conditions et limitations imposées et d'arriver à un système fonctionnel sur la plateforme FPGA, l'outil de synthèse et d'implantation de XILINX ont été guidés en spécifiant plusieurs contraintes de synthèse et d'implantation pour chacune des phases correspondantes.

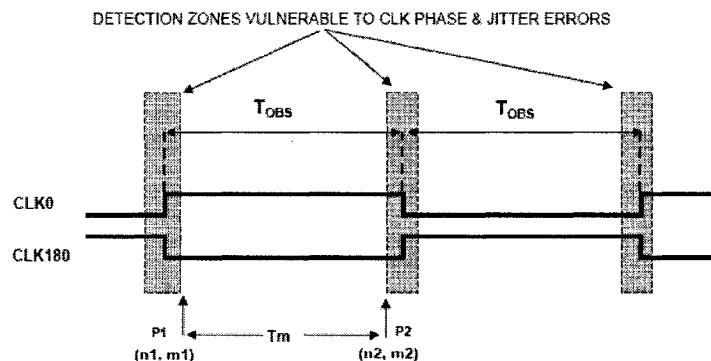

Les principales sources d'erreurs sont liées à l'incertitude dans l'uniformité des délais des cellules à retard et la présence de biais dans les lignes d'horloge. De plus, la performance du système est aussi affectée par d'autres facteurs tels que les variations dans les paramètres de l'horloge comme les variations de la période (Jitter), de la phase, et du duty cycle, ainsi que les fluctuations des délais de propagation des éléments identiques sur une même puce, qui sont principalement causées par les fluctuations des paramètres du procédé de fabrication et de l'environnement.

## 0.6 Conclusion et travaux futurs

Ce projet de recherche propose un circuit TDC à base d'une nouvelle méthode d'interpolation de temps. La technique d'interpolation proposée divise la période d'horloge de référence en tranches de  $N$  pas de temps et chacun des pas est ensuite divisé en  $M$  plus petits pas. Cette interpolation à deux niveaux réduit le temps de mesure en éliminant beaucoup de propagation successive de données à travers les lignes de retard pour couvrir la gamme dynamique de l'interpolator. Les impulsions à l'entrée sont propagées avec des pas de temps plus grands jusqu'à ce que le temps restant à propager devienne plus petit que le pas en question. Ensuite, les plus petits pas de temps sont utilisés pour obtenir une meilleure résolution. Le circuit prototype a été réalisé sur une plate-forme SPARTAN<sup>TM</sup>-3 FPGA de Xilinx. La résolution de mesure atteinte est de l'ordre de 100-120 ps.

Les travaux futurs sur ce projet consisteraient en l'amélioration de la performance du circuit TDC par, possiblement, une re-implémentation du circuit sur un prototype de FPGA plus récent avec les chemins d'horloges améliorés. Ainsi, l'amélioration des interconnexions entre les éléments des cellules adjacentes par un algorithme approprié garantissant un routage équilibré et uniforme afin de respecter l'uniformité des délais est fortement suggérée. De plus, il serait très intéressant de réaliser une implémentation sur ASIC du système permettant d'avoir des routages symétriques, et en conséquence, des délais de propagation plus uniformes.

## TABLE OF CONTENTS

|                                                                                       |              |

|---------------------------------------------------------------------------------------|--------------|

| <b>ACKNOWLEDGEMENT.....</b>                                                           | <b>V</b>     |

| <b>RESUMÉ .....</b>                                                                   | <b>VI</b>    |

| <b>ABSTRACT.....</b>                                                                  | <b>VIII</b>  |

| <b>CONDENSÉ EN FRANÇAIS .....</b>                                                     | <b>X</b>     |

| 0.1    INTRODUCTION .....                                                             | X            |

| 0.2    REVUE DE LITTERATURE DES METHODES D'INTERPOLATION DE TEMPS<br>EXISTANTES ..... | XII          |

| 0.3    ARCHITECTURE TDC PROPOSÉE .....                                                | XV           |

| 0.4    RÉSULTATS .....                                                                | XIX          |

| 0.5    CONSTRAINTES DE PERFORMANCE.....                                               | XX           |

| 0.6    CONCLUSION ET TRAVAUX FUTURS.....                                              | XXI          |

| <b>TABLE OF CONTENTS .....</b>                                                        | <b>XXII</b>  |

| <b>LIST OF TABLES.....</b>                                                            | <b>XXVI</b>  |

| <b>LIST OF FIGURES .....</b>                                                          | <b>XXVII</b> |

| <b>LIST OF FIGURES .....</b>                                                          | <b>XXVII</b> |

| <b>LIST OF SIGNS AND ABREVIATION .....</b>                                            | <b>XXX</b>   |

| <b>LIST OF SIGNS AND ABREVIATION .....</b>                                            | <b>XXX</b>   |

| <b>CHAPTER 1 - INTRODUCTION.....</b>                                                  | <b>1</b>     |

| 1.1    GENERAL TERMS AND CHARACTERISTICS .....                                        | 3            |

| 1.2    PROJECT INTENT .....                                                           | 5            |

| <b>CHAPTER 2 - OVERVIEW OF TIME INTERPOLATION TECHNIQUES.....</b>                     | <b>7</b>     |

| 2.1    TIME-TO-AMPLITUDE CONVERTER (TAC) .....                                        | 7            |

| 2.2    TIME INTERVAL (TI) STRETCHING .....                                            | 9            |

| 2.3    DELAY LINE AS TIME DIGITIZER.....                                              | 10           |

|       |                                                               |           |

|-------|---------------------------------------------------------------|-----------|

| 2.4   | CARRY-RIPPLE MULTI-BIT ADDER AS TIME INTERPOLATOR.....        | 12        |

| 2.5   | PULSE SHRINKING TECHNIQUE .....                               | 13        |

| 2.6   | THE VERNIER PRINCIPLE .....                                   | 15        |

| 2.6.1 | Buffer-Buffer Vernier Delay Line (VDL) .....                  | 16        |

| 2.6.2 | Buffer-Latch Vernier Delay Line (VDL).....                    | 18        |

| 2.7   | MULTIPLE SAMPLING TECHNIQUES.....                             | 19        |

| 2.7.1 | Delay Locked Loop (DLL) and Adjustable RC line.....           | 19        |

| 2.7.2 | Array of Time Samplers.....                                   | 20        |

| 2.8   | ARRAY OF DLL .....                                            | 22        |

| 2.9   | CHAPTER SUMMARY .....                                         | 23        |

|       | <b>CHAPTER 3 - PERFORMANCE ANALYSIS IN TDC CIRCUITS .....</b> | <b>24</b> |

| 3.1   | PERFORMANCE PARAMETERS .....                                  | 26        |

| 3.1.1 | Differential Non-Linearity (DNL) .....                        | 26        |

| 3.1.2 | Integral Non-Linearity (INL) .....                            | 27        |

| 3.2   | ERROR SOURCES.....                                            | 28        |

| 3.2.1 | Reference clock jitter .....                                  | 29        |

| 3.2.2 | Skew in clock paths .....                                     | 29        |

| 3.2.3 | Variation in delays .....                                     | 31        |

|       | <b>CHAPTER 4 - PROPOSED TDC ARCHITECTURE.....</b>             | <b>32</b> |

| 4.1   | INTRODUCTION .....                                            | 32        |

| 4.2   | PRESENTATION OF THE TDC ARCHITECTURE .....                    | 32        |

| 4.2.1 | Architecture Requirements .....                               | 32        |

| 4.2.2 | Proposed Design Specifications.....                           | 33        |

| 4.2.3 | The Time Interpolator .....                                   | 36        |

| 4.2.4 | Overall TDC Architecture.....                                 | 47        |

| 4.3   | COMPONENTS AND SYSTEM INTEGRATION .....                       | 49        |

| 4.3.1 | Target Implementation Platform.....                           | 49        |

| 4.3.2 | Delay Matrix .....                                            | 53        |

|                                                                |                                                        |           |

|----------------------------------------------------------------|--------------------------------------------------------|-----------|

| 4.3.3                                                          | Coarse Counter.....                                    | 55        |

| 4.3.4                                                          | Data Encoder.....                                      | 55        |

| 4.3.5                                                          | Synchronous FIFO Unit.....                             | 57        |

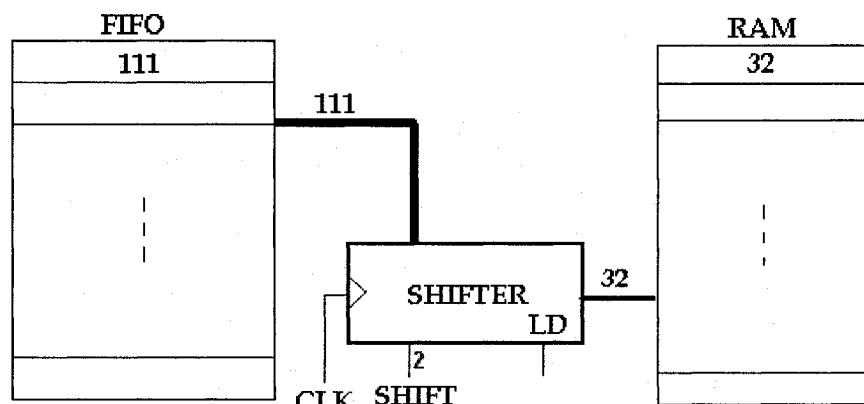

| 4.3.6                                                          | 32-bit Shifter .....                                   | 57        |

| 4.3.7                                                          | Data RAM.....                                          | 58        |

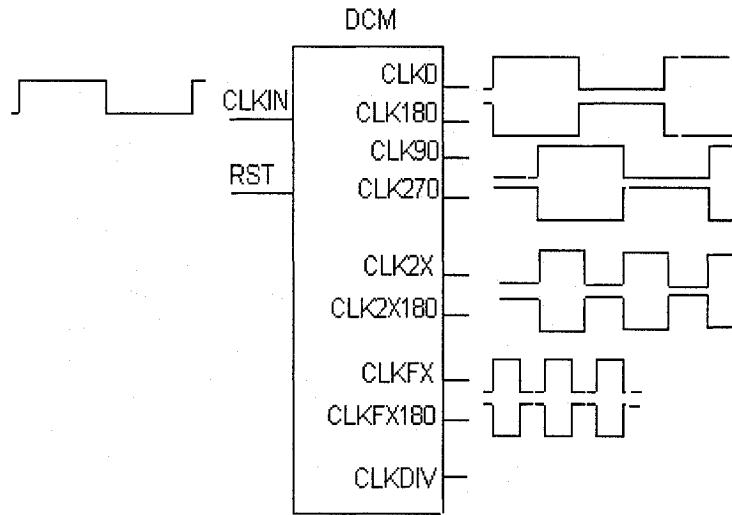

| 4.3.8                                                          | Digital Clock Manager (DCM) for Clock Generation.....  | 58        |

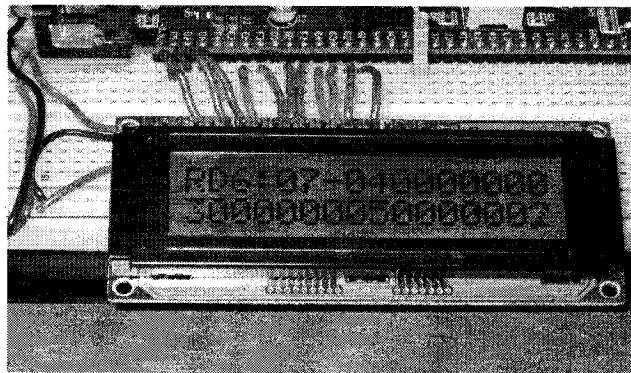

| 4.3.9                                                          | LCD Driver .....                                       | 59        |

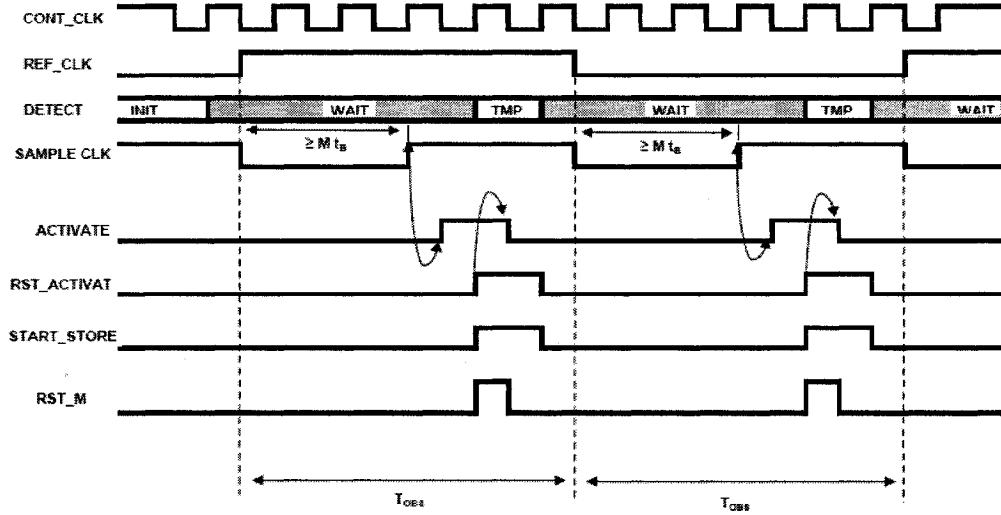

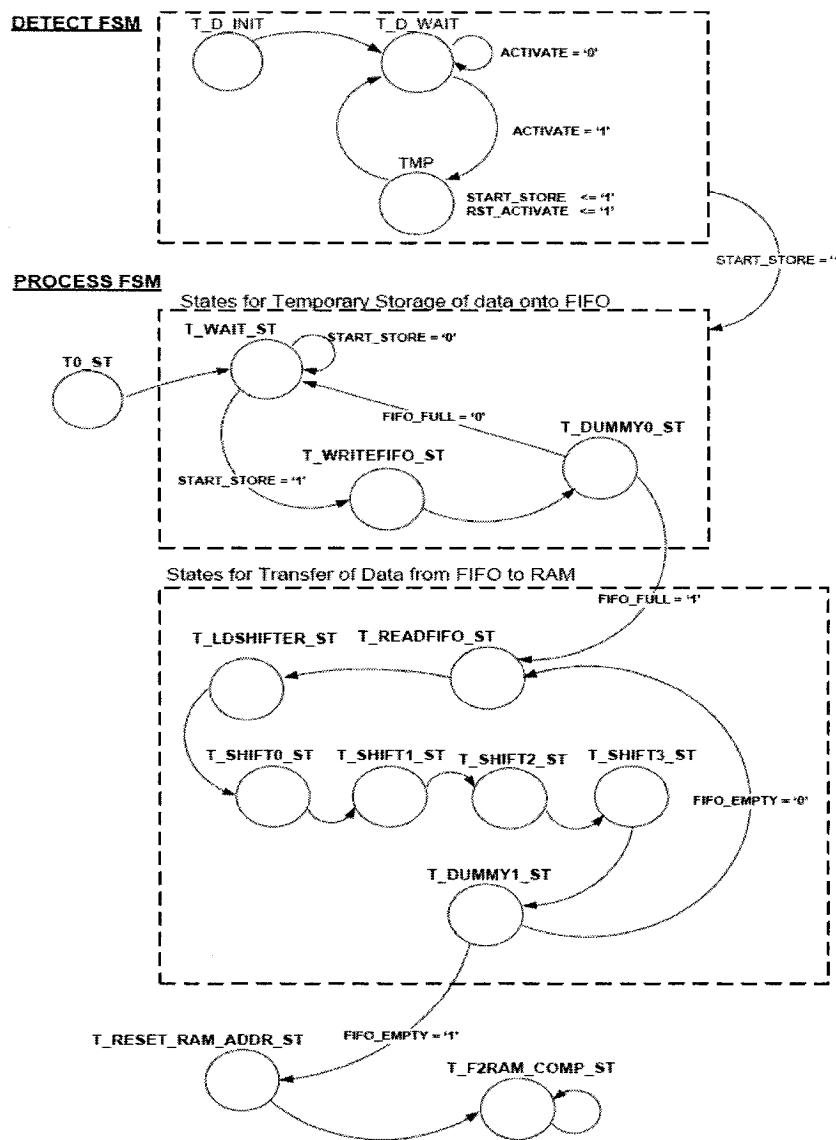

| 4.3.10                                                         | System Control Unit .....                              | 61        |

| 4.4                                                            | DELAY CALIBRATION .....                                | 66        |

| 4.4.1                                                          | RO-based Calibration Scheme.....                       | 66        |

| 4.4.2                                                          | Analytic method of Calibration .....                   | 73        |

| 4.5                                                            | CHAPTER SUMMARY .....                                  | 75        |

| <b>CHAPTER 5 - ISSUES AND DISCUSSIONS .....</b>                |                                                        | <b>77</b> |

| 5.1                                                            | LOGIC PLACEMENT ONTO FPGA SURFACE .....                | 77        |

| 5.1.1                                                          | Design Optimization.....                               | 78        |

| 5.1.2                                                          | Why Manual Logic Placement?.....                       | 79        |

| 5.1.3                                                          | Directional-Dependent D-latch Propagation Delays ..... | 80        |

| 5.1.4                                                          | Delay Matrix Constraints.....                          | 80        |

| 5.1.5                                                          | Other Constraints .....                                | 82        |

| 5.2                                                            | DESIGN & IMPLEMENTATION LIMITING FACTORS.....          | 85        |

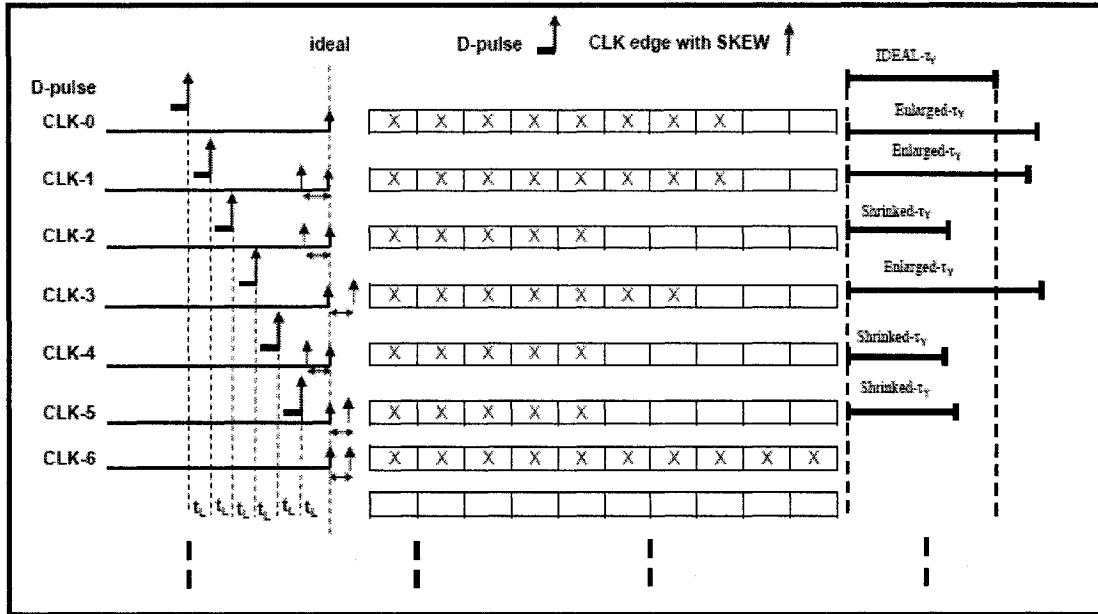

| 5.2.1                                                          | Skew In Clock Lines.....                               | 85        |

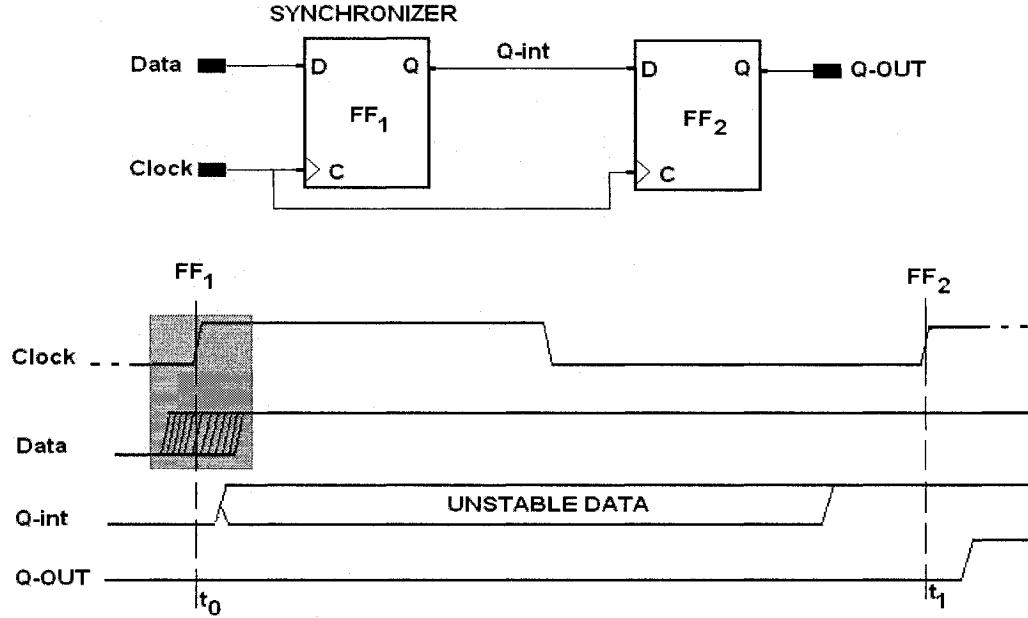

| 5.2.2                                                          | Meta-stability In Flip-Flop Elements.....              | 87        |

| 5.2.3                                                          | Delay Mismatch In Identical Components .....           | 88        |

| 5.3                                                            | CHAPTER SUMMARY .....                                  | 90        |

| <b>CHAPTER 6 - SIMULATION &amp; EXPERIMENTAL RESULTS .....</b> |                                                        | <b>91</b> |

| 6.1                                                            | TEST STRATEGIES .....                                  | 91        |

| 6.1.1                                                          | Functional Simulation.....                             | 91        |

| 6.1.2                                                          | Timing Simulation .....                                | 93        |

|                                                                                |            |

|--------------------------------------------------------------------------------|------------|

| 6.1.3 Experimental Testing .....                                               | 95         |

| 6.2 ACQUIRED DATA AND ANALYSIS.....                                            | 102        |

| 6.2.1 Timing Analyzer Data.....                                                | 102        |

| 6.2.2 Calibration Data.....                                                    | 104        |

| 6.2.3 Code Density Test Data .....                                             | 108        |

| 6.2.4 Test Interval Measured Data.....                                         | 113        |

| 6.2.5 Clock Skew Estimation.....                                               | 114        |

| 6.2.6 Accuracy/Precision Analysis .....                                        | 116        |

| 6.2.7 FPGA Area Utilization .....                                              | 117        |

| 6.3 DISCUSSIONS.....                                                           | 118        |

| 6.4 CHAPTER SUMMARY .....                                                      | 120        |

| 6.4.1 Performance evaluation with comparable designs.....                      | 121        |

| <b>CHAPTER 7 - CONCLUSION AND FUTURE WORK .....</b>                            | <b>123</b> |

| <b>REFERENCES.....</b>                                                         | <b>127</b> |

| <b>BIBLIOGRAPHY .....</b>                                                      | <b>132</b> |

| <b>APPENDIX-I.....</b>                                                         | <b>134</b> |

| CONFERENCE PAPERS.....                                                         | 134        |

| <b>APPENDIX-II .....</b>                                                       | <b>143</b> |

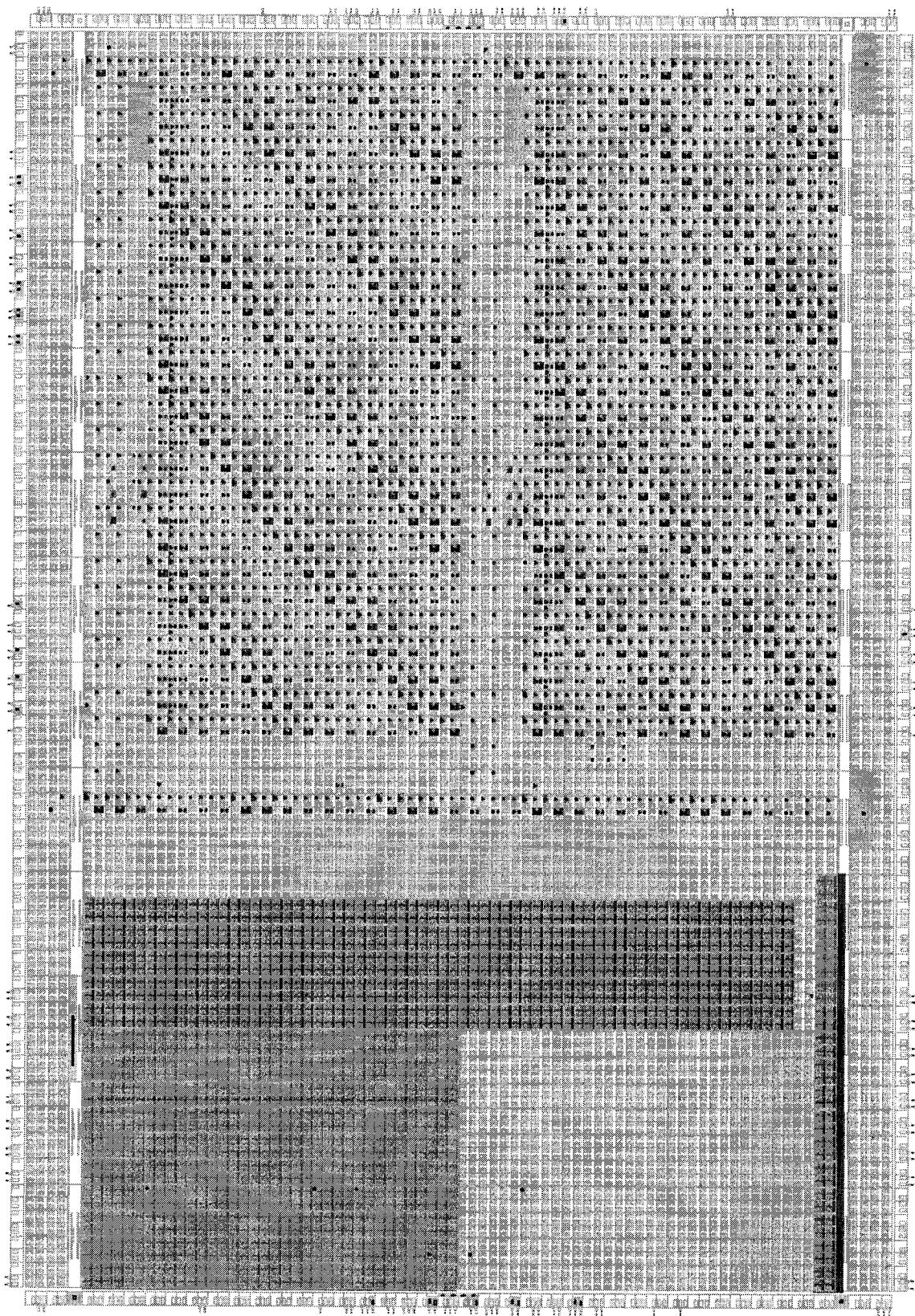

| SCHEMATIC OF FLOORPLANNED TDC LOGIC ON XC3S1000 -SPARTAN <sup>TM</sup> -3 FPGA |            |

| SURFACE.....                                                                   | 143        |

| TDC TOP-LEVEL SCHEMATIC.....                                                   | 143        |

| <b>APPENDIX-III.....</b>                                                       | <b>146</b> |

| VHDL SOURCE CODE .....                                                         | 146        |

| <b>APPENDIX-IV .....</b>                                                       | <b>188</b> |

| C++ SOURCE CODE FOR PRPG EMULATION PRESENTED IN CHAPTER 6.....                 | 188        |

## LIST OF TABLES

|                                                                                            |     |

|--------------------------------------------------------------------------------------------|-----|

| Table 4.1 : Summary of features of Xc3s1000 FPGA Device [36] .....                         | 51  |

| Table 6.1 : Delay analysis using Timing Analyzer.....                                      | 103 |

| Table 6.2 : Determination of $\tau_Y$ using Ring Oscillator-based Calibration .....        | 104 |

| Table 6.3 : Determination of $\tau_X$ using Ring Oscillator-based Calibration .....        | 105 |

| Table 6.4 : Analytical calibration results using different intervals T1 and T2 .....       | 106 |

| Table 6.5 : Analytical calibration results using $T_{CAL}$ .....                           | 107 |

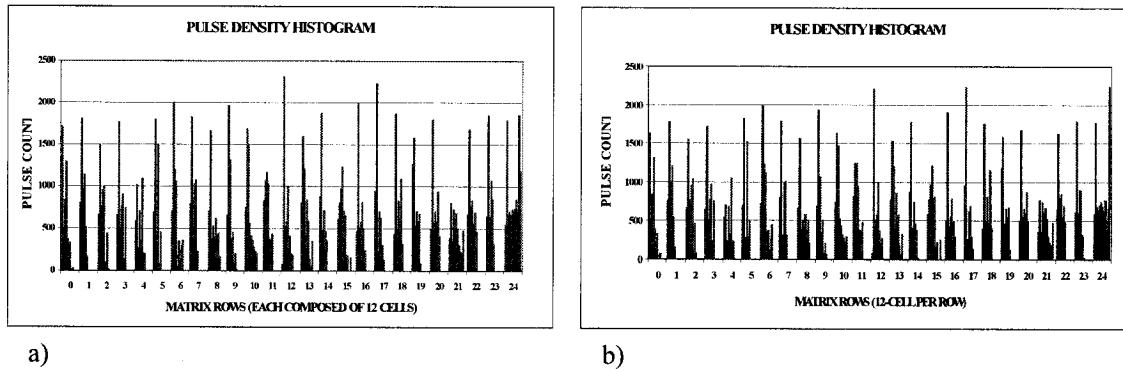

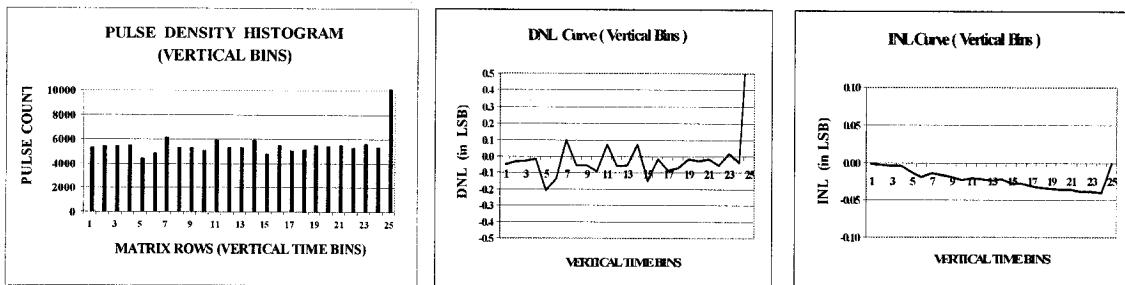

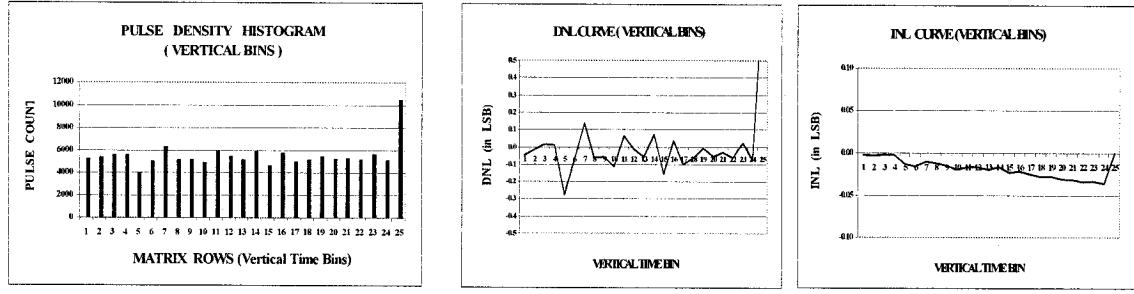

| Table 6.6 : CDT results from application of pseudo-randomly generated pulses .....         | 109 |

| Table 6.7 : CDT results obtained from pulse sweeping.....                                  | 109 |

| Table 6.8 : Estimation of $(\tau_Y)$ using CDT results for $T_{OBS} = 27.5\text{ns}$ ..... | 110 |

| Table 6.9 : Sample Timing Analyzer data for ROW-1 of delay matrix M-1.....                 | 113 |

| Table 6.10 : Sample Interval Measurement Data.....                                         | 113 |

| Table 6.11 : Clock net delays from source to destination cells of the matrices.....        | 114 |

| Table 6.12 : Estimation of Skew from CDT data .....                                        | 115 |

| Table 6.13 : SPATRAN <sup>TM</sup> -3 FPGA Resource Utilization Summary .....              | 118 |

| Table 6.14 : Summary of TDC characteristic parameters.....                                 | 121 |

## LIST OF FIGURES

|                                                                                                          |    |

|----------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 : Abstract view of a TDC circuit .....                                                        | 2  |

| Figure 1.2 : The interval $d$ ( $T_m$ ) in terms of its constituent sub-intervals .....                  | 2  |

| Figure 1.3 : Further refined view of a TDC circuit.....                                                  | 3  |

| Figure 2.1 : TAC circuit diagram.....                                                                    | 8  |

| Figure 2.2 : Time Interval Stretching Circuit Diagram.....                                               | 10 |

| Figure 2.3 : Delay line as time interpolator .....                                                       | 10 |

| Figure 2.4 : DLL circuit schematic .....                                                                 | 12 |

| Figure 2.5 : N-bit carry ripple adder used as fine time interpolator .....                               | 12 |

| Figure 2.6 : simple pulse shrinking circuit topology .....                                               | 14 |

| Figure 2.7 : Cyclic pulse shrinking circuit topology.....                                                | 14 |

| Figure 2.8 : A pulse shrinking delay cell .....                                                          | 14 |

| Figure 2.9 : VDL principle exploiting the difference in propagation delays of logic<br>elements .....    | 16 |

| Figure 2.10 : Buffer-implemented VDL used in jitter characterization circuit [28].....                   | 17 |

| Figure 2.11 : VDL implemented by Latch and Buffer lines .....                                            | 18 |

| Figure 2.12 : Time interpolator based on a DLL and an RC delay line.....                                 | 19 |

| Figure 2.13 : Time interpolation using multiple time sampling .....                                      | 21 |

| Figure 2.14 : TDC circuit diagram based on a DLL array .....                                             | 23 |

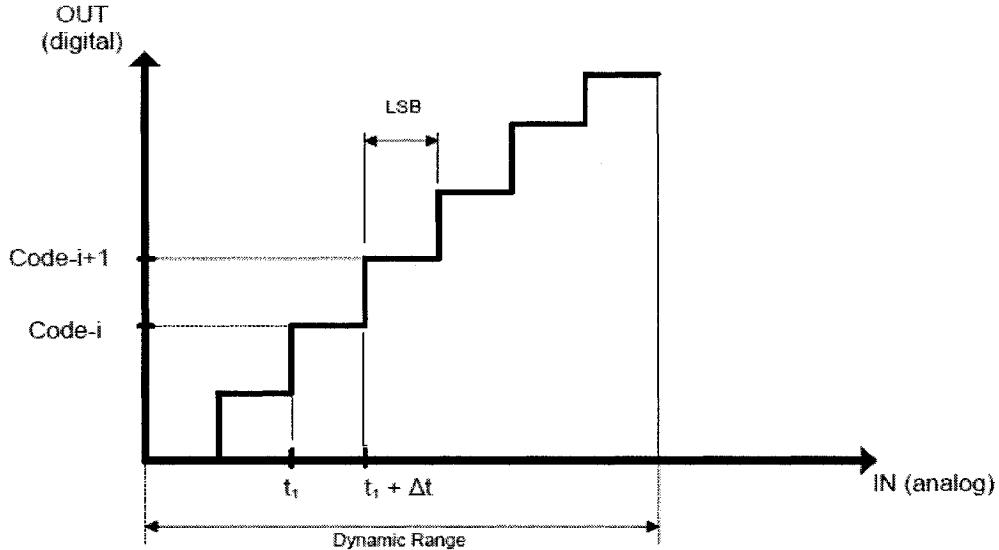

| Figure 3.1 : Input-output transfer response for an ideal converter .....                                 | 26 |

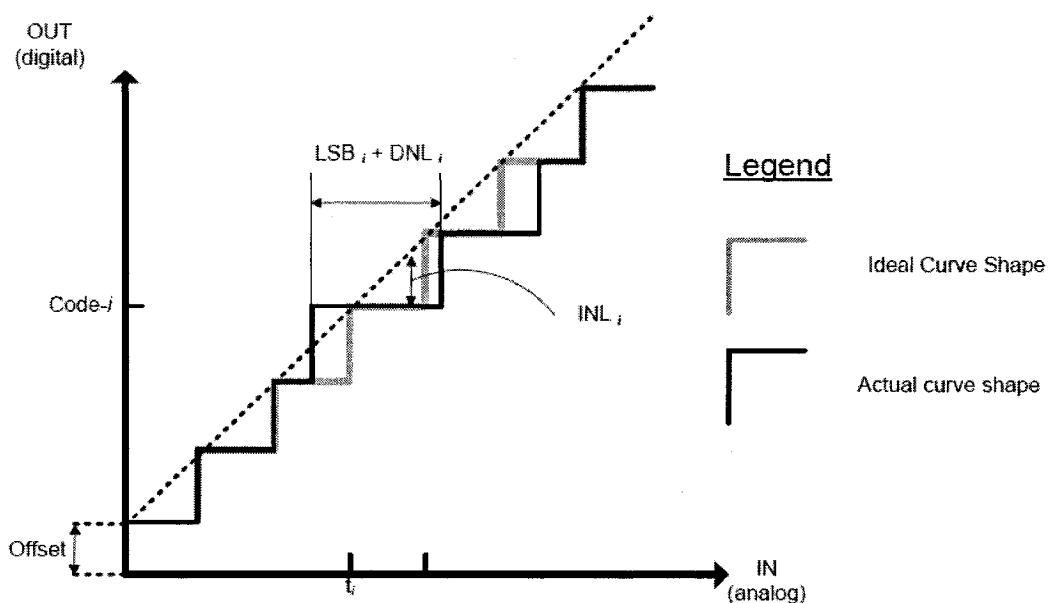

| Figure 3.2 : Transfer curve for a non-ideal converter .....                                              | 27 |

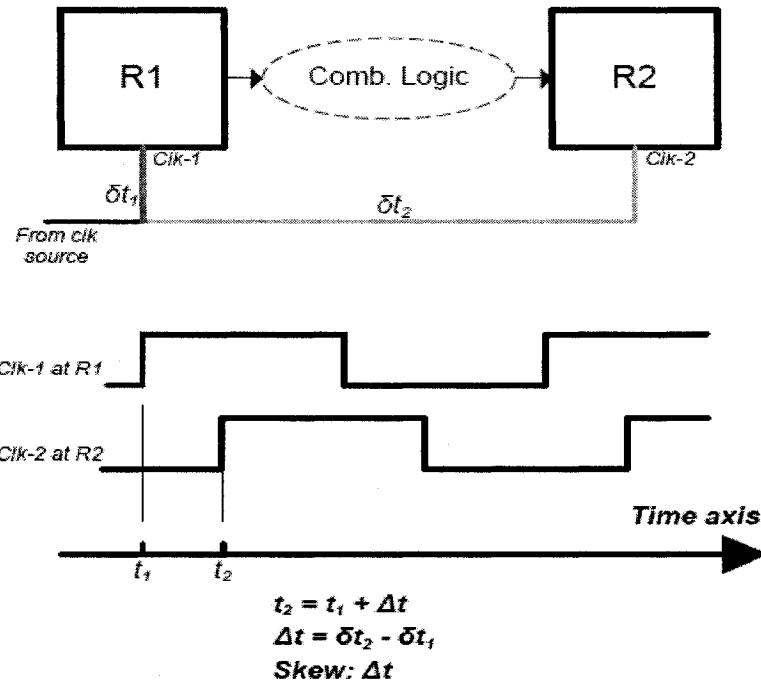

| Figure 3.3 : Clock skew .....                                                                            | 30 |

| Figure 4.1 : Two-level time interpolation .....                                                          | 35 |

| Figure 4.2 : Delay matrix topology.....                                                                  | 36 |

| Figure 4.3 : Interval of Interest .....                                                                  | 38 |

| Figure 4.4 : Pulse arrival time.....                                                                     | 38 |

| Figure 4.5 : Interpolation of $T_{REF}$ into $N$ smaller time bins of magnitude $\tau_Y$ .....           | 39 |

| Figure 4.6 : Interpolation of $T_{REF}$ into smaller time bins of magnitudes $\tau_Y$ and $\tau_X$ ..... | 39 |

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Figure 4.7 : $T_{OBS}$ decomposition.....                                                           | 42 |

| Figure 4.8 : New matrix topology including the reset generators.....                                | 44 |

| Figure 4.9 : Self-reset FF used as constant-width pulse generator .....                             | 44 |

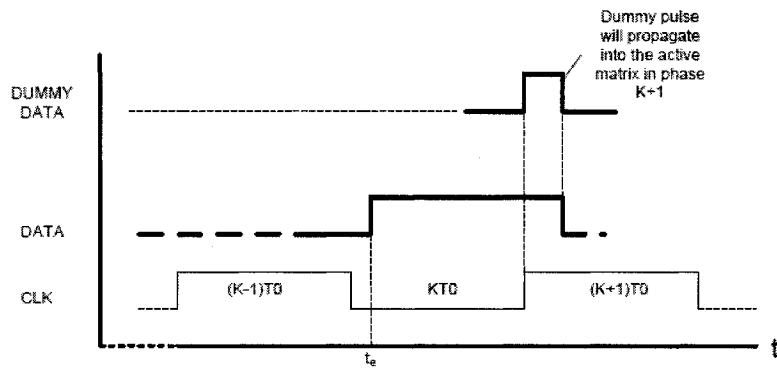

| Figure 4.10 : Erroneous dummy pulse propagation.....                                                | 45 |

| Figure 4.11 : Parallel operation of delay matrices .....                                            | 47 |

| Figure 4.12 : Overall TDC system.....                                                               | 48 |

| Figure 4.13 : Snapshots of the test system on Spartan <sup>TM</sup> -3 FPGA Platform .....          | 49 |

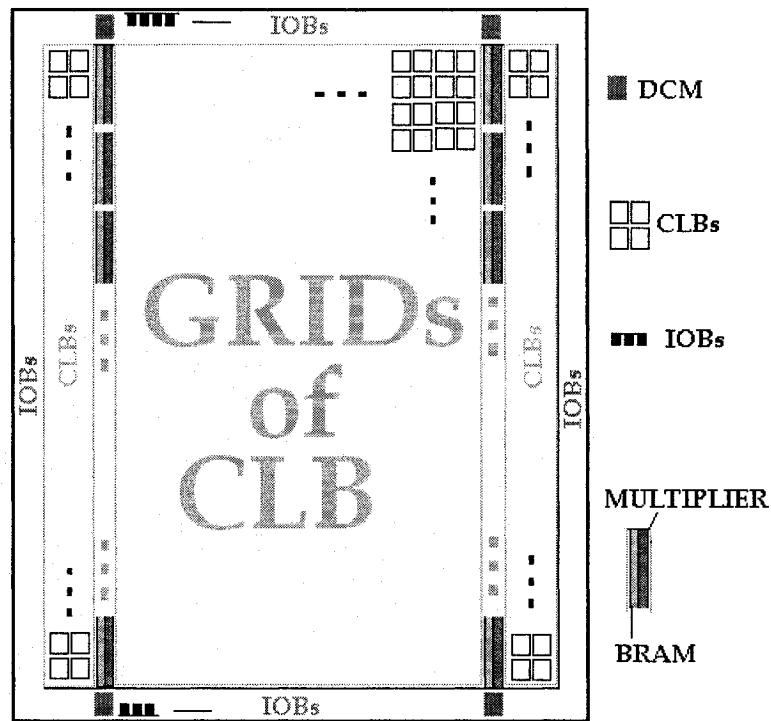

| Figure 4.14 : Spartan <sup>TM</sup> -3 general surface view [36].....                               | 52 |

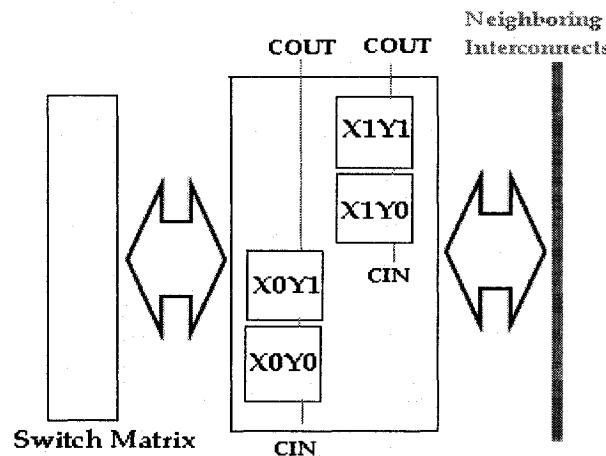

| Figure 4.15 : CLB structure [36].....                                                               | 52 |

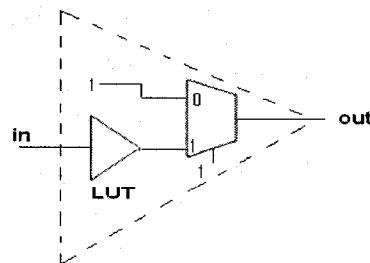

| Figure 4.16 : Buffer implementation .....                                                           | 53 |

| Figure 4.17 : 32-bit Shifter in Operation .....                                                     | 57 |

| Figure 4.18 : Simplified DCM block diagram.....                                                     | 59 |

| Figure 4.19 : Typical data display on LCD.....                                                      | 60 |

| Figure 4.20 : Waveforms showing DETECT state transitions .....                                      | 62 |

| Figure 4.21 : State Diagrams for DETECT and PROCESS FSMs.....                                       | 63 |

| Figure 4.22 : State diagram for DISPLAY FSM .....                                                   | 64 |

| Figure 4.23 : ASM-CHART for NORMAL OPERATION.....                                                   | 65 |

| Figure 4.24 : Buffer and latch line reconfigured as RO.....                                         | 67 |

| Figure 4.25 : Cell delay estimation for vertical propagation .....                                  | 68 |

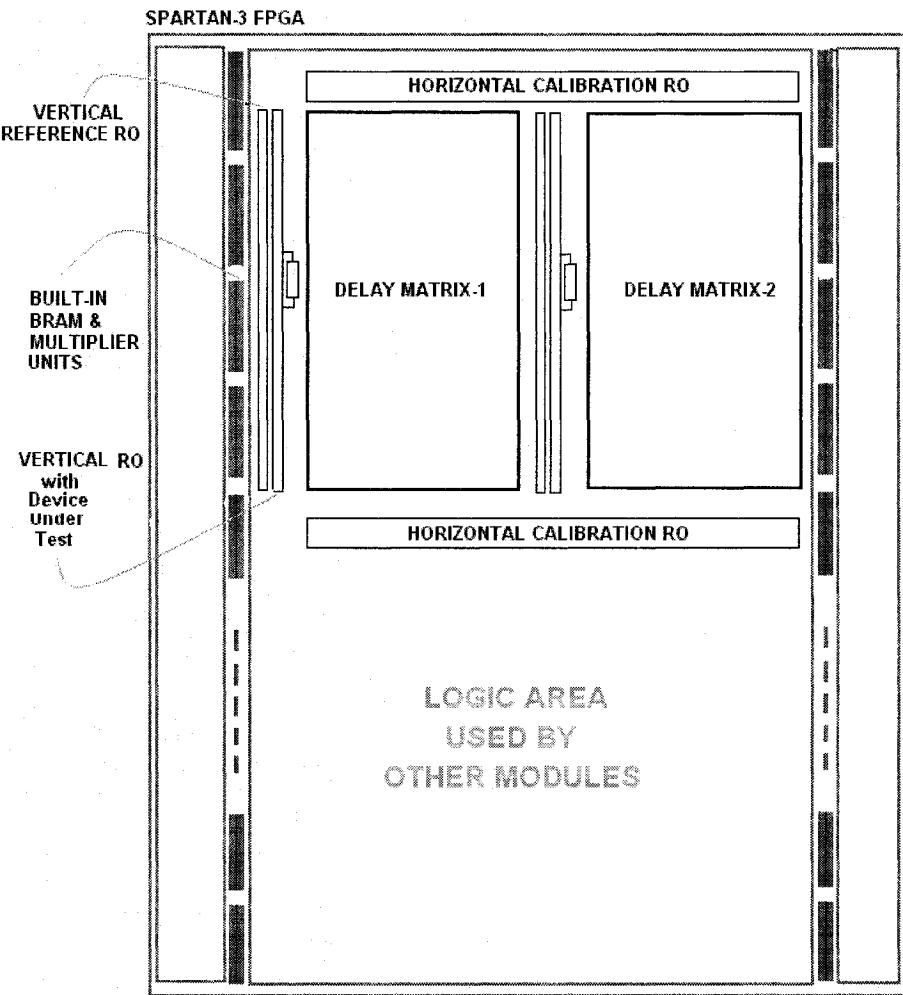

| Figure 4.26 : Partial calibration lines of the TDC system on FPGA surface .....                     | 69 |

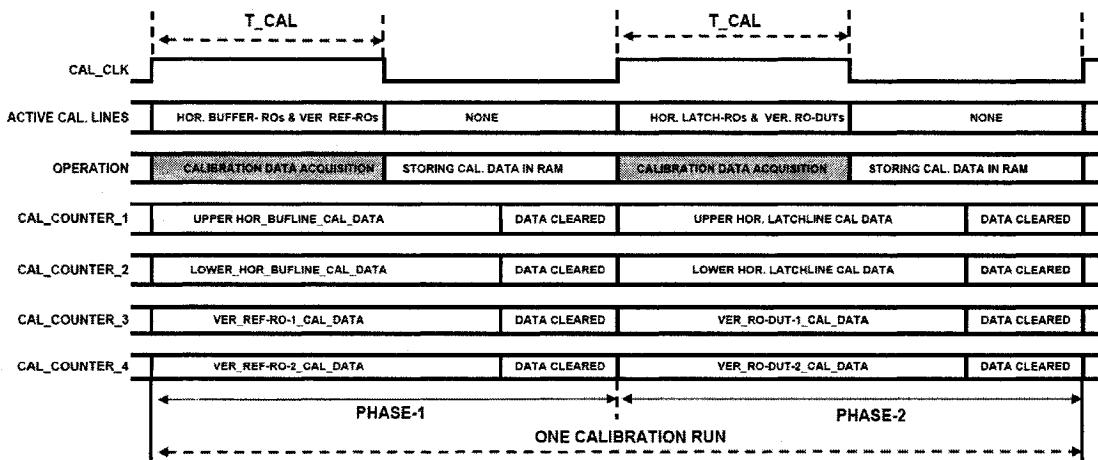

| Figure 4.27 : A single calibration run divided in two phases .....                                  | 70 |

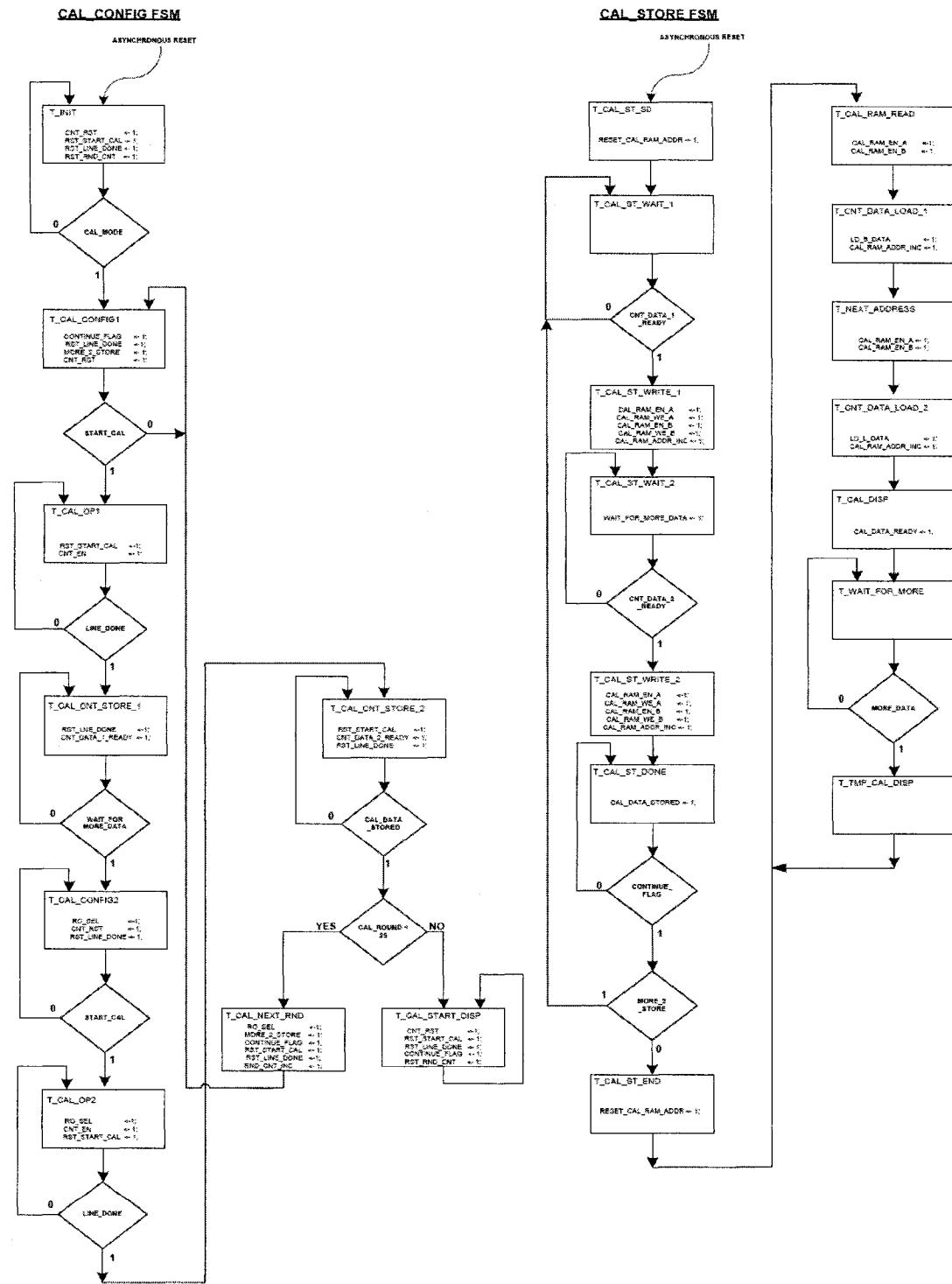

| Figure 4.28 : ASM charts for calibration operation involving CAL_CONFIG and<br>CAL_STORE FSMs ..... | 72 |

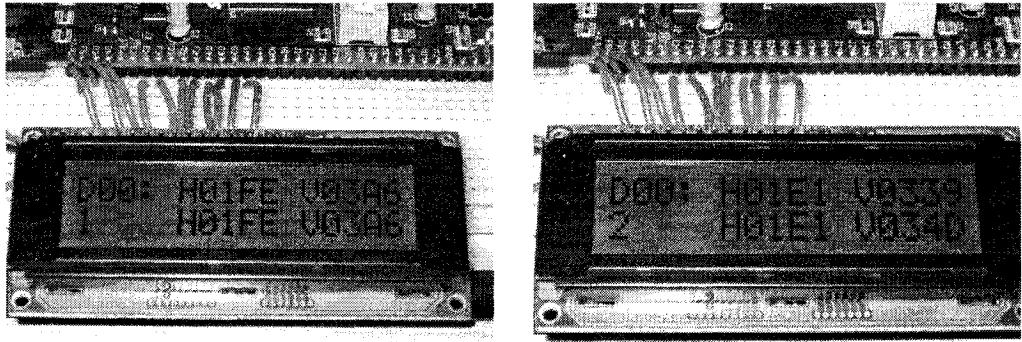

| Figure 4.29 : Sample calibration data display.....                                                  | 73 |

| Figure 4.30 : Equidistance pulses within the same time window .....                                 | 74 |

| Figure 5.1 : CLB placement scheme for delay cells of the delay matrix.....                          | 81 |

| Figure 5.2 : Side effects of skew on vertical time bin ( $\tau_Y$ ) ..                              | 87 |

| Figure 5.3 : Double-FF used to improve metastability .....                                          | 88 |

| Figure 5.4 : Vulnerable zones of the reference clocks for pulse detection .....                     | 89 |

|                                                                                                                                                                      |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

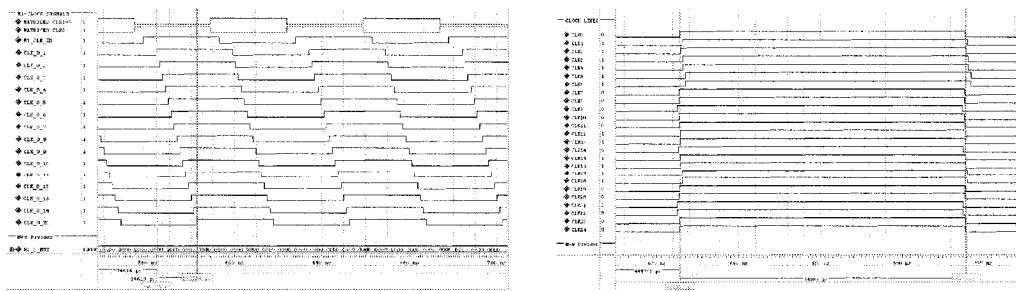

| Figure 6.1 : Sample waveforms for data storage onto FIFO & BRAM.....                                                                                                 | 92  |

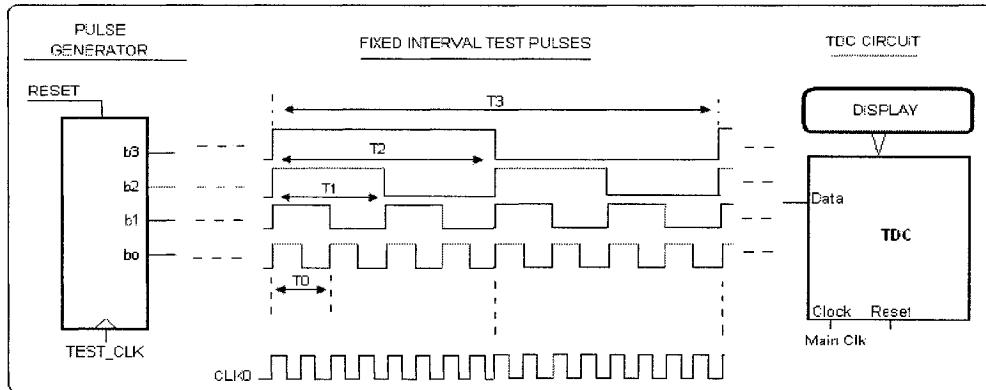

| Figure 6.2 : Binary counter as fixed interval generator .....                                                                                                        | 93  |

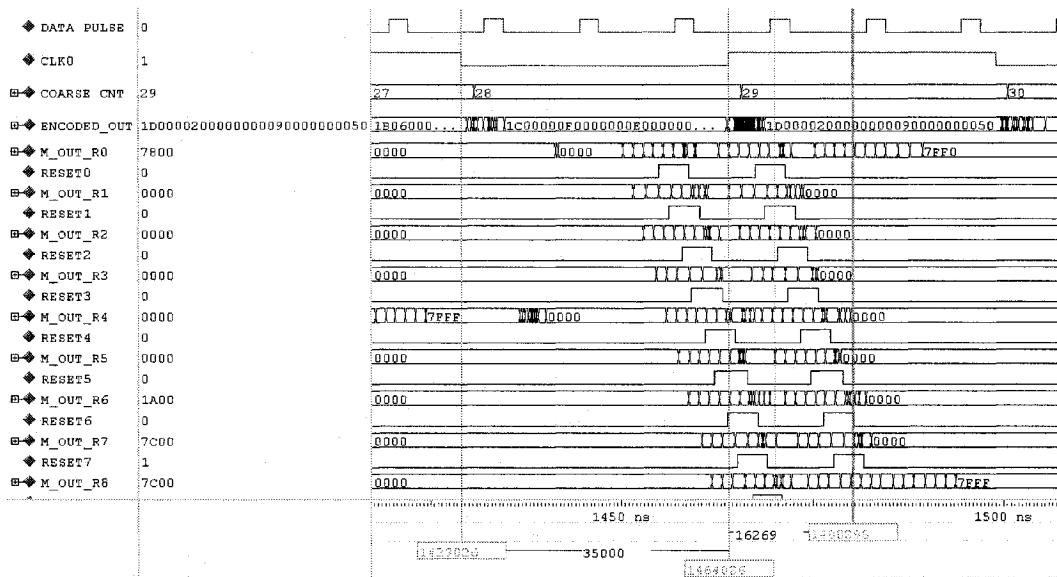

| Figure 6.3 : Sample timing waveforms for a detected pulse & corresponding encoding.                                                                                  | 94  |

| Figure 6.4 : Clock delaying waveform and clock misalignment due to skew .....                                                                                        | 94  |

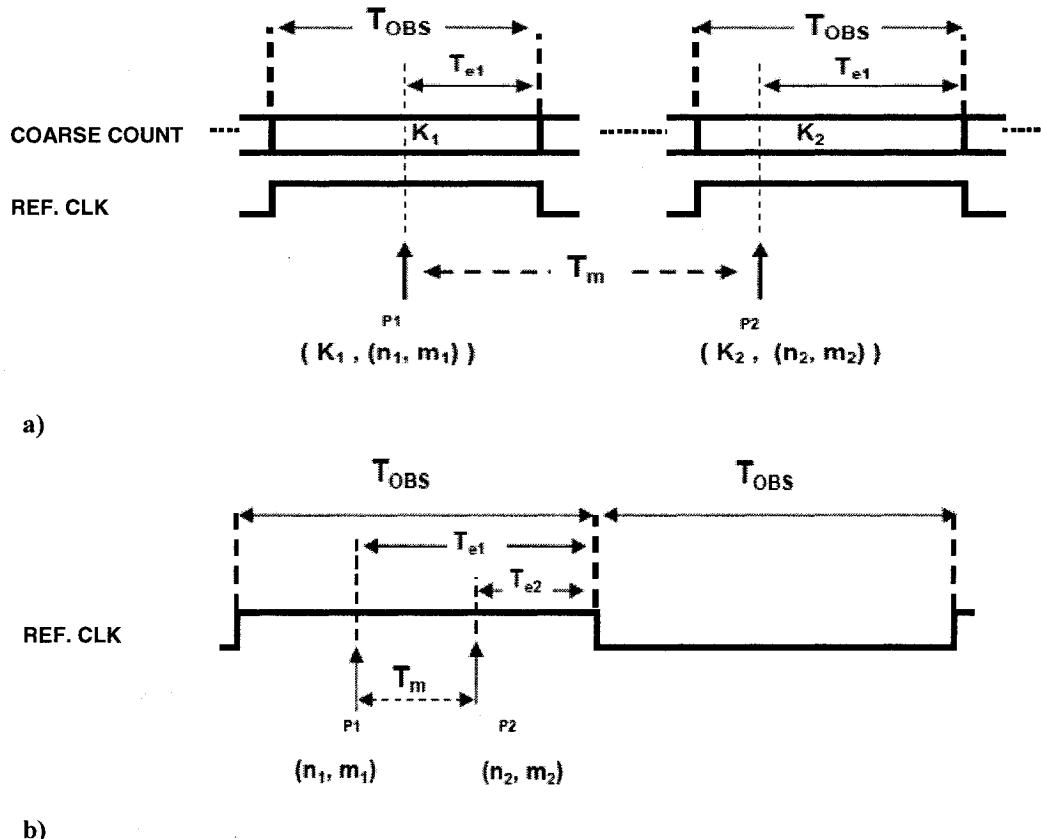

| Figure 6.5 : Demonstration of interval Calculation a) $T_m > T_{OBS}$ b) $T_m < T_{OBS}$ .....                                                                       | 95  |

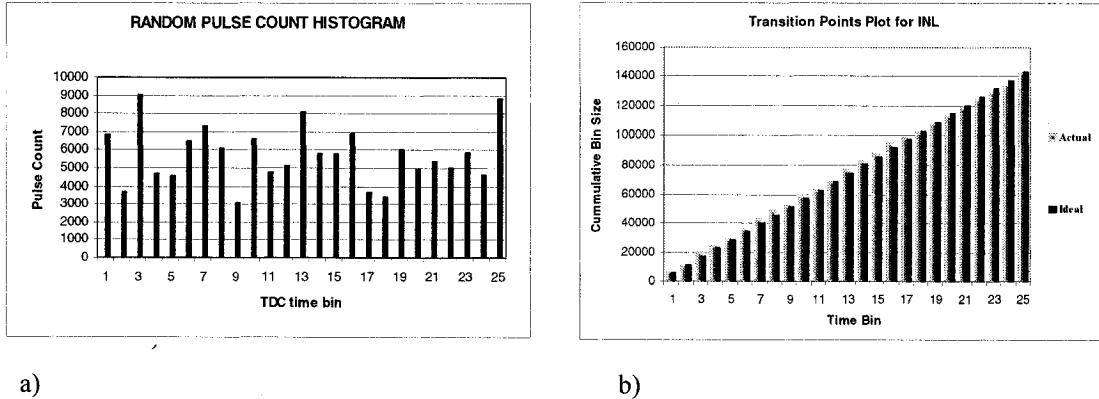

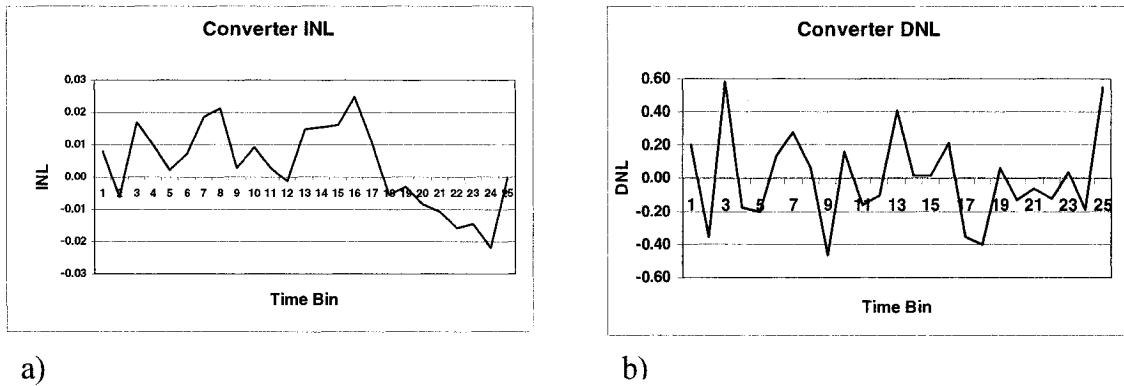

| Figure 6.6 : a) Data Histogram b) Histogram representing transition points.....                                                                                      | 97  |

| Figure 6.7 : a) Sample Converter INL b) Sample Converter DNL.....                                                                                                    | 98  |

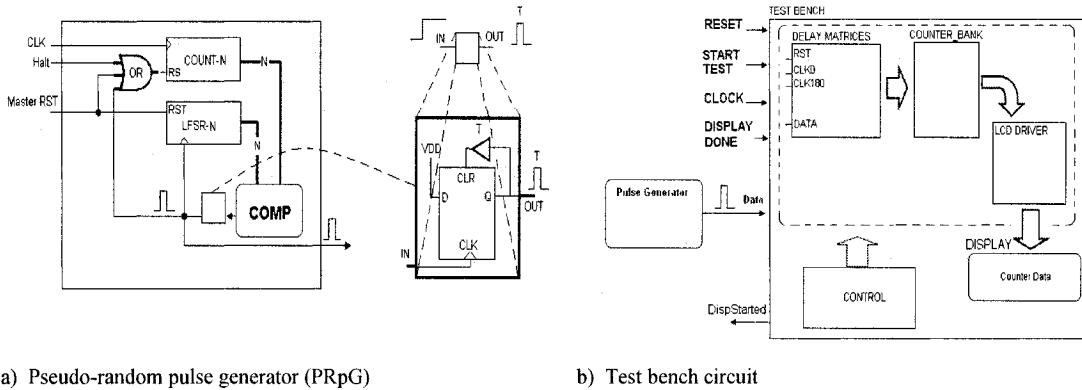

| Figure 6.8 : Code density test circuit block diagrams.....                                                                                                           | 99  |

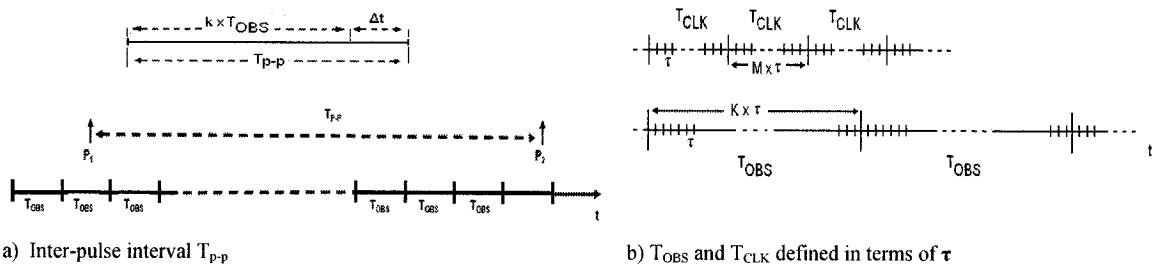

| Figure 6.9 : $T_{p-p}$ , $T_{OBS}$ and $T_{CLK}$ .....                                                                                                               | 100 |

| Figure 6.10 : Emulation results for pulse distribution of 25000 pulses within $T_{OBS}$ for $K=$<br>$270$ , $\tau = 100\text{ps}$ and $T_{CLK} = 5.9\text{ns}$ ..... | 101 |

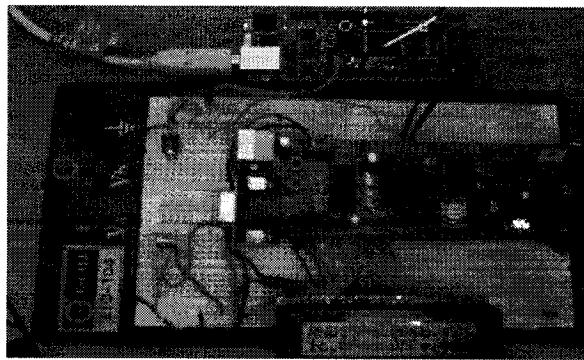

| Figure 6.11 : FPGA platforms implementing the TDC system and CDT Test Circuitry                                                                                      | 101 |

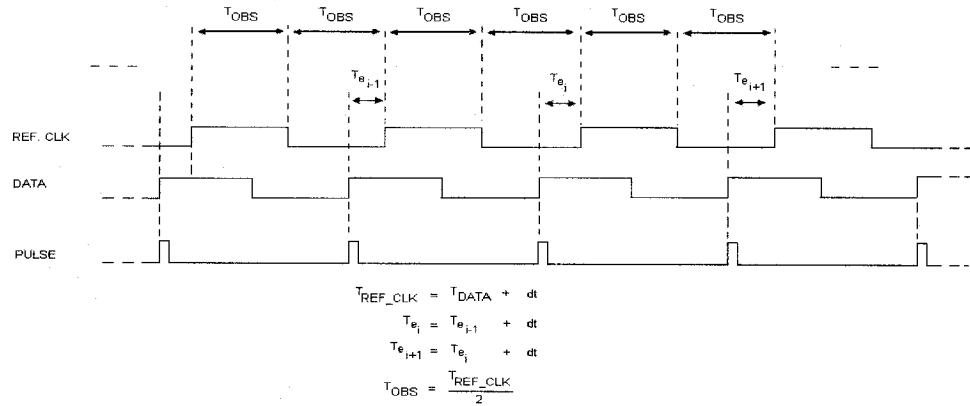

| Figure 6.12 : Pulse sweep generation for $T_{REF\_CLK} = T_{DATA} + \delta t$ .....                                                                                  | 102 |

| Figure 6.13 : Pulse distribution histograms across finer time bins ( $\tau_X$ ) .....                                                                                | 108 |

| Figure 6.14 : Row-wise pulse density, DNL & INL curves from pulse sweeping .....                                                                                     | 110 |

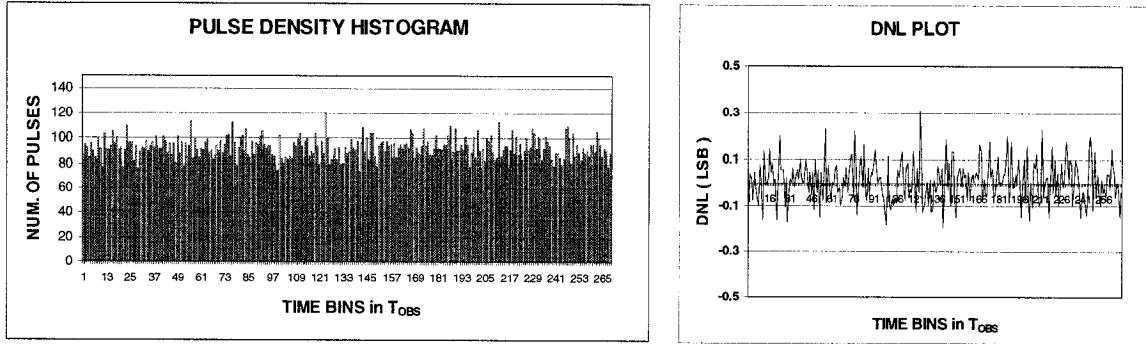

| Figure 6.15 : Row-wise pulse density DNL & INL curves from PRpG.....                                                                                                 | 111 |

| Figure 6.16 : Measurement Accuracy and Precision definitions .....                                                                                                   | 116 |

## LIST OF SIGNS AND ABREVIATION

|          |                                                              |

|----------|--------------------------------------------------------------|

| A/D      | Analog-to-Digital Converter                                  |

| ASIC     | Application-Specific Integrated Circuit                      |

| ASM      | Algorithmic State Machine                                    |

| BEL      | Placement constraint used by Xilinx PAR tool                 |

| BRAM     | Block Random Access Memory                                   |

| CDT      | Code Density Test                                            |

| CLB      | Configurable Logic Block                                     |

| DCM      | Digital Clock Manager                                        |

| DLL      | Delay-Locked Loop                                            |

| DNL      | Differential Non-Linearity                                   |

| FF       | Flip-Flop                                                    |

| FIFO     | First-In-First-Out                                           |

| FPGA     | Field Programmable Gate Array                                |

| FSM      | Finite State Machine                                         |

| GCD      | Greatest Common Divisor                                      |

| INL      | Integral Non-Linearity                                       |

| LCD      | Liquid Crystal Display                                       |

| LOC      | Placement and synthesis constraint in Xilinx Synthesis Tool  |

| LSB      | Least Significant Bit                                        |

| LUT      | Look-up Table                                                |

| MAXDELAY | XILINX timing constraint for maximum delay on a net          |

| MAXSKEW  | XILINX timing constraint for maximum skew among shared paths |

| MSB      | Most Significant Bit                                         |

| NCD      | Native Generic Database                                      |

| NGC      | Native Circuit Description                                   |

| PPR      | Pulse Pair Resolution                                        |

| PRPG     | Pseudo-Random Pulse Generation/Generator                     |

| RAM      | Random Access Memory                                         |

|           |                                                                 |

|-----------|-----------------------------------------------------------------|

| RO        | Ring Oscillator                                                 |

| TAC       | Time-to-Amplitude Conversion                                    |

| $t_B$     | Propagation delay of a buffer logic element                     |

| TDC       | Time-to-Digital Converter                                       |

| TIM       | Time Interval Meter                                             |

| TIS       | Time Interval Stretching                                        |

| $t_L$     | Propagation delay of a latch                                    |

| $T_m$     | Interval-to-be-measured                                         |

| $T_{OBS}$ | Observation Time Window (Detection time window for Measurement) |

| TOF       | Time-of-Flight                                                  |

| $T_{REF}$ | Period of the reference clock                                   |

| $T_{RO}$  | Period of Ring Oscillator                                       |

| $\tau_X$  | Single shot measurement resolution                              |

| $\tau_Y$  | Vertical measurement resolution (larger time step)              |

| UCF       | User Constraint File                                            |

| VCDL      | Voltage-Controlled Delay Line                                   |

| VDL       | Vernier Delay Line                                              |

| HDL       | Hardware Description Language                                   |

| XST       | Xilinx Synthesis Tool                                           |

## CHAPTER 1 - INTRODUCTION

Many applications in science and engineering require precise measurement of time intervals or the time elapsed between occurrences of two physical events. Depending on the nature and the requirements set by the application of concern, some applications need precise measurements for shorter intervals of time while some others may necessitate relatively longer time interval measurements. Regardless of the magnitude, it is often desirable to achieve timing measurements that are accurate and well representative of the actual elapsed time.

Applications involving time interval measurement are wide-spread in various fields of science and engineering. In electronic circuits, the time interval of interest could represent the propagation delay of a logic block from the rising/falling edge of a test signal at the input to the corresponding rising/falling edge at the output. Similarly, the jitter present in consecutive periods of a periodic signal such as the system clock is a good candidate for the interval of interest [1]. In Time-Of-Flight (TOF) and mass spectrometry experiments [2][3][4][5][6], the distance in time between two or more adjacent pulses or particles liberated from the collision point are to be measured for finding the molecular mass of the particles released. In instrumentation, the high resolution digital oscilloscopes and logic analyzers require precise measurements of time intervals for sampling digital waveforms and signal timings [7]. Other applications where timing measurement is one of the key elements of the overall process include applications such as positron lifetime spectroscopy [8] and laser range finder devices [9] used in finding an object's distance from the reference point (the device location).

A Time-to-Digital Converter (TDC), also referred as Time Interval Meter (TIM), is an electronic circuit designed to measure the time elapsed between two timing events/pulses. With the rapidly advancing digital world, many of the originally analog-domain parameters have been embedded into the digital domain for better and easier data

processing. A TIM circuit is one of such structures that have evolved from its earlier analog domain time measurement methods to the most recent digital ones [10][11]. Using a TDC, the time interval of interest is converted into a binary word representation that can easily be used in other digital blocks for further processing.

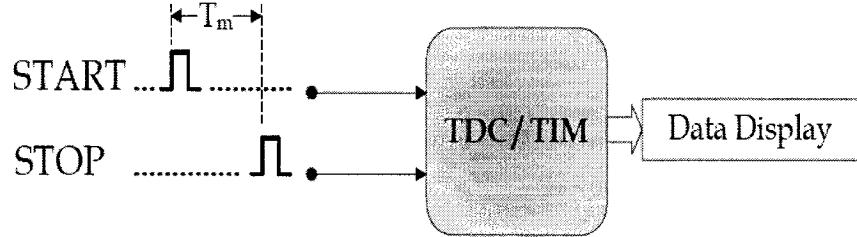

**Figure 1.1:** Abstract view of a TDC circuit

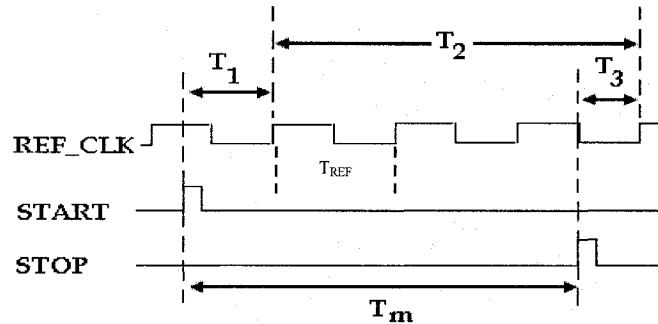

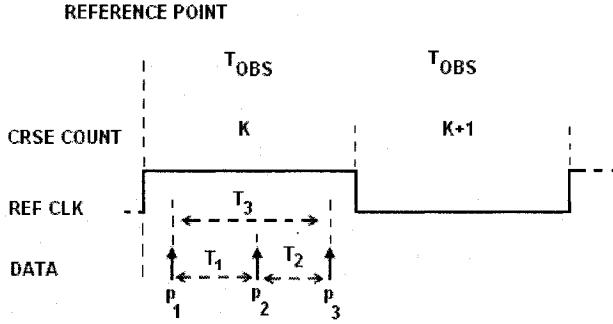

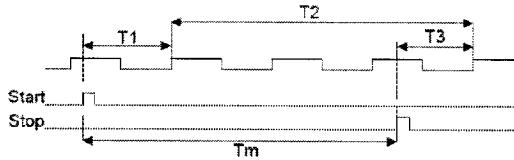

A time interval to be measured ( $T_m$ ) is defined between rising edges of two pulses commonly named as START and STOP. The interval  $T_m$  is usually described in terms of fine and coarse subintervals. The coarse section of  $T_m$  ( $T_2$  in Figure 1.2) is divisible by the system clock period, hence measurable with a resolution of  $T_{REF}$  by a binary counter clocked with a frequency of  $1/T_{REF}$ . However, to measure the fine constituents of  $T_m$  ( $T_1$ ,  $T_3$  in Figure 1.2), further interpolation of the system clock (division of system clock period into many smaller time bins) is needed. From Figure 1.2, it is seen that with the fine and coarse subintervals measured,  $T_m$  can be given as:

$$T_m = T_1 + T_2 - T_3 \quad (1.1)$$

**Figure 1.2:** The interval ( $T_m$ ) in terms of its constituent sub-intervals

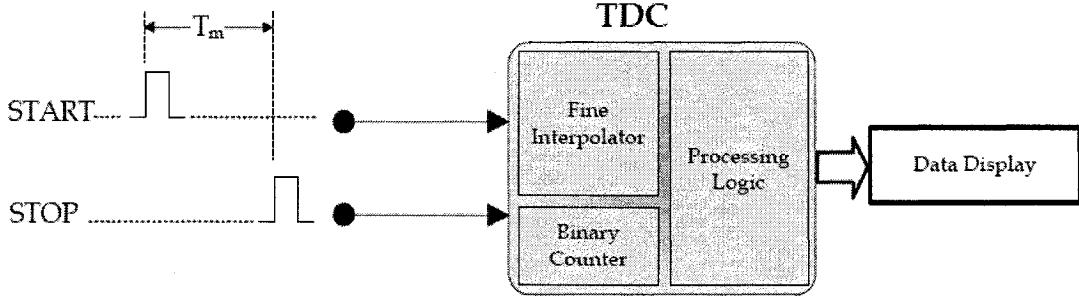

With  $T_m$  defined by eq. 1.1, typical TDC circuits consist of a coarse time counter running with some reference clock and a fine interpolator as depicted in Figure 1.3.

Figure 1.3: Further refined view of a TDC circuit

While digital counter design methods have been pretty much well established to address coarse timing measurements, the focus of the recent research efforts have mostly been in the area of time interpolators to provide finer resolutions. In theory, a particular time interpolator slicing the reference clock period into  $N$  equal intervals will achieve a resolution of  $T_{REF} / N$ . In practice, however, the finer resolution of the interpolator is affected by factors such as the quantization error, signal jitter in reference clock signal, offset errors and other design-dependent factors. Throughout the years, researchers have come up with many TDC solutions, each targeting a particular performance metric of the TDC. Some of the early-proposed solutions are further discussed in the next chapter.

## 1.1 General Terms and Characteristics

Similar to any electronic circuit, a TDC comes with its own performance metrics that are of interest and concern to designers during the design phase. Some of the important terms and characteristics associated with TDC circuits are as follows:

**Measurement Resolution:** The smallest time unit that a time interval  $T_m$  can be described with is referred to as the measurement resolution. It is the smallest time

quantity that can be discriminated in a timing measurement. For instance, a measured time interval  $T_m = 25.6$  ns has a resolution of 0.1ns or 100 picoseconds.

**Dynamic/Measurement Range:** Usually extended by a binary counter, the dynamic or measurement range is the maximum time interval measurable by a TDC.

**Conversion/Measurement Time:** Conversion time of a TDC can be defined as the processing time of the interval to be measured from the detection of the STOP pulse up to the binary word or any other form used to represent the time interval.

**Dead time:** The shortest time required by a TDC from the end of a measurement to come back to the initial ready state is commonly referred as conversion dead time.

**Multi-hit:** This is the capability of a TDC circuit to measure more than one time interval, possibly from a common reference point in time, in a single measurement phase without having to go back to an initial ready state.

**Pulse-Pair Resolution (PPR):** PPR is the minimum distance in time between two incoming data pulses that can be measured by a multi-hit capable TDC circuit.

**Non-Linearity Errors:** Similar to analog-to-digital and digital-to-analog converters, the transfer curve of a TDC circuit may deviate from the expected response. Non-linearity of a converter is a measure of output deviation from the expected values under differential and integral non-linearity errors. *Differential non-linearity* refers to the difference between the actual time width corresponding to a digital code and the ideal one. *Integral non-linearity* of a TDC refers to the difference between the actual code transition points and a line connecting the ideal end points of the conversion.

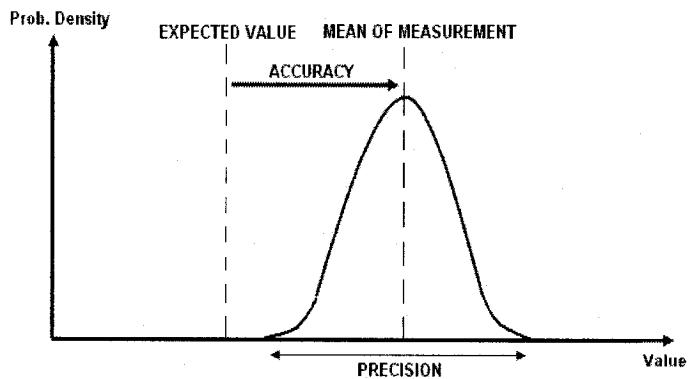

**Measurement Precision:** Precision of the measurement refers to the degree of coherence among several time interval measurements.

**Measurement Accuracy:** Accuracy portrays the degree of agreement of the measured value with respect to the actual value of the unknown.

While all the associated characteristics are important to meet the requirements for proper operation of a TDC circuit, researchers have given more attention to certain parameters such as resolution, dead time, dynamic range, and multi-hit capability. Timing resolution is important as it reduces the measurement uncertainty while increasing the accuracy of the measurement. In Time-of-Flight experiments, an improved timing resolution has a direct impact on the effectiveness of the particle identification [12]. Reducing the dead time increases performance of the TDC circuit by increasing the number of applicable measurements in a given time window. Similarly, having a large dynamic range, a TDC is no longer confined to short time intervals and it can process relatively larger time intervals.

## 1.2 Project Intent

Understanding the importance of the various characteristics of the TDC circuits, the current work focuses on achieving high measurement resolution, low dead time, and multi-hit capability with a reasonable pulse-pair resolution. Furthermore, inspired by the recent advances in the programmable logic devices such as Field Programmable Gate Array (FPGA), we have chosen to focus on portability and low cost aspects of designs targeting FPGA technology by implementing our prototype on the low-cost SPARTAN-3 FPGA from the SPARTAN™ family by XILINX. A partial objective of the project is also to explore the degree of feasibility of timely constraint designs such as a TDC on an FPGA platform. FPGA-targeted designs have several advantages such as low cost, fast prototyping and implementation, re-usability of silicon, easy integration within a larger system, and the flexibility of upgrading and modification of the design over the ASIC counterpart. However, despite the various advantages, designs targeting FPGA platforms may suffer from relatively lower performance compared to the corresponding ASIC solution.

With a general introduction to TDC circuits in this chapter, the organization of the subsequent chapters is as follows: Chapter 2 compiles a study of several time

interpolation methodologies used in accomplishing high resolution TDC circuits. In chapter 3 some important performance metrics are discussed. Chapter 4 presents the proposed TDC solution by discussing all details relating to the design and implementation. The test strategies along with simulation/experimental results are presented in chapter 5. Finally, the concluding remarks and the future work are contained in chapter 6.

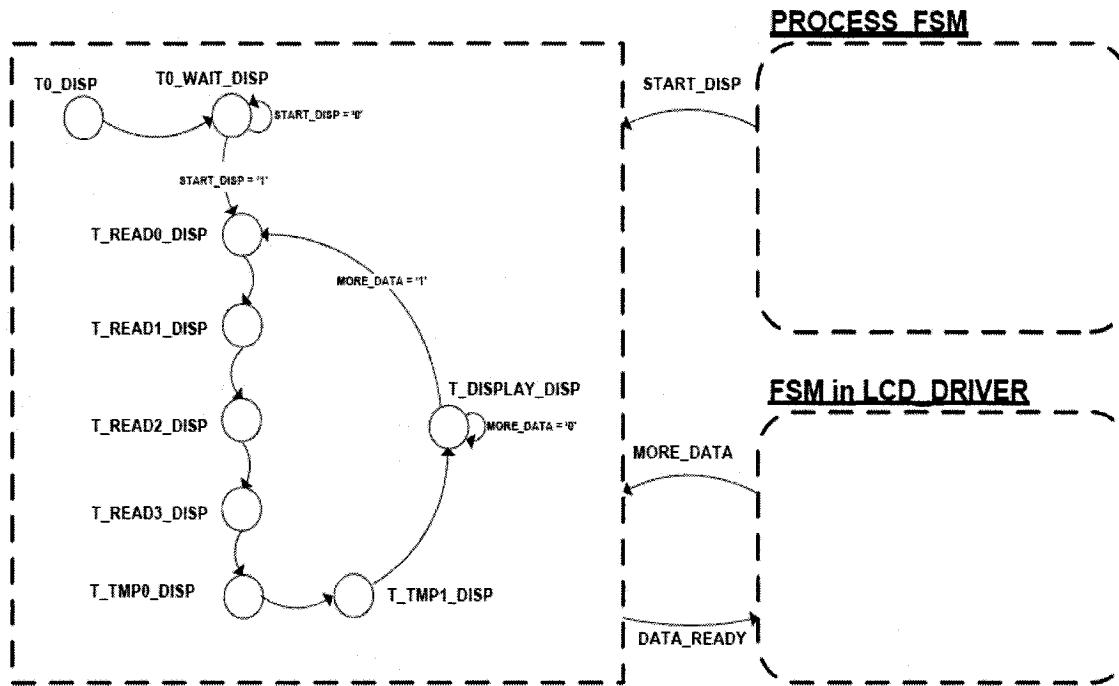

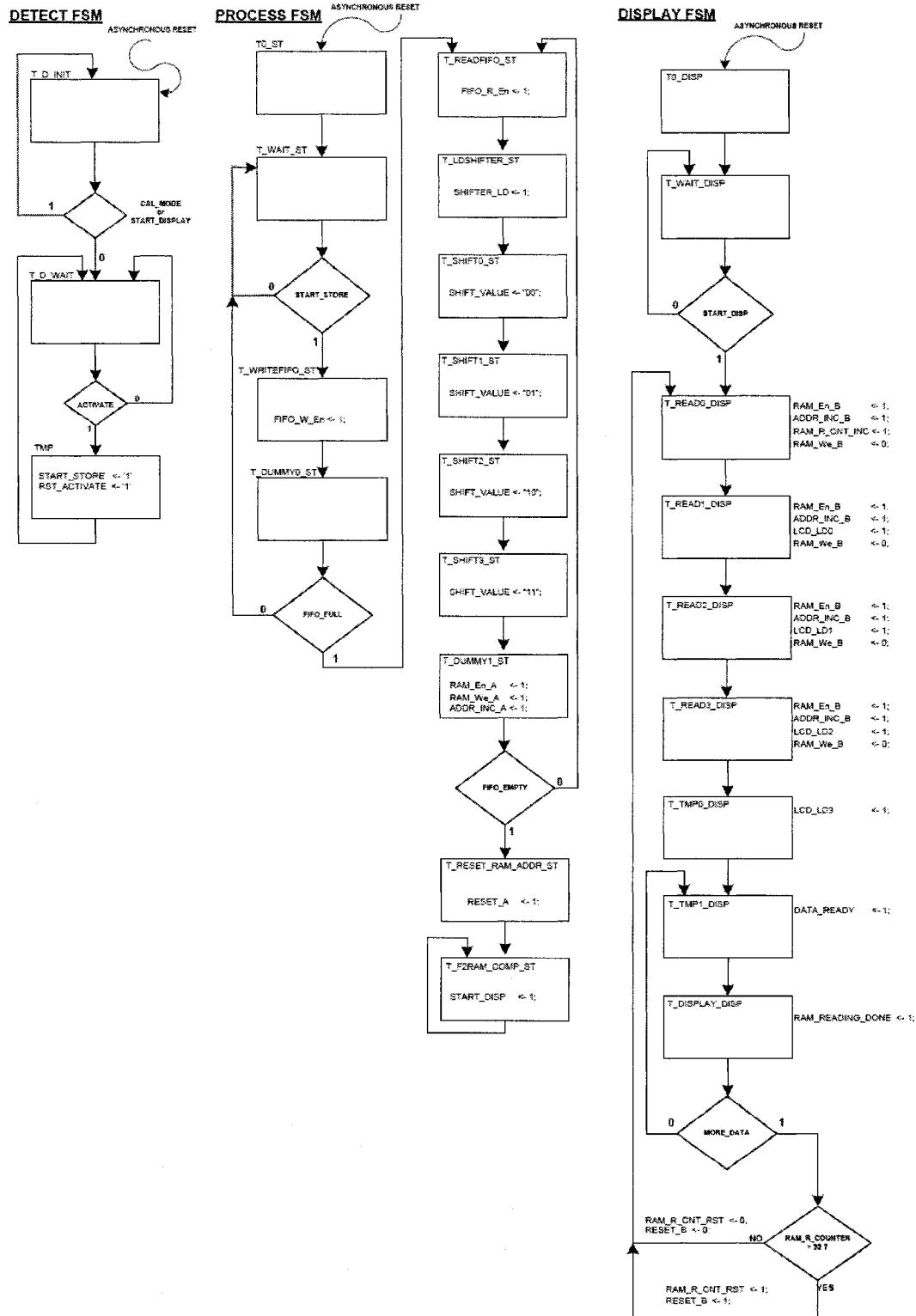

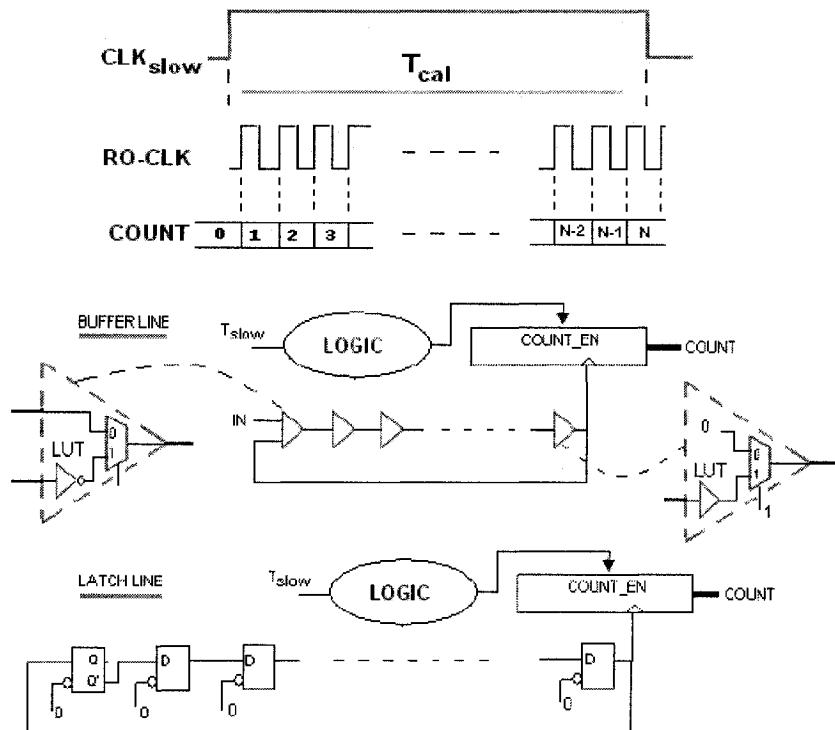

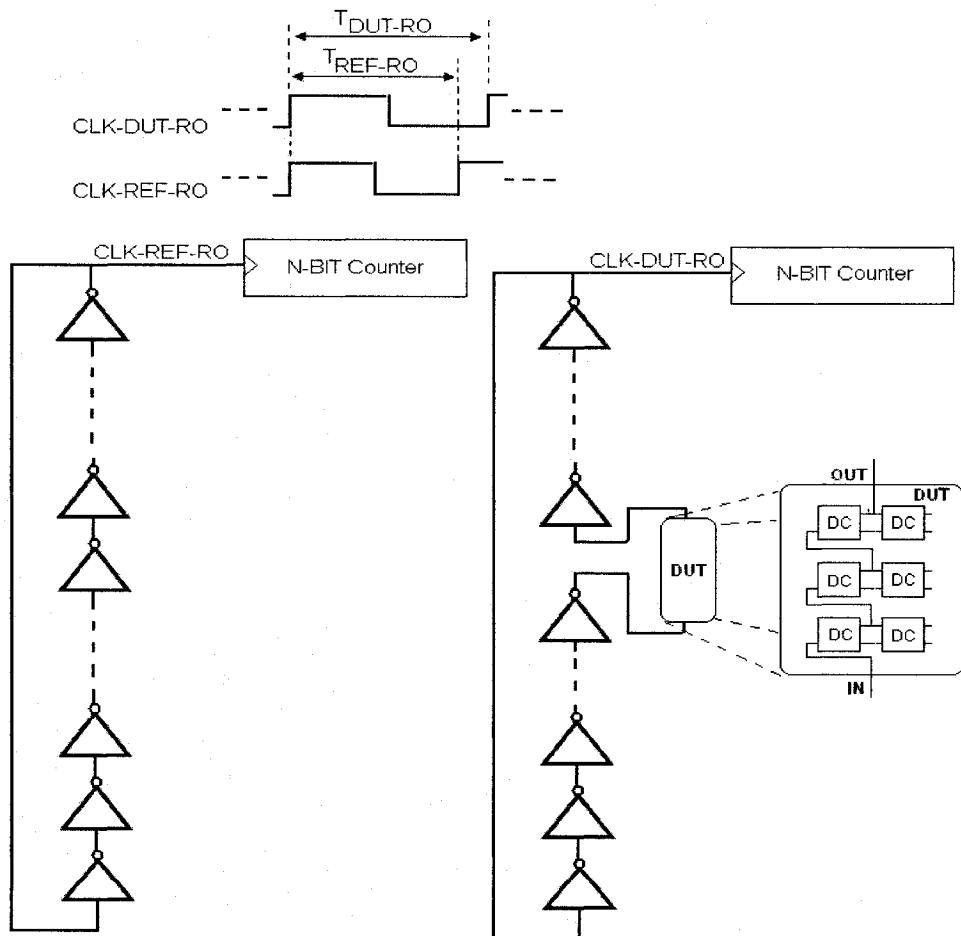

## CHAPTER 2 - OVERVIEW OF TIME INTERPOLATION TECHNIQUES