**Titre:** Accélération d'une plateforme d'encodage MPEG-4 à l'aide de

Title: processeurs configurables

**Auteur:** Simon Provost

Author:

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Provost, S. (2006). Accélération d'une plateforme d'encodage MPEG-4 à l'aide de

processseurs configurables [Master's thesis, École Polytechnique de Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/7921/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7921/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & Gabriela Nicolescu

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

ACCÉLÉRATION D'UNE PLATEFORME D'ENCODAGE MPEG-4 À L'AIDE

DE PROCESSEURS CONFIGURABLES

SIMON PROVOST

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

DÉCEMBRE 2006

Library and

Archives Canada

Bibliothèque et

Archives Canada

Published Heritage

Branch

Direction du

Patrimoine de l'édition

395 Wellington Street

Ottawa ON K1A 0N4

Canada

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-25567-4

*Our file* *Notre référence*

ISBN: 978-0-494-25567-4

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

---

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

ACCÉLÉRATION D'UNE PLATEFORME D'ENCODAGE MPEG-4 À L'AIDE

DE PROCESSEURS CONFIGURABLES

présenté par: PROVOST Simon

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. LANGLOIS Pierre, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

Mme NICOLESCU Gabriela, Doct., membre et codirectrice de recherche

M. ABOULHAMID Mostapha, Ph.D., membre

## REMERCIEMENTS

Je tiens tout d'abord à remercier mon directeur de recherche, M. Guy Bois, et ma codirectrice, Mme Gabriela Nicolescu pour leur support tout au long de cette recherche. Je désire également remercier Guy, et lui offrir mes sympathies, pour avoir dû utiliser une bonne partie de ses soirées et fins de semaine pour lire ce présent document.

Je me dois de dire un gros merci à Bruno Lavigueur pour l'immense aide qu'il a apporté tout au long de cette recherche. Ses innombrables questions, commentaires et suggestions ont grandement facilité l'avancement des travaux réalisés. Les contributions de Bruno à cette recherche ont largement dépassé toutes les attentes. Encore une fois merci.

Mes collègues de travail ont également tenu un rôle important lors de ces travaux de recherche. À cet égard, j'aimerais remercier (dans aucun ordre précis): J-F, Frank, Frank (vous déciderez entre vous lequel est lequel), Pat, Max, Cédric, Luc, Morti, David, Fouad, Nick et tous les autres membres du Circus. Ils ont su contribuer par des discussions intéressantes sur les projets de recherche, mais surtout par des activités moins constructives et hautement divertissantes. Grâce à eux, je sors de l'université riche de plusieurs amitiés supplémentaires.

Bien qu'ils n'aient pas contribué directement aux travaux de recherche, j'aimerais remercier plusieurs personnes pour leur aide dans des activités connexes. Tout d'abord, Alex et Réjean, nos deux techniciens du GRM pour leur excellent support et efficacité. Par la suite, Madeleine, Jeanne, Chantal, Marie-Yannick et Ghislaine pour avoir été toujours si serviable.

Je tiens à remercier mes parents pour m'avoir toujours appuyés dans mes choix de carrière et m'avoir enduré chez eux toutes ces années. Finalement, j'aimerais remercier Chantal Perreault pour son support inconditionnel et pour avoir apporté une aide bien plus grande qu'elle ne saurait le croire.

## RÉSUMÉ

Le marché des systèmes embarqués et systèmes sur puce modernes connaît une croissance impressionnante depuis quelques années. Les outils et techniques de conception classiques ne permettent plus de rencontrer les contraintes du marché en matière de coûts, de puissance de calcul et de délai de conception. Pour répondre à ces nouveaux défis, le domaine des systèmes sur puce a vu apparaître plusieurs techniques ou outils visant à accélérer le développement et augmenter la puissance de calcul tout en gardant les coûts faibles et un bon niveau de flexibilité.

Les processeurs configurables sont un de ces outils ayant vu récemment le jour. Cette nouvelle classe de processeurs, grâce à l'ajout d'instructions spécialisées, vise à offrir un niveau de performance rivalisant avec celui d'un couple processeur général et coprocesseur. Par contre, ces processeurs possèdent l'avantage d'être plus flexibles étant donné qu'ils permettent de maintenir une solution entièrement logicielle. De plus, les outils fournis avec ces processeurs offrent un soutien à la conception des instructions spécialisées et dans certains cas offrent même de les déterminer automatiquement, ce qui permet d'accélérer le délai de conception et réduit le risque d'erreurs. Une des principales contributions de cette recherche est de montrer comment les instructions spécialisées peuvent être utilisées pour réaliser des gains importants et de présenter les résultats obtenus pour une application d'encodage MPEG-4.

Un autre aspect vers lequel se sont penchés les concepteurs de systèmes sur puce est le développement de systèmes sur puce multiprocesseurs. Ces systèmes visent à atteindre la performance voulue en distribuant une application sur plusieurs processeurs. Malheureusement, l'ajout de plusieurs processeurs complexifie considérablement le développement du système à cause de tous les problèmes de synchronisation, de cohérence de données, de communication entre différents éléments hétérogènes et de

congestion. Dans le but de favoriser la conception de tels systèmes, des outils ont été développés afin d'élever le niveau d'abstraction lors de la conception de plateformes, masquant ainsi plusieurs des problèmes reliés aux plateformes multiprocesseurs. Par exemple, la bibliothèque SystemC permet de modéliser un système complet, comme le fait VHDL, mais en utilisant le langage C++. Il existe également des plateformes de développement à haut niveau d'abstraction permettant de facilement brancher, simuler et faire la synthèse de plusieurs composants d'une plateforme et qui automatisent une bonne partie du processus de conception d'un système sur puce multiprocesseurs.

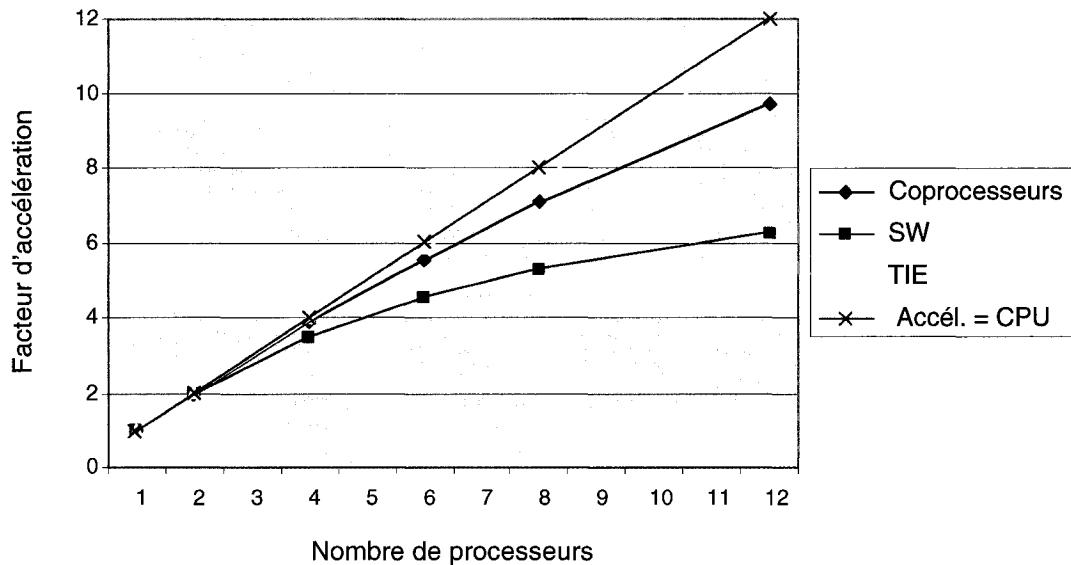

La deuxième contribution principale de cette recherche est d'utiliser une plateforme de développement à haut niveau d'abstraction, nommée StepNP, pour simuler un système sur puce multiprocesseurs utilisant des processeurs configurables. Nous montrerons qu'un tel système permet d'obtenir des gains en performance très intéressants et que la puissance de calcul croît presque linéairement avec le nombre de processeurs en l'absence de contention.

## ABSTRACT

Modern embedded systems and systems on chip have known an impressive growth in the last few years. Traditional tools and design techniques are becoming insufficient to meet the constraints of the market in regard to costs, processing power and design time. To answer these new challenges, the field of systems on chip saw the appearance of several techniques or tools aimed at accelerating the development cycle and increasing the processing power while keeping the costs low and a good level of flexibility.

Configurable processors are one of these tools which appeared recently. This new class of processors, thanks to the addition of specialized instructions, aims at offering a level of performance competing with that of a general processor coupled with a coprocessor. However, these processors also have the advantage of being more flexible since they make it possible to maintain an entirely software solution. Moreover, the tools provided with these processors offer a support to the design of the specialized instructions and in certain cases even offer to determine them automatically, which makes it possible to accelerate the design time and reduces the risk of errors. One of the main contributions of this research is to show how the specialized instructions can be used to obtain important speedup and to present results obtained for an MPEG-4 encoding application.

Another aspect towards which systems on chip designers are leaning is the development of multiprocessors systems on chip. These systems aim at reaching the performance needed by distributing an application over several processors. Unfortunately, the addition of several processors complexes considerably the development of the system because of all the problems related to synchronization, data coherency, communication between various heterogeneous elements and congestion. In the hope of supporting the design of such systems, tools were developed to raise the level of

abstraction when designing platforms, thus masking several of the problems related to multiprocessors platforms. For example, the SystemC library makes it possible to model a complete system, as with VHDL, but by using the C++ language. There are also high abstraction level development platforms which allow to easily connect, simulate and make the synthesis of several components of a platform and which automate a good part of the development process of a multiprocessors system on chip.

The second main contribution of this research is to use a high level development platform, named StepNP, to simulate a multiprocessors system on chip using configurable processors. We will show that such a system makes it possible to obtain very interesting performance speedups and that the computing power scales very well with the number of processors.

**TABLE DES MATIÈRES**

|                                                                                                   |       |

|---------------------------------------------------------------------------------------------------|-------|

| REMERCIEMENTS . . . . .                                                                           | iv    |

| RÉSUMÉ . . . . .                                                                                  | v     |

| ABSTRACT . . . . .                                                                                | vii   |

| TABLE DES MATIÈRES . . . . .                                                                      | ix    |

| LISTE DES FIGURES . . . . .                                                                       | xiii  |

| LISTE DES ACRONYMES . . . . .                                                                     | xv    |

| LISTE DES TABLEAUX . . . . .                                                                      | xviii |

| LISTE DES ANNEXES . . . . .                                                                       | xix   |

| INTRODUCTION . . . . .                                                                            | 1     |

| CHAPITRE 1 REVUE DE LA CONCEPTION AU NIVEAU SYSTÈME ET<br>DES PROCESSEURS CONFIGURABLES . . . . . | 7     |

| 1.1 Conception au niveau système . . . . .                                                        | 7     |

| 1.1.1 Langages de design au niveau système . . . . .                                              | 7     |

| 1.1.1.1 SystemC . . . . .                                                                         | 8     |

| 1.1.1.2 SystemVerilog . . . . .                                                                   | 11    |

| 1.1.1.3 Autres langages . . . . .                                                                 | 13    |

| 1.1.2 Plateformes de développement . . . . .                                                      | 16    |

| 1.1.2.1 SPACE . . . . .                                                                           | 16    |

| 1.1.2.2 Virtual Platform Designer . . . . .                                                       | 18    |

| 1.1.2.3 Roses . . . . .                                                                           | 21    |

| 1.1.2.4 Autres Plateformes . . . . .                                                              | 23    |

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| 1.2 Processeurs configurables . . . . .                                   | 25 |

| 1.2.1 Xtensa . . . . .                                                    | 27 |

| 1.2.1.1 Xtensa T1050 . . . . .                                            | 27 |

| 1.2.1.2 Xtensa LX . . . . .                                               | 28 |

| 1.2.2 Autres processeurs configurables . . . . .                          | 33 |

| 1.2.2.1 Stretch . . . . .                                                 | 33 |

| 1.2.2.2 Garp . . . . .                                                    | 34 |

| 1.2.2.3 APU . . . . .                                                     | 35 |

| 1.2.2.4 Triton-Builder . . . . .                                          | 36 |

| CHAPITRE 2 EXTENSION DU JEU D'INSTRUCTIONS POUR UN EN-                    |    |

| CODEUR MPEG-4 . . . . .                                                   | 37 |

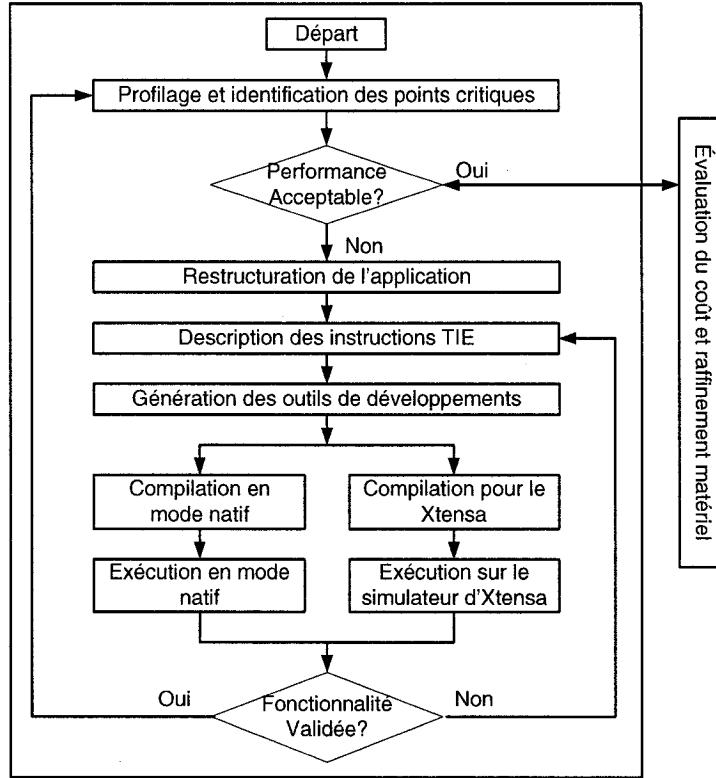

| 2.1 Méthodologie . . . . .                                                | 37 |

| 2.1.1 Méthodologie de Quinn et Lavigueur . . . . .                        | 37 |

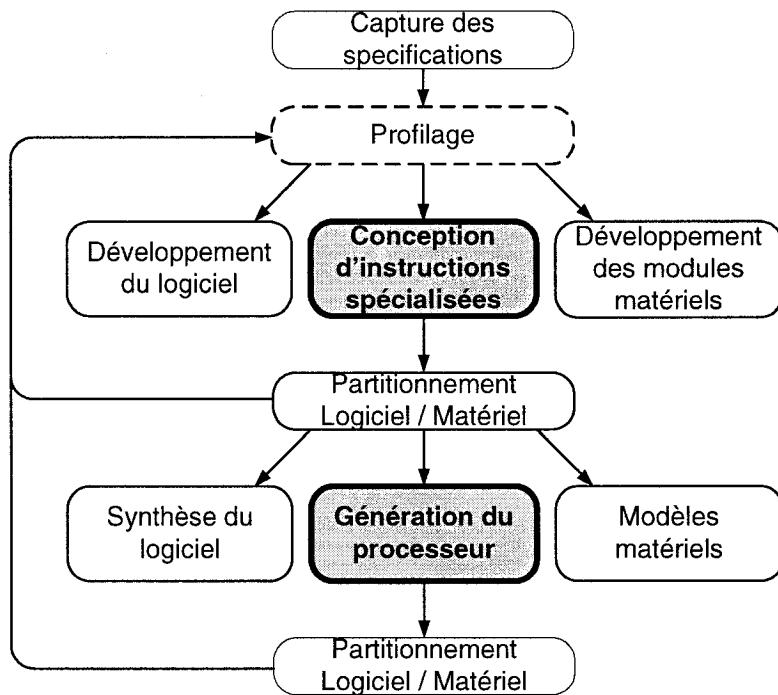

| 2.1.2 Méthodologie de Tensilica . . . . .                                 | 39 |

| 2.1.3 Méthodologie utilisée . . . . .                                     | 41 |

| 2.2 Instructions TIE . . . . .                                            | 44 |

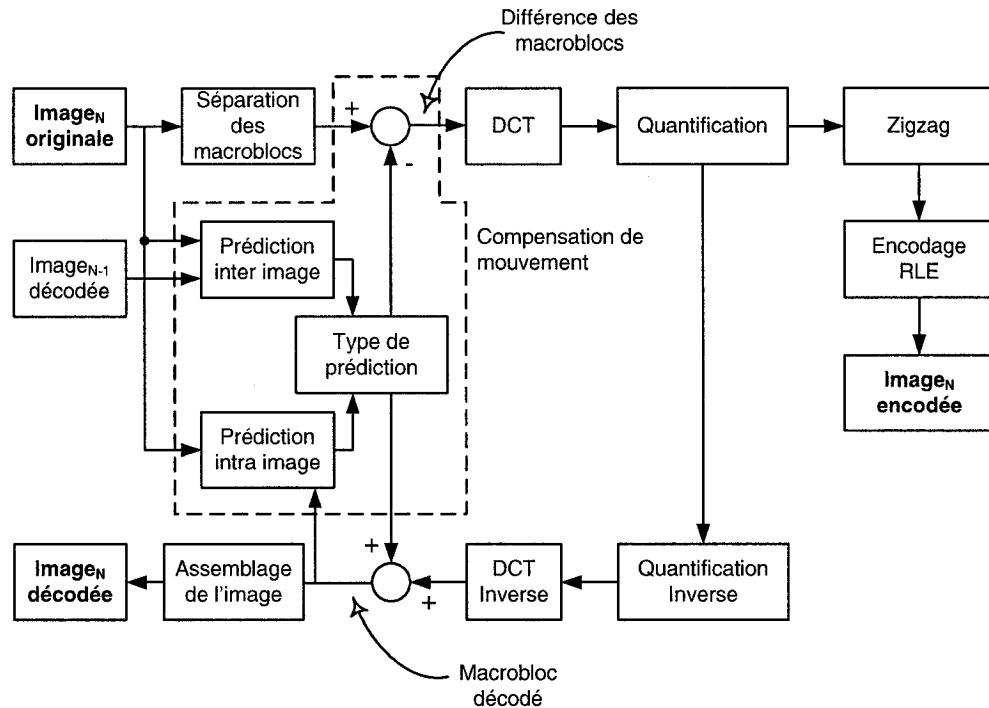

| 2.3 Application d'encodage MPEG-4 . . . . .                               | 46 |

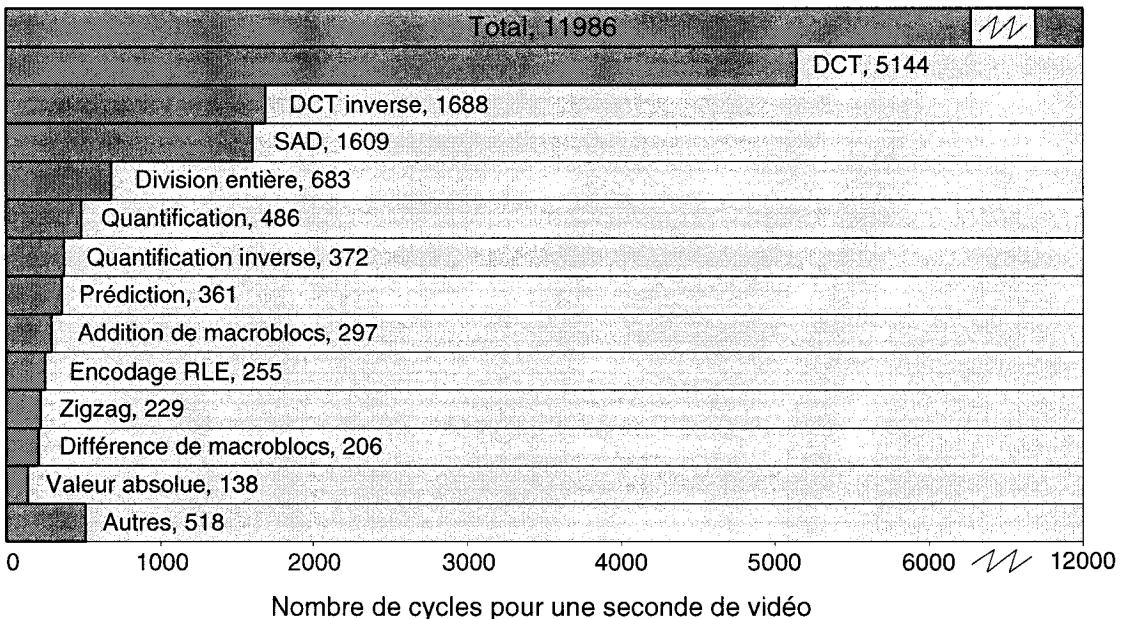

| 2.3.1 Profilage de l'application et configuration du processeur . . . . . | 50 |

| 2.4 Conception d'instructions spécialisées pour le MPEG-4 . . . . .       | 51 |

| 2.4.1 Détails des instructions spécialisées . . . . .                     | 52 |

| 2.4.1.1 DCT . . . . .                                                     | 52 |

| 2.4.1.2 DCT inverse . . . . .                                             | 55 |

| 2.4.1.3 SAD . . . . .                                                     | 55 |

| 2.4.1.4 Quantification et quantification inverse . . . . .                | 57 |

| 2.4.1.5 Addition et soustraction de blocs . . . . .                       | 58 |

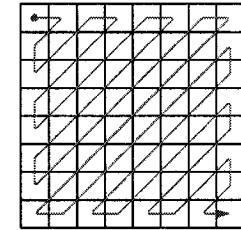

| 2.4.1.6 Zigzag . . . . .                                                  | 59 |

| 2.4.1.7 Encodage RLE . . . . .                                            | 60 |

| 2.4.2 Résultats obtenus . . . . .                                         | 62 |

|                                                                                |                                                   |     |

|--------------------------------------------------------------------------------|---------------------------------------------------|-----|

| 2.4.3                                                                          | Améliorations possibles . . . . .                 | 65  |

| CHAPITRE 3 SIMULATION D'UN MPSOC . . . . .                                     |                                                   | 67  |

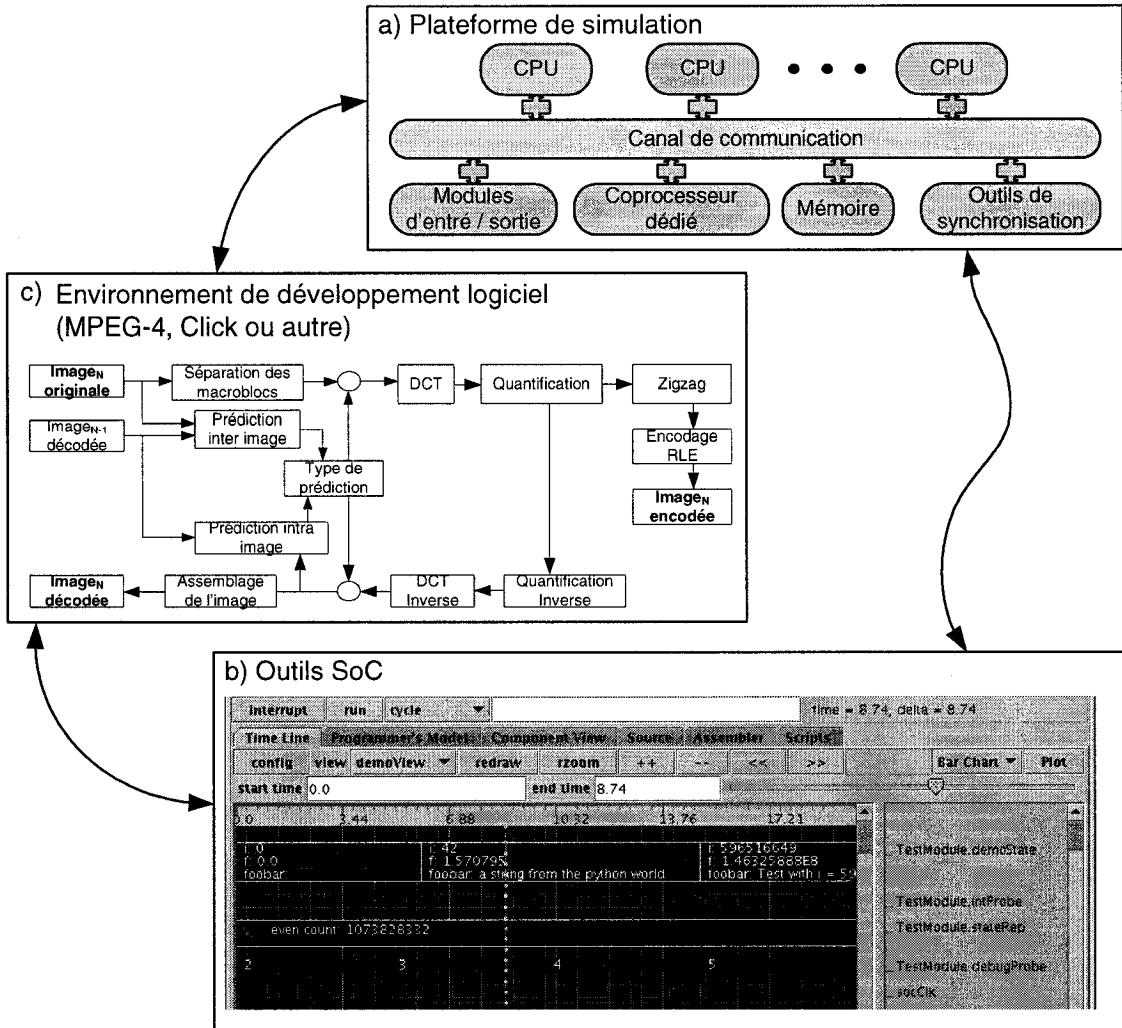

| 3.1                                                                            | La plateforme StepNP . . . . .                    | 68  |

| 3.1.1                                                                          | Environnement de développement logiciel . . . . . | 68  |

| 3.1.1.1                                                                        | Modèle DSOC . . . . .                             | 70  |

| 3.1.1.2                                                                        | Modèle SMP . . . . .                              | 72  |

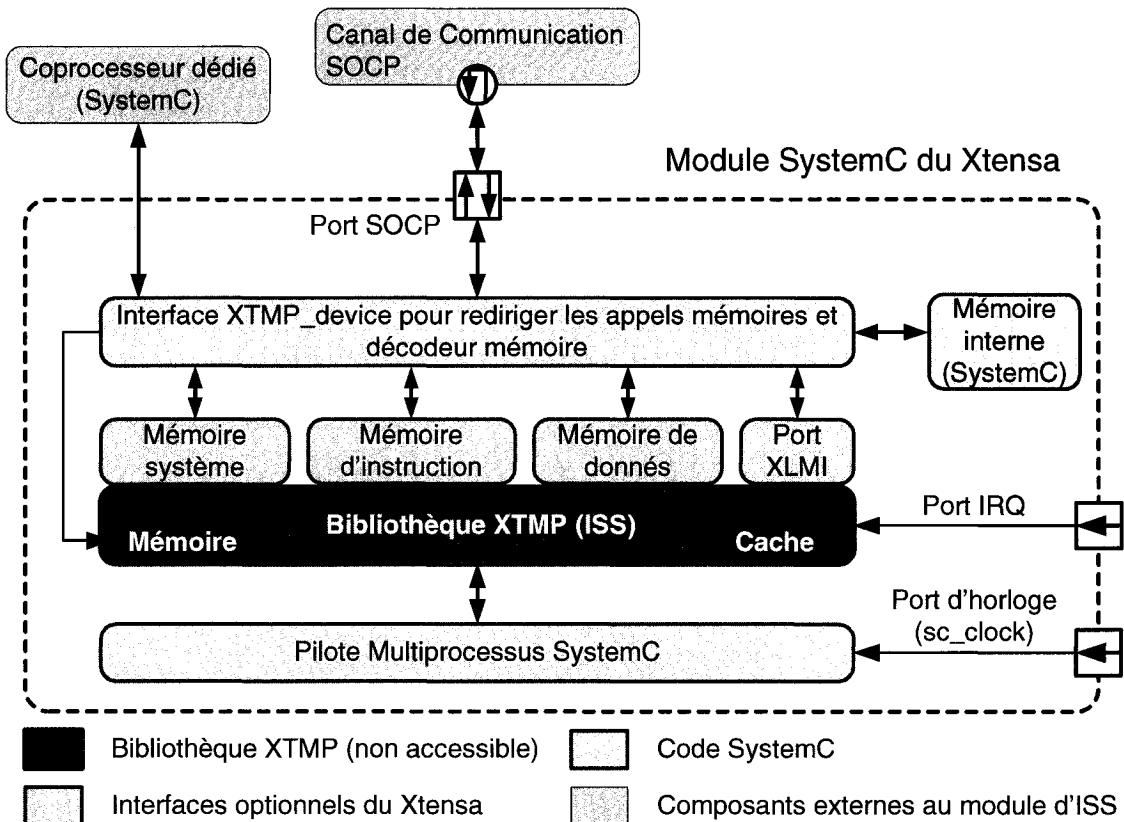

| 3.2                                                                            | Intégration du Xtensa dans StepNP . . . . .       | 73  |

| 3.2.1                                                                          | Résumé des travaux antérieurs . . . . .           | 73  |

| 3.2.2                                                                          | Ajouts réalisés . . . . .                         | 75  |

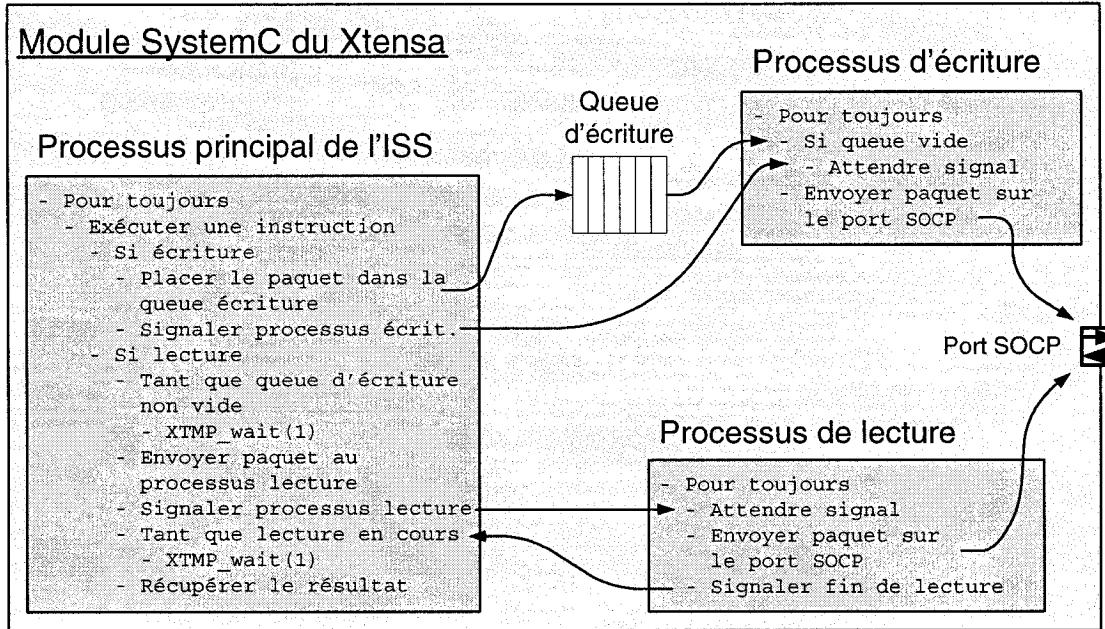

| 3.2.2.1                                                                        | Processus d'écriture et de lecture . . . . .      | 78  |

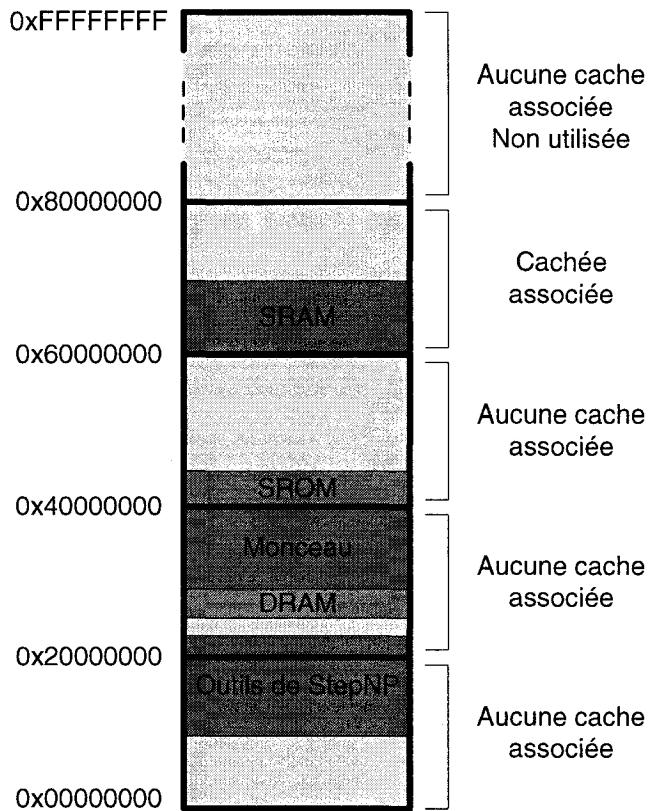

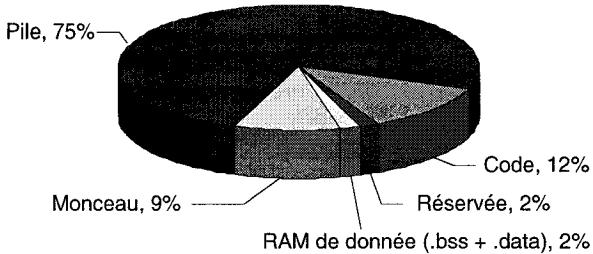

| 3.2.2.2                                                                        | Gestion de la mémoire et de la cache . . . . .    | 80  |

| 3.2.3                                                                          | Améliorations possibles . . . . .                 | 85  |

| CHAPITRE 4 CONCEPTION D'UNE PLATEFORME D'ENCODAGE MPEG-4 POUR STEPNP . . . . . |                                                   | 87  |

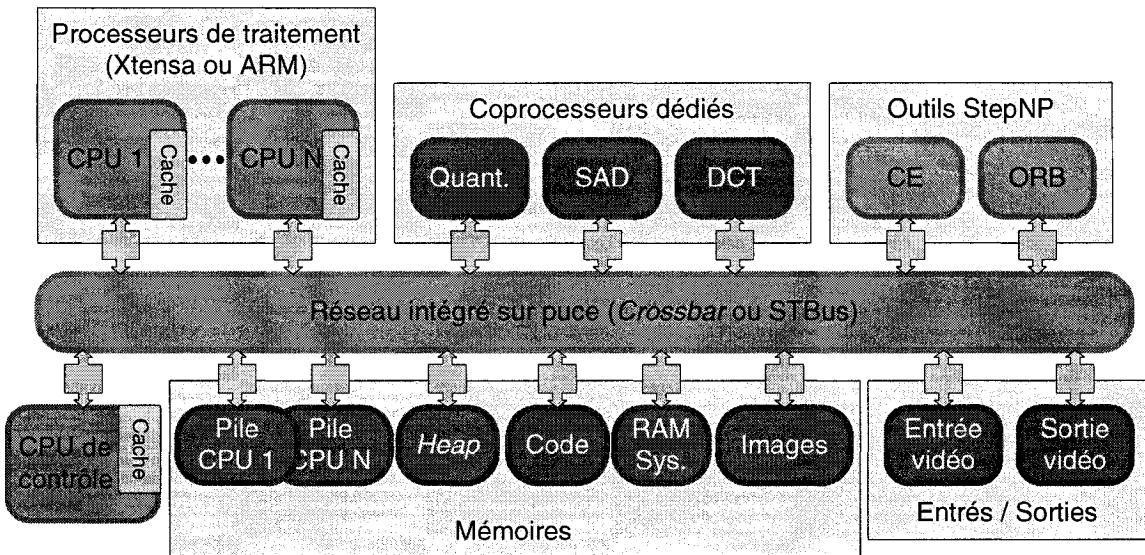

| 4.1                                                                            | Description de la plateforme . . . . .            | 87  |

| 4.1.1                                                                          | Plateforme matérielle . . . . .                   | 87  |

| 4.1.2                                                                          | Plateforme logicielle . . . . .                   | 90  |

| 4.1.3                                                                          | Contributions . . . . .                           | 92  |

| 4.2                                                                            | Résultats de simulation . . . . .                 | 92  |

| 4.2.1                                                                          | Latence de communication nulle . . . . .          | 93  |

| 4.2.2                                                                          | Canal avec latence sans contention . . . . .      | 97  |

| 4.2.3                                                                          | Canal avec latence et contention . . . . .        | 97  |

| 4.3                                                                            | Améliorations possibles . . . . .                 | 98  |

| CONCLUSION ET TRAVAUX FUTURS . . . . .                                         |                                                   | 101 |

| RÉFÉRENCES . . . . .                                                           |                                                   | 105 |

## LISTE DES FIGURES

|            |                                                                                                                                                                           |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1   | Écart de productivité . . . . .                                                                                                                                           | 3  |

| Figure 1.1 | Niveaux de raffinement de SPACE . . . . .                                                                                                                                 | 17 |

| Figure 1.2 | Environnement de Roses . . . . .                                                                                                                                          | 22 |

| Figure 1.3 | Position des processeurs configurables . . . . .                                                                                                                          | 25 |

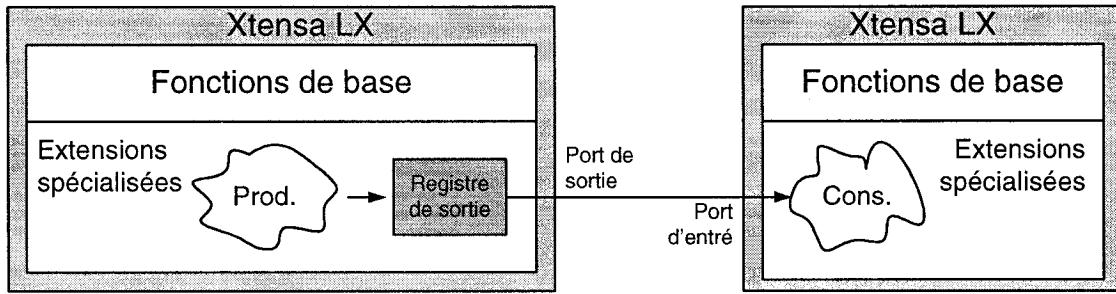

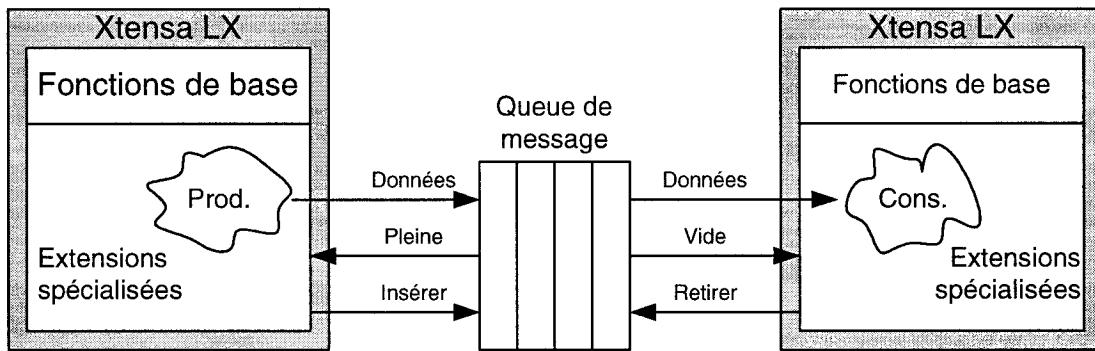

| Figure 1.4 | Schéma d'un port TIE . . . . .                                                                                                                                            | 32 |

| Figure 1.5 | Schéma d'une queue TIE . . . . .                                                                                                                                          | 32 |

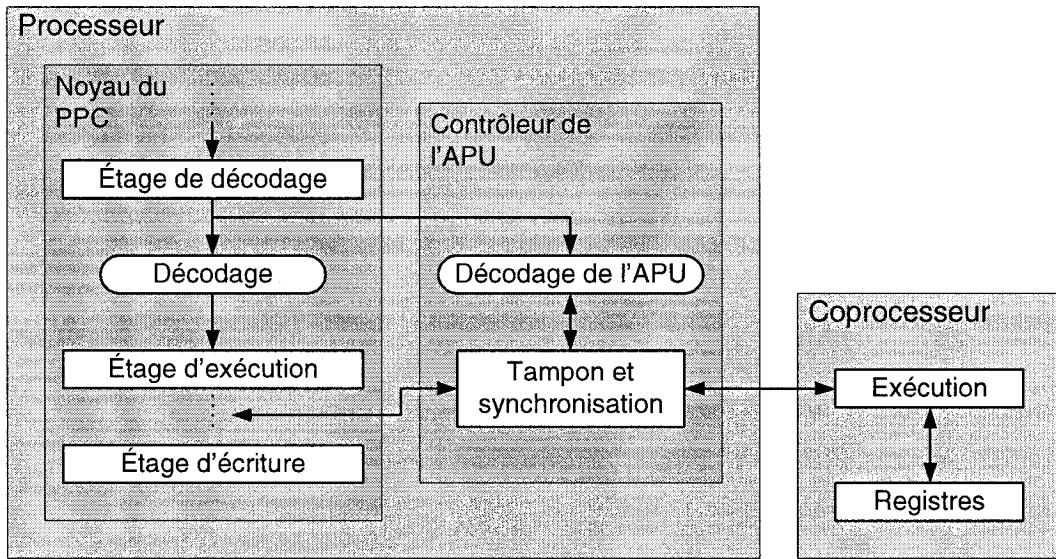

| Figure 1.6 | APU de Xilinx . . . . .                                                                                                                                                   | 36 |

| Figure 2.1 | Méthodologie de codesign de Quinn et Lavigueur . . . . .                                                                                                                  | 38 |

| Figure 2.2 | Méthodologie de Tensilica . . . . .                                                                                                                                       | 40 |

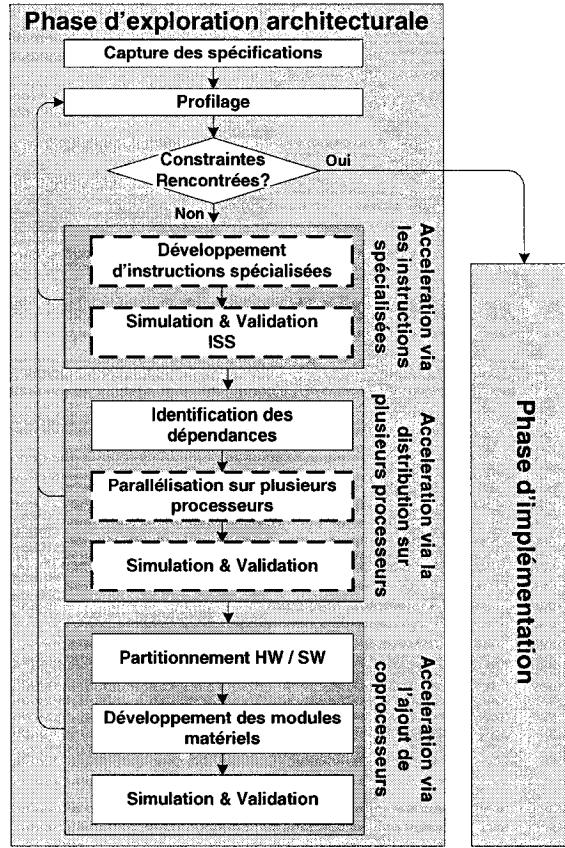

| Figure 2.3 | Méthodologie utilisée . . . . .                                                                                                                                           | 42 |

| Figure 2.4 | Encodage MPEG-4 . . . . .                                                                                                                                                 | 47 |

| Figure 2.5 | Zigzag . . . . .                                                                                                                                                          | 49 |

| Figure 2.6 | Profilage de l'application MPEG-4 . . . . .                                                                                                                               | 52 |

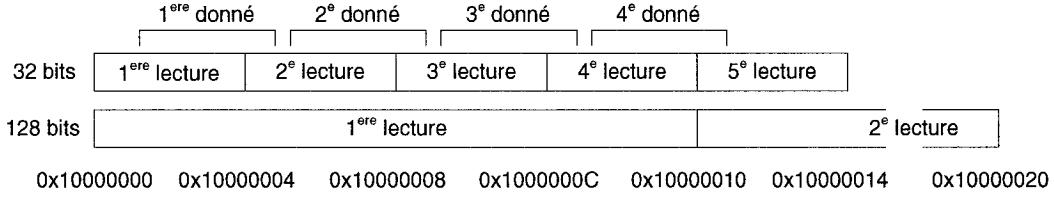

| Figure 2.7 | Multiples accès non alignés . . . . .                                                                                                                                     | 56 |

| Figure 3.1 | Les trois environnements de StepNP . . . . .                                                                                                                              | 69 |

| Figure 3.2 | Module Xtensa intégré à StepNP . . . . .                                                                                                                                  | 76 |

| Figure 3.3 | Les trois processus SystemC du module Xtensa . . . . .                                                                                                                    | 79 |

| Figure 3.4 | Zones mémoire du Xtensa . . . . .                                                                                                                                         | 83 |

| Figure 3.5 | Distribution des accès mémoire . . . . .                                                                                                                                  | 85 |

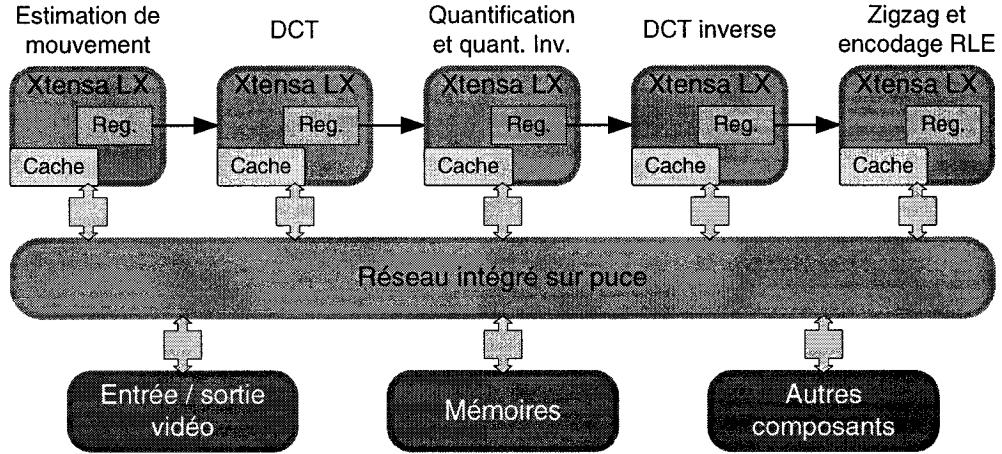

| Figure 4.1 | Plateforme d'encodage MPEG-4 . . . . .                                                                                                                                    | 88 |

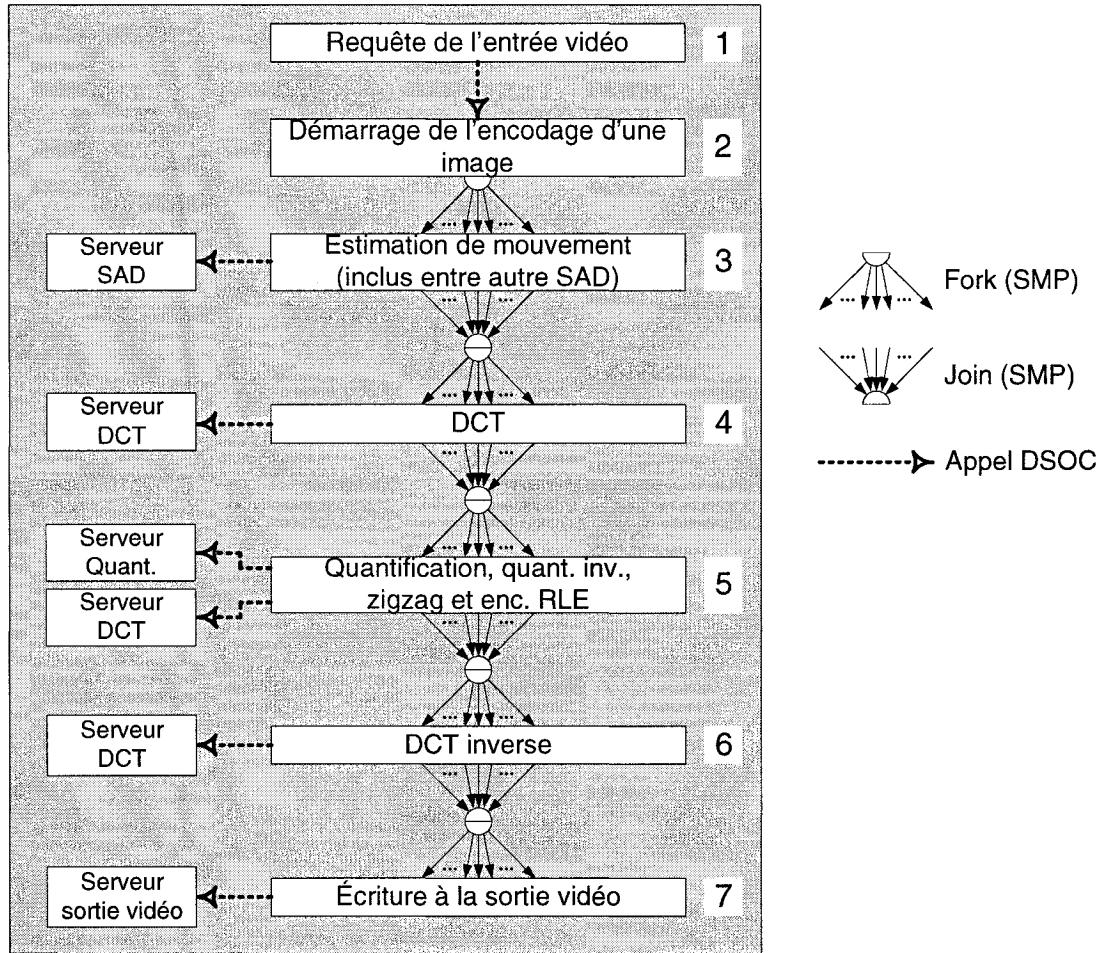

| Figure 4.2 | Flot de contrôle de l'application MPEG-4 . . . . .                                                                                                                        | 91 |

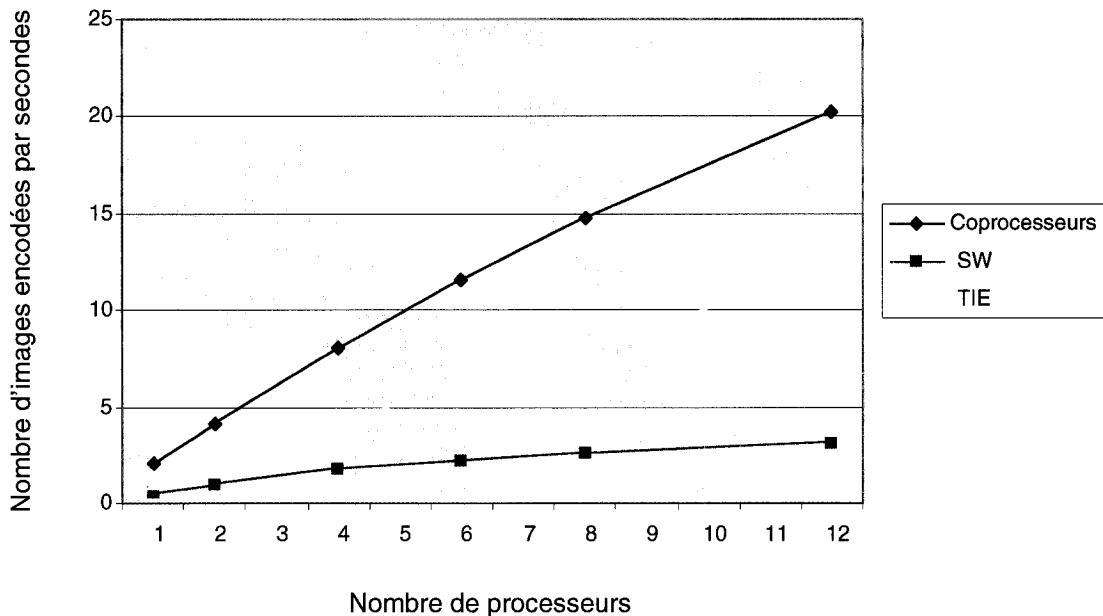

| Figure 4.3 | Vitesse d'encodage pour une latence de communication nulle .                                                                                                              | 93 |

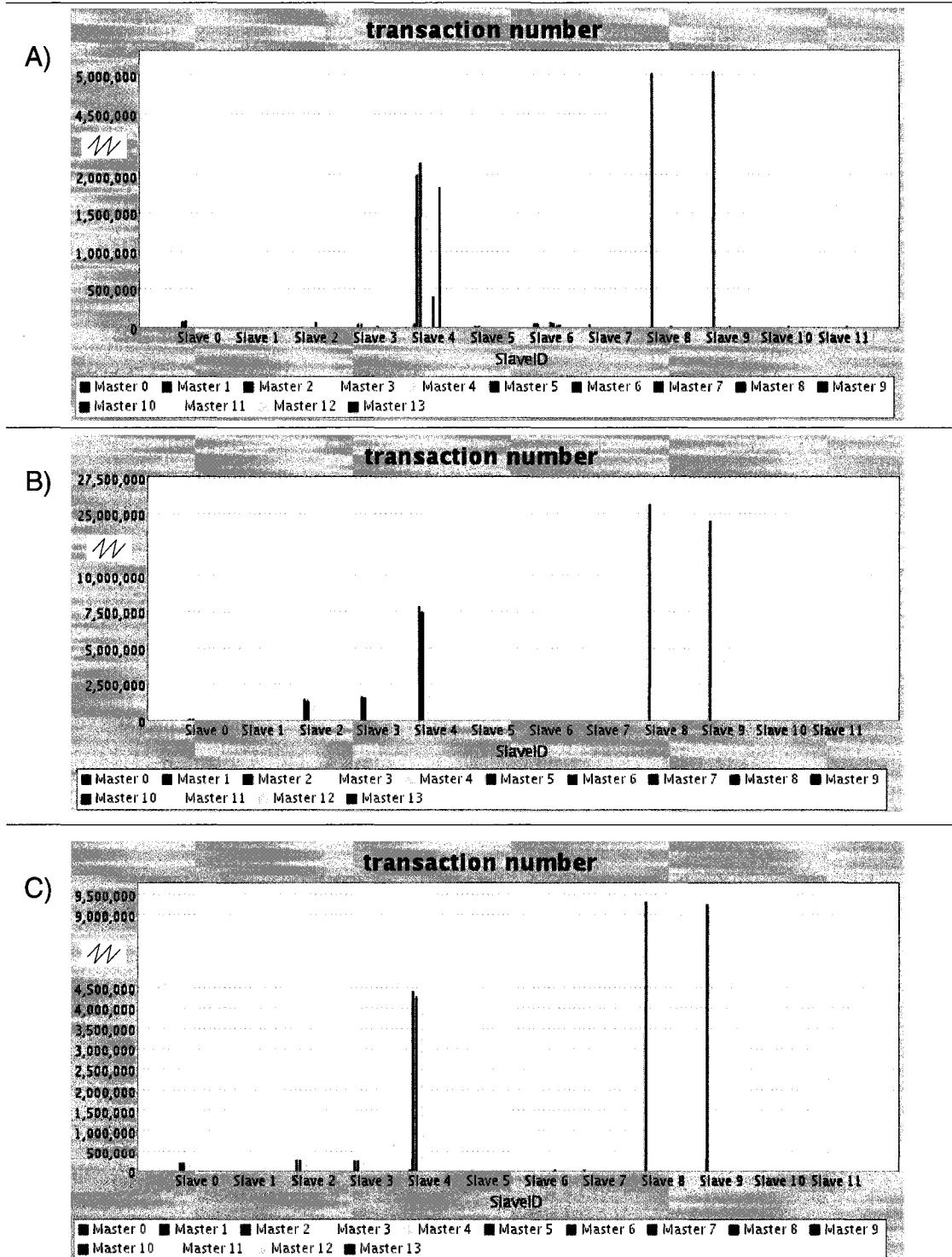

| Figure 4.4 | Nombre de transactions pour une simulation à quatre processeurs. A) Cas des coprocesseurs. B) Cas entièrement logiciel.<br>C) Cas des instructions spécialisées . . . . . | 95 |

| Figure 4.5 | Facteur d'accélération en fonction du nombre de processeurs .                                                                                                             | 96 |

|            |                                                                   |     |

|------------|-------------------------------------------------------------------|-----|

| Figure 4.6 | Distribution de type flot de données avec les Xtensa LX . . . . . | 99  |

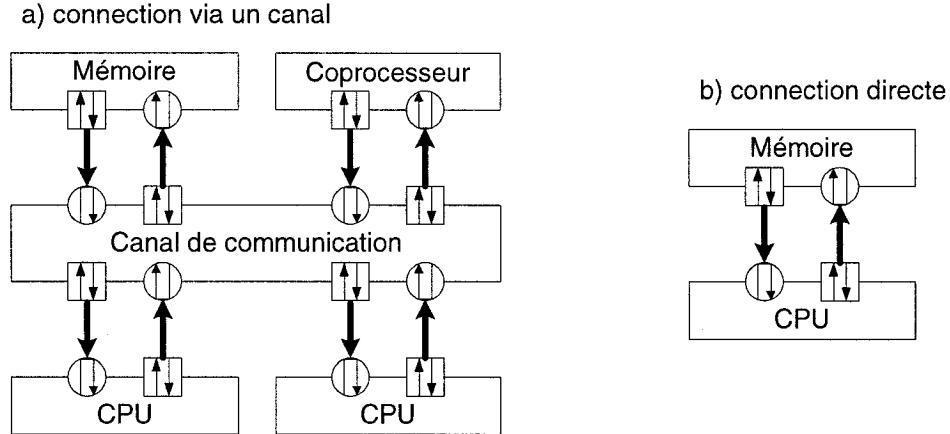

| Figure I.1 | Communications dans StepNP . . . . .                              | 115 |

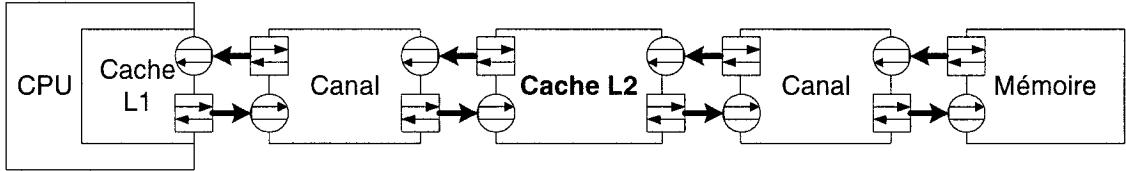

| Figure I.2 | Cache L2 dans StepNP . . . . .                                    | 116 |

## LISTE DES ACRONYMES

|                  |                                                 |

|------------------|-------------------------------------------------|

| <b>AMBA</b>      | Advanced Microcontroller Bus Architecture       |

| <b>ANSI</b>      | American National Standards Institute           |

| <b>API</b>       | Application Programming Interface               |

| <b>APU</b>       | Auxiliary Processing Unit                       |

| <b>ArchiFlex</b> | Architecture Flexible                           |

| <b>ASIC</b>      | Application Specific Integrated Circuit         |

| <b>ASIP</b>      | Application Specific Instructions Set Processor |

| <b>BCA</b>       | Bus Cycle Accurate                              |

| <b>CE</b>        | Concurrency Engine                              |

| <b>CAO</b>       | Conception Assistée par Ordinateur              |

| <b>CIL</b>       | Common Intermediate Language                    |

| <b>CORBA</b>     | Common Object Request Broker Architecture       |

| <b>DCOM</b>      | Distributed Component Object Model              |

| <b>DCT</b>       | Discrete Cosine Transform                       |

| <b>DSP</b>       | Digital Signal Processing                       |

| <b>DFG</b>       | Dataflow Graph                                  |

| <b>DSOC</b>      | Distributed System Object Component             |

| <b>DSP</b>       | Digital Signal Processing                       |

| <b>ESL</b>       | Electronic System Level                         |

| <b>FLIX</b>      | Flexible-Length Instructions Extensions         |

| <b>FPGA</b>      | Field Programmable Gate Array                   |

| <b>GIPS</b>      | Giga-Instructions Par Secondes                  |

| <b>GPP</b>       | General Purpose Processor                       |

| <b>HDL</b>       | Hardware Description Language                   |

| <b>HW</b>        | Hardware                                        |

| <b>IC</b>        | Integrated Circuit                              |

|               |                                                                 |

|---------------|-----------------------------------------------------------------|

| <b>IMC</b>    | Interface Method Call                                           |

| <b>ISA</b>    | Instruction Set Architecture                                    |

| <b>ISEF</b>   | Instruction Set Extension Fabric                                |

| <b>ISS</b>    | Instruction Set Simulator                                       |

| <b>LISA</b>   | Language for Instruction Set Architecture                       |

| <b>MAC</b>    | Multiply And Accumulate                                         |

| <b>MESCAL</b> | Modern Embedded Systems, Compilers, Architectures and Languages |

| <b>MPE</b>    | Message Passing Engine                                          |

| <b>MPEG-4</b> | Motion Picture Expert Group 4                                   |

| <b>MPSoC</b>  | Multiprocessor System on Chip                                   |

| <b>NoC</b>    | Network on Chip                                                 |

| <b>NOP</b>    | No Operation                                                    |

| <b>OCP</b>    | Open Core Protocol                                              |

| <b>ORB</b>    | Object Request Broker                                           |

| <b>OSCI</b>   | Open SystemC Initiative                                         |

| <b>PE</b>     | Processing Element                                              |

| <b>RISC</b>   | Reduced Instruction Set Computing                               |

| <b>RPC</b>    | Remote Procedure Call                                           |

| <b>RLE</b>    | Run Length Encoding                                             |

| <b>RTL</b>    | Register Transfer Level                                         |

| <b>RTOS</b>   | Real Time Operating System                                      |

| <b>SAD</b>    | Sum of Absolute Differences                                     |

| <b>SCIDE</b>  | SystemC Integrated Development and Debug Environment            |

| <b>SIMD</b>   | Single Instruction Multiple Data                                |

|               |                                                                                         |

|---------------|-----------------------------------------------------------------------------------------|

| <b>SISSMA</b> | SPACE Engine for Synchronization of SystemC Multiprocessor / Multithreaded Applications |

| <b>SoC</b>    | System on Chip                                                                          |

| <b>SocGen</b> | SoC Generation                                                                          |

| <b>SocMon</b> | SoC Monitor                                                                             |

| <b>SOCP</b>   | SystemC Open Core Protocol                                                              |

| <b>SMP</b>    | Symmetric Multiprocessing                                                               |

| <b>SPACE</b>  | SystemC Partitioning of Architectures for Codesign of Embedded Systems                  |

| <b>StepNP</b> | System-Level Exploration Platform for Network Processors                                |

| <b>SW</b>     | Software                                                                                |

| <b>TF</b>     | Timed functionnal                                                                       |

| <b>TIE</b>    | Tensilica Instruction Extension                                                         |

| <b>TLM</b>    | Transaction Level Modeling                                                              |

| <b>TTL</b>    | Task Transaction Level                                                                  |

| <b>UAL</b>    | Unité Arithmétique et Logique                                                           |

| <b>UTF</b>    | Untimed Functionnal                                                                     |

| <b>VCC</b>    | Virtual Component Co-Design                                                             |

| <b>VHDL</b>   | VHSIC Hardware Description Language                                                     |

| <b>VHSIC</b>  | Very High Speed Integrated Circuit                                                      |

| <b>VLIW</b>   | Very Long Instruction Word                                                              |

| <b>XLMI</b>   | Xtensa Local Memory Interface                                                           |

| <b>XPRES</b>  | Xtensa processor extension synthesis                                                    |

| <b>XTMP</b>   | Xtensa Modeling Protocol                                                                |

**LISTE DES TABLEAUX**

|             |                                                                |    |

|-------------|----------------------------------------------------------------|----|

| Tableau 2.1 | Opérations disponibles dans le langage TIE . . . . .           | 46 |

| Tableau 2.2 | Exploration de la cache . . . . .                              | 50 |

| Tableau 2.3 | Table pour l'encodage RLE . . . . .                            | 61 |

| Tableau 2.4 | Résultats des instructions TIE . . . . .                       | 63 |

| Tableau 3.1 | Zones mémoire du Xtensa . . . . .                              | 82 |

| Tableau 4.1 | Identification des maîtres et esclaves . . . . .               | 94 |

| Tableau 4.2 | Délai d'encodage d'une image avec et sans latence . . . . .    | 97 |

| Tableau 4.3 | Résultats de simulation avec contention sur le canal . . . . . | 98 |

## **LISTE DES ANNEXES**

ANNEXE I

PLATEFORME MATÉRIELLE ET OUTILS SOC DE STEPNP113

## INTRODUCTION

Le marché des systèmes embarqués, depuis quelques années, ne cesse de croître. On doit cette avancée en grande partie à la loi de Moore, établie en 1965 par Gordon Moore co-fondateur de IBM, qui prédisait à l'époque que le nombre de transistors sur une même puce augmenterait de 50% par année. Quarante ans plus tard, cette loi tient toujours la route et les développeurs de circuits intégrés (IC, *Integrated Circuit*) travaillent d'arrache pied pour maintenir cette croissance. L'intégration d'un nombre toujours grandissant de composants électroniques sur une simple puce, qu'on appelle système sur puce (SoC, *System On Chip*), permet aux compagnies de systèmes embarqués de séduire leurs clients avec de plus en plus de fonctionnalités. On n'a qu'à regarder le marché des téléphones cellulaires pour voir l'effet de cette croissance. Il n'y a pas si longtemps, un téléphone ne servait, sans aucune surprise, qu'à téléphoner. Aujourd'hui, ils permettent d'observer son interlocuteur, de prendre des photos et films, d'envoyer et recevoir des courriels et une panoplie d'autres caractéristiques intéressantes. Avec la barrière de un milliard de transistors à l'horizon [13], il y a fort à parier que cette croissance n'est pas finie.

Une technique utilisée récemment, et rendue possible grâce à l'augmentation de la densité de transistors sur une puce, pour combler les demandes toujours plus grandes en puissance de calcul est la combinaison de plusieurs processeurs sur une même puce. Cette technique a fait naître le concept de systèmes sur puce multiprocesseurs (MPSoC, *Multiprocessor System on Chip*). Les MPSoC, par contre, sont plus qu'un simple système visant à augmenter la puissance de calcul par l'ajout de processeurs [36]. Ceux-ci sont des architectures complexes réunissant ensemble un grand nombre de composants dédiés et hétérogènes, comme différents types de processeurs, de mémoires et de canaux de communication.

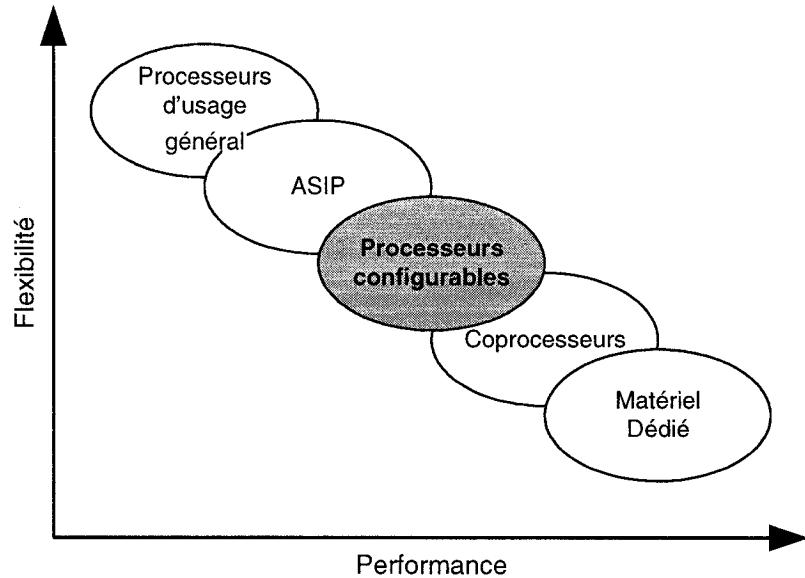

Un autre élément important ayant récemment fait son entrée dans le domaine des systèmes embarqués est l'utilisation d'unités de traitement configurables. Ce nouveau type d'unité de calcul présente principalement les mêmes avantages qu'un processeur d'usage général (GPP, *General Purpose Processor*) mais possède en plus la possibilité d'étendre le jeu d'instruction avec des instructions spécialisées et de modifier certains paramètres architecturaux. Avant cette venue, le traitement d'une application était séparé entre des partitions logicielles, lentes mais plus facilement programmables et plus flexibles, et des partitions matérielles, rapides mais complexes à développer. Maintenant, grâce aux unités de traitement configurables, les concepteurs de SoC disposent d'une alternative à mi chemin entre les deux.

## Problématique

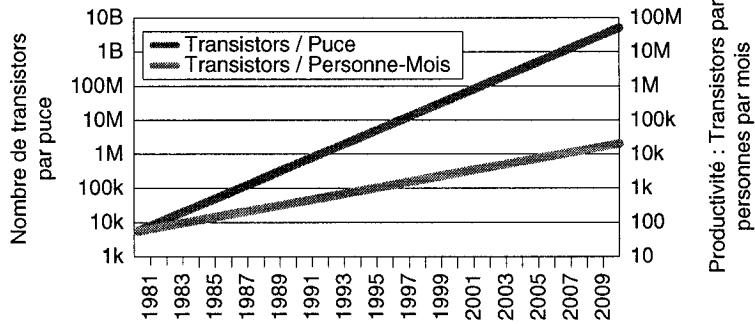

Bien que la loi de Moore suit son cours, les développeurs de systèmes embarqués sont confrontés à bien d'autres problèmes que l'intégration de plusieurs transistors sur une même puce. Comme le montre la figure 1, la productivité des développeurs, liée en grande partie aux outils de programmation, ne croît pas au rythme de la loi de Moore, ce qui crée un écart de productivité important qui ne cesse de grandir avec les années. Le besoin d'avoir des outils de développement adéquats est illustré par le fait que ceux-ci soient le facteur numéro un influençant le choix d'un produit plutôt que celui d'un compétiteur [60].

Par le passé, pour atteindre les nouveaux standards de performance et rencontrer les délais de mise en marché, les concepteurs de systèmes ont toujours dû éléver le niveau d'abstraction de leurs designs. Ainsi, nous sommes passés de programmes écrits en assembleur à des langages haut niveau (e.g. C, Java), des dessins en portes logiques aux RTL (*Register Transfer Level*) (e.g. VHDL, Verilog). Nous en sommes arrivés à un point où le marché devra à nouveau éléver ce niveau d'abstraction pour tenir en

Figure 1 Écart de productivité

compte les nouveaux défis posés par les MPSoC.

Un des problèmes auxquels sont confrontés les développeurs de systèmes embarqués est au niveau de l'intégration des composants. L'approche classique pour la conception de SoC consiste à réaliser la partie matérielle du système en premier et la partie logicielle ensuite. Cette approche comporte son lot d'inconvénients. Premièrement, la difficulté, et par conséquent le délai, liée à la conception du logiciel croît exponentiellement avec les années. Cette situation vient en grande partie de la difficulté à distribuer et synchroniser adéquatement l'application sur l'ensemble des processeurs du système. La conception du logiciel a d'ailleurs remplacé la consommation de puissance au premier rang des facteurs nuisant à la continuation de la loi de Moore [31]. Deuxièmement, il est fort probable que la conception et la réalisation de la partie logicielle révèle des failles non anticipées dans la partie matérielle, ce qui peut nécessiter un retour en arrière et des retards importants [33]. Troisièmement, cette approche ne permet pas de tester plusieurs options de partitionnement puisque la partie matérielle précède la partie logicielle. Un autre problème relié à l'approche classique de conception est que les spécifications d'un système à concevoir sont décrites dans une langue native (e.g. anglais, français) et sont généralement très lourdes. Malgré tous les efforts pour les rendre les plus claires possible, ces spécifications restent généralement floues et sont la plus grande source

d'erreurs dans le design [44]. Finalement, pour tenir compte de l'arrivée des unités de traitement configurables dans le choix des composants, il est nécessaire de se doter d'outils permettant d'exploiter la conception d'instructions spécialisées.

Pour contrer les problèmes mentionnés, l'industrie a récemment vu l'apparition du concept d'*ESL* (*Electronic System Level*). La notion exacte d'*ESL* n'est pas encore bien définie, mais elle implique entre autre la modélisation des communications logicielles / matérielles, la conception au niveau système et l'élévation du niveau d'abstraction [40]. Cette nouvelle approche de conception possède plusieurs avantages considérables :

- Le modèle haut niveau constitue la spécification du système. Puisque celle-ci est écrite dans un langage exécutable / simulable, ceci permet d'éliminer toute ambiguïté et permet de vérifier plus aisément que l'implémentation correspond aux spécifications [12].

- Le développement de la partie logicielle peut débuter plus rapidement étant donné qu'un modèle de la partie matérielle est disponible plus tôt dans le processus de développement.

- Cette approche favorise une meilleure exploration architecturale. Un modèle décrit à un haut niveau d'abstraction est plus rapide à simuler qu'un modèle à bas niveau. De plus, comme le système entier est initialement décrit dans un seul langage, cela implique que le partitionnement logiciel / matériel n'est pas fixe. Ceci permet donc aux concepteurs de rapidement évaluer plusieurs possibilités d'architecture ou de partitionnement et de raffiner la meilleure solution pour le système.

- Le niveau système se prête bien à l'exploration des diverses possibilité offertes par les processeurs configurables puisque l'architecture n'est pas encore fixée [41].

## Objectifs

L'objectif principal de ce travail consiste à évaluer l'avantage offert par les processeurs configurables dans un système embarqué multiprocesseurs requérant une grande puissance de calcul. L'approche classique pour atteindre le niveau de performance requis consiste à utiliser plusieurs processeurs couplés de coprocesseurs dédiés. Nous visons à mesurer les gains qu'il est possible d'obtenir en utilisant des instructions spécialisées plutôt que des accélérateurs matériels conventionnels. De plus, la conception se fera à un haut niveau d'abstraction, permettant d'évaluer la facilité avec laquelle il est possible de modéliser un MPSoC complet. Bien que l'implémentation physique du circuit modélisé ne fasse pas partie des objectifs, le modèle haut niveau permettra d'obtenir des conclusions intéressantes sur l'utilisation des processeurs configurables dans un MPSoC.

## Méthodologie

Pour montrer l'atteinte des objectifs, nous utiliserons une application d'encodage MPEG-4 (*Motion Picture Expert Group 4*) comme cas de test. Cette application fut choisie puisqu'elle est très exigeante en puissance de calcul.

La méthodologie utilisée consistera à accélérer l'application en question à l'aide de deux grandes étapes. Premièrement, nous étendrons le jeu d'instruction standard d'un processeur configurable avec des instructions spécialisées, procurant un premier niveau d'accélération. Dans un deuxième temps, nous distribuerons l'application sur plusieurs processeurs configurables pour obtenir un gain supplémentaire. Par la suite, nous comparerons la vitesse d'encodage, en images par secondes, avec celle obtenue à l'aide d'une plateforme utilisant des processeurs d'usage général et des coprocesseurs dédiés.

## Contributions

La réalisation de ce travail entraîne deux principales contributions. En premier lieu, nous montrons comment il est possible d'obtenir des gains en performance très intéressants, pour une application d'encodage vidéo, en utilisant les processeurs configurables et particulièrement les instructions spécialisées. La deuxième contribution est l'intégration d'un modèle simulable du processeur Xtensa à l'intérieur de la plateforme de simulation haut niveau StepNP. La version de StepNP utilisée lors de cette recherche est plus récente que celle utilisée par Bruno Lavigueur [38]. On y inclut entre autre plusieurs nouvelles fonctionnalités visant principalement les MPSoC.

## Organisation du mémoire

Le reste du mémoire est divisé comme suit. Le chapitre 1 passe en revue un éventail des langages de conception au niveau système, des plateformes de développement à haut niveau d'abstraction et des processeurs configurables. Le chapitre 2 explique les techniques utilisées pour étendre le jeu d'instruction du processeur configurable et présente les résultats obtenus pour l'accélération d'une application d'encodage MPEG-4. Le chapitre 3 présente en détail la plateforme StepNP et les opérations nécessaires pour y intégrer un modèle du processeur Xtensa. Le chapitre 4 montre la plateforme multiprocesseurs d'encodage MPEG-4 réalisée à l'aide de StepNP et donne les résultats obtenus suite à l'ajout de processeurs configurables.

## CHAPITRE 1

### REVUE DE LA CONCEPTION AU NIVEAU SYSTÈME ET DES PROCESSEURS CONFIGURABLES

Comme il est expliqué dans l'introduction, ce chapitre présente un aperçu de diverses techniques récentes utilisées pour la conception de MPSoC. On y décrit dans un premier temps la conception au niveau système, soit plus précisément les langages qui l'accompagnent et les plateformes de développement disponibles. Dans un deuxième temps, on présente un éventail de processeurs configurables.

#### 1.1 Conception au niveau système

Pour résumer, la conception au niveau système est une élévation du niveau d'abstraction pour le design de systèmes embarqués. Comme il est expliqué dans l'introduction, ceci comporte plusieurs avantages notables et est nécessaire pour contrer les nouveaux problèmes apportés par les systèmes multiprocesseurs.

##### 1.1.1 Langages de design au niveau système

Les langages utilisés lors du développement classique d'un système embarqué sont mal adaptés pour le développement au niveau système. Les langages de conception matérielle comme VHDL ou Verilog sont évidemment adéquat pour le raffinement de la partie matérielle. Par contre, ces langages ne permettent pas de décrire le fonctionnement du système à un haut niveau d'abstraction. D'un autre côté, les langages de programmation comme le C/C++ permettent de décrire toute la

fonctionnalité d'un système à un haut niveau d'abstraction, mais ils ne sont pas bien adaptés pour modéliser les communications logicielles/matérielles et les composantes matérielles. De plus, ils ne permettent pas le raffinement vers un niveau d'abstraction plus bas. Pour combler ce problème, plusieurs langages ont été proposés pour permettre la conception au niveau système. Ces langages possèdent une combinaison de constructions propres aux langages de programmation haut niveau et aux langages de conception matérielle.

Le principal intérêt de ces langages est qu'ils permettent de conserver le même langage tout au long des étapes de raffinement. Comme mentionné précédemment, ceci permet d'évaluer plus aisément différents types de partitionnement. Autre avantage important, l'utilisation d'un langage unique permet de conserver les mêmes tests à chacune des différentes étapes et limite le risque d'erreurs liées à porter le système d'un langage à un autre.

#### 1.1.1.1 SystemC

SystemC fut développé et est maintenu par le consortium OSCI (*Open SystemC Initiative*), regroupant plusieurs entreprises telles Mentor, Coware, Synopsys et autres. SystemC n'est pas un nouveau langage à proprement parler, mais plutôt une bibliothèque de fonctionnalités ajoutées au populaire langage C++, et c'est d'ailleurs là une de ses principales forces. La bibliothèque offre deux principaux intérêts pour la conception au niveau système. Premièrement, on y retrouve plusieurs types d'éléments propres à la conception matérielle et deuxièmement, elle offre un noyau de simulation similaire à celui qu'on retrouve dans d'autres langages de conception matérielle tels VHDL [47].

Plusieurs éléments de modélisation en SystemC ont été empruntés d'autres HDL (*Hardware Description Language*). On retrouve, premièrement, le concept de

modules, comparable à une entité en VHDL, qui se traduit sous la forme d'une classe en C++ de laquelle hérite tous les modules du système. Ces modules peuvent également être créés de manière hiérarchique, permettant l'assemblage de systèmes complexes à partir de composants simples. La bibliothèque ajoute également les processus et la liste de sensibilité qui leur est associée, émulant ainsi le comportement concurrent inhérent aux systèmes matériels. Les processus peuvent également synchronisés sur des événements ou par des délais temporels. Un ajout intéressant apporté par la version 2.1 de SystemC est que ces processus peuvent être instanciés de manière statique, comme en VHDL, ou de manière dynamique en cours d'exécution, procurant ainsi plus de flexibilité au concepteur.

Un élément important apporté pas SystemC, et autres langages de conception au niveau système, est l'abstraction des communications entre les modules. On y introduit la notion de ports représentant les connections à un bas niveau d'abstraction. On y introduit également les canaux de communication et les interfaces, permettant de modéliser à un haut niveau d'abstraction les communications entre modules. Cette fonctionnalité permet de modéliser des protocoles de communication plus complexe comme ceux offerts par les réseaux sur puce (NoC, *Network on Chip*), qui sont devenu très populaires ces dernières années [9]. Les interfaces sont représentées par une fonction C qui peut être appelée par un port qui lui est connecté et qui peut passer n'importe quel type de donnée comme argument, comme par exemple une structure contenant les divers paramètres nécessaires, élevant ainsi le niveau d'abstraction. Ce type de communication est aussi appelé niveau transactionnel (TLM, *Transaction Level Modeling*) puisqu'on se concentre sur le passage de paquets en faisant abstraction des détails du protocole [14].

L'opération de test en SystemC constitue également un avantage d'utiliser ce langage. SystemC possède toute les fonctionnalités du langage C/C++, permettant ainsi la réalisation de bancs d'essais plus complexes que ce qu'il est possible en VHDL ou

en Verilog [24]. Ce banc d'essai prend la forme d'un programme C/C++ exécutable dans lequel on instancie et connecte nos différents modules.

Le noyau de simulation utilisé dans SystemC, basé sur un mécanisme d'évaluation et de mise à jour, est très similaire à celui qu'on retrouve dans VHDL et autres HDL. Le concept de delta cycles, fréquemment utilisé dans les langages de description matérielle, y est également présent. Le processus de simulation possède cinq grandes étapes qui sont brièvement décrites ci-dessous [46].

- 1 - Initialisation : Au début de la simulation, le système est initialisé et tous les processus sont exécutés, à l'exception de ceux sensibles à l'horloge ou que le programmeur a spécifié explicitement comme non initialisés.

- 2 - Évaluation : Le système exécute successivement tous les processus présents dans la liste des processus prêts. Le noyau de SystemC étant non préemptif, lorsqu'un processus est exécuté, il l'est jusqu'à ce qu'il se suspende lui-même suite à un appel à l'instruction `wait`, qui peut être explicite ou implicite du point de vue du programmeur. Encore une fois pour imiter le langage VHDL, les signaux ne sont pas mis à jour instantanément mais plutôt cédulés pour l'être à la phase 3.

- 3 - Mise à jour : Les signaux sont mis à jour suite aux changements ayant été apportés à l'étape 2.

- 4 - Notification d'un delta cycle : Dans le cas où un processus aurait demandé une attente ou une notification avec un délai d'un delta cycle (e.g. en utilisant `wait(0)`), on détermine la liste des processus sensibles à cet événement qui formeront la liste de processus prêts, et on retourne à l'étape 2.

- 5 - Notification d'un délai : Le temps de simulation est avancé jusqu'au prochain événement, la liste des processus prêts est déterminée et on passe à l'étape 2. Lorsqu'il n'existe aucun événement dans le futur, la simulation est terminée.

### 1.1.1.2 SystemVerilog

Comme son nom l'indique, ce langage est une extension du très populaire langage de conception matérielle Verilog. À l'origine, les développeurs de ce langage avaient deux objectifs principaux lors de sa conception [28]. Le premier était d'étendre les fonctionnalités de conception de Verilog, en partie en empruntant certaines des fonctionnalités présentes en VHDL. Le deuxième était d'augmenter le support offert par Verilog au niveau de la vérification.

Parmi les ajouts présents dans SystemVerilog, on retrouve plusieurs types de données pour mémoriser les entiers, points flottants ou signaux logiques. On y retrouve également le type Chandle (*C handle*) qui s'apparente à un pointeur sécuritaire tel qu'on les retrouve dans certains langages de programmation haut niveau. SystemVerilog possède également des types de données utilisées lors de la synchronisation interprocessus. Premièrement, on retrouve les événements, qui contrairement à SystemC, sont actifs pendant tout le cycle de simulation. Ainsi, lorsqu'un processus déclenche un événement, si un autre processus se met en attente de celui-ci par la suite mais au même cycle, le processus reprendra son exécution immédiatement. Outre les événements, SystemVerilog possède deux autres types de données de synchronisation soit les boîte de messages et les sémaphores. Pour favoriser la modélisation à un haut niveau d'abstraction et la réalisation de bancs d'essais, on a également ajouté la programmation orientée objet. SystemVerilog supporte la majorité des concepts reliés à ce type de programmation comme illustré ci-dessous :

- Encapsulation    - Héritage simple    - Classes abstraites    - Classes paramétrées

- Pointeur *this*    - Surcharge              - Polymorphisme        - Méthodes virtuelles

- Variables et méthodes statiques

On retrouve également plusieurs concepts dans SystemVerilog analogues à ceux de SystemC. Notamment, SystemVerilog possède les interfaces, permettant de séparer

les communications des modules, et permet de créer dynamiquement des processus.

La principale force de SystemVerilog vient de son support à la vérification et particulièrement des assertions. Premièrement, la syntaxe utilisée pour les assertions est la même que pour le design, permettant ainsi de les inclure directement dans le code aux endroits appropriés. Ensuite, on nous garantit que les assertions sont construites de manière à produire le même résultat lors de la simulation, qui est basée sur les événements, que lors d'une vérification formelle par des outils externes, qui est basée sur les cycles d'horloge [27]. Ceci est réalisé en échantillonnant les signaux impliqués dans les assertions à chaque cycle d'horloge lors de la simulation.

La nouveauté introduite par SystemVerilog est l'assertion concorrente qui permettent de décrire le comportement du système dans le temps. Pour définir ce comportement, on utilise les expressions séquentielles. Ceux-ci permettent de spécifier des expressions booléennes accompagnées de leur relation temporelle. Par exemple, si A et B sont des expressions booléennes, il serait possible de spécifier que A doit se produire un cycle après B. On peut également combiner les expression séquentielles ensembles pour spécifier qu'une séquence doit être inclue dans une autre, que deux séquences doivent se terminer en même temps ou encore que la fin d'une séquence doit entraîner le départ d'une autre. Un autre attrait très intéressant de SystemVerilog pour la vérification est la génération aléatoire de contraintes, qui est inclus à la programmation orientée objet. Ainsi, les contraintes sur un attribut d'une classe sont spécifiées à l'intérieur de la classe même. Au moment d'instancier la classe en question, l'utilisateur n'a qu'à indiquer qu'il veut générer aléatoirement les valeurs des paramètres et l'outil va déterminer une solution satisfaisant les contraintes données. Le solveur va toujours trouver une valeur respectant les contraintes s'il en existe une [27]. Une classe qui hérite d'une autre hérite également de toutes les contraintes qui lui sont associées, favorisant la réutilisation et le raffinement des contraintes pour des cas plus spécifiques.

### 1.1.1.3 Autres langages

Il existe bien d'autres langages permettant de faire de la conception de SoC au niveau système dont quelques uns sont décrits ci-dessous.

**SpecC** [29]: Originalement développé à l'université de Californie, SpecC est l'un des premiers langages de conception au niveau système à avoir vu le jour. Bien que la syntaxe soit basée sur celle du ANSI-C, il s'agit bien d'un nouveau langage et non d'une simple bibliothèque comme dans le cas de SystemC. L'objectif des concepteurs était de définir un langage permettant d'intégrer les spécifications et les premières phases de design lors de la conception d'un SoC. Comme pour la plupart des langages de conception au niveau système, un des principaux avantages de SpecC est de séparer les communications entre modules des modules eux-mêmes. SpecC permet de définir le comportement des différents modules en utilisant une classe nommée `behavior` et ces modules peuvent être connectés ensemble via des interfaces ou encore regroupés ensemble pour former des modules hiérarchiques. SpecC supporte quatre types d'exécution des modules hiérarchiques :

**Séquentielle** : Dans ce type d'exécution, les modules sont tous exécutés un à la suite de l'autre. Ce mode permet de simuler un comportement logiciel.

**Concurrent** : Tous les modules sont exécutés de manière concurrente, permettant de modéliser un comportement matériel.

**Pipeline** : Le mode pipeline permet d'exécuter plusieurs modules de manière concurrente, mais comme son nom l'indique, de manière pipelinée. Plus concrètement, le mode pipeline prend la forme d'une boucle `for` où chaque module représente un étage du pipeline. À la première itération, seulement le premier étage du pipeline est exécuté. À la seconde, les deux premiers étages sont exécutés en parallèle, et ainsi de suite jusqu'à ce que le pipeline soit rempli.

Lorsque la condition de la boucle *for* est fausse,  $n-1$  ( $n$  étant le nombre d'étages) itérations supplémentaires sont exécutées pour vider les étages du pipeline. Des variables de type *file* permettent également le passage de valeurs entre les étages du pipeline.

**Machine à états :** SpecC permet également de modéliser le comportement d'une machine à états. Dans ce mode, chaque module représente un état de la machine et le test de certaines conditions de sortie des modules permet de spécifier quel sera le module suivant à être exécuté.

**ESys.Net [37]:** ESys fut développé à l'université de Montréal par le groupe de recherche de M. Mostapha Aboulhamid. Le but premier de ce langage était de couvrir les lacunes présentes dans SystemC, comme le manque de support au déverminage et la difficulté de modéliser la partie logicielle d'un SoC. Alors que SystemC est une bibliothèque C++, c'est à l'aide de C# que le développement de ESys.Net fut réalisé. L'utilisation de .Net pour le développement d'un langage de conception à haut niveau offre plusieurs avantages soient :

- La gestion des processus, incluant le contrôle de ceux-ci et la préemption, permet de mieux modéliser le comportement de la partie logicielle.

- La gestion automatique de la mémoire allège la tâche des programmeurs et réduit le risque d'erreur.

- La présence d'un format intermédiaire commun (CIL, *Common Intermediate Language*) permet de faire du développement indépendant de la plateforme et du langage. De plus, ce format intermédiaire peut être utilisé comme entrée par les outils de conception assistés par ordinateur (CAO).

- Le mécanisme de réflexion présent dans .Net permet de construire plus aisément l'hiérarchie du système et favorise l'introspection de la plateforme sous test.

- Les interfaces font partie des fonctionnalités de base de .Net, simplifiant la conception des canaux de communication.

- Les services Web offerts par .Net permettent à plusieurs équipes de travailler conjointement au développement.

- L'ajout d'étiquettes donne la possibilité de spécifier plus aisément certaines directives d'exécution, comme par exemple les différents processus, listes de sensibilité, initialisation.

**Rosetta** [4]: Ce nouveau langage de modélisation tire son nom de la pierre de Rosette, ayant permis de déchiffrer les hiéroglyphes égyptiens. L'approche utilisée par Rosetta pour la modélisation diffère sensiblement des autres langages illustrés précédemment. Un problème rencontré lors de la modélisation est que les diverses parties d'un système hétérogène sont généralement mieux décrites en utilisant une certaine sémantique qui leur est propre. Par exemple, un système combinant des éléments mécaniques, optiques et électriques analogiques / numériques pourrait présenter un tel problème. Ou encore, la modélisation des contraintes d'un système qui peut combiner la puissance, la surface et le délai. Le langage Rosetta permet de définir un système par une combinaison de plusieurs facettes qui illustrent chacune une perspective du système. Chaque facette est associée à un domaine spécifique (e.g. mécanique, machine à états, temps discret) qui fournit une sémantique pour ce domaine. La force de Rosetta est qu'il permet de définir les interactions entre les domaines, ou encore comment traduire les facettes d'un domaine à un autre. Cette capacité permet donc de spécifier toutes les parties et contraintes d'un système en utilisant la sémantique la mieux adaptée pour chacune. Par la suite, ces différentes parties et contraintes sont combinées ensemble pour former un système complet. Ceci fait donc de Rosetta un langage très puissant lors de la conception de systèmes hétérogènes.

### 1.1.2 Plateformes de développement

#### 1.1.2.1 SPACE

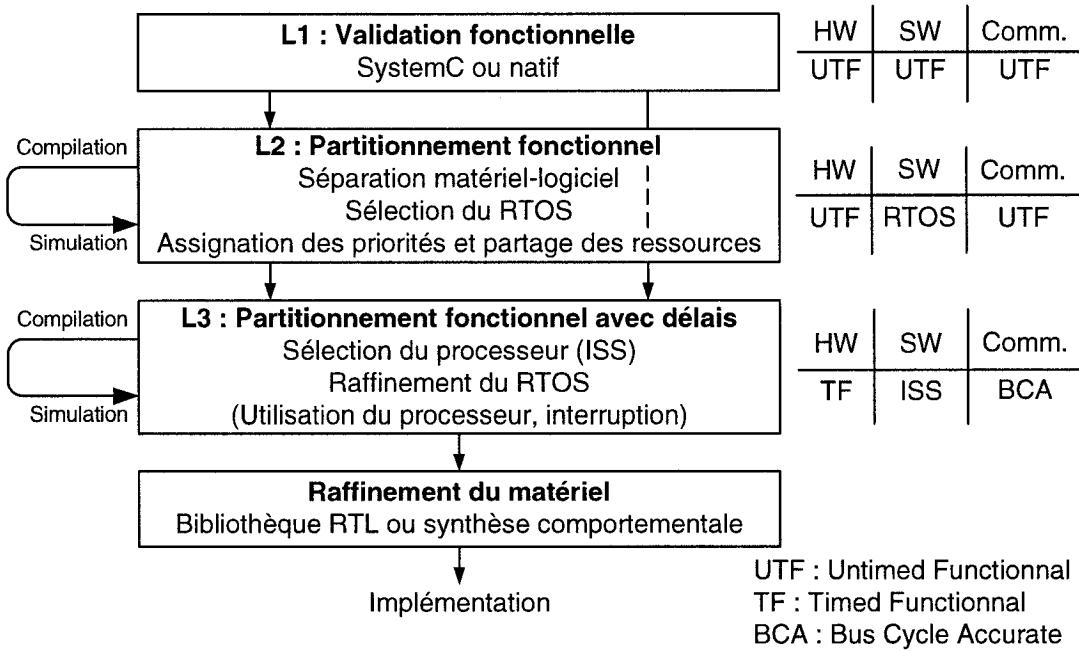

Développé à l'École Polytechnique de Montréal, SPACE (*SystemC Partitioning of Architectures for Codesign of Embedded Systems*) a pour but premier de combler les lacunes de SystemC en matière de simulation de la partie logicielle d'un système embarqué [10]. Étant donné que tous les processus créés en SystemC sont exécutés de manière concurrente, ou simulés comme tel, ceci représente mal le comportement de processus exécutés sur un processeur puisque ceux-ci devraient être exécutés séquentiellement. De plus, les processus de SystemC ne supportent pas la préemption ou l'ordonnancement selon la priorité, qui sont des éléments souvent requis par les systèmes embarqués. Pour résoudre ce problème, SPACE intègre un système d'exploitation temps réel (RTOS, *Real Time Operating System*) à une plateforme SystemC. Le second objectif de SPACE est de faciliter le partitionnement logiciel / matériel. Tous les modules suivent des règles de conception qui permettent de les déplacer d'une partition logicielle à une partition matérielle, ou vice-versa, sans aucune modification du module lui-même. Pour ce faire, SPACE fournit une interface générique aux modules qui redirige les appels de fonction vers ceux de SystemC ou du RTOS dépendamment si le module est sur une partition matérielle ou logicielle. Finalement, SPACE fournit une méthodologie de conception pour les systèmes embarqués basée sur le raffinement en trois niveaux successifs. Ces trois niveaux sont décrits ci-dessous et résumés à la figure 1.1 [19].

Le premier niveau, L1, permet de rapidement valider le fonctionnement de l'application. À cette étape, aucune distinction n'est faite entre les modules logiciels et matériels, ils sont tous représentés par des modules SystemC de base. De plus, tous ces modules sont connectés ensemble par un canal de communication au niveau transactionnel sans délai, ce qui permet de simuler très rapidement.

Figure 1.1 Niveaux de raffinement de SPACE

Le deuxième niveau, L2, donne une première approximation du partitionnement logiciel / matériel. À ce stade, les partitions logicielles sont prises en charge par un RTOS (*Real Time Operating System*) (i.e. MicroC/OS-II) qui exécute sur la machine hôte alors que le canal de communication et les partitions matérielles restent inchangés. Ce niveau permet de vérifier le réglage des priorités et de s'assurer qu'il n'y a pas d'interblocage. Tous les modules logiciels sont exécutés sur la machine hôte qui utilise l'interface générique pour rediriger les appels de fonctions vers le RTOS. Afin de communiquer avec la partie matérielle du système, incluant la mémoire principale, la partie logicielle est munie d'une couche qui communique par interface de connexion (*socket*) avec la partie matérielle du système. Puisque plusieurs détails architecturaux ne sont pas encore fixés (e.g. processeurs, communications), le niveau L2 reste beaucoup plus rapide à simuler que le niveau L3. Une amélioration en cours vise à éliminer la communication par interface de connexion et fournir une première approximation des délais de la plateforme dès le niveau L2. Cette simulation se fait sans simuler au niveau du cycle, ce qui est l'objectif du niveau L3 et nécessite plus

de temps de simulation. Les détails d'implémentation du nouveau L2, par contre, ne sont pas connus à ce moment.

Le troisième niveau, L3, implémente plusieurs détails architecturaux. Premièrement, on y introduit un simulateur de jeu d'instruction (ISS, *Instruction Set Simulator*) du processeur cible (e.g. ARM, Microblaze) sur lequel seront exécutés le RTOS et les modules logiciels. Cet ISS est encapsulé dans un module SystemC et relié au canal de communication de la plateforme. Le canal de communication est remplacé par un modèle précis au cycle près et des délais sont ajoutés aux modules matériels. La plateforme obtenue au niveau L3 permet d'obtenir des délais relativement précis tout en étant plus rapide à simuler qu'un model RTL, ceci procure donc la possibilité de tester plusieurs choix architecturaux et de raffiner la meilleure solution trouvée.

SPACE fournit également un outil de gestion de la concurrence, nommé SISSMA (*SPACE Engine for Synchronization of SystemC Multiprocessor/Multithreaded Applications*), permettant de contrôler l'accès aux zones partagées [55]. L'outil SISSMA fournit un module matériel, connecté sur le canal de communication de la plateforme, qui centralise la gestion des sémaphores partagés par plusieurs éléments de calcul. Ainsi, la prise d'un sémaphore se fait par un simple accès mémoire au module SISSMA, ce qui assure l'atomicité des opérations. Il est également possible d'utiliser des sémaphores locaux dans le cas où ceux-ci ne sont utilisés que par un seul processeur. Pour ce deuxième type de sémaphore, SISSMA réutilise ceux incluent à MicroC/OS-II.

### 1.1.2.2 Virtual Platform Designer

Cette suite d'outils de la compagnie CoWare fournie un éventail complet de fonctionnalités permettant de créer des plateformes virtuelles basées sur la bibliothèque SystemC. Virtual Platform Designer est une combinaison de plusieurs outils inter-

reliés dont Model Libraries, Processor Designer et Platform Architect<sup>1</sup>, qui sont décrits ci-dessous [1].

**1) Model Libraries.** Cet outil de développement donne accès à une bibliothèque de composants, décrits en SystemC, parmi lesquels on retrouve des processeurs, mémoires, bus de communication et périphériques. CoWare a travaillé en collaboration avec ARM, MIPS et LSI afin d'inclure à la bibliothèque un ISS pour leurs processeurs respectifs, assurant ainsi une correspondance exacte et une simulation rapide. De plus, des options de déverminage et d'analyse, compatibles avec les autres outils de CoWare, y ont été ajoutées. Plusieurs architectures de bus sont présentes dans la bibliothèque et peuvent être représentées au niveau transactionnel ou RTL selon le besoin. De plus, il est possible d'y connecter en même temps des composants décrits à ces deux niveaux d'abstraction grâce à des interfaces automatiquement adaptables. Les bus sont munis d'une bonne capacité d'analyse, permettant d'identifier les goulots d'étranglement, et offrent un support particulier pour les architectures AMBA et OCP.

**2) Processor Designer.** Ce deuxième outil de CoWare permet de créer des processeurs sur mesure pour une application donnée. La conception de processeurs est réalisée en utilisant LISA 2.0 (*Language for Instruction Set Architecture*) qui est, comme son nom l'indique, un langage permettant de décrire avec formalisme et précision l'architecture et le jeu d'instruction d'un processeur [52]. Le langage LISA, dont la syntaxe s'inspire fortement du langage C, vise à couvrir plusieurs classes de processeurs (e.g. RISC, DSP, VLIW). Un des objectifs principaux du langage LISA était de permettre la modélisation au cycle près d'un processeur, ce qui n'est pas chose facile étant donné la présence d'un pipeline complexe pour certaines classes de processeurs. À partir de la description du processeur en langage LISA, l'outil Processor Designer génère automatiquement une série d'outils et de modèles

---

<sup>1</sup>Jusqu'à récemment, ces outils étaient nommés respectivement ConvergenSC Model Libraries, LISATek Processor Designer et ConvergenSC Platform Architect

permettant son utilisation:

- un compilateur optimisateur pour le langage C, un éditeur de lien et un archiveur permettant de générer un exécutable pour l'architecture cible,

- des outils de profilage et d'analyse intégrés permettant d'optimiser le logiciel pour l'architecture donnée avec une emphase sur la puissance, la surface ou la vitesse du processeur,

- un ISS pouvant être intégré dans une plateforme SystemC, telle Platform Architect de la même compagnie, ou autres types de plateforme,

- une description VHDL ou Verilog synthétisable du processeur permettant de l'implémenter dans un produit final.

3) **Platform Architect.** Ce logiciel de CoWare favorise la conception et l'intégration de SoC complet. Il offre principalement un environnement de développement et de vérification basé sur Eclipse, nommé SCIDE (*SystemC Integrated Development and Debug Environment*), pour la réalisation de modules décrits en SystemC ou importés d'autres outils de la suite comme Model Libraries, Processor Designer ou Signal Processing Designer (non décrit ici). L'environnement graphique offre la possibilité de facilement assembler des blocs ensemble, mais l'intérêt principal de Platform Architect est au niveau de la vérification et du déverminage. Premièrement, le dévermineur est adapté aux constructions de SystemC comme l'exécution sur plusieurs processus. Deuxièmement, l'outil permet de générer un graphique en forme d'onde des différents signaux et horloges du système. Troisièmement, il permet de tracer l'ordre des événements, processus et appels aux fonctions des différentes interfaces (IMC, *Interface Method Call*) sous forme graphique. Un autre avantage de SCIDE est que son compilateur permet d'optimiser les changements de contextes dus aux processus, signaux et ports de SystemC, accélérant ainsi la simulation.

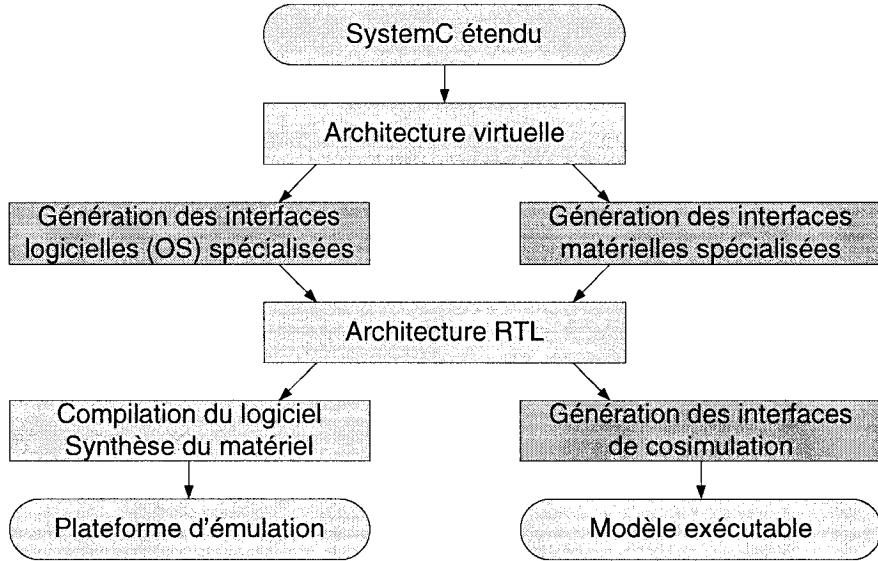

### 1.1.2.3 Roses

La plateforme Roses, issue du groupe de recherche TIMA à Grenoble, vise à générer automatiquement les interfaces de communication dans un MPSoC hétérogène. La conception de ces interfaces spécialisées nécessite normalement une couche de OS décrite à bas niveau qui est entremêlée avec l’application. La programmation de cette couche est généralement fastidieuse et présente un goulot d’étranglement pour le développement des systèmes embarqués. L’objectif de Roses est de générer automatiquement cette couche et de fournir un API qui permet de lui accéder facilement. L’approche utilisée par Roses est de type ascendante ou encore basée sur les composants [18]. Ce type d’approche démarre avec un ensemble de composants et vise à générer les API de communication. Par opposition, une approche descendante démarre avec une architecture fonctionnelle, généralement décrite à un haut niveau d’abstraction, et raffine vers le bas pour obtenir une implémentation RTL de la plateforme. SPACE aborde ce deuxième type d’approche. La génération d’interfaces de Roses procure trois avantages importants [17] :

1. le logiciel dédié n’a pas à se soucier de l’interface vers le matériel;

2. l’application peut être développée indépendamment de l’implémentation matérielle; et,

3. offre un niveau de flexibilité et de portabilité accru sans perte de performance.

Un système sur Roses est défini en utilisant SystemC auquel on a étendu certaines fonctionnalités. Roses utilise une architecture virtuelle composée de modules virtuels, de ports virtuels et de canaux virtuels. Un module virtuel représente un module de la plateforme accompagné d’une interface constituée de plusieurs ports virtuels. Un port virtuel quant à lui est composé de plusieurs ports internes et externes aux composants. Celui-ci permet de relier les ports internes et externes en convertissant

Figure 1.2 Environnement de Roses

le protocole ou le niveau d'abstraction lorsque nécessaire. Finalement, les canaux virtuels permettent de relier ensemble les ports virtuels tout en masquant la plupart des détails de communication. De plus, pour des fins de raffinement, le modèle est annoté à l'aide de paramètres architecturaux, comme par exemple le protocole utilisé.

La figure 1.2 illustre l'environnement de Roses et les trois types d'interfaces automatiquement générées. Les interfaces matérielles sont générées à partir d'une bibliothèque de services préconfigurée pour chaque processeur ciblé. Un avantage est qu'un graphe de dépendance permet de n'inclure que les services nécessaires, réduisant au minimum la taille de l'OS. Les interfaces matérielles sont générées à partir d'une bibliothèque contenant des modèles de processeurs et de protocoles pour les canaux. Finalement, le générateur de cosimulation produit un modèle exécutable SystemC. De plus celui-ci agit également à titre de pilote pour d'autres simulateurs (e.g. VHDL, Verilog, ISS) grâce à des adaptateurs.

Bien que Roses soit un outil puissant pour interfaçer ensemble des composants d'un système hétérogène, il n'offre pas de support pour l'exploration architecturale et le

partitionnement. Pour combler cette lacune, une approche a été proposée combinant Roses et VCC (*Virtual Component Co-Design*) pour obtenir un flot de conception complet permettant d'obtenir une implémentation RTL à partir des spécifications du système [26]. VCC est une autre plateforme de développement qui se concentre sur l'exploration architecturale [56], c'est donc une approche descendante telle que décrit précédemment. VCC fourni des outils permettant d'associer des blocs fonctionnels à des composants architecturaux, créant un partitionnement logiciel / matériel. Par la suite, les performances du système sont analysées et on peut jouer avec la configuration de l'architecture pour obtenir un partitionnement idéal. On obtient donc à la fin un modèle abstrait du système. C'est là que Roses entre en jeu, pour procurer en lien direct et automatique du modèle abstrait de VCC vers une plateforme Roses. Une fois le système converti en Roses, il devient possible de générer les interfaces des modules et de raffiner le système vers une implémentation RTL.

#### 1.1.2.4 Autres Plateformes

Il existe plusieurs autres plateformes de développement à haut niveau. Parmi ces autres plateformes, notons le projet MESCAL (*Modern Embedded Systems, Compilers, Architectures and Languages*) qui vise à fournir une approche formelle au développement de SoC [43]. Leurs outils visent à trouver une correspondance entre la concurrence présente dans une application et la concurrence présente dans la plateforme. L'exploitation de la concurrence se fait à quatre niveaux [7]:

1. Au niveau bit via des unités fonctionnelles spécialisées

2. Au niveau instruction grâce à des processeurs VLIW

3. Au niveau processus légers par des processeurs multiprocessus

4. Au niveau processus par l'utilisation de plusieurs processeurs

L'utilisateur spécifie d'abord une architecture pour le système. Des outils de compilation et de simulation pour la partie logicielle sont alors automatiquement

générés. Le compilateur de MESCAL analyse ensuite l'application et permet d'exploiter le parallélisme en fonction de l'architecture choisie. Finalement, du code est généré pour chaque élément de calcul (PE, *processing element*) qui inclue l'ordonnancement et la synchronisation.

TTL (*Task Transaction Level*) est une autre de ces plateformes de développement pour les MPSoC [61]. Leur approche est basée sur la définition d'un système par un ensemble de tâches et par les interfaces entre ces tâches. TTL supporte plusieurs types de communication en offrant une grande variété de types d'interfaces (e.g. bloquant ou non-bloquant, requêtes ordonnées ou non ordonnées). La fonction de multi-tâches de TTL est réalisée en offrant trois types de tâches :

1. Processus qui correspond à une tâche n'ayant pas d'interaction explicite avec d'autres tâches. Celles-ci n'interagissent pas directement avec l'ordonnanceur, bien qu'elles peuvent être suspendues par la plateforme, comme par exemple un OS.

2. Co-routine qui sont des tâches exécutant en collaboration avec d'autres tâches et qui interagissent avec l'ordonnanceur du système.

3. Acteur qui représente une tâche ayant un début et une fin. Autrement dit, celle-ci correspond plus à une fonction qu'à une tâche, un peu comme les `sc_method` de SystemC.

ArchiFlex (*Architecture Flexible*) présente une solution pour l'exploration architecturale différente de celles présentées précédemment. Cette plateforme n'en est pas une de simulation mais d'émulation, c'est à dire qu'elle permet d'avoir une implémentation physique de la plateforme et non pas un modèle. Comme il a été expliqué, l'élévation du niveau d'abstraction permet d'obtenir des vitesses de simulation accrues, mais celles-ci ne se comparent pas à la vitesse d'exécution du circuit réel, c'est donc là l'avantage principal d'une plateforme d'émulation. L'autre avantage d'ArchiFlex est que la plateforme procure une grande flexibilité au niveau

Figure 1.3 Position des processeurs configurables

des choix architecturaux, principalement grâce à un réseau sur puce reconfigurable et des interfaces de communication génériques, contrairement à ses compétiteurs dont la plateforme est centrée sur leurs propres produits [45].

Finalement, parmi les plateformes de développement, notons la présence de la plateforme StepNP qui sera présentée en détail à la section 3.1 puisqu'elle fait l'objet de ce travail.

## 1.2 Processeurs configurables