**Titre:** Unité de contrôle et de compression de données pour la partie

Title: implantable d'un capteur d'électroneurogrammes

**Auteur:** Jean-François Roy

Author:

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Roy, J.-F. (2006). Unité de contrôle et de compression de données pour la partie

implantable d'un capteur d'électroneurogrammes [Master's thesis, École

Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7904/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7904/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan, & Abdelhakim Khouas

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

UNITÉ DE CONTRÔLE ET DE COMPRESSION DE DONNÉES POUR LA PARTIE

IMPLANTABLE D'UN CAPTEUR D'ÉLECTRONEUROGRAMMES

JEAN-FRANÇOIS ROY

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

Août 2006

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-19324-2

*Our file* *Notre référence*

ISBN: 978-0-494-19324-2

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

**Canada**

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

UNITÉ DE CONTRÔLE ET DE COMPRESSION DE DONNÉES POUR LA PARTIE

IMPLANTABLE D'UN CAPTEUR D'ÉLECTRONEUROGRAMMES

Présenté par : JEAN-FRANÇOIS ROY

En vue de l'obtention du diplôme de : Maitre ès sciences appliquées

M. SAVARIA, Yvon, Ph. D., président

M. SAWAN, Mohamad, Ph. D., membre et directeur de recherche

M. KHOUAS, Abdelhakim Ph. D., membre et codirecteur de recherche

## REMERCIEMENTS

Je voudrais d'abord remercier Monsieur Mohamad Sawan, mon directeur qui m'a laissé la chance de faire cette recherche passionnante dans un environnement aussi enviable que le laboratoire Polystim. Je remercie aussi messieurs Yvon Savaria et Abdelhakim Khouas, professeurs à l'École Polytechnique, pour avoir accepté de participer au jury de ce mémoire.

Merci à mes collègues de Polystim, avec qui j'ai eu des discussions et des partages de connaissances très intéressants. En particulier quelques membres de l'équipe Cortisens : Benoit Gosselin, pour son organisation, sa disponibilité et son dévouement, Virginie Simard, pour sa rigueur et sa justesse, Cyprien Dumortier, pour l'apport considérable de son travail à mes recherches, Pierre-Yves Robert et Amer Ayoub.

Merci au CRSNG (Conseil de Recherche en Sciences Naturelles en Génie du Canada) pour leur apport financier ainsi qu'à la CMC (Canadian Microelectronics Corporation) pour leur soutien technique et le partage de leurs ressources.

Je voudrais souligner l'aide que mes amis m'ont apportée, chacun à sa manière, par leurs idées, leurs conseils, leur motivation et leurs sourires. Pierre-Alexandre Fournier, Guillaume Germain, Olivier Duval, Ghislain Provost et Mathieu Plante, pour ne pas tous les nommer.

Je voudrais dire un merci spécial à ma famille pour être là, sans qui je ne serais pas qui je suis.

Un merci unique à Mélanie, ma fiancée, qui me stimule et m'incite toujours à continuer. On a fait beaucoup ensemble et il reste encore beaucoup plus à partager.

## RÉSUMÉ

Les scientifiques s'entendent pour dire que les neurones communiquent entre eux par la transmission de signaux par impulsions ou potentiels d'action qui sont les unités de base pour l'encodage neuronal. Ce mémoire propose une analyse et un système spécialisé de contrôle et de compression de données pour la partie implantable d'un électroneurogramme.

Le signal neuronal que le système doit acquérir est masqué en partie par les artefacts rencontrés par ce système comme le bruit, la superposition d'impulsions et les salves de potentiels d'action. Une revue de la littérature montre que plusieurs équipes se sont penchées sur ce problème et ont proposé des solutions fonctionnelles mais pas nécessairement optimisées pour notre type d'application : un implant cortical pour les expérimentations chroniques.

Ce mémoire présente une nouvelle étude des méthodes et algorithmes pertinents pour la réalisation en circuits intégrés d'un système implantable. L'équipe Cortisens du laboratoire de neurotechnologies Polystim propose une solution basée sur l'utilisation de la transformée en ondelettes pour la compression du signal.

Les résultats de simulation montrent qu'il est possible d'obtenir une reconstitution quasi parfaite (spécificité de 99% et sélectivité de 100%) avec un taux de transmission aussi bas que 1.5%. Ce résultat n'est atteignable qu'avec cette méthode en ne considérant que les techniques envisageables pour une implémentation sur puce. Afin d'obtenir ces résultats prometteurs, une méthodologie par seuillage est choisie pour faire la détection de l'activité neuronale qui est la base d'une compression par événements. Cette méthode est la base puisqu'elle suppose que les potentiels d'action ne surviennent que de temps en temps et que la majorité du temps, ce n'est que du bruit qui est observé.

Différentes méthodes de détection neuronales sont donc comparées pour en conclure

que l'implémentation d'un seuil simple après une transformée en ondelettes est suffisante pour une acquisition acceptable. Les méthodes adaptatives proposées dans la littérature fournissent une bonne approche pour une configuration continue et peuvent être appliquées par un logiciel plutôt qu'en matériel. Ce qui permettra une plus grande latitude expérimentale pour le système développé par l'équipe Cortisens.

Ce mémoire met l'emphase sur la réalisation et l'optimisation du contrôleur numérique. Il se compose d'un lien entièrement bidirectionnel qui permet une configuration continue sans influencer le flot sortant de données, par l'écriture aux registres. Il comprend aussi une unité de détection de l'activité neuronale ainsi que le bloc majeur qui gère l'accès aux cellules mémoire tout en accomplissant la compression des données.

Bien que les tests préliminaires ont été effectués sur une plate-forme de prototypage rapide avec FPGA, chacun des blocs a été optimisé pour finalement obtenir une consommation logique minimisant la surface sur puce nécessaire pour une même fonctionnalité. Dans le but d'obtenir un prototype complet sur puce avec une surface restreinte, certains compromis ont dû être pris. Le bloc de transformée en ondelettes prenant manifestement plus d'espace que d'autres blocs a été retiré lors de la réalisation du prototype matériel car il utiliserait  $0.92 \text{ mm}^2$  (56%) de l'espace, tandis que le deuxième bloc d'importance, les cellules mémoire, utilisent  $0.41 \text{ mm}^2$  (25%) et doivent absolument faire partie du système final car la mémoire représente la fondation du système par fenêtrage basé sur l'occurrence de potentiels d'action. Ce premier prototype sur puce permettra de valider la preuve de concept en faisant l'acquisition de signaux qui corroboreront les résultats de ce mémoire.

La densité finale du système obtenu en circuits intégrés est de 92% pour une surface d'implémentation du cœur de  $0.65 \text{ mm}^2$ . Ce qui donne une surface totale sur silicium de  $1.86 \text{ mm}^2$  incluant les tampons d'entrée/sortie et les contacts permettant la réalisation d'un premier prototype complet par l'assemblage de plusieurs puces superposées avec une matrice d'électrodes interconnectées par micro-manipulations.

## ABSTRACT

Scientists agree that neurons communicate information by firing sequences of spikes which are the neuronal code unity. This master's thesis propose an analysis and a specialized system for control and data compression for an implantable electroneurogram.

The neuronal signal acquired with this system can be masked by artifacts like noise, spike superposition and spike train special behaviour. A literature review shows that many teams worked on these problems and proposed functional solutions but not optimized for our application : a cortical implant for chronic experimentations.

This master's thesis presents a new study of pertinent methods and algorithms for the realization in integrated circuits of an implantable system. The Cortisens team of the neurotechnologies Laboratory Polystim proposes a solution based on a wavelet transform for signal characterization and compression.

The simulation results show that it is possible to obtain an almost perfect reconstruction of the signal (specificity of 99% and selectivity of 100%) with a transmission rate as low as 1.5%. These results can be achieved only with this method while considering only the techniques which are conceivable for low power integrated circuits. These results are possible due to a thresholding methodology which is the basis of the compression behaviour. This method is based on the assumption that spikes only occur with low duty cycle and noise is normally observed on the signal seen on the electrodes.

Different methods for neuronal activity detection are compared before concluding that a simple threshold after a wavelet transform is enough for an acceptable acquisition. The adaptive methods proposed in literature give great insight for continuous configuration and can easily be implemented in software instead of hardware. This will let more experimental capabilities for the system still in development by the Cortisens

team.

This master's thesis emphasizes on the realization and the optimization of the digital controller. It includes a full duplex link to enable continuous configuration through writable registers without interrupting the uplink data flow. It also includes a neuronal activity detection module and, finally, the most important module which is dedicated to manage the memory blocks while compressing data.

Even if preliminary tests had been done on a fast prototyping platform with a FPGA, each block had been optimized focusing on the minimization of the logic usage using the least chip area as possible for the same functionality. In order to obtain a first complete prototype with integrated circuits using a constrained area, some trade-offs were necessary. The biggest block, the wavelet transform processor, would have used  $0.92 \text{ mm}^2$  (56%) of the space, the second biggest part, the memory blocks, use  $0.41 \text{ mm}^2$  (25%) and must be part of the final system because it is used as the foundation for a windowing system based on spike event occurrence. This first integrated circuit prototype will validate the proof of concept by acquiring signal that will corroborate results of this master's thesis.

The final density of the realized system is 92% for an implementation area of the core of  $0.65 \text{ mm}^2$ . This ends with a total area of  $1.86 \text{ mm}^2$  including the input/output buffers and the metal contacts forming the chip. This chip will be assembled with other chips and a microelectrode array to constitute a complete stacked dies system.

**TABLE DES MATIÈRES**

|                                                            |      |

|------------------------------------------------------------|------|

| REMERCIEMENTS . . . . .                                    | iv   |

| RÉSUMÉ . . . . .                                           | v    |

| ABSTRACT . . . . .                                         | vii  |

| TABLE DES MATIÈRES . . . . .                               | ix   |

| LISTE DES FIGURES . . . . .                                | xiv  |

| LISTE DES TABLEAUX . . . . .                               | xvi  |

| LISTE DES NOTATIONS ET DES SYMBOLES . . . . .              | xvii |

| LISTE DES ANNEXES . . . . .                                | xix  |

| INTRODUCTION . . . . .                                     | 1    |

| CHAPITRE 1    LES NEURONES ET LEURS SYSTÈMES D'ACQUISITION | 4    |

| 1.1    Introduction . . . . .                              | 4    |

| 1.2    Interface cerveau-ordinateur . . . . .              | 5    |

| 1.2.1    L'acquisition . . . . .                           | 6    |

| 1.2.2    La stimulation électrique neuronale . . . . .     | 10   |

| 1.2.3    La variété des tâches . . . . .                   | 10   |

| 1.3    Caractérisation des potentiels d'action . . . . .   | 11   |

| 1.3.1    Le bruit . . . . .                                | 14   |

| 1.3.2    La superposition d'impulsions . . . . .           | 15   |

| 1.3.3    Les salves d'impulsions . . . . .                 | 17   |

| 1.3.4    Les potentiels d'action en équations . . . . .    | 17   |

|                                                                                   |                                                               |           |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------|-----------|

| 1.4                                                                               | Les signaux d'intérêt pour l'acquisition . . . . .            | 20        |

| 1.4.1                                                                             | Les potentiels d'action . . . . .                             | 20        |

| 1.4.2                                                                             | L'information neuronale . . . . .                             | 21        |

| 1.5                                                                               | Système d'acquisition neuronaux existants . . . . .           | 22        |

| 1.5.1                                                                             | Systèmes avec processeurs et microcontrôleurs . . . . .       | 23        |

| 1.5.2                                                                             | Systèmes intégrés sur puce . . . . .                          | 24        |

| 1.5.3                                                                             | Autres domaines reliés . . . . .                              | 25        |

| <b>CHAPITRE 2 LE TRAITEMENT ET LA COMPRESSION DES SIGNAUX NEURONAUX . . . . .</b> |                                                               | <b>27</b> |

| 2.1                                                                               | Introduction . . . . .                                        | 27        |

| 2.2                                                                               | Analyse pour une compression optimale . . . . .               | 28        |

| 2.2.1                                                                             | Points de comparaison . . . . .                               | 29        |

| 2.2.2                                                                             | Débit de transfert . . . . .                                  | 30        |

| 2.2.3                                                                             | L'erreur quadratique moyenne . . . . .                        | 33        |

| 2.2.4                                                                             | Complexité d'implémentation . . . . .                         | 34        |

| 2.3                                                                               | Filtres et transformées en temps réel envisageables . . . . . | 35        |

| 2.3.1                                                                             | Transformée rapide de Fourier . . . . .                       | 37        |

| 2.3.2                                                                             | Transformée discrète en cosinus . . . . .                     | 38        |

| 2.3.3                                                                             | Transformée discrète en ondelettes . . . . .                  | 40        |

| 2.3.4                                                                             | Analyse par composants principaux . . . . .                   | 45        |

| 2.3.5                                                                             | Autres méthodes . . . . .                                     | 47        |

| 2.4                                                                               | Les schèmes ou flots de données . . . . .                     | 47        |

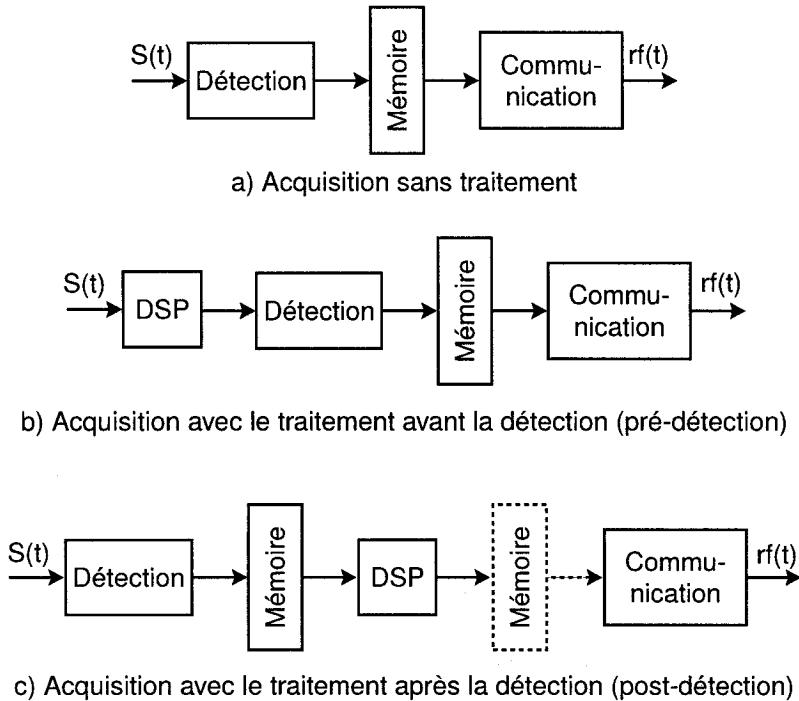

| 2.4.1                                                                             | Acquisition sans traitement . . . . .                         | 48        |

| 2.4.2                                                                             | Acquisition avec traitement pré-détection . . . . .           | 48        |

| 2.4.3                                                                             | Acquisition avec traitement post-détection . . . . .          | 49        |

| 2.5                                                                               | Les techniques de détection d'activité neuronale . . . . .    | 50        |

|                                                                          |                                                                  |           |

|--------------------------------------------------------------------------|------------------------------------------------------------------|-----------|

| 2.5.1                                                                    | Détection par seuil simple . . . . .                             | 51        |

| 2.5.2                                                                    | Détection par mesure d'énergie . . . . .                         | 52        |

| 2.5.3                                                                    | Détection par extraction de propriétés . . . . .                 | 54        |

| 2.5.4                                                                    | Méthodes adaptatives . . . . .                                   | 54        |

| 2.5.5                                                                    | Transformée discrète en ondelettes . . . . .                     | 55        |

| <b>CHAPITRE 3     IMPLÉMENTATIONS MATÉRIELLE ET LOGICIELLE . . . . .</b> |                                                                  | <b>57</b> |

| 3.1                                                                      | Introduction . . . . .                                           | 57        |

| 3.2                                                                      | Le projet Cortisens . . . . .                                    | 57        |

| 3.2.1                                                                    | Interface Électrodes-Tissu . . . . .                             | 58        |

| 3.2.2                                                                    | Amplification analogique et échantillonnage . . . . .            | 59        |

| 3.2.3                                                                    | Contrôleur numérique . . . . .                                   | 60        |

| 3.2.4                                                                    | Communication sans-fil . . . . .                                 | 61        |

| 3.2.5                                                                    | Module externe . . . . .                                         | 61        |

| 3.2.6                                                                    | Assemblage et prototypes . . . . .                               | 62        |

| 3.3                                                                      | Problématiques du contrôleur numérique . . . . .                 | 62        |

| 3.3.1                                                                    | Interface avec le module RF . . . . .                            | 62        |

| 3.3.2                                                                    | Interface avec les convertisseurs analogique numérique . . . . . | 64        |

| 3.3.3                                                                    | Gestion des horloges . . . . .                                   | 66        |

| 3.3.4                                                                    | Le choix des cellules mémoire . . . . .                          | 71        |

| 3.3.5                                                                    | La mémoire circulaire . . . . .                                  | 72        |

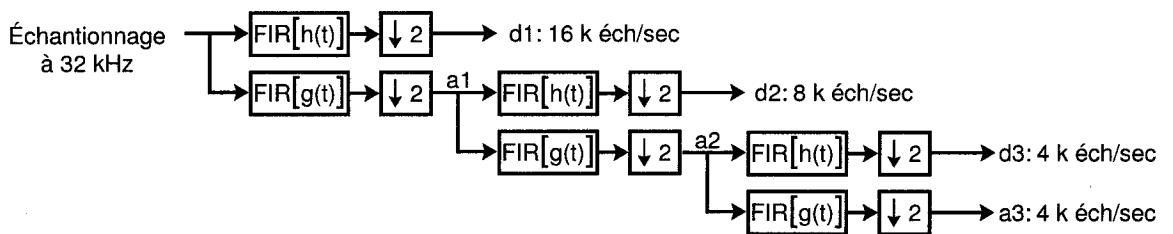

| 3.3.6                                                                    | Architectures DWT . . . . .                                      | 73        |

| 3.4                                                                      | Le protocole de communication . . . . .                          | 74        |

| 3.4.1                                                                    | La signification des registres . . . . .                         | 74        |

| 3.4.2                                                                    | Lien de données et trame physique . . . . .                      | 75        |

| 3.4.3                                                                    | Compression avec DWT . . . . .                                   | 77        |

| 3.5                                                                      | Description du contrôleur numérique . . . . .                    | 78        |

|                                       |                                                                   |           |

|---------------------------------------|-------------------------------------------------------------------|-----------|

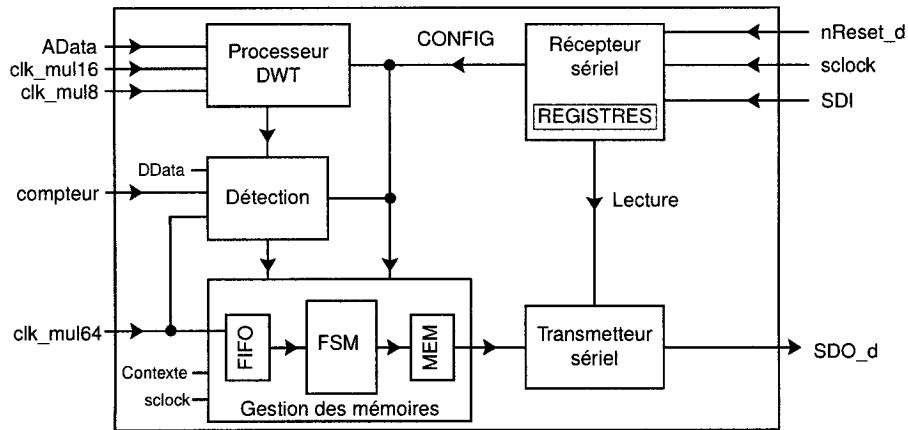

| 3.5.1                                 | Architecture globale du contrôleur . . . . .                      | 78        |

| 3.5.2                                 | Le récepteur série . . . . .                                      | 79        |

| 3.5.3                                 | Le transmetteur série . . . . .                                   | 80        |

| 3.5.4                                 | Le module de processeur d'ondelettes . . . . .                    | 81        |

| 3.5.5                                 | Le module de détection . . . . .                                  | 81        |

| 3.5.6                                 | Le module de gestion des mémoires . . . . .                       | 82        |

| 3.5.7                                 | Les modes de fonctionnement . . . . .                             | 83        |

| <b>CHAPITRE 4 RÉSULTATS . . . . .</b> |                                                                   | <b>86</b> |

| 4.1                                   | Introduction . . . . .                                            | 86        |

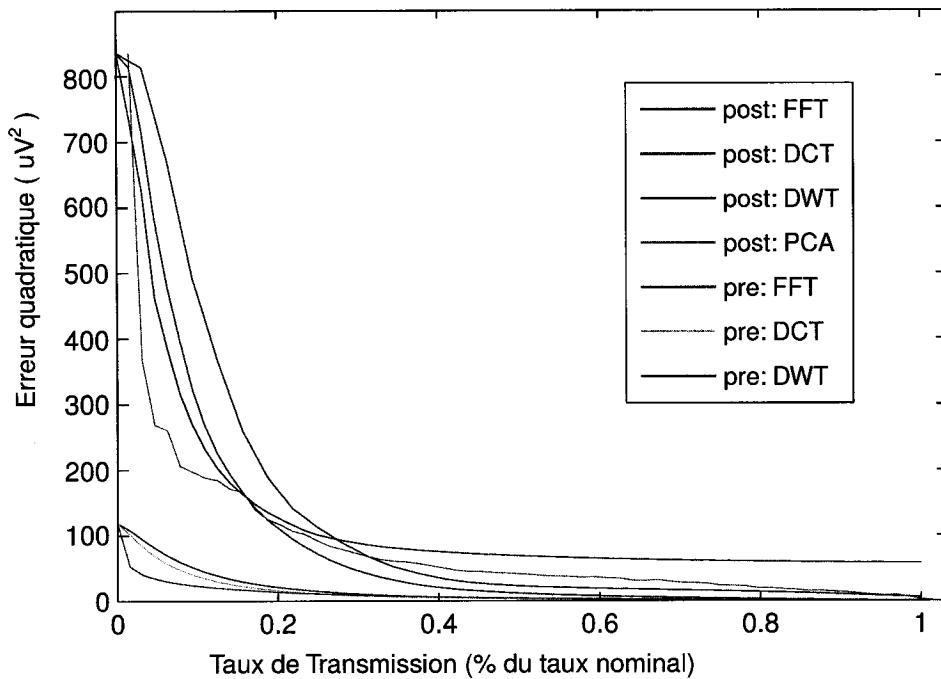

| 4.2                                   | Analyse des filtres et transformées pour la compression . . . . . | 87        |

| 4.2.1                                 | Taux de compression comparés . . . . .                            | 88        |

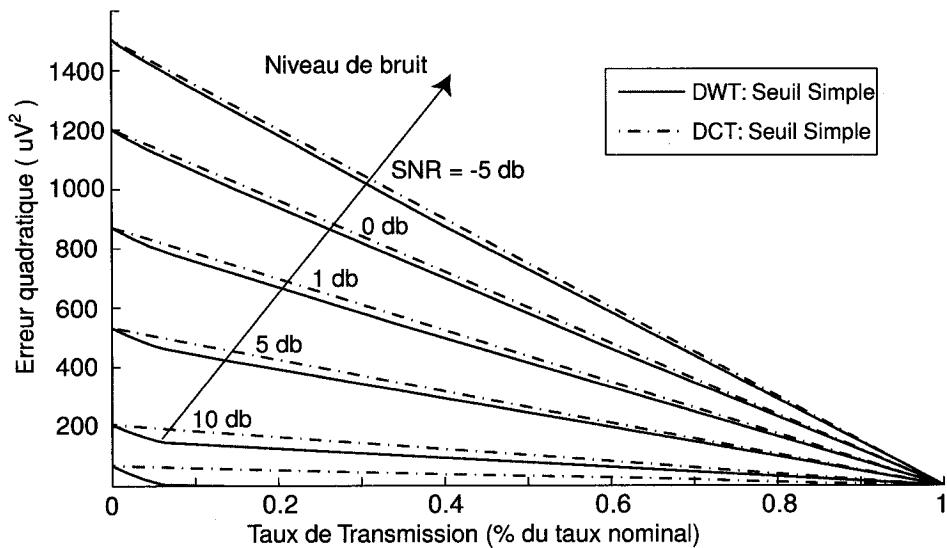

| 4.3                                   | Analyse des techniques de détection d'activité . . . . .          | 89        |

| 4.3.1                                 | Taux de détection comparés . . . . .                              | 90        |

| 4.3.2                                 | Taux de compression avec bruit variable . . . . .                 | 93        |

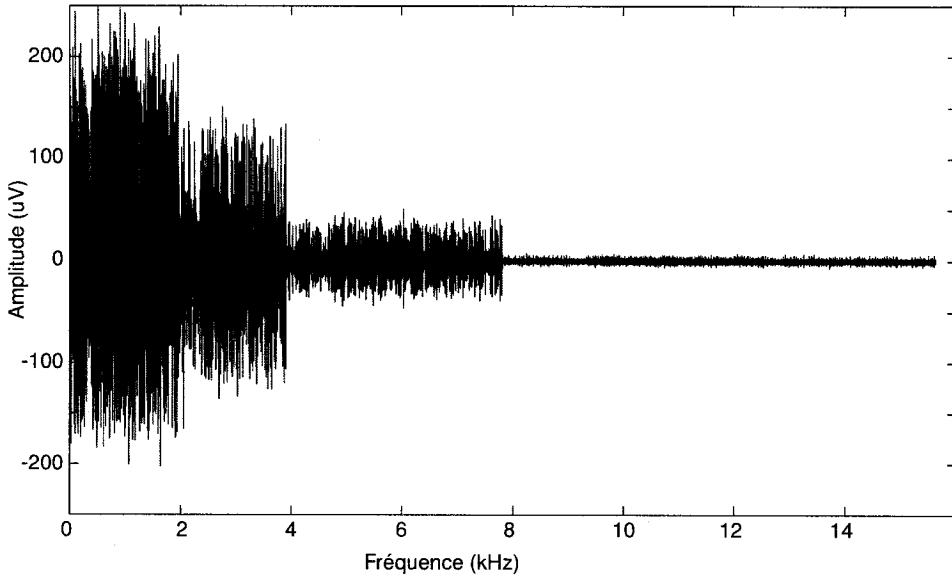

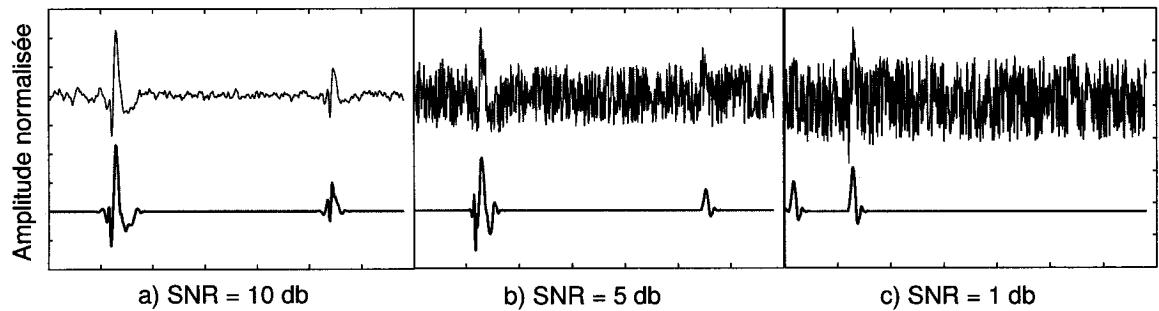

| 4.4                                   | Débruitage par compression DWT . . . . .                          | 94        |

| 4.5                                   | Les simulations en langage matériel . . . . .                     | 95        |

| 4.5.1                                 | Méthodologie Co-Design . . . . .                                  | 95        |

| 4.5.2                                 | Implémentation avec Modelsim . . . . .                            | 96        |

| 4.6                                   | Logiciel de gestion de contrôle . . . . .                         | 98        |

| 4.6.1                                 | Le seuillage par méthode adaptative . . . . .                     | 99        |

| 4.6.2                                 | Implémentation du logiciel de contrôle . . . . .                  | 99        |

| 4.7                                   | Réalisation sur plate-forme de prototypage rapide . . . . .       | 101       |

| 4.7.1                                 | Prototype Xilinx avec lien USB . . . . .                          | 102       |

| 4.7.2                                 | Prototype Altera avec processeur NIOS . . . . .                   | 103       |

| 4.8                                   | Réalisation d'un ASIC . . . . .                                   | 104       |

| 4.8.1                                 | Compromis architecturaux . . . . .                                | 105       |

|                                                               |     |

|---------------------------------------------------------------|-----|

| 4.8.2 Module simple et sécuritaire sans mémoire RAM . . . . . | 106 |

| 4.8.3 Module avec détection et cellules mémoire . . . . .     | 107 |

| 4.8.4 Les outils de développements . . . . .                  | 108 |

| 4.8.5 Utilisation des ressources . . . . .                    | 108 |

| CONCLUSION . . . . .                                          | 111 |

| RÉFÉRENCES . . . . .                                          | 115 |

| ANNEXES . . . . .                                             | 124 |

## LISTE DES FIGURES

|                  |                                                                                    |    |

|------------------|------------------------------------------------------------------------------------|----|

| <b>FIG. 1.1</b>  | Parties essentielles d'une interface cerveau-ordinateur . . . . .                  | 6  |

| <b>FIG. 1.2</b>  | Signal typique à basse fréquence . . . . .                                         | 8  |

| <b>FIG. 1.3</b>  | Trois sites d'enregistrement neuronal possibles . . . . .                          | 12 |

| <b>FIG. 1.4</b>  | Potentiel d'action . . . . .                                                       | 13 |

| <b>FIG. 1.5</b>  | Caractéristiques des potentiels d'action . . . . .                                 | 16 |

| <b>FIG. 1.6</b>  | Système exemple, module DSP du projet VSAMUEL . . . . .                            | 24 |

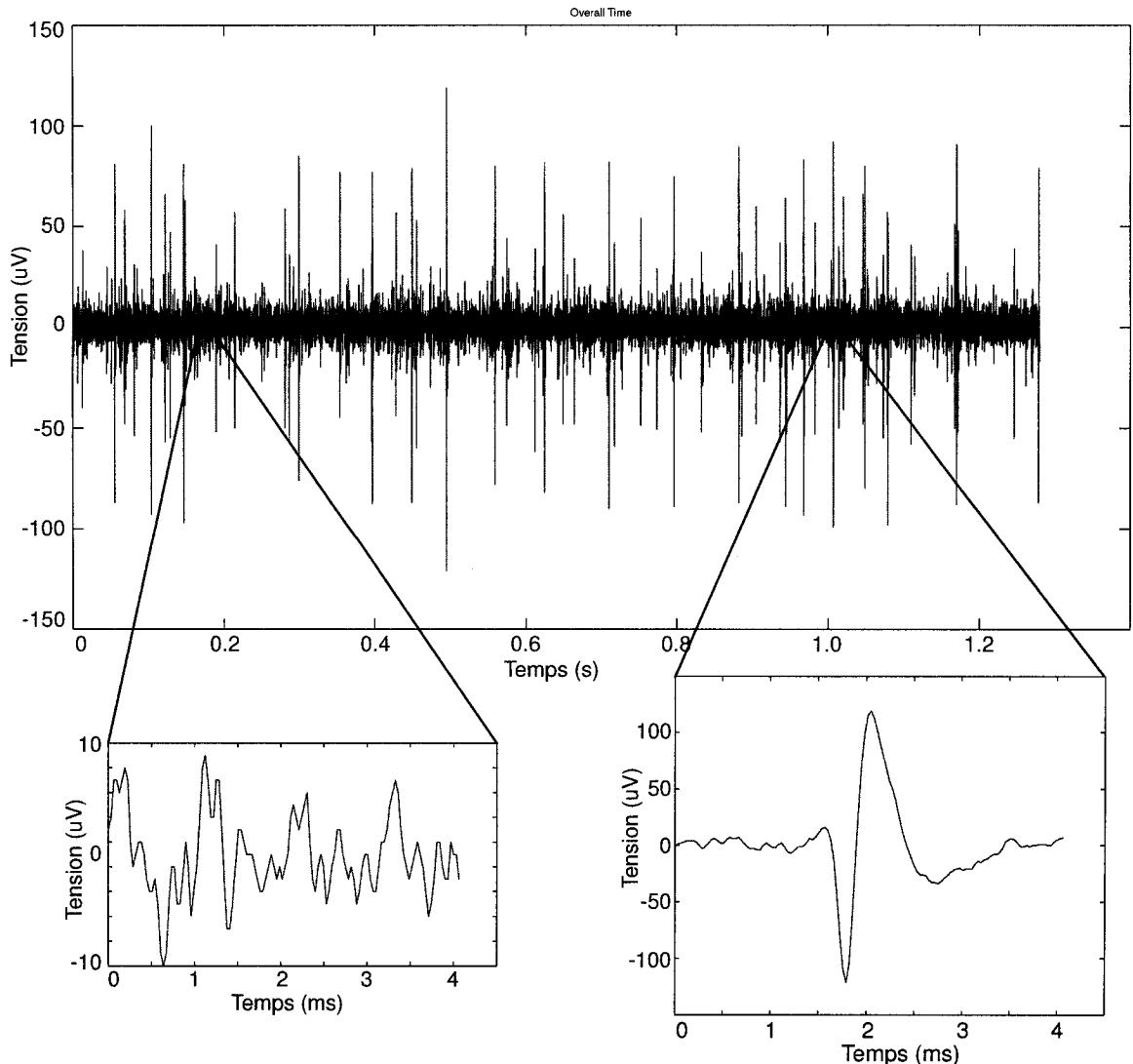

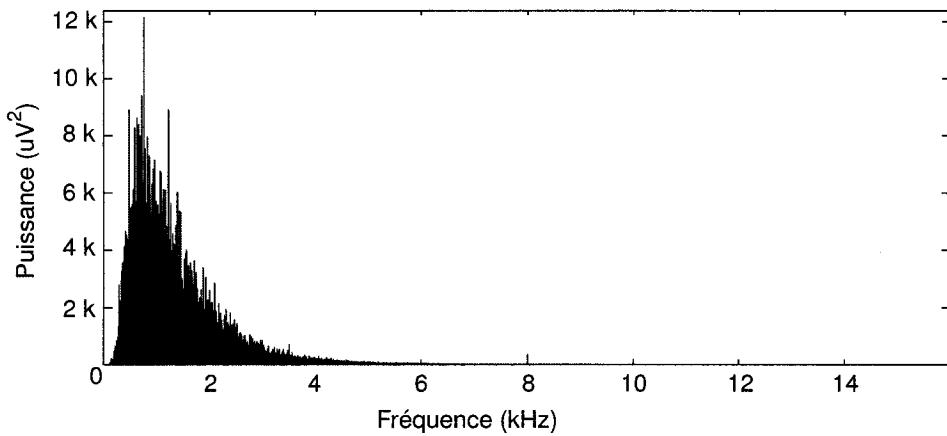

| <b>FIG. 2.1</b>  | Signal de référence avec agrandissement sur du bruit et sur un AP . . . . .        | 36 |

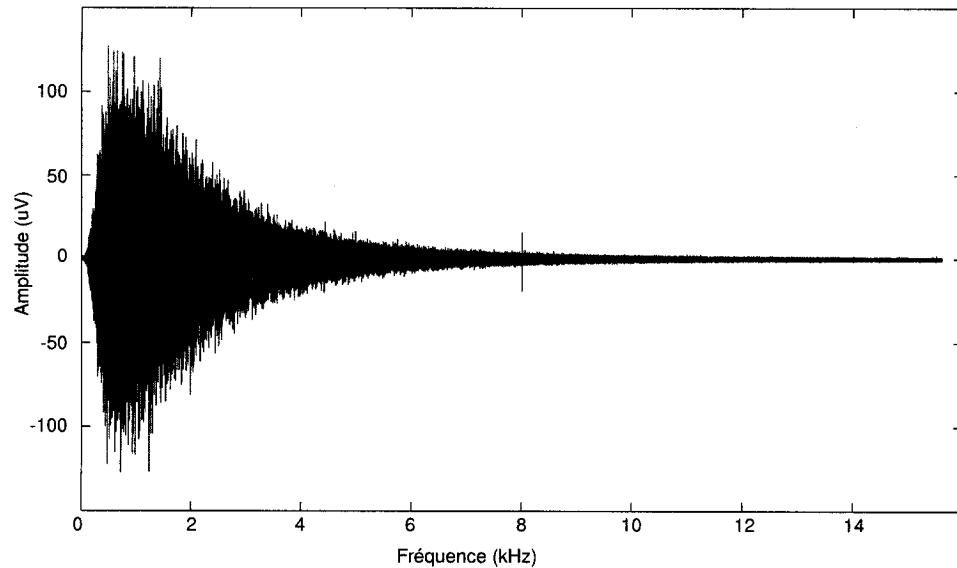

| <b>FIG. 2.2</b>  | Contenu spectral d'un signal neuronal . . . . .                                    | 37 |

| <b>FIG. 2.3</b>  | Transformée DCT . . . . .                                                          | 39 |

| <b>FIG. 2.4</b>  | Changement d'échelle et de translation pour l'ondelette Daubechies (db4) . . . . . | 41 |

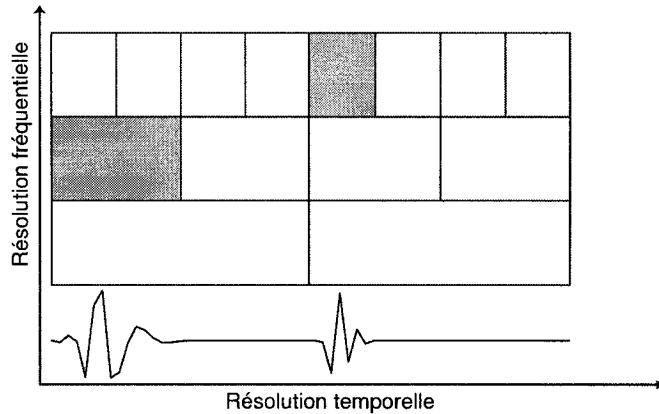

| <b>FIG. 2.5</b>  | Structure en arbre de la DWT . . . . .                                             | 43 |

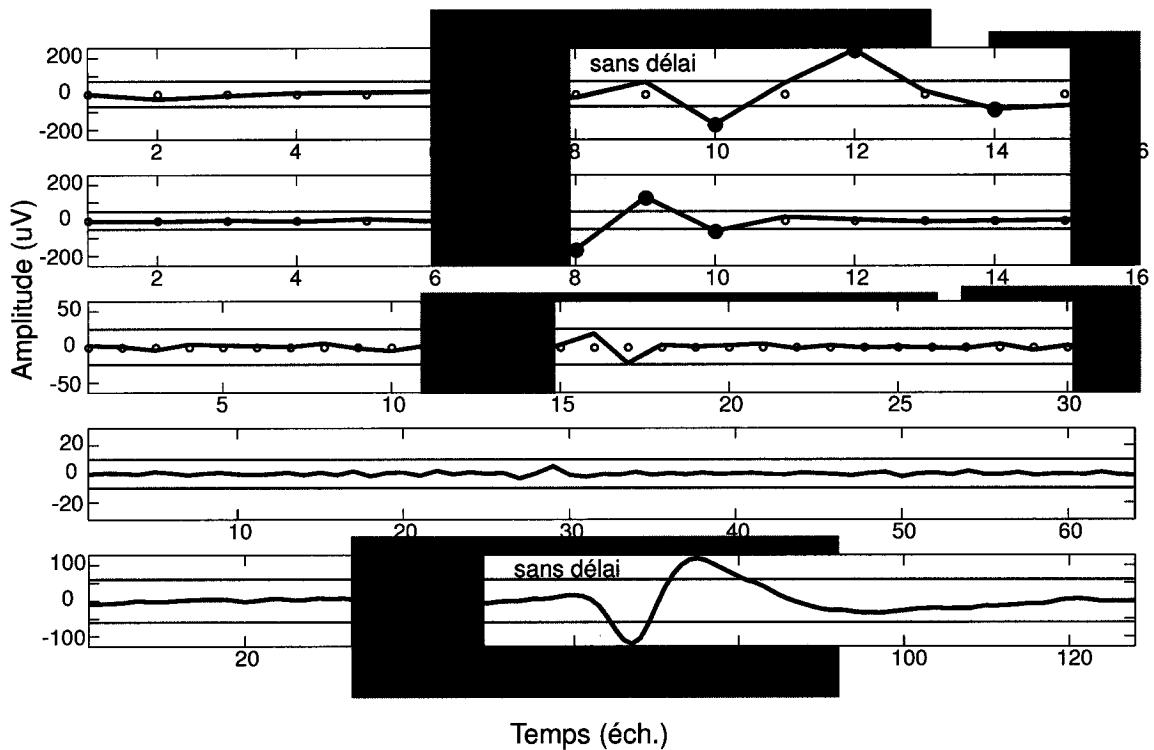

| <b>FIG. 2.6</b>  | Transformée en ondelettes . . . . .                                                | 44 |

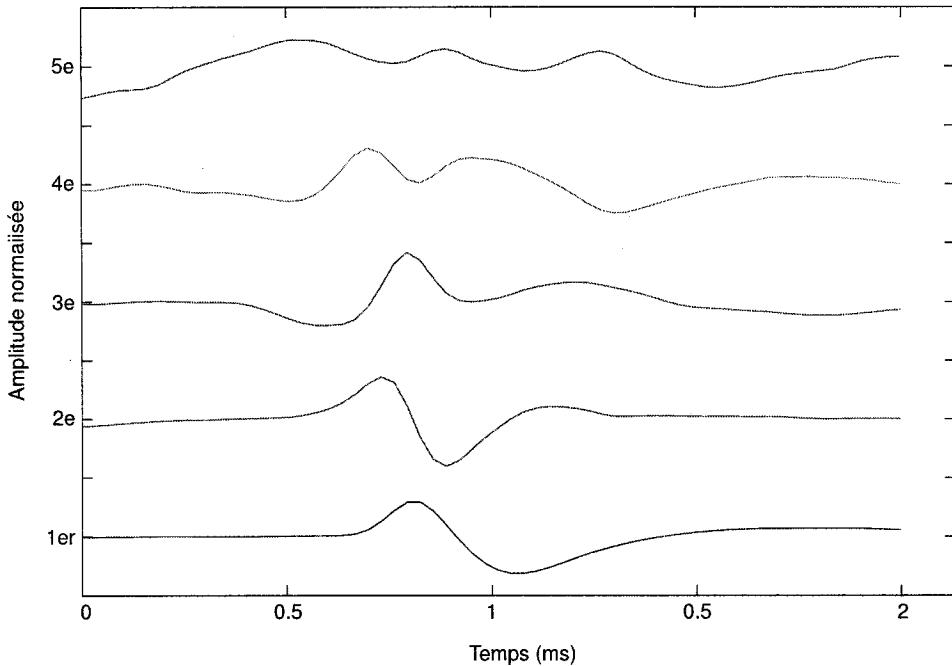

| <b>FIG. 2.7</b>  | Cinq composants principaux de AP pré-sélectionnés . . . . .                        | 46 |

| <b>FIG. 2.8</b>  | Schèmes de flot de données . . . . .                                               | 49 |

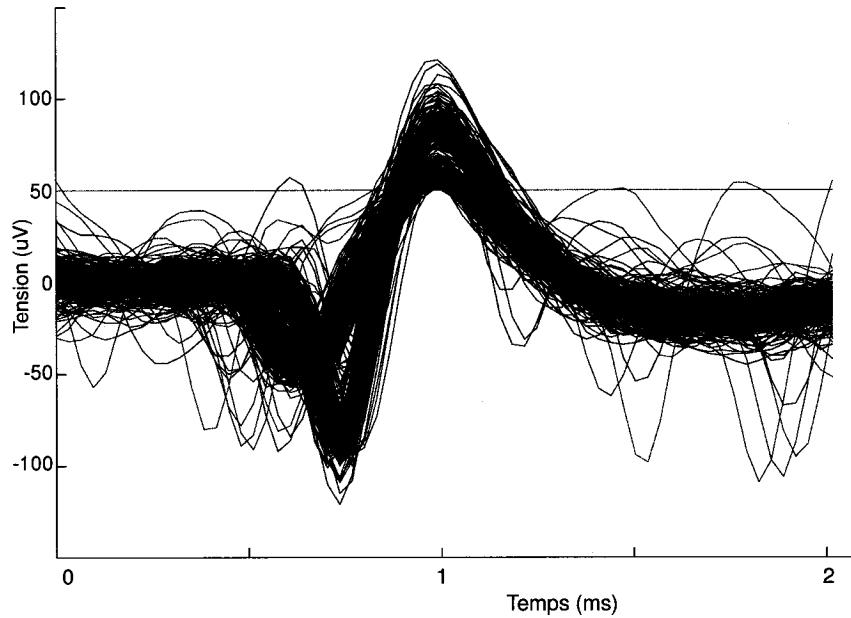

| <b>FIG. 2.9</b>  | Seuil simple avec détecteur de front montant et alignement . .                     | 52 |

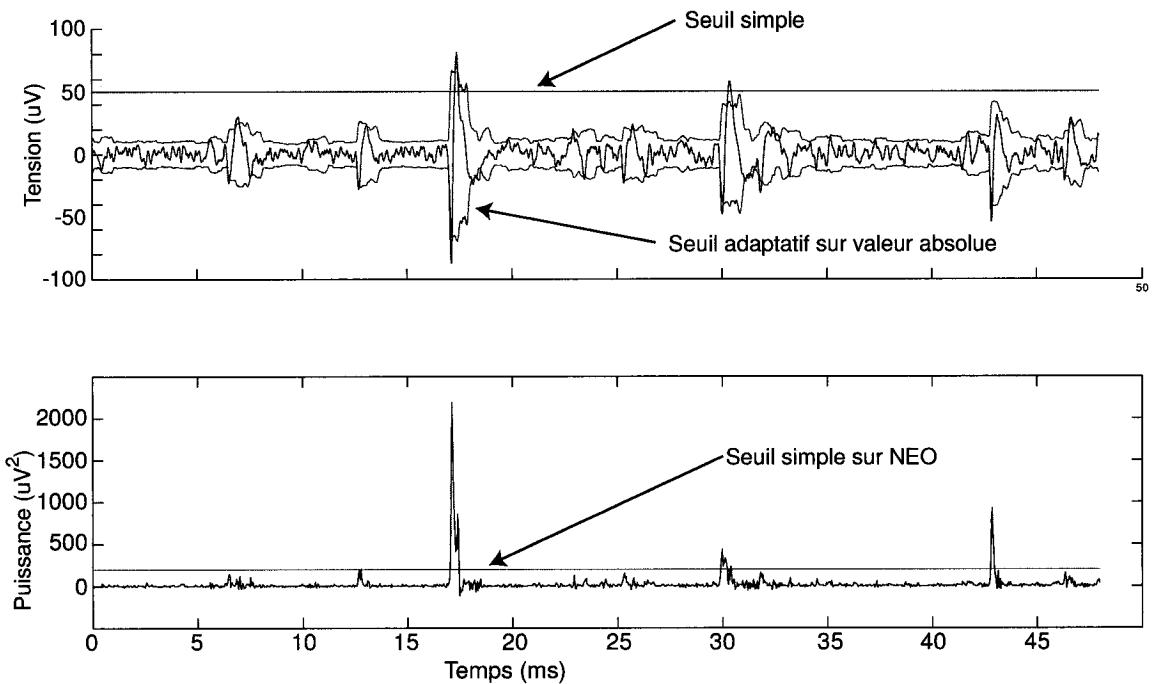

| <b>FIG. 2.10</b> | Exemple d'application des seuils . . . . .                                         | 53 |

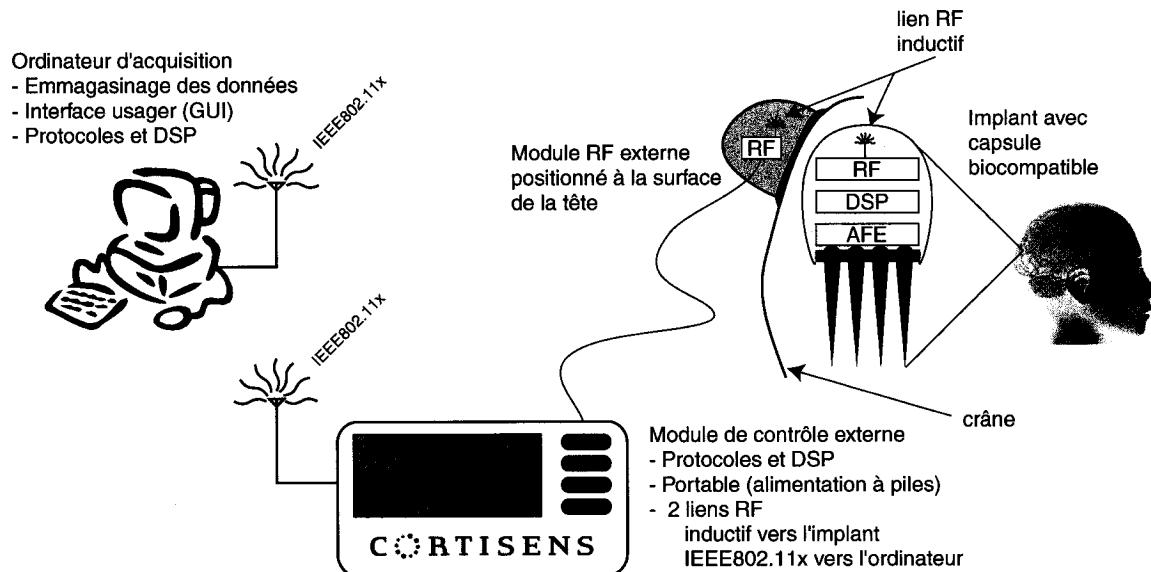

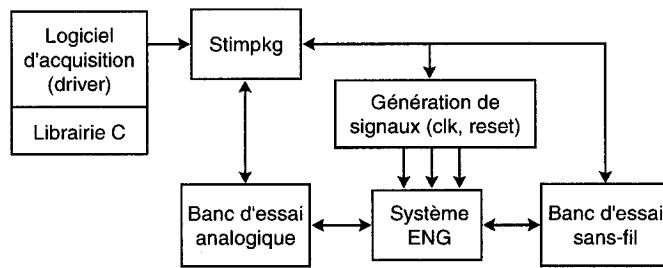

| <b>FIG. 3.1</b>  | Système conçu par l'équipe Cortisens . . . . .                                     | 58 |

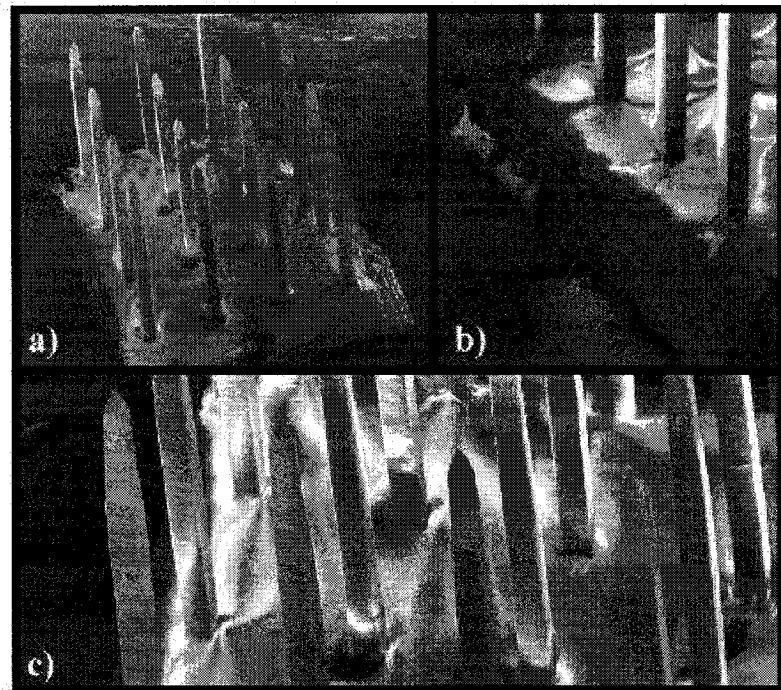

| <b>FIG. 3.2</b>  | Matrice d'électrodes fabriquée par Polystim . . . . .                              | 59 |

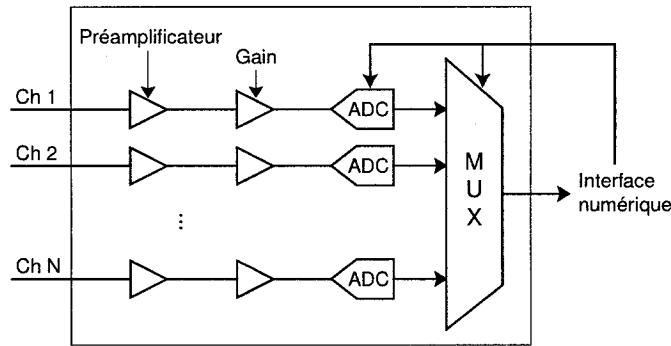

| <b>FIG. 3.3</b>  | Filtrage analogique et amplification . . . . .                                     | 60 |

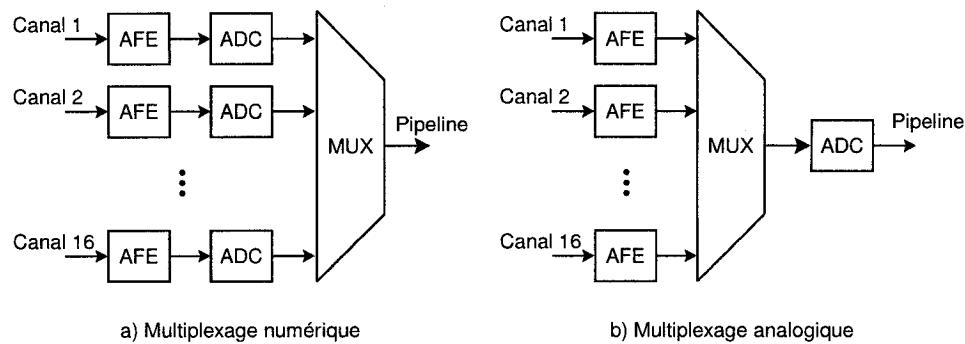

| <b>FIG. 3.4</b>  | Multiplexeur analogique vs numérique . . . . .                                     | 65 |

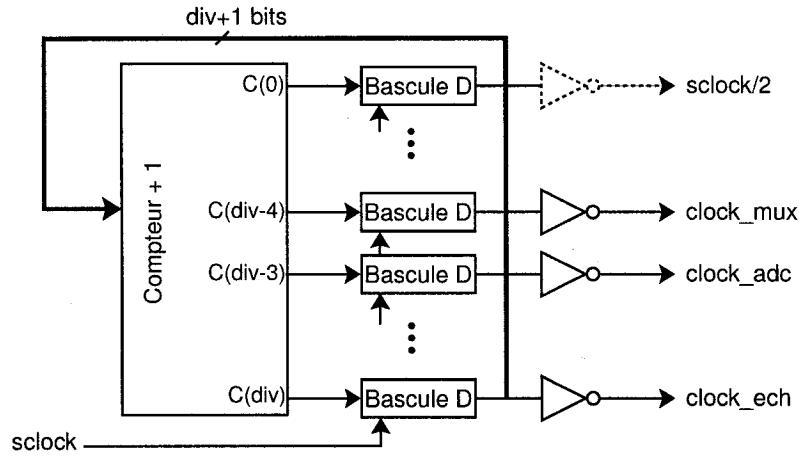

| <b>FIG. 3.5</b>  | Génération d'horloges avec un compteur libre . . . . .                             | 68 |

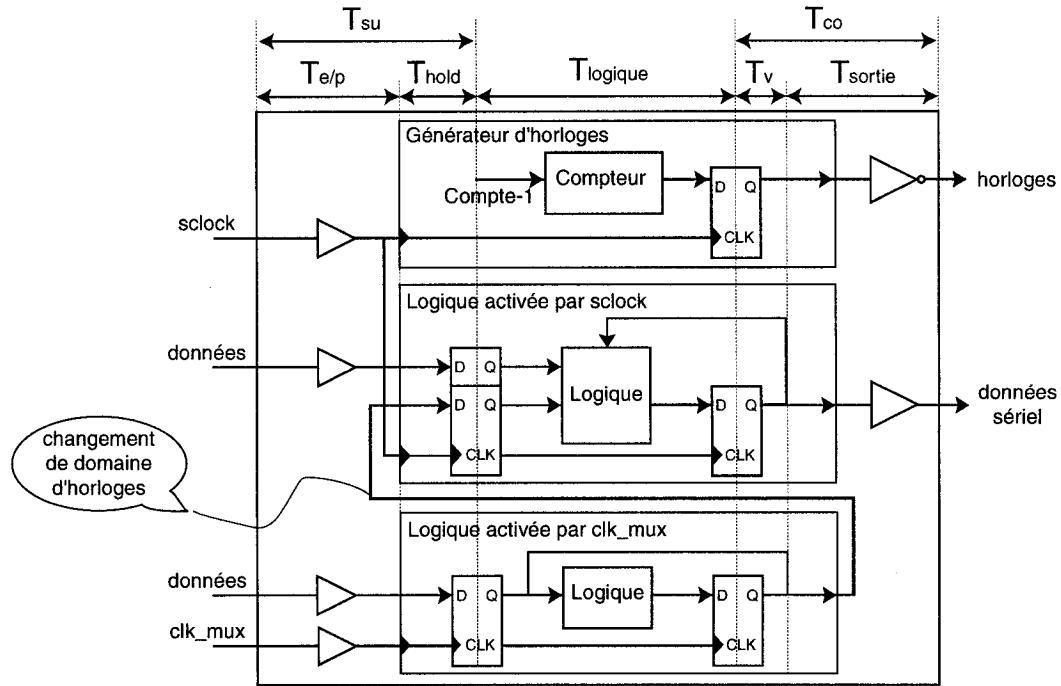

| <b>FIG. 3.6</b>  | Description des délais par rapport à la génération d'horloges .                    | 70 |

| <b>FIG. 3.7</b>  | Architecture globale du contrôleur numérique . . . . .                             | 79 |

|          |                                                                                         |     |

|----------|-----------------------------------------------------------------------------------------|-----|

| FIG. 3.8 | Fonctionnement de base du système . . . . .                                             | 85  |

| FIG. 3.9 | Fonctionnement du système avec l'utilisation du processeur d'ondelettes . . . . .       | 85  |

| FIG. 4.1 | Compression sans en-tête pour le protocole . . . . .                                    | 89  |

| FIG. 4.2 | Compressions DWT et DCT comparées . . . . .                                             | 93  |

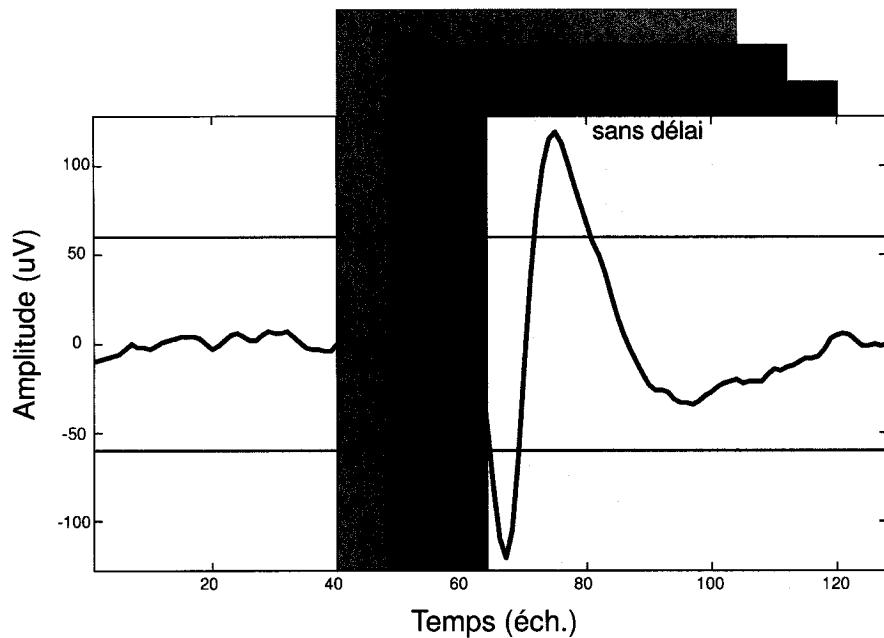

| FIG. 4.3 | Débruitage lors de la compression DWT . . . . .                                         | 94  |

| FIG. 4.4 | Schéma du dispositif de test et de validation . . . . .                                 | 96  |

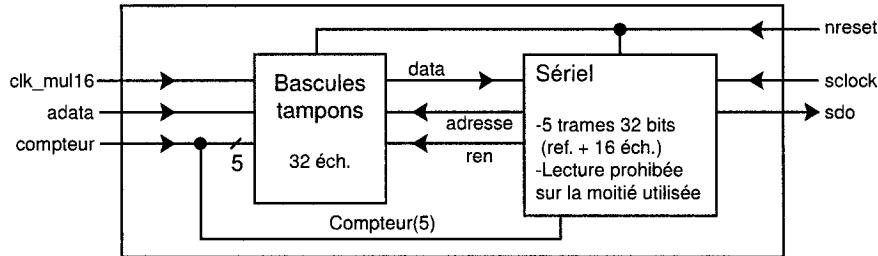

| FIG. 4.5 | Interface sérielle simple et sécuritaire avec changement de domaine d'horloge . . . . . | 107 |

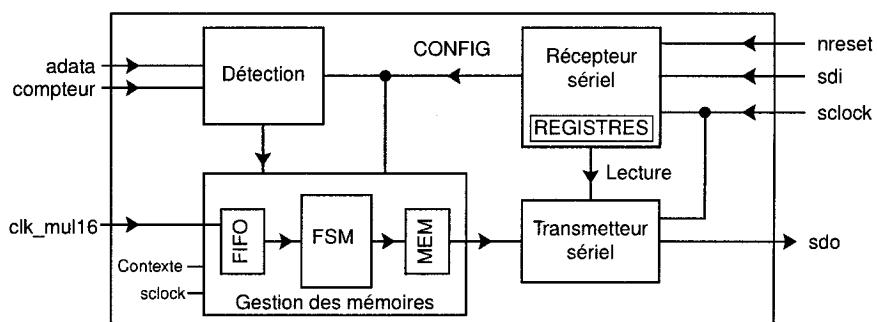

| FIG. 4.6 | Architecture du Système ASIC numérique . . . . .                                        | 107 |

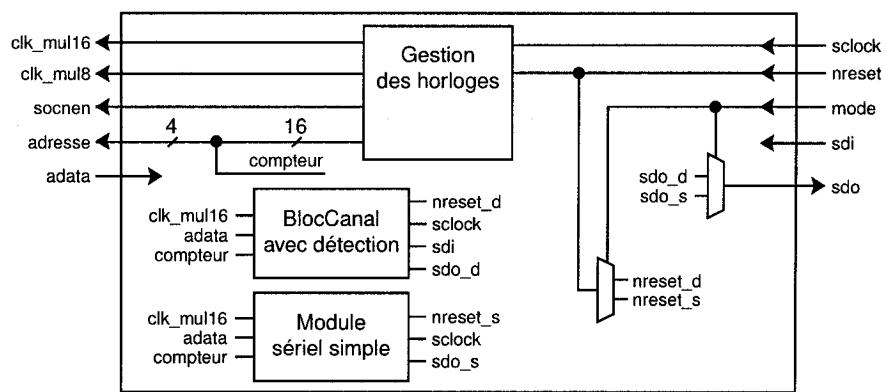

| FIG. 4.7 | Système ASIC conçu par l'équipe Cortisens . . . . .                                     | 108 |

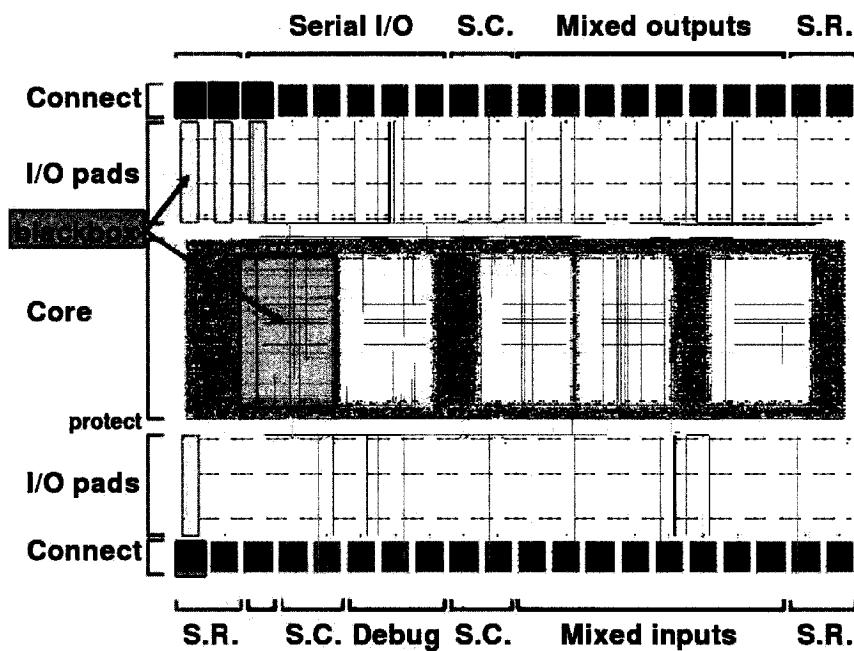

| FIG. 4.8 | Vue physique du système ASIC numérique . . . . .                                        | 110 |

| FIG. I.1 | Placement des mémoires et des lignes d'alimentation du cœur . . . . .                   | 124 |

| FIG. I.2 | Placement des unités logiques de base . . . . .                                         | 125 |

| FIG. I.3 | Routage de l'arbre d'horloge . . . . .                                                  | 125 |

| FIG. I.4 | Routage des alimentations . . . . .                                                     | 126 |

| FIG. I.5 | Routage final des cellules logiques . . . . .                                           | 126 |

| FIG. I.6 | Photo de la puce une fois fabriquée . . . . .                                           | 127 |

**LISTE DES TABLEAUX**

|          |                                                                                |     |

|----------|--------------------------------------------------------------------------------|-----|

| TAB. 2.1 | Décision par seuillage . . . . .                                               | 50  |

| TAB. 3.1 | Horloges impliquées dans le système . . . . .                                  | 67  |

| TAB. 3.2 | Délais typiques . . . . .                                                      | 69  |

| TAB. 3.3 | Trame de commande pour les accès aux registres de configuration                | 75  |

| TAB. 3.4 | Exemple de séquences de trames . . . . .                                       | 76  |

| TAB. 3.5 | Trame d'en-tête de paquet de données . . . . .                                 | 77  |

| TAB. 3.6 | Séquence de trames avec compression DWT . . . . .                              | 78  |

| TAB. 3.7 | Échantillonnage des coefficients DWT . . . . .                                 | 82  |

| TAB. 3.8 | Modes de fonctionnement . . . . .                                              | 84  |

| TAB. 4.1 | Comparaison des techniques de seuillage . . . . .                              | 91  |

| TAB. 4.2 | Utilisation logique du premier prototype . . . . .                             | 102 |

| TAB. 4.3 | Utilisation logique et surface estimée pour le système ENG . .                 | 104 |

| TAB. 4.4 | Résumé de la surface d'implémentation sur silicium du prototype ASIC . . . . . | 110 |

## LISTE DES NOTATIONS ET DES SYMBOLES

ADC = Analog Digital Converter

AFE = Analog Front End

AP = Action Potential

ASIC = Application Specific Integrated Circuit

BCI = Brain Computer Interface

CWT = Continuous Wavelet Transform

DCT = Discrete Cosinus Transform

DRC = Design Rule Check

DFT = Discrete Fourier Transform

DSP = Digital Signal Processing

DUT = Design Under Test

DWT = Discrete Wavelet Transform

ECoG = Electrocorticogramme

EEG = Electroencephalogramme

EDM = Electrical Discharge Micromachining

ENG = Electroneurogramme

ERD = Event-Related Desynchronization

ERP = Event-Related Potential

FIR = Finite Impulse Response

FFT = Fast Fourier Transform

FLI = Foreign Language Interface

GUI = Graphic User Interface

LFP = Low Field Potential

LVS = Layout Versus Schematics

MEG = Magnetoencephalogramme

MRP = Movement-Related Potential

MSE = Mean Square Error

PCA = Principal Component Analysis

SCP = Slow Cortical Potential

SNR = Signal Noise Ratio

STFT = Short Time Fourier Transform

TDM = Time Division Multiplexing

VHDL = VHSIC Hardware Description Language

VHSIC = Very-High-Speed Integrated Circuit

VLSI = Very Large Scale Integration

**LISTE DES ANNEXES**

|           |                                                                |     |

|-----------|----------------------------------------------------------------|-----|

| ANNEXE I  | PROCESSUS DE PLACEMENT ET ROUTAGE DE LA PUCE<br>ASIC . . . . . | 124 |

| ANNEXE II | PORT VHDL DU CONTRÔLEUR NUMÉRIQUE . . . . .                    | 128 |

## INTRODUCTION

De nos jours, les systèmes d'interface humain-machine montrent de plus en plus leurs utilités en apportant une aide aux handicapés. Ces systèmes représentent l'aboutissement de plusieurs années de recherche mettant en relation plusieurs disciplines complémentaires : l'électrophysiologie avec l'étude du système nerveux, la microélectronique avec la réalisation d'implants, le traitement de signal pour l'analyse, la robotique et plusieurs autres.

Dans le cas qui nous intéresse, nous nous concentrerons sur un type particulier d'interface humain-machine qui a pour but de faire l'acquisition des signaux électriques en provenance du cerveau (*Brain Computer Interface-BCI*). Parmi les percées scientifiques dans ce domaine, l'électroencéphalogramme (EEG) a été le premier type d'appareil dédié aux signaux corticaux. Grâce à lui, les scientifiques ont pu caractériser les grandes régions d'activité cérébrales comme les cortex moteur et visuel. Dans un même ordre d'idée, l'électroneurogramme (ENG) est une suite logique de l'EEG pour des besoins accrus de précision, de qualité et de sensibilité.

L'équipe Cortisens du laboratoire de recherche en neurotechnologies Polystim s'est intéressée aux techniques d'acquisition de signaux corticaux. Suivant cette direction, Polystim a développé, et développe encore, une matrice d'électrodes implantable. Chacune des électrodes permettra de suivre l'évolution localisée des stimuli corticaux. L'idée est la réalisation d'une puce implantable qui permettrait de prendre des mesures *in vivo*.

Le but du système d'acquisition consiste à faire l'échantillonnage des signaux électriques du cerveau qui se propagent par impulsions aussi appelées des potentiels d'action. Les signaux sont d'abord amplifiés et filtrés par un circuit analogique (*Analog*

*Front End-AFE) puis échantillonnés par des convertisseurs analogique-à-numérique. L'unité de contrôle et de compression numérique coordonne l'échantillonage en synchronisant les différentes fréquences d'horloges pour finalement transférer les données compressées et regroupées par paquets au lien de communication sans-fil.*

Ce mémoire se penche sur une partie de ce système, l'unité de contrôle et de compression de données pour la partie implantable d'un ENG. Les points d'importance y sont exposés en partant de la théorie du signal cortical pour aboutir à la réalisation matérielle d'une puce électronique.

Une mise en contexte au chapitre 1 mène à une description des signaux corticaux qui permet d'expliquer quelle information la BCI doit transmettre pour faire l'acquisition neuronale. Les données peuvent être interprétées différemment : une série d'exemples provenant de systèmes existants montrent comment il est possible d'y parvenir.

Dans le chapitre 2 sont présentés les algorithmes qui permettront de compresser le signal afin d'économiser sur la bande passante et ainsi offrir un système multi-canal avec la plus grande densité pour un même lien de communication. De plus, différentes techniques de détection de l'activité neuronale montrent les compromis rencontrés lors de la description et de l'optimisation du système. Le système en tant que tel est décrit en détails au chapitre 3 où le contrôleur numérique est situé dans l'ENG global conçu par l'équipe Cortisens.

Les décisions architecturales expliquées au chapitre 3 proviennent des résultats de simulation pour les comparaisons des algorithmes de compression et des techniques de détection d'activité neuronale décrits au chapitre 2. Tous les résultats sont concentrés dans le chapitre 4 afin de réunir dans un même contexte toutes les preuves décisionnelles.

Finalement, la méthodologie de design est présentée pour expliquer le cheminement et les étapes de développement qui ont menés à la réalisation de prototypes sur plate-forme de prototypage rapide et finalement d'un prototype ASIC (*Application Specific Integrated Circuit*).

## CHAPITRE 1

### LES NEURONES ET LEURS SYSTÈMES D'ACQUISITION

#### 1.1 Introduction

Depuis longtemps la population scientifique s'est intéressée à l'information que l'on peut extraire de signaux neuronaux. Lui méritant son prix Nobel en 1906 en collaboration avec Camillo Golgi sur la structure du système nerveux, le célèbre Santiago Ramón y Cajal introduit l'idée que les neurones représentent la structure fonctionnelle du cerveau, (Ramón y Cajal 1911). Depuis, les travaux ont beaucoup évolué, en particulier avec l'apport substantiel de Hebb qui amena le postulat d'apprentissage. Par contre, son influence prit du temps pour atteindre la communauté des sciences appliquées (Haykin 1998).

Plusieurs groupes se sont penchés sur le problème et ont développé le concept d'interface cerveau-ordinateur plus connu sous l'acronyme BCI (*Brain Computer Interface*). De telles recherches impliquent l'implémentation matérielle de composants dédiés pour l'observation du comportement animal, et pour l'interpréter ensuite. Ces composants se divisent en deux groupes : les implants pour usage chronique et ceux pour usage aiguë. Le transfert et le traitement ne s'appliquent pas de la même façon pour les deux cas. Dans notre contexte, le but final est de réaliser un système entièrement implantable, soit de la catégorie à usage chronique. Certaines restrictions et astuces sont donc applicables pour l'accomplissement de cette tâche. Une description des différents aspects est faite dans la section 1.2. Ces caractéristiques sont la base de la conception de prothèses neurologiques permettant de pallier certaines dysfonctions

dont souffrent les patients visés.

La caractérisation des potentiels d'action (*Action Potential-AP*) faite à la section 1.3 permet d'établir une approche plus pragmatique des tâches d'acquisition. Ce qui nous mène à la réalisation d'un système d'acquisition de signaux neuronaux actionné par l'occurrence d'évènements, soient les AP.

L'époque de la validation expérimentale a débuté depuis plusieurs années. Déjà en 1986, l'équipe Motorlab (Georgopoulos *et al.* 1986) publiait un article montrant l'application de l'encodage du mouvement provenant d'une population de neurones. Aujourd'hui, Motorlab a un bras robotisé activé par l'analyse en temps réel des signaux corticaux. Ainsi, Motorlab performe des algorithmes sur la perception et les intentions de mouvement (Schwartz *et al.* 2004). Une description des différents systèmes existants est faite dans la section 1.5.

## 1.2 Interface cerveau-ordinateur

Certaines applications BCI ont pour but le contrôle en temps réel, d'autres prônent plutôt l'acquisition pure et dure avec une bonne qualité. Ces deux approches se complètent dans le sens où l'un tente d'interpréter les signaux fournis par l'autre afin d'interagir. La différence survient dans les restrictions d'application. Par exemple, un système entièrement implantable ne pourra pas offrir autant de quantité et de qualité qu'un autre système avec fils. Les contraintes varient en ce qui concerne la superficie sur le silicium, la consommation de puissance et la bande passante pour le transfert des données.

Parlant de l'intelligence artificielle, Sage décrit un système qui devrait savoir faire trois choses : emmagasiner des connaissances, appliquer les connaissances connues pour

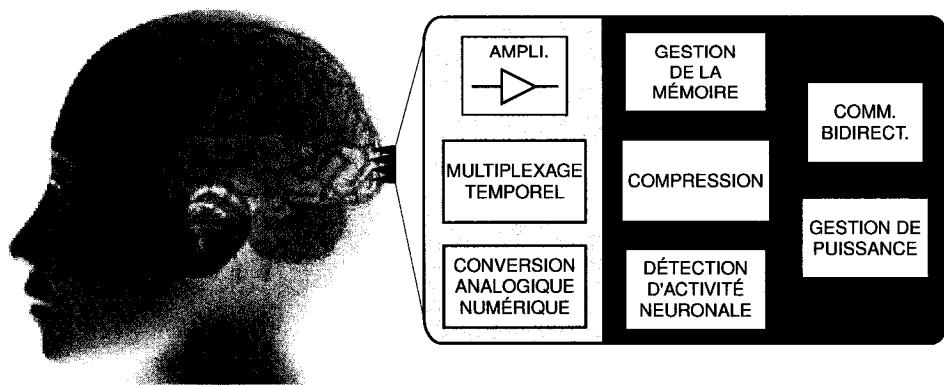

résoudre des problèmes et, finalement, acquérir de nouvelles connaissances (Sage 1990). Haykin le cite et ajoute que les connaissances ne désignent en fait que des données, c'est la représentation ; l'application doit pouvoir se contrôler pour choisir les chemins logiques, c'est le raisonnement ; finalement, les nouvelles connaissances s'incluent dans un système par algorithme, c'est l'apprentissage (Haykin 1998). La figure 1.1 montre les différents modules essentiels de la partie implantable d'une BCI.

FIG. 1.1 Parties essentielles d'une interface cerveau-ordinateur

L'objectif d'une BCI est d'établir un canal de communication afin de traduire les intentions humaines, reflétées par les signaux corticaux, en un signal de contrôle pour une application logicielle ou une prothèse neurologique (Dornhege *et al.* 2003). L'important devient de se représenter les états courants possibles du cerveau en comparant les caractéristiques des signaux observés avec les paradigmes prédéfinis comme l'idée de mouvements et la vision, par exemple.

### 1.2.1 L'acquisition

Bien que plusieurs méthodes aient été développées pour faire l'acquisition des signaux neuronaux, trois grandes classes en sont ressorties, l'électroencéphalogramme (EEG),

l'électroneurogramme (ENG) et le magnétoencéphalogramme (MEG). Chacune offre une méthodologie applicable pour des potentiels d'action. Faisant une analogie entre l'enregistrement d'un orchestre symphonique et l'enregistrement neuronal, Buzaki explique bien les perspectives de l'acquisition d'un ensemble de neurones. Il sépare l'acquisition en trois composants critiques qui sont l'interface neurone-électrode, l'identification et la classification des AP, et les outils d'analyse et d'interprétation des salves d'impulsions. Le développement de méthodes objectives et de systèmes novateurs devient nécessaire afin de percer l'incompréhension de l'encodage neuronal, de l'intérieur du cerveau (Buzsaki 2004).

### L'électroencéphalogramme

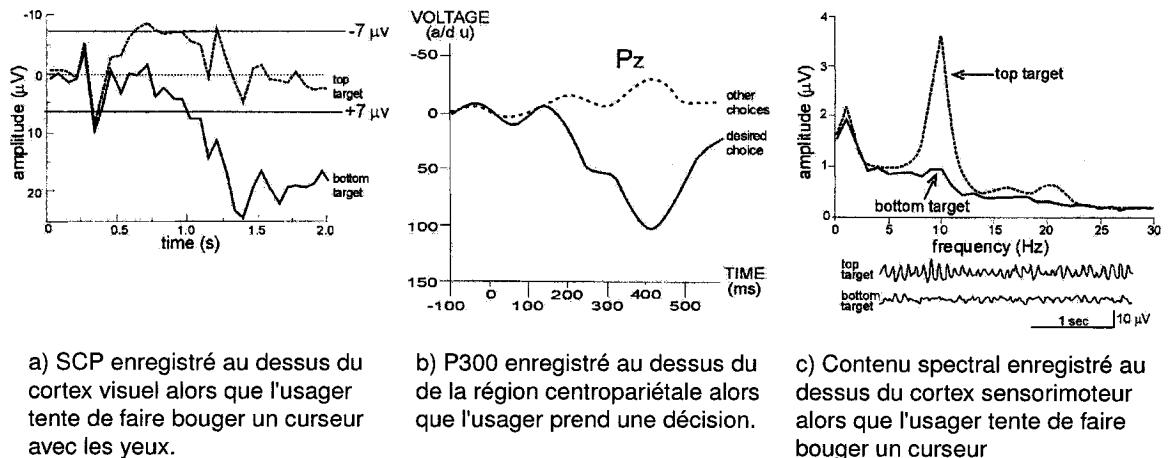

L'électroencéphalogramme (EEG) est une méthode non envahissante qui est aussi considérée comme étant une des plus simples. Elle consiste à placer des électrodes sur la surface de la tête, préférablement directement sur la peau pour plus de stabilité et pour obtenir un meilleur rapport signal sur bruit (*Signal Noise Ratio-SNR*). Par contre, la présence importante de bruit limite son utilisation à des signaux de basses fréquences. De toute façon, d'après Wolpaw, les signaux d'intérêt seraient les SCP (*Slow Cortical Potentials*), plus précisément les ondes  $\mu$  ou  $\beta$  (Wolpaw *et al.* 2002). Les SCP sont aussi connus sous le nom de LFP (*Low Field Potentials*) et ont la forme montrée aux figures 1.2a-c.

Puisque cette technique est non envahissante, elle offre de nombreuses applications allant de l'aide aux invalides à un dispositif de jeu vidéo. Le problème majeur associé à cette technique est le mauvais SNR dû à l'atténuation des signaux au travers du crâne. Une vaste panoplie de traitements de signaux peut être appliquée à cette méthode d'acquisition, comme pour les autres méthodes d'ailleurs.

Dans son étude de cas, Meinicke résume les quatre principales approches pour ce

type d'acquisition. La première, l'approche de Wolpaw présentée précédemment et considérant seulement les SCP, aurait besoin d'un transfert de données dans les environs de 20-25 bits/min (Wolpaw *et al.* 2002). Une autre approche, basée sur les travaux de Blankertz, analyse particulièrement les ERP (*Event Related Potentials*) afin de déduire l'intention humaine, ce genre de calcul pourrait offrir une classification de signaux neuronaux avec 23 bits/min (Blankertz *et al.* 2001). La troisième approche rejoint les travaux faits par Hinterberger dans un scénario de rétroaction biologique qui nécessite beaucoup de traitements préalables pour aboutir à un transfert aussi bas que 6 bits/min dans un système pseudo temps-réel (Hinterberger *et al.* 2004). La dernière approche analysée regarde principalement les signaux P300, qui représentent une impulsion survenant environ 300 ms après une intention de mouvement. Leur modèle permet une vraie gestion temps réel avec un débit prometteur de 12 bits/min (Meinicke *et al.* 2002).

FIG. 1.2 Signal typique à basse fréquence, source : (Wolpaw *et al.* 2002)

## L'électroneurogramme

Cette méthode envahissante aussi appelée ECoG pour électrocorticogramme est un procédé qui consiste à la disposition de micro-électrodes directement dans le cortex

pour faire l'enregistrement électrique de l'activité. Cette méthode est particulièrement appropriée pour des implants chroniques qui permettent aux sujets de vaquer à leurs occupations normales.

La résolution spatiale de l'électroneurogramme (ENG) est nettement supérieure à celle de l'EEG puisque le crâne n'est plus là pour atténuer les signaux ; il offre donc une meilleure qualité d'acquisition en augmentant le SNR. De plus, étant donnée sa résolution, il permet une plus grande densité d'analyse qui pourrait permettre de couvrir plus exactement la région désirée. Il ouvre ainsi la voie à l'observation de région prédéfinie comme le cortex visuel ou moteur pour en extraire plus facilement les ERP qui y sont associés.

Le plus grand point négatif de cette méthode est l'obligation de recourir à la chirurgie pour insérer les électrodes jusqu'au cortex. Vu cette contrainte, cette méthode offre malheureusement une expérimentation limitée de nos jours.

### **Le magnétoencéphalogramme**

Le magnétoencéphalogramme (MEG) est une méthode non envahissante qui consiste à lire le champ magnétique induit par les courants circulant dans les dendrites. Ces courants appelés dipôles permettent d'identifier l'activité d'un ensemble de neurones plutôt qu'un neurone en particulier en déduisant la position, la direction et la magnitude des dipôles.

On pourrait aussi inclure dans cette catégorie toutes les méthodes moyennement envahissantes comme le PET (*Positron Emission Tomography*) qui utilise un bio-traceur radioactif, le fMRI (*functional Magnetic Resonance Imaging*) et l'imagerie par laser. Ces méthodes se rapportent principalement au flux sanguin plutôt qu'à une représentation électrique, ce qui permet tout de même de faire une corrélation

entre cette activité et l'activité neuronale. Ces techniques sont toutes freinées par une longue constante de temps et sont encore très demandantes en matériel pour un système complet et portable. Ce travail n'en fera plus allusion.

### **1.2.2 La stimulation électrique neuronale**

La stimulation électrique neuronale est un domaine de recherche en tant que tel et ne fait pas partie de cette recherche. Il implique le développement de modèles pour l'interface tissu-électrode et pour une carte neurotopique qui permet de déterminer à quel endroit, à quel moment et de quelle façon il convient de stimuler. Sans ce modèle, on ne peut pas estimer l'impact de l'injection d'un courant ou de l'application d'une tension sur les tissus nerveux. En effet, avant de stimuler, il est important de comprendre comment les signaux transmettent et reflètent l'information pour ensuite être en mesure de reconstituer l'effet désiré.

### **1.2.3 La variété des tâches**

Un système BCI temps-réel complet requiert grossièrement cinq tâches importantes afin d'acquérir des AP et d'agir rétroactivement.

1. Une détection d'activité neuronales permet d'identifier les données consistantes.

2. Une caractérisation des signaux permet de représenter les données en préservant le maximum d'information. Le concept d'extraction de propriétés (*feature extraction*) réfère à cette tâche.

3. Une localisation temporelle permet de reconstituer le signal échantillonné.

4. Une classification permet d'associer l'information à un comportement connu.

5. Une rétroaction permet d'agir directement par des actions spécifiques en fonction du contexte comme le cortex moteur pour activer un bras robotisé.

Les tâches dédiées à l'acquisition se résument par les trois premières tâches énumérées, tandis que les deux dernières représentent plutôt les traitements spécifiques à l'application, pour un système BCI complet.

### 1.3 Caractérisation des potentiels d'action

Un neurone est une cellule particulièrement adaptée à la propagation des signaux électriques générés en réponse à une réaction chimique ou d'autres stimuli. De plus, ces signaux se propagent rapidement d'une cellule à une autre. Deux approches globales peuvent être choisies pour en faire l'étude. Premièrement, l'encodage neuronal est le lien entre le stimulus et la réponse du nerf sous la forme de AP, aussi appelés impulsions. Comme le décrit Dayan, les neurones encodent et transmettent l'information sous forme de séquences de AP. Deuxièmement, à l'opposé, le décodage neuronal considère la quantité d'information contenue dans la séquence de AP et son défi est de reconstruire un stimulus en fonction de la réponse (Dayan et Abbott 2001).

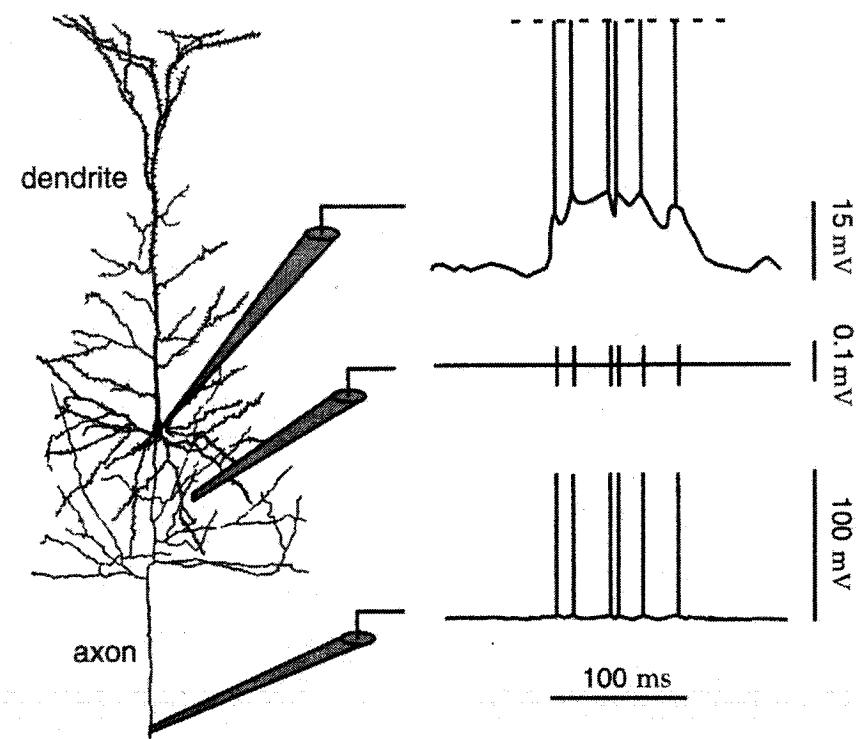

L'architecture biologique simplifiée d'un neurone est dessinée à la figure 1.3. Les dendrites reçoivent des signaux d'entrée provenant d'autres neurones et les transmettent au soma. Le soma, non montré, est la cellule centrale où les échanges chimiques se produisent selon une évolution non linéaire. Si l'accumulation électrique des entrées dépasse un certain seuil, un autre signal est émis en sortie par l'axone vers d'autres cellules. L'arbre de branchement des dendrites permet à plusieurs neurones de s'interconnecter au travers d'une ou plusieurs connexions synaptiques. Un neurone simple dans le cortex d'un vertébré fait la connexion à plus de  $10^4$  autres neurones (Gerstner et Kistler 2002).

La figure 1.3 présente les endroits propices à l'observation neuronale. Le signal du haut représente le potentiel intracellulaire du soma, le signal du centre montre des potentiels d'action et le signal du bas représente le potentiel intracellulaire au niveau de l'axone (Dayan et Abbott 2001).

FIG. 1.3 Trois sites d'enregistrement neuronal possibles,

source : (Dayan et Abbott 2001)

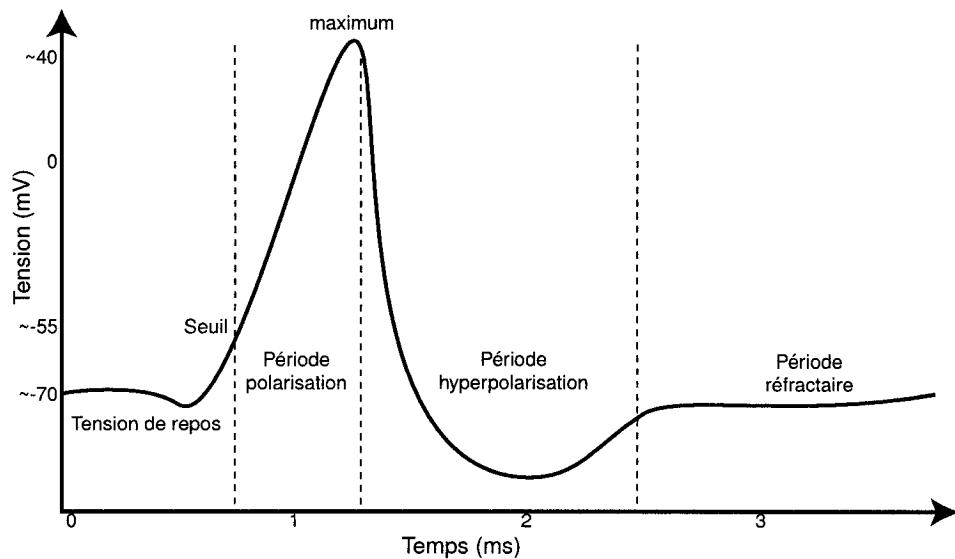

Plus précisément, le signal électrique est le résultat de la différence entre les potentiels intérieurs et extérieurs de la membrane neuronale. Le signal électrique est présenté à la figure 1.4. Une pompe à ions située dans cette membrane maintient le gradient de concentration pour maintenir le potentiel (environ -70 mV). Lorsque le gradient atteint un certain niveau de seuil de 15 à 20 mV de plus que la tension de repos, le canal ionique s'ouvre et survient la phase de montée du AP, la polarisation, qui rééquilibre

ainsi les charges ioniques. La montée dure environ 1 ms, puis le canal se referme et la phase de descente s'amorce jusqu'à un certain niveau, c'est l'hyperpolarisation qui porte ce nom puisque la tension redescend à un niveau inférieur au potentiel de repos.

En dernier, vient la période réfractaire, introduit par Hodgkin et Huxley en 1952. Cette période représente le temps durant lequel les canaux ioniques sont inactifs, donc le temps durant lequel un AP ne peut avoir lieu. Dans les faits, la réactivation des canaux ioniques se fait selon une manière stochastique et le seuil d'activation peut être atteint prématûrement si le potentiel d'excitation est suffisamment élevé.

FIG. 1.4 Potentiel d'action

La période réfractaire est le temps suivant immédiatement un AP, aucune nouvelle impulsion n'est possible à ce moment car c'est le temps nécessaire à la pompe à ions pour se recharger. Sa durée s'estime entre 5 et 20 ms et un nouveau AP est fortement probable 10 ms plus tard (Pouzat *et al.* 2004). Cette définition devient particulièrement significative lorsqu'il s'agit de calculer un possible taux de compression du signal (section 2.2).

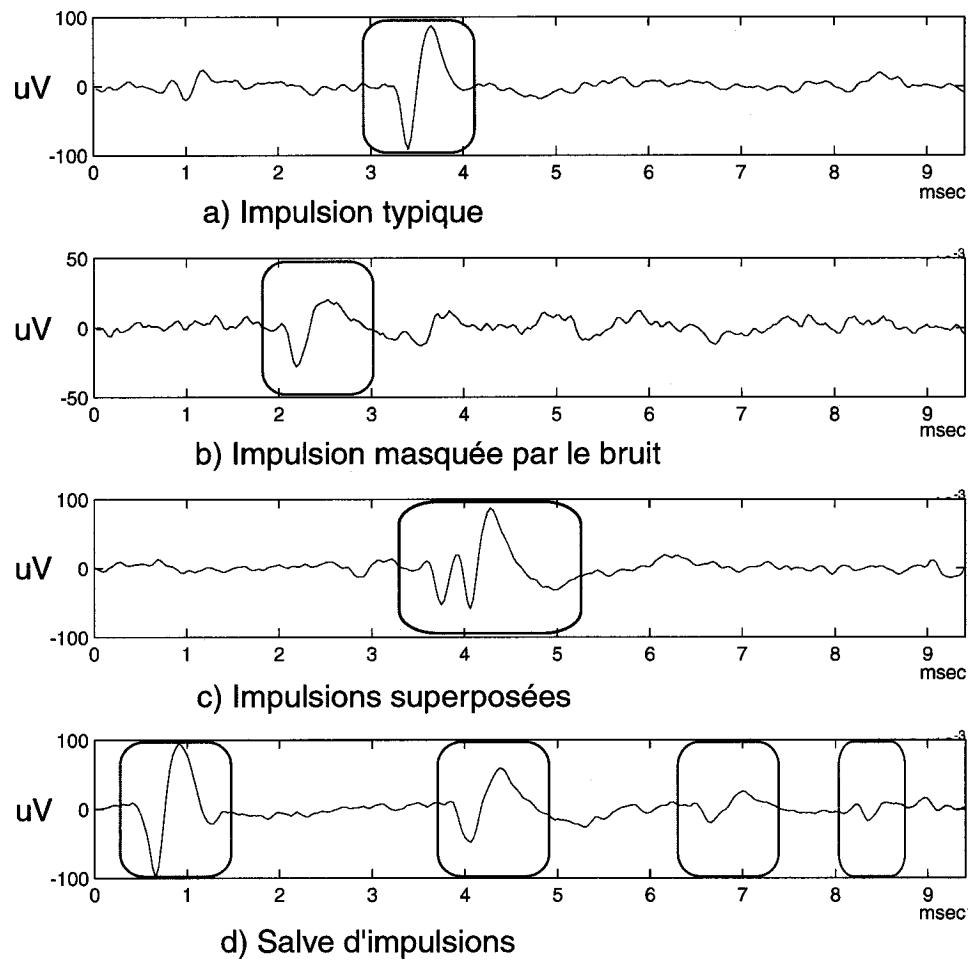

Quelques obstacles peuvent obstruer l'acquisition et nuire à l'analyse et à la reconnaissance des signaux enregistrés. Premièrement, le bruit peut masquer un AP généré par un neurone qui serait placé trop loin d'un site d'enregistrement. Deuxièmement, la superposition de plusieurs AP sur un même site qui pourrait être causée par la proximité relative de plusieurs neurones. Troisièmement, l'atténuation d'amplitude entre deux AP d'un même neurone produit lors d'un train consécutif d'impulsions. De plus, le volume d'information à considérer est trop grand pour tout conserver, surtout en considérant que plusieurs sites sont enregistrés simultanément d'où la nécessité de faire un traitement de base permettant de choisir les échantillons significatifs.

### 1.3.1 Le bruit

L'acquisition des signaux neuronaux est sujette à plusieurs types de bruit et parfois, il peut même devenir impossible de discerner le signal utile, on dit alors qu'il est entièrement couvert et que le SNR est pauvre ou petit. Le bruit peut provenir de toutes les sources qui ne sont pas les neurones que le système a pour but d'enregistrer.

Le bruit observé peut provenir autant de l'environnement que des outils et circuits servant à faire la lecture du signal (Oweiss et Anderson 2000). Premièrement, le bruit thermique dû aux amplificateurs composant l'étage d'entrée du circuit et faisant l'interface avec les tissus nerveux. Le bruit thermique est par définition un bruit dit blanc. Deuxièmement, le bruit de quantification qui est introduit par le convertisseur analogique-numérique (*Analog Digital Converter-ADC*). Ces deux causes peuvent être classées comme non corrélées donc indépendantes. De plus, dans cette catégorie peut s'ajouter les variations dues au déplacement du capteur par rapport au site d'enregistrement, l'impédance de l'électrode et bien d'autres sources indépendantes comme présentées dans (Musial *et al.* 2002).

Un autre type de bruit observable est directement lié à l'activité des autres neurones environnants et qui ne sont pas reconnus comme des AP. Ce type de sources contient un mélange de bruit corrélé, provenant de neurones proches mais trop éloignés pour être identifiés comme tels, ainsi que du bruit non corrélé provenant d'activité locale mais faible. Ce type de bruit est considéré comme coloré (Chandra et Optican 1997).

Bien que certains ne soient pas d'accord avec cette méthode (Kim et Kim 2000), le problème se simplifie en considérant le bruit comme étant du type blanc gaussien (Pouzat *et al.* 2002). Une bonne description<sup>1</sup> :

*”Un bruit blanc est un signal aléatoire dont la densité spectrale de puissance est constante quelle que soit sa fréquence. En d'autres termes, la probabilité qu'un bruit blanc possède une certaine puissance est la même pour toutes les fréquences.”*

Étant donné que le bruit est indépendant du signal, le signal échantillonné s'exprime donc comme à l'équation (1.1) où  $s(t)$  est le signal d'intérêt, tandis que  $b(t)$  est le bruit. Le signal observé pourrait ressembler au signal de la figure 1.5b.

$$s_e(t) = s(t) + b(t) \quad (1.1)$$

### 1.3.2 La superposition d'impulsions

Cette caractéristique est directement liée à la position spatiale de l'électrode par rapport aux neurones environnants. Si un site d'enregistrement est spatiallement situé au centre de deux neurones, par exemple, des impulsions quasi simultanées pourraient être difficilement identifiables.

La figure 1.5c montre une possibilité d'occurrence d'impulsions quasi simultanées.

---

<sup>1</sup>[http://fr.wikipedia.org/wiki/Bruit\\_blan](http://fr.wikipedia.org/wiki/Bruit_blan) consultée le 6 octobre 2005

FIG. 1.5 Caractéristiques des potentiels d'action,

source du signal : université Duke (même qu'aux chapitres 2 et 4)

En d'autres occasions il serait possible que le signal résultant soit interprété comme du bruit, même par des yeux d'experts. À ce sujet, Wood présente justement les divergences d'analyses faites par différents experts (Wood *et al.* 2004).

### 1.3.3 Les salves d'impulsions

Lorsqu'un neurone est fortement actif, c'est-à-dire que si les dendrites alimentant un neurone permettent d'accumuler suffisamment de charges dans le soma, le neurone en question peut émettre une salve d'impulsions dont l'intervalle dépend de la période réfractaire. Selon Pouzat, suivant un AP, un nouveau AP est fortement probable 10 ms plus tard avec une atténuation significative en amplitude comme on peut l'observer sur la figure 1.5D (avec une période réfractaire plus courte) (Pouzat *et al.* 2004).

Lewicki disait en 1998 que le taux d'occurrence pouvait s'estimer entre 20 et 100 Hz, ce qui correspond à la période réfractaire. Par contre, il ajoutait que le contenu fréquentiel des AP allait jusqu'à 4 kHz (Lewicki 1998). Cette dernière information est cruciale pour le choix de la fréquence d'échantillonage. Une discussion plus approfondie est faite dans la section 2.2.

### 1.3.4 Les potentiels d'action en équations

Si l'on simplifie le problème à sa plus simple expression en ignorant la durée du potentiel d'action qui devrait être environ 1 ms, on obtient une série de fonctions de Dirac ( $\delta$ ) où le temps  $t_i$  est l'occurrence d'un AP et n le nombre de AP dans la séquence analysée.

$$s(t) = \sum_{i=1}^n \delta(t - t_i) \quad (1.2)$$

La quantité d'information à transférer pour une séquence de données est représentée par le taux d'activité moyen ( $T_{act}$ ) pour une période d'analyse T :

$$T_{act} = \frac{n}{T} \quad (1.3)$$

Par contre, cette information ne nous informe pas suffisamment. Il serait plus pratique de connaître l'évolution temporelle de cette fonction ; surtout si le but est de l'associé à un stimulus. Prenons une moyenne de ce taux d'activité sur une fenêtre coulissante de grandeur  $\Delta t$ . Cette fenêtre doit être suffisamment grande pour calculer un bon estimé de la moyenne.

$$T_{act}(t) = \frac{1}{\Delta t} \int_t^{t+\Delta t} s(\tau) d\tau \quad (1.4)$$

où  $s(\tau)$  est l'extension continue du signal de l'équation (1.2). La probabilité qu'une impulsion soit vue sur un intervalle  $\Delta t$  autour de  $t_i$  est simplement

$$p[t_i] = T_{act}(t) \cdot \Delta t \quad (1.5)$$

Il est important de concevoir l'acquisition de signaux neuronaux comme un procédé temporel variant et stochastique. En fait, il est impossible de prédire à quel moment et selon quelle amplitude un neurone va générer une impulsion. Pour le savoir, il faudrait connaître toutes les séquences possibles qui relient un stimulus avec les émissions d'impulsions, donc l'encodage neuronal (ce qui n'est pas encore le cas). Il serait donc plus juste de dire simplement que la probabilité qu'un neurone émette une impulsion à un moment donné est nulle si  $\Delta t \rightarrow 0$ .

Le  $T_{act}(t)$  ne fournit malheureusement pas suffisamment d'information pour nous prédire la probabilité de l'occurrence d'une impulsion. Par exemple, la probabilité que deux neurones émettent un AP n'est pas nécessairement le produit des deux probabilités individuelles parce qu'il est possible que la présence de l'un influence l'occurrence de l'autre. Par contre, puisque la génération d'un AP dépend directement de son historique et que les intervalles successifs sont indépendants, donc les événements eux-mêmes sont indépendants ; nous avons donc un processus de Poisson (Dayan et Abbott 2001).

## Le processus de Poisson

Dans plusieurs applications comme le comptage des AP, l'intérêt est de compter le nombre d'occurrence dans un certain laps de temps ou dans l'espace. La variable aléatoire de Poisson est tout indiquée pour caractériser cette situation “imprévisible” (Leon-Garcia 1994). Sa probabilité  $p_k$  pour  $k$  occurrences est :

$$p_k = \frac{(T_{act})^k}{k!} e^{-T_{act}} \quad (1.6)$$

La moyenne, ou l'espérance  $E[X]$ , et la variance  $VAR[X]$  sont équivalentes avec ce type de variables aléatoires. La variance est une mesure qui permet de voir l'étendue des données aux alentours d'une moyenne

$$E[X] = VAR[X] = T_{act} \quad (1.7)$$

## Fonction de densité d'intervalle

Par définition, une fonction de densité de probabilité est une manière utile de spécifier l'information contenue dans une fonction de distribution comme l'avènement d'un AP par rapport à un précédent. Une caractéristique intéressante de la distribution de Poisson est que le nombre d'occurrences pendant un certain temps implique que l'intervalle entre chaque évènement est distribué exponentiellement (Leon-Garcia 1994). Une variable aléatoire exponentielle n'a pas la propriété de mémoire, c'est-à-dire que les évènements ne sont pas influencés par leurs précédents. Ce qui est pratiquement le cas pour un neurone si l'on ne considère pas la période réfractaire ou aucune activité n'est possible. Donc, puisque l'intervalle suit une exponentielle, il est fort probable que le temps entre deux AP soit court et peu probable qu'il soit long.

On pourrait exprimer ce taux d'activité par l'intervalle inter-impulsions, ou ISI (*Inter*

*Spike Interval*). Suivant une probabilité exponentielle, la moyenne donne donc :

$$E[ISI] = \frac{1}{T_{act}} \quad (1.8)$$

et la variance :

$$VAR[ISI] = \frac{1}{(T_{act})^2} \quad (1.9)$$

Cette densité représente l'activité générale du neurone plutôt que sa forme donnant seulement l'information sur l'état actuel. Cette fonction de densité semble mieux adaptée pour l'analyse de population à l'instar de l'analyse d'échantillons indépendants (Pouzat *et al.* 2004, Wood *et al.* 2004).

## 1.4 Les signaux d'intérêt pour l'acquisition

Plusieurs méthodes et procédés ont été mis en oeuvre pour les différents types de signaux. Que ce soient les signaux à basse fréquence ou les impulsions, chacune des caractéristiques importe ; allant de sa forme à sa fréquence d'occurrence en passant par le synchronisme des différents neurones. Dans le domaine de la computation de signaux corticaux, le terme propriétés des signaux revient souvent, surtout lorsqu'il est question de faire de l'extraction de propriété (*feature extraction*) (Dornhege *et al.* 2002). Cette tâche est effectuée par des filtres particuliers et des algorithmes dédiés.

### 1.4.1 Les potentiels d'action

La méthode d'acquisition d'ENG, bien qu'envahissante, est aussi beaucoup plus précise que les autres méthodes. Elle sert souvent de point de comparaison pour corroborer

les résultats obtenus avec les signaux à basse fréquence (Dornhege *et al.* 2002) car il est assez aisément de reconstituer des signaux similaires aux enregistrements EEG avec des signaux ENG.

Les types de filtres applicables pour des signaux comme les potentiels d'action couvrent une grande gamme de filtres possibles (Wilson et Emerson 2002, Lewicki 1998). Ces catégories incluent le filtrage du bruit, la détection d'événements et la compression du signal. Ces points seront couverts dans le chapitre 2.

En supposant qu'un neurone émet toujours de la même façon par son axone vers les autres neurones, la forme de l'impulsion pourrait sembler ne pas avoir d'importance pour une reconstitution fidèle. Positionner temporellement les impulsions sur une droite pourrait sembler suffisant. Par contre, ne connaissant pas la position spatiale exacte de l'électrode lors de l'acquisition, les signaux provenant de neurones distincts avoisinant peuvent être identifiés comme tels si et seulement si la forme du signal a été préalablement reconnue afin de faire la déduction. Hulata propose une méthode pour le tri des AP basée sur les paquets d'ondelettes et l'information mutuelle de Shannon (Hulata *et al.* 2002). Pouzat et Wood suggèrent l'analyse ISI (section 1.3) comme étant adéquate pour voir l'évolution de l'information (Pouzat *et al.* 2004, Wood *et al.* 2004).

#### 1.4.2 L'information neuronale

Dans son travail de renom, Shannon propose que “*le problème fondamental est de reproduire à un point, soit l'exactitude ou l'approximation, d'un message choisi à un autre point*” (Shannon 1948). Shannon définit donc une bonne mesure du contenu de l'information ( $I$ ) d'un message ainsi que l'entropie ( $H$ ) qui est une moyenne de

l'information transmise par message.

$$I(x_k) = \log\left(\frac{1}{p(x_k)}\right) = -\log[p(x_k)] \quad (1.10)$$

$$H(X) = E[I(x_k)] = \sum_k p(x_k) \cdot I(x_k) = -\sum_k p(x_k) \cdot \log[p(x_k)] \quad (1.11)$$

où  $p(x_k)$  est la probabilité d'occurrence d'un message  $x_k$ . Cela indique que si un message survient nécessairement, aucune information supplémentaire n'est apportée en le notant ( $p(x_k) = 1 \rightarrow I = 0$ ) ; donc on peut aussi conclure que moins l'occurrence d'un événement est probable plus l'information qui découle de sa notification est grande. Cette théorie est la base pour la construction d'un système de communication qui sera efficace et fiable. (French *et al.* 2003) utilise ce théorème comme point de comparaison pour évaluer l'efficacité d'algorithmes de compression ; bien que leur méthode est un peu douteuse du point de vue qualité, l'idée reste intéressante.

De plus, on peut aussi prouver que si les variables sont indépendantes, l'entropie est additive.

$$H(X, Y) = H(X) + H(Y) \quad (1.12)$$

Cette dernière équation est d'ailleurs appliquée dans l'équation du signal bruité (1.1) où les signaux peuvent simplement être considérés comme superposés.

## 1.5 Système d'acquisition neuronaux existants

Plusieurs groupes de recherche ont déjà étudié la question et ont développé des prototypes. La compagnie Cyberkinetics en collaboration avec l'université de l'Utah (Branner *et al.* 2004) offre un système commercial d'enregistrement et de traitement temps-réel pour des expérimentations aiguës. Cyberkinetics a évolué à partir de tra-

vaux présentés par l'équipe de Normann qui avaient proposé un système à 100 canaux (Guillory et Normann 1999). Des chercheurs de l'Université du Michigan ont développé une électrode multi-sites à différents niveaux (Wise *et al.* 2004). Les systèmes existants se divisent grossièrement en trois groupes, soient les systèmes avec processeurs, les systèmes intégrés et les autres systèmes connexes.

### 1.5.1 Systèmes avec processeurs et microcontrôleurs

Certains groupes décrivent leurs systèmes de façon détaillée comme Nicolelis qui présente une méthode pour l'enregistrement simultané d'ensembles neuronaux. Ce groupe a bâti un système de 96 canaux avec des micro-fils implantés chroniquement avec une grande capacité de calcul fournie par des modules commerciaux disponibles, soient des processeurs dédiés et autres DSP (*Digital Signal Processing*) (Nicolelis 1999).

Des chercheurs du Centre de recherche de Wadsworth (Wolpaw *et al.* 2003) proposent de leur côté un système basé sur des EEG enregistrés sur la tête. Cette équipe offre un système d'enregistrement générique non envahissant et partage ouvertement son logiciel baptisé BCI-2000. Les membres de cette équipe développent actuellement des applications utiles pour les invalides du cortex moteur, comme faire bouger un curseur sur un écran d'ordinateur sans l'usage des mains.

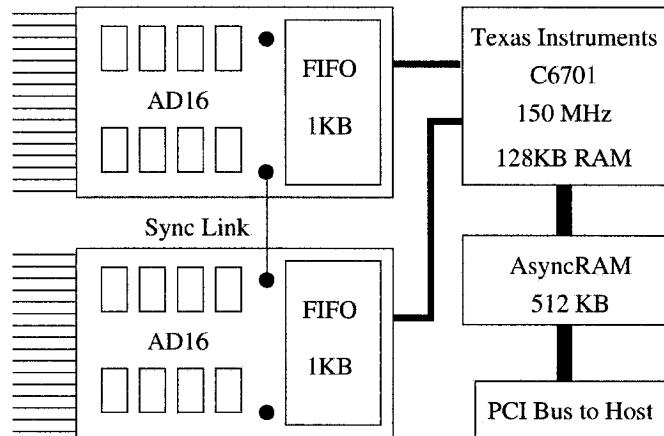

Un projet européen appelé VSAMUEL (Folkers *et al.* 2003) présentait un système permettant l'acquisition de 128 canaux avec un échantillonnage de 50k éch/s. Le système se compose de puces commercialement disponibles : des électrodes implantables, des étages d'amplification, des ADC ainsi que des plate-formes DSP. Un module DSP est montré en exemple à la figure 1.6. Leur système permet une gestion

et un traitement en temps-réel qui utilise une DWT (*Discrete Wavelet Transform*) par banque de filtres afin de faire la compression des signaux. Ce projet est celui qui ressemble le plus à ce que notre équipe Cortisens voudrait réaliser, à l'exception que nous visons une implémentation matérielle complète sur micro-puce.

FIG. 1.6 Système exemple, module DSP du projet VSAMUEL,

source : (Folkers *et al.* 2003)

### 1.5.2 Systèmes intégrés sur puce

Suivant une autre approche, les systèmes entièrement implantables occupent une bonne partie de l'intérêt des chercheurs car ils sont mieux adaptés pour des implantations à long terme. L'équipe de Wise propose un système hybride avec une technique avancée de micromachinage permettant une bonne densité du côté des électrodes avec un système externe non intégré (Wise *et al.* 2004).

Boahen présente dans son article une méthode de utilisant l'adressage d'événements. C'est-à-dire qu'il considère seulement si un AP est produit ou non et transmet simplement sa position spatiale plutôt que l'information intégrale. Boahen en vient à la conclusion qu'il est mieux d'utiliser un système de communication avec un lien

partagé et un arbitre plutôt qu'un lien dédié, car les informations proviennent majoritairement par accès sporadiques et un lien n'est que rarement utilisé à sa pleine capacité pour une longue période de temps. Il propose une solution originale pour la gestion de queues et de files (Boahen 2000).

### **Électronique analogique et mixte**

L'équipe de l'université Duke (Obeid *et al.* 2004a, Obeid *et al.* 2004b) présente un système de télémétrie à seize canaux réalisant 31.5 k échantillons/s supportés par un système embarqué personnalisé comprenant un PC et une interface sans-fil 802.11b<sup>2</sup>. Le système est léger, alimenté avec une batterie, portable mais pas entièrement implantable.

De son côté, l'équipe de l'université de Tübingen (Hinterberger *et al.* 2004) propose aussi un système s'intéressant aux SCP mais pour en extraire la pensée. Le système utilise une boucle de rétroaction afin d'établir un lien entre les stimuli visuels et les 64 sites d'enregistrement EEG. La société Danica<sup>3</sup> offre un système complet avec ordinateur, écran, panneau de commande, chariot et supports.

#### **1.5.3 Autres domaines reliés**

En regardant comment des ingénieurs s'intéressent à d'autres domaines d'activité ont résolu leurs problèmes, on en tire une information précieuse. Par exemple, l'équipe de Segura-Juarez a développé un système de très grande précision et de haute densité. Les membres de cette équipe ont développé un système basé sur l'occurrence d'événements pour 512 canaux échantillonnés à 100 MHz avec une résolution de 1 kHz entre chaque événement. Bien que leur but était d'analyser l'identification de parti-

---

<sup>2</sup><http://grouper.ieee.org/groups/802/11/> standard adopté depuis 1999

<sup>3</sup><http://www.danica.nl/neuro/neuro.htm> consultée le 27 septembre 2005

cules subatomiques, leur application présente des similitudes flagrantes avec l'acquisition de signaux neuronaux (Segura-Juarez *et al.* 2004).

Dans un autre ordre d'idées, Chueh et Hatfield présentent un système d'acquisition temps-réel pour l'analyse des odeurs, un nez électronique ( $H^2EN$ ). Ils utilisent une matrice de capteurs spécialisés couplés à une application logicielle qui peut fournir une rétroaction. L'intéressant de leur article est qu'il présente le problème dans son intégralité, allant du capteur à l'utilisation graphique en passant par les algorithmes utilisés et les mathématiques s'y rattachant (Chueh et Hatfield 2002).

L'équipe Euratom (Batista *et al.* 2002) a aussi exploré les systèmes de commande basés sur l'occurrence d'événements. Ils ont particulièrement ciblé l'amélioration des performances en ce qui concerne le transport de données, le traitement de signal, la synchronisation de systèmes et l'emmagasinage de données pour de grands débits. Ils résument bien les compromis entre les différents liens de communication disponibles et compare l'utilisation de FPGA versus celle de DSP.

## CHAPITRE 2

### LE TRAITEMENT ET LA COMPRESSION DES SIGNAUX NEURONaux

#### 2.1 Introduction

Dans le chapitre 1, les signaux d'intérêts pour un système d'acquisition cortical ont été présentés. Différents systèmes et algorithmes ont été introduits et seront développés plus en détails dans ce chapitre. Afin de choisir et de valider la méthode d'application la plus pertinente, plusieurs avenues ont été évaluées. En partant des caractéristiques décrites dans le chapitre 1, et considérant qu'il est superflu de transmettre toutes les données échantillonnées, le présent travail utilise le modèle classique de la théorie de l'information de Shannon pour développer un système de traitement dédié.

Une analyse pour une compression optimale est faite dans la section 2.2. Le barème de sélection se construit en comparant les fonctions de coût utilisées dans les systèmes de contrôle intelligent associés aux paramètres décisifs tels que :

- minimiser le taux de transfert

- minimiser l'erreur quadratique moyenne (*Mean Square Error-MSE*)

- minimiser la consommation d'énergie pour une tâche spécifique, ou minimiser la complexité de l'algorithme

D'après les résultats prometteurs aperçus dans la littérature, différents traitements de données applicables pour une implémentation matérielle sont comparés dans la section 2.3. Cette section survole principalement l'application de la transformée rapide de Fourier (*Fast Fourier Transform-FFT*), de la transformée discrète en cosinus (*Dis-*

*crete Cosinus Transform-DCT) et de la transformée discrète en ondelettes (Discrete Wavelet Transform-DWT).* L'application des filtres dans un système en particulier peut varier en fonction des goulets d'étranglement rencontrés dans le flot de données désiré. C'est pourquoi une analyse des mouvements d'ensemble, des processus, ou des schèmes possibles est faite dans la section 2.4.

Par la suite, les différentes méthodes de seuillage pour la détection d'activité neuronale sont présentées à la section 2.5. Ceci permet de finalement déterminer l'architecture qui sera réalisée sous la forme d'un système numérique temps réel au chapitre 3.

## 2.2 Analyse pour une compression optimale

En science computationnelle et dans la théorie de l'information, la compression est l'action d'encoder l'information en moins de bits que la représentation non encodée. Dans le cas d'un système de communication, l'encodeur qui transmet doit correspondre avec le décodeur qui reçoit l'information. Cette action devient possible car les cas normaux sont redondants.

L'idéal, pour obtenir une compression maximale, est d'approcher le plus possible le taux optimal proposé par Shannon (Shannon 1948). La problématique de choisir un type de compression se pose et se résout différemment en fonction du problème. La compression d'une chaîne de caractères ne se traitera certainement pas de la même façon qu'un encodage neuronal.

Mackay analyse globalement ce problème en le contraignant à un "compresseur" de fichiers et il le divise simplement en deux (Mackay 2003) :

1. Un compresseur *avec pertes* compresse des fichiers, mais il pourrait associer

le même encodage à différentes données. Assumons que l'usager requiert une reconstitution parfaite, alors cette possible confusion mène à une erreur (dans le cas d'applications sur des images, une compression avec perte est normalement considérée comme satisfaisante). Donc pour qu'un compresseur avec perte soit pratique, il faut minimiser la probabilité que la confusion survienne.

2. Un compresseur *sans perte* associe chaque groupe de données dans un fichier à un encodage singulier. Si cette méthode réduit la taille de certains fichiers, elle cause nécessairement que d'autres pourraient être plus long.

### 2.2.1 Points de comparaison