**Titre:** Modélisation et conception d'une architecture à flots d'exécution multiples selon une approche de réutilisation

Title: multiples selon une approche de réutilisation

**Auteur:** Mortimer Hubin

Author:

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Hubin, M. (2006). Modélisation et conception d'une architecture à flots d'exécution multiples selon une approche de réutilisation [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

Citation: <https://publications.polymtl.ca/7894/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7894/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & Robert Roy

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

**MODÉLISATION ET CONCEPTION D'UNE ARCHITECTURE À

FLOTS D'EXÉCUTION MULTIPLES SELON UNE APPROCHE DE

RÉUTILISATION.**

MORTIMER HUBIN

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

AOÛT 2006

Library and

Archives Canada

Bibliothèque et

Archives Canada

Published Heritage

Branch

Direction du

Patrimoine de l'édition

395 Wellington Street

Ottawa ON K1A 0N4

Canada

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-19309-9

*Our file* *Notre référence*

ISBN: 978-0-494-19309-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

**UNIVERSITÉ DE MONTRÉAL**

**ÉCOLE POLYTECHNIQUE DE MONTRÉAL**

Ce mémoire intitulé :

**MODÉLISATION ET CONCEPTION D'UNE ARCHITECTURE À

FLOTS D'EXÉCUTION MULTIPLES SELON UNE APPROCHE DE

RÉUTILISATION.**

présenté par : HUBIN Mortimer

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

Mme. NICOLESCU Gabriella, Doct., présidente

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. ROY Robert, Ph.D., membre et codirecteur de recherche

M. SAVARIA Yvon, Ph.D., membre

## Remerciements

Je tiens d'abord à remercier mon directeur de recherche Guy Bois pour sa patience, sa confiance et son implication auprès de ses étudiants. J'aimerais surtout le remercier pour son soutien autant technique que financier, sans quoi je n'aurais pu participer à une telle aventure.

Je désire aussi souligner l'implication de tous les étudiants qui ont participé de près ou de loin à la réalisation de ce projet. Je pense principalement à mes collègues, David Quinn, Simon Provost, Francis St-Pierre, Patrick Samson ainsi que Jean-François Thibeault faisant tous partie du CIRCUS et certains membres du GRM qui ont contribué à mon bonheur durant mes deux années de maîtrise, rendant l'ambiance d'étude stimulante, plaisante et toujours relevée de défi.

Finalement, j'aimerais remercier ma femme Brigitte qui m'a soutenu, supporté et surtout poussé à terminer la longue rédaction de ce mémoire qu'elle a brillamment lu, relu et corrigé.

## Résumé

Poussé par la loi de Moore, le degré de miniaturisation et d'intégration permet désormais de créer des systèmes embarqués sur une seule puce toujours plus performante et offrant un plus vaste éventail de fonctionnalités. Ainsi, l'émergence des systèmes sur puce améliore constamment les performances de nombreux systèmes possédant de la logique dédiée. De ce fait, plusieurs domaines se sont tournés vers cette technologie qui permet sans cesse de repousser les limites.

La demande croissante des applications multimédia et de télécommunication nécessite la puissance des fonctionnalités dédiées, le parallélisme et la performance qu'offre de telles puces. Cependant, le prix à payer est fort dispendieux. Une alternative plus qu'intéressante consiste à utiliser des puces reprogrammables pour atteindre le même but. Évidemment, comme ces possède de la logique reprogrammable, elles ne peuvent atteindre les mêmes performances même si leur conception est basée sur une même technologie. Par contre, le degré de parallélisme et les fonctionnalités dédiées se retrouvent autant sur ces puces que sur des systèmes embarqués spécialisés.

Malheureusement, malgré ces performances hors de l'ordinaire, les applications orientées données rencontrent leurs goulots d'étranglement au niveau des latences de communication. Plusieurs techniques ont été proposées dans divers systèmes commerciaux pour alléger ce problème. La prélecture de données, la cohérence de cache ainsi que le multi-processus matériel en font partie. Ainsi, ce projet présente une approche différente basée sur le principe du multi-processus matériel permettant de cacher les latences de communication. L'architecture proposée contient plusieurs processeurs et vise à utiliser les modules disponibles dans les bibliothèques d'une puce reprogrammable Virtex II pro.

Le concept consiste à partager le temps d'exécution de quatre microprocesseurs pré-synthétisé. Chacun de ces myaux fonctionne à une fréquence réduite pour obtenir une

part égale dans un domaine de fréquence plus élevé. Cette organisation émule quatre contextes matériels de flots d'exécution générant un genre de parallélisme à grains fins. Ce parallélisme réduit considérablement des périodes vides, imposées par des latences de communication, à l'intérieur d'un microprocesseur.

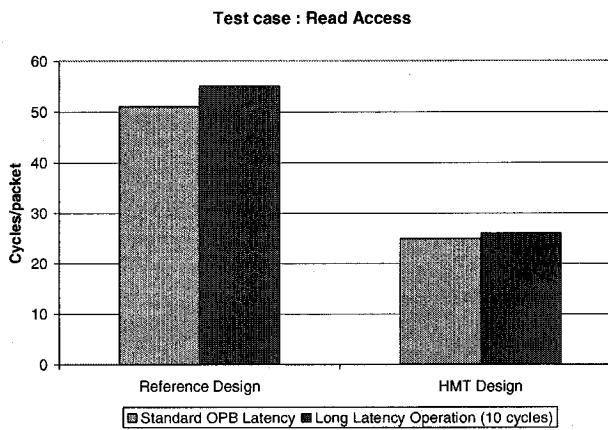

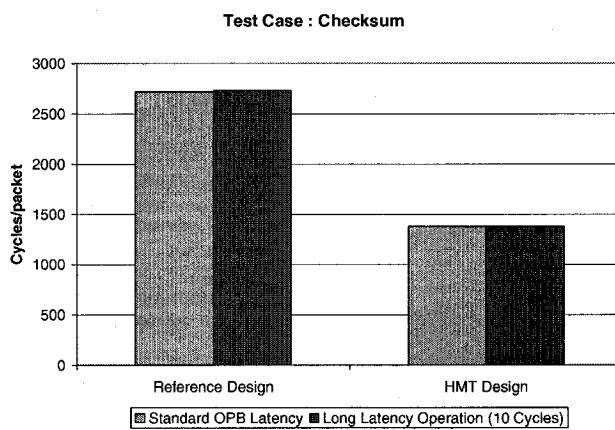

Ensuite, l'architecture est analysée à l'aide de trois applications de test. La première permet d'évaluer l'impact sur les accès mémoire. La seconde, quant à elle, calcule une somme de contrôle sur plusieurs morceaux de données. Cette application permet d'observer les gains obtenus avec une fonctionnalité typique de traitement de paquets. Les résultats démontrent clairement les capacités de l'architecture à cacher la latence de communication.

## Abstract

Modern chip design techniques constantly improve system performances. This progress continuously encounters growing communication bottlenecks. Several techniques have been proposed in commercial systems to alleviate this issue, such as data prefetching, cache coherency and hardware multithreading. However, they are relatively recent techniques in the field of system-on-chip (SoC). This paper presents a multiprocessor approach to latency-hiding based on hardware multithreading. The proposed multiprocessor architecture is targeted for a reconfigurable SoC based on the Virtex II Pro FPGA library. It essentially consists in interleaving the execution of four soft-core microprocessors each running at a reduced frequency to obtain an equal share of a faster communication channel. This organization emulates four hardware contexts implementing a fine-grain thread parallelism mode. This parallelism greatly reduces idle times inside the microprocessor imposed by long-latency operations. The design is evaluated with two test applications. The first one evaluates the pure memory-hiding abilities of the hardware multithreading platform while the second one implements a packet-processing application. The results clearly demonstrate the latency-hiding ability of hardware multithreaded processors.

## Table des matières

|                                                                   |             |

|-------------------------------------------------------------------|-------------|

| <b>REMERCIEMENTS .....</b>                                        | <b>IV</b>   |

| <b>RÉSUMÉ.....</b>                                                | <b>V</b>    |

| <b>ABSTRACT.....</b>                                              | <b>VII</b>  |

| <b>TABLE DES MATIÈRES .....</b>                                   | <b>VIII</b> |

| <b>LISTE DES FIGURES .....</b>                                    | <b>X</b>    |

| <b>LISTE DES TABLEAUX .....</b>                                   | <b>XI</b>   |

| <b>LISTE DES ACRONYMES.....</b>                                   | <b>XII</b>  |

| <b>LISTE DES ANNEXES .....</b>                                    | <b>XIII</b> |

| <b>INTRODUCTION.....</b>                                          | <b>1</b>    |

| <b>CHAPITRE 1 REVUE DE LITTÉRATURE .....</b>                      | <b>5</b>    |

| 1.1.    FPGA .....                                                | 6           |

| 1.1.1.    FPGA orienté logique .....                              | 8           |

| 1.1.2.    FPGA orienté système .....                              | 11          |

| 1.1.3.    Ce que le futur nous réserve .....                      | 14          |

| 1.2.    Processeurs présynthétisés .....                          | 16          |

| 1.2.1.    Nios II .....                                           | 16          |

| 1.2.2.    MicroBlaze .....                                        | 22          |

| 1.2.3.    Comparaison des processeurs présynthétisées.....        | 27          |

| 1.3.    Interconnexion.....                                       | 28          |

| 1.3.1.    AMBA.....                                               | 28          |

| 1.3.2.    CoreConnect.....                                        | 29          |

| 1.3.3.    Avalon.....                                             | 30          |

| 1.4.    Multi-Processus matériel. ....                            | 31          |

| 1.4.1.    Processeurs RISC .....                                  | 32          |

| 1.4.2.    Processeurs superscalaires.....                         | 33          |

| 1.4.3.    Multi-processus Matériel.....                           | 33          |

| 1.4.4.    Multiprocessus avancés.....                             | 36          |

| <b>CHAPITRE 2 RESSOURCES LOGICIELLES ET MATÉRIELLES UTILISÉES</b> | <b>38</b>   |

| 2.1.    Choix architecturaux .....                                | 38          |

|                                                                    |                                                            |           |

|--------------------------------------------------------------------|------------------------------------------------------------|-----------|

| 2.1.1.                                                             | Plateforme reconfigurable .....                            | 38        |

| 2.1.2.                                                             | Processeur.....                                            | 39        |

| 2.1.3.                                                             | Communication.....                                         | 39        |

| 2.2.                                                               | Outils logiciels .....                                     | 46        |

| 2.2.1.                                                             | Xilinx EDK (“Embedded Developpment Kit”) .....             | 47        |

| <b>CHAPITRE 3 ORGANISATION ARCHITECTURALE ET APPLICATION .....</b> |                                                            | <b>49</b> |

| 3.1.                                                               | Vue d’ensemble .....                                       | 49        |

| 3.1.1.                                                             | Prérequis .....                                            | 52        |

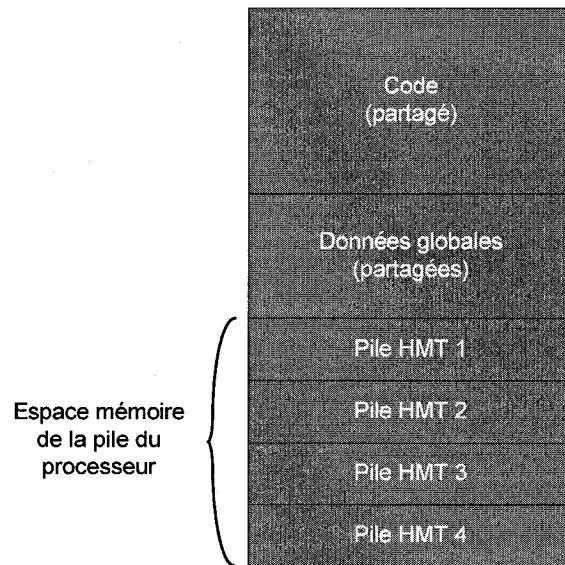

| 3.2.                                                               | Organisation de la mémoire .....                           | 53        |

| 3.3.                                                               | Détails d’implantation.....                                | 54        |

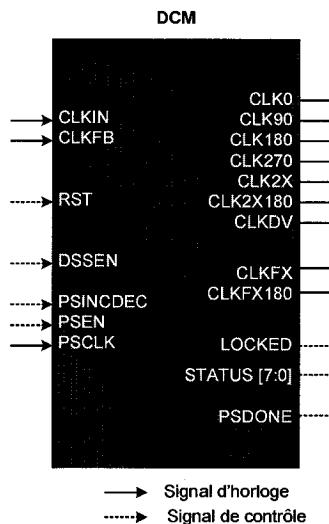

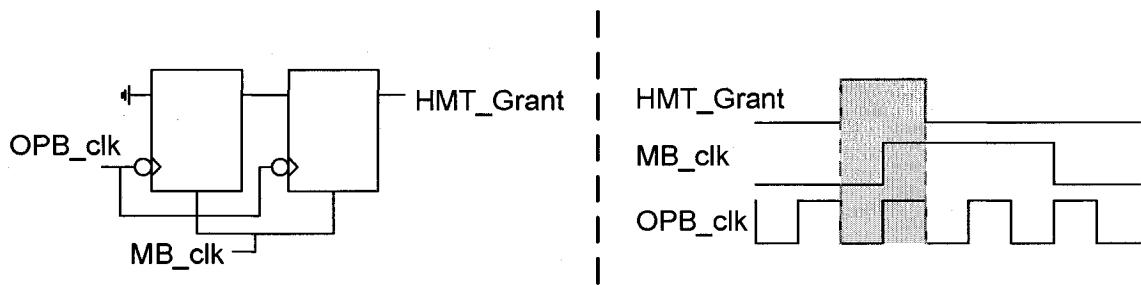

| 3.3.1.                                                             | Horloges .....                                             | 55        |

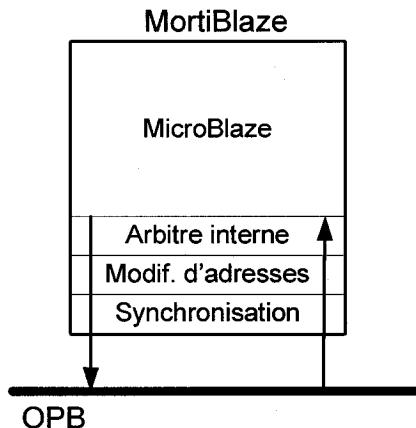

| 3.3.2.                                                             | Processeur.....                                            | 56        |

| 3.3.3.                                                             | OPB.....                                                   | 61        |

| 3.3.4.                                                             | Modification des autres périphériques existants .....      | 61        |

| 3.3.5.                                                             | Nouveaux périphériques.....                                | 63        |

| <b>CHAPITRE 4 ANALYSE DES RÉSULTATS .....</b>                      |                                                            | <b>66</b> |

| 4.1.                                                               | Environnement et application test.....                     | 66        |

| 4.2.                                                               | Applications .....                                         | 68        |

| 4.2.1.                                                             | Accès mémoire.....                                         | 68        |

| 4.2.2.                                                             | Somme de contrôle .....                                    | 68        |

| 4.2.3.                                                             | Somme de contrôle partagée.....                            | 69        |

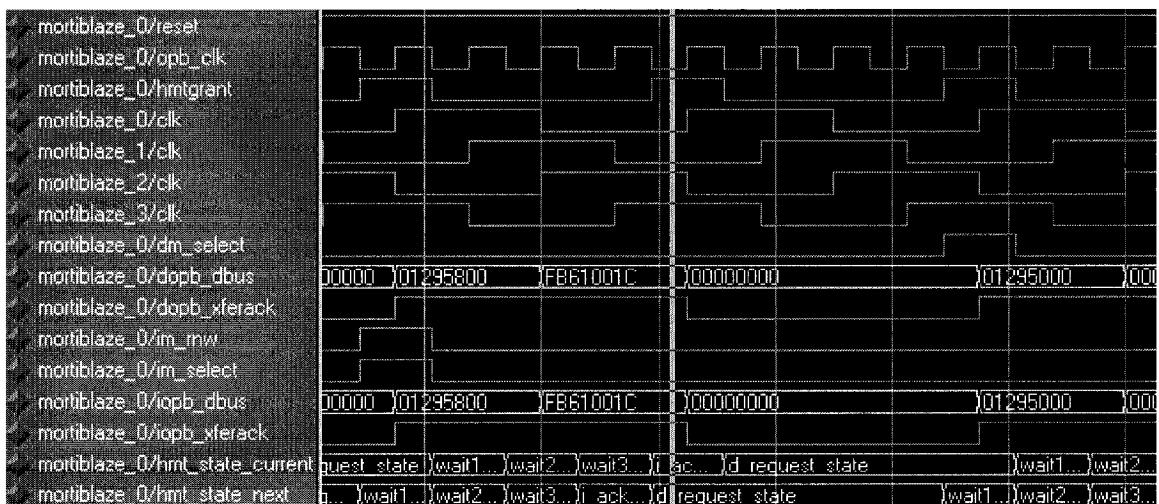

| 4.3.                                                               | Simulation .....                                           | 70        |

| 4.3.1.                                                             | Fenêtre d’opération .....                                  | 70        |

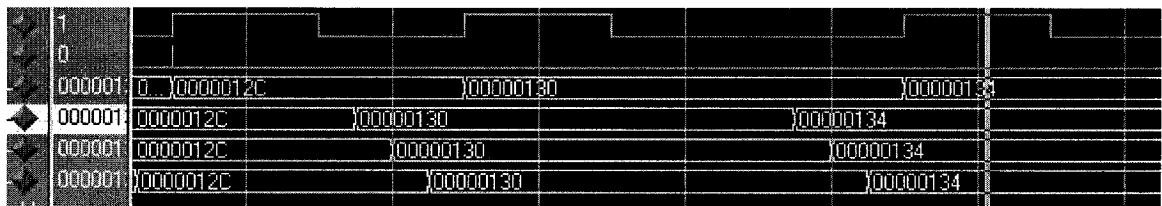

| 4.3.2.                                                             | Flot d’exécution .....                                     | 71        |

| 4.4.                                                               | Résultats.....                                             | 72        |

| 4.4.1.                                                             | Test 1 – Accès mémoires, application orientée données..... | 72        |

| 4.4.2.                                                             | Test 2 – Calcul des sommes de contrôle .....               | 73        |

| 4.4.3.                                                             | Test 3 – Calcul du «checksum » partagé.....                | 75        |

| <b>CONCLUSION ET TRAVAUX FUTURS .....</b>                          |                                                            | <b>76</b> |

| <b>RÉFÉRENCES .....</b>                                            |                                                            | <b>80</b> |

| <b>ANNEXES .....</b>                                               |                                                            | <b>86</b> |

## Liste des figures

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

| Figure 1.1 : Évolution du contenu des FPGA de Altera [ALTE04] .....                      | 7  |

| Figure 1.2 : Arrangement d'une tranche d'un Virtex 2 et Virtex 2 Pro [XILI04].....       | 12 |

| Figure 1.3 : Vue d'ensemble de l'architecture d'un Virtex 2 Pro [XILI04] .....           | 13 |

| Figure 1.4 : Caractéristiques de la famille Virtex 4 [XILI04] .....                      | 15 |

| Figure 1.5 : Schéma bloc du Nios II [ALTE04a].....                                       | 17 |

| Figure 1.6 : Flot des instructions spécialisées du Nios II [ALTE04].....                 | 18 |

| Figure 1.7 : Schéma bloc du Microblaze et de certains périphériques [XILI04c].....       | 24 |

| Figure 1.8 : Interface FSL dans le pipeline du Microblaze [XILI04c] .....                | 26 |

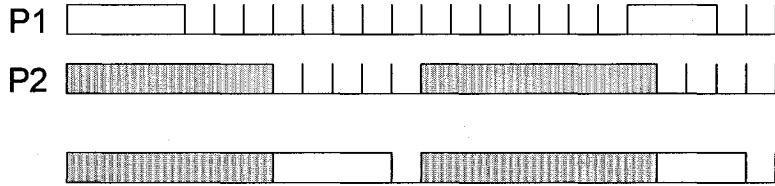

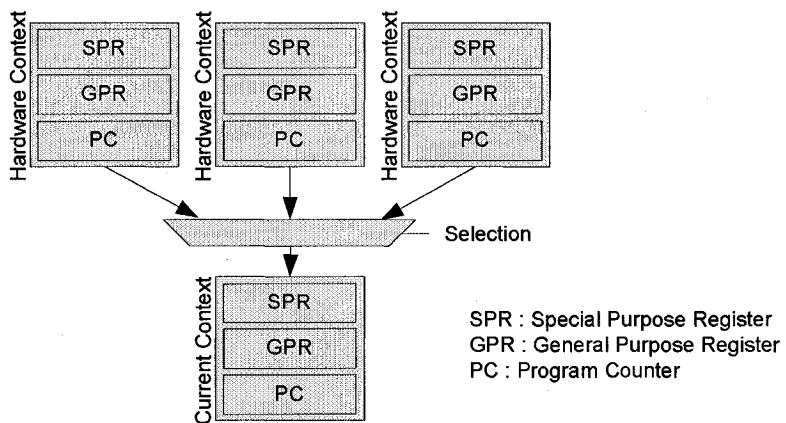

| Figure 1.9 : Cacher la latence.....                                                      | 34 |

| Figure 1.10 : Ordonnanceurs à grains fins. ....                                          | 35 |

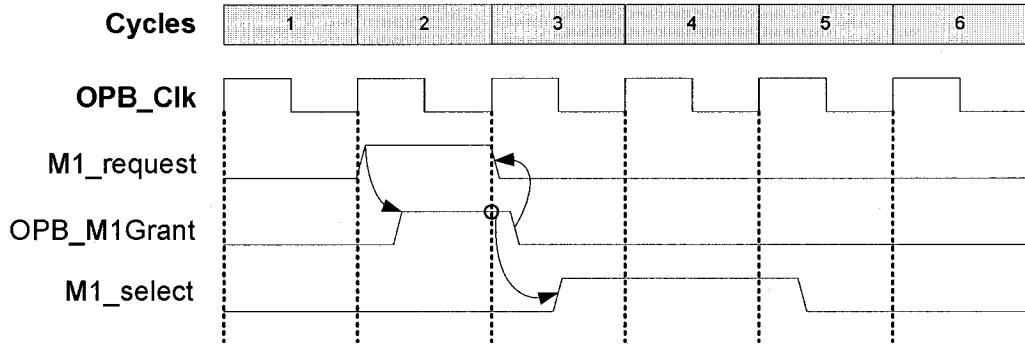

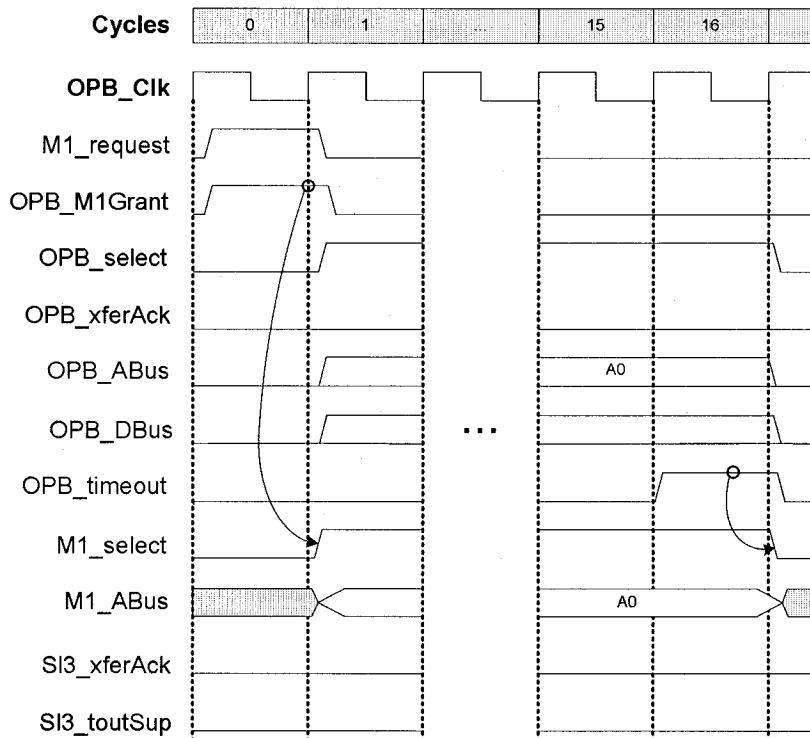

| Figure 2.1 : Protocole d'arbitrage typique de l'OPB [IBM02] .....                        | 41 |

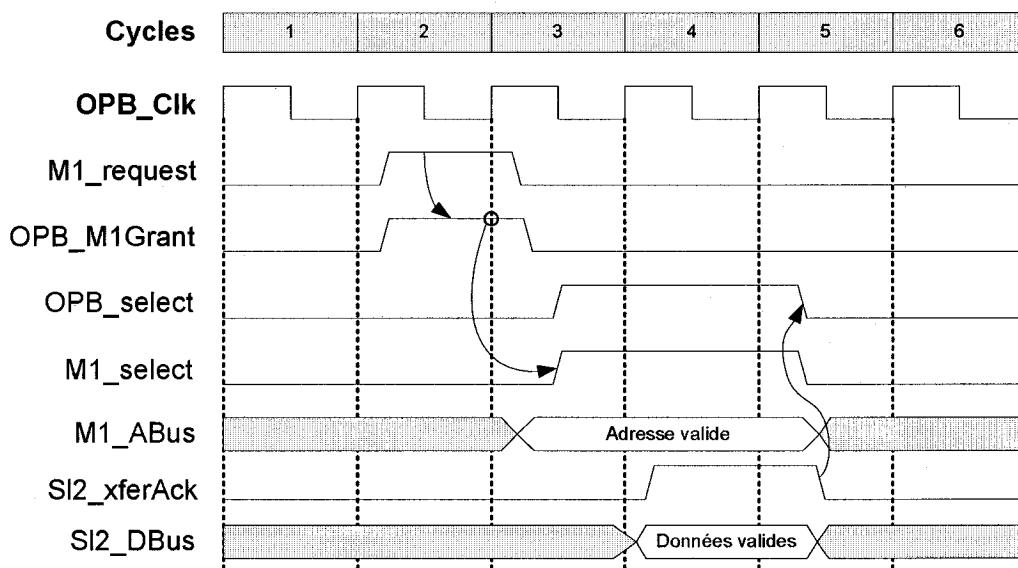

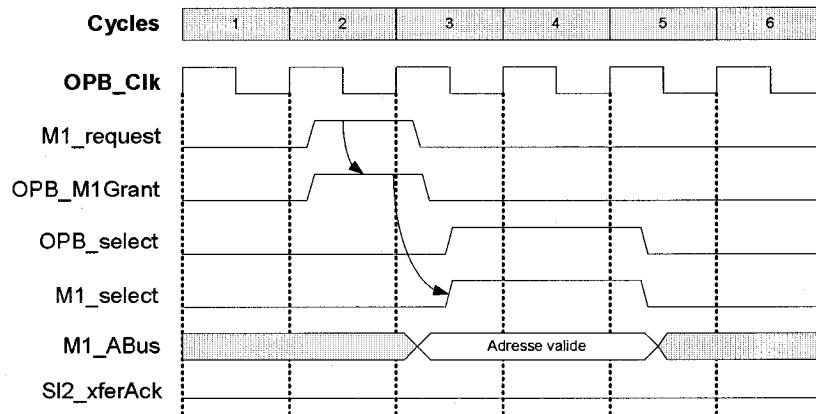

| Figure 2.2 : Transaction de bus typique [IBM02].....                                     | 42 |

| Figure 2.3 : Transaction trop longue : génération d'un timeout [IBM02] .....             | 44 |

| Figure 2.4 : Annulation de requête [IBM02] .....                                         | 46 |

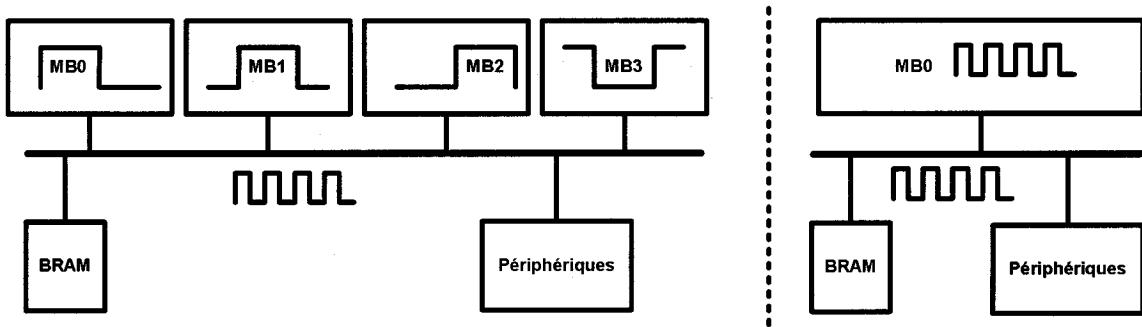

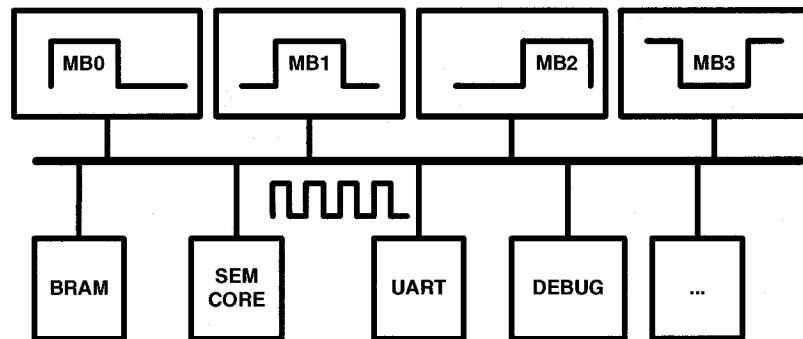

| Figure 3.1 : Système à quatre processeurs plus lent versus un seul processeur rapide.... | 49 |

| Figure 3.2: Vue d'ensemble du système .....                                              | 49 |

| Figure 3.3: Fenêtre d'opération et domaines de fréquence .....                           | 51 |

| Figure 3.4: Organisation de la mémoire .....                                             | 54 |

| Figure 3.5: Shema bloc d'un DCM [XILI04] .....                                           | 55 |

| Figure 3.6: Shema bloc d'un « Mortiblaze » .....                                         | 56 |

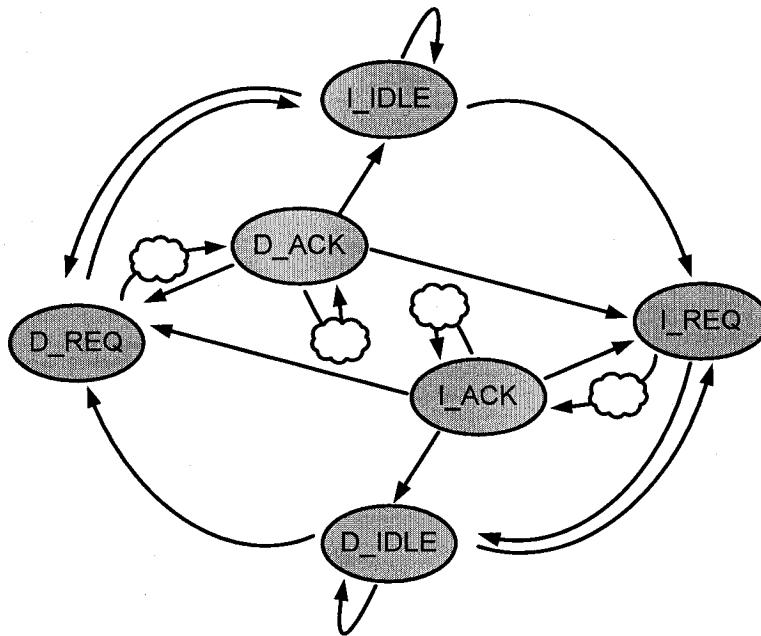

| Figure 3.7: Machine à état du « Mortiblaze ».....                                        | 58 |

| Figure 3.8 : Génération du signal de synchronisation.....                                | 60 |

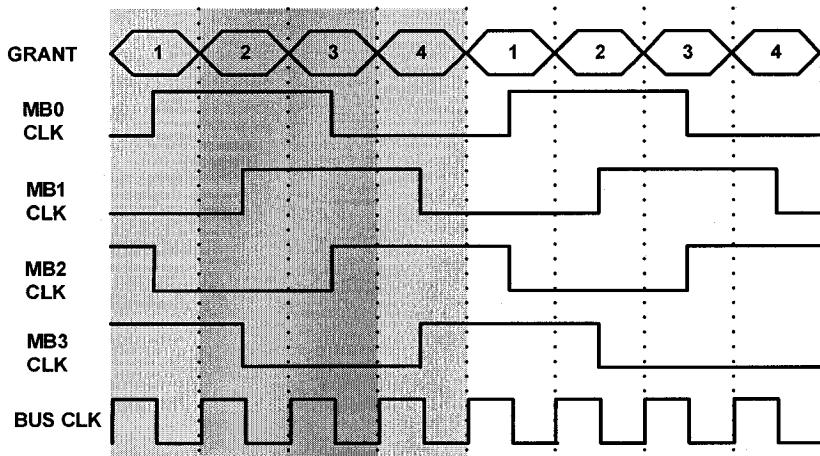

| Figure 4.1 : Simulation de la fenêtre d'opération du Microblaze 0 .....                  | 70 |

| Figure 4.2 : Flots d'exécution des Microblazes .....                                     | 71 |

| Figure 4.3 : Détachement de flot d'exécution.....                                        | 72 |

| Figure 4.4 : Comparaison des gains du test1 .....                                        | 73 |

| Figure 4.5 : Comparaison des gains du test2 .....                                        | 74 |

## Liste des tableaux

|                                                                  |    |

|------------------------------------------------------------------|----|

| Tableau 1.1: Vue d'ensemble de la famille Cyclone II.....        | 10 |

| Tableau 1.2: Performance du Microblaze [XILI04] .....            | 23 |

| Tableau 1.3: Comparaison des processeurs logiciels.....          | 27 |

| Tableau 2.1 : Quelques modules disponibles avec EDK .....        | 48 |

| Tableau 3.1 : Adresses des piles des différents processeurs..... | 61 |

| Tableau 4.1: Résultats du test sur les accès mémoires.....       | 72 |

| Tableau 4.2: Résultats du test du calcul des “checksum” .....    | 74 |

| Tableau 4.3: Resultats du test sur le “checksum” partagé .....   | 75 |

## Liste des acronymes

|             |                                         |

|-------------|-----------------------------------------|

| <b>ASIC</b> | Application Specific Integrated Circuit |

| <b>CLB</b>  | Configurables Logic Blocs               |

| <b>DCM</b>  | Digital Clock Managment                 |

| <b>DLL</b>  | Digital Lock Loops                      |

| <b>DSP</b>  | Digital Signal Processor                |

| <b>E/S</b>  | Entrées / Sorties                       |

| <b>FIFO</b> | First-in First-out                      |

| <b>FIR</b>  | Finite Impulse Response                 |

| <b>FFT</b>  | Fast Fourier Transform                  |

| <b>FPGA</b> | Field Programmable Gate Array           |

| <b>FSL</b>  | Fast Simplex Link                       |

| <b>IP</b>   | Intellectual Property                   |

| <b>IP</b>   | Iternet Protocol                        |

| <b>LC</b>   | Logic Cells                             |

| <b>LE</b>   | Logic Element                           |

| <b>LUT</b>  | Look-up Table                           |

| <b>NoC</b>  | Network-on-a-Chip                       |

| <b>NCO</b>  | Numerically Controlled Oscillator       |

| <b>PLL</b>  | Phase-Locked Loops                      |

| <b>PLD</b>  | Programmable Logic Device               |

| <b>RAM</b>  | Read Access Memory                      |

| <b>RISC</b> | Reduce Instruction Set Computer         |

| <b>SOC</b>  | System On Chip                          |

| <b>SOCP</b> | System On Programmable Chip             |

| <b>V2P</b>  | Virtex 2 Pro                            |

| <b>V4</b>   | Virtex 4                                |

## **Liste des annexes**

|          |                          |    |

|----------|--------------------------|----|

| ANNEXE A | Code du Mortiblaze ..... | 86 |

|----------|--------------------------|----|

## Introduction

Depuis les dernières décennies, la pénétration des systèmes embarqués sur le marché des semi-conducteurs continue de croître à un rythme incroyable. Effectivement, ces systèmes de plus en plus complexes que l'on retrouve désormais souvent sur une seule puce sont maintenant exploités dans plusieurs domaines importants, dont les télécommunications, le multimédia, l'automobile et bien d'autres. Pourtant, bien que très performants, ces systèmes sur puce (SOC) sont très coûteux, autant au niveau du développement qu'à celui de la fabrication. Pour pallier à ce problème, une grande proportion, voire près de 90%, des nouvelles puces contiennent au moins un processeur, qu'il soit d'usage général ou pour le traitement de signaux digitaux [JERR04]. Bien que le temps de conception soit sensiblement réduit par la réutilisation des modules de propriétés intellectuelles (IP) pré-développées et de la partie logicielle exécutée sur le processeur, l'intégration et la vérification du système en entier représentent toujours une large portion du temps de conception. En plus, le coût de fabrication de ces puces reste énorme. Ce désavantage majeur de ce type de circuits dédiés fait partie des raisons de la croissance des FPGA depuis leur introduction en 1985 [JAWC94]. Effectivement, leur quantité de logique programmable combinée à une facilité de développement équivalente amène une mise en marché plus rapide, et ce tout en gardant une performance plus qu'acceptable.

De plus, pour améliorer les performances de ces puces, les FPGA ne contiennent plus que de la logique programmable depuis déjà un certain temps. En effet, la majorité de ces puces reprogrammables possède maintenant plusieurs modules intéressants pour l'élaboration d'un système sur puce complet. Ainsi, on retrouve très souvent, sur ce type de puce, de la mémoire, des modules de communication et même des processeurs embarqués sur la puce.

Le FPGA devient donc, pour plusieurs, plus intéressant qu'un simple outil de prototypage. Ainsi on le retrouve de plus en plus, dans les systèmes orientés données, tel que dans les domaines du multimédia et de la réseautique.

### **Problématique**

L'émergence d'Internet et le transfert grandissant des données multimédias ont amené des défis de taille dans l'industrie des télécommunications et du multimédia. Ainsi, il n'est pas rare d'avoir à décompresser de la vidéo et de l'audio en temps réel afin de traiter leurs données. Effectivement, les applications orientées données souffrent des longues latences de communication ainsi que des collisions au niveau du réseau. Or, les processeurs disponibles dans les FPGA n'exploitent pas le parallélisme nécessaire permettant de réduire de telles latences et ainsi d'atteindre des performances qui pourraient être acceptables dans ces domaines [EEL98].

De nombreuses recherches ont tenté de découvrir plusieurs mécanismes permettant de réduire le délai d'attente dû aux latences des communications. Parmi ceux-ci, on retrouve le multi-processus matériel (HMT) qui, quant à lui, ne propose pas d'éliminer la latence de communication, mais plutôt de la cacher [EEL98]. Effectivement, ce concept propose de donner le temps d'attente d'un processeur à un autre flot d'exécution pour débuter ou compléter d'autres instructions. Ainsi, les trous créés par les latences de communication demeurent mais elles sont recyclées pour exécuter d'autres tâches.

Pour obtenir ce comportement, il faut multiplier les registres matériels et modifier le pipeline du processeur ciblé. Cependant, il serait intéressant d'utiliser plusieurs processeurs de base disponibles dans les bibliothèques des FPGA pour créer une architecture simple permettant d'obtenir un tel comportement.

## **Objectifs**

Le principal objectif de ce mémoire consiste à démontrer qu'il est possible, à l'aide de composants existants et disponibles sur le marché, de concevoir un système pouvant être déployé sur un FPGA et possédant un amalgame de processeurs de base supportant une version de multi-processus matériel. Il s'agira ensuite d'analyser les gains possibles avec ce système, autant au niveau de la performance qu'au niveau de l'effort à déployer pour en tirer profit. Ainsi, si très peu de modifications aux modules disponibles sur le marché sont nécessaires afin d'obtenir une architecture performante, une solution de ce genre devient beaucoup plus intéressante que la création d'un système embarqué sur puce qui entraînerait une perte de temps de développement ainsi qu'un coût de fabrication beaucoup plus élevé.

Le second objectif consiste à explorer les diverses facultés et le potentiel des outils fournis par Xilinx pour le développement.

## **Méthodologie**

Afin d'atteindre ces objectifs, plusieurs tâches devront être réalisées. D'abord, il semble impératif de commencer par l'exploration des différentes possibilités de l'outil EDK de Xilinx. Ensuite, il sera important de concevoir et de tester les modules utiles qui n'existent pas sur le marché et dont nous avons besoin pour la suite du projet. Ces modules nous permettront de réaliser une version hybride d'une architecture multi-processus matérielle. Une fois cette architecture conçue, l'effort sera déployé sur l'adaptation de plusieurs applications tests. Ces applications nous permettront de recueillir les résultats et de les comparer à des résultats compilés sur une architecture de référence.

## **Contribution**

Bien que beaucoup de tâches et projets connexes aient dû être réalisés pour l'obtention de ces objectifs, ma principale contribution constitue un modèle simulable d'une architecture supportant le multi-processus matériel. Ce modèle a permis de recueillir les

données nécessaires pour démontrer qu'il est possible de créer ce type d'architecture à l'aide de modules existants. Ma seconde contribution provient directement de l'exploration des possibilités des outils de Xilinx et de la carte de développement. En effet, parallèlement à ce projet, j'ai créé une architecture, un module configurable, ainsi qu'une application actuellement utilisée dans le cadre du cours « Systèmes temps réel ». Cette réalisation a engendré la publication d'un article expliquant la nature des travaux préparatifs effectués [THDS05]. Finalement, l'élaboration d'un modèle d'enveloppe en couche permettant de garder une partie générique dans l'interface lors d'un changement de système constitue ma dernière contribution.

### **Distribution des chapitres**

Ce mémoire se divise en quatre chapitres. Le premier chapitre survole et décrit certains des différents FPGA, certains processeurs logiciels ainsi que leurs modules de communication associés. Ce chapitre détaille aussi le concept de multi processus matériel. Le second chapitre quant à lui définit les choix architecturaux adoptés pour le projet, et explique plus en détails le comportement de chacun des composants choisis. L'avant dernier chapitre traite du design de l'architecture, des modifications apportées aux modules existants ainsi que de la présentation des modules créés spécialement pour le système. Finalement, le dernier chapitre, le quatrième, présente les applications utilisées pour tester l'architecture ainsi que les résultats et l'analyse découlant de ces derniers.

## CHAPITRE 1

### Revue de littérature

Avec la croissance incroyable du marché des semi-conducteurs et des autres technologies, de nombreuses possibilités de produits s'offrent aux architectes pour la confection d'un système sur puce. Ainsi il devient difficile de choisir chacun des composants nécessaires au bon fonctionnement de l'architecture voulue.

En effet, la conception d'une architecture embarquée sur puce avec des technologies récentes nécessite généralement une connaissance importante des différents composants nécessaires à son élaboration. Ainsi les architectes doivent connaître les types de processeurs, de mémoire, ainsi que différents périphériques qui pourraient devenir, une fois réunis, un système fiable, peu coûteux, performant et rapide à mettre en marché. Le choix des technologies de chacun des éléments est crucial pour atteindre les objectifs fixés, tant au niveau de la puissance, de la performance, de l'espace occupé par le système sur puce, ou encore du temps de mise en marché.

On retrouve actuellement en abondance des modules matériels qui permettent de créer des systèmes sans devoir réinventer la roue. Ces modules, offerts ou vendus, sont appelés « IP », acronyme tiré du terme anglais « Intellectual Property ». La majorité de ces IP sont testés et optimisés pour certaines plateformes, certaines puces reprogrammable nommés FPGA (« Field Programmable Gate Array ») ou encore certaines architectures. Parmi ces IP, on retrouve entre autres des processeurs logiciels pour systèmes embarqués, des modèles de bus, arbitres et ponts, ainsi que différents autres périphériques nécessaires à la conception d'un système sur puce. Ces éléments sont aussi généralement interfacés avec les bus auxquels ils devraient être connectés. L'utilisation de ces modules n'est donc pas évidente sur toutes les architectures : un certain travail de compatibilité peut être nécessaire au bon fonctionnement du système. Cette diversité de solutions pour la création d'un système amène un architecte à devoir

faire plusieurs choix importants, que ce soit le choix de la bibliothèque d'IP ou celui du bon FPGA. Ces décisions deviennent cruciales pour les performances du nouveau système, et c'est pourquoi il apparaît essentiel de connaître le matériel avant de se lancer dans la grande aventure. En ce sens, le présent chapitre vise à débattre de certains choix possibles pour créer un système sur puce programmable (SOPC). Plusieurs processeurs logiciels, certaines structures d'interconnexion disponibles ainsi que quelques familles de FPGA qui se trouvent actuellement sur le marché, seront donc abordés.

## 1.1. FPGA

Gordon Moore, co-fondateur d'Intel, prédit en 1965 que la densité des transistors intégrés sur puces allait doubler chaque 18 mois. Cette prédiction, maintenant connue comme la Loi de Moore, s'est avérée assez juste jusqu'à ce jour.

Cette croissance incroyable de la densité des transistors a permis aux ingénieurs et architectes de créer des systèmes sur puce toujours plus denses, plus complexes et plus rapides qu'auparavant. Au fil des ans, le coût d'une puce de complexité donnée a diminué grandement. Malheureusement, cette diminution n'empêche pas que leur coût de production demeure toujours très élevé, et généralement, la complexité augmente les coûts de développement [ALTE04]. Ainsi, la création de circuits intégrés à application spécifique (ASIC) étant très dispendieuse, elle n'est vraiment pas une solution viable pour une production moyenne. Par ailleurs, la capacité de programmation des FPGA continue à croître, alors que leur coût d'exploitation s'avère inférieur à celui d'un ASIC [ALTE04]. Ces deux facteurs non-négligeables ont permis aux FPGA de passer d'outil de prototypage à un médium de production de SOPC. Cette solution viable et moins coûteuse devient donc de plus en plus utilisée sur le marché des architectures embarquées.

L'évolution des FPGA ne s'arrête pas à la simple croissance de cellules logiques à l'intérieur d'une puce. Bien que très convoité et toujours grandissant, le pourcentage de

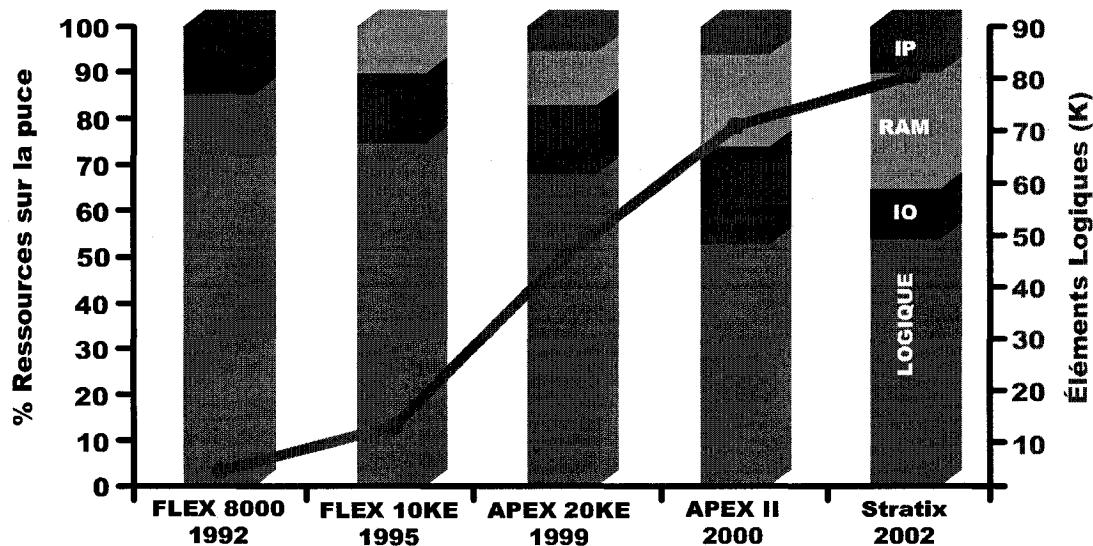

cette capacité de programmation logique tend à diminuer avec les dernières familles de FPGA, remplaçant une partie de superficie gagnée de logique par plusieurs éléments intégrés très intéressants pour nombre d'architectures sur puces. La figure 1.1 illustre la diminution de la proportion des ressources disponibles sous forme de cellules logiques et l'ajout de modules au sein des FPGA. En effet, plusieurs sociétés compétitionnent quant à la valeur ajoutée de leurs FPGA. Outre la quantité de mémoire et les entrées/sorties rapides, certains de ces PLD (« Programmable Logic Device »)) offrent des options plus surprenantes mais très intéressantes, illustrées par la portion IP dans la figure 1.1. On y retrouve notamment l'intégration d'un processeur embarqué, des processeurs de signal numérique (DSP), des modules de gestion digitale d'horloge et bien d'autres. Bien que la proportion des ressources consacrées à la logique diminue, il n'en demeure pas moins que la densité de cellules programmables dans un FPGA continuera de croître pour les futures générations de FPGA.

Figure 1.1 : Évolution du contenu des FPGA de Altera [ALTE04]

Parmi les éléments supplémentaires, on peut remarquer l'arrivée des processeurs directement intégrés dans la puce. Ce nouvel élément n'est pas une évolution mais une branche supplémentaire dans la généalogie des FPGA. En effet, les FPGA avec et sans processeur embarqué continuent d'évoluer chacun de leur côté. Cette distinction permet donc désormais de classer les FPGA en deux groupes : les puces orientées logique par opposition à celles orientées système.

### **1.1.1. FPGA orienté logique**

Les FPGA orientés logique représentent généralement les éléments programmables les plus denses. En réalité, ce sont les puces qui, généralement, contiennent le plus grand pourcentage de cellules programmables. Ces FPGA représentent la continuité logique des tout premiers PLD. Ce groupe de puces est spécialement utilisé pour créer un design personnalisé, un module d'accélération, un petit système, une fonction DSP, ou encore un système complet avec un processeur logiciel. La majorité des PLD font partie de ce groupe. Parmi tous les FPGA disponibles sur le marché, la génération des « Cyclone 2 » d'Altera, considérée, selon la société, comme « les FPGA les moins chers de tous les temps », est choisie pour représenter ce groupe dans le présent chapitre. Altera propose également ses fameux « Stratix 2 » qu'elle vante comme étant les plus gros et les plus performants. Du côté de Xilinx, les « Spartan » et les « Virtex » figurent dans cette catégorie de PLD. Il est possible d'obtenir plus de renseignements sur les pages web respectives de ces sociétés [ALTE04b] et [XILI04].

Il est actuellement difficile de comparer des familles de FPGA car chacune des sociétés conceptrices utilise des métriques qui les avantagent. En effet, Altera quantifie la densité de ses produits en terme d'éléments logiques (LE), alors que Xilinx, de son côté, utilise les cellules logiques (LC) ou encore les portes logiques équivalentes. Comme les deux sociétés utilisent des tables de conversion (LUT) à quatre entrées, il semble plus sage d'utiliser cette métrique pour faire des comparaisons. Par exemple, une LE d'Altera correspond à une LUT de quatre entrées avec quelques modifications [ALTE03].

### 1.1.1.1. Cyclone 2

« Le FPGA le moins cher de tous les temps », c'est ce que scande Altera à propos de la génération « Cyclone™ II » qui vient surpasser la famille précédente, « Cyclone », en tous points. Cette famille orientée logique offre, selon Altera, le meilleur prix par élément logique. En effet, ce FPGA, produit sur des gaufres de 300mm et issu d'une technologie de 90 nm, offre, en plus d'un faible coût d'exploitation, une plus grande densité et plusieurs options exceptionnelles. Parmi celles-ci figurent l'intégration de multiplicateurs et de mémoires embarquées, l'ajout d'entrées/sorties à très hauts débits et l'utilisation possible de boucles à verrouillage de phase (PLL) pour la gestion efficace des horloges internes au FPGA. Cette solution permet donc la création d'un système à des prix défiant celui des ASIC, et ce, avec moins de risques et un temps de mise en marché beaucoup plus rapide. Cette nouvelle génération est principalement utilisée dans l'industrie de l'automation, en communication sans-fil, dans le domaine médical et bien d'autres [ALTE04c].

La mémoire embarquée sur ces puces est instanciée de façon matérielle par blocs de 4Kb, et la totalité de sa capacité peut atteindre jusqu'à 1.1 Mb sur les plus gros FPGA de cette famille. Cette mémoire satisfait la demande nécessaire pour la création de systèmes nécessitant de la mémoire embarquée, du tamponnage de données, de la translation d'horloge et d'architecture basée sur des queues de type premier entré, premier sorti (FIFO). Cette mémoire ambivalente peut être configurée comme une mémoire vive (RAM) à double port, une mémoire vive à simple port, une mémoire morte (ROM) ou encore une structure de données de type FIFO.

Les multiplicateurs, quant à eux, se retrouvent au nombre de 180 et comportent 18 bits de large ; ils sont capables d'opérer à une fréquence d'horloge d'environ 250MHz. Cet opérateur embarqué permet de modéliser plusieurs fonctions DSP communes, telles que des filtres à réponse instantanée (FIR), des fonctions de transformation de Fourier rapide

(FFT), des encodeurs/décodeurs et des oscillateurs contrôlés de façon numérique (NCO), tout en augmentant les performances du système et en allégeant le travail du reste de la logique programmée.

Le « Cyclone 2 » contient jusqu'à 68416 éléments logiques (l'équivalent d'une LUT à quatre entrées) et offre quatre PLL pour la gestion d'horloge. Ses entrées/sorties à haut débit permettent un transfert en amont de 622 Mbps, ainsi qu'un transfert en aval pouvant atteindre les 805 Mbps. Les autres caractéristiques sont présentées sur la figure suivante, selon les modèles disponibles actuellement.

**Tableau 1.1: Vue d'ensemble de la famille Cyclone II**

| Fonction                  | EP2C5   | EP2C8   | EP2C20  | EP2C35  | EP2C50  | EP2C70    |

|---------------------------|---------|---------|---------|---------|---------|-----------|

| Éléments logiques         | 4 608   | 8 256   | 18 752  | 33 216  | 50 528  | 68 416    |

| Blocs RAM M4K             | 26      | 36      | 52      | 105     | 129     | 250       |

| Total bits RAM            | 119 808 | 165 888 | 239 616 | 483 840 | 594 432 | 1 152 000 |

| Mult 18x18 Embarqués      | 13      | 18      | 26      | 35      | 86      | 150       |

| PLL                       | 2       | 2       | 4       | 4       | 4       | 4         |

| Broches utilisateur d'E/S | 142     | 182     | 315     | 475     | 450     | 622       |

De plus, sur ce type de FPGA, il est possible, entre autres, d'utiliser les cellules logiques encore disponibles pour instancier le processeur logiciel « Nios 2 », conçu par Altera, qui permettra de créer un système sur puce complet. La section 1.2 introduit les processeurs logiciels.

### **1.1.2. FPGA orienté système**

Le groupe orienté système est généralement utilisé dans le but ultime de faire un système complet possédant un ou plusieurs processeurs performants, des fonctions DSP, un système d'interconnexion, une bonne quantité de mémoire et un grand nombre de périphériques propres à un système sur puce (SOC). Ce type de FPGA contient d'habitude un processeur intégré directement dans sa logique. Par exemple, les modèles de la famille « Excalibur », développée par Altera, possèdent, en plus de la mémoire, des cellules programmables, des entrées/sorties rapides et certains « IP », ainsi qu'un ARM 9 directement intégré dans le FPGA [ALTE99]. De plus, pour un maximum d'opérabilité, la majorité des modules pouvant être ajoutés à cette puce sont compatibles avec le bus AMBA, ce qui permet une communication facile avec le processeur embarqué. Les détails de cette famille d'Altera ne sont pas présentés dans cette section. Pour plus d'informations, consulter [ALTE99].

#### **1.1.2.1. Virtex 2 Pro**

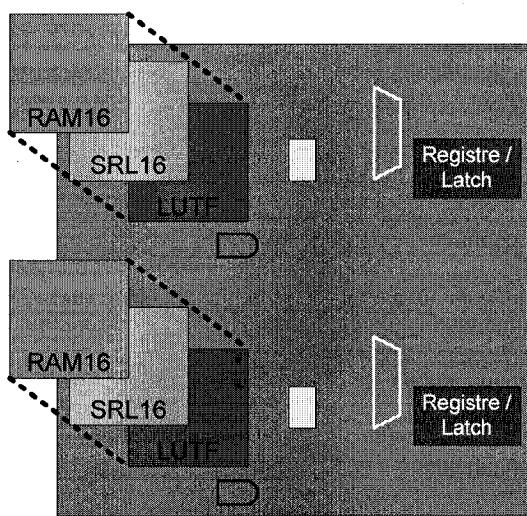

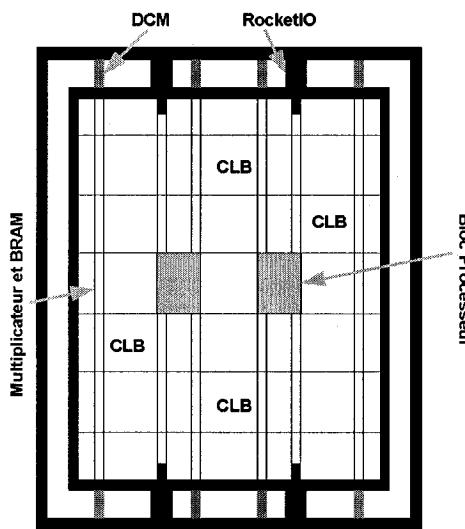

Pour sa part, Xilinx offre le « Virtex 2 Pro », la seule famille de cette société qui figure entièrement parmi les FPGA orientés système. La partie FX des tout nouveaux « Virtex 4 », décrits dans la section suivante, représentent également les FPGA orientés systèmes. Le « Virtex 2 Pro » est sans équivoque l'évolution naturelle du populaire « Virtex 2 ». Ce circuit intégré est conçu selon un procédé technologique à 0.13 micron. Xilinx a utilisé une combinaison de 9 couches et ces puces ont été produites sur des gaufres de 300 mm. Pour terminer la description technique, le boîtier est capable de détenir jusqu'à 1200 broches [XILI04]. Le « Virtex 2 Pro » est basé sur le même arrangement physique que le « Virtex 2 ». Cet arrangement consiste en une matrice de 2 dimensions qui contient des blocs logiques configurables couramment appelés CLB. Chacun de ces blocs contient quatre tranches<sup>1</sup>, tel qu'illustré à la figure suivante, qui contiennent à leur

---

<sup>1</sup> Terme généralement utilisé en anglais : Slice

tour deux LUT (« Look-up Tables »), deux registres flip-flop, ainsi que deux entrées dédiées pour la retenue de somme. Avec cette configuration, chaque LUT peut être utilisé comme n'importe quelle fonction, registrée ou non, de 4 bits d'entrée, dont un registre à décalage programmable de 16 bits ou encore une mémoire RAM de 16 bits. Chaque CLB contient des composants intégrés pour interconnecter tous les éléments qui y sont inclus.

Figure 1.2 : Arrangement d'une tranche d'un Virtex 2 et Virtex 2 Pro [XILI04]

On retrouve, en périphérie de cette grande matrice de blocs logiques programmables, un amalgame d'entrées/sorties qui peuvent supporter environ 25 différentes normes de communication. La vitesse maximale que peuvent atteindre ces blocs est de 840 Mbps.

L'architecture de cette famille contient aussi un large éventail d'autres composantes intéressantes. Parmi celles-ci, on retrouve une grande quantité de blocs de mémoire RAM de 18Kbits. Ces blocs de mémoire vive (BRAM) peuvent être configurés de plusieurs façons, notamment en mémoire à double port de différentes grandeurs et profondeurs. Outre la mémoire intégrée au FPGA, on observe aussi une variété de fonctions DSP, dont une quantité plus qu'intéressante de multiplieurs dédiés d'une largeur de 18 bits. Finalement, cette puce inclut également plusieurs modules de gestion

numérique d'horloge (DCM) permettant de gérer efficacement un système à plusieurs domaines de temps. [XILI05]

Enfin, un processeur « Power PC » 405 d'IBM est directement intégré dans le FPGA, ce qu'on appelle généralement un « Hard Core ». Ce dernier module est en fait un processeur 32-bits, basé sur une architecture de style « Harvard<sup>2</sup> » et pouvant fonctionner théoriquement à 300 MHz et 420 Dhystone MIPS. Certains FPGA de la famille ont un seul PPC, mais il en existe aussi à deux. De plus, il y a une série d'entrées/sorties supportant de très hauts débits, nommé communément « RocketIO », communiquant jusqu'à 3.125 Gbps. De ceux-ci, on en retrouve de 4 à 24, selon le « Virtex 2 Pro » choisi. [XILI05]

Figure 1.3 : Vue d'ensemble de l'architecture d'un Virtex 2 Pro [XILI04]

Pour communiquer avec le PPC405, IBM procure sa suite « CoreConnect » décrite plus loin dans ce mémoire. Afin de rendre la tâche de conception de système plus facile aux ingénieurs, Xilinx, en conjonction avec IBM, offre un amalgame de noyaux déjà

---

<sup>2</sup> Architecture Harvard : processeur possédant un bus de données et un bus d'instructions séparés.

interfacés avec les protocoles de communication de « CoreConnect ». Il devient donc aussi facile que quelques clics de créer un système contenant un processeur, de la mémoire et une interface d'entrées/sorties, quasi complet et fonctionnel. Évidemment, ces quelques manipulations nécessitent la connaissance préalable des outils de design offerts par ces sociétés. Les outils proposés par Xilinx pour le design de leurs FPGA et CPLD sont décrits dans le chapitre 2 de ce mémoire.

### **1.1.3. Ce que le futur nous réserve**

Il est difficile de concevoir que les « Virtex 2 Pro » puissent finir par être surclassés. Effectivement, avec tous les ajouts récents sur les FPGA, ce que nous réserve le domaine des FPGA dans un futur très proche devient difficilement imaginable.

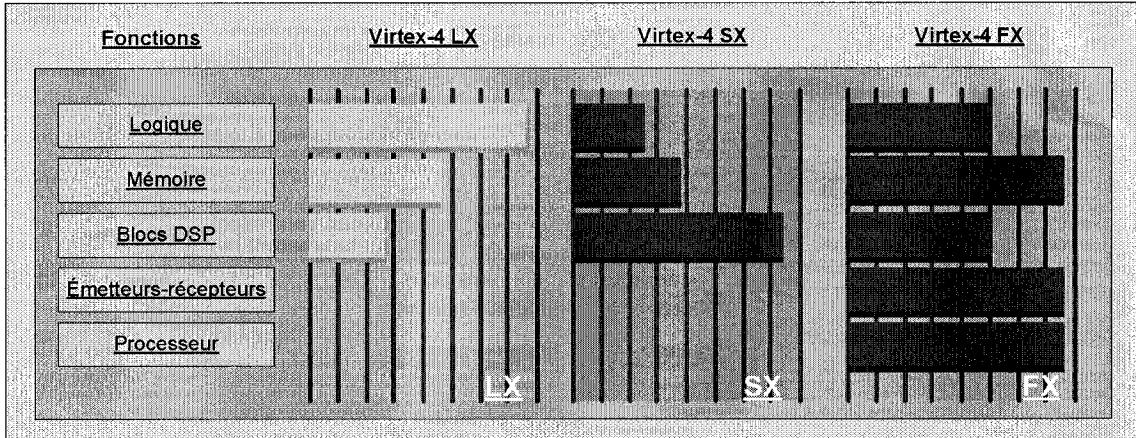

Du coté de Xilinx, on continue de sortir les dernières sous-familles des « Virtex 2 Pro ». Parmi toutes les puces de Xilinx, ces dernières contiennent plus de logiques programmables, de mémoires, de fonctions DSP (digital signal processing), etc. De plus, une toute nouvelle famille a fait son apparition dernièrement, il s'agit des « Virtex 5 » qui, basé sur une technologie de 65 nm, contient une toute nouvelle architecture constitué de LUT à 6 entrées. Cette technologie, conjuguée a sa nouvelle structure de base et aux nombreux blocs embarqués et fonction DSP ajoutée à la puce, lui permet d'effectuer un éventail de fonctionnalité plus rapidement et avec une moins grande dissipation de puissance [XILI06] par rapport aux autres familles de FPGA que Xilinx possède. Cependant, cette section détaillera plutôt une autre famille tel le « Virtex 4 » [XILI04]. Il s'agit d'une puce permettant trois types d'exploitation. En effet, cette famille comporte trois types de puces permettant de réaliser des systèmes complètement différents. À la fois orientée logique, et orientée système, cette famille de FPGA est sûrement la plus versatile de notre époque. Son coté design composé des puces V4 LX, possédant un très grand rapport de logique programmable versus le nombre de cellules totales, et des V4 SX spécialisées pour les design nécessitant beaucoup de fonctions DSP. D'autre part, elle est également orientée système grâce aux V4 FX qui contiennent un processeur

embarqué et de multiples autres composants à cet effet. La figure suivante illustre très bien la flexibilité de la famille « Virtex 4 ».

Figure 1.4 : Caractéristiques de la famille Virtex 4 [XILI04]

Altera, pour sa part, semble prendre un tournant différent. Tout en continuant de déployer tous les efforts requis pour continuer à développer ses familles actuelles de FPGA et procurer une impressionnante bibliothèque de IP intégrable à leur puce dont le processeur logiciel Nios II, une branche de cette société se tourne désormais vers les ASIC structurés dont leur premier essai se nomme le « HardCopy ». En résumé, les ASIC structurés consistent en des ASIC configurables où la puce n'est pas entièrement complétée. Il ne reste alors qu'à appliquer quelques couches de métal pour que la puce soit terminée [BEHR03]. En réalité, ces couches de métal permettent d'intégrer le comportement désiré dans la puce. Ainsi, le « HardCopy » permet de joindre la flexibilité à la performance. Effectivement, Altera propose de conjuguer le flot de conception rapide et efficace des FPGA et la performance des ASIC. Le « HardCopy » est basé sur la technologie « Stratix » (une des familles classiques de Altera), ce qui permet à l'entreprise d'utiliser ses outils de conception. Une fois le système entièrement réalisé avec un FPGA « Stratix », Altera s'engage à migrer le « netlist » du système vers un « HardCopy ». De plus, ce composant possède exactement la même empreinte de puce que la famille « Stratix ». Il devient donc facile de les interchanger sur une carte.

Ces quelques étapes de plus procurent un nouveau flot permettant de garder un temps de conception rapide, d'augmenter les performances de 50% et de diminuer la consommation de puissance d'un facteur 40% par rapport à un FPGA Stratix équivalent [ALTE03a].

Les familles d'Altera sont autant diversifiées que celles de Xilinx. Par contre, Altera semble avoir abandonné le concept de processeur intégré au FPGA, comme le PPC dans le V2P, et semble mettre plus d'emphase sur leur concept de ASIC structuré et sur l'évolution de leur bibliothèque de modules logiciels (IP) [ALTE04].

Pour sa part, Actel se lance aussi dans la guerre des modules logiciels, parmi leur bibliothèque se retrouve une version du ARM7 qui, selon cette société, semble être le processeur embarqué le plus utilisé au monde. Évidemment, leur bibliothèque procure aussi les modules nécessaires à la communication du ARM7, soit la suite de bus AMBA. Cette bibliothèque conjuguée a une impressionnante liste de FPGA leur donne assurément une place importante de le marché de la puce programmable [ACTE05].

## 1.2. Processeurs présynthétisés

En plus d'offrir une gamme complète de FPGA et CPLD, Altera et Xilinx offrent aussi des processeurs pré-synthétisés qu'on peut programmer dans leurs FPGA respectifs. Pour Xilinx, il s'agit du « Microblaze », alors qu'Altera propose le « Nios » et le « Nios II ». Nous détaillerons principalement les processeurs « Microblaze » ainsi que le « Nios II » dans les sous-sections suivantes.

### 1.2.1. Nios II

Le fameux « Nios II » se présente en fait comme une famille de processeurs pré-synthétisés. En effet, un peu de la même façon que Xilinx avec son « Virtex 4 », Altera cherche à élargir le champ d'application de son processeur. Fort de son architecture

RISC, ce noyau de 32 bits se divise en trois processeurs distincts : le « Nios II/e », le « Nios II/s » ainsi que le « Nios II/f » [ALTE04b]

Malgré moult différences, ces trois processeurs distincts possèdent une architecture semblable. En effet, leurs nombreux points communs leur permettent de garder une compatibilité logicielle. La figure suivante illustre le schéma bloc global des « Nios II ».

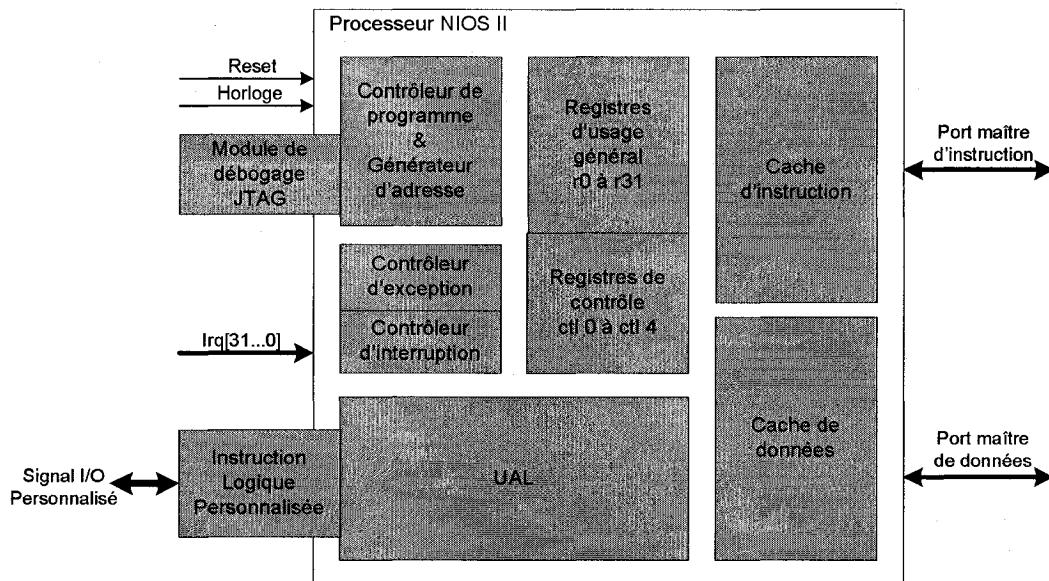

Figure 1.5 : Schéma bloc du Nios II [ALTE04a]

Ces processeurs utilisent un fichier de registres contenant 32 registres d'usage général ainsi que cinq registres de contrôle. Comme la majorité des RISC, chacun de ces registres possède une capacité de 32 bits.

L'unité arithmétique et logique possède un jeu d'instruction riche permettant d'effectuer de nombreuses opérations différentes. De plus, certaines instructions demeurent dépendantes du matériel : elles restent donc non implémentées. Effectivement, dépendamment du noyau choisi, les instructions de multiplication et de division sont simulées de façon logicielle. Afin que cette simulation reste transparente à l'utilisateur, lorsqu'une instruction de ce type est appelée, une exception se lève et la routine de

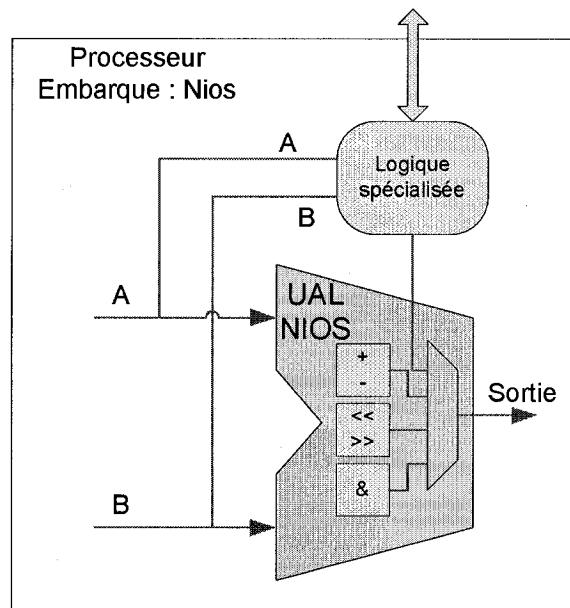

simulation de l'instruction s'exécute. De plus, chacun de ces processeurs peut utiliser des instructions spécialisées préalablement programmées par l'utilisateur. Effectivement, les outils de développement permettent de créer des instructions matérielles qui seront insérées en parallèle à ALU. Suite à l'utilisation de l'instruction spécialisée, le flot de données sera dévié vers le module matériel. Ainsi, le calcul résultant de l'instruction aura été exécutée par un module généré par le programmeur.

**Figure 1.6 : Flot des instructions spécialisées du Nios II [ALTE04]**

Toutes les exceptions et les interruptions matérielles restent liées à une seule adresse mémoire. Cette adresse contient généralement une méthode d'aiguillage des événements. Ainsi, toutes les exceptions et les interruptions finissent par atteindre leur routine prédéterminée.

Comme le schéma bloc de la Figure 1.7 l'illustre, le « Nios II » possède un contrôleur d'interruption intégré pouvant supporter jusqu'à 32 niveaux d'interruptions. De plus, cette architecture supporte les interruptions imbriquées.

Tous les « Nios II » possèdent une architecture « Harvard » : leurs bus d'instruction et de données se trouvent donc séparés. Ces deux bus sont implémentés selon le protocole de bus « Avalon » développé par Altera. Ce protocole sera survolé dans les sections suivantes. Par ailleurs, les processeurs « Nios II » sont « little endian » et permettent des accès par mot ou par demi-mot.

De plus, des caches d'instructions et de données sont disponibles pour certains des trois processeurs. Ces caches se gèrent de façon logicielle, directement à l'aide d'instructions prévues à cet effet. Plusieurs paramètres dont la grandeur des caches restent pourtant configurables par l'utilisateur.

Finalement, les « Nios II » contiennent un module JTAG complet pour le débogage. Ce module permet de :

- transférer du code,

- démarrer et arrêter le code en exécution,

- ajouter des points d'arrêt,

- analyser les registres et la mémoire,

- obtenir des données de traçage en temps réel.

Certains noyaux ne possèdent qu'un sous-ensemble de ces fonctionnalités. Les caractéristiques de chacun des trois processeurs sont présentées brièvement dans la prochaine section, afin de mieux comprendre leurs différences

#### 1.2.1.1. «Nios II/e»

Le premier membre de la famille le «Nios II/e », aussi appelé le « Nios 2 Economy », vise principalement à utiliser le moins de ressources possible pour atteindre le noyau le plus petit possible, tout en gardant sa compatibilité avec les instructions standard des « Nios II ». De ce fait, ce noyau se montre beaucoup moins performant que les autres membres de sa famille, mais il est environ deux fois plus petit que le « Nios II/s ». En

effet, ce noyau peut atteindre 200MHz mais ne peut pas dépasser 31 Dhystone MIPS.

[ALTE04b]

Pour épargner de l'espace et des ressources, tout doit être sacrifié. C'est pourquoi ce noyau ne contient qu'un pipeline d'un seul étage. Il en découle qu'aucune dépendance de données entre les étages n'est possible, et on peut ainsi sauver l'espace dédié pour résoudre les aléas de données.

L'espace adressable par ce processeur est de 2Go. Ce processeur économique ne supporte en aucun cas les caches de données, ni celles d'instructions.

La performance maximale de ce petit processeur est de 6 cycles par instruction, et ce, seulement si le bus d'instruction est assez performant pour récupérer l'instruction courante en un seul cycle.

Pour atteindre ces objectifs, les unités de multiplication, de division et les registres à barillet ne sont pas disponibles dans ce noyau. Par le fait même, les instructions non-implémentées sont automatiquement résolues de façon logicielle, suite à une exception émise par le processeur.

Finalement, l'interface de débogage logiciel via JTAG reste disponible, mais avec des fonctionnalités réduites. Dans cette version minimalistre, le module JTAG ne supporte pas les points d'arrêt matériels, ni le traçage de signaux en temps réel.

### **1.2.1.2. “Nios II/s”**

Le second noyau, appelé « Nios II Standard », a pour objectif de rester petit et performant. Tout comme pour son homologue économique, toute réduction de la taille du processeur se fait au détriment de ses performances. Ce noyau « Standard » utilise approximativement 20% moins de logique programmable que le « Nios /f », mais semble aussi 40% moins performant que celui-ci.

Pour atteindre ces objectifs, seuls les modules avec les plus grands rapport utilisation de ressources versus impact sur la performance on été bannis. Ce type de processeur est parfait pour tout système nécessitant un petit processeur avec des performances moyennes. Malgré tout, ce noyau peut atteindre 127 Dhystone MIPS à 165 MHz.

Le pipeline de ce noyau ressemble étrangement à celui du classique DLX décrit dans [HEPA90]. Effectivement, ce pipeline contient 5 étages définis comme suit : « Fetch », « Decode », « Execute », « Memory », « Writeback ». Une politique de prédition de branchement statique est utilisée pour réduire les pénalités dues à une erreur de branchement. Pour plus d'informations sur les politiques utilisées pour le pipeline des « Nios II », le lecteur peut se référer à [ALTE04b].

Comme le « Nios II Economy », l'espace adressable de ce processeur est de 2Go. Par contre, le « NIOS II/s » supporte les caches d'instructions. Ses performances lui permettent également d'exécuter une instruction à chaque 1 ou 2 cycles.

De plus, si le FPGA cible le permet, le processeur supporte les instructions matérielles de multiplication. Par contre, les opérations de division sont toujours simulées en logiciel.

Finalement, le module de débogage via JTAG offre toutes les fonctionnalités dont le débogage logiciel, ainsi que le traçage des signaux matériels en temps réel.

#### 1.2.1.3. «Nios II/f»

Le dernier membre de cette famille de processeur pré-synthétisé demeure le plus performant d'où son nom : « Nios II Fast ». Les objectifs de ce noyau consistent à maximiser le rapport instructions par cycle tout en optimisant sa fréquence maximale d'exécution. Ainsi, ce noyau s'avère parfait pour les systèmes devant traiter une grande quantité de données et dont les performances deviennent essentielles. Il reste à noter que ce processeur peut atteindre 218 Dhystone MIPS à 185 MHz.

Si le FPGA cible contient les modules DSP nécessaires, toutes les instructions non-implémentées (multiplication, division, rotation et décalage de bits) s'exécutent directement en matériel.

Contrairement au « Nios II/s », le modèle rapide possède un pipeline de 6 étages : « Fetch », « Decode », « Execute », « Memory », « Align », « Writeback ». De plus, ce noyau utilise une technique de prédition de branchement dynamique pour restreindre les pénalités de branchements. Ainsi ce processeur peut exécuter une instruction à chaque cycle ou plus.

Comme les deux autres processeurs de sa famille, l'espace adressable de ce processeur est de 2Go. Pour sa part, le « NIOS II/f » supporte autant les caches d'instructions que les caches de données. La grandeur de chacune de ces caches est configurable par les utilisateurs.

Comme le « Nios II Standard », toutes les fonctionnalités du module de débogage intégré dans le noyau sont disponibles dans la version rapide. Ces fonctionnalités comprennent le débogage logiciel, les points d'arrêt matériel ainsi que le traçage en temps réel.

### 1.2.2. MicroBlaze

Le « Microblaze » ressemble beaucoup au « Nios II » : c'est un processeur pré-synthétisé performant, configurable à sa manière et offrant diverses possibilités.

Également un RISC à 32-bits, ce processeur est optimisé spécialement pour son intégration dans des FPGA de Xilinx. De ce fait, il peut atteindre une fréquence théorique de 150MHz sur un « Virtex 2 Pro », et de 185 MHz sur un « Virtex 4 ». Comme ce processeur est paramétrable, ses performances peuvent différer dépendamment de la configuration du processeur à générer. Le tableau suivant expose des données obtenues

par Xilinx avec un Microblaze optimisé pour la performance d'une application de recherche de patron. Le processeur utilisé contient un multiplieur intégré, un décaleur à binaire ainsi qu'une instruction spécialisée interfacée par FSL.

**Tableau 1.2: Performance du Microblaze [XILI04]**

| FPGA                          | Grandeur   | Fréquence | Dhrystone 2.1 | Performance       |

|-------------------------------|------------|-----------|---------------|-------------------|

|                               |            | d'horloge |               |                   |

| Virtex-4<br>(4VLX25-12)       | 1,269 LUTs | 180 MHz   | 166 DMIPS     | 0.92<br>DMIPS/MHz |

| Virtex-II<br>Pro<br>(2VP20-7) | 1,225 LUTs | 150 MHz   | 138 DMIPS     | 0.92<br>DMIPS/MHz |

| Spartan-3<br>(3S1500-5)       | 1,318 LUTs | 100 MHz   | 92 DMIPS      | 0.92<br>DMIPS/MHz |

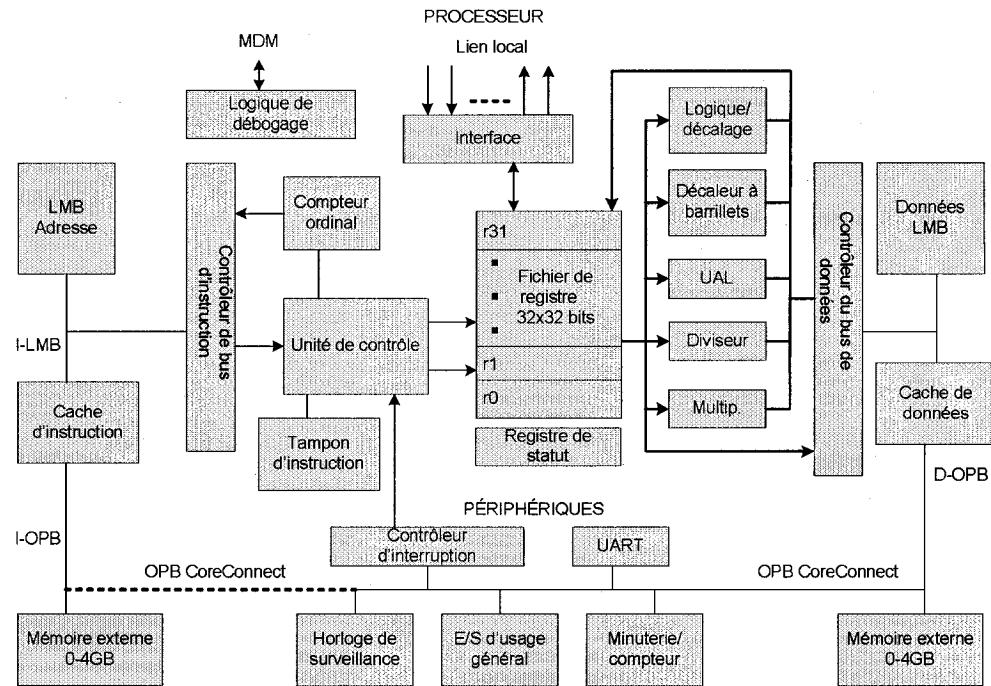

L'illustration suivante représente un diagramme bloc de ce processeur avec plusieurs des périphériques disponibles dans la bibliothèque d'IP offerte par Xilinx. Ces périphériques sont connectés directement sur le bus OPB, mais toutes ces connexions se font très facilement grâce aux outils fournis. À partir du diagramme, on observe que le processeur suit une architecture « Harvard » avec ses bus de données et ses bus d'instructions séparés. On remarque également les modules optionnels, tels que l'unité de division matérielle, le binaire à décalage, les caches de données et d'instructions disponibles, ainsi que le bus FSL, qui donnent une tout autre dimension à ce processeur.

Figure 1.7 : Schéma bloc du Microblaze et de certains périphériques [XIL104c]

Ce processeur possède 32 registres d'usage général, ainsi que deux registres à usage spécialisé de 32 bits de large. Les instructions sont codées également sur 32 bits, et naturellement, ses bus de données et d'instructions sont de cette largeur.

Comme la majorité des RISC, le « Microblaze » est pipeliné. Son pipeline est composé de trois étages (« Fetch, decode, execute »), et deux techniques de réduction de pénalités de branchement sont implémentées, afin d'augmenter les performances d'exécution.

De plus, ce processeur « big endian » possède un jeu d'instructions très complet, permettant même d'utiliser les multiplieurs et le diviseur intégrés dans le FPGA. Ces instructions sont divisées en deux types, soient A et B. Le type A permet d'effectuer des opérations sur deux registres sources, alors que le type B utilise une valeur immédiate et un registre source.

Il est aussi intéressant de remarquer, sur la figure précédente, que le « Microblaze » peut communiquer sur deux types de bus : le LMB, pour « Local Memory Bus », ainsi que l'OPB, pour « On-Chip Peripheral Bus », ce dernier faisant partie de la suite « CoreConnect » de IBM présentée dans la section suivante. Comme son nom l'indique, le « LMB » permet d'interfacer de la BRAM localement au processeur : la latence de communication devient ainsi très faible. Comme il n'y a qu'une faible quantité de BRAM sur des FPGA, ce type de connexion est parfait pour créer un niveau de cache dans un système. On pourrait imaginer un second niveau de cache directement sur l'OPB, qui pourrait être partagée, ainsi qu'une mémoire principale, à l'extérieur du FPGA, à laquelle on accède par un contrôleur branché également sur l'OPB. Il existe six différentes configurations de mémoire possibles avec le « Microblaze ». Il est à noter que chaque configuration doit posséder minimalement une connexion pour les instructions et au moins une pour les données.

Le « Microblaze » possède aussi des contrôleurs de cache pour ses instructions et ses données. Plusieurs paramètres du « Microblaze » sont dédiés à la configuration des caches. Par exemple, la taille de ces caches peut être configurée par l'utilisateur. De plus, ce type de mémoire peut être utilisé soit via l'OPB ou encore via l'interface « CacheLink »<sup>3</sup>. Cette nouvelle interface se connecte par le biais du FSL pour effectuer les opérations de cache.

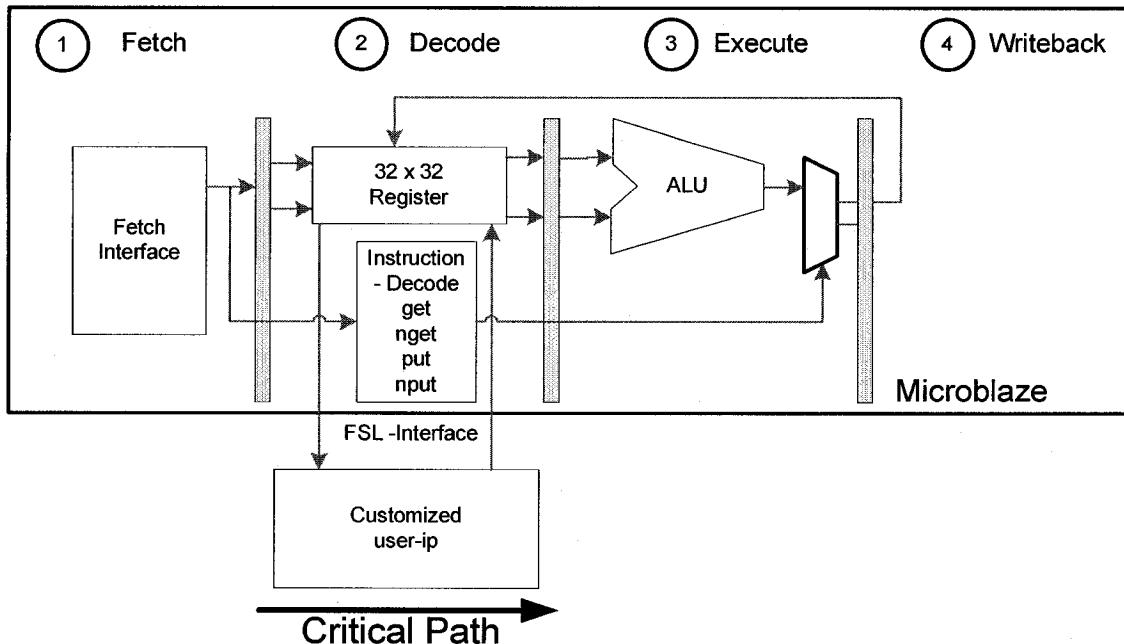

Comme le montre la figure suivante, le bus « Fast Simplex Link » est en fait une interface permettant de connecter n'importe quel périphérique directement et localement au Microblaze. La communication avec les co-processeurs via FSL se fait facilement grâce à un API écrit en C. Chaque processeur possède 8 entrées et 8 sorties FSL de 32 bits chacune : il est donc possible de créer un coprocesseur FSL pouvant transférer des paquets allant jusqu'à 32 octets. L'avantage de ce type d'ajout, comparativement à un

---

<sup>3</sup> Le « CacheLink » est seulement disponible dans les versions supérieures à la 3.00a du « Microblaze »

processeur possédant un jeu d'instructions configurable, consiste dans le fait que le co-processeur ne bloque pas l'exécution du « Microblaze » pendant ces opérations. Les performances de l'interface FSL peuvent atteindre jusqu'à 300 MB/sec. Ce type d'interconnexion se montre idéal pour communiquer d'un « Microblaze » à un autre « Microblaze ».

Figure 1.8 : Interface FSL dans le pipeline du Microblaze [XILIO4c]

Contrairement au « Nios II », aucun module de débogage n'est directement intégré dans le « Microblaze ». Cependant, une interface JTAG est disponible pour connecter certains modules permettant de parcourir le code en exécutions pas par pas, d'insérer des points d'arrêt, et d'examiner des variables, des registres et des plages mémoires. Un second aspect du débogage est également disponible grâce à cette interface. En effet, l'outil « Chipscope Pro » permet de tracer des diagrammes temporels des signaux internes au FPGA pendant l'exécution du projet. Pour ce faire, quelques modules propres à l'outil doivent être instanciés dans le système.

### 1.2.3 Comparaison des processeurs présynthétisés

Le tableau suivant compare certaines caractéristiques discutées dans les sections précédentes sur les trois « Nios II » et le « Microblaze.

Tableau 1.3: Comparaison des processeurs logiciels

|                            | NIOS II                            |                                    |                                        | Microblaze                               |

|----------------------------|------------------------------------|------------------------------------|----------------------------------------|------------------------------------------|

|                            | Economy                            | Standard                           | Fast                                   |                                          |

| Max DMIPS                  | 31 <sup>4</sup>                    | 127 <sup>4</sup>                   | 218 <sup>4</sup>                       | 125 <sup>5</sup>                         |

| F <sub>MAX</sub>           | 200 MHz <sup>4</sup>               | 265 MHz <sup>4</sup>               | 185 MHz <sup>4</sup>                   | 150 MHz <sup>5</sup>                     |

| Surface                    | < 700 LEs <sup>4</sup>             | < 1400 LEs <sup>4</sup>            | < 1800 LEs <sup>4</sup>                | < 900 LCs <sup>5</sup>                   |

| Pipeline                   | 1 étage                            | 5 étages                           | 6 étages                               | 3 étages                                 |

| ICache                     | Non                                | Oui<br>512o à 64Ko                 | Oui<br>512o à 64Ko                     | Oui<br>2Ko à 64Ko                        |

| DCache                     | Non                                | Non                                | Oui<br>512o à 64Ko                     | Oui<br>2Ko à 64Ko                        |

| Multiplication et division | Opérations logicielles             | Mult. matérielles <sup>6</sup>     | Mult. et div. matérielles <sup>6</sup> | Mult. et div. matérielles <sup>6</sup>   |

| Débogage                   | Logiciel seulement                 | Logiciel et matériel               | Logiciel et matériel                   | Logiciel et matériel via modules séparés |

| Interruptions              | Contrôleur d'interruption intégré. | Contrôleur d'interruption intégré. | Contrôleur d'interruption intégré.     | Contrôleur d'interruption séparé.        |

| Options                    | Instructions spécialisées          | Instructions spécialisées          | Instructions spécialisées              | FSL                                      |

<sup>4</sup> Calculé avec les Stratix les plus rapides [ALTE04b]

<sup>5</sup> Calculé avec les Virtex 4 les plus rapides [XILI04]

<sup>6</sup> Si le FPGA cible possède les fonctions DSP nécessaires. [ALTE04b] et [XILI04]

### 1.3. Interconnexion

Afin que ces processeurs, autant les pré-synthétisés que les autres, puissent communiquer avec le reste des modules présents dans le système, il semble important de choisir un protocole de communication adéquat. Actuellement, sur le marché des systèmes-sur-puce, les structures de bus représentent le moyen le plus répandu pour communiquer entre un processeur et ses périphériques. Évidemment, on aurait pu choisir tout autre réseau sur puce (NOC) plus efficace pour l'application utilisée dans ce projet [DESL05], mais le but du projet réside dans l'aisance de la création d'une architecture efficace, et les protocoles de bus se montrent plus répandus et souvent offerts avec les outils de développement des FPGA. De plus, la majorité des modules fournis possèdent déjà une interface compatible avec certains protocoles de bus. Le choix du FPGA n'est donc pas seulement un choix de technologie physique mais aussi le choix du processeur et de ses interconnexions. Bien entendu, il reste possible de déroger à la tendance d'utiliser les interfaces de communication, les périphériques et le processeur généralement optimisé pour un FPGA, mais le gain possible ne vaut pas les complications attendues. Les structures de bus suivantes auraient pu être utilisées dans le projet : AMBA, CoreConnect, Avalon

#### 1.3.1. AMBA

Conçu par ARM, le protocole AMBA [ARM04] est une spécification de bus de communication pour système sur puce que l'entreprise propose comme norme pour les SOC. L'entièreté de cette spécification comprend trois protocoles qui permettent une utilisation différente, dépendamment des besoins du système. Le plus connu des protocoles AMBA est le AHB « Advanced High-Speed Bus ». Celui-ci est particulièrement utilisé pour créer des systèmes très performants contenant généralement des processeurs rapides, des DMA, et des DSP. Le ASP, quant à lui, représente l'acronyme de « Advanced System Bus » et se trouve actuellement remplacé par le AHB. Le dernier, l'APB, pour «Advanced Peripheral Bus», permet l'utilisation de

périphériques et modules plus lents. Son protocole, plus simple que les deux autres, rend aisée la génération de nouveaux modules, son interface étant plus facile à comprendre et à tester.

Ce protocole AHB, largement utilisé, possède plusieurs caractéristiques intéressantes, comme le support de plusieurs maîtres, les transactions en rafales et les transactions partagées dites « split ». Il offre aussi un mécanisme de protection des accès privilégiés ainsi qu'un algorithme d'arbitrage pour éviter les conflits sur des système multi-maîtres. Un pont AHB-APB reste disponible pour assurer la communication entre les modules à haut débit et les périphériques plus lents.

AHB dispose aussi d'un nouveau modèle qui se nomme AHB-CLI pour « cycle level interface », qui consiste en fait en un modèle RTL pour SystemC du protocole de bus.

### 1.3.2. CoreConnect

Très semblable à AMBA, cette spécification est aussi divisée en trois protocoles distincts. Le premier nommé PLB pour « Processor Local Bus », se montre semblable au AHB d'AMBA : il est utilisé dans des systèmes à haut débit et pour séparer la majeure partie des périphériques du processeur utilisé. Souvent en conjonction avec son homologue, l'OPB, « On-Chip Peripheral Bus », s'avère beaucoup plus simple à comprendre et les modules qui lui sont connectés sont plus faciles à tester et à intégrer au système. Ce protocole est utilisé pour contenir les périphériques lents, comme le APB de AMBA. Finalement, le dernier des trois protocoles offerts par CoreConnect se nomme le DCR, pour « Device Control Register ». Celui-ci se connecte en anneau avec le PowerPc, permettant d'aligner plusieurs esclaves en série sur cette interconnexion. Ce type de connexion semble intéressant pour les modules très lents : il est principalement utilisé pour connecter les contrôleurs d'interruptions au processeur.

Pour sa part, le « Microblaze » possède une interface qui n'est compatible qu'avec l'OPB. Par contre, le PowerPc 405 de IBM utilise une interface PLB. Certains considèrent CoreConnect comme trop lourd et trop compliqué pour intégrer à un SOC [USSE01]; Xilinx, par contre, tente de contrer cette croyance en intégrant ce protocole et une quantité intéressante d'IP compatibles à ses outils de développement de FPGA. Effectivement, CoreConnect, avec son Microblaze, peut être instancié sur tous les FPGA de Xilinx possèdant assez de ressources configurables.

Puisque la création d'interfaces pour ces protocoles reste souvent inévitable et fastidieuse, IBM offre certains outils de vérification et de génération de tests, afin d'assurer la compatibilité du protocole. Ainsi, il devient plus simple de connecter son propre périphérique au système.

### 1.3.3. Avalon

Le dernier protocole présenté est particulièrement simple. En effet, cette particularité est l'objectif principal que les architectes ont voulu atteindre. Effectivement, ce protocole de bus, créé par Altera et complètement dédié aux systèmes utilisant un « Nios » ou un « Nios II », vise principalement à rester facile d'apprentissage pour les concepteurs de systèmes sur puce. De plus, il est optimisé pour l'utilisation de « LE », principal élément dans les FPGA de Altera.

Comme les deux premiers protocoles, il se base sur des transactions maîtres-esclaves et peut supporter plusieurs maîtres. Afin d'éviter les problèmes d'accès simultanés, un arbitre esclaves est directement intégré dans le protocole. Ce type d'arbitrage détermine quel maître peut communiquer un esclave si les requêtes des maîtres sont émises simultanément pour un même module.

Finalement, les outils d'Altera procurent un assistant permettant de générer facilement et automatiquement le bus à partir des paramètres spécifiés par l'utilisateur. [ALTE04a]

#### 1.4. Multi-Processus matériel.

Depuis plusieurs décennies, des ingénieurs du monde entier tentent, en vain, de maintenir la cadence de développement face à rapidité de l'évolution de la loi de Moore au niveau de la performance des systèmes informatiques. De ce fait, plusieurs recherches portant sur des architectures multiprocesseurs émergent chaque année. Ces systèmes à grande échelle utilisant des mémoires partagées génèrent des latences de communications de plusieurs dizaines, voire centaines de cycles [GHGM91, KHKA92]. Ce problème de latence peut facilement faire écrouler les performances du système utilisé. Pour remédier à cet obstacle, plusieurs mécanismes sont encore étudiés. Parmi ceux-ci on retrouve notamment les protocoles de cohérence de caches [GHGM91, BORA92, TUEG93], la prélecture de données [GHGM91, BORA92, TUEG93] ou encore des architectures basées sur les flots de données [GHGM91, PDWO92, HAFU88, KHKA92, BORA92].

Toutes ces techniques comportent leurs avantages et leurs inconvénients. En fait, elles peuvent réduire significativement la latence de communication, sans toutefois l'éliminer. Individuellement, ces mécanismes peuvent produire globalement des gains variant d'un facteur 1 à 2. Cependant, la meilleure solution consisterait en une composition de plusieurs techniques. Effectivement, une combinaison de mécanismes de réduction/masquage de la latence peut générer une augmentation de performance d'un facteur 4 à 7, dépendamment de l'application utilisée [GHGM91].

Le but ultime de ces mécanismes consiste à augmenter le taux d'utilisation des processeurs inclus dans les systèmes [EEL98]. Les prochaines sections présentent d'ailleurs des mécanismes tirés des architectures orientées données.

#### 1.4.1. Processeurs RISC

Au début des années 80, Berkley, Stanford et IBM se sont penchés, chacun de leur côté, sur une nouvelle architecture afin de faciliter le support de langages sur le matériel. De ces recherches, il en résulte, quelques années plus tard, l'apparition de l'architecture RISC [HEPA90].

Cette philosophie architecturale se base principalement sur la simplification des instructions. En effet, seules les instructions « load » et « store » utilisent la mémoire, toutes les autres instructions travaillent de registres à registres. Cette technique simplifie le décodage et uniformise le format des instructions [PATT85]. De plus, cette architecture utilise un pipeline afin que les instructions se recouvrent pendant leur exécution. Ce mécanisme augmente ainsi le taux d'utilisation du processeur en exécutant une instruction par cycle [HEPA90]. Cependant, ces performances ne s'atteignent que dans les conditions idéales : un code possédant le moins de branchements possible et très peu de dépendances de données. Si un seul de ces deux facteurs est présent, des bulles s'installent dans le pipeline et diminuent le nombre d'instructions par cycle. Dans les processeurs actuels, plusieurs solutions sont apportées pour éviter les bulles ou pour diminuer l'impact des pénalités dans le pipeline, dont la prédiction de branchement.

Parmi les processeurs embarqués, le ARM, le PowerPc, les « Nios I/II » et le « Microblaze » font partie des noyaux dit RISC.

Évidemment, ces processeurs ne possèdent aucun mécanisme matériel de multi-processus. Pour y arriver, ces processeurs doivent utiliser des bibliothèques logicielles prévues à cet effet. De plus, aucun parallélisme matériel ne s'exploite dans ce type de processeurs.

#### **1.4.2. Processeurs superscalaires**