**Titre:** Plate-forme de communication pour systèmes embarqués

Title: multipuces utilisant HyperTransport

**Auteur:** Ami Castonguay

Author:

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Castonguay, A. (2006). Plate-forme de communication pour systèmes embarqués multipuces utilisant HyperTransport [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7868/>

Citation:

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7868/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

PLATE-FORME DE COMMUNICATION POUR SYSTÈMES

EMBARQUÉS MULTIPUCES UTILISANT HYPERTRANSPORT

AMI CASTONGUAY

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AOÛT 2006

© Ami Castonguay, 2006.

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-19287-0

*Our file* *Notre référence*

ISBN: 978-0-494-19287-0

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

**Canada**

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

PLATE-FORME DE COMMUNICATION POUR SYSTÈMES

EMBARQUÉS MULTIPUCES UTILISANT HYPERTRANSPORT

présenté par : CASTONGUAY Ami

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M<sup>me</sup> NICOLESCU Gabriela, Ph.D., présidente

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. DAVID Jean-Pierre, Ph.D., membre

## Remerciements

Ce travail a été accompli grâce aux contributions de nombreuses personnes et organismes :

**Yvon Savaria** – Tout d’abord un grand merci à mon directeur pour m’avoir proposé un projet qui a su me passionner tout au long de ma maîtrise. Sa vision et ses conseils m’ont toujours gardé dans le droit chemin afin d’atteindre les objectifs visés. Malgré son horaire chargé, il a toujours su être présent lorsque nécessaire.

**Bernard Racine** – Ses idées à l’avant-garde de la technologie ont permis de donner un sens à cette recherche. Il a su partager sa passion pour le sujet, tout en donnant de précieux conseils.

**Conseil de recherches en sciences naturelles et en génie du Canada** – Pour son grand appui financier grâce à son programme de bourses d’études supérieures.

**CMC Microsystèmes** – Pour l’accès à tous les outils de microélectronique qui ont permis de compléter le présent mémoire.

**Francis St-Pierre** – L’intégration de son réseau embarqué avec le tunnel HyperTransport présenté dans ce mémoire a permis de donner une dimension supplémentaire très intéressante au projet.

**Jean-François Bélanger, Laurent Aubray, Michel Morneau, Max-Élie Salomon et Martin Chabot-Corriveau** – Ils ont tous participé à la conception d’une première implémentation du tunnel HyperTransport. Ce fut un énorme coup de pouce!

## Résumé

Même s'il est possible d'intégrer une multitude de fonctionnalités à l'intérieur d'un système embarqué sur puce, il est parfois nécessaire de distribuer ces fonctionnalités sur plusieurs puces à cause de limites technologiques ou afin d'offrir une plus grande flexibilité au système. Pour qu'un environnement multipuce fonctionne adéquatement, les composants embarqués sur différentes puces doivent pouvoir communiquer entre eux de façon performante. Ce mémoire explore la conception d'une plate-forme de communication pour de tels systèmes embarqués sur plusieurs puces.

En premier lieu, il est important de bien connaître les besoins de notre plate-forme : il est nécessaire d'avoir accès à un protocole de communication interpuces qui est à la fois performant et compatible avec les méthodes de communication actuelles des systèmes embarqués. Les protocoles de communications PCI Express, RapidIO, HyperTransport et SPI 4-2 sont comparés en terme de fonctionnalités et c'est le protocole HyperTransport qui est retenu pour la plate-forme.

Afin d'avoir accès à cette technologie de communication interpuces, la conception d'un tunnel HyperTransport a été effectuée. L'architecture et la méthode de développement du tunnel sont présentées en détail. Le tunnel a été conçu à l'aide de SystemC, à la fois pour la validation de l'architecture, la conception matérielle et pour la vérification de son bon fonctionnement. Le tunnel, qui est disponible sous une licence libre, est grandement paramétrable et supporte plusieurs fonctionnalités dont le mode *retry* qui permet de corriger des erreurs de transmission.

Les résultats de synthèse du tunnel permettent tout d'abord d'obtenir une compréhension d'où vient la grande complexité des contrôleurs de communication de haute performance. La complexité logique du tunnel se situe à 131,9 milliers de portes logiques, ce qui exclut les 43,2 Kibits de mémoires embarquées qui sont également

nécessaires. Le tunnel peut être implémenté à la fois pour la technologie de cellules normalisées TSMC 0,18 µm pour obtenir une bande passante de 8000 Mb/s et pour des FPGAs tels que ceux d'Altera et de Xilinx avec une bande passante de 2400 Mb/s et 3200 Mb/s respectivement. L'aspect paramétrable du tunnel permet également de comprendre les effets des divers paramètres du circuit sur sa complexité et sa performance.

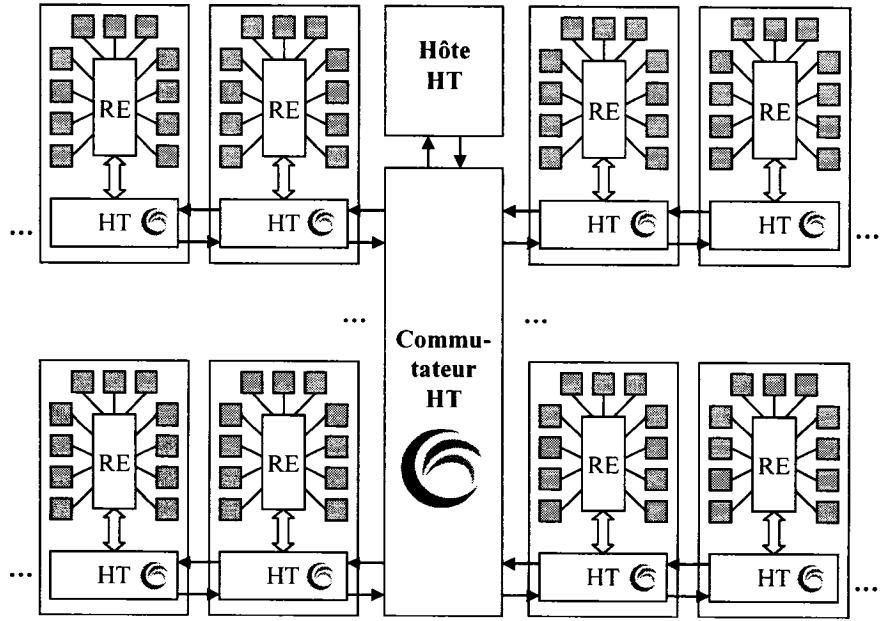

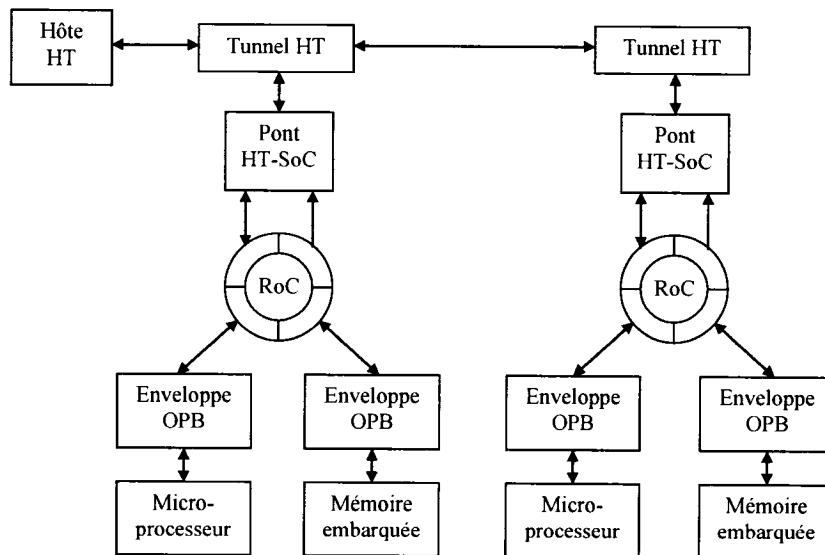

Un pont a été conçu afin de permettre à des systèmes embarqués d'interagir avec un réseau HyperTransport. Son architecture et les résultats de synthèse sont également détaillés dans le mémoire. Ce pont a permis d'intégrer, en simulation, plusieurs réseaux embarqués RoC avec une chaîne de communication HyperTransport constitués de deux tunnels HyperTransport. La simulation d'une chaîne de communication HyperTransport a nécessité la conception d'un hôte HyperTransport, qui a été simulée à l'aide d'un modèle transactionnel en SystemC.

## Abstract

Even if it is possible to integrate a great deal of functionalities inside a system on a chip, it is sometimes necessary to distribute the functionalities on multiple chips because of technological limitations or in order to achieve greater system flexibility. To obtain adequate system performance in a multiple chip environment, high performance communication is required. This thesis explores the development of a communication platform for such systems on multiple chips.

It is first necessary to fully understand all the needs of the communication platform: a high performance interchip communication protocol is needed that is compatible with existing system on chip communication. PCI Express, RapidIO, HyperTransport and SPI 4-2 are compared in terms of functionalities and the HyperTransport protocol was chosen for the platform.

In order to obtain such an interchip communication technology, a HyperTransport tunnel was developed. The tunnel architecture and the development method that was used are presented in details. SystemC was used for the validation of the architecture of the tunnel, the hardware design and to verify that all the functionalities were correct. The tunnel, that is available under an open license, is highly configurable and supports many functionalities, such as the *retry* mode that allows error correction.

Synthesis results provide a better understanding of the complexity of high performance communication controllers. The tunnel has a complexity of 131 900 logic gates, which excludes the 43,2 Kibits of embedded memory that are also required. The tunnel can be implemented in a TSMC 0,18  $\mu\text{m}$  technology to obtain a bandwidth of 8000 Mb/s and for FPGAs such as those from Altera and Xilinx with a resulting bandwidth of 2400 Mb/s and 3200 Mb/s respectively. The effects of the various parameters on the circuit complexity and performance are also explored in details.

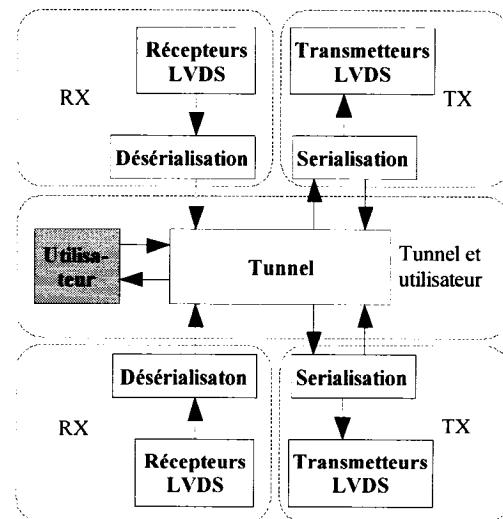

A bridge was developed to allow system on chips to communicate with the HyperTransport network. The architecture and synthesis results of the bridge are also presented in details. The bridge allowed the integration of many RoC network on chips with a HyperTransport communication chain composed of two HyperTransport tunnels. Such a simulation also required a HyperTransport host controller that was simulated using a SystemC transactional model.

## Table des matières

|                                            |       |

|--------------------------------------------|-------|

| REMERCIEMENTS .....                        | IV    |

| RÉSUMÉ.....                                | V     |

| ABSTRACT .....                             | VII   |

| TABLE DES MATIÈRES .....                   | IX    |

| LISTE DES TABLEAUX .....                   | XIV   |

| LISTE DES FIGURES.....                     | XV    |

| LISTE DES SIGLES ET DES ABRÉVIATIONS ..... | XVIII |

| INTRODUCTION.....                          | 1     |

| CONTRIBUTIONS DU PRÉSENT MÉMOIRE .....     | 3     |

| PLAN DU MÉMOIRE .....                      | 4     |

| CHAPITRE 1. REVUE DE LITTÉRATURE.....      | 6     |

| 1.1 COMMUNICATION INTERPUCES .....         | 6     |

| 1.2 HYPERTRANSPORT.....                    | 10    |

| 1.2.1 Lien physique et initialisation..... | 10    |

| 1.2.2 Format des paquets .....             | 11    |

| 1.2.3 Ordonnancement des paquets .....     | 14    |

| 1.2.4 Contrôle de flux .....               | 15    |

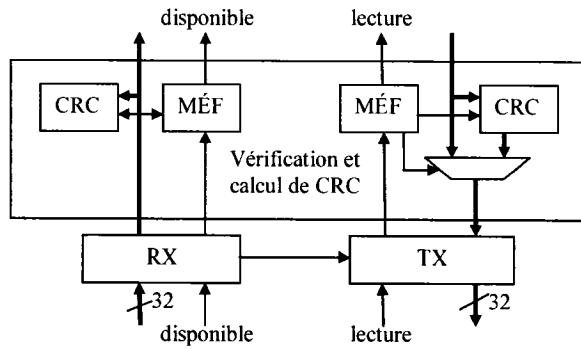

| 1.2.5 Vérification d'erreurs.....          | 16    |

|                                                               |           |

|---------------------------------------------------------------|-----------|

| 1.2.6    Configuration des fonctionnalités .....              | 17        |

| 1.3    SYSTÈMES ET RÉSEAUX EMBARQUÉS .....                    | 17        |

| 1.4    CONCEPTION MATÉRIELLE UTILISANT SYSTEMC .....          | 20        |

| 1.5    CONCLUSION.....                                        | 25        |

| <b>CHAPITRE 2. ARCHITECTURE DU SYSTÈME .....</b>              | <b>27</b> |

| 2.1    ARCHITECTURE GLOBALE DE COMMUNICATION .....            | 27        |

| 2.2    CHOIX D'UNE TECHNOLOGIE DE LIEN INTERPUCES.....        | 28        |

| 2.3    INTERACTION AVEC UN SYSTÈME EMBARQUÉ .....             | 29        |

| 2.4    CONCLUSION.....                                        | 31        |

| <b>CHAPITRE 3. ARCHITECTURE DU TUNNEL HYPERTRANSPORT.....</b> | <b>32</b> |

| 3.1    LICENCE DE DÉVELOPPEMENT ET DE DISTRIBUTION .....      | 32        |

| 3.1.1    Choix de licence.....                                | 33        |

| 3.1.2    Distribution .....                                   | 33        |

| 3.2    APERÇU DE L'ARCHITECTURE .....                         | 34        |

| 3.2.1    Options supportées.....                              | 34        |

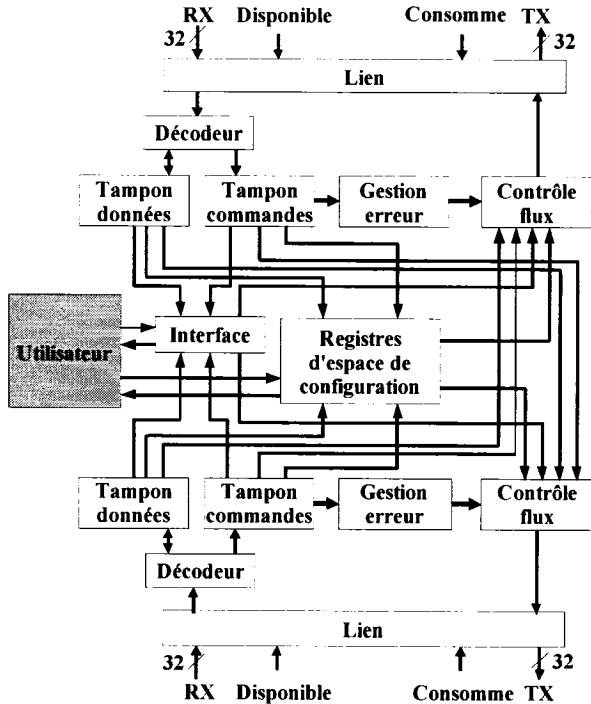

| 3.2.2    Aperçu des modules.....                              | 35        |

| 3.3    MÉTHODE DE CONCEPTION .....                            | 37        |

| 3.4    ASPECTS PARAMÉTRABLES .....                            | 39        |

|                                                                   |                                                           |    |

|-------------------------------------------------------------------|-----------------------------------------------------------|----|

| 3.4.1                                                             | Exemples d'utilisation du précompilateur .....            | 40 |

| 3.5                                                               | ARCHITECTURE DÉTAILLÉE.....                               | 41 |

| 3.5.1                                                             | Domaines d'horloge.....                                   | 41 |

| 3.5.2                                                             | Initialisation du circuit .....                           | 45 |

| 3.5.3                                                             | Lien .....                                                | 45 |

| 3.5.4                                                             | Décodeur .....                                            | 47 |

| 3.5.5                                                             | Tampon de données .....                                   | 49 |

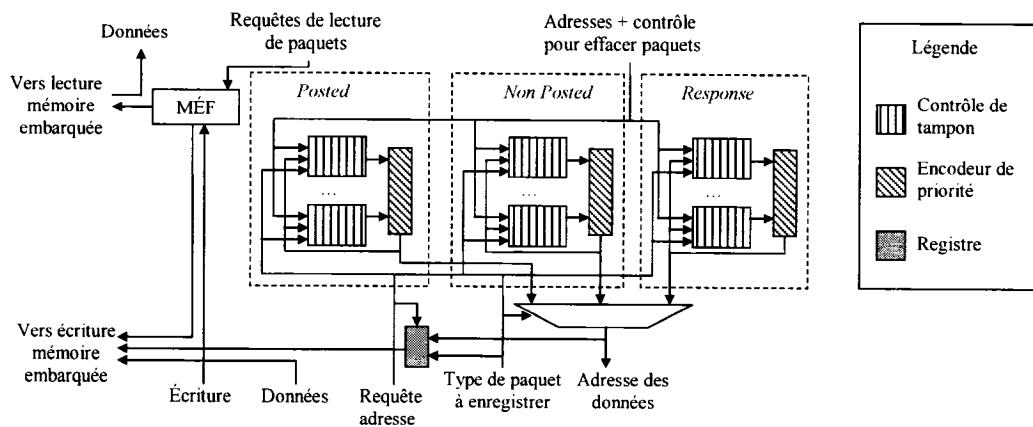

| 3.5.6                                                             | Tampon de commandes .....                                 | 51 |

| 3.5.7                                                             | Module <i>Gestion erreur</i> .....                        | 56 |

| 3.5.8                                                             | Registres d'espace de configuration .....                 | 57 |

| 3.5.9                                                             | Interface .....                                           | 58 |

| 3.5.10                                                            | Contrôle de flux .....                                    | 60 |

| 3.6                                                               | COMPARAISON AUX ARCHITECTURES COMMERCIALES ACTUELLES..... | 63 |

| 3.7                                                               | CONCLUSION.....                                           | 64 |

| CHAPITRE 4. RÉSULTATS DE SYNTHÈSE ET VÉRIFICATION DU TUNNEL ..... | 65                                                        |    |

| 4.1                                                               | DONNÉES DE SYNTHÈSE .....                                 | 65 |

| 4.1.1                                                             | Distribution de la complexité.....                        | 67 |

|                                                           |                                                         |    |

|-----------------------------------------------------------|---------------------------------------------------------|----|

| 4.1.2                                                     | Effets des paramètres de synthèse.....                  | 70 |

| 4.1.3                                                     | Chemin critique.....                                    | 74 |

| 4.2                                                       | AMÉLIORATION DE LA COMPLEXITÉ ET DE LA PERFORMANCE..... | 76 |

| 4.2.1                                                     | Lien .....                                              | 76 |

| 4.2.2                                                     | Tampon de données .....                                 | 76 |

| 4.2.3                                                     | Tampon de commandes .....                               | 77 |

| 4.2.4                                                     | Contrôle de flux .....                                  | 78 |

| 4.2.5                                                     | Augmentation de la taille du chemin de données .....    | 78 |

| 4.3                                                       | VÉRIFICATION DU TUNNEL.....                             | 79 |

| 4.4                                                       | CONCLUSION.....                                         | 80 |

| CHAPITRE 5. INTÉGRATION ENTRE HT ET UN SYSTÈME EMBARQUÉ.. |                                                         | 82 |

| 5.1                                                       | OPÉRATIONS SUPPORTÉES PAR LE PONT .....                 | 82 |

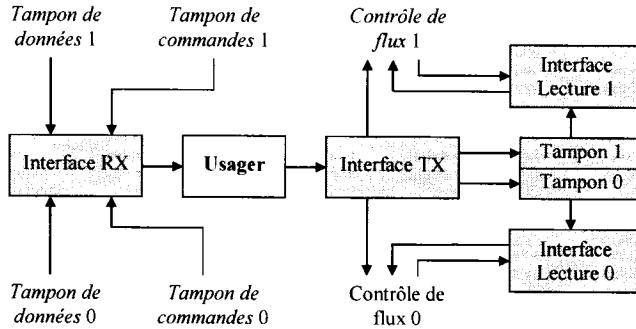

| 5.2                                                       | STRUCTURE DU PONT .....                                 | 84 |

| 5.3                                                       | VÉRIFICATION DU PONT .....                              | 85 |

| 5.4                                                       | HÔTE DE CHAÎNE HT.....                                  | 86 |

| 5.5                                                       | INTÉGRATION DES COMPOSANTS.....                         | 87 |

| 5.5.1                                                     | Démonstration de concept.....                           | 88 |

| 5.5.2                                                     | Résultats.....                                          | 89 |

|                                                                     |    |

|---------------------------------------------------------------------|----|

| 5.6 COMPARAISON DE LA COMPLEXITÉ DES DIVERS ÉLÉMENTS DU SYSTÈME ... | 90 |

| 5.7 CONCLUSION.....                                                 | 92 |

| CONCLUSION .....                                                    | 94 |

| TRAVAUX FUTURS .....                                                | 97 |

| RÉFÉRENCES.....                                                     | 99 |

## Liste des tableaux

|                                                                                                                                  |    |

|----------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 1 - Comparaison des protocoles de communication interpuces PCI-Express,<br>RapidIO série, Hypertransport et SPI 4-2..... | 8  |

| Tableau 2 - Format de la famille de paquet <i>Request</i> .....                                                                  | 12 |

| Tableau 3 - Format de la famille de paquet <i>Response</i> .....                                                                 | 14 |

| Tableau 4 - Règles d'ordonnancement des paquets .....                                                                            | 15 |

| Tableau 5 - Méthodes pour pallier aux différences d'horloges entre deux éléments HT..                                            | 44 |

| Tableau 6 - Données de synthèse du tunnel HT pour diverses technologies.....                                                     | 66 |

| Tableau 7 - Effet des paramètres du tunnel sur les résultats.....                                                                | 71 |

| Tableau 8 - Latence moyenne des communications à l'intérieur de la chaîne HT.....                                                | 89 |

| Tableau 9 - Comparaison de résultats de synthèse des nœuds élémentaires pour les<br>réseaux HT et RoC.....                       | 91 |

## Liste des figures

|                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 - Topologie d'une chaîne HT .....                                                              | 10 |

| Figure 1.2 - Topologies de réseaux embarqués .....                                                        | 18 |

| Figure 1.3 - RoC à 4 ports.....                                                                           | 19 |

| Figure 2.1 - Intégration HT avec des réseaux embarqués (RE).....                                          | 30 |

| Figure 3.1 - Architecture du tunnel HyperTransport .....                                                  | 36 |

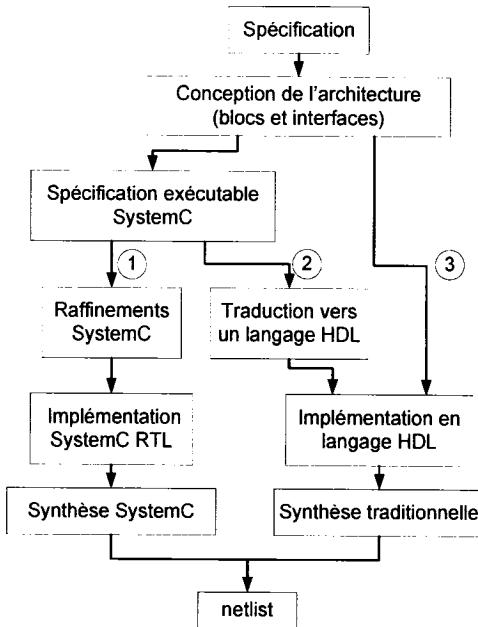

| Figure 3.2 - Divers flots de conception avec SystemC.....                                                 | 38 |

| Figure 3.3 - Domaines d'horloge du tunnel.....                                                            | 43 |

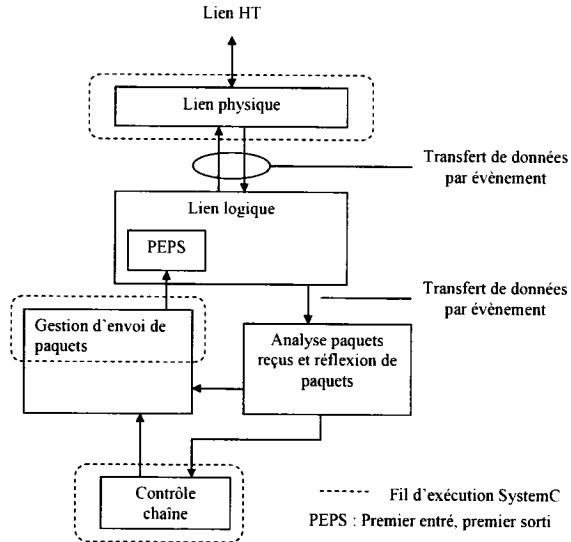

| Figure 3.4 - Schéma bloc du <i>Lien</i> .....                                                             | 46 |

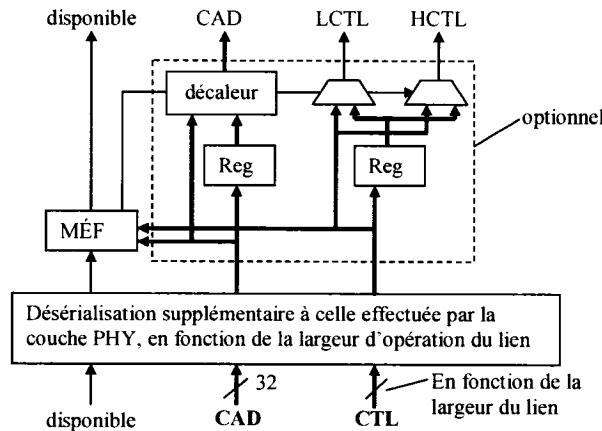

| Figure 3.5 - Schéma bloc du sous-module RX du <i>Lien</i> .....                                           | 47 |

| Figure 3.6 - Schéma bloc du <i>Décodeur</i> .....                                                         | 48 |

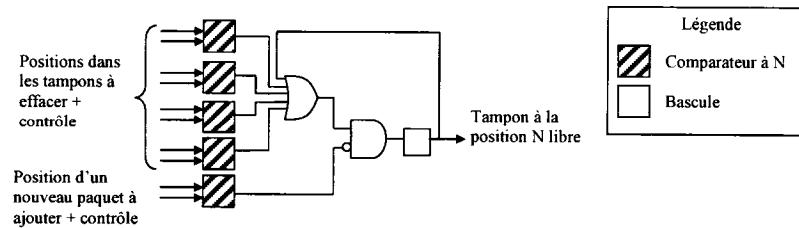

| Figure 3.7 - Bascule pour mémoriser si une position est disponible dans le <i>Tampon de données</i> ..... | 49 |

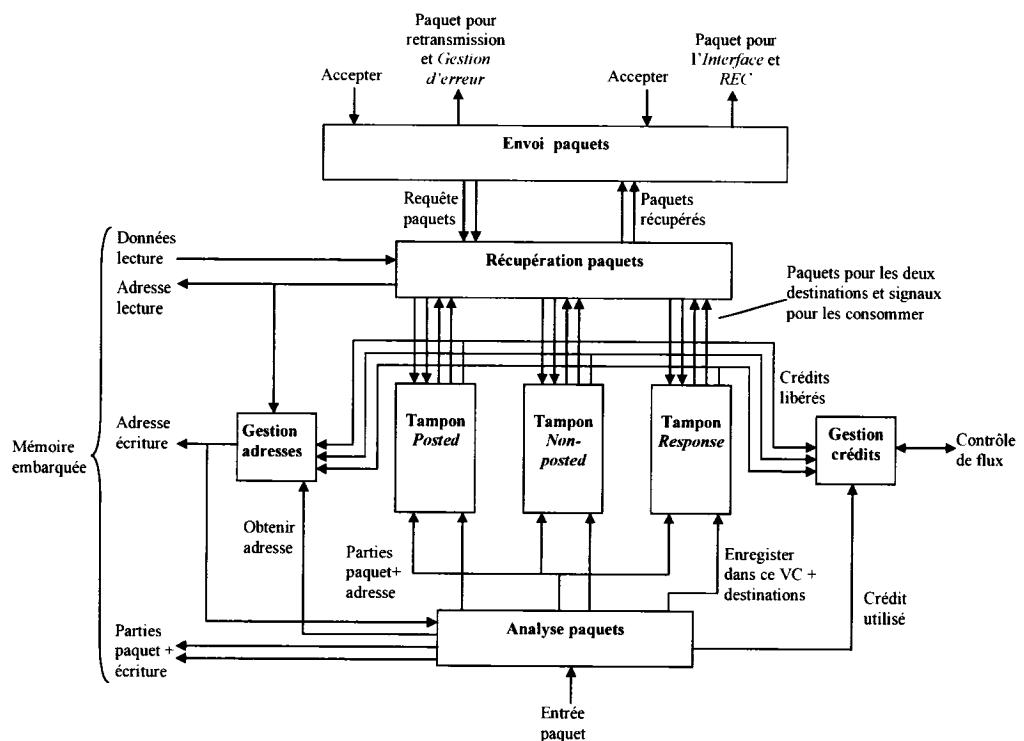

| Figure 3.8 - Schéma bloc du <i>Tampon de données</i> .....                                                | 50 |

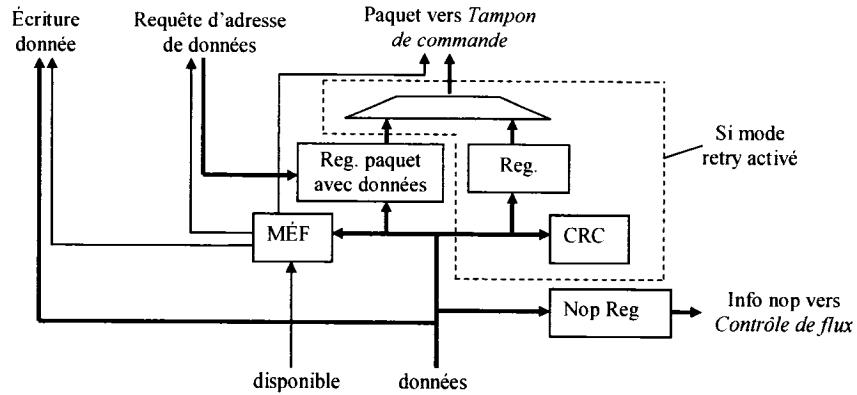

| Figure 3.9 - Schéma bloc du <i>Tampon de commandes</i> .....                                              | 51 |

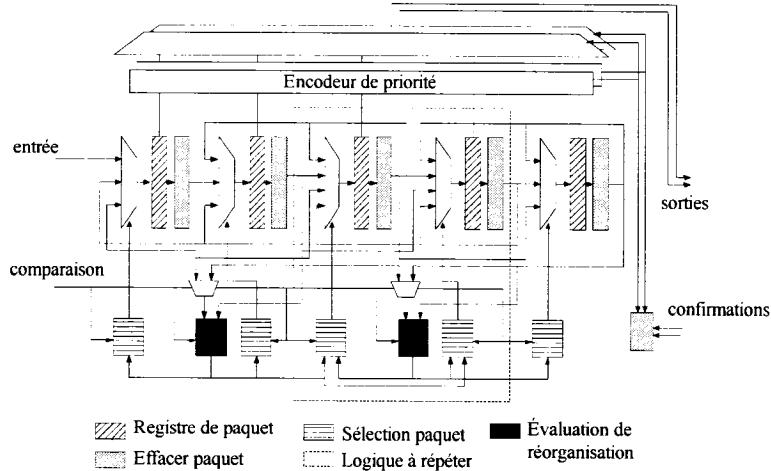

| Figure 3.10 - Circuit de réorganisation des paquets .....                                                 | 54 |

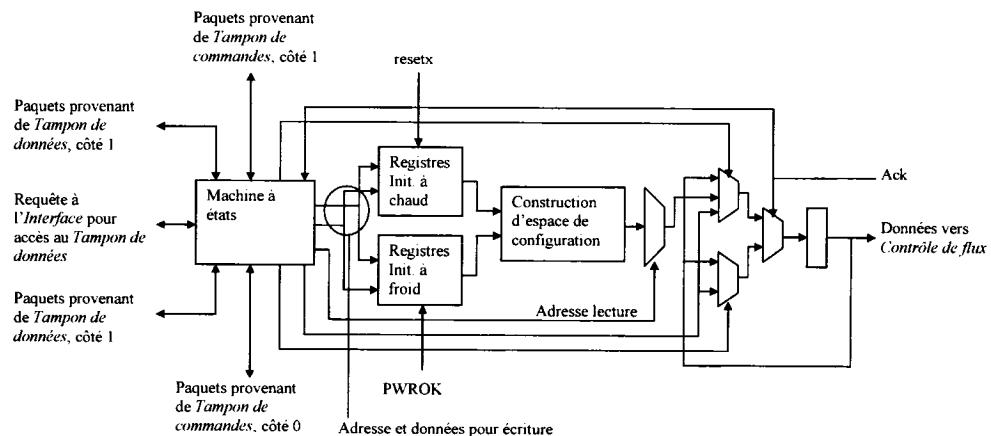

| Figure 3.11 - Schéma bloc des <i>Registres d'espace de configuration (REC)</i> .....                      | 57 |

| Figure 3.12 - Schéma bloc de l' <i>Interface</i> .....                                                    | 59 |

|                                                                                                                                |    |

|--------------------------------------------------------------------------------------------------------------------------------|----|

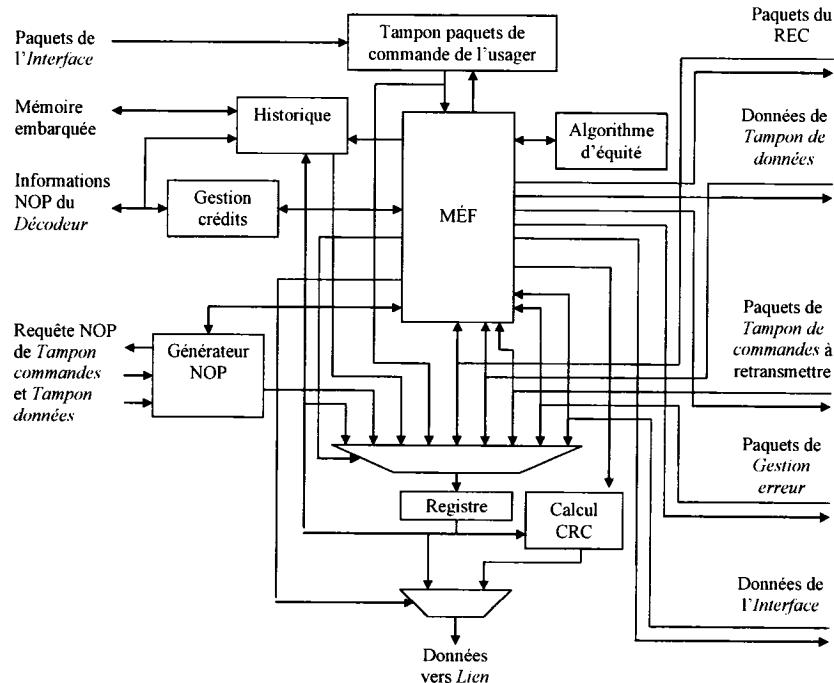

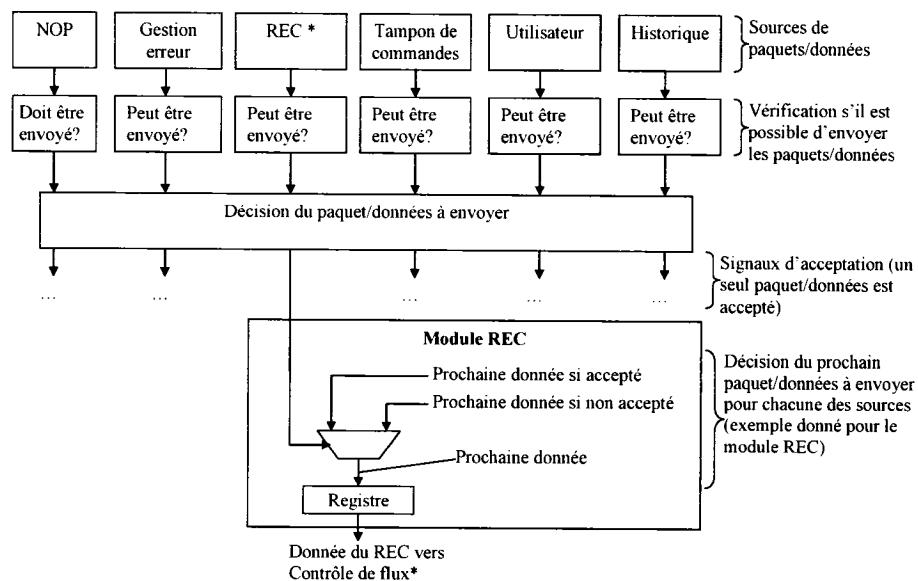

| Figure 3.13 - Schéma bloc du module <i>Contrôle de flux</i> .....                                                              | 60 |

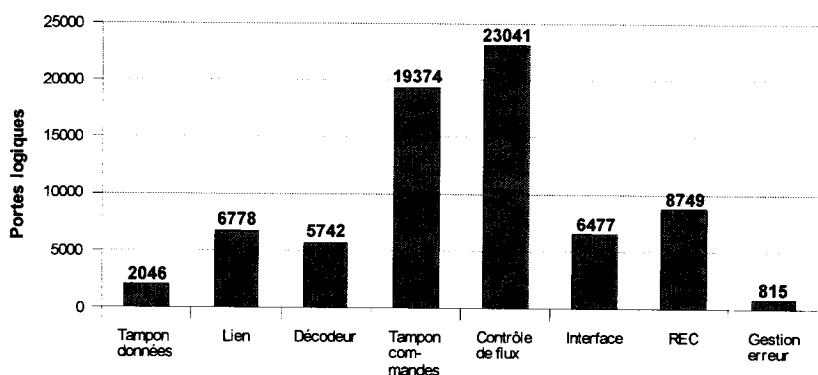

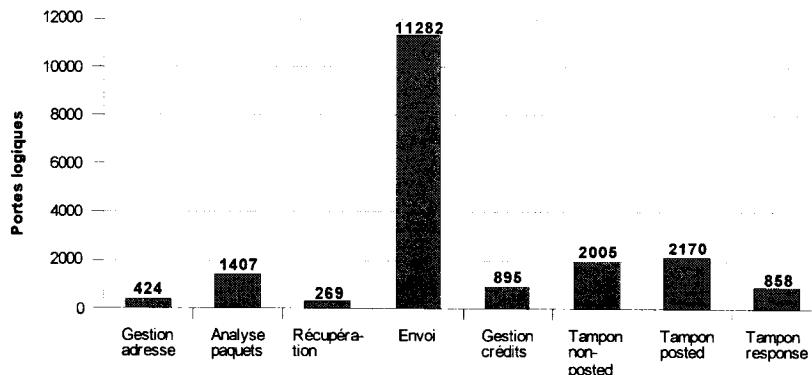

| Figure 4.1 - Répartition de la complexité du tunnel entre les modules .....                                                    | 67 |

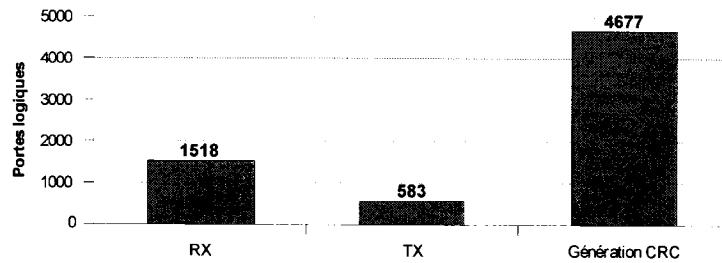

| Figure 4.2 - Répartition de la complexité à l'intérieur du module <i>Lien</i> .....                                            | 68 |

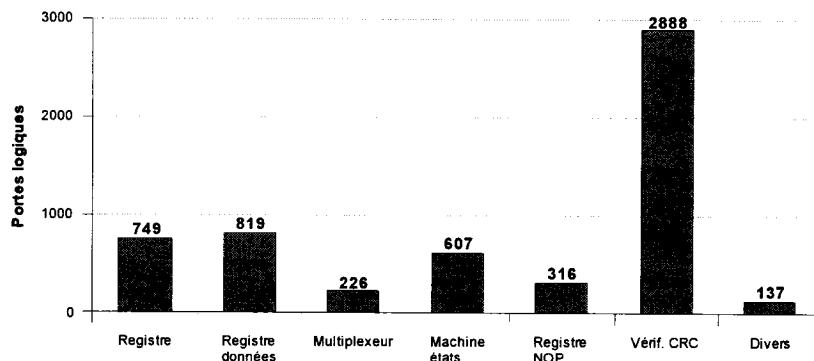

| Figure 4.3 - Répartition de la complexité à l'intérieur du module <i>Décodeur</i> .....                                        | 68 |

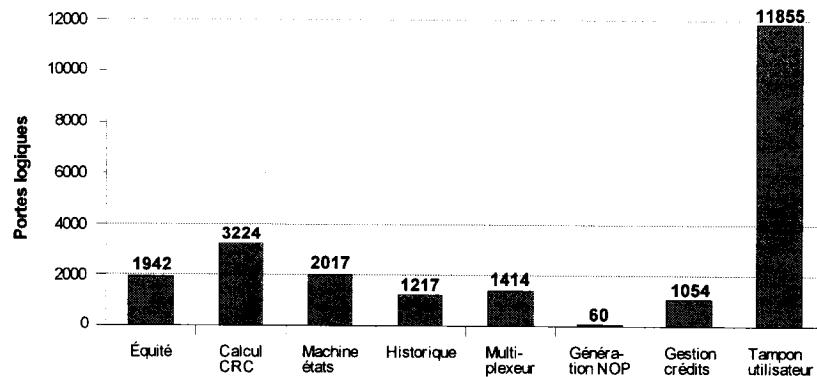

| Figure 4.4 - Répartition de la complexité à l'intérieur du module <i>Tampon de commandes</i> .....                             | 69 |

| Figure 4.5 - Répartition de la complexité à l'intérieur du module <i>Contrôle de flux</i> .....                                | 70 |

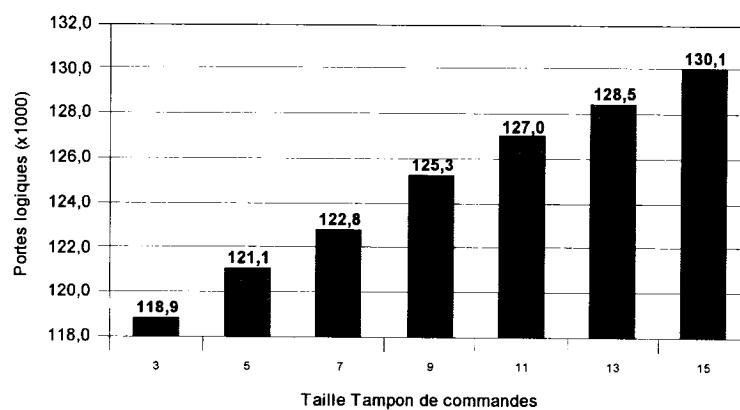

| Figure 4.6 - Complexité du tunnel en fonction de la profondeur des tampons de commandes .....                                  | 72 |

| Figure 4.7 - Complexité du tunnel en fonction de la profondeur des tampons de commandes, sans réorganisation des paquets ..... | 72 |

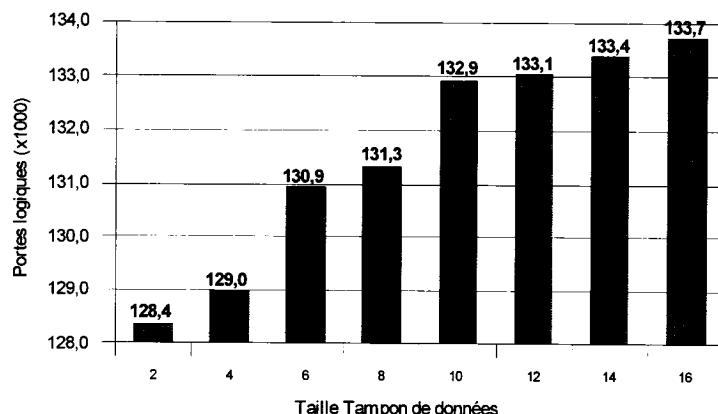

| Figure 4.8 - Complexité du tunnel en fonction de la profondeur des tampons de données .....                                    | 73 |

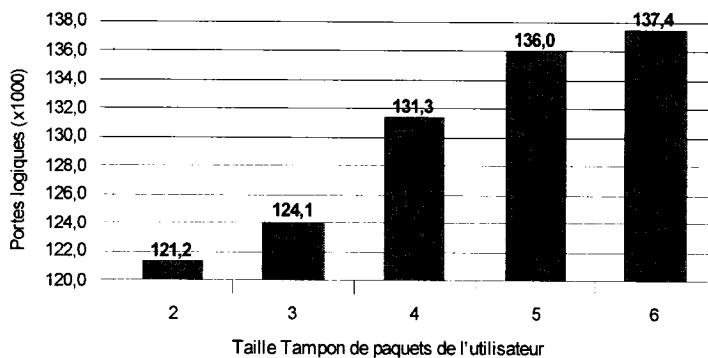

| Figure 4.9 - Complexité du tunnel en fonction de la profondeur des tampons de paquets envoyés par l'utilisateur .....          | 74 |

| Figure 4.10 - Chemin critique du tunnel.....                                                                                   | 75 |

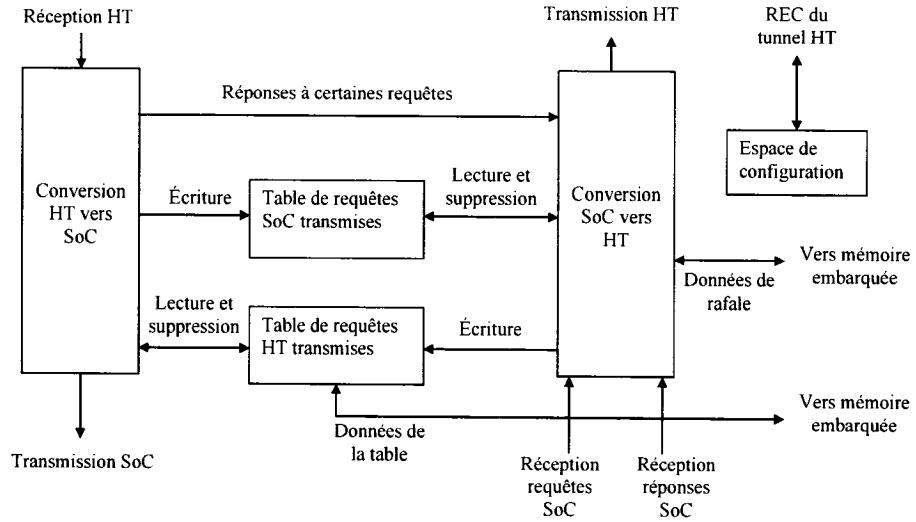

| Figure 5.1 - Schéma bloc du pont HT – Système embarqué .....                                                                   | 85 |

| Figure 5.2 - Architecture de l'hôte HT (haut niveau d'abstraction) .....                                                       | 87 |

| Figure 5.3 - Schéma bloc de l'intégration d'une chaîne HT et de réseaux embarqués RoC .....                                    | 88 |

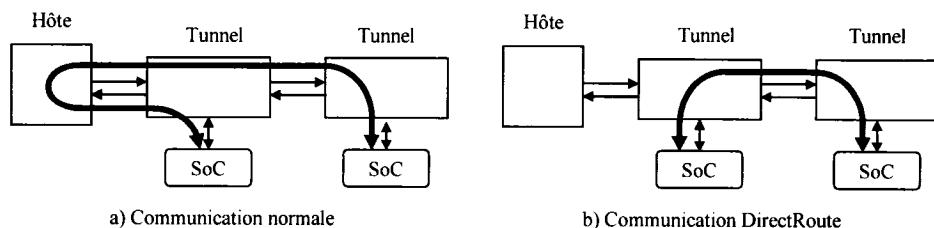

Figure 5.4 - Effet de DirectRoute sur la communication entre deux éléments d'une chaîne HT ..... 89

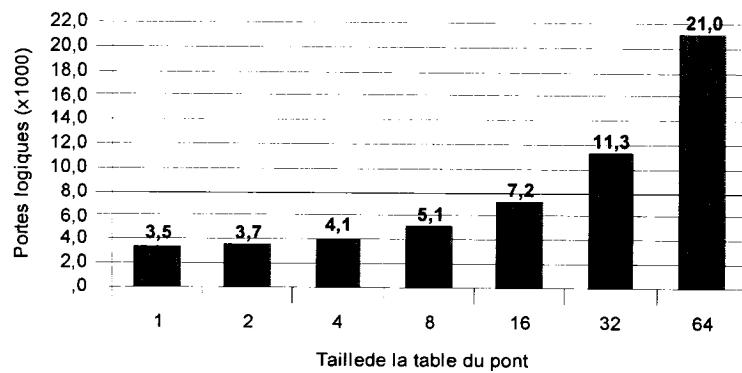

Figure 5.5 - Complexité du pont en fonction de la taille de la table qui enregistre la source d'une lecture HT ..... 90

## Liste des sigles et des abréviations

|      |                                                                            |

|------|----------------------------------------------------------------------------|

| CMOS | Semi-conducteur à oxyde de métal complémentaire                            |

| CRC  | Contrôle par redondance cyclique                                           |

| FIFO | « <i>First In First Out</i> » (Premier entré, premier sorti)               |

| FPGA | Réseau prédiffusé programmable par l'utilisateur                           |

| HT   | HyperTransport                                                             |

| LVDS | Signalisation différentielle à basse tension                               |

| MÉF  | Machine à états finis                                                      |

| MPL  | Licence publique Mozilla                                                   |

| NOP  | Paquet qui n'effectue aucune opération.                                    |

| PCI  | « <i>Peripheral Component Interconnect</i> »                               |

| RE   | Réseau embarqué                                                            |

| REC  | Registres d'espace de configuration (module du tunnel HyperTransport)      |

| RoC  | « <i>Rotator on chip</i> » (type de réseau embarqué)                       |

| RX   | Réception                                                                  |

| SoC  | « <i>System on a chip</i> » (système embarqué sur une puce)                |

| SPI  | « <i>System Packet Interface</i> » (protocole de communication interpuces) |

|      |                                                                             |

|------|-----------------------------------------------------------------------------|

| TSMC | Taiwan Semiconductor Manufacturing Company Ltd.                             |

| TX   | Transmission                                                                |

| VHDL | « <i>Very-High-Speed Integrated Circuit Hardware Description Language</i> » |

## Introduction

La capacité de calcul des systèmes électroniques a vu une augmentation fulgurante au cours de la dernière décennie. Cette augmentation de capacité de calcul est le résultat de l'amélioration des procédés de fabrication, ce qui permet un accroissement de la complexité des circuits intégrés. La technologie a toutefois ses limites et, pour obtenir une performance et un coût adéquats, il est parfois nécessaire de partitionner les fonctionnalités d'un système sur plusieurs composants. Cela permet de faire des circuits plus petits qui ont un taux de rejet plus faible lors de la fabrication, en plus de permettre d'obtenir un système plus extensible en permettant de faire varier le nombre de composants inclus dans le système. Distribuer un calcul sur plusieurs puces nécessite implicitement que les divers composants communiquent entre eux. Le présent mémoire de maîtrise présente une architecture de communication qui permet à de tels composants embarqués sur plusieurs puces de communiquer entre eux de façon efficace.

Il existe présentement plusieurs protocoles de communication interpuces de haute performance dont HyperTransport [16], PCI Express, RapidIO [28] et System Packet Interface (SPI) [25]. HyperTransport (HT) a été retenu comme protocole convenant le mieux au besoin du projet pour des raisons qui seront expliquées plus en détail dans la suite de ce document. HT est un protocole par paquet de grande performance et à faible latence. Des circuits HT commerciaux sont disponibles mais ces derniers sont coûteux et laissent peu de flexibilité pour répondre aux différents besoins d'une grande variété d'applications. Une première étape du projet de recherche fut donc de faire le développement d'un circuit de contrôle HT, une étape qui a occupé une majeure partie du projet à cause de la grande complexité du protocole.

Puisque HT est un protocole de communication par paquet, il faut divers types de composants pour diriger les paquets à l'intérieur d'un système incluant des routeurs. Un

routeur est un composant qui comprend plus de deux ports HT et qui permet de diriger les paquets d'un port à un autre. Puisqu'un routeur est un élément complexe, débuter par faire la conception d'un tunnel était préférable, puisque c'est un élément de base plus simple. Un tunnel HT est similaire à un routeur HT, mais celui-ci ne comporte que deux liens. Il est donc beaucoup plus simple à concevoir qu'un routeur, tout en comportant une série de composants qui pourraient être réutilisés pour faire la conception d'un routeur. Une part importante de ce document porte donc sur les détails de conception de ce circuit ainsi que sur les résultats obtenus qui permettent une analyse approfondie de la complexité d'un tel circuit. Les données détaillées nécessaires à une telle analyse n'étaient jusqu'à maintenant pas disponibles dans la littérature. Afin de rendre le plus disponible possible les résultats de notre recherche, le tunnel a été rendu librement disponible sous la licence MPL (Mozilla Public Licence) [22].

Un aspect intéressant de la conception du tunnel est qu'il a été développé en utilisant exclusivement SystemC [32], à la fois pour la vérification et la synthèse. SystemC est une bibliothèque C++ qui permet de modéliser le comportement d'un circuit à divers niveaux d'abstraction. Cette capacité du C++ de définir la fonctionnalité d'un circuit à haut niveau d'abstraction permet de valider rapidement en simulation le bon fonctionnement de son architecture. Des outils de synthèse de SystemC sont également disponibles et ceux-ci permettent de rapidement prototyper un circuit sans devoir utiliser un langage de synthèse plus traditionnel tel que le VHDL ou le Verilog. L'utilisation d'un tel flot de conception comporte des avantages pour permettre de rendre paramétrable le circuit, mais comporte aussi des désavantages, puisque c'est un flot de conception peu conventionnel.

L'effort de développement nécessaire pour concevoir des circuits numériques intégrés est en constante croissance à cause de leur complexité grandissante. Une solution pour limiter l'ampleur de la tâche de conception est de réutiliser des circuits et de les intégrer dans un système embarqué qui regroupe une multitude de composants. La

réutilisation de circuits permet de faire la conception d'un système avec des ressources de développement limitées.

Tout comme pour un système comprenant plusieurs puces, un système embarqué sur une puce nécessite une architecture de communication permettant à ses divers composants d'échanger de l'information. Si l'on veut créer un système embarqué extensible, le système de communication doit être en mesure de communiquer avec d'autres puces. La méthode proposée dans ce mémoire pour effectuer cette tâche est d'intégrer à un système embarqué la capacité de communiquer par un protocole interpuces de haute performance. HT est par contre un protocole complexe et les composants d'un système embarqué sont souvent conçus pour communiquer avec les autres composants à l'aide de protocoles beaucoup plus simples. Pour que tous les éléments d'un système embarqué puissent profiter de communication interpuces, il faut donc un pont pour effectuer une traduction de la communication entre HT et le système embarqué.

La création d'un pont pour lier un réseau embarqué avec le réseau HT est donc une étape afin de permettre à une multitude de puces contenant des systèmes embarqués de communiquer entre elles. L'intégration grâce à un réseau HT d'un système embarqué comprenant divers éléments ainsi que des ponts pour lier tous ces éléments permet donc d'obtenir une architecture de communication pour système embarqué sur plusieurs puces, dont on peut ensuite vérifier le bon fonctionnement à l'aide de simulations.

## ***Contributions du présent mémoire***

Dans un premier temps, le présent projet donne à la communauté scientifique accès à un tunnel HyperTransport, puisque celui-ci est librement disponible. Ce tunnel pourra être modifié et réutilisé pour des projets nécessitant des liens interpuces performants. Le développement de ce tunnel permet également de recueillir quantité de données sur la conception de contrôleur pour lien interpuces de haute performance. Il permet

d'approfondir les connaissances sur la complexité de tels contrôleurs puisqu'aucune donnée sur le sujet n'est disponible dans la littérature. L'utilisation du langage SystemC pour faire la conception du tunnel permet en plus de faire la mise au point sur l'état des outils de synthèse de SystemC, un langage qui est encore très peu utilisé pour cette tâche.

D'autre part, la partition d'une application embarquée entre plusieurs puces n'est pas un aspect nouveau [33], mais la méthode à utiliser pour effectuer la communication entre plusieurs systèmes embarqués distribués sur plusieurs puces l'est. Des systèmes embarqués peuvent souvent inclure des liens de communication interpuces mais la solution présentée est innovatrice du fait qu'elle s'intègre de façon entièrement transparente au système de façon à ce qu'une communication intra puce s'effectue de façon identique à une communication hors puce.

## ***Plan du mémoire***

Le mémoire débute par faire une revue de littérature pour bien établir le contexte présent du sujet de recherche. On y retrouve une discussion sur une variété de thèmes abordés par le projet, de la communication interpuces jusqu'aux systèmes embarqués, en passant par les méthodes de conception en utilisant SystemC.

Le chapitre 2 continue en présentant l'architecture d'un système de calcul distribué sur plusieurs puces, la raison pour laquelle le projet a pris forme. On y fait le choix d'un protocole de communication interpuces et on y présente comment celui-ci peut interagir avec des systèmes embarqués.

Le chapitre 3 aborde pour sa part les détails techniques de la conception du tunnel HT. On débute en présentant la licence qui couvre le tunnel HT. On voit ensuite un survol de l'architecture, la méthode de conception qui a été utilisée et les éléments paramétrables du tunnel. Le chapitre se termine avec une présentation détaillée de

l'architecture du tunnel. La présentation du tunnel se poursuit ensuite au chapitre 4 où les résultats de synthèse du tunnel sont présentés.

Le chapitre 5 décrit l'intégration du tunnel avec un système embarqué à l'aide du pont. On y présente donc le pont, utilisé pour lier HT et le tunnel, ainsi qu'un hôte HT qui permet de contrôler la chaîne de communication HT.

# Chapitre 1. Revue de littérature

Le développement de systèmes de communication est un aspect extrêmement important pour une multitude d'applications et il est possible de trouver dans la littérature une variété d'informations dans ce domaine. Dans le cadre de ce projet, quatre grands sujets attirent notre attention : les technologies de communication interpuces, HyperTransport plus spécifiquement, les méthodes de développement de circuits en utilisant le langage SystemC et finalement les réseaux embarqués et la façon dont ils peuvent s'intégrer à un tissu de communication interpuces.

## 1.1 *Communication interpuces*

Une première étape pour permettre de bien comprendre le domaine de la communication interpuces est de connaître les différents grands joueurs de ce domaine. HyperTransport, RapidIO, PCI-Express et System Packet Interface (SPI) sont quatre protocoles dominants présentement. Toutes les spécifications de ces protocoles ont été créées par des regroupements de sociétés : le consortium HyperTransport pour HyperTransport, RapidIO Trade Association pour RapidIO, PCI-SIG pour PCI-Express et Optical Internetworking Forum pour SPI. Il peut également être pertinent de mentionner la technologie FlexIOTM de Rambus pour laquelle peu d'information est librement disponible, ainsi que Cray qui utilise dans ses superordinateurs une combinaison de HyperTransport et de protocoles propriétaires pour permettre à des milliers de processeurs de communiquer entre eux à l'intérieur d'une matrice de communication tridimensionnelle [5].

Tous ces protocoles utilisent des liens électriques différentiels qui comportent deux fils sur lesquels on envoie une tension différentielle. Ce mode de transmission permet une plus grande immunité au bruit que l'utilisation d'un fil unique et permet donc d'utiliser des tensions plus basses et d'atteindre des fréquences de transmission plus

élevées. Un aspect également très important de ces protocoles est qu'ils utilisent tous deux groupes indépendants de signaux pour la transmission et la réception d'information, permettant donc d'envoyer et de recevoir de l'information de façon simultanée. Les spécifications électriques de ces liens varient par contre d'un protocole à un autre. PCI Express et RapidIO utilisent tous deux des liens sériels utilisant un encodage qui intègre l'horloge et les données dans un même flot de données tandis que HyperTransport et SPI utilisent des liens parallèles avec des signaux de contrôle et d'horloge indépendants des signaux de transfert de données. L'utilisation d'un lien serial occasionne un surdébit par rapport à l'utilisation d'un lien parallèle, mais elle permet d'utiliser des lignes de transmission plus longues. Un aspect extrêmement important de tous ces protocoles est qu'ils effectuent tous du contrôle de flux de façon matérielle. Le contrôle de flux est nécessaire afin de s'assurer que la destination d'un paquet est en mesure de le recevoir et de le traiter sans perte de données.

Du côté des fonctionnalités, HyperTransport, RapidIO et PCI Express sont tous relativement similaires. Ces trois protocoles définissent des paquets et effectuent de la détection et de la correction d'erreurs si désiré. Un paquet consiste en un en-tête qui contient la destination du paquet ainsi que d'autres informations de contrôle suivie de données. Un paquet peut donc être acheminé à l'intérieur d'un réseau de puces jusqu'à une destination bien précise. Pour tous ces protocoles, les paquets peuvent passer à l'intérieur de canaux virtuels indépendants, évitant ainsi que certains types de paquets empêchent d'autres types de paquets de passer, ce qui permet d'éviter des interblocages ou d'améliorer la performance pour acheminer des paquets prioritaires. Par contre, HyperTransport et PCI Express utilisent un système de mémoire partagée afin de diriger les paquets à l'intérieur d'un système tandis que RapidIO définit une couche de transport qui fait complètement abstraction du contenu du paquet. De son côté, SPI est un protocole plus simple qui permet d'envoyer des données à une destination précise, sans définir des types de paquets spécifiques. SPI est bien adapté pour transmettre un flux de

données vers des destinations, puisqu'il ne comprend qu'un canal de transmission pour chaque destination. Une comparaison détaillée de ces protocoles est effectuée par [6] et est reprise au tableau 1 avec l'ajout du protocole SPI-4.2.

**Tableau 1 - Comparaison des protocoles de communication interpuces PCI-Express, RapidIO sériel, Hypertransport et SPI 4-2**

|                  | PCI Express                                                                                                                                                                                                                                                                                                                                                                                                                                          | RapidIO Sériel                                                                                                                                                                                                                                                                                                                                                                                                                            | HyperTransport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SPI-4.2                                                                                                                                                                                                                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Couche physique  | <ul style="list-style-type: none"> <li>Lien LVDS série (2.5 GHz)</li> <li>1, 2, 4, 8, 16 ou 32 liens</li> <li>Compensation et récupération d'horloge</li> <li>Séparation en couloirs et correction d'alignement</li> <li>Codage 8/10b</li> <li>Verrouillage de trame : Code de début/fin et codes de commande</li> <li>Brouillage pour réduire les émissions électromagnétiques</li> </ul>                                                           | <ul style="list-style-type: none"> <li>Lien LVDS série (1.25, 2.5 ou 3.125 GHz)</li> <li>1 ou 4 liens</li> <li>Compensation et récupération d'horloge</li> <li>Séparation en couloirs et correction d'alignement</li> <li>Codage 8/10b</li> <li>Verrouillage de trame : Code de début et codes de commande</li> </ul>                                                                                                                     | <ul style="list-style-type: none"> <li>Lien LVDS parallèle (0.4 – 2.4 GHz)</li> <li>2 – 32 données, 1 contrôle, 1-4 horloge</li> <li>Compensation d'horloge</li> <li>Séparation en couloirs et correction d'alignement</li> <li>Pas de codage</li> <li>Pas de verrouillage de trame</li> </ul>                                                                                                                                                                                                                                                         | <ul style="list-style-type: none"> <li>Lien LVDS parallèle (0.311 GHz et plus)</li> <li>16 données, 1 contrôle, 1 horloge et 2 données et 1 horloge pour statut de contrôle de flux</li> <li>Compensation d'horloge</li> <li>Pas de couloir</li> <li>Pas de codage</li> <li>Pas de verrouillage de trame</li> </ul> |

| Couche de lien   | <ul style="list-style-type: none"> <li>Protection de CRC 16 bits par paquet de lien et CRC de 32 bits pour la communication bout à bout</li> <li>Protocole Ack/Nack pour chaque lien</li> <li>Classification de type de paquet et assemblage</li> <li>Paquets de lien de données de 6 octets</li> </ul>                                                                                                                                              | <ul style="list-style-type: none"> <li>Protection de CRC 16 bits par paquet de lien et CRC de 5 bits pour les codes de contrôle</li> <li>Protocole Ack/Nack pour chaque lien</li> <li>Classification de type de paquet et assemblage</li> <li>Paquets de lien de données de 3 octets</li> </ul>                                                                                                                                           | <ul style="list-style-type: none"> <li>Protection de CRC 32 bits pour chaque tranche de 512 octets transmis (détection erreur) et protection 32 bits par paquet optionnelle</li> <li>Protocole Ack/retry optionnel</li> <li>Classification de type de paquet (pas d'assemblage : la taille des paquets est connue)</li> <li>Pas de paquet de lien</li> </ul>                                                                                                                                                                                           | <ul style="list-style-type: none"> <li>Protection par parité diagonale entrelacée de 4 bits pour les données et 2 bits pour le contrôle de flux</li> <li>Pas de correction d'erreur</li> <li>Pas de classification puisqu'il n'y a pas de type de paquet, assemblage</li> <li>Pas de paquet de lien</li> </ul>      |

| Couche transport | <ul style="list-style-type: none"> <li>Trois types de trafic : posted, non-posted et completion, avec des canaux individuels</li> <li>8 priorités de trafic à l'aide de canaux virtuels</li> <li>Transferts de données jusqu'à 4096 octets, en-tête typique de 12 à 16 octets</li> <li>Contrôle de flux par crédit. Les crédits sont gérés par type de trafic.</li> <li>Jusqu'à 32 transactions en cours</li> <li>Espace de configuration</li> </ul> | <ul style="list-style-type: none"> <li>Pas de canal individuel par type de trafic</li> <li>4 priorités de trafic avec des canaux indépendants</li> <li>Transferts de données jusqu'à 256 octets. En-tête typique de 6 octets</li> <li>Contrôle de flux au niveau de la couche physique par essais successifs ou par crédit</li> <li>Jusqu'à 256 transactions en cours, dont 32 non confirmées</li> <li>Espace de configuration</li> </ul> | <ul style="list-style-type: none"> <li>Trois types de trafic : posted, non-posted et response, avec des canaux individuels</li> <li>Possibilité de relaxer les règles de réorganisation et un deuxième niveau de priorité optionnel (isoc)</li> <li>Transferts de données jusqu'à 64 octets, en-tête typique de 4 à 8 octets</li> <li>Contrôle de flux par crédit. Les crédits sont gérés par type de trafic.</li> <li>Jusqu'à 32 transactions en cours par UnitID : un noeud peut avoir plus d'un UnitID.</li> <li>Espace de configuration</li> </ul> | <ul style="list-style-type: none"> <li>Pas de priorité de trafic</li> <li>Transfert de données maximal déterminé par l'application, en-tête de 2 octets</li> <li>Contrôle de flux par combinaison d'échange de statut de tampons et de crédits</li> </ul>                                                           |

HyperTransport est le bus de communication utilisé par les processeurs les plus récents de la société AMD, ce qui veut dire qu'il se retrouve dans une grande quantité d'ordinateurs et occupe donc une bonne part du marché. HT est également utilisé sur les cartes mères pour permettre aux différentes puces d'un jeu de puces de communiquer entre elles. Il est également utilisé par des processeurs réseaux. Jusqu'à tout dernièrement, HT ne pouvait pas servir pour la mise en œuvre de fond de panier (*backplane* : ensemble de connecteurs permettant l'ajout de cartes amovibles) puisqu'aucun connecteur HT n'était défini, mais cela vient tout récemment de changer avec l'introduction de la norme HTX [17]. HTX utilise le même connecteur physique que PCI Express, mais orienté différemment afin d'éviter de placer une carte PCI Express dans ce connecteur. RapidIO de son côté a été fortement adopté par les processeurs de traitement de signal en plus de servir également pour des processeurs de réseau par Motorola, l'entreprise qui en est l'instigatrice. PCI Express est un joueur beaucoup plus récent mais qui a su prendre de l'ampleur très rapidement puisque ce protocole est devenu la norme pour les cartes vidéo d'ordinateurs personnels. Son succès est lié au fait qu'il est supporté par Intel qui est un joueur de taille dans l'industrie des ordinateurs personnels. De son côté, SPI est utilisé dans les commutateurs réseaux de grande performance.

Pour ce qui est de faire la conception de circuits pour utiliser ces divers protocoles, aucune information n'est facilement disponible à ce sujet. Il existe toutefois des circuits que l'on peut acheter, pour utilisation à l'intérieur d'un FPGA, qui fournissent des spécifications expliquant les grandes lignes de leur architecture et la quantité de ressources qu'ils requièrent. Ces spécifications ne donnent par contre pas de détails au sujet de la distribution de la complexité. Il y a donc un intérêt de déterminer d'où vient la complexité des circuits utilisés pour ces protocoles.

## 1.2 HyperTransport

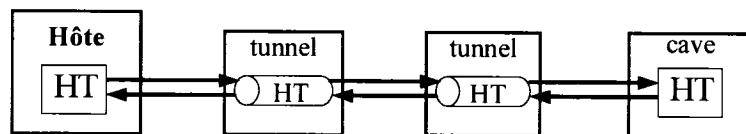

Suite à une analyse qui sera élaborée avec plus de détails au cours de ce document, la technologie de communication interpuces HyperTransport [16] a été retenue pour effectuer la communication interpuces au sein de notre système. HT est un protocole de communication interpuces qui permet à une grande variété de composants électroniques d'échanger de l'information de façon performante. La topologie de base d'un réseau HT est une chaîne de composants qui sont reliés par des connexions point à point, tel qu'il est démontré à la figure 1.1. Une chaîne comporte toujours un hôte, un élément de fin de chaîne nommé « Cave » et un nombre variable de tunnels qui comportent chacun deux liens de communication HT. Une topologie en étoile peut également être utilisée grâce à l'utilisation de commutateurs HT.

Figure 1.1 - Topologie d'une chaîne HT

### 1.2.1 Lien physique et initialisation

Le lien électrique de HyperTransport comprend plusieurs lignes permettant de transmettre des données, un signal horloge et un signal de contrôle, et cela pour la transmission et la réception de données. Chaque ligne est un lien différentiel LVDS offrant une grande résistance au bruit électromagnétique tout en ayant une faible consommation énergétique. Le nombre de lignes de données peut varier de 2 à 32 en fonction de la bande passante requise, et cela pour la transmission et la réception. Les données sont transmises aux deux fronts du signal d'horloge. Le récepteur doit se baser sur le signal d'horloge reçu afin de faire la lecture des données.

Les signaux sont regroupés en couloir qui sont composés d'un maximum de 8 signaux de données, un signal de contrôle et un signal d'horloge. Toutes les lignes d'un

couloir doivent avoir la même longueur, afin que les signaux électriques prennent le même temps à atteindre la destination et demeurent ainsi le plus possible en phase. La séparation des signaux en couloirs facilite la conception de circuits imprimés puisqu'il n'est pas nécessaire que toutes les lignes du lien aient la même longueur.

Chaque couloir doit être initialisé individuellement à l'aide d'une séquence d'initialisation. Cette séquence permet de s'assurer qu'à la fois le récepteur et le transmetteur sont prêts à débuter la communication et sert également à indiquer à quel moment les paquets commencent à être transmis.

### 1.2.2 Format des paquets

L'information transmise par HT transite par divers types de messages qui incluent des écritures, des lectures et des réponses. Un système d'adressage de 40 bits ou de 64 bits, au choix du concepteur, est utilisé pour acheminer les paquets à leur destination. HT est un protocole de type stockage et retransmission : chaque nœud HT contient trois groupes indépendants de tampons qui permettent d'accumuler divers types de paquets :

- *Posted* – requête qui ne requiert pas de réponse, telle qu'une écriture.

- *Non-Posted* – requête qui requiert une réponse, telle qu'une lecture.

- *Response* – réponse à une requête, telle qu'une réponse à une lecture.

L'en-tête qui contient toutes les informations sur le type de paquet se nomme un paquet de commande, tandis que les données associées à l'opération, s'il y en a, se nomment un paquet de données. Il existe quatre grandes familles de paquets : *Info*, *Request*, *Address Extension* et *Response*.

Les paquets de la famille *Info* ont une taille de 4 octets et ne servent qu'à la communication entre deux voisins. Cette catégorie comprend le paquet *NOP* qui est

transmis afin d'échanger de l'information sur l'espace tampon disponible ou lorsqu'aucun autre paquet ne peut être transmis. Il comprend également le paquet *Sync* qui est envoyé lorsqu'une erreur critique est détectée et que la chaîne entière doit être réinitialisée.

Le support pour les paquets de la famille *Address Extension* est optionnel et permet d'ajouter, à certains paquets de requête, 24 bits supplémentaires d'adresse pour obtenir une adresse de 64 bits au lieu de 40 bits.

Les paquets de la famille *Request* ont une taille de 4 ou 8 octets et permettent d'effectuer une requête. Cette famille comprend les paquets de type *Read*, *Write*, *Atomic-RMW*, *Broadcast*, *Flush* et *Fence*. Les paquets de type *Read*, *Write* et *Atomic-RMW* permettent d'accéder et/ou de modifier le contenu d'un espace mémoire spécifique. *Broadcast* permet d'envoyer un message à toute la chaîne de communication HT. *Fence* permet de séparer plusieurs groupes de requêtes, puisque la majorité des requêtes n'ont pas le droit de dépasser ce type de paquet. Finalement, *Flush* permet d'obtenir une réponse lorsque toutes les requêtes de type *posted* envoyées précédemment vers l'hôte ont atteint ce dernier.

**Tableau 2 - Format de la famille de paquet *Request***

| Octet | 7      | 6          | 5          | 4 | 3                | 2           | 1 | 0 |

|-------|--------|------------|------------|---|------------------|-------------|---|---|

| 0     |        | SeqID[3:2] |            |   |                  | Cmd[5:0]    |   |   |

| 1     | PassPW |            | SeqID[1:0] |   |                  | UnitID[4:0] |   |   |

| 2     |        |            |            |   | Spécifique à Cmd |             |   |   |

| 3     |        |            |            |   | Spécifique à Cmd |             |   |   |

| 4     |        |            |            |   | Addr[15:8]       |             |   |   |

| 5     |        |            |            |   | Addr[23:16]      |             |   |   |

| 6     |        |            |            |   | Addr[31:24]      |             |   |   |

| 7     |        |            |            |   | Addr[39:32]      |             |   |   |

Les paquets de la famille *Request* ont tous le format présenté au tableau 2. Le champ *Cmd* détermine le type exact du paquet tandis que les champs spécifiques à *Cmd* ont une fonctionnalité qui varie en fonction du type exact du paquet. *SeqID* détermine si ce paquet fait partie d'une séquence. Des paquets d'une même séquence doivent absolument être traités dans l'ordre dans lequel ils sont transmis. *UnitID* permet de déterminer quel est l'émetteur du paquet afin de permettre à un paquet de réponse de revenir à celui qui a émis la requête. Finalement, le champ *PassPW* détermine si ce paquet a le droit de dépasser les paquets de type *Posted Write*, ce qui permet d'assouplir les règles de maintien de l'ordre des paquets afin d'améliorer les performances du système.

Les paquets qui jouent le rôle d'entête pour des données, tel qu'un paquet *Write* ou *Atomic-RMW*, contiennent tous deux un champ *Count* qui détermine la taille, en nombre de double mot (32 bits), du paquet de données qui suit la requête. Les paquets qui doivent effectuer une opération à une adresse spécifique contiennent le champ *Addr* qui se trouve à être l'adresse ou doit s'effectuer l'opération. C'est le champ *Addr* qui détermine la destination du paquet. Il est important de noter que plusieurs plages d'adresses sont réservées afin de permettre d'envoyer des paquets spécifiquement à un élément de la chaîne sans devoir nécessairement connaître la plage mémoire utilisée par cet élément (*Device Messaging*), d'envoyer des interruptions et de supporter plusieurs autres fonctionnalités. Les paquets pour lesquels une réponse doit être générée lorsqu'arrivés à destination contiennent également un champ *SrcTag* qui est un identificateur unique permettant d'associer la réponse à la bonne requête.

Les paquets de la famille *Response* sont générés en réponse à une requête et ont toujours une taille de 4 octets. Cela peut être le résultat de l'opération *Read* et *Atomic-RMW*, ou pour avertir qu'une opération tel qu'un *Write* ou *Flush* est complétée avec succès.

**Tableau 3 - Format de la famille de paquet *Response***

| <b>Octet</b> | <b>7</b>         | <b>6</b> | <b>5</b> | <b>4</b>               | <b>3</b>    | <b>2</b>         | <b>1</b> | <b>0</b> |  |

|--------------|------------------|----------|----------|------------------------|-------------|------------------|----------|----------|--|

| 0            | Spécifique à Cmd |          |          |                        | Cmd[5:0]    |                  |          |          |  |

| 1            | Spécifique à Cmd |          | Rsv      |                        | UnitID[4:0] |                  |          |          |  |

| 2            | PassPW           | Bridge   | Error0   |                        | SrcTag[4:0] |                  |          |          |  |

| 3            | Rsv/RqUID        |          | Error1   | Fonctionnalité avancée |             | Spécifique à Cmd |          |          |  |

Les paquets de la famille *Response* ont tous le format présenté au tableau 3. Le champ *Cmd* détermine le type exact du paquet tandis que les champs spécifiques à *Cmd* ont une fonctionnalité qui varie en fonction du type exact du paquet. Les champs *UnitID* et *RqUID* permettent de déterminer la destination du paquet de réponse tandis que le champ *SrcTag* permet d'identifier à quelle requête est associée la réponse. Les bits *Error0* et *Error1* permettent d'identifier si des erreurs sont survenues lors du traitement de la requête et les bits *Rsv* sont réservés pour un usage futur.

### 1.2.3 Ordonnancement des paquets

Puisque HyperTransport comporte trois canaux virtuels indépendants et afin d'optimiser la performance du réseau, il est possible que certains paquets dépassent d'autres paquets lorsqu'un canal virtuel est bloqué. Afin de bien comprendre les règles régissant la réorganisation des paquets, il faut savoir que deux paquets sont considérés dans le même flot lorsqu'ils sont dans la direction *downstream* ou qu'ils sont dans la direction *upstream* et qu'ils ont la même source (le même *UnitID*). Un paquet *upstream* se dirige vers l'hôte et un paquet *downstream* s'éloigne de l'hôte. Voici les règles d'ordonnancement de HyperTransport :

1. Les paquets étant dans des flots différents peuvent être réorganisés librement.

2. Les paquets étant dans le même flot et ayant une valeur identique et non zéro du champ SeqID ne peuvent pas être réorganisés : ils font partie d'une séquence ordonnée.

3. Les paquets étant dans le même flot et ne faisant pas partie d'une séquence doivent suivre les règles du tableau 4.

Tableau 4 - Règles d'ordonnancement des paquets

| Ligne peut passer colonne?       | Requête <i>Posted</i> |         | Requête<br><i>Nonposted</i> | Response |         |

|----------------------------------|-----------------------|---------|-----------------------------|----------|---------|

|                                  | PPW=0                 | PPW =1  |                             | PPW =0   | PPW =1  |

| Requête <i>Posted</i> , PPW=0    | Non                   | Non     | Oui                         | Oui      | Oui     |

| Requête <i>Posted</i> , PPW=1    | Oui/Non               | Non     | Oui                         | Oui      | Oui     |

| Requête <i>Nonposted</i> , PPW=0 | Non                   | Non     | Oui/Non                     | Oui/Non  | Oui/Non |

| Requête <i>Nonposted</i> , PPW=1 | Oui/Non               | Oui/Non | Oui/Non                     | Oui/Non  | Oui/Non |

| <i>Response</i> , PPW=0          | Non                   | Non     | Oui                         | Non      | Non     |

| <i>Response</i> , PPW=1          | Oui/Non               | Oui/Non | Oui                         | Oui/Non  | Non     |

**Non** – La transaction ne peut pas être complétée avant celle qui la précède.

**Oui** – La transaction doit pouvoir passer en avant de celle qui la précède si cette dernière ne peut pas être complétée (par exemple à cause d'un canal virtuel bloqué).

**Oui/Non** – Il n'y a pas de dépendance entre les deux transactions, mais la réorganisation des paquets n'est pas nécessaire. Une implémentation peut décider d'effectuer la réorganisation si elle y voit un avantage.

**PPW** – Champ *PassPW* du paquet

#### 1.2.4 Contrôle de flux

Un paquet de données a une taille variant de 4 à 64 octets et est toujours associé à un paquet de commande, puisque ce dernier contient toute l'information sur la destination et le rôle de ces données. Le paquet de type *NOP* permet d'effectuer du contrôle de

flux puisqu'il contient des champs permettant d'échanger de l'information sur l'espace disponible dans les tampons.

Afin d'éviter le dépassement de capacité lors de la réception de paquets, HT utilise un système de crédits. Lorsqu'un espace tampon devient disponible afin de recevoir un certain type de paquet, un crédit est alloué et envoyé au nœud HT voisin. La fonctionnalité de base de HT prévoit deux types de crédits pour chaque grande catégorie de paquets : un pour les paquets de commandes et un autre pour les paquets de données. Avant d'envoyer un paquet, un émetteur doit avoir un crédit pour le type de paquet à envoyer. Dans le cas d'un paquet qui joue le rôle d'en-tête de données, il est nécessaire d'avoir à la fois un crédit pour le paquet et un autre pour le paquet de données qui suivra.

### 1.2.5 Vérification d'erreurs

HyperTransport prévoit deux types de vérification d'erreurs. Le premier type est une vérification de l'intégrité du lien entre deux voisins. Chaque couloir HT doit insérer périodiquement un code CRC calculé à partir des données transmises. Le récepteur effectue le même calcul de CRC sur les données reçues et le compare au code CRC reçu. Si le code CRC calculé diffère du code reçu, cela veut dire qu'au moins une erreur est survenue à l'intérieur de la fenêtre de calcul de ce code CRC. Puisqu'il n'est pas possible de corriger l'erreur, la façon dont la détection de telles erreurs est traitée est spécifique à chaque application.

Le deuxième type de vérification d'erreur se nomme le mode *retry*. Celui-ci est optionnel et permet d'assurer l'intégrité de tous les transferts de paquets. Un code CRC est inséré à la suite de chaque paquet, et chaque paquet transmis est enregistré temporairement dans une mémoire. Si le code CRC calculé à la réception n'est pas identique à celui reçu, le lien de communication est réinitialisé et le paquet est retransmis. Si aucune erreur n'est détectée, le paquet peut être retiré de la mémoire du transmetteur.

### 1.2.6 Configuration des fonctionnalités

Chaque élément HT comprend un espace de registres de configuration. Certains registres sont en lecture seule et permettent d'afficher les options supportées par le tunnel tandis que d'autres sont également accessibles en écriture et permettent de configurer les fonctionnalités du noeud HT. Par exemple, tous les éléments HT ont un registre qui permet de leur donner un numéro *UnitID* unique qui permet de les identifier dans la chaîne. Une plage mémoire est réservée pour l'accès à l'intérieur de cet espace de configuration. Chaque élément est responsable de détecter si un paquet reçu s'adresse à son espace de configuration et si oui, de traiter la requête adéquatement.

## 1.3 Systèmes et réseaux embarqués

L'amélioration des procédés de fabrication de circuits intégrés permet d'intégrer sur une même puce de plus en plus de fonctionnalités. Cette augmentation constante du niveau d'intégration a par contre l'effet d'augmenter de façon significative l'effort de développement nécessaire. Pour réduire cet effort de développement, l'industrie se penche de plus en plus sur la réutilisation de composants qui peuvent être intégrés dans ce que l'on appelle un système embarqué.

De façon traditionnelle, les composants d'un système embarqué communiquent entre eux à l'aide d'un bus. Un bus a l'avantage d'utiliser peu de ressources, mais un seul composant à la fois peut utiliser le bus pour envoyer ou recevoir de l'information. Cette méthode peut donc causer un goulot d'étranglement lorsque plusieurs composants veulent communiquer simultanément. Une méthode alternative est d'utiliser un réseau embarqué qui permet d'échanger des paquets entre les composants. Cela a l'avantage d'éliminer le goulot d'étranglement qu'est traditionnellement le bus et donc d'intégrer une plus grande quantité de composants, mais à un coût également plus élevé puisqu'il faut des éléments pour diriger les paquets jusqu'à la bonne destination.

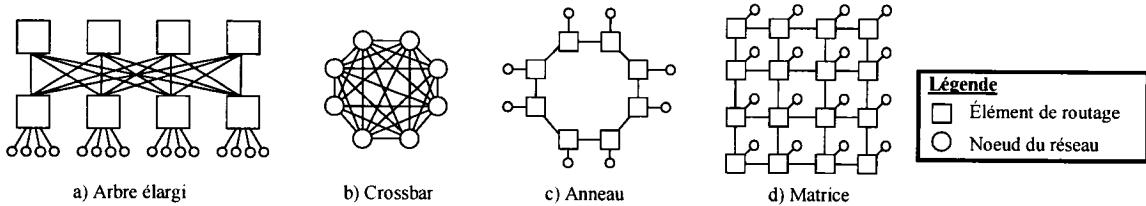

Il existe une grande variété de topologies de réseaux embarqués. On y retrouve des réseaux en anneaux où tous les éléments d'un réseau sont placés les uns à la suite des autres, tel qu'il est proposé pour un réseau compatible à HyperTransport [30]. Les réseaux en anneaux sont très simples et ne demandent pas un grand nombre de ressources, mais ceux-ci sont peu extensibles puisque la latence à l'intérieur d'un tel réseau est proportionnelle à sa taille. Un *crossbar* tel qu'il est utilisé par le réseau *STbus crossbar* [29] permet à chaque élément de communiquer directement avec chaque autre élément du réseau. Un *crossbar* est une topologie parmi les plus performantes, puisqu'elle contient un lien direct entre chaque noeud du réseau. Cette performance vient par contre au coût d'une très grande complexité.

Certains groupes de recherche travaillent plutôt sur des réseaux en arbres où les paquets passent par des concentrateurs pour être redirigés vers la bonne destination, tels que le *Butterfly Fat Tree* [3] et le réseau *SPIN* [26]. Une matrice de noeuds est également une topologie explorée par le réseau embarqué *Eclipse* [20]. Ces deux derniers types de réseaux effectuent un compromis entre performance et complexité, puisqu'ils sont beaucoup plus efficaces que les anneaux, mais également beaucoup moins complexes qu'un *crossbar*.

**Figure 1.2 - Topologies de réseaux embarqués**

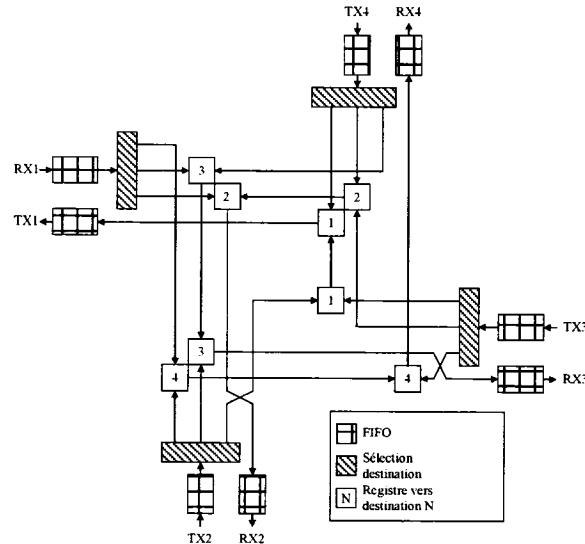

Le réseau RoC [11] est un réseau embarqué développé à l'École Polytechnique en collaboration avec la société STMicroelectronics. Celui-ci combine une topologie à anneau avec la technique crossbar : chaque élément du réseau a un anneau dédié pour recevoir des paquets. La figure 1.3 montre un RoC de 4 ports. Afin d'absorber les

variations de débits des paquets dans le réseau, le RoC utilise des mémoires tampons de type premier entré, premier sorti (FIFO) lors de la transmission et de la réception de paquets. Chaque paquet transmis dans un RoC contient un champ de destination ainsi qu'un champ de données. Pour envoyer un paquet vers une destination donnée, il suffit de l'insérer dans le FIFO de transmission et le paquet sera dirigé vers le bon registre de destination par le bloc de sélection de destination. Au cours de plusieurs cycles d'horloge, les paquets sont dirigés vers la destination voulue. Bien que la figure 1.3 ne montre qu'un RoC de 4 éléments, la taille de ce réseau embarqué peut s'adapter aux besoins des applications.

**Figure 1.3 - RoC à 4 ports**

Un désavantage des bus et des réseaux embarqués est qu'ils ne fournissent pas de garantie de performance, on les appelle des réseaux « *service au mieux* ». Si le bus du réseau est déjà fortement sollicité, il est possible que la performance de la communication soit très basse. Cela peut causer de graves problèmes dans des systèmes embarqués qui doivent répondre à des critères de performance très rigoureux. Une alternative à l'utilisation d'un réseau embarqué par paquets est d'utiliser un réseau embarqué avec routage par circuit [27]. Lorsqu'une route entre deux points est établie, la bande passante

et la latence entre les deux points est fixe. Cette méthode a l'avantage de garantir la performance, mais elle peut fortement limiter la flexibilité du système. Une méthode pour permettre de garantir la performance tout en gardant une certaine flexibilité est de combiner à la fois les réseaux à performance garantie ainsi que des réseaux *service au mieux* [15][9]. Certains systèmes tel que le processeur RAW [21] utilisent la tactique d'utilisation de deux réseaux distincts dont un de type *service au mieux*.

Un système embarqué doit en général être en mesure de communiquer avec le monde extérieur. La communication extérieure peut être utilisée afin de traiter des données provenant de l'extérieur, tandis que d'autres systèmes nécessitent des liens de communication externes pour partager les tâches de calcul comme pour les puces de la société AMD [4] qui peuvent communiquer avec plusieurs autres processeurs à l'aide du protocole HT. Le processeur Cell [7] est également une architecture intéressante qui combine sur une même puce un microprocesseur et 7 coprocesseurs, le tout lié par un bus interne et un lien FlexIOT<sup>TM</sup> pour communiquer avec d'autres puces.

#### **1.4 Conception matérielle utilisant SystemC**

SystemC [32] est une bibliothèque C++ qui permet de modéliser le fonctionnement d'un circuit à divers niveaux d'abstraction. Il permet donc de rapidement modéliser un circuit très complexe de façon comportementale afin de valider son architecture, ou de générer des vecteurs de test pour effectuer la validation d'un circuit. Il est également possible de modéliser un circuit à un niveau d'abstraction très bas pour définir très précisément le comportement d'un circuit, tout comme il est possible de le faire avec le langage de description matérielle VHDL. Lorsque le niveau d'abstraction est suffisamment bas, il devient possible de faire la synthèse du code SystemC pour obtenir un circuit numérique.

Les circuits numériques ont la particularité de traiter toutes les données à leurs entrées en parallèle, tandis que les logiciels informatiques doivent en général effectuer

des traitements de séquentiels. SystemC permet de modéliser ce parallélisme puisqu'il comprend des structures qui permettent de définir plusieurs fils d'exécution qui doivent s'exécuter en parallèle lorsque certains évènements se produisent. Cette bibliothèque comprend également plusieurs structures qui permettent de représenter des entrées, des sorties et des signaux de circuits. SystemC intègre toute la structure nécessaire pour gérer tous les fils d'exécution et la mise à jour des signaux du système. Un exécutable produit à partir d'un code source utilisant la bibliothèque SystemC comprend donc à la fois le modèle du circuit et tout ce qui est nécessaire pour effectuer la simulation du circuit. Lors de l'exécution du modèle du circuit, il est possible de produire un fichier contenant la valeur des signaux du circuit modélisé lors de la simulation.

Ce qui suit est un compteur matériel utilisé dans le tunnel HyperTransport. Le premier fichier `cd_counter_l3.h` est l'en-tête du compteur. Tout composant qui utilise une instance de module n'a qu'à inclure ce fichier pour obtenir la définition de son interface. Ce même fichier inclut à son tour l'en-tête `<systemc.h>` qui définit la bibliothèque SystemC. Le fichier `cd_counter_l3.cpp` contient quant à lui l'implémentation du compteur. Un circuit modélisé en SystemC est une classe qui est dérivée de la classe `sc_module`. Les membres de cette classe incluent les entrées et les sorties du circuit, ainsi que ses signaux internes. Les méthodes de la classe représentent les fonctionnalités du circuit.

### **Fichier `cd_counter_l3.h` :**

```

#ifndef CD_COUNTER_L3_H

#define CD_COUNTER_L3_H

//Inclusion de la bibliothèque SystemC

#include <systemc.h>

///Compteur pour le module decoder_12

/**

* @class cd_counter_13

* @description Compte le nombre de données reçues et active

*             un signal lors de la fin de réception des données

*/

class cd_counter_13 : public sc_module

```

```

{

///La valeur du compte

sc_signal<sc_uint<4> > countVal;

public:

//***** Entrées *****

//Signal d'horloge de synchronisation

sc_in< bool > clk;

//Signal d'initialisation (actif bas)

sc_in< bool > resetx;

//Permet de fixer le nombre de données à recevoir

sc_in< bool > setCnt;

//Permet de décrémenter le compte interne

sc_in< bool > decrCnt;

//Paquet d'en-tête, les bits (25,22) contiennent le nombre de données qui suivent

sc_in<sc_bv<32> > data;

//***** Sorties *****

//La prochaine donnée sera la dernière à recevoir

sc_out< bool > end_of_count;

/**

Processus sensible au front montant de l'horloge qui compte

Le nombre de données reçues

*/

void count_process();

//Macro SystemC : la classe contient des processus

SC_HAS_PROCESS(cd_counter_13);

//Constructeur

cd_counter_13(sc_module_name name);

};

#endif

```

### Fichier cd\_counter\_13.cpp :

```

#include "cd_counter_13.h"

cd_counter_13::cd_counter_13(sc_module_name name) : sc_module(name)

{

//SC_METHOD means veut dire que cette méthode sera exécutée à chaque fois

//qu'un signal dans la liste de processus est modifié

SC_METHOD(count_process);

sensitive_neg << resetx;

sensitive_pos<<clk;

}

void cd_counter_13::count_process()

{

sc_bv<4> count;

```

```

count = data.read().range(25,22);

//À l'initialisation, le compte tombe à 0

if (!resetx.read()){

countVal = 0;

end_of_count = true;

}

else{

//Si nous devons enregistrer une nouvelle valeur

if(setCnt.read()){

countVal = sc_uint<4>(count);

//Si le compte est à 0, il ne reste qu'une seule et dernière donnée

if(sc_uint<4>(count) == 0){

end_of_count = true;

}

else{

end_of_count = false;

}

}

//Décrémenté, si ce n'est pas la dernière donnée

else if (decrCnt.read() && countVal.read() !=0){

countVal = countVal.read() - 1;

if(countVal.read() == 1){

end_of_count = true;

}

else{

end_of_count = false;

}

}

//Sinon, décrémenter et c'est la dernière donnée

else if (decrCnt.read()){

countVal = countVal.read();

end_of_count = true;

}

}

}

```

Le langage C++ permet de faire de la programmation à un niveau d'abstraction pour lequel il n'est pas toujours possible de générer un circuit matériel qui a un comportement équivalent. Un pointeur, par exemple, trouve difficilement son équivalent en matériel. Un outil qui effectue la synthèse de SystemC doit donc précisément définir quels éléments du langage sont supportés ou ne le sont pas. De façon générale, les outils présentement disponibles commercialement pour effectuer la synthèse de SystemC ne supportent pas les fonctionnalités de la programmation par objets. Néanmoins, un groupe s'est penché sur la possibilité d'utiliser les possibilités qu'offre la programmation par objets pour des fins de synthèse à l'aide d'un outil maison nommé ODETTE [8]. On y retrouve des fonctionnalités telles que l'utilisation de classes dérivées qui réutilisent du code provenant des classes de base et l'utilisation de patrons (*template*) pour définir une fonctionnalité générique.