**Titre:** Abstraction de la synchronisation dans une stratégie de co-design

Title: logiciel/matériel sur une plateforme (SOC) multiprocesseur

**Auteur:** Patrick Samson

Author:

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Samson, P. (2006). Abstraction de la synchronisation dans une stratégie de co-design logiciel/matériel sur une plateforme (SOC) multiprocesseur [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie.

**Citation:** <https://publications.polymtl.ca/7831/>

**Document en libre accès dans PolyPublie**

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7831/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & El Mostapha Aboulhamid

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

ABSTRACTION DE LA SYNCHRONISATION DANS UNE STRATÉGIE DE

CO-DESIGN LOGICIEL/MATÉRIEL SUR UNE PLATEFORME (SOC)

MULTIPROCESSEUR

PATRICK SAMSON

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

DÉCEMBRE 2006

Library and

Archives Canada

Bibliothèque et

Archives Canada

Published Heritage

Branch

Direction du

Patrimoine de l'édition

395 Wellington Street

Ottawa ON K1A 0N4

Canada

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-25574-2

*Our file* *Notre référence*

ISBN: 978-0-494-25574-2

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

ABSTRACTION DE LA SYNCHRONISATION DANS UNE STRATÉGIE DE

CO-DESIGN LOGICIEL/MATÉRIEL SUR UNE PLATEFORME (SOC)

MULTIPROCESSEUR

présenté par: SAMSON Patrick

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. ROY Robert, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. ABOULHAMID Mostapha, Ph.D., membre et codirecteur de recherche

MME. NICOLESCU Gabriela, Doct., membre

Un condensé des leçons apprises au cours des présents travaux de recherche.

« The road of life twists and turns and no two directions are ever the same. Yet our lessons come from the journey, not the destination. » - Don Williams, Jr.

« The greatest danger in modern technology isn't that machines will begin to think like people, but that people will begin to think like machines. » - Anonyme

## REMERCIEMENTS

Il convient d'abord de remercier les gens qui m'ont offert un support remarquable tout au long de ma maîtrise: ma famille proche et ma copine. Mario, Ginette et Karine, sans vos encouragements et votre aide, cette maîtrise n'aurait peut-être jamais vue le jour. Il va de soi qu'une présence régulière offre une contribution marquée dont l'essence perdure au fil des années. C'est pourquoi, dans le même ordre d'idée, je tiens à remercier mes confrères de travail. Ces partenaires de recherche et amis ont toujours su apporter conseils, support moral et divertissements dans les moments de gloire et dans les moments plus difficiles. Merci à Simon, Jean-François, François, Francis, Mortimer et au CIRCUS.

Je ne peux poursuivre avant de remercier mon directeur et mon co-directeur de recherche, Guy Bois et Mustapha Alboulhamid. Leur expérience et leurs judicieux conseils m'ont permis d'amorcer mon projet dans une avenue novatrice et de lui donner l'orientation qu'il connaît aujourd'hui.

Un remerciement final s'applique aussi au personnel technique (Alex) et administratif qui a facilité mon travail, mon développement et mon apprentissage durant mon séjour à l'École Polytechnique de Montréal.

## RÉSUMÉ

Un nombre croissant de systèmes embarqués sont aujourd’hui implantés sur une même puce électronique. De tels systèmes prennent alors l’appellation systèmes-sur-puce ou SoC. La conception et l’implantation de SoC reposent sur les technologies des semi-conducteurs qui permettent des niveaux d’intégration en constante croissance. Bien que ces systèmes soient plus compacts, consomment une faible puissance et offrent des performances inégalées en comparaison à leurs ancêtres, ils sont plus complexes à concevoir. Cette augmentation de la complexité est amplifiée par l’avènement des MPSoCs, les systèmes-sur-puce multiprocesseurs.

La plateforme de conception SPACE cherche à faciliter la conception et l’implantation de systèmes-sur-puce. SPACE opère à un niveau d’abstraction supérieur au niveau RTL plus conventionnel: le niveau système (ESL). SPACE repose sur l’assemblage de composants IP afin de créer un système électronique. Dans l’ensemble, SPACE se veut une solution plus rapide et plus économique à la création de SoCs performants. SPACE cherche à étendre ses capacités afin de supporter la création de MPSoCs. À ce titre, les plateformes multiprocesseurs requièrent des fonctionnalités additionnelles. La bibliothèque SISSMA développée dans le cadre de cette recherche intègre des services de synchronisation pour MPSoC dans SPACE.

La bibliothèque SISSMA sert d’abord d’analyse initiale à l’intégration de supports de synchronisation génériques, indépendants de la plateforme matérielle utilisée. Son attrait tient aussi du fait qu’elle est aisément configurable afin de tenir compte d’un facteur de conception propre à l’ESL: le partitionnement logiciel/matériel des tâches du système. Ainsi, fidèle à la méthodologie de conception au niveau système et à la plateforme SPACE, une application n’a pas à être personnalisée suite à son partitionnement logiciel/matériel, puisque SISSMA assure les changements grâce à ses options de configuration. Enfin, il est montré que les performances de la bibliothèque SISSMA sont négligeables lors de synchronisations dites locales. Dans

le cas de synchronisations dites à distance, elle requiert moins de deux fois le temps d'exécution requis par une synchronisation faite par le système d'exploitation temps-réel MicroC/OS-II.

## ABSTRACT

A growing number of embedded systems today are manufactured on a single electronic chip. In such a case, a system is called a system-on-chip or SoC. The design and implementation of SoCs rely on semiconductor technologies which nowadays increase in terms of integration levels. Considering that such systems are more compact, operate with lower power and offer unprecedented performances in comparison to their ancestors, they are more complex to design. This increase in complexity is amplified by the introduction of MPSoCs, the multiprocessor systems-on-chip.

SPACE, a design platform, is meant to facilitate the design and implementation of systems-on-chip. SPACE operates at an abstraction level higher than the more conventional RTL level: the electronic system level (ESL). SPACE relies on IP component assembly in order to create an electronic system. Overall, SPACE offers a faster and cheaper solution to creating efficient SoCs.

SPACE seeks to expand its services in order to support the creation of MPSoCs. Multiprocessor platforms require additional functionalities. The SISSMA library developed in this research integrates synchronization services for MPSoC into SPACE. The SISSMA library first serves as an initial analysis to the integration of generic synchronization support, independent of the hardware platform used. Its configurability makes it attractive in considering a key factor of ESL design: hardware/software partitioning of system tasks. Hence, in complete harmony with electronic system level methodology and with the SPACE platform, an application does not require custom tuning following its hardware/software partitioning since SISSMA ensure the changes through its configuration options. To conclude, it is demonstrated that the performance overhead of the SISSMA library are negligible during local synchronizations. For remote synchronizations, they demand less than twice the synchronization time required by the MicroC/OS-II real-time operating system.

**TABLE DES MATIÈRES**

|                                                    |      |

|----------------------------------------------------|------|

| DÉDICACE . . . . .                                 | iv   |

| REMERCIEMENTS . . . . .                            | v    |

| RÉSUMÉ . . . . .                                   | vi   |

| ABSTRACT . . . . .                                 | viii |

| TABLE DES MATIÈRES . . . . .                       | ix   |

| LISTE DES FIGURES . . . . .                        | xiv  |

| LISTE DES ACRONYMES . . . . .                      | xvi  |

| LISTE DES TABLEAUX . . . . .                       | xix  |

| LISTE DES ANNEXES . . . . .                        | xxi  |

| CHAPITRE 1 INTRODUCTION . . . . .                  | 1    |

| 1.1 Les systèmes embarqués d'aujourd'hui . . . . . | 1    |

| 1.1.1 Loi de Moore . . . . .                       | 3    |

| 1.1.2 Loi de Wirth . . . . .                       | 4    |

| 1.1.3 Loi de Rock . . . . .                        | 5    |

| 1.2 Problématique . . . . .                        | 5    |

| 1.3 Objectifs . . . . .                            | 7    |

| 1.4 Méthodologie . . . . .                         | 7    |

| 1.5 Contributions . . . . .                        | 8    |

| 1.6 Organisation de ce mémoire . . . . .           | 9    |

|            |                                                                              |    |

|------------|------------------------------------------------------------------------------|----|

| CHAPITRE 2 | SYSTÈME-SUR-PUCE: DÉFINITION, PROBLÉMATIQUE<br>ET CONCEPTION . . . . .       | 10 |

| 2.1        | Définitions: Soc et MPSoC . . . . .                                          | 11 |

| 2.1.1      | Système-sur-Puce (SoC) . . . . .                                             | 11 |

| 2.1.2      | Système-sur-Puce Multiprocesseur (MPSoC) . . . . .                           | 11 |

| 2.1.2.1    | Origine des systèmes multiprocesseurs . . . . .                              | 12 |

| 2.2        | Complexité de la conception de systèmes-sur-puce au niveau système . . . . . | 13 |

| 2.2.1      | Synthèse logicielle et matérielle . . . . .                                  | 13 |

| 2.2.2      | Architecture système et partitionnement logiciel/matériel . . . . .          | 14 |

| 2.2.3      | Performance des communications . . . . .                                     | 15 |

| 2.2.4      | Synchronisation . . . . .                                                    | 16 |

| 2.2.5      | La nature hétérogène des composants . . . . .                                | 16 |

| 2.2.6      | La pile logicielle . . . . .                                                 | 16 |

| 2.3        | Conception de systèmes-sur-puce multiprocesseurs . . . . .                   | 18 |

| 2.3.1      | Approche traditionnelle à la conception . . . . .                            | 19 |

| 2.3.2      | Codesign logiciel/matériel . . . . .                                         | 20 |

| 2.3.3      | Conception au niveau système . . . . .                                       | 23 |

| 2.3.3.1    | TLM . . . . .                                                                | 24 |

| 2.3.3.2    | Raffinement progressif . . . . .                                             | 26 |

| 2.3.4      | Alternatives de conception au niveau système . . . . .                       | 28 |

| 2.3.4.1    | Synthèse système . . . . .                                                   | 28 |

| 2.3.4.2    | Conception basée sur l'utilisation de noyaux IP . . . . .                    | 30 |

| 2.3.4.3    | Conception basée sur une plateforme . . . . .                                | 33 |

| CHAPITRE 3 | LA SYNCHRONISATION DANS UN SYSTÈME MULTI-<br>PROCESSEUR . . . . .            | 36 |

| 3.1        | La synchronisation : un besoin . . . . .                                     | 36 |

| 3.2        | La synchronisation dans les systèmes multiprocesseurs . . . . .              | 37 |

|                                                                                                     |                                                                                                                          |    |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----|

| 3.2.1                                                                                               | Protocoles de synchronisation . . . . .                                                                                  | 37 |

| 3.2.2                                                                                               | Problèmes typiques de la synchronisation multiprocesseur . . . . .                                                       | 38 |

| 3.2.2.1                                                                                             | Contention . . . . .                                                                                                     | 38 |

| 3.2.2.2                                                                                             | Point chaud (« Hot spot ») . . . . .                                                                                     | 39 |

| 3.2.2.3                                                                                             | Préemption . . . . .                                                                                                     | 40 |

| 3.2.3                                                                                               | Algorithmes de synchronisation par attente active . . . . .                                                              | 41 |

| 3.2.3.1                                                                                             | Objet de synchronisation basé sur le spin ( <i>Test-and-Set</i> )                                                        | 41 |

| 3.2.3.2                                                                                             | Objet de synchronisation basé sur le spin avec lecture<br>( <i>Test-and-Test-and-Set</i> ) (« Snooping Lock ») . . . . . | 42 |

| 3.2.3.3                                                                                             | Objet de synchronisation basé sur l'évitement des<br>collisions . . . . .                                                | 43 |

| 3.2.3.4                                                                                             | Objet de synchronisation basé sur un ticket « Ticket<br>Lock » [1][2] . . . . .                                          | 44 |

| 3.2.3.5                                                                                             | Objet de synchronisation MCS . . . . .                                                                                   | 44 |

| 3.2.3.6                                                                                             | Analyse des performances des algorithmes de synchro-<br>nisation présentés . . . . .                                     | 45 |

| 3.2.3.7                                                                                             | Autres supports matériels pour la synchronisation de<br>plateformes multiprocesseurs . . . . .                           | 46 |

| 3.2.4                                                                                               | Optimisations apportées aux algorithmes existants . . . . .                                                              | 51 |

| 3.2.4.1                                                                                             | Objet de synchronisation de type rédacteur/lecteur .                                                                     | 51 |

| 3.2.4.2                                                                                             | Objet de synchronisation avec temps d'arrêt . . . . .                                                                    | 54 |

| 3.2.5                                                                                               | Variantes des algorithmes basés sur le spin avec délais adaptatifs                                                       | 55 |

| 3.2.5.1                                                                                             | Protocoles adaptatifs . . . . .                                                                                          | 56 |

| 3.3                                                                                                 | Conclusion . . . . .                                                                                                     | 58 |

| CHAPITRE 4 SISSMA : SYNCHRONISATION MULTIPROCESSEUR DANS<br>LA PLATEFORME VIRTUELLE SPACE . . . . . |                                                                                                                          | 60 |

| 4.1                                                                                                 | Terminologie . . . . .                                                                                                   | 60 |

|                                                       |                                                                                 |    |

|-------------------------------------------------------|---------------------------------------------------------------------------------|----|

| 4.2                                                   | SISSMA : introduction et objectifs . . . . .                                    | 61 |

| 4.3                                                   | Définition : SISSMA . . . . .                                                   | 63 |

| 4.3.1                                                 | Services disponibles . . . . .                                                  | 63 |

| 4.3.2                                                 | Configuration : synchronisation locale ou à distance . . . . .                  | 64 |

| 4.3.3                                                 | Optimisations dans un contexte temps-réel . . . . .                             | 66 |

| 4.3.3.1                                               | Optimisation du temps de blocage : recul adaptatif .                            | 68 |

| 4.3.3.2                                               | Optimisation de la concurrence : section critique longue et promotion . . . . . | 69 |

| 4.3.3.3                                               | Optimisation de la concurrence : accès rédacteur/lecteur                        | 69 |

| 4.4                                                   | Conception des composants SISSMA . . . . .                                      | 70 |

| 4.4.1                                                 | Réutilisation du concept de tickets . . . . .                                   | 70 |

| 4.4.2                                                 | API SISSMA : modélisation système et conception logicielle .                    | 71 |

| 4.4.2.1                                               | Structure . . . . .                                                             | 71 |

| 4.4.2.2                                               | Configuration du mode de synchronisation . . . . .                              | 72 |

| 4.4.3                                                 | Moteur de synchronisation SISSMA : conception matérielle .                      | 72 |

| 4.4.3.1                                               | Modèle SystemC . . . . .                                                        | 72 |

| 4.4.3.2                                               | Modèle VHDL . . . . .                                                           | 76 |

| 4.5                                                   | Intégration dans la plateforme SPACE . . . . .                                  | 83 |

| CHAPITRE 5 ÉVALUATION DES PERFORMANCES ET ANALYSE . . |                                                                                 | 85 |

| 5.1                                                   | Environnement d'analyse . . . . .                                               | 85 |

| 5.1.1                                                 | Outils et plateforme cible . . . . .                                            | 85 |

| 5.1.2                                                 | Architecture et configuration des systèmes-sur-puce d'analyse                   | 86 |

| 5.2                                                   | Métriques statiques . . . . .                                                   | 89 |

| 5.2.1                                                 | Métriques logicielles . . . . .                                                 | 90 |

| 5.2.1.1                                               | Méthode d'évaluation . . . . .                                                  | 90 |

| 5.2.1.2                                               | Analyse des métriques statiques . . . . .                                       | 90 |

| 5.2.2                                                 | Métriques matérielles . . . . .                                                 | 94 |

|            |                                                         |     |

|------------|---------------------------------------------------------|-----|

| 5.3        | Métriques dynamiques                                    | 97  |

| 5.3.1      | Application d'analyse: multiplication de matrices       | 97  |

| 5.3.2      | Accélération par l'utilisation de plusieurs processeurs | 99  |

| 5.4        | Conclusion                                              | 102 |

| CONCLUSION |                                                         | 103 |

| RÉFÉRENCES |                                                         | 109 |

| ANNEXES    |                                                         | 122 |

## LISTE DES FIGURES

|             |                                                                                                                                  |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1  | Écart de la productivité . . . . .                                                                                               | 4  |

| Figure 2.1  | Processus de partitionnement logiciel/matériel . . . . .                                                                         | 14 |

| Figure 2.2  | Les différents éléments de la couche logicielle . . . . .                                                                        | 17 |

| Figure 2.3  | Flot de conception du codesign logiciel/matériel . . . . .                                                                       | 21 |

| Figure 2.4  | Configuration d'une co-simulation logicielle/matérielle entre un simulateur de jeux d'instructions et une partition matérielle . | 22 |

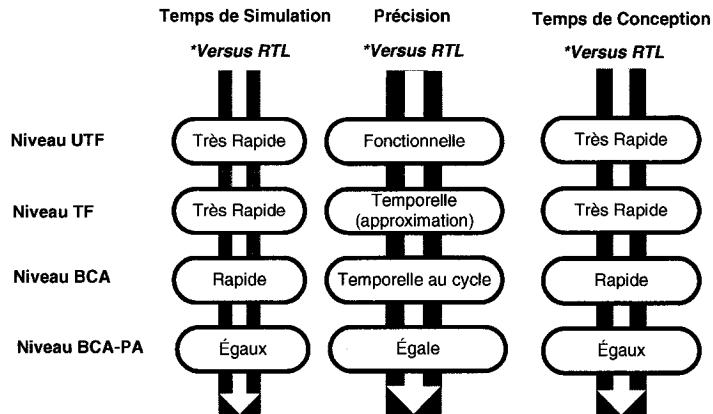

| Figure 2.5  | Raffinement progressif . . . . .                                                                                                 | 27 |

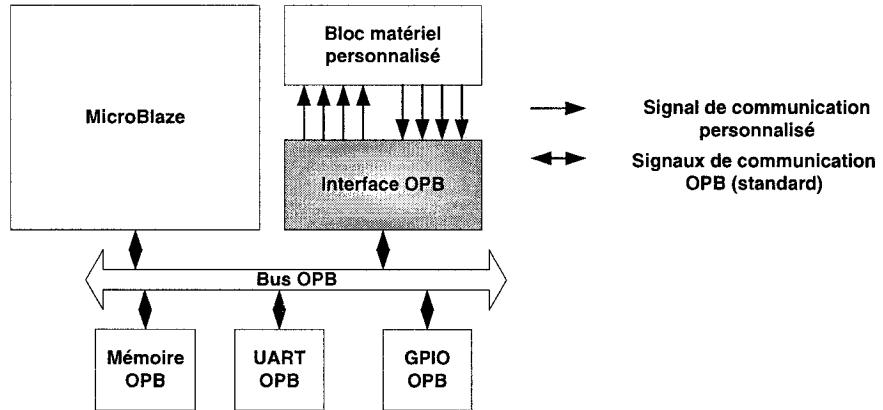

| Figure 2.6  | Plateforme conçue à partir de la méthodologie de conception basée sur l'assemblage de noyaux IP . . . . .                        | 31 |

| Figure 2.7  | Architecture de la plateforme SPACE . . . . .                                                                                    | 33 |

| Figure 2.8  | Architecture de la plateforme Nomadik (STMicroelectronics) .                                                                     | 34 |

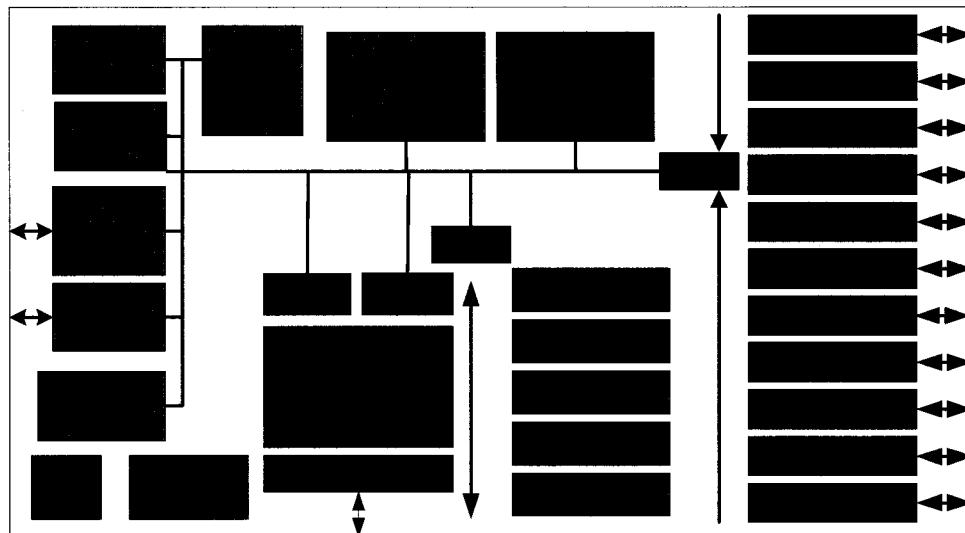

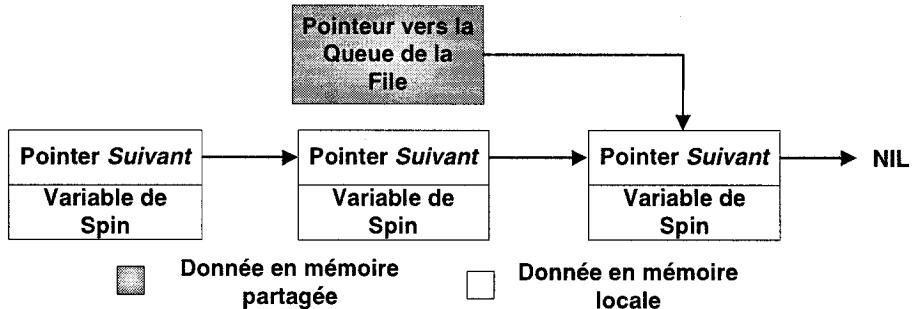

| Figure 2.9  | Architecture de la plateforme OMAP (Texas Instruments) .                                                                         | 35 |

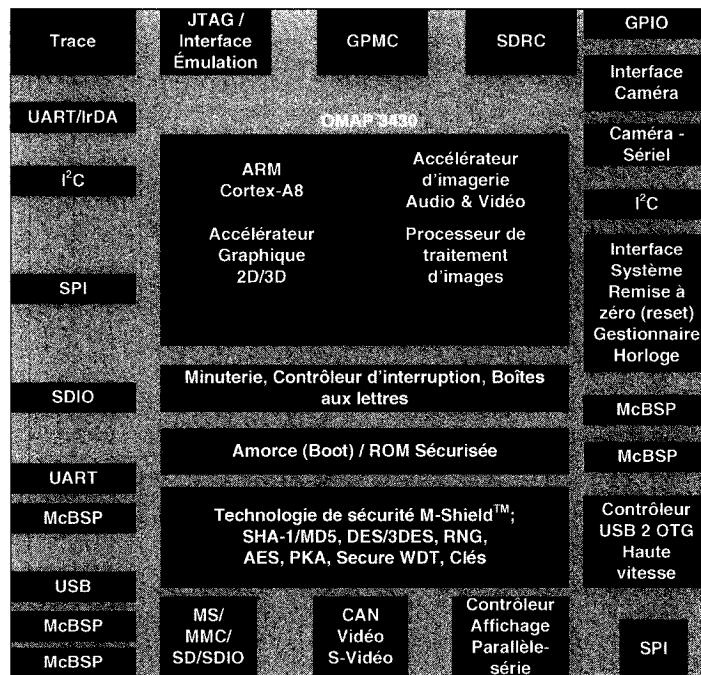

| Figure 2.10 | Architecture de la plateforme Nexperia (Philips) . . . . .                                                                       | 35 |

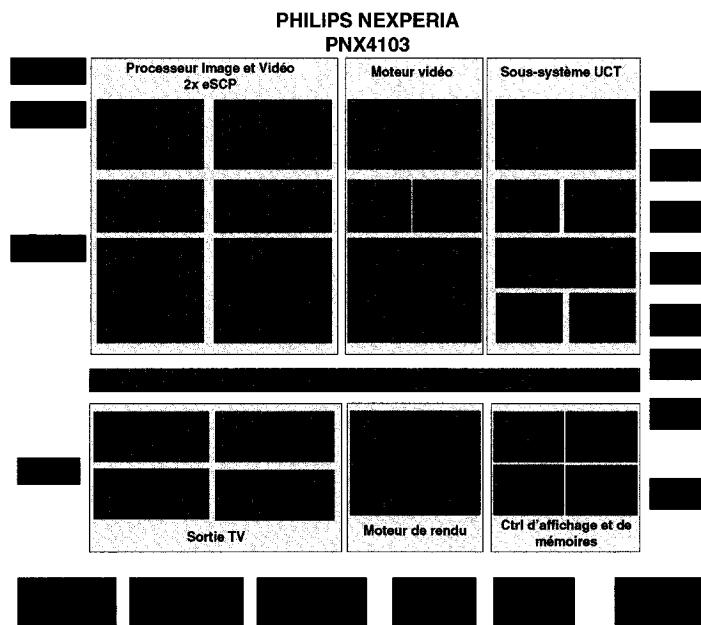

| Figure 3.1  | Organisation de la mémoire des objets de synchronisation MCS à exclusion mutuelle . . . . .                                      | 45 |

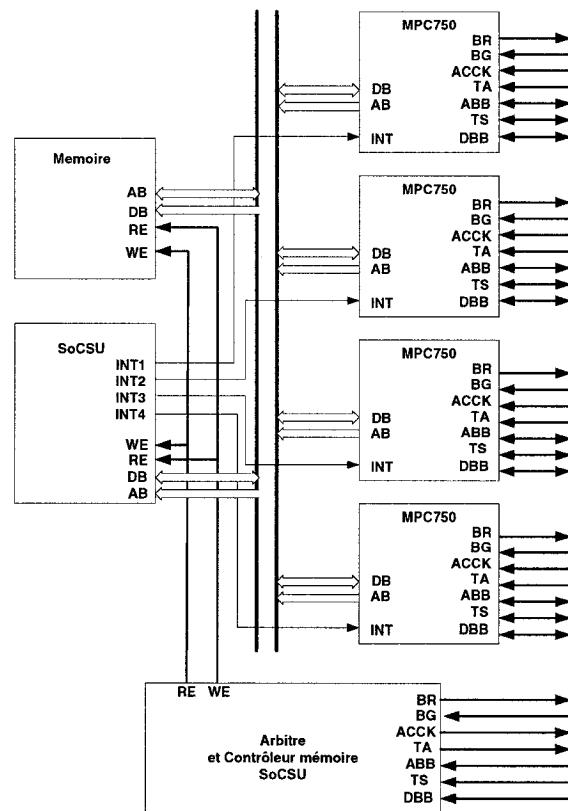

| Figure 3.2  | Architecture matérielle d'un système à 4 processeurs utilisant le composant SoCSU/SoCLC . . . . .                                | 49 |

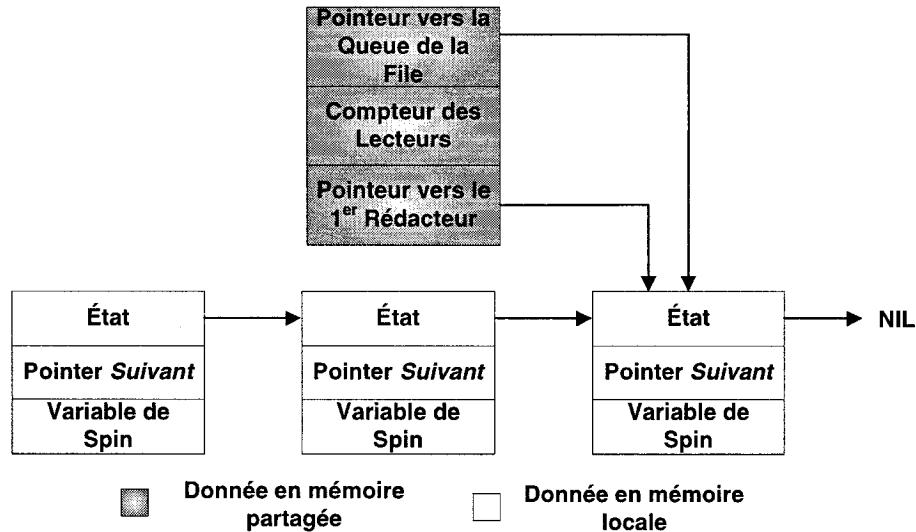

| Figure 3.3  | Organisation de la mémoire des objets de synchronisation MCS de type rédacteur/lecteur . . . . .                                 | 52 |

| Figure 4.1  | MPSoC typique ciblé par les présents travaux . . . . .                                                                           | 63 |

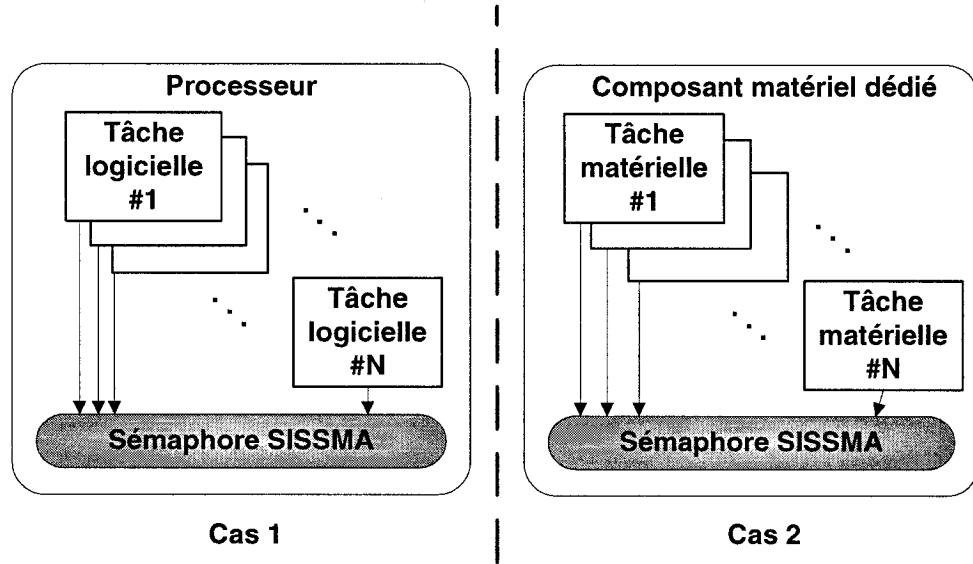

| Figure 4.2  | Cas d'utilisation de la synchronisation locale lors de la configuration d'un sémaphore SISSMA . . . . .                          | 66 |

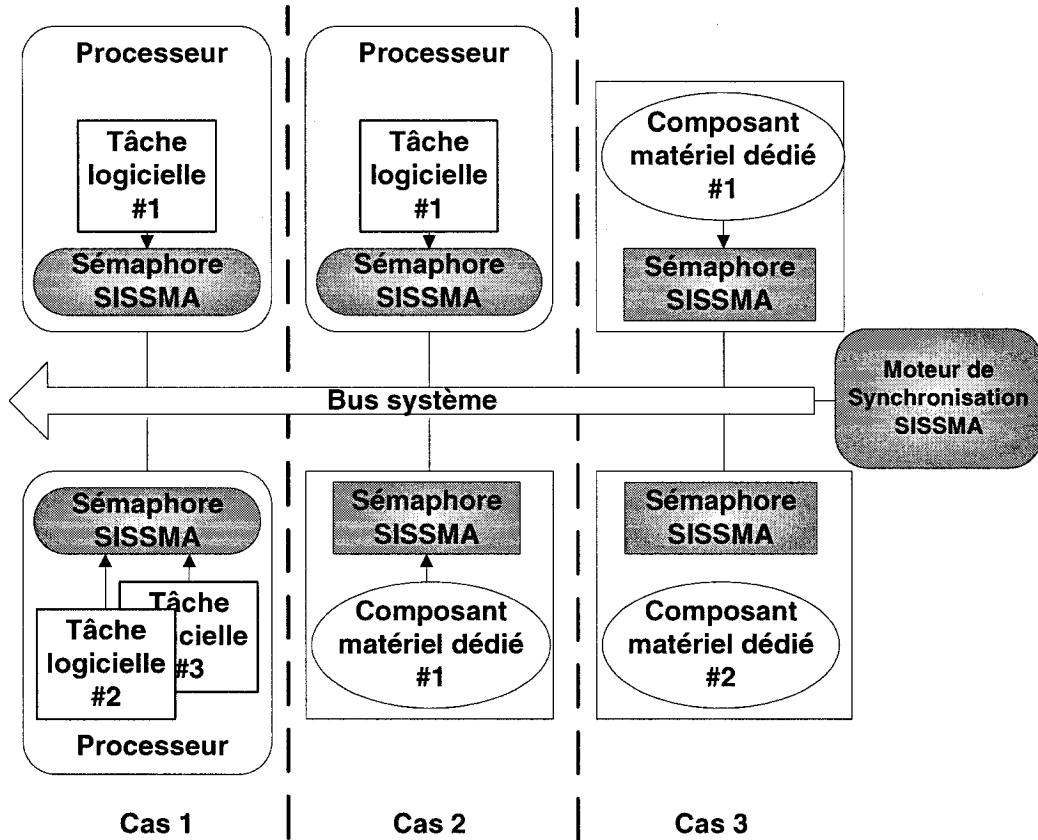

| Figure 4.3  | Cas d'utilisation de la synchronisation à distance lors de la configuration d'un sémaphore SISSMA . . . . .                      | 67 |

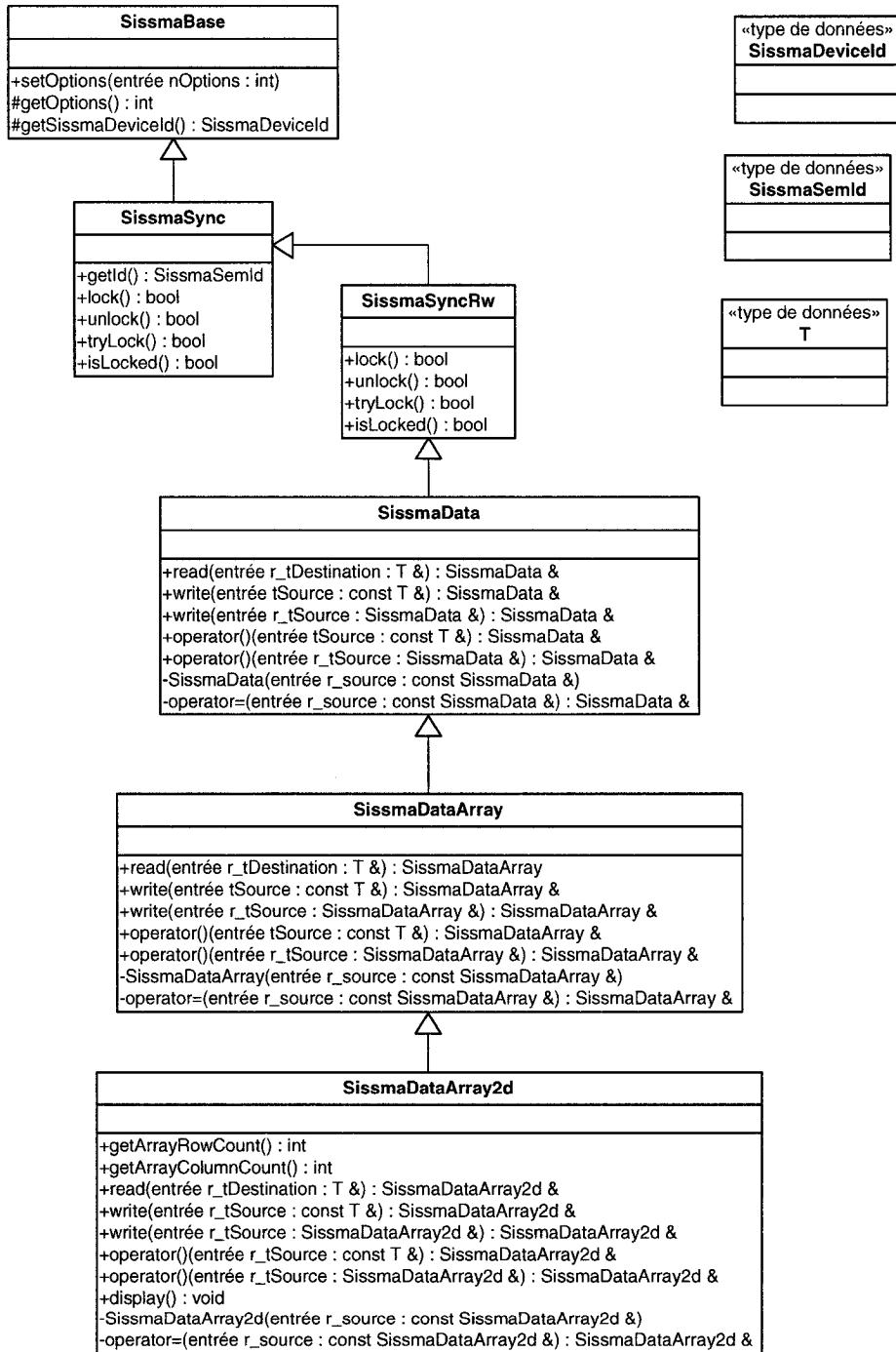

| Figure 4.4  | Diagramme de classe simplifié de l'API SISSMA . . . . .                                                                          | 73 |

|              |                                                                                                                               |     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|-----|

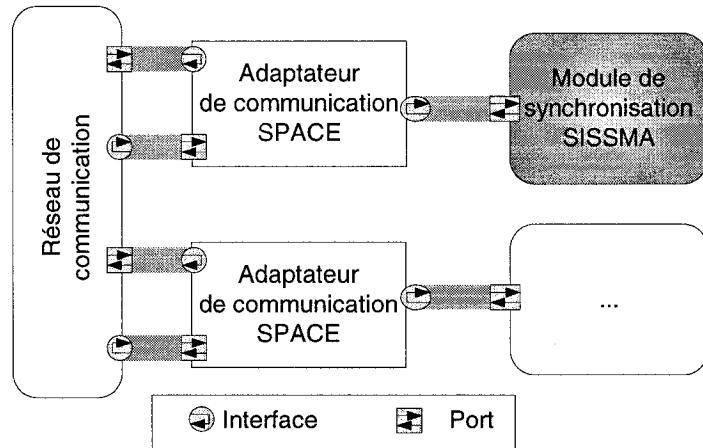

| Figure 4.5   | Organisation architecture du module SISSMA dans la plate-forme SPACE . . . . .                                                | 74  |

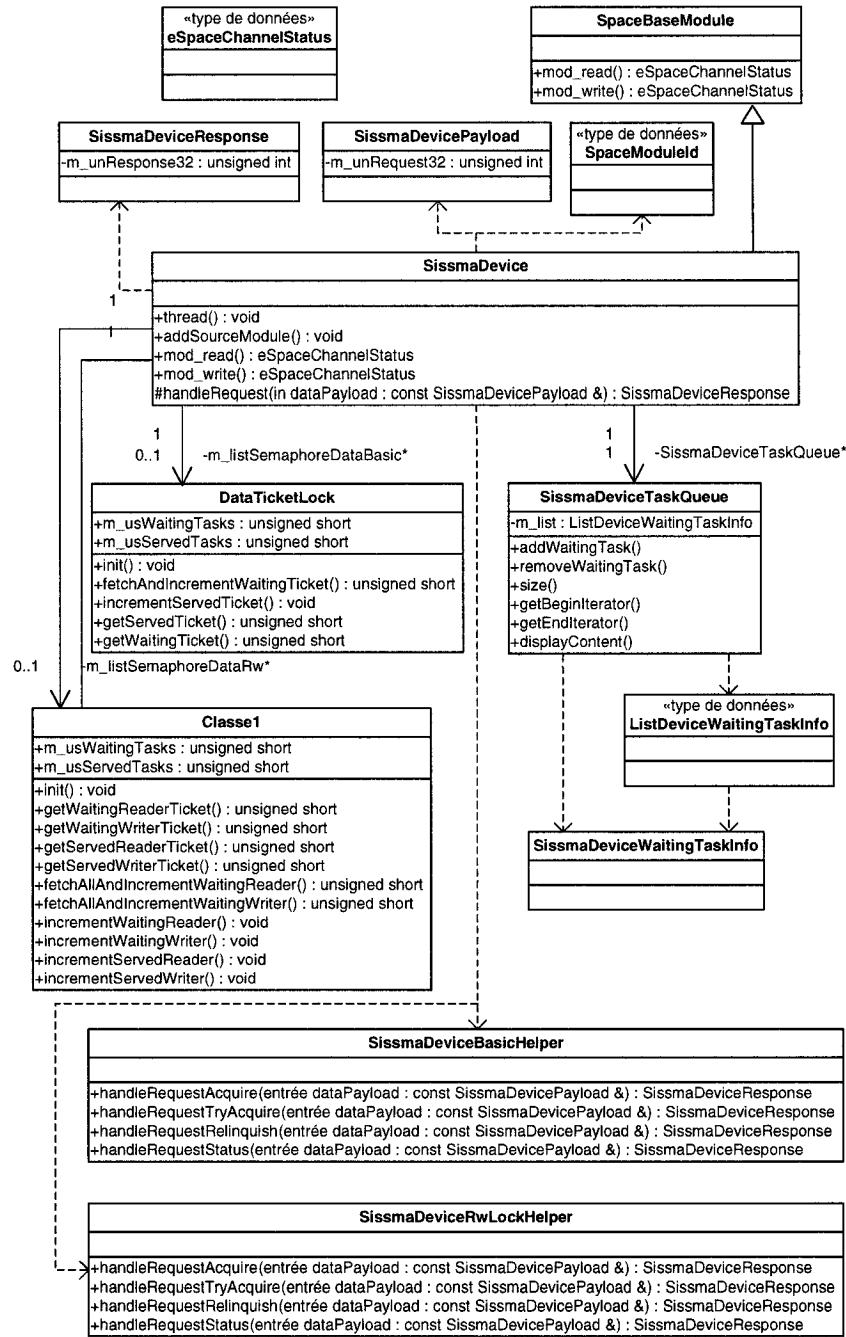

| Figure 4.6   | Diagramme de classe simplifié du modèle TLM du moteur de synchronisation SISSMA . . . . .                                     | 77  |

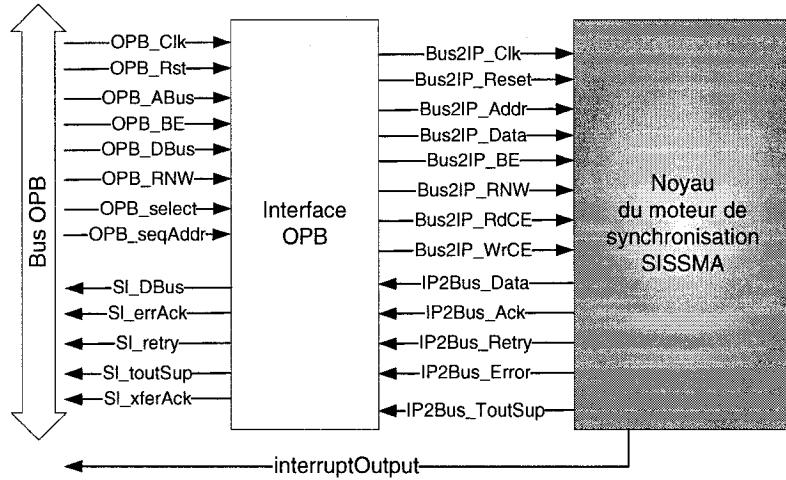

| Figure 4.7   | Interface de communication et noyau logique du moteur de synchronisation SISSMA . . . . .                                     | 78  |

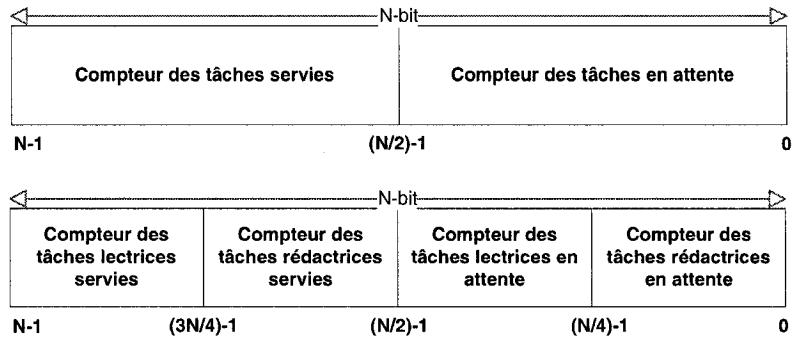

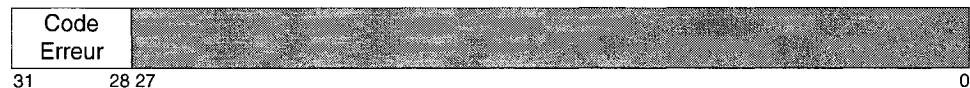

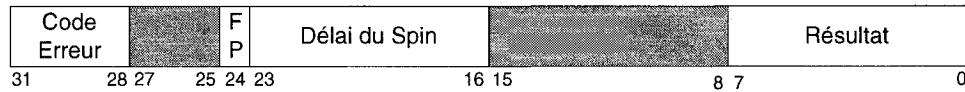

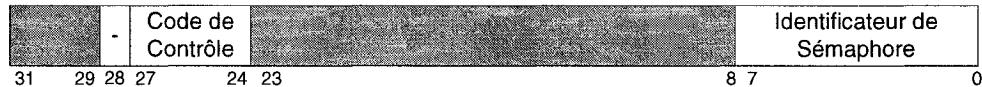

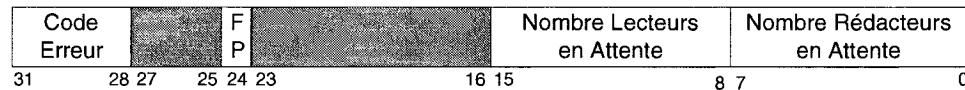

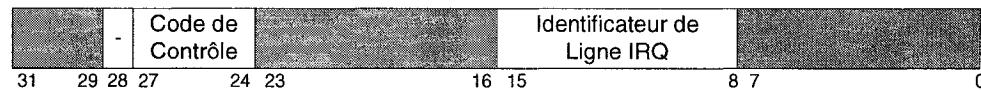

| Figure 4.8   | Structure du registre d'état d'un sémaphore du moteur de synchronisation SISSMA . . . . .                                     | 79  |

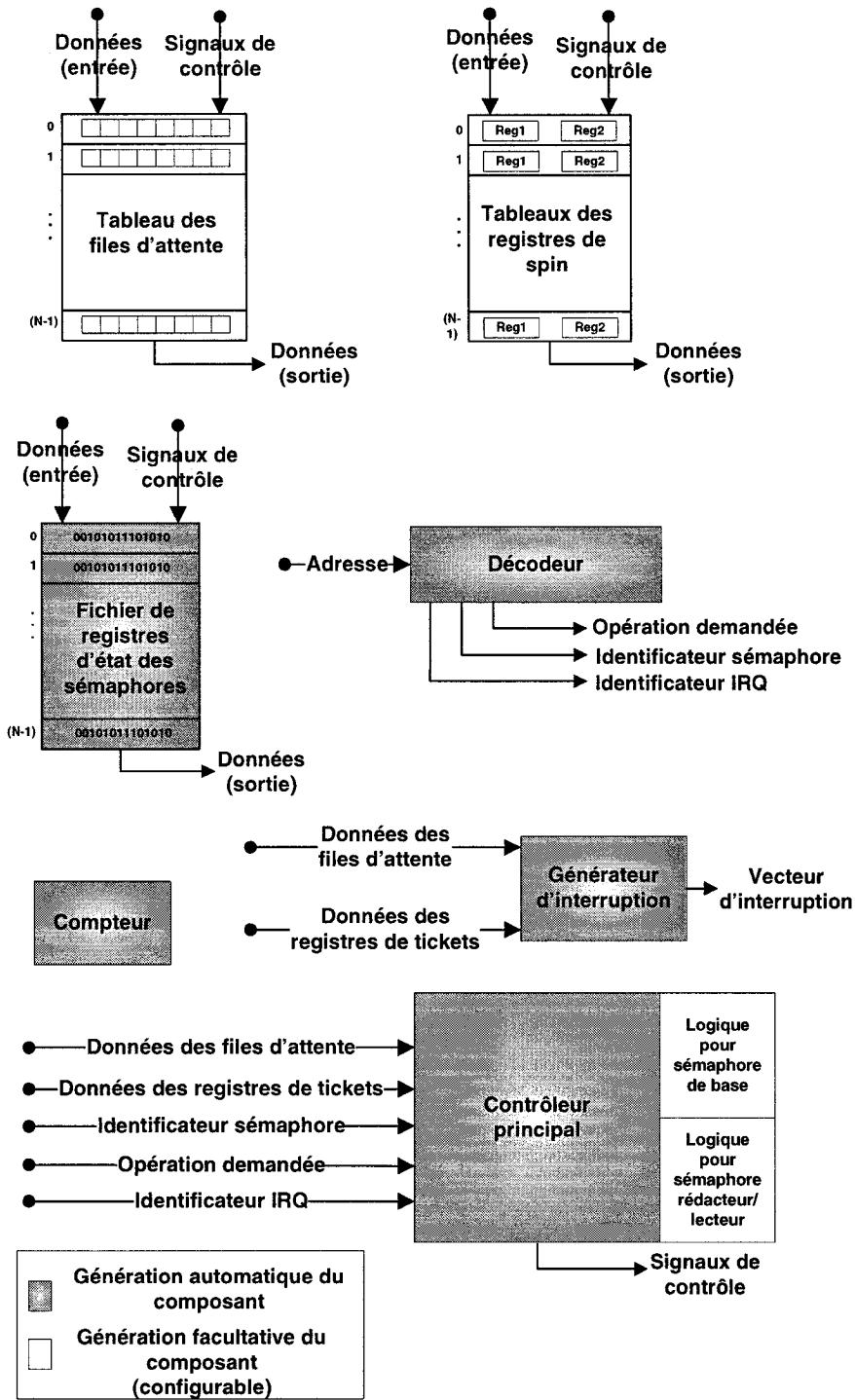

| Figure 4.9   | Composition matérielle du moteur de synchronisation SISSMA                                                                    | 82  |

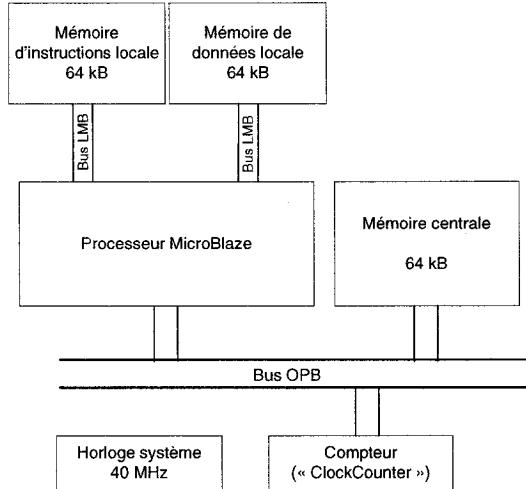

| Figure 5.1   | Architecture de la plateforme d'analyse monoprocesseur utilisée                                                               | 87  |

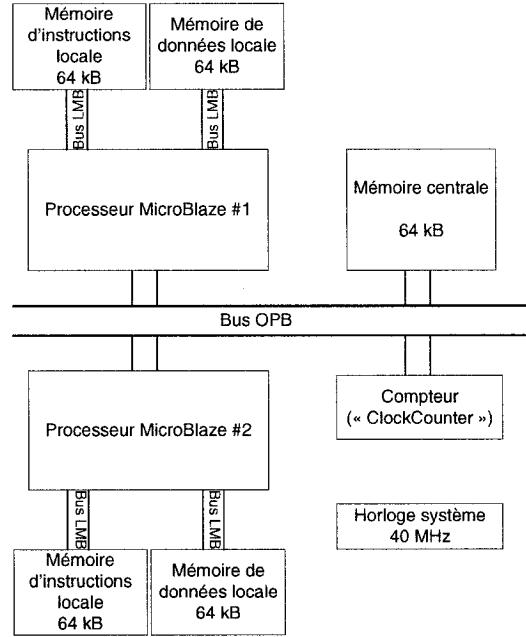

| Figure 5.2   | Architecture de la plateforme d'analyse multiprocesseur utilisée                                                              | 88  |

| Figure 5.3   | Organisation du compteur du temps d'exécution . . . . .                                                                       | 88  |

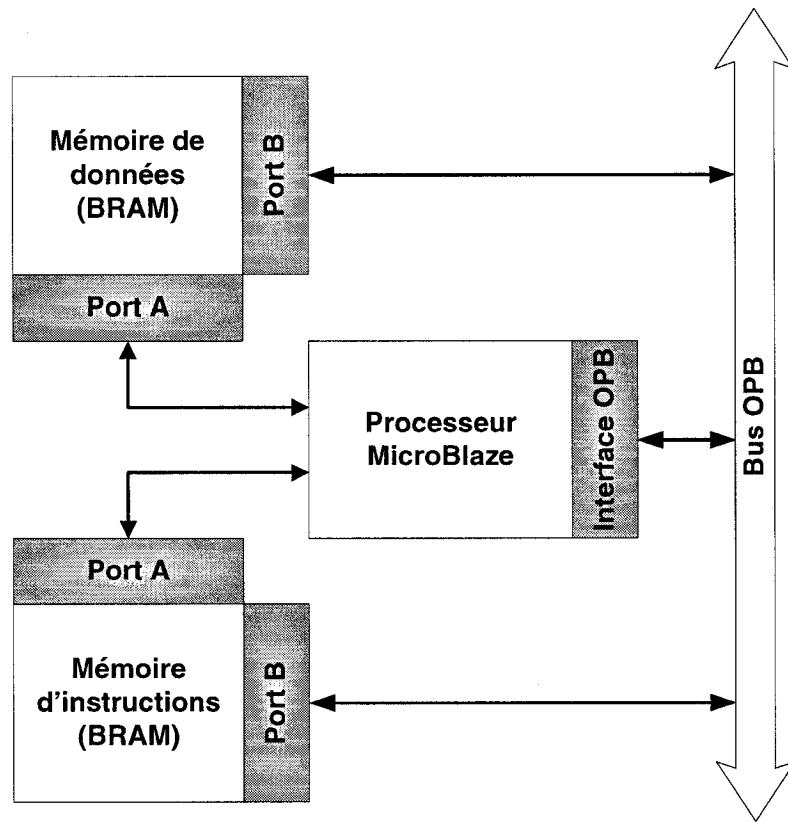

| Figure 5.4   | Organisation architecturale simplifiée d'un processeur MicroBlaze utilisant des mémoires locales accessibles globalement. . . | 107 |

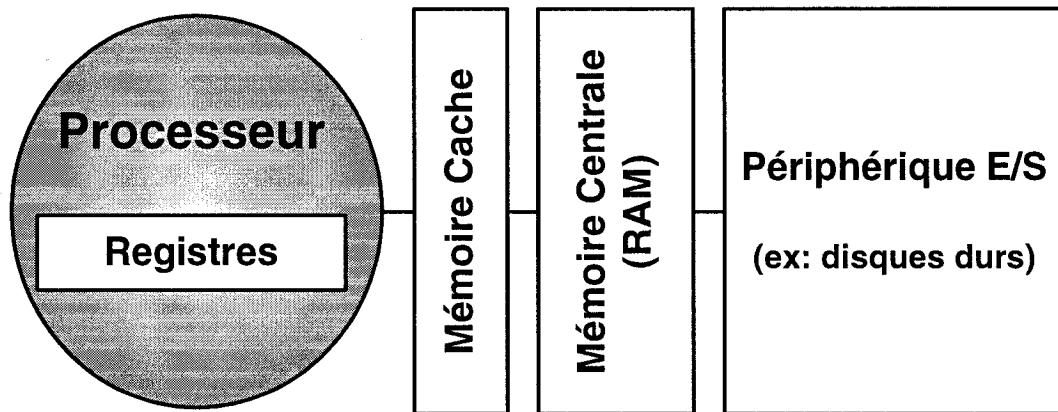

| Figure I.1   | Hiérarchie de mémoire dans un système embarqué typique . .                                                                    | 123 |

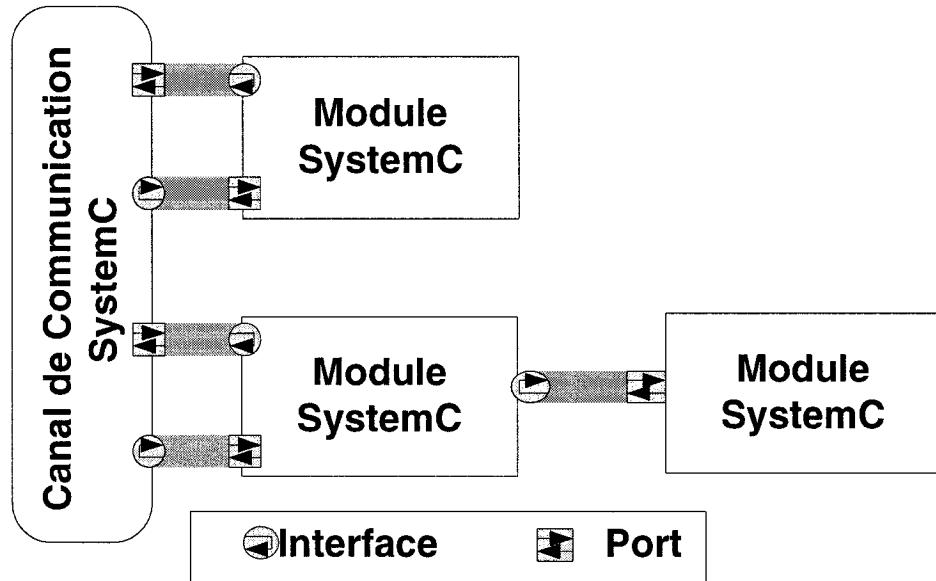

| Figure II.1  | Structure architecturale des composants SystemC . . . . .                                                                     | 126 |

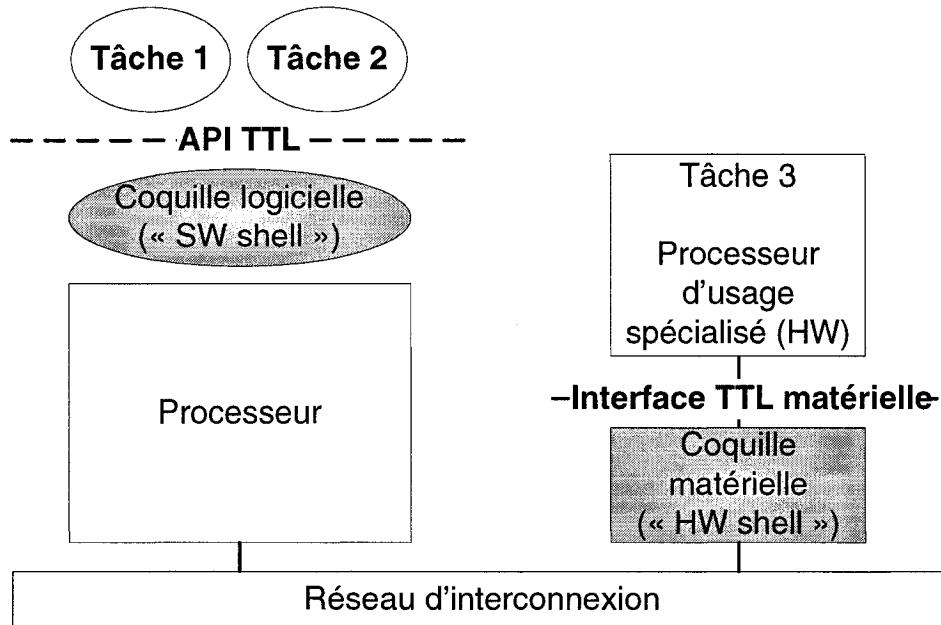

| Figure III.1 | L'interface TTL et ses coquilles logicielles et matérielles [3] . .                                                           | 133 |

## LISTE DES ACRONYMES

|                |                                                       |

|----------------|-------------------------------------------------------|

| <b>API</b>     | <b>Application Programmer Interface</b>               |

| <b>ASIC</b>    | <b>Application Specific Integrated Circuit</b>        |

| <b>ASIP</b>    | <b>Application Specific Instruction-set Processor</b> |

| <b>BRAM</b>    | <b>Block Random Access Memory</b>                     |

| <b>BCA</b>     | <b>Bus Cycle Accurate</b>                             |

| <b>CC-NUMA</b> | <b>Cache Coherent Nonuniform Memory Architecture</b>  |

| <b>CMP</b>     | <b>Chip MultiProcessors</b>                           |

| <b>CAF</b>     | <b>Co-Array Fortran</b>                               |

| <b>CAS</b>     | <b>Compare-And-Swap</b>                               |

| <b>CLB</b>     | <b>Configurable Logic Block</b>                       |

| <b>CMOS</b>    | <b>Complementary Metal Oxide Semiconductor</b>        |

| <b>DCM</b>     | <b>Digital Clock Manager</b>                          |

| <b>DSP</b>     | <b>Digital Signal Processor</b>                       |

| <b>E/S</b>     | <b>Entrée/Sortie</b>                                  |

| <b>EDA</b>     | <b>Electronic Design Automation</b>                   |

| <b>ESL</b>     | <b>Electronic System Level</b>                        |

| <b>FF</b>      | <b>Flip-Flop</b>                                      |

| <b>FIFO</b>    | <b>First-In-First-Out</b>                             |

| <b>FPGA</b>    | <b>Field Programmable Gate Array</b>                  |

| <b>HAL</b>     | <b>Hardware Abstraction Layer</b>                     |

| <b>IC</b>      | <b>Integrated Circuit</b>                             |

| <b>IDE</b>     | <b>Integrated Development Environment</b>             |

| <b>I/F</b>     | <b>Interface</b>                                      |

| <b>IP</b>      | <b>Intellectual Property</b>                          |

| <b>IPCP</b>    | <b>Immediate Priority Ceiling Protocol</b>            |

|        |                                                                                                                                           |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| IPIF   | <b>IP</b> InterFace                                                                                                                       |

| LMB    | <b>L</b> ocal <b>M</b> emory <b>B</b> us                                                                                                  |

| LUT    | <b>L</b> ook <b>U</b> p <b>T</b> able                                                                                                     |

| OS     | <b>O</b> perating <b>S</b> ystem                                                                                                          |

| MCS    | <b>M</b> ellor- <b>C</b> rummey et <b>S</b> cott                                                                                          |

| MPI    | <b>M</b> essage <b>P</b> assing <b>I</b> nterface                                                                                         |

| MPSoC  | <b>M</b> ulti <b>P</b> rocessor <b>S</b> ystem- <b>O</b> n- <b>C</b> hip                                                                  |

| NOC    | <b>N</b> etwork- <b>o</b> n- <b>C</b> hip                                                                                                 |

| NUCA   | <b>N</b> onuniform <b>C</b> ommunication <b>A</b> rchitecture                                                                             |

| NUMA   | <b>N</b> onuniform <b>M</b> emory <b>A</b> rchitecture                                                                                    |

| OPB    | <b>O</b> n-chip <b>P</b> eripheral <b>B</b> us                                                                                            |

| QOSB   | <b>Q</b> ueue <b>O</b> n <b>S</b> ync <b>B</b> it                                                                                         |

| PA     | <b>P</b> in <b>A</b> ccurate                                                                                                              |

| RAM    | <b>R</b> andom <b>A</b> ccess <b>M</b> emory                                                                                              |

| RoC    | <b>R</b> otator <b>O</b> n <b>C</b> hip                                                                                                   |

| RTU    | <b>R</b> eal <b>T</b> ime <b>U</b> nit                                                                                                    |

| SISSMA | <b>S</b> PACE engIne for <b>S</b> ynchronization of <b>S</b> ystemC <b>M</b> ultiprocessor/<br><b>M</b> ultithreaded <b>A</b> pplications |

| SLD    | <b>S</b> ystem <b>L</b> evel <b>D</b> esign                                                                                               |

| SLIC   | <b>S</b> ystem <b>L</b> ink and <b>I</b> nterrupt <b>C</b> ontroller                                                                      |

| SMP    | <b>S</b> ymmetric <b>M</b> ulti <b>P</b> rocessing                                                                                        |

| SMT    | <b>S</b> imultaneous <b>M</b> ulti <b>T</b> hreading                                                                                      |

| SoC    | <b>S</b> ystem- <b>O</b> n- <b>C</b> hip                                                                                                  |

| SoCLC  | <b>S</b> ystem- <b>O</b> n- <b>C</b> hip <b>L</b> ock <b>C</b> ache                                                                       |

| SoCSU  | <b>S</b> ystem- <b>O</b> n- <b>C</b> hip <b>S</b> ynchronization <b>U</b> nit                                                             |

| SPIN   | <b>S</b> calable <b>P</b> rogrammable <b>I</b> nterconnection <b>N</b> etwork                                                             |

|       |                                                                            |

|-------|----------------------------------------------------------------------------|

| SPMD  | <b>S</b> ingle <b>P</b> rogram <b>M</b> ultiple <b>D</b> ata               |

| SMT   | <b>S</b> imultaneous <b>M</b> ultithreading                                |

| RTOS  | <b>R</b> eal <b>T</b> ime <b>O</b> perating <b>S</b> ystem                 |

| TAS   | <b>T</b> est-and- <b>S</b> et                                              |

| TATAS | <b>T</b> est-and- <b>T</b> est-and- <b>S</b> et                            |

| TF    | <b>T</b> imed <b>F</b> unctionnal                                          |

| TLM   | <b>T</b> ransactional <b>L</b> evel <b>M</b> odel                          |

| TTL   | <b>T</b> ask <b>T</b> ransaction <b>L</b> evel <b>I</b> nterface           |

| UPC   | <b>U</b> nified <b>P</b> arallel <b>C</b>                                  |

| UTF   | <b>U</b> n <b>T</b> imed <b>F</b> unctional                                |

| VLIW  | <b>V</b> ery <b>L</b> ong <b>I</b> nstruction <b>W</b> ord                 |

| VHDL  | <b>V</b> HSIC <b>H</b> ardware <b>D</b> escription <b>L</b> anguage        |

| VHSIC | <b>V</b> ery <b>H</b> igh <b>S</b> peed <b>I</b> ntegrated <b>C</b> ircuit |

| UPC   | <b>U</b> nified <b>P</b> arallel <b>C</b>                                  |

## LISTE DES TABLEAUX

|             |                                                                                                                                                 |     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 3.1 | Pseudo code de l'opération Test-and-Set (TAS) . . . . .                                                                                         | 42  |

| Tableau 3.2 | Pseudo code de l'opération Test-and-Test-and-Set [4] . . . . .                                                                                  | 43  |

| Tableau 4.1 | Type de requêtes supportées par le modèle SystemC du moteur de synchronisation SISSMA . . . . .                                                 | 75  |

| Tableau 4.2 | Rôle des classes du modèle TLM du moteur de synchronisation SISSMA . . . . .                                                                    | 76  |

| Tableau 4.3 | Description des paramètres de configuration du module SISSMA en VHDL . . . . .                                                                  | 83  |

| Tableau 5.1 | Caractéristiques de la puce FPGA utilisée . . . . .                                                                                             | 86  |

| Tableau 5.2 | Performance de synchronisation offerte par le RTOS MicroC/OS-II . . . . .                                                                       | 91  |

| Tableau 5.3 | Tableau comparatif de la synchronisation locale sans optimisation                                                                               | 92  |

| Tableau 5.4 | Tableau comparatif de la synchronisation locale avec l'optimisation rédacteur/lecteur . . . . .                                                 | 93  |

| Tableau 5.5 | Tableau comparatif de la synchronisation à distance sans optimisation . . . . .                                                                 | 94  |

| Tableau 5.6 | Tableau comparatif de la synchronisation à distance avec l'optimisation rédacteur/lecteur . . . . .                                             | 95  |

| Tableau 5.7 | Temps d'exécution de la multiplication de deux matrices sur la plateforme monoprocesseur . . . . .                                              | 100 |

| Tableau 5.8 | Temps d'exécution de la multiplication de deux matrices sur la plateforme multiprocesseur . . . . .                                             | 100 |

| Tableau 5.9 | Tableau comparatif des gains d'accélération par l'utilisation d'une plateforme multiprocesseur pour la multiplication de deux matrices. . . . . | 101 |

|                |                                                                                                                                  |     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau V.1    | Description des codes d'erreur du moteur de synchronisation SISSMA . . . . .                                                     | 141 |

| Tableau V.2    | Encodage des commandes du moteur de synchronisation SISSMA                                                                       | 142 |

| Tableau V.3    | Description des acronymes . . . . .                                                                                              | 143 |

| Tableau VII.1  | Acronymes utilisés dans l'affichage des métriques logicielles . . . . .                                                          | 151 |

| Tableau VII.2  | Performance de synchronisation locale sans optimisation offerte par la bibliothèque SISSMA . . . . .                             | 151 |

| Tableau VII.3  | Performance de synchronisation à distance sans optimisation offerte par la bibliothèque SISSMA . . . . .                         | 152 |

| Tableau VII.4  | Performance de synchronisation locale avec l'optimisation rédacteur/lecteur offerte par la bibliothèque SISSMA . . . . .         | 152 |

| Tableau VII.5  | Performance de synchronisation à distance avec l'optimisation rédacteur/lecteur offerte par la bibliothèque SISSMA . . . . .     | 152 |

| Tableau VIII.1 | Acronymes utilisés dans l'affichage des métriques matérielles . . . . .                                                          | 153 |

| Tableau VIII.2 | Métriques matérielles - désactivation de l'optimisation rédacteur/lecteur et des sections critiques longues . . . . .            | 154 |

| Tableau VIII.3 | Métriques matérielles - désactivation de l'optimisation rédacteur/lecteur et activation des sections critiques longues . . . . . | 155 |

| Tableau VIII.4 | Métriques matérielles - activation de l'optimisation rédacteur/lecteur et désactivation des sections critiques longues . . . . . | 157 |

| Tableau VIII.5 | Métriques matérielles - activation de l'optimisation rédacteur/lecteur et des sections critiques longues . . . . .               | 158 |

**LISTE DES ANNEXES**

|             |                                                                                       |     |

|-------------|---------------------------------------------------------------------------------------|-----|

| ANNEXE I    | HIÉRARCHIE DE MÉMOIRE . . . . .                                                       | 122 |

| ANNEXE II   | SYSTEMC: COMPOSITION D'UN MODÈLE . . . . .                                            | 125 |

| ANNEXE III  | COMPLÉMENT À LA REVUE DE LITTÉRATURE . . . . .                                        | 127 |

| ANNEXE IV   | BIBLIOTHÈQUE SISSMA: VERSION PERSONNALISÉE .                                          | 135 |

| ANNEXE V    | BIBLIOTHÈQUE SISSMA : IMPLANTATION PERSONNALISÉE ET ENCODAGE DES REQUÊTES . . . . .   | 137 |

| ANNEXE VI   | INSTRUCTIONS ATOMIQUES SPÉCIALISÉES POUR LA SYNCHRONISATION MULTIPROCESSEUR . . . . . | 149 |

| ANNEXE VII  | MÉTRIQUES LOGICIELLES . . . . .                                                       | 151 |

| ANNEXE VIII | MÉTRIQUES MATÉRIELLES . . . . .                                                       | 153 |

## CHAPITRE 1

### INTRODUCTION

Cette section sert d'introduction au thème des systèmes-sur-puce. Il traite des aspects impliqués dans leur conception et des méthodes prédominantes de conception et de raffinements de ces derniers.

#### 1.1 Les systèmes embarqués d'aujourd'hui

Les systèmes embarqués sont omniprésents dans notre environnement. On les retrouve dans une multitude de domaines d'application, autant dans notre environnement quotidien (micro-onde, machine à laver, thermostats numériques, téléphone cellulaire) qu'au travail et dans les transports (assistant numérique personnel, lecteur de musique MP3 portatif, système de GPS portatif). De nos jours, une automobile contient en moyenne de 20 à 80 ordinateurs [5]. Dans cette optique, il n'est pas surprenant de constater que plus de 90 % des microprocesseurs vendus sur le marché, incluant les microcontrôleurs, soient destinés à des applications embarquées [6], plutôt qu'à des ordinateurs de travail (PC) ou des serveurs.

Le marché de l'électronique impose de constantes pressions aux concepteurs de systèmes embarqués. Les systèmes à concevoir doivent fournir un nombre croissant de fonctionnalités tout en offrant des performances améliorées. Il suffit d'observer l'évolution d'un système embarqué très populaire, le téléphone cellulaire. Les téléphones cellulaires ont non seulement diminué de format de génération en génération, mais offrent constamment plus de services, au-delà de la fonction d'émettre ou de recevoir des appels téléphoniques: carnet d'adresses, mini plateformes

de jeux, lecteur de musique numérique, prise de photos et enregistrement de vidéos numériques, etc.

Il est important de noter qu'une telle demande a un impact marqué sur la complexité des systèmes embarqués. Les systèmes embarqués de dernières générations comportent maintenant plusieurs processeurs, souvent de nature hétérogène, et de la logique personnalisée en plus de devoir répondre à des contraintes de performance. Alors que le terme performance faisait jadis référence au temps d'exécution d'une application ou à son débit, il prend désormais une toute autre signification. Malgré que ce dernier aspect de la performance soit toujours présent, d'autres qualificatifs sont venus s'y greffer. Les termes puissance et énergie font aujourd'hui partie de la définition de performance. Il n'est pas rare de constater que les systèmes embarqués opèrent à partir de batteries. Il est donc requis qu'ils performent correctement sur une longue période de temps sans demander le remplacement constant des piles utilisées.

Dans le même ordre d'idée, la dissipation de puissance reliée à un système embarqué prend de plus en plus d'importance. Cette dissipation d'énergie affecte directement le coût du système à concevoir [7], car il requiert l'utilisation d'un système de refroidissement et l'encapsulation du circuit intégré.

Il y a un besoin, dans le domaine de la conception de systèmes embarqués, pour de nouveaux outils. Ces outils devront nécessairement attaquer de face les complexités identifiées précédemment. Plus particulièrement, une des problématiques actuelles se situe au niveau de la productivité des méthodes utilisées. Essentiellement, les méthodes de conception utilisées depuis les dix dernières années ne parviennent plus à soutenir la cadence requise.

Bref, la conception et la fabrication de systèmes embarqués est un monde complexe où interagissent plusieurs domaines d'application: informatique, microélectronique,

réseautique et télécommunication, pour n'en nommer que quelques-uns.

### 1.1.1 Loi de Moore

Cette loi, qui représente plutôt une observation résultant de données empiriques, fut formulée en avril 1965 par Gordon E. Moore, co-fondateur de la compagnie Intel. Dans sa formulation la plus connue, la loi fait état de l'avancement de la technologie et constate que le nombre de transistors des circuits intégrés double tous les 18 mois. Il est indiqué de mentionner que la formulation désirée de la loi fait référence à une période de 24 mois, plutôt qu'à 18, avant que le nombre de transistors ne double [8].

La Loi de Moore, bien qu'elle se soit révélée correcte dans les années suivant sa formulation, est en fait devenue un objectif de performance pour l'ensemble de l'industrie de la microélectronique. Effectivement, l'industrie de semi-conducteurs s'est fixée comme objectif de pouvoir suivre cette tendance formulée à travers cette loi.

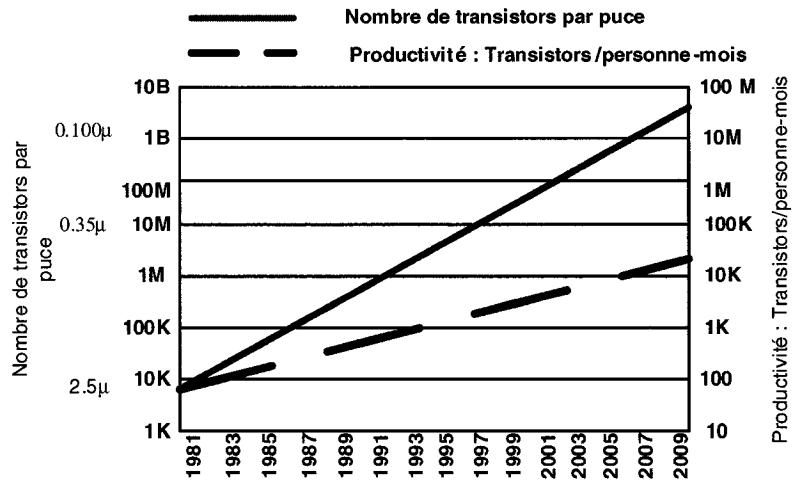

Toutefois, bien que les technologies de fabrication des circuits intégrés rendent disponibles tous ces transistors, il en résulte que les concepteurs ne parviennent pas à suivre cette cadence exposée dans la Loi de Moore. Bref, les systèmes à concevoir augmentent en termes de contenu (quantité de transistors) et en termes de performance (puissance, bande passante, latence, etc.). Par contre, les méthodes courantes de conception et de vérification ne permettent pas une telle progression. En somme, il en résulte la tendance montrée à la Figure 1.1.

Ainsi, il est possible d'observer que chaque nouvelle génération de technologie des semi-conducteurs creuse le fossé entre la productivité des concepteurs et le potentiel offert au niveau matériel par tous ces transistors. Un premier besoin se fait entendre afin de disposer de nouveaux outils permettant d'accroître la productivité des

Figure 1.1 Écart de la productivité

concepteurs. À titre d'exemple, aucun design, basé sur la technologie 90-nanomètres, n'excédait 50 millions de transistors d'utilisation, alors qu'ils disposaient du double de ressources [9].

### 1.1.2 Loi de Wirth

Dans un même ordre d'idée, il n'y a pas que la productivité dans le domaine matériel qui élargit ce fossé. Il apparaît que la conception logicielle requiert elle aussi un gain de productivité. Le domaine de la conception logicielle a fort à gagner à utiliser de nouvelles stratégies de vérification et de génération de code. D'une manière analogue à la Loi de Moore, Wirth a formulé en 1995 sa loi exposant une partie du problème dans le domaine logiciel. Il affirme ainsi que le « logiciel ralentit plus rapidement que le matériel accélère » [10]. Bref, Wirth remarque que bien que le matériel devienne de plus en plus rapide, cela ne signifie pas que le travail à accomplir se fait plus rapidement. En fait, les programmes conçus croissent et deviennent de plus en plus complexes, mais finalement, requièrent le même temps pour s'exécuter.

### 1.1.3 Loi de Rock

Cet aspect touchant le développement logiciel prend de l'ampleur lorsque l'on considère l'aspect économique de la fabrication de circuits intégrés. Effectivement, chaque nouvelle technologie des semi-conducteurs est plus coûteuse que la précédente. Arthur Rock, de par sa Loi (« Rock's Law »), arrive aux mêmes conclusions: « le coût de fabrication d'une nouvelle fabrique de semi-conducteurs double à tous les 4 ans » [11].

En somme, il est nécessaire d'adapter les méthodes de conception actuelles, tant matérielles que logicielles, afin de pallier ces difficultés.

Bien que différentes embûches se présentent afin de mieux exploiter les ressources offertes par l'industrie des semi-conducteurs, fidèles jusqu'à maintenant à la Loi de Moore, des systèmes des plus en plus compacts et performants sont produits. L'ère des systèmes-sur-puce débute.

## 1.2 Problématique

Les concepteurs de systèmes électroniques font face à plusieurs défis de taille. Non seulement sont-ils d'abord soumis à de fortes pressions afin de produire des systèmes plus avancés et plus complexes à chaque génération d'un produit, mais ils doivent accomplir cette tâche avec l'aide d'outils qui n'offrent pas la productivité nécessaire. À cette complexité propre au matériel s'ajoute une vérification aussi complexe ainsi qu'un contenu logiciel qui augmente constamment avec le temps [5].

De surcroît, il est essentiel d'accélérer et de faciliter la conception et l'implantation de systèmes-sur-puce multiprocesseurs, des plateformes qui gagnent en popularité, mais qui sont, elles aussi, négligées par les outils de conception actuels. Les approches

utilisées présentement parviennent de peine et de misère à développer de telles solutions. Leur contenu logiciel demande plusieurs milliers de lignes de code. Ce développement logiciel à bas niveau d'abstraction, où tous les détails sont pris en compte, demande beaucoup de temps [12]. La situation est similaire au niveau du matériel: concevoir au niveau RTL en plus de s'assurer du bon fonctionnement d'une plateforme contenant plusieurs processeurs demande d'énormes ressources, tant temporelles que financières.

D'une manière similaire, la conception d'une application et de sa plateforme associée se doit d'être dissociée à part entière de son implantation finale. Ainsi, les méthodes actuelles doivent être abstraites afin d'éliminer du processus de conception les dépendances envers le partitionnement possible du système et de ses détails de bas niveau.

Globalement, les systèmes conçus sont bel et bien validés. Toutefois, cette validation a lieu une fois l'intégration de tous les composants complétée. Une telle approche ne peut suffire face aux courts temps d'accès au marché et au nombre croissant de fonctionnalités à valider [13].

La bibliothèque SystemC adresse plusieurs de ces problèmes. SystemC permet d'abstraire un grand nombre de détails propres à l'implantation d'un système-surpuce, mais superflus quant à son design. La plateforme de conception SPACE [14], qui se base sur SystemC lui sert de complément tout en adressant des aspects négligés par SystemC. Ainsi, l'approche supportée par SPACE quant à la conception d'un produit électronique au niveau système vise la réduction des temps de conception et de vérification en plus de faciliter l'optimisation de ce dernier.

### 1.3 Objectifs

L'objectif principal de ce travail consiste à augmenter les fonctionnalités de la plateforme SPACE avec des services de synchronisation propices à une plateforme multiprocesseur. Ceux-ci se veulent complémentaires aux services de communication existants, qui reposent sur la transmission de messages. Ces services de synchronisation doivent être indépendants de la plateforme matérielle choisie tout en étant aisément configurables afin de ne pas restreindre les capacités de SPACE à déplacer des composants entre les couches logicielle et matérielle sans effort. Cette indépendance de la plateforme matérielle gagne en importance lorsque des composants, ne présentant pas des services particulièrement adaptés pour une solution multiprocesseur, telle l'utilisation de cache, cohérente ou pas, ou d'architecture mémoire particulière, sont utilisés afin de constituer une plateforme multiprocesseur. Cette importance implique que les services de synchronisation fournis doivent offrir un compromis satisfaisant entre flexibilité et performance.

### 1.4 Méthodologie

Pour débuter, une familiarisation avec la plateforme SPACE, sans oublier la bibliothèque SystemC, est de mise. Puisque SPACE repose sur le concept de modélisation au niveau système et de modélisation transactionnelle, il est essentiel d'être familier avec ces approches.

Par la suite, l'interface de programmation, à travers laquelle les services de synchronisation sont disponibles, sera conçue. Cette interface, bien que développée et implantée dans le langage C++ avec la complicité de SystemC, se doit d'être utilisable tant par des tâches logicielles que matérielles, tel que requis par la plateforme SPACE.

Ensuite, les mécanismes architecturaux génériques, référencés sous le nom du moteur de synchronisation, seront conçus. La conception de ce bloc matériel comprendra deux étapes. En premier lieu, un modèle transactionnel (TLM) de ce dernier sera conçu et par la suite optimisé. Une fois le modèle optimisé au niveau transactionnel, une version synthétisable sera implantée avec l'aide du langage de description matérielle VHDL.

Enfin, l'ensemble des composants définis, à savoir l'interface de programmation ainsi que son support matériel générique, sera utilisé afin d'exécuter la multiplication de deux matrices. Pour ce faire, un système-sur-puce multiprocesseur (MPSoC) sera conçu et le tout exécutera à partir d'une plateforme matérielle basée sur une puce reprogrammable (FPGA).

## 1.5 Contributions

Ce travail a d'abord permis d'explorer la littérature existante quant aux méthodes de synchronisation, développées pour les systèmes multiprocesseurs, et des applications dans un contexte de conception au niveau système pour des systèmes-sur-puce. Ainsi, une interface de programmation générique est désormais disponible dans SPACE afin de synchroniser des tâches. Ces tâches peuvent être implantées en logiciel comme en matériel et s'exécuter sur un même processeur tout comme être partitionnées sur des processeurs indépendants.

Ces interfaces utilisent leurs propres mécanismes, basés sur un module matériel générique, si nécessaire, et ne dépend donc aucunement de l'architecture choisie pour le système-sur-puce implanté. L'interface permet par conséquent d'abstraire tous les détails de synchronisation facilitant la conception au niveau système et la portabilité du code source créé.

Les services de synchronisation offerts tiennent aussi compte des contraintes possibles en temps réel et offrent des optimisations favorisant de meilleures performances: différents mode de synchronisation et d'éveil, un ordonnancement FIFO aux ressources de synchronisation et concurrence.

De plus, cette interface ainsi que son support matériel est entièrement intégrée dans SPACE, permettant de nouvelles possibilités quant à la conception de plateforme multiprocesseur, pavant la voie à de futurs travaux sur la modélisation de plateformes multiprocesseurs.

Enfin, les travaux effectués offrent la base requise afin de pouvoir extraire des métriques sur le système simulé par rapport à la synchronisation entre ses composants.

## 1.6 Organisation de ce mémoire

Ce mémoire est constitué de cinq chapitres. Le présent chapitre introduit le monde des systèmes embarqués et de la conception de systèmes électroniques. Le second chapitre introduit les systèmes-sur-puce multiprocesseurs. Il présente aussi d'une manière plus générale tous les aspects propres à leur conception. Enfin, il conclut avec une introduction aux différentes méthodes de conception au niveau système. Le chapitre 3 constitue une revue de littérature sur les techniques de synchronisation développées pour des plateformes multiprocesseurs. L'intégration de ces protocoles de synchronisation dans un environnement de codesign logiciel/matériel est ensuite décrit dans le chapitre 4. Ce chapitre décrit les objectifs ainsi que la conception de la bibliothèque de synchronisation SISSMA, dédiée à la conception au niveau système dans la plateforme SPACE. Le chapitre 5 présente les performances de cette bibliothèque de synchronisation. Enfin, une conclusion résume les travaux de recherche accomplis et propose des travaux futurs.

## CHAPITRE 2

### SYSTÈME-SUR-PUCE: DÉFINITION, PROBLÉMATIQUE ET CONCEPTION

Les technologies de conception de circuits intégrés offrent des densités d'intégration en constante augmentation. Au rythme actuel, il sera possible, d'ici une dizaine d'années, d'intégrer un milliard de transistors sur une même puce d'une taille raisonnable [15]. Il est essentiel d'identifier un parallélisme afin de tirer profit de toutes ces ressources.

Traditionnellement et encore aujourd'hui, il relève du microprocesseur d'exploiter le parallélisme inhérent à un programme. Les microprocesseurs disposent de nombreux mécanismes afin d'optimiser l'utilisation parallèle de leurs ressources afin d'augmenter leur performance. Ainsi, ils tirent profit du parallélisme au niveau du jeu d'instruction (« Instruction Level Parallelism (ILP) »), du pipeline d'exécution ou de la prédition de branche, pour nommer quelques techniques disponibles.

Toutefois, l'utilisation d'un seul fil d'exécution limite le parallélisme disponible pour de nombreuses applications. En fait, il devient de plus en plus coûteux, tant en complexité qu'en surface et en temps de conception ou de vérification, d'extraire ce parallélisme [15].

Depuis quelques années, les plateformes multiprocesseurs ont gagné en intérêt. Cet intérêt renouvelé pour de telles plateformes vient principalement des nouvelles technologies de la microélectronique, qui permettent leur intégration sur une même puce.

Le présent chapitre constitue une présentation générale des plateformes multipro-

cesseurs. Une courte description de leur début est d'abord donnée. Elle sera suivie par une description des différents types de plateformes multiprocesseurs ainsi que leurs distinctions. Dans un second volet, une revue littéraire de plusieurs plateformes multiprocesseurs commerciales est montrée.

## 2.1 Définitions: Soc et MPSoC

### 2.1.1 Système-sur-Puce (SoC)

Tout d'abord, il convient de définir ce qu'est un système-sur-puce, communément référé sous l'appellation « System-on-Chip » ou SoC dans la littérature. Un système-sur-puce est un circuit intégré qui implante la majorité ou l'ensemble des fonctions d'un système électronique complexe. De façon générale, un système-sur-puce est principalement constitué de logique numérique. Il peut contenir un processeur de jeu d'instructions, de la mémoire, des bus de communication, de la logique spécialisée ou d'autres fonctions numériques. Les systèmes-sur-puce se retrouvent dans différentes catégories de produits, tel le domaine de la télécommunication par leur utilisation dans les téléphones cellulaires [7].

Des besoins croissants en termes de performance ont amené les concepteurs à concevoir des systèmes-sur-puce multiprocesseurs.

### 2.1.2 Système-sur-Puce Multiprocesseur (MPSoC)

Les systèmes-sur-puce multiprocesseurs, ou « Multiprocessor System-on-Chip (MP-SoC) », constituent une simple extension au système-sur-puce. Ainsi, un système-sur-puce multiprocesseur est simplement un système-sur-puce qui utilise plusieurs

processeurs. Les MPSoCs sont complexes à concevoir en partie dû aux fonctions sophistiquées qu'ils implémentent et en partie à cause de la grande variété de technologies impliquées afin d'accomplir le travail [5].

Enfin, bien que les systèmes-sur-puce multiprocesseurs soient relativement récents, ce n'est pas le cas des systèmes multiprocesseurs. La section qui suit donne un bref historique des systèmes multiprocesseurs. L'expérience acquise au cours des 45 dernières années avec ces systèmes peut maintenant être transmise aux concepteurs de MPSoC.

Toutefois, bien que ce transfert de connaissance ne soit pas nouveau en tant que soi, il reste néanmoins que beaucoup de connaissances acquises au niveau des systèmes de traitement parallèle relèvent d'applications scientifiques, de bases de données ou d'autres applications qui diffèrent beaucoup des systèmes embarqués. Deux nouveaux aspects notables apportés par les systèmes-sur-puce multiprocesseurs sont [16]:

1. Les opérations en temps réel

2. Les opérations à faible consommation d'énergie et de puissance.

#### 2.1.2.1 Origine des systèmes multiprocesseurs

Les systèmes multiprocesseurs ont fait leur apparition au début des années 1960 [17]. L'intérêt principal pour de tels systèmes émanait du fait qu'ils étaient fiables et redondants, qu'ils couvraient plusieurs gammes de prix et de performance, et ce, pour un nombre réduit de designs différents, et qu'ils supportaient des mises à jour incrémentales [17]. Toutefois, il fut déjà identifié à cette époque que tous ces avantages des systèmes multiprocesseurs étaient contrebalancés par un certain nombre d'inconvénients. Les systèmes multiprocesseurs demandent notamment des temps de conception allongés, leur extensibilité (« scalability ») est limitée et l'obsolescence

rapide de certains composants matériels limite l'application de mises à jour. De plus, un manque flagrant de supports logiciels, particulièrement au niveau des systèmes d'exploitation et des modèles de programmation, affecte négativement les systèmes multiprocesseurs par rapport aux systèmes monoprocesseurs existants [17].

Gorden Bell et Catharine Van Ingen présentent un résumé de l'évolution des systèmes multiprocesseurs, depuis leur tout début jusqu'en 1999, dans [17].

## **2.2 Complexité de la conception de systèmes-sur-puce au niveau système**

La conception et l'implantation d'un système-sur-puce (SoC), multiprocesseur ou non, englobent de nombreux aspects. La section suivante identifie et donne une description de chacun de ces aspects. Cette section a pour objectif de donner une vue globale de ce qu'un tel design implique.

### **2.2.1 Synthèse logicielle et matérielle**

Tout d'abord, tous les systèmes électroniques se composent d'une partie matérielle et d'une partie logicielle, aussi simple peut-elle être. Le processus de génération de ces deux couches porte le nom de synthèse logicielle et de synthèse matérielle. La génération logicielle implique la création de l'application qui s'exécutera sur le SoC. La génération matérielle implique la création de la plateforme qui supportera la couche logicielle. Il est essentiel de distinguer la synthèse matérielle du processus de synthèse numérique qui peut être utilisé pour générer automatiquement cette couche matérielle. Toutefois, la synthèse numérique n'est pas la seule avenue disponible pour y arriver. D'autres approches sont décrites dans la section 2.3.4, notamment l'utilisation de plateformes préconçues ou de plateformes constituées par l'assemblage

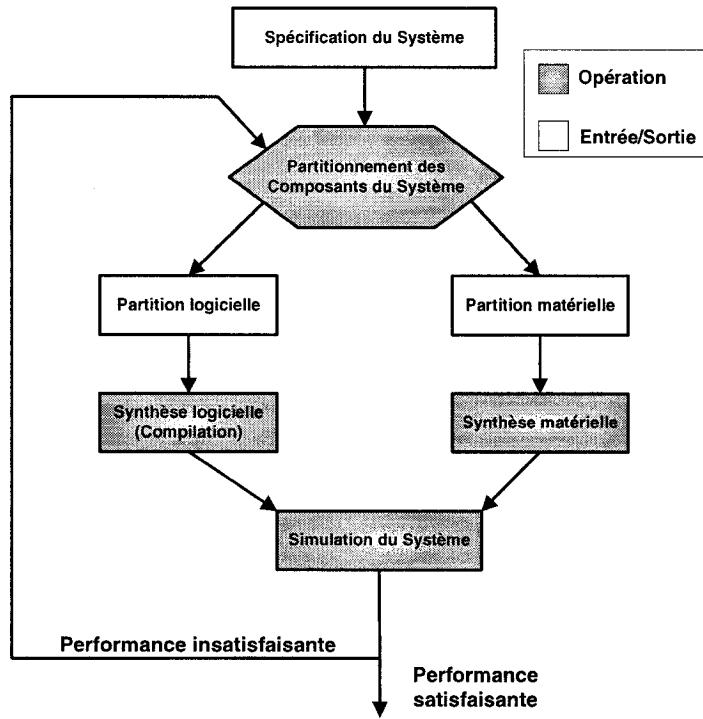

Figure 2.1 Processus de partitionnement logiciel/matériel

de composants existants.

### 2.2.2 Architecture système et partitionnement logiciel/matériel

L'étape de génération des couches logicielles et matérielles ne constitue que la conclusion du processus de conception et l'implantation d'un SoC. De prime abord, il est primordial de concevoir ce système afin qu'il réponde aux requis tant en termes de fonctionnalités que de performance.

Le partitionnement logiciel/matériel est défini comme le processus décisionnel à travers lequel l'ensemble des fonctionnalités du système est partagé entre les couches logicielles et matérielles. La Figure 2.1 illustre ce processus.

Tel qu'illustré, le processus de partitionnement logiciel/matériel cherche la solution optimale répondant aux contraintes du système. Les contraintes typiques à respecter peuvent être techniques (énergie requise, puissance dissipée, surface consommée, temps d'exécution, bande passante, consommation de mémoire) ou économiques. Économiquement, il est généralement moins dispendieux de développer des composants logiciels comparativement à leur équivalent matériel. Toutefois, ils sont aussi moins performants et requièrent l'utilisation d'un processeur adapté à leurs besoins (processeur d'usage général, microcontrôleur, processeur VLIW, DSP ou ASIP).

### 2.2.3 Performance des communications

Bien que le partitionnement logiciel/matériel identifie quels composants constitueront les couches logicielle et matérielle, il n'indique pas nécessairement comment ils y sont organisés. D'ailleurs, l'architecture d'un SoC identifie non seulement la nature des composants présents, mais surtout leurs interconnexions. Le réseau de communication qui unit tous les composants du SoC est un facteur déterminant de ses performances et de la surface requise pour son implantation. Traditionnellement, ce réseau reposait sur l'utilisation d'un bus de communication. Depuis quelques années, une variété de réseaux-sur-puce ont fait leur apparition. Il y a notamment les réseaux basés sur une topologie en anneau (Token Ring, Rotator-on-Chip [18][19]), ceux basés sur des arbres (SPIN [20]) ou encore ceux prenant une topologie en maille (Hot Potato [21]) ou le typique crossbar. Bref, la gestion des communications constitue un autre aspect important de la conception d'un SoC.

#### 2.2.4 Synchronisation

Un aspect qui gagne en importance avec l'avènement des systèmes-sur-puce multiprocesseurs (MPSoC) est la synchronisation. La synchronisation englobe l'ensemble des aspects relatifs à l'exécution correcte de multiples fils d'exécution, tel dans une plateforme multiprocesseur ou avec une application multitâche, ainsi que la protection des ressources partagées. De plus, l'exécution des comportements désirés de l'application au moment approprié relève de la synchronisation.

#### 2.2.5 La nature hétérogène des composants

La conception d'un SoC constitue l'agglomération de plusieurs composants, souvent de nature hétérogène, augmentant par le fait même la complexité de ce processus. Des exemples de SoC sont donnés à la section 2.3.4.3. Il est possible de remarquer que ces plateformes sont souvent constituées d'un processeur à usage général en plus d'un processeur spécifique (DSP, processeur réseau, accélérateurs spécifiques), sans oublier le support d'une gamme de périphériques distincts, des mémoires, un réseau de communication et des unités de traitement spécifiques (« custom logic »).

#### 2.2.6 La pile logicielle

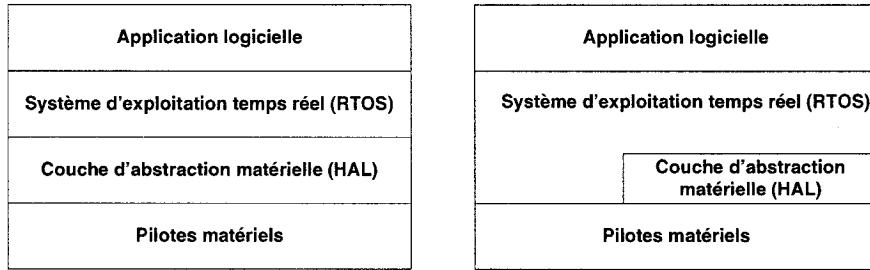

La couche logicielle d'un SoC peut prendre différentes saveurs en fonction des besoins requis. Ainsi, bien que cette couche semble n'abriter que l'application s'exécutant en coopération avec les services fournis dans la couche matérielle, celle-ci cache en fait une pile complète de services. Les principaux éléments de cette pile sont montrés à la Figure 2.2.

Typiquement, le premier niveau implante les comportements de l'application. Ils

Figure 2.2 Les différents éléments de la couche logicielle

sont typiquement modélisés dans un langage de programmation tel le C/C++ ou même en assembleur. À l'autre extrême de cette pile, les pilotes (ou « drivers ») servent d'interface vers la couche matérielle. Les pilotes sont propres aux composants de la couche matérielle. Ils permettent l'interaction entre une application et un composant matériel. Par exemple, une minuterie, un contrôleur d'interruption, un contrôleur Ethernet et un UART possèdent chacun leur propre pilote spécifique à leurs fonctionnalités.

Bien que ces deux éléments de la pile logicielle peuvent répondre à tous les besoins d'une application destinée à un SoC, deux autres couches peuvent être présentes afin d'offrir des services additionnels.

Il est possible qu'une application requière les services d'un système d'exploitation (« Operating System, OS ») ou d'un système d'exploitation temps réel (« Real Time Operating System, RTOS »). D'une manière générale, le système d'exploitation est essentiellement un programme logiciel qui gère les ressources logicielles et matérielles d'un système. De la même façon, un système d'exploitation temps réel constitue une classe spécialisée des systèmes d'exploitation. Toutefois, ceux-ci sont destinés à des applications temps-réel. Bref, ils sont conçus afin d'être déterministes et ainsi répondre à des contraintes de temps dans des échéances prescrites. eCos [22], INTEGRITY [23], QNX [24], MicroC/OS-II [25], Nucleus [26], RTEMS [27], RTLinux

[28], ThreadX [29] et VxWorks [30] sont quelques exemples de systèmes d'exploitation temps réel.

La couche d'abstraction du matériel, communément appelée « Hardware Abstraction Layer » ou HAL, sert d'interface entre l'application ou le RTOS et les pilotes. Bref, cette couche permet une séparation entre les détails de bas niveau requis pour interagir avec le matériel et l'application logicielle [13]. Il est possible que cette couche fasse partie du système d'exploitation, ce qui explique les deux représentations de la Figure 2.2.

Les systèmes embarqués, nonobstant les SoC, étant des systèmes répondant à des besoins précis, il n'est pas inhabituel qu'une combinaison de ces différentes couches se retrouve dans la pile logicielle en fonction des besoins exprimés par l'application. Ces différentes couches favorisent la modularité et la réutilisation des éléments logiciels conçus. Il est à noter que la couche logicielle sert parfois de facteur différentiateur entre deux produits qui, sous toutes apparences, utilisent une même plateforme matérielle. La couche logicielle prend de plus en plus d'ampleur avec le gain de popularité des plateformes programmables, où un SoC peut contenir plusieurs millions de lignes de code [31].

Cette section a identifié les principales étapes présentes dans le processus de conception d'un système-sur-puce. La section suivante présente l'évolution des méthodologies de conception.

### 2.3 Conception de systèmes-sur-puce multiprocesseurs

Alors que l'intégration de multiples processeurs sur une même puce n'était qu'une tendance il y a quelques années [12], de tels systèmes font maintenant partie de la

réalité. Toutefois, les méthodes de conception traditionnelles se doivent d'évoluer au même rythme que les besoins qu'ils rencontrent. Les sections qui suivent présentent l'évolution des méthodes de conception de systèmes embarqués et de systèmes-surpuce, à partir de l'approche plus traditionnelle de conception jusqu'à la conception au niveau système.

### 2.3.1 Approche traditionnelle à la conception

Le point de départ de tout système implique **la définition de ses requis et spécifications**. Cette première étape cible le fonctionnement du système: ses fonctionnalités et son mode d'opération. Une fois le système défini, les concepteurs traversent une phase d'**exploration architecturale**. Cette phase identifie, pour chaque module, s'il sera implanté dans la couche logicielle ou dans la couche matérielle du système. Le processus décisionnel de ce partitionnement logiciel/matériel repose sur les contraintes du système, à savoir la surface qu'il occupe, ses restrictions au niveau de la consommation d'énergie, sa puissance d'opération et les performances d'exécution qui lui sont imposées ou requises. Par la suite, une fois les spécifications définies et l'architecture choisie, une séparation se produit : **le développement de la couche logicielle et de la couche matérielle** débute de façon parallèle, mais séparée [32]. Néanmoins, il se trouve que les équipes logicielles et matérielles reposent sur la qualité et l'exactitude des spécifications initiales, souvent rédigées dans un langage informel.

La faiblesse principale d'une telle approche repose sur le fait que la décision du partitionnement logiciel/matériel se fait a priori, sans expérimentation concrète sur le système cible. De plus, la solution implantée, étant fortement dépendante de la partition choisie, il devient coûteux et complexe en temps de conception de changer de partitions par la suite [33]. Enfin, l'approche traditionnelle au partitionnement

consiste souvent à chercher une solution offrant le plus de contenu logiciel possible. Dans l'éventualité où les performances ne sont pas satisfaisantes, une partie des fonctionnalités est alors transférée en matériel.

Bref, l'approche traditionnelle de la conception peut tirer profit d'un environnement unifié où le logiciel et le matériel sont représentés. Cet environnement permet la vérification complète du système en plus de clairement démarquer la séparation logicielle/matérielle. Également, le choix préétabli de la partition mène à des designs sous-optimaux. La décision de partitionnement doit reposer sur des métriques réelles, vérifiables, applicables aux systèmes en cours de conception. Somme toute, un flot de conception mieux défini offrirait de meilleures garanties quant à la complexité du système à concevoir ainsi qu'au temps d'accès au marché.

### 2.3.2 Codesign logiciel/matériel

Devant les faiblesses de l'approche traditionnelle, le codesign logiciel/matériel a pris forme. Cette approche se veut une évolution de l'approche traditionnelle. Voici un bref aperçu de ce qu'est le codesign logiciel/matériel [34].

Les méthodologies de codesign cherchent d'abord à apporter une solution aux concepteurs pris avec des méthodes ad hoc quant au partitionnement logiciel/matériel de leur système. L'objectif du codesign logiciel/matériel est d'identifier un flot de conception dirigée permettant d'optimiser le processus de partitionnement logiciel/matériel et de réduire les coûts de conception et le temps d'accès au marché. Par le fait même, ce flot de conception évolué réduit les coûts directs du produit, facilite l'intégration du système et génère automatiquement les interfaces entre le logiciel et le matériel.

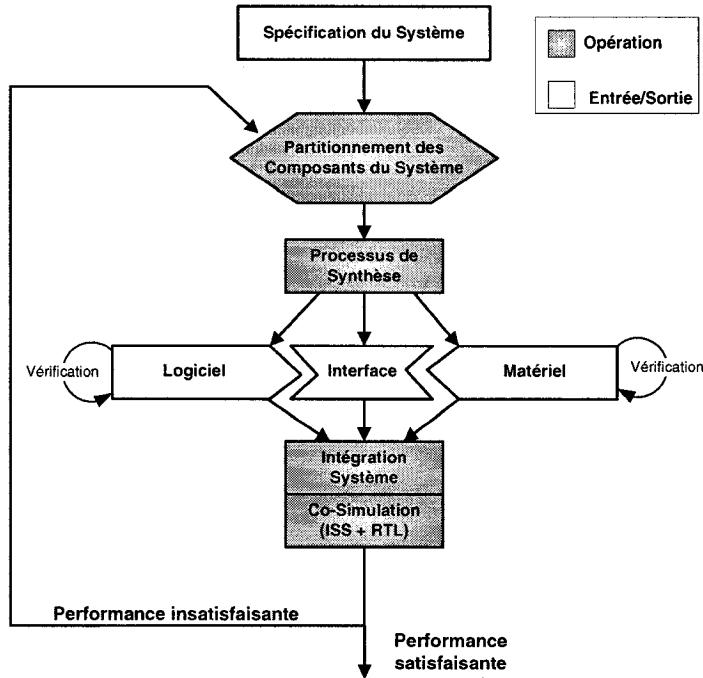

La Figure 2.3 illustre le flot de conception suggéré par la méthodologie de codesign logiciel/matériel.

Figure 2.3 Flot de conception du codesign logiciel/matériel

Le point de départ reste le même : la spécification du système. Toutefois, une variante apparaît. La modélisation du système requiert un processus itératif plus efficace afin d'identifier le partitionnement logiciel/matériel optimal. Le codesign utilise un environnement intégré de cosimulation où le logiciel et le matériel interagissent. Cet environnement permet un retour plus rapide sur les décisions de la conception initiale du système comme suite aux informations obtenues durant la cosimulation.

La faiblesse principale de la méthodologie de codesign logiciel/matériel, telle que décrite plus tôt, tient d'abord du temps de développement qu'elle impose. La décision de partitionnement repose sur les métriques de performance obtenues lors de la cosimulation des composants logiciels et matériels. D'une part, les composants matériels sont modélisés dans un langage de description matériel (HDL) tel que VHDL ou Verilog. Parallèlement, les composants logiciels sont typiquement implantés dans

Figure 2.4 Configuration d'une co-simulation logicielle/matérielle entre un simulateur de jeux d'instructions et une partition matérielle

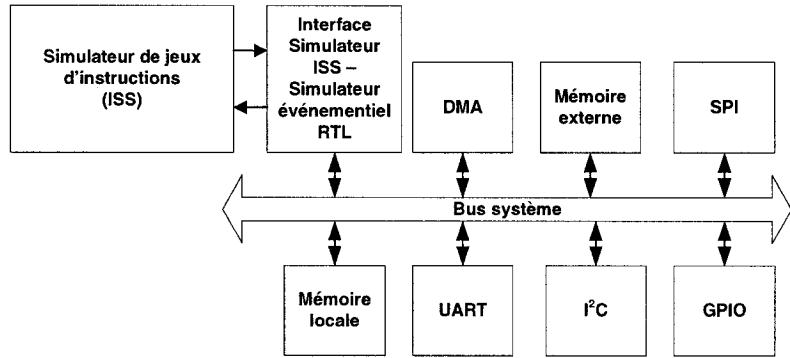

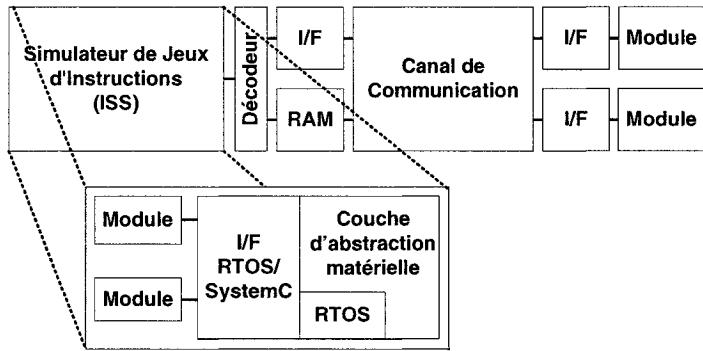

un langage de programmation tel C/C++ ou en assembleur. Durant la simulation, l'application logicielle s'exécute sur un simulateur de jeux d'instructions, ou ISS pour « Instruction Set Simulator ». Ce simulateur de jeux d'instructions interagit avec les blocs matériels afin d'émuler les comportements du système conçu. Cet arrangement est présenté à la Figure 2.4.

Bien qu'un tcl environnement procure un niveau de précision très élevé, il requiert aussi un long temps de simulation. Effectivement, les blocs matériels, étant implantés au niveau RTL, ou « Register Transfer Level », et le simulateur de jeux d'instructions, offrant le même niveau de précision, prennent beaucoup de temps à s'exécuter dû à la grande quantité de détails disponibles durant la simulation du système. À cela, s'ajoute un temps de conception relativement long des composants du système qui sont implantés avec le maximum de détails et de précision. Bref, cela affecte directement le temps de développement, principalement en ce qui a trait au processus d'identification de la partition optimale.