**Titre:** Paramétrisation et reconfiguration automatique du chemin de données d'un processeur synthétisable

Title: [Paramétrisation et reconfiguration automatique du chemin de données d'un processeur synthétisable](#)

**Auteur:** Alexandre Fortin

Author: [Alexandre Fortin](#)

**Date:** 2000

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Fortin, A. (2000). Paramétrisation et reconfiguration automatique du chemin de données d'un processeur synthétisable [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7814/>

Citation: [Fortin, A. \(2000\). Paramétrisation et reconfiguration automatique du chemin de données d'un processeur synthétisable \[Mémoire de maîtrise, École Polytechnique de Montréal\]. PolyPublie. https://publications.polymtl.ca/7814/](#)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7814/>

PolyPublie URL: [https://publications.polymtl.ca/7814/](#)

**Directeurs de recherche:** Yvon Savaria, & Mohamad Sawan

Advisors: [Yvon Savaria](#), [Mohamad Sawan](#)

**Programme:** Non spécifié

Program: [Non spécifié](#)

UNIVERSITÉ DE MONTRÉAL

PARAMÉTRISATION ET RECONFIGURATION

AUTOMATIQUE DU CHEMIN DE DONNÉES

D'UN PROCESSEUR SYNTHÉTISABLE

ALEXANDRE FORTIN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ET DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

AOÛT 2000

National Library

of Canada

Acquisitions and

Bibliographic Services

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque nationale

du Canada

Acquisitions et

services bibliographiques

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-65561-X

Canadä

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

PARAMÉTRISATION ET RECONFIGURATION

AUTOMATIQUE DU CHEMIN DE DONNÉES

D'UN PROCESSEUR SYNTHÉTISABLE

Présenté par : FORTIN Alexandre

En vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

M. BOIS Guy, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

M. SAWAN Mohamad, Ph.D., membre et codirecteur de recherche

M. ABOULHAMID Moustapha, Ph.D., membre

## RÉSUMÉ

Les processeurs de traitement de signaux (*DSP*) sont utilisés dans un nombre d'applications toujours grandissant. De plus, ceux-ci doivent être performants et optimisés aux tâches à accomplir tout en minimisant le temps de développement. Ce mémoire présente donc l'architecture d'un chemin de données hautement parallèle et configurable, de type SIMD (*Single Instruction Multiple Data*).

Le point de départ étant un processeur développé en vue d'une implantation dans un ASIC, la première partie du travail consistait à adapter l'architecture afin de porter l'implantation vers un FPGA de la série Virtex de Xilinx. La seconde étape de développement, plus complexe, nous a amené à effectuer plusieurs transformations du code VHDL, de telle sorte que le chemin de données puisse être complètement configurable. En effet, selon l'application demandée, l'architecture peut dorénavant être optimisée, lors de la synthèse du circuit, à l'aide de quelques paramètres contrôlant entre autres la largeur des mots de donnée, les dimensions des registres et des mémoires et le nombre d'éléments de calcul (*PE*) composant le chemin de données. De plus, le chemin de données est modulaire. En effet, chaque module composant un PE peut être individuellement inclus ou exclus de l'architecture, sans affecter le fonctionnement des autres modules. Toutes les stratégies déployées pour l'atteinte de ces résultats sont expliquées dans le présent mémoire, en accordant une importance particulière au multiplicateur en raison de son architecture difficilement paramétrable.

## ABSTRACT

DSPs are used in a continuously growing number of applications. They should provide a high performance, while offering a short development time. This master thesis presents the architecture of a highly parallel and configurable datapath, which is a SIMD (*Single Instruction Multiple Data*) type.

The starting point of this work was a processor first developed as an ASIC. Hence, the first task to realize was to adapt the architecture to a FPGA implementation, specifically a model part of the Virtex family produced by Xilinx. The second stage of the development, more complex, was to modify the VHDL code of the datapath in order to make it completely configurable. In fact, the architecture can now be optimised to the desired application with only a few parameters that adapt the circuit during the synthesis phase. For example, the bit width of the data words, the depth of the registers and the memories, and the number of processing elements (*PE*) that compose the datapath are all parameterizable. In addition, the datapath is modular by allowing each module part of a *PE* to be included or excluded, without affecting the function of the other modules. All the strategies deployed to reach these results are explained in this thesis. Finally, a particular attention is given to the multiplier since its architecture is particularly complex to parameterize.

## TABLE DES MATIÈRES

|                                                                             |             |

|-----------------------------------------------------------------------------|-------------|

| <b>Résumé .....</b>                                                         | <b>iv</b>   |

| <b>Abstract.....</b>                                                        | <b>v</b>    |

| <b>Table des matières .....</b>                                             | <b>vi</b>   |

| <b>Liste des tableaux .....</b>                                             | <b>x</b>    |

| <b>Liste des figures .....</b>                                              | <b>xi</b>   |

| <b>Liste des abréviations.....</b>                                          | <b>xiii</b> |

| <b>Introduction .....</b>                                                   | <b>15</b>   |

| <b>Revue de littérature.....</b>                                            | <b>21</b>   |

| 1.1 Processeur ARC .....                                                    | 22          |

| 1.2 Processeur Xtensa .....                                                 | 25          |

| 1.3 Comparaison et applications .....                                       | 27          |

| 1.4 Méthodes de conception de processeurs configurables.....                | 28          |

| 1.4.1 Modules nécessaires et optionnels .....                               | 29          |

| 1.4.2 Flexibilité versus complexité .....                                   | 30          |

| 1.4.3 Architecture basée sur les transferts de données à haute vitesse..... | 30          |

| 1.4.4 Utilisation de librairies hiérarchiques de modules VHDL .....         | 31          |

| 1.4.5 Synthèse de processeurs DSP par analyse d'algorithmes .....           | 34          |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| <b>1.5 Exemples de designs configurables.....</b>           | <b>36</b> |

| 1.5.1 Module VS_DSP .....                                   | 36        |

| 1.5.2 MetaCore .....                                        | 37        |

| 1.5.3 Générateur de processeurs RISC configurables .....    | 37        |

| 1.5.4 PINE .....                                            | 38        |

| 1.5.5 RaPID .....                                           | 39        |

| <b>1.6 Reconfigurabilité .....</b>                          | <b>40</b> |

| 1.6.1 Reconfigurabilité statique .....                      | 41        |

| 1.6.2 Reconfigurabilité dynamique .....                     | 42        |

| <b>Multiplicateur configurable, signé et pipeliné .....</b> | <b>45</b> |

| 2.1 Introduction .....                                      | 46        |

| 2.2 Multiplier architecture.....                            | 49        |

| 2.3 Algorithm .....                                         | 56        |

| 2.4 Pipelining strategy.....                                | 58        |

| 2.5 Results .....                                           | 63        |

| 2.6 Conclusion.....                                         | 72        |

| <b>Architecture initiale et technologie visée.....</b>      | <b>74</b> |

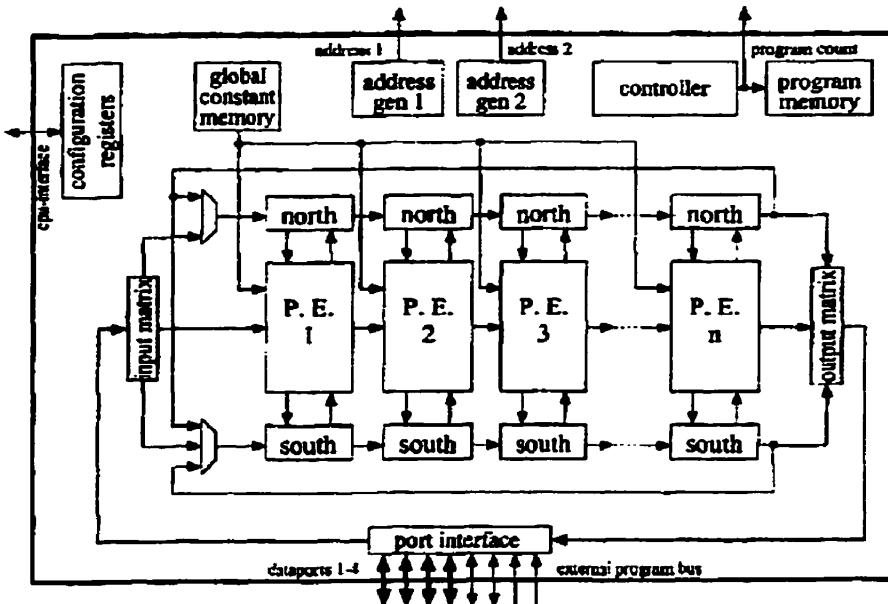

| 3.1 Architecture PULSE.....                                 | 75        |

| 3.1.1 Architecture de haut niveau.....                      | 75        |

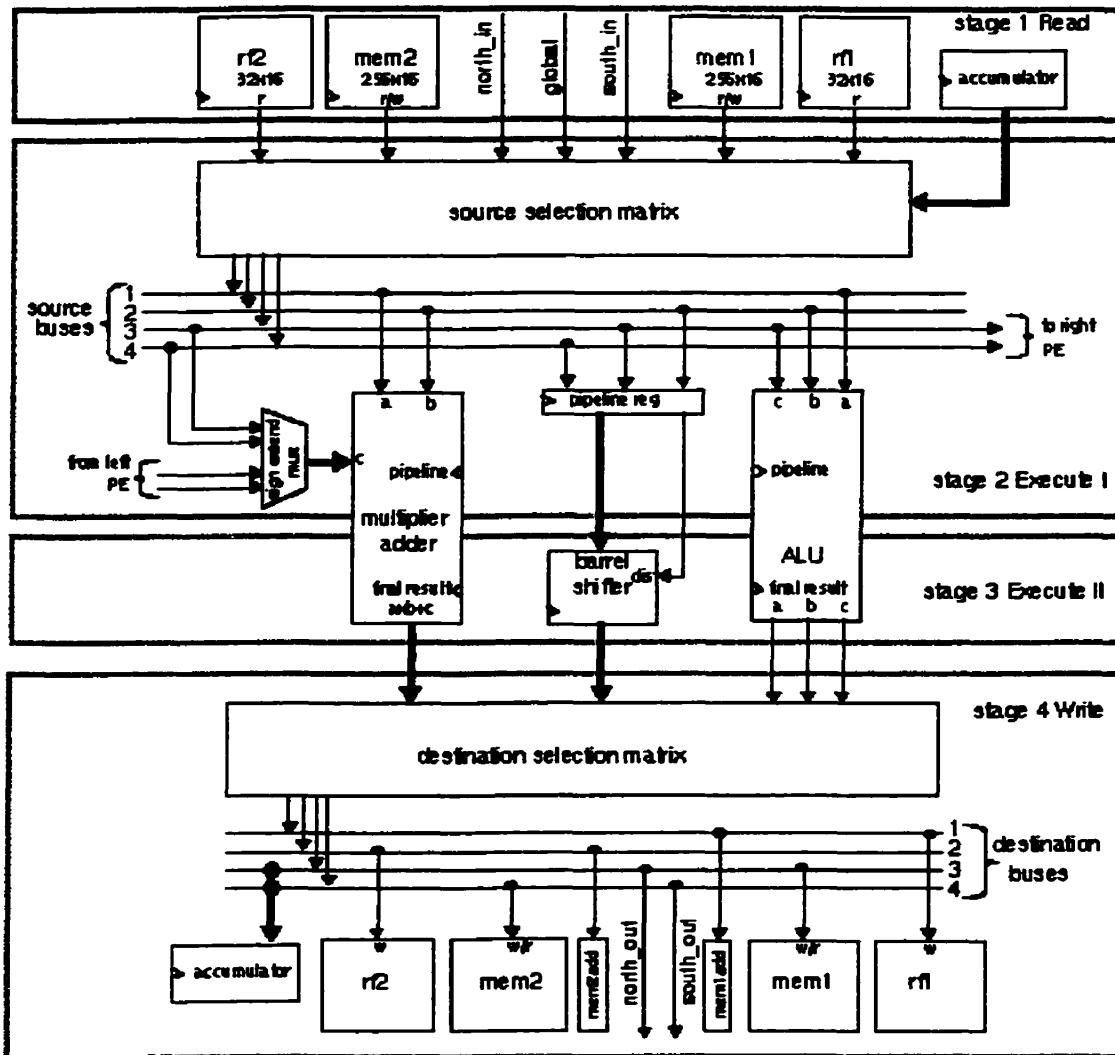

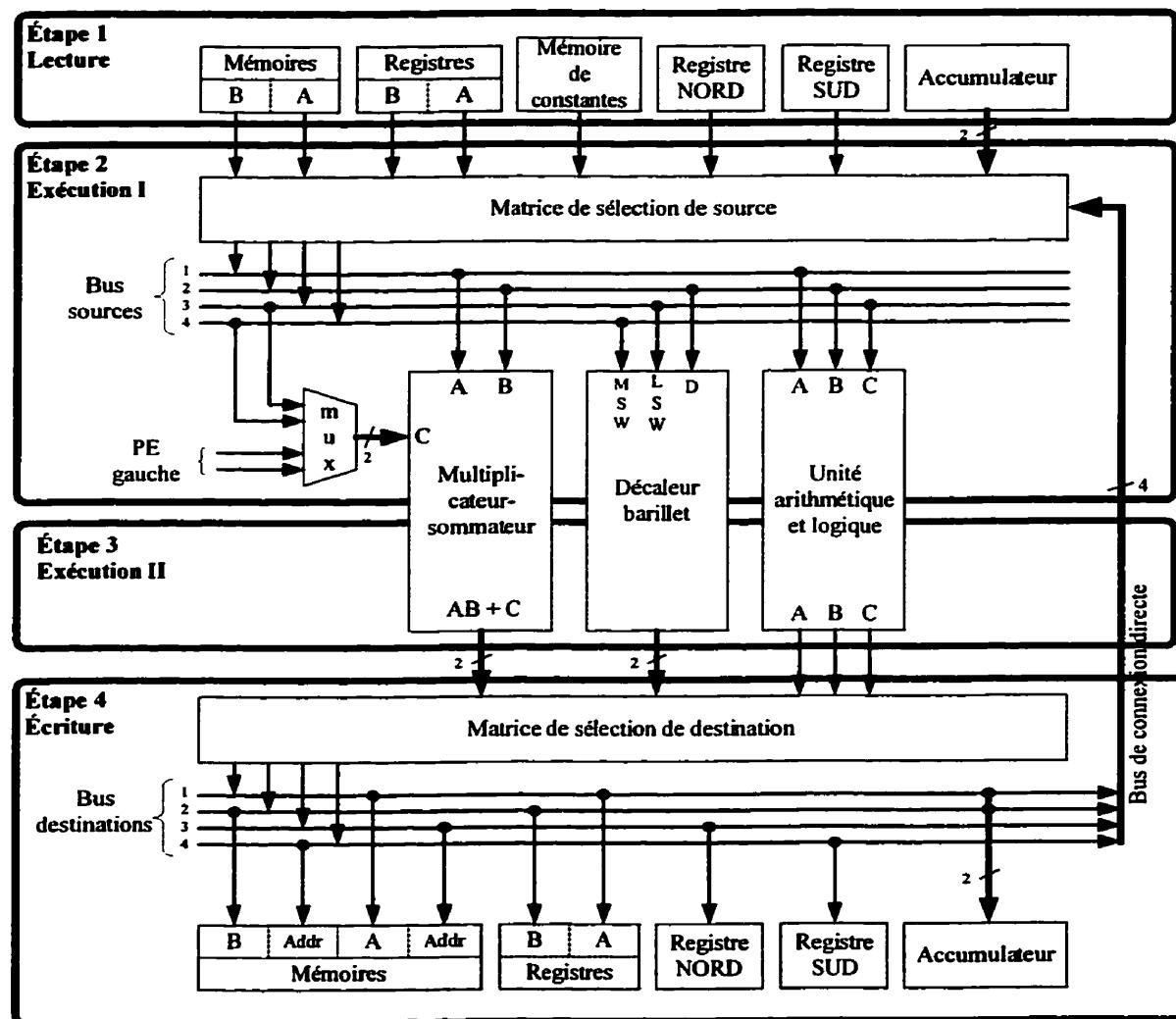

| 3.1.2 Architecture du chemin de données .....               | 76        |

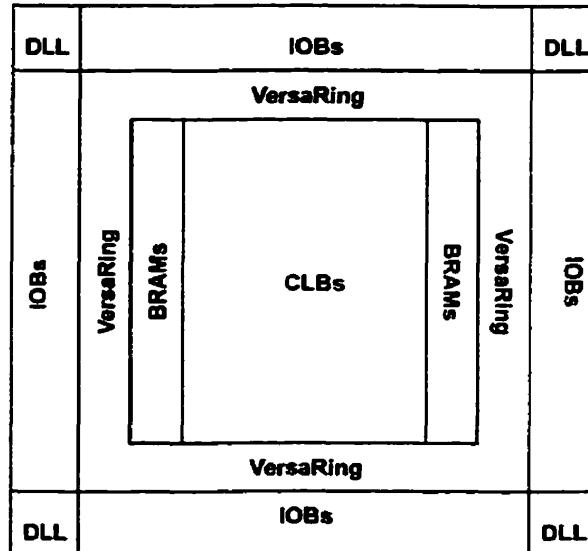

| 3.2 Technologie d'implantation .....                        | 80        |

|       |                                                                       |           |

|-------|-----------------------------------------------------------------------|-----------|

| 3.2.1 | Mémoire disponible.....                                               | 82        |

| 3.2.2 | Interconnexions .....                                                 | 83        |

| 3.2.3 | Logique arithmétique .....                                            | 84        |

| 3.2.4 | Tampons à trois états.....                                            | 85        |

| 3.3   | Outils logiciels.....                                                 | 85        |

| 3.3.1 | Simulation et validation .....                                        | 86        |

| 3.3.2 | Synthèse .....                                                        | 87        |

| 3.3.3 | Placement et routage .....                                            | 88        |

|       | <b>Optimisation et paramétrisation.....</b>                           | <b>91</b> |

| 4.1   | Optimisation et modification de l'architecture.....                   | 92        |

| 4.1.1 | Modification des sélecteurs de bus .....                              | 93        |

| 4.1.2 | Modification des mémoires et registres .....                          | 95        |

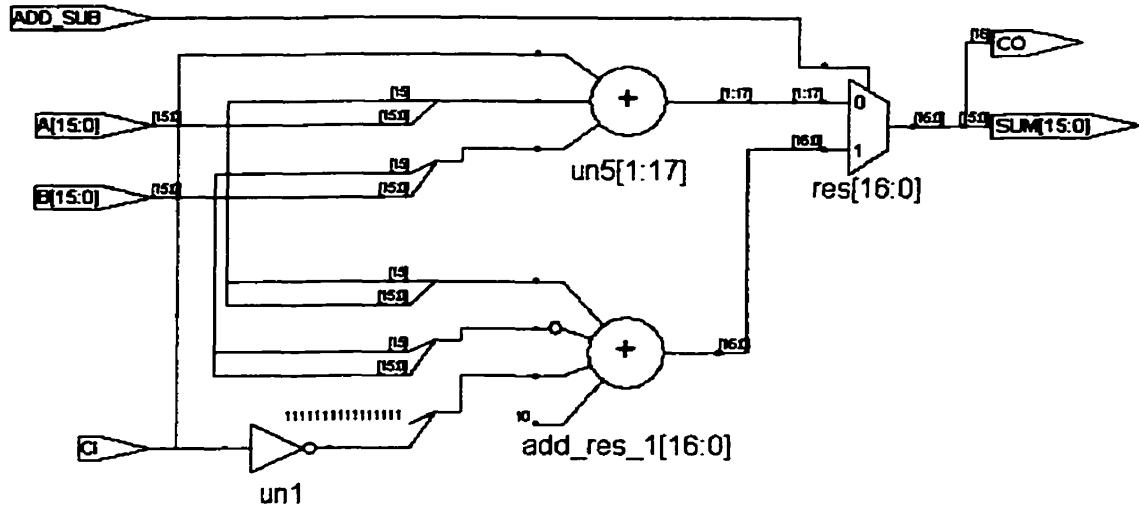

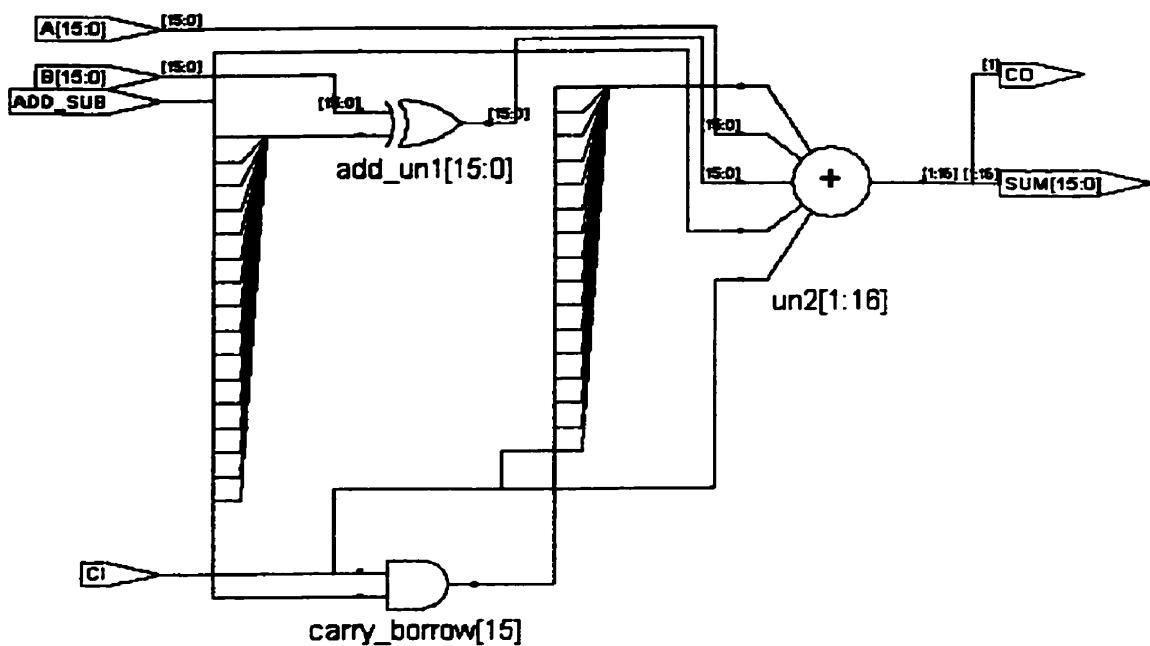

| 4.1.3 | Optimisation du module additionneur-soustracteur .....                | 96        |

| 4.1.4 | ROM de décodage .....                                                 | 100       |

| 4.1.5 | Modifications des bus.....                                            | 102       |

| 4.1.6 | Résultats des optimisations et modifications de l'architecture .....  | 105       |

| 4.2   | Configuration du chemin de données.....                               | 106       |

| 4.2.1 | Utilisation de types globaux.....                                     | 107       |

| 4.2.2 | Paramétrisation.....                                                  | 109       |

| 4.2.3 | Modularité .....                                                      | 112       |

| 4.2.4 | Résultats de la paramétrisation et de la modularité.....              | 116       |

| 4.2.5 | Méthodologie de migration et d'adaptation pour la configuration ..... | 119       |

|                                           |            |

|-------------------------------------------|------------|

| 4.3 Validation du chemin de données ..... | 122        |

| <b>Conclusion.....</b>                    | <b>126</b> |

| <b>Références .....</b>                   | <b>132</b> |

## **LISTE DES TABLEAUX**

|                                                                                                                                                                                                                                                                                                  |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 1.1 Modules configurables .....                                                                                                                                                                                                                                                          | 29  |

| Tableau 1.1 Contenu des différentes banques .....                                                                                                                                                                                                                                                | 33  |

| Table 2.1 Performances (MHz), in a Xilinx XCV800 -5 FPGA, for combinational and pipelined carry chain of different lengths adders .....                                                                                                                                                          | 62  |

| Table 2.1 Performances (MHz) for all pipeline configurations of three different lengths multipliers. Binary numbers represents configurations, where each bit indicates the presence (1) or absence (0) of registers at corresponding position. Results are grouped by identical latencies ..... | 65  |

| Table 2.2 Comparison between generic length multipliers and multipliers from Xilinx's "Reference Designs" library synthesized for a Xilinx Virtex XCV800 -5 .....                                                                                                                                | 66  |

| Tableau 3.1 Délais d'exécution d'opérations arithmétiques .....                                                                                                                                                                                                                                  | 85  |

| Tableau 4.1 Comparaison entre les architectures d'additionneur-soustracteur.....                                                                                                                                                                                                                 | 100 |

| Tableau 4.1 Influence du nombre de décodeurs.....                                                                                                                                                                                                                                                | 102 |

| Tableau 4.1 Comparaison des versions du chemin de données et des PE .....                                                                                                                                                                                                                        | 105 |

| Tableau 4.1 Influence de la modularité sur la complexité .....                                                                                                                                                                                                                                   | 117 |

| Tableau 4.2 Influence de la longueur des mots du PE sur la complexité.....                                                                                                                                                                                                                       | 118 |

| Tableau 4.3 Influence du nombre de PE du chemin de données sur la complexité.....                                                                                                                                                                                                                | 119 |

## LISTE DES FIGURES

|                                                                                                                                                                                                   |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure I.1 Évolution du marché des DSP ( <i>Market Background. Lexra, Inc.</i> ).....                                                                                                             | 16 |

| Figure 1.1 Unité de calcul fondamentale ( <i>Grayver et Daneshrad, 1998</i> ).....                                                                                                                | 31 |

| Figure 1.1 Hiérarchie des librairies hiérarchiques ( <i>McCanny et al., 1996</i> ) .....                                                                                                          | 32 |

| Figure 1.1 Architecture RaPID ( <i>Cronquist et al., 1999</i> ).....                                                                                                                              | 40 |

| Figure 1.1 Avantages des architectures reconfigurables dynamiquement (Bhatia, 1997)                                                                                                               | 43 |

| Figure 2.1 Partial products of a complete signed multiplication, with S1, S2 and S3 being used for signed representation.....                                                                     | 52 |

| Figure 2.2 Schematic representation of a 10x10 multiplier, with $shl\ x$ being a left-shift by x bits, and partial products S1, S2 and S3 being defined in equation (2.1) to equation (2.6) ..... | 53 |

| Figure 2.1 Schematic representation of a 17x17 pipelined multiplier. Dotted vertical lines indicate all the useful positions where pipeline registers can be inserted.....                        | 60 |

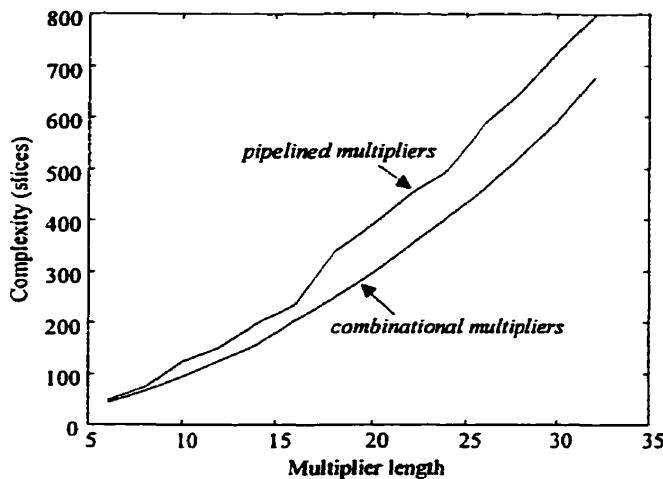

| Figure 2.1 Variation of the maximum frequency for pipelined and combinational multipliers depending on multiplier length .....                                                                    | 69 |

| Figure 2.2 Variation of complexity for pipelined and combinational multipliers depending on multiplier length .....                                                                               | 70 |

| Figure 3.1 Canaux de communication ( <i>Marriott et al., 1998</i> ) .....                                                                                                                         | 76 |

| Figure 3.1 Architecture interne initiale des PE ( <i>Marriott et al., 1998</i> ).....                                                                                                             | 78 |

| Figure 3.1 Disposition des BlockRAM et de l'anneau VersaRing ( <i>Virtex product specifications. Xilinx, Inc.</i> ).....                                                                          | 83 |

|                                                                                                        |            |

|--------------------------------------------------------------------------------------------------------|------------|

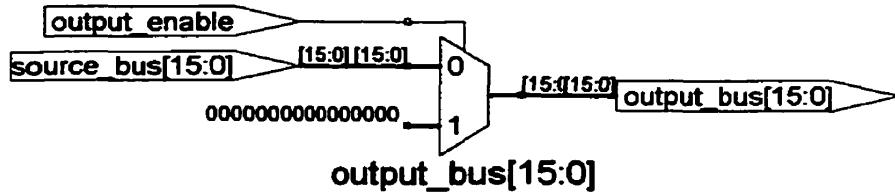

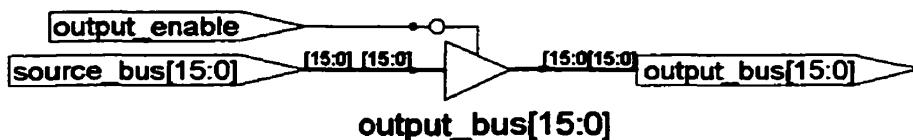

| <b>Figure 4.1 Multiplexeur d'un sélecteur de bus de la version initiale du chemin de données .....</b> | <b>94</b>  |

| <b>Figure 4.2 Sélecteur de bus utilisant les tampons à trois états des FPGA Virtex .....</b>           | <b>94</b>  |

| <b>Figure 4.1 Architecture originale du module additionneur-soustracteur .....</b>                     | <b>97</b>  |

| <b>Figure 4.2 Architecture optimisée du module additionneur-soustracteur .....</b>                     | <b>99</b>  |

| <b>Figure 4.1 Architecture interne des PE modifiés et optimisés .....</b>                              | <b>103</b> |

## LISTE DES ABRÉVIATIONS

|             |                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>ALU</b>  | <i>(Arithmetic and Logic Unit)</i> Unité de calcul arithmétique et logique comprise dans un DSP.                                                                                                                  |

| <b>ASIC</b> | <i>(Application-Specific Integrated Circuit)</i> Circuit Intégré conçu pour une application visée. Ils sont très performants et offrent le plus haut niveau d'intégration de tous les types de circuits intégrés. |

| <b>CLB</b>  | <i>(Configurable Logic Block)</i> Bloc de logique configurable constituant l'élément de circuit fondamental à l'intérieur d'un FPGA. Un assemblage de CLB liés forme un circuit logique.                          |

| <b>DLL</b>  | <i>(Delay-Locked Loop)</i> Circuit utilisé pour stabiliser les signaux d'horloge dans les circuits intégrés.                                                                                                      |

| <b>DSP</b>  | <i>(Digital Signal Processor)</i> Processeur spécialisé dans le traitement de signaux.                                                                                                                            |

| <b>FPGA</b> | <i>(Field Programmable Gate Array)</i> Circuit intégré programmable, permettant un temps de développement plus court mais des performances et un niveau d'intégration moindres qu'un ASIC.                        |

| <b>IP</b>   | <i>(Intellectual Property)</i> Se dit de modules fonctionnels vendus par une société en possédant les droits d'utilisation.                                                                                       |

| <b>PE</b>   | <i>(Processing Element)</i> Élément de traitement d'un DSP. L'arrangement de plusieurs PE fonctionnant simultanément donne les architectures parallèles.                                                          |

|              |                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>PULSE</b> | <i>(Parallel Ultra-Large Scale Engine)</i> Projet de DSP à architecture massivement parallèle, développé en vue du traitement d'images vidéo.                  |

| <b>RAM</b>   | <i>(Random-Access Memory)</i> Type de circuit de mémoire permettant les lectures et les écritures.                                                             |

| <b>ROM</b>   | <i>(Read-Only Memory)</i> Type de circuit de mémoire ne permettant que les lectures.                                                                           |

| <b>SIMD</b>  | <i>(Single Instruction Multiple Data)</i> Une seule instruction pour plusieurs données. Type d'architecture parallèle employée dans les DSP.                   |

| <b>VHDL</b>  | <i>(Very high density Hardware Description Language)</i> Langage de programmation permettant la représentation de circuits logiques et la synthèse de ceux-ci. |

## INTRODUCTION

De nos jours, les microprocesseurs sont présents dans presque tous les aspects de la vie quotidienne. Bien sûr, l'application la plus flagrante est sans doute le microprocesseur que l'on retrouve au cœur de tout ordinateur, mais il existe un autre type de processeur encore plus courant : le processeur embarqué. Celui-ci est optimisé et spécialisé pour une tâche précise. Par exemple, une voiture moderne possède une puissance de calcul équivalente à six processeurs Pentium, pour contrôler une foule de paramètres allant du fonctionnement du climatiseur à l'admission d'essence au moteur, en passant par l'activation des freins antiblocages.

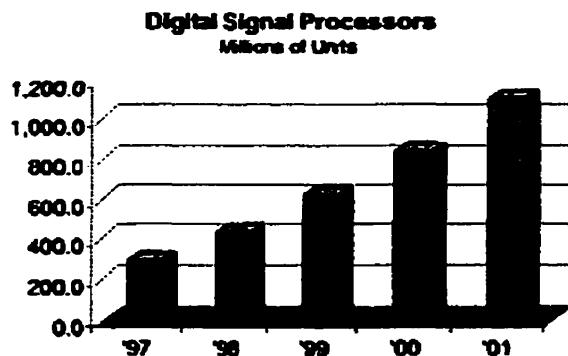

Les domaines d'application des processeurs spécialisés ne cessent de s'élargir avec le développement des nouvelles technologies de l'information. Pour réaliser la transmission et l'interprétation des données à des débits de plus en plus rapides, on a recours à des processeurs de traitement de signaux (DSP). En fait, la majorité des applications comportant un flot important de données à traiter font appel actuellement à de tels types de processeurs. La popularité des DSP se reflète sur l'évolution du marché actuel, illustré à la Figure I.1, qui affiche le taux de croissance le plus important à l'intérieur du marché des processeurs embarqués (Market Background. Lexra, Inc.).

Figure I.1 Évolution du marché des DSP (*Market Background. Lexra, Inc.*)

Afin d'offrir des processeurs de mieux en mieux adaptés aux applications pour lesquelles ils sont destinés, certaines compagnies ont fait un pas en avant en introduisant des processeurs configurables. De plus, parmi ces entreprises, certaines vont même jusqu'à laisser toute la liberté de développement à leurs clients en fournissant des outils de développement qui leur permettent de configurer leur propre processeur sur mesure, à partir des options disponibles. La majorité de ces solutions se présentent sous forme de modules IP<sup>1</sup>. Ces processeurs configurables comportent plusieurs avantages notables sur leurs cousins à architecture fixe. On peut entre autres mentionner qu'ils sont sensiblement plus compacts et plus rapides, offrent plus de flexibilité de liaison avec d'autres modules, consomment moins d'énergie, permettent l'ajout de fonctionnalités et d'instructions spécifiques et ils sont compatibles avec une grande variété de technologies

---

<sup>1</sup> Un module IP ou « Intellectual Property Core » est un module fonctionnel conçu pour s'insérer dans une puce avec d'autres modules ou circuits logiques, dédiés à une application.

d'implantation lorsque distribués sous forme de modules IP. Finalement, tous ces avantages en font des candidats idéaux pour les applications de systèmes complets sur un seul circuit intégré (*system-on-chip*).

Avec la flexibilité grandissante qu'offrent aujourd'hui les manufacturiers de circuits intégrés, de nouvelles stratégies de développement de processeurs ont vu le jour. En effet, il est maintenant possible d'avoir recours à des circuits intégrés programmables comme des FPGA (*Field Programmable Gate Array*) pour la réalisation de ces derniers. Les FPGA actuels permettent un haut niveau d'intégration, en plus d'être programmables en quelques fractions de secondes. De plus, la majorité des modèles qui sont disponibles actuellement peuvent même être reprogrammés à volonté. L'avantage qu'ont les FPGA au niveau de la rapidité de réalisation des circuits par rapport aux circuits dédiés ASIC (*Application Specific Integrated Circuit*) est énorme, compte tenu du délai de plusieurs semaines nécessaire à la réalisation de ces derniers. L'utilisation des FPGA permet donc un déverminage beaucoup plus efficace grâce aux corrections qui peuvent être rapidement apportées au circuit. L'aspect reprogrammable de ces circuits est aussi intéressant du point de vue de l'évolutivité, car les modifications apportées dans les versions subséquentes d'un produit pourront être incorporées dans les versions initiales. Cependant, l'avantage le plus marqué demeure un délai de mise en marché qui est grandement diminué comparativement aux ASIC, ce qui peut être déterminant pour le succès commercial d'un produit.

Ce mémoire expose les grandes lignes du développement et de l'optimisation d'un chemin de données configurable, faisant partie intégrante d'un processeur DSP. Le point de départ de ce travail est un modèle VHDL synthétisable du processeur PULSE (*Parallel Ultra-Large Scale Engine*), initialement développé pour être réalisé dans un circuit ASIC (Marriott et al., 1998). Ce processeur est de type SIMD (*Single Instruction Multiple Data*), ce qui signifie qu'il est composé principalement d'une matrice d'éléments de traitement ou PE (*Processing Elements*) effectuant tous les mêmes opérations simultanément sur des données différentes. C'est donc une architecture de calcul hautement parallèle, adaptée principalement pour effectuer du traitement numérique d'images.

Le modèle VHDL a dû être modifié et optimisé en vue d'une implantation dans un FPGA de la famille Virtex de Xilinx (Virtex product specifications. Xilinx, Inc.). Toutefois, la majeure partie de ce travail consiste à rendre le chemin de données configurable. Ainsi, une série de paramètres permet de contrôler différents aspects de l'architecture lors de la synthèse, tels que la largeur des mots traités, la profondeur des mémoires et des registres, la configuration de pipeline du multiplicateur et le nombre de PE du chemin de données. Cependant, la propriété la plus intéressante est la possibilité d'adapter le chemin de données à une application spécifique, en incluant ou en excluant divers modules composant les PE. Ainsi, le circuit généré lors de la synthèse du code VHDL sera optimisé exclusivement pour l'application visée, ce qui permet, tel que vu précédemment, un circuit plus compact. La complexité du PE étant diminuée, deux options se présentent

alors au concepteur : le choix d'un FPGA plus compact et moins dispendieux ou la génération d'un plus grand nombre de PE dans le chemin de données, ce qui apporte une plus grande capacité de traitement et donc, un processeur plus rapide.

D'autres modifications touchant l'architecture ont été apportées au modèle afin d'obtenir une meilleure exploitation des ressources disponibles à l'intérieur des PE. En ajoutant des bus et des connexions supplémentaires, la communication entre les différents modules devient plus flexible et permet ainsi de simplifier la tâche de programmation du processeur. Finalement, la dernière étape consiste à valider la fonctionnalité du nouveau modèle de chemin de données afin d'y apporter les correctifs nécessaires.

Le premier chapitre de ce mémoire est une revue de littérature ayant pour but d'exposer les différents travaux ayant été effectués à ce jour dans le domaine des processeurs configurables. Différentes méthodologies de conception ainsi que plusieurs exemples de réalisations y sont exposés. La revue se termine par une introduction aux processeurs et circuits reconfigurables dynamiquement, c'est-à-dire de façon simultanée avec l'exécution d'un programme par le processeur.

Le second chapitre présente un algorithme de génération de multiplicateurs signés, pipelinés et configurables. Selon les paramètres d'entrée, les multiplicateurs générés peuvent traiter des données de tailles diverses et comporter des configurations de pipeline variées, engendrant différentes latences. Cet algorithme, une fois programmé, fait partie

du modèle VHDL global du chemin de données configurable. Ce cas particulier est traité séparément des autres modules, étant donné la complexité de sa réalisation et son intérêt dans le contexte de différents circuits configurables et reconfigurables dynamiquement.

Le troisième chapitre présente l'architecture PULSE utilisée comme point de départ dans ce travail. Une attention particulière est accordée au chemin de données étant donné le fait qu'il constitue l'objet principal de ce mémoire. La technologie d'implantation ciblée, la famille de FPGA Virtex de Xilinx, est ensuite exposée en expliquant différentes caractéristiques intéressantes pour notre réalisation. Le chapitre se termine par la description des différents outils de développement utilisés.

Le quatrième et dernier chapitre constitue le cœur de cet ouvrage en proposant une méthodologie de développement pouvant être appliquée lors de la transformation de circuits conventionnels en circuits configurables. Toutes les étapes encourues pour la transformation du chemin de données sont décrites en détails, en partant du modèle original jusqu'au modèle final. La stratégie de validation mise en œuvre est explicitée ainsi que différents résultats visant à mettre en évidence l'impact de la modularité du chemin de données sur la complexité et la performance du circuit résultant.

## **CHAPITRE 1**

### **REVUE DE LITTÉRATURE**

Ce chapitre a pour but d'exposer brièvement au lecteur les différents travaux réalisés dans le domaine des processeurs et chemins de données configurables. La première partie de cette revue de littérature couvre les principaux produits offerts actuellement sur le marché des processeurs configurables. Quelques spécifications importantes ainsi que les outils de développement et les différentes options au niveau de la conception sont exposés. Les méthodes mises en œuvre pour la création et la validation de ces processeurs configurables ne sont cependant pas dévoilées publiquement par les sociétés en question. La seconde partie du chapitre traite de certaines méthodologies développées en vue de rendre modulaires certains designs existants, ainsi que des procédures proposées pour l'implantation de ces circuits. De plus, cette partie montre plusieurs prototypes réalisés dans différents domaines d'applications. La revue de littérature se termine par un survol des circuits à reconfiguration dynamique qui, bien que peu répandus pour l'instant, permettent déjà d'entrevoir des performances intéressantes, couplées à des avantages considérables sur les circuits conventionnels.

Il est opportun ici d'expliquer la différence entre certains termes employés dans cet ouvrage. Premièrement, il faut faire la nuance entre les circuits configurables et les circuits reconfigurables. Les premiers permettent à un utilisateur de créer un circuit optimisé et adapté à une application donnée sans toutefois pouvoir modifier ce circuit une

fois implanté. Les circuits reconfigurables ont cependant cette flexibilité accrue de pouvoir modifier le circuit à plusieurs reprise selon les utilisations qu'on compte en faire. De plus, il existe deux types de circuits reconfigurables. La section 1.6 aborde ce sujet en définissant la reconfigurabilité statique comme étant une seule configuration par application, contrairement à la reconfigurabilité dynamique qui implique des modifications au circuit pendant l'exécution d'une application. On peut ajouter que lorsqu'elle n'est pas spécifiée, c'est généralement de la reconfigurabilité statique dont on parle.

## 1.1 Processeur ARC

La compagnie ARC (ARC Cores, Ltd) fut la première à offrir commercialement un processeur sous la forme d'un module IP hautement configurable. Celui-ci comporte une architecture RISC (*Reduced Instruction Set Computing*) de 32 bits, entièrement nouvelle et développée exclusivement pour la flexibilité de configuration. Il peut atteindre des fréquences d'opération avoisinant 200 MHz lorsque implanté avec une technologie CMOS de 0,18 micron. Sa complexité est estimée à 16 000 portes logiques pour une configuration typique. Un des facteurs que la compagnie a su privilégier lors de la conception de ce processeur est la faible consommation d'énergie. En effet, parmi les applications visées pour un tel processeur, on retrouve plusieurs appareils mobiles ou portatifs qui nécessitent une alimentation à pile. Une autre propriété intéressante est la possibilité d'interconnecter plusieurs processeurs ARC ensemble, ce qui est intéressant

pour les applications intensives, afin d'obtenir une plus grande capacité de traitement. Par exemple, certains concepteurs ont déjà fabriqué des designs fonctionnels comportant 32 processeurs regroupés sur un seul circuit intégré.

La compagnie ARC affirme que son processeur peut être utilisé avec trois niveaux de configuration de plus en plus évolués. Le premier ne fait appel à aucune configuration de la part du concepteur qui peut utiliser directement le processeur ARC comme tout autre machine RISC de 32 bits. Le second consiste à sélectionner, dans une liste, différentes modifications et des modules variés qui se grefferont à l'architecture de base lors de la synthèse. Cette méthode offre un bon niveau de flexibilité tout en demeurant facile à utiliser, car toutes ces options et leur intégration dans le modèle général ont été préalablement optimisées et validées par la compagnie ARC. Le troisième et dernier niveau de configuration est rendu possible grâce à la disponibilité du code VHDL pour les concepteurs. En fait, ils ont la possibilité de modifier eux-mêmes le modèle VHDL synthétisable du processeur, afin d'y inclure les fonctionnalités nécessaires. ARC est d'ailleurs la seule société qui distribue présentement son processeur sous cette forme. Sa philosophie fait la promotion d'une démocratisation de la phase de conception, car elle juge qu'elle ne connaît pas à fond toutes les exigences des clients et qu'ils sont les mieux placés pour créer un processeur vraiment adapté à leurs besoins.

Les options disponibles pour le second niveau de configuration sont nombreuses et de nouvelles sont régulièrement ajoutées par la compagnie. Voici cependant les principales options disponibles :

- Synthèse en vue d'une faible complexité ou d'une fréquence élevée

- Sélection de la mémoire cache d'instructions

- Sélection des instructions requises à l'application

- Taille des registres

- Ajout de registres à usages spécifiques

- Choix de divers codes de condition

- Inclusion de mémoires RAM tampon localisées

- Bibliothèque d'extensions multimédia pour les applications 3D

- Fonctions pour le traitement de signal

L'outil de travail utilisé pour la configuration du processeur se nomme ARChitect et se présente sous la forme d'une interface graphique simple à utiliser. Le concepteur peut choisir parmi plusieurs bibliothèques d'options disponibles selon le type de processeur visé. L'outil donne un estimé du nombre de portes logiques totales et de la fréquence maximale d'opération pour chaque ajout ou retrait d'options sélectionnées. Les autres outils de développement disponibles comprennent de la documentation, une interface de simulation et un compilateur pour le langage C, permettant la simulation du code et son déverminage. À ces outils logiciels s'ajoute un système de prototype, basé sur des FPGA.

reprogrammables, utilisé pour simuler de façon réelle le processeur avant la phase finale d'implantation.

## 1.2 Processeur Xtensa

La seconde compagnie majeure dans le domaine des processeurs configurables, Tensilica (Tensilica, Inc.), vend aussi son produit sous forme de module IP. Celui-ci est basé sur une architecture de 32 bits, optimisée pour la configuration et entièrement propre à Tensilica. Sa fréquence maximale d'opération est spécifiée à 250 MHz pour une technologie d'implantation CMOS de 0,25 micron, grâce à un pipeline à cinq niveaux. Un modèle type du processeur Xtensa comporte environ 25 000 portes logiques. Tout comme la compagnie ARC, Tensilica favorise une faible consommation énergétique pour son processeur. Cependant, elle a fait un pas de plus en implantant une fonctionnalité qui coupe dynamiquement l'alimentation des portions de circuit inutilisées.

Le processeur Xtensa est distribué en librairies de cellules disponibles pour différentes technologies. En effet, la compagnie Tensilica opte plutôt pour s'assurer que toutes les configurations possibles pour son processeur sont valides, en empêchant le troisième niveau de configuration alloué par ARC. Elle pense aussi qu'en voulant accélérer une partie du processeur, l'utilisateur peut en ralentir une autre car il ne connaît pas profondément l'architecture du processeur. Tensilica offre donc des outils qui ajustent

automatiquement les paramètres critiques selon les configurations choisies, au détriment d'un niveau de configuration supérieur.

Voici maintenant un aperçu des différentes options disponibles pour configurer le processeur Xtensa. Tensilica ajoute régulièrement de nouvelles possibilités et introduira des fonctions pour les calculs en virgule flottante.

- Résultat en fonction de la fréquence et de la complexité

- Inclusion d'un multiplicateur 16 bits

- Inclusion d'une unité de multiplication-sommation 16 bits

- Taille des registres de 32 ou 64 mots

- Différentes architectures de mémoire

- Support de signaux d'interruption

- Test par interface JTAG

- Fonctions pour le traitement de signal

Les deux outils principaux pour la création de processeurs dédiés comprennent un générateur de processeur et un environnement de développement logiciel. Le premier s'apparente à l'outil ARChitect et permet au concepteur de sélectionner les différentes options du processeur de façon graphique, tout en affichant aussi une approximation de la fréquence d'opération et du nombre de portes nécessaires pour la technologie visée. Il peut même analyser automatiquement le code C de l'application et optimiser le

processeur en conséquence. Des gains de performance variant de 5 à 50 fois ont été observés pour l'utilisation de cette fonction. L'environnement de développement logiciel génère tous les outils de programmation nécessaires adaptés au processeur créé. Ceci comprend un compilateur C/C++, un assembleur et différents outils de simulation et de déverminage. Un système de prototype est aussi inclus pour les simulations matérielles.

### 1.3 Comparaison et applications

Ces deux produits sont présentement les plus évolués sur le marché et offrent une suite intéressante d'outils de développement. Un aspect important pour la flexibilité est la portabilité qu'offrent ces processeurs, particulièrement pour celui de ARC distribué en VHDL. Un article (How Much Configurability Do You Need? Issues Forum, Silicon Strategies) soulève plusieurs points importants en présentant une conférence entre les représentants des compagnies ARC et Tensilica. Les avantages et inconvénients des processeurs configurables sont exposés, ainsi que plusieurs autres aspects situant la position de ces produits parmi les processeurs en général.

Bien que plusieurs réalisations effectuées à l'aide des processeurs configurables touchent des applications domestiques telles que les caméras numériques, les imprimantes et les systèmes de télévision numériques, le domaine des communications est présentement celui qui semble le mieux adapté à l'utilisation de ces processeurs. Due à l'émergence continue de nouveaux protocoles, à la mise en marché qui doit se faire très rapidement

et aux mises à jour fréquentes, les concepteurs adoptent rapidement ces processeurs qui leur offrent un niveau de flexibilité inégalé. Contrairement aux processeurs traditionnels qui ne possèdent qu'un jeu d'instruction basé sur des opérations logiques et arithmétiques, les processeurs de ARC et Tensilica rendent possible la création d'instructions dédiées aux communications, telles que « extraction et décodage d'en-tête ». Cette nouvelle possibilité permet une meilleure utilisation des ressources matérielles mais surtout, elle permet à une compagnie d'implanter des algorithmes spécifiques confidentiels directement sous forme d'instructions, sans crainte de voir la concurrence récupérer ces algorithmes alors implantés de façon matérielle.

En intégrant ces processeurs dans des circuits programmables à haute densité, certains périphériques et coprocesseurs peuvent être inclus à même le circuit, afin de supprimer les bus de communication. Cette approche permet de meilleures performances tout en supprimant plusieurs problèmes reliés à l'utilisation de bus comme les délais de transfert, les protocoles de synchronisation ou l'allocation de bande passante.

## 1.4 Méthodes de conception de processeurs configurables

Bien que ARC et Tensilica gardent confidentielles les idées et les procédés mis en œuvre lors de la conception de leurs processeurs configurables, certains articles ont été publiés à ce sujet et proposent différentes méthodes à adopter pour la confection de tels processeurs.

### 1.4.1 Modules nécessaires et optionnels

La première méthode (Dyck et al., 1999) propose simplement l'idée que pour offrir un niveau de flexibilité suffisant, un processeur configurable doit permettre certaines variations au modèle de base et comporter une banque de modules optionnels pouvant être intégrés à l'architecture. Les options proposées sont résumées dans le Tableau 1.1.

**Tableau 1.1 Modules configurables**

| Module                                         | Type       | Choix possible             |

|------------------------------------------------|------------|----------------------------|

| registre à usage général                       | nécessaire | 4-64 mots                  |

| mémoire de programme                           | nécessaire | 16-512 mots                |

| registre d'état                                | nécessaire | 4-32 bits                  |

| mémoire                                        | optionnel  | au besoin                  |

| mémoire FIFO ( <i>First-In-First-Out</i> )     | optionnel  | au besoin                  |

| bus PCI                                        | optionnel  | taille des mémoires tampon |

| unité CRC ( <i>Cyclic Redundancy Checker</i> ) | optionnel  | selon performance visée    |

| unité MAC ( <i>Multiply-Acumulate</i> )        | optionnel  | selon performance visée    |

L'article présente également une stratégie de communication entre processeurs où la transmission de données se fait par les registres à usage général. Deux processeurs échangent des données en intervertissant une portion de leurs registres en un cycle d'horloge.

#### **1.4.2 Flexibilité versus complexité**

Pour un processus de configuration efficace, un bon compromis entre la flexibilité et la complexité architecturales doit être atteint (Smith et al., 1989). Un processeur configurable doit être composé de blocs fondamentaux ayant une granularité appropriée à la variété d'applications supportées. En effet, une porte NON-ET est un bloc fondamental avec une grande flexibilité mais sans complexité. En contrepartie, un PE possède une grande complexité au détriment de la flexibilité de configuration. Cet équilibre doit être planifié dès le début de la conception d'un circuit configurable afin de minimiser le temps de développement (complexité architecturale des blocs élevée) tout en conservant un bon niveau de configurabilité (flexibilité du circuit élevée).

#### **1.4.3 Architecture basée sur les transferts de données à haute vitesse**

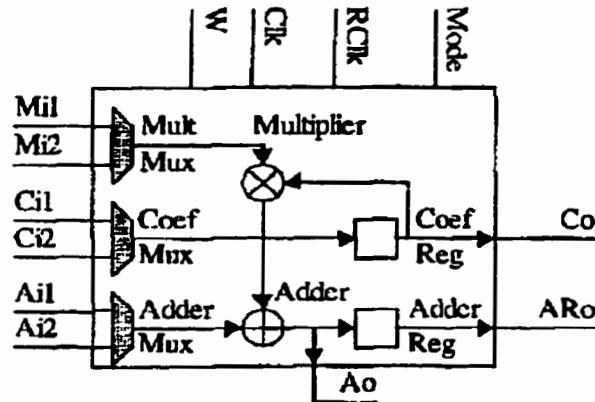

Afin d'être en mesure de traiter les débits élevés requis par le transfert d'images vidéo, de voix ou de données à travers les réseaux, une architecture configurable a été proposée pour supporter plusieurs protocoles de communication existants (Grayver et Daneshrad, 1998). Les modes d'opération possibles comprennent le filtrage numérique FIR/IIR réel et complexe, le filtrage basé sur l'erreur quadratique moyenne minimale, les transformées discrètes de Fourier et la synthèse de fréquences numériques directes. Tous ces modes sont supportés par un seul chemin de données composé d'unités de calcul interconnectées selon des patrons spécifiques à chaque application. Cette unité fondamentale de calcul est

en fait le plus petit dénominateur commun des algorithmes supportés et elle est illustrée à la Figure 1.1.

Figure 1.1 Unité de calcul fondamentale (*Grayver et Daneshrad, 1998*)

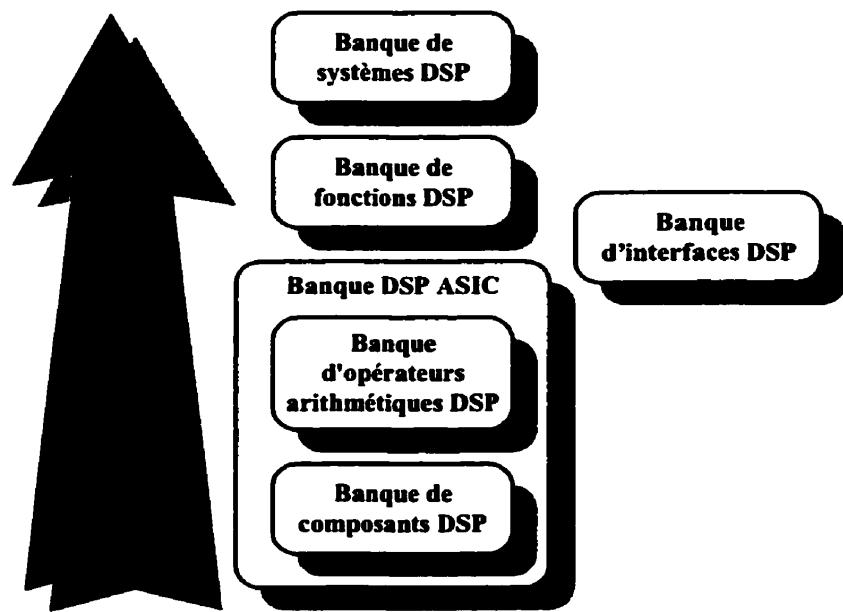

#### 1.4.4 Utilisation de librairies hiérarchiques de modules VHDL

Cette approche implique la création de modules de base paramétrables et synthétisables en VHDL pour ensuite en faire l'organisation en banques hiérarchiques (McCanny et al., 1996). Chacun des modules d'une banque est composé de modules de la banque se situant au niveau inférieur. Cette méthode accélère considérablement le processus de conception car elle ne nécessite que l'assemblage de blocs entre eux selon la fonctionnalité désirée du processeur. La hiérarchie des banques est montrée à la Figure 1.2, où les banques du bas comprennent les modules de bas niveau et celles du haut, les modules fonctionnels de haut niveau.

Figure 1.2 Hiérarchie des librairies hiérarchiques (*McCanny et al., 1996*)

Pour mieux illustrer le rôle de chaque banque, quelques exemples types des blocs que l'on retrouve dans celles-ci sont présentés dans le Tableau 1.2.

**Tableau 1.2 Contenu des différentes banques**

| <b>Banque de composants DSP</b> |  | <b>Banque de fonctions DSP</b> |                               | <b>Banque de systèmes DSP</b> |  |

|---------------------------------|--|--------------------------------|-------------------------------|-------------------------------|--|

| compteurs                       |  |                                | multiplicateurs               |                               |  |

| comparateurs                    |  |                                | accumulateurs                 |                               |  |

| éléments de délai               |  |                                | multiplicateurs-sommateurs    |                               |  |

| convertisseurs de données       |  |                                | opérateurs de racines carrées |                               |  |

| mémoires                        |  |                                | divideurs                     |                               |  |

| décaleurs                       |  |                                | sommateurs                    |                               |  |

| <b>Banque d'interfaces</b>      |  |                                |                               |                               |  |

| contrôleurs de mémoire          |  |                                |                               |                               |  |

| interfaces de microprocesseurs  |  |                                |                               |                               |  |

| contrôleurs d'interface de bus  |  |                                |                               |                               |  |

| contrôleurs graphiques          |  |                                |                               |                               |  |

- La banque de composants DSP comporte plus de 70 blocs dont la paramétrisation doit permettre de supporter les différents formats de données possibles (non-signées, complément à deux, virgule flottante...).

---

<sup>2</sup> Adaptive Differential Pulse Code Modulation

- La banque d'opérateurs arithmétiques DSP est composée de plus de 100 blocs optimisés. Le type de paramétrisation requis pour ceux-ci concerne principalement les structures arithmétiques utilisées (*carry-save, carry-look-ahead, carry-ripple...*).

- La banque de fonctions DSP nécessite une paramétrisation propre à chaque fonction (niveau de troncation, profondeur du pipeline, paramètres des filtres...).

- La banque de systèmes DSP se situe au sommet de la hiérarchie et regroupe les fonctionnalités de haut niveau destinant le processeur à une application spécifique. La paramétrisation possible de cette banque doit simplement adapter et optimiser le système choisi à l'application.

- La banque d'interfaces doit être en mesure de supporter les communications entre le processeur DSP conçu et les périphériques externes grâce à une série d'interfaces disponibles.

#### 1.4.5 Synthèse de processeurs DSP par analyse d'algorithme

Cette technique synthétise automatiquement un processeur DSP adapté spécifiquement pour une application en réalisant son algorithme (Ramanathan et al., 1999). Cet algorithme doit être représenté sous forme d'un graphe de flot de données et de contrôle.

L'outil de synthèse utilise alors ce graphe pour générer les structures de calcul requises pour l'exécution de l'application. Le processus de synthèse se décompose en trois grandes étapes :

1. **Identification des structures de calcul minimales.** Elles correspondent à des sous-graphes du graphe de flot de données et de contrôle de l'algorithme à planter. Ces structures minimales sont ensuite converties en différents circuits de base permettant de réaliser la fonctionnalité demandée, tout en obtenant les performances visées. Dans le cas contraire, les structures de calcul sont modifiées en y appliquant des transformations affines équivalentes, afin de générer de nouveaux circuits de base. De telles modifications sont itérées jusqu'à l'atteinte des objectifs.

2. **Synthèse de l'architecture correspondant à l'algorithme.** Les circuits de base sont interconnectés de telle sorte qu'ils forment un circuit de haut niveau exécutant l'algorithme demandé. Cette étape est itérative et peut exiger un retour à la première étape.

3. **Synthèse des structures de contrôle.** Les structures de contrôle nécessaires à l'algorithme sont synthétisées pour l'intégration dans l'architecture précédemment générée. Certaines séquences de contrôle peuvent nécessiter des modifications à l'architecture globale pour leur implantation.

## 1.5 Exemples de designs configurables

Quelques processeurs ou portions de processeurs ont été développés à ce jour à des fins expérimentales. Bien que fonctionnels et offrant des caractéristiques de configuration intéressantes, aucun de ces designs n'est devenu un produit commercial en mesure de se mesurer à ceux des deux compagnies principales, ARC et Tensilica. Cette section présente des processeurs et des chemins de données ayant atteint divers niveaux de configuration.

### 1.5.1 Module VS\_DSP

Le module VS\_DSP (Kuulusa et al., 1997; Nurmi et Takala, 1997), s'apparente particulièrement avec le travail dont il est question dans ce mémoire. C'est un DSP avec une architecture à trois étages de pipeline, globalement composée d'un chemin de données, d'un contrôleur, d'un générateur d'adresses, d'une mémoire de programme et de deux mémoires de données. Tous ces éléments sont connectés à l'aide de trois bus. Plusieurs paramètres peuvent être modifiés, mais les plus intéressants sont la longueur de mots de données paramétrable de 8 à 64 bits, la longueur du microcode choisie avec un minimum de 32 bits, un nombre d'accumulateur compris entre 2 et 4, 3 différents types d'adressage et plusieurs variantes de décaleur, ALU (*Arithmetic and Logic Unit*) et multiplicateur-sommateur. Des instructions peuvent aussi être ajoutées au jeu de base. Une fois la configuration choisie par le concepteur, les outils de développement génèrent

le processeur sous forme de cellules adaptées pour une des technologies supportées, ce qui n'offre pas la flexibilité d'un modèle VHDL entièrement portable.

### 1.5.2 MetaCore

Un second exemple présente MetaCore (Jin-Hyuk et al., 1998), un module DSP configurable avec un jeu d'instructions extensible. Son architecture se compose de trois parties distinctes fonctionnant en parallèle : une ALU, un générateur d'adresses pour la mémoire et un contrôleur. Celles-ci peuvent être configurées pour la longueur des mots de données et d'adresses et la taille de la mémoire, des registres et de l'accumulateur. Par ailleurs, les instructions inutiles à une application peuvent être supprimées et d'autres plus utiles peuvent être ajoutées. Le processeur final est synthétisé à partir de code VHDL pouvant être utilisé pour la simulation. Un premier prototype de 16 bits, le MDSP16, implanté sur une technologie CMOS de 0,6 micron, affiche une performance de pointe de 50 millions d'instruction par seconde (*MIPS*).

### 1.5.3 Générateur de processeurs RISC configurables

Cet outil (Berekovic et al., 1998) génère différents processeurs RISC à partir de paramètres sélectionnés par le concepteur. Le niveau de configuration disponible permet entre autres la sélection des longueurs de mots du chemin de données et d'instructions pour des valeurs comprises entre 8 et 64 bits pour le chemin de données et entre 8 et 32 bits pour les instructions. Un multiplicateur-sommateur de 64 bits et un accumulateur

peuvent être intégrés au besoin, alors que le nombre et la capacité des registres sont ajustables. Finalement, la profondeur du pipeline peut varier entre 1 et 5 étages. Une particularité intéressante de ce générateur est qu'il produit des modules codés en VHDL directement synthétisable, ce qui apporte une grande portabilité. Le nombre de portes logiques utilisées pour son implantation dépend des options choisies et peut varier entre un minimum de 900 portes pour un processeur 8 bits sans pipeline et un maximum de 10 000 portes dans le cas d'un processeur 32 bits à 5 étages de pipeline et 8 registres. Les prototypes réalisés ont permis de constater une fréquence d'opération maximale de 100 MHz pour un procédé CMOS de 0,5 micron.

#### 1.5.4 PINE

Le module DSP PINE (Be'ery et al., 1993) est un processeur 16 bits à trois niveaux de pipeline, spécialement conçu pour les applications portables nécessitant une gestion d'économie d'énergie, afin d'obtenir une plus grande autonomie. Cette caractéristique autorise trois modes de fonctionnement, allant de l'inactivité complète à la pleine activité, en passant par un mode de fonctionnement au ralenti. Le processeur est principalement composé d'un contrôleur, d'un générateur d'adresses et d'une unité de calcul. Cette dernière comporte un multiplicateur, une ALU, ainsi que deux accumulateurs. Bien que moins flexible que les processeurs précédents, l'architecture PINE permet différents niveaux de configuration au niveau de ses RAM, ROM et de ses types d'entrées/sorties.

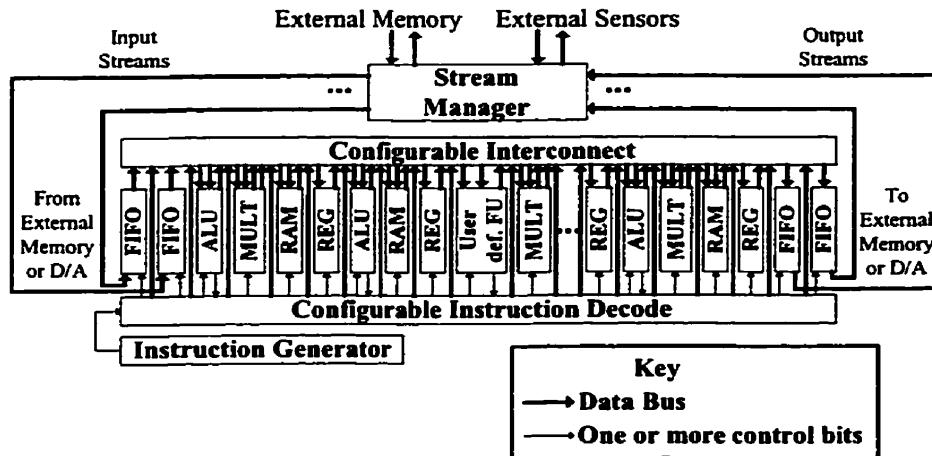

### 1.5.5 RaPID

L'architecture RaPID (*Reconfigurable Pipelined Datapath*) (Cronquist et al., 1999; Ebeling et al., 1997) est un chemin de données se basant sur les réseaux systoliques. Il comporte plusieurs cellules reliées sérielement qui peuvent être des ALU, des multiplicateurs, des décaleurs, des registres, des mémoires, mais aussi des modules de calcul spécialisés à un traitement de données en particulier (Figure 1.3). Certaines de ces cellules, comme les registres et les mémoires, peuvent être configurées par le concepteur. Cependant, la paramétrisation se situe principalement au niveau des interconnexions et du décodage d'instruction. En fait, c'est l'algorithme à planter qui détermine la configuration du décodeur, des interconnexions entre les cellules et les délais à insérer aux sorties de celles-ci. Comme l'indique son nom, RaPID est un chemin de données hautement pipeliné et c'est pourquoi les sorties de données doivent être synchronisées selon les différentes phases du pipeline pour permettre une réalisation adéquate de l'algorithme. Il faut toutefois mentionner que, de par sa nature serielle, cette architecture est exclusivement optimisée pour des calculs hautement répétitifs et de faible complexité. Finalement, la fréquence d'opération atteinte par l'implantation de ce chemin de données sur une technologie CMOS de 0,5 micron est de 100 MHz, pour l'équivalent d'environ 1,5 BOPS (*Billion of Operations Per Second*).

Figure 1.3 Architecture RaPID (*Cronquist et al., 1999*)

## 1.6 Reconfigurabilité

Nous terminerons cette revue de littérature en traitant des architectures reconfigurables, ce qui est justifiable par la popularité grandissante de cette méthode et les avantages qu'elle procure. La reconfigurabilité est définie comme étant la capacité de configurer une machine de façon répétée, pour effectuer différentes fonctions (Bhatia, 1997). Par opposition, le travail relaté dans ce mémoire, ainsi que tous les exemples de processeurs configurables cités précédemment, ne peuvent plus être modifiés une fois qu'ils ont été implantés. Cependant, la frontière entre ces deux types de circuits est mince, d'autant plus que l'utilisation de FPGA reprogrammables ouvre de nouveaux horizons aux concepteurs, en leur offrant une flexibilité supérieure (Fawcett, 1995). Il existe deux types principaux de reconfigurabilité : la statique et la dynamique.

### 1.6.1 Reconfigurabilité statique

La reconfigurabilité statique implique une seule configuration par application. En fait, une seule architecture spécialisée est employée pour la réalisation complète d'une tâche à effectuer. Ce n'est qu'une fois l'application terminée que le circuit peut être modifié de nouveau, afin d'être mieux adapté et optimisé à une différente tâche à effectuer. La reconfigurabilité statique est utilisée présentement par certains constructeurs électroniques pour leur permettre de modifier leurs circuits afin d'évoluer vers de nouveaux algorithmes ou protocoles et ainsi garder leurs produits compatibles avec les nouvelles normes. D'ailleurs, le domaine spatial considère de plus en plus cette méthode pour le développement de sondes et de satellites reconfigurables à partir de la Terre (Matsumoto, 1999). En ayant cette particularité, les engins spatiaux pourront être réutilisables à plusieurs missions et réparables à distance dans le cas d'une erreur d'implantation de circuit. De plus, ils pourront même n'être configurés et programmés qu'une fois rendus en orbite, ce qui offre plus de souplesse dans les délais de conception.

L'idée de la reconfiguration à distance peut cependant être ramenée à l'échelle terrestre, à travers différents réseaux de communication existants. Bien qu'intéressante, cette manière de procéder peut entraîner de sérieux problèmes auxquels il faudra faire face éventuellement (Westfeld, 1999). En effet, l'utilisation de réseaux publics implique une visibilité accrue et donc une ouverture au piratage des données. Une société pourrait voir l'architecture de son circuit copiée par une société concurrente lors du transfert de celui-ci vers un FPGA distant. Ces données pourraient aussi être altérées afin d'en modifier la

fonctionnalité une fois l'implantation réalisée, un peu à la manière des virus informatiques actuels. Finalement, un autre problème risque d'apparaître avec la capacité grandissante des FPGA; les fichiers utilisés pour l'implantation de circuits complexes pourraient nécessiter des temps de transfert trop longs. Tous ces nouveaux obstacles devront être franchis en ayant recours à de nouvelles techniques d'encryption et de compression de données, apportant une sécurité, une fiabilité et une efficacité accrues.

### **1.6.2 Reconfigurabilité dynamique**

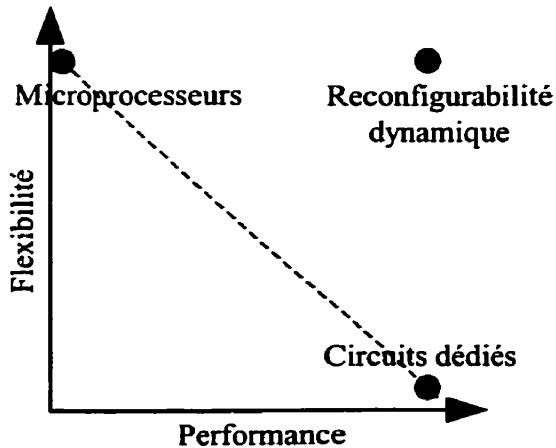

La reconfigurabilité dynamique implique que des modifications à la configuration d'un circuit puissent être faites simultanément avec l'exécution d'une application. Ces changements peuvent affecter toute l'architecture ou seulement une portion. L'utilisation de la reconfiguration dynamique est encore relativement récente et peu répandue, étant donné sa difficulté d'implantation. Généralement, de tels processeurs sont utilisés sous forme de coprocesseurs, en conjonction avec une plate-forme stable qui n'est pas reconfigurable. Malgré sa complexité de réalisation, les avantages de la reconfigurabilité dynamique sont nombreux. Tel qu'illustré à la Figure 1.4, la flexibilité s'approche de celle des microprocesseurs programmables et la performance atteint celle des circuits dédiés qui ne sont optimisés que pour une seule application.

Figure 1.4 Avantages des architectures reconfigurables dynamiquement (Bhatia, 1997)

Une utilisation intéressante de ce type de reconfigurabilité fait appel à un seul FPGA pour émuler un design complexe destiné à être implanté sur un ASIC (Gajjalapurna et Bhatia, 1998). Un algorithme partitionne et réordonne temporellement l'architecture initiale pour ensuite adapter le contrôle des opérations. La nouvelle architecture fractionnée peut ensuite être implantée sur un FPGA de moindre capacité, tout en conservant la même fonctionnalité, en effectuant de la reconfiguration dynamique. Cette stratégie a permis la simulation d'un design de 75 000 portes logiques sur un seul FPGA de 13 000 portes. Il existe aussi différents exemples de processeurs et coprocesseurs implantés dans des FPGA reconfigurables dynamiquement : le nano-processeur (Wirthlin et al., 1994), Enable++ (Hogl et al., 1995), qui permet un gain en performance variant entre 100 et 1000 dépendant de l'algorithme implanté, et un coprocesseur spécialisé pour le traitement des bases de données du génome humain (Lemoine et Merceron, 1995), qui affiche aussi

une amélioration de deux à trois ordres de grandeur comparativement à un processeur conventionnel.

## CHAPITRE 2

### MULTIPLICATEUR CONFIGURABLE, SIGNÉ ET PIPELINÉ

Pour rendre un processeur configurable, plusieurs modifications sont nécessaires afin de rendre chacun des modules flexibles au niveau des paramètres sélectionnés. Certaines structures sont facilement adaptables alors que d'autres sont beaucoup plus complexes à rendre configurables. Dans le cadre de ce travail, le multiplicateur utilisé dans le chemin de données, fut le module qui nécessita le plus de modifications. La principale difficulté vient du fait que l'architecture du multiplicateur signé est étroitement liée à la longueur des mots de données traités.

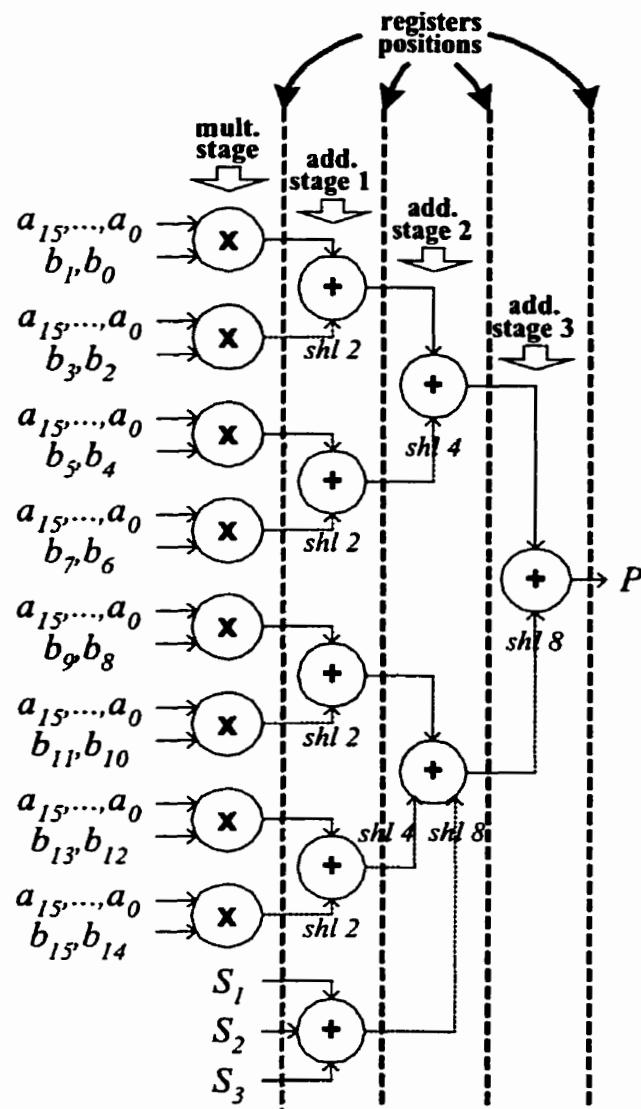

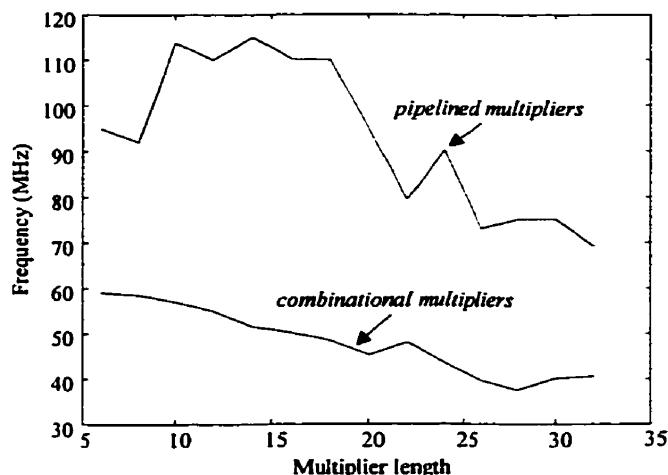

Ce chapitre présente un article intitulé « A configurable generic two's complement pipelined multiplier » soumis à la revue « IEEE Design and Test of Computers » au mois de février 2000. Cet article présente la démarche employée pour développer un algorithme codé en VHDL, permettant la synthèse d'un multiplicateur aux caractéristiques voulues. Les paramètres d'entrée permettent la sélection de la longueur des mots de données et le nombre d'étages du pipeline ainsi que leur disposition. L'article décrit en détail l'architecture retenue et les relations mathématiques reliant celle-ci aux paramètres de configuration. Finalement, une étude comparative permet de situer le multiplicateur développé par rapport aux modèles existants dans les bibliothèques de modules arithmétiques de Xilinx.

## A CONFIGURABLE GENERIC TWO'S COMPLEMENT PIPELINED MULTIPLIER

Alexandre Fortin, Yvon Savaria and Mohamad Sawan,

Department of ECE, Ecole Polytechnique de Montreal

*Abstract --* In the context of reconfigurable processors, there is a need for generic multipliers that can compute operands of different bit-lengths and have a latency that can be adjusted to the environment. We propose in this paper an algorithm that can synthesize signed, pipelined and parallel multipliers optimized for any length greater than five bits. The Baugh-Wooley algorithm is used to process the sign. Pipeline depth and registers locations are also fully parameterizable. The algorithm has been successfully implemented in VHDL, tested, placed and routed for a state-of-the-art FPGA. Speed and complexity comparisons with fixed multipliers from Xilinx's library are made and demonstrate an increase in speed at the expense of a larger area.

### 2.1 Introduction

Nowadays, time-to-market is a very significant factor in the commercial success of a new product. A new device, even if it is greatly improved compared to existing products, could be a commercial failure if it does not reach the market on time. This principle is particularly relevant to electronic systems, where evolution is lightning fast. For this reason, hardware designers must complete their circuits quickly, without wasting

precious time in all design and test phases. To minimize the development time, designers have used different design methodologies and tools. One of such strategies is to have a generic architectural model, that the designers can adapt and modify to suit their needs (Levy, 1999). By using a customisable processor, developers are freed from the tasks of defining, implementing and validating a suitable architecture. This idea is growing in popularity in industry and some companies even restrict their activity to this field and provide hardware cores which can be adapted on demand.

Recent availability of high-performance field programmable gate arrays (*FPGA*), with densities in excess of one million system gates, providing dedicated datapaths for high-speed arithmetic and integrated high-bandwidth RAM (Virtex product specifications. Xilinx, Inc.), is a very interesting medium to implement embedded processors with flexible architectures. FPGAs have at least two major advantages over their application-specific integrated circuits (*ASIC*) counterparts. Firstly, they are programmable in a fraction of a second, which contributes to reduce turnaround compared to ASIC devices. Secondly, SRAM FPGAs are reprogrammable, and some systems even allow a dynamic reprogramming, that let some parts of the device be reconfigured while others are running. This flexibility allows a high level of optimisation never reached before, by having a chip whose architecture can be modified to best fit the requirements of a specific application.

At the current level of complexity, hardware description languages (*HDL*) are indispensable to design configurable processor cores. Not only do they significantly decrease the development time of new devices over a schematic design methodology, but they also make them easily configurable. It is even possible to modify an existing design to adapt it for another use. For example, a core is easily customizable for its data length, memories sizes, instructions set, pipeline depth, number of processing elements and for inclusion of custom modules. Languages like VHDL even allow a designer to use generic parameters, wherever needed in the code, to subsequently change the structure of the resulting circuit, just by changing their values and re-synthesising the code. Designs that have a regular architecture are easily made generic, while more complex designs, with irregular structures, cannot be adapted without a thorough rearrangement of their architecture.

Multipliers are common components found in almost every processor dedicated to execute mathematical functions or to perform signal processing. The architecture of these multipliers depends on their use, but also on the design goals. In fact, multipliers can be signed or unsigned and they can work with fixed-point or floating-point numbers. Furthermore, many hardware algorithms have been developed, each one offering a different compromise between speed and complexity. However, multiplier architectures are generally dependent on word length, especially with signed numbers. For that reason, generic variable length multipliers with a reasonable level of optimisation can be difficult to realise.

The algorithm proposed in this paper generates circuits to multiply two signed integers having the same number of bits represented in two's complement format. It can support any multiplicand and multiplier lengths greater than or equal to 6 bits. Also, the algorithm has the capability to insert registers at different places selected by the designer. As a result, the multiplier has a parameterizable latency. All these properties are very useful to designers, since they permit the use of this multiplier in different processor architectures, each one generally supporting a unique fixed latency and data width in their modules. Therefore, no deep modification in the rest of the architecture is required, which is then compatible with our main goal of providing a designer with a fast development time without extensive revalidation. The algorithm was implemented in VHDL 93, targeting the Virtex series of FPGAs from Xilinx (Virtex product specifications. Xilinx, Inc.).

## 2.2 Multiplier architecture

The architecture of the proposed multiplier is based on the Baugh-Wooley algorithm (Baugh and Wooley, 1973). The main advantage of using this algorithm is to generate only positive partial products, allowing to calculate the product by simply adding all the partial products. Also, it processes the signs simultaneously with the multiplication, without additional delay. As explained in the following, the multiplier structure is composed of a first stage of parallel two-bit multipliers, followed by a binary tree of adders to quickly execute as many additions as possible in parallel. In addition to the first

multiplication stage and the following tree of adders, the Baugh-Wooley algorithm requires an additional structure to calculate the sign of the result by producing a unique partial product, which is then added to the other partial products. This architecture is relatively fast, while maintaining a good regularity suitable for FPGAs and compatible with our objective of producing a generic length multiplier. Interesting work has been done on recursive generation of multipliers in VHDL (McCluskey, Practical Applications of Recursive VHDL Components in FPGA Synthesis) and, while signed multipliers are not as regular and cannot exploit easily their method, unsigned multiplier may be implemented that way to reduce the algorithm complexity.

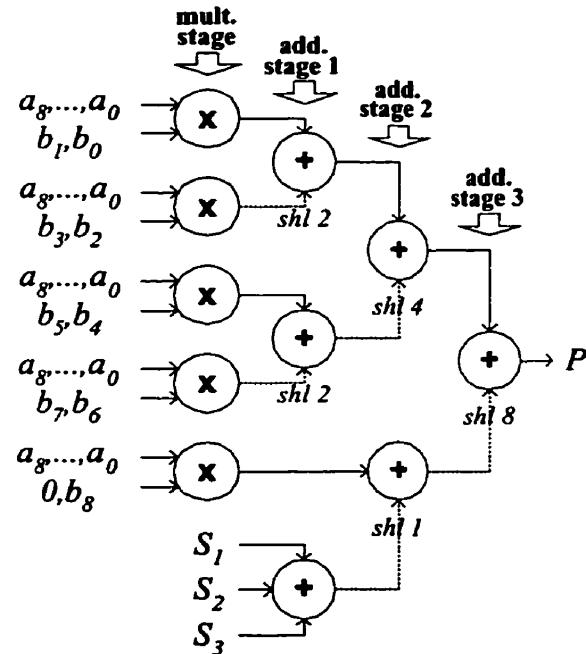

For a signed multiplication, let  $A = (a_{n-1}, \dots, a_0)$  be the multiplicand,  $B = (b_{n-1}, \dots, b_0)$  the multiplier and  $P = (p_{2n-1}, \dots, p_0)$  the product. All these vectors are expressed using two's complement representation. When the multiplicand and the multiplier have the same length  $n$ , the Baugh-Wooley algorithm can be slightly simplified to generate one less partial product than the original algorithm. Figure 2.1 shows the multiplication procedure with all the partial products generated according to this reduced Baugh-Wooley algorithm. It should be noted that the first  $n-1$  partial products correspond to the ones that would have been generated by the unsigned multiplication of  $A$  and  $B$ , without their most significant bits  $(a_{n-2}, \dots, a_0) \times (b_{n-2}, \dots, b_0)$ . The following three partial products are generated by the most significant bits  $a_{n-1}$  and  $b_{n-1}$  to take care of the sign in the two's complement representation. The first of these three partial products,  $S1$ , is formed by

producing the bit-wise inverse of  $(b_{n-2}, \dots, b_0)$  and then multiplying the resulting vector by  $a_{n-1}$ :

$$S1 = (a_{n-1}b_{n-2}^*, a_{n-1}b_{n-3}^*, \dots, a_{n-1}b_0^*) \quad (2.1)$$

The second partial product used for the sign,  $S2$ , is calculated by inverting  $(a_{n-2}, \dots, a_0)$  and multiplying it by  $b_{n-1}$ :

$$S2 = (b_{n-1}a_{n-2}^*, b_{n-1}a_{n-3}^*, \dots, b_{n-1}a_0^*) \quad (2.2)$$

The third partial product,  $S3$ , is a little more complex to generate and it is composed as follows:

$$S3_0 = a_{n-1} \text{ XOR } b_{n-1} \quad (2.3)$$

$$S3_1 = a_{n-1} \text{ AND } b_{n-1} \quad (2.4)$$

$$S3_{n-2}, \dots, S3_2 = 0 \quad (2.5)$$

$$S3_n = S3_{n-1} = a_{n-1} \text{ OR } b_{n-1} \quad (2.6)$$

Once the three partial products described above are computed, they must be added, and the resulting sum of  $S1$ ,  $S2$  and  $S3$  is finally added to all the other partial products.

|                     |                     |           |                 |                          |                 |

|---------------------|---------------------|-----------|-----------------|--------------------------|-----------------|

|                     | $b_{n-1}$           | $b_{n-2}$ | ...             | $b_1$                    | $b_0$           |

| $a_{n-1}$           | $a_{n-2}$           | ...       | $a_1$           | $a_0$                    |                 |

|                     | $a_0 b_{n-2}$       | ...       | $a_0 b_1$       | $a_0 b_0$                |                 |

|                     | $a_1 b_{n-2}$       | ...       | $a_1 b_1$       | $a_1 b_0$                |                 |

|                     | ...                 | ...       | ...             | ...                      |                 |

|                     | $a_{n-2} b_{n-2}$   | ...       | $a_{n-2} b_1$   | $a_{n-2} b_0$            | $\Leftarrow S1$ |

|                     | $a_{n-1} b_{n-2}^*$ | ...       | $a_{n-1} b_1^*$ | $a_{n-1} b_0^*$          | $\Leftarrow S2$ |

|                     | $b_{n-1} a_{n-2}^*$ | ...       | $b_{n-1} a_1^*$ | $b_{n-1} a_0^*$          | $\Leftarrow S3$ |

| $a_{n-1} + b_{n-1}$ | $a_{n-1} + b_{n-1}$ | 0...      | ...0            | $a_{n-1} \oplus b_{n-1}$ |                 |

| $p_{2n-1}$          | $p_{2n-2}$          | ...       | ...             | $p_n$                    | $p_{n-1}$       |

|                     |                     |           |                 |                          | $\dots$         |

|                     |                     |           |                 |                          | $\dots$         |

|                     |                     |           |                 |                          | $p_1$           |

|                     |                     |           |                 |                          | $p_0$           |

Figure 2.1 Partial products of a complete signed multiplication, with S1, S2 and S3 being used for signed representation

Processing independently the most significant bits of the multiplicand and the multiplier, and the reduced unsigned multiplication of the other  $n-1$  bits, by independently generating the partial products before adding them, is a standard way to complete a multiplication. In the rest of this paper, all the real numbers are floored ( $\lfloor x \rfloor$ ). This means that all the fractional values are ignored, as in VHDL where each number  $x$  is automatically truncated to the nearest integer smaller or equal to  $x$ .

The first step, shown in Figure 2.2, is realised using several two-bit multiplication modules having the same multiplicand ( $a_{n-2}, a_{n-3}, \dots, a_0$ ).