|                         | Digital background calibration for pipelined and time-interleaved analog-to-digital converters                                                                                                                                                                                          |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur: Author:         | Kamal Elsankary                                                                                                                                                                                                                                                                         |

| Date:                   | 2006                                                                                                                                                                                                                                                                                    |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                                               |

| Référence:<br>Citation: | Elsankary, K. (2006). Digital background calibration for pipelined and time-<br>interleaved analog-to-digital converters [Thèse de doctorat, École Polytechnique<br>de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7764/">https://publications.polymtl.ca/7764/</a> |

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

| <b>URL de PolyPublie:</b> PolyPublie URL: | https://publications.polymtl.ca/7764/ |

|-------------------------------------------|---------------------------------------|

| Directeurs de recherche: Advisors:        | Mohamad Sawan                         |

| Programme:                                | Non spécifié                          |

#### UNIVERSITÉ DE MONTRÉAL

## DIGITAL BACKGROUND CALIBRATION FOR PIPELINED AND TIME-INTERLEAVED ANALOG-TO-DIGITAL CONVERTERS

# Kamal Elsankary DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR (PH.D.)

(GÉNIE ÉLECTRIQUE)

Juin 2006

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-20824-3 Our file Notre référence ISBN: 978-0-494-20824-3

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## UNIVERSITÉ DE MONTRÉAL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

### DIGITAL BACKGROUND CALIBRATION FOR PIPELINED AND TIME-INTERLEAVED ANALOG-TO-DIGITAL CONVERTERS

présentée par: <u>Elsankary Kamal</u>

en vue de l'obtention du diplôme de <u>Philosophiae Doctor</u>

a été dûment acceptée par le jury d'examen constitué de:

- M. SAVARIA Yvon, Ph.D., président

- M. SAWAN Mohamad, Ph.D., membre et directeur de recherche

- M. AUDET Yves, Ph.D., membre

- M. ISMAIL Mohamed, Ph.D., membre externe

To all my beloved

#### **ACKNOWLEDGMENTS**

It is only by the will and help of God that I have been able to accomplish this thesis.

I would like to express my sincerest gratitude to my advisor Professor Mohamad Sawan for all the help and guidance he has provided me throughout my Ph.D. His advice on technical and also non-technical matters has taught me how to excel as successful researcher. I will always consider him not only as a mentor but also as a big brother.

I thank Professor Yvon Savaria, for his valuable comments along this project and also for chairing the committee of this thesis. I also thank Professor Yves Audet for accepting being member of my thesis committee and Professor Mohamed Ismail of Ohio University for accepting being the external reviewer of my thesis. I would like also to thank Professor Mourad El-Gamal of McGill University and Professor Fadhel Ghannouchi of Calgary University for being on my qualification exam.

I would like to thank the fabrication services and design facilities from CMC Microsystems and the financial support from the NSERC and Prompt-Quebec. Also I thank Polystim fellow students, secretaries, and technicians, especially, Ghyslaine, Robert, Abdallah, Abbas, Abdelouahab, Mohamad, Saeid, Ibrahim, Roula, Lisheng, louis-francois, Jonathan, Claudine, Diane, Martin, Réjean and Alex for their supports.

I would like to thank all my friends especially Salma for the joyful and priceless time we spent together and for the unconditional help and understanding.

Finally, I would like to express my deepest gratitude to my family, especially my mother and my precious sisters Gana and Ghina, for their love, support and encouragements.

#### RÉSUMÉ

L'apparition rapide, de nos jours, de différentes normes pour les systèmes de télécommunications a conduit au besoin de développer de nouvelles architectures de convertisseurs analogiques-numériques (CAN) à grande largeur de bande et à haute résolution. Parmi ces architectures, on retrouve les CAN pipelines qui présentent un bon compromis entre la surface du silicium occupée, la consommation de puissance et le débit de conversion. De plus, dans la plupart des architectures des CAN, la précision est limitée par l'appariement réel des éléments analogiques, nominalement à taille égale, et par le gain fini des amplificateurs opérationnels (ampop) résultant de la diminution de la tension d'alimentation. Cependant, la résolution de l'appariement et la précision du gain de l'ampop sont loin d'être conformes aux caractéristiques exigées par les CAN actuellement. Aussi, le mésappariement dans les canaux parallèles, utilisés pour concevoir des CAN pipeline à grande vitesse, et temporellement entrelacés, crée des distorsions non-désirées dans la bande passante. Ces distorsions doivent être évitées ou compensées.

Quant à la technologie de fabrication de CAN, le CMOS (Complementary Metal-Oxide Semiconductor) submicronique présente la solution la plus prometteuse pour l'intégration de système sur une seule puce (System-on-Chip - SoC). Cette intégration permet la réduction de la surface et de la puissance des circuits numériques plus rapidement qu'elle se permet pour les circuits analogiques. Par conséquence, la solution d'employer des techniques de calibration numérique afin d'améliorer la performance des CAN implémentés en technologie CMOS est devenue très attirante et convaincante.

Dans cette thèse, nous présentons de nouvelles méthodes et circuits numériques opérant en arrière plan dédiés à calibrer des CAN pipelinés et temporellement entrelacés.

Les nouvelles contributions proposées dans cette recherche sont récapitulées comme suit:

- Une nouvelle méthode d'échantillonnage, implémentée dans le domaine numérique, dédiée à surmonter les limitations des CAN temporellement entrelacés. Dans cette méthode, une permutation numérique aléatoire totale, pour n'importe quel nombre des canaux du CAN, peut être obtenue en échangeant aléatoirement la distribution des échantillons entre chaque groupe de deux CAN et en effectuant la rotation parmi ces différents groupes.

- Une technique de calibration aveugle surmontant les non-linéarités résultant du mésappariement de la capacité et du gain fini de l'ampop dans le CAN pipeline de 1.5-bit/étage, sans affecter ni la vitesse ni la gamme dynamique du signal d'entrée du CAN.

- Une nouvelle technique de calibration numérique obtenue en adoptant une injection de la tension de calibration imprécise opérant en arrière plan pour compenser la non-linéarité dans le CAN pipeline de multi-bits/étage.

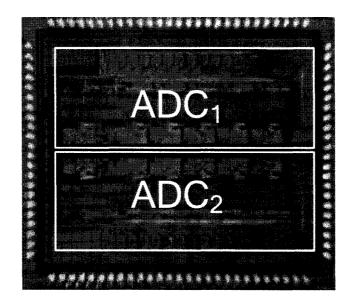

- Un prototype de CAN 10-bit, 100 MS/s, pipeline de deux canaux temporellement entrelacés et implémentés dans la technologie CMOS standard de 0.18 μm, est présenté avec ses résultats expérimentaux. Le mésappariement du gain statique entre les canaux est compensé par la méthode de corrélation basée sur l'injection de la tension, tandis que le mésappariement du gain dynamique est réduit en utilisant la technique d'échantillonnage insensible au biais (skew) de l'horloge.

L'analyse et les résultats de ces méthodes proposées prouvent leurs capacités afin de réduire les limites technologiques et d'accroître la performance de ce CAN lorsqu'il est implémenté avec des technologies CMOS submicroniques

#### **ABSTRACT**

The fast emergence of different standards for telecommunication systems has urged the need for high-resolution wide-bandwidth analog-to-digital converters (ADCs) to accommodate nowadays applications. On the other hand, pipelined ADCs offer an excellent trade-off between die area, power consumption and throughput among the various available ADC architectures. In most ADCs, the accuracy is limited by the actual matching of nominally equal-sized passive elements and the finite operational amplifier (opamp) gain stemming from power supply voltage reduction. These matching accuracy and opamp gain are far from being compliant with the up-to-date required specifications. Moreover, mismatches in the parallel ADCs' channels, used to form a wide bandwidth time-interleaved ADC (TIADC), create unwanted in-band distortions that have to be compensated.

Knowing that the CMOS technology presents the most promising solution for SoC (System on Chip) designs and that the digital circuits scale faster than the analog circuits, using digital techniques to improve the performance of CMOS type ADC has become very attractive.

In this thesis, the following new research contributions associated with the digital background calibration of high-performance time-interleaved and pipelined ADCs are presented:

Sampling method to improve spurious free dynamic range of TIADC. Firstly, the

mathematical background describing the effect of randomizing the samples

among the ADC channels in TIADC was analyzed and consequently a digitally

- oriented implementation, amenable to integration in deep submicron technology, was proposed.

- Digital blind background calibration method for 1.5b-per-stage pipelined ADC without affecting the speed or the input dynamic range was presented. In this method, a simple modification to the conventional MDAC allowed the ADC to toggle between different configurations to create a reference signal used to calibrate blindly the ADC in the background.

- Multi-bit-per-stage pipelined ADC calibration using imprecise voltage injection and correlation-based background calibration with duration shortening. By injecting subtractive voltages in a modified conventional multi-bit MDAC and performing correlation based successive coefficient measurements, a background calibration was achieved.

- A prototype of two-channel 10-bit, 100 MS/s time-interleaved ADC was designed and fabricated in 0.18μm CMOS technology. The front-end S/Hs circuits of this ADC were modified to enable the injection of calibration voltage to compensate for the static gain-mismatch. Dynamic gain-mismatch was reduced by applying skew-insensitive sampling.

Analysis and experimental results of the new methods demonstrated their effectiveness to improve significantly pipelined and time-interleaved ADCs performances.

## CONDENSÉ EN FRANÇAIS

#### 1. Introduction

L'apparition rapide, de nos jours, de différentes normes pour les systèmes de télécommunications a conduit au besoin de développer de nouvelles architectures de convertisseurs analogiques-numériques (CAN), à grande largeur de bande et à haute résolution, destinés à des applications à haute vitesse [MIT00]. Parmi ces architectures, on trouve les CAN pipelines [LEW87] qui présentent un des meilleurs compromis entre la surface de la puce, la consommation de la puissance et le débit de conversion parmi toutes les architectures des CAN. Cependant, l'augmentation de la vitesse au-delà des limites des technologies d'intégration nécessite que la fréquence d'échantillonnage de l'interface analogique-numérique soit ainsi accrue en employant des CAN pipelines multiples et temporellement entrelacés [SUM01]. Aussi, dans la plupart des architectures des CAN, la précision est limitée par l'appariement réel des éléments analogiques, nominalement à taille égale, et par le gain fini de l'amplificateur opérationnel (ampop) résultant de la diminution de la tension d'alimentation. Cependant, la résolution de l'appariement et la précision du gain de l'ampop sont loin d'être conformes aux caractéristiques exigées à ce jour. D'ailleurs, le mésappariement dans les canaux parallèles utilisés pour implémenter un CAN pipeline à grande vitesse, et temporellement entrelacés, provoque des distorsions non-désirées dans la bande passante qui doivent être évitées ou compensées.

Quant à la technologie de fabrication de CAN, le CMOS (Complementary Metal-Oxide Semiconductor) submicronique présente la solution la plus prometteuse pour l'intégration de système sur une seule puce (System-on-Chip - *SoC*). Cette intégration permet la réduction de la surface et la puissance des circuits numériques plus rapidement qu'elle se permet pour les circuits analogiques. Par conséquence, la solution d'employer des techniques de calibration numérique afin d'améliorer la performance des CAN implémentés dans la technologie CMOS est devenue très attirante et convaincante.

Dans cette thèse, nous présentons de nouvelles méthodes et circuits CMOS de calibration numériques opérant en arrière plan qui sont dédiés à calibrer le CAN afin d'en réduire les limitations technologiques et d'accroître les performances.

Cette thèse est divisée en sept sections. Après une brève introduction, la section 2 présente une revue de la théorie de base des CAN pipelines et temporellement entrelacés. Dans la section 3, une nouvelle méthode d'échantillonnage, dédiée à surmonter les limitations des CAN temporellement entrelacés, est présentée. Une technique de calibration «aveugle» opérant en arrière plan pour réduire les non-linéarités provenant du mésappariement de la capacité et du gain fini d'ampop dans le CAN pipeline de 1.5-bit/étage est présentée dans la section 4. La section 5 couvre une nouvelle technique de calibration numérique opérant en arrière plan compensant la non-linéarité dans le CAN pipeline de multi-bits/étage. Un prototype de CAN pipeline de deux-canaux temporellement entrelacés et implémentés dans la technologie CMOS 0.18 µm est présenté ainsi que ses résultats expérimentaux dans la section 6. Finalement, la conclusion et des recommandations pour des travaux futures terminent ce travail dans la

section 7. Notons que toutes les références aux figures aux équations et aux indications bibliographiques dans ce document réfèrent au texte de cette thèse en anglais.

## 2. Problèmes de la conception des CAN pipelines et temporellement entrelacés

#### 2.1 CAN pipeline

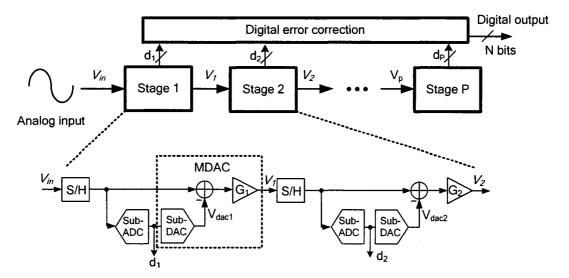

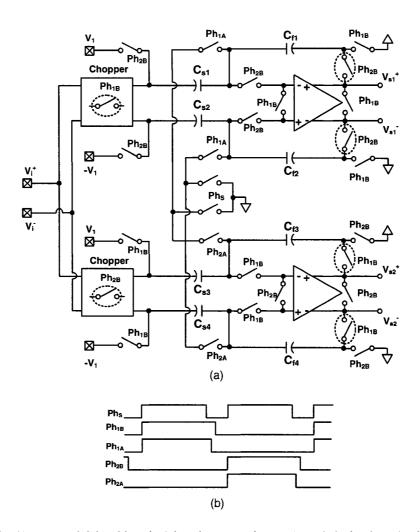

La figure 2.1 illustre le diagramme bloc d'un CAN pipeline général utilisant P étages. Dans cette structure pipelinée, la conversion est répartie sur plusieurs étages mis en cascade. Chaque étage (excepté le dernier représentant uniquement un CAN type flash), le signal d'entrée est d'abord quantifié en utilisant un CAN de résolution réduite (sub-CAN - SCAN), ensuite la sortie du code numérique est convertie à nouveau à un signal analogique en utilisant un convertisseur numérique-analogique à basse résolution (sub-CNA - SCNA). Ce signal analogique quantifié est alors soustrait du signal d'entrée, ayant pour résultat un résidu qui est amplifié par une valeur G égale à 2n, où n représente la résolution d'étage. Ensuite, ce résidu est transmis à l'étage suivant et le processus est répété.

Un étage avec une résolution n fournit un mot numérique de n+1 bit qui est transmis au bloc numérique de correction d'erreurs. Ce dernier contient des registres à décalage et des circuits numériques de correction. La redondance d'un symbole binaire dans chaque étage est habituellement désignée sous le nom de redondance de 0.5 bit. Ainsi, un étage avec une résolution de 1-bit et un symbole binaire redondant par étage est décrit comme un module à 1.5 bit/étage. Cette redondance compense le décalage du comparateur utilisé dans le SCAN [LEW87].

L'avantage principal de la conversion en plusieurs étages pipelines est l'augmentation du taux de la conversion, puisqu'il y a une conversion complète à chaque période de l'horloge. En outre, la taille de la puce est réduite puisque la résolution est linéairement liée au nombre d'étages pipelinés.

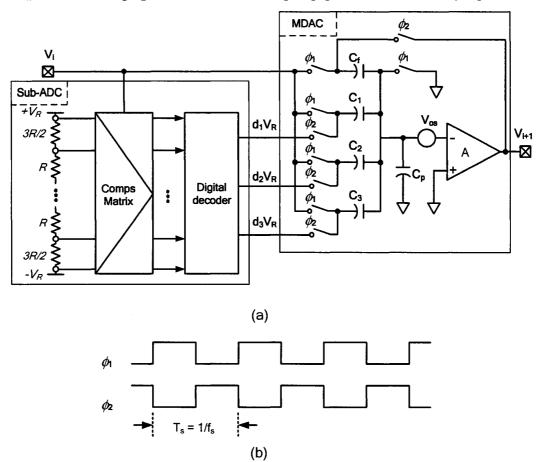

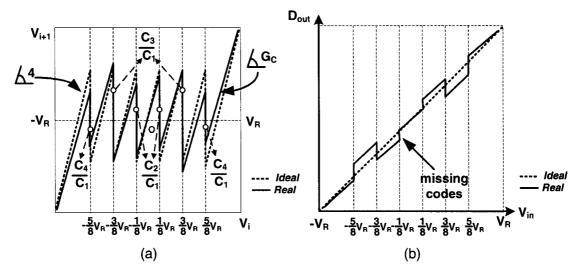

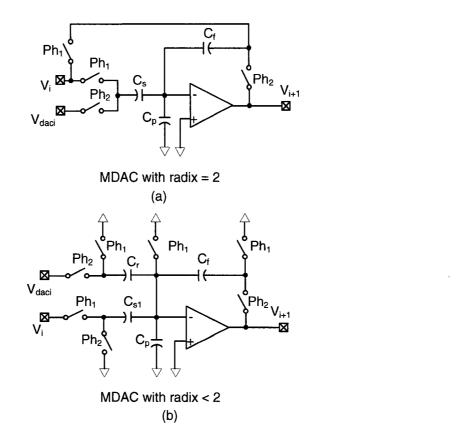

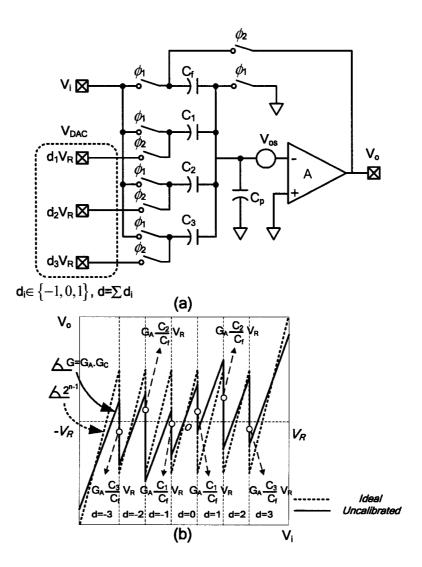

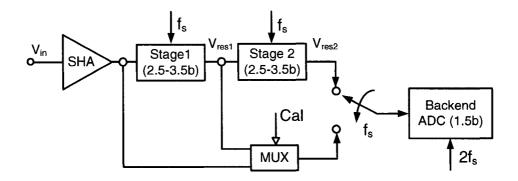

Dans la réalisation d'un CAN pipeline par des circuits à capacités commutées, les opérations du SCNA, incluant la soustraction, et l'amplification sont conjointement combinées et désignées sous le nom du CAN multiplicateur (CNAM). Le SCAN est composé du CNA flash et d'un encodeur numérique. Un étage pipeliné, basé sur le CNAM à 2.5 bit/étage est illustré dans la Fig. 5.3.

La tension du résidu reliée à l'étage i peut être dérivée par l'éq. (5.1). Tels que  $C_T = C_f + C_I + C_2 + C_3$ ,  $G_C = C_T/C_f$ , et  $G_A = 1/(1+1/Af)$  dont A représente le gain DC de l'ampop, f représente le facteur de rétroaction donné par  $f = C_f/(C_T + C_p)$ ,  $C_p$  représente la capacité parasite connectée à la masse virtuelle et  $V_{os}$  représente la tension de décalage. La sortie du SCNA est donnée par  $V_{daci} = ((d_1.C_1 + d_2.C_2 + d_3.C_3)/C_T) \cdot V_R$ , où  $V_R$  représente la tension de référence et  $d_i$  représente la sortie numérique du SCAN dont  $d_i \in \{-1, 0, 1\}$  et  $d = \sum_{i=1}^3 d_i$ .

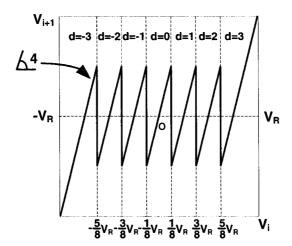

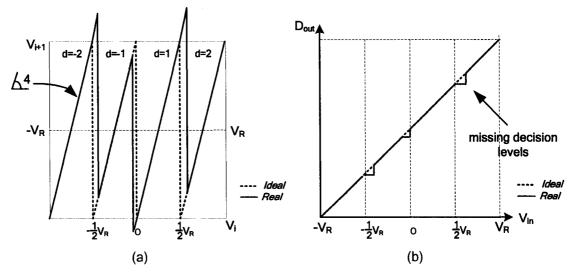

La figure 5.3(b) illustre le tracé du résidu d'un CNAM réel de 2.5-bit donné par l'éq. (5.1) et comparé à celui idéal. Cependant, la non-linéarité du SCNA et l'erreur du gain entre étages introduisent le mésappariement dans les sauts du résidu aux différentes bornes du code numérique  $d_i$ . Ces erreurs produisent des discontinuités dans la relation d'entrée-

sortie du CNA non-calibré et par conséquent provoquent des distorsions harmoniques qui vont dégrader considérablement la performance du CNA.

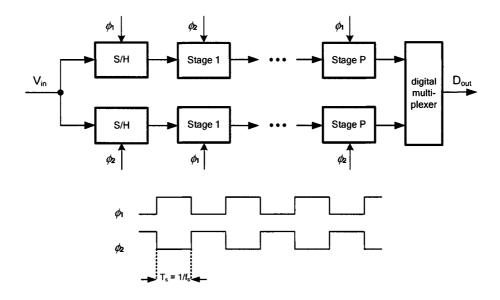

#### 2.2 CAN temporellement entrelacé

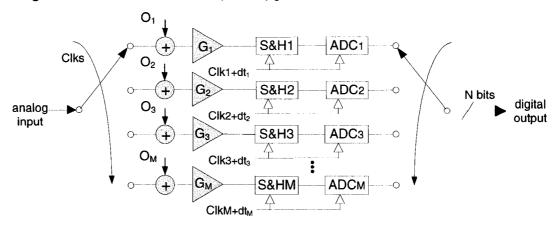

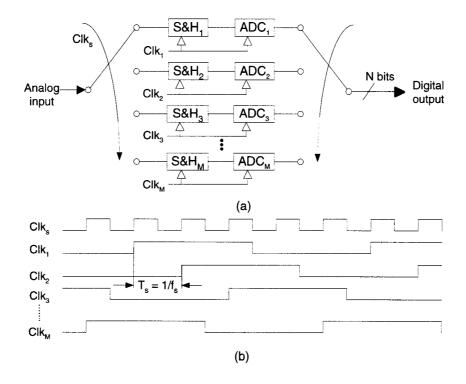

Figure 3.1 illustre un diagramme bloc du CAN temporellement entrelacé (CAN-TE). Chaque canal du CAN (CNA<sub>1</sub>, CNA<sub>2</sub>, ..., CNA<sub>M</sub>) opère, respectivement, à une phase d'horloge parmi M (CK<sub>1</sub>, CK<sub>2</sub>, ..., CK<sub>M</sub>) et au taux d'échantillonnage  $f_s/M$ , où M et  $f_s$  désignent, respectivement, le nombre de canaux parallèles du CNA et la fréquence globale de l'échantillonnage. Idéalement, tous les canaux du CNA-TE possèderaient la même fonction de transfert.

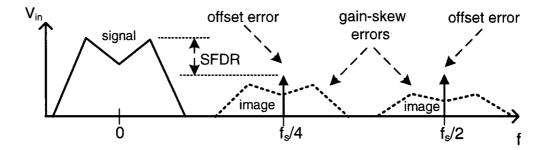

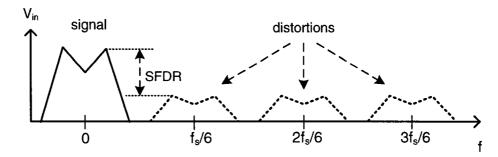

Malheureusement, n'importe quel mésappariement entre les canaux du CAN-TE mène à une dégradation de la performance de la linéarité. En particulier, les mésappariements de décalage, du gain et du biais de l'horloge (skew) engendrés dans les canaux parallèles sont imprévisibles et ils produisent des distorsions harmoniques dans la bande passante du signal d'entrée. Ces distorsions empirent la plage dynamique exemptée des parasites (Spurious Free Dynamic Range - *SFDR*) et par conséquent dégradent la performance du rapport signal sur bruit et la distorsion (Signal to Noise and Distortion Ratio - *SNDR*).

#### 2.3 Calibration des CAN pipelines et temporellement entrelacés

Plusieurs techniques de calibration ont été proposées afin de surmonter les limitations reliées à la technologie et d'accroître la linéarité des CAN pipelines et temporellement entrelacés. Cependant, chaque méthode présente des avantages et des limitations. La

méthode d'avant plan [SUM02a] par exemple, interrompt l'opération normale du CAN. Quant à la méthode de la moyenne de l'erreur [CHI04a], elle augmente la résolution tout en diminuant la bande passante du CAN. Aussi, l'addition d'un signal de calibration avec le signal d'entrée [JEW97] entraîne une diminution de la gamme dynamique utile du convertisseur. Cependant, l'ajout des convertisseurs et des circuits analogiques [CHU04b] augmente largement la complexité et le coût du CAN. Dans les sections suivantes, nous présentons de nouvelles méthodes et techniques de calibration du CAN pipeline et temporellement entrelacé surmontant les limitations de ces méthodes existantes.

#### 3. Nouvelle méthode d'échantillonnage pour les CAN-TE à large bande

L'échantillonnage à un taux élevé peut être réalisé par plusieurs canaux d'un CAN pipeline (section 2.2). Cependant, les mésappariements entre les canaux du CAN infligent un modèle de distorsion additif et périodique à la sortie du CAN-TE. Dans ce qui suit, M et  $T = 1/f_s$  représentent, respectivement, le nombre des canaux en parallèles et la période de l'échantillonnage globale du CAN-TE.

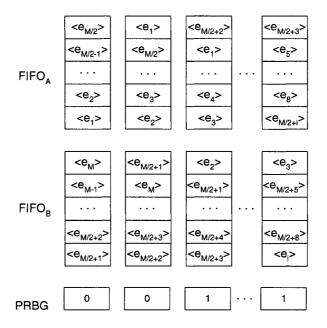

Quand un signal d'entrée de forme d'ondes sinusoïdale, de fréquence  $f_{in}$  et d'amplitude  $A_0$ , est appliqué à l'entrée du CAN-TE et que les erreurs du gain et de décalage sont présentées en ajoutant des termes dépendants du canal  $a_m$  et  $d_m$ , respectivement; le spectre du signal résultant à la sortie du CAN-TE est donné par l'éq. (3.1). Cette équation montre que les erreurs du gain et de décalage présentent des raies indésirables, centrées aux fréquences  $kf_s/M \pm f_{in}$  et  $kf_s/M$ .

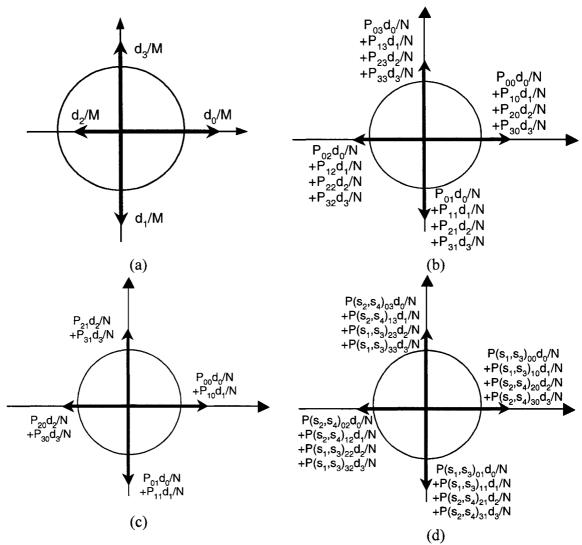

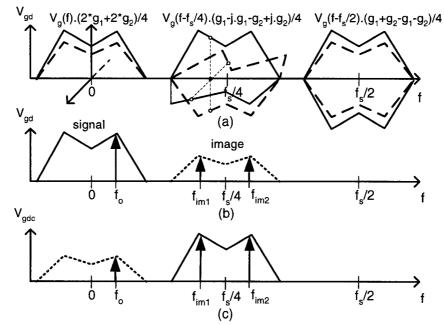

Par exemple dans le cas d'un CAN à quatre canaux, la sortie de CAN-TE est une séquence constituée des échantillons prélevés à partir de chaque canal dans l'ordre suivant : CAN<sub>1</sub>, CAN<sub>2</sub>, CAN<sub>3</sub>, CAN<sub>4</sub>, CAN<sub>1</sub>, etc. Cette séquence périodique crée des raies centrées aux fréquences  $kf_s/4 \pm f_{in}$  et  $kf_s/4$ . Dans ce qui suit, nous étudierons les raies produites par l'erreur de décalage  $d_m$ , et nous considérons l'étude d'un CAN à quatre canaux. Pour k = 1, nous avons des raies ayant des valeurs centrées à  $f_s/4$  donnée par l'éq. (3.3) (figure 3.3(a)). Ces raies centrées à  $f_s/4$  et aux autres fréquences dégradent le SFDR à des valeurs intolérables.

Cependant, dans le but de réduire la concentration des raies reliée à ces fréquences, une certaine permutation à l'intérieur de la séquence  $d_0d_1d_2d_3$  est requise. Par exemple, cette permutation peut être de l'ordre de  $d_0d_2d_1d_3$  ou n'importe quel autre ordre de permutation. Tout d'abord, si nous effectuons une permutation aléatoire des échantillons à l'entrée du CAN-TE, nous devons remplacer M dans l'éq. (3.1) par la période de cette séquence aléatoire. En d'autres termes, si un générateur de nombre binaire pseudo-aléatoire de période P est employé afin de contrôler cette permutation aléatoire, les séquences qui se répètent périodiquement, pour chaque N échantillons égal à 4P, sont donc obtenues et la période de la DFT donnée par l'éq. (3.1) deviendra N = 4P. Et par conséquent, l'erreur du mésappariement est distribuée d'une manière que nous pouvons trouver  $d_i/N$  dans chaque direction et ce qui réduit ainsi la somme due à ce mésappariement à la fréquence  $f_s/4$  (k=M/2), comme illustré dans la figure 3.3 (b) où  $P_{ij}$  sont données par l'éq.(3.5). Quand N est élevé, ces  $P_{ij}$  sont presque égales à P/4 pour chaque valeur de i et la somme de l'erreur due à chaque mésappariement est réduite au

minimum. Une technique pour mettre en application une permutation aléatoire presque complète concerne à ajouter plusieurs CAN aux *M* canaux du CAN-TE. Par conséquent, à un instant donné, deux CAN peuvent être disposés à recevoir deux échantillons aléatoirement choisis du signal d'entrée.

Ici nous proposons une solution de permutation aléatoire complète qui ne nécessite pas une complexité matérielle analogique supplémentaire mais en revanche, elle est basée sur des circuits numériques simples. Premièrement, supposons que nous pouvons permuter aléatoirement entre  $d_0$  et  $d_1$  et également entre  $d_2$  et  $d_3$  pendant une longue période d'échantillons de valeurs N. En effectuant cette procédure, les séquences comme  $(d_0d_1d_2d_3, d_1d_0d_2d_3, d_0d_1d_3d_2,$  etc..) peuvent être obtenues. Pour  $f = f_s/4$ , les raies sont distribuées dans chaque direction comme montré dans la figure 3.3(c).

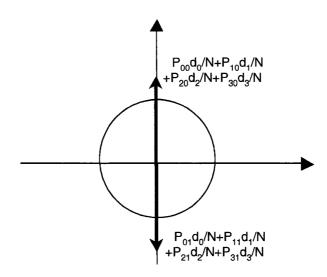

Cette permutation aléatoire élimine complètement la raie centrée à la fréquence  $f = f_s/2$  puisqu'il existe des erreurs  $d_i$  dans toutes les directions. Quant à la fréquence  $f_s/4$ , une grande réduction des raies est obtenue dans tous les cas sauf  $d_0.d_1 > 0$  et  $d_2.d_3 > 0$ , dont les raies ne sont pas réduites. Cependant, afin d'obtenir une permutation aléatoire totale, nous proposons d'effectuer une technique de rotation des positions des CAN. Par exemple, au lieu d'avoir une séquence répétée à chaque N échantillons comme ( $d_0d_1d_2d_3$ ,  $d_1d_0d_2d_3$ ,  $d_0d_1d_3d_2$ ,...), on peut s'arranger à avoir des séquences différentes.

Pour cela, on divise les N échantillons périodiques en quatre ensembles, le premier ensemble d'éléments peut disposer la même séquence à savoir  $(d_0d_1d_2d_3, d_1d_0d_3d_2)$ , tandis que le deuxième ensemble peut être obtenu en tournant simultanément les positions de deux couples des deux CAN, résultant d'une nouvelle séquence  $(d_2d_3d_0d_1, d_3d_2d_1d_0)$ , et

ensuite, on permute deux fois les deux séquences précédentes durant les N échantillons. En effectuant cette procédure, les erreurs du mésappariement  $d_i$  sont distribuées dans toutes les directions, et par conséquent, une réduction considérable de l'erreur totale est produite (figure 3.3 (d)). Cette réduction sera similaire à celle obtenue à partir de la permutation aléatoire complète des séquences. Cependant, le nombre des rotations effectuées, qui est égal à quatre dans cet exemple, est largement petit comparé au nombre N d'échantillons.

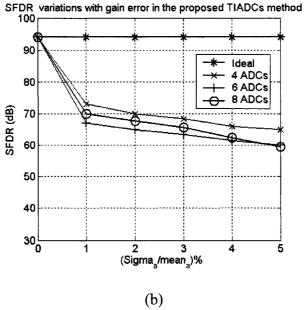

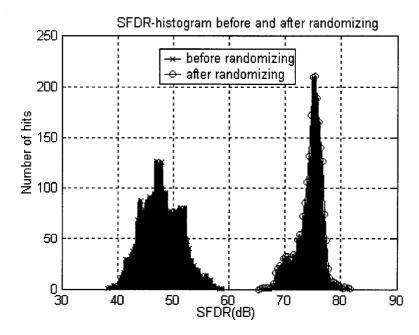

En effet, une permutation numérique aléatoire totale pour n'importe quel nombre de canaux du CAN peut être obtenue en permutant aléatoirement uniquement la distribution des échantillons entre chaque groupe de deux CAN et en effectuant la rotation parmi ces différents groupes. L'analyse et les résultats prouvent que cette méthode proposée peut être adaptée jusqu'a 5%pp de mésappariement de gain et un mésappariement de décalage atteignant  $\pm V_R/10$  tout en préservant une performance de 10 bits de SFDR

#### 4. Calibration «aveugle» opérant en arrière plan pour les CAN pipelines

Ces dernières années, l'architecture pipelinée des circuits à capacités commutées émergeait comme une approche particulièrement attrayante afin de réaliser des CAN type Nyquist ayant une moyenne-à-haute résolution et un moyen-à-haut taux de conversion. L'architecture 1.5-b/étage, où n = 2 avec un symbole binaire redondant, est généralement utilisée pour maximiser le taux de conversion tout en offrant une consommation raisonnable de puissance. Dans une implémentation pratique, le résidu analogique  $V_{i+1}$  de l'étage i d'un CAN pipeline utilisant 1.5-b/étage est exprimé par l'éq. (4.2). Dans cette

équation,  $C_1/C_2 = 1+\alpha_i$ ,  $\alpha_i$  représente le mésappariement de la capacité,  $\varepsilon_i$  représente l'erreur due au gain fini de l'ampop, et  $V_{ofi}$  représente la tension de l'offset. Prenant uniquement en considération le mésappariement de la capacité, l'éq. (4.2) peut être exprimée par l'éq. (4.3).

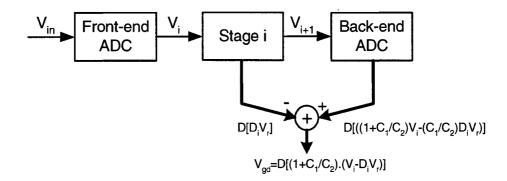

Cette valeur est numérisée par la partie restante du CAN de l'étage i à l'étage P (figure 4.1) dont le résultat est donné par l'éq.(4.4), où D[V] dénote la valeur numérique de V.

La soustraction de l'éq. (4.4) par la valeur numérique de  $V_i$  générée par l'étage i,  $(D[D_iV_r])$ , comme illustrée dans la figure 4.1, donne l'éq. (4.5) où  $g_l$  et  $V_g$  sont donnés par les équations (4.6) et (4.7).

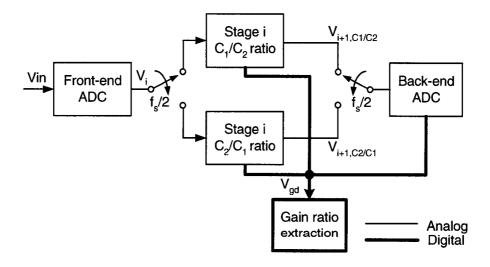

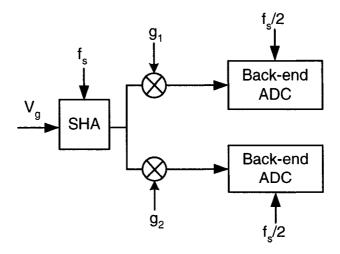

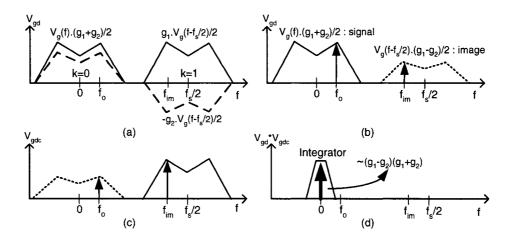

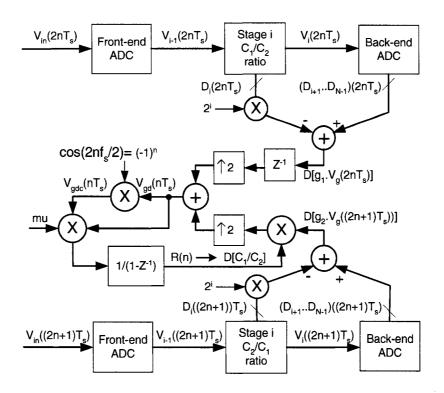

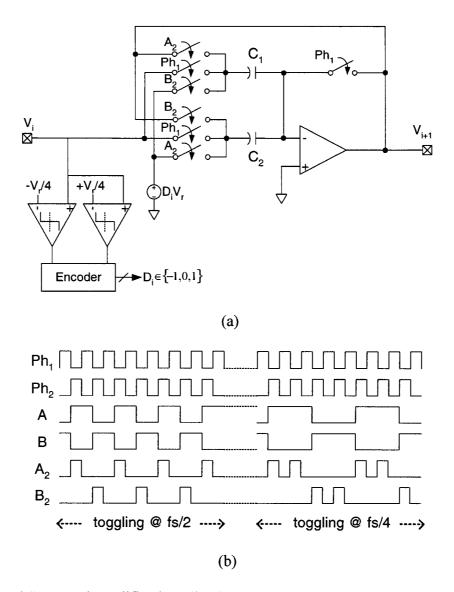

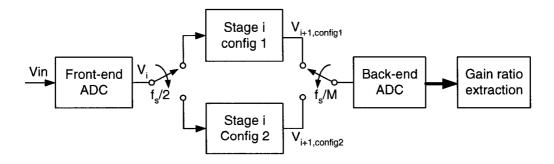

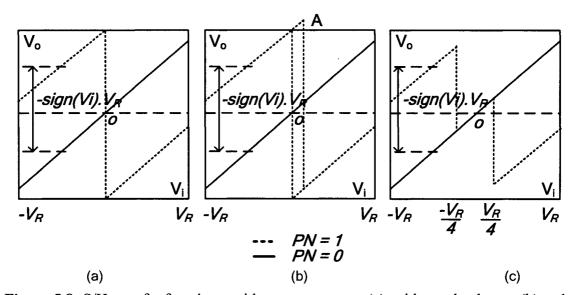

Maintenant, en échangeant le rôle de  $C_1$  et  $C_2$ , l'éq. (4.5) devient être exprimée par l'éq. (4.8) où  $g_2$  est donné par l'éq. (4.9). En permutant l'étage i à une fréquence  $f_s/2$  entre les deux configurations obtenues à partir de la permutation de rôle de  $C_1$  et  $C_2$ , comme illustré dans la Fig.4.2, la tension  $V_g$  est considérée d'être échantillonnée par un CAN-TE à deux canaux où le premier canal possède un gain  $g_1$  et le deuxième possède un gain  $g_2$ .

Basé sur la théorie du CAN-TE [CON93], la différence des gains  $g_1$  et  $g_2$  entre les deux canaux créera une image centrée à la fréquence  $kf_s/2 \pm f_{in}$  dans le spectre du signal  $V_{gd}$  où  $f_{in}$  dénote la fréquence du signal  $V_g$  donnée par l'équation (4.7) et  $f_s$  dénote la fréquence d'échantillonnage. Le spectre du signal numérique  $V_{gd}$  est donné par l'éq. (4.10). Cette équation indique qu'un signal sinusoïdal de fréquence  $f_o$  possédera une image à la fréquence  $f_{im}=f_s/2-f_o$ .

Les auteurs dans [JAM02] présentent une méthode pour égaliser le gain dans un CAN-TE à deux canaux. Dans cette méthode la sortie du CAN, dans notre cas  $V_{gd}$ , est multipliée par  $(-1)^n$  et le signal  $V_{gdc}$  est obtenu. Cette multiplication déplacera l'image centrée à la fréquence  $f_{im}$  à  $f_o$  et le signal d'entrée centrée à la fréquence  $f_o$  à  $f_{im}$ . La multiplication de  $V_{gd}$  par  $V_{gdc}$  dans le domaine temporel résultera à une composante DC proportionnelle au mésappariement du gain. En multipliant ensuite cette composante DC par mu et à l'aide d'un intégrateur, un signal R(n) proportionnel au mésappariement du gain est extrait. Ce signal, R(n) multiplie le gain  $g_2$  afin de forcer l'élimination de l'image. À l'équilibre, R(n) convergera vers la valeur  $g_1/g_2$ . Ce rapport de gain est employé afin de corriger le mésappariement de la capacité et le gain fini de l'ampop.

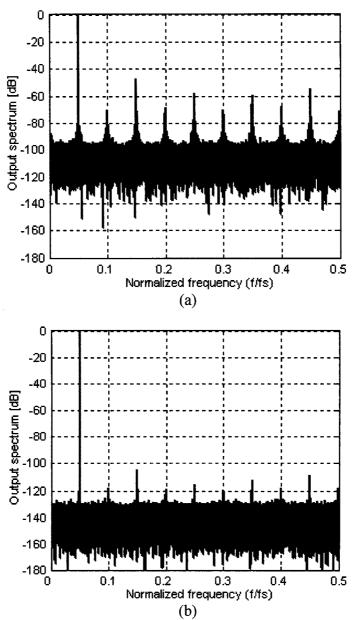

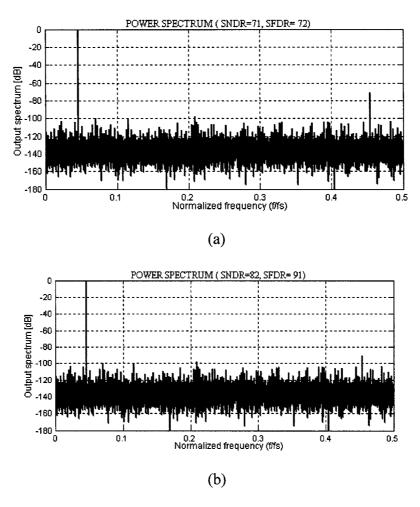

Des simulations ont été effectuées afin de vérifier l'efficacité de cette nouvelle technique de calibration opérant en arrière plan. Un mésappariement de la capacité de 3% et une tension de décalage du comparateur de  $\pm V_R/10$  ont été ajoutés dans tous les étages d'un CAN pipeline de 15 bits.

Un signal sinusoïdal à amplitude pleine échelle et de fréquence égale à 1/20 la fréquence d'échantillonnage ( $f_s$ ) a été appliqué à l'entrée du CAN avant et après le calibrage. Cependant, avant la calibration, le SNDR est de l'ordre de 43.9 dB, ayant pour résultat un nombre de bits effectifs (Effective Number Of Bit - *ENOB*) égal à 7 bits, et un SFDR de l'ordre de 47 dB. Aussi, après la calibration le SNDR devient de l'ordre de 89.3 dB, correspondant à un ENOB de 14.5 bits, et par conséquent, le SFDR est amélioré jusqu'au 103 dB.

## 5. Calibration numérique en arrière plan en utilisant l'injection de tension imprécise

Pour des CANs pipelines de haute résolution, la conversion de plusieurs bits par étage diminue généralement la consommation de puissance [CLI96]. Ceci est principalement dû au fait que la conversion de plusieurs bits par étage réduit considérablement le nombre total d'étages nécessaires.

Ainsi, comme mentionné dans la section 2.1, la non-linéarité du SCNA et l'erreur du gain entre étages introduisent le mésappariement dans les sauts du résidu aux différentes bornes du code numérique comme illustré dans la Fig. 5.3. Cependant, en mesurant précisément la valeur des sauts  $G_A(C_i/C_f)V_R$  dans le résidu et en employant l'équation (5.2), la sortie du résidu devient linéaire si elle se référera à l'entrée de l'étage i en dépit des erreurs produites du SCAN et du gain fini de l'ampop.

Après cette correction en utilisant l'éq. (5.2), le CAN, composé maintenant de l'étage i et les étages suivants, est linéaire avec un gain global  $G_A \cdot G_C$ . Dans la technique de calibration proposée, le terme  $G_A(C_i/C_f)V_R$  est mesuré à partir de différentes valeurs de  $C_i$  afin de permettre la correction en utilisant l'éq. (5.2).

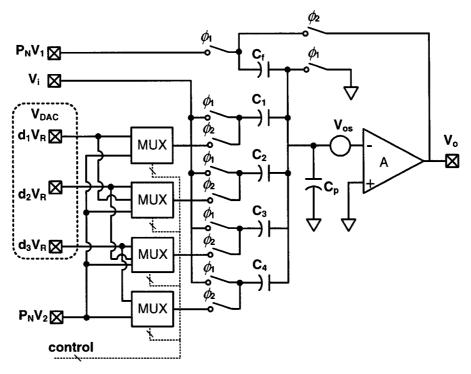

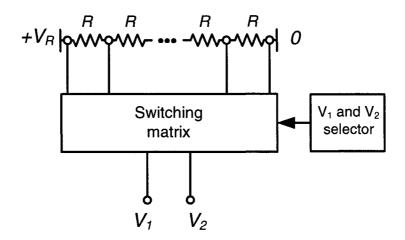

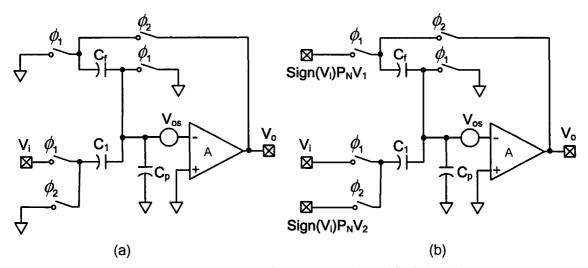

Un schéma du CNAM de 2.5-bit utilisant le calibrage proposé est illustré dans la Fig. 5.4. La modification apportée au CNAM par rapport au conventionnel est l'ajout d'une capacité supplémentaire  $C_4$  et de quelques circuits de contrôle numérique. En outre, la tension  $V_1 \cdot P_N$  est échantillonnée par la capacité de rétroaction  $C_\ell$  quand  $\phi$  est élevée, tel

que  $P_N$  est un signal pseudo-aléatoire alternant entre 0 et 1. La capacité  $C_4$  est utilisée au lieu de  $C_f$  pour échantillonner la tension d'entrée quand  $\phi$  est élevée.

En effectuant cette procédure, une tension égale à  $G_A \cdot V_1$  est injectée dans la sortie du résidu. Cependant, afin de ne pas trop limiter la plage de tension allouée pour la correction de la tension de décalage du SCAN, la tension  $V_1$  doit être suffisamment petite. Pour cette raison, une tension  $V_2 \cdot P_N$  est échantillonnée par la capacité  $C_4$  dans la phase suivante où la phase  $\phi_2$  est élevée. En injectant ces tensions suivant cette procédure, une tension est prélevée à la sortie du résidu de l'étage sous-calibrage est donnée par l'éq. (5.3). Tel que  $G_C = (C_1 + C_2 + C_3 + C_4)/C_f$  et  $V_{o1}$  désigne le terme restant dans la tension  $V_o$  qui représente la sortie du résidu dans l'absence des tensions injectées.

En effectuant une corrélation entre la valeur numérisée  $D[V_o]$  de la sortie du résidu  $V_o$  et  $P_N$ , le terme  $\Delta V = G_A \cdot (V_1 - (C_4/C_f)V_2)$  est mesuré. De plus, le terme  $G_A(C_4/C_f)V_R$  est obtenu par l'injection des tensions de calibration et en effectuant des mesures successives des coefficients. En effet, pour mesurer le premier coefficient  $(g_1)$ , la tension  $V_1$  est choisie égale à  $(K-1)V_R/K$  et la tension  $V_2$  est égale à  $V_R$ , où K est un entier pair. Dans ce cas, le terme égal à  $g_1$ , représentant le premier coefficient, serait mesuré. Aussi, pour mesurer le 2ieme coefficient  $(g_2)$ , la tension  $V_1$  est choisie égale à  $(K-1)V_R/K$  et la tension  $V_2$  est égale à  $(K-1)V_R/K$  et la tension  $V_2$  est égale à  $(K-1)V_R/K$  et la tension  $V_3$  est égale à  $(K-1)V_R/K$  et la tension  $V_4$  est égale à  $(K-1)V_R/K$  et la tension  $(K-1)V_R/K$  et la tension  $(K-1)V_R/K$  et la tension  $(K-1)V_R/K$  et la tension  $(K-1)V_R/K$  et la te

le coefficient  $g_K$ , la tension  $V_1$  est choisie égale à  $V_R/K$  et la tension  $V_2$  est reliée à la masse. Le terme  $G_A(C_4/C_f)V_R$  est obtenu par l'éq. (5.8).

La même procédure est répétée pour chaque capacité dont les multiplexeurs illustrés dans la Fig. 5.4 choisissent la capacité correspondante à la valeur à mesurer et acheminent sa ligne de contrôle numérique à une capacité de remplacement.

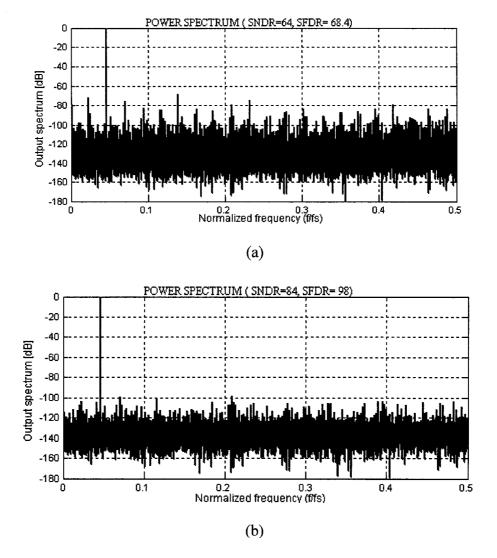

Des simulations ont été effectuées afin de vérifier l'efficacité de la technique proposée de calibrage dans un CAN pipeline de 14-bit. Un mésappariement de la capacité de  $\pm 0.2\%$ , une tension de décalage du comparateur de  $\pm V_R/12$  et un gain DC de l'ampop de l'ordre de 60 dB ont été ajoutés dans tous les étages.

Un signal sinusoïdal à amplitude pleine échelle et de fréquence égale à 1/20 la fréquence d'échantillonnage ( $f_s$ ) a été appliqué à l'entrée du CAN de 14-bit avant et après la calibration. Nous avons obtenu avant la calibration un SNDR de l'ordre de 64 dB, ayant pour résultat un ENOB égal à 10.3 bits, et un SFDR de l'ordre de 68.4 dB. Après le calibration, le SNDR devient de l'ordre de 84 dB, ayant pour résultat un ENOB égal à 13.7 bits, et par conséquent, le SFDR s'est accru à 98 dB.

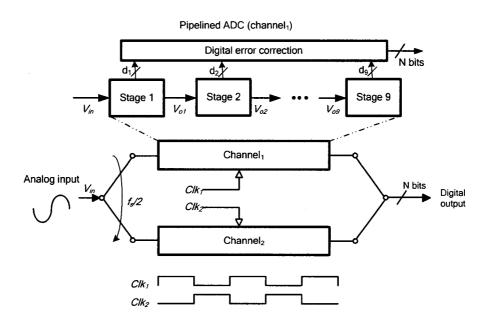

#### 6. CAN-TE pipeline à 2 canaux de 10-b et 100-MÉ/s

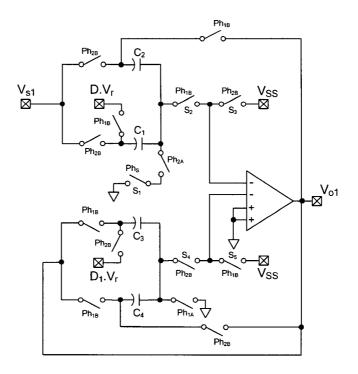

Dans cette section, un CAN-TE pipeline à deux canaux, conçu et fabriqué dans la technologie CMOS standard 0.18µm, est présenté. Le diagramme bloc de ce CAN proposé est illustré dans la Fig. 6.1. Chaque canal possède à l'entrée un échantillonneur-bloqueur (É/B) d'une large bande passante et implémenté en employant une architecture de neuf étages pipelinés en cascade d'une résolution de 1.5-bit-par-étage. Cependant,

chaque étage est composé d'un CNAM suivi d'un CAN complètement différentiel d'une résolution de 1.5 bit-par-étage.

Cependant, le mésappariement du gain statique entre les canaux est compensé en utilisant la méthode de calibration opérant en arrière plan basée sur l'injection de la tension sans affecter la gamme d'entrée du CAN comme présenté dans la section 3. De même, le mésappariement du gain dynamique, due à l'établissement incomplet de la tension à la sortie de l'É/B, est réduit en employant la technique d'échantillonnage insensible au biais de l'horloge, appliquée au premier étage de chaque canal du CAN pipeline.

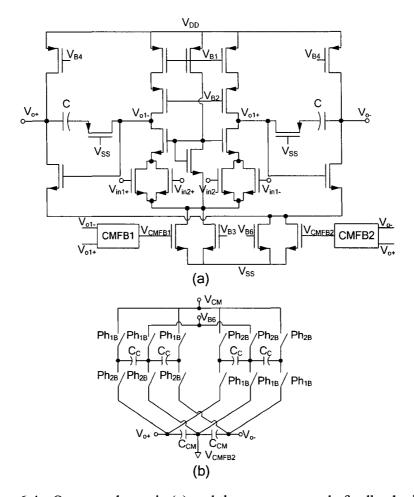

Ainsi, afin de réduire la consommation de la puissance et la surface de la puce, le partage de l'ampop entre deux étages consécutifs du CAN pipeline est employé. Les commutateurs additionnels dédiés à réaliser le partage conventionnel de l'ampop engendrent des capacités supplémentaires à l'entrée de l'ampop. En conséquence, ces capacités supplémentaires accumulées avec les capacités disposées à l'entrée de l'ampop ne sont jamais remises à zéro entre les échantillons ce qui introduira une non-linéarité dans le CAN. Afin de réduire la non-linéarité du CAN, nous proposons un ampop à quatre entrées dont chaque CNAM dispose deux entrées désignées. Cet ampop proposé est illustré dans la Fig. 6.5. Cet ampop est implémenté en utilisant une architecture complètement différentielle à deux étages d'amplification avec une compensation type Miller. Cet ampop fournit à la fois une performance au niveau du gain DC de l'ordre de 78 dB et au niveau de la fréquence du gain unitaire de l'ordre de 400 MHz.

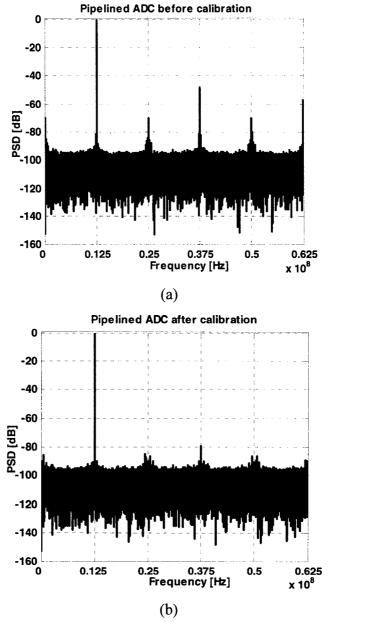

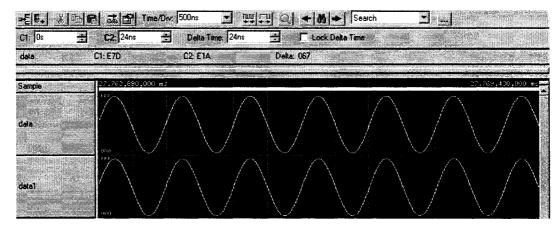

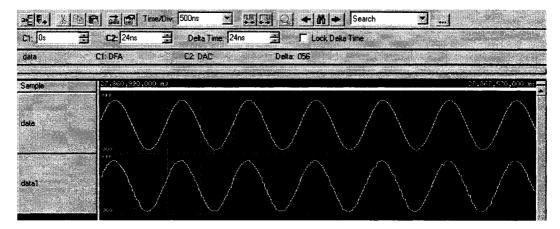

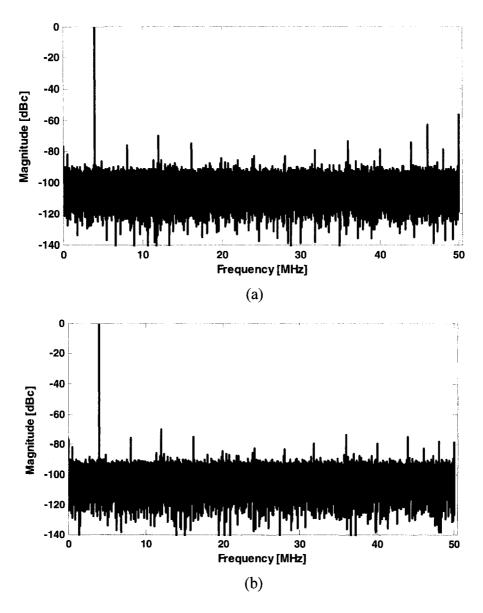

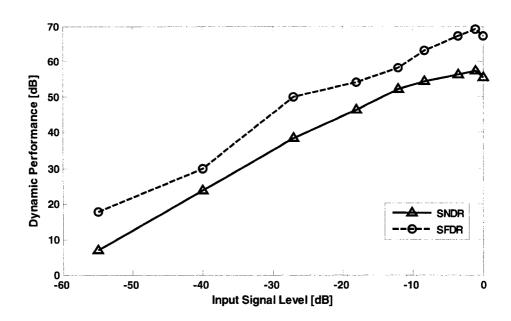

Le convertisseur est implémenté et fabriqué dans la technologie CMOS de TSMC standard  $0.18\mu m$ . Ce CAN consomme 76 mW et occupe une surface de  $3.6 \text{ mm}^2$ . La Fig. 6.15 présente le spectre de la sortie du CAN avant et après le calibrage. Le signal d'entrée, appliqué à ce convertisseur, est un signal sinusoïdal en pleine échelle de 1.6Vpp et de fréquence ( $f_{in}$ ) de 3.99 MHz telle que la fréquence de l'échantillonnage ( $f_s$ ) est égale à 100 MHz. Avant la calibration, le SNDR et le SFDR mesurés étaient de l'ordre de 48dB et 57dB, respectivement. La performance est limitée par l'existence des raies de distorsion, due au mésappariement de l'offset, de l'ordre de -57dBc à la fréquence  $f_s/2$  d'une part et d'autre part due au désappareillement du gain de l'ordre de -61dBc à la fréquence  $f_s/2-f_{in}$ . Après la calibration, le SNDR et le SFDR sont améliorés à 57dB et à 69dB, respectivement. Le tableau 6.2 récapitule les performances mesurées.

#### 7. Conclusion et recommandations

Dans cette thèse, nous avons examiné la calibration numérique opérant en arrière plan de CNA pipeline et temporellement entrelacé. Les nouvelles contributions proposées dans cette recherche ont été présentées et sont récapitulées comme suit:

- Une nouvelle méthode d'échantillonnage, implémentée dans le domaine numérique, dédiée à surmonter la limitation de CAN temporellement entrelacé.

- Une technique de calibrage «aveugle» surmontant les non-linéarités provenant du mésappariement de la capacité et du gain fini de l'ampop dans le CAN pipeline de 1.5-bit/étage, sans affecter ni la vitesse ni la gamme dynamique du signal d'entrée du CAN.

- Une nouvelle technique de calibrage numérique obtenue en adoptant une injection de la tension de calibration imprécise opérant en arrière plan compensant la nonlinéarité dans le CAN pipeline de multi-bits/étage.

- Un prototype de CAN pipeline de deux canaux temporellement entrelacés, et implémenté dans la technologie CMOS standard de 0.18 μm est présenté avec ses résultats expérimentaux. Le mésappariement du gain statique entre les canaux est compensé par la méthode de corrélation basée sur l'injection de la tension tandis que le mésappariement du gain dynamique est réduit en utilisant la technique d'échantillonnage insensible au biais de l'horloge.

Finalement, nous présentons certaines recommandations pour des recherches futures reliées à la conception du CAN pipeline, temporellement entrelacé de haute performance:

- Étudier la limitation pratique liée à la consommation de la puissance des CAN, et développer une architecture et des circuits mixtes afin d'atteindre la limite optimale de cette consommation. Une solution destinée à réduire cette dernière peut être réalisée en substituant l'ampop par un circuit analogique imprécis nécessitant une faible consommation de puissance. Un tel circuit peut être basé sur un circuit passif à capacité commutée à faible linéarité. Les méthodes proposées dans cette thèse peuvent être utilisées pour calibrer les non-linéarités des CAN basés sur cette sorte des circuits imprécis.

- Vérification expérimentale des méthodes proposées, en particulier la méthode de calibration «aveugle» grâce à sa faible complexité d'intégration au niveau des circuits analogiques et sa performance prometteuse.

Dans le SoC à haute densité d'intégration, le couplage des circuits numériques avec les modules analogiques génère un bruit se propageant dans les substrats communs. Ce phénomène de propagation est appelé le couplage de substrat. Malheureusement, ce couplage de substrat dégrade l'intégrité des signaux analogiques dans les circuits mixtes en y injectant des perturbations de l'ordre des centaines de millivolts durant les transitions de l'horloge. Pour cette bonne raison, la modélisation de l'effet de ce bruit sur la performance du CAN et la proposition de solution est un sujet de recherche vivement recommandé.

## TABLE OF CONTENTS

| DEDICATION                                                 | iv      |

|------------------------------------------------------------|---------|

| ACKNOWLEDGMENTS                                            | v       |

| RÉSUMÉ                                                     | V       |

| ABSTRACT                                                   | ix      |

| CONDENSÉ EN FRANÇAIS                                       | xi      |

| TABLE OF CONTENTS                                          | xxix    |

| LIST OF FIGURES                                            | xxxii   |

| LIST OF TABLES                                             | xxxvi   |

| LIST OF ABBREVIATIONS                                      | xxxviii |

| LIST OF SYMBOLS                                            | x       |

|                                                            |         |

| CHAPTRE 1: INTRODUCTION                                    | 1       |

| 1.1. Trends and Motivation                                 | 1       |

| 1.2. Research Problem                                      | 4       |

| 1.3. Research Contributions                                | 6       |

| 1.4. Thesis Organization                                   | 8       |

|                                                            |         |

| CHAPITRE 2: PIPELINED AND TIME-INTERLEAVED ADCS: ARCHITECT | URES    |

| AND CALIBRATION METHODES                                   | 10      |

| 2.1. Introduction                                          | 10      |

| 2.2. Pipelined ADC                                         | 11      |

| 2.2.1. Basic Operation                                                               |

|--------------------------------------------------------------------------------------|

| 2.2.2. Error Sources in Pipelined ADCs                                               |

| 2.3. Time-Interleaved ADC                                                            |

| 2.3.1. Structure                                                                     |

| 2.3.2. Error Sources in Time-Interleaved ADCs                                        |

| 2.4. Calibration of Pipelined and Time-Interleaved ADCs                              |

|                                                                                      |

| CHAPITRE 3: NEW SAMPLING METHOD FOR WIDE BANDWIDTH TIME-                             |

| INTERLEAVED ADCS                                                                     |

| 3.1. Introduction                                                                    |

| 3.2. Paper # 1 - New Sampling Method to Improve the SFDR of Wide Bandwidth ADC       |

| Dedicated to Next Generation Wireless Transceiver                                    |

|                                                                                      |

| CHAPITRE 4: DIGITAL BLIND BACKGROUND CALIBRATION FOR PIPELINED                       |

| ADCS64                                                                               |

| 4.1. Introduction                                                                    |

| 4.2. Paper # 2 - A Digital Blind Background Capacitor Mismatch Calibration Technique |

| for Pipelined ADC                                                                    |

| 4.3. Background Finite Opamp Gain Compensation Technique in Medium Resolution        |

| 1.5b/stage Pipelined ADC                                                             |

| 4.3.1. Gain ratio extraction                                                         |

| 4.3.2. Gain ratio construction                                                       |

| 4.3.3. MDAC configuration                                               | 84            |

|-------------------------------------------------------------------------|---------------|

| 4.3.4. Results                                                          | 86            |

| CHAPITRE 5: DIGITAL BACKGROUND CALIBRATION USING IMP                    | 'RECISE       |

| VOLTAGE INJECTION                                                       | 89            |

| 5.1. Introduction                                                       | 89            |

| 5.2. Paper # 3 - A Background Calibration Technique for Multi-bit/Stage | Pipelined and |

| Time-Interleaved ADCs                                                   | 92            |

| CHAPITRE 6: RESULTS AND DISCUSION                                       | 112           |

| 6.1. Introduction                                                       | 112           |

| 6.2. Two-Channel Time Interleaved ADC                                   | 113           |

| 6.2.1. Front-end Sample and Holds                                       | 113           |

| 6.2.2. Pipelined ADC Stages Implementation                              | 115           |

| 6.3. Experimental Results and Discussions                               | 119           |

| 6.4. Conclusion                                                         | 125           |

| CHAPITRE 7: CONCLUSION AND RECOMMENDATIONS                              | 126           |

| 7.1. Contributions of this Thesis                                       | 126           |

| 7.2. Recommendation for Future Work                                     | 127           |

| BIBLIOGRAPHY                                                            | 129           |

### LIST OF FIGURES

| Figure 1.1.  | An ideal SDR receiver                                                        |

|--------------|------------------------------------------------------------------------------|

| Figure 1.2.  | The digital radio receiver architecture employing IF-sampling2               |

| Figure 1.3.  | The direct conversion architecture                                           |

| Figure 2.1.  | Diagram of the conventional multi-bit/stage pipelined ADC                    |

| Figure 2.2.  | Switched capacitor implementation for 2.5 bit/stage of a pipelined ADC       |

|              | (a) and its clocks control signals (b)                                       |

| Figure 2.3.  | Residue plot of a 2.5 bit ideal pipeline stage                               |

| Figure 2.4.  | The residue plot of a 2 bit/stage with comparator offset error (a) and the   |

|              | input-output relationship of the overall pipelined ADC                       |

| Figure 2.5.  | The residue plot of a 2.5 bit/stage with comparator offset error (a) and the |

|              | input-output relationship of the overall pipelined ADC                       |

| Figure 2.6.  | The residue plot of a 2.5 bit/stage with opamp offset error (a) and the      |

|              | input-output relationship of the overall pipelined ADC                       |

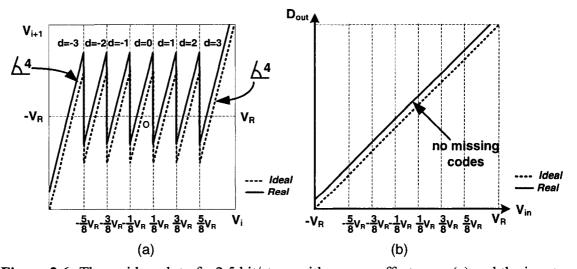

| Figure 2.7.  | The residue plot of a 2.5 bit/stage with opamp finite gain error (a) and the |

|              | input-output relationship of the overall pipelined ADC                       |

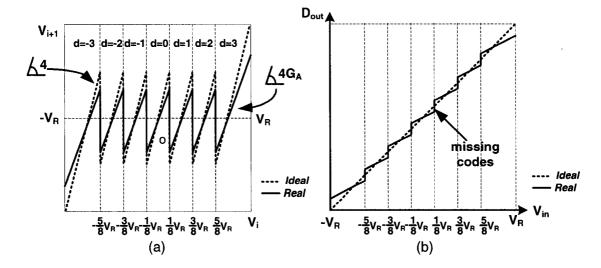

| Figure 2.8.  | The residue plot of a 2.5 bit/stage with capacitor mismatch error (a) and    |

|              | the input-output relationship of the overall pipelined ADC                   |

| Figure 2.9.  | A two-channel parallel pipeline ADC clocking example21                       |

| Figure 2.10. | Offset, gain and time skew mismatches model                                  |

| Figure 2.11. | High performance ADC for SDR transceivers                                    |

| Figure 2.12. | Principle of digital self-calibration: (a) error coefficient measurement, a | nd |

|--------------|-----------------------------------------------------------------------------|----|

|              | (b) missing code elimination                                                | 27 |

| Figure 2.13. | Schematic diagram of passive capacitor error-averaging technique            |    |

|              | [CHI00]                                                                     | 28 |

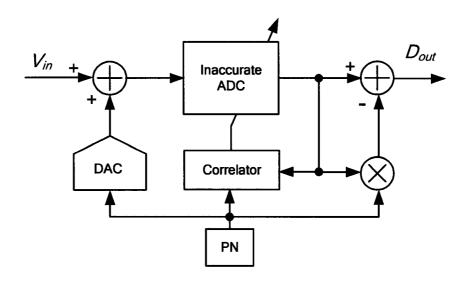

| Figure 2.14. | Error correction of pipelined ADC in channel equalizer like scheme          |    |

|              | [CHU04b]                                                                    | 31 |

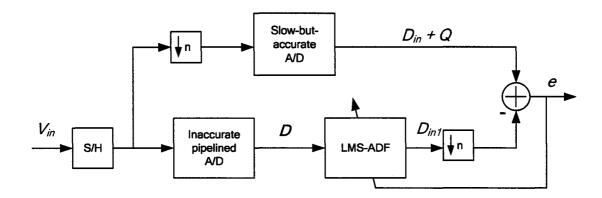

| Figure 2.15. | Correlation-based techniques to calibrate pipelined ADC [JEW97]             | 32 |

| Figure 3.1.  | Conventional time-interleaved ADC: (a) structure and (b) clock              |    |

|              | waveforms                                                                   | 40 |

| Figure 3.2.  | Spurs distribution for four channels conventional TIADC                     | 41 |

| Figure 3.3.  | Spurs distribution for $f = fs/4$ : (a) without randomizing, (b) with total |    |

|              | randomizing, (c) with the new randomizing, and (d) with the new             |    |

|              | randomizing and rotation                                                    | 43 |

| Figure 3.4.  | Spurs distribution for $f = fs/2$ with the new randomizing                  | 45 |

| Figure 3.5.  | Architecture of the new random time-interleaved ADC                         | 47 |

| Figure 3.6.  | The distribution of the samples at the inputs of the two ADCs sets: (a)     |    |

|              | waveforms, (b) set 1, (c) set 2                                             | 49 |

| Figure 3.7.  | Possible values of vectors <a> and <b></b></a>                              | 49 |

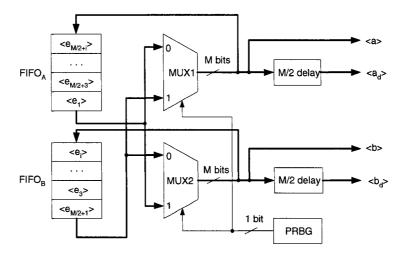

| Figure 3.8.  | Block diagram of the new random TIADC controller                            | 50 |

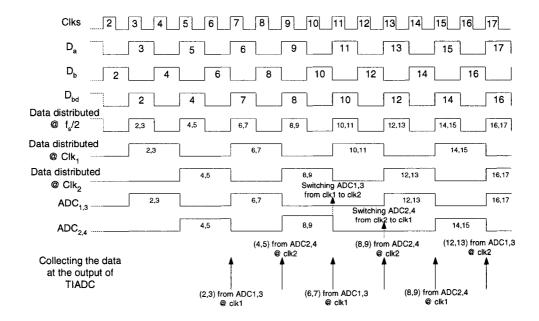

| Figure 3.9.  | Examples of the FIFOs cycles during the randomizing                         | 50 |

| Figure 3.10. | Distortion due to periodic rotation                                         | 53 |

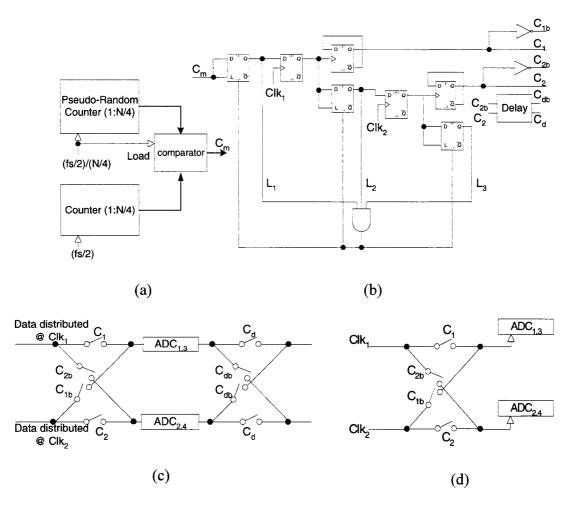

| Figure 3.11. | Rotation circuits implementation: (a) rotation trigger, (b) control signal | S    |

|--------------|----------------------------------------------------------------------------|------|

|              | generation, (c) switches to rotate the ADCs, and (d) switches to rotate    | the  |

|              | clocks                                                                     | . 54 |

| Figure 3.12. | Waveforms at the inputs of the four ADCs                                   | . 55 |

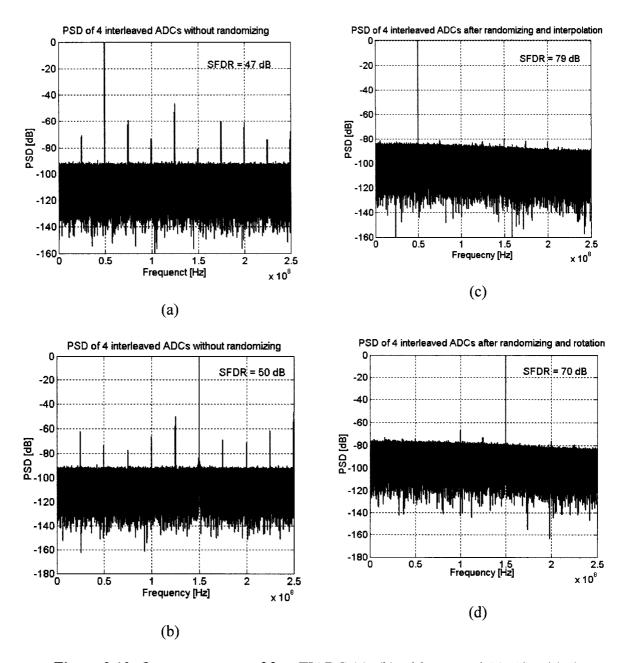

| Figure 3.13. | Output spectrum of four TIADC (a), (b) without, and (c), (d) with the      |      |

|              | proposed method                                                            | . 57 |

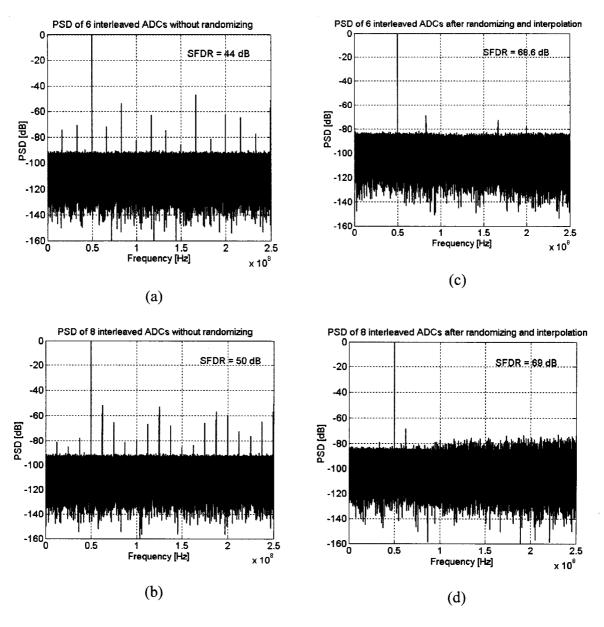

| Figure 3.14. | Output spectrum of 6 and 8 TIADCs (a), (b) without, and (c), (d) with t    | the  |

|              | proposed method                                                            | . 58 |

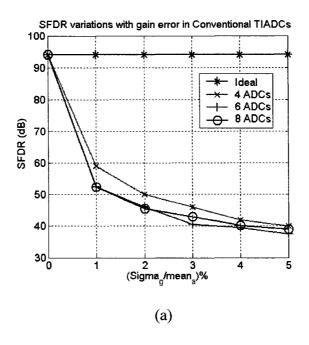

| Figure 3.15. | SFDR in terms of gain error mismatches: (a) without, and (b) with the      |      |

|              | proposed method                                                            | . 59 |

| Figure 3.16. | SFDR-histogram of the TIADC before and after the randomizing               | . 60 |

| Figure 4.1.  | Digital transformation of the capacitor mismatch in capacitor-flip-over    |      |

|              | MDAC to gain error                                                         | . 68 |

| Figure 4.2.  | The new background calibration principle                                   | . 69 |

| Figure 4.3.  | Drawing the ADC like two channels TIADC                                    | . 70 |

| Figure 4.4.  | Output spectrums for fs/2 swapping frequency in (a) and (b). The           |      |

|              | spectrum after (c) chopping and (d) convolution                            | . 71 |

| Figure 4.5.  | Gain ratio extraction diagram                                              | . 72 |

| Figure 4.6.  | Spectrum outputs for fs/4 swapping frequency in (a) and (b) and the        |      |

|              | spectrum after chopping in (c)                                             | . 73 |

| Figure 4.7.  | MDAC modification allowing the swapping between (a) the different          |      |

|              | capacitor ratios, the (b) MDAC control signals                             | . 75 |

| Figure 4.8.  | Spectrum of the output of a 15-b pipelined ADC (a) without and (b) with    |

|--------------|----------------------------------------------------------------------------|

|              | the proposed calibration technique                                         |

| Figure 4.9.  | Swapping the stage i between two configurations                            |

| Figure 4.10. | MDAC implementations for 1 bit/stage pipelined ADC: (a) radix 2 and (b)    |

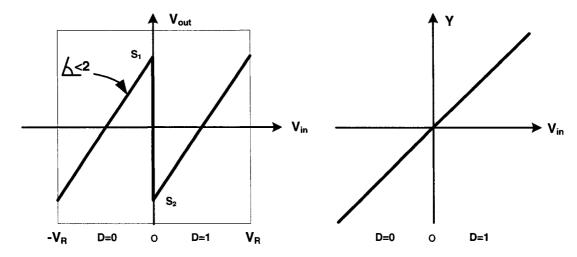

|              | radix <2                                                                   |

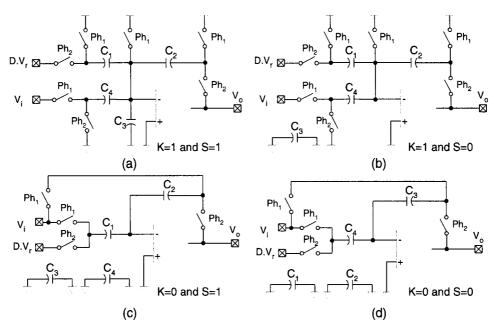

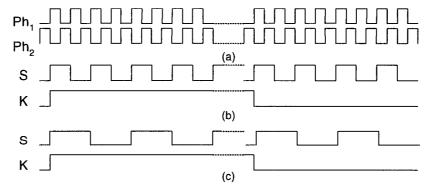

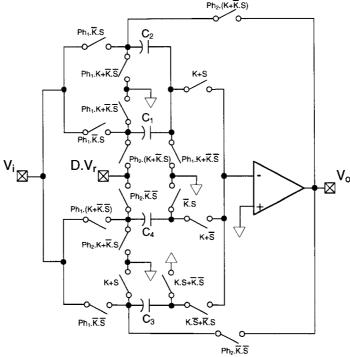

| Figure 4.11. | MDAC configurations: (a) $K=1$ and $S=0$ (radix < 2), (b) $K=1$ and $S=1$  |

|              | (radix <2), (c) K=0 and S=1 (radix 2), (d) K=0 and S=0 (radix 2)           |

| Figure 4.12. | Control signals for the MDAC: (a) S/H clock phases, (b) the control signal |

|              | to swap the TIADCs at fs/2,(c) fs/485                                      |

| Figure 4.13. | MDAC modifications with the control signals                                |

| Figure 4.14. | Spectrum of the output of the 10-bit pipelined ADC: (a) without and (b)    |

|              | with the proposed calibration technique                                    |

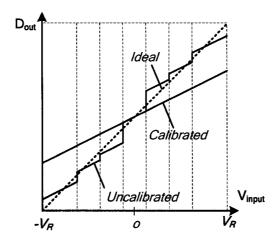

| Figure 5.1.  | The input-output relationship of the overall pipelined ADC90               |

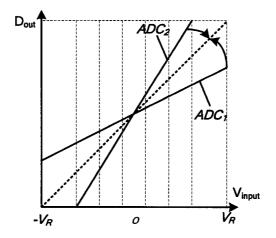

| Figure 5.2.  | Global gain correction for 2 ADCs                                          |

| Figure 5.3.  | MDAC implementation for 2.5 bit/stage pipelined (a), and the residue plot  |

|              | of a realistic stage compared with an ideal one (b)                        |

| Figure 5.4.  | 2.5-bit MDAC employing the proposed calibration                            |

| Figure 5.5.  | The SCV technique is applied to the first stage                            |

| Figure 5.6.  | Switching matrix used to generate the voltages $V_1$ and $V_2$             |

| Figure 5.7.  | Conventional (a), and modified (b) S/H                                     |

| Figure 5.8.  | S/H transfer functions: with one comparator (a), with overload error (b)   |

|              | and when two comparators are used (c)                                      |

| Figure 5.9.  | Using the 1.5b/stage backend ADC to shorten the calibration cycles 105               |  |  |

|--------------|--------------------------------------------------------------------------------------|--|--|

| Figure 5.10. | Spectrum of the output of a 14-bit pipelined ADC without (a) and with the            |  |  |

|              | proposed calibration technique (b)                                                   |  |  |

| Figure 5.11. | Spectrum of the output of a 14-bit pipelined ADC without (a) and with the            |  |  |

|              | proposed calibration technique (b)                                                   |  |  |

| Figure 6.1.  | The block diagram of the proposed two-channel ADC 112                                |  |  |

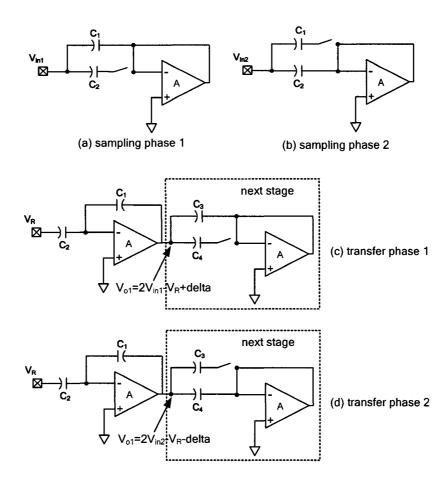

| Figure 6.2.  | Front-end S/H Circuits' implementation: (a) and their signals timing (b)             |  |  |

|              |                                                                                      |  |  |

| Figure 6.3.  | The MDACs of stages 1 and 2 of ADC <sub>1</sub>                                      |  |  |

| Figure 6.4.  | Opamp schematic (a) and the common-mode feedback circuit (b) 118                     |  |  |

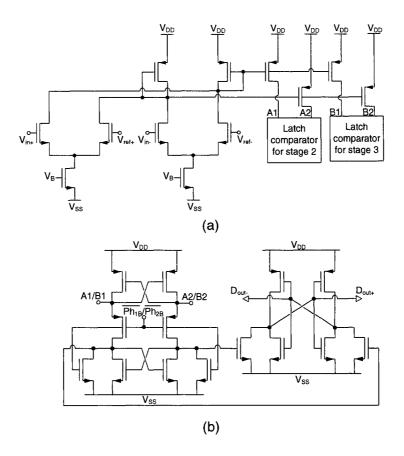

| Figure 6.5.  | Current-mirrored fully differential preamp (a) and latch stage (b) 119               |  |  |

| Figure 6.6.  | Die photograph of the prototype ADC                                                  |  |  |

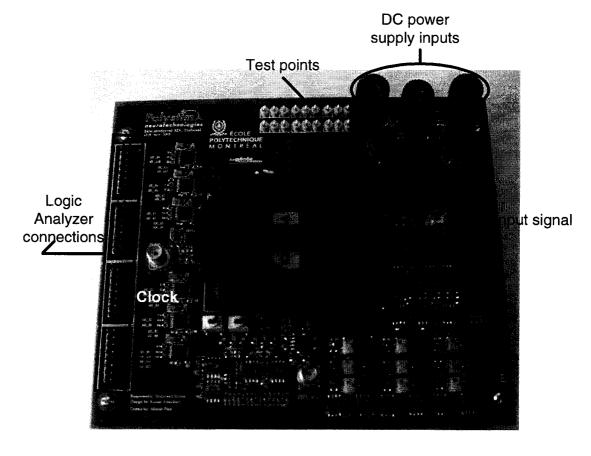

| Figure 6.7.  | Top side photo of the PCB                                                            |  |  |

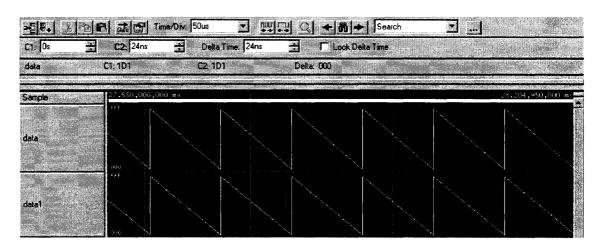

| Figure 6.8.  | Logic analyzer output for 10 KHz ramp input                                          |  |  |

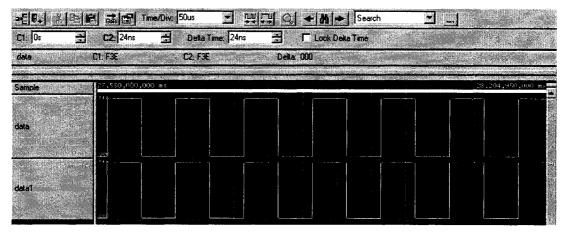

| Figure 6.9.  | Logic analyzer output for 10 KHz square input                                        |  |  |

| Figure 6.10. | Logic analyzer output for 1 MHz sinusoidal input                                     |  |  |

| Figure 6.11. | Logic analyzer output for 99 MHz sinusoidal input                                    |  |  |

| Figure 6.12. | ADC output spectrum (a) without calibration and (b) with calibration. ( $f_s$ =      |  |  |

|              | 100 MS/s, $V_{\text{in}} = 1.6 \text{Vpp}$ , and $f_{\text{in}} = 3.9 \text{ MHz}$ ) |  |  |

| Figure 6.13. | Measured dynamic performance versus input signal level                               |  |  |

# LIST OF TABLES

| Table 6.1: Performance summary                                             | 124 |

|----------------------------------------------------------------------------|-----|

| Table 6.2: Performance comparison with state-of-the-art 10-b, 100MS/s ADCs | 125 |

## LIST OF ABBREVIATIONS

|  | ADC | Analog-to-Digital | Converter |

|--|-----|-------------------|-----------|

|--|-----|-------------------|-----------|

BPF Bandpass Filter

CDS Correlated Double Sampling

CMOS Complementary Metal Oxide Semiconductor

DAC Digital-to-Analog Converter

DCR Direct Conversion Receiver

DNC DAC Noise Cancellation

DNL differential nonlinearity

DFCA DAC and Feedback Capacitor Averaging

DFT Discrete Fourier Transform

DRR Digital Radio Receive

FS Full-Scale

GEC Gain Error Correction

ICM Input Common Mode

IF Intermediate Frequency

INL integral nonlinearity

IR Image Reject

LMS Least Mean Square

LNA Low Noise Amplifier

LSB Least Significant Bit

MDAC Multiplying Digital-to-Analog Converter

MNC Mismatch Noise Cancelling

MSB Most Significant Bit

PRBG Pseudo-Random Bit Generator number

RF Radio Frequency

SADC Sub Analog-to-Digital Converter

SCM Successive Coefficient Measurement

SCV Subtractive Calibration Voltage

SDAC Sub Digital-to-Analog Converter

SD-CGC Subtractive Dither-Continuous Gain Correction

SDR Software Defined Radio

SFDR Spurious Free Dynamic Range

S/H Sample and Hold

SMA SubMiniature version A

SNDR Signal-to-Noise-and-Distortion Ratio

SNR Signal-to-Noise Ratio

SoC System on Chip

TIADC Time-Interleaved ADC

TSMC Taiwan Semiconductor Manufacturing Company

# LIST OF SYMBOLS

| $\alpha_i$               | Capacitor mismatch                           |

|--------------------------|----------------------------------------------|

| Δ                        | Quantization error                           |

| $oldsymbol{\phi}_{ m l}$ | Sampling phase                               |

| $\phi_2$                 | Amplifying phase                             |

| μm                       | Micrometer                                   |

| $\sigma^2$               | Variance                                     |

| $\boldsymbol{A}$         | Finite opamp gain                            |

| $C_p$                    | Virtual ground parasitic capacitance         |

| dB                       | Decibel                                      |

| dBm                      | dB referenced to one milliwatt               |

| $d_i$                    | Digital output code                          |

| E[]                      | Expected value                               |

| f                        | Feedback factor                              |

| $f_s$                    | Sampling frequency                           |

| $g_{m}$                  | Gate small-signal transconductance           |

| $G_A$                    | Interstage gain due to the finite opamp gain |

| $G_C$                    | Interstage gain due to sub-DAC               |

| $G_i$                    | Interstage gain of stage i                   |

| MHz                      | Megahertz                                    |

| MS/s                     | Mega-sample-per-second                       |

| n                        | Stage resolution                             |

| N                        | Number of bits                               |

| $V_{daci}$               | SDAC analog output of stage i                |

| $V_{i+1}$                | Output residue of stage i                    |

| $V_{os}$                 | Input-referred offset voltage                |

$V_R$  Reference voltage

T Time

V Voltage

W Watt

## Chapter 1

### **INTRODUCTION**

#### 1.1 Trends and Motivation

The continuous growth of demand for wireless communications has led to the proliferation of different standards. The highly competitive market demands low-cost, low-power, and small form-factor devices. This calls for the development of single-chip receivers capable of adapting to the various communication standards, preferably in low-cost technologies [LI02]. New transceiver architectures are evolving toward enabling software defined radio (SDR) to allow global roaming for wireless users.

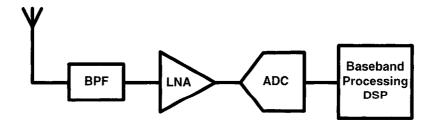

The ideal SDR receiver [MIT00] has very few analog stages: the only analog components are the antenna, the bandpass filter (BPF), the low noise amplifier (LNA), and the analog-to-digital converter (ADC) as illustrated in Fig. 1.1.

Figure 1.1: An ideal SDR receiver.

In this architecture, analog-to-digital conversion is achieved immediately at the radio frequency (RF) in order to process the signal completely in the digital domain. In addition to the difficulty concerning the design of wide bandwidth LNAs and antennas, this architecture puts stringent requirements on the analog-to-digital converter (ADC). To sample directly the RF input signals, which can rise to several giga-hertz, an ADC capable of handling signals ranging from –120 dBm to –30 dBm is needed [BUR00]. An ADC with sampling rate of several gigahertz and a dynamic range around 90 dB is far from being realized due to technological, technical, and fundamental physical limitations with today's technologies. Moreover, the configurability of the receiver means that its front-end interface should be highly adjustable. This configurability is difficult to obtain at the analog side of the receiver and for this reason it should be transferred to the digital domain. Thus, the most promising nowadays solutions for receivers are the digital radio receiver (DRR) and the direct conversion receiver (DCR) [MIR00], shown in Figs. 1.2 and 1.3 respectively.

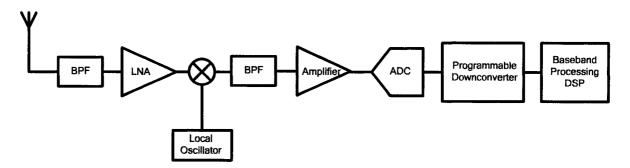

Figure 1.2: The digital radio receiver architecture employing IF-sampling.

In DRR, the ADC samples the overall spectrum allocated to the system at an intermediate frequency (IF) selected upon a compromise between selectivity and sensitivity of the receiver. It is desirable to choose a high IF to reduce the requirements

on the image reject (IR) filter to make it implementable on-chip. For a sufficiently high IF, the band selection filter can play the role of IF filter as well [RAZ97].

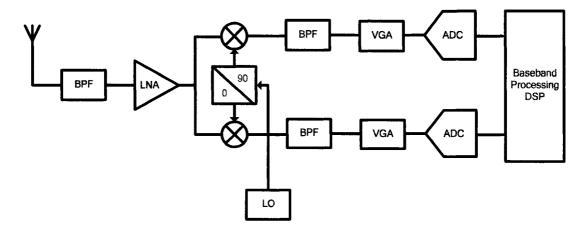

Figure 1.3: The direct conversion architecture.

The programmable downconverter (Fig. 1.2) deals with down conversion, channelization and sample rate adaptation. This kind of receiver overcomes some problems of the DCR architecture such as dynamic dc offset, flicker noise and second-order intermodulation. Also this DRR has the advantage of avoiding I and Q mismatches in DCR. However, this technique requires a fast and high resolution ADC that is currently limiting its utilization almost to base stations only. Providing wide bandwidth, high resolution and low power ADC, the DRR architecture becomes also a viable solution for mobile receivers.

In DCR, the desired channel is centered at zero frequency (DC), which relaxes the sampling frequency required from the ADC. Solving the shortcomings of the DCR could make it the most favorable solution for mobile receivers.

Since signal processing functions are moved to the digital domain, where all nonidealities of the analog domain can be avoided, the ADC stage has become a key bottleneck in these developments. Therefore in DRR and DCR, ADCs with specifications ranging between 50 to 200 MS/s, and 10 to 14 bits with high spurious free dynamic range (SFDR) are required.

Since the complementary metal oxide semiconductor (CMOS) technology permits the free mixture of analog and digital functions owing to its inexpensive fabrication process and its superiority for the digital applications, CMOS is the best technology for the SoC (System on Chip) design that enables single chip transceivers.

On the other hand, pipelined ADCs offer an excellent trade-off between die area, power consumption and throughput among all the ADC architectures [LEW87]. For this reason the pipelined ADC in CMOS technology is the perfect choice for DRR and DCR receivers. Moreover, to increase the speed beyond the technological limit of the CMOS technology: the sampling frequency of the analog-to-digital interface can be increased by using multiple ADCs that are time interleaved [SUM01].

#### 1.2 Research Problem

In the following paragraphs we will state the major limitations facing the implementation of the high dynamic range wide-bandwidth pipelined ADCs in CMOS technologies:

A. In most ADCs, the accuracy is limited by the actual matching of nominally equalsized analog elements (resistors, capacitors, or current sources). This matching accuracy is far from being compliant with the up-to-date required specifications. To improve matching between components, their geometrical sizes and therefore the area

- of the circuit increases. Large analog elements (e.g. capacitors) limit the speed of the ADC and increase also its power consumption.

- B. The supply voltage of digital CMOS circuits is decreasing to minimize the power consumption per logic cell. In addition, the shrinking of device dimensions lowers the maximum allowed supply voltage. While high-performance ADCs rely on fast and high gain operational amplifiers (opamps), lowering the supply voltage reduces the available signal swing and makes the design of high gain opamp topologies with many stacked transistors unfeasible. One way to overcome this problem is to use multistage opamps with nested Miller-effect compensation. Although such opamps can give large enough gains, they slow down the frequency compared to simple single-stage structures.

- C. To achieve higher sampling rates, parallelism can be introduced to multiple ADC channels to form a single wide bandwidth time-interleaved ADC (TIADC). In CMOS technology, TIADCs using pipelined ADCs for the parallel channels represent the most suitable solution to obtain high frequency and resolution simultaneously. Mismatches in the parallel ADCs channels create unwanted in-band distortions that have to be avoided or compensated. For nowadays configurable receivers, the digital channel selection is performed after digitizing the whole utilized spectrum, with wide bandwidth high dynamic range TIADC needed to support a large number of wireless standards. Channel selection after the ADC will increase the signal-to-noise ratio (SNR) but it cannot overcome distortion in the ADC bandwidth, which makes the SFDR a very important parameter to feature the efficiency of an ADC for

telecommunication applications. TIADCs, as we mentioned earlier, suffer from inband distortions that undermine the SFDR performance.

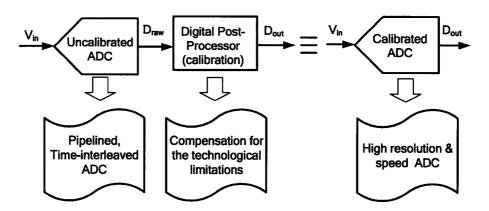

The aforementioned problems motivate the development of calibration methods to compensate for the technological limitations and enhance the ADCs performance. Knowing that the digital circuits in current deep submicron technologies scale faster in terms of power and area compared with the analog circuits, digital solutions to improve ADC performance are now very attractive.

#### 1.3 Research Contributions

The contributions presented in this thesis have been reported in several journals and conferences as summarized below.

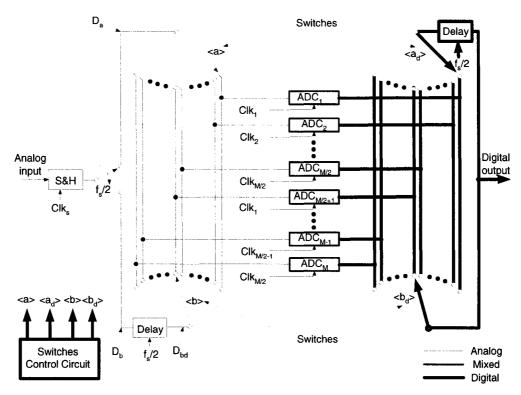

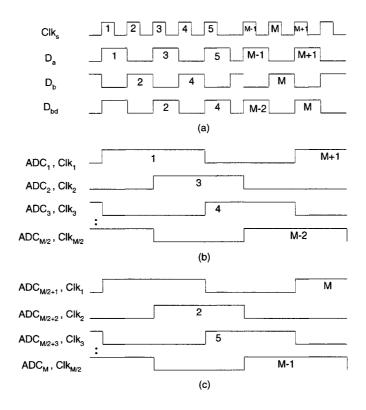

We presented, in [ELS03] and [ELS04a], a new sampling method to overcome the limitation of time-interleaved analog-to-digital converters (TIADC). Ideally in TIADC all the channels would have the same transfer function. In fact, mismatches between these channels inflict periodic additive spurious components to the output that undermine the ADC performance. To overcome this problem in the digital domain, a randomizing and rotation technique to average out the effect of the mismatches among the ADC channels was proposed. The mathematical background describing the effect of randomizing the samples among the ADC channels was analyzed and consequently a digitally oriented implementation, amenable to integration in deep submicron technology, was proposed. Analysis

- and results of the new method demonstrated its effectiveness to improve significantly the TIADC performance.

- In [ELS04b], we proposed a new digital background calibration technique to compensate the capacitor mismatch in pipelined ADCs. A major limitation in the switched-capacitor pipelined ADC is the capacitor mismatch due to the finite resolution of the technology. In this work, a digital signal from the ADC output is constructed so as to transform the capacitor mismatch to gain error. A simple modification to the conventional multiplying digital-to-analog converter (MDAC) allows the ADC to toggle between different configurations to create a reference signal used to calibrate blindly the ADC in the background. The creation of this signal does not produce any limitation for the ADC in terms of speed or degradation of the input dynamic range. Also, we extended this to calibrate in the background the finite opamp gain in one-bit/stage pipelined ADCs [ELS04c].

- In [ELS06a], a method to calibrate multi-bit/stage pipelined ADC has been presented. According to one aspect of this method, a new digital background calibration technique to compensate for the nonlinearity and gain error and opamp finite dc gain in multi-bit/stage pipelined ADC was provided. By injecting subtractive voltages in a modified conventional multi-bit multiplying digital-to-analog converter (MDAC) and performing correlation based successive coefficient measurements, a background calibration was achieved. This calibration does not need accurate calibration voltages or increasing the MDAC resolution and the coefficients measurement is independent from the input signal.

Further, we presented a global gain correction for time-interleaved ADCs. Techniques to shorten the calibration duration are further provided. This method demonstrates linearity improvement by several bits in single and multi-channel multi-bit/stage pipelined ADC.

A two-channel, 10-bit, 100-MS/s, time-interleaved pipelined ADC was designed and fabricated in 0.18μm CMOS technology. Static gain mismatch between the channels was compensated for by a background correlation scheme based on voltage injection without affecting the ADC input range as we proposed in [ELS06a]. Dynamic gain mismatch due to incomplete linear settling in the frontend S/Hs was reduced by applying skew-insensitive sampling in the first stage of every pipelined ADC channel. Power consumption and chip area were minimized by using four-input opamps sharing and comparators' preamplifiers sharing between each two consecutive stages. At sampling rate of 100 MS/s, this ADC achieved peak signal-to-noise-and-distortion ratio (SNDR) and SFDR of 57 dB and 69 dB respectively for a 3.99 MHz input signal, and it consumes 76 mW from 1.8 V power supply.

#### 1.4 Thesis Organization

The thesis is organized into seven chapters. After the introduction, chapter 2 reviews the basic theory of pipelined and time-interleaved ADCs and their known calibration methods. In chapter 3, a new sampling method to overcome the limitation of TIADCs is presented. Blind background calibration techniques to overcome the nonlinearities

stemming from capacitor mismatch and finite opamp gain in 1.5-bit/stage pipelined ADC are presented in chapter 4. Chapter 5 covers a new digital background calibration technique to compensate for the nonlinearity in multi-bit/stage pipelined ADC. A prototype 2-channel calibrated TIADC fabricated in 0.18 µm CMOS technology is presented in chapter 6. Finally, we conclude in chapter 7 with main contribution's summary and recommendations for future research works.

## Chapter 2

# PIPELINED AND TIME-INTERLEAVED ADCs: ARCHITECTURES AND CALIBRATION METHODS

#### 2.1 Introduction

Modern analog to digital converters are divided into two main categories, Nyquistrate ADCs, and oversampled ADCs [WAL99]. Flash and pipelined ADCs are Nyquistrate type. Sigma-delta ADCs belong to the oversampled ADC category. Although the pipeline architecture is inherently not as fast as a flash scheme, its serial nature results in a linear scaling of power and area with resolution, as opposed to the exponential scaling which occurs in a flash, resulting in the pipelined architecture being a more attractive solution around and above the 10 bit resolution level. Similarly, for very high resolution conversion, sigma delta architectures are generally used. However the oversampling nature of such schemes limits the maximum speed to a fraction of the fastest possible sampling rate. Thus, pipelined ADC is an excellent architecture to realize wide bandwidth ADC with high resolution. To increase the speed beyond the technological limits, time-interleaving several pipelined ADCs will increase the global sampling frequency, enabling the realization of high resolution and high speed ADCs suitable for direct conversion IF/RF transceivers. This chapter focuses on the architectures and nonidealities of pipelined and time-interleaved ADCs. The final section of the chapter reviews existing techniques to calibrate these ADCs.

#### 2.2 Pipelined ADC

#### 2.2.1 Basic Operation

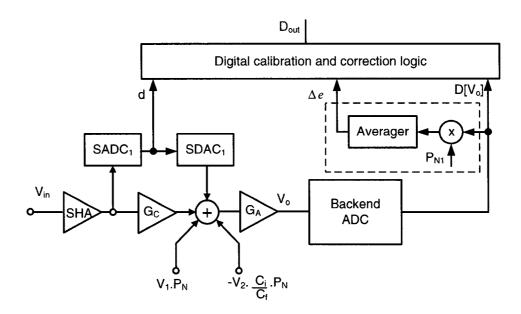

Figure 2.1 shows the block diagram of a general pipelined ADC with P stages. In each stage (except the last stage which has only a flash ADC), the input signal is first quantized by a sub-ADC (SADC), then the output digital code is converted back to an analog signal by a sub-DAC (SDAC). This quantized analog signal is then subtracted from the input signal, resulting in a residue that is amplified by a gain G equals to  $2^n$ , where n is the stage resolution. This residue is sent to the following stage and the process is repeated.

Figure 2.1: Diagram of the conventional multi-bit/stage pipelined ADC.

The output residue  $V_{i+1}$  of stage i is expressed as:

$$V_{i+1} = G_i \cdot \left( V_i - V_{daci} \right) \tag{2.1}$$

where  $V_{daci}$  and  $G_i$  are the SDAC analog output and the interstage gain of stage i respectively. The input of the entire pipelined ADC can be obtained by: