|                         | High-speed CMOS design techniques for multi-gigahertz transceivers                                                                                                                                                                                |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Hung Tien Bui                                                                                                                                                                                                                                     |

| Date:                   | 2006                                                                                                                                                                                                                                              |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                         |

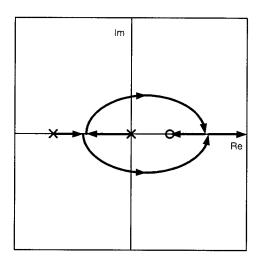

| Référence:<br>Citation: | Bui, H. T. (2006). High-speed CMOS design techniques for multi-gigahertz transceivers [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7740/">https://publications.polymtl.ca/7740/</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

IIPL do PolyPublica

| URL de PolyPublie:<br>PolyPublie URL: | https://publications.polymtl.ca/7740/ |

|---------------------------------------|---------------------------------------|

| Directeurs de recherche: Advisors:    | Yvon Savaria                          |

| <b>Programme:</b> Program:            | Non spécifié                          |

#### UNIVERSITÉ DE MONTRÉAL

# HIGH-SPEED CMOS DESIGN TECHNIQUES FOR MULTI-GIGAHERTZ TRANSCEIVERS

# HUNG TIEN BUI DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR (PH.D.)

(GÉNIE ÉLECTRIQUE)

FÉVRIER 2006

Library and Archives Canada

rchives Canada Archives Canada

Published Heritage Branch

Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Bibliothèque et

Your file Votre référence ISBN: 978-0-494-17973-4 Our file Notre référence ISBN: 978-0-494-17973-4

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### UNIVERSITÉ DE MONTRÉAL

#### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

# HIGH-SPEED CMOS DESIGN TECHNIQUES FOR MULTI-GIGAHERTZ TRANSCEIVERS

présentée par: BUI Hung Tien

en vue de l'obtention du diplôme de: Philosophiae Doctor

a été dûment acceptée par le jury d'examen constitué de:

- M. SAWAN Mohamad, Ph.D., président

- M. SAVARIA Yvon, Ph.D., membre et directeur de recherche

- M. AUDET Yves, Ph.D., membre

- M. AL-KHALILI Asim, Ph.D., membre externe

## Dedications

To the memory of my grand-parents.

To my family.

#### Acknowledgments

First and foremost, I would like to thank my research supervisor Dr. Yvon Savaria who supported me technically, morally and financially through this process. He took me under his wing and showed me a whole new level of excellence. His guidance has helped me evolve both as a researcher and as a person. He is truly an inspirational man.

I would also like to thank Dr. Mohamad Sawan, Dr. Yves Audet and Dr. Asim Al-Khalili for taking time off their busy schedule to be part of my jury. Each of these people has had significant accomplishments and I am honored to have them on my committee.

This thesis would not have been completed in time had it not been for the participation of several key contributors. A heartfelt "thank you" goes out to my proof-reading team that consists of the following people (in alphabetical order): Andria Alter, Robert Grou-Szabo, Bill Pontikakis, Bruno Tanguay and Guillaume Wild.

My research was supported financially by FQRNT and NSERC. The CAD tools and technologies used to complete the project were supplied by the CMC. Their contributions are much appreciated.

The years I spent at the GRM were made so pleasant due to the great office support from Mrs. Ghyslaine Carrier and to the flawless technical support provided by Mr. Rejean Lepage. I also want to thank everyone else at the GRM for creating such a great working environment.

Finally, where would I be without my family? I owe everything to my parents who have supported me in all imaginable ways while I was busy completing my degree. I also

want to thank my brother and my sister-in-law who have provided some much-needed distractions and who have helped me stay grounded. A final "thank you" goes out to my niece Minh Nhi, who always knew how to put a smile on my face.

Thank you all. None of this would have been possible without you.

#### Résumé

La croissance continuelle de l'Internet a provoqué une demande grandissante pour la bande passante. Cette demande a amené le développement de nouvelles normes en télécommunication telles que le OC-192 et le OC-768 qui spécifient des vitesses de transmission de données allant jusqu'à 10 Gb/s (OC-192) et 40 Gb/s (OC-768). Pour pouvoir mettre à profit ces liens, il est important de développer des circuits pouvant fonctionner à ces vitesses.

Le premier problème rencontré dans la conception de ces circuits est celui de la bande passante. Pour augmenter celle-ci, plusieurs utilisent la technique de la pointe-inductive avec des inductances en spirales. Cependant, les inductances en spirale ont une grande superficie et ne sont pas facile à optimiser. Pour résoudre ce problème, nous proposons d'utiliser des inductances actives. En simulation, avec les inductances actives, il était possible d'augmenter la bande passante des portes logiques jusqu'à 17%. Le défaut majeur des inductances actives est la sensibilité aux variations de procédés et de température. Pour pallier ce problème, nous proposons une nouvelle structure d'inductances et un système de mesure et de compensation de ces variations. Pour tester la structure de mesure de variations de procédés et de température, nous avons conçu et fait fabriquer une puce. Les mesures expérimentales démontrent que le système fonctionne tel que spécifié.

Bien que certaines portes logiques CMOS en mode courant soient capables de fonctionner à des vitesses de plusieurs GHz, elles ont très souvent la caractéristique d'être

asymétriques. Ceci est d'autant plus important que plusieurs transcepteurs utilisent des portes XOR pour aligner le signal d'horloge aux données. Cette thèse propose trois approches pour concevoir des structures symétriques qui éliminent théoriquement la gigue en sortie. En utilisant ces solutions, la gigue peut être réduite jusqu'à 95% à basse fréquence et 75% à une vitesse de 10 Gb/s. Pour confirmer les résultats de simulation, une puce a été conçue et fabriquée. Les mesures démontrent clairement que la structure fabriquée est en fait symétrique.

Nous savons que les détecteurs de phases ne sont pas capables de distinguer des différences de fréquences en entrée. Il est donc attendu que, lorsque la différence en fréquence entre les données et l'horloge est trop élevée, le transcepteur ne soit pas capable de converger. Une technique pour aider la convergence est d'utiliser une boucle d'asservissement de fréquence. Pour ce faire, nous proposons un nouvel algorithme et des nouveaux circuits pour créer un convertisseur fréquence-tension. Avec ce convertisseur, nous avons conçu une boucle d'asservissement de fréquence qui fonctionne à 5 GHz en simulation. Le circuit a aussi été implanté sur une puce et les résultats de mesures montrent que le circuit opère bien à des vitesses de jusqu'à 3.65 GHz. Une étude plus poussée révèle que cette différence en fréquences est probablement due aux variations de procédés.

Une technique populaire pour la détection de phases utilise une horloge à demie fréquence. Avec cette technique, pour bien récupérer les données, il faut que le rapport cyclique de l'horloge soit de 50%. Pour ce faire, nous proposons une nouvelle boucle de contrôle de rapport cyclique. Ce circuit, qui se sert du convertisseur fréquence-tension,

transforme un signal déformé en un signal d'horloge à rapport cyclique de 50%. Même à une vitesse de 5 GHz le circuit a été capable de transformer une horloge ayant un rapport cyclique de 25% et un déphasage de 49 ps en un signal d'horloge utilisable.

Les techniques proposées servent à améliorer différents aspects des transcepteurs de haute vitesse. En utilisant ces méthodes, il est possible d'améliorer la performance des transcepteurs sans toutefois être exposé aux difficultés associées aux approches conventionnelles.

#### **Abstract**

With the development of standards such as OC-192 and OC-768, the design of transceivers has become increasingly difficult. Designers are faced with the task of making circuits operate at speeds of multiple GHz which is not a trivial task. Numerous factors are responsible for the difficulty in designing high speed transceivers.

The main problem with multi-GHz design is the bandwidth. In an effort to resolve the bandwidth limitation issue, this thesis proposes the use of active inductors in the design of shunt-peaked MOS current-mode logic (MCML) gates. Conventionally, shunt-peaking is done with spiral inductors. However, they tend to be very large and optimizing shunt-peaked circuits can be long and difficult. For bandwidth improvement without much area penalty and design effort, we propose the use of active inductors. Results show that it can improve the performance of the MCML gates by up to 17%. One drawback to this approach is that active inductors are sensitive to process and temperature variations. To solve this problem, a new active inductor topology is proposed to allow the inductance value to be changed. The required changes in inductance are determined by a new method of measuring process and temperature variations on chip. This measurement technique has been implemented on a chip and has shown good measured results.

At high speeds, recovered signal quality becomes an issue. The second contribution of this thesis addresses this issue by proposing techniques for the design of high speed and low jitter XOR gates. XOR gates are crucial in the design of many clock and data recovery circuits as they are used to measure the precise phase alignment of the clock.

The problem is that the conventional XOR gate is asymmetric and generates output jitter. To resolve this, three design techniques have been suggested for the design of high speed symmetric XOR gates. Results show that, at low speeds, the jitter could be reduced from 26% to 95%, while at speeds of 10 Gb/s, the jitter can be reduced by up to 75%. A chip containing one of the proposed topology was made to demonstrate its functionality. Measurement results show that the implemented device is symmetric and works as described.

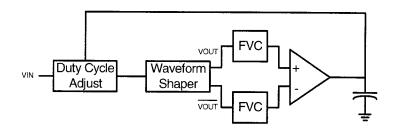

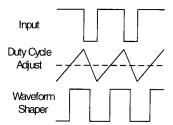

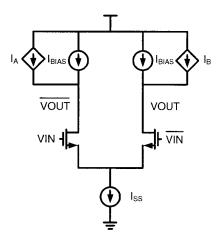

The last contributions of this thesis revolve around a novel frequency-to-voltage converter. Frequency-to-voltage converters can be used in transceivers for functions such as frequency acquisition and clock duty cycle adjustment. To implement this converter, a novel algorithm is proposed as well as new circuits techniques. Simulation results show that the resulting circuit is able to operate at speeds of 5 GHz.

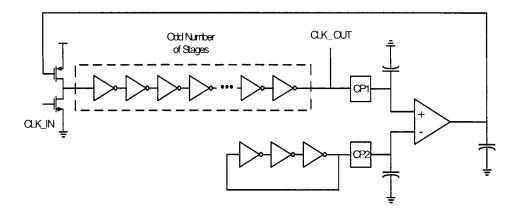

Using this converter, a novel pulse width control loop has been designed. This circuit is useful in half-rate phase detectors which are becoming increasingly popular. Since these phase detectors use both edges of a clock, they require that the clock signal have 50% duty cycle. While the oscillator can be designed to have this characteristic, process variations and layout mismatches can change the signal's symmetry. To restore 50% duty cycle, a new differential pulse width control loop has been designed and simulations show that it can operate up to 5 GHz.

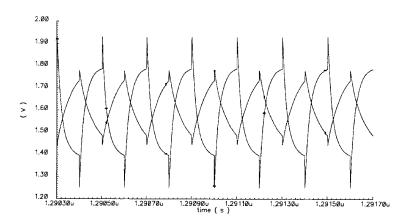

To improve the frequency acquisition range of a transceiver, a frequency locked loop based on this converter has been designed and fabricated. Simulation results show that it can operate at 5GHz. After fabrication, however, measurements show that the

implemented frequency locked loop only operates reliably up to 3.65 GHz. Further investigations indicated that this difference in expected and measured frequencies is probably due to process variations.

The design techniques proposed throughout this thesis help increase the bandwidth, improve the quality of the recovered signals and proposes new approaches to designing multi-GHz transceivers. It is the author's belief that these techniques will help design high speed circuits with less silicon area, better signal quality and with less design effort.

#### Condensé en Français

La croissance continuelle de l'Internet a provoqué une demande grandissante pour la bande passante. Cette demande a amené le développement de nouvelles normes en télécommunication telles que le OC-192 et le OC-768 qui spécifient des vitesses de transmission de données allant jusqu'à 10 Gb/s (OC-192) et 40 Gb/s (OC-768). Pour pouvoir mettre à profit ces liens, il est important de développer des circuits pouvant fonctionner à ces vitesses. La conception de ces circuits a traditionnellement été faite avec des technologies telles que le GaAs et le SiGe, qui permettent d'obtenir des transistors plus rapides. Cependant, ces technologies sont coûteuses et consomment beaucoup de puissance.

Dans le passé, la technologie CMOS n'était pas communément utilisée dans la conception de circuits de haute performance puisqu'elle était considérée comme étant trop lente. Cependant, avec la réduction à l'échelle, il est désormais possible d'atteindre des vitesses de plusieurs GHz en technologie CMOS 0.18µm. Les chercheurs s'intéressent à la possibilité de réaliser des transcepteurs en technologie CMOS, puisque celle-ci coûte moins cher, consomme moins de puissance et peut s'intégrer aux autres circuits CMOS sur une même puce.

Un lien de communication comprend trois parties importantes: un transmetteur, un canal et un récepteur. Le transmetteur envoie des bits de données à travers un canal et ces bits sont ensuite récupérés par le récepteur. La transmission et la réception doivent se faire à la même vitesse. De plus, l'échantillonnage des données doit être faite au milieu

du bit pour réduire les possibilités d'erreurs. Pour ce faire, les systèmes de réception doivent utiliser un circuit de recouvrement d'horloge et de données (RHD).

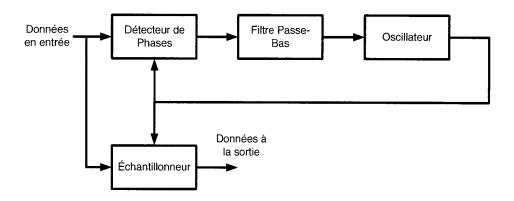

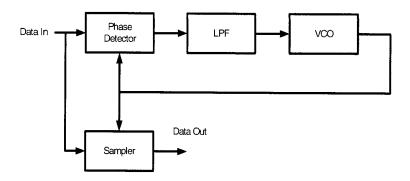

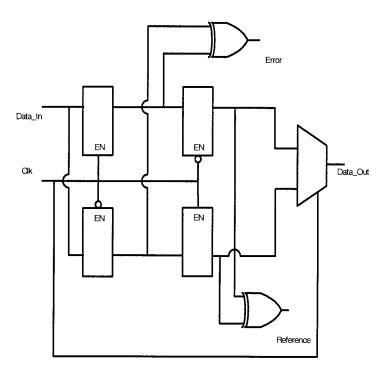

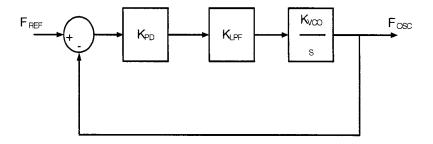

Le circuit RHD, dont le diagramme bloc est présenté à la Figure 0.1, est un des éléments qui posent les plus grand défi dans la conception de transcepteurs de haute performance. La raison est que ce circuit doit être précis et doit également être en mesure d'opérer à des vitesses de plusieurs GHz.

Figure 0.1. Diagramme bloc d'un circuit RHD

Le détecteur de phase est utilisé pour mesurer la différence entre la position d'échantillonnage optimale et la position d'échantillonnage actuelle. Ce signal est filtré pour éliminer le bruit de haute fréquence avant d'être envoyé à l'oscillateur. En réponse au signal de contrôle, ce dernier déplace la phase de l'horloge dans la direction qui permet à la boucle de converger vers l'échantillonnage optimal.

Il y a plusieurs problèmes liés à la conception de circuits RHD. Le premier problème est celui de la bande passante. Les techniques de conception conventionnelles sont

poussées au-delà des limites faisables avec une technologie donnée. Quand un système opère à une vitesse de quelques GHz, la qualité des signaux devient un autre problème. Plusieurs circuits importants ont des propriétés asymétriques. Sachant que l'asymétrie est une propriété indésirable et que la qualité des résultats est directement liée à ces circuits, il est important de les améliorer. Un troisième problème est celui de l'acquisition de fréquence. Les détecteurs de phase sont normalement incapables de signaler une différence de fréquences. Or, si les fréquences des deux entrées sont trop éloignées, le RHD peut perdre la capacité de converger. Ce problème, de même que les autres problèmes mentionnés ci-dessus, sera traité tout au long de cette thèse.

Lorsque la vitesse d'opération atteint quelques GHz, la logique complémentaire CMOS n'est plus en mesure de fonctionner. Le temps requis pour effectuer des transitions entre VDD et VSS devient trop long. Pour les circuits de haute vitesse, les concepteurs adoptent une technique appelée la logique en mode courant CMOS (LMCC). La technique est basée sur des paires de transistors connectées à la source qui commutent le courant d'une branche à l'autre. Le courant passe presque exclusivement dans une des branches quand le signal différentiel à l'entrée est plus élevé que :

$$\Delta V = \sqrt{\frac{2ISS}{\mu_N C_{OX}(W/L)}} \tag{0.1}$$

Quand le courant passe dans une branche, une chute de tension égale à  $ISS*R_L$  est observée à la sortie. L'autre sortie, qui théoriquement ne devrait être traversée par aucun courant, voit son potentiel s'élever vers VDD par l'intermédiaire de la résistance. En ajustant la valeur du courant et de la résistance, il est donc possible de régler le niveau de

l'excursion de tension en sortie. Avec une plus petite transition, il est possible d'atteindre des vitesses plus élevées.

Cette technique peut être généralisée pour concevoir n'importe quelle porte logique complexe. Celles-ci peuvent être conçues en empilant plusieurs paires de transistors les unes sur les autres.

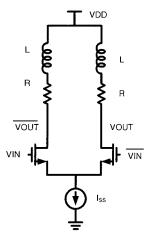

#### <u>Inductances actives</u>

La technique LMCC trouve ses limites avant de satisfaire les besoins des applications courantes quand elle est utilisée seule dans le but de concevoir des transcepteurs à haute vitesse avec une technologie populaire. Par exemple, ses limites pratiques se trouvent à quelques GHz en technologie CMOS 0.18µm. En 1996, Mohan et al. ont proposé une méthode pour augmenter la bande passante dans les amplificateurs. Cette technique, appelée la pointe-inductive, consiste à placer une inductance en parallèle avec la sortie. Cette approche peut, en théorie, augmenter la bande passante jusqu'à 85%. Récemment, la pointe-inductive a aussi été appliquée à la conception de portes LMCC de haute performance.

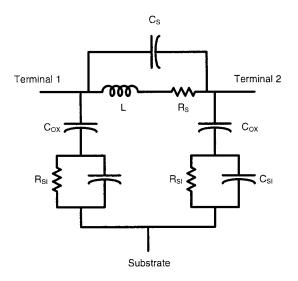

Bien que cette technique offre des améliorations significatives, elle a ses défauts. À l'intérieur des puces, les inductances sont fabriquées en forme de spirales tel qu'illustré à la Figure 0.2.

Figure 0.2. Inductance en Spirale

La taille de ces spirales est rarement plus petite que 100µm par 100µm. De plus, l'espace autour de ces inductances doit être libéré afin de limiter les risques d'interférence électromagnétique. Un autre problème lié aux inductances en spirales est la difficulté avec laquelle on conçoit les circuits comportant ces éléments. En effet, la conception d'inductances doit être faite dans un environnement spécialisé spécifique à la conception de circuits radiofréquences tandis que la conception de circuits intégrés doit être faite dans un environnement spécifique à cette tâche. Par conséquent, l'optimisation, qui est un processus itératif, peut s'avérer très longue.

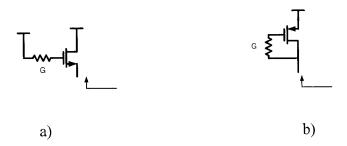

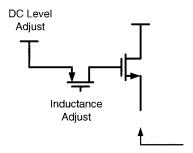

Pour résoudre ces problèmes, nous proposons d'utiliser des inductances actives. Ces inductances, qui sont faites à partir d'au moins un transistor, imitent le fonctionnement des inductances pour un modèle linéaire petit-signal. Cependant, les améliorations en terme de vitesse apportées par l'utilisation d'inductances actives ne sont pas aussi importantes que celles offertes par les inductances en spirales. L'amélioration en performance varie d'une application à l'autre. Dans les portes LMCC, il était possible d'augmenter la bande passante jusqu'à 17%. De plus, le temps requis pour la conception tout comme la taille du circuit résultant sont réduits.

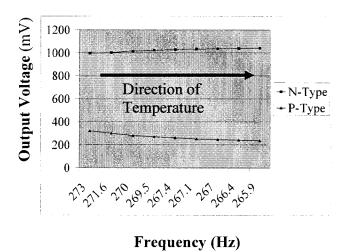

Un des grands défauts des inductances actives est leur sensibilité aux variations de procédés et de température. Cette sensibilité a pour effet de changer les caractéristiques des inductances actives lorsqu'il y a un changement au niveau de la température ou des procédés de fabrication. Pour résoudre ce problème, nous proposons un système de mesure et de compensation. Ce système a pour but de quantifier les changements de température et de procédés et d'ajuster les paramètres pour en annuler les effets. Afin de s'assurer que le système fonctionne, une partie du circuit a été conçue et fabriquée en technologie CMOS 0.18µm. Les résultats expérimentaux confirment que le système de mesure des variations de procédés et de températures se comporte bien.

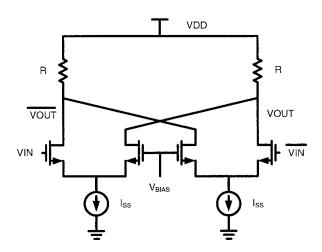

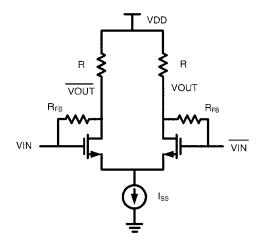

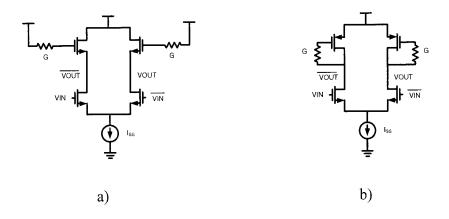

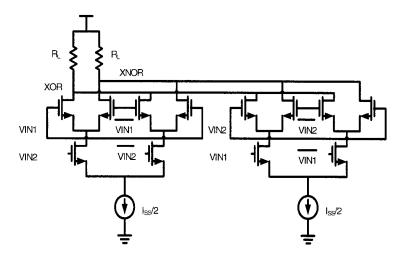

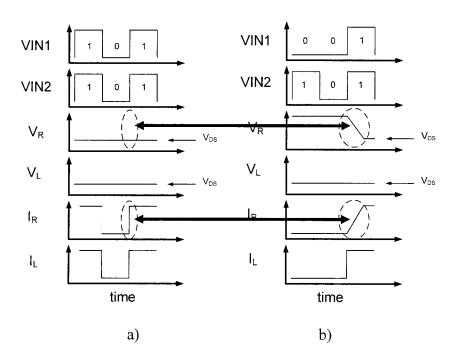

#### Porte XOR symétrique

Bien que les portes logiques de type LMCC soient capables de fonctionner à des vitesses de plusieurs GHz, elles ont la caractéristique d'être asymétriques. Ceci est d'autant plus important que plusieurs circuits RHD utilisent des portes XOR de type LMCC pour aligner le signal d'horloge aux données. Lorsqu'une gigue est présente à la sortie de la porte XOR, la qualité du signal d'horloge est réduite. Puisque la qualité des données récupérées est déterminée par la qualité du circuit RHD, il est important de résoudre le problème d'asymétrie lié aux portes XOR LMCC.

Une analyse théorique du premier ordre peut aider à trouver les tailles des transistors qui permettent de concevoir une porte XOR sans gigue. Cependant, les tailles qui éliminent la gigue ne sont pas nécessairement les tailles qui augmentent la vitesse de ces

portes. Si seul l'ajustement de la taille des transistors est fait, il n'est généralement pas possible d'optimiser la vitesse et la gigue en même temps.

Une des techniques proposée est d'ajuster les circuits qui contrôlent les entrées en plus d'ajuster la taille des transistors du XOR LMCC. De cette façon, il y a plus de degrés de liberté et l'optimisation en terme de gigue et de vitesse peut se faire indépendamment.

Un des problèmes avec cette approche est que la performance de ces portes est étroitement liée aux modèles du premier ordre et à la précision des procédés de fabrication. Il y a plusieurs effets qui ne sont pas inclus dans le modèle et qui peuvent affecter la performance de la porte XOR. De plus, même si le XOR est conçu pour n'avoir aucune gigue, les variations de procédés peuvent dégrader la performance de ces portes.

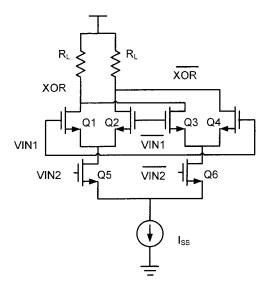

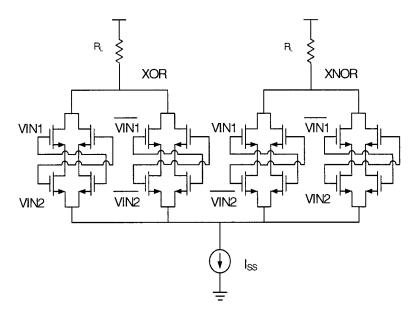

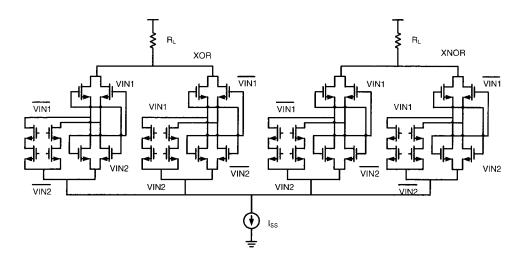

L'approche favorisée est celle qui utilise des structures symétriques. De cette façon, même les effets qui ne sont pas modélisés sont compensés. Nous proposons quatre circuits XOR symétriques qui éliminent théoriquement la gigue en sortie. En utilisant ces solutions, la gigue peut être réduite jusqu'à 95% à basse fréquence et 75% à une vitesse de 10 Gb/s.

Pour prouver l'efficacité des portes symétriques, un des circuits proposés a été fabriqué en technologie CMOS 0.18µm. Les résultats expérimentaux indiquent que le circuit fonctionne bien et qu'il a en fait des caractéristiques symétriques.

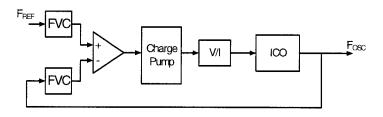

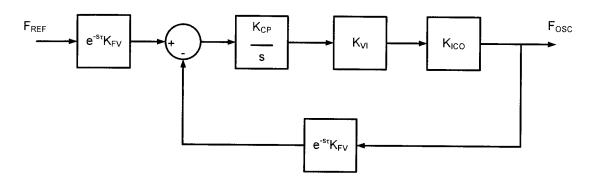

#### Convertisseur fréquence-tension

Nous savons que les détecteurs de phase ne sont pas capables de distinguer des différences de fréquences en entrée. Il est donc attendu que, lorsque la différence en fréquence entre les données et l'horloge est trop élevée, le circuit RHD ne soit pas capable de converger. Pour résoudre ce problème, nous avons recours à une boucle de verrouillage en fréquences (BVF). Cette boucle sert à rapprocher la fréquence de l'horloge de la fréquence des données. Lorsque la différence en fréquence est assez basse, le BVF se désactive et le RHD prend le contrôle de la boucle.

Pour réaliser le circuit BVF, on a recours à un circuit de conversion fréquencetension. Un des circuits populaires de ce genre a été proposé par Djemouai et al. Ce circuit opère très bien à des vitesses modérées de l'ordre de centaines de MHz. Pour des applications dans les GHz, ce circuit a des caractéristiques qui l'empêchent de bien fonctionner.

Le premier problème est associé à l'usage de signaux de pleine amplitude (VSS à VDD). Nous avons vu précédemment que cette technique n'est pas recommandée pour des circuits de haute vitesse. Le deuxième problème est lié à l'utilisation de pulsations pour gérer les phases d'opération du circuit (S1, S2 et S3). Le circuit utilise un signal oscillatoire en entrée pour générer ces pulsations. La première demie période du signal en entrée sert a générer la phase S1. Les phases S2 et S3 sont générées durant la deuxième demie période. Les phases S2 et S3 doivent être assez longues pour transférer des charges et doivent être de pleine amplitude. Puisque ces phases doivent en plus être

générées de façon mutuellement exclusive, il s'en suit que la période minimale supportée par ce circuit doit être plus grande que la durée de quatre pulsations de durée minimale. Ceci devient une contrainte importante lorsqu'un circuit doit opérer à plusieurs GHz.

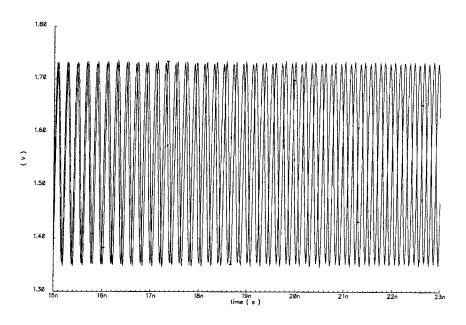

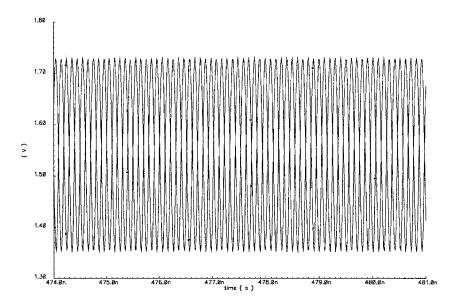

Pour régler ces problèmes, nous proposons un nouvel algorithme de fonctionnement et de nouveaux circuits. Le nouvel algorithme proposé s'exécute en deux phases et peut être contrôlé directement par le signal en entrée sans l'intermédiaire de pulsations générées à l'interne. De plus, les techniques proposées au niveau circuit permettent au convertisseur fréquence-tension de fonctionner à des vitesses de 5 GHz. Le convertisseur a été utilisé pour créer une BVF qui opère à 5 GHz en simulation. Quand cette même BVF a été fabriquée en technologie CMOS 0.18µm, les résultats expérimentaux montrent qu'elle peut fonctionner jusqu'à 3.65GHz. Des tests additionnels ont montré que la différence en performance était probablement due aux variations de procédés.

Un des problèmes rencontré dans la conception de transcepteurs à haute vitesse est la conception d'un oscillateur. À haute vitesse, il n'est pas évident de parvenir à cumuler toutes les caractéristiques désirables telles que la gamme dynamique de fréquence, la stabilité de l'oscillation, etc. Pour cette raison, le concept de RHD à demie fréquence a été introduit. Les RHD conventionnels utilisent une horloge rapide qui n'a qu'un seul front actif. Dans le cas du RHD à demie fréquence, les deux fronts de l'horloge sont mis à profit. Pour s'assurer de bien récupérer les données, il faut que le rapport cyclique de l'horloge soit de 50%. Pour ce faire, une nouvelle boucle de contrôle de rapport cyclique a été proposée. Ce circuit se sert du convertisseur fréquence-tension pour transformer un signal déformé en un signal d'horloge à rapport cyclique de 50%. Même à une vitesse de

5 GHz, le circuit a été capable de transformer une horloge ayant un rapport cyclique de 25% et un déphasage de 49 ps en un signal d'horloge utilisable. Dans ce cas extrême, le signal résultant est une horloge avec un rapport cyclique de 48% qui a une légère disparité dans le niveau DC de ses composantes différentielles. Ce problème peut être réglé simplement en ajoutant des étages de gain pour restituer le signal.

Les techniques proposées tout au long de cette thèse servent à améliorer différents aspects des transcepteurs de haute vitesse. Puisque ces techniques sont orthogonales, elles peuvent être combinées. En utilisant ces méthodes, il est possible d'améliorer la performance des transcepteurs sans toutefois être exposé aux difficultés associées aux approches conventionnelles.

## Table of Contents

| DEDICATIONS                  | iv     |

|------------------------------|--------|

| ACKNOWLEDGMENTS              | V      |

| RÉSUMÉ                       | vii    |

| ABSTRACT                     |        |

| CONDENSÉ EN FRANÇAIS         | xii    |

| TABLE OF CONTENTS            | xxiii  |

| LIST OF FIGURES              | xxvii  |

| LIST OF TABLES               | xxxi   |

| LIST OF ABBREVIATIONS        | xxxiii |

| CHAPTER 1: INTRODUCTION      | 1      |

| 1.1. CONTEXT                 | 2      |

| 1.2. ORGANIZATION            | 4      |

| 1.3. CONTRIBUTIONS           | 5      |

| CHAPTER 2: BACKGROUND        | 8      |

| 2.1. INTERCONNECTIONS        | 9      |

| 2.2. CLOCK AND DATA RECOVERY | 12     |

| 2.3. FREQUENCY ACQUISITION   | 19     |

| 2.4. MOS CURRENT-MODE LOGIC  | 21     |

| 2.4.1. SYMMETRIC XOR         | 24     |

| 2.5. BANDWIDTH IMPROVEMENT TO MCML GATES                   | 26 |

|------------------------------------------------------------|----|

| 2.6. SUMMARY                                               | 34 |

| CHAPTER 3: BANDWIDTH ENHANCEMENT USING ACTIVE INDUCTIVE    |    |

| LOADS IN MCML GATES                                        | 35 |

| 3.1. THEORETICAL ANALYSIS OF ACTIVE INDUCTORS              | 37 |

| 3.2. SIMULATION RESULTS                                    | 44 |

| 3.3. PROCESS VARIATIONS                                    | 47 |

| 3.3.1. PROCESS/TEMPERATURE VARIATIONS AND                  |    |

| MEASUREMENT                                                | 47 |

| 3.3.2. ACTIVE INDUCTOR COMPENSATION                        | 52 |

| 3.3.3. SIMULATION RESULTS AND ANALYSIS                     | 53 |

| 3.3.4. EXPERIMENTAL RESULTS                                | 55 |

| 3.4. CONCLUSIONS                                           | 59 |

| CHAPTER 4: HIGH-SPEED AND LOW JITTER DESIGN TECHNIQUES FOR |    |

| MCML XOR GATES                                             | 61 |

| 4.1. JITTER ANALYSIS OF THE MCML XOR GATE                  | 61 |

| 4.1.1. UNEVEN DRIVE STRENGTH                               | 63 |

| 4.1.2. UNEVEN INPUT LOADING                                | 66 |

| 4.1.3. GLITCHES                                            | 68 |

| 4.1.4. TOTAL DETERMINISTIC JITTER                          | 72 |

| 4.1.5 HTTER COMPENSATION THROUGH SIZING                    | 72 |

| 4.1.6. JITTER COMPENSATION THROUGH CONTROLLED                |     |

|--------------------------------------------------------------|-----|

| IMBALANCED DRIVERS                                           | 73  |

| 4.2. SYMMETRIC GATES                                         | 74  |

| 4.2.1. CRISS-CROSSED XOR GATES                               | 75  |

| 4.2.2. 4-BRANCH SYMMETRIC XOR                                | 77  |

| 4.2.3. 4-BRANCH SYMMETRIC XOR WITH RESET                     | 80  |

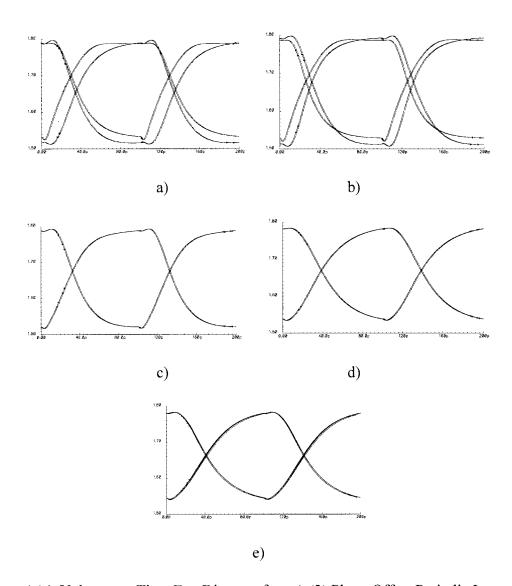

| 4.3. SIMULATION RESULTS                                      | 83  |

| 4.4. EXPERIMENTAL RESULTS                                    | 90  |

| 4.5. CONCLUSIONS                                             | 93  |

| CHAPTER 5: DESIGN OF A HIGH-SPEED DIFFERENTIAL FREQUENCY-TO- |     |

| VOLTAGE CONVERTER AND ITS APPLICATIONS                       | 95  |

| 5.1. SINGLE-PHASE ARCHITECTURE                               | 97  |

| 5.2. CIRCUIT-LEVEL IMPLEMENTATION                            | 104 |

| 5.3. SAMPLE APPLICATION: PULSE WIDTH CONTROL LOOP            | 109 |

| 5.3.1. PROPOSED PWCL                                         | 112 |

| 5.3.1.1 DUTY CYCLE ADJUST                                    | 114 |

| 5.3.1.2 FVC                                                  | 115 |

| 5.3.2. SIMULATION RESULTS                                    | 116 |

| 5.4. FREQUENCY LOCKED LOOP: A Second Sample Application      | 119 |

| 5.4.1. ANALYTICAL MODEL                                      | 120 |

| 5.4.2. BUILDING BLOCKS                                       | 127 |

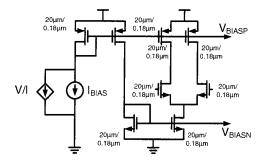

| 5.4.2.1 ICO                                                  | 127 |

| 5.4.2.2. COMPARATOR                          | 128 |

|----------------------------------------------|-----|

| 5.4.2.3. V/I                                 | 128 |

| 5.4.2.4. DIVIDE-BY-64                        | 129 |

| 5.4.3. TOP-LEVEL SIMULATIONS AFTER EXTRACTED |     |

| LAYOUT                                       | 130 |

| 5.4.4. EXPERIMENTAL RESULTS                  | 131 |

| 5.5. CONCLUSIONS                             | 135 |

| CHAPTER 6: CONCLUSIONS                       | 137 |

| 6.1. FUTURE WORK                             | 139 |

| REFERENCES                                   | 141 |

# List of Figures

| Figure 0.1. Diagramme Bloc d'un RHD                                           | xiv |

|-------------------------------------------------------------------------------|-----|

| Figure 0.2. Inductance en Spirale                                             | xvi |

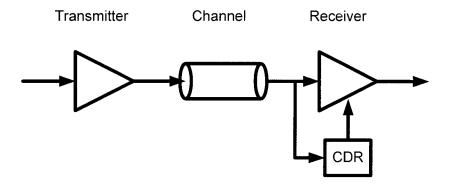

| Figure 1.1. Typical Communications Link                                       | 2   |

| Figure 2.1. Sample Eye Diagram Showing Non-Ideal Sampling Instants            | 11  |

| Figure 2.2. Block Diagram of a CDR                                            | 13  |

| Figure 2.3. Determination of Phase Relations in 2X Oversampling               | 14  |

| Figure 2.4. Hogge's Phase Detector                                            | 15  |

| Figure 2.5. Waveforms Showing Different Clocking Schemes                      | 16  |

| Figure 2.6. Savoj's Half-Rate Phase Detector                                  | 17  |

| Figure 2.7. Example of 4-Phase Time-Interleaving CDR                          | 18  |

| Figure 2.8. Ideal Model of Djemouai's Frequency-to-Voltage Converter          | 19  |

| Figure 2.9. Input Clock Showing the Different Phases for Frequency-to-Voltage |     |

| Conversion                                                                    | 20  |

| Figure 2.10. MCML Buffer                                                      | 22  |

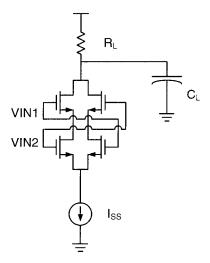

| Figure 2.11. MCML XOR Gate                                                    | 23  |

| Figure 2.12. Single Ended Symmetric XOR                                       | 25  |

| Figure 2.13. Buffer with Compensated Miller C <sub>GD</sub>                   | 27  |

| Figure 2.14. Differential $f_t$ Doubler                                       | 28  |

| Figure 2.15. Buffer with Negative Feedback                                    | 20  |

| Figure 2.16. Representation of a Spiral Inductor                                       |

|----------------------------------------------------------------------------------------|

| Figure 2.17. Shunt-Peaked Buffer                                                       |

| Figure 2.18. Lumped Model of a Spiral Inductor                                         |

| Figure 2.19. Active Inductors                                                          |

| Figure 3.1. Active Inductors                                                           |

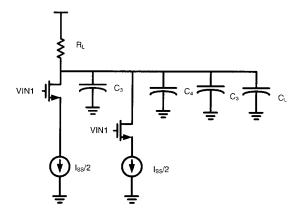

| Figure 3.2. MCML Buffers Loaded with Active Inductors                                  |

| Figure 3.3. Small Signal Model of the Buffer Loaded with an NMOS Active                |

| Inductor                                                                               |

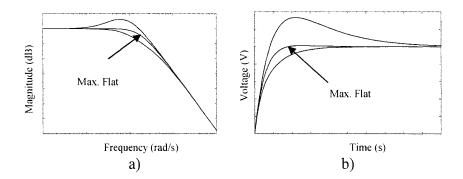

| Figure 3.4. a) Bode Plot and b) Transient Step Response for Different Pole-Zero        |

| Positions41                                                                            |

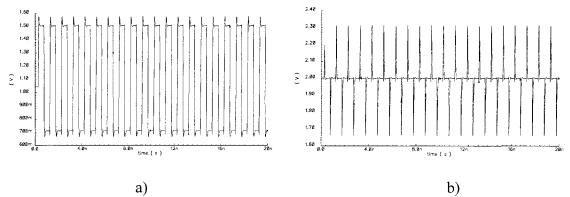

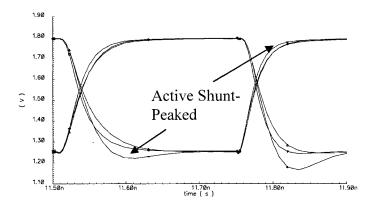

| Figure 3.5. Simulation Results for a) the Output of a Buffer with Active Shunt-Peaking |

| and b) the Corresponding Voltage at the Gate of the Active Inductor's Transistor43     |

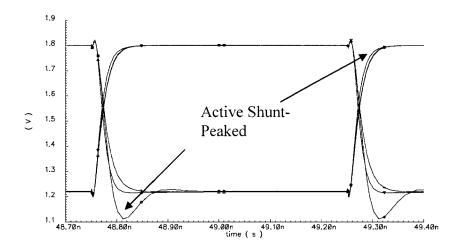

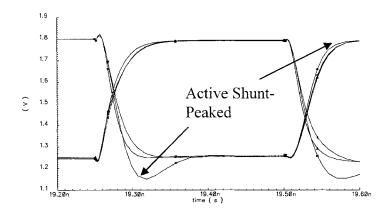

| Figure 3.6. Simulation Results for the Resistor-Loaded, NMOS-Loaded and Active         |

| Shunt-Peaked Buffers45                                                                 |

| Figure 3.7. Simulation Results for the Resistor-Loaded, NMOS-Loaded and Active         |

| Shunt-Peaked AND Gates                                                                 |

| Figure 3.8. Simulation Results for the Resistor-Loaded, NMOS-Loaded and Active         |

| Shunt-Peaked XOR Gates                                                                 |

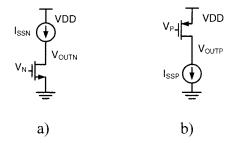

| Figure 3.9. a) N-Type and b) P-Type Process and Temperature Measurement Circuits48     |

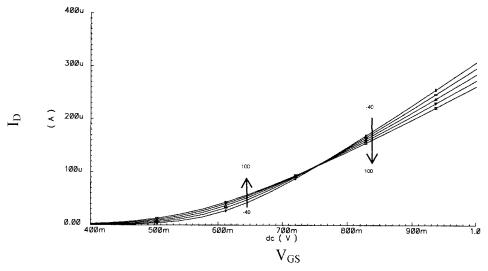

| Figure 3.10. I <sub>D</sub> vs. V <sub>GS</sub> for Different Temperatures50           |

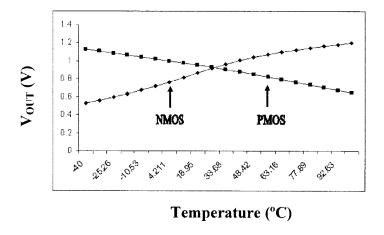

| Figure 3.11. Measurement Output for Different Temperatures in a Typical Process52      |

| Figure 3.12. Adjustable Active Inductor53                                              |

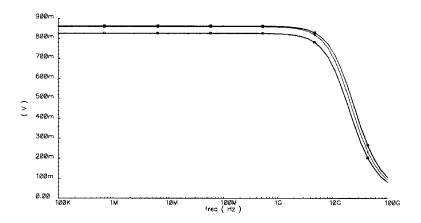

| Figure 3.13. Frequency Response of Active Shunt-Peaked Buffer in Presence of Process                                   |

|------------------------------------------------------------------------------------------------------------------------|

| Variations54                                                                                                           |

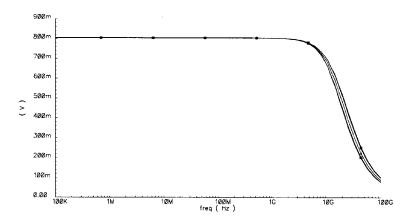

| Figure 3.14. Frequency Response of Active Shunt-Peaked Buffer after Process Variation                                  |

| Compensation55                                                                                                         |

| Figure 3.15. Process and Temperature Measurement Circuit and Test Circuit56                                            |

| Figure 3.16. Sample Output of the Test Circuit                                                                         |

| Figure 3.17. Output Voltage as a Function of Oscillator Frequency                                                      |

| Figure 4.1. MCML XOR Gate62                                                                                            |

| Figure 4.2. MCML XOR Gate Output Branch                                                                                |

| Figure 4.3. Small-Signal Model for XOR Gate with Transition on a) VIN1 and b)                                          |

| VIN264                                                                                                                 |

| Figure 4.4. Possible Change in Current Path Causing Glitches                                                           |

| Figure 4.5. Jitter Measurement                                                                                         |

| Figure 4.6. Gate Level Criss-Crossed Symmetric XOR                                                                     |

| Figure 4.7. Criss-Crossed Symmetric XOR Gate                                                                           |

| Figure 4.8. Small-Signal Model for the Criss-Crossed Symmetric XOR Gate76                                              |

| Figure 4.9. 4-Branch Symmetric XOR Gate                                                                                |

| Figure 4.10. Single Branch of the 4-Branch Symmetric XOR Gate78                                                        |

| Figure 4.11. Symmetric XOR Model                                                                                       |

| Figure 4.12. Intermediate Nodes of the 4-Branch Symmetric XOR Gate with Reset when                                     |

| Inputs are a) $VIN1 - VIN2 = 11 \rightarrow 00 \rightarrow 11$ and b) $VIN1 - VIN2 = 01 \rightarrow 00 \rightarrow 11$ |

| Figure 4.13. 4-Branch Symmetric XOR Gate with Reset82                                                                  |

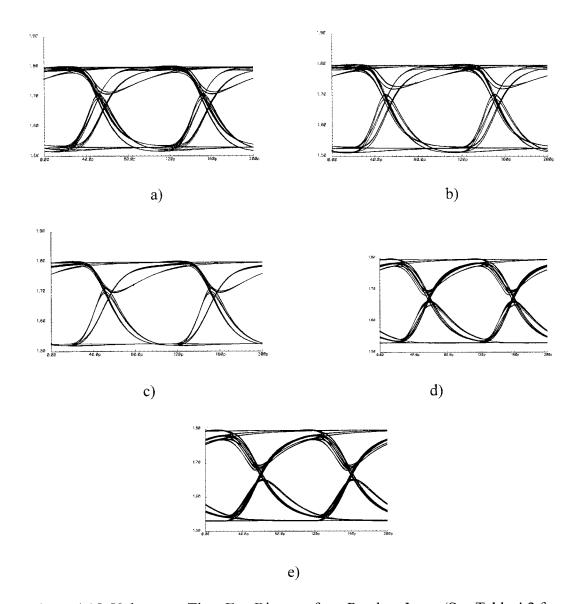

| Figure 4.14. Voltage vs. Time Eye Diagram for a $(\pi/2)$ Phase Offset Periodic Input | 85  |

|---------------------------------------------------------------------------------------|-----|

| Figure 4.15. Voltage vs. Time Eye Diagram for a Random Input                          | 87  |

| Figure 4.16. Jitter as a Function of Bit Period.                                      | 89  |

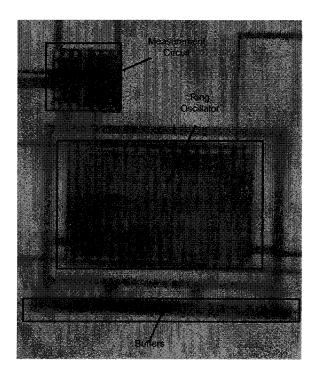

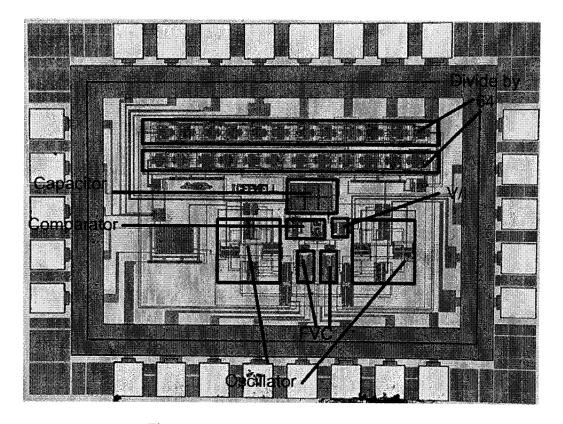

| Figure 4.17. Micrograph of the 4-Branch Symmetric XOR Gate                            | 90  |

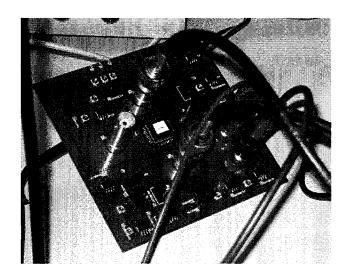

| Figure 4.18. Experimental Setup for the XOR Gate                                      | 91  |

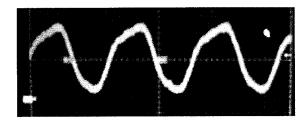

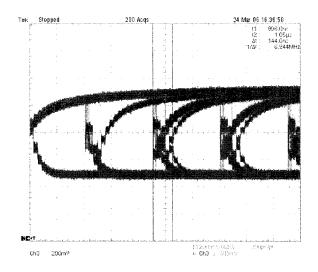

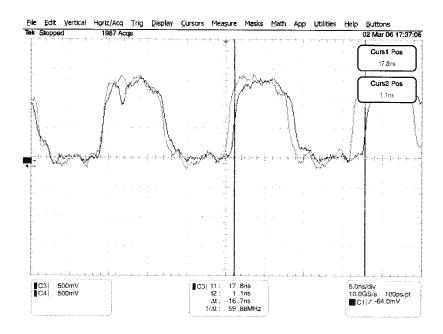

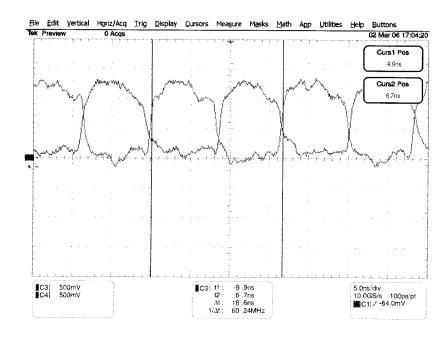

| Figure 4.19. Chip Output in Response to $\pi/2$ Phase Offset Square Waves             | 92  |

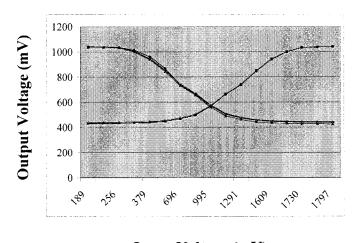

| Figure 4.20. DC Measurements of the 4-Branch Symmetric XOR Gate                       | 9   |

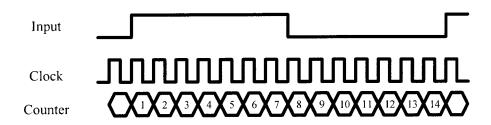

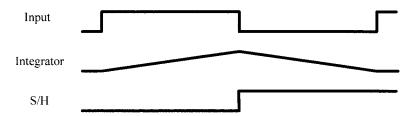

| Figure 5.1. Counter-Based Conversion.                                                 | 9   |

| Figure 5.2. Integrator-Based Conversion.                                              | 96  |

| Figure 5.3. Model of Single Phase Algorithm                                           | 97  |

| Figure 5.4. Steps in Single Phase Operation.                                          | 9   |

| Figure 5.5. Ideal Simulation Waveform of Single Phase Algorithm                       | 99  |

| Figure 5.6. MATLAB Simulation with Two Different Values of C2                         | 103 |

| Figure 5.7. Charging/Discharging Switch                                               | 105 |

| Figure 5.8. Charge Transfer Switch                                                    | 106 |

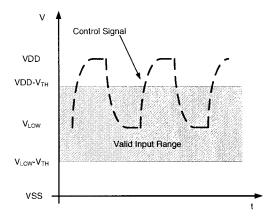

| Figure 5.9. Valid Input Voltages                                                      | 10′ |

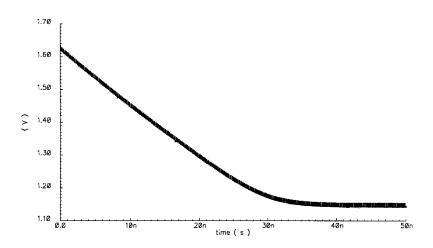

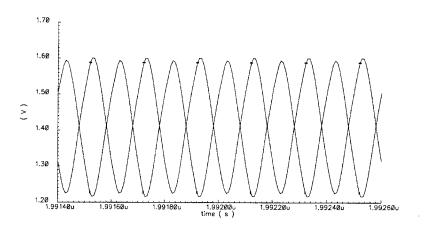

| Figure 5.10. Frequency-to-Voltage Conversion at 5 GHz                                 | 108 |

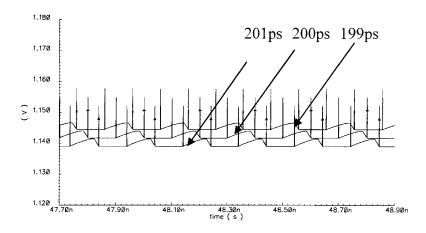

| Figure 5.11. Outputs when Input Signal Periods are 199, 200 and 201 ps                | 108 |

| Figure 5.12. Conventional PWCL                                                        | 111 |

| Figure 5.13. Block Diagram of PWCL                                                    | 113 |

| Figure 5.14. Ideal Waveform for PWCL                                                  | 113 |

| Figure 5.15. Differential Duty Cycle Adjust                                           | 114 |

| Figure 5.16. Input Signal with Uneven Loading Condition                | 11  |

|------------------------------------------------------------------------|-----|

| Figure 5.17. Output Signal with Uneven Loading Condition               | 11  |

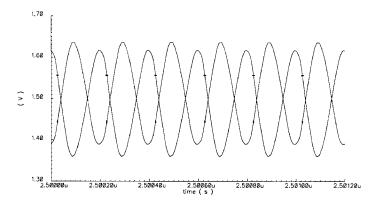

| Figure 5.18. Input Signal with 25% Duty Cycle and 49ps Skew            | 118 |

| Figure 5.19. Output Signal when Input has 25% Duty Cycle and 49ps Skew | 119 |

| Figure 5.20. Block Diagram of FLL                                      | 120 |

| Figure 5.21. Linearized Model of a PLL                                 | 121 |

| Figure 5.22. Block Diagram of FLL with Transfer Function of Each Block | 122 |

| Figure 5.23. Root Locus Plot of FLL                                    | 126 |

| Figure 5.24. Biasing Scheme and Single Delay Element                   | 127 |

| Figure 5.25. Fully Differential Two Stage Amplifier                    | 128 |

| Figure 5.26. V/I Circuit                                               | 129 |

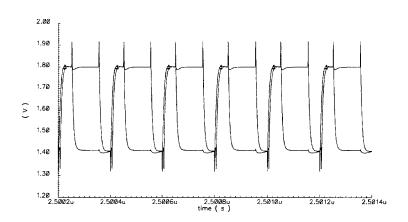

| Figure 5.27. Full Speed Oscillators Before Lock                        | 130 |

| Figure 5.28. Full Speed Oscillators after Lock                         | 131 |

| Figure 5.29. Chip Micrograph of the FLL                                | 132 |

| Figure 5.30. Experimental Setup for FLL.                               | 133 |

| Figure 5.31. Output Signals Before Lock                                | 134 |

| Figure 5.32. Output Signals After Lock                                 | 134 |

### List of Tables

| Table 3.1. Summary of Different Design Parameters for NMOS Active Inductors        | 42    |

|------------------------------------------------------------------------------------|-------|

| Table 3.2. Summary of Performance.                                                 | 46    |

| Table 3.3. Measurement Output for Process Corners                                  | 49    |

| Table 3.4. Measurements of Process Variation Chips                                 | 57    |

| Table 4.1. XOR Truth Table                                                         | 63    |

| Table 4.2. Description of Simulated XOR Gates                                      | 84    |

| Table 4.3. Eye Diagram Measurements for $(\pi/2)$ Phase Offset Input (100ps output | t bit |

| time)                                                                              | 86    |

| Table 4.4. Eye Diagram Measurements for Random Input                               | 88    |

xxxiii

#### List of Abbreviations

#### **Abbreviations**

AHDL Analog Hardware Description Language

CDR Clock and Data Recovery

CMOS Complementary MOS

CQFP Ceramic Quad-Flat Package

DC Direct Current

DDR Double Data Rate

ECL Emitter-Coupled Logic

FLL Frequency Locked Loop

f<sub>t</sub> Frequency at which current gain of a transistor is 1 (Transition Frequency)

FVC Frequency to Voltage Converter

GaAs Gallium Arsenide

IC Integrated Circuits

ICO Current Controlled Oscillator

L Channel Length

MCML MOS Current Mode Logic

MOS Metal Oxide Semiconductor

NMOS MOS transistor having electrons as majority carriers (N-Type)

PCB Printed Circuit Board

PLL Phase Locked Loop

PMOS MOS transistor having holes as majority carriers (P-Type)

PWCL Pulse Width Control Loop

RAM Random Access Memory

SCL Source-Coupled Logic

S/H Sample and Hold

SiGe Silicon Germanium

VCO Voltage Controlled Oscillator

VDD Power Supply Voltage

V/I Voltage to Current Converter

VSS Ground Voltage

VTH Threshold Voltage of a Transistor

W Channel Width

#### Chapter 1

#### Introduction

The increasing demand for high speed communications has led to the development of multi-GHz transceivers. Modern optical transmission standards such as OC-192 and OC-768 specify links operating at speeds of 10 Gb/s and 40 Gb/s respectively. To implement these links, transceiver circuitry must be able to support these data rates.

Multi-GHz transceivers have traditionally been designed in technologies such as GaAs and SiGe, because of their fast intrinsic device speed. Within the last few decades, CMOS technology has improved tremendously and has been used successfully in the design of high speed circuits. There are many benefits to using CMOS in the design of transceivers, including lower power consumption and reduced cost. In addition, CMOS is a mature technology for which many tools and design techniques have been developed. Due to these characteristics, there is widespread interest in CMOS technology which has been driving the aggressive transistor scaling and performance improvements seen over the years. Since CMOS provides higher levels of integration, lower cost and lower power consumption, it is an appealing solution for the design of high speed transceivers.

The goal of this research is to provide techniques for improving the performance of high speed interface circuits in CMOS technology. As much as possible, the developed techniques aim to be orthogonal, in that they can be combined to achieve even better performance. The contributions of this thesis are made at the algorithmic, architectural and at the circuit level.

#### 1.1. Context

The work presented in this thesis is focused on ways of improving communications links through the design of better transceivers. A communications link primarily consists of three parts: a transmitter, a channel and a receiver (Figure 1.1). Data from the transmitter side are sent as a series of bits through a channel. These bits are then recovered at the receiver end.

Figure 1.1. Typical Communications Link

The transmitter sends data at a given frequency through the channel and these data need to be recovered at the same speed. In addition to having the right frequency, there are also instances during the period where data recovery is less prone to errors. It is highly desirable to sample data at those specific moments. Consequently, receivers need to have a clock that oscillates with the right frequency and also needs to have the right phase.

Receivers typically have a local oscillator that operates at about the same frequency as the transmitter's clock. However, the required phase information is not known. To solve this problem, some systems use a source-synchronous approach, where a clock signal is transmitted along with the data. The transmitted clock is then used to sample the data. This technique greatly facilitates the design of a receiver. However, since source-synchronous approaches are not always possible, as in the case of optical links, receivers often require a clock and data recovery circuit (CDR). CDRs typically use the transient characteristics of the incoming data to extract the phase information.

The CDR is perhaps the most challenging part of the transceiver. It needs to derive timing information from the incoming data which can arrive at rates of multi-Gb/s. The task becomes even more difficult because the channel attenuates and distorts the transmitted signals. While some solutions have been proposed to recover clock and data signals at 10 and 40 Gb/s [13][37][64], the circuits are large and these results are not easily reproducible. Integration of a number of these devices onto a single chip can be difficult and costly.

This thesis proposes a series of algorithmic, architectural and circuit-level techniques to provide more efficient solutions for high speed CDRs. As it will be shown throughout, these techniques help reduce silicon area, ease design efforts and improve the quality of the recovered signals.

### 1.2. Organization

To understand the contributions of this thesis, it is essential to explore the significant research that has been done in the field. A thorough literature survey is provided in Chapter 2. It explains the theoretical background required to understand the remaining parts of the thesis. It describes CDRs and how their different components are pieced together. It also examines the logic style and design techniques that are typically used in these applications.

One of the most difficult aspects of transceiver design for OC-192 and OC-768 is making circuits that can respond to the specified data rates. The simplest way of making a transceiver operate faster is to increase its clock speed. Unfortunately, many circuits cannot operate reliably when the clock speed is increased too much due to large parasitic capacitances. This problem is addressed in Chapter 3, where a method of increasing the bandwidth of conventional logic gates is proposed. The technique allows for devices to operate faster with minimal area penalty and minimal design effort.

As will be shown in Chapter 2, device symmetry is a very important issue especially at high speeds. Typical CDR circuits use XOR gates to align the local clock to the incoming data. Since the XOR gate directly controls this alignment, it is important to have a well-behaved XOR gate that can operate at high speeds. Chapter 4 proposes several techniques to design these gates.

It is known that communications are facilitated when the clock frequency of the transmitter and receiver are the same. In practice, however, this is usually not the case, thus the need for CDR circuits. When the difference between these frequencies is too large, typical CDRs will not be able to lock because they do not have enough frequency acquisition range. To address this problem, Chapter 5 introduces a differential high speed frequency-to-voltage converter (FVC). As will be shown, this FVC can be applied to the design of a frequency-locked loop (FLL) to increase the frequency acquisition range of a CDR.

An important class of CDRs uses a concept called half-rate clocks to facilitate the design of the local oscillator. These CDRs require a clock with 50% duty cycle. As will be shown in Chapter 5, the proposed FVC can also be used in the design of a pulse-width control loop (PWCL) to restore a 50% duty cycle clock from distorted signals.

Finally, Chapter 6 summarizes the results that have been brought forth in this thesis. In addition, a list of future research directions is proposed.

#### 1.3. Contributions

The goal of this thesis is to help improve the design of multi-GHz transceivers. A number of contributions have been made throughout this research and they are summarized as follows:

1. Application of shunt-peaking to non-linear circuits. By using shunt-peaking with MCML gates, it was possible to design a half-rate clock and data recovery circuit operating at 20 Gb/s [5].

- 2. Implementation of shunt-peaking using active inductors. The use of active inductors in shunt-peaking helps improve the bandwidth of MCML gates with little penalty in terms of area and design effort [7].

- 3. Design and analysis of high speed and low jitter XOR gates. We provided a model for deterministic jitter in XOR gates and proposed several design techniques to reduce this jitter [6]. A test chip has also been successfully fabricated and tested in 0.18µm CMOS technology.

- 4. Design of a 5 GHz differential frequency-to-voltage circuit [8]. Frequency-to-voltage converters can have numerous applications in multi-GHz transceivers such as controlling the duty-cycle of clock signals [11]. A correct duty cycle is crucial in half-rate clock and data recovery circuits.

- 5. Design, fabrication and testing of a 5 GHz frequency-locked loop. The frequency-to-voltage converter proposed in [8] was also used to implement a 5 GHz frequency-locked loop in  $0.18 \, \mu m$  CMOS technology.

- 6. Development of a process and temperature measurement and compensation technique [10]. The effects of process and temperature variations are important and need to be considered in the design of circuits. By using this method, fabricated circuits can have predictable and reliable performance despite process and temperature variations. The

measurement technique has been implemented and tested in  $0.18\mu m$  CMOS technology with success.

7. Design of a 10 GHz PLL. Using some of the techniques previously described, a 10 GHz PLL has been designed [9].

# Chapter 2

# Background

While advances in silicon technology have led to a rapid increase in speed and scaling of current integrated circuits (IC), the bandwidth of interconnections between systems has not improved as much. For many applications, such as multi-processor and processor-memory interconnections, the bottleneck lies in the links. Even systems that can process data at multiple Gb/s may not be able to transmit or receive data at that same rate. While the issue can be partly addressed by improving the packaging or the channel, this thesis is mainly concerned with the design of electronic transceivers that are often the dominant bottleneck in high bandwidth interconnections.

The design of transceivers and links involves a number of architectural decisions. The interconnection could be point-to-point or in the form of a bus, serial or parallel. Such interconnections may be source-synchronous or have an embedded clock, and signals may carry a single-bit or multiple bits. These choices must be made carefully in order to maximize the performance of a given system within the bounds of the given specifications.

#### 2.1. Interconnections

The bus paradigm is based on a communication medium that is shared by various modules. The transaction between these modules is scheduled by an arbiter to ensure that bus contention does not occur while maximizing the efficiency of the bus. The bus is very popular with systems-on-chip as it facilitates design-reuse. To make a design easily reusable for different applications, it is necessary to have a known interface. It is common to see intellectual property (IP) blocks being developed for a given bus type. Though the bus eases design reuse and facilitates the interconnection between modules, it does have its drawbacks. Since multiple modules are competing for bandwidth, bus latency is inevitable. In a bus with more than one master, a module will have to wait for a bus-grant from the arbiter before any type of transaction can be initiated. The second drawback lies in the fact that the bus is a shared medium. Since the bus is connected to multiple modules, the capacitance associated to the lines tends to be large. This could contribute to slowing down data transmission. Using a point-to-point link increases the attainable bandwidth by effectively removing the two main drawbacks of the bus. Given that the link only connects two devices, the load is reduced and arbitration becomes unnecessary. and it becomes easier to use well defined and terminated transmission lines.

To increase the bandwidth of communications links, it is common practice to have multiple bits transmitted through the medium. One way of transmitting multiple bits is to send them in parallel [67]. Most parallel links are source-synchronous, which means that

the clock signal is sent along with the parallel data word. Since the clock signal is provided, it easily allows the module at the receiving end to recover the data. At high-speeds, however, several design aspects need to be considered. When designing the parallel link, it is often difficult to match the transmission lines through which individual bits of the link are transmitted. If the electrical lengths are not matched, the arrival time of the individual bits could be different. In severe cases, this could lead to incorrect data transmission. To address some of the skew problems, several deskewing circuits have been proposed in the recent years [2]. In an effort to reduce the matching problem, parallel bits of a link are usually routed next to each other so that they would have approximately the same electrical length. However, having the bit lines in close proximity could cause cross-talk and inductive coupling between the bits, which could have unmodeled and unexpected pattern-dependent behavior. When designed carefully, one of the advantages for such source-synchronous systems is that they do not require complicated clock and data recovery (CDR) circuits.

An alternative to parallel links is the single wire serial link [38][80]. Using this method, the data are serialized at the transmitting end before being sent through the channel. The circuit at the receiving end descrializes the stream and recovers the data. The system is plesiochronous, which means that the transmitter and the receiver use separate local clocks that oscillate at the same frequency, but not with a predefined phase relationship.

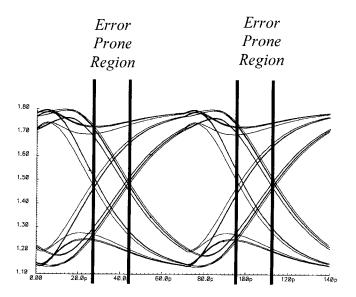

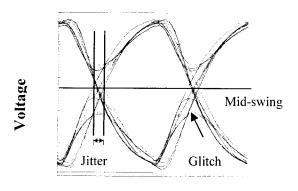

Having a plesiochronous system also implies that the sampling edge of the receiver clock and the incoming data are not necessarily aligned. Without this proper alignment, sampling of the data could be prone to errors. This can be seen in a sample data eye shown in Figure 2.1. For instance, if the sampling edge of the clock occurred close to a data transition, the recovered data could be incorrect or even metastable. In order to avoid errors, it is usually recommended to sample the data at the middle of the bit time. To find this middle, extra circuitry is required. The action of aligning the active transition of the local clock to the middle of the data bit is known as clock recovery. Despite the extra design requirements, serial links could inherently transfer data more rapidly. Since serial links do not have multiple wires to handle, it does not suffer from skew problems.

Figure 2.1. Sample Eye Diagram Showing Non-Ideal Sampling Instants

It is known that parallel links offer a way of sending multiple bits every clock cycle. In recent years, another technique has been proposed: multi-level signaling [22][72].

Static CMOS systems use two discrete levels of logic, which associate VDD to logic '1' and VSS to logic '0'. Multi-level signaling is a system that uses intermediate values between VDD and VSS to increase the amount of information per bit time. For example, PAM-4 divides the voltage range into equal sections so as to allow for four distinct levels of logic (two bits) to be transmitted at a time. The advantage of this method is that more information can be sent in a single bit time. The drawbacks are the added complexity in the design of the receiver and the reduced noise margin. The receiver needs to use high-performance analog-to-digital converters (ADC) and novel CDR algorithms. Another drawback to multi-level signaling is that it cannot be used for optical links.

## 2.2. Clock and Data Recovery

CDRs have been the topic of many works over the years [1][5][13][37][59][64][70]. While numerous different architectures have been proposed, all CDRs accomplish two main tasks: clock recovery and data recovery.

As discussed previously, the clocks of the receiver and of the transmitter oscillate at about the same frequency without any predefined phase relationships. Clock recovery is the task of deriving the required clock phase and frequency to correctly retrieve the data. Data recovery uses the recovered clock to sample the data and retime the bits so that they can be used in a synchronous manner by the receiver. The block diagram of a simple CDR is shown in Figure 2.2.

Figure 2.2. Block Diagram of a CDR

In the figure, the upper loop consists of the modules required for clock recovery. It consists of a phase detector, a low pass filter (LPF) and a voltage controlled oscillator (VCO). The sampler located at the bottom of the Figure is shown here for illustrative purposes, since it is generally incorporated into the phase detector.

Clock recovery typically uses the transitions in the incoming data pattern to help align the active transition of the local clock to the middle of the data bit, where it is least prone to errors. To accomplish this task, the CDR relies on a phase detector, which is a module that checks the position of the active clock edge with respect to the data. When the clock is misaligned, the output of the phase detector helps the CDR adjust the clock phase.

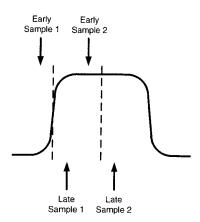

Phase detectors can generally be classified into two categories: binary (bang-bang) and linear [4]. A binary phase detector is a circuit that indicates whether the clock transition occurred early or late with respect to the data transition. If the data are sampled before the middle of the bit time, they are considered early. Similarly, when the sampling

is done after the middle, it is considered late. An example of binary phase detection is a double-rate (2X) oversampling scheme, which is shown in Figure 2.3. Using this technique, each bit is sampled twice: once in the middle of the data bit and once during data transition. The dotted lines in the Figure show the location of the ideal sampling points. Let the mid-transition sample be known as *Sample 1* and the mid-bit sample be known as *Sample 2*. Assuming that the oscillator frequency is correct, when the values of *Sample 1* and *Sample 2* are different, it indicates that *Sample 1* occurred before mid-swing. *Sample 2* would therefore occur before the middle of the bit time. In this case, the clock is considered early. Conversely, when the values of *Sample 1* and *Sample 2* are the same, the clock is considered late. Assuming the sampler does not become metastable, the binary phase detector will continuously detect early or late clocks and will keep adjusting its control signal. This can cause rippling on the VCO control line.

Figure 2.3. Determination of Phase Relations in 2X Oversampling

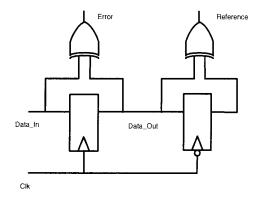

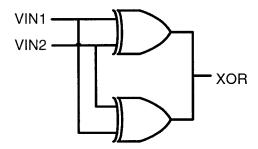

As previously discussed, binary phase detectors operate by indicating whether a clock is early or late. However, it does not give information as to how early or how late the clock actually is. On the other hand, linear phase detectors give a response that is proportional to the data-clock misalignment. A classic way of providing linear phase detection is to measure the time between a data transition and a clock transition. The goal is to adjust the clock signal until the time difference between the transitions becomes equal to half of a bit time. Hogge's phase detector [29], shown in Figure 2.4, is a linear phase detector that makes use of flip-flops and XOR gates to accomplish this task. The flip-flop and the XOR gate on the left of the Figure are used to measure the time difference between the data transition and a clock transition. It generates a pulse with a duration that is proportional to the time difference. The right-most XOR gate, combined with the two flip-flops, operates as an edge-detector. It generates a pulse of duration equal to half of a bit time when a transition is detected on the data line. When the clock is properly aligned with the data, both pulses should have equal width.

Figure 2.4. Hogge's Phase Detector

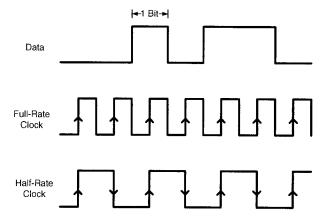

Hogge's phase detector, along with many other phase detectors, is classified in a group known as full-rate circuits. Full-rate circuits operate using a single active-edge of a clock during any given period. That means that the full-rate clock needs to make two transitions during a single data bit time. When the data rate is fast, it is difficult to design a VCO that functions at the full-rate. In an effort to alleviate this constraint, the concept of half-rate phase detection has been proposed [65][70]. Using such architecture allows the clock to function at a speed equal to half of the full-rate clock. Figure 2.5 illustrates the different clocking schemes.

Figure 2.5. Waveforms Showing Different Clocking Schemes

Perhaps the most significant half-rate phase detector in recent years has been proposed by Savoj (Figure 2.6). The structure of the phase detector can be seen as consisting of two of Hogge's phase detectors working in parallel: one operating on the rising clock edge and one operating on the falling clock edge. Note that each of the

sampling devices in Figure 2.6 is a level-sensitive latch as opposed to the conventional edge-triggered flip-flop. In addition to operating as a phase detector, the circuit is also used to sample and retime the incoming data. The data retrieved through the top and bottom portions are combined using a multiplexer. While the half-rate concept is useful in reducing constraints on the VCO, the main drawback is that it requires a 50% duty cycle clock.

Figure 2.6. Savoj's Half-Rate Phase Detector

Another way of reducing the constraint on the VCO and on the samplers is to use the concept of time-interleaving [69]. Time-interleaving consists of using N phases of a clock

that are separated by T/N, where T is the clock period. The incoming data are then retrieved using N samplers, each of which only needs to operate with clock period T. The benefits of using this technique are that, for a given data rate, the VCO only needs to operate at a speed of 1/N of a full-rate clock and the samplers can operate N times slower. This, of course, assumes that the samplers can handle the bandwidth of the incoming data. A drawback to this approach is the increased number of devices connected to the input data line. This can potentially add large amounts of load capacitance to the driver of the data line.

An example of time-interleaving using four clock phases is shown in Figure 2.7.

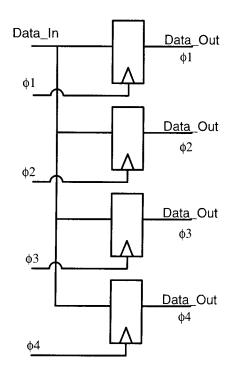

Figure 2.7. Example of 4-Phase Time-Interleaving CDR

### 2.3. Frequency Acquisition

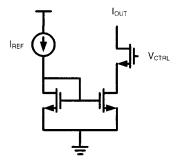

CDRs do not usually have a good frequency acquisition range due to the fact that they rely on phase detectors. When the frequency difference is large, the CDR may fail to lock. In order to increase the acquisition range, it is customary to include a module, which brings the VCO close to the target frequency. As soon as the frequency difference is small enough, it lets the phase detector take control. The frequency-adjusting module can be seen as providing coarse-tuning for the CDR, whereas the phase detector provides fine-tuning. Many frequency-measuring circuits exist in literature, although most of them cannot operate in the GHz range. An important class of frequency measurement circuits is known as integrator-based frequency-to-voltage converters (FVCs). A significant architecture, shown in Figure 2.8, was proposed by Djemouai [20].

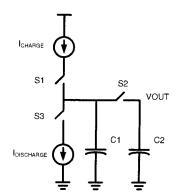

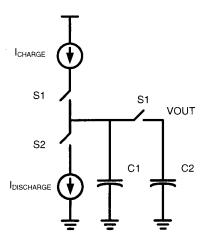

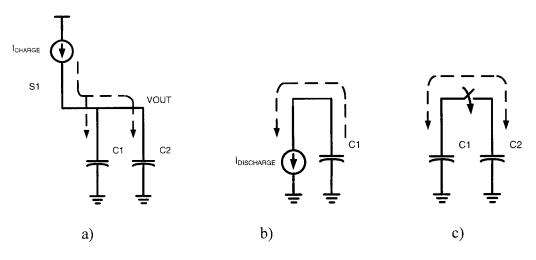

Figure 2.8. Ideal Model of Djemouai's Frequency-to-Voltage Converter

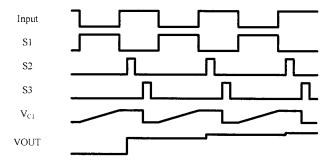

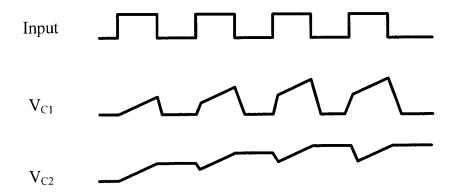

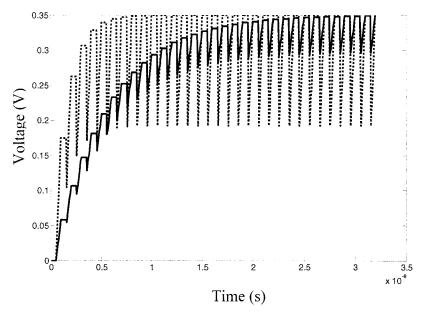

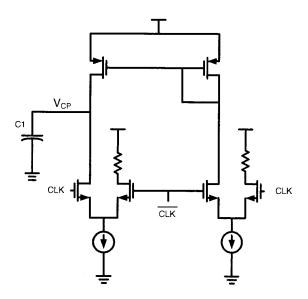

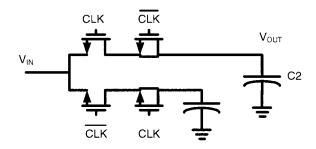

Its principle of operation relies on three control phases. These three phases controlled by switches S1, S2 and S3, are generated in response to the input waveform. The relationship between the input signal and the control signals are shown in Figure 2.9.

Figure 2.9. Input Clock Showing the Different Phases for Frequency-to-Voltage

Conversion

During the first half period, S1 conducts and capacitor C1 works as an integrator by accumulating charges from a constant current source. The voltage at the capacitor node is proportional to the duration of the half-period. During the second half of the period, the accumulated charges are transferred to a second capacitor through switch S2 and the integrating capacitor C1 is discharged through S3. Switches S2 and S3 are controlled by pulses that are generated internally when the first phase is complete. After a few cycles, the output voltage stabilizes to a constant value representing the associated frequency.

Although the circuit operates well at moderate frequencies, several factors limit its performance in the GHz range. The first problem lies in the fact that the circuit makes use

of two pulses that are generated internally. The minimum duration of a half-period is therefore two pulses. In addition, it relies on these pulses to control NMOS switches: the switches typically require full-swing pulses with a duration that is long enough for charge transfer. These constraints set the minimum clock period to be equal to four full-swing pulses. Even with its limits, the FVC is able to function properly at speeds of 200 MHz. Provided its operating speed can be increased, the use of such FVC circuit can contribute to the design of a frequency-acquisition aid that would extend the frequency range of the CDR.

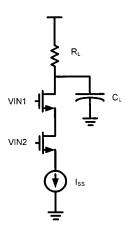

# 2.4. MOS Current-Mode Logic

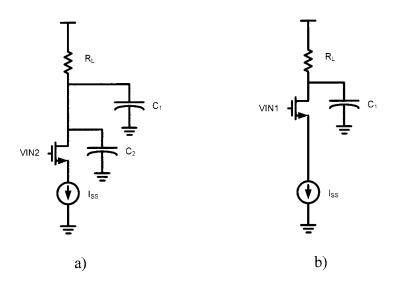

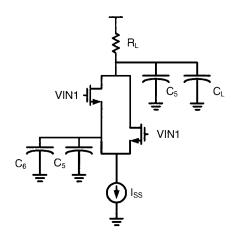

These days, transceivers operate at frequencies that are in the multi-GHz range. This operating speed cannot be achieved with conventional design techniques using static CMOS gates. At such frequencies, circuits requiring rail-to-rail output transitions are not feasible with the 0.18 µm technology used in our work. At such operating speeds, MOS current-mode logic (MCML) is the preferred design technique [79]. The principle of operation of MCML gates is best described using an example. Consider the buffer/inverter circuit, which is the simplest MCML gate, shown in Figure 2.10.

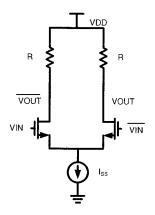

Figure 2.10. MCML Buffer

Its functionality essentially relies on a differential pair that steers a tail current according to the input voltage. When the same voltage is applied to VIN and  $\overline{VIN}$ , the tail current is split equally between the branches. If the voltage at VIN is increased while decreasing the voltage at  $\overline{VIN}$ , more current will start flowing through the VIN branch. When the differential input voltage,  $VIN - \overline{VIN}$ , is larger than a given  $\Delta V$ , the tail current is completely steered to one branch, leaving the output voltage of the other controlled by a passive pull up. This  $\Delta V$  is approximated by the following equation [28]:

$$\Delta V = \sqrt{\frac{2ISS}{\mu_N C_{OX}(W/L)}} \tag{2.1}$$

In this case, the output voltage on the current-carrying branch drops by  $I_{SS}*R_L$ , whereas the other branch goes to VDD. By adjusting the values of  $I_{SS}$  and  $R_L$ , the swing of the gate can be adjusted, which could lead to higher operating speeds.

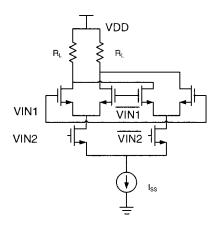

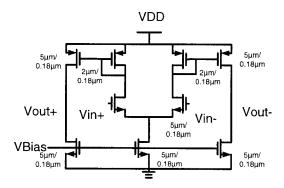

More complex gates can be designed simply by connecting a number of these differential pairs together. For instance, the XOR gate shown in Figure 2.11 can be

implemented with two parallel differential pairs stacked on top of a third differential pair. The tail-current is first steered through the bottom transistors and is then switched between the top transistors. More complete discussions on the design of MCML gates can be found in [50].

Figure 2.11. MCML XOR Gate

Besides its potential for achieving higher speed, MCML has several other advantages. The current drawn by MCML gates does not vary much with frequency and consequently, the power dissipated is also nearly constant. On the other hand, CMOS gates consume more power as the switching activity increases. It can be shown that in the gigahertz range, MCML gates often dissipate less power than their CMOS counterpart. In addition to consuming less power at high frequencies, since the current is nearly constant, the L (di/dt) noise is minimized [50], which greatly alleviates signal integrity issues that often become the bottleneck in high speed systems. Finally, the fully differential topology of the MCML gates reduces its sensitivity to common-mode noise.

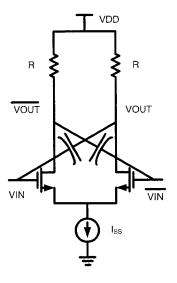

#### 2.4.1 Symmetric XOR

One of the problems encountered when using multiple-input MCML gates in high speed applications, such as CDRs, is gate asymmetry. Gate asymmetry gives rise to some uncertainty regarding the time an output transition is generated in response to switching inputs. While this timing variation is a negligible jitter in most low-speed applications, its effect becomes more significant as the speed increases. In applications such as CDRs, the XOR gate is often used to measure the precise phase difference between two signals [29][64]. An asymmetric XOR would introduce jitter that generates errors in the phase measurements, ultimately causing data recovery errors. It is therefore important to reduce the jitter introduced by the XOR gate.

While most of the work in recent years has dealt with speed and power issues, only a limited number of designs have addressed jitter. For instance, the work in [19][52] perform a theoretical jitter analysis on the use of XOR gates in CDR applications. In an attempt to reduce output jitter in XOR gates, several works have proposed symmetric circuit topologies. The first symmetric XOR gate was proposed in 1990 [66]. The authors in [66] suggest a criss-crossed connection of bipolar emitter-coupled logic (ECL) XOR gates, which would eliminate any asymmetry in the output signal. This topology has recently been adapted to CMOS technology in [58], where the authors implemented the circuit using MCML [79], or source-coupled logic (SCL) as it is sometimes known [16].

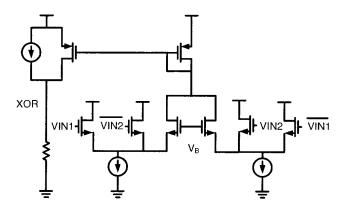

Another significant XOR gate is the one proposed by Savoj and Razavi in [64] (Figure 2.12). This circuit is a symmetric XOR gate with symmetric drive strength and

symmetric loading. It operates as follows. When VINI and VIN2 have different values, both input transistors on one branch carry the tail current. On the other branch, none of the input transistors are selected and consequently, the tail current flows through one of the  $V_B$ -biased transistors. The current through that  $V_B$ -biased transistor is then copied through the current mirror which brings the output node high. In the case where inputs VIN1 and VIN2 are equal, only one input transistor on each branch carries its respective tail current. Since there is no current flow through the  $V_B$  transistors, no extra current is injected at the output node and the resistor pulls the output low. The current source located at the output node is used to set the DC level of the XOR gate.

Figure 2.12. Single-Ended Symmetric XOR

The benefits of this topology are that input drivers are loaded equally and only have to drive a single transistor. The main drawback of this circuit is its single-ended output. While it performs the required functionality in the CDR presented in [64], its single-ended output limits its versatility and the gate cannot be used in many applications. Therefore, it will not be considered any further in this thesis.

## 2.5. MCML Gate Bandwidth Improvement

Although MCML provides the highest achievable speed compared to most other CMOS design techniques, it is quickly reaching its limits. In 0.18 µm CMOS, the gain of the fastest MCML gate, namely the buffer, drops below unity soon after 10 GHz. Most other MCML gates cannot operate reliably at speeds beyond 5 GHz. To push back the limits of these MCML gates, numerous techniques have been proposed in recent years. This section will provide a brief overview of the significant developments.

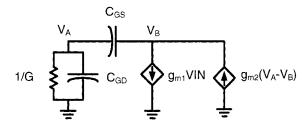

As stated previously, the structure of MCML gates is based on differential amplifiers. It is also known that differential amplifiers and other inverting amplifiers are subject to Miller capacitance, which can potentially reduce the maximum bandwidth that can be achieved by the circuit. Due to the Miller effect, part of the capacitance (C<sub>GD</sub>) seen at the input node is effectively multiplied by the gain of the amplifier. Since MCML gates are based on differential pairs, they are also affected by the Miller capacitance.

In an effort to extend the maximum bandwidth, researchers have attempted to cancel the Miller effect by including a series capacitor between the non-inverting input and the drain node, as shown in Figure 2.13 [28].

Figure 2.13. Buffer with Compensated Miller C<sub>GD</sub>