**Titre:** Conception d'une architecture alternative à la technologie

Title: "mémoire adressable par contenu"

**Auteur:** Patrick Mahoney

Author:

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Mahoney, P. (2006). Conception d'une architecture alternative à la technologie

"mémoire adressable par contenu" [Mémoire de maîtrise, École Polytechnique de

Montréal]. PolyPublie. <https://publications.polymtl.ca/7726/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7726/>

PolyPublie URL:

**Directeurs de

recherche:** Guy Bois, & Yvon Savaria

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

CONCEPTION D'UNE ARCHITECTURE ALTERNATIVE À LA

TECHNOLOGIE "MÉMOIRE ADRESSABLE PAR CONTENU"

PATRICK MAHONEY

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

AVRIL 2006

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-17955-0

*Our file* *Notre référence*

ISBN: 978-0-494-17955-0

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

CONCEPTION D'UNE ARCHITECTURE ALTERNATIVE À LA

TECHNOLOGIE "MÉMOIRE ADRESSABLE PAR CONTENU"

présenté par: MAHONEY Patrick

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

Mme NICOLESCU Gabriela, Doct., présidente

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. SAVARIA Yvon, Ph.D., membre et codirecteur de recherche

M. DAVID Jean-Pierre, Ph.D., membre

## REMERCIEMENTS

Je remercie mon directeur Guy Bois pour avoir grandement facilité mon retour à l'École Polytechnique. Il a su être disponible tout au long de cette aventure en me fournissant support et conseils.

Je remercie mon co-directeur Yvon Savaria grâce à qui j'ai pu découvrir le monde de la microélectronique tout en ayant le nécessaire pour payer le loyer et l'épicerie. Je remercie Patrice Plante pour avoir pris le temps de répondre à mes nombreuses questions ainsi que pour m'avoir donné accès aux ressources de son employeur pendant la durée du projet.

Je remercie mes parents sans qui tout ceci n'aurait pas été possible.

## RÉSUMÉ

La technologie *Content Addressable Memory* (CAM) est une technologie mémoire qui permet d'accéder aux données à partir de la donnée même plutôt qu'à partir de son adresse. Elle est utilisée par une grande portion des applications nécessitant un haut débit d'accès mémoire. La raison est simple: elle effectue ses opérations de recherche et d'insertion en un seul cycle.

La technologie CAM parvient à réaliser des recherches en un seul cycle comparant simultanément la donnée fournie par l'usager à toutes les données présentes en mémoire. Si la donnée recherchée est présente, l'information associée à la donnée recherchée est présentée à l'usager.

Elle possède toutefois plusieurs inconvénients majeurs. Tout d'abord, le parallélisme des comparaisons demande une grande quantité de comparateurs qui réalisent leur tâche en même temps. Ainsi, pour une capacité donnée, la technologie CAM occupe une grande quantité d'aire de silicium. Aussi, le fonctionnement simultané des comparateurs demande une grande quantité d'énergie à chaque opération de recherche. Les designers doivent donc tenir compte de la grande consommation de puissance et de la grande dissipation de chaleur qu'implique l'utilisation de la technologie CAM. Finalement, les fournisseurs des compilateurs de CAM exigent des frais de licence qui rendent la technologie inabordable pour plusieurs.

Les alternatives consistent principalement au recours à la technologie *Random Access Memory* (RAM) utilisée en combinaison avec des algorithmes de recherche et d'insertion conventionnels: structures arborescentes, hashing, etc. Les performances qu'elles permettent d'atteindre ne sont tout simplement pas les mêmes.

Le présent projet consiste en la conception d'une architecture mémoire offrant des performances similaires à celles des CAM tout en tirant profit des caractéristiques de la technologie RAM: faible coût, forte densité et faible consommation.

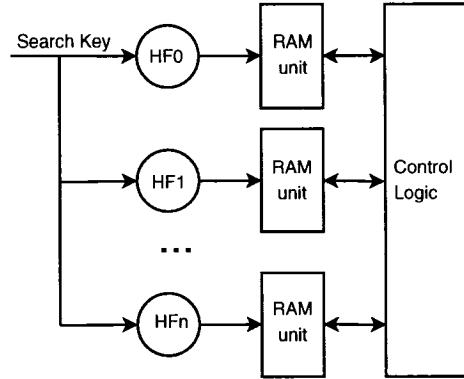

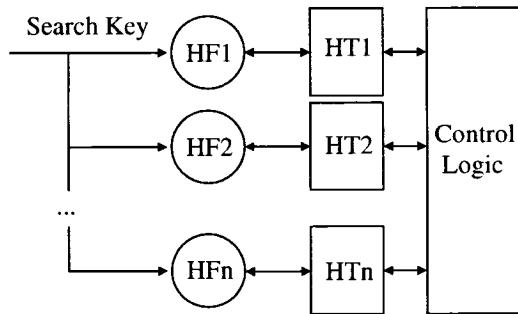

L'architecture propose de disposer un certain nombre d'unités de RAM en parallèle et de les utiliser comme table de hashing, chaque table ayant une unité réalisant une fonction de hashing et la combinaison des deux représentant une couche. Lors d'une insertion, chaque couche vérifie si la rangée à laquelle correspond la donnée à insérer est libre. L'insertion est faite dans la première table présentant une entrée disponible. Lors d'une recherche, chaque couche accède à la rangée de l'unité de RAM à laquelle correspond la donnée recherchée et compare la donnée accédée à celle fournie par l'usager. Une logique se charge de rassembler les résultats des comparaisons et d'acheminer l'information pertinente en sortie.

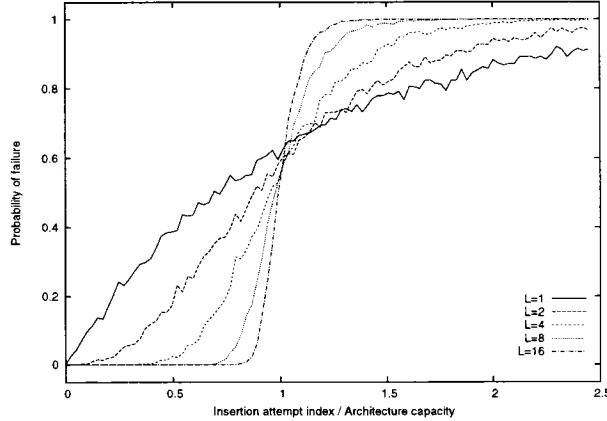

Cette architecture tire profit de la technologie RAM, mais ne peut garantir l'absence de tout échec lors des insertions. En effet, si les rangées de toutes les couches sont occupées lors d'une tentative insertion, celle-ci ne peut être réalisée. Le présent projet analyse donc les performances de l'architecture et tente d'évaluer son coût. Tout d'abord, le comportement de l'architecture a été modélisé par un simulateur et les premiers indices de performances ont ainsi pu être obtenus. Un peu comme il était permis de croire, les simulations nous ont confirmé que pour un nombre d'insertions donné, une augmentation du nombre de couches ou une augmentation de la capacité totale de l'architecture permettent d'obtenir un plus petit nombre d'échecs. Ces constatations sont toutefois basées sur la présence de fonctions de hashing idéales. Ces fonctions ont la caractéristique de briser toute corrélation dans les données à insérer pour ainsi disperser de façon uniforme les adresses mémoire générées.

Toutefois, les simulations ne nous permettent que difficilement d'identifier les configurations qui mènent à des taux d'échecs inférieurs à  $10^{-4}$ . Pour combler ce manque, un modèle analytique a donc été conçu. Celui-ci nous permet d'identifier les configurations menant à des taux d'échecs de n'importe quel ordre de grandeur. Il permet ainsi de définir de façon précise les performances de l'architecture. Il est important de noter que ce modèle se base aussi sur l'hypothèse de fonctions de

hashing idéales.

Pour évaluer le coût de l'architecture, une réalisation VLSI a été effectuée. Les métriques obtenues se comparent avantageusement aux fiches techniques des modules CAM. Elles nous permettent d'estimer que pour une capacité donnée, le rapport d'aire de l'architecture proposée par rapport à une cellule de CAM est de 2.4. En ce qui concerne la consommation, ce rapport est de 4.7.

Ces résultats nous indiquent que pour reproduire le comportement d'une unité de CAM, il est possible de recourir à une architecture de hashing parallèle possédant une capacité supérieure à cette unité sans nécessairement avoir à débourser pour une plus grande consommation d'aire de silicium, de consommation de puissance ou encore de dissipation de chaleur.

## ABSTRACT

Content Addressable Memories (CAMs) allow lookup operations to be executed in a single cycle. This feature enables many applications to sustain high data throughput in a deterministic manner. It does so by comparing the value to look for with every item in memory. On a successful lookup, information associated with the sought after data is gated to the output.

These parallel comparisons cause CAM units to have high area and power consumption metrics. Another key liability of CAM technology resides in the high licensing fees imposed by CAM vendors.

These factors have designers looking for alternatives. Most of them consist in using Random Access Memory (RAM) technology combined with classic algorithms such as hashing or tree-based algorithms. The performances of the alternatives do not match the performances of CAMs.

The current project aims at offering a RAM based alternative offering performances similar to ones of CAMs while leveraging on RAM technology to offer improved area and power consumption metrics.

The proposed architecture is structured as sets of modules implementing multiple processing layers, each consisting of a hashing function, a static RAM unit and some combinational logic. The hashing functions translate the incoming data into an address used by the RAM cell. When an insertion attempt is made, all RAM units verify the availability of the row associated with the data to insert. The insertion is made on the highest layer among those signaling an empty row. On lookup operations, all layers access the row associated with the sought after data and compare it with the accessed value. Glue logic takes care of regrouping the results and gating the relevant information to the output.

The proposed architecture offers an interesting cost saving alternative to CAMs, yet it cannot guarantee to successfully realize every insertion attempt. Attempts

will fail if corresponding rows in all layers are occupied. The current project aims at analyzing and quantifying this performance behaviour so as to provide designers all the tools they need to fully benefit from this architecture.

A simulator was first used to obtain the first performances metrics. As we had guessed it, for a given number of insertions attempts, performances are enhanced by increasing the number of layers or by increasing the total architecture capacity. However, it is important to note that the simulator uses high quality hashing functions in its architecture model. These hashing functions possess the characteristic of breaking any correlation in search key traffic so as to yield uniformly dispersed hash keys. Another drawback of the simulator was to severely limit the analysis of the performance domain where collision rates get lower than  $10^{-4}$ . Prohibitive simulation times make it very difficult to identify architecture configurations yielding to lower failure rates.

In order to fill this gap, an analytical model of the architecture was created. This model assumes perfect hashing functions, yet it covers all of the performance domain. The analytical model allows to identify configurations yielding to failure rates of any magnitude.

In order to evaluate the cost of this architecture, a VLSI implementation was realized. It allowed us to make certain comparisons with commercial CAMs. Among them, it was found that the parallel hashing architecture consumed less die area than CAM units by a factor of 2.4. The value reaches 4.7 when comparing power consumption metrics.

In order to emulate a CAM unit of a given size, it is thus possible to use an oversized unit of parallel hashing memories while still offering improved die area and power consumption metrics.

**TABLE DES MATIÈRES**

|                                                            |       |

|------------------------------------------------------------|-------|

| REMERCIEMENTS . . . . .                                    | iv    |

| RÉSUMÉ . . . . .                                           | v     |

| ABSTRACT . . . . .                                         | viii  |

| TABLE DES MATIÈRES . . . . .                               | x     |

| LISTE DES FIGURES . . . . .                                | xii   |

| LISTE DES TABLEAUX . . . . .                               | xv    |

| LISTE DES ANNEXES . . . . .                                | xvi   |

| LISTE DES NOTATIONS ET DES SYMBOLES . . . . .              | xviii |

| AVANT PROPOS . . . . .                                     | xix   |

| INTRODUCTION . . . . .                                     | 1     |

| CHAPITRE 1 REVUE DE LITTÉRATURE . . . . .                  | 6     |

| 1.1 Modifications à la cellule de base de la CAM . . . . . | 6     |

| 1.2 Modifications Architecturales . . . . .                | 10    |

| 1.3 Positionnement du projet . . . . .                     | 15    |

| CHAPITRE 2 SYNTHÈSE DES TRAVAUX . . . . .                  | 17    |

| 2.1 Mise en Contexte . . . . .                             | 17    |

| 2.2 Description de l'Architecture . . . . .                | 19    |

| 2.3 Évaluation de Performances . . . . .                   | 21    |

| 2.4 Implantation de l'Architecture . . . . .               | 23    |

|                                                         |    |

|---------------------------------------------------------|----|

| 2.5 Résumé de l'article . . . . .                       | 24 |

| CHAPITRE 3 RÉALISATION VLSI DE L'ARCHITECTURE . . . . . | 31 |

| 3.1 Méthodologie . . . . .                              | 31 |

| 3.2 Description Comportementale . . . . .               | 31 |

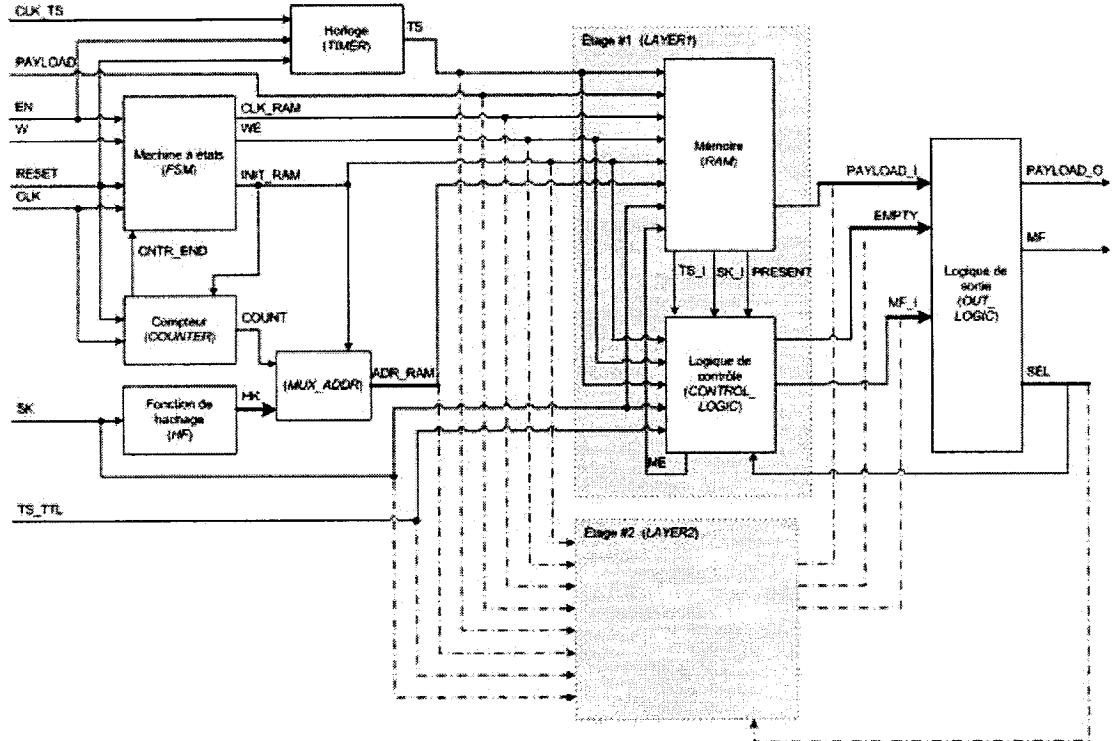

| 3.3 Fonctionnement Interne . . . . .                    | 32 |

| 3.4 Choix d'implantation . . . . .                      | 39 |

| 3.5 Simulations et Vérifications . . . . .              | 42 |

| 3.6 Résultats . . . . .                                 | 43 |

| CHAPITRE 4 DISCUSSION GÉNÉRALE . . . . .                | 46 |

| CONCLUSION . . . . .                                    | 48 |

| RÉFÉRENCES . . . . .                                    | 50 |

| ANNEXES . . . . .                                       | 53 |

## LISTE DES FIGURES

|            |                                                                                                                                                 |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1   | Fonctionnement interne de la CAM . . . . .                                                                                                      | 2  |

| Figure 2   | Les acteurs d'une architecture de hashing. . . . .                                                                                              | 4  |

| Figure 1.1 | Cellule CAM de base . . . . .                                                                                                                   | 7  |

| Figure 1.2 | Mosaïque de cellules de CAM. . . . .                                                                                                            | 8  |

| Figure 1.3 | Cellule CAM de base proposée par Lin (Lin, 2003) . . . . .                                                                                      | 9  |

| Figure 1.4 | La précharge sélective est un compromis entre la latence et la consommation proposé par Zukowski (Zukowski 1997). . . . .                       | 10 |

| Figure 1.5 | Lin et Chang (Lin 2000) proposent de comparer la donnée seulement si la comparaison du paramètre est réussie. . . . .                           | 11 |

| Figure 1.6 | Seznec (Seznec 1993) propose un système de cache avec deux fonctions de hashing pour minimiser les collisions. . . . .                          | 12 |

| Figure 1.7 | Lim (Lim 2002) propose une table de débordement utilisant la technologie CAM pour conserver les données qui n'ont pas pu être insérées. . . . . | 14 |

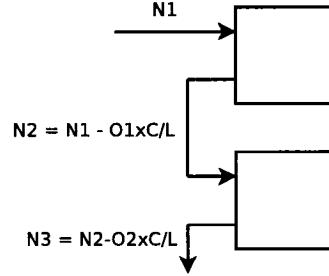

| Figure 2.1 | Architecture proposée . . . . .                                                                                                                 | 20 |

| Figure 3.1 | Schéma bloc de l'architecture . . . . .                                                                                                         | 33 |

| Figure 3.2 | Disposition des champs en RAM . . . . .                                                                                                         | 34 |

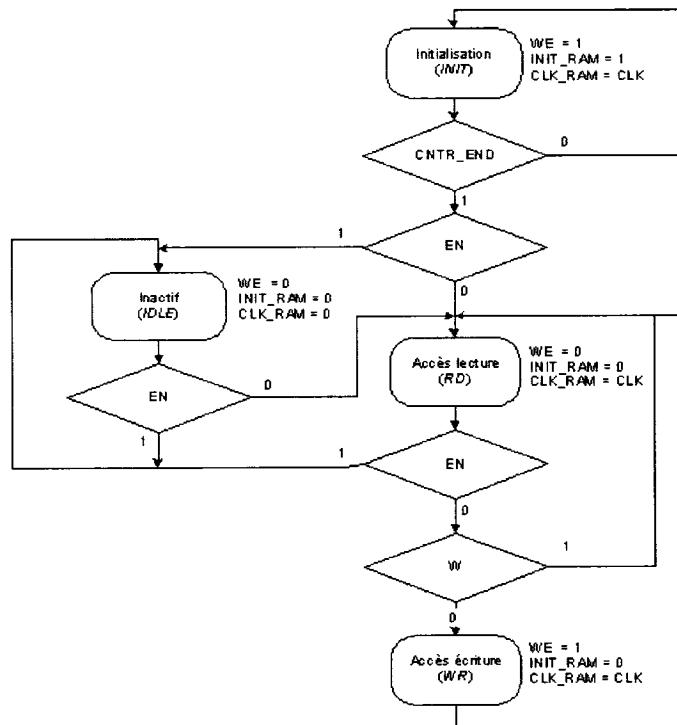

| Figure 3.3 | Machine à États . . . . .                                                                                                                       | 35 |

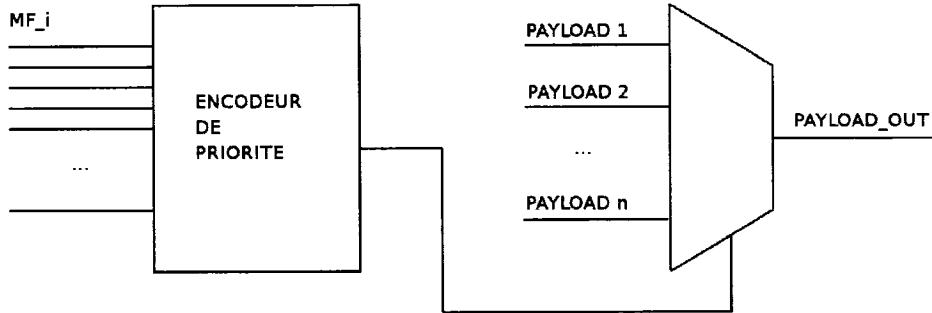

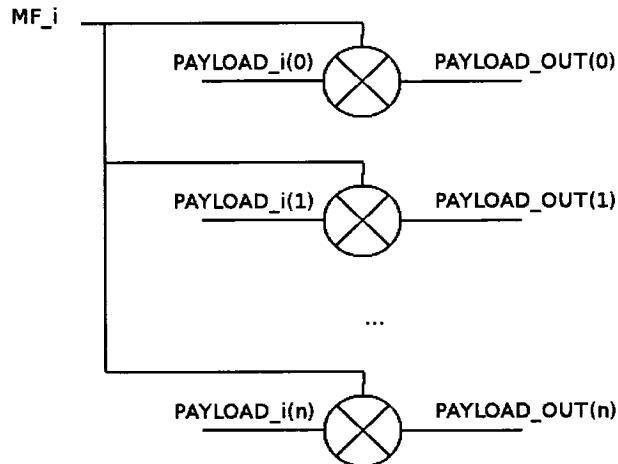

| Figure 3.4 | Circuit de sélection du signal PAYLOAD réalisé à l'aide d'un encodeur de priorité . . . . .                                                     | 41 |

| Figure 3.5 | Circuit de sélection du signal PAYLOAD réalisé à l'aide de portes de transmission . . . . .                                                     | 41 |

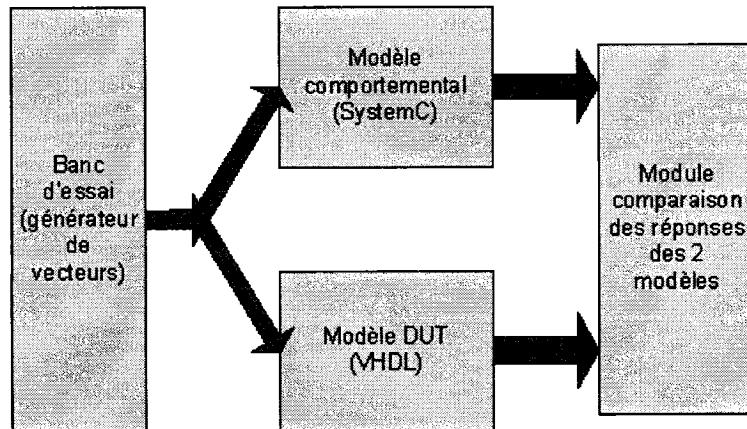

| Figure 3.6 | Stratégie de simulations mixtes . . . . .                                                                                                       | 42 |

| Figure 3.7 | Simulation pré-synthèse du bloc HF . . . . .                                                                                                    | 44 |

| Figure 3.8 | Simulation post-synthèse du bloc HF . . . . .                                                                                                   | 44 |

| Figure I.1 | Proposed hardware structure . . . . .                                                                                                           | 57 |

|             |                                                                                                                          |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------|----|

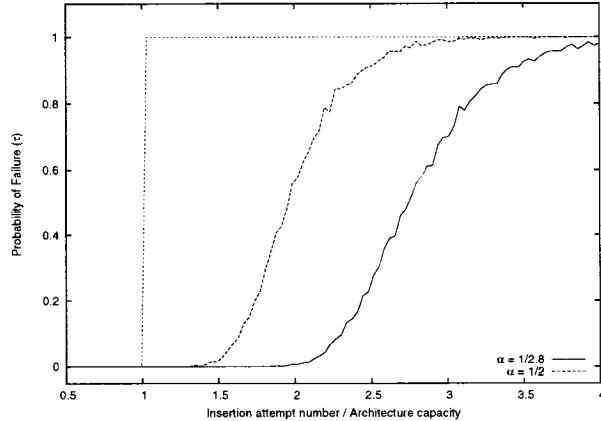

| Figure I.2  | The sigmoid behaviour of the probability of failure as the number of insertion attempts varies . . . . .                 | 61 |

| Figure I.3  | Performance comparison with CAM at $L=8$ and $\alpha = 1/2.8$ (cost per bit equivalent) and $\alpha = 1/2$ . . . . .     | 62 |

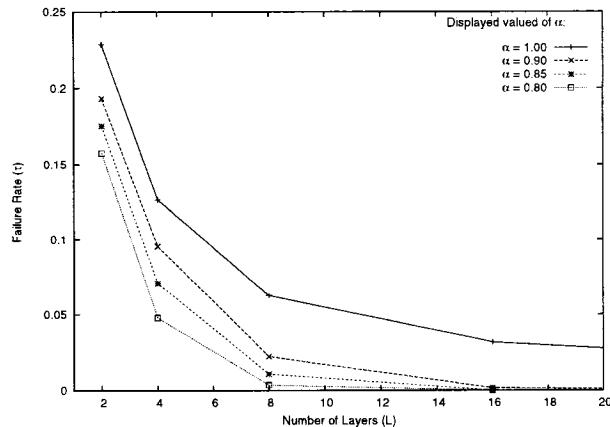

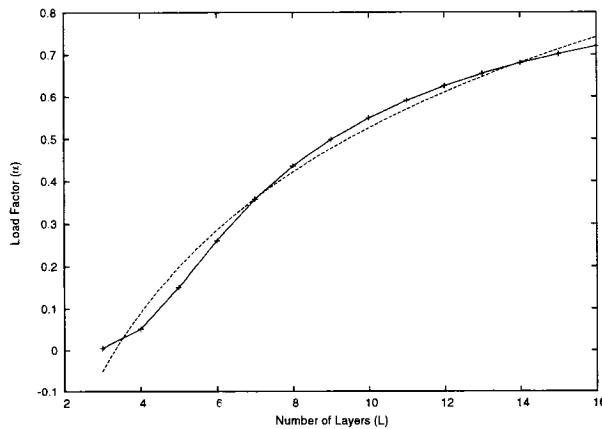

| Figure I.4  | $\tau$ vs $L$ for several $\alpha$ values with constant total architecture capacity . . . . .                            | 63 |

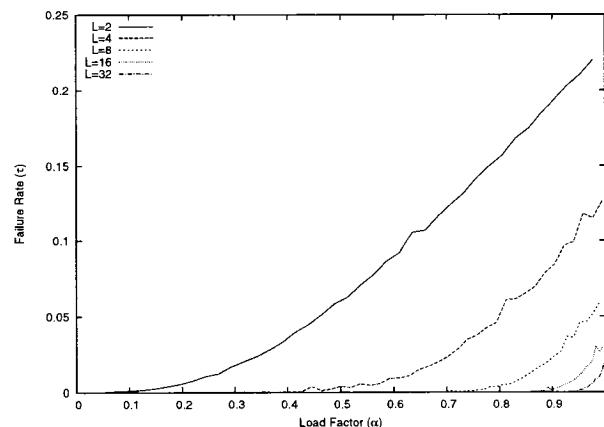

| Figure I.5  | $\tau$ vs $\alpha$ for several $L$ values with constant total architecture capacity . . . . .                            | 63 |

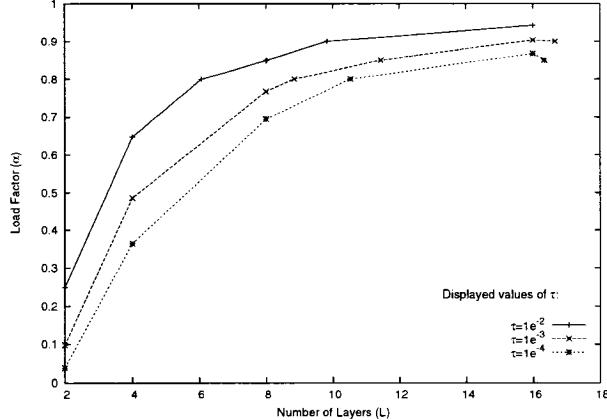

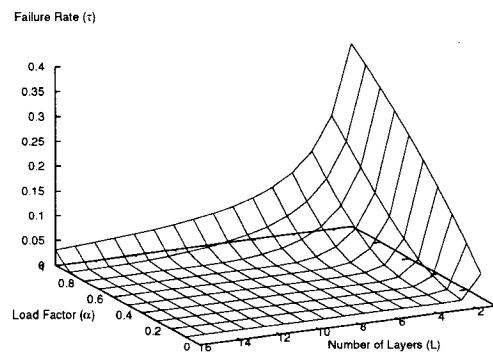

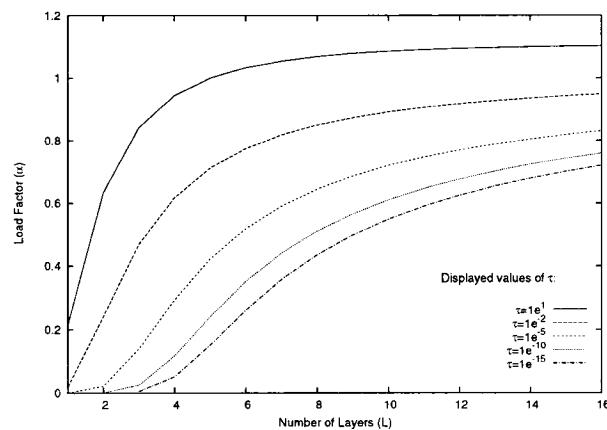

| Figure I.6  | $L, \alpha$ pairs yielding to constant $\tau$ values . . . . .                                                           | 64 |

| Figure I.7  | If the insertion attempt of an element in a layer causes a collision, it is said to percolate to the next layer. . . . . | 67 |

| Figure I.8  | Joined $\tau$ vs $R$ and $\tau$ vs $\alpha$ relations . . . . .                                                          | 69 |

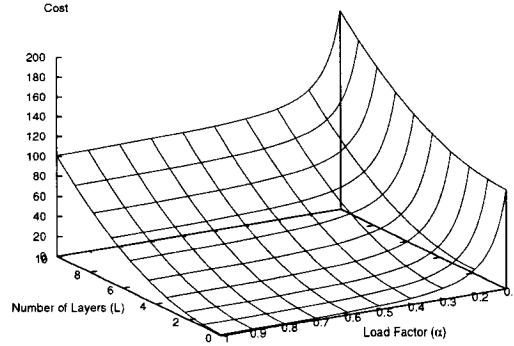

| Figure I.9  | $\alpha/L$ relations yielding to same $\tau$ . . . . .                                                                   | 69 |

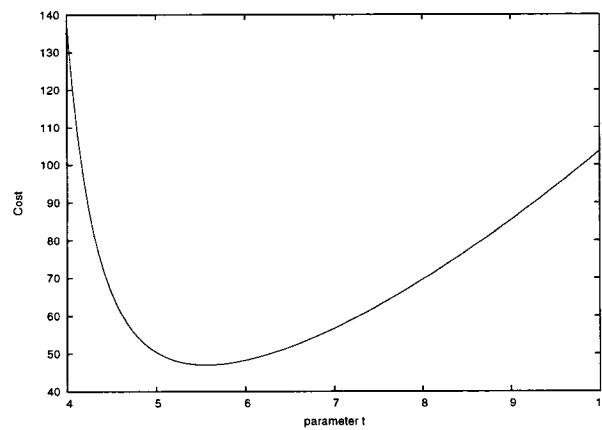

| Figure I.10 | Cost Model . . . . .                                                                                                     | 71 |

| Figure I.11 | Model of $\alpha$ vs $L$ relation for $\tau = 10^{-15}$ . . . . .                                                        | 72 |

| Figure I.12 | Minimal cost configuration for $\tau = 10^{-15}$ . . . . .                                                               | 72 |

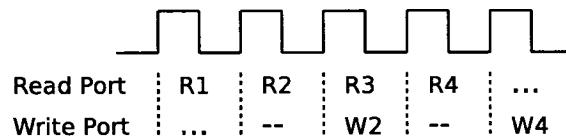

| Figure I.13 | Dual Port RAM design optimisation. Operations 2 and 4 represent insertions. . . . .                                      | 74 |

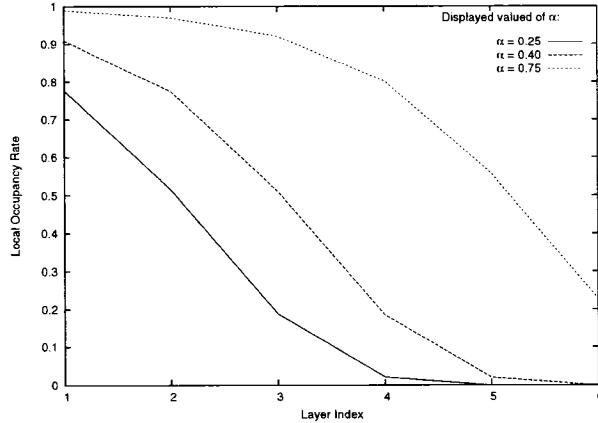

| Figure I.14 | The occupancy rate of the individual layers decreases as the layer index increases. . . . .                              | 76 |

| Figure II.1 | Proposed hardware structure . . . . .                                                                                    | 86 |

| Figure II.2 | Hash table entry layout . . . . .                                                                                        | 87 |

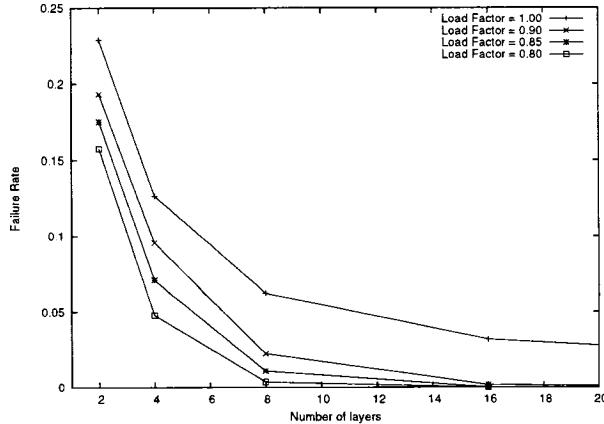

| Figure II.3 | $\tau$ vs $L$ for several $\alpha$ values with constant total architecture capacity . . . . .                            | 88 |

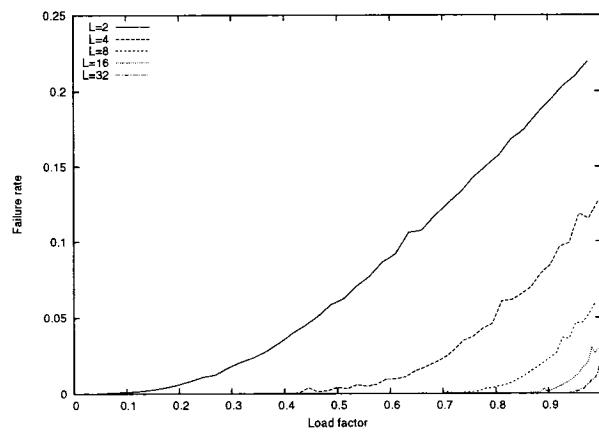

| Figure II.4 | $\tau$ vs $\alpha$ for several $L$ values with constant total architecture capacity . . . . .                            | 88 |

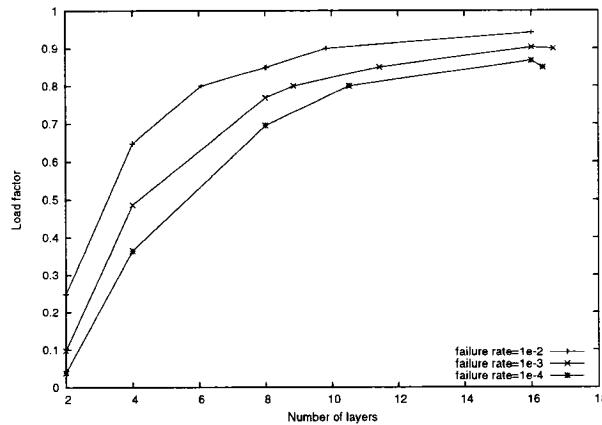

| Figure II.5 | $L, \alpha$ pairs yielding to constant $\tau$ values . . . . .                                                           | 89 |

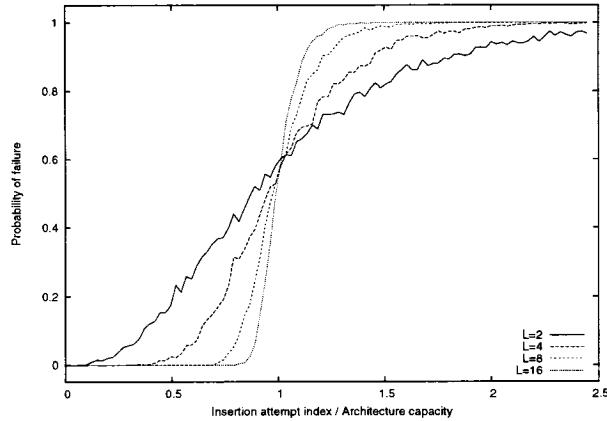

| Figure II.6 | Probability of failure vs $\frac{\text{InsertionAttemptIndex}}{\text{TotalCapacity}}$ for $L=2,4,8,16$ .                 | 90 |

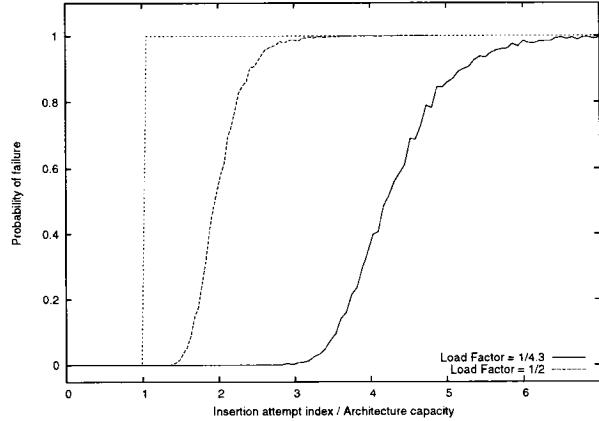

Figure II.7 Performance comparison with CAM at  $L=8$  and  $\alpha = 1/4.3$

(cost per bit equivalent) and  $\alpha = 1/2$  . . . . . 93

## LISTE DES TABLEAUX

|              |                                                                                                                                                                                                                     |    |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 1    | Comparaison de métriques d'une cellule de RAM statique avec celles d'une CAM binaire. Technologie CMOS $0.18\mu m$ . Fréquence d'opération 100 MHz. . . . .                                                         | 3  |

| Tableau 2.1  | Performance des principaux algorithmes de recherche. . . . .                                                                                                                                                        | 17 |

| Tableau 2.2  | Comparaison des métriques de la réalisation VLSI de l'architecture proposée avec une cellule CAM commerciale. Métrique issues de la technologie 180nm et évaluées avec une fréquence d'opération de 200MHz. . . . . | 28 |

| Tableau 2.3  | La diminution de la période d'horloge d'influence pas la portion de l'aire occupée par les cellules de RAM. . . . .                                                                                                 | 29 |

| Tableau I.1  | Static RAM and binary CAM technologies comparison. CMOS $0.18\mu m$ technology. 100 MHz operating frequency. . . . .                                                                                                | 54 |

| Tableau I.2  | Six layers are necessary to obtain a value of $\tau = 10^{-16}$ . $N_1=4000$ . . . . .                                                                                                                              | 68 |

| Tableau I.3  | Bringing the clock period from over 25ns down to under 5ns does not affect significantly the portion of the total area occupied by the RAMs. 180nm technology. . . . .                                              | 73 |

| Tableau I.4  | Comparisons of design with commercial CAMs. All values are for 180nm implementations running at 200MHz with a RAM access time of 2.8 ns. . . . .                                                                    | 74 |

| Tableau II.1 | Static RAM and binary CAM technologies comparison. CMOS $0.13\mu m$ technology. 100 MHz operating frequency. . . . .                                                                                                | 85 |

## LISTE DES ANNEXES

|           |                                                                                                                                                            |    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| ANNEXE I  | PARALLEL HASHING MEMORIES: AN ALTERNATIVE<br>TO CONTENT ADDRESSABLE MEMORIES. SOUMIS LE<br>31 MARS 2006 AU JOURNAL ACM TRANSACTIONS ON<br>STORAGE. . . . . | 53 |

| I.1       | abstract . . . . .                                                                                                                                         | 53 |

| I.2       | Introduction . . . . .                                                                                                                                     | 53 |

| I.3       | Previous Work . . . . .                                                                                                                                    | 55 |

| I.4       | Proposed Architecture . . . . .                                                                                                                            | 57 |

| I.5       | Performance Characterization . . . . .                                                                                                                     | 59 |

| I.6       | Analytical Modeling of the Proposed Architecture . . . . .                                                                                                 | 64 |

| I.7       | Proposed Methodology . . . . .                                                                                                                             | 70 |

| I.8       | Hardware Implementation and Metric Comparison . . . . .                                                                                                    | 71 |

| I.9       | Proposed Optimisations . . . . .                                                                                                                           | 74 |

| I.10      | Conclusions . . . . .                                                                                                                                      | 77 |

| I.11      | acknowledgments . . . . .                                                                                                                                  | 78 |

| ANNEXE II | PARALLEL HASHING MEMORIES: AN ALTERNATIVE<br>TO CONTENT ADDRESSABLE MEMORIES. PRÉSENTÉ<br>À LA CONFÉRENCE IEEE NEWCAS 2005. . . . .                        | 82 |

| II.1      | abstract . . . . .                                                                                                                                         | 82 |

| II.2      | Introduction . . . . .                                                                                                                                     | 82 |

| II.3      | Previous Schemes . . . . .                                                                                                                                 | 84 |

| II.4      | Binary CAM vs RAM . . . . .                                                                                                                                | 85 |

| II.5      | Proposed Architecture . . . . .                                                                                                                            | 86 |

| II.6      | Simulation Results . . . . .                                                                                                                               | 88 |

|                                 |    |

|---------------------------------|----|

| II.7 Results Analysis . . . . . | 91 |

| II.8 Conclusion . . . . .       | 92 |

| II.9 Acknowledgments . . . . .  | 93 |

**LISTE DES NOTATIONS ET DES SYMBOLES**

|          |                                      |

|----------|--------------------------------------|

| CAM      | Content Addressable Memory           |

| RAM      | Random Access Memory                 |

| CRC      | Cyclic Redundancy Check              |

| VLSI     | Very Large Scale Intergrated Circuit |

| PDT      | Pulled Down Transistor               |

| $\alpha$ | Taux de charge de l'architecture     |

| $L$      | Nombre de couches de l'architecture  |

## AVANT PROPOS

Le présent document prend la forme d'un mémoire par articles, tel que défini par le Bureau des Affaires Académiques (BAA) de l'École Polytechnique de Montréal. Les règlements du BAA stipulent que seuls les articles de revue permettent la rédaction d'un mémoire par article. Comme de fait, l'annexe de ce mémoire en contient un en annexe. Cependant, l'auteur de ce mémoire a cru pertinent d'y insérer en plus un article de conférence. Cet article brosse un portrait des étapes initiales du projet qui ont mené au travaux présentés dans l'article de revue.

L'information que contient le corps du mémoire a pour but de synthétiser, de complémer et de supporter les deux publications écrites par le groupe de recherche dont fait parti l'auteur de ce mémoire.

Le lecteur saura trouver dans le corps du mémoire une synthèse globale des travaux effectués dans le cadre du projet. La lecture des articles n'est pas essentielle à la compréhension d'ensemble. Cependant, elle permettra aux lecteurs curieux de saisir l'ensemble des tâches accomplies par l'équipe de recherche.

## INTRODUCTION

Les dix dernières années ont donné lieu à une explosion de la demande générale en services réseau de toutes sortes. L'intégration de services comme la téléphonie cellulaire, la messagerie SMS, les Blackberries et le *podcasting* dans le quotidien d'une tranche importante de la population est en partie responsable de ce phénomène. Les conséquences de ces généralisation et décentralisation de la demande en services réseau sont nombreuses. Du point de vue des fournisseurs, les deux plus importantes sont l'amélioration des services et la baisse des coûts.

Ces transformations à la demande se reflètent directement chez les fabricants d'équipements réseau et ce, à tous les niveaux de l'échelle de production. Les fournisseurs de solutions intégrées tout comme les fabricants de puces doivent se soumettre aux nouvelles contraintes. Les produits offerts doivent intégrer un plus grand nombre de solutions et être offerts à un coût moindre.

L'explosion du nombre d'applications réseau a entraîné un accroissement important de la quantité d'information transférée à l'échelle mondiale. Les applications de traitement de paquets ont ainsi connu une grande effervescence, elles aussi. Plusieurs de ces applications ont un point commun, l'avantage que leur procure un recours à la technologie des "Content Addressable Memories", ou CAM.

### Description la Technologie CAM

La technologie mémoire CAM se prête très bien à plusieurs applications de traitement de paquets, puisqu'elle permet d'effectuer les opérations de recherche et d'insertion en un seul cycle. Elle permet ainsi de soutenir des débits très élevés.

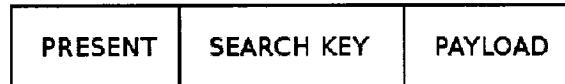

Les rangées des unités de CAM contiennent typiquement au moins deux informations essentielles: l'étiquette et la donnée utile. Sur la première sont effectuées les comparaisons avec les données recherchées. La seconde représente la donnée que cherche à obtenir l'usager. Par exemple, dans une application d'aiguillage de paquets, les adresses seraient contenues dans la portion étiquette, tandis que les identificateurs des ports permettant de rejoindre les adresses seraient présents dans la portion donnée utile.

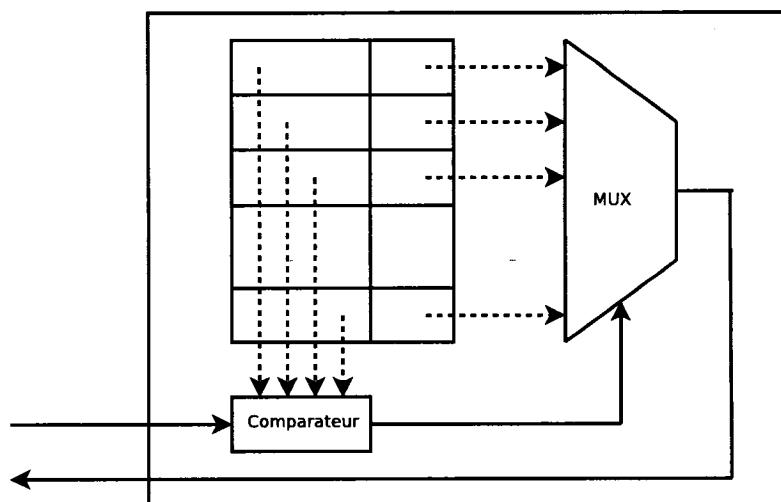

Lors des opérations de recherche, l'élément recherché est comparé à la portion étiquette de toutes les entrées en mémoire. Si une comparaison s'avère réussie, la portion donnée utile de cette rangée est acheminée vers la sortie. La Fig.1 illustre le fonctionnement interne d'une CAM.

Figure 1 Fonctionnement interne de la CAM

Ces comparaisons parallèles entraînent toutefois une grande consommation de puissance, ainsi qu'une forte dissipation de chaleur. En plus de ces inconvénients, les frais non-récurrents très élevés exigés par les fournisseurs rendent l'accès à la technologie très difficile. Finalement, la superficie de silicium qu'occupent les cellules

de CAM représente un autre aspect du coût très élevé associé à l'utilisation de cette technologie. La table II.1 compare quelques métriques de la CAM avec celles de la technologie RAM.

Tableau 1 Comparaison de métriques d'une cellule de RAM statique avec celles d'une CAM binaire. Technologie CMOS  $0.18\mu m$ . Fréquence d'opération 100 MHz.

|                                                       | CAM  | RAM  | Facteur |

|-------------------------------------------------------|------|------|---------|

| Coût<br>( $mm^2/Mbit$ )                               | 19.2 | 6.75 | 2.8     |

| Consommation<br>Opération de lecture<br>( $mW/Mbit$ ) | 410  | 80.9 | 5.1     |

| Consommation<br>Opération d'écriture<br>( $mW/Mbit$ ) | 735  | 89.3 | 8.23    |

Le présent projet propose une architecture alternative à la technologie CAM. Elle a recours à la technologie RAM pour pouvoir pallier aux inconvénients mentionnés ci-haut. Elle a recours au *hashing* pour parvenir à offrir une fonctionnalité similaire à celle de la technologie CAM.

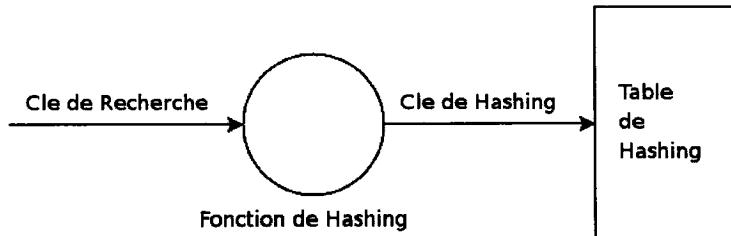

## Hashing

Le hashing est un algorithme qui permet d'effectuer des recherches et des insertions de données en un seul accès mémoire. Une donnée à insérer en mémoire (la clé de recherche) est associée à une adresse de cette mémoire (la clé de hashing) à l'aide d'une logique déterministe (la fonction de hashing). Lors d'une opération de recherche, ce n'est qu'à cette adresse que la mémoire doit être accédée. Pour les insertions, ce n'est qu'à cette adresse qu'il est permis d'insérer la donnée. L'algorithme de hashing, qui tente de produire un patron d'écriture aussi aléatoire que possible, offre donc des performances intéressantes, mais il est nécessaire de

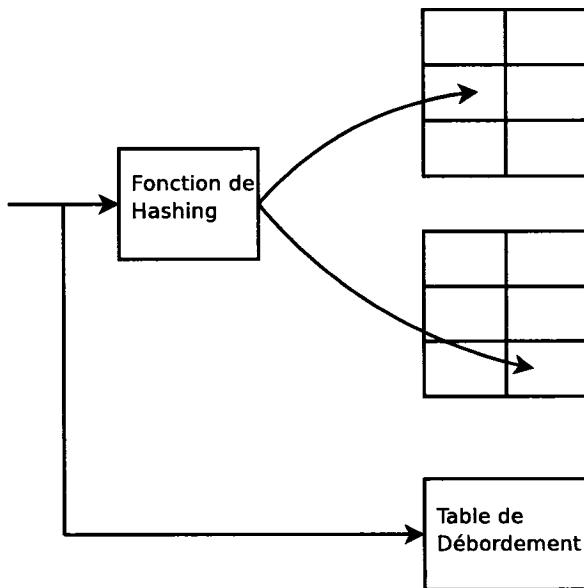

gérer les collisions qui en résultent. Celles-ci surviennent lorsqu'une insertion doit être faite à une adresse qui est déjà occupée par une autre donnée. La figure 2 illustre les différents participants de l'algorithme de hashing.

Figure 2 Les acteurs d'une architecture de hashing.

L'architecture présentée dans ce document offre une alternative économique à la technologie CAM. En effet, en ayant recours à l'algorithme de hashing et tirant profit des caractéristiques de la technologie RAM, l'architecture présentée parvient à émuler le comportement des CAM tout en offrant des métriques d'aire et de consommation avantageuses.

### Présentation du Mémoire

Le mémoire contient trois sections en plus des annexes. Tout d'abord, le second chapitre consiste en une revue de littérature portant sur la technologie CAM. Le troisième chapitre, quant à lui, présente au lecteur l'information nécessaire à la pleine compréhension des articles. Il décrit les différentes décisions qui ont défini les bases du projet de recherche. De plus, il résume le contenu des deux articles insérés en annexe pour fournir au lecteur une vue d'ensemble lui permettant de saisir les principaux aspects techniques en jeu.

Le quatrième chapitre traite de la réalisation VLSI. Il aborde tout d'abord le design de la réalisation ainsi que la méthodologie employée, pour finalement présenter

les performances résultantes en les comparant à celles de la CAM. Finalement, les annexes contiennent les deux articles écrits par l'équipe impliquée dans cette recherche.

## CHAPITRE 1

### REVUE DE LITTÉRATURE

Ce chapitre présente un survol de l'état de la recherche dans le domaine de la technologie CAM en 2006. Sa lecture permettra au lecteur de situer l'apport exact du projet par rapport à ce qui a déjà été fait.

Comme le lecteur pourra le constater, plusieurs travaux tentent de pallier aux lacunes de la technologie CAM. Plusieurs proposent des modifications à la cellule de base de la CAM permettant une réduction de sa consommation, souvent au détriment d'une autre métrique comme le délai de l'opération ou encore l'aire de silicium. D'autres proposent des solutions logicielles ou architecturales. Les différentes solutions seront tout d'abord décrites. Ensuite, le présent projet sera situé par rapport aux autres travaux, permettant ainsi au lecteur d'identifier sa contribution exacte.

#### 1.1 Modifications à la cellule de base de la CAM

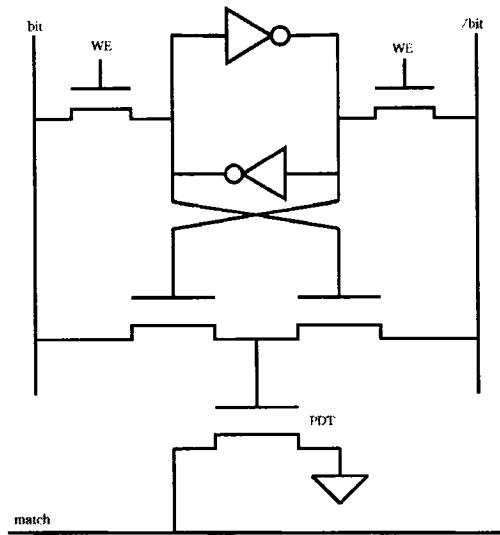

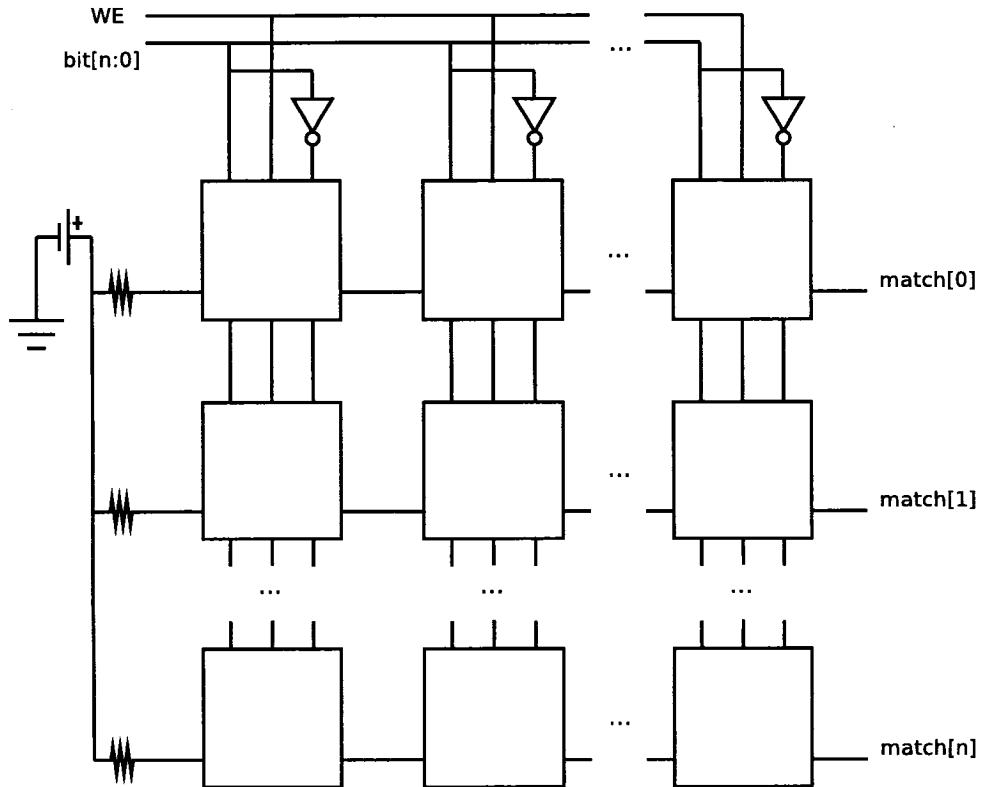

Une grande portion des efforts investis pour pallier au problème de consommation de la technologie CAM est centrée sur la cellule de base mémorisant un bit de CAM.

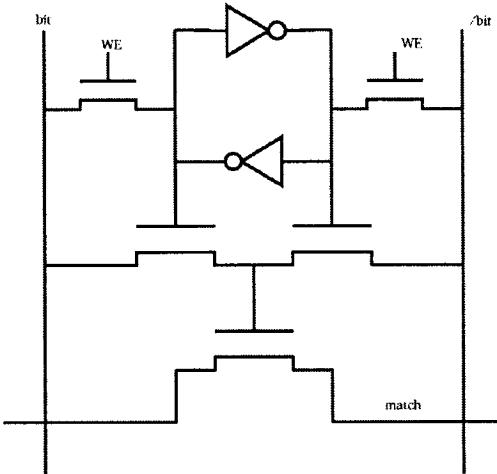

La Fig. 1.1 illustre une cellule de base typique d'une unité CAM. Elle est composée d'une cellule SRAM jumelée à une porte XOR dont la sortie contrôle une résistance de rappel vers le niveau bas, le PDT (*pulled down transistor*). Si un bit en entrée, représenté à la Fig. 1.1 par les valeurs complémentaires bit et /bit, n'est pas

Figure 1.1 Cellule CAM de base

identique à la valeur en mémoire, le PDT sera activé et le signal *match* sera amené à la terre. Sinon, le signal *match* sera dans un état HZ (haute impédance). Le signal WE (write enable), si activé, permettra à la donnée d'être écrite à la cellule SRAM.

Une unité de CAM dispose les cellules en mosaïque en joignant les signaux *WE*, */bit*, *bit* et *match* des cellules voisines. La valeur par défaut du signal *match* est obtenue à l'aide d'un simple mécanisme de résistance de rappel vers le niveau haut. Le signal *match* d'une rangée donnée sera dans l'état HZ si et seulement si toutes les cellules de base de la rangée contiennent une valeur identique à leur bit d'entrée respectif. La matrice résultante est illustrée à la Fig. 1.2.

Le désavantage principal de la cellule décrite ci-haut se situe au niveau du déchargement fréquent du signal *match* au travers du PDT. En effet, le signal *match* se décharge pour toutes les rangées contenant une portion étiquette non identique à la donnée présente en entrée. Plusieurs projets ((Natarajan 2003),(Efthymiou, 2002), (Pa-

Figure 1.2 Mosaïque de cellules de CAM.

giamtzis 2004),(Delgado-Frias 2005),(Liu 2001)) ont entrepris de modifier la cellule de base de la CAM dans le but de minimiser sa consommation. Par exemple, Lin (Lin, 2003) a tenté de réduire au minimum le nombre de cellules avec un PDT actif. Il propose la cellule illustrée à la figure 1.3 dans laquelle les sorties complémentaires de la cellule SRAM sont inversées par rapport à celles de la figure 1.1. Ainsi, le transistor présent sur le signal *match* sera actif si le bit en entrée est identique à celui contenu en mémoire. Une configuration “NAND” est obtenue en liant à la terre le signal *match* à l’entrée de la première cellule et en plaçant une résistance de rappel vers le signal haut à la sortie. Le signal *match* obtenu sera ainsi à la terre si et seulement si la rangée contient un champ étiquette identique à la donnée

recherchée.

Figure 1.3 Cellule CAM de base proposée par Lin (Lin, 2003)

Dans cette configuration, seules les rangées contenant un mot identique à celui présenté en entrée posséderont un signal *match* déchargé à la terre. Il en résulte une réduction de la consommation au détriment d'un plus grand délai. En effet, en disposant les portes de façon serielle, il en résulte un réseau de portes de transmission dont le délai est proportionnel au carré du nombre de portes (Savaria 1988). Cet inconvénient limite la largeur des rangées de CAM pour lesquelles la configuration serielle représente une solution adéquate. Zukowski (Zukowski 1997) propose à cet effet une solution intermédiaire qui laisse le choix à l'usager de la configuration exacte.

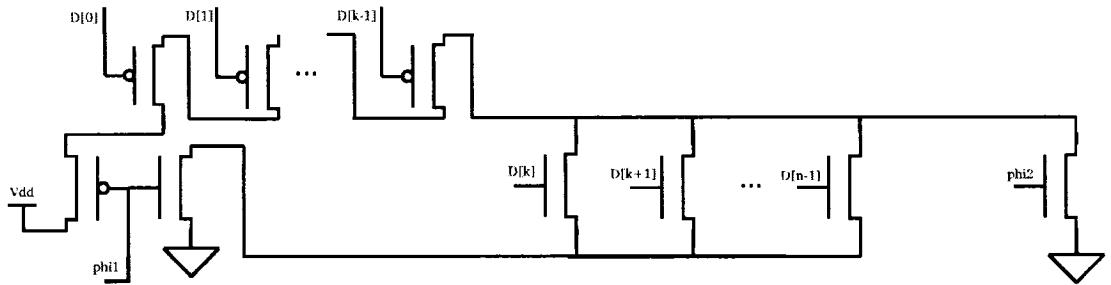

La figure 1.4 présente une configuration qui permet au concepteur de limiter les effets de la sérialisation des portes sur le délai. En effet, il est libre de disposer  $k$  portes de façon serielle et les autres, en parallèle. De cette façon, le signal *match* ne pourra être déchargé qu'en la présence d'une comparaison partielle réussie puisque le signal *match* ne sera préchargé que si les bits  $D_0$  à  $D_{k-1}$  sont tous identiques à leur bit d'entrée respectifs. Le concepteur est ainsi libre de définir le meilleur

Figure 1.4 La précharge sélective est un compromis entre la latence et la consommation proposé par Zukowski (Zukowski 1997).

compromis entre la consommation et le délai.

## 1.2 Modifications Architecturales

L'intégration à un design d'une unité de CAM optimisée à l'aide d'une modification à la cellule de base n'est pas une tâche simple. En effet, il est tout d'abord nécessaire que cette cellule soit intégrée à un compilateur de CAM pour que celui-ci puisse générer l'unité de CAM optimisée. En ce sens, il est plus simple et surtout plus rapide d'intégrer à un design une unité de CAM optimisée à l'aide de modifications faites au niveau architectural.

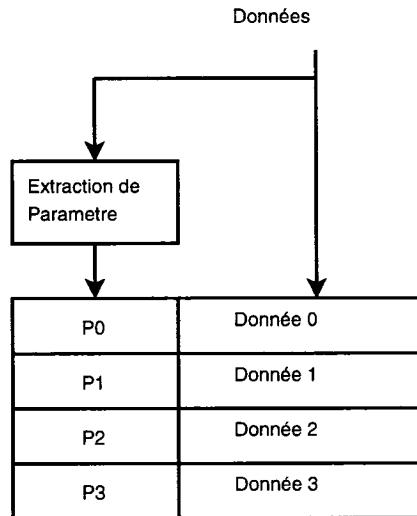

Lin et Chang (Lin 2000) proposent une architecture en plusieurs points similaires à celle présentée dans cet ouvrage. Elle rajoute aux rangées de la CAM une clé de hashing, appelée "paramètre" par les auteurs, obtenue en appliquant une fonction de hashing choisie par le concepteur sur la donnée à conserver en mémoire. La figure 1.5 illustre cette architecture. Chaque rangée de la CAM est ainsi composée du paramètre et de la donnée à conserver. Les comparateurs sont conçus de façon à tout d'abord comparer le paramètre et ensuite n'effectuer la comparaison de la donnée que si la comparaison du paramètre est réussie. Puisque le paramètre est

choisi de façon à être beaucoup plus petit que la donnée, il en résulte une économie du nombre moyen de bits comparés à chaque accès.

Figure 1.5 Lin et Chang (Lin 2000) proposent de comparer la donnée seulement si la comparaison du paramètre est réussie.

Certains chercheurs (Kartalopoulos 1998) suggèrent aussi d'utiliser des unités de RAM en mode “correspondance directe” pour émuler le comportement d'une CAM. Cette méthode consiste à associer une donnée à l'adresse égale à cette même donnée. Les avantages de cette méthode sont évidents, puisqu'elle permet d'obtenir des performances de la CAM avec des unités issues de la technologie RAM. Toutefois, un nombre limité d'applications se prêtent à ce genre d'architecture. En effet, la correspondance directe nécessite une entrée disponible en RAM pour chaque élément qu'il est possible de rencontrer durant l'exécution de l'application. Par exemple, si l'application nécessite l'entreposage en CAM d'adresses IPv4, dont la taille est de 32 bits, la cellule de RAM se devrait alors de posséder  $2^{32}$  entrées. Le coût d'une telle cellule serait alors démesuré. Ce genre de design est donc réservé pour des applications possédant un domaine de données de taille restreinte. Par exemple, une application de traitement de paquets ATM, utilisant le champ de 12

bits VCI (*virtual circuit identifier* ou le champs de 16 bits VPI *virtual path identifier* comme clés de recherche, serait un bon candidat.

Certains chercheurs ont identifié le hashing (Sedgewick 2002) comme étant un outil très efficace pour pallier à ce problème. Cette technique consiste à utiliser la correspondance directe, mais avec une clé de hashing agissant comme indice, plutôt qu'avec la donnée à insérer. Il s'agit d'ailleurs d'un processus utilisé fréquemment dans des systèmes de cache utilisant la technologie RAM (Hennessy 2003). Le problème propre au hashing se situe au niveau des collisions. Dépendamment des besoins de l'application, il peut être acceptable ou non de rejeter certaines données à insérer.

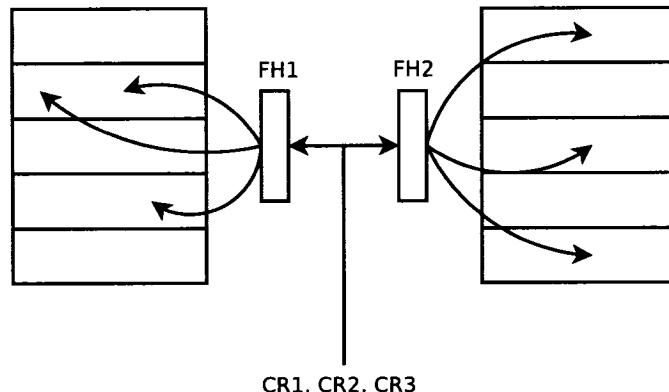

Plusieurs méthodes sont utilisées pour gérer les collisions. Par exemple, Seznec (Seznec 1993) propose une architecture de hashing multiple dans le cadre d'une unité de mémoire cache. La figure 1.6 illustre le tout.

Figure 1.6 Seznec (Seznec 1993) propose un système de cache avec deux fonctions de hashing pour minimiser les collisions.

L'architecture illustrée à la figure 1.6 comporte deux bancs de cache, chacun étant composé d'une unité de RAM et d'un bloc réalisant la fonction de hashing. Lors d'une insertion, les bancs sont accédés selon un ordre de priorité. Ainsi, une inser-

tion ne sera faite dans le second banc que s'il y a collision dans le premier. De plus, s'il y a collision dans le second banc, une certaine logique se chargera de gérer la situation, rejetant une des trois données en jeu selon un algorithme prédéfini. La présence de deux fonctions de hashing distinctes permet à un groupe d'éléments qui entrent en collision dans un banc de cache d'avoir de fortes probabilités de pouvoir être tous contenus dans le second.

L'architecture des caches "skewed associative" n'est pas sans rappeler celles des caches associatifs par ensembles. La principale différence se situe au niveau du nombre de fonctions de hashing utilisées. En effet, les bancs de mémoire des caches associatifs par ensembles utilisent une fonction de hashing commune qui consiste généralement en une simple extraction de bits. Bien que ces fonctions de hashing ne soient pas reconnues comme étant les meilleures (Jain 1992), ils ont l'avantage de diminuer la consommation de mémoire de l'architecture. En effet, puisque il est possible de récupérer les bits extraits de la clé de recherche à l'aide de la clé de hashing, seuls les bits non-extrai ts de la clé de recherche doivent être conservés en mémoire.

Certains chercheurs ont quant à eux exploré les différentes possibilités qui permettraient d'optimiser le taux de réussite des insertions. Lim (Lim 2002) propose d'ajouter une table de débordement, qui saurait contenir les éléments causant des collisions pour l'une et l'autre des fonctions de hashing.

La figure 1.7 illustre le cheminement possible d'un élément à insérer dans l'architecture mémoire. Tout d'abord, l'insertion est tentée à l'adresse spécifiée par la première clé de hashing. Dans le cas d'une collision, elle est tentée à nouveau à l'adresse spécifiée par la deuxième clé de hashing. Finalement, s'il y a échec aux deux adresses, l'élément est inséré dans une table de débordement. Lim (Lim 2002) propose d'avoir recours à une unité de CAM pour la réalisation de celle-ci. Lors d'une

Figure 1.7 Lim (Lim 2002) propose une table de débordement utilisant la technologie CAM pour conserver les données qui n'ont pas pu être insérées.

opération de recherche, trois accès mémoire sont effectués simultanément: deux en mémoire RAM aux adresses spécifiées par les clés de hashing, et une en mémoire CAM. Un circuit logique simple se charge alors de diriger vers la sortie la donnée associée à l'accès réussi s'il y en a un.

Le concept du hashing multiple n'est pas nouveau en soi. Broder (Broder, 1990) a proposé un processus similaire réalisé en logiciel. Cet algorithme consiste en une solution au problème des collisions propre au hashing. L'application réservait un certain nombre de tables et chaque insertion était tentée successivement dans une table après l'autre jusqu'à ce qu'elle soit réussie. Broder propose cependant une technique de re-hashing dans le cas où une insertion cause une collision dans chacune des tables. Cette technique consiste à redéfinir les fonctions de hashing pour que l'ensemble des données puissent être contenues dans les tables. Évidemment, cette technique est très difficilement réalisable en matériel.

Quelques autres pistes architecturales ont été explorées dans le cadre de différents projets. Meribout (Meribout 2003) a conçu une architecture reconfigurable reprenant certains éléments du Cell Processor de IBM. Tarassenko (Tarassenko 1991) a pour sa part étudié la possibilité d'émuler le comportement de la technologie CAM à l'aide de réseaux neuronaux.

### 1.3 Positionnement du projet

Les projets de recherche décrits ci-haut proposent des méthodes permettant de réduire certains aspects du coûts de la CAM au détriment d'autres métriques. Comme le lecteur a été en mesure de le constater, la majorité des chercheurs se sont concentrés sur le problème de consommation de la CAM. Les pistes proposées consistent essentiellement en des modifications à la cellule de base de la CAM ou encore en des architectures ayant recours au hashing et à la technologie RAM.

Les solutions avancées représentent des pistes de solution intéressantes. Toutefois, les modifications à la cellule de base de la CAM doivent d'abord être intégrées à un compilateur de CAM avant de pouvoir être intégrées à un design. Ces designs sont ainsi inaccessibles tant et aussi longtemps qu'un concepteur de compilateur de CAM ne les supporte pas.

En ce qui concerne les solutions ayant recours à la technologie RAM et aux techniques de hashing, elles peuvent être facilement intégrées à un design. Leur lacune se situe toutefois dans la rigidité de leur design. Ces alternatives peuvent représenter des solutions très intéressantes, mais seulement pour un ensemble d'applications restreint. En effet, ces designs, tels qu'ils sont présentés, sont inaptes à s'adapter aux besoins très variables des applications. Par exemple, l'architecture de Lim (Seznec 1993) possède deux modules, contenant chacun une clé de hashing et

une unité de mémoire RAM. Certaines applications nécessitent assurément un plus grand nombre de bancs de mémoire. Et pour ce qui est de la table de débordement suggérée par Lim (Lim 2002), la présence d'un bloc de CAM, si petite soit-elle, va à l'encontre d'un des objectifs premiers du présent projet qui est de contourner les frais non-récurrents exigés par les vendeurs de CAM.

Le présent projet retient les avantages des solutions proposant le recours à des bancs de mémoire combinant hashing et technologie RAM, tout en laissant au concepteur le soin de configurer l'architecture selon une granularité très fine en fonction des besoins exacts de son application. En effet, le concepteur pourra décider du nombre de bancs de mémoire et de la taille des cellules de RAM intérieures aux bancs.

Le présent projet offre une méthode facile et rapide d'intégrer à un design une solution alternative à la CAM. Il permet d'obtenir un comportement équivalent à la CAM tout en diminuant la consommation d'énergie et les frais de licences. Ces frais peuvent même être considérés nuls si on assume que les frais associés à la licence d'un compilateur RAM ainsi qu'à un outil de synthèse sont déjà amortis.

## CHAPITRE 2

### SYNTHÈSE DES TRAVAUX

#### 2.1 Mise en Contexte

Dans le but de concevoir une architecture permettant de réaliser en un seul cycle les opérations d'insertion et de recherche, nous examinons d'abord les différents algorithmes de recherche habituellement associés au domaine du logiciel. Le but de l'exercice est d'étudier la possibilité de réaliser en matériel un de ces algorithmes qui saurait offrir les performances recherchée, ou encore une variante de celui-ci.

Tableau 2.1 Performance des principaux algorithmes de recherche.

|                        |                  |

|------------------------|------------------|

| Recherche Séquentielle | $\theta(n)$      |

| Arbres Binaires        | $\theta(\log n)$ |

| Arbre Balancé          | $\theta(\log n)$ |

| Recherche par Racine   | $\theta(\log n)$ |

| Correspondance Directe | $\theta(1)$      |

| Hashing                | $\theta(1)$      |

| Mémoires CAM           | $\theta(1)$      |

Le tableau 2.1 présente la performance offerte par les principaux algorithmes de recherche, tels que présentés dans la référence (Sedgewick 2002). Il est facile de constater que seuls les algorithmes de hashing et de correspondance directe sont en mesure de rivaliser avec les performances des CAMs. Toutefois, comme il a été mentionné dans la section précédente, la correspondance directe n'est qu'un cas particulier de l'algorithme de hashing qui ne peut être utilisé que pour certaines applications. L'algorithme de hashing apparaît comme étant le candidat le plus prometteur.

L'algorithme de hashing possède des opérations d'insertion et de recherche de complexité  $\theta(1)$ . Lors d'une opération d'insertion, les données à insérer (les clés de recherche) sont utilisées pour générer l'indice de la table auquel sera effectué l'insertion (la clé de hashing). L'opération de recherche effectue un processus analogue. La comparaison sera faite entre la donnée recherchée et celle présente dans la table à l'indice correspondant à la clé de hashing générée à partir de la donnée recherchée. La fonction de hashing se charge de générer les clés de hashing de manière déterministe. Par exemple, si une fonction de hashing se définit comme effectuant l'extraction des bits 9 à 15 de l'adresse source d'un paquet IPv4, alors tous les paquets provenant de l'adresse "192.168.123.456" seront insérés à l'entrée 123 de la table.

Il est toutefois possible que deux clés de recherche soient associées à une seule et même clé de hashing. Lorsque cette situation survient, on dit qu'il y a collision. Il existe plusieurs méthodes pour gérer les collisions, mais elles nécessitent toutes un nombre d'accès supplémentaires potentiellement grand à la mémoire (Sedgewick 2002).

Le choix du hashing est prometteur, mais la réalisation matérielle se devra de gérer les cas de collision de manière efficace. Lim et Jung (Lim 2002) proposent une approche fort intéressante en ce sens. Celle-ci présente une architecture de hashing parallèle supportant une collision par table et possédant une table de débordement, accueillant les éléments qui n'ont pu être insérés dans les autres tables. Les opérations d'insertion et de recherche sont exécutées en un cycle. Elle tire ainsi profit du parallélisme et des caractéristiques de la technologie RAM pour obtenir des performances équivalentes à celles offertes par la technologie CAM. Il s'agit d'une alternative intéressante qui présente toutefois deux inconvénients majeurs. Tout d'abord, elle ne répond aux besoins que d'un ensemble très restreint d'applications. Sa configurabilité est faible, voire nulle. De plus, elle peut difficile-

ment être considérée comme alternative complète à la CAM, puisqu'elle y a recours pour réaliser la table de débordement. Les coûts non-récurrents de la technologie CAM ne peuvent donc pas être évités.

## 2.2 Description de l'Architecture

L'architecture présentée dans le cadre du présent projet de recherche reprend quelques concepts à la base de l'architecture présentée par (Lim 2002) sans toutefois figer sa configuration. Elle innove en ce sens qu'elle permet au concepteur de définir sa forme exacte pour répondre de façon optimale aux besoins de l'application. Son plus grand avantage se situe toutefois au niveau de l'absence de toute présence de technologie CAM. En effet, l'architecture de (Lim 2002) a recours à une CAM pour la réalisation de la table de débordement. Même si celle-ci est de petite taille, sa seule présence ajoute les frais de licences au coût total du design.

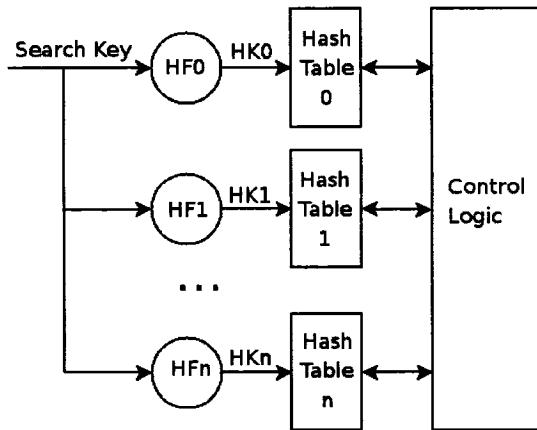

La figure 2.1 présente l'architecture proposée. Elle permet au concepteur de choisir une configuration éliminant toute possibilité d'échec, ou la réduisant à une valeur négligeable, faisant de l'architecture une alternative de choix pour combler les lacunes de la CAM.

L'architecture consiste en une fonction de hashing associée à chaque table de hashing en plus d'un bloc de logique de contrôle. Lors d'une insertion, la fonction de hashing génère une clé de hashing pour chaque table. L'insertion est alors faite à la table possédant la priorité la plus élevée parmi celles qui ne donnent pas lieu à une collision. Pour ce qui est des opérations de recherche, toutes les tables sont accédées en parallèle. Chacune d'elles compare la donnée accédée à la clé de recherche fournie par l'usager, et envoie le résultat de la comparaison accompagnée par la donnée accédée à la logique de contrôle. Celle-ci filtre les données reçues et

Figure 2.1 Architecture proposée

dirige vers la sortie la donnée accédée par la table à laquelle il y a eu une comparaison réussie. Si aucune table ne signale une comparaison réussie, la logique de sortie signale que l'opération de recherche a échoué.

En plus de laisser tomber la table de débordement pour les raisons décrites ci-haut, l'architecture se distingue de celle décrite par Lim et Jung en (Lim 2002) aussi par l'absence du concept de réservoir (*buckets*). En effet, le concept n'a pas été considéré afin de simplifier le problème en lui enlevant une de ses variables. À première vue, des gains de performance semblables à ceux réalisés par les réservoirs pouvaient très bien être obtenus en modifiant d'autres paramètres architecturaux sans nécessairement avoir à payer davantage. Une analyse plus poussée est nécessaire est donc nécessaire pour déterminer s'il d'agit d'un avantage ou d'une limitation. La plus grande différence par rapport à l'architecture décrite en (Lim 2002) réside toutefois au niveau de la configurabilité. L'architecture proposée laisse le soin à l'usager de définir le nombre de couches de l'architecture, tout en lui fournissant les outils pour estimer les performances du système en fonction de l'utilisation de l'application. Le concepteur peut ainsi atteindre les performances que requièrent une application donnée, sans avoir à débourser davantage.

### 2.3 Évaluation de Performances

Le besoin d'un modèle d'évaluation de performances pour cette architecture provient du fait qu'il est possible qu'une tentative d'insertion résulte en un échec. Cette possibilité est nulle avec la technologie CAM tant et aussi longtemps que l'unité CAM n'est pas remplis à capacité. La présente étude aborde la quantification de performances selon deux métriques: le taux d'échec et la probabilité d'échec des tentative d'insertion.

Le taux d'échecs est défini comme étant le rapport entre le nombre d'insertions résultant en un échec par rapport au nombre de tentatives d'insertion effectuées. Quant à la probabilité d'échec associée à chaque insertion, l'architecture offre des performances qui se dégradent progressivement. Cet aspect fait contraste avec les unités CAM qui acceptent de nouvelles données jusqu'à ce que leur capacité soit atteinte. À ce moment, chaque tentative d'insertion résulte en un échec. Cette différence peut être considérée comme un avantage ou comme un inconvénient, dépendamment de l'application.

Les différentes configurations de l'architecture sont définies à partir de trois paramètres: le nombre de couches, la capacité totale de l'architecture et le taux d'utilisation. À ces paramètres seront respectivement associés les symboles  $L$ ,  $C$  et  $\alpha$  dans le cadre des documents relatifs à ce projet de recherche. Le taux d'utilisation,  $\alpha$ , est défini comme étant le rapport entre le nombre de données qu'une application vise à emmagasiner dans l'architecture par rapport à la capacité totale de l'architecture.

Le modèle de performances démontre que l'architecture proposée peut offrir des performances de n'importe quel ordre de grandeur, dépendamment de la configuration dans laquelle elle était utilisée. Dans une configuration minimaliste, elle peut agir comme une simple table de hashing avec toutes les limites qu'on lui

connaît. À l'opposé, dans une configuration dégénérée, dans laquelle chaque table est de capacité unitaire, elle peut reproduire les performances exactes d'une unité de CAM.

Il est important de noter que le modèle de performance considère les fonctions de hashing comme étant idéales. Une fonction de hashing idéale disperse de façon parfaitement aléatoire les clés de hashing générées et ce, indépendamment des clés de recherche lues. Dans le cadre d'une application d'aiguillage de paquets par exemple, une fonction de hashing idéale briserait tout lien de corrélation présent dans l'ensemble des adresses réseau actives. Ce genre de corrélation est reconnue comme étant omniprésente et source de plusieurs problèmes de performance dans des designs comme celui-ci. Il s'agit d'une simplification qui nécessite une attention particulière par un concepteur qui considère utiliser l'architecture. La littérature identifie certains algorithmes de CRC comme étant ceux se rapprochant le plus de la définition des fonctions de hashing idéales (Jain 1992). L'implantation faite dans le cadre du présent projet utilise un algorithme de CRC sans toutefois apporter de justifications supplémentaires quant à son choix.

La première constatation se trouve au niveau du taux d'échecs d'une simple table de hashing. Celui-ci semble être constant pour un nombre donné de tentatives d'insertion faites sur des éléments distincts. Lorsque le nombre de tentatives d'insertion est égal à la capacité de l'architecture ( $\alpha = 1.0$ ), le taux d'échecs est de 0.63, une valeur se rapprochant étrangement de  $1 - e^{-1}$ . Il reste à savoir comment l'ajout de couches et des variation au paramètre  $\alpha$  influencent cette valeur de taux d'échecs. C'est une des questions à laquelle tente de répondre le premier article.

## 2.4 Implantation de l'Architecture

Pour ce qui est de l'implantation de l'architecture, nous avons d'abord examiné la possibilité d'avoir recours à un processeur à instructions spécialisées: le XTensa V de Tensilica. Cette voie semblait très prometteuse, d'autant plus que le GRM possède une certaine expertise en la matière ainsi que les licences nécessaires pour utiliser les outils de Tensilica. Le design initial consistait en quelques instructions "TIE" réalisant la fonction de hashing et la logique de contrôle, le tout interagissant avec les unités RAM présentes sur le processeur. Il s'agissait d'un design idéal qui permettait de réaliser l'architecture en logiciel. Toutefois, les contraintes techniques du XTensa ont compliqué les choses. En effet, la cadence du processeur combinée à la quantité maximale de RAM sur la puce ainsi que la taille maximale du bus mémoire limitaient la configurabilité de l'architecture, que l'on voulait sans limite.

L'idée de recourir à des instructions spécialisées n'a pas été écartée immédiatement. Un second design d'implantation a été considéré. Il consistait à sortir du XTensa les tables de hashing et la logique de comparaison. Lors d'une opération de recherche, les instructions spécialisées se chargeaient d'abord d'évaluer les clés de hashing qui étaient transférées à notre ASIC en compagnie de la clé de recherche fournie par l'usager. Les tables de hashing étaient accédées et les données obtenues, comparées à la clé de recherche. Les résultats de la comparaison étaient retournés au processeur qui se chargeait du reste de la logique. Les instructions d'insertion représentaient une plus grande complexité dans ce design puisque le processeur devait initier une deuxième communication avec le ASIC pour lui indiquer l'indice de la table à laquelle devait avoir lieu l'insertion. La présence de deux blocs de logique permettait un certain parallélisme, mais ajoutait toutefois une grande complexité supplémentaire. Encore une fois, ce design a été écarté en raison d'une spécification technique du processeur XTensa. En effet, la largeur maximale de son port IO lim-

ite le nombre de clés de hashing qu'il était possible de transférer du processeur vers le ASIC en un cycle. La configurabilité de l'architecture se voyait encore une fois réduite.

Il a donc été décidé que l'implantation de l'architecture allait se passer de toute forme de processeur et se faire sur un ASIC. Cette décision impliquait l'ajout d'un autre volet à la comparaison avec la technologie CAM, celle du coût en aire d'un bit. En effet, il était pertinent de déterminer si à taille égale, il en coûtait moins d'avoir recours à une unité de l'architecture de hashing parallèle plutôt qu'à une unité de CAM. Si cette hypothèse était validée, il serait alors possible d'affirmer que sans même considérer les coûts non-récurrents de la technologie CAM, l'architecture de hashing parallèle offrait des performances équivalentes à un coût moindre.

## 2.5 Résumé de l'article

Tout d'abord, les technologies RAM et CAM sont comparées selon différentes métriques. La comparaison révèle que le coût d'aire de silicium en  $mm^2/Mbit$  de la CAM est 2 fois supérieur à celui de la RAM, que sa consommation lui est entre 4 fois supérieure. La comparaison faite au niveau de la latence ne montre qu'un léger avantage. La comparaison des métriques ne révèle toutefois qu'une partie de la vérité puisque les frais de licence exigés par les vendeur d'unité issus de la technologie CAM représentent les coûts les plus importants.

L'article définit le comportement interne de l'architecture, permettant au concepteur de la reproduire avec la technologie et les outils qu'il désire. Il aborde ensuite le thème des performances. Pour ce faire, il a été nécessaire de réaliser un simulateur “from scratch” qui reproduisait le comportement de l'architecture. Il est important que l'analyse de ses résultats soit mise en contexte avec l'hypothèse des fonctions

de hashing idéales. En effet, le simulateur implante cette hypothèse à l'aide d'un générateur de nombres aléatoires au niveau des adresses utilisées, éliminant ainsi toutes corrélation possible et permettant à une fonction de hashing très simple de générer des clés de hashing réparties uniformément.

Le simulateur a été utilisé pour illustrer la variation des performances de l'architecture selon un certain nombre de configurations possibles. Les résultats obtenus permettent d'illustrer le comportement exponentiel du décroissement du taux d'échecs lorsque le nombre de couches augmente ainsi que de son accroissement alors que le taux d'utilisation augmente. Ces illustrations fournissent les bases de connaissances aux concepteur désireux de configurer l'architecture en fonction des spécifications d'une application donnée.

L'article fournit de plus une description du comportement de la probabilité d'échec de l'architecture en fonction de l'indice de la tentative d'insertion selon un certain nombre de configurations. L'aspect progressif de la dégradation des performances de l'architecture est un élément clé de leur analyse. En effet, une augmentation du nombre de couches diminue le rythme de l'accroissement de la probabilité d'échec, reportant ainsi l'atteinte d'une valeur non-négligeable à un indice d'insertion plus élevé. Le concepteur peut ainsi juger approprié d'augmenter le nombre de couches tout en diminuant la capacité totale de l'architecture tout en conservant l'atteinte d'une probabilité d'échec critique à un indice d'insertion constant.

Les résultats de simulation illustrent efficacement le comportement de l'architecture selon les différentes configurations dans lesquelles elle peut se trouver. Par contre, elles ne permettent pas d'identifier les configurations menant à des taux d'échecs inférieures à  $10^{-4}$  en raison des temps de simulation trop grands. Or, pour plusieurs applications, un taux d'échecs non-négligeable n'est tout simplement pas acceptable. Pour résoudre ce problème, une première approche étudiée fut de déployer

le simulateur sur une architecture de type “cluster”. Cette stratégie aurait permis d’atteindre des ordres de grandeur intéressants. Il était toutefois plus efficace et précis de modéliser de façon analytique le comportement du système pour pouvoir obtenir les métriques de performances de manière analytique. C’est cette dernière approche qui est élaborée dans la seconde publication.

L’article abord ensuite quatre nouveaux thèmes. Il définit d’abord le modèle analytique, pour ensuite présenter une méthodologie pour définir la configuration optimale d’une application donnée. Les métriques de l’implantation faite sur ASIC sont ensuite présentées. Finalement, certaines optimisations mettant l’emphase sur certaines métriques de performance ou de coût au détriment de certaines autres sont décrites.

Le modèle analytique se base sur l’hypothèse de distribution uniforme des clés de hashing, qui assigne une probabilité de  $1/m$  à chaque entrée d’une table d’être associée à une clé de recherche donnée où  $m$  représente la taille de chaque table. Elle affirme que la probabilité qu’une entrée d’une table soit occupée est égale à  $1 - P_0$ , où  $P_0$  est égal à la probabilité que cette entrée n’ait été associée à aucune clé de recherche sur laquelle une tentative d’insertion a été effectuée antérieurement. Ces données sont suffisantes pour estimer  $P_0$  à l’aide d’une variable aléatoire de Poisson, et permettent ainsi de définir le taux d’occupation local à une table comme étant  $1 - e^{-\alpha}$ . Le taux d’occupation global est ainsi facilement obtenu à l’aide d’une relation de récurrence qui définit le nombre de tentatives d’insertions faite sur une table donnée à partir du nombre de collisions qui ont eu lieu à la table précédente. Cette valeur combinée au nombre de tentatives d’insertion faites dans l’architecture globale permet d’obtenir le taux d’échecs de manière analytique.

En fixant un des paramètres de la configuration et à partir d’un taux d’échecs cible visé par une application, cette méthode permet d’identifier l’autre paramètre

permettant d'atteindre le taux d'échecs visé. Pour les applications ne supportant pas un taux d'échecs non-nul, une règle du pouce utilisée régulièrement est de considérer comme étant négligeable la présence d'un échec durant 10 ans d'utilisation continue de l'application. Cette règle combinée par exemple avec une fréquence d'événements de 100 MHz mène à un taux d'échecs de l'ordre de  $3.171 \times 10^{-16}$ . Cette valeur était inaccessible par le simulateur. Seul le modèle analytique nous permet de l'atteindre.

Théoriquement, il est possible d'identifier une infinité de configurations menant à un taux d'échecs donné. Il est donc à l'avantage d'un concepteur d'identifier la configuration possédant le plus faible coût de production parmi celles menant aux performances visées. L'article propose ainsi une méthode pour effectuer cette tâche. La première étape consiste à définir un modèle de coût à partir des technologies et autres variables propres au projet du concepteur. Ensuite, la méthode amène le concepteur à obtenir la courbe iso de la surface de performance obtenue à l'aide du modèle analytique associant un taux d'échecs à chaque configuration possible. Le minimum de la courbe paramétrique résultant de la projection de la courbe iso sur la surface de coût représente ainsi le coût minimal qu'il est nécessaire de débourser pour atteindre les performances visées.

L'article présente ensuite un aperçu des métriques obtenues grâce à l'implantation de l'architecture réalisée à l'aide d'outils VLSI. L'utilisation d'un compilateur de cellules RAM a permis d'obtenir des métriques performantes et sur lesquelles il est possible de baser une analyse sérieuse. L'implantation a d'ailleurs eu recours à quelques éléments de la librairie *DesignWare* de Synopsys. La réutilisation de ces blocs réduit l'influence que la qualité du concepteur a sur les métriques obtenues tout en augmentant leur reproductibilité.

La table 2.2 présente le résumé des métriques obtenues suite à la réalisation VLSI

de l'architecture. Les métriques sont assez révélatrices. Elle montrent entre autres qu'à capacité égale, l'aire de la cellule de CAM est 2 fois plus grande, et qu'elle consomme 4 fois davantage d'énergie. Il est normal que ces données soient similaires à celles issues de la comparaison avec la technologie RAM puisque les cellules de RAM occupent plus de 98% de l'aire totale de l'architecture.

Tableau 2.2 Comparaison des métriques de la réalisation VLSI de l'architecture proposée avec une cellule CAM commerciale. Métrique issues de la technologie 180nm et évaluées avec une fréquence d'opération de 200MHz.

| Architecture de Hashing Parallèle | Portion Occupée par les RAMs | CAM    | Facteur CAM / HP |

|-----------------------------------|------------------------------|--------|------------------|

| Aire ( $mm^2/Mbit$ )              | 8.02                         | 98.10% | 19.2             |

| Puissance ( $mW/Mbit$ )           | 309                          | 68.8%  | 1454             |

Il est d'ailleurs intéressant de noter que peu importe le type de contraintes d'optimisation imposée à l'outil de synthèse, l'aire du design final sera occupée en très grande majorité par les cellules de RAM. Faire passer la fréquence d'horloge maximale d'une valeur inférieure à 40 MHz à une valeur supérieure à 200 MHz augmente l'aire de la logique combinatoire par un facteur de 40%. Par contre, la portion occupée par cette logique est tellement faible par rapport à l'aire totale que ces modifications n'ont pratiquement aucune influence sur l'aire totale et sur la portion occupée par les cellules RAM, qui elles occupent plus de 98% du design. Il est intéressant de noter que plus de 65% de la période d'horloge optimale est consommée par les accès parallèles aux cellules de RAM. Il serait ainsi possible d'obtenir une fréquence d'horloge beaucoup plus grande en ayant recours à des cellules de RAM plus rapides. La table 2.3 illustre la situation.

Finalement, l'article présente trois optimisations applicables à l'implantation originale. Tout concepteur se doit de les considérer et de les évaluer en fonction des besoins de l'application.

L'implantation initiale utilise des cellules RAM ne possédant qu'un seul port de lecture et d'écriture. Elle est considérée comme étant "multicycle" puisqu'elle réalise les opérations de lecture en un cycle et celles d'écriture, en deux. Cet aspect est reconnu comme étant source de maints problèmes de synchronisation. La première optimisation résout cet inconvénient en ayant recours à des cellules RAM possédant deux ports. Elle cache le second cycle des opérations d'écriture en utilisant le deuxième port des cellules de RAM pour réaliser l'insertion en mémoire, seule opération effectuée dans le second cycle d'une opération d'insertion. Il apparaît ainsi à l'usager que l'architecture est prête à réaliser une nouvelle opération dès le cycle suivant. Cette optimisation permet d'augmenter le débit des opérations et de diminuer leur latence moyenne. Il en résulte aussi une augmentation de l'aire de sillicium requise et de la consommation d'énergie. En effet, les cellules RAM à deux ports consomment davantage que les cellules RAM à port unique et occupent près du double de leur aire.

La seconde optimisation consiste à pipeliner le design pour ainsi atteindre un débit d'opérations plus grand. La période d'horloge serait définie par l'opération atomique la plus lente, soit l'accès aux cellules de RAM, qui dans notre cas demande 2,8ns. Le pipeline nécessiterait un étage de pré-traitement et un de post-traitement en plus de l'étage d'accès aux mémoires. Cette optimisation, combinée à à la

Tableau 2.3 La diminution de la période d'horloge d'influence pas la portion de l'aire occupée par les cellules de RAM.

| Période d'horloge (ns) | Aire Totale (sq $\mu$ m) | Aire de la logique Combinatoire (sq $\mu$ m) | Portion occupée par les RAMs |

|------------------------|--------------------------|----------------------------------------------|------------------------------|

| 26.98                  | 1,699,135                | 22,955                                       | 98.65%                       |

| 9.48                   | 1,699,518                | 23,338                                       | 98.63%                       |

| 4.35                   | 1,704,266                | 28,086                                       | 98.35%                       |

| 4.27                   | 1,707,043                | 30,863                                       | 98.19%                       |

| 4.24                   | 1,708,629                | 32,449                                       | 98.10%                       |

précédente, permettrait d'atteindre un débit supérieur à  $350 \times 10^6$  opérations par seconde.

La troisième et dernière optimisation permet de minimiser la consommation de puissance de l'architecture en effectuant les recherches dans les couches non plus de façon simultanée, mais bien de façon séquentielle. Les couches sont rassemblées en groupes et ces groupes sont accédés les uns après les autres. Pour des valeurs de  $\alpha < 1$ , les tables supérieures contiennent un nombre d'éléments plus grand que les tables inférieures. Il est ainsi plus probable de retrouver un élément recherché dans une des premières tables plutôt que dans un des dernières. Puisque les tables qui ne sont pas accédées ne consomment pas, il en résulte une économie de consommation de puissance. Cette économie est évidemment réalisée aux dépens d'une augmentation de la latence moyenne.

## CHAPITRE 3

### RÉALISATION VLSI DE L'ARCHITECTURE

#### 3.1 Méthodologie

Pour réaliser l'implantation VLSI de l'architecture, l'équipe a choisi de développer en parallèle ses modèles VHDL et SystemC et d'avoir recours à un simulateur mixte. Cette façon de faire permet de définir les cas de tests en SystemC, de les exécuter sur les deux modèles, de valider le modèle VHDL en comparant son comportement avec celui du modèle SystemC. Les deux modèles sont considérés valides si leur comportement est identique pour l'ensemble des tests. Une fois cette étape franchie, le modèle synthétisé se doit à son tour passer la batterie de tests pour s'assurer qu'aucune contrainte de délai n'est violée.

#### 3.2 Description Comportementale