**Titre:** Circuits analogiques intégrés programmables basés sur des matrices de transconductances

Title: matrices de transconductances

**Auteur:** Eric Lebel

Author:

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Lebel, E. (2006). Circuits analogiques intégrés programmables basés sur des matrices de transconductances [Master's thesis, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7718/>

Citation:

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7718/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan

Advisors:

**Programme:** Unspecified

Program:

UNIVERSITÉ DE MONTRÉAL

CIRCUITS ANALOGIQUES INTÉGRÉS PROGRAMMABLES BASÉS SUR DES

MATRICES DE TRANSCONDUCTANCES

ERIC LEBEL

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

MARS 2006

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-17950-5

*Our file* *Notre référence*

ISBN: 978-0-494-17950-5

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

CIRCUITS ANALOGIQUES INTÉGRÉS PROGRAMMABLES BASÉS SUR DES

MATRICES DE TRANSCONDUCTANCES

Présenté par : LEBEL, Eric

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment acceptée par le jury d'examen constitué de :

M. Yvon Savaria, Ph.D., président

M. Mohamad Sawan, Ph.D., membre et directeur de recherche

M. Yves Audet, Ph.D., membre du jury

## **REMERCIEMENTS**

Je souhaite d'abord remercier le professeur Mohamad Sawan pour m'avoir donner la chance de travailler sur ce projet dans d'excellentes conditions au sein de l'équipe Polystim. Mes remerciements s'adressent aussi au professeur Ali Assi de la «United Arab Emirates University» pour sa précieuse collaboration.

Mes collègues de Polystim m'ont permis d'évoluer dans un cadre de travail très agréable par leur support et leur camaraderie. La disponibilité des secrétaires et des techniciens du GRM a aussi été très appréciée.

Je remercie également mes parents et ma copine Martine pour leurs encouragements tout au long de mes études.

Enfin, je suis reconnaissant envers le Conseil de Recherche en Sciences Naturelles et en Génie (CRSNG) pour la bourse qui m'était accordée ainsi que la Société Canadienne de Microélectronique (CMC Microsystems) pour le soutien matériel et logiciel ayant rendu possible la réalisation de ce projet.

## RÉSUMÉ

Les circuits programmables permettent de mettre au point des systèmes électroniques flexibles et des prototypes rapidement. Dans le monde numérique, les FPGA (Field Programmable Gate Array) sont maintenant largement utilisés et permettent l'implémentation de circuits numériques complexes sans que l'usager n'ait à se soucier des contraintes physiques des circuits intégrés. Du côté analogique, des circuits avec une telle polyvalence sont également recherchés et commencent à émerger sous la forme de FPAA (Field Programmable Analog Array). Ils constituent un champ de recherche actif et quelques modèles sont apparus sur le marché. Par contre, les performances notamment en bande passante sont pour le moment limitées.

Ce projet vise donc à réaliser des circuits analogiques programmables numériquement. Certains choix technologiques ont mené à l'utilisation de la technologie CMOS 0.18  $\mu\text{m}$  pour réaliser des circuits basés sur une matrice de cellules de transconductance (Gm). La majeure partie du projet porte sur un filtre programmable biquadratique passe-bas et passe-bande dont la fréquence centrale et le facteur de qualité sont programmables. La technique de programmation repose sur l'activation sélective de Gm en parallèle ainsi que l'utilisation de capacités programmables. Ce circuit intégré a été fabriqué et testé.

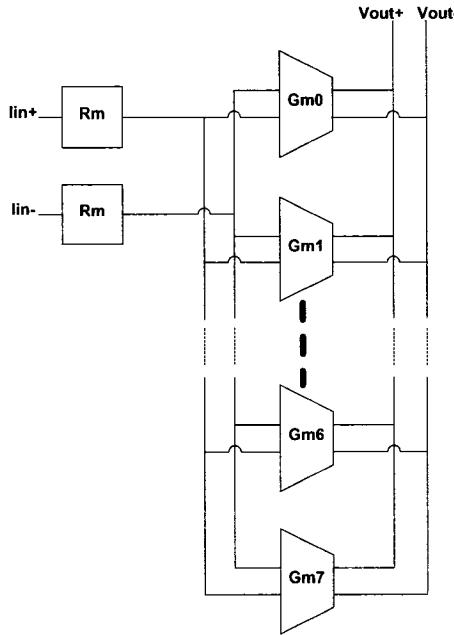

Dans le même ordre d'idées, un amplificateur de courant a été conçu et simulé. Des Gm en parallèle sont branchés à une cellule de transrésistance. L'activation sélective des Gm permet dans ce cas de programmer le gain de l'amplificateur.

Les simulations de même que les résultats expérimentaux ont permis de démontrer que la technique de programmation innovatrice permet la programmation des paramètres des circuits (fréquence centrale, largeur de bande, gain) sur une large plage.

## ABSTRACT

Programmable circuits allow for rapid prototyping of flexible electronic systems. In the digital world, FPGAs (Field Programmable Gate Arrays) are now widely used to implement complex digital circuits without needing the user to care about the physics of integrated circuits. On the analog side, circuits with such versatility are also wanted and are starting to emerge as FPAs (Field Programmable Analog Arrays). They represent an active research area and a few commercial devices have already entered the market. However, performances, especially bandwidth, are still limited at this time.

The goal of the project is to design analog circuits that are digitally programmable. Technological choices led us to design circuits based on a transconductors ( $G_m$ ) array using CMOS 0.18 $\mu m$  technology. The cornerstone of this project is a programmable biquadratic low-pass and band-pass filter. The center frequency and the quality factor of the filter are programmable parameters. The programming technique consists essentially in selectively activating transconductors connected in parallel. Programmable capacitors are also used for finer tuning. This circuit was fabricated and extensively tested.

In a similar fashion, a current amplifier was also designed and simulated. With a transresistance connected to parallel transconductors selectively activated, it is possible to program the amplifier gain.

Simulations and experimental results have demonstrated that the innovative programming technique is working properly to control circuits parameters (frequency, bandwidth, gain) over a wide range.

## TABLE DES MATIÈRES

|                                                                             |      |

|-----------------------------------------------------------------------------|------|

| REMERCIEMENTS .....                                                         | iv   |

| RÉSUMÉ.....                                                                 | v    |

| ABSTRACT .....                                                              | vi   |

| TABLE DES MATIÈRES .....                                                    | vii  |

| LISTE DES TABLEAUX.....                                                     | x    |

| LISTE DES FIGURES.....                                                      | xi   |

| LISTE DES ABRÉVIATIONS ET SYMBOLES.....                                     | xiii |

| LISTE DES ANNEXES .....                                                     | xv   |

| Chapitre 1 Introduction .....                                               | 1    |

| 1.1    Organisation du mémoire .....                                        | 3    |

| 1.2    Capacités commutés versus temps continu .....                        | 4    |

| 1.3    FPAAs commerciaux .....                                              | 6    |

| Chapitre 2 Aperçu des FPAAs et des architectures de transconductances ..... | 8    |

| 2.1    Introduction .....                                                   | 8    |

| 2.2    Architectures de circuits FPAAs.....                                 | 8    |

| 2.3    Transconductance (Gm) .....                                          | 13   |

| 2.3.1    Paire différentielle .....                                         | 15   |

| 2.3.2    Paires différentielles croisées .....                              | 15   |

| 2.3.3    Gm à base d'un transistor en triode.....                           | 16   |

| 2.3.4    Étage de sortie .....                                              | 17   |

| 2.4    Programmation de la transconductance.....                            | 18   |

| 2.4.1    Source de courant programmable.....                                | 18   |

|                                                               |                                                                                         |    |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|----|

| 2.4.2                                                         | Contrôle en tension .....                                                               | 19 |

| 2.4.3                                                         | Gm multiples.....                                                                       | 20 |

| 2.5                                                           | Transrésistance.....                                                                    | 20 |

| 2.5.1                                                         | Rm grille commune.....                                                                  | 21 |

| 2.5.2                                                         | Rm à 2 transistors.....                                                                 | 23 |

| 2.5.3                                                         | Rm à étages multiples .....                                                             | 24 |

| 2.6                                                           | Conclusion .....                                                                        | 25 |

| Chapitre 3 Filtres Gm-C hautes fréquences programmables ..... |                                                                                         | 26 |

| 3.1                                                           | Présentation de l'article .....                                                         | 26 |

| 3.2                                                           | PROGRAMMABLE MONOLITHIC GM-C BAND-PASS FILTER:<br>DESIGN AND EXPERIMENTAL RESULTS ..... | 27 |

| 3.2.1                                                         | Introduction.....                                                                       | 28 |

| 3.2.2                                                         | The band-pass filter architecture.....                                                  | 29 |

| 3.2.3                                                         | The filter results .....                                                                | 35 |

| 3.2.4                                                         | Conclusion .....                                                                        | 36 |

| 3.2.5                                                         | Acknowledgments.....                                                                    | 36 |

| 3.2.6                                                         | References.....                                                                         | 36 |

| 3.2.7                                                         | List of figures.....                                                                    | 38 |

| 3.2.8                                                         | List of tables.....                                                                     | 38 |

| 3.2.9                                                         | Figures.....                                                                            | 39 |

| 3.2.10                                                        | Tables.....                                                                             | 45 |

| Chapitre 4 Tests et validation de filtres programmables ..... |                                                                                         | 46 |

| 4.1                                                           | Traitemet de signaux différentiels .....                                                | 46 |

| 4.2                                                           | Carte de test.....                                                                      | 47 |

| 4.4                                                           | Divergences entre les résultats expérimentaux et de simulation .....                    | 50 |

| Chapitre 5 Amplificateur de courant programmable .....        |                                                                                         | 57 |

|                                                                    |                                     |    |

|--------------------------------------------------------------------|-------------------------------------|----|

| 5.1                                                                | Introduction.....                   | 57 |

| 5.2                                                                | Conception .....                    | 57 |

| 5.3                                                                | Résultats.....                      | 60 |

| 5.4                                                                | Conclusion .....                    | 64 |

| Chapitre 6 Discussion Générale, Conclusion et Recommandations..... |                                     | 65 |

| 6.1                                                                | Discussion Générale.....            | 65 |

| 6.2                                                                | Conclusion et Recommandations ..... | 66 |

| BIBLIOGRAPHIE.....                                                 |                                     | 68 |

## LISTE DES TABLEAUX

|                                                              |    |

|--------------------------------------------------------------|----|

| Table 3.1 Results summary .....                              | 45 |

| Table 3.2 Results comparisons.....                           | 45 |

| Tableau 4.1 Résumé comparatif du filtre Gm-C proposé .....   | 56 |

| Tableau 5.1 Résumé des performances de l'amplificateur ..... | 63 |

## LISTE DES FIGURES

|                                                                                                  |    |

|--------------------------------------------------------------------------------------------------|----|

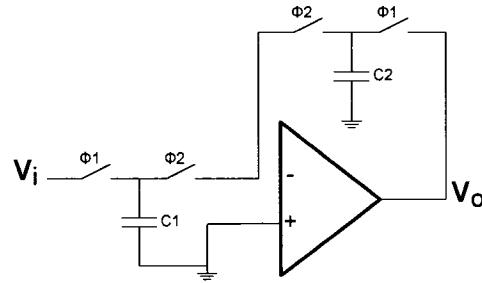

| Figure 1.1 Exemple de circuit à capacités commutées.....                                         | 5  |

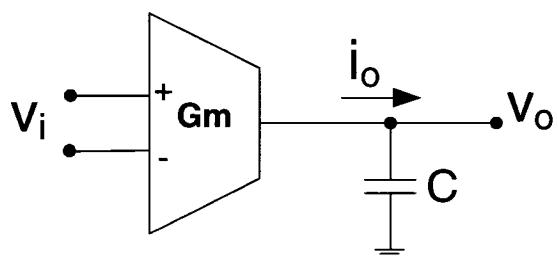

| Figure 1.2 Exemple de circuit en temps continu.....                                              | 5  |

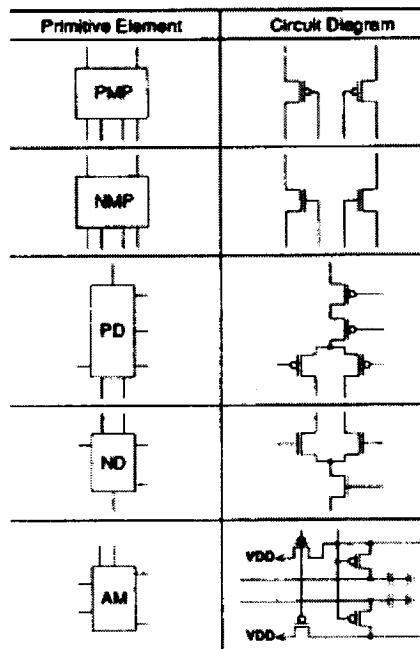

| Figure 2.1 Cellules de base du FPAA (Lee et Gulak, 1991).....                                    | 9  |

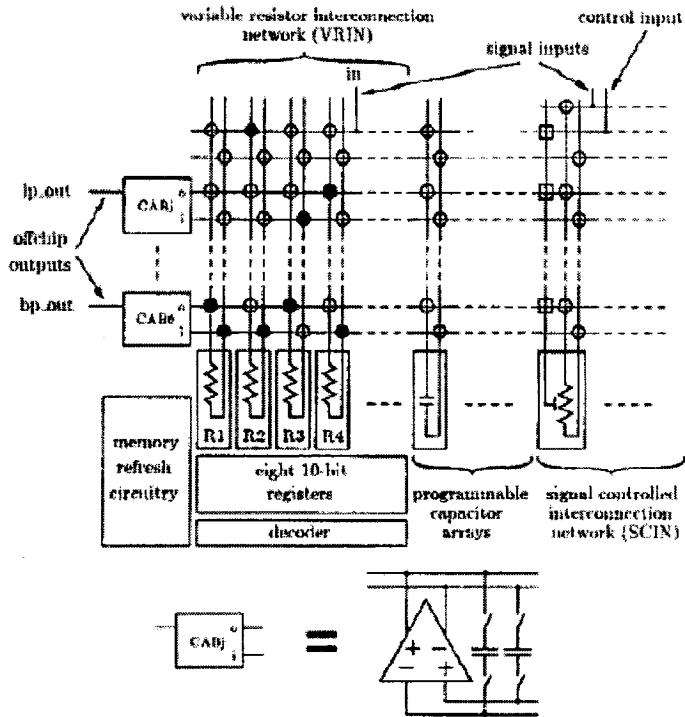

| Figure 2.2 Réseau d'interconnexions avec des résistances programmables (Lee et Gulak, 1995)..... | 10 |

| Figure 2.3 Transistor à grille flottante (Hall et al., 2005) .....                               | 11 |

| Figure 2.4 Disposition en nid d'abeille (Becker et al., Mai 2004) .....                          | 12 |

| Figure 2.5 Nombre de CAB limité (Lon-Kou et al, 2004) : a) schéma bloc b)CAB .....               | 13 |

| Figure 2.6 Paire différentielle.....                                                             | 15 |

| Figure 2.7 Paires différentielles croisées.....                                                  | 16 |

| Figure 2.8 Gm à base d'un transistor en triode .....                                             | 17 |

| Figure 2.9 Source de courant programmable .....                                                  | 19 |

| Figure 2.10 Topologie à grille commune .....                                                     | 21 |

| Figure 2.11 Rm grille commune et cascode .....                                                   | 22 |

| Figure 2.12 Deux transistors branchés en diode .....                                             | 23 |

| Figure 2.13 Deux transistors avec contre-réaction.....                                           | 24 |

| Figure 2.14 Rm à étages multiples .....                                                          | 25 |

| Figure 3.1 Proposed filter architecture .....                                                    | 39 |

| Figure 3.2 Programming logic building block .....                                                | 40 |

| Figure 3.3 Transconductance circuit .....                                                        | 40 |

| Figure 3.4 CMFB circuit .....                                                                    | 41 |

| Figure 3.5 Bias circuit .....                                                                    | 41 |

| Figure 3.6 Buffer circuit.....                                                                   | 42 |

| Figure 3.7 Programmable capacitor array .....                                                    | 42 |

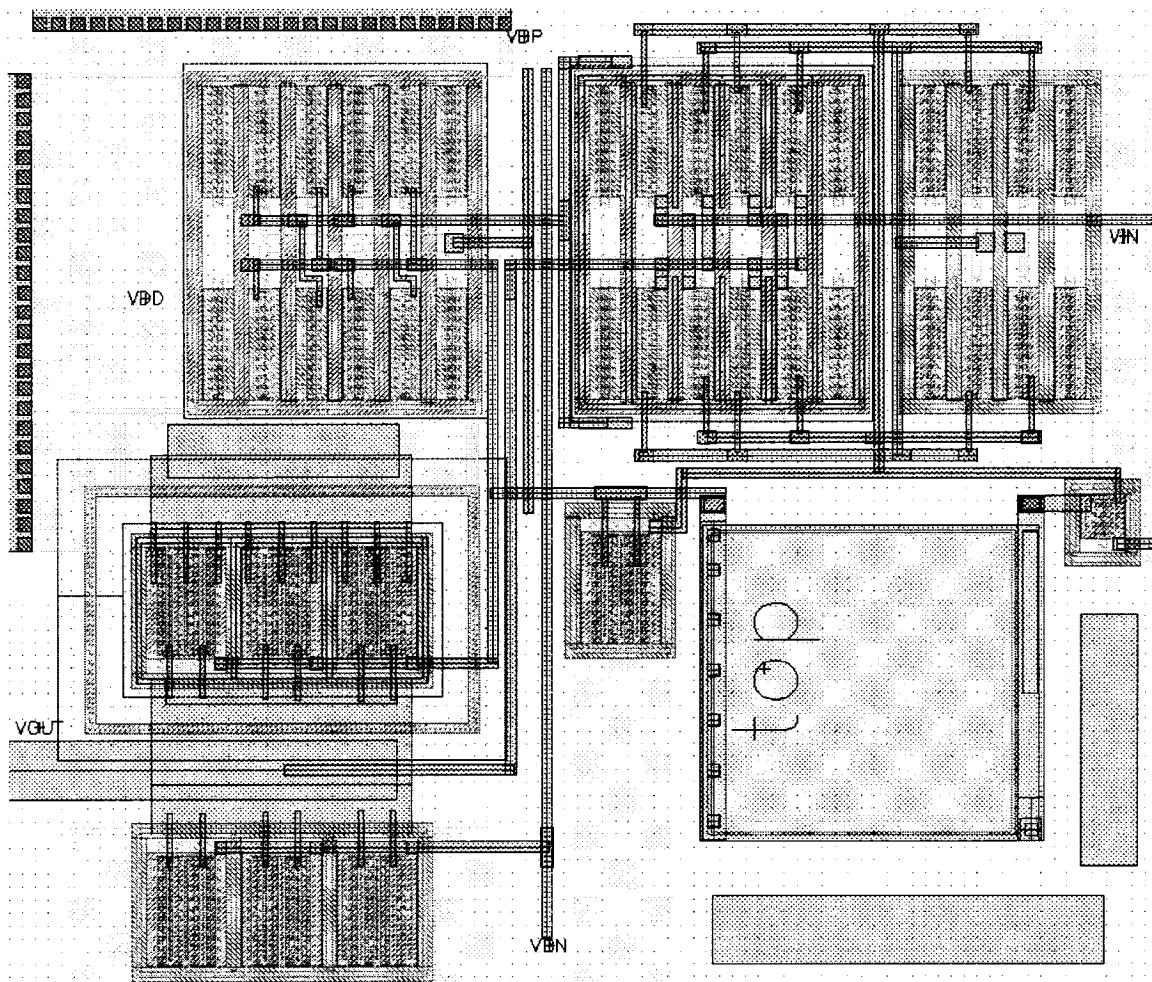

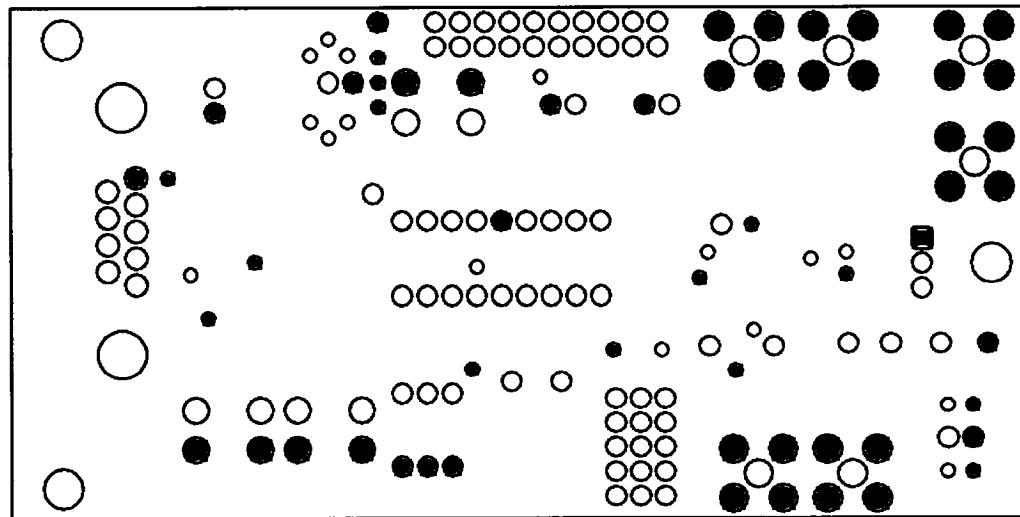

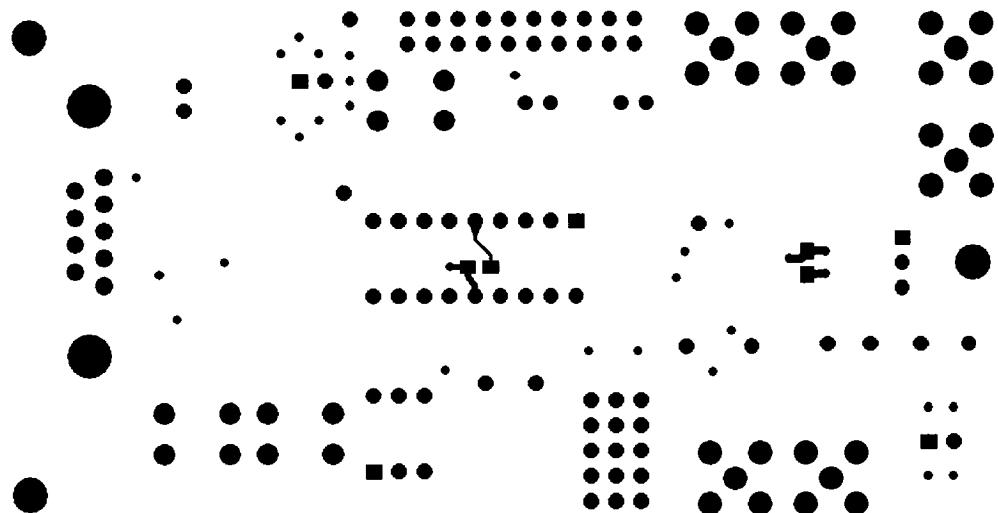

| Figure 3.8 Chip microphotograph .....                                                            | 43 |

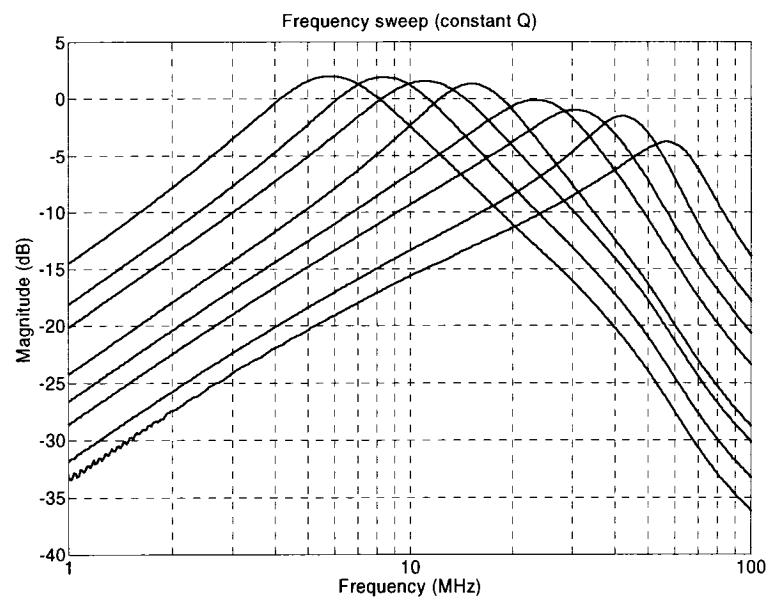

| Figure 3.9 Various frequency settings for constant quality factor .....                          | 43 |

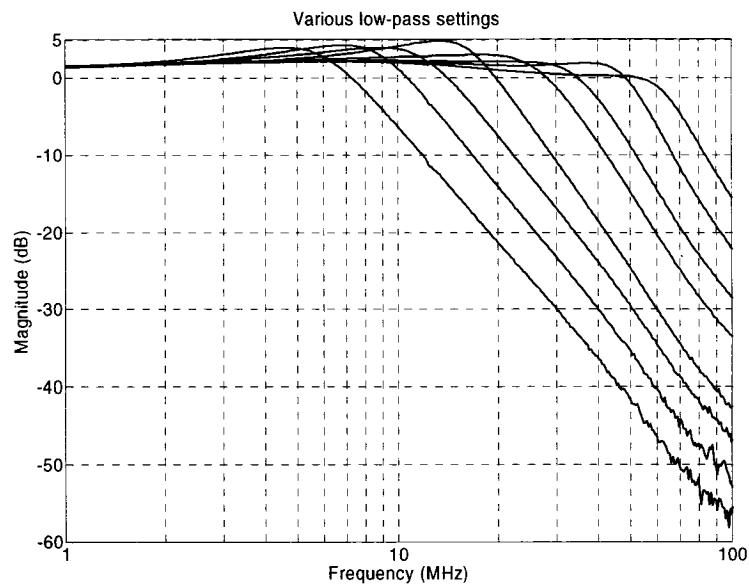

| Figure 3.10 Various low-pass settings .....                                                      | 44 |

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

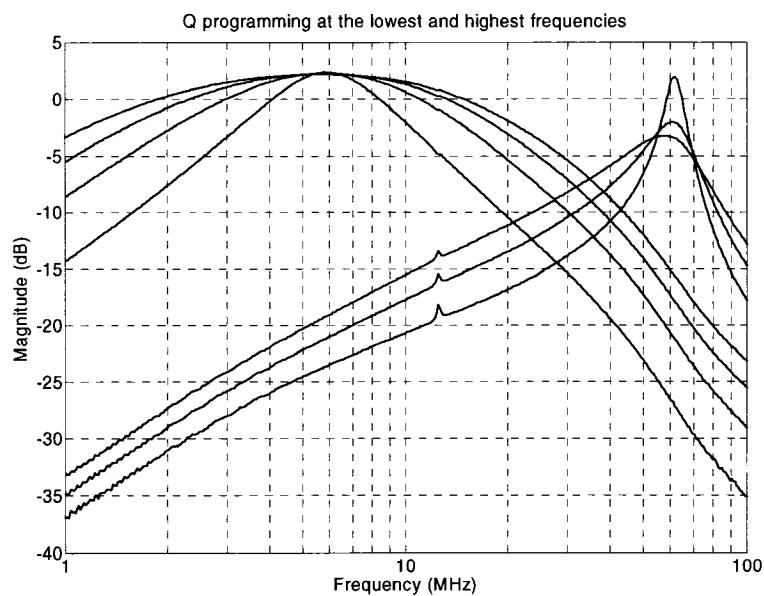

| Figure 3.11 Q programming at the lowest and highest frequencies.....                     | 44 |

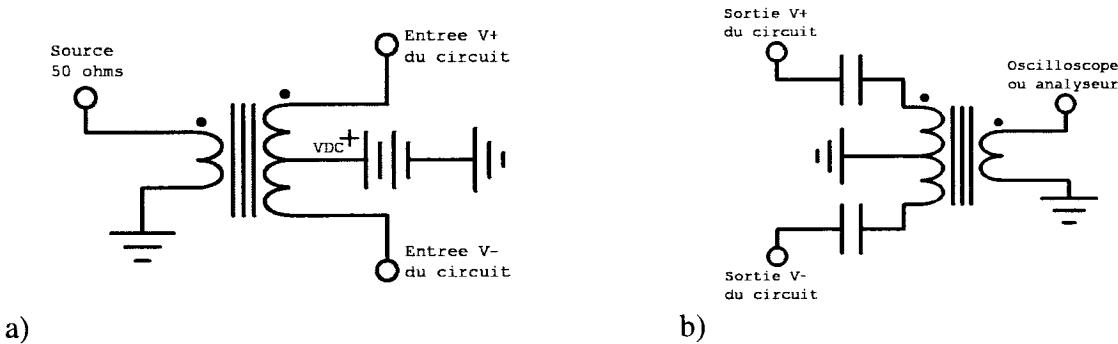

| Figure 4.1 Transformateurs haute-fréquence : a) entrée du circuit b) sortie du circuit.. | 47 |

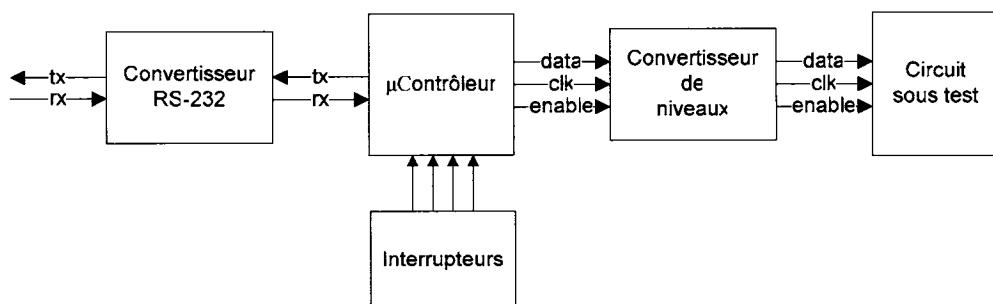

| Figure 4.2 Photo de la carte de test .....                                               | 48 |

| Figure 4.3 Schéma bloc de la carte de test .....                                         | 48 |

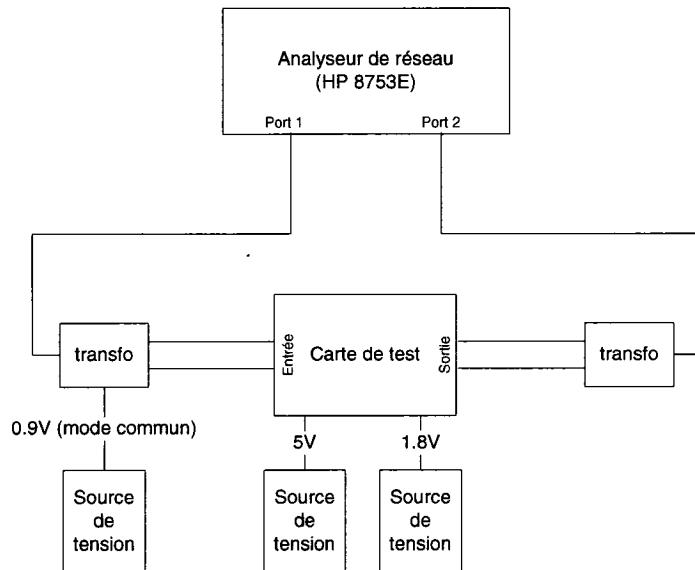

| Figure 4.4 Montage de test pour étude fréquentielle.....                                 | 49 |

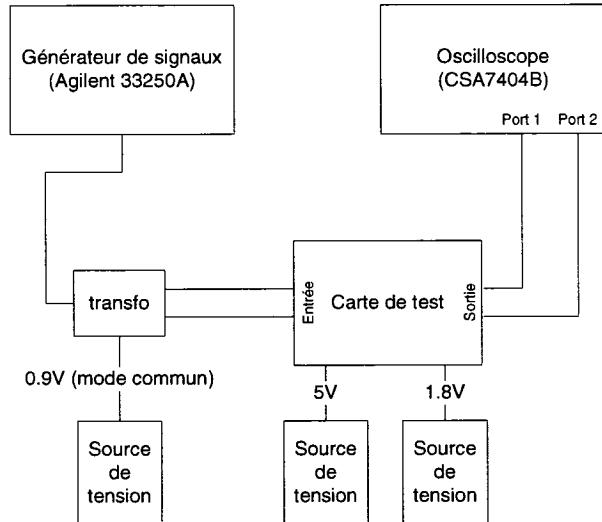

| Figure 4.5 Montage de test pour étude temporelle.....                                    | 50 |

| Figure 4.6 Balayage en fréquence à Q constant (simulation CMOSP18 V4.6) .....            | 51 |

| Figure 4.7 Balayage en fréquence à Q constant (simulation CMOSP18 V5) .....              | 52 |

| Figure 4.8 Simulation pour un facteur de qualité élevé (CMOSP18 V5) .....                | 53 |

| Figure 4.9 Résultats expérimentaux pour un facteur de qualité élevé .....                | 54 |

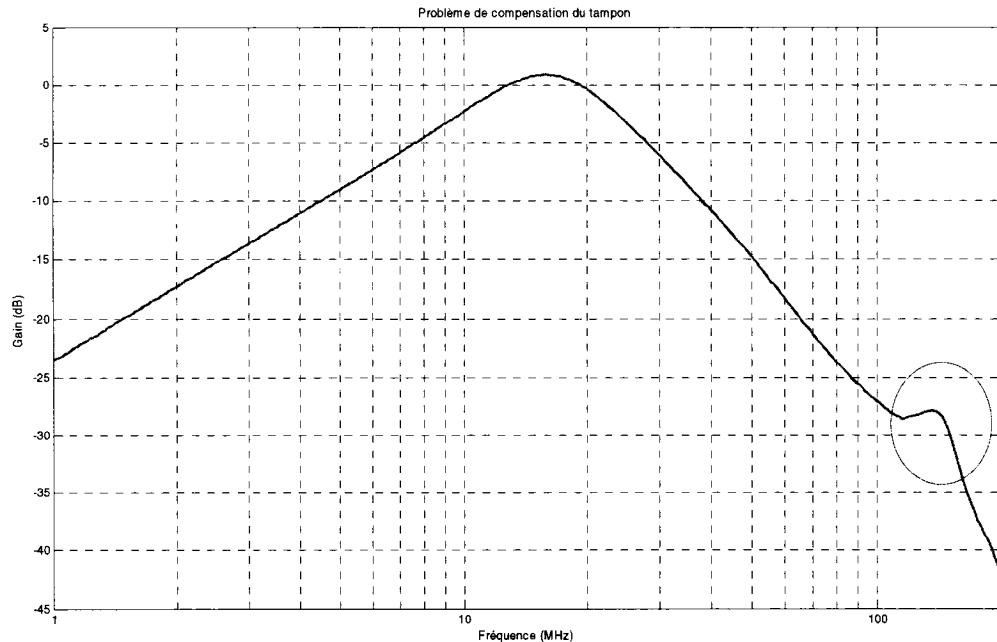

| Figure 4.10 Illustration des problèmes du tampon (expérimentale).....                    | 55 |

| Figure 5.1 Architecture de transrésistance choisie.....                                  | 58 |

| Figure 5.2 Architecture de l'amplificateur de courant.....                               | 60 |

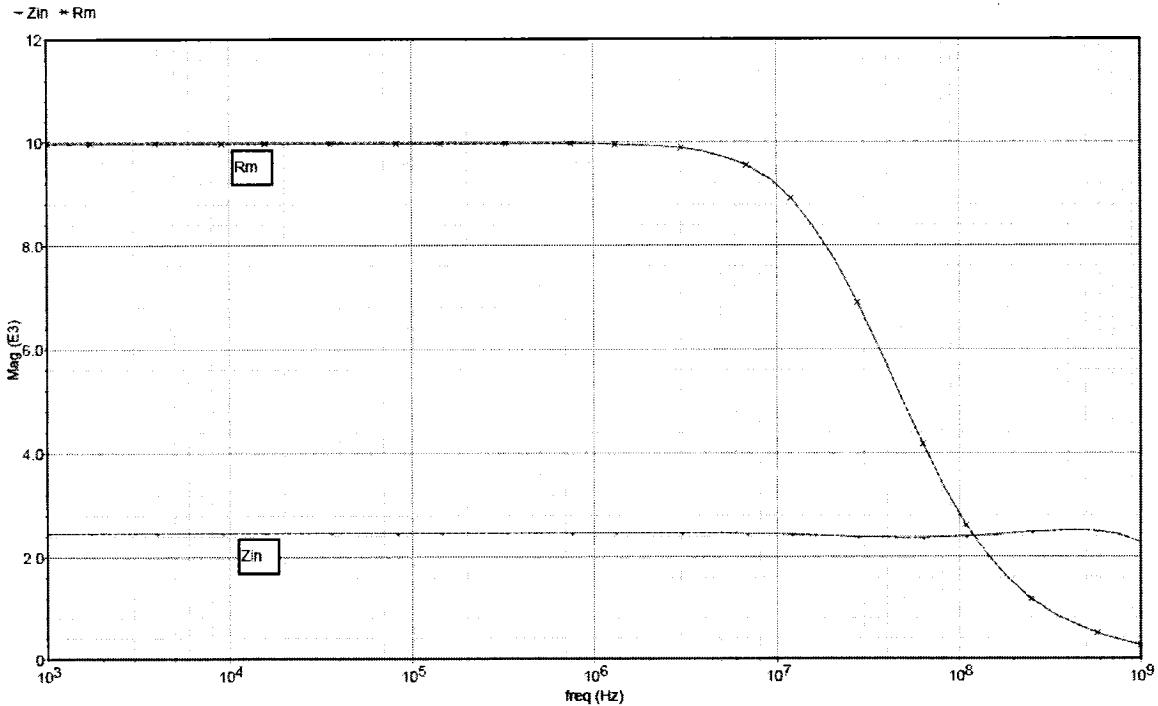

| Figure 5.3 Zin et Rm vs Fréquence .....                                                  | 61 |

| Figure 5.4 Gain vs Fréquence (8 configurations).....                                     | 62 |

| Figure 5.5 Gain/Phase vs Fréquence (4 Gm activés) .....                                  | 63 |

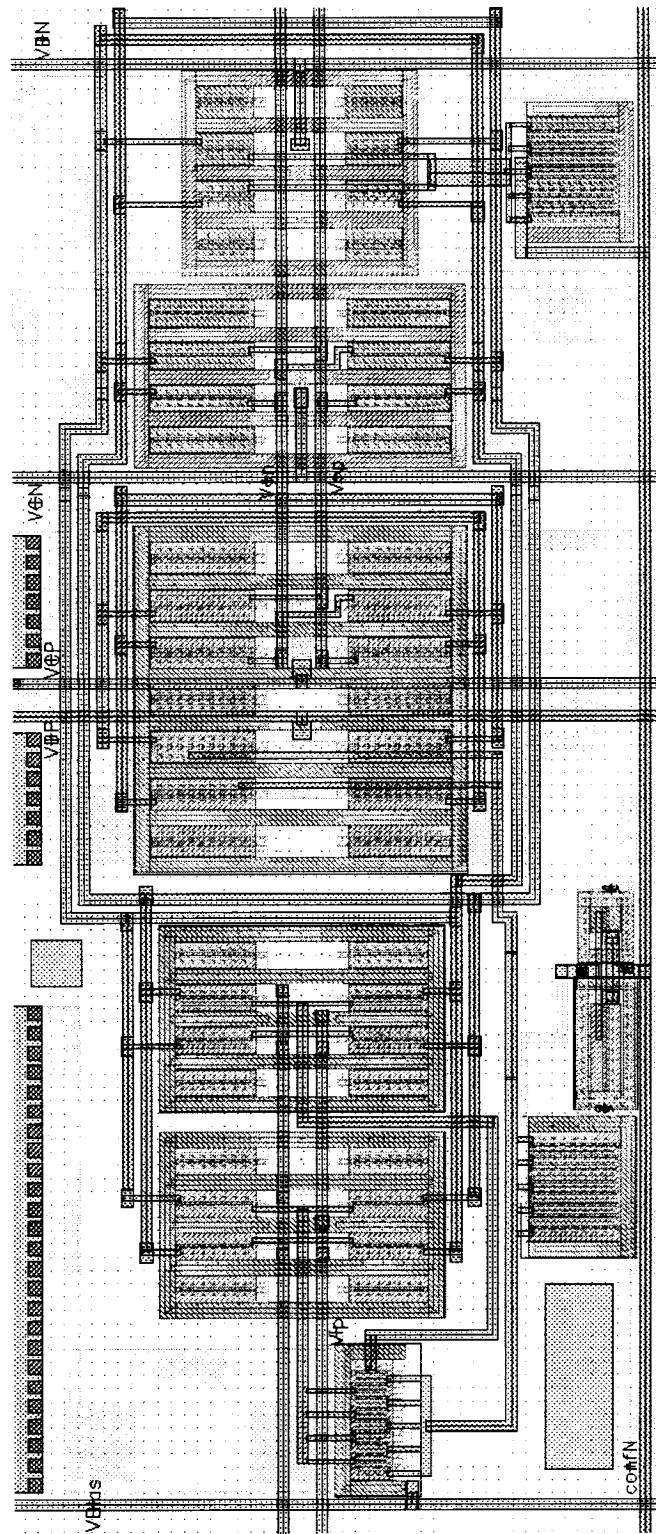

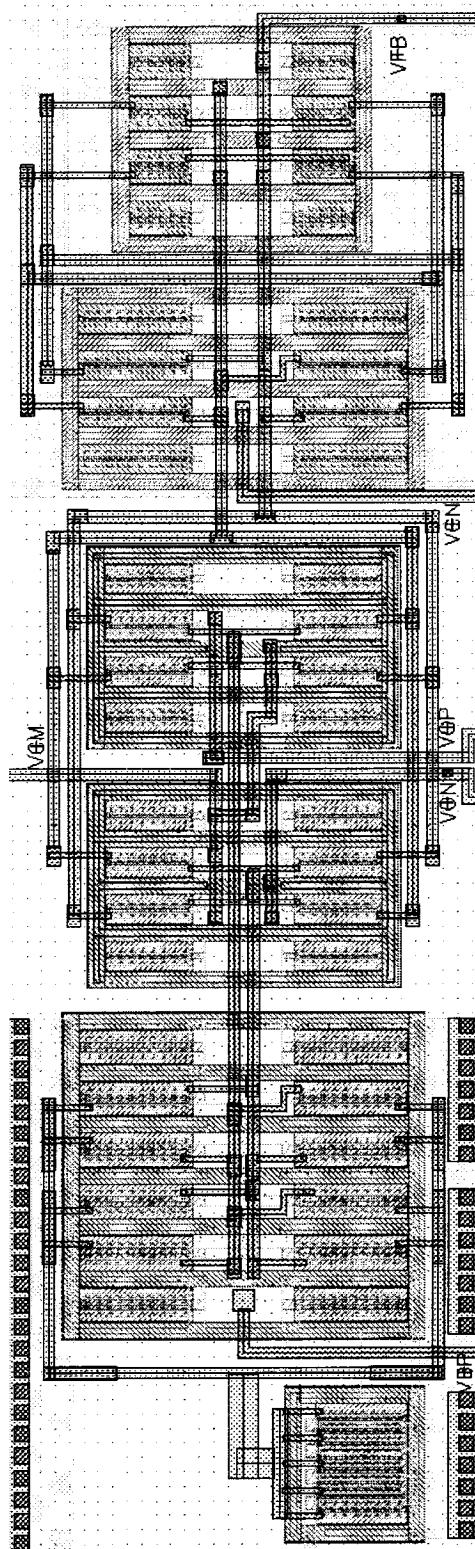

| Figure A.1 Dessin de masque du suiveur .....                                             | 71 |

| Figure A.2 Dessin de masque du Gm.....                                                   | 72 |

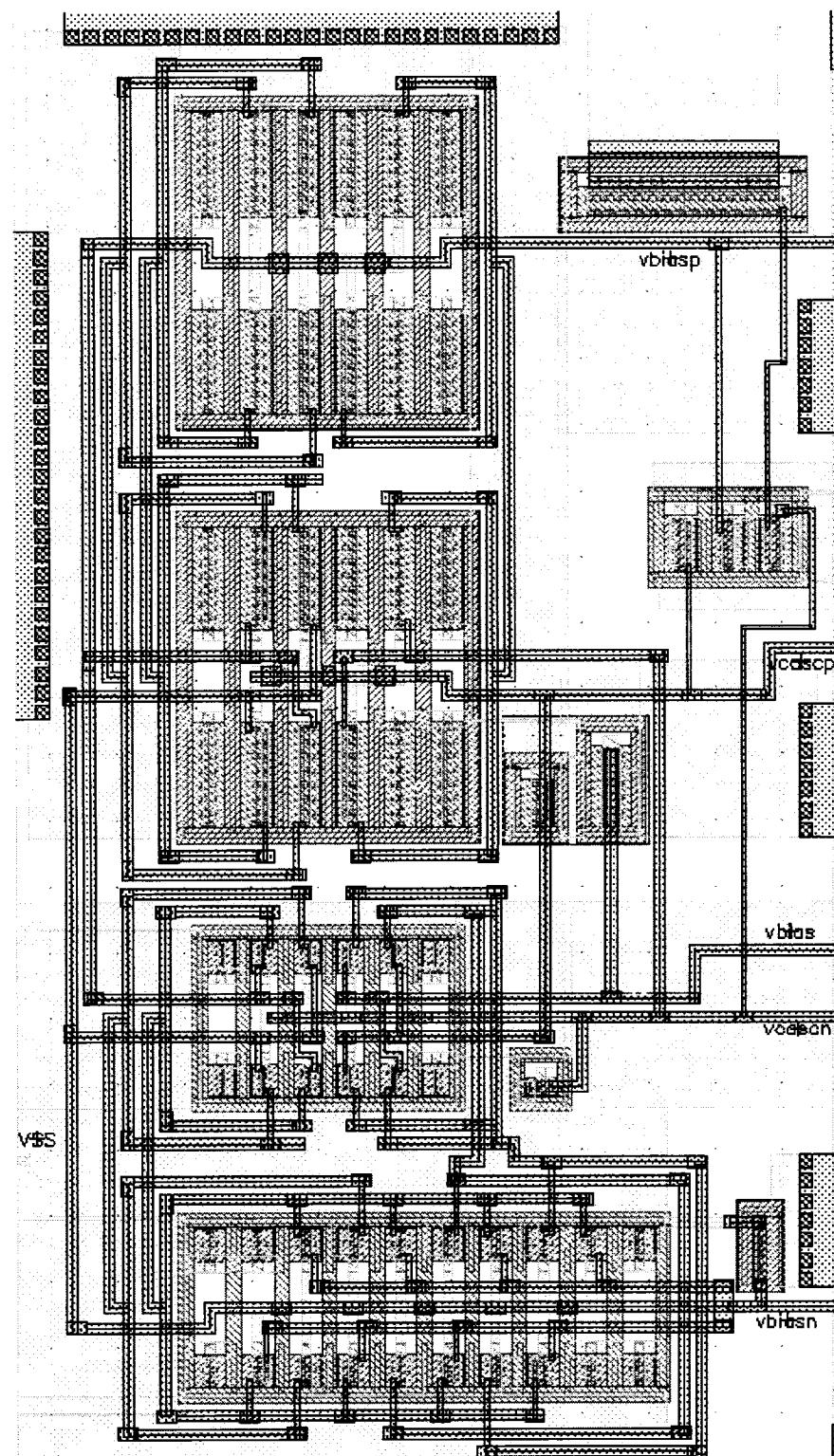

| Figure A.3 Dessin de masque du CMFB.....                                                 | 73 |

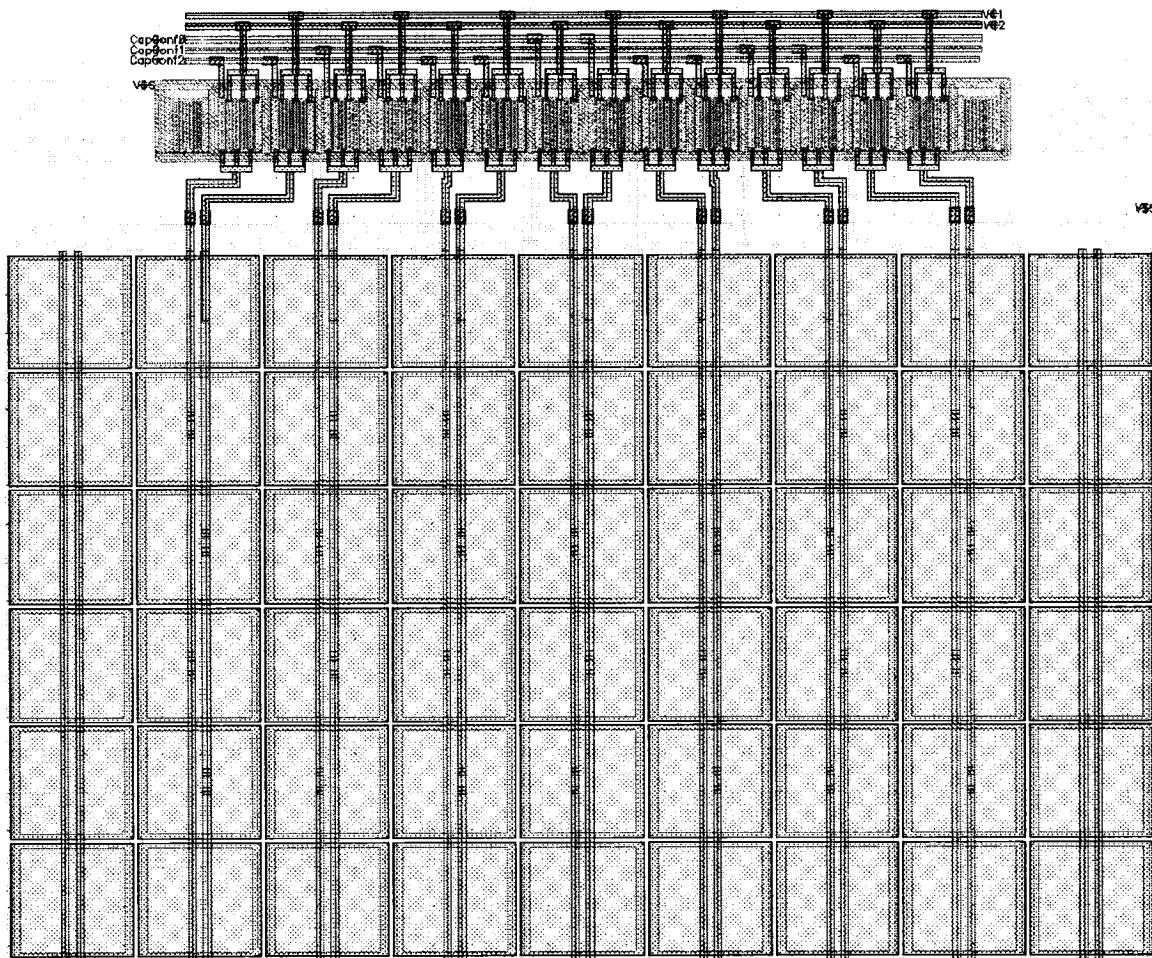

| Figure A.4 Dessin de masque du condensateur programmable .....                           | 74 |

| Figure A.5 Dessin de masque du circuit de polarisation.....                              | 75 |

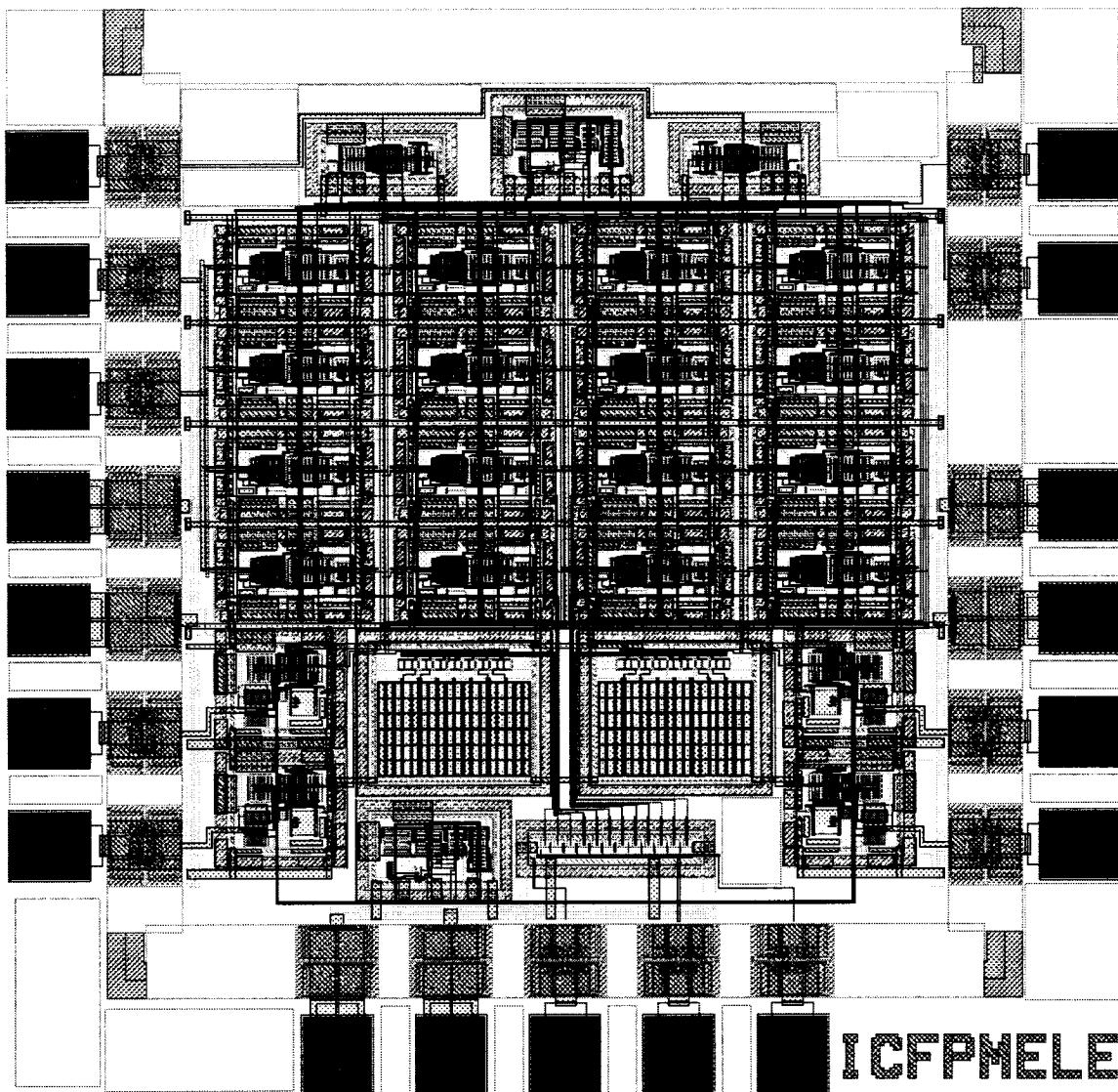

| Figure A.6 Dessin de masque du circuit complet.....                                      | 76 |

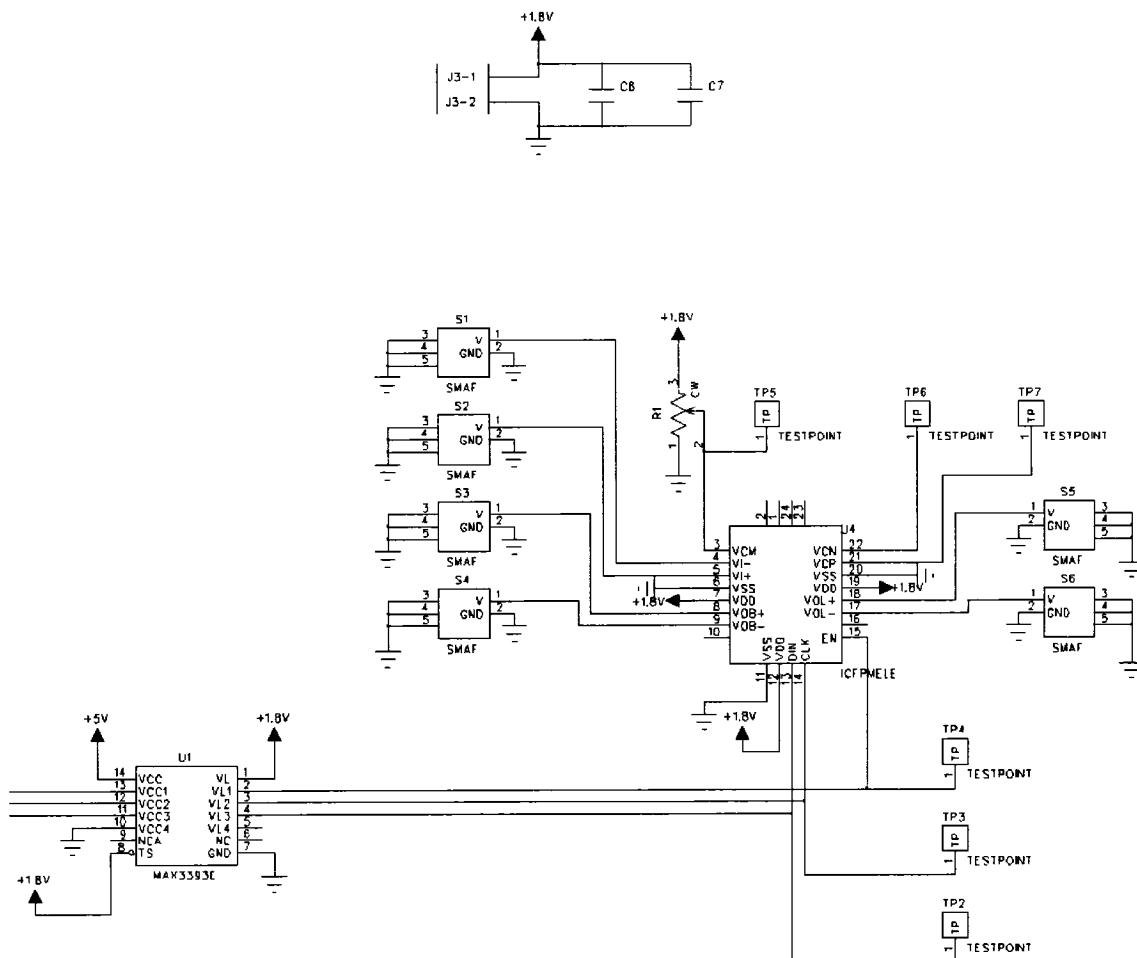

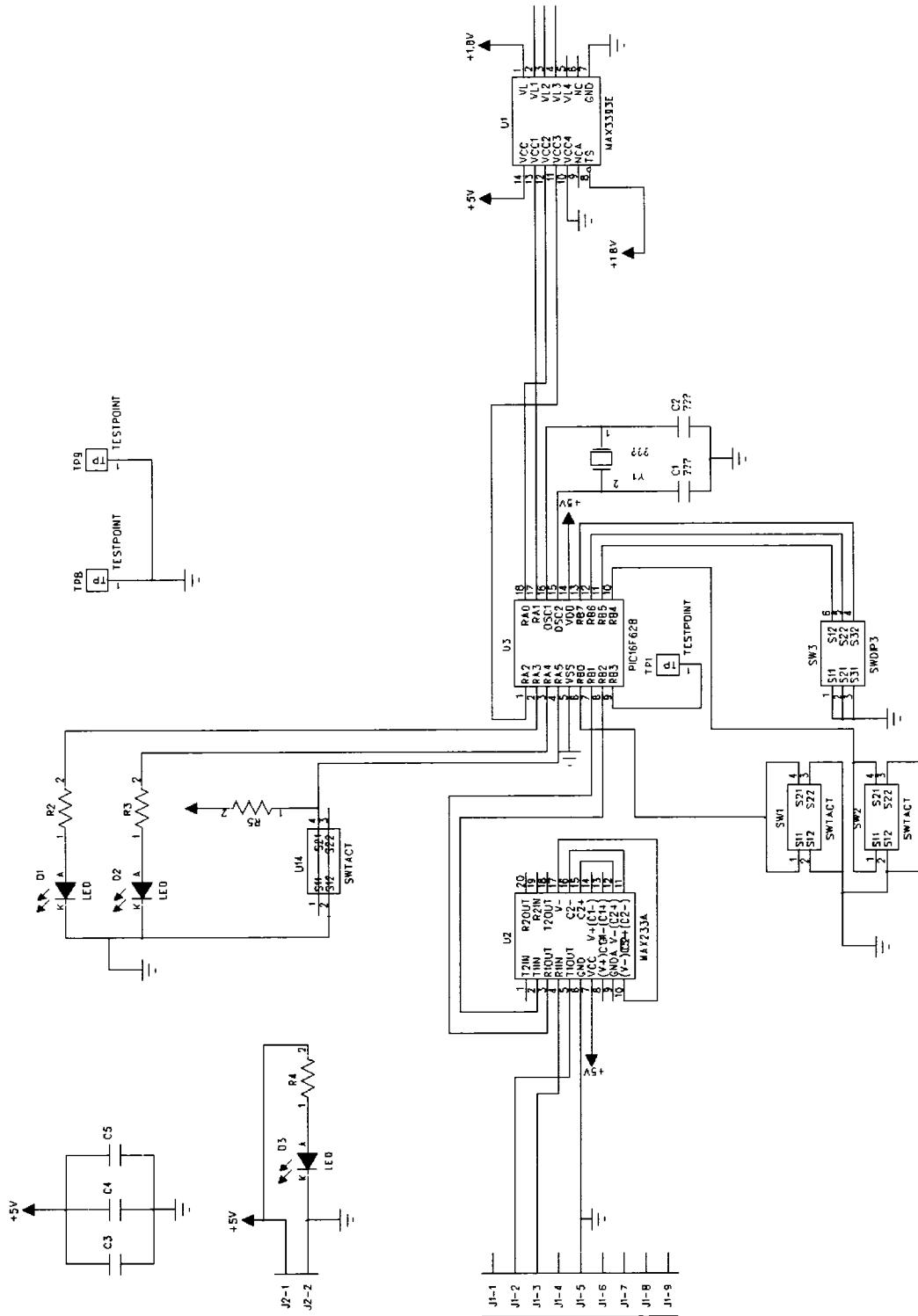

| Figure B.1 Circuit de la carte de test (partie 1.8 V) .....                              | 77 |

| Figure B.2 Circuit de la carte de test (partie 5 V) .....                                | 78 |

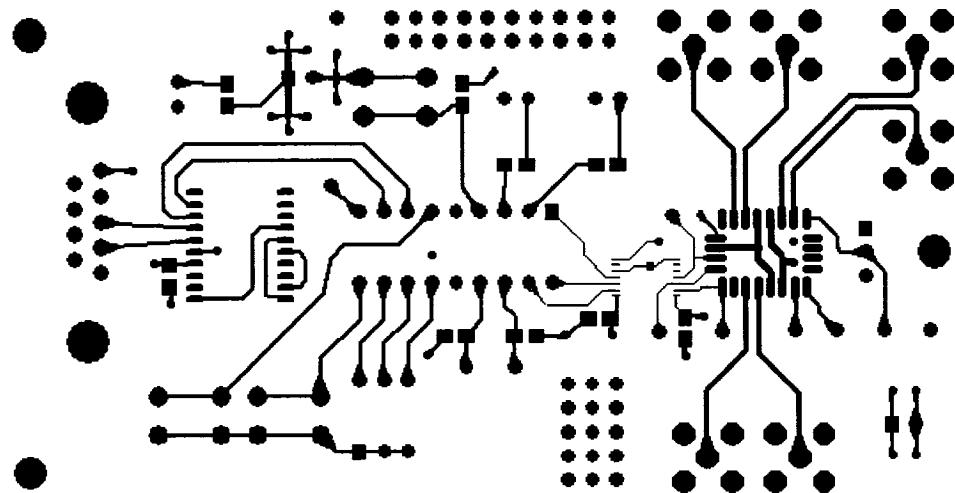

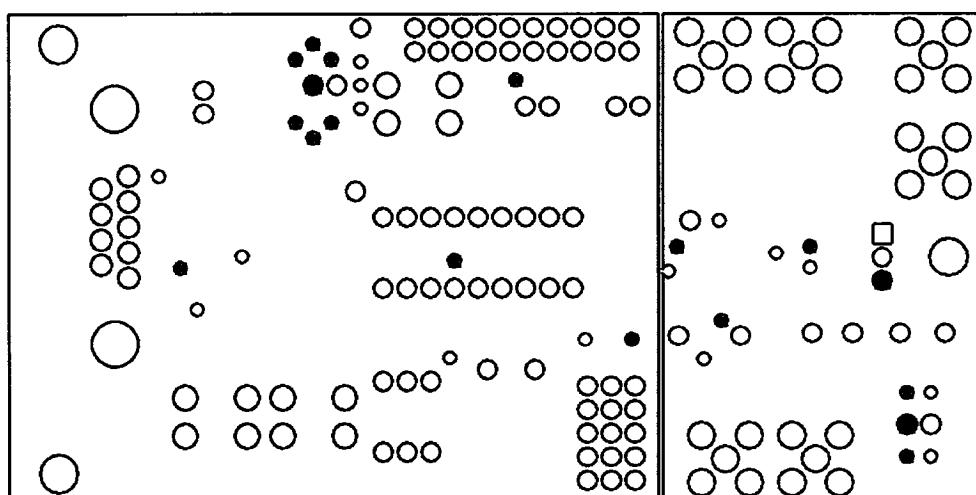

| Figure B.3 Dessin de masque du circuit imprimé (couche supérieure) .....                 | 79 |

| Figure B.4 Dessin de masque du circuit imprimé (couche VDD) .....                        | 79 |

| Figure B.5 Dessin de masque du circuit imprimé (couche VSS).....                         | 80 |

| Figure B.6 Dessin de masque du circuit imprimé (couche inférieure).....                  | 80 |

## LISTE DES ABRÉVIATIONS ET SYMBOLES

### ABRÉVIATIONS

|        |                                                     |

|--------|-----------------------------------------------------|

| AC     | Alternative Current (signaux variationnels)         |

| CAB    | Configurable Analog Block                           |

| CC     | Capacité Commutée                                   |

| CMFB   | Common-mode FeedBack                                |

| CMOS   | Complementary Metal Oxyde Semiconductor             |

| DC     | Direct Current (signaux fixes)                      |

| EEPROM | Electrically Erasable Programmable Read-Only Memory |

| FFT    | Fast Fourier Transform                              |

| FPAA   | Field Programmable Analog Array                     |

| FPGA   | Field Programmable Gate Array                       |

| FPMA   | Field Programmable Mixed-Signal Array               |

| MOS    | Metal Oxyde Semiconductor                           |

| NMOS   | Transistor MOS négatif                              |

| PMOS   | Transistor MOS positif                              |

| P-P    | Pointe à Pointe                                     |

| RF     | Radio Fréquence                                     |

| SDR    | Software Defined Radio                              |

| THD    | Total Harmonic Distortion                           |

### SYMBOLES

|          |                                         |

|----------|-----------------------------------------|

| $C_{ox}$ | Capacité de grille par unité de surface |

| dB       | Décibel                                 |

| Gm       | Transconductance                        |

| Hz       | Hertz                                   |

|                      |                                            |

|----------------------|--------------------------------------------|

| $I_B$ ou $I_{SS}$    | Courant de polarisation DC                 |

| $I_D$ ou $i_D$       | Courant de drain (DC ou AC respectivement) |

| $i_O$                | Courant de sortie                          |

| $L$                  | Longueur de transistor                     |

| $m$                  | mètre                                      |

| $mW$                 | milliWatt                                  |

| $Q$                  | Facteur de qualité                         |

| $R$                  | Résistance                                 |

| $R_m$                | Transrésistance                            |

| $V_b$                | Tension de polarisation (DC)               |

| $v_{cm}$             | Tension de mode commun                     |

| $V_{cn}$             | Tension de polarisation cascode du NMOS    |

| $V_{cp}$             | Tension de polarisation cascode du PMOS    |

| $V_{DD}$             | Tension d'alimentation positive            |

| $V_{DS}$             | Tension drain-source du transistor MOS     |

| $V_{GS}$ ou $v_{gs}$ | Tension grille-source du transistor MOS    |

| $v_{in}$ ou $v_{ip}$ | Tension d'entrée (négative ou positive)    |

| $V_{SS}$             | Tension d'alimentation négative (ou masse) |

| $V_{tn}$             | Tension de seuil du transistor MOS         |

| $W$                  | Largeur de transistor                      |

| $\mu_n$              | Constante de mobilité des électrons        |

| $\Omega$             | Ohms                                       |

| $\omega_0$           | Fréquence centrale en radians par seconde  |

## **LISTE DES ANNEXES**

|                                          |    |

|------------------------------------------|----|

| Annexe A : Dessins de masque .....       | 71 |

| Annexe B : Carte de test.....            | 77 |

| Annexe C : Code du microcontrôleur ..... | 81 |

## Chapitre 1

### Introduction

Le développement de la portion analogique d'un circuit mixte occupe une importante proportion du temps de design. La difficulté de la conception analogique s'explique par les compromis à plusieurs niveaux que ces circuits impliquent : bruit, linéarité, vitesse, consommation, impédance entrée/sortie, plage de tension/courant, etc. Les choix à faire requièrent donc des compétences spécialisées et de l'expérience.

Dans le monde de l'électronique numérique, la venue des circuits programmables, plus particulièrement les **FPGA**, a permis d'améliorer plusieurs aspects de la conception numérique. En effet, ces circuits couplés à des outils de synthèse permettent de réduire considérablement le temps de design d'une application numérique. De plus, l'utilisateur n'a nul besoin de connaître les détails du fonctionnement interne du dispositif pour l'utiliser. Il n'en demeure pas moins que l'interfaçage avec le monde extérieur nécessite toujours de l'électronique analogique. Il est donc souhaitable de vouloir amener la polyvalence et l'efficacité des **FPGA** dans le monde analogique en créant des circuits analogiques programmables.

De multiples applications peuvent bénéficier de circuits analogiques programmables, particulièrement si ceux-ci peuvent fonctionner à des fréquences de plusieurs dizaines de mégahertz. Des domaines d'applications sont, par exemple, l'acquisition et la conversion de données, le conditionnement de signaux, le filtrage et l'amplification de signaux dans le domaine des communications et du contrôle industriel.

En raison des différents compromis de la conception analogique, il n'est pas vraiment possible de concevoir un circuit analogique programmable pouvant réaliser n'importe quelle fonction à n'importe quelle fréquence. C'est pourquoi les circuits programmables

réalisés dans le cadre de cette maîtrise ciblaient principalement des fonctions de filtrages et d'amplification à hautes fréquences (100 MHz). Un filtre passe-bande et passe-bas de type biquadratique programmable au niveau de la fréquence de coupure ainsi que du facteur de qualité a été conçu et fabriqué. L'objectif était également de valider une nouvelle technique de programmation. En effet, les paramètres du filtre sont contrôlés par l'activation ou la désactivation de cellules de transconductance en parallèle. Un ajustement plus fin est également réalisé à l'aide d'une capacité programmable. Les dessins de masque de cette capacité ont été exécutés de manière à assurer un rapport fiable entre les différentes configurations possibles.

Un exemple d'application visé avec ce filtre est la radio numérique configurable (Software Defined Radio - SDR). Typiquement, un tel filtre pourrait servir en tant que sélecteur de bande dans une radio pouvant être reconfigurée en cours d'utilisation.

En utilisant la même technique de programmation, un amplificateur de courant constitué d'une cellule de transimpédance suivie de cellules de transconductance en parallèle a été conçu et simulé. Ce circuit pourrait donc être placé dans le même circuit intégré que le filtre décrit précédemment de manière à s'approcher de la versatilité des circuits intégrés analogiques programmables (Field Programmable Analog Array – FPAA) tout en conservant de bonnes performances à haute fréquence.

Une définition simple de FPAA serait : « un circuit intégré qui peut être programmé pour implémenter des circuits analogiques en utilisant des blocs analogiques flexibles et des interconnexions. Le circuit est doté de mémoire permettant de modifier la configuration et les paramètres. » (Sun, 2004). Les FPMA qui sont mentionnés plus tard sont quant à eux des circuits intégrés contenant à la fois un FPGA et un FPAA. Ce projet ne s'inscrit donc pas parfaitement sous l'appellation FPAA puisque les interconnexions proprement dites n'existent pas pour maximiser les performances en éliminant les interrupteurs dans le chemin du signal.

## ***1.1 Organisation du mémoire***

Ce mémoire débute par une discussion des raisons justifiant le choix des circuits en temps continu plutôt que commutés temporellement. Un survol des FPAA disponibles commercialement est présenté pour ensuite s'attarder aux travaux de recherche de pointe dans le domaine. Les différentes architectures de cellules de transconductance et de transimpédance dominent cette revue de littérature. Les différentes composantes du circuit intégré fabriqué sont décrites dans un chapitre incluant un article de journal soumis à Springer Analog Integrated Circuits and Signal Processing Journal. Les principaux résultats expérimentaux en font également partie. Un complément de résultats suit pour apporter des précisions sur les simulations et les résultats expérimentaux. Un autre chapitre est consacré à l'amplificateur de courant. En conclusion, un retour sur le projet est accompagné de recommandations pour de futurs travaux.

## 1.2 Capacités commutées versus temps continu

Les FPAA à base de MOS peuvent être regroupés en deux catégories : les circuits à base capacités commutées (CC) et ceux fonctionnant en temps continu. Il est utile de décrire dès maintenant ces catégories, puisque ce projet est centré sur les circuits en temps continu, mais bon nombre de FPAA sont à base de capacités commutées

Les cellules utilisant des capacités commutées (CC) se composent généralement d'un amplificateur opérationnel dont les résistances de contre-réaction sont remplacées par des capacités entourées d'interrupteurs, contrôlés par des horloges sans recouvrement comme à la Figure 1.1. Le signal à traiter est donc échantillonné. Il est démontrable que, suivant le théorème de Nyquist, les blocs capacité/interrupteurs se présentent comme des résistances si la fréquence de contrôle des interrupteurs est au moins 2 fois plus grande que celle du signal à traiter. De plus, la valeur apparente des résistances varie en fonction de la fréquence d'horloge.

Cette technique limite toutefois à quelques MHz la fréquence maximale des signaux pouvant être traités. En effet, un temps minimum est nécessaire à la charge des capacités forçant ainsi une durée minimum de l'application du signal d'horloge. Les paramètres du circuit dépendent généralement de rapports de capacités et il est possible d'en obtenir des assez précis dans les circuits intégrés (0.1%) (Johns et al., 1997). De plus la fréquence d'horloge est aussi contrôlable précisément de sorte que les circuits à CC offrent une bonne précision et linéarité. Par ailleurs, les commutations présentent le désavantage d'introduire du bruit.

**Figure 1.1 Exemple de circuit à capacités commutées**

La catégorie temps continu comprend tous les autres circuits où le signal n'est pas échantillonné (disponible en tout temps). Il peut donc s'agir de cellules à base de transconductances (Figure 1.2), de convoyeurs de courant, d'amplificateurs opérationnels ou de transrésistances. Le fait de ne pas échantillonner élimine la nécessité d'un filtre anti-recouvrement et offre de meilleures performances au niveau du bruit. On peut également s'attendre à une consommation de puissance moindre que les circuits à capacités commutées. Le principal avantage demeure la possibilité de traiter des signaux de l'ordre des centaines de MHz. Les circuits en temps continu sont toutefois plus dépendant des variations du procédé, donc moins précis. Il peut également être plus difficile d'obtenir de bonnes performances en linéarité.

**Figure 1.2 Exemple de circuit en temps continu**

Cette maîtrise vise des applications haute-vitesse, c'est pourquoi il a été choisi de se concentrer sur les circuits en temps continu. Pour différentes raisons qui seront exposées plus tard, la cellule de transconductance a été choisie comme bloc de base.

### **1.3 FPAA commerciaux**

La recherche industrielle et celle académique sont liées et s'inspirent mutuellement. Cette section se veut un survol des manufacturiers de FPAA et de leurs produits disponibles sur le marché. Ce survol permettra de mieux situer notre contribution dans ce domaine.

La compagnie Anadigm est sans doute le chef de file dans le domaine des FPAA. Le manufacturier en est à sa deuxième génération de composants. Le principe des capacités commutées est utilisé, ce qui limite la bande passante des signaux analogiques traités à 2 MHz. L'architecture consiste en une petite matrice (2x2 ou 2x1) de blocs configurables interconnectés (Anadigm, 2006). Ces blocs configurables (Configurable Analog Block - CAB) dynamiquement peuvent réaliser plusieurs fonctions analogiques différentes : amplificateur, différentiateur, comparateur, intégrateur, filtre, additionneur, multiplicateur, redresseur, etc. De plus, l'implémentation du circuit sur le FPAA est facilitée par le logiciel AnadigmDesigner.

Toujours suivant le principe des CC, la compagnie Lattice propose une approche différente avec sa série ispPAC (Lattice, 2006). En effet, les différentes fonctions à bande passante faible sont réalisables et configurables et se retrouvent dans des circuits intégrés différents plus spécialisés. On retrouve donc un circuit de conditionnement de signal (ispPAC10), de contrôle de système (ispPAC20) et d'interfaçage analogique (ispPAC30) qui réalisent principalement des fonctions d'amplification et de filtrage de base. Le ispPAC80/81 pour sa part est un filtre programmable de 5<sup>e</sup> ordre (limité à 750 kHz).

Cypress est une des rares compagnies actives dans le domaine des circuits programmables en temps continu, plus particulièrement des FPMA. Dans une optique d'acquisition de données, le PSoC (Cypress, 2006) de Cypress est un système sur puce

comprenant des éléments programmables d'amplification et de filtrage ayant une bande passante de l'ordre de 10 MHz.

Bien que le produit n'est plus en production, Zetex s'était démarqué avec son TRAC (Totally Reconfigurable Analog Circuit) . Vingt cellules en temps continu réalisant des fonctions arithmétiques configurables (log, intégration, somme, soustraction, multiplication et division) sont interconnectables pour former une fonction de traitement de signal complète supportant des signaux de l'ordre des 10 MHz.

Sans pouvoir les qualifier de FPAA, il est pertinent de mentionner également les manufacturiers de microcontrôleurs qui intègrent de plus en plus des blocs analogiques plus ou moins configurables à leurs produits. Par exemple, chez Microchip et Atmel, on retrouve abondamment des microcontrôleurs équipés de comparateurs, de convertisseurs numérique-analogique et analogique-numérique. Ces pratiques confirment l'intérêt de l'industrie pour les FPMA.

Notons également que la majorité des fabricants de circuits intégrés (Advanced Linear Devices, Maxim, Micrel, etc.) offre une gamme de circuits programmables (amplificateur opérationnel, résistance, potentiomètres et références de tension).

Nous constatons que les principaux acteurs dans le monde des FPAA commerciaux offrent dans la majorité des cas des circuits à capacités commutées limitées en bande passante. Les autres circuits commerciaux basés sur d'autres principes ne dépassent guère les 10 MHz. Ceci laisse donc beaucoup de place pour la recherche sur des circuits en temps continu programmables permettant le traitement de signaux à des fréquences beaucoup plus élevées (> 100 MHz).

## Chapitre 2

# Aperçu des FPAA et des architectures de transconductances

### 2.1 *Introduction*

Les FPAA représentent un champ de recherche actif. Un survol des FPAA disponibles commercialement a déjà été présenté et ce chapitre met l'accent sur les travaux de recherche de pointe dans ce domaine. Le circuit programmable réalisé dans le cadre de ce projet étant à base de cellules de transconductance, différentes architectures seront passées en revue afin de justifier le choix de celle utilisée. L'amplificateur de courant programmable faisant appel à une cellule de transrésistance, les options qui s'offrent pour ce circuit seront également présentées.

### 2.2 *Architectures de circuits FPAA*

Il est possible d'identifier plusieurs points communs entre les différents FPAA issus de la recherche académique, mais aussi commerciale. On y retrouve systématiquement un bloc analogique configurable (Configurable Analog Block - CAB) à l'instar des blocs de logique configurable d'un FPGA. La nature de ces blocs et leur nombre varient grandement d'un FPAA à l'autre. Un réseau de routage est également inévitable pour relier les CAB entre eux. Des éléments de mémoire, souvent des registres, sont également une constante dans le monde des FPAA, puisqu'ils sont nécessaires pour permettre des modifications et une rétention de différentes configurations. D'autres éléments ne sont pas utilisés systématiquement, mais peuvent s'avérer utiles. Des mécanismes de calibration permettent d'améliorer la fiabilité des gains et/ou des fréquences de coupures selon l'utilisation du FPAA. De plus, les références de tension

sont un élément important des circuits analogiques et ils se retrouvent donc souvent à l'intérieur d'un FPAA. La suite de ce chapitre présente les réalisations de différents chercheurs en matière de FPAA et met l'accent sur les particularités des designs.

(Lee et al., 1991) ont misé sur l'utilisation d'éléments relativement primitifs comme à la Figure 2.1: paire différentielle, miroir de courant. Plusieurs interrupteurs contrôlés par des bits en mémoire relient ces éléments. Le CAB ainsi formé permet plusieurs configurations : comparateur, multiplicateur, étage tampon de courant ou de tension. L'objectif était la réalisation de réseaux de neurones configurables. La grande flexibilité des CAB limite toutefois la bande passante du FPAA qui en découle.

© IEEE 1991

**Figure 2.1 Cellules de base du FPAA (Lee et Gulak, 1991)**

L'utilisation de cellules de transconductance est également répandue comme dans le design de la Figure 2.2 (Lee et al., 1995). Des résistances variables sont utilisées pour contrôler les paramètres du FPAA plutôt que des interrupteurs. La linéarité en est

améliorée selon les auteurs. Encore une fois, il s'agit des débuts des FPAA en temps continu et la bande passante est de l'ordre du kHz.

© IEEE 1995

**Figure 2.2 Réseau d'interconnexions avec des résistances programmables (Lee et Gulak, 1995)**

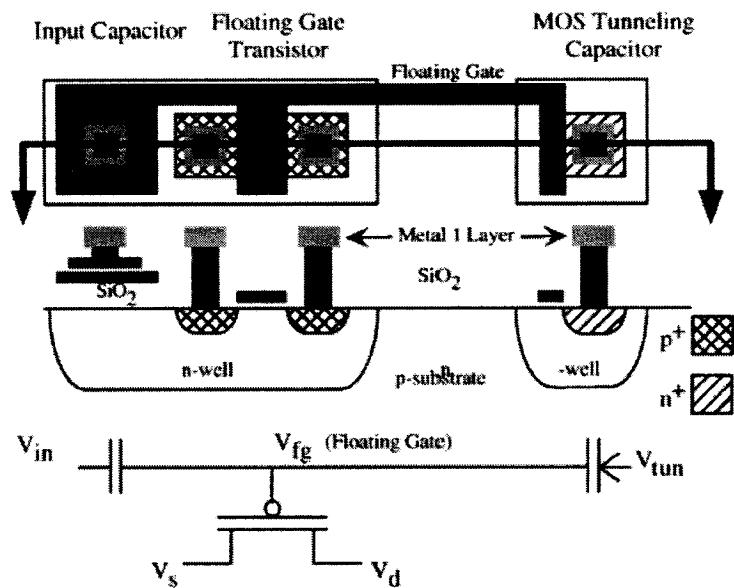

Plus récemment, les transistors à grille flottante ont fait leur entrée dans le domaine des FPAA (Hall et al., 2005). Le principe de ces transistors tel qu'illustré à la Figure 2.3 consiste à n'avoir aucun chemin DC à la grille du transistor. Les connexions à la grille sont toutes faites à travers une capacité. Une capacité sert à appliquer un signal à la grille tandis qu'une autre sert à y injecter des électrons afin de modifier la charge à la grille. Un avantage certain de cette technologie est que telle une mémoire EEPROM, la charge sur la grille est maintenue même en l'absence d'alimentation. Ceci permet par exemple la création de vastes réseaux d'interconnexions comme dans ce FPAA. Ces

interrupteurs peuvent également agir comme résistances programmables permettant un contrôle accru. De plus, ce FPAA utilise des CAB à base de transconductances. L'utilisation de transistors à grille flottante à l'intérieur de ces cellules permet donc de pouvoir contrôler (et programmer) les courants de polarisation et par conséquent les paramètres de transconductance. Cette technologie est prometteuse vu la grande versatilité qu'elle apporte. Les résultats présentés dans (Hall et al., 2005) comprennent d'ailleurs plusieurs configurations de filtres programmables réalisables avec cette technologie dans un FPAA. Des bandes passantes de l'ordre du MHz sont réalisées mettant en évidence une fois de plus que la perte de bande passante est le prix à payer pour la versatilité. Dans le même ordre d'idées, Yasunari et al, 2004 utilisent également des résistances programmables (MOS cette fois) dans ses FPAA. (Yasunari et al., 2004).

© IEEE 2005

**Figure 2.3 Transistor à grille flottante (Hall et al., 2005)**

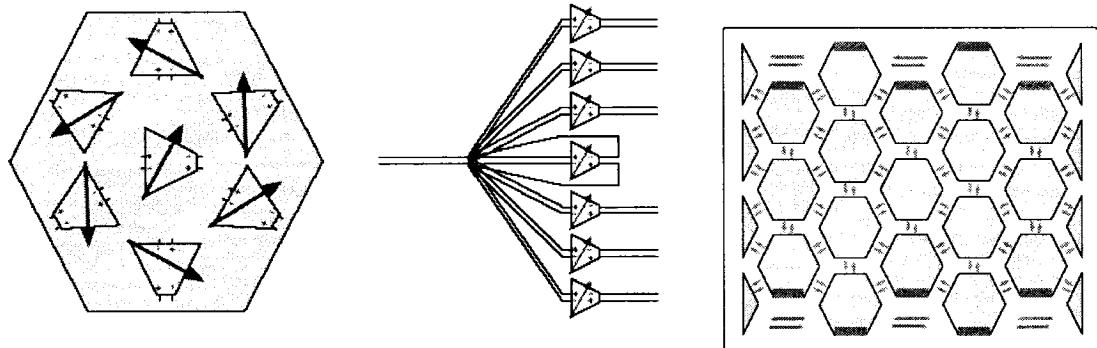

Certaines innovations sont aussi possibles au niveau structurel. Becker et al. utilisent des CAB de forme hexagonale (Figure 2.4) composés de transconductance qui sont disposés en nid d'abeille. Une grande flexibilité au niveau des interconnexions est possible. Les

performances attendues sont de l'ordre des dizaines de MHz. Similairement au projet de cette maîtrise, la technique de programmation fait appel au branchement en parallèle de transconductances.

© IEEE 2004

**Figure 2.4 Disposition en nid d'abeille (Becker et al., Mai 2004)**

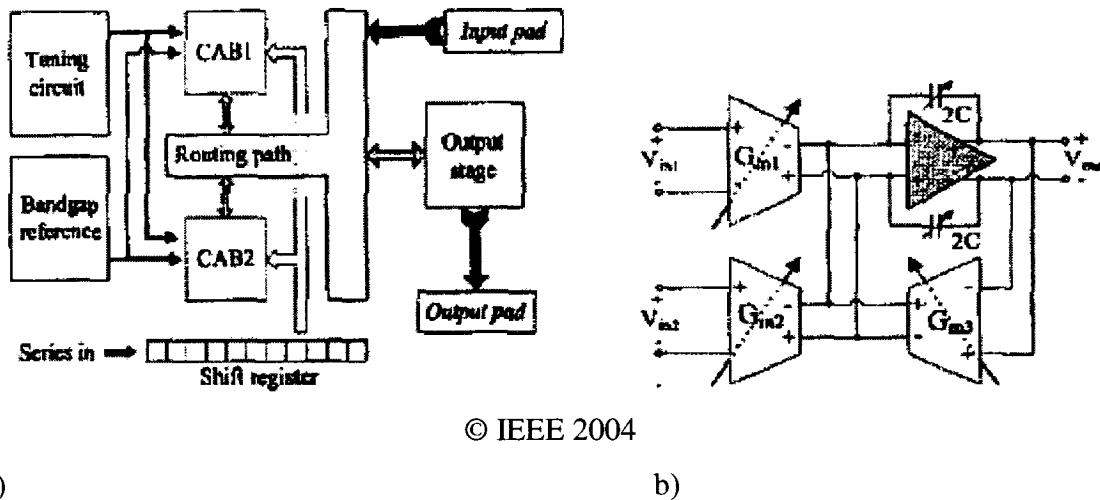

À l'instar de ce projet, plusieurs préconisent un réseau d'interconnexions et un nombre de cellules de transconductance limité afin de favoriser les performances en fréquence (Pankiewicz et al., 2002; Lon-Kou et al., 2004). Dans les deux cas, la programmabilité est basée sur des condensateurs programmables ainsi que le contrôle de la transconductance. L'architecture de Lon-Kou et al, 2004 est montrée à la Figure 2.5. Avec seulement deux CAB, la création de filtres de 1<sup>er</sup> et de 2<sup>e</sup> ordre opérant à des fréquences autour de 1 MHz est possible.

Figure 2.5 Nombre de CAB limité (Lon-Kou et al, 2004) : a) schéma bloc b) CAB

En conclusion, il est à noter qu'une grande proportion des FPAA récents est à base de transconductances. Les principaux avantages sont la possibilité de les fabriquer facilement avec la technologie CMOS maintenant incontournable en analogique. En effet, la CMOS est plus avantageuse pour les circuits numériques et ceux-ci représentent une plus grande proportion des circuits fabriqués. Les  $G_m$  peuvent aussi bien fonctionner aux tensions d'alimentation toujours plus faibles suivant la miniaturisation des procédés de fabrication. De plus, comparativement à un amplificateur opérationnel, les  $G_m$  démontrent une meilleure linéarité et sont performants en fréquences.

### 2.3 Transconductance (Gm)

Différentes architectures de Gm et techniques pour faire varier la transconductance existent. La section suivante présente les principales approches pour créer des Gm dans un environnement CMOS. L'accent est toutefois mis sur les architectures différentielles puisque ces dernières sont les plus couramment utilisées dans les circuits modernes. En effet, les circuits complètement différentiels (entrée et sortie différentielles) présentent l'avantage de minimiser la distorsion causée par les harmoniques d'ordres paires. Deux

catégories de Gm peuvent être dressées : ceux impliquant des transistors opérant dans la région triode et ceux composés uniquement de transistors opérant dans la région de saturation (ou active).

Ces derniers fonctionnent en suivant le principe de la loi carré des transistors MOS donnée par l'équation (2.1).

$$I_D = \frac{\mu_n C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{in})^2 \quad (2.1)$$

Où  $I_D$  est le courant de drain,  $\mu_n$  la constante de mobilité des électrons,  $C_{ox}$  la capacité de grille par unité de surface,  $W$  la largeur du transistor,  $L$  sa longueur,  $V_{GS}$  la tension grille-source et  $V_{in}$  la tension de seuil du transistor. Le rôle d'un Gm étant de générer un courant de sortie en fonction d'une tension, le plus simple Gm pourrait donc être un unique transistor.

Tel que désiré dans un Gm, l'impédance d'entrée est élevée (la tension est appliquée à une grille), mais l'impédance de sortie (idéalement infinie) ne satisferait pas à de véritables applications surtout avec des signaux différentiels. Le problème le plus évident pour un unique transistor en région active est le terme au carré qui anéantirait toute linéarité entre l'entrée et la sortie. D'ailleurs, la plupart des efforts en matière de Gm se concentrent à produire une bonne linéarité.

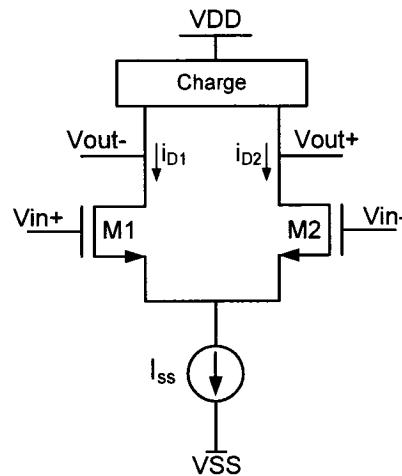

### 2.3.1 Paire différentielle

Ceci nous amène à introduire les Gm à base de paires différentielles (Figure 2.6) pour lesquelles la linéarité repose sur une somme constante des tensions grille-source. En effet, pour 2 transistors Q1 et Q2, le comportement sera donné par l'équation (2.2).

$$i_{D1} - i_{D2} = \frac{\mu_p C_{ox}}{2} \frac{W}{L} (v_{GS1} + v_{GS2} - 2V_m)(v_{GS1} - v_{GS2}) \quad (2.2)$$

Donc pour des tensions d'entrée parfaitement symétriques, le courant différentiel ne dépend que de la différence des tensions d'entrée ( $v_{GS1} - v_{GS2}$ ). Ceci suppose toutefois, une tension de mode commun assurant le maintien des transistors dans la région active. De plus, en pratique, des signaux d'entrée non balancés sont courants.

Figure 2.6 Paire différentielle

### 2.3.2 Paires différentielles croisées

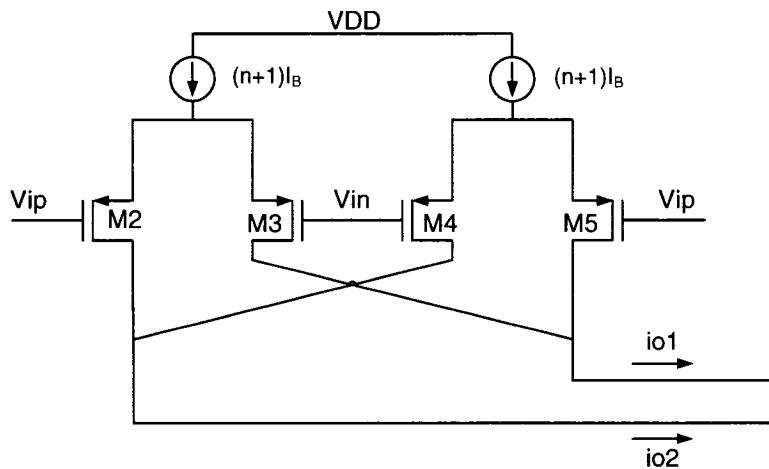

L'avantage de cette topologie montrée à la Figure 2.7 est de conserver une bonne linéarité même en présence de signaux d'entrée qui ne sont pas parfaitement symétriques (débalancés). Elle est originalement attribuée à (Nedungadi et al., 1984) et a

aussi été améliorée (par l'ajout d'un étage de sortie cascode replié) et exploitée au sein de notre laboratoire Polystim (Voghell et al., May 2000). L'expression des courants différentiels est la suivante :

$$i_{o1} - i_{o2} = \left( \frac{n}{n+1} \right) 4 \sqrt{\frac{\mu_p C_{ox}}{2} \frac{W}{L} I_B} (v_{ip} - v_{in}) \quad (2.3)$$

Où  $i_{o1}$  et  $i_{o2}$  sont les courants de sortie,  $v_{ip}$  et  $v_{in}$  les tensions d'entrée et  $n$  le rapport des largeurs M3/M2 et M5/M4. On constate que contrairement à la formule de la simple paire différentielle, la somme des tensions de grille n'entre pas en ligne de compte, favorisant ainsi une meilleure linéarité. La grande intensité des courants DC devant traverser ce type de circuit est toutefois un désavantage en termes de consommation.

Figure 2.7 Paires différentielles croisées

### 2.3.3 Gm à base d'un transistor en triode

L'expression du courant de drain d'un transistor MOS dans la région triode est la suivante :

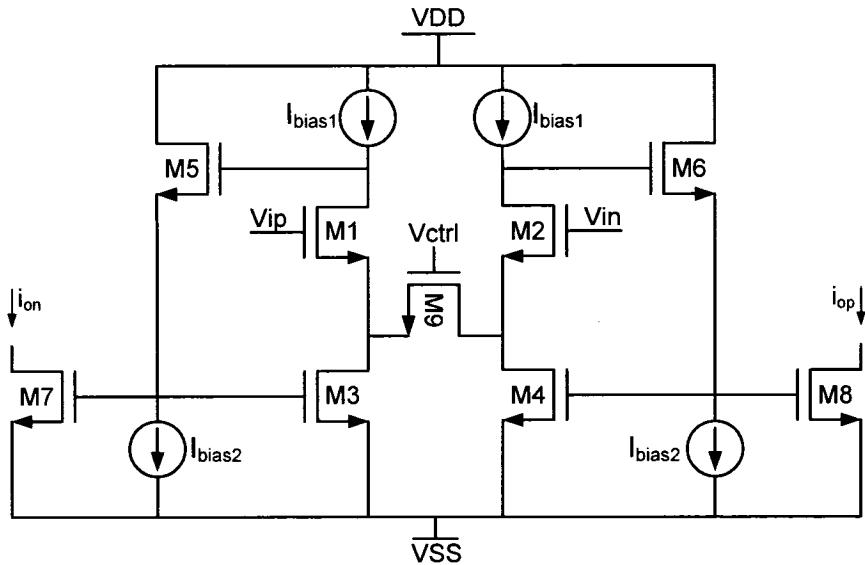

$$I_D = \mu_p C_{ox} \left( \frac{W}{L} \right) \left[ (V_{GS} - V_m) V_{DS} - \frac{V_{DS}^2}{2} \right] \quad (2.4)$$

$V_{GS}$  n'étant plus élevé au carré, il est déjà possible de s'attendre à une meilleure linéarité en comparaison à un Gm à base de transistors en région active seulement. La Figure 2.8 montre un Gm à base d'un transistor en région triode. La fonction du transistor M9 dans ce circuit est de maintenir  $V_{GS1}$  et  $V_{GS2}$  constants. La transconductance de ce circuit est donnée par :

$$Gm = \mu_n C_{ox} \left( \frac{W}{L} \right) [V_{gs9} - V_m] \quad (2.5)$$

L'amélioration de la linéarité se fait au détriment des performances en vitesse. Par ailleurs, cette topologie présente l'avantage de permettre facilement l'ajout de branches de sortie pour la conception de Gm à sorties multiples.

Figure 2.8 Gm à base d'un transistor en triode

#### 2.3.4 Étage de sortie

Dans tous les cas présentés, l'impédance de sortie est relativement faible. Afin de l'augmenter pour pouvoir alimenter une charge à une vitesse respectable, un étage de sortie est généralement nécessaire. Le choix le plus commun est un étage cascode replié

ou une de ses variantes (Bruun et al., 1995). Pour les architectures totalement différentielles, un circuit de rétroaction du mode commun (Commun Mode FeedBack - CMFB) est nécessaire pour éviter que le niveau DC à la sortie ne se retrouve à VDD ou VSS.

Le choix de la topologie de cellule Gm, le choix de l'étage de sortie, l'intensité des courants y circulant viendront influencer la vitesse d'opération. Par contre, le facteur le plus déterminant est le procédé de fabrication qui permet des gains en vitesse au fur et à mesure que la technologie permet de miniaturiser les transistors et par le fait même les capacités parasites.

## **2.4 Programmation de la transconductance**

Que ce soit pour contrôler le gain d'un amplificateur à base de Gm ou les paramètres d'un filtre, différentes approches pour programmer des circuits à transconductance sont possibles. Comme il a déjà été mentionné, l'utilisation de capacités ou de résistances programmables sont des éléments qu'il est possible d'utiliser à l'extérieur du circuit Gm lui-même. Par contre, la plupart des FPAA implique également une programmation du Gm (valeur de transconductance) lui même. Quelques techniques de programmation des Gm sont présentées dans cette section.

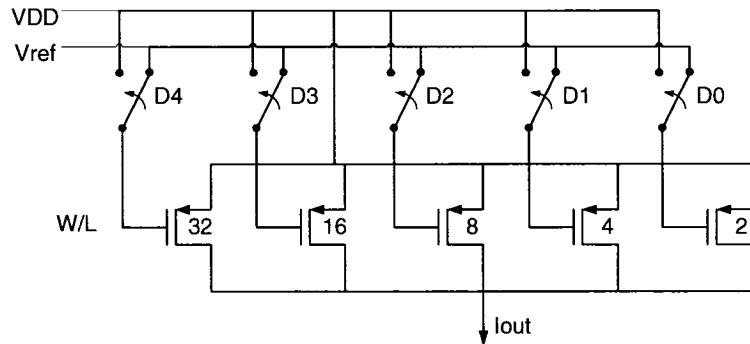

### **2.4.1 Source de courant programmable**

Comme la plupart des circuits CMOS actifs, les Gm présentés dans la section précédente comporte au moins une source de courant pour des fins de polarisation. Tout comme pour un transistor individuel, la transconductance d'un circuit sera influencée par l'intensité du courant qui le traverse. Le contrôle de l'intensité du courant aura donc une influence sur la transconductance. Ceci est réalisable en utilisant un circuit tel que celui de la Figure 2.9 (Voghell et al., 1998).

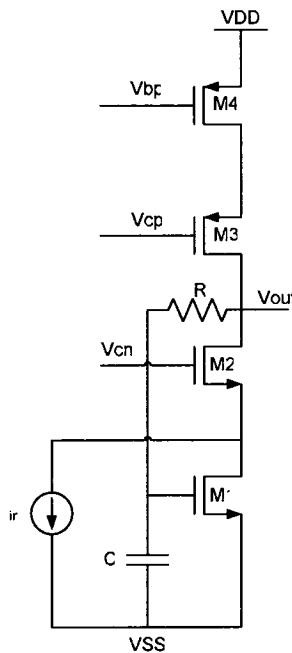

**Figure 2.9 Source de courant programmable**

Il s'agit en fait d'un convertisseur numérique à analogique (CNA) en mode courant. Des interrupteurs activent ou non des transistors ayant un poids binaire de par leur taille (ou plus pratiquement du nombre de transistors en parallèle). Ces transistors constituent un miroir de courant basé sur une tension  $V_{ref}$ . La Figure 2.9 montre donc un CNA de 5 bits. La plage de courant couverte peut toutefois être limitée puisqu'il faut s'assurer de maintenir les autres transistors du circuit dans leur région active.

#### 2.4.2 Contrôle en tension

Bien qu'il soit généralement plus facile de générer des courants avec précision, un contrôle en tension est aussi possible. Plus particulièrement dans le cas des  $G_m$  basés sur un transistor opérant dans la région triode, la programmation peut s'effectuer en faisant varier une tension qui est appliquée à une grille. Ceci est également applicable à la technologie des transistors à grille flottante précédemment présentée. Aussi, la tension qui alimente une branche du circuit peut permettre de contrôler le courant qui y circule et par conséquent la transconductance du circuit (Assi et al., August 1997). Pour ces exemples, un traditionnel CNA en tension peut apporter un contrôle numérique sur les circuits analogiques.

### 2.4.3 Gm multiples

Les techniques de programmation précédemment introduites présentent toutes un problème similaire : la plage sur laquelle il est possible de faire varier la transconductance est limitée puisqu'il faut maintenir la plupart des transistors dans leur région active. Une approche à la base de ce projet (Lebel et al., 2005) consiste à placer de multiples Gm en parallèle et à les activer au besoin pour faire varier la transconductance résultante. Cette technique sera donc discutée plus en détail dans le prochain chapitre. Des approches similaires ont également été proposées dans (Becker et al., Mai 2004) et (Quan et al., Mai 1998). Dans tous les cas, les désavantages sont des capacités parasites, une consommation et une surface de silicium plus élevées.

## 2.5 Transrésistance

Tel que mentionné dans l'introduction, une autre facette de ce projet consiste à réaliser un amplificateur de courant faisant appel à une cellule de transrésistance (ou transimpédance) suivi d'une cellule de transconductance. En effet, un amplificateur de courant résulte de cet agencement puisque la transrésistance convertit un courant en tension et la transconductance, une tension en courant. Cette section présentera donc les principales topologies de transrésistance.

La transrésistance ( $R_m$ ) idéale présente une impédance d'entrée la plus faible possible afin de minimiser l'excursion en tension engendrée par le courant d'entrée. Ceci est particulièrement important pour les procédés à faibles tensions d'alimentation. L'amplitude maximale des courants qui pourront être traités en dépend aussi. Pour toutes les architectures présentées, l'entrée du courant s'effectue donc sur un drain (ou une source) plutôt que sur une grille comme c'était le cas pour les Gm. Une application typique des  $R_m$  est l'acquisition de signaux en provenance de photodiodes qui sont de faibles courants.

### 2.5.1 Rm grille commune

Tel qu'utilisé dans un contexte d'amplificateur de courant dans (Bruun, 1994), l'étage de transrésistance est constitué d'une topologie à grille commune (Figure 2.10). L'impédance d'entrée (vue à la source de M1) est approximativement :

$$R_{in} = \frac{2}{g_{m1} + g_{mb1}} \quad (2.6)$$

Où  $g_{m1}$  et  $g_{mb1}$  sont respectivement la transconductance de M1 et la transconductance attribuable au substrat. Les paires de transistors M2-M3 et M4-M5 forment chacune une source de courant pour polariser l'étage grille-commune.

Figure 2.10 Topologie à grille commune

Il est donc possible de s'attendre à des impédances d'entrée de l'ordre des Kohms. Pour une transrésistance, il est toutefois souhaitable de maximiser l'impédance de sortie afin de maximiser du même coup la valeur de la transrésistance elle-même. C'est donc la

fonction du miroir de courant formé des transistors M6-M7 et M10-M11 dont l'impédance de sortie est environ :

$$R_{out} = g_{m10} (r_{ds10})^2 \quad (2.7)$$

Où  $r_{ds10}$  est la résistance drain-source de M10.

Toujours du type grille commune, l'architecture de type cascode de la Figure 2.11 (Baker, 2005) est surtout attirante par sa simplicité bien qu'on tente généralement d'éviter les résistances dans les circuits intégrés. L'impédance d'entrée est du même ordre que celle de l'architecture précédente. La résistance et le condensateur de grandes valeurs permettent quant à eux d'assurer la polarisation des transistors M1 et M2 indépendamment des signaux AC.

Figure 2.11 Rm grille commune et cascode

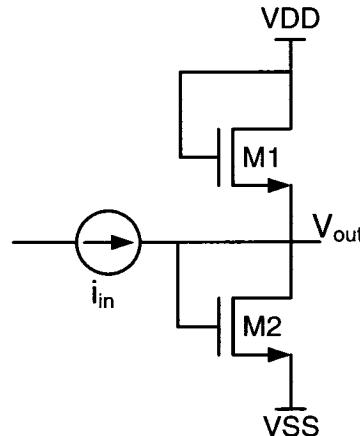

### 2.5.2 Rm à 2 transistors

Il existe plusieurs architectures à seulement 2 transistors. Sur la Figure 2.12, la transrésistance est formée de 2 transistors en diode (Wang, 1990). La valeur de transrésistance résultante est :

$$R = \frac{V_o}{I_{in}} = \frac{L}{WC_{ox}(VDD - V_T)} \quad (2.8)$$

La sortie et l'entrée étant le même nœud, on doit toutefois faire un compromis entre une faible impédance d'entrée ou une grande valeur de transrésistance. Selon les auteurs, ce circuit procure de bonnes performances en distorsion et en fréquence (vu sa simplicité).

**Figure 2.12 Deux transistors branchés en diode**

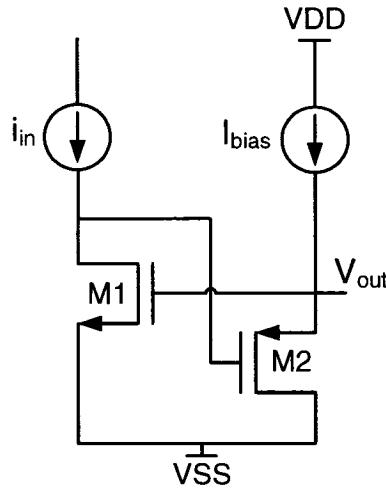

Une autre topologie fait appel à un transistor en région triode comme sur la Figure 2.13 (Schlannann et al., 2000).

**Figure 2.13 Deux transistors avec contre-réaction**

Le transistor M1 doit être dans la région triode et M2 en saturation. La contre-réaction permet de maintenir cet état. Par contre, le fonctionnement interne hautement non linéaire de ce circuit rend son expression mathématique difficile. Il offre tout de même de bonnes performances en fréquence et en linéarité. Une version complètement différentielle est également envisageable. Son ajustement s'est toutefois avéré difficile en CMOS 0.18um.

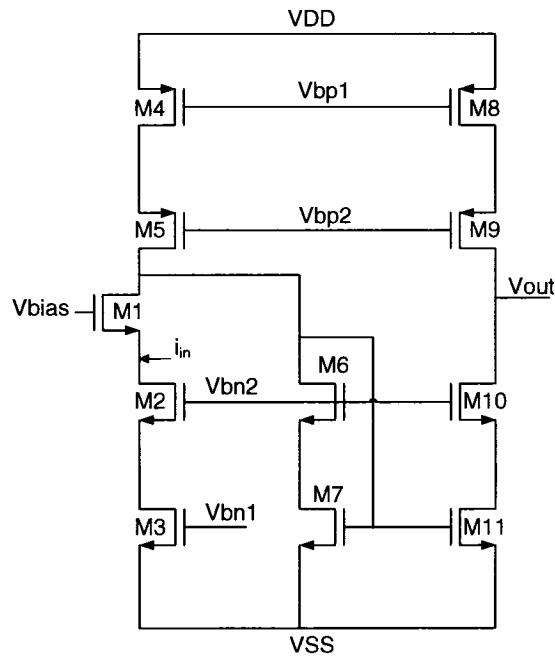

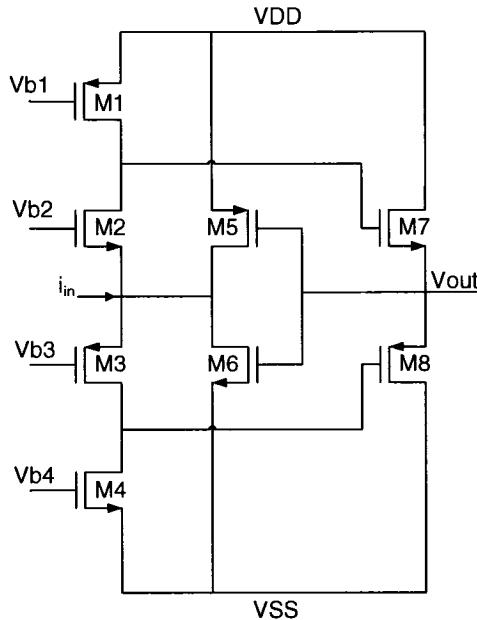

### 2.5.3 Rm à étages multiples

Plusieurs architectures de transrésistance sont similaires à celle de (Ping-Hsing et al., 1994) et (Parnklang et al., 2000) de la Figure 2.14. L'étage typique grille commune (avec M2 et M3) se retrouve à l'entrée. M7 et M8 forme un étage tampon de type suiveur de source. L'étage formé de M5 et M6 constitue une transconductance suivant un modèle d'inverseur. Sa fonction est de créer une contre réaction de type shunt-shunt afin d'améliorer la bande passante, la linéarité du circuit de transrésistance. Cet étage contribue également au principal avantage du circuit : procurer à la fois une faible impédance d'entrée et de sortie. L'impédance de sortie peut ne pas être critique si ce circuit est branché à la grille du transistor d'un autre étage. Une faible impédance peut toutefois être primordiale si une ligne de transmission y est branchée.

Figure 2.14 Rm à étages multiples

## 2.6 Conclusion

Dans ce chapitre, quelques architectures de FPAA en temps continu à base de cellules de transconductance ont été présentées. Différentes topologies de Gm complètement différentielles ont aussi été passées en revue. Différents compromis sont faits au niveau, entre autres, de la linéarité, de la plage d'opération en fréquence et en tension. Les circuits programmables nécessitent de pouvoir faire varier les transconductances et quelques techniques ont été abordées. Le chapitre suivant présentera l'architecture choisie et son application dans un filtre programmable.

Quelques architectures de transrésistance ont également été présentées. On retrouve un étage typique d'une grille commune dans la plupart des cas, de sorte que l'impédance d'entrée est souvent du même ordre de grandeur. Les autres paramètres comme l'impédance de sortie, la valeur de la transrésistance du circuit complet et sa bande passante dépendent davantage des étages subséquents qui peuvent ou non impliquer de la contre-réaction. Le choix d'architecture sera discuté dans le chapitre qui traite de l'amplificateur de courant.

## Chapitre 3

# Filtres Gm-C hautes fréquences programmables

### 3.1 Présentation de l'article

Le chapitre 2 présentait différentes architectures de FPAA ainsi que différentes topologies de Gm qui peuvent en être à la base. Dans le cas particulier d'un FPAA implémentant un filtre programmable, il a été mentionné que le problème qui revient souvent est une plage de fréquence limitée. Le présent chapitre propose un filtre programmable haute-fréquence sous forme d'un article soumis à la revue « *Analog Integrated Circuits And Signal Processing* » de Springer en janvier 2006. Le filtre en question a été fabriqué avec la technologie CMOS 0.18  $\mu\text{m}$ . Afin de favoriser les performances en fréquence, le concept de FPAA a été délaissé un peu pour se concentrer sur un filtre. Ce dernier est tout de même basé sur une matrice de Gm et offre une sortie passe-bande et passe-bas. De plus, la programmation permet de contrôler à la fois la fréquence centrale du filtre et son facteur de qualité sur une large plage. L'originalité réside dans l'utilisation de cellules Gm en parallèle (pour les ajustements grossiers) branchées à des condensateurs programmables pour les ajustements plus fins.

L'organisation de l'article consiste en une introduction qui expose l'intérêt des circuits Gm-C pour la réalisation de filtres programmables en hautes fréquences. Différents travaux concurrents trouvés dans la littérature sont également présentés. Le principe de fonctionnement et l'architecture du filtre ainsi que les différents blocs le composant sont ensuite expliqués : Gm, CMFB, polarisation, étage tampon et capacité programmable. Les principaux résultats expérimentaux sont finalement présentés de même qu'une comparaison avec des réalisations similaires.

Afin de présenter de façon plus complète le circuit intégré, l'article est suivi d'un complément expliquant la méthode de tests et donnant davantage de résultats de simulation et expérimentaux.

### **3.2 PROGRAMMABLE MONOLITHIC GM-C BAND-PASS FILTER: DESIGN AND EXPERIMENTAL RESULTS**

*E. Lebel<sup>1</sup>, A. Assi<sup>1,2</sup>, and M. Sawan<sup>1</sup>*

<sup>1</sup>Polystim Neurotechnologies Laboratory,

Department of Electrical Engineering, Ecole Polytechnique de Montréal,

Montreal, Quebec, Canada

<sup>2</sup>Department of Electrical Engineering, United Arab Emirates University

eric.lebel@polymtl.ca

**Abstract** - We propose in this paper a programmable band-pass filter based on an array of fully differential transconductance circuits that controls the filter parameters. The signal path does not contain any switch in the interconnection network, and fine-tuning of the filter parameters is implemented using programmable capacitors. A digital building block is implemented in the proposed band-pass filter to tune its central frequency as well as its bandwidth. The filter circuit is based on a biquad topology, which is designed and implemented with CMOS 0.18 $\mu$ m technology. Experimental results show a programming ability of the center frequency between 5.9 MHz and 58 MHz, and the quality factor can be tuned from 0.36 to 10. These features are obtained for a total power consumption of less than 10.5 mW from a single 1.8V power supply.

**Keywords:** CMOS analog circuits, transconductance, programmable band-pass filters, continuous-time filters, capacitor arrays, digital tuning.

### 3.2.1 Introduction

Analog filters are key circuits in electronic systems involving signal processing. In order to decrease the development time or to increase the flexibility of systems using such filters, programmability is one of the important features required in filters. Programmability in terms of not only the center frequency but also the bandwidth can be useful in applications such as Software Defined Radio and front-end biomedical signal acquisition systems. Commercially available programmable filters and Field Programmable Analog Arrays (FPAs) have already hit the market, but most of the available circuits are switched capacitor based filters [1, 2]. For signals with frequencies higher than few tens of megahertz, continuous-time circuits are the best choice for designers to achieve such frequencies. On the other hand, transconductor-based circuits are currently an active research area [3-11]. The linearity and relatively wide bandwidth of transconductors make these circuits appropriate for continuous-time filters.

Programming techniques based on current or voltage tuning of the programmed circuit are widely used in filtering systems [5, 8-11], but keeping the transistors in the saturation region over a wide range is one of the limiting problems in such techniques [6], for instance, linearity and noise performances become a concern when using these techniques.

We propose in this paper a new approach to design and implement programmable band-pass filters using transconductors as basic building blocks. Transconductor blocks connected in parallel are activated and deactivated by controlling their power supply [12]. This technique has been used also in realizing a programmable current amplifier [3]. The parallelism technique has already been exploited for the design of band-pass filters [4, 6, 7], in this work we use this technique without switches in the signal path (except at the programmable capacitors); this will let our band-pass filter operates at a wider frequency range. Moreover, integrated grounded programmable capacitors allow for finer tuning of the filter parameters. The band-pass filter presented in this paper has

three basic advantages: 1) Use of simple transconductance (Gm) circuits, 2) Simplicity of the digital tuning scheme, and 3) Integration of the whole filter circuitry on a single chip.

The proposed band-pass filter has been designed and fabricated with the TSMC 0.18 $\mu$ m CMOS process. It operates from a single 1.8V power supply. The architecture is presented in section II. The building blocks are described in section III. Experimental results along with comparisons against similar works are presented in section IV.

As mentioned previously, all the Gm's in the array are identical. It is true that binary-weighted rows would lead to more possible combinations and therefore a better control on the filter parameters. For instance, row #2 Gm's could be formed by 2 basic Gm cells in parallel, row #3 Gm's by 4 basic cells and row #4 Gm's by 8 basic cells. However, the resulting circuit would be too large. Different Gm cells with different transconductance in each row is another approach. However, it was decided not to follow this path either because the transconductance of the Gm's used in this work cannot be tuned on a large scale (multiplied by 2, 4 or 8). This would inevitably lead to a different frequency response from one row to another. Moreover, linearity issues would arise since transistors would leave their saturation region as the transconductance is scaled.

### 3.2.2 The band-pass filter architecture

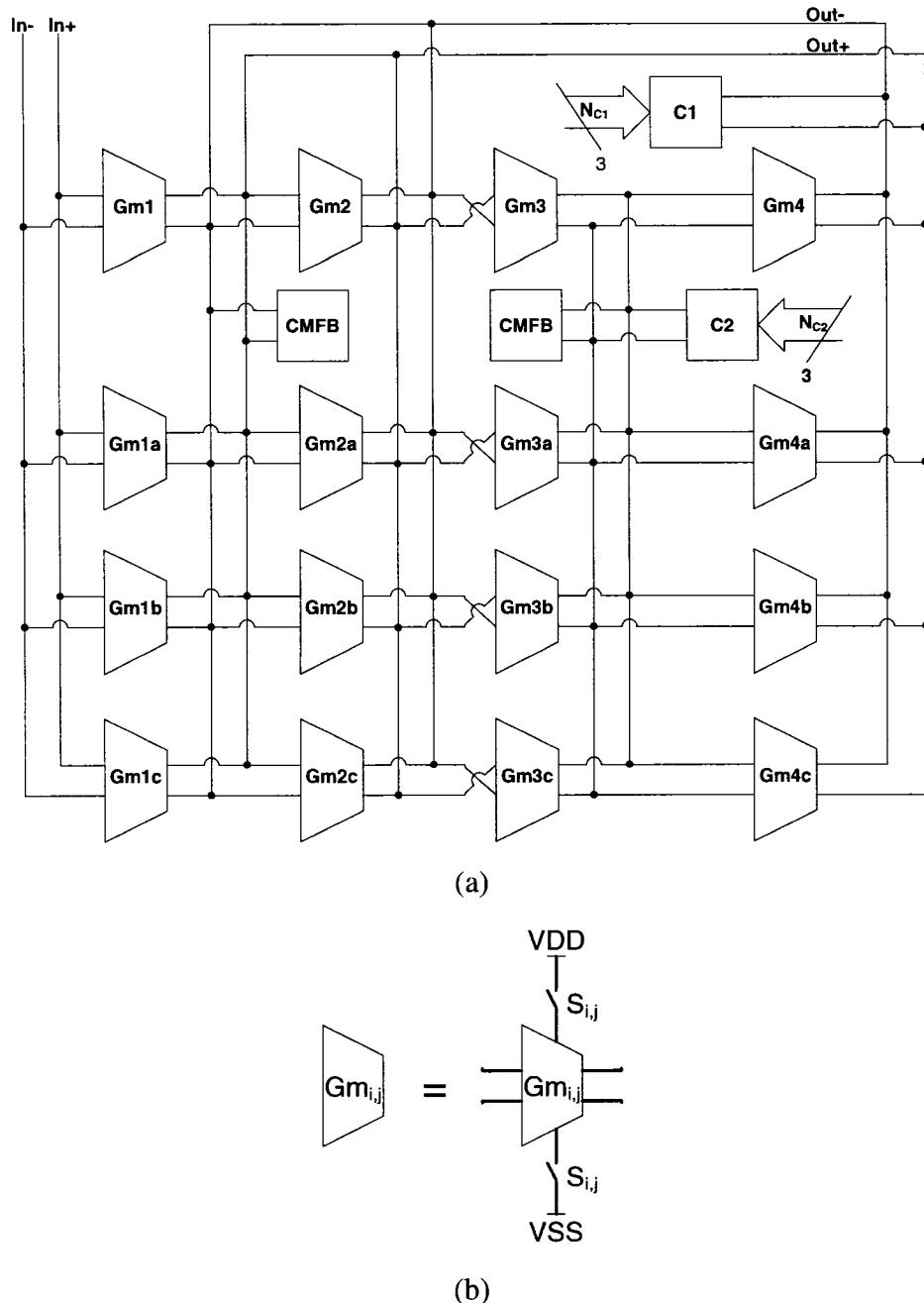

Figure 3.1 shows the proposed Gm-C array to build the programmable band-pass filter. It consists of four groups of four Gm blocks. Each Gm block includes two switches as shown in Figure 3.1. The programmability of the band-pass filter is implemented using switches that control whether the Gm blocks are connected (powered) or disconnected to the power supply sources VDD and VSS. The switches are merely large N-transistors for VSS and P-transistors for VDD.

### 3.2.2.1. Circuit Analysis

Horizontally, the Gm blocks are connected as a second order filter providing low-pass and band-pass outputs. Vertically, they are connected in parallel. Therefore, they share the same inputs, outputs and capacitive loads. Selectively activating and deactivating the Gm blocks can set four different transconductance values for a given column. Therefore, several bandwidth and center frequency configurations can be obtained for the filter. To control the filter parameters, it is not necessary to control all columns independently as it will be indicated by the equations of the next section. Switches selecting the Gm's of the first two columns ( $Gm_{1,j}$  and  $Gm_{2,j}$  with  $j = a, b$  or  $c$ ) are controlled by the same three bits ( $S_{1a}$ ,  $S_{1b}$  and  $S_{1c}$ ) (Figure 3.2). Three other bits configure the last two columns ( $S_{2a}$ ,  $S_{2b}$  and  $S_{2c}$ ). Switches are included in the first row even if they are always on. This is to ensure constant voltage drop caused by the switches among all Gm blocks in the array.

The fully differential nature of the Gm blocks requires the use of a common mode feedback (CMFB) circuit to stabilize the output voltage around the common mode voltage. Only two CMFB circuits are necessary since the Gm blocks in columns 1, 2 and 4 share the same output. In order to drive the output pads of the chip, buffers are used at the low-pass and band-pass outputs.

Programmable capacitors are used to allow finer tuning of the filter parameters while coarse tuning (band selection) is implemented using switches. The 3-bit programmable capacitor allows for 7 different capacitance values. Capacitors  $C_1$  and  $C_2$  are respectively controlled by the configuration words  $N_{C1}$  and  $N_{C2}$ .

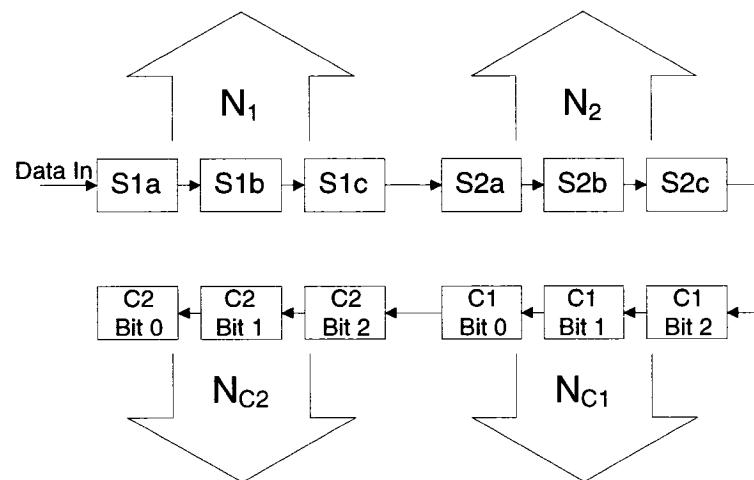

The configuration words of the circuit are fed serially and stored in registers at the power up or as needed during operation. A total of 12 bits is required to program the array and they are arranged as shown on Figure 3.2.

The transfer function of a quadratic filter (neglecting second order effects) is given by equation (1):

$$H(s) = \frac{(Gm_1/C_1)s}{s^2 + (Gm_2/C_1)s + Gm_3Gm_4/C_1C_2} \quad (3.1)$$

where

$$\omega_0 = \sqrt{\frac{Gm_3Gm_4}{C_1C_2}} \quad (3.2)$$

and

$$\frac{\omega_0}{Q} = \frac{Gm_1}{C_1} = \frac{Gm_2}{C_1} \quad (3.3)$$

As mentioned previously, all the Gm blocks have the same transconductance value and the same bits control columns 1 and 2. Therefore, the actual transconductance value of either column 1 or 2 is given by:

$$Gm_1 = Gm_2 = N_1 Gm \quad (3.4)$$

where  $N_1$  is the number of activated Gm blocks in the column that can be 1, 2, 3 or 4.  $N_1$  is applied to the switches controlling  $Gm_{1,j}$  and  $Gm_{2,j}$ . The same technique also applies to columns 3 and 4:

$$Gm_3 = Gm_4 = N_2 Gm \quad (3.5)$$

The capacitors can take a value that is multiple of 1 to 7 of the basic capacitor ( $C = 0.4$  pF):

$$C_1 = N_{c1} C \quad (3.6)$$

and

$$C_2 = N_{c2} C \quad (3.7)$$

The equations describing the global array will be:

$$\omega_0 = \frac{N_2}{\sqrt{N_{c1}N_{c2}}} \frac{Gm}{C} \quad (3.8)$$

and

$$Q = \frac{N_2}{N_1} \sqrt{\frac{N_{C1}}{N_{C2}}} \quad (3.9)$$

The parasitic capacitance  $C_p$  at the outputs is not negligible and taking it into account leads to a more accurate equation:

$$\omega_0 = \frac{N_2}{\sqrt{N_{C1}N_{C2}}} \frac{Gm}{C + C_p} \quad (3.10)$$

Although the center frequency depends on the actual transconductance and capacitor values, the quality factor of the filter depends only on the programmed settings. It can already be expected that the minimum and maximum  $Q$  will be 0.1 and 10.6 respectively. In theory 784 different configurations can be programmed: 4 different possible values for  $N_1$  and  $N_2$ , and 7 for  $N_{C1}$  and  $N_{C2}$  ( $N_{C1}$  or  $N_{C2} = 0$  is not used since only the parasitic capacitances would be left) so  $4 \times 4 \times 7 \times 7 = 784$ . However, several configurations lead to the same or very similar frequency response. Moreover, it is not possible, for example, to have the highest  $Q$  (or the lowest  $Q$ ) at any frequency because of the dependency between  $\omega_0$  and  $Q$ . We can see from equations (8) and (9) that  $\omega_0$  and  $Q$  are both proportional to  $N_2$ . For any given frequency, it is always possible to have at least 4 different  $Q$ s (by varying  $N_1$  only). Sixteen different  $Q$ s can be achieved if the product  $N_{C1} \times N_{C2}$  remains constant e.g.  $N_{C1} \times N_{C2} = 6 \times 1, 3 \times 2, 2 \times 3$  or  $1 \times 6$ . Nevertheless, several useful configurations can be programmed.

### 3.2.2.2. Building blocks

- **The transconductance circuit**

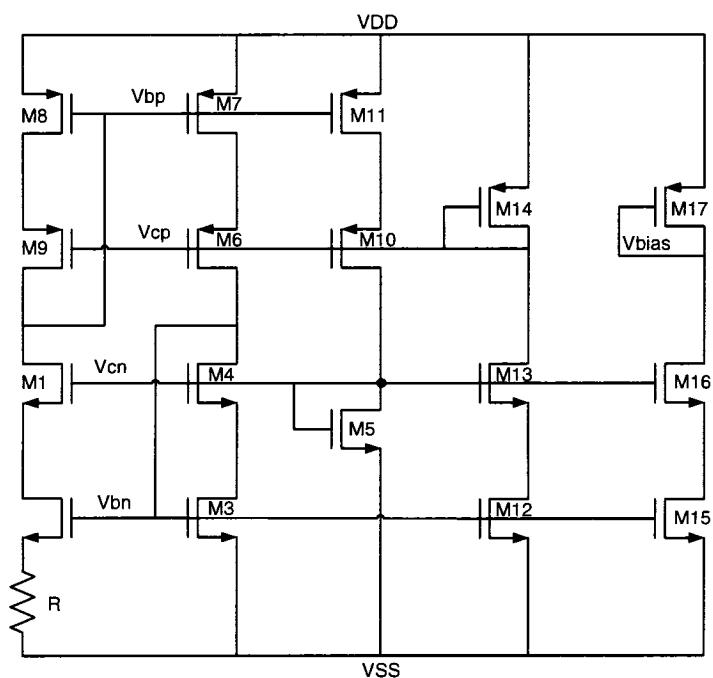

The basic building block of the band-pass filter circuit is the Gm circuit (Figure 3.3). The circuit of the Gm block has been designed originally within our Polystim team using the  $0.35\mu\text{m}$  technology[8]. In this work we use the same transconductor topology and redesign it with the  $0.18\mu\text{m}$  CMOS process. The cross-coupled input stage provides the circuit with good linearity and the wide-swing folded cascode output stage provides

it with high output impedance. For the circuit shown in Figure 3.3, we can write the following:

$$\begin{aligned} G_m &= \frac{i_{out}}{v_{ip} - v_{in}} \\ &= \sqrt{2\mu_p C_{ox} (W_{2,3,4,5}/L)} (\sqrt{I_{D0}} - \sqrt{I_{D1}}) \end{aligned} \quad (3.11)$$

where  $i_{out} = i_{o1} - i_{o2}$ , M1, M2, M3, M4 and M5 are matched and the dimensions ratio between M0 and M1 is equal to k, taking into account this fact, equation (11) becomes:

$$G_m = \sqrt{2\mu_p C_{ox} (W_{2,3,4,5}/L)} I_{D0} \left( 1 - \frac{1}{\sqrt{k}} \right) \quad (3.12)$$

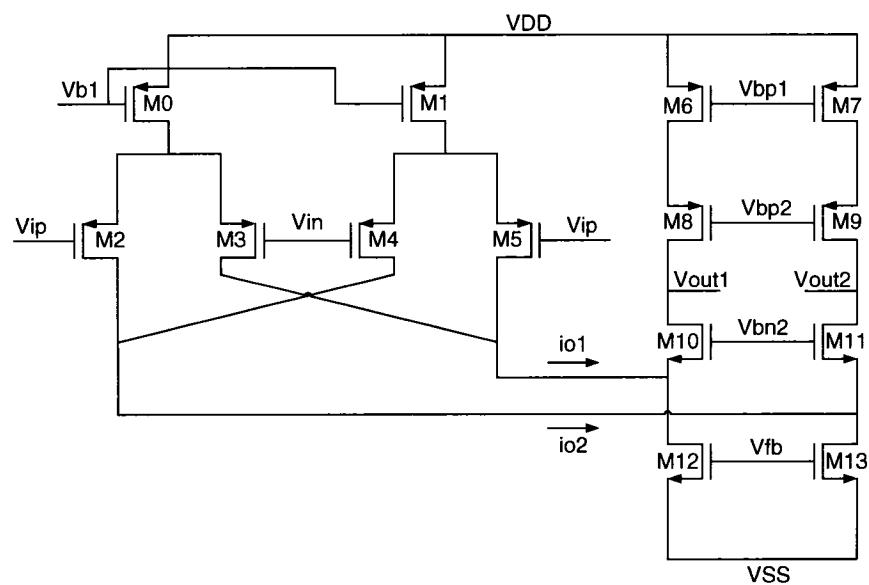

#### • The CMFB block

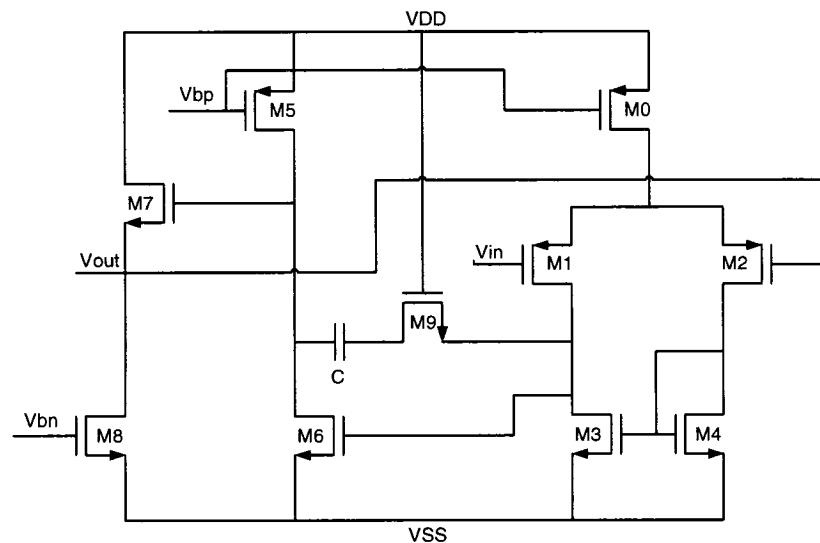

The purpose of this circuit (Figure 3.4) is to maintain a constant common mode voltage at the differential output of a Gm (Von and Vin) without affecting the AC mode. Transistors M1 and M2 are matched to provide branches M7-M9 and M8-M10 with the same current. The desired common mode voltage is applied to Vcm. The circuit is sensitive to common mode voltage difference between Vcm and Von and Vop. For instance, a voltage drop at Vin and Vop relative to Vcm will cause the current in M8-M9 to increase. Consequently, the current in M7-M9 will decrease so will the voltage Vfb. Vfb is the feedback voltage applied as a bias voltage to gate of the lower N transistors in the output stage of the Gm blocks whose outputs are connected to the CMFB circuit. In this example, the Vfb voltage drop will cause a drain-source resistance increase, so the common mode voltage will also increase to finally stabilize around the desired Vcm.

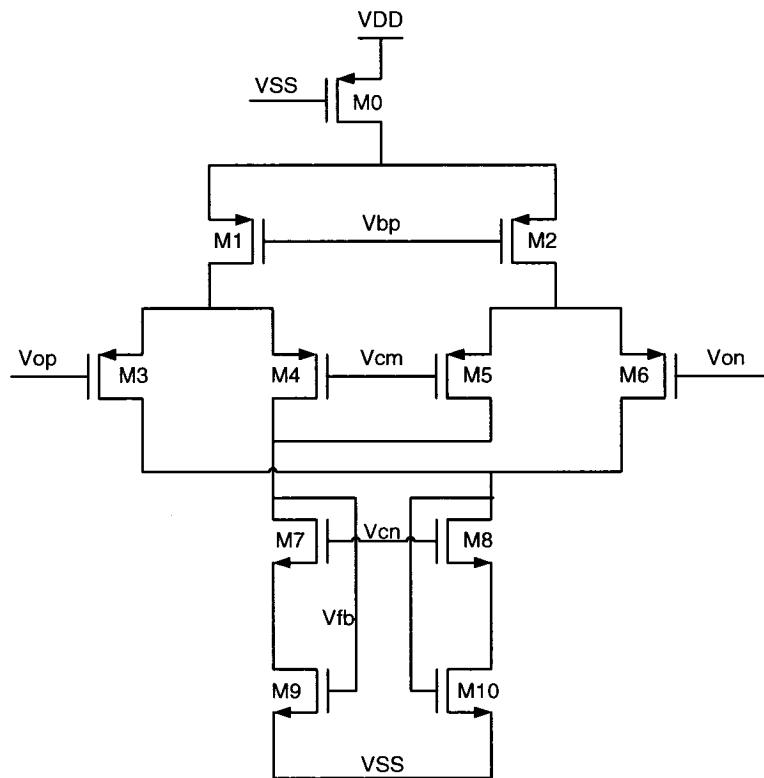

#### • The Bias circuit

A wide-swing constant-transconductance bias circuit (Figure 3.5) was chosen. The main characteristic of this circuit is that the Gm of all transistors depends on the resistor as

proposed in [13]. Therefore, the transconductance of transistors are independent of the power supply and are more immune to temperature variations. Since the purpose of this circuit is to provide Gm blocks with bias voltage, stable Gm values; consequently stable filter characteristics can be expected.

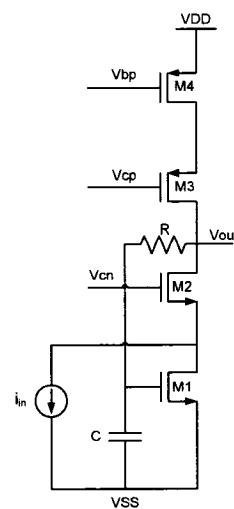

- **The Buffer circuit**

The buffers (Figure 3.6) used to drive the pads are typical single-ended operational amplifiers. They are internally wired as voltage follower. The pads and the instrument probes were modeled by a 20 pF capacitor. The design and the compensation were tuned to obtain a constant gain (ideally 0 dB); constant to frequencies well over the filter range. A large source-follower output stage allows for output currents of about 100  $\mu$ A. In further designs, it would be advisable to use fully differential buffers.

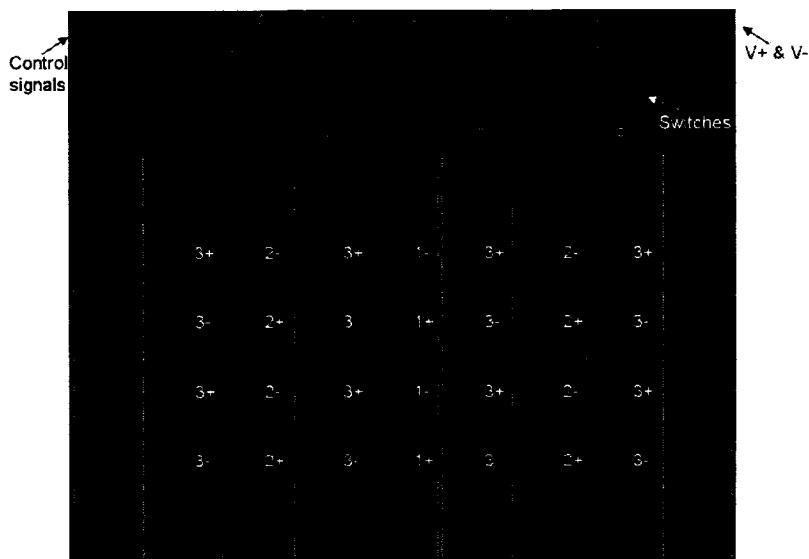

- **The Programmable capacitor array**

The layout of the programmable capacitors is shown in Figure 3.7. To maximize the linearity, grounded capacitors were used. However, being in a fully differential environment, this means that the negative and the positive signals are connected to different capacitors. It is suitable to have the same capacitance for both signals. The 0.2 pF unit capacitors were connected in a way to maximize the matching. The numbers shown in Figure 3.7 indicate to which bit a given unit capacitor is associated. Moreover, the active capacitors are surrounded by dummies.

As in [5], switches were used to program the capacitors. The size of the switches allowing the signal in and out of the capacitors was chosen in order to minimize the resistance and to maximize the linearity.

### 3.2.3 The filter results

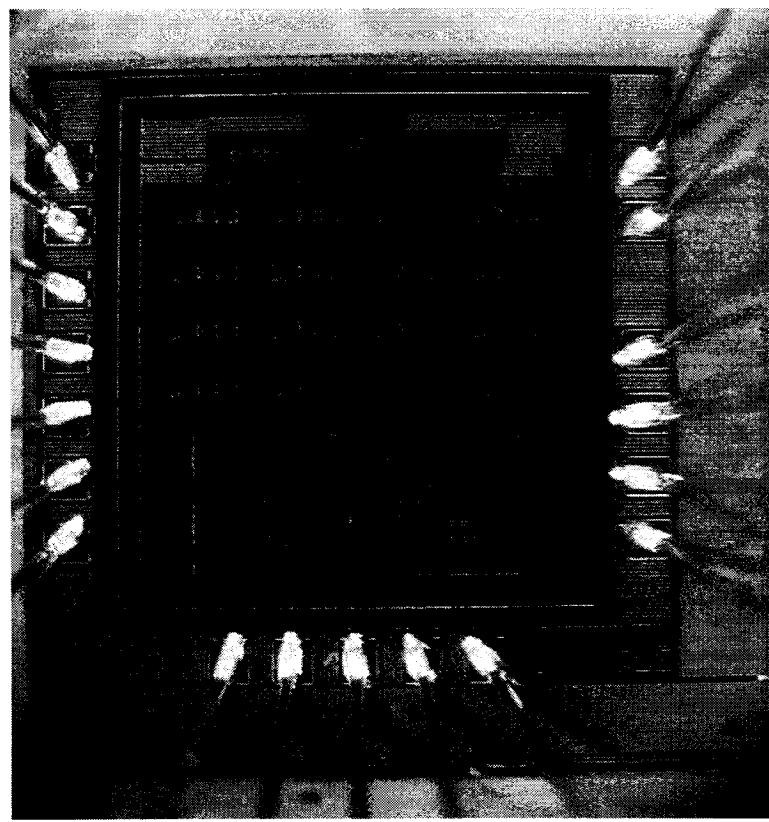

Three sample chips of this filter have been fabricated in a  $0.18\mu\text{m}$  six-metal one-poly CMOS technology offered by TSMC. Figure 3.8 shows the microphotograph of one of the measured chips, whose die area is  $1\text{ mm}^2$ . All measurements were performed using RF transformer with a center-tap in order to produce differential signals from single-ended signal generator.

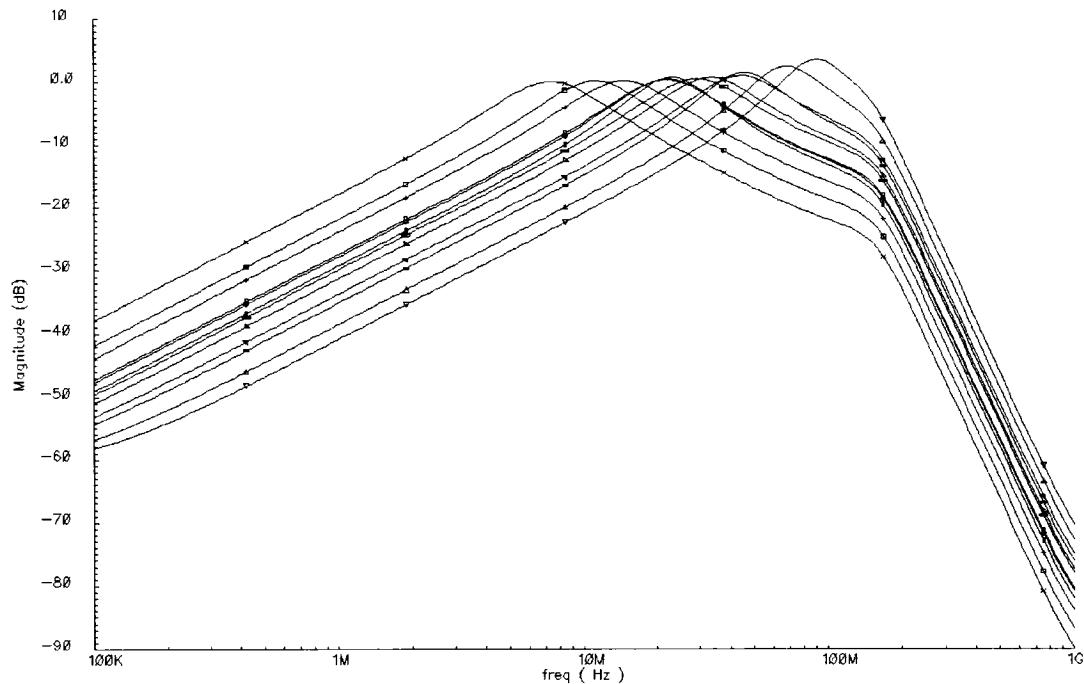

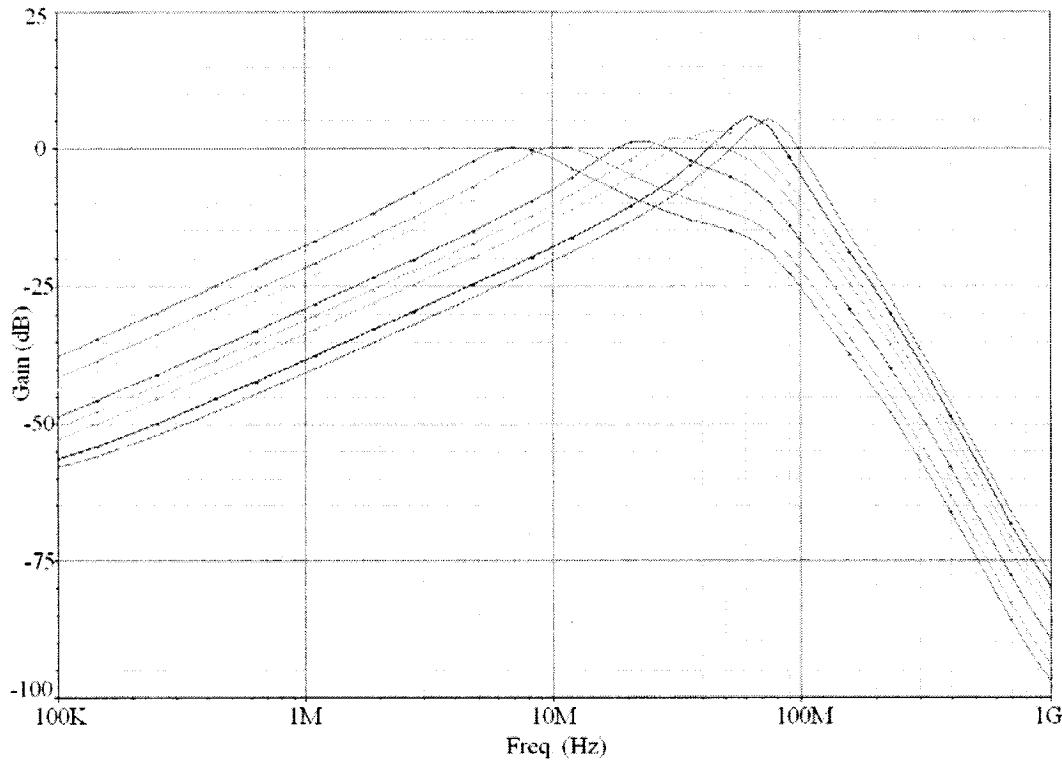

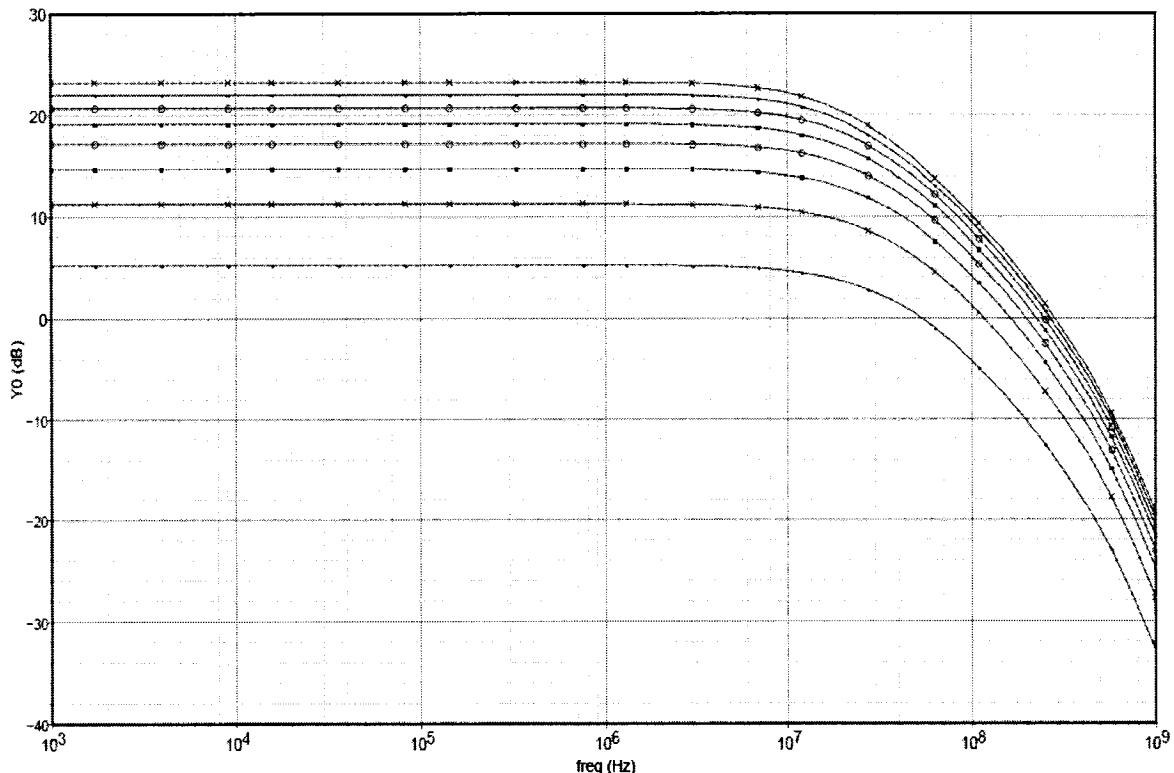

Figure 3.9 shows the frequency response with constant quality factor  $Q$ . The center frequency can be tuned from 5.9 MHz to 58 MHz. The quality factor ( $Q = 1$  in theory) is actually located between 1.2 and 1.7.

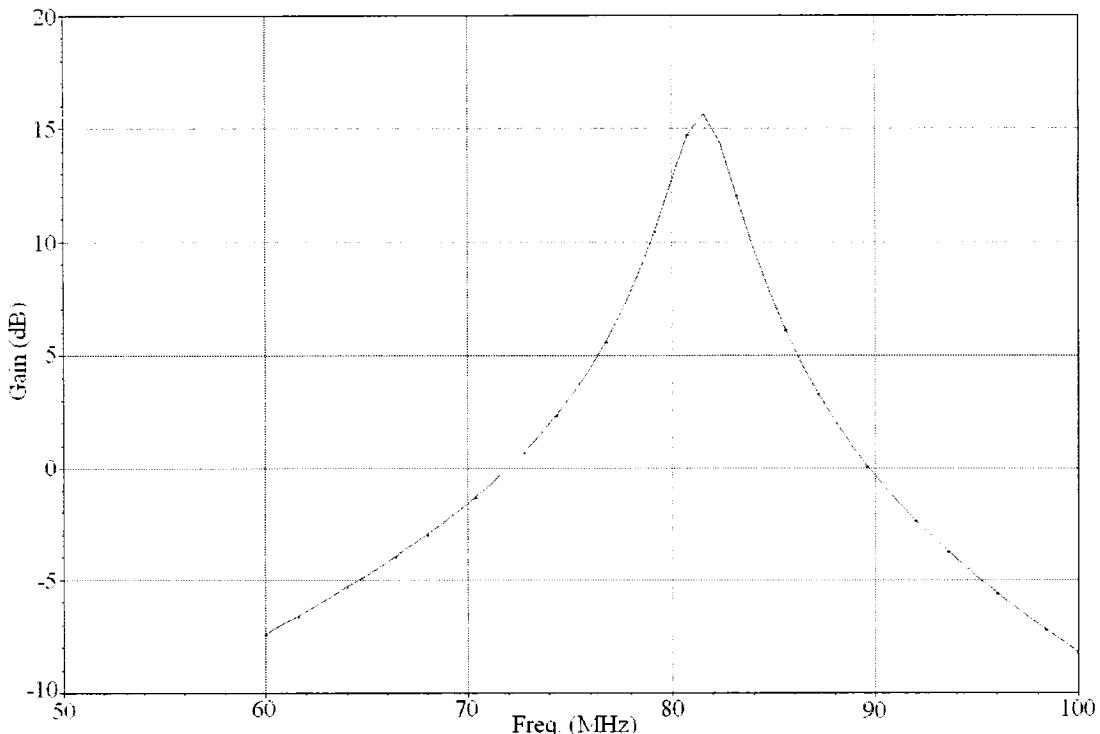

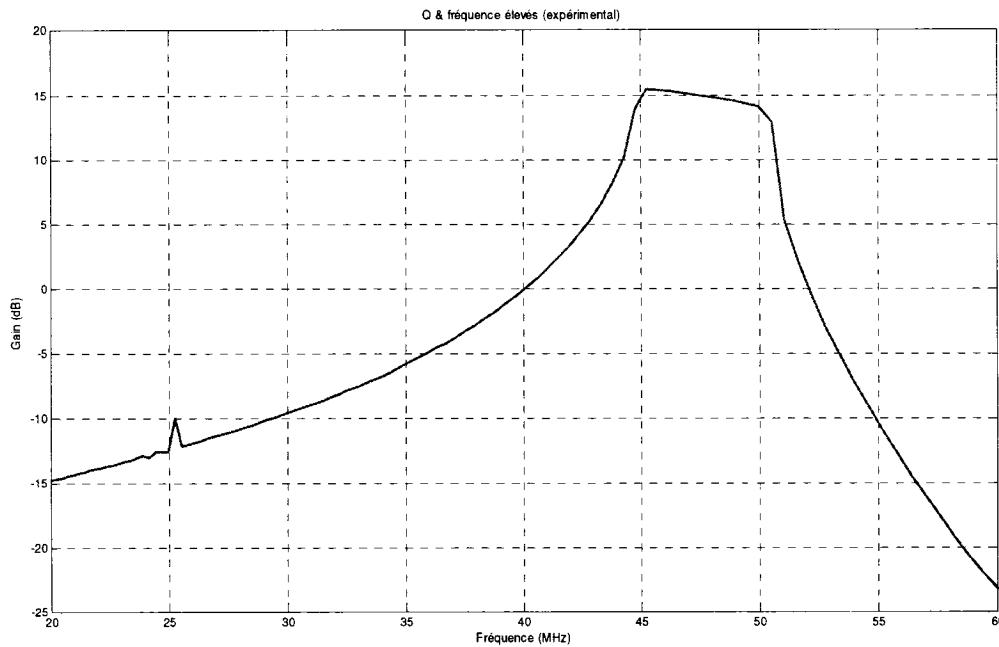

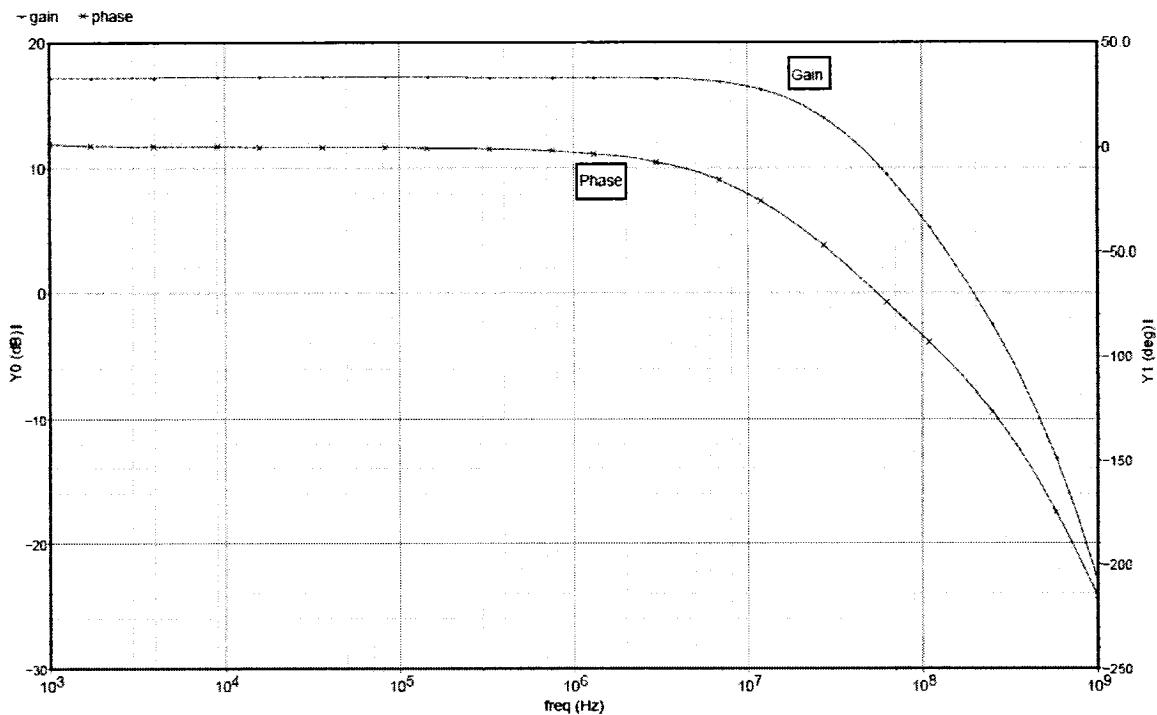

The measured reduction in the frequency range compared to the theoretical and simulation results is attributed to larger parasitic capacitances even if they were taken into account during post-layout simulations. Figure 3.10 presents similar settings, but the low-pass output is observed here. Also, Figure 3.11 shows the ability to program  $Q$  at a fixed frequency. Three fabricated chips have been measured and Table 3.1 summarizes the performance of the worst case among the three chips.

Table 3.2 presents a comparison with other programmable filter designs based on Gm-C architecture. Our circuit has the advantages to provide a low-pass and a band-pass output with good quality factor and frequency range although the frequency range could certainly be improved considering the advanced technology used ( $0.18\mu\text{m}$  CMOS process). The use of several transconductor cells in the circuit can be a drawback in terms of power consumption, but still the results obtained are excellent considering the achieved flexibility of the proposed programmable filter.

### 3.2.4 Conclusion

A high performance programmable band-pass filter using an array of transconductance circuits is presented. The filter parameters are controlled by selectively activating and deactivating transconductance blocks so current source and biasing voltages are fixed. Fine-tuning is implemented with programmable capacitors. Silicon measurements showed frequency operating range from 5.9 MHz to 58 MHz and a quality factor that can be tuned from 0.36 to 10. Future work involves the design of an FPAAs that can be configured to provide more analog functions such as programmable current and voltage amplifiers within the same chip.

### 3.2.5 Acknowledgments

The authors would like to thank the Natural Sciences and Engineering Research Council of Canada (NSERC) for the financial support and the Canadian Microelectronics Corporation (CMC Microsystems) for providing the design tools.

### 3.2.6 References

- [1] M. Jankovec and M. Topic, "Analog circuit development system", in *Proc. IEEE Region 8 Computer as a Tool EUROCON*, vol. 1, pp. 125-129, September 2003.

- [2] P. G. Gulak, "Field programmable analog arrays: past, present and future perspectives", in *Proc. IEEE Region 10 International Conference on Microelectronics and VLSI*, pp. 123-126, November 1995.