**Titre:** Conception d'un processeur à vitesse variable et synthèse d'horloge à période ajustable

Title: [Conception d'un processeur à vitesse variable et synthèse d'horloge à période ajustable](#)

**Auteur:** Dimitri Gabriel Epassa Habib

Author: [Dimitri Gabriel Epassa Habib](#)

**Date:** 2006

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Epassa Habib, D. G. (2006). Conception d'un processeur à vitesse variable et synthèse d'horloge à période ajustable [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7709/>

Citation: [Epassa Habib, D. G. \(2006\). Conception d'un processeur à vitesse variable et synthèse d'horloge à période ajustable \[Mémoire de maîtrise, École Polytechnique de Montréal\]. PolyPublie. https://publications.polymtl.ca/7709/](#)

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7709/>

PolyPublie URL: [https://publications.polymtl.ca/7709/](#)

**Directeurs de recherche:** Yvon Savaria, & François-Raymond Boyer

Advisors: [Yvon Savaria](#), [François-Raymond Boyer](#)

**Programme:** Non spécifié

Program: [Non spécifié](#)

UNIVERSITÉ DE MONTRÉAL

CONCEPTION D'UN PROCESSEUR À VITESSE VARIABLE ET

SYNTHÈSE D'HORLOGE À PÉRIODE AJUSTABLE

EPASSA HABIB DIMITRI GABRIEL

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE INFORMATIQUE)

AVRIL 2006

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-17940-6

*Our file* *Notre référence*

ISBN: 978-0-494-17940-6

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

**CONCEPTION D'UN PROCESSEUR À VITESSE VARIABLE ET

SYNTHÈSE D'HORLOGE À PÉRIODE AJUSTABLE**

présenté par : EPASSA Habib Dimitri Gabriel

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

Mme NICOLESCU Gabriela, Doct., Présidente

M. BOYER François-Raymond, Ph.D., membre et directeur de recherche

M. SAVARIA Yvon, Ph.D., membre et codirecteur de recherche

M. ABOULHAMID El Mostapha, Ph.D., membre

## REMERCIEMENTS

Je tiens à remercier Messieurs Francois-Raymond Boyer et Yvon Savaria, respectivement directeur et co-directeur de maîtrise pour leur disponibilité, leurs conseils et suggestions, ainsi que le support financier qu'ils ont apporté afin de mener à bien ce projet de recherche jusqu'à sa consécration.

Mes remerciements vont aussi à tous les collègues et camarades du GRM (Groupe de Recherche en Microélectronique) sans exception, des étudiants aux techniciens et personnel administratif. En un mot, tous ceux qui ont fait partie de mon quotidien durant ces trois ans d'études supérieures. En particulier, à M. Bill Pontikakis qui a partagé avec moi les tâches au tout début du projet.

Une mention spéciale à mes parents, et ma famille étendue du Cameroun au Canada, pour leur présence et leur soutien moral tout au long de mes études. Sans oublier, mes amis qui m'ont permis de m'épanouir en dehors du milieu étudiantin.

## RÉSUMÉ

Avec l'avancée technologique des produits électroniques portables, les manufacturiers essaient du mieux qu'ils peuvent de se rapprocher des performances des ordinateurs de bureaux. Ces derniers, puisant leur source d'énergie directement des prises du réseau électrique domestique, ne sont pas confrontés aux mêmes problèmes sévères d'économie d'énergie. En revanche, les équipements portatifs fonctionnant à l'aide de batteries ont besoin d'une autonomie satisfaisante pour les usagers tout en maintenant un niveau de performance suffisant. Étant donné que la performance est proportionnelle à la consommation d'énergie, un compromis s'impose lors du design des processeurs actuels. La majeure partie de la recherche, concernant les manufacturiers populaires comme Intel, AMD, IBM, etc. est axée sur la conception de processeurs embarqués à consommation d'énergie réduite.

Plusieurs méthodes sont employées pour la conception de tels processeurs, la plupart allient l'ajustement de la tension d'alimentation avec la variation de la fréquence de l'horloge système, méthode utilisée par les processeurs DVS (Dynamic Voltage Scaling). Dans ce rapport, les différentes architectures et méthodes de réduction de l'énergie consommée dans les processeurs embarqués sont explorées. Ces derniers utilisent des circuits de génération d'horloge dynamiquement ajustables ou synthétiseurs d'horloge programmables.

Nous présenterons dans ce mémoire la conception d'un processeur embarqué à vitesse variable (VSP) dont la période de l'horloge est ajustée à chaque cycle, selon les instructions qui se présentent pour exécution dans le pipeline. Pour atteindre nos objectifs, le projet de recherche est effectué en deux volets : En premier lieu, la conception du VPCS, un circuit de synthèse d'horloge à période d'horloge variable, est

effectuée en technologie ASIC 0,18 $\mu$ m. Le circuit permet d'effectuer la multiplication ainsi que la division de la fréquence de l'horloge de référence par un facteur fractionnel quelconque, contrairement au DDPS de la littérature existante qui ne permet que de multiplier la fréquence par un facteur plus grand que un. Le circuit proposé suit les règles de conception des circuits à consommation réduite de puissance, et est comparable en performance aux circuits de la littérature. Il se présente sous forme d'un noyau logiciel codé en VHDL facilement intégrable avec tout processeur dont le noyau serait accessible.

En second lieu, le processeur proposé est basé sur un processeur RISC standard de type Nios provenant de la société Altera®. En combinaison avec le VPCS et modifié pour obtenir les fonctionnalités désirées, il est implémenté dans la plateforme de systèmes embarqués du FPGA Stratix™. Un prototype est réalisé avec succès, fonctionnant avec une horloge dont la fréquence oscille entre 110 MHz et 147 MHz selon que les instructions soient « lentes » ou « rapides », permettant d'obtenir une accélération par rapport au Nios standard à performance maximale avec une consommation d'énergie par opération bien réduite.

## ABSTRACT

With the technology advances applied to electronic portable devices, the main goal for their manufacturers is to achieve as much as possible the same performance as desktop personal computers. With the latter, the energy source is taken from domestic electric outlet and there is no pressing need to save energy, while battery-powered portable devices need long lasting battery life, keeping a sufficient level of performance. Since having an increase in performance leads to an increase in energy consumption, energy efficient processors design becomes a very pressing issue. Manufacturers of popular processors such as Intel, AMD, IBM, etc. address that issue with some commercial embedded processors designed to be low power.

Many methods exist to design the above processors. The major methods will achieve energy reduction by adjusting the supply voltage along with the operating frequency which is used in Dynamic Voltage Scaling (DVS) processors. In this thesis, we explore different methods and architectures for energy reduction in embedded processors, which use dynamic adjustable clock generators or programmable frequency synthesizers.

We present a Variable Speed Processor (VSP), which is an embedded processor with a system clock period that can change every cycle, according to the instructions being executed by the pipeline. To achieve our goal, the design process is done in two steps. First, we designed a Variable Period Clock Synthesis Circuit (VPCS) in ASIC 0,18 $\mu$ m technology, which can multiply and divide on the fly the reference clock frequency with a fractional number that can be larger than unity, compared to the Direct Digital Period Synthesis Circuit (DDPS) that can only multiply the frequency (multiply the period by a number below unity). The proposed circuit design follows the low power design rules and is comparable to clock generators found in the literature in terms of performance.

Secondly, the proposed processor is implemented by coupling the VPCS and the standard RISC Nios processor from Altera. The Nios core is modified so that the desired functionalities are achieved. The design is prototyped into the embedded systems platform for the Stratix™ FPGA. The experimental circuit runs with a 110 MHz frequency for “slow” instructions and 147 MHz for “fast” instructions, giving a speedup upon the standard Nios at peak performance with energy per operation savings.

## TABLE DES MATIÈRES

|                                                                                 |     |

|---------------------------------------------------------------------------------|-----|

| REMERCIEMENTS .....                                                             | IV  |

| RÉSUMÉ .....                                                                    | V   |

| ABSTRACT .....                                                                  | VII |

| TABLE DES MATIÈRES .....                                                        | IX  |

| LISTE DES FIGURES.....                                                          | XII |

| LISTE DES TABLEAUX.....                                                         | XIV |

| SIGLES ET ABRÉVIATIONS.....                                                     | XV  |

| LISTE DES ANNEXES.....                                                          | XVI |

| CHAPITRE 1 INTRODUCTION .....                                                   | 1   |

| 1.1 MOTIVATIONS .....                                                           | 1   |

| 1.2 OBJECTIFS DE LA RECHERCHE .....                                             | 1   |

| 1.3 CONTRIBUTIONS ET PUBLICATIONS .....                                         | 2   |

| 1.4 PLAN DU MÉMOIRE.....                                                        | 4   |

| CHAPITRE 2 REVUE DE LITTÉRATURE .....                                           | 5   |

| 2.1 CIRCUITS DE SYNTHÈSE D'HORLOGE .....                                        | 5   |

| 2.1.1 Synthèse d'horloge traditionnelle : les PLL.....                          | 5   |

| 2.1.2 Synthèse numérique directe d'ondes (DDS) .....                            | 14  |

| 2.1.3 Synthèse numérique directe de périodes (DDPS) .....                       | 18  |

| 2.1.4 Autres méthodes de synthèse d'horloge.....                                | 21  |

| 2.2 PROCESSEURS À FAIBLE CONSOMMATION DE PUISSANCE ET À FRÉQUENCE VARIABLE..... | 23  |

| 2.2.1 Modèle : puissance et énergie .....                                       | 23  |

|                                                                                                                               |                                                                       |    |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----|

| 2.2.2                                                                                                                         | Techniques de réduction d'énergie dans les processeurs embarqués..... | 24 |

| 2.2.3                                                                                                                         | Réduction d'énergie appliquée aux processeurs DVS .....               | 25 |

| CHAPITRE 3 MÉTHODOLOGIE D'IMPLÉMENTATION.....                                                                                 |                                                                       | 31 |

| 3.1                                                                                                                           | MÉTHODOLOGIE DE CONCEPTION ASIC DU VPCS.....                          | 31 |

| 3.1.1                                                                                                                         | Spécifications .....                                                  | 32 |

| 3.1.2                                                                                                                         | Description VHDL et simulation .....                                  | 33 |

| 3.1.3                                                                                                                         | Synthèse et optimisations.....                                        | 34 |

| 3.1.4                                                                                                                         | Simulation après synthèse .....                                       | 35 |

| 3.1.5                                                                                                                         | Estimation de la puissance dynamique consommée .....                  | 35 |

| 3.2                                                                                                                           | MÉTHODOLOGIE D'IMPLÉMENTATION FPGA POUR LE VSP .....                  | 38 |

| 3.2.1                                                                                                                         | Spécifications et configuration du système.....                       | 39 |

| 3.2.2                                                                                                                         | Analyse du jeu d'instructions.....                                    | 41 |

| 3.2.3                                                                                                                         | Profilage des délais d'instructions .....                             | 41 |

| 3.2.4                                                                                                                         | Adaptation du VPCS en technologie FPGA .....                          | 42 |

| 3.2.5                                                                                                                         | Estimation de la puissance consommée .....                            | 43 |

| 3.2.6                                                                                                                         | Configuration et prototypage .....                                    | 43 |

| CHAPITRE 4 PROCESSEUR EMBARQUÉ À FAIBLE CONSOMMATION DE<br>PUISSEANCE AVEC VITESSE VARIABLE À CHAQUE CYCLE<br>D'HORLOGE ..... |                                                                       | 46 |

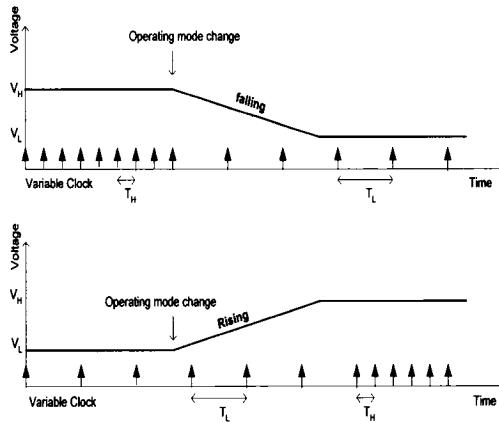

| 4.1                                                                                                                           | ARCHITECTURE DU GÉNÉRATEUR D'HORLOGE .....                            | 48 |

| 4.2                                                                                                                           | APERÇU ARCHITECTURAL DU VSP .....                                     | 52 |

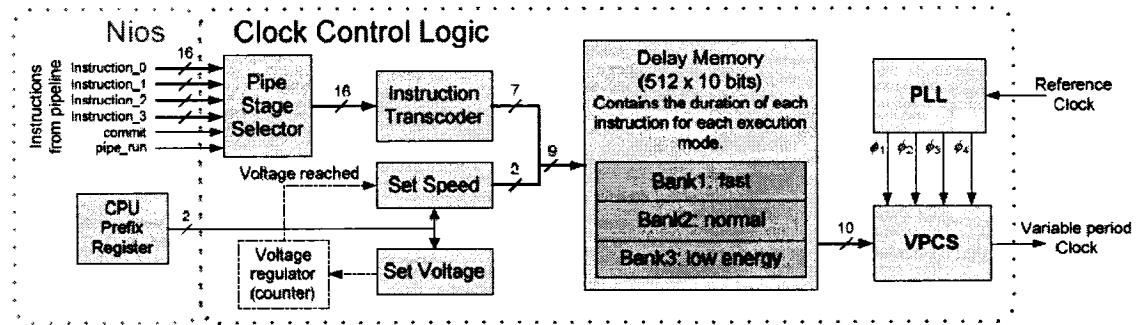

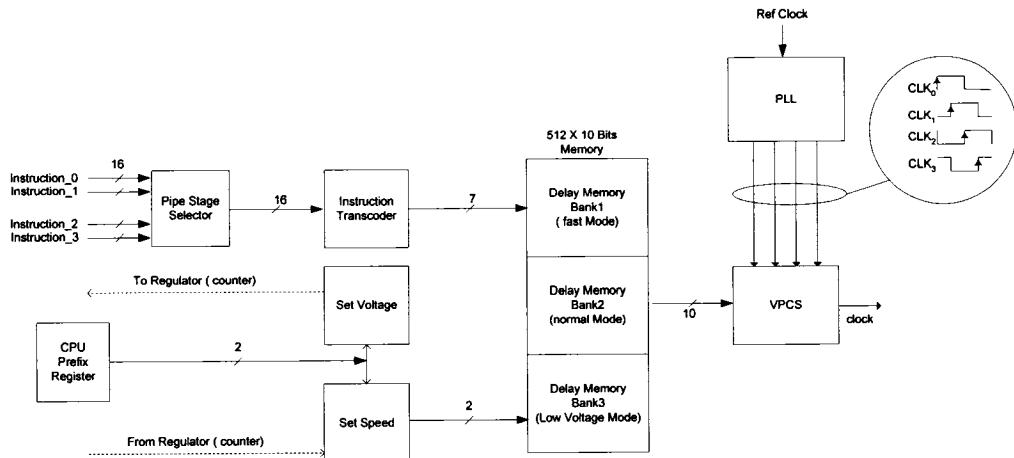

| 4.2.1                                                                                                                         | Diagramme Bloc .....                                                  | 53 |

| 4.2.2                                                                                                                         | La logique de contrôle.....                                           | 55 |

| 4.2.3                                                                                                                         | Aléas du Pipeline.....                                                | 57 |

| 4.2.4                                                                                                                         | Résultats de synthèse du VPCS.....                                    | 58 |

| 4.3                                                                                                                           | RÉSULTATS D'EXPÉRIMENTATION DU VSP ET DISCUSSION.....                 | 60 |

| 4.4                                                                                                                           | ANALYSE D'EFFICACITÉ DU VSP.....                                      | 61 |

|                                     |                                                     |    |

|-------------------------------------|-----------------------------------------------------|----|

| 4.5                                 | IMPACT DES INSTRUCTIONS SPÉCIALISÉES .....          | 63 |

| 4.6                                 | SYNCHRONISATION ENTRE LE VSP ET LE PORT SÉRIE ..... | 63 |

| 4.7                                 | ACCÉLÉRATION MAXIMALE DU NIOS.....                  | 64 |

| CHAPITRE 5 CONCLUSION GÉNÉRALE..... |                                                     | 66 |

| 5.1                                 | SYNTHÈSE DES TRAVAUX .....                          | 66 |

| 5.2                                 | INDICATIONS DE RECHERCHES FUTURES.....              | 69 |

| ANNEXES .....                       |                                                     | 75 |

## LISTE DES FIGURES

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Figure 2-1 : Diagramme bloc général d'un PLL [D. Abravomitch, 2002].                              | 7  |

| Figure 2-2 : Schéma de principe de circuit oscillant.                                             | 8  |

| Figure 2-3. Oscillateur à boucle d'inverseurs [Yalcin Elper Eken et Al, 2004].                    | 9  |

| Figure 2-4 : Principe d'asservissement.                                                           | 9  |

| Figure 2-5 : Diagramme Bloc d'un PLL numérique classique.                                         | 10 |

| Figure 2-6 : Diagramme Bloc d'un PLL complètement numérique.                                      | 10 |

| Figure 2-7 : Diagramme bloc d'un PLL.                                                             | 11 |

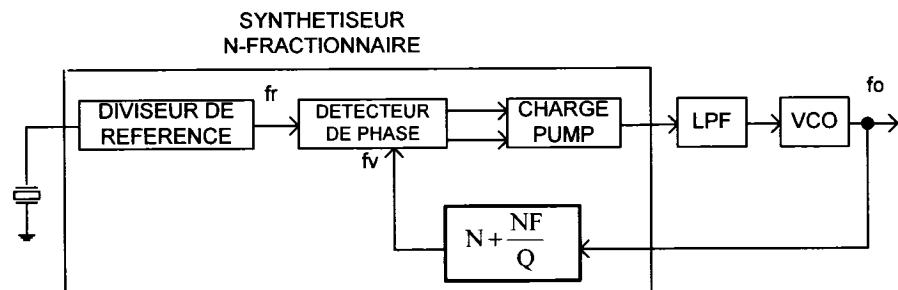

| Figure 2-8 : Synthétiseur de fréquence N-fractionnaire.                                           | 13 |

| Figure 2-9 : Diviseur modulaire N-Fractionnaire.                                                  | 14 |

| Figure 2-10 : Structure générale du DDS.                                                          | 15 |

| Figure 2-11 : Signal du DDS [Calbaza, 01].                                                        | 17 |

| Figure 2-12 : Diagramme bloc du DDPS [Calbaza et Al, 99].                                         | 19 |

| Figure 2-13 : Diagramme temporel du DDPS (Calbaza, 1999).                                         | 19 |

| Figure 2-14 : Architecture d'un "Flying Adder".                                                   | 22 |

| Figure 2-15 : Mesures voltage vs fréquence pour le ARM926EJ-ST <sup>TM</sup> [Clive Watts, 2003]. | 26 |

| Figure 2-16 : Régulateur de voltage [Kuroda T, 24].                                               | 28 |

| Figure 2-17 : Régulation par boucle de fréquence à voltage [BURD T.D, 10].                        | 29 |

| Figure 3-1 : Flot de design pour implémentation en ASIC.                                          | 32 |

| Figure 3-2 : Méthodologie et flux de donnée de l'analyse de puissance.                            | 36 |

| Figure 3-3 : Flot de création de fichiers saif.                                                   | 37 |

| Figure 3-4 : Flot de design avec Quartus II [Altera design flow].                                 | 38 |

| Figure 3-5 : Exemple de système généré par SOPCBuilder.                                           | 40 |

| Figure 3-6 Diagramme Block de la carte de développement [Altera Corporation].                     | 45 |

|                                                                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

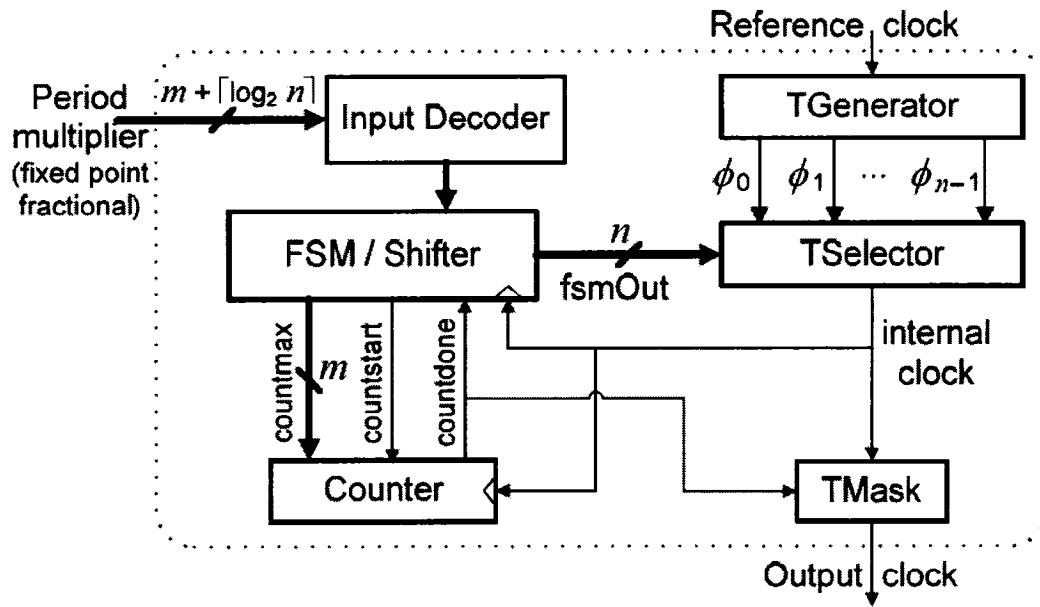

| Figure 4-1 : Diagramme Bloc du VPCS.....                                                                                                                                                                                        | 48 |

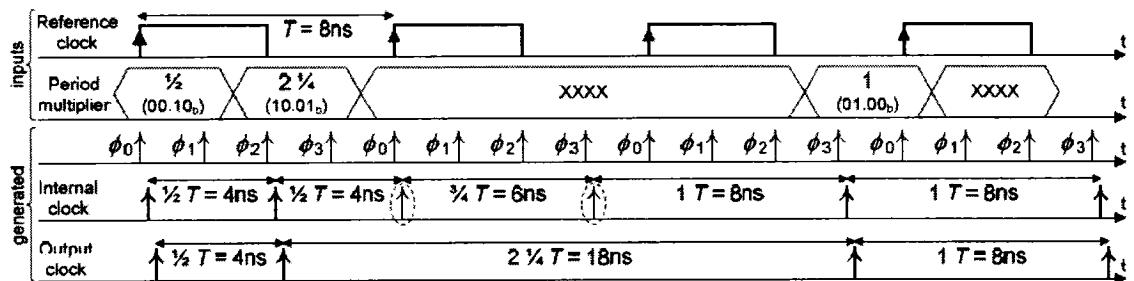

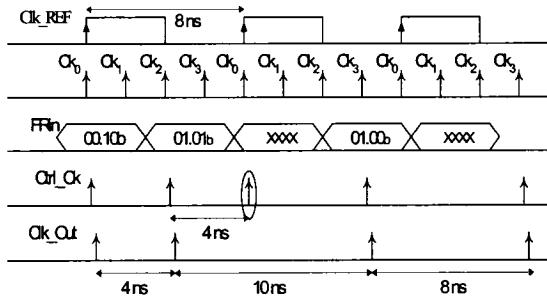

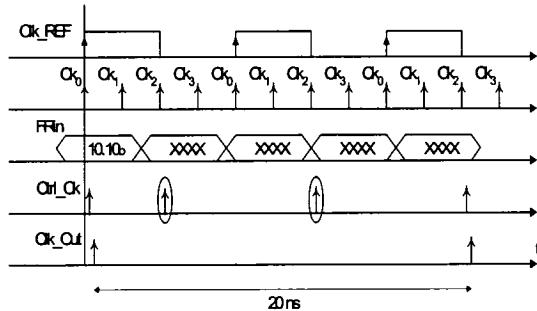

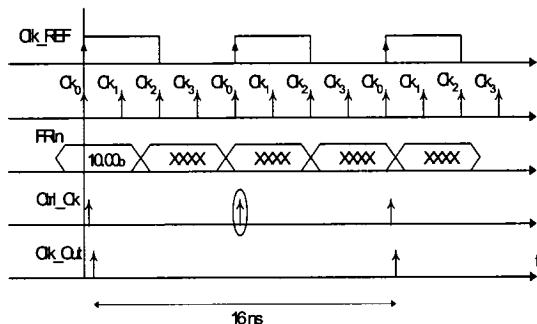

| Figure 4-2 : Diagramme Temporel.....                                                                                                                                                                                            | 50 |

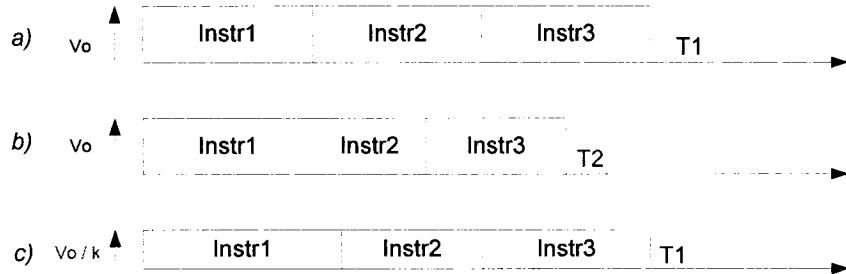

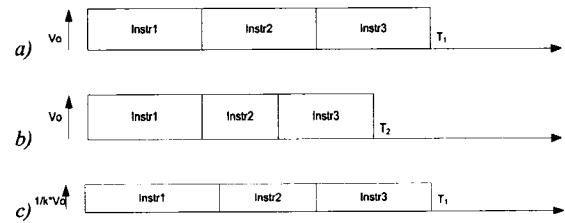

| Figure 4-3 a) Application sans l'ajustement des cycles d'horloge, b) même application utilisant les cycles variables, c) l'application à la même vitesse que celle en a) , mais avec moins d'énergie et un voltage réduit. .... | 53 |

| Figure 4-4 : Architecture du VSP prototype implémenté sur FPGA. ....                                                                                                                                                            | 54 |

| Figure 4-5 : Aperçu de la plateforme VSP.....                                                                                                                                                                                   | 54 |

| Figure 4-6 : Régulation de voltage.....                                                                                                                                                                                         | 56 |

| Figure 4-7 : Caractéristiques de Synthèse ASIC du VPCS. ....                                                                                                                                                                    | 59 |

| Figure 4-8 : Table de mesures expérimentales sur 100 $\mu$ s de simulation.....                                                                                                                                                 | 63 |

**LISTE DES TABLEAUX**

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| Tableau 2-1 Rapports de division communs entre fréquences vidéo et audio.....    | 12 |

| Tableau 2-2 Caractéristiques de quelques processeurs DVS commerciaux connus..... | 27 |

## SIGLES ET ABRÉVIATIONS

|       |                                               |

|-------|-----------------------------------------------|

| ADPLL | : All Digital PLL                             |

| CPU   | : Central Processing Unit                     |

| CVS   | : Clustered Voltage Scaling                   |

| DCO   | : Digitally Controlled Oscillator             |

| DDPS  | : Direct Digital Period Synthesis             |

| DDS   | : Direct Digital Synthesis                    |

| DFCS  | : Dynamic Frequency Clocking Scheme           |

| DPCD  | : Dynamic Clock Programmable Divider          |

| DPM   | : Dynamic Power Management                    |

| DVS   | : Dynamic Voltage Scaling                     |

| PIO   | : Parallel Interface Output                   |

| PLL   | : Phase Locked Loop                           |

| SAIF  | : Switching Activity Input File               |

| SDF   | : Standard Delay File                         |

| UART  | : Universal Asynchronous Receiver Transmitter |

| VCO   | : Voltage Controlled Oscillator               |

| VSP   | : Variable Speed Processor                    |

## **LISTE DES ANNEXES**

|                        |           |

|------------------------|-----------|

| <b>Annexe A.</b> ..... | <b>76</b> |

| <b>Annexe B.</b> ..... | <b>82</b> |

# CHAPITRE 1

## Introduction

### 1.1 Motivations

Les designs des processeurs actuels ne se consacrent pas seulement aux besoins de haute performance à combler, mais de plus en plus, ils répondent à une nécessité de dissiper le moins de chaleur possible, c'est-à-dire de consommer moins de puissance que les processeurs employés dans les ordinateurs personnels de bureau. Il s'agit aussi de diminuer la consommation de l'énergie provenant des piles ou des batteries, pour ce qui est des processeurs d'équipements embarqués tels que les téléphones cellulaires, les organisateurs numériques personnels, etc.. L'idée première qui a orienté la rédaction de ce mémoire était de vérifier dans quelle mesure un circuit électronique digital, qui s'adapterait aux conditions variables de fonctionnement, serait implanté. Cette variabilité pourrait venir des changements de température du circuit, des variations des procédés de fabrication, des changements de la tension d'alimentation ainsi que des variations de la source d'énergie. Ce circuit réduirait ainsi dynamiquement sa vitesse au fur et à mesure que la température augmente, ou lorsque les délais du circuit s'allongent, ou encore quand la tension ou l'énergie restante dans la batterie baissent. Les grands constructeurs de processeurs tels que Intel® et AMD® intègrent déjà ces astuces, fabriquant ainsi des processeurs alliant haute performance et faible consommation.

### 1.2 Objectifs de la recherche

Faire varier la vitesse d'opération selon les conditions de fonctionnement est un facteur clé dans la conception de processeurs à faible consommation de puissance et d'énergie. Plusieurs circuits dans la littérature courante sont capables de synthétiser l'horloge à

partir d'une horloge de référence. Cette fonction est paramétrable, donc la cadence de l'horloge peut être ajustée selon les besoins du concepteur.

L'objectif principal du projet réalisé tout au long de ce mémoire est de concevoir un circuit électronique qui change dynamiquement sa période d'horloge dans un intervalle d'un seul cycle d'horloge.

Nos recherches ont conduit à l'ajout de plusieurs fonctions aux circuits existants dans la littérature, en concevant un circuit de synthèse d'horloge à période variable aussi dynamique, complètement numérique et intégrable sur puce que le DDPS, mais avec une couverture de fréquence plus élevée vue sa capacité à diviser et multiplier la période de l'horloge.

Les applications courantes les plus en demande de variabilité de la fréquence des opérations sont les processeurs à consommation de puissance faible et ajustable selon la charge de travail. Le projet de recherche vise, par la même occasion, à fabriquer un tel processeur en s'aidant du circuit de synthèse d'horloge à période variable, avec une méthodologie compatible aux architectures à faible consommation de puissance existantes, mais différentes du point de vue de l'ajustement de la fréquence d'opération.

### **1.3 Contributions et publications**

Ce mémoire contient les fruits d'une recherche avancée qui ont été synthétisés dans la production de 2 articles de conférence et d'un article soumis auprès d'une revue scientifique.

Le premier article présente la conception du circuit de VPCS, le générateur d'horloge à période variable adapté aux circuits de faible consommation de puissance. Le second article présente un processeur embarqué à vitesse variable utilisant le VPCS pour ajuster la période de son horloge selon chaque instruction issue de son pipeline prête à être exécutée. Le troisième article, soumis pour publication dans une revue présente le processeur à vitesse variable avec son générateur d'horloge à période variable en détails, et effectue une analyse de la performance ainsi que de la réduction en consommation d'énergie atteinte.

**Articles de Conferences:**

1 - Boyer, F-R.; Epassa, H.G.; Pontikakis, B.; Savaria, Y.; Wei Ling, - “A variable period clock synthesis (VPCS) architecture for next-generation power-aware SoC applications”

Circuits and Systems, 2004. NEWCAS 2004. The 2nd Annual IEEE Northeast Workshop on, 20-23 June 2004 Page(s):145 - 148

2 - Epassa, H.G; Boyer, F-R; Savaria, Y – “Implementation of a Cycle by Cycle Variable Speed Processor” Circuits and Systems, 2005. ISCAS 2005. IEEE International Symposium on 23-26 May 2005 Page(s):3335 - 3338

**Article de Revue:**

Boyer, F-R; Epassa, H.G; Savaria, Y – “Embedded Power-Aware Cycle by cycle Variable Speed Processor”

Soumis pour publication au *IEE Proceedings Computers & Digital Techniques*

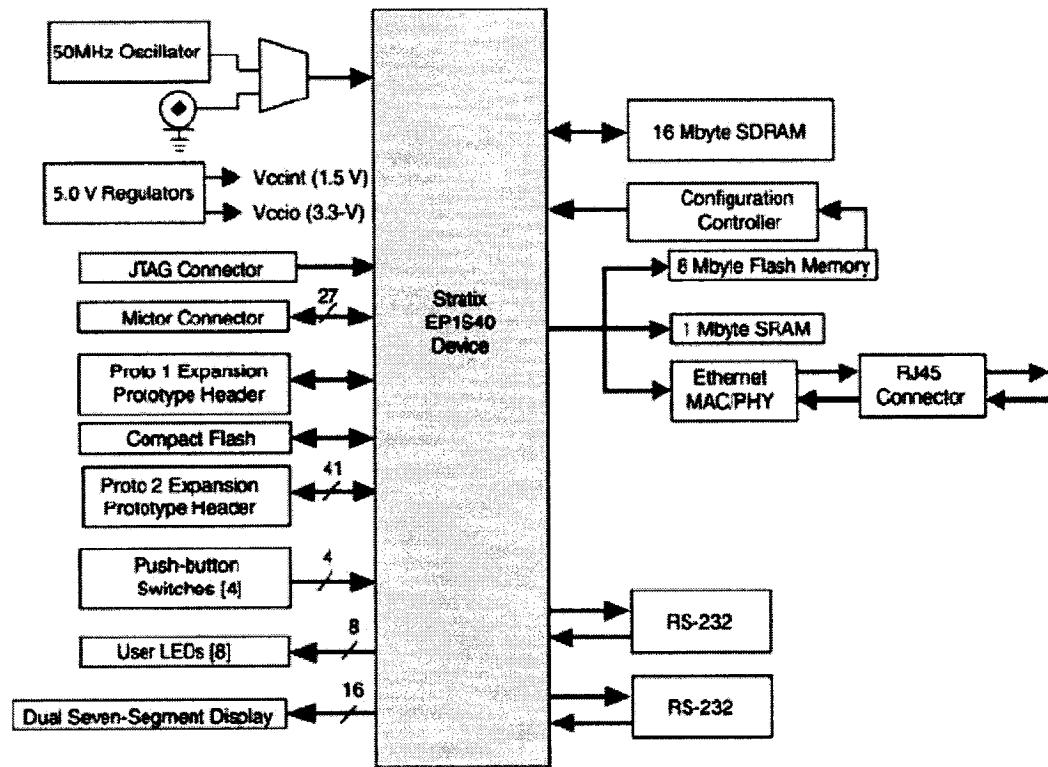

**Circuits de prototypage :** Carte de développement de système embarqué FPGA Stratix™ EPS140

Le circuit a été implémenté sur la plateforme de prototypage rapide « *Embedded System development platform, Stratix Edition* » de la société Altera qui contient un processeur RISC Nios dont le noyau logiciel est disponible et modifiable.

## 1.4 Plan du mémoire

Ce mémoire est composé de cinq chapitres répartis comme suit :

Le chapitre 2 présente une revue de littérature sur l'évolution de la synthèse d'horloge à l'aide de PLL, incluant les circuits de synthèse numérique d'horloge récemment utilisés, ainsi que les différentes architectures de processeurs à basse puissance, utilisant les techniques de réduction de la consommation d'énergie et de puissance.

Le chapitre 3 élabore sur les méthodes de conception qui ont contribué à la réalisation de ce projet. Ce chapitre décrit de manière détaillée, la méthodologie et les outils utilisés spécifiquement lors de la conception d'un processeur à vitesse variable sur une plateforme FPGA avec un processeur embarqué.

Le chapitre 4 présente les résultats issus de notre travail. Il s'agira d'une compilation des travaux effectués tout au long du projet, allant de la conception du générateur d'horloge VPCS à l'implémentation du VSP. On y retrouve également des résultats d'implémentation, une étude détaillée et comparative de la méthode à période d'horloge variable appliquée au processeur embarqué NIOS. Le chapitre est un condensé de l'article de revue, soumis pour publication auprès du journal « *Computer and Digital techniques* » de la société IEE.

Enfin, en guise de conclusion, le dernier chapitre fait un bilan du travail de recherche effectué et propose des ouvertures éventuelles pour des travaux futurs.

## CHAPITRE 2

### Revue de littérature

Dans les systèmes à microprocesseurs, on retrouve toujours une partie de circuit dédiée à la génération de l'horloge du système. Ce type de circuiterie réalise ce qui est communément appelé une synthèse de fréquence. L'horloge provenant du cristal de quartz est retransformée pour rencontrer les spécifications requises pour les circuits numériques synchrones, ainsi que pour les réseaux de distribution d'horloge. Ce chapitre explore les différentes architectures de circuits de synthèse d'horloge existants, ainsi que les différentes architectures de processeurs embarqués à basse puissance, dont la fréquence de l'horloge est dynamiquement variable. Ceci permettra de faire une comparaison entre ces architectures et la notre.

#### 2.1 Circuits de synthèse d'horloge

Depuis la découverte des propriétés oscillatoires des cristaux, les travaux sur les circuits de synthèses d'horloge se sont intensifiés. Ce paragraphe présente ces circuits en partant du traditionnel PLL jusqu'aux circuits de synthèse d'horloge actuels.

##### 2.1.1 Synthèse d'horloge traditionnelle : les PLL

Il y a environ un siècle, l'effet piézoélectrique des cristaux fut découvert par les chercheurs Pierre et Jacques Curie. En effet, en appliquant un champ électrique autour d'un cristal, sa structure subit une distorsion, lui donnant une propriété oscillatoire.

Avec l'évolution du « sans-fil », les besoins en précision de fréquence se sont accrus, ce qui a conduit à l'évolution des recherches sur les oscillateurs à cristal.

Malgré cela, les oscillateurs à cristal sont limités, car la gamme de fréquences qu'ils peuvent fournir n'est pas assez étendue. Pour pallier à cette limitation, certaines méthodes proposent d'utiliser des capacités variables ou des circuits répondant aux harmoniques de la fréquence fondamentale du cristal, mais n'entraînent qu'une variation très légère de cette dernière. D'autres solutions ont aussi été longtemps utilisées. Notamment, celles qui consistent en l'usage d'une structure hétérodyne ou de mixage afin d'utiliser la somme et la différence entre deux fréquences d'oscillateurs. Elles ont permis d'avoir une plus large gamme de fréquences, tout en maintenant la stabilité de l'horloge des oscillateurs à cristal.

L'utilisation des boucles de verrouillage de phase (PLLs) est apparue depuis plusieurs années, présentés par Gupta [21] et Lindsey [25], et continue toujours d'être populaire. Plusieurs ouvrages [3],[5],[7],[10],[17],[26],[27],[32],[37],[39],[42], ont été publiés sur la théorie et la conception des PLLs dont l'utilisation est avantageuse, grâce à leur structure de boucle fermée à asservissement. Ils servent notamment à effectuer des recouvrements de porteuses, des recouvrements d'horloge, la démodulation de fréquence et de phase, la modulation de phase, la synchronisation d'horloges et la synthèse d'horloge.

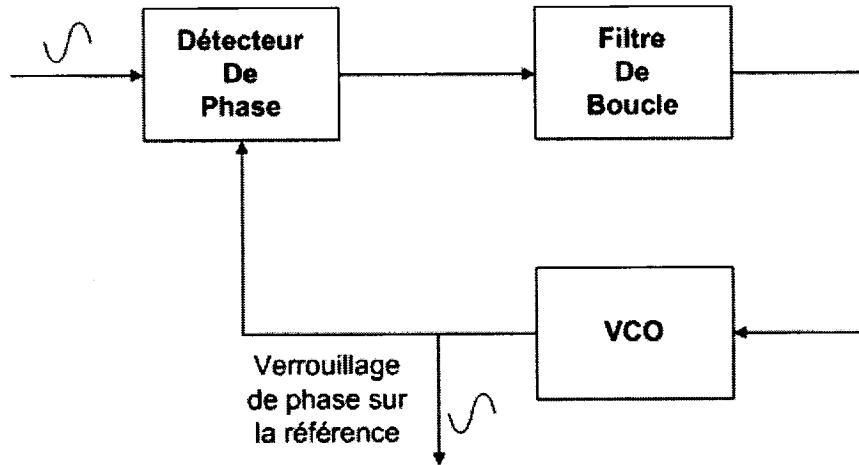

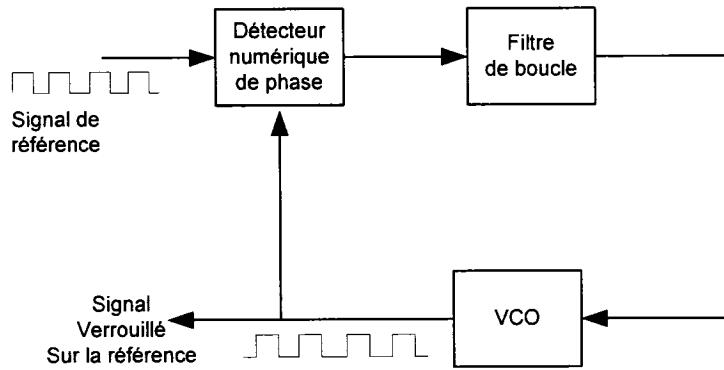

La méthode de verrouillage de phase est donc la méthode de synthèse de fréquence qui est la plus communément utilisée pour la production des oscillations à hautes fréquences dans les équipements modernes de communication. Sa structure la plus simple est représentée à la **Figure 2-1**.

**Figure 2-1 :** Diagramme bloc général d'un PLL [D. Abravomitch, 2002].

Les éléments qui y sont illustrés font normalement partie de toutes les variantes de PLL, notamment :

- Le DéTECTEUR De Phase (PD). C'est un circuit non linéaire qui détecte la différence de phase entre les deux signaux oscillatoires et produit un niveau de tension quasiment continu et proportionnel à cette différence;

- Le VCO produit une fréquence de sortie qui dépend du niveau de tension de son signal en entrée;

- Le filtre de boucle (LF) qui peut être omis, est un filtre passe bas, qui sert à la conception de PLL de premier ordre. Il sert à choisir la composante continue venant du détecteur de phase;

- La connexion en boucle permet d'assurer le verrouillage de la fréquence.

La propriété qui permet de varier la fréquence est réalisée par l'Oscillateur Contrôlé par tension (VCO). L'avantage de ce circuit vient du fait que sa fréquence est contrôlable

électriquement, ce qui n'était pas le cas pour les anciens oscillateurs à fréquence variable (VFO), pour lesquels les propriétés du circuit devaient être modifiées pour réaliser le changement de fréquence. Les VCOs sont souvent structurés comme une boucle d'inverseurs. Ils sont parfois structurés comme des oscillateurs à relaxation ou des oscillateurs résonants. L'oscillateur en boucle est très souvent utilisé dans les topologies monolithiques, comme illustré à la Figure 2-3. Il se compose souvent d'un nombre impair d'inverseurs connectés les uns aux autres et formant une boucle grâce à une connexion en rétroaction. L'oscillateur à relaxation utilise souvent un Trigger de Schmitt pour générer une onde carrée stable.

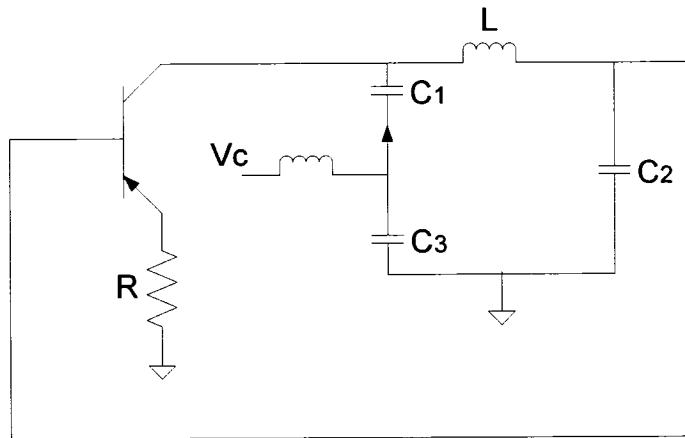

**Figure 2-2 :** Schéma de principe de circuit oscillant.

En ce qui concerne les VCO à oscillateurs résonants, un circuit résonnant comme celui de la Figure 2-2 est placé sur le feedback positif à la sortie d'un amplificateur de tension à courant ayant un gain proche de l'unité. Cette approche est illustrée à la Figure 2-4. La fréquence est contrôlée grâce à la présence d'une diode polarisée en inverse. Ainsi, la capacité de jonction varie selon la valeur instantanée de la tension. Une telle diode à capacité variable est parfois appelée Varicaps™.

**Figure 2-3.** Oscillateur à boucle d'inverseurs [Yalcin Elper Eken et Al, 2004].

D'autres formes de VCO utilisées sont les cristaux contrôlés par tension (VCXO), et les oscillateurs de types YIG qui se différencient tout simplement des autres par l'architecture des circuits résonnants.

**Figure 2-4 :** Principe d'asservissement.

La conception présentée précédemment d'un PLL trouve ses limites avec l'évolution des circuits intégrés à grande échelle, étant donné son caractère analogique. Il est difficilement intégrable sur une puce à cause des éléments analogiques passifs comme les inductances et les capacités. Les PLLs numériques ont non seulement pour rôle de pallier à cet inconvénient, mais ils se servent aussi du fait que l'horloge présente dans

les systèmes numériques, les ordinateurs et les systèmes de transmission numérique, utilise des ondes carrées au lieu des sinusoïdes.

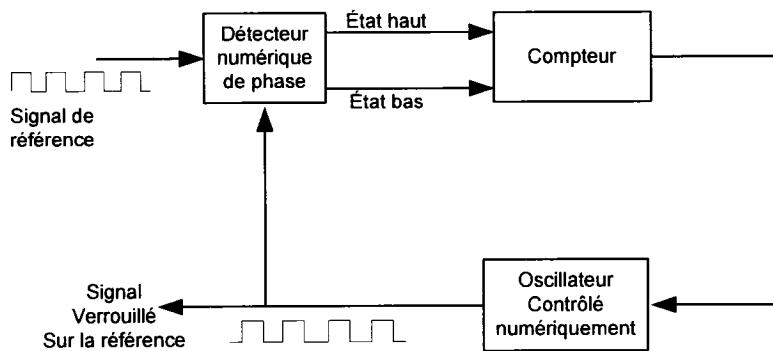

**Figure 2-5 :** Diagramme Bloc d'un PLL numérique classique.

La littérature [3] distingue deux sortes de PLLs numériques : les PLLs numériques classiques (CDPLL) dont l'architecture est illustré à la Figure 2-5, où seul le détecteur de phases est numérique, et les PLLs complètement numériques (ADPLL) qui utilisent des oscillateurs numériquement contrôlables (DCO) à la place des VCO, comme l'illustre la Figure 2-6.

**Figure 2-6 :** Diagramme Bloc d'un PLL complètement numérique.

La description précédente des PLL montre qu'ils permettent de générer un signal d'horloge stable et flexible dans le VCO, à la fréquence de référence, qui est celle de

l'horloge du cristal utilisé. Par contre, si l'on insère un diviseur de fréquence entre le détecteur de phase et le VCO, il sera possible de verrouiller le détecteur de phase à une fréquence qui est une fraction de la fréquence désirée dans le VCO. Par exemple, pour un diviseur par 2, et un cristal fonctionnant à 10 MHz, le détecteur de phase essaiera de verrouiller le VCO à 20MHz. De manière générale, la fréquence du signal à la sortie du VCO est tirée de la formule suivante :

$$\frac{f_{VCO}}{N} = f_{Clk} \quad (2.1)$$

Où  $N$  représente le facteur de division, et  $f_{Clk}$  la fréquence de l'horloge de référence.

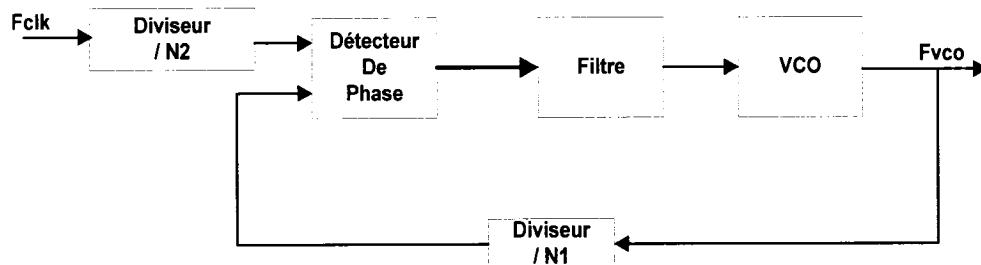

Une architecture plus complète du PLL est présentée à la Figure 2-7. Elle est à la base de nombreux travaux sur les circuits à fréquence variable, étant donné la possibilité de programmer le facteur de division.

**Figure 2-7 :** Diagramme bloc d'un PLL.

Notons la présence d'un diviseur additionnel inséré entre le générateur de l'horloge de référence et le détecteur de phase, afin d'obtenir un rapport de division de la fréquence de l'horloge à la sortie du VCO, exprimé de la sorte :

$$f_{VCO} = \frac{N1}{N2} \times f_{Clk} \quad (2.2)$$

Le rapport N1/N2 est utile pour la synchronisation entre les signaux audio et vidéo, étant donné qu'ils sont de fréquences différentes. Le Tableau 2-1 nous montre un exemple des normes de la télévision numérique, illustrant les rapports possibles entre les fréquences audio et vidéo.

Tableau 2-1 Rapports de division communs entre fréquences vidéo et audio

|                     |                 | Fréquences Audio       |                         |                         |

|---------------------|-----------------|------------------------|-------------------------|-------------------------|

|                     |                 | 4.0960<br>MHz          | 5.6448<br>MHz           | 6.1440<br>MHz           |

| Fréquences<br>Vidéo | 27.00000<br>MHz | <u>512</u><br>3375     | <u>392</u><br>1875      | <u>256</u><br>1125      |

|                     | 28.63636<br>MHz | <u>5632</u><br>39375   | <u>616</u><br>3125      | <u>2816</u><br>13125    |

|                     | 35.46895<br>MHz | <u>81920</u><br>709379 | <u>112896</u><br>709379 | <u>122880</u><br>709379 |

|                     | 36.00000<br>MHz | <u>128</u><br>1125     | <u>98</u><br>625        | <u>64</u><br>375        |

Les termes respectifs des rapports de division indiquent les nombres de cycles d'horloge requis de chacun des signaux avant de se synchroniser entre eux..

Comme il a été précisé dans les paragraphes précédents, les facteurs de division peuvent être changés automatiquement selon plusieurs méthodes. Certaines architectures utilisent des diviseurs d'horloge dynamiquement programmables [7], [9], qui permettent de diviser la fréquence de l'horloge autant par des nombres pairs que par des nombres impairs.

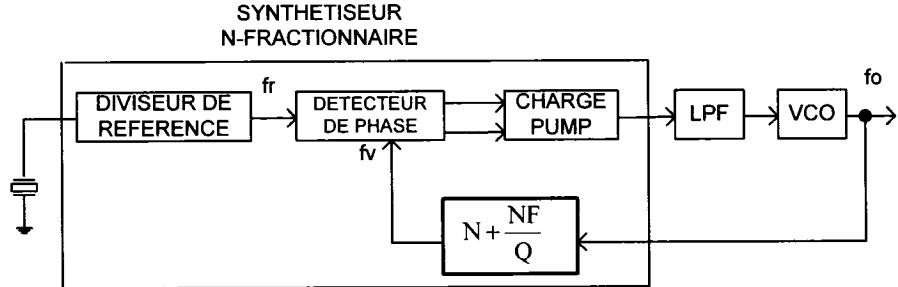

Il existe d'autres formes d'architectures à PLL qui permettent d'effectuer une division fractionnaire de la fréquence de l'horloge en moyenne. Ce sont les synthétiseurs

fractionnaires dont un exemple est illustré à la

Figure 2-8.

**Figure 2-8 :** Synthétiseur de fréquence N-fractionnaire [Rhee W , 00].

La division fractionnaire y est interpolée en utilisant un compteur bi modulaire qui est commandé soit par un accumulateur tel qu'illustré à la Figure 2-9 , soit par un modulateur delta sigma. En effet, le diviseur programmable a une valeur de division de N pour un certain nombre de périodes de l'horloge, et change à la valeur N+1 pour un autre nombre de cycles d'horloge. La valeur moyenne de la fréquence obtenue en sortie est une valeur contenant une partie fractionnaire qui dépend du signal de contrôle et de sa résolution en bits. Plusieurs types [16][34][35] de circuits de synthèse N-Fractionnaire d'horloge, avec plusieurs modes de contrôle des diviseurs programmables, existent dans la littérature.

**Figure 2-9 :** Diviseur modulaire N-Fractionnaire.

### 2.1.2 Synthèse numérique directe d'ondes (DDS)

La technique de synthèse numérique de fréquence (DDS) a vu le jour au début des années 1970, en tant que technique capable de générer des signaux sinusoïdaux avec une grande précision. La fréquence du signal à la sortie peut être contrôlée et ajustée à haute vitesse. Cependant ...L'article de J. Tierney [38] qui est l'un des pionniers de ce type circuit, présente un schéma global du DDS, explique sa fonctionnalité, et en énumère quelques applications possibles.

Dans le domaine des communications, le DDS est devenu une technique populaire compte tenu du besoin de produire des signaux sinusoïdaux précis, et de contrôler avec précision leur fréquence, phase et amplitude. Avec quelques modifications, cette technique est aussi utilisée pour générer d'autres types de forme d'ondes, tels les ondes triangulaires ou de forme arbitraire. D'autres applications incluent le domaine des radars, où la rapidité avec laquelle la fréquence change dans le DDS est un facteur

important. Les communications mobiles, telles que les systèmes de téléphonie cellulaire, utilisent le DDS pour générer des fréquences de référence.

Beaucoup d'articles dans la littérature présentent l'utilisation d'un circuit DDS dans chacun de ces domaines [19].

Ce circuit est aussi utilisé par D. Calbaza [12] pour effectuer la synchronisation entre les horloges vidéo et audio en DTV, car il permet de contrôler avec une précision accrue le rapport de division entre les fréquences de deux signaux – c'est à dire d'obtenir un signal qui a une fréquence contrôlée avec grande précision en utilisant une autre fréquence comme référence.

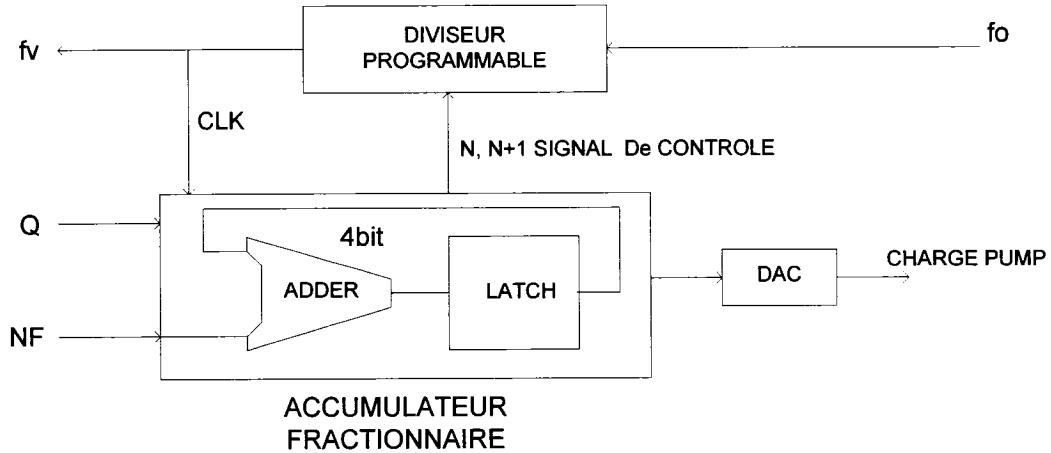

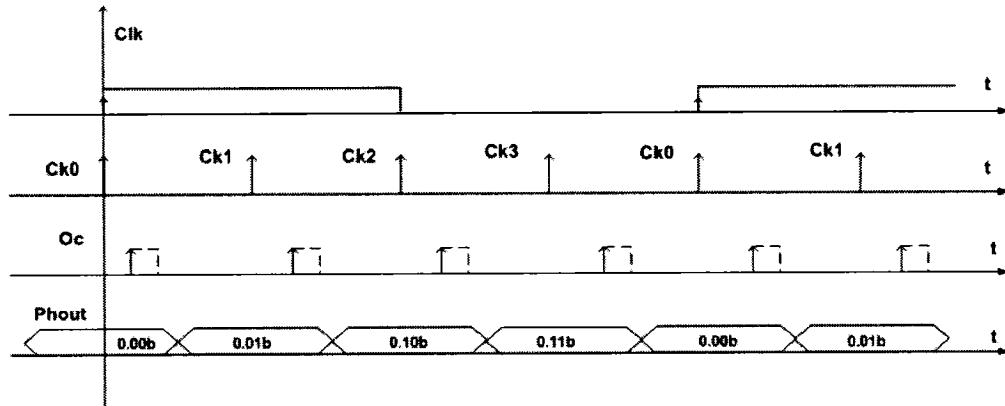

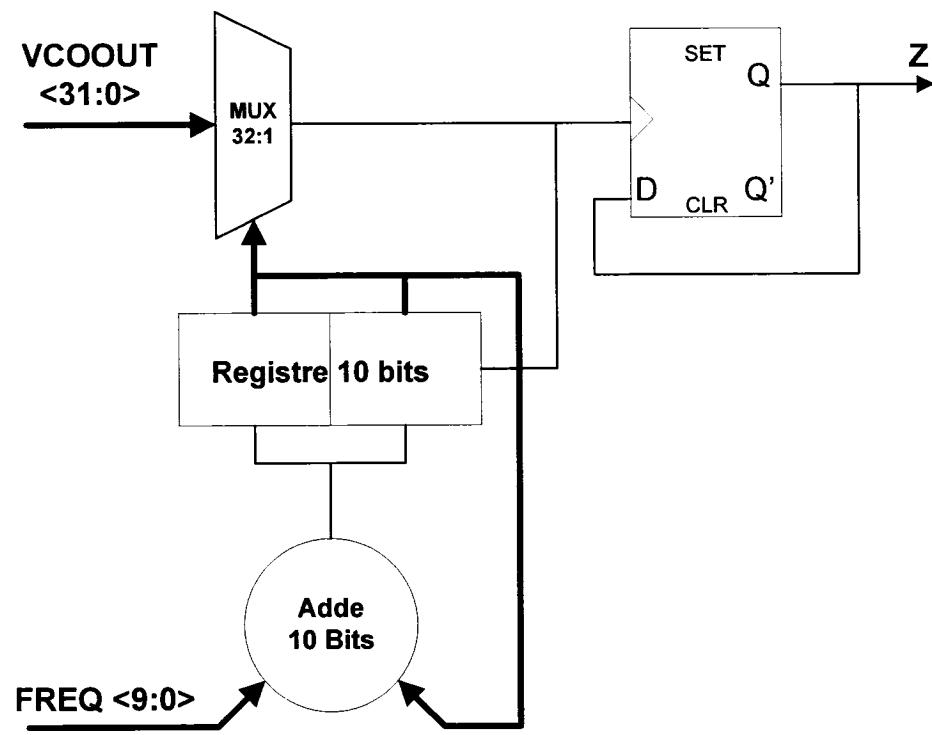

**Figure 2-10 :** Structure générale du DDS [Calbaza, 01].

La Figure 2-10 présente la structure générale d'un DDS. Le circuit DDS contient l'accumulateur de phase (Acc), une table de Conversion (LUT), un convertisseur numérique analogique (DAC), un filtre (F) et un comparateur (C).

L'accumulateur de phase ajoute l'incrément de phase (P) à la phase accumulée à chaque cycle d'horloge. Le nombre de bits de l'accumulateur,  $n$  dans ce cas, nous donne la précision du calcul. On observe que la phase accumulée, présente à la sortie de l'accumulateur, a une période répétitive déterminée par : le nombre de bits de l'accumulateur, l'incrément de phase et la période de l'horloge Clk [19].

La phase accumulée réduite de  $n$  bits à ses  $m$  bits les plus significatifs, est convertie par la table de conversion, LUT, dans la forme d'onde désirée. La plupart des circuits DDS

utilisent comme table de conversion une mémoire ROM, qui donne à la sortie la valeur numérique correspondant au sinus de l'argument représenté par les  $m$  bits les plus significatifs de la phase accumulée.

Cette valeur numérique est convertie en signal analogique par le convertisseur numérique analogique (DAC). Le filtre (F) est utilisé pour couper les harmoniques supérieures du signal produit par le DAC. À la sortie du filtre, on aura un signal sinusoïdal ayant une fréquence donnée par [15] :

$$f_a = \frac{N \times f_{Clk}}{2^n} \quad (2.3)$$

Où  $f_a$  est la fréquence de sortie et  $f_{Clk}$  est la fréquence de l'horloge Clk, et  $N$  est le nombre binaire présent à l'entrée de l'accumulateur de phase.

Le comparateur (C) permet de transformer le signal sinusoïdal en une onde carrée qui pourra être utilisée comme horloge pour les systèmes numériques. Ce signal est à la même fréquence que celle obtenue à l'équation 2.3.

À la sortie du DDS, la fréquence maximale qu'on puisse atteindre est la moitié de la fréquence de référence. En pratique, cette fréquence ne peut atteindre que le tiers de la fréquence de référence à cause des caractéristiques physiques du filtre.

Le signal à la sortie du DAC est de la forme suivante :

$$A_d(t) = \sin(\omega_a \cdot t) = \sin(2 \cdot \pi \cdot f_a \cdot t) \quad (2.4)$$

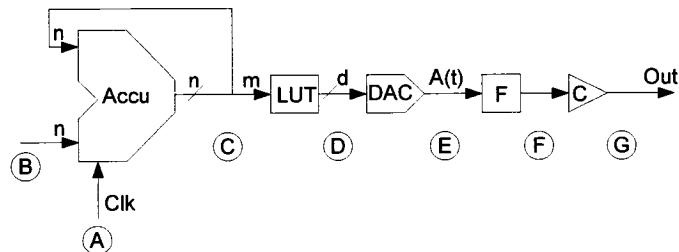

Le signal A (t) est représenté à la Figure 2-11 [6] et [18] :

Figure 2-11 : Signal du DDS [Calbaza, 01].

$A(t)$  n'est pas encore une sinusoïde, le filtre après le DAC permet d'obtenir la fondamentale  $A_1(t)$  qui est un signal presque parfaitement sinusoïdal à la fréquence désirée. Son expression analytique est la suivante :

$$A_1 = \sin c\left(\frac{\omega_a \cdot T}{2}\right) \cdot \sin\left(\omega_a \cdot t - \frac{\omega_a \cdot T}{2}\right) = a_1 \cdot \sin[\omega_a \cdot (t - \phi_1)] \quad (2.5)$$

On peut noter que cette composante est déphasée de la moitié de la période de l'horloge d'entrée Clk. Ce déphasage est exprimé par le terme  $\phi_1 = T/2$ . L'amplitude de cette composante est donnée par le terme :

$$a_1 = \sin c\left(\frac{\omega_a \cdot T}{2}\right) \quad (2.6)$$

Étant donné le caractère analogique du filtre, les autres harmoniques du signal venant du DAC ne sont pas parfaitement filtrées, ce qui introduit une gigue.

Dans ce travail, nous ne ferons pas une étude de gigue, puisque le circuit que nous concevons est purement numérique, ce qui apporte un avantage face au DDS en termes de consommation de puissance et de plage de fonctionnement en fréquence.

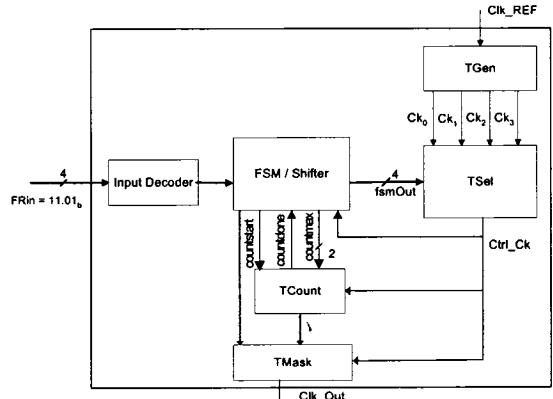

### 2.1.3 Synthèse numérique directe de périodes (DDPS)

Calbaza [10] présente un nouveau type de circuit de synthèse d'horloge, le circuit de synthèse numérique de période (DDPS). Ce circuit produit une onde carrée, comparativement au DDS qui produit une onde sinusoïdale.

Ce faisant, la table de sinus LUT, le convertisseur numérique analogique et le filtre ne sont plus utilisés. Ce circuit a l'avantage d'apporter plus de simplicité, avec une réduction de la consommation de puissance grâce à l'élimination de la mémoire LUT. Il peut atteindre des fréquences en sortie plus élevées, et il s'en suit une réduction de la gigue de l'horloge produite.

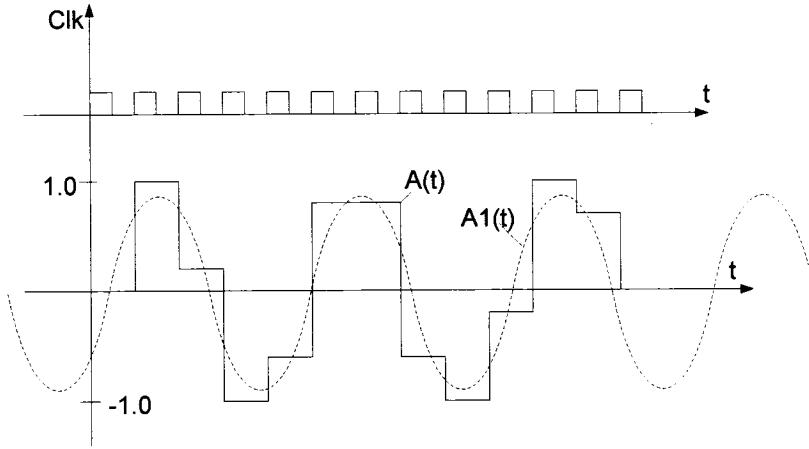

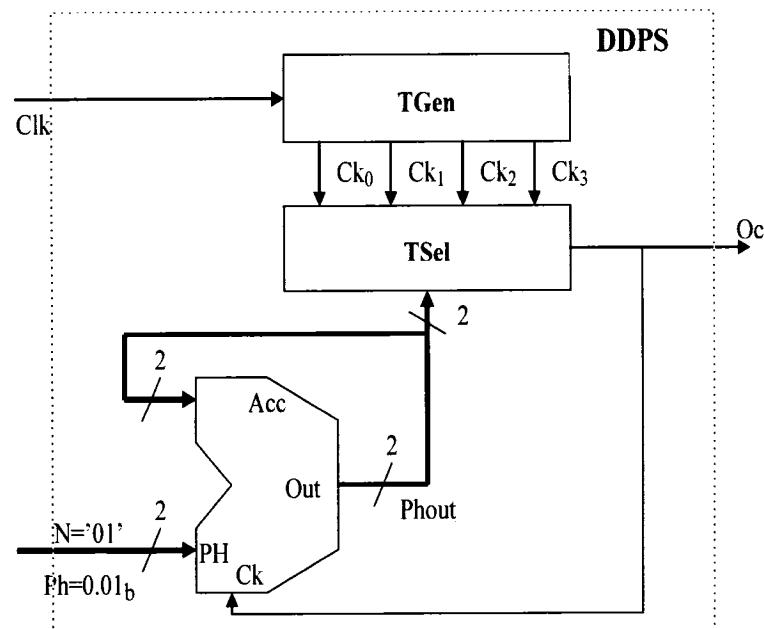

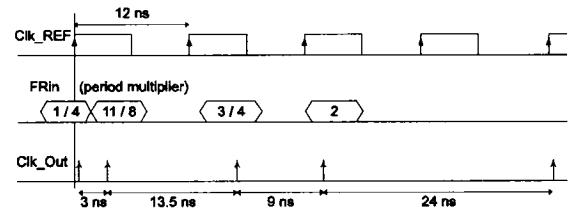

Le diagramme bloc du DDPS est présenté à la Figure 2-12.

**Figure 2-12 :** Diagramme bloc du DDPS [Calbaza et Al, 99].

Le DDPS peut multiplier la fréquence de l'horloge de référence par un nombre fractionnaire. Le diagramme temporel de la Figure 2-13 illustre un exemple de son fonctionnement.

**Figure 2-13 :** Diagramme temporel du DDPS (Calbaza, 1999).

Le module générateur de transitions (TGen) produit plusieurs phases à la même fréquence que l'horloge de référence (Clk), à la même distance les unes des autres. Le module de sélection des transitions (TSel) choisit les transitions du TGen. Cette dernière est propagée à l'horloge de sortie (Oc). Le choix de la transition est déterminé par l'accumulateur de phase (Acc).

Le fait de pouvoir sélectionner la transition qui pourra être propagée à l'horloge de sortie permet au DDPS de contrôler numériquement la période de sortie. Tandis que les circuits de la littérature couramment utilisés pour multiplier la fréquence propagent les transitions dans leur ordre naturel, produisant un signal de période fixe. Cette capacité est due au fait que le signal de sortie Oc contrôle directement l'accumulateur de phase. Cette astuce est aussi retrouvée dans l'article de Mair [29]. En utilisant le signal Oc, la

période peut être une fraction de la période (T) de l'horloge de référence Clk. Cette fraction est déterminée par l'incrément de phase (Ph).

Le diagramme temporel de la Figure 2-13 représente le cas où Ph=0.01b qui est la représentation binaire de  $\frac{1}{4}$ . À chaque coup d'horloge venant des impulsions de Oc sur l'accumulateur, les phases en sortie varient de 0.00b à 0.01b, 0.10b, 0.11b et la séquence se répète.

La séquence ci-dessus permet de sélectionner respectivement les front montants des phases de l'horloge : Ck0, Ck1, Ck2, Ck3 qui seront propagées l'une après l'autre comme impulsions de l'horloge de sortie Oc.

La fréquence à la sortie est déterminée par l'équation suivante :

$$f_{Oc} = \frac{f_{Clk}}{Ph} \quad (2.6)$$

Où Ph, inférieur à 1, est l'incrément de phase et  $f_{Clk}$  est la fréquence de référence de toutes les phases Ck<sub>i</sub>. Comme Ph est plus petit que 1, la fréquence du signal de sortie est plus élevée que la fréquence de l'horloge de référence.

Selon cette équation, on peut théoriquement produire une fréquence de sortie infiniment grande, mais évidemment, les propriétés physiques des éventuelles mises en œuvre vont limiter cette valeur.

En effet lorsque la séparation entre les phases est trop faible, l'impulsion à choisir pour obtenir la durée de période désirée arrive avant que les éléments du circuit qui constituent le chemin entre le TGen et le signal Oc ne prennent la nouvelle valeur dictée par l'accumulateur. Ceci est une cause d'aléas dans le cas où la mise à jour du chemin critique est très proche de la transition à sélectionner, ou ceci conduirait à sauter un cycle entier de la période de l'horloge Clk si cette mise à jour est faite trop tard, résultant à une division de fréquence exprimée comme suit :

$$f_{oc} = \frac{f_{clk}}{1.0 + Ph} \quad (2.7)$$

Choisir un Ph très bas n'est pas acceptable car la sortie résultante contiendrait des aléas. Pour déterminer l'intervalle dans lequel on pourrait utiliser n'importe quelle valeur de Ph, il faut tenir compte des variations de délais dues au procédé et les conditions d'opérations significatives (température, tension alimentation). La fréquence maximale du DDPS est donc déterminée par sa boucle critique : cette boucle inclut le délai entre la transition Oc, en passant par l'accumulateur qui permet de mettre à jour l'incrément de phase, auquel s'ajoute le délai de propagation d'un multiplexeur utilisé pour la sélection de la phase propagée en sortie. L'auteur de ce circuit estime qu'avec une implémentation optimisée, la fréquence du circuit tournerait autour du 1GHz avec la technologie CMOS 0,25µm, étude qui n'a pas été confirmée expérimentalement. Une étude sur la gigue a plutôt été réalisée, démontrant une amélioration face au circuit du DDS.

#### 2.1.4 Autres méthodes de synthèse d'horloge

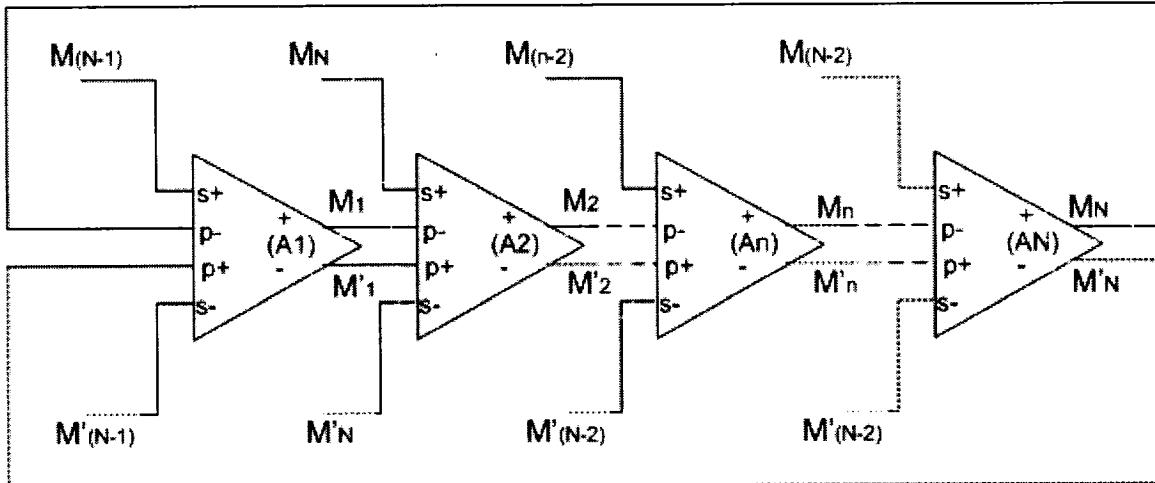

Plusieurs autres circuits qui sont des prédecesseurs ou des successeurs aux circuits présentés ci-dessus ont été rapportés. L'un des plus utilisé, très ressemblant au DDPS, est le synthétiseur de fréquence et de phase « flying-adder » [29]. Une illustration de cette architecture est présentée à la Figure 2-14. Les phases du VCO sont utilisées pour effectuer une multiplication de l'horloge. Un registre est utilisé à sa sortie pour obtenir un « duty cycle » de 50%.

**Figure 2-14 :** Architecture d'un "Flying Adder".

## 2.2 Processeurs à faible consommation de puissance et à fréquence variable

Ce paragraphe présente une revue des techniques qui permettent une réduction effective de la consommation d'énergie dans les systèmes sur puces de génération récente en mettant une emphase sur les processeurs embarqués.

### 2.2.1 Modèle : puissance et énergie

La puissance dissipée dans les circuits VLSI en technologie CMOS est constituée de deux composantes relatives aux propriétés dynamiques et statiques de ces circuits :

$$P = P_{\text{Dynamique}} + P_{\text{Statique}} \quad (2.8)$$

Avec approximativement ;

$$P_{\text{Dynamique}} = CV_{DD}^2 f_{\text{Clock}} \quad (2.9)$$

Et

$$P_{\text{Statique}} = V_{DD} I_Q \quad (2.10)$$

Où  $C$  est la capacitance active du circuit durant son fonctionnement,  $f_{\text{Clock}}$  est la fréquence de l'horloge,  $V_{DD}$  la tension d'alimentation et  $I_Q$  le courant de fuite.

Cependant l'énergie qu'une pile ou une batterie fournirait à un tel circuit ne dépend pas de la fréquence d'opération. Sa composante dynamique est exprimée par :

$$E_{\text{Dynamique}} = \alpha \cdot CV_{DD}^2 \quad (2.11)$$

Avec  $\alpha$  qui représente le coefficient d'activité du circuit.

### 2.2.2 Techniques de réduction d'énergie dans les processeurs embarqués

Pour une réduction effective de la consommation de l'énergie selon les équations du paragraphe précédent, plusieurs techniques s'appliquant aux processeurs embarqués ont été développées. Elles sont appliquées soit individuellement, soit combinées à une autre. Selon [4] et [28] ces différentes techniques peuvent être résumées comme suit:

- La technique de *voltage scaling* qui peut être appliquée dynamiquement (DVS) ou statiquement (CVS), nécessite plusieurs niveaux de voltage ;

- La technique de *clock gating* où le signal de l'horloge est contrôlé à l'aide de portes ET pour permettre d'arrêter le signal ;

- La gestion dynamique de puissance (DPM) ;

- La technique d'optimisation de puissance de la mémoire : méthode de partitionnement de l'accès à la cache ;

- Techniques d'optimisation de puissance par le contrôle du flux des données, par transformation du graphe de contrôle de flux de données (CDFG) ;

- Les méthodes d'optimisation de puissance au niveau d'abstraction des instructions ;

- La méthode de conception asynchrone globalement et synchrone localement (GALS) pour réduire la consommation de puissance du réseau de distribution de l'horloge

L'utilisation des ces méthodes de réduction d'énergie touchent tous les niveaux hiérarchiques de conception incluant le niveau algorithmique, architectural, le niveau circuit et la technologie de fabrication.

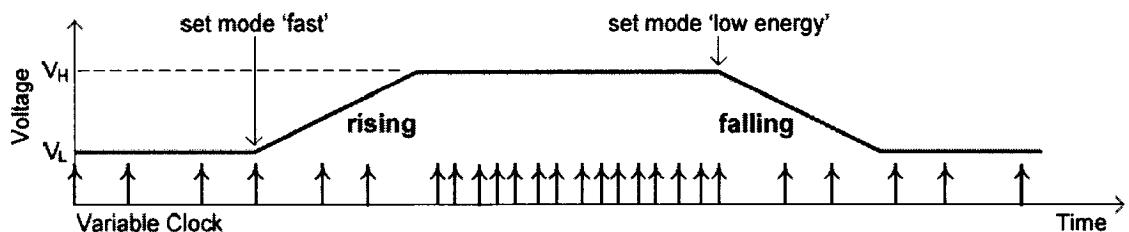

La conception de notre VSP est du domaine architectural avec une possibilité d'y appliquer les algorithmes d'ajustement dynamique du voltage (DVS) et de fréquence. Les lignes suivantes se consacreront aux différents travaux de la littérature concernant le DVS ainsi que la gestion dynamique de la puissance consommée.

### **2.2.3 Réduction d'énergie appliquée aux processeurs DVS**

Historiquement, pour atteindre l'objectif de réduire la consommation de puissance dans les processeurs embarqués, les concepteurs ont longtemps utilisé la technique qui consiste à se mettre en mode de faible consommation lors des moments de repos. Or de plus en plus ces processeurs exécutent des tâches beaucoup plus sophistiquées qui requièrent un plus haut niveau de performance, ainsi les nouvelles applications audio et vidéo ainsi que les jeux vidéo s'exécutent pendant des périodes de temps énormes, ce qui entraîne une augmentation du rapport du temps d'exécution sur le temps de repos. Ceci étant, ces techniques de gestion de puissance, très efficaces lors des périodes de repos, ne permettent pas de préserver l'autonomie des batteries pendant les moments d'opérations actives.

Bien qu'on observe une évolution dans la conception des batteries (qui se traduit par une durée de vie prolongée et une réduction de leur taille), les demandes des nouveaux design de nouvelle génération en consommation d'énergie ont en revanche augmentées plus rapidement, les moyens conventionnels de gestion de puissance ne conservant pas l'autonomie des batteries à un niveau acceptable par les usagers.

Pour remplir les objectifs de performance et ceux de faible consommation de puissance, il suffit de permettre aux processeurs de rouler à différents niveaux de performances selon la charge de travail. Par exemple, un lecteur de vidéo MPEG demande plus de performance qu'un lecteur audio MP3. Il serait donc possible de ralentir le processeur

pour les applications MP3 sans pour autant perdre la qualité. Avec l'équation 2.11, l'énergie peut être sauvée en réduisant la tension d'alimentation du processeur pendant que sa fréquence est réduite.

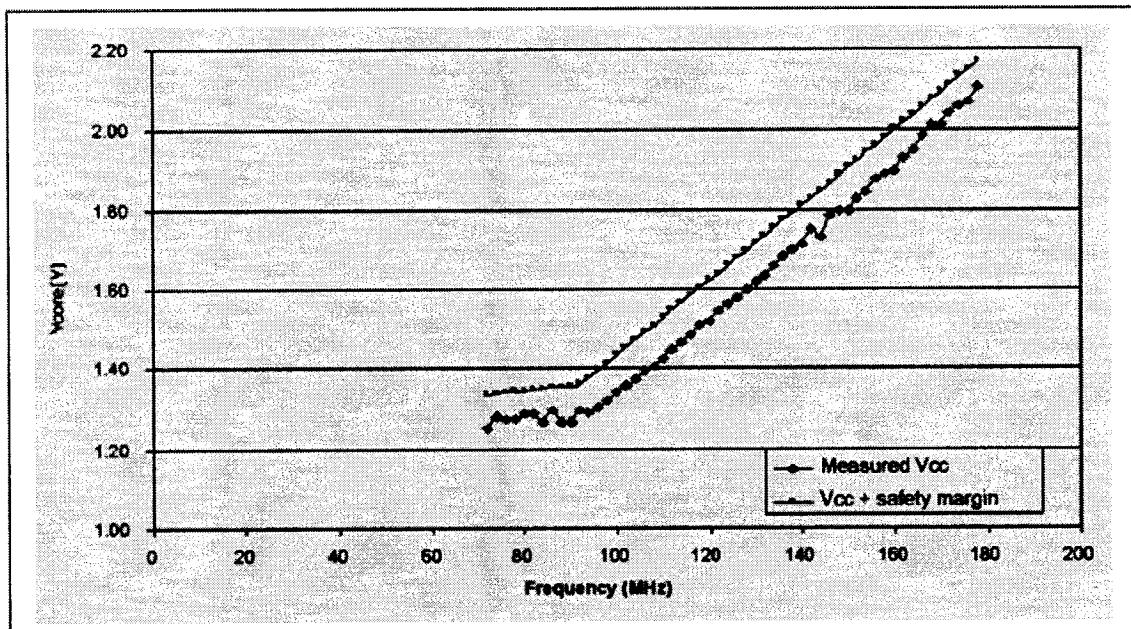

La méthode DVS exploite le fait que la fréquence de pic du processeur implantée en technologie CMOS est proportionnelle à sa tension d'alimentation. La Figure 2-15 illustre bien cette relation entre la fréquence et la tension d'alimentation en technologie CMOS  $0.18\mu\text{m}$ .

**Figure 2-15 :** Mesures voltage vs fréquence pour le ARM926EJ-S<sup>TM</sup> [Clive Watts, 2003].

Autour de la fréquence 90MHz on constate que l'intervalle des niveaux de tension a une limite qui ne peut être dépassée pour l'ajustement de tension.

La réduction du voltage et de la fréquence permet une réduction quadratique de l'énergie dynamique avec pour autre conséquence le rallongement du temps de fonctionnement. Étant donné que l'énergie conservée dans la batterie n'est pas infinie, cette méthode est très utile pour augmenter l'autonomie de la batterie.

La conception d'un processeur compatible DVS nécessite la présence non seulement d'un processeur à faible puissance supportant une gamme de niveaux de voltage et de fréquences, mais aussi un régulateur dynamique de voltage et de fréquence, le tout commandé par un gestionnaire de voltage et d'énergie. Le DVS est utilisée déjà dans certains processeurs commerciaux à faible puissance dont les caractéristiques sont illustrées au tableau 2-2.

**Tableau 2-2 Caractéristiques de quelques processeurs DVS commerciaux connus**

|                                 | Intervalle de Voltage | Intervalle de fréquences |

|---------------------------------|-----------------------|--------------------------|

| IBM PowerPC<br>405LP [22]       | 1.0V – 1.8V           | 153MHz – 333 MHz         |

| Transmeta Crusoe<br>TM5800 [39] | 0.8V – 1.3V           | 300MHz – 1GHz            |

| Intel Xscale 80200<br>[23]      | 0.85V – 1.55V         | 333MHz – 733MHz          |

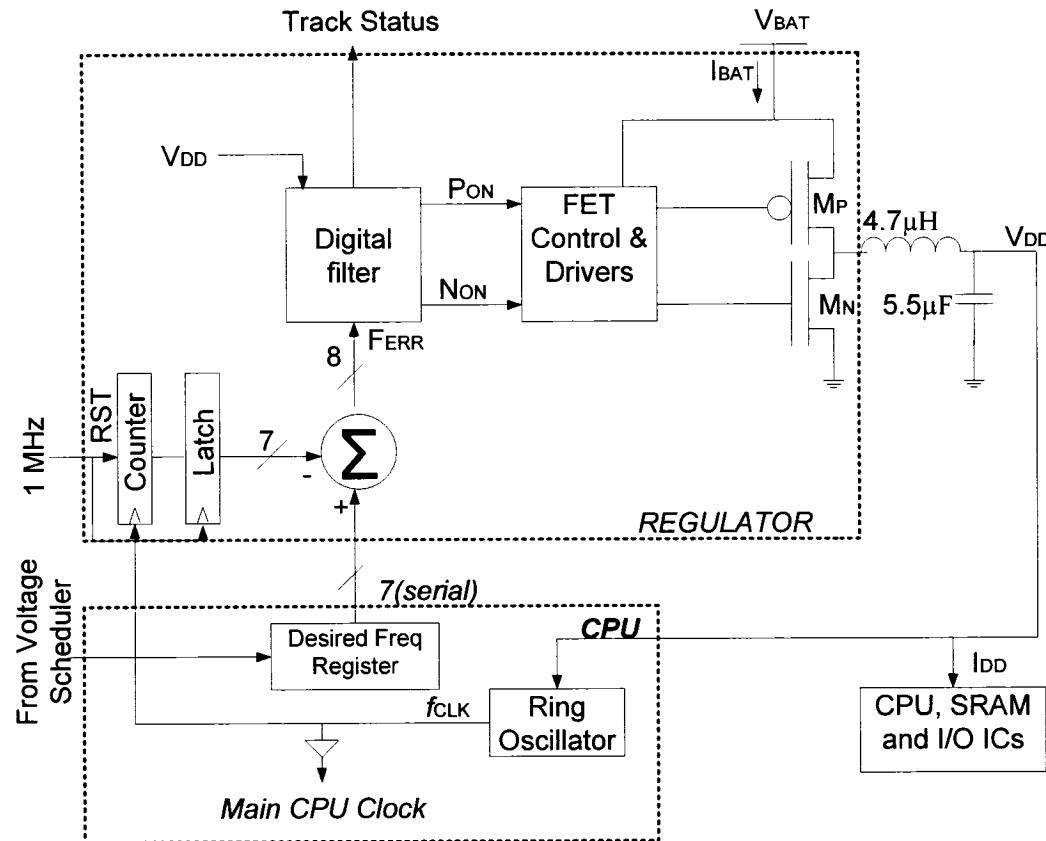

Kuroda [24] est l'un des premiers à avoir publié les résultats expérimentaux de la méthode de « *voltage scaling* » sur un processeur à utilisation générale. La tension minimale requise dans le processeur RISC R3900 pour la fréquence d'opération est toujours obtenue dynamiquement en comparant la fréquence avec le délai d'une copie du chemin critique du système alimentée à la tension minimale VDDL; ainsi le processeur est toujours alimenté au voltage minimum nécessaire. Le R3900 fonctionne entre 1.9V à 40MHz et 1.3V à 10MHz supportant toutes les fréquences intermédiaires.

Son régulateur de tension, à la Figure 2-16, est adaptatif à la fréquence de fonctionnement et consomme 140mW à 40MHz. [20] présente la plateforme Itsy, une expérience sur une plate forme Linux. Elle utilise le processeur StrongARM SA1100 qui supporte le *voltage scaling*. Seulement deux niveaux de tension y sont implémentés, 1,5V pour des fréquences au dessus de 162MHz et 1,23V en dessous, les réductions en énergie ne sont donc pas importantes. La différence de consommation de puissance est de 15% entre les 2 niveaux de tension. De meilleurs résultats ont été obtenus avec la plateforme SmartBadge [36] similaire à Itsy. Des mesures expérimentales de puissance en utilisant les opérations en temps réel de décodage audio MP3 et de décodage vidéo MPEG montrent qu'il est possible d'atteindre des gains en énergie de 40% avec cette plateforme.

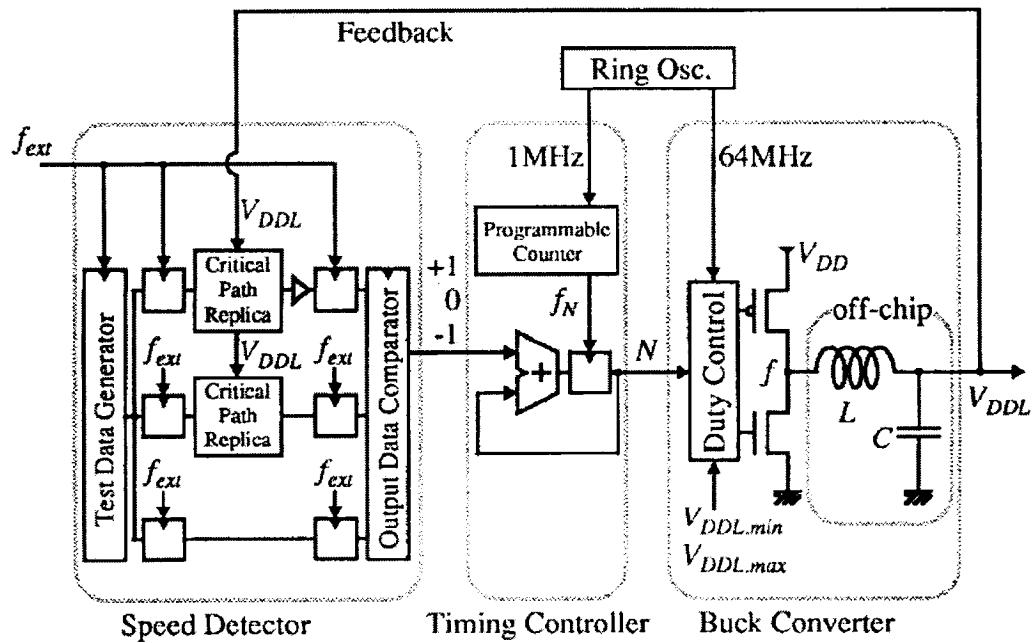

**Figure 2-16 :** Régulateur de voltage [Kuroda T, 24].

Burd T. [10] implémente un processeur basé sur un noyau de processeur ARM8 qui supporte l'échelonnage de la tension d'alimentation. Le circuit est fabriqué en technologie 600nm et contribue à l'économie de l'énergie. En mode haute performance,

il exécute à 80MHz et consomme 476mW à 3.8V. Avec une vitesse de 5MHz, il consomme 3,24mW à 1.2V. On note une réduction de la puissance par un facteur de 147 pour une performance réduite au seizième.

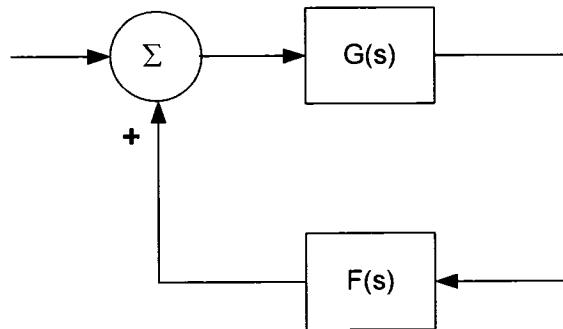

Le circuit de la Figure 2-17 qui se charge de la régulation de la fréquence, est une boucle fermée qui régule la tension d'alimentation en fonction de la fréquence. Il est implémenté sur deux puces distinctes : celle du régulateur et celle du CPU.

**Figure 2-17 :** Régulation par boucle de fréquence à voltage [Burd T.D, 10].

L'oscillateur en boucle du CPU fournit une horloge dont la fréquence est fonction de la tension d'alimentation  $V_{DD}$ . Le signal de l'horloge est envoyé sur la puce du régulateur et commande un compteur qui est réinitialisé à une cadence de 1MHz et permet de quantifier la fréquence en un mot de 7 bits. Cette valeur est soustraite de la valeur de fréquence désirée (en MHz) qui est donnée par le système d'exploitation, ce qui génère un mot de 8 bits représentant l'erreur en fréquence  $F_{ERR}$ . Le filtre numérique effectue une modulation de largeur et de fréquence d'impulsions (PMW/PFM) pour activer les transistors de puissance à effet de champ (TEC) via les signaux  $P_{ON}$  et  $N_{ON}$ . Ensuite le circuit de niveling de tension convertit la tension de la pile VBATT (3.3-6.0V) à la tension régulée  $V_{DD}$  qui alimente le CPU pour fermer la boucle. La clé de l'adaptation aux changements de la température et du procédé est l'implémentation sur puce de l'oscillateur en boucle contrôlé par voltage. Il s'adapte aux conditions réelles de fonctionnement. Le temps de transition maximal lors du changement de voltage de 1,2V à 3,8V est de 70 $\mu$ s, avec la fréquence qui change de 5MHz à 80MHz. Il existe une énergie dissipée lors de la transition qui est de 70 $\mu$ J.

L'article [30] présente la conception d'une plateforme autour d'un processeur 32-bits basé sur le PowerPC, qui supporte en plus les algorithmes DVS. Il permet aussi d'ajuster la fréquence de l'horloge en temps réel, s'adaptant dynamiquement aux changements des demandes en performance aux contraintes de faible consommation de puissance. À 1,8V il atteint une fréquence de 380MHz pour une consommation de 500mW, et réduit sa consommation à 53mW pour un voltage de 1,0V et une fréquence de 152MHz. L'ajustement de la tension et de la fréquence peut aussi être effectuée par logiciel, ainsi [32] propose des algorithmes d'ordonnancements selon la priorité en énergie, qui utilise les descriptions des charges de travail des applications pour gérer l'exécution des tâches. Le design est basé sur le processeur StrongARM d'Intel et supporte les applications à puissance consommée réduite. La plateforme supporte 128 niveaux de tension. À 0,79V il roule à 59MHz et à 1,65V la fréquence est de 251MHz.

## CHAPITRE 3

### Méthodologie d'implémentation

La méthodologie de conception du processeur à vitesse variable est présentée dans ce chapitre sous deux volets :

- la méthodologie en conception ASIC pour le synthétiseur d'horloge à période variable, le VPCS ;

- la méthodologie de conception pour FPGA du processeur à vitesse variable.

Ces méthodologies suivent les mêmes principes que celles de base mais avec un accent sur les différences qui s'appliquent à la méthode de cycles d'horloge variables.

#### 3.1 Méthodologie de conception ASIC du VPCS

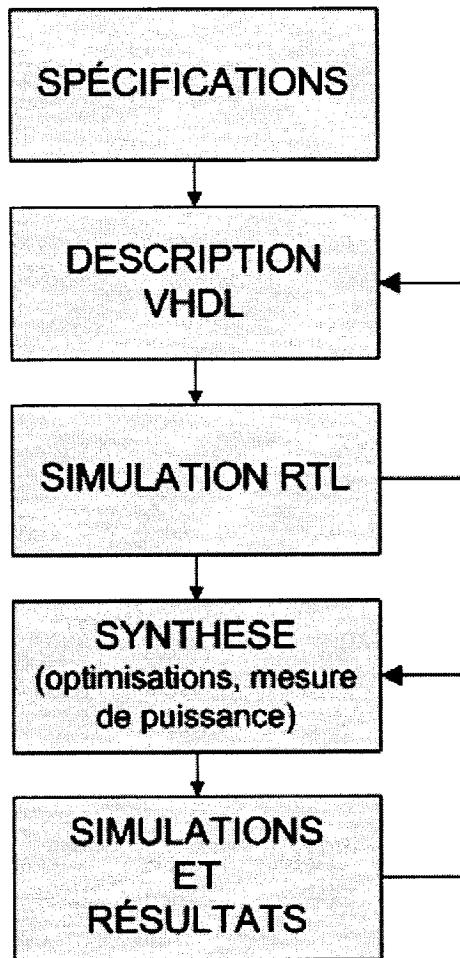

Le flot de conception du VPCS illustré à la Figure 3-1 est le même que pour tout circuit implanté en technologie ASIC. En premier lieu, il faut définir les spécifications du circuit à réaliser selon les objectifs à atteindre. Ensuite il faut passer à la description en langage de haut niveau (VHDL) et sa compilation, qui formera la description RTL du design et permettra de faire la simulation fonctionnelle au niveau RTL. Une fois la fonctionnalité du circuit vérifiée après simulation RTL, on procède à la synthèse du circuit. Durant cette étape nous nous concentrerons sur l'analyse du timing et l'évaluation de la puissance dynamique du circuit pour optimiser le design. Nous nous sommes arrêtés à la simulation après synthèse, autrement dit la simulation au niveau des portes logiques. La validation des résultats en ce qui concerne les performances en fréquence du circuit est effectuée durant cette dernière étape. Les sections suivantes décrivent en grandes lignes, l'implémentation de notre générateur d'horloge.

**Figure 3-1 :** Flot de design pour implémentation en ASIC.

### 3.1.1 Spécifications

Ce paragraphe décrit les spécifications du VPCS qui ont mené à la concrétisation de sa réalisation.

Le cahier de charge initial voulait qu'on puisse obtenir un circuit qui change la période d'une horloge selon un mot de commande en entrée. Le défi était ensuite d'effectuer le changement sans délais, puis de pouvoir le faire à chaque cycle selon la commande

présente. Ainsi, à la transition montante marquant la fin du cycle précédent, le calcul de la période suivante doit commencer.

Inspiré des récents DLL et des travaux sur le DDPS, il s'agissait de pouvoir obtenir à la sortie un signal de fréquence plus élevée que celui en entrée en sélectionnant les phases intermédiaires de l'horloge de référence.

La description du circuit est faite en VHDL pour lui donner un caractère purement numérique, le calcul de la durée de la période à synthétiser est fait par une Machine à états (FSM), la description du circuit est générique c'est-à-dire qu'on peut configurer le circuit selon le nombre de phases disponibles en autant que ce nombre est une puissance de 2. Le diagramme du flux de donnée de la FSM se trouve en Annexe B. Le mot en entrée qui est le facteur multiplicatif est un nombre arbitraire fractionnel à point fixe, la partie entière étant large de  $m$  bits, la partie fractionnaire de  $\log_2(n)$  bits avec  $n$  qui représente le nombre de phases disponibles en entrée.

Le circuit sera utilisé dans un processeur supportant autant les applications de haute performance que celles à faible consommation d'énergie. Il s'agit donc de pouvoir générer différentes fréquences selon ces applications.

### 3.1.2 Description VHDL et simulation

La description VHDL selon les spécifications précédentes est présentée en Annexe A. L'analyse et la simulation du circuit sont faites grâce au simulateur HDL *Modelsim®*, pour compiler le programme en langage VHDL et faire une simulation fonctionnelle selon les vecteurs en entrée précisés par le banc de test. Il s'agit ici de vérifier qu'on obtient bien à la sortie la forme de signal escomptée. Les délais ne sont pas pris en compte, les phases de l'horloge sont fournies par le simulateur.

### 3.1.3 Synthèse et optimisations

À l'aide de l'outil *Design Analyzer*<sup>TM</sup> de *SYNOPSYS*<sup>®</sup>, la synthèse et l'analyse statique du Timing dans le circuit est effectuée. Après la compilation, le design est transformé en portes logiques prêt à être optimisé selon les contraintes et spécifications.

L'analyse du timing est différente des circuits conventionnels dans la mesure où la sortie du VPCS est réutilisée comme horloge pour certains registres. Il a fallu créer une horloge supplémentaire artificielle pour ce signal afin d'avoir des résultats plus réalistes, puisque l'analyseur ne comprend pas ce qu'implique la boucle dans le circuit. De plus, l'existence de plusieurs phases de l'horloge utilisées rend la tâche difficile à l'outil d'analyse. Il était donc nécessaire de spécifier une valeur de fréquence au signal de sortie correspondant à la fonction voulue. (Par exemple, avec une fréquence de référence **CLOCK\_REF** de 50MHz, pour multiplier cette fréquence par 4, on spécifie que le signal de sortie devrait être à 200MHz). Pour une version du circuit à 4 phases, l'analyse du timing nous montre l'existence de 5 domaines d'horloges et les distances entre les phases des différents domaines sont prises en considération dans le calcul du délai critique. À cette étape nous faisons une estimation de la fréquence grâce à la valeur de la période maximale admissible selon l'outil de Synopsys. Si la fréquence de l'horloge en sortie est trop élevée, il y a une violation des règles de contraintes de temps selon la technologie CMOS 180nm, il faut donc modifier cette fréquence jusqu'à ce qu'elles soient respectées. Une autre synthèse est nécessaire une fois toutes les horloges créées et les modifications des fréquences faites, afin d'obtenir un circuit qui respecte les contraintes.

### 3.1.4 Simulation après synthèse

L'outil de simulation est *Modelsim®*. Il permet d'effectuer une simulation assez fidèle du comportement du circuit. Pour une simulation plus proche de la réalité, on applique au circuit obtenu après synthèse, les délais de chaque élément qui se trouvent dans le fichier contenant ces délais, d'extension *sdf*. Le dit fichier étant créé automatiquement par le *design compiler®* de *Synopsys* selon les bibliothèques standards de la technologie CMOS 180nm. La commande utilisée pour créer le fichier des délais est « **write – constraints nonmdufichier.sdf** ». Le fichier ainsi obtenu est chargé dans Modelsim afin de tenir compte des délais des portes. Les formes d'ondes obtenues ne sont pas exemptes d'éventuels aléas et représentent le comportement du circuit sans tenir compte des capacités parasites ou de l'effet ajouté au cas où on implémenterait le circuit sur une puce. Tous les cas de simulations sont couverts (division et multiplication de la fréquence de l'horloge avec ou sans partie fractionnaire), il suffit de préciser les vecteurs d'entrée du VPCS correspondants à chacun des modes de fonctionnement.

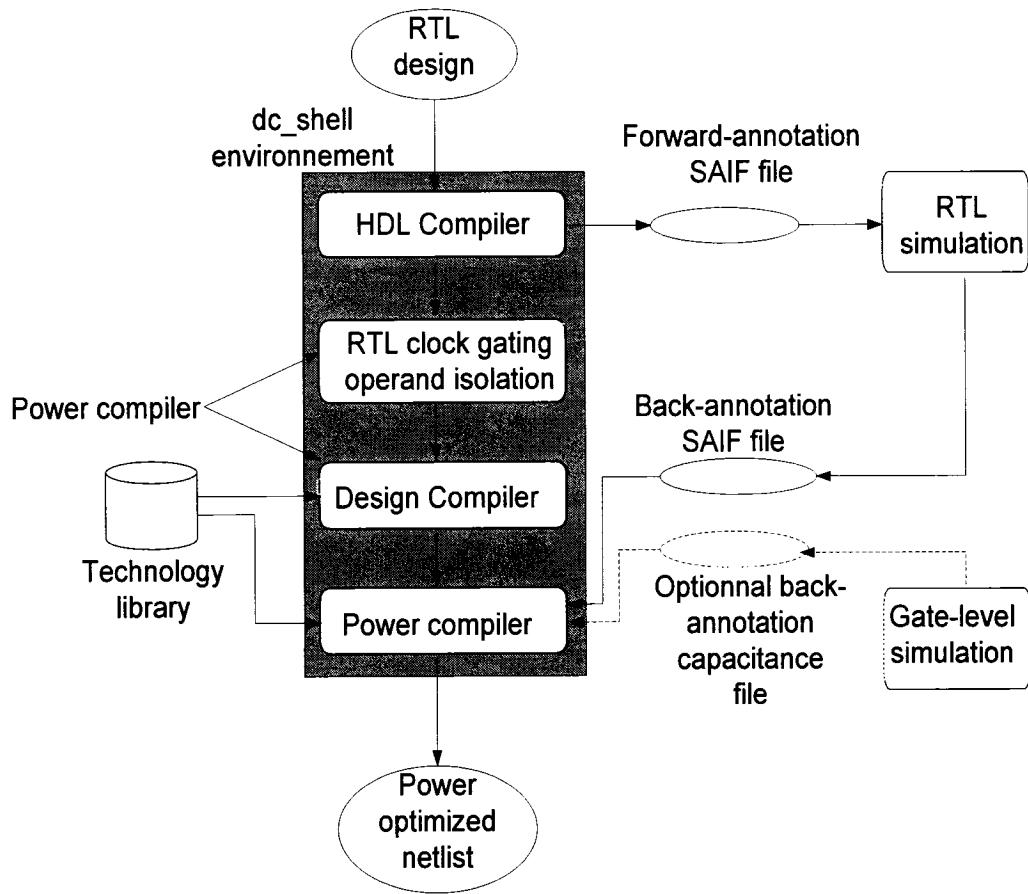

### 3.1.5 Estimation de la puissance dynamique consommée

Le cheminement général de l'analyse de la consommation de puissance est illustré à la Figure 3-2. Pour des circuits à une seule phase d'horloge, l'estimation de la puissance se fait assez aisément car l'outil *Power Compiler* de *Synopsys* peut estimer fidèlement la puissance consommée par le circuit sans avoir à effectuer une simulation du circuit. Il suffit de préciser la fréquence désirée, et d'utiliser la commande **report power –out fichierdesortie.out** pour avoir le rapport contenant les détails de la puissance consommée. Il faut aussi annoter les changements d'états (switching activity) de tous les signaux du circuit grâce à la commande **set switching activity** à laquelle on spécifie les paramètres suivants de façon arbitraire selon les caractéristiques de l'horloge:

- la probabilité  $P_1$  que le signal soit à 1 dans un cycle d'horloge ;

- le nombre de fois TR que le signal change d'état (0,1) à l'intérieur d'un cycle d'horloge.

Lorsque les changements d'états dans le circuit ne sont pas annotés, l'outil estime que le signal d'horloge défini a une probabilité par défaut  $P_1 = 0.5$  et la fréquence de changements d'états par défaut est  $TR = 0.5f_{CLK}$ .

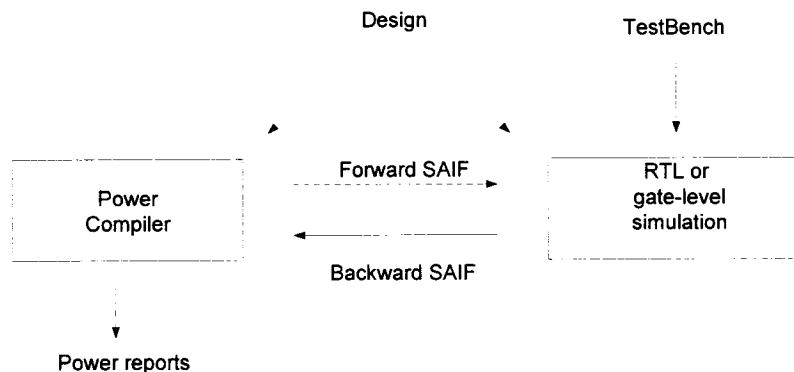

**Figure 3-2 :** Méthodologie et flux de donnée de l'analyse de puissance.

Avec le VPCS, il faut absolument annoter le circuit après simulation car les changements de phases durant le fonctionnement du circuit, ainsi que le fait que les signaux générés sont des impulsions, ne nous permettent pas d'annoter arbitrairement le

design, et encore moins d'utiliser les valeurs par défaut de l'outil d'analyse. Pour ce faire, il faut générer un fichier d'extension *saif* (Switching Activity Input File) tel qu'illustré à la Figure 3-3 qui contient toutes les informations sur les activités dynamiques du circuit après simulation (Backward SAIF) pour ainsi annoter le design à analyser.

**Figure 3-3 :** Flot de création de fichiers saif.

Le fichier d'annotation *saif* est généré par le simulateur *Modelsim* en passant par la création de fichiers *vcd* (value change dump) qui contient les informations de l'activité du circuit après simulation sous un autre format. Ces derniers sont créés grâce à la commande *vcd add*, puis la conversion se fait grâce à la commande *vcd2saif*.

Une fois le fichier *saif* utilisé pour l'annotation du circuit, la puissance dynamique peut être estimée. Les outils nous montrent qu'elle est constituée en 2 parties. La puissance interne qui est celle que dissipe toute cellule à l'interne, et la puissance de transitions (switching) qui est celle dissipée par les capacités de charges en se chargeant et se déchargeant tour à tour.

### 3.2 Méthodologie d'implémentation FPGA pour le VSP

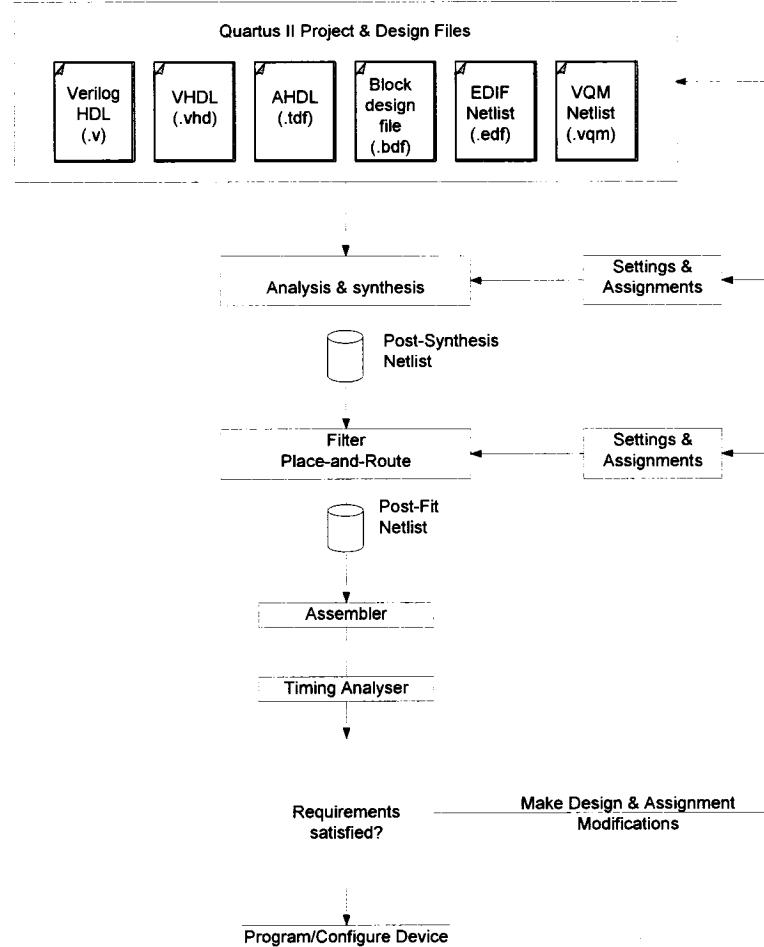

En somme, la méthodologie d'implémentation du VSP est similaire à celle utilisée pour toute implémentation de systèmes sur puce programmable (SOPC), plus précisément sur FPGA. L'outil fourni par Altera est Quartus II. Il assiste le concepteur depuis l'élaboration du design jusqu'au placement et routage du circuit suivant le flux illustré à la Figure 3-4.

**Figure 3-4 :** Flot de design avec Quartus II [Altera design flow].

### 3.2.1 Spécifications et configuration du système

Les spécifications du VSP requièrent un processeur duquel on extrait les signaux de l'état du pipeline, qui seront utilisés comme commande du VPCS. Ceci requiert que la logique interne du processeur soit pleinement accessible. Une fois les opcodes venant du pipeline et de la mémoire d'instructions extraits, il faut s'assurer qu'à chaque cycle la durée de la période d'horloge est toujours plus longue que l'étage du pipeline le plus long, ceci en comparant les différents opcodes issus des différents étages.

Il peut arriver dans le pipeline des aléas provenant des données et même du contrôle, créant ainsi des cycles de suspensions. Aussi certaines instructions peuvent s'exécuter en plusieurs cycles, il est donc nécessaire de prédire à quels moments on aurait un cycle de plus, pour que la modification de la durée s'effectue au bon cycle. Ces événements sont signalés par les signaux *commit* et *pipe\_run* issus du processeur.

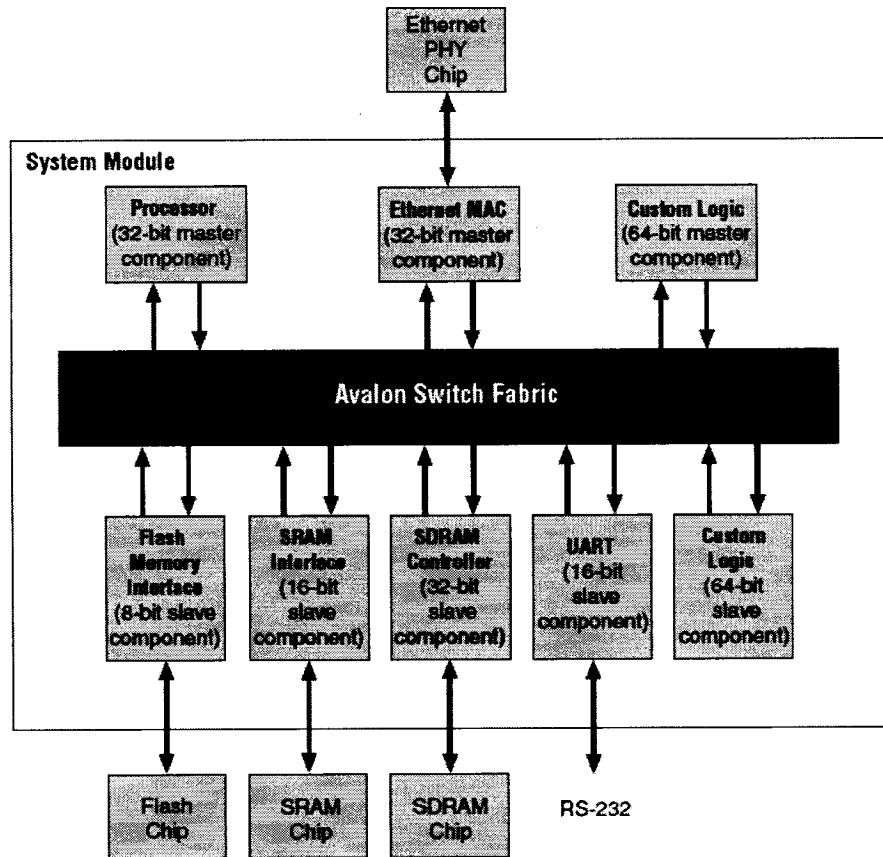

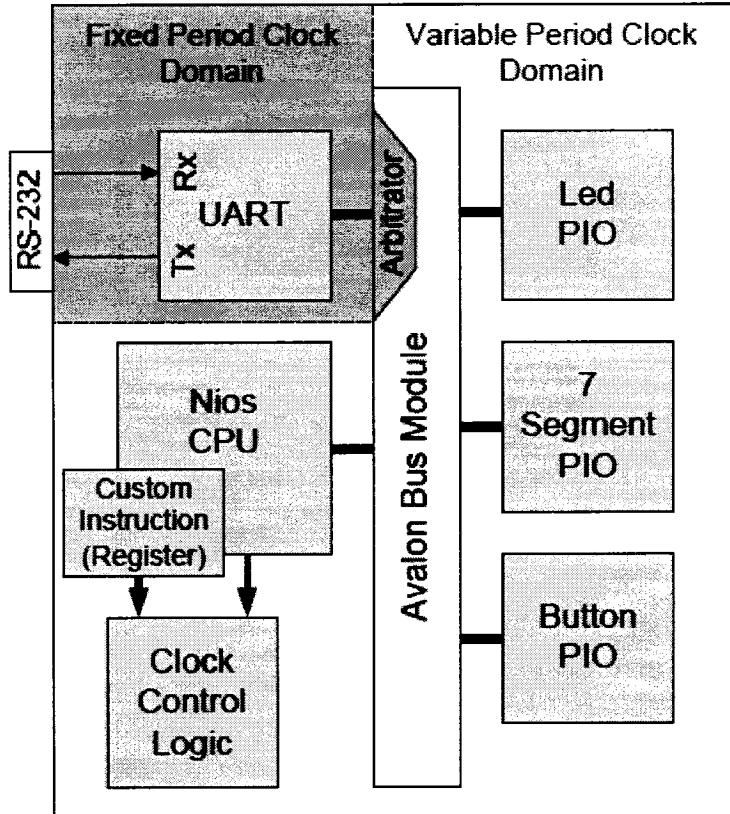

Le Nios est un processeur RISC configurable contenant un pipeline à 5 étages. Le noyau logiciel est disponible, selon les choix du concepteur, sous les formats VHDL ou Verilog, et sa configuration initiale se fait grâce à l'outil SOPCBuilder disponible pour la plateforme de développement Stratix. Un exemple typique de système généré avec SOPCBuilder est illustré à la Figure 3-5.

**Figure 3-5 :** Exemple de système généré par SOPCBuilder.

Il permet de configurer le système au complet en quelques minutes, en connectant plusieurs composants autour d'une architecture de bus. Il génère ainsi un bus appelé *Avalon® Switch fabric* qui gère toute la logique pour connecter les périphériques à l'intérieur et hors du FPGA Stratix. Une fois le système configuré, SOPCBuilder génère le code VHDL de tout le système. Compte tenu de la nécessité de modifier le code source du noyau du processeur, un défi à relever est de comprendre et analyser le code automatiquement généré afin de déterminer les registres du pipeline.

Le VSP devrait pouvoir supporter les algorithmes de DVS, donc pouvoir fonctionner à des voltages différents. Une instruction spécialisée est donc créée pour changer le mode

de fonctionnement. Globalement, cette instruction sera utilisée par le logiciel du système d'exploitation responsable de l'ordonnancement selon la technique de DVS.

### 3.2.2 Analyse du jeu d'instructions

Le jeu d'instruction du Nios contient un peu plus de 70 instructions. Le format est de 16 bits quel que soit la configuration choisie (16 ou 32 bits, qui correspondent à la largeur du bus de donnée). Il supporte les programmes compilés en C ou en C++, permettant d'effectuer les opérations standard arithmétiques et logiques ainsi que les opérations sur les bits, l'extraction des octets, les mouvements de données, la modification du contrôle et les instructions conditionnelles. Le Nios contient 32 registres, dont l'adressage est effectué par 5 bits du champ instructions. La plupart des instructions sont exécutées en un cycle, sauf pour le cas de la multiplication et des opérations de décalage, qui respectivement consomment trois et deux cycles.