**Titre:** Modélisation d'un réseau intégré sur puce basé sur une architecture en anneau

Title: en anneau

**Auteur:** François Deslauriers

Author:

**Date:** 2005

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Deslauriers, F. (2005). Modélisation d'un réseau intégré sur puce basé sur une architecture en anneau [Master's thesis, École Polytechnique de Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/7696/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7696/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois, & Yvon Savaria

Advisors:

**Programme:** Unspecified

Program:

Université de Montréal

**MODÉLISATION D'UN RÉSEAU INTÉGRÉ SUR PUCE BASÉ SUR

UNE ARCHITECTURE EN ANNEAU**

François Deslauriers

Département de Génie informatique

École Polytechnique de Montréal

Mémoire présenté en vue de l'obtention du

Diplôme de Maîtrise ès Sciences Appliquées

(Génie électrique)

Août 2005

© François Deslauriers, 2005

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-16871-4

*Our file* *Notre référence*

ISBN: 978-0-494-16871-4

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

**MODÉLISATION D'UN RÉSEAU INTÉGRÉ SUR PUCE BASÉ SUR UNE ARCHITECTURE EN

ANNEAU**

présenté par : DESLAURIERS François

en vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de :

MME NICOLESCU Gabriela, Doct., présidente

M. BOIS Guy, Ph.D., membre et directeur de recherche

M. SAVARIA Yvon, Ph.D., membre et codirecteur de recherche

M. ABOULHAMID El Mostapha, Ph.D., membre

## Remerciements

Je tiens d'abord à remercier mon directeur de recherche, Guy Bois. Son soutien moral constant m'a permis de mener à terme ce projet. Par ailleurs, je voudrais également remercier mon co-directeur de recherche, Yvon Savaria, de même que Michel Langevin pour l'apport d'idées et de pistes à exploiter qu'ils ont pu me fournir tout au long du projet.

Je ne pourrais pas passer sous silence l'immense contribution de mes confrères de travail : Bruno Lavigne, Olivier Benny, Luc Filion, David Quinn, Mortimer Hubin, Jean-François Thibeault, Simon Provost, Patrick Samson et Francis « The Tank » St-Pierre. Grâce à eux, la maîtrise a parfois pu prendre la forme d'une récréation.

Mes parents sont également du nombre des gens à qui je dois une fière chandelle pour m'avoir encouragé dans mes démarches. Il en est de même pour ma copine Laurence et mon frère Yann.

Un beau merci par ailleurs à Réjean Lepage et Alexandre Vesey pour leur soutien technique, de même qu'à notre chère Ghislaine qui est une mère pour nous.

Finalement, je me dois de profiter de l'occasion qui m'est offerte pour me remercier moi-même d'avoir persévétré tout au long de cette aventure. Je dois une partie de cette persévérence aux contributions immenses de mes fidèles amis Ghislain Raza, Jonathan Zerg, Gregory Superi et Gary Broslma.

## Résumé

La constante miniaturisation du transistor a révolutionné le marché des systèmes embarqués des dernières années. Grâce aux progrès réalisés dans le domaine des semi-conducteurs et aux possibilités offertes par les nouvelles technologies, la porte a été ouverte aux systèmes multiprocesseurs, systèmes qui permettent à plusieurs unités de se répartir les tâches à effectuer de façon à atteindre une vitesse de traitement bien supérieure aux systèmes utilisant un seul processeur.

Une des conditions essentielles pour atteindre de tels gains de performance est de diminuer autant que possible le temps de communication entre les composants. En effet, la synchronisation entre diverses unités de traitement implique en général une communication constante entre ces derniers. De plus, l'intégration d'une centaine de blocs sur une même puce engendre une imposante quantité de transactions. L'architecture de communication utilisée se doit d'être en mesure de supporter cette hausse des communications.

Les architectures de communication dominant le marché actuel sont celles utilisant les bus, que ce soit dans leur forme la plus simple ou dans une version hiérarchisée. Or, ces architectures de bus seront prochainement déficientes puisqu'elles ne permettent d'accommoder qu'un nombre limité de blocs (moins de cinq processeurs, par exemple). Ceci est nettement insuffisant pour les systèmes intégrés sur puce du futur qui comprennent des centaines de composants.

Pour contourner ce problème, un nouveau concept a fait son apparition depuis quelques années : le réseau intégré sur puce. L'utilisation de ce type d'architecture permet de rencontrer les besoins en bande passante et en extensibilité.

Ce travail met d'abord en lumière les déficiences des architectures de bus en mettant l'accent sur leurs carences les plus importantes. Ensuite il présente le concept de réseau pur puce. Ce type d'architecture incorpore des notions générales associées aux réseaux à grande échelle. Il est donc primordial de présenter quelles sont ces notions générales qui seront ensuite intégrées au monde des systèmes sur puce.

Il existe par ailleurs plusieurs façons d'agencer entre eux les composants qui forment le réseau. On parle ici de la notion de *topologie*. Plusieurs topologies sont étudiées et caractérisées selon leurs avantages et inconvénients. Une dizaine de réseaux intégrés sur puce, issus de travaux universitaires ou commerciaux sont d'ailleurs présentés pour valider la théorie sur les topologies.

Une nouvelle architecture de réseau intégré, basée sur le modèle de l'anneau par jeton (en anglais *Token Ring*) et baptisée RoC (*Rotator on Chip*), est présentée et détaillée. Cette architecture facilement extensible se veut un réseau qui maximise le taux d'utilisation de ses composants, ce qui le rend très peu coûteux en espace tout en permettant d'obtenir de bonnes performances. Les simulations montrent qu'il est plus lent que les architectures en mailles, mais qu'il nécessite un espace plus restreint sur la puce. En ayant en tête le perpétuel compromis performance/coût, le RoC se démarque particulièrement lorsque le concepteur doit se soucier de la surface occupée par le réseau en même temps que de la puissance qu'il dissipe. Le RoC se démarque également pour les applications nécessitant un trafic local et il est un choix avantageux lorsqu'utilisé pour traiter les applications de type *streaming*.

## Abstract

In recent years, technology scaling caused the embedded systems' world to change drastically. Because of constant progress and interesting outcomes connected to new technologies, multiprocessor systems have emerged as the ultimate solution to process many embedded applications such as multimedia and telecommunications.

The expected performance gains can be reached only to one condition: communication time between components must be lowered as much as possible. Indeed, synchronisation between processing units involves high and constant communications. Moreover, integrating hundreds of IP cores on a single chip leads to a significant increase in the number of transactions. The communication infrastructure must then be able to sustain the required bandwidth and latency.

Currently, bus-based architectures are very popular, whether simple shared based or advanced hierarchical structures. Nevertheless, typically, these architectures can only support up to 5 processors and up to twelve masters before becoming the system bottleneck. This is obviously insufficient for systems on chip integrating over a hundred cores, which will be widely used in the near future.

To solve this problem, a new paradigm has emerged since the year 2000: the network on chip approach. Such networks easily allows meeting bandwidth needs and scalability requirements.

This work highlights bus-based architecture deficiencies by showing why they are not suitable for multiprocessor SoCs and then presents the network on chip concept. This type of architecture uses general notions associated with wide area networks. Those concepts are thus presented in this work

In addition, it is possible to connect network components together in many ways, leading to various topologies. Several of those topologies are presented in this work and are discussed in order to highlight their pros and cons. Some NoC architectures are then presented to go along with the discussions.

A new NoC architecture, based on the token ring model and called RoC (*Rotator on Chip*) is the main focus of this thesis. Its architecture is easily scalable and can support a high utilization rate, which makes it less expensive in area than other networks while still preserving acceptable performance. Simulations show that RoC is slower than mesh-based networks on chip, while being less expensive. Having in mind the performance/cost tradeoff, RoC is very suitable when area and power consumption are significant issues. RoC also provides very good performance when used to process stream-based applications.

## Table des matières

|                                                        |           |

|--------------------------------------------------------|-----------|

| Remerciements.....                                     | iv        |

| Résumé.....                                            | v         |

| Abstract.....                                          | vii       |

| Table des matières .....                               | ix        |

| Liste des figures .....                                | xiii      |

| Liste des tableaux.....                                | xvi       |

| Liste des acronymes.....                               | xvii      |

| Liste des annexes .....                                | xix       |

| Introduction.....                                      | 1         |

| <b>CHAPITRE 1 Revue de littérature .....</b>           | <b>6</b>  |

| 1.1.    L'état actuel .....                            | 6         |

| 1.1.1.    L'écart de productivité .....                | 6         |

| 1.1.2.    Raffinement progressif.....                  | 7         |

| 1.1.3.    Réutilisation .....                          | 8         |

| 1.1.4.    Applications du présent et du futur .....    | 9         |

| 1.2.    Limitations des systèmes sur puce actuels..... | 10        |

| 1.2.1.    Systèmes sur puce .....                      | 11        |

| 1.2.2.    Premier problème : les fils .....            | 12        |

| 1.2.3.    Deuxième problème : la synchronisation ..... | 13        |

| 1.2.4.    Troisième problème : les communications..... | 14        |

| 1.3.    Les architectures de bus .....                 | 15        |

| 1.3.1.    AMBA.....                                    | 15        |

| 1.3.2.    CoreConnect.....                             | 16        |

| 1.3.3.    SiliconBackplane III .....                   | 17        |

| 1.3.4.    Wishbone .....                               | 18        |

| 1.3.5.    Limitations des bus .....                    | 19        |

| 1.3.6.    Défis .....                                  | 21        |

| <b>CHAPITRE 2 Les réseaux intégrés sur puce.....</b>   | <b>23</b> |

|          |                                                           |    |

|----------|-----------------------------------------------------------|----|

| 2.1.1.   | Modèle OSI .....                                          | 23 |

| 2.1.1.1. | La couche physique .....                                  | 24 |

| 2.1.1.2. | La couche liaison .....                                   | 24 |

| 2.1.1.3. | La couche réseau .....                                    | 25 |

| 2.1.1.4. | La couche transport .....                                 | 25 |

| 2.1.1.5. | La couche session .....                                   | 25 |

| 2.1.1.6. | La couche présentation .....                              | 25 |

| 2.1.1.7. | La couche application .....                               | 26 |

| 2.1.1.8. | Couches couvertes par un NoC .....                        | 26 |

| 2.1.2.   | Caractéristiques / Catégories de NOC .....                | 26 |

| 2.1.3.   | Interface réseau .....                                    | 28 |

| 2.1.4.   | VCI .....                                                 | 29 |

| 2.1.5.   | OCP .....                                                 | 30 |

| 2.2.     | Concepts réseau .....                                     | 31 |

| 2.2.1.   | Réseaux vs NoC .....                                      | 31 |

| 2.2.2.   | Concepts réseau .....                                     | 32 |

| 2.2.3.   | Trafic .....                                              | 32 |

| 2.2.4.   | Commutation par paquets et commutation de circuit .....   | 33 |

| 2.2.5.   | Routage .....                                             | 35 |

| 2.2.5.1. | Stockage et réémission ( <i>store and forward</i> ) ..... | 36 |

| 2.2.5.2. | Par raccourcis ( <i>virtual-cut-through</i> ) .....       | 36 |

| 2.2.5.3. | Trou de ver ( <i>wormhole</i> ) .....                     | 36 |

| 2.3.     | Topologies existantes .....                               | 36 |

| 2.3.1.   | Maille .....                                              | 37 |

| 2.3.2.   | Papillon .....                                            | 38 |

| 2.3.3.   | Arbre élargi .....                                        | 39 |

| 2.3.4.   | Autres topologies .....                                   | 40 |

| 2.3.5.   | Black-Bus .....                                           | 42 |

| 2.3.6.   | ClearConnect® .....                                       | 42 |

| 2.3.7.   | STBus .....                                               | 43 |

| 2.3.8.   | SPIN .....                                                | 43 |

|                                              |                                                                  |    |

|----------------------------------------------|------------------------------------------------------------------|----|

| 2.3.9.                                       | Hot Potato .....                                                 | 44 |

| 2.3.10.                                      | SoCIn .....                                                      | 44 |

| 2.3.11.                                      | ECLIPSE .....                                                    | 45 |

| 2.3.12.                                      | NoCGEN .....                                                     | 45 |

| 2.3.13.                                      | Et les autres .....                                              | 46 |

| CHAPITRE 3 : Le <i>Rotator on Chip</i> ..... |                                                                  | 47 |

| 3.1.                                         | Vue d'ensemble .....                                             | 47 |

| 3.2.                                         | Le noeud .....                                                   | 49 |

| 3.3.                                         | La banque .....                                                  | 51 |

| 3.4.                                         | Cheminement des données .....                                    | 53 |

| 3.5.                                         | Détails d'implantation .....                                     | 57 |

| 3.6.                                         | Caractéristiques du RoC .....                                    | 62 |

| CHAPITRE 4 Optimisation du RoC.....          |                                                                  | 63 |

| 4.1.                                         | Requête sous forme d'une matrice de bits ( <i>bitmap</i> ) ..... | 63 |

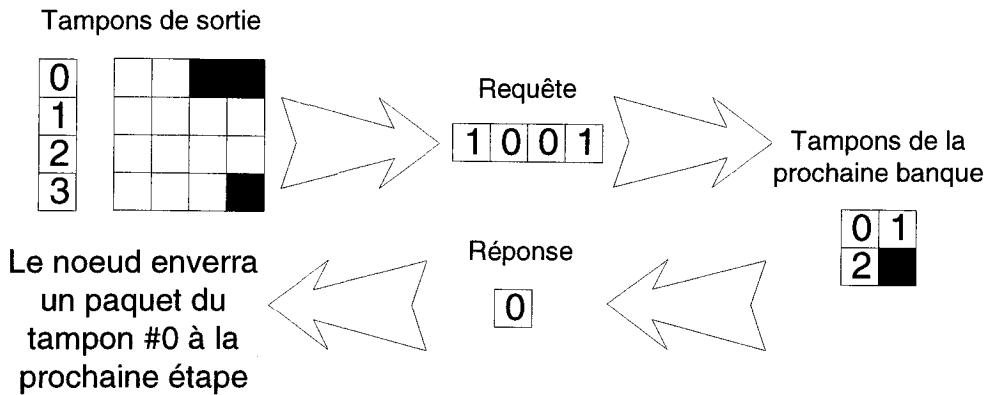

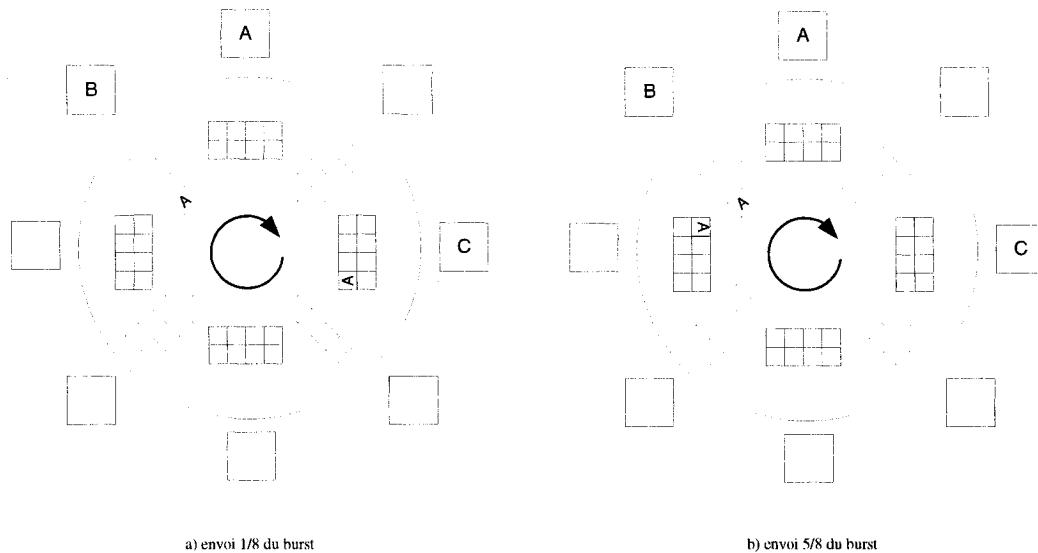

| 4.2.                                         | Mode rafale .....                                                | 65 |

| 4.3.                                         | RoC bidirectionnel .....                                         | 67 |

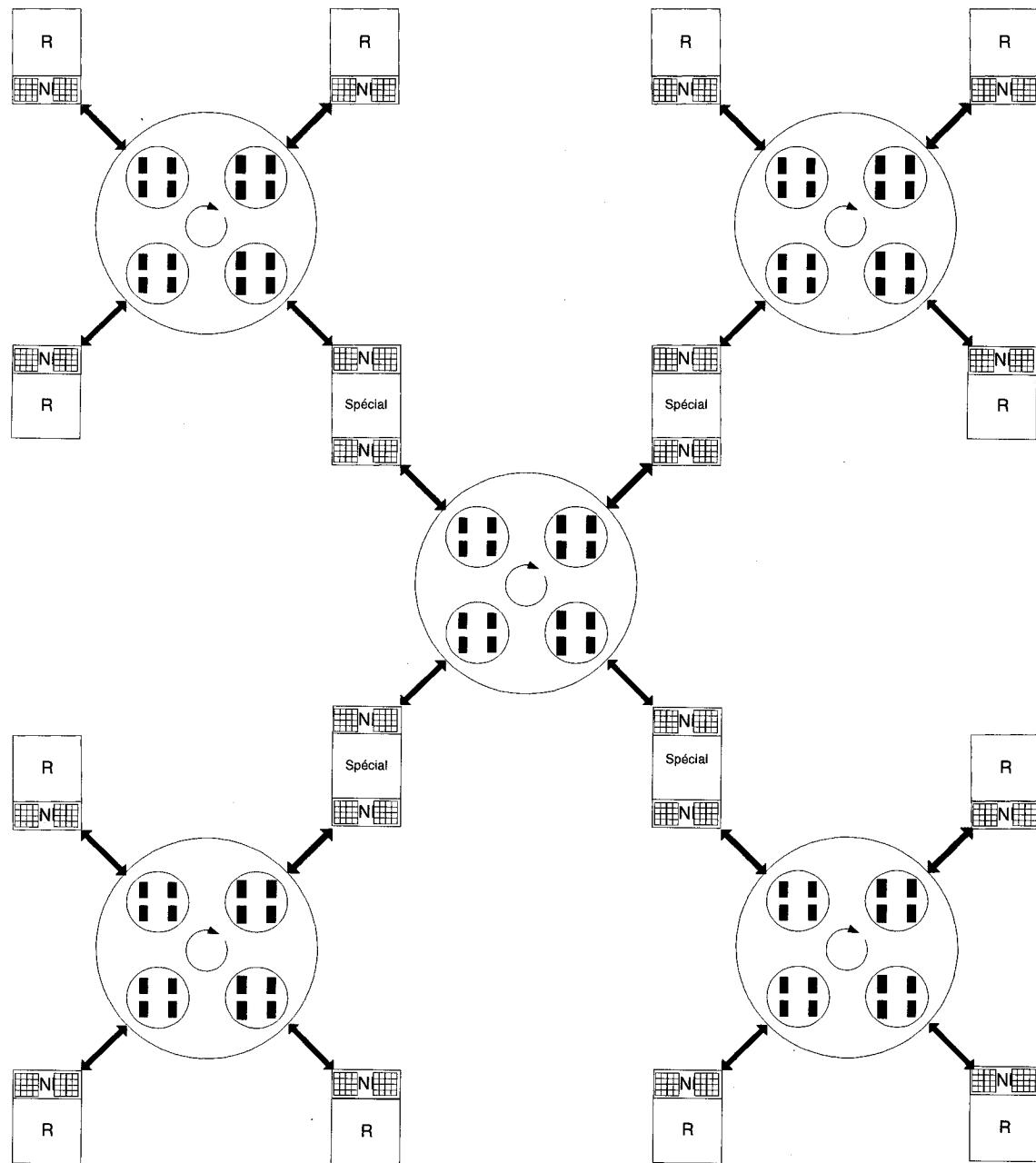

| 4.4.                                         | RoC hiérarchique .....                                           | 70 |

| CHAPITRE 5 : Résultats et analyse .....      |                                                                  | 73 |

| 5.1.                                         | Description des simulations fonctionnelles .....                 | 73 |

| 5.1.1.                                       | Détails sur l'environnement .....                                | 74 |

| 5.1.2.                                       | Types de trafic .....                                            | 75 |

| 5.1.2.1.                                     | Trafic aléatoire .....                                           | 75 |

| 5.1.2.2.                                     | Trafic « même endroit » .....                                    | 75 |

| 5.1.2.3.                                     | Trafic « voisin » .....                                          | 75 |

| 5.1.3.                                       | perNOC .....                                                     | 76 |

| 5.2.                                         | Résultats des simulations fonctionnelles .....                   | 76 |

| 5.2.1.                                       | Trafic aléatoire .....                                           | 77 |

| 5.2.1.1.                                     | Résultats de base .....                                          | 77 |

| 5.2.1.2.                                     | Effets de l'augmentation du nombre de nœuds .....                | 78 |

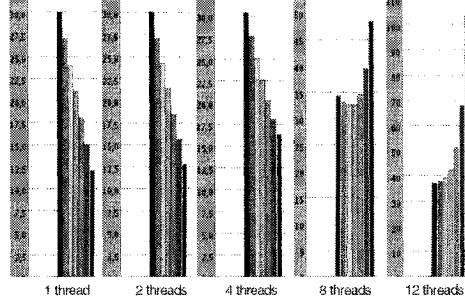

| 5.2.1.3.                                     | Effets de l'augmentation du nombre de threads .....              | 78 |

|          |                                                                            |     |

|----------|----------------------------------------------------------------------------|-----|

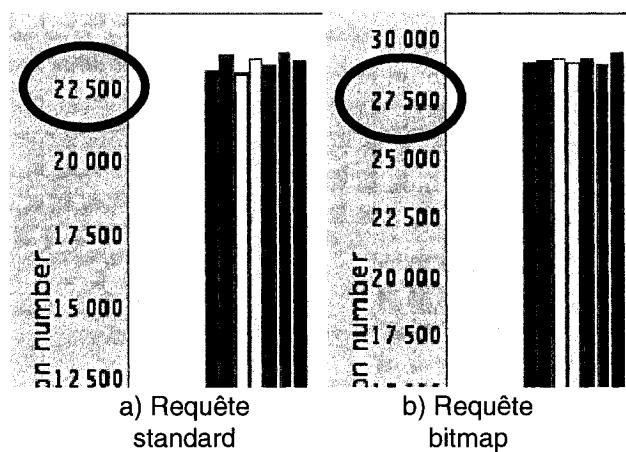

| 5.2.1.4. | Effets de l'utilisation de la requête <i>bitmap</i> .....                  | 80  |

| 5.2.1.5. | Utilisation du RoC bidirectionnel .....                                    | 81  |

| 5.2.1.6. | Utilisation du RoC hiérarchique .....                                      | 81  |

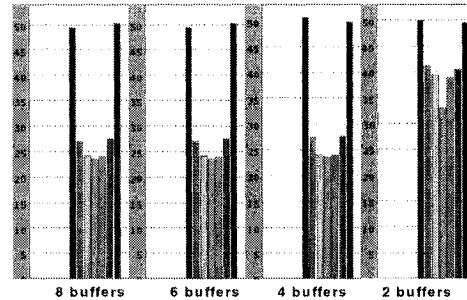

| 5.2.1.7. | Effets de la diminution du nombre de tampons sur une banque .....          | 83  |

| 5.2.1.8. | Comparaisons avec les réseaux <i>Token Ring</i> et <i>Hot Potato</i> ..... | 85  |

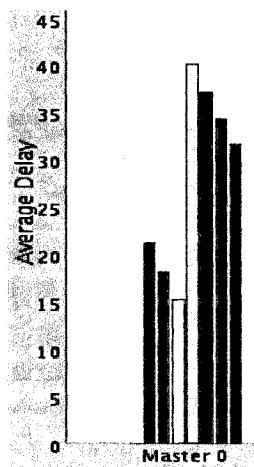

| 5.2.2.   | Trafic dirigé.....                                                         | 88  |

| 5.2.3.   | Trafic voisin .....                                                        | 90  |

| 5.3.     | Simulations du RoC avec une application multimédia .....                   | 91  |

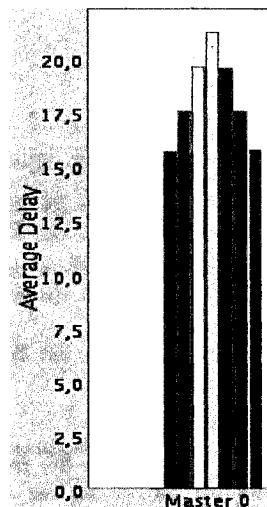

| 5.3.1.   | RoC classique / 26 nœuds .....                                             | 93  |

| 5.3.2.   | RoC bidirectionnel / 14 nœuds.....                                         | 93  |

| 5.3.3.   | RoC hiérarchique / 14 nœuds .....                                          | 94  |

| 5.3.4.   | Résultats obtenus.....                                                     | 95  |

|          | Conclusion et travaux futurs .....                                         | 99  |

|          | Considérations pour le futur.....                                          | 100 |

|          | Travaux futurs.....                                                        | 103 |

|          | Travaux reliés.....                                                        | 104 |

|          | Références.....                                                            | 107 |

|          | Annexes .....                                                              | 112 |

## Liste des figures

|                                                                                                                  |    |

|------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 : Allure de la loi de Moore .....                                                                     | 6  |

| Figure 1.2 : L'écart de productivité .....                                                                       | 7  |

| Figure 1.3 : Le raffinement progressif.....                                                                      | 8  |

| Figure 1.4 : Fractionnement de la puce en systèmes hétérogènes .....                                             | 11 |

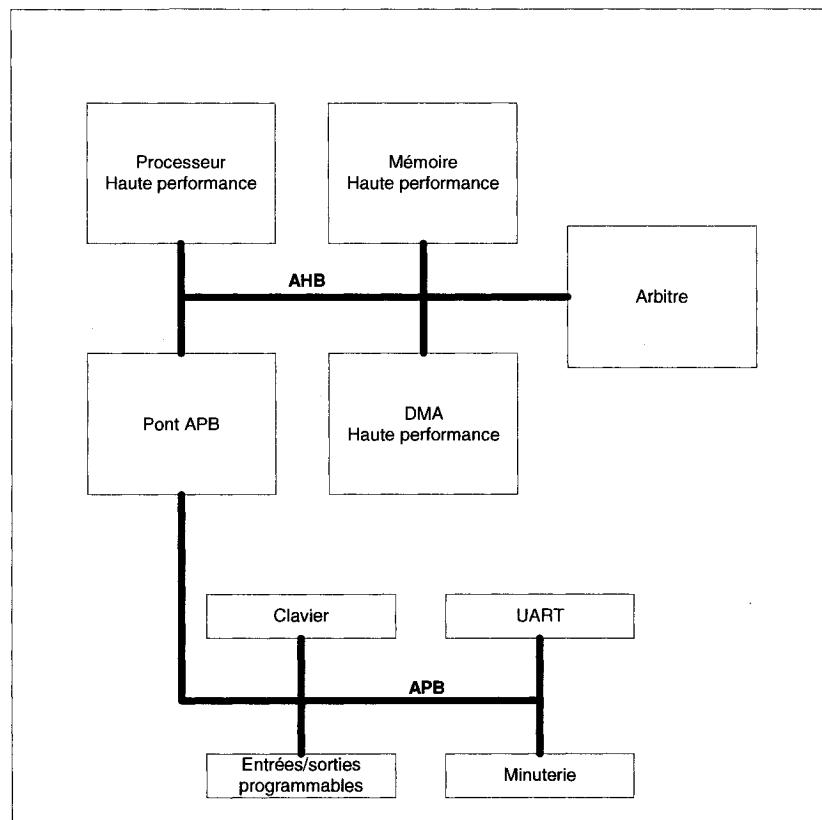

| Figure 1.5 : Structure du bus AMBA.....                                                                          | 15 |

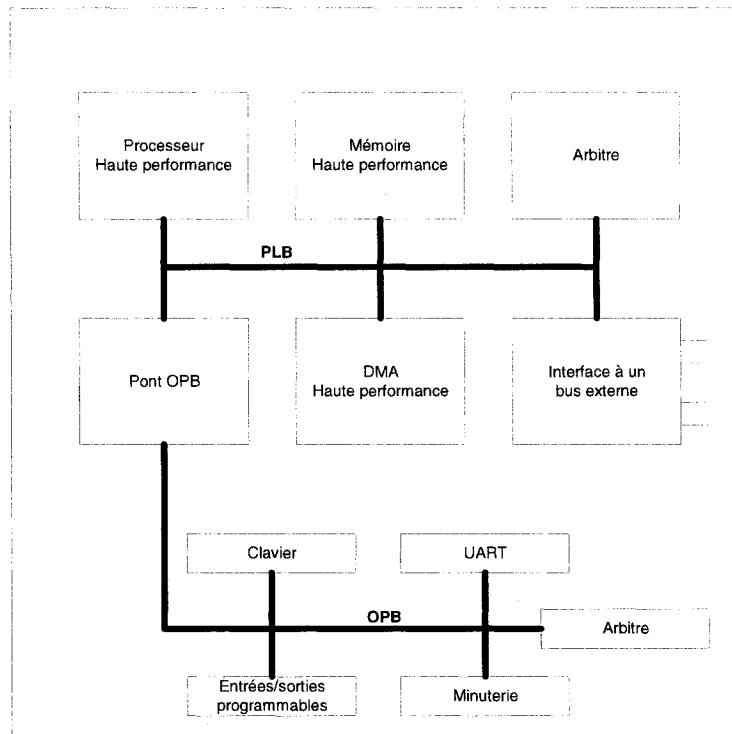

| Figure 1.6 : Structure du bus CoreConnect.....                                                                   | 17 |

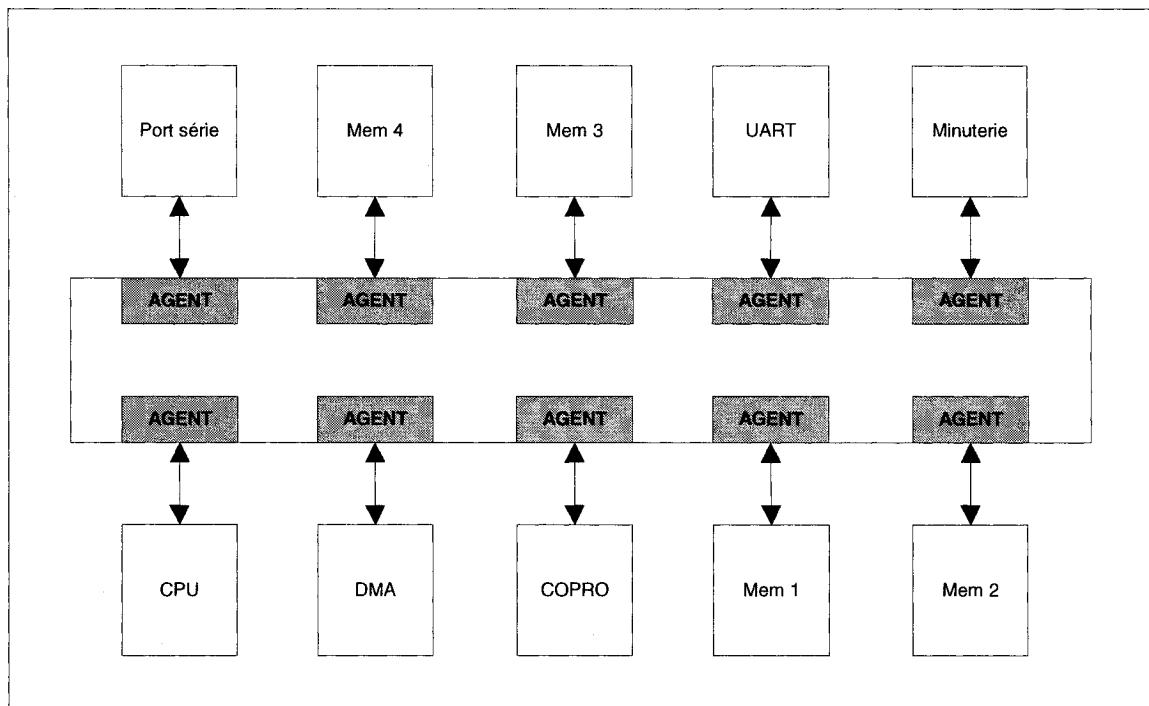

| Figure 1.7 : Structure du bus SiliconBackplane.....                                                              | 18 |

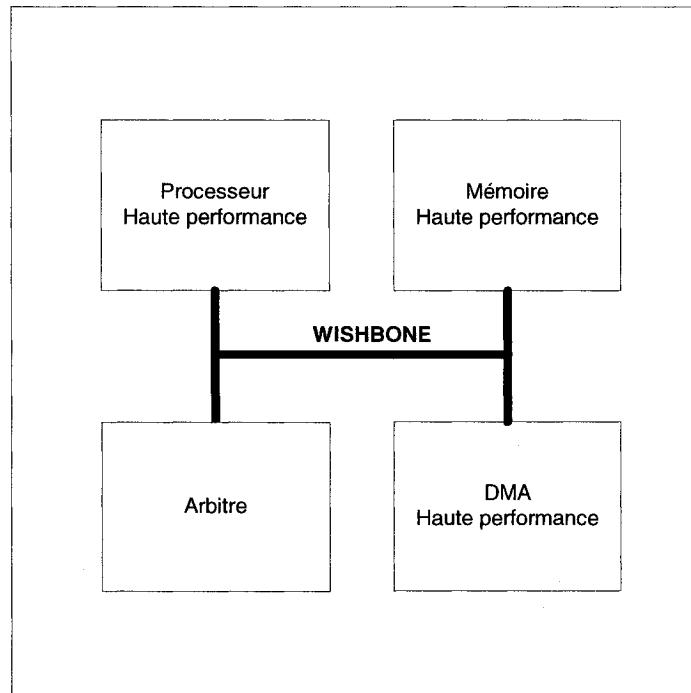

| Figure 1.8 : Structure du bus Wishbone.....                                                                      | 19 |

| Figure 1.9 : Situation sur un bus partagé menant à un conflit réglé par l'utilisation d'un bus hiérarchique..... | 20 |

| Figure 2.1 : Modèle OSI .....                                                                                    | 24 |

| Figure 2.2 : Modèle OSI appliqué aux réseaux intégrés sur puce .....                                             | 26 |

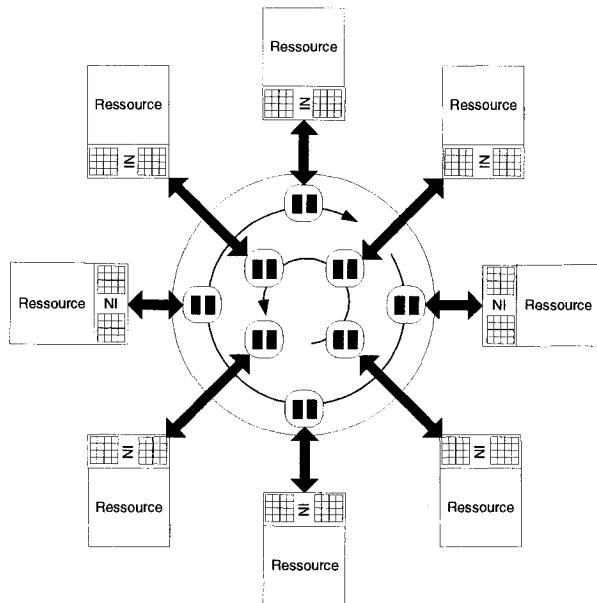

| Figure 2.3 : Exemple d'utilisation d'une interface réseau commune pour tous les blocs                            | 29 |

| Figure 2.4 : Rôle de l'interface OCP .....                                                                       | 30 |

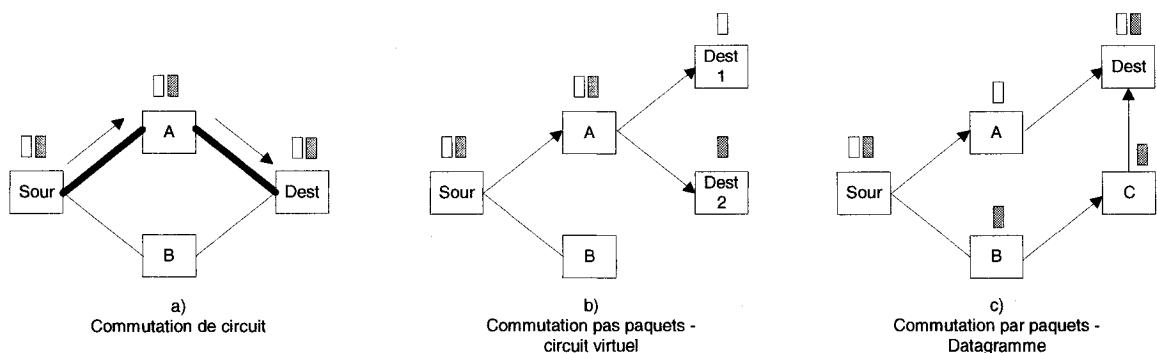

| Figure 2.5 : Différentes sortes de commutation.....                                                              | 34 |

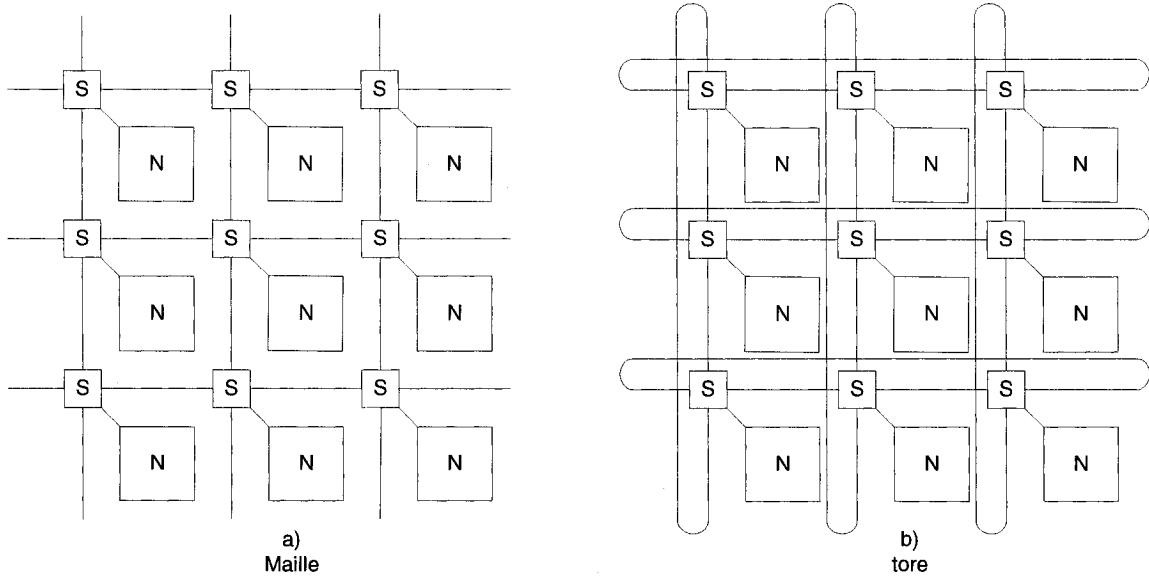

| Figure 2.6 : Topologies <i>maille</i> et <i>tore</i> .....                                                       | 38 |

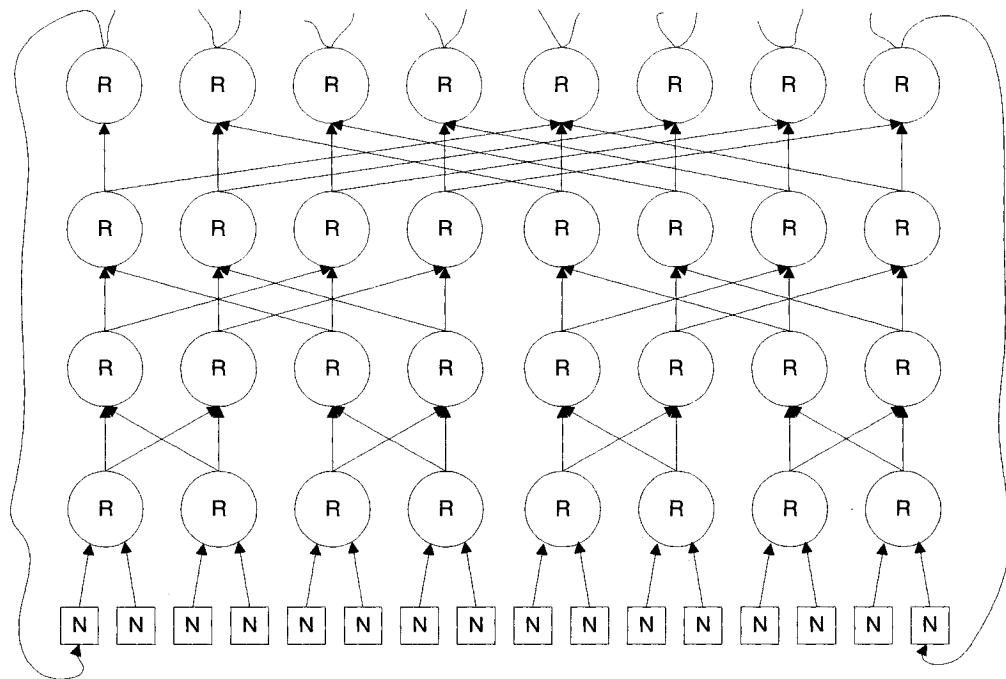

| Figure 2.7 : Schéma de la topologie papillon .....                                                               | 39 |

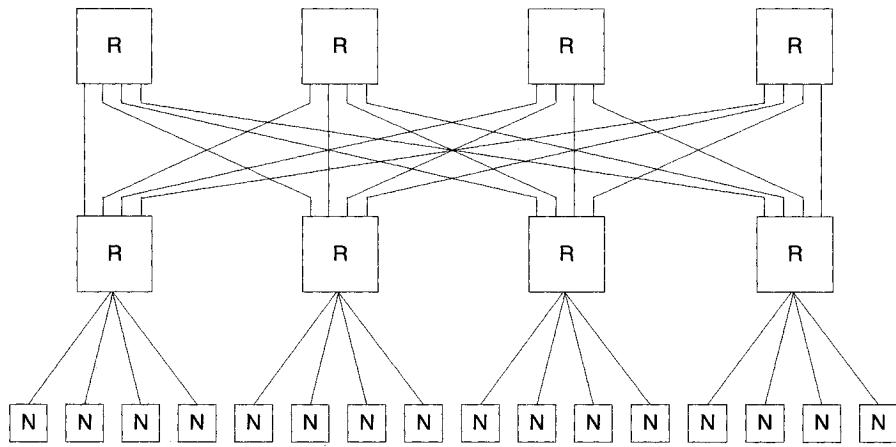

| Figure 2.8 : Schéma de la topologie en arbre élargi .....                                                        | 40 |

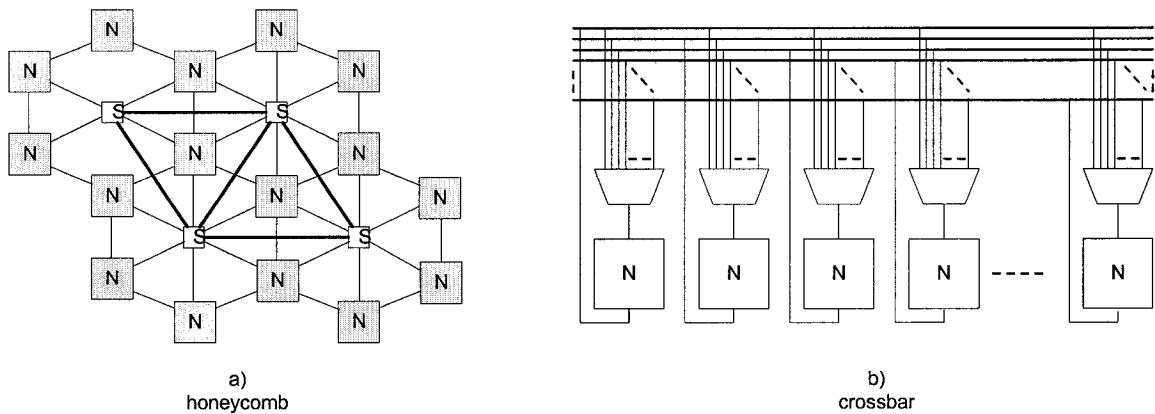

| Figure 2.9 : Allure des topologies <i>honeycomb</i> et <i>crossbar</i> .....                                     | 41 |

| Figure 2.10 : Allure du réseau ClearConnect® .....                                                               | 43 |

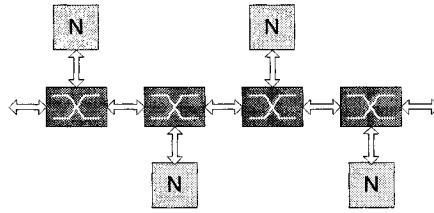

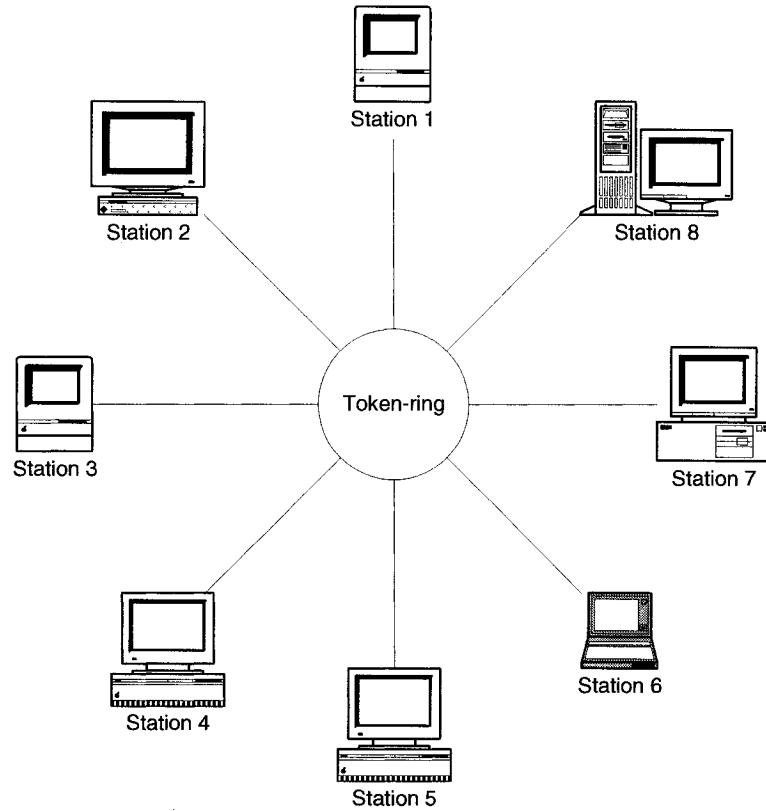

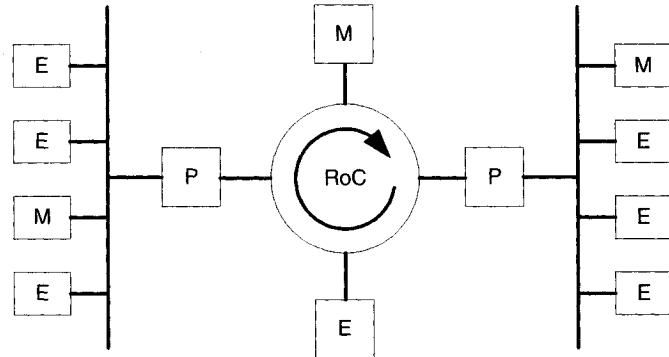

| Figure 3.1 : Architecture Token Ring.....                                                                        | 48 |

| Figure 3.2 : Vue d'ensemble du RoC.....                                                                          | 49 |

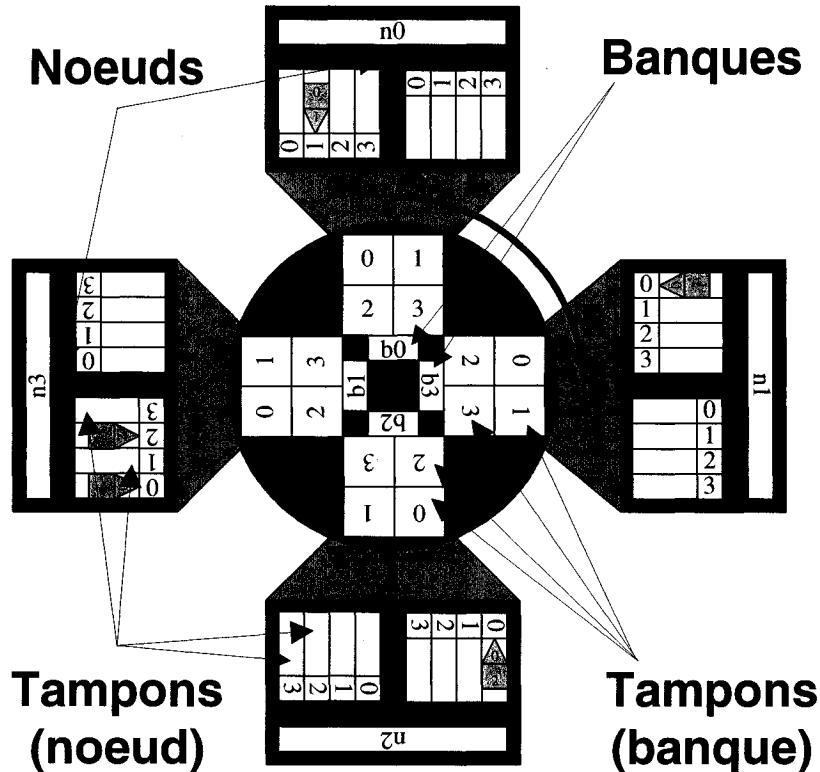

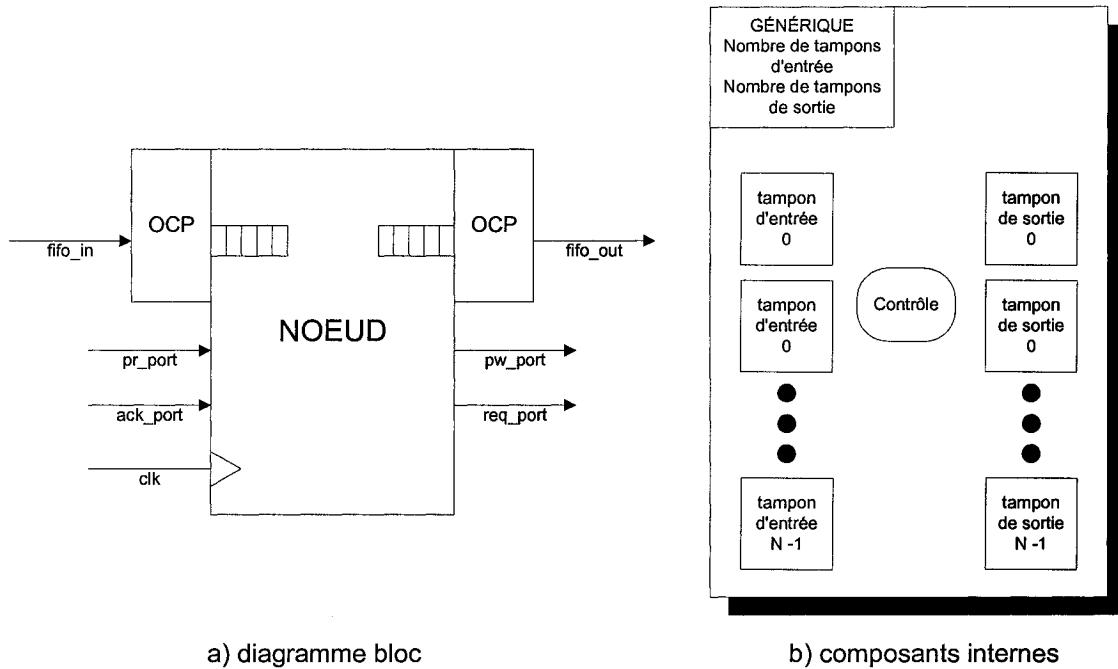

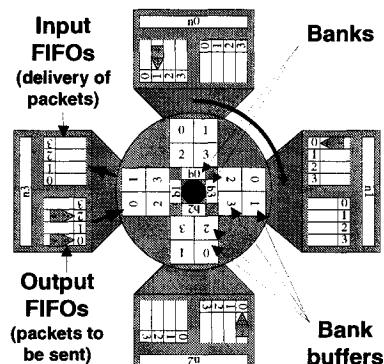

| Figure 3.3 : Description du noeud.....                                                                           | 50 |

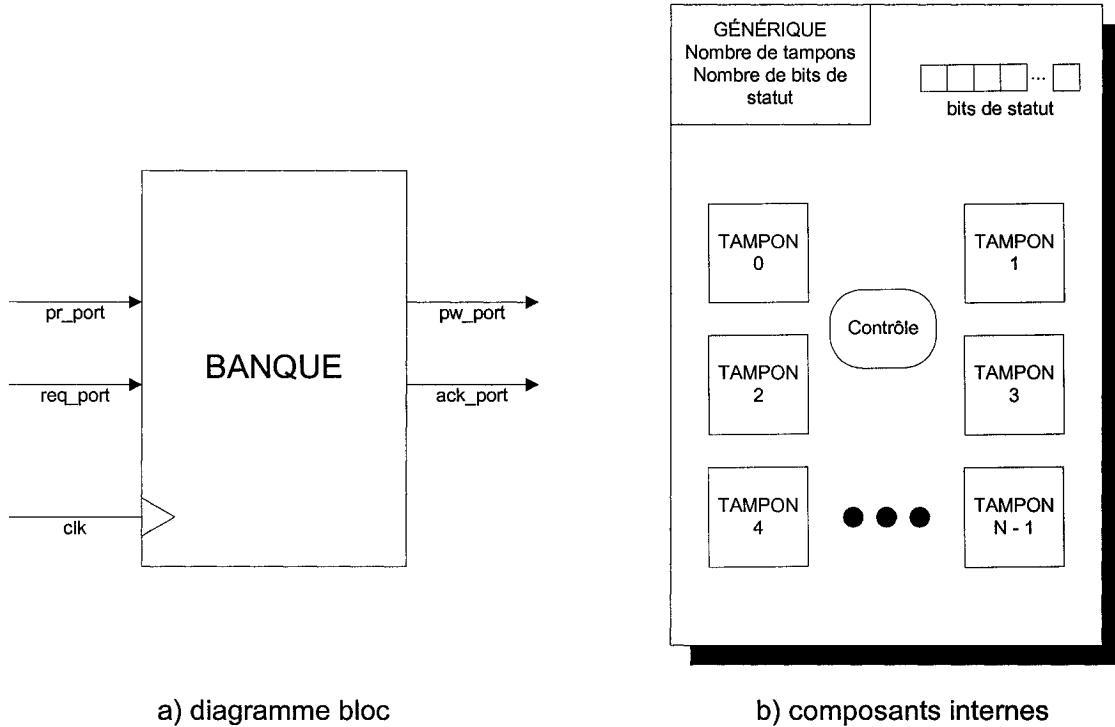

| Figure 3.4 : Description d'une banque.....                                                                       | 52 |

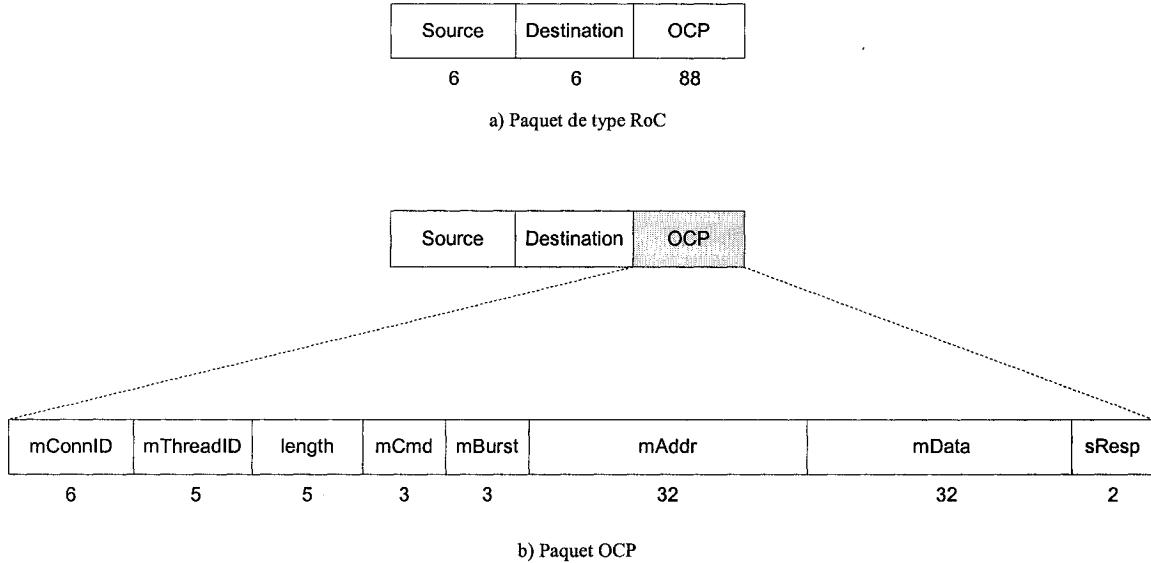

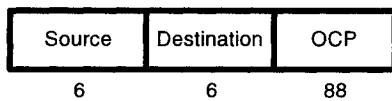

| Figure 3.5 : Représentation des paquets .....                                                                    | 54 |

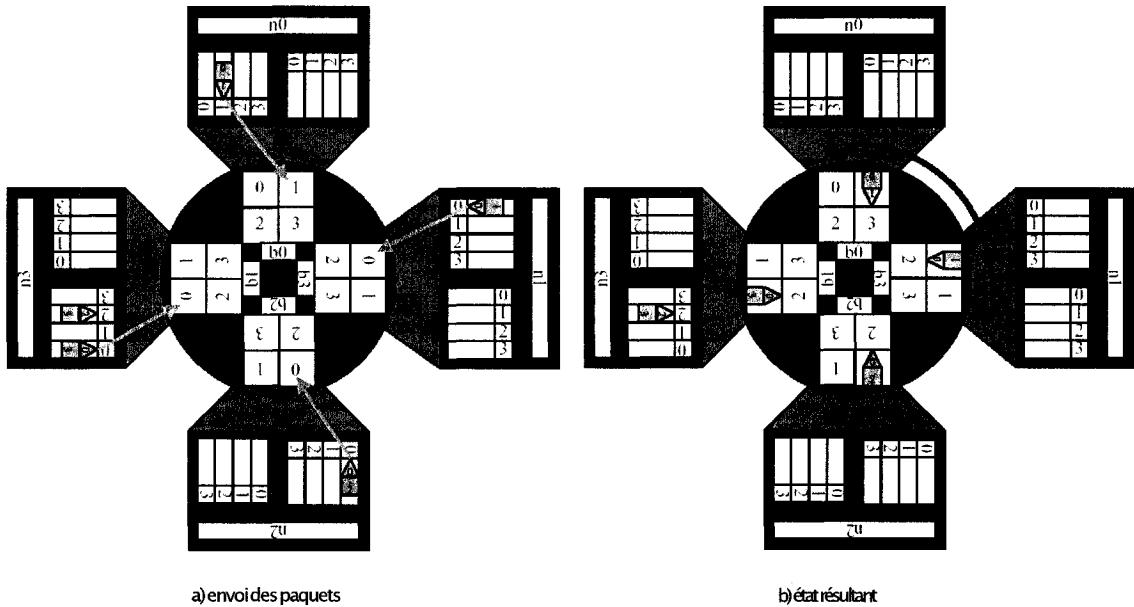

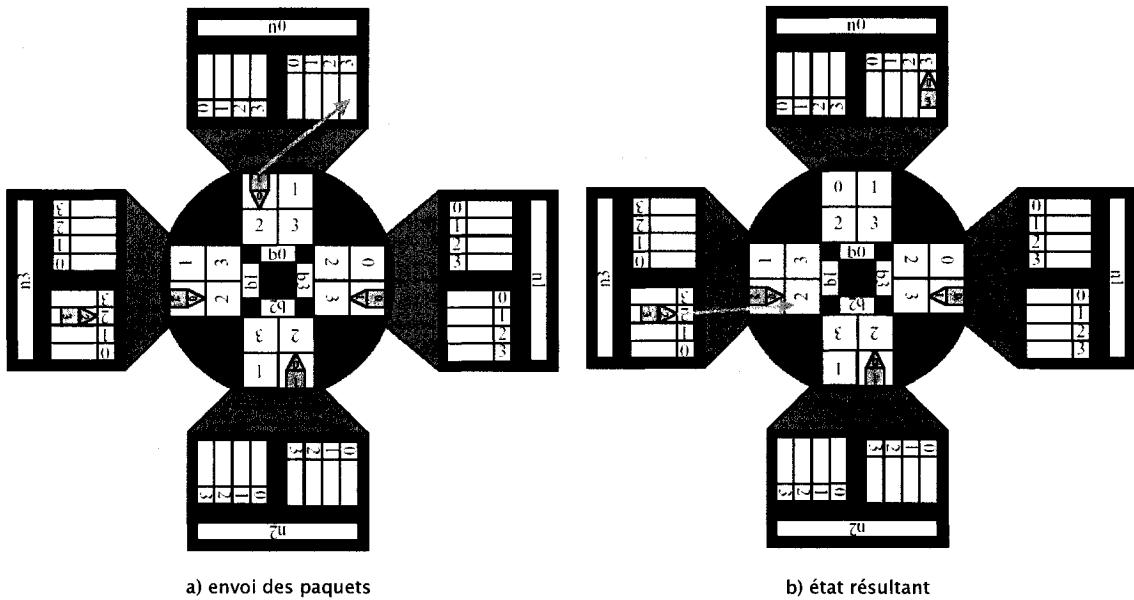

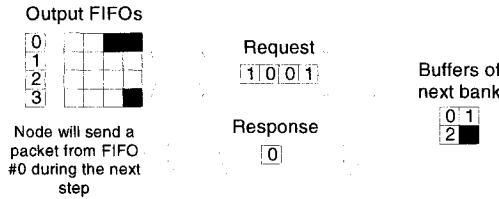

| Figure 3.6 : Transfert d'un paquet d'un noeud à une banque .....                                                 | 55 |

| Figure 3.7 : Transfert d'un paquet d'une banque à un noeud .....                                                 | 56 |

|                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------|----|

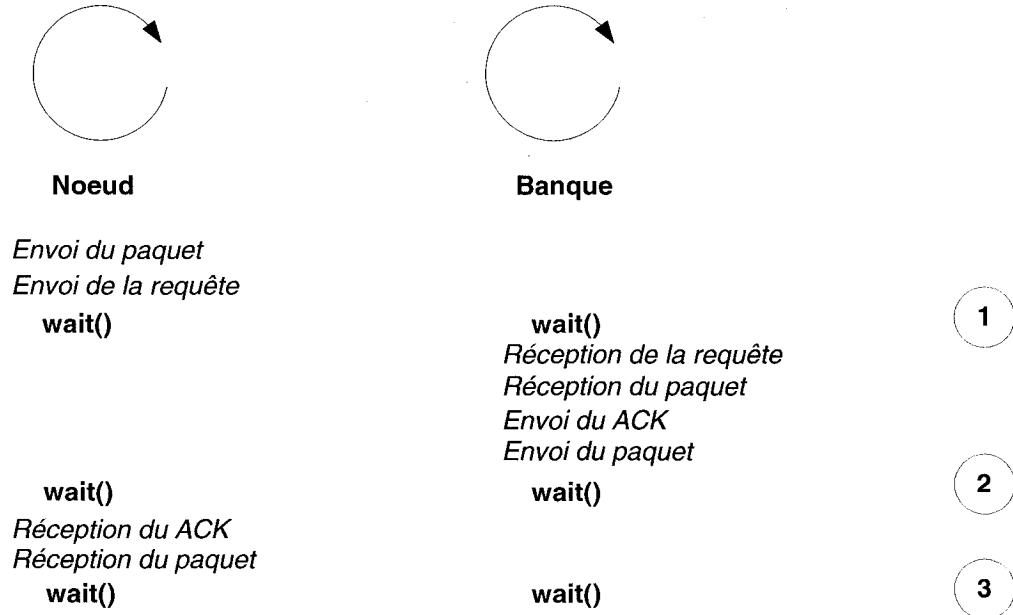

| Figure 3.8 : Séquence d'exécution du nœud et de la banque.....                                                       | 57 |

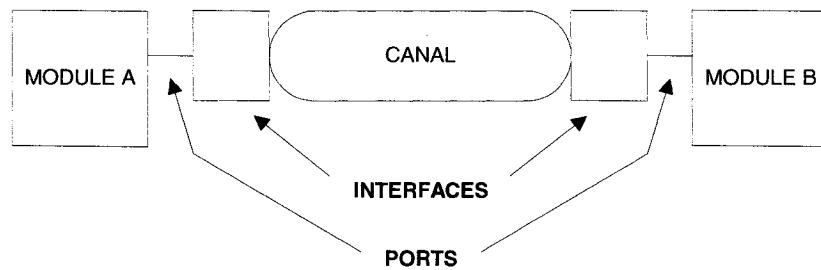

| Figure 3.9 : Interaction des modules, canaux, ports et interfaces dans SystemC .....                                 | 58 |

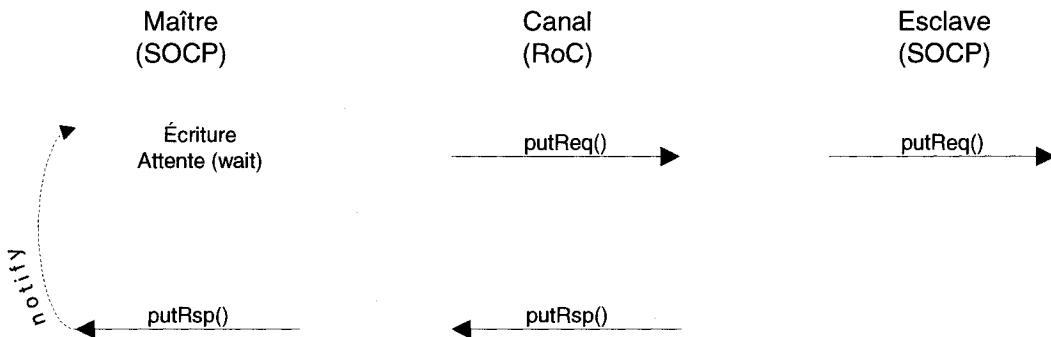

| Figure 3.10 : Fonctionnement des communications sous SystemC.....                                                    | 58 |

| Figure 3.11 : Suite d'appels de fonction menant à une transaction entre maître et esclave .....                      | 60 |

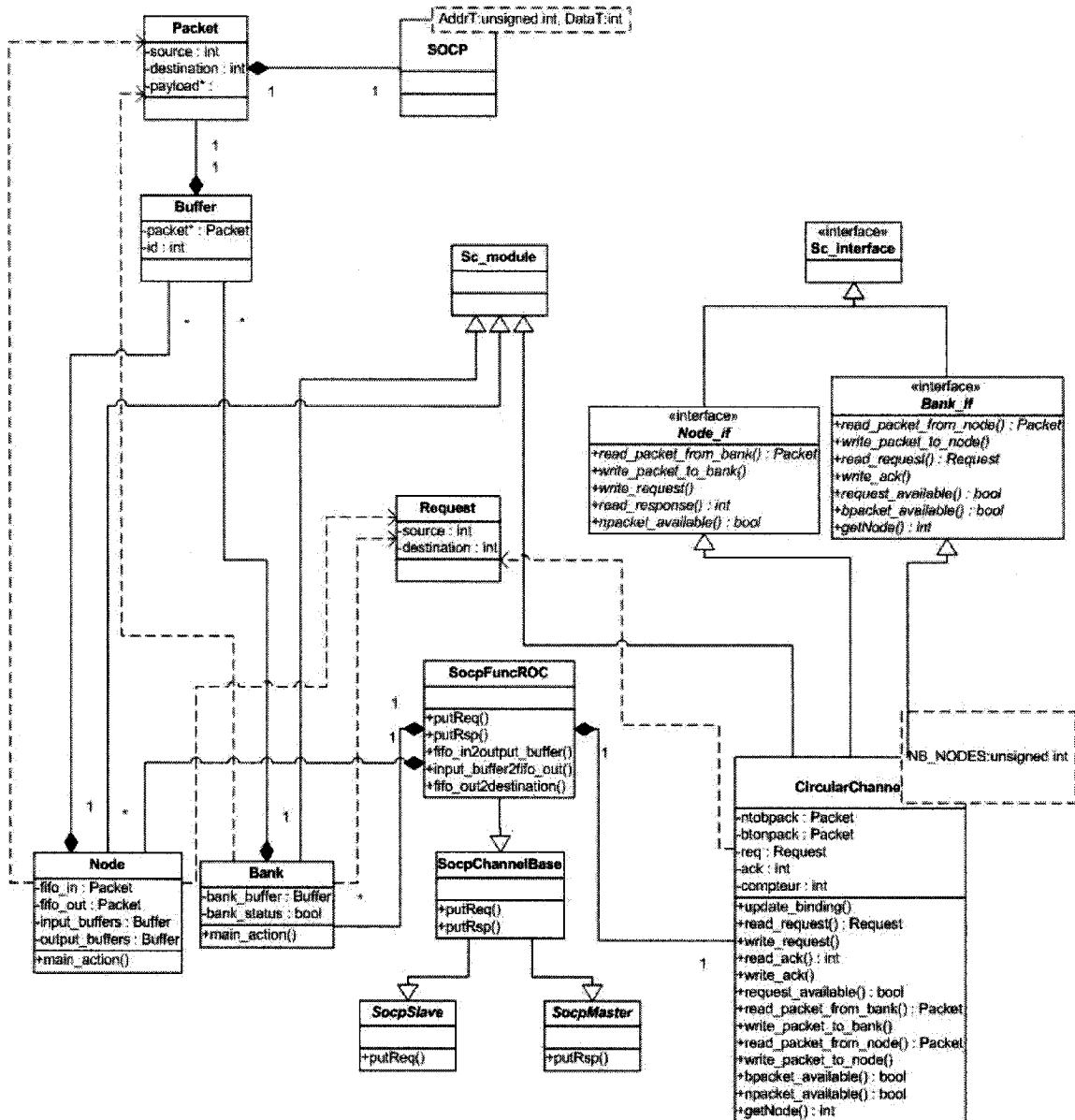

| Figure 3.12 : Diagramme de classes simplifié .....                                                                   | 61 |

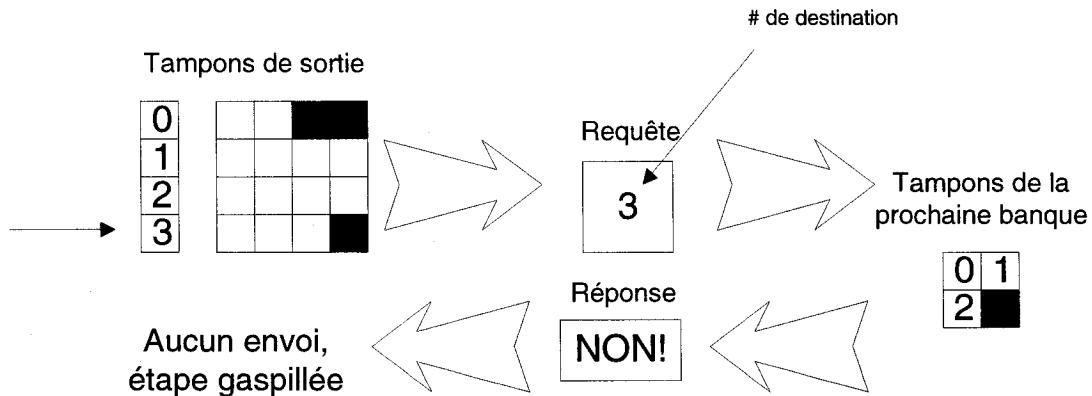

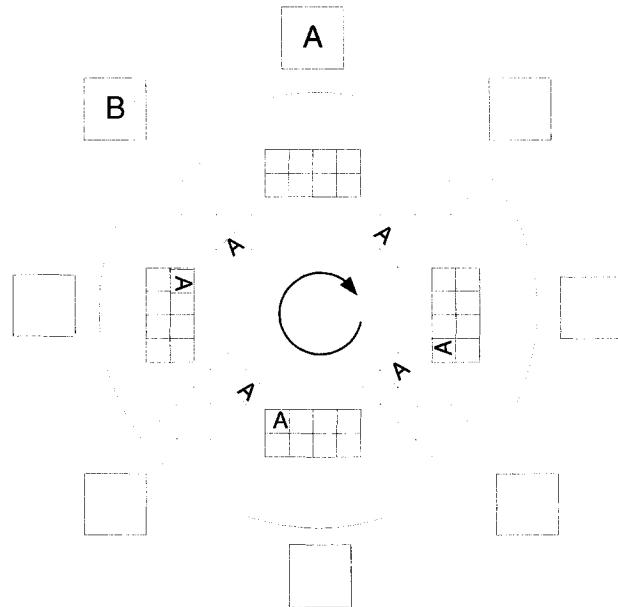

| Figure 4.1 : Situation menant à un cycle inutilisé.....                                                              | 64 |

| Figure 4.2 : Situation réglée par l'emploi de la requête <i>bitmap</i> .....                                         | 65 |

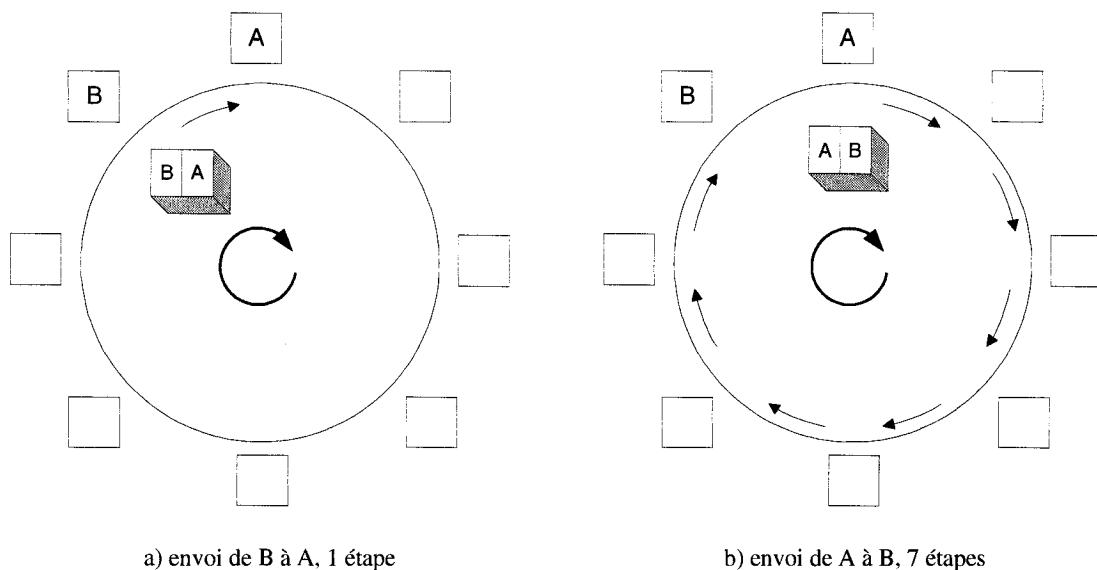

| Figure 4.3 : Problème lors d'un envoi en rafale de B à A .....                                                       | 66 |

| Figure 4.4 : Problème causé par l'architecture unidirectionnelle .....                                               | 67 |

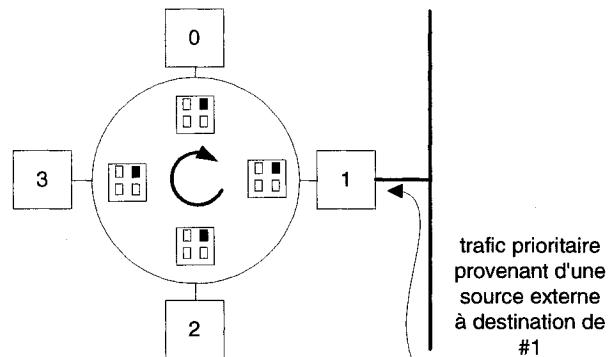

| Figure 4.5 : Situation qui conduit à l'incapacité d'un nœud à envoyer un paquet à son voisin immédiat.....           | 68 |

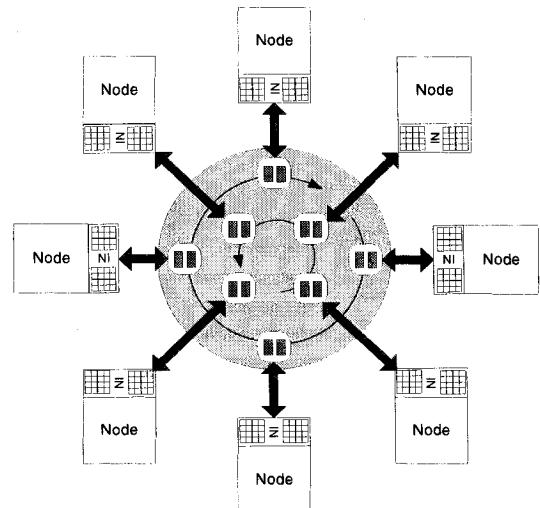

| Figure 4.6 : RoC bidirectionnel .....                                                                                | 69 |

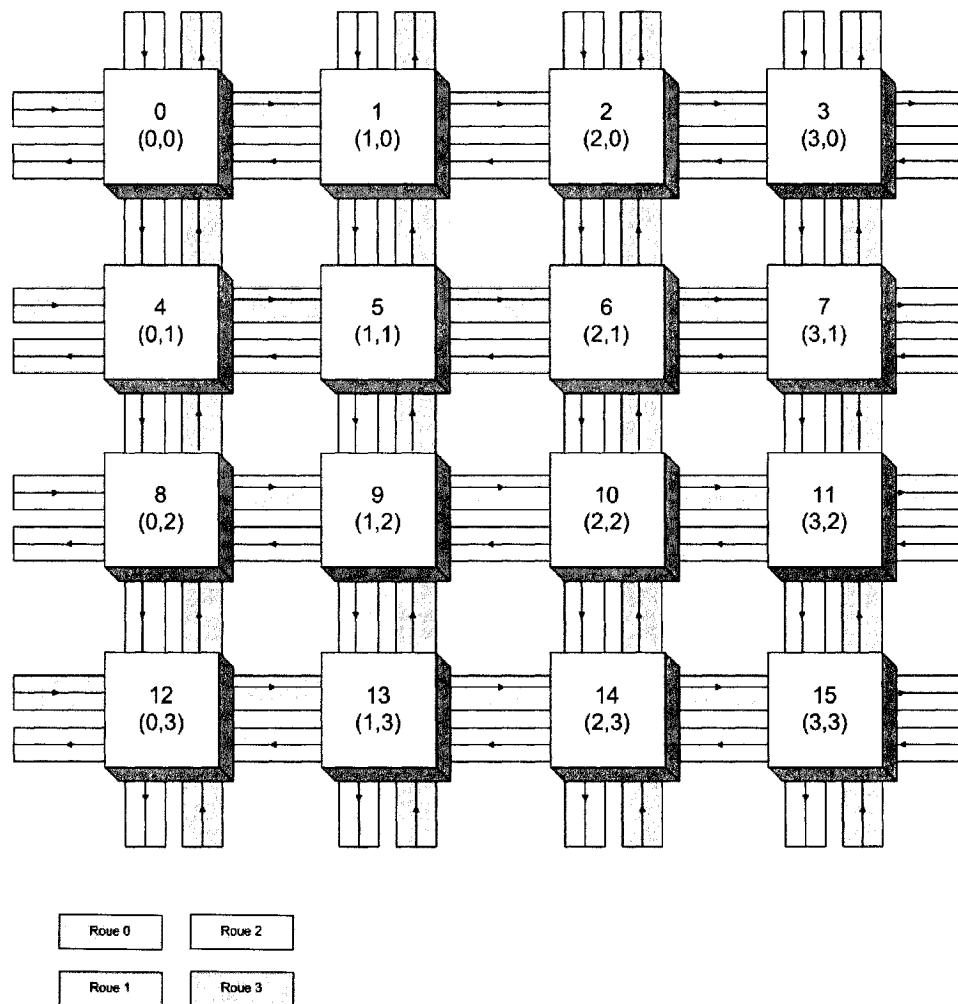

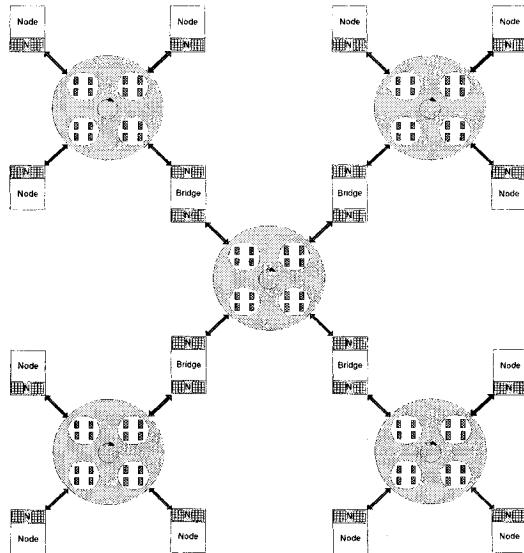

| Figure 4.7 : RoC hiérarchique.....                                                                                   | 71 |

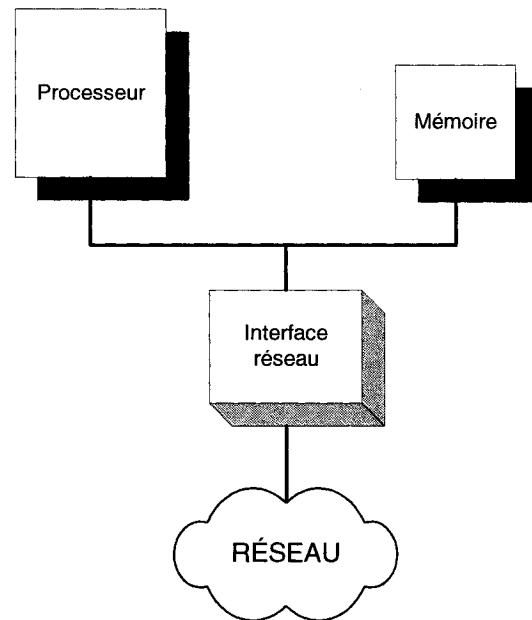

| Figure 5.1 : Utilisation d'une interface maître/esclave .....                                                        | 74 |

| Figure 5.2 : Affichage des résultats de performance avec perNOC .....                                                | 76 |

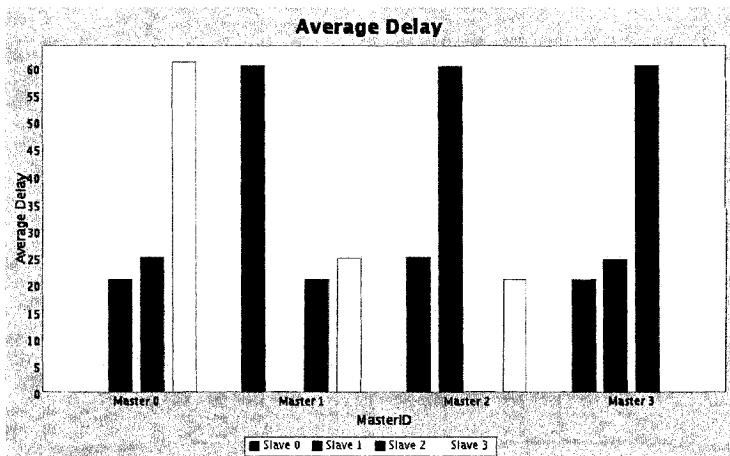

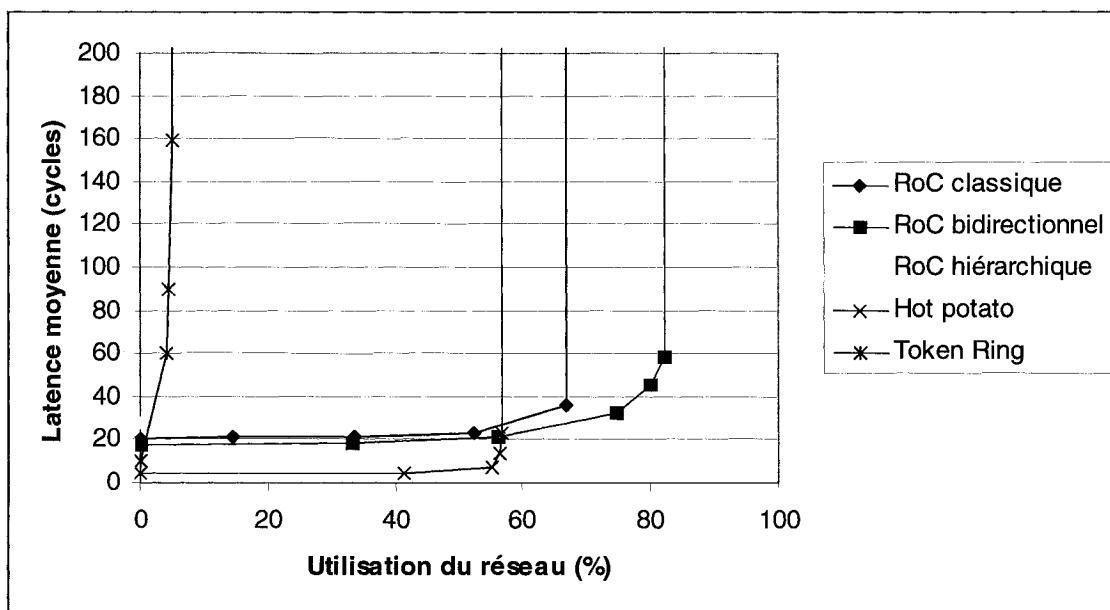

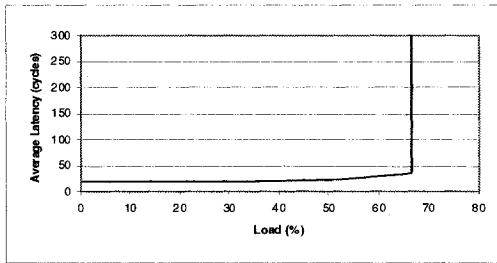

| Figure 5.3 : Résultat typique du RoC pour la latence .....                                                           | 77 |

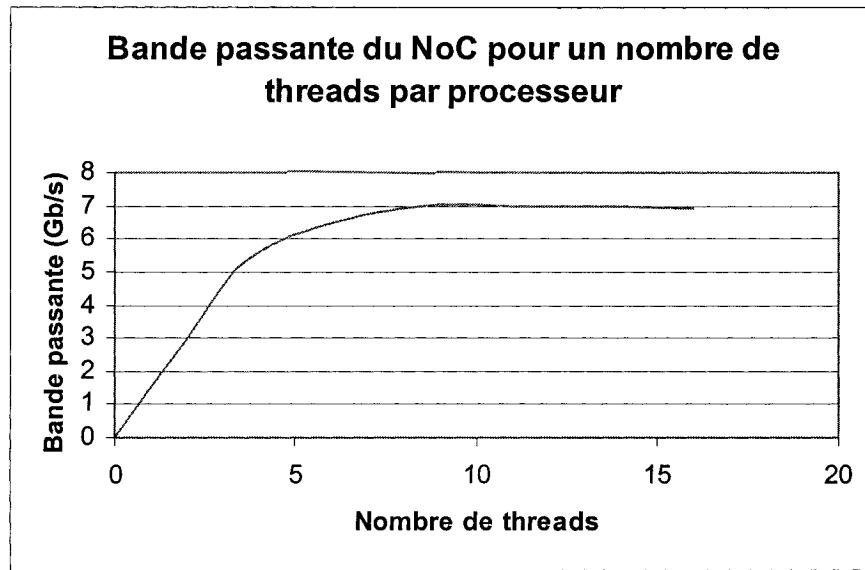

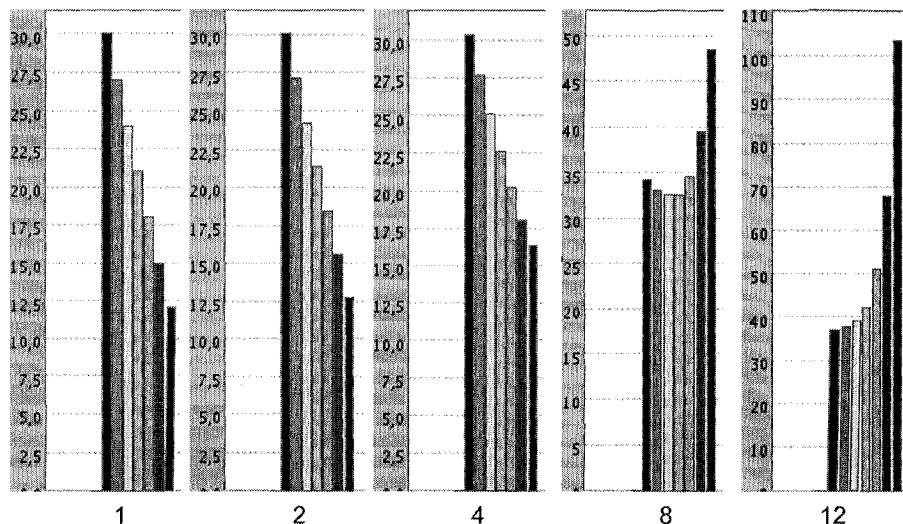

| Figure 5.4 : Saturation de la bande passante.....                                                                    | 79 |

| Figure 5.5 : Dégénérescence de la latence pour un transfert entre deux ressources voisines .....                     | 79 |

| Figure 5.6 : Augmentation de la bande passante effective avec une requête bitmap .....                               | 80 |

| Figure 5.7 : Résultat typique du RoC bidirectionnel pour la latence.....                                             | 81 |

| Figure 5.8 : Résultat typique du RoC hiérarchique pour la latence .....                                              | 82 |

| Figure 5.9 : Effet de la diminution du nombre de tampons sur la latence avec un RoC bidirectionnel à 8 noeuds .....  | 84 |

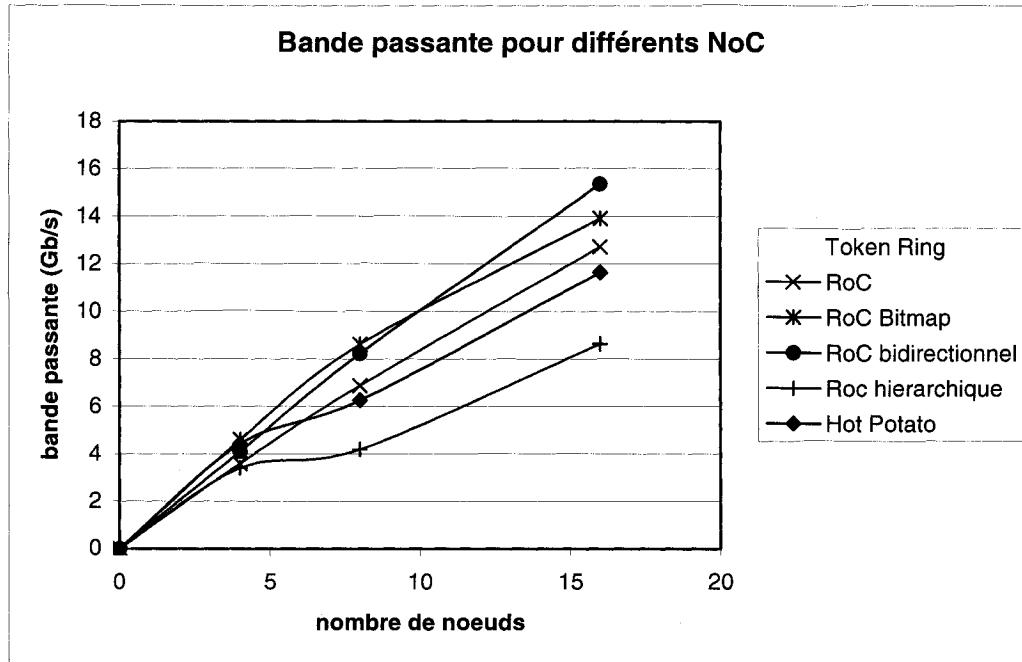

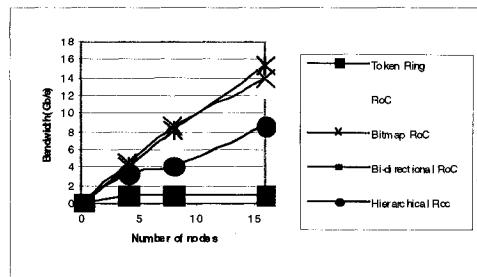

| Figure 5.10 : Bande passante pour différents NoC .....                                                               | 85 |

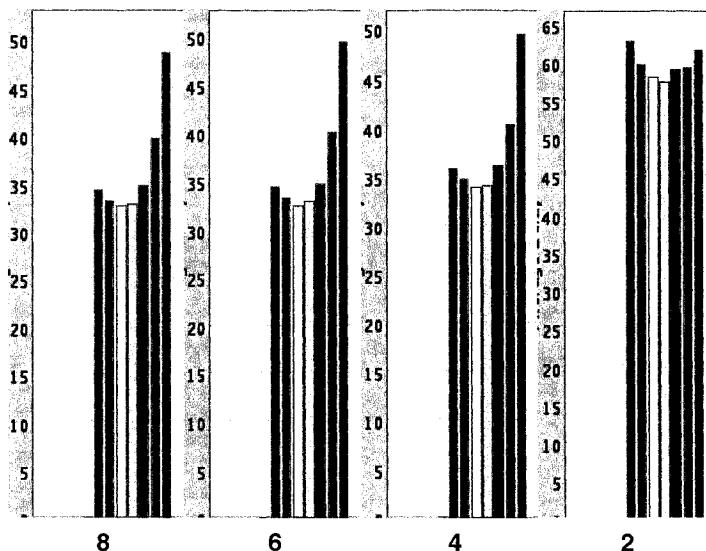

| Figure 5.11 : Pourcentage d'utilisation de l'interface réseau (nœud) .....                                           | 87 |

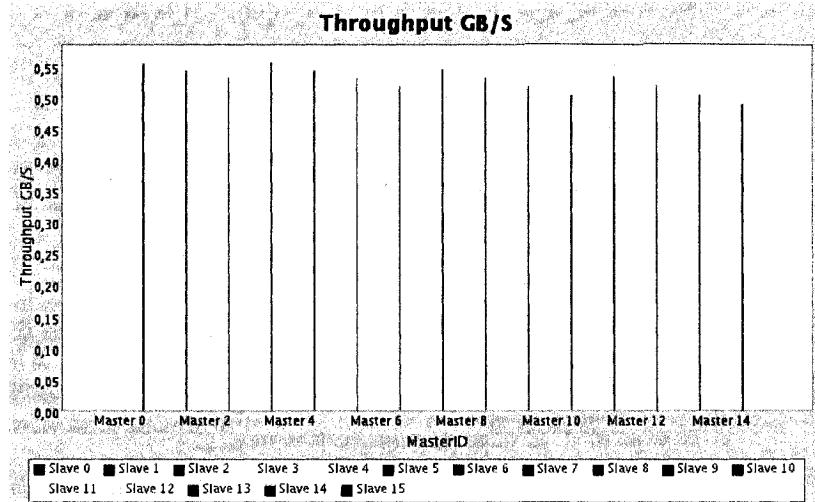

| Figure 5.12 : Bande passante pour un RoC standard à 16 nœuds suivant un trafic dirigé (8 threads / processeur) ..... | 89 |

|                                                                                                   |     |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 5.13: Bande passante pour un réseau Hot Potato à 16 nœuds suivant un trafic dirigé .....   | 90  |

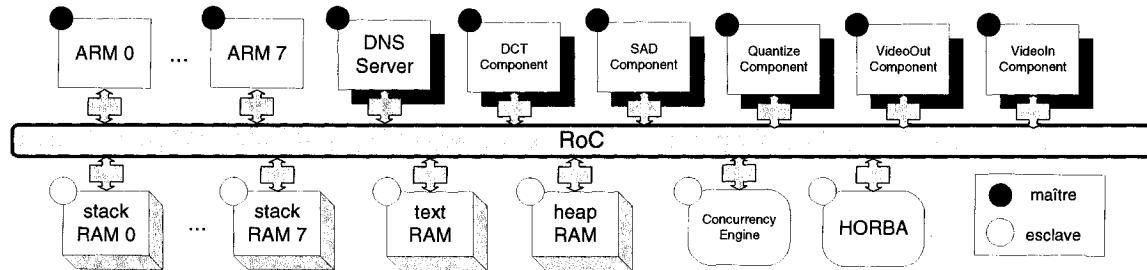

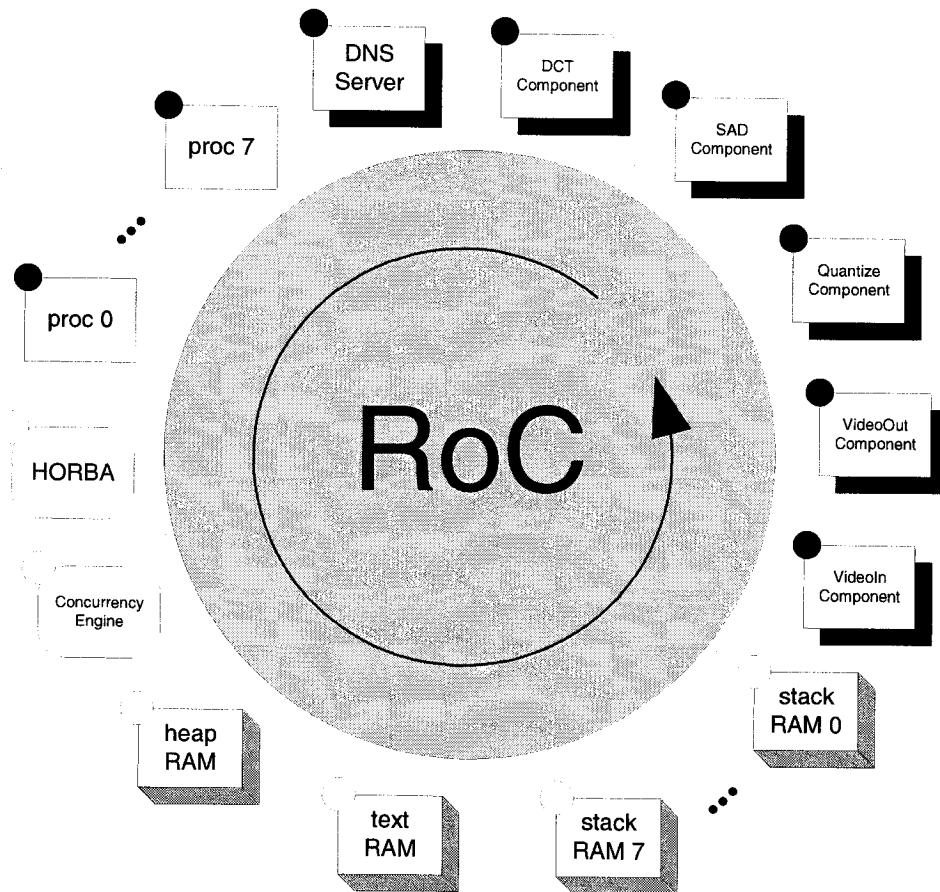

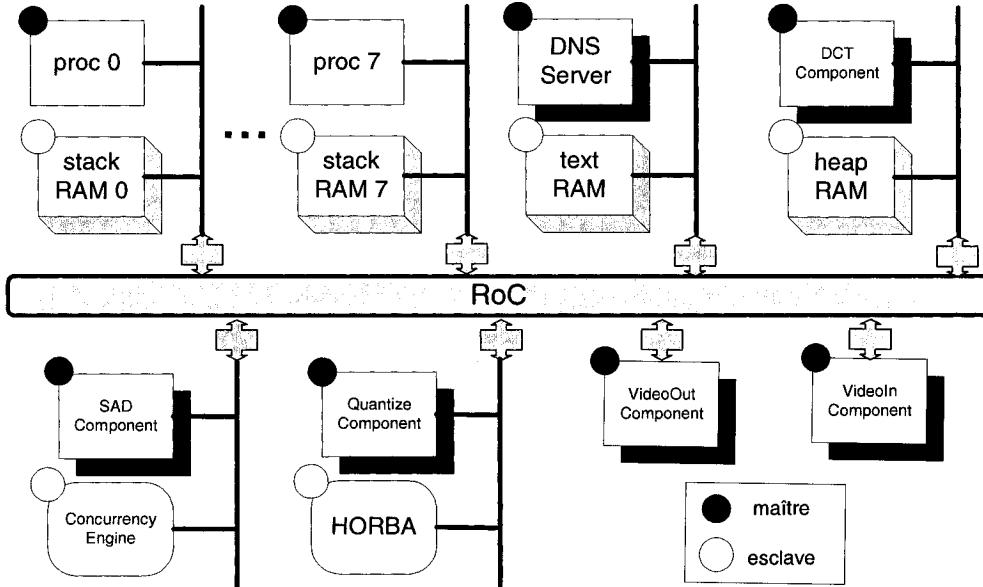

| Figure 5.14 : Configuration à 26 nœuds .....                                                      | 93  |

| Figure 5.15 : Ordre des ressources dans la rotation .....                                         | 94  |

| Figure 5.16 : Configuration à 14 nœuds .....                                                      | 95  |

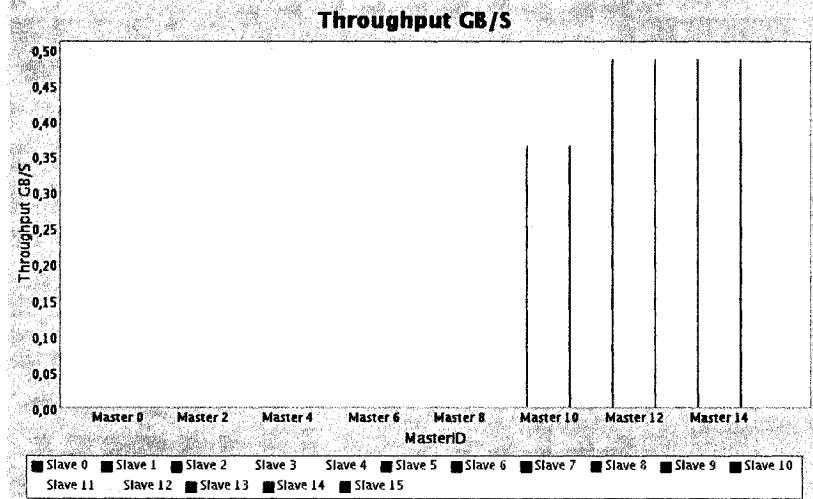

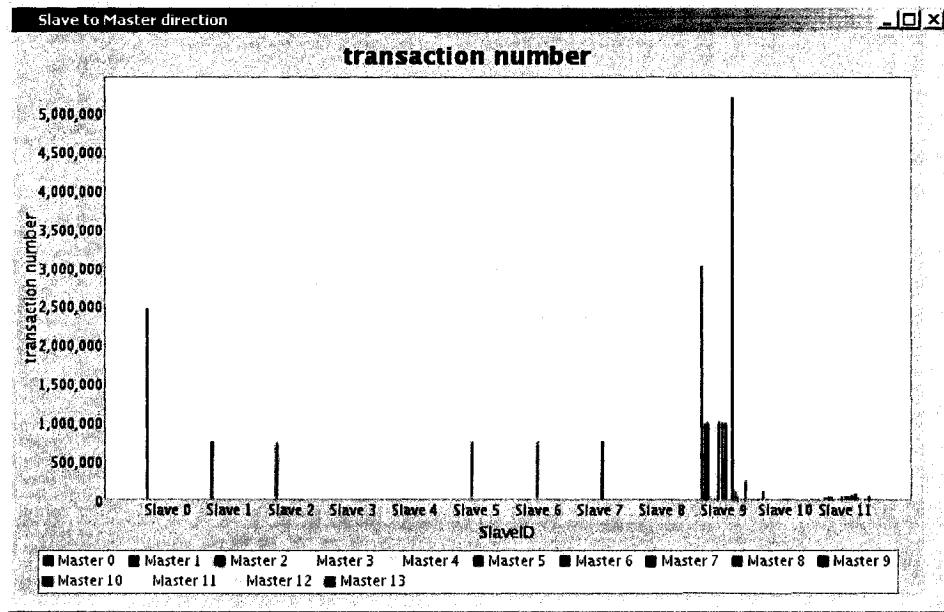

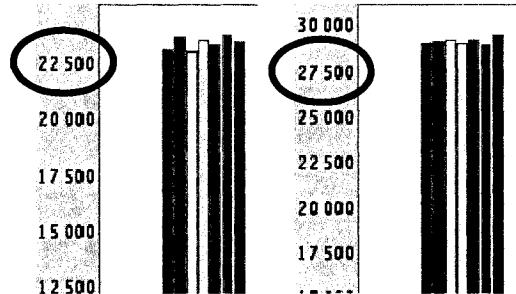

| Figure 5.17 : Nombre de transactions traitées par les esclaves (réponses) .....                   | 96  |

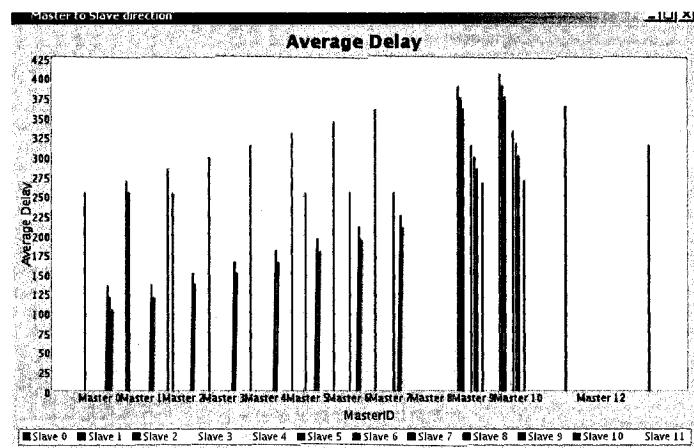

| Figure 5.18 : Latence moyenne des paquets (en ns) en utilisant le RoC classique .....             | 97  |

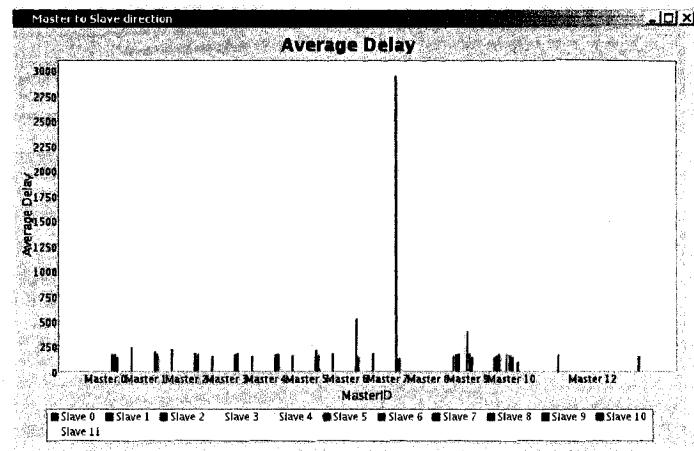

| Figure 5.19 : Latence moyenne des paquets (en ns) en utilisant le RoC bidirectionnel ...          | 97  |

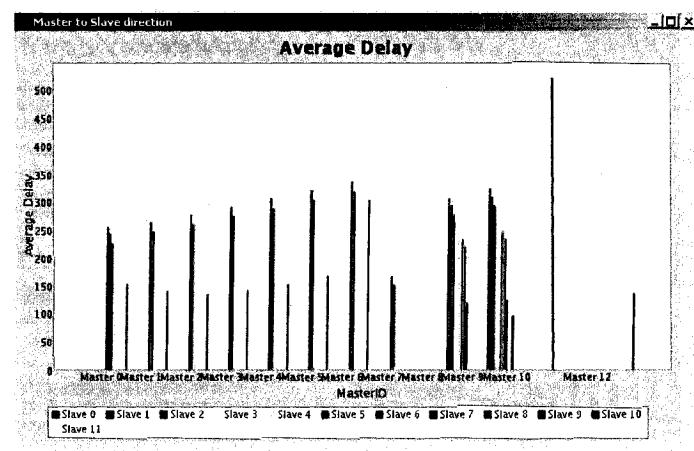

| Figure 5.20 : Latence moyenne des paquets (en ns) en utilisant le RoC hiérarchique .....          | 97  |

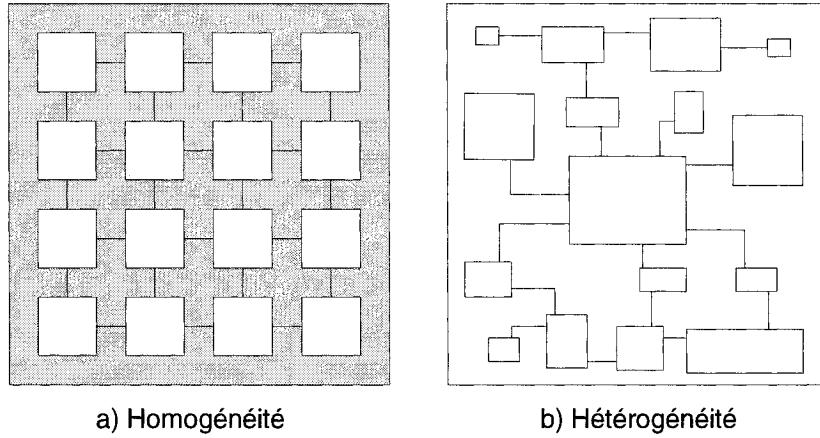

| Figure 1 : Homogénéité de la topologie versus hétérogénéité des blocs et des communications ..... | 102 |

| Figure 2 : Utilisation d'un NoC conjointement à une architecture de bus .....                     | 103 |

| Figure 3 : Exemple de contrôle de flot .....                                                      | 104 |

| Figure 4 : Vue d'ensemble du HyRoC (Hyper Ring-on-Chip) .....                                     | 106 |

## Liste des tableaux

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Tableau 2.1 : Caractéristiques des topologies.....                                                  | 41 |

| Tableau 3.1 : Description des ports d'un nœud .....                                                 | 50 |

| Tableau 3.2 : Description des ports d'une banque .....                                              | 52 |

| Tableau 3.3 : Description des champs d'un paquet OCP.....                                           | 54 |

| Tableau 3.4 : Rôle des classes du RoC .....                                                         | 62 |

| Tableau 4.1 : Nombre maximal d'étapes requises pour l'acheminement d'un paquet.....                 | 70 |

| Tableau 5.1 : Effet de l'ajout de nœuds sur la bande passante du RoC.....                           | 78 |

| Tableau 5.2 : Taux d'occupation moyen des banques pour un RoC à 8 nœuds .....                       | 83 |

| Tableau 5.3 : Taux d'occupation moyen des banques pour un RoC à 8 nœuds .....                       | 91 |

| Tableau 5.4 : Description des modules de l'encodeur MPEG4 .....                                     | 92 |

| Tableau 5.5 : Paramètres de simulation.....                                                         | 92 |

| Tableau 5.6 : Latence maximale observée avec le trafic MPEG4 selon différentes configurations ..... | 98 |

## Liste des acronymes

|                |                                                       |

|----------------|-------------------------------------------------------|

| <b>ACK</b>     | Acknowledge                                           |

| <b>AHB</b>     | Advanced High-speed Bus                               |

| <b>AMBA</b>    | Advanced Microcontroller Bus Architecture             |

| <b>APB</b>     | Advanced Peripheral Bus                               |

| <b>ASIC</b>    | Application Specific Integrated Circuits              |

| <b>AVI</b>     | Audio Video Interleaved                               |

| <b>BCA</b>     | Bus Cycle Accurate                                    |

| <b>BE</b>      | Best Effort                                           |

| <b>DCT</b>     | Discrete Cosine Transform                             |

| <b>DMA</b>     | Direct Memory Access                                  |

| <b>DNS</b>     | Domain Name System                                    |

| <b>ECLIPSE</b> | Embeddeb Chip-Level Integrated Parallel Supercomputer |

| <b>FIFO</b>    | First In First Out                                    |

| <b>flit</b>    | flow control digit                                    |

| <b>GALS</b>    | Globally Asynchronous Locally Synchronous             |

| <b>GT</b>      | Guaranteed Traffic                                    |

| <b>HyRoC</b>   | Hyper Ring on Chip                                    |

| <b>IP</b>      | Intellectual Property                                 |

| <b>ISO</b>     | International Standards Organisation                  |

| <b>Ko</b>      | Kilo octects                                          |

| <b>LAN</b>     | Local Area Network                                    |

| <b>MOPS</b>    | Million Operations Per Second                         |

| <b>MP3</b>     | Motion Picture Experts Group Audio Layer 3            |

| <b>MPEG4</b>   | Motion Picture Experts Group - 4                      |

| <b>MPSoC</b>   | Multi-Processor System on Chip                        |

| <b>NACK</b>    | Non Acknowledge                                       |

|               |                                                          |

|---------------|----------------------------------------------------------|

| <b>NI</b>     | Network Interface                                        |

| <b>NoC</b>    | Network on Chip                                          |

| <b>NoCGEN</b> | Network on Chip Generator                                |

| <b>OPB</b>    | On-chip Peripheral Bus                                   |

| <b>OCP</b>    | Open Core Protocol                                       |

| <b>OSI</b>    | Open Systems Interconnection                             |

| <b>PA</b>     | Pin Accurate                                             |

| <b>PCI</b>    | Peripheral Component Interconnect                        |

| <b>PerNoC</b> | Performance Network on Chip                              |

| <b>PLB</b>    | Processor Local Bus                                      |

| <b>RAM</b>    | Random Access Memory                                     |

| <b>RoC</b>    | Rotator on Chip                                          |

| <b>RTOS</b>   | Real Time Operating System                               |

| <b>SAD</b>    | Sum of Absolute Difference                               |

| <b>SoC</b>    | System on Chip                                           |

| <b>SoCIN</b>  | System on Chip Interconnection Network                   |

| <b>SOCP</b>   | SystemC Open Core Protocol                               |

| <b>SPIN</b>   | Scalable Programmable Interconnection Network            |

| <b>StEPNP</b> | System-Level Exploration Platform for Network Processors |

| <b>TDMA</b>   | Time Division Multiple Access                            |

| <b>TF</b>     | Timed Functional                                         |

| <b>TOPS</b>   | Tera Operations Per Second                               |

| <b>UART</b>   | Universal Asynchronous Receiver Transmitter              |

| <b>UCT</b>    | Unité Centrale de Traitement                             |

| <b>UTF</b>    | UnTimed Functional                                       |

| <b>VCI</b>    | Virtual Component Interface                              |

| <b>VHDL</b>   | VHSIC Hardware Description Language                      |

| <b>VHSIC</b>  | Very High Speed Integrated Circuit                       |

| <b>VSIA</b>   | Virtual Socket Interface Alliance                        |

## Liste des annexes

|                                                                      |     |

|----------------------------------------------------------------------|-----|

| ANNEXE A .....                                                       | 113 |

| Fichier d'intégration du RoC classique à la plate-forme StepNP ..... | 113 |

| ANNEXE B .....                                                       | 123 |

| Programme de test pour les simulations fonctionnelles.....           | 123 |

| ANNEXE C .....                                                       | 131 |

| Fichier de configuration pour MPEG4 .....                            | 131 |

| ANNEXE D .....                                                       | 144 |

| Article soumis à la conférence ICCD 2005 .....                       | 144 |

## Introduction

Depuis une quinzaine d'années, les grands progrès technologiques dans le domaine des systèmes intégrés sur puce (SoC, pour *System on Chip*) ont fait considérablement croître les possibilités. Il n'y a pas si longtemps, un processeur pouvait occuper à lui seul un dé (puce). Les communications avec les mémoires et autres périphériques se faisaient via l'utilisation d'une carte (board). Chacun des composants du système conçu était une puce dont l'ensemble constituait la carte.

Or, les progrès réalisés au niveau transistor permettent aujourd'hui d'inclure plusieurs blocs fonctionnels sur une seule et même puce. Avec la poursuite de cette évolution, les transistors étant de plus en plus petits et de plus en plus rapides, il sera possible d'ici quelques années de concevoir un SoC comportant l'équivalent d'un milliard de portes logiques pouvant opérer à des fréquences avoisinant la dizaine de giga hertz (GHz) [ITRS04]. Cela ouvre la porte à l'intégration de fonctionnalités multiples dans un même système. Les champs d'opération sont immenses. Que ce soit dans le domaine de la sécurité des systèmes (caméras de surveillance), de la santé (prothèses auditives), des communications (téléphonie cellulaire), du divertissement (lecteurs MP3) ou de la photographie (caméras numériques), les SoC sont tout désignés pour remplir les exigences du marché en termes de performance et de coût [HEWC04]. L'avènement récent des SoC apporte donc une solution intéressante aux besoins propres de ces domaines. Ils offrent la possibilité d'intégrer un ensemble de processeurs et de coprocesseurs spécialisés pour exécuter les différentes tâches du système.

Les SoC du futur seront basés sur le traitement de signaux numériques, avec des charges allant de 10 MOPS pour du traitement audio jusqu'à 1 TOPS pour la génération synthétique de vidéo. Pour accomplir ce traitement, un seul processeur ne suffira pas à la tâche, d'où l'apparition prochaine des systèmes sur puce multiprocesseurs (MPSoC) [BEBE04].

## **Problématique**

Sur un système monoprocesseur, la fonctionnalité d'un système est décortiquée puis séparée en tâches spécifiques et relativement indépendantes entre elles. Ces tâches peuvent être ordonnancées sur l'unité centrale de traitement (UCT) par un système d'exploitation temps réel (RTOS), par exemple. Elles s'exécuteront concurremment sur l'UCT, laissant croire à un parallélisme pourtant absent.

Il est possible d'ajouter du parallélisme avec l'introduction de modules matériels dédiés qui permettent, selon la tâche à effectuer, d'obtenir des gains substantiels sur la performance comparativement à une même tâche effectuée par une UCT (de l'ordre d'une centaine de fois plus rapide). D'ailleurs, un intéressant domaine de recherche est le partitionnement logiciel/matériel des modules de façon à obtenir un compromis optimal entre performances et coûts [CBRB04].

Qui plus est, la naissance des MPSoC apporte obligatoirement avec elle le concept de parallélisme dans les opérations. Plusieurs UCT peuvent se partager une portion d'exécution de tâche (par exemple, l'encodage d'une image) ou exécuter plusieurs tâches indépendantes (par exemple, un système de surveillance par caméra). Tel que mentionné plus tôt, la technologie actuelle permet d'intégrer plusieurs de ces processeurs, coprocesseurs et modules matériels. Le nombre d'opérations s'exécutant en même temps se trouve alors augmenté de façon drastique.

D'un autre côté, l'augmentation du nombre d'opérations implique aussi l'augmentation des communications sur la puce. En effet, un processeur a parfois besoin d'obtenir une information se trouvant sur une mémoire externe, de demander à un coprocesseur d'effectuer une opération spécifique, etc. Ces communications entraînent un mouvement de données d'un composant à un autre. La multiplication des initiateurs de telles transactions apporte donc la multiplication des données circulant sur la puce. Selon

[BEBE04], les systèmes de demain seront dominés par les communications plutôt que par le traitement.

Actuellement, les architectures de communication sont assez rudimentaires, bien qu'elles soient tout à fait adéquates pour les besoins actuels. Les architectures de bus [IBM03] [ARM01] [SILI02] [SONI01] permettent d'acheminer une transaction ayant été initiée par un module maître (ex : processeur) vers un module esclave (ex : mémoire). Toutefois, lorsqu'un système comporte plus d'une dizaine de modules maître, les communications deviennent le goulot d'étranglement du système et ne permettent plus de profiter du parallélisme, puisque plusieurs modules peuvent attendre le résultat des transactions qu'ils ont initiées [BEDE02].

Depuis quelques années, un nouveau concept a fait son apparition dans le design d'un SoC : les réseaux intégrés sur puce (NoC pour *Network on Chip*). Les NoC procurent une amélioration significative aux communications en permettant à plusieurs transactions de s'effectuer en même temps, à l'instar des grands réseaux informatiques tels que le réseau Internet.

## **Objectifs**

Le principal objectif de ce mémoire est de concevoir un modèle de NoC et d'évaluer ses performances par rapport à des topologies connues. En effet, plusieurs recherches ont déjà été entamées dans ce domaine, recherches ayant conduit à l'élaboration de plusieurs configurations possibles pour obtenir un NoC. Par contre, il n'existe toujours pas de consensus à ce sujet et l'on en est encore à l'exploration architecturale de même qu'à l'évaluation de la contribution réelle d'un réseau dans un SoC. Par conséquent, un second objectif se veut une réflexion sur l'utilisation des NoC selon leurs caractéristiques et selon le type d'application.

## **Méthodologie**

Afin de répondre aux objectifs fixés, plusieurs tâches devront être réalisées. Une première étape est l'exploration des opportunités offertes par la plate-forme StepNP, développée en langage SystemC [OSCI03] par la société StMicroelectronics. Cette plate-forme de haut niveau renferme une bibliothèque de blocs de propriété intellectuelle tels que processeurs, mémoires et réseaux d'interconnexions [PAPB02]. Une architecture en développement peut être facilement modifiable par l'ajout ou le changement d'un composant par un autre, ce qui facilite les comparaisons et les prises de décision. De plus, tous les outils essentiels au développement d'une architecture à haut niveau (simulateur, débogueur et différents mécanismes d'analyse de performance) sont fournis et leur utilisation est relativement simple. Enfin, le code source de la plate-forme nous était disponible et gratuit, ce qui est très utile dans le contexte académique où les travaux ont été réalisés.

Une deuxième étape sera de construire le modèle de base du réseau. Deux niveaux d'abstraction seront explorés: UTF (*untimed functional*) et TF (*timed functional*), selon la méthodologie de co-design. Le niveau UTF permet de ne pas tenir compte des notions de temps pour permettre de se concentrer sur la fonctionnalité du système, c'est-à-dire ce qu'il doit accomplir. Le niveau TF ajoute du *timing*.

Une troisième étape sera d'apporter plusieurs améliorations à l'algorithme de base, d'où en découlera plusieurs variantes du modèle initial. L'analyse de ces variantes donnera des informations sur leur utilisation dans un contexte donné et selon le type d'application. Une application complète préalablement développée, MPEG4 (*Motion Picture Experts Group 4*), servira de banc d'essai.

## **Originalité et contribution**

Une analyse récente des NoC existants, effectuée par [HEWC04], suggérait l'exploration du concept de hiérarchisation dans les réseaux, pour maximiser les avantages offerts par la localisation des ressources. Il est de plus en plus important d'exploiter cette localité

dans le contexte des SoC où le temps de propagation des signaux devient une source de problèmes pour les concepteurs. Les réseaux sur puce modélisés ici tentent de remédier à ce problème et invitent les concepteurs à profiter des avantages de la localité des ressources lorsque vient le temps de faire l'assignation des composants sur la puce.

Par ailleurs, ce travail se veut un apport important à l'exploitation d'une plate-forme multiprocesseurs, puisqu'il offre au concepteur d'une telle plate-forme différentes configurations possibles du réseau dans le but de satisfaire le plus possible à ses besoins en termes de bande passante et de latence.

Finalement, ce réseau sur puce tente de pousser au maximum la réutilisation de ses composantes ainsi que leur taux d'utilisation afin de donner une justification solide pour l'espace supplémentaire que le réseau occupe sur la puce ainsi que la puissance qu'il consomme, tout ceci dans un contexte très contraignant pour les développeurs de systèmes intégrés sur puce.

### **Distribution des chapitres**

Ce mémoire est constitué de cinq chapitres. Le chapitre 1 survole le monde des systèmes intégrés sur puce, en mettant l'accent sur les limitations des architectures actuelles de communication. Le chapitre 2 introduit une idée qui se veut une solution prometteuse aux problèmes de communication : les réseaux intégrés sur puce. Une partie de ce chapitre est aussi consacrée à l'explication de différents concepts que l'on peut retrouver dans les réseaux à grande échelle. En effet, plusieurs similarités existent entre ces types de réseaux et les réseaux intégrés sur puce. Le chapitre 3 décrit ensuite les composants du modèle de base du réseau développé alors que le chapitre 4 regroupe tous les ajouts apportés à ce modèle de même que les améliorations qu'ils procurent au niveau des performances du réseau. Puis, les résultats sont présentés au chapitre 5. Enfin, pour clore ce mémoire, la conclusion résume le travail accompli et renferme également une courte discussion portant sur les travaux futurs et autres considérations.

# CHAPITRE 1 Revue de littérature

## 1.1. L'état actuel

Les systèmes, les applications et la technologie sont en constante évolution. Cette situation donne lieu à de nouveaux besoins. Afin de mieux cerner ces besoins, il est important de bien comprendre dans quelle portion de l'évolution nous nous retrouvons.

### 1.1.1. L'écart de productivité

Un des enjeux actuels des systèmes sur puce est que la technologie évolue trop rapidement par rapport aux capacités des développeurs d'en tirer profit.

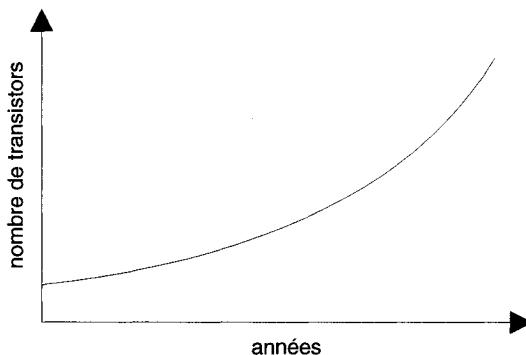

Gordon Moore, co-fondateur d'Intel et de Fairchild, annonça en 1965 que la densité des transistors intégrés sur une puce doublerait tous les 18 mois. Cette prédiction, éventuellement nommée « Loi de Moore », est encore validée de nos jours et est illustrée à la Figure 1.1.

Figure 1.1 : Allure de la loi de Moore

D'un côté, cette importante croissance de la densité des transistors permet aux ingénieurs de créer des systèmes sur puce toujours plus denses, plus complexes et plus rapides

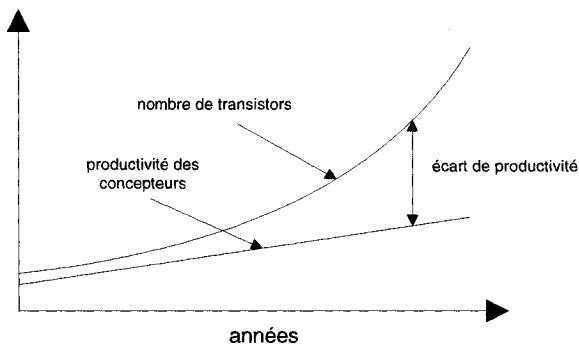

qu'auparavant. D'un autre côté, la productivité d'un concepteur augmente également avec le temps, mais de façon beaucoup plus limitée. L'amélioration des outils de développement et de synthèse se fait lentement par rapport à la vitesse à laquelle la technologie évolue. Le fossé qui se creuse entre technologie et productivité est représenté par la Figure 1.2.

Figure 1.2 : L'écart de productivité

Par ailleurs, la loi de Moore devrait encore s'appliquer pour une période variant entre cinq et dix ans. Par conséquent, pour la prochaine décennie à venir, les concepteurs de systèmes devront adapter les méthodologies de conception de façon à leur permettre d'exploiter le maximum des ressources qui seront mises à leur disposition.

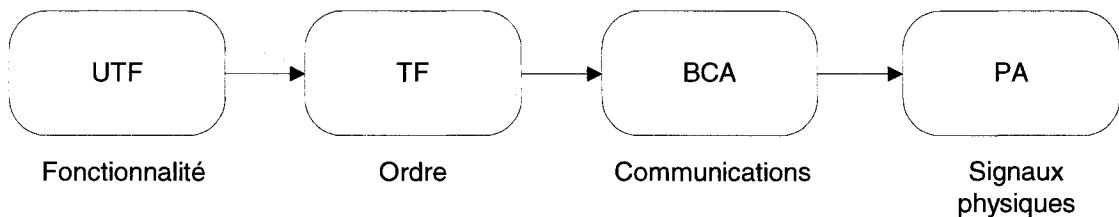

### 1.1.2. Raffinement progressif

Il existe plusieurs techniques qui tentent de réduire l'écart de productivité. Une première technique, appelée *raffinement progressif*, consiste à développer sur plusieurs niveaux successifs d'abstraction [FILI02]. On appelle *niveau d'abstraction* le fait de négliger des spécificités de l'implantation pour se concentrer sur une partie du problème. Par exemple, au niveau *UTF* aucune notion de temps n'est considérée et seuls les fonctionnalités du système de même que les algorithmes sont validés. Lorsque ce niveau de développement est complété, on passe au niveau d'abstraction suivant, nommé *TF*, où une certaine notion

de temps est introduite (l'ordre des opérations est important et une synchronisation entre les modules doit être présentée).

Par la suite, on passe au niveau BCA (*bus cycle accurate*) où les communications entre modules sont décrites abstraitements sous forme de transactions. Cela conduit au dernier niveau PA (*pin accurate*) qui représente l'évolution des signaux proprement dits dans le temps. Le niveau PA est celui qui exprime le niveau le plus élevé de détail avant la synthèse elle-même. La Figure 1.3 récapitule les différentes étapes de la méthodologie.

Figure 1.3 : Le raffinement progressif

Plusieurs compagnies, comme par exemple Synopsys [SYNO03], tentent de développer des outils et des langages qui couvrent toutes les étapes pour accélérer et automatiser la conception jusqu'à la synthèse du système, de façon à réduire son temps de développement.

### 1.1.3. Réutilisation

Une deuxième technique, appelée *réutilisation*, permet d'intégrer les fonctionnalités d'un module déjà existant sans avoir à le concevoir de nouveau. Les développeurs se sont rapidement aperçus qu'il était impossible de construire un système entier (comme par exemple un encodeur MPEG ou un routeur sophistiqué) à partir de rien. Les systèmes sont maintenant si complexes qu'il est très ardu d'obtenir les résultats escomptés en partant d'une plate-forme complètement générique. Également, de plus en plus de pression est mise sur l'ingénieur afin de réussir à concevoir ces systèmes dans un délai

raisonnable. En effet, les échéanciers pour demeurer concurrentiel dans le marché sont de plus en plus courts (parfois moins d'une année).

La réutilisation des composants est apparue comme étant une solution bénéfique dans le processus de conception. Les compagnies productrices de systèmes ont commencé à se doter d'une bibliothèque de composants réutilisables, au premier rang desquels se trouvent les simples portes logiques. Plus tard, des blocs relativement primitifs tels qu'additionneurs, compteurs et multiplexeurs se sont joints aux entités réutilisables. De nos jours, des processeurs entiers, des mémoires et d'autres modules spécialisés et complexes sont réutilisés dans la conception puisqu'il n'est pas avantageux de les redéfinir. Bon an mal an, les sociétés qui conçoivent des puces ont accès à des centaines de blocs IP (*intellectual property (modules)*) pour élaborer leur système global. Dans une vision naïve du processus de conception, les concepteurs n'ont qu'à intégrer les blocs requis en les faisant interagir entre eux adéquatement à travers des interfaces communes et par des communications appropriées. Cette portion du travail représente tout de même un défi important au niveau de la standardisation des communications. Ce sujet sera approfondi plus loin.

La réutilisation est donc une technique omniprésente dans la réalisation de systèmes sur puce et continuera de l'être. Dans le chapitre suivant, le concept de réseau intégré sur puce sera décrit et on notera que les avantages qu'offrent la réutilisation ne seront pas mis de côté.

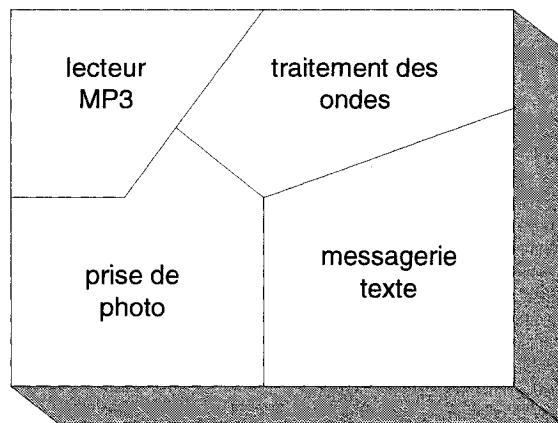

#### **1.1.4. Applications du présent et du futur**

Tel que mentionné plus tôt, les champs d'application des SoC sont très vastes. De plus en plus de systèmes électroniques peuvent être intégrés sur une seule et même puce. Ces systèmes peuvent regrouper plusieurs fonctionnalités souvent indépendantes les unes des autres. On n'a qu'à penser aux téléphones cellulaires qui permettent également la

navigation sur Internet, l'envoi de messages texte, la prise de photos numériques et la capture de séquences vidéo.

On considère deux types d'applications : les applications orientées *données* ainsi que les applications orientées *contrôle*. Les applications orientées données manipulent un grand flot d'information. Par exemple, une caméra vidéo numérique échantillonne plusieurs fois par seconde des images de l'environnement filmé pour ensuite les convertir en pixels (points de couleur) pouvant être affichés simultanément sur un écran. Les données traversent plusieurs blocs d'un même système où elles subissent différents traitements (ex. : conversion en pixels, correction gamma, amplification, encodage, etc.).

Les applications orientées contrôle, comme le nom l'indique, doivent contrôler un environnement. Par exemple, un simple thermostat permet d'ajuster la température ambiante à un niveau précis. Un système orienté contrôle est souvent composé de senseurs qui sont responsables de prendre des mesures de l'environnement contrôlé (ex. : la température d'une pièce). Ces résultats de mesure sont alors envoyés au système exploitation qui vérifie si une action doit être apportée à l'environnement.

Dans ces deux types d'application, les communications sont généralement nombreuses mais leurs caractéristiques diffèrent. Une application orientée données enverra une grande quantité d'information et nécessitera donc une grande bande passante. Une application orientée contrôle générera beaucoup moins de trafic; par contre, ce trafic devra être acheminé le plus rapidement possible puisque le contrôle de l'environnement en dépend.

## 1.2. Limitations des systèmes sur puce actuels

Cette section se veut une présentation des défis qui attendent la prochaine génération de systèmes sur puce. Les requis de performance y sont présentés, de même que les moyens à prendre pour atteindre ces nouveaux standards.

### 1.2.1. Systèmes sur puce

Les systèmes sur puce fournissent des solutions intégrées aux problèmes de design rencontrés dans les domaines des télécommunications, du multimédia et autres domaines grands consommateurs d'électroniques [Bede02]. Le monde des SoC est en pleine effervescence et surtout en continue progression. Dans quelques années, des systèmes comprenant quatre milliards de transistors opérant à une fréquence de dix GHz seront monnaie courante. Actuellement, plusieurs modules IP remplissant différentes fonctions et opérant à différentes fréquences doivent être intégrés sur une même puce, ce qui augmente le défi de conception [GPIS03]. Les ressources disponibles sur une puce étant immenses, un simple processeur ne peut plus utiliser l'ensemble des transistors du dé. Il est donc possible de fractionner la puce en différentes régions ayant des fonctionnalités distinctes (voir Figure 1.4) [KJSF02].

Figure 1.4 : Fractionnement de la puce en systèmes hétérogènes

Une nouvelle façon de concevoir le système peut alors être envisagée. Notamment l'approche GALS (*Globally Asynchronous, Locally Synchronous*) permet à plusieurs régions de la puce d'opérer à des fréquences différentes (il est aussi possible qu'elles

opèrent à la même fréquence mais dans des domaines de phase différents; le sujet sera approfondi plus loin).

### **1.2.2. Premier problème : les fils**

Il n'y a pas si longtemps, il était possible de négliger le temps de propagation d'un signal sur un fil sans que cette négligence n'entraîne une erreur catastrophique de conception. Le délai de propagation des fils était largement inférieur aux délais d'un transistor ou d'une porte logique. Avec la largeur du canal d'un transistor qui sera bientôt de 50 nm, la fréquence d'opération de ce transistor pourra atteindre 10 GHz. C'est donc dire que deux fronts montants d'horloge seront séparés par 100 picosecondes seulement. La vitesse de propagation de la tension étant limité à une fraction de celle de la lumière, le signal a le temps de parcourir moins de 30 mm avant que le prochain front montant ne survienne! Dans une puce où les fils sont très entremêlés, un signal pourrait prendre entre six et dix périodes d'horloge pour se propager sur la puce entière [GPIS03b]. Le problème est déjà rencontré dans les designs actuels, où le temps de propagation d'un signal s'étend sur une période complète d'horloge. Même si les longs délais peuvent être contrôlés par des techniques de pipelinage, l'incertitude apportée par ces délais sera tout de même considérable pour les développeurs [BEDE02b]. L'ajout de répéteurs pour garder le délai linéaire plutôt que quadratique est donc requis et il est difficile de placer proprement ces répéteurs, d'autant plus qu'ils s'ajoutent aux contraintes d'espace et de puissance déjà présentes [DATO01].

Par ailleurs, la taille réduite des transistors permet d'inclure plus de blocs sur la puce, ce qui engendre forcément plus de fils pour relier les blocs en question. Du point de vue global, plus de fils sont sollicités à la fois, ce qui cause une augmentation sensible de la puissance dissipée [BEDE02]. Aussi, des fils ne suivant aucune structure ont une capacité parasite difficile à prévoir tôt dans le processus de conception. Ils engendrent également des interférences (en anglais : *crosstalk*) envers les fils adjacents, ce qui rend le comportement hautement imprévisible [DATO01].

De même, un filage *ad hoc* présente souvent la caractéristique qu'une importante proportion des fils ne sont utilisés que 10% du temps ou moins, ce qui n'est pas souhaitable dans le mesure où les fils prennent une importance grandissante dans le système [WIGO02]. Finalement, la miniaturisation fait en sorte que les transistors nécessitent maintenant des tensions d'opération de plus en plus faible pour éviter qu'ils ne claquent. Prochainement, il ne sera pas rare d'observer des tensions inférieures à 1V. L'intégrité du signal est donc menacée, puisqu'une légère variation de la tension peut maintenant faire la différence entre un 1 logique et un 0 logique. Somme toutes, les fils deviennent un enjeu majeur dans le développement de systèmes sur puce. Il est à noter que les impacts des problèmes mentionnés plus haut deviennent encore plus grands au fur et à mesure que la technologie évolue.

### **1.2.3. Deuxième problème : la synchronisation**

Les enjeux entourant les fils ont des conséquences directes sur la synchronisation du circuit. Puisqu'il sera bientôt impossible qu'un signal se propage d'une extrémité de la puce à l'autre en une période d'horloge, la synchronisation globale de tous les blocs IP perdra sa signification. Il sera donc important de limiter la distance parcourue par les signaux critiques de façon à garantir la performance du système global [BEBE02].

Une solution intéressante est donc de fragmenter le système en plusieurs sous-systèmes distincts. Ainsi, tous les blocs d'un même sous-système seraient synchronisés entre eux sur le même signal d'horloge. Par contre, les sous-systèmes n'auraient pas cette synchronisation et devraient se synchroniser par les communications. Le réseau d'interconnexions devrait donc être en mesure d'assumer cette synchronisation. Voilà pourquoi cette approche, présentée plus tôt comme l'approche *GALS*, devient attrayante : les ingénieurs peuvent se séparer la tâche en travaillant parallèlement sur des sous-systèmes différents sans se soucier du détail fin de la synchronisation avec les autres. Les communications devraient en principe ramener tout les signaux au même niveau lorsque

vient le temps des échanges d'informations. Ces communications deviendront omniprésentes au fur et à mesure que le nombre de modules sur une puce continuera d'augmenter.

#### **1.2.4. Troisième problème : les communications**

La possibilité d'inclure plusieurs dizaines d'unités de traitement sur une puce représente une solution intéressante pour un ingénieur toujours avide de concevoir des systèmes performants et rapides. Le parallélisme dans les opérations est une façon rêvée d'accomplir une tâche le plus rapidement possible. Toutefois, le fait d'exécuter cette tâche avec  $N$  processeurs ne garantit pas que le traitement se fera  $N$  fois plus rapidement, surtout si le degré de dépendance est grand entre les processeurs. On peut faire l'analogie avec un groupe d'ingénieurs qui travaillent sur un système commun. Bien que chaque ingénieur puisse travailler sur une portion du système, chacun doit être au courant des travaux exécutés par les autres, via des réunions et des rencontres de mise à jour. L'ingénieur ne passera donc pas tout son temps à faire progresser son travail; la communication prendra une grande part de son temps. Il en sera de même dans les futurs systèmes sur puce multiprocesseurs. Un modèle souvent cité dans les systèmes futurs est composé de processeurs esclaves faisant « ce qu'on leur demande » et de maître(s) répartissant le travail à effectuer aux autres unités de traitement. Ceci engendre une importante communication entre tous ces modules qui doivent communiquer entre eux. À cela s'ajoute la communication que l'on retrouve sur les SoC actuels, comme par exemple les échanges traditionnels de données entre maîtres et esclaves (écritures et lectures en mémoire). Les communications deviendront donc rapidement le goulot d'étranglement de la prochaine génération des systèmes sur puce, c'est donc ce qui en limitera les performances.

### 1.3. Les architectures de bus

Présentement, les communications sont assurées par des architectures de bus sur puce qui sont une adaptation des bus sur carte que l'on retrouve sur des ordinateurs personnels, le bus *PCI* par exemple. La prochaine section présente un survol des architectures de bus existantes ainsi que leurs limitations.

#### 1.3.1. AMBA

Depuis 1999, ARM [ARM01] propose le protocole AMBA en tant que norme pour les systèmes sur puce. La spécification offre deux protocoles qui peuvent être utilisés selon les besoins.

Figure 1.5 : Structure du bus AMBA

Tout d'abord, le *Advanced High-speed Bus* est adapté pour les communications à haute vitesse requises par les modules performants du système comme les processeurs, par exemple. Ensuite, le *Advanced Peripheral Bus* est utilisé pour connecter les modules qui n'ont pas besoin de la performance offerte par AHB. Les périphériques comme les minuteries et les contrôleurs d'entrées/sorties sont tout désignés pour ce genre de protocole. Un pont APB permet de relier des bus gérés selon les deux protocoles. Selon les spécifications de AMBA, ce pont n'a comme utilité que de fournir une interface plus simple. Toute latence présentée par un périphérique de basse performance sera reflétée par le pont APB au bus AHB. Le pont ne peut agir comme maître qu'au niveau APB, où il sera d'ailleurs le seul maître. Un exemple de système utilisant le protocole AMBA est illustré à la Figure 1.5. Le lecteur est invité à consulter [BERT03] pour plus de détails sur les spécifications du protocole AMBA.

### 1.3.2. CoreConnect

CoreConnect [IBM03] est un protocole conçu par IBM et ayant plusieurs similarités avec AMBA. Le protocole est illustré à la Figure 1.6. On retrouve premièrement le *Processor Local Bus* pour les modules à haute performance tels que les processeurs, mémoires cache et DMA (*Direct Memory Access*). Il est à noter qu'une interface à un bus externe peut être ajoutée à ce niveau.

Le deuxième niveau, appelé *On-Chip Peripheral Bus* (OPB), est un bus secondaire dont le but principal est d'augmenter la performance du bus principal en diminuant la charge capacitive sur le PLB. Les périphériques comme les ports série, ports parallèles, UART (*Universal Asynchronous Receiver-Transmitter*), minuteries et autres modules de faible performance peuvent adéquatement être branchés à ce bus. Plusieurs maîtres sont supportés à ce niveau. Un pont fait également le lien entre le niveau PLB et OPB. Il est à noter que ce pont agit comme maître au niveau OPB et comme esclave au niveau PLB, contrairement à AMBA.

Figure 1.6 : Structure du bus CoreConnect

CoreConnect est un protocole de bus complet qui peut très bien faire parti d'un système de haute performance tel qu'une station de travail. Il supporte une lecture concurrente à une écriture, de même que des transactions de type *différé (split)*, où le maître laisse le contrôle du bus après avoir effectué sa requête pour le reprendre lorsque la réponse sera prête. Le désavantage de CoreConnect est qu'il est possiblement trop compliqué, en ce sens qu'il offre trop de fonctionnalités qui ne seront pas utilisées dans une simple application embarquée [USSE01]. Près d'une quarantaine de sociétés et d'organismes ont une licence de CoreConnect, dont l'École Polytechnique de Montréal.

### 1.3.3. SiliconBackplane III

SiliconBackplane III est un système d'interconnexions commercialisé par Sonics [SONI01] pour les applications multimédia. Ce système est implanté un peu différemment des architectures de bus AMBA et CoreConnect. Une représentation est

illustrée à la Figure 1.7. Chacun des composants est relié au réseau via un agent [WING01]. L’arbitration est basée selon un système rotatif à priorité qui découle du TDMA (*Time Division Multiple Access*). À chaque coup d’horloge, l’arbitre sélectionne l’agent correspondant à la période de temps en cours. Si l’agent n’a aucun message à envoyer, l’intervalle de temps est alloué à un autre agent selon l’algorithme *round-robin*.

Figure 1.7 : Structure du bus SiliconBackplane

#### 1.3.4. Wishbone

Wishbone [SILI02], développée par Silicore, est une spécification qui propose de réduire au minimum l’ensemble des signaux de façon à permettre des accès simples via un bus. Il n’y a donc pas de notion de bus opérant à différentes fréquences ni de ponts pour les relier (voir Figure 1.8). Si le concepteur souhaite avoir un système avec deux niveaux de bus, il est possible de le faire en créant deux interfaces *Wishbone*, plutôt qu’en définissant deux interfaces différentes (PLB et OPB par exemple). Par contre, le développeur doit

définir lui-même les sous-standards de Wishbone, comme par exemple l'ordre des données (*Little endian* versus *Big endian*). Aussi, des fonctionnalités supplémentaires pourraient devoir être ajoutées si nécessaires puisque non présentes dans la version de base de Wishbone.

Figure 1.8 : Structure du bus Wishbone

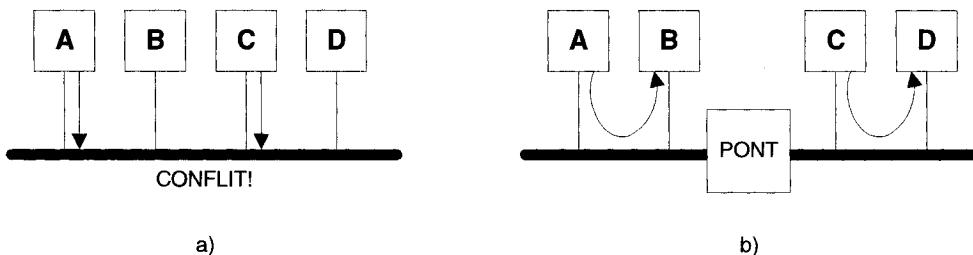

### 1.3.5. Limitations des bus

Dans un bus partagé, lorsque plusieurs requêtes sont générées simultanément par plusieurs maîtres, l'arbitre décide de donner l'accès à un maître en particulier selon des règles d'arbitrage. Un problème significatif de telles architectures est une dégradation de la performance causée par le nombre excessif de conflits. Une solution, telle qu'adoptée par AMBA et CoreConnect, entre autres, est d'instaurer une hiérarchie de bus contenant chacun les modules communiquant fréquemment ensemble, autant que possible. Cette solution est présentée à la Figure 1.9. Deux requêtes sur un bus partagé

(Figure 1.9a) produisent un conflit qui peut être évité par l'utilisation d'un bus hiérarchique (Figure 1.9b).

**Figure 1.9 : Situation sur un bus partagé menant à un conflit réglé par l'utilisation d'un bus hiérarchique**

Si on examine les considérations physiques, on observe une contradiction qui rend problématique l'utilisation des bus comme médium de communication dans un système complexe. D'un autre côté, plus il y a de modules connectés à un segment de bus, plus ce bus devra opérer à une fréquence d'horloge petite, ceci étant dû à la charge capacitive présente sur le bus. Pour garder une performance acceptable, il faut donc réduire le nombre de modules connectés à un même segment et par conséquent augmenter le nombre de segments. D'un autre côté, plus il y a de segments, plus la performance (latence) s'en trouve affectée à cause de la surcharge qu'apporte chaque pont reliant deux segments [YOO03]. Le bus le plus lent déterminera la performance des communications inter-segments. La solution pour diminuer la surcharge est donc de diminuer le nombre de segments, ce qui est contradictoire avec le problème précédent.

Par ailleurs, dans le cas où l'arbitrage est fait selon la priorité de la requête, une requête de faible priorité pourrait prendre un temps considérable à être traitée si les requêtes de plus haute priorité se multiplient, ce qui peut entraîner un problème de famine. Il serait souhaitable, si on parle de qualité de service, de garantir une certaine bande passante à ce type de module. Toutefois, la bande passante du bus n'augmente pas avec le nombre de modules connectés à celui-ci, contrairement aux réseaux

conventionnels où la bande passante augmente lorsqu'on y insère un nœud supplémentaire [GPIS03b]. On dira alors du bus qu'il n'est pas extensible (en anglais *scalable*), ce qui est son problème majeur puisqu'au-delà d'un seuil limite, il est incapable de recevoir une charge supplémentaire. Finalement, les architectures de bus ne sont pas en mesure de répondre aux contraintes temps réel associées aux applications de réseautique, de télécommunications et de multimédia, puisqu'il est presque impossible de déterminer avec précision leur pire temps de réponse [WING01].

Néanmoins, les architectures de bus restent tout de même adéquates pour les SoC actuels qui intègrent moins de cinq processeurs et tout au plus une dizaine de maîtres [BEDE02]. Cependant, ces architectures seront inappropriées pour les futurs systèmes qui comprendront des centaines d'unités pouvant générer de l'information à être transférée. Avec des IP opérant à des fréquences de l'ordre du GHz, un seul bus (ou même plusieurs bus synchronisés) ne sera pas une solution viable, en raison des charges capacitives et de la résistance des fils qui ralentissent la propagation du signal [MAMA04].

Comme nous le verrons dans ce travail, il y a toutefois de l'espoir en ce qui a trait aux perspectives d'utilisation des bus dans les SoC du futur. En effet, dans l'architecture que nous proposons, le bus standard occupera encore une place de choix dans les communications.

### 1.3.6. Défis

Suite à la problématique énoncée dans la section précédente, voici une liste des principaux défis qui attendent les concepteurs dans le domaine des communications sur puce et des SoC en général :

- Fournir un réseau d'interconnexions dont les composants assureront des transmissions fonctionnelles et fiables. On peut y parvenir en exploitant des infrastructures et des protocoles déjà existants dans le domaine des réseaux à

grande échelle. Les interconnexions formeraient maintenant un micro-réseau sur puce, ce qui constituerait une adaptation du traditionnel modèle OSI.

- Parvenir au compromis flexibilité versus efficacité énergétique. Le système se doit de faire une gestion intelligence de la puissance dissipée. En effet, l'énergie résultante des communications globales ne diminue pas avec les nouvelles technologies, contrairement à l'énergie résultante du traitement. Cela s'explique par le fait que plus un transistor est petit, moins il consomme de puissance. Par contre, un fil ne change pas sensiblement d'une technologie à l'autre. L'énergie devient donc de plus en plus dominante dans les communications [BOZZ04].

- Fournir une qualité de service avec un budget limité en consommation d'énergie et en espace, le tout en tenant compte des limitations de la technologie. Une qualité de service inclut la performance et la fiabilité, sans se limiter à ces métriques. La performance est nécessaire pour répondre aux applications toujours plus exigeantes tandis que la fiabilité découle plutôt de la dépendance des consommateurs face à l'utilisation qu'ils font des accessoires électroniques dans la vie de tous les jours [BEDE02b].

- Étendre la réutilisation aux réseaux d'interconnexion pour permettre au concepteur d'utiliser les composants du réseau sur plusieurs systèmes [DATO01]. La réutilisation, si importante dans la méthodologie de conception des SoC, peut être facilitée par l'emploi d'interfaces communes qui attacheraient chacunes des composants au réseau.

- Permettre l'extensibilité des communications, ce qu'une architecture de bus n'est pas en mesure de faire. Il serait souhaitable que le réseau en place supporte l'ajout d'un nouveau bloc sans altérer les performances pour les blocs déjà en place. Ceci serait donc un bénéfice découlant directement de la réutilisation du réseau.

Ces défis sont intéressants pour les ingénieurs qui auront comme contraintes supplémentaires des échéanciers à respecter pour la mise en marché de nouvelles technologies en plus des problèmes d'intégrité de signal et une surface de puce limitée.

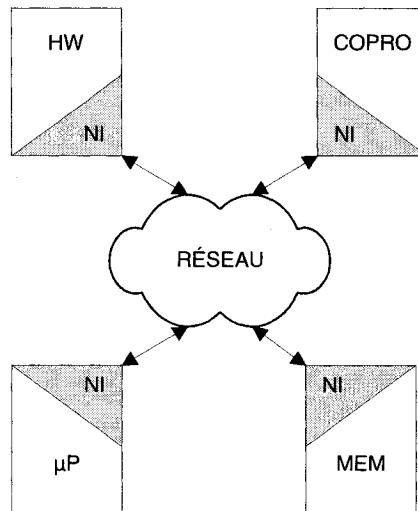

## CHAPITRE 2 Les réseaux intégrés sur puce

Depuis quelques années, un nouveau concept a émergé dans le domaine des systèmes sur puce. Ce concept vise, essentiellement, à améliorer considérablement les communications dans les systèmes. L'idée est de reproduire sur une puce les infrastructures de communication que l'on retrouve dans les grands réseaux d'ordinateurs, comme les LAN et Internet. On parlera donc de réseaux intégrés sur puce (en anglais NoC pour *Network on Chip*). Cette section décortique plusieurs concepts réseau et NoC en présentant leurs caractéristiques ainsi que le contexte dans lequel ils s'inscrivent.

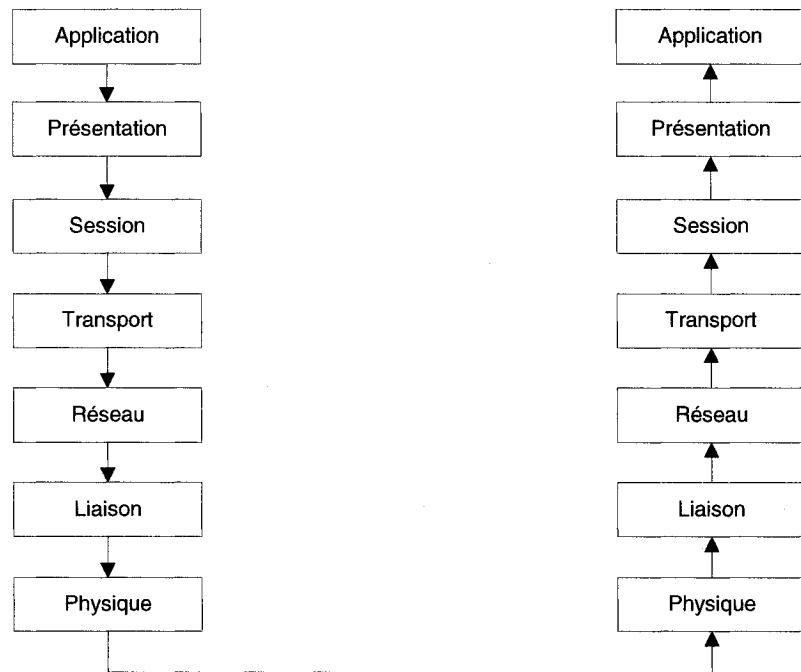

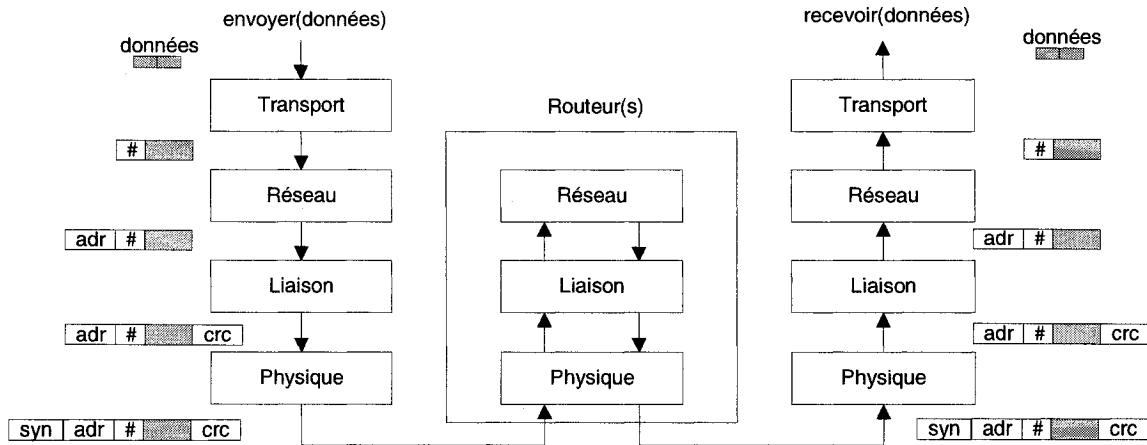

### 2.1.1. Modèle OSI

Pour éviter la multiplication des solutions d'interconnexion d'architectures hétérogènes, l'ISO (*International Standards Organisation*) a développé un modèle de référence appelé modèle OSI (*Open Systems Interconnection*). Ce modèle décrit les concepts utilisés et la démarche suivie pour normaliser l'interconnexion de systèmes ouverts (un réseau est composé de systèmes ouverts lorsque la modification, l'adjonction ou la suppression d'un de ces systèmes ne modifie pas le comportement global du réseau). Le modèle OSI n'est pas une véritable architecture de réseau, car il ne précise pas réellement les services et les protocoles à utiliser pour chaque couche. Il décrit plutôt ce que doivent faire les couches. Cette norme a été adoptée depuis une vingtaine d'années. Le modèle OSI comporte sept couches (voir Figure 2.1). Les couches basses (1, 2, 3 et 4) sont nécessaires à l'acheminement des informations entre les extrémités concernées et dépendent du support physique. Les couches hautes (5, 6 et 7) sont responsables du traitement de l'information relative à la gestion des échanges entre systèmes informatiques. La suite de cette section résume le rôle des diverses couches.

Figure 2.1 : Modèle OSI

### 2.1.1.1. La couche physique

La couche physique s'occupe de la transmission des bits de façon brute sur un canal de communication. L'unité d'information typique de cette couche est le bit, représenté par une différence de potentiel.

### 2.1.1.2. La couche liaison

Elle va transformer les signaux reçus de la couche physique en une liaison a priori exempte d'erreurs pour la couche réseau. Elle fractionne les données d'entrée de l'émetteur en trames, transmet ces trames en séquence et gère les trames d'acquittement renvoyées par le récepteur. De manière générale, un rôle important de cette couche est la détection et la correction d'erreurs apparues sur la couche physique. Cette couche intègre également une fonction de contrôle de flux pour éviter l'engorgement du récepteur. L'unité d'information de la couche liaison de données est la trame.

#### **2.1.1.3. La couche réseau**

C'est la couche qui permet de gérer le routage des paquets et l'interconnexion des différents sous-réseaux entre eux. La couche réseau contrôle également l'engorgement du sous-réseau. L'unité d'information de la couche réseau est le *paquet*.

#### **2.1.1.4. La couche transport**

Cette couche est responsable du bon acheminement des messages complets au destinataire. Le rôle principal de la couche transport est de prendre les messages de la couche session, de les découper s'il le faut en unités plus petites et de les passer à la couche réseau, tout en s'assurant que les morceaux arrivent correctement de l'autre côté. Cette couche effectue donc aussi le réassemblage du message à la réception des morceaux. Cette couche est également responsable du type de service à fournir aux utilisateurs du réseau : service en mode connecté ou non, avec ou sans garantie d'ordre de délivrance, diffusion du message à plusieurs destinataires à la fois, etc. L'unité d'information de la couche réseau est le *message*.

#### **2.1.1.5. La couche session**

Cette couche organise et synchronise les échanges entre des tâches distribuées. Elle établit également une liaison entre deux programmes d'application devant coopérer et commander leur dialogue (qui doit parler, qui parle...).

#### **2.1.1.6. La couche présentation**

Cette couche s'intéresse à la syntaxe et à la sémantique des données transmises : c'est elle qui traite l'information de manière à la rendre compatible entre les tâches communicantes.

### 2.1.1.7. La couche application