**Titre:** Méthodologie de codesign pour les systèmes sur puce programmable

Title: programmable

**Auteur:** Loïc Pierron

Author:

**Date:** 2005

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Pierron, L. (2005). Méthodologie de codesign pour les systèmes sur puce programmable [Mémoire de maîtrise, École Polytechnique de Montréal].

Citation: PolyPublie. <https://publications.polymtl.ca/7665/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7665/>

PolyPublie URL:

**Directeurs de recherche:** Guy Bois

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

MÉTHODOLOGIE DE CODESIGN POUR LES SYSTÈMES SUR PUCE

PROGRAMMABLE

LOÏC PIERRON

DÉPARTEMENT DE GÉNIE INFORMATIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2005

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-16834-9

*Our file* *Notre référence*

ISBN: 978-0-494-16834-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

MÉTHODOLOGIE DE CODESIGN POUR LES SYSTÈMES SUR PUCE

PROGRAMMABLE

présenté par: PIERRON Loïc

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. ABOULHAMID El Mostapha, Ph.D., président

M. BOIS Guy, Ph.D., membre et directeur de recherche

Mme. NICOLESCU Gabriela, Doct., membre

To us.

## REMERCIEMENTS

Tout d'abord, je remercie mon directeur de recherche, Guy Bois, pour son aide financière m'ayant permis de commencer ma maîtrise dans de bonnes conditions.

Je remercie ensuite énormément les personnes qui m'ont aidé en fin de parcours : d'une part mes parents, et surtout ma maman, Nadine, pour leur soutien financier ; d'autre part mon frère d'armes, Quentin Bleton, qui m'a gracieusement accueilli chez lui pendant presque six mois, et sur lequel je peux vraiment compter.

Pour l'efficacité avec laquelle ils ont régulièrement répondu à mes besoins et réglé mes problèmes, je remercie les administrateurs systèmes du groupe de recherche, Réjean Lepage et Alexander Vesey. Je remercie également Marc Minato, de la compagnie Mentor Graphics, pour son support technique irréprochable à un moment crucial de mon travail.

## RÉSUMÉ

Depuis le début de la microélectronique, les performances des puces disponibles n'ont cessé de s'améliorer, mais c'est actuellement dans le domaine des puces à architecture reprogrammable que les progrès sont les plus importants, ces progrès dépassant même les prévisions de la loi de Moore au cours des dix dernières années. Le succès croissant des FPGA s'explique également par l'apparition encore récente des FPGA plateformes, des FPGA sur lesquels, en plus des blocs logiques programmables et du réseau d'interconnexions programmable, ont été ajoutées en matériel des propriétés intellectuelles comme un microprocesseur.

Compte tenu de la taille et de la complexité toujours croissantes des systèmes sur puces, l'utilisation de méthodologies et d'outils appropriés est primordiale si l'on souhaite pouvoir tirer profit au maximum des possibilités offertes par ces nouvelles puces. La réutilisation de la propriété intellectuelle, par exemple, fait déjà partie intégrante des flots de conception pour FPGA. Dans ce travail, nous avons exploré une autre piste, celle de la cosimulation, et étudié comment l'utilisation d'un outil de covérification comme Mentor Seamless CVE peut bénéficier au flot de conception classique pour Xilinx Virtex-II Pro.

Nous avons commencé par créer un modèle cosimulable d'un design de base. À partir de cette expérience, nous avons établi une méthode de transformation d'un design quelconque obtenu avec les outils Xilinx vers un modèle cosimulable dans Seamless. Nous avons fait rouler un système d'exploitation temps réel avec ce modèle, puis à partir de cette plateforme de référence, nous avons défini une méthodologie de codesign pour systèmes sur puce programmable, adaptée au flot de conception Xilinx et utilisant la cosimulation. Nous sommes capables de cosimuler des designs possédant des modules matériels modélisés à différents niveaux d'abs-

traction et communiquant avec le processeur à différents niveaux d'abstraction également. Notre méthodologie permet donc de concevoir des modules matériels par raffinement progressif et de valider leur fonctionnement à chaque niveau d'abstraction.

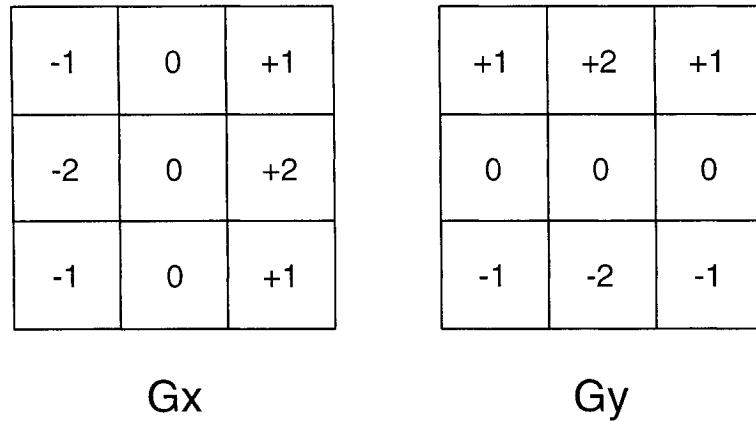

Afin de démontrer le fonctionnement de la méthodologie mise au point, nous l'avons appliquée à un exemple de détection de contours, et nous avons mesuré et analysé les résultats obtenus. En conclusion, l'intégration de la cosimulation dans le flot de conception FPGA permet d'accélérer le cycle de conception d'un design, et en particulier de faciliter grandement la phase d'exploration architecturale.

## ABSTRACT

Since the beginning of microelectronics, chip performance has constantly been improved, but nowadays the most significant progress is being made in the field of reprogrammable architecture chips, so that it even surpassed Moore's law's predictions in the last ten years. The increasing success of FPGAs also comes from the still recent platform FPGAs, FPGAs that don't only feature reprogrammable logic blocks in a reprogrammable interconnection network, but also integrate hardwired IP cores such as microprocessors.

Because of the exploding complexity of system-on-chip design, it is extremely important to use adequate methodologies and tools in order to harness all the possibilities offered by these new chips. IP reuse, for example, is already a part of current FPGA design flows. In this work, we explored the idea of using co-simulation, and studied how the use of a co-verification tool like Mentor Seamless CVE can improve the classical design flow for Xilinx Virtex-II Pro.

From the experience of creating a first co-simulation model of a reference design, we established a way to transform any design obtained with Xilinx' tools into a co-simulation model for Seamless. We had a real-time operating system run with this model, and we defined a co-design methodology for system-on-programmable-chip design that is adapted to the classical Xilinx design flow and uses co-simulation. We are able to co-simulate designs integrating hardware modules modelled at different abstraction levels and communicating with the processor at different abstraction levels as well. Our methodology therefore allows us to design hardware modules through progressive refining and validate them at each abstraction level.

To demonstrate how our methodology works, we applied it to accelerate an edges detection algorithm, and we measured and analyzed the results. To conclude, inte-

grating the use of co-simulation into the classical FPGA design flow can accelerate the design cycle, in particular by facilitating the architectural exploration phase.

## TABLE DES MATIÈRES

|                                                   |      |

|---------------------------------------------------|------|

| DÉDICACE . . . . .                                | iv   |

| REMERCIEMENTS . . . . .                           | v    |

| RÉSUMÉ . . . . .                                  | vi   |

| ABSTRACT . . . . .                                | viii |

| TABLE DES MATIÈRES . . . . .                      | x    |

| LISTE DES TABLEAUX . . . . .                      | xiv  |

| LISTE DES FIGURES . . . . .                       | xv   |

| LISTE DES SIGLES ET ABRÉVIATIONS . . . . .        | xvii |

| INTRODUCTION . . . . .                            | 1    |

| CHAPITRE 1 ÉTAT DE L'ART . . . . .                | 10   |

| 1.1 Les SoC . . . . .                             | 10   |

| 1.2 Le codesign . . . . .                         | 11   |

| 1.3 Les types de puces . . . . .                  | 15   |

| 1.3.1 ASIC . . . . .                              | 16   |

| 1.3.1.1 ASIC sur mesure . . . . .                 | 17   |

| 1.3.1.2 ASIC précaractérisés . . . . .            | 17   |

| 1.3.2 ASIC structurés . . . . .                   | 18   |

| 1.3.3 Puces à architecture programmable . . . . . | 19   |

| 1.3.3.1 CPLD . . . . .                            | 19   |

| 1.3.3.2 FPGA . . . . .                            | 20   |

|                                            |                                                                                   |    |

|--------------------------------------------|-----------------------------------------------------------------------------------|----|

| 1.3.4                                      | Récapitulatif                                                                     | 22 |

| 1.4                                        | La montée en puissances des FPGA                                                  | 23 |

| 1.5                                        | FPGA plateformes                                                                  | 24 |

| 1.5.1                                      | Triscend                                                                          | 25 |

| 1.5.2                                      | Altera                                                                            | 25 |

| 1.5.3                                      | Xilinx                                                                            | 26 |

| 1.5.4                                      | Comparaison                                                                       | 27 |

| 1.6                                        | Outils                                                                            | 31 |

| 1.6.1                                      | Xilinx                                                                            | 31 |

| 1.6.2                                      | Altera                                                                            | 31 |

| 1.6.3                                      | Récapitulatif                                                                     | 32 |

| 1.7                                        | Applications des FPGA plateformes                                                 | 32 |

| 1.8                                        | La covérification avec Seamless                                                   | 35 |

| 1.8.1                                      | Épargner le temps gaspillé en synthèses et placements/routages successifs         | 35 |

| 1.8.2                                      | Accélérer la cosimulation                                                         | 36 |

| 1.8.3                                      | Gérer les modèles matériels décrits dans des langages à haut niveau d'abstraction | 38 |

| 1.8.4                                      | Autres solutions                                                                  | 39 |

| CHAPITRE 2 ARCHITECTURE DE RÉFÉRENCE CIBLE |                                                                                   | 41 |

| 2.1                                        | Carte de développement                                                            | 41 |

| 2.1.1                                      | Principaux composants                                                             | 41 |

| 2.1.2                                      | Méthodes de démarrage                                                             | 43 |

| 2.1.3                                      | Mécanismes de communication                                                       | 44 |

| 2.1.4                                      | Différences entre les modèles                                                     | 45 |

| 2.2                                        | Design de départ                                                                  | 46 |

| 2.2.1                                      | Processeur                                                                        | 47 |

| 2.2.2                                      | Bus d'interconnexion                                                              | 47 |

|                                                        |                                                              |    |

|--------------------------------------------------------|--------------------------------------------------------------|----|

| 2.2.3                                                  | Périphériques                                                | 48 |

| <b>CHAPITRE 3 MÉTHODOLOGIE</b>                         |                                                              | 50 |

| 3.1                                                    | Vers un design de départ dans Seamless                       | 50 |

| 3.1.1                                                  | Test du PSP du Virtex-II Pro dans Seamless                   | 50 |

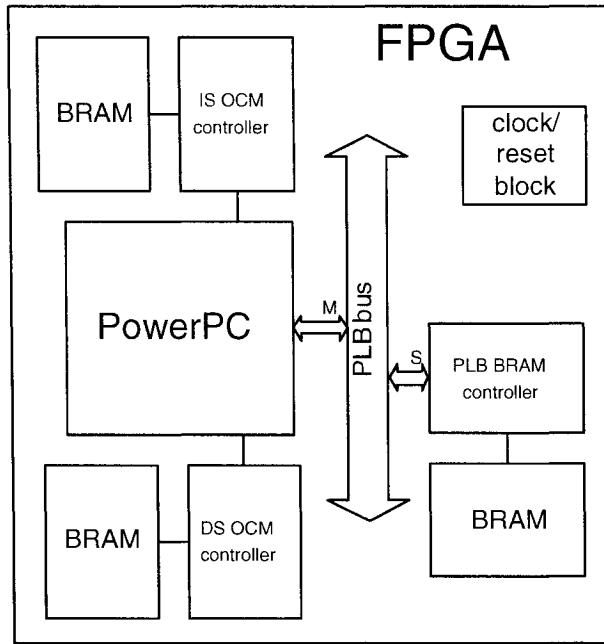

| 3.1.2                                                  | Conception d'un design minimal dans XPS                      | 52 |

| 3.1.3                                                  | Méthodologie de seamlesssation des designs XPS               | 54 |

| 3.1.3.1                                                | Processeur                                                   | 54 |

| 3.1.3.2                                                | Mémoires                                                     | 55 |

| 3.1.3.3                                                | Touches finales                                              | 56 |

| 3.1.4                                                  | Seamlesssation du design baseline                            | 57 |

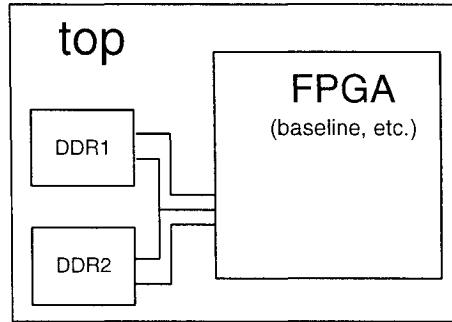

| 3.1.5                                                  | Ajout de la mémoire externe                                  | 58 |

| 3.1.6                                                  | Récapitulatif sur les possibilités du modèle de cosimulation | 60 |

| 3.2                                                    | Comment faire des ajouts ou des modifications                | 61 |

| 3.2.1                                                  | Côté logiciel                                                | 61 |

| 3.2.2                                                  | Côté matériel                                                | 63 |

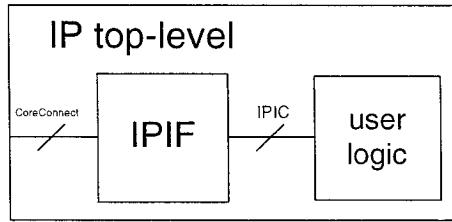

| 3.2.2.1                                                | IPIF                                                         | 63 |

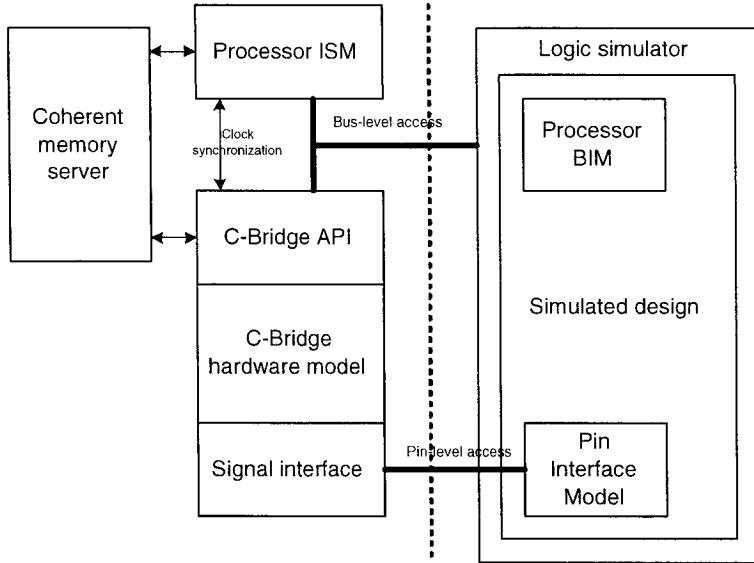

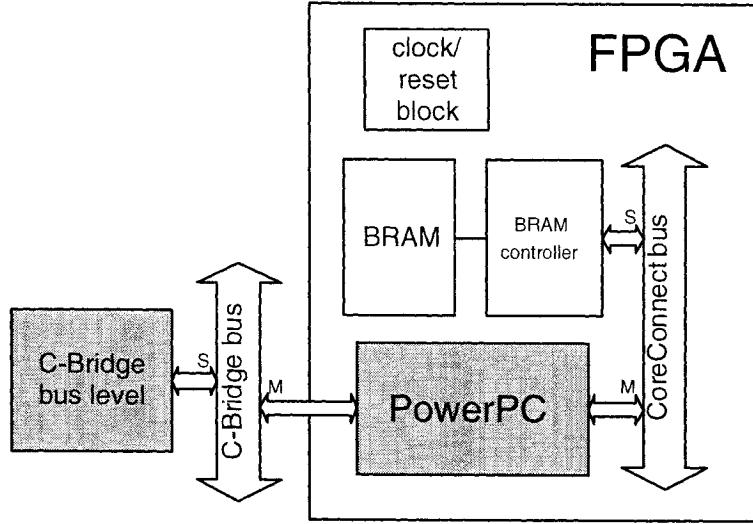

| 3.2.2.2                                                | C-Bridge niveau bus                                          | 65 |

| 3.2.2.3                                                | C-Bridge niveau pins                                         | 67 |

| 3.3                                                    | Vérification et performance                                  | 69 |

| 3.3.1                                                  | Vérification du fonctionnement                               | 70 |

| 3.3.2                                                  | Performance de la cosimulation                               | 70 |

| 3.3.3                                                  | Performance du modèle                                        | 71 |

| <b>CHAPITRE 4 APPLICATION, RÉSULTATS ET DISCUSSION</b> |                                                              | 74 |

| 4.1                                                    | Exemple d'application                                        | 74 |

| 4.2                                                    | Application de la méthodologie                               | 76 |

| 4.2.1                                                  | Obtention d'un modèle de base cosimulable dans Seamless      | 76 |

| 4.2.1.1                                                | Matériel                                                     | 76 |

|         |                                                                     |    |

|---------|---------------------------------------------------------------------|----|

| 4.2.1.2 | Logiciel                                                            | 77 |

| 4.2.1.3 | Seamlessisation                                                     | 78 |

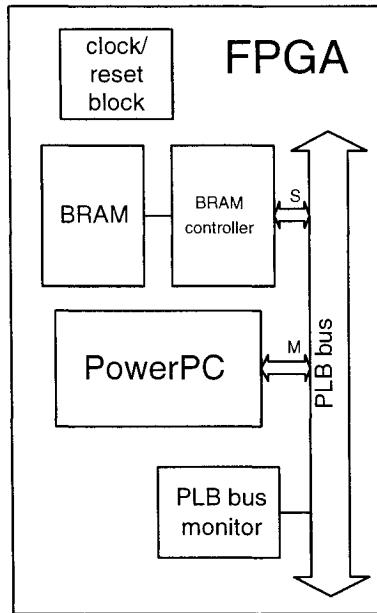

| 4.2.2   | Ajout du moniteur de bus                                            | 78 |

| 4.2.3   | Profilage et choix de partitionnement                               | 79 |

| 4.2.4   | Partitionnement pseudo-matériel/logiciel avec uC/OS-II              | 80 |

| 4.2.5   | Partitionnement matériel/logiciel avec C-Bridge niveau bus          | 82 |

| 4.2.6   | Partitionnement matériel/logiciel avec IPIF et C-Bridge niveau pins | 83 |

| 4.2.7   | Partitionnement matériel/logiciel avec IPIF et VHDL                 | 84 |

| 4.2.8   | Récapitulatif                                                       | 84 |

| 4.3     | Mesures                                                             | 85 |

| 4.3.1   | Profilage de l'application                                          | 85 |

| 4.3.2   | Durée des cosimulations                                             | 85 |

| 4.3.3   | Performances diverses                                               | 87 |

| 4.4     | Analyse des résultats et discussion                                 | 89 |

| 4.4.1   | Durées de simulation                                                | 89 |

| 4.4.2   | Autres informations                                                 | 91 |

| 4.4.3   | Temps de développement                                              | 92 |

| 4.4.4   | Seamless ou non                                                     | 93 |

|         | CONCLUSION                                                          | 94 |

|         | RÉFÉRENCES                                                          | 97 |

**LISTE DES TABLEAUX**

|             |                                                                                 |    |

|-------------|---------------------------------------------------------------------------------|----|

| Tableau 1.1 | Comparaison des puces Altera et Xilinx . . . . .                                | 30 |

| Tableau 2.1 | Différences principales entre les puces XC2VP7, XC2VP20 et<br>XC2VP30 . . . . . | 45 |

| Tableau 4.1 | Différences entre code récupéré et code de départ . . . . .                     | 78 |

| Tableau 4.2 | Récapitulatif des propriétés des modèles matériels . . . . .                    | 85 |

| Tableau 4.3 | Durée de la cosimulation pour chacune des implémentations                       | 87 |

## LISTE DES FIGURES

|             |                                                                                   |    |

|-------------|-----------------------------------------------------------------------------------|----|

| Figure 1.1  | Les étapes du codesign . . . . .                                                  | 12 |

| Figure 1.2  | Influence de la cosimulation sur le cycle de développement d'un produit . . . . . | 14 |

| Figure 1.3  | Structure d'un CPLD . . . . .                                                     | 20 |

| Figure 1.4  | Structure d'un FPGA . . . . .                                                     | 21 |

| Figure 1.5  | Récapitulatif des caractéristiques des types de puces . . . . .                   | 22 |

| Figure 1.6  | Architecture de l'Excalibur . . . . .                                             | 26 |

| Figure 1.7  | Architecture du Virtex-II Pro . . . . .                                           | 27 |

| Figure 1.8  | Flot de conception classique pour FPGA plateforme . . . . .                       | 34 |

| Figure 1.9  | Flot de conception pour FPGA plateforme avec cosimulation                         | 35 |

| Figure 1.10 | Serveur mémoire Seamless . . . . .                                                | 37 |

| Figure 1.11 | C-Bridge dans Seamless . . . . .                                                  | 38 |

| Figure 2.1  | Schéma blocs de la carte AP100 . . . . .                                          | 42 |

| Figure 2.2  | Vue du design baseline dans Xilinx Platform Studio . . . . .                      | 46 |

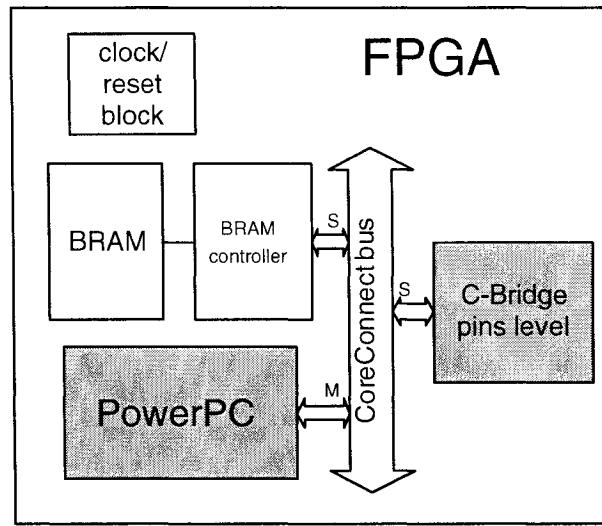

| Figure 3.1  | Design utilisé pour le test du PSP . . . . .                                      | 51 |

| Figure 3.2  | Schéma blocs du premier design créé dans XPS . . . . .                            | 52 |

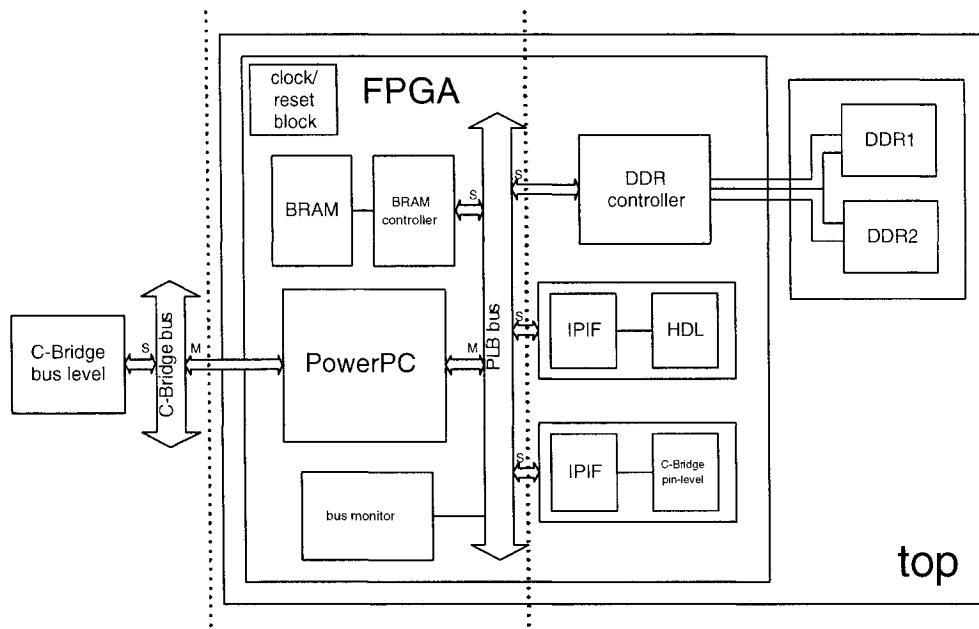

| Figure 3.3  | Modèle top-level avec mémoire externe . . . . .                                   | 60 |

|            |                                                                            |    |

|------------|----------------------------------------------------------------------------|----|

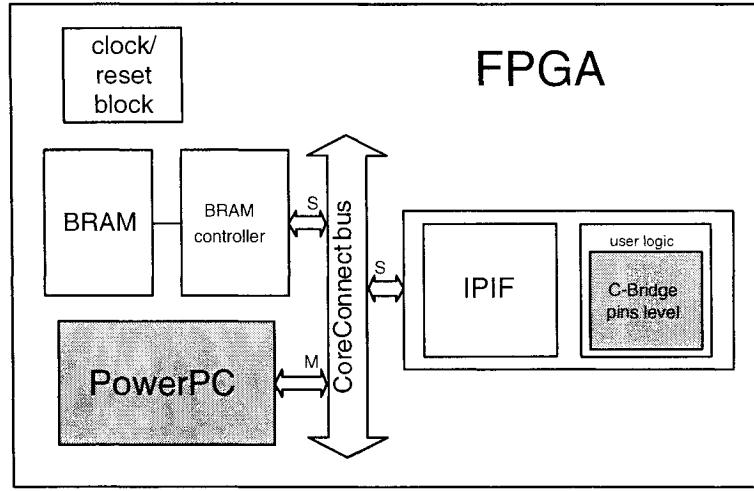

| Figure 3.4 | Structure d'un patron d'IP utilisant IPIF . . . . .                        | 64 |

| Figure 3.5 | Cosimulation avec un module C-Bridge communiquant au niveau bus . . . . .  | 66 |

| Figure 3.6 | Cosimulation avec un module C-Bridge communiquant au niveau pins . . . . . | 67 |

| Figure 3.7 | Principe de fonctionnement d'un module IPIF+C-Bridge . .                   | 68 |

| Figure 3.8 | Instanciation du moniteur de bus dans le modèle de cosimulation . . . . .  | 72 |

| Figure 4.1 | Masques de convolution de Sobel . . . . .                                  | 75 |

| Figure 4.2 | Plateforme finale . . . . .                                                | 77 |

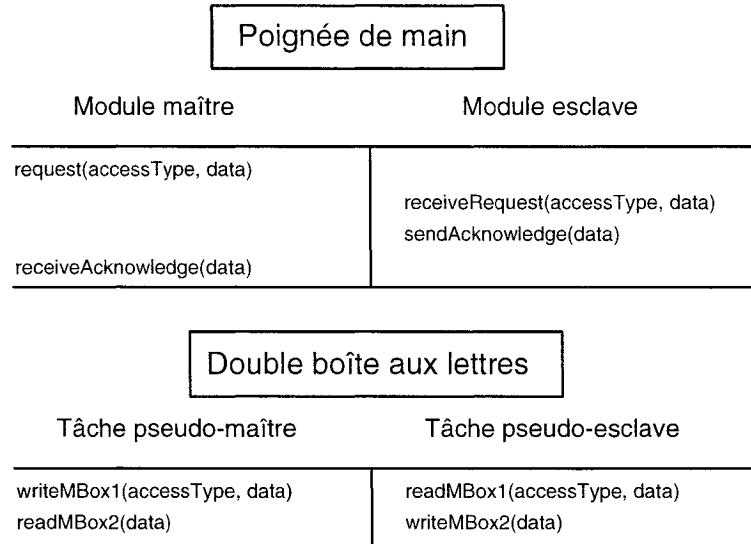

| Figure 4.3 | Simulation d'une poignée de main avec des boîtes aux lettres               | 82 |

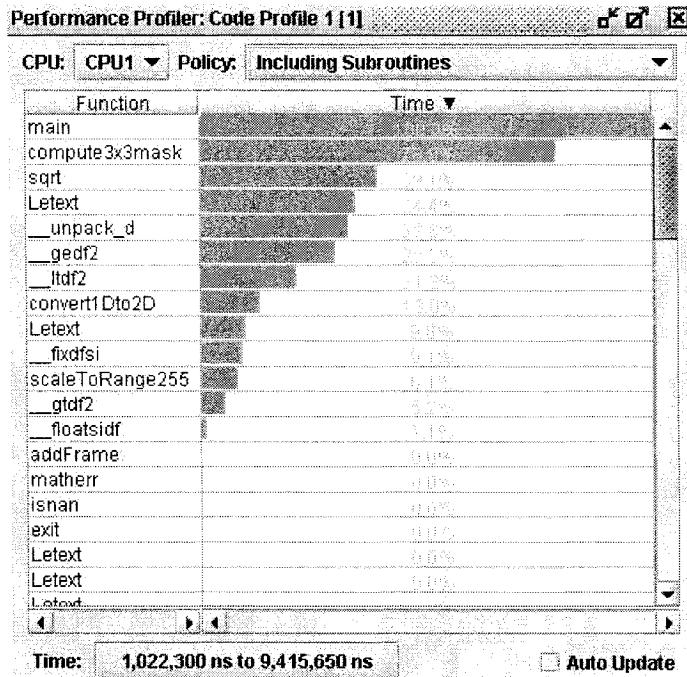

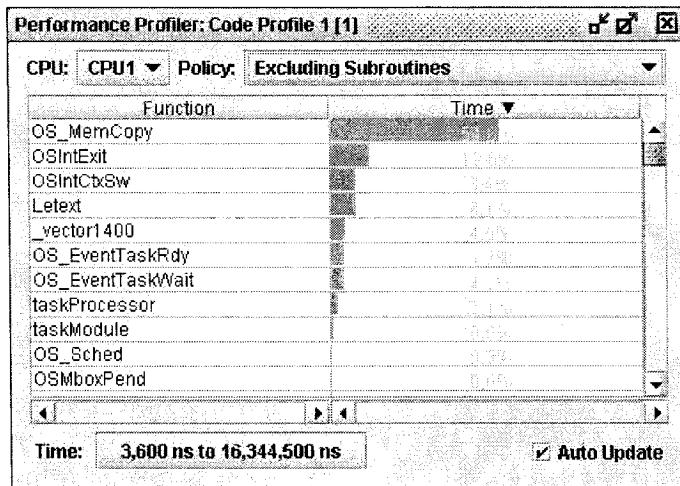

| Figure 4.4 | Profilage de l'application logicielle avec SPP . . . . .                   | 86 |

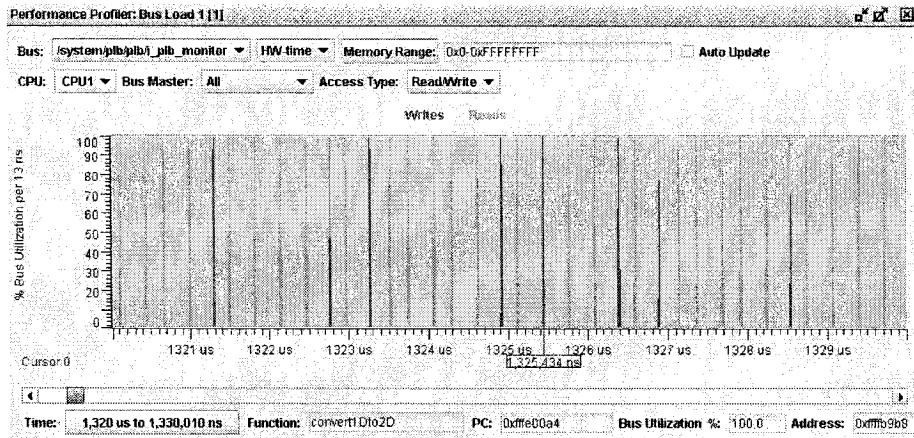

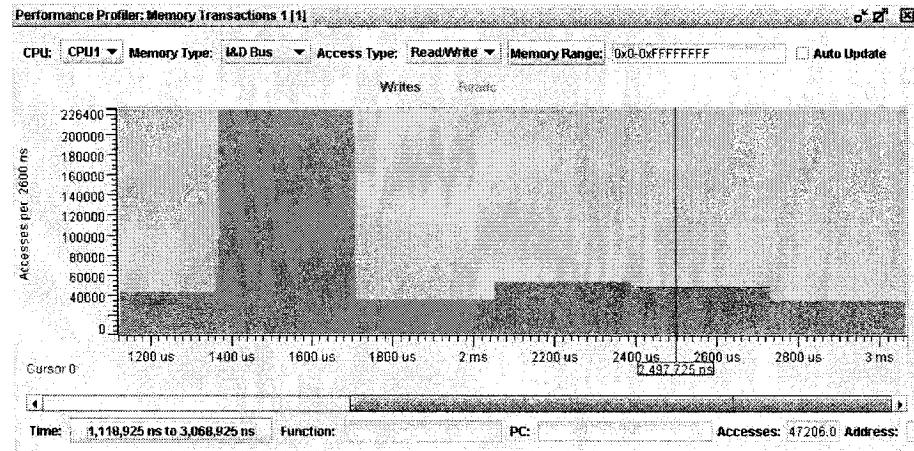

| Figure 4.5 | Informations sur les transactions à travers le bus PLB dans SPP . . . . .  | 88 |

| Figure 4.6 | Informations sur les transactions mémoire dans SPP . . . . .               | 88 |

| Figure 4.7 | Profilage de l'application uC/OS-II avec SPP . . . . .                     | 90 |

## LISTE DES SIGLES ET ABRÉVIATIONS

|       |                                         |

|-------|-----------------------------------------|

| AHB   | Advanced High Performance               |

| API   | Application Programming Interface       |

| ASIC  | Application-Specific Integrated Circuit |

| BRAM  | BlockRAM                                |

| CAM   | Content-Addressable Memory              |

| CPLD  | Complex Programmable Logic Device       |

| CVE   | Co-Verification Environment             |

| DCR   | Device Control Register                 |

| DDR   | Double Data Rate                        |

| DPRAM | Dual Port RAM                           |

| EDK   | Embedded Development Kit                |

| ESB   | Embedded System Block                   |

| FIFO  | First In First Out                      |

| FIT   | Fixed Interval Timer                    |

| FPGA  | Field-Programmable Gate Array           |

| HDL   | Hardware Description Language           |

| IP    | Intellectual Property                   |

| IPIC  | IP InterConnect                         |

| IPIF  | IP InterFace                            |

| ISE   | Integrated Software Environment         |

| ISS   | Instruction Set Simulator               |

| MGT   | Multi-Gigabit Transceiver               |

| MMU   | Memory Management Unit                  |

|       |                                             |

|-------|---------------------------------------------|

| OPB   | On-chip Peripheral Bus                      |

| PCI   | Peripheral Component Interconnect           |

| PIT   | Programmable Interval Timer                 |

| PLA   | Programmable Logic Array                    |

| PLB   | Processor Local Bus                         |

| PMC   | PCI Mezzanine Card                          |

| PSP   | Processor Support Package                   |

| RAM   | Random Access Memory                        |

| ROM   | Read Only Memory                            |

| RTOS  | Real Time Operation System                  |

| SDRAM | Synchronous Dynamic RAM                     |

| SoC   | System-on-Chip                              |

| SPP   | Seamless Performance Profiler               |

| SRAM  | Static RAM                                  |

| UART  | Universal Asynchronous Receiver/Transmitter |

| VHDL  | Very high speed integrated circuit HDL      |

| XPS   | Xilinx Platform Studio                      |

## INTRODUCTION

Aujourd’hui, nous sommes entourés d’appareils électroniques de plus en plus variés, de plus en plus petits, de plus en plus puissants. Prenons l’exemple du téléphone cellulaire. Cette petite merveille de technologie qui tient dans la main peut, entre autres choses, prendre des photos, lire des films, envoyer et recevoir des courriels, jouer de la musique, et, chose à laquelle peu de personnes font encore attention, nous permettre de parler en temps réel à n’importe qui sur la planète.

Le téléphone cellulaire est un excellent exemple de système embarqué, un système informatique - matériel et logiciel, dédié à l’exécution de tâches spécifiques. Il contient un processeur qui exécute du code (la partie logicielle), et il contient du matériel spécialisé pour certains traitements, le tout relié par un système d’interconnexions permettant aux différents composants de communiquer entre eux.

Mais avant d’en arriver là, il a non seulement fallu que les chercheurs et les ingénieurs inventent de nouveaux composants, mais aussi qu’ils réduisent énormément leur taille. C’est justement un des principaux accomplissements de la microélectronique, qui est le cœur de l’électronique d’aujourd’hui. Pour bien comprendre comment on en est arrivé aux technologies actuelles, il est intéressant de revenir un peu en arrière dans notre histoire, de disons deux siècles.

### **Historique de l’électronique et de la microélectronique**

Le dix-neuvième siècle a été celui de la révolution industrielle. Parallèlement au triomphe de la vapeur et de la force thermodynamique, il a également marqué une période de grandes découvertes dans le domaine de l’électromagnétisme. Alors qu’au début du siècle, on était tout juste capable de construire la première pile, la

fin du siècle voyait l'apparition de la machine à rayons X. Grâce aux applications de l'électromagnétisme, le dix-neuvième siècle a également été celui des premières communications, avec des appareils comme le télégraphe puis le téléphone.

Au cours du siècle dernier, tout s'est accéléré. En effet, dès le début du vingtième siècle, toutes sortes d'appareils électriques ont fait leur apparition dans les foyers et ont progressivement changé la vie de tout un chacun. Du côté des communications, on apprend à se passer de médium de transmission métallique et c'est la naissance des communications sans fil, dont les applications mènent à la radio et à la télévision. Mais jusqu'à la moitié du vingtième siècle, ces premiers appareils de communication sans fil sont très encombrants et peu fiables.

Une invention va changer tout ça et lancer la révolution électronique : celle du transistor, en 1947. Le transistor est utilisé en remplacement du tube électronique, jusqu'alors notamment responsable d'amplifier le courant dans les circuits, et est non seulement plus petit, mais aussi plus fiable et moins coûteux. On se met donc à fabriquer des postes de radio portables, moins chers, et offrant à la fois AM et FM. Ces mêmes postes de radio "à transistors" ont d'ailleurs longtemps été incorrectement appelés transistors.

Les premiers transistors sont très vite remplacés par des transistors faits à partir de matériaux semiconducteurs. Tout d'abord de germanium, puis de silicium, qui est encore aujourd'hui principalement utilisé, plus de cinquante ans après ses débuts en 1954. Progressivement, on met de plus en plus de transistors sur une seule et même tranche de silicium, avant de la découper pour produire les composants discrets.

Puis vient l'idée de fabriquer des puces de silicium contenant non seulement des transistors, mais aussi d'autres composants électroniques de base comme des résistances et des condensateurs, permettant ainsi de mettre un circuit électronique complet sur une puce. En 1958, seulement une dizaine d'années après l'invention

du premier transistor, c'est la naissance des circuits intégrés.

De même que le transistor a révolutionné le domaine des communications, il a aussi, par l'intermédiaire des circuits intégrés, révolutionné celui des ordinateurs. Alors que les ordinateurs du milieu du vingtième siècle occupaient des salles entières et étaient réservés à des groupes d'utilisateurs privilégiés, l'apparition du microprocesseur au début des années 1970 permit dès la fin de la décennie de construire des ordinateurs personnels tenant sur un bureau [Museum (2005)]. Depuis, la taille des transistors n'a cessé de diminuer, et on s'est mis à parler de microélectronique.

### **Les mécanismes de l'évolution en électronique**

Avant de tourner cette page historique, essayons de voir comment se fait l'évolution dans le domaine de l'électronique. Prenons le cas de la télévision. La télévision a ceci d'intéressant qu'elle a relativement peu évolué - la couleur existait déjà - depuis le début de sa démocratisation, au milieu du siècle dernier. En effet, en dehors de quelques innovations récentes et encore peu répandues comme la télévision haute définition, la télévision a gardé le même principe de fonctionnement. Cependant, au fil des années, les téléviseurs se sont faits de plus en plus petits, de moins en moins chers, de plus en plus performants et de plus en plus perfectionnés ; la télécommande est devenue son inséparable compagne, la qualité de l'image ainsi que celle du son se sont améliorées.

Derrière ces améliorations, il y a plusieurs phénomènes. Tout d'abord, il y a la miniaturisation des composants électroniques. Cette miniaturisation a plusieurs conséquences bénéfiques : bien évidemment, la taille des circuits électroniques se trouve diminuée en conséquence, et on peut donc construire des téléviseurs plus petits et plus légers ; si on souhaite en revanche construire des téléviseurs de même taille, on peut alors utiliser l'espace gagné pour ajouter de nouvelles fonctionnalités

au téléviseur. Il y a aussi l'amélioration des composants électroniques existants, ce qui permet d'améliorer la performance des circuits, et il y a encore l'apparition de nouveaux composants, qui permet quant à elle de créer de nouveaux types de circuits.

Cette évolution est généralisable à la plupart des domaines de l'électronique, et notamment à celui qui nous intéresse plus particulièrement, celui de la microélectronique. Au niveau de la miniaturisation, les progrès réalisés au cours des années sont considérables. On parle aujourd'hui de transistors dont les dimensions peuvent être aussi petites que 90 nanomètres (et bientôt 65 nm), et on fabrique des puces de grande consommation destinées aux ordinateurs contenant plus de cent millions de transistors, là où le premier microprocesseur, fabriqué par Intel en 1971, contenait environ 2300 transistors.

Il y a eu évolution au niveau des types de composants, avec par exemple la découverte du transistor à effet de champ, mais aussi au niveau des technologies de fabrication, avec par exemple la technologie CMOS. On a également vu l'apparition de nouvelles classes de circuits ou de puces. Au début des années 1970, peu après l'invention du premier microprocesseur, les puces à architecture programmable ont fait leur apparition. Ces circuits (PLD puis CPLD, FPGA), initialement utilisés pour des fonctions combinatoires simples, sont désormais très versatiles et peuvent mélanger des éléments aussi divers qu'une simple porte logique ou un microprocesseur complet.

## **Les défis de la microélectronique**

Les défis posés par la microélectronique sont multiples et complexes. D'une manière évidente, il y a une grande différence d'accessibilité entre une puce et un circuit électronique classique. En effet, Monsieur Tout-le-Monde peut très facile-

ment, avec très peu d'équipement spécialisé (en gros, une insoleuse et quelques produits chimiques), fabriquer ses propres circuits imprimés. Ensuite, il peut acheter des composants dans le magasin d'électronique le plus proche, se munir de son fer à souder, et le reste n'est qu'une question d'huile de coude. Même s'il s'agit de composants CMS (Composants Montés en Surface, en anglais SMC pour Surface Mounted Components), chaque composant est macroscopique et aisément manipulable.

En revanche, pour fabriquer une puce contenant des millions de transistors concentrés sur moins d'un centimètre carré, il faut adopter une approche totalement différente. Même avec une excellente vue et une incroyable dextérité, il est humainement impossible (aujourd'hui du moins) de graver une tranche de silicium manuellement. En microélectronique, dès qu'on veut produire, il faut donc obligatoirement utiliser des machines. Pour que la microélectronique continue de progresser, il a donc fallu sans cesse améliorer les procédés de fabrication, et donc les machines dont ils dépendent.

En fait, depuis longtemps, on utilise également des machines pour aider à la conception des puces. Le microordinateur, qui est l'un des principaux produits de la microélectronique, a très vite été utilisé pour permettre à la microélectronique d'aller encore plus loin. Même si ça semble ironique, on ne pourrait pas améliorer les ordinateurs sans les ordinateurs eux-mêmes ! L'utilisation de l'ordinateur comme aide à la conception n'est pas propre à la microélectronique et, d'une manière générale, on appelle ça la conception assistée par ordinateur (CAO, en anglais CAD pour Computer-Aided Design).

Pour progresser, la microélectronique a donc bénéficié de la création de nouvelles méthodologies de conception et de l'utilisation d'outils informatiques spécialisés. Ces outils de conception électronique automatisée (en anglais EDA tools, pour

Electrical Design Automation tools) constituent un domaine de recherche à part entière de la microélectronique. Méthodologies et outils vont souvent de paire, mais on peut même considérer que tous les aspects de la microélectronique sont interdépendants. En effet, si une nouvelle technologie est mise au point mais qu'il n'existe aucun outil approprié, cette technologie reste alors inexploitable pour les concepteurs de puces.

Les outils développés et les méthodologies mises au point sont dépendants de la technologie visée. Par exemple, le flot de conception sera sensiblement différent selon qu'on veuille produire des ASIC (Application Specific Integrated Circuit) ou des FPGA (Field Programmable Gate Array). Cependant, certaines étapes sont communes à toutes les méthodologies, quelle que soit la technologie cible. On peut même, dépendamment de l'application, avoir des étapes, dans le flot de conception, qui sont complètement indépendantes de la technologie visée.

Dans ce mémoire, nous nous penchons sur l'étude d'une méthodologie de code-sign sur FPGA plateforme (de l'anglais platform FPGA). Elle s'articule autour de l'utilisation de deux outils en particulier, et se propose de réaliser une intégration, un mélange des flots de conception proposés par chacun d'eux, afin d'accélérer le processus de conception sur ce type de puces.

## Problématique

Puisque le nombre de transistors qu'il est possible d'intégrer augmente régulièrement, la taille et la complexité des systèmes embarqués ne cessent d'augmenter. Ce phénomène touche notamment les systèmes sur puce programmable, qui en plus jouissent d'un succès croissant. Afin de concevoir efficacement des systèmes, il est devenu nécessaire d'utiliser des outils d'aide à la conception électronique, mais les outils seuls ne peuvent pas tout faire. Aussi est-il important de définir des métho-

dologies permettant non seulement de tirer profit au maximum des outils, mais aussi de définir une approche systématique à la conception de systèmes.

Nous nous intéressons au développement de systèmes sur puce programmable Virtex-II Pro en particulier parce que notre laboratoire allait être équipé de cartes de développement et de prototypage équipées de ce type de puce. Naturellement, la compagnie Xilinx fournit une suite d'outils pour la conception de systèmes sur ces FPGA, et ces outils feront partie intégrante de la méthodologie mise au point.

Un autre aspect que nous voulons explorer est celui de la cosimulation. La compagnie Mentor venait d'annoncer le support du PowerPC 405 D5, le processeur contenu dans les Virtex-II Pro, dans son outil Seamless CVE. L'utilisation de la cosimulation permettrait par ailleurs de créer un design de référence et des applications pour le Virtex-II Pro avant de recevoir les cartes de développement. Seamless venant évidemment lui aussi avec sa propre méthodologie de conception, nous allons regarder comment il est possible de combiner les outils et les méthodologies afin de créer une nouvelle méthodologie de conception de systèmes sur puce programmable, le but étant d'améliorer la vitesse ou la facilité de conception.

## Objectifs

Le premier objectif lors de ce travail était simplement de se familiariser avec les outils offerts par Xilinx, et d'évaluer le support du Virtex-II Pro dans Seamless en tentant de créer un design de référence.

Lorsque le laboratoire a reçu les cartes de développement, le principal objectif est devenu d'obtenir un modèle de cosimulation du design de référence fourni avec les cartes Amirix dans Seamless.

Enfin, l'objectif final de ce travail est de mettre au point une méthodologie de

codesign, adaptée à la conception de systèmes sur puce programmable, pouvant servir de complément à l'utilisation des cartes.

## **Méthodologie**

Nous avons commencé par utiliser les outils chacun de leur côté, afin de comprendre leur fonctionnement, et de trouver comment il était possible de les combiner dans un flot de conception unique, permettant entre autres d'obtenir facilement un modèle de cosimulation à partir d'une plateforme conçue avec les outils de Xilinx.

Nous avons ensuite commencé à utiliser ces outils de manière combinée afin de créer des plateformes très simples, avant d'entreprendre la mise au point du modèle pour le design de référence des cartes de prototypage. Ceci nous a permis de créer une technique largement automatisée pour obtenir le modèle cosimulable dans Seamless d'un design conçu avec l'outil XPS (Xilinx Platform Studio).

Enfin, pour accélérer et faciliter la création de modules matériels, nous avons exploré toutes les diverses possibilités offertes par Seamless et nous nous sommes efforcés de les inclure dans une méthodologie de codesign adaptée à la conception de systèmes sur puce reprogrammable.

## **Originalité et contributions**

Pour ce qui est de l'originalité, lorsque ce projet a été commencé, l'idée d'associer XPS et Seamless dans un flot de conception unique, et surtout celle d'automatiser l'obtention de modèles de cosimulation Seamless à partir d'un système conçu avec XPS étaient toutes deux nouvelles. Depuis, les deux compagnies, ont ajouté dans leurs outils respectifs plusieurs assistants dont l'utilisation combinée permet d'au-

tomatiser grandement le passage d’XPS vers Seamless. Il reste que nous avons fait la même chose avant eux.

Du côté des contributions, on notera surtout la création d’une méthodologie de création de modules matériels par raffinement progressif, rendue possible grâce à l’utilisation conjointe de caractéristiques propres à chacun des outils. Cette méthodologie est utile de la phase d’exploration architecturale à la phase d’implémentation des modules. Il y a aussi le fait que la plateforme finale obtenue pour l’exemple d’application présenté intègre toutes les caractéristiques possibles de Seamless. Cette plateforme représente donc non seulement un outil de recherche et développement, mais aussi un outil éducatif sur Seamless et le codesign en général.

## Plan du mémoire

Entre sa présente introduction et sa conclusion, ce mémoire est constitué de quatre chapitres. Le chapitre 1 fait l’état de l’art dans le domaine du codesign et des FPGA. On y aborde tout d’abord des sujets vastes avant de préciser les choses et d’arriver à ce qui nous intéresse plus particulièrement : les FPGA plateformes et la cosimulation. Le chapitre 2 présente la carte de développement et le design de référence ciblés. Ceci définit le cadre dans lequel le travail a été réalisé, et explique certains des choix qui ont été faits par la suite. Le chapitre 3 définit et explique, étape par étape, la méthodologie de conception de systèmes sur puce programmable mise au point dans ce travail. Le chapitre 4 illustre cette méthodologie à l’aide d’un exemple de détecteur de contours utilisant les masques de Sobel, et présente et discute les résultats obtenus.

## CHAPITRE 1

### ÉTAT DE L'ART

La microélectronique est un domaine de recherche très vaste, et il est donc important de situer un peu plus précisément le travail dont il est question dans ce mémoire. Nous nous intéressons ici à une méthodologie de codesign de systèmes sur puces embarqués.

#### 1.1 Les SoC

Les systèmes sur puce (en anglais SoC pour System on Chip) sont en quelque sorte la seconde étape d'intégration après les circuits intégrés. Là où les circuits intégrés ont révolutionné l'électronique en rassemblant plusieurs composants sur une seule puce (microprocesseur, mémoire, puce de décodage video, etc.), le système sur puce va plus loin, en combinant ce qui était autrefois sur plusieurs puces sur une seule et même puce. On a désormais un système complet (au minimum un processeur, de la mémoire, et un réseau d'interconnexions) sur une seule puce.

Les SoC sont des systèmes mixtes combinant logiciel et matériel, et ils sont très adaptés à la conception de systèmes embarqués. Ils permettent donc de tirer profit à la fois des avantages du logiciel (versatilité, prix...) et de ceux du matériel (performance...) afin de trouver le meilleur compromis pour l'application désirée.

Un avantage important des SoC, en outre celui de la possibilité d'intégration, est celui de la vitesse. Puisque tout se fait à l'intérieur d'une puce, les communications entre les différents modules du système, par exemple à travers un bus sur puce,

sont beaucoup plus rapides qu'elles le seraient entre différentes puces reliées par un bus.

Les SoC apportent également leur lot d'inconvénients. Comme ils contiennent une faune diversifiée de modules pouvant réaliser des fonctions très différentes, ils peuvent être extrêmement complexes à concevoir, surtout avec les progrès croissants au niveau des technologies de fabrication. Alors que l'écart de productivité dû à la différence entre le nombre de transistors qu'il est possible d'intégrer sur une puce et le nombre de transistors que peuvent gérer les concepteurs a été grandement réduit aux cours des précédentes décennies grâce au développement des outils de conception électronique automatisée, on fait désormais face à un nouvel écart de productivité cette fois entraîné par la différence entre la complexité des technologies des procédés de fabrication et les capacités de conception [Wakabayashi et Okamoto (2004)].

Pour pallier les problèmes rencontrés dans la conception de SoC, il est nécessaire de développer de nouveaux outils et de nouvelles façons de concevoir, des méthodologies.

## 1.2 Le codesign

Une méthodologie de codesign, ou de conception conjointe logicielle/matérielle, est une méthodologie de conception qui combine les flots de conception matériel et logiciel à l'intérieur d'un flot unique. Bien évidemment, le produit final aura des parties matérielles et des parties logicielles, mais une méthodologie de codesign prévoit et permet de gérer cette dualité dans la nature du système tout au long du processus de conception.

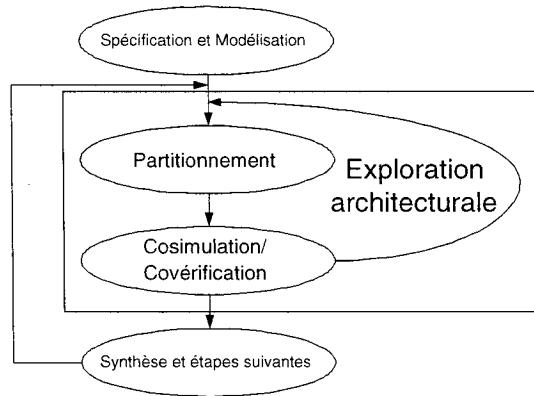

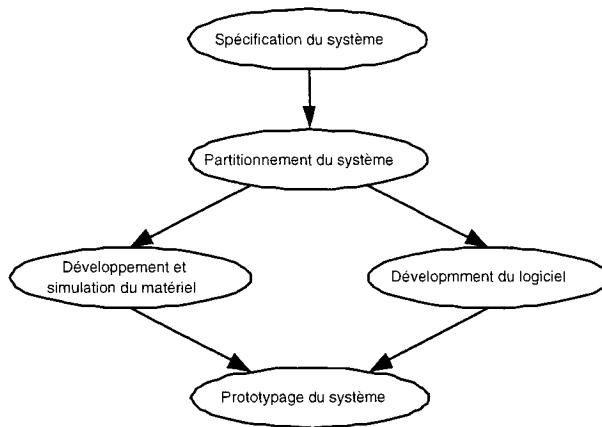

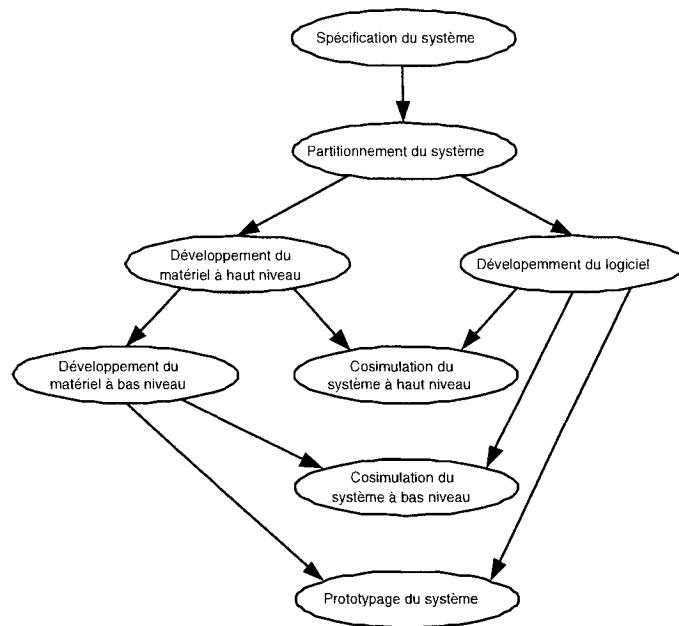

La figure 1.1 présente les étapes générales d'une méthodologie de codesign.

Figure 1.1 Les étapes du codesign

Nous avons ici divisé la méthodologie de codesign en cinq étapes (ou quatre plus une, l'exploration architecturale étant plutôt un ensemble de sous-étapes) :

- Spécification et modélisation : il s'agit de traduire le cahier des charges dans un langage (ou une représentation) plus approprié pour la suite du flot de conception. Il peut en résulter la mise au point d'un modèle exécutable écrit à haut niveau d'abstraction, mais encore indépendant des futurs choix architecturaux.

- Partitionnement : on choisit comment organiser le système d'un point de vue architectural, et en particulier on décide quelles parties seront exécutées en logiciel et lesquelles seront implémentées sous forme de bloc matériel.

- Cosimulation ou covérification : le design ayant été partitionné en un système mixte logiciel-matériel, on le simule grâce à un outil permettant la simulation hétérogène, afin de vérifier le système et valider le choix de partitionnement dont il découle.

- Exploration architecturale : l'exploration architecturale vise, par une succession d'itérations au cours de chacune desquelles on réalise un partitionnement et la cosimulation correspondante, à trouver dans un premier temps des solutions res-

pectant les contraintes de la spécification, puis dans un deuxième temps à identifier la solution qui offre le meilleur compromis performance/prix/versatilité.

- Synthèse et étapes suivantes : une fois l'exploration architecturale terminée, et le choix de partitionnement arrêté, on peut passer à la suite du flot de conception, qui sera alors le même que dans une méthodologie classique, i.e. synthèse, placement, routage, etc. Il se peut néanmoins qu'apparaîsse ici une violation de contrainte, ce qui entraîne alors des coûts beaucoup plus importants que lorsque ça arrive à l'étape précédente.

Dans une méthodologie de conception classique (par opposition à une méthodologie de codesign), le logiciel et le matériel sont développés séparément. Ceci pose quelques problèmes sérieux : premièrement, avant de pouvoir tester le logiciel, il est nécessaire de disposer d'un prototype fonctionnel du matériel. L'avancement côté logiciel est donc bloqué jusqu'à ce que le développement côté matériel atteigne une phase presque terminale. Deuxièmement, puisque le logiciel et le matériel sont développés chacun de leur côté, leur intégration est une étape très problématique.

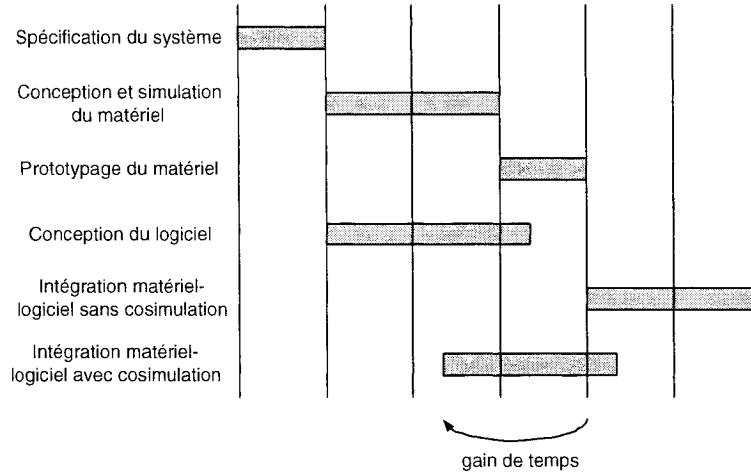

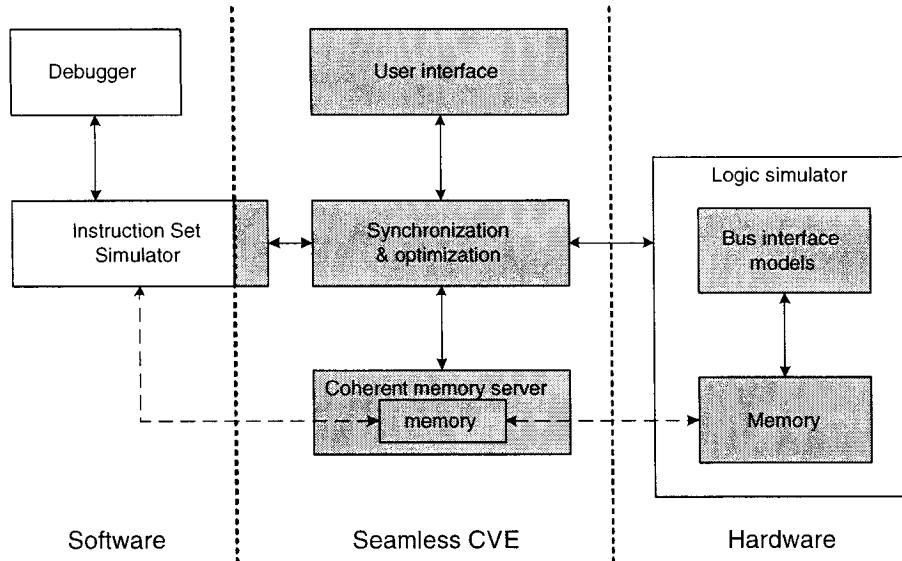

Grâce à la cosimulation/covérification, qui constitue une étape cruciale dans la méthodologie de codesign, il est possible de réduire la durée du développement d'un produit. Dès qu'on a une version simulable du matériel, on peut réaliser une cosimulation logicielle/matérielle, et ainsi commencer à tester l'exécution du logiciel sur le matériel. Plus l'outil de cosimulation utilisé supporte des modèles matériels décrits à haut niveau d'abstraction, plus tôt on peut commencer à tester le logiciel et donc plus le temps d'accès au marché peut être diminué. La figure 1.2 illustre comment l'utilisation de la cosimulation permet d'accélérer le cycle de développement d'un produit.

Le codesign présente plusieurs avantages intéressants (par rapport aux méthodolo-

Figure 1.2 Influence de la cosimulation sur le cycle de développement d'un produit

gies classiques), mais il pose aussi des problèmes importants. Au niveau de la spécification et de la modélisation tout d'abord, car il est difficile de décrire le système logiciel/matériel au complet dans un langage unique, indépendamment des futurs choix d'architecture et de partitionnement, et sans influencer ces derniers. [Jerraya et Nicolescu (2003)] souligne l'importance de la spécification/modélisation dans une méthodologie de codesign et affirme qu'il n'existe aujourd'hui aucun langage capable de satisfaire tous les besoins, et en particulier de modéliser correctement à tous les niveaux d'abstraction. Puisqu'il est presque admis qu'aucun langage ne pourra jamais tout faire, l'approche gagnante est donc peut-être de développer un nouveau langage prévu dès le début pour être interconnecté à d'autres langages dans un environnement multilangages [ESys.Net (2005)].

Un autre gros problème du codesign se situe au niveau de la validation des essais de partitionnement, car on ne dispose pas toujours de bonnes métriques de performance. Il est donc important de développer des moyens de quantifier la performance tout au long du processus de codesign, en utilisant par exemple du profilage [Dubois *et al.* (2005)].

Enfin, le codesign pose des problèmes liés à l'exploration architecturale et à la re-

cherche d'un choix de partitionnement optimal<sup>1</sup>. En plus du temps consommé en cycles d'exploration architecturale avant d'arriver à la solution optimale, puisque la nature (logicielle ou matérielle) des blocs fonctionnels du système est potentiellement modifiée à chaque nouvel essai, cela peut nécessiter beaucoup de travail additionnel (double codage de chaque bloc fonctionnel). Divers travaux se penchent sur ces problèmes et tentent de leur apporter des solutions. En particulier, [SPACE (2005)] propose une plateforme de codesign en SystemC [SystemC (2005)] qui, d'une part, facilite l'exploration architecturale en permettant le passage des modules en logiciel ou en matériel à partir d'un codage unique et, d'autre part, offre une approche par raffinement progressif avec un raffinement automatique des communications.

Ces travaux visent à faciliter ou accélérer la conception des SoC. Pour la plupart des méthodologies de conception, une partie des étapes est indépendante du type de puce et de la technologie de fabrication visés. En revanche, les dernières étapes en dépendent systématiquement. Nous allons maintenant regarder les différents types de puces que les fonderies sont aujourd'hui capables de produire.

### 1.3 Les types de puces

Aujourd'hui, il y a trois grandes classes de puces destinées à la production des SoC : les circuits intégrés spécifiques à une application (en anglais ASIC pour Application-Specific Integrated Circuit), les ASIC structurés et les puces à architecture programmable. Aucune d'entre elles n'est absolument meilleure que les autres, et le choix de l'une sur l'autre doit se faire en fonction du projet entrepris.

---

<sup>1</sup>Ou tout au moins relativement optimal, puisque pour garantir un choix optimal, il faudrait tester toutes les architectures possibles, et comme le nombre d'architectures augmente exponentiellement avec le nombre de blocs fonctionnels, en pratique, on ne testera jamais tous les cas.

Il faut alors considérer plusieurs critères :

- performance : par exemple la latence maximum ou bien la fréquence d'horloge ou le débit minimum qu'il faut achever ;

- consommation : la puissance consommée ;

- temps d'accès au marché vs. temps de conception et production : le temps dont on dispose pour mener le project à terme par rapport au temps lié d'une part à la conception de la puce et d'autre part à sa fabrication ;

- coût unitaire : le coût de chaque puce ;

- quantité : le nombre de puces ;

- coûts d'ingénierie non récurrents (en anglais NRE costs pour Non Recurring Engineering costs) : somme d'argent chargée par le fondeur pour chaque nouveau design de puce, notamment pour les coûts des masques.

Chaque type de puce offre un certain compromis entre ces différents critères. Nous allons maintenant étudier chaque catégorie de puces un peu plus en détails.

### 1.3.1 ASIC

De nos jours, les fondeurs proposent des ASIC qui, dépendamment de la technologie, possèdent typiquement une ou deux couches de poly (de l'anglais polycrystalline silicon) et de quatre à dix couches métalliques (aluminium ou, de plus en plus, cuivre). Même si on se concentre dans le présent mémoire sur l'électronique numérique, on notera qu'il est possible de fabriquer des circuits ASIC mixtes combinant des blocs analogiques et des blocs numériques.

### 1.3.1.1 ASIC sur mesure

Ces puces (en anglais full custom ASIC) sont la version la plus personnalisée des ASIC. Chaque élément est dessiné sur mesure et toutes les couches sont gravées sur mesure.

Avantages : performance, consommation, prix unitaire (surface de silicium utile réduite).

Inconvénients : coûts non récurrents très élevés, temps de conception et de fabrication très longs.

Les ASIC sur mesure sont principalement utilisés pour des designs nécessitant le maximum de performance, comme un processeur ou une mémoire. En revanche, lorsqu'il s'agit de SoC, on n'emploiera jamais d'ASIC totalement sur mesure mais, à la limite, un ASIC partiellement sur mesure et partiellement précaractérisé.

### 1.3.1.2 ASIC précaractérisés

Pour ces puces (en anglais standard cell ASIC ou cell-based ASIC), les circuits doivent cette fois être conçus à partir de cellules élémentaires fournies par le fondeur (sous forme d'une bibliothèque) mais, là encore, toutes les couches sont gravées en fonction du circuit désiré.

Avantages et inconvénients : ce sont les mêmes que pour les ASIC sur mesure, à part qu'ils sont moins prononcés (dans un sens comme dans l'autre).

Les ASIC précaractérisés seront typiquement le choix de prédilection lorsqu'on veut produire un SoC en très grande quantité et qu'on dispose de temps (grand temps d'accès au marché).

Nous omettons ici volontairement les ASIC prédiffusés (en anglais gate array ASIC) car ils perdent énormément en popularité et tendent à être remplacés par les ASIC structurés.

### 1.3.2 ASIC structurés

Le but des ASIC structurés (en anglais structured ASIC ou platform ASIC) est de proposer une puce ayant des performances de l'ordre de celles des ASIC précaractérisés, tout en réduisant substantiellement le temps de conception. Pour cela, les fondeurs préfabriquent des puces contenant plusieurs tranches de silicium dites plateformes. Ces tranches plateformes intègrent divers modules, afin de pouvoir adresser une grande variété d'applications. Puis, à travers la personnalisation de juste quelques couches métalliques, il est possible de configurer et d'interconnecter les tranches afin d'obtenir une puce ayant les fonctionnalités voulues [Lipman (2004)] [Khalilollahi (2004)]. Afin de permettre aux concepteurs de puces de tirer profit des ASIC structurés, les fondeurs fournissent en fait non seulement les puces, mais aussi une méthodologie et un ensemble d'outils associés.

Par rapport aux ASIC précaractérisés, les ASIC structurés ont comme avantage de réduire grandement à la fois le temps et les coûts liés à la conception et à la fabrication de la puce. En revanche, ils présentent une bien moins bonne densité d'intégration, et ont donc un prix unitaire plus élevé. Alors que performance et densité d'intégration atteindraient un très honnête 80% de ces mêmes caractéristiques pour des ASIC précaractérisés, les coûts seraient quant à eux diminués de 80% [Zakharia (2003)].

Les ASIC structurés seront donc typiquement choisis lorsqu'on veut produire des SoC en quantité moyenne ou quand on veut produire de grosses quantités mais qu'on n'a pas le temps de développer un ASIC précaractérisé.

### 1.3.3 Puces à architecture programmable

Ces circuits, également appelés circuits à réseaux logiques programmables, sont des circuits dont l'architecture logique interne peut être programmée, voire reprogrammée, après leur fabrication chez le fondeur. Ils permettent de réaliser n'importe quelle fonction logique en reliant, par des connexions programmables, des blocs programmables eux aussi contenant des fonctions logiques élémentaires.

On trouve aujourd'hui deux principales familles de circuits logiques programmables : les CPLD (Complex Programmable Logic Device) et les FPGA (Field Programmable Gate Array). Indépendamment de leur appartenance à l'une de ces deux familles, les puces à architecture programmable présentent les mêmes avantages et inconvénients.

Avantages : coûts de conception et surtout<sup>1</sup> de fabrication peu élevés ; temps d'accès au marché court.

Inconvénients : prix unitaire élevé dû à une faible densité d'intégration ; performance très inférieure à celle des ASIC ; consommation plus importante.

Une caractéristique intéressante des puces à architecture programmable est la capacité de reprogrammation. En effet, dépendamment de la technologie employée, ces puces pourront être programmées une seule fois ou bien plusieurs fois.

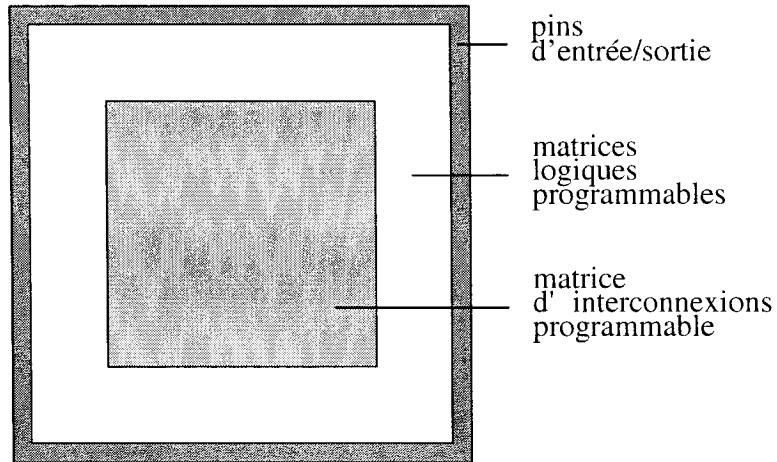

#### 1.3.3.1 CPLD

Les CPLD combinent plusieurs matrices logiques programmables ou PLA (de l'anglais Programmable Logic Array) en périphérie de la puce avec une matrice d'in-

---

<sup>1</sup>Surtout de fabrication, car il n'y a pas de coûts d'ingénierie non récurrents, la spécificité des puces n'étant pas ici dans ce qui est gravé dans silicium, mais dans la façon dont les éléments programmables vont être utilisés dans chaque puce.

Figure 1.3 Structure d'un CPLD

terconnexions programmable au centre.

Chaque PLA est une matrice logique à réseaux ET et OU programmables, capable de réaliser n'importe quelle fonction logique sous forme de somme de produits. Les blocs peuvent ensuite être reliés entre eux à travers la matrice d'interconnexions. Grâce à cette organisation, les délais de propagation entre les blocs à travers la matrice d'interconnexions sont fixes, et connus avant les étapes de placement et routage. En conséquence, ces phases du cycle de conception sont faciles et donc peu gourmandes en temps.

La grande majorité des CPLD sont reprogrammables.

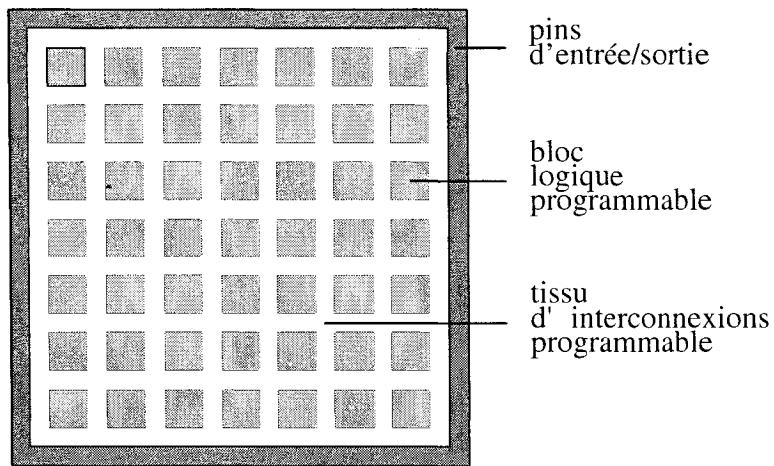

### 1.3.3.2 FPGA

Plutôt que de définir des zones bien séparées de logique programmable et d'autres d'interconnexions programmables, on trouve dans un FPGA de nombreux blocs logiques programmables simples éparpillés dans un tissu d'interconnexions programmable.

Figure 1.4 Structure d'un FPGA

Avec ce type d'organisation, on gagne beaucoup en densité d'intégration sur les CPLD et on peut tirer meilleur profit des ressources disponibles. En revanche, les phases de placement et routage sont gourmandes en temps, surtout si on souhaite exploiter les possibilités de la puce au maximum, et les délais dus aux interconnexions ne peuvent être connus qu'après ces étapes.

Du point de vue de la reprogrammabilité, on trouve des deux cas dans les FPGA. D'un côté, par exemple, les FPGA utilisant la technologie anti-fusible au niveau des interconnexions ne sont programmables qu'une seule fois, mais c'est cette technologie qui offre la meilleure densité d'intégration et les meilleures performances. D'un autre côté, les FPGA utilisant la technologie SRAM pour les interconnexions sont reprogrammables. Cette technologie facilite en outre l'intégration de mémoire RAM dans le circuit, i.e. directement sur la puce [Rabasté (2002)] [FPGA-FAQ (2005)].

Typiquement, les FPGA seront utilisés pour les projets ayant d'importantes contraintes de temps (temps d'accès au marché petit) et/ou nécessitant la production d'un petit nombre de puces.

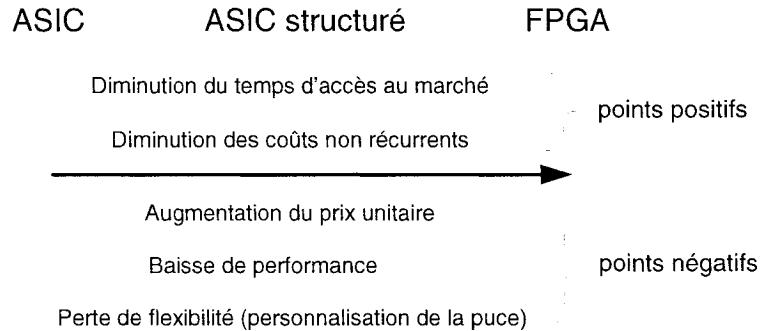

Figure 1.5 Récapitulatif des caractéristiques des types de puces

#### 1.3.4 Récapitulatif

Pour conclure sur les différents types de puces, la figure 1.5 présente un récapitulatif de leurs avantages et inconvénients. Plus exactement, elle montre les tendances observées lorsqu'on va des ASIC vers les FPGA en passant par les ASIC structurés. Si on réfléchit dans le sens opposé, migrer d'un FPGA vers un ASIC permet un gain de performance et une diminution du coût unitaire des puces au prix d'importants temps et coûts de conception et d'ingénierie non récurrents.

Il est difficile de comparer numériquement les ASIC et les FPGA en termes de performances, notamment parce que les métriques utilisées diffèrent d'une catégorie à l'autre et d'un vendeur à l'autre. Si l'on souhaite malgré tout se risquer à donner des chiffres : fin 2005, pour une technologie 90 nm, la fréquence de l'horloge dans un design FPGA atteint 500 MHz alors qu'elle peut aisément dépasser 1 Gz dans un design ASIC ; le nombre de portes pour un ASIC peut atteindre 100 millions alors que les plus gros FPGA proposent l'équivalent d'un peu plus de 2 millions de portes ASIC ; enfin, pour effectuer la même fonction logique, la puissance consommée est 5 à 10 fois supérieure pour un FPGA que pour un ASIC.

On notera que sur le marché hyperdynamique d'aujourd'hui, celui de l'électronique grand public, les critères de choix les plus importants sont un temps d'accès au

marché petit et un prix unitaire faible. Or ces deux données suivent des évolutions opposées. Il n'est donc pas rare pour les concepteurs de réaliser leur circuit d'abord sur des FPGA ou des ASIC structurés avant de migrer leur design vers des ASIC. Ceci permet en effet de pénétrer un nouveau marché plus rapidement et, si le produit marche, de baisser les coûts de production pour les générations suivantes.

#### 1.4 La montée en puissances des FPGA

Si les progrès de la microélectronique ont pour effet d'améliorer les performances de tous les types de puces, c'est dans le domaine des FPGA que l'on voit actuellement le plus de progrès. En conséquence, le niveau de performance des FPGA se rapproche de plus en plus de celui des ASIC. L'écart au niveau de la densité d'intégration se réduit lui aussi de plus en plus. Ceci a pour effet de réduire les coûts unitaires qui, comme nous l'avons vu précédemment, représentent le principal désavantage des FPGA. Les constructeurs de solutions reprogrammables annoncent même depuis quelque temps des solutions FPGA moins chères que les ASIC structurés [Krishnan et Thirumalai (2004)].

Par ailleurs, bien qu'il existe des différences entre les ASIC et les FPGA, ces derniers bénéficient de plus en plus des outils et méthodologies initialement développés et utilisés pour les ASIC, comme la synthèse physique [Southard (2004)]. Déjà en 2003, 53% des concepteurs de SoC n'utilisaient que des FPGA, alors que seulement 13% n'en utilisaient pas du tout [Celoxica (2003)]. Aujourd'hui, tout le monde semble être d'accord pour dire que l'utilisation des FPGA continue d'augmenter.

Avec d'un côté une forte amélioration de leurs points faibles (i.e. des performances et des coûts unitaires se rapprochant de ceux des ASIC) et un nombre croissant d'outils et méthodologies utilisables, et avec d'un autre côté une consolidation de leurs avantages évoqués plus tôt, les FPGA apparaissent comme la solution

gagnante du moment pour la conception de systèmes sur puce. Au cours des dix dernières années, les progrès qu'ils ont connus ont dépassé les prévisions de la loi de Moore, et la compétition est très féroce [Morris (2005)].

Une autre raison du succès croissant des FPGA est l'apparition récente d'un nouveau produit : le FPGA plateforme.

## 1.5 FPGA plateformes

Les FPGA plateformes sont des FPGA sur lesquels, en plus des blocs logiques programmables et du réseau d'interconnexions programmable, ont été ajoutées en dur (de l'anglais hard core) des propriétés intellectuelles (en anglais IP pour Intellectual Property), comme par exemple un microprocesseur. Ces modules existant en dur ne font pas partie de l'architecture programmable, et il n'est donc pas possible de les remplacer par autre chose. En revanche, ils ne consomment aucun bloc logique, et ils sont plus petits (en termes de surface occupée) et plus performants que le seraient leurs équivalents en logique programmable.

Afin que les concepteurs puissent tirer profit au maximum de ces puces, leurs fabricants offrent des outils et méthodologies associés, incluant une bibliothèque d'IP. Ces outils permettent d'adopter une approche plateforme, et les concepteurs peuvent ainsi, à partir d'un système standard réalisé à partir des IP fournies, venir greffer leurs modules personnalisés.

Comme il s'agit de produits encore récents, il n'y a pas encore de véritable consensus au niveau de la terminologie les concernant. Dans ce mémoire, les puces seront toujours appelées FPGA plateformes (platform FPGA en anglais). Pour désigner les systèmes qu'elles contiendront, nous préférerons en revanche parler de systèmes sur puce programmable (de l'anglais SOPC pour System On Programmable Chip).

Nous allons maintenant passer en revue les fabricants de FPGA plateformes, et présenter leurs offres (puces et suite d'outils) respectives.

### 1.5.1 Triscend

Triscend, Corp. fut la première compagnie, en août 2000, à lancer un FPGA plateforme, le A7, qui incorpore le très populaire microprocesseur ARM7TDMI de la compagnie ARM Ltd [ARM (2005)]. Depuis, Triscend a été rachetée (en mars 2004) par Xilinx, Inc. [Xilinx (2005)] et a cessé de produire ses puces et de fournir son outil, FastChip. Nous n'en parlerons donc pas davantage.

### 1.5.2 Altera

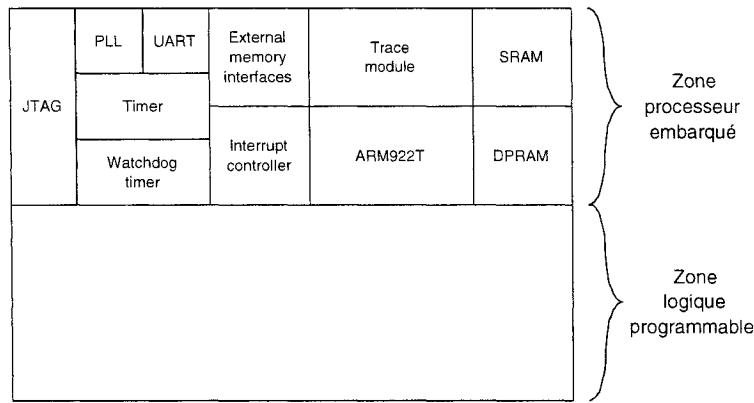

La compagnie Altera [Altera (2005)] a lancé son FPGA plateforme, nommé Excalibur, en octobre 2001. Du côté logique programmable, l'Excalibur repose sur les FPGA Altera APEX 20KE. Du côté IP en dur, Altera a choisi d'intégrer un système complet fonctionnel sur la puce. Les figure 1.6 montrent l'architecture des puces Excalibur, où l'on voit clairement apparaître les deux zones de la puce : la zone processeur embarqué (embedded processor stripe dans la terminologie Altera) et la zone logique programmable.

On trouve donc à l'intérieur de la puce, en dur : un bloc processeur ARM922T, de la mémoire SRAM, des minuteries, un contrôleur d'interruptions, un émetteur-récepteur asynchrone universel (en anglais UART pour Universal Asynchronous Receiver-Transmitter) et une boucle à vérouillage de phase. Ces éléments, qui forment le cœur de la zone processeur embarqué, sont interconnectés grâce à deux instances du bus sur puce ARM AHB. La puce intègre également un contrôleur de mémoire SDRAM externe et un bus EIB (Extension Bus Interface) permettant de

Figure 1.6 Architecture de l'Excalibur

connecter au système des éléments externes tels qu'une mémoire flash.

Il est intéressant de noter que le système contenu dans la zone processeur embarqué est capable de fonctionner indépendamment de ce qu'on décide de mettre en logique programmable, ce qui présente évidemment des avantages et des inconvénients, sur lesquels nous reviendront plus tard.

Une autre particularité de la puce Altera vient de sa partie logique programmable, qui incorpore, à l'instar des APEX 20KE, des ESB (Embedded System Block) permettant d'implémenter différents types de blocs mémoires, comme par exemple des files (FIFO).

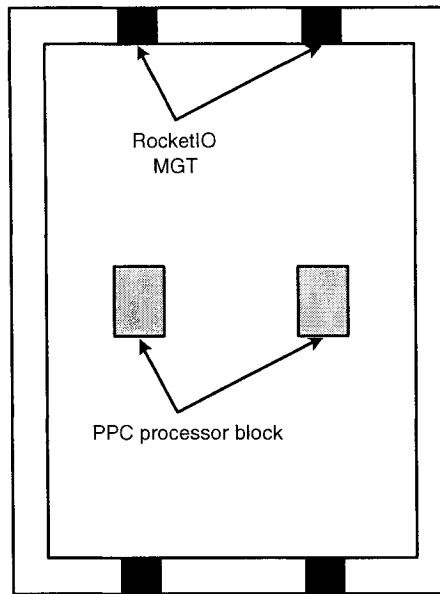

### 1.5.3 Xilinx

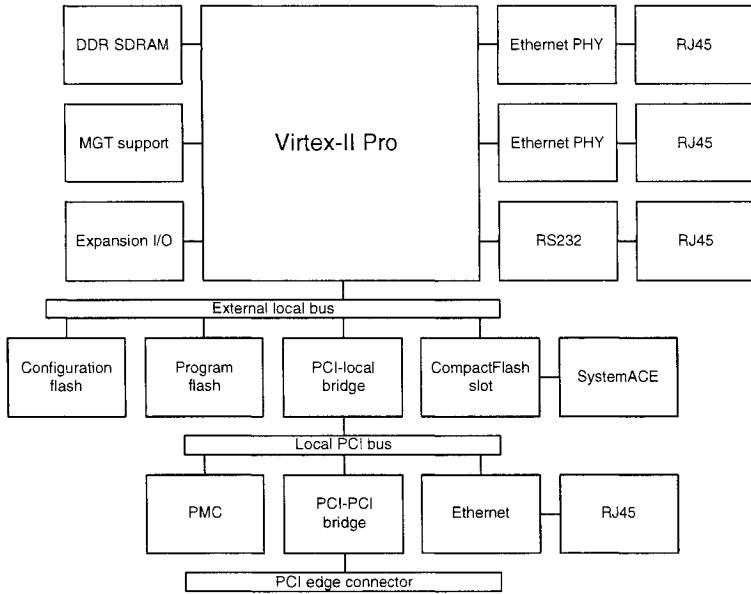

La compagnie Xilinx est arrivée la dernière sur le marché des FPGA plateformes quand elle a sorti le Virtex-II Pro, en mars 2002. Ces puces reposent sur le Virtex-II pour ce qui est de la logique programmable et, du côté des IP en dur, elles intègrent un ou deux microprocesseurs PowerPC 405 de IBM Corp. [IBM (2005)] et un nombre variable d'émetteurs-récepteurs multigigabit (en anglais MGT pour Multi-Gigabit Transceiver). La figure 1.7 illustre l'architecture du Xilinx Virtex-II

Figure 1.7 Architecture du Virtex-II Pro

Pro.

L'approche de Xilinx est radicalement différente de celle d'Altera. En effet, si le concepteur ne crée pas de système, le Virtex-II Pro n'est pas capable de faire quoi que ce soit. Autrement dit, le concepteur a la liberté d'utiliser à sa guise ce que la puce met à sa disposition.

Tout comme le Virtex-II, le Virtex-II Pro intègre également des multiplicateurs 18 bits par 18 bits, qui sont très utiles pour des applications telles que le traitement de signal.

#### 1.5.4 Comparaison

Avant de tenter une comparaison entre les produits d'Altera et de Xilinx, il est important de préciser que la guerre que se mènent les deux compagnies est très féroce, et qu'à travers la quantité d'informations plus ou moins pertinentes et

à cause de la façon dont les constructeurs les manipulent, il est difficile de s'y retrouver. En particulier, comme le mentionne [Morris (2005)], la bataille sur le nombre de portes est une bataille perdue d'avance...pour le client potentiel en quête de vérité. Nous nous contenterons donc ici de comparer ce qui est réellement comparable.

Premièrement, et de façon évidente, la principale distinction entre l'Excalibur d'Altera et le Virtex-II Pro de Xilinx se fait au niveau des approches diamétralement opposées que les compagnies ont retenues. D'un côté, Altera a décidé de prendre son APEX 20KE et de lui accoler un système complet, pouvant potentiellement fonctionner de manière totalement indépendante du reste de la puce, et non modifiable. D'un autre côté, Xilinx a préféré modifier son Virtex-II pour y éparpiller quelques modules supplémentaires, complètement dépendants de ce qui est programmé sur le reste de la puce.

Avec Xilinx, on a donc une plateforme entièrement personnalisable. Le concepteur pourra par exemple décider de n'utiliser qu'un PowerPC, ou de relier les modules de son système à l'aide d'un réseau sur puce au lieu d'utiliser les IP du bus sur puce IBM CoreConnect fournis avec la suite d'outils. Ceci signifie aussi qu'il faudra passer du temps à créer une plateforme de base avant de pouvoir utiliser la puce. Néanmoins, le Virtex-II Pro est une meilleure solution que l'Excalibur si l'on souhaite par exemple tester différents moyens d'interconnexions.

En revanche, avec Altera, on dispose directement d'une puce contenant un système fonctionnel et utilisable, mais aussi beaucoup moins personnalisable, ce qui en soit présente assez peu d'avantages. Ce qui est beaucoup plus intéressant, c'est que ceci permet de reconfigurer complètement la logique programmable en cours d'utilisation, puisque le système dur ne sera pas affecté du tout par cette reprogrammation. En comparaison, le Virtex-II Pro n'est capable que de reconfiguration

partielle. Pour des travaux comme par exemple le partitionnement logiciel/matériel dynamique [Stitt *et al.* (2003)] nécessitant la reconfiguration de la logique programmable en cours d'exécution, l'Excalibur apparaît donc comme la solution la plus avantageuse.

Deuxièmement, il y a une différence importante au niveau des microprocesseurs embarqués. Sur la puce Altera, il s'agit d'un ARM922T, au cœur duquel on trouve un noyau de microprocesseur à usage général ARM9TDMI, à architecture Harvard 32 bits, et possédant un pipeline à 5 étages. Il contient également deux mémoires caches (instructions et données) et une unité de gestion de mémoire (en anglais MMU pour Memory Management Unit), et est cadencé à 200 MHz.

Du côté Xilinx, on trouve un (ou plusieurs) IBM PowerPC 405D5, reprenant les caractéristiques du ARM922T (architecture Harvard 32 bits, pipeline 5 étages, deux caches, MMU), capable d'atteindre une fréquence d'horloge de 400 MHz, et offrant quelques suppléments tels qu'un moltiplicateur matériel. Il est d'une manière générale plus performant que son concurrent.

Troisièmement, ces puces diffèrent de part le type et la quantité de mémoire qu'elles intègrent. Dans l'Excalibur, on a de la SRAM réservée à la zone processeur, de la SRAM à double port partagée entre la zone processeur embarqué et la logique programmable, et des blocs de mémoire (les ESB) dans la zone logique programmable. Les ESB peuvent au choix être utilisés comme RAM, DPRAM, ROM ou CAM.

Dans le Virtex-II Pro, on a seulement des blocs de mémoire (Block SelectRAM+) distribués à travers le réseau de logique programmable et pouvant être utilisés comme RAM ou comme DPRAM. Au final, aucune des solutions n'est vraiment meilleure que l'autre, l'absence de flexibilité au niveau des SRAM que contient l'Excalibur étant contrebalancée par la grande flexibilité de ses ESB.

Tableau 1.1 Comparaison des puces Altera et Xilinx

| Altera Excalibur EPXA10<br>(APEX 20KE)                                                                          | Xilinx Virtex-II Pro XC2VP100<br>(Virtex-II)                                                                                        |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Zone processeur embarqué contenant un sous-système complet fonctionnel                                          |                                                                                                                                     |

| 1 ARM922T<br><br>ARM AMBA                                                                                       | 2 IBM PowerPC 405D5<br>– multiplicateur matériel<br>IBM CoreConnect                                                                 |

| 1 bloc 256 ko SRAM<br>2 blocs 64 ko DPSRAM<br>160 blocs ESB, 2 kb par bloc<br>Total : environ 700 ko de mémoire | 444 blocs Block SelectRAM+,<br>18 kb par bloc<br><br>Total : environ 1 Mo de mémoire<br><br>444 multiplicateurs 18 bits par 18 bits |

Quatrièmement, le Virtex-II Pro propose quelques blocs fonctionnels supplémentaires. Cette puce sera donc avantageuse pour certaines classes d'applications telles que le traitement de signal (multiplicateurs 18 bits par 18 bits) ou les réseaux (MGT).

Le tableau 1.1 résume les différences existant entre les puces Altera et Xilinx. Les caractéristiques quantitative citées ici sont celles du modèle le plus performant de chaque constructeur [Altera (2005)] [Xilinx (2005)].

On notera qu'on a pour l'instant comparé les deux solutions uniquement sur les différences matérielles au niveau des puces. D'autres éléments font pourtant partie intégrante de la solution globale, comme c'est notamment le cas pour la bibliothèque d'IP fournie. Les bibliothèques d'IP sont à peu près équivalentes pour les deux constructeurs, mais une différence émerge pourtant, au niveau des processeurs logiciels (en anglais soft processor) développés par chacune des compagnies : le NIOS-II d'Altera qui se connecte sur un bus Altera Avalon, et le MicroBlaze de Xilinx qui se connecte sur un bus IBM CoreConnect OPB.

Les outils de conception sont également importants. Ils font l'objet de la partie

suivante.

## 1.6 Outils

### 1.6.1 Xilinx

En plus de son environnement classique de développement sur FPGA ISE (Integrated Software Environment), Xilinx propose EDK (Embedded Development Kit), une suite d'outils de développement plus adaptée aux FPGA plateformes. EDK propose principalement une grande bibliothèque d'IP et XPS (Xilinx Platform Studio), un outil assez complet permettant de concevoir le système, que ce soit la partie matérielle ou la partie logicielle.

Dans XPS, on construit le système en utilisant le principe du glisser-déposer à partir des blocs IP fournis ou créés par l'utilisateur. On peut alors configurer certaines propriétés des blocs insérés et choisir comment les relier entre eux. Les versions récentes proposent plusieurs assistants, permettant par exemple de créer un système de base, de générer une carte d'adressage mémoire ou un script de compilation, ou encore d'importer des IP créées avec ISE. L'outil permet ensuite de synthétiser le code et de le charger dans un FPGA.

### 1.6.2 Altera

L'environnement de développement Altera, Quartus-II, permet également de concevoir les parties logicielle et matérielle du système embarqué. En outre, l'outil Altera permet, dans une seule et unique vue hiérarchique, et ce sans avoir à passer par un quelconque autre outil, de mélanger des IP complexes provenant des bibliothèques d'IP avec de simples portes logiques, et d'entrer directement des blocs de code

HDL (Hardware Description Language). Cette possibilité de mélanger des blocs à différents niveaux est très pratique et impossible avec les outils Xilinx.

De façon à faciliter et accélérer la création de systèmes, Quartus-II intègre SOPC Builder, un outil permettant de générer automatiquement et facilement des systèmes complets, simples ou complexes, et de configurer les blocs IP du système. SOPC Builder permet également de créer des versions personnalisées du processeur logiciel NIOS-II d'Altera.

### 1.6.3 Récapitulatif