**Titre:** Conception d'un convertisseur analogique à numérique 10 bits /

Title: 200 MÉ/s pipeliné et calibré numériquement

**Auteur:** Dominic Morin

Author:

**Date:** 2005

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Morin, D. (2005). Conception d'un convertisseur analogique à numérique 10 bits /

200 MÉ/s pipeliné et calibré numériquement [Mémoire de maîtrise, École

Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7650/>

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7650/>

PolyPublie URL:

**Directeurs de recherche:** Yvon Savaria, & Mohamad Sawan

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

CONCEPTION D'UN CONVERTISSEUR ANALOGIQUE À

NUMÉRIQUE 10 BITS / 200 MÉ/S PIPELINÉ ET CALIBRÉ

NUMÉRIQUEMENT

DOMINIC MORIN

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

NOVEMBRE 2005

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-16820-2

*Our file* *Notre référence*

ISBN: 978-0-494-16820-2

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

**Canada**

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé :

CONCEPTION D'UN CONVERTISSEUR ANALOGIQUE À

NUMÉRIQUE 10 BITS / 200 MÉ/S PIPELINÉ ET CALIBRÉ

NUMÉRIQUEMENT

Présenté par : MORIN, Dominic

En vue de l'obtention du diplôme de : Maîtrise ès sciences appliquées

A été dûment accepté par le jury d'examen constitué de :

M. KHOUAS Abdelhakim, Ph.D., président

M. SAVARIA Yvon, Ph.D., membre et directeur

M. SAWAM Mohamad, Ph.D., membre et co-directeur

M. AUDET Yves, Ph.D., membre

## REMERCIEMENTS

J'aimerais avant toute chose remercier mon directeur de recherche, Yvon Savaria, pour m'avoir accepté au sein du groupe de recherche en microélectronique. Il m'a guidé tout au long de mes études supérieures, non seulement pour mes recherches, mais aussi dans l'optique de ma carrière professionnelle. En plus de s'être investi dans ce projet, il m'a trouvé un support financier et m'a donné la chance de participer à la formation d'autres étudiants. Je remercie également mon codirecteur de recherche, Mohamad Sawan, ses suggestions et l'aide apportées par lui et ses étudiants ont contribué grandement à la complétion de ce projet.

Ce travail a été supporté financièrement et rendu possible par Gennum Corp. par l'entremise du programme de support financier de Micronet R&D.

Merci à mes collègues, pour leur aide, support et encouragement qu'ils m'ont apportés. Plus particulièrement à Manuel Robert, Tien Bui, Frédéric Normandin, Marie-Ève Grandmaison, Hung Dang, Bruno Tanguay, Ghislain Provost, Kamal El-Sankary, Robert Chebli et Maria Mbaye. Merci également à Alexander Vesey, Ghyslaine E-Carrier, Réjean Lepage, et Martin Paré pour leur support.

Je désire apporter des remerciements spéciaux à mes parents, Florent et Huguette, et à mes frères, Frédéric et Martin qui tout au long de mes études m'ont encouragé et supporté dans des moments souvent difficiles. Merci à tous mes amis pour leur contribution et appui.

## RESUMÉ

Les convertisseurs analogique à numérique (CAN) permettent de convertir des signaux du domaine analogique au domaine numérique. Le traitement des signaux est beaucoup plus simple dans le domaine numérique que dans le domaine analogique. Même si le domaine de recherche liée aux CAN est très actif, les architectures standards de convertisseurs atteignent difficilement les spécifications de certaines applications modernes. C'est le cas de la télévision haute définition qui requiert une bonne linéarité et une fréquence d'opération élevée. Pour cette application, l'utilisation d'une architecture pipelinée et parallèle semble être le choix le plus judicieux. Avec cette configuration, il est plutôt facile d'atteindre la cadence de conversion nécessaire, mais à cette vitesse, la linéarité de la fonction de transfert est souvent inadéquate. Ce problème est lié aux non-idealités des circuits analogiques. C'est pourquoi, il est nécessaire d'améliorer les techniques actuelles.

La technique utilisée pour améliorer la linéarité des CAN dans ce projet est la calibration numérique. Par des traitements numériques, le dispositif permettra de compenser les non-idealités des circuits analogiques telles que le mauvais mariage des composants, les gains finis et les distorsions provoquées par la nature analogique des éléments. L'utilisation de cette technique permettra aussi de réduire considérablement la complexité des circuits analogiques. Par cette méthode, il est possible d'obtenir un gain en vitesse, car les non-idealités d'un circuit analogique simple peuvent être compensées

dans le domaine numérique. En effet, un circuit analogique simple et imprécis est beaucoup plus rapide qu'un circuit complexe et précis.

Quoique simple, la technique de calibration numérique utilisée reste néanmoins difficilement applicable pour un convertisseur pipeliné standard. En effet, il est nécessaire d'identifier quels critères doivent être respectés pour que cette technique soit complètement fonctionnelle sur toute la plage de fonctionnement du convertisseur. Afin, de maximiser les résultats du prototype, un modèle mathématique des CAN pipelinés a été utilisé pour déterminer les limitations de la calibration numérique. Aussi un simulateur utilisant une procédure de type Monte-Carlo a été conçu pour valider le concept dans les plages de variation des paramètres pour la technologie utilisée.

Un prototype a été conçu, afin de vérifier le concept de calibration numérique proposé. Les simulations après dessin de masques, montrent que le prototype atteint 200 Méchantillons/s à une précision de 9.8 bits effectifs et ce en utilisant les paramètres qui correspondent aux coins de l'espace des paramètres de la technologie CMOS  $0.18\mu\text{m}$ .

## ABSTRACT

Analog to digital converters (ADC) convert signals from the analog world to digital signals. Processing of the converted signals is much simpler in the digital domain than in the analog domain. Even if the research field related to the ADC is very active, standard converter architectures have difficulties to reach the needed specifications of modern applications. It is the case of high definition televisions which require good linearity and high operating frequency. For this application, the use of pipelined and parallel architectures seems to be the most judicious choice. With this configuration, it is easy to reach the necessary conversion rate, but at this speed, the linearity of the transfer function is inadequate. This problem is related to the non-idealities of analog circuits. So, it is essential to improve the current techniques.

The technique used to improve the linearity of ADCs explored in this project is digital calibration. By digital post-processing, the device can be compensated for the non-idealities of the analog circuit such as components mismatch, finite gain and distortions caused by the analog nature of electronic components. This technique reduces considerably the complexity of the analog circuits. Using this technique, it is possible to enhance the operating frequency, because the non-idealities of a simple analog circuit can be compensated in the digital domain. Indeed, a simple and imprecise analog circuit is much faster than a complex and precise circuit.

Though simple in principle, digital calibration is not easily applicable to standard pipelined converters. In fact, criteria must be respected so that this technique is

completely functional over the operating range of the converter. Thus, to help optimize performances of a prototype, a mathematical model of the pipelined ADC was created and used to determine the limitations of digital calibration. Also a simulator using a Monte-Carlo procedure was developed to validate the proposed concept with respect to expected variations of technology parameters.

A prototype was designed, in order to validate the proposed digital calibration method. Post-layout simulations show that the prototype can operate at 200 MS/s with an accuracy of 9.8 effective bits by using corners parameters of the CMOS 0.18 $\mu$ m technology.

## TABLE DES MATIÈRES

|                                                       |       |

|-------------------------------------------------------|-------|

| REMERCIEMENTS .....                                   | iv    |

| RESUMÉ .....                                          | v     |

| ABSTRACT .....                                        | vii   |

| TABLE DES MATIÈRES .....                              | ix    |

| LISTE DES FIGURES.....                                | xiii  |

| LISTE DES TABLEAUX.....                               | xviii |

| LISTE DES ABBRÉVIATIONS .....                         | xix   |

| LISTE DES ANNEXES.....                                | xx    |

| 1. CHAPITRE I : INTRODUCTION .....                    | 1     |

| 2. CHAPITRE II : REVUE DE LITTÉRATURE .....           | 4     |

| 2.1. Convertisseurs analogique à numérique .....      | 4     |

| 2.2. Spécifications .....                             | 6     |

| 2.2.1. Spécifications statiques : .....               | 6     |

| 2.2.2. Spécifications dynamiques : .....              | 9     |

| 2.3. Architecture.....                                | 10    |

| 2.3.1. Convertisseur à approximation successive ..... | 10    |

| 2.3.2. Convertisseur à intégration .....              | 11    |

|                                                  |    |

|--------------------------------------------------|----|

| 2.3.3. Convertisseur Sigma Delta.....            | 15 |

| 2.3.4. Convertisseur Flash.....                  | 16 |

| 2.3.5. Convertisseurs Flash pliés.....           | 17 |

| 2.3.6. Convertisseurs à plusieurs étapes.....    | 19 |

| 2.3.7. Convertisseurs en pipeline .....          | 20 |

| 2.3.8. Convertisseurs parallèles .....           | 21 |

| 2.4.    Perfectionnements.....                   | 23 |

| 2.4.1. Correction numérique des erreurs .....    | 23 |

| 2.4.2. Calibration externe.....                  | 27 |

| 2.4.3. Auto-calibration .....                    | 27 |

| 2.5.    Choix d'une architecture.....            | 37 |

| 3.    CHAPITRE III : MODÈLE ET CALIBRATION ..... | 40 |

| 3.1.    Modèle des convertisseurs pipelinés..... | 40 |

| 3.2.    Calibration.....                         | 43 |

| 3.2.1. Architecture.....                         | 44 |

| 3.2.2. Simulation.....                           | 46 |

| 4.    CHAPITRE IV : PROTOTYPE.....               | 51 |

| 4.1.    Règles de conception .....               | 51 |

|        |                                                   |    |

|--------|---------------------------------------------------|----|

| 4.2.   | Spécifications et hypothèses .....                | 53 |

| 4.2.1. | Convertisseur .....                               | 53 |

| 4.2.2. | Étages pipelinés et échantillonneur bloqueur..... | 54 |

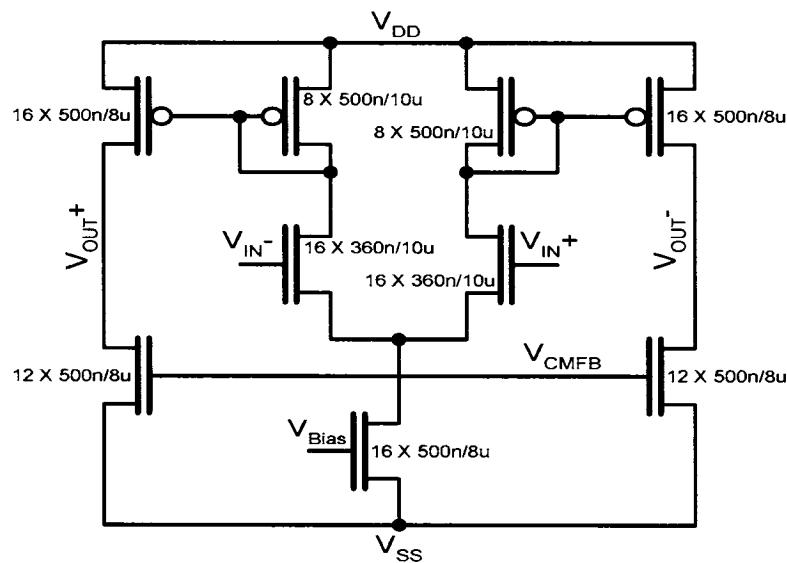

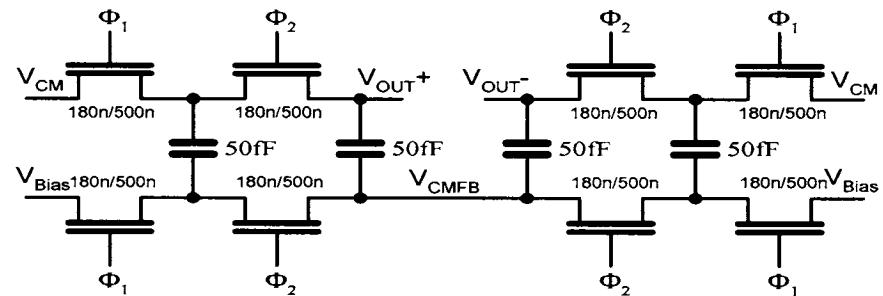

| 4.2.3. | Amplificateur opérationnel .....                  | 59 |

| 4.2.4. | Comparateur.....                                  | 60 |

| 4.3.   | Conception .....                                  | 60 |

| 4.3.1. | Amplificateur opérationnel .....                  | 61 |

| 4.3.2. | Comparateur.....                                  | 66 |

| 4.3.3. | Étages pipelinés et échantillonneur bloqueur..... | 69 |

| 4.3.4. | Réseaux de commutation .....                      | 72 |

| 4.3.5. | Générateur d'horloges.....                        | 74 |

| 4.4.   | Intégration .....                                 | 77 |

| 4.4.1. | Étages pipelinés et échantillonneur bloqueur..... | 77 |

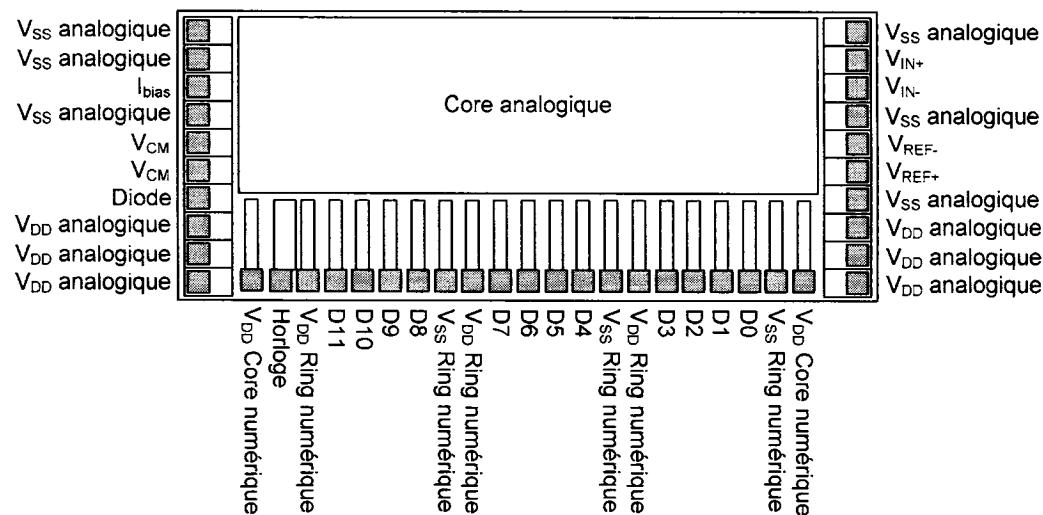

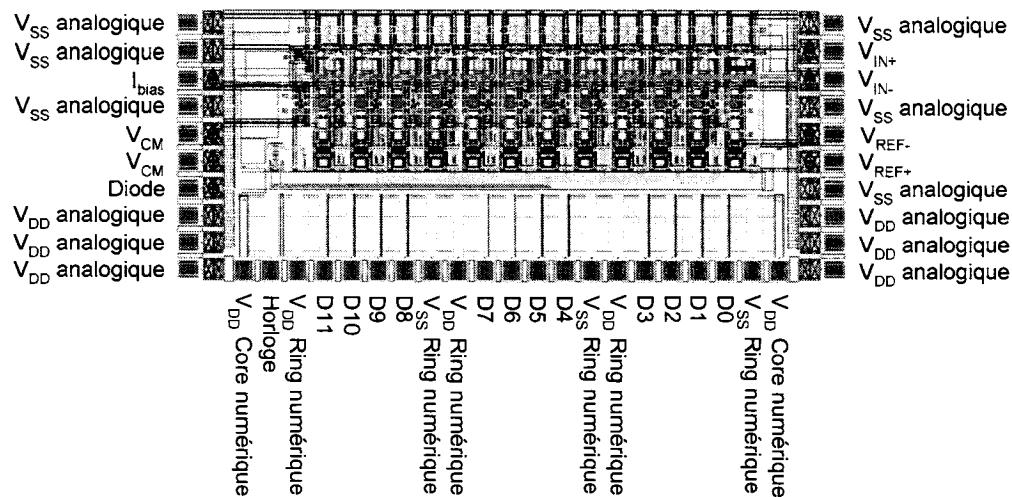

| 4.4.2. | Noyau .....                                       | 83 |

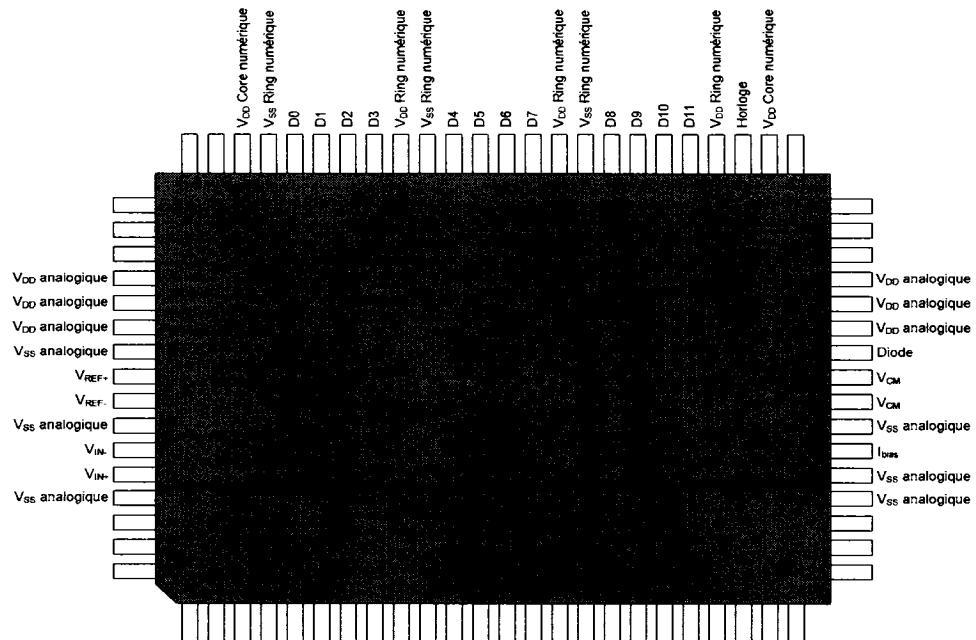

| 4.4.3. | Disposition des plots .....                       | 84 |

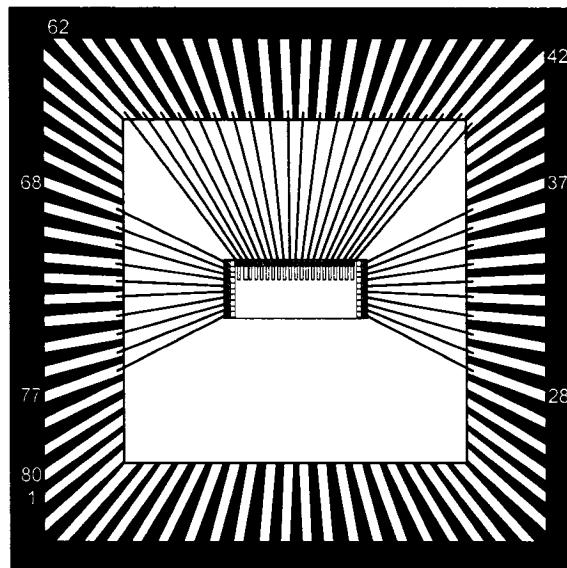

| 4.4.4. | Circuit intégré final .....                       | 86 |

| 4.4.5. | Encapsulation du circuit intégré.....             | 86 |

| 5.     | CHAPITRE V : TESTS .....                          | 88 |

|        |                                |     |

|--------|--------------------------------|-----|

| 5.1.   | Circuit Imprimé.....           | 88  |

| 5.1.1. | Partie Analogique.....         | 90  |

| 5.1.2. | Partie numérique .....         | 93  |

| 5.1.3. | Circuit imprimé final.....     | 94  |

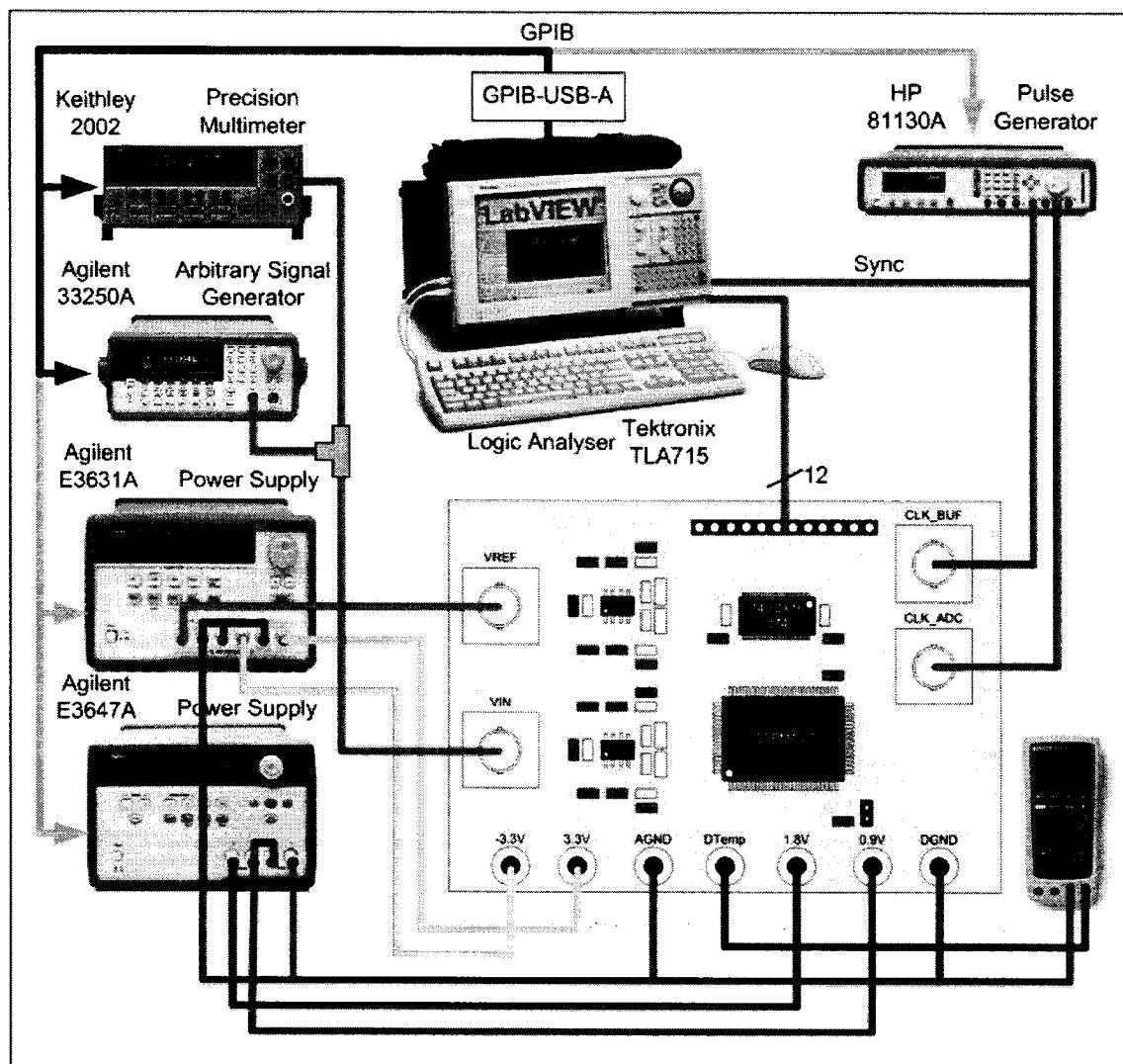

| 5.2.   | Banc de test.....              | 95  |

| 5.3.   | Résultats préliminaires.....   | 97  |

| 6.     | CHAPITRE VI : RÉSULTATS .....  | 102 |

| 7.     | CHAPITRE VII : CONCLUSION..... | 106 |

| 8.     | REFERENCES .....               | 109 |

## LISTE DES FIGURES

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

| Figure 2.1 – (a) Signal analogique, (b) Signal échantillonné et (c) Signal numérique ..... | 5  |

| Figure 2.2 – Exemples illustratifs des INL et DNL .....                                    | 8  |

| Figure 2.3 - Convertisseur à approximations successives .....                              | 10 |

| Figure 2.4 - Principe de fonctionnement d'un convertisseur à simple pente .....            | 12 |

| Figure 2.5 - Chronogramme d'un convertisseur à simple pente .....                          | 12 |

| Figure 2.6 - Principe de fonctionnement d'un convertisseur à double pente.....             | 13 |

| Figure 2.7 - Chronogramme d'un convertisseur à double pente.....                           | 14 |

| Figure 2.8 - Bloc d'un convertisseur Sigma Delta.....                                      | 15 |

| Figure 2.9 - Modulateur Sigma-Delta du premier ordre .....                                 | 15 |

| Figure 2.10- Convertisseur Flash standard .....                                            | 17 |

| Figure 2.11 - (a) Convertisseur à pliage (b) Fonction de transfert du plieur .....         | 18 |

| Figure 2.12 - Convertisseur à plusieurs étapes, deux étapes.....                           | 19 |

| Figure 2.13 - Convertisseur en pipeline .....                                              | 21 |

| Figure 2.14 - convertisseur parallèle.....                                                 | 22 |

| Figure 2.15 - Architecture requise pour la correction numérique des erreurs .....          | 23 |

| Figure 2.16 - Fonction de transfert d'un étage de 1.5 bits et de 2 bits.....               | 24 |

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Figure 2.17 - Effet d'une tension de décalage sur les fonctions de transfert .....  | 25 |

| Figure 2.18 - Exemple de traitement de l'unité de correction d'erreur.....          | 26 |

| Figure 2.19 - Architecture de calibration mixte LMS.....                            | 29 |

| Figure 2.20 – Décomposition d'un convertisseur pipeliné .....                       | 30 |

| Figure 2.21 – Architecture de calibration numérique simplifiée .....                | 31 |

| Figure 2.22 – Architecture de calibration numérique LMS .....                       | 32 |

| Figure 2.23 – Architecture de calibration numérique par changement de configuration | 35 |

| Figure 2.24 – Fonction de transfert des configurations utilisées .....              | 36 |

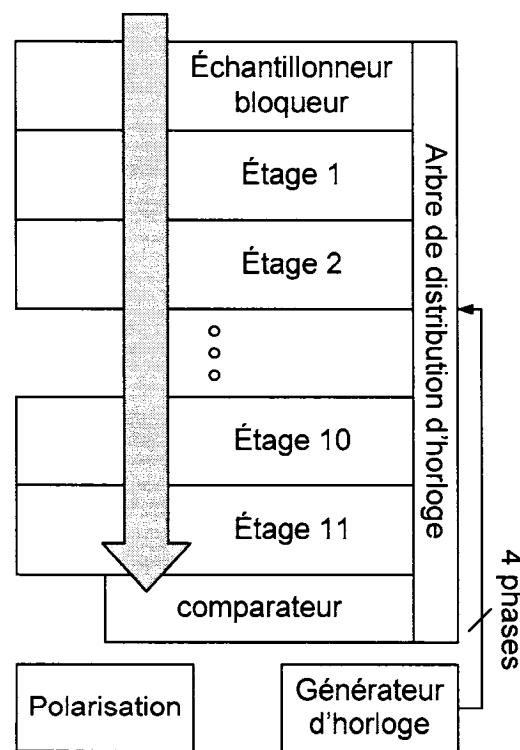

| Figure 3.1 - Convertisseur pipeliné de n étages .....                               | 40 |

| Figure 3.2 – Modèle d'un étage pipeliné.....                                        | 41 |

| Figure 3.3 - Architecture de calibration numérique .....                            | 45 |

| Figure 3.4 - Représentation du gain non linéaire utilisé .....                      | 47 |

| Figure 4.1 - Cheminement de conception .....                                        | 52 |

| Figure 4.2 - Modèle du bruit généré par un convertisseur pipeliné .....             | 55 |

| Figure 4.3 - Diagramme simplifié d'un étage pipeliné .....                          | 58 |

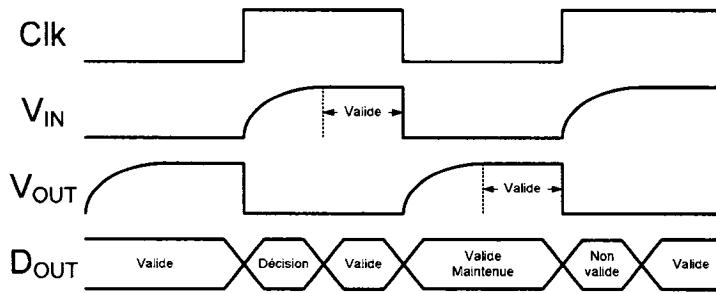

| Figure 4.4 - Chronogramme des signaux de l'étage pipeliné .....                     | 59 |

| Figure 4.5 - Schéma au niveau des transistors de l'amplificateur opérationnel ..... | 61 |

| Figure 4.6 - Circuit de rétroaction du mode commun.....                             | 61 |

|                                                                                                                                |    |

|--------------------------------------------------------------------------------------------------------------------------------|----|

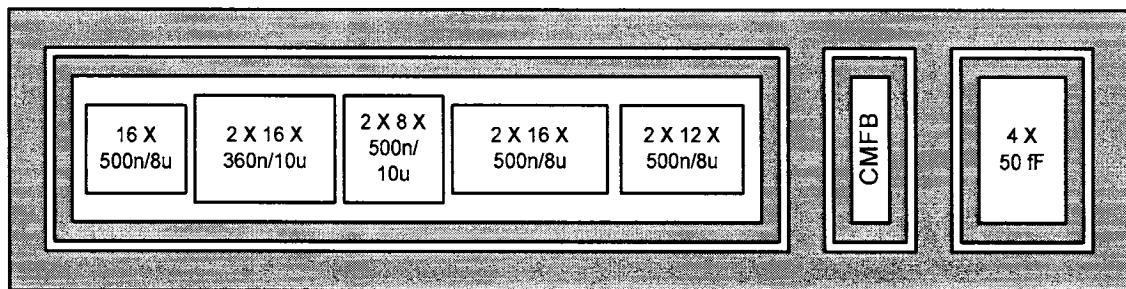

| Figure 4.7 - Disposition des transistors et modules de l'amplificateur opérationnel.....                                       | 62 |

| Figure 4.8 - Dessin de masques de l'amplificateur opérationnel.....                                                            | 62 |

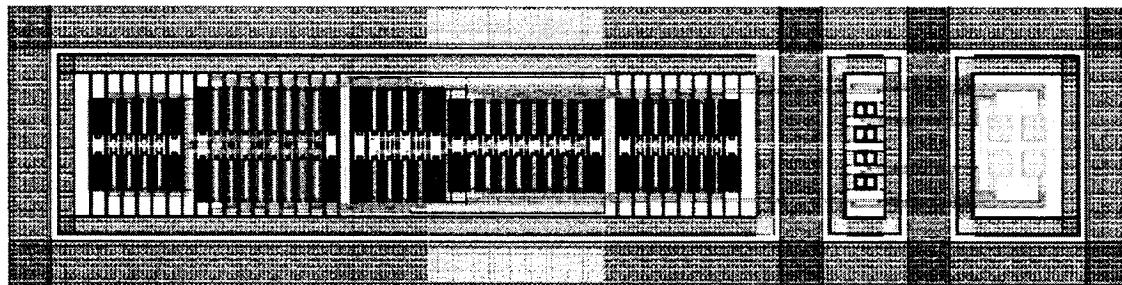

| Figure 4.9 - Réponse dynamique de l'amplificateur opérationnel.....                                                            | 63 |

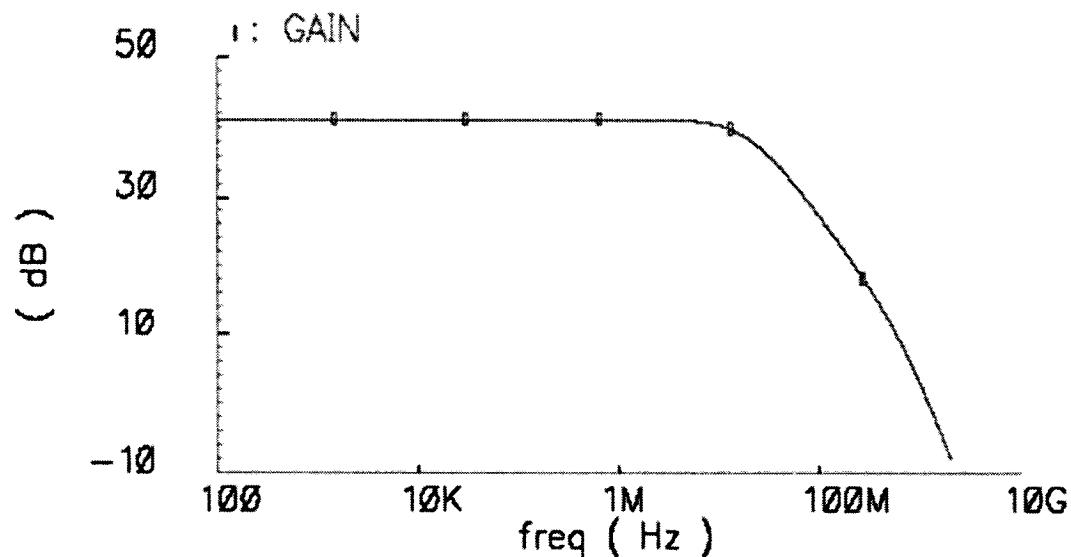

| Figure 4.10- Gain DC selon la température de jonction .....                                                                    | 64 |

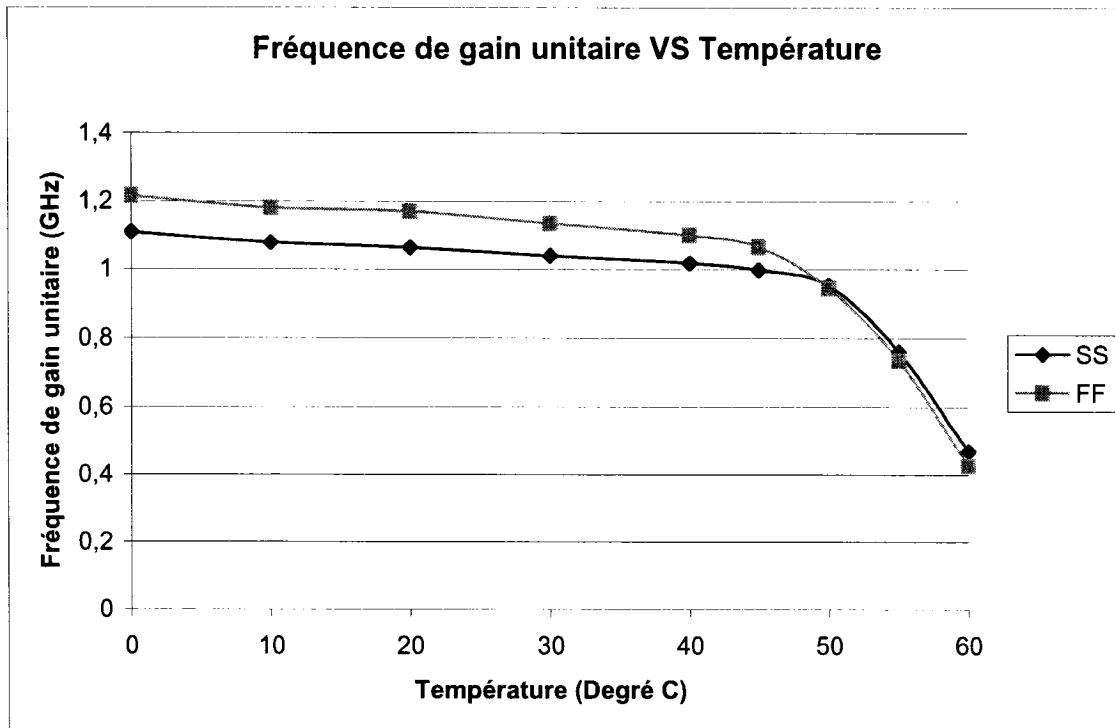

| Figure 4.11 - Fréquence de gain unitaire selon la température de jonction .....                                                | 65 |

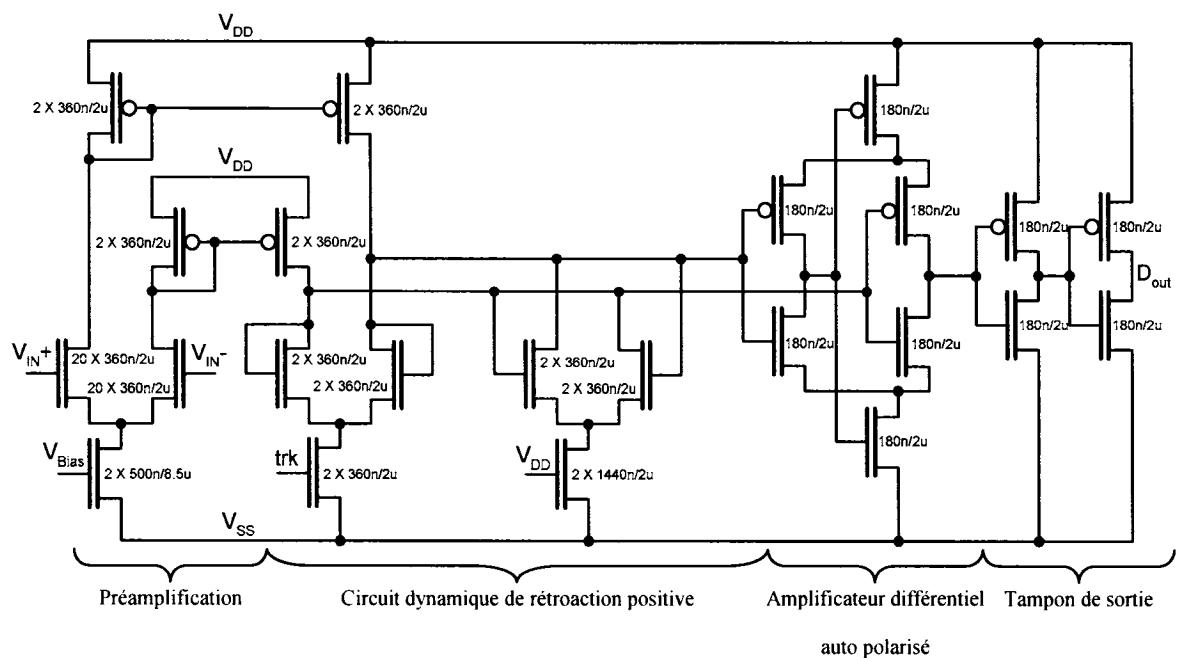

| Figure 4.12 - Circuit final du comparateur dynamique.....                                                                      | 66 |

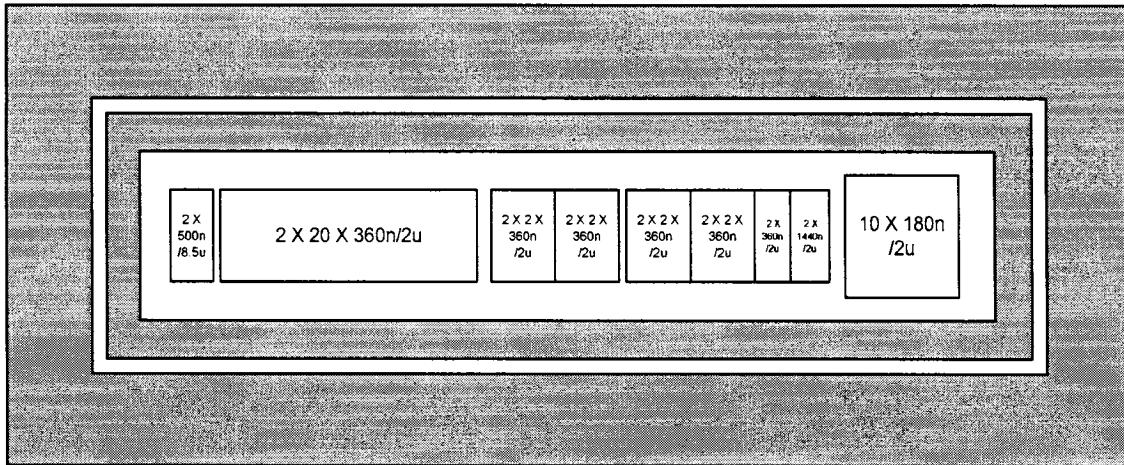

| Figure 4.13 - Disposition des transistors appariés du comparateur .....                                                        | 67 |

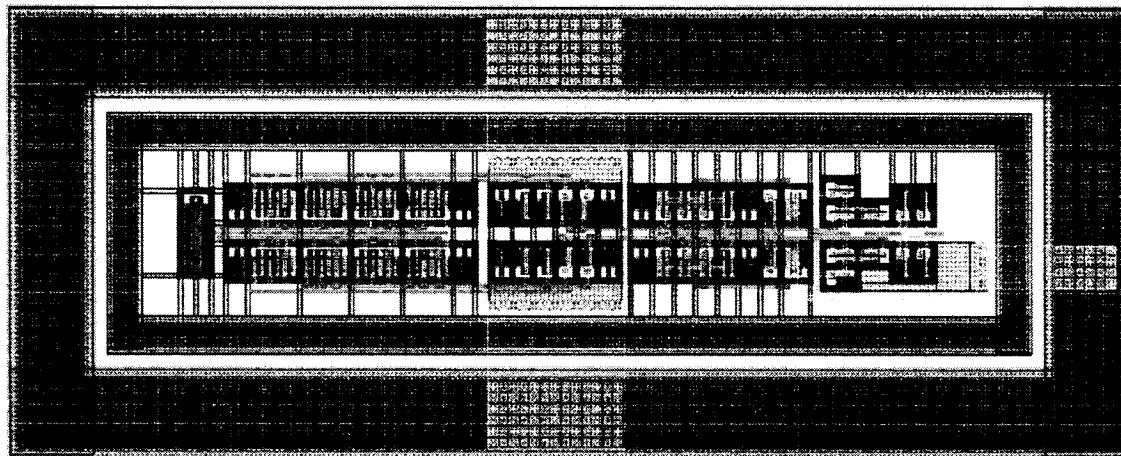

| Figure 4.14 - Dessin de masques du comparateur .....                                                                           | 67 |

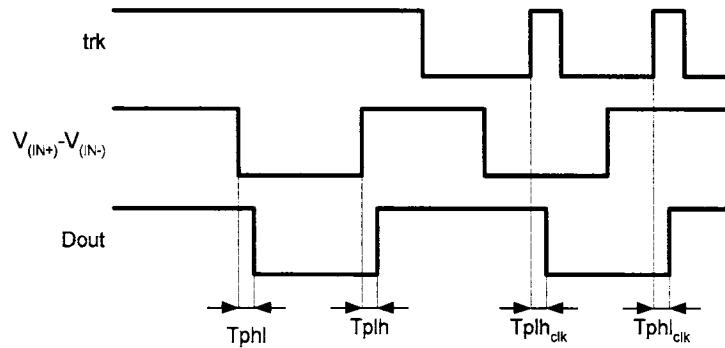

| Figure 4.15 - Chronogramme du comparateur.....                                                                                 | 68 |

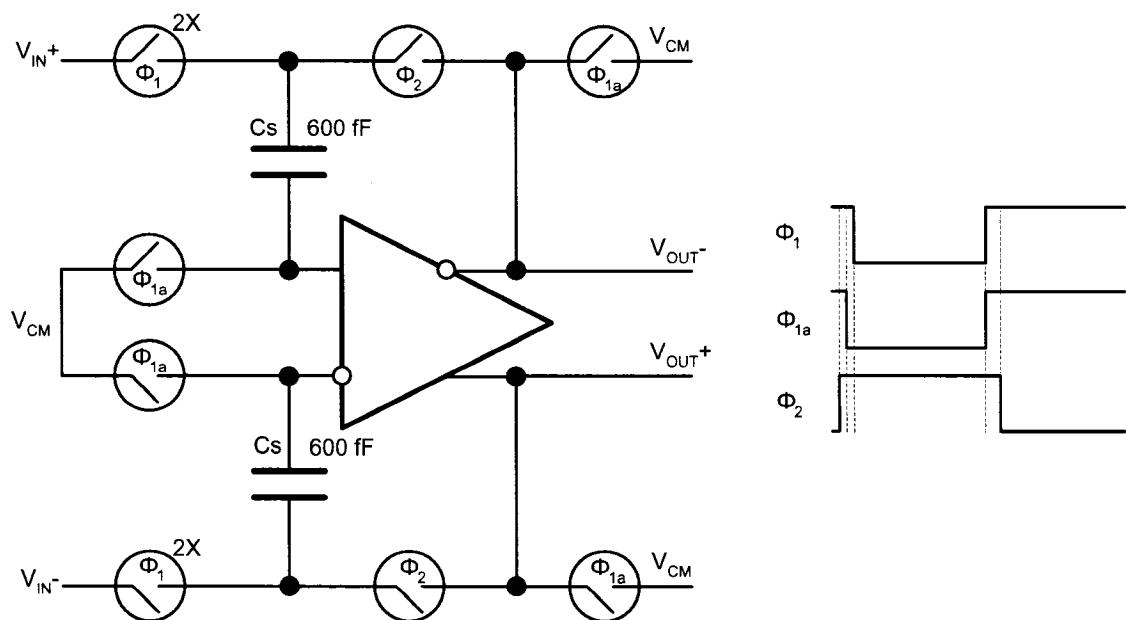

| Figure 4.16- Architecture de l'échantillonneur bloqueur et son diagramme de phase ....                                         | 70 |

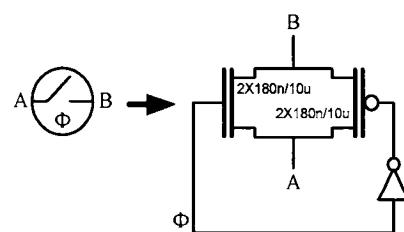

| Figure 4.17 - Porte de transmission des réseaux de commutation.....                                                            | 70 |

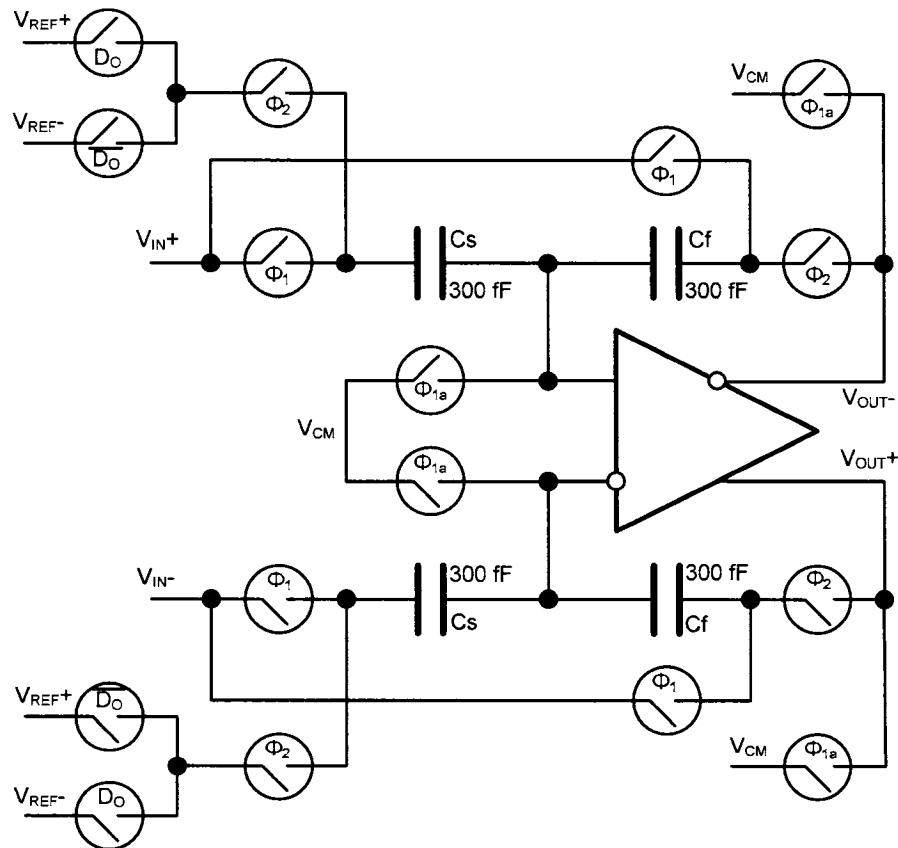

| Figure 4.18 - Architecture des étages pipelinés .....                                                                          | 71 |

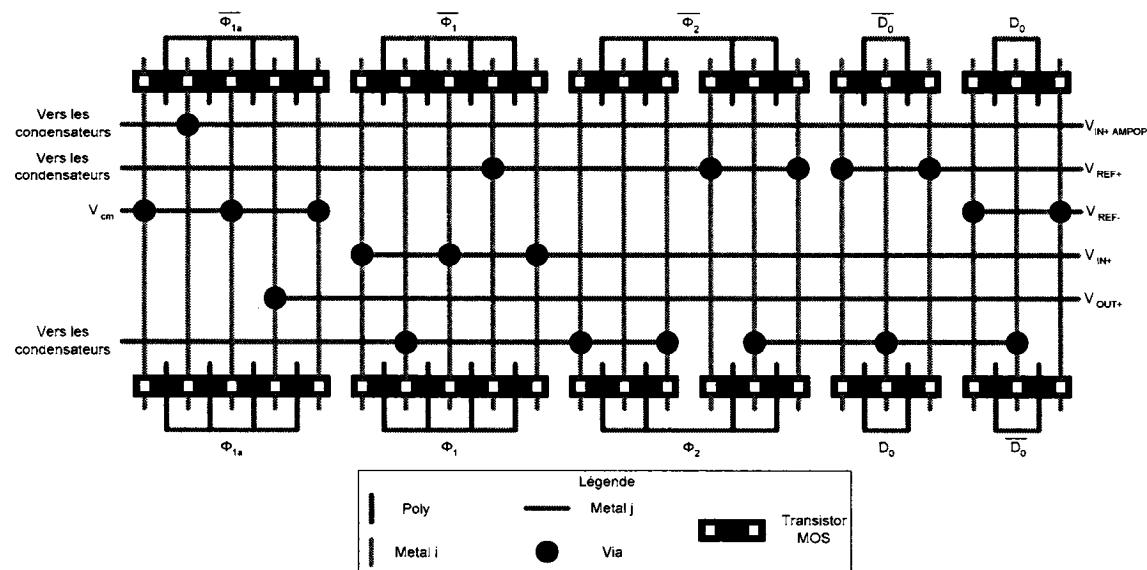

| Figure 4.19 - Diagramme squelettisé du réseau de commutation des étages pipelinés ...                                          | 72 |

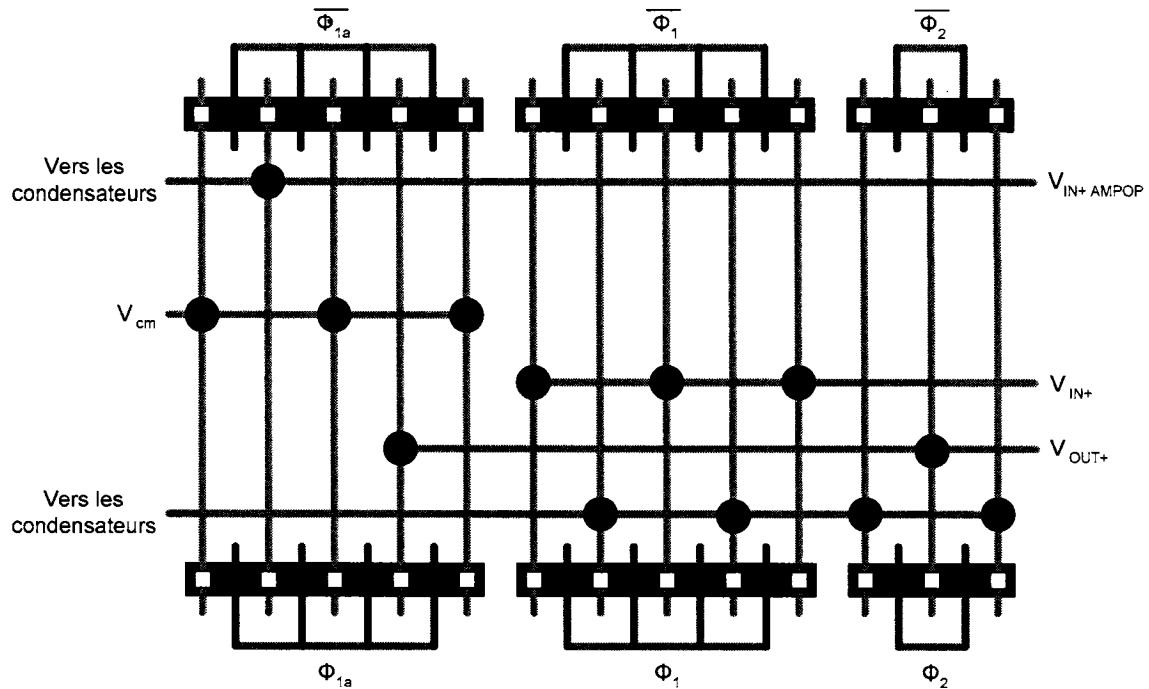

| Figure 4.20 - Diagramme squelettisé du réseau de commutation de l'échantillonneur<br>bloqueur .....                            | 73 |

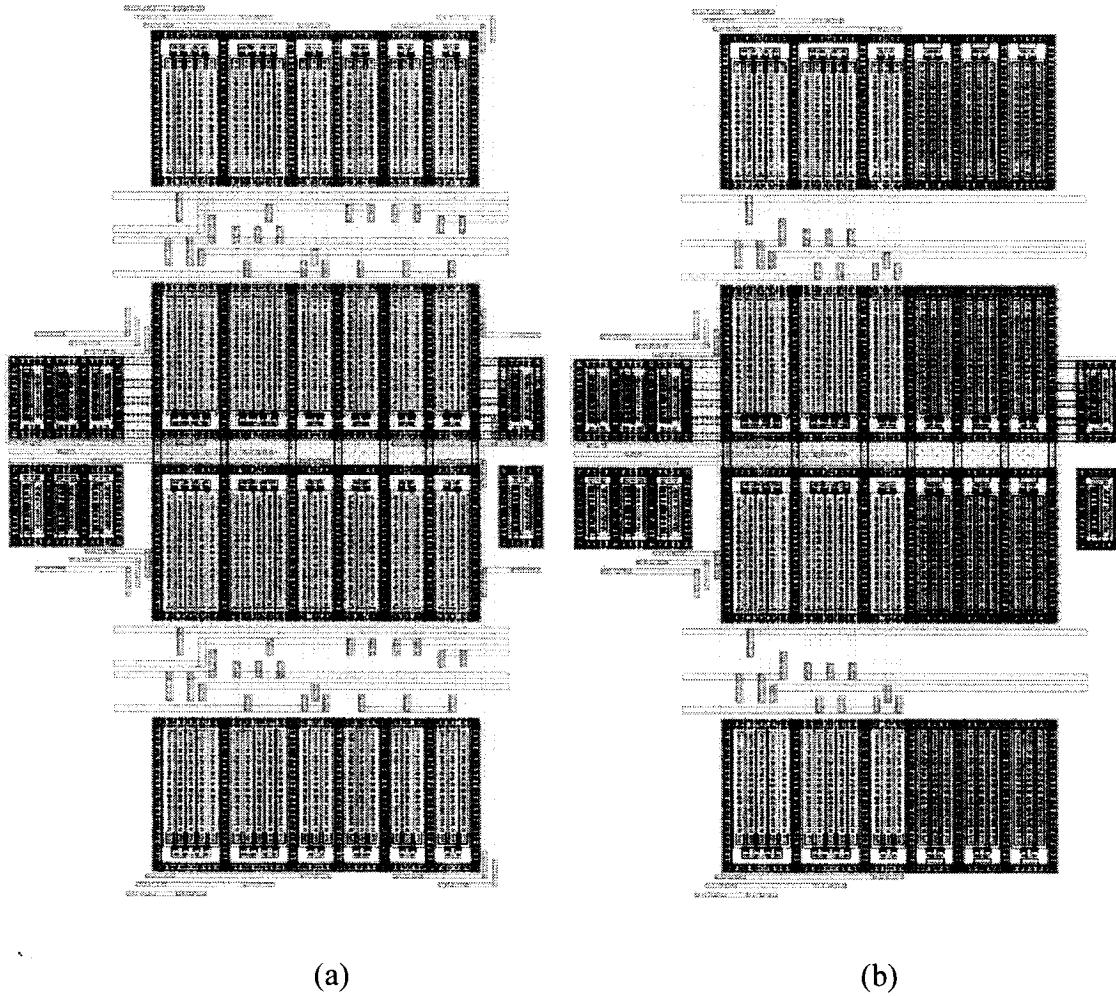

| Figure 4.21 - Dessin de masques du réseau de commutation (a) des étages pipelinés et<br>(b) de l'échantillonneur bloqueur..... | 74 |

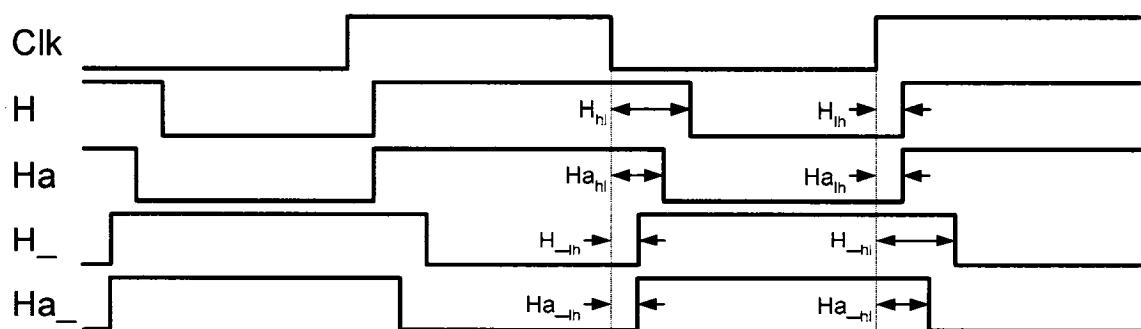

| Figure 4.22 - Schéma du générateur d'horloges .....                                                                            | 75 |

| Figure 4.23 - Chronogramme des phases du générateur d'horloges.....                                                            | 75 |

|                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------|----|

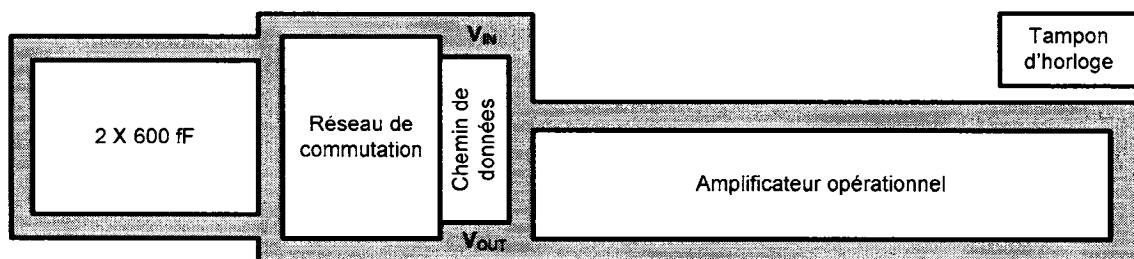

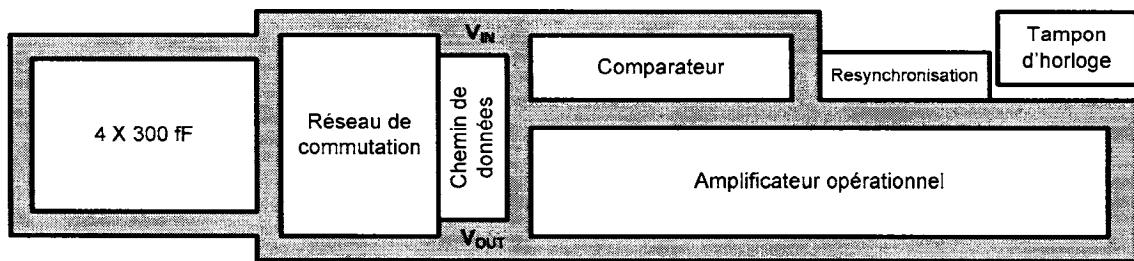

| Figure 4.24- Disposition des sous modules de l'échantillonneur bloqueur .....                          | 77 |

| Figure 4.25 - Dessin de masques de l'échantillonneur bloqueur .....                                    | 77 |

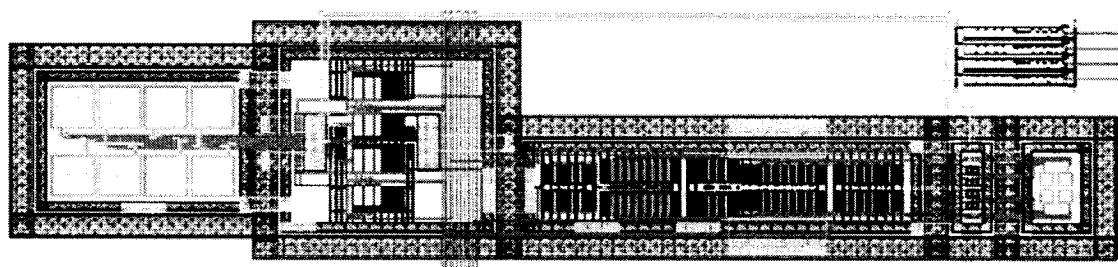

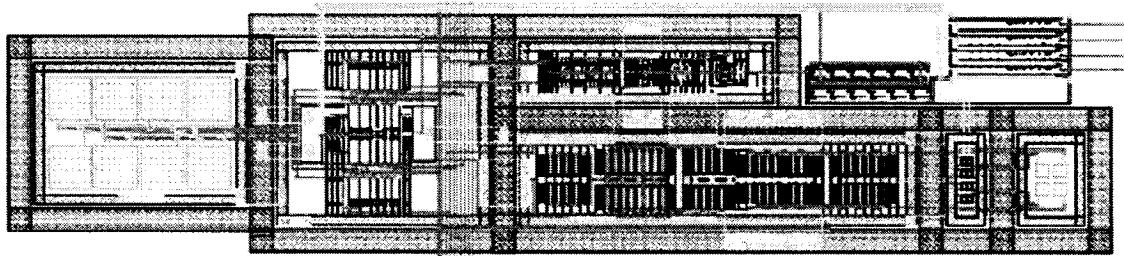

| Figure 4.26 - Disposition des sous modules d'un étage pipeliné.....                                    | 78 |

| Figure 4.27 - Dessin de masques d'un étage pipeliné.....                                               | 78 |

| Figure 4.28 - Banc de test des étages pipelinés.....                                                   | 79 |

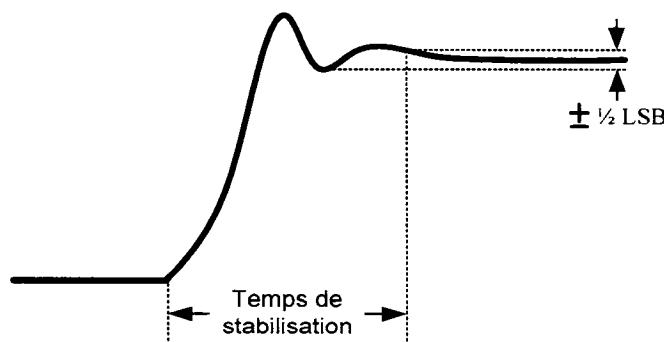

| Figure 4.29 - Temps de stabilisation.....                                                              | 80 |

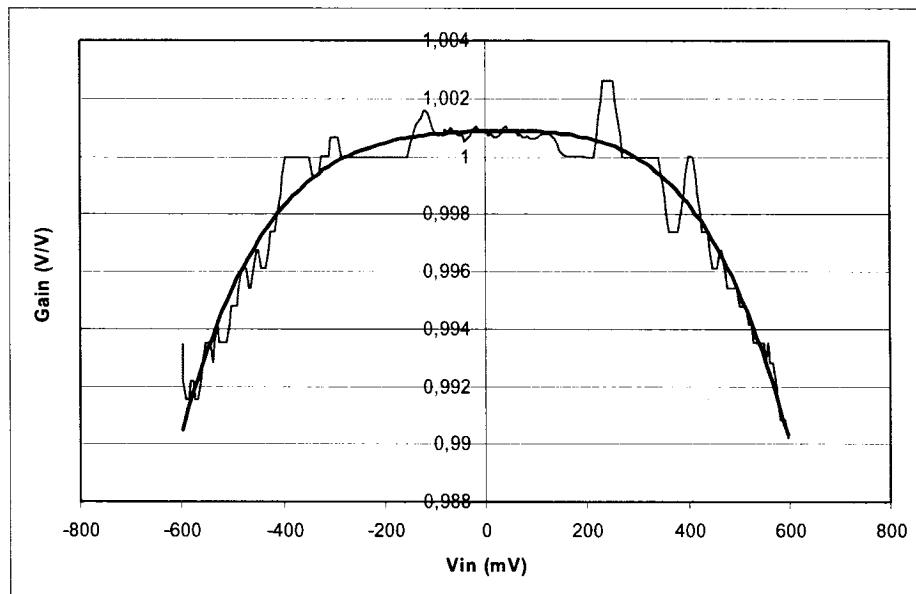

| Figure 4.30 - Gain de l'échantillonneur bloqueur selon son entrée .....                                | 82 |

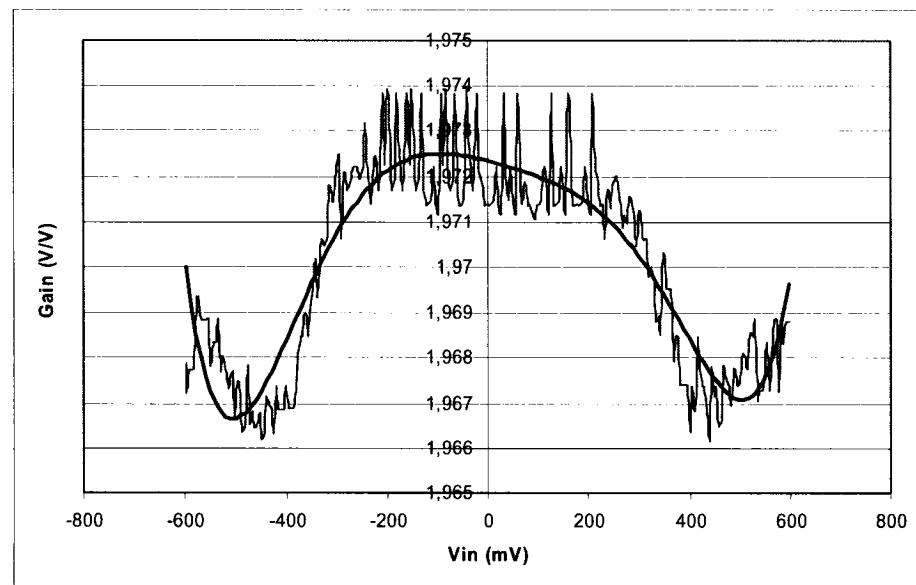

| Figure 4.31 - Gain d'un étage pipeliné selon son entrée.....                                           | 82 |

| Figure 4.32 - Disposition des modules du noyau.....                                                    | 83 |

| Figure 4.33 - Disposition des plots d'entrée/sortie et d'alimentation .....                            | 85 |

| Figure 4.34 - Dessin de masques final .....                                                            | 86 |

| Figure 4.35 - Connexions des plots aux pins du boîtier.....                                            | 87 |

| Figure 4.36 - Circuit intégré final .....                                                              | 87 |

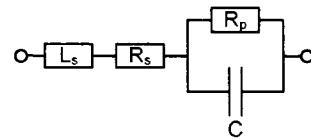

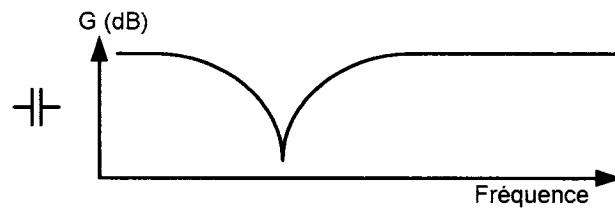

| Figure 5.1 - Modèle d'un condensateur commercial .....                                                 | 89 |

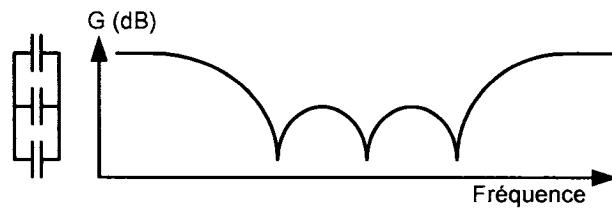

| Figure 5.2 - Réponse en fréquence d'un filtre passe-bas basé sur un condensateur<br>commercial.....    | 89 |

| Figure 5.3 - Réponse en fréquence d'un filtre passe-bas basé sur une batterie de<br>condensateurs..... | 89 |

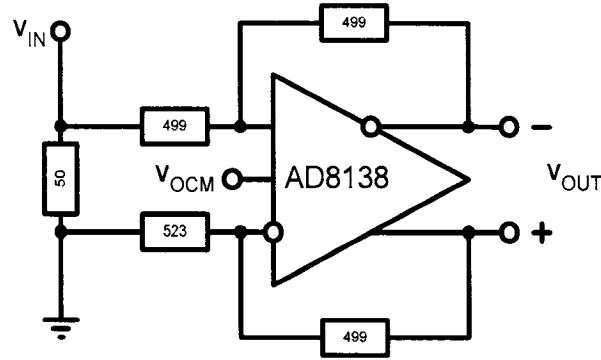

| Figure 5.4 - Convertisseur « single-ended » à différentiel.....                                        | 91 |

|                                                                 |     |

|-----------------------------------------------------------------|-----|

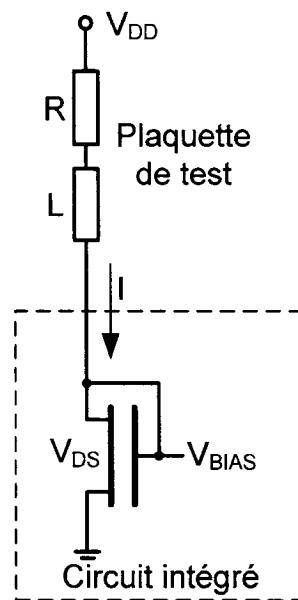

| Figure 5.5 - Génération du courant de polarisation .....        | 92  |

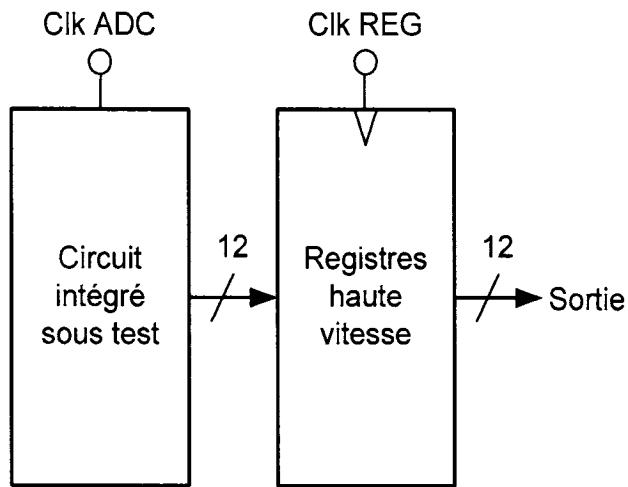

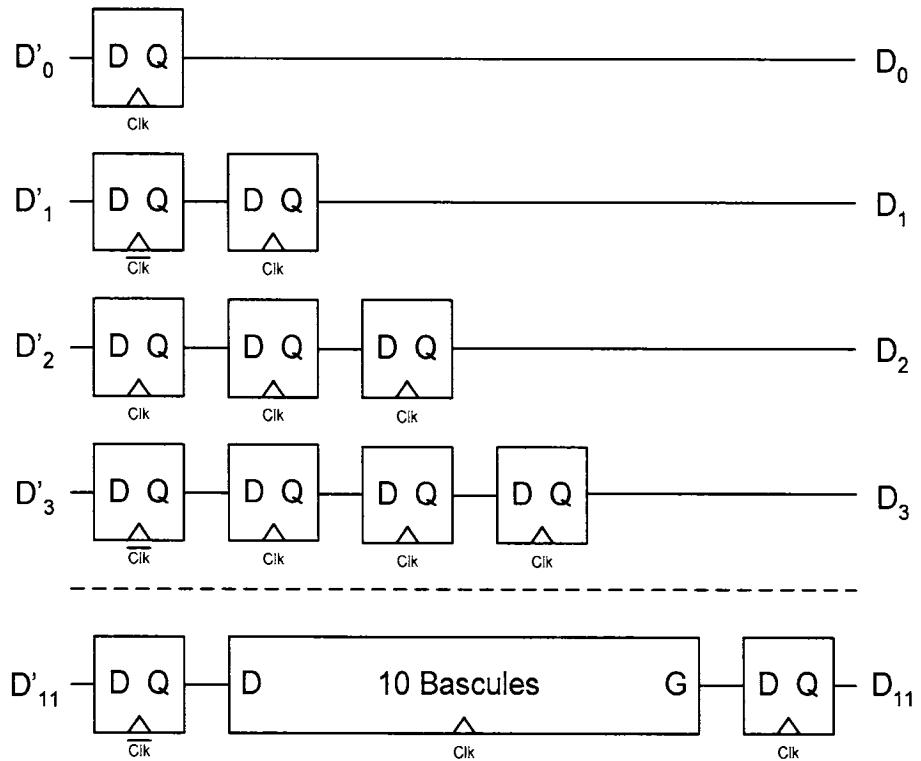

| Figure 5.6 - Architecture des registres de sortie .....         | 93  |

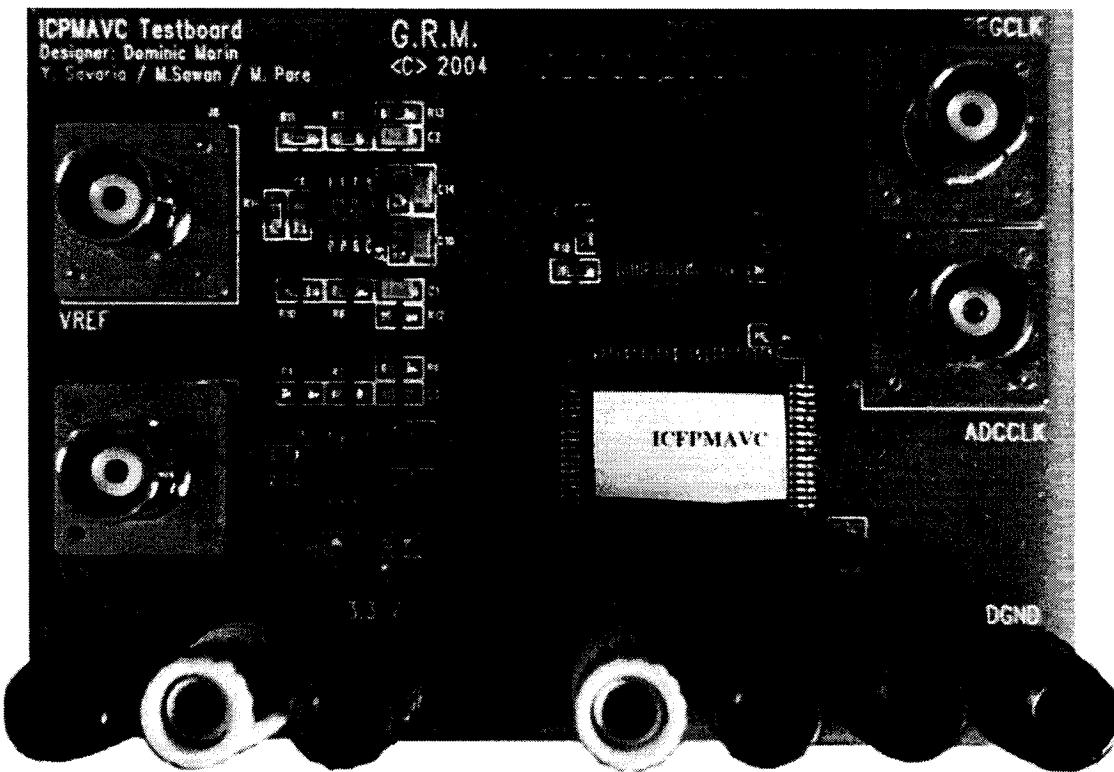

| Figure 5.7 - Circuit imprimé final .....                        | 95  |

| Figure 5.8 - Banc de test final .....                           | 96  |

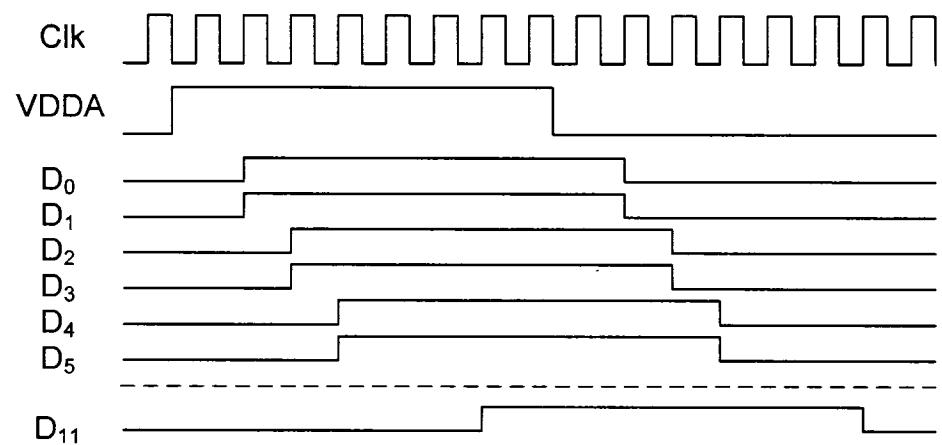

| Figure 5.9 - Resynchronisation des étages pipelinés .....       | 99  |

| Figure 5.10 - Chronogramme du test de la partie numérique ..... | 99  |

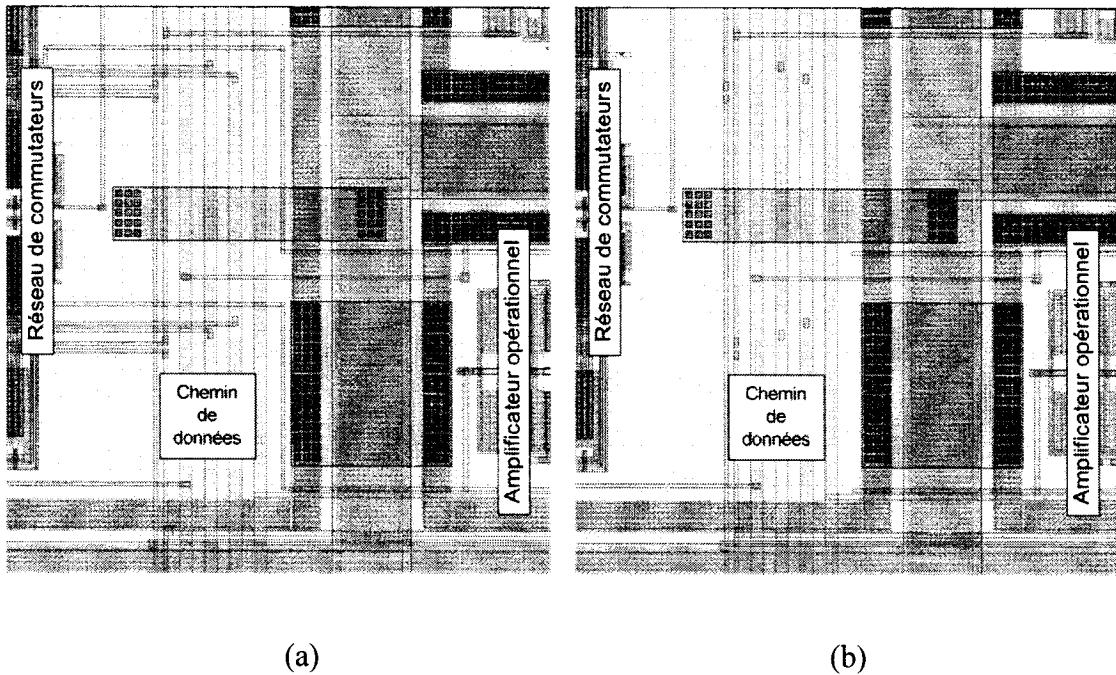

| Figure 5.11 - Section problématique du dessin de masques .....  | 100 |

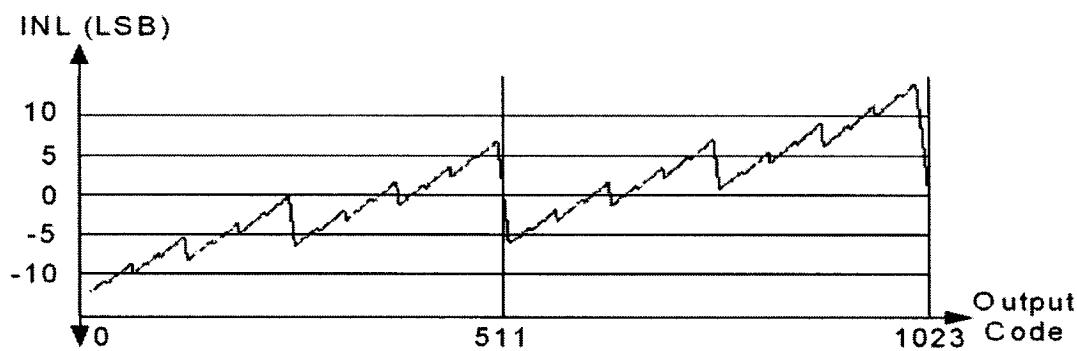

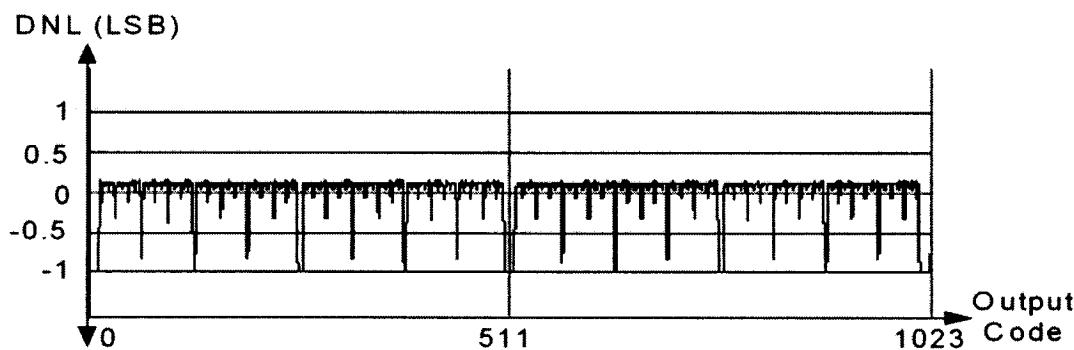

| Figure 6.1 - INL avant calibration (résultat typique) .....     | 103 |

| Figure 6.2 - DNL avant calibration (résultat typique) .....     | 103 |

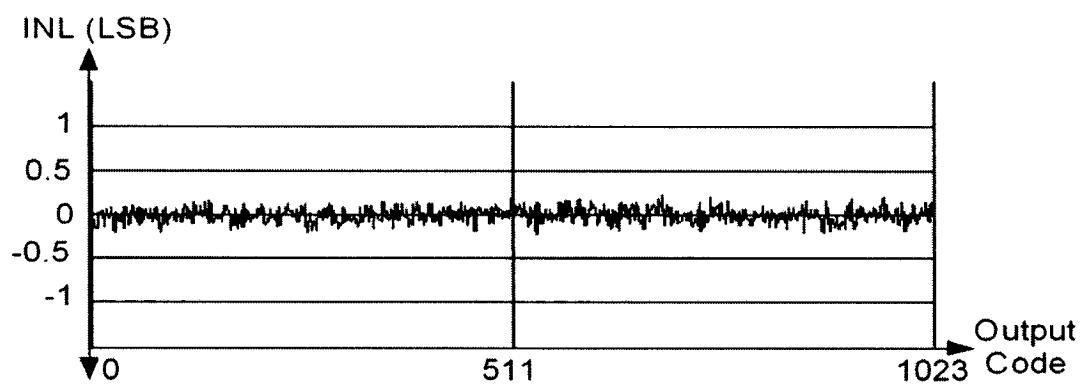

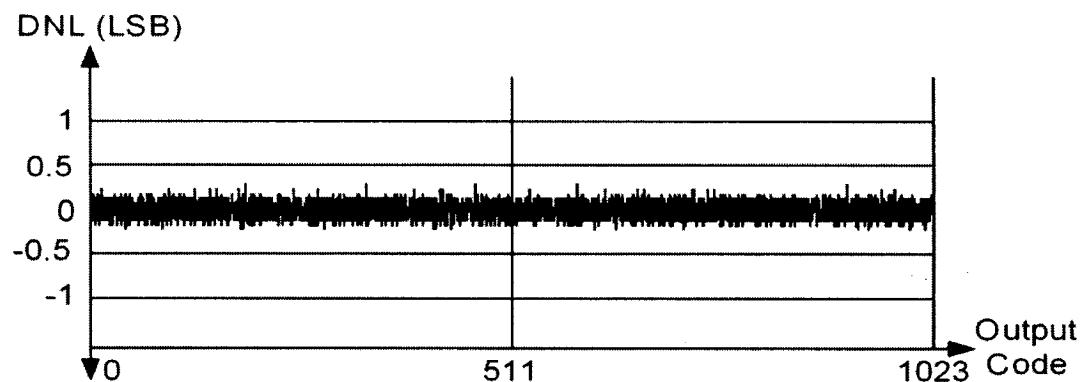

| Figure 6.3 - INL après calibration (résultat typique) .....     | 104 |

| Figure 6.4 - DNL après calibration (résultat typique).....      | 104 |

## LISTE DES TABLEAUX

|                                                                                                                                                      |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 2.1 - Exemple de performance pour une architecture donnée.....                                                                               | 38  |

| Tableau 3.1- Paramètres du modèle d'un étage pipeliné.....                                                                                           | 42  |

| Tableau 3.2 - Valeurs appliquées aux simulations.....                                                                                                | 48  |

| Tableau 3.3 - Résultats des simulations sans redondance.....                                                                                         | 48  |

| Tableau 3.4 - Résultats des simulations avec redondance .....                                                                                        | 49  |

| Tableau 4.1- Gain DC et fréquence de gain unitaire de l'amplificateur opérationnel pour les paramètres de performance typique et de coin .....       | 63  |

| Tableau 4.2- Temps associé à différents cas de figure et paramètres coins du comparateur.....                                                        | 68  |

| Tableau 4.3 - Temps de décision maximale du comparateur pour différentes températures de jonction .....                                              | 69  |

| Tableau 4.4 - Temps (ps) associé aux différentes phases du générateur d'horloge pour différents ensembles de paramètres de coins technologiques..... | 76  |

| Tableau 4.5 - Temps de stabilisation (ns) pour T=27°C.....                                                                                           | 81  |

| Tableau 4.6 - Temps de stabilisation (ns) pour T=40°C.....                                                                                           | 81  |

| Tableau 6.1 - Résumé des résultats des simulations .....                                                                                             | 105 |

## LISTE DES ABRÉVIATIONS

- ADC Analog to digital converter (CAN)

CAN Convertisseur analogique à numérique (ADC)

CMC Canadian Microelectronics Corporation (SCM)

CMOS Complementary Metal Oxyde Semiconductor

CNA Convertisseur numérique à analogique (DAC)

DAC Digital to analog converter (CNA)

DNL Non-linéarité différentielle ( Differential Non Linearity)

ENOB Résolution effective ou Nombre de bits effectifs (Effective Number Of Bits)

INL Non-linéarité intégrale (Integral Non Linearity)

IEEE Institute of Electrical and Electronics Engineers, Inc.

LSB Bit le moins significatif (Least Significant Bit)

MSB Bit le plus significatif (Most Significant Bit)

RMS Valeur efficace (Root Mean Squared)

SCM Société canadienne de microélectronique

SFDR Spurious Free Dynamic Range

SNR Ratio signal sur bruit (Signal to Noise Ratio)

## LISTE DES ANNEXES

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| ANNEXE I : Spécification de base.....                                             | 114 |

| ANNEXE II : Analyse de la technique de correction des erreurs par redondance..... | 115 |

# CHAPITRE I

## INTRODUCTION

Les choix technologiques actuels nous amènent de plus en plus vers une société du « tout numérique » où l'on décide de restreindre les technologies analogiques. Ceci est explicable par la multitude d'avantages qu'apporte le traitement numérique des signaux. En effet, la conception de circuits numériques permettant le traitement des signaux est beaucoup moins complexe que sa contrepartie analogique, ce qui amène une réduction de coût, une miniaturisation et une flexibilité incomparable. Qui plus est, dans une optique de performance, le traitement numérique est extrêmement stable, robuste et insensible au bruit, ce qui permet d'atteindre de très grandes précisions.

Évidemment, le monde qui nous entoure n'étant que phénomène analogique, les circuits analogiques ne disparaîtront sans doute jamais. De ce fait, les signaux analogiques doivent être numérisés pour ainsi être traités de façon numérique. C'est ici que les convertisseurs analogique à numérique (CAN) sont utilisés en guise de pont entre les deux domaines. La demande croissante en performance des applications, due en grande partie aux avantages qu'offrent les technologies numériques, amène à développer des convertisseurs analogiques à numériques plus performants.

Une application de plus en plus visible est celle de la télévision haute définition (HDTV). Le standard HDTV requiert des CAN de 10 bits opérant à une cadence de 75 Méchantillons/s (MÉ/s) [18], [30]. Pour améliorer la qualité des images, plusieurs

manufacturiers utilisent un échantillonnage à une cadence deux fois plus élevé que le taux de transfert des pixels. Ainsi, avec une fréquence d'échantillonnage de 150 MÉ/s, on obtient une meilleure résolution horizontale, car le nombre de lignes est un paramètre invariant dans le standard HDTV. Les spécifications voulues pour ce projet sont présentées en Annexe I.

Les objectifs de ce projet sont en premier lieu de donner à l'auteur une base dans le domaine de la microélectronique analogique et mixte, ainsi que les connaissances nécessaires à la réalisation de ce projet. En second lieu, il s'agit de déterminer les architectures et techniques nécessaires pour atteindre les spécifications demandées par le standard amélioré HDTV. Finalement, ce projet vise la réalisation d'un prototype intégré pour valider l'architecture proposée.

Dans le but d'identifier les techniques actuelles utilisées en industrie ou en développement dans le milieu de la recherche, une revue de littérature a été effectuée dès le début du projet. Un aperçu de cette revue de littérature sera exposé au deuxième chapitre. De ce chapitre découlent certaines limitations des architectures actuellement utilisées. En effet, le lecteur verra que de nouvelles techniques peuvent être utilisées pour atteindre nos objectifs. C'est ainsi que le troisième chapitre exposera les principes de base de la calibration numérique. Dans ce chapitre, le lecteur pourra voir l'utilisation judicieuse de circuits numériques et analogiques dont les avantages de chacun seront utilisés de façon à atteindre les spécifications visées dans ce projet. Le quatrième chapitre exposera la conception d'un prototype de circuit intégré ayant les spécifications nécessaires au standard HDTV amélioré. Ce chapitre montrera toutes les étapes et choix

de conception du prototype, en débutant par les spécifications jusqu'à l'encapsulation du microcircuit. Afin de tester ce circuit intégré, un plan de test a été élaboré, le cinquième chapitre portera sur ce plan de test. Le sixième chapitre présentera les résultats de simulation au niveau du dessin de masques. En guise de conclusion, le septième chapitre fermera ce mémoire de maîtrise.

## CHAPITRE II

### REVUE DE LITTÉRATURE

#### 2.1. Convertisseurs analogique à numérique

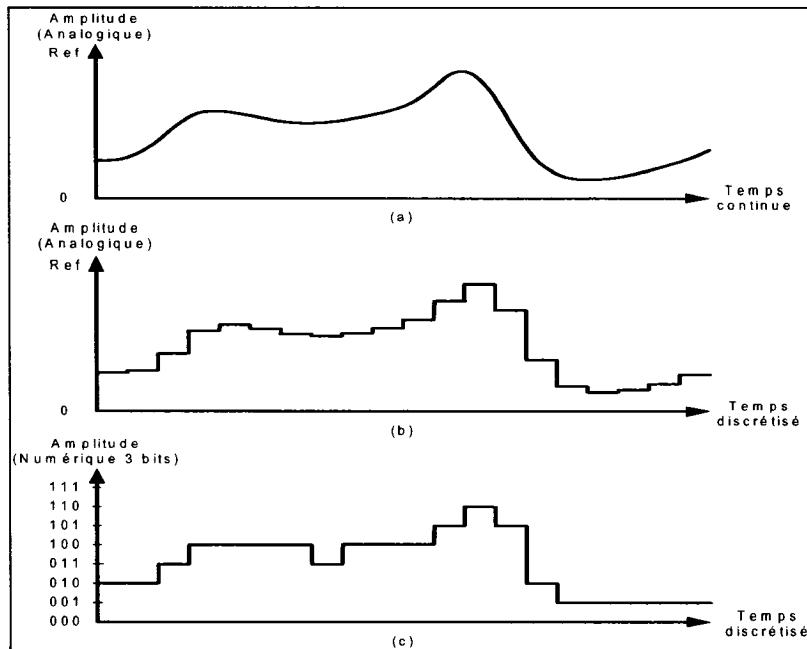

Les convertisseurs analogique à numérique (CAN), comme leurs noms l'expriment si clairement, sont le lien entre les domaines analogique et numérique. Un signal analogique est un signal arbitraire qui possède la propriété d'être continu en amplitude et en temps, voir figure 2.1.a. Le convertisseur utilise deux opérations pour effectuer sa conversion : L'échantillonnage et la quantification.

Lorsque le signal analogique est échantillonné, ce dernier perd sa propriété de continuité temporelle. Ainsi, le signal analogique échantillonné est idéalement invariant sur une période de temps donnée, voir figure 2.1.b. Par le théorème de Nyquist, un signal peut être reconstruit si ce dernier a été échantillonné à une fréquence égale ou supérieure au double de la fréquence maximale contenue dans le signal.

Le signal devient numérique lorsque l'amplitude du signal échantillonné est quantifiée ou discrétisée, c'est-à-dire que l'amplitude ne peut prendre qu'un nombre fini de valeurs identifiables séparément, voir figure 2.1.c. Le nombre de valeurs ou de codes possibles représente la résolution du convertisseur. La résolution est habituellement exprimée par le nombre de bits pouvant représenter ce nombre. Ainsi, un convertisseur ayant 1024 ( $2^{10}$ ) valeurs numériques identifiables est un convertisseur de 10 bits. Plus la

résolution est élevée plus le signal quantifié peut être proche du signal analogique échantillonné.

**Figure 2.1 – (a) Signal analogique, (b) Signal échantillonné et (c) Signal numérique**

Les CAN sont utilisés dès que les caractéristiques d'un signal analogique (tension, courant ou charge) sont nécessaires au fonctionnement d'un dispositif numérique. Par exemple, le simple comparateur d'un thermostat peut être considéré comme un CAN. En effet, le signal est échantillonné au temps de transition du comparateur et discrétisé en deux valeurs possibles. On parle ici d'un CAN ayant une résolution de 1 bit. À un autre extrême, les CAN utilisés dans les systèmes sonores pour audiophiles peuvent avoir une résolution de plus de 24 bits soit près de 16.7 millions de codes possibles. Par contre,

tous ces codes ne sont pas nécessairement justes. En effet, la plupart des CAN audio offrant une précision de 24 bits que l'on retrouve sur le marché ont une exactitude de 16 à 20 bits. Plusieurs phénomènes peuvent causer la dégradation de l'exactitude d'un convertisseur: Le bruit de quantification, le bruit généré par les composants actifs et passifs, et les non-idéalités.

Il existe plusieurs façons de représenter un signal analogique et un code numérique, mais ils sont toujours physiquement analogiques. Ainsi, un signal analogique à convertir peut être soit une tension, un courant, une charge, etc. ; de même que les codes numériques sont représentés par deux niveaux en tension, en courant, etc. Ce document se restreint à la conversion des tensions analogiques en tensions numériques.

## 2.2. Spécifications

Pour bien comprendre les enjeux, il est primordial de connaître les spécifications reliées aux convertisseurs analogique à numérique. Les spécifications associées au CAN peuvent être de deux types : statique (DC) ou dynamique (AC) [28]. Les spécifications statiques seront décrites en premier lieu pour ainsi en arriver ensuite aux spécifications dynamiques.

### 2.2.1. Spécifications statiques :

La spécification la plus utilisée est la résolution, elle représente la largeur, en bit, de la sortie du convertisseur. Ainsi, la résolution se réfère au nombre maximal de niveaux

de quantification que le convertisseur peut représenter. Elle peut aussi être représentée en décibels (dB) à partir de la plage dynamique du convertisseur. La plage dynamique étant le rapport entre la plus grande quantité et la petite quantité pouvant être représentées par le CAN.

La précision d'un convertisseur peut être vue de deux façons ; absolue et relative. La précision absolue est déterminée par la fonction caractéristique du convertisseur en rapport avec une référence provenant d'un standard. Cette dernière inclut tous les défauts qu'un convertisseur peut posséder, elle est habituellement reliée aux erreurs des références. La précision relative ou linéarité est la déviation de la fonction caractéristique d'un convertisseur avec une ligne droite parcourant la plage dynamique du convertisseur. Cette dernière façon est majoritairement utilisée pour caractériser l'exactitude des CAN, elle sera donc utilisée dans ce document.

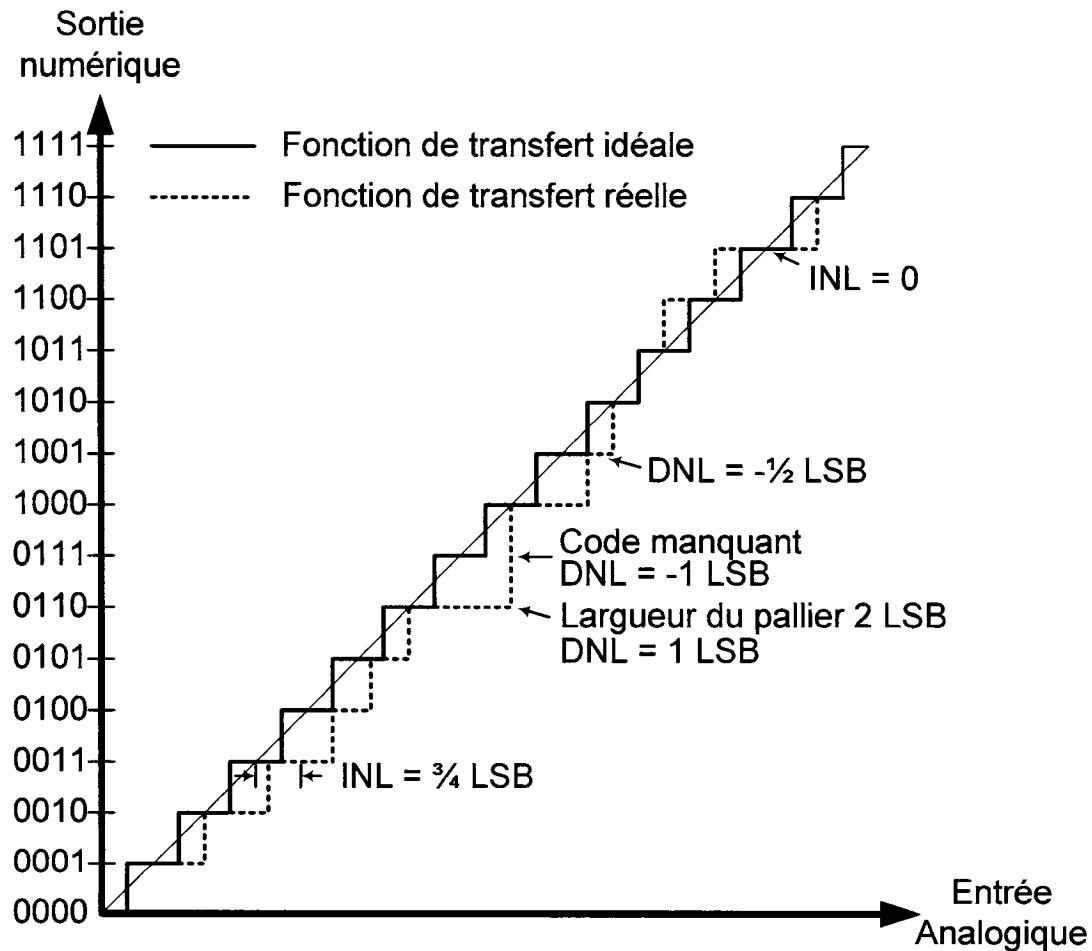

La linéarité est l'écart entre la courbe caractéristique idéale qui se réduit généralement à une droite de pente déterminée et la courbe caractéristique réelle d'un convertisseur. Elle peut être exprimée soit par l'indice de linéarité intégrale (INL) ou l'indice de linéarité différentielle (DNL). La linéarité intégrale est la différence entre la fonction caractéristique du CAN avec un CAN idéal. Les CAN ayant un nombre de niveaux finis, le INL est déterminé seulement sur les niveaux, plus précisément au centre de ces derniers. Ainsi, l'indice de linéarité intégrale est la différence entre le centre d'un niveau et une ligne droite représentant le CAN idéal.

La linéarité différentielle est la différence entre la largeur d'un niveau du CAN et la largeur de niveau d'un CAN idéal.

Les indices INL et DNL sont exprimés par rapport au bit le moins significatif (LSB) du convertisseur. La figure 2.2 montre un exemple de CAN avec quelques valeurs des indices INL et DNL.

Figure 2.2 – Exemples illustratifs des INL et DNL

### 2.2.2. Spécifications dynamiques :

Une façon d'évaluer la qualité d'un convertisseur est de déterminer son nombre effectif de bits (ENOB). Ce paramètre provient du rapport signal à bruit (SNR) représenté par l'équation suivante.

$$SNR = 20 \log \left( \frac{V_{Signal\ RMS}}{V_{Bruit\ RMS}} \right) \quad (2.1)$$

Pour un convertisseur de n bits de précision, on obtient la relation suivante [11].

$$SNR = 6.02n + 1.76dB \quad (2.2)$$

Ainsi, pour un convertisseur ayant un rapport signal à bruit donné, il est possible de déterminer sa précision en bit. Ce paramètre, exprimé par l'équation 2.3, est appelé nombre effectif de bits

$$ENOB = \frac{SNR - 1.76}{6.02} \quad (2.3)$$

Un autre indice de performance dynamique est le “ *spurious free dynamic range* ” (SFDR). Ce dernier est évalué à partir de la plus grande raie spectrale produite par le convertisseur. La bande passante analogique du convertisseur est aussi un bon indice de performance de ce dernier, à cette fréquence, le signal analogique a un gain de -3 dB.

## 2.3. Architecture

Afin de déterminer une architecture ayant le potentiel d'atteindre les spécifications nécessaires à ce projet (voir Annexe 1), il est primordial d'accumuler une connaissance de base des architectures présentement utilisées dans l'industrie. Les prochaines sections exposeront les architectures de base et certaines techniques permettant de les améliorer.

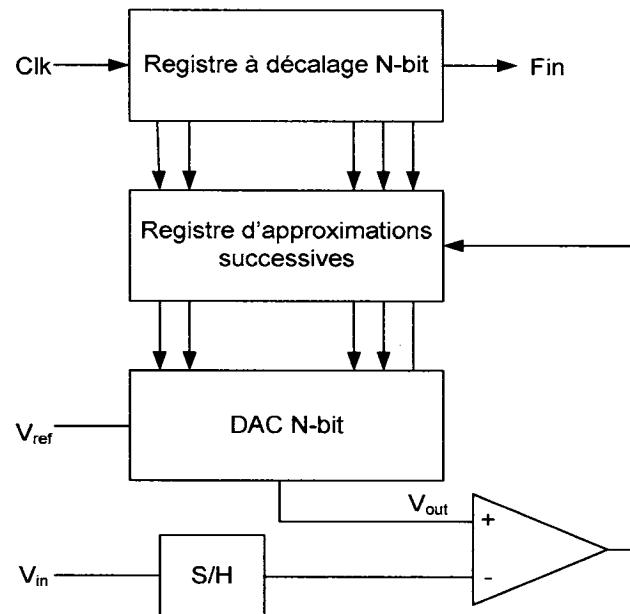

### 2.3.1. Convertisseur à approximation successive

Les convertisseurs à approximations successives font une recherche binaire sur tous les niveaux possibles de discréétisation en convergeant vers une valeur finale [28]. La figure 2.3 présente le principe standard d'un convertisseur à approximation successive.

Figure 2.3 - Convertisseur à approximations successives

Les algorithmes optimisés dans une telle architecture sont capables de faire une conversion de N bits en, au plus N essais. Le comparateur utilisé dans cette architecture sert à orienter les essais dans le bon sens. Ce type de convertisseur se retrouve dans les applications dont les résolutions peuvent atteindre 14 bits à une fréquence de conversion de l'ordre de 200 KHz.

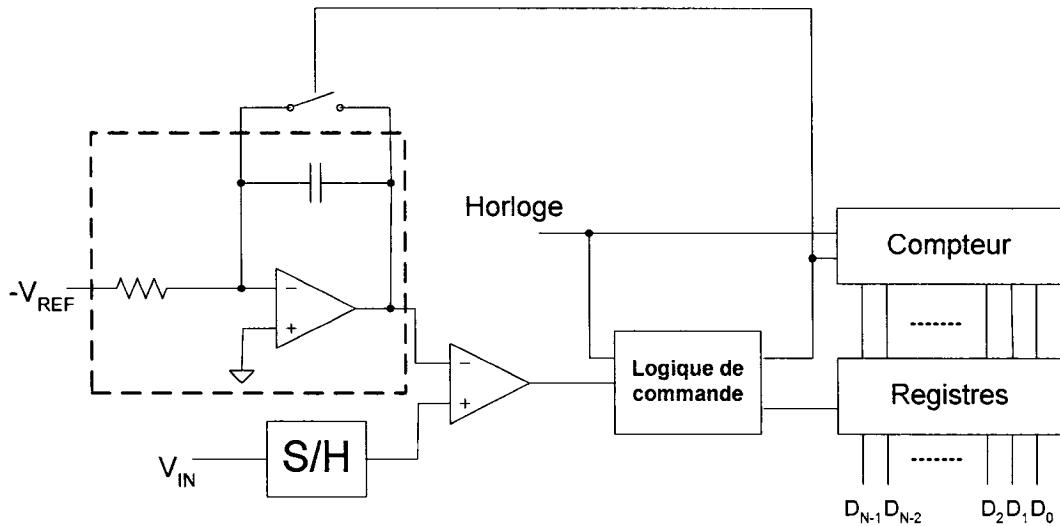

### 2.3.2. Convertisseur à intégration

Un autre type d'architecture permet de faire une conversion en déterminant le temps d'intégration avec un compteur digital. Deux types de convertisseurs à intégration seront expliqués dans cette revue de littérature ; les convertisseurs à simple pente et à double pente. Ces types de convertisseurs sont utilisés dans des applications économiques nécessitant une haute résolution à basse vitesse de conversion [28].

#### 2.3.2.1. Convertisseurs à simple pente

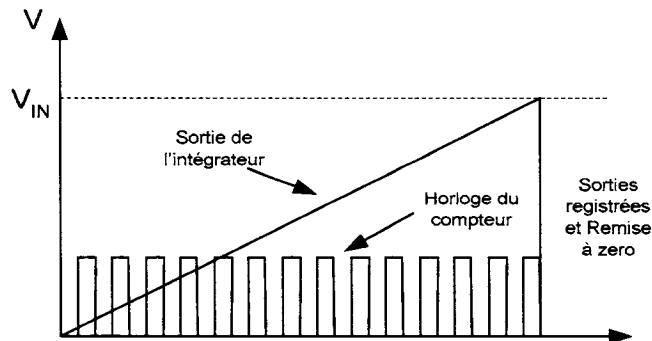

Les figures 2.4 et 2.5 représentent le principe d'une conversion avec un convertisseur à simple pente.

**Figure 2.4 - Principe de fonctionnement d'un convertisseur à simple pente**

**Figure 2.5 - Chronogramme d'un convertisseur à simple pente**

La tension de référence est intégrée par un amplificateur opérationnel en configuration intégrateur. La sortie de l'intégrateur est ensuite comparée avec la tension d'entrée du convertisseur. La comparaison commande le compteur digital qui détermine le temps nécessaire pour que l'intégration atteigne la tension d'entrée. Étant donné que

la tension intégrée est constante, la pente produite par l'intégrateur est constante. Ainsi, le temps déterminé par le compteur est directement proportionnel à la tension d'entrée. Par contre, la sortie du convertisseur est fonction de l'entrée et de la valeur du condensateur d'intégration, il est donc primordial de bien fixer cette valeur.

### 2.3.2.2. Convertisseurs à double pente

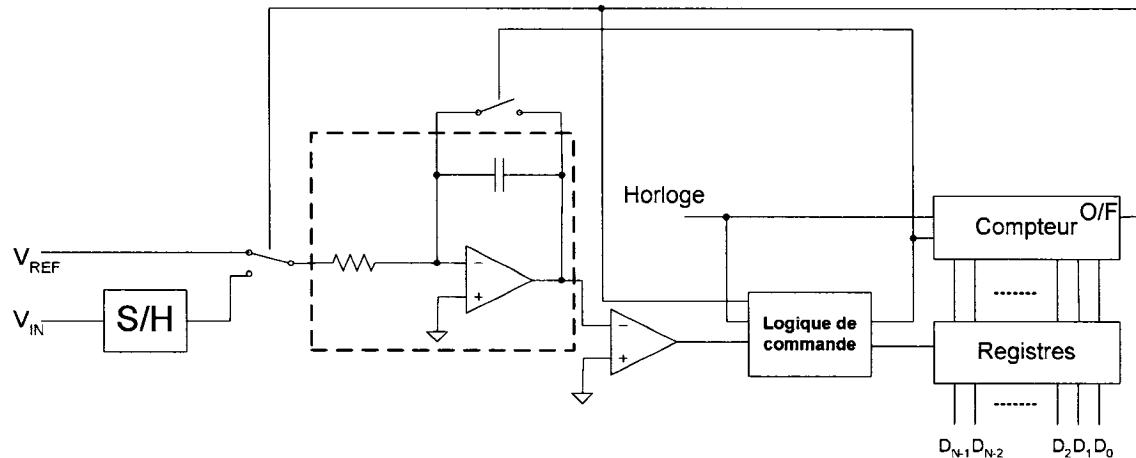

Une architecture un peu plus sophistiquée est souvent utilisée, elle peut éliminer certains problèmes liés à l'exactitude des conversions. Les figures 2.6 et 2.7 représentent cette architecture et son chronogramme.

**Figure 2.6 - Principe de fonctionnement d'un convertisseur à double pente**

**Figure 2.7 - Chronogramme d'un convertisseur à double pente**

Ce convertisseur effectue deux intégrations ; une avec la tension d'entrée et l'autre avec la tension de référence. La première intégration est de durée précise, fixée par la limite de dépassement du compteur. Cette première intégration charge le condensateur de l'intégrateur et permet d'atteindre une tension maximale lorsque le compteur dépasse sa limite. La deuxième intégration décharge la capacité d'intégration jusqu'à une tension nulle. Le temps de la décharge est directement proportionnel à la tension d'entrée. En plus, étant donné qu'il y a deux intégrations avec le même intégrateur, la sortie du convertisseur n'est plus fonction du condensateur, mais seulement de la tension d'entrée. Ceci a pour effet de rendre le convertisseur beaucoup plus exact que la configuration à simple pente. Il existe des convertisseurs à double pente d'une précision de 16 bits capable d'opérer à une fréquence de 44 KHz.

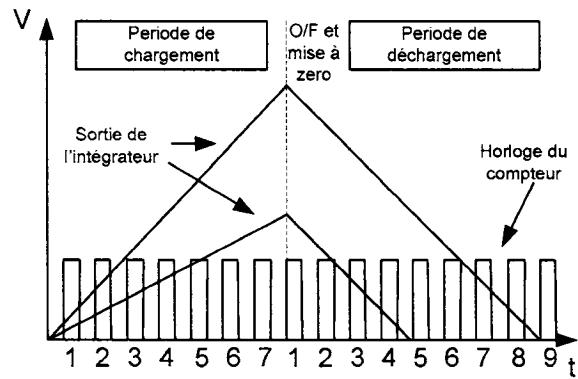

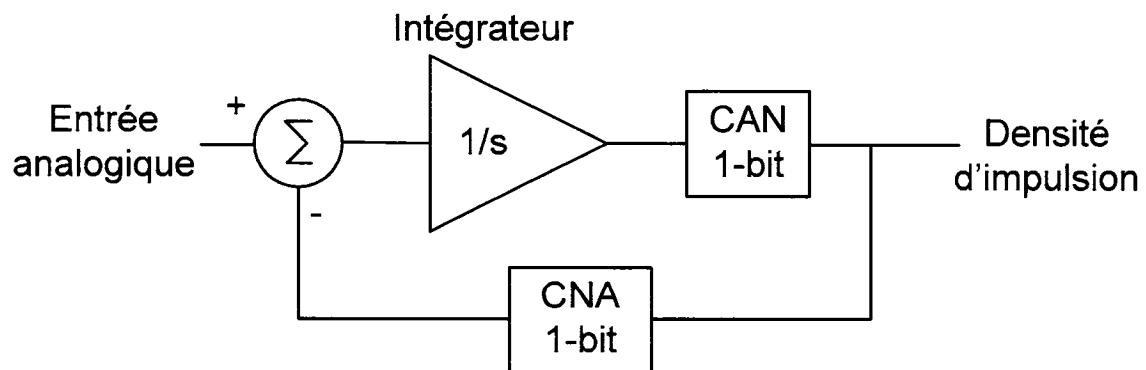

### 2.3.3. Convertisseur Sigma Delta

Les convertisseurs de type Sigma Delta sont des convertisseurs à suréchantillonnage [11], ils échantillonnent un grand nombre de tensions d'entrée pour générer une sortie. La sortie de tels convertisseurs est reliée à la valeur moyenne du signal d'entrée sur la période de suréchantillonnage. La figure 2.8 représente le schéma bloc classique d'un convertisseur Sigma Delta. La figure 2.9 montre en détail les composants d'un modulateur Sigma-Delta du premier ordre, un composant essentiel de ces convertisseurs.

Figure 2.8 - Bloc d'un convertisseur Sigma Delta

Figure 2.9 - Modulateur Sigma-Delta du premier ordre

Les modulateurs Sigma-Delta génèrent une densité d'impulsion à sa sortie semblable à une modulation de largeur d'impulsion. Le filtre numérique effectue la moyenne associée à la densité d'impulsion. Il est facile de retrouver des convertisseurs Sigma-Delta d'une résolution de 24 bits. Par contre, il est rare d'en trouver un qui opère à plus de 200 KHz.

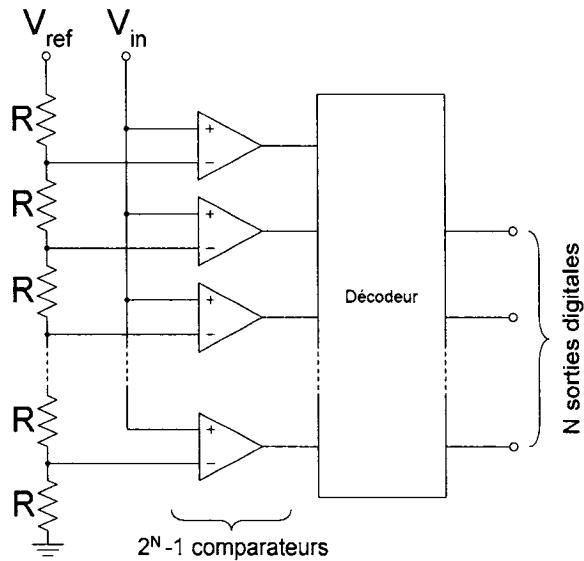

### 2.3.4. Convertisseur Flash

Le convertisseur «Full-Flash» est le plus rapide [2] et le plus simple des convertisseurs analogiques. Il compare chaque palier de la fonction de transfert idéale avec la tension d'entrée. Un réseau de comparateurs convertit la tension analogique d'entrée à partir de références analogiques en code de type thermomètre. Ainsi, un décodeur est nécessaire pour la conversion de ce code en un code binaire de pratique plus courante. Les tensions de comparaison sont générées habituellement par une échelle de résistances pondérées. Ces tensions de référence sont divisées en  $2^N$  niveaux analogiques qui sont respectivement comparés avec la tension d'entrée du convertisseur. La figure 2.10 représente un convertisseur de type Flash standard.

**Figure 2.10- Convertisseur Flash standard**

Ce type de convertisseur occupe un espace qui croît exponentiellement avec la résolution. Par exemple, un convertisseur de 8 bits nécessite 255 comparateurs. Habituellement, les concepteurs de convertisseurs se limitent à une résolution de 8 bits pour des raisons de surface et de puissance consommée. L'exactitude de ce convertisseur repose sur l'idéalité de l'échelle de résistances et des comparateurs.

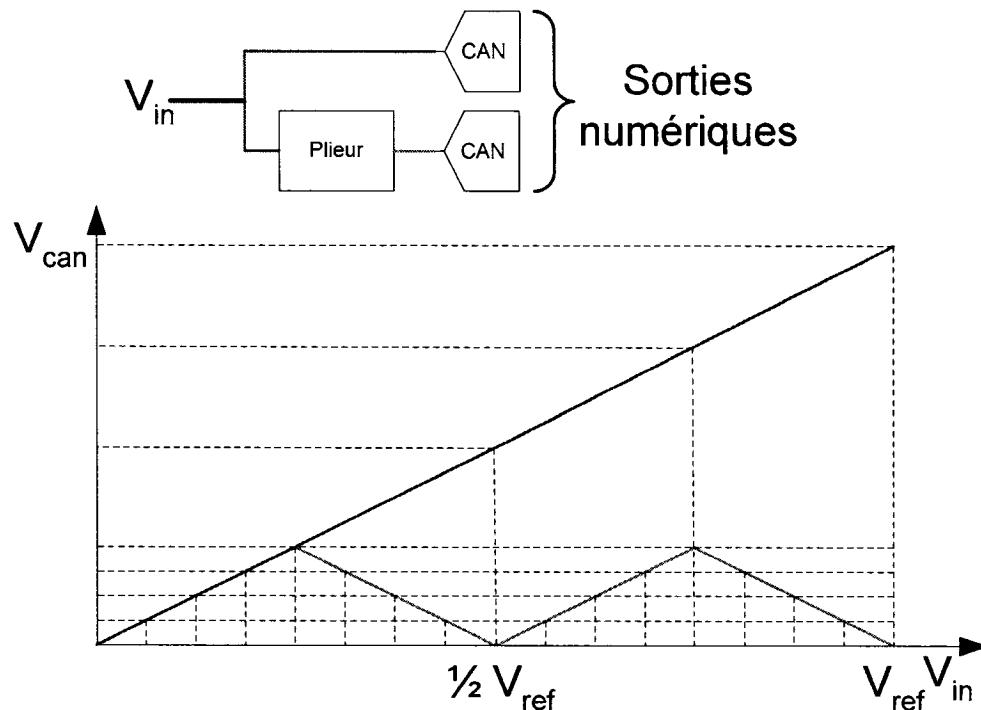

### 2.3.5. Convertisseurs Flash pliés

Les convertisseurs à pliage sont considérés comme des convertisseurs de type Flash. Le principe de ces convertisseurs est de séparer le signal en deux pour être ensuite convertis par deux convertisseurs ayant une plus faible résolution, mais étant beaucoup

plus rapides. La fonction de transfert du module « Plier » est représentée à la figure 2.11.

**Figure 2.11 - (a) Convertisseur à pliage (b) Fonction de transfert du plieur**

Cette configuration permet de séparer les deux CAN indépendamment dans le temps. Ceci signifie que le deuxième convertisseur ne doit pas attendre la fin de la conversion du premier. Ils sont utilisés dans des applications à haute vitesse, mais nécessitant une faible résolution. Les modules « plieurs » sont souvent complexes et non linéaires, ce qui explique que les concepteurs ne les utilisent que dans des applications à basse résolution nécessitant de hautes fréquences d'opération. Par exemple, les convertisseurs qu'on retrouve dans les appareils de mesure de laboratoire performants

peuvent atteindre des fréquences d'échantillonnage de quelques Giga Hertz, mais ils n'ont que 6 ou 7 bits de résolution [28].

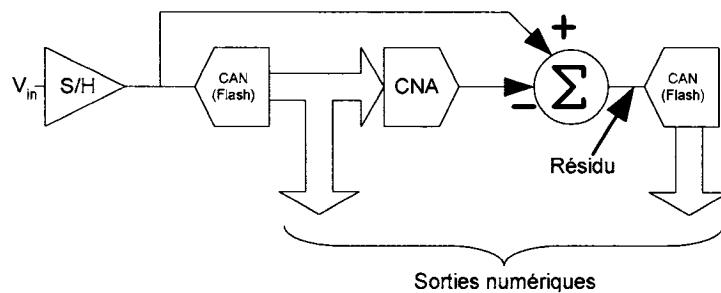

### 2.3.6. Convertisseurs à plusieurs étapes

Un autre type de convertisseur est appelé convertisseur à plusieurs étapes. Le principe de base est présenté à la figure 2.12 avec l'exemple d'un convertisseur à deux étapes. Le CAN est séparé en deux convertisseurs « Flash complet ». Le premier convertisseur donne une estimation grossière de l'entrée, tandis que le second effectue une conversion affinée. Ainsi, la sortie est une concaténation des mots de sortie des deux convertisseurs. Cette architecture permet de réduire considérablement le nombre de comparateurs utilisés dans le convertisseur ; pour un convertisseur « Flash complet » de 8 bits, plus de 255 comparateurs ( $2^N-1$ ) doivent être utilisés, tandis qu'avec un convertisseur à deux étapes, seulement 30 comparateurs  $2(2^{N/2}-1)$  sont nécessaires.

Figure 2.12 - Convertisseur à plusieurs étapes, deux étapes

Cette architecture a un temps de conversion plus important qu'un convertisseur « Flash » complet. Le temps de conversion est multiplié par le nombre d'étage plus le temps nécessaire pour faire la soustraction. Habituellement, le résidu est amplifié avant d'entrer dans un étage subséquent. Ce type de convertisseur nécessite un soin important de la conception du soustracteur et de l'amplificateur de résidu, car dans un convertisseur ayant plusieurs étages, les troncations dues au dépassement de la plage d'entrée sont courantes. Aussi les amplificateurs créent des distorsions et du bruit, ce qui rend encore plus complexe leurs réalisations.

### 2.3.7. Convertisseurs en pipeline

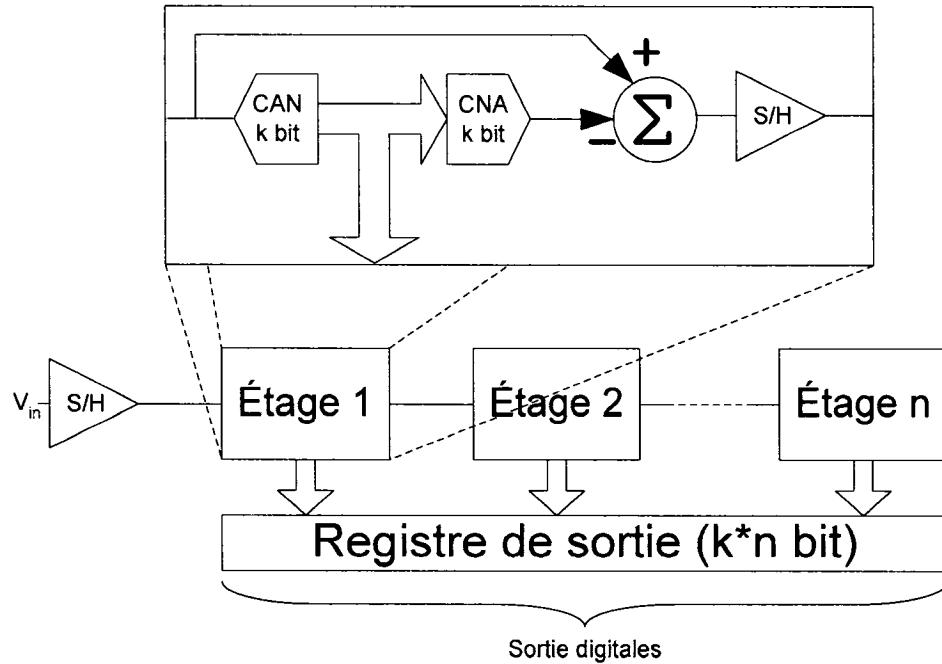

Étant donné que le dernier étage d'une architecture à plusieurs étapes doit attendre tous les autres étages pour faire sa conversion, la vitesse s'en voit grandement diminuée. Ainsi, il est possible d'utiliser la technique du pipeline pour réduire le temps perdu en attente d'un signal valide. En ajoutant un échantillonneur/bloqueur à la fin de chaque étage d'un convertisseur à plusieurs étapes, les étages de conversion deviennent quasi indépendantes dans le temps. La figure 2.13 montre un schéma bloc d'un convertisseur en pipeline.

**Figure 2.13 - Convertisseur en pipeline**

Les registres de sortie doivent synchroniser les mots de chaque étage pour les rendre valide entre eux. De simples registres en cascade font facilement le travail. Ce type de convertisseur est malheureusement plus sensible aux non-idealités provenant des échantillonneurs/bloqueurs qui sont habituellement porteurs de distorsion. Ce type de convertisseur peut atteindre des cadences de 50 MÉ/s à une résolution de 10 bits.

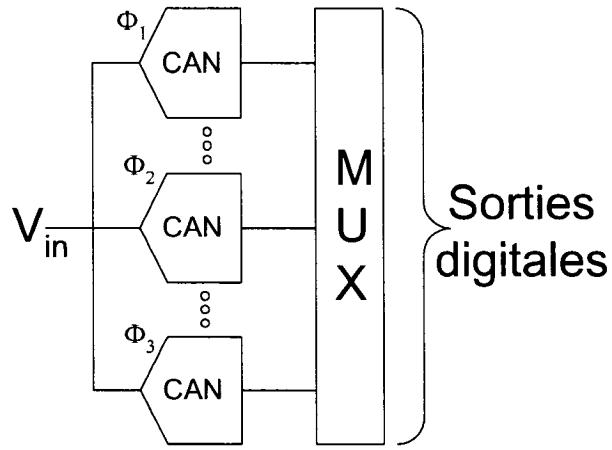

### 2.3.8. Convertisseurs parallèles

Lorsqu'une meilleure vitesse de conversion est nécessaire dans une application, les règles du parallélisme peuvent être appliquées. La figure 2.14 présente le principe derrière le parallélisme.

**Figure 2.14 - convertisseur parallèle**

L’architecture est composée de plusieurs canaux ayant leurs propres convertisseurs.

Chaque canal a sa propre phase dans la conversion d’un signal. Ainsi tous les autres canaux sont déphasés par rapport aux autres. Cette architecture permet théoriquement de multiplier la fréquence d’opération par un facteur égalant le nombre de canaux. Par contre, le fait de rajouter des canaux multiplie le matériel utilisé par ce même facteur. Un autre désavantage potentiel est dû à l’appariement non idéal des canaux entre eux, ce qui génère du bruit harmonique dans les conversions à la fréquence du convertisseur pour ainsi diminuer de façon considérable l’indice SFDR.

## 2.4. Perfectionnements

Pour améliorer les performances en terme d'exactitude, les concepteurs ont élaboré plusieurs techniques ne nécessitant pas d'intervention extérieure. Ces techniques permettent de rendre les convertisseurs insensibles aux variations extérieures. Deux des techniques les plus utilisées dans l'industrie sont expliquées dans cette section; la correction digitale des erreurs par redondance [14] et la calibration.

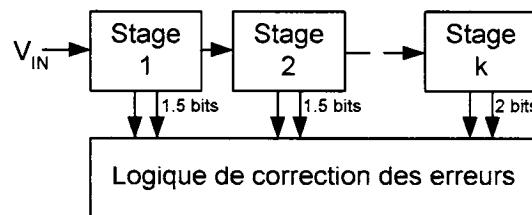

### 2.4.1. Correction numérique des erreurs

Cette technique améliore la linéarité des CAN dans les étages d'un convertisseur à plusieurs étapes. À l'aide de la redondance, il est possible après traitement numérique d'obtenir une linéarité accrue. Elle permet de diminuer la sensibilité aux imperfections des comparateurs présents dans les convertisseurs « Flash ». En fait, elle annule les effets de décalage pouvant être présents dans les convertisseurs « Flash » internes. La figure 2.15 représente la structure requise pour effectuer cette correction d'erreur.

**Figure 2.15 - Architecture requise pour la correction numérique des erreurs**

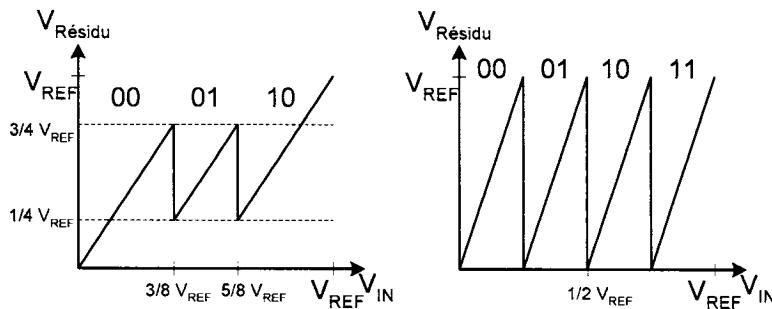

Ainsi, ce type d'amélioration n'est possible qu'avec les architectures à plusieurs étapes ou les architectures pipelinées. Les premiers convertisseurs « Flash » ne sont pas de 2 bits mais bien de 1.5 bits bien qu'il y ait 2 lignes de donnée permettant une transmission de 2 bits. La figure 2.16 montre les fonctions de transfert associées à un étage de 1.5 bits et à un étage de 2 bits standard.

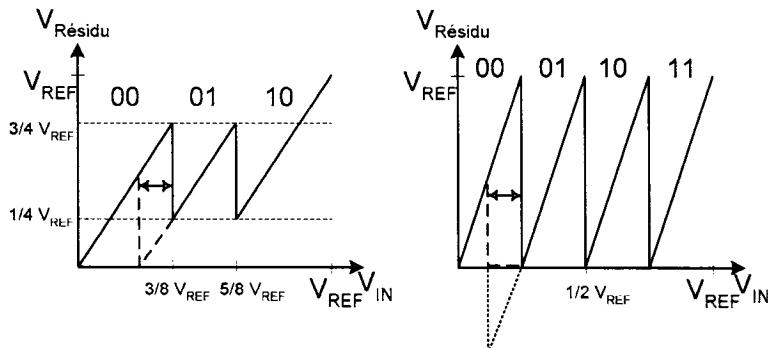

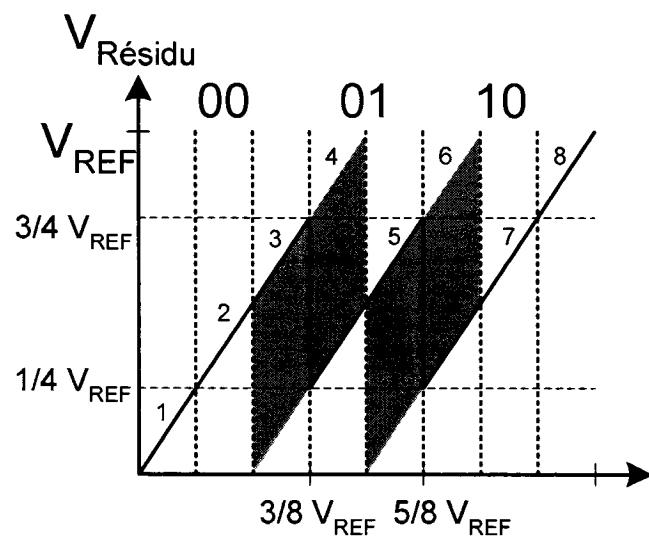

Figure 2.16 - Fonction de transfert d'un étage de 1.5 bits et de 2 bits

Ces fonctions de transfert montrent le cheminement du résidu ( $V_{\text{Résidu}}$ ) dans un étage de convertisseur, les discontinuités représentent le moment où un comparateur du CAN bascule dans un autre état. Ainsi, cette discontinuité représente directement les tensions de référence des comparateurs et leur tension de décalage. Un code est manquant dans le convertisseur de 1.5 bits et le résidu n'excède les limites de  $\frac{1}{4}$ - $\frac{3}{4} V_{\text{REF}}$  qu'aux extrémités de la fonction de transfert. La figure 2.17 montre l'effet d'une tension de décalage sur les fonctions de transfert de convertisseurs de 2 bits et de 1.5 bits.

**Figure 2.17 - Effet d'une tension de décalage sur les fonctions de transfert**

Dans le cas d'un convertisseur de 2 bits, il y a troncation du résidu, ce qui implique une perte d'information ; tandis que dans un convertisseur de 1.5 bits, il n'y a pas ce type de saturation sauf pour une tension de décalage trop grande. Lorsqu'il y a une erreur de décalage dans la fonction de transfert, il y a nécessairement un dépassement de la limite du résidu de  $\frac{1}{4}$ - $\frac{3}{4}$   $V_{REF}$  ce qui permet de détecter rapidement les erreurs. Ainsi, lorsque le résidu est inférieur à  $\frac{1}{4} V_{REF}$ , le résultat est nécessairement faux et inférieur à ce qu'il doit être. De l'autre côté de la limite, le résultat est supérieur à la valeur obtenue. À partir de cette méthode de détection des erreurs, les étages subséquents doivent pouvoir d'une certaine façon remédier à la lacune de cet étage. Pour une valeur supérieure à la réalité, il faut additionner un « 1 » logique par-dessus le dernier bit de la valeur erronée. Pour une valeur inférieure à la réalité, il n'y a tout simplement rien à faire, car la valeur associée à la conversion est déjà plus petite que dans un convertisseur standard. De cette façon, il est facile de corriger les erreurs en effectuant une addition standard et en juxtaposant les derniers bits d'un étage au premier de l'étage suivant. La

figure 2.18 montre un exemple de correction d'erreur pour un convertisseur de 8 bits composé de 6 étages de 1.5 bits et d'un dernier de 2 bits standard.

|         |   |   |   |   |   |   |   |   |

|---------|---|---|---|---|---|---|---|---|

| Étage 1 | 1 | 0 |   |   |   |   |   |   |

| Étage 2 |   | 0 | 1 |   |   |   |   |   |

| Étage 3 |   |   | 0 | 1 |   |   |   |   |

| Étage 4 |   |   |   | 0 | 1 |   |   |   |

| Étage 5 |   |   |   |   | 0 | 1 |   |   |

| Étage 6 |   |   |   |   |   | 0 | 1 |   |

| Étage 7 |   |   |   |   |   |   | 1 | 0 |

| Sortie  | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

**Figure 2.18 - Exemple de traitement de l'unité de correction d'erreur**

Il est essentiel d'utiliser un convertisseur standard au dernier étage pour que le convertisseur parcoure toute la plage de conversion. En effet, si le convertisseur n'est composé que d'étage à redondance, le code le plus élevé ne peut être généré par l'unité de correction des erreurs.

Aussi, il est possible d'utiliser la même logique pour des étages ayant une résolution supérieure ; par exemple, un étage de 2.5 bits. L'annexe II de ce document démontre en détail le fonctionnement de la correction des erreurs par redondance.

#### 2.4.2. Calibration externe

Les manufacturiers utilisent des techniques de calibration externes pour améliorer la linéarité des convertisseurs. Ces techniques consistent habituellement à une calibration matérielle par laser pour ajuster les valeurs relatives des résistances ou des condensateurs utilisés. En plus, certaines architectures permettent une calibration numérique ; les résultats sont traités par une unité logique programmable qui associe les résultats du convertisseur aux résultats réels contenus dans une table de correspondance programmée à la fabrication. Ces techniques ne sont pas robustes, car une variation de l'environnement du circuit peut facilement rendre la calibration inutile.

#### 2.4.3. Auto-calibration

Pour rendre le système insensible aux variations des gains et des tensions de décalage entre les étages d'un convertisseur, les chercheurs ont présentés plusieurs méthodes pour effectuer une calibration interne. Ces différentes méthodes peuvent se regrouper en deux catégories, soit les méthodes analogiques ou mixtes et les méthodes numériques.

##### 2.4.3.1. Auto-calibration mixte

Les méthodes dites analogiques interviennent en modifiant des paramètres matériels du circuit. Les premiers types de convertisseur auto-calibrable [13], [15], modifient les propriétés du convertisseur en ajustant les rapports de capacité des condensateurs. Les

capacités utilisées sont modifiées par l'ajout ou la soustraction d'une capacité en parallèle et parfois même en série. Par exemple, la technique utilisée par Lin [15], détermine si deux condensateurs sont égaux en modifiant quelque peu la configuration d'un étage pipeliné. La technique permet aussi de déterminer le sens de l'inégalité grâce au comparateur déjà utilisé dans l'architecture. Un algorithme permet, en plusieurs essais, de converger vers cette égalité voulue. Ainsi, il est possible d'ajuster le gain et la soustraction des étages pipelinés à la précision voulue. Il faut noter que ces techniques n'utilisent aucun élément de référence, si ce n'est que leur propre tension de référence. Les convertisseurs répertoriés utilisant ce type de calibration opèrent à une cadence maximale de 5 MHz et ont une précision d'une douzaine de bits.

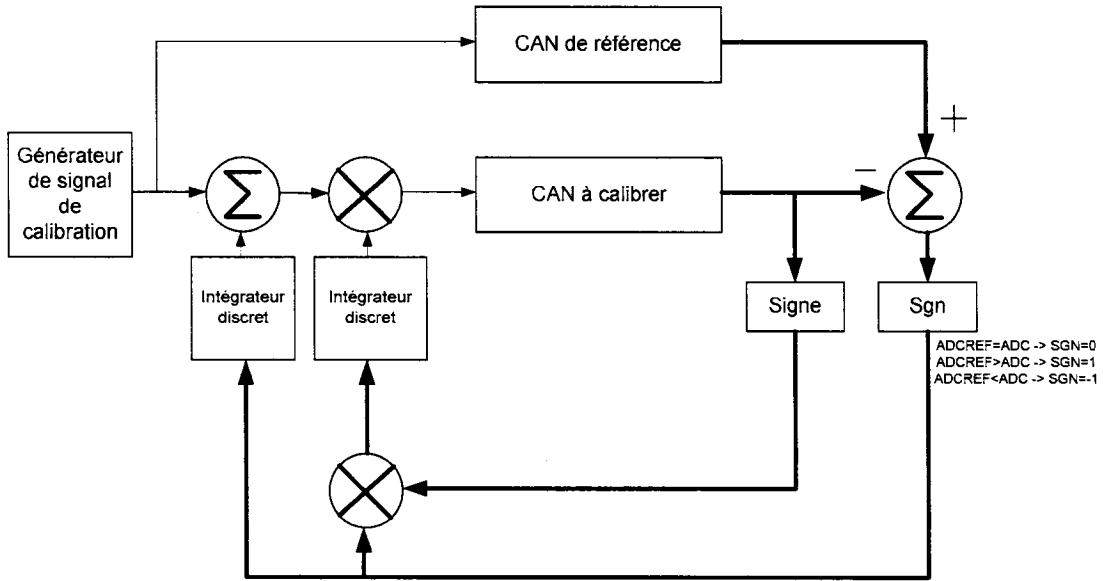

D'autres techniques mixtes, utilisent un convertisseur de référence [3], [8]. Ces convertisseurs de références sont typiquement des convertisseurs mis en œuvre selon une autre architecture qui produit des résultats beaucoup plus exacts, mais qui a une fréquence d'opération relativement lente. Les convertisseurs Sigma-Delta sont souvent utilisés pour cette besogne. La figure 2.19 propose une architecture de calibration mixte [3] utilisant une boucle des moindres moyennes carrées (LMS). Un signal de calibration analogique est converti par un CAN de référence et par le CAN à calibrer. L'algorithme LMS permet de converger vers un gain et une tension de décalage optimale.

**Figure 2.19 - Architecture de calibration mixte LMS**

Cette technique vise essentiellement à marier plusieurs canaux parallèles éliminant les problèmes de dégradations du “Spurious Free Dynamic Range” (SFDR). Ainsi, la calibration s’effectue seulement devant chaque canal d’un convertisseur parallèle.

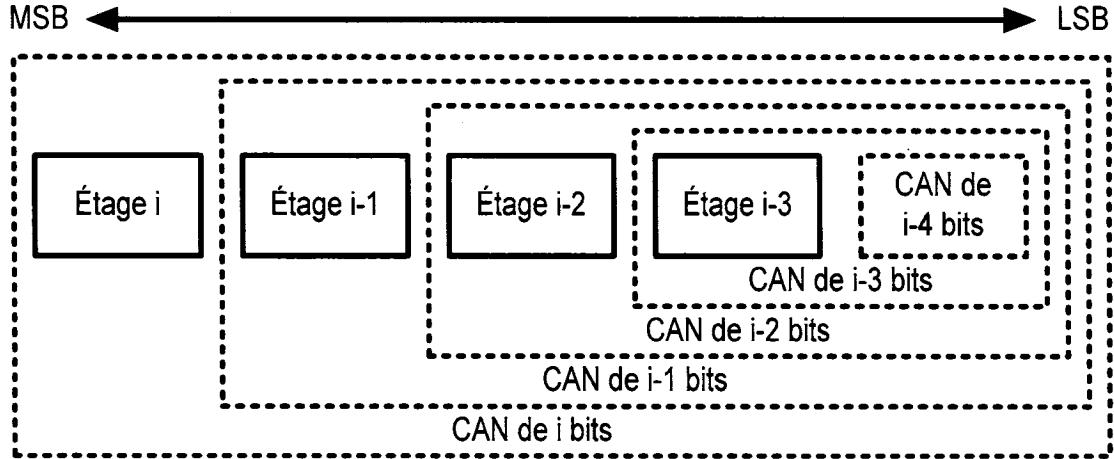

Il est possible d’utiliser cette même architecture et algorithme pour calibrer les étages internes d’un convertisseur pipeliné [16]. En effet, un convertisseur pipeliné peut se décomposer en plusieurs convertisseurs selon la figure 2.20.

**Figure 2.20 – Décomposition d'un convertisseur pipeliné**

La calibration commence par le convertisseur le plus petit, l'étage le moins significatif. Lorsque cet étage est calibré, ces caractéristiques maintenant quasi idéales permettent de créer un convertisseur ayant un étage de plus. Maintenant, il est possible de calibrer ce premier étage du nouveau convertisseur sans que l'étage subséquent affecte la calibration. Cette procédure est répétée jusqu'à ce que tous les étages du convertisseur soient calibrés.

Aucune technique de calibration mixte ne peut corriger les erreurs causées par le gain non linéaire ou la distorsion des étages. Ainsi, pour utiliser ce type de technique, il est de mise d'avoir des étages ayant des caractéristiques analogiques très linéaires.

### 2.4.3.2. Auto-calibration numérique

Les méthodes dites numériques modifient directement la sortie du convertisseur non calibré à partir d'un traitement numérique ou d'une table de correction. La figure 2.21 présente un schéma simplifié de ce type de technique.

**Figure 2.21 – Architecture de calibration numérique simplifiée**

Le traitement numérique utilise un modèle du convertisseur ainsi que des paramètres de non-idealité extraits du convertisseur. Aussi, le convertisseur peut être calibré par une table de correction contenant les codes idéaux associés aux codes non idéaux.

D'une technique à l'autre, seule la façon d'estimer ou d'évaluer les corrections différencie les techniques. Le reste de cette section, portera sur plusieurs façons d'estimer ou d'évaluer les corrections.

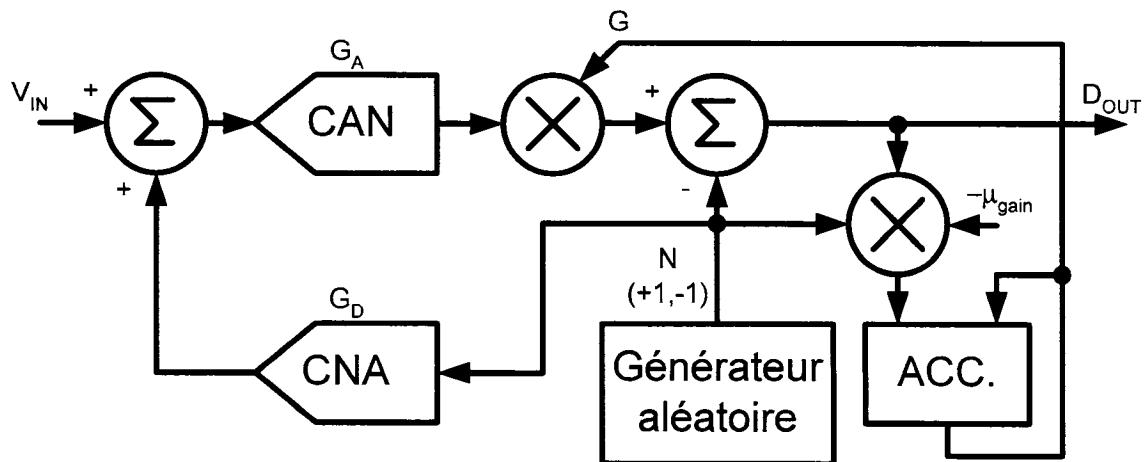

La technique suivante proposée par Dyer [7] permet de déterminer le gain adéquat pour compenser un convertisseur. La figure 2.22 montre le schéma bloc de cette architecture de calibration. Cette technique utilise un algorithme des moindres moyennes carrées pour ajuster le gain du convertisseur à calibrer.

Figure 2.22 – Architecture de calibration numérique LMS

L'équation 2.4 détermine le gain de compensation  $G$  où  $\mu_{\text{gain}}$ ,  $N$  et  $D_{\text{out}}$  sont respectivement le pas de l'algorithme, une valeur produite par un générateur pseudo-aléatoire et la sortie du convertisseur.

$$G[n + 1] = G[n] - \mu_{\text{gain}}N[n]D_{\text{out}}[n] \quad (2.4)$$

L'équation 2.5 permet de déterminer la sortie du convertisseur calibré par rapport au gain du CAN sous calibration  $G_A$ , du gain du CNA  $G_D$ , du gain de compensation, du nombre aléatoire  $N$  et de l'entrée analogique.

$$Dout[n] = G_A G[n] Vin[n] + G_D G_A G[n] N[n] - N[n] \quad (2.5)$$

$\mu gain$  étant le pas utilisé par l'algorithme.

Il est à noter que le signal ajouté avant la conversion est soustrait plus tard dans le traitement numérique. La substitution, de 2.5 dans 2.4 donne,

$$G[n+1] = G[n] + \mu gain - \mu gain G_A G_D G[n] - \mu gain G_A G[n] N[n] S[n] \quad (2.6)$$

En considérant que  $N[n]$  possède une moyenne égalant zéro car cette variable est générée par un générateur pseudo aléatoire, alors,

$$\overline{G[n+1]} = \mu gain + \overline{G[n]}(1 - \mu gain G_A G_D) \quad (2.7)$$

Si la moyenne de variable  $G[n]$  converge,

$$\lim_{n \rightarrow \infty} \overline{G[n+1]} = \lim_{n \rightarrow \infty} \overline{G[n]} \quad (2.8)$$

Par substitution de 2.8 dans 2.7,

$$G[\infty] = \frac{1}{G_D G_A} \quad (2.9)$$

Donc,

$$G_A G[\infty] = \frac{1}{G_D} \quad (2.10)$$

L'algorithme de cette technique permet de trouver le gain de compensation ( $G$ ) pour que le gain du CAN calibré ( $G_A G$ ) soit égal à l'inverse du gain du CNA ( $1/G_D$ ). Cette technique est surtout utile pour marier plusieurs canaux de conversion parallèles car elle ne calibre que le gain global d'un convertisseur. Cette technique ne tient pas compte de la non-linéarité du convertisseur. Une méthode légèrement modifiée permet de compenser les tensions de décalage entre plusieurs canaux.

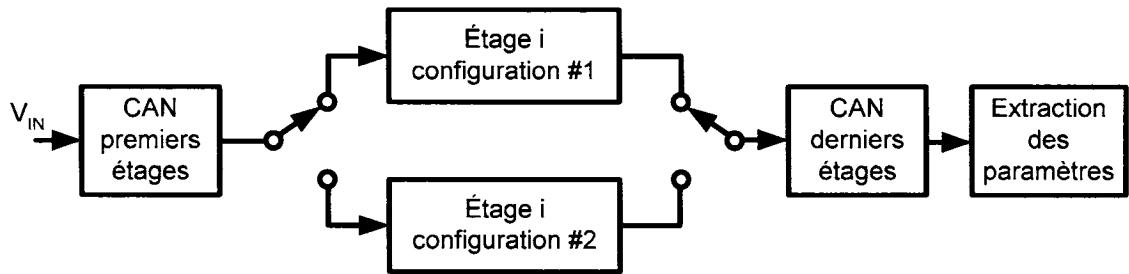

El-Sankary a développé un algorithme permettant de déterminer les gains de chaque étage d'un convertisseur pipeliné [5]. La technique proposée nécessite des étages ayant plusieurs configurations. C'est en changeant ces configurations fréquemment et en analysant leur réponse dans le domaine fréquentiel qu'elle peut déterminer le gain adéquat pour chaque étage. La figure 2.23 montre le principe de base de cette technique.

**Figure 2.23 – Architecture de calibrage numérique par changement de configuration**

En se basant sur la théorie de convertisseur parallèle [3], l'erreur de gain entre les deux configurations génère une image de bande lorsque les deux configurations s'interchangent à une fréquence donnée. L'analyse fréquentielle permet d'extraire les ratios de gain entre les configurations utilisées. En obtenant ces ratios de gain, il est possible de déterminer avec précision le gain à utiliser pour chaque étage. Toujours de type linéaire, cette technique ne corrige pas les gains non-linéaires. Par contre, elle permet d'ajuster le gain entre chaque étage et ainsi réduire considérablement les spécifications de gain des amplificateurs opérationnels.

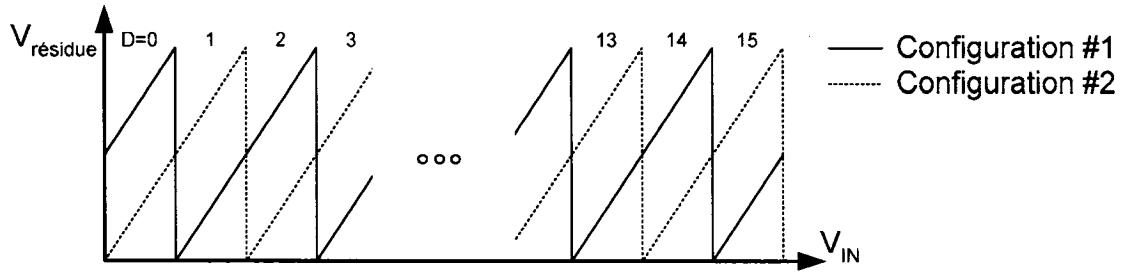

Murmann et Boser [17] ont pour leur part utilisé une technique similaire pour leur convertisseur. Leurs étages peuvent se changer en deux configurations, les fonctions de transfert de ces configurations sont présentées à la figure 2.24.

**Figure 2.24 – Fonction de transfert des configurations utilisées**

Il est à noter que la première configuration correspond à un étage de 4 bits standard tandis que la deuxième configuration correspond à un étage de 4 bits avec redondance.

Par un algorithme d'estimation de paramètre basé sur la statistique, il est possible de déterminer les compensations adéquates des gains non linéaires selon un modèle du troisième ordre. Aussi, l'algorithme tient compte des tensions de décalage et des erreurs présentes dans les CNA internes aux étages. Le prototype créé à partir de cette technique atteint une cadence de 75 MÉ/s avec 11 bits effectifs d'exactitude. Ici, la calibration corrige assez de non-idealité pour laisser tomber les amplificateurs à rétroaction habituellement nécessaire à cette précision.

Les techniques d'estimation de la linéarité par histogramme telle que celle présentée par Eduri [4], construisent un histogramme de densité de code qui permet de déterminer les non-linéarités et d'estimer les compensations nécessaires. La technique présentée par Eduri construit une table de correspondance à partir des histogrammes de deux CAN. Le premier CAN est le convertisseur à calibrer, le second est un CAN du même type que le

premier mais échantillonne le signal d'entrée avec une atténuation. Le système de calibration construit un histogramme par CAN avec un nombre élevé d'échantillon. Les histogrammes normalisés dans le cas de deux CAN parfaitement linéaires devraient être identiques. L'algorithme tente par la suite de déterminer en premier lieu la tension de décalage et l'atténuation entre les deux CAN. Lorsque ces paramètres sont déterminés, il est possible de déterminer les non-linéarités provoquant les différences entre les deux histogrammes.

D'autre technique de calibration numérique [12], [20] utilisent des façons plus directes pour déterminer les paramètres de compensation. L'injection de signaux de calibration et le forçage d'état de comparateur peuvent déterminer les gains et les tensions de décalage présents dans un étage. La technique proposée par Ravindran [20] permet même l'estimation non linéaire des gains.

## 2.5. Choix d'une architecture

Le tableau 2.1 présente des exemples de performance provenant de la littérature pour chaque architecture vue précédemment. Il est clair qu'une architecture pipelinée est indispensable pour atteindre les spécifications de ce projet. En effet, c'est la seule architecture qui permet d'obtenir un nombre effectif de bit se rapprochant de 10 à une cadence acceptable élevée. Comme énoncé dans la section 2.3, ce type de convertisseur peut atteindre des cadences de 50 MÉ/s. Alors, deux choix s'imposent, utilisez la technique de convertisseur parallèle ou améliorer le pipeline pour atteindre les 200 MÉ/s requis avec une résolution de 10 bits.

**Tableau 2.1 - Exemple de performance pour une architecture donnée**

| Architecture                  | ENOB (bit) | Fréquence d'échantillonnage (É/s) |

|-------------------------------|------------|-----------------------------------|

| Approximation successive [21] | 8.9        | 150K                              |

| Intégration [10]              | 12         | 1K                                |

| Sigma Delta [29]              | 18.5       | 384K                              |

| Flash [27]                    | 5          | 1.3G                              |

| Pliée [24]                    | 5.9        | 200M                              |

| 2 étapes [31]                 | 9.67       | 10M                               |

| Pipelinée [6]                 | 9.8        | 50M                               |

| Parallèle/Pipelinée [25]      | 8.8        | 200M                              |

Sumanem [25] montre qu'il est possible d'atteindre la cadence voulue en utilisant la technique de parallélisation avec l'architecture pipelinée. Par contre, même en utilisant la technique de correction des erreurs par redondance et une technique numérique d'annulation des tensions de décalage, il est difficile d'atteindre les spécifications de linéarité voulues sans utiliser d'autres techniques.

Ainsi, le choix se portera sur l'utilisation d'un convertisseur pipeliné utilisant une technique de calibration numérique. La calibration analogique étant écartée, car les distorsions produites par les amplificateurs sont très difficilement compensables analogiquement [16]. La calibration numérique permettra d'atteindre les spécifications de linéarité voulues. Pour ce qui est de la vitesse de conversion, la technique de parallélisation pourra être utilisée si nécessaire, car en utilisant la technique de

calibration numérique, il est possible d'utiliser des circuits simples et rapides pour atteindre les spécifications de linéarité.

## CHAPITRE III

### MODÈLE ET CALIBRATION

#### 3.1. Modèle des convertisseurs pipelinés

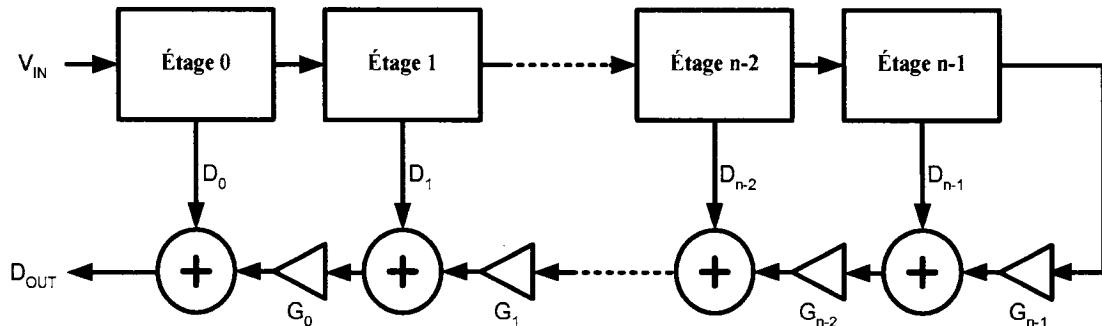

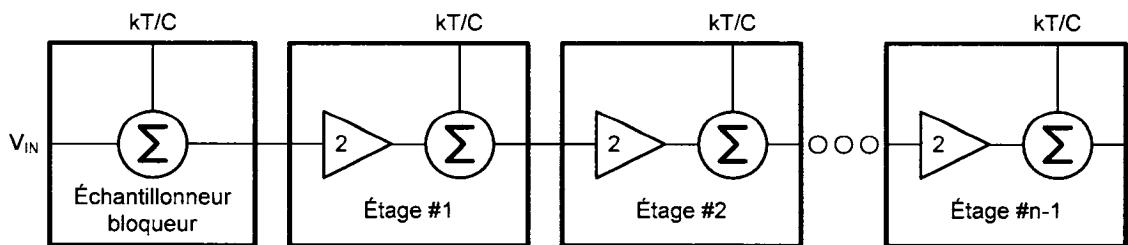

Un convertisseur pipeliné de  $n$  étages peut être représenté par le modèle de la figure 3.1. Le code de sortie est reconstruit selon les gains numériques ( $G_0$  à  $G_{n-1}$ ). Ces gains ont pour valeur l'inverse des gains analogiques de chaque étage. Par exemple, si l'étage  $n-1$  est un étage de 1 bit idéal, il faut que son gain analogique soit idéalement de  $2^1$ . Donc, le gain numérique  $G_{n-1}$  doit être de  $1/2^1$ . Pour un convertisseur n'ayant que des étages idéaux standards, les sorties numériques ( $D_0$  à  $D_{n-1}$ ) peuvent être transposées directement à la sortie, quelle que soit la largeur binaire de chaque étage.

Figure 3.1 - Convertisseur pipeliné de  $n$  étages

Il est à noter à cette étape, que l'erreur produite par un premier étage non idéal a un impact  $1/G_0$  fois plus important que son étage adjacent.

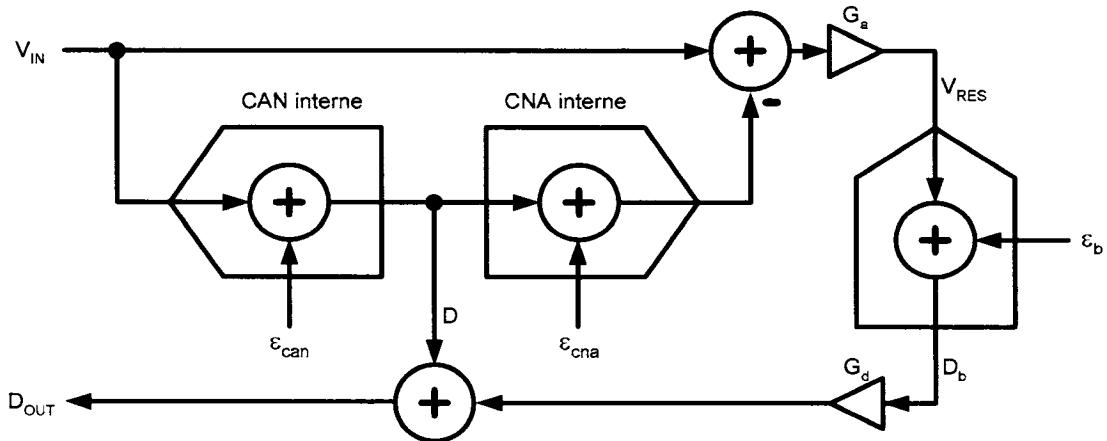

La figure 3.2 présente le modèle d'un étage pipeline non idéal de n bits. Les différents paramètres qu'on retrouve dans la figure 3.2 sont expliqués au tableau 3.1. Ce modèle a été élaboré à partir d'un modèle simplifié provenant des travaux de Murmann et Boser [17].

Figure 3.2 – Modèle d'un étage pipeliné

Les équations 3.1 et 3.2 montrent la relation entre la sortie, l'entrée et les différents paramètres de la figure 3.2.

$$D_{OUT} = (V_{IN} + \varepsilon_{CAN}) + (G_d(G_a(V_{IN} - (V_{IN} + \varepsilon_{CAN} + \varepsilon_{CNA})) + \varepsilon_b)) \quad (3.1)$$

$$D_{OUT} = (V_{IN} + \varepsilon_{CAN}) + (G_d(-G_a(\varepsilon_{CAN} + \varepsilon_{CNA}) + \varepsilon_b)) \quad (3.2)$$

La fonction de transfert du gain analogique ( $G_a$ ) est rarement linéaire sur toute la plage du convertisseur. Pour obtenir une conversion idéale, il faut que  $D_{OUT}$  soit égal à  $V_{IN}$ . Ainsi, on peut déterminer le gain digital à appliquer pour obtenir une conversion idéale.

$$G_d = \frac{\varepsilon_{CAN}}{G_a(\varepsilon_{CAN} + \varepsilon_{CNA}) - \varepsilon_b} \text{ si } D_{OUT} = V_{IN} \quad (3.3)$$

**Tableau 3.1- Paramètres du modèle d'un étage pipeliné**

| Paramètre           | définition                                                                                                       |

|---------------------|------------------------------------------------------------------------------------------------------------------|

| $\varepsilon_{CAN}$ | Erreur de quantification et de non-idéalité du CAN interne (fonction de type échelon)                            |

| $\varepsilon_{CNA}$ | Erreur du CNA interne provenant des non-idéalités (fonction de type échelon)                                     |

| $\varepsilon_b$     | Erreur de quantification et de non-idéalité des étages pipelinés subséquents combinés (fonction de type échelon) |

| $G_a$               | Gain analogique (comprend les non linéarités)                                                                    |

| $G_d$               | Gain digital                                                                                                     |

| $V_{RES}$           | Résidu de conversion de l'étage                                                                                  |

| $D$                 | Code obtenu par l'étage                                                                                          |

| $D_b$               | Code obtenu par les étages pipelinés subséquents                                                                 |

Il devient donc possible de compenser un convertisseur pipeliné complet en appliquant à la partie numérique une fonction de transfert adéquate. Une autre façon de procéder serait d'appliquer des compensations à chaque étage. De cette façon le terme  $\varepsilon_b$  est compensé à chaque étage, ainsi l'équation 3.4 devrait être utilisée pour compenser localement les non-idéalités.

$$G_d = \frac{\varepsilon_{CAN}}{G_a(\varepsilon_{CAN} + \varepsilon_{CNA})} \quad (3.4)$$

Il va sans dire que ces analyses ne sont valides que si la fonction de conversion possède une fonction inverse. De cette façon, il est possible de trouver l'inverse de la fonction et de linéariser le convertisseur. Pour que la fonction de conversion possède un inverse, il faut que la fonction de conversion soit strictement croissante. En termes pratiques, il faut éviter la saturation et s'assurer que les erreurs des CAN et des CNA internes ne provoquent pas des retours arrière.

### 3.2. Calibration

Cette section présente un exemple d'architecture de calibration numérique et les simulations effectuées pour la valider. Cet exemple sera utilisé plus tard pour les simulations et l'intégration du circuit intégré réalisé dans le cadre de cette recherche.

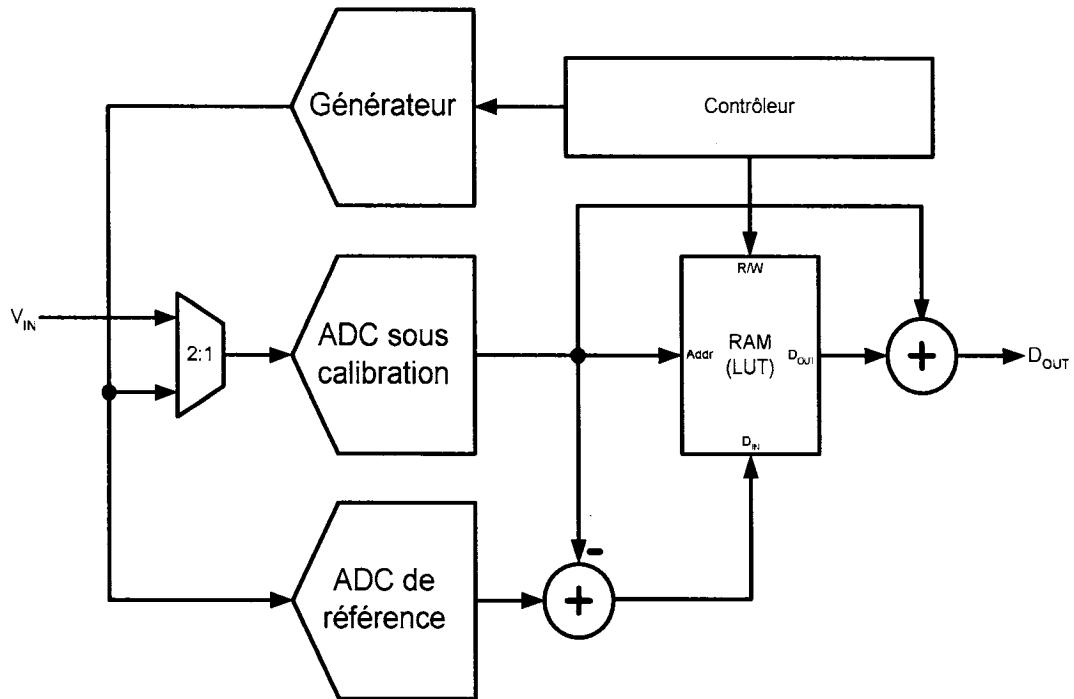

### 3.2.1. Architecture

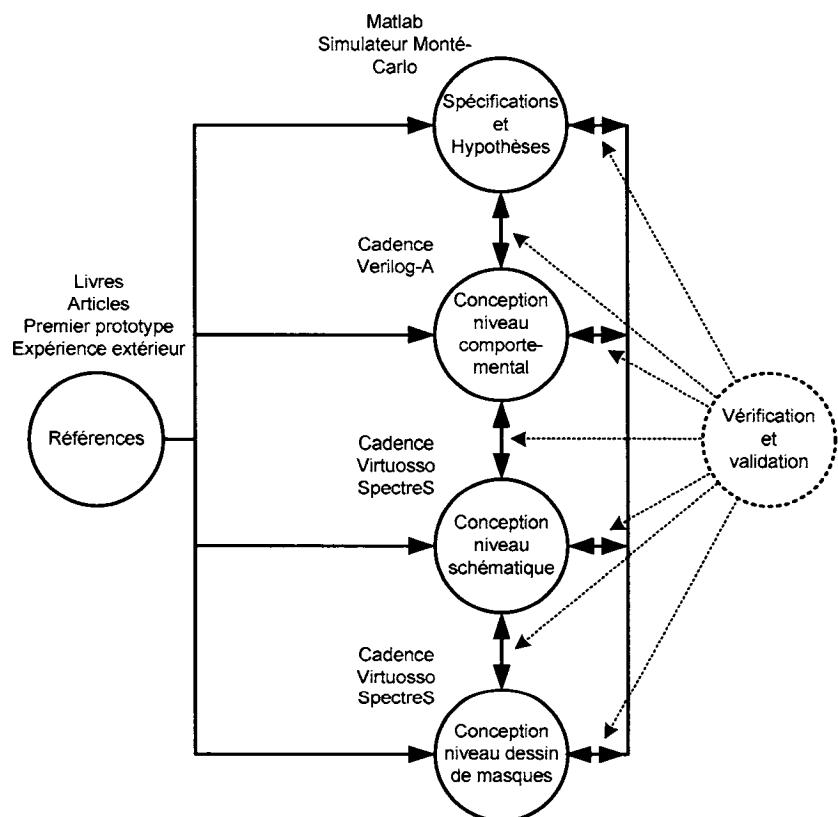

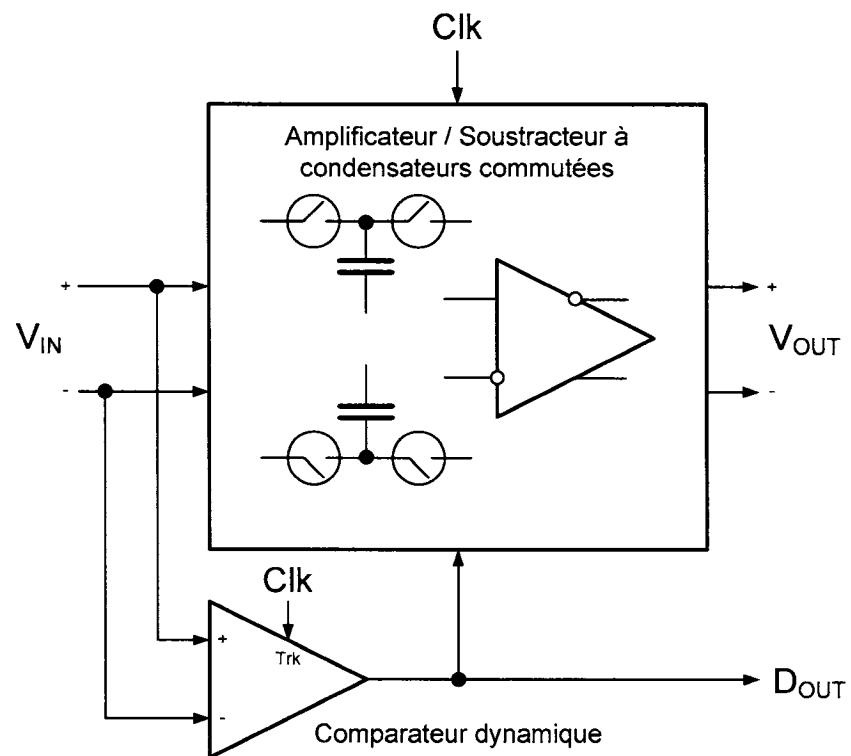

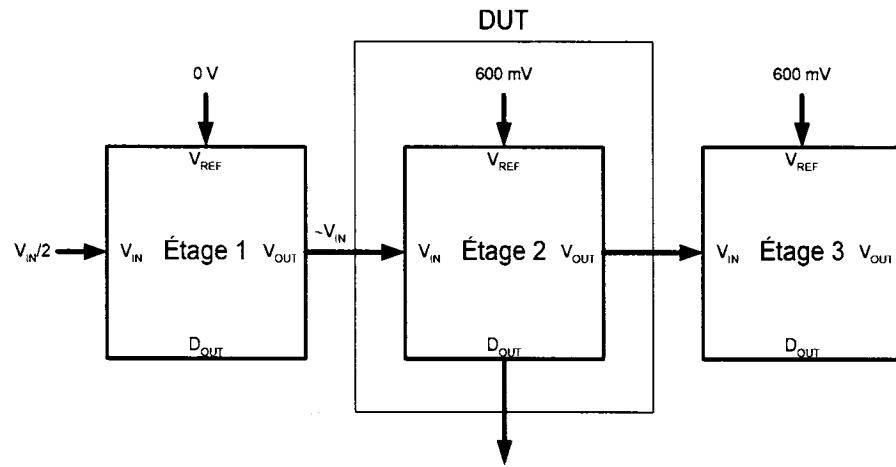

La figure 3.3 montre une architecture possible et simplifiée de calibration numérique. On peut analyser cette architecture en deux opérations. La première étant l'opération de conversion, l'entrée analogique  $V_{IN}$  est dirigée vers le convertisseur sous calibration par un multiplexeur analogique. Le convertisseur effectue la conversion qui sert d'entrée d'adressage d'une mémoire RAM. Dans cette mémoire se retrouve la compensation adéquate pour chaque code de sortie du convertisseur sous calibration. En emmagasinant seulement la compensation et non les codes compensés, il est possible de réduire considérablement la taille de la mémoire à utiliser.

La deuxième opération permet de remplir la mémoire avec une compensation idéale. Un générateur de signaux injecte simultanément un signal de calibration dans le convertisseur sous calibration et dans un convertisseur de référence. Le convertisseur de référence doit posséder la linéarité voulue pour le convertisseur sous calibration. Les convertisseurs de haute précision tels que les convertisseurs Delta Sigma ou à approximations successives ont habituellement une bonne linéarité, mais nécessitent un temps plus important pour effectuer la conversion. Lorsque les conversions sont terminées, la différence entre les deux codes de sortie est enregistrée dans la mémoire. Cette opération doit être effectuée plusieurs fois pour parcourir toute la plage d'entrée du convertisseur sous calibration. De cette façon, chaque code de sortie du convertisseur sous calibration aura sa compensation dans la mémoire.

**Figure 3.3 - Architecture de calibration numérique**

Lorsque l'opération de calibration est terminée, le convertisseur sous calibration est totalement compensé, mais cela ne s'arrête pas là. En effet, tous les dispositifs électroniques sont sujets à des variations environnementales qui ont pour effet de modifier leurs caractéristiques et comportements. Ici, les variations de température sont montrées du doigt. Ainsi, à intervalle régulier ou par monitorage des variations de température, l'opération de calibration doit être répétée.

On voit que la technique de calibration nécessite un arrêt de l'opération normale du convertisseur. Dans certaines applications cet arrêt peut être critique, c'est pourquoi,

certaines techniques permettent de minimiser ou de rendre inexistant ce laps de temps ou il n'y pas de conversion [3].

Étant donné que les deux conversions ne prennent pas le même temps lors de l'opération de calibration, il faut prévoir un dispositif permettant au convertisseur sous calibration d'opérer en mode conversion normale pendant que la conversion lente s'effectue pour réduire les pénalités de calibration.

### 3.2.2. Simulation

Un simulateur utilisant une procédure de type Monte-Carlo a été conçu en vue d'explorer les limites de la méthode de calibration proposée. Ce simulateur inclut le modèle de la figure 3.2 pour chaque étage. Le simulateur génère des convertisseurs en se basant sur une plage d'erreur délimitée par l'usager. Chaque étage du convertisseur créé possède ses propres caractéristiques aléatoires provenant des plages d'erreur spécifiées. Ce simulateur support la technique de redondance (chapitre II) et il permet l'évaluation de la linéarité sous forme dynamique (ENOB) et statique (INL et DNL). Ce simulateur a été codé en C++ orienté objet permettant une très grande flexibilité tout en assurant une facilité de réutilisation.

Plus de 20 milles convertisseurs ont été générés et caractérisés avant et après calibration. La moitié de ces convertisseurs possèdent que des étages de 1 bit standard tandis que le reste utilise la technique de redondance avec des étages de 1.5 bits. Le tableau 3.2 montre les plages d'erreur appliquées à une série de ces convertisseurs, ces

dernières ont été déterminées arbitrairement à l'aide de simulations analogiques utilisant les paramètres dits de coins technologiques, et des tolérances standards découlant des règles d'appariement. Aussi, ces plages d'erreur ont été sélectionnées en considérant un design analogique rapide ayant des caractéristiques assez modestes en termes de linéarité.

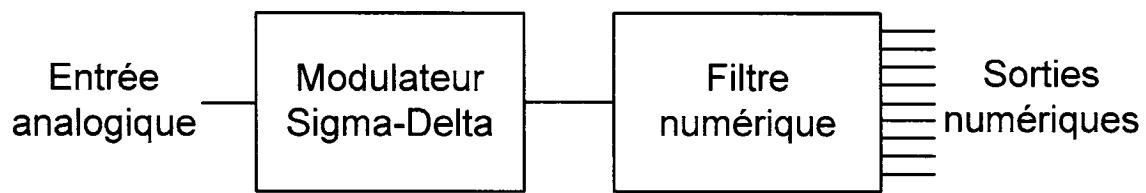

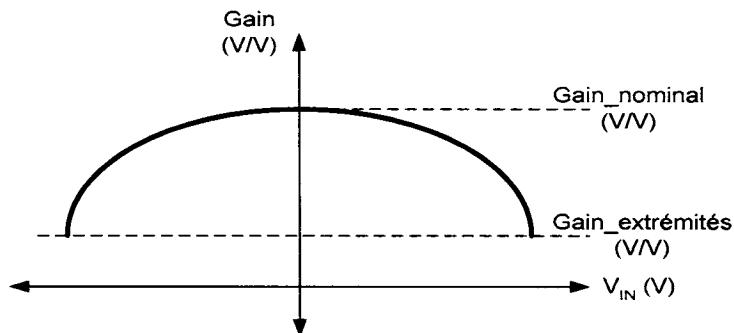

Dans ces simulations, un gain non linéaire d'ordre 2 est utilisé, le paramètre *Gain\_nominal* est le gain à 0V tandis que le paramètre *Gain\_nonlinéaire* est la variation en pourcentage aux extrémités de la plage dynamique d'entrée (figure 3.4 et équation 3.5). L'hypothèse suivante est donc utilisée : Le gain non linéaire est symétrique et sans décalage car c'est habituellement le cas pour une architecture complètement différentielle.

**Figure 3.4 - Représentation du gain non linéaire utilisé**

$$Gain\_nonlinéaire(\%) = \frac{Gain\ nominal - Gain\ extrémités}{Gain\ nominal} \quad (3.5)$$

Avant d'effectuer la calibration numérique, le simulateur vérifie si le convertisseur créé peut être calibré. Pour ce faire, il détermine si la fonction de transfert du dit convertisseur possède une fonction inverse.

**Tableau 3.2 - Valeurs appliquées aux simulations**

|                             | Minimun | Maximun |

|-----------------------------|---------|---------|

| <i>Gain_nominal (V/V)</i>   | 1.95    | 2       |

| <i>Gain_nonlinéaire (%)</i> | 0       | 2       |

| $\varepsilon_{CAN} (LSB^*)$ | -5      | 5       |

| $\varepsilon_{CNA}(LSB^*)$  | -5      | 5       |

\*Relatif au premier étage d'un convertisseur de 10 bits.

Les résultats de ces simulations pour une architecture sans redondance sont présentés au tableau 3.3.

**Tableau 3.3 - Résultats des simulations sans redondance**

|                                       | Minimum    | Maximum    |

|---------------------------------------|------------|------------|