**Titre:** Nouvelle approche de conception d'un CAN parallèle 1.25-gigaéchantillons/s utilisant la technique MCML

Title: gigaéchantillons/s utilisant la technique MCML

**Auteur:** Hung Dang

Author:

**Date:** 2005

**Type:** Mémoire ou thèse / Dissertation or Thesis

**Référence:** Dang, H. (2005). Nouvelle approche de conception d'un CAN parallèle 1.25-gigaéchantillons/s utilisant la technique MCML [Mémoire de maîtrise, École Polytechnique de Montréal]. PolyPublie. <https://publications.polymtl.ca/7606/>

Citation:

## Document en libre accès dans PolyPublie

Open Access document in PolyPublie

**URL de PolyPublie:** <https://publications.polymtl.ca/7606/>

PolyPublie URL:

**Directeurs de recherche:** Mohamad Sawan, & Yvon Savaria

Advisors:

**Programme:** Non spécifié

Program:

UNIVERSITÉ DE MONTRÉAL

NOUVELLE APPROCHE DE CONCEPTION D'UN CAN PARALLÈLE 1.25-

GIGAÉCHANTILLONS/S UTILISANT LA TECHNIQUE MCML

HUNG DANG

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION

DU DIPLÔME DE MAÎTRISE ES SCIENCES APPLIQUÉES

(GÉNIE ÉLECTRIQUE)

JUIN 2005

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street

Ottawa ON K1A 0N4

Canada

Bibliothèque et

Archives Canada

Direction du

Patrimoine de l'édition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

*Your file* *Votre référence*

ISBN: 978-0-494-16772-4

*Our file* *Notre référence*

ISBN: 978-0-494-16772-4

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

\*\*

Canada

UNIVERSITÉ DE MONTRÉAL

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

Ce mémoire intitulé:

NOUVELLE APPROCHE DE CONCEPTION D'UN CAN PARALLÈLE 1.25-

GIGAÉCHANTILLONS/S UTILISANT LA TECHNIQUE MCML

présenté par: HUNG DANG

en vue de l'obtention du diplôme de: Maîtrise ès sciences appliquées

a été dûment accepté par le jury d'examen constitué de:

M. AUDET Yves, Ph.D, président

M. SAWAN Mohamad, Ph.D, membre et directeur de recherche

M. SAVARIA Yvon, Ph.D, membre et co-directeur de recherche

M. BRAULT Jean-Jules, Ph.D, membre

*À mes très chers parents, qui m'ont apporté tous leurs soutiens moral et matériel,*

*À ma famille, qui m'a toujours encouragé dans chaque démarche de ma vie,*

*À mes amis*

*À Minh-Nhi...*

## REMERCIEMENTS

Je remercie,

L'ensemble des membres du GRM, et tout particulièrement à mes deux directeurs de recherche Mohamad Sawan et Yvon Savaria pour m'avoir permis d'effectuer ma maîtrise au sein de leur équipe.

Monsieur Yves Audet et Monsieur Jean-Jules Brault d'avoir accepté de participer à l'examen de ce travail.

Mon collègue Abdel Djemouai et les stagiaires Philippe Ménard et Amine Moumain, pour leur apport dans le processus de développement.

Mes collègues du bureau D6207 pour leur sagesse et leur apport technique dans la réalisation de mon projet.

La société canadienne en microélectronique (SCM) pour la fabrication des puces.

Les Fonds sur la Natures et les Technologies du Québec (Nateq) pour l'aide financière.

## RÉSUMÉ

Dans le cadre d'application radio configurable (Software Defined Radio - SDR) définie purement par logiciel, le convertisseur analogique à numérique (CAN) doit au moins atteindre une résolution de 6 bits et un taux de 1 giga échantillons par seconde (GÉPS) ou plus. L'architecture parallèle est la plus appropriée pour accéder à de tel taux d'échantillonnage. Néanmoins, elle a le défaut de consommer beaucoup de puissance.

Les objectifs de ce mémoire sont, d'une part, de réaliser avec la technologie CMOS 0.18  $\mu$ m un convertisseur analogique à numérique parallèle compétitif de 6 bits fonctionnant à une cadence supérieure à 1 GÉPS, et d'autre part, de réduire la consommation de puissance à un niveau inférieur à ceux obtenus dans les travaux existants. À travers ce projet, nous analysons les différentes méthodes permettant de minimiser les tensions de décalage qui affectent la linéarité du convertisseur. Par conséquent, notre objectif est d'obtenir une non linéarité différentielle (Differential Non Linearity – DNL) et une non linéarité intégrale (Integral Non Linearity – INL) inférieures à 0.5 LSB. Nous nous concentrerons aussi sur les techniques de décodage du code thermomètre au code binaire, permettant de minimiser les erreurs de conversion. Par ailleurs, une première dans ce domaine est de concevoir un convertisseur parallèle entièrement avec la technique MCML pour optimiser la cadence de conversion et réduire la consommation de puissance, qui, rappelons-le, est notre principal objectif.

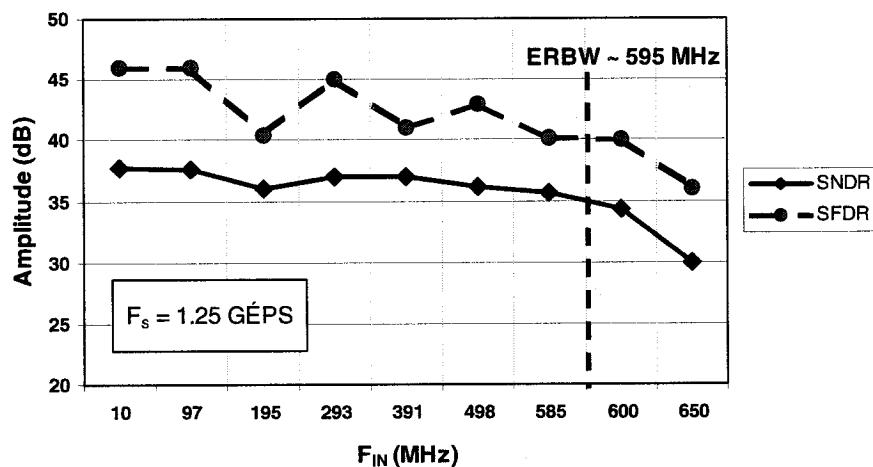

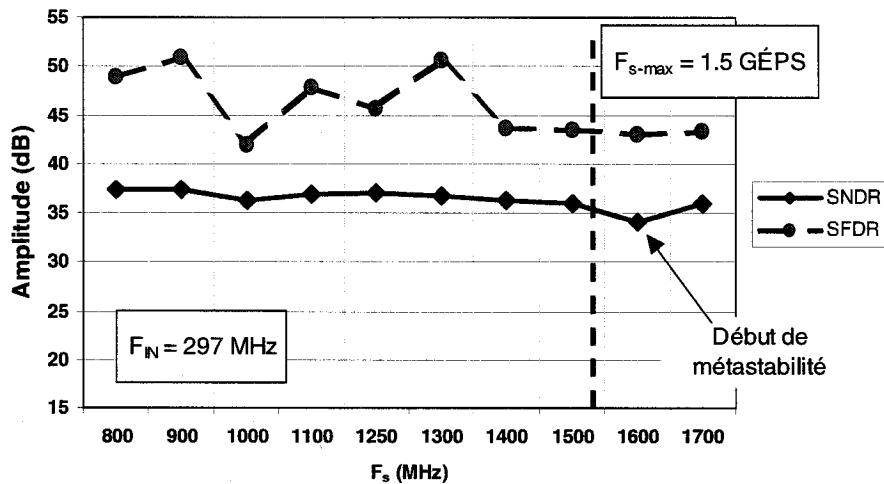

Nous avons conçu, modélisé et fait fabriquer une puce dédiée pour valider nos travaux au niveau matériel. La puce fonctionne avec deux sources d'alimentation, 1.2 V et 1.8 V. Les simulations « post-layout » démontrent que le CAN opère à une fréquence maximale de 1.5 GÉPS. À la fréquence de 1.25 GÉPS, la bande passante la plus large

offerte par ce CAN est d'environ 595 MHz. Le CAN consomme 172.0 mW, ce qui représente la moitié de la consommation du CAN CMOS parallèle de 6 bits comparable le plus rapide rapporté à ce jour (1.6 GÉPS).

## ABSTRACT

In order to support the popular concept of a fully software defined radio (SDR), analog to digital converters (ADC) must offer at least a 6-bit resolution at 1 gigasamples per second (GSPS) or more. The flash architecture is the most appropriate to achieve such sampling rates. Nevertheless, the architecture dissipates large amounts of power.

The objectives of this master thesis are, on the one hand, to design a competitive 6-bit flash ADC operating at a sampling rate greater than 1 GSPS when implemented with a CMOS 0.18  $\mu\text{m}$  technology, and on the other hand, to reduce its power consumption below existing state of the art ADCs using MCML techniques. Throughout this project, we study various existing methods to minimize the effect of offset voltages at the preamplifier and comparator circuit levels, which adversely affect the linearity of the ADC. We therefore target a differential non linearity (DNL) and an integral non linearity (INL) below 0.5 LSB. Moreover, to minimize the conversion errors, we focus our attention on an efficient decoding scheme that is most appropriate to our design methodology.

The ADC has been designed, modeled and implemented in CMOS 0.18  $\mu\text{m}$  technology to validate our work. The chip works with two supply voltages, 1.2 V and 1.8 V. Post-layout simulations show that the ADC operates at a maximum sampling rate of 1.5 GSPS. The largest bandwidth offered by this ADC is obtained at 1.25 GSPS and is 595 MHz. Its total power consumption is 172.0 mW, which is half the consumption of the fastest comparable CMOS 6-bit flash ADC reported to date (1.6 GSPS).

# TABLE DES MATIÈRES

|                                             |       |

|---------------------------------------------|-------|

| REMERCIEMENTS .....                         | v     |

| RÉSUMÉ .....                                | vi    |

| ABSTRACT .....                              | viii  |

| TABLE DES MATIÈRES .....                    | ix    |

| LISTE DES FIGURES .....                     | xiv   |

| LISTE DES TABLEAUX .....                    | xviii |

| LISTE DES ABRÉVIATIONS .....                | xx    |

| LISTE DES SYMBOLES .....                    | xxiii |

| LISTE DES ANNEXES .....                     | xxvii |

| CHAPITRE 1 : INTRODUCTION .....             | 1     |

| 1.1. Motivation .....                       | 1     |

| 1.2. Applications .....                     | 2     |

| 1.2.1. Équipements de test .....            | 2     |

| 1.2.2. Système de stockage magnétique ..... | 2     |

| 1.2.3. Télécommunication radio .....        | 3     |

| 1.3. Nos objectifs .....                    | 4     |

| 1.4. Organisation du mémoire .....          | 5     |

| CHAPITRE 2 : NOTIONS SUR LES CAN .....      | 6     |

| 2.1. Introduction .....                     | 6     |

| 2.2. Concepts de base .....                 | 7     |

| 2.2.1. Bruit de quantification .....        | 8     |

| 2.2.1.1. Fonction de transfert .....        | 9     |

| 2.2.1.2. Rapport signal sur bruit .....     | 10    |

| 2.2.2. Critères de performance .....        | 11    |

|                                                                   |    |

|-------------------------------------------------------------------|----|

| 2.2.2.1. Non linéarité.....                                       | 12 |

| 2.2.2.2. Nombre de bits effectifs .....                           | 13 |

| 2.2.2.3. Plage dynamique exempte de parasites.....                | 13 |

| 2.2.2.4. Résolution effective de la bande passante.....           | 14 |

| 2.2.2.5. Taux d'erreurs de bit .....                              | 14 |

| 2.3. Architectures ultra-rapides .....                            | 15 |

| 2.3.1. Modèle probabiliste de la tension de décalage.....         | 15 |

| 2.3.2. Architecture parallèle .....                               | 18 |

| 2.3.2.1. Description .....                                        | 18 |

| 2.3.2.2. Performance des comparateurs .....                       | 19 |

| 2.3.2.3. Avantages et inconvénients.....                          | 19 |

| 2.3.3. L'architecture interpolée (Interpolating).....             | 20 |

| 2.3.4. L'architecture pliée (Folding) .....                       | 21 |

| 2.3.5. L'architecture à temps-entrelacé (Time-Interleaving) ..... | 22 |

| 2.4. Choix de l'architecture parallèle .....                      | 22 |

| CHAPITRE 3 : REVUE DES CANS ULTRA-RAPIDES .....                   | 24 |

| 3.1. Introduction .....                                           | 24 |

| 3.2. Échantillonneur bloqueur (É/B) .....                         | 25 |

| 3.2.1. Motivation .....                                           | 25 |

| 3.2.2. Approches .....                                            | 26 |

| 3.2.2.1. Pré-échantillonnage.....                                 | 26 |

| 3.2.2.2. Échantillonnage distribué.....                           | 27 |

| 3.3. Moyennage « Averaging » .....                                | 29 |

| 3.3.1. Motivation.....                                            | 29 |

| 3.3.2. Concept .....                                              | 30 |

| 3.3.3. Problématique .....                                        | 32 |

| 3.3.4. Approches et exemples .....                                | 32 |

| 3.3.4.1. Approche de filtre spatial « Spatial Filter » .....      | 32 |

| 3.3.4.2. Méthode de Scholtens et Vertregt .....                   | 33 |

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| 3.4. « Autozeroing » de préamplificateurs .....                         | 35        |

| 3.4.1. Motivation .....                                                 | 35        |

| 3.4.2. Concept mathématique .....                                       | 36        |

| 3.4.3. Problème envisageable .....                                      | 37        |

| 3.5. Décodage et correction d'erreurs .....                             | 38        |

| 3.5.1. Types d'erreurs .....                                            | 38        |

| 3.5.2. Techniques de correction de bulles .....                         | 38        |

| 3.5.2.1. Décodeur Gray .....                                            | 38        |

| 3.5.2.2. Décodeur Q-Gray (Quasi-Gray) .....                             | 40        |

| 3.5.2.4. Décodeur en arbre « Fat Tree » .....                           | 41        |

| 3.5.3. Techniques pour gérer la métastabilité .....                     | 42        |

| 3.5.3.1. Pipelinage des comparateurs .....                              | 42        |

| 3.5.3.2. Circuits d'arbitrage .....                                     | 43        |

| 3.6. Approches et innovations .....                                     | 44        |

| <b>CHAPITRE 4 : MODÉLISATION DU CAN PARALLÈLE DE 6 BITS .....</b>       | <b>45</b> |

| 4.1. Introduction .....                                                 | 45        |

| 4.2. Description du MCML .....                                          | 46        |

| 4.2.1. Performance MCML versus CMOS .....                               | 47        |

| 4.2.2. Conception de la logique MCML .....                              | 48        |

| 4.3. CAN parallèle de 6 bits .....                                      | 49        |

| 4.3.1. Architecture dans sa vue d'ensemble .....                        | 49        |

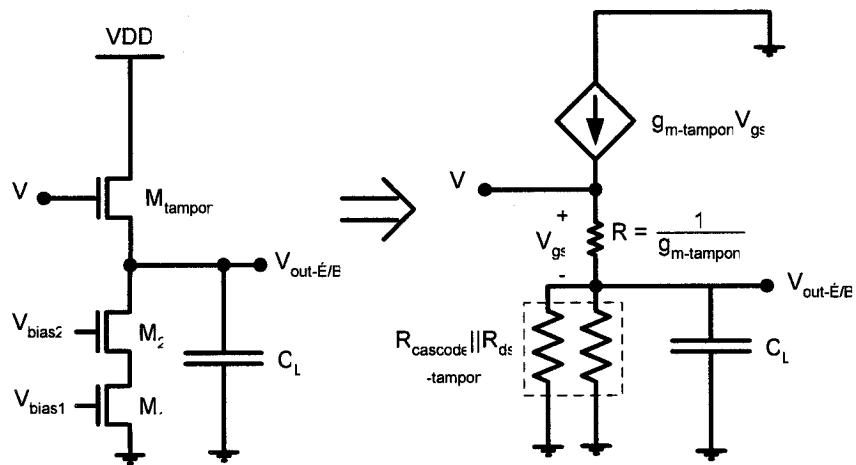

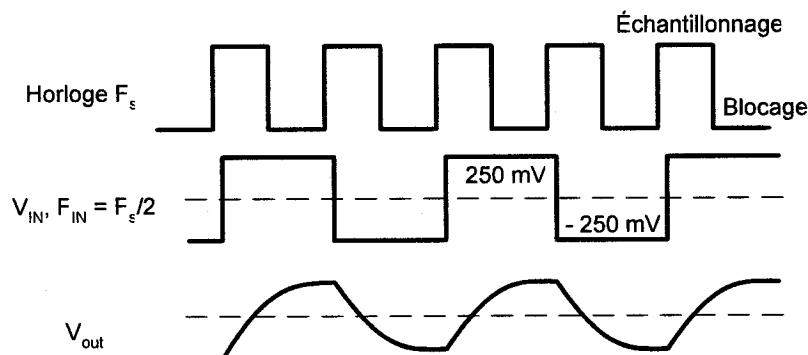

| 4.3.2. Pré échantillonneur bloqueur (pré-É/B) .....                     | 51        |

| 4.3.2.1. Schéma électrique et conception .....                          | 51        |

| 4.3.2.2. Spécifications ciblées pour le pré-É/B .....                   | 53        |

| 4.3.2.3. Modélisation et optimisation .....                             | 53        |

| 4.3.2.4. Résultats de la simulation schématique .....                   | 55        |

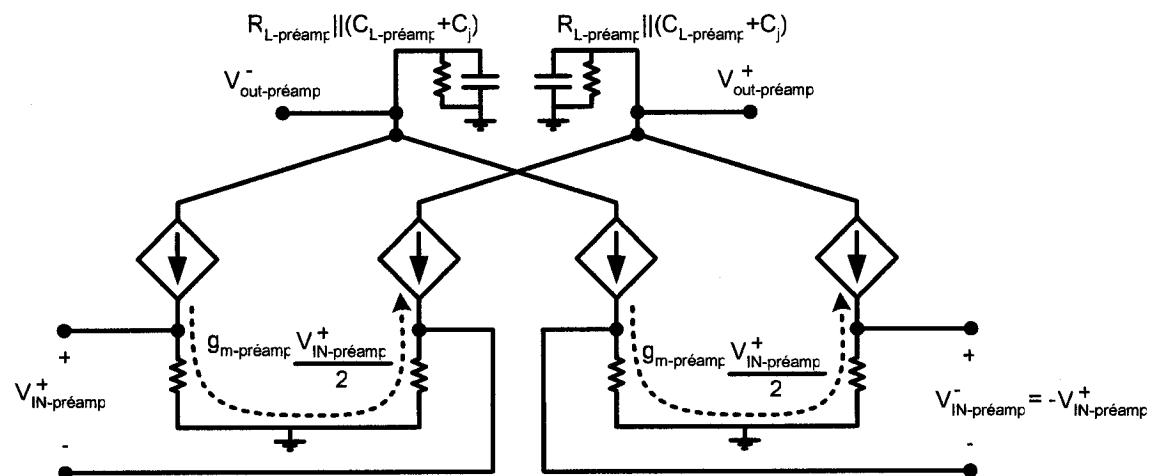

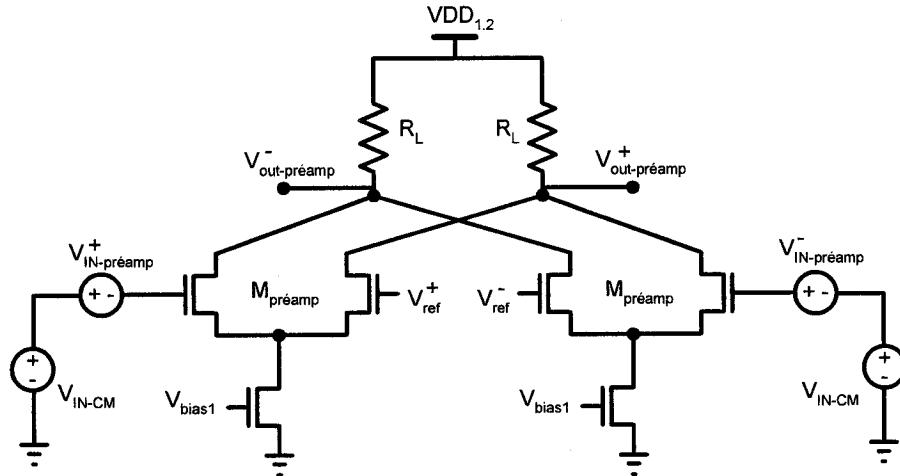

| 4.3.3. Préamplificateur .....                                           | 56        |

| 4.3.3.1. Schéma électrique et conception .....                          | 56        |

| 4.3.3.2. Spécifications et résultats de la simulation schématique ..... | 58        |

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| 4.3.4. Réseau de moyennage .....                                                 | 58 |

| 4.3.4.1. Méthode de conception .....                                             | 58 |

| 4.3.4.2. Résultats de la simulation schématique.....                             | 60 |

| 4.3.5. Comparateur MCML.....                                                     | 61 |

| 4.3.5.1. Comparateur MCML versus comparateur CMOS .....                          | 61 |

| 4.3.5.2. Conception .....                                                        | 61 |

| 4.3.5.3. Spécifications et résultats de la simulation du modèle schématique..... | 63 |

| 4.3.7. Échelle résistive .....                                                   | 64 |

| 4.3.7.1. Conception .....                                                        | 64 |

| 4.3.7.2. Résultats de la simulation du modèle schématique.....                   | 65 |

| 4.3.8. Décodeur en arbre MCML.....                                               | 66 |

| 4.3.8.1. Conception .....                                                        | 66 |

| 4.3.8.2. Spécifications et résultats de simulation du modèle schématique .....   | 68 |

| 4.3.9. Simulation du modèle schématique du CAN parallèle .....                   | 68 |

| CHAPITRE 5 : DESSINS DE MASQUES ET RÉSULTATS .....                               | 72 |

| 5.1. Introduction .....                                                          | 72 |

| 5.2. Dessins de masques.....                                                     | 73 |

| 5.2.1. Précautions pour minimiser les éléments parasites .....                   | 73 |

| 5.2.2. Principes de dessins pour réduire le mésappariement.....                  | 75 |

| 5.2.3. Astuces et principes de dessins pour minimiser le bruit .....             | 76 |

| 5.2.4. Autres astuces.....                                                       | 79 |

| 5.2.5. Deep-N-Well et résistance métallique .....                                | 81 |

| 5.3. Résultats des simulations post-layout .....                                 | 82 |

| 5.4. Banc de test .....                                                          | 86 |

| 5.5. Résultats expérimentaux .....                                               | 88 |

| 5.6. Comparaison des performances .....                                          | 91 |

| CHAPITRE 6 : CONCLUSION .....                                                    | 92 |

| 6.1. Travaux futurs .....                                                        | 94 |

| RÉFÉRENCES.....                                                                  | 95 |

|               |     |

|---------------|-----|

| ANNEXES ..... | 103 |

|---------------|-----|

# LISTE DES FIGURES

|                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1. Diagrammes blocs typiques pour des architectures de (a) récepteur hétérodyne et de (b) concept du radio configurable..... | 4  |

| Figure 2.1. Effet du bruit de quantification sur un signal échantillonné.....                                                         | 8  |

| Figure 2.2. CAN idéal : (a) Fonction de transfert, (b) erreur de quantification associée...                                           | 9  |

| Figure 2.3. Principe de sur-échantillonnage.....                                                                                      | 11 |

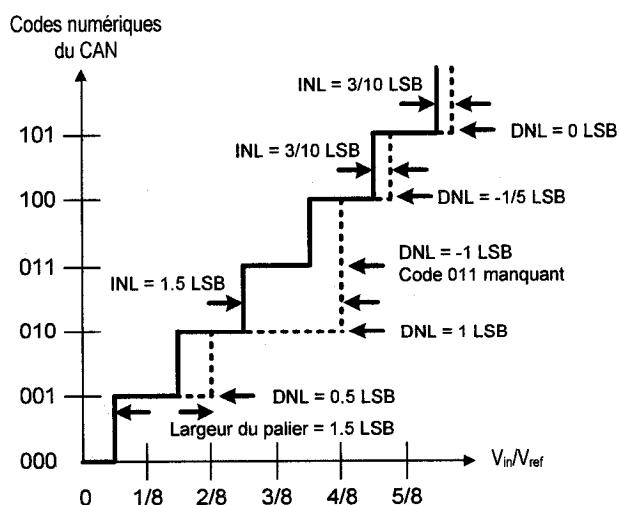

| Figure 2.4. Illustration des non-linéarités (DNL et INL) des CAN. ....                                                                | 12 |

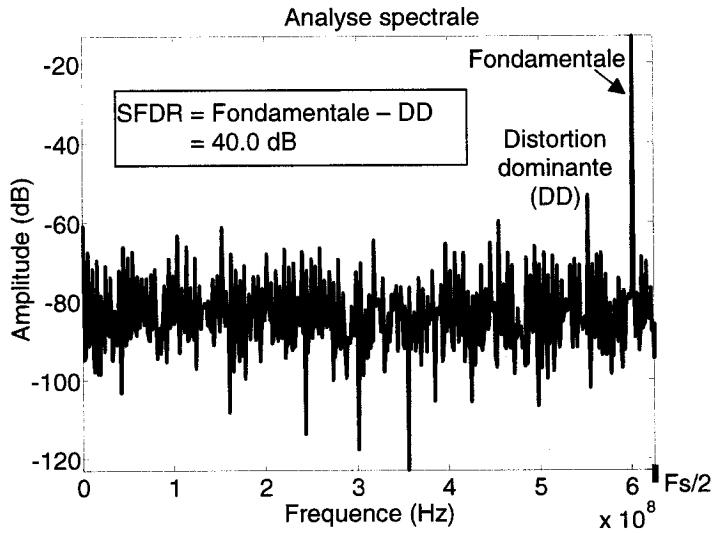

| Figure 2.5. Analyse spectrale et SFDR .....                                                                                           | 14 |

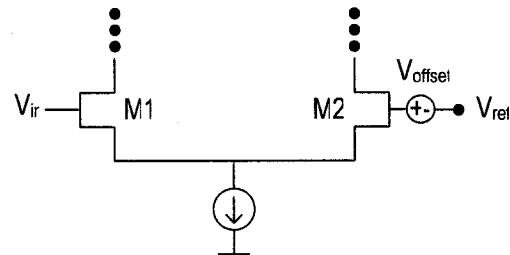

| Figure 2.6. Paire différentielle affichant une tension de décalage ( $V_{\text{offset}}$ ). .....                                     | 15 |

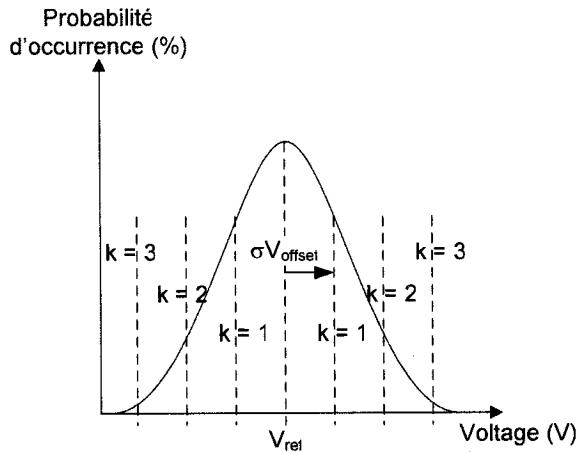

| Figure 2.7. Distribution gaussienne du $V_{\text{ref}}$ résultant.....                                                                | 17 |

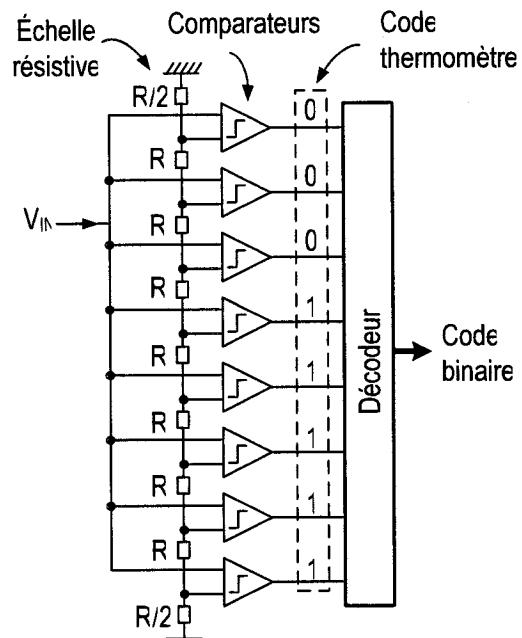

| Figure 2.8. Architecture du convertisseur parallèle. ....                                                                             | 18 |

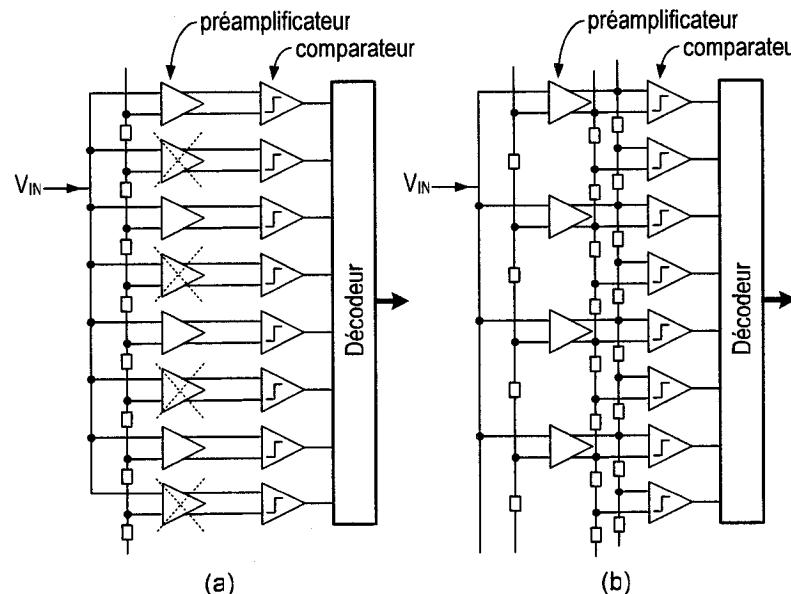

| Figure 2.9. Architecture du convertisseur : (a) parallèle, (b) interpolé.....                                                         | 20 |

| Figure 2.10. Architecture du convertisseur (a) parallèle, (b) pliée [16].....                                                         | 21 |

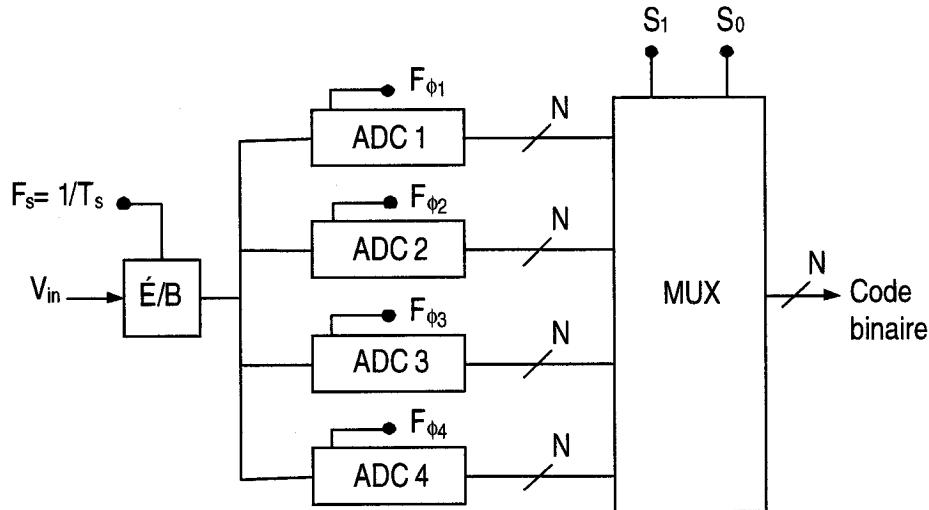

| Figure 2.11. Architecture du convertisseur à temps-entrelacé.....                                                                     | 22 |

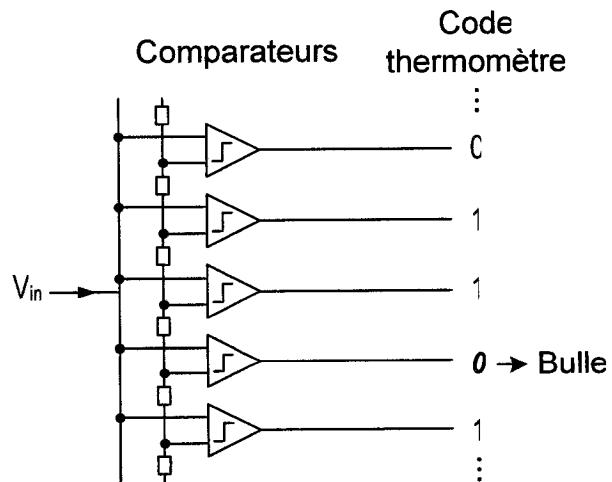

| Figure 3.1. Exemple d'occurrence d'une bulle dans un code thermomètre (CT).....                                                       | 25 |

| Figure 3.2. Couplage capacitif entre $V_{\text{IN}}$ et l'échelle resistive. ....                                                     | 26 |

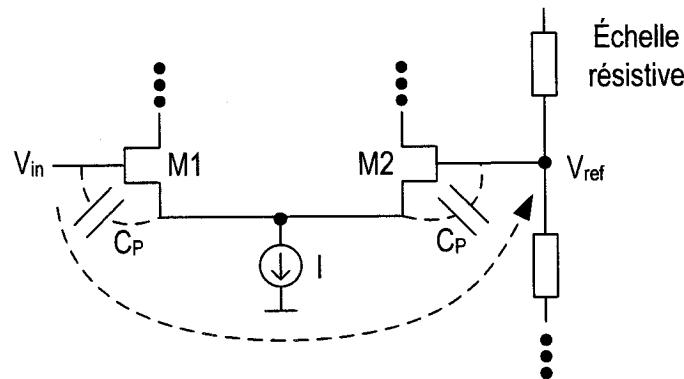

| Figure 3.3. Pré-échantillonnage utilisant un pré-É/B différentiel [6, 42]. .....                                                      | 27 |

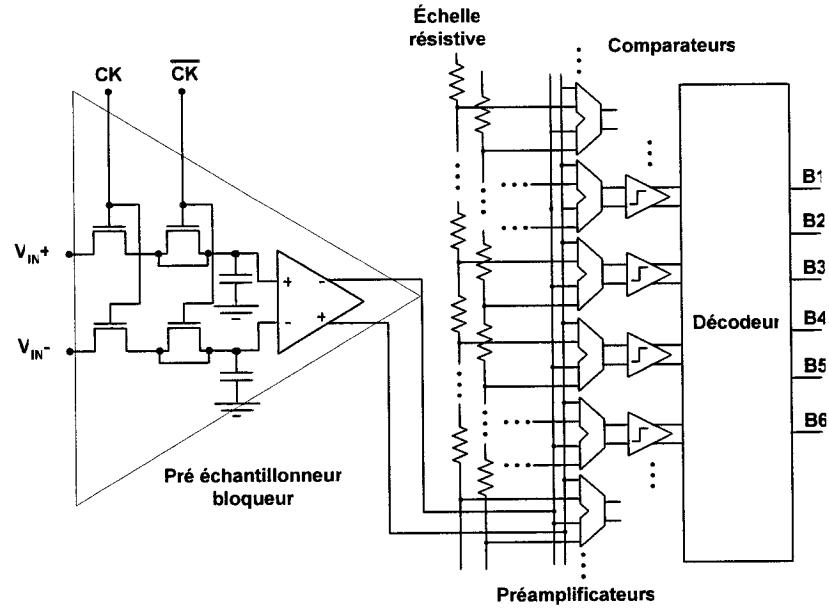

| Figure 3.4. É/B distribués a) à l'entrée du CAN et, b) derrière la rangée de préamplificateurs.....                                   | 28 |

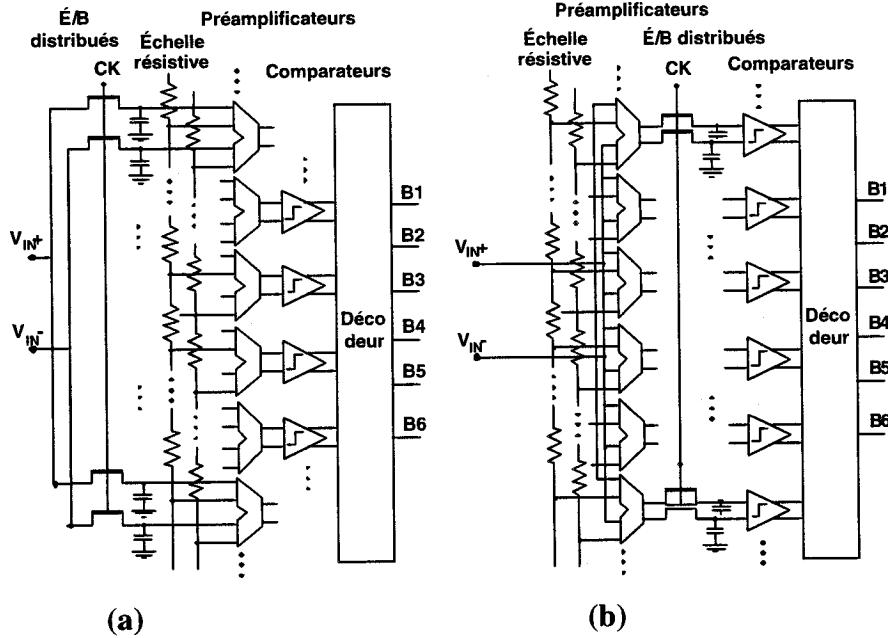

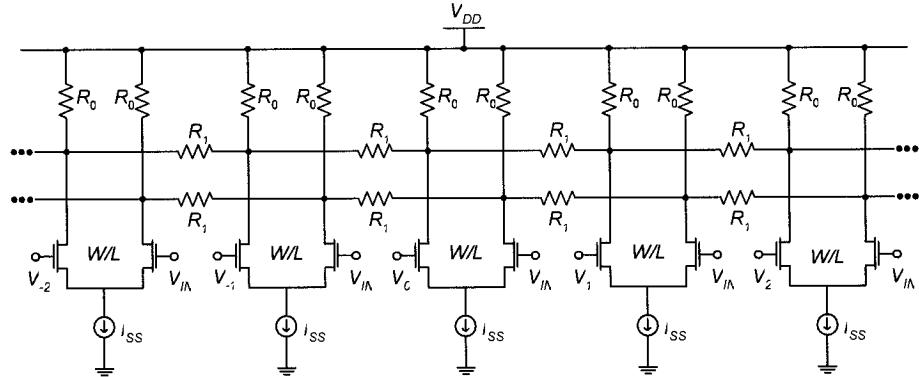

| Figure 3.5. Étage de préamplificateurs d'un CAN flash employant la technique de moyennage. ....                                       | 30 |

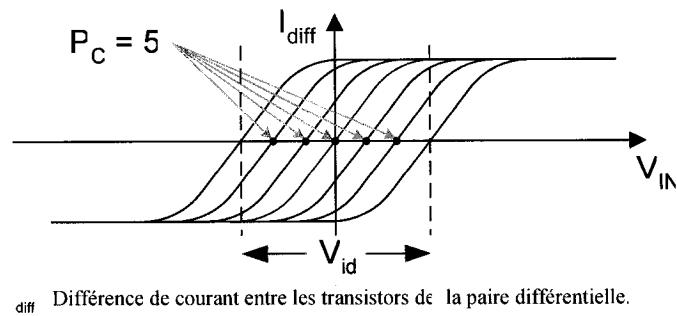

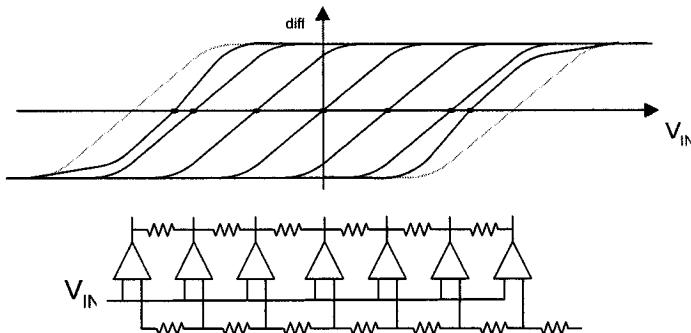

| Figure 3.6. Fonctions de transfert des préamplificateurs du réseau de moyennage.....                                                  | 30 |

| Figure 3.7. Effet de bordure dans le réseau de moyennage. ....                                                                        | 32 |

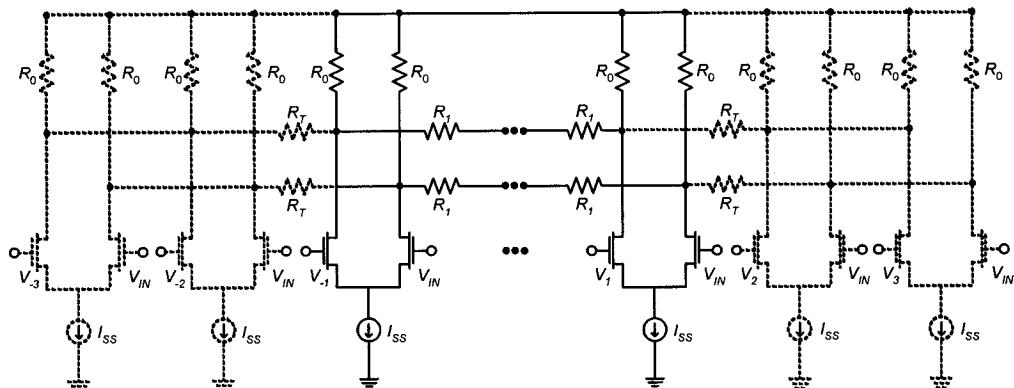

| Figure 3.8. Réseau de moyennage et terminaison proposé par H. Pan [41]. ....                                                          | 33 |

|                                                                                                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.9. Réseau de moyennage et terminaison proposé par Scholtens et Vertregt [56].                                                                                            | 34 |

| Figure 3.10. Préamplificateur avec le principe « autozeroing ».                                                                                                                   | 35 |

| Figure 3.11. La réponse transitoire a) d'un préamplificateur classique, et b) d'un préamplificateur avec « autozeroing ».                                                         | 36 |

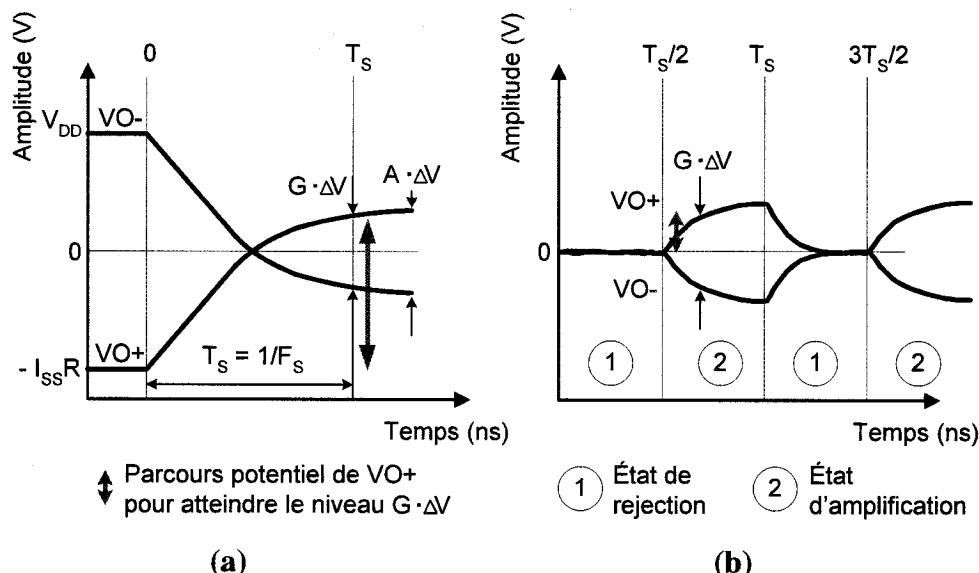

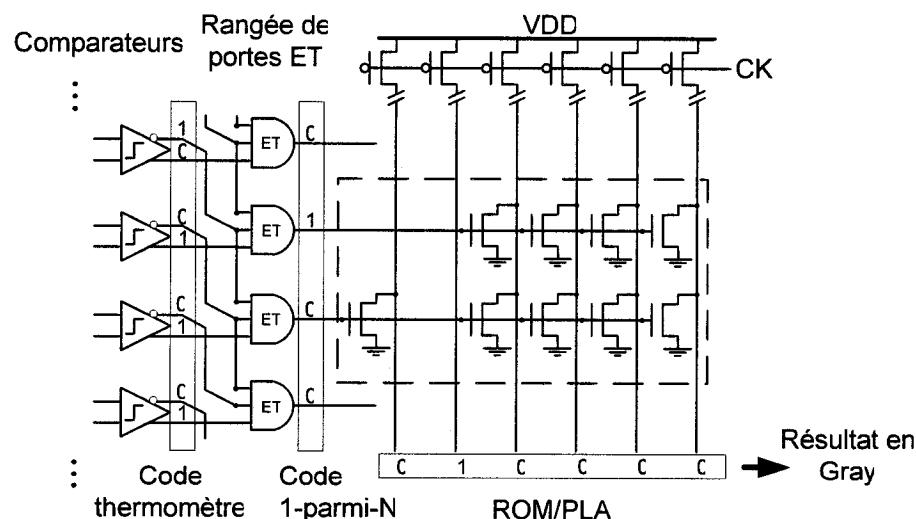

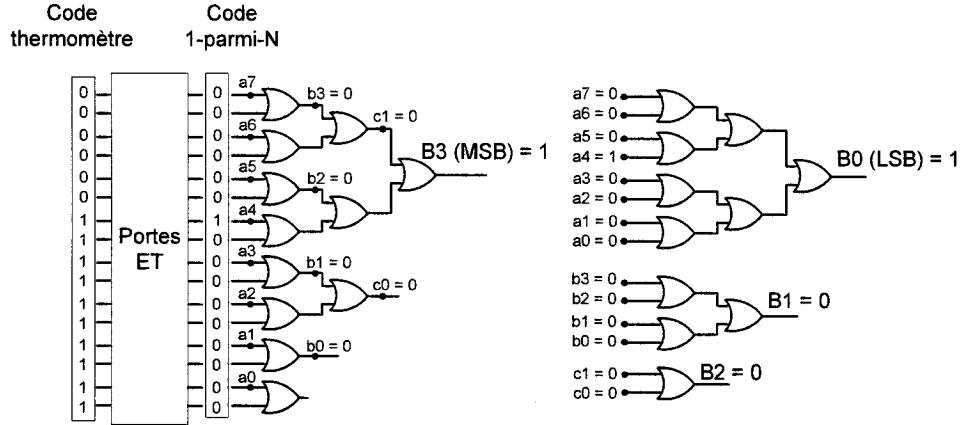

| Figure 3.12. Décodeur Gray conçu via un décodeur 1-parmi-N et un circuit ROM.....                                                                                                 | 39 |

| Figure 3.13. Décodeur en arbre.....                                                                                                                                               | 42 |

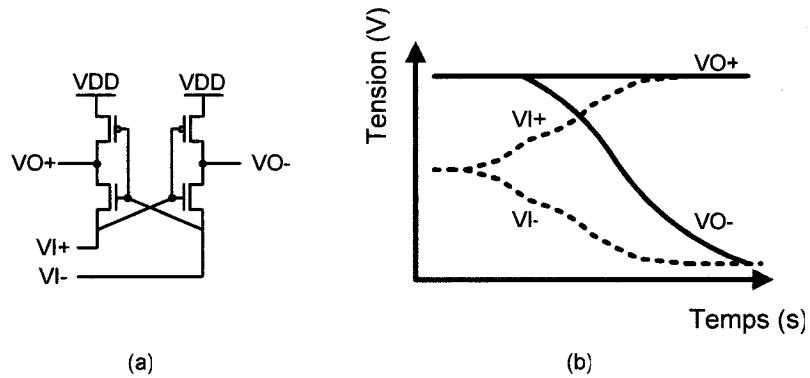

| Figure 3.14. a) Circuit d'arbitrage différentiel [49], et sa b) réponse transitoire.....                                                                                          | 43 |

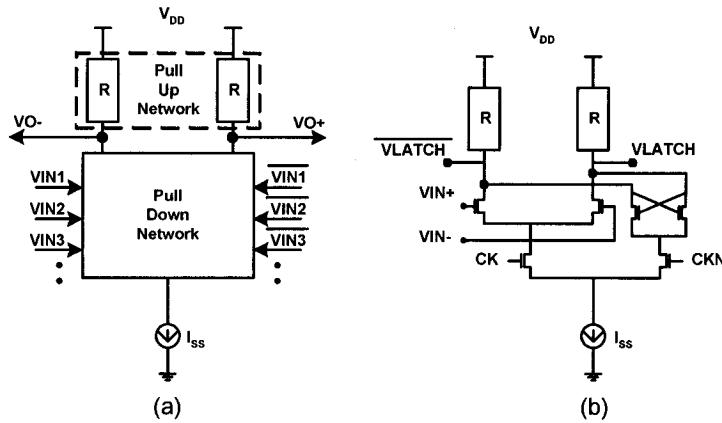

| Figure 4.1. Diagramme MCML illustrant (a) sa structure de base, et (b) son circuit à verrou (Latch).....                                                                          | 46 |

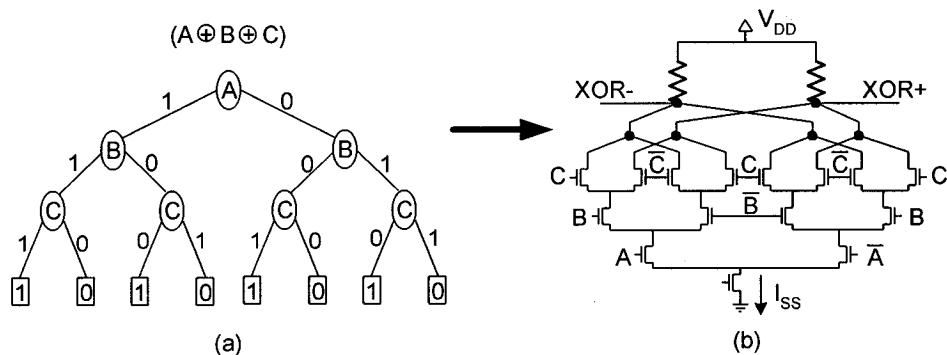

| Figure 4.2. Conception de la $F = A \oplus B \oplus C$ en logique MCML : (a) à partir du BDD, (b) schéma électrique correspondant. ....                                           | 48 |

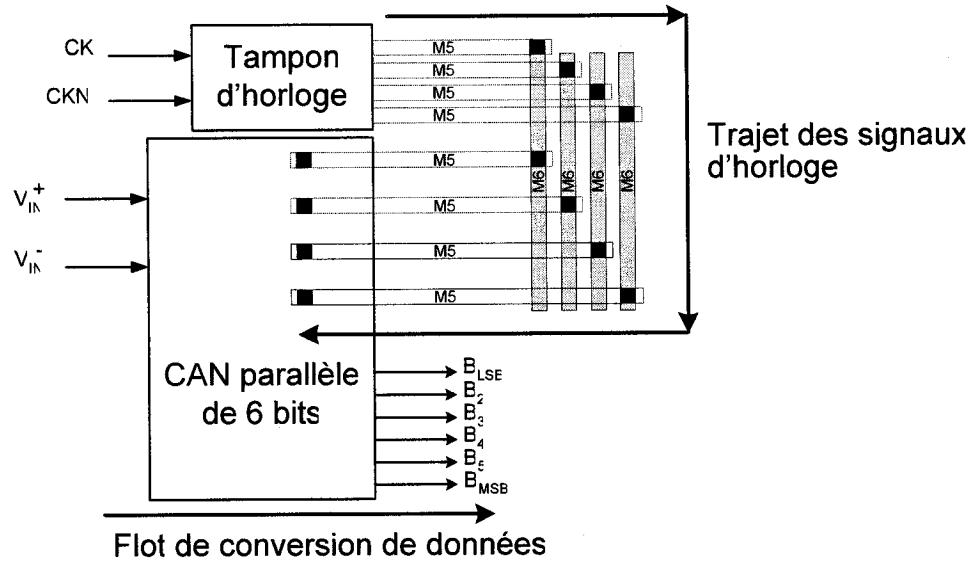

| Figure 4.3. Schéma simplifié du CAN parallèle de 6 bits conçu en partie avec les circuits MCML. ....                                                                              | 50 |

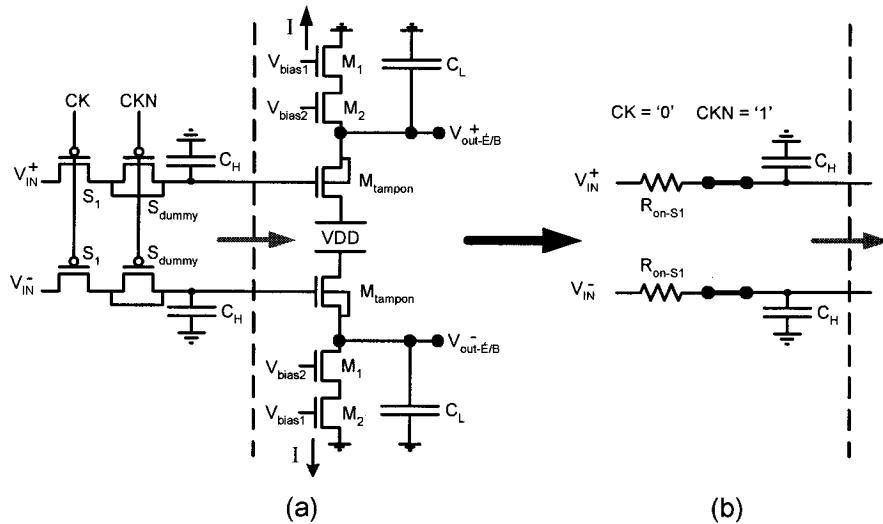

| Figure 4.4. Illustration du pré-É/B : (a) au niveau schématique, (b) circuit RC équivalent, excluant les tampons de sortie, (c) valeur des principaux paramètres. ....            | 51 |

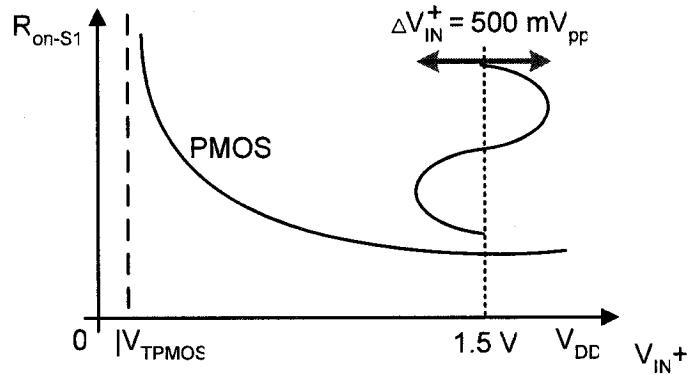

| Figure 4.5. Variation de la valeur de $R_{on-S1}$ du PMOS en fonction de $V_{IN+}$ .....                                                                                          | 54 |

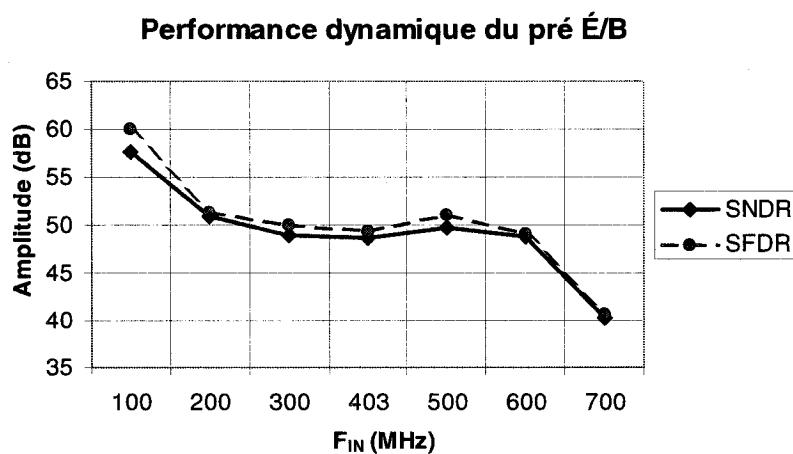

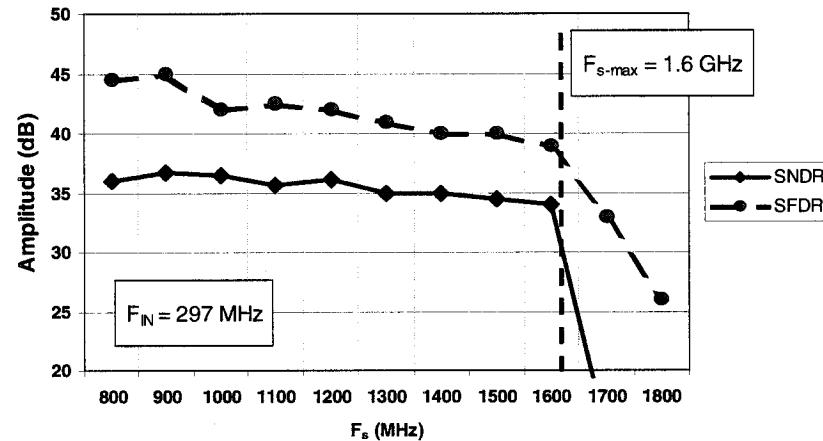

| Figure 4.6. Performances dynamiques en SNDR et SFDR du pré-É/B à $F_s = 1.6$ GÉPS. ....                                                                                           | 55 |

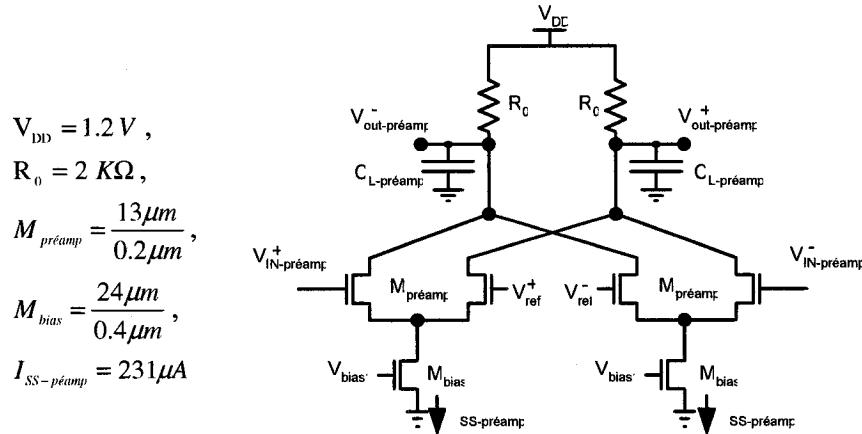

| Figure 4.7. Schéma électrique du préamplificateur différentiel.....                                                                                                               | 56 |

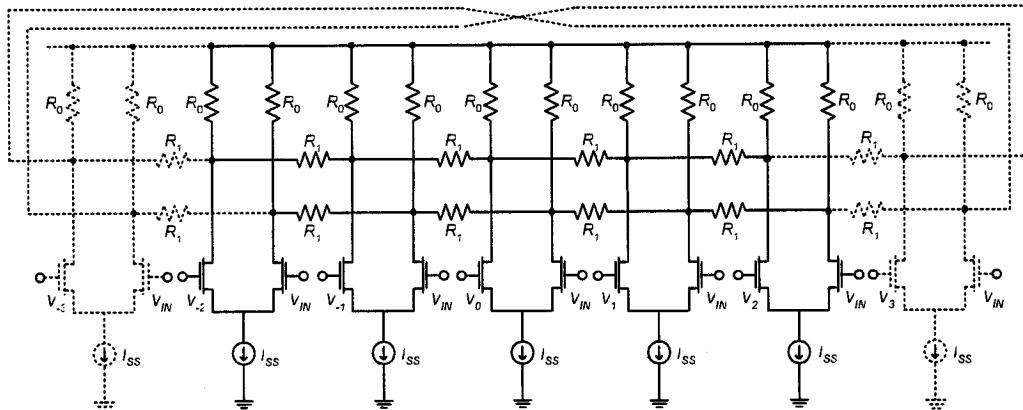

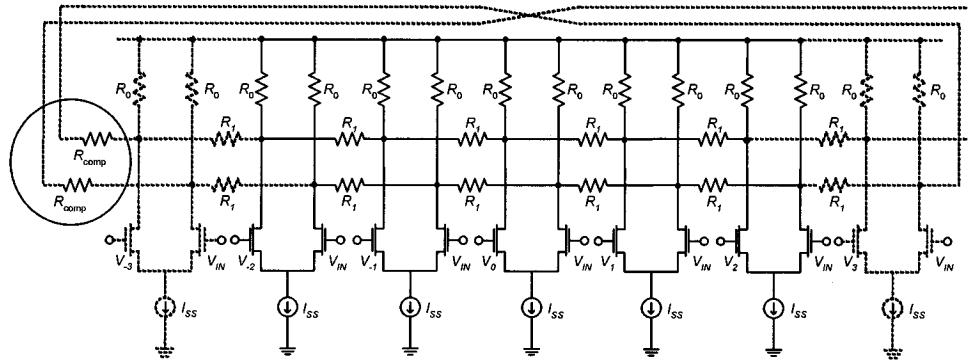

| Figure 4.8. Réseau de moyennage du CAN avec l'ajout de $R_{comp}$ .....                                                                                                           | 59 |

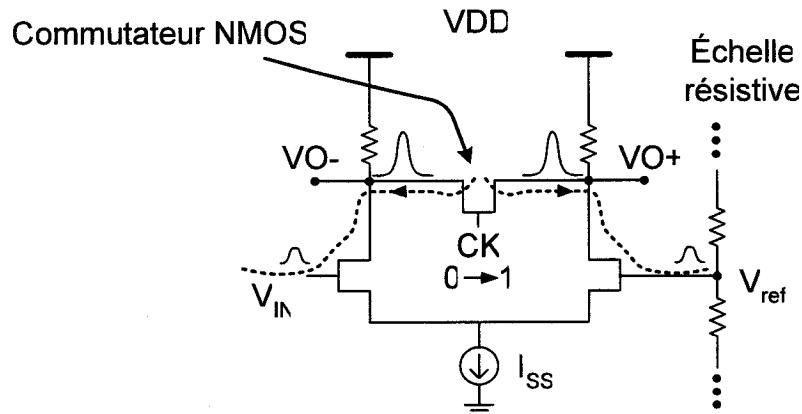

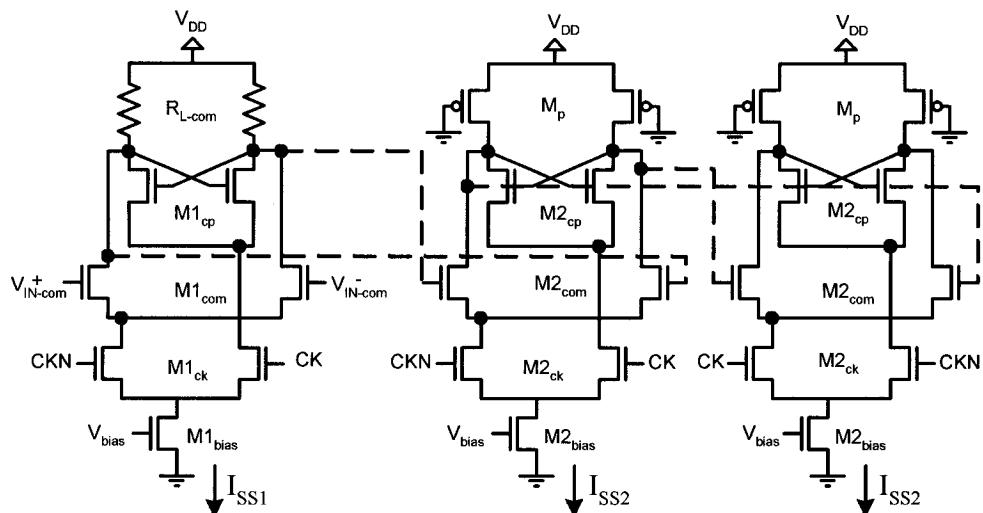

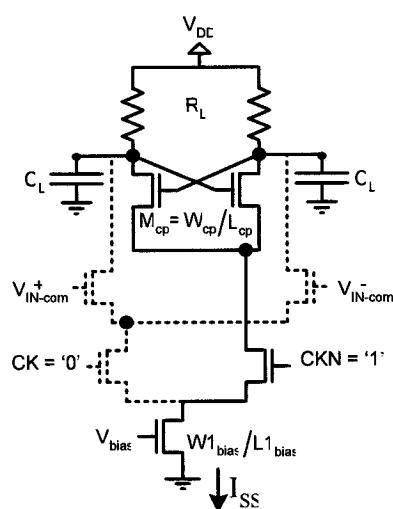

| Figure 4.9. Schéma électrique du comparateur MCML.....                                                                                                                            | 61 |

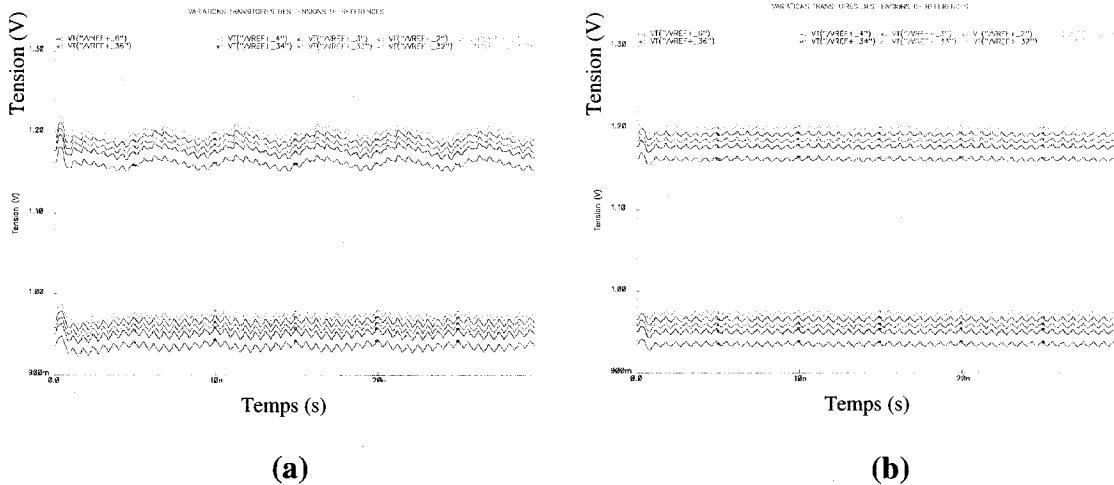

| Figure 4.10. Variations transitoires des niveaux de référence, lorsque $F_s = 1.6$ GÉPS et $F_{IN} = 100$ MHz, dans le cas de (a) $R = 10 \Omega$ , et (b) $R = 1 \Omega$ . ....  | 65 |

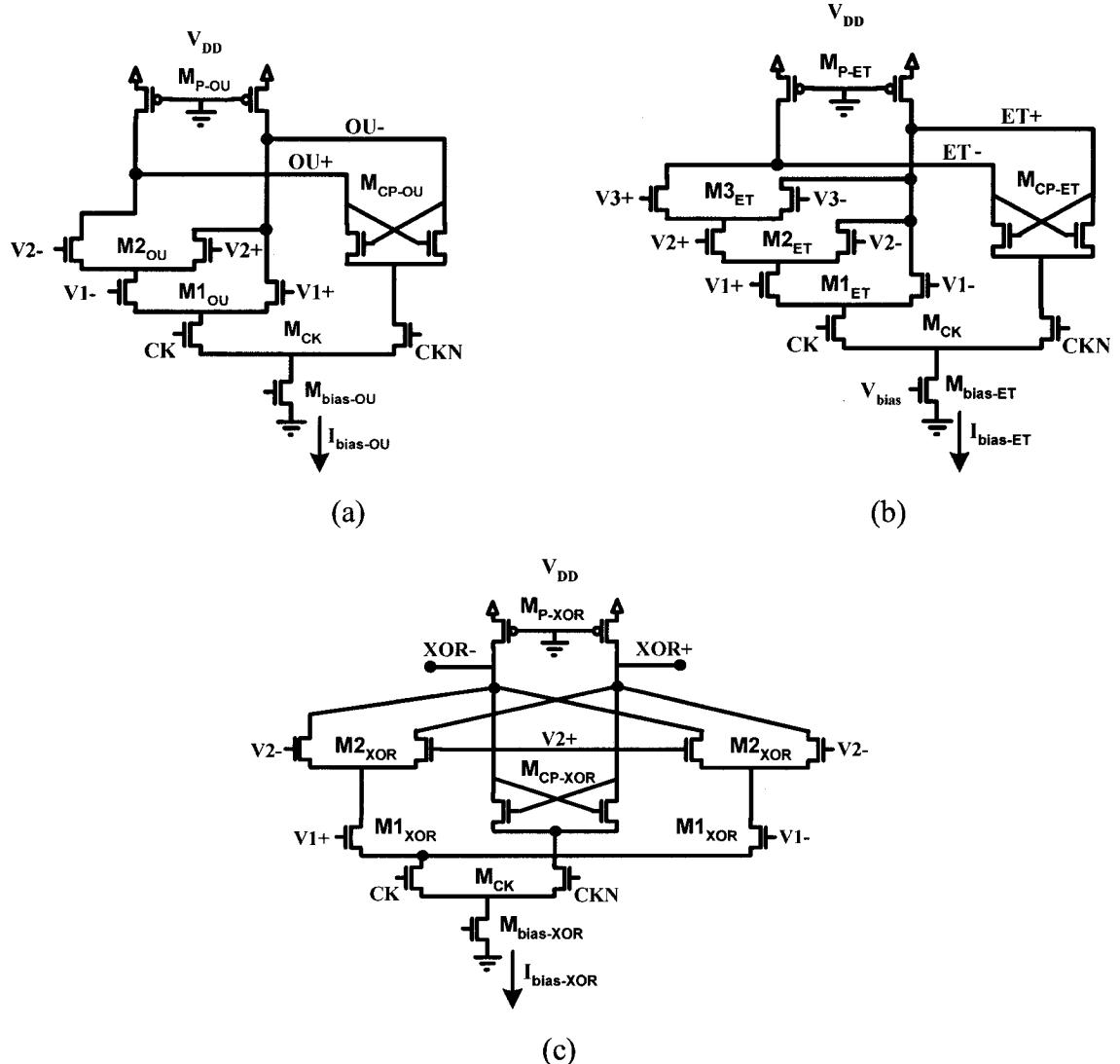

| Figure 4.11. Schéma électrique de la porte (a) OU MCML à 2 entrées, (b) ET MCML à 3 entrées, et (c) XOR MCML à 2 entrées, combinée à la structure de circuit à verrou.....        | 67 |

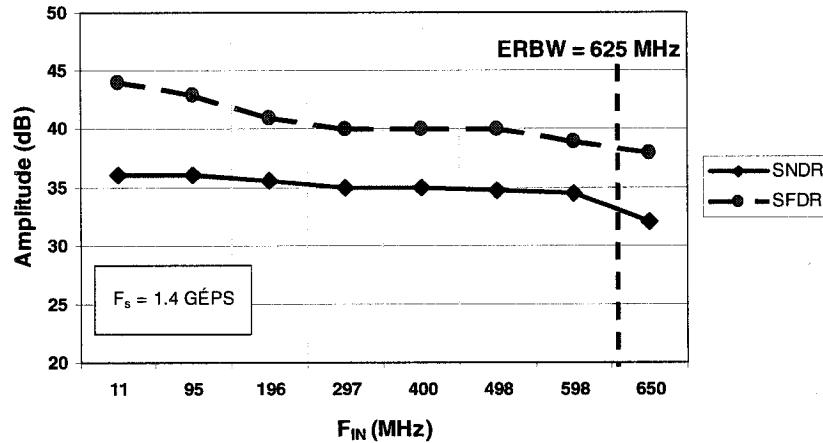

| Figure 4.12. La performance dynamique du CAN en SNDR et en SFDR pour $F_s = 1.4$ GÉPS, simulées avec $\sigma V_{offset-total} = 5$ mV et $\sigma V_{offset-préamp} = 3.8$ mV..... | 71 |

|                                                                                                                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.13. Performance dynamique du CAN en fonction de $F_s$ , simulée avec $\sigma V_{offset-total} = 5 \text{ mV}$ et $\sigma V_{offset-préamp} = 3.8 \text{ mV}$ .....                                  | 71 |

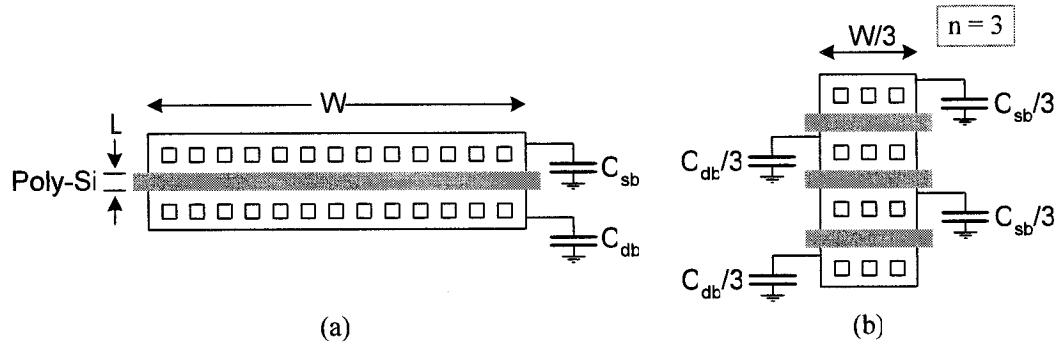

| Figure 5.1. Dessin de masques d'un transistor avec rapport W/L élevé (a) en une pièce, (b) séparé en $n = 3$ unités parallèles.....                                                                          | 74 |

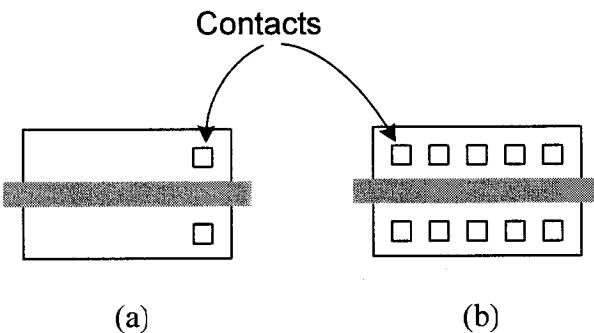

| Figure 5.2. Dessin de masques d'un contact à un transistor formé (a) d'un seul contact, (b) d'un grand nombre de contacts.....                                                                               | 74 |

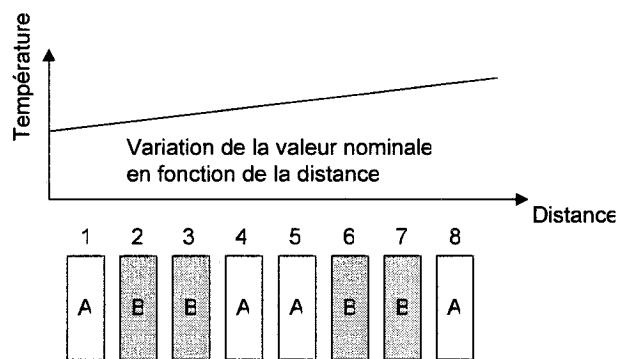

| Figure 5.3. Configuration de centroïde commun de type « ABBA », pour contrer la variation due aux gradients.....                                                                                             | 75 |

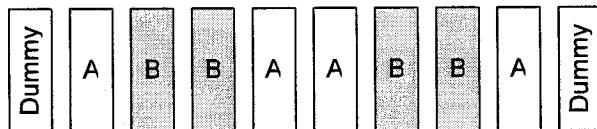

| Figure 5.4. Configuration de centroïde commun de type « ABBA » avec la présence de « dummies ».....                                                                                                          | 76 |

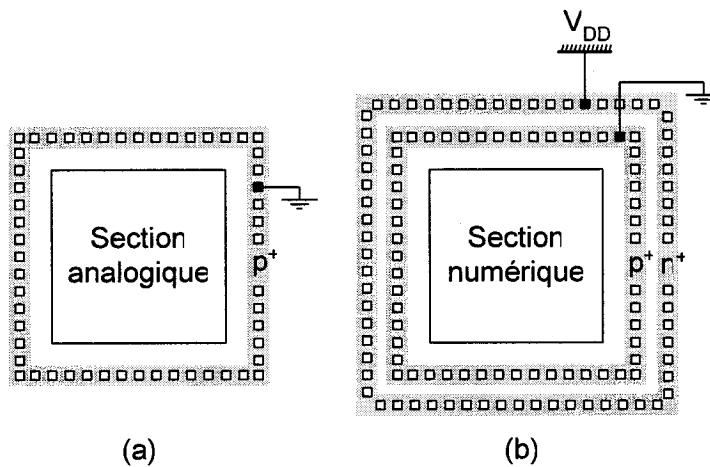

| Figure 5.5. Anneau de garde (a) section analogique dopée $p^+$ , b) section numérique offrant une double protection, dopée de $p^+$ et $n^+$ .....                                                           | 77 |

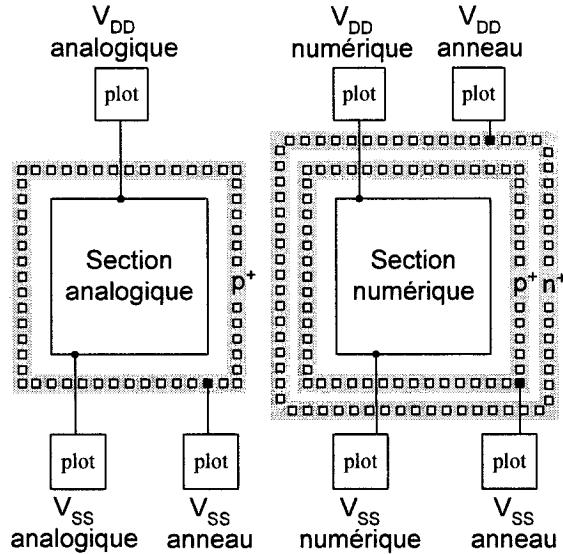

| Figure 5.6. Séparation des alimentations et de la masse entre la section analogique et la section numérique, et entre les anneaux de gardes. ....                                                            | 78 |

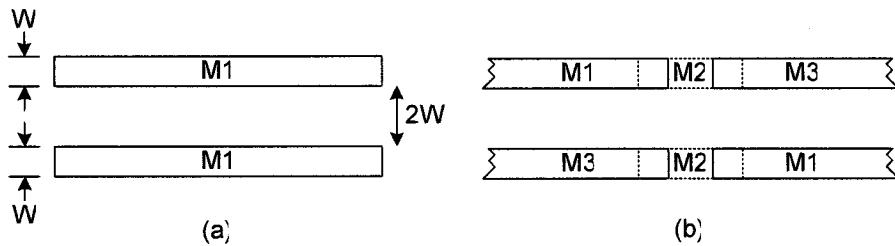

| Figure 5.7. Techniques de dessins employées pour minimiser le couplage diaphonique (a) en distançant le plus possible deux traces parallèles, (b) en interchangeant les couches de métal. ....               | 79 |

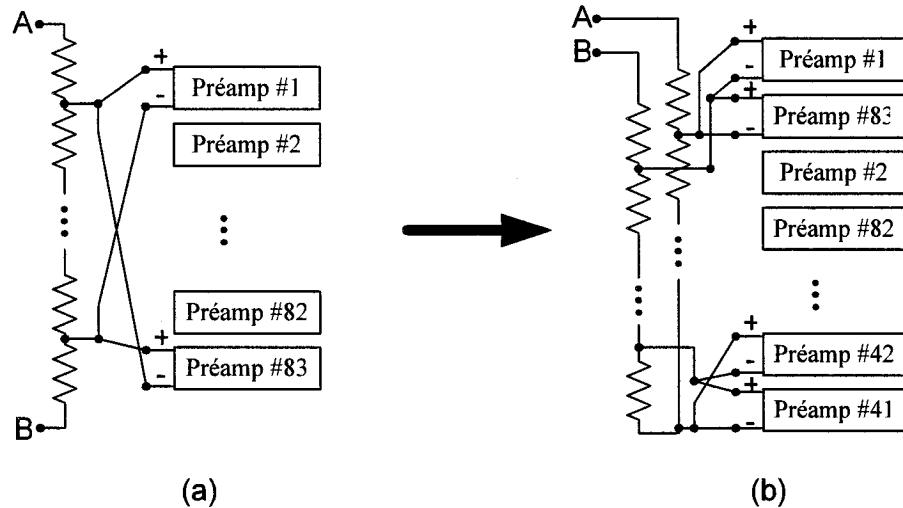

| Figure 5.8. Échelle résistive (a) connexion linéaire qui génère des complications au niveau du routage dans le plan de masques, et (b) connexion pliée qui facilite le routage dans le plan de masques. .... | 80 |

| Figure 5.9. Routage des signaux d'horloge permettant le biais positif. ....                                                                                                                                  | 81 |

| Figure 5.10. La performance dynamique du CAN en SNDR et en SFDR pour $F_s = 1.25 \text{ GÉPS}$ , simulée au niveau post-layout. ....                                                                         | 83 |

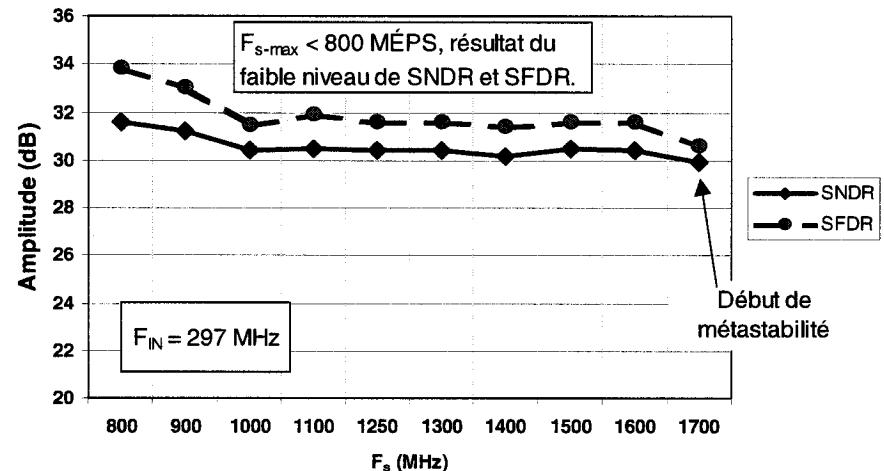

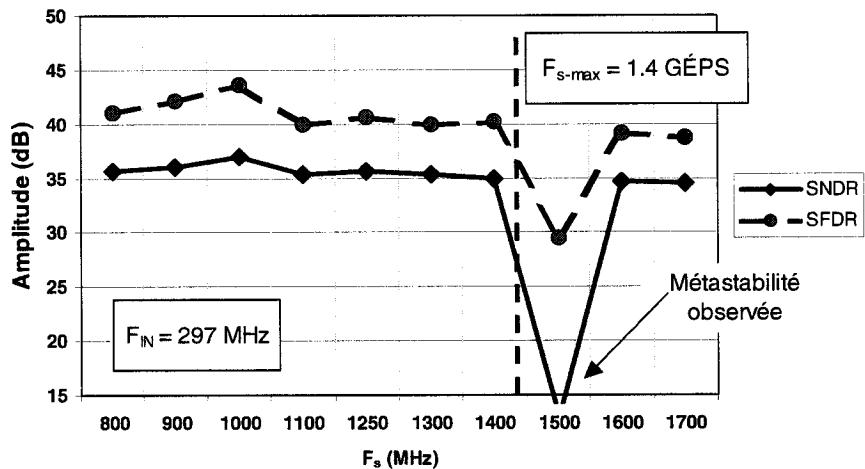

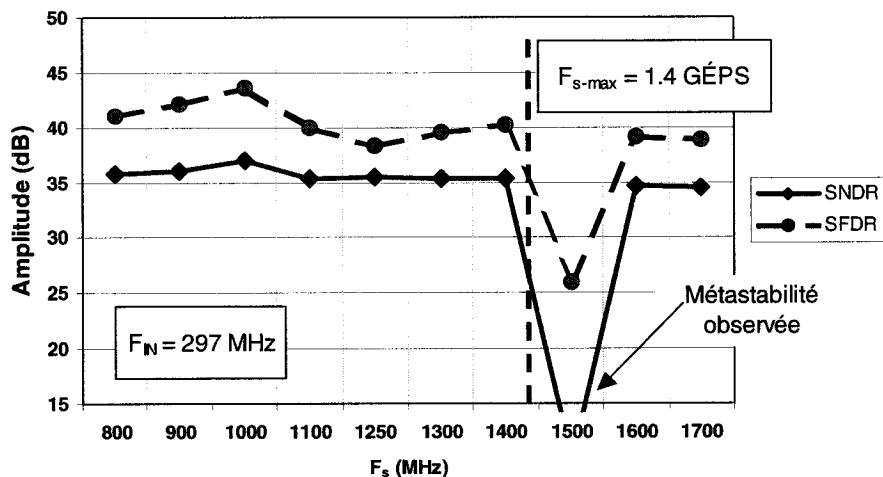

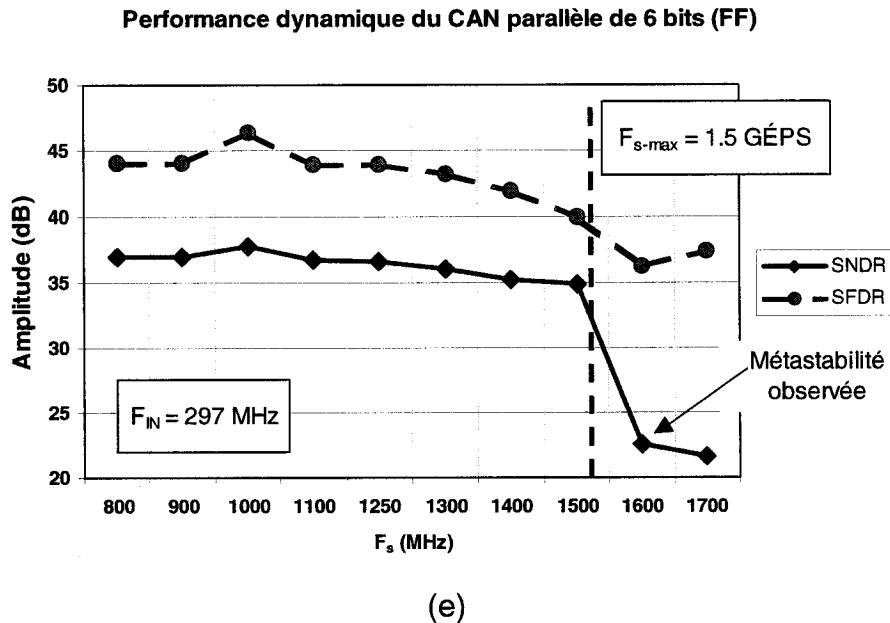

| Figure 5.11. Performance dynamique du CAN en fonction de $F_s$ , simulée au niveau post-layout dans les coins de procédés (a) TT, (b) SS, (c) SF, (d) FS, et (e) FF. ....                                    | 86 |

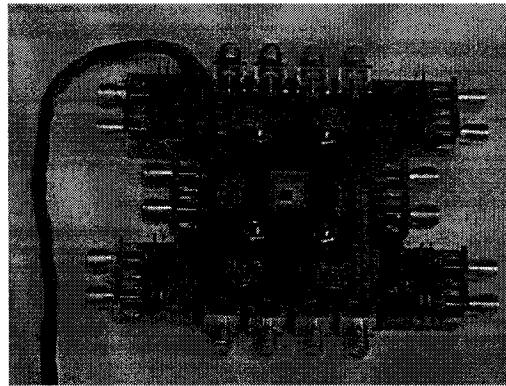

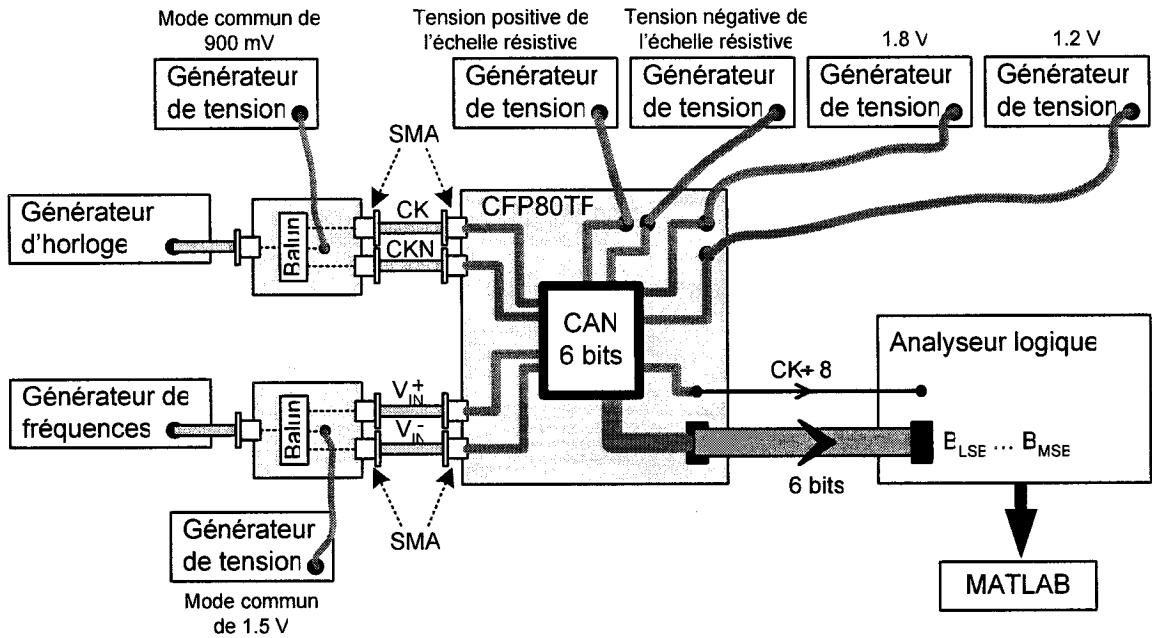

| Figure 5.12. Carte de test CFP80TF fournie par la CMC. ....                                                                                                                                                  | 87 |

| Figure 5.13. Configuration du banc de test du CAN.....                                                                                                                                                       | 88 |

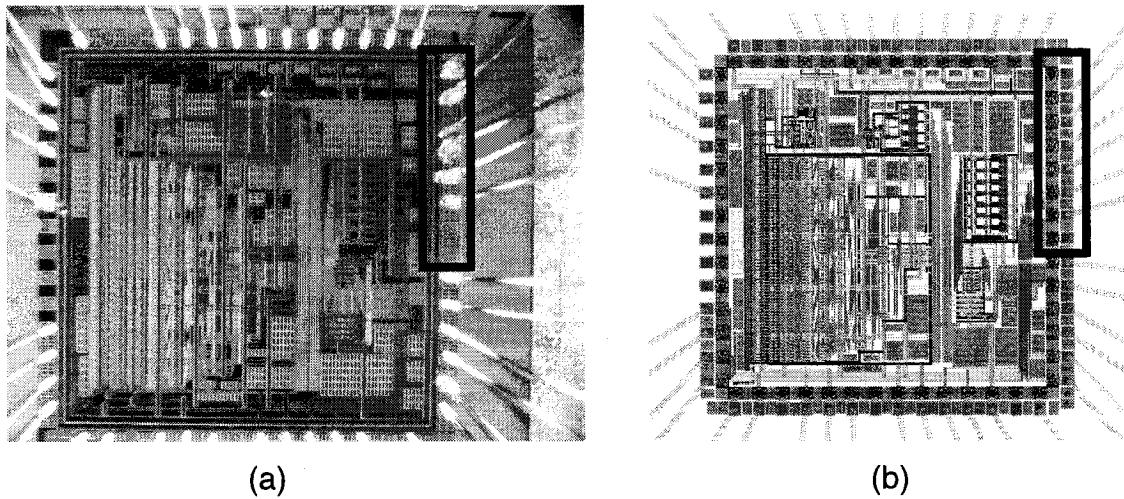

| Figure 5.14. Erreur de connexion des liaisons électriques (a) au niveau de la puce après la fabrication, (b) au niveau du plan de masques. ....                                                              | 89 |

|                                                                                                                                                                                                                                               |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

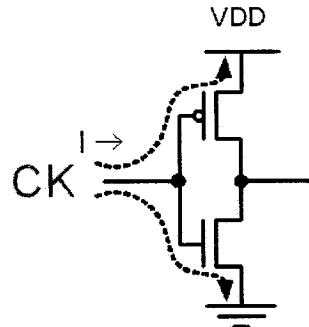

| Figure 5.15. Passage du courant DC à travers les grilles des transistors de l'inverseur à l'entrée du tampon d'horloge.....                                                                                                                   | 90  |

| Figure A.1. Circuit équivalent du préamplificateur différentiel. ....                                                                                                                                                                         | 104 |

| Figure B.1. Exemple d'un modèle d'échantillonnage.....                                                                                                                                                                                        | 108 |

| Figure C.1. Circuit équivalent du préamplificateur différentiel.....                                                                                                                                                                          | 110 |

| Figure D.1. Circuit du préamplificateur différentiel. ....                                                                                                                                                                                    | 113 |

| Figure E.1. Portion régénérative du circuit à vérrou MCML. ....                                                                                                                                                                               | 115 |

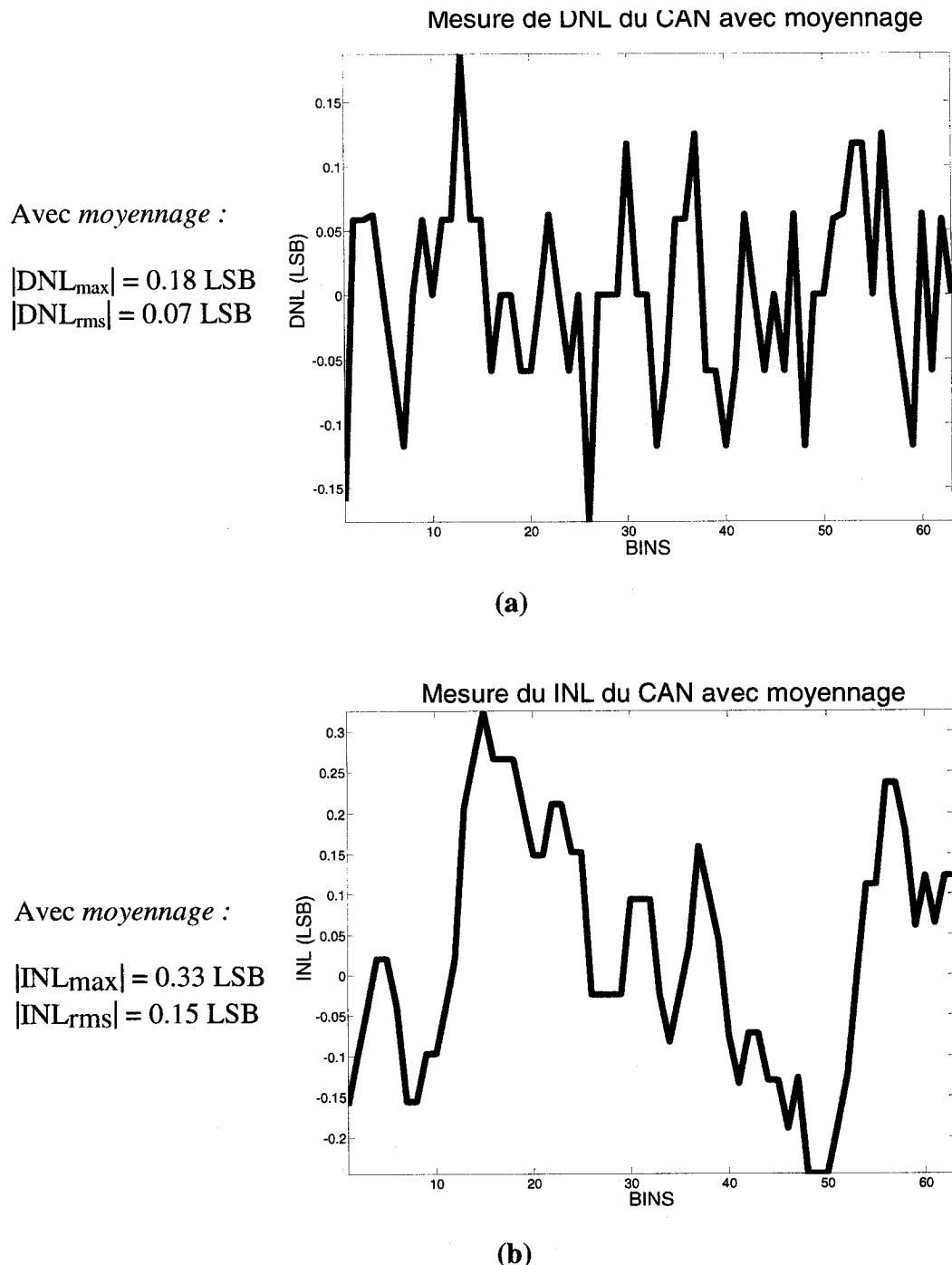

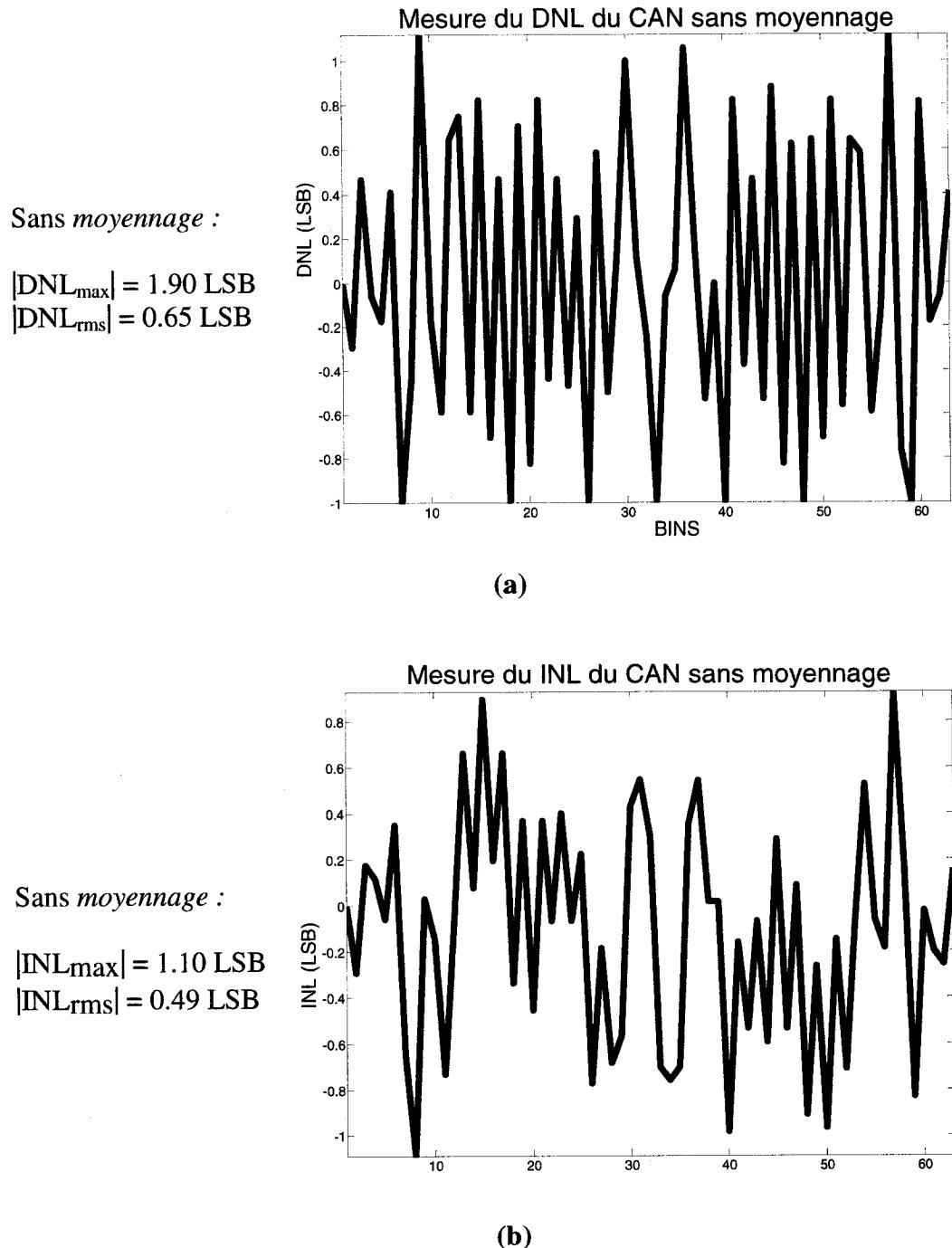

| Figure G.1. Illustration de la linéarité du CAN parallèle de 6 bits, avec $\sigma V_{\text{offset-total}} = 5$ mV et $\sigma V_{\text{offset-préamp}} = 3.8$ mV, avec moyennage (a) DNL, (b) INL.....                                         | 121 |

| Figure G.2. Illustration de la linéarité du CAN parallèle de 6 bits, avec $\sigma V_{\text{offset-total}} = 5$ mV et $\sigma V_{\text{offset-préamp}} = 3.8$ mV, sans moyennage (a) DNL, (b) INL. ....                                        | 122 |

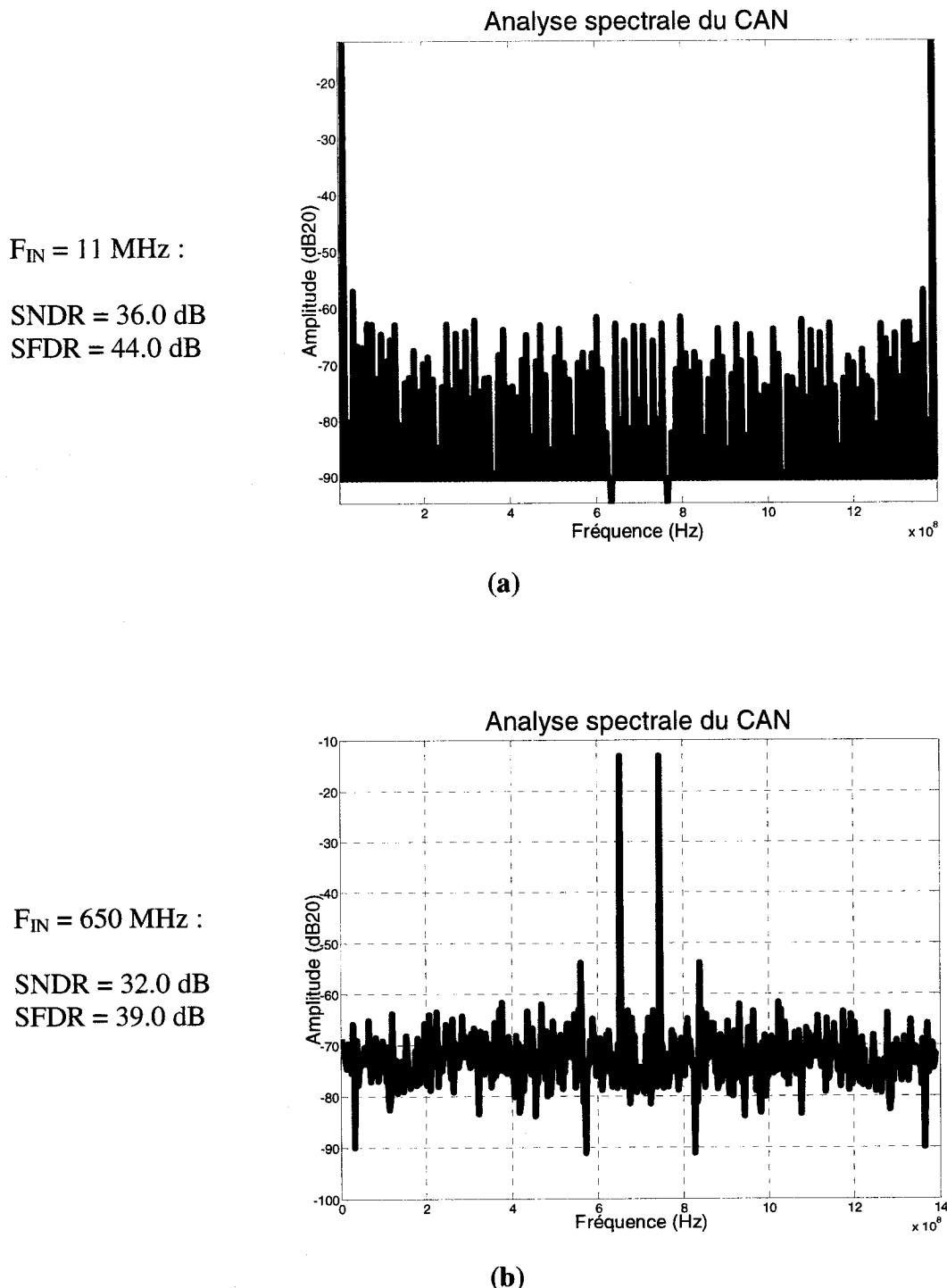

| Figure G.3. Analyse spectrale du CAN, avec $\sigma V_{\text{offset-total}} = 5$ mV et $\sigma V_{\text{offset-préamp}} = 3.8$ mV, pour $F_s = 1.4$ GÉPS et (a) $F_{\text{IN}} = 11$ MHz, et (b) $F_{\text{IN}} = 650$ MHz respectivement..... | 123 |

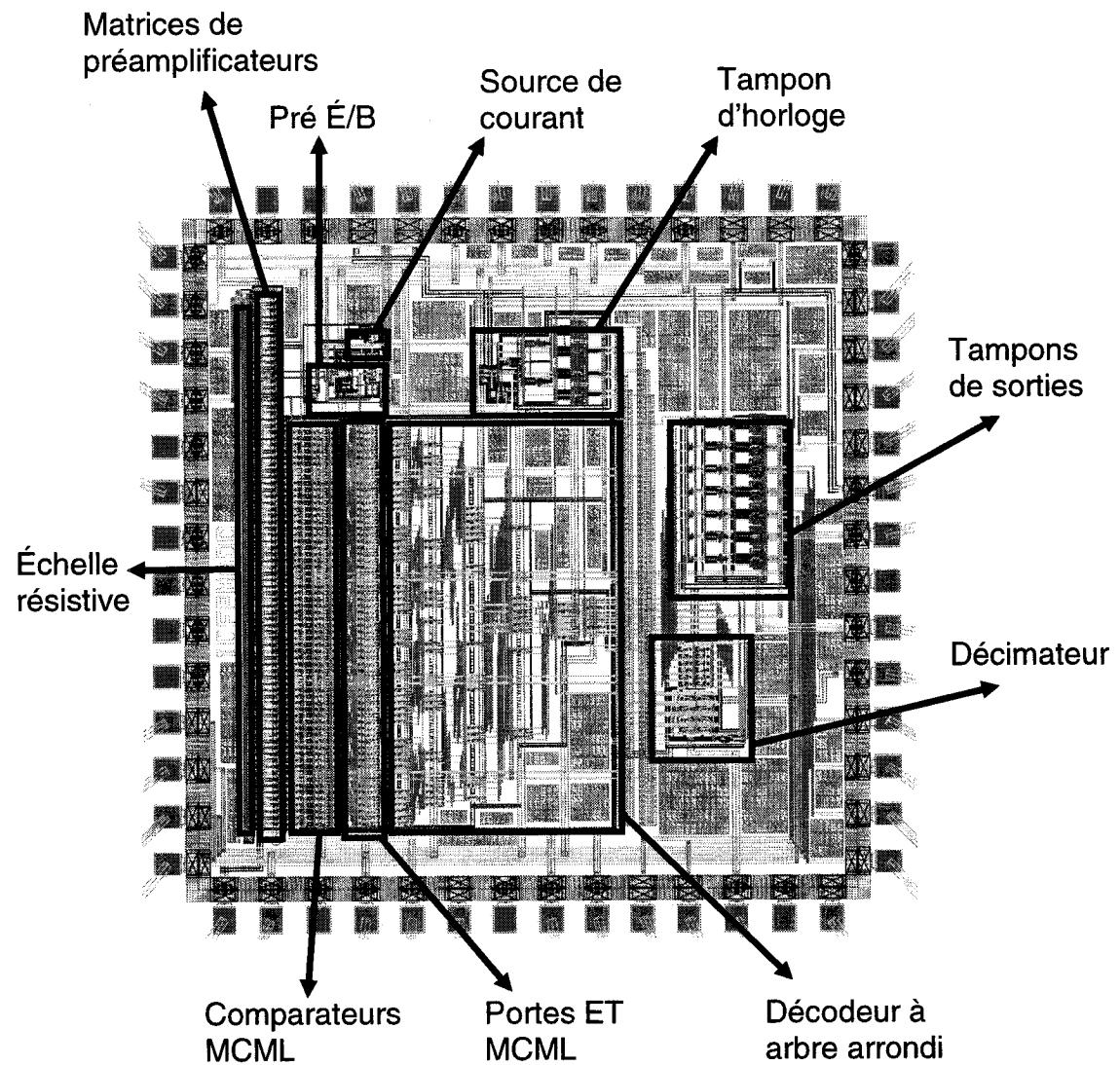

| Figure H.1. Plan de masques de la puce entière, illustrant le CAN parallèle de 6 bits et des modules servant à la testabilité. ....                                                                                                           | 125 |

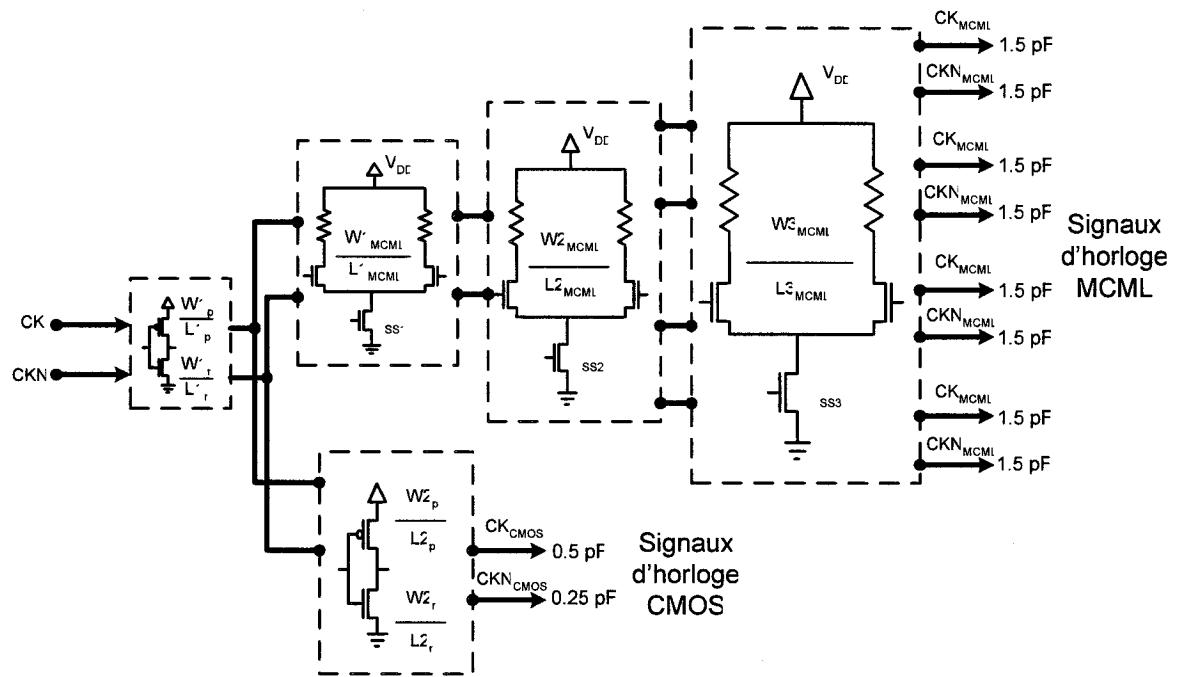

| Figure I.1. Circuit interne du tampon d'horloge mixte, CMOS et MCML.....                                                                                                                                                                      | 127 |

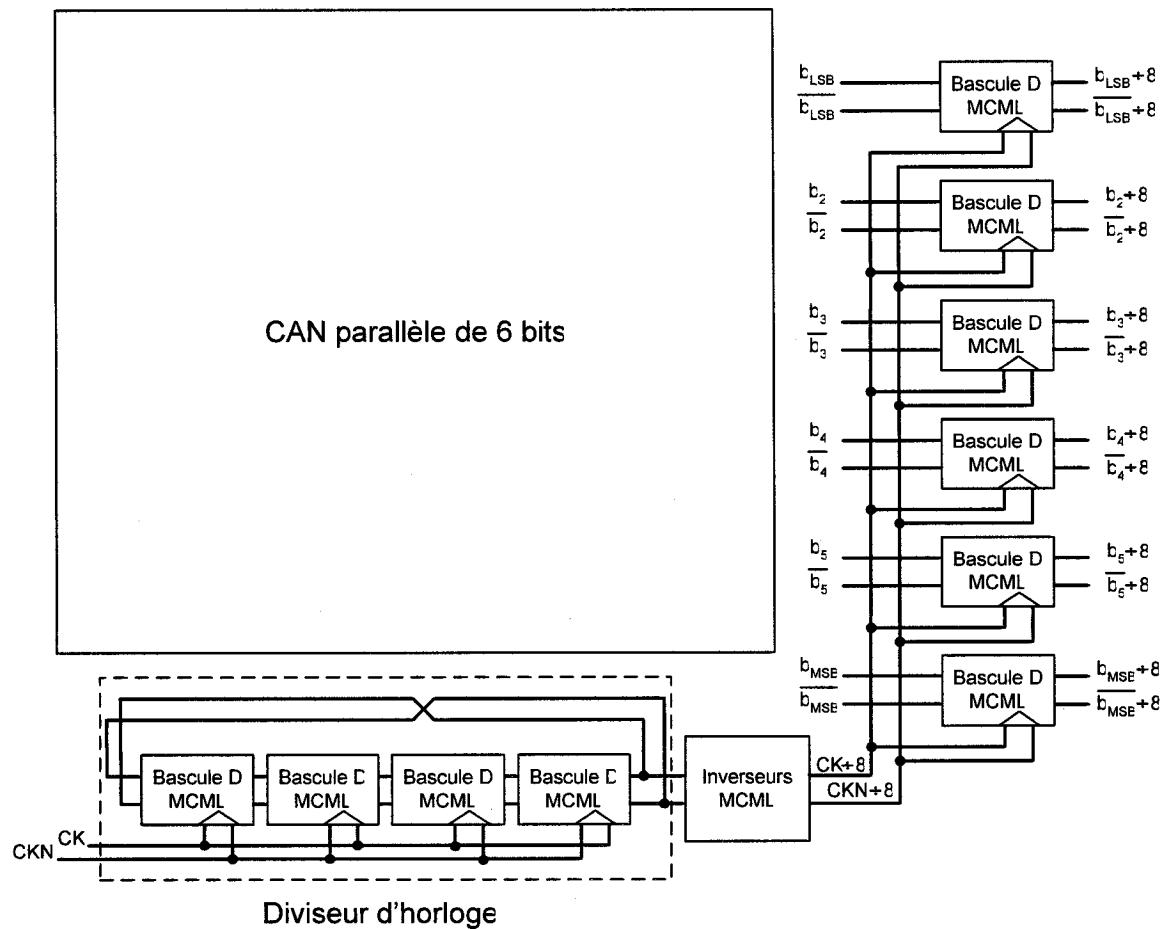

| Figure J.1. Circuit interne du décimateur, réduisant la fréquence d'échantillonnage par un facteur de 8.....                                                                                                                                  | 129 |

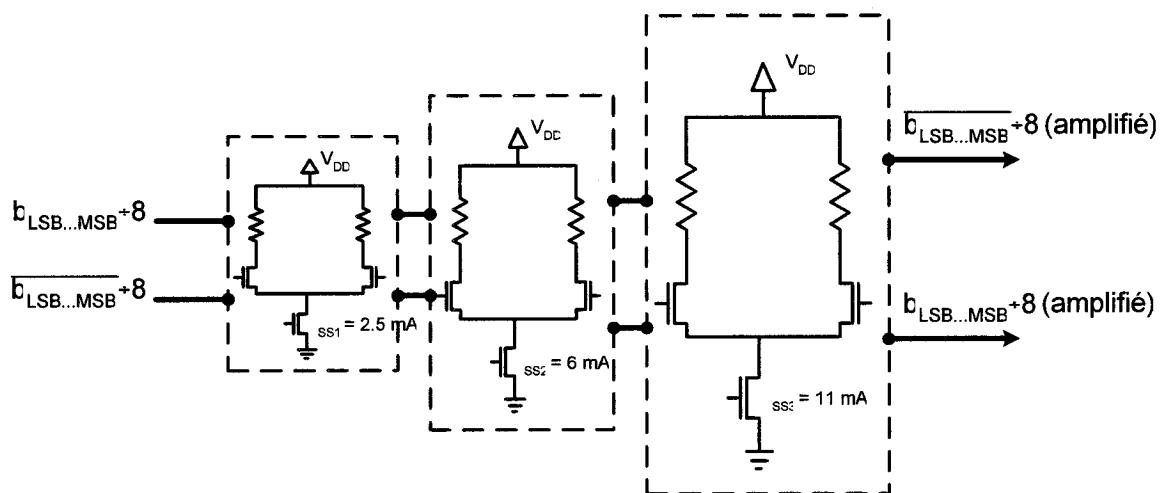

| Figure K.1. Circuit interne du tampon de sortie.....                                                                                                                                                                                          | 130 |

# LISTE DES TABLEAUX

|                                                                                                                                                                                                 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 2.1. Classes d'architectures. ....                                                                                                                                                      | 7  |

| Tableau 2.2. Résultats de l'intégrale donnés par l'équation (2.16) pour différentes valeurs de « k ». ....                                                                                      | 17 |

| Tableau 3.1. Représentation du code thermomètre et sa correspondance en codes binaire, Gray et Q-Gray respectivement. ....                                                                      | 39 |

| Tableau 3.2. Corrections d'erreurs obtenues par les décodeurs binaires, Gray et Q-Gray en fonction de l'ordre de bulles dans le code CT. ....                                                   | 40 |

| Tableau 3.3. Conversion (a) binaire en Q-Gray, et (b) Q-Gray en binaire. ....                                                                                                                   | 40 |

| Tableau 3.4. Résumé des résultats du décodeur en arbre versus ceux du décodeur ROM de 6 bits, conçus avec la technologie CMOSP18 [7]. ....                                                      | 41 |

| Tableau 4.1. Spécifications ciblées pour le CAN parallèle. ....                                                                                                                                 | 50 |

| Tableau 4.2. Spécifications ciblées pour le pré É/B. ....                                                                                                                                       | 53 |

| Tableau 4.3. Résultats obtenus de la simulation schématique du pré-É/B. ....                                                                                                                    | 55 |

| Tableau 4.4. Spécifications ciblées et résultats de simulation d'un modèle schématique du préamplificateur. ....                                                                                | 58 |

| Tableau 4.5. Spécifications ciblées et résultats de la simulation du modèle schématique du comparateur MCML. ....                                                                               | 64 |

| Tableau 4.6. Comparaison des résultats de simulation schématique de l'échelle résistive pour $R = 1 \Omega$ et $R = 10 \Omega$ . ....                                                           | 66 |

| Tableau 4.7. Spécifications ciblées et résultats de simulation du modèle schématique du décodeur en arbre MCML. ....                                                                            | 68 |

| Tableau 4.8. Résultats de la simulation schématique pour le CAN parallèle de 6 bits, simulé avec $\sigma V_{offset-total} = 5 \text{ mV}$ et $\sigma V_{offset-preamp} = 3.8 \text{ mV}$ . .... | 70 |

|                                                                                                                                                                 |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 5.1. Résultats de la simulation post-layout pour le CAN parallèle de 6 bits, simulés sans $\sigma V_{offset-total}$ et $\sigma V_{offset-préamp}$ ..... | 83  |

| Tableau 5.2. Valeurs des résistances de l'échelle résistive compilées sur 3 puces.....                                                                          | 91  |

| Tableau 5.4. Comparaison des performances du CAN avec certains travaux sur des CAN implémentés en technologie CMOS 0.18 $\mu\text{m}$ . .....                   | 91  |

| Tableau B.1. Variation de l'amplitude du circuit É/B ( $V_{out}$ ) en fonction du temps.....                                                                    | 108 |

## LISTE DES ABRÉVIATIONS

|         |                                                                               |

|---------|-------------------------------------------------------------------------------|

| BB      | Fréquence de base « Base-Band frequency »                                     |

| BDD     | Diagramme de décision binaire « Binary Decision Diagram »                     |

| BER     | Taux d'erreur de bit « Bit Error Rate »                                       |

| CAN     | Convertisseur Analogique à Numérique                                          |

| CFP80TF | Carte de test pour les boîtiers de type CFP80, fournie par la CMC             |

| CK      | Horloge d'échantillonnage du convertisseur                                    |

| CKN     | Horloge d'échantillonnage du convertisseur, déphasée de 180° par rapport à CK |

| CMC     | « Canadian Microelectronics Corporation »                                     |

| CMOS    | « Complementary Metal Oxyde Semiconductor »                                   |

| CT      | Code thermomètre                                                              |

| DNL     | Non linéarité différentielle « Differential Non-Linearity »                   |

| DSP     | « Digital Signal Processing »                                                 |

| É/B     | Échantillonneur bloqueur                                                      |

| ENOB    | Nombre de bits effectifs « Effective Number Of Bit »                          |

| ERBW    | Résolution effective de la bande passante « Effective Resolution Bandwidth »  |

| ESD     | Décharge électrostatique « Electrostatic discharge »                          |

| FF      | Simulation limite dans le coin « fast-fast »                                  |

|      |                                                                                 |

|------|---------------------------------------------------------------------------------|

| FS   | Simulation limite dans le coin « fast-slow »                                    |

| GÉPS | Giga échantillons par seconde                                                   |

| IF   | Fréquence intermédiaire « Intermediate Frequency »                              |

| INL  | Non linéarité intégrale « Integral Non-Linearity »                              |

| LSB  | Bit le moins significatif « Least Significant Bit »                             |

| M3   | Couche de métal du 3 <sup>e</sup> niveau de la technologie CMOS 0.18 µm         |

| MCML | « MOS Current Mode Logic »                                                      |

| MSB  | « Bit le plus significatif « Most Significant Bit »                             |

| NMOS | « Channel-N Metal Oxyde Semiconductor »                                         |

| PDN  | Réseau de rappel vers le niveau bas « Pull-down Network »                       |

| PMOS | « Channel-P Metal Oxyde Semiconductor »                                         |

| PUN  | Réseau de rappel vers le niveau haut « Pull-up Network »                        |

| RF   | Radio Fréquence                                                                 |

| ROM  | « Read-Only-Memory »                                                            |

| SCM  | Société Canadienne de Microélectronique                                         |

| SDR  | « Software-Defined-Radio »                                                      |

| SF   | Simulation limite dans le coin « slow-fast »                                    |

| SFDR | Plage dynamique exempte de parasites « Spurious Free Dynamic Range »            |

| SNDR | Rapport signal sur bruit et distorsion « Signal to Noise and Distortion Ratio » |

| SNR  | Rapport signal sur bruit « Signal to Noise Ratio »                              |

| SOC  | « System-on-Chip »                                                              |

| SS   | Simulation limite dans le coin « slow-slow »                                    |

TSMC

« Taiwan Semiconductor Manufacturing Company »

## LISTE DES SYMBOLES

|                             |                                                                                                                            |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|

| $\beta$                     | Transconductance                                                                                                           |

| $\mu$                       | Constante de mobilité des électrons dans le silicium (Si)                                                                  |

| $\sigma(\Delta\beta/\beta)$ | Déviation standard du désappareillement entre les transistors d'une paire différentielle, causé par l'effet de $\beta$ (%) |

| $\sigma(\Delta V_T)$        | Déviation standard du désappareillement entre les transistors d'une paire différentielle, causé par l'effet de $V_T$ (V)   |

| $\tau_{CMOS}$               | Délai dans une porte CMOS (s)                                                                                              |

| $\tau_{MCML}$               | Délai dans une porte MCML (s)                                                                                              |

| $\Delta V$                  | Différence de potentiel entre $V_{IN}$ et $V_{ref}$ du préamplificateur (V)                                                |

| $\sigma V_{offset}$         | Déviation standard de la tension de décalage (V)                                                                           |

| $\Delta V_{out}$            | Dynamique des transitions des sorties du décodeur MCML (V)                                                                 |

| $A_\beta$                   | Coefficient de mésappariement du $\beta$ par unité de surface de la grille (%· $\mu m$ )                                   |

| $A_{\text{préamp}}$         | Gain DC du préamplificateur (V/V)                                                                                          |

| $A_{\text{préamp-com}}$     | Gain DC du comparateur (V/V)                                                                                               |

| $A_{VT}$                    | Coefficient de mésappariement du $V_T$ par unité de surface de la grille (V· $\mu m$ )                                     |

| $C_{db}$                    | Capacité de déplétion au drain d'un transistor (fF)                                                                        |

| $C_H$                       | Capacité de charge à l'entrée du pré E/B (fF)                                                                              |

| $C_{ox}$                    | Capacité de grille par unité de surface (F/m <sup>2</sup> )                                                                |

| $C_P$                       | Capacités parasites (F)                                                                                                    |

|                           |                                                                                      |

|---------------------------|--------------------------------------------------------------------------------------|

| $C_{sb}$                  | Capacité de déplétion à la source d'un transistor (fF)                               |

| $D_{LSB}$                 | Distorsion de l'échelle résistive exprimée en LSB                                    |

| $E_Q$                     | Erreur de quantification                                                             |

| $F_{3dB}$                 | Fréquence de coupure ou bande passante (Hz)                                          |

| $F_{3dB-com}$             | Bande passante du comparateur MCML à l'échantillonnage (Hz)                          |

| $F_{3dB-É/B}$             | Fréquence de coupure ou bande passante de l'échantillonneur bloqueur (Hz)            |

| $F_{3dB-É/B}$             | Fréquence de coupure ou bande passante de l'échantillonneur bloqueur (Hz)            |

| $F_{3dB-échantillonnage}$ | Bandé passante du circuit commuté à l'entrée du pré É/B (Hz)                         |

| $F_{3dB-préamp}$          | Bandé passante du préamplificateur (Hz)                                              |

| $F_{3dB-préamp}$          | Bandé passante d'un préamplificateur (Hz)                                            |

| $F_{3dB-tampon}$          | Bandé passante du transistor $M_{tampon}$ du pré É/B (Hz)                            |

| $f_{CK}$                  | Fréquence des signaux d'horloge CK et CKN (Hz)                                       |

| $F_{IN}$                  | Fréquence d'entrée (Hz)                                                              |

| $F_N$                     | Taux de Nyquist (Hz)                                                                 |

| $F_s$                     | Fréquence d'échantillonnage (Hz)                                                     |

| $F_{s-max}$               | Fréquence d'échantillonnage limite du CAN (Hz)                                       |

| $g_{m-tampon}$            | Transconductance de $M_{tampon}$ (mA/V)                                              |

| $G_{préamp}$              | Gain du préamplificateur obtenu à la fin de la période d'échantillonnage $T_s$ (V/V) |

| $G_{tampon}$              | Gain DC du transistor $M_{tampon}$ à l'intérieur du pré É/B (V/V)                    |

| $I_{SS}$                  | Courant de commande de la paire différentielle (A)                                   |

| $L$                       | Longueur de grille d'un transistor MOS ( $\mu m$ )                                   |

|                  |                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| $M_{tampon}$     | Transistor de tampon de sortie du pré É/B                                                                             |

| $N$              | Résolution en nombre de bits                                                                                          |

| $P_C$            | Nombre de préamplificateurs en couplage ou de préamplificateurs excédentaires « dummies » dans le réseau de moyennage |

| $P_{CMOS}$       | Dissipation de la puissance dynamique des portes MCML (mW)                                                            |

| $P_M$            | Probabilité d'observer la métastabilité                                                                               |

| $P_{MCML}$       | Dissipation de la puissance statique des portes MCML (mW)                                                             |

| $R_0$            | Résistance de charge du préamplificateur ( $\Omega$ )                                                                 |

| $R_1$            | Résistance latérale servant à construire le réseau de moyennage ( $\Omega$ )                                          |

| $R_{comp}$       | Résistance de compensation du réseau de moyennage ( $\Omega$ )                                                        |

| $R_{on-S1}$      | Valeur de la résistance commutée du transistor S1 ( $\Omega$ )                                                        |

| $R_T$            | Résistance de terminaison dans le réseau de moyennage ( $\Omega$ )                                                    |

| $S_1$            | Transistor commuté de type P situé à l'entrée du pré É/B                                                              |

| $S_{dummy}$      | Transistor factice du pré É/B                                                                                         |

| $T_S$            | Période d'échantillonnage (s)                                                                                         |

| $V_{DD}$         | Tension d'alimentation (V)                                                                                            |

| $V_{eff}$        | Tension de saturation d'un transistor (V)                                                                             |

| $V_{eff-préamp}$ | Tension de saturation des transistors de la paire différentielle (V)                                                  |

| $V_{gs}$         | Différence de potentiel entre la grille et la source du transistor (V)                                                |

| $V_{id}$         | Étendue de la plage d'entrée du préamplificateur (V)                                                                  |

| $V_{IN}$         | Signal d'entrée (V)                                                                                                   |

| $V_{IN^-}$       | Signal d'entrée $V_{IN}$ déphasé de $180^0$ (V)                                                                       |

| $V_{IN^+}$       | Signal d'entrée $V_{IN}$ non déphasé (V)                                                                              |

|              |                                                     |

|--------------|-----------------------------------------------------|

| $V_{IN-CM}$  | Tension commune de $V_{IN}$ à l'entrée du CAN (V)   |

| $V_{IN-dyn}$ | Plage dynamique de la tension d'entrée $V_{IN}$ (V) |

| $V_{LSB}$    | Différence de potentiel correspondant à 1 LSB (V)   |

| $V_{offset}$ | Tension de décalage (V)                             |

| $V_{ref}$    | Tension de référence d'une paire différentielle (V) |

| $V_T$        | Tension de seuil (V)                                |

| W            | Largeur de grille d'un transistor MOS ( $\mu m$ )   |

## LISTE DES ANNEXES

|                                                                                        |     |

|----------------------------------------------------------------------------------------|-----|

| ANNEXE A : TRANSISTOR TAMPON DU PRÉ É/B .....                                          | 104 |

| ANNEXE B : ÉCHANTILLONNAGE DU PRÉ É/B .....                                            | 107 |

| ANNEXE C : BANDE PASSANTE ( $F_{3\text{dB-}\text{préamp}}$ ) DU PRÉAMPLIFICATEUR ..... | 110 |

| ANNEXE D : RÉSEAU DE MOYENNAGE .....                                                   | 112 |

| ANNEXE E : COMPARATEUR MCML .....                                                      | 115 |

| ANNEXE F : SCRIPT MATLAB .....                                                         | 117 |

| ANNEXE G : COURBES OBTENUES DES SIMULATIONS SCHÉMATIQUES ...                           | 120 |

| ANNEXE H : DESSIN DE MASQUES DU CAN PARALLÈLE DE 6 BITS .....                          | 124 |

| ANNEXE I : TAMPON D'HORLOGE .....                                                      | 126 |

| ANNEXE J : LE DÉCIMATEUR .....                                                         | 128 |

| ANNEXE K : LE TAMPON DE SORTIE .....                                                   | 130 |

# **CHAPITRE 1**

---

## **INTRODUCTION**

### **1.1. MOTIVATION**

L'univers est majoritairement analogique et le traitement de l'information en découlant est essentiellement numérique. Le passage de l'un à l'autre nécessite une approche plutôt élaborée, tenant compte des différents aspects d'une telle transformation. Toutefois, qu'est-ce qui motive une telle conversion? Et quel est le moyen par lequel cette conversion se fait ?

Pour répondre à la première question, la transmission par voies numériques est plus avantageuse que par voies analogiques. En effet, ces voies sont plus résistantes aux perturbations dans un environnement bruité et aux atténuations sur de longues distances de transmission [33]. De plus, la transmission numérique donne lieu à des traitements avancés permettant d'améliorer la qualité et la sécurité de l'information par des techniques de correction d'erreurs et d'encryption. Ainsi, le traitement numérique reste une nécessité pour les nombreux avantages listés ci-haut.

Pour la deuxième question, elle introduit le fondement même du sujet de ce mémoire : les convertisseurs analogiques numériques (CAN). En effet, hors de toutes

surprises, la conversion analogique à numérique se fait à l'aide des circuits microélectroniques dédiés que sont les CAN. Ils agissent comme des éléments clés dans plusieurs domaines d'applications : équipements de mesures et de tests, systèmes de stockage à support magnétique, et télécommunication radio.

## 1.2. APPLICATIONS

### 1.2.1. Équipements de test

Dans le monde des équipements de mesures et de test, les CAN sont utilisés pour numériser les signaux sortant du module de test, pour les stocker dans un tampon local ou disque rigide servant à l'acquisition de données ou encore à l'affichage sur un écran. Des exemples de tels équipements sont : les analyseurs logiques, les oscilloscopes et les analyseurs de spectre. Les oscilloscopes numériques et les analyseurs logiques les plus performants à ce jour utilisent typiquement des CAN de 8 bits implantés avec la technologie bipolaire ou Arsenic de Gallium (GaAs). Ces CAN opèrent généralement à quelques giga échantillons par seconde (GÉPS). Jusqu'à nos jours, ces technologies offrent des performances inégalées en termes de rapidité en comparaison avec la technologie CMOS. Toutefois, les CAN conçus consomment énormément de puissance, ce qui limite l'étendue de leurs applications. Alors que l'aspect de consommation est peu critique dans le domaine des équipements de test, il est d'une importance fondamentale dans des projets de systèmes sans fil les plus ambitieux.

### 1.2.2. Système de stockage magnétique

En 2001, les systèmes de stockages à support magnétique pour disques rigides à grandes densités nécessitaient des CAN ayant une précision de 6 bits et un taux de conversion supérieur à 1 GÉPS afin de permettre une lecture efficace du canal d'entrée [2]. Il est prévu que ce taux de conversion augmentera en parallèle avec la croissance de la densité de stockage dans les années à venir. Dans cette optique, non seulement le CAN doit être rapide, mais il doit aussi avoir une basse consommation en puissance,

plus particulièrement en ce qui a trait au développement des disques rigides dédiés aux ordinateurs portables. Ainsi, il est clair que les CAN rapides à forte consommation destinés aux équipements de test ne sont pas pertinents dans ce cadre d'application.

### 1.2.3. Télécommunication radio

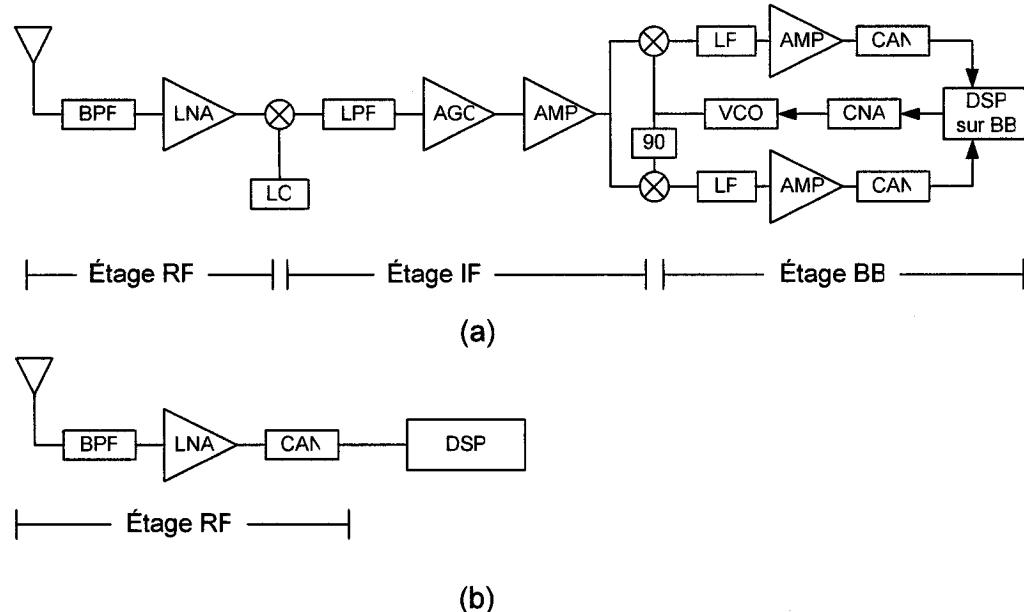

Dans un autre ordre d'idées, les innovations techniques de plus en plus développées dans le monde des CAN ont permis de frayer un chemin dans le progrès du monde de la communication numérique, plus particulièrement les récepteurs pour ondes radar [33]. Il existe plusieurs types d'architectures de récepteurs radios, qui sont : le récepteur hétérodyne, le récepteur homodyne, le récepteur « low-IF » et bien d'autres [57]. La plus connue étant certainement le récepteur hétérodyne, illustré à la Figure 1.1a. Cette architecture opère dans 3 paliers de fréquences, soit : le niveau des radio fréquences (Radio Frequency – RF), le niveau de fréquence intermédiaire (Intermediate Frequency - IF) et le niveau bande de base (BB). Toutefois, l'architecture est d'une complexité accablante, et par conséquent, très demandant en terme de consommation de puissance.

Le concept radio configurable souvent appelée radio définie par logiciel (Software Defined Radio - SDR) a été élaboré dans le but de s'adapter aux différentes normes de communication sans fils qui existent à travers le monde. Les systèmes radio découlant du concept doivent être flexibles et reprogrammables. Les systèmes SDR dits à conversion directe sont une classe de systèmes qui visent une flexibilité maximale. Pour ce faire, le récepteur radio doit directement numériser le signal RF à la sortie de l'antenne de réception pour permettre aux logiciels ou modules de traitement numérique de signaux (DSP : « digital signal processing ») de traiter numériquement le signal en question, et de reprogrammer le récepteur sur une autre fréquence de porteuse d'intérêt à tout moment. Ultimement, ce système radio configurable ne nécessite qu'un seul CAN, comme illustré à la Figure 1.1b. À l'opposé du récepteur hétérodyne, il doit aussi être très rapide afin d'échantillonner le signal RF. Sa consommation en puissance doit être

minimisée pour satisfaire au critère de portabilité. En somme, le concept SDR requiert un CAN extrêmement performant.

**Figure 1.1. Diagrammes blocs typiques pour des architectures de (a) récepteur hétérodyne et de (b) concept du radio configurable.**

### 1.3. NOS OBJECTIFS

L'objectif principal de ce mémoire est de concevoir un CAN de type parallèle (flash) à basse consommation, ultra-rapide et avec un taux d'échantillonnage supérieur à 1 GÉPS, adapté pour des applications SDR. Toutefois, il y a un compromis entre le taux d'échantillonnage et la résolution du CAN. Ainsi, plus le CAN est rapide, moins il est précis et vice et versa. Par conséquent, nous visons une précision de 6 bits, et nous limitons son application dans le domaine de la détection de signaux radios. Cette application exige une faible consommation de puissance, ce qui est un critère essentiel et même primordial dans ce cas. À cette fin, nous examinerons la technique de conception « MOS Current Mode Logic » (MCML) pour réduire la consommation en énergie du CAN.

## 1.4. ORGANISATION DU MÉMOIRE

Le restant du mémoire sera réparti en cinq chapitres. Les notions introducives des CAN ultra-rapides sont introduites dans le chapitre 2. Nous présenterons le bruit de quantification, ainsi que les critères essentiels de performances se rattachant à ces CAN. De plus, nous mettrons l'accent sur les architectures ultra-rapides telles que l'architecture parallèle, l'architecture interpolée (interpolating), l'architecture pliée (folding) et celle à temps-entrelacé (time-interleaving).

La revue de littérature des CAN ultra-rapides fait l'objet du chapitre 3. Nous nous axerons sur la nécessité d'utiliser un échantillonneur bloqueur (É/B). De même, nous introduirons la technique dite de moyennage (averaging). Aussi, nous mettrons en évidence les techniques récentes de décodage et de correction d'erreurs.

Au chapitre 4, qui porte sur la conception du CAN parallèle, nous modélisons ce CAN et nous discutons l'innovation apportée au CAN parallèle. Nous discuterons notamment des circuits MCML, et nous y présenterons des résultats de simulations au niveau schématique.

Le chapitre 5 est consacré aux considérations pratiques pour les dessins de masques ainsi que les résultats « post-layout ». Les résultats de test de la puce fabriquée compléteront le chapitre. Nous terminons le mémoire avec nos conclusions présentées au chapitre 6.

## CHAPITRE 2

---

### Notions sur les convertisseurs analogiques numériques

#### 2.1. INTRODUCTION

Il existe deux principales catégories de CAN: les CAN à taux de Nyquist (Nyquist-rate converters) et les CAN à sur-échantillonnage (oversampling converters). En théorie, les CAN de la première catégorie sont ceux pour lesquels la fréquence d'échantillonnage ( $F_s$ ) coïncide avec le taux de Nyquist ( $F_N$ ) du CAN, *i.e.*  $F_N = 2F_{IN\text{-}max}$  où  $F_{IN\text{-}max}$  est la fréquence maximale du signal d'entrée. La théorie entourant les CAN est très riche, voire même complexe, de telle sorte qu'il est difficile de faire une revue complète sur le sujet. Dans ce présent chapitre, nous examinons les concepts de base des CAN ainsi que leurs critères de performance. Nous présenterons principalement les CAN à taux de Nyquist, et en particulier les architectures rapides telles que les architectures parallèle, interpolée (interpolating), pliée (folding) et à temps-entrelacé (time-interleaved), résumées au Tableau 2.1.

**Tableau 2.1. Classes d'architectures.**

| Catégorie de convertisseurs | Vitesse faible, Grande précision (14-20 bits)             | Vitesse moyenne, Moyenne précision (10-14 bits)         | Vitesse haute, Basse précision (4-10 bits)                                                       |

|-----------------------------|-----------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| <i>Taux de Nyquist</i>      | <i>Intégrateur</i>                                        | <i>Approximation successive</i><br><i>Algorithmique</i> | <i>Parallèle</i><br><i>Interpolé</i><br><i>Plié</i><br><i>Pipeliné</i><br><i>Temps-entrelacé</i> |

| <i>Sur-échantillonnage</i>  | <i>Sigma-Delta</i><br><i>Sigma-Delta à bande-passante</i> |                                                         |                                                                                                  |

## 2.2. CONCEPTS DE BASE

En principe, les CAN convertissent un signal analogique en un mot binaire représenté sur un certain nombre de bits (N) de résolution. Dans la terminologie des convertisseurs, l'unité de mesure sur l'erreur est souvent exprimée selon la résolution du convertisseur qui correspond à l'amplitude du bit le moins significatif (Least significant bit – LSB) associée à la précision du CAN et elle est notée par :

$$1 \text{ LSB} = \frac{1}{2^N} \quad (2.1)$$

Également, nous désignons par  $V_{\text{LSB}}$  le changement de potentiel entre 2 niveaux de décision du CAN, autrement dit :

$$V_{\text{LSB}} = \frac{V_{\text{IN-dyn}}}{2^N} = \frac{2 \cdot V_{\text{IN}}}{2^N} \quad (2.2)$$

où  $V_{\text{IN-dyn}}$  est la plage dynamique de la tension d'entrée et  $V_{\text{IN}}$  est l'amplitude absolue de la tension d'entrée, *i.e.*  $V_{\text{IN-dyn}} = 2V_{\text{IN}}$ . La relation entre le signal d'entrée analogique et le mot binaire en sortie est reprise par l'équation (2.3) [10] :

$$V_{IN-dyn} \cdot (b_1 \cdot 2^{-1} + b_2 \cdot 2^{-2} + \dots + b_N \cdot 2^{-N}) = V_{IN} \pm V_{err} \quad (2.3)$$

où

$$-\frac{1}{2}V_{LSB} \leq V_{err} \leq \frac{1}{2}V_{LSB}$$

Ici,  $b_1$  est le bit le plus significatif (most significant bit – MSB) et  $b_N$  le moins significatif (least significant bit – LSB) du mot binaire généré par le CAN. L'équation 2.3 décrit le comportement du convertisseur dans le cas où la quantification n'est pas idéale et qu'il y a une certaine erreur ( $V_{err}$ ) sur chaque conversion du signal  $V_{IN}$ . Cette erreur génère ce qu'on appelle le *bruit de quantification*.

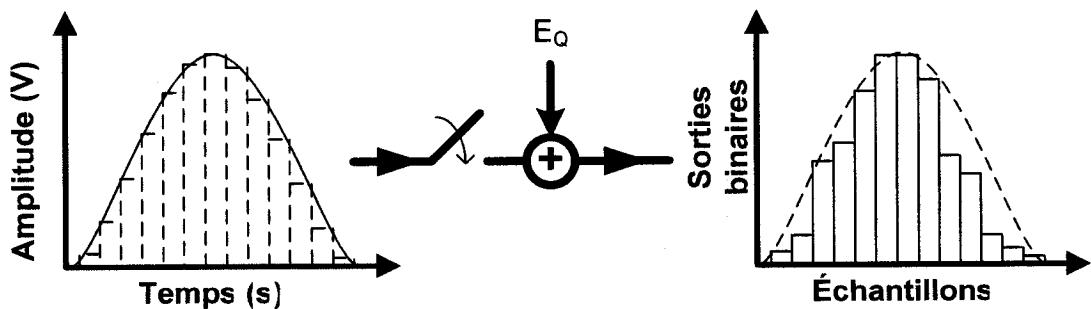

### 2.2.1. Bruit de quantification

Le bruit de quantification est un paramètre qui dépend essentiellement de la résolution ( $N$ ) du convertisseur. Comparé à sa tension d'entrée  $V_{IN}$ , la sortie du CAN produit un ensemble de valeurs discrètes se limitant à  $2^N$  possibilités. Dans cette optique, l'erreur introduite dans chaque conversion associée à la résolution finie du convertisseur est appelée erreur de quantification ( $E_Q$ ).

La quantification de  $V_{IN}$  est représentée par un modèle d'échantillonnage idéal dans lequel on a ajouté une source de bruit, comme illustré à la Figure 2.1.

**Figure 2.1. Effet du bruit de quantification sur un signal échantillonné.**

Il serait intéressant d'investiguer ce cas et d'essayer de caractériser le bruit de quantification ( $E_Q$ ) résultant.

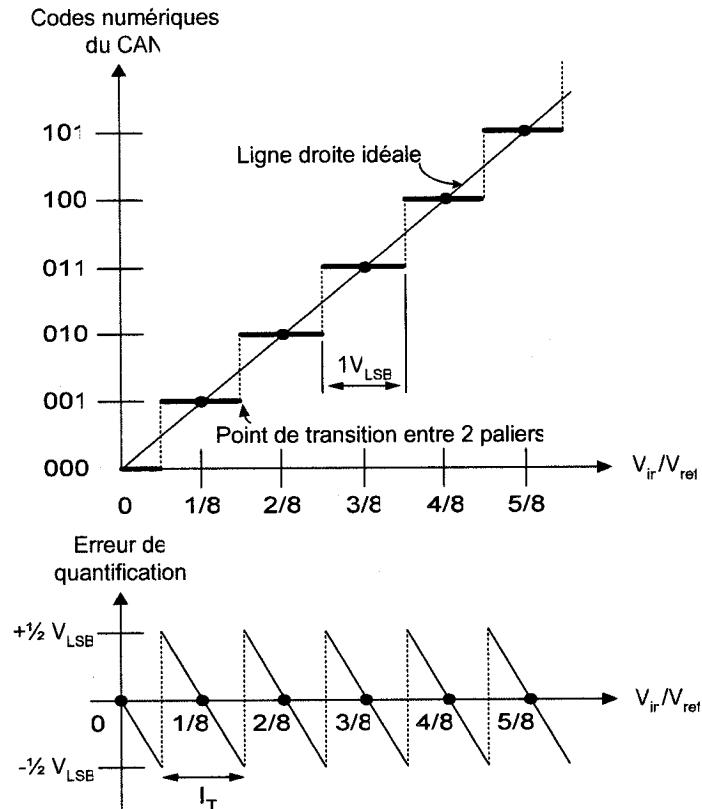

### 2.2.1.1. Fonction de transfert

La fonction de transfert d'un CAN idéal et la courbe d'énergie du bruit ( $E_Q$ ) associée aux niveaux de tension  $V_{IN}$  sont illustrées à la figure 2.2:

**Figure 2.2. CAN idéal : (a) Fonction de transfert, (b) erreur de quantification associée.**

Chaque étage de la Figure 2.2a s'étend exactement sur un intervalle correspondant à 1  $V_{LSB}$ . Par conséquent, l'erreur maximale perçue par chacun des étages de décision du CAN est de 0.5  $V_{LSB}$ , comme le fait valoir la Figure 2.2b. Il est intéressant de noter qu'il existe deux approches pour modéliser  $E_Q$  : une approche déterministe qui se base sur la forme de l'erreur de quantification (Figure 2.2b) pour calculer l'erreur  $E_Q$ , et une approche stochastique, s'appuyant quant à elle sur les principes de probabilité pour déterminer la déviation standard du niveau d'erreur. Étonnamment, ces deux approches donnent le même résultat. Afin d'alléger le texte, nous exposerons seulement la première approche qui est l'approche déterministe.

En effet, la forme d'onde de  $E_Q$  est périodique, par conséquent, il est possible de calculer le niveau RMS du signal en intégrant la fonction sur une période entière ( $I_T$ ) :

$$E_{Q-rms}(V_{LSB}) = \sqrt{\frac{1}{I_T} \int_{I_T} E_Q^2 dI} = \sqrt{\frac{1}{I_T} \int_{I_T} \left(1V_{LSB} \frac{-I}{I_T}\right)^2 dI} = \frac{1V_{LSB}}{\sqrt{12}} \quad (2.4)$$

### 2.2.1.2. Rapport signal sur bruit

À partir de l'équation (2.4), il est envisageable de calculer le rapport signal sur bruit (Signal to noise ratio – SNR) qu'un CAN est capable d'atteindre avec une certaine précision. Lorsque le signal d'entrée  $V_{IN}$  du convertisseur est une sinusoïde, le SNR est donné par l'expression suivante :

$$\begin{aligned} SNR &= 20 \cdot \log \left| \frac{V_{IN-rms}}{E_{Q-rms}} \right| \\ &= 20 \cdot \log \left| \frac{V_{IN} / \sqrt{2}}{V_{LSB} / \sqrt{12}} \right| \\ &= 20 \cdot \log \left| \frac{V_{IN} / \sqrt{2}}{2 \cdot V_{IN} / 2^N \cdot \sqrt{12}} \right| \end{aligned} \quad (2.5)$$

$$SNR = 6.02 \cdot N + 1.76 \text{ dB}$$

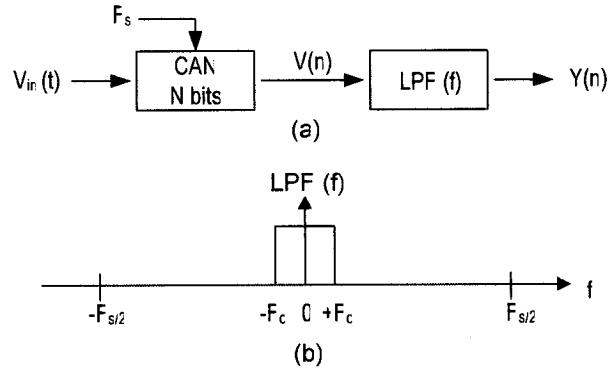

Par convention, la mesure du SNR se fait avec une entrée sinusoïdale. Il est à noter que l'équation (2.5) s'applique seulement sur les CAN à taux de Nyquist, où la bande passante du convertisseur s'étend jusqu'à  $F_s/2$ . Toutefois, dans un CAN à sur-échantillonnage se servant d'un filtre passe-bas (Low pass filter – LPF), comme illustré à la Figure 2.3, il est possible d'obtenir des SNR élevés.

**Figure 2.3. Principe de sur-échantillonnage.**

Le LPF limite la bande passante du CAN à une fréquence ( $F_0$ ) et élimine le bruit de quantification se trouvant au-delà de cette fréquence. Généralement,  $F_0$  est choisi pour être de loin inférieure à  $F_s/2$ . À toutes fins utiles, le sur-échantillonnage peut être employé pour augmenter la résolution du CAN à taux de Nyquist. L'équation du SNR résultant du sur-échantillonnage ( $SNR_{sur}$ ) est donnée par :

$$SNR_{sur} = 6.02 \cdot N + 1.76 + 10 \cdot \log \left| \frac{F_s}{2 \cdot F_0} \right| \quad (2.6)$$

La technique de sur-échantillonnage représente une alternative intéressante pour augmenter le SNR dans les applications rapides.

### 2.2.2. Critères de performance

Les termes fréquemment utilisés dans le domaine des CAN pour quantifier leurs performances sont : la non linéarité différentielle (Differential non linearity – DNL), la non linéarité intégrale (Integral non linearity – INL), le nombre de bits effectifs (Effective number of bits – ENOB), la plage dynamique exempte de parasites (Spurious free dynamic range – SFDR), la résolution effective de la bande passante (Effective resolution bandwidth – ERBW) et le taux d'erreur de bit (Bit error rate – BER).

### 2.2.2.1. Non linéarité

Le niveau de linéarité d'un CAN est caractérisé par la DNL et l'INL. La Figure 2.4 montre une fonction de transfert idéale d'un CAN à 3 bits, et une non idéale affichant des DNL et INL. Par définition, le DNL représente la différence entre la largeur du palier d'un CAN non idéal et celle d'un CAN idéal soit 1 LSB :

$$DNL_k = \text{Largeur du } k^{\text{ième}} \text{ palier non idéal (en LSB)} - 1 \text{ LSB} \quad (2.7)$$

Ainsi, lorsque le palier non idéal a une largeur de 1 LSB, l'erreur DNL correspondante est nulle. Lorsque le DNL dépasse  $\pm 1$  LSB, il y a un risque pour que le CAN ait un code manquant « missing code ». Toutefois, lorsque cette dernière situation se présente, il est certain que la fonction de transfert a un DNL de  $\pm 1$  LSB, comme illustré à la Figure 2.4. L'INL se définit comme étant l'accumulation des  $DNL_k$  de la fonction de transfert :

$$INL = \sum_{k=0}^{2^N-1} DNL_k \quad (2.8)$$

Une manière plus inspirée de le percevoir est de le considérer comme étant la déviation des points de transition du palier non idéal par rapport au palier de la courbe idéale, comme indiqué à la Figure 2.4. Dans la majorité des cas, un CAN est considéré comme étant parfaitement linéaire lorsque le DNL et le INL sont chacun de  $\pm 0.5$  LSB.

Figure 2.4. Illustration des non-linéarités (DNL et INL) des CAN.

### 2.2.2.2. Nombre de bits effectifs

L'ENOB découle directement de l'équation (2.5), qui exprime le SNR en termes de bits au lieu de l'unité décibel. En réalité, un CAN comporte du bruit de quantification auquel vient s'ajouter de la distorsion. Il est alors pertinent et rigoureux d'employer la terminologie rapport signal sur bruit et distorsion (Signal to noise and distortion ratio – SNDR) au lieu du SNR, lorsque le CAN est non idéal. Ainsi, en isolant le terme N et en remplaçant SNR par SNDR dans l'équation (2.5), l'ENOB s'affiche comme :

$$ENOB = \frac{SNDR - 1.76 \text{ dB}}{6.02 \text{ dB}} \quad (2.9)$$

### 2.2.2.3. Plage dynamique exempte de parasites

Les différentes erreurs de conversion créent des raies spectrales à des harmoniques bien définies par rapport à  $F_{IN}$ . Dans des applications où la pureté spectrale est importante, le SFDR devient un critère d'évaluation dans la sélection d'un CAN. Le SFDR se définit comme étant la différence en dB entre la fondamentale et la composante de distorsion la plus élevée du spectre fréquentiel, comme le démontre la Figure 2.5. De plus, sa plage dynamique diminue au fur et à mesure que le CAN est stimulé par une fréquence  $F_{IN}$  de plus en plus grande. Ce comportement s'explique par des pertes de performance au niveau des composants circuits constituant le CAN comme les échantillonneurs bloqueurs (É/H), les préamplificateurs, les amplificateurs opérationnels et les comparateurs.

**Figure 2.5. Analyse spectrale et SFDR**

#### 2.2.2.4. Résolution effective de la bande passante

L'ERBW est la fréquence  $F_{IN}$  pour laquelle le SNDR du CAN chute de 3 dB par rapport à la valeur SNDR au niveau DC. La plupart des applications s'attendent à une conversion fidèle du CAN pour tout signal d'entrée affichant  $F_{IN}$  inférieure à la fréquence de Nyquist, *i.e.*  $F_{IN} \leq F_s/2$ . Toutefois, beaucoup de CAN affichent une sévère dégradation du SNDR à des fréquences bien en dessous de  $F_s/2$  [32, 50, 63]. Pour cette raison, la littérature rapporte souvent la vitesse d'un convertisseur par l'ERBW plutôt que par la fréquence d'échantillonnage  $F_s$ .

#### 2.2.2.5. Taux d'erreurs de bit

Le BER indique le nombre de décisions erronées effectué par le CAN sur un grand nombre défini d'échantillons [52]. Certains auteurs l'interprètent comme la probabilité d'erreurs du CAN [49]. Ces erreurs sont directement proportionnelles à la probabilité du comparateur de tomber dans un état métastable, qui se définit par un niveau de tension dont l'état logique « 1 » ou « 0 » ne peut être clairement défini. Généralement, cet événement survient lorsque :

1. La tension d'entrée du comparateur est trop faible;

2. Le temps alloué pour amplifier ce potentiel à la sortie est insuffisant.

Un CAN haut de gamme doit avoir un BER se situant entre  $10^{-10}$  et  $10^{-15}$  [52].

## 2.3. ARCHITECTURES ULTRA-RAPIDES

Dans cette section, nous examinons les architectures des CAN à taux de Nyquist supérieures à quelques centaines de MHz. Les architectures présentées sont les architectures parallèle, interpolée, pliée et à temps entrelacé. Avant d'entreprendre cette discussion, nous allons faire un survol sur un modèle probabiliste pour prédire la tension de décalage ( $V_{\text{offset}}$ ) dans une paire différentielle. Rappelons que cette dernière est généralement une partie intégrante dans les préamplificateurs ainsi que les comparateurs.

### 2.3.1. Modèle probabiliste de la tension de décalage

Les variations de procédés font en sorte que le circuit fabriqué ne se comporte plus de façon idéale. Dans une paire différentielle, ces variations causent des mésappariements entre les valeurs des tensions de seuil ( $V_T$ ) et des transconductances ( $\beta$ ) de transistors M1 et M2, ce qui résulte en un décalage de la tension ( $V_{\text{offset}}$ ) à l'entrée de la paire différentielle, comme illustré à la Figure 2.6.

Figure 2.6. Paire différentielle affichant une tension de décalage ( $V_{\text{offset}}$ ).

Lors de la conception, il est impératif d'avoir un modèle probabiliste pour prédire la déviation standard de la tension de décalage ( $\sigma V_{\text{offset}}$ ), car elle a une implication directe sur le DNL et INL [65]. De ce fait,  $\sigma V_{\text{offset}}$  dans une paire différentielle est donné par [53]:

$$\sigma V_{\text{offset}} = \sigma(\Delta V_T) + \sigma\left(\frac{\Delta\beta}{\beta}\right) \cdot \frac{V_{\text{gst}}}{2} \quad (2.10)$$

où  $V_{\text{gst}} = (V_{\text{gs}} - V_T)$  est la tension de saturation, et  $\sigma(\Delta V_T)$  et  $\sigma(\Delta\beta/\beta)$  sont les déviations standards des mésappariements entre les valeurs  $V_T$  et  $\beta$  des transistors M1 et M2 respectivement.

Suite à de longues recherches, Pelgrom [45] a pu démontrer que  $\Delta V_T$  et  $\Delta\beta/\beta$  ont des distributions gaussiennes, et que leurs déviations standards respectives sont données par les équations suivantes :

$$\sigma(\Delta V_T) = \frac{A_{V_T}}{\sqrt{W \cdot L}} \quad (2.11)$$

$$\sigma\left(\frac{\Delta\beta}{\beta}\right) = \frac{A_\beta}{\sqrt{W \cdot L}} \quad (2.12)$$

où  $W$  et  $L$  sont la largeur et la longueur des transistors M1 et M2. Les mêmes résultats ont été confirmés par la suite à plusieurs reprises [3, 30, 47, 55]. Dans la pratique,  $A_{V_T}$  et l'intervalle des valeurs de  $A_\beta$  sont approximativement de l'ordre de [65, 53] :

$$A_{V_T} \approx (1.5 \cdot t_{\text{ox}}) V/\mu\text{m} \quad (2.13)$$

$$A_\beta = 1 - 3 \% \quad (2.14)$$

La fonction densité de probabilité  $f_v(v)$  de la Figure 2.7 est donnée par :

$$f_v(v) = \frac{1}{\sqrt{2\pi} \cdot \sigma V_{\text{offset}}} \exp\left[-\frac{(v - V_{\text{ref}})^2}{2 \cdot \sigma V_{\text{offset}}^2}\right] \quad (2.15)$$

où  $v$  est une variable indiquant une valeur de tension, et  $V_{\text{ref}}$  est la valeur moyenne de la tension de référence. L'intégrale de l'équation (2.15) évalue la probabilité d'avoir une référence de tension dans l'intervalle  $v = V_{\text{ref}} \pm k \cdot \sigma V_{\text{offset}}$  :

$$P\left(v \begin{cases} \leq V_{\text{ref}} + k \cdot \sigma V_{\text{offset}} \\ \geq V_{\text{ref}} - k \cdot \sigma V_{\text{offset}} \end{cases}\right) = \int_{V_{\text{ref}} - k \cdot \sigma V_{\text{offset}}}^{V_{\text{ref}} + k \cdot \sigma V_{\text{offset}}} \frac{1}{\sqrt{2\pi} \cdot \sigma V_{\text{offset}}} \exp\left[-\frac{(v - V_{\text{ref}})^2}{2 \cdot \sigma V_{\text{offset}}^2}\right] dv \quad (2.16)$$

Le Tableau 2.2 présente les résultats de l'intégrale de l'équation (2.16) pour différentes valeurs de «  $k$  » [44].

**Figure 2.7. Distribution gaussienne du  $V_{ref}$  résultant.**

**Tableau 2.2. Résultats de l'intégrale donnés par l'équation (2.16) pour différentes valeurs de «  $k$  ».**

| $k$ | Probabilité d'occurrence (%) dans l'intervalle $V_{ref} \pm k \cdot \sigma V_{offset}$ |

|-----|----------------------------------------------------------------------------------------|

| 0.2 | 15.9                                                                                   |

| 0.6 | 45.1                                                                                   |

| 1.0 | 68.3                                                                                   |

| 1.4 | 83.8                                                                                   |

| 1.8 | 92.8                                                                                   |

| 2.2 | 97.2                                                                                   |

| 2.6 | 99.1                                                                                   |

| 3.0 | 99.7                                                                                   |

À partir du Tableau 2.2, si nous voulons avoir 99.7% de chances d'obtenir un  $V_{offset} \leq 0.5 V_{LSB}$ , il faut attribuer  $W$  et  $L$  des équations (2.11) et (2.12) de manière à ce que le résultant  $\sigma V_{offset}$  de l'équation (2.10) soit 3 fois moins que  $0.5 V_{LSB}$ , *i.e.*  $\sigma V_{offset} = 0.167 V_{LSB}$ .

## 2.3.2. Architecture parallèle

### 2.3.2.1. Description