|                         | Numerical calibration techniques and applications of planar integrated microwave structures                                                                                                                                                                            |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteur:<br>Author:      | Lin Li                                                                                                                                                                                                                                                                 |

| Date:                   | 2005                                                                                                                                                                                                                                                                   |

| Type:                   | Mémoire ou thèse / Dissertation or Thesis                                                                                                                                                                                                                              |

| Référence:<br>Citation: | Li, L. (2005). Numerical calibration techniques and applications of planar integrated microwave structures [Thèse de doctorat, École Polytechnique de Montréal]. PolyPublie. <a href="https://publications.polymtl.ca/7579/">https://publications.polymtl.ca/7579/</a> |

## Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:    | https://publications.polymtl.ca/7579/ |

|------------------------------------------|---------------------------------------|

| Directeurs de<br>recherche:<br>Advisors: | Ke Wu                                 |

| <b>Programme:</b><br>Program:            | Non spécifié                          |

#### UNIVERSITÉ DE MONTRÉAL

# NUMERICAL CALIBRATION TECHNIQUES AND APPLICATIONS OF PLANAR INTEGRATED MICROWAVE STRUCTURES

# LIN LI DÉPARTEMENT DE GÉNIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIAE DOCTOR (Ph.D.)

(GÉNIE ÉLECTRIQUE)

DÉCEMBRE 2005

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-17004-5 Our file Notre référence ISBN: 978-0-494-17004-5

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### UNIVERSITÉ DE MONTRÉAL

#### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

# NUMERICAL CALIBRATION TECHNIQUES AND APPLICATIONS OF PLANAR INTEGRATED MICROWAVE STRUCTURES

présenté par : <u>LI Lin</u>

en vue de l'obtention du diplôme de: <u>Philosophiae Doctor</u>

a été dûment accepté par le jury d'examen constitué de :

M. BOSISIO Renato G., M.Sc., président

M. WU Ke, Ph. D., membre et directeur de recherche

M. CALOZ Christophe, Ph. D., membre

M. RONI Khazaka, Ph. D., membre

#### **AKNOWLEDGEMENTS**

I would like to express my gratitude to my director, Professor Ke Wu, for his continuous support, invaluable guidance and encouragement throughout the work involved in this thesis, which gave me four extremely memorable and fruitful years of studing at École polytechnique de Montréal.

I would like to also thank to M. Jules Gauthier, M. Steve Dubé, and M. Roch Brassard for their patient during the elaboration of the prototypes and their technical assistance, to M. René Archambault and M. Jean-Sebastien Décarie for their software support.

I appreciate the friendly help provided by Yves Cassive, Ping yang, Dominic Deslandes, Feng Xu, Eric marson, Guifu Gong, Taijun Liu, John Linden and everyone in Poly-Grames.

Finally I would like to dedicate this thesis to my wife and to my parents. It is their love and support that have enabled me to complete this thesis successfully.

### RÉSUMÉ

Dans cette thèse, des techniques de calibration numérique thru-reflect-line (TRL) et thru-resistor (TR) sont proposées pour éliminer l'effet de discontinuité du port qu'entraîne la source d'excitation discrète de l'algorithme de la Méthode des Moments (MoM) déterministe. Ainsi, le modèle équivalent au circuit planaire peut être extrait correctement. Ces techniques sont compatibles avec les logiciels de simulation électromagnétique commerciaux.

A l'aide des techniques de calibration numérique, les modèles de circuit des discontinuités de port sont extraits rigoureusement. Les erreurs causées par la discontinuité de port sont analysées en se basant sur la transformation des paramètres S en paramètres Y/Z. La technique de calibrage numérique proposée est utilisée pour extraire les modèles de circuit du circuit-ouvert microruban, de la ligne espacée microruban, du saut d'impédance de la ligne microruban, du condensateur interdigital (CID) et des lignes microruban. En se basant sur les modèles de circuit complets, un filtre passe-bas, un résonateur et un filtre passe-bande utilisant une ligne à onde lente sont conçus. Il a été démontré que les modèles complets sont critiques pour la conception de circuits intégrés sur la base de stratégies de conception bien établies pour l'analyse et l'optimisation des circuits. Un nouveau combineur de puissance planaire quasi-optique est proposé. La technique de calibrage numérique est utilisée pour extraire les paramètres de la structure de distribution/combinaison de puissance.

#### **ABSTRACT**

In this work, a set of numerical thru-reflect-line (TRL) and thru-resistor (TR) calibration techniques are proposed and combined with commercial planar electromagnetic (EM) simulation software. Such numerical calibration techniques are used to eliminate port discontinuities brought by the lumped current/voltage exciting sources in a deterministic method-of-moments (MoM) algorithm. Therefore, accurate equivalent full-wave-based circuit models of the planar discontinuities can be extracted and established for CAD and optimization purposes.

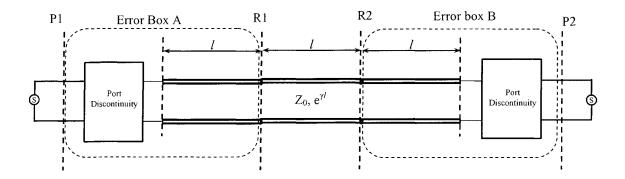

The TRL calibration makes use of three standards, namely, through, reflect and line connections. The TRL calibration standards are easy to realize in both practical circuit measurements and numerical EM simulations. The error boxes, which consist of the port discontinuity effects and guided (or feed) line sections from the exciting source planes to DUT (device-under-test), can be set up by using these standards. Then, accurate parameters that electrically characterize the DUT can be obtained. In a TRL calibration procedure, the characteristic impedance of the line standard should be known exactly a priori. To obtain this characteristic impedance for the TRL calibration, a resistor standard is introduced in this work as impedance reference for extracting a three-dimensional (3D) characteristic impedance of the line standard. Generally, the numerical TRL calibration is bandwidth-limited and it is difficult to extend to a scenario of multiport calibration. To remedy this situation, we have proposed numerical 2-port TR and multi-parallel port TR calibration techniques. The 2-port TR calibration procedure

deploys through and resistor standards while the multi-parallel port TR calibration uses through, match and multi-resistors standards. Comparing results obtained from our proposed numerical calibration techniques with published results as well as the static modeling results has validated the proposed numerical calibration techniques.

With the help of a numerical calibration technique, field-based equivalent circuit models of the port discontinuities are rigorously extracted. Generally, the circuit model of a port discontinuity can be represented by a shunt capacitor and a series inductor. Values of those elements in the circuit model might unfortunately be different when different exciting schemes are applied. From the analysis that is based on a transformation from S parameters to Z or Y parameters, we can observe that a small port discontinuity change can generate huge errors in the extracted equivalent circuit elements of planar circuits and this verily confirms that the calibration is absolutely necessary to remove the errors.

The proposed numerical calibration techniques are implemented to extract the equivalent full-wave circuit models of various microstrip discontinuities such as open, step and gap. Also, the 3D characteristic impedance of microstrip line and microstrip couple line is calculated. Based on the extracted full-wave circuit models of those microstrip circuit elements, a microstrip low-pass-filter and a microstrip resonator are designed. Measurement results are in a very good agreement with the predicted ones. With the calibrated circuit models of planar discontinuities, the design of planar circuit becomes more accurate than a design based on static models and more efficient than a design based on EM simulations.

The proposed numerical calibration techniques are also implemented to extract the equivalent circuit model of Interdigital-Capacitor (IDC) in CPW interface. The circuit model of IDC can be represented by one series capacitor (the dominant parameter which is related to coupling), two shunt capacitors (which are much smaller than their series counterpart), and other loss-related resistors and conductors. By using the circuit model of the IDC, we can realize a slow wave line by loading IDC onto a CPW line. The slow-wave line has a much smaller phase velocity than its bold counterpart. A 2-pole band-pass-filter (BPF) is designed by using the IDC as converter and using the slow wave line as half wavelength resonator. The design and simulation of this BPF is based on lumped-element network topologies. Measured results have confirmed the extracted full-wave circuit model of the IDC as well as the model of the slow wave line loaded with IDC.

The numerical calibration technique is also used to extract the parameters of a novel planar power distributing/combining structure. An approximate circuit model of the power distributing/combining structure is proposed. The power distributing/combining structures are realized by the transition between an oversized microstrip line and parallel multi-microstrip lines. By using the planar power distributing/combining structures, a quasi-optic power combiner is designed, which operates over 25-31 GHz, using 4 amplifier ICs. Measured results show a good agreement with simulated ones, and a combining efficiency 79.5% is obtained at 25 GHz. The whole quasi-optical power combiner is in a planar form, and of course it can be fabricated with a conventional planar circuit technology. Therefore, no complicated mechanical

assembling is needed, and the circuitry is very compact. It is very convenient for the power combiner to interconnect with other planar circuits. This quasi-optical power combiner manifests how a quasi-optical combiner circuit works.

#### CONDENSÉ EN FRANÇAIS

Dans cette thèse, des techniques de calibration numérique sont proposées pour éliminer l'effet de discontinuité du port qu'entraîne la source d'excitation discrète de l'algorithme de la Méthode des Moments (MoM) déterminée. Ainsi, le modèle équivalent au circuit planaire peut être extrait correctement.

#### 0.1 Technique de calibration TRL numérique

La simulation de discontinuités planaires ou de façon plus générale, le Dispositif Sous Test (DST), s'effectue en appliquant une source d'excitation reliée au DST par un guide. La discontinuité de port se trouve entre le guide et la source d'excitation. Les sources d'erreurs comprennent le guide de transmission et la discontinuité du port. La procédure de calibrage TRL utilise trois types de standards: le *passe-tout*, le *réflecteur* et la *ligne*. Ces standards de calibration sont simples et faciles à réaliser à la fois pour la mesure et la simulation MoM.

On effectue la connexion des standards *passe-tout*, *réflecteur* et l*igne* aux plans de référence du DST, R1 et R2, et on simule les paramètres S pour ces trois cas aux plans de référence de la source d'excitation, P1 et P2. On transfert ensuite les paramètres S en paramètres T. Les paramètres des boîtes d'erreur du DST peuvent être calculés par l'entremise de l'algorithme TRL. La procédure de calibrage est directe et permet d'obtenir les termes d'erreur sous forme d'expressions explicites. Le modèle de circuit complet de la discontinuité planaire peut être extrait des paramètres du DST.

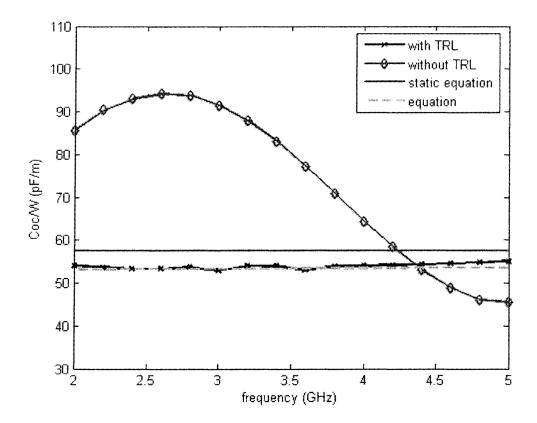

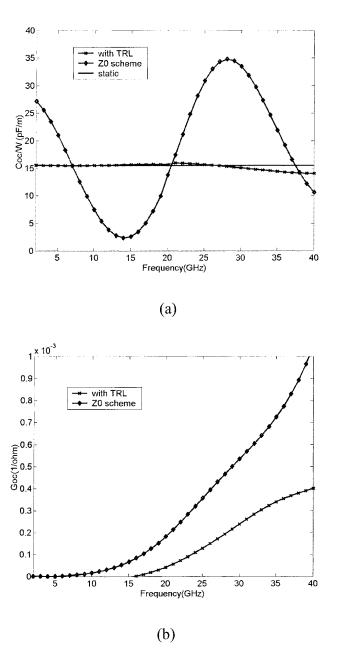

Le modèle équivalent de deux circuits ouverts microruban sur des substrats différents, alumine ( $\varepsilon_r = 9.9$ , W = h = 0.635mm, 2-5 GHz) et Duroid 5880 ( $\varepsilon_r = 2.2$ , h = 0.254mm, W=0.762mm, 2GHz to 40GHz) sont extraits par la technique de calibrage TRL. Le logiciel IE3D est utilisé pour la simulation électromagnétique. Les résultats provenant du calibrage TRL ne présentent que très peu de variation en fréquence et sont fortement en accord avec ceux obtenus des formules [38] et [39] alors que les résultats sans calibrage fluctuent de bas en haut avec l'augmentation de la fréquence.

Pour déterminer l'impédance caractéristique en trois dimensions du standard *ligne*, un standard alternatif appelé "standard de résistance" est introduit dans le calibrage TRL numérique [33]. L'impédance caractéristique du standard *ligne* est définie par Z. La matrice T du standard *ligne* est :

$$N_{2} = \begin{bmatrix} ch(\gamma l) - \frac{Z^{2} + Z_{0}^{2}}{2ZZ_{0}} sh(\gamma l) & \frac{Z^{2} - Z_{0}^{2}}{2ZZ_{0}} sh(\gamma l) \\ -\frac{Z^{2} - Z_{0}^{2}}{2ZZ_{0}} sh(\gamma l) & ch(\gamma l) + \frac{Z^{2} + Z_{0}^{2}}{2ZZ_{0}} sh(\gamma l) \end{bmatrix} = \begin{bmatrix} 1 & a \\ a & 1 \end{bmatrix} \begin{bmatrix} e^{-\gamma l} & 0 \\ 0 & e^{+\gamma l} \end{bmatrix} \begin{bmatrix} 1 & a \\ a & 1 \end{bmatrix}^{-1}$$

$$, \quad a = \frac{Z - Z_{0}}{Z + Z_{0}}$$

$$(0.1)$$

Cependant, si l'impédance caractéristique du standard ligne n'est pas précisément connue, la procédure de calibrage TRL ne peut être complétée. De plus, si l'impédance caractéristique du standard ligne est connue mais erronée, de faux paramètres seront extraits du DST. L'impédance caractéristique du standard ligne ne peut être obtenue que par le coefficient de réflexion  $\Gamma$  du standard résistance.

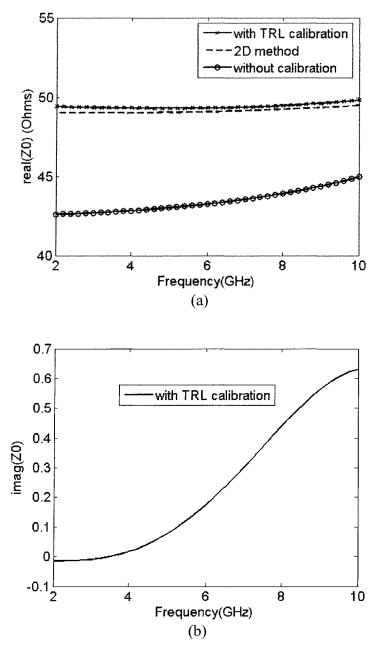

L'impédance caractéristique d'une ligne microruban sur un substrat d'alumine est calculée. Les résultats obtenus démontrent que la partie réelle de l'impédance caractéristique du standard *ligne* est équivalente à celle rapportés dans [33]. La partie imaginaire de l'impédance caractéristique est due aux pertes du standard et est de beaucoup inférieure à la partie réelle.

#### 0.2 Technique de calibrage numérique TR

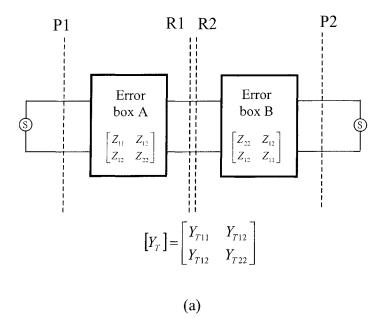

La technique de calibrage TR est proposée pour extraire le modèle de circuit de discontinuités planaires sur une large bande de fréquence. Les boîtes d'erreur sont supposées être symétriques et réciproques. La technique de calibrage TR utilise deux standards : passe-tout et résistance. Le standard résistance a pour valeur R. L'algorithme de calibrage TR peut être dérivé en se fondant sur les paramètres Y ou T.

Des circuit-ouverts microruban sur deux différents substrats sont étudiés en utilisant le calibrage TR à deux ports. La valeur de R est 50 ohms. Le résultat de la capacitance de bord obtenu du calibrage TR est en accord avec le résultat obtenu du calibrage TRL. La validité de la technique de calibrage TR est donc prouvée.

Le calibrage TR à ports multi-parallèles utilise trois standards: passe-tout, adapté et multi-résistance. En simulant le réseau connecté aux standards, il est possible de retirer les boîtes d'erreur que sont les lignes multi-guides et la discontinuité du port entre les ports d'excitation et les lignes multi-guides. Donc, les paramètres du DST peuvent être obtenus. L'algorithme du calibrage TR multi-parallèle est fondé sur les paramètres T. L'exemple de lignes couplées sur un substrat Duroid 5880 est étudié. Les lignes couplées ont deux ensemble de constantes de propagation: une pour le mode paire et

l'autre pour le mode impaire. Les résultats obtenus du calibrage numérique TR multiparallèle sont en accord avec les résultats statiques.

#### 0.3 Discontinuité du port et analyse d'erreur

Pour obtenir le modèle de circuit de la discontinuité de port entre le port d'excitation et le guide microruban, on utilise, au lieu du DST, la même section de ligne de transmission que le guide [20]. Puisque la ligne de transmission est physiquement identique au guide, la boîte d'erreur A peut être exprimée par

$$[T_A] = [T_P][T_L]$$

(0.2)

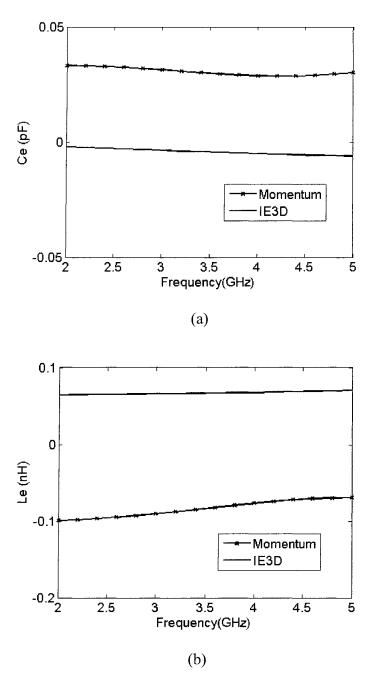

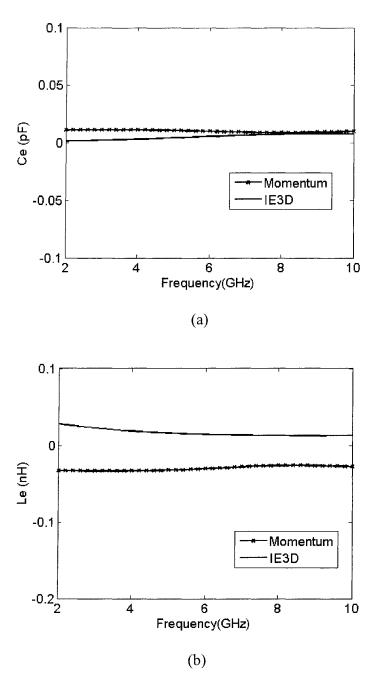

où [Tp] est la matrice T de la discontinuité de port et [Tt] est la matrice T de la ligne de transmission. Par le calibrage numérique, on peut retirer la boîte d'erreur et obtenir les paramètres corrigés de la ligne de transmission, [Tt]. Ensuite, on peut calculer les paramètres de la discontinuité de port en retirant le guide de la boîte d'erreur. Tel qu'en [20], le modèle de circuit équivalent de la discontinuité de port peut être représenté par un condensateur parallèle et une inductance série (Les pertes infimes reliées à la résistance ou au conducteur sont négligées). Les modèles de circuit des discontinuités de port sur différents substrats (alumine ou Duroid 5880) sont extraits en utilisant plusieurs types de simulateurs électromagnétiques (Momentum d'Agilent ou IE3D de Zeland). On remarque que les valeurs des éléments du modèle de circuit de la discontinuité de port demeurent presque inchangées en fonction de la fréquence. Avec différents substrats ou différents logiciels de simulation électromagnétique, la valeur des éléments du modèle

diffèrent. Ceci s'explique par la différence entre les méthodes d'excitation (verticale ou horizontale, source de courant ou de tension) utilisées par les logiciels.

Les paramètres S de la discontinuité de port démontrent que la magnitude de S11 est très petite et que S21 est presque égale à 1. Cependant, si l'on désire extraire le modèle de circuit de la discontinuité planaire, la discontinuité de port peut entraîner une erreur importante. En regardant de plus près la transformation des paramètres S en Y/Z, on constate que le dénominateur des paramètres Y/Z atteint zéro sur certaines régions. Lorsque le dénominateur approche zéro, les erreurs des paramètres S calculées du circuit seront amplifiées ce qui résulte en d'importantes erreurs une fois converties en paramètres Z. Si la discontinuité de port n'est pas calibrée, la valeur des paramètres Y/Z présente une variation périodique autour de la valeur réelle. La variation périodique est imputable à la longueur de la ligne guide reliant le port d'excitation au DST. Les effets de la discontinuité de port sur un circuit ouvert et un saut d'impédance microruban sont démontrés. Les résultats indiquent que la procédure de calibrage est absolument nécessaire pour l'extraction précise du modèle de circuit.

#### 0.4 Application aux discontinuités microruban

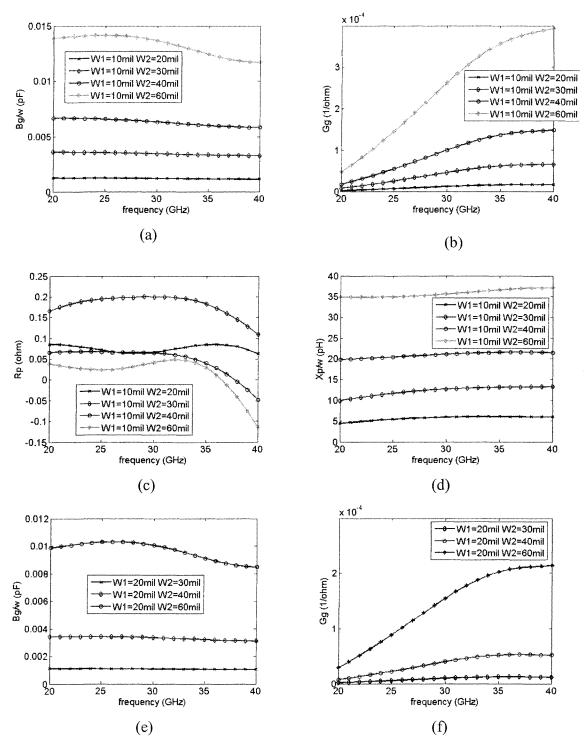

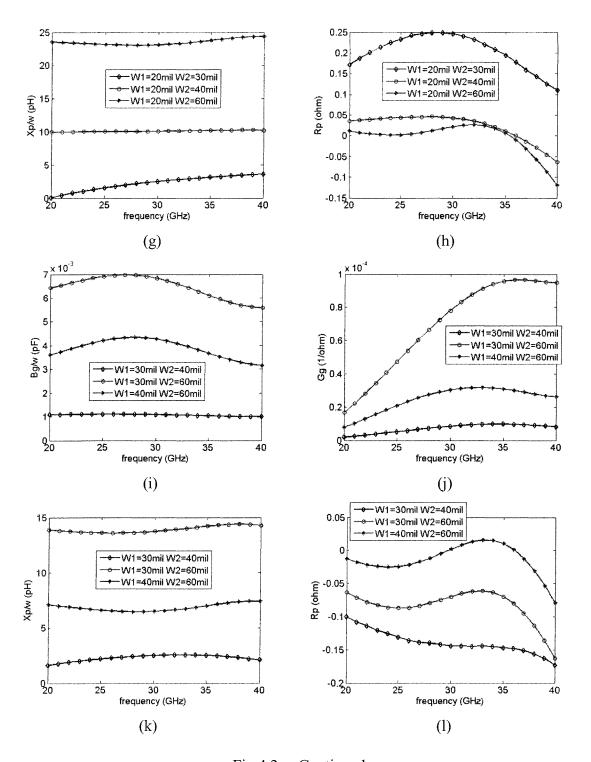

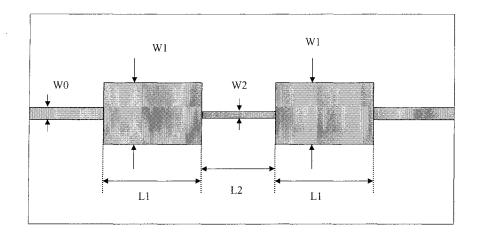

La technique de calibrage numérique proposée est utilisée pour extraire les modèles de circuits de lignes espacées série et à saut de largeur sur un substrat Duroid 5880. Pour cette application, la hauteur du substrat est de 0,254 mm et la plage de fréquence s'étend de 20 GHz à 40 GHz.

La largeur de la ligne microruban aux deux extrémités du saut varie de 0,254 mm à 1,524 mm. Puisque les impédances caractéristiques des deux côtés sont différentes, nous

devons utiliser deux procédures de calibrage TRL sur la base de différentes impédances de référence pour calculer les deux boîtes d'erreur, respectivement. Le modèle de circuit complet de la discontinuité de saut peut être exprimé par une admittance capacitive parallèle, deux impédances série inductives et les résistances et conductances reliées à la Lorsque W2 est plus petit ou égal à 1,016 mm, les paramètres du radiation [18]. modèle de circuit indiquent que lorsque la fréquence augmente, l'inductance Xp/ω et la capacitance Bg/ω ne varient presque pas (Xp/ω augmente légèrement mais Bg/ω décroît légèrement et ils démontrent les propriétés d'éléments discrets), et les pertes par radiation reliées à la conductance Gg augmentent. À mesure que la ligne W2 s'élargit Xp/ω, Bg/ω et Gg augmentent. Inversement, à mesure que la ligne plus mince W1 s'élargie, Xp/ω, Bg/ω et Gg diminuent. On observe également que plus le saut est important, plus grands seront Xp/ω, Bg/ω et Gg. Ceci s'explique par la transition du flux de courant de la direction longitudinale à transverse au bord de la ligne plus large près du saut, ce qui se traduit en une augmentation de la courbure de la densité de courant. Dans le cas où W2 serait égale à 1,524 mm, Xp/ω et Bg/ω varient de façon irrégulière lorsque la fréquence augmente. Ce phénomène est dû aux conditions d'application du modèle discret. En effet, le saut ne peut être considéré sous forme d'éléments discrets qu'à la condition que sa dimension soit beaucoup plus petite que la longueur d'onde.

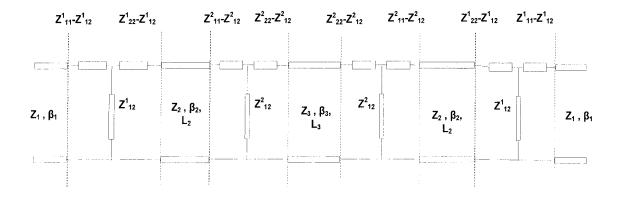

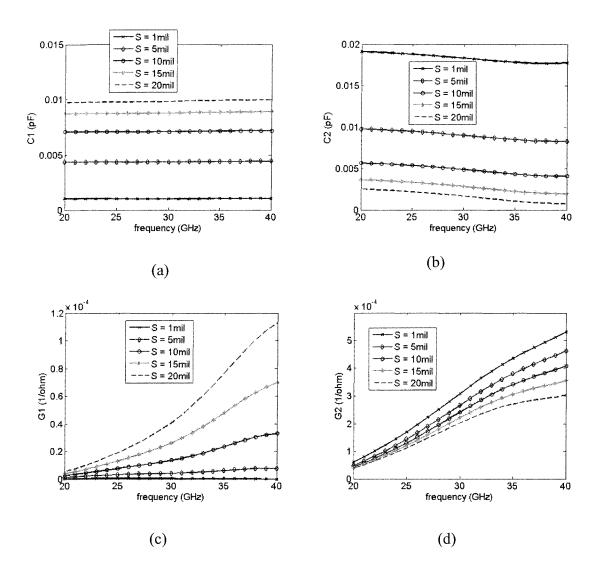

La largeur de la ligne microruban de l'espacement est de 0,762 mm et l'espacement varie de 0,025 mm à 0,508 mm. Le modèle équivalent complet de l'espacement microruban peut être représenté par deux admittances parallèles capacitives, une admittance capacitive parallèle, une résistance et une conductance reliée aux pertes par

radiation [19]. Les résultats obtenus du calibrage numérique démontrent que lorsque la fréquence augmente, les conductances G1 et G2 reliées à la radiation augmentent, C1 demeure presque constant et C2 décroît légèrement. Lorsque la largeur de l'espacement augmente, C1 et G1 augmentent alors que C2 et G2 décroissent, indiquant une diminution de l'effet de couplage.

En se basant sur les modèles de circuit complets de l'espacement et de saut de la ligne microruban, un filtre passe-bas et un résonateur opérant en bande Ka sont conçus. Les circuits sont analysés tel un réseau formé par la cascade de lignes et de discontinuités microruban. La simulation et l'optimisation des circuits deviennent directes et très facile. La validité des modèles de circuits extraits est démontrée par des résultats de mesure. Les modèles complets de circuit extraits procure une méthode de conception efficace et précise.

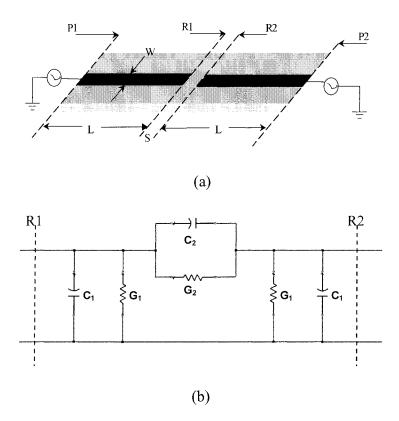

#### 0.5 Conception d'un filtre utilisant la ligne à onde lente

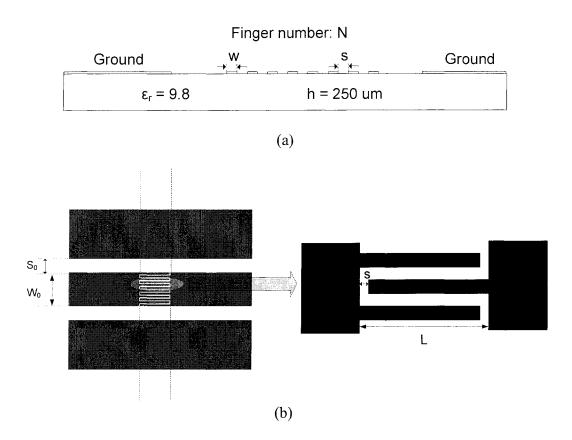

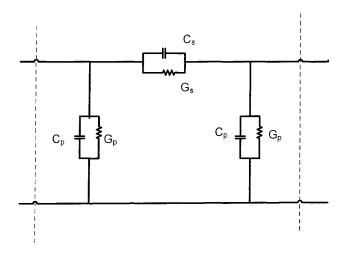

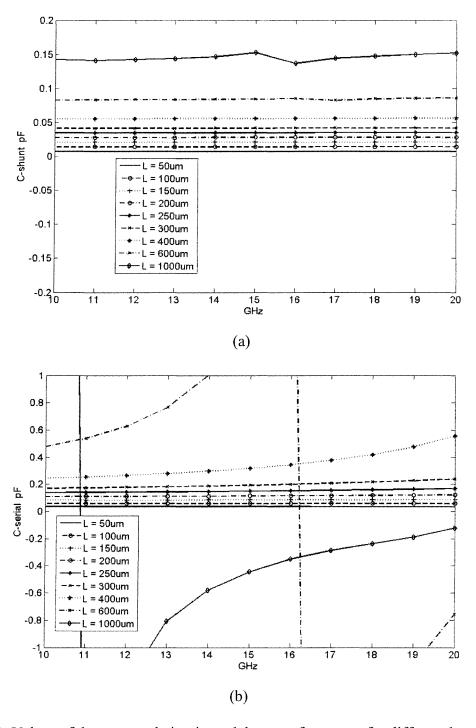

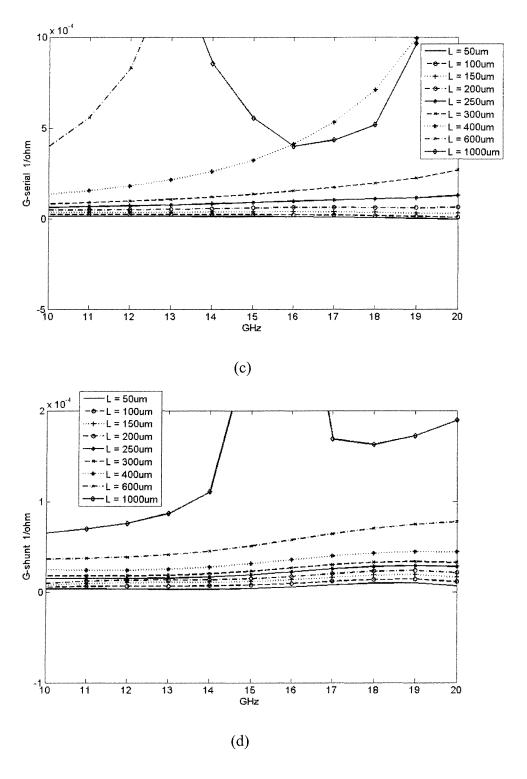

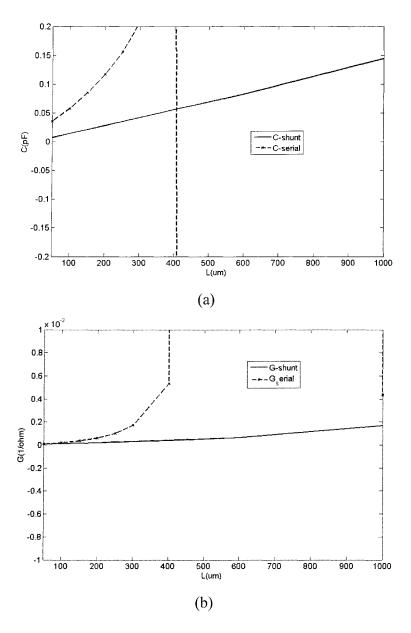

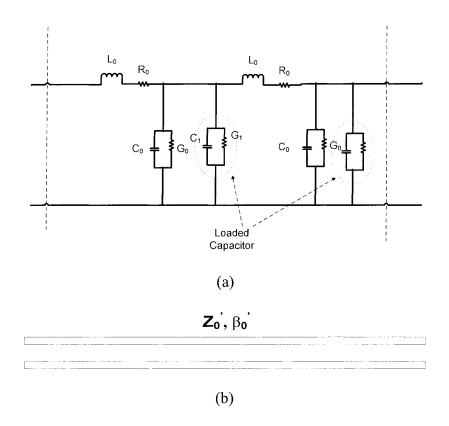

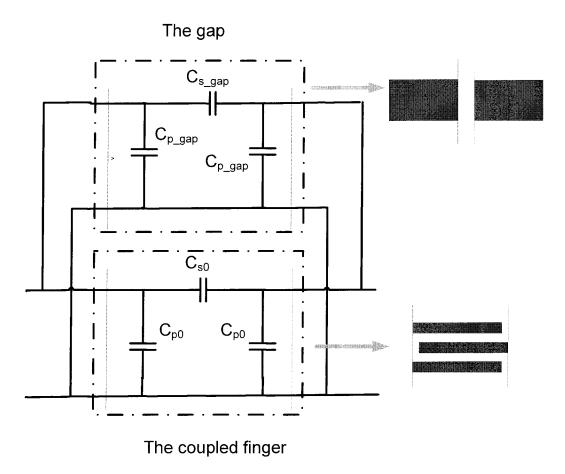

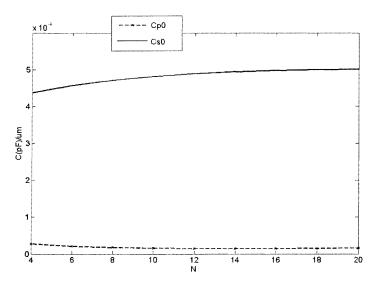

Le condensateur interdigital (CID) sur guide coplanaire (GCP) est étudié en utilisant les techniques de calibrage numérique et le modèle extrait est implanté pour la conception d'un filtre utilisant une ligne à onde lente. Le CID est placé sur un GCP sans plan de masse sous le substrat. Les dimensions physiques du CID et du GCP sont : N=12,  $w=s=10\mu m$ ,  $S_0=100\mu m$ ,  $W_0=230$   $\mu m$  et l'épaisseur de la couche métallique est de 2  $\mu m$ . Le modèle de circuit complet du CID consiste en deux condensateurs parallèles  $C_p$ , un condensateur série  $C_s$  (le composant dominant représentant la capacité de couplage) et les conductances  $G_p$  et  $G_s$  reliées aux pertes par radiation et par la couche métallique. Puisque le CID est symétrique, le modèle de circuit équivalent l'est

également. La plage de fréquence pour l'extraction du modèle est de 10 GHz à 20 GHz. La longueur du CID varie de 50 μm à 1 mm alors que les autres dimensions demeurent inchangées. Le modèle extrait montre que les condensateurs équivalents  $C_p$ ,  $C_s$  et les conductances  $G_p$ ,  $G_s$ , augmentent presque linéairement avec un accroissement de la longueur L à la condition que L demeure inférieur à 0,3 mm. Lorsque L est supérieur à 0,4 mm, les valeurs des condensateurs et des conductances fluctuent grandement avec la fréquence et le CID ne se comporte plus tel un condensateur discret. Ceci s'explique par le fait que le condensateur n'est plus suffisamment petit par rapport à la longueur d'onde.

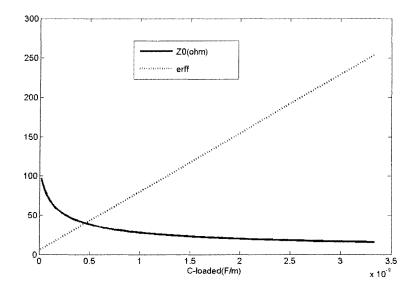

En chargeant la ligne GCP périodiquement par une capacitance par unité de longueur  $C_1$ , on réalise une ligne à onde lente. Les paramètres de transmission de la ligne à onde lente sont:

$$C_0' = C_0 + C_1 \tag{0.4}$$

$$Z_{0}' = \sqrt{\frac{L_{0}}{C_{0}}} \tag{0.5}$$

$$v' = \frac{1}{\sqrt{L_0 C_0'}} \tag{0.6}$$

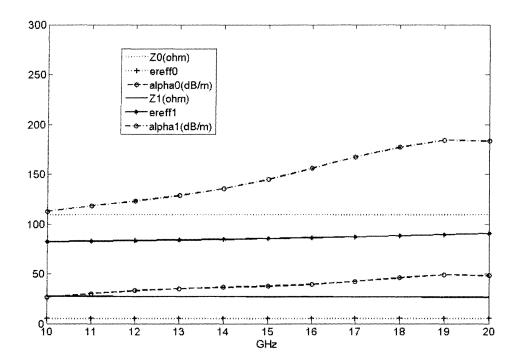

Théoriquement, la valeur de la capacitance par unité de longueur  $C_1$  devrait être calculée depuis un CID infiniment long. Cependant, pour faciliter la modélisation, on peut calculer approximativement la valeur de  $C_1$  depuis un CID de longueur finie. Les paramètres du substrat, de la ligne GCP et du CID sont respectivement:  $\varepsilon_r$ =9,8, h=250 $\mu$ m, w=s=10 $\mu$ m,  $S_0$ =100 $\mu$ m et  $W_0$ =30  $\mu$ m. L'épaisseur de la couche métallique

est de 2 µm. À 17 GHz, les paramètres de propagation de la ligne GCP chargée sont :  $Z_0$ = 109 ohms, permittivité effective  $\varepsilon_{reff}$ =5,24 et facteur de perte  $\alpha$ =42,3 dB/m. En chargeant la ligne classique par des CID aux deux extrémités, les paramètre de la ligne à onde lente sont :  $Z_0$ = 26,8 ohms, permittivité effective  $\varepsilon_{reff}$ =87,2 et facteur de perte  $\alpha$ =167,1 dB/m. La longueur d'onde de la ligne à onde lente est plus courte que celle de la ligne GCP non chargée par un facteur de quatre. Ceci s'explique par le fait que la capacité de charge  $C_1$  est beaucoup plus grande que  $C_0$ . Il est donc possible de réaliser un circuit plus compact en utilisant la ligne à onde lente.

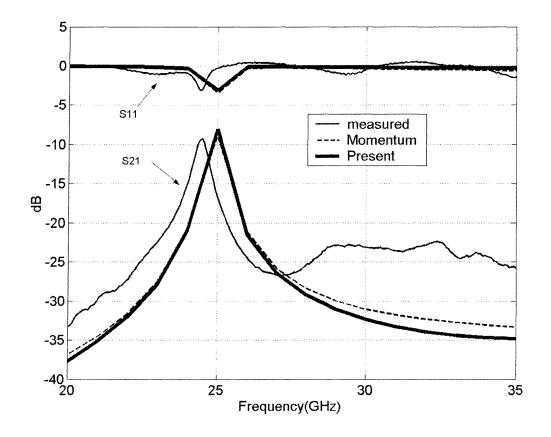

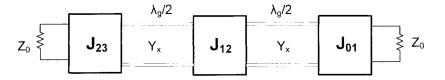

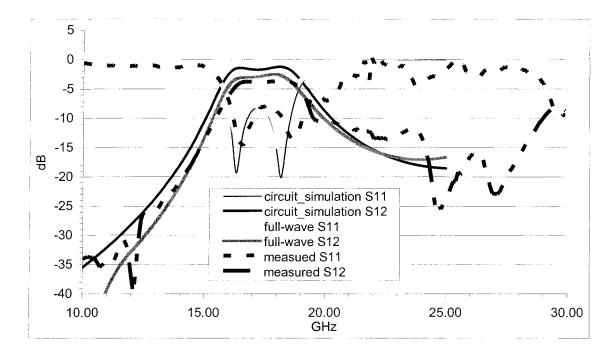

Un filtre passe-bande (FPB) a été conçu en utilisant le modèle du circuit de la ligne à onde lente et le CID décrit plus haut. Le FPB est réalisé par la cascade série de résonateurs à onde lente d'une demi-longueur d'onde et de CID de couplage. Les paramètres du filtre sont :

- N=2 de type Chebyshev.

- Fréquence centrale, f0 = 17.5 GHz.

- La bande passante se situe de 16.5 GHz à 18.5 GHz.

- Ondulation de 0.5 dB.

La longueur totale du FPB est de 2,4 mm. Les résultats de simulation du FPB fondés sur le modèle de la ligne à onde lente et le CID sont très près des résultats de mesure et des simulations électromagnétiques. Cet exemple de conception d'un FPB démontre que l'extraction du modèle complet est très efficace pour la conception de circuit sous forme de schéma.

#### 0.6 Combineur planaire quasi-optique

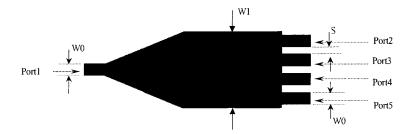

Une nouvelle structure de combinaison de puissance est proposée. La structure de distribution/combinaison de puissance est réalisée par la transition en une ligne microruban surdimensionnée et des lignes microruban multi parallèles. Un diviseur de puissance de 1 à 4 ports opérant à 25-31 GHz est conçu. Le substrat utilisé est le Duroid 5870 et a pour paramètres  $\varepsilon_r = 2.33$  et h = 0,254 mm. Les quatre lignes microruban parallèles sont espacées également. La relation entre le nombre de lignes microruban multi parallèles 2N, l'impédance caractéristique de la ligne mince  $Z_2$  et l'impédance caractéristique de la ligne surdimensionnée  $Z_1$  est définie par :

Puisque la structure agit selon un mode électromagnétique quasi transverse et que la distribution de courant sur le métal est foncièrement plane selon la direction transverse, la puissance d'entrée est presque également divisée aux quatre sorties. Le mode TE10 de la ligne microruban surdimensionnée doit être évité puisqu'il réduit l'efficacité de combinaison de puissance. La transition de largeur de la ligne d'entrée à la ligne surdimensionnée réalise l'adaptation d'impédance et réduit les modes supérieurs pouvant se propager. Les lignes microruban multi parallèles fonctionnent principalement selon un mode paire et le couplage entre chacune d'elle est très faible. Les résultats de simulation démontrent que les magnitudes et les phases des signaux distribués aux ports 2-5 et aux ports 3-4 n'ont que très peu de différence. L'application du calibrage TR à ports multi parallèles permet d'obtenir les paramètres de la transition de la ligne microruban surdimensionnée aux lignes microruban multi parallèles. Le modèle de circuit équivalent de la transition peut être approximativement considéré tel quatre sauts

microruban connectées à une ligne microruban surdimensionnée. Deux diviseurs de puissance 1-4 connectés dos à dos ont été fabriqués et mesurés. Les résultats de mesure sont en accord avec les résultats obtenus par simulation. La magnitude du paramètre  $S_{21}$  mesurée se situe entre -0.8 dB et -1.6 dB.

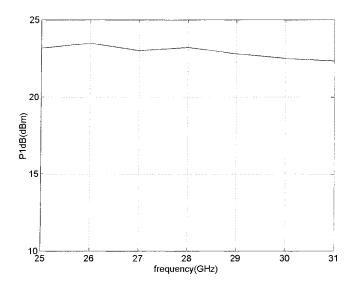

Quatre amplificateurs MMIC HMC283 fabriqués sur Arsénure de Galium (GaAs) par *Hittite Microwave Corporation* sont utilisés pour construire le combineur de puissance. Le gain de cet amplificateur est de 21 dB et le point P<sub>1dB</sub> se situe typiquement à 18 dBm. Les résultats de mesure sont près des résultats simulés. La mesure montre un P<sub>1dB</sub> de 23 dBm signifiant une efficacité de combinaison de puissance de l'ordre de 79,5%. L'ensemble de la structure de combinaison est planaire et le combineur de puissance quasi-optique possède un concept de circuit clair.

#### 0.7 CONCLUSION

Des techniques de calibrage numérique ont été proposées pour résoudre le problème des discontinuités de port engendré par les sources d'excitation courant/tension discrètes dans l'algorithme MoM déterminé. L'utilisation des ces techniques permet d'extraire précisément le modèle de circuit équivalent complet de structures planaires. De plus, ces techniques sont compatibles avec les logiciels de simulation électromagnétique commerciaux.

Il a été démontré que les modèles complets sont critiques pour la conception de circuits intégrés sur la base de stratégies de conception bien établies pour l'analyse et l'optimisation des circuits. L'utilisation de modèles de circuits de discontinuités planaires permet une conception plus précise que celle réalisée à partir des modèles

statiques et s'avère plus efficace qu'une conception par simulation électromagnétique.

Les techniques de calibrage proposées sont puissantes et efficaces pour faire le pont entre la simulation de champs et la conception de circuits.

## TABLE OF CONTENTS

| Acknowledg     | rementsiv                                                       |

|----------------|-----------------------------------------------------------------|

| Résumé         | v                                                               |

| Abstract       | vi                                                              |

| Condensé en    | Françaisx                                                       |

| Table of con   | tentsxxii                                                       |

| List of figure | es and tablesxxv                                                |

| List of abbre  | viationxxxii                                                    |

|                | CTION1                                                          |

| CH 1 NUM       | IERICAL TRL CALIBRATION TECHNIQUE6                              |

| 1.1 Introd     | duction6                                                        |

| 1.2 Num        | erical TRL calibration7                                         |

| 1.2.1          | TRL calibration                                                 |

| 1.2.2          | Examples15                                                      |

| 1.3 Deter      | mination of the characteristic impedance of a transmission line |

| by us          | ing a resistor standard in TRL calibration22                    |

| 1.3.1          | Theory                                                          |

| 1.3.2          | Examples33                                                      |

| 1.4 Sumn       | nary                                                            |

| CH 2 | 2 NUM  | ERICAL TR CALIBRATION TECHNIQUE                                     | 36 |

|------|--------|---------------------------------------------------------------------|----|

| 2.1  | Introd | uction                                                              | 36 |

| 2.2  | Two-p  | oort TR calibration                                                 | 37 |

|      | 2.2.1  | Theory                                                              | 39 |

|      | 2.2.2  | TR calibration-based parameter extraction of planar discontinuities | 43 |

| 2.3  | Multi- | parallel-port TR calibration                                        | 47 |

|      | 2.3.1  | Theory                                                              | 48 |

|      | 2.3.2  | Example                                                             | 54 |

| 2.4  | Summ   | ary                                                                 | 56 |

|      |        |                                                                     |    |

| СН 3 | PORT   | DISCONTINUITY AND ERROR ANALYSIS                                    | 57 |

| 3.1  | The eq | uivalent circuit model of the port discontinuity                    | 57 |

| 3.2  | Effect | of the port discontinuity on the extracted one-port circuit model   | 62 |

| 3.3  | Effect | of the port discontinuity on the extracted two-port circuit models  | 65 |

| 3.4  | Summa  | ary                                                                 | 76 |

|      |        |                                                                     |    |

| CH 4 | ACCU   | RATE MODELING OF MICROSTRIP DISCONTINUITIES                         | 77 |

| 4.1  | Intro  | duction                                                             | 77 |

| 4.2  | Circu  | ait model of microstrip step and low pass filter design             | 78 |

|      | 4.2.1  | Extraction of the circuit model of microstrip step                  | 78 |

|      | 4.2.2  | Low pass filter design.                                             | 83 |

| 4.3   | Circuit model of microstrip gap and resonator design            | 86              |

|-------|-----------------------------------------------------------------|-----------------|

| 4     | Extraction of the circuit model of microstrip gap               | 86              |

| 4     | Microstrip resonator                                            | 89              |

| 4.4   | Summary                                                         | 91              |

|       |                                                                 |                 |

| CH 5  | SLOW-WAVE LINE FILTER DESIGN                                    | 92              |

| 5.1   | Introduction                                                    | 92              |

| 5.2   | Circuit model of Interdigital capacitor                         | 93              |

| 5.3   | CPW slow-wave line with loaded IDC                              | 98              |

| 5.4   | Band pass filter using slow-wave lines                          | 106             |

| 5.5   | Summary                                                         | 112             |

|       |                                                                 |                 |

| CH 6  | PLANAR QUASI-OPTICAL POWER COMBINER                             | 114             |

| 6.1   | Introduction                                                    | 114             |

| 6.2   | Operating principle                                             | 115             |

| 6.3   | Circuit model of the transition by using multi-parallel-port TR | calibration 125 |

| 6.4   | Experiments                                                     | 130             |

| 6.5   | Summary                                                         | 135             |

| CONC  | LUSION                                                          | 137             |

| DEEDI | DENCES                                                          | 1.41            |

## LIST OF FIGURES AND TABLES

| Fig.1.1. | Two-port microstrip discontinuity under modeling (a) and                             |

|----------|--------------------------------------------------------------------------------------|

| Fig.1.2. | Block diagram of the numerical TRL calibration procedure. (a) Thru                   |

|          | connection; (b) Line connection; (c) Reflect connection                              |

| Fig.1.3. | Geometry and generalized equivalent circuit model of a microstrip open-              |

|          | end circuit                                                                          |

| Fig.1.4. | The layout of the three connections (IE3D). (a) Thru connection; (b)                 |

|          | Reflect connection; (c) Line connection                                              |

| Fig.1.5. | The de-embedding procedure based on a simple transmission line theory 18             |

| Fig.1.6. | TRL-extracted open-end fringing capacitance together with those                      |

|          | obtained from the non-TRL parameter extraction scheme and two                        |

|          | closed-form design equations [38][39] (w = h = 0.635mm, $\epsilon_r$ = 9.9, L =      |

|          | 10.4 mm)                                                                             |

| Fig.1.7. | Extracted parameters of the circuit model of microstrip open-end                     |

|          | obtained from TRL calibration compared with those calculated from                    |

|          | other two methods: Z <sub>0</sub> -scheme (without calibration), and static equation |

|          | [39] ( $\varepsilon_r$ = 2.2, h = 0.254mm, W=0.762mm)                                |

| Fig.1.8. | Resistor standard connection of the proposed improved numerical TRL                  |

|          | calibration procedure24                                                              |

| Fig.1.9. A section of microstrip line to be calculated for the characteristic    |     |

|----------------------------------------------------------------------------------|-----|

| impedance.                                                                       | 33  |

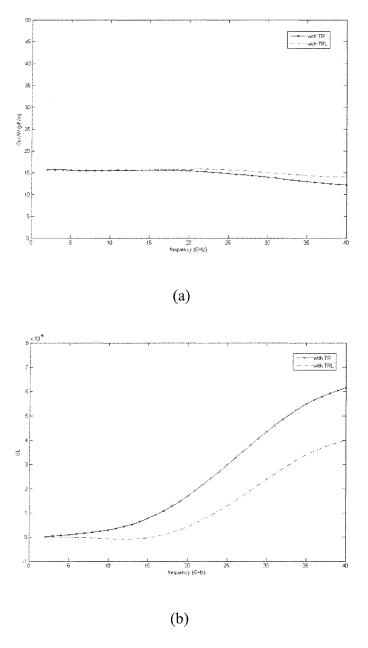

| Fig.1.10. Characteristic impedance of a microstrip line obtained from the        |     |

| improved numerical TRL method compared with the data obtained                    |     |

| without calibration and the data obtained from the 2D method. (a) real           |     |

| part, and (b) image part. ( $\varepsilon_r = 9.9$ , w = h = 0.635mm)             | 35  |

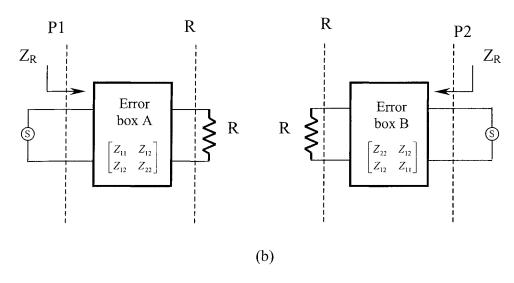

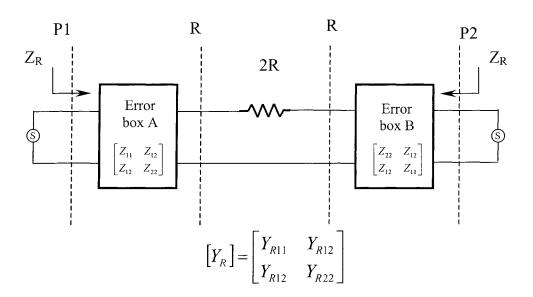

| Fig.2.1. Equivalent error box model for the TR calibration                       | 37  |

| Fig.2.2. Block diagram of the TR calibration procedure. (a) Thru connection; (b) |     |

| Resistor connection.                                                             | 38  |

| Fig.2.3. Modified connection of Resistor standard for the TR calibration.        | 40  |

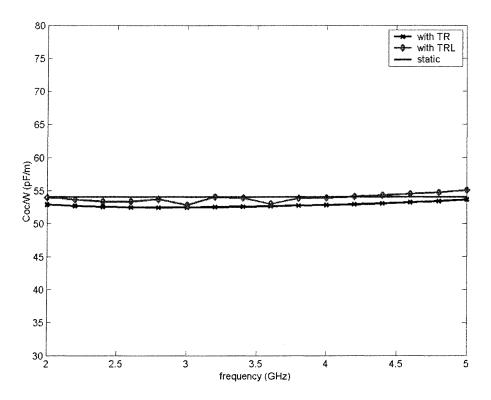

| Fig.2.4. TR-extracted open-end fringing capacitance together with those obtained |     |

| from the TRL parameter extraction scheme in section I and a closed-              |     |

| form design equation (w = h = 0.635mm, $\varepsilon_r$ = 9.9)                    | 43  |

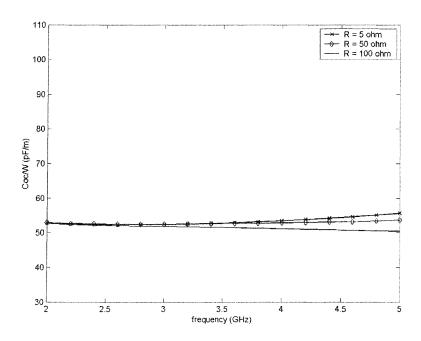

| Fig.2.5. TR-extracted open-end fringing capacitance using different values of R  |     |

| $(w = h = 0.635 \text{mm}, \epsilon_r = 9.9).$                                   | 44  |

| Fig.2.6. Extracted open-end fringing capacitance Coc and radiation-related       |     |

| conductance GL by using the TR calibration ( $\epsilon_r$ = 2.2, h = 10mil,      |     |

| W=30mil)                                                                         | 46  |

| Fig.2.7. Block diagrams for a multi-port circuit.                                | 48  |

| Fig.2.8. Connection scheme of standards in a multi-parallel TR calibration. (a)  |     |

| Thru connection; (b) Resistor connection; (c) Multi-resistor connection          | .49 |

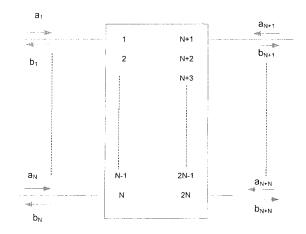

| Fig.2.9. A 2N port network.                                                      | .50 |

| Fig.2.10. The connection of multi-parallel resistor standard                                                                   | 53     |

|--------------------------------------------------------------------------------------------------------------------------------|--------|

| Fig.2.11. A coupled microstrip line under study                                                                                | 55     |

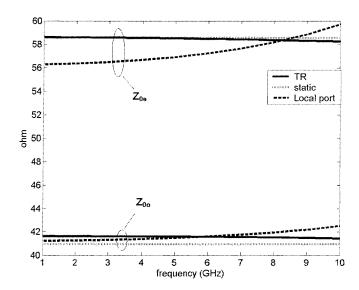

| Fig.2.12. 3D properties of the characteristic impedance of a microstrip                                                        | line   |

| obtained from a multi-parallel-port TR calibration together with the                                                           | e data |

| obtained without the calibration (local port) and the data obtained fr                                                         | rom a  |

| 2D method [reference ???] ( $\epsilon_r$ = 2.2, w = 30 mil, h = 10 mil and                                                     | s = 5  |

| mil)                                                                                                                           | 55     |

| Fig.3.1. Equivalent network connection of a transmission line section                                                          | 57     |

| Fig.3.2. Equivalent circuit model of the port discontinuity.                                                                   | 58     |

| Fig.3.3. Calculated parameters of a port discontinuity with alumina substrate                                                  | (w =   |

| $h = 0.635 \text{mm}, \ \epsilon_r = 9.9$ ).                                                                                   | 60     |

| Fig.3.4. Calculated parameters of a port discontinuity with Duroid                                                             | 5880   |

| substrate( $\epsilon_r$ = 2.2, h = 0.254mm, W=0.762mm)                                                                         | 61     |

| Fig.3.5. Network representation of an open-end capacitor.                                                                      | 63     |

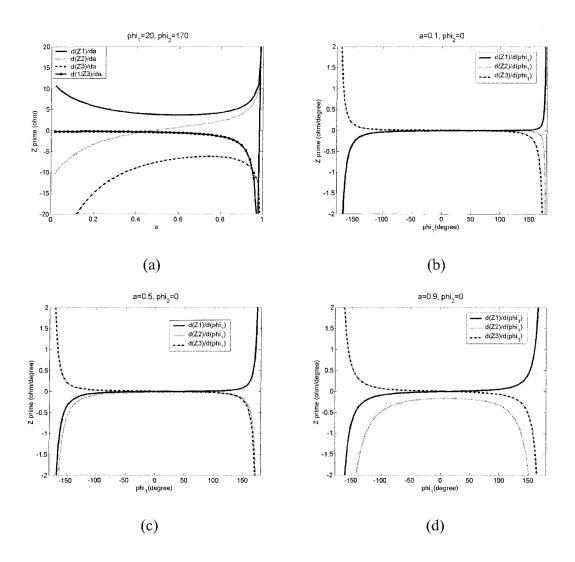

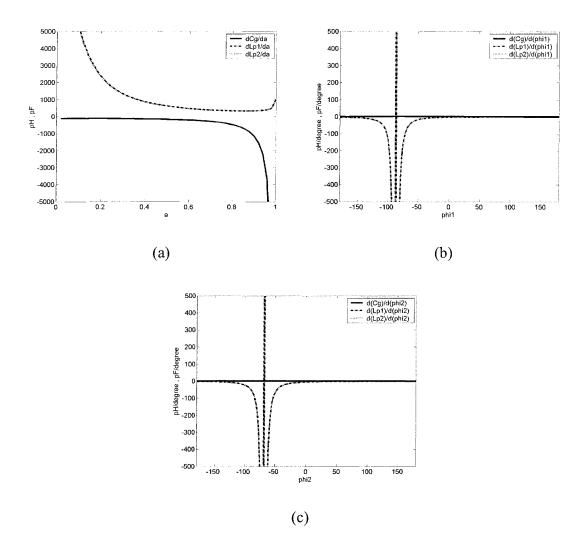

| Fig.3.6. Examples of correlations between $d\overline{Z}/da$ , $d\overline{Z}/d\phi$ and $a$ , $\phi$ . (a) $d\overline{Z}/da$ | when   |

| $\phi_1$ =20 and $\phi_2$ =170. (b), (c), (d) $\overline{dZ}/d\phi_1$ when $\phi_2$ =0 and a=0.1, 0.5                          | 5, 0.9 |

| respectively. (e)(f)(g) $\overline{dZ}/d\phi_1$ when $\phi_2$ =90 and a=0.1, 0.5,                                              | 0.9    |

| respectively.                                                                                                                  | 69     |

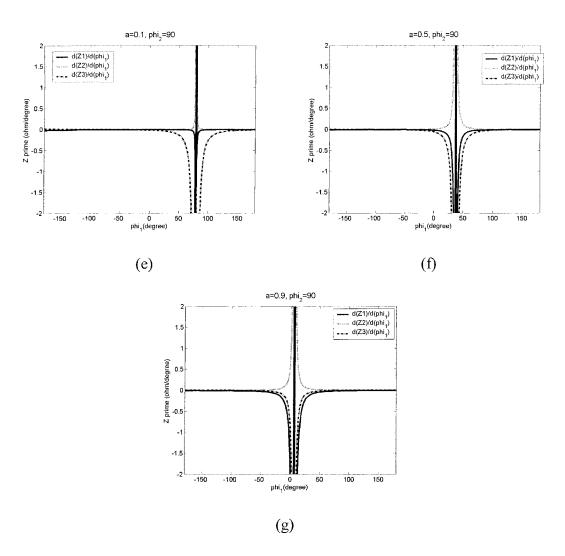

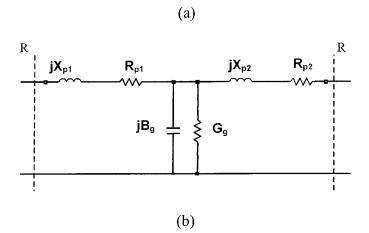

| Fig.3.7. Geometry and equivalent circuit model of a step discontinuit                                                          | y of   |

| microstrip line. (a) Physical layout in Momentum. (b) Equiv                                                                    | alent  |

| network. (c) Circuit model of the step discontinuity                                                                           | 72     |

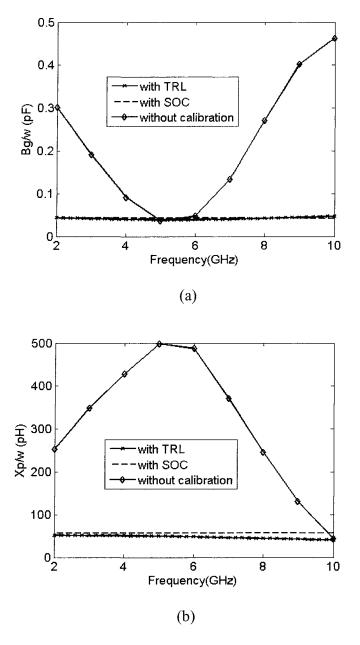

| Fig.3.8. TRL-extracted parameters of a step discontinuity compared with those                    |    |

|--------------------------------------------------------------------------------------------------|----|

| generated from other three methods: static, SOC technique [18] and $Z_0$ -                       |    |

| scheme (without calibration)[18] ( $\epsilon_r$ = 10.2, h = 0.635mm, W <sub>1</sub> =2.0mm,      |    |

| $W_2 = 0.4$ mm) $(X_p = X_{p1} + X_{p2})$ . (a) Bg/ $\omega$ . (b) Xp/ $\omega$                  | 74 |

| Fig.3.9. Typical numerical correlations between $L$ , $C$ and $a$ , $\phi$ . (a) dCg/da and      |    |

| $dLp/da$ . (b) $dCg/d\varphi_1$ and $dLp/d\varphi_1$ . (c) $dCg/d\varphi_2$ and $dLp/d\varphi_2$ | 75 |

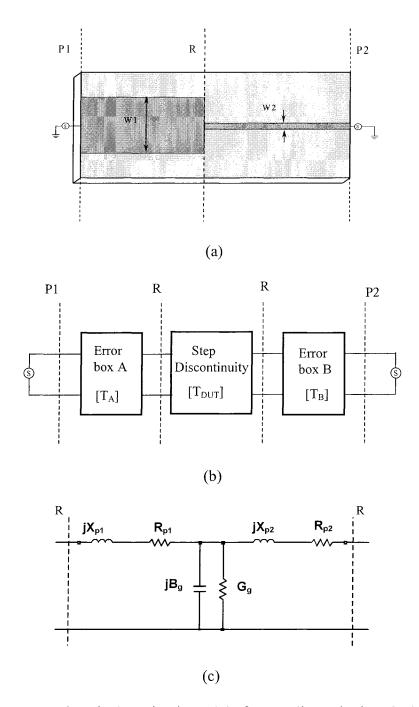

| Fig.4.1. Geometry and equivalent circuit model of a step discontinuity.                          |    |

| (a)Physical layout in Momentum; (b)Circuit model of the step                                     |    |

| discontinuity                                                                                    | 79 |

| Fig.4.2. Extracted parameters of the circuit model of microstrip step ( $\epsilon_r$ = 2.2, h =  |    |

| 0.254mm) $(X_p = X_{p1} + X_{p2}, R_p = R_{p1} + R_{p2})$                                        | 81 |

| Fig.4.3. Layout of the microstrip low pass filter. ( $\epsilon_r = 2.2$ , h = 0.254mm,           |    |

| W0=30mil, W1=60mil, W2=10mil, L1=160mil, L2=170mil)                                              | 84 |

| Fig.4.4. Equivalent network of the microstrip low pass filter                                    | 84 |

| Fig.4.5. Comparison of the frequency responses of the low pass filter obtained                   |    |

| from simulation based on the extracted circuit model, Momentum, and                              |    |

| measurements                                                                                     | 85 |

| Fig.4.6. (a), (b) Geometry and equivalent circuit model of a microstrip gap                      | 87 |

| Fig.4.7. Extracted parameters of the circuit model of a microstrip gap ( $\epsilon_r$ = 2.2, h   |    |

| = 0.254mm, W=0.762mm)                                                                            | 88 |

| Fig.4.8. Layout of the microstrip resonator. ( $\varepsilon_r$ = 2.2, h = 0.254mm, W=30mil,      |    |

| S=5mil, L=160 mil)                                                                               | 89 |

| Fig.4.9. | Equivalent circuit network of the microstrip resonator.                                                          | 90  |

|----------|------------------------------------------------------------------------------------------------------------------|-----|

| Fig.4.10 | ). Frequency responses of the microstrip resonator obtained from                                                 |     |

|          | simulation and measurement.                                                                                      | 90  |

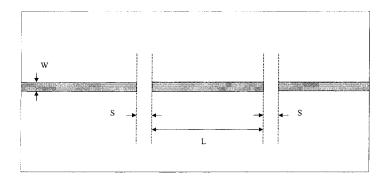

| Fig.5.1. | Physical layout of IDC in CPW. (a) Cross section of IDC. (b) Top view                                            |     |

|          | of IDC.                                                                                                          | 93  |

| Fig.5.2. | Equivalent full-wave circuit model of IDC.                                                                       | 94  |

| Fig.5.3. | Values of the extracted circuit model versus frequency for different                                             |     |

|          | length L of the IDC. (a) Shunt capacitor $C_p$ . (b) Series capacitor $C_s$ . (c)                                |     |

|          | Shunt conductance G <sub>p</sub> . (d) Series conductance G <sub>s</sub> ,                                       | 95  |

| Fig.5.4. | Values of the extracted circuit model versus length L of the IDC,                                                |     |

|          | f=17GHz. (a) Capacitors C <sub>p</sub> and C <sub>s</sub> . (b) Conductances G <sub>p</sub> and G <sub>s</sub> , | 97  |

| Fig.5.5. | (a) Bald transmission line. (b) Equivalent circuit model of the bald                                             |     |

|          | transmission line.                                                                                               | 98  |

| Fig.5.6. | Capacitance loaded transmission line. (a) Equivalent lumped circuit                                              |     |

|          | model of the loaded transmission line. (b) New equivalent transmission                                           |     |

|          | line                                                                                                             | 100 |

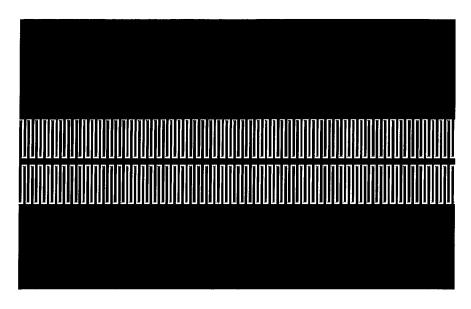

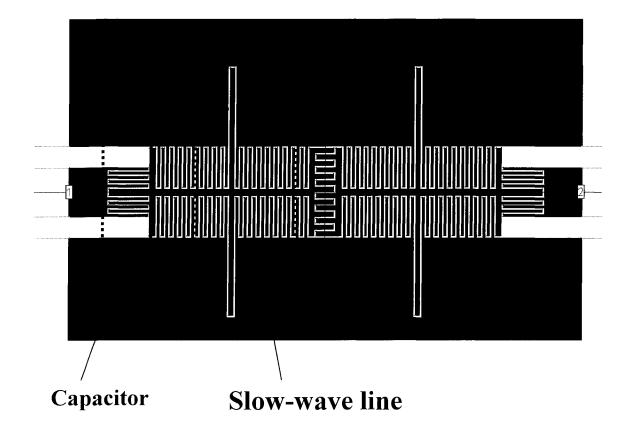

| Fig.5.7. | Structure of a slow-wave line realized by CPW transmission line loaded                                           |     |

|          | by parallel IDCs.                                                                                                | 101 |

| Fig.5.8. | Capacitances in the extracted IDC circuit model involve two parts: the                                           |     |

|          | capacitances of gap and the capacitances of coupled finger                                                       | 102 |

| Fig.5.9. | Extracted capacitances per unit length of the coupled fingers when a                                             |     |

|          | different number of fingers N is selected.                                                                       | 103 |

| Fig.5.10. Transmission parameters calculated for both the loaded CPW line and       |       |

|-------------------------------------------------------------------------------------|-------|

| the unloaded CPW line                                                               | 105   |

| Fig.5.11. The transmission parameters of the slow-wave line loaded with different   |       |

| value of capacitance to the same bald CPW line.                                     | 106   |

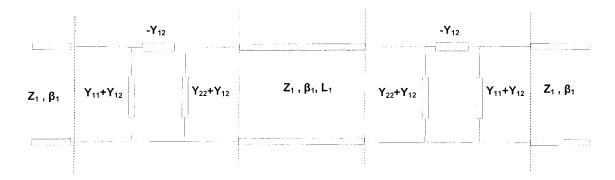

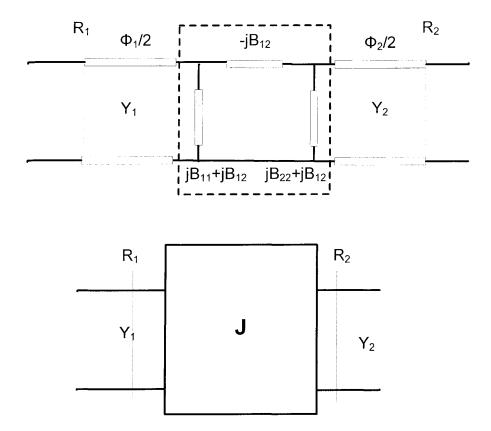

| Fig. 5.12. Equivalent network of the 2-pole BPF.                                    | . 107 |

| Fig. 5.13. J-converter network.                                                     | .108  |

| Fig.5.14. Structural layout of a 2-pole BPF using the slow-wave line resonator      | .110  |

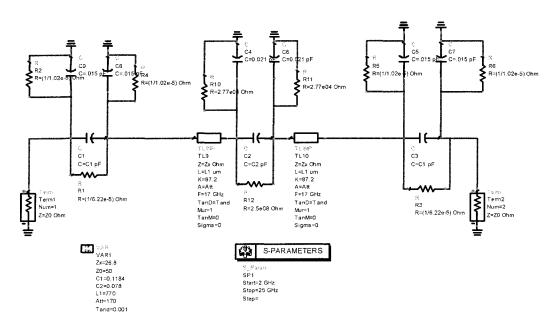

| Fig.5.15. Equivalent network of the 2-pole BPF used in ADS schematic                |       |

| simulation                                                                          | .111  |

| Fig.5.16. Measured results of the slow-wave line 2-pole BPF compared with the       |       |

| simulated results.                                                                  | .112  |

| Fig.6.1. The proposed structure for realizing a 1-to-4 power divider/combiner in    |       |

| our case study                                                                      | .116  |

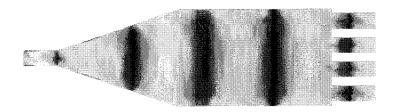

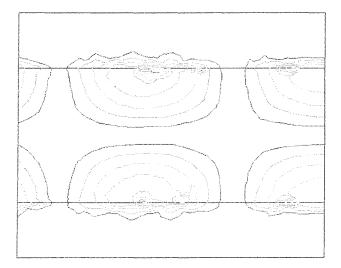

| Fig.6.2. Surface current distribution at 31 GHz generated by Momentum when          |       |

| port 1 is excited.                                                                  | .117  |

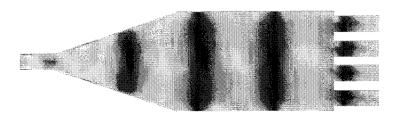

| Fig.6.3. Surface current distribution at 31 GHz generated by Momentum when          |       |

| ports 2 to 5 are excited equally (coherently)                                       | .117  |

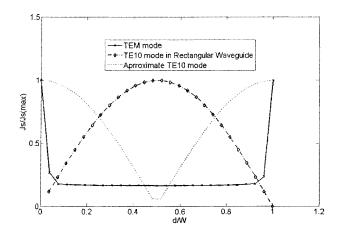

| Fig.6.4. Current distribution density on surface of the oversized microstrip line   | .118  |

| Fig.6.5. Electrical field distribution of the TE10 mode in the oversized microstrip |       |

| line (generated by HFSS).                                                           | .119  |

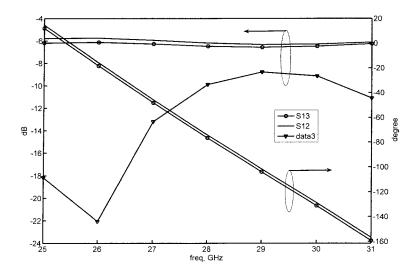

| Fig.6.6. Simulated S parameters of an 1-to-4 power divider as a function of         |       |

| frequency.                                                                          | .121  |

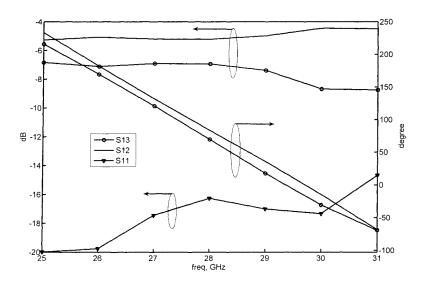

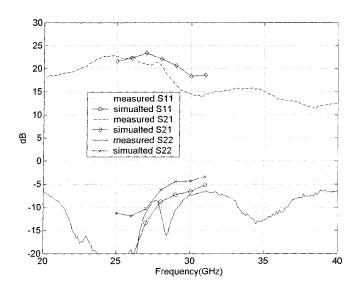

| Fig.6.7. (a) The back-to-back connected 1 to 4 power divider; (b) The measured S |       |

|----------------------------------------------------------------------------------|-------|

| parameters compared with simulated ones.                                         | .122  |

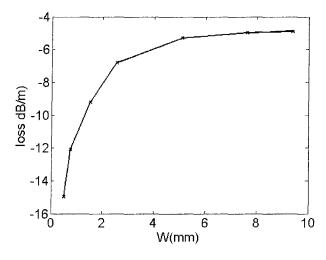

| Fig.6.8. The loss factors versus width of the microstrip line.                   | .124  |

| Fig.6.9. Cascade connection of two networks that have different port numbers     | .126  |

| Fig.6.10. Approximate equivalent circuit model and simulated results of the      |       |

| transition from the oversized microstrip line to the parallel multi              |       |

| microstrip lines                                                                 | .129  |

| Fig.6.11. The structure of the 1-to-4 power divider/combiner to be used in the   |       |

| power combiner                                                                   | .130  |

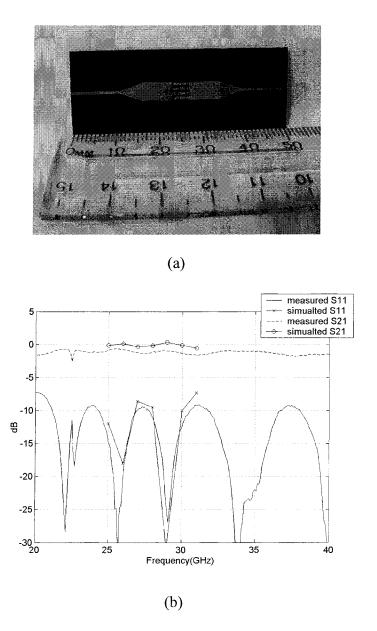

| Fig.6.12. The surface current distribution at 31GHz plotted by Momentum          | .131  |

| Fig.6.13. Simulated S parameters of the 1-to-4 power divider                     | .131  |

| Fig.6.14. The photography of the fabricated quasi-optical planar power           |       |

| combiner.(the size is 69*40 mm <sup>2</sup> )                                    | . 133 |

| Fig.6.15. Frequency response of measured S parameters compared with simulated    |       |

| ones.                                                                            | . 133 |

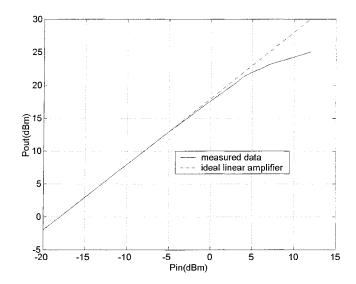

| Fig.6.16. Input power versus output power performance at 25 GHz                  | .134  |

| Fig.6.17. The P1B parameters of the power combiner plotted against frequency     | .134  |

|                                                                                  |       |

| Table 3.1. The S-parameters of a port discontinuity with alumina substrate       |       |

| $(w = h = 0.635 mm, \epsilon_r = 9.9)$                                           | 62    |

| Table 6.1. The calculated maximum potential combining                            |       |

| efficiency                                                                       | 124   |

#### LIST OF ABBREVATIONS

2D Two-dimensional

3D Three-dimensional

ABCD parameter Transmission Parameter or Chain Parameter

BPF Band Pass Filter

CAD Computer Aided Design

CPS Coplanar Stripline

CPW Coplanar Waveguide

DUT Device Under Test

EM Electromagnetic

FGCPW Finite-Ground Coplanar Waveguide

IC Integrated Circuit

IDC Interdigital Capacitor

MMIC Monolithic Microwave Integrated Circuit

MOM Method of Moments

SOC Short-open Calibration

SOLT short-open-load-through

S parameter Scattering Parameter

TE Transverse Electric

TEM Transverse Electromagnetic

TR Thru-Resistor

TRL Thru-Reflect-Line

T parameter Chain Scattering Parameter or Scattering Transfer Parameter

Y parameter Admittance Parameter

Z parameter Impedance Parameter

#### INTRODUCTION

The state-of-the-art design of planar microwave and millimeter-wave circuits and components is generally made in two different ways. One way is based on lumpedelement network topologies, which are developed with static or quasi-static equivalent circuit models of electrically small-sized structures or discontinuities and connecting transmission lines such as planar microstrip or coplanar waveguide elements. This design procedure is quite similar or even identical to the schemes commonly used for low-frequency electronic circuits. A large variety of equivalent circuit models for planar discontinuities has been established and widely used in commercial software packages including Agilent Advanced Design System (ADS), Agilent EEsof EDA, Ansoft Designer and others. However, these models and their network parameters are generally formulated by static/quasi-static closed-form equations with approximations or assumptions, which do not account for high frequency effects such as frequency dispersion, high-order modes, parasitic coupling, space radiation and substrate leakage. In addition, a commercial software package may be able to handle only a limited number of all possible planar discontinuities in its design library, and the designer has to develop his/her own models for the other portion of planar discontinuities. Nevertheless, the equivalent network approach is still the most powerful and preferred technique for the designer.

The other way which is more accurate and reliable is completely based on full-wave electromagnetic modeling and simulation. The terminology "full-wave" means that the

field model is directly developed from the Maxwell's equations although certain assumptions or approximations may also be considered in the model construction such as lossless structures and vanishing conductor thickness. A handful of commercial method-of-moments (MoM) simulators including Agilent Momentum, Ansoft Ensemble, Sonnet EM Suite, Zeland IE3D and other field-based software packages present popular design tools, allowing one to implement accurate full-wave simulation and optimization of planar integrated circuits and antennas. Generally, the full-wave packages are related to simulation and modeling aspects rather than design and optimization processes even though a sophisticated field-based scheme may be possible at the expense of requiring a huge computational resource. This is in particular true when an electrically large planar structure is designed and optimized. Therefore, the global field-based optimization of such a complete structure is impractical and sometimes impossible with the commonly used computing facility. So the most efficient way is to segment the overall complex geometrical layout into a number of electrically small and geometrically simple discontinuities together with uniform transmission line sections and then carry out a direct synthesis and optimization procedure based on its equivalent circuit network topology, which is constructed by characterization and establishment of an equivalent circuit model of each individual part. In this way, element-to-element and adjacent couplings can be involved through multi-level segmentation procedure. However, the fundamental problem in this procedure is whether it is able to obtain very accurate equivalent circuit models with full-wave electromagnetic modeling and simulation techniques for such electrically small structures.

The deterministic MOM algorithms [1]-[13] have been recognized as probably the most powerful candidates for accurate and efficient modeling of planar or quasi-planar structures. However, lumped current/voltage sources such as delta-voltage are generally used to excite the structure, allowing the deterministic and efficient calculations of field parameters. Since the artificial sources can never describe the exact field profile at the ports of excitation because of multilayered geometry and non-uniform field profile, the resulting "artificial" field discontinuities or differences between the lumped sources and the "true" fields can bring errors or parasites to the calculated network parameters or equivalent circuit models. To solve this problem of port discontinuities, several techniques such as double-delay calibration, external exciting and de-embedding, were presented [13]-[17]. But no further attempts were published for systematic understanding of this critical problem until the proposal of short-open calibration (SOC) technique [18]-[30].

The SOC technique, which was inspired from the real-world measurement techniques, makes use of the even/odd excitations with one section of uniform line to formulate the open/short standards and then calculate the error boxes of the structure. Such SOC calibration techniques have successfully been used in equivalent circuit modeling and applications of various microwave planar structures including microstrip, coplanar stripline (CPS), and finite-ground coplanar waveguide (FGCPW) circuits. The original 2-port SOC calibration technique has also been extended to the multi-port SOC [30]. The use of SOC techniques requires intermediate field calculations within the MoM software, which has to be implemented by the software developer. Considering

that nearly all commercial MoM simulators can only provide the calculated network parameters at a specified external location along the feeding line, the SOC technique was found difficult in theory for its compatibility and integration with them. Therefore, it is not practical for us to consider the SOC technique in the commercial electromagnetic simulation and analysis. To remove this hurdle, we propose thru-reflect-line (TRL) and thru-resistor (TR) numerical calibration techniques that can be combined with such commercial EM software packages as Agilent Momentum and Zeland IE3D to model the port discontinuities and extract the circuit model of planar discontinuities[31]-[33] in a similar way as the SOC scheme.

It is well known that the TRL calibration technique [34]-[37] has widely been used in microwave measurements and it was also deployed in [17] to numerically extract the S-parameters of planar circuits from full-wave MoM simulations. The TRL standards are easily realized in both practical measurements and numerical simulations. Distinct technical merits of the TRL and TR calibration techniques can be summarized by two aspects, namely, easily realizable calibration standards and complete compatibility with commercial EM software. With the TRL and TR calibration techniques and commercial packages, one can easily formulate full-wave based equivalent circuit model of planar circuits. In this work, these calibration techniques will be described and discussed with respect to their applications as microstrip circuits, slow wave line filter and planar quasi-optical power combiner.

Slow wave lines are widely implemented in microwave circuits because the size of the circuit using slow-wave line can be greatly reduced. However, the accurate full-wave

models of slow-wave line are difficult to be extracted. The full-wave equivalent circuit model of interdigital capacitors (IDC) in Coplanar waveguides (CPW) configuration will be extracted by using numeric TRL calibration technique combined with commercial EM software and will be implemented in the slow-wave line filter design. In addition, a new planar quasi-optical power combiner will be proposed in this work. The power distributing/combining structures are simply realized by transition between the oversized microstrip line and the parallel multi microstrip lines. With the numerical calibration technique we proposed, we can extract the equivalent circuit model of the power distributing/combining structures. Such structure is a planar structure and has merits of both the circuit based power combiner and the traditional quasi-optics power combiner. It can be fabricated using planar circuit technology. No complicated mechanical assembling is needed, and the volume can be greatly reduced. The interconnections with other planar circuits are very easy.

To avoid any possible confusion of terminology in connection with the use of discontinuity, we should point out that the modeling of a planar discontinuity is concerned with the investigation of a "useful" circuit element and its equivalent circuit model will be developed by numerical calibration and parameter extraction while the port discontinuity is related to parasites due to the "artificial" source or excitation mechanism required in the numerical methods.

#### **CHAPTER 1**

# NUMERICAL TRL CALIBRATION TECHNIQUE

## 1.1 Introduction

A variety of error models and calibration procedures has been proposed and developed for practical measurements. Two of the most popular schemes are the full 2-port short-open-load-through SOLT calibration and TRL calibration. All the proposed calibration procedures rely on simple and idealized standards. The difference between the calibration procedures is in number, specific nature, complexity of the used standards, and type of measurement to be performed. In a real measurement, for example, both SOLT and TRL calibrations can be used if the device-under-test (DUT) has a coaxial structure. If the DUT has a microstrip structure, however, the TRL calibration is better than the SOLT calibration because the SOLT calibration cannot remove discontinuity effects of the transition from coaxial connector to microstrip. Also, the standards in the TRL calibration are much easier to realize than those in the SOLT calibration.

Theoretically, all the calibration procedures proposed in real measurement can also be used in numerical EM simulations. The ideal open and short standards are not easy to realize in an EM simulation of planar structures when we make use of those commercial EM simulation packages based on MOM algorithm. For example, the open always has a

capacitance effect, and the short that is realized by the via connecting to ground always has an inductance effect. However, the TRL calibration standards are much easier to realize. The reflect standards do not need to be perfect. The line and through standards can easily be implemented. Therefore, we believe that the TRL calibration is much more proper for use in the numerical calibration combined with the commercial EM simulation packages based on MOM algorithm.

## 1.2 Numerical TRL calibration

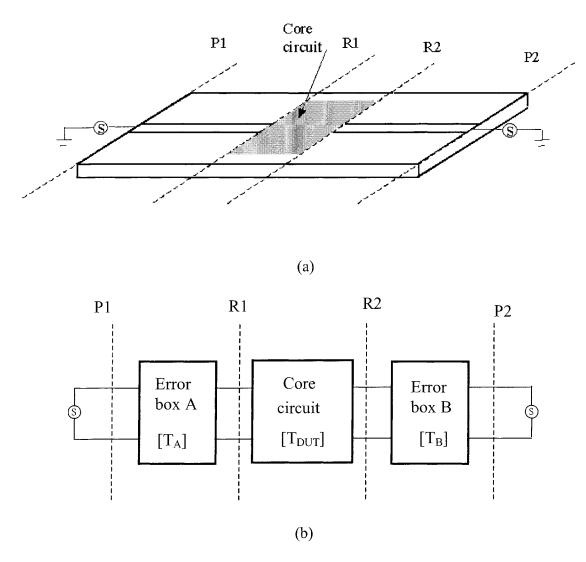

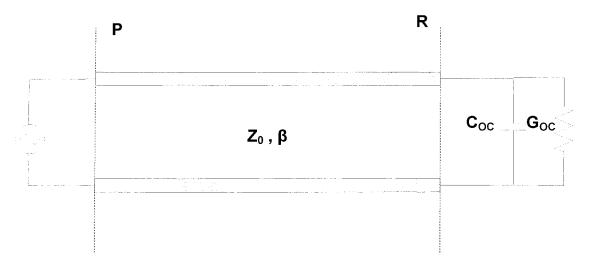

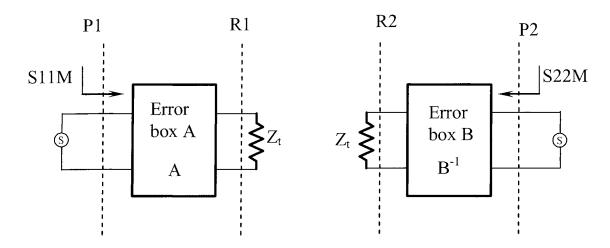

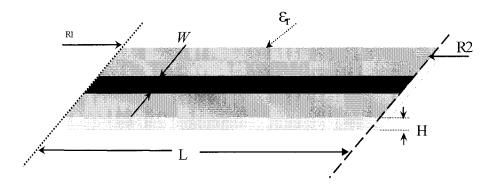

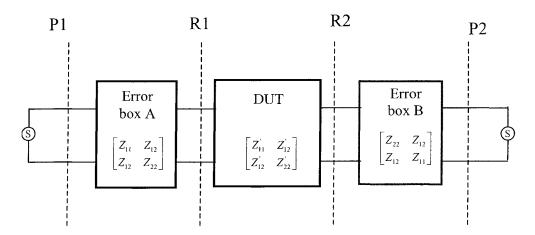

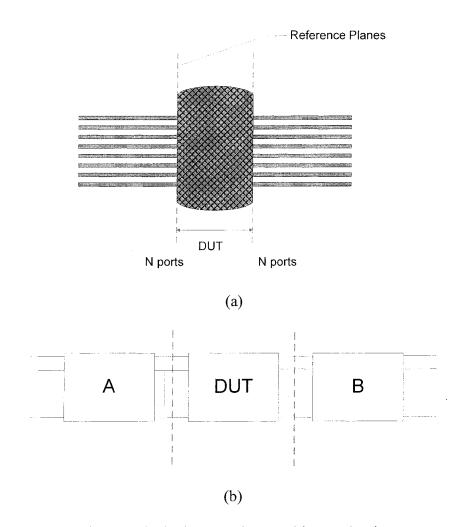

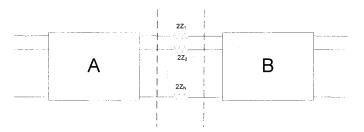

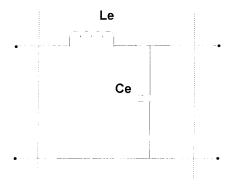

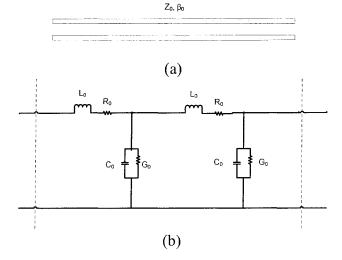

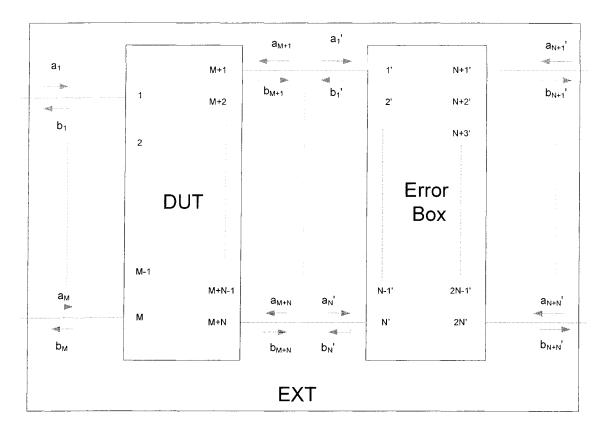

Fig.1.1(a) illustrates a two-port microstrip discontinuity under modeling. The shadow region between reference planes R1 and R2 represents the discontinuity from which we want to extract the circuit model. The discontinuity is named as device under test (DUT). The port discontinuities exist between microstrip feed lines and exciting sources. The equivalent network is shown in Fig.1.1 (b). The error boxes involve the transmission feed line and port discontinuity.

Fig.1.1. Two-port microstrip discontinuity under modeling (a) and its equivalent network (b).

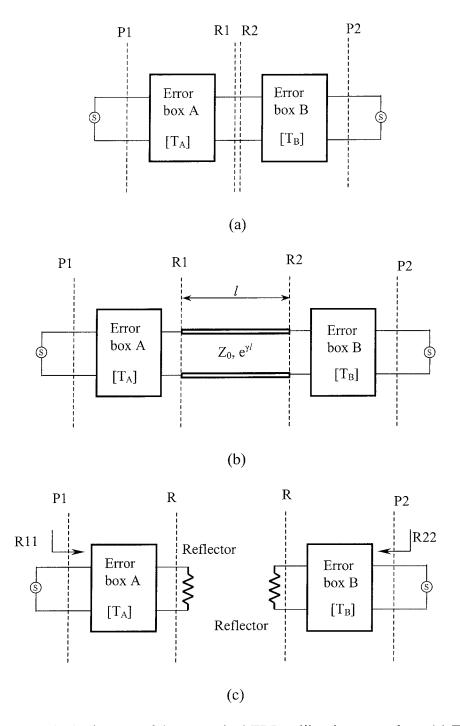

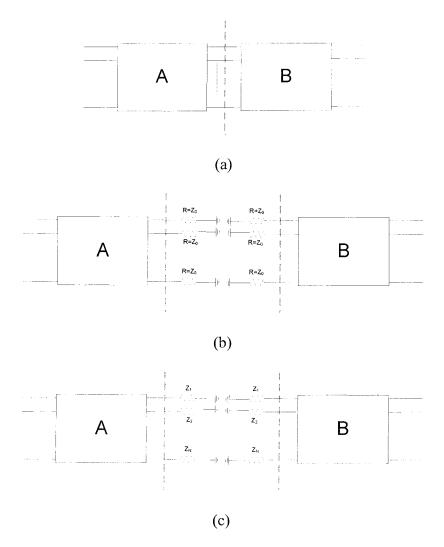

A calibration procedure is used to characterize the error boxes; then the actual errorcorrected parameters of the DUT can be calculated. The simplest way to do calibration is to use three or more known standards, such as short, open, and match loads. The problem with this approach is that such standards are always imperfect to some degree, and consequently introduce errors into the calibrated parameters of the DUT. The TRL calibration scheme does not rely on exactly known standards. The TRL calibration technique makes use of three standards: thru, reflect, and line, which are shown in Fig.1.2.

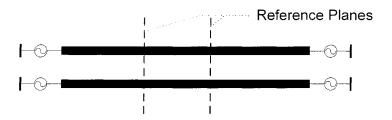

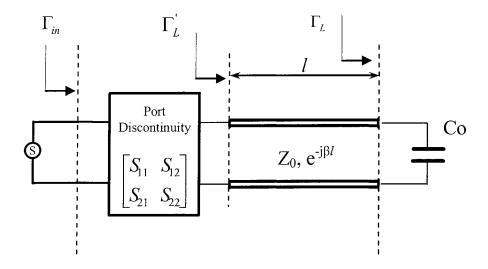

In Fig.1.2, the thru connection is made by directly connecting port at reference plane R1 and port at reference plane R2; the reflect connection uses a load having a high reflection coefficient,  $\Gamma_L$ , as this will be determined in the TRL calibration procedure while the line connection is made by connecting port at reference plane R1 to port at reference plane R2 through a section of uniform transmission line. It is not necessary to know the exact length of the line, and it is not required that the line be lossless as such parameters will be determined in the TRL procedure.

The TRL calibration standards are simple and easily realizable in both practical measurement and numerical MOM simulation. The only critical parameter is the characteristic impedance  $Z_0$  of connecting or reference lines. The calibration procedure is straightforward and results in explicit analytical expressions for the error terms. The TRL calibration technique does have some limitations. Higher-order modes can affect the calibration accuracy and they must be eliminated. For best accuracy, the line standard should be less than 1/2 wavelength long at the highest frequency. However, the difference in length between the line standard and the through standard should be discernible (greater than  $\approx 20^{\circ}$ ) at the lowest frequency. These restrictions limit the frequency span for a given set of standards to a ratio of 8:1. Thus, for a larger desired frequency range, multiple standards and calibrations must be applied.

Fig.1.2. Block diagram of the numerical TRL calibration procedure. (a) Thru connection; (b) Line connection; (c) Reflect connection.

## 1.2.1 TRL calibration algorithm

We apply the through, reflect, and line connections over the reference planes at DUT, R1 and R2, and simulate the S-parameters for these three cases at the reference planes of an exciting source, P1 and P2. Thereafter, we can transfer these S-parameters into T parameters. The following derivation of the TRL algorithm similar to the derivation in [34][35] can be set up. Each connection of standard or DUT which has generalized transfer matrix  $N_x$  will lead to the following matrix  $M_x$ :

$$M_x = AN_x B^{-1}, (1.1)$$

in which A and  $B^{-1}$  are the cascading matrices of error boxes A and B;  $N_x$  are the cascading matrices of the standards or the cascading matrices of the DUT and  $M_x$  are the cascading matrices obtained at reference planes  $P_1$  and  $P_2$ .

From the thru connection, we have

$$M_1 = AN_1B^{-1}, (1.2)$$

$$N_1 = \begin{bmatrix} I & 0 \\ 0 & I \end{bmatrix}. \tag{1.3}$$

From the line connection, we can get the following expressions

$$M_2 = AN_2B^{-1}, (1.4)$$

$$N_2 = \begin{bmatrix} e^{-\gamma l} & 0\\ 0 & e^{+\gamma l} \end{bmatrix}. \tag{1.5}$$

Because the length of the line standard is an unknown, so is  $N_2$  in equation (1.4). Two similar matrices P and Q are defined as follows

$$Q = M_2 M_1^{-1} \text{ and } P = N_2 N_1^{-1},$$

(1.6)

$$P = A^{-1}QA. (1.7)$$

From equation (1.7) we can see that such similar matrices have equal eigenvalues:

$$eig(P) = eig(Q) = \lambda_{1,2}, \quad \Lambda = \begin{bmatrix} \lambda_1 & 0 \\ 0 & \lambda_2 \end{bmatrix},$$

(1.8)

where eig() is the eigenvalue operator.  $\Lambda$  denotes the matrix of eigenvalues which is related to P and Q via the following transformation

$$\Lambda = X^{-1}PX = Y^{-1}PY, \tag{1.9}$$

where the columns of the transformation matrices X and Y are composed of the eigenvectors of P and Q, respectively. Since P is equal to  $N_2$ ,  $N_2$  and  $\Lambda$  have identical eigenvalues, the unknown propagation constants of the line standard can be derived by

$$N_2 = \begin{bmatrix} e^{-\gamma l} & 0 \\ 0 & e^{+\gamma l} \end{bmatrix} = \Lambda = \begin{bmatrix} \lambda_1 & 0 \\ 0 & \lambda_2 \end{bmatrix}. \tag{1.10}$$

As P and Q are known (Q is the measured data at reference planes  $P_1$  and  $P_2$ ), the eigenvectors can be evaluated except for an arbitrary factor, we can write

$$X = X_0 \beta , \qquad \beta = diag(\beta_1, \beta_2), \qquad (1.11)$$

$$Y = Y_0 \delta$$

,  $\delta = diag(\delta_1, \delta_2)$ , (1.12)

where  $\beta_i$  and  $\delta_i$  are arbitrary constants,  $X_0$  and  $Y_0$  can be computed from equation (1.9). As P is diagonal, one possible solution for  $X_0$  is a unit matrix. From equation (1.9) we have

$$P = XY^{-1}QYX^{-1}. (1.13)$$

From equation (1.13) we can partly determine A as

$$A = YX^{-1} = Y_0 \delta \beta^{-1} = A_0 K, \qquad (1.14)$$

where  $A_0 = Y_0$ , and  $K = diag(\frac{\delta_1}{\beta_1}, \frac{\delta_2}{\beta_2}) = \begin{bmatrix} k_1 & 0 \\ 0 & k_2 \end{bmatrix}$ , k1 and k2 are arbitrary constants.

B can be derived by

$$B = M_1^{-1} A N_1 = M_1^{-1} A = M_1^{-1} A_0 K = B_0 K, (1.15)$$

where  $B_0 = M_1^{-1} A_0$ .

So far, there are two unknowns to be determined in A and B:  $k_1$  and  $k_2$ . The reflect standard is used to determine these two unknowns. The reflection coefficient of the reflect standard is not known exactly, but it can be chosen to be an imperfect short or an imperfect open which has a reflect coefficient  $|\Gamma| \approx 1$ . So we have the reflect coefficient at the reference planes  $P_1$  and  $P_2$

$$\Gamma_{Xa} = (A_{11}\Gamma + A_{12})(A_{21}\Gamma + A_{22})^{-1}, \tag{1.16}$$

$$\Gamma_{xb} = (B_{22}\Gamma + B_{21})(B_{12}\Gamma + B_{11})^{-1}. \tag{1.17}$$

From equation (1.16)(1.17), we can get

$$\Gamma = k_2^{-1} X_2 k_1 = k_1^{-1} X_1 k_2, \tag{1.18}$$

$$X_{1} = (A_{0,11} - \Gamma_{Xa} A_{0,21})^{-1} (\Gamma_{Xa} A_{0,22} - A_{0,12}), \qquad (1.19)$$

$$X_2 = (B_{0,22} - \Gamma_{Xb} B_{0,12})^{-1} (\Gamma_{Xb} B_{0,11} - B_{0,21}). \tag{1.20}$$

Solving equation (1.18) yields

$$k_2 k_1^{-1} = \pm \sqrt{\frac{X_2}{X_1}} \ . \tag{1.21}$$

The sign in equation (1.21) can be determined by evaluating the sign of  $\Gamma$  in equation (1.18). So we have

$$k_2 = \alpha k_1, \qquad \alpha = \pm \sqrt{\frac{X_2}{X_1}}, \qquad (1.22)$$

$$K = \begin{bmatrix} k_1 & 0 \\ 0 & k_2 \end{bmatrix} = k_1 \begin{bmatrix} 1 & 0 \\ 0 & \alpha \end{bmatrix}. \tag{1.23}$$

We can now complete the calibration because we can derive the T parameters of any DUT by

$$N_{x} = A^{-1}M_{x}B = K^{-1}A_{0}^{-1}M_{x}B_{0}K = \begin{bmatrix} 1 & 0 \\ 0 & \alpha \end{bmatrix}^{-1}A_{0}^{-1}M_{x}B_{0}\begin{bmatrix} 1 & 0 \\ 0 & \alpha \end{bmatrix}.$$

(1.24)

Furthermore, the value of  $k_1$  can be determined by using the reciprocity property. We assume that the error box has a reciprocity property. Such property exists in most of passive structures in the full-wave electromagnetic simulations.

From the reciprocity property of error box A, we have

$$A_{11}A_{22} - A_{12}A_{21} = 1. (1.25)$$

From equations (1.14), (1.23) and (1.25), we can calculate the value of  $k_1$  by

$$k_1^2 = \frac{1}{\alpha(A_{0.11}A_{0.22} - A_{0.12}A_{0.22})}. (1.26)$$

By using three standards: thru, line and reflect connections, we can calculate the parameters of the error boxes, and the correct core parameter of the DUT can be obtained by removing the error boxes through equation (1.24). The TRL calibration

technique can be implemented in both practical measurement and full-wave MOM simulation.

# 1.2.2 Examples

In full-wave MOM simulations, it has been known that port discontinuities brought by the imposed lumped current/voltage exciting source will cause errors in the calculated parameters of the circuit of interest (as in the measurement, we name it as DUT). By using our numerical TRL calibration technique, the port discontinuities can be considered in the error boxes, and their effects can be removed in order to extract the correct parameters of the DUT. Therefore, we can use the numerical TRL calibration to extract parameters of planar discontinuities such as microstrip open, step, gap and so forth. In the following, an example will be studied to validate the proposed numerical TRL calibration technique.

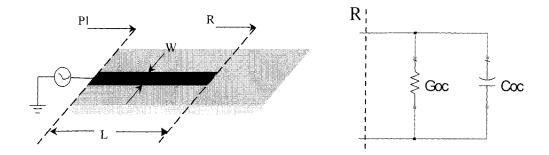

A simple microstrip open-end circuit is studied in this work. Fig.1.3 depicts the physical layout arranged for the TRL-based de-embedding of equivalent open-end capacitance (Coc). The radiation-related conductance (Goc) is negligible at low frequency. The substrate of this open circuit is Alumina  $\varepsilon_r = 9.9$ , W = h = 0.635mm, L = 10.4mm. We use IE3D to carry out the EM simulation. A local port model is selected instead of other port models for the deterministic or direct MoM algorithm as detailed in [19]. Therefore, network parameters at the port can directly be derived from the calculated port quantities such as port voltages/currents or amplitudes of

incident/reflected waves, without resorting to any additional simulation of current density distributions along the feeding line in the indirect MoM algorithm as in [19].

Fig.1.3. Geometry and generalized equivalent circuit model of a microstrip open-end circuit.

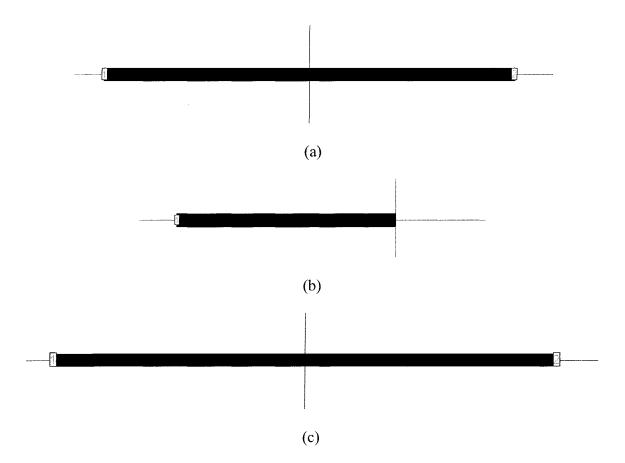

First, the complex reflection coefficient at the port can numerically be calculated and then converted to its corresponding input admittance with the help of characteristic impedance. Next, the three microstrip thru, line and reflect connections are realized in the EM simulation and the S parameters are generated. The length of the line standard is chosen to be 5.6mm. From the static calculation, the electrical length of the line standard is about 35° at 2GHz and 87° at 5GHz, which can satisfy the necessary condition from 20° to 160° in the frequency range from 2 to 5 GHz. We choose the open-end (the same open-end we want to study) as the reflect standard. All the S parameters corresponding to the thru and the line standard are transferred to the T parameters. Then we use the TRL calibration algorithm as described above to do the calibration and the network parameters of the error terms with regard to the feed line section (port-to-end section in Fig.1.1(a)) can be obtained. The layouts of the connection of the three standards in IE3D

are shown in Fig.1.4. As a result, the load admittance at the open-end can be derived in an analytical way by removing out the error box. Actually, because we use the reflect standard that is the same as the open-end during the TRL calibration procedure, we can calculate the reflection coefficient  $\Gamma$  of the open-end from equation (1.18). Then we can obtain the input admittance of the open-end by

$$Y_{in} = Y_0 \frac{1 - \Gamma}{1 + \Gamma} \,. \tag{1.27}$$

Fig.1.4. The layout of the three connections (IE3D). (a) Thru connection; (b) Reflect connection; (c) Line connection.

And the capacitance of the equivalent circuit model as shown in Fig.1.3 can be calculated by

$$C_{oc} = \frac{IM(Y_{in})}{2\pi f_0}, \ G_{oc} = RE(Y_{in}).$$

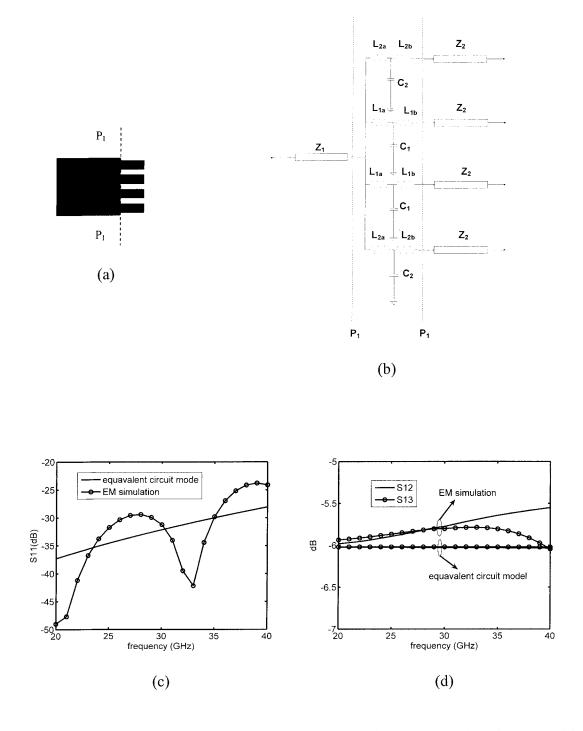

(1.28)